Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

83 results about "XNOR gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The XNOR gate (sometimes ENOR, EXNOR or NXOR and pronounced as Exclusive NOR) is a digital logic gate whose function is the logical complement of the exclusive OR (XOR) gate. The two-input version implements logical equality, behaving according to the truth table to the right, and hence the gate is sometimes called an "equivalence gate". A high output (1) results if both of the inputs to the gate are the same.

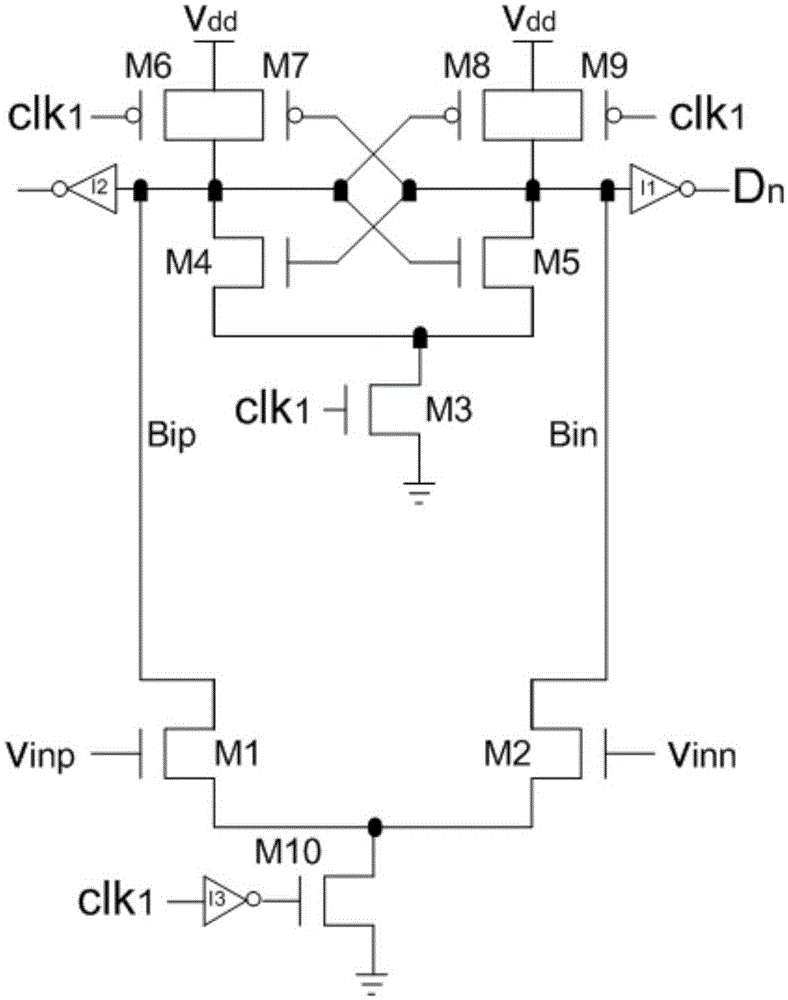

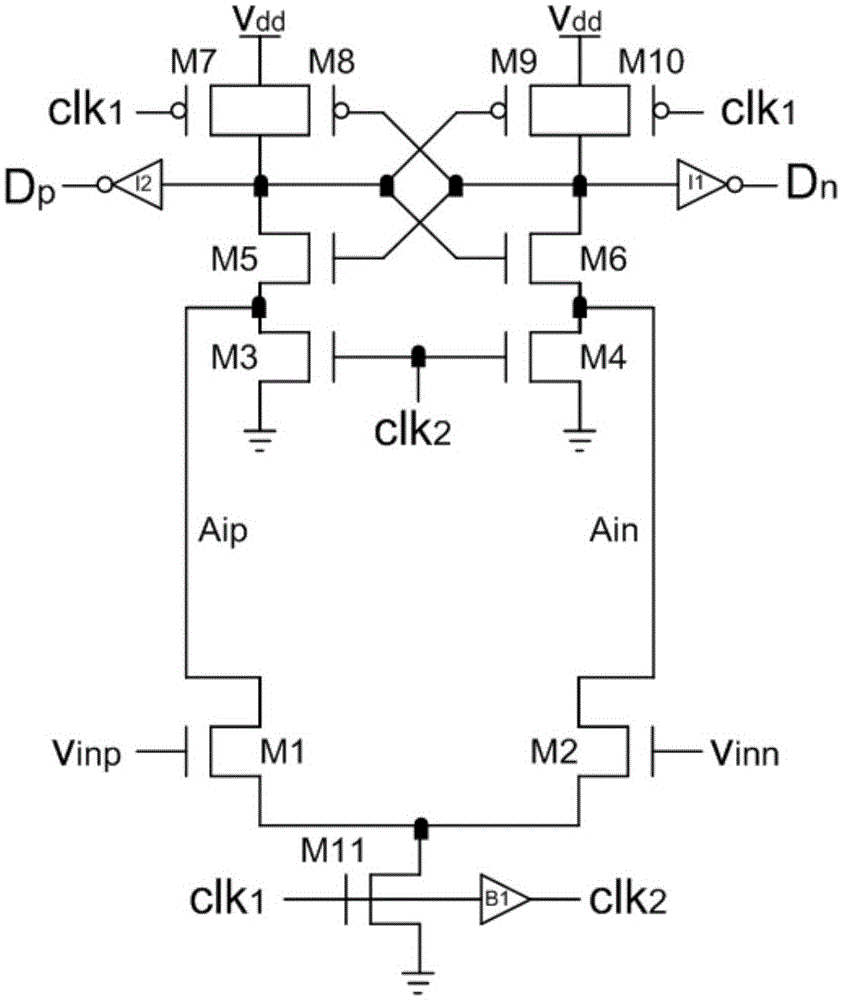

High-speed low-power-consumption dynamic comparator

ActiveCN105162441AGive full play to the advantages of high speedAddressing Static Power IssuesPower reduction in field effect transistorsReliability increasing modificationsControl signalLow power dissipation

The invention discloses a high-speed low-power-consumption dynamic comparator. The high-speed low-power-consumption dynamic comparator comprises a latch, an AND gate, a delay unit and an XNOR gate, wherein the latch is provided with first to third control ends; the output of the latch generates a first comparator output signal and a second comparator output signal through phase inverter I1 and I2 respectively; the first comparator output signal and the second comparator output signal generate an output signal through the XNOR gate; the output signal and a control signal clk1 are taken as input signals of the AND gate; an output signal of the AND gate controls a grid of a sixth NMOS (N-channel Metal Oxide Semiconductor) transistor P10; a delay signal clk2 of the clk1 is generated through the delay unit; and the clk2 is input into a third control end of the latch. According to the high-speed low-power-consumption dynamic comparator, the comparator output signals Dp and Dn generate the output signal through the XNOR gate, and the output signal and the control signal clk1 generate the control signal of the NMOS tube P10 through the AND gate, so that the problem of static power consumption in a conventional structure is solved.

Owner:CHONGQING GIGACHIP TECH CO LTD

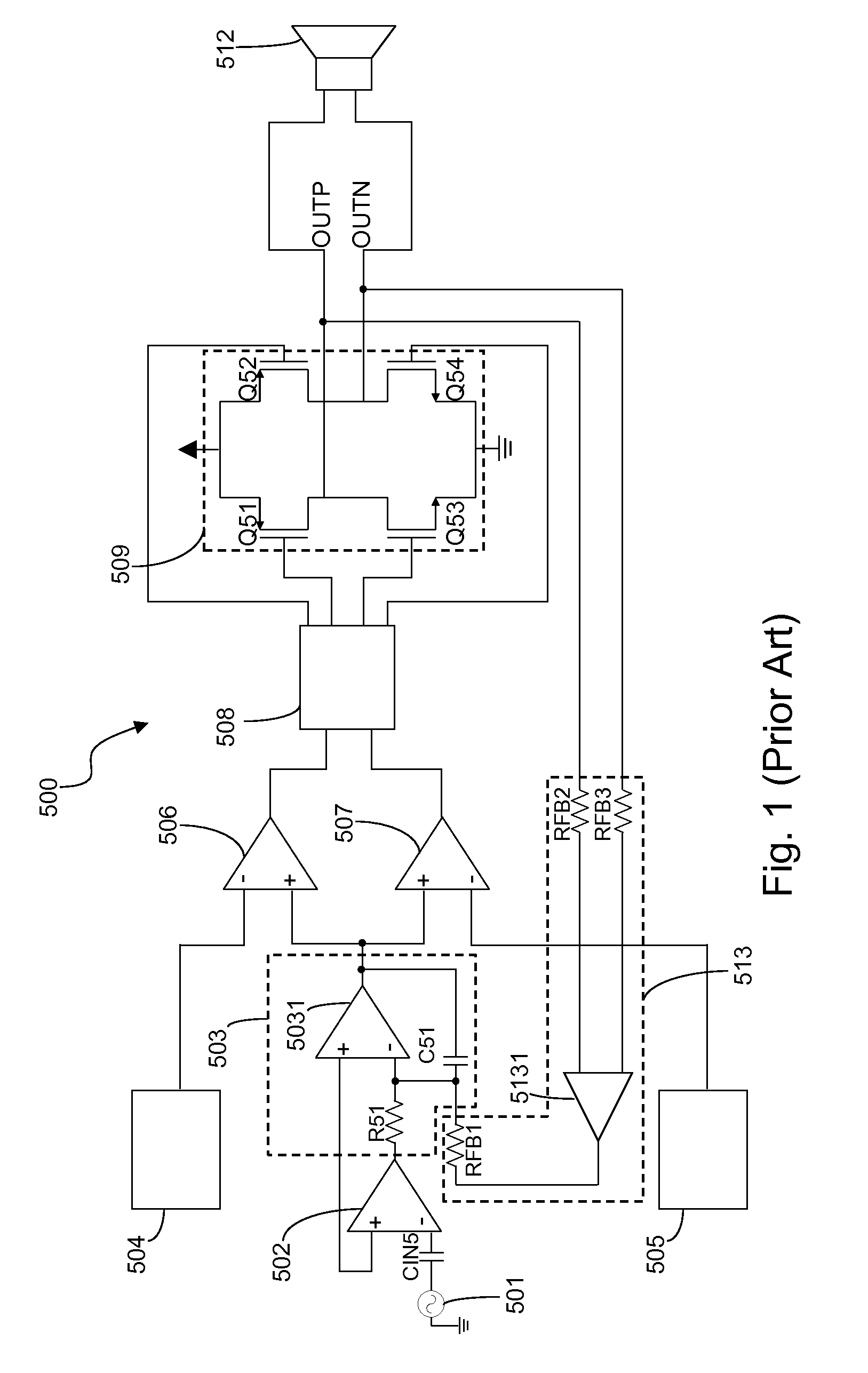

Class-D power amplifier having distortion-suppressing function

InactiveUS7852156B1Prevent audio distortionEnsuring quality of outputNegative-feedback-circuit arrangementsAmplifier modifications to reduce noise influenceAudio power amplifierAudio frequency

A Class-D power amplifier having a distortion-suppressing function includes a gain control unit, a first PWM unit, a second PWM unit, a current control unit, and a level control unit. The level control unit includes at least one D flip-flop and at least one XNOR gate. The D flip-flop has an output end coupled with the gain control unit and an R end coupled with an output end of the XNOR gate. When the Class-D power amplifier has its positive output end and negative output end respectively and simultaneously outputting a high-level signal and a low-level signal to the XNOR gate, the XNOR gate outputs the high-level signal to the D flip-flop. Then the D flip-flop outputs the high-level signal to the gain control unit as feedback for controlling the gain control unit to reduce audio gain, thereby suppressing audio distortion.

Owner:AMAZING MICROELECTRONICS

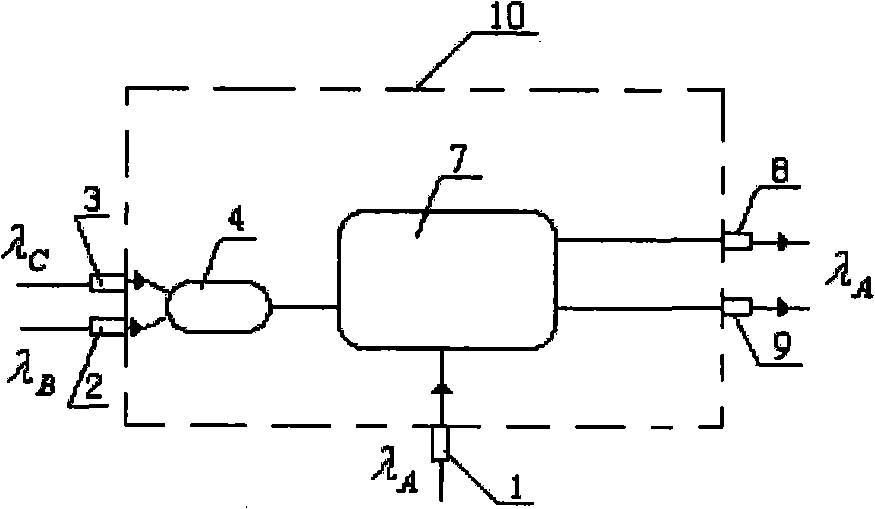

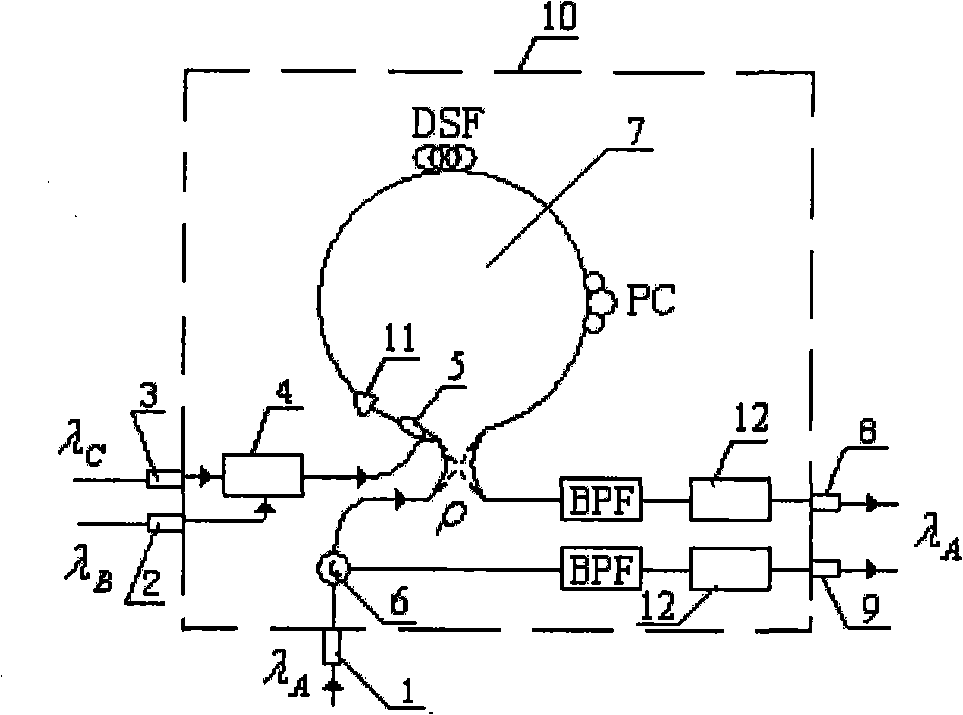

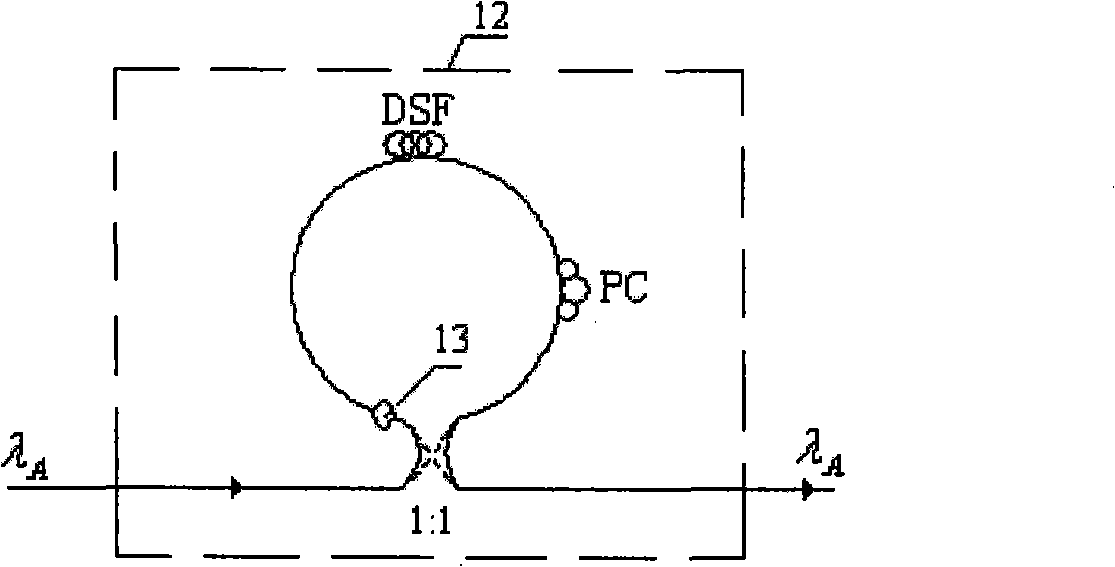

Full-optical logic gate

InactiveCN101526715AReduce the incident light powerReduce Sagnac loop lengthLogic circuits using opto-electronic devicesNon-linear opticsControl signalNOR gate

The invention relates to a full-optical logic gate (10), which can be reused to achieve opposite phase operations of an AND gate, an OR gate, an NOT gate, an NAND gate, an NOR gate, an XOR gate, an XNOR gate and combination thereof, and can also achieve a half adder. The full-optical logic gate comprises light input ports (2, 3) for receiving two control light signals respectively, a light input port (1) for receiving a synchronous light clock signal, a light output port (8) for outputting the result for expressing logic application, and a light output port (9) for outputting opposite phase operation. The full-optical logic gate is characterized by comprising a light combination device (4) and a nonlinear optical device (7), wherein the light combination device (4) is used for combining the two control light signals to generate corresponding combined signals with a wavelength division multiplexer or a polarization beam combiner; and the nonlinear optical device (7) is used for receiving the combined signals and the synchronous light clock signal and emitting two paths of light output signals mutual in opposite phase operations. The full-optical logic function depends on the characteristic of the nonlinear optical device, wherein the characteristic is selected so that the power of the output signals and the light power of the clock signal are redistributed and associated through the selected logic function.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

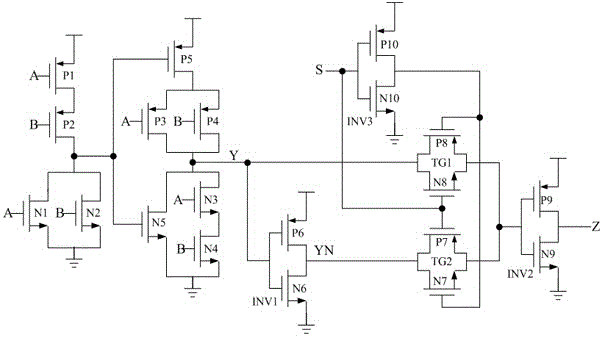

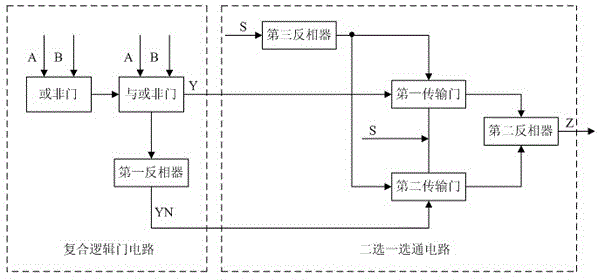

Circuit capable of realizing multiplexing of exclusive-OR gate or XNOR gate

ActiveCN105471425AReduce power consumptionReduce in quantityLogic circuits characterised by logic functionMultiplexingExclusive or

The invention discloses a circuit capable of realizing multiplexing of an exclusive-OR gate or an XNOR gate, belonging to the technical field of integrated circuits. The circuit comprises a compound logic gate circuit and an either-or gating circuit which are cascaded; the compound logic gate circuit comprises a NOR gate unit, an AND-OR-NOT gate unit and a first phase inverter, an input end of the NOR gate unit and the input end of the AND-OR-NOT gate unit are respectively connected with two paths of input signals, an output end of the NOR gate unit is connected with a control end of the AND-OR-NOT gate unit, the output end of the AND-OR-NOT gate unit is connected with the input end of the first phase inverter and outputs an exclusive-OR operation result, and the output end of the first phase inverter outputs an XNOR operation result; and the either-or gating circuit performs gating on an exclusive-OR gate unit composed of the NOR gate unit and the AND-OR-NOT gate unit, or an XNOR gate unit composed of the NOR gate unit, the AND-OR-NOT gate unit and the first phase inverter. The circuit provided by the invention realizes simple multiplexing of the exclusive-OR gate or XNOR gate circuit, reduces the number of transistors of the whole circuit system, and consequently reduces the layout area and circuit power consumption.

Owner:WUXI XINXIANG ELECTRONICS TECH

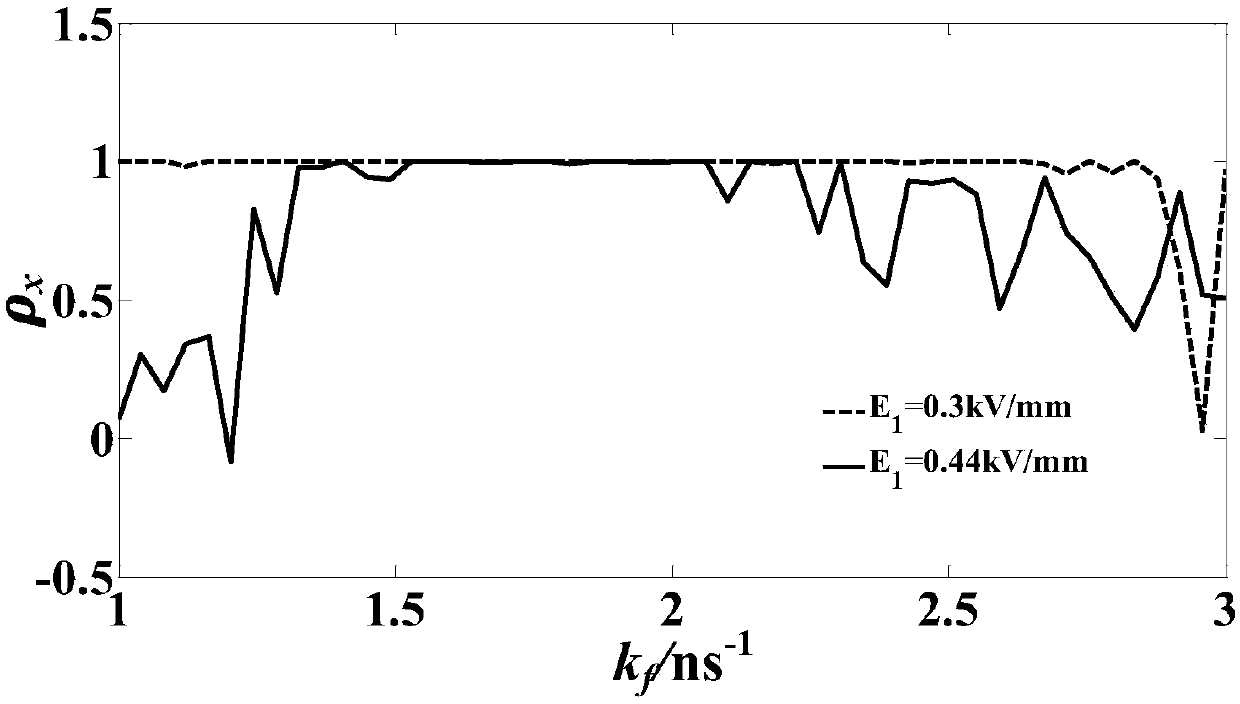

True random number generator based on time delay feedback oscillators

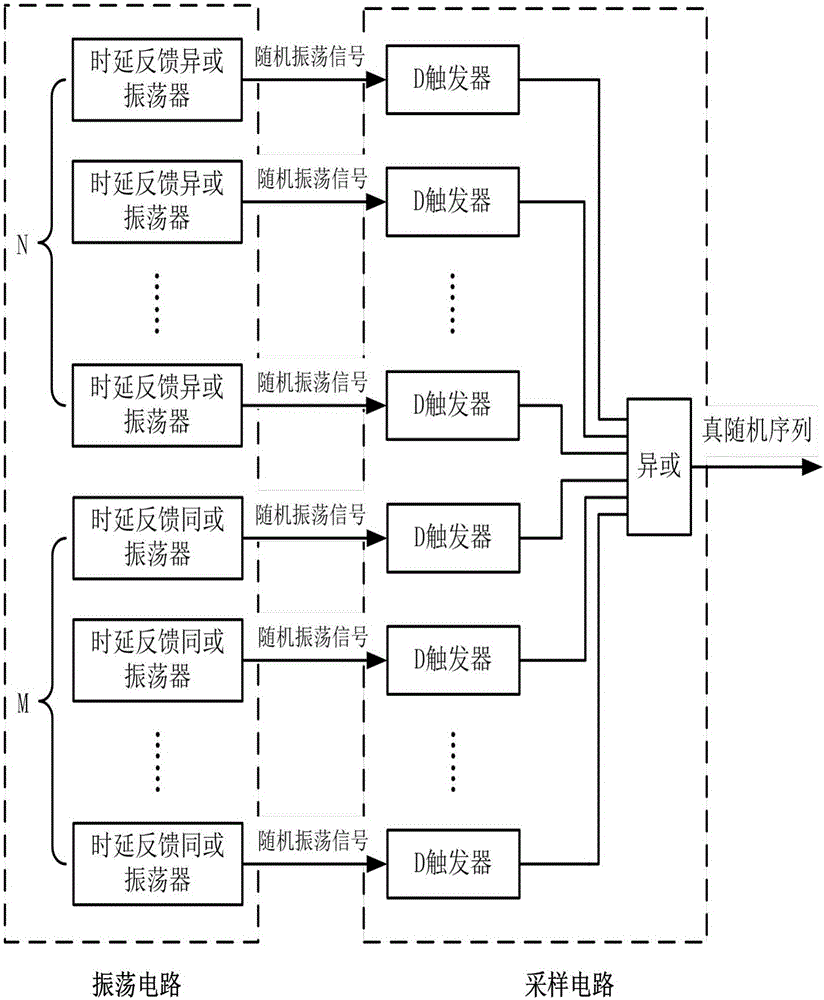

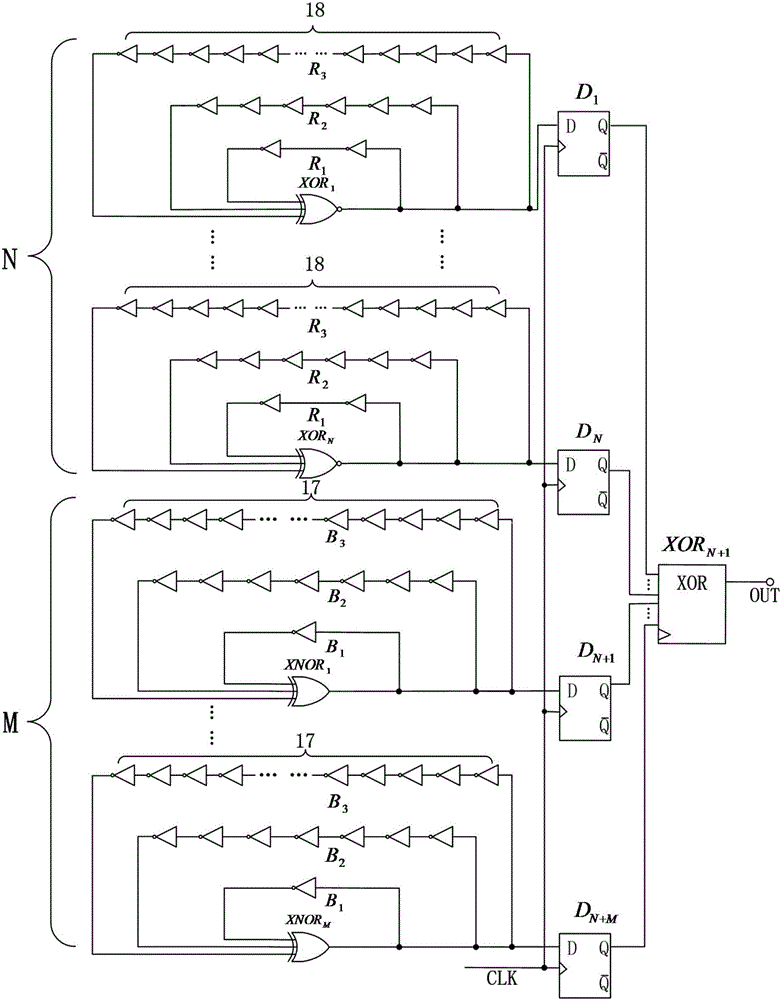

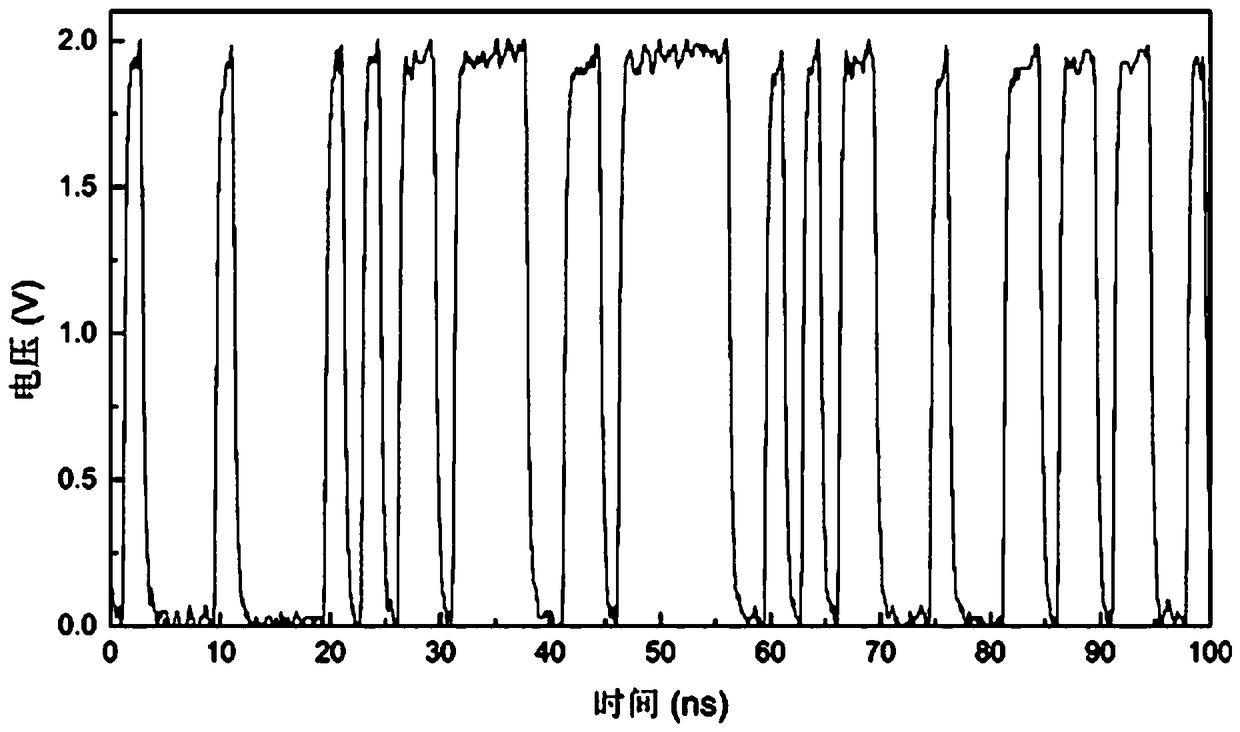

The invention discloses a true random number generator based on time delay feedback oscillators. The true random number generator mainly solves the problems that a true random number generator in the prior art is low in true random number generating speed and poor in randomness. The true random number generator comprises an oscillating circuit and a sampling circuit. The oscillating circuit is used for generating random oscillating signals and is composed of a plurality of time delay feedback exclusive-or oscillators and a plurality of time delay feedback exclusive-nor oscillators, each time delay feedback exclusive-or oscillator is composed of an exclusive-or gate and three upper inverter sets, each time delay feedback exclusive-nor oscillator is composed of an exclusive-nor gate and three lower inverter sets, and the inverter sets comprise different numbers of inverters. The sampling circuit is used for sampling the random oscillating signals generated by the oscillating circuit and is composed of a plurality of D triggers and an exclusive-or gate, and output of all the D triggers generates true random numbers with the speed of 100 Mbit / s or above through the exclusive-or gate. The true random number generator is simple in structure and good in entropy source randomness and can be used for secret communication.

Owner:XIDIAN UNIV

High-speed random number generation method and apparatus

ActiveCN108345446AIncrease spawn rateSimple structureRandom number generatorsFrequency spectrumBoolean network

The invention discloses a high-speed random number generation method and apparatus. The apparatus comprises two parts including an entropy source module and an entropy sampling module. The entropy source module is an autonomous Boolean network consisting of digital logic gates; the network consists of an XNOR gate and N-1 XOR gates; N is equal to 3n (n is a positive integer); and the entropy source module can generate a chaotic signal with a wide and flat spectrum. The entropy sampling module is composed of a D trigger, and performs sampling and quantization on the chaotic signal to generate arandom number sequence. The generated random number sequence can pass random number industry test standards (NIST and Diehard statistical tests), and has good random statistical characteristic. The apparatus consists of the digital logic gates, and is simple in circuit structure and easy to integrate and manufacture; and a post-processing algorithm or circuit necessary for a conventional random number generation apparatus is not required, so that the power consumption can be greatly reduced. The high-speed random number generation method and apparatus can be widely applied to the field of information security of secret communication, key distribution, data encryption and the like.

Owner:TAIYUAN UNIV OF TECH

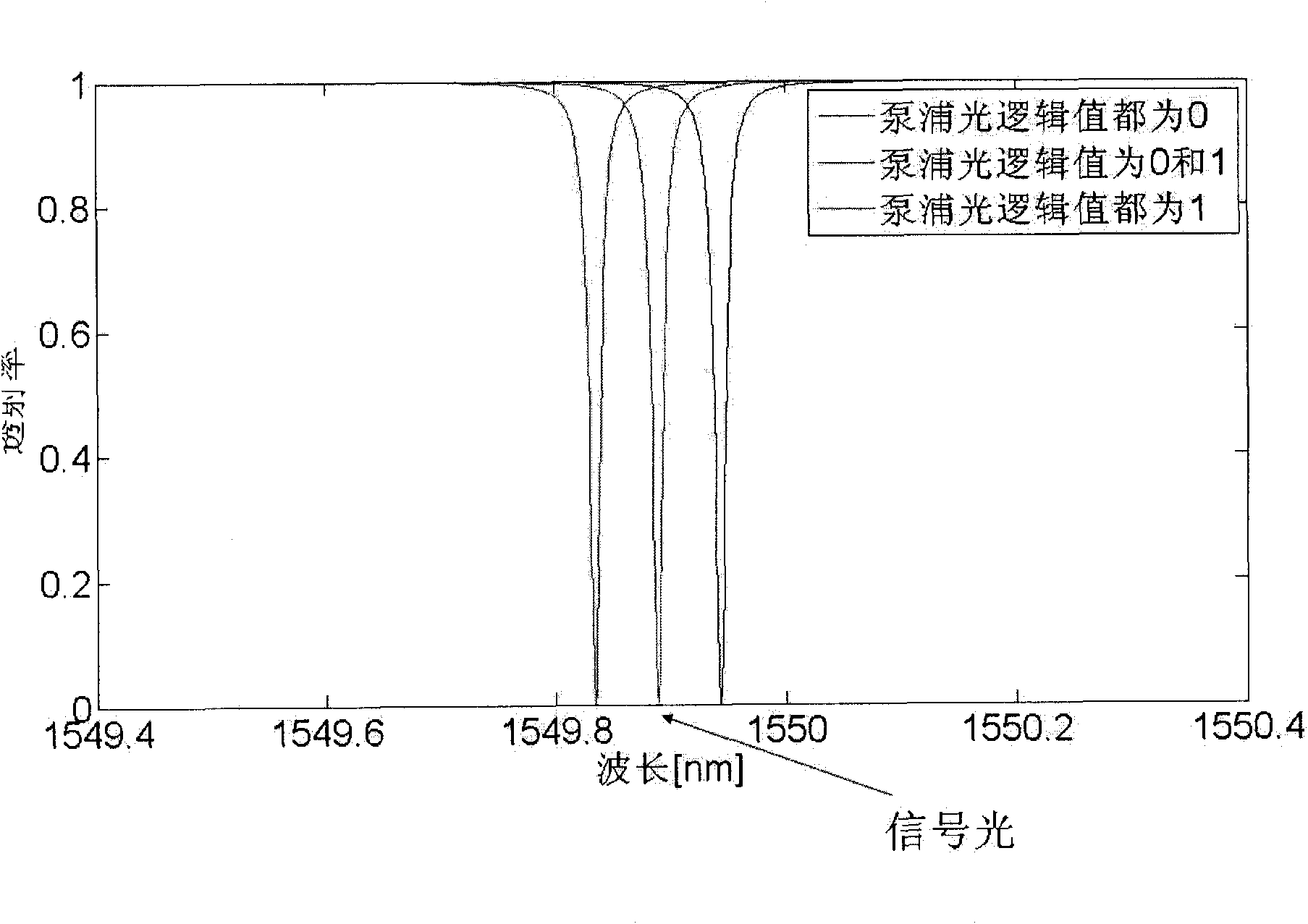

Full-gloss logic XNOR gate structure based on micro-ring resonator structure

InactiveCN101794053ARealize the logic functionReduce working optical powerLogic circuits using opto-electronic devicesNon-linear opticsTwo-photon absorptionResonant cavity

The invention relates to a full-gloss logic XNOR gate structure based on a micro-ring resonator structure, comprising a first nanowire waveguide, a second nanowire waveguide and a micro-ring resonant cavity, wherein the first nanowire waveguide and the second nanowire waveguide are parallel to each other, the micro-ring resonant cavity is positioned between the first nanowire waveguide and the second nanowire waveguide, gaps are respectively arranged between the micro-ring resonant cavity and the first nanowire waveguide and between the micro-ring resonant cavity and the second nanowire waveguide and ensure that the micro-ring resonant cavity satisfies critical coupling conditions so that light waves satisfying the resonant wavelength of the micro-ring resonant cavity can be completely coupled in the micro-ring resonant cavity through the first nanowire waveguide or the second nanowire waveguide, and the light extinction is realized on the output end of the first nanowire waveguide or the second nanowire waveguide. The invention utilizes the two-photon absorption effect in the micro-ring resonant cavity to realize the logic function of full-gloss 'XNOR'.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

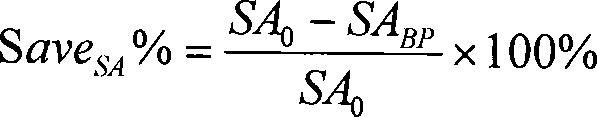

Optimum polarity search method for digital integrated circuit design

InactiveCN101216865AReduce power consumptionWhile optimizing power consumptionEnergy efficient computingSpecial data processing applicationsMulti inputElectrical polarity

The invention discloses an optimum polarity search method for the design of a digital integrated circuit, which comprises the following steps: establishing a XNOR / OR circuit power consumption estimation model through optimizing the power consumption algorithm of a multi-input XNOR gate, so as to obtain the switching activity of the whole XNOR / OR circuit; utilizing the rapid list polarity conversion algorithm to realize conversion from the maximum item of a Boolean function to the XNOR / OR circuit expansion under the 0 polarity; carrying out the list technology-based polarity conversion algorithm according to the order of Gray code, so as to obtain the XNOR / OR circuit expansion under the other 2<N> minus 1 polarities; and finally obtaining the minimum power consumption, the minimum area and the minimum cost value and the optimum polarity of the XNOR / OR circuit. The invention has the advantages that the XNOR / OR logic circuit with the lower power consumption can be obtained; by measuring 10 MCNC Benchmark circuits, the XNOR / OR circuit corresponding to the optimum polarity searched via the method of the invention can save the switching activity and the area respectively by 94.4 percent and 82.2 percent at the most when comparing with the polarity 0,, and the 10 circuits can averagely save the witching activity and the area by 68.4 percent and 34.2 percent respectively.

Owner:NINGBO UNIV

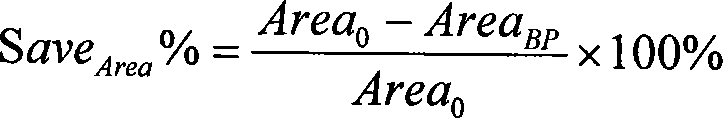

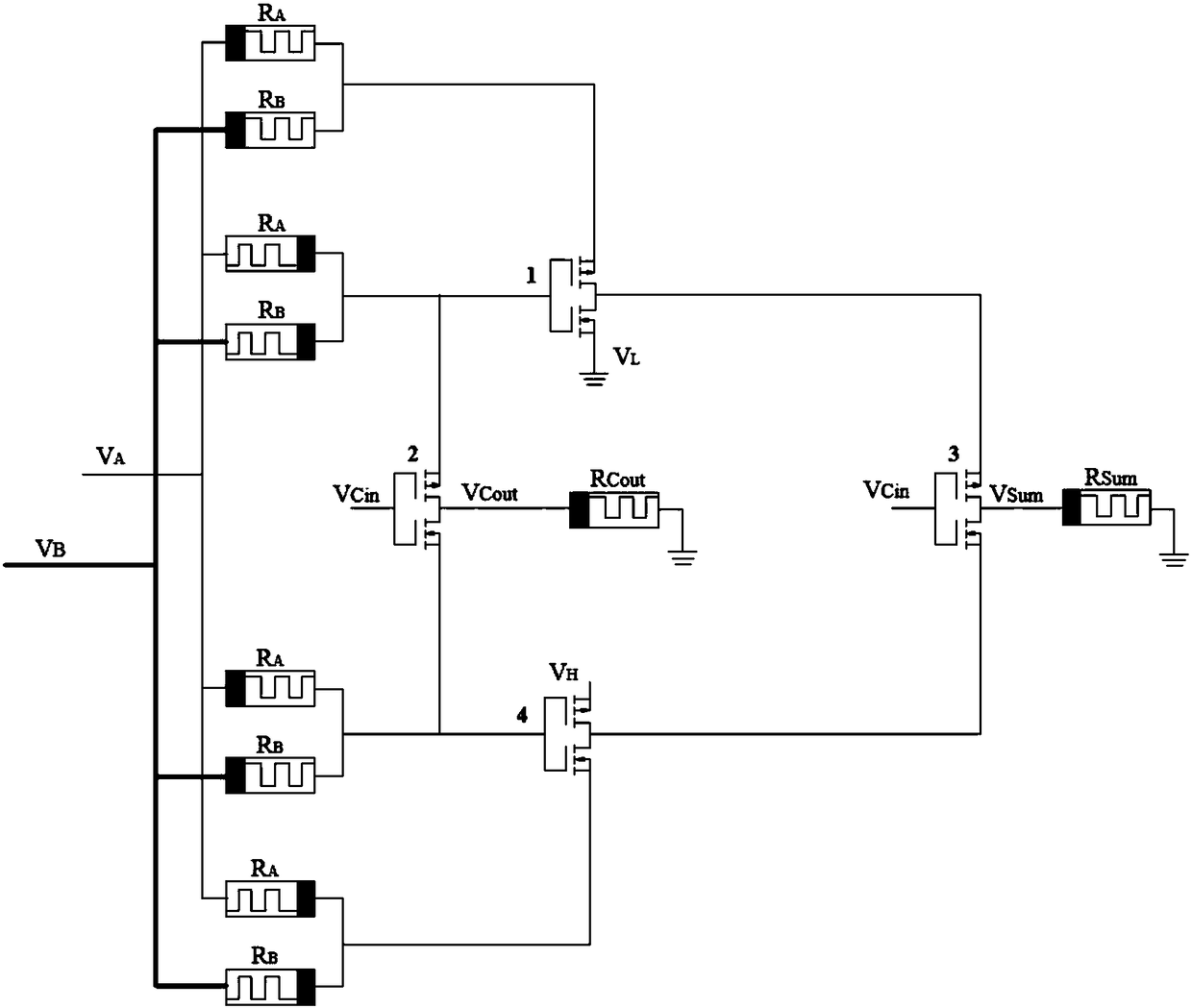

Full-addition circuit composed of CMOS inverters and memristors

The invention discloses a full-addition circuit composed of CMOS inverters and memristors. The full-addition circuit comprises four CMOS inverters, wherein the first inverter and four memristors forman XOR gate circuit, the fourth inverter and another four memristors form an XNOR gate circuit, the second inverter and the third inverter separately receive initial carry signals VCin, the upper endof the second inverter is connected to the input end of the first inverter, the lower end of the second inverter is connected to the input end of the fourth inverter, the second inverter outputs a carry signal VCout, the output end of the XOR gate circuit is connected to the upper end of the third inverter, the output end of the XNOR gate circuit is connected to the lower end of the third inverter, and the third inverter outputs a sum voltage VSum. The scheme of the invention has the effects that: according to the circuit, a logical circuit integrates computing and storage functions, logical operation steps can be greatly reduced, components required by the circuit can be simplified, the circuit costs can be further reduced, and the integration degree of the circuit can be improved.

Owner:SOUTHWEST UNIVERSITY

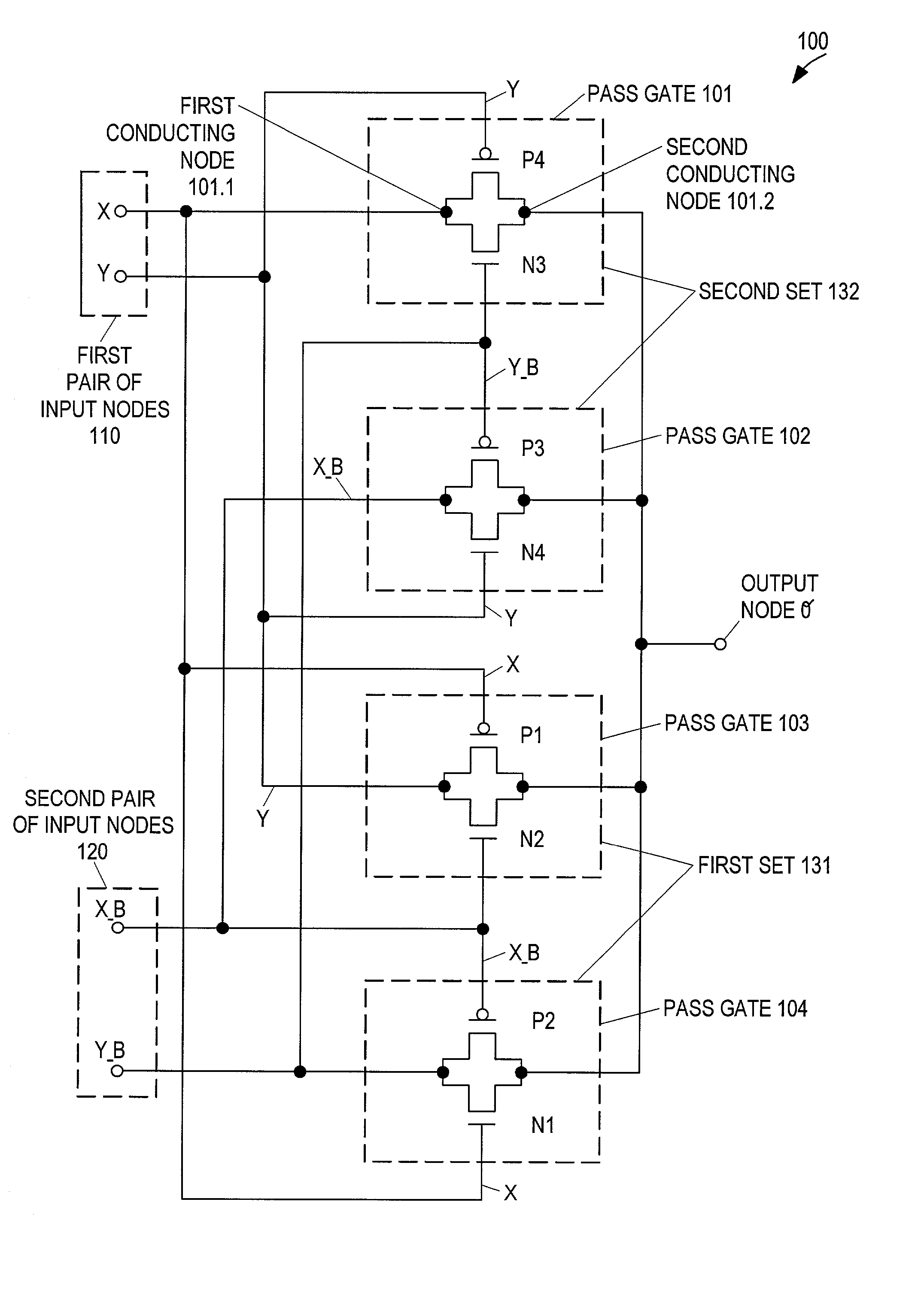

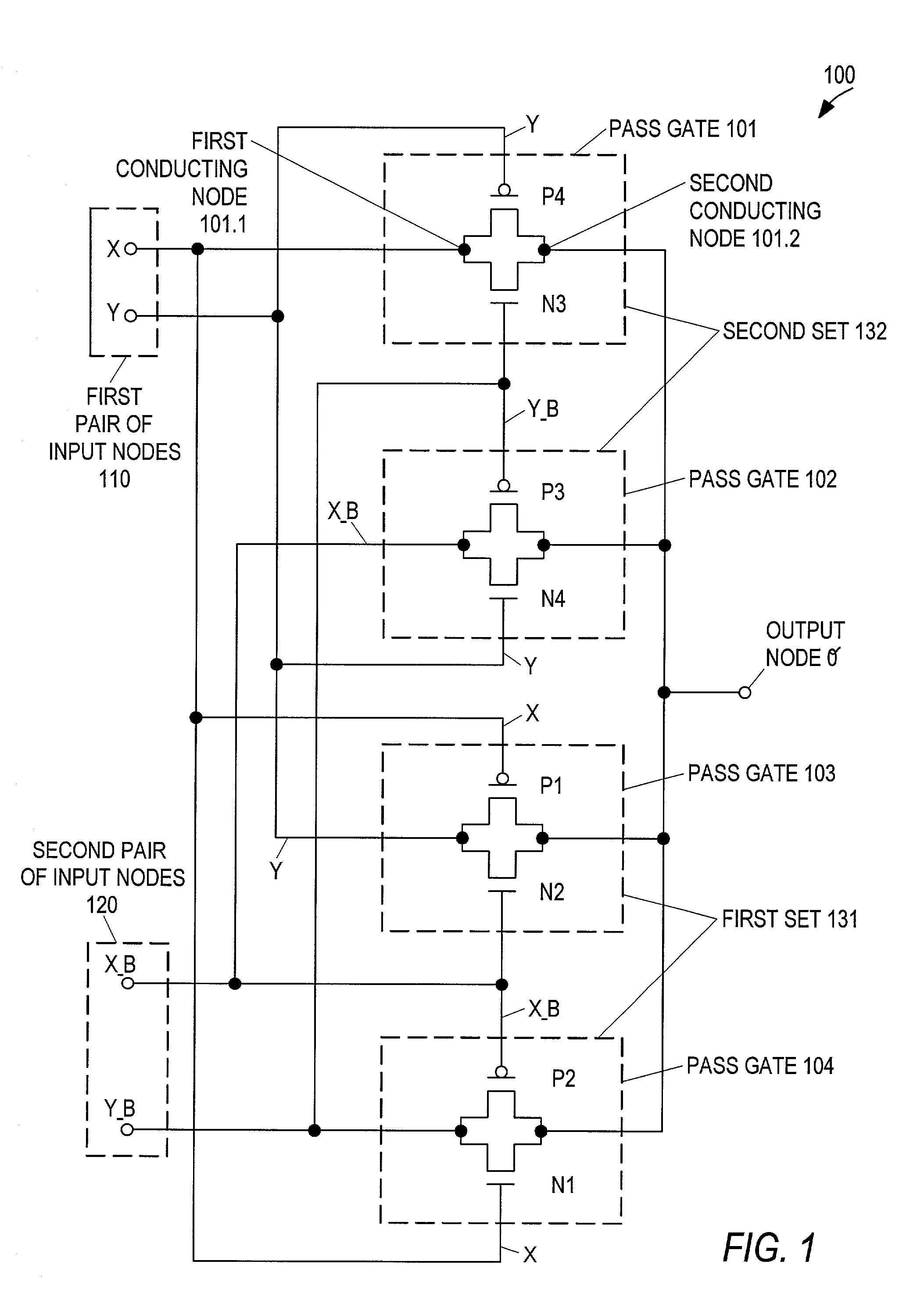

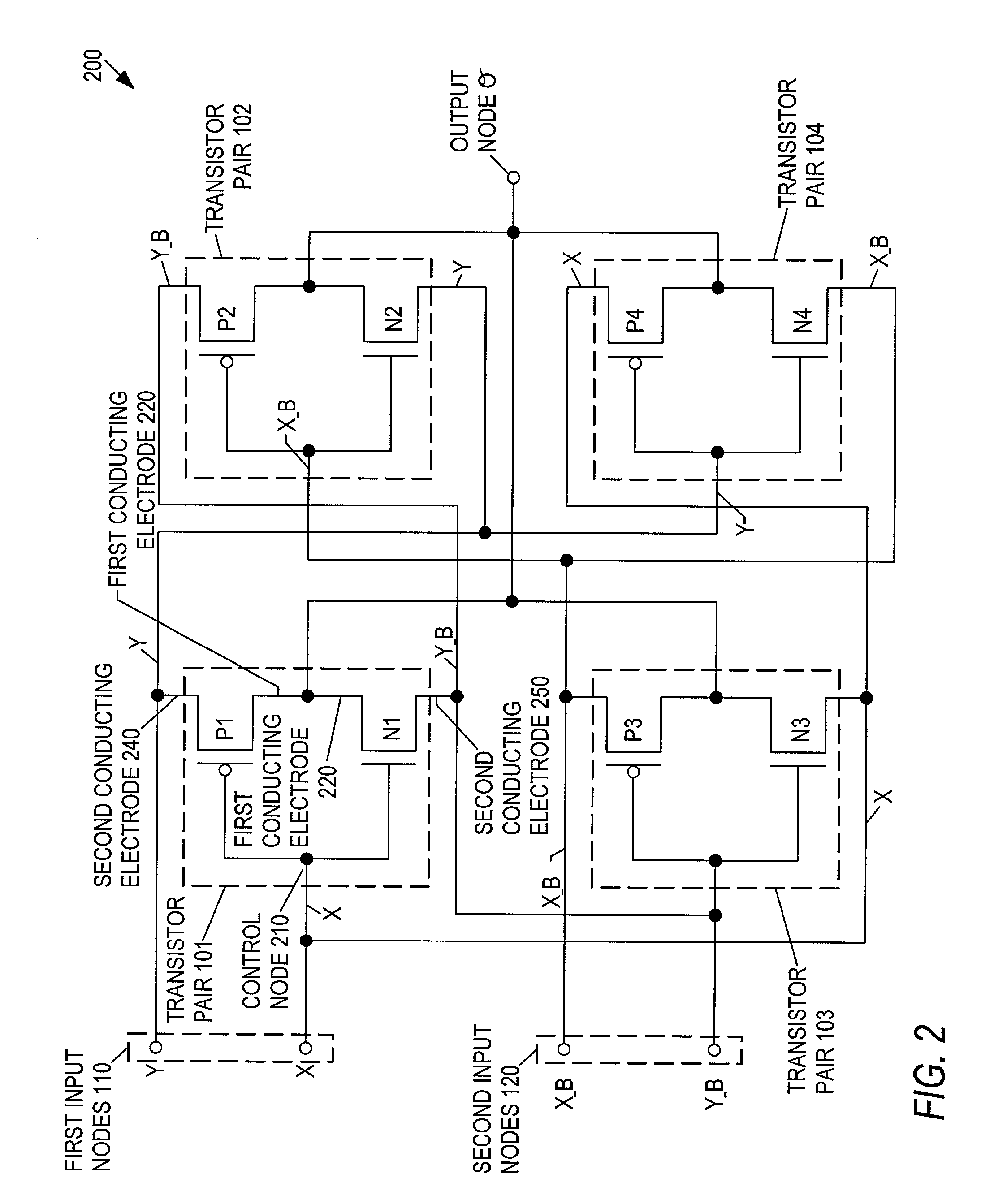

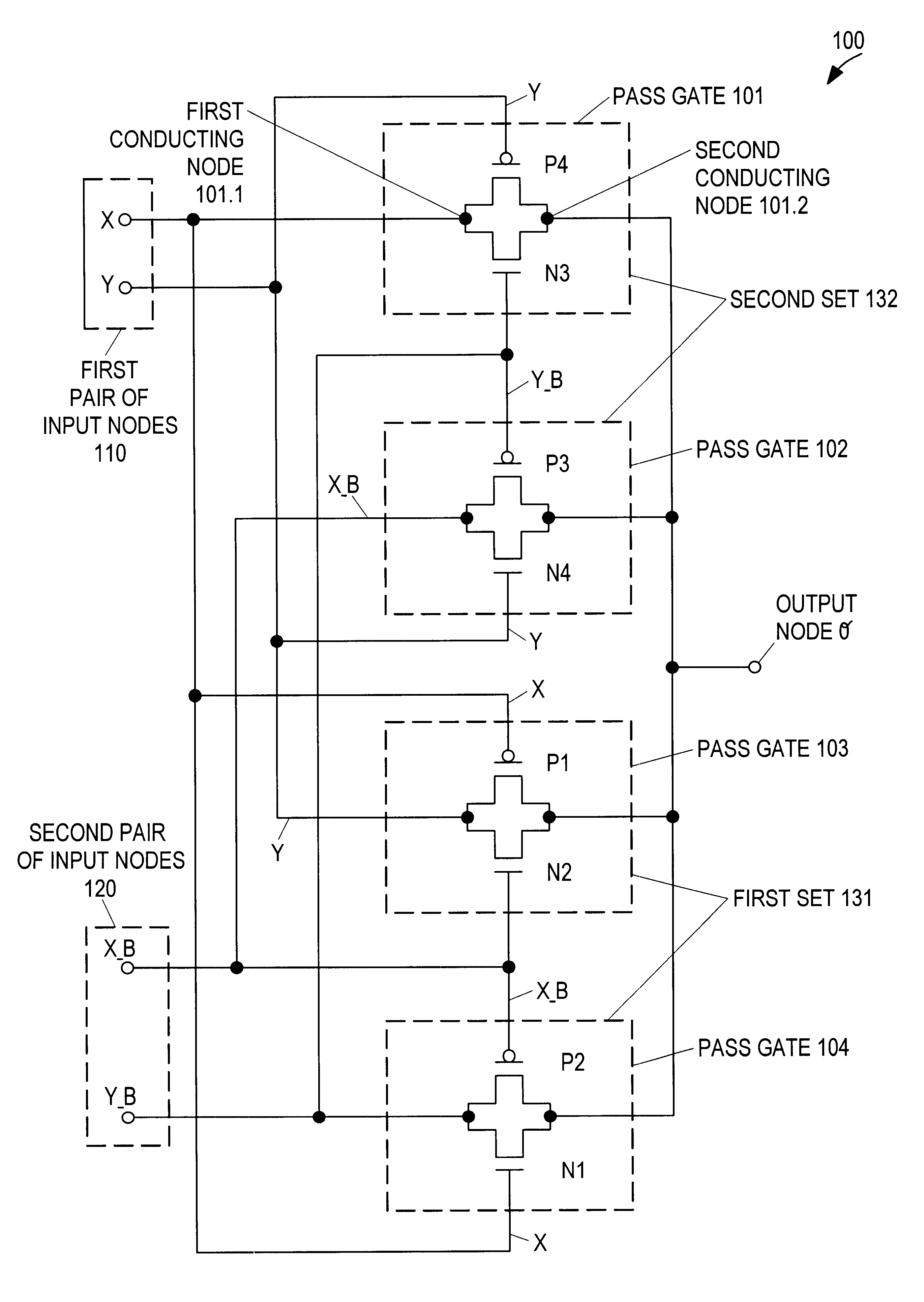

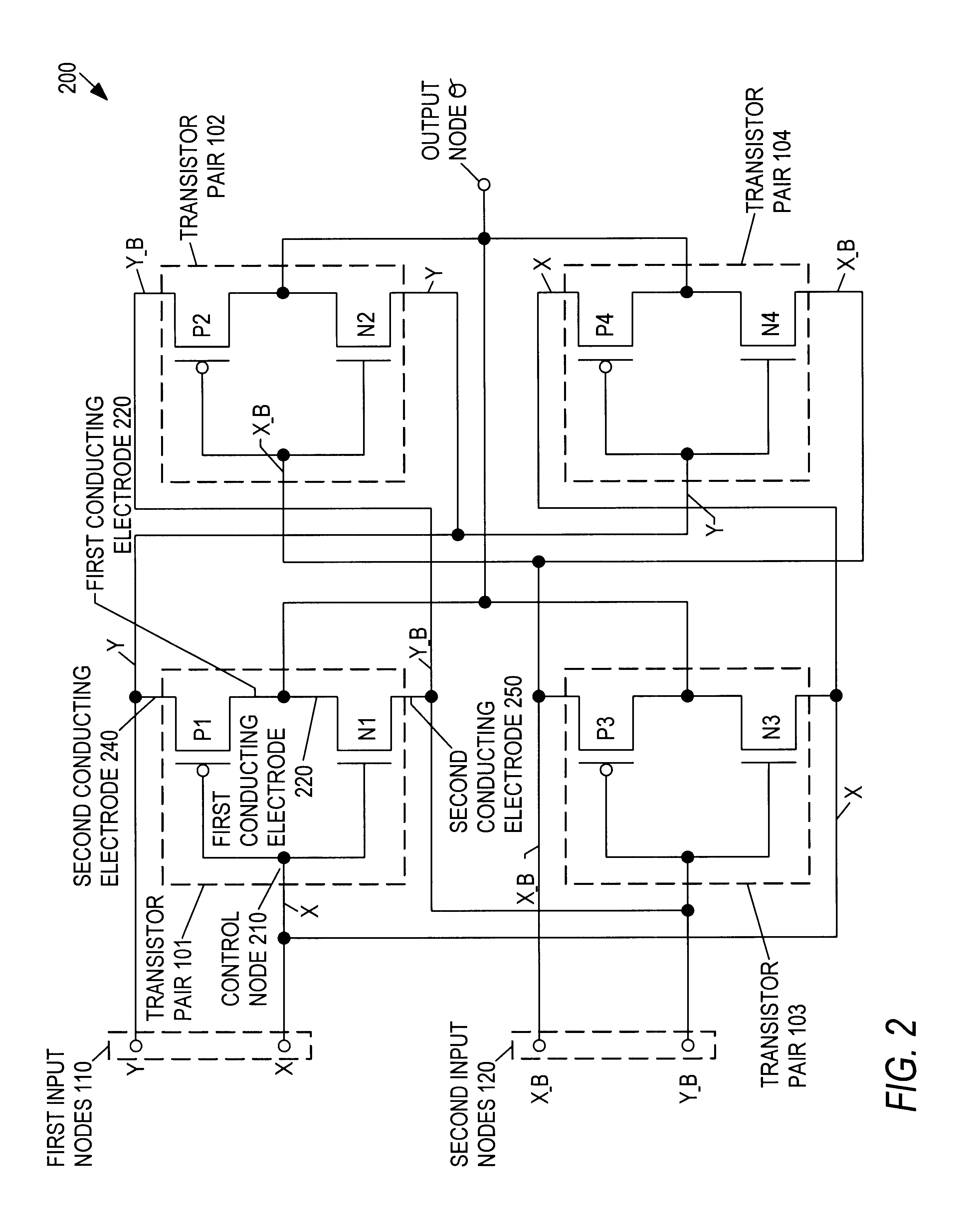

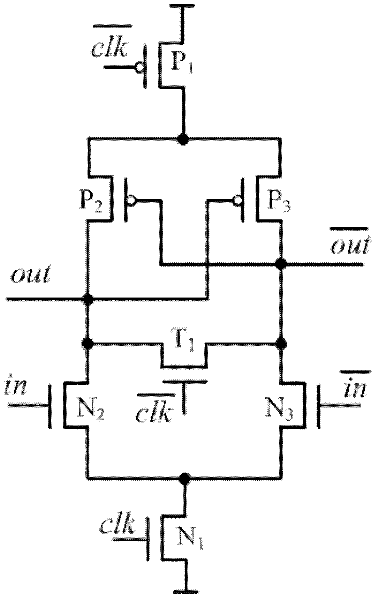

Fast, symmetrical XOR/XNOR gate

InactiveUS20030058001A1Exclusive-OR circuitsComputation using non-contact making devicesEngineeringPass gate

In one aspect, circuitry for a digital logic function includes a first pair of input nodes for receiving respective first and second input signals, a second pair of input nodes for receiving respective complements of the first and second input signals, and an output node. The circuitry has a plurality of PFET-NFET pass gates. Such a pass gate has a first conducting electrode of the pass gate PFET connected to a first conducting electrode of the pass gate NFET, providing a first conducting node of the pass gate, and a second conducting electrode of the pass gate PFET connected to a second conducting electrode of the pass gate NFET, providing a second conducting node of the pass gate. The input nodes are connected to first conducting nodes of respective ones of the plurality of pass gates, and the second conducting nodes of the plurality of pass gates are connected to the circuitry output node.

Owner:GOOGLE LLC

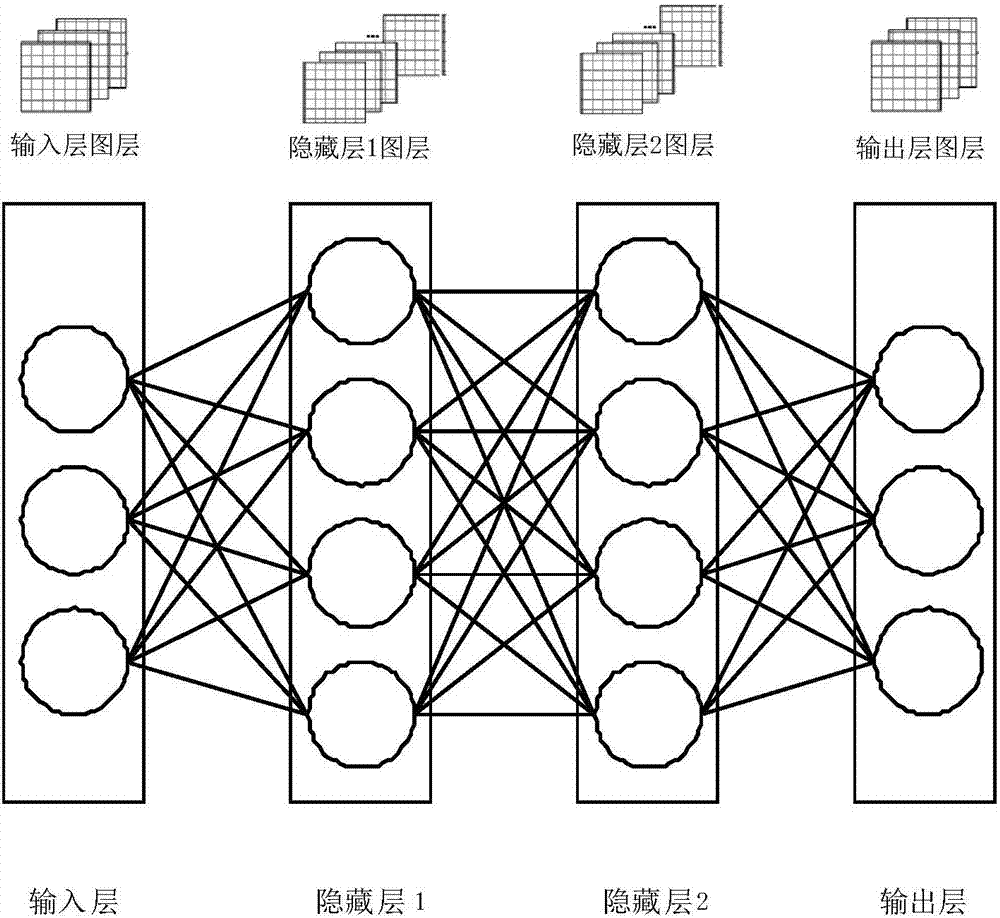

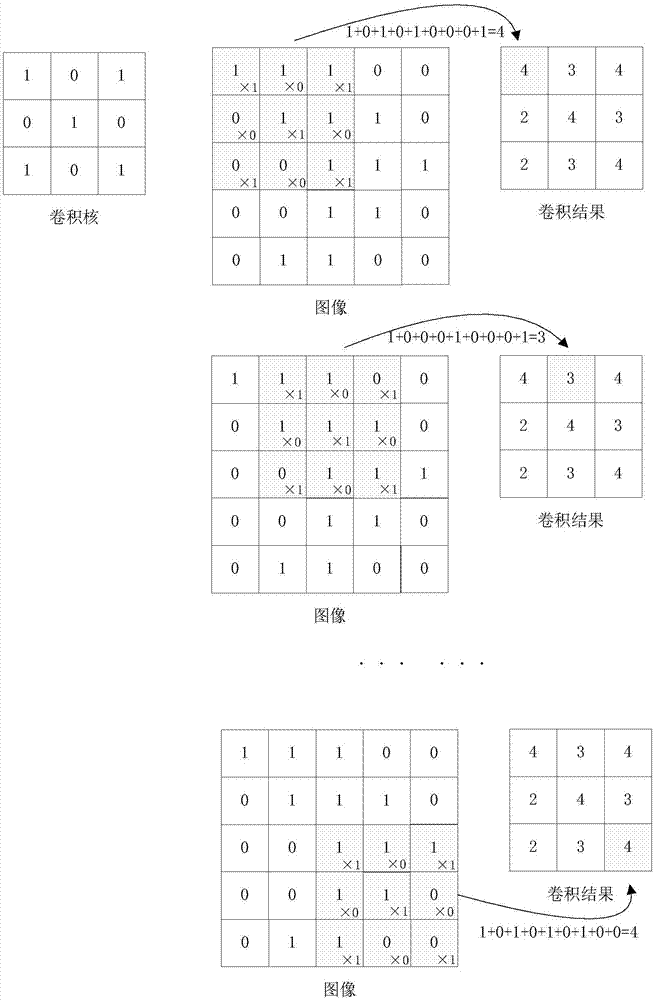

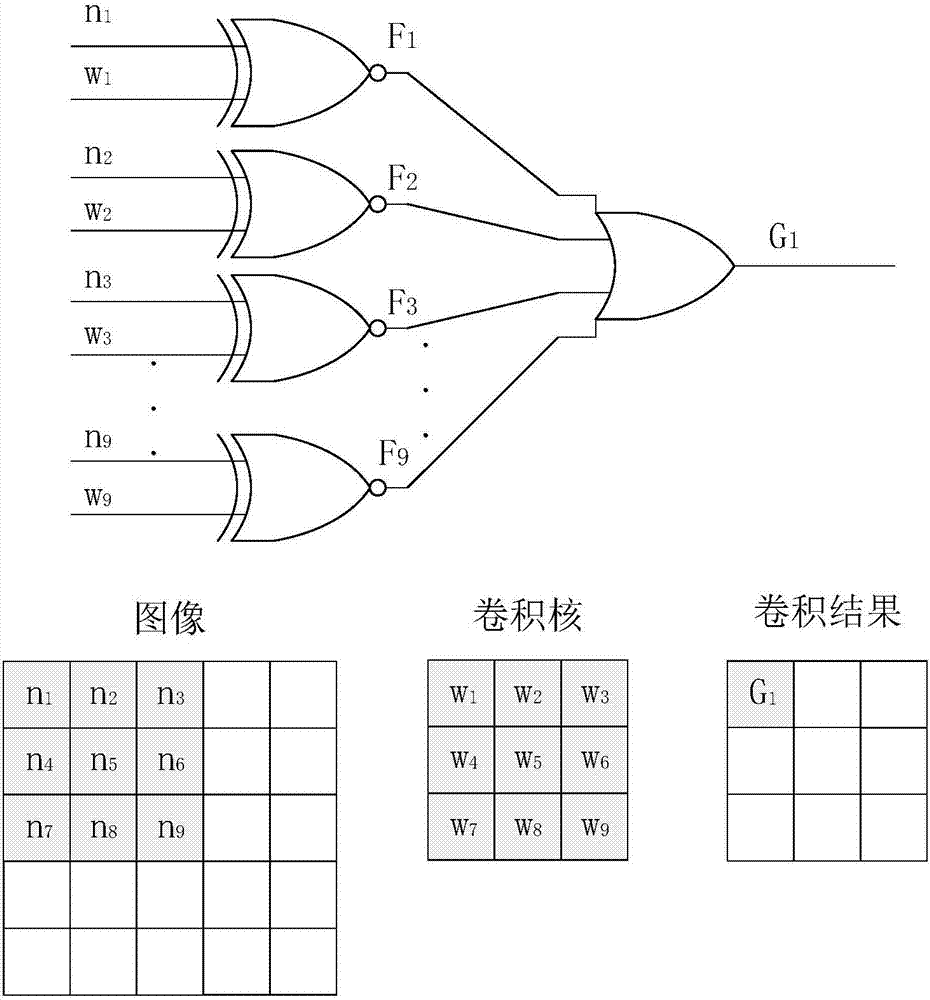

Binary convolutional device and corresponding binary convolutional neural network processor

ActiveCN107203808AReduce bit widthImprove computing efficiencyPhysical realisationParallel computingConvolution theorem

The present invention provides a binary convolutional device and a corresponding binary convolutional neural network processor. The binary convolutional device comprises: an XNOR gate taking elements in an employed convolution kernel and corresponding elements in data to be subjected to convolution as input, wherein the elements in the employed convolution kernel and the corresponding elements in the data to be subjected to convolution are both binary forms; and an accumulation device taking the output of the XNOR gate as input and configured to perform accumulation of the output of the XNOR gate to output a binary convolutional result. According to the technical scheme, the bit wide of data for calculation is reduced in the operation process so as to reach the effect of improving operation efficiency and reduce storage capacity and energy consumption.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

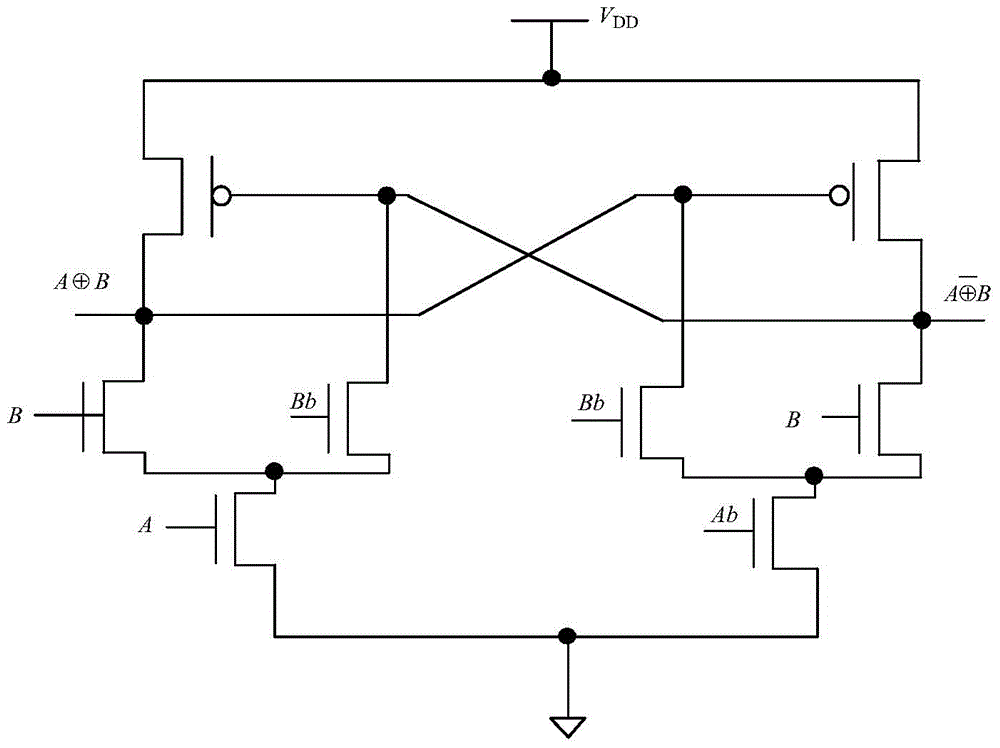

XOR/XNOR gate circuit based on FinFET devices

The invention discloses an XOR / XNOR gate circuit based on FinFET devices. The circuit comprises a first FinFET transistor, a second FinFET transistor, a third FinFET transistor, a fourth FinFET transistor, a fifth FinFET transistor, and a sixth FinFET transistor, the first FinFET transistor and the fourth FinFET transistor are both P-type FinFET transistors, the second FinFET transistor, the third FinFET transistor, the fifth FinFET transistor, and the sixth FinFET transistor are all N-type FinFET transistors, the first FinFET transistor and the fourth FinFET transistor are both low-threshold FinFET transistors, the second FinFET transistor, the third FinFET transistor, the fifth FinFET transistor, and the sixth FinFET transistor are all high-threshold FinFET transistors, the numbers of the fins of the first FinFET transistor and the fourth FinFET transistor are both 1, and the numbers of the fins of the second FinFET transistor, the third FinFET transistor, the fifth FinFET transistor, and the sixth FinFET transistor are all 2. The circuit is advantageous in that the logic function is correct, the circuit area is small, the time delay is short, the power consumption is low, and the consumption-delay product is small.

Owner:NINGBO UNIV

Power consumption optimizing method for mixed polarity XNOR/OR circuit

InactiveCN103020331AMixed Polarity OptimizationMixed Polarity SavingsPower supply for data processingSpecial data processing applicationsMulti inputElectrical polarity

The invention discloses a power consumption optimizing method for a mixed polarity XNOR / OR circuit. The method comprises the following steps: improving a quick list technology according to the characteristics of an expression of the mixed polarity XNOR / OR circuit, so as to realize the mixed polarity conversion of the XNOR / OR circuit; on the basis of a power consumption estimation model, utilizing a Hoffman algorithm to realize the low power consumption decomposition of an OR gate, and dividing input signals of a multi-input XNOR gate into three sets according to the distribution characteristics of input signal probability and output signal probability of a two-input XNOR gate, wherein the three sets are as follows: the input signal probability being more than 0.5, the input signal being less than 0.5 and the input signal being equal to 0.5; synthesizing in each set, realizing the low power consumption decomposition of the multi-input XNOR gate and synthesizing the low power consumption decomposition of the OR gate and that of the multi-input XNOR gate, thereby obtaining a mixed polarity fitness function; establishing a corresponding relation between the mixed polarity and particle swarm; and adopting a particle swarm optimizing algorithm for performing the optimized power consumption mixed polarity searching on the XNOR / OR circuit. The power consumption optimizing method has the advantages that a test for a MCNC Benchmark circuit shows that the corresponding circuit power consumption is averagely saved for 53.98% and the searching speed is obviously increased.

Owner:NINGBO UNIV

Sensitive amplifier used for EEPROM and read circuit constituted of the same

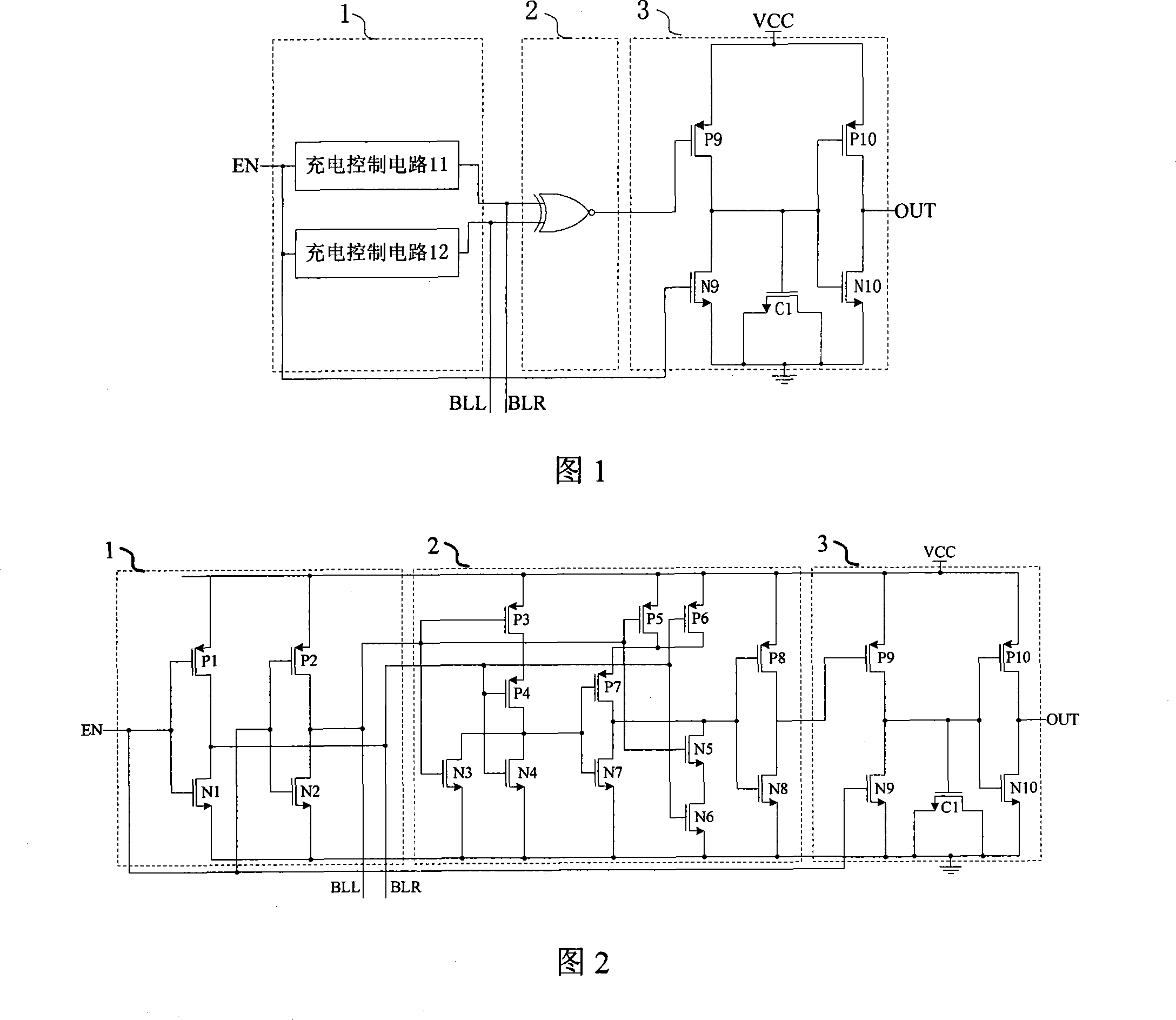

InactiveCN101221814AGuaranteed stabilityReduce static power consumptionRead-only memoriesBit lineAudio power amplifier

The invention discloses a sensitive amplifier for an EEPROM and a read circuit consisting of the sensitive amplifier. The sensitive amplifier for the EEPROM provided by the invention comprises a charge control circuit, a detection circuit and an output maintaining and shaping circuit, wherein, the charge control circuit consists of two same charge control sub-circuits; the detection circuit has a XNOR gate; the output maintaining and shaping circuit maintains the output of the detection circuit and shapes the output into a standard digital level. The read circuit formed by the sensitive amplifier comprises a first memory module and a second memory module which are completely symmetrical, two bit lines of each sensitive amplifier are respectively switched to corresponding bit lines of the first memory module and the second memory module. The sensitive amplifier has a circuit with simple structure, small occupied area, high read speed, low dynamic power, wide range of operation voltage and almost-zero static power and does not need a biasing circuit; the read circuit formed by the sensitive amplifier has the characteristics of anti-degradation of the properties of elements and stable performance.

Owner:HUAZHONG UNIV OF SCI & TECH

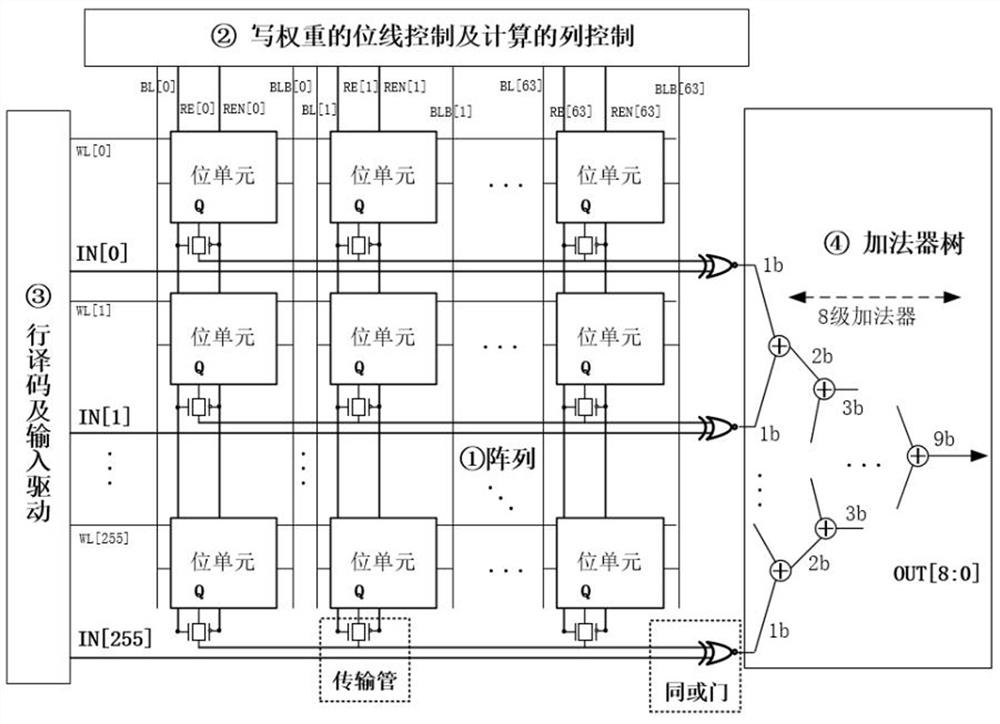

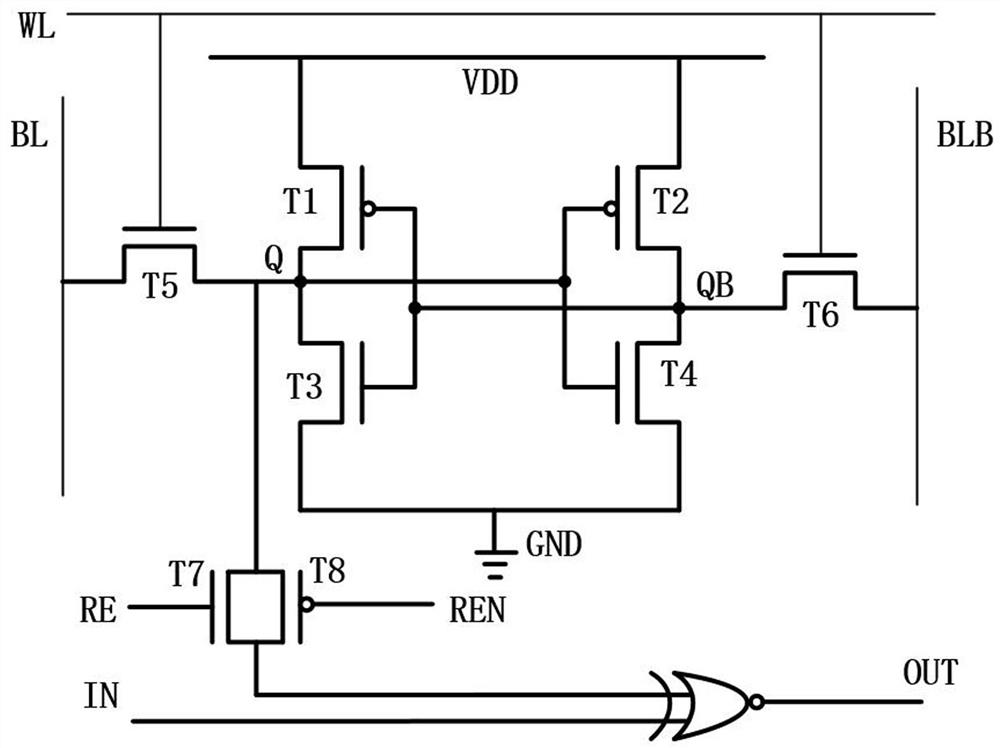

Digital in-memory computing array device

ActiveCN113035251ANo lossDigital data processing detailsDigital storageComputer architectureTransmission gate

The invention relates to a digital in-memory computing array device, which comprises 256 row * 64 column in-memory computing modules, each in-memory computing module comprises a bit cell, a tube T7, a tube 8 and an XNOR gate, and the tube T7 and the tube 8 form a transmission gate; the weight storage point Q of the bit cell is connected with the input end of the transmission gate, the output end of the transmission gate is connected with the first input end of the XNOR gate, the second input end of the XNOR gate is connected with an input signal, the output of the XNOR gate serves as the output of the bit cell, the grid electrode of the tube T7 is connected with a control signal RE, and the grid electrode of the tube T8 is connected with a control signal REN; an input signal input by each bit unit and the weight storage point Q are subjected to XNOR operation through an XNOR gate; and a column of bit cells is calculated each time, and thus accumulating 1bit outputs of 256 bit cells and then outputting a 9bit multiply-accumulate result. According to the invention, the calculation precision is improved.

Owner:中科南京智能技术研究院

Fast, symmetrical XOR/XNOR gate

InactiveUS6573758B2Exclusive-OR circuitsComputation using non-contact making devicesTelecommunicationsTransmission gate

In one aspect, circuitry for a digital logic function includes a first pair of input nodes for receiving respective first and second input signals, a second pair of input nodes for receiving respective complements of the first and second input signals, and an output node. The circuitry has a plurality of PFET-NFET pass gates. Such a pass gate has a first conducting electrode of the pass gate PFET connected to a first conducting electrode of the pass gate NFET, providing a first conducting node of the pass gate, and a second conducting electrode of the pass gate PFET connected to a second conducting electrode of the pass gate NFET, providing a second conducting node of the pass gate. The input nodes are connected to first conducting nodes of respective ones of the plurality of pass gates, and the second conducting nodes of the plurality of pass gates are connected to the circuitry output node.

Owner:GOOGLE LLC

All-optical logic gate with Michelson structure

InactiveCN101598884AReduce incident powerLower requirementLogic circuits using opto-electronic devicesNon-linear opticsSignal onNOR gate

The invention relates to an all-optical logic gate with a Michelson structure, which can be reused for realizing an AND gate, an OR gate, an NOT gate, an NAND gate, an NOR gate, an XOR gate and an XNOR gate as well as the reverse operation thereof, and also realizing a half-adder. The all-optical logic gate with a Michelson structure comprises two control optical signals, a synchronous optical detection signal and an output detection signal, wherein the two control optical signals are input into an arm (2) of symmetrical Michelson interferometers by a coupler (1); the synchronous optical detection signal is divided into two beams of equal light to be projected into the arm (2) and an arm (3) of the Michelson interferometers and used for outputting a reflecting output opening (4) for expressing the application of the logic result and a transmitting output opening (5) of the reverse operation; the output detection signal is results of the self-phase modulation of a detection optical signal, the intersection phase modulation of the two control optical signals on detection light and average intersection phase modulation on the detection light in two times of arm length and is expressed into a corresponding logic gate relation. The all-optical logic gate has the characteristic of self-phase modulation in the symmetrical Michelson interferometers, preferably the two arms adopt different nonlinear optical fibers and the input arm (2) of the control optical signals adopts a high nonlinear optical fiber.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

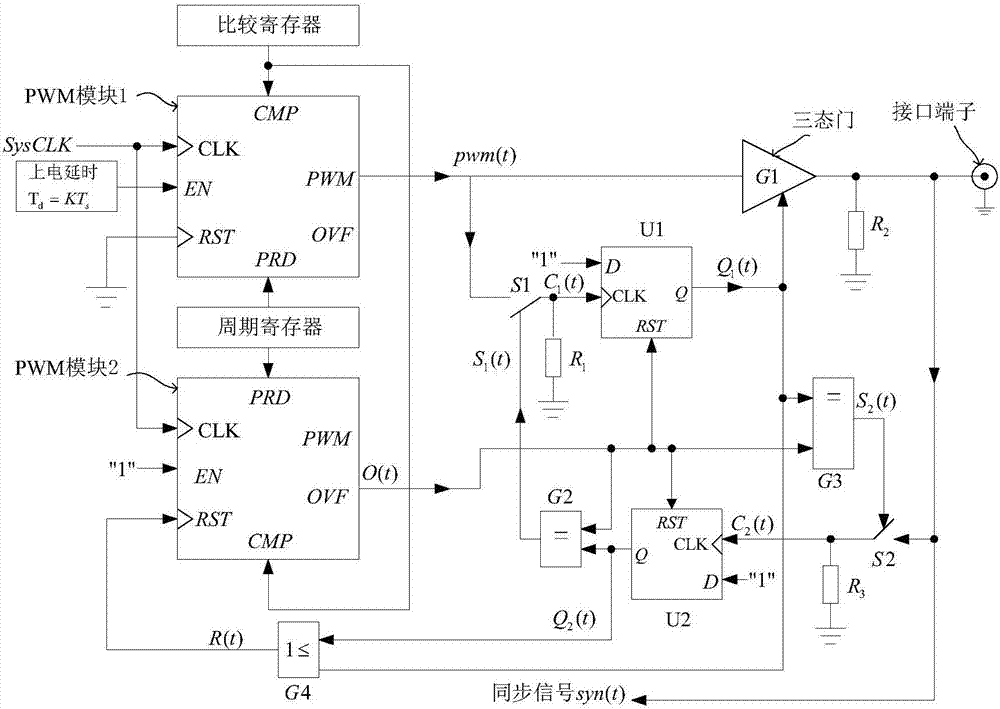

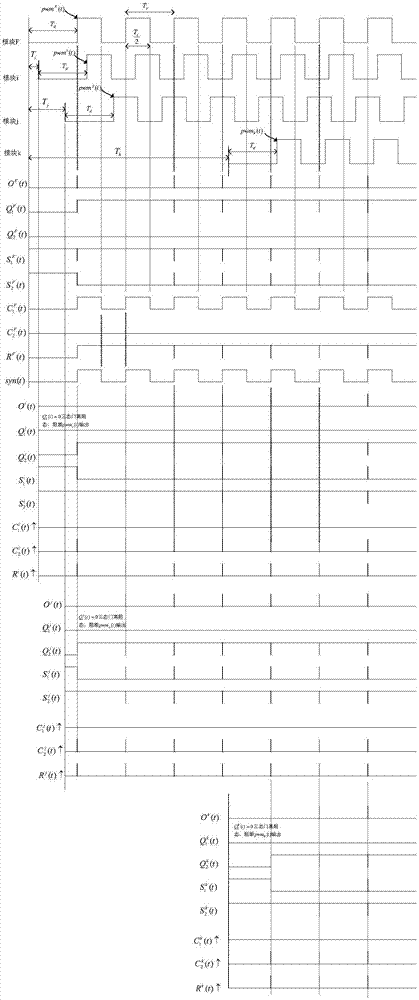

Synchronous control signal generating circuit

ActiveCN107425828AImprove reliabilityNo loss of sync signalEfficient power electronics conversionPulse manipulationControl signalTime delays

The invention provides a synchronous control signal generating circuit. The generating circuit comprises a PWM module 1, a PWM module 2, a power-on time delay circuit, a D trigger U1, a D trigger U2, an electric control switch S1, an electric control switch S2, a three-state gate G1, an XNOR gate G2, an XNOR gate G3, an OR gate G4, and a synchronous signal syn input-output connection terminal; the generating circuit adopts the non-master-slave and dynamic synchronization scheme, and has higher reliability in comparison with the static master-slave synchronization scheme; a synchronous clock signal source is produced through a competition way in the parallel control, the synchronous clock signal source is from the module with the three-state gate being at the on-state at the earliest in the synchronous control signal generating circuit, so that the synchronous signal source is unique. The generating circuit provided by the invention supports the hot-plugging under the parallel system working condition and cannot lose the synchronous signal. Compared with the synchronous control scheme performed through a communication bus, the synchronous control signal generating circuit has the advantage that the synchronization of the controller can be realized by only using a conductor to connect, the structure is simple and practicability is good.

Owner:WENZHOU UNIVERSITY

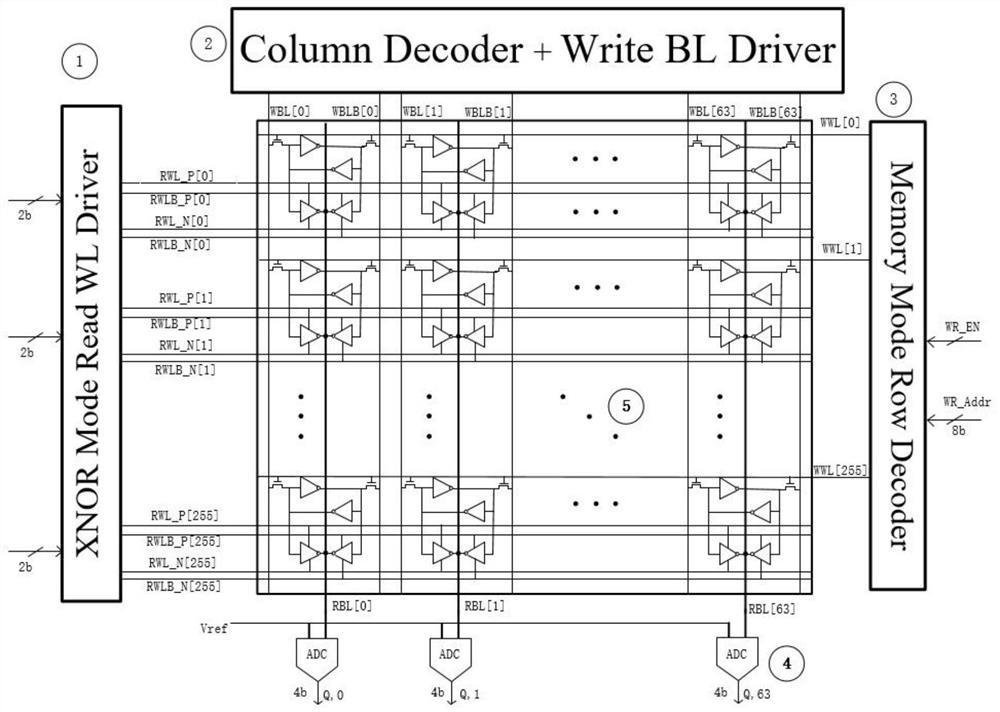

Voltage accumulation in-memory calculation circuit based on SRAM bit line XNOR

PendingCN111816234AReduce selection timeReduce propagation timeDigital storageEnergy efficient computingWrite bitHemt circuits

The invention relates to a voltage accumulation in-memory calculation circuit based on SRAM bit line XNOR. The voltage accumulation in-memory calculation circuit is characterized in that a read word line driver module in an XNOR mode is connected with a storage operation unit through a read word line; the row decoder module in the storage mode is connected with a storage arithmetic unit through awriting line; the write bit line driving and column decoding module in the storage mode is connected with the storage arithmetic unit through a write bit line; the read bit line in each storage arithmetic unit is directly connected with one analog-to-digital converter; and analog accumulation is carried out on bitwise ternary XNOR gate results of each read bit line voltage in the storage array module, and the analog-to-digital converter is used for digitally outputting the read bit line voltage. The circuit can shorten the propagation time of the output voltage.

Owner:中科南京智能技术研究院

Clock frequency error injection attack resisting defense circuit of security chip

ActiveCN106096457ASimple structureReduce areaInternal/peripheral component protectionTransmission gateSchmitt trigger

The invention discloses a clock frequency error injection attack resisting defense circuit of a security chip. The defense circuit is characterized by comprising a detection module and a judgment module; the detection module comprises a first NMOS transistor M1, a second NMOS transistor M2, a first transmission gate TG1, a second transmission gate TG2, a third transmission gate TG3 and a fourth transmission gate TG4, and the judgment module comprises a first Schmitt trigger A1, a second Schmitt trigger A2, a first D trigger D1, a second D trigger D2 and an XNOR gate XNOR. By means of the defense circuit, the clock frequency can be limited within a security frequency range, and thus clock frequency error injection attacks can be effectively prevented.

Owner:HEFEI UNIV OF TECH

Clock switching structure having automatic resetting function

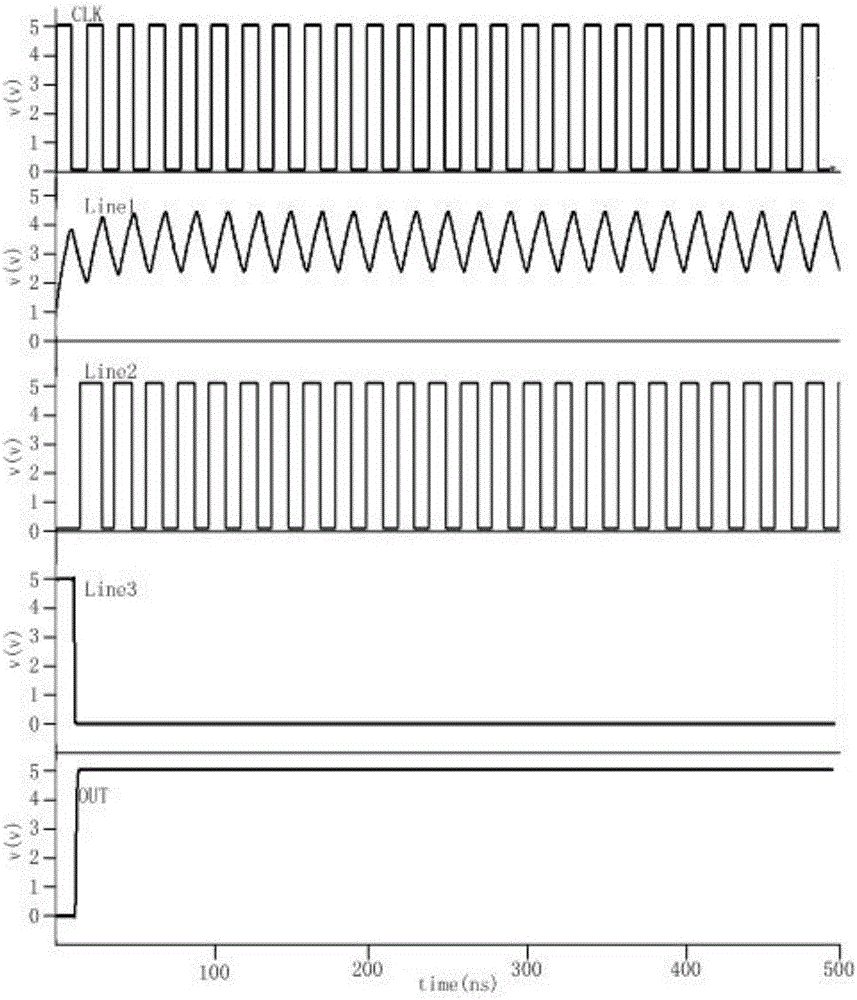

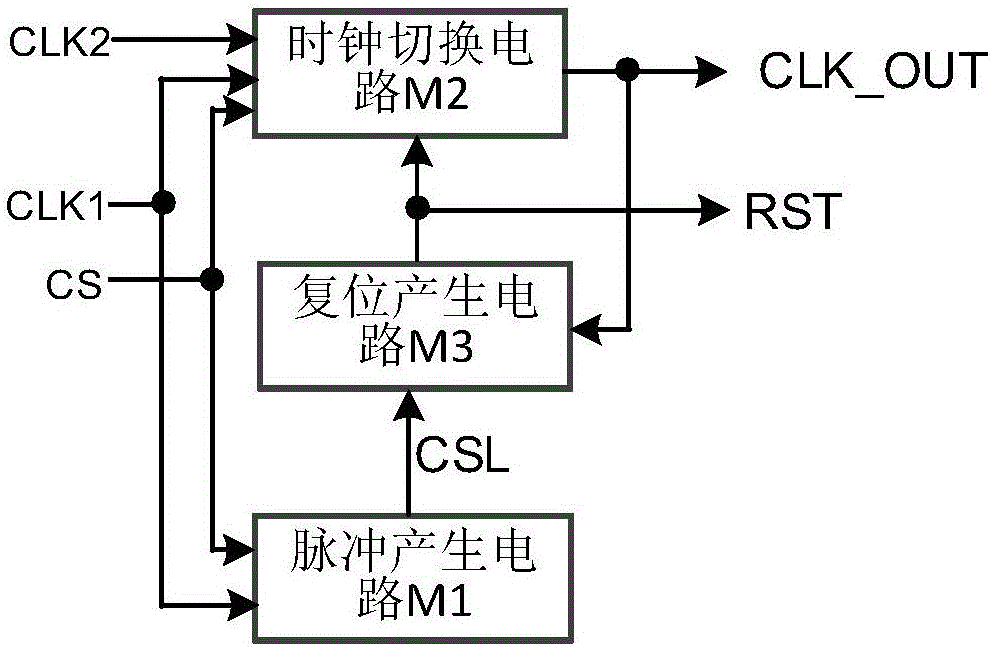

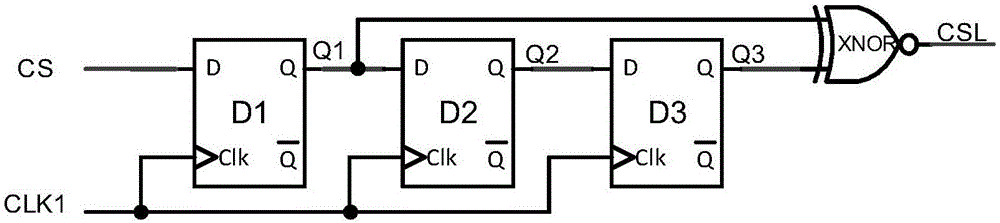

ActiveCN106452394AAvoid influenceVariable durationData resettingPulse manipulationControl circuitVIT signals

The invention discloses a clock switching structure having an automatic resetting function. The clock switching structure comprises a pulse generating circuit M1, a clock switching circuit M2, and a resetting generating circuit M3. The pulse generating circuit M1 is used for monitoring changing of a clock selection signal CS, and comprises three D triggers triggered by a rising edge of a clock and an XNOR gate. The clock switching circuit M2 is used to switch an output clock between a clock source CLK1 and a clock source CLK2, which are different from each other, and comprises a D trigger D4 used for triggering a rising edge of an enabling end, two two-input AND gates, and a two-input OR gate. The resetting generating circuit M3 is used to generate and eliminate a resetting signal automatically, and comprises three D triggers triggered by a rising edge provided with an asynchronous clearing end and a phase inverter INV. The clock switching structure is advantageous in that only the clock selection signal is required to be provided, and when the clock selection signal is changed, the resetting signal is generated automatically, and the clock switching is carried out; after the switching is completed, the resetting signal is eliminated after a certain period, and a controlled circuit can work normally.

Owner:TIANJIN UNIV

XNOR gate circuit, regulating method and XOR gate circuit

The embodiments of the invention provide a XNOR gate circuit, a regulating method and an XOR gate circuit, and relates to the field of logic circuits. The XNOR gate circuit includes a first input module, a second input module, an output module and a time-delay module. An input end of the first input module is in electrical connection to a first signal source. A first output end of the first inputmodule and a first end of the time-delay module are in electrical connection. A second output end of the first input module and one end of the output module are in electrical connection. An input endof the second input module is in electrical connection to a second signal source. An output end of the second input module and a second end of the time-delay module are in electrical connection. A third end of the time-delay module and the other end of the output module are in electrical connection. The time-delay module is intended for when a first signal is faster than a second signal by T time,postponing the first signal for T time, such that the first signal that is postponed for T time is synchronous with the second signal so as to acquire an output signal from the other end of the output module. The XNOR gate circuit prevents the output signal from having blurr.

Owner:成都声立德克技术有限公司

Relay anti-adhesion circuit

The invention provides a relay anti-adhesion circuit comprising a first relay and a second relay which comprise two-path contact points, a first XNOR gate and a second XNOR gate. The first-path contact points of the two relays are both connected in an application circuit. The second-path contact points and the first-path contact points are simultaneously controlled to act so that a signal reflecting the adhesion state of the first-path contact points is outputted. The input end of the first XNOR gate is respectively connected with a control signal of the first relay and the adhesion state signal of the first relay, and the output end is connected with a control circuit of the second relay. The input end of the second XNOR gate is respectively connected with the control signal of the second relay and the adhesion state signal of the second relay, and the output end is connected with the control circuit of the first relay. When an adhesion fault occurs in the relay with passing of high current, the situation can be timely reported and connection of the other relay can be cut off so that safety performance and reliability of an electric vehicle can be greatly enhanced, functions can be realized only by using a few commonly used components and parts, and thus the relay anti-adhesion circuit is low in cost.

Owner:HUIZHOU EPOWER ELECTRONICS

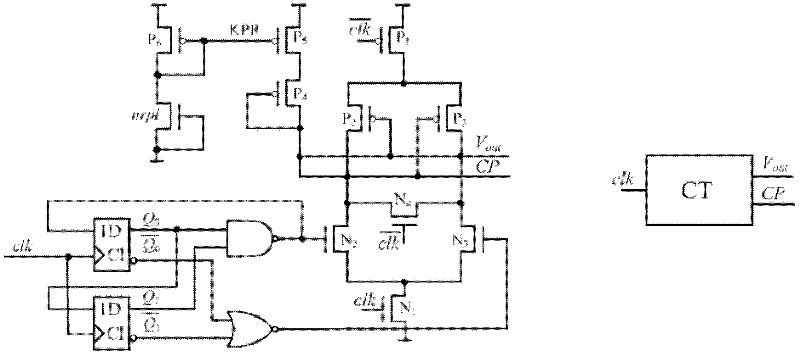

Anti-differential power attack ternary counter based on sense amplification logic

InactiveCN102394637AGood anti-differential energy attack effectImprove reliabilityCounting chain synchronous pulse countersConstant powerField-effect transistor

The invention discloses an anti-differential power attack ternary counter based on sense amplification logic, characterized by comprising a binary logic switching circuit and a sense amplification logic switching circuit, wherein the sense amplification logic switching circuit is provided with a current compensation circuit; the binary logic switching circuit is composed of a first D flip-flop, a second D flip-flop, an NAND gate and an XNOR gate; the sense amplification logic switching circuit is composed of a first PMOS (P-channel Metal Oxide Semiconductor) FET (Field Effect Transistor), a second PMOS FET, a third PMOS FET, a first NMOS (N-channel Metal Oxide Semiconductor) FET, a second NMOS FET, a third NMOS FET and a fourth NMOS FET; and a first signal output end and a second signal output end of the sense amplification logic switching circuit are connected in parallel with the current compensation circuit. The invention has the advantages that the circuit of the ternary counter has the characteristic of constant power consumption, the ternary counter has good anti-differential power attack effect, the complexity and cost of wire connection among circuits are greatly reduced, and the reliability of the circuits is improved.

Owner:HANGZHOU MAEN TECH

Neural network circuit device, neural network, neural network processing method, and neural network execution program

Provided are a neural network circuit device, a neural network, a neural network processing method, and a neural network execution program, each of which does not require a bias. A binarized neural network circuit includes: an input part configured to allow input of an input node which allows input of input values x1-xn (xi) (binary), and input of weights w1-wn (wi) (binary); an XNOR gate circuit configured to receive the input values x1-xn and the weights w1-wn and to take XNOR logic; a sum circuit configured to sum XNOR logical values; a batch normalization circuit configured to correct a variance due to binarization, by extending a range of normalization and shifting a center thereof; and an activating function circuit configured to convert a signal B obtained by batch-normalizing a signal Y generated by taking the sum, by means of an activating function f sgn(B).

Owner:TOKYO ARTISAN INTELLIGENCE CO LTD

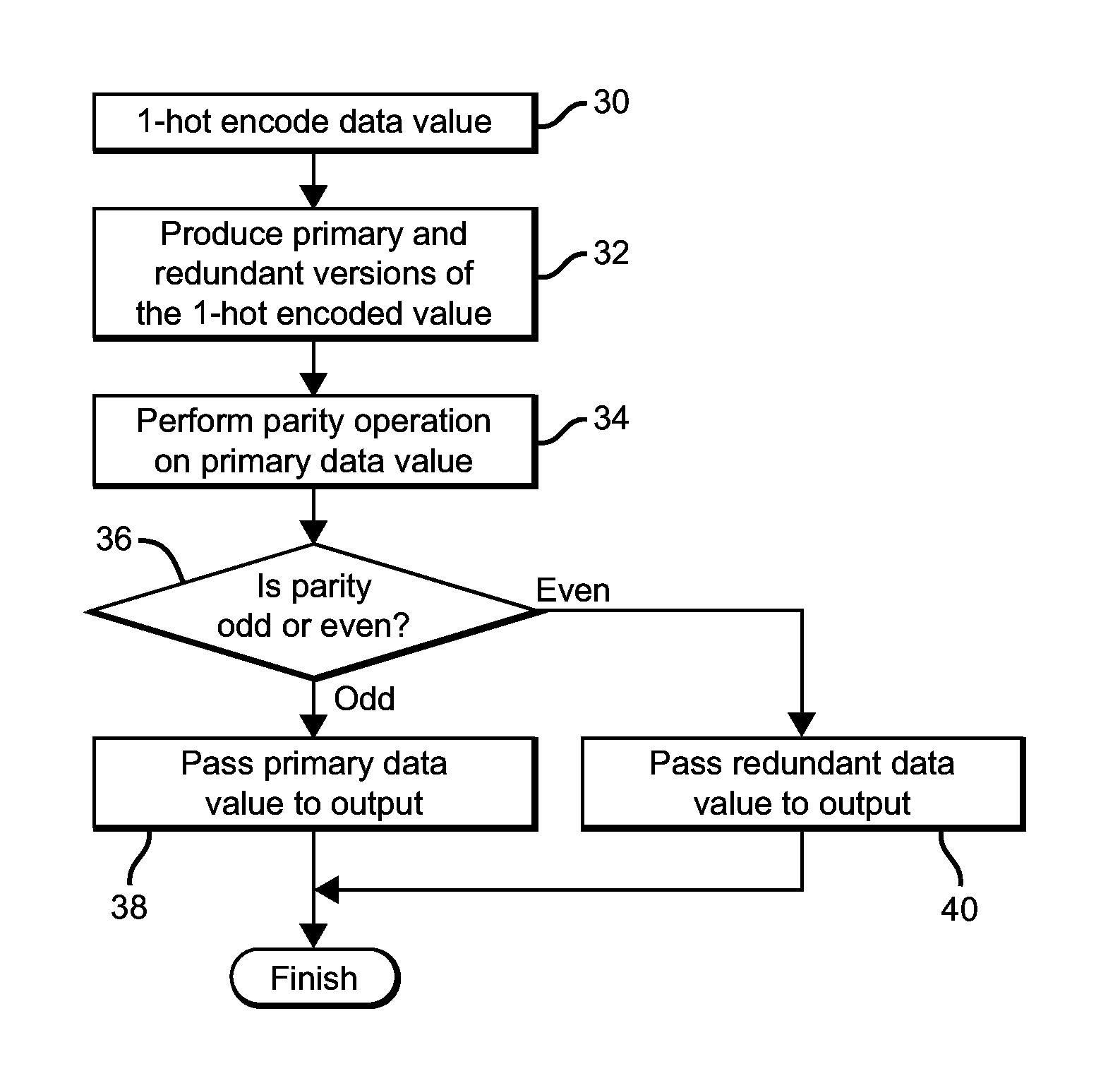

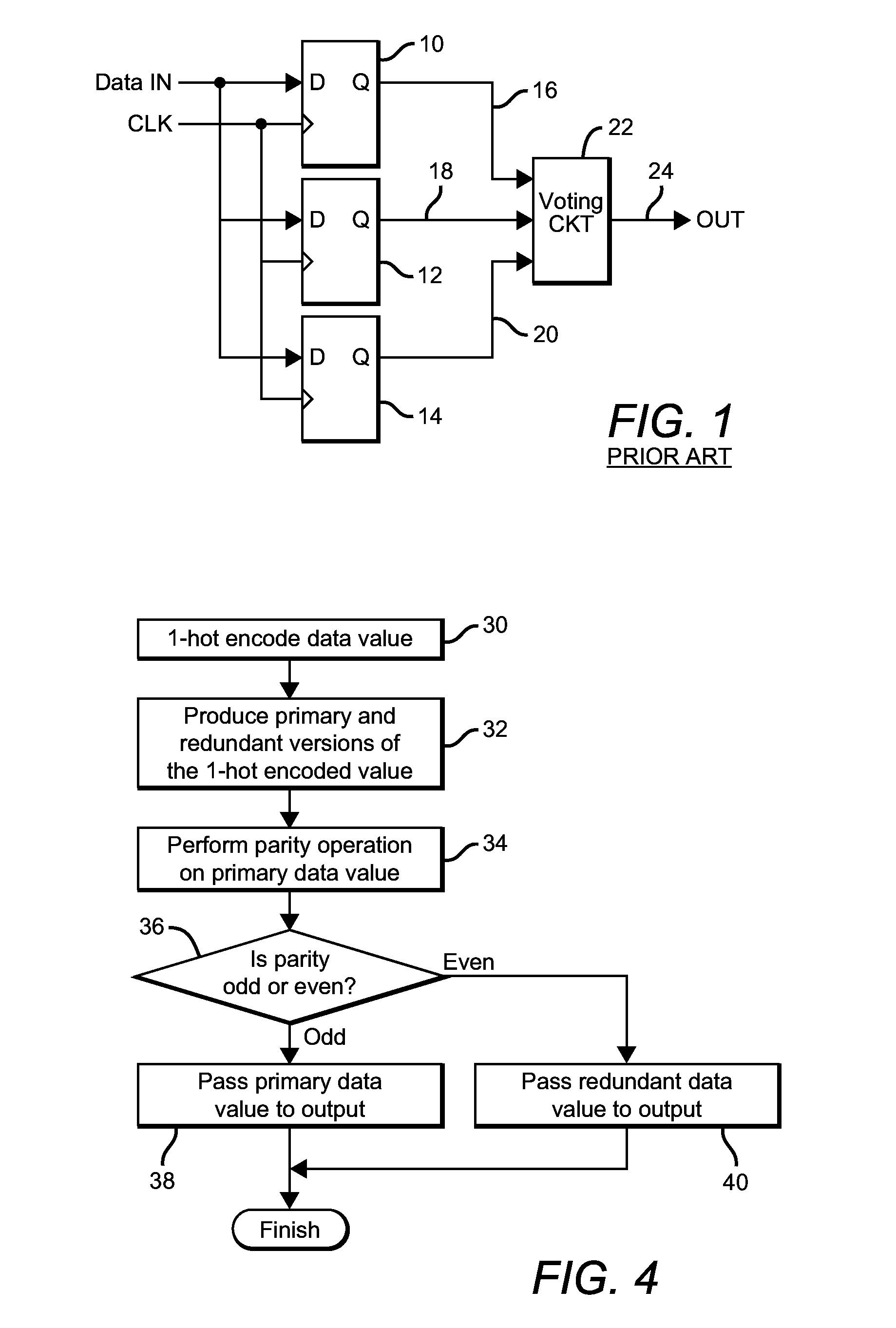

Single event upset protection circuit and method

An SEU protection circuit comprises first and second storage means for receiving primary and redundant versions, respectively, of an n-bit wide data value that is to be corrected in case of an SEU occurrence; the correction circuit requires that the data value be a 1-hot encoded value. A parity engine performs a parity operation on the n bits of the primary data value. A multiplexer receives the primary and redundant data values and the parity engine output at respective inputs, and is arranged to pass the primary data value to an output when the parity engine output indicates ‘odd’ parity, and to pass the redundant data value to the output when the parity engine output indicates ‘even’ parity. The primary and redundant data values are suitably state variables, and the parity engine is preferably an n-bit wide XOR or XNOR gate.

Owner:TELEDYNE SCI & IMAGING

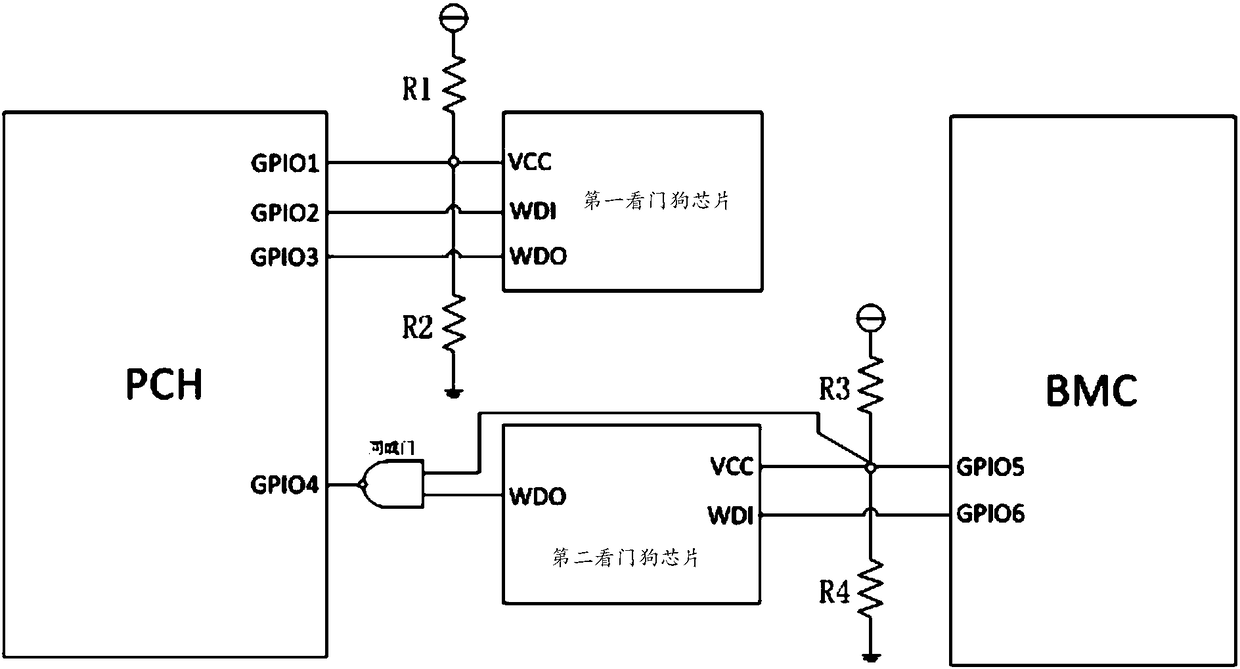

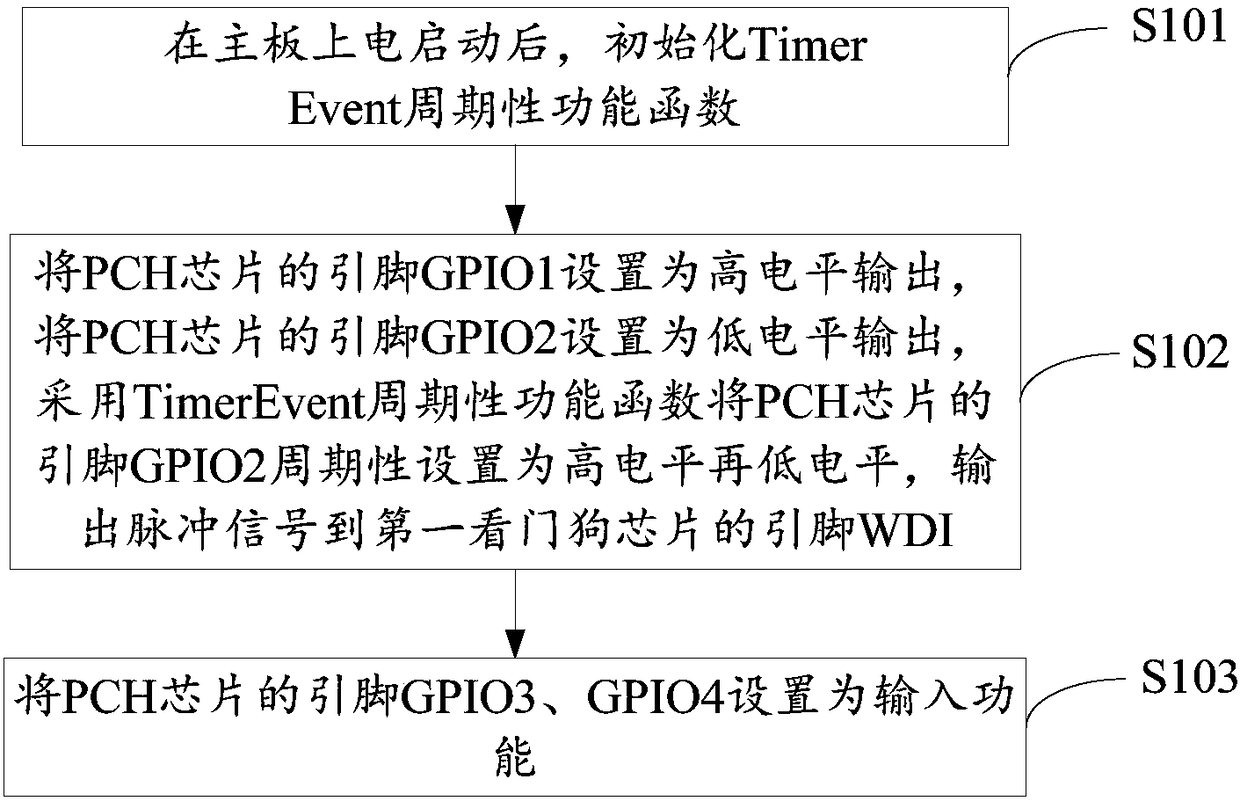

Hardware fault diagnosis circuit and method, and mainboard

InactiveCN108446198AAccurately locate faultsRealize automatic diagnosisError detection/correctionElectrical resistance and conductanceSmall probability

The invention discloses a hardware fault diagnosis circuit and method, and a mainboard. The circuit comprises a resistor R1, a resistor R2, a resistor R3, a resistor R4, an XNOR gate, a first watchdogchip and a second watchdog chip. For the problem of jamming due to hardware initialization failure, an effective solution is given; through cooperation of BIOS software, BMC software and hardware, hardware faults can be automatically diagnosed for whether BMC Boot loader-based hardware initialization failure or BIOS-based hardware initialization failure in whether a development stage or a user scene; locating is accurate; convenience and quickness are achieved; each mainboard can be covered; and small-probability faults can be solved.

Owner:深圳市国鑫恒宇科技有限公司

Positive feedback exclusive-OR/exclusive-OR gate and hybrid logic adder

ActiveCN111313889AReduce in quantityReduce layout areaExclusive-OR circuitsDigital data processing detailsControl engineeringInverter

The invention discloses a positive feedback XOR / XNOR gate and a hybrid logic adder. The hybrid logic adder comprises a positive feedback XOR / XNOR gate and an output circuit. The positive feedback exclusive-OR / XNOR gate comprises a first PMOS tube and a second PMOS tube which are used as transmission tubes, and a first NMOS tube and a second NMOS tube which form a pull-down network. The third PMOStube, the third NMOS tube and the fourth NMOS tube form a positive feedback loop; when the exclusive-OR logic output end of the positive feedback exclusive-OR / exclusive-OR gate is pulled down to be below the switching threshold value of an inverter composed of a third PMOS tube and a fourth NMOS tube, the exclusive-OR logic output end of the positive feedback exclusive-OR / exclusive-OR gate is switched off. The positive feedback loop starts to work, so that the exclusive-OR logic output end of the positive feedback exclusive-OR / XNOR gate enters an accelerated pull-down period and is successfully pulled down to a low level, and threshold-voltage-loss-free is realized; the invention has the advantages of no threshold voltage loss, and small time delay and power consumption time delay product.

Owner:NINGBO UNIV

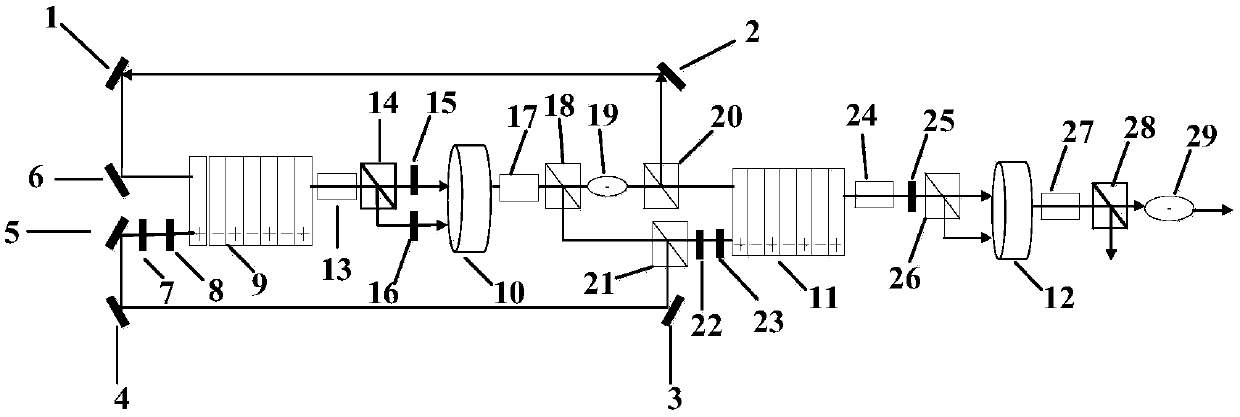

Reconfigurable dynamic all-optical chaotic logic gate capable of performing delay storage

ActiveCN108919589ARealize arbitrary switchingEffective delayed storageLogic circuits using opto-electronic devicesInstrumentsVertical-cavity surface-emitting laserBeam splitter

The invention discloses a reconfigurable dynamic all-optical chaotic logic gate capable of performing delay storage. The reconfigurable dynamic all-optical chaotic logic gate comprises a vertical cavity surface emitting laser, a beam splitter, an optical isolator, a polarization beam splitter, a subtractor, a variable attenuator, a half-wave plate and a periodically poled lithium niobate crystal.According to the reconfigurable dynamic all-optical chaotic logic gate, the arbitrary switching between basic all-optical chaotic logic gate operations is achieved, effective delay storage can be performed, and specifically, any switching and delay storage of AND gate, NAND gate, OR gate, NOR gate, XOR gate and XNOR gate operations are achieved. The reconfigurable dynamic all-optical chaotic logicgate capable of performing delay storage can be popularized and applied to all-optical digital chaotic timing and combinatorial logic computing devices.

Owner:WUYI UNIV

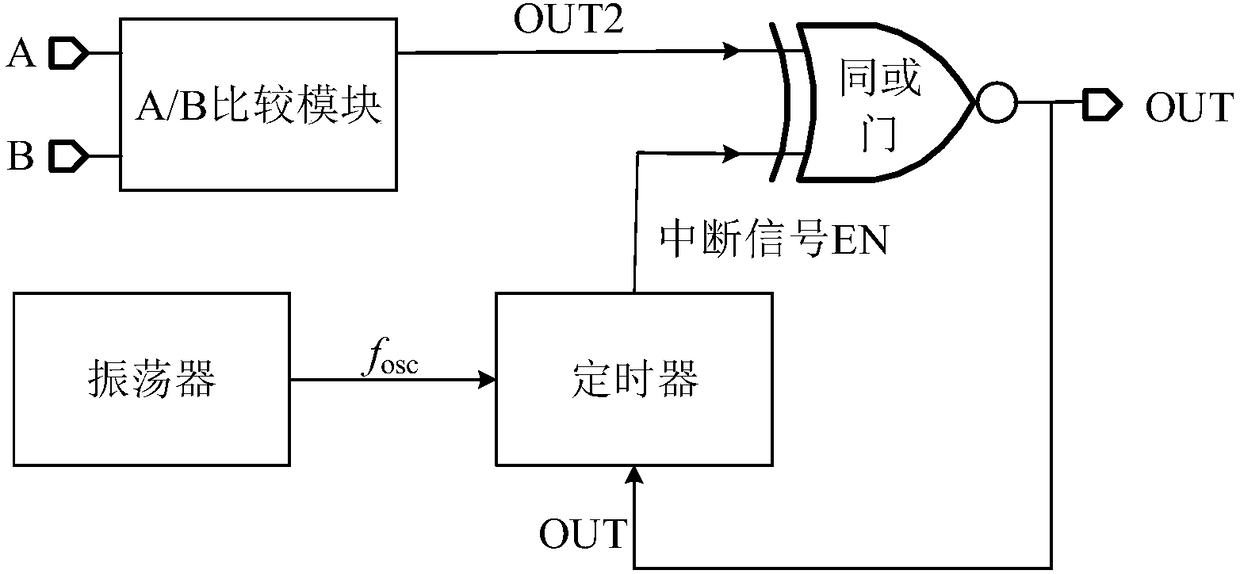

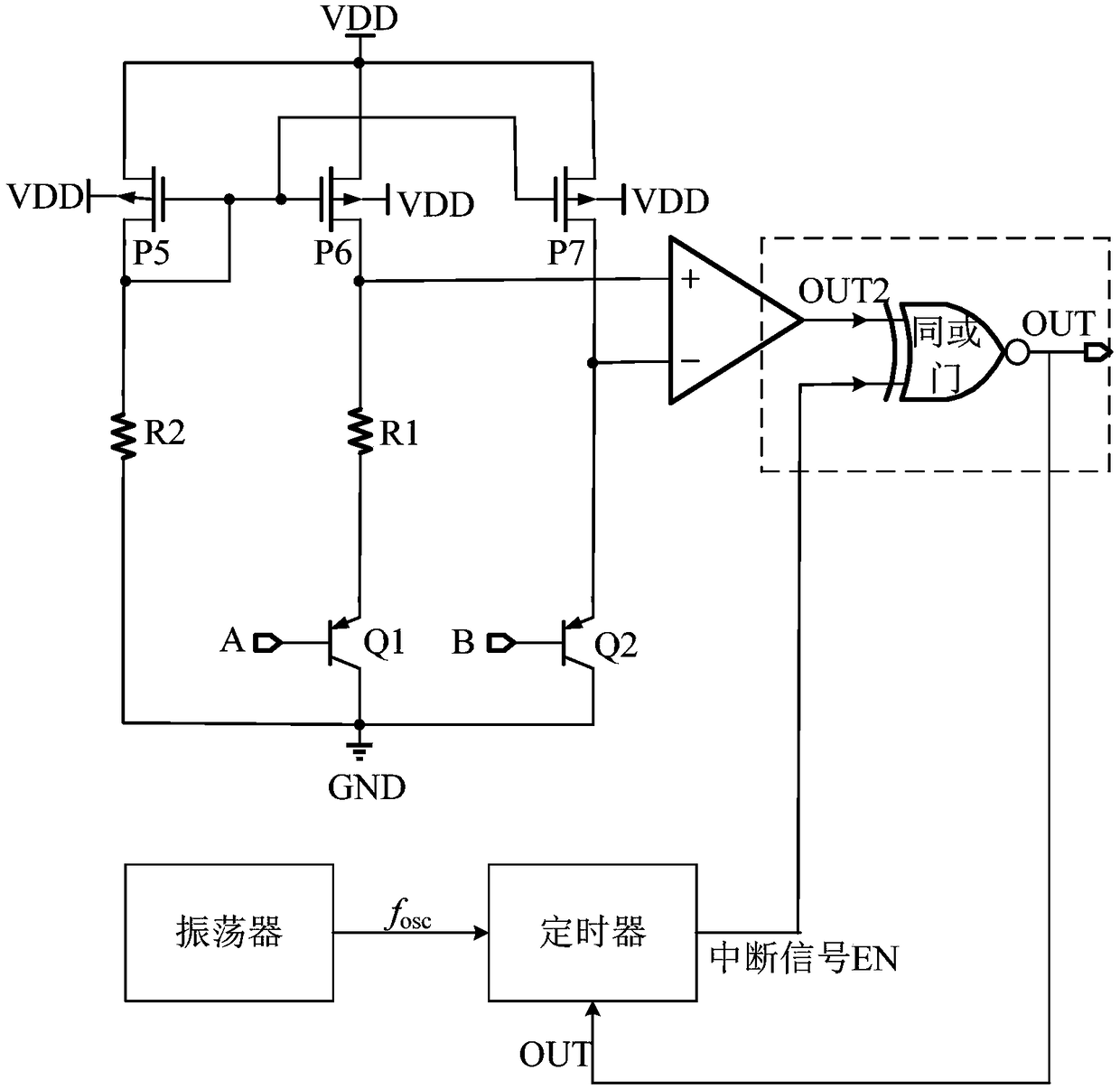

Circuit for realizing polarity turnover of non-polar RS485

ActiveCN108988845AImprove yieldEliminate the effects ofLogic circuits coupling/interface using field-effect transistorsElectrical polarityComputer module

The invention relates to a circuit for realizing polarity turnover of a non-polar RS485. The circuit comprises an A / B comparison module, an oscillator, a timer, an XNOR Gate and an RS485 interface circuit, wherein the A / B comparison module comprises a first PMOS tube, a second PMOS tube, a third PMOS tube, a first resistor, a second resistor, a first triode, a second triode and a comparator. The circuit realizes polarity switching by adopting a novel logic structure which replaces MOS switches, and four MOS switches in a traditional scheme are removed, the output signals OUT2 of the A / B comparison module and interrupt signal en generated by the timer are subjected to XNOR processing to realize polarity switching. Therefore, the influence of an MOS switch can be eliminated, and the polarity(data) turnover threshold consistency of different circuits and the consistency of parameters before and after the polarity turnover of a single circuit can be improved. The yield of the circuit is improved, and the method has a wide application range.

Owner:CRM ICBG (WUXI) CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com