Hardware fault diagnosis circuit and method, and mainboard

A hardware fault diagnosis circuit technology, applied in the computer field, can solve problems such as difficulties in motherboard fault diagnosis and troubleshooting, and achieve the effect of accurately locating hardware faults

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

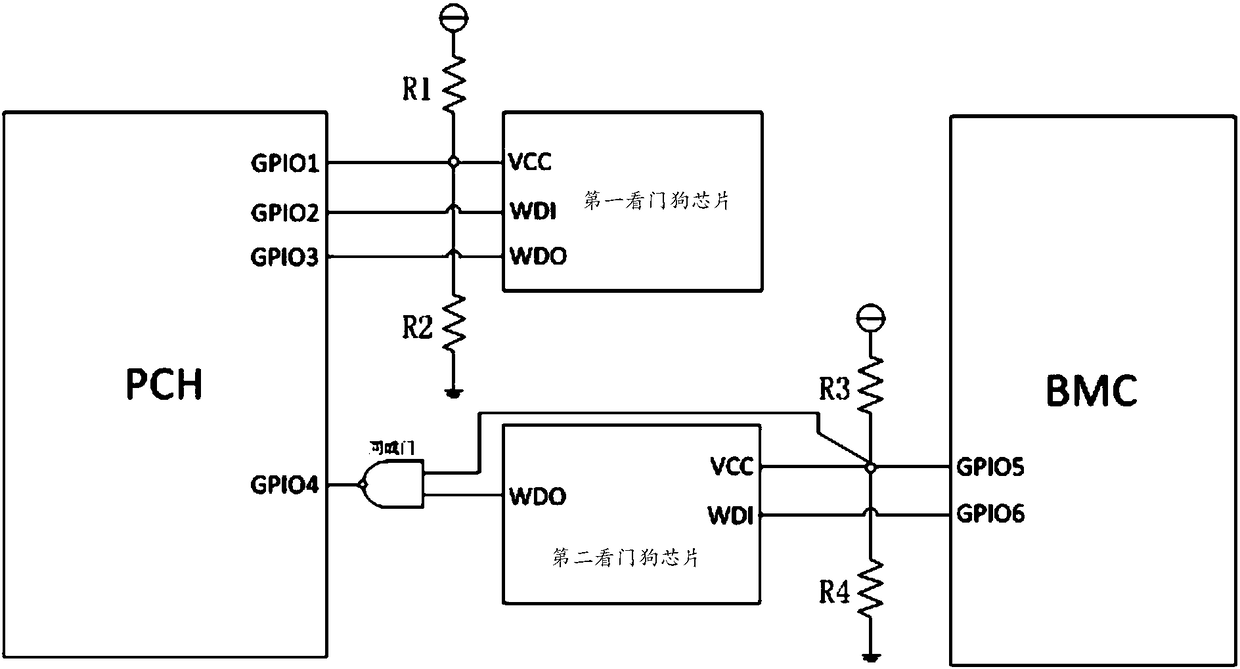

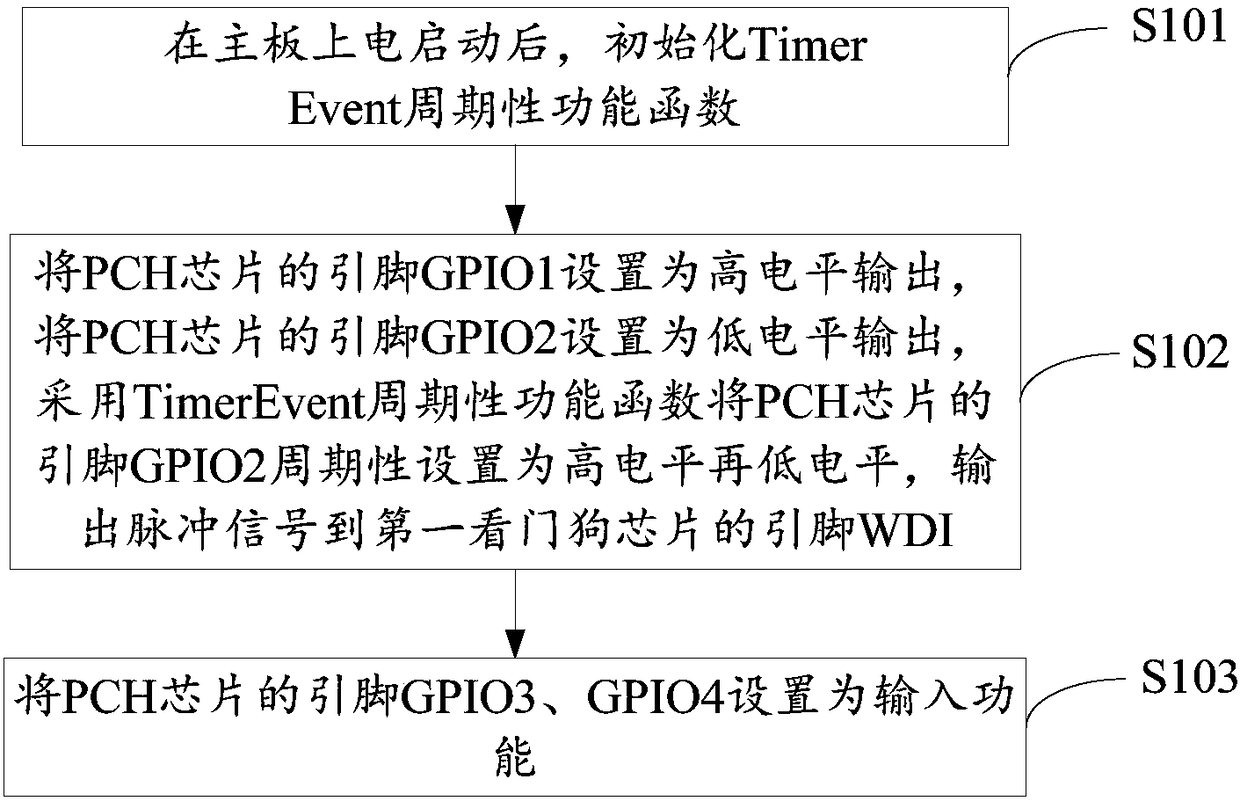

[0065] Such as figure 2 As shown, the first embodiment of the hardware fault diagnosis method of the present invention includes the following steps:

[0066] Step S100 , after the motherboard is powered on, run the BIOS to initialize the pins GPIO1 , GPIO2 , GPIO3 , and GPIO4 of the PCH chip.

[0067] It should be noted that after the motherboard is powered on, the BIOS does not run in the standby state. After the power-on sequence, the BIOS starts to run, and completes the self-test and initialization of the CPU and memory, and the initialization of peripheral devices such as PCIE and SATA. functions such as booting the operating system.

[0068] Specifically, please refer to image 3 , image 3 yes figure 2 Schematic diagram of the refinement process of step S100.

[0069] Such as image 3 As shown, as an implementation, the above step S100, after the motherboard is powered on, runs the BIOS, and initializes the pins GPIO1, GPIO2, GPIO3, and GPIO4 of the PCH chip, in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com