Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

64 results about "Indium bump" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

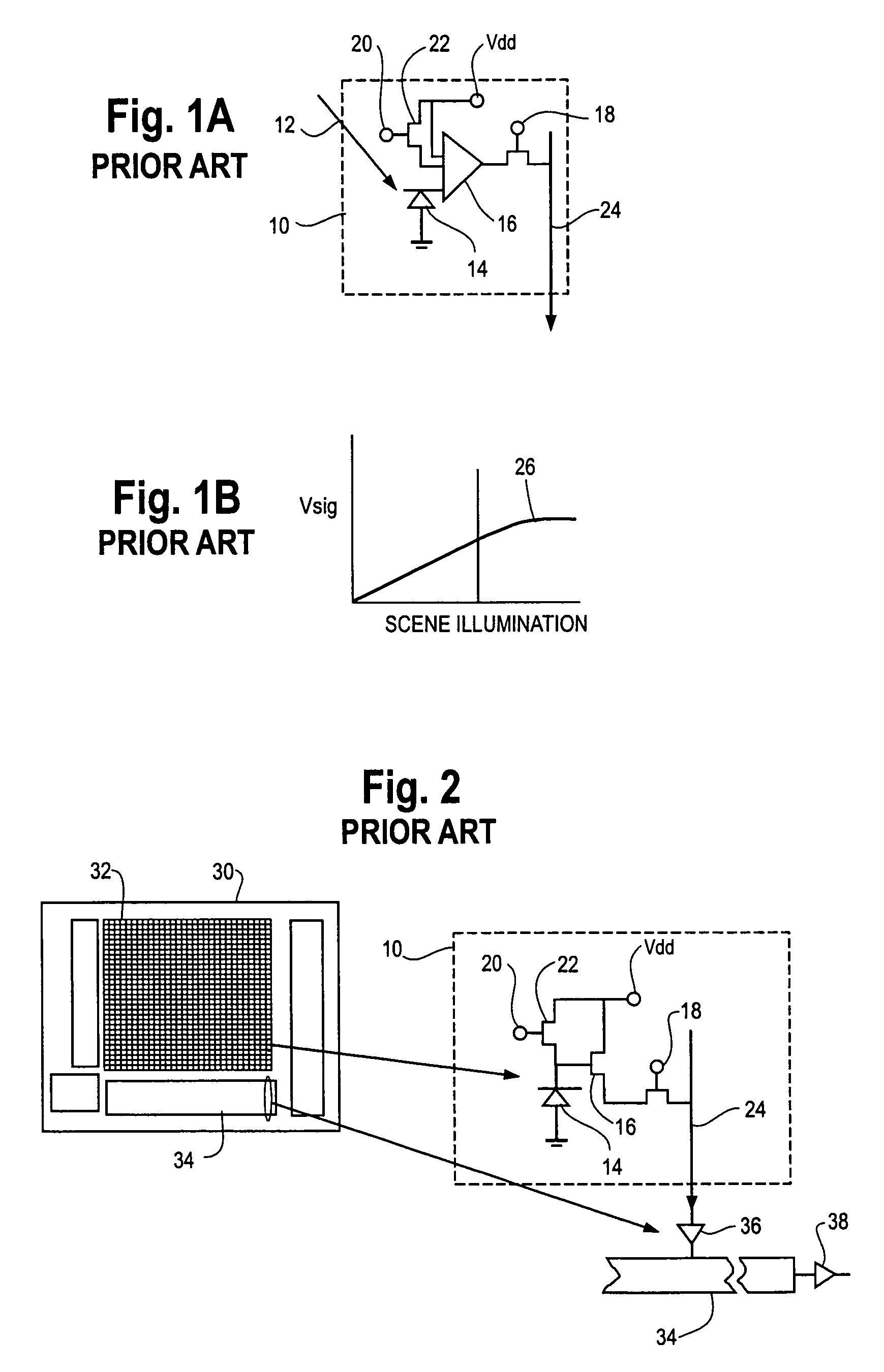

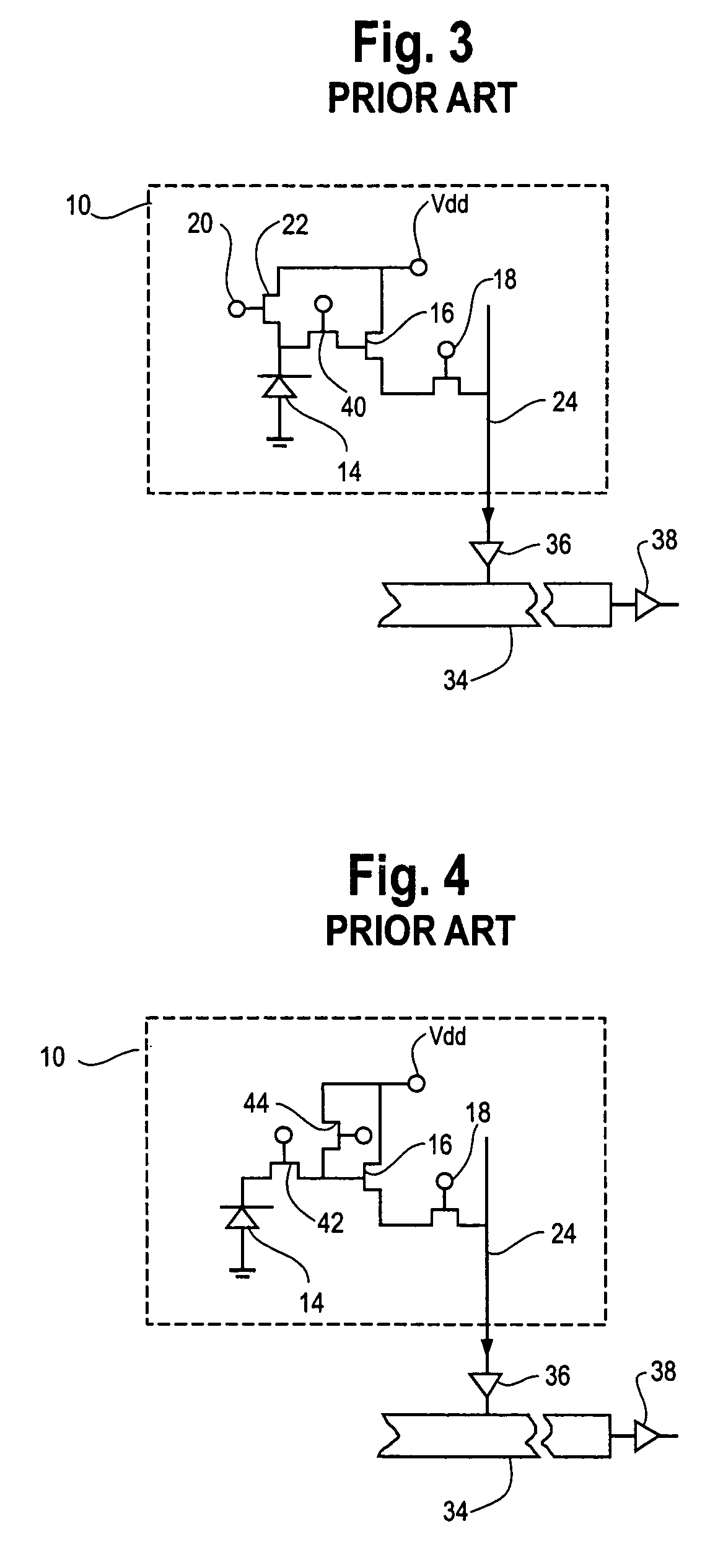

Hybrid infrared detector array and CMOS readout integrated circuit with improved dynamic range

ActiveUS20060181627A1High gainReduced dynamic rangeTelevision system detailsTelevision system scanning detailsIndium bumpDetector array

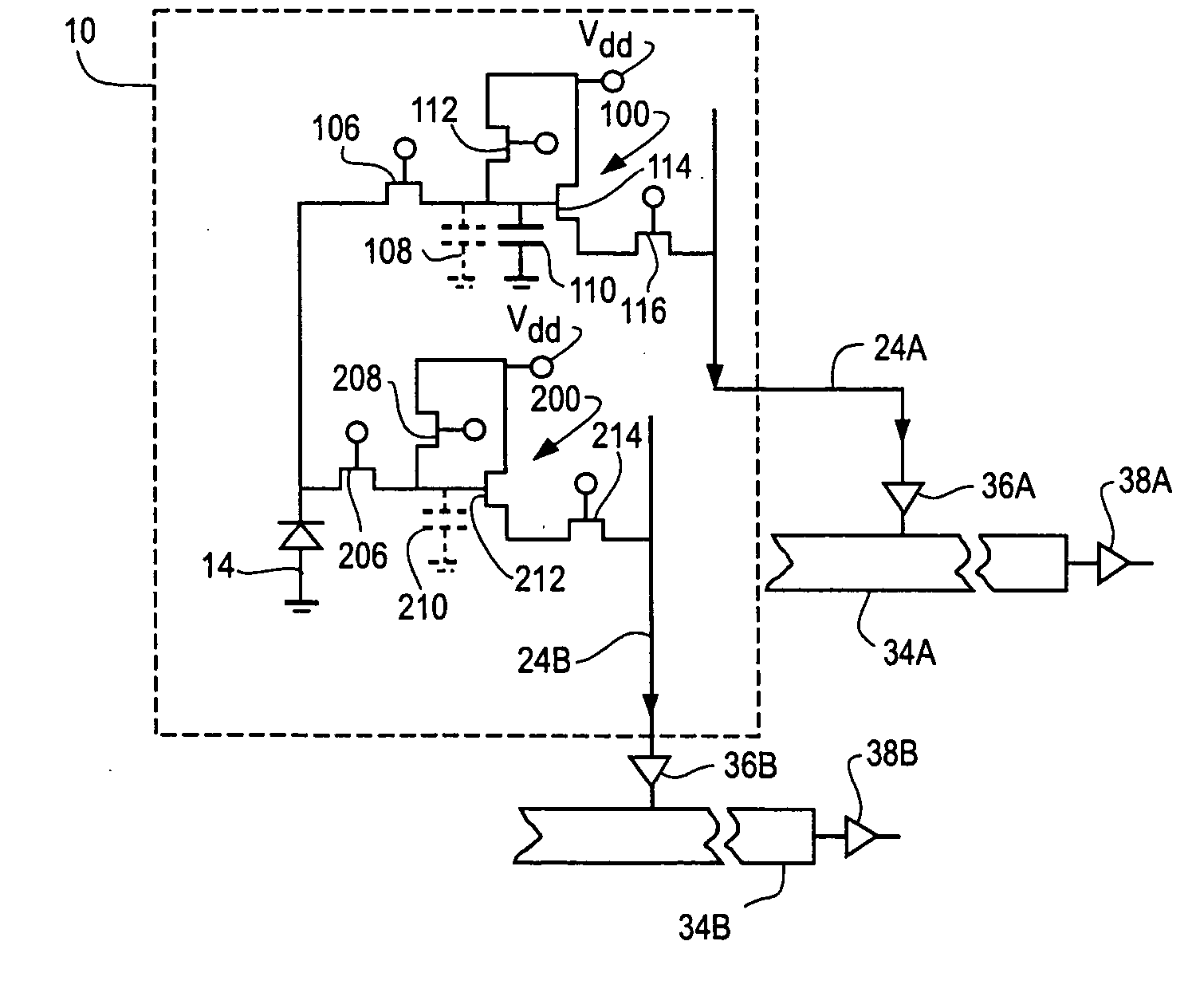

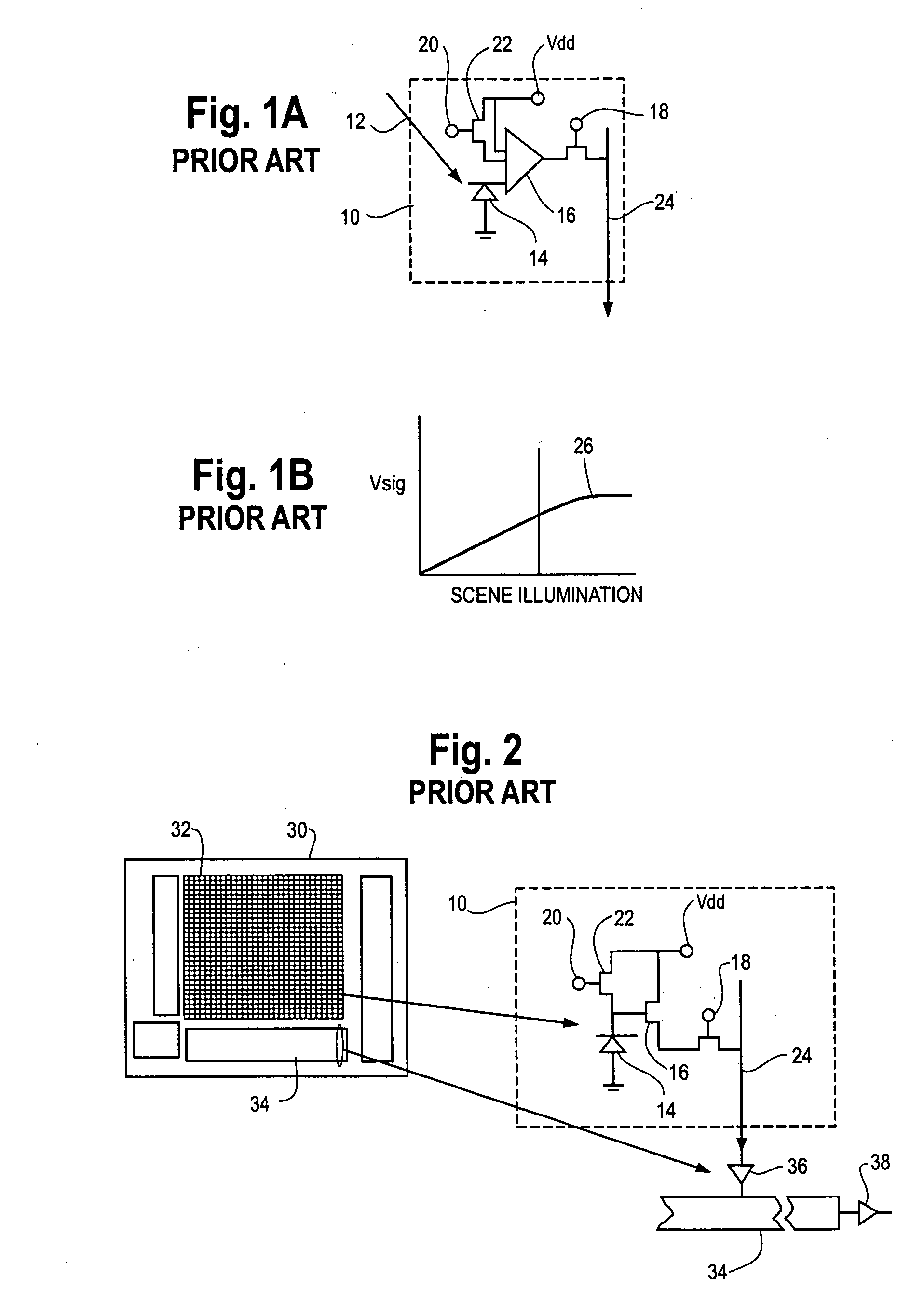

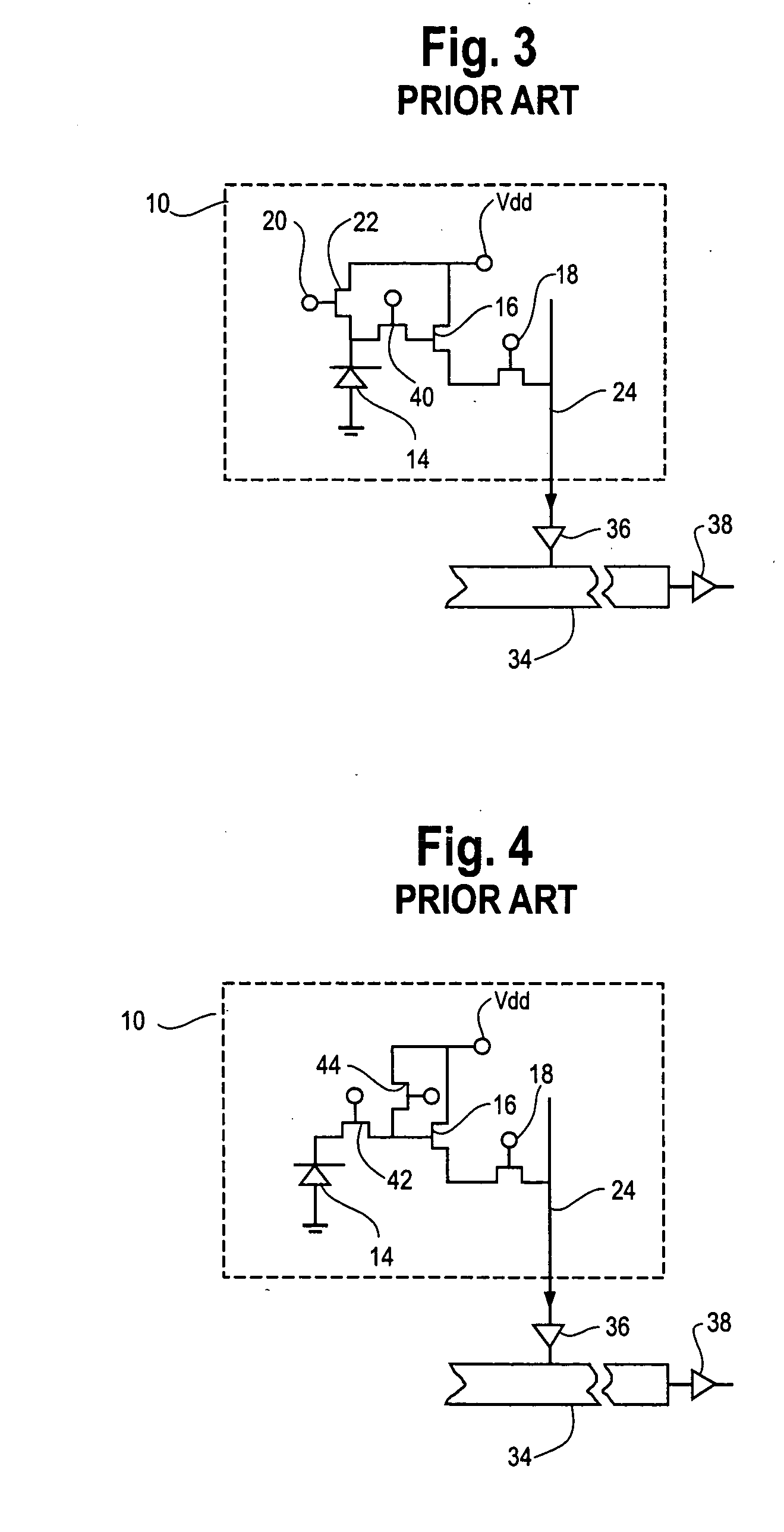

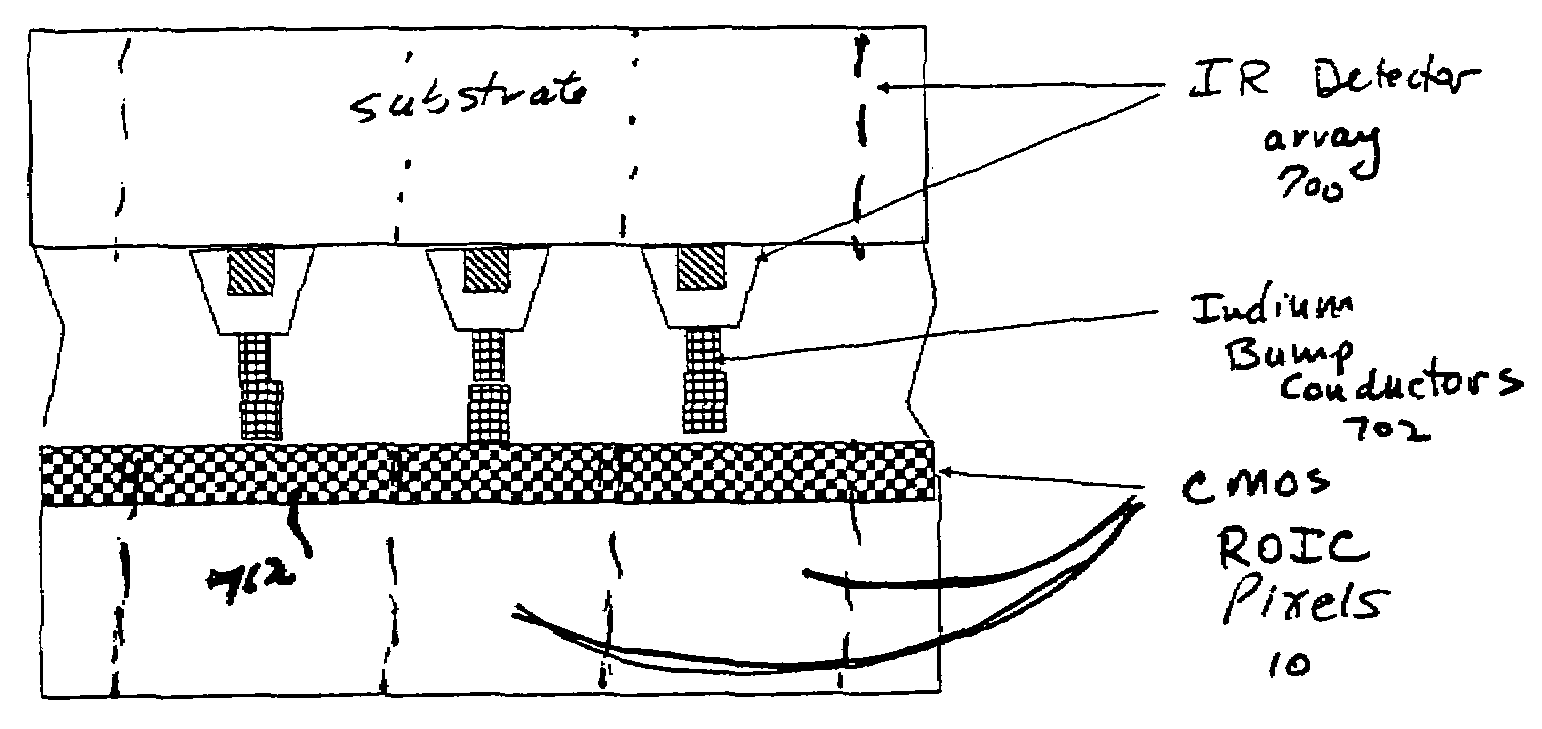

A hybrid image sensor includes an infrared detector array and a CMOS readout integrated circuit (ROIC). The CMOS ROIC is coupled to at least one detector of the IR detector array, e.g., via indium bump bonding. Each pixel of the CMOS ROIC includes a first, relatively lower gain, wide dynamic range amplifier circuit which is optimized for a linear response to high light level input signals from the IR detector. Each pixel also includes a second, relatively higher gain, lower dynamic range amplifier circuit which is optimized to provide a high signal to noise ratio for low light level input signals from the IR detector (or from a second IR detector). A first output select circuit is provided for directing the output of the first circuit to a first output multiplexer. A second output select circuit is provided for directing the output of the second circuit to a second output multiplexer. Thus, separate outputs of the first and second circuits are provided for each of the individual pixel sensors of the CMOS imaging array.

Owner:THE BF GOODRICH CO

Hybrid infrared detector array and CMOS readout integrated circuit with improved dynamic range

ActiveUS7551059B2High gainReduced dynamic rangeTelevision system detailsTelevision system scanning detailsIndium bumpDetector array

A hybrid image sensor includes an infrared detector array and a CMOS readout integrated circuit (ROIC). The CMOS ROIC is coupled to at least one detector of the IR detector array, e.g., via indium bump bonding. Each pixel of the CMOS ROIC includes a first, relatively lower gain, wide dynamic range amplifier circuit which is optimized for a linear response to high light level input signals from the IR detector. Each pixel also includes a second, relatively higher gain, lower dynamic range amplifier circuit which is optimized to provide a high signal to noise ratio for low light level input signals from the IR detector (or from a second IR detector). A first output select circuit is provided for directing the output of the first circuit to a first output multiplexer. A second output select circuit is provided for directing the output of the second circuit to a second output multiplexer. Thus, separate outputs of the first and second circuits are provided for each of the individual pixel sensors of the CMOS imaging array.

Owner:THE BF GOODRICH CO

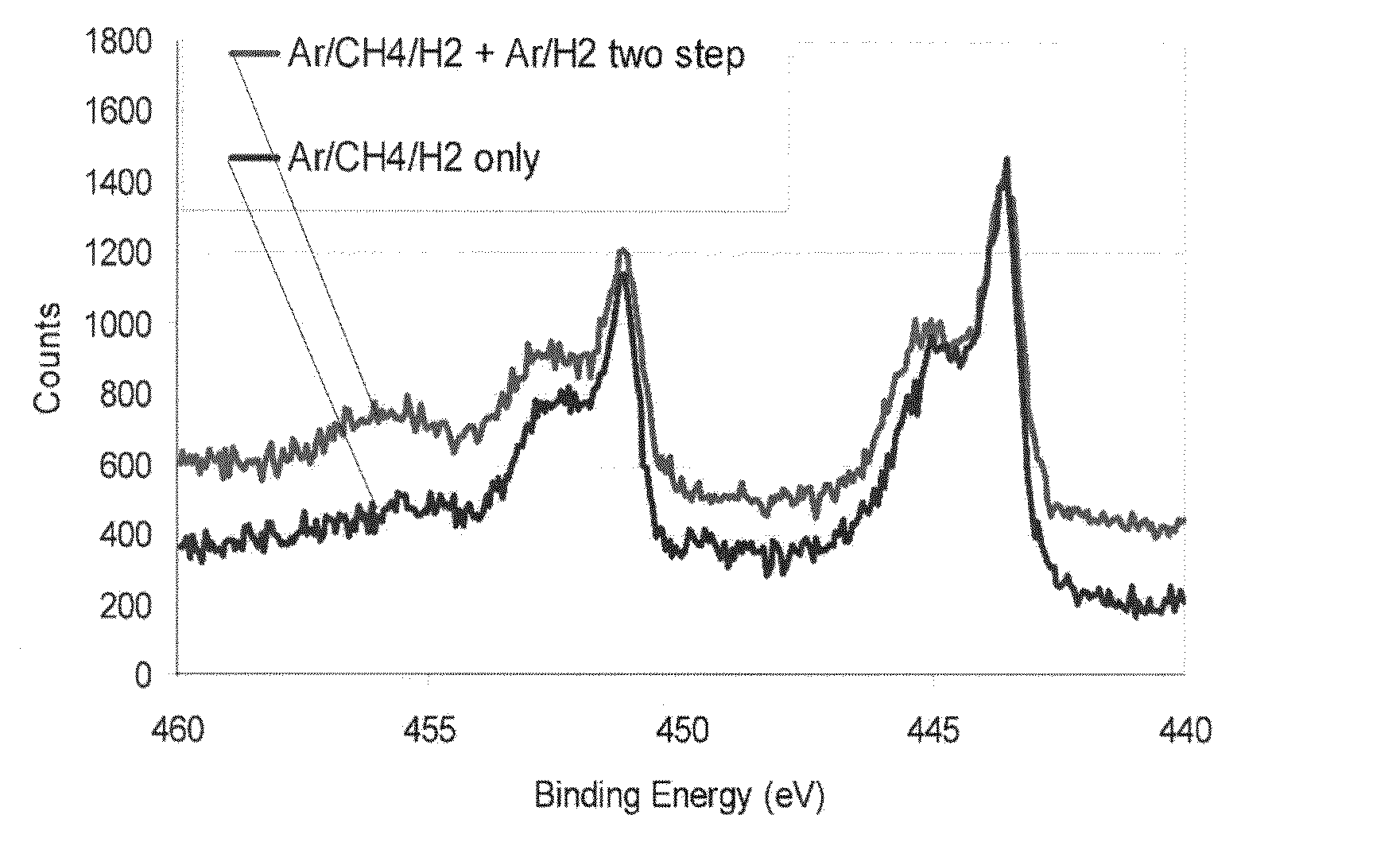

Method to improve indium bump bonding via indium oxide removal using a multi-step plasma process

A process for removing indium oxide from indium bumps in a flip-chip structure to reduce contact resistance, by a multi-step plasma treatment. A first plasma treatment of the indium bumps with an argon, methane and hydrogen plasma reduces indium oxide, and a second plasma treatment with an argon and hydrogen plasma removes residual organics. The multi-step plasma process for removing indium oxide from the indium bumps is more effective in reducing the oxide, and yet does not require the use of halogens, does not change the bump morphology, does not attack the bond pad material or under-bump metallization layers, and creates no new mechanisms for open circuits.

Owner:NASA

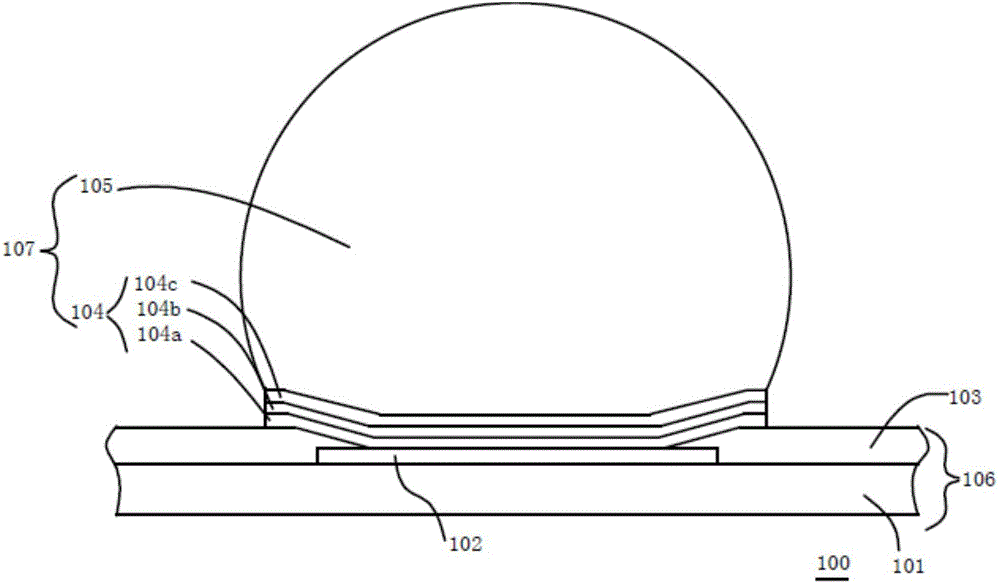

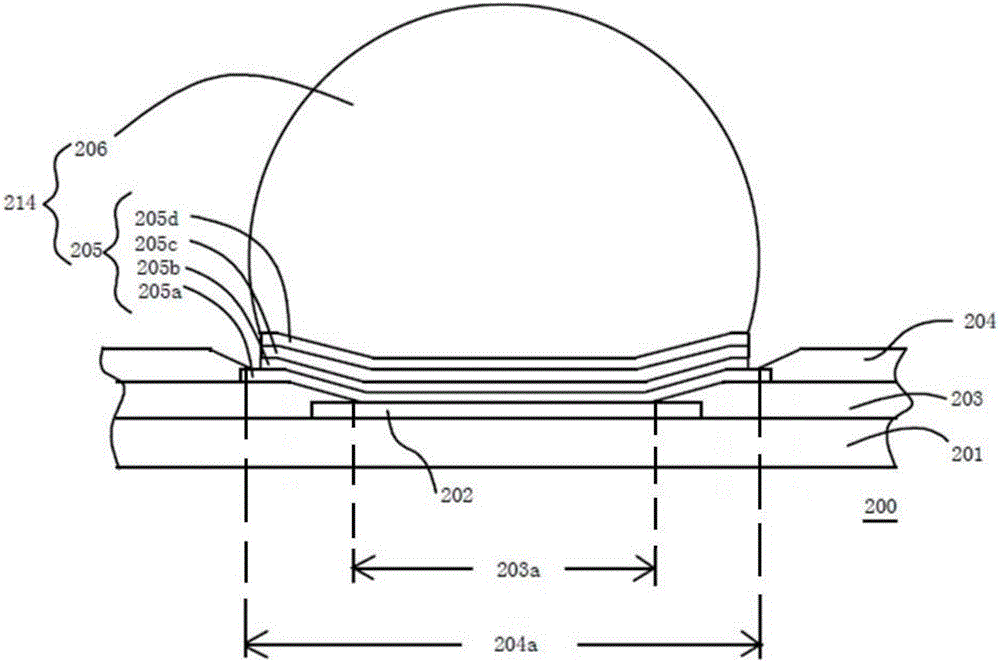

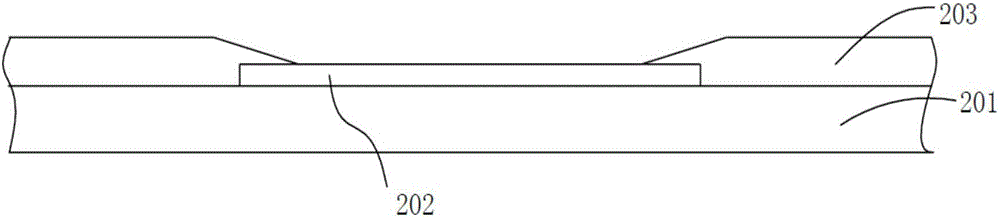

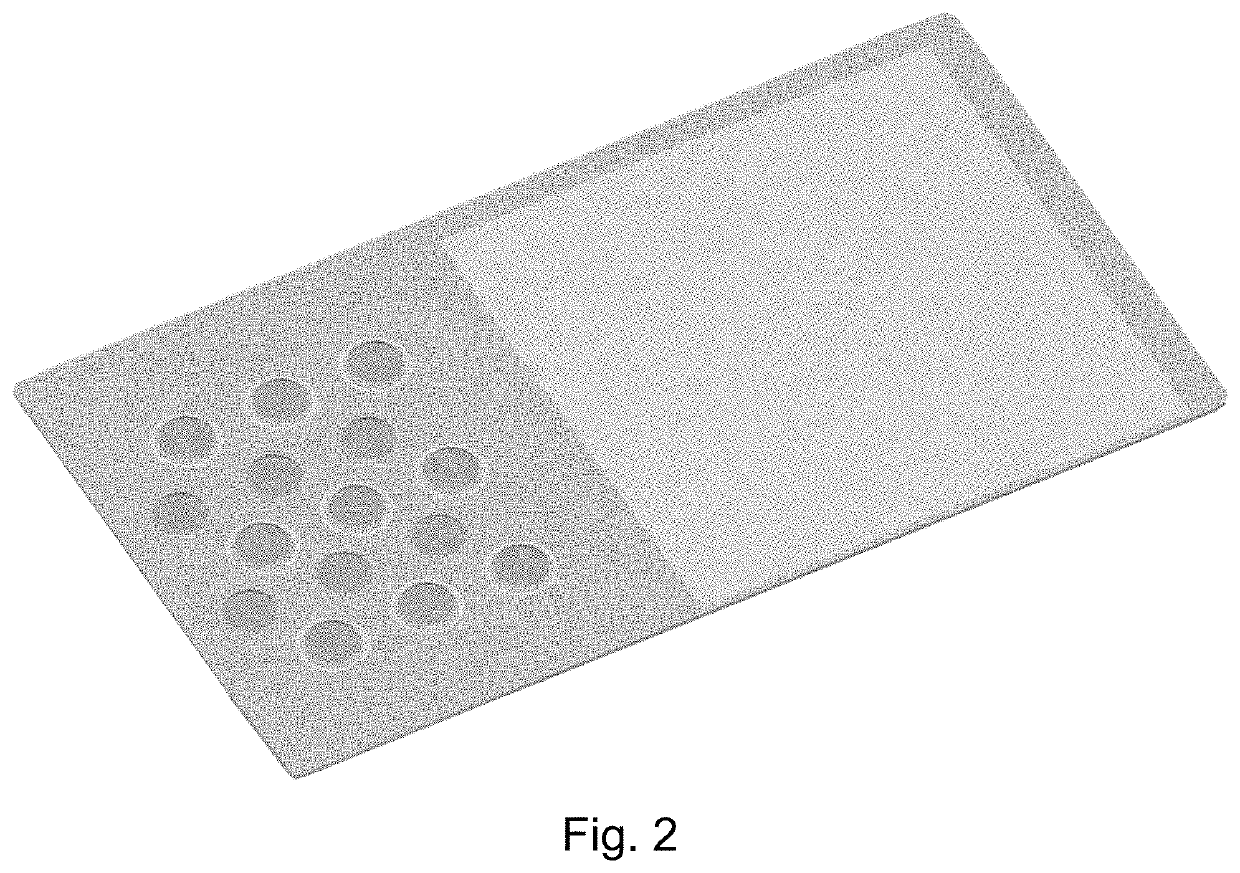

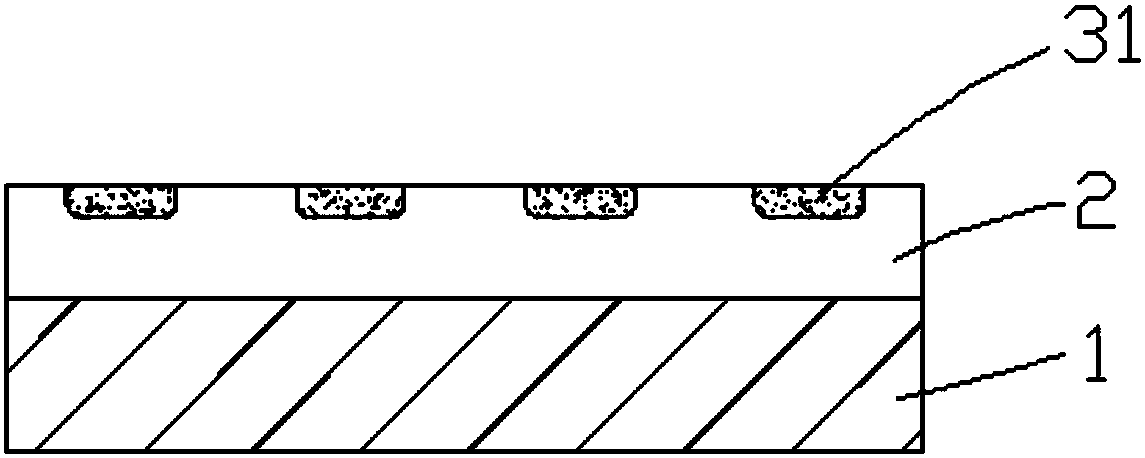

Indium bump device structure and preparation method for same

InactiveCN105826421AImprove structural strengthAvoid sheddingFinal product manufactureSemiconductor devicesIndium bumpUltimate tensile strength

The invention relates to an indium bump device structure and a preparation method for the same and belongs to the technical field of preparation of indium bump devices. The device structure comprises a semiconductor substrate, a welding disk, a first passivation layer, a second passivation layer, a UBM metal layer and an indium bump, wherein the UBM metal layer comprises an adhesion layer, a blocking layer, a buffer layer and a wetting layer; and in the device structure, a part of the first passivation layer is covered by the adhesion layer, and a part of the adhesion layer is covered by the second passivation layer. High structural intensity is provided by the stacking structure, so that the structure composed of the indium bump and the UBM is prevented from being separated along an interface of the adhesion layer and the first passivation layer under effects of thermal stress when the device surfers from thermal shocks. In addition, internal stress changes between the substrate and the UBM during backflow are mitigated by setting of the buffer layer, so that the indium bump is prevented from being separated from the wetting layer under too large internal stress changes. Hence, the device structure provided by the invention has higher stability and a longer service life.

Owner:KUNMING INST OF PHYSICS

System and method for superconducting multi-chip module

ActiveUS20200119251A1Shorten the timeReduce leakageSemiconductor/solid-state device detailsSolid-state devicesIndium bumpEngineering physics

A method for bonding two superconducting integrated circuits (“chips”), such that the bonds electrically interconnect the chips. A plurality of indium-coated metallic posts may be deposited on each chip. The indium bumps are aligned and compressed with moderate pressure at a temperature at which the indium is deformable but not molten, forming fully superconducting connections between the two chips when the indium is cooled down to the superconducting state. An anti-diffusion layer may be applied below the indium bumps to block reaction with underlying layers. The method is scalable to a large number of small contacts on the wafer scale, and may be used to manufacture a multi-chip module comprising a plurality of chips on a common carrier. Superconducting classical and quantum computers and superconducting sensor arrays may be packaged.

Owner:SEEQC INC

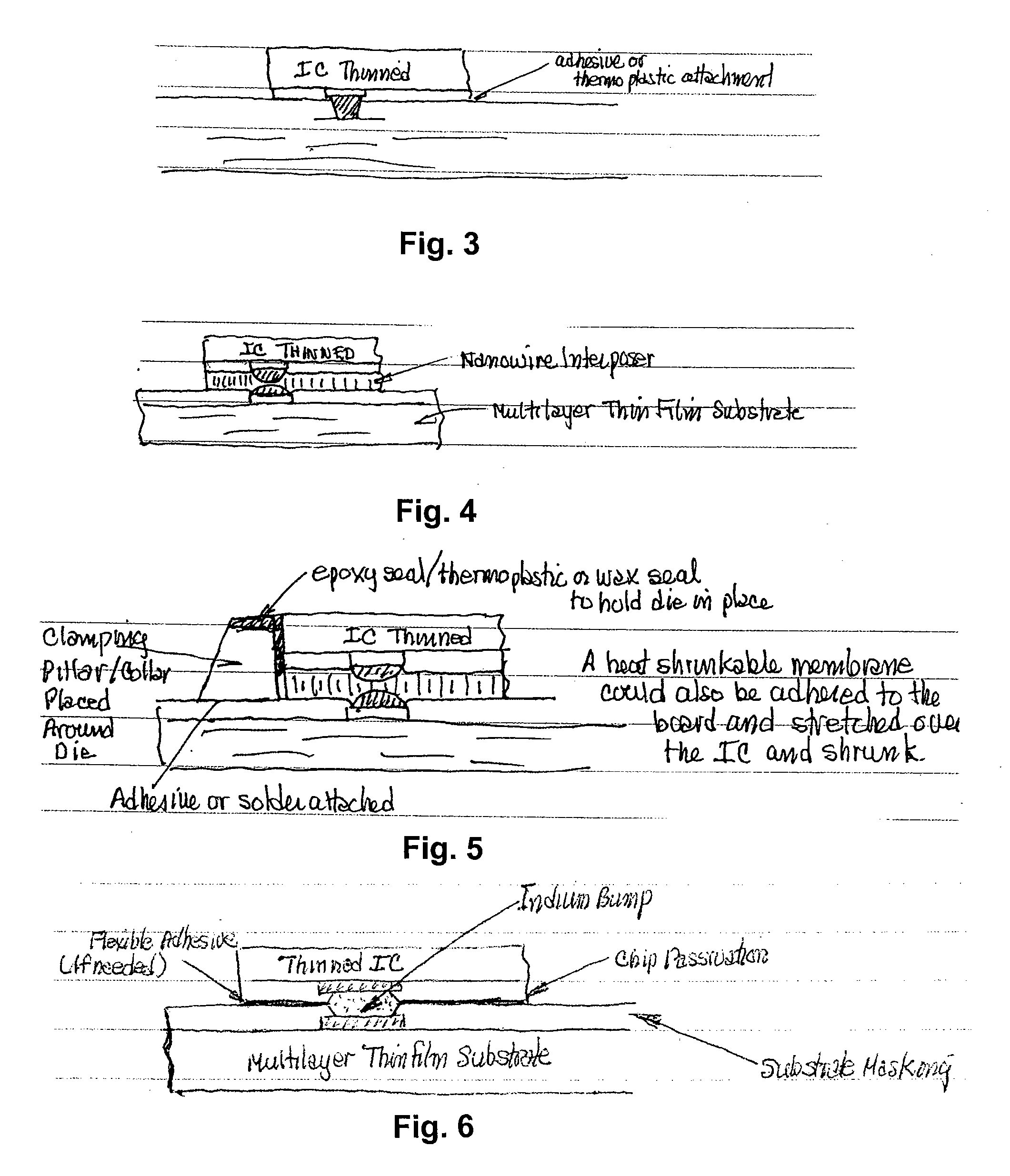

Advanced Thin Flexible Microelectronic Assemblies and Methods for Making Same

InactiveUS20080009095A1Wide rangeSolid-state devicesSemiconductor/solid-state device manufacturingNanowireIndium bump

A thin, flexible microelectronic assembly using thinned die (5-10 microns and lower) produced by growing a 1 μm-10 μm silicon epitaxial (Epi) layer on an oxidized silicon carrier. The integrated circuit process takes place in the standard manner in the Epi layer. The oxide layer and the silicon carrier serve as the backside handle. Once processed, the wafer can be bumped and singulated just like a normal chip without the need for the extra handle attachment processes or the backside thinning operation. Once the integrated circuits are flipped and solder reflowed to a substrate, the handle can be removed by etching the oxide. In one assembly embodiment, wells are etched in the flexible circuit board material to allow the interconnect to be recessed below the circuit board surface. An adhesive can then be placed on the board surface, locking the die to the flexible substrate. Alternatively, a nanowire interposer can be sandwiched between a bumped multilayer substrate and a bumped thin die. Further, indium bumps can be substituted for solder bumps to provide a more flexible assembly.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

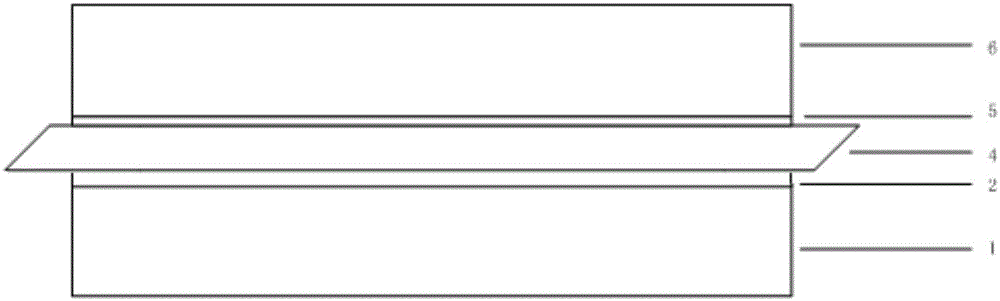

Back-illuminated mercury cadmium telluride long-wave light-guide type infrared flat-panel detector

ActiveCN101728403AReduce intervalImprove accuracySemiconductor/solid-state device detailsPhotometryEpoxyZinc selenide

The invention discloses a back-illuminated mercury cadmium telluride long-wave light-guide type infrared flat-panel detector. The detector is characterized by comprising a zinc selenide substrate and a mercury cadmium telluride sheet fixed on the substrate by epoxy glue, wherein one face of the mercury cadmium telluride sheet, which is in contact with the substrate, is provided with an anodized layer and a ZnS anti-reflection layer, and the double-layer passivation surface on the surface of the mercury cadmium telluride sheet forms an a photosensitive element area array and a signal extraction electrode area and a common electrode area which are respectively positioned at both ends of a photosensitive element by photoengraving. The signal extraction electrode area and the common electrode area are both extracted from the back side of a light collection surface, an indium bump grows in a specified area, another indium bump grows on a signal reading circuit board, and the indium bumps are interconnected. An indium bump of a chip electrode and an indium bump of an electrode plate are connected together. An indium layer, an aurum layer and indium bumps are orderly grow on the signal electrode area and the common electrode area, thereby forming the back-illuminated mercury cadmium telluride long-wave light-guide type infrared flat-panel detector.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

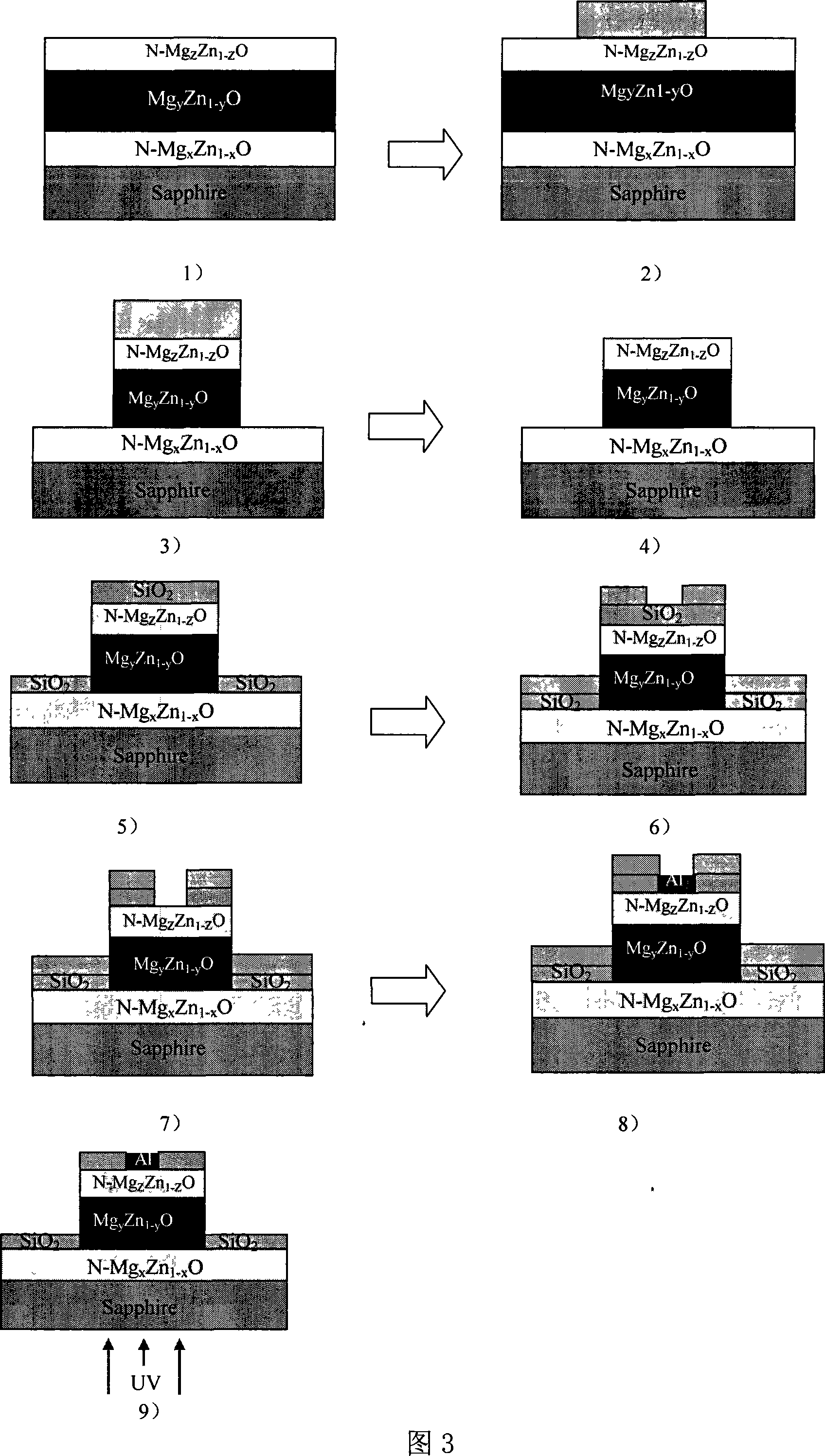

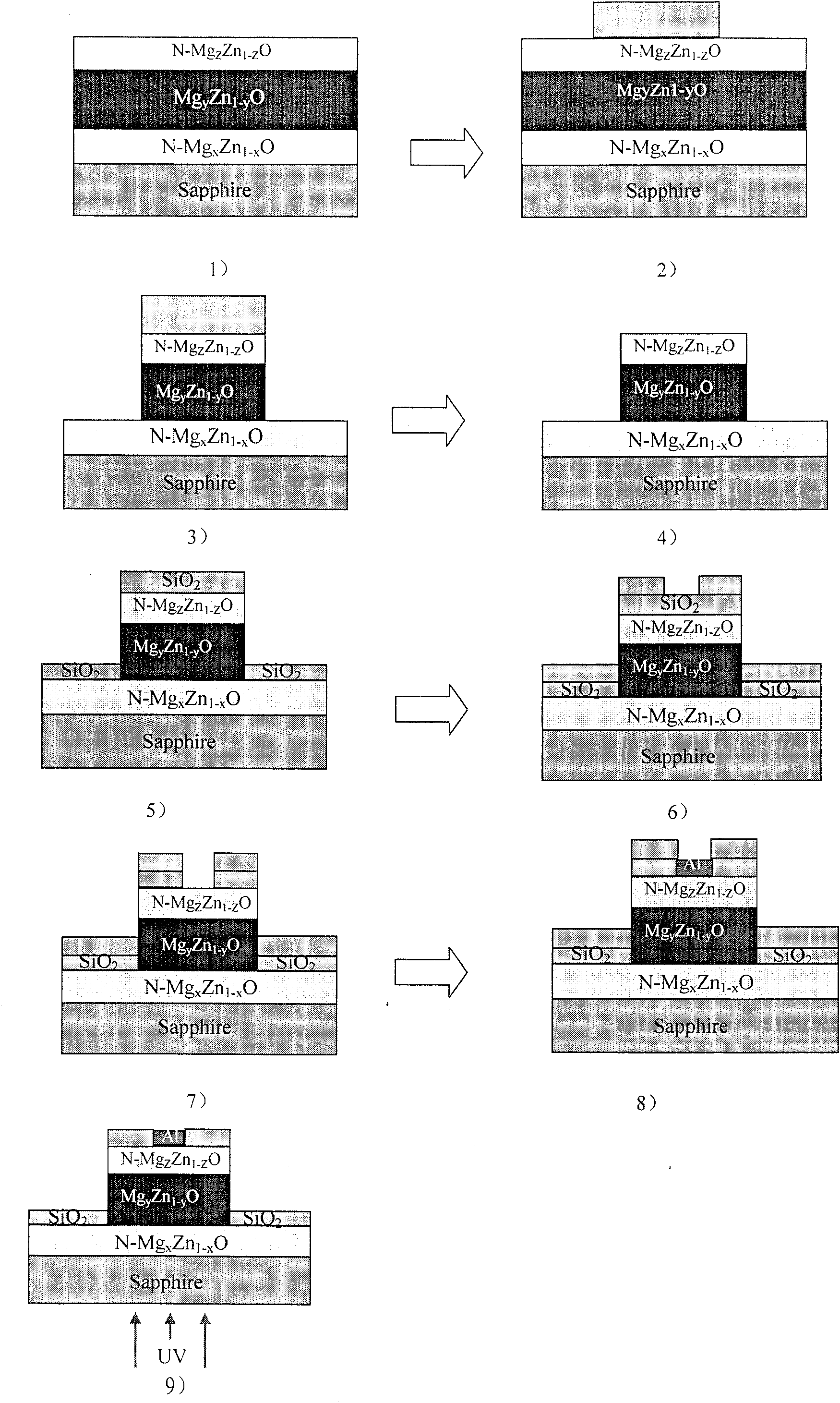

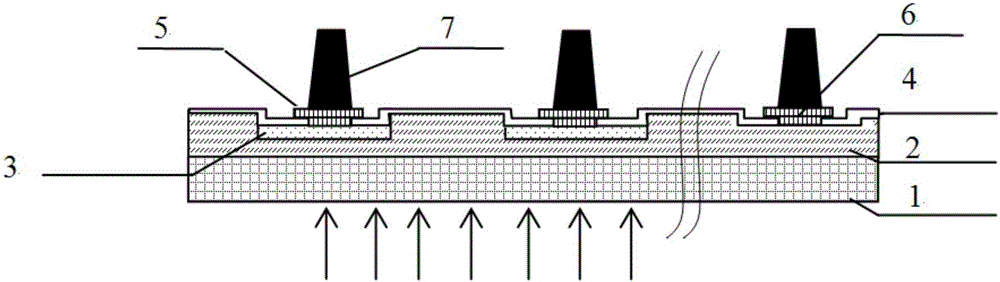

Back shining type ZnO base ultraviolet imaging solid state focal plane detection array and its preparation

InactiveCN101055881AFinal product manufactureSemiconductor/solid-state device manufacturingIndium bumpUltraviolet lights

The invention relates to a backlight ZnO-based ultraviolet imaging solid focal plane surveying array and preparation, which on the sapphire (0001)substrate of double-face polishing, uses laser molecular beam to epitaxially grow a MgxZn1-xO(BexZn1-xO) nesa heavily doped with Al, then epitaxially growing a MgyZn1-yO layer without adulterant, sensitive to ultraviolet light. Then a MgzZn1-zO ohm contact epitaxial layer heavily doped with Al is gengerated on the upper surface. An array pixel cell structure is formed by using a photoetching and ICP ion etching method, then uses RF magnetron sputtering to plate a SiO2 passivation layer, based on the etched graph. An Al contact of electrodes etched by reactive ion uses a method of evaporation plated film to form a metallic contact, for rapid annealing activation of an ultraviolet sensitive active layer to form an ohm contact, thus getting a backlight ZnO-based ultraviolet imaging solid focal plane surveying array. The invention and the matched Si-CMOS readout circuit chip are interconnected through indium bumps, which are put on the focal plane of the ultraviolet lens, added with the corresponding image processing, memory circuit and software to form a complete ultraviolet imaging device.

Owner:XI AN JIAOTONG UNIV

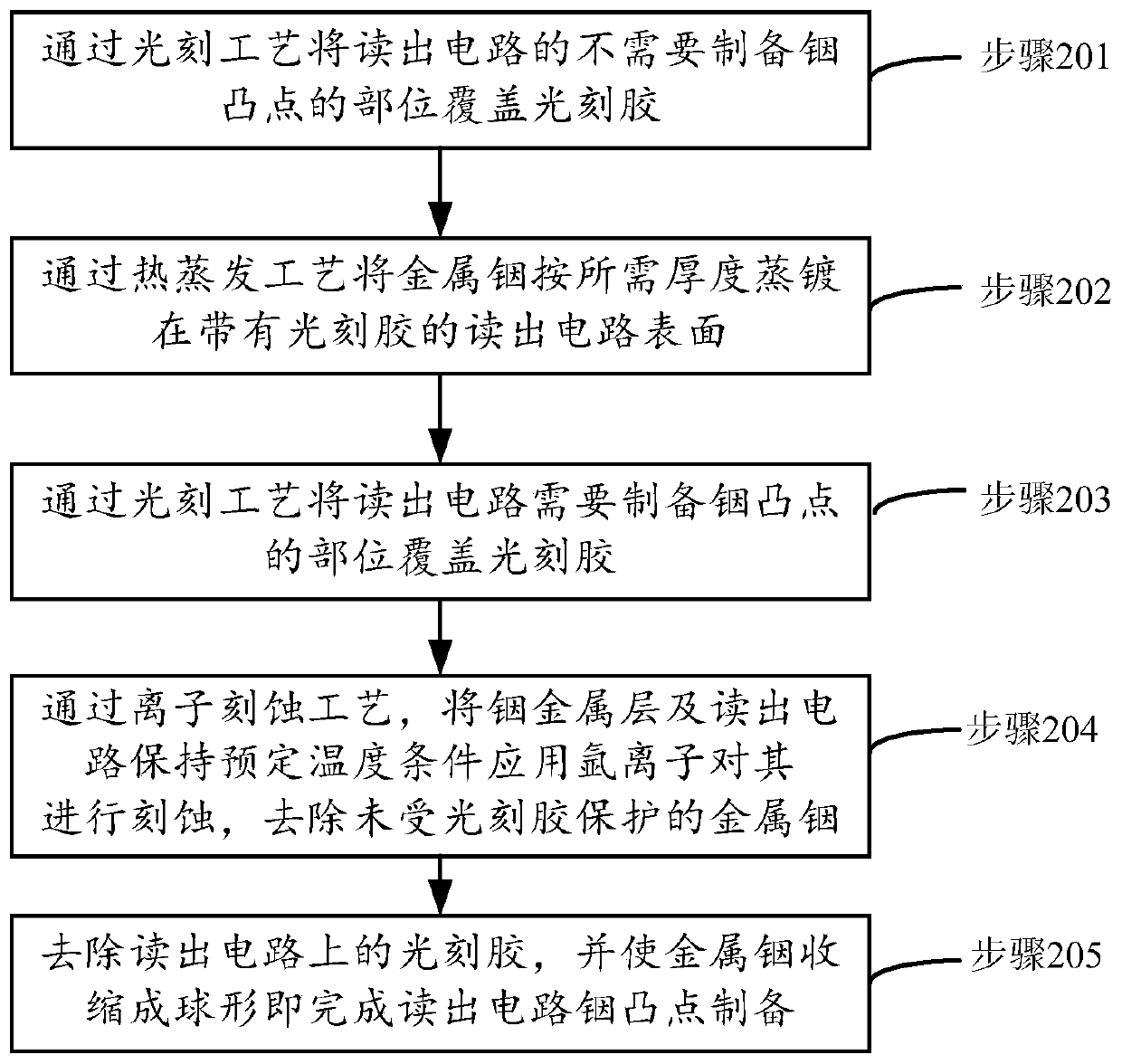

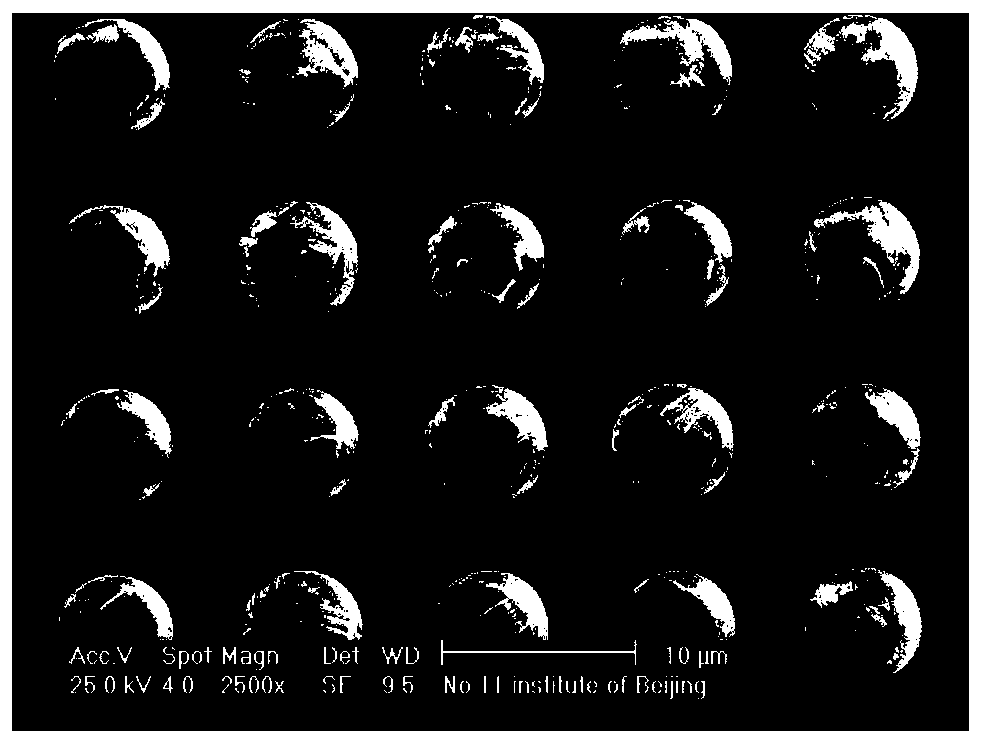

Method for preparing indium bumps of reading circuit of infrared detector

ActiveCN110660690AImprove uniformityReduce manufacturing difficultySolid-state devicesSemiconductor/solid-state device manufacturingIndium metalLithography process

The invention discloses a method for preparing indium bumps of a reading circuit of an infrared detector. The method comprises steps of covering photoresist on a part, which does not need to be provided with indium bumps, of the reading circuit through the photoetching process; evaporating metal indium on a surface of the reading circuit with the photoresist according to the required thickness through the thermal evaporation process; covering photoresist on the part of the reading circuit, which needs to be provided with the indium bumps, through the photoetching process; through the ion etching process, etching the indium metal layer and the reading circuit by using argon ions while keeping the preset temperature condition, and removing the metal indium which is not protected by the photoresist; and removing the photoresist on the reading circuit, and shrinking the metal indium into a sphere to finish preparation of the indium bumps of the reading circuit.

Owner:11TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

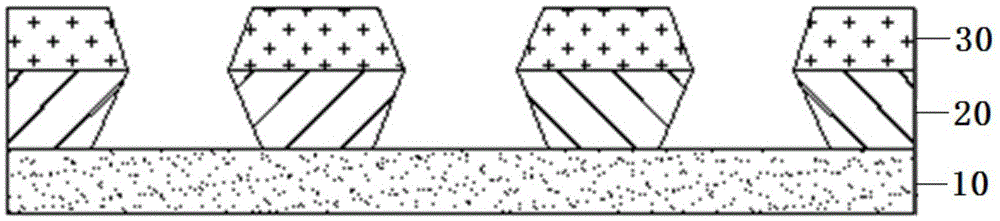

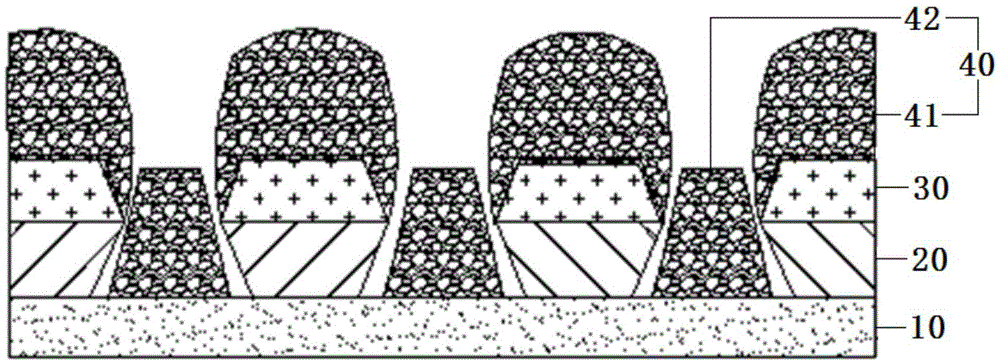

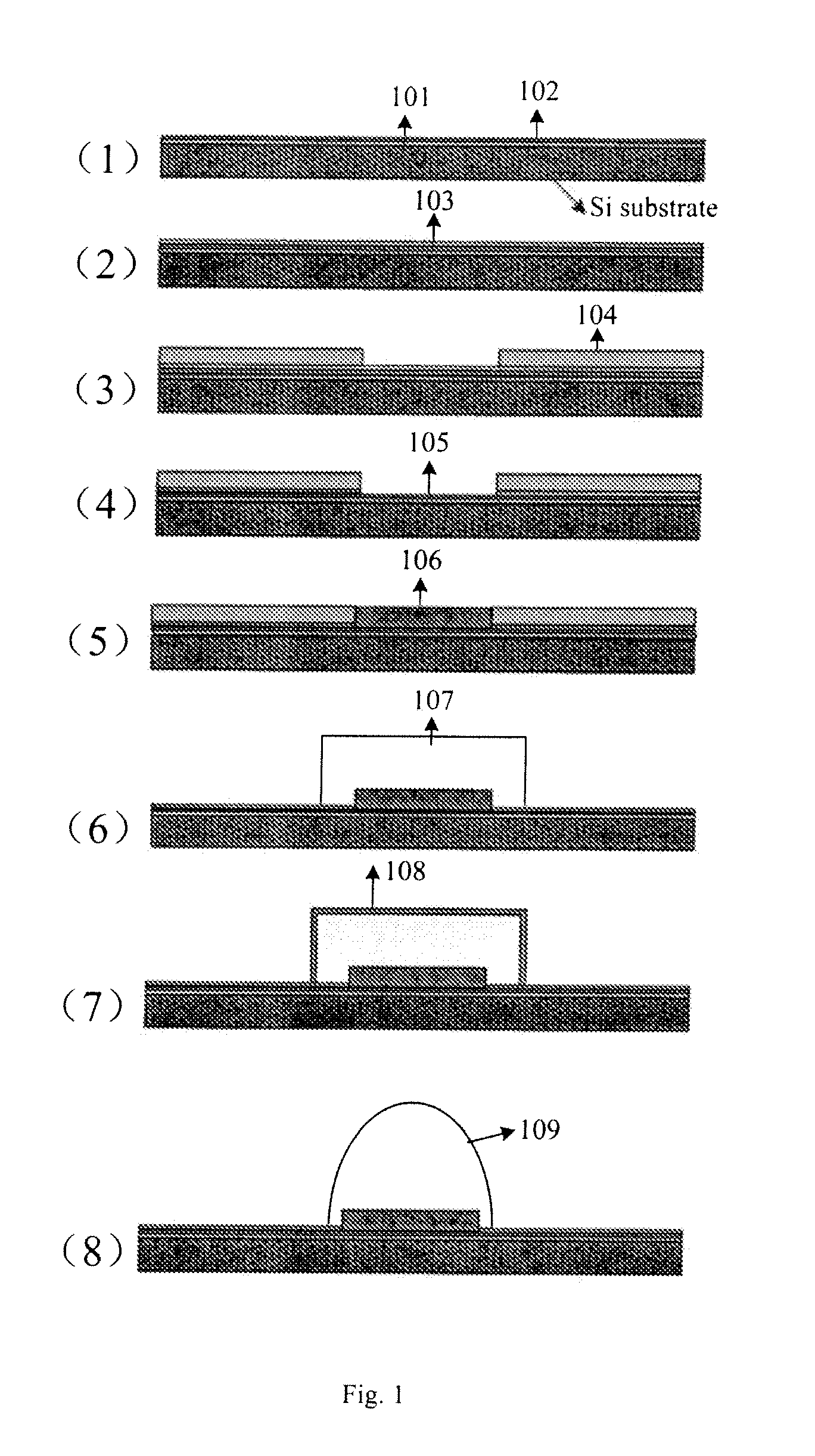

Indium bump preparation method and infrared focal plane array detector

ActiveCN105633008AReduce processing timeImprove yieldSemiconductor/solid-state device manufacturingIndium bumpGallium arsenide

The present invention discloses an indium bump and a preparation method thereof. The preparation method comprises the steps of A, coating a photoresist layer (20) on a chip (10); B, forming a deposition hole (21) on the photoresist layer (20); C, depositing the metal and the indium orderly, forming a bottom metal layer (30) and an indium layer (41) on the photoresist layer (20) orderly, and forming the bottom metal layer (30) and an indium bump (42) in the deposition hole (21) orderly; D, removing the photoresist layer (20) and the bottom metal layer (30) and the indium layer (41) which are located on the photoresist layer (20). The preparation method enables the process time of the indium bump preparation to be shortened and the working efficiency and the indium bump yield to be improved, at the same time, can avoid the fragmentation of the fragile samples, such as the gallium arsenide, etc., in a device. The present invention also discloses the application of the indium bump prepared according to the preparation method in an infrared focal plane array detector, the indium bump can avoid the problems, such as the pixel short circuit caused by a wet stripping technology, etc., and enables the performance of the device to be improved.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

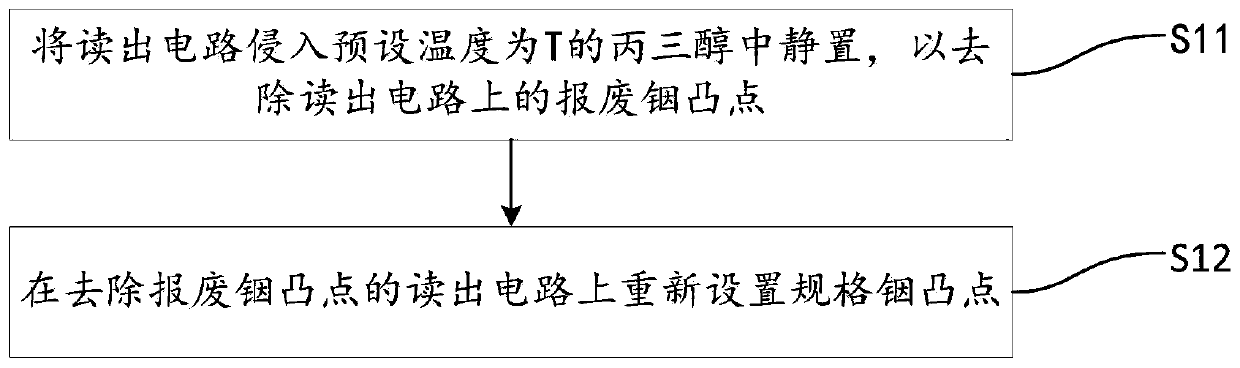

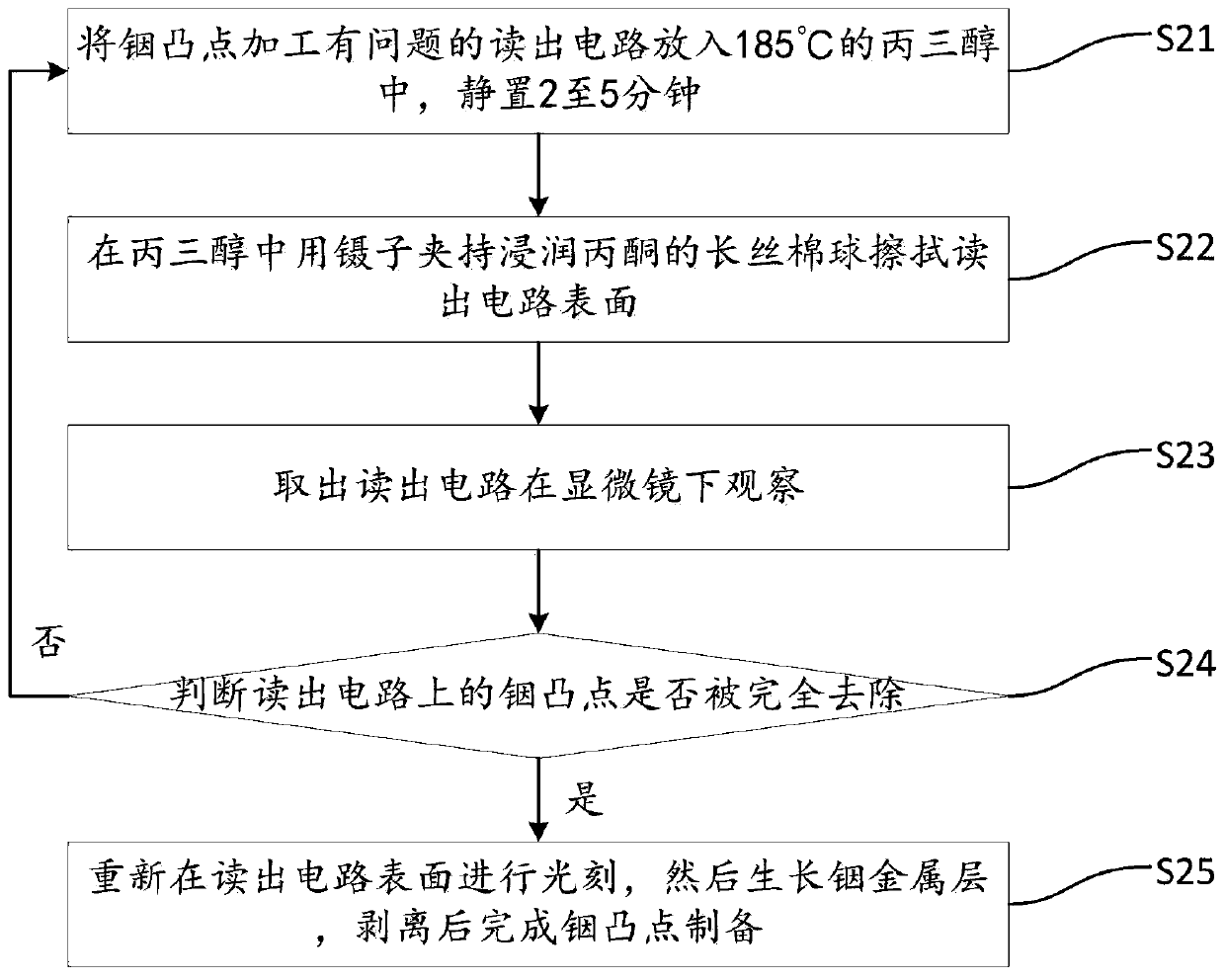

Indium bump resetting method for infrared detector reading circuit

ActiveCN110993729AImprove performanceAvoid problemsFinal product manufactureSemiconductor devicesIndium bumpPhysical chemistry

The invention discloses an indium bump resetting method for an infrared detector reading circuit, and the method comprises the steps: enabling the reading circuit to be immersed in glycerol at a preset temperature T for standing, so as to remove a scrapped indium bump on the reading circuit; and resetting the specification indium bumps on the reading circuit from which the scrapped indium bumps are removed. According to the invention, resetting of the indium bumps of the readout circuit is realized, the indium bumps on the reading circuit can be removed by adopting a physical method, and thenthe indium bumps are grown again, so that waste products of the reading circuit due to the indium bump processing problem can be avoided, the 100% yield of indium bump processing of the reading circuit is realized, and the reading circuit with the good performance can be repeatedly used for many times.

Owner:11TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

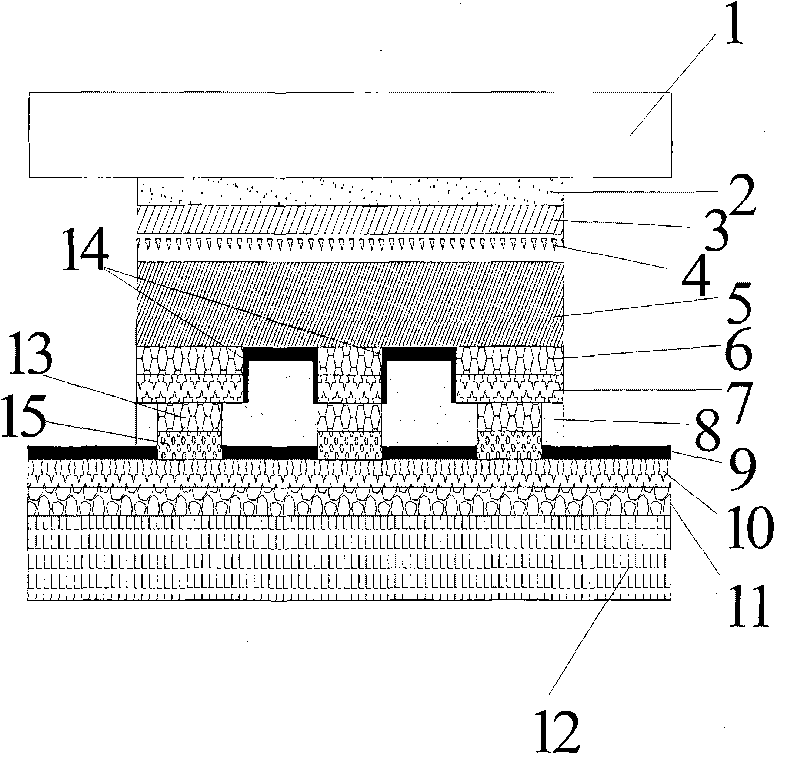

Focal plane array detector and preparation method thereof

ActiveCN108257987AImprove signal-to-noise ratioSolve hidden dangersSolid-state devicesPhotometry using electric radiation detectorsIndium bumpP–n junction

The invention discloses a focal plane array detector and a preparation method thereof. The focal plane array detector comprises an epitaxial layer. The lower surface of the epitaxial layer is providedwith multiple concave first doped regions. The interfaces of the epitaxial layer and the first doped regions are first PN junctions. A pixel element hole is arranged between the adjacent first PN junctions. The lower surface of the epitaxial layer is covered by a first passivation film. The first passivation film arranged on the surface of the first doped regions is provided with first contact holes. The exact middle of the first passivation film arranged on the surface of the pixel element holes is provided with second contact holes. The first contact holes and the second contact holes are filled with first indium bumps and second indium bumps respectively. The first indium bumps and the second indium bumps protrude out of the epitaxial layer. The upper surface of the epitaxial layer isprovided with multiple concave second doped regions. The first doped regions and the second indium bumps are connected in a one-to-one correspondence way. The objective of the invention is to solve the technical problems of crosstalk of the PN junctions of the adjacent pixel elements and small effective utilization area of the pixel elements.

Owner:WUHAN GAOXIN TECH

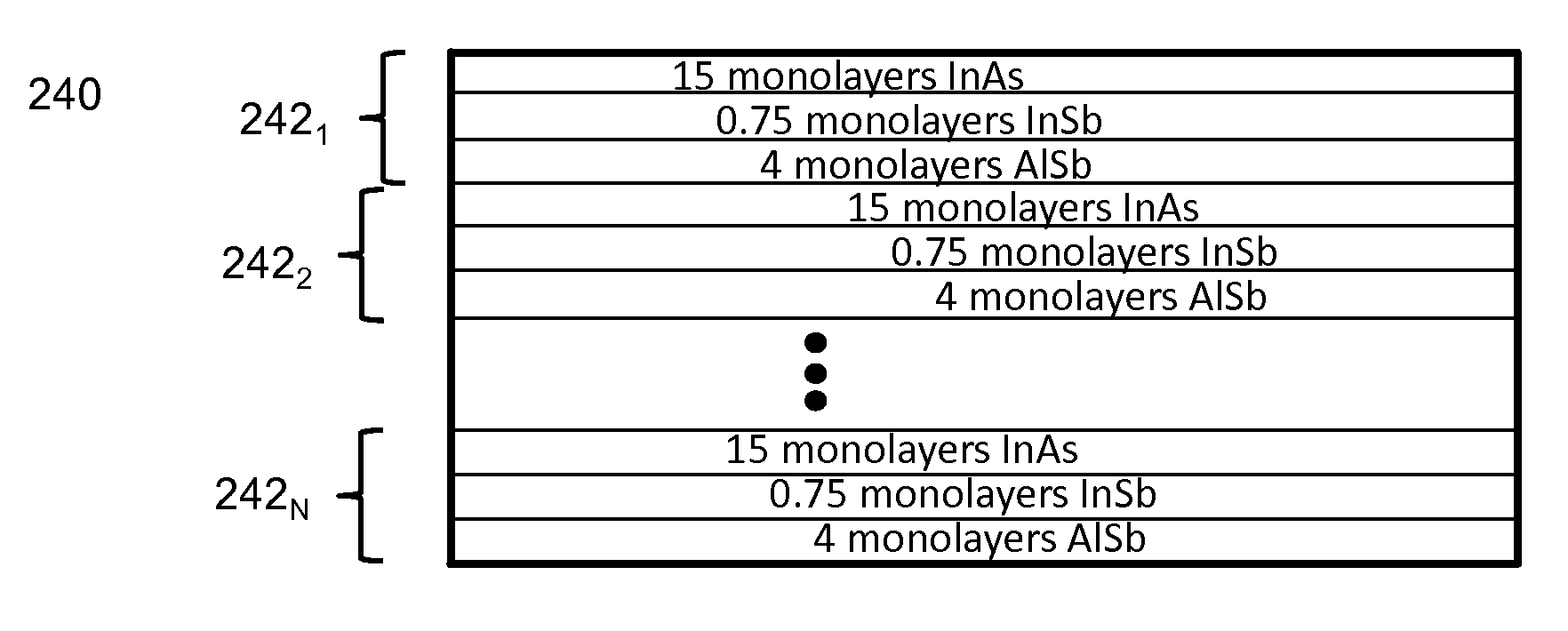

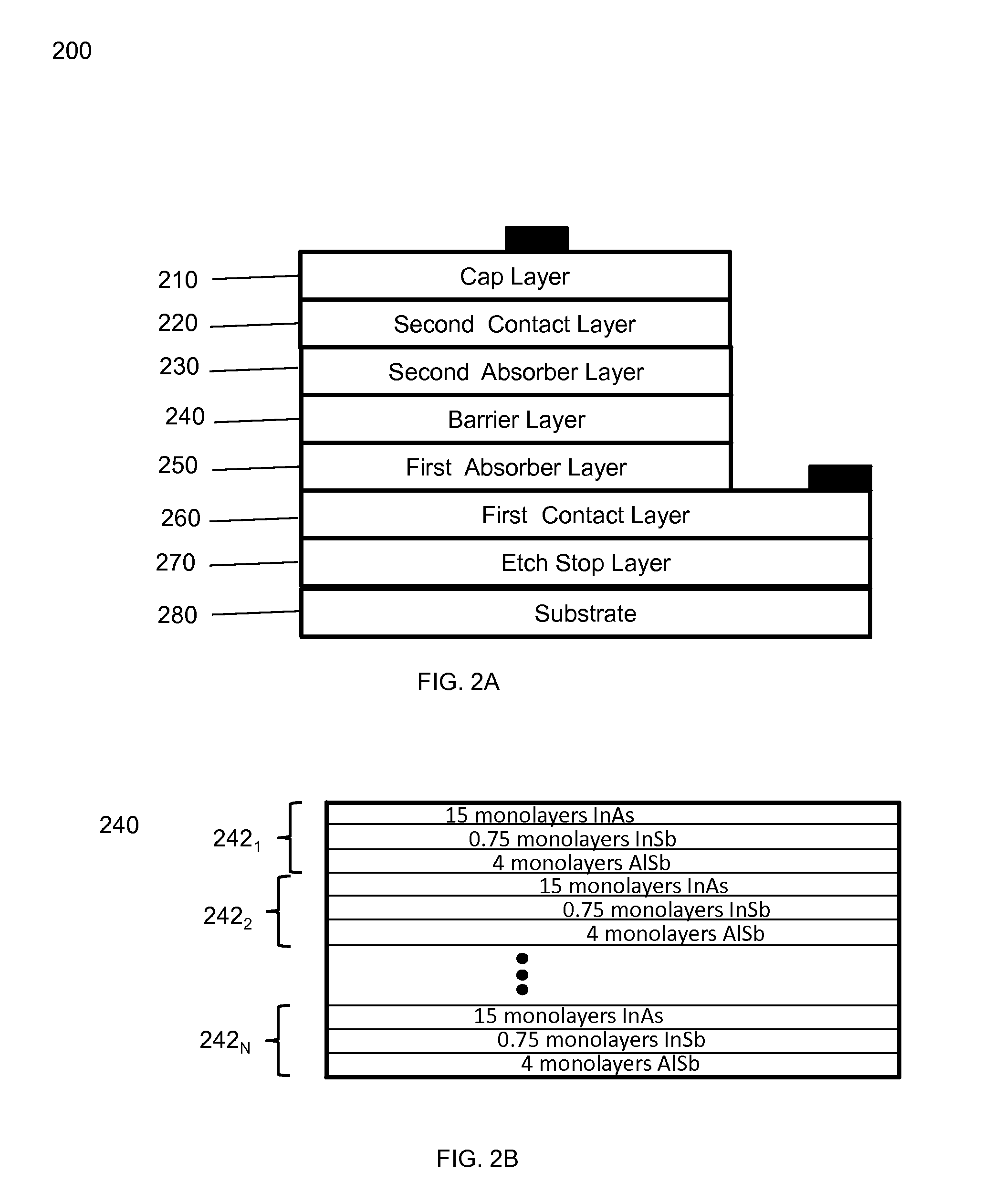

Method of fabricating dual-band type-II superlattice detectors based on p-B-p design

A dual-band infrared detector structure based on Type-II superlattices (T2SL) has been developed and experimentally validated. The structure according to the principles of the present invention is designed for a single Indium bump architecture and utilizes a T2SL barrier design that omits the traditional p-n junction region. The barrier design comprises multiple periods where each period comprises multiple monolayers doped P type. By selecting the composition, number of monolayers per period and number of periods, a transition region is created in the conduction band between a first absorber layer and a second absorber layer that allows operation at low biases (<100 mV for both bands) and exhibits a dark current density in the longer wavelength band comparable to that obtained with single-color detectors.

Owner:HRL LAB

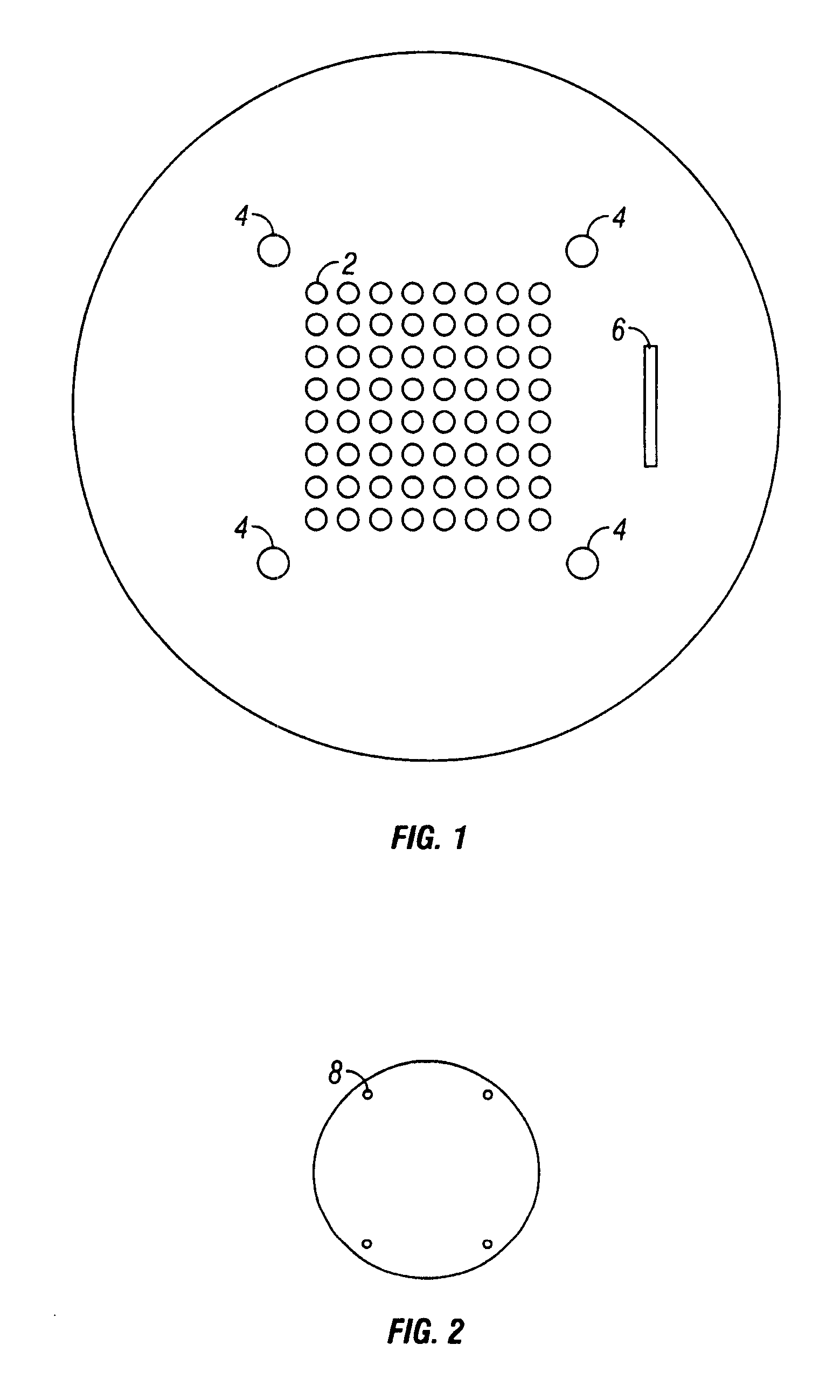

Indium features on multi-contact chips

InactiveUS20070224722A1Improve leakage currentThicker regionSolid-state devicesSemiconductor/solid-state device manufacturingIndium metalIndium bump

A device comprising a pixilated semiconductor detector or VLSI chip having plurality of individual indium bumps arrayed on a surface of the detector, wherein the indium bumps are in electrical contact with the surface and are situated in defined locations on the surface is provided. Additionally, a hybrid detector comprising a pixilated detector in electrical contact with a VLSI chip, wherein electrical contacts formed from indium metal are made between the pixels of the semiconductor and regions on the VLSI chip corresponding thereto is provided. In another embodiment, a method of forming electrical contacts on a pixilated detector comprising the steps of constraining a shadow mask having an array of holes in predetermined locations above a surface on the detector, aligning the mask above the detector, and evaporating indium metal under vacuum through holes in the mask onto the surface of the detector to form the contacts is described.

Owner:CALIFORNIA INST OF TECH

Technical method of infrared detector indium bump

ActiveCN105575892AEasy to makeCheap manufacturingSolid-state devicesSemiconductor/solid-state device manufacturingIndium bumpPhotoresist

The invention provides a technical method of an infrared detector indium bump. The method comprises spin-coating two layers of photoresist on a chip in a superposing manner, and further comprises the following steps: firstly, spin-coating a layer of negative photoresist on the chip, and then spin-coating a layer of inversion photoresist on the negative photoresist; through a masking plate exposure and masking plate-free exposure, enabling the contours of the sections of the upper half portions of the two layers of photoresist on the chip to be trapezoidal and the contours of the sections of the lower half portions to be inverted-trapezoidal; and performing indium membrane precipitation, wherein an indium precipitation window is not obviously reduced and an indium bump is platform-shaped so that subsequent preparation is facilitated. By means of the method provided by the invention, the technical problem of preparing a flat-top indium bump on the chip is solved, and good effects of easy preparation, low cost and facilitated combination with external equipment are achieved.

Owner:WUHAN GAOXIN TECH

Field emission electrode and preparation method thereof

ActiveCN109585238ASimple preparation processImprove adsorption capacityMaterial nanotechnologyDischarge tube/lamp detailsNanowireLow voltage

The invention discloses a field emission electrode. The field emission electrode comprises a substrate and a metal electrode layer formed on the substrate, the metal electrode layer is provided with aplurality of indium bumps arranged in an array, and the top surface of each indium bump is provided with a plurality of nanowires. The preparation method comprises the steps of: S10, providing a substrate, and performing depositing on the substrate to form a metal electrode layer; S20, preparing a photoresist mask having a hole array on the metal electrode layer; S30, depositing indium materialson the photoresist mask to peel off the photoresist mask to obtain the indium bumps arranged in the array; and S40, putting the substrate with the formed indium bumps in a reaction furnace, wherein the top surface of each indium bump grows and forms the plurality of nanowires. The field emission electrode has an excellent field emission performance and is simple in preparation process, the growthof the nanowires can be performed in the low temperature and the low voltage, the growth condition is simple and gentle and easy to control, and therefore, the quality of products can be effectively improved and the production cost is reduced.

Owner:SHENZHEN INST OF ADVANCED TECH

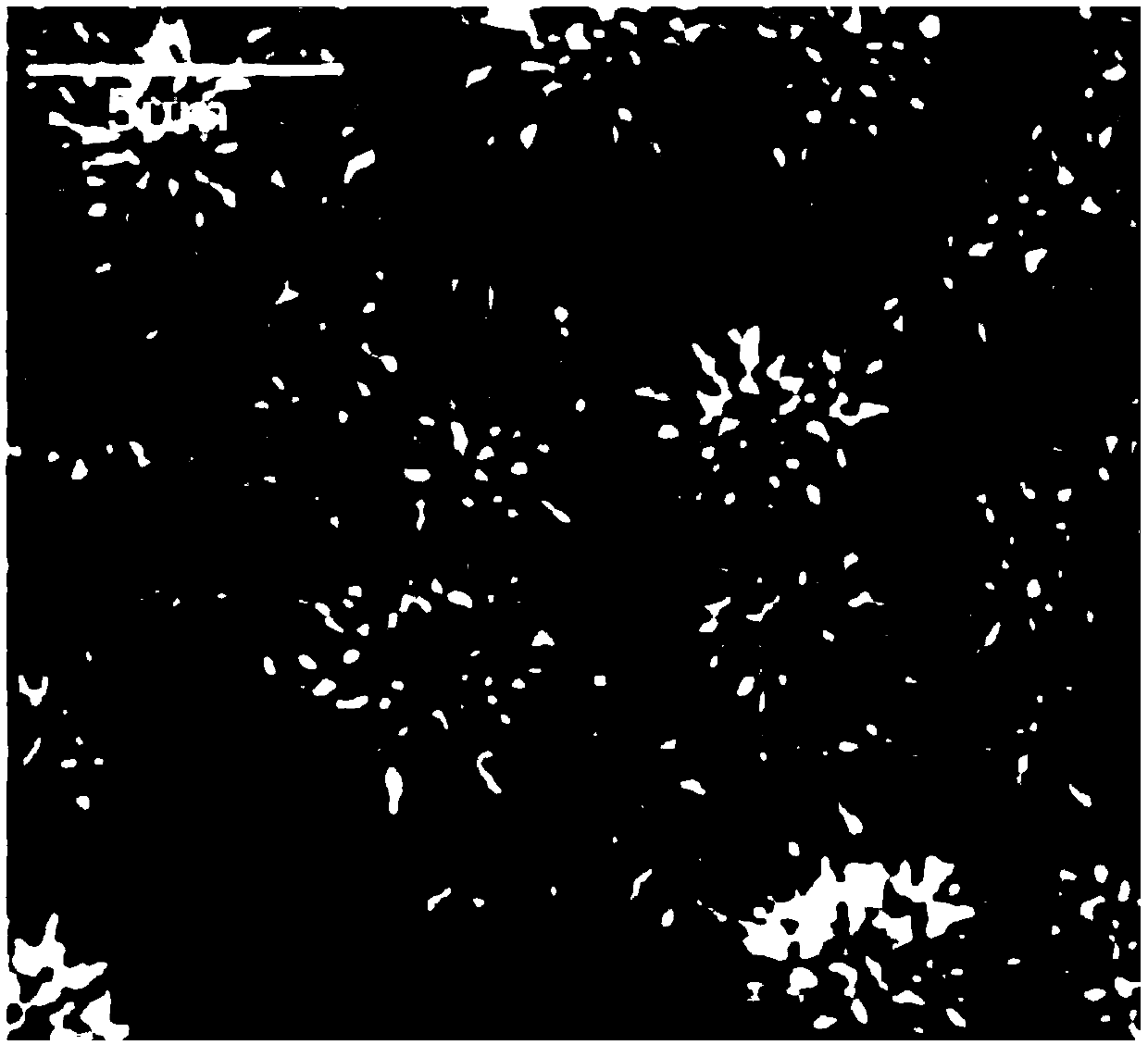

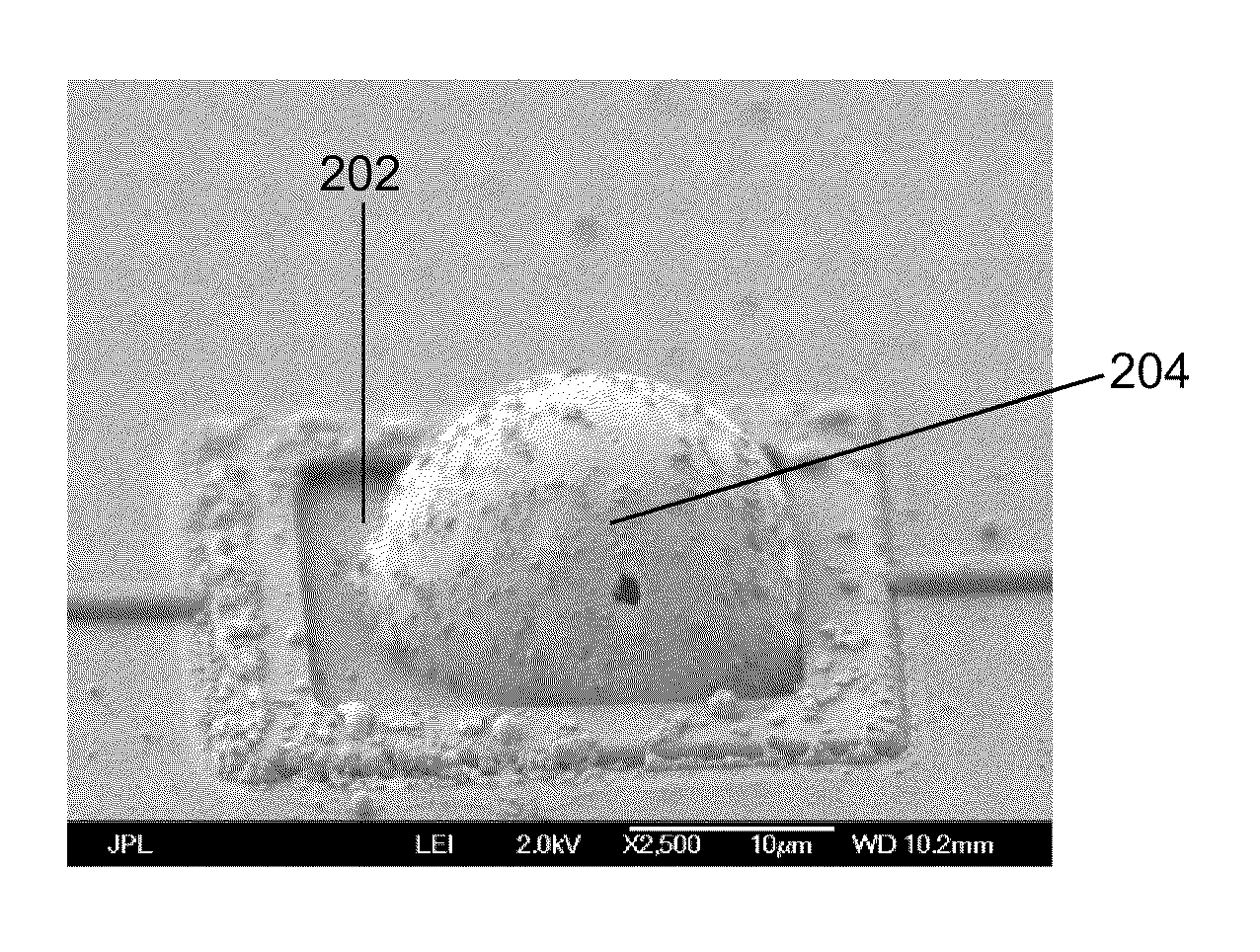

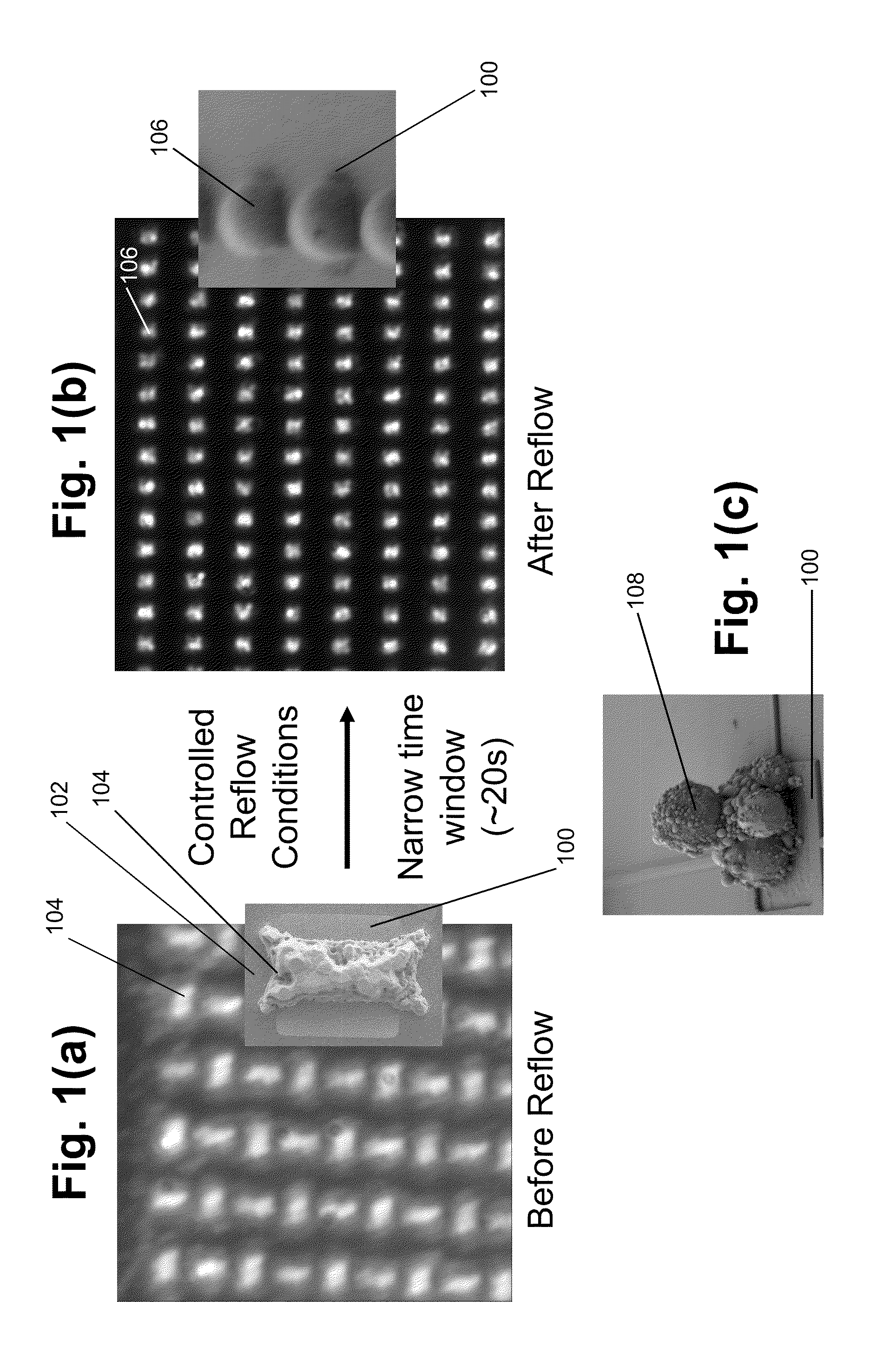

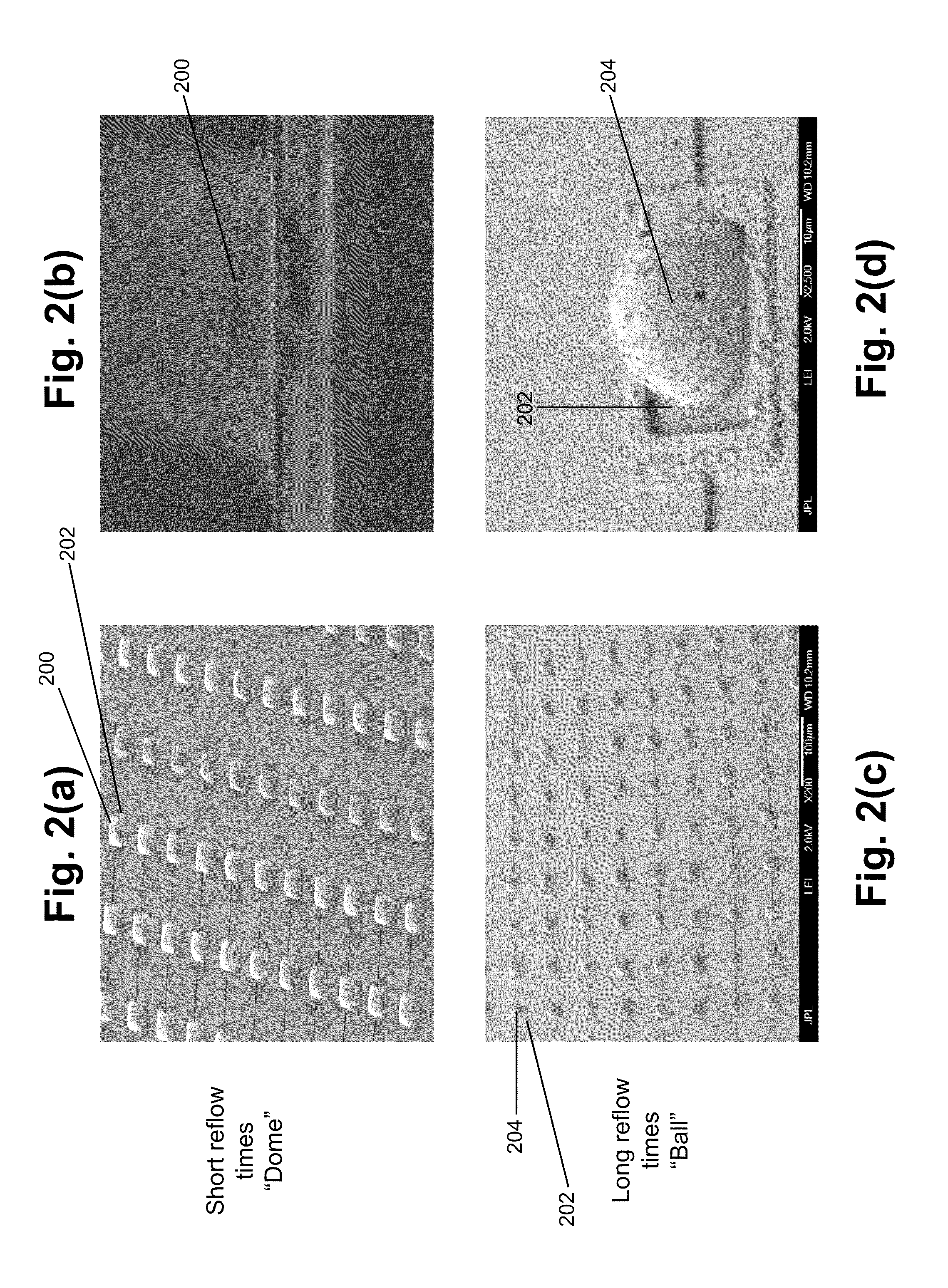

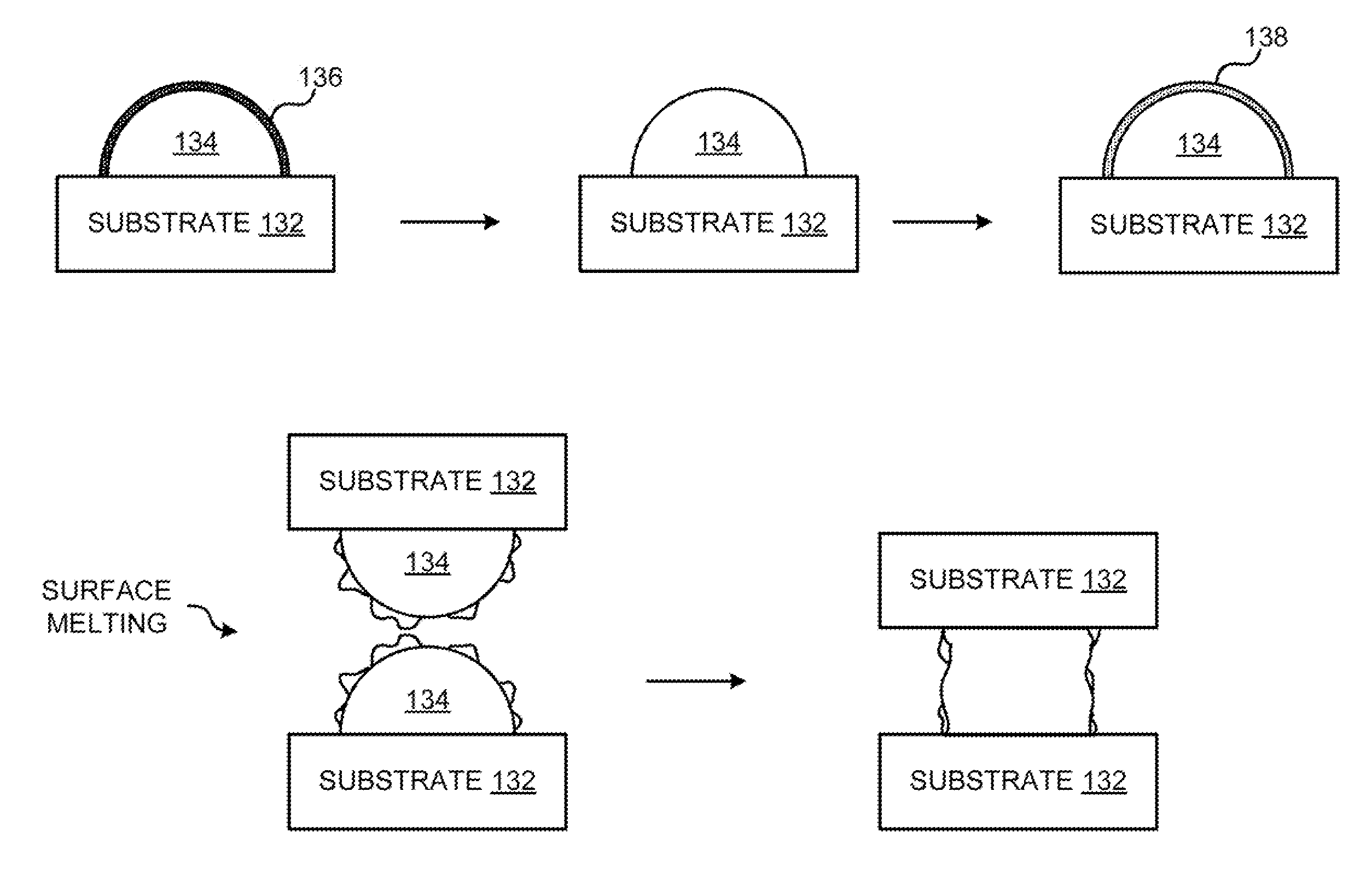

Real time monitoring of indium bump reflow and oxide removal enabling optimization of indium bump morphology

InactiveUS20110169160A1Maximize and optimize wettingAutomatic control devicesPrecision positioning equipmentIndium bumpMaterials science

A method, apparatus, system, and device provide the ability to form one or more solder bumps on one or more materials. The solder bumps are reflowed. During the reflowing, the solder bumps are monitored in real time. The reflow is controlled in real time, thereby controlling a morphology of each of the solder bumps. Further, the wetting of the solder bumps to a surface of the materials is controlled in real time.

Owner:CALIFORNIA INST OF TECH

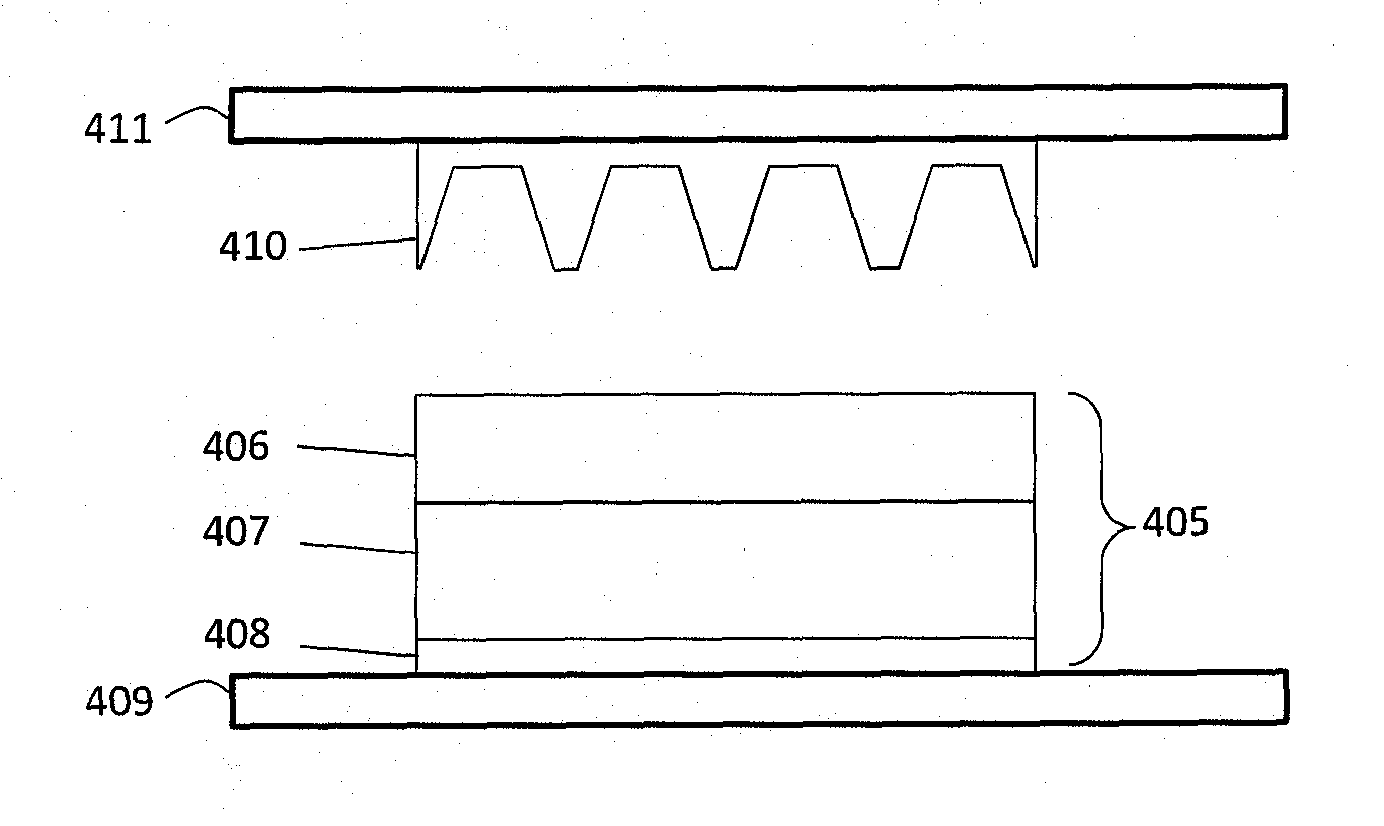

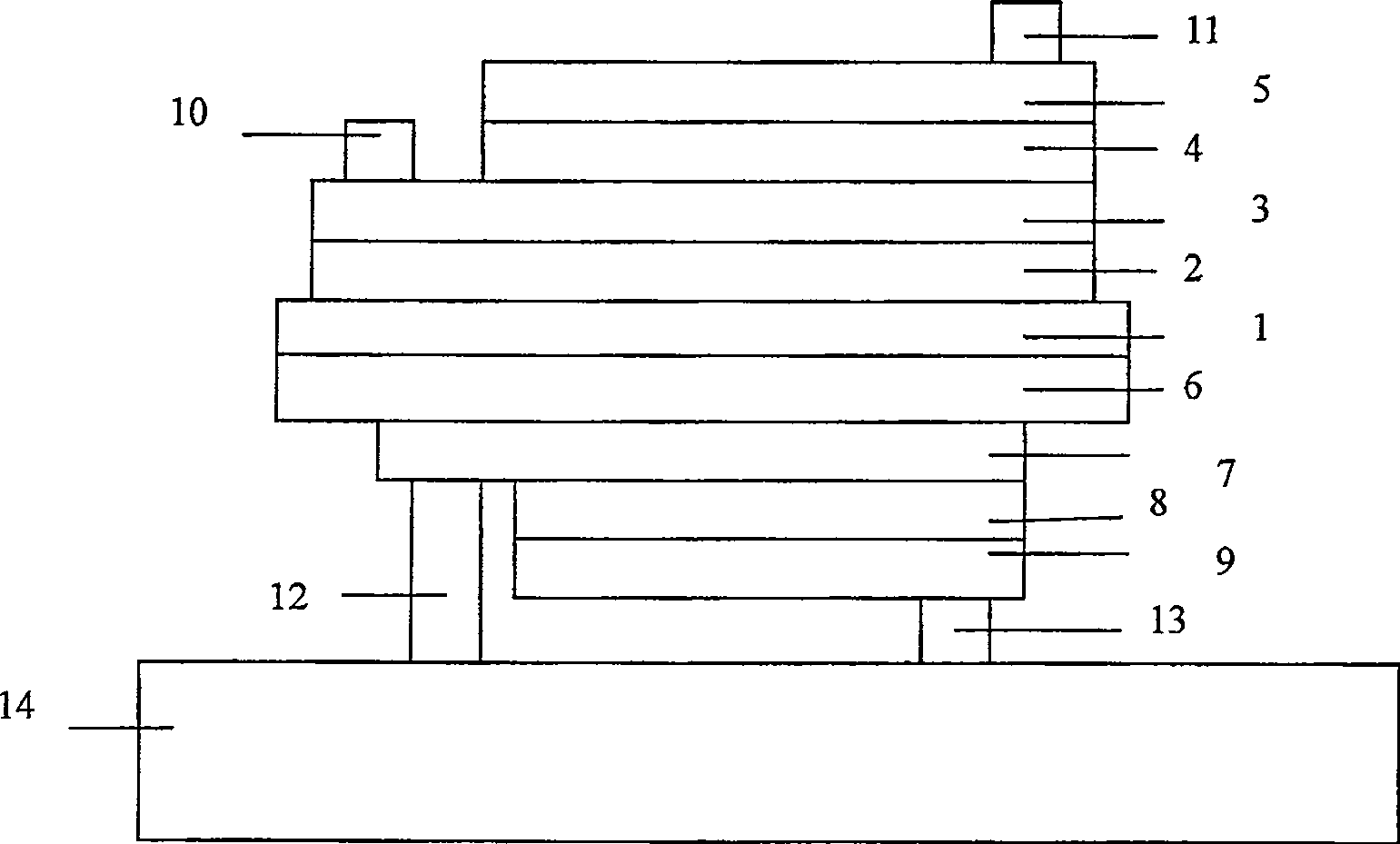

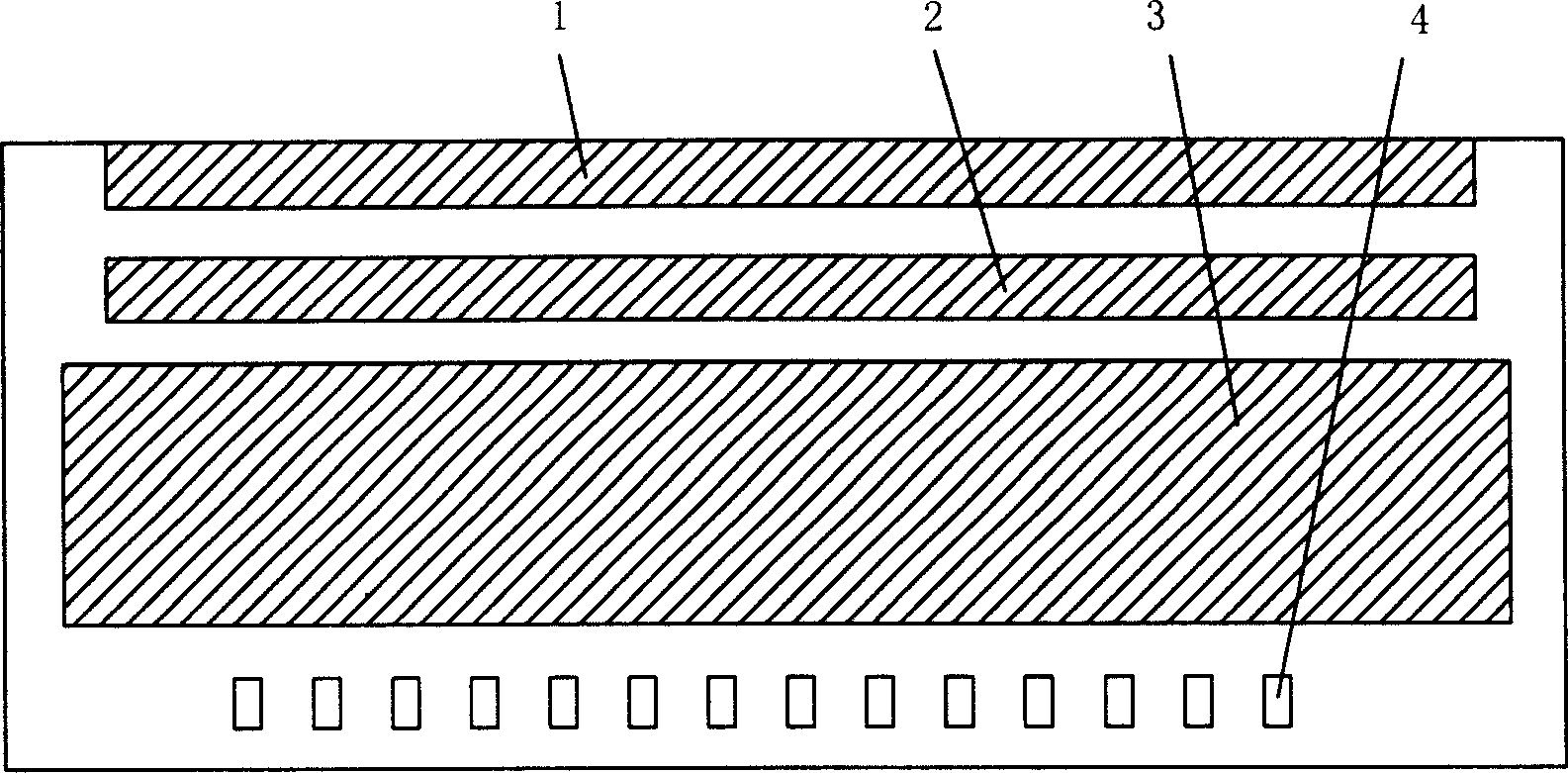

Indium antimonide infrared focal plane array detector chip and manufacturing method thereof

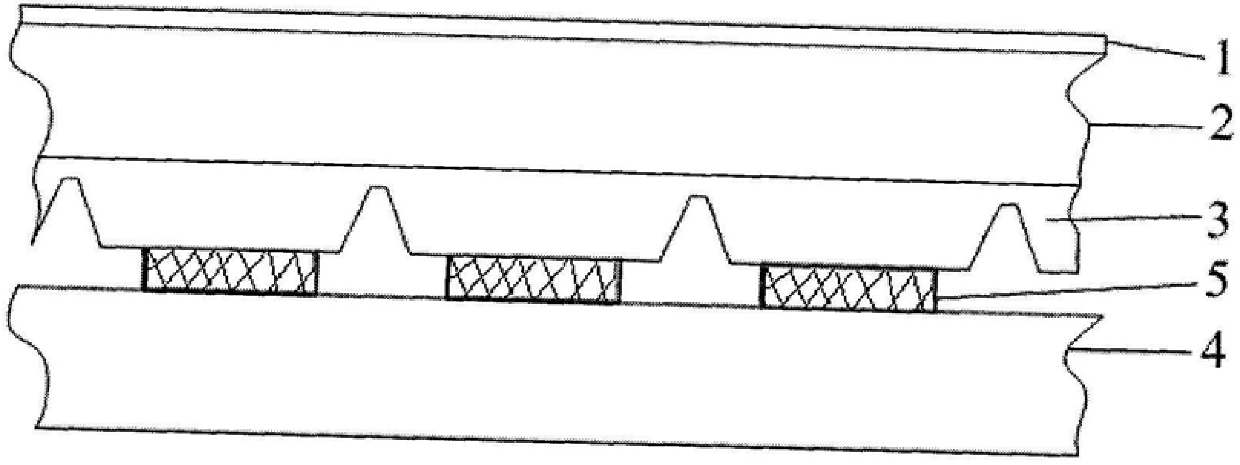

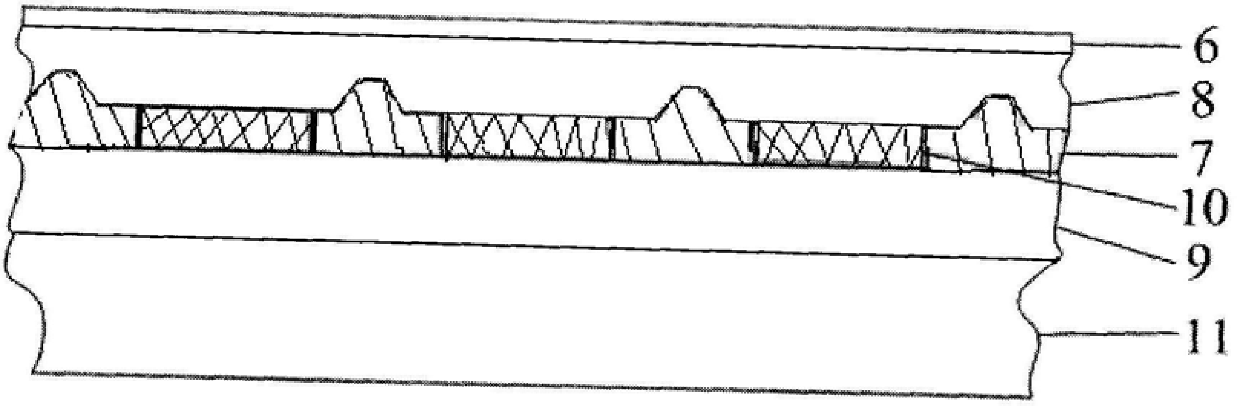

An indium antimonide infrared focal plane array detector chip, which includes an antireflection film [6], a low-temperature glue [7], an indium antimonide photosensitive array [8], a silicon readout circuit [9], and an indium column [10] , InSb substrate [11]. Wherein, the indium antimonide photosensitive array [8] is provided with an antireflection film [6] on the back, and an indium pillar [10] is provided on the front. The other end of the indium column [10] is connected to the silicon readout circuit [9], and the backside of the silicon readout circuit [9] is provided with an indium antimonide substrate [11], and the indium antimonide photosensitive array [8], the silicon A low-temperature glue [7] is arranged in the gap between the readout circuit [9] and the indium column [10]. The indium antimonide infrared focal plane array detector chip of the invention achieves thermal matching with the indium antimonide photosensitive array and the silicon readout circuit, reduces strain, and makes the indium antimonide infrared focal plane array detector have higher reliability. In addition, the invention provides a method for manufacturing the indium antimonide infrared focal plane array detector chip.

Owner:CHINA AIR TO AIR MISSILE INST

Back shining type ZnO base ultraviolet imaging solid state focal plane detection array and its preparation

InactiveCN100561742CFinal product manufactureSemiconductor/solid-state device manufacturingIndium bumpUltraviolet lights

The invention relates to a backlight ZnO-based ultraviolet imaging solid focal plane surveying array and preparation, which on the sapphire (0001)substrate of double-face polishing, uses laser molecular beam to epitaxially grow a MgxZn1-xO(BexZn1-xO) nesa heavily doped with Al, then epitaxially growing a MgyZn1-yO layer without adulterant, sensitive to ultraviolet light. Then a MgzZn1-zO ohm contact epitaxial layer heavily doped with Al is gengerated on the upper surface. An array pixel cell structure is formed by using a photoetching and ICP ion etching method, then uses RF magnetron sputtering to plate a SiO2 passivation layer, based on the etched graph. An Al contact of electrodes etched by reactive ion uses a method of evaporation plated film to form a metallic contact, for rapid annealing activation of an ultraviolet sensitive active layer to form an ohm contact, thus getting a backlight ZnO-based ultraviolet imaging solid focal plane surveying array. The invention and the matched Si-CMOS readout circuit chip are interconnected through indium bumps, which are put on the focal plane of the ultraviolet lens, added with the corresponding image processing, memory circuit and software to form a complete ultraviolet imaging device.

Owner:XI AN JIAOTONG UNIV

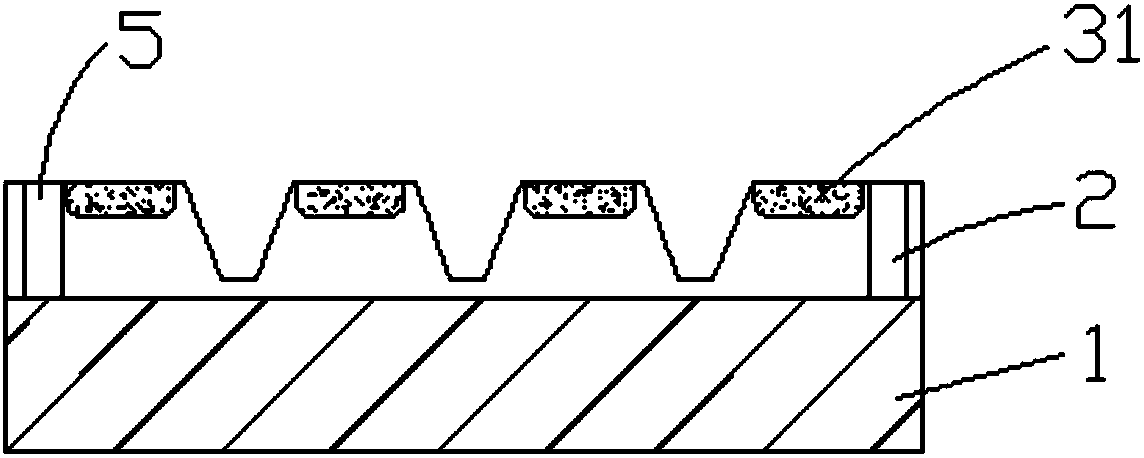

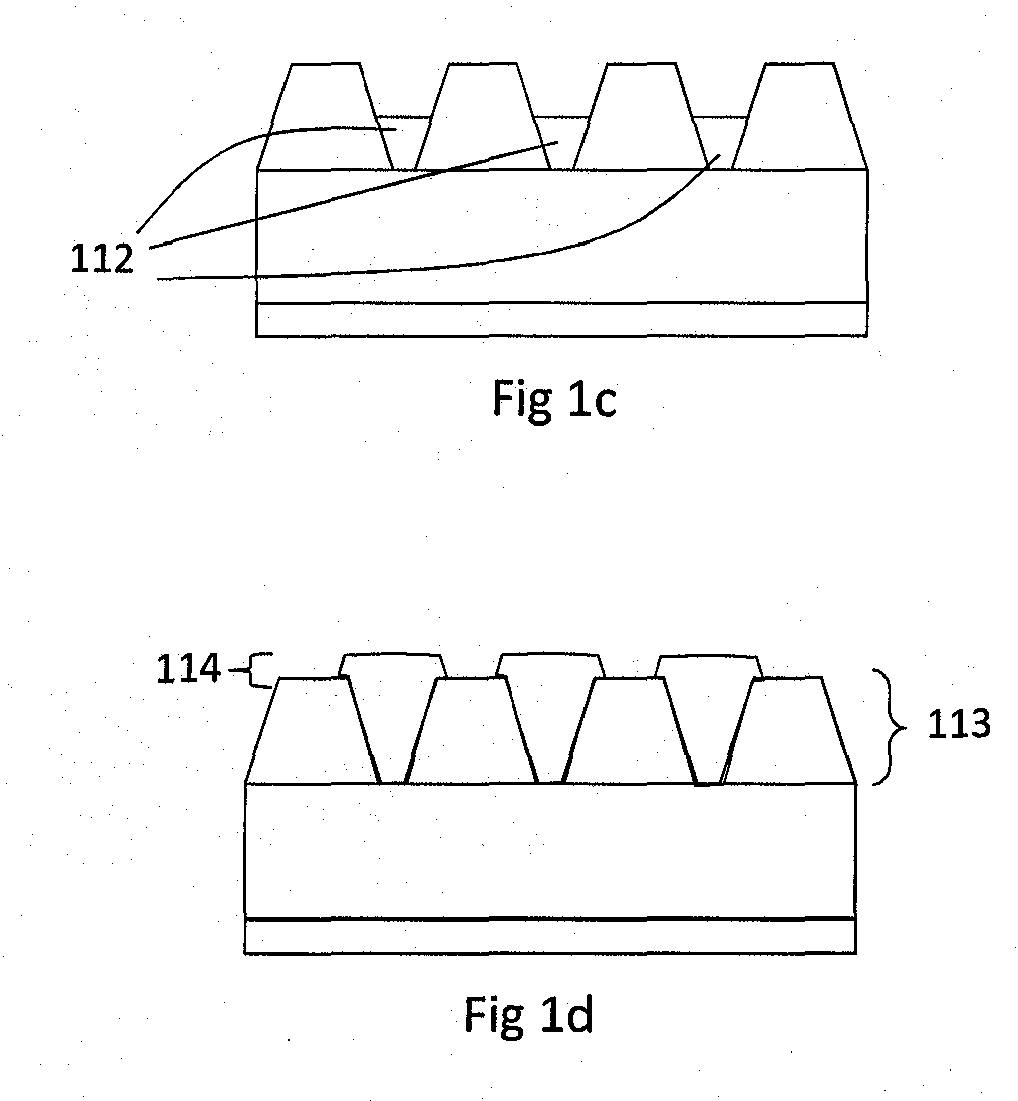

Template Process for Small Pitch Flip-Flop Interconnect Hybridization

InactiveUS20110079894A1Eliminate unevennessHigh densitySemiconductor/solid-state device detailsSolid-state devicesHigh densityImage resolution

A process is disclosed for high density indium bumping of microchips by using an innovative template wafer upon which the bumps are initially fabricated. Once fabricated, these bumps are transferred to the microchip, after which can be hybridized to another microchip. Such a template wafer is reusable, and thus provides an economical way to fabricate indium bumps. Reusability also eliminates nonuniformities in bump shape and size in serial processing of separate microchips, which is not the case for other indium bump fabrication processes. Such a fabrication process provides a way to form relatively tall indium bumps and accomplishes this without the standard thick photoresist liftoff process. The described process can be suitable for bump pitches under 10 microns, and is only limited by the resolution of the photolithography equipment used.

Owner:UNITED STATES OF AMERICA THE AS REPRESENTED BY THE SEC OF THE ARMY

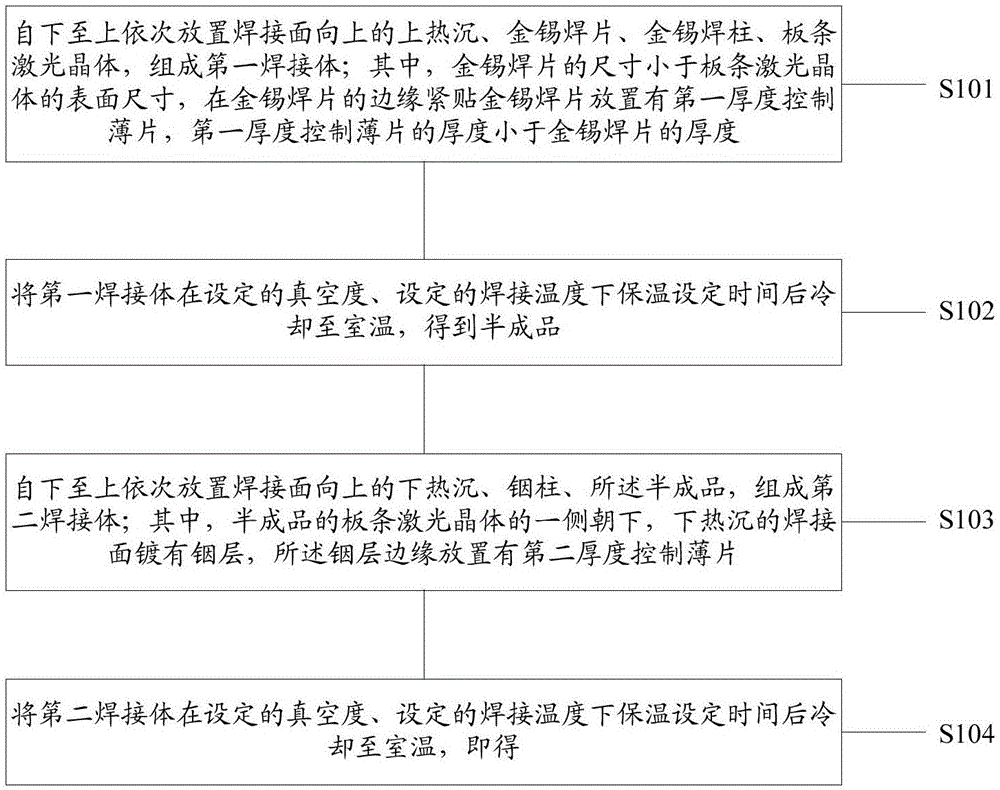

Double-sided packaging method of slab laser crystal

The invention discloses a double-sided packaging method of a slab laser crystal. The method comprises the following steps that an upper heat sink of which the welding surface is upward, a gold and tin welding sheet, a gold and tin welding column and the slab laser crystal are arranged in turn from the bottom to the top so as to from a first welding body, wherein a first thickness control piece is arranged at the edge of the gold and tin welding sheet in a way of being fit with the gold and tin welding sheet; the first welding body is welded so as to obtain a semi-finished product; a lower heat sink of which the welding surface is upward, an indium bump and the semi-finished product are arranged in turn from the bottom to the top so as to from a second welding body, wherein one side of the semi-finished slab laser crystal is downward, an indium layer is plated on the welding surface of the lower heat sink, and a second thickness control piece is arranged at the edge of the indium layer; and the second welding body is welded so as to obtain the slab laser crystal. With application of the technical scheme, the problems that large-size holes and large-area pseudo welding are liable to occur on the welding layer can be solved.

Owner:11TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

Low-damage buried mercury cadmium telluride detector chip

ActiveCN105762209AAvoid photosensitive cell performance degradationSemiconductor devicesIndium bumpMercury cadmium telluride

The invention discloses a low-damage buried mercury cadmium telluride detector chip, the chip comprises a substrate, a mercury cadmium telluride p-type epitaxial thin film, an ion implantation n-type region, a passivation layer, an n-type region electrode, a p-type electrode and an indium bump array, and the invention relates to the technology of photoelectric detector. According to the invention, a structure scheme of p-n node being prepared in a mercury cadmium telluride material etch pit is adopted, so that the position of the node region is far away from the material surface, problems including detector performance reduction, blind pixels increasing and the like caused by defects increasing caused by the acting force of a photosensitive element region form technologies such as cleaning, adhesive removing and the like are avoided. The chip has a great help to reduce blind pixel ratio of a mercury cadmium telluride plane.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Method for preparing large-scale small-pixel indium gallium arsenide focal plane detector

InactiveCN109449238AReduce the risk of conductionAvoid damageFinal product manufactureSemiconductor devicesLithographic artistIndium bump

The invention discloses a method for preparing a large-scale small-pixel indium gallium arsenide focal plane detector. The method comprises the specific steps as follows: 1) depositing a silicon nitride diffusion mask, 2) opening a diffusion window, 3) performing closing-tube diffusion, 4) growing a P electrode, 5) performing rapid thermal annealing, 6) opening an N groove, 7) depositing the silicon nitride passivation film, 8) opening P and N electrode holes, 9) growing a thickened electrode, 10) metallizing, and 11) growing an indium bump. The invention has the advantages that: 1, the preparation process is simpler, and the technique of first growing the P-region electrode is used to reduce the risk of conduction between the P-region electrode and the N-region InP material caused by lithography deviation and over-etching; 2, the inductively coupled plasma chemical vapor deposition (ICPCVD) technology is used to grow the low-temperature silicon nitride passivation film, and the surface passivation layer of the chip is dense, which reduces the damage caused by the process to the surface of the material and improves the surface passivation effect; and 3, the lithographic growth technique is adopted for the metalized region and the indium bump region to reduce the contact resistance of the device.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Method to realize flux free indium bumping

InactiveUS20130273730A1Prevent indium bumpingHigh melting pointSemiconductor/solid-state device detailsSolid-state devicesIndium bumpMaterials science

A method to realize flux free indium bumping process includes several steps including substrate metallization, contact holes opening, underbump metallization (UBM) layer thickening, indium bump preparation and Ag layer coating. The method can be used in the occasion for some special application, e.g., the packaging of the photoelectric chip (with optical lens), MEMS and biological detection chip, where the usage of flux is prohibited.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

AlGaN/PZT ultraviolet/infrared double-waveband detector

InactiveCN100524842CImprove reliabilityReduce false alarm rateSemiconductor devicesIndium bumpHigh energy

The invention discloses an AlGaN / PZT ultraviolet / infrared dual-band detector, which uses the dual-band absorption characteristics of the composite detection material AlGaN / PZT to simultaneously realize the detection of ultraviolet light and infrared light. The incident beam first passes through the AlGaN PIN structure, and the ultraviolet light with higher energy is absorbed and converted into ultraviolet photocurrent; the infrared light with lower energy passes through the sapphire substrate and is absorbed by the PZT ferroelectric film, and the formed photocurrent passes through the indium column. soldered out. The dual-band detector of the present invention makes full use of the detection advantages of different materials and realizes the simultaneous detection of two bands; meanwhile, the detector works at room temperature and is easy to use.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

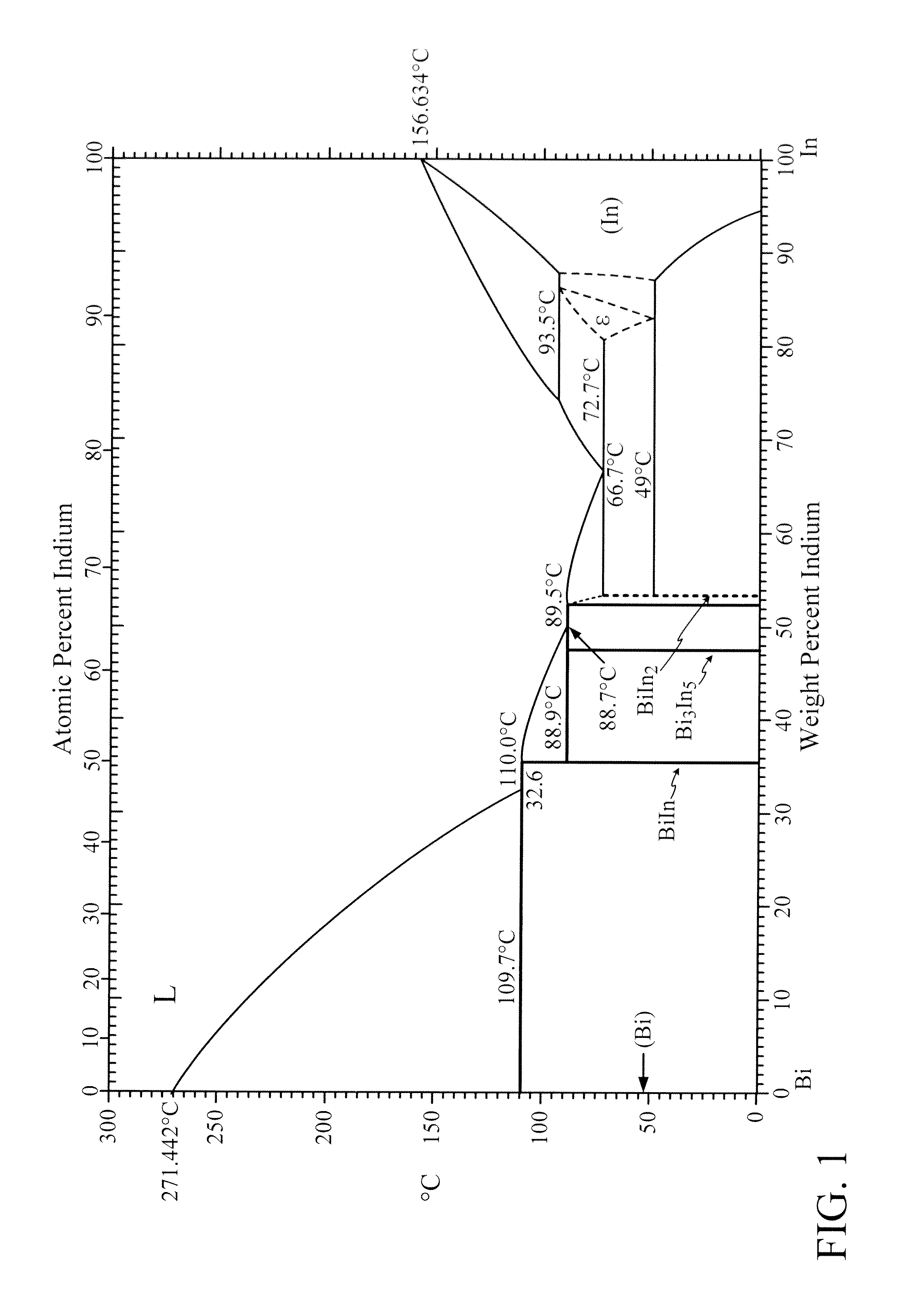

Metal coating for indium bump bonding

ActiveUS20110315429A1Increase temperatureNon-insulated conductorsSoldering apparatusMetal coatingIndium bump

A process of making efficient metal bump bonding with relative low temperature, preferably lower than the melting point of Indium, is described. To obtaining a lower processing temperature (preferred embodiments have a melting point of <100° C.), a metal or alloy layer is deposited on the indium bump surface. Preferably, the material is chosen such that the metal or alloy forms a passivation layer that is more resistant to oxidation than the underlying indium material. The passivation material is also preferably chosen to form a low melting temperature alloy with indium at the indium bump surface. This is typically accomplished by diffusion of the passivation material into the indium to form a diffusion layer alloy. Various metals, including Ga, Bi, Sn, Pb and Cd, that can be used to form a binary to quaternary low melting point alloy with indium. In addition, diffusion of metal such as Sn, Sn—Zn into Ga—In alloy; Sn, Cd, Pb—Sn into Bi—In alloy; Cd, Zn, Pb, Pb—Cd into Sn—In alloy can help adjust the melting point of the alloy.

Owner:INDIUM CORPORATION

Indium features on multi-contact chips

InactiveUS20040195516A1Improve leakage currentImprove mechanical stabilitySolid-state devicesMaterial analysis by optical meansIndium bumpSemiconductor detector

A device comprising a pixilated semiconductor detector or VLSI chip having plurality of individual indium bumps arrayed on a surface of the detector, wherein the indium bumps are in electrical contact with the surface and are situated in defined locations on the surface is provided. Additionally, a hybrid detector comprising a pixilated detector in electrical contact with a VLSI chip, wherein electrical contacts formed from indium metal are made between the pixels of the semiconductor and regions on the VLSI chip corresponding thereto is provided. In another embodiment, a method of forming electrical contacts on a pixilated detector comprising the steps of constraining a shadow mask having an array of holes in predetermined locations above a surface on the detector, aligning the mask above the detector, and evaporating indium metal under vacuum through holes in the mask onto the surface of the detector to form the contacts is described.

Owner:CALIFORNIA INST OF TECH

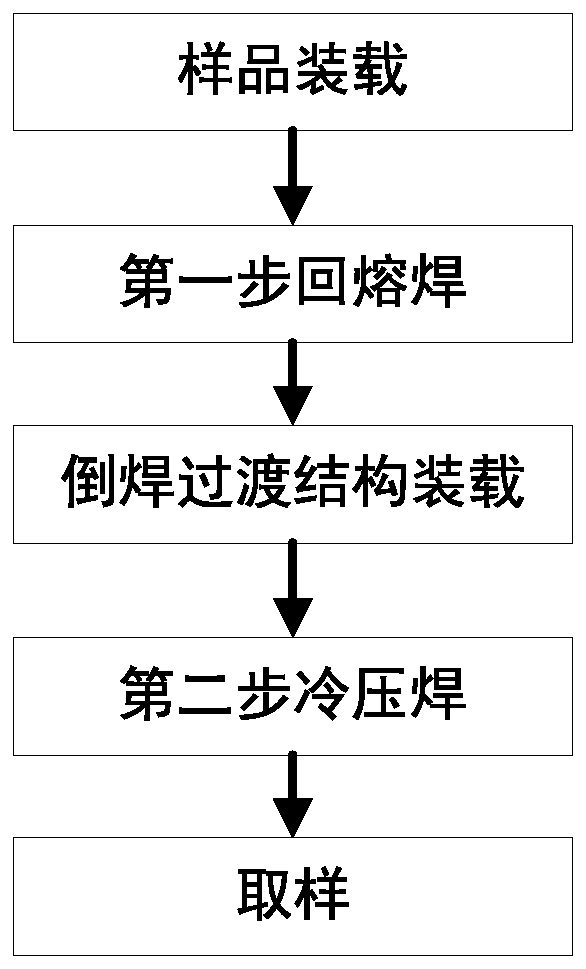

Two-step flip chip bonding technique of focal-plane detector

The invention discloses a two-step flip chip bonding technique of a focal-plane detector. The two-step flip chip bonding technique of the focal-plane detector comprises the steps that a photosensitivechip and a reading circuit are interconnected preliminarily through a meltback welding technology; then a high-flatness material is adopted as a flip chip bonding transitional structure; and throughsecondary cold pressure welding of the flip chip bonding transitional structure and a preliminarily-interconnected focal-plane module, the photosensitive chip and the reading circuit are completely interconnected. According to the two-step flip chip bonding technique of the focal-plane detector, the meltback welding technology and the cold pressure welding technology are organically integrated; full play is given to advantages of the two technologies; flip chip bonding random shifting is reduced, and meanwhile, the problem of dis-interconnection caused by chip flatness and the indium bump quality is solved; thus the connectivity rate and the flip chip bonding finished product rate of a large-scale high-density focal-plane detector are effectively improved; and the technique is not limitedby array scales or pixel sizes and can be conveniently applied to various area array devices.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

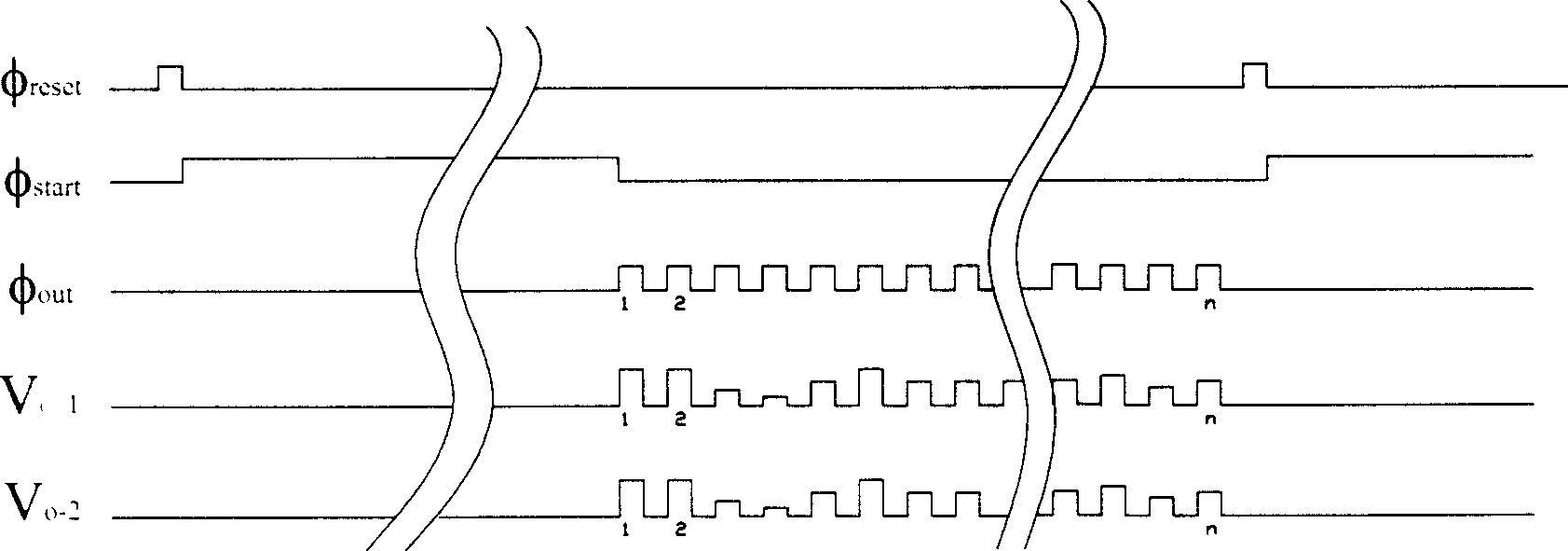

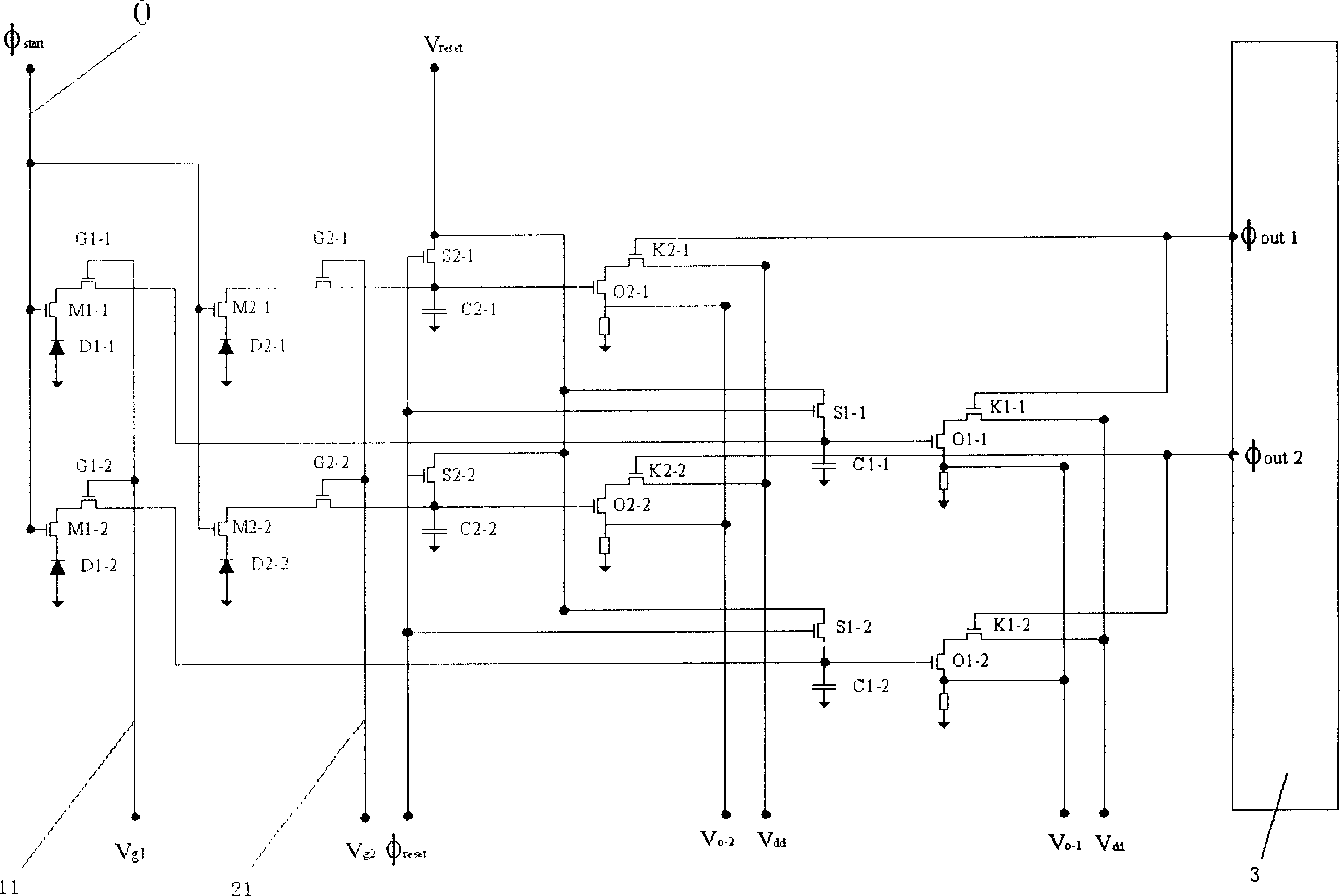

Reading circuit structure of double-colour line-array infrared focus plane detector

InactiveCN1210548CCompact structureEasy to usePhotometry electrical circuitsSemiconductor devicesShift registerCapacitance

A two-color linear column infrared focal plane detector readout circuit structure, including a band-one input stage, a band-two input stage, a shift register and an external lead key pressure point working together with the two input stages, and its characteristic is that it consists of two A series of switching tubes, photosensitive elements, gate control tubes, integral capacitors, reset switches and source limit followers are connected to form, and the photosensitive element array and each input end of the readout circuit are electrically connected through the interconnection of indium columns. The circuit structure of the present invention is compact, the working points of the photosensitive element array of the two bands, and the corresponding integral capacitors can be set independently, and the response signals of the two bands are output respectively, and the readout circuit made with this structure has a modular form, which can Realize the seamless splicing of multiple modules to form a two-color long-line infrared focal plane detector.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

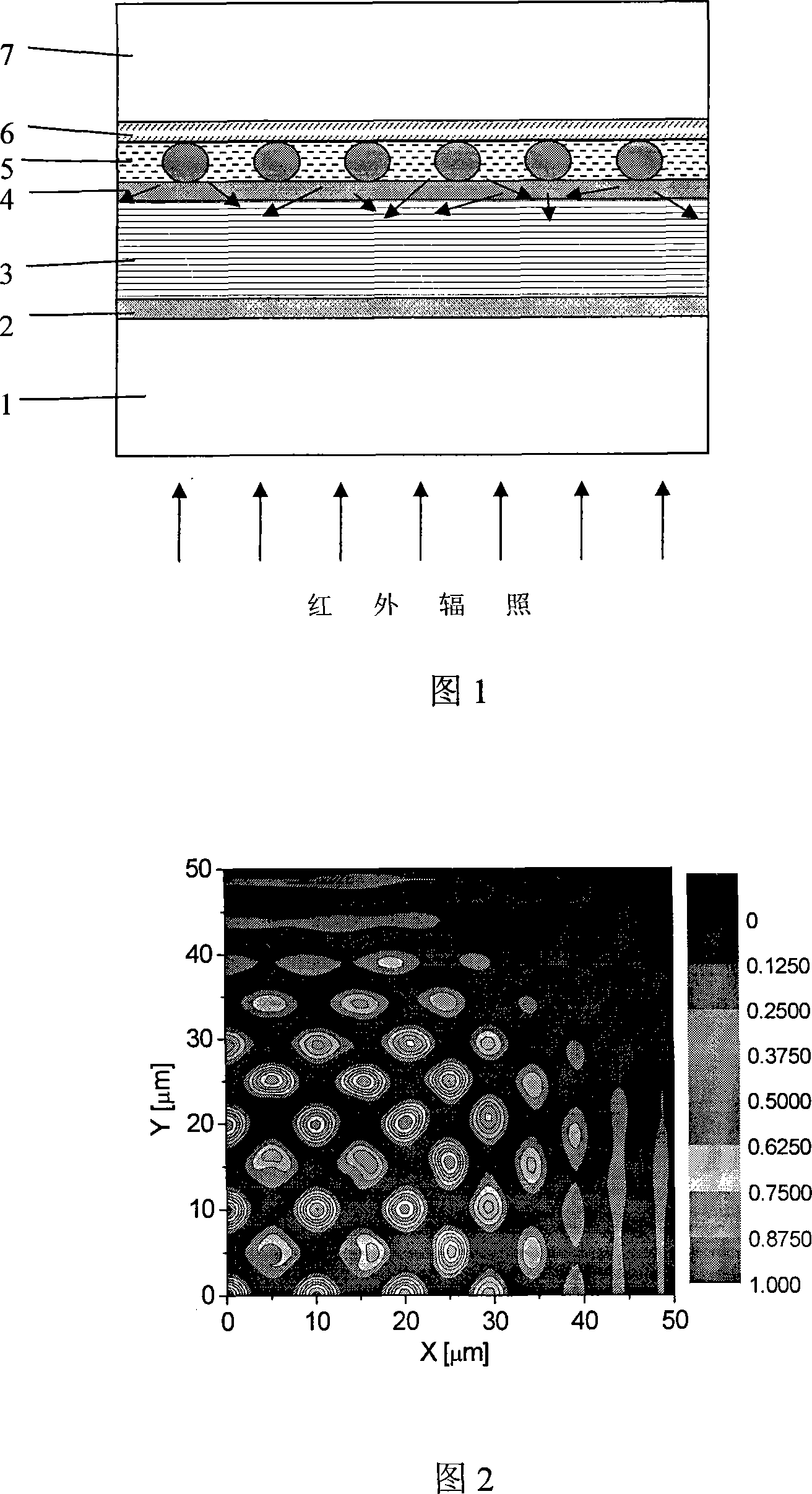

Quanta trap infrared detector for multi-folded light dispersion coupling

InactiveCN101188234AImprove coupling efficiencyReduce processing difficultySemiconductor/solid-state device detailsSolid-state devicesLight dispersionGrating

The invention discloses a quantum well infrared detector of multiple light scattering coupling. The detector comprises a substrate layer, a lower electrode layer which grows successively layer by layer, a multiple quantum well layer with 50 periods and an upper electrode layer. An array layer made of metallic balls which are immersed in organic adhesive or balls which are coated with metal is provided on the upper electrode layer. The array layer is provided with a metal contacting layer, and the metal contacting layer is provided with a readout circuit by means of flip-chip bonding interconnection to realize the readout detection signals. The invention has the advantages that: firstly, the metal ball array replaces the traditional grating. The electric rector which can be absorbed with transition by a quantum well belt is produced by multiple light coupling among the metallic balls. The electric rector parallels to the component of the quantum well layer, so the coupling between the normal incidence lights and the quantum well is realized. Secondly, the metallic ball array replaces the traditional indium column of flip-chip bonding interconnection to form an anisotropic conducting layer, so the conductive function is realized. Because of the advantages, on one hand, the coupling efficiency of normal incidence lights is improved; on the other hand, the deposition of indium bump is saved, and the flip-chip bonding process is simplified.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com