Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

76results about How to "Reduce on-state voltage drop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

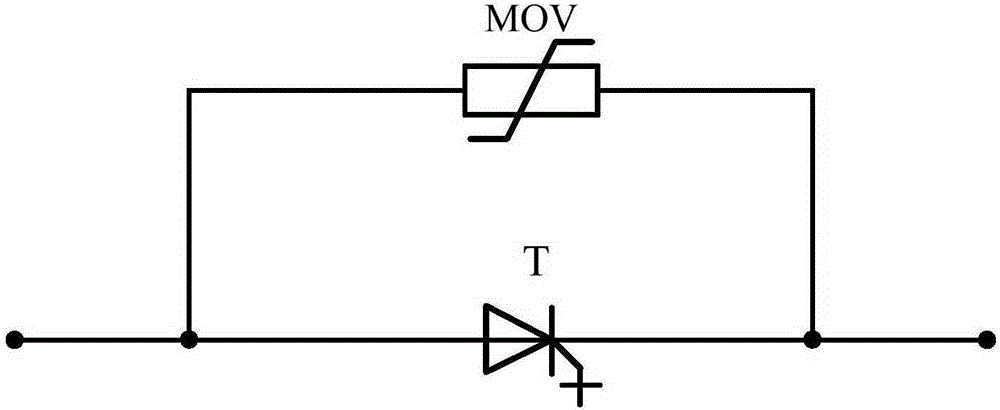

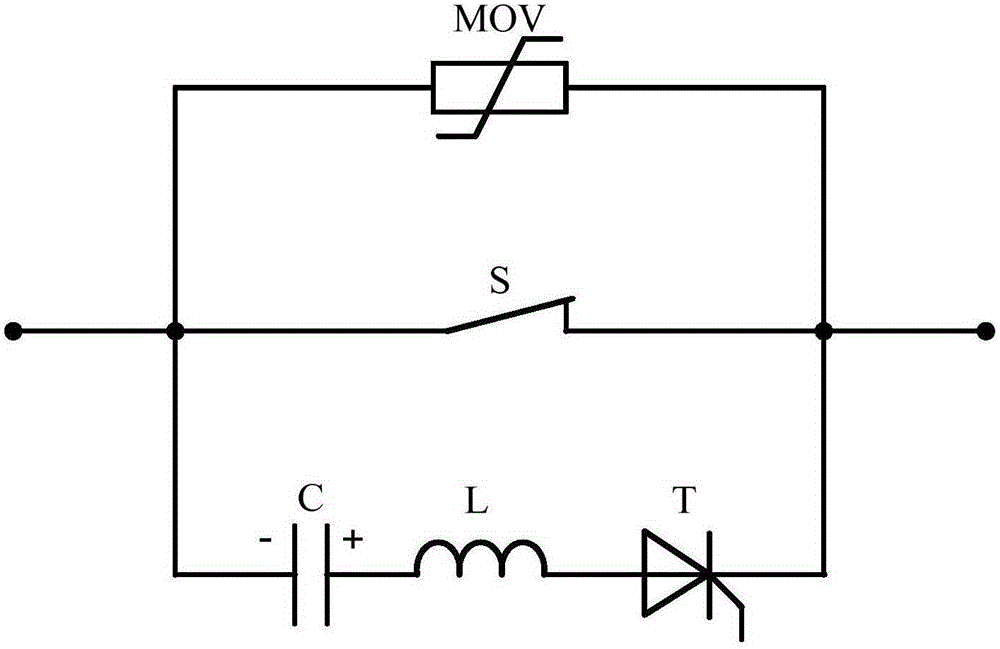

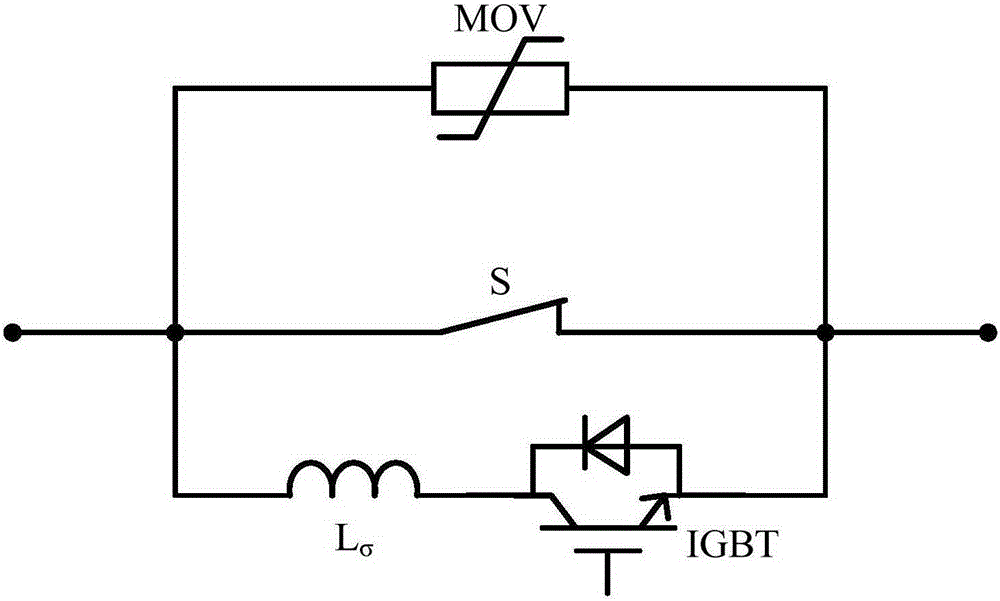

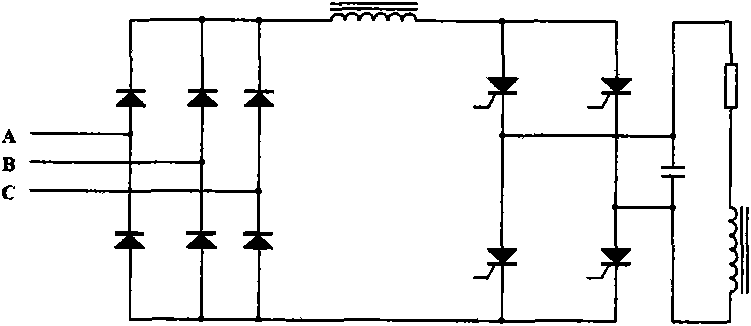

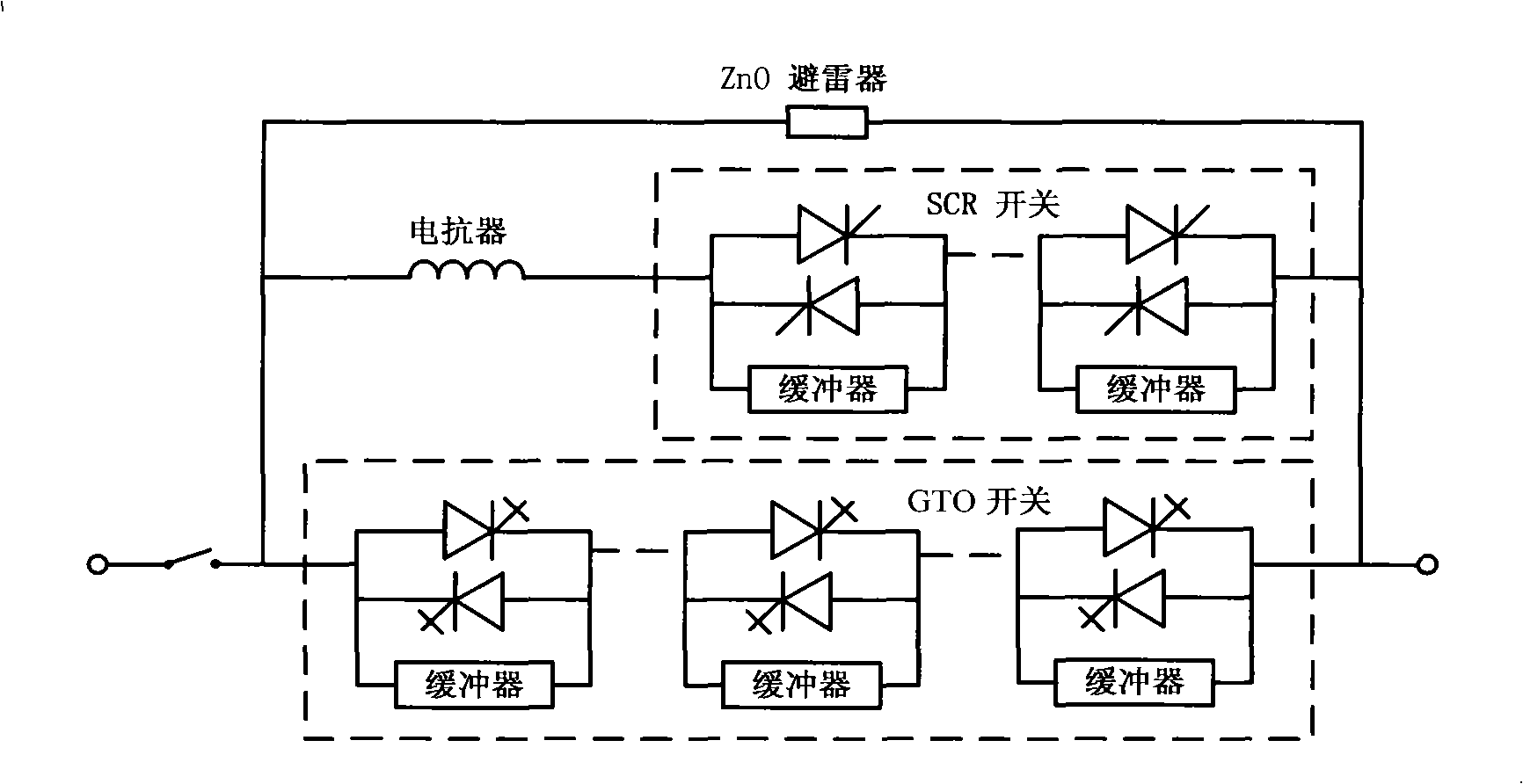

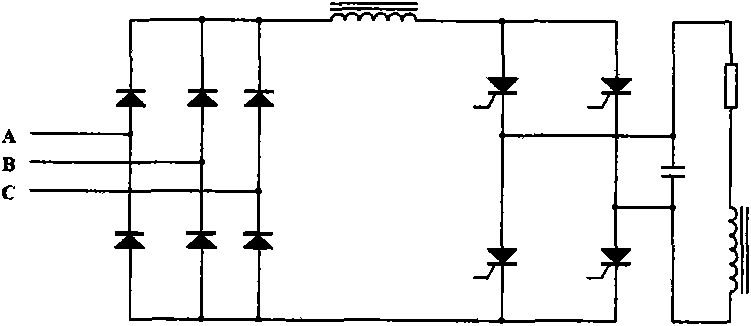

Bidirectional combined type direct current breaker and control method thereof

ActiveCN105281289AReduce on-state voltage dropFast current transferEmergency protective arrangements for automatic disconnectionVaristorThyratron

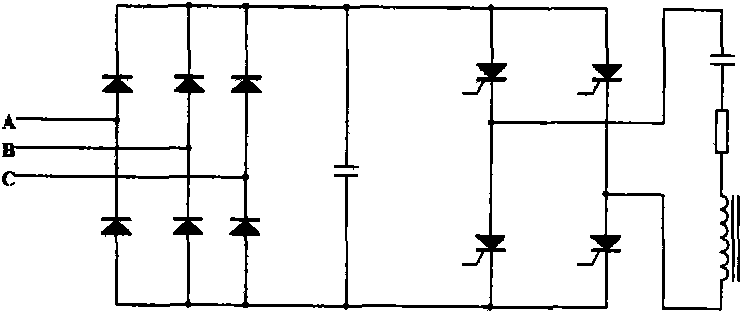

The present invention discloses a bidirectional combined type direct current breaker and a control method thereof. The bidirectional combined type direct current breaker comprises a principal current circuit, a no-voltage circuit, a null-current circuit and an energy absorption circuit, wherein the principal current circuit, the no-voltage circuit, the null-current circuit and the energy absorption circuit are in parallel. The principal current circuit employs a mechanical switch; the no-voltage circuit employs a bi-directional semiconductor switch formed through anti-parallel thyristors; the null-current circuit is a bi-directional pulse current circuit formed by a precharge capacitor, an inductor and a thyristor bridge; and the energy absorption circuit employs a metal-oxide varistor. The present invention further discloses a control method of the bidirectional combined type direct current breaker. According to the invention, the no-voltage circuit employs thyristors so that the on-state voltage drop is small and the current commutation speed is fast, and a mechanical switch has sufficient dielectric recovery time and post arc dielectric recovery is reliable; a null-current circuit is adopted to realize quick shutdown of the thyristors, and the breaking capacity of a breaker is great; and two working modes are convenient to be realized, and the working capability of the breaker is easy to be improved. The bidirectional combined type direct current breaker and the control method thereof are applicable to the fault protection of a bi-directional direct current power system, with small loss of long-term flow passage, rapid breaking motion, high work reliability and the like.

Owner:中国船舶重工集团公司第七一二研究所

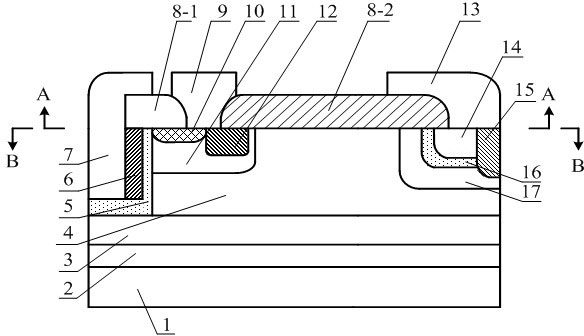

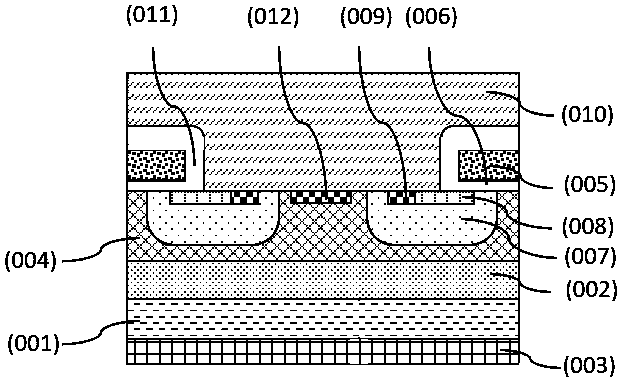

SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

ActiveCN102157550AReduce adverse effectsImprove vertical pressure resistanceSemiconductor devicesMetal electrodesConductivity modulation

The invention relates to an SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with a p buried layer and a longitudinal channel. The existing products restrict the improvement of the device structures and the electrical properties. The device unit comprises a p-type semiconductor substrate, a buried oxide layer and a p buried layer region in sequence, wherein a metal gate, an n-type heavily doped polysilicon gate, a gate oxide layer and an n-type lightly doped drift region are arranged at the top of the p buried layer region side by side in sequence; a first p-type well region and an n-type buffer region are respectively embedded at the two sides at the top of the n-type lightly doped drift region; an n-type cathode region and a first p well ohmic contact region are embedded at the top of the first p-type well region; a second p-type well region and an anode short-circuit point region are embedded at the top of the n-type buffer region; a second p well ohmic contact region is embedded at the top of the second p-type well region; and a first field oxide layer, a second field oxide layer, an anode metal electrode and a cathode metal electrode are arranged at the top of the device unit. The device unit has the beneficial effects of reducing the spreading resistance, improving the conductivity modulation effect of the drift region, reducing the on-state power consumption and obviously improving the thermal property of the device.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

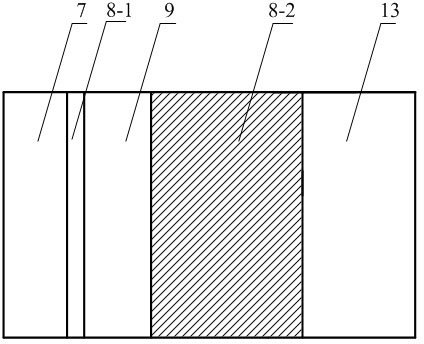

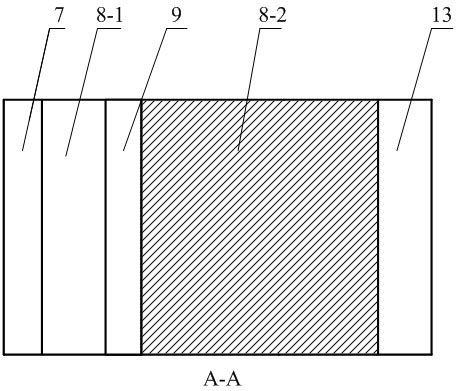

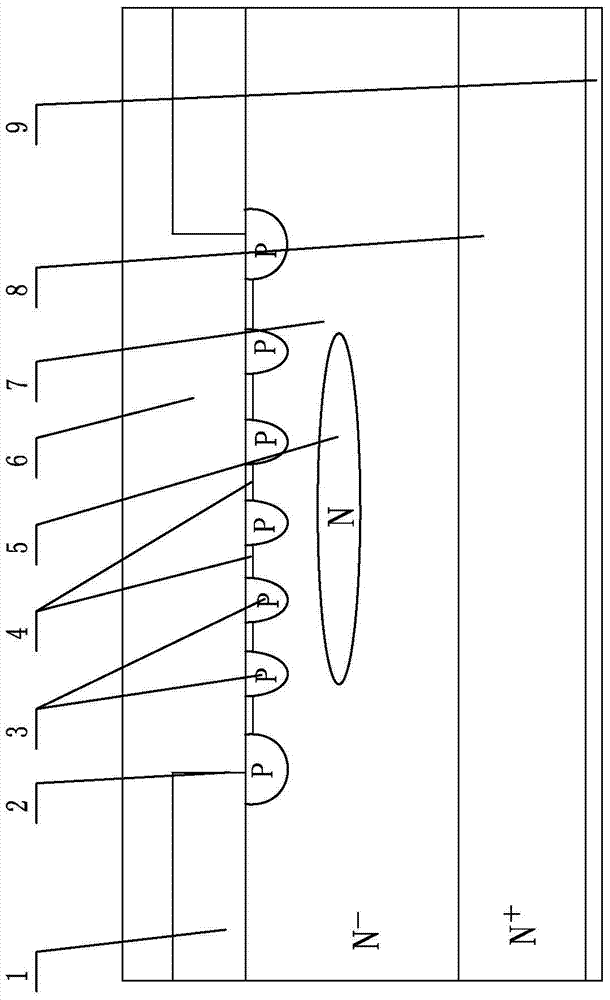

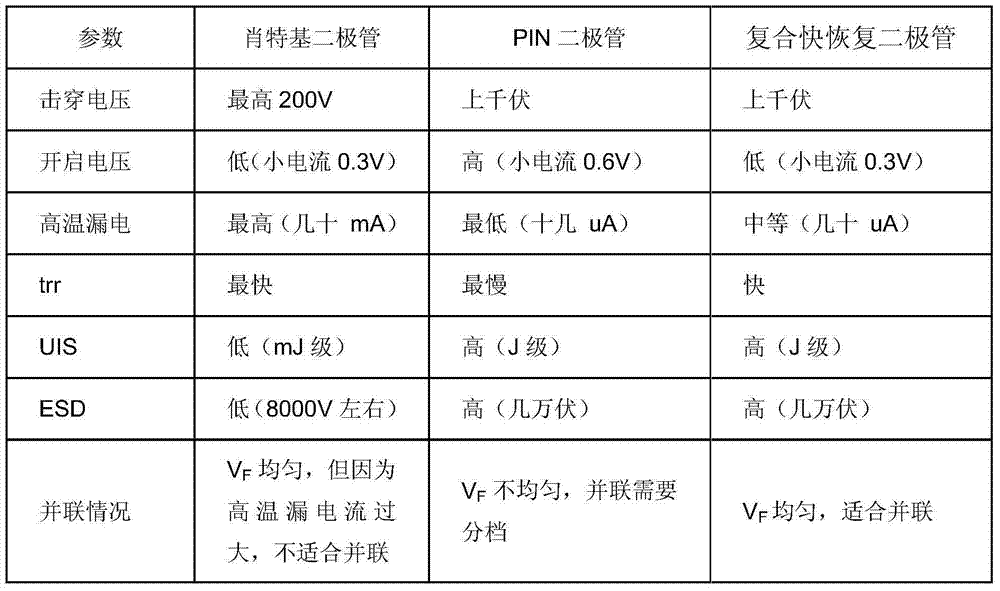

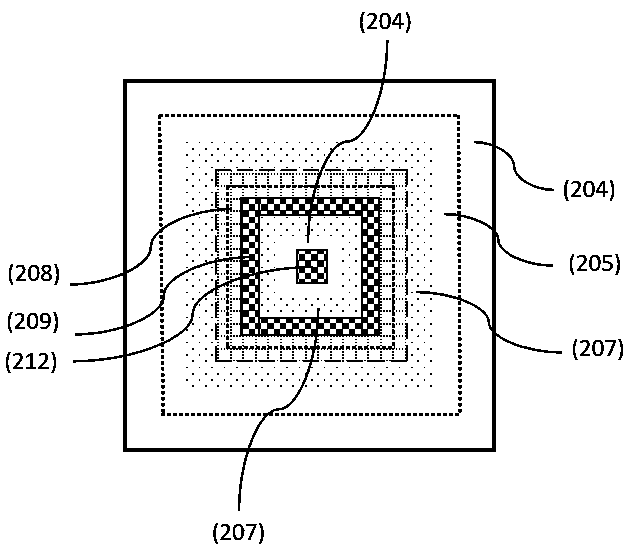

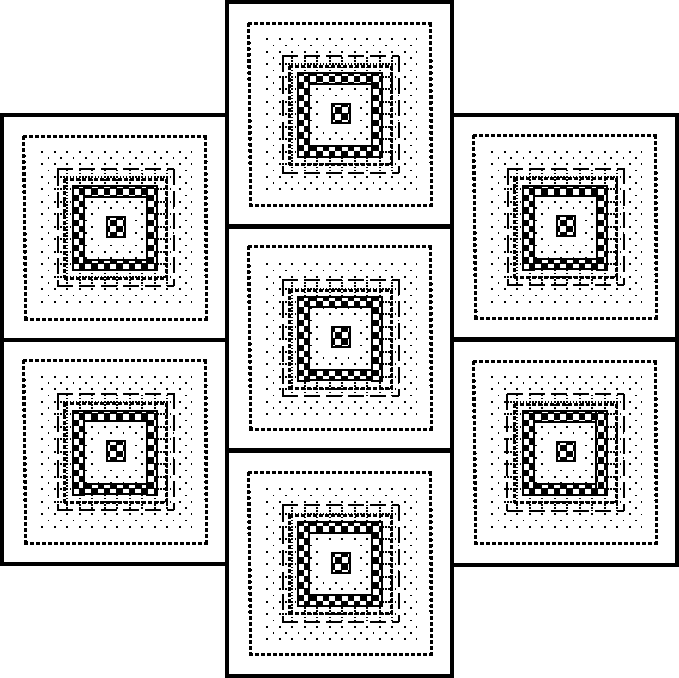

Composite fast recovery diode and preparation method thereof

ActiveCN104716038AImproved Forward Voltage Drop ConsistencyImprove consistencySemiconductor/solid-state device manufacturingSemiconductor devicesImpurity ionsForward voltage

The invention relates to a preparation method for a composite fast recovery diode. The method comprises the steps that 1, an active area is subjected to oxidization and photoetching; 2, N-typed impurity ions are injected; 3, N knot pushing is conducted; 4, P-area injection windows are formed; 5, P-typed impurity ions are injected; 6, knot pushing is conducted; 7, Schottky areas are formed; 8, metal film deposition is conducted; 9, back reduction is conducted; 10, back metallization is conducted to obtain the composite fast recovery diode. The composite fast recovery diode has the advantages that the forward voltage drop consistence is good, the avalanche tolerance capacity is high and the recovery property is good.

Owner:MACMIC SCIENCE & TECHNOLOGY CO LTD

Deep groove side oxygen controlled planar isolated gate bipolar transistor

InactiveCN102184949AImprove breakdown voltageSoft reverse recovery characteristicsSemiconductor devicesParasitic bipolar transistorPeak value

The invention discloses a deep groove side oxygen controlled planar isolated gate bipolar transistor, belonging to the technical field of semiconductor power devices. A deep groove body electrode structure consisting of a P-type floating layer, a deep groove silicon dioxide oxide layer and a deep groove body electrode is prevented from being introduced to a planar isolated gate bipolar transistor in the conventional electric field, the introduction of an extra electric field is realized, and transverse consumption of an N-pillar is facilitated, so that the doping concentration of the N-pillar can be increased under the same withstand voltage, and the on-state voltage drop during positive break-over is lowered. A reverse electric field opposite to the original electric filed can be generated on the top of a device by applying a certain positive voltage to the body electrode, so that the original peak-value electric field is lowered and the breakdown voltage of the device is raised. By adopting the P-type floating layer in the deep groove body electrode structure, electric field concentration at the bottom of the deep groove can be prevented effectively. During positive break-over of the device, an electron accumulation layer can be formed at one side of a thick oxide layer by optimizing the positive voltage at one side of the body electrode, so that a low-impedance channel is provided for electric current.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

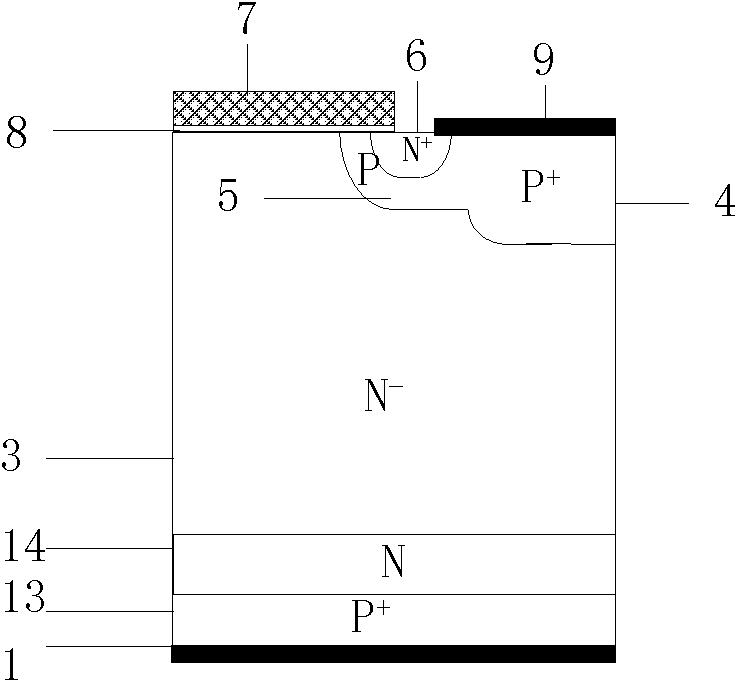

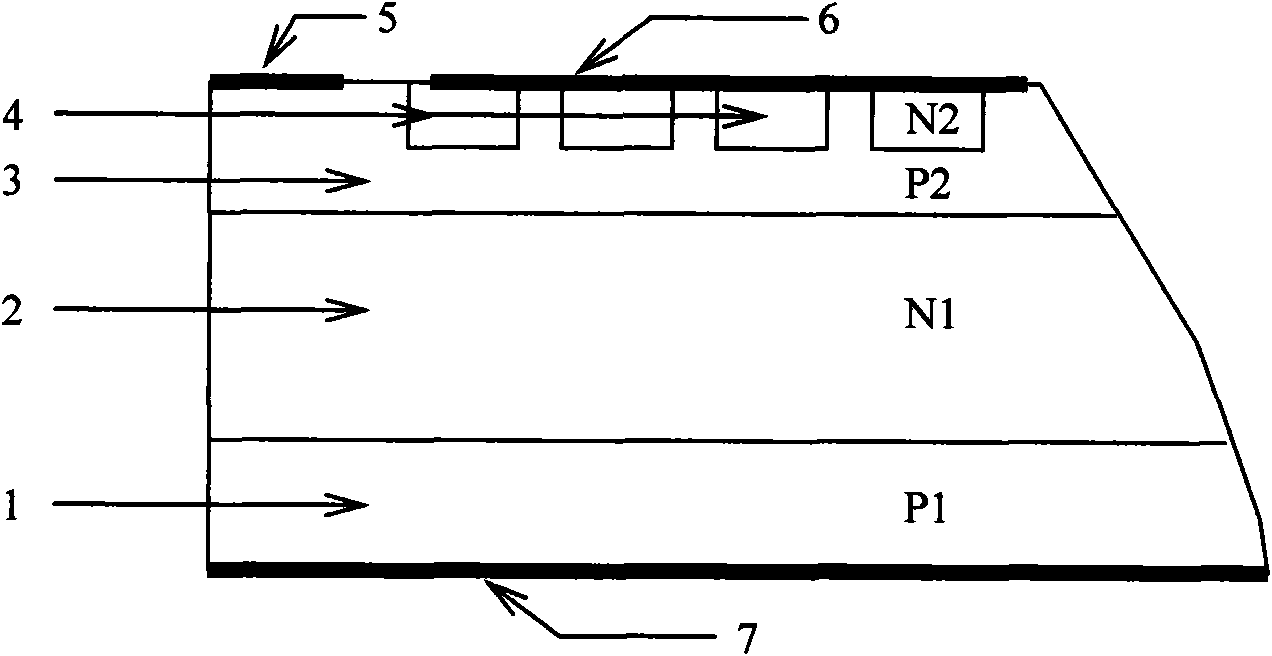

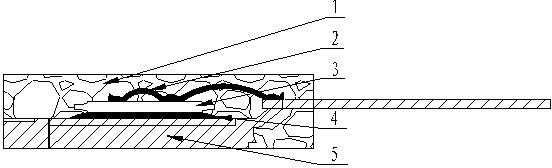

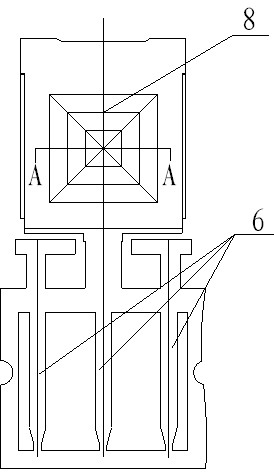

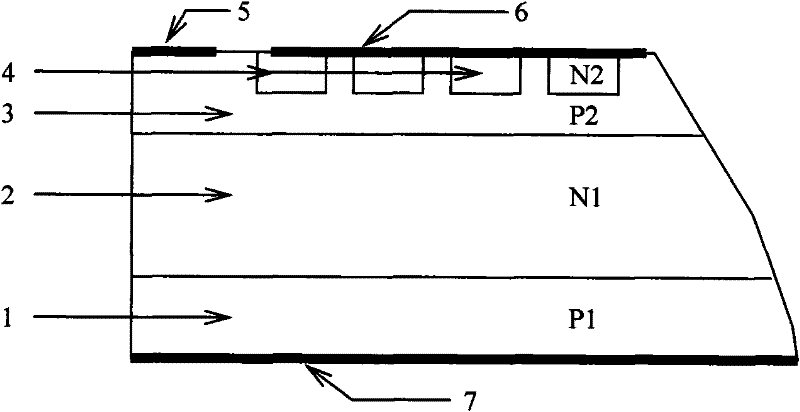

Asymmetrical fast thyristor

ActiveCN101931001AReduce on-state voltage dropReduce stored chargeThyristorHigh concentrationPower semiconductor device

The invention provides an asymmetrical fast thyristor, belonging to the technical field of a power semiconductor device, and mainly aiming at solving the problems of the large pressure drop, the wore dynamic characteristic and the like of the existing fast thyristor when being applied to series inversion. The asymmetrical fast thyristor is mainly characterized by comprising a thyristor shell and a semiconductor chip which is packed in the thyristor shell and has a PNPN four-layer and three-end structure; the junction depth of a P1 anode area 1 of the semiconductor chip is 20-70 of that of a cathode end P2 area 3; and the P1 anode area 1 is internally provided with a P+ high-concentration area 8. When being applied to the series inversion, the asymmetrical fast thyristor can obviously reduce the on-state pressure drop to improve the on-state capability and the work reliability, has the characteristics of being capable of preferably optimizing the inner structure, reducing the large-injection stored electric charge, and improving the resumed softness, and can be applied to a large-power series inverted power supply device.

Owner:HUBEI TECH SEMICON

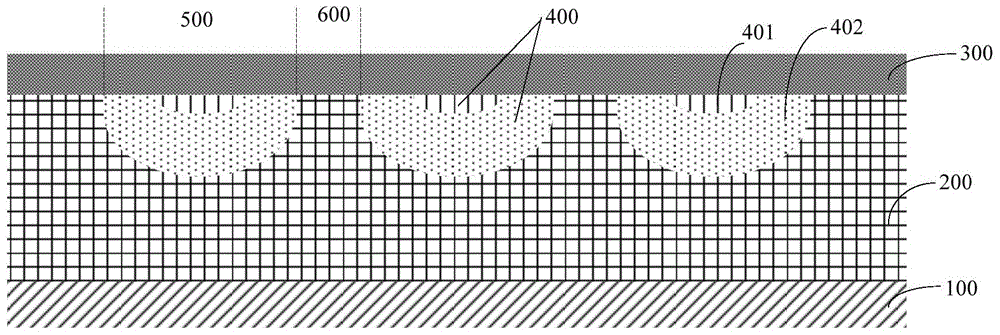

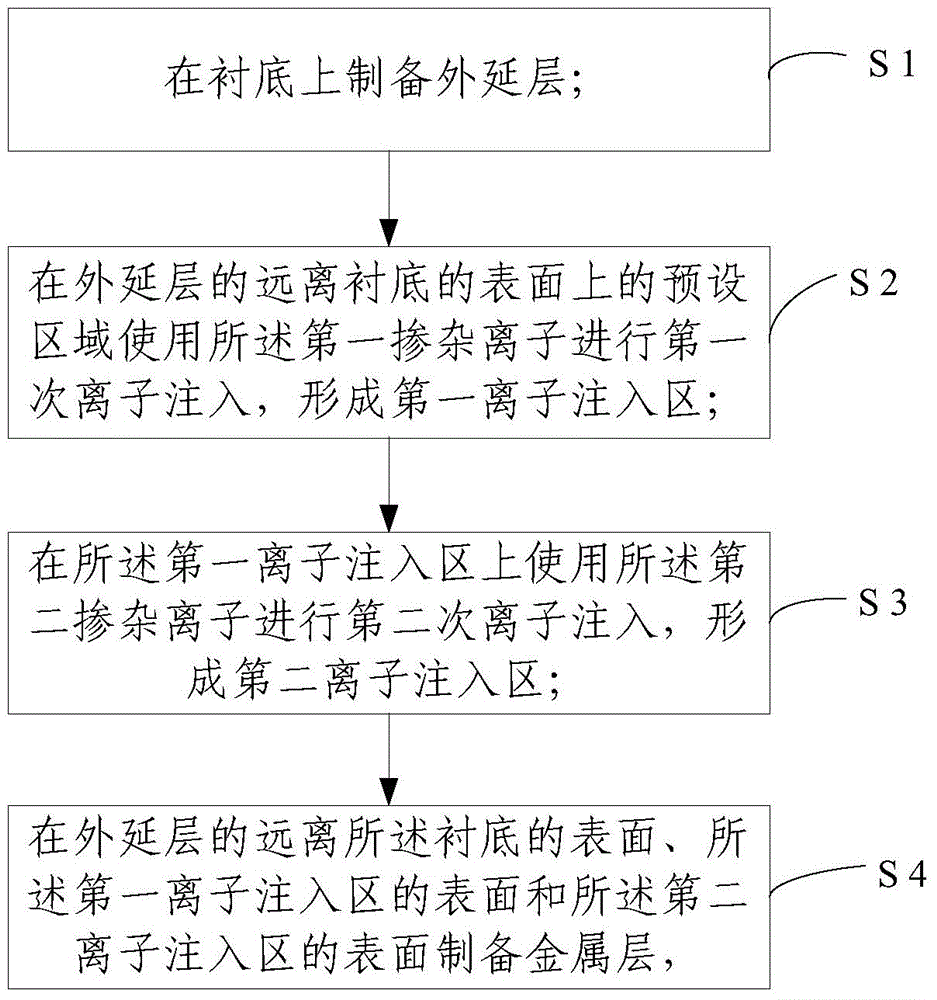

MPS diode and manufacturing method therefor

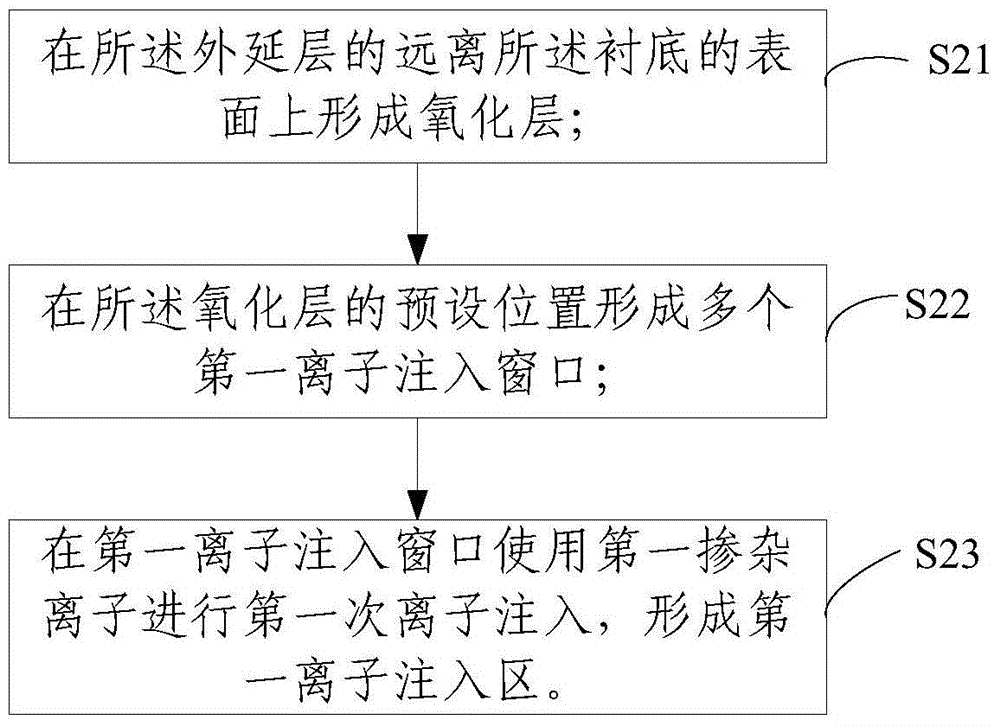

InactiveCN106298774AReduce surface damageReduce on-state voltage dropSolid-state devicesSemiconductor/solid-state device manufacturingVoltage dropIon implantation

The invention relates to an MPS diode and a manufacturing method therefor. The MPS diode comprises a substrate, and an epitaxial layer and a metal layer which are arranged on the substrate in sequence, wherein the diode also comprises multiple ion implantation regions which are embedded in the epitaxial layer and are in contact with the metal layer; the ion implantation regions are formed by implanting doped ions in the epitaxial layer; each ion implantation region comprises a first ion implantation region and a second ion implantation region; the second ion implantation region is embedded in the first ion implantation region; and in addition, the upper surface of the first ion implantation region and the upper surface of the second ion implantation region are both in contact with the metal layer. According to the MPS diode and the manufacturing method therefor, through the multiple times of ion implantation, the leakage current of a device is lowered; the on-state voltage drop of the device is lowered; and the performance of the device is improved.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

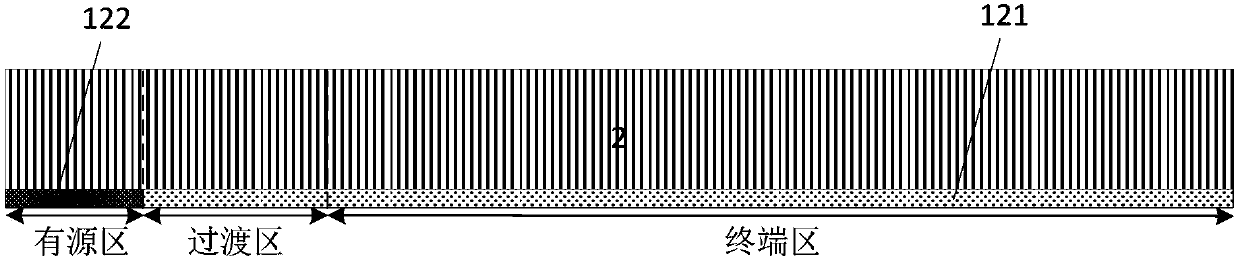

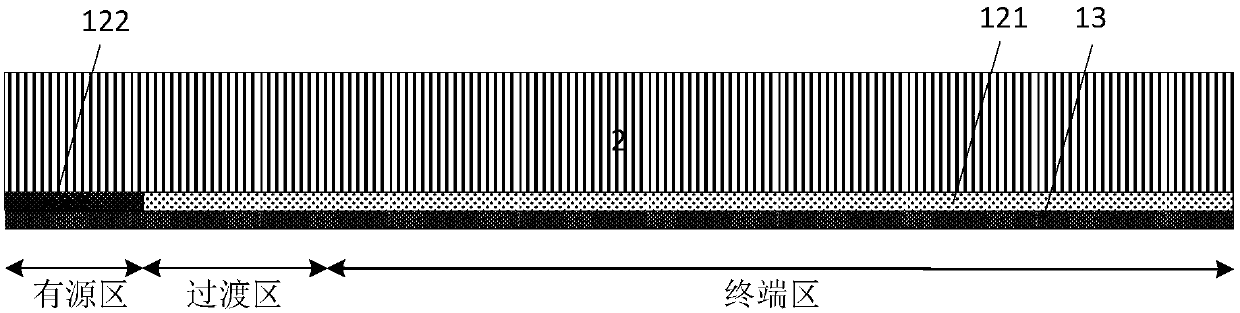

Back surface structure of IGBT chip, IGBT chip structure and preparation method thereof

ActiveCN109671771AImprove reliabilityAvoid overheatingTransistorSemiconductor/solid-state device manufacturingState of artOhmic contact

The invention discloses a back surface structure of an IGBT chip, an IGBT chip structure and a preparation method thereof. The back surface structure comprises: a buffer layer and a doped layer, the doped layer is formed by ion implantation in the buffer layer; the doped layer of a terminal region and a transition region is subjected to high-temperature annealing treatment; a doped layer of the active region is subjected to twice high-temperature annealing treatment to achieve different hole injection efficiencies of the active region and the terminal region so as to improve the current concentration problem in the IGBT transition region and improve the reliability. Compared to the prior art of a treatment mode that a photolithography process is used to implant different doses of doping ions on the back side of the active region and the terminal region to achieve different injection efficiencies of the back surface collectors of the active region and the terminal region, the back surface structure of the IGBT chip, the IGBT chip structure and the preparation method thereof only employ the annealing process to omit the photolithography process so as to save the manufacturing cost. An inert ion defect layer is implanted in the buffer layer to form a defect layer, so that the IGBT back surface collector can adopt a higher doping concentration, and the IGBT back surface and the back surface metal easily form good ohmic contact, thereby reducing the IGBT on-state voltage drop.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

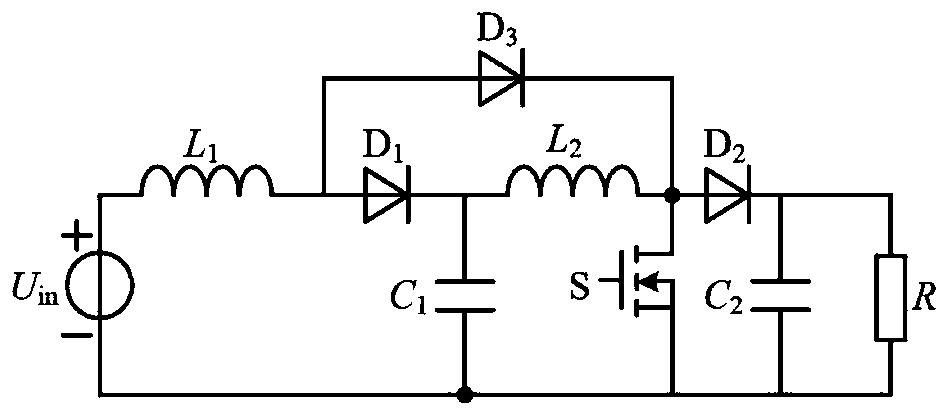

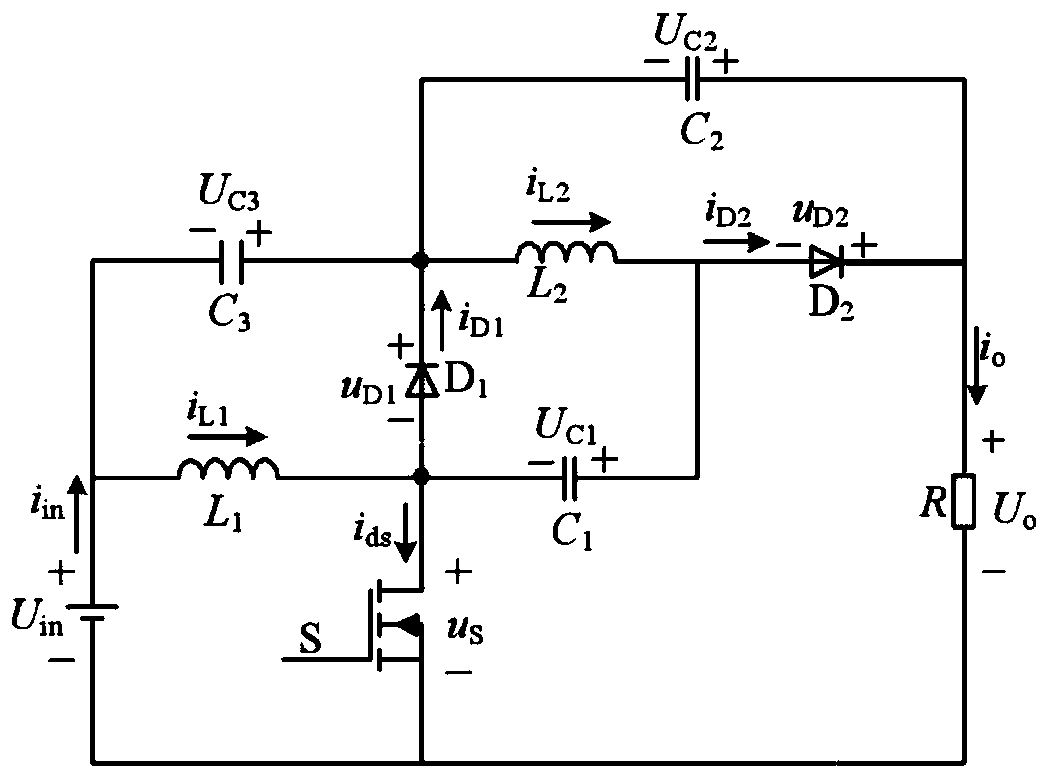

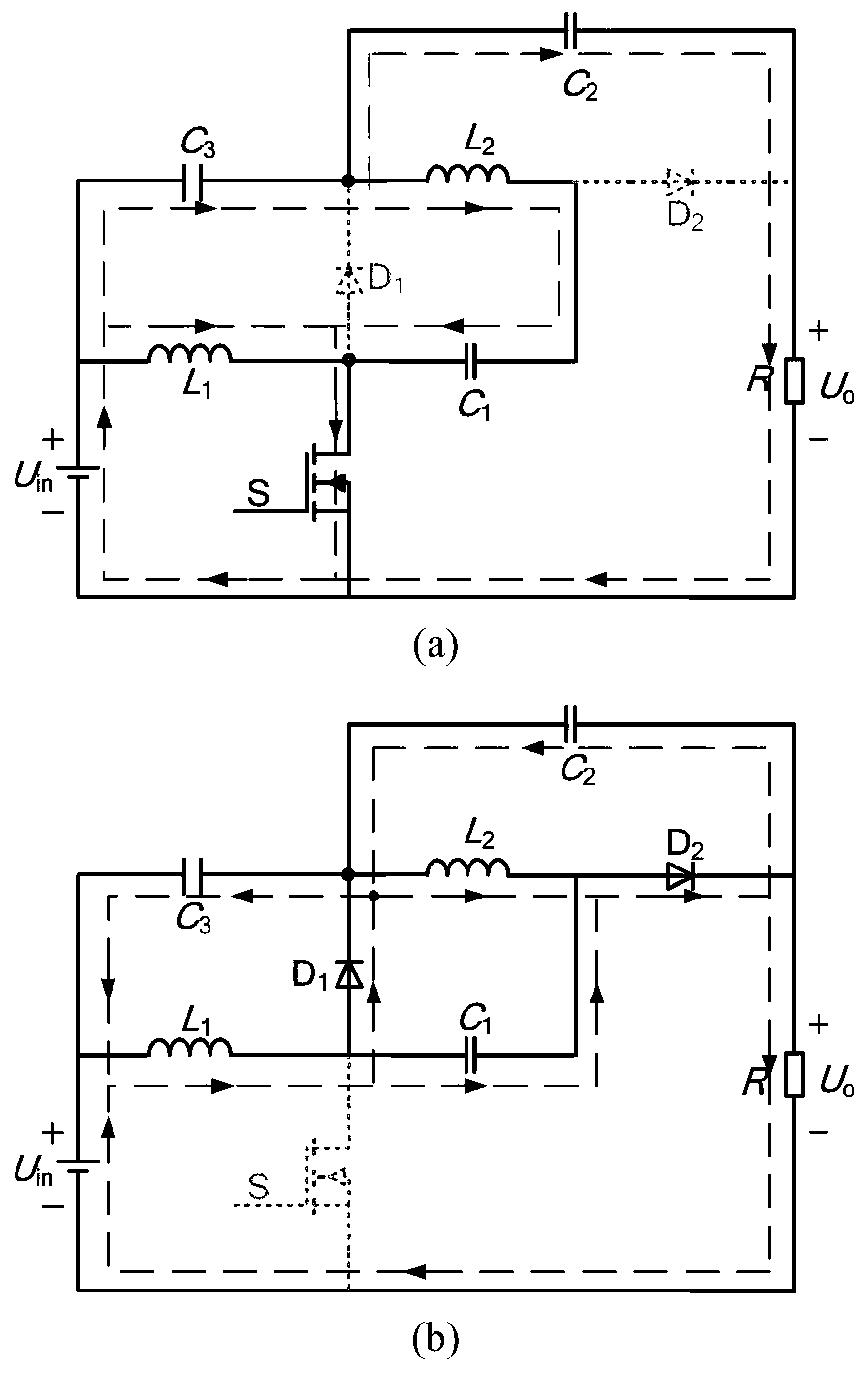

High-gain Boost converter

ActiveCN110649805AReduce voltage stressLow costEfficient power electronics conversionApparatus without intermediate ac conversionCapacitanceControl theory

The invention discloses a high-gain Boost converter which comprises a direct-current voltage source, a switching tube, a first diode, a second diode, a first inductor, a second inductor, a first capacitor, a second capacitor, a third capacitor and a load. The voltage gain of the high-gain Boost converter is G=(1+D) / (1-D), and higher voltage gain can be achieved under the condition of lower duty ratio. The voltage stresses of all power devices are (Uin+Uo) / 2, and the voltage stresses of all the capacitors are (Uo-Uin) / 2. Compared with a traditional quadratic Boost converter, the voltage stresses of the switching tube, part of the diodes and the capacitors of the high-gain Boost converter of the invention are reduced to a certain extent under the same working condition, the number of diodesis reduced by one, the system loss, the device model selection difficulty and the device model selection cost are reduced, and the conversion efficiency is improved. The high-gain Boost converter is suitable for application occasions requiring medium boosting capability (the voltage gain G is less than or equal to 9), such as a single-phase UPS and a direct-current micro-grid.

Owner:NANTONG UNIVERSITY

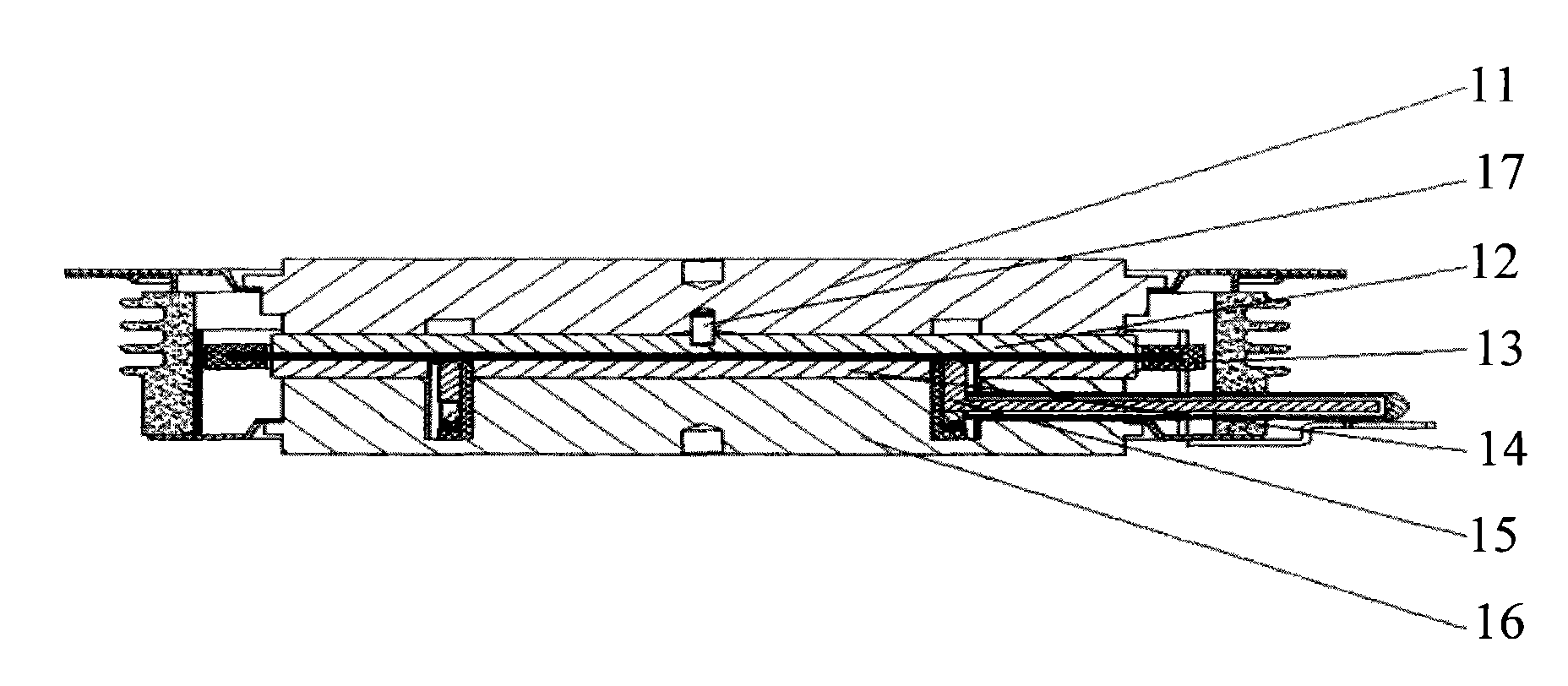

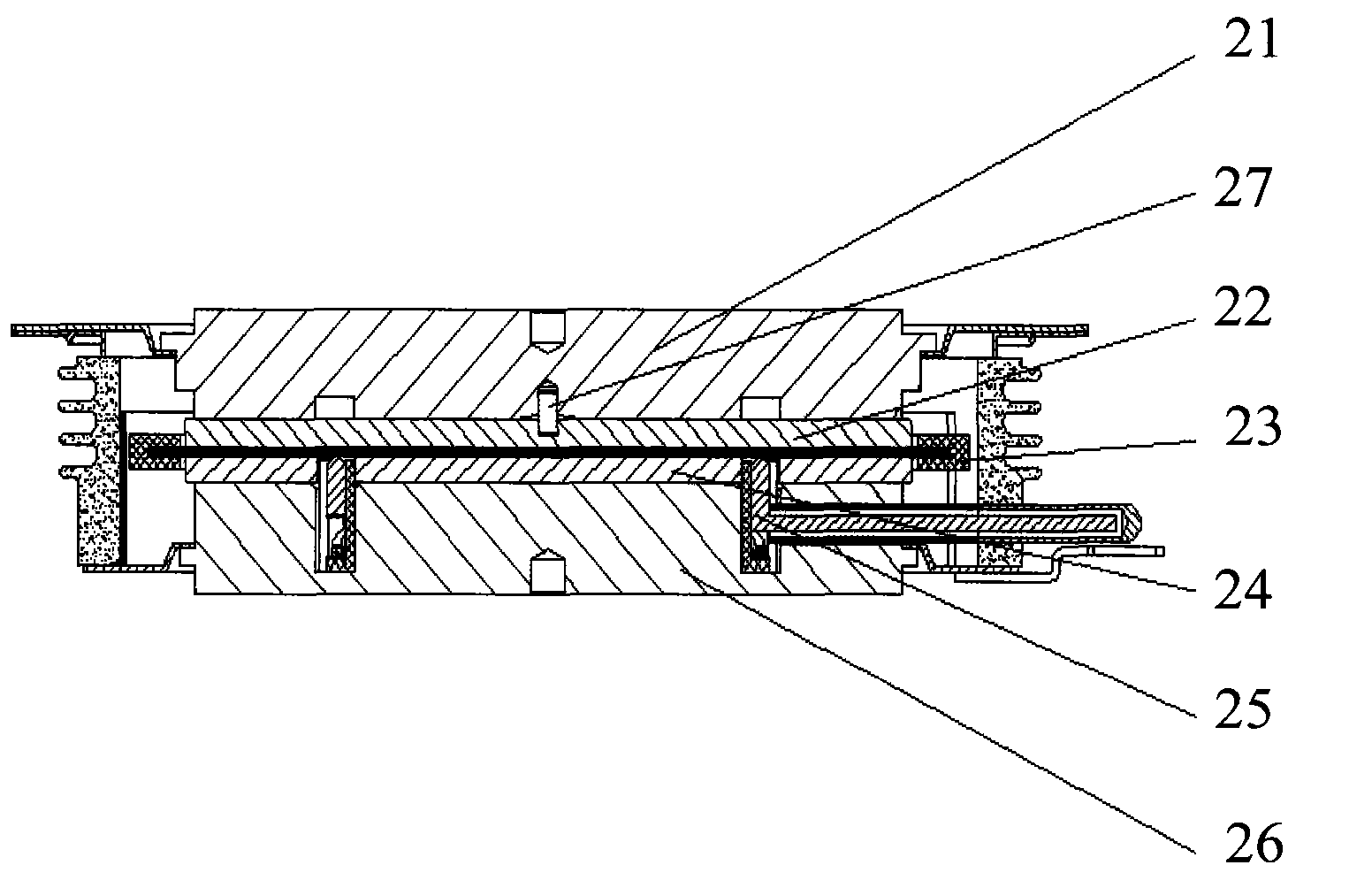

Semiconductor device, test mould and test method

ActiveCN101615602AReduce testing costsReduce on-state voltage dropSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsTube socketTest fixture

The embodiment of the invention provides a semiconductor device, a test mould and a test method. The semiconductor device comprises a tube cap, an aluminum alloy anode, a tube core chip, an aluminum alloy cathode, a gate pole and a tube socket orderly stacked; and adjacent layers of components are electrically connected, and the gate pole is electrically connected with the tube core chip. The test method for the semiconductor device comprises the following steps: assembling a tube core chip to be tested, the gate pole component and an aluminum alloy test sheet group into a test fixture, wherein the tube core chip to be tested is sandwiched between the anode and the cathode of the aluminum alloy test sheet group; and performing dynamic testing. The method adopts the aluminum alloy sheet group to replace a rhodium plated molybdenum sheet group in the prior art, not only reduces testing cost, but also reduces turn on voltage drop, improves thermal resistance performance, and improves the combination with the surface of the tube core chip.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

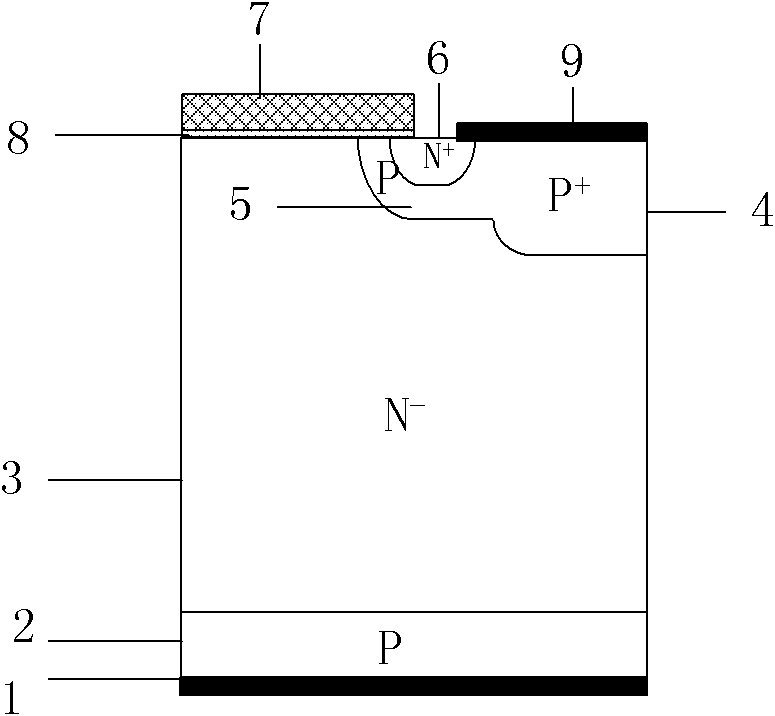

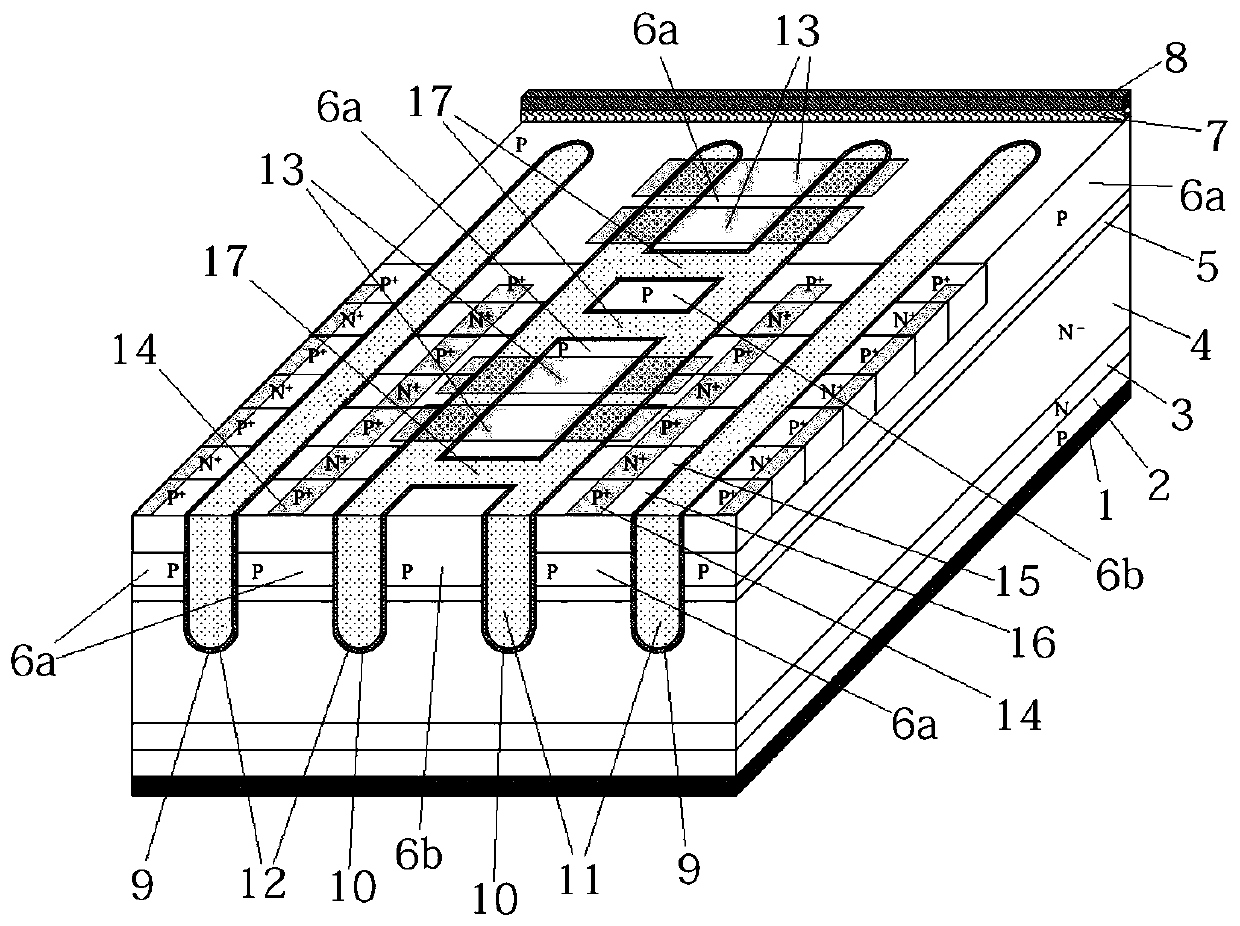

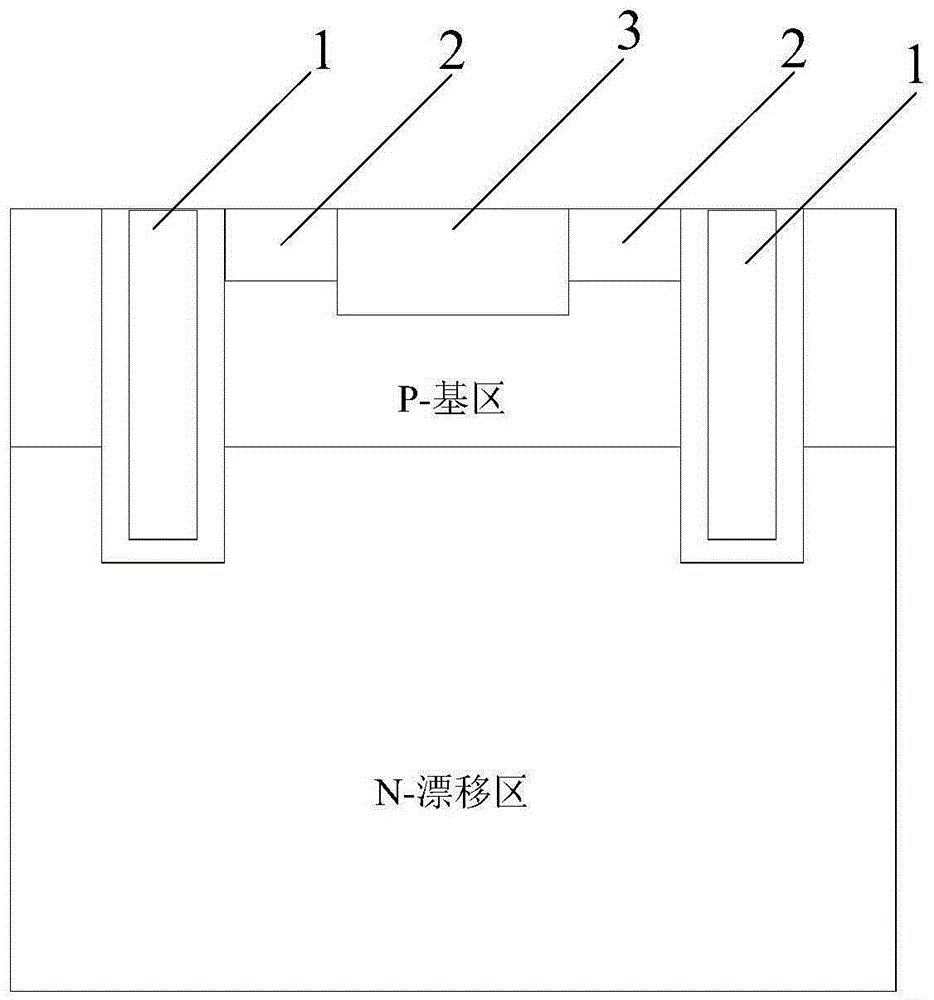

Novel power semiconductor device

InactiveCN103887332ANo conductance modulationReduce on-state voltage dropSemiconductor devicesPower semiconductor deviceBody region

The invention relates to a semiconductor device, and discloses a novel power semiconductor device comprising a substrate (1), an anode P+ region (5), an anode N+ region (4), anode metal (12), an N-type drift region (3), a field oxide layer (16), a cathode P+ region (8), a cathode P-type body region (7), a P-type channel region (6), an emitting electrode N+ region (9), cathode metal (11), a poly-silicon gate (14), a gate oxide layer (10), poly-silicon gate metal (13) and P-type cylinder regions (17,18). The two P-type cylinder regions (17, 18) are additionally arranged in the P-type channel region (6) and the anode P+ region (5), and the structure that the anode P+ region (5) and the anode N+ region (4) are arranged in an alternating way is adopted so that the inverse resistance effect of the device is inhibited, the latch-up effect of the device in the high-current working state is overcome, turn-off speed and voltage resistance of the device are enhanced and power consumption of the device is reduced.

Owner:HANGZHOU ENNENG TECH

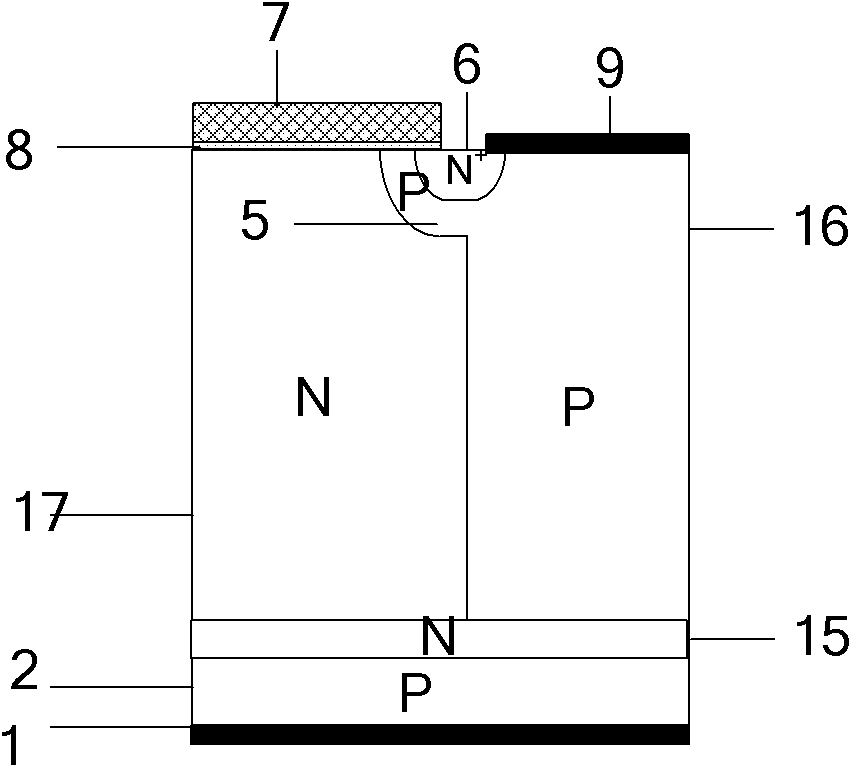

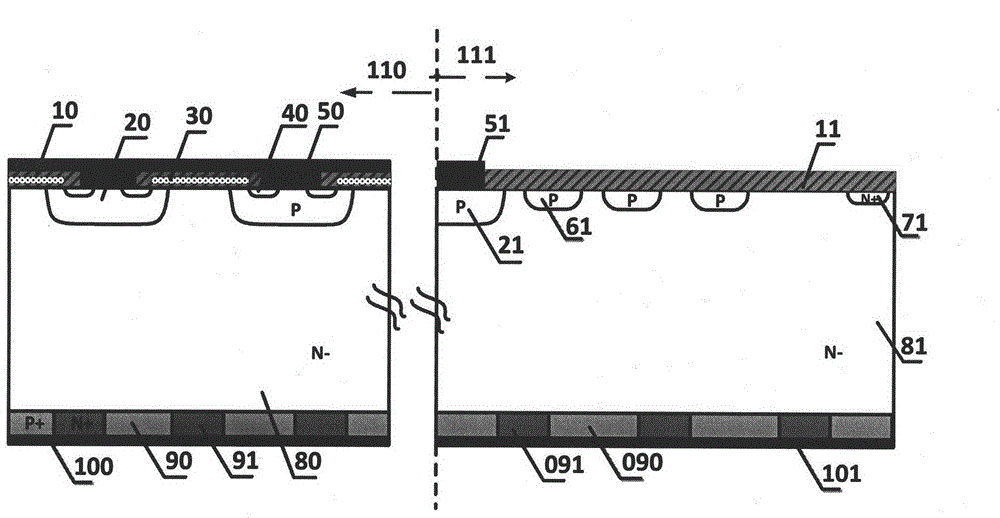

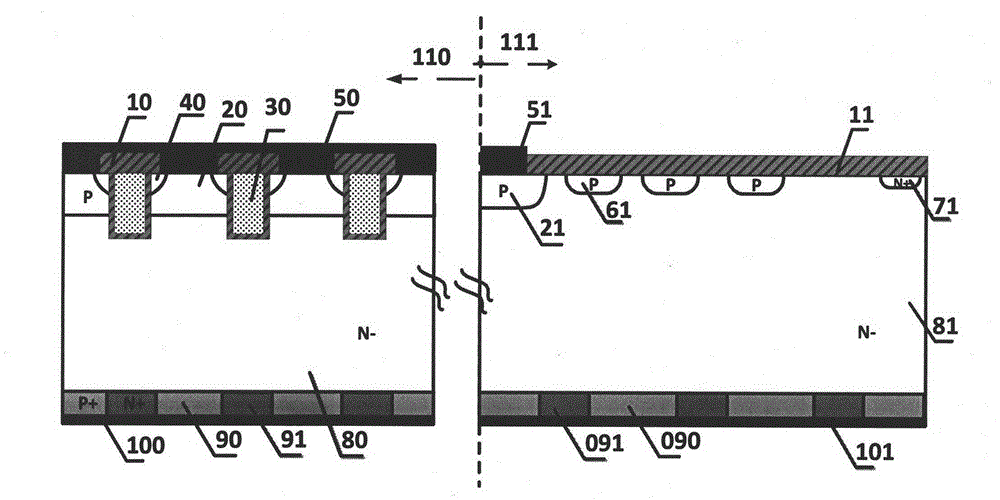

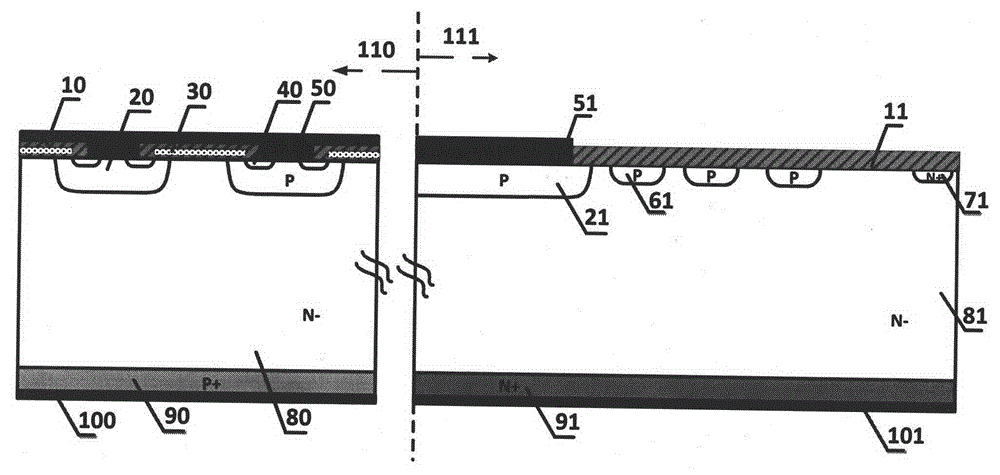

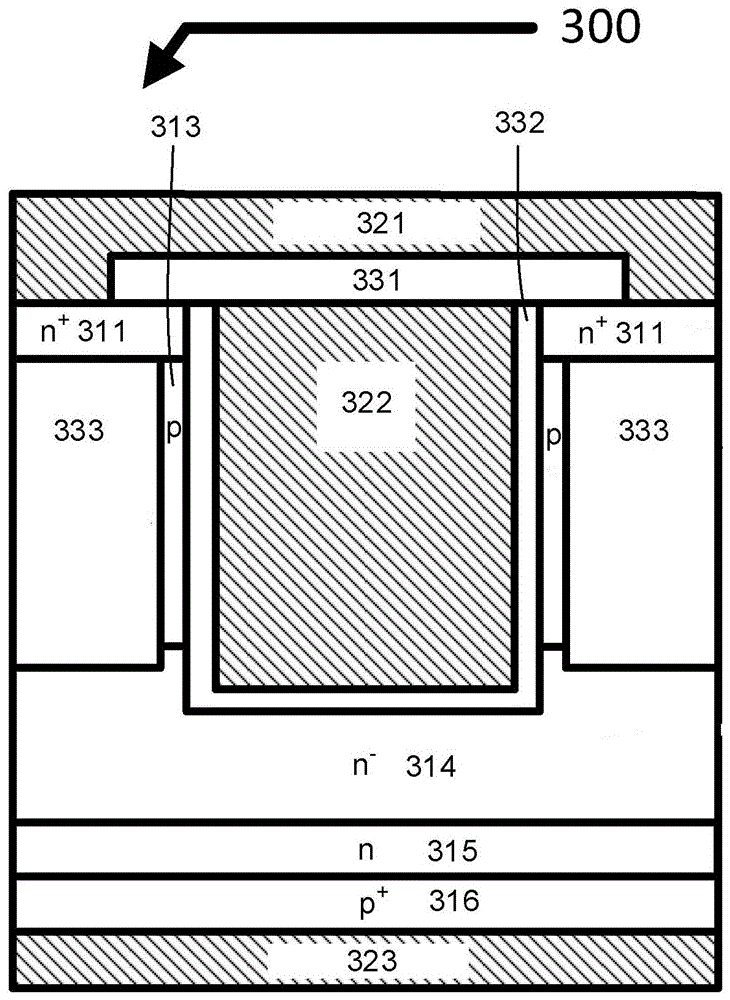

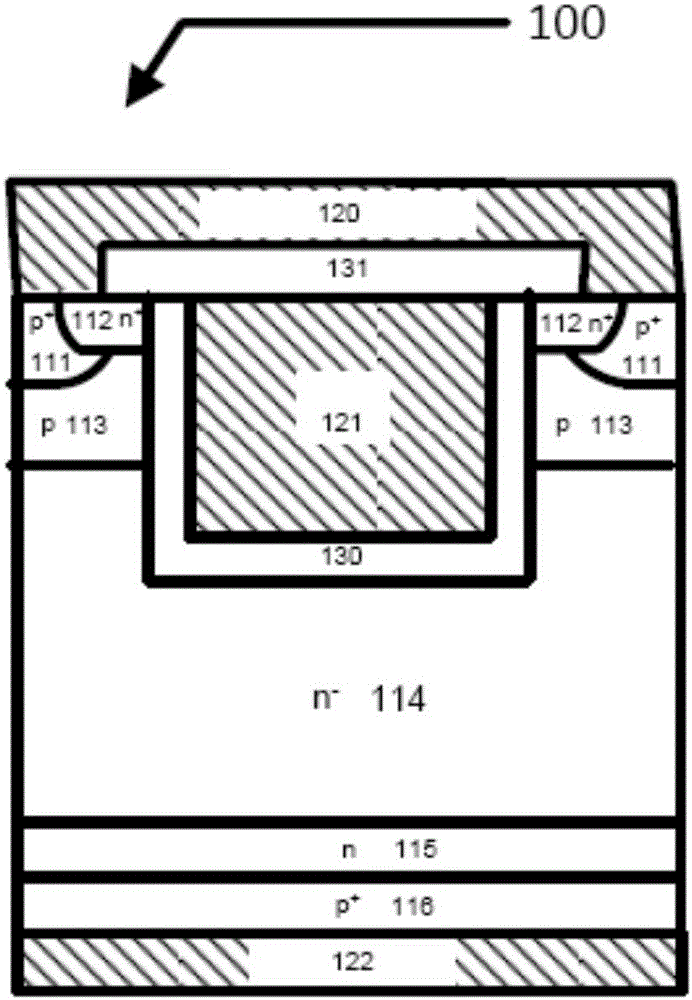

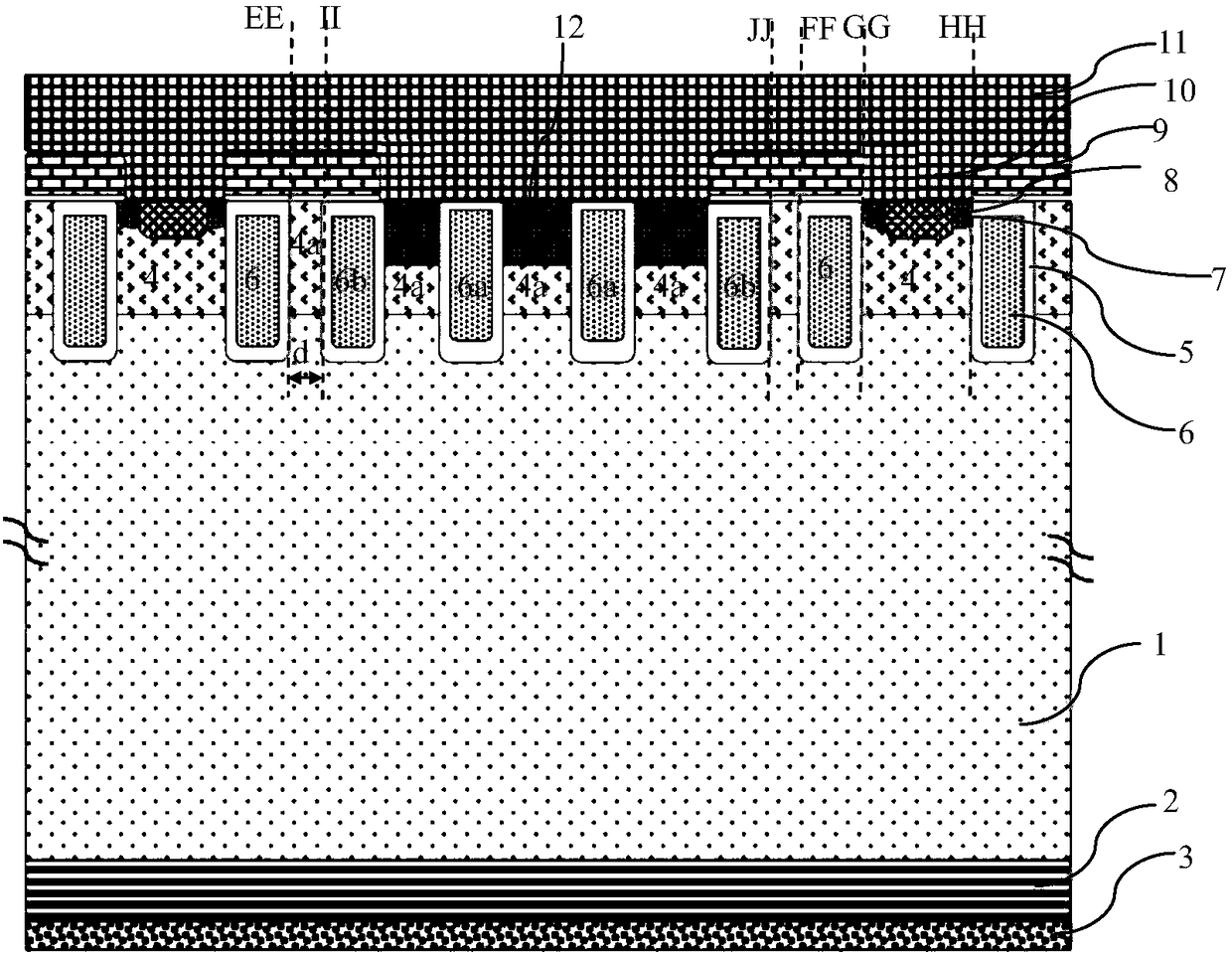

Collector-electrode short-circuit IGBT structure integrating diode

InactiveCN103606557ANo conductance modulationReduce on-state voltage dropTransistorPower semiconductor deviceBlock effect

The invention discloses a collector-electrode short-circuit IGBT structure integrating a diode. The structure includes a cellular area (110) and a terminal area (111) surrounding the cellular area (110) and belongs to the technical field of power semiconductor devices, wherein the cellular area (110) includes an insulating layer (10), polycrystalline silicon gates (30), emitting-electrode metal (50), P-body areas (20), an emitting-electrode N+ area (40), an N- drift area (80), an collector-electrode P+ area (90) and a collector-electrode area (100). The terminal area (111) includes a main junction (21), field limiting rings (61), a channel cutoff ring (71), an N- drift area (81), an N+ collector-electrode short-circuit area (91), emitting-electrode metal (51), collector-electrode metal (101) and an insulating layer (11). The main junction (21), the N- drift area (81) and a collector-electrode N+ area (91) form an antiparallel PiN diode. The structure not only reduces the overall area and packaging cost of a device, but also improves the switching speed of the device and overcoming a reverse-blocking effect of traditional collector-electrode short circuits.

Owner:FOSHAN XINGUANG SEMICON

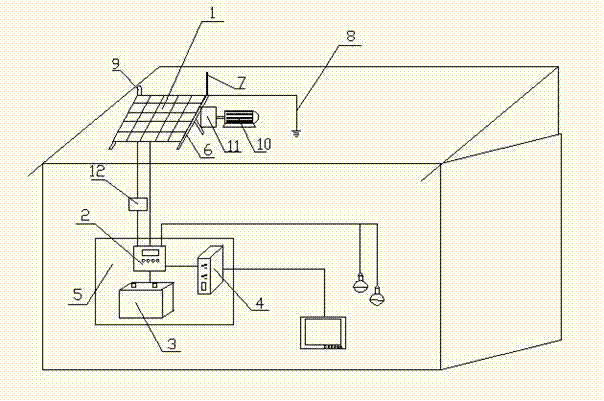

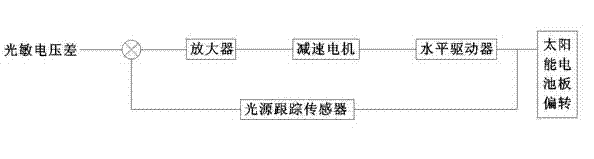

Domestic photovoltaic power generation system

ActiveCN102780244AIncrease power generation capacityReduce dosageBatteries circuit arrangementsPV power plantsEngineeringElectric network

The invention discloses a domestic photovoltaic power generation system. Compared with the ordinary system, the domestic photovoltaic power generation system has the advantages that the effective light illumination time and the service life of a batter pack are greatly prolonged, and the goal of utilizing the solar energy to the greatest degree is reached. The domestic photovoltaic power generation system is provided with lightning protection measures for protecting the whole system, the east and west self-tracking sun movement is also adopted, in addition, the alternating current and direct current inverse power supply is automatically switched, when the effective light illumination time cannot be reached, alternating current and direct current are automatically and linearly superposed, and the solar energy is fully utilized for charging a storage battery pack. The system adopts the double-input alternating current and direct current superposition technology for solving the problems of higher harmonic elimination and phase position regulation of the ordinary photovoltaic converted direct current and electric network superposition. The domestic photovoltaic power generation system can solve the ordinary power consumption requirement of families, the system structure is simple, the use is more precise, and the domestic photovoltaic power generation system has the advantages that the stability is high, the installation is convenient, the operation is simple, the dismounting and the moving are convenient, and the like. The domestic photovoltaic power generation system is particularly suitable for the daily power supply of regions far away from an electric network, power limitation regions or disperse resident villages.

Owner:SHANDONG JIEYANG NEW ENERGY

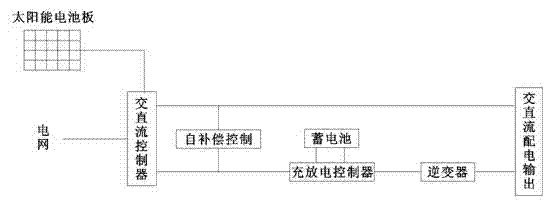

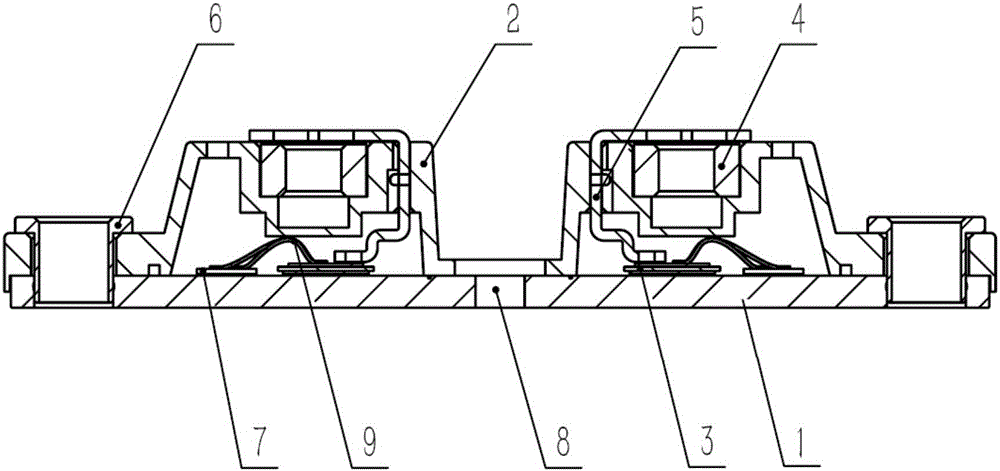

Non-insulating dual-tower type diode module

InactiveCN106783773ALower resistanceReduce feverPrinted circuit assemblingSemiconductor/solid-state device detailsIntegrated circuit manufacturingInternal resistance

The invention relates to the technical field of integrated circuit manufacturing, particularly to a non-insulating dual-tower type diode module. A diode chip is directly welded on a bottom plate, and the diode chip is connected with a main terminal through aluminum wires and a ceramic copper-clad plate; the mechanical stress and internal resistance of the diode chip are lowered in installation and operating processes, and the operating reliability of the diode is improved; and meanwhile, by adoption of the main terminal with a specific bending shape, when the main terminal on the module suffers from stress, external stress can be buffered by the bending shape on the main terminal, so that the internal structure of the module can be further protected.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

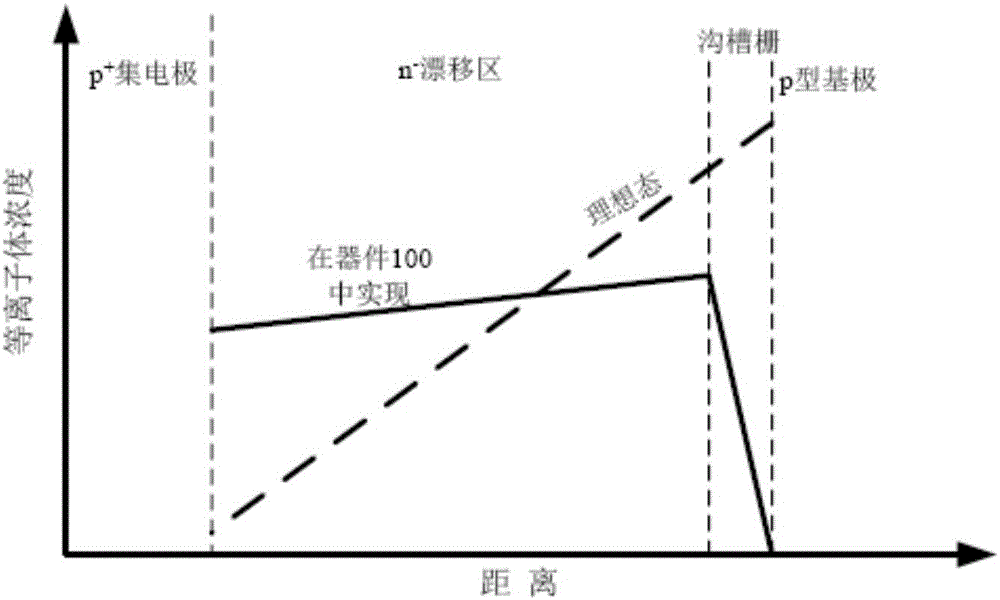

IGBT device structure

ActiveCN110416283AReduce on-state voltage dropIncrease current densitySemiconductor devicesPower semiconductor deviceCharge carrier

The invention discloses an IGBT device structure in the technical field of power semiconductor devices, aims to solve the technical problems that in the prior art, when an IGBT device adopting a virtual trench gate structure is turned off, the on-state voltage drop of a device cannot be reduced due to the fact that the concentration of carriers accumulated below a trench region is too low, and thedifficulty of opening a contact window from the middle of virtual trench polycrystalline silicon is increased as the width of a virtual trench is designed to be narrower and narrower. The top surfaceof the device is downwards provided with a plurality of active trenches and virtual trench regions which are distributed at intervals. Each virtual trench region comprises at least one bridge and a plurality of virtual trenches connected through the bridge, and a dielectric layer is provided with a contact window; and P-type well regions comprise a first P-type well region connected with the metal emitter through the contact window and a second P-type well region in a potential floating state.

Owner:NARI TECH CO LTD

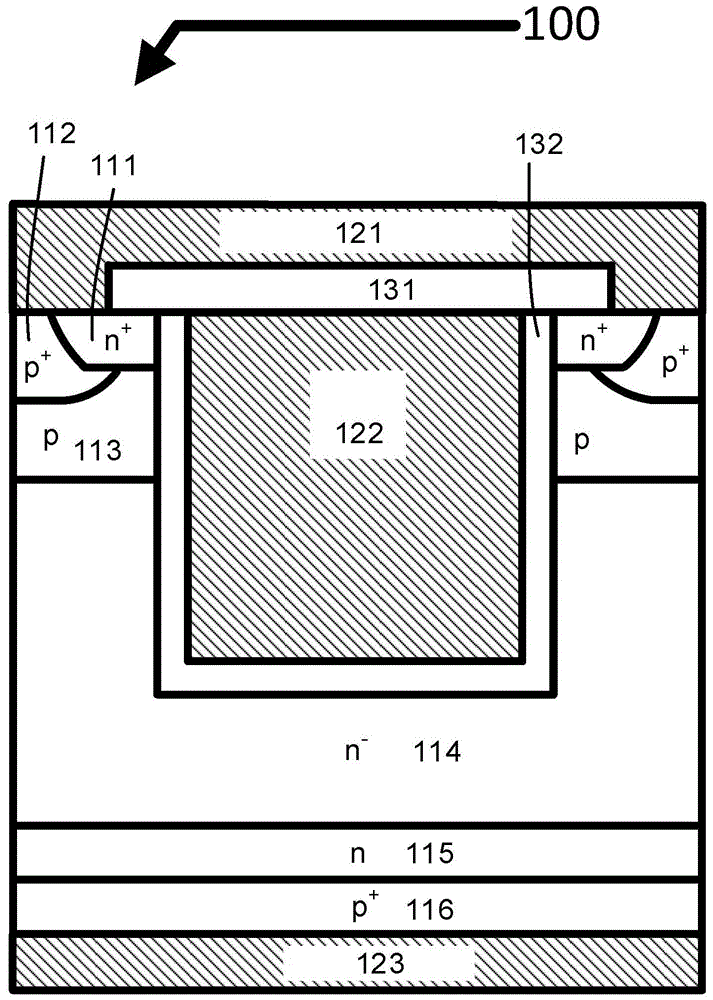

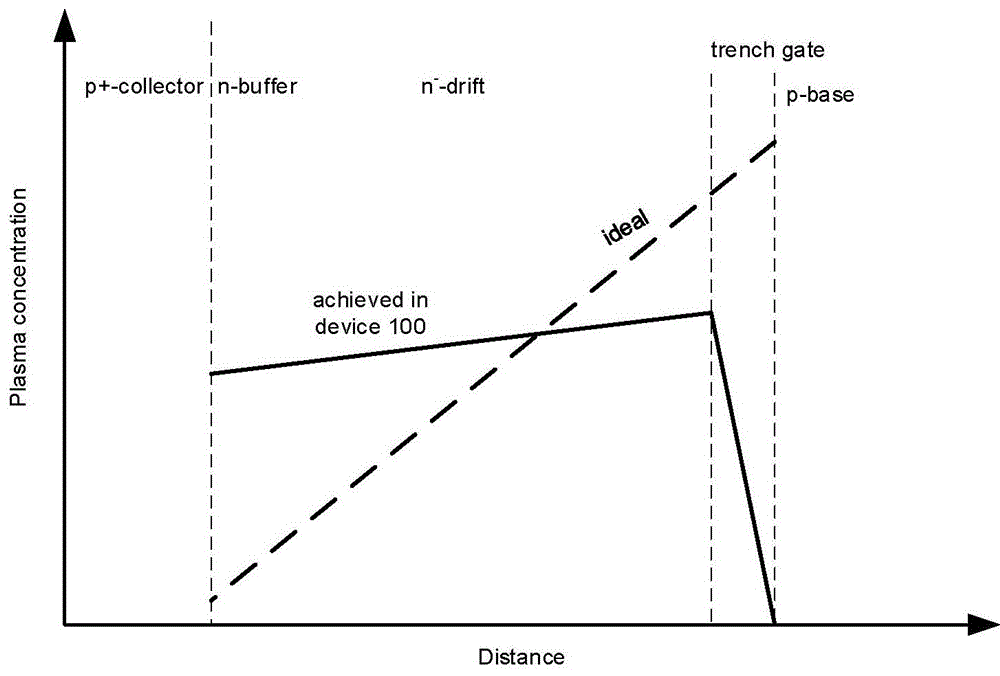

Insulated gate bipolar transistor structure

The invention discloses an insulated gate bipolar transistor structure. The insulated gate bipolar transistor structure includes a collector located at the bottom of the insulated gate bipolar transistor structure, a collection region of a second conductivity type arranged on the top of the collector, a buffer region of a first conductivity type which is arranged at the top of the collection region, a drift region of the first conductivity type which is arranged at the top of the buffer region, a buried dielectric which is partially enclosed by the upper surface of the drift region and is made of an insulation material, an ultra-thin polysilicon base region of the second conductivity type which is arranged at the top of the drift region and is adjacent to the buried dielectric, a gate dielectric which is partially enclosed by the upper surface of the drift region and is adjacent to the polysilicon base region, a gate electrode which is partially enclosed by the gate dielectric, a polysilicon emission region of the first conductivity type which is adjacent to the gate dielectric and is located at the tops of the base region and the buried dielectric, a polysilicon diffusion region of the second conductivity type which is parallel to the emission region, an emitter which is in short connection with the emission region and the diffusion region, and an interlayer dielectric which isolates the emitter from the gate electrode. The insulated gate bipolar transistor structure has theoretical minimum on-state voltage drop.

Owner:宁波安建半导体有限公司

Controlled silicon for large-size silicon chip employing plastic entity package and packaging process thereof

ActiveCN102254879ASimple structureCompact structureSemiconductor/solid-state device detailsSolid-state devicesPlastic materialsVoltage drop

The invention relates to a controlled silicon for a large-size silicon chip employing a plastic entity package and a packaging process for the controlled silicon. The controlled silicon comprises a copper substrate and pins; a silicon chip is welded on the copper substrate through a lead-tin solder; an aluminum wire internal lead is welded on the silicon chip; the aluminum wire internal lead is plastically packaged through a plastic material; and a plastic groove is formed between the pins. The invention also relates to a process for packaging the controlled silicon for the large-size siliconchip employing the plastic entity package. The method comprises the following steps of: sintering, cleaning, welding, packaging, cutting ribs and testing. The invention has the advantages that: the process is simple and has the advantages of low thermal resistance and low state voltage drop, and the product reliability is improved.

Owner:JIANGSU JIEJIE MICROELECTRONICS

Method for manufacturing SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

ActiveCN102157434AImprove vertical pressure resistanceLittle impact on performanceSemiconductor/solid-state device manufacturingVoltage dropEngineering

The invention relates to a method for manufacturing an SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with a p buried layer and a longitudinal channel. The SOI LIGBT device manufactured by the existing method abruptly degrades and even becomes invalid under a high temperature and large current. In the method, SOI materials with p-type buried layers are adopted to manufacture the SOI LIGBT device with the longitudinal channel; the longitudinal withstand voltage is mainly borne by a reversely biased pn junction depletion layer formed by a p-type buried layer with backward impurity concentration distribution and an n-type top layer semiconductor with forward impurity concentration distribution; and the SOI LIGBT device unit is manufactured through ten-time etching and seven-time oxidizing. The method has the beneficial effects of effectively reducing the on-state resistance, on-state voltage drop and on-state power consumption of the device, improving the on-state current and working efficiency of the device, obviously improving the performance of the SOI LIGBT device and improving the reliability of the device.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

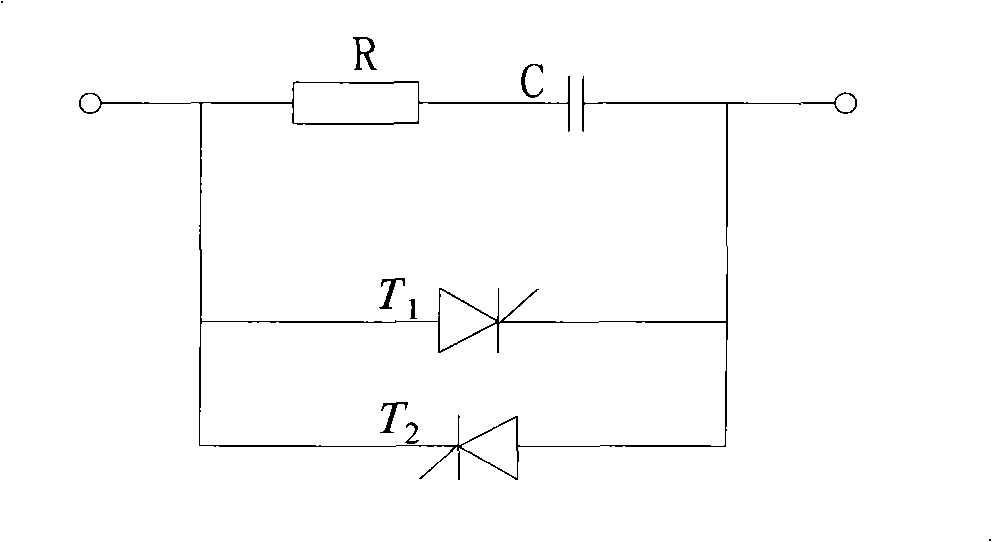

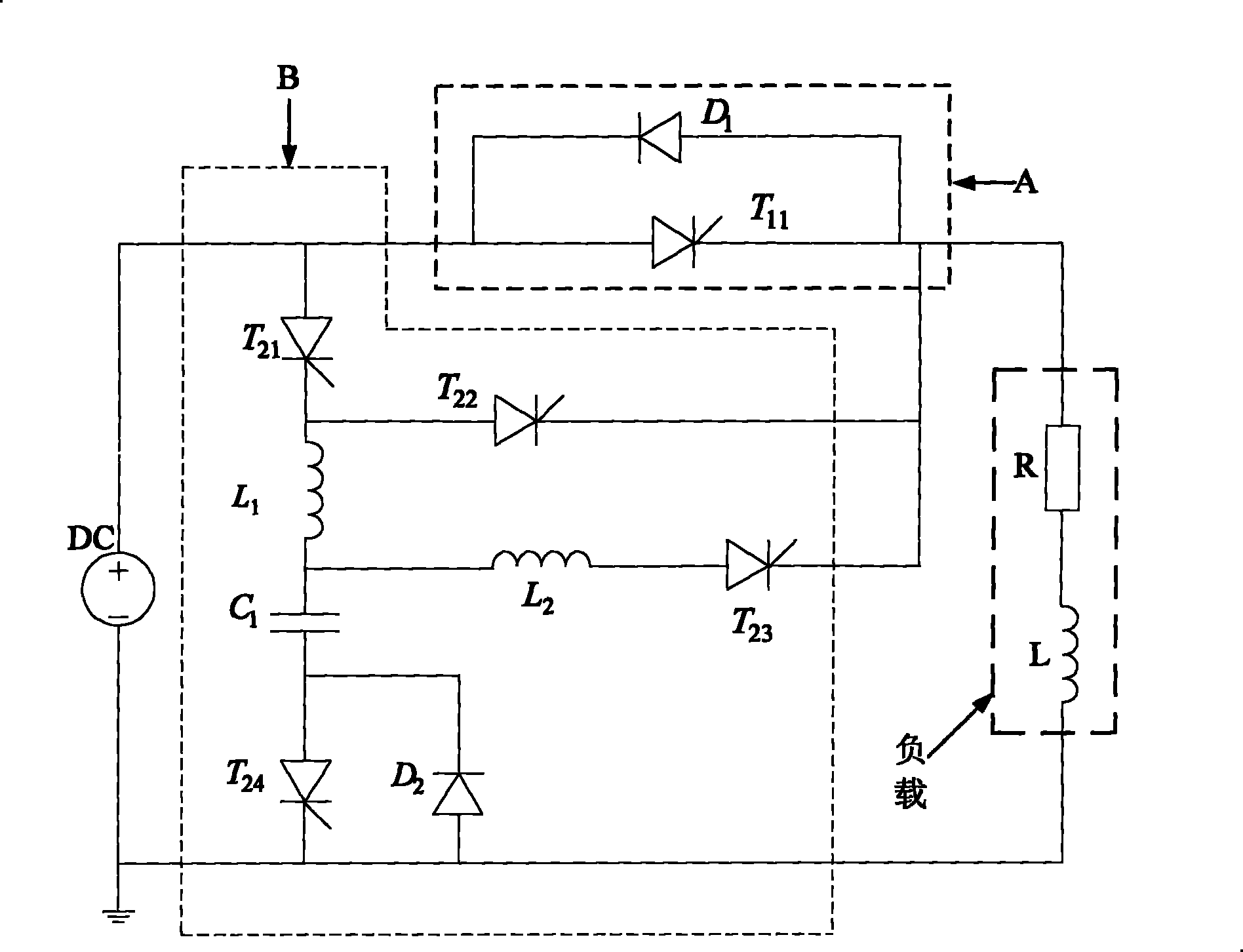

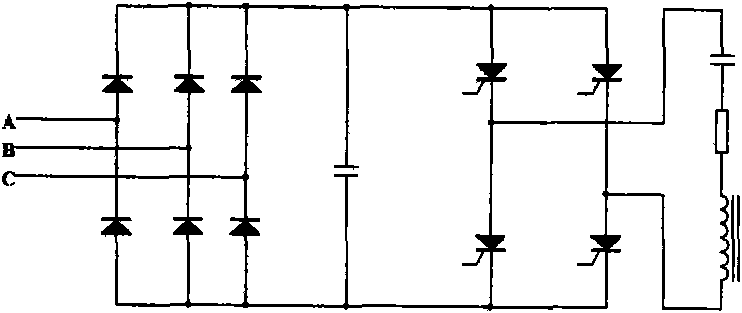

Resonance type DC solid circuit breaker

InactiveCN101540493BAvoid the disadvantage of low overload multiple setting valueImprove reliabilityElectronic switchingEmergency protective arrangements for automatic disconnectionCapacitanceResonance

The invention discloses a resonance type DC solid circuit breaker which belongs to a solid circuit breaker and comprises a DC power supply, a main switching unit A, an auxiliary switching unit B and a load, wherein the main switching unit A comprises a main switching thyristor and a main switching power diode; the auxiliary switching unit B comprises a first thyristor, a second thyristor, a thirdthyristor, a fourth thyristor, a first inductor, a second inductor, an energy-storing impulse capacitor and an auxiliary switching power diode. The invention improves the capacity of the breaker, lowers the cost, realizes the soft starting (shutoff) of a solid switch, and improves the reliability of the breaker.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

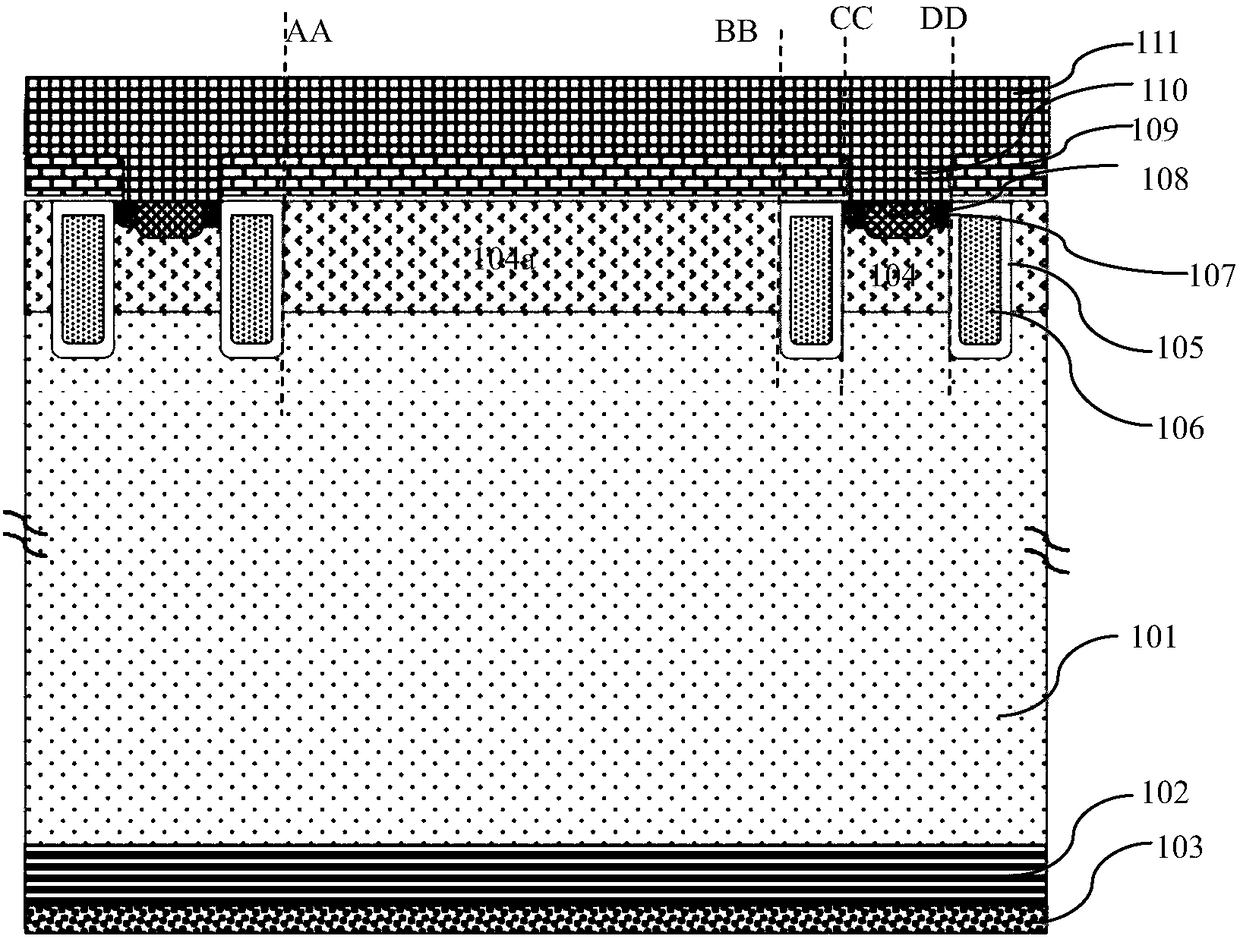

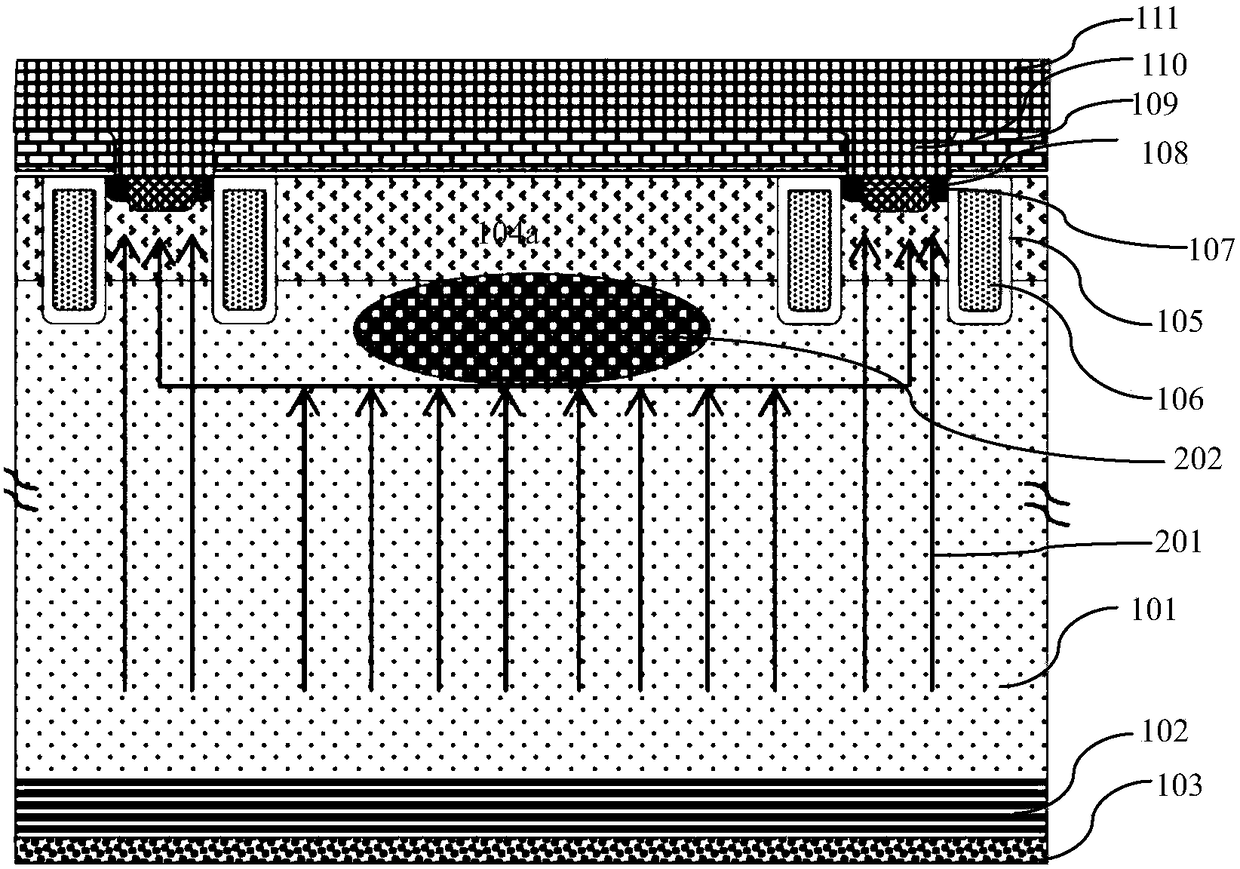

Insulated gate bipolar transistor structure and manufacturing method thereof

ActiveCN106098761AReduce on-state voltage dropTransistorSemiconductor/solid-state device manufacturingBuried oxideInsulated-gate bipolar transistor

The invention provides an insulated gate bipolar transistor (IGBT) structure and a manufacturing method thereof. The structure is a planar IGBT structure; and the insulated gate bipolar transistor (IGBT) structure is characterized by comprising an ultra-thin channel and a buried oxide located under the channel. By the structure, a theoretic lowest on-state voltage drop can be provided.

Owner:宁波吉赛半导体有限公司

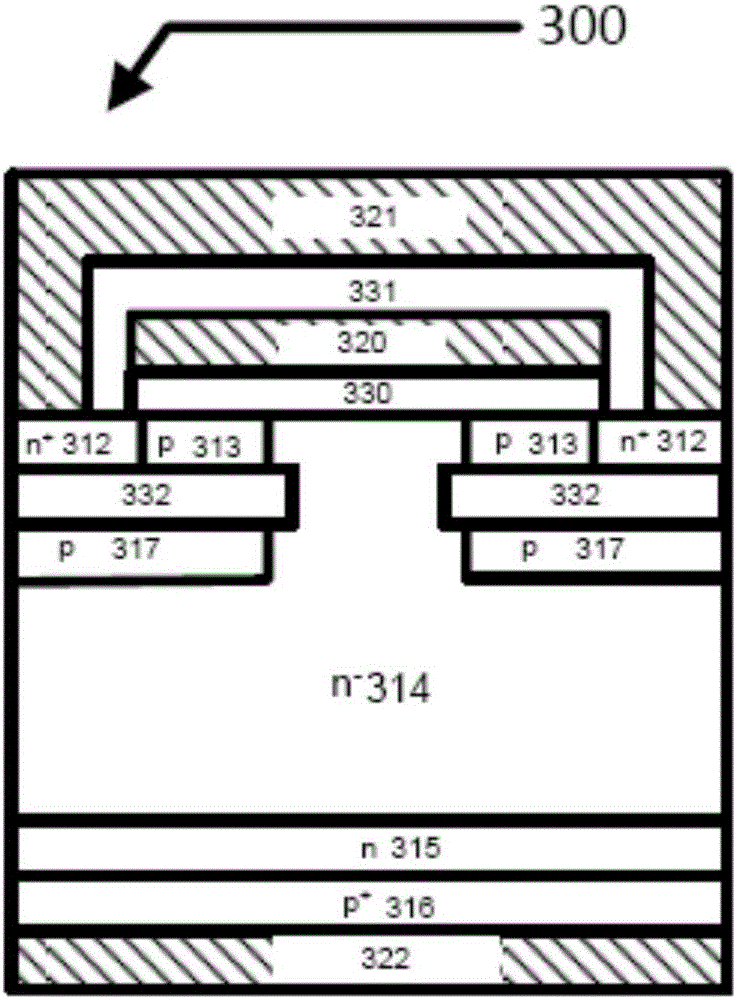

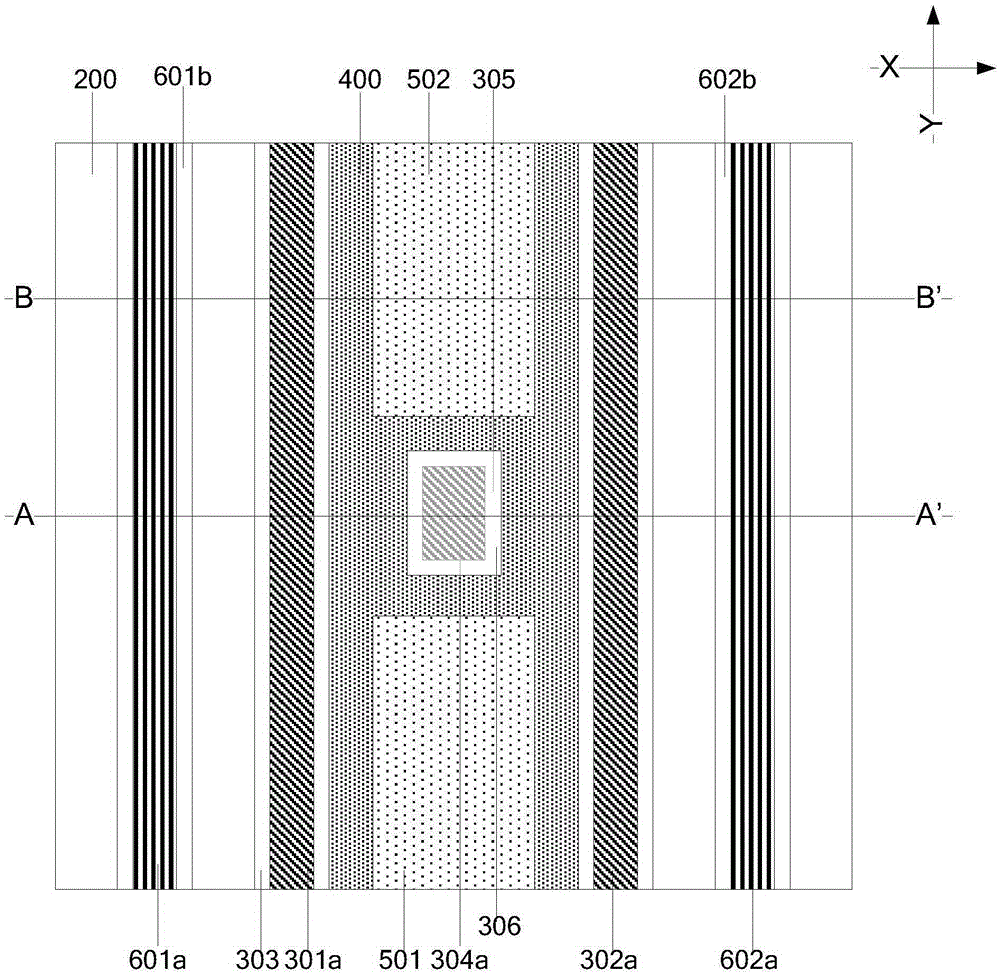

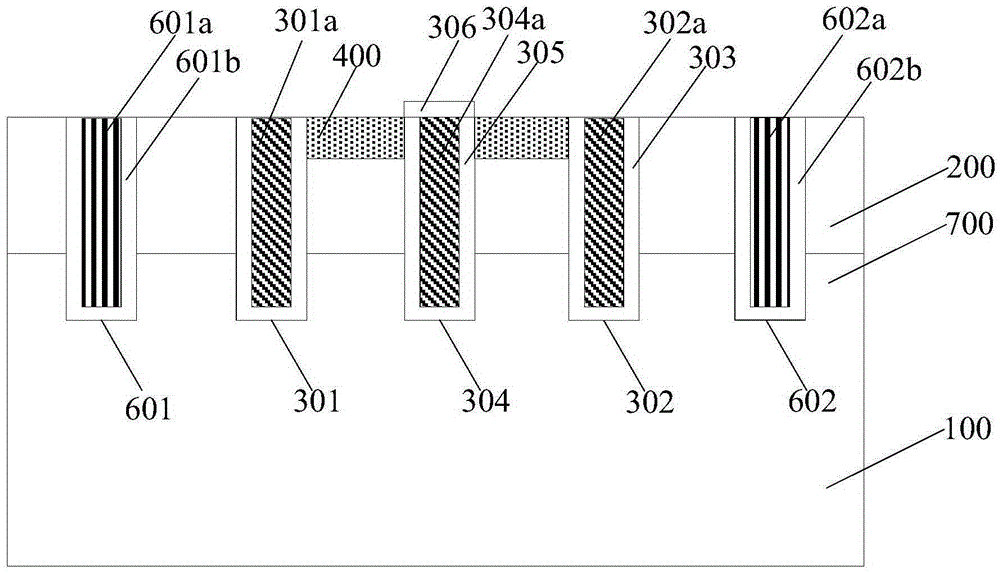

Insulated gate bipolar transistor (IGBT) device

ActiveCN108417622AReduce on-state voltage dropIncrease current densitySemiconductor devicesInsulated-gate bipolar transistorCharge carrier

The invention discloses an insulated gate bipolar transistor (IGBT) device. The IGBT device comprises at least two first groove gates and at least one flotation region, wherein a channel region is formed on at least one side surface of each first groove gate, two sides of the flotation region are limited by side surfaces of the two corresponding first groove gates, at least one second groove gateis formed in the flotation region and penetrates through the floating region, a first well region oppositely doped is formed on a surface of the flotation region, an emission region is formed on a surface of the channel region, a surface of the emission region is connected to an emitter via a contact hole, a surface of the first well region is also connected to the emitter via the contact hole, the second groove gate is connected to a control signal, the channel on the side surface of the second groove gate is switched off by the control signal when the IGBT device is conducted so that carriers are accumulated in the flotation region, and the channel on the side surface of the second groove gate is switched on by the control signal when the IGBT device is switched off so that the accumulated carriers are released. By the IGBT device, the on-state voltage drop of the device can be simultaneously reduced, and the switch-off loss of the device is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Trench gate IGBT and manufacturing method thereof

ActiveCN105390537AIncrease groove densityReduce on-state voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropGate oxide

The present invention discloses a trench gate IGBT and a manufacturing method thereof. A cell comprises a first emitter electrode metal electrode, at least one auxiliary groove and a second emitter electrode metal electrode which are located at one side of a source region departed from a base region and are arranged along a second direction; wherein both the first emitter electrode metal electrode and the second emitter electrode metal electrode extend to the base region, the auxiliary groove is contacted with the source region, and the auxiliary groove extends to a drift region, the auxiliary groove is provided with an auxiliary gate layer therein, a second gate oxide layer is arranged between the inner wall of the auxiliary groove and the auxiliary gate layer, wherein, a first direction is intersected with the second direction. According to the technical solution provided by the present invention, at least one auxiliary groove is formed between a first conventional trench and a second conventional trench, so that trench density of the trench gate IGBT is increased, a conductivity modulation effect is improved, and on-state voltage drop of the trench gate IGBT is further reduced, and the performance of the trench gate IGBT is improved.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

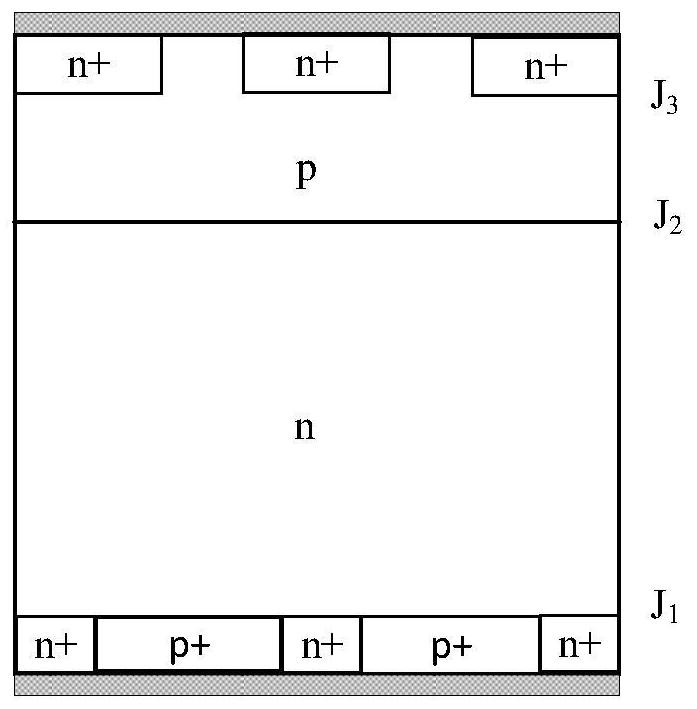

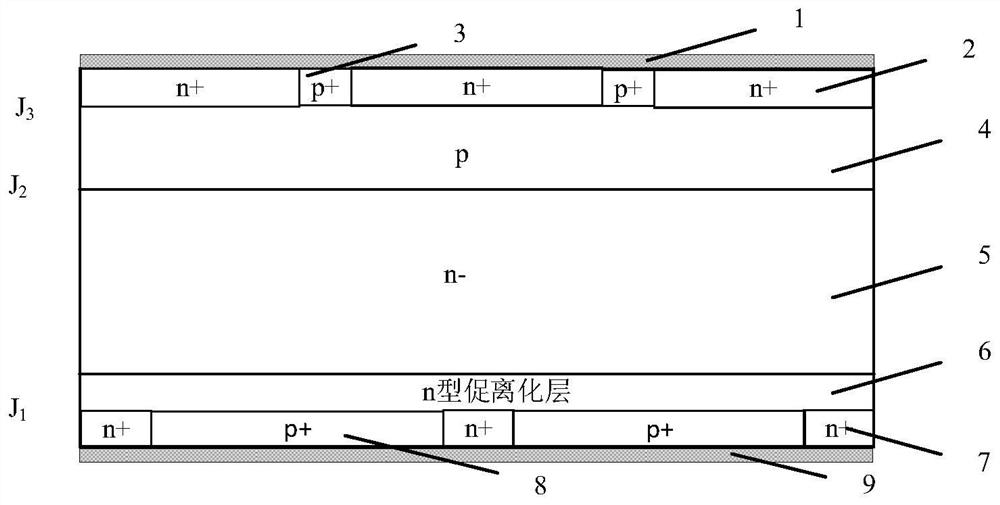

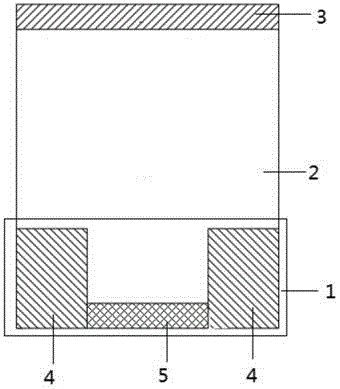

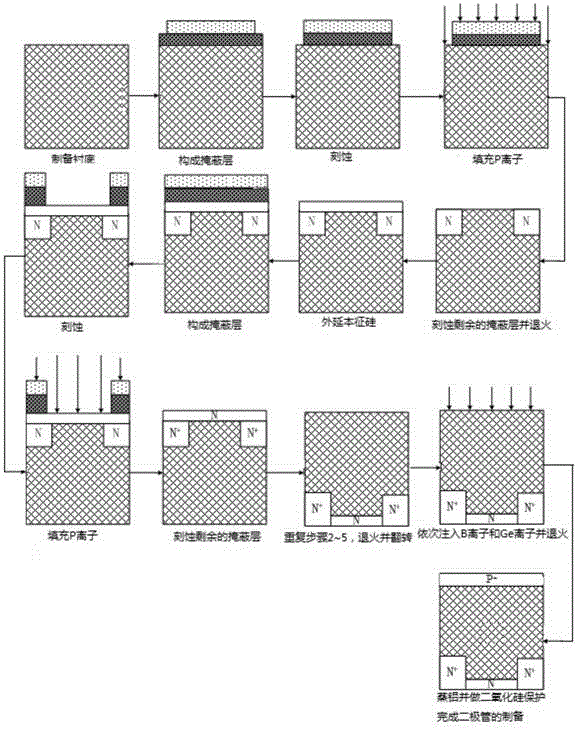

Rapid ionization device and preparation method thereof

ActiveCN112071898AIncrease the opening speedLimit area widthFinal product manufactureSemiconductor/solid-state device manufacturingDevice materialImpact ionization

The invention belongs to the field of pulse power semiconductor devices, and particularly relates to a rapid ionization device and a preparation method thereof. The rapid ionization device comprises ametallized cathode, a highly-doped n+ region, a cathode-side highly-doped p+ short-circuit point, a p base region, an n- base region, an n-type ionization promoting layer, an anode-side highly-dopedn+ short-circuit point, a highly-doped p+ region and a metallized anode which are adjacently arranged in sequence. According to the invention, the n-type ionization promoting layer with higher dopingconcentration than the n- base region is introduced into the FID device structure, and the expansion of the space charge region of the n- base region is limited, so that the width of the region to bepenetrated by the collision ionization front edge is limited, the penetration range of the collision ionization front edge is reduced, the propagation time of the collision ionization front edge is shortened, and the reliability of the device is improved, so the switching-on speed of the device is improved.

Owner:HUAZHONG UNIV OF SCI & TECH

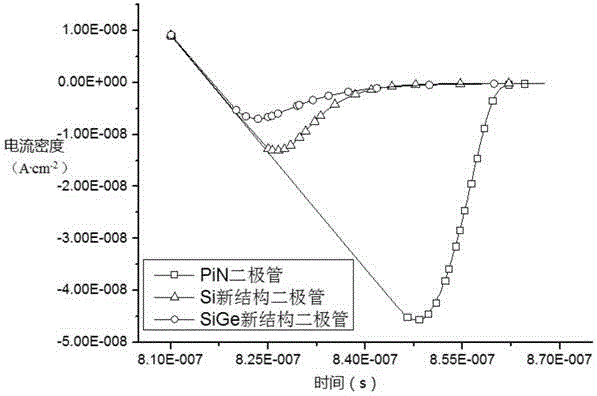

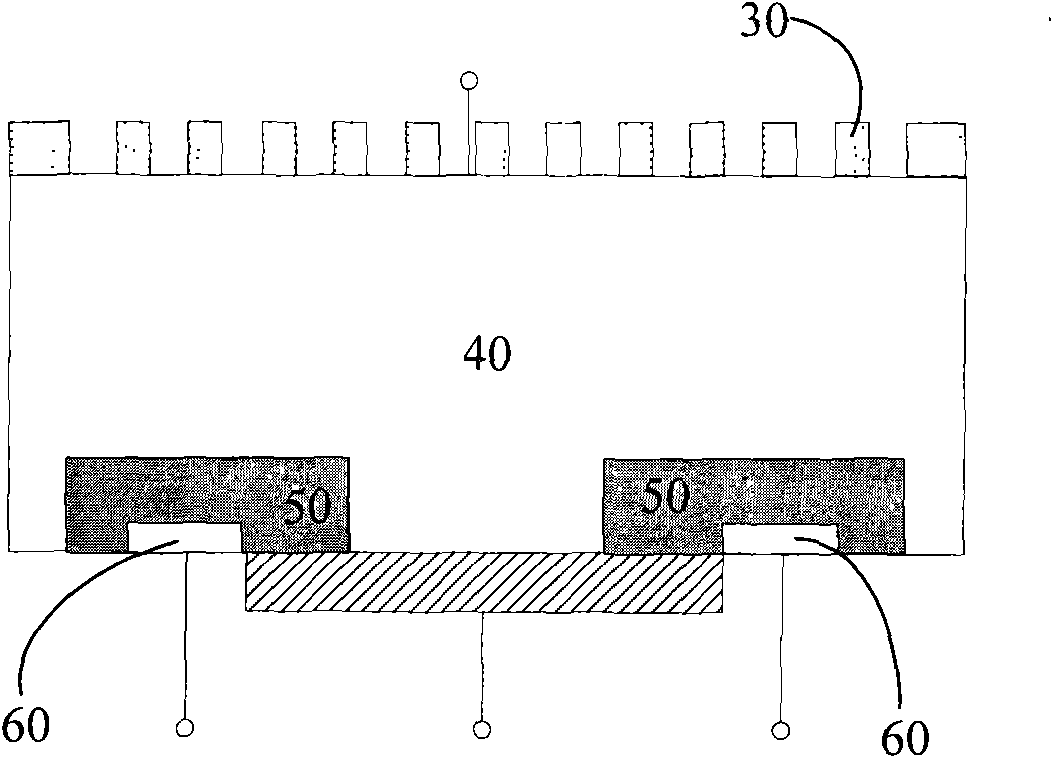

Power diode and preparation method thereof

ActiveCN105140112AShort reverse recovery timeReduce reverse recovery peak currentSemiconductor/solid-state device manufacturingSemiconductor devicesPeak currentIon implantation

The invention discloses a power diode which comprises a cathode N+ region, a voltage withstand layer and an anode P+ region successively from bottom to top, wherein the cathode N+ region comprises two N+ regions, arranged horizontally, and an N region therebetween. The invention also discloses a preparation method of the power diode, a Si material of the P+ region is replaced with a SiGe material, the cathode is arranged in the N+ / N / N+ structure, the reverse recovery peak current is greatly reduced, the reverse recovery time of the diode is effectively shortened, and lower on-state voltage drop and higher switching speed can be obtained simultaneously. A break-through design can reduce the thickness of a drift region, the on-state voltage drop can be reduced, the storage charge is reduced, and power consumption of reverse recover is reduced; and according to the preparation method, expitaxy is combined with multi-time ion implantation to ensure that well N+ and N regions are formed, energy is greatly saved, and the utilization rate of electric energy is improved.

Owner:西安国创电子股份有限公司

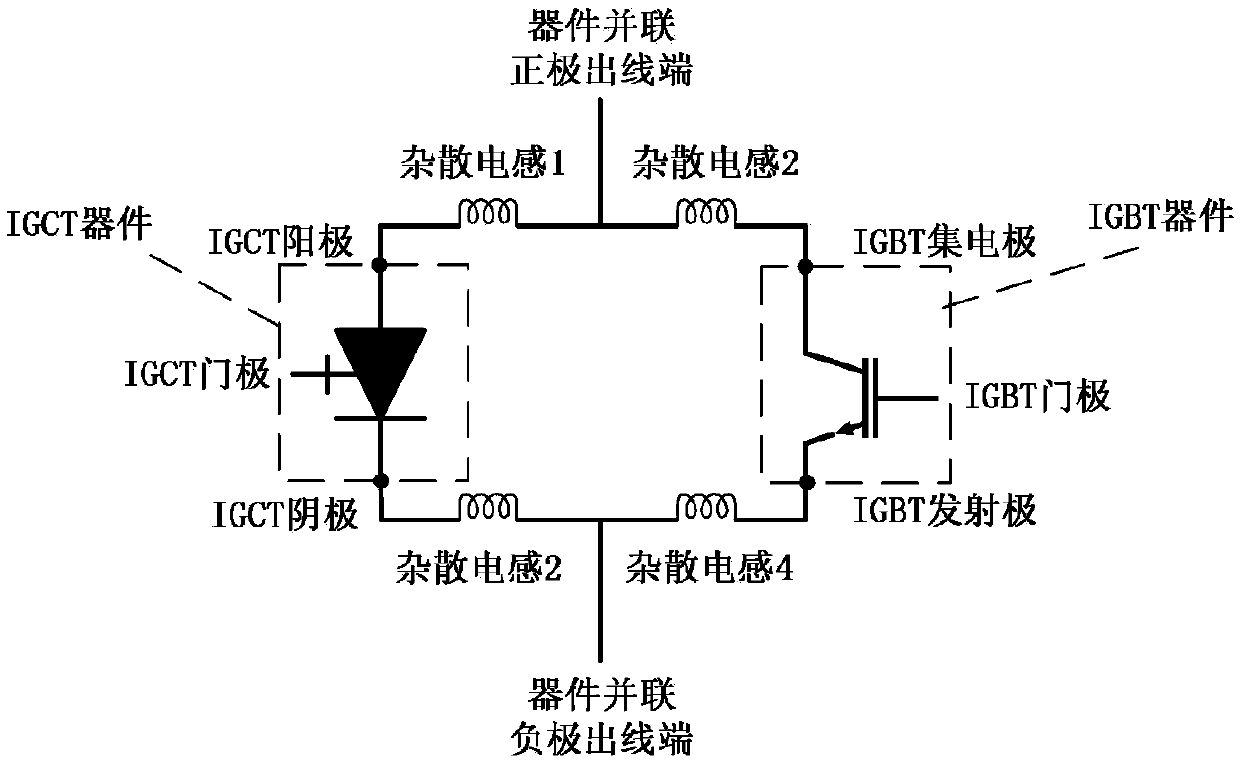

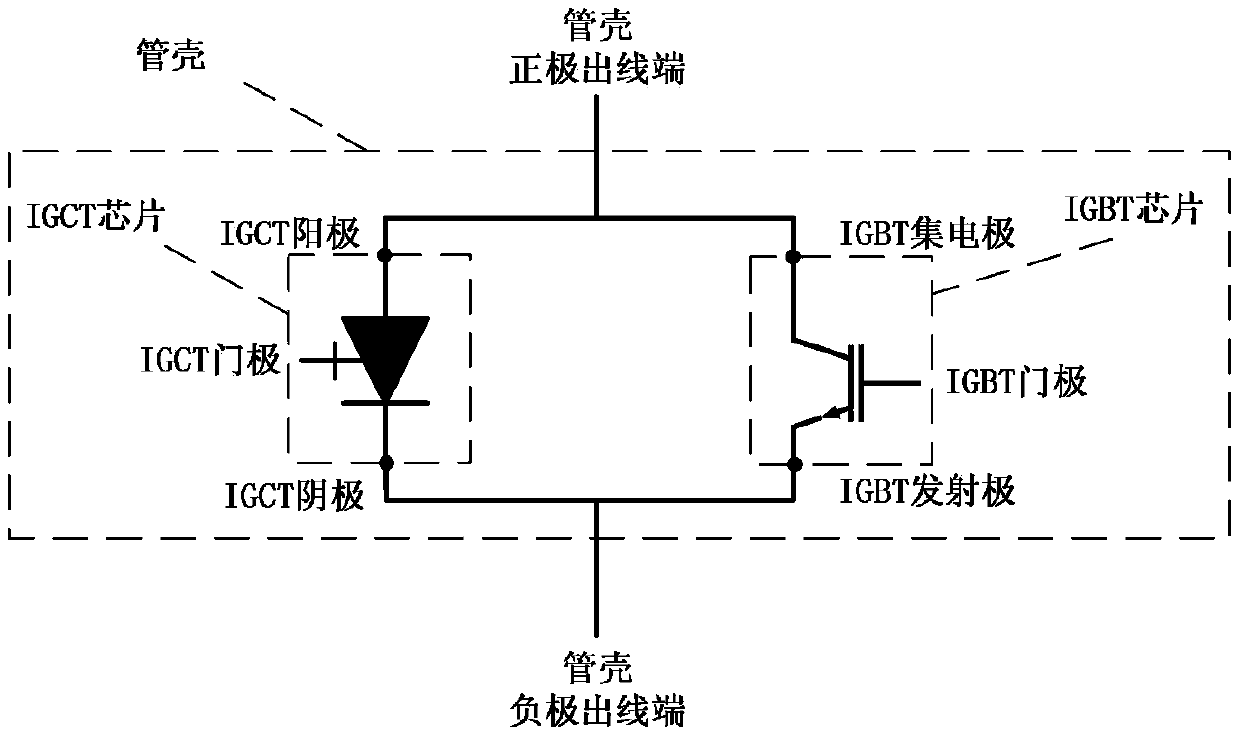

High-power power electronic device applied to MMC and operation method thereof

PendingCN108054943AAvoid damageControl current rate of change (di/dt) speedEfficient power electronics conversionAc-dc conversionPower flowStray inductance

The invention provides a high-power power electronic device applied to an MMC and an operation method thereof. The power electronic device comprises an IGCT device and an IGBT device which are in parallel connection, and the IGCT device and the IGBT device have the equal voltage class and a certain current class proportion; furthermore, the IGCT device and the IGBT device can be sealed into a device tube shell with a special design, and therefore the stray inductance between the two devices is reduced. According to the high-power power electronic device applied to the MMC, the whole on-state voltage drop can be lowered, and the working efficiency of the MMC is improved; the loss is lowered, the size of the whole device is reduced, and the cost is lowered.

Owner:TSINGHUA UNIV

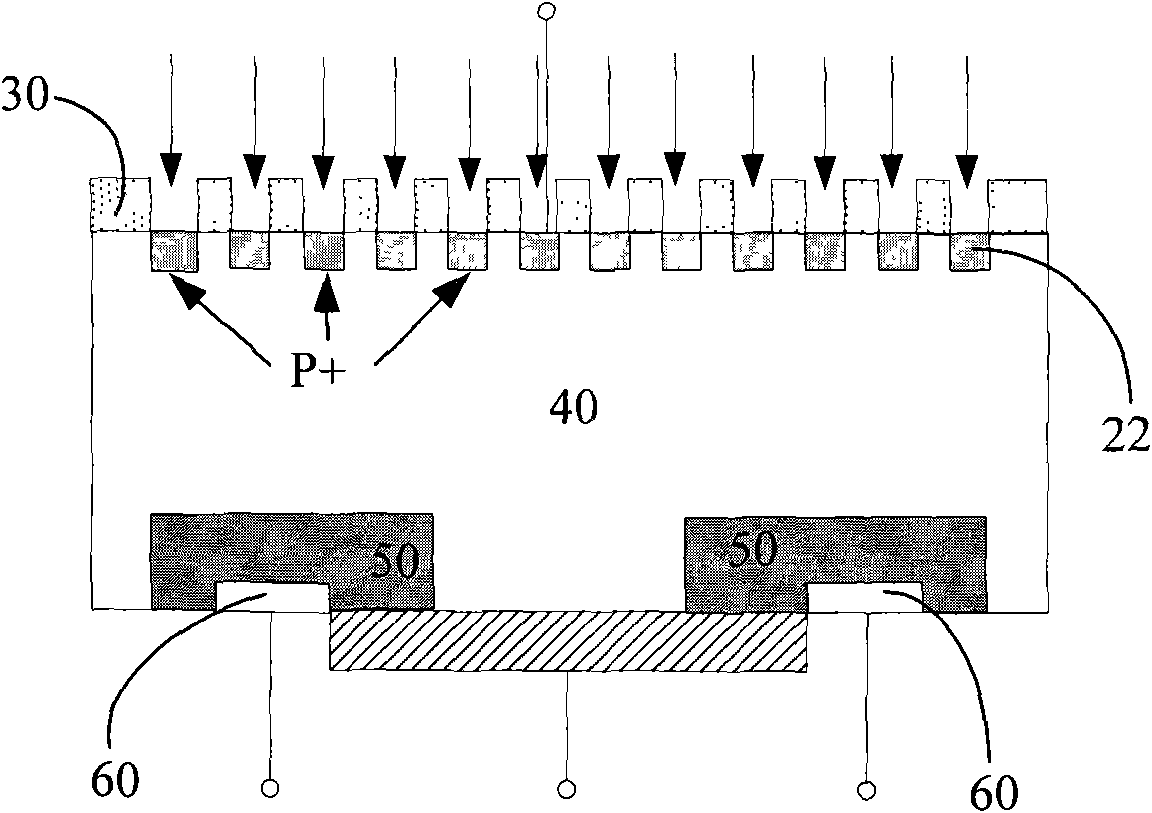

Insulated gate bipolar transistor and manufacturing method thereof

InactiveCN101877359AEnhanced conductance modulation effectIncrease the effective areaSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic bipolar transistorVoltage drop

The invention provides an insulated gate bipolar transistor, which is manufactured by using a silicon chip. The insulated gate bipolar transistor comprises a P+ region, an N- region, a P region and an N+ region, wherein the P region and the N+ region are positioned on the front surface of the silicon chip; the P+ region is positioned on the back surface of the silicon chip; and the P+ region comprises a plurality of P-type impurity regions which are longitudinally distributed in a doping way. The invention also provides a method for manufacturing the insulated gate bipolar transistor. As the P+ region comprises the plurality of P-type impurity regions to increase the effective area of an emitter and increase injected P-type impurities, cavity minority carriers injected into the N- region are increased, conductivity modulation effect on the N- region is enhanced, the on-state voltage drop of the insulated gate bipolar transistor is reduced and the loss of own power of the insulated gate bipolar transistor is further reduced.

Owner:商海涵

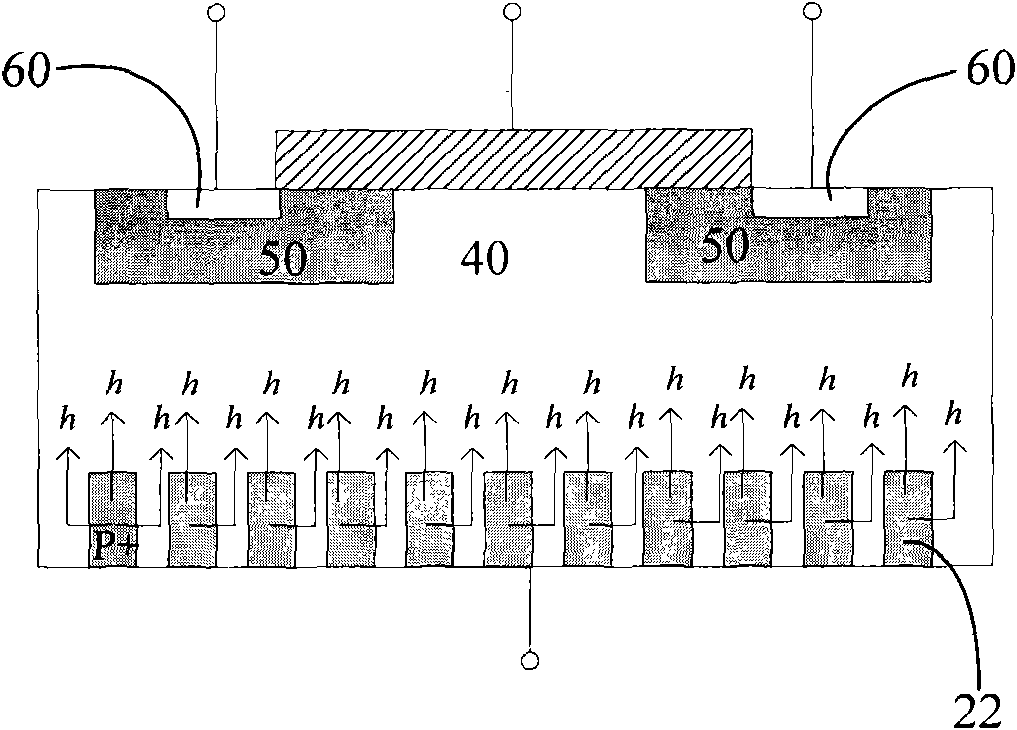

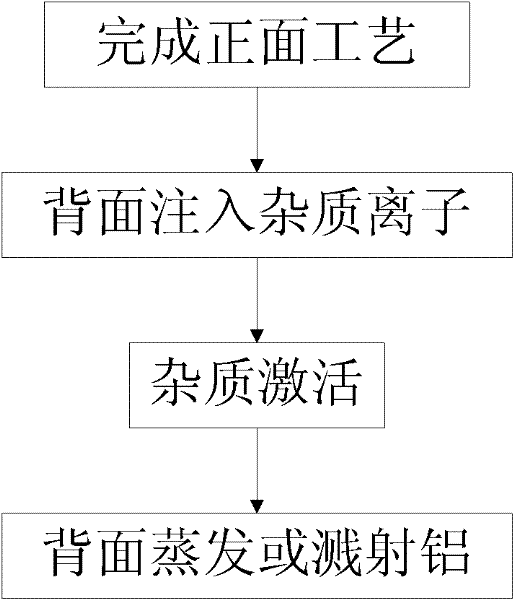

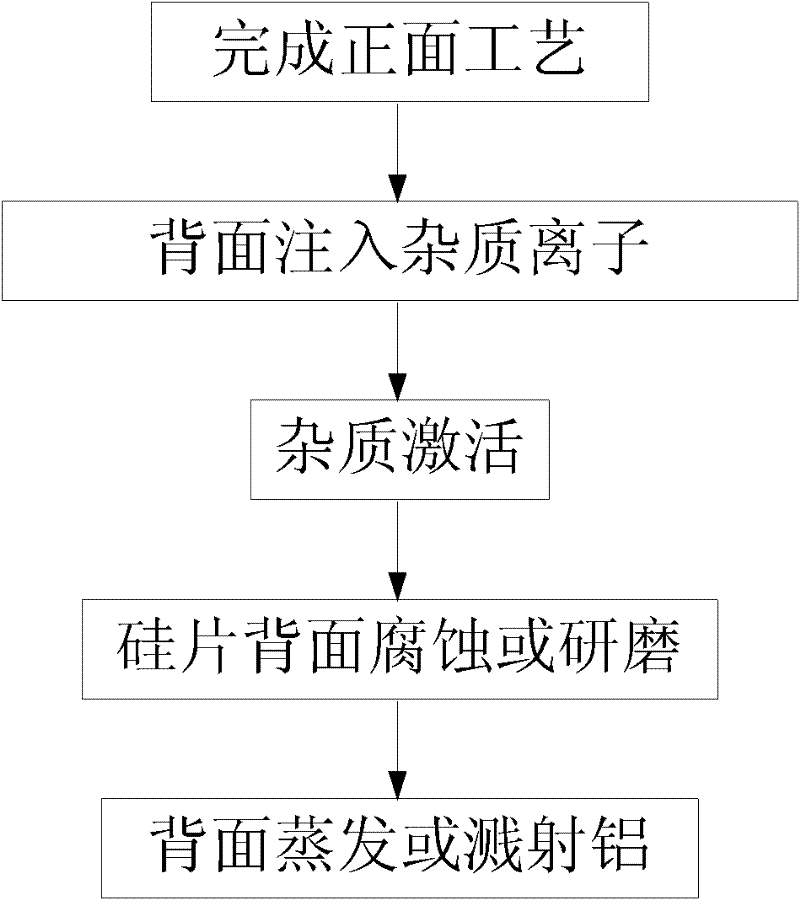

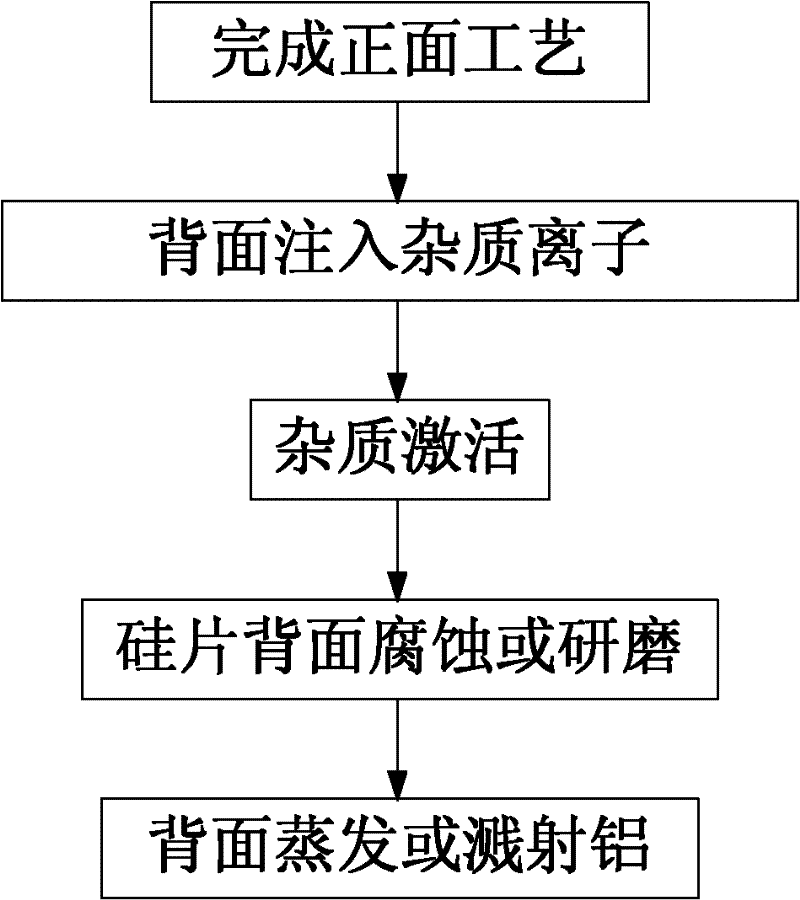

Ion implantation method of substrate back of power device

InactiveCN102157363BReduce leakage currentReduce on-state voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsBiological activation

The invention relates to an ion implantation method of a substrate back of a power device, belonging to the technical field of semiconductor power devices. The ion implantation method disclosed by the invention comprises the following steps of: after finishing steps of a front face process of the power device, thinning the substrate back to an impurity implantation layer and then depositing a metal aluminum layer by utilizing a corrosion or grinding method after ion implantation (thinning or non-thinning process can be carried out on the substrate back before the ion implantation) and ion activation are finished, but not directly carrying out metal aluminum layer deposition like the traditional process. Therefore, the contact resistance between the subsequently deposited metal aluminum and the substrate can be reduced, unnecessary parasitic multi-layer structures can be eliminated, the leakage current and the on-state voltage drop of the power device are reduced, and the switching time of the power device is shortened. The ion implantation method of the substrate back of the power device, disclosed by the invention, is suitable for semiconductor power devices made from semiconductor materials, such as bulk-silicon, silicon carbide, gallium arsenide, indium phosphide or germanium silicon and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Silicon carbide MOS device with majority carrier diode

InactiveCN110473872AReduce conduction lossLower turn-on voltageSolid-state devicesSemiconductor devicesPower flowReverse recovery

The invention provides a silicon carbide MOS device with a majority carrier diode. When the MOS device is turned off, the majority carrier diode is connected in parallel with a PN junction diode, andmeanwhile, on the basis of the characteristics of the low opening voltage and single-polarity current conduction of the majority carrier diode and the large breakover current and high voltage resistance of the PN junction diode, the conduction loss of the device during reverse follow current is reduced, the reverse follow current capability and breakdown voltage of the device are improved, the reverse recovery charges of the device are reduced, and the reliability and integration of the silicon carbide MOS device are improved. When the silicon carbide MOS device is turned on, in order to reduce on resistance, the conduction loss of the MOS transistor is reduced. According to the silicon carbide MOS device of the invention, a current reinforcing injection region is additionally arranged inan active region, and the problem of excessively large JFET resistance due to excessively low epitaxial doping concentration can be solved.

Owner:PN JUNCTION SEMICON HANGZHOU CO LTD

A manufacturing method of a power diode and the power diode

InactiveCN107579120AImprove reliabilityGuaranteed withstand voltage characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPower diodeAnisotropic etching

The invention provides a manufacturing method of a power diode and the power diode, wherein the manufacturing method comprises the steps of sequentially forming an N type epitaxial layer and an N typejunction region of a preset area of the N type epitaxial layer on an N type substrate; sequentially forming a field oxide layer, a polycrystalline silicon layer and an insulating layer mask structureon the N type epitaxial layer after forming the N type junction area; and the insulating layer mask structure and the N type junction area are vertically aligned; using the insulating layer mask structure as a mask and sequentially carrying out anisotropic etching on the polycrystalline silicon layer and the field oxide layer so as to expose a designated area for manufacturing an epitaxial layerof a body region; forming a P type body region in a prescribed region of the epitaxial layer and forming a P- type region at an edge of the P type body region; and forming an N+ type area and electrode separated from the P- type area in the epitaxial layer on the inner side of the P- type area so as to complete manufacturing of the power diode. Through the technical scheme of the present invention, the on-state pressure drop of the device is reduced, and the reliability of the power diode is further raised.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

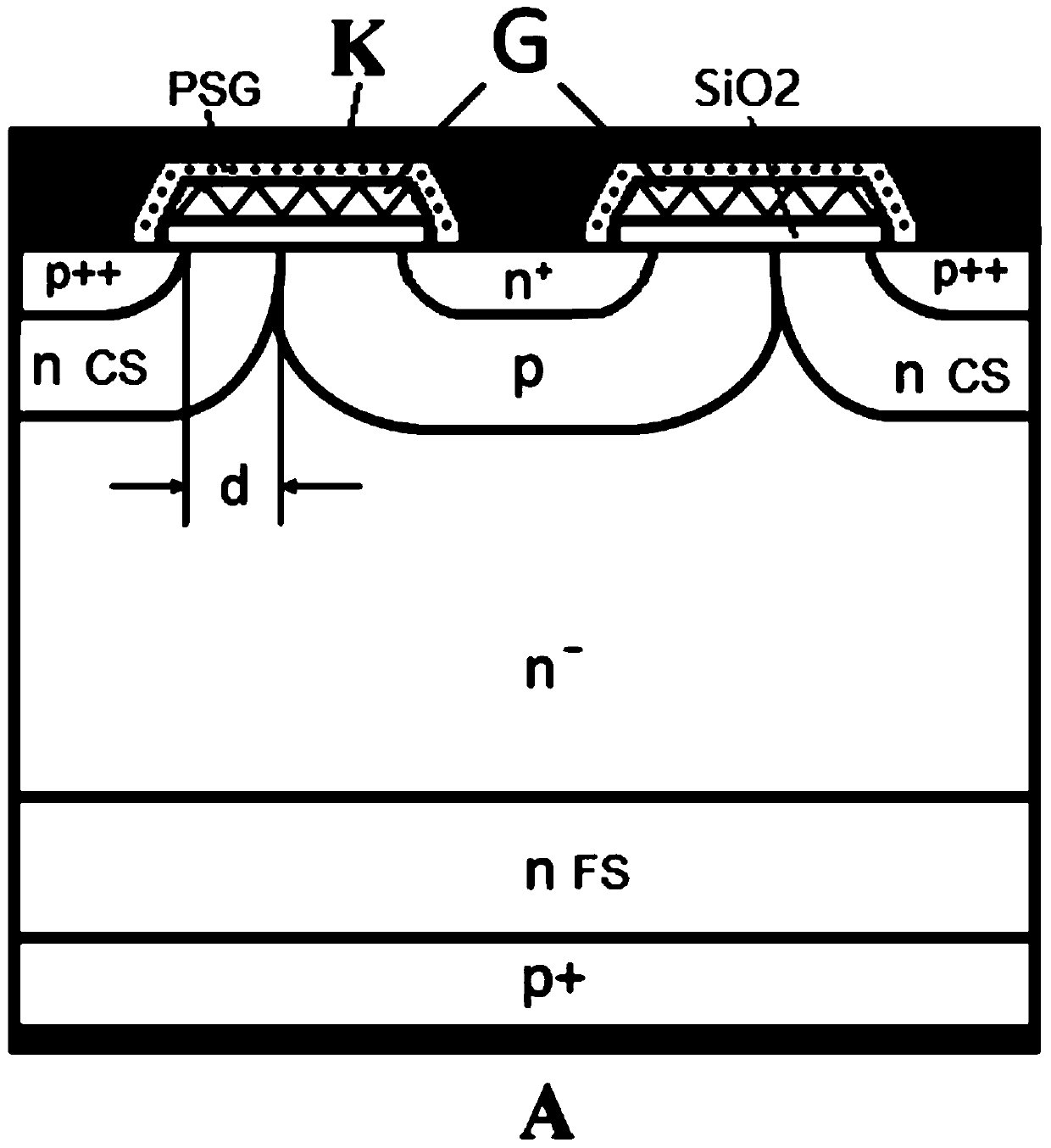

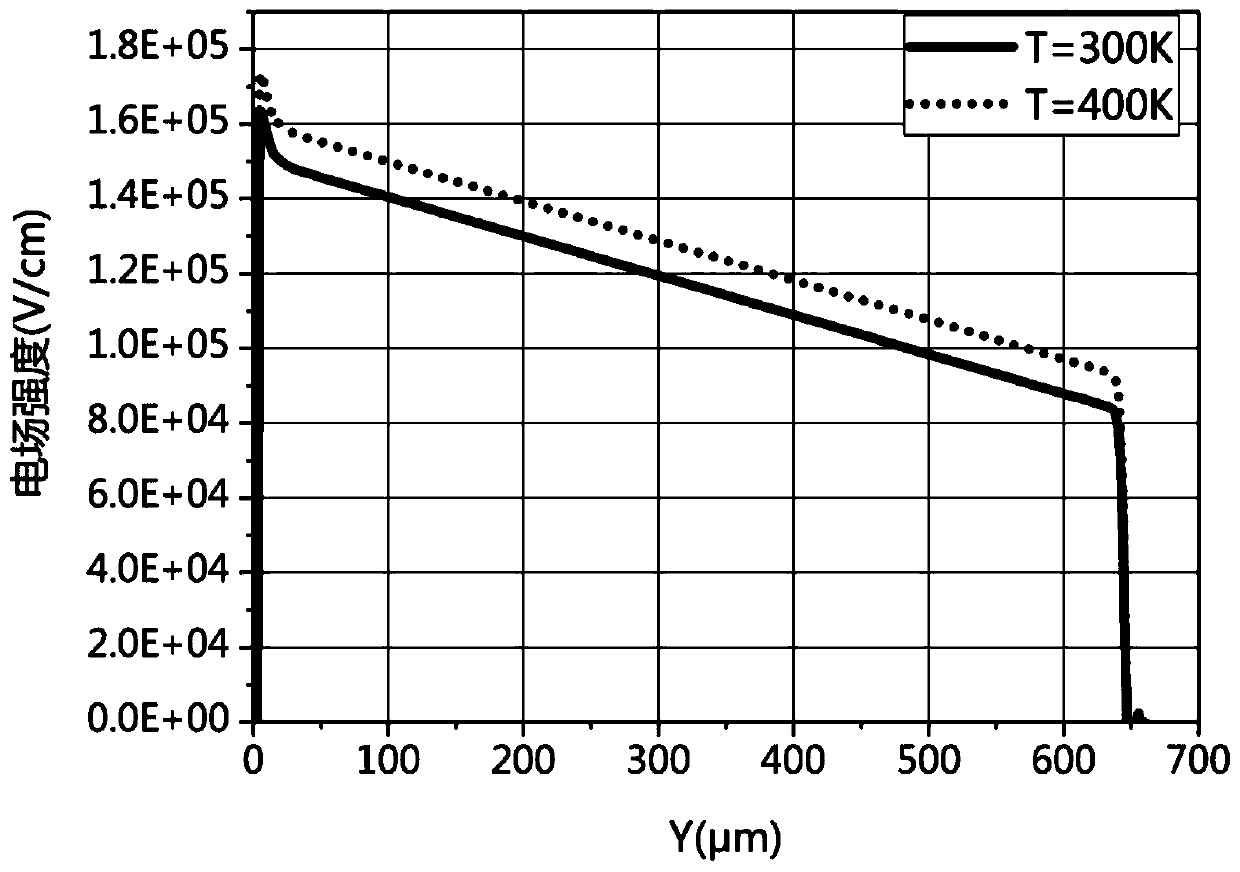

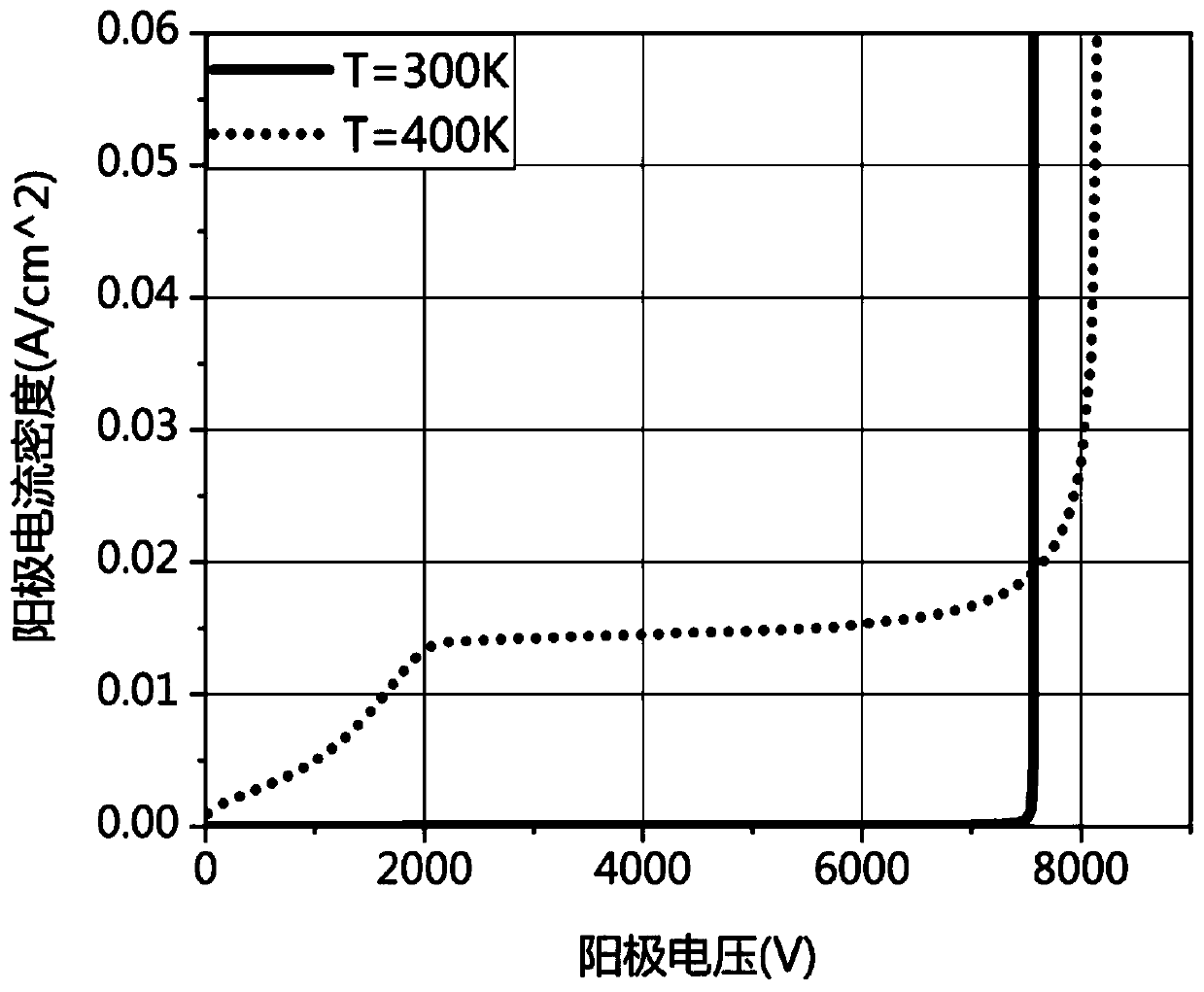

Electron injection enhanced dual-mode MOS controlled thyristor and manufacturing method thereof

ActiveCN110212027AIngenious structural designReduce on-state voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesElectron injectionDual mode

The invention discloses an electron injection enhanced dual-mode MOS controlled thyristor. An n<+> cathode region is arranged inside a p base region in the center of the upper part of an n<-> drift region; a p<++> shunt region is arranged outside the upper part of an n CS layer around the periphery of the p base region, and a cathode electrode K is formed by aluminum layers on the upper surface ofthe p<++> shunt layer and the upper surface of the n<+> cathode region together; the upper surfaces of a part of the n<+> cathode region, the p base region, the n CS layer and a part of the p<++> shunt region are provided with a gate oxide layer together, and a polycrystalline silicon layer is arranged on the upper surface of the gate oxide layer as a grid electrode G; a phosphorosilicate glass layer is arranged between the cathode electrode K and the grid electrode G; and the n<-> drift region is provided with an n FS layer, a p<+> anode region and a metallized anode A downwards in sequence.The invention also discloses a preparation method of an IE-Bi-MCT. According to the IE-Bi-MCT structure disclosed by the invention, the on-state voltage drop of the device can be reduced obviously, and the cellular maximum controllable current is improved.

Owner:合肥森思功率半导体有限公司

Asymmetrical fast thyristor

ActiveCN101931001BReduce on-state voltage dropReduce stored chargeThyristorHigh concentrationPower semiconductor device

The invention provides an asymmetrical fast thyristor, belonging to the technical field of a power semiconductor device, and mainly aiming at solving the problems of the large pressure drop, the wore dynamic characteristic and the like of the existing fast thyristor when being applied to series inversion. The asymmetrical fast thyristor is mainly characterized by comprising a thyristor shell and a semiconductor chip which is packed in the thyristor shell and has a PNPN four-layer and three-end structure; the junction depth of a P1 anode area 1 of the semiconductor chip is 20-70 of that of a cathode end P2 area 3; and the P1 anode area 1 is internally provided with a P+ high-concentration area 8. When being applied to the series inversion, the asymmetrical fast thyristor can obviously reduce the on-state pressure drop to improve the on-state capability and the work reliability, has the characteristics of being capable of preferably optimizing the inner structure, reducing the large-injection stored electric charge, and improving the resumed softness, and can be applied to a large-power series inverted power supply device.

Owner:HUBEI TECH SEMICON

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com