Controlled silicon for large-size silicon chip employing plastic entity package and packaging process thereof

A silicon chip, large-scale technology, used in the packaging field of semiconductor devices, can solve the problems of large plastic curing stress and thermal stress of silicon chips, power limitation of device products, low packaging qualification rate and reliability, etc., and achieve uniform current distribution. , Reduce the probability of hot spots, the effect of simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

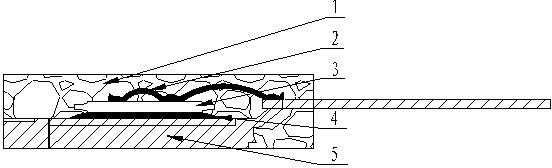

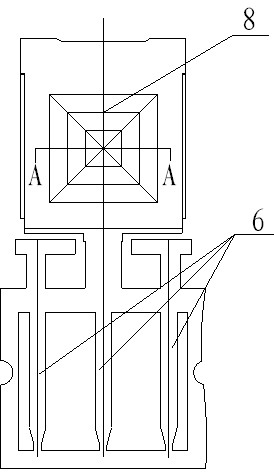

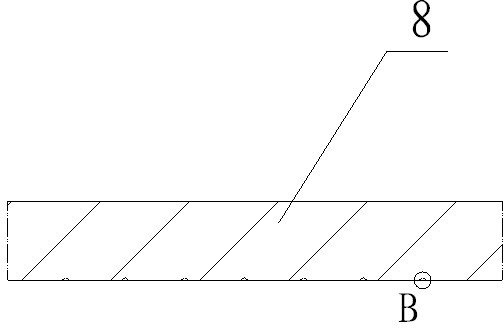

[0035] like Figures 1 to 6 As shown, a kind of large-size silicon chip of the present invention adopts the silicon controlled rectifier of plastic entity package, comprises copper base plate 5 and pin 6, is welded with silicon chip 3 by lead-tin solder 4 on copper base plate 5, welds on silicon chip 3 There are aluminum wire inner leads 2, and the outside of the aluminum wire inner leads 2 is plastic-sealed by a plastic sealing compound 1. The plastic sealing compound 1 is made of a low-stress plastic sealing compound. There are plastic grooves 7 between the pins 6, and a drainage groove 8 is opened on the copper base plate 5. The drainage groove 8 is square, and the section of the drainage groove 8 is V-shaped. Five aluminum wire inner leads 2 are welded on the silicon chip 3, and each aluminum wire inner lead 2 is pressed with two solder joints 9 on the silicon chip 3. The upper surface of the chip 3 is covered with a thickened Al layer with a thickness of 18 μm, and the lo...

Embodiment 2

[0037] like Figures 1 to 6 As shown, a kind of large-size silicon chip of the present invention adopts the silicon controlled rectifier of plastic entity package, comprises copper base plate 5 and pin 6, is welded with silicon chip 3 by lead-tin solder 4 on copper base plate 5, welds on silicon chip 3 There are aluminum wire inner leads 2, and the outside of the aluminum wire inner leads 2 is plastic-sealed by a plastic sealing compound 1. The plastic sealing compound 1 is made of a low-stress plastic sealing compound. There are plastic grooves 7 between the pins 6, and a drainage groove 8 is opened on the copper base plate 5. The drainage groove 8 is circular, and the section of the drainage groove 8 is V-shaped. Five aluminum wire inner leads 2 are welded on the silicon chip 3, and each aluminum wire inner lead 2 is pressed with two solder joints 9 on the silicon chip 3. The upper surface of the silicon chip 3 is covered with a thickened Al layer with a thickness of 20 μm, ...

Embodiment 3

[0039] like Figures 1 to 6 As shown, a kind of large-size silicon chip of the present invention adopts the silicon controlled rectifier of plastic entity package, comprises copper base plate 5 and pin 6, is welded with silicon chip 3 by lead-tin solder 4 on copper base plate 5, welds on silicon chip 3 There are aluminum wire inner leads 2, and the outside of the aluminum wire inner leads 2 is plastic-sealed by a plastic sealing compound 1. The plastic sealing compound 1 is made of a low-stress plastic sealing compound. There are plastic grooves 7 between the pins 6, and a drainage groove 8 is opened on the copper base plate 5. The drainage groove 8 is in the shape of a square plus a diagonal line, and the section of the drainage groove 8 is V-shaped. There are five aluminum wire inner leads 2 welded on the silicon chip 3, and each aluminum wire inner lead 2 is pressed on the silicon chip 3 with two Solder spot 9, the upper surface of the silicon chip 3 is covered with a thick...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com