Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

100results about How to "Reduce the number of photolithography" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

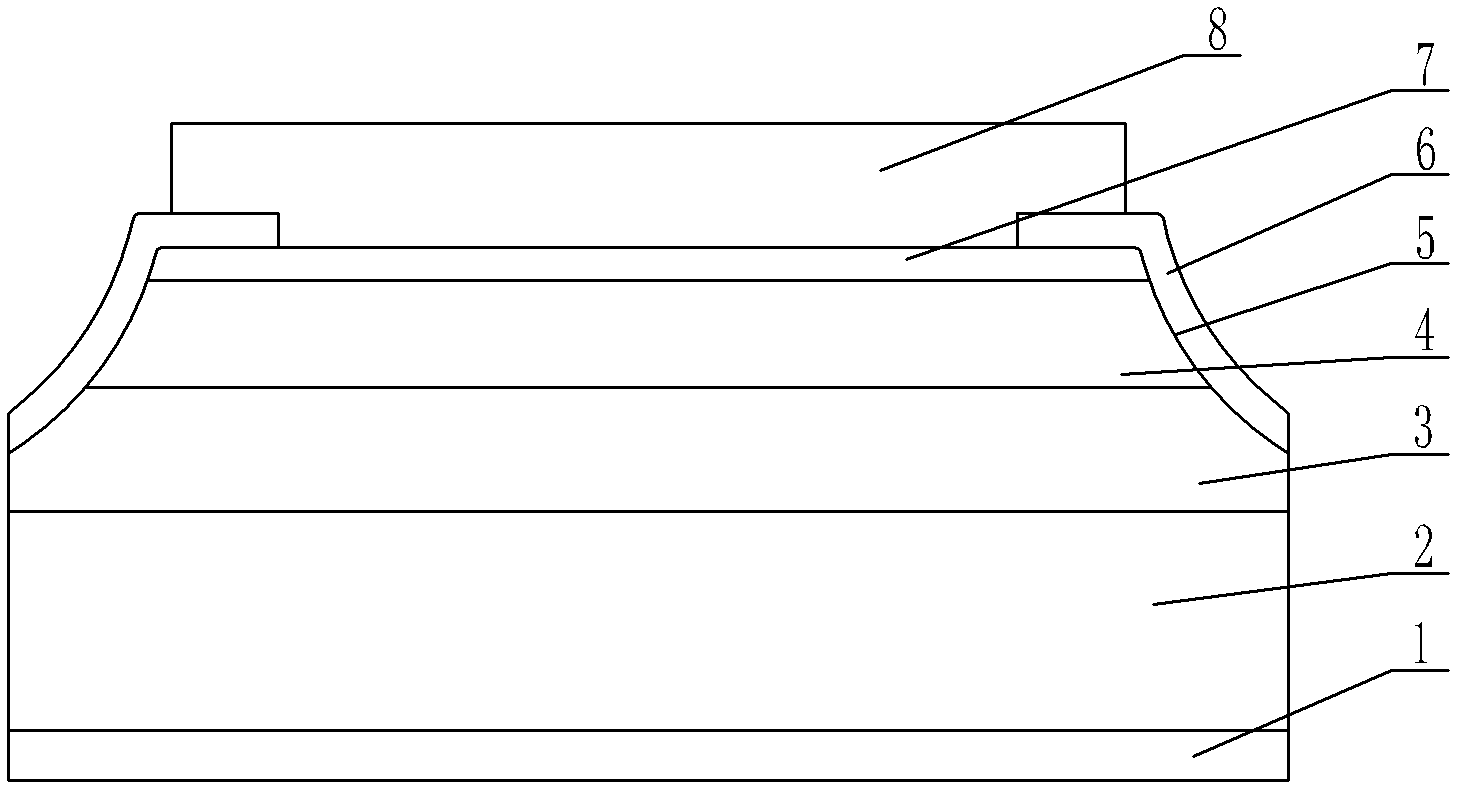

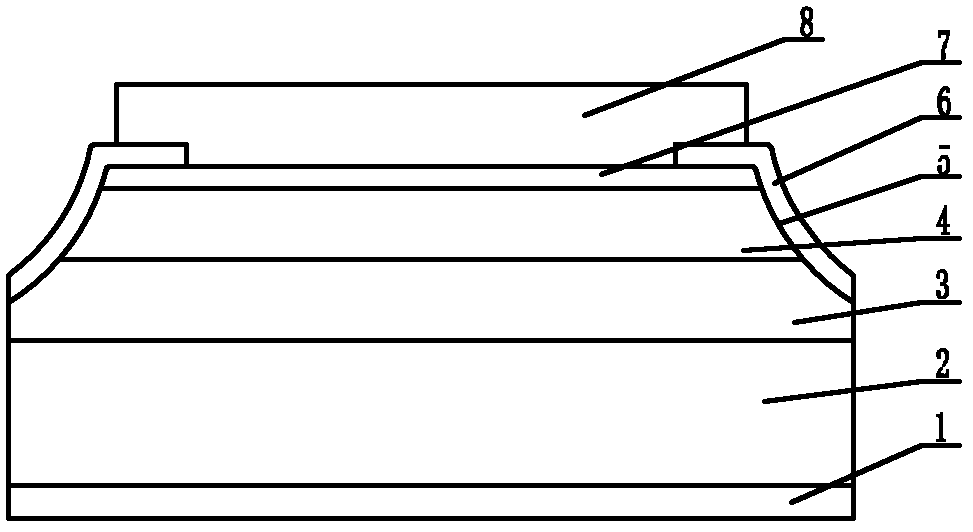

Fast recovery epitaxial diode and preparation method thereof

InactiveCN102496572AGood ohmic contactPrevent extensionSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropSilicon chip

The invention relates to a fast recovery epitaxial diode comprising a metal cathode layer, an N + substrate silicon chip, a first epitaxial layer, a second epitaxial layer, a third epitaxial layer, wherein the above-mentioned parts are successively connected. A mesa silicon groove penetrates the third epitaxial layer and is extended into the second epitaxial layer; a glass passivation layer that is arranged inside the mesa silicon groove and is provided with a window is extended to the top surface of the third epitaxial layer; and a metal anode layer that is arranged at the upper portion of the glass passivation layer passes through the window that is arranged on the glass passivation layer and then is connected with the third epitaxial layer. According to the invention, an epitaxial technology is used to accurately control impurity concentration and thickness of all the epitaxial layers; and a mesa channeling technology and a glass passiviation technology are utilized to manufacture a terminal structure, thereby substantially reducing a technology flow. Besides, the fast recovery epitaxial diode has good consistency and repeatability; high quality characteristics including low forward direction voltage drop, super speediness, and soft recovery characteristic and the like of the fast recovery epitaxial diode can be easily realized.

Owner:MACMIC SCIENCE & TECHNOLOGY CO LTD

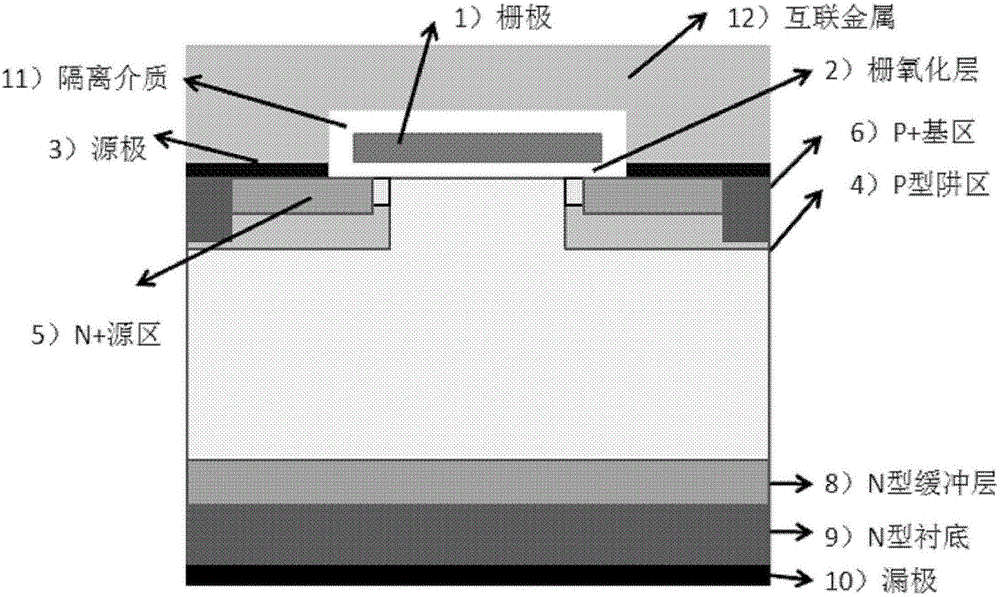

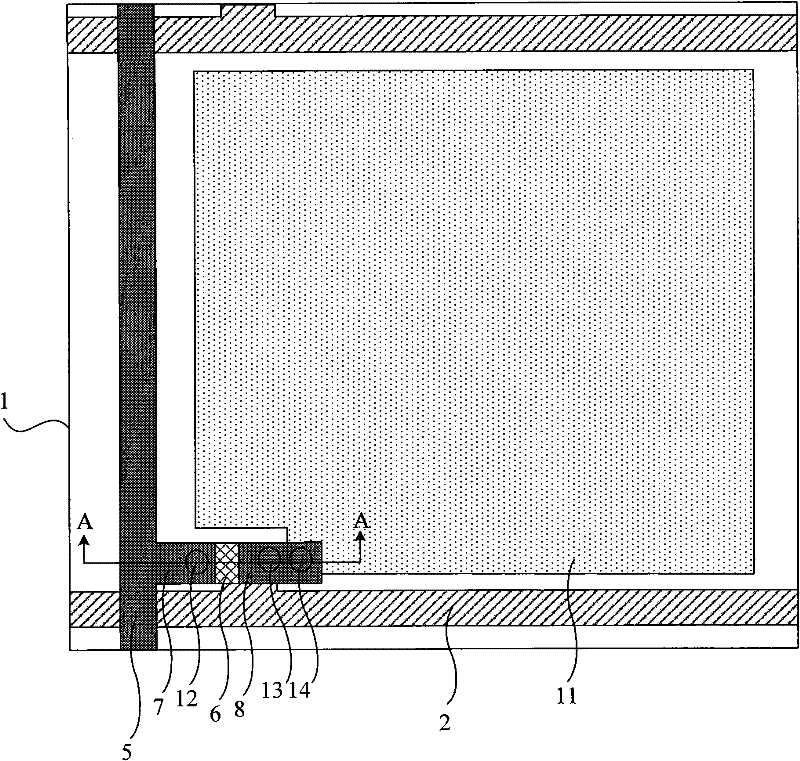

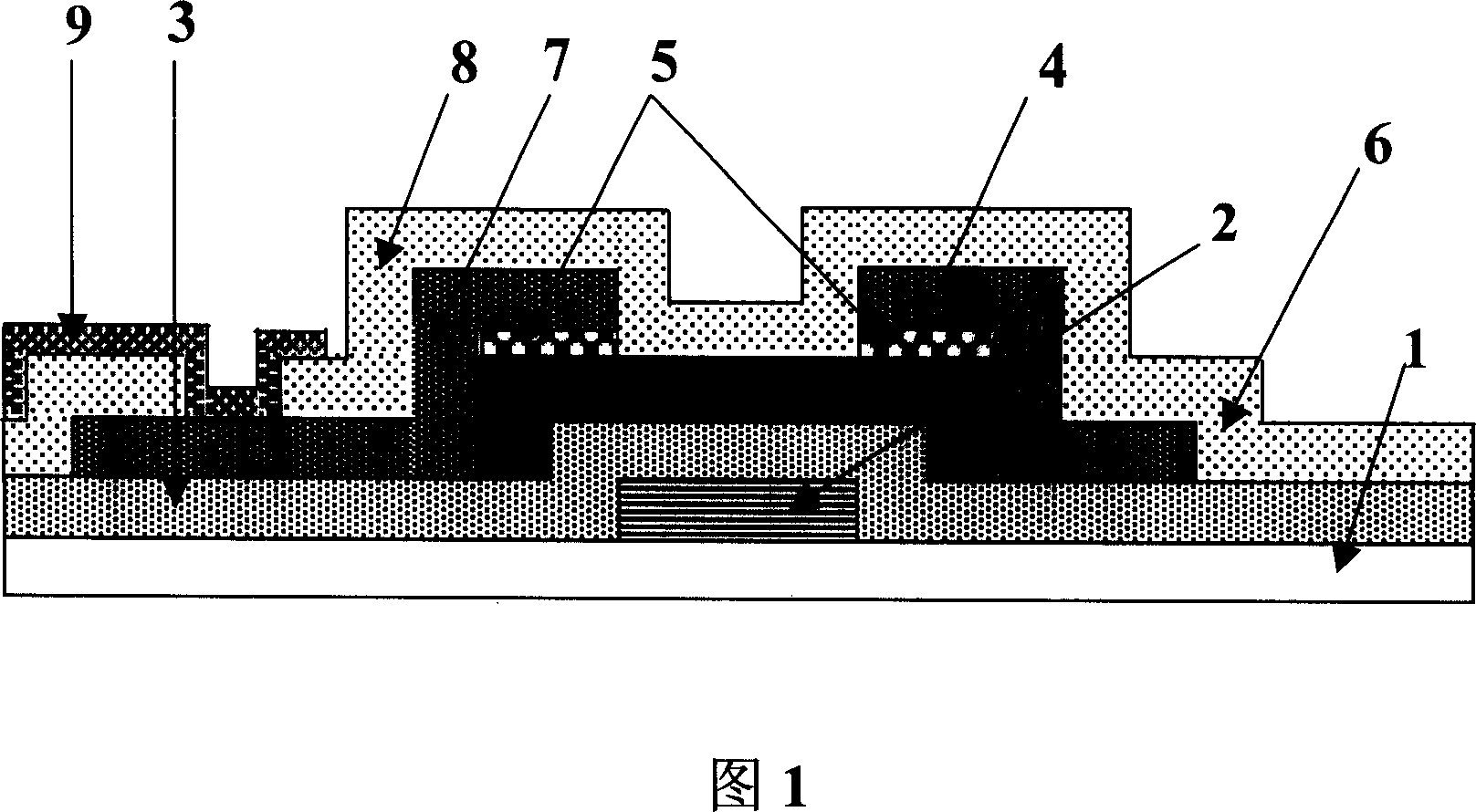

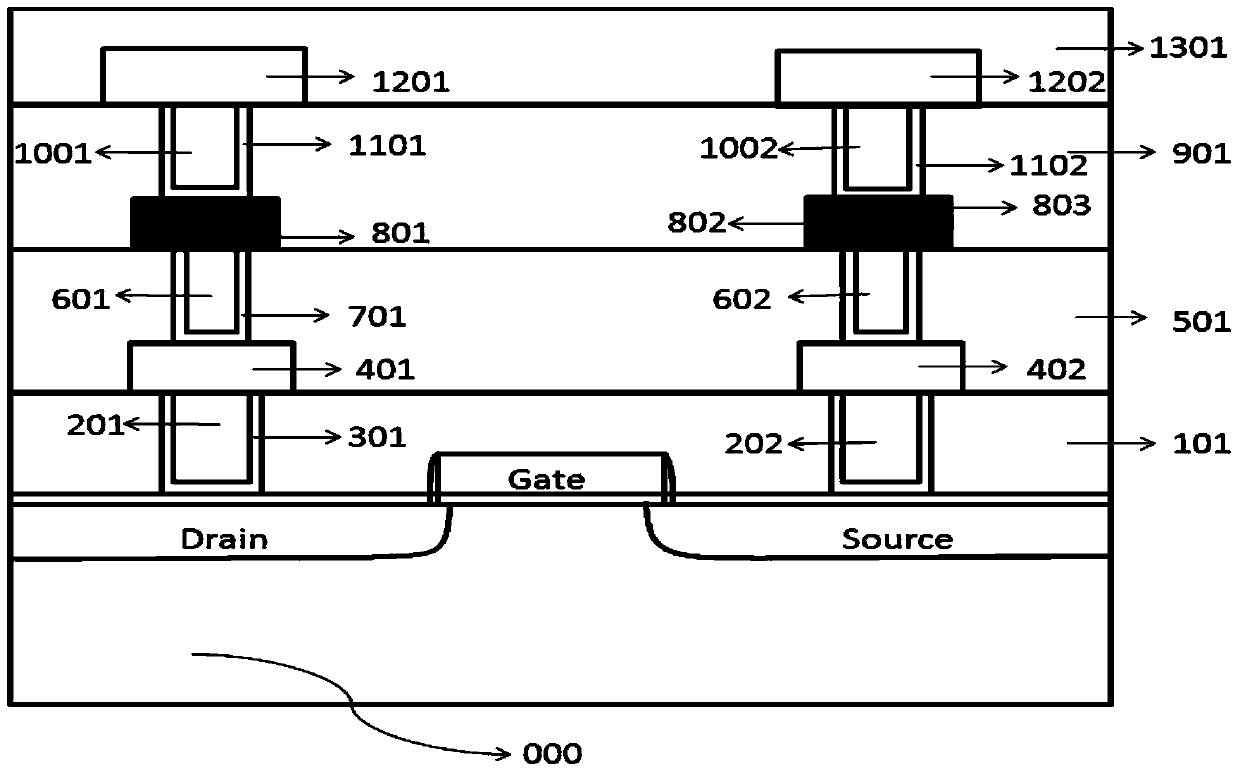

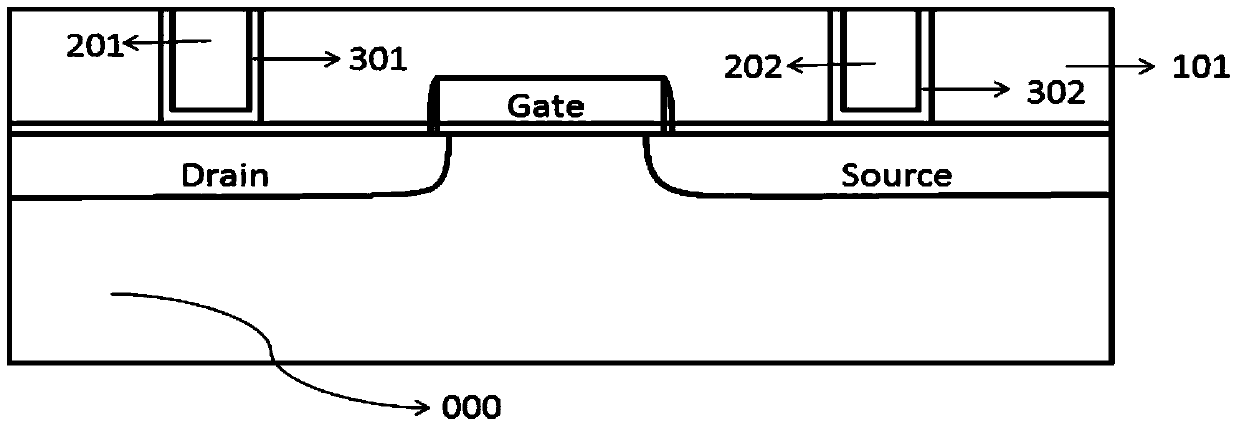

SiC metal-oxide-semiconductor field-effect transistor (MOSFET) device and fabrication method thereof

ActiveCN105810722AShort processReduce the number of photolithographySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETInterconnection

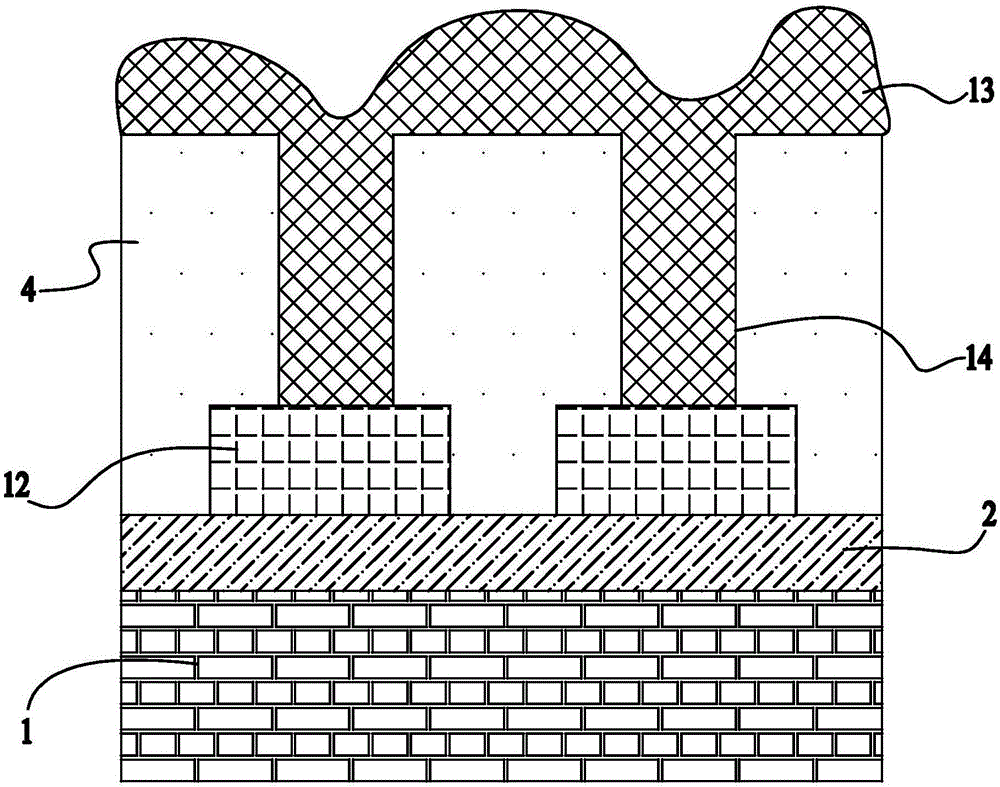

The invention discloses a SiC metal-oxide-semiconductor field-effect transistor (MOSFET) device and a fabrication method thereof. The SiC MOSFET device comprises a plurality of cells, wherein the cells are connected through interconnection metal (12), each cell comprises a grid, a grid oxide layer, two sources, an N-type drift layer, an N+ buffer layer, an N+ substrate, a drain and an isolation medium. According to the process step disclosed by the invention, in a photoetching plate subjected to tapping in a contact region, contact metal evaporation and stripping, a source electrode region is provided with a pattern, and a pattern also exists in a pad region of the grid.

Owner:ZHEJIANG XINKE SEMICON CO LTD

Array base plate, liquid crystal display and manufacturing method for array base plate

InactiveCN102446925AImprove performanceIncrease productivitySolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayEngineering

The invention discloses an array base plate, a liquid crystal display and a manufacturing method for the array base plate. The array base plate comprises a substrate base plate; a grid line, a data wire, a thin film transistor, a pixel electrode, an active layer, a passivation layer and a grid insulating layer are formed on the substrate base plate; the thin film transistor comprises a grid electrode connected with the grid line, a source electrode connected with the data wire and a drain electrode connected with the pixel electrode; the grid insulating layer is formed above the grid electrode; the passivation layer is arranged among the active layer, the source electrode and the drain electrode; the passivation layer is provided with a source electrode through hole and a drain electrode through hole; and the source electrode and the drain electrode are respectively connected with the active layer through the source electrode through hole and the drain electrode through hole. According to the technical scheme, the active layer, the passivation layer and the grid insulating layer are formed by one-time composition, so that the composition number is reduced and the production efficiency is improved; and meanwhile, the array base plate structure in which the passivation layer is positioned above the active layer is realized, and damage to a thin film transistor (TFT) channel when the source electrode and the drain electrode are formed is avoided.

Owner:BOE TECH GRP CO LTD

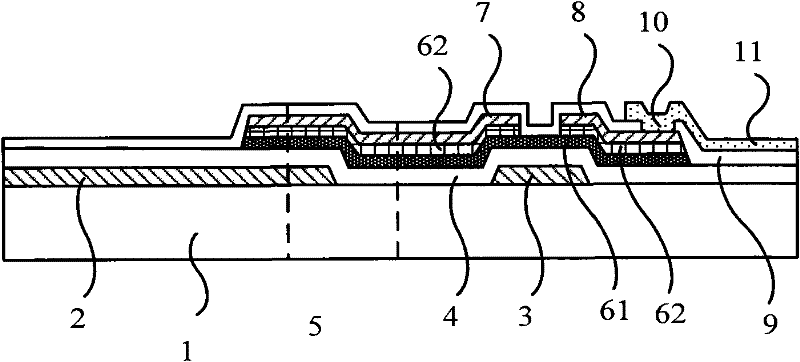

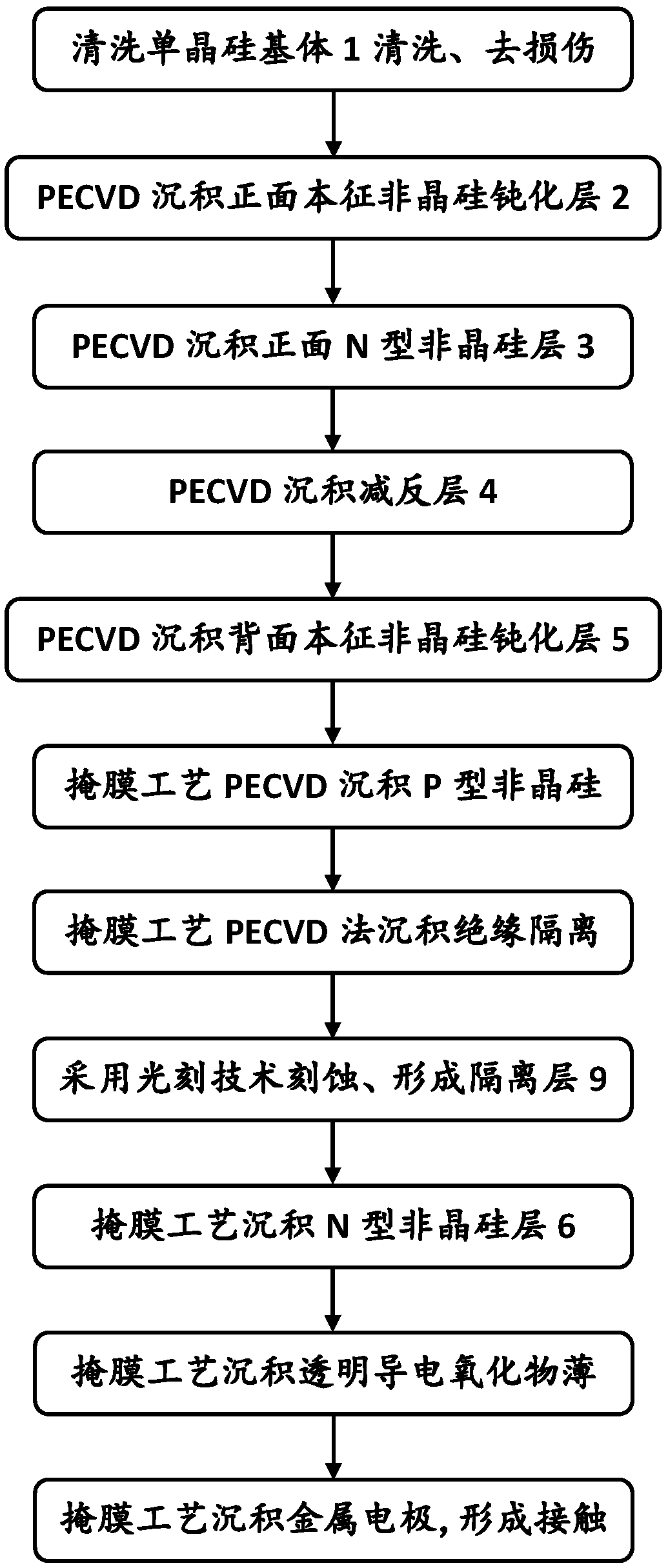

A preparation method of a back-contact heterojunction solar cell

ActiveCN109216509AReduce widthIncrease collection rateFinal product manufacturePhotovoltaic energy generationHeterojunctionContact layer

The invention discloses a preparation method of a back-contact heterojunction solar cell. A pre-passivation layer of intrinsic amorphous silicon, an N-type amorphous silicon layer and an anti-reflection layer are sequentially deposited on the front side of the washed and dedamaged layer and the velveted monocrystalline silicon substrate; Depositing an intrinsic amorphous silicon back passivation layer on the back surface of the battery; The P-type amorphous silicon layer is deposited on the surface of the back passivation layer by a mask method, and then the insulation isolation layer betweenthe P-type amorphous silicon layer and the N-type amorphous silicon layer is directly deposited, and the insulation isolation layer is etched according to the preset width of the insulation isolationlayer by a photolithography method; Further depositing an N-type amorphous silicon layer on the back surface by a mask method; At last, that transparent conductive film is sequentially deposite by adopting a mask proces, and the metal film forms a contact layer, thereby completing the preparation of the solar cell of the invention. The invention improves the preparation process precision of the back surface structure pattern of the HBC single crystal silicon solar cell, reduces the width of the isolation layer, and improves the collection probability of the photogenerated carriers and the short-circuit current density of the HBC solar cell.

Owner:XIAN UNIV OF TECH

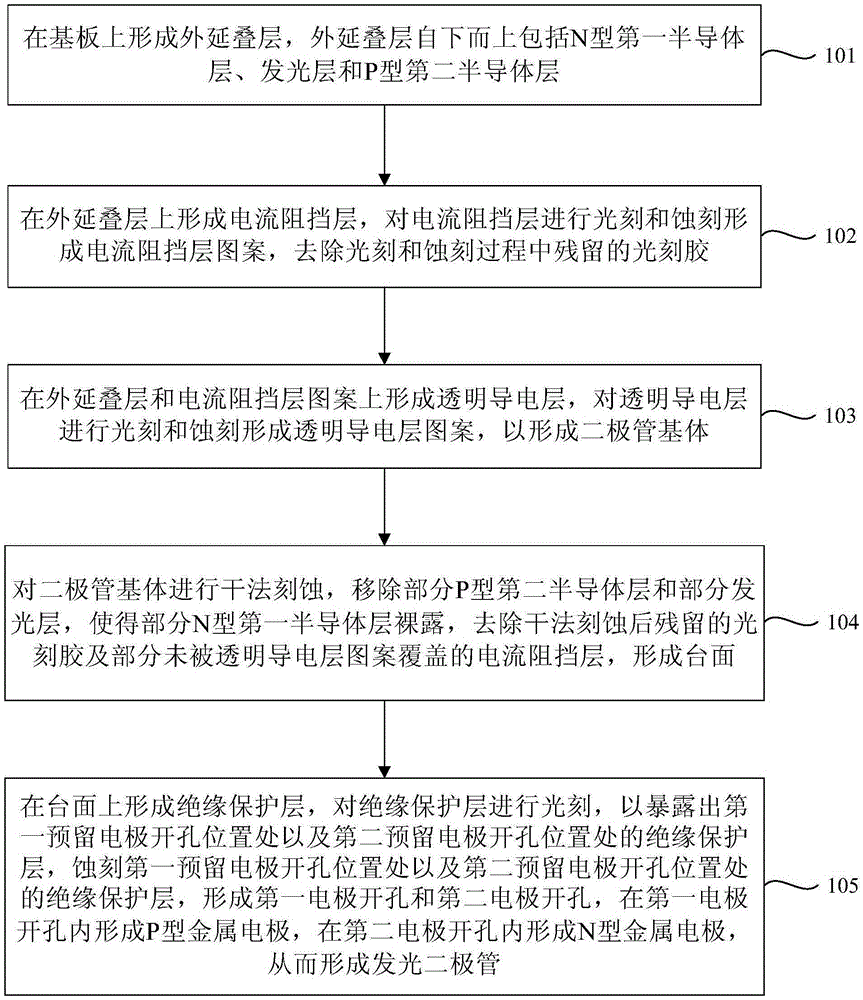

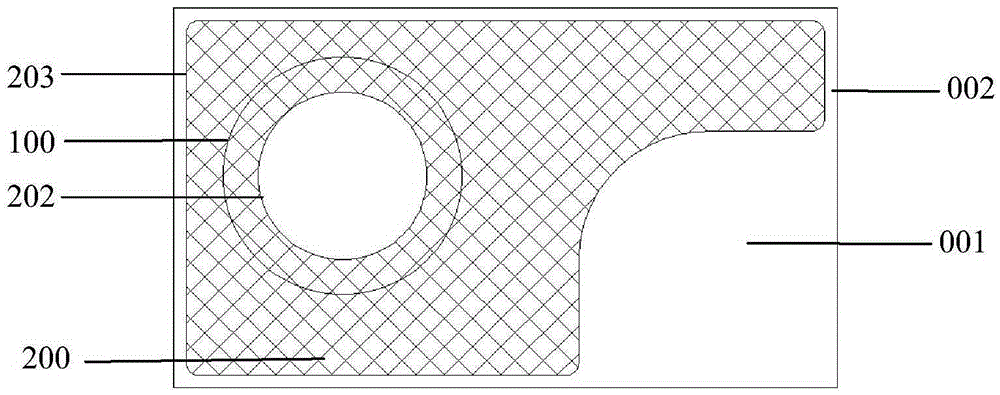

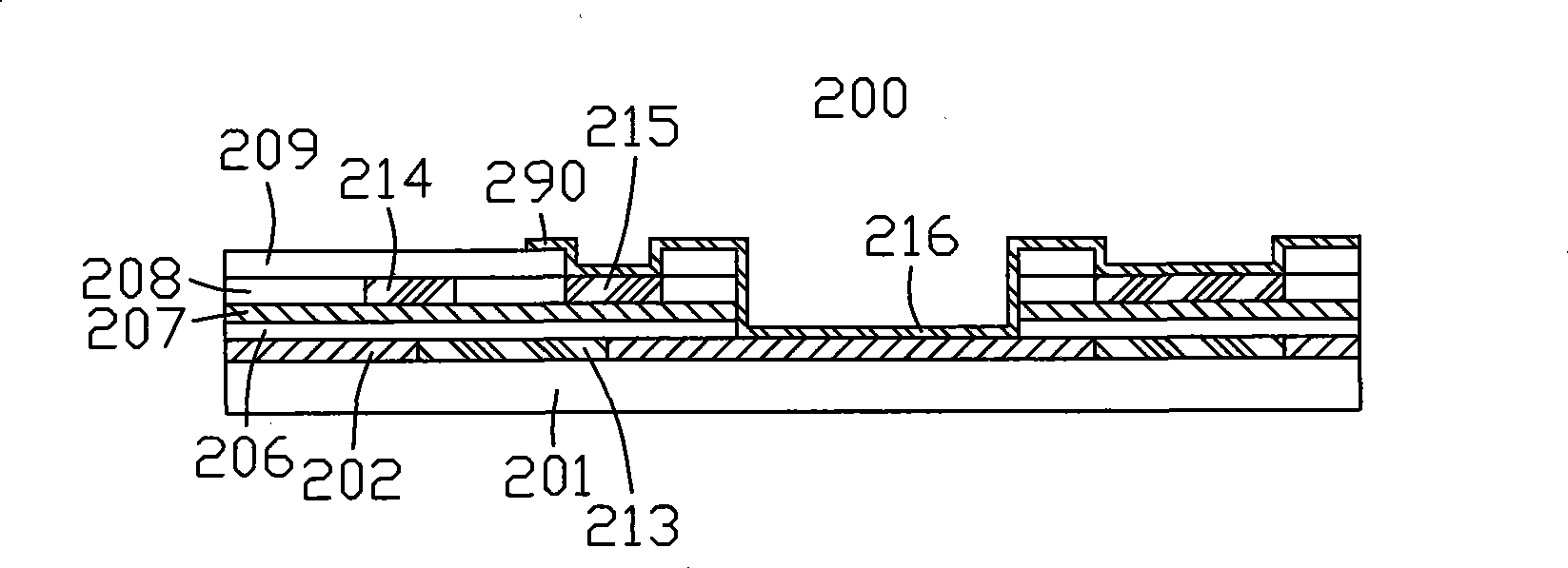

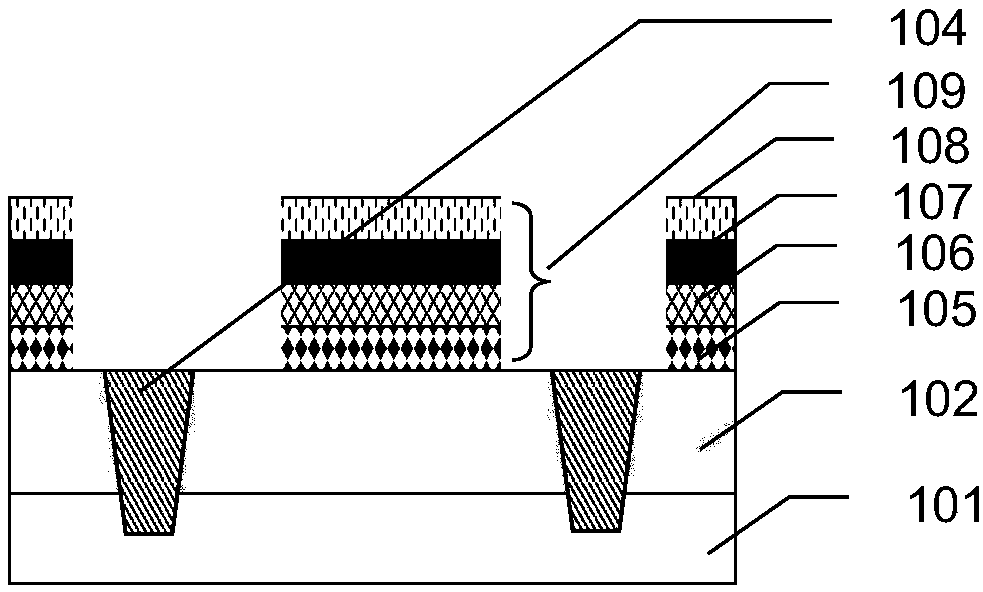

Manufacturing method of GaN-based light emitting diode

Embodiments of the invention provide a manufacturing method of a GaN-based light emitting diode. The method comprises the following steps of forming an epitaxial lamination on a substrate; forming a current barrier layer pattern and a transparent conducting layer pattern on the epitaxial lamination; carrying out dry etching so that a part of N-type first semiconductor layer is exposed so as to form a table board; forming an insulation protection layer on the table board, carrying out electrode lithography on the insulation protection layer so as to form a first electrode opening and a second electrode opening, and forming a metal electrode in each electrode opening so as to form a light emitting diode. By using the manufacturing method of the GaN-based light emitting diode, through adjusting lithography of each structure and an etching sequence, in a total process flow, the lithography only needs to be performed for three times so that the light emitting diode which has a same structure with the structure of the light emitting diode obtained through using a routine technology is acquired; manufacturing time of the light emitting diode is shortened; and material cost and production cost are reduced.

Owner:EPITOP PHOTOELECTRIC TECH

Thin-film transistor manufacturing method

InactiveCN101364572AReduce the number of photolithographySimple processSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor

The invention relates to a method for manufacturing a thin-film transistor baseplate, which comprises the following steps: an insulating base is provided; a grid groove is formed on the insulating base; a grid metal layer is deposited; chemical and mechanical grinding is performed to the grid metal layer to form a grid electrode; a grid insulating layer, a semiconductor layer and a first passivation layer are deposited in sequence; a source electrode groove and a drain electrode are formed; a source / drain electrode metal layer is deposited; chemical and mechanical grinding is performed to the source / drain electrode metal layer to form a source electrode and a drain electrode; a second passivation layer is deposited; a pixel electrode groove is formed and the drain electrode is exposed; a conductor layer is deposited; and a pixel electrode is formed.

Owner:INNOCOM TECH SHENZHEN +1

High-density phase change memory and preparation method thereof

ActiveCN109686755AReduce power consumptionReduce contact areaSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing cost reductionPhase-change memory

The invention discloses a high-density phase change memory including a Schottky diode, a phase change layer and an upper electrode from bottom to top. The Schottky diode includes a semiconductor layerand a metal layer forming a Schottky barrier with the semiconductor layer. The metal layer serves as a lower electrode of the phase change layer at the same time. The semiconductor layer, the metal layer, the phase change layer and the upper electrode are of a flat layer structure stacked from bottom to top, or the semiconductor layer, the phase change layer and the upper electrode are of a planar structure arranged from bottom to top, the metal layer is connected with a planar bottom surface and a vertical sidewall, the metal layer is overlapped with the semiconductor layer below the metal layer through the bottom surface and is connected to the phase change layer above the metal layer through the sidewall, and the phase change layer is stacked on the upper electrode. The memory can effectively improve the density of phase change memory units, reduce the number of lithography, simplify the process and reduce the manufacturing cost. The invention also discloses a preparation method ofthe high-density phase change memory.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

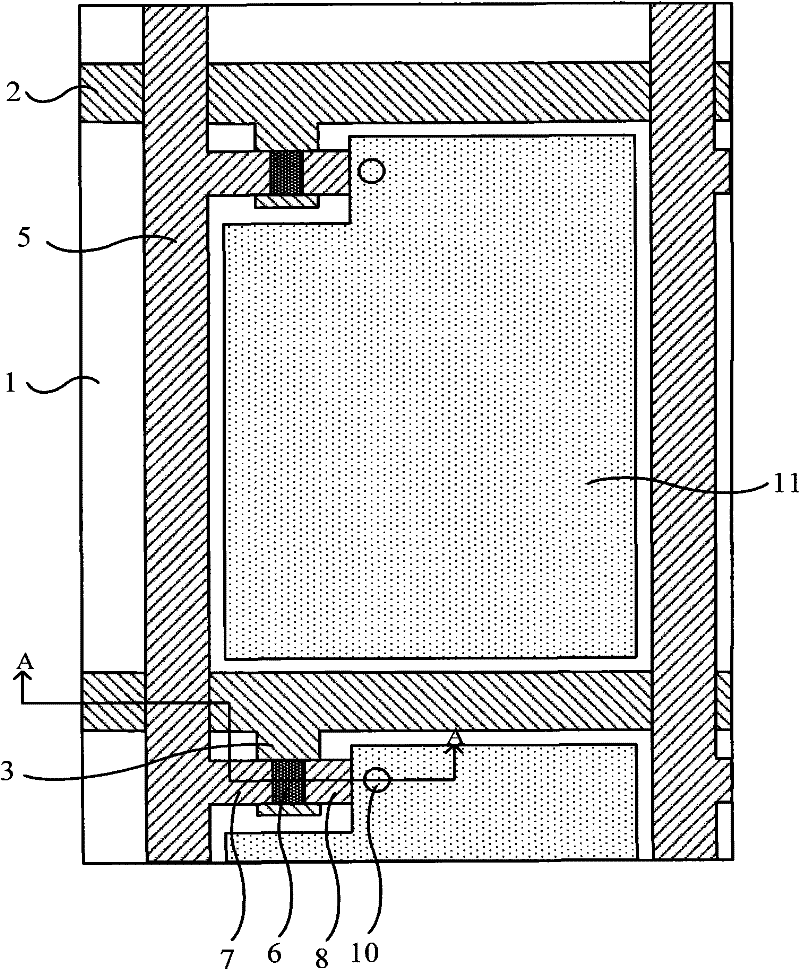

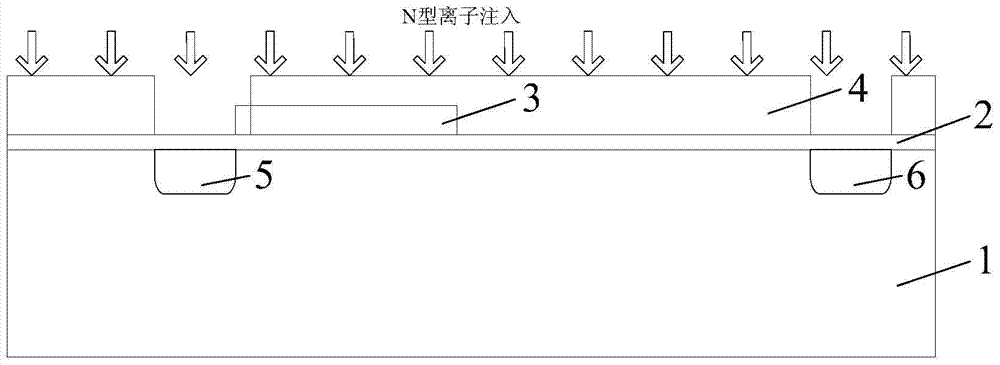

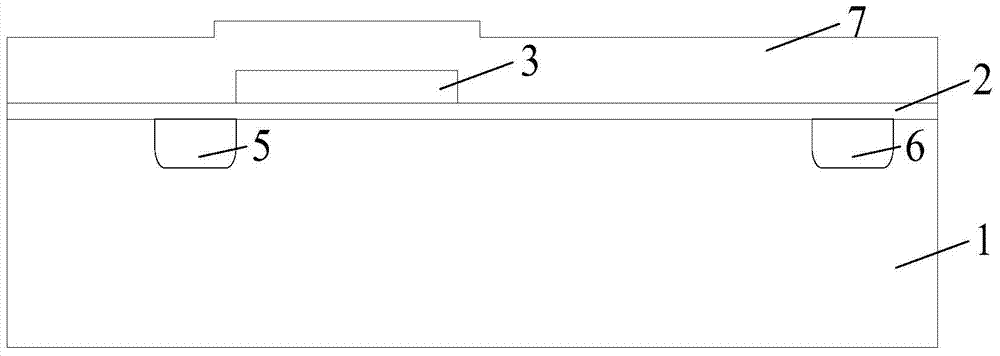

Power MOS field effect pipe with poly-silicon field plate and manufacturing method thereof

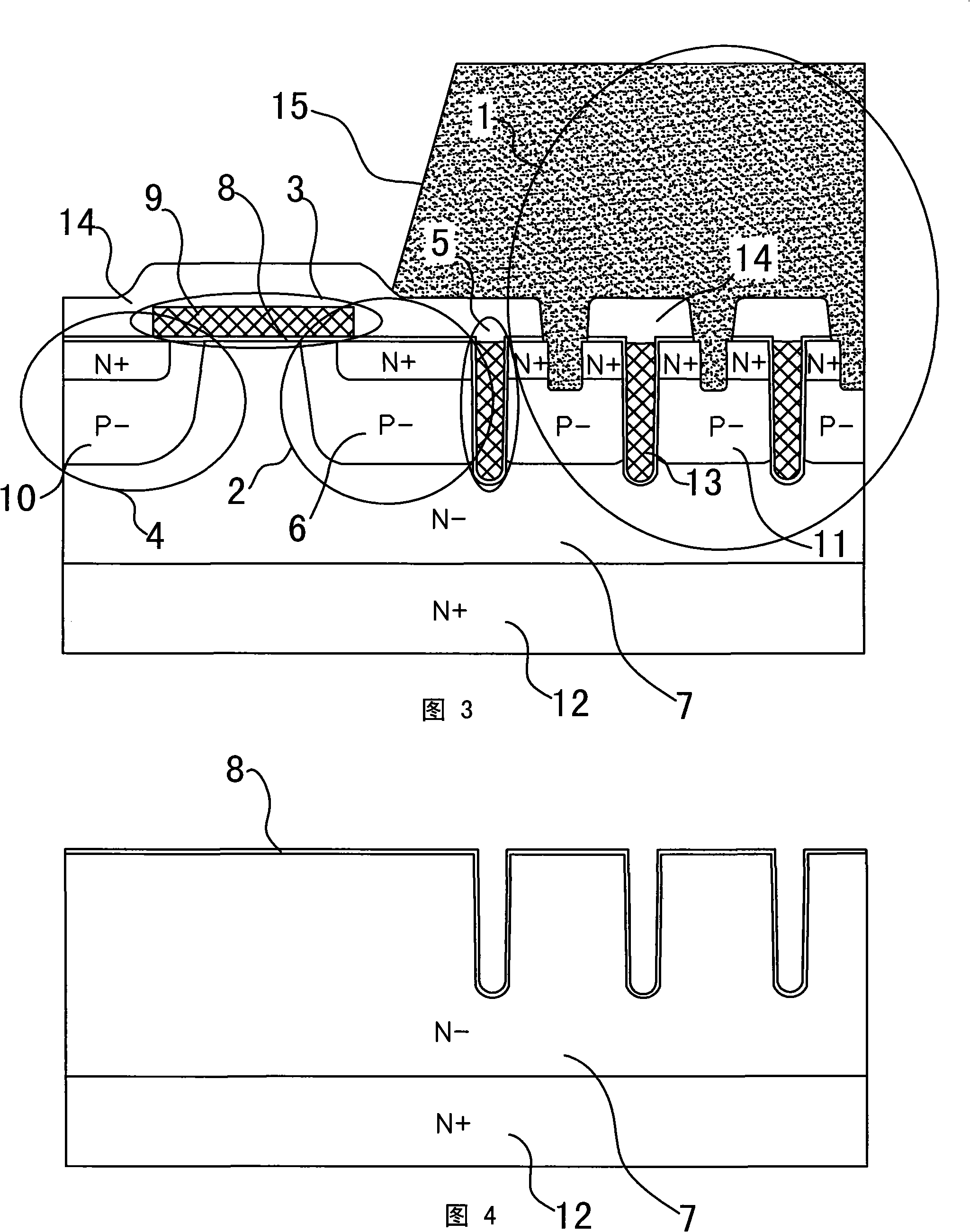

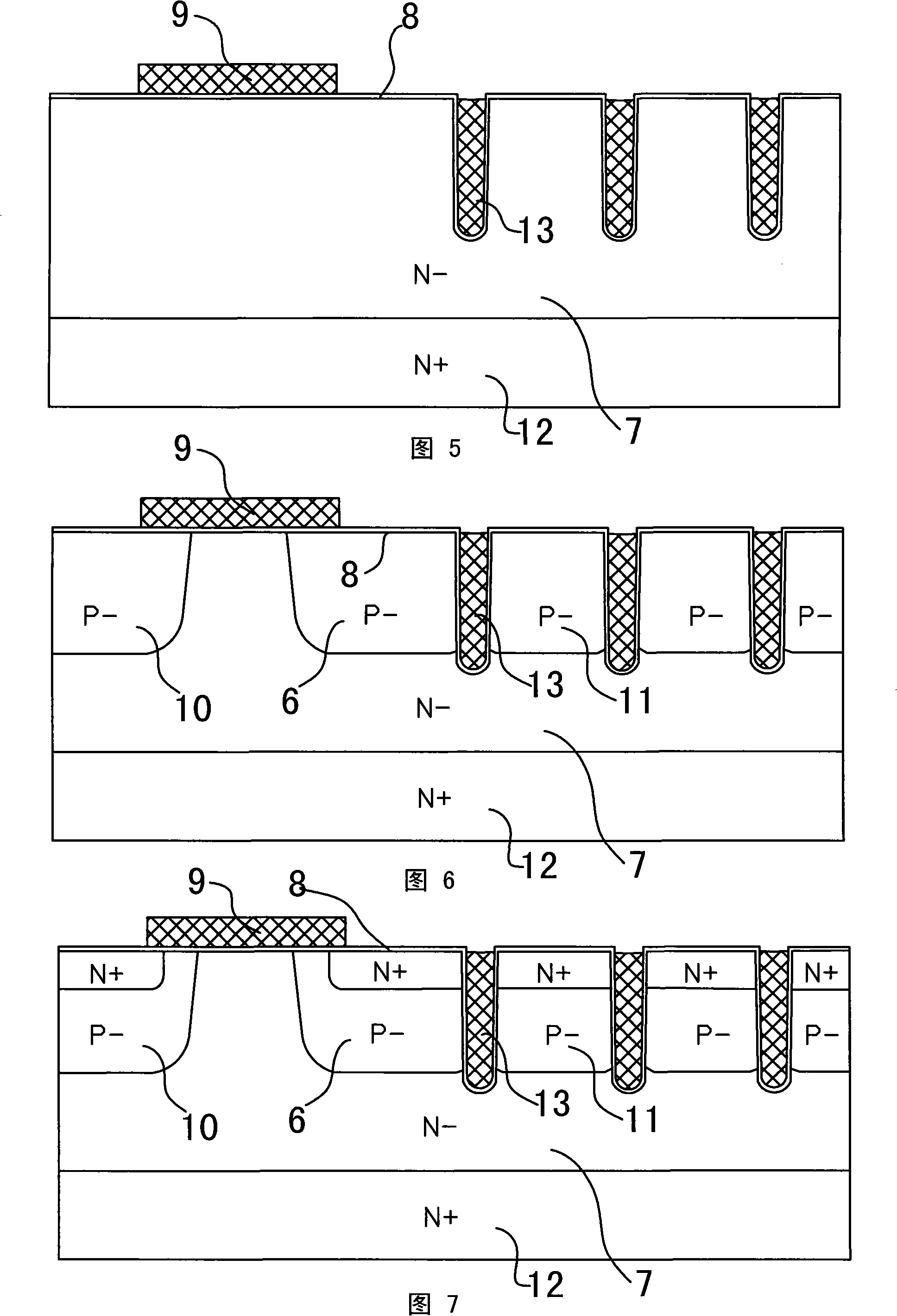

InactiveCN101271898AAdjustable widthActs as a field limiting ringTransistorSemiconductor/solid-state device manufacturingManufacturing cost reductionImpurity ions

A power MOS field effect transistor with polysilicon field plate and a manufacture method thereof are characterized in that a terminal protection structure of the periphery of an active region of the MOS field effect transistor is improved in the following aspects: 1. a P<-> trap of the periphery of edged unit cells of a unit cell array is directly treated as a field limiting ring; 2. a field limiting ring P<-> area, a cut-off ring P<-> area and a P<-> trap of the unit cell array are treated as the same manufacturing layer which is formed by P-shaped doping simultaneously; 3. field oxygen is omitted, the structure of the field plate is changed in composition and composed by a grid silica layer and polysilicon; 4. the polysilicon in the field plate is treated as a barrier layer injected with P-shaped impurity ions, and the field limiting ring P<-> area, the cut-off ring <-> area and the P<-> trap of the unit cell are formed directly; 5. N-shaped doping is carried out after P-shaped doping, thus causing upper parts of the field limiting ring P<-> area, the cut-off ring P<-> area and the P<-> trap of the unit cell array have an N<+> area. The power MOS field effect transistor with polysilicon field plate and a manufacture method thereof of the invention have the advantages of saving the photoglith plate of the active region, the photoglith plate of the field limiting ring and the photoglith plate with three layers injected in the active region, on the premise of guaranteeing performance of products, reducing times of photoetching, reducing manufacture cost greatly, which are suitable for manufacturing the power MOS field effect transistor with low cost on a large scale.

Owner:SUZHOU SILIKRON SEMICON CO LTD

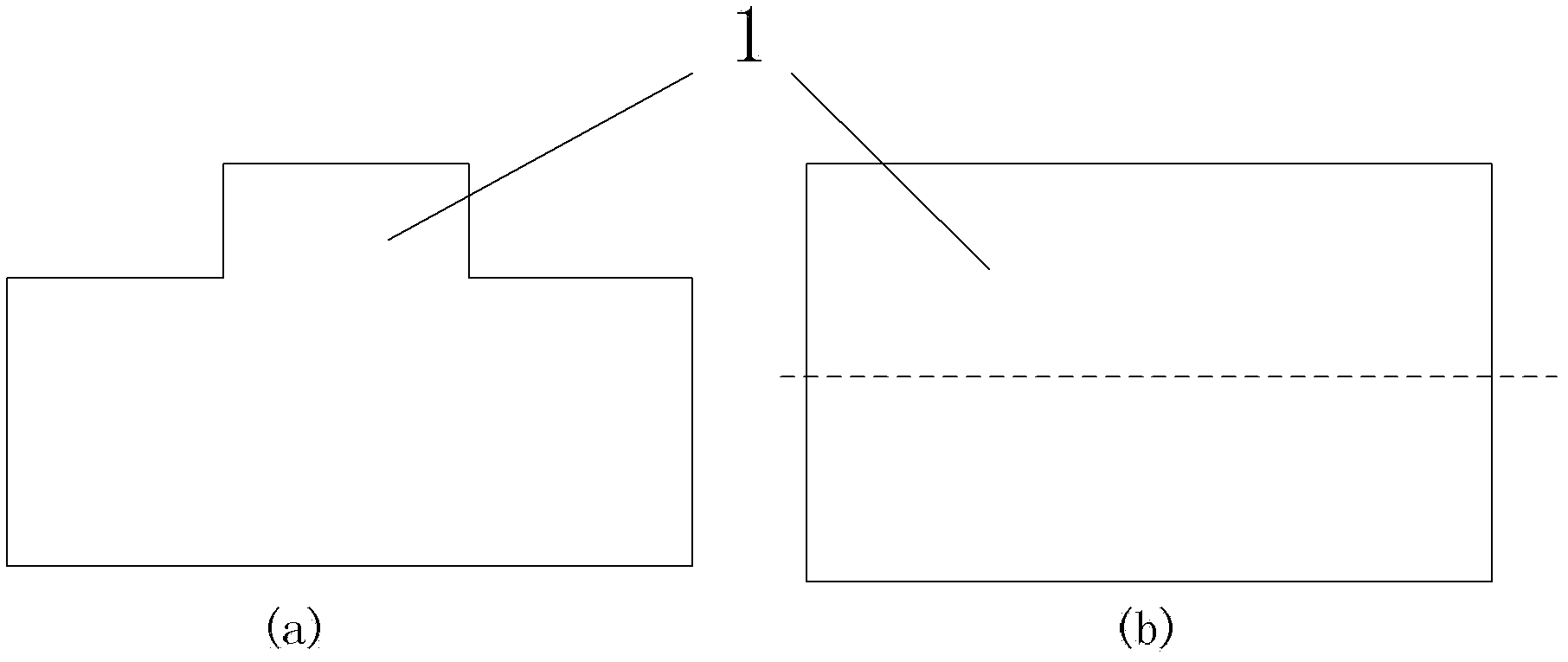

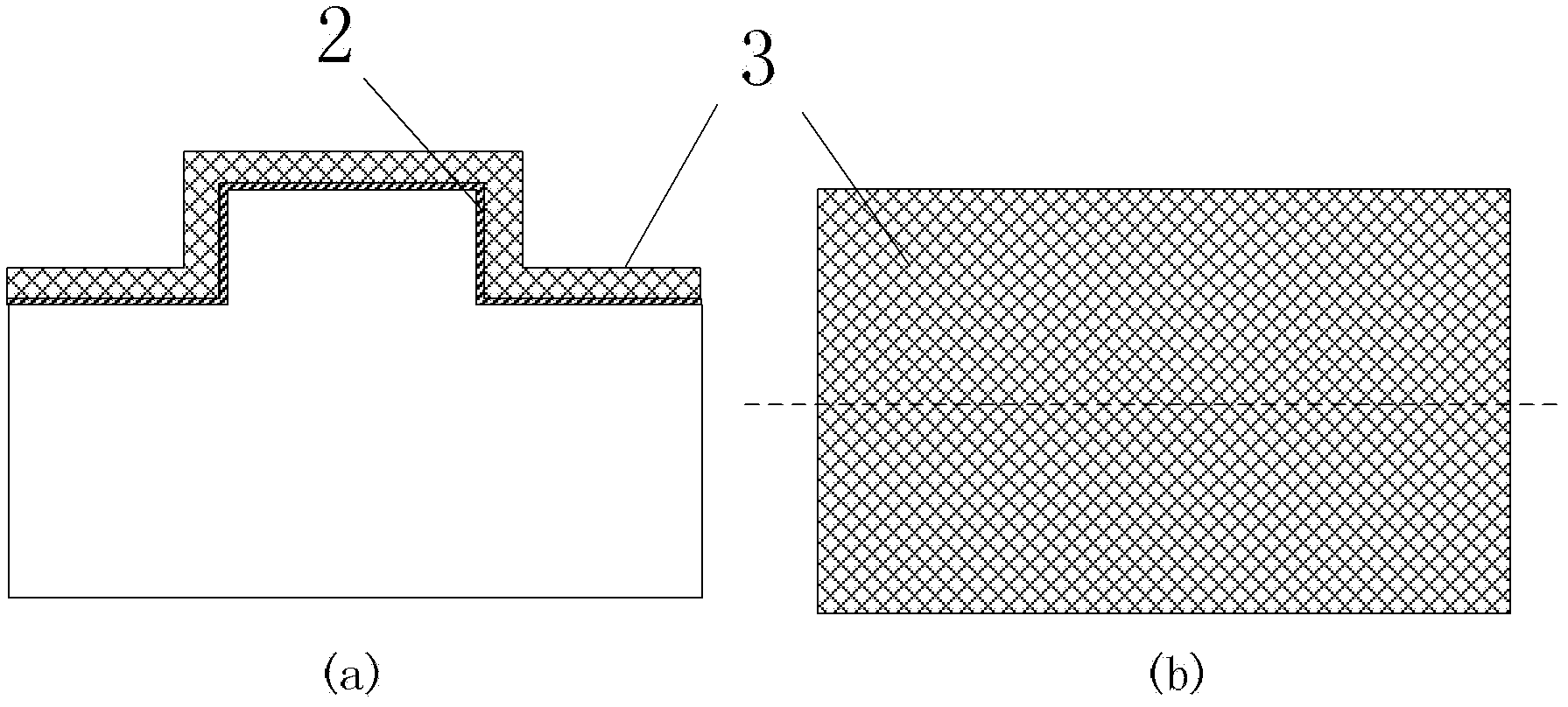

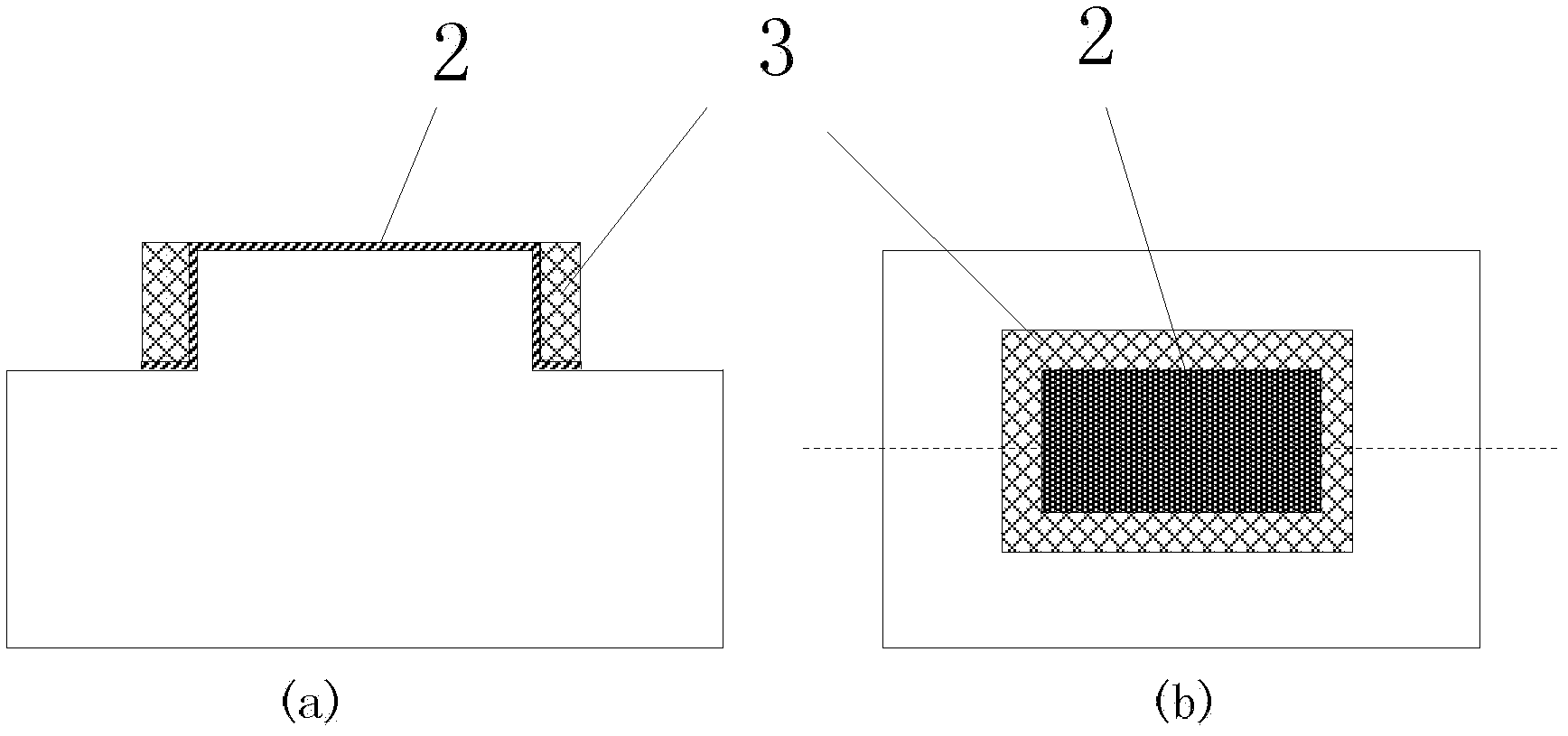

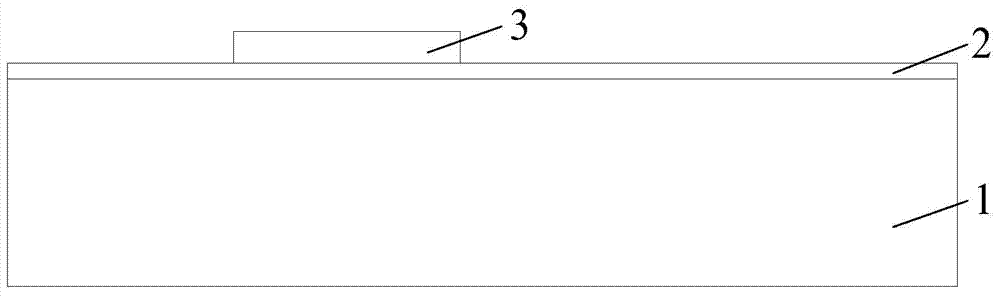

Schottky barrier metal oxide semiconductor (MOS) transistor and preparation method thereof

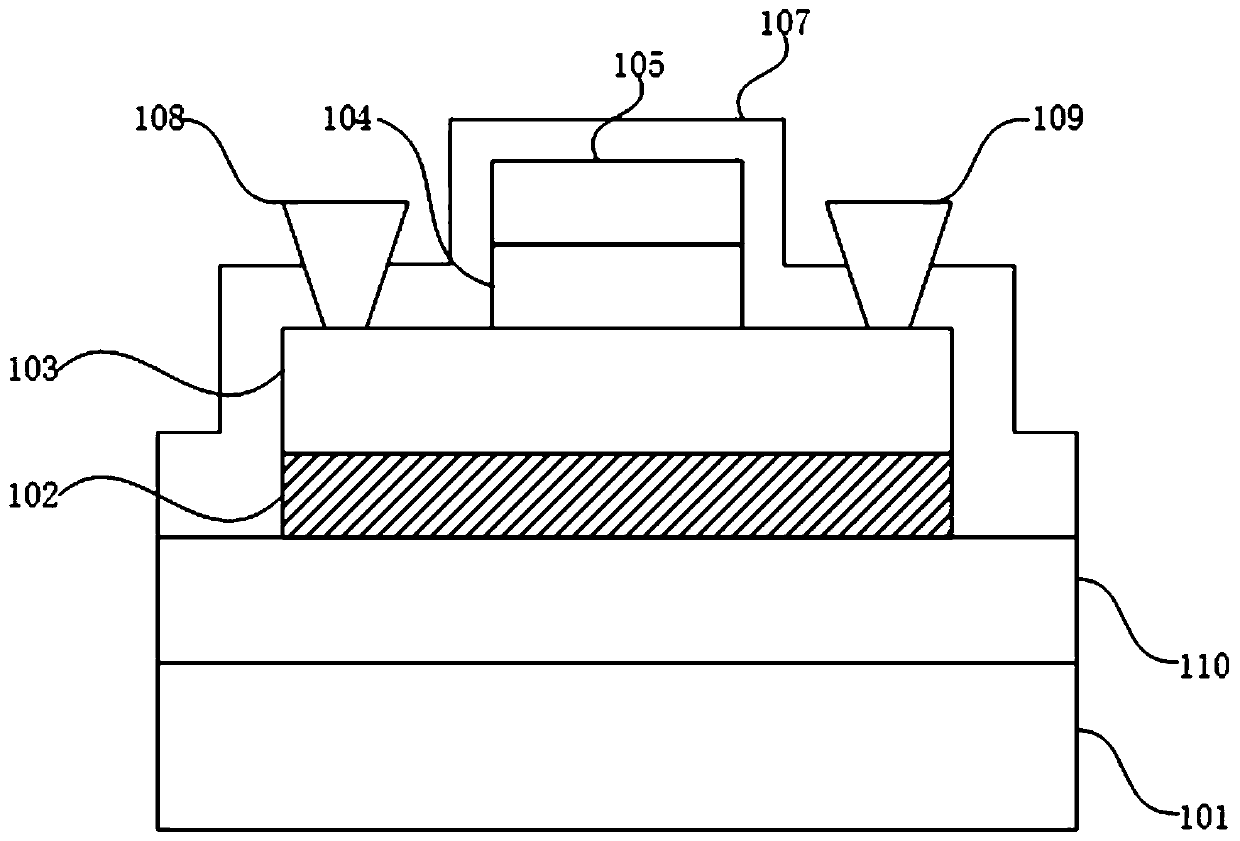

ActiveCN102324434AReduce parasitic resistanceEliminate uncovered areasSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

The invention discloses a Schottky barrier metal oxide semiconductor (MOS) transistor, which comprises a ring-shaped gate electrode (3), a ring-shaped gate dielectric layer (2), a ring-shaped gate electrode side wall (4), a semiconductor substrate, a source region (5) and a ring-shaped drain region (6). The Schottky barrier MOS transistor is characterized in that: the semiconductor substrate is provided with a convex step structure; the source region is positioned on a high plane of a convex step; the ring-shaped drain region surrounds the convex step and is positioned on a low plane; the gate dielectric layer and the gate electrode are positioned at a corner of the convex step, surrounds the step and is raised into a ring shape; and the gate electrode side wall is ring-shaped, surrounds on the outer side of the gate electrode and has a certain thickness to serve as a shelter to form an underlap structure of a drain terminal. The Schottky barrier MOS transistor adopts a step structurecombining a ring-shaped gate structure and an asymmetric source / drain structure, so on the basis of inheriting advantages of traditional SB-MOSFET, the on-state conduction current is improved, a dipolar effect is inhibited, and the process is simplified.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Three-dimensional stacked phase change memory and preparation method thereof

ActiveCN109524543AReduce the number of photolithographyReduce the size of the phase transition regionSolid-state devicesSemiconductor devicesPhase-change memoryMiniaturization

The invention discloses a three-dimensional stacked phase change memory and a preparation method thereof. The preparation method comprises a step of preparing first horizontal electrodes with spacingfrom each other on a substrate, a step of preparing first strip-shaped phase change layers with gaps in the centers in areas corresponding to the spacing of the first horizontal electrodes, a step ofpreparing first gate tubes between the gaps of the first strip-shaped phase change layers, a step of preparing a first insulating layer, a step of preparing second horizontal electrodes at the same vertical positions on the first insulating layer, a step of preparing second strip-shaped phase change layers, a step of preparing second gate tubes, a step of preparing horizontal insulating holes in the spacing of the horizontal electrodes, and a step of preparing a vertical electrode between adjacent insulating holes and then forming a multi-layer stacked phase change memory with a vertical structure. According to the invention, the overall process design of the key preparation method, the shape setting of each detail structure and the like are improved, and the problems of complicated multi-layer stacking steps, difficult process realization and the miniaturization of a unit size of the three-dimensional stacked phase change memory in the process preparation are solved.

Owner:HUAZHONG UNIV OF SCI & TECH

Method for improving alignment of lithography mark, epitaxial layer for alignment of lithography mark, and preparation method for super-junction

ActiveCN108346581APrevent closurePreserve integritySemiconductor/solid-state device detailsSolid-state devicesLithographic artistEngineering

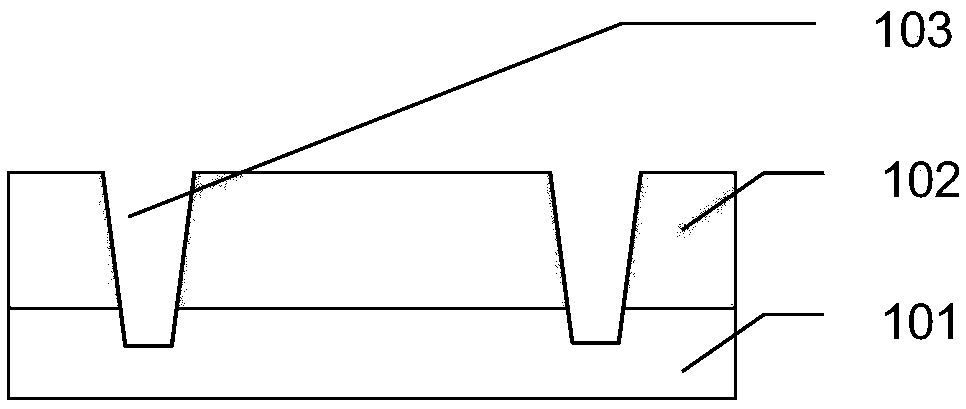

The invention discloses a method for improving the alignment of a lithography mark, an epitaxial layer for the alignment of the lithography mark, and a preparation method for a super-junction, and belongs to the field of micro-electronic chips. The method comprises the steps: providing a substrate with an epitaxial layer, wherein the epitaxial layer is provided with a groove which is far from thetop surface far of the substrate and extends inwards from the top surface, the groove is limited by a bottom wall and a side wall, the bottom wall is parallel to the top surface of the epitaxial layer, and the side wall extends towards the epitaxial layer along the top surface; and forming films on a part of the side wall or on the whole side wall. The method facilitates the obtaining of the better and easier alignment effect in the subsequent manufacturing process during lithography marking.

Owner:JILIN SINO MICROELECTRONICS CO LTD

Method for forming varied doping region and device thereof

InactiveCN104851799AReduce manufacturing costReduce the number of photolithographySemiconductor/solid-state device manufacturingSemiconductor devicesComposite filmGate oxide

The invention provides a method for forming a varied doping region and a device thereof. The method comprises the steps of growing a multilayer composite film on the surfaces of a gate and a gate oxide layer, wherein the multilayer composite film comprises at least two dielectric layers which are made of different materials, namely a first dielectric layer and a second dielectric layer, furthermore a corresponding step is formed by the dielectric layers because of existence of the gate; performing photolithography for exposing the surface of the first dielectric layer in an area which corresponds with the area from the gate edge to the drain edge, performing primary ion implantation in an area from the step edge to the drain edge on the first dielectric layer, thereby forming a first varied doping region; etching the surface of the second dielectric layer in an area which corresponds with the area from the gate edge to the drain edge, performing secondary ion implantation in an area from the step edge to the drain edge on the second dielectric layer, thereby forming a second varied doping region; and etching the surface of the gate oxide layer in an area which corresponds with the area from the gate edge to the drain edge, and performing third ion implantation in an area from the gate edge to the drain edge, thereby forming a third varied doping region. Compared with the prior art, the method of the invention is advantageous in that the cost is reduced.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

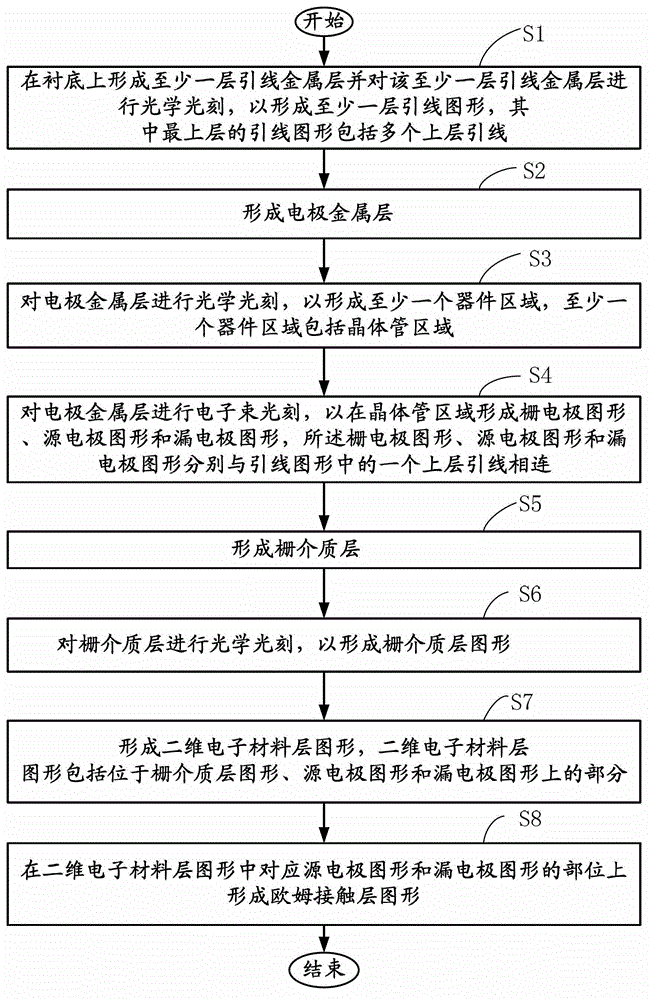

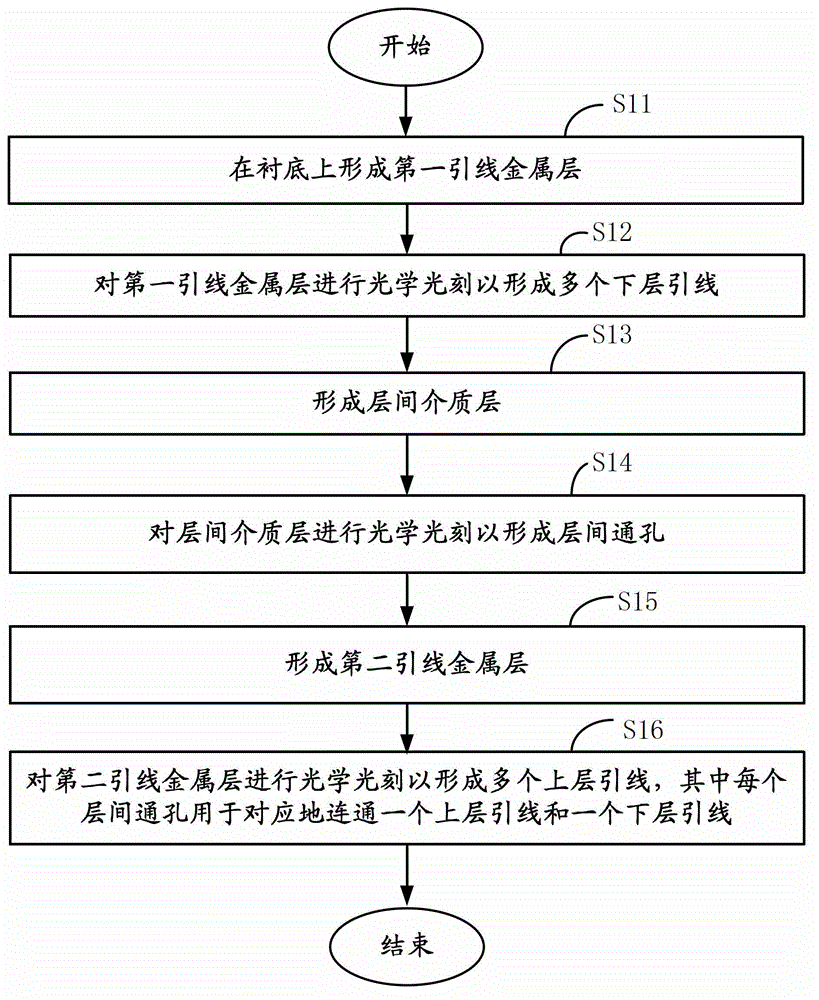

Two-dimensional electronic material device and mixed photoetching method thereof

ActiveCN102945794AReduce the number of photolithographySimple processSemiconductor/solid-state device detailsSolid-state devicesLead MetalElectronic materials

The invention relates to a two-dimensional electronic material device and a mixed photoetching method thereof, wherein the method comprises the following steps: forming at least one lead metal layer on a substrate, and performing optical photoetching on the at least one lead metal layer so as to form at least one layer of lead figures, wherein an uppermost layer comprises a plurality of upper layer leads, and a grid electrode, a source electrode and a drain electrode are respectively connected with one upper layer lead; forming an electrode metal layer; performing the optical photoetching on the electrode metal layer so as to form a transistor region; performing electron-beam photoetching on the electrode metal layer so as to form the figures of the grid electrode, the source electrode and the drain electrode; forming a grid dielectric layer; performing the optical photoetching on the grid dielectric layer so as to form the figure of the grid dielectric layer; forming the figure of a two-dimensional electronic material layer; and forming the figure of an ohmic contact layer. The device is capable of eliminating or decreasing the destruction of intrinsic properties of the two-dimensional electronic material, capable of greatly improving the photoetching precision of small-size devices based on guaranteeing the process cost and improving the performance of the devices, and capable of saving the processing time based on guaranteeing the processing precision.

Owner:TSINGHUA UNIV

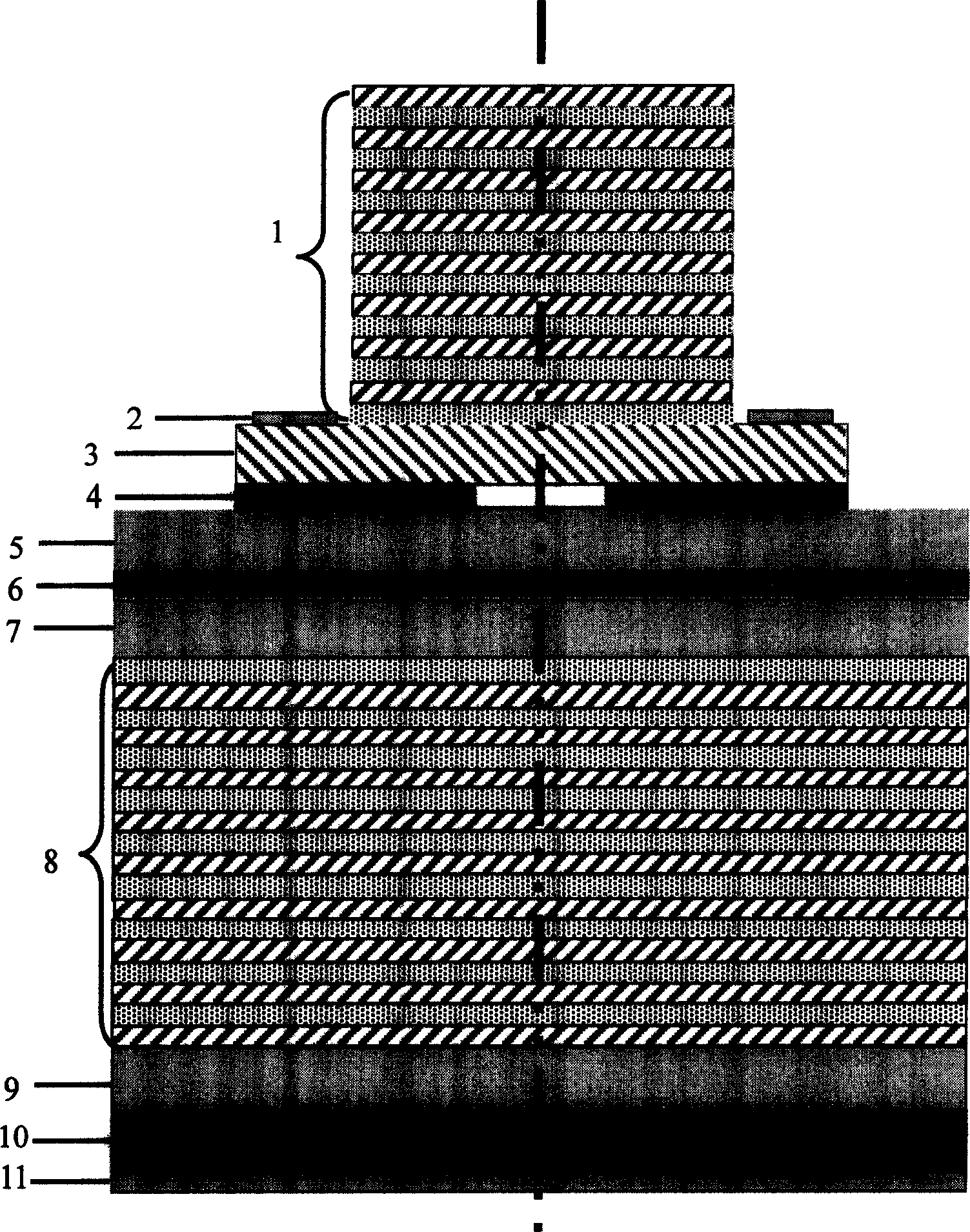

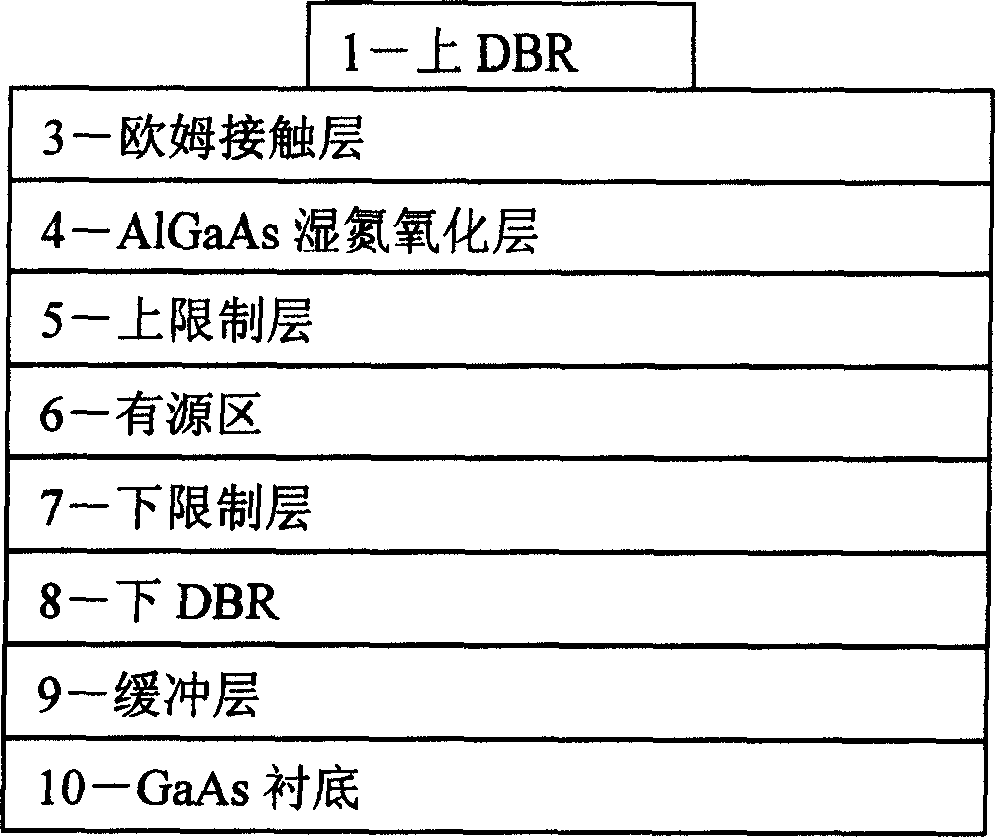

Prepn. of inner chanber contacting vertical chamber emitting laser by 3-shaft self-aligning process

InactiveCN1564405AReduce the number of photolithographyReduced requirements for lithography precisionLaser detailsSemiconductor lasersOhmic contactDistributed Bragg reflector

Following steps are carried out by using traditional technique: photo etching from up distributed Bragg reflector to ohmic contact layer in dual groove shape; depositing P type ohmic contact electrode Ti / Pt / Au; peeling off procedure reserves Ti / Pt / Au on ohmic contact layer only; etching down no mask protected up distributed Bragg reflector, ohmic contact layer and AlxGa1-xAs(x is greater than or equal to 0.9) wet nitrogen oxidation respectively in registration photoetching procedure by using photoresist and P type ohmic contact electrode Ti / Pt / A as masks; Removing photoresist, wet nitrogen oxidating forming oxidation aperture; n type ohmic contact electrode obtained after thinning and polishing. Disclosed method obtains product by using photoetching device in low precision.

Owner:BEIJING UNIV OF TECH

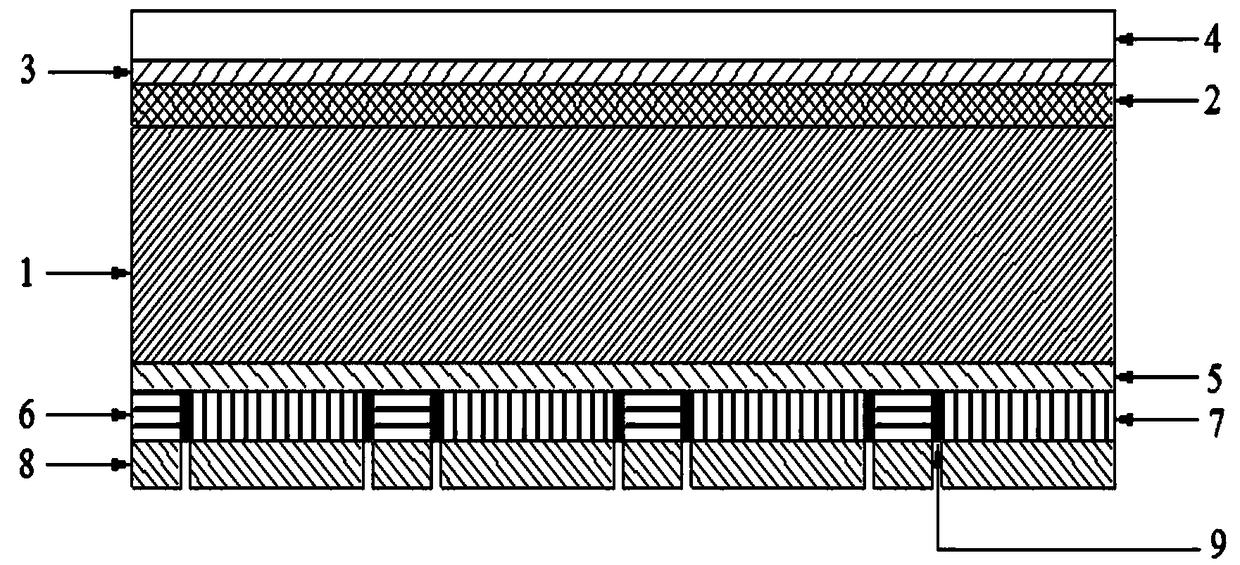

Infrared transmitting high sensitivity visible light detector and preparation method thereof

ActiveCN109742178AGood through abilityImprove collection efficiencySemiconductor devicesPhysicsInfrared

The invention discloses an infrared transmitting high sensitivity visible light detector and a preparation method thereof. The detector is composed of a passivation layer, an upper electrode, a heterojunction, a lower electrode and an intrinsic monocrystalline silicon substrate. The upper electrode is made of a material which is conductive and is transparent to visible light and infrared. The heterojunction comprises an upper heterojunction layer and a lower heterojunction layer. The upper heterojunction layer is nano-film which is sensitive to the visible light and can transmit the infrared.The lower heterojunction layer is intrinsic monocrystalline silicon. When the visible light and the infrared transmit the upper electrode and the upper heterojunction layer, the visible light stimulates electron hole pairs in the heterojunction, the electron hole pairs are collected by the upper electrode and the lower electrode and are discharged from longitudinally set metal columns, and the infrared passes through a whole detection structure, so the visible light is detected, and moreover, transmission of the infrared is not influenced. Compared with a conventional structure, the detector has the advantages that distance between the electrodes and a junction area is low, so recombination rates of the electron hole pairs can be reduced before the electron hole pairs reach the electrodes,and collection efficiency of photon-generated carriers is improved. Through longitudinal metal structure design, light shielding is reduced, and sensitivity is improved.

Owner:XIAN TECHNOLOGICAL UNIV

Thinfilm transistor device for reducing leaping voltage

ActiveCN1937254AImprove display qualityReduce the number of photolithographyTransistorSolid-state devicesLiquid-crystal displayDielectric

The thin film transistor device includes following parts: a transparent glass base plate; gate electrode; insulating layer of gate electrode for partitioning scan line of gate electrode from scan line of source electrode; active layer, doping layer; source / drain electrodes; passivation layer for partitioning scan line of source electrode from transparent pixel electrode. Gate insulating layer under the active layer includes three layers of insulating medium. Dielectric constant of middle insulating-film is lower than Dielectric constants of insulating-film at upper layer and insulating-film at lower layer. Thus, the device possesses lower leaping voltage so as to restrain flicker and crosstalk on liquid crystal display of using the thin film transistor as well as improve quality of displayed images.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD +1

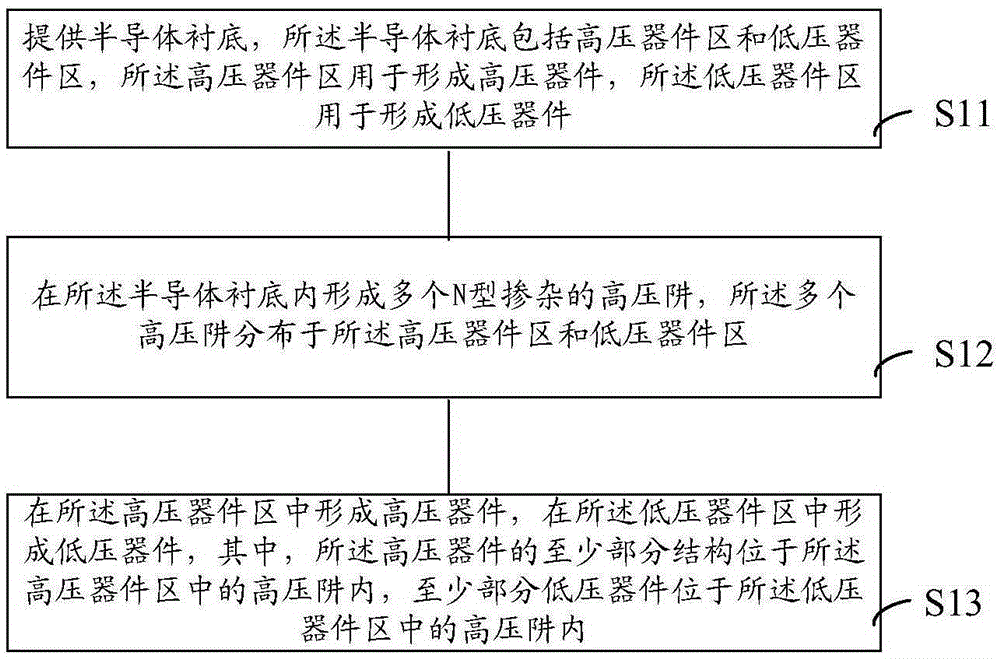

BCD device and manufacturing method thereof

ActiveCN105336736ASave forming stepsReduce the number of photolithographySolid-state devicesSemiconductor/solid-state device manufacturingCMOSLow voltage

The invention provides a BCD (Bipolar-CMOS-DMOS) device and a manufacturing method thereof. The BCD device comprises a semiconductor substrate and a plurality of N type doped high voltage wells, wherein the semiconductor substrate includes a high voltage device area and a low voltage device area; the high voltage device area is used for forming high voltage devices; the low voltage device area is used for forming low voltage devices; the plurality of N type doped high voltage wells are distributed in the high voltage device area and the low voltage device area; at least part of the component structures of the high voltage devices are formed in the high voltage wells of the high voltage device area; and at least part of the low voltage devices are formed in the high voltage wells of the low voltage device area. The BCD device and the manufacturing method thereof can reduce the frequency for the photoetching process, and can be conductive to cost reduction and efficiency improvement.

Owner:HANGZHOU SILAN MICROELECTRONICS

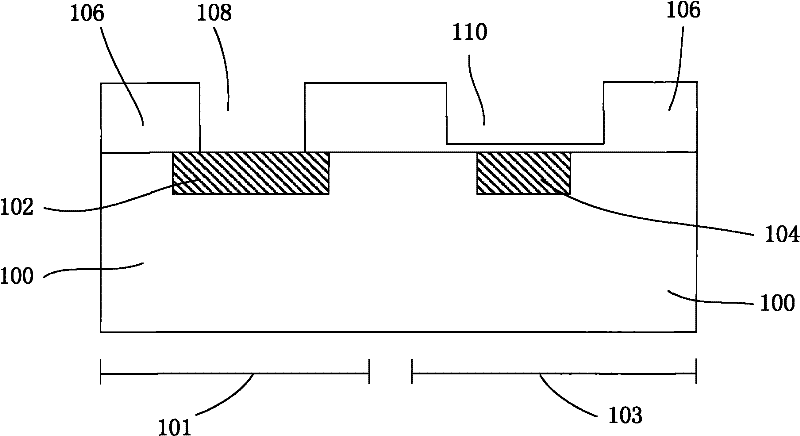

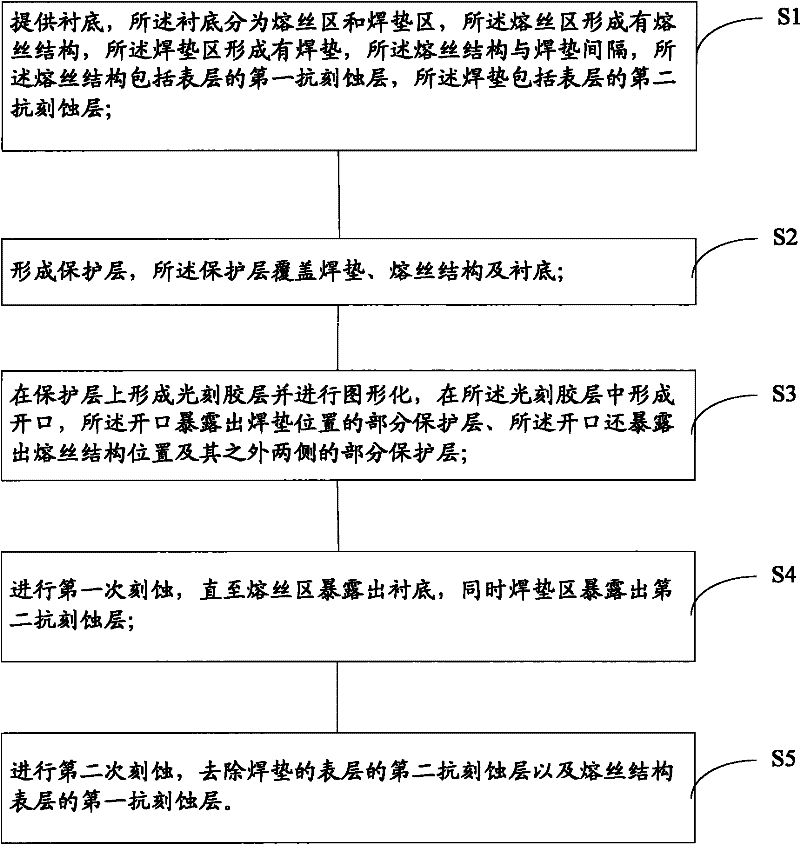

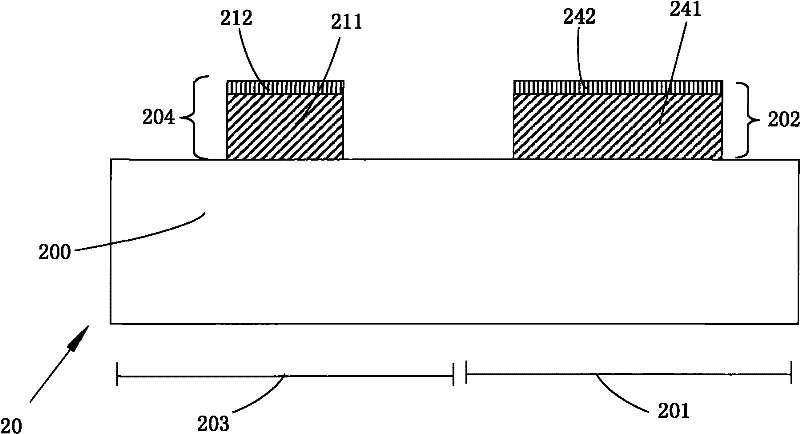

Fabrication method of semiconductor structure

ActiveCN102263011AReduce the number of photolithographySave time and costSemiconductor/solid-state device detailsSolid-state devicesPhotoresistEtching

The invention discloses a semiconductor structure manufacturing method, which comprises the following steps of: providing a substrate, wherein the substrate is divided into a fuse region with a fuse structure and a bonding pad region with a bonding pad, the fuse structure comprises a first anti-etching layer on a surface layer and the bonding pad comprises a second anti-etching layer on the surface layer; forming a protective layer; forming a photoresist layer on the protective layer, patterning the photoresist layer and forming an opening in the photoresist layer, wherein the opening exposesthe protective layer at a part of a bonding pad position, at a fuse structure position and on the two sides of the fuse structure position; performing primary etching until the first anti-etching layer of the fuse region and the second anti-etching layer of the bonding pad region are exposed at the same time; and performing secondary etching to remote the second anti-etching layer on the surface layer of the bonding pad and the first anti-etching layer on the surface layer of the fuse structure. In the method, a process of performing single photoetching and then sequentially performing the primary and secondary etching is adopted to reduce photoetching times.

Owner:CSMC TECH FAB2 CO LTD

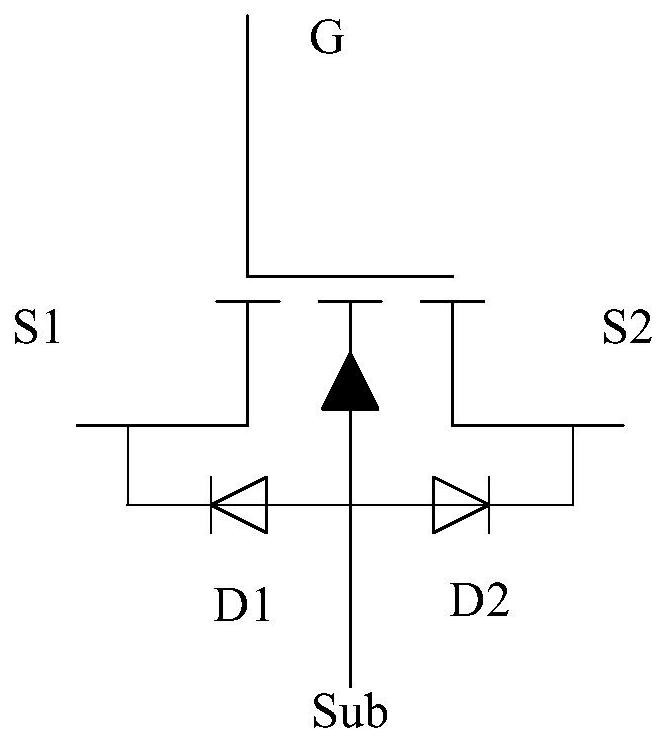

Manufacturing method of bidirectional power device

PendingCN112309975AReduce areaLower bulk resistanceSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricElectrical conductor

The invention discloses a manufacturing method of a bidirectional power device. The manufacturing method comprises the following steps: forming a first doped region in a semiconductor layer; forming aplurality of trenches in a first trench region, wherein the plurality of trenches of the first trench region are located in the first doped region and divide the first doped region into alternating first-type sub-doped regions and second-type sub-doped regions; forming a gate dielectric layer covering the side walls of the lower parts of the plurality of trenches of the first trench region; forming a shielding dielectric layer covering the side walls of the upper parts of the plurality of trenches of the first trench region; and forming gate conductors respectively in contact with the gate dielectric layer and the shielding dielectric layer in the plurality of trenches of the first trench region, wherein the gate conductors comprise control gates and shielding gates which are connected with each other, the control gates are in contact with the gate dielectric layer, and the shielding gates are in contact with the shielding dielectric layer. According to the manufacturing method, the first doped region is divided into the first-type sub-doped regions and the second-type sub-doped regions which are alternated by the trenches to form a source region and a drain region of the bidirectional power device, so the area of the device is reduced.

Owner:HANGZHOU SILAN MICROELECTRONICS

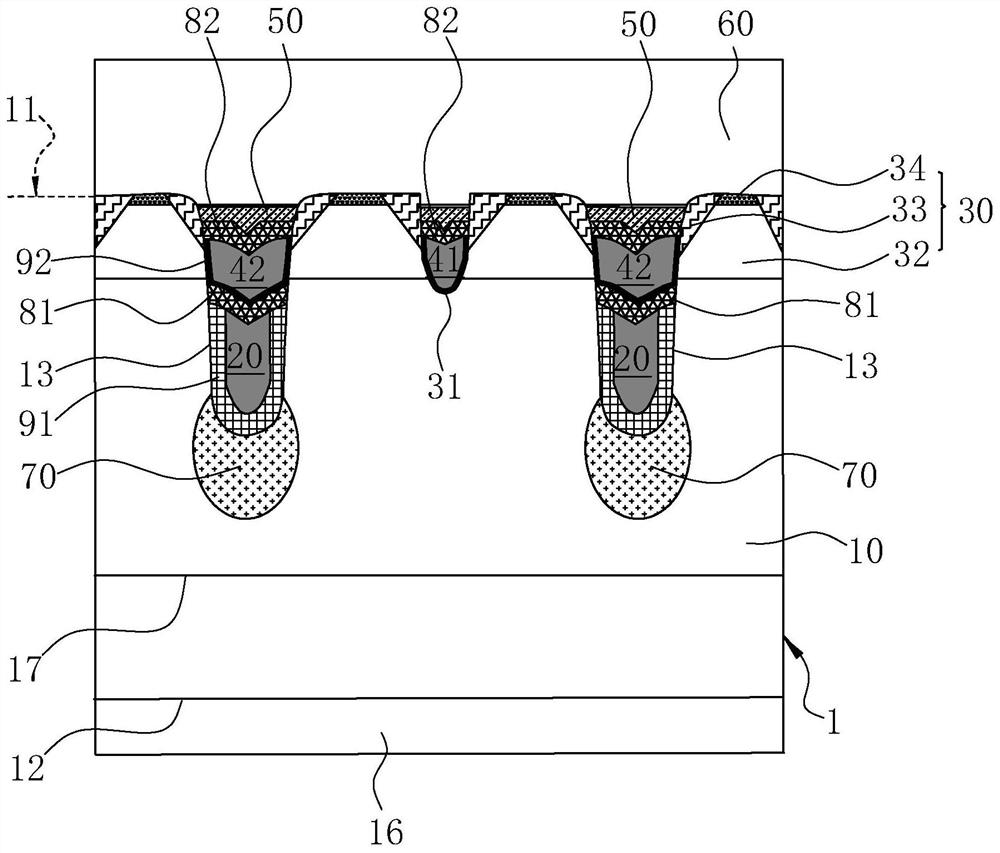

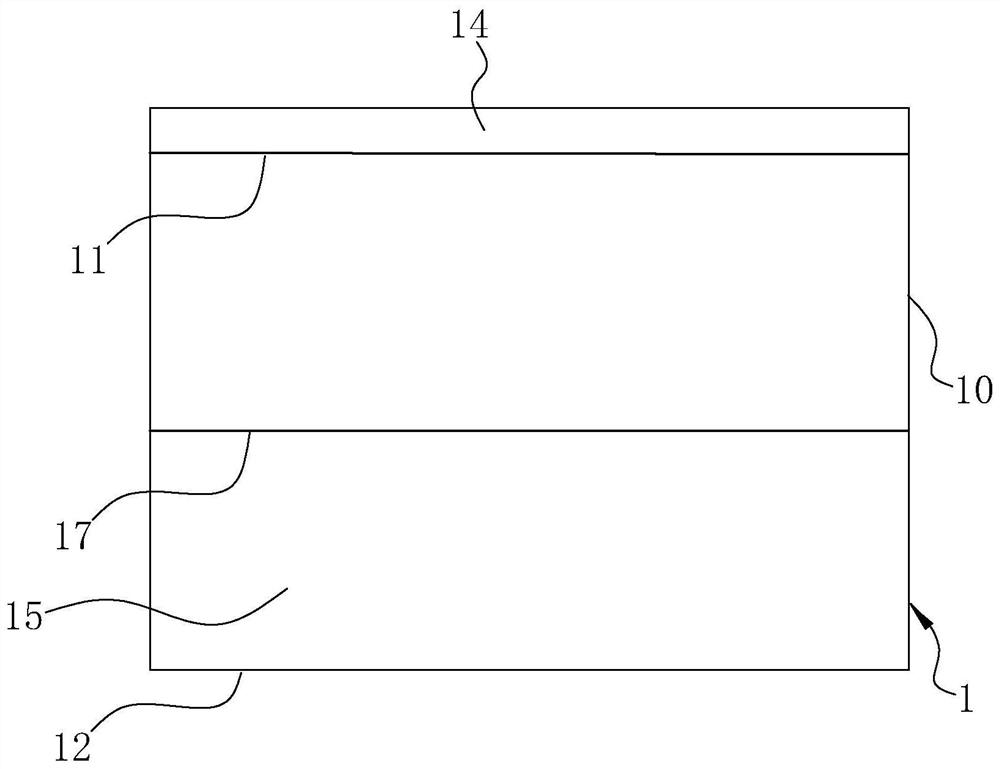

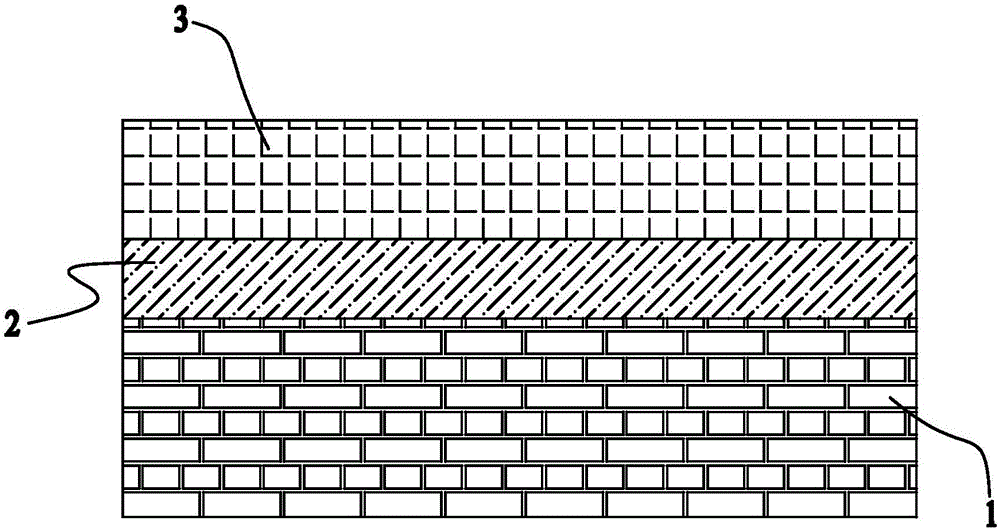

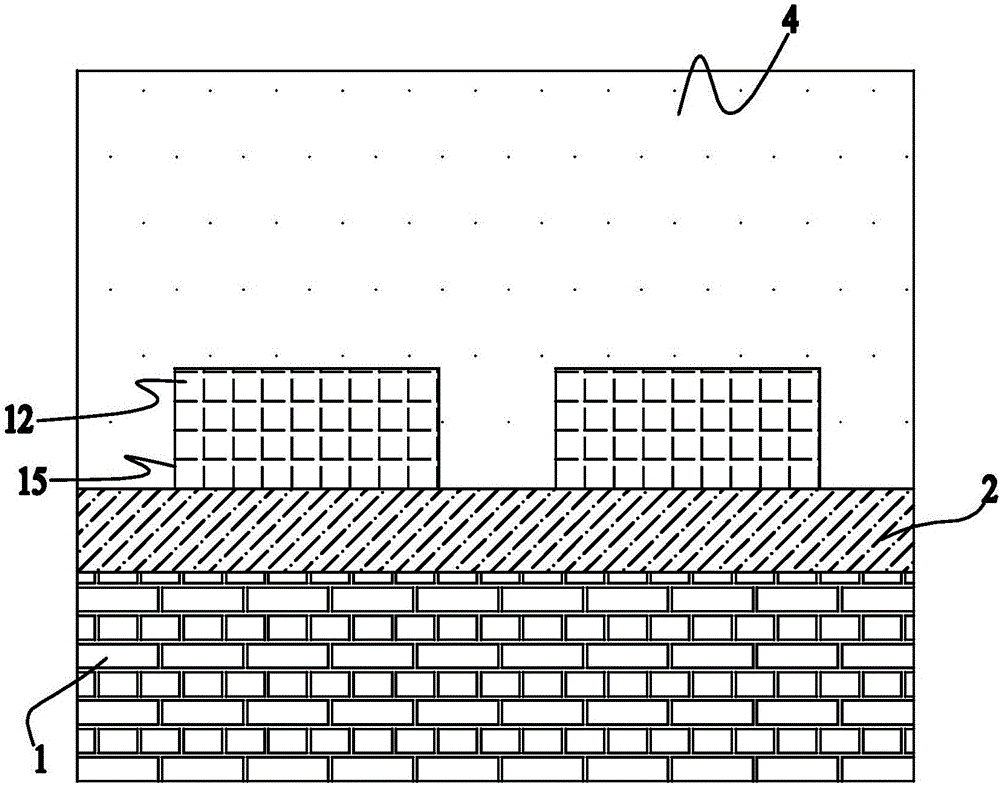

Silicon carbide MOS device with groove type JFET and preparation process thereof

PendingCN111509037AReduce the problem of excessive JFET resistanceReduce excessive resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconJFET

The invention discloses a silicon carbide MOS device with a groove type JFET and a preparation process of the silicon carbide MOS device. The silicon carbide MOS device with the groove type JFET comprises a silicon carbide substrate, the doping type of the silicon carbide substrate material is a first conductive type, a first conductive type semiconductor epitaxial layer and a drain electrode arerespectively arranged on a front surface and a back surface of the silicon carbide substrate, wherein a JFET region is arranged on an active region of the first conductive type semiconductor epitaxiallayer, a first surface, a second surface and a third surface are arranged on the JFET region, and a first conductive type source region and a second conductive type base region are arranged on the first surface and the second surface respectively from outside to inside, a source electrode is arranged above the first surface, a gate medium and a gate electrode are arranged above the third surface,a second conductive type injection body region is arranged between the second conductive type base region and the source electrode, and an inter-electrode isolation medium is arranged between the source electrode and the gate electrode.

Owner:PN JUNCTION SEMICON HANGZHOU CO LTD

Double-gate electrode metal oxide thin film transistor and preparation method thereof

InactiveCN111710725AImprove stabilitySimple processTransistorSemiconductor/solid-state device manufacturingOxide thin-film transistorBottom gate

The invention discloses a double-gate electrode metal oxide thin film transistor and a preparation method thereof. The double-gate electrode metal oxide thin film transistor comprises a substrate; a bottom gate electrode, a bottom gate insulating layer, a metal oxide semiconductor layer and a passivation layer sequentially arranged on the substrate, and a source electrode, a drain electrode, a first top gate electrode and a second top gate electrode arranged on the passivation layer; a flat layer and a pixel electrode layer. The source electrode, the drain electrode, the first top gate electrode and the second top gate electrode are located on the same layer, and the second top gate electrode is connected with the bottom gate electrode through a bottom gate electrode contact hole. The topgate electrode, the source electrode and the drain electrode are made of the same layer of metal, the top gate and the bottom gate are in signal communication to form the double-gate structure device,the process is simple, and the cost is saved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

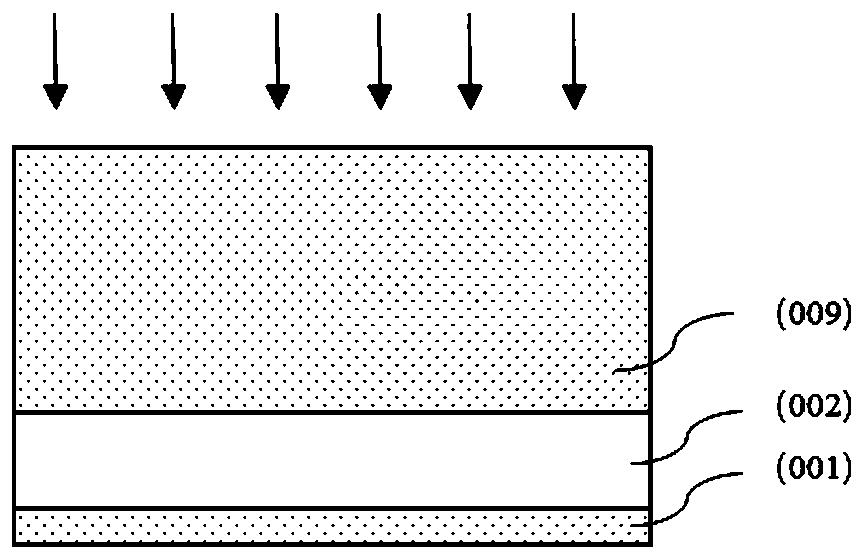

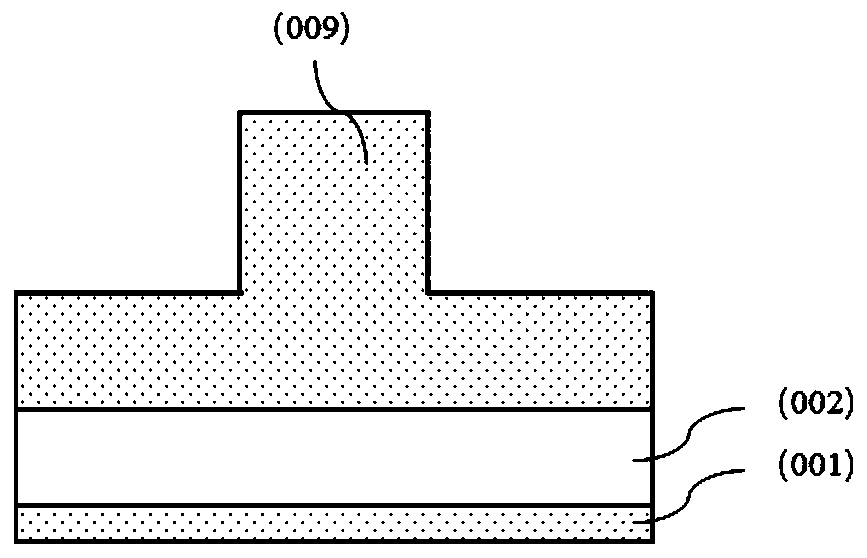

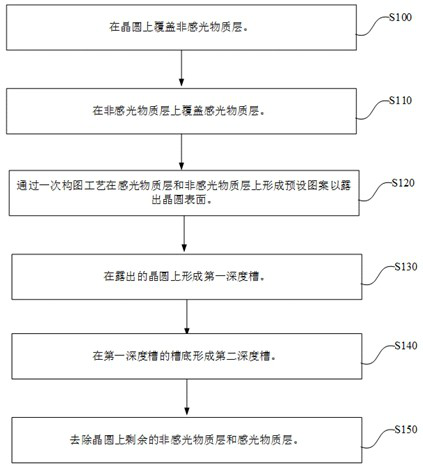

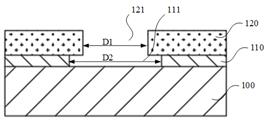

Preparation method of semiconductor device

ActiveCN112802747AReduce photolithography stepsReduce the number of photolithographySemiconductor/solid-state device manufacturingPhysicsPhotoresist

The invention provides a preparation method of a semiconductor device, and relates to the technical field of a semiconductor preparation process, and the method comprises the steps of: covering a wafer with a non-photosensitive substance layer; covering the non-photosensitive substance layer with a photosensitive substance layer; forming preset patterns on the photosensitive substance layer and the non-photosensitive substance layer through a one-time composition process to expose the surface of the wafer, wherein a first opening is formed in the photosensitive substance layer, a second opening is formed in the non-photosensitive substance layer, and the caliber of the first opening is smaller than that of the second opening; forming a first depth groove in the exposed wafer; forming a second depth groove in the groove bottom of the first depth groove, wherein the width of the second depth groove is smaller than or equal to that of the first depth groove; and removing the remaining non-photosensitive substance layer and photosensitive substance layer on the wafer. The semiconductor device can be formed through a one-time composition process, thereby saving the photoetching step, reducing the step of removing photoresist, and improving the preparation efficiency by reducing the photoetching times.

Owner:度亘激光技术(苏州)有限公司

A kind of preparation method of interdigitated back contact heterojunction solar cell

ActiveCN109216509BReduce widthIncrease collection rateFinal product manufacturePhotovoltaic energy generationHeterojunctionEngineering

Owner:XIAN UNIV OF TECH

Multi-grid changing field effect transistor structure, manufacturing method thereof and chip device

ActiveCN113224133AReduce areaIncrease current densitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsEngineering

The invention relates to a multi-grid changing field effect transistor structure, a manufacturing method thereof and a chip device. A transistor comprises a drain epitaxial layer located at a bottom layer, a source layer located at a top layer, and source extension inverted fins, a first grid and a second grid which are embedded in the drain epitaxial layer; the first grid electrode is arranged between the source electrode extension inverted fins, the second grid electrode is aligned to the source electrode extension inverted fins, and symmetrical channels which are connected in parallel from the source electrode layer to the interior of the drain electrode epitaxial layer in pairs are formed in the two sides of the first grid electrode and the two sides of the second grid electrode respectively; and in a preferred example, the drain epitaxial layer forms a shield gate bottom floating antipolar column bottom junction at a bottom portion corresponding to the source extension inverted fin. The field effect transistor architecture provided by the invention is a multi-grid-electrode change densification, and has the effects of uniformizing electron flow partitions of the drain electrode on the back surface of the substrate and the source electrode on the top surface of the substrate and reducing the grooving process.

Owner:深圳真茂佳半导体有限公司

MTM anti-fuse structure on through hole and preparation process thereof

InactiveCN106601718AImprove process toleranceImprove conductivitySemiconductor/solid-state device detailsSolid-state devicesLithographic artistEngineering

The invention relates to an MTM anti-fuse structure on a through hole and a preparation process thereof. The structure comprises a substrate and a device layer on the substrate. The device layer is pressed and covered by a fuse sealing body which is internally provided with a fuse lower electrode. A fuse upper electrode is arranged outside the fuse sealing body and is just above the fuse lower electrode. An anti-fuse dielectric structure and an anti-fuse bottom layer blocking body are arranged between the fuse upper electrode and the fuse lower electrode. The anti-fuse bottom layer blocking body coats the top end of the fuse lower electrode in the fuse sealing body. The anti-fuse dielectric structure is supported on the anti-fuse bottom layer blocking body, and the fuse upper electrode is supported on the anti-fuse dielectric structure. The structure of the MTM anti-fuse structure is compact, the times of lithography can be reduced, the process operation is simple, the process cost is reduced, the integration degree is raised, and the reliability of anti-fuse is improved.

Owner:58TH RES INST OF CETC

Preparation method of laminated anode of strong microcavity device

ActiveCN113380967ASimple stepsAvoid damageFinal product manufactureSolid-state devicesPhysical chemistryLayer thickness

The invention provides a preparation method of a laminated anode of a strong microcavity device. The preparation method of the laminated anode of the strong microcavity device is applied to the technical field of strong microcavity devices. The preparation method of the laminated anode of the strong microcavity device comprises the steps: S1, enabling a metal reflecting layer and a B anode to form a film; S2, preparing B-HM; during B-HM preparation, performing a PECVD (plasma enhanced chemical vapor deposition) film forming process on a wafer subjected to a B anode process, selecting a SiO or SiN film layer, and selecting the thickness of the film layer is selected to be 3000A-4000A; S3, preparing a G-anode; S4, preparing G-HM; S5, preparing an R-anode; and S6, removing HM, and completing laminated anode preparation. According to the preparation method of the laminated anode of the strong microcavity device, the preparation process is changed, dislocation photoetching is carried out, the photoetching times are reduced, each sub-pixel anode is protected in the preparation process under the condition that the few photoetching times are ensured, the yield of the anode manufacturing process is ensured, and the yield of the anode manufacturing process is ensured, and through hard mask protection. damage to the pixel anode in the preparation process is avoided, so that preparation of the laminated anode is completed.

Owner:ANHUI SEMICON INTEGRATED DISPLAY TECH CO LTD

Top-gate type thin film transistor and manufacturing method thereof

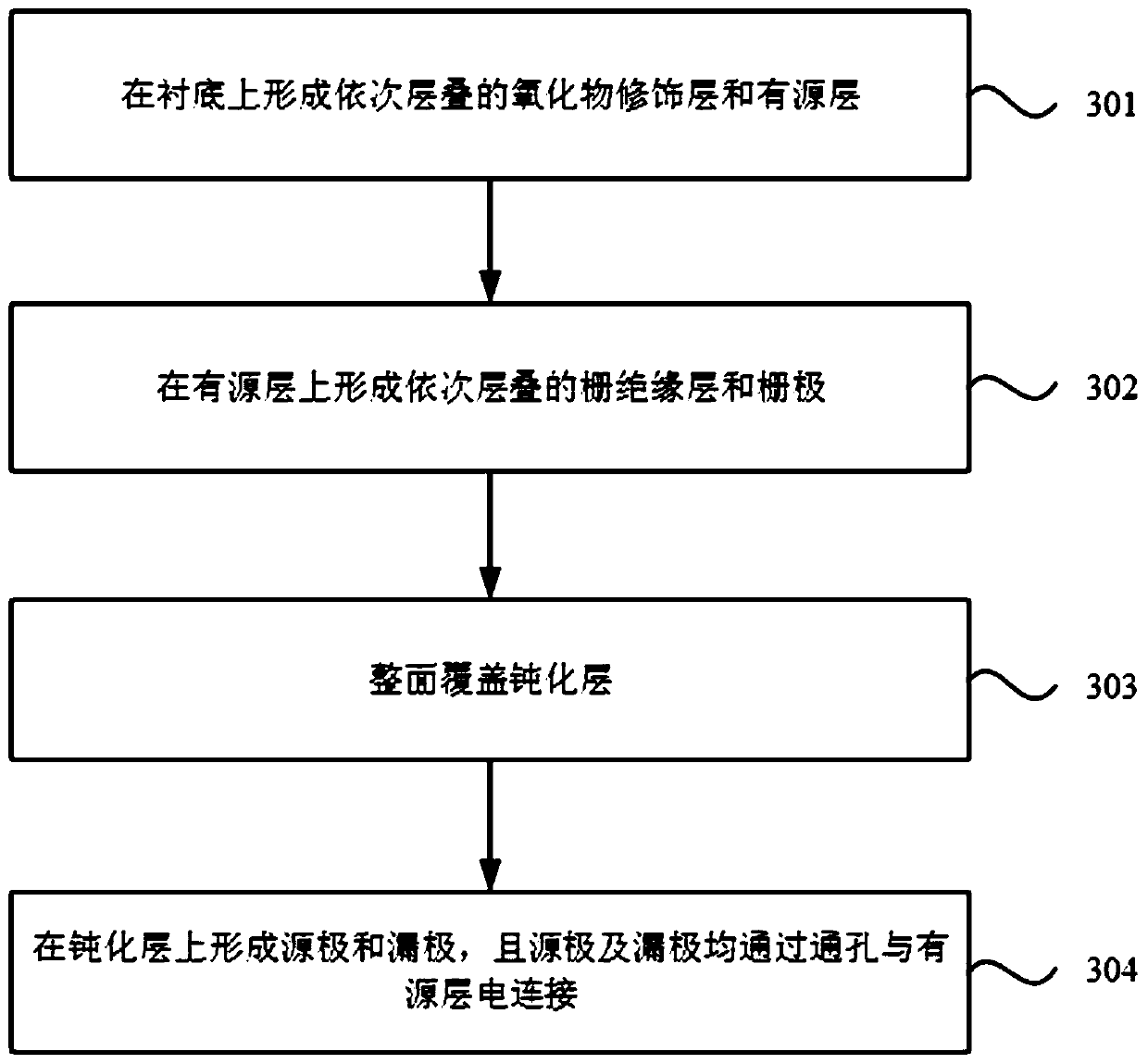

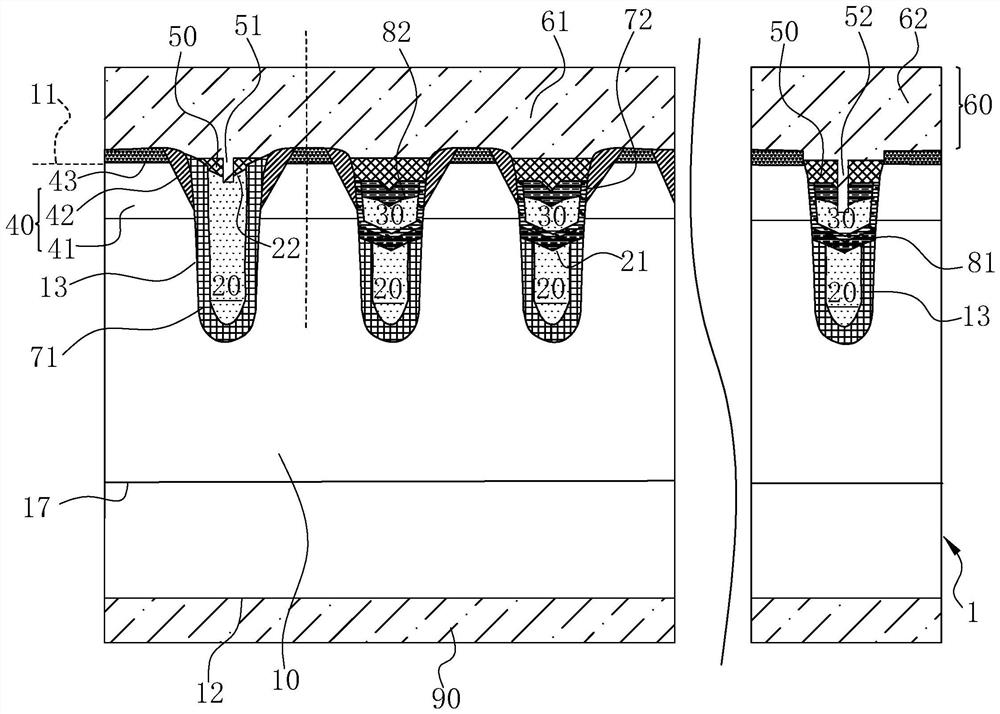

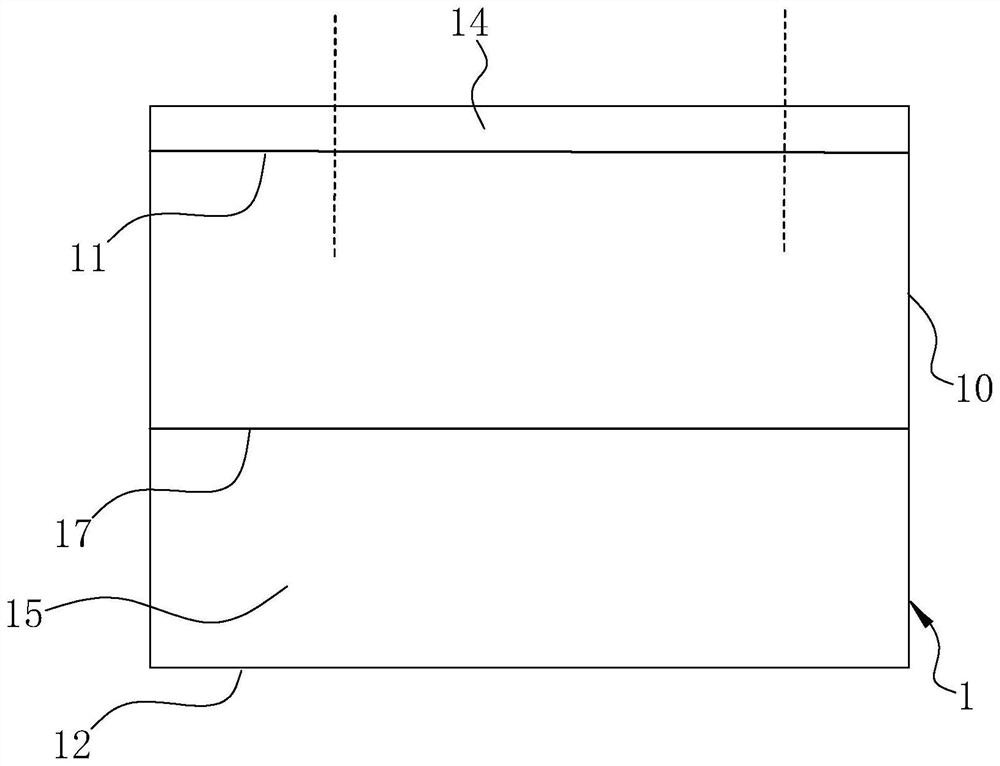

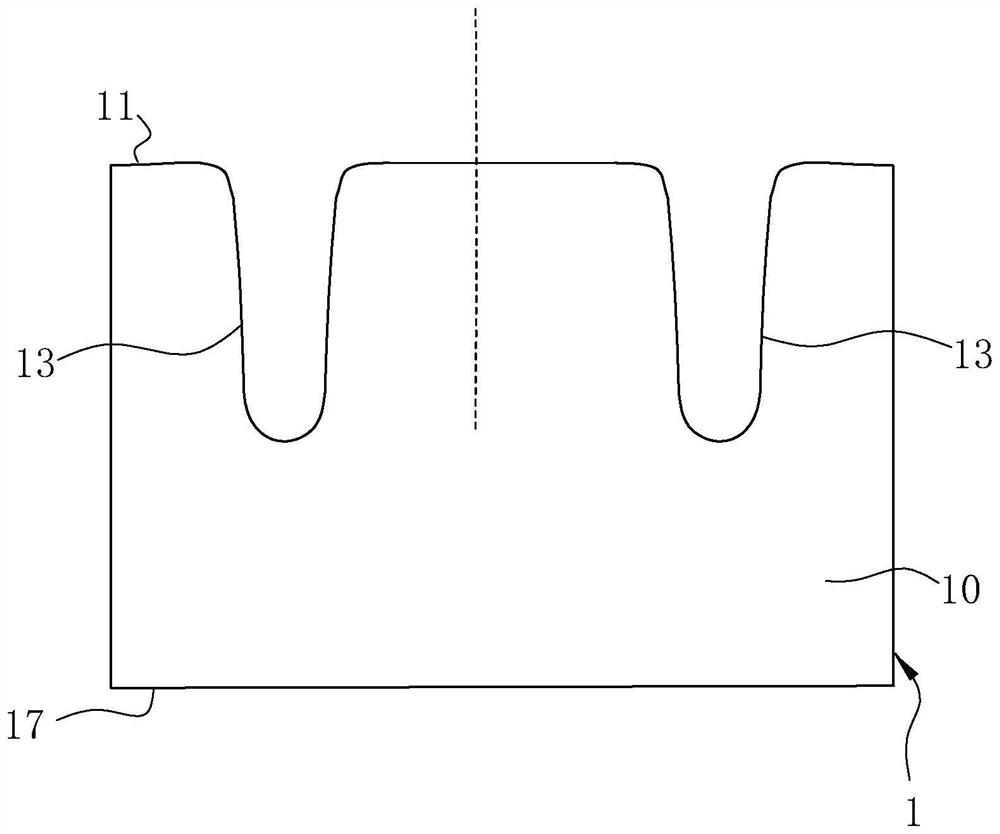

ActiveCN109950322AImprove performanceImprove stabilityTransistorSemiconductor/solid-state device manufacturingInsulation layerEngineering

The invention discloses a top-gate type thin film transistor. The top-gate type thin film transistor comprises a substrate, an oxide modification layer, an active layer, a grid insulation layer, a grid electrode, a passivation layer, a source electrode and a drain electrode. The oxide modification layer is arranged between the substrate and the active layer. The oxide modification layer can adjustthe performance of the top-gate type thin film transistor, so as to achieve the effect of improving the stability. Meanwhile, the oxide modification layer and the active layer can be patterned at thesame time, and the photoetching frequency can be not increased, thereby improving the performance of the top gate type thin film transistor on the premise that the photoetching cost is not increased.

Owner:SOUTH CHINA UNIV OF TECH

Embedded gate top surface contact field effect transistor structure and manufacturing method thereof

ActiveCN113284944AIncrease the areaIncrease current densitySemiconductor/solid-state device manufacturingSemiconductor devicesElectron currentElectron flow

The invention relates to an embedded gate top surface contact field effect transistor structure and a manufacturing method thereof. The transistor comprises a drain epitaxial layer, a surface metal layer which is located on the top layer and can be divided into a source metal pad and a gate metal pad, and an embedded source extension inverted fin and a gate which are located in the drain epitaxial layer. The gate is aligned to the source extension inverted fin, and symmetrical channels which are connected in parallel from the surface metal layer to the interior of the drain epitaxial layer in pairs are formed on the two sides of the gate respectively; by means of the design that the embedded source extension inverted finand the gate are in the same groove and are not in the same area, the source metal pad and the gate metal pad are individually conducted outside the mesa area, and the condition that the mesa area needs to be provided with a contact hole is avoided. The field effect transistor architecture provided by the invention has the effect of reducing the gate trench pitch to improve the electron current density.

Owner:深圳真茂佳半导体有限公司

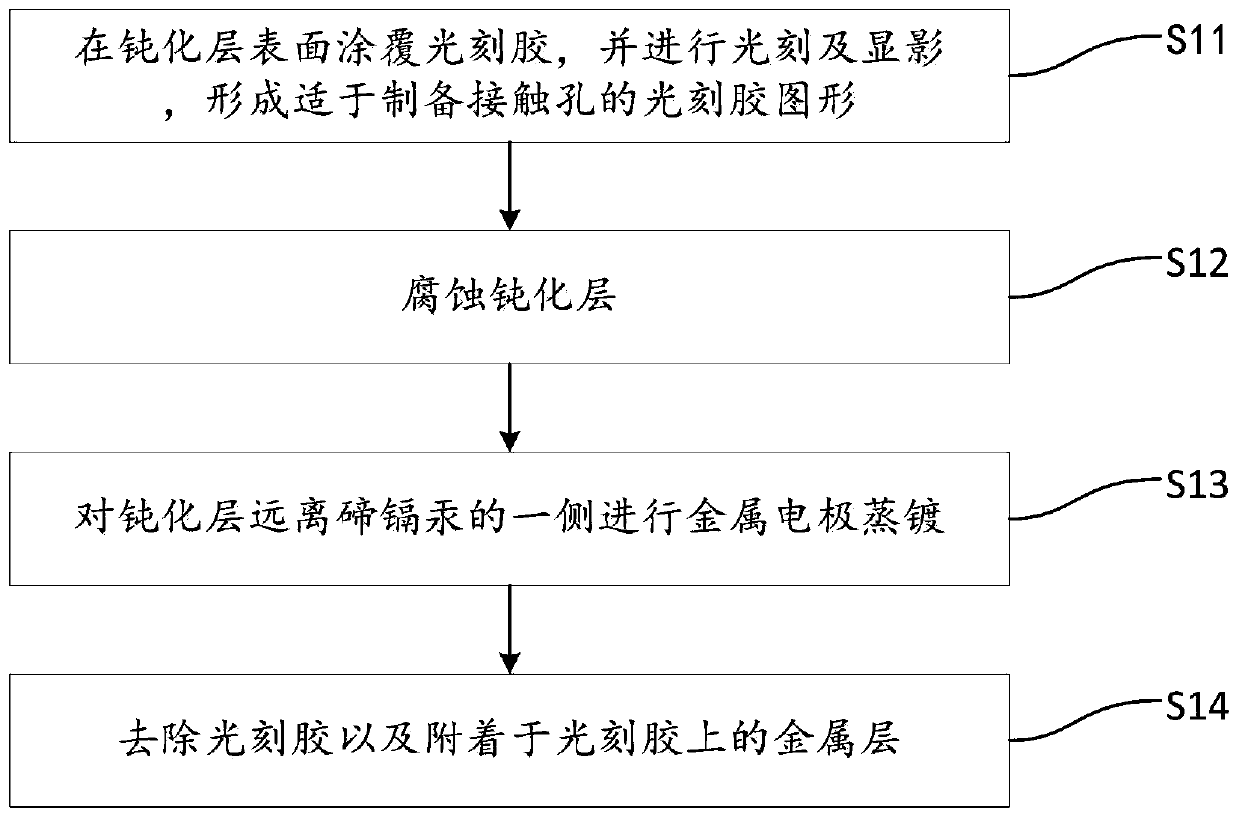

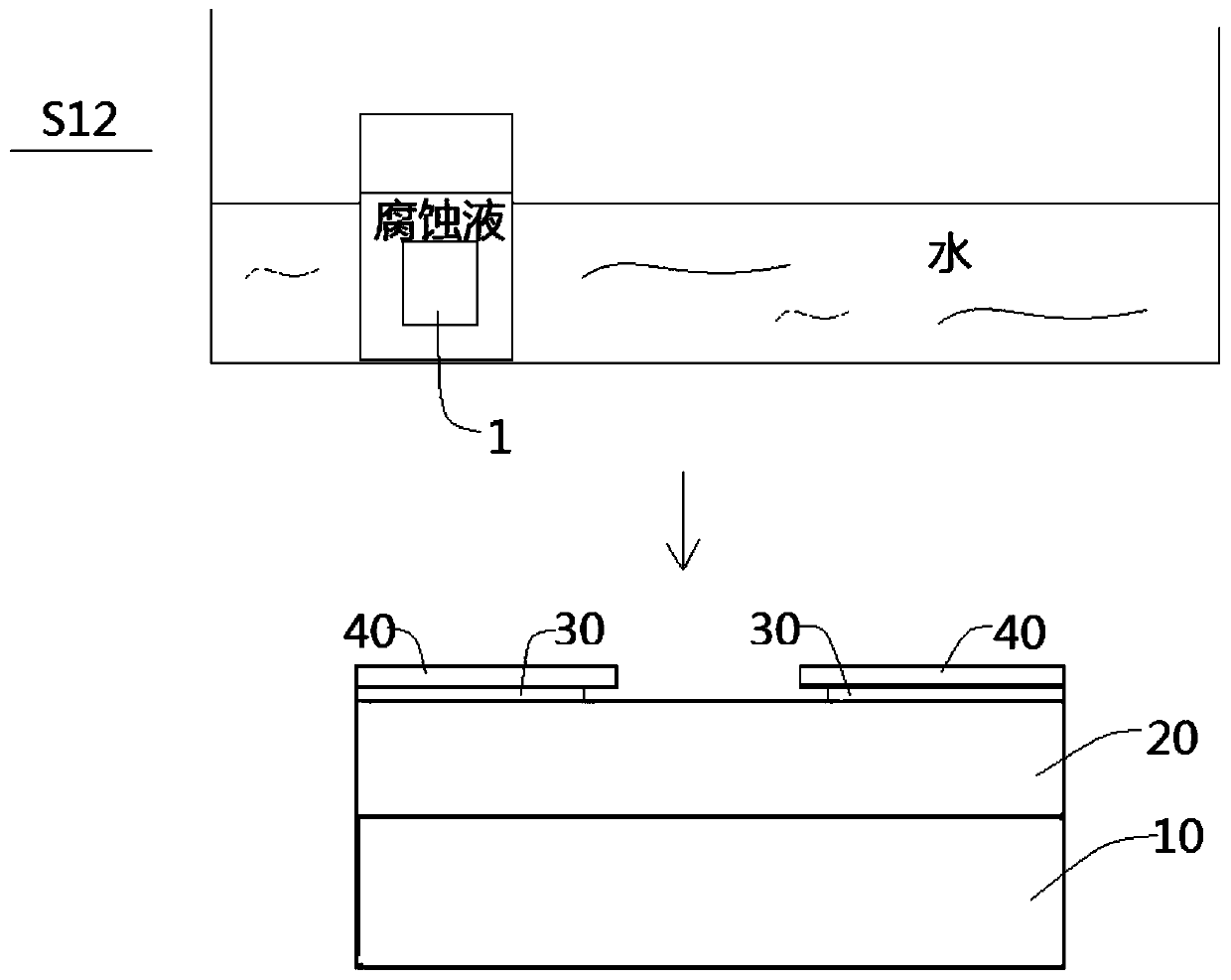

Method for preparing contact electrode of infrared detector chip

InactiveCN111403502AAvoid damageReduce the number of photolithographyFinal product manufactureSemiconductor devicesMetallic electrodePhotoresist

The invention discloses a method for preparing a contact electrode of an infrared detector chip, which comprises the following steps of: coating photoresist on the surface of a passivation layer, photoetching and developing to form a photoresist pattern suitable for preparing a contact hole; corroding the passivation layer; performing metal electrode evaporation on the side, away from tellurium, cadmium and mercury, of the passivation layer; and removing the photoresist and the metal layer attached to the photoresist. By the adoption of the method, a passivation layer corrosion process and anelectrode stripping process are combined, damage to tellurium, cadmium and mercury and the passivation layer in the process is avoided, the number of photoetching times is reduced, process steps are reduced, lateral corrosion of passivation layer corrosion is ingeniously utilized, the stripping process difficulty is greatly reduced, and the rate of finished products is increased.

Owner:11TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

1T1R and 1R resistive random access memory integrated structure and implement method thereof

ActiveCN103441135ARealize concatenationEasy to compareSolid-state devicesDigital storageStatic random-access memoryInter layer

The invention discloses a 1T1R and 1R resistive random access memory integrated structure and an implement method thereof. Resistive random access memory structures with MIM structures are manufactured on a drain electrode and a source electrode of an original substrate transistor respectively at the same time, a first layer of metal front medium, a first layer of plug, a first layer of metal, a second layer of inter-layer medium, a second layer of plug, an MIM structure layer, a third layer of inter-layer medium, a third layer of plug, a second layer of metal and a passivation layer are sequentially and respectively formed above the drain electrode and the source electrode of the substrate transistor, and the substrate transistor is connected with resistive random access memories in series. The resistive random access memory in the 1T1R structure and the resistive random access memory in the 1R structure are manufactured at the same time, the technological conditions are completely the same, the photo-etching times can be reduced, manufacturing cost is reduced, meanwhile, the 1T1R structure and the 1R structure are integrated, the characteristics of the resistive random access memories in the two structures can be compared conveniently, and the effect on the changing characteristic of a device from the current overshoot can be studied.

Owner:PEKING UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com