Power MOS field effect pipe with poly-silicon field plate and manufacturing method thereof

A technology of polysilicon field plates and field effect transistors, which is applied in transistors, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as edge breakdown of devices, shorten manufacturing time, reduce manufacturing costs, and reduce photolithography times Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

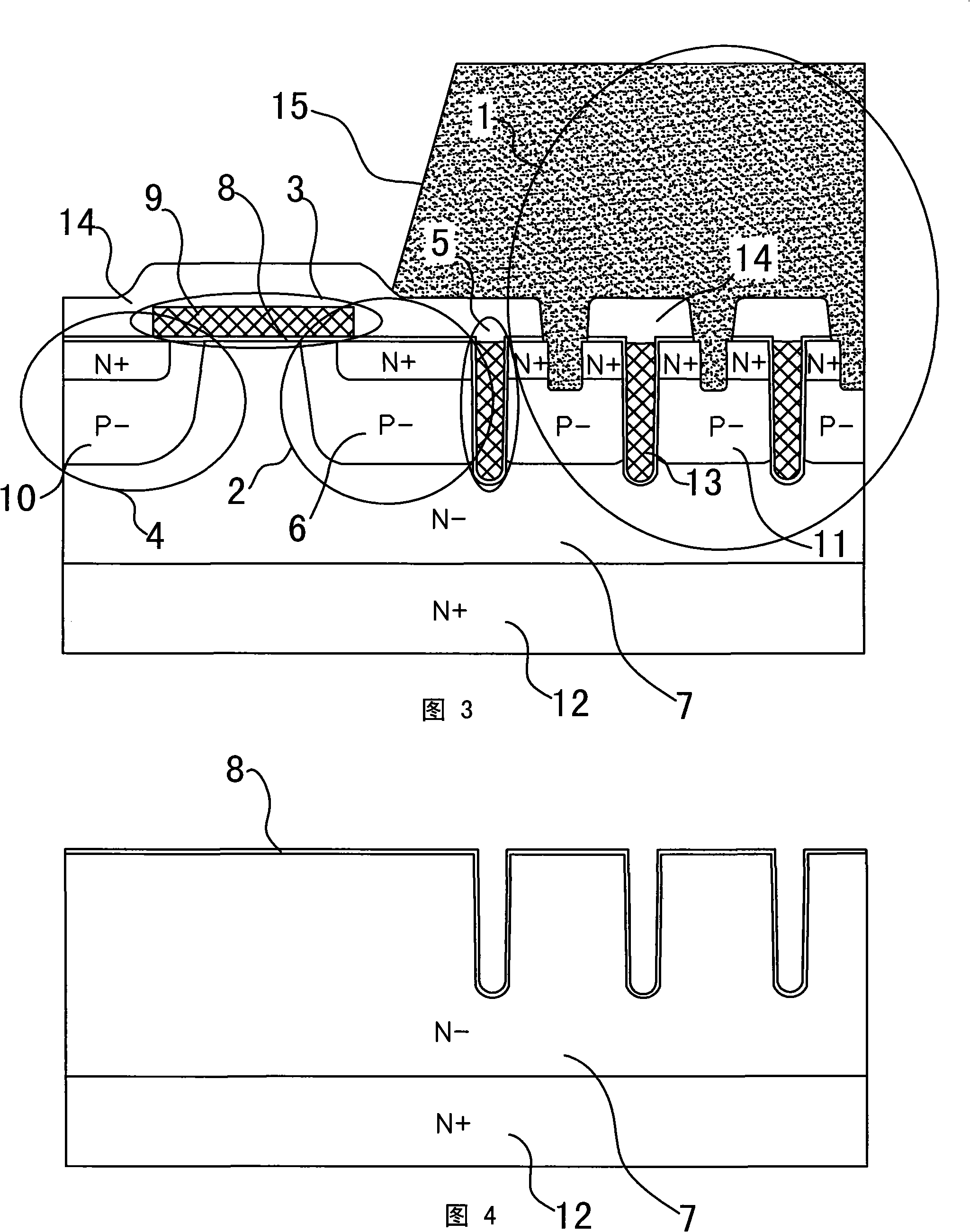

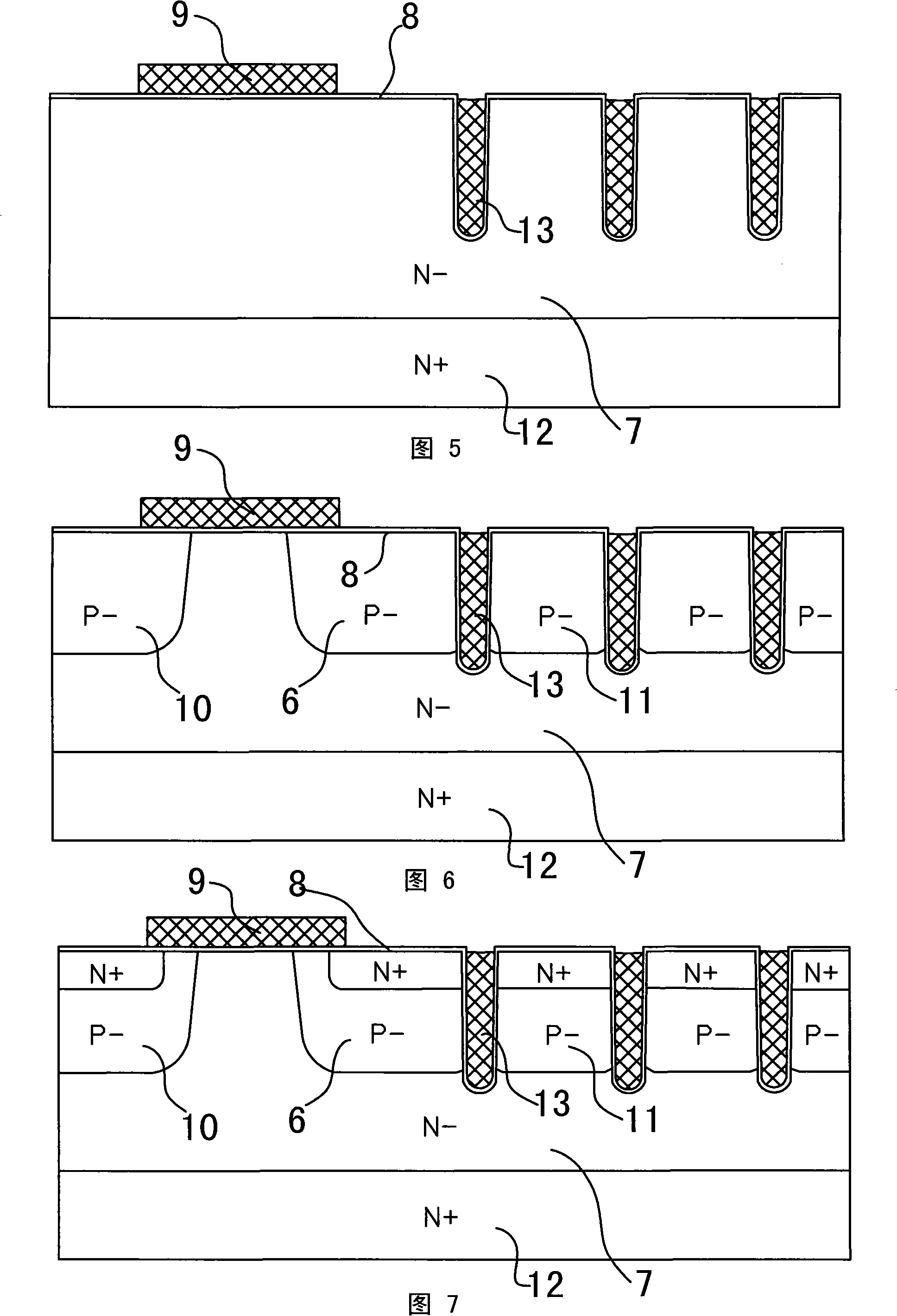

[0076] Embodiment 1: A power trench MOS field effect transistor

[0077] As shown in Figure 2, on the top plane, the middle of the MOS field effect transistor is a unit cell array 1 connected in parallel, and the periphery of the unit cell array 1 is provided with a terminal protection structure. The MOS field effect transistor is also provided with a gate (in the figure) Not shown), the position of the gate is determined according to the packaging requirements. The terminal protection structure is composed of a field limiting ring 2, a field plate 3 and a stop ring 4.

[0078] As shown in Figure 3, in the cross section, starting from the periphery of the edge unit cell 5 of the active area, the terminal protection structure is arranged in the order of the field limiting ring 2, the field plate 3, and the stop ring 4 from the inside to the outside, and the edge unit cell 5 is directly outside the periphery. Connect the field limit ring 2.

[0079] Field limit ring 2 consists of N ...

Embodiment 2

[0094] Embodiment 2: A power MOS field effect tube

[0095] Such as Picture 10 As shown, the difference between this embodiment and the first embodiment is that the terminal protection structure is composed of two field limiting rings 2, two field plates 3 and one stop ring 4, starting from the periphery of the edge unit cell 5 of the active area, The terminal protection structure is arranged regularly from the inside to the outside according to the field limit ring 2, the field plate 3, the field limit ring 2, the field plate 3, and the final stop ring 4, and the periphery of the edge unit cell 5 is directly connected to the field limit ring 2. The other structure and the content of the manufacturing method are the same as in the first embodiment, and the description is not repeated here.

[0096] From this embodiment, it can be directly derived that the terminal protection structure is composed of three field limiting rings 2, three field plates 3, and one stop ring 4. It can a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com