Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

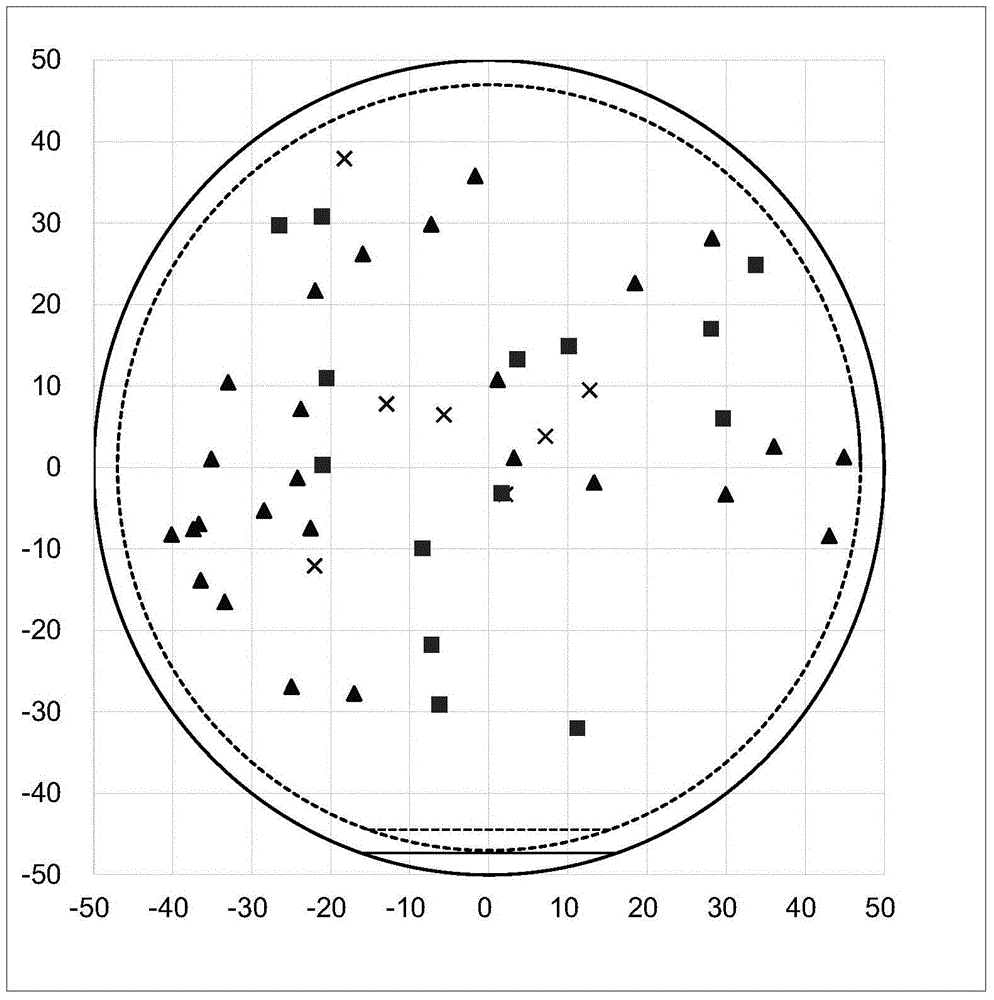

33results about How to "Reduce surface defect density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Molecular beam epitaxy growth of ternary and quaternary metal chalcogenide films

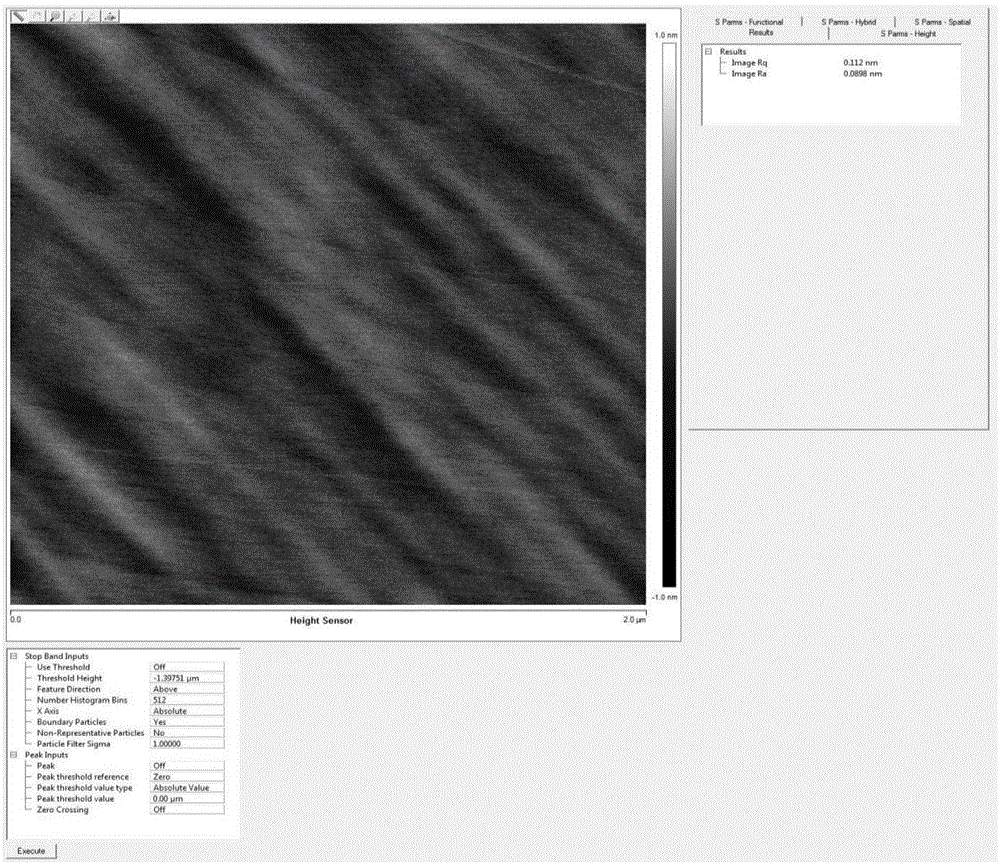

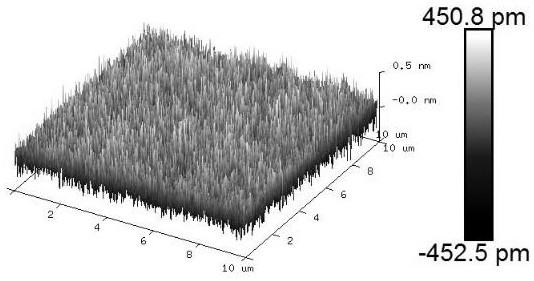

InactiveUS7518207B1Improve surface morphologyReduce surface defect densitySemiconductor/solid-state device manufacturingPhotovoltaic energy generationRocking curveSulfur

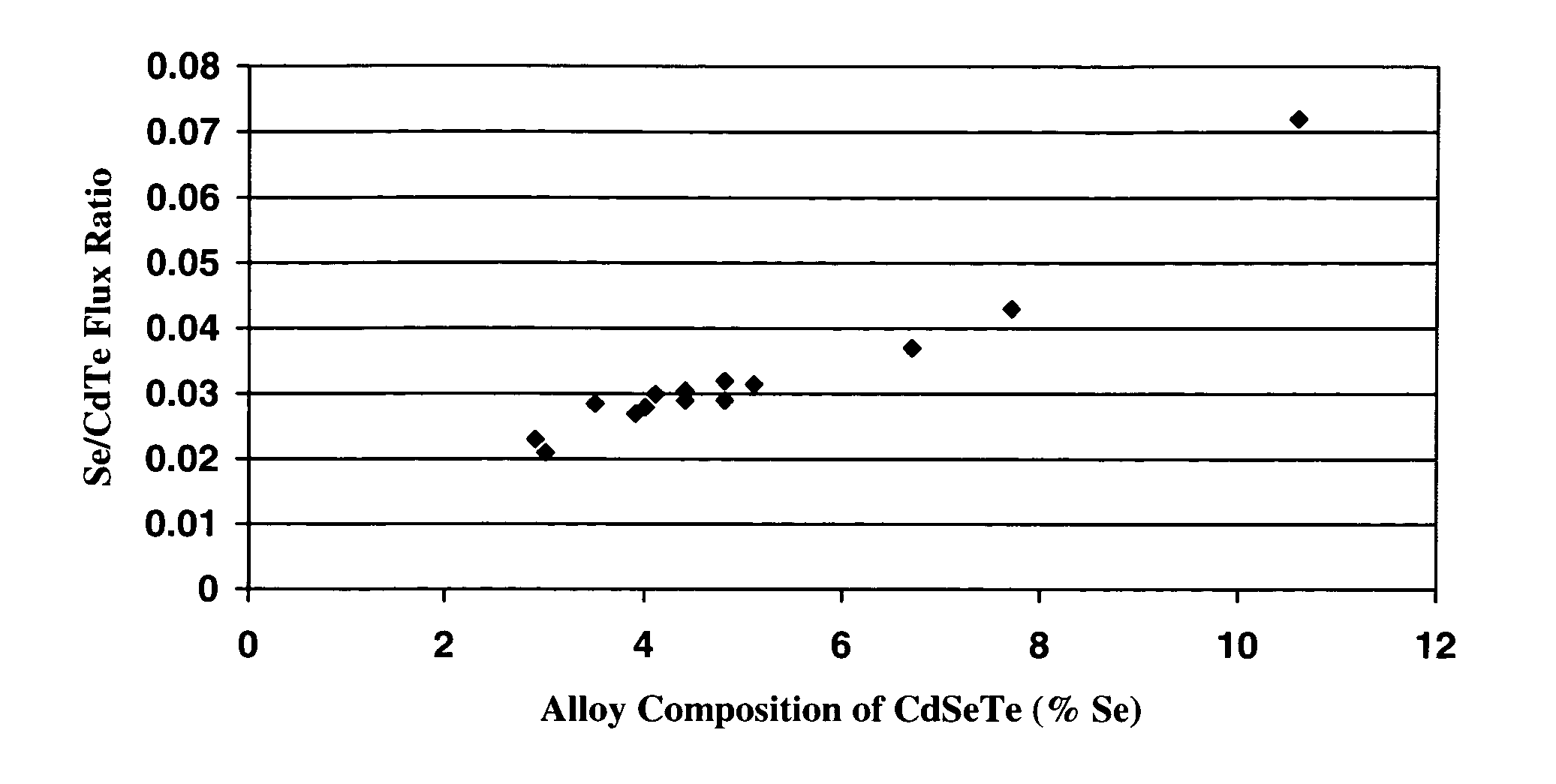

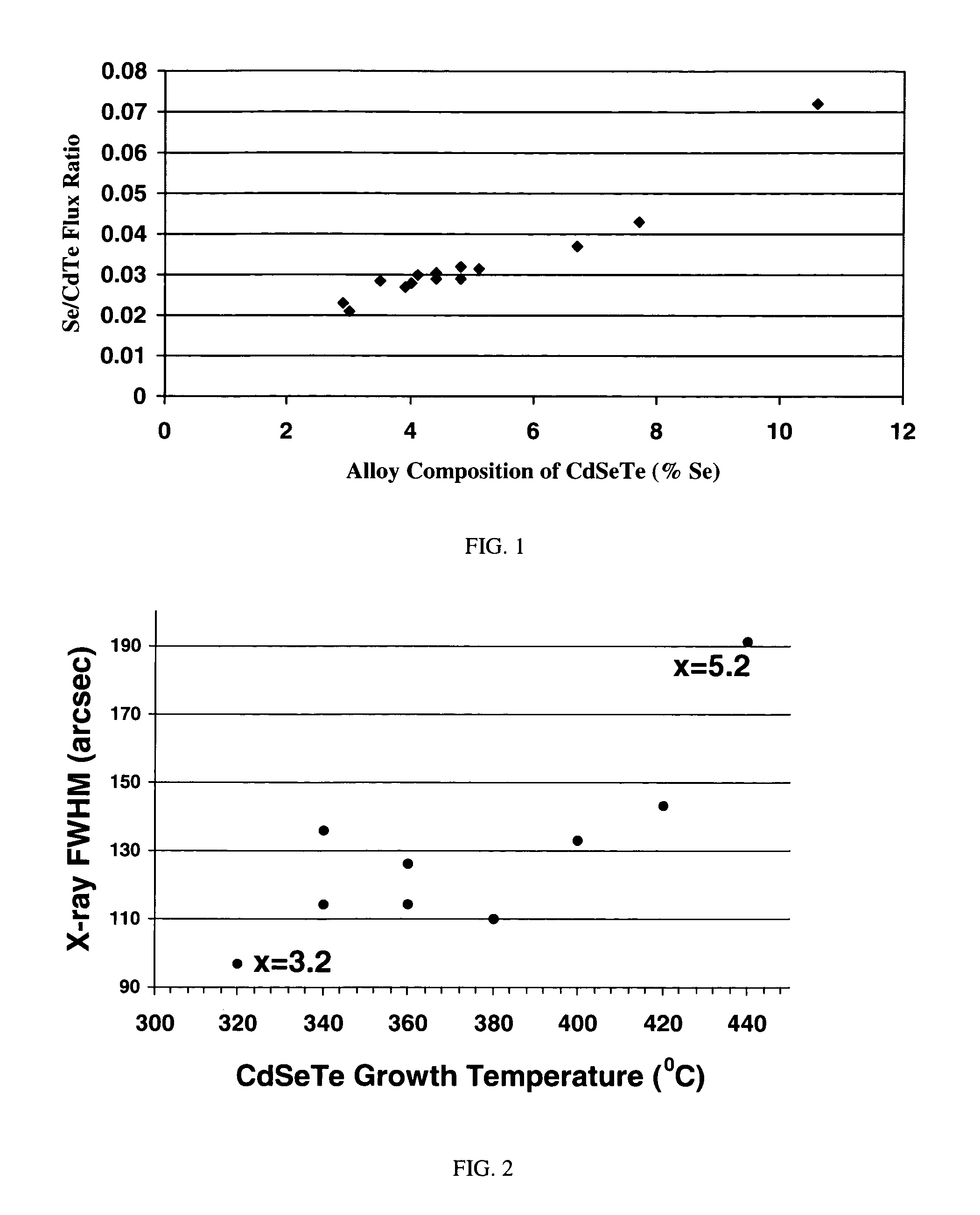

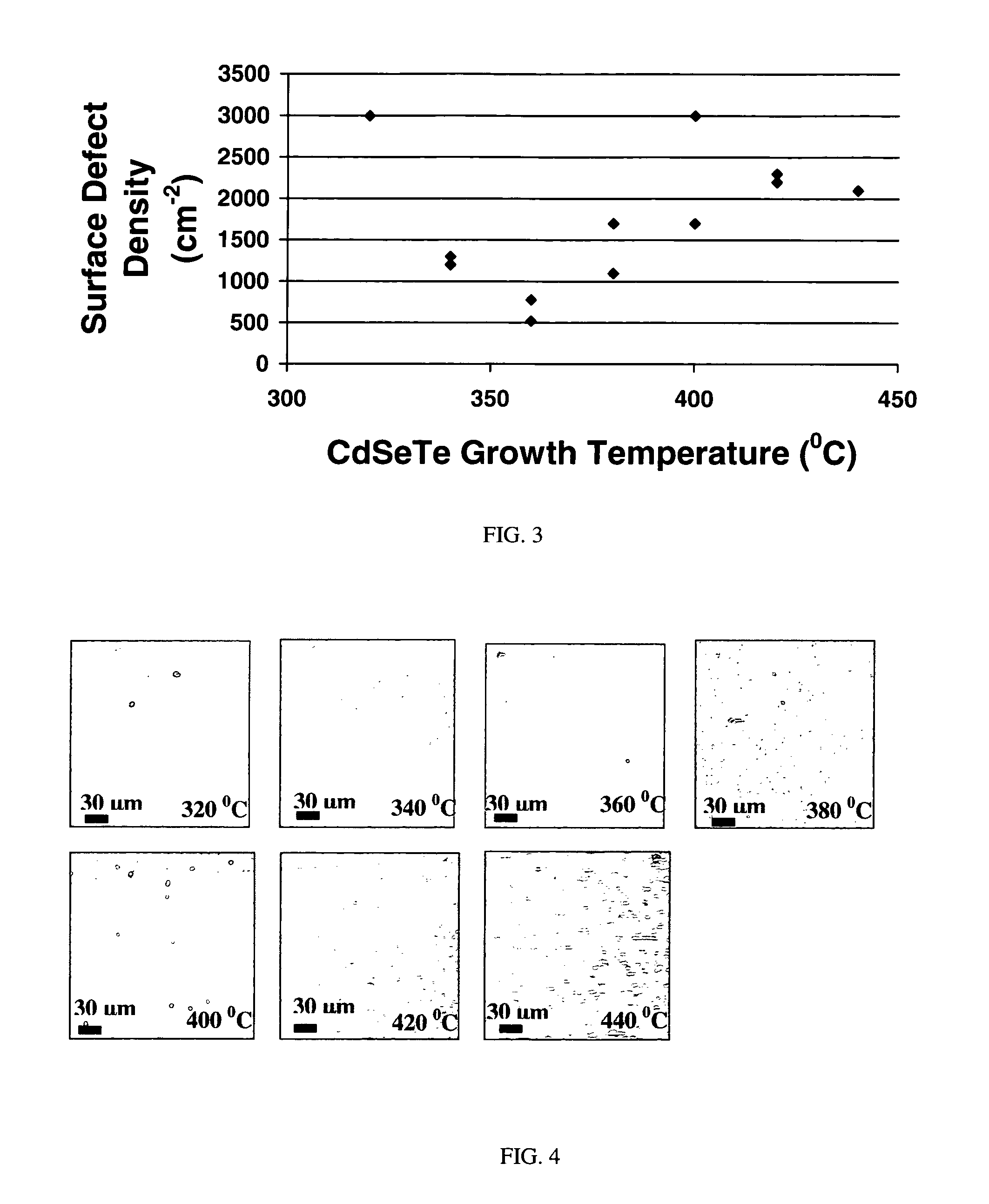

The ternary alloy CdSexTe1-x(2 1 1) and the quaternary alloy Cd1-zZnzSexTe1-x have been grown on Si(2 1 1) substrates using molecular beam epitaxy (MBE). The growth of CdSeTe is facilitated using a compound CdTe effusion source and a Se effusion source while the growth of CdZnSeTe is facilitated using a compound CdTe effusion source, a compound ZnTe effusion source, and an elemental Se source. The alloy compositions (x) and (z) of CdSexTe1-x ternary compound and Cd1-zZnzSexTe1-x are controlled through the Se / CdTe and ZnTe / CdTe flux ratios. The rate of Se incorporation is higher than the rate of Te incorporation as growth temperature increases. As-grown CdSeTe with 4% Se and CdZnSeTe with 4% Zn+Se, which is substantially lattice matched to long-wavelength infrared HgCdTe materials, exhibits excellent surface morphology, low surface defect density (less than 500 cm2), and a narrow X-ray rocking curve (a full-width at half maximum of 103 arcsec).

Owner:UNITED STATES OF AMERICA THE AS REPRESENTED BY THE SEC OF THE ARMY

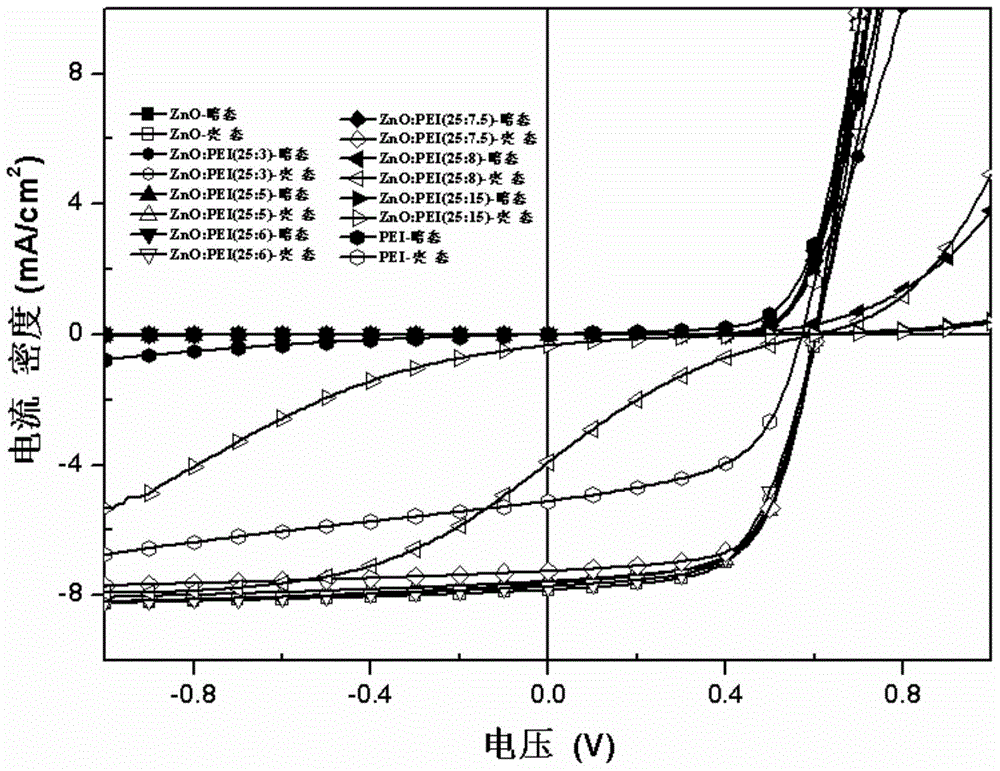

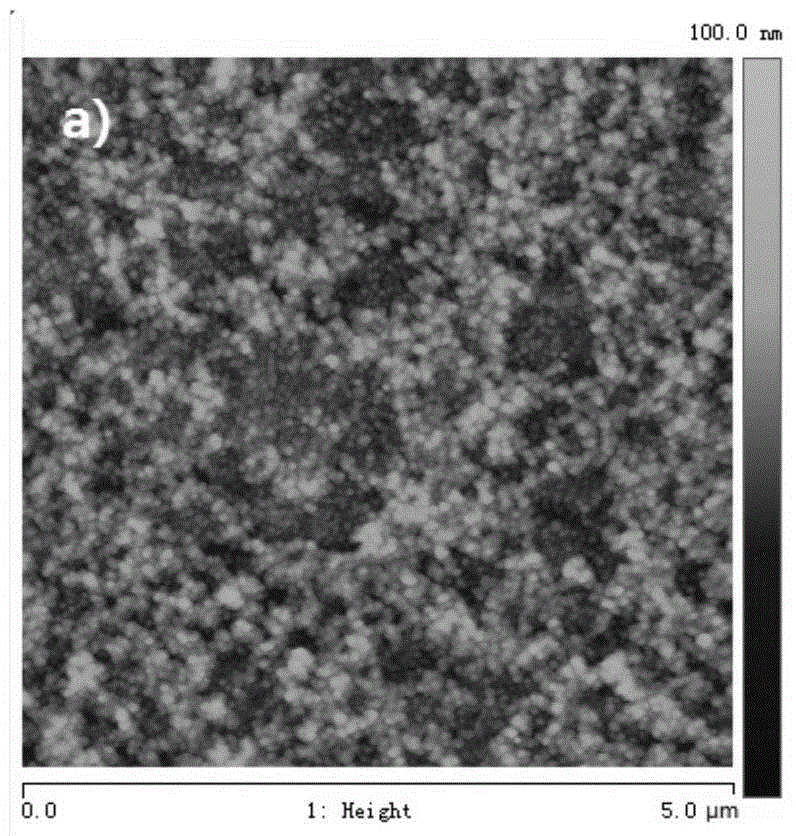

Polymer-nanometer metal oxide composite ink, and preparation method and application thereof

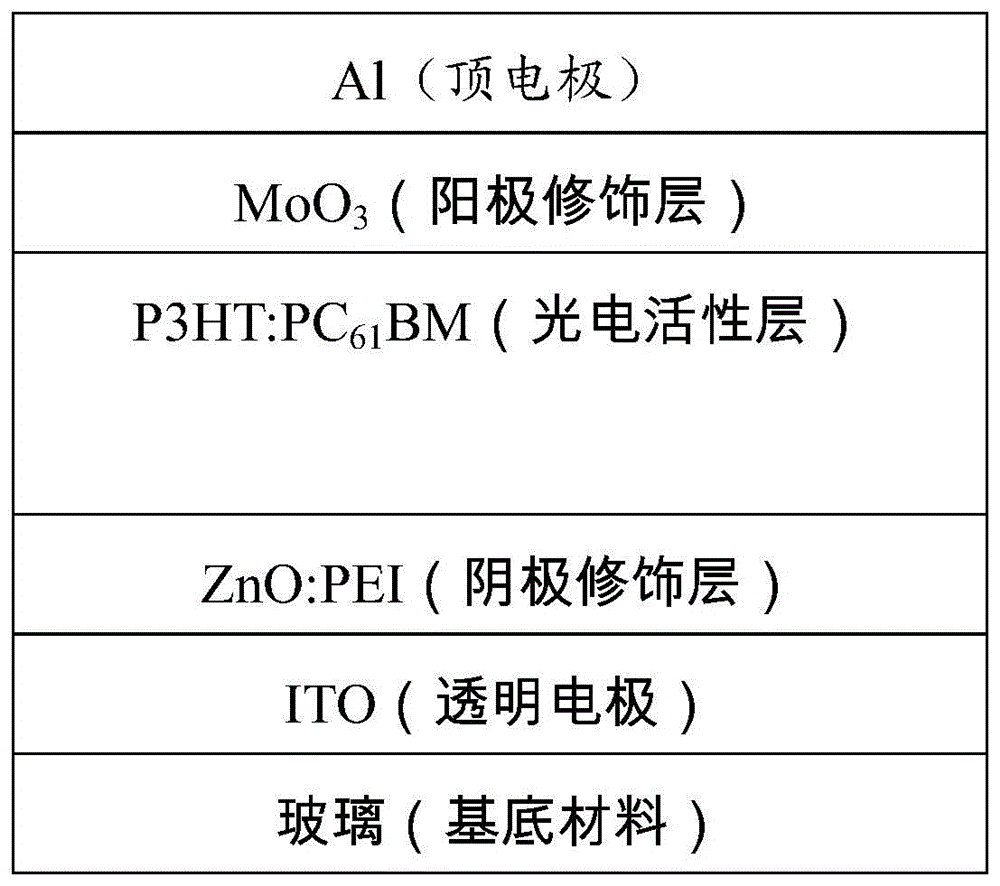

The invention discloses a polymer-nanometer metal oxide composite ink. The polymer-nanometer metal oxide composite ink comprises at least one polymer with a fatty amine unit, at least one nano-metal oxide particle and at least one organic alcohol solvent used as a solvent, wherein the polymer is preferably selected from linear or branched polyethylene imine, end position ethoxylated or ethylaminated polyethylene imine, or a polyethylene imine fragment-containing copolymer. The invention also discloses a preparation method of the composite ink. A composite film is produced through spin-coating or printing the composite ink, and can be applied in solar batteries, light emitting diodes and other optoelectronic devices as an electrode modification layer to improve contact performances between the electrode and an organic active layer in order to improve the performances of the optoelectronic devices.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

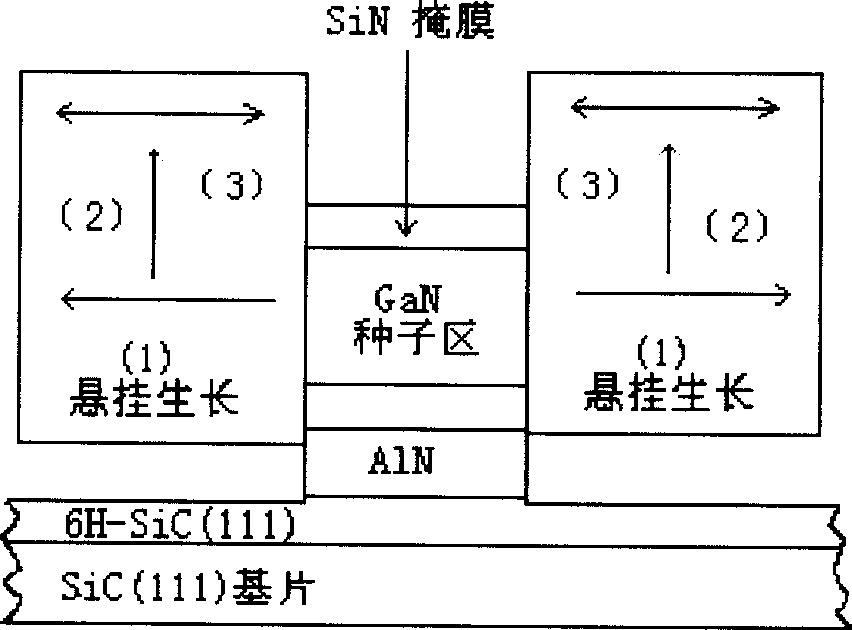

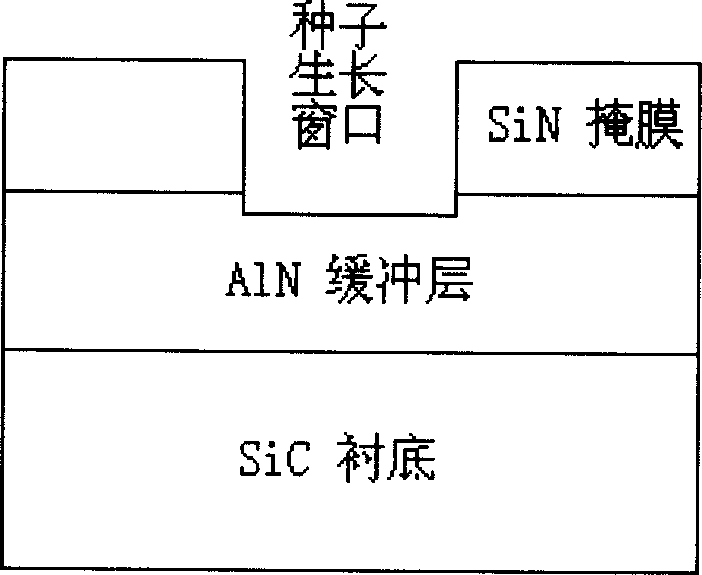

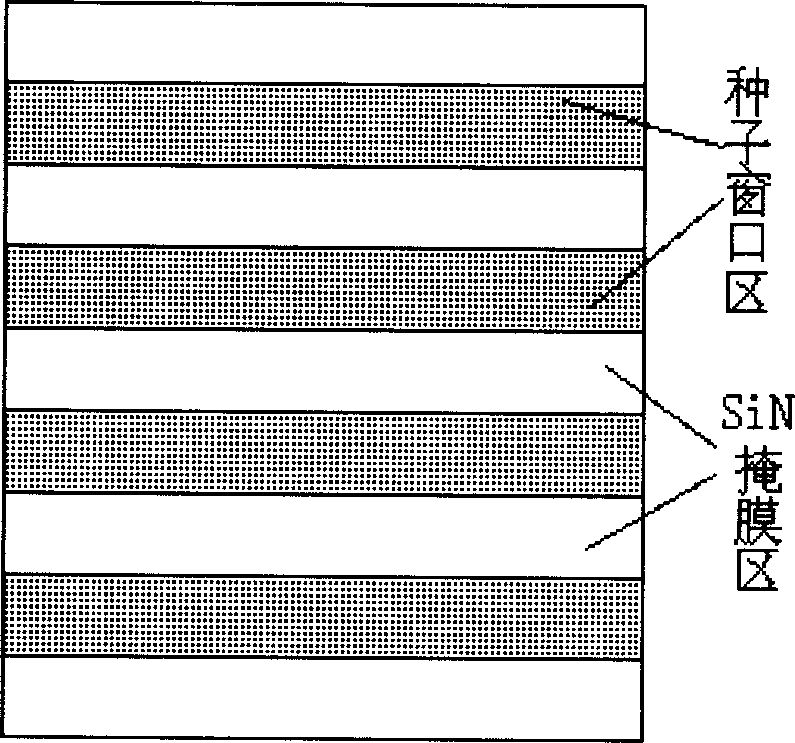

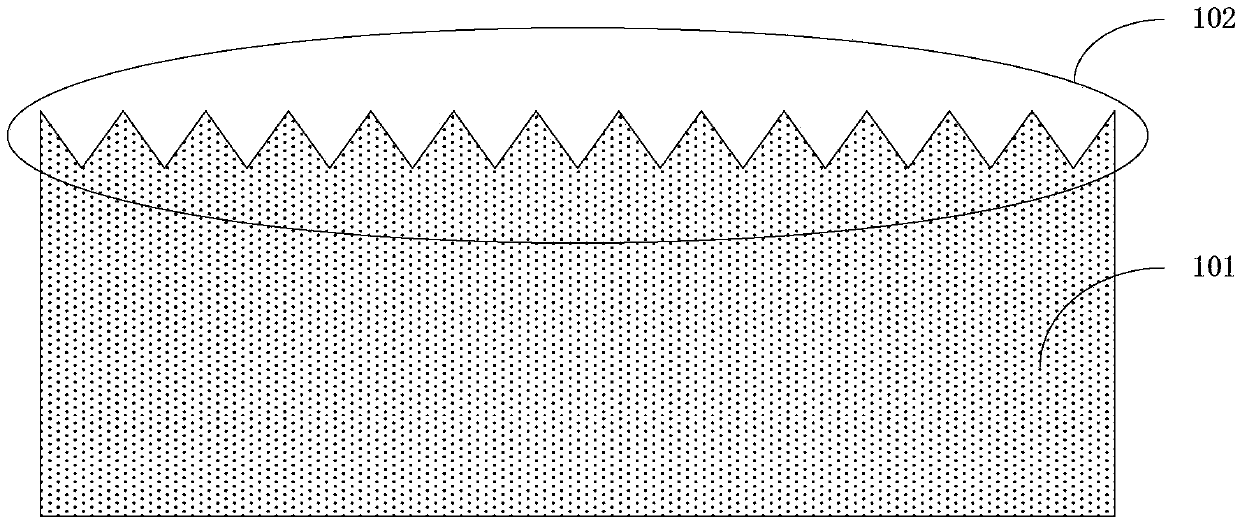

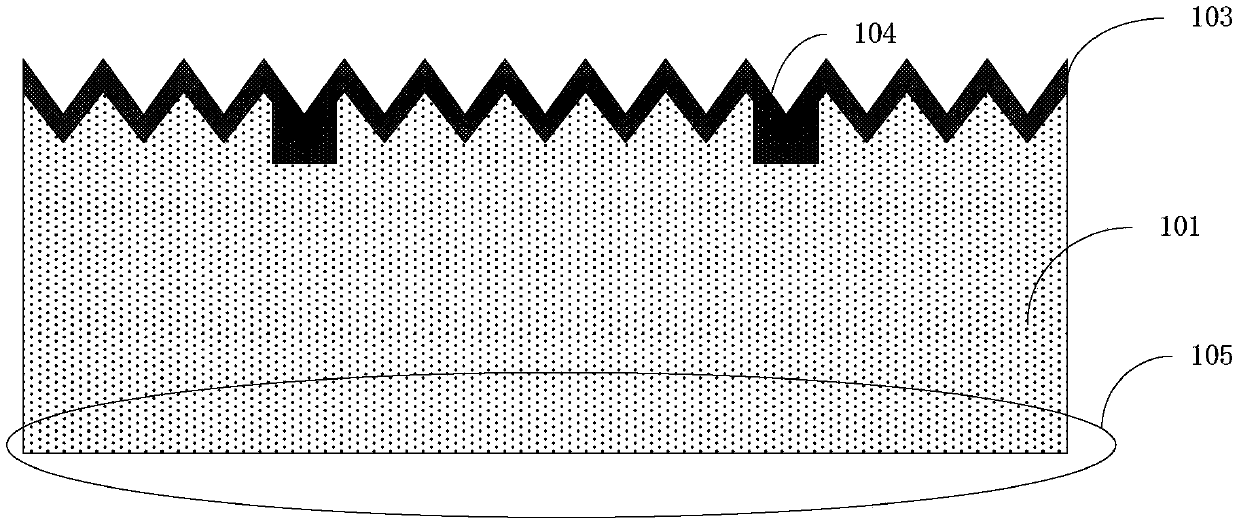

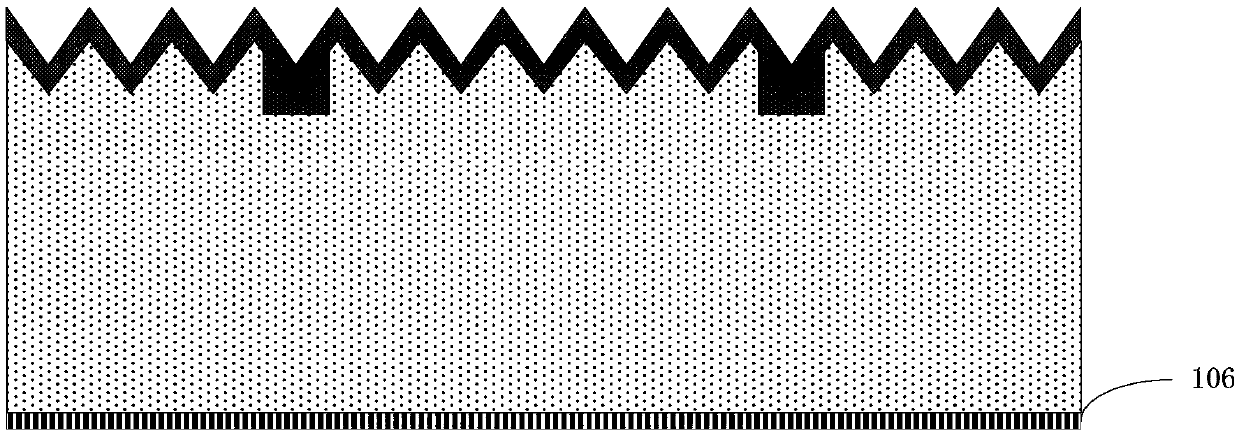

Heteroepitaxy method for GaN semiconductor material

InactiveCN1738000AQuality improvementLarge storage capacitySemiconductor/solid-state device manufacturingSemiconductor materialsGas phase

The invention discloses a heterogeneous epitaxial method of GaN semi-conducting material. First, utilizing the technology of metallorganics chemical vapor deposition, deposing the buffer layer and mask on the surface of SiC substrate (111) and sapphire substrate (0001), etching the mask according the relative pattern, entering and exposing the buffer layer AlN as the area for growing seeds; then, arranging the growing temperature of said area in 1050~110 Deg. C, the pressure beside 40tor, and the seeds in the type of stone can be attained on the buffer layer AlN to grow epitaxially in the form of pyramid, growing mainly in the longitudinal vertical direction while crosswise slow; when reaching the correct height in the vertical direction, changing the growth processing parameters to enter the coronal growing process which covering the upper part of SiN mask by net, as crosswise growing mainly while the vertical growing is slow. The invention has the advantages of simple processing, high performance of film, and the application to the preparation of low defect concentration semi-conducting film material.

Owner:XIDIAN UNIV

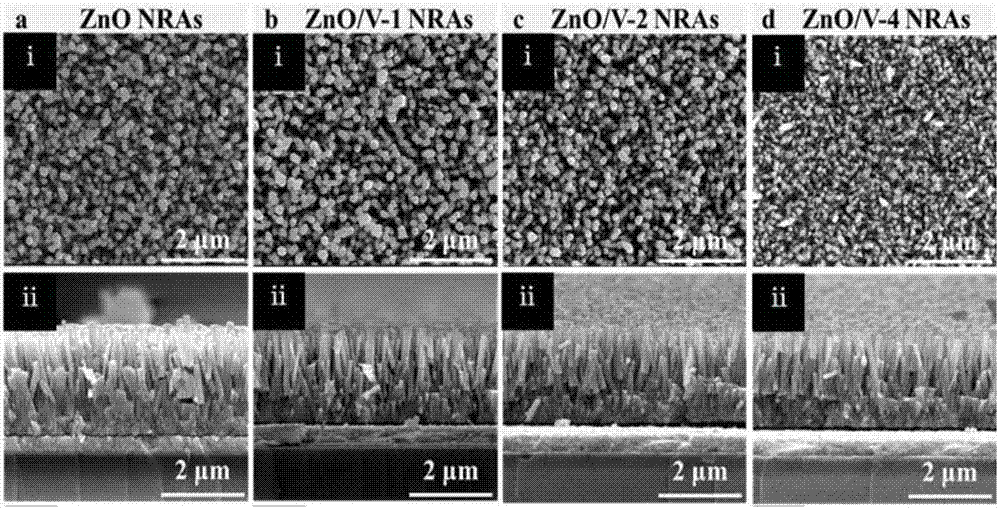

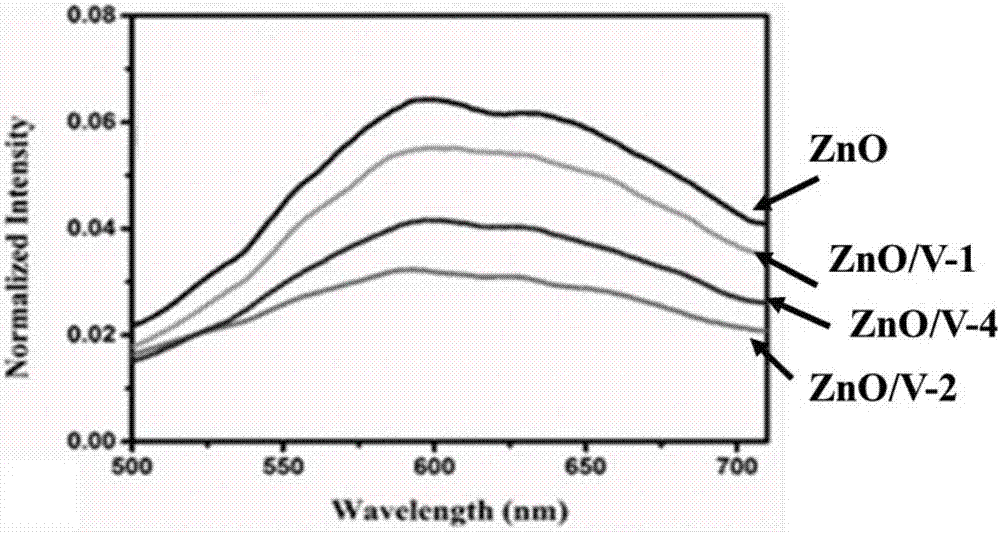

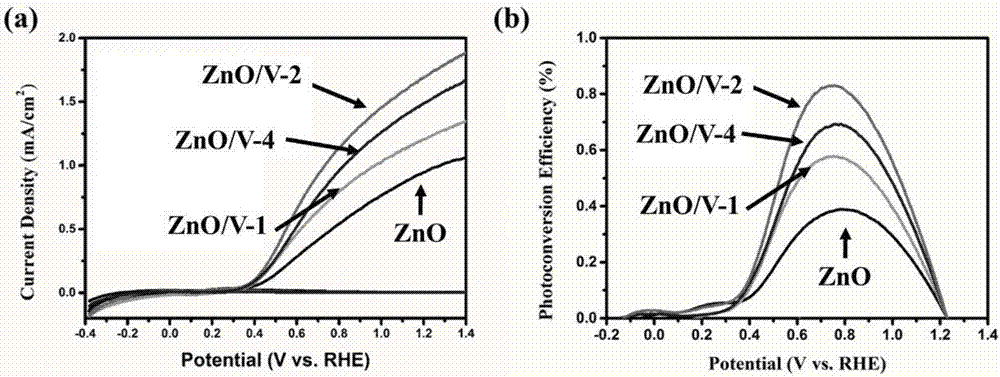

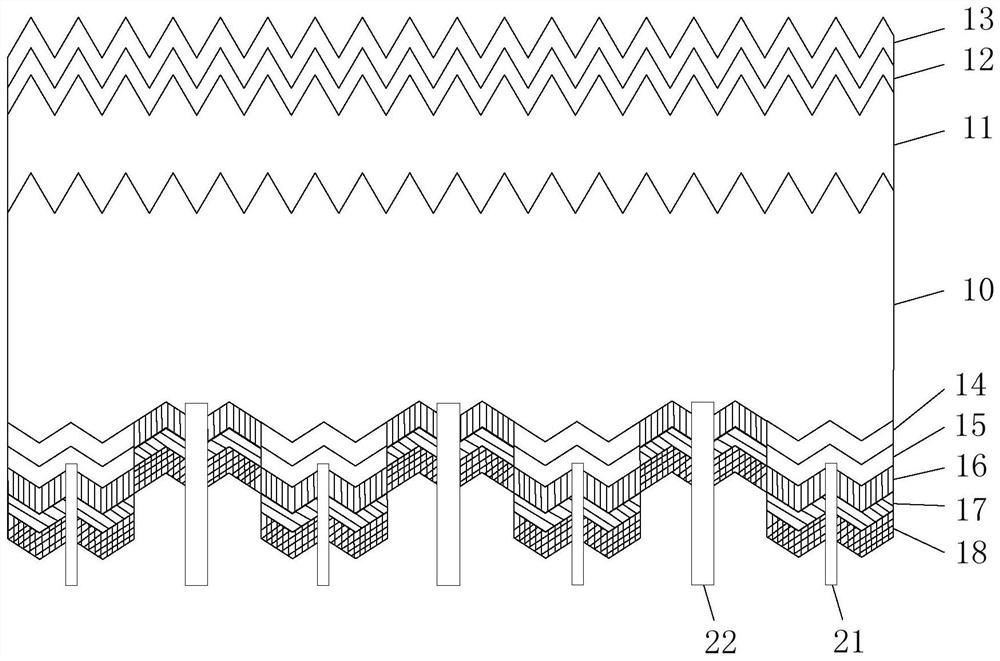

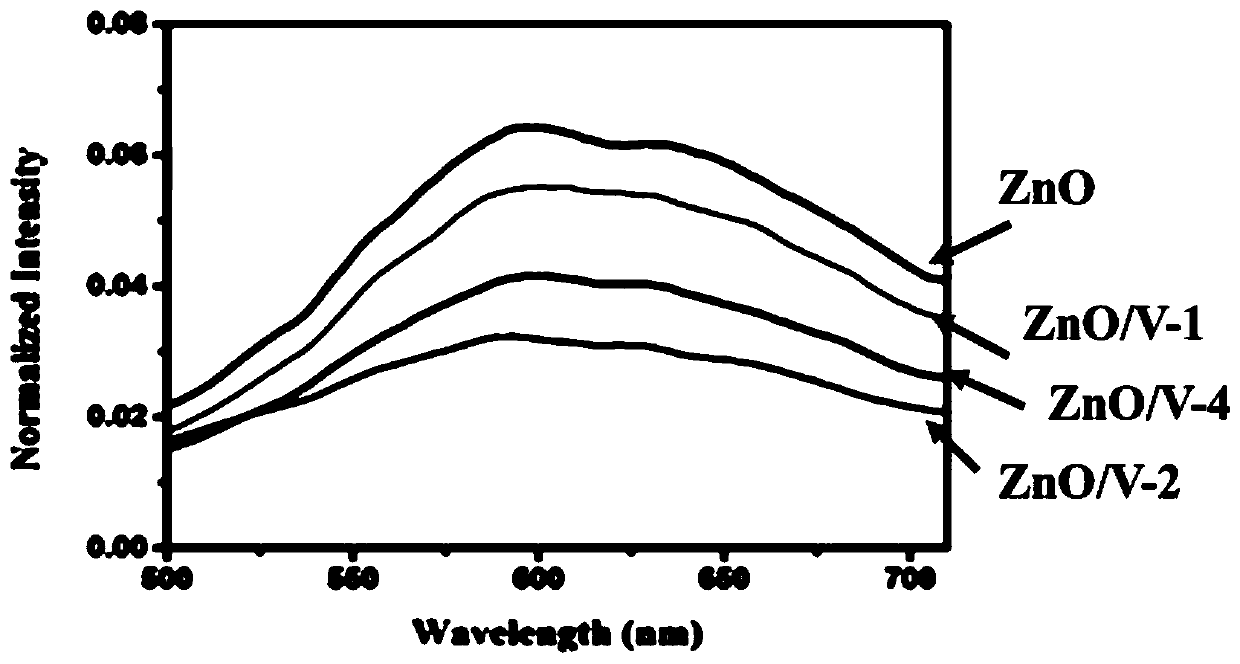

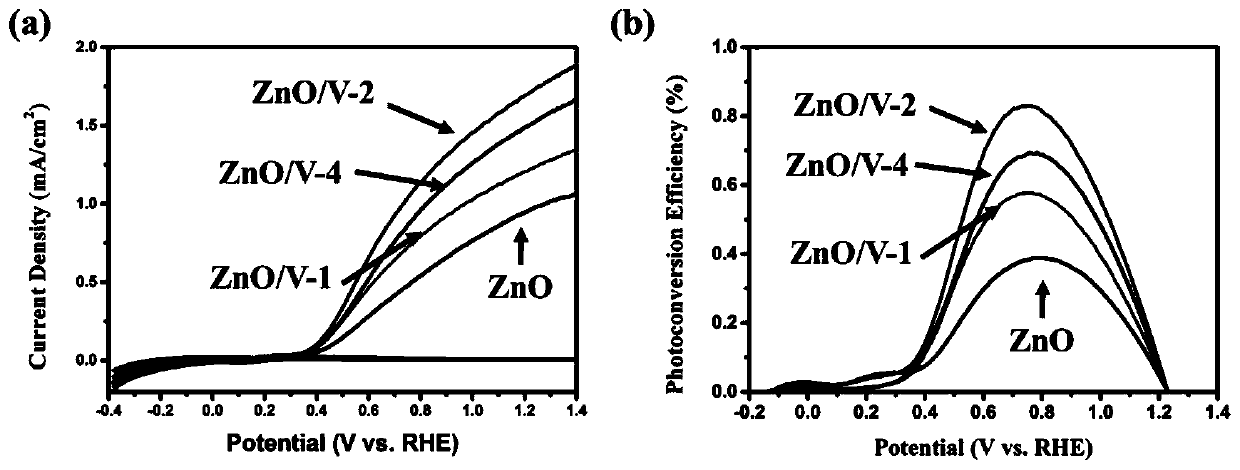

Vanadium-doped ZnO nanorod array photo-anode, and preparation method and application thereof

ActiveCN107287615ASimple processEasy to implementMaterial nanotechnologyEnergy inputVanadium dopingZinc oxide nanorod

The invention mainly belongs to the field of photoelectrochemistry water-splitting for hydrogen production and particularly relates to a vanadium-doped ZnO nanorod array photo-anode, a preparation method of the vanadium-doped ZnO nanorod array photo-anode and an application of the vanadium-doped ZnO nanorod array photo-anode in photoelectrochemistry water-splitting for hydrogen production. The method comprises the steps of preparing a ZnO seed crystal solution, a vanadium-doped solution and a growth solution correspondingly; conducting spin-coating on conducting glass with the ZnO seed crystal solution and obtaining the conducting glass with the surface covered with a ZnO seed crystal layer after spin-coating and annealing; pulling the conducting glass with the surface covered with the ZnO seed crystal layer into a mixed solution of the vanadium-doped solution and the growth solution for a hydrothermal reaction, washing the conducting glass with deionized water after completion of the reaction, conducting annealing in a muffle furnace and then obtaining an vanadium-doped ZnO nanorod array. By adopting the vanadium-doped ZnO nanorod array photo-anode provided by the invention, the carrier life is prolonged, combination of electron holes is reduced, and the photoelectrochemistry water-splitting performance is improved.

Owner:UNIV OF SCI & TECH BEIJING

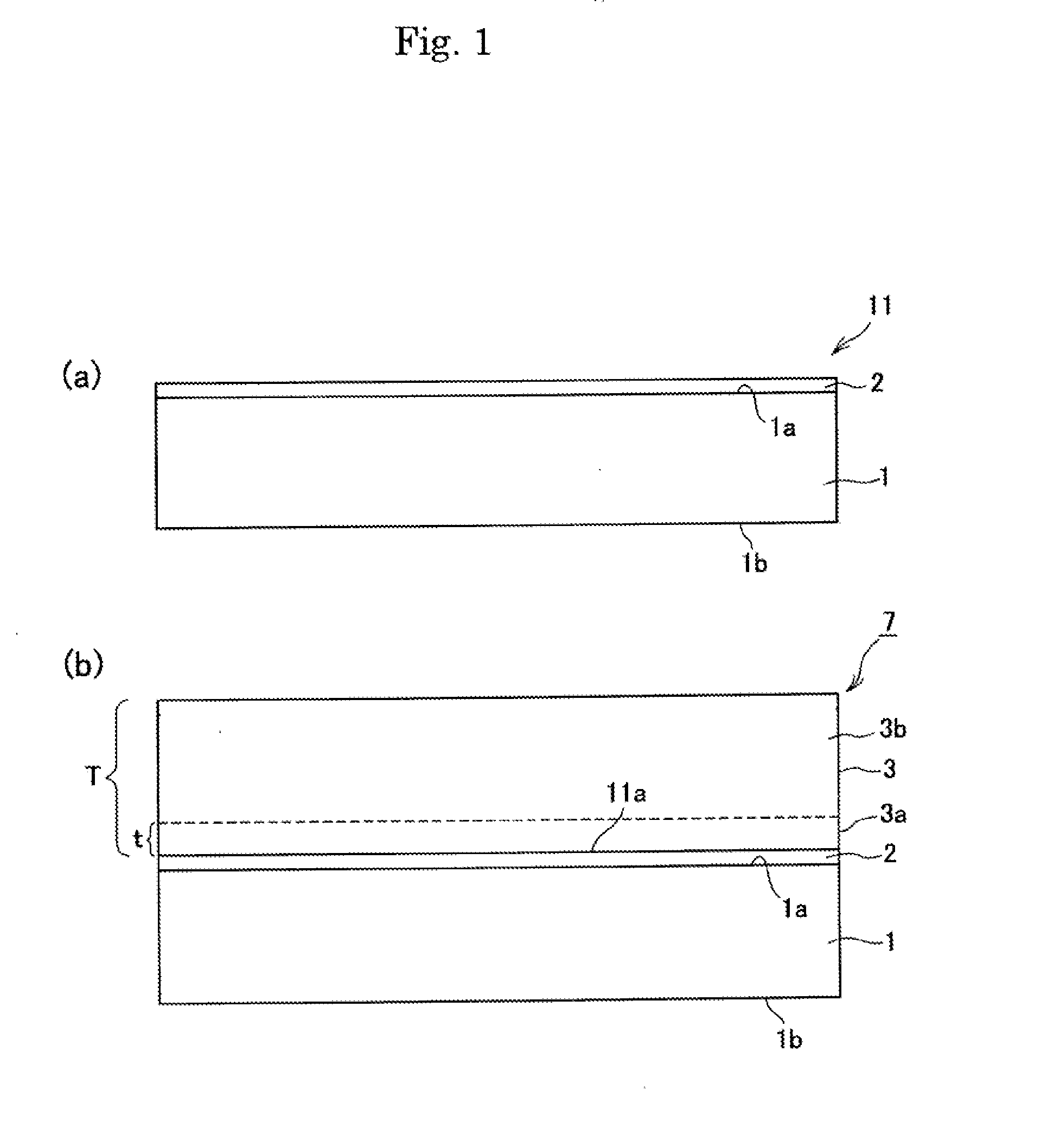

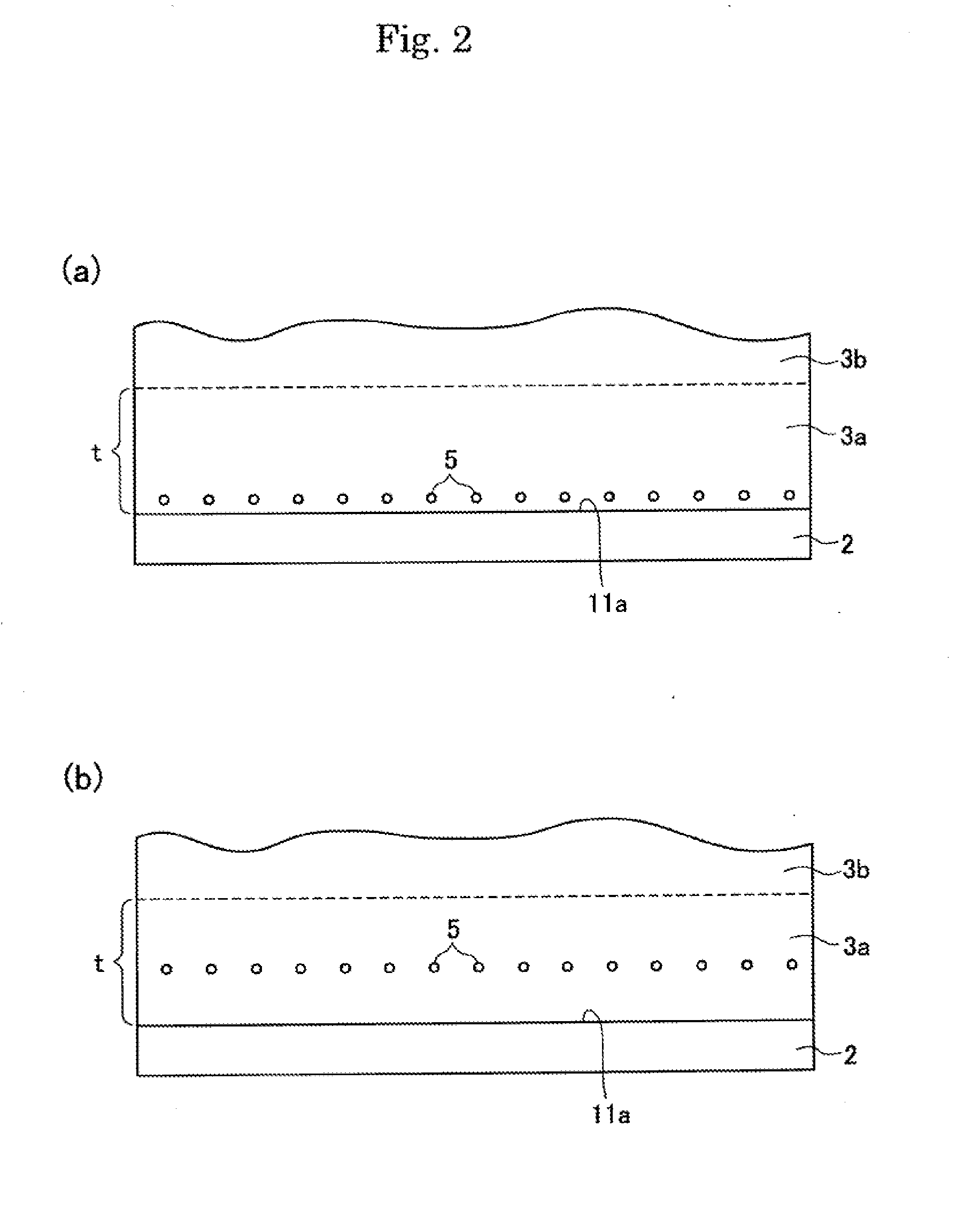

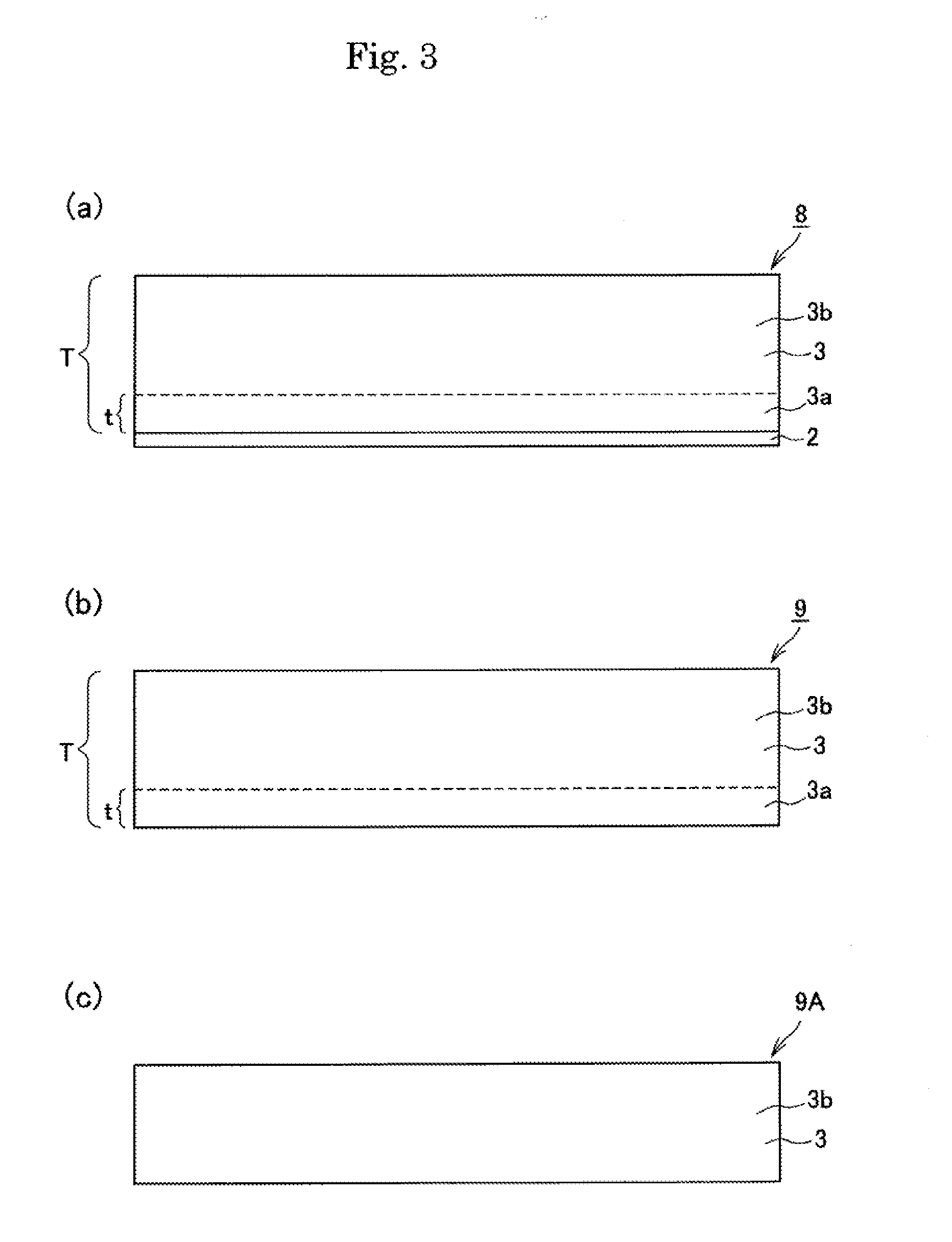

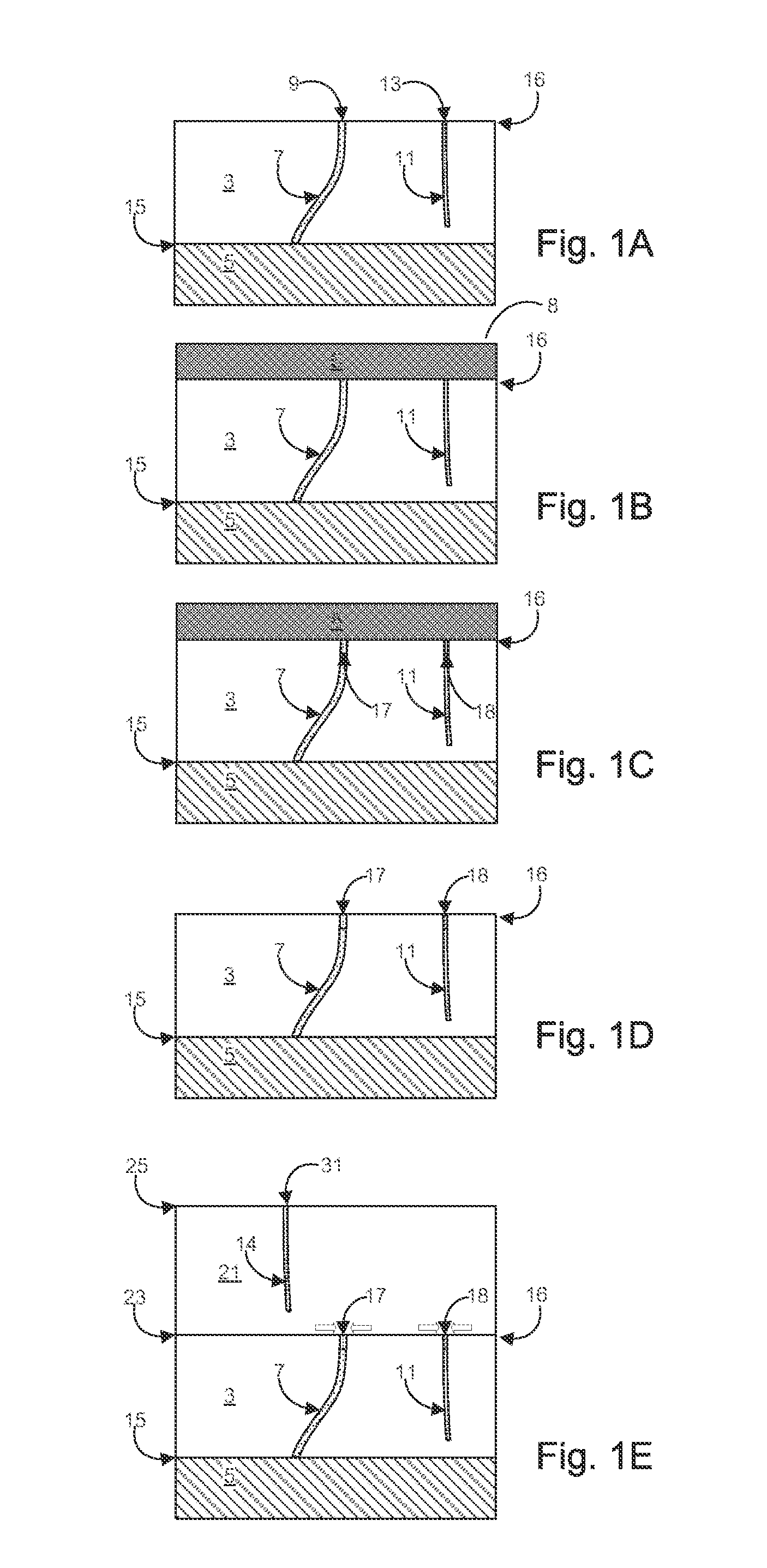

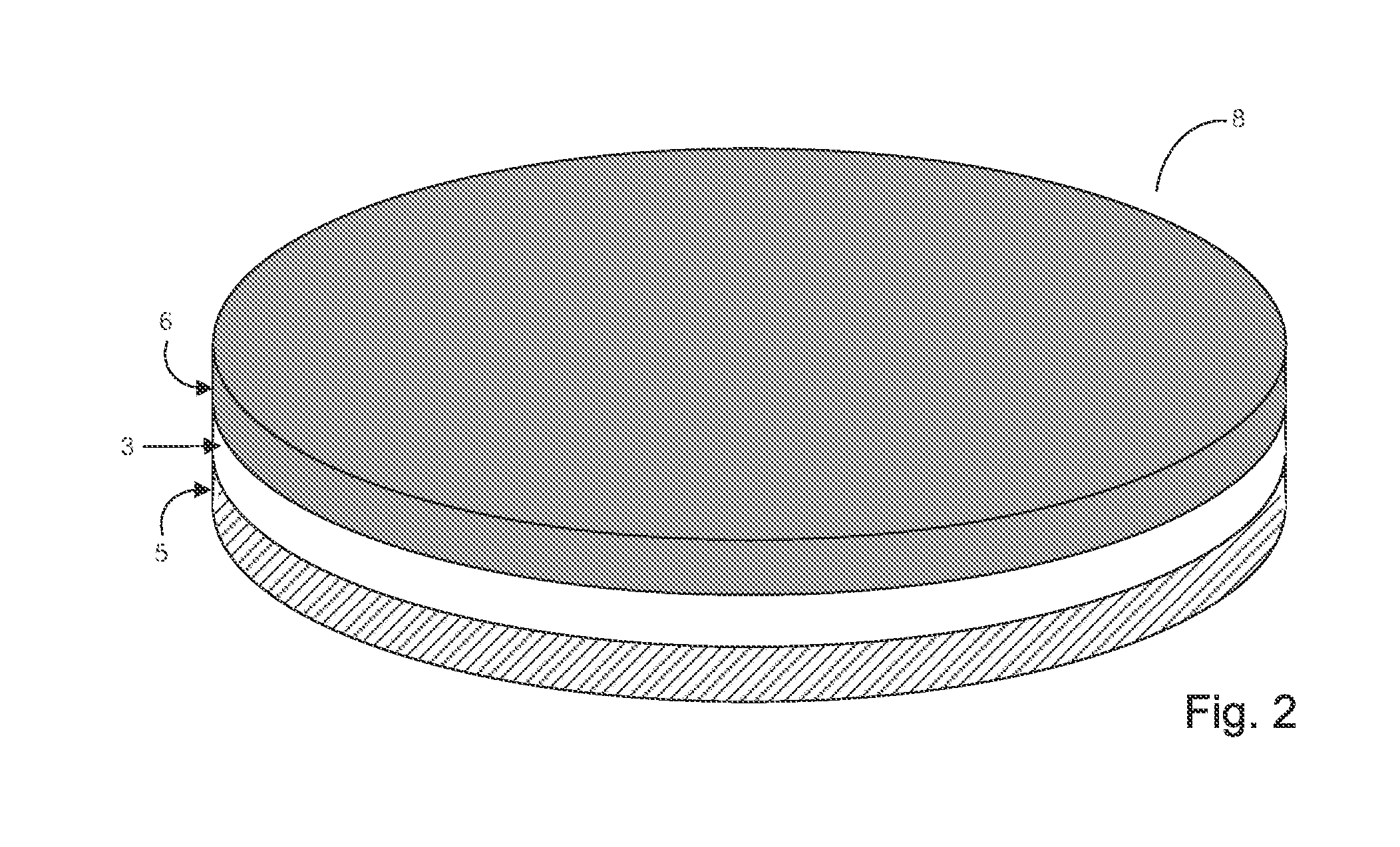

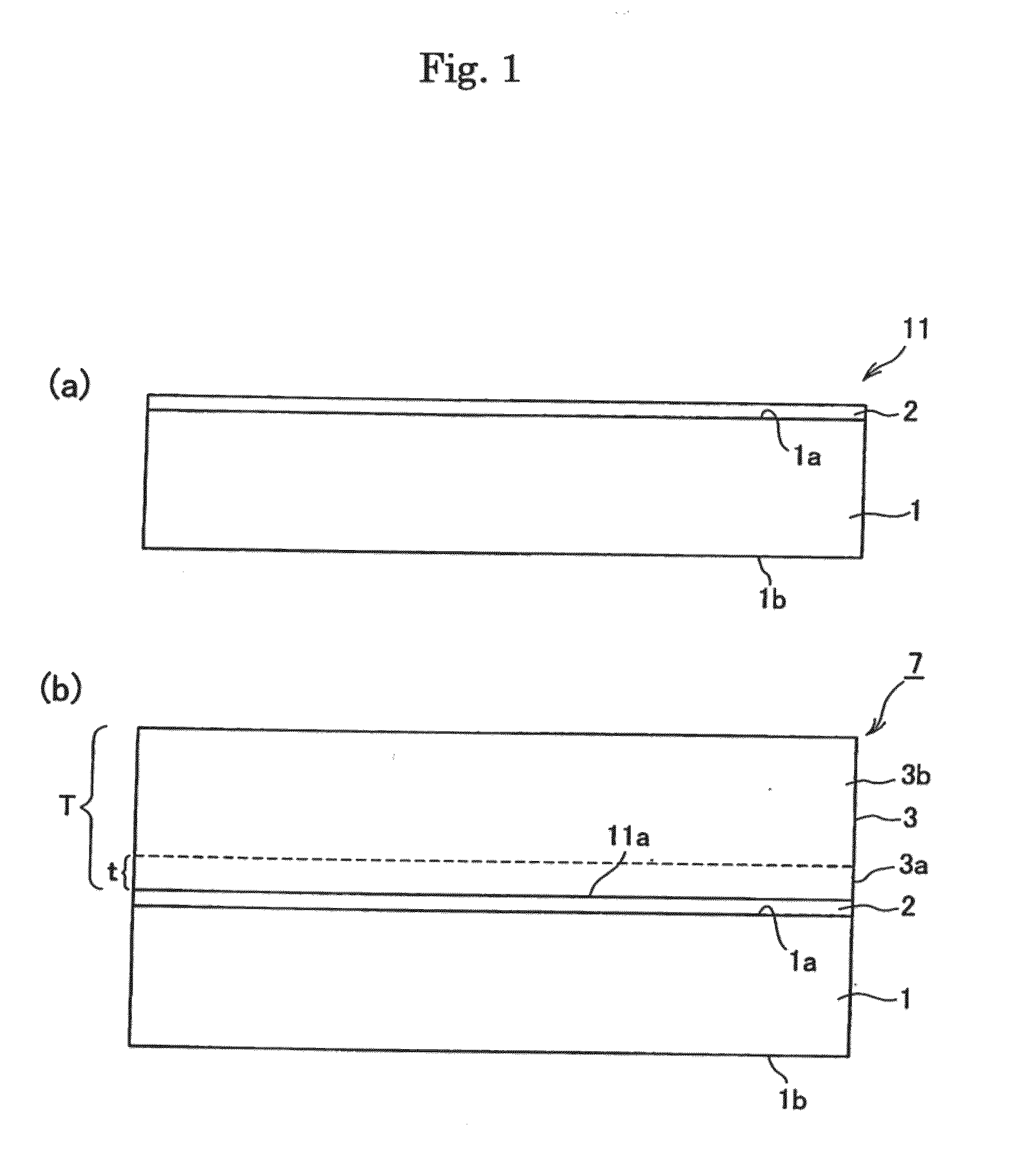

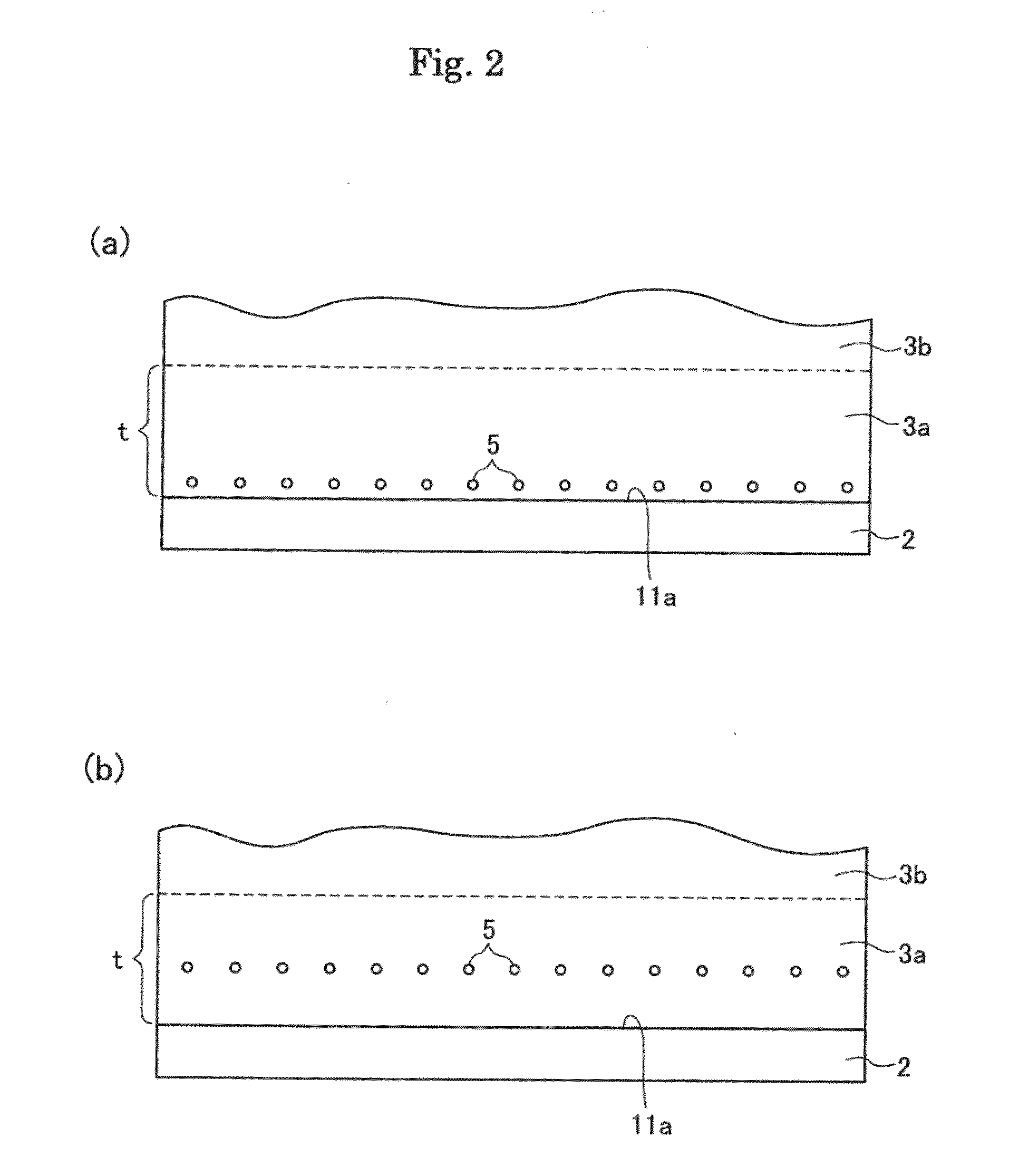

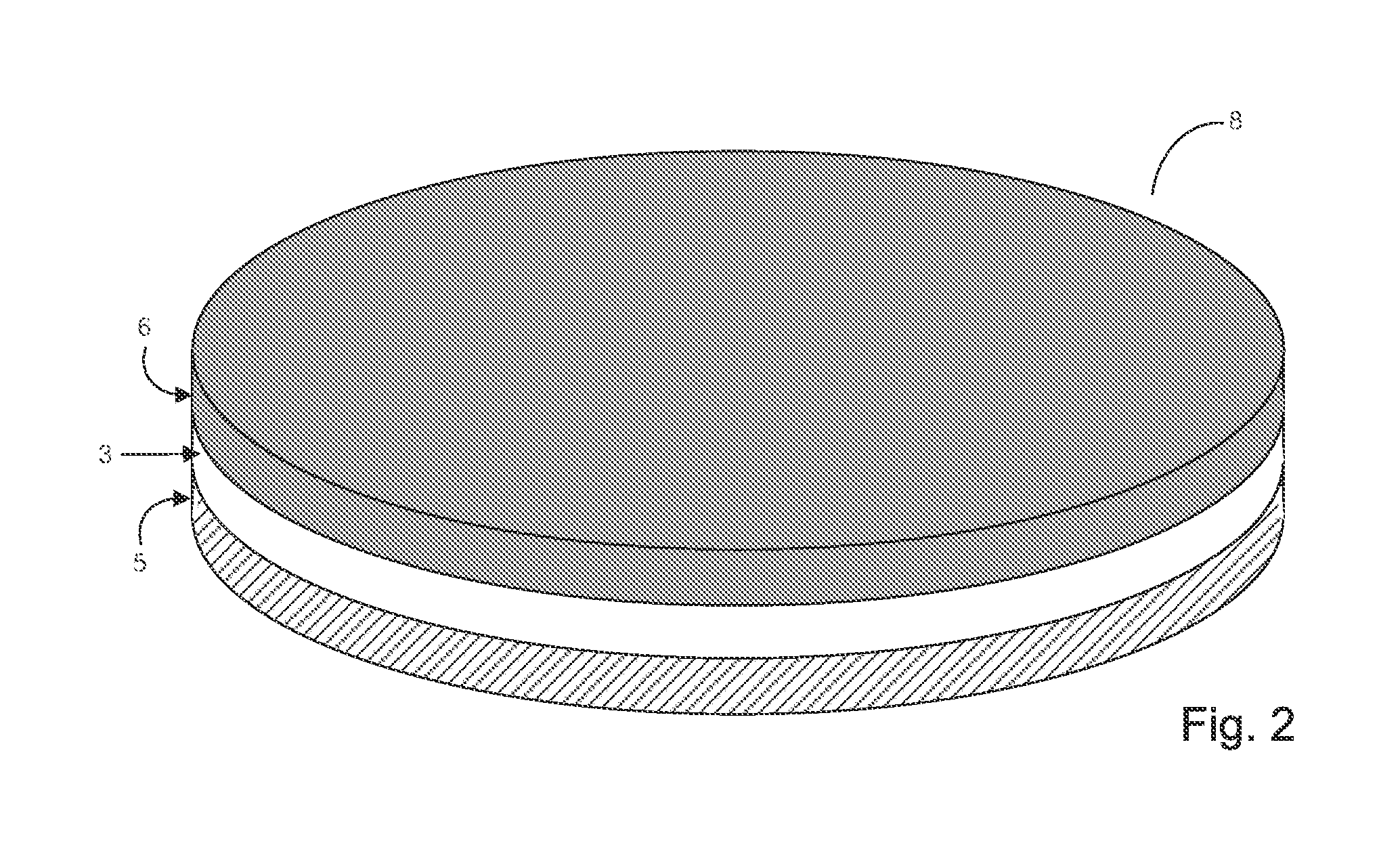

Films of Nitrides of Group 13 Elements and Layered Body Including the Same

ActiveUS20140197420A1Reduce misalignmentPreferable propertyPolycrystalline material growthLiquid-phase epitaxial-layer growthNitrogenNitride

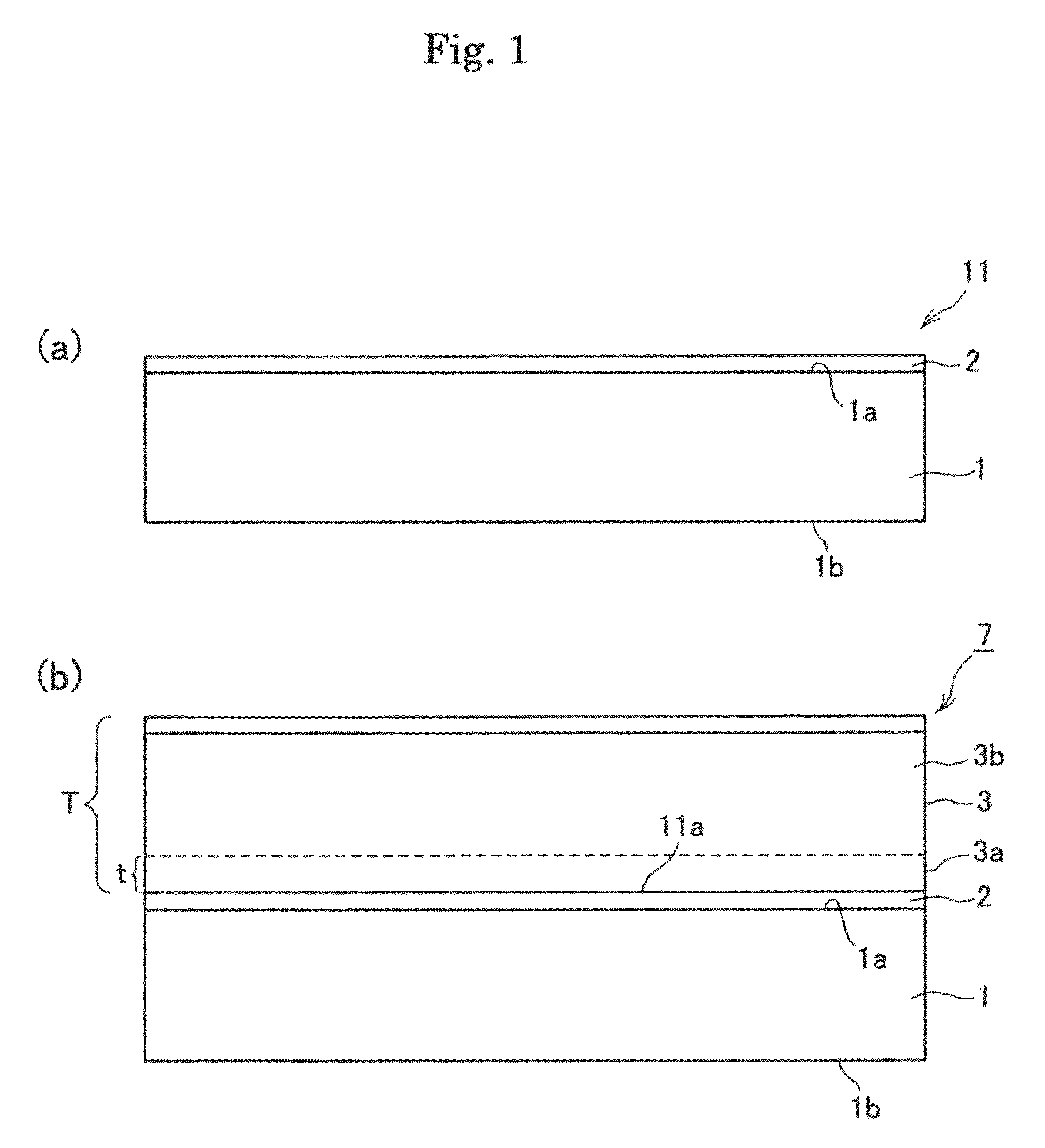

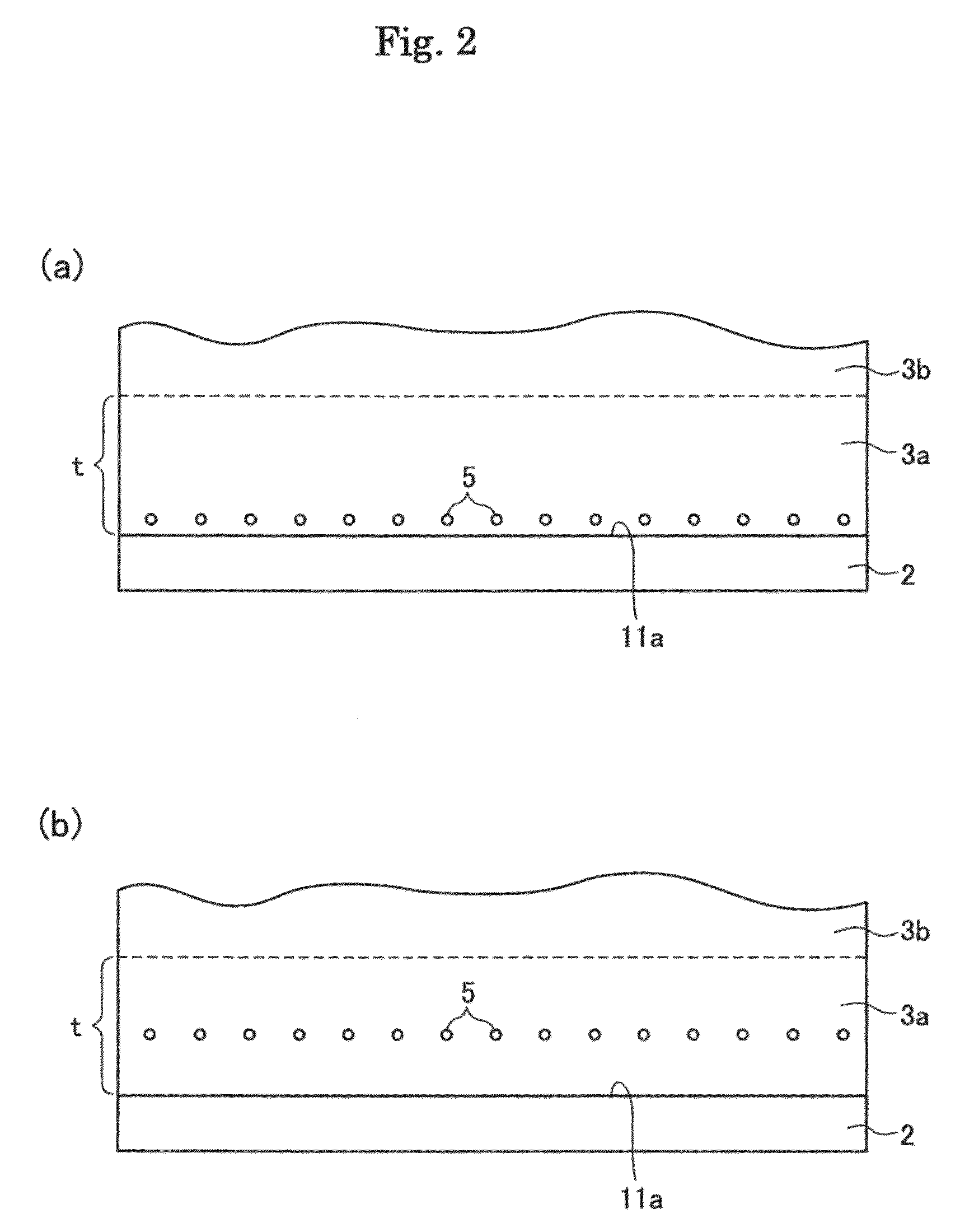

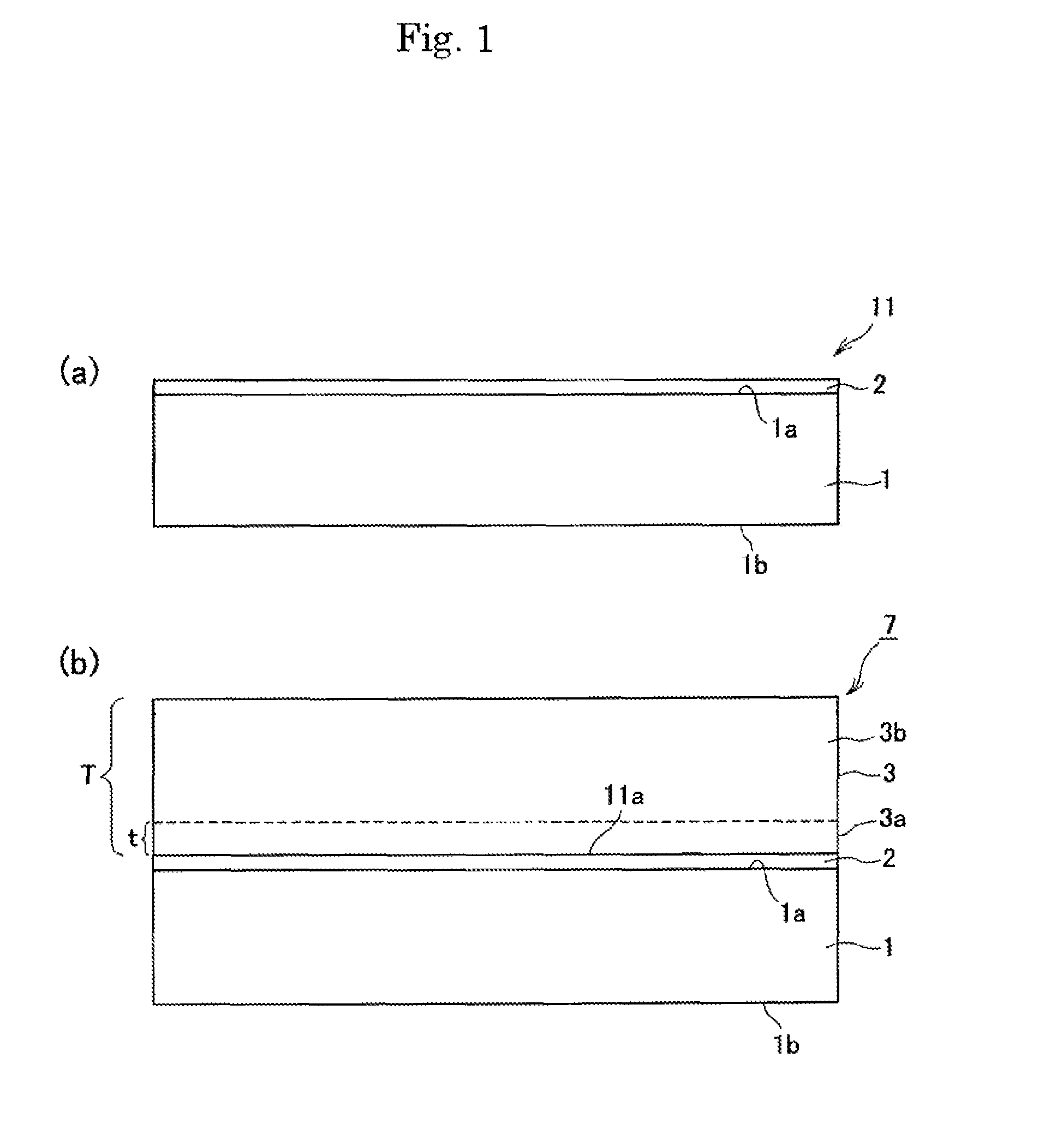

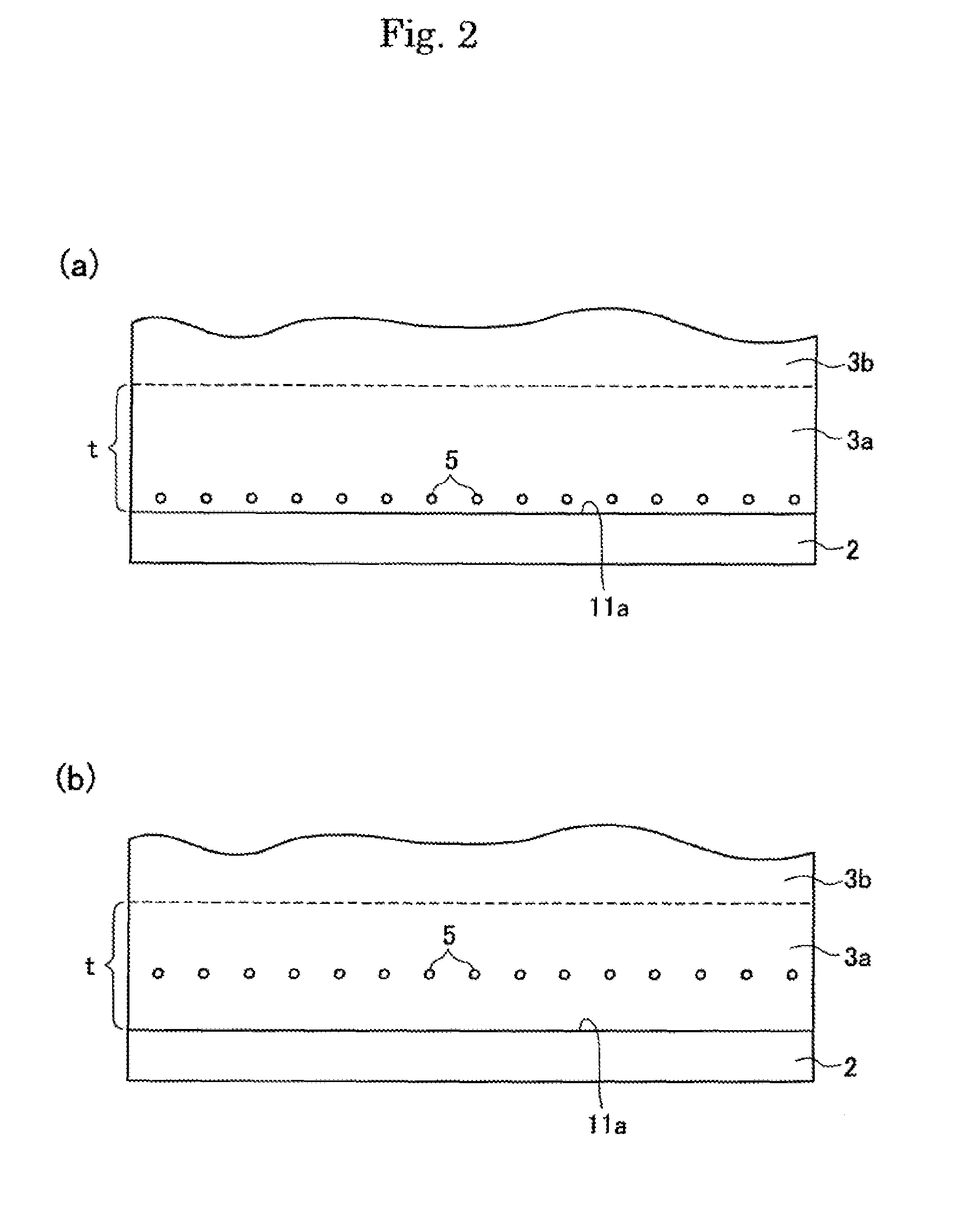

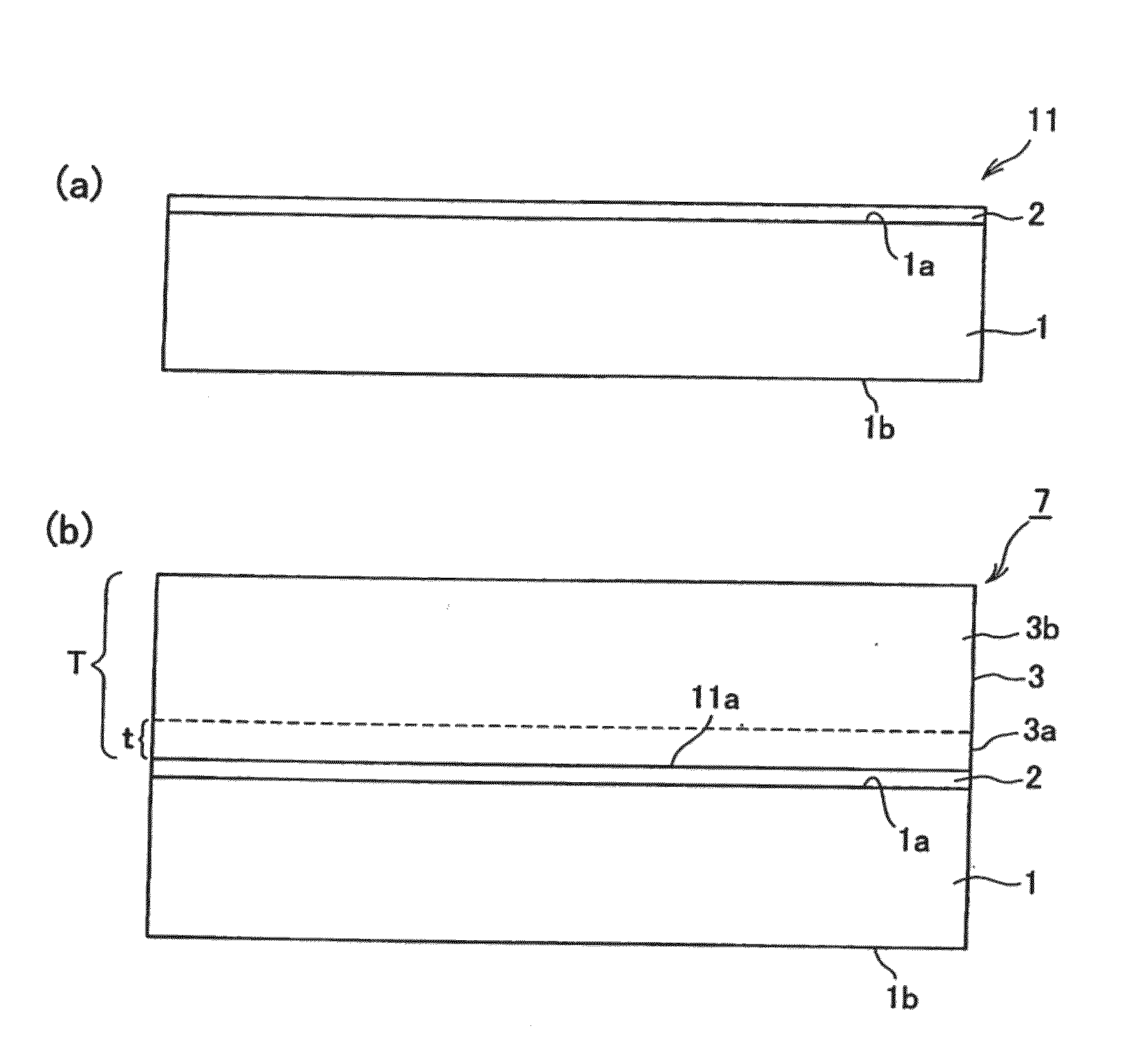

A film 3 of a nitride of a group 13 element is grown on a seed crystal substrate 11 by flux process from a melt containing a flux and a group 13 element under nitrogen containing atmosphere. The film 3 of a nitride of a group 13 element includes an inclusion distributed layer 3a in a region distant from an interface of the film of a nitride of group 13 element on the side of the seed crystal substrate 11 and containing inclusions derived from components of the melt, and an inclusion depleted layer 3b, with the inclusion depleted. provided on the layer 3a.

Owner:NGK INSULATORS LTD

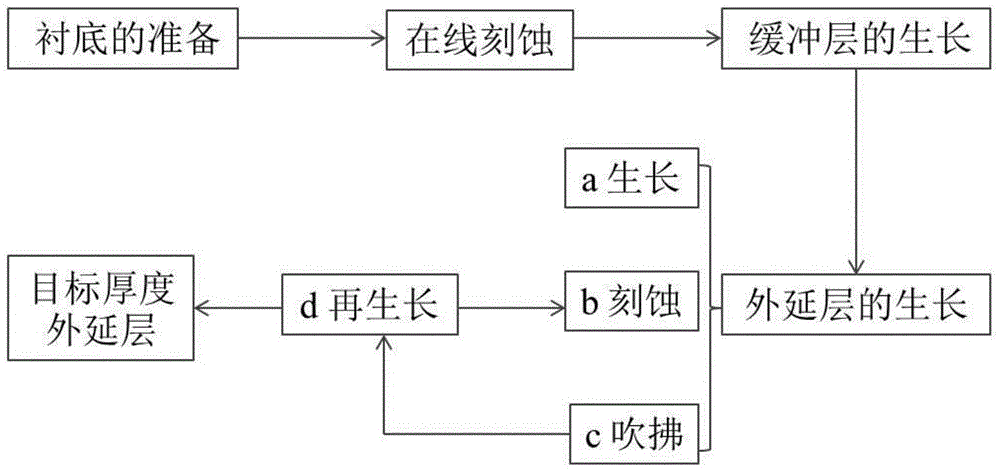

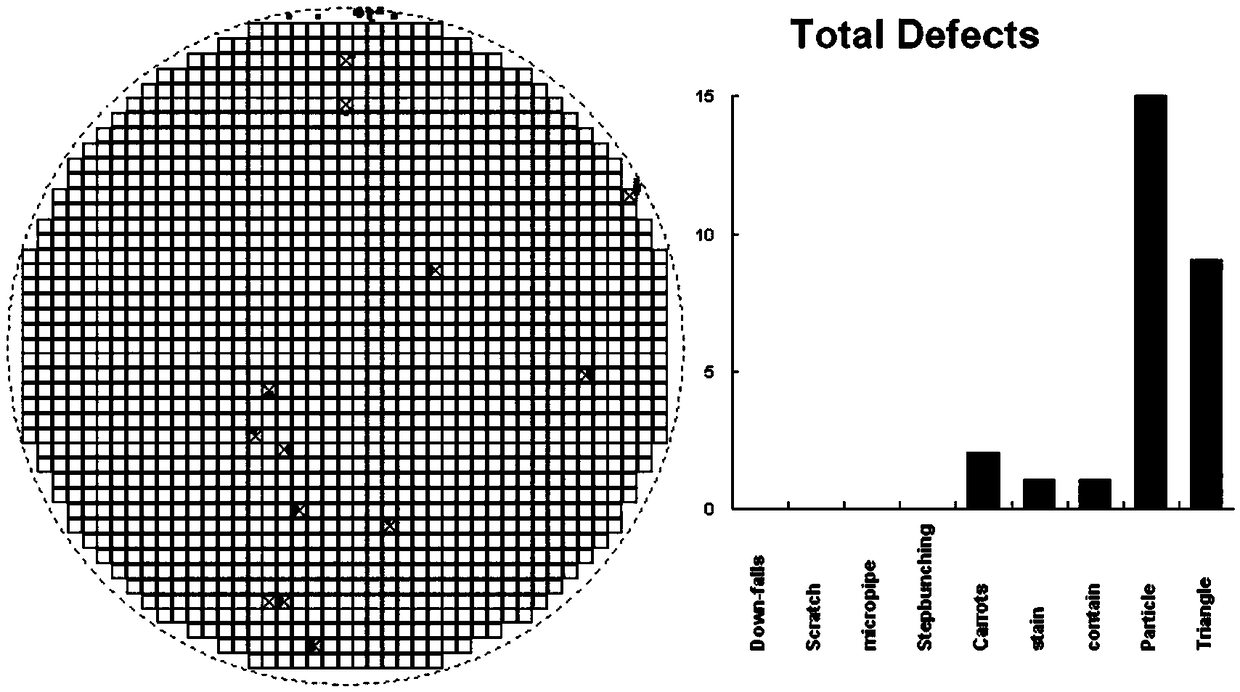

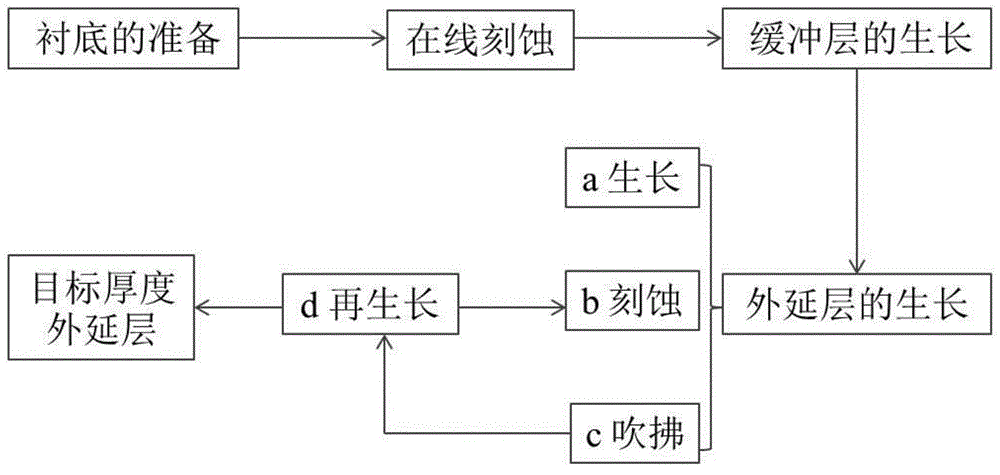

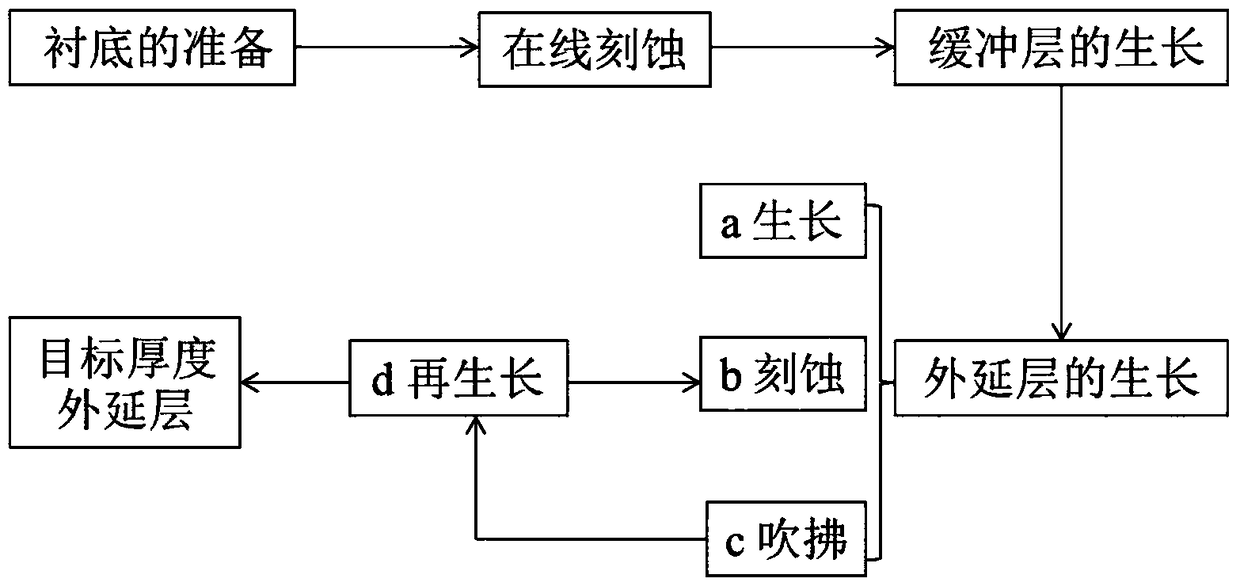

Preparation method of N-type low-defect silicon carbide epitaxial wafer

ActiveCN104934318AGood effectLow densitySemiconductor/solid-state device manufacturingEtchingEpitaxial material

The invention provides a preparation method of an N-type low-defect silicon carbide epitaxial wafer. The method comprises the steps of preparation of a substrate, online substrate etching, growth of a buffer layer and growth of an epitaxial layer, wherein growth of the epitaxial layer includes growth, etching, blowing and re-growth. The method can be used to effectively reduce the dislocation density of the base, reduce deposit in the cavity, reduce the defect density of the surface of the silicon carbide epitaxial wafer, improve the quality of a silicon carbide epitaxial material, and is wide in application range, low in processing cost and suitable for industrial production.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

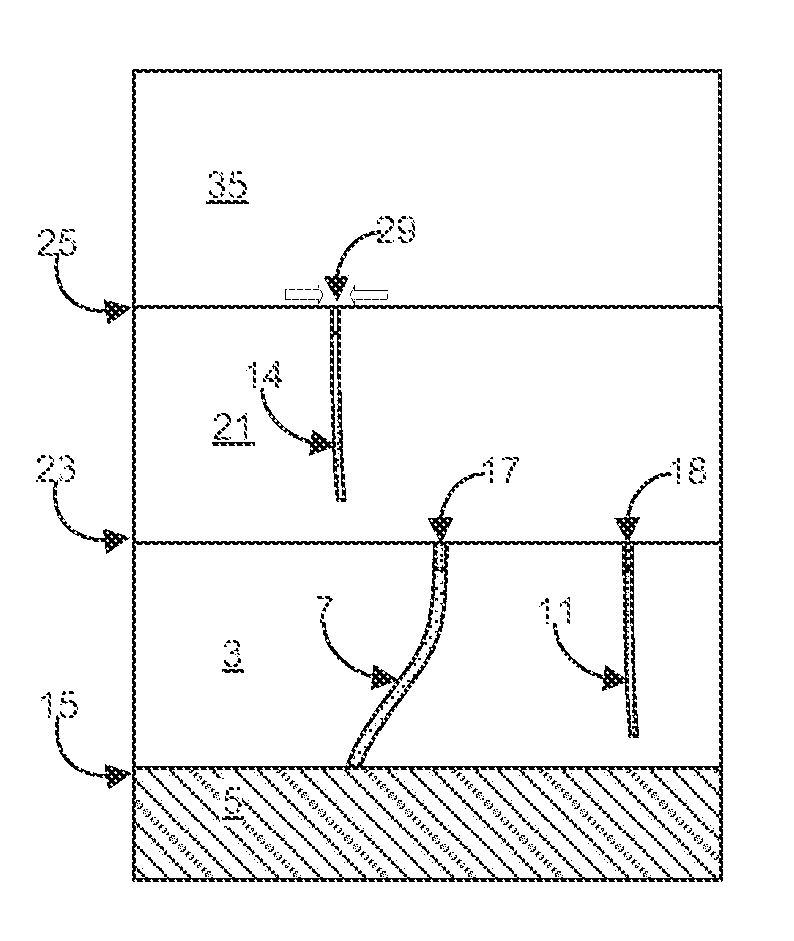

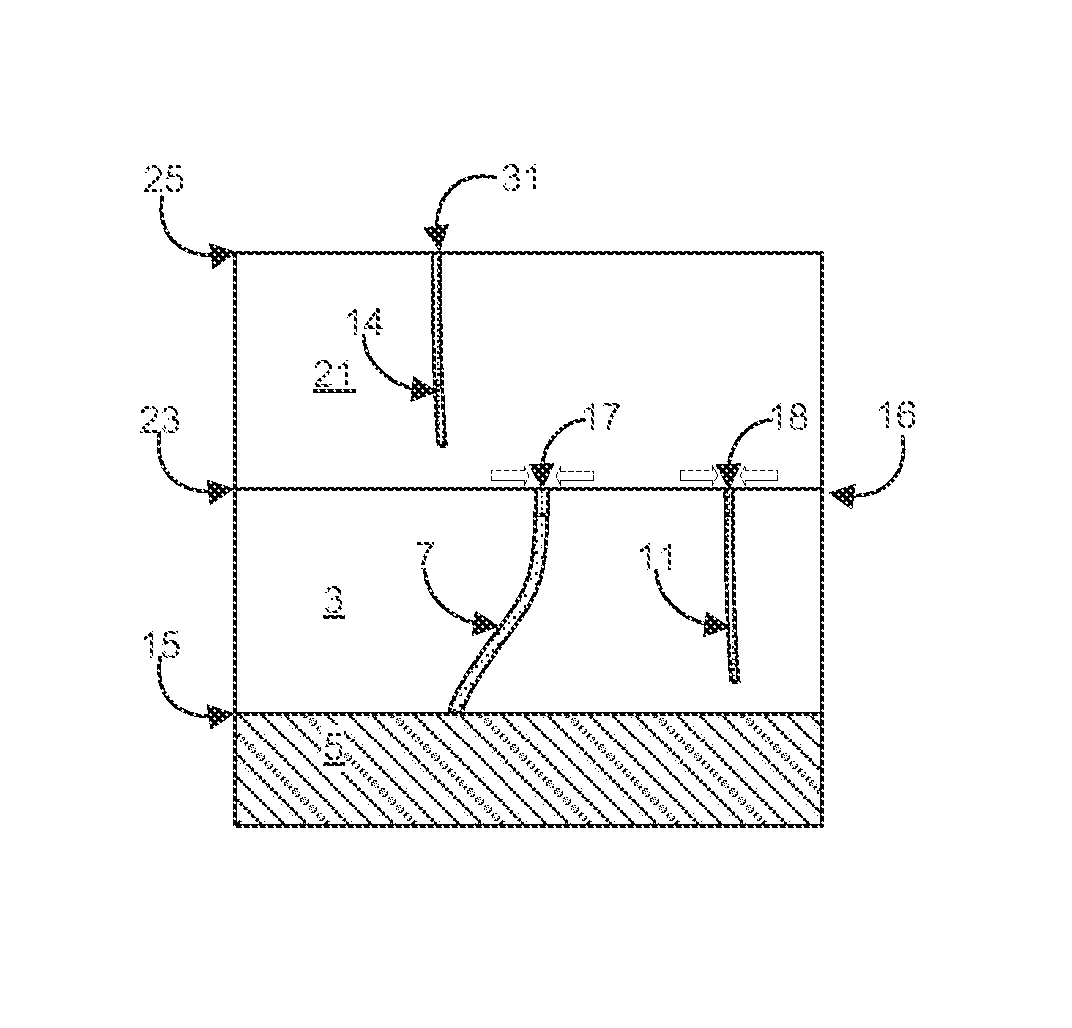

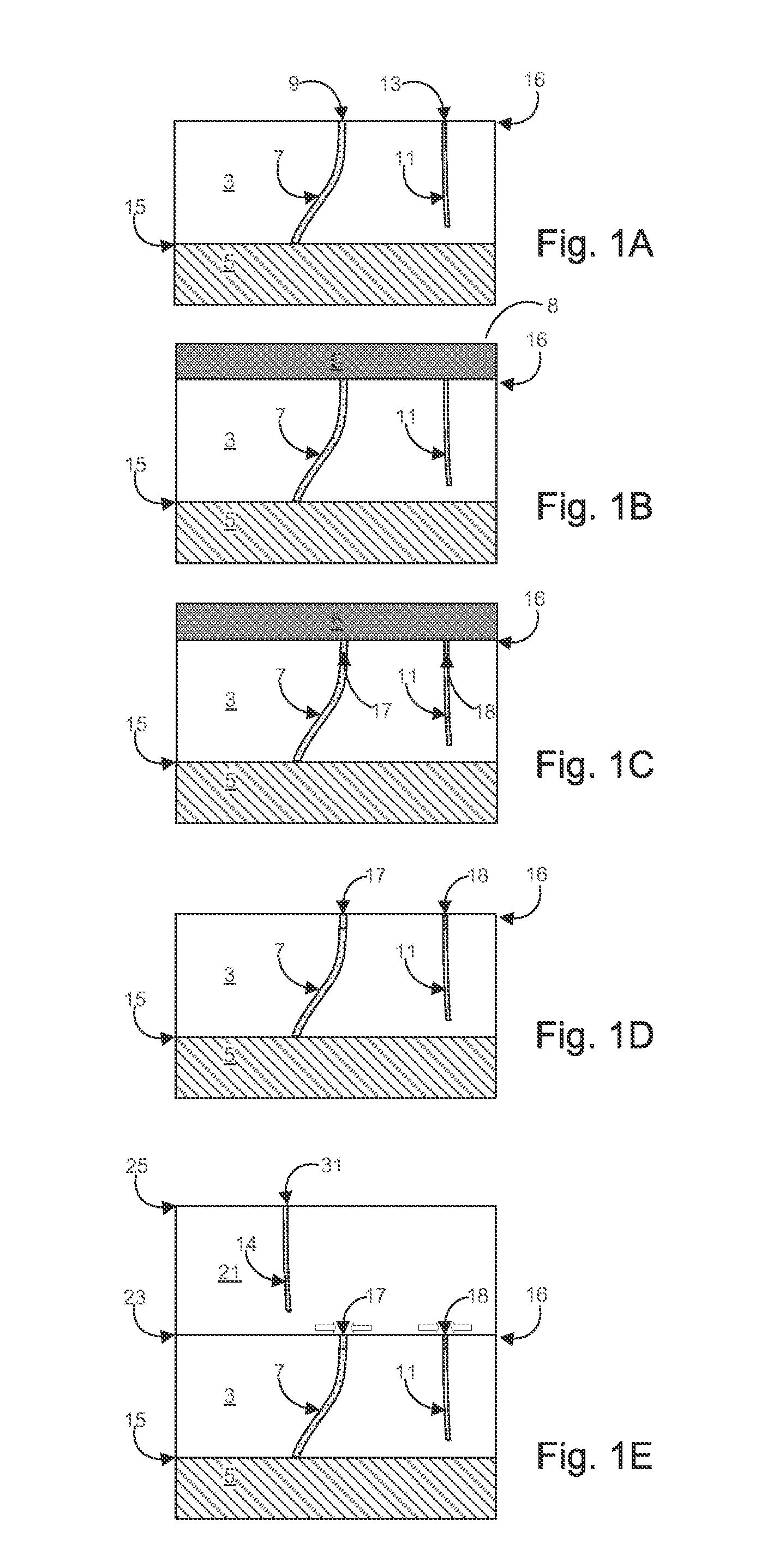

Methods for improving the quality of group iii-nitride materials and structures produced by the methods

ActiveUS20110024747A1Reduce surface defect densityAvoid decompositionSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureDislocation

The invention provides methods which can be applied during the epitaxial growth of two or more layers of Group III-nitride semiconductor materials so that the qualities of successive layer are successively improved. In preferred embodiments, surface defects interact with a protective layer of a protective material to form amorphous complex regions capable of preventing the further propagation of defects and dislocations. The invention also includes semiconductor structures fabricated by these methods.

Owner:SOITEC SA +1

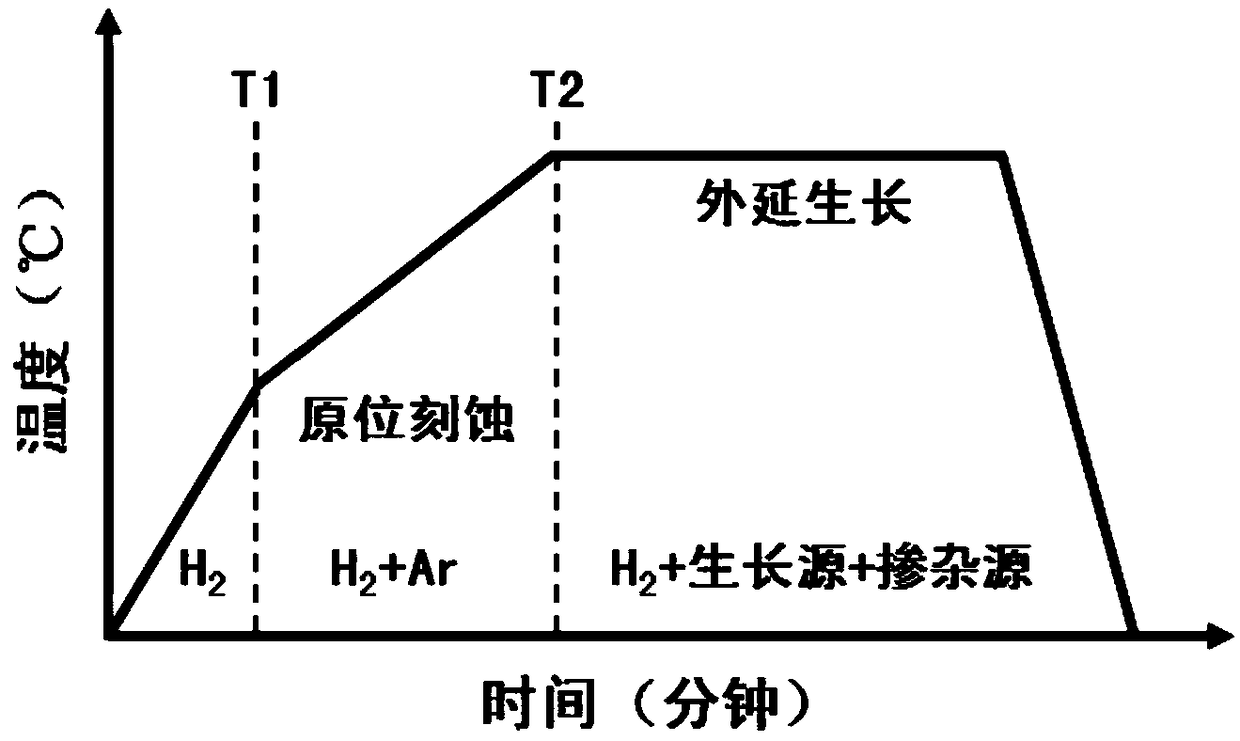

Method for reducing the density of silicon carbide epitaxial surface defects

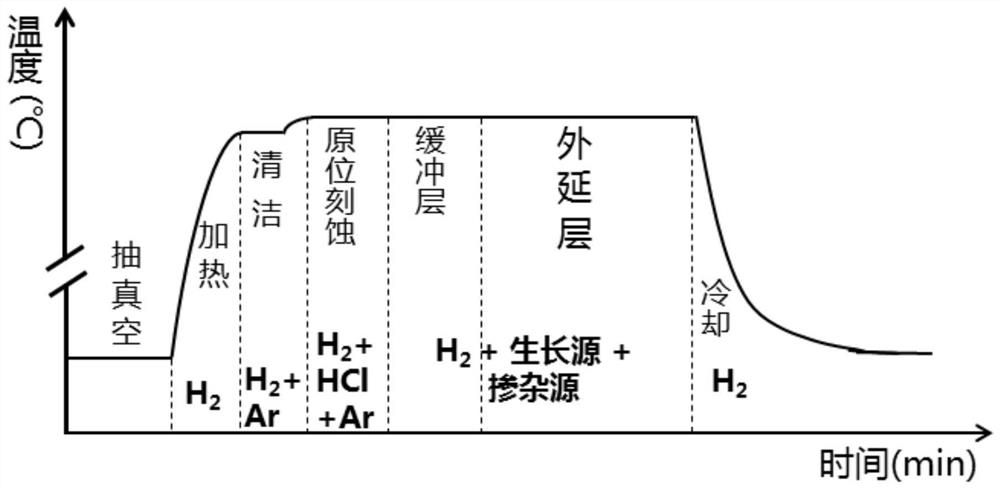

ActiveCN108878257AReduce unintentional injuriesReduce surface defect densitySemiconductor/solid-state device manufacturingHydrogenEtching

The invention discloses a method for reducing the density of silicon carbide epitaxial surface defects, a silicon carbide substrate is treated by in-situ composite etching with hydrogen-argon mixed atmosphere before epitaxial growth, by introducing relatively mild argon gas, the problem of large surface damage caused by pure hydrogen etching is solved, compared with pure hydrogen etching, the temperature field is more uniform, and the surface instability of the substrate in the initial epitaxial stage is reduced or even eliminated while the damaged layer introduced by the chemical mechanical polishing of the substrate is effectively treated, so that the defects of the surface extended into the epitaxial layer due to the substrate are greatly reduced, and the surface defect density in the epitaxial layer can be effectively reduced. The method of the invention is simple, feasible and compatible with the existing epitaxial process, and has high popularization value.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

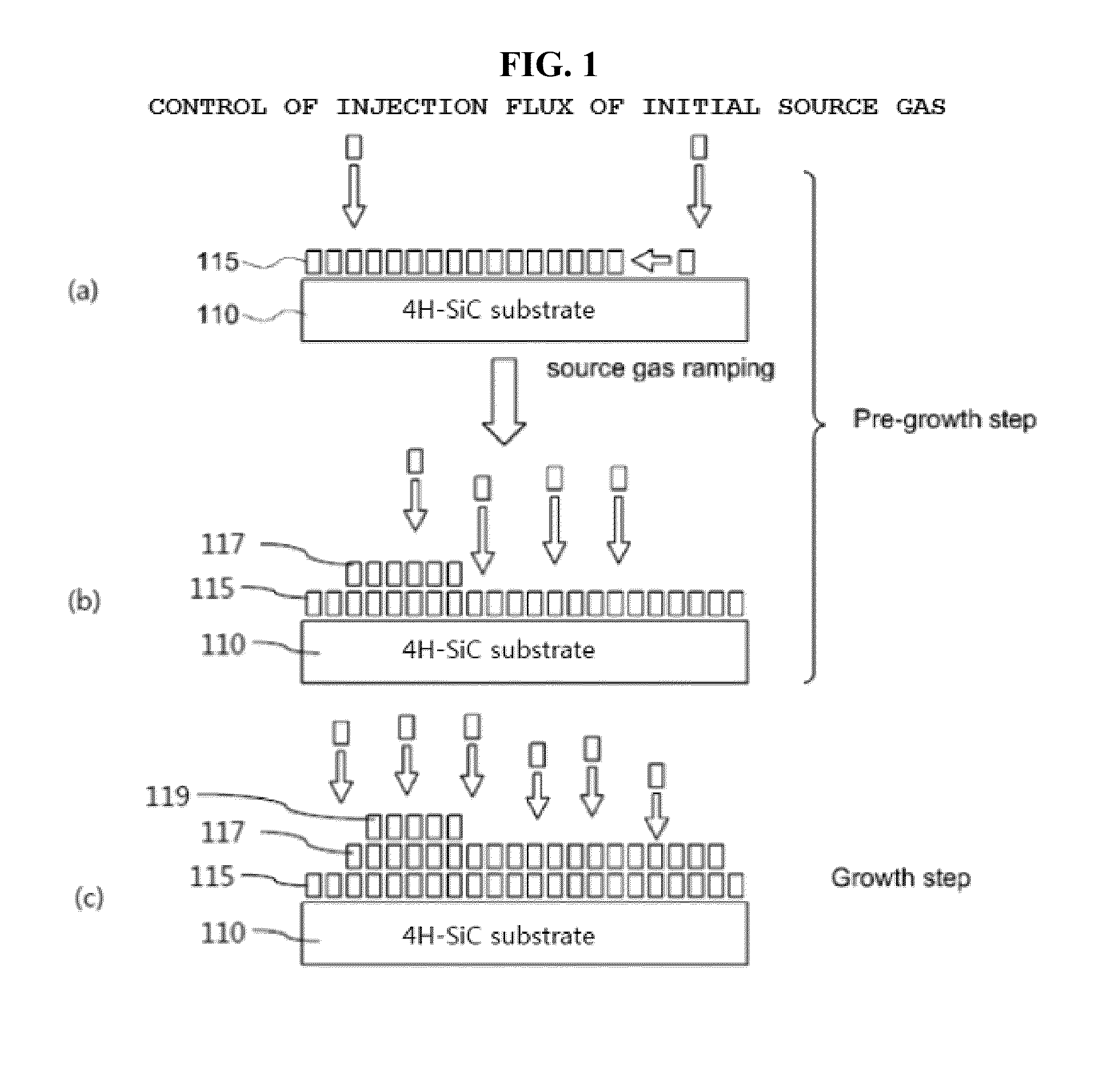

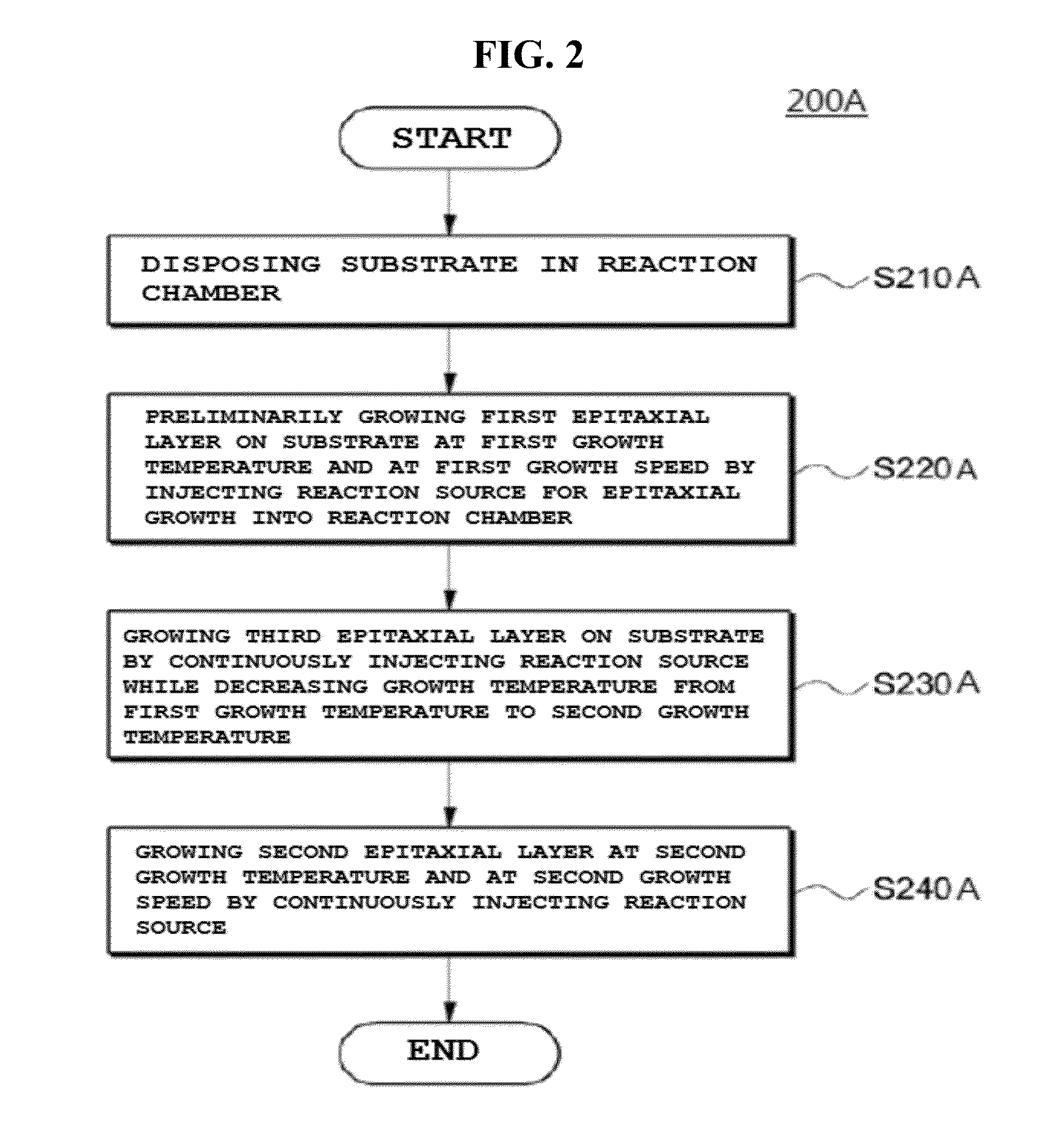

Epitaxial Wafer, Method for Fabricating the Wafer, and Semiconductor Device Including the Wafer

InactiveUS20140117382A1Reduce surface defect densityImprove propertiesPolycrystalline material growthSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

Disclosed is an epitaxial wafer including a substrate, and an epitaxial structure disposed on the substrate, wherein the epitaxial structure includes a first epitaxial layer, a second epitaxial layer disposed on the first epitaxial layer, and a third epitaxial layer disposed between the first epitaxial layer and the second epitaxial layer, the third epitaxial layer having a first doping concentration around a first boundary adjacent to the first epitaxial layer and a second doping concentration different from the first doping concentration around a second boundary adjacent to the second epitaxial layer.

Owner:LG INNOTEK CO LTD

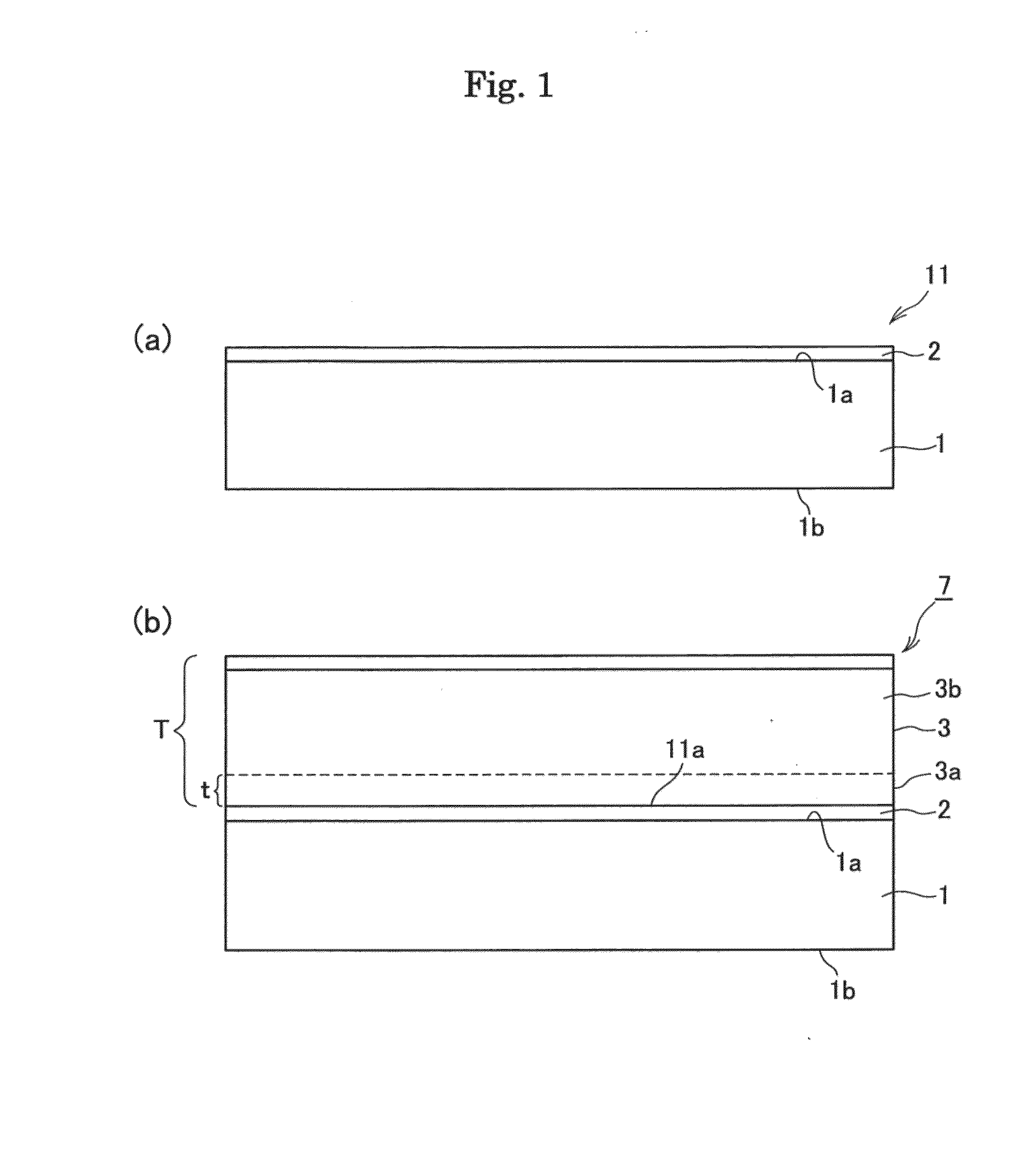

Method for Peeling Group 13 Element Nitride Film

InactiveUS20140147953A1Reduce misalignmentPreferable propertyPolycrystalline material growthAfter-treatment detailsNitrogenLaser light

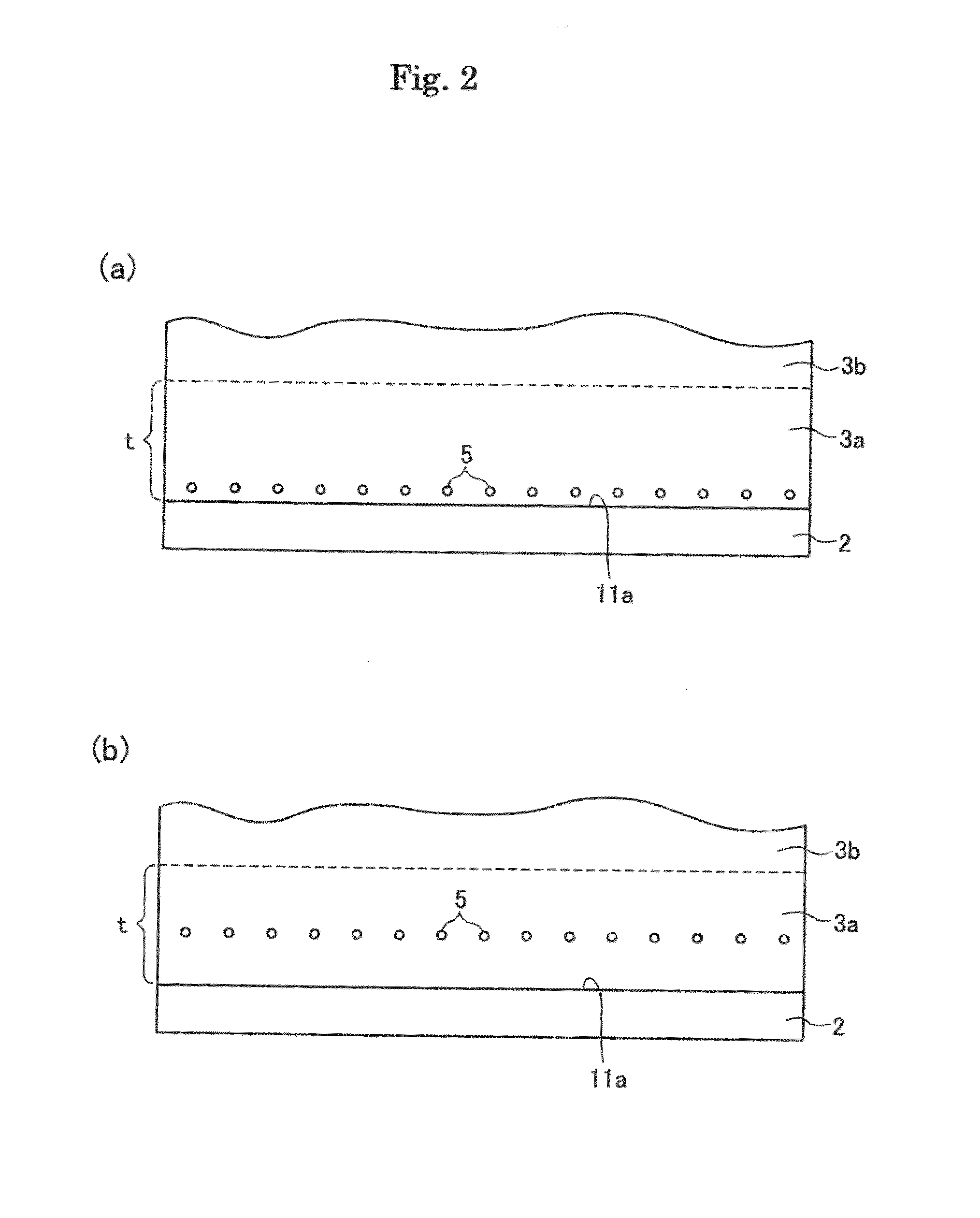

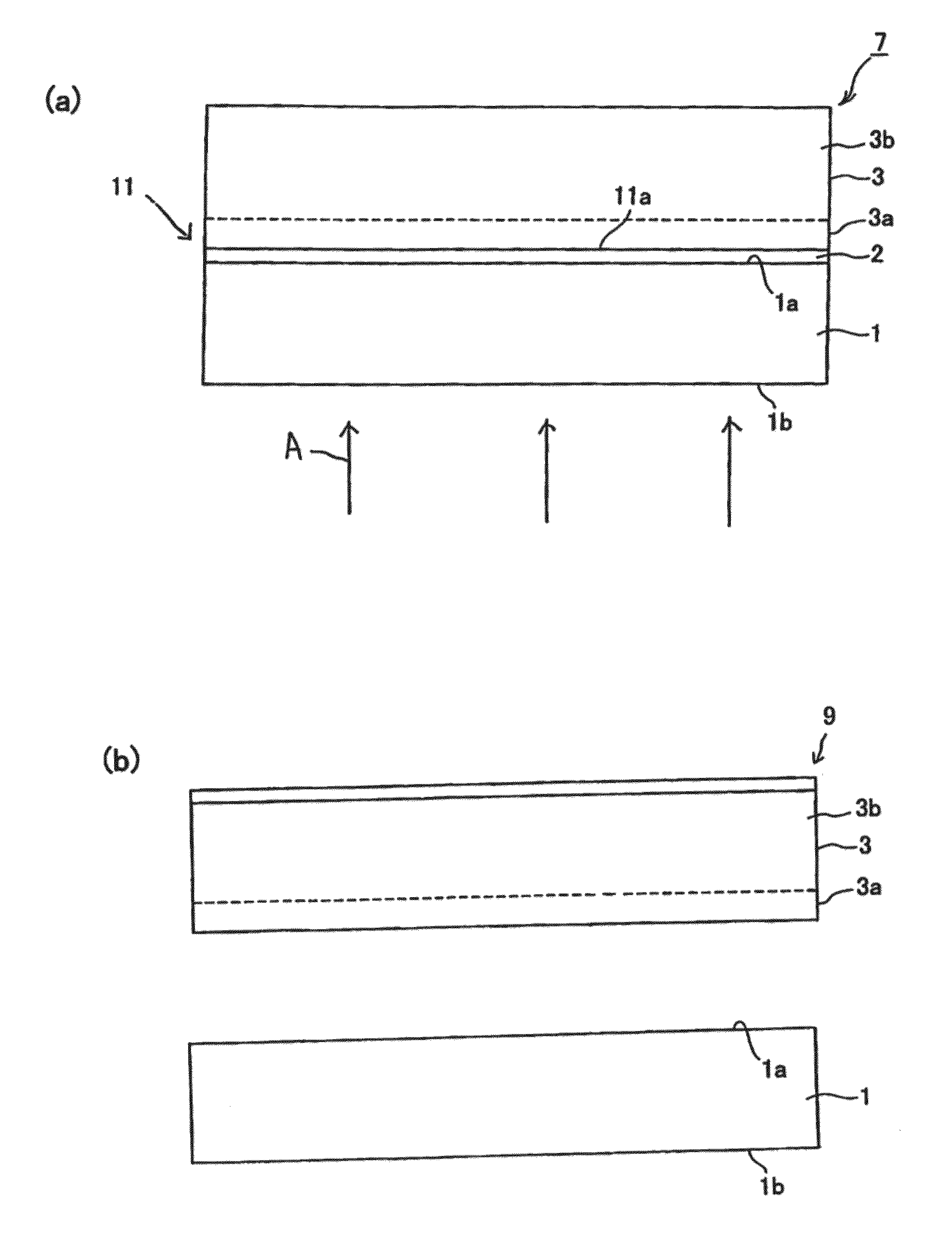

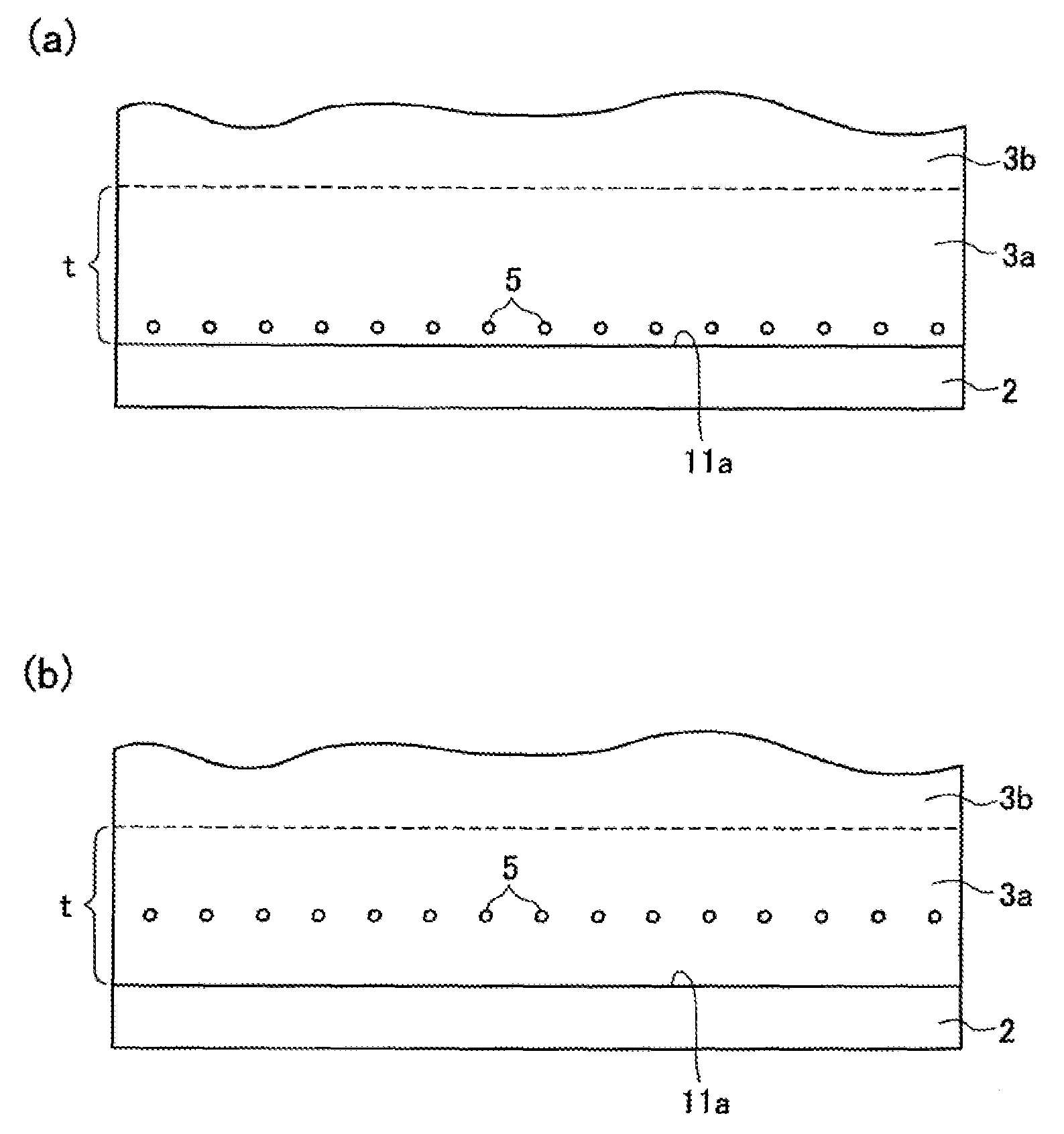

A film 3 of a nitride of a group 13 element is grown on a seed crystal substrate 11 by flux process from a melt containing a flux and the group 13 element under nitrogen containing atmosphere. The film 3 of the nitride of the group 13 element includes an inclusion distributed layer 3a in a region distant from an interface 11a of the film 3 of the nitride of the group 13 element on the side of the seed crystal substrate 11 and containing inclusions derived from components of the melt, and an inclusion depleted layer 3b, with the inclusion depleted. provided on the layer 3a. Laser light A is irradiated from the side of the back face 1b of the seed crystal substrate 11 to peel the single crystal 3 of the nitride of the group 13 element from the seed crystal substrate 11 by laser lift-off method.

Owner:NGK INSULATORS LTD

Method for peeling group 13 element nitride film

InactiveUS9045844B2Reduce surface defect densityReduce misalignmentPolycrystalline material growthAfter-treatment detailsNitrogenLaser light

A film 3 of a nitride of a group 13 element is grown on a seed crystal substrate 11 by flux process from a melt containing a flux and the group 13 element under nitrogen containing atmosphere. The film 3 of the nitride of the group 13 element includes an inclusion distributed layer 3a in a region distant from an interface 11a of the film 3 of the nitride of the group 13 element on the side of the seed crystal substrate 11 and containing inclusions derived from components of the melt, and an inclusion depleted layer 3b, with the inclusion depleted. provided on the layer 3a. Laser light A is irradiated from the side of the back face 1b of the seed crystal substrate 11 to peel the single crystal 3 of the nitride of the group 13 element from the seed crystal substrate 11 by laser lift-off method.

Owner:NGK INSULATORS LTD

Films of nitrides of group 13 elements and layered body including the same

ActiveUS9041004B2Reduce surface defect densityReduce misalignmentPolycrystalline material growthLiquid-phase epitaxial-layer growthNitrogenNitride

Owner:NGK INSULATORS LTD

Semiconductor Light-Emitting Element and Laminate Containing Same

InactiveUS20140158978A1Reduce misalignmentPreferable propertyPolycrystalline material growthLiquid-phase epitaxial-layer growthNitrogenNitrogen gas

A semiconductor light emitting device includes a film of a nitride of a group 13 element grown on a seed crystal substrate by flux method from a melt including a flux and a group 13 element under nitrogen containing atmosphere, an n-type semiconductor layer provided on the film of the nitride, a light emitting region provided on the n-type semiconductor layer, and a p-type semiconductor layer provided on the light emitting region. The film includes an inclusion distributed layer in a region distant by 50 μm or less from an interface of the film on the side of the seed crystal substrate and including inclusions derived from components of the melt, and an inclusion depleted layer with the inclusion depleted formed on the inclusion distributed layer.

Owner:NGK INSULATORS LTD

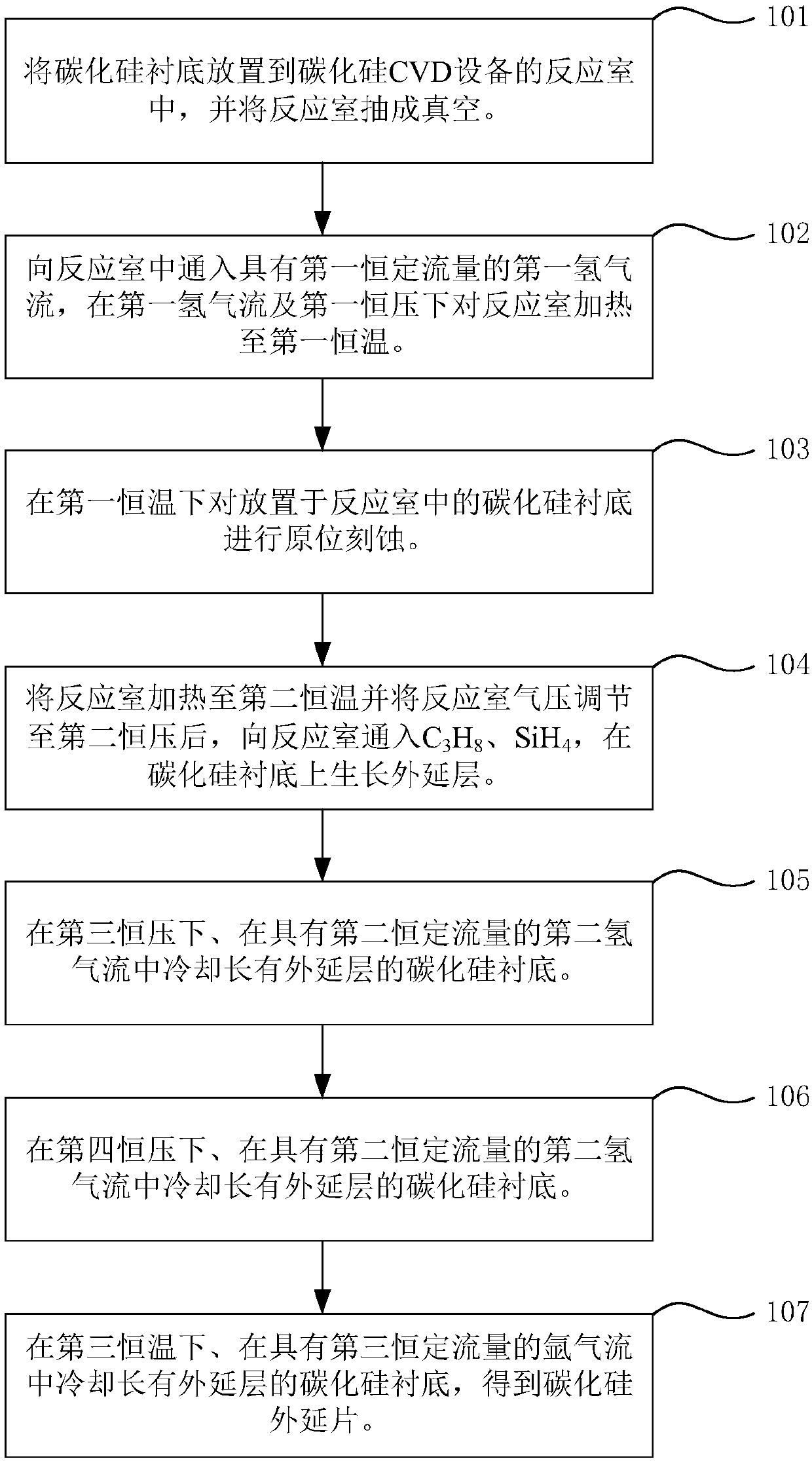

Low-pressure preparation method for silicon carbide thin film epitaxy

InactiveCN110117816ALow unintentional doping concentrationQuality improvementPolycrystalline material growthFrom chemically reactive gasesAtmospheric pressureHydrogen flow

The invention relates to a low-pressure preparation method for a silicon carbide thin film epitaxy. The method comprises the steps that a silicon carbide substrate is placed in a reaction chamber of silicon carbide CVD equipment, and the reaction chamber is vacuumized; first hydrogen flow with a first constant flow rate is introduced into the reaction chamber, and under the first hydrogen flow andthe first constant pressure, the reaction chamber is heated to a first constant temperature; at the first constant temperature, the silicon carbide substrate placed in the reaction chamber is subjected to in-situ etching; after the reaction chamber is heated to a second constant temperature, the air pressure of the reaction chamber is adjusted to the second constant pressure, C3H8 and SiH4 are introduced into the reaction chamber, and an epitaxial layer grows on the silicon carbide substrate; under the third constant pressure, the silicon carbide substrate with the epitaxy layer growing on iscooled in second hydrogen flow with a second constant flow rate; under the fourth constant pressure, the silicon carbide substrate with the epitaxy layer growing on is cooled in the second hydrogen flow; at a third constant temperature, the silicon carbide substrate with the epitaxy layer growing on is cooled in argon flow with a third constant flow rate, and a silicon carbide epitaxy wafer is obtained.

Owner:XIDIAN UNIV

Methods for improving the quality of group III-nitride materials and structures produced by the methods

ActiveUS8318612B2Reduce surface defect densityAvoid decompositionSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureDislocation

The invention provides methods which can be applied during the epitaxial growth of two or more layers of Group III-nitride semiconductor materials so that the qualities of successive layer are successively improved. In preferred embodiments, surface defects interact with a protective layer of a protective material to form amorphous complex regions capable of preventing the further propagation of defects and dislocations. The invention also includes semiconductor structures fabricated by these methods.

Owner:SOITEC SA +1

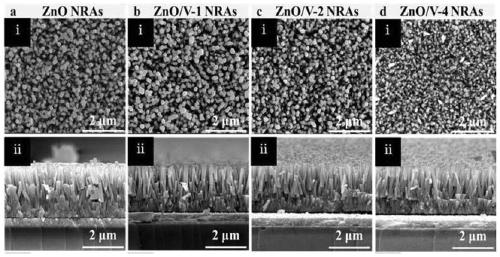

Preparation process of front oxide layer of novel crystalline silicon PERC battery

ActiveCN111564530AImprove performanceAvoid damageFinal product manufactureChemical vapor deposition coatingSilicon oxideRadio frequency

The invention relates to the field of crystalline silicon PERC battery passivation. The invention discloses a preparation process of a front oxide layer of a novel crystalline silicon PERC battery. The preparation process is carried out according to the technological processes of cleaning and texturing, diffusion and junction making, back etching, double-sided aluminum oxide preparation, front silicon nitride film preparation, back silicon nitride film preparation, back laser grooving and front and back electrode preparation. In the preparation process of the double-sided aluminum oxide, a silicon wafer is inserted into an aluminum flower basket, TMA and water vapor are circularly introduced, and a layer of aluminum oxide film of 3-5 nm is prepared on each of the front surface and the backsurface of the silicon wafer; in the preparation process of the front silicon nitride film, the prepared silicon wafer with the double-sided aluminum oxide is put into a graphite boat, silicon nitride is prepared in tubular PECVD, NH3 and N2 gas is introduced, then a radio frequency source is connected, the front aluminum oxide film layer is knocked off through high-energy plasma, and meanwhile asilicon oxide layer is formed.

Owner:SHANXI LUAN PHOTOVOLTAICS TECH

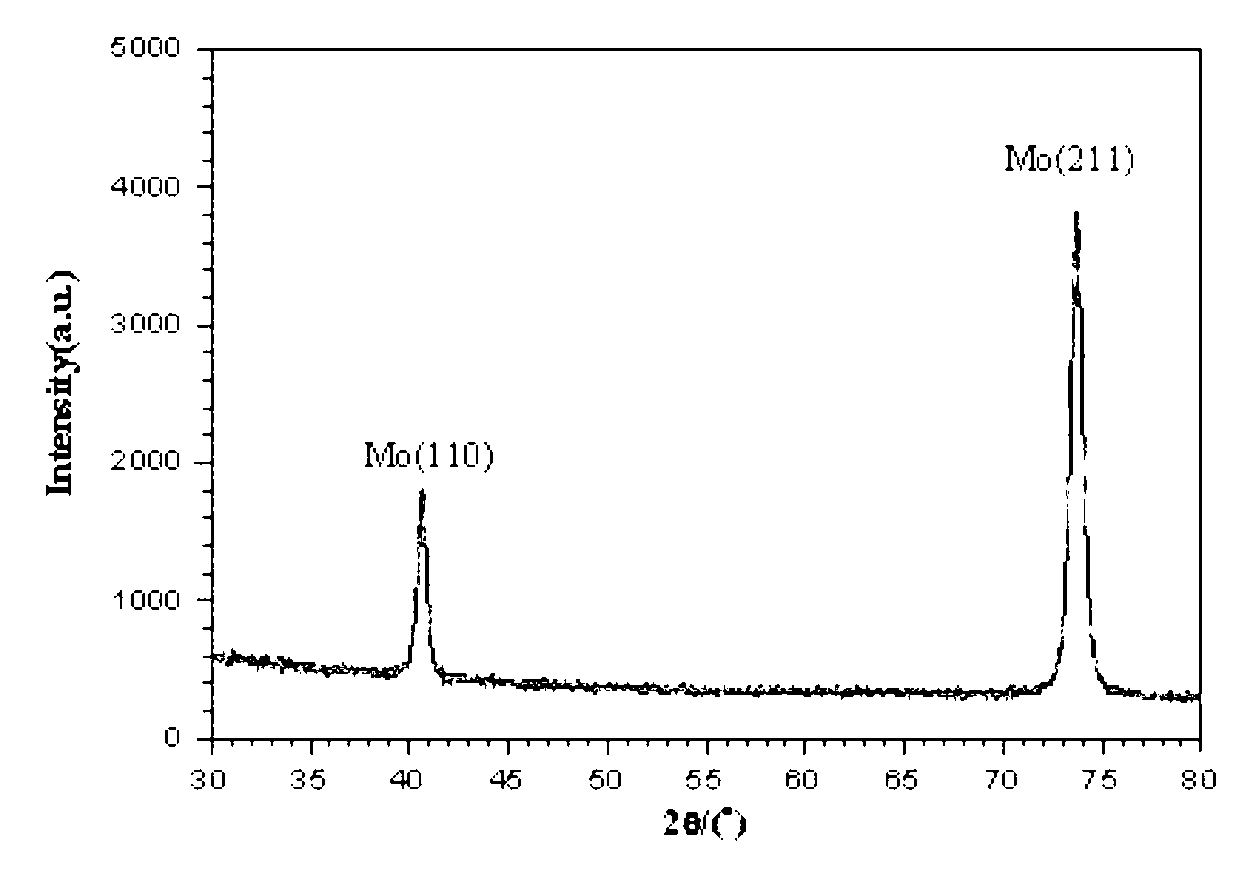

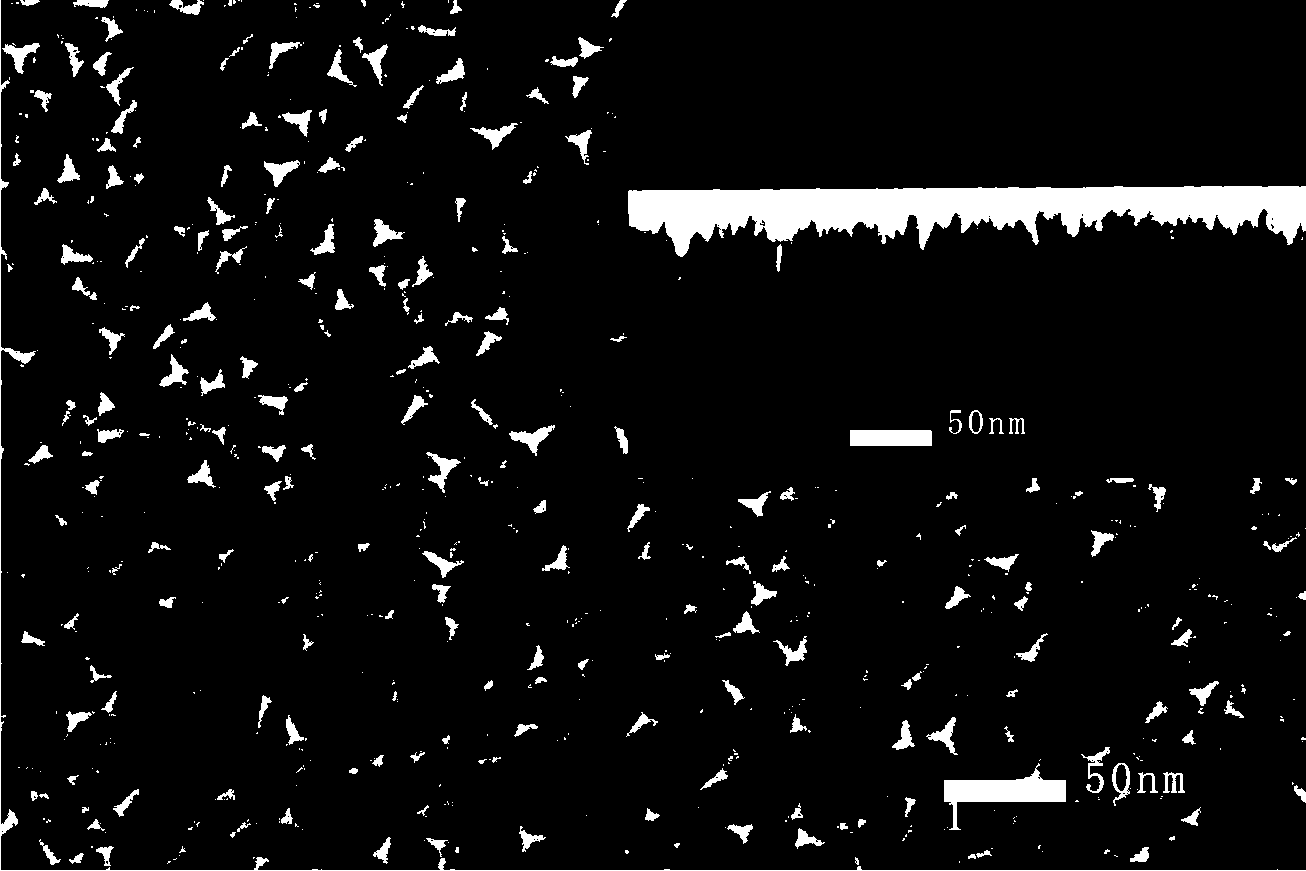

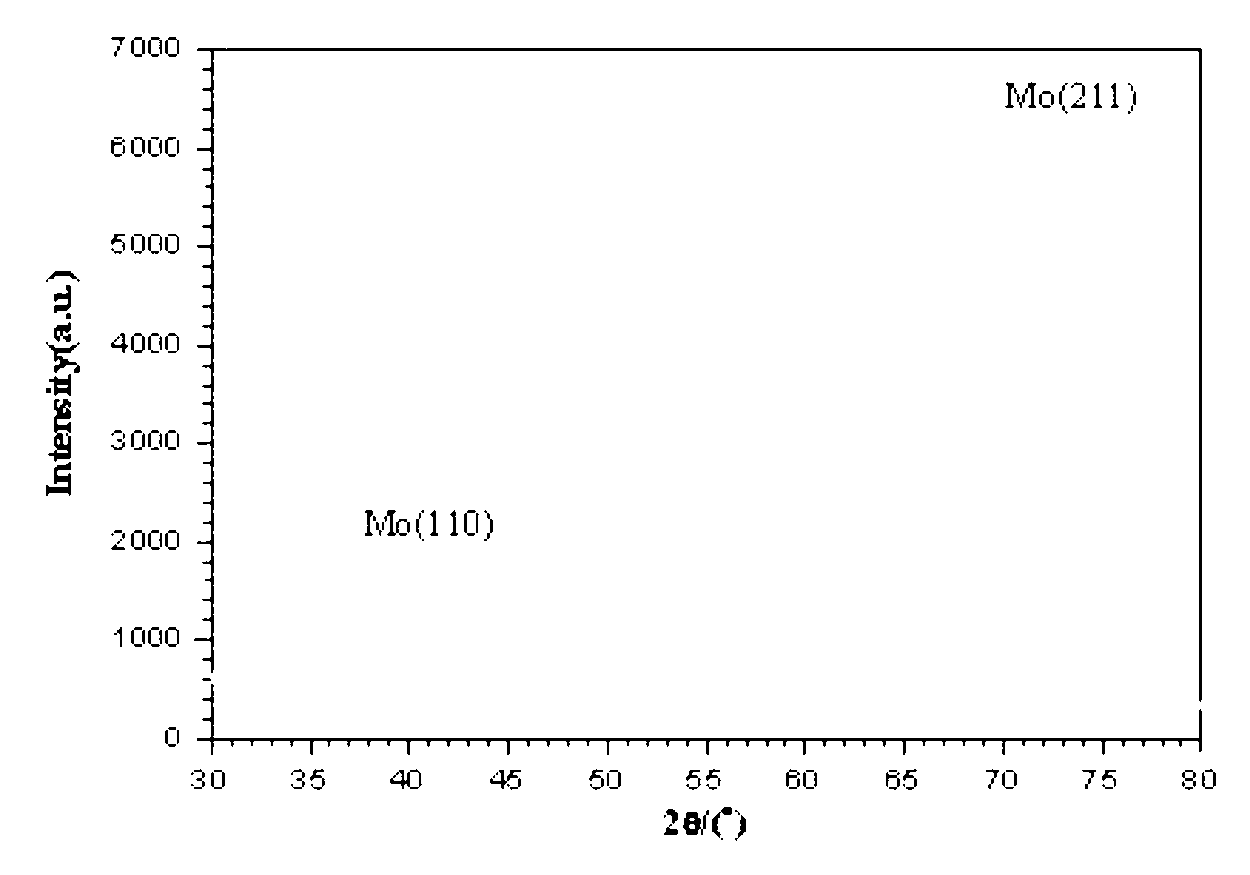

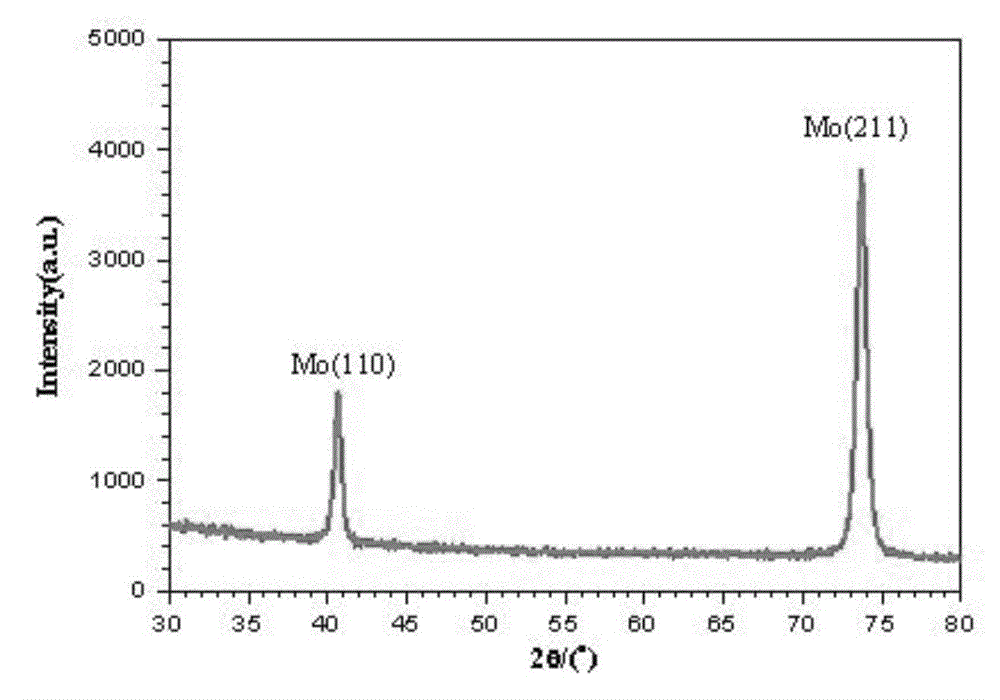

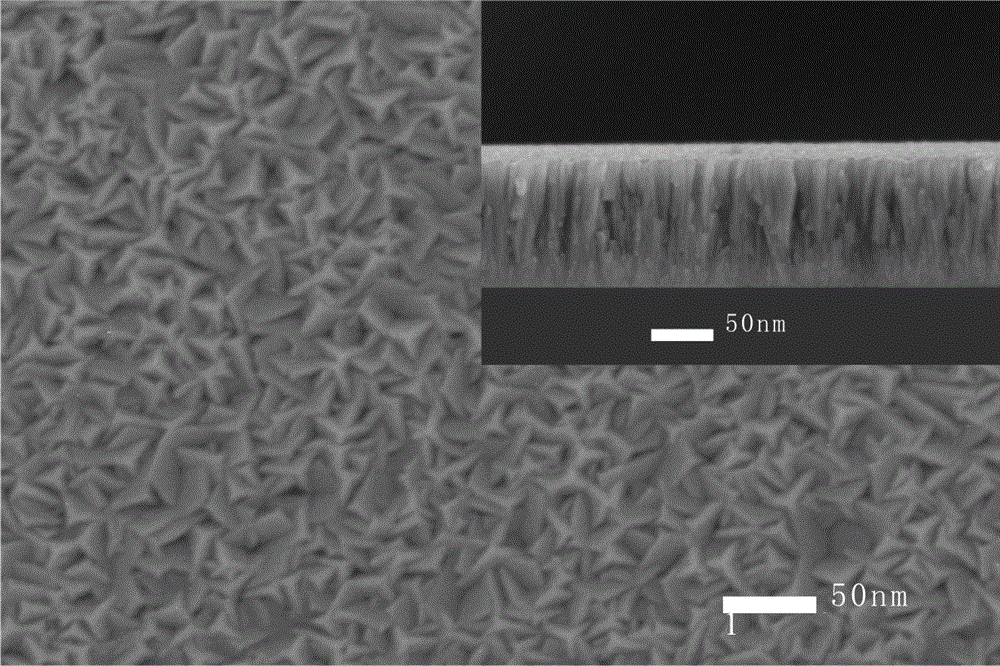

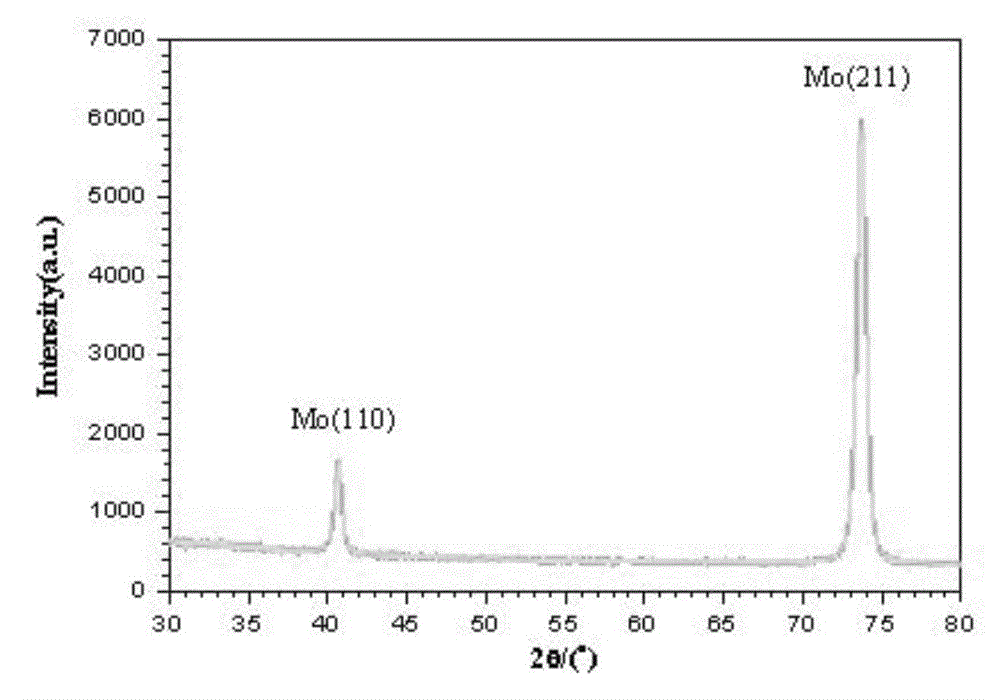

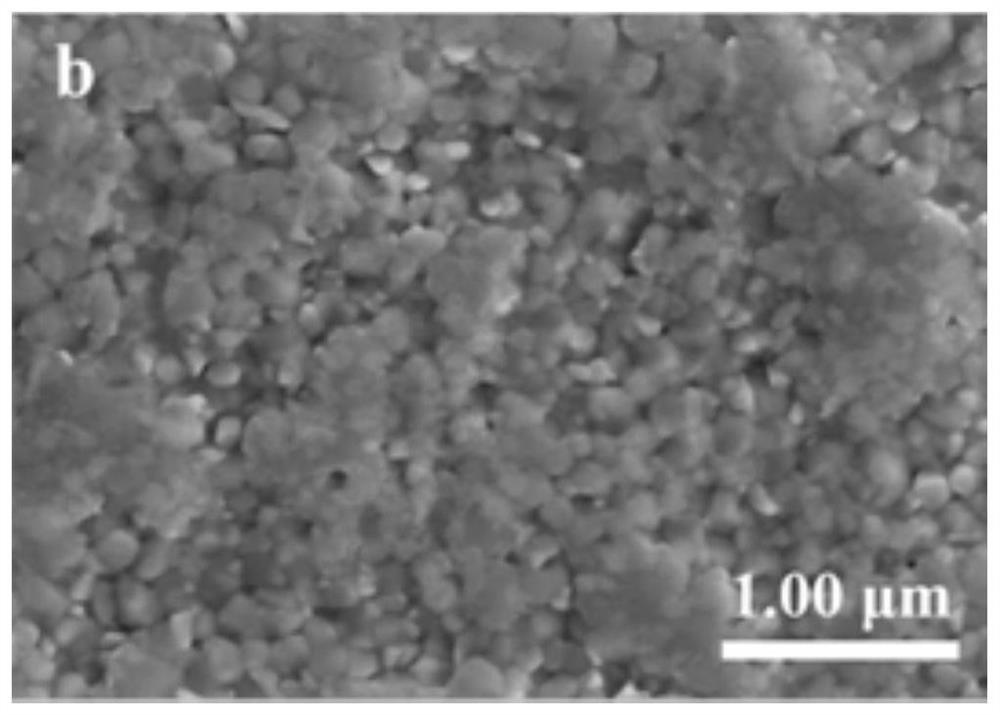

Preparation method of (211) preferred orientation Mo film

InactiveCN102912304AEfficient manufacturing methodLow resistivityVacuum evaporation coatingSputtering coatingIndiumVacuum chamber

The invention discloses a preparation method of a (211) preferred orientation Mo film. The preparation method comprises the steps of: (1) cleaning a substrate, ultrasonically cleaning the substrate in acetone, ethanol and deionized water for 10 minutes respectively, and putting the substrate into a sputtering vacuum chamber after drying by nitrogen; (2) sputtering the Mo film, installing a high-purity Mo target on a magnetron sputtering target gun, adjusting a distance from the magnetron sputtering target gun to the substrate to be 50mm after purity achieves 99.99%, and vacuumizing a background in vacuum to be less than 3.0*10<-4>Pa, leading 99.995% of high-purity argon, adjusting sputtering work pressure to 0.15Pa and sputtering power to 5W / cm<2>, pre-sputtering the target for 10 minutes to remove surface contaminants after glow is stabilized, then beginning to deposit the film, and stopping after depositing for 20-40 minutes to obtain the Mo film with (211) preferred orientation. The film is high in crystal quality, even in surface appearance, low in resistivity and suitable for being used as a back electrode layer of a copper indium gallium diselenide film battery.

Owner:CHENGDU XINYUAN PV TECH

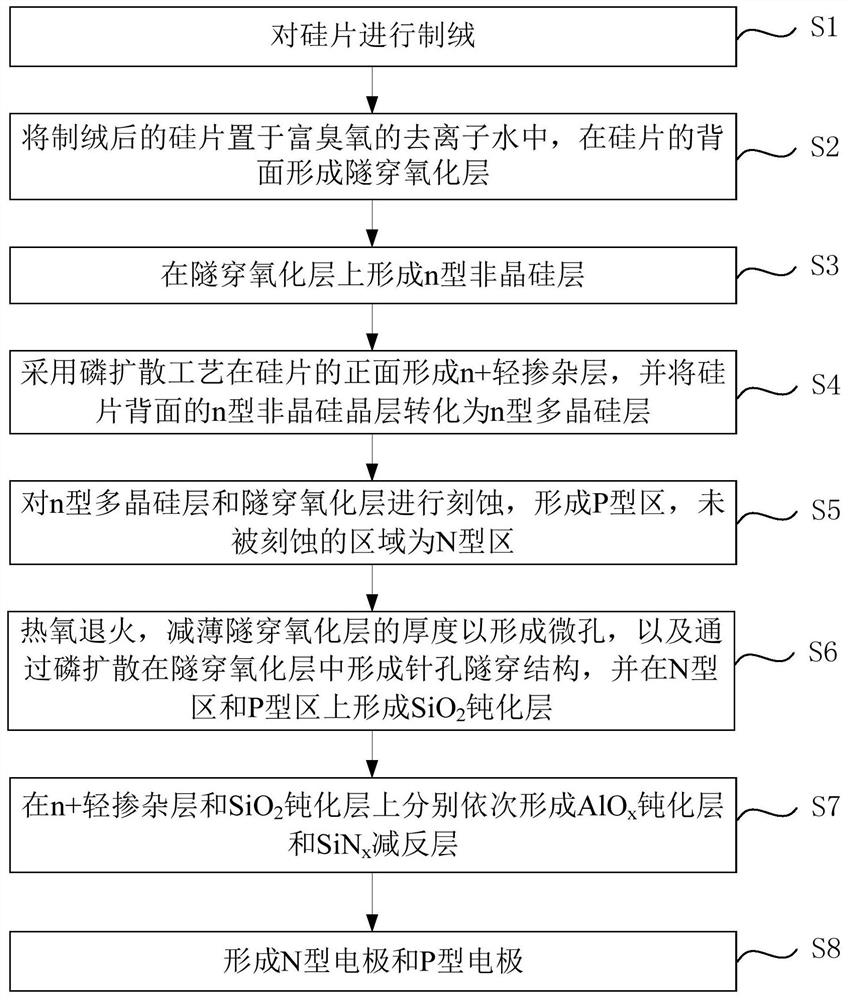

POLO-IBC solar cell and preparation method thereof

ActiveCN113224202ASimple processReduce processFinal product manufacturePhotovoltaic energy generationOxygen annealingAmorphous silicon

The invention discloses a POLO-IBC solar cell and a preparation method thereof. The method comprises the following steps of: S1, texturing a silicon wafer; S2, forming a tunneling oxide layer on the back surface of the silicon wafer; S3, forming an n-type amorphous silicon layer on the tunneling oxide layer; S4, forming an n + lightly doped layer on the front surface of the silicon wafer, and converting the n-type amorphous silicon layer on the back surface of the silicon wafer into an n-type polycrystalline silicon layer; S5, forming a P-type region and an N-type region; S6, performing thermal oxygen annealing; S7, respectively forming an AlOx passivation layer and a SiNx antireflection layer on the n + lightly doped layer and a SiO2 passivation layer in sequence; and S8, forming an N-type electrode and a P-type electrode. The preparation method is simple in process, short in production period and low in cost.

Owner:ZHEJIANG AIKO SOLAR ENERGY TECH CO LTD +2

A kind of vanadium-doped zno nanorod array photoanode and its preparation method and application

ActiveCN107287615BSimple processEasy to implementMaterial nanotechnologyEnergy inputVanadium dopingZinc oxide nanorod

The invention mainly belongs to the field of photoelectrochemistry water-splitting for hydrogen production and particularly relates to a vanadium-doped ZnO nanorod array photo-anode, a preparation method of the vanadium-doped ZnO nanorod array photo-anode and an application of the vanadium-doped ZnO nanorod array photo-anode in photoelectrochemistry water-splitting for hydrogen production. The method comprises the steps of preparing a ZnO seed crystal solution, a vanadium-doped solution and a growth solution correspondingly; conducting spin-coating on conducting glass with the ZnO seed crystal solution and obtaining the conducting glass with the surface covered with a ZnO seed crystal layer after spin-coating and annealing; pulling the conducting glass with the surface covered with the ZnO seed crystal layer into a mixed solution of the vanadium-doped solution and the growth solution for a hydrothermal reaction, washing the conducting glass with deionized water after completion of the reaction, conducting annealing in a muffle furnace and then obtaining an vanadium-doped ZnO nanorod array. By adopting the vanadium-doped ZnO nanorod array photo-anode provided by the invention, the carrier life is prolonged, combination of electron holes is reduced, and the photoelectrochemistry water-splitting performance is improved.

Owner:UNIV OF SCI & TECH BEIJING

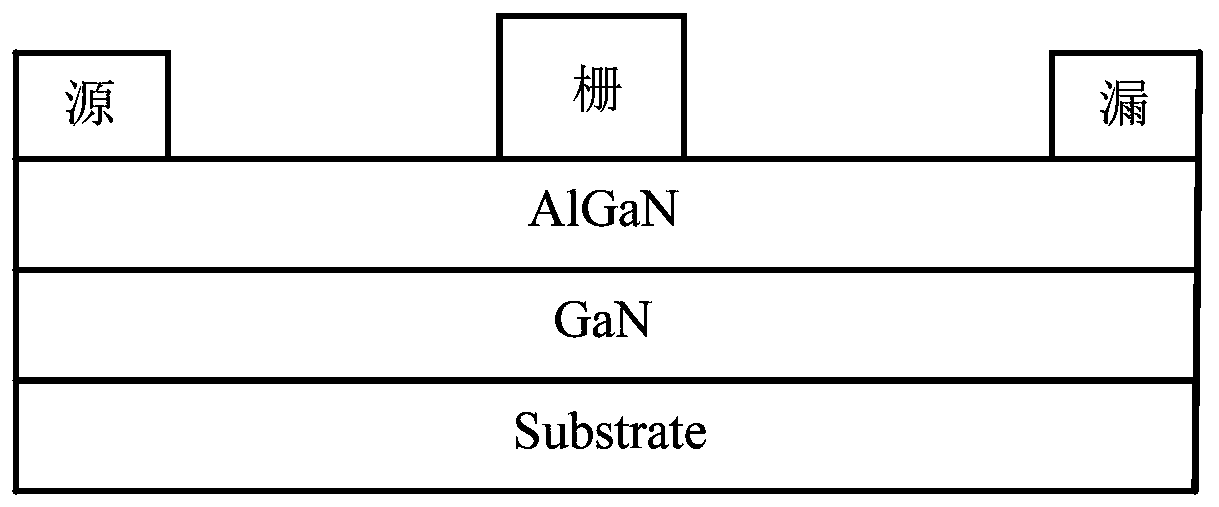

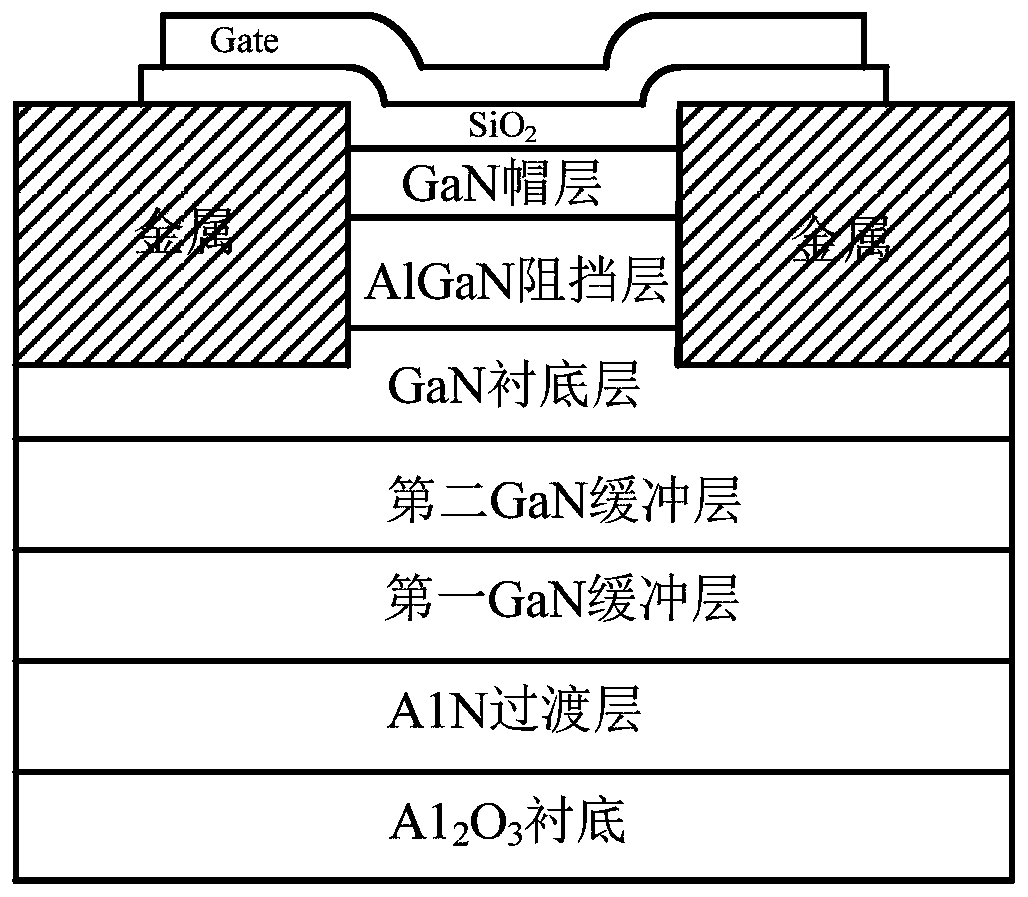

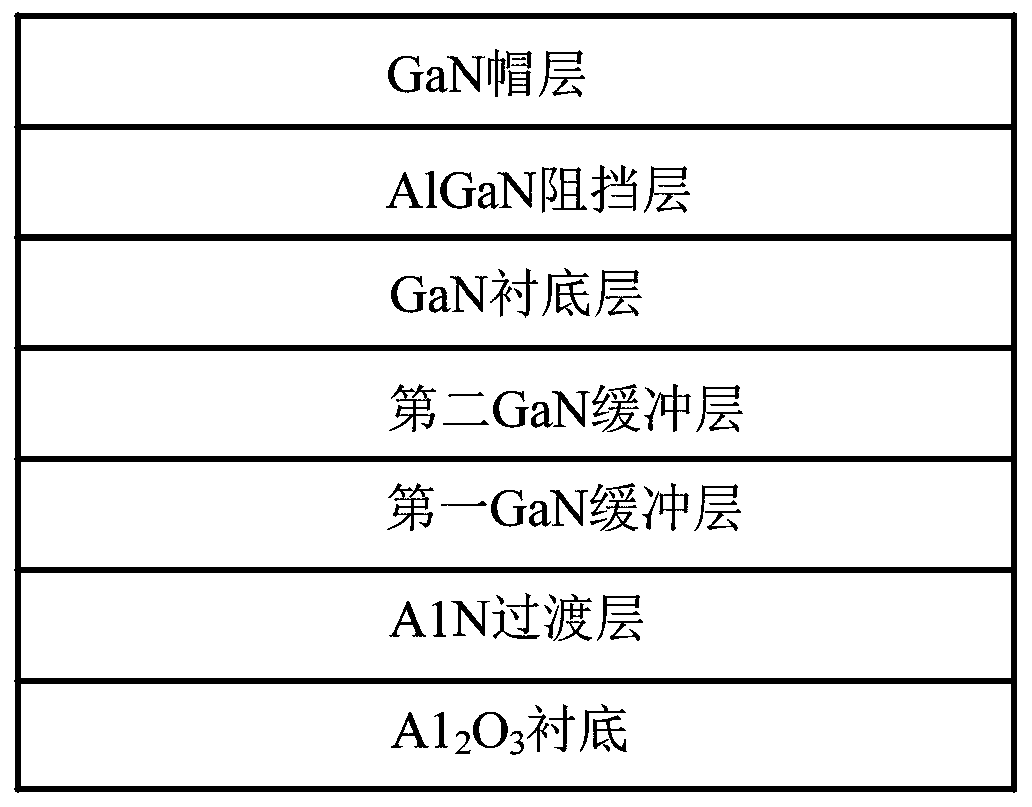

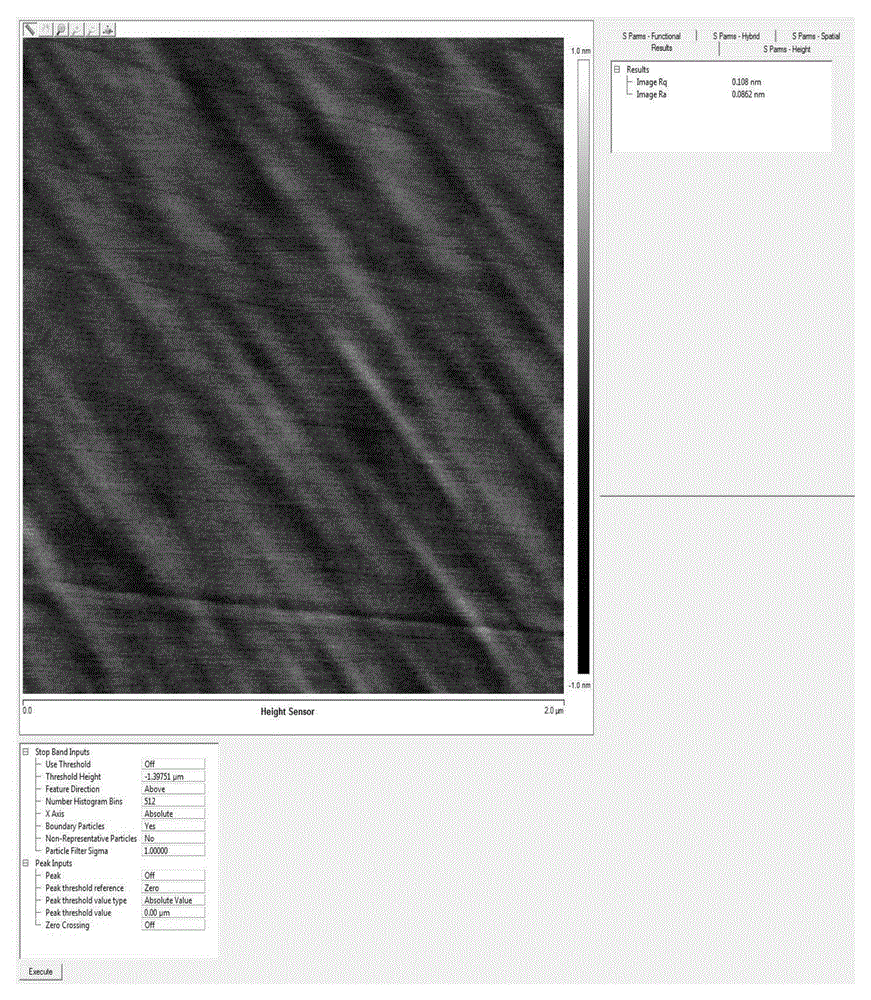

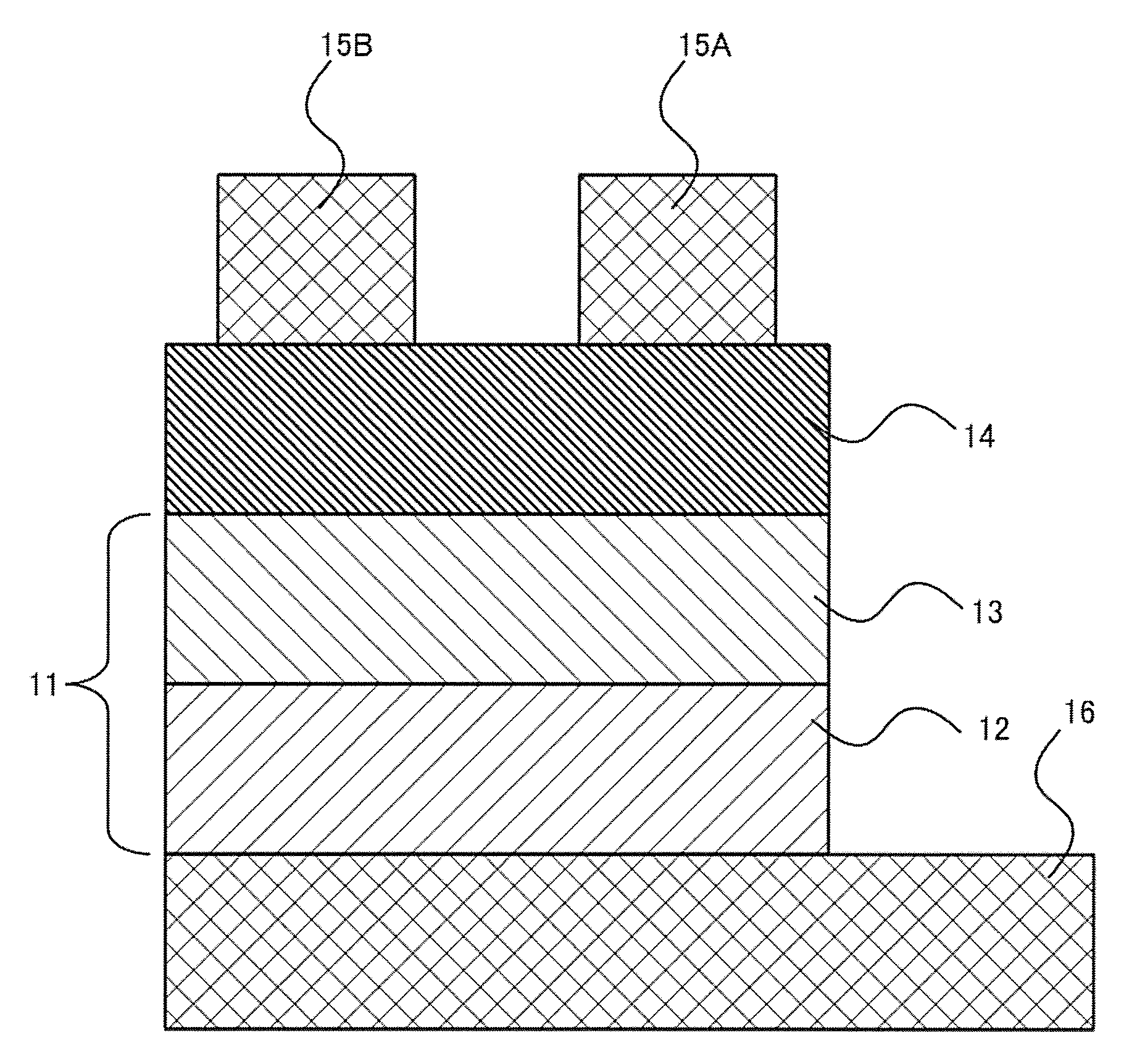

Enhanced AlGaN/GaN MOS(Metal Oxide Semiconductor)-HEMT(High Electron Mobility Transistor) device structure

PendingCN110600549AImprove reliabilityReduce surface defect densitySemiconductor/solid-state device manufacturingSemiconductor devicesGate leakage currentDriving current

The invention provides an enhanced AlGaN / GaN MOS(Metal Oxide Semiconductor)-HEMT(High Electron Mobility Transistor) device structure. The structure comprises an Al2O3 substrate, a first intrinsic GaNbuffer layer, a second intrinsic GaN buffer layer, a GaN substrate layer, an AlGaN barrier layer and a GaN cap layer, wherein the first intrinsic GaN buffer layer, the second intrinsic GaN buffer layer, the GaN substrate layer, the AlGaN barrier layer and the GaN cap layer are sequentially stacked on the Al2O3 substrate, the GaN cap layer to the GaN substrate layer are etched to form a left sourceregion and a right drain region, metalized ohmic contact protruding out of a surface of the device is formed on surfaces of the left source region and the right drain region, a gate oxide layer is formed in a gate region corresponding to the GaN cap layer and the ohmic contact surface, and gate metal is formed on a surface of the gate oxide layer. The invention also provides a preparation methodof the device structure. The structure is advantaged in that reliability of the device can be improved, surface density and a channel driving current of the 2DEG can be improved, the gate leakage current of the device can be reduced, the preparation method can be compatible with the mainstream compound semiconductor process, the substrate quality is good, process repeatability is high, and large-scale manufacturing is easy.

Owner:中证博芯(重庆)半导体有限公司

Method for preparing P-type low-defect silicon carbide epitaxial wafer

The invention provides a method for preparing a P-type low-defect silicon carbide epitaxial wafer, comprising the steps of substrate preparation, online substrate etching, buffer layer growth and epitaxial layer growth, wherein the epitaxial layer is grown in an approach of 'growing, etching, blowing and re-growing'. By adopting the method, the dislocation density of the base plane is reduced effectively, the sediment in the cavity is reduced, the defect density of the silicon carbide epitaxial surface is reduced, and the quality of the silicon carbide epitaxial material is improved. Moreover, the method has a wide range of applications, makes the production cost low, and is suitable for industrial production.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

Preparation method of (211) preferred orientation Mo film

InactiveCN102912304BEfficient manufacturing methodLow resistivityVacuum evaporation coatingSputtering coatingIndiumVacuum chamber

The invention discloses a preparation method of a (211) preferred orientation Mo film. The preparation method comprises the steps of: (1) cleaning a substrate, ultrasonically cleaning the substrate in acetone, ethanol and deionized water for 10 minutes respectively, and putting the substrate into a sputtering vacuum chamber after drying by nitrogen; (2) sputtering the Mo film, installing a high-purity Mo target on a magnetron sputtering target gun, adjusting a distance from the magnetron sputtering target gun to the substrate to be 50mm after purity achieves 99.99%, and vacuumizing a background in vacuum to be less than 3.0*10<-4>Pa, leading 99.995% of high-purity argon, adjusting sputtering work pressure to 0.15Pa and sputtering power to 5W / cm<2>, pre-sputtering the target for 10 minutes to remove surface contaminants after glow is stabilized, then beginning to deposit the film, and stopping after depositing for 20-40 minutes to obtain the Mo film with (211) preferred orientation. The film is high in crystal quality, even in surface appearance, low in resistivity and suitable for being used as a back electrode layer of a copper indium gallium diselenide film battery.

Owner:CHENGDU XINYUAN PV TECH

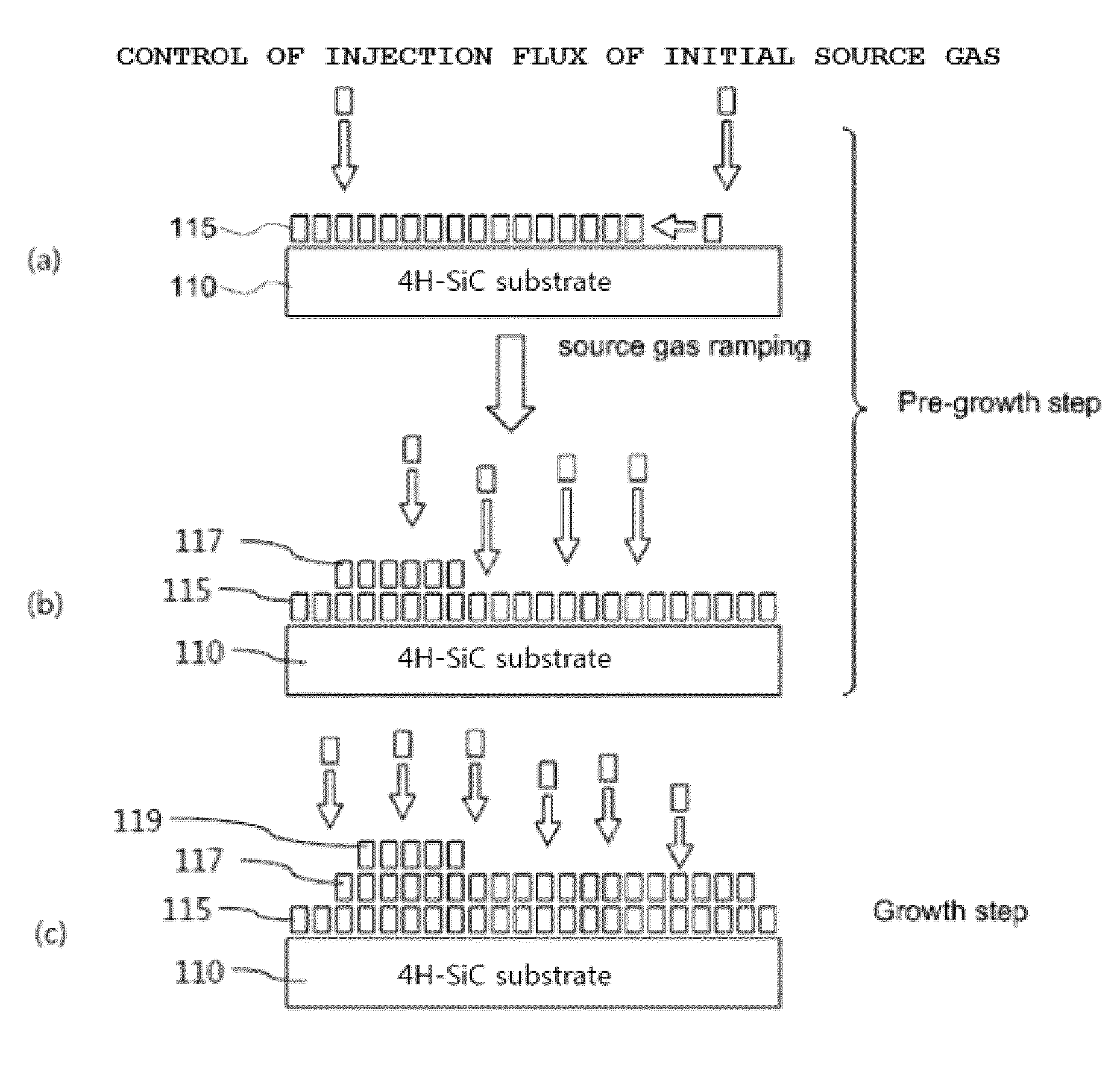

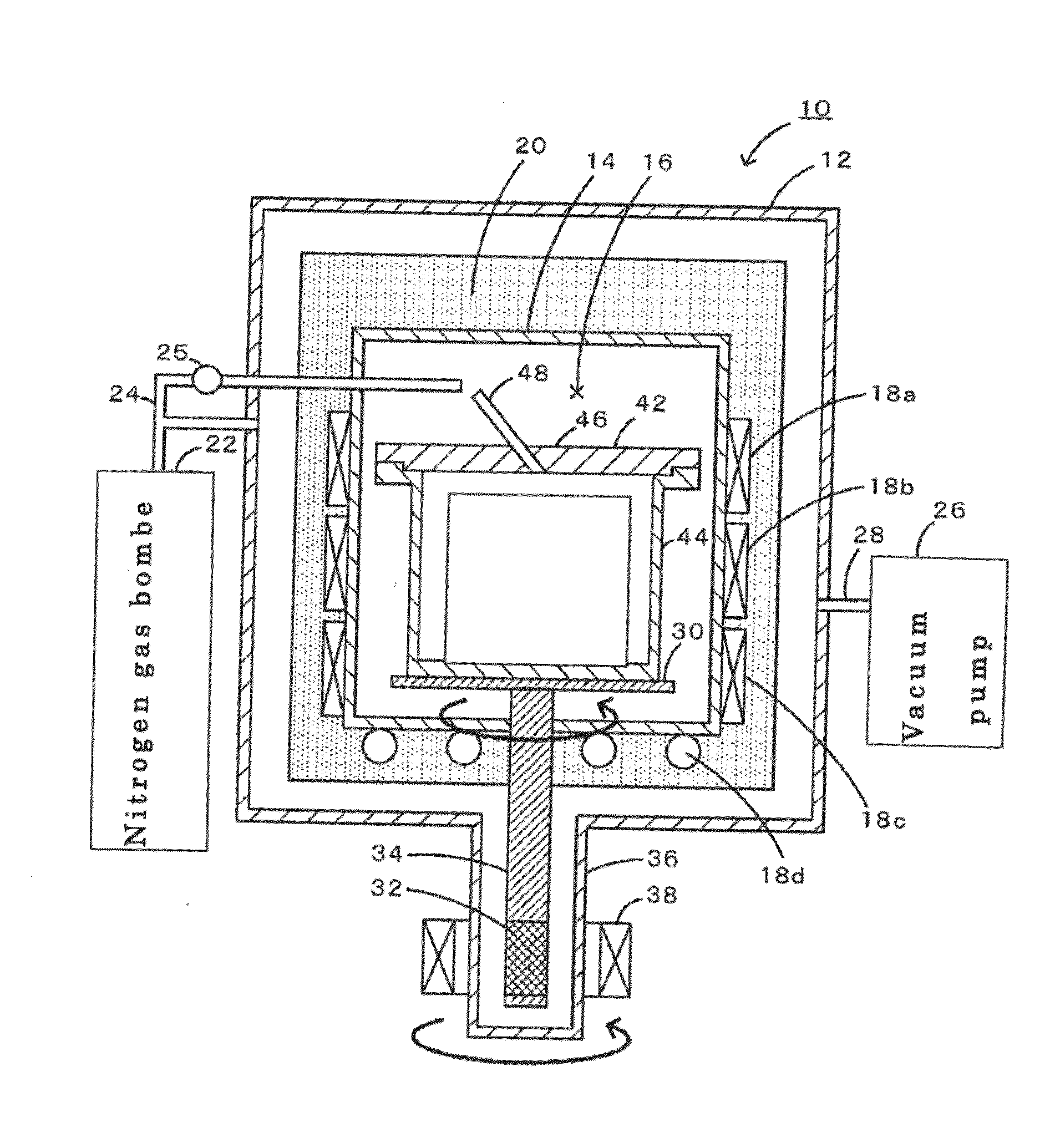

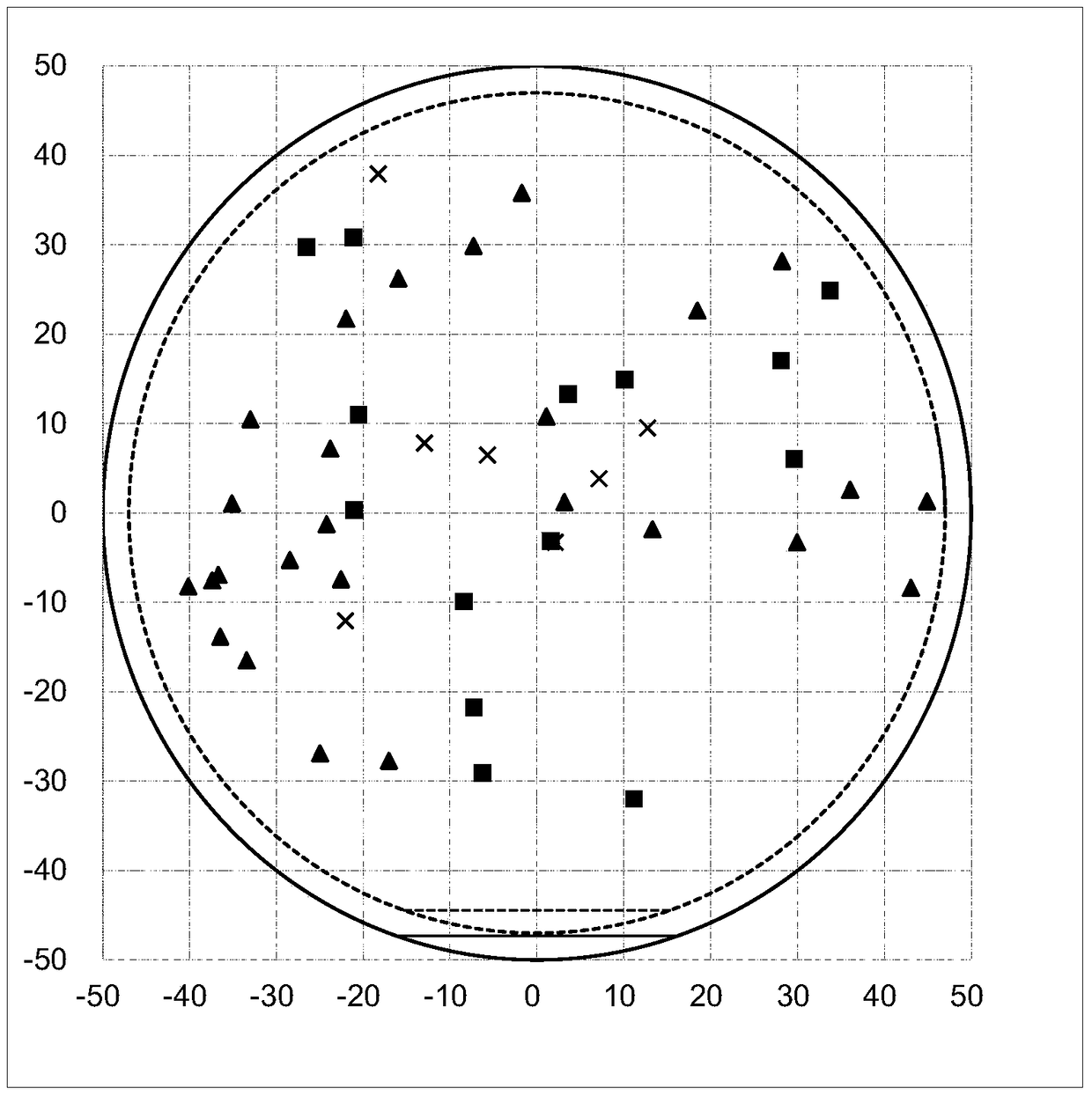

Silicon carbide epitaxial wafer, method for manufacturing silicon carbide epitaxial wafer, device for manufacturing silicon carbide epitaxial wafer, and silicon carbide semiconductor element

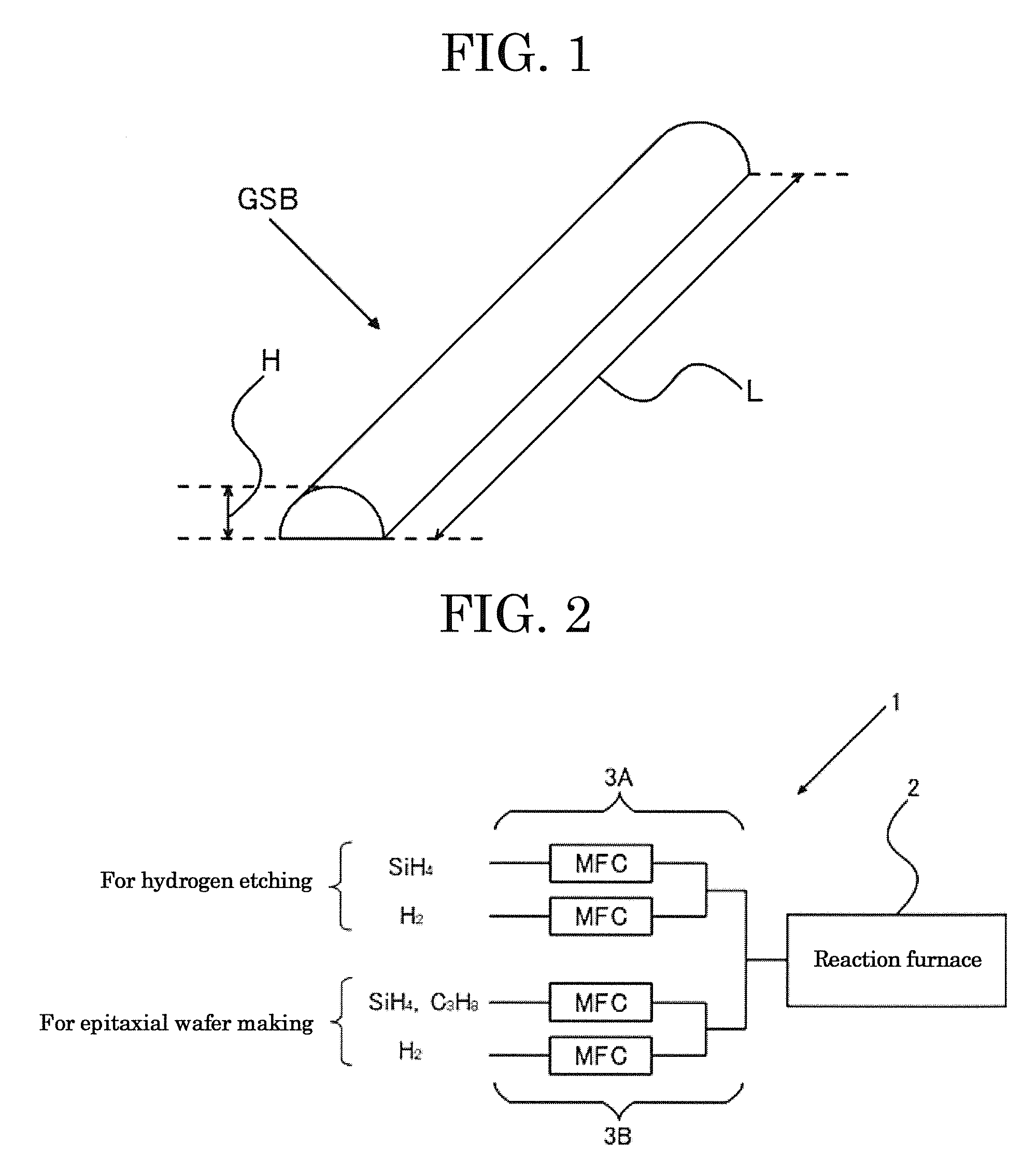

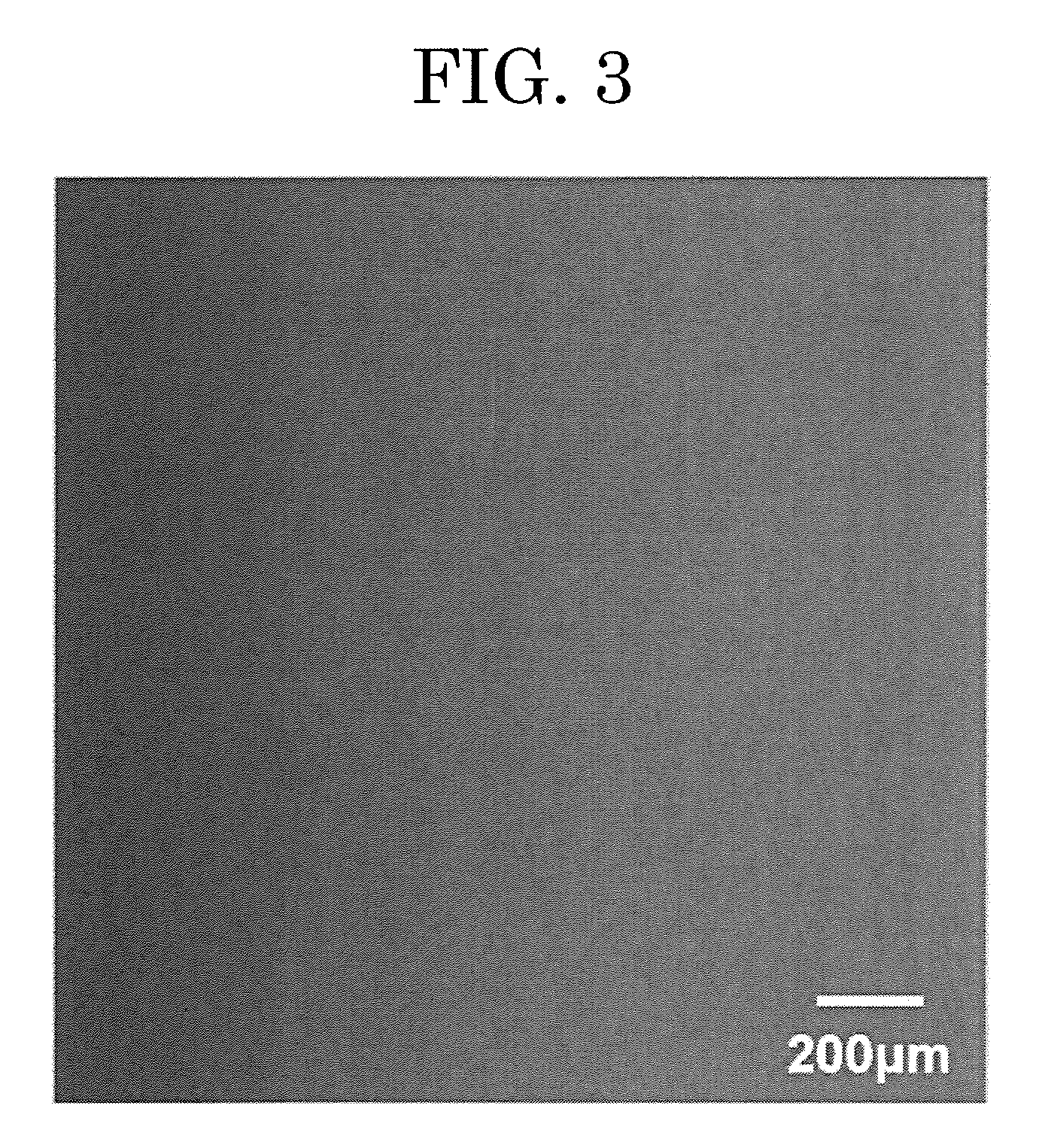

InactiveUS9587326B2Reduce surface defect densityImprove reliabilityPolycrystalline material growthSemiconductor/solid-state device manufacturingWaferingHydrogen

To provide silicon carbide epitaxial wafer in which occurrence of giant step bunchings (GSBs) caused by basal plane dislocations (BPDs) that occur during hydrogen etching is suppressed on low off-angle silicon carbide substrate to decrease surface defect density of epitaxially grown layer to allow formation of silicon carbide semiconductor device having high reliability, method for manufacturing the wafer, and apparatus for manufacturing the wafer, and silicon carbide semiconductor device having the wafer.A silicon carbide epitaxial wafer of the present invention is such that epitaxially grown layer is disposed on silicon carbide substrate which has α-type crystal structure and in which (0001) Si face is tilted at greater than 0° and less than 5°, wherein surface defect density of the epitaxially grown layer based on giant step bunching caused by basal plane dislocation on substrate surface of the silicon carbide substrate is ≦20 / cm2.

Owner:NAT INST OF ADVANCED IND SCI & TECH

Preparation method of low-defect silicon carbide epitaxial material

PendingCN114496728AReduce uniformityReduce surface defect densitySemiconductor/solid-state device manufacturingCrystallographyCarbide silicon

The invention provides a preparation method of a low-defect silicon carbide epitaxial material, which relates to the technical field of silicon carbide epitaxial materials, and comprises the following steps: introducing argon and mixed gas consisting of hydrogen chloride and hydrogen into a reaction chamber to carry out in-situ etching on a silicon carbide off-axis substrate for 5-20 minutes. The introduction of hydrogen chloride and hydrogen enables a Si component and a C component on the surface of the silicon carbide off-axis substrate to reach similar removal speeds, so that a smoother substrate surface is obtained, the introduction of argon enables a temperature field in the reaction chamber to be more uniform, anisotropy generated when the silicon carbide off-axis substrate is etched by hydrogen chloride and hydrogen in the reaction chamber is reduced, and the yield of the silicon carbide off-axis substrate is improved. The non-uniformity of surface etching and the surface defects of the substrate extending to the epitaxial layer are reduced, and the silicon carbide epitaxial material obtained through the growth of the buffer layer and the growth of the epitaxial layer has the advantages of low surface defect density and high uniformity.

Owner:ZHEJIANG UNIV HANGZHOU GLOBAL SCI & TECH INNOVATION CENT

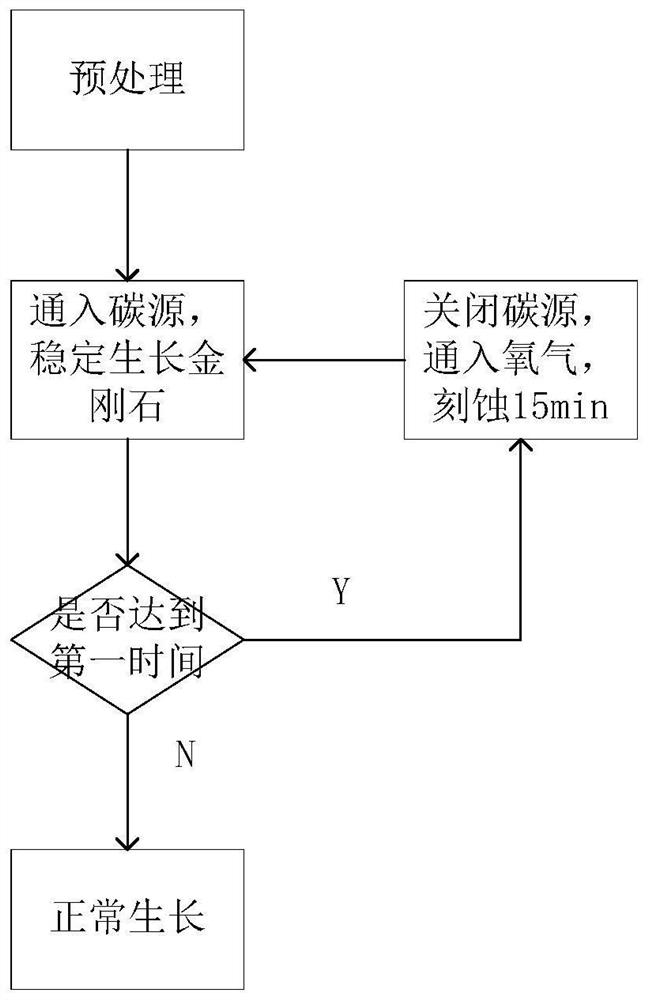

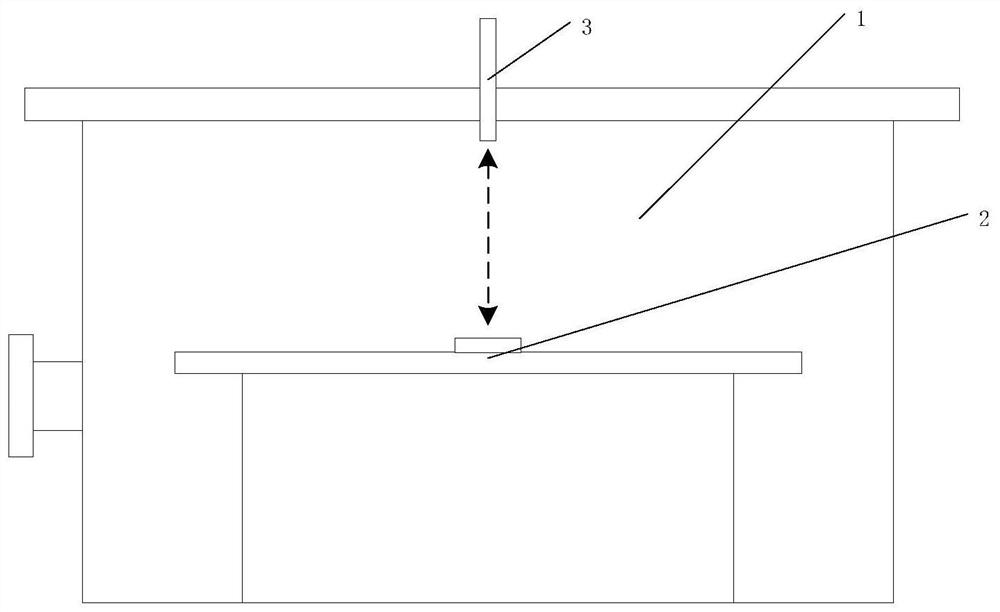

A low-defect high-transmittance diamond growth method and system

ActiveCN110835746BIncrease oxygen contentReduce surface defect densityPolycrystalline material growthFrom chemically reactive gasesCarbon ionSeed crystal

The invention relates to a diamond growth method and system with low defects and high light transmittance. A diamond growth method with low defects and high light transmittance, comprising the steps of: feeding oxygen in stages: pretreating the surface of the seed crystal and putting it into a growth chamber, feeding microwaves with a certain power, and then feeding hydrogen and oxygen to the seed crystal Etch the surface for 15‑60min; then, stop feeding oxygen, feed a certain amount of argon, feed carbon source to generate carbon ion clusters, and then grow diamond stably; stop feeding carbon source, feed oxygen every first time Etching for 10-30min; substrate table lifting: while the stable growth, real-time detection of the thickness data of diamond growth, according to the thickness data, the height of the substrate table is controlled, so that the diamond growth surface is always in the best growth position . The present invention provides a low-defect high-transmittance diamond growth method and system. The grown diamond has a layered structure, and the content of oxygen element is periodically distributed as the thickness of the diamond increases.

Owner:CHANGSHA ADVANCED MATERIALS IND RES INST CO LTD

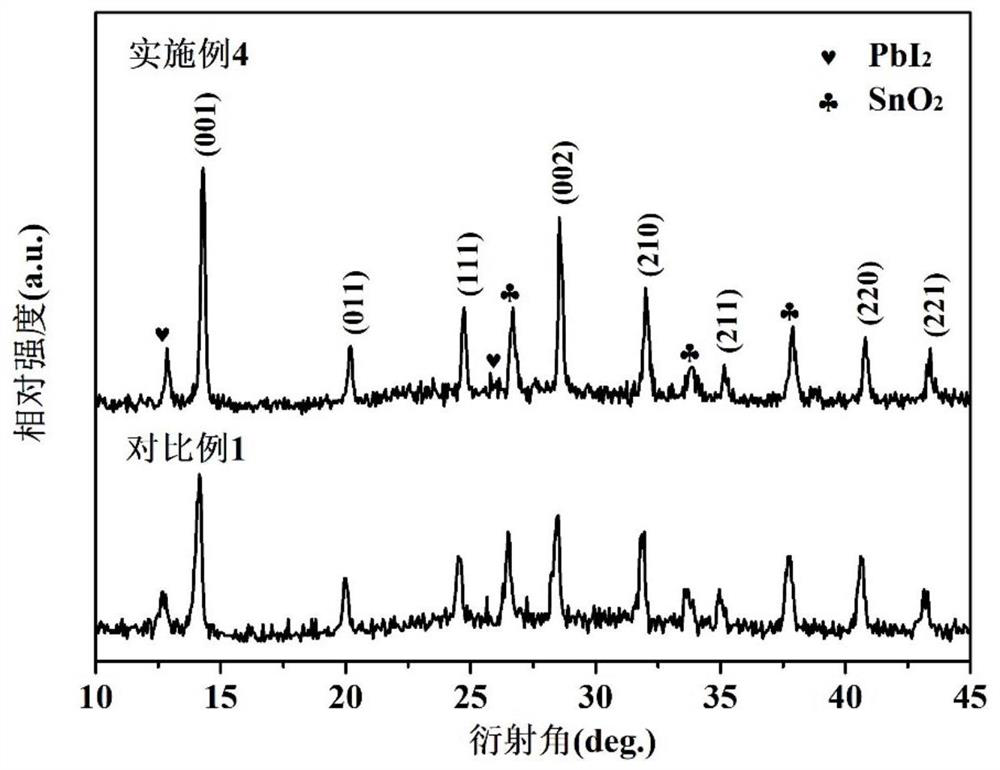

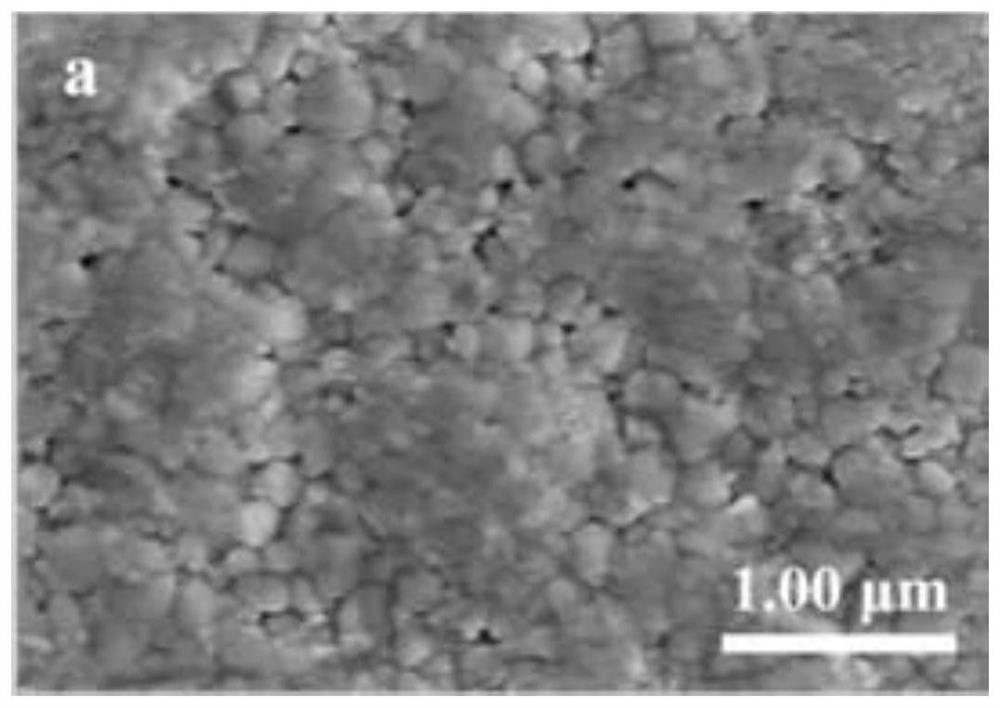

Perovskite light absorption layer film and surface defect passivation method thereof

PendingCN113675345AQuality improvementStop erosionSolid-state devicesSemiconductor/solid-state device manufacturingArgon atmosphereOrganosolv

The invention discloses a perovskite light absorption layer film and a surface defect passivation method thereof. The method comprises the steps of 1, dissolving PbI2, FAI, PbBr2, MABr and CsIb in a mixed solvent of N, N-dimethylformamide and dimethyl sulfoxide, and preparing a perovskite precursor solution, 2, dissolving pyrrole in an organic solvent to prepare an additive solution, 3, dispensing the perovskite precursor solution on an FTO conductive glass substrate, starting a spin coater, accelerating to a rotating speed of 1000rpm at an acceleration of 1000rpm s<-1> and rotating for 10s, then accelerating to a rotating speed of 5500rpm at an acceleration of 2000rpm s<-1> and rotating for 25s, and preparing a perovskite thin film, quickly dropwise adding the additive solution obtained in the step 2 on the surface of the perovskite thin film 5 seconds before the high-speed rotation is stopped, and drying in an argon atmosphere to obtain the perovskite thin film. A pyrrole additive is introduced to the surface of a perovskite light absorption layer film, so that the surface defect density is reduced, and a hydrophobic layer is formed on the surface.

Owner:SHAANXI UNIV OF SCI & TECH

A kind of preparation method of n-type low-defect silicon carbide epitaxial wafer

ActiveCN104934318BLow densityPromote conversionSemiconductor/solid-state device manufacturingEtchingEpitaxial material

The invention provides a preparation method of an N-type low-defect silicon carbide epitaxial wafer. The method comprises the steps of preparation of a substrate, online substrate etching, growth of a buffer layer and growth of an epitaxial layer, wherein growth of the epitaxial layer includes growth, etching, blowing and re-growth. The method can be used to effectively reduce the dislocation density of the base, reduce deposit in the cavity, reduce the defect density of the surface of the silicon carbide epitaxial wafer, improve the quality of a silicon carbide epitaxial material, and is wide in application range, low in processing cost and suitable for industrial production.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

A method for surface modification of metal materials with high strength and toughness

The invention discloses a method for modifying the high-toughness surfaces of metal materials, relating to a surface modification technique for materials. The method comprises the following main steps: 1) pretreating the surface of a metal material; 2) carrying out laser shot blasting treatment on the pretreated surface of the material; 3) carrying out magnetic field nitriding on the surface subjected to laser shot blasting treatment; 4) carrying out magnetic field quenching on the surface subjected to nitriding; 5) carrying out low-energy laser shot blasting treatment on the surface subjected to magnetic field quenching; 6) carrying out magnetic field quenching again on the surface subjected to low-energy laser shot blasting treatment, so that a flat high-toughness surface is obtained. According to the invention, the grain structure of a surface can be effectively refined, the thickness of a nitriding layer can be increased, the nitriding time can be shortened, the brittleness of the nitriding layer can be reduced, and the toughness of the surface can be improved. The method disclosed by the invention is simple in technological process, easy in operation, high in efficiency, and suitable for mass production in a large scale.

Owner:常熟市通顺纺织有限责任公司

P-type crystalline silicon solar cell and preparation method thereof

InactiveCN109560149AIncrease concentrationReduce compoundingFinal product manufacturePhotovoltaic energy generationOhmic contactP type silicon

The invention provides a p-type crystalline silicon solar cell and a preparation method thereof. The p-type crystalline silicon solar cell is characterized in that the back surface of a p-type crystalline silicon substrate is provided with a first oxide layer, a doped p-type silicon-based thin film layer, a second oxide layer and a silicon-based thin film layer which are sequentially stacked so asto form a laminated structure; a back contact window is formed in the laminated structure, and a metal grid line electrode is formed in the back contact window, wherein an ohmic contact is formed between the metal grid line electrode and one or both of the p-type crystalline silicon substrate and the doped p-type silicon-based thin film layer. According to the method, the hole concentration and the transverse transmission performance of the surface of the p-type crystalline silicon substrate can be improved, and recombination and loss of carriers are reduced; and compared with an existing PERC battery (Passivated Emitter and Rear Cell), a passivation emitter back battery), higher open-circuit voltage and photoelectric conversion efficiency can be obtained.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

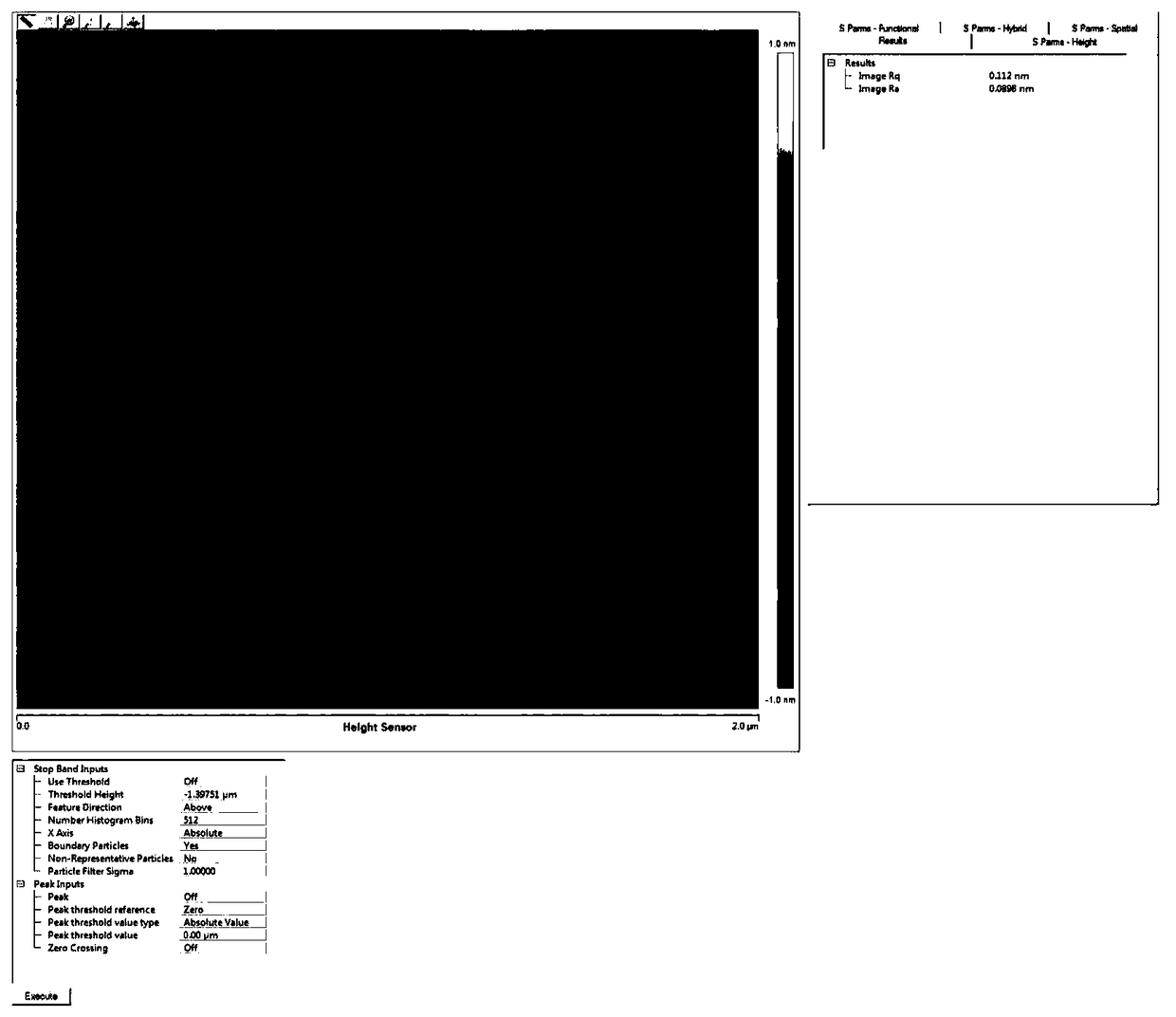

Surface treatment method for molecular beam epitaxy InAs substrate

ActiveCN114753007AControllable corrosion ratePolished evenlyPolycrystalline material growthFrom chemically reactive gasesSilicon dioxideMaterials science

The invention belongs to the technical field of compound semiconductor wafer polishing, and particularly relates to a surface treatment method for a molecular beam epitaxy InAs substrate. The method comprises chemical mechanical polishing and surface vulcanization passivation treatment, and chemical mechanical polishing adopts an alkaline polishing solution containing colloidal silicon dioxide, a weakly alkaline oxidizing agent, organic sodium salt, a pH regulator and water. According to the method, the problems that scratches and particle pollution are easily generated when the InAs substrate which is a soft compound substrate is polished, and the surface is difficult to deoxidize during epitaxial growth are well solved, and the InAs substrate treated by the method can stably grow a high-quality superlattice infrared detector epitaxial wafer.

Owner:SUZHOU KUNYUAN OPTOELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com