Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

41results about How to "Rapid thermal annealing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Solvent-assisted lithographic process using photosensitive sol-gel derived glass for depositing ridge waveguides on silicon

InactiveUS6054253ARapid thermal annealingSimple wayPhotomechanical apparatusOriginals for photomechanical treatmentRidge waveguidesSolvent

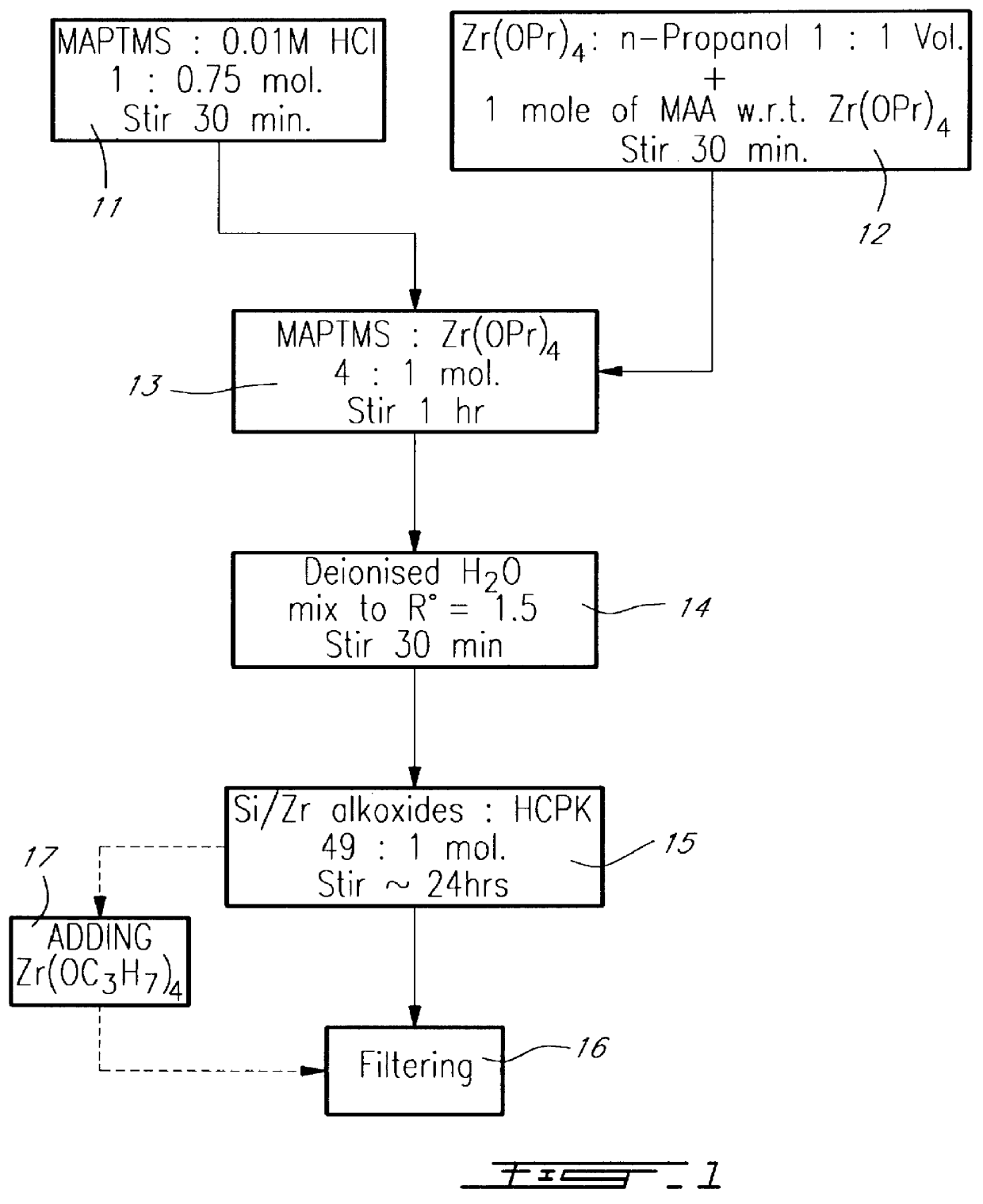

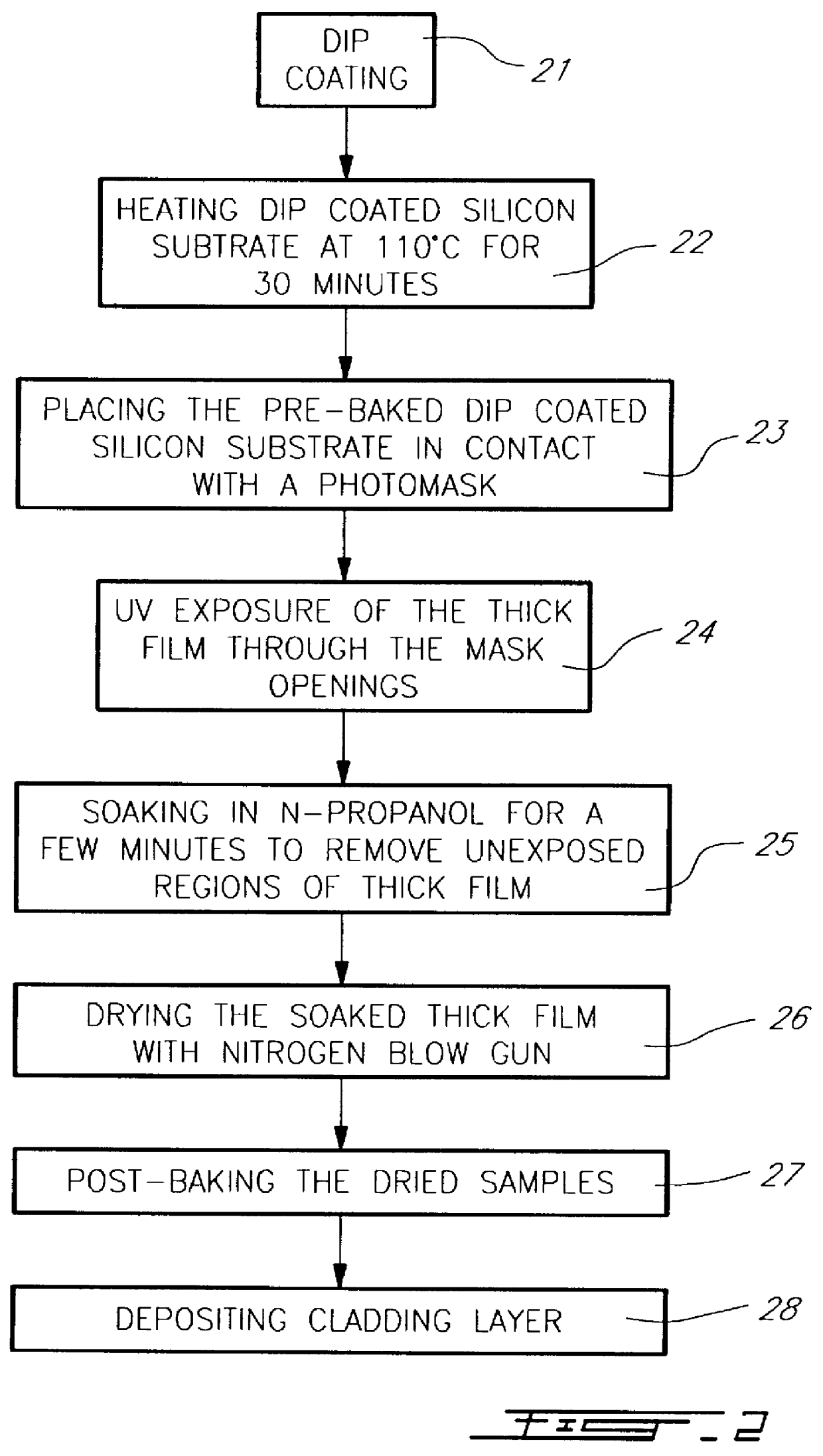

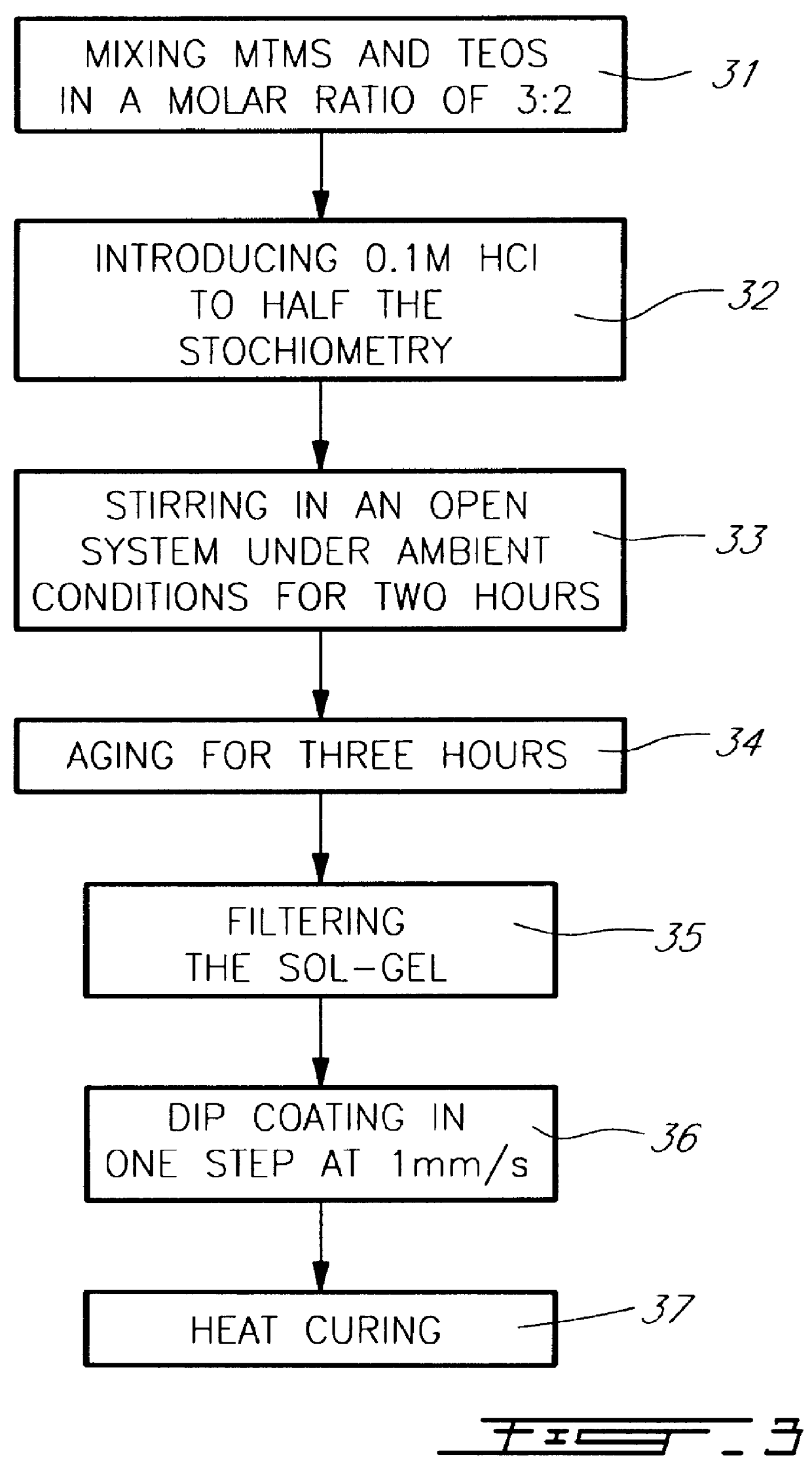

The process for fabricating a ridge waveguide on a substrate uses a photosensitive sol-gel glass material prepared, according to a first embodiment, by mixing methacryloxypropyltrimethoxysilane (H2C=C(CH3)CO2(CH2)3Si(OCH3)3) and methacrylic acid (H2C=C(CH3)COOH) or, according to a second embodiment, by mixing methacryloxypropyltrimethoxysilane (H2C=C(CH3)CO2(CH2)3Si(OCH3)3) with bis(s-butoxy)aluminoxytriethoxysilane. A thick film of photosensitive sol-gel glass material is first dip coated on at least a portion of the substrate. A photomask is applied to the film of photosensitive sol-gel glass material, and this sol-gel material is exposed to ultraviolet radiation through the opening(s) of the photomask to render a portion of the film insoluble to a given solvent and thereby imprint the ridge waveguide in that film. The thick film is then soaked in this solvent, for example n-propanol to dissolve the unexposed portion of the sol-gel film and leave on the substrate the exposed film portion and therefore the ridge waveguide. The ridge waveguide is heat cured and the heat cured ridge waveguide is covered with a cladding layer.

Owner:MCGILL UNIV - THE ROYAL INSTION FOR THE ADVANCEMENT OF LEARNING

Process for fabricating an MOS device having highly-localized halo regions

Owner:INT BUSINESS MASCH CORP

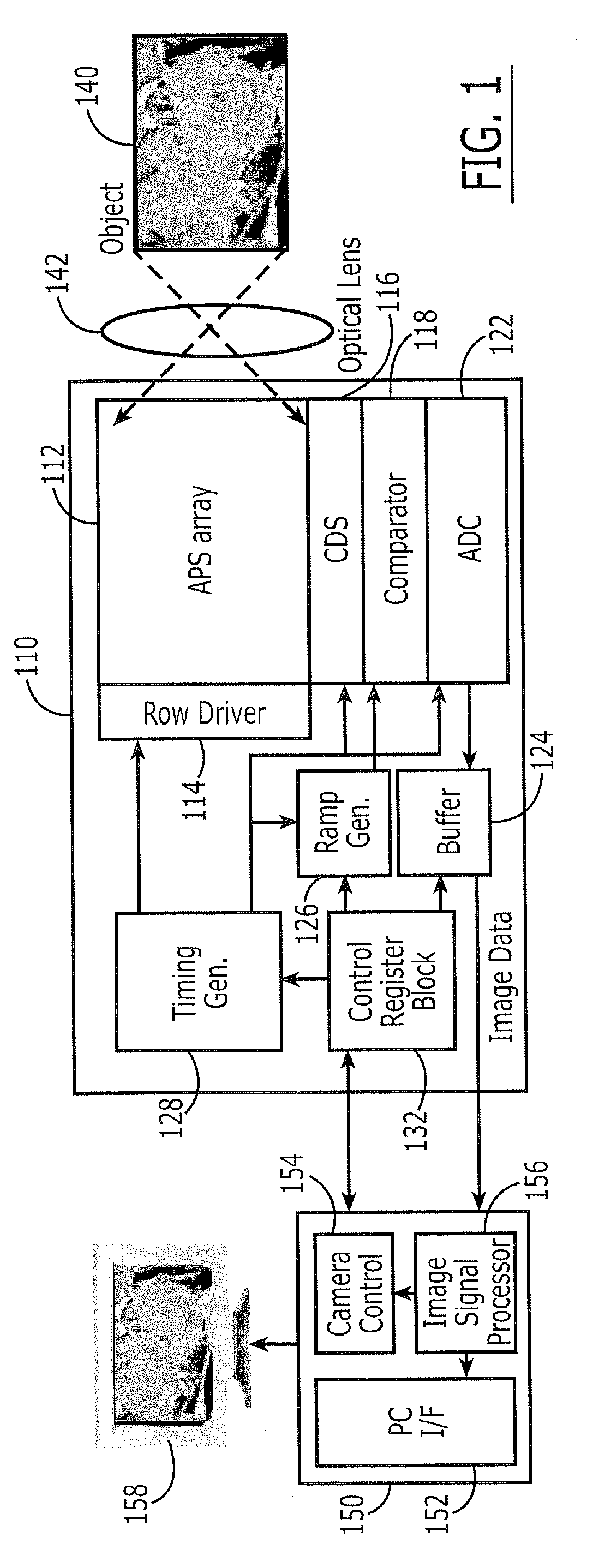

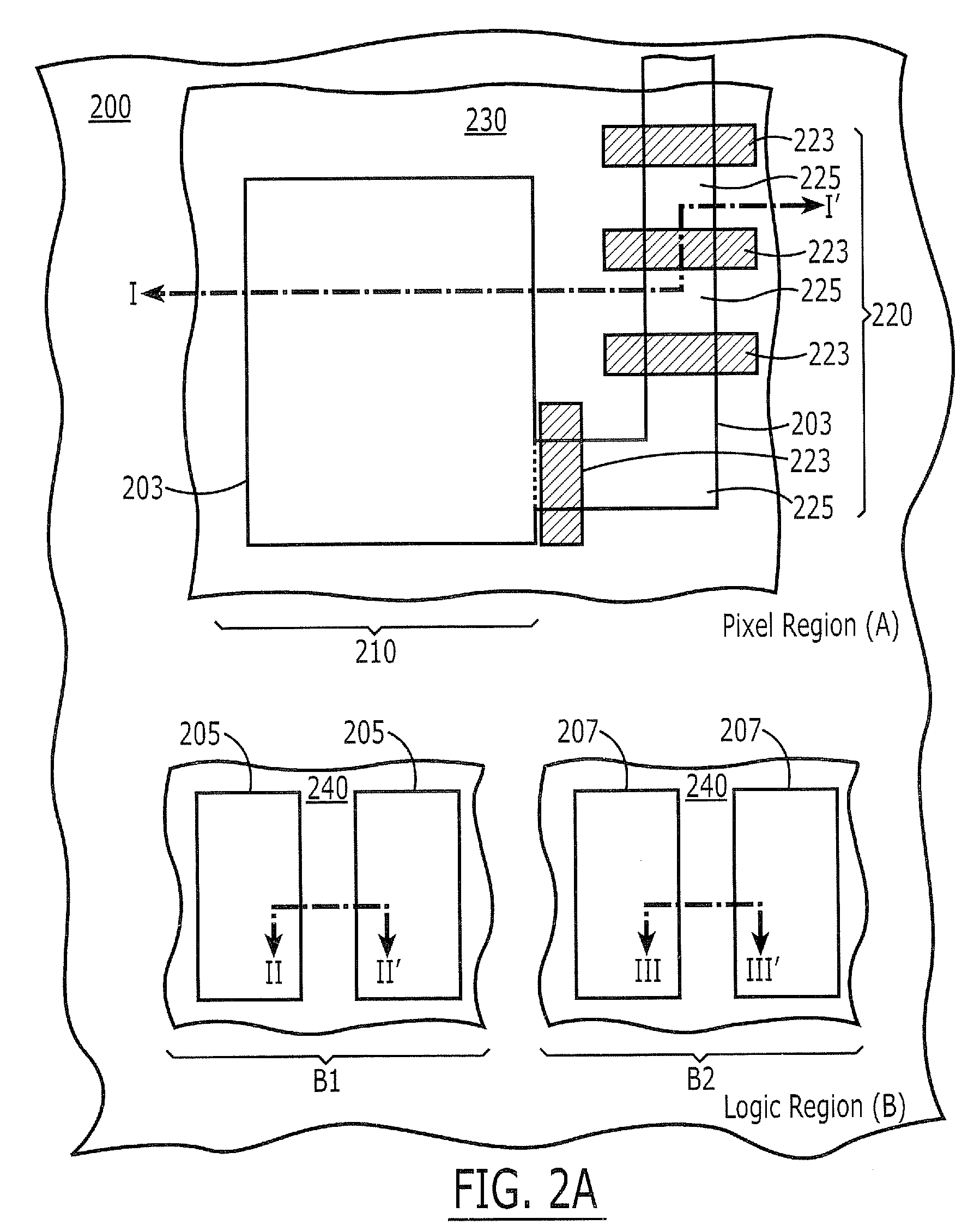

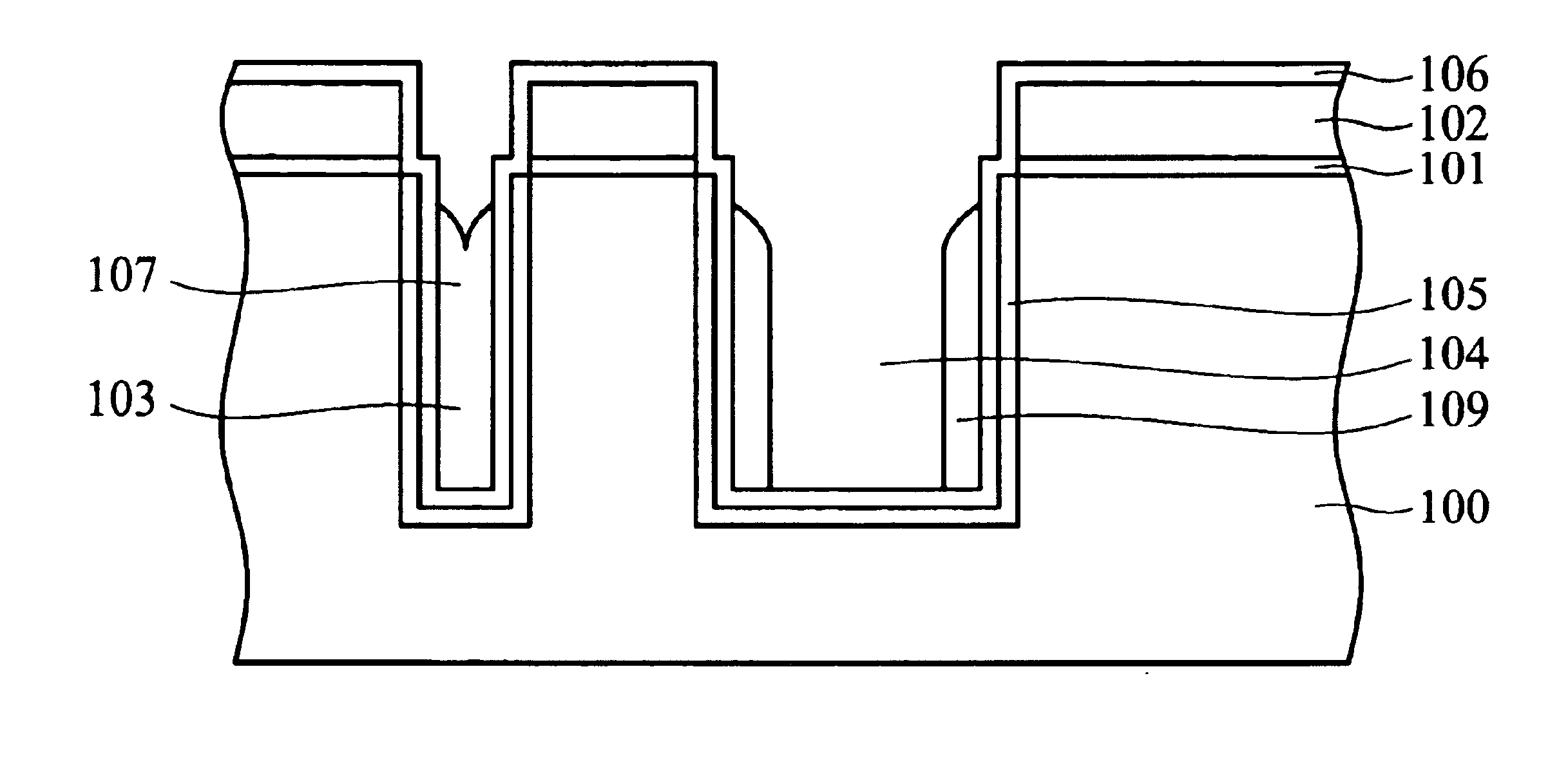

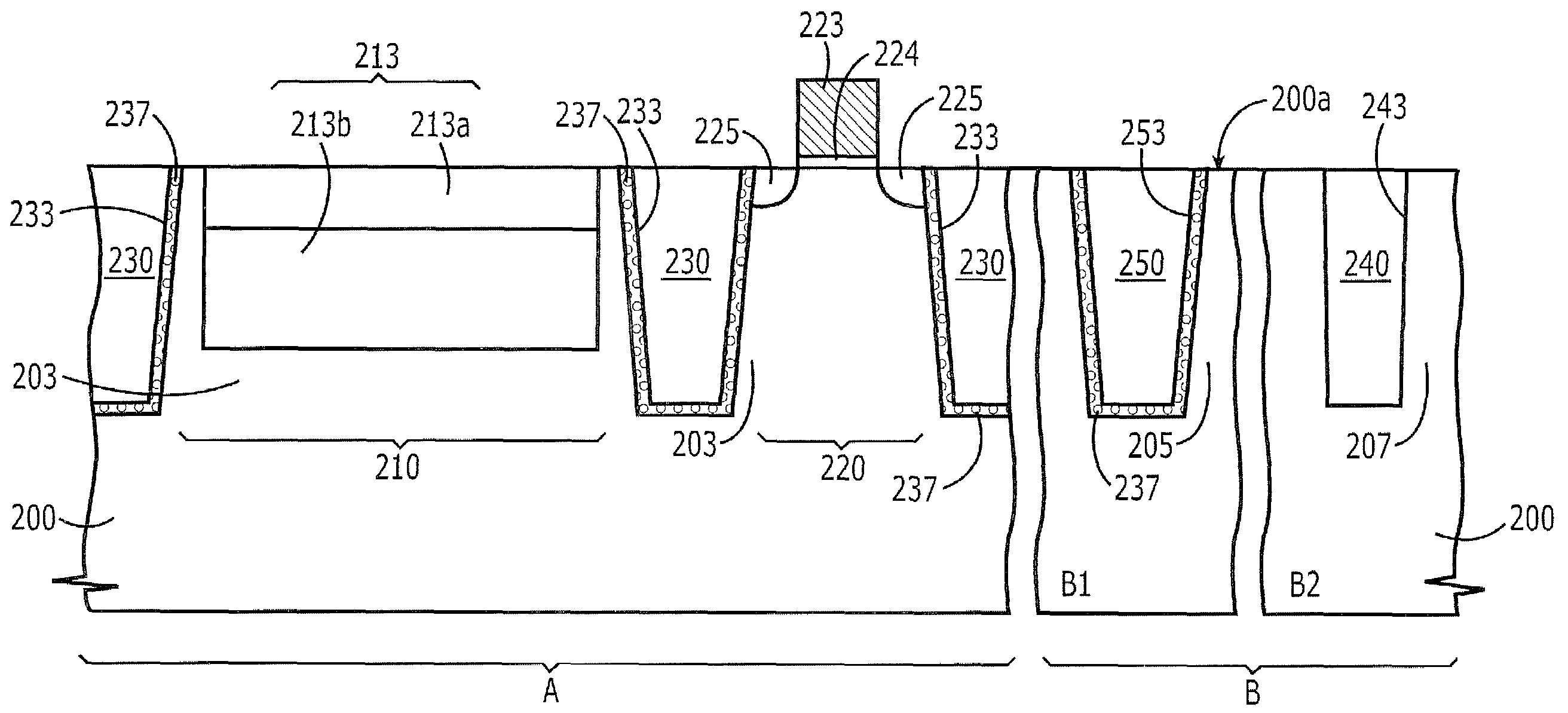

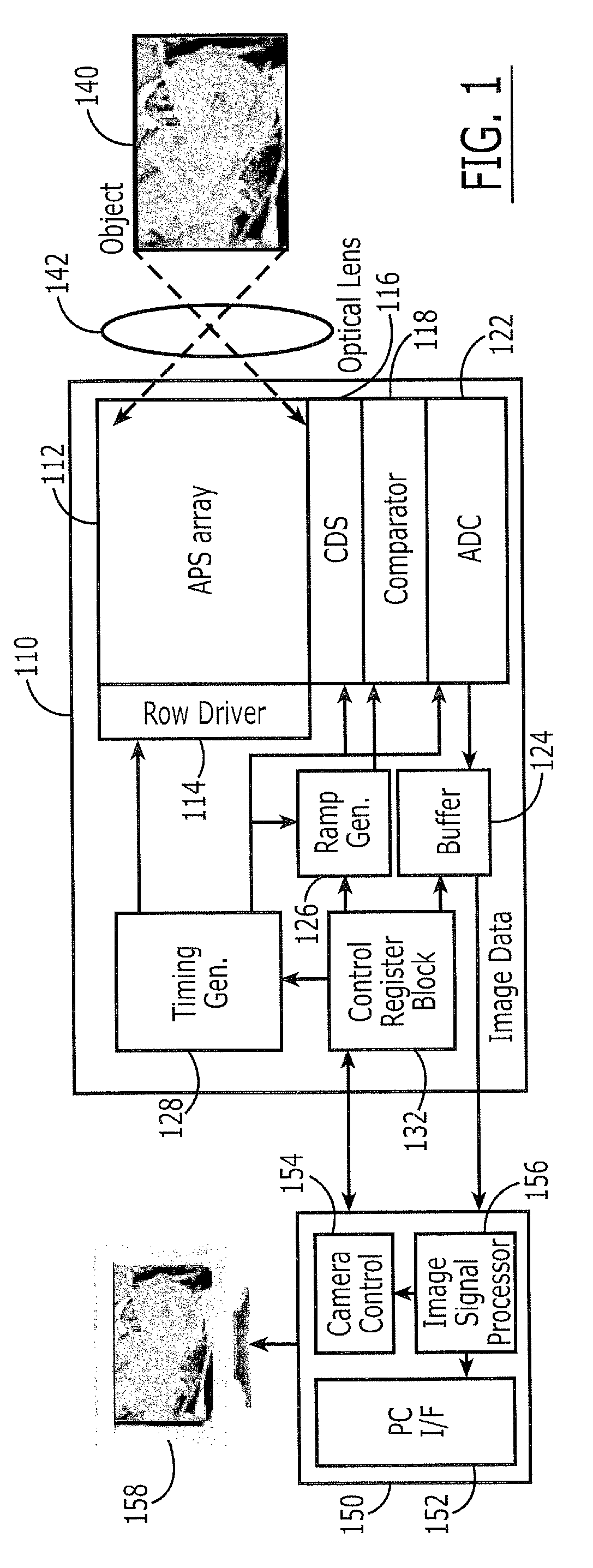

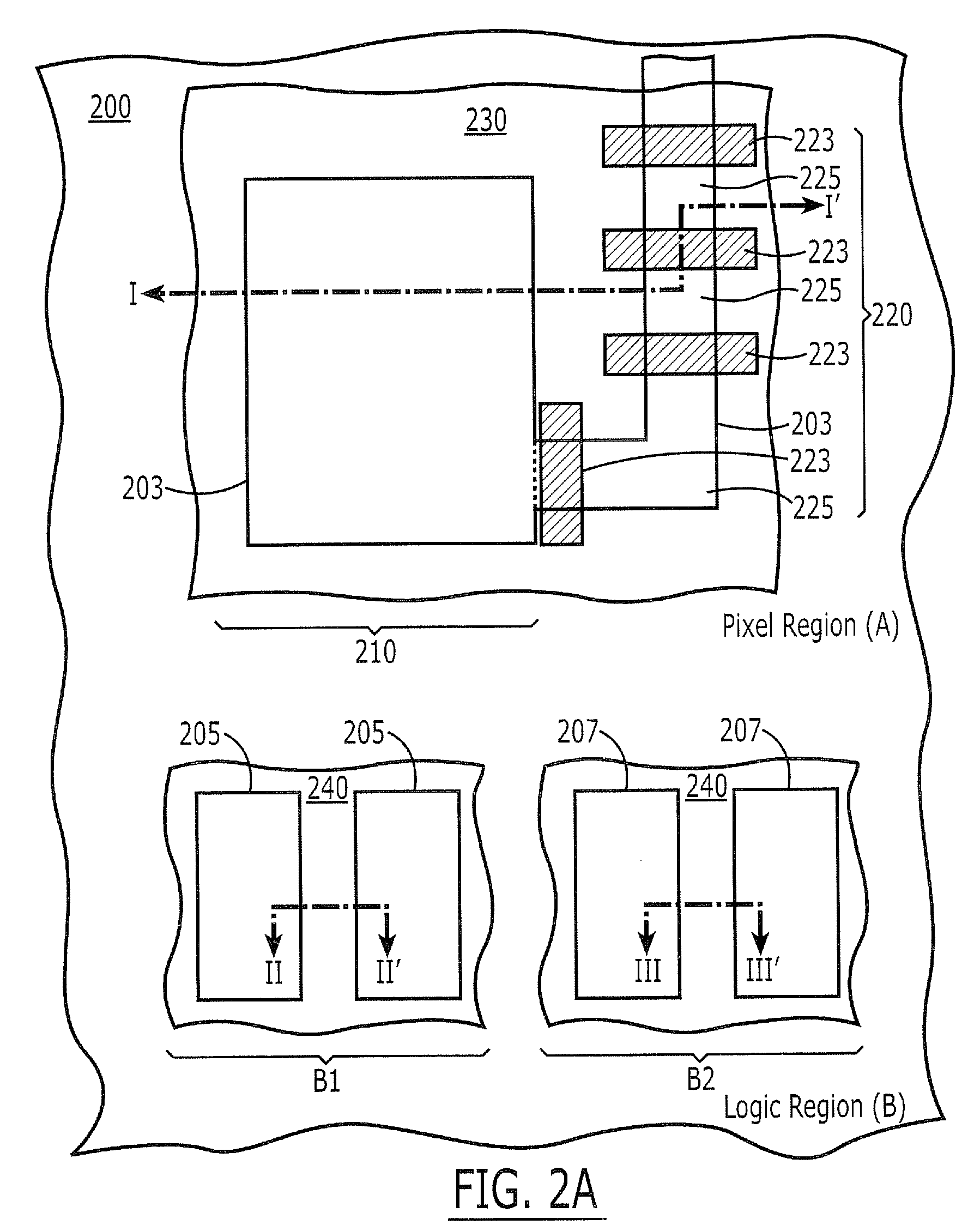

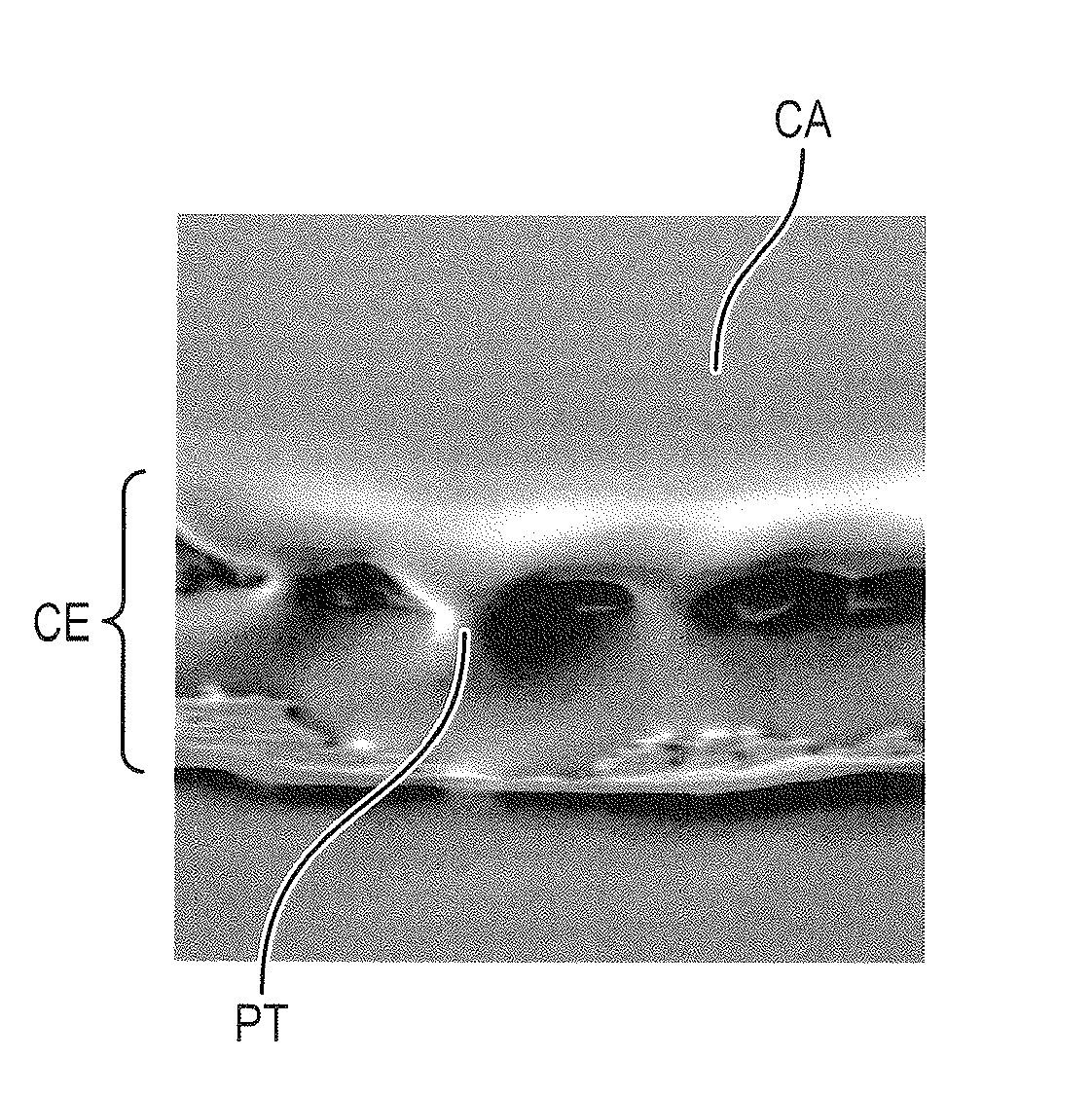

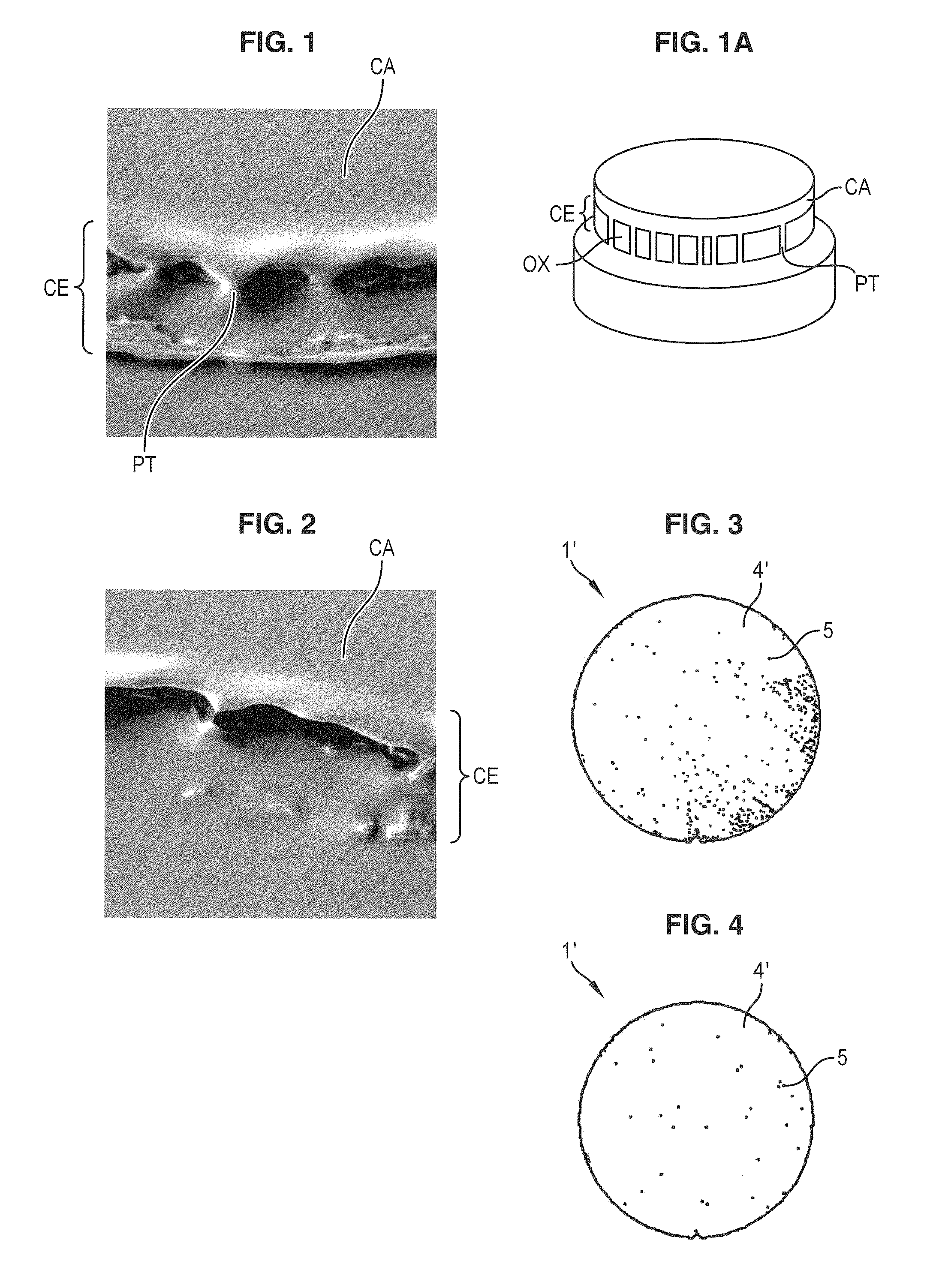

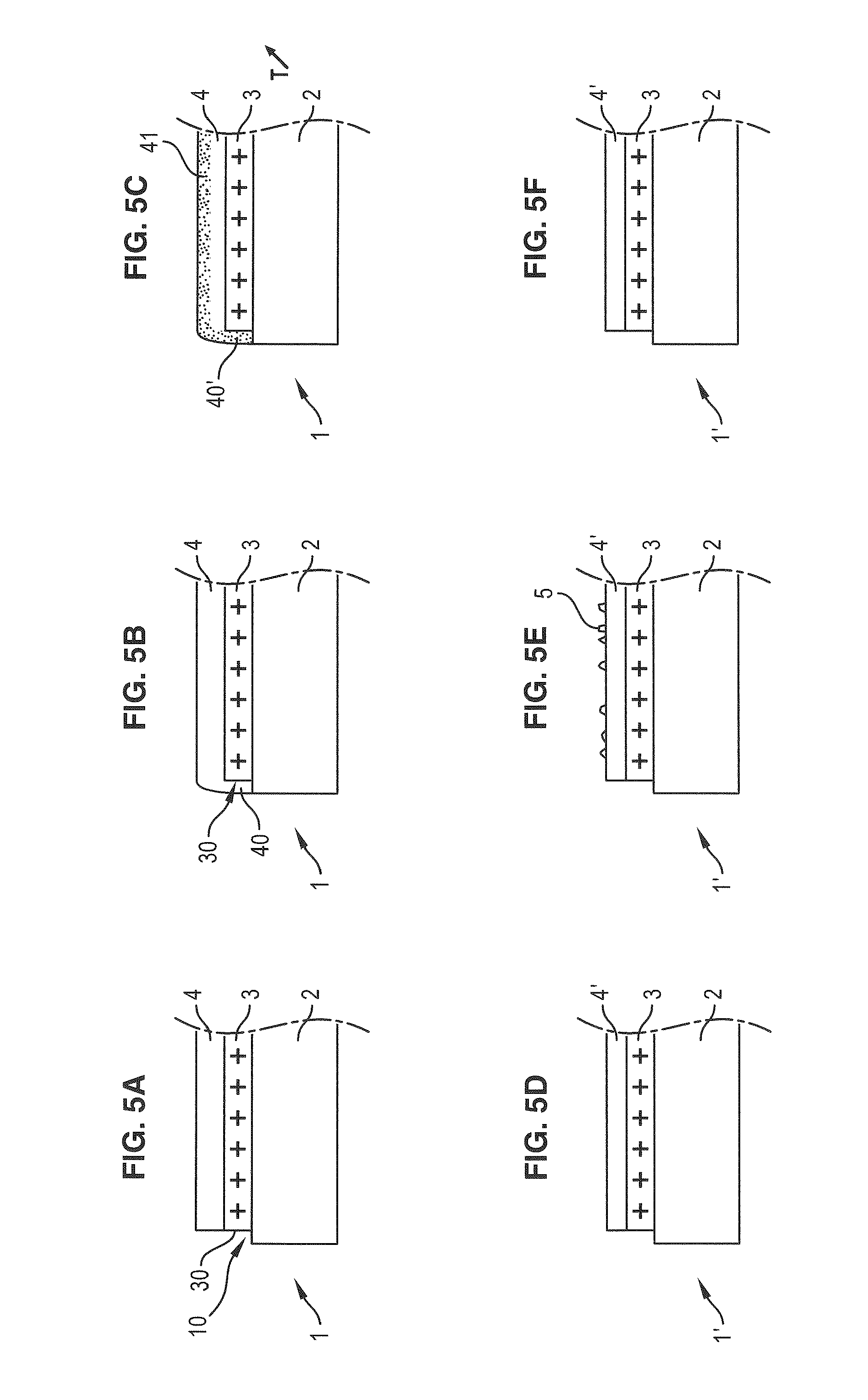

Image sensors including multiple slope/impurity layer isolation regions, and methods of fabricating same

ActiveUS20080035963A1Reduce dark currentRapid thermal annealingSolid-state devicesRadiation controlled devicesComputer scienceImpurity

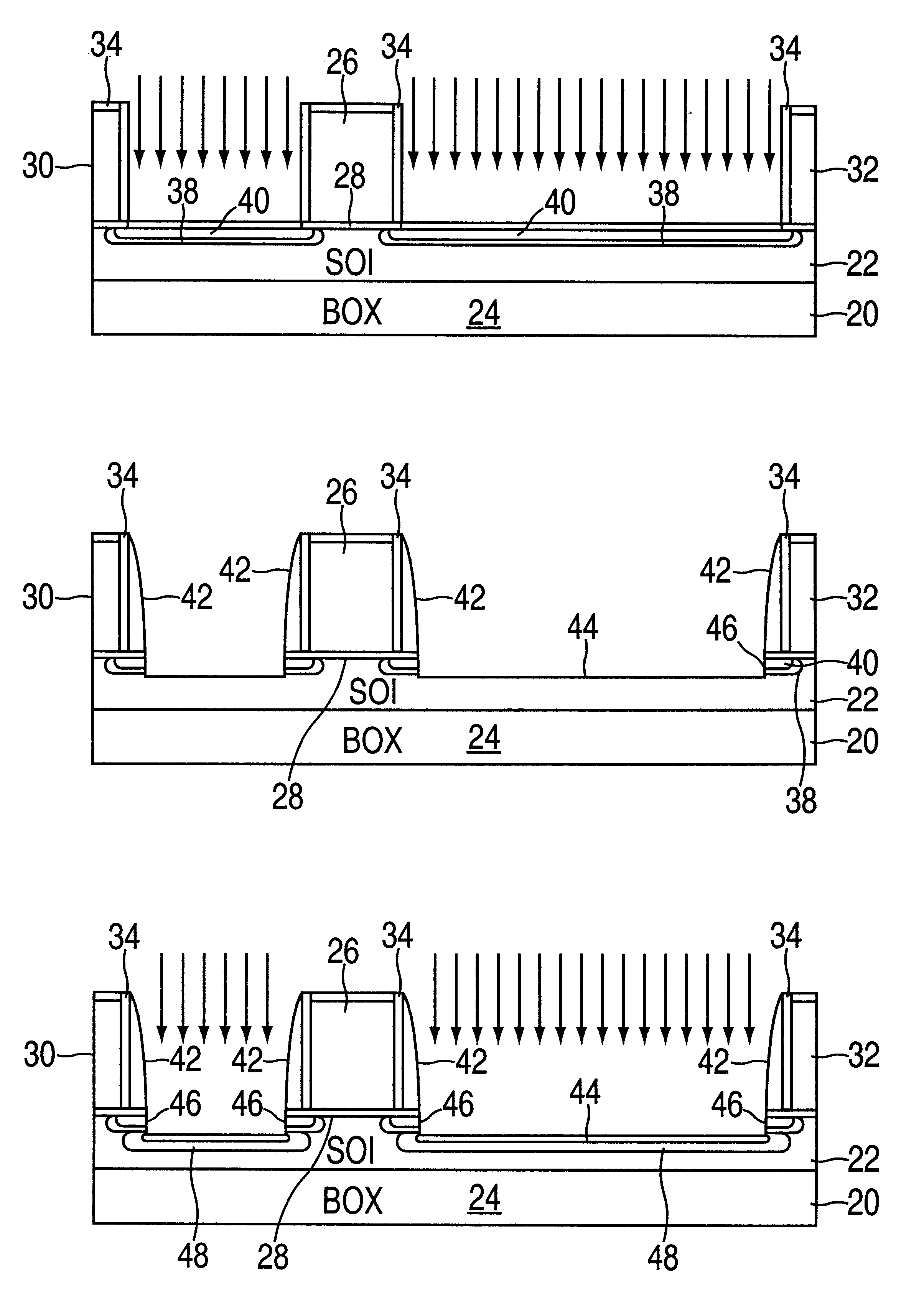

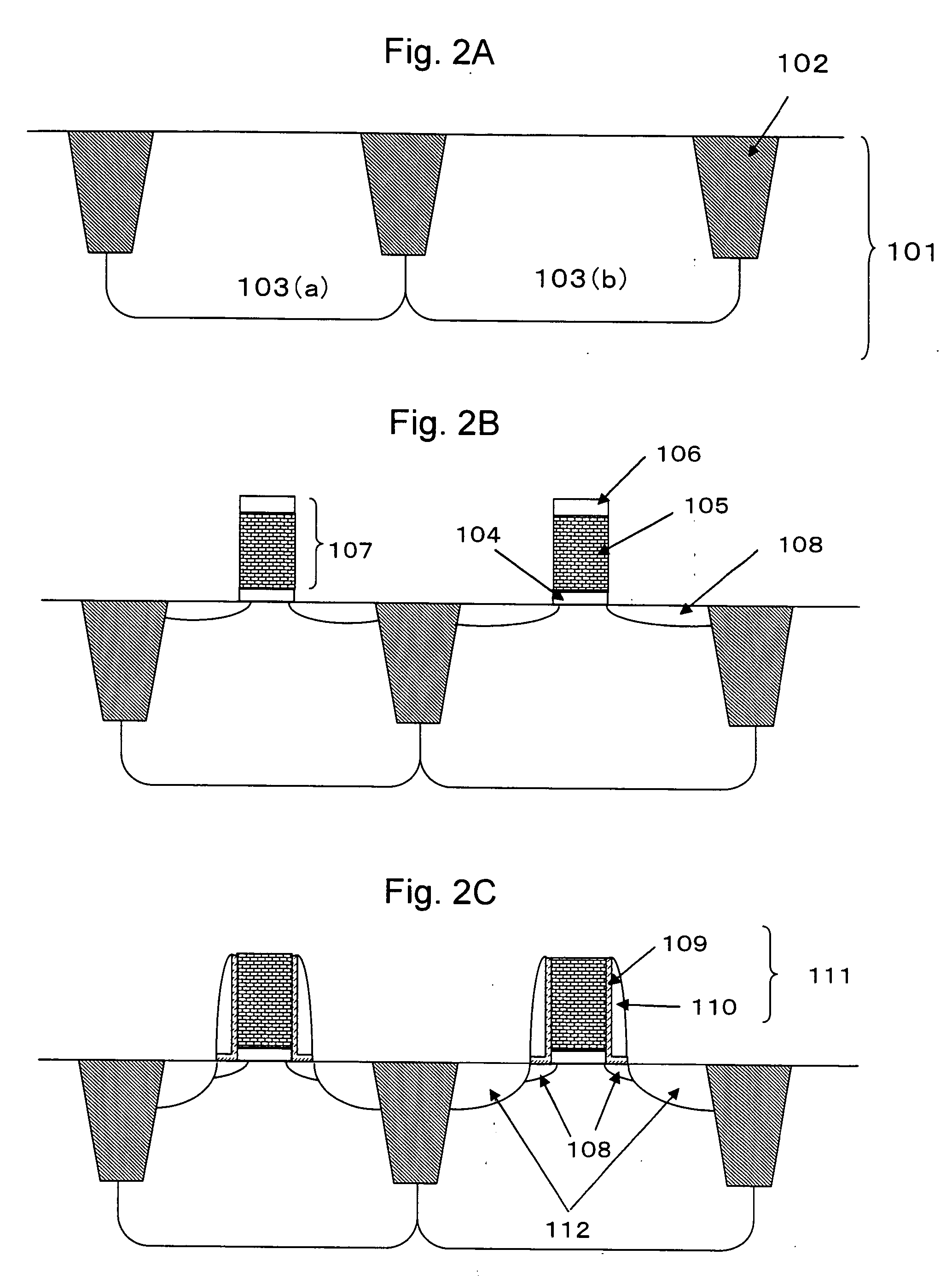

Image sensors include a pixel region and a logic region. Pixel isolation regions in the pixel region include pixel isolation region walls that are less sloped than logic isolation region walls in the logic region. An impurity layer also may be provided adjacent at least some of the pixel isolation region walls, wherein at least some of the logic isolation region walls are free of the impurity layer. The impurity layer and / or the less sloped logic isolation region walls may also be provided for NMOS devices in the logic region but not for PMOS devices in the logic region. Doped sacrificial layers may be used to fabricate the impurity layer.

Owner:SAMSUNG ELECTRONICS CO LTD

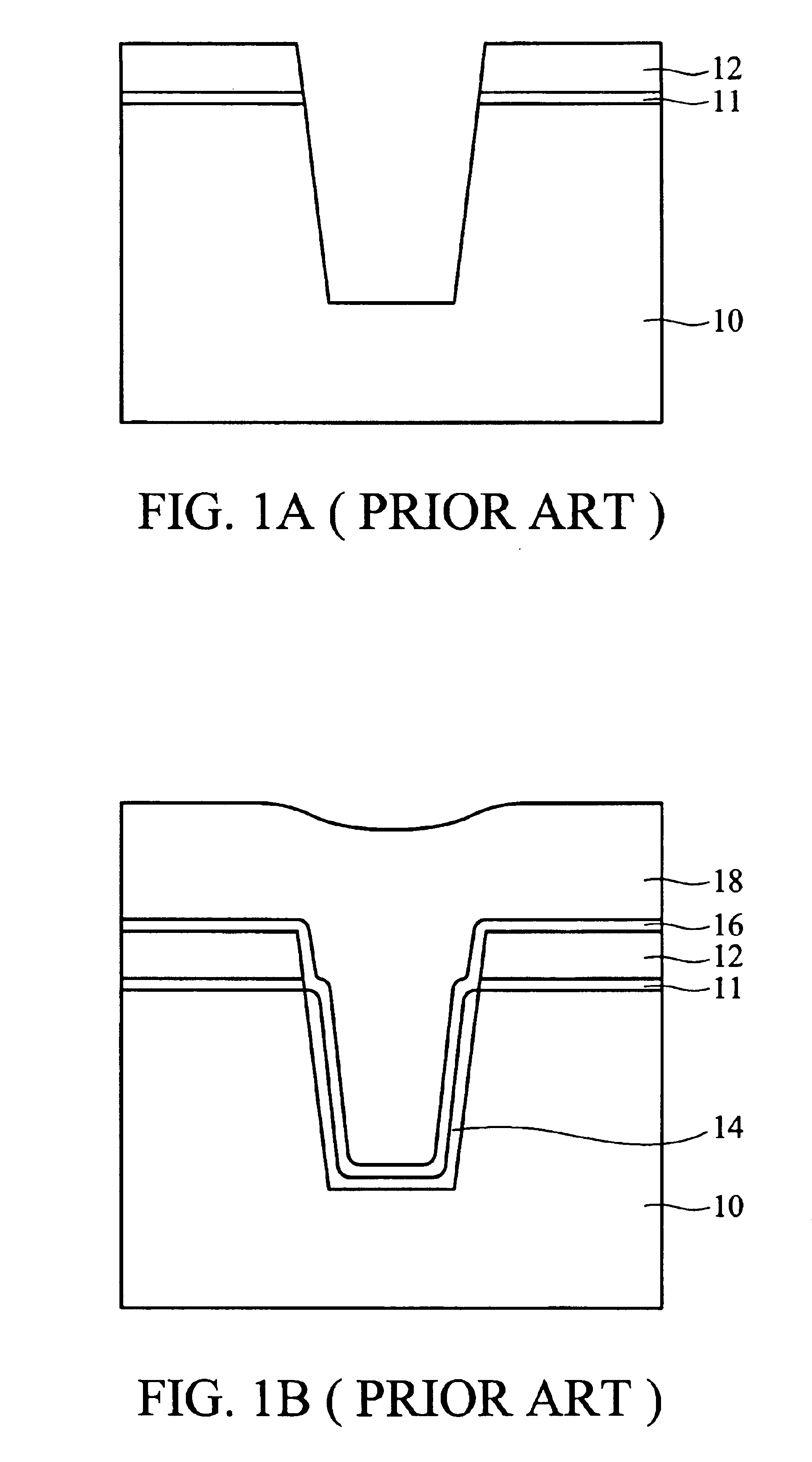

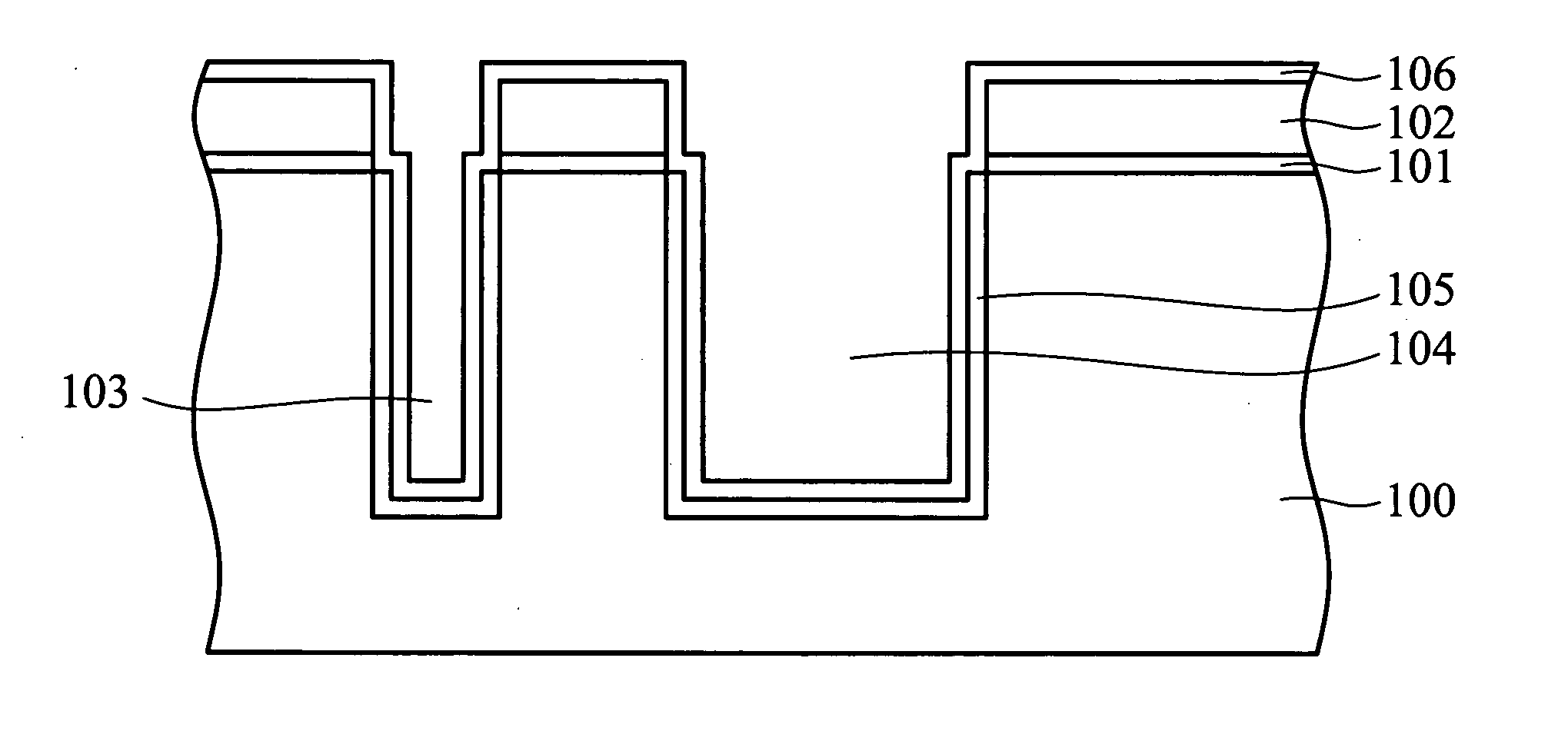

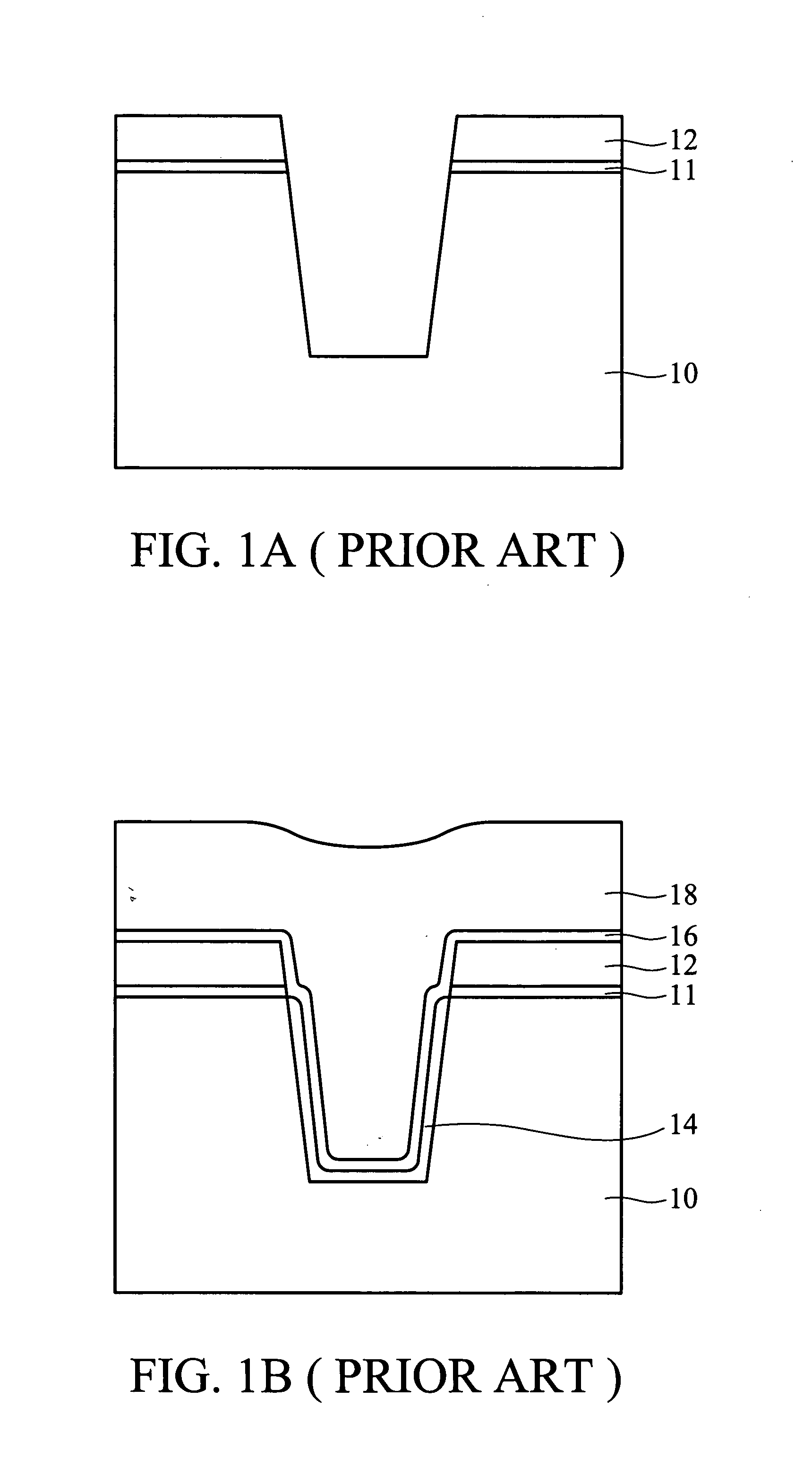

Method for fabricating trench isolations with high aspect ratio

InactiveUS6946359B2Excellent gap fillingQuicker procedureSemiconductor/solid-state device manufacturingCable/conductor manufactureHigh densityCompound (substance)

A method of fabricating a trench isolation with high aspect ratio. The method comprises the steps of: providing a substrate with a trench; depositing a first isolation layer filling the trench by low pressure chemical vapor deposition; etching the first isolation layer so that its surface is lowered to the opening of the trench; depositing a second isolation layer to fill the trench without voids by high density plasma chemical vapor deposition and achieving global planarization by chemical-mechanical polishing then providing a rapidly annealing procedure. Accordingly, the present invention achieves void-free trench isolation with high aspect ratio.

Owner:NAN YA TECH

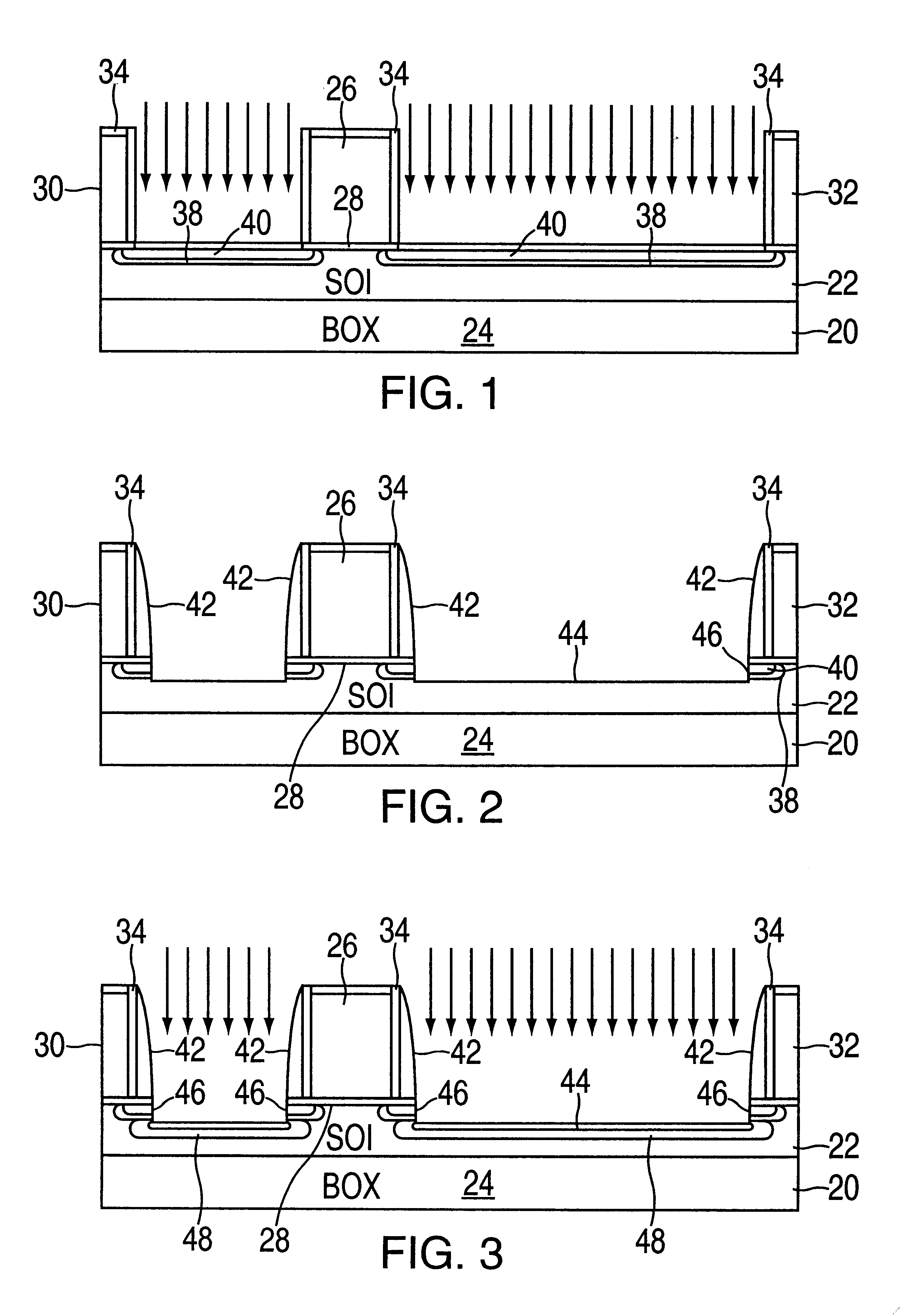

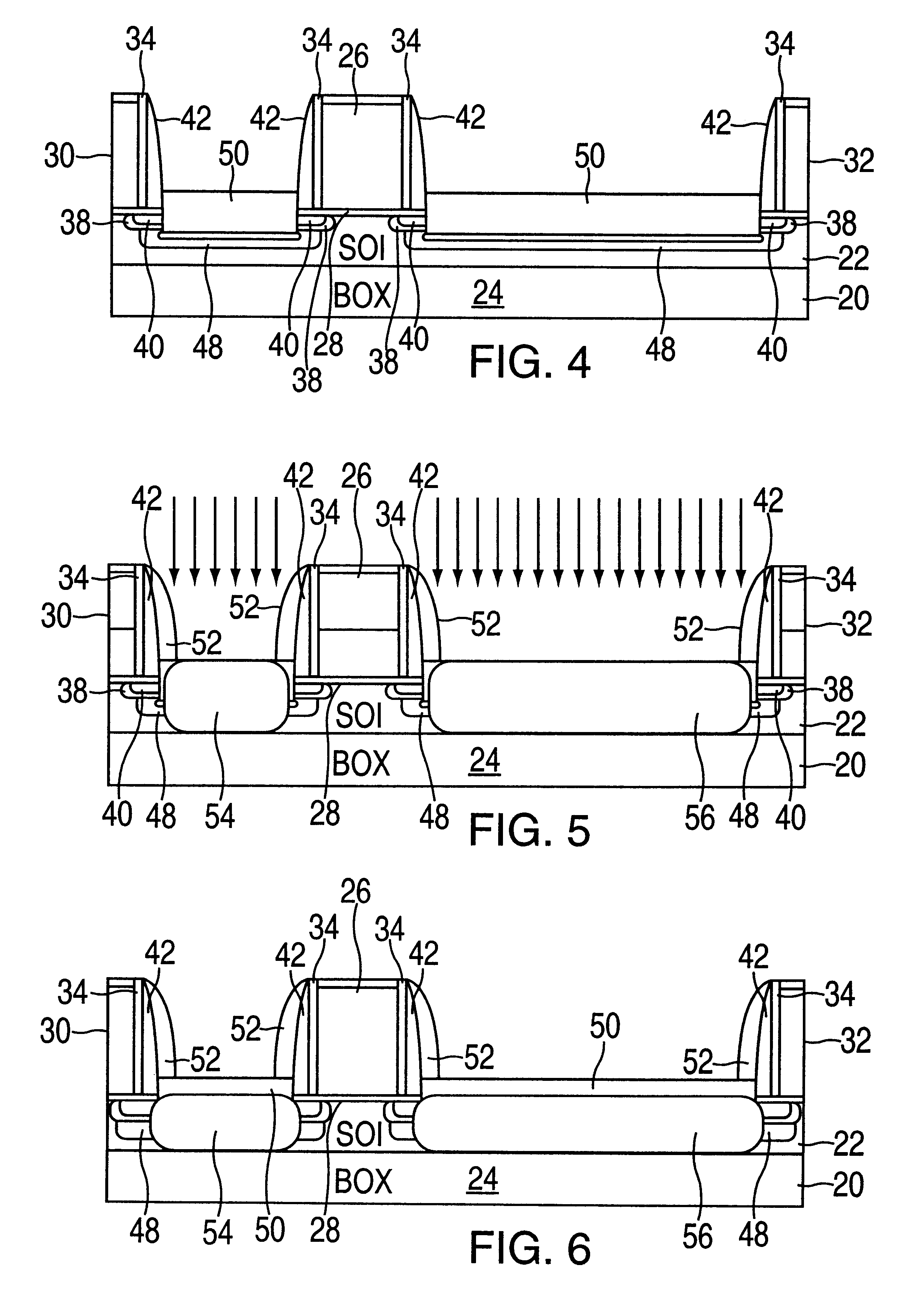

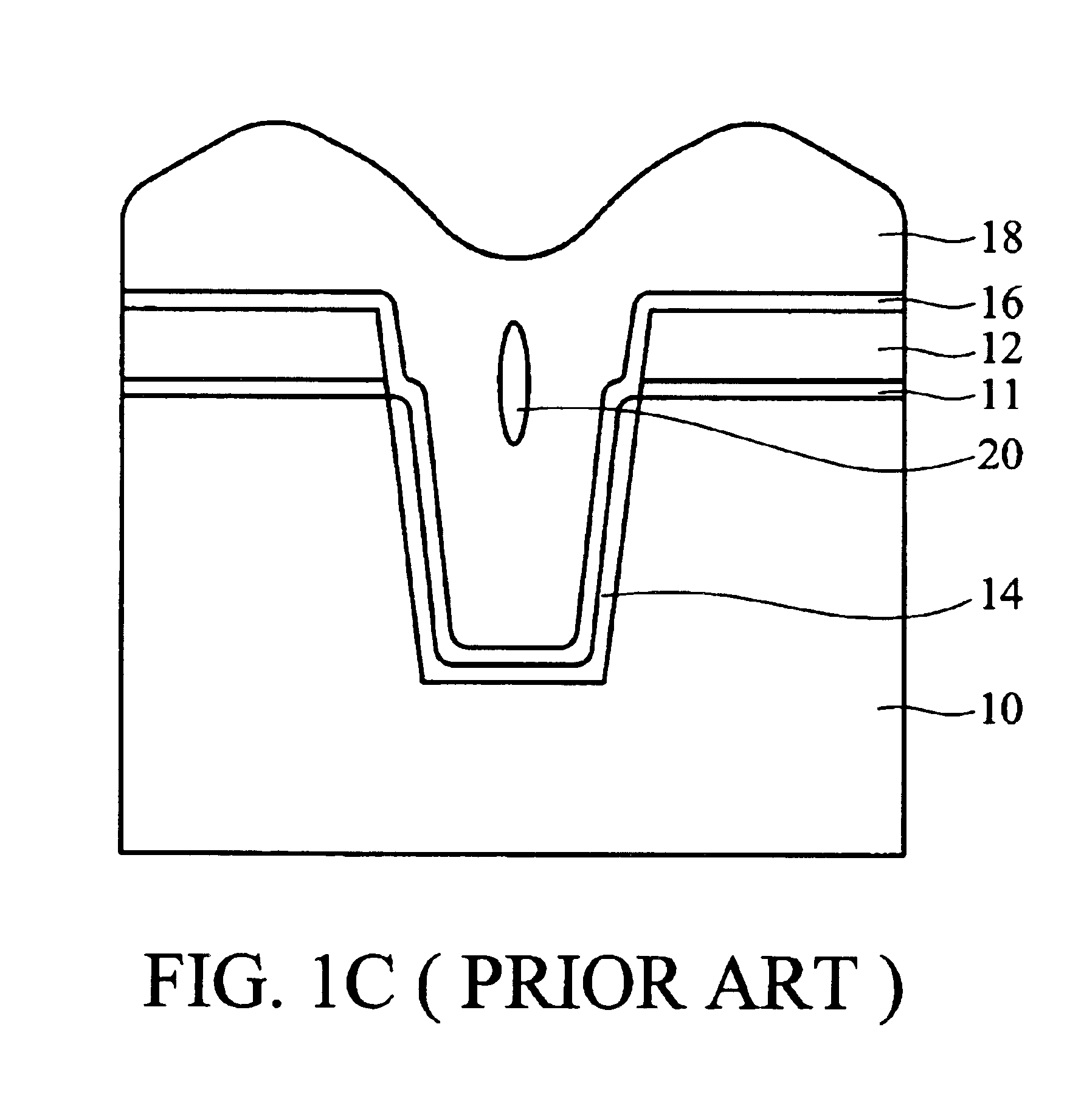

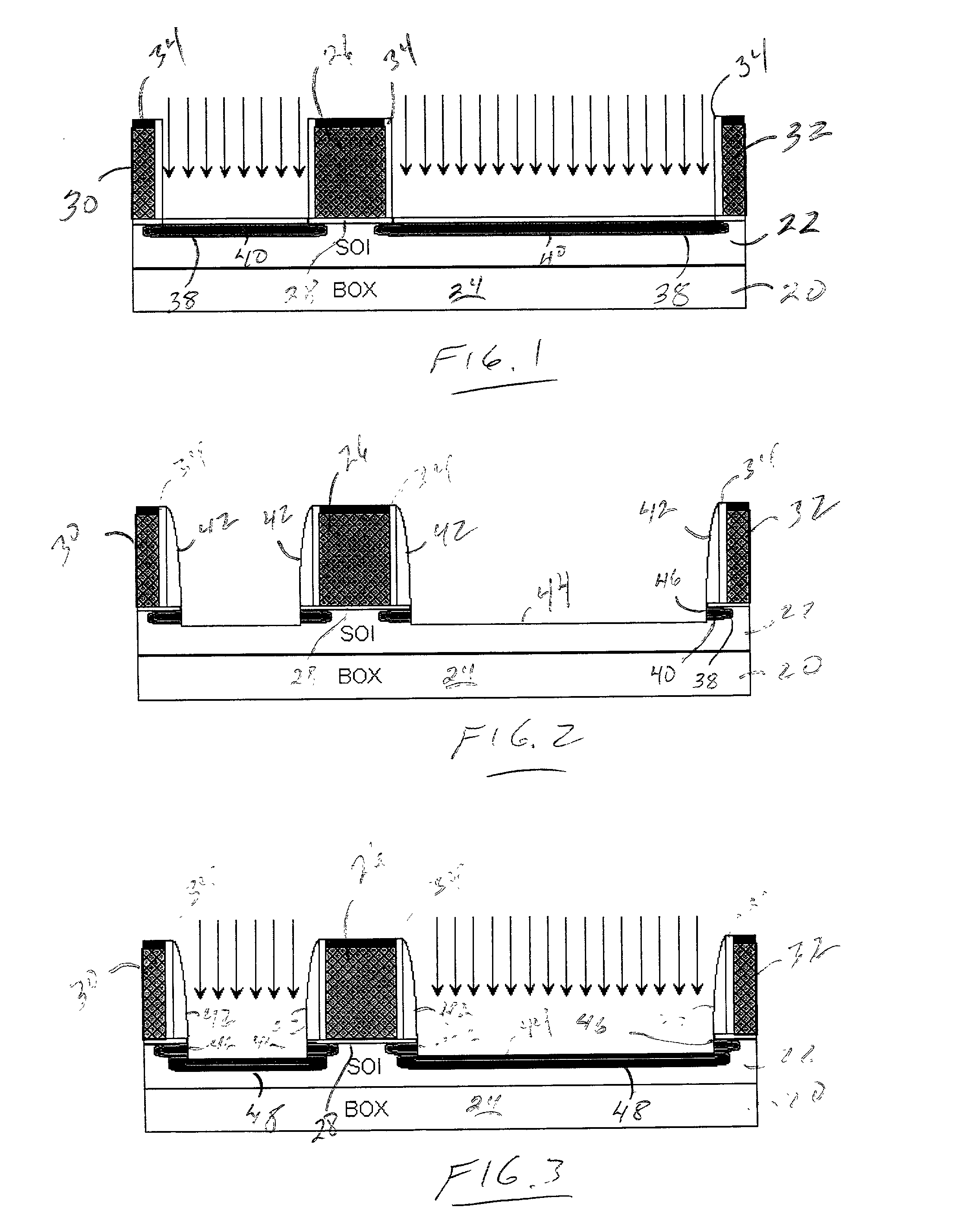

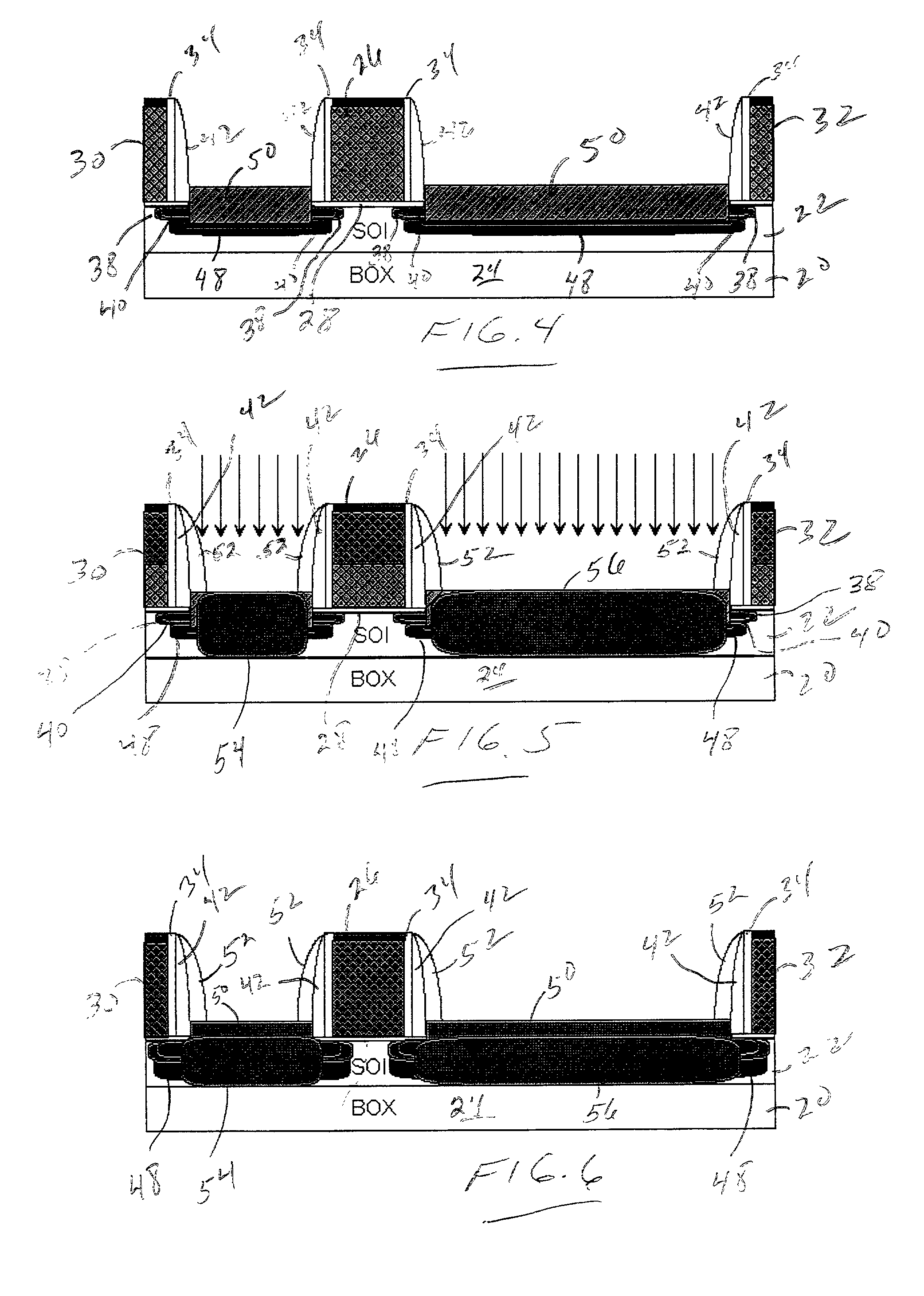

Process for fabricating an MOS device having highly-localized halo regions

InactiveUS20020072176A1Large diffusionEasy to makeTransistorSolid-state devicesBoronIon implantation

A process for fabricating an MOS device having a highly-localized halo region includes the formation of a first halo region at a first surface of a silicon substrate, and a second halo region at a second surface of the silicon substrate. The second surface of the silicon substrate is formed by anisotropically etching the first surface of the silicon substrate to remove a portion of the material from the substrate. Both the first and second halo regions are formed by low-energy ion implantation. For the fabrication of an n-channel device, boron is implanted at an energy of no more than about 1 keV. Upon implantation and a subsequent annealing process, the first and second halo regions form a continuous halo region within the semiconductor substrate.

Owner:IBM CORP

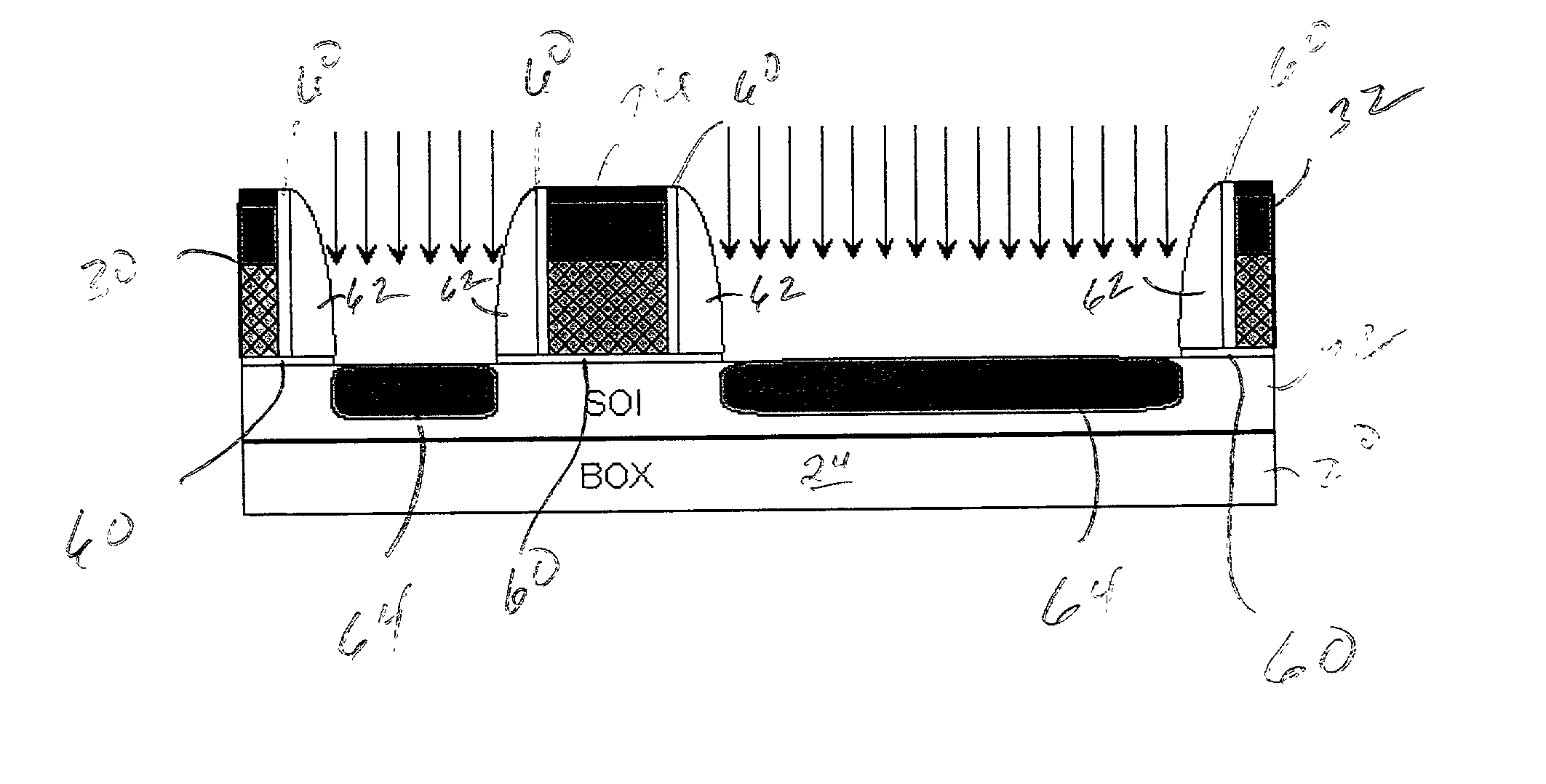

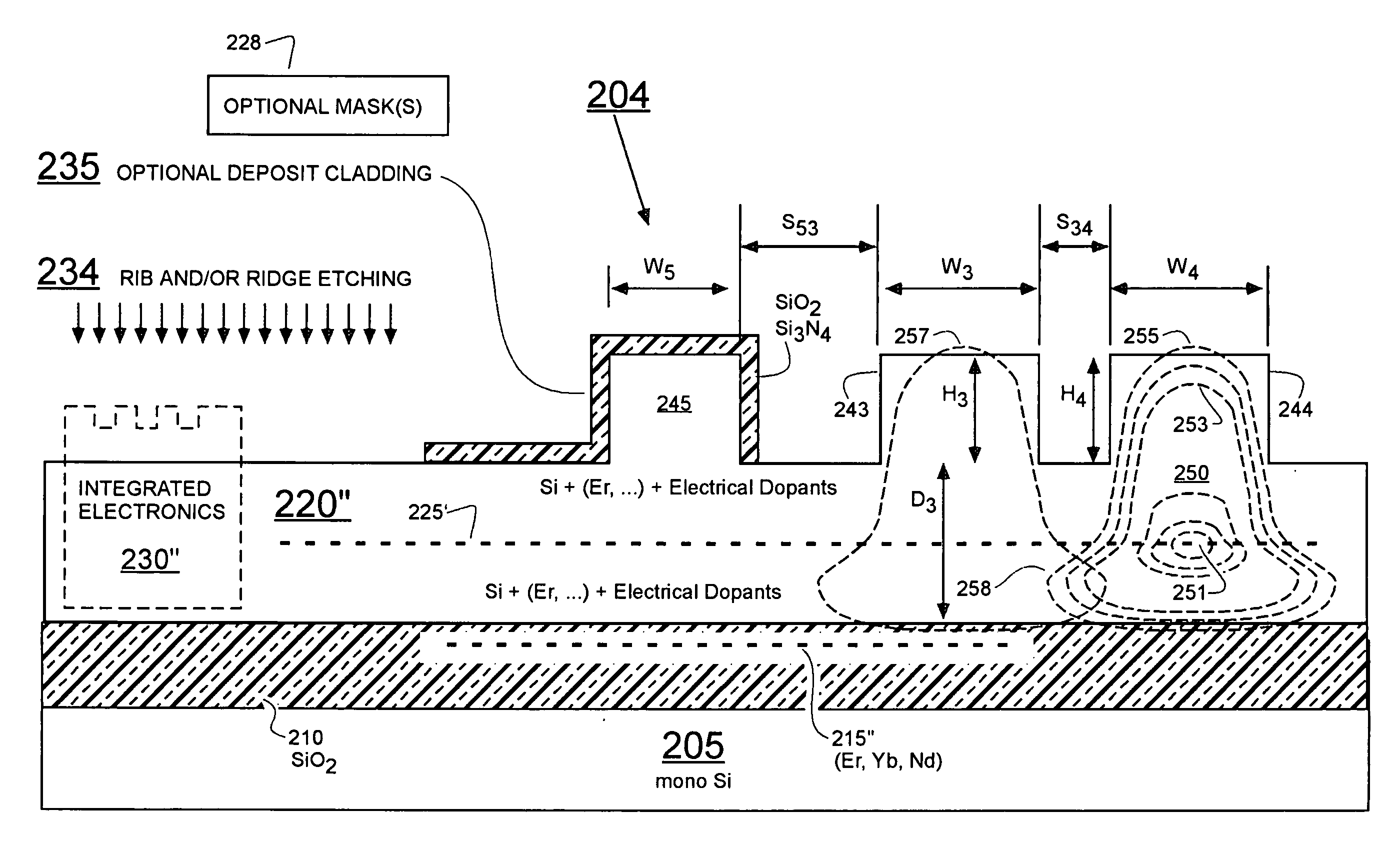

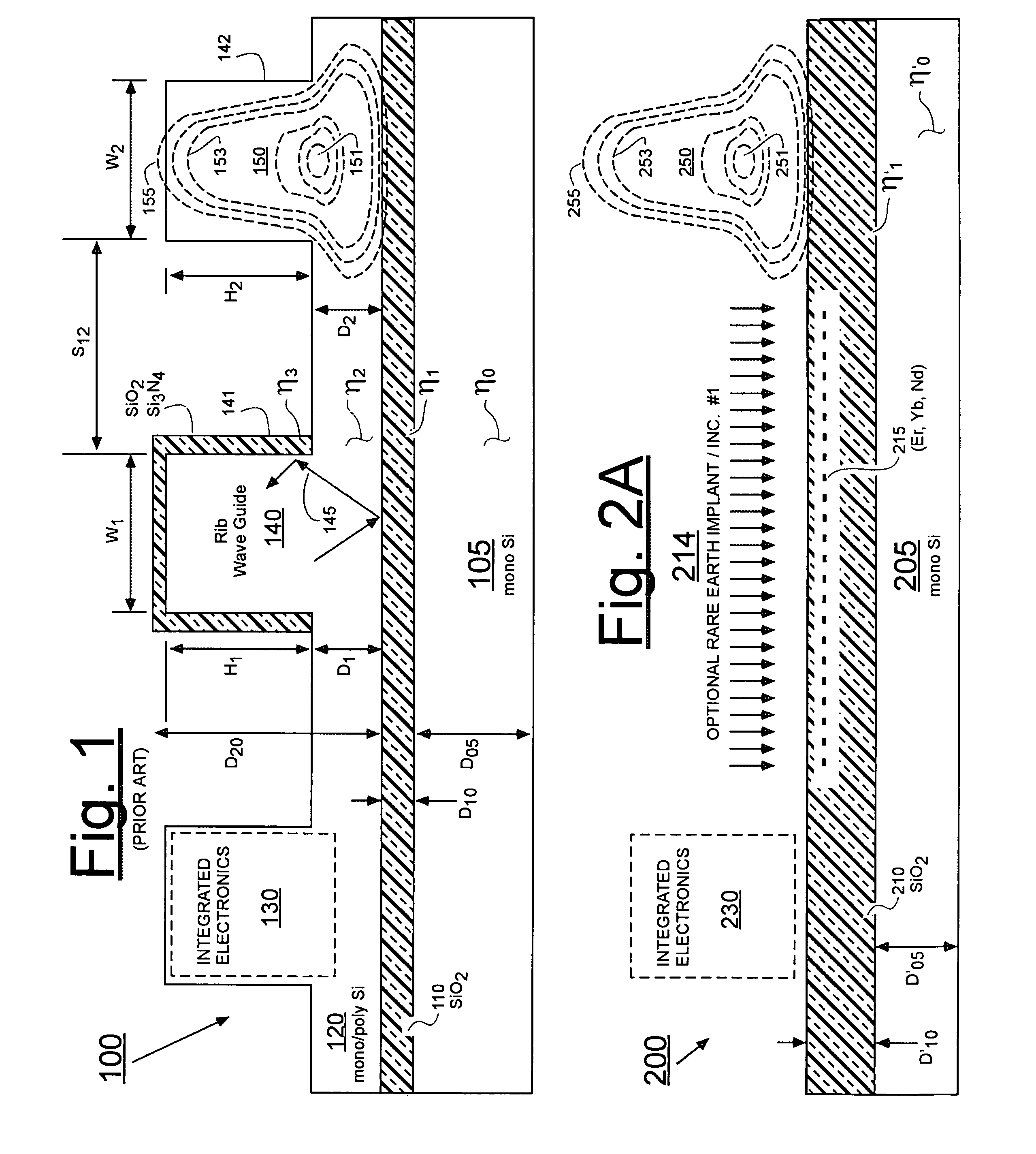

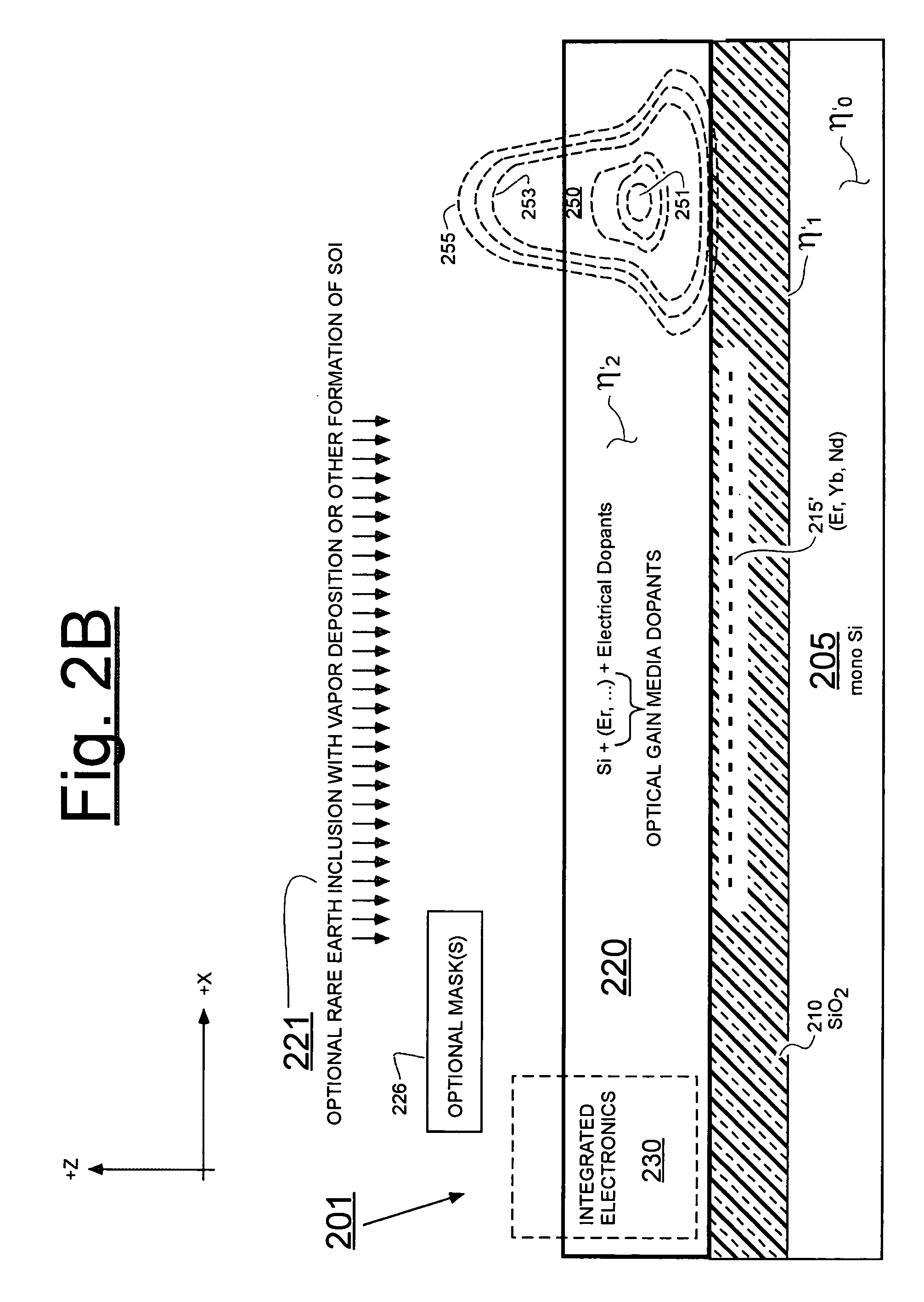

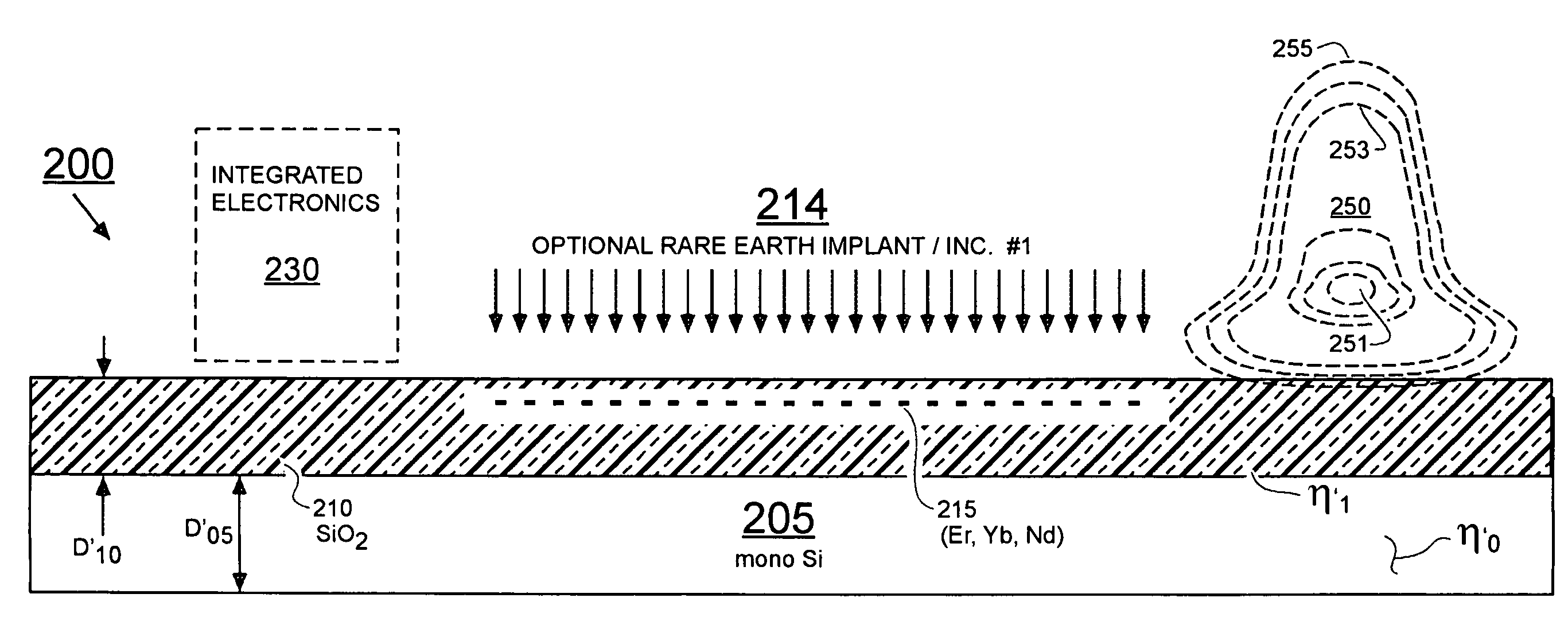

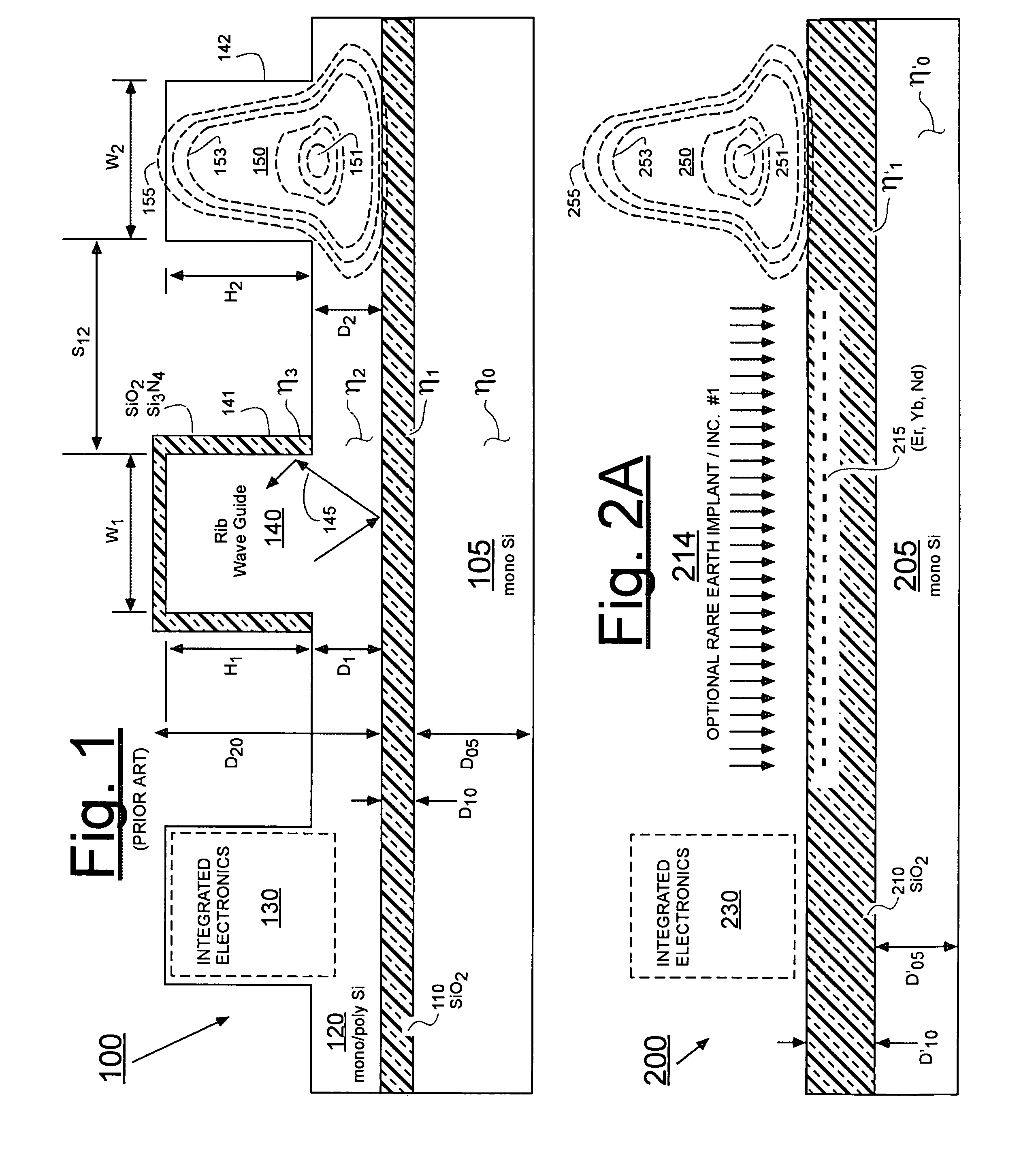

Integration of rare-earth doped amplifiers into semiconductor structures and uses of same

InactiveUS20050195472A1Eliminating passive waveguide lossSmall sizeExcitation process/apparatusActive medium materialAudio power amplifierSemiconductor structure

An integrated device is disclosed which has a substrate and a Rare-Earth Doped Semiconductor layer (REDS layer) integrated with the substrate. The REDS layer is patterned to define one or more optically amplifying structures each having a first I / O port for receiving or outputting a first optical signal, and at least one pump energy receiving port for receiving pumping energy in the form of at least one of electrical pump energy and / or optical pump energy. In one particular set of embodiments, at least one of the optical amplifying structures is a Raman type amplifier where a corresponding pump energy receiving port is structured for receiving Raman type pumping energy having an effective frequency which is about one optical phonon frequency higher than a signal frequency of an optical signal supplied at a corresponding I / O port. Methods are disclosed for fabricating Rare-Earth Doped Semiconductor layers, including providing such layers in semiconductor-on-insulator (SOI) structures and for enhancing the effective, long-term concentrations of incorporated, rare earth atoms. Additionally, non-parallel pumping techniques are disclosed.

Owner:TANG YIN S

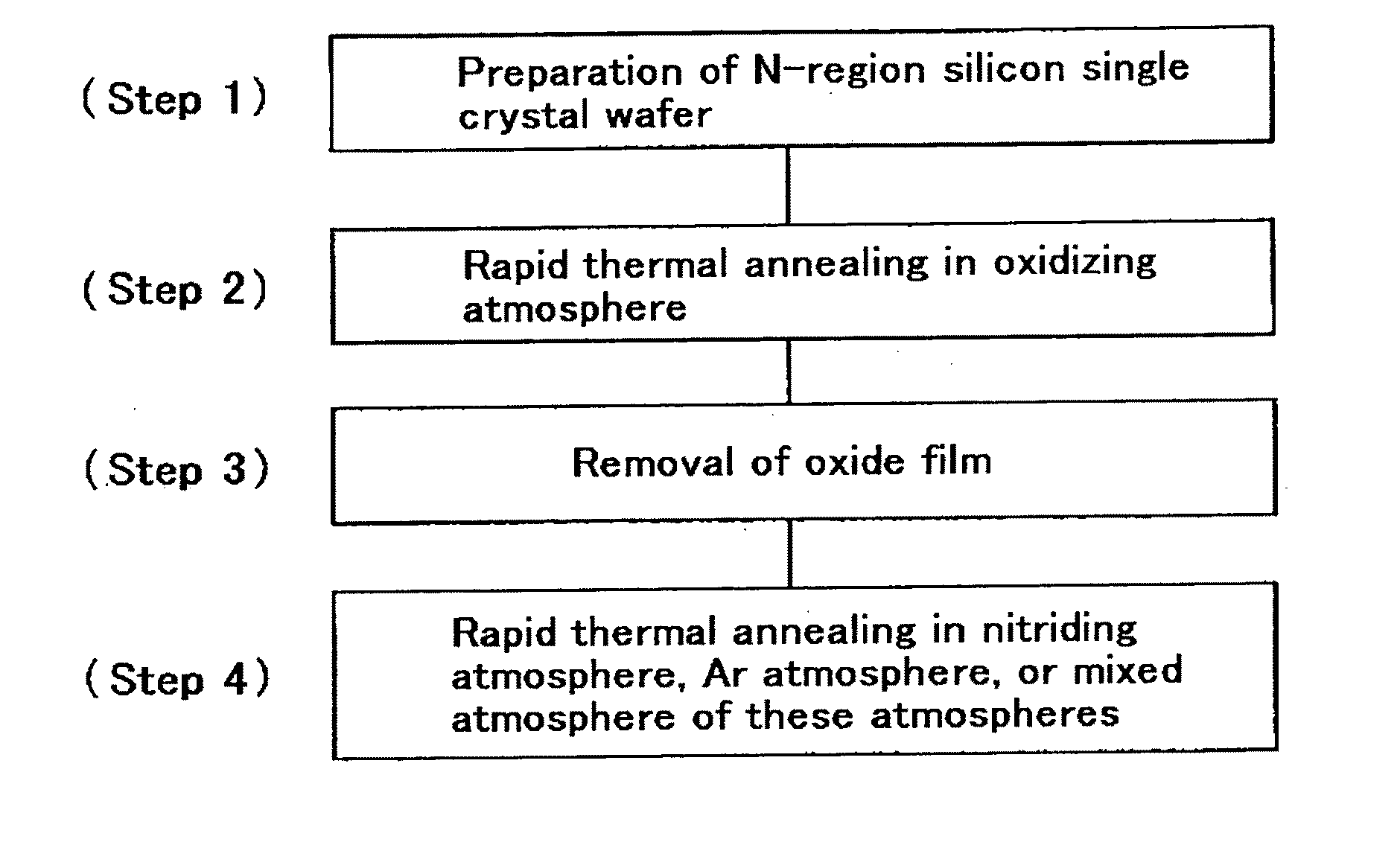

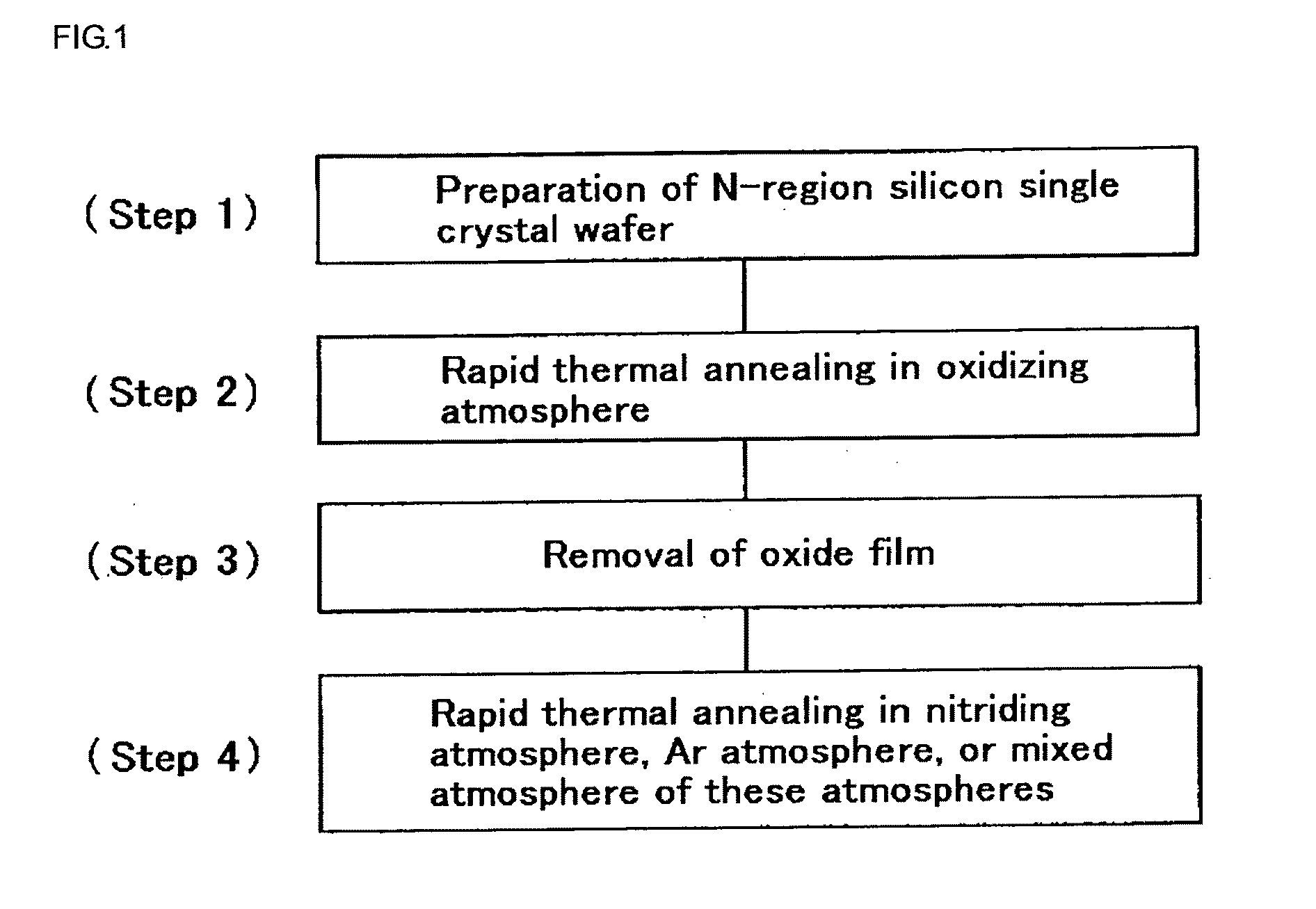

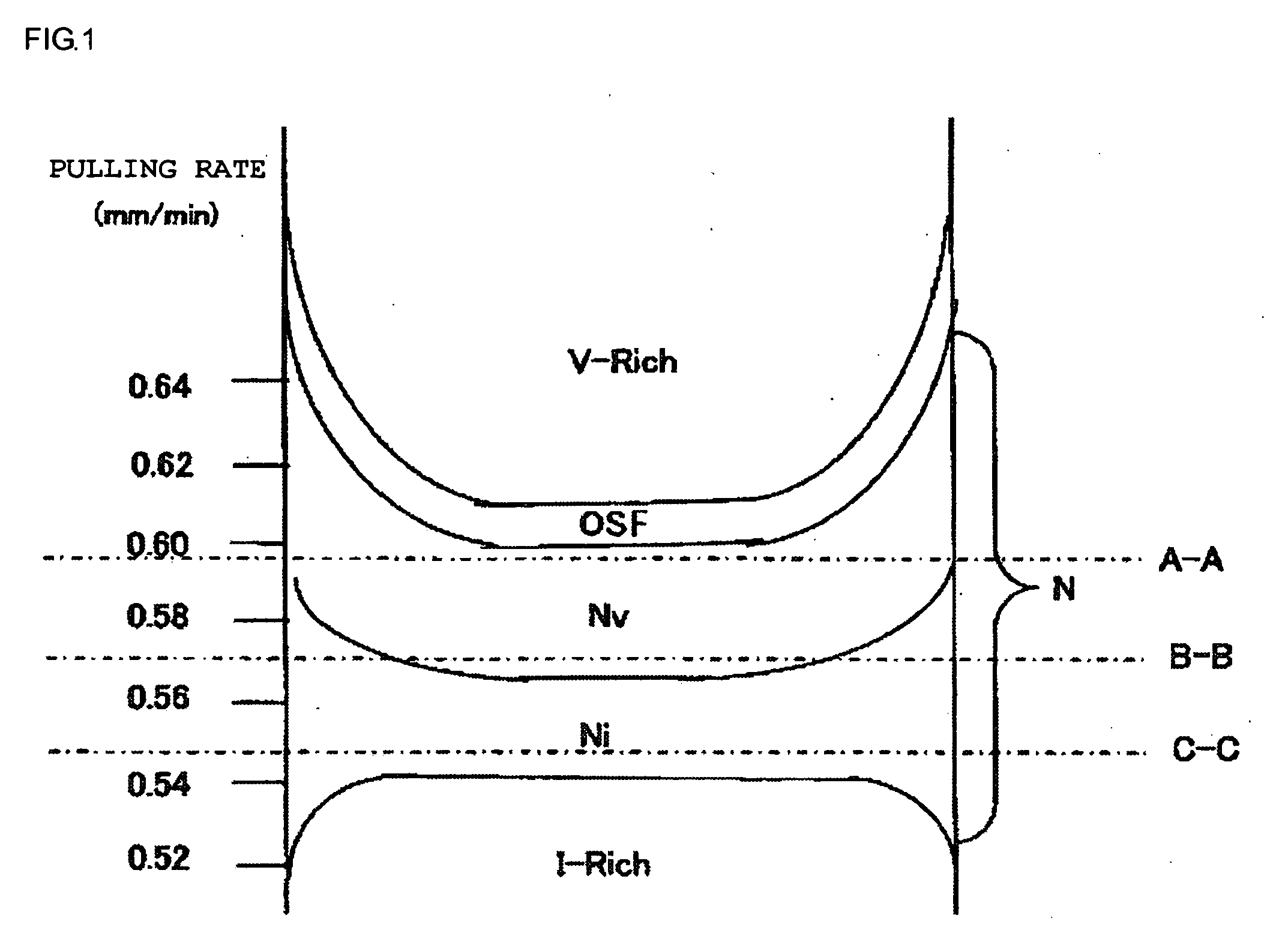

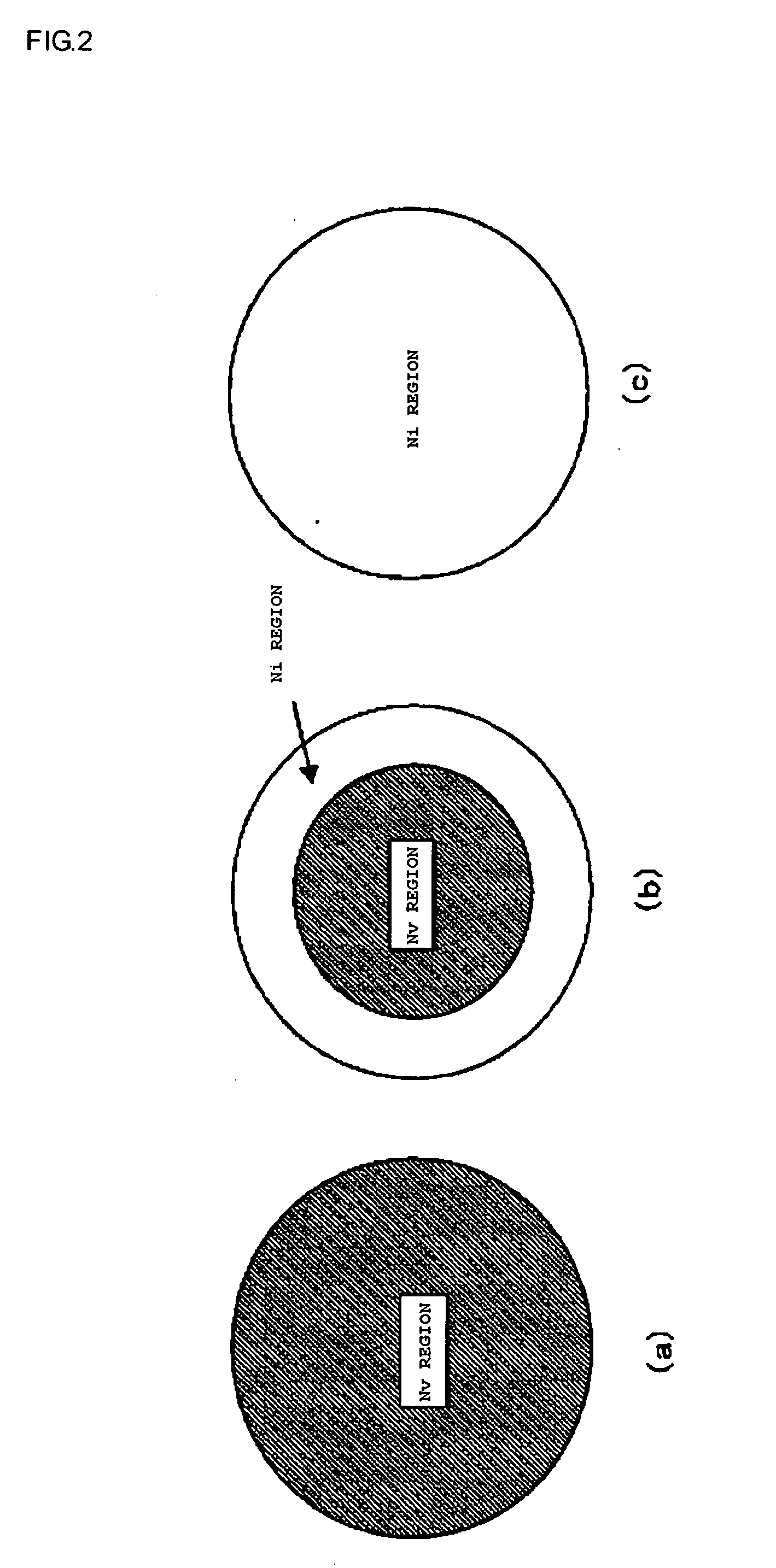

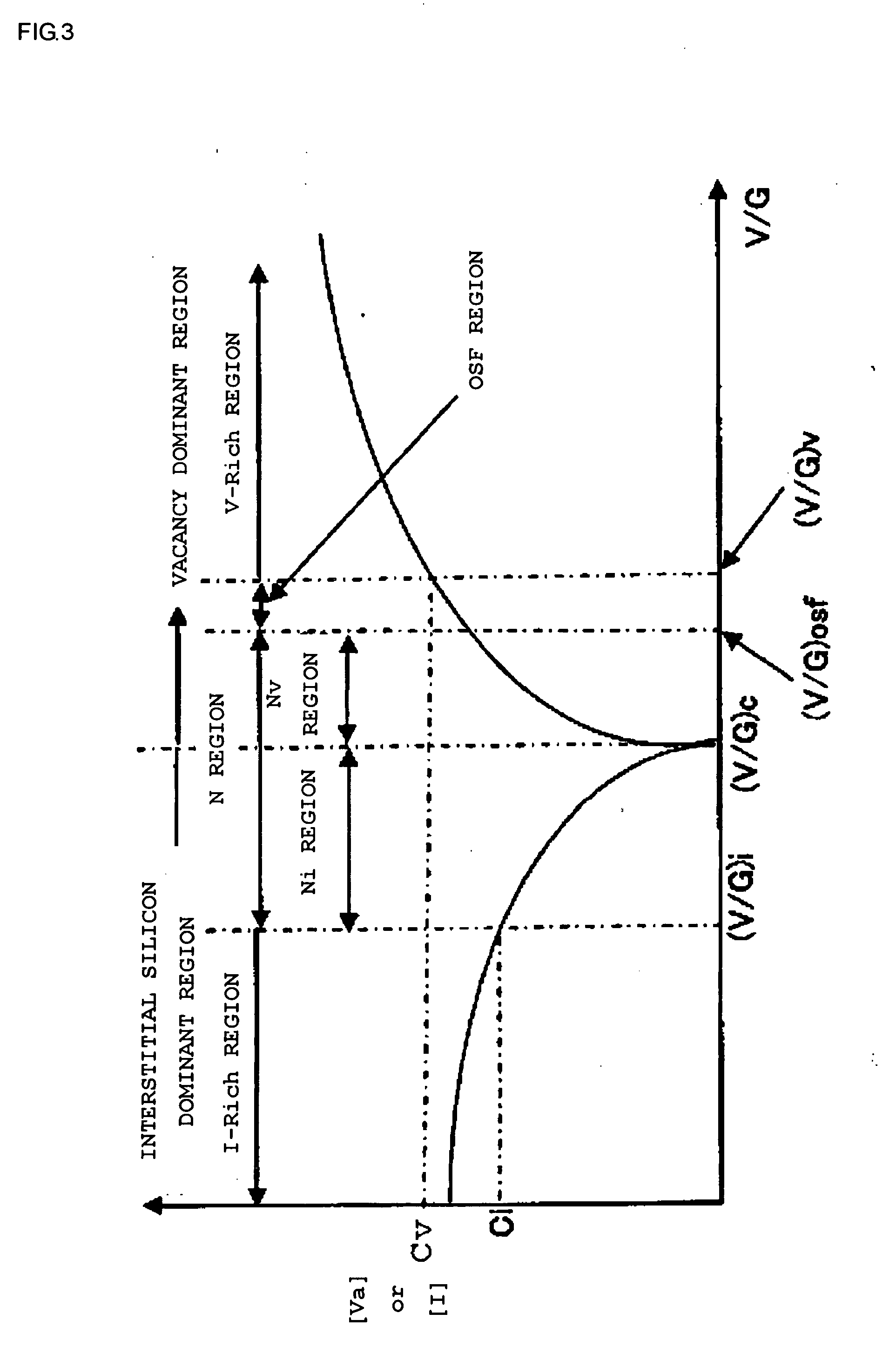

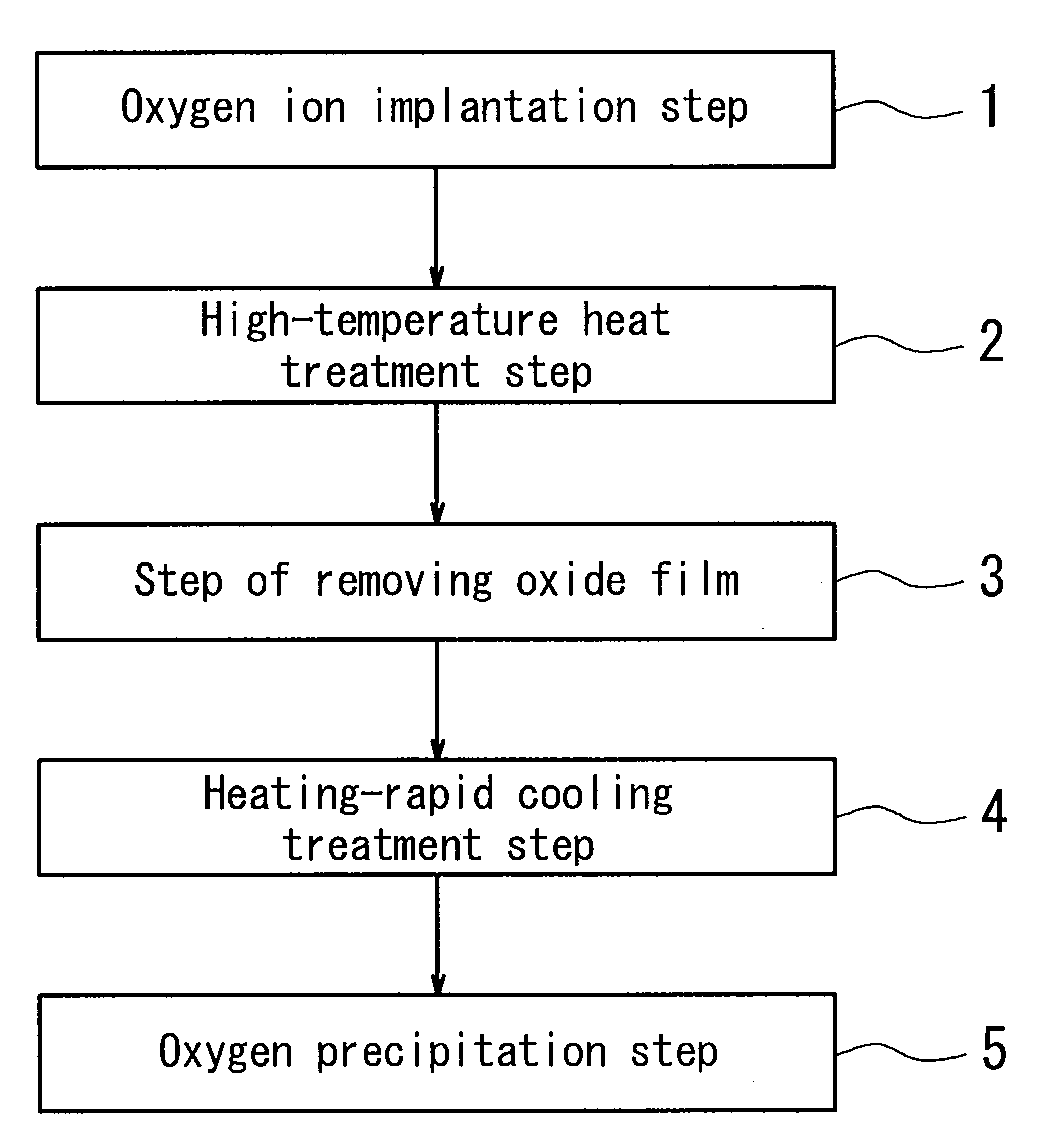

Method for manufacturing silicon single crystal wafer

ActiveUS20100105191A1High gettering capabilityLarge manufacture marginPolycrystalline material growthAfter-treatment detailsOxideSurface layer

Owner:SHIN-ETSU HANDOTAI CO LTD

Method for fabricating trench isolations with high aspect ratio

ActiveUS20050016948A1Excellent gap fillingRapid thermal annealing procedureSemiconductor/solid-state device manufacturingCable/conductor manufactureAspect ratioHigh density

A method of fabricating a trench isolation with high aspect ratio. The method comprises the steps of: providing a substrate with a trench; depositing a first isolation layer filling the trench by low pressure chemical vapor deposition; etching the first isolation layer so that its surface is lowered to the opening of the trench; depositing a second isolation layer to fill the trench without voids by high density plasma chemical vapor deposition and achieving global planarization by chemical-mechanical polishing then providing a rapidly annealing procedure. Accordingly, the present invention achieves void-free trench isolation with high aspect ratio.

Owner:NAN YA TECH

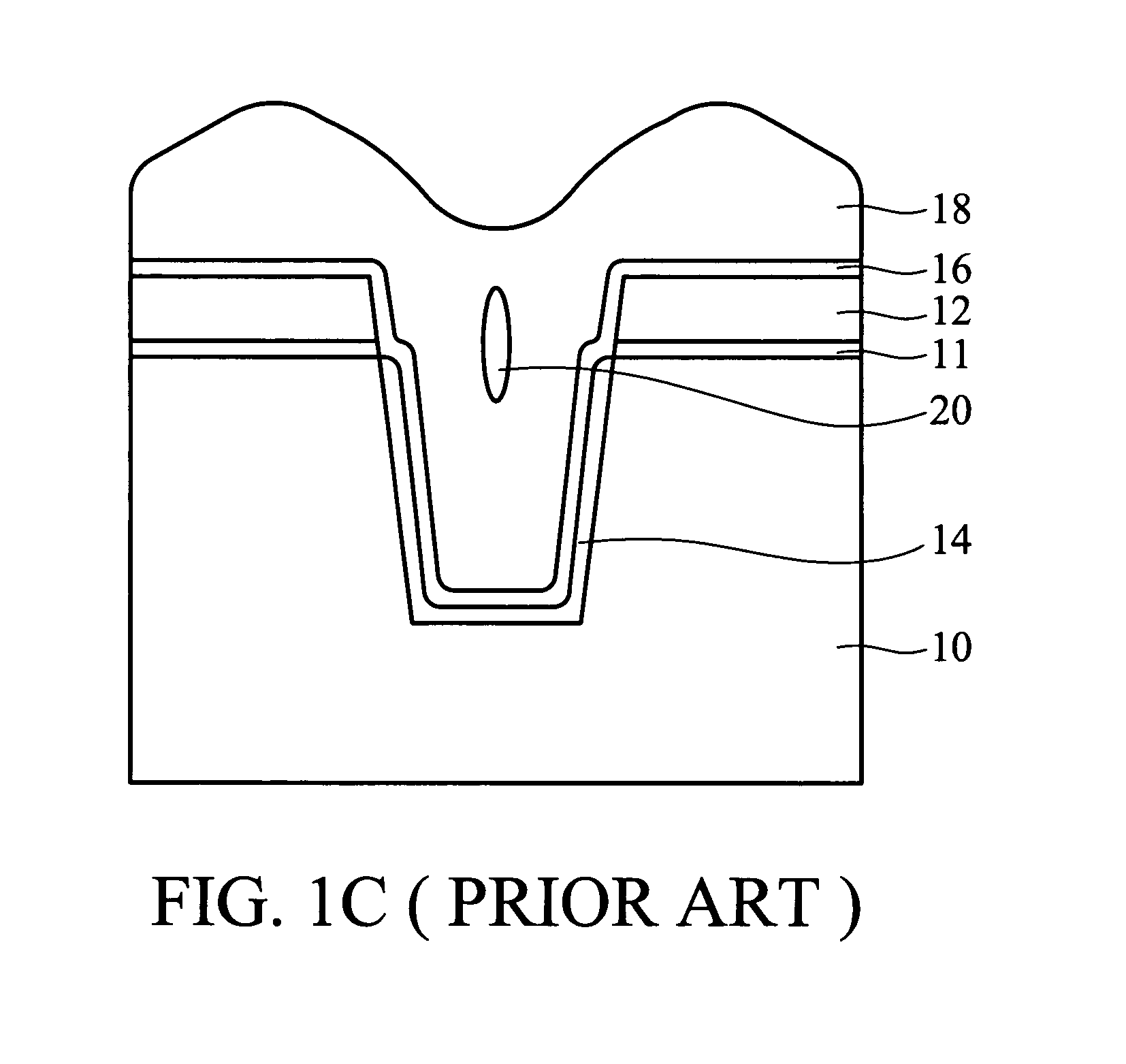

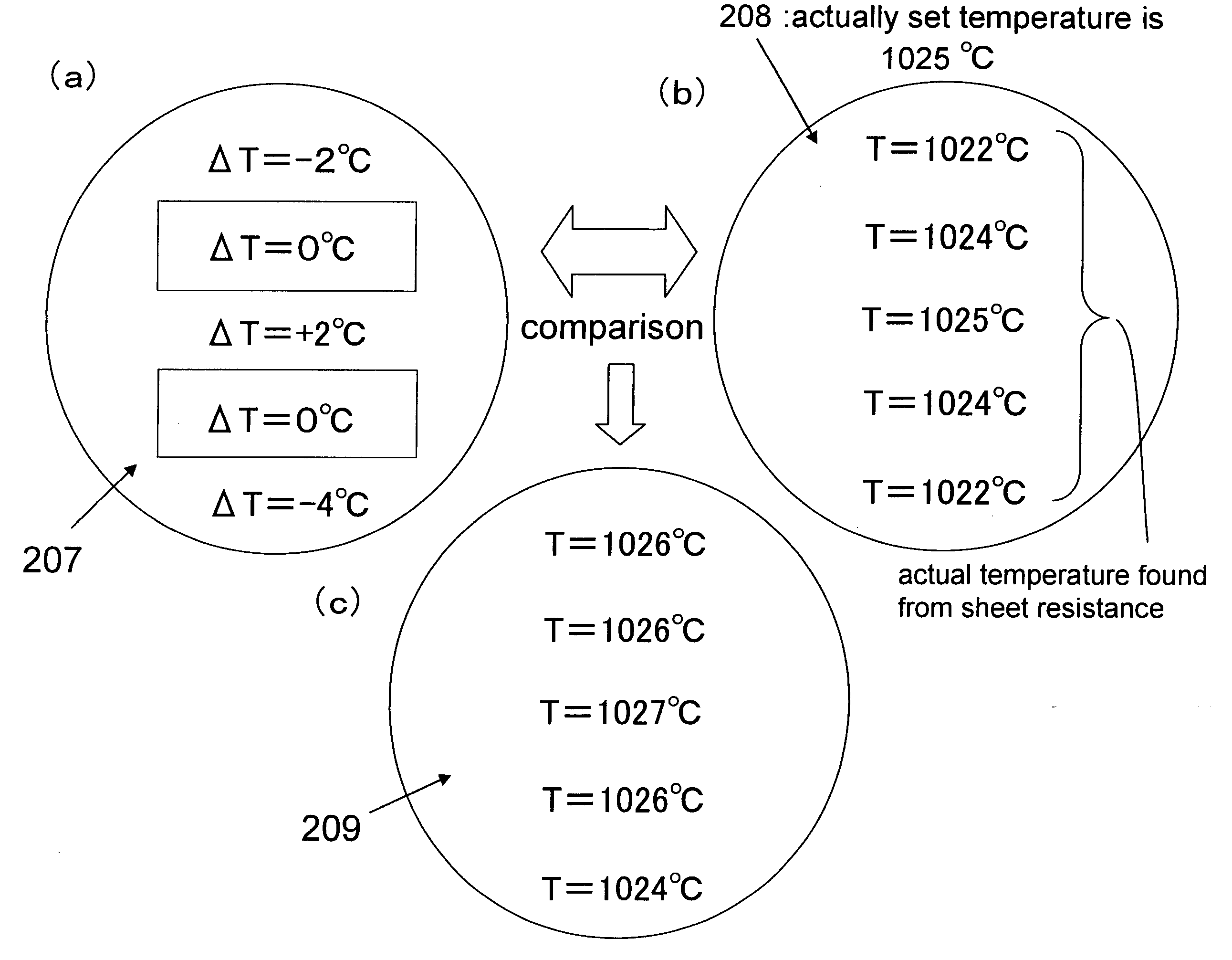

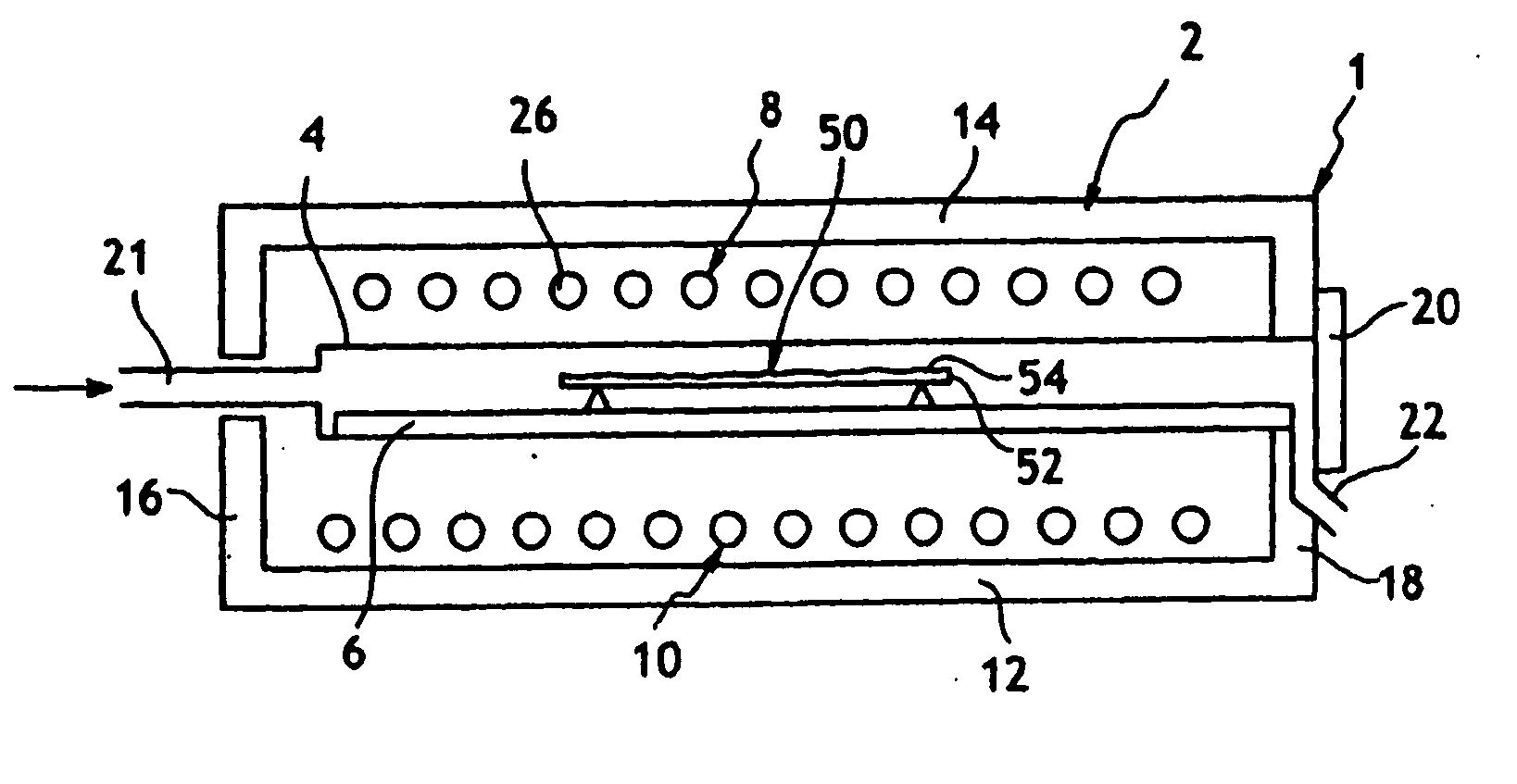

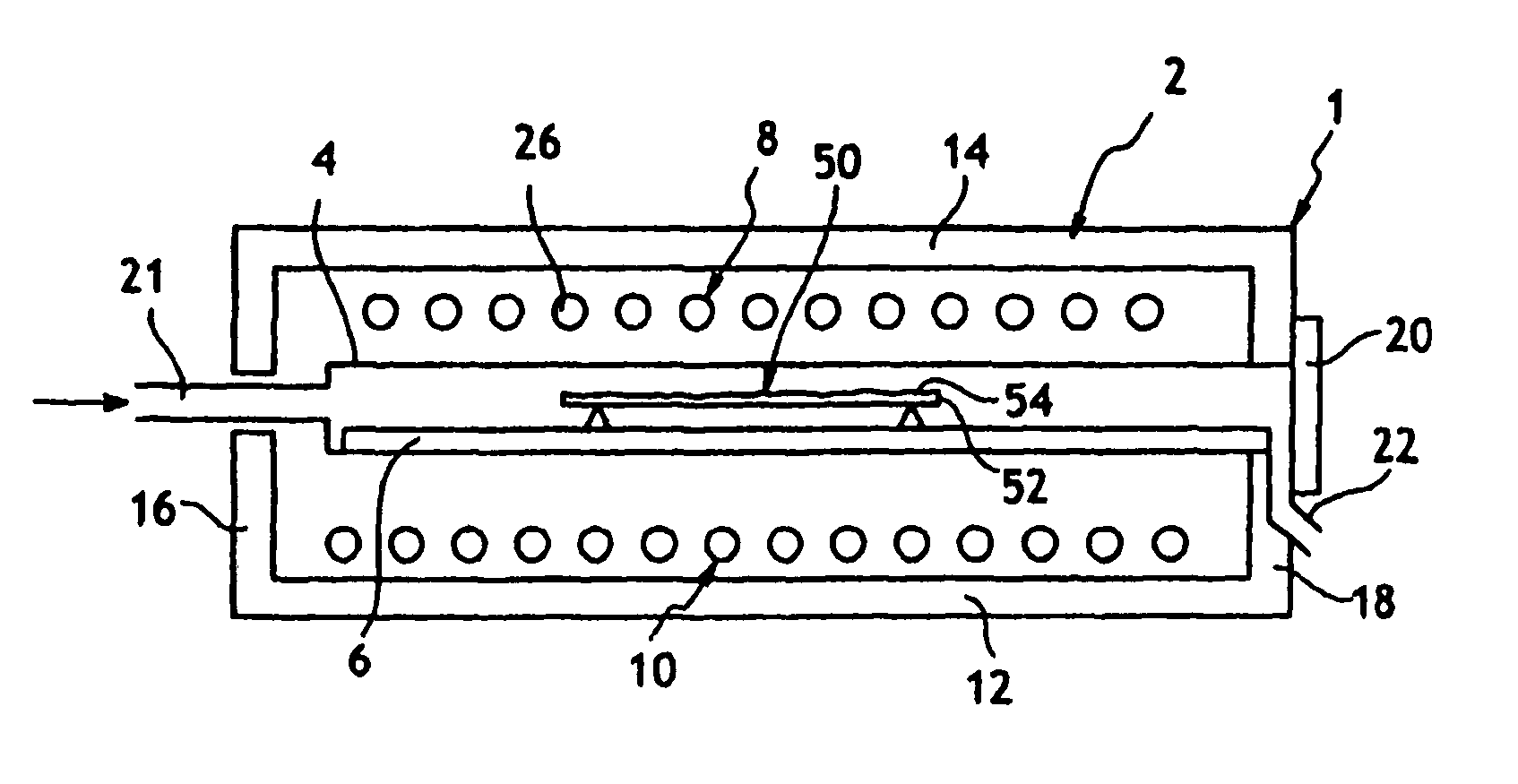

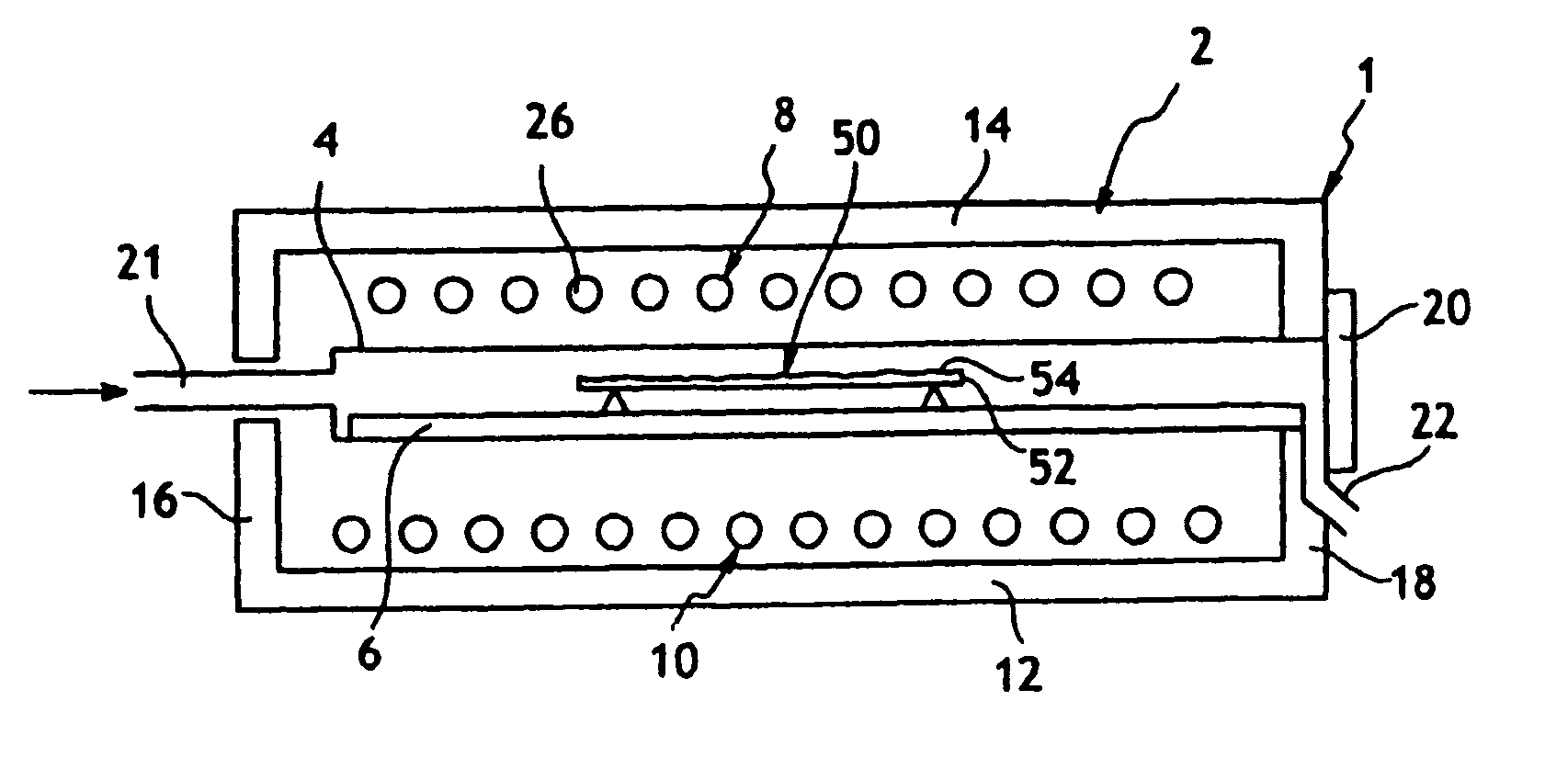

Manufacturing method for semiconductor device and rapid thermal annealing apparatus

InactiveUS20060183290A1Rapid thermal annealingUniform qualitySemiconductor/solid-state device testing/measurementSolid-state devicesElectricityDevice material

During a manufacturing process for a semiconductor device, the size of gate electrodes is measured within the wafer surface. The gained measurement data is compared with the data which depends on the gate length-electrical properties of the semiconductor elements, and thus, distribution in the electrical properties within the wafer surface is expected. Next, the difference between the expected data on the electrical properties and the designed value is calculated, and this difference is compared with the data which depends on the temperature-electrical properties, so that the electrical property values a reconverted to temperature values. Next, the temperature distribution within the surface which makes inconsistency in said electrical properties within the surface minimal is determined from the gained data on the temperature distribution within the surface and the data on the temperature distribution within the surface which is gained from the equipment management data of the thermal annealing apparatus.

Owner:PANASONIC CORP

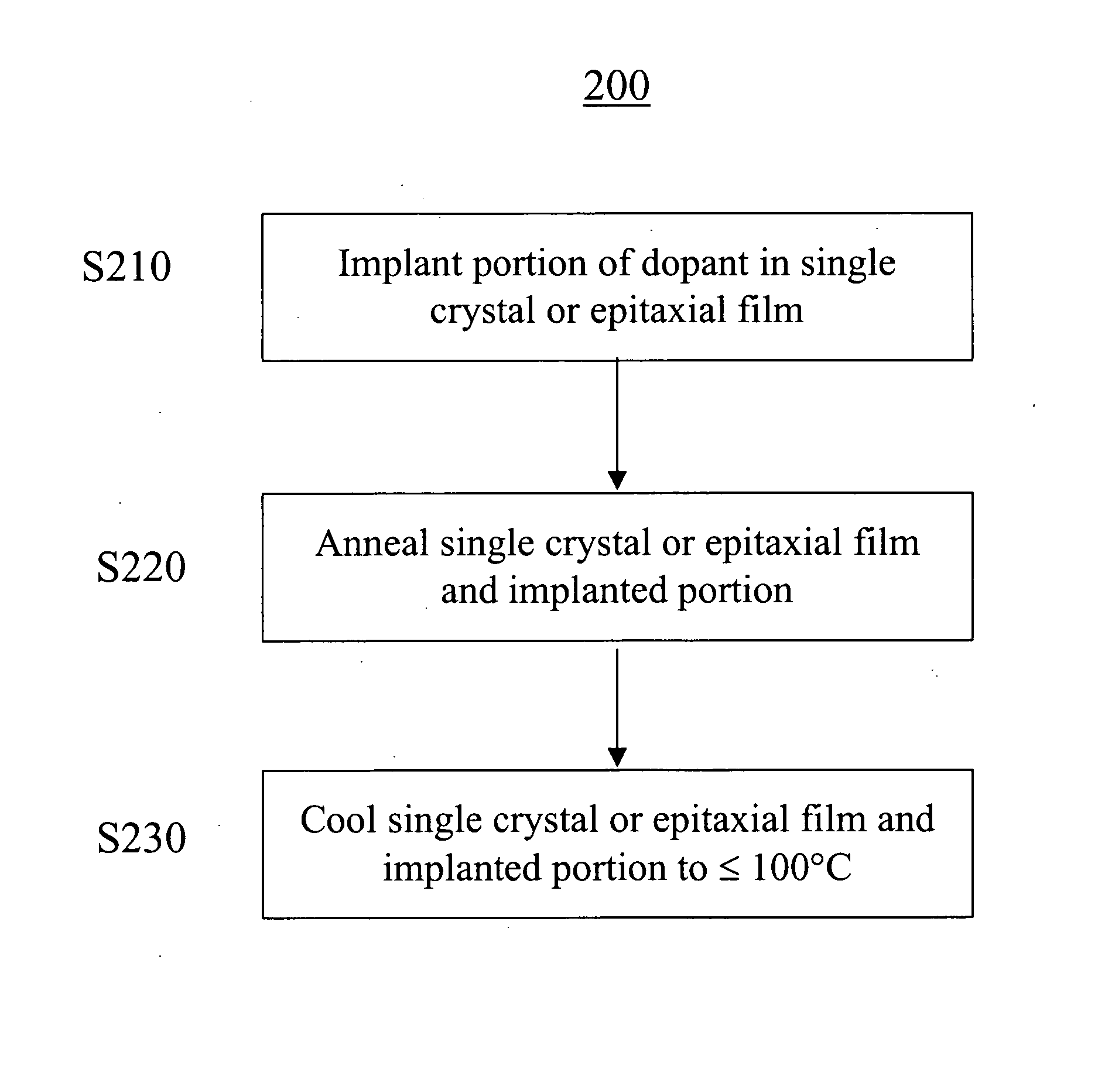

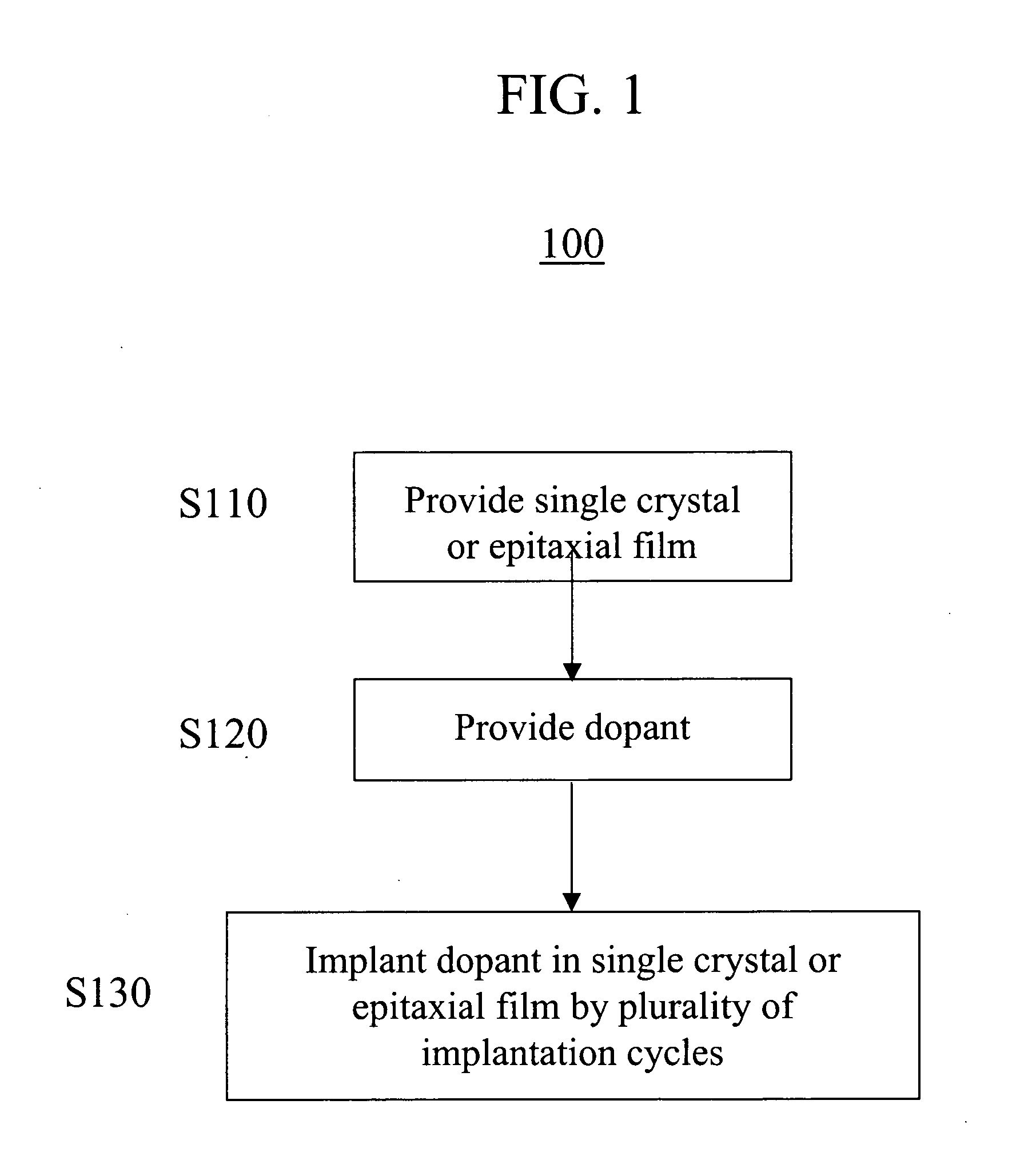

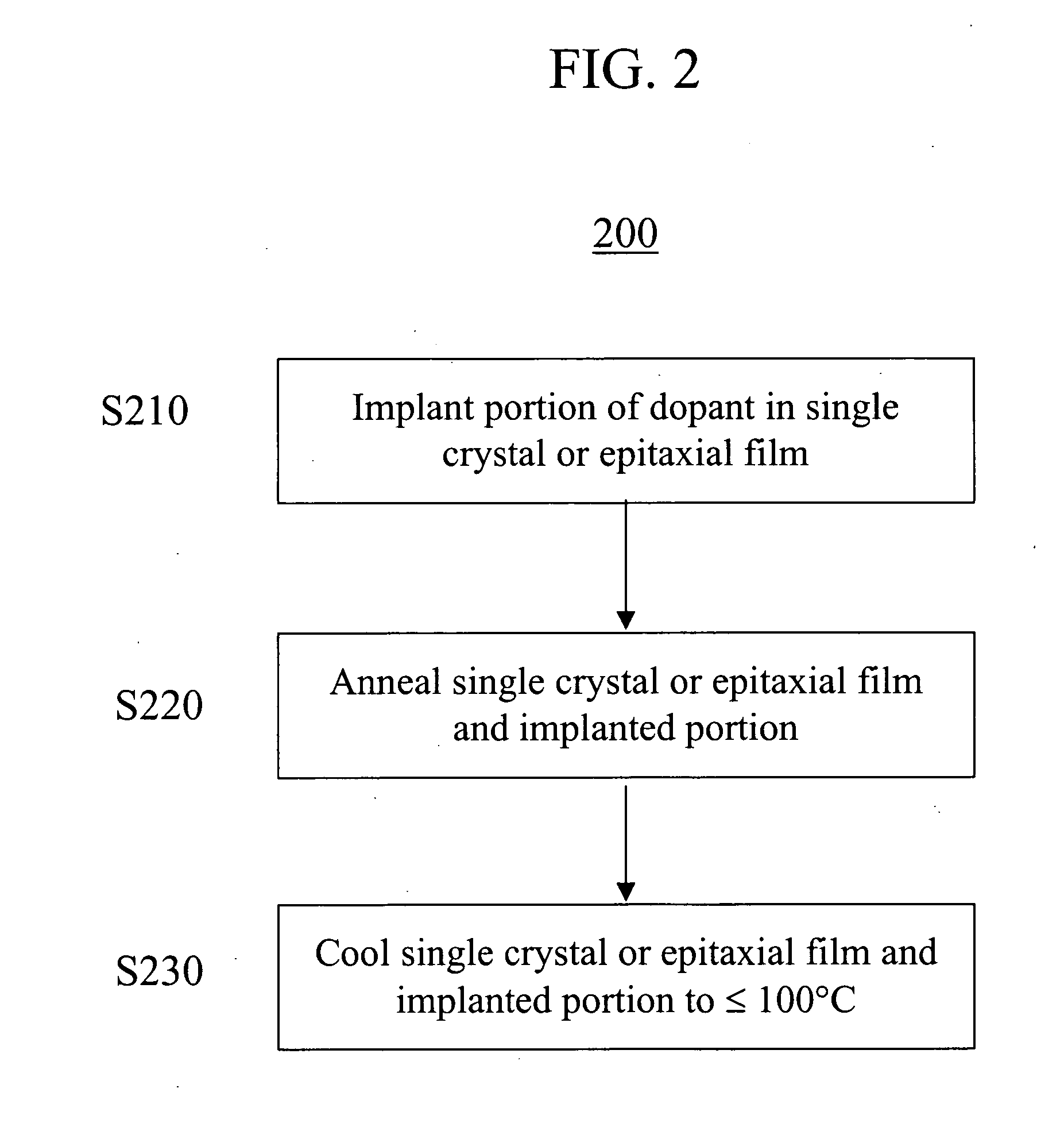

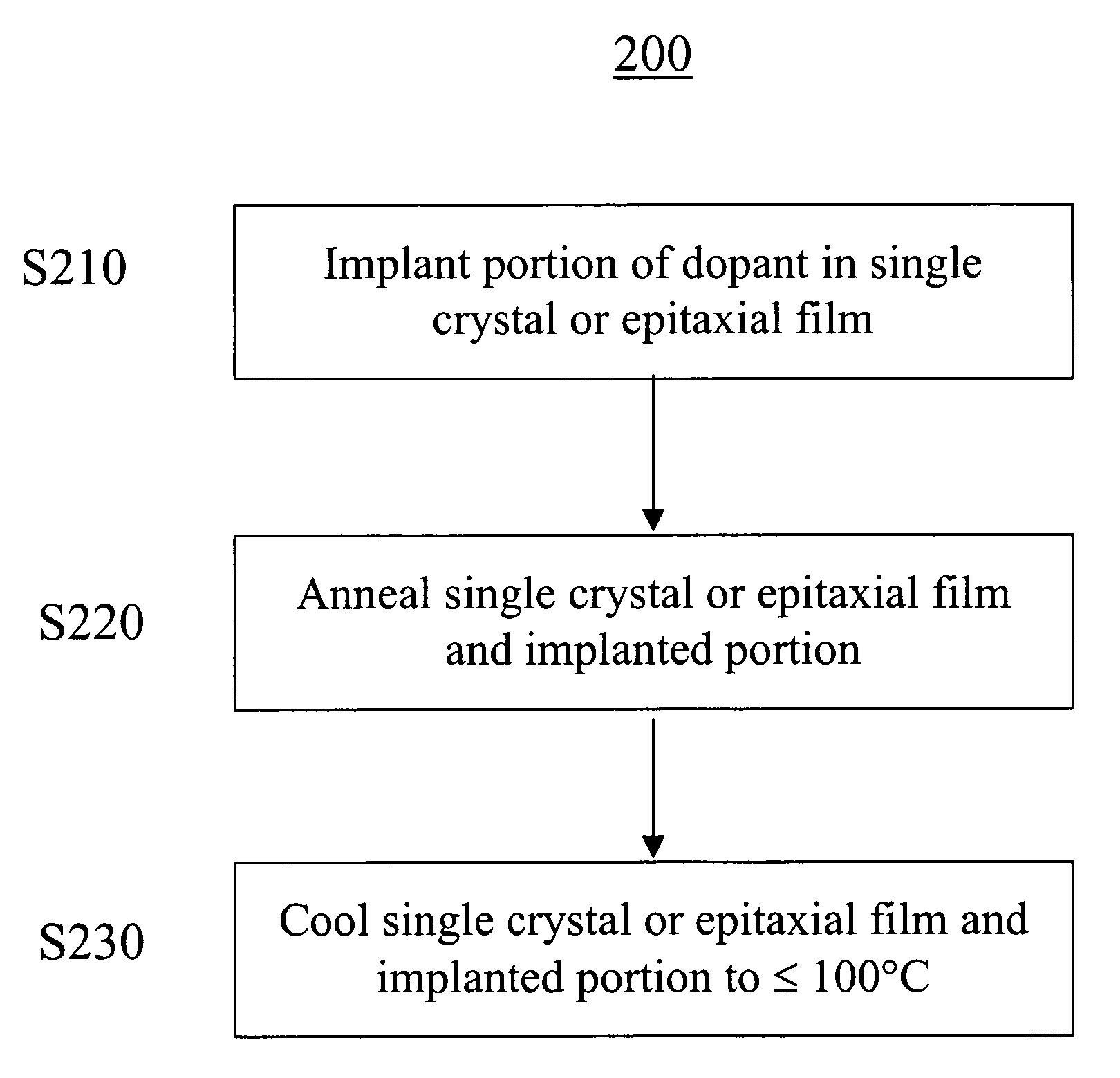

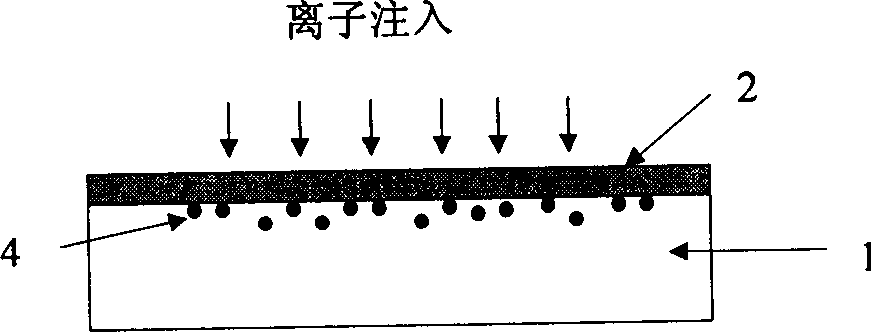

Method for implantation of high dopant concentrations in wide band gap materials

InactiveUS20060286784A1Increase concentrationMinimizing defect concentrationSemiconductor/solid-state device manufacturingHigh concentrationDopant

A method that combines alternate low / medium ion dose implantation with rapid thermal annealing at relatively low temperatures. At least one dopant is implanted in one of a single crystal and an epitaxial film of the wide band gap compound by a plurality of implantation cycles. The number of implantation cycles is sufficient to implant a predetermined concentration of the dopant in one of the single crystal and the epitaxial film. Each of the implantation cycles includes the steps of: implanting a portion of the predetermined concentration of the one dopant in one of the single crystal and the epitaxial film; annealing one of the single crystal and the epitaxial film and implanted portion at a predetermined temperature for a predetermined time to repair damage to one of the single crystal and the epitaxial film caused by implantation and activates the implanted dopant; and cooling the annealed single crystal and implanted portion to a temperature of less than about 100° C. This combination produces high concentrations of dopants, while minimizing the defect concentration.

Owner:LOS ALAMOS NATIONAL SECURITY

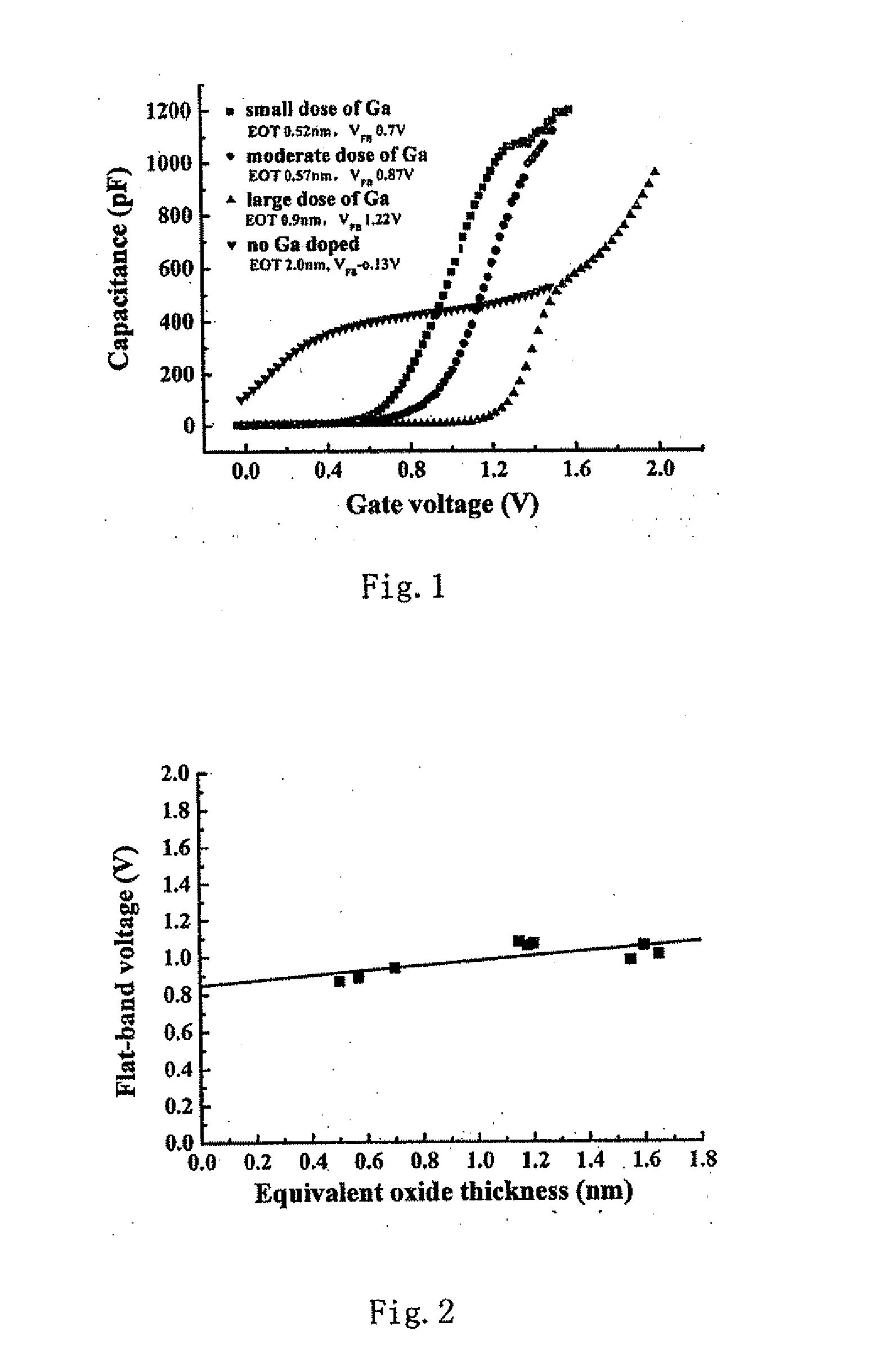

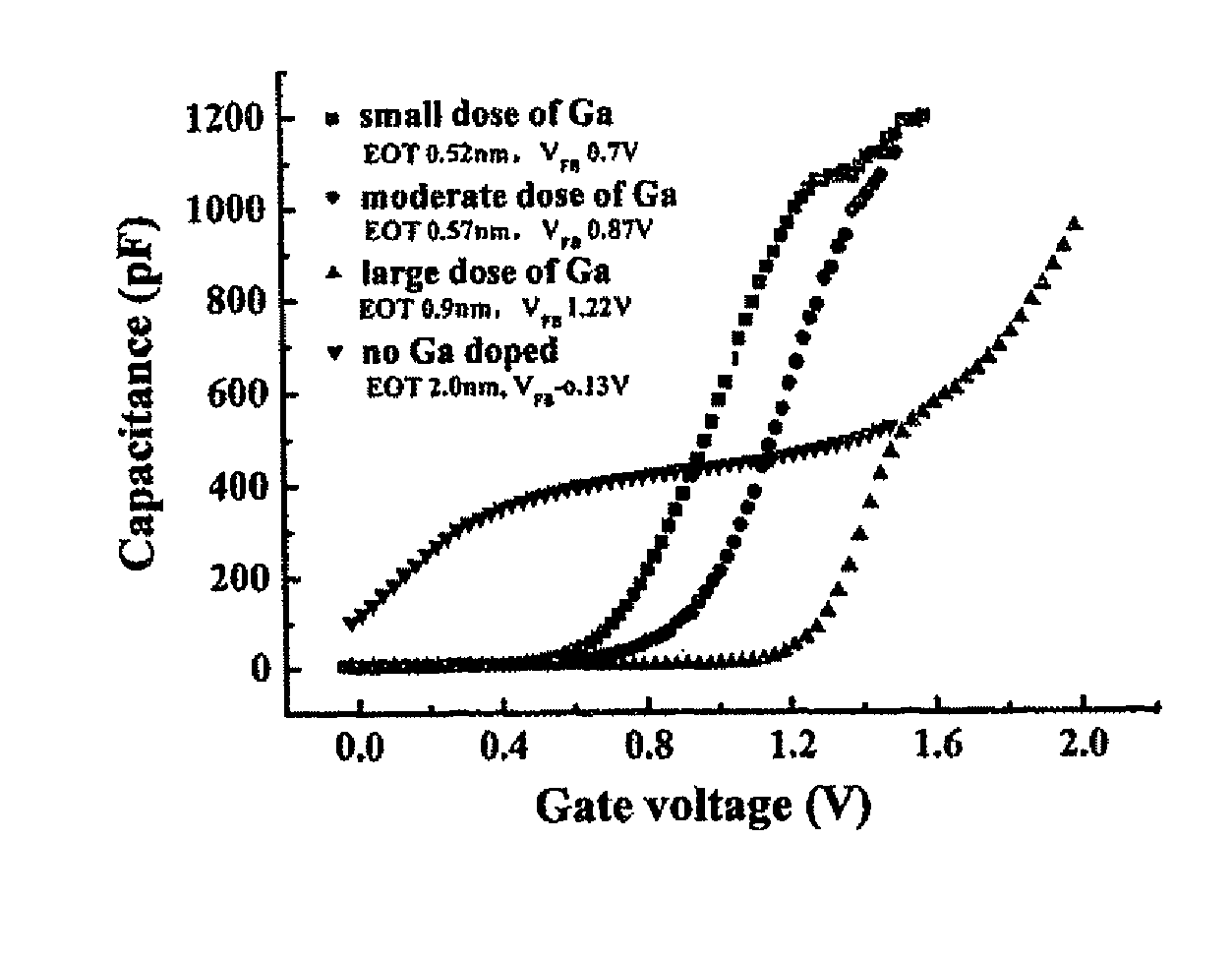

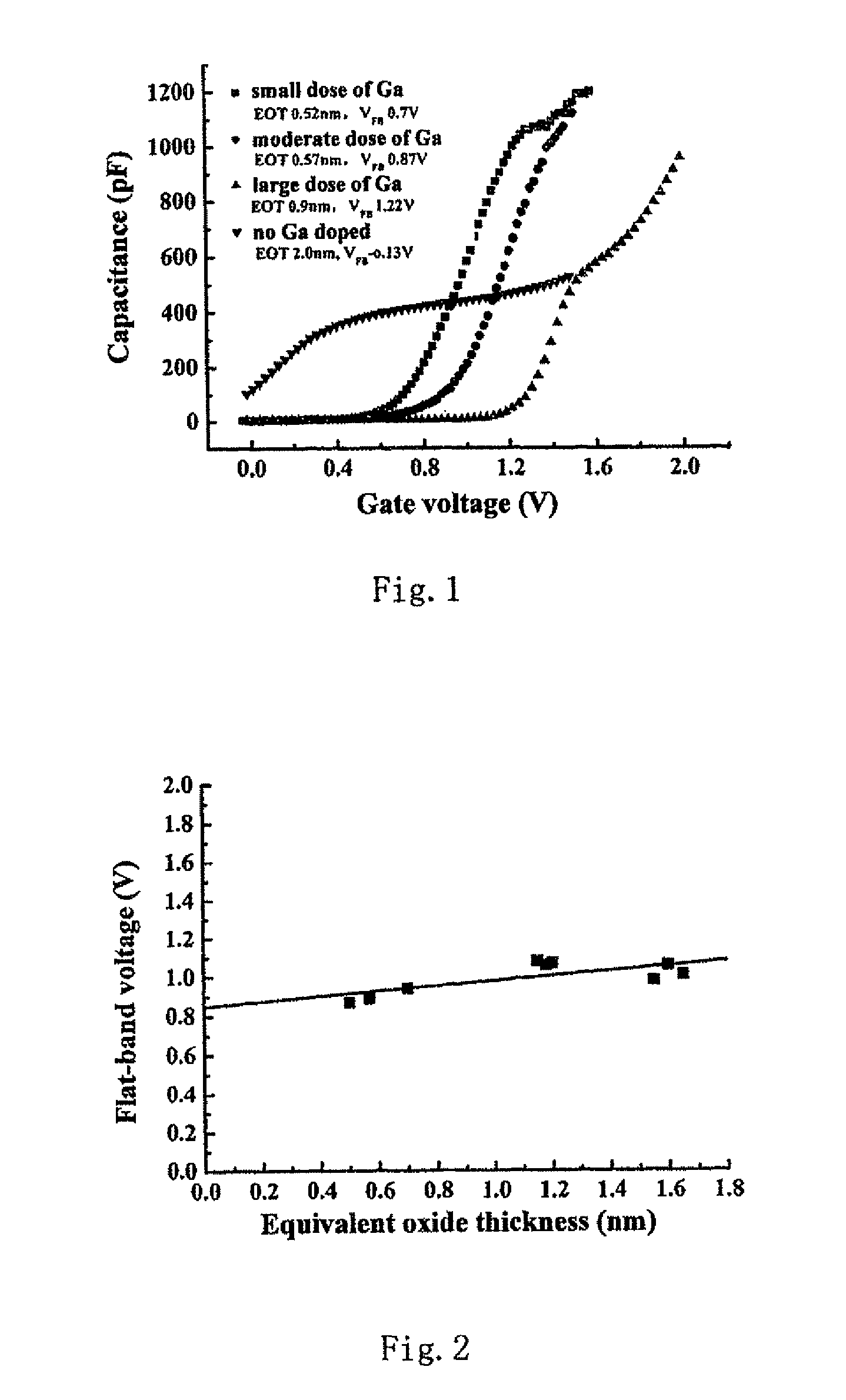

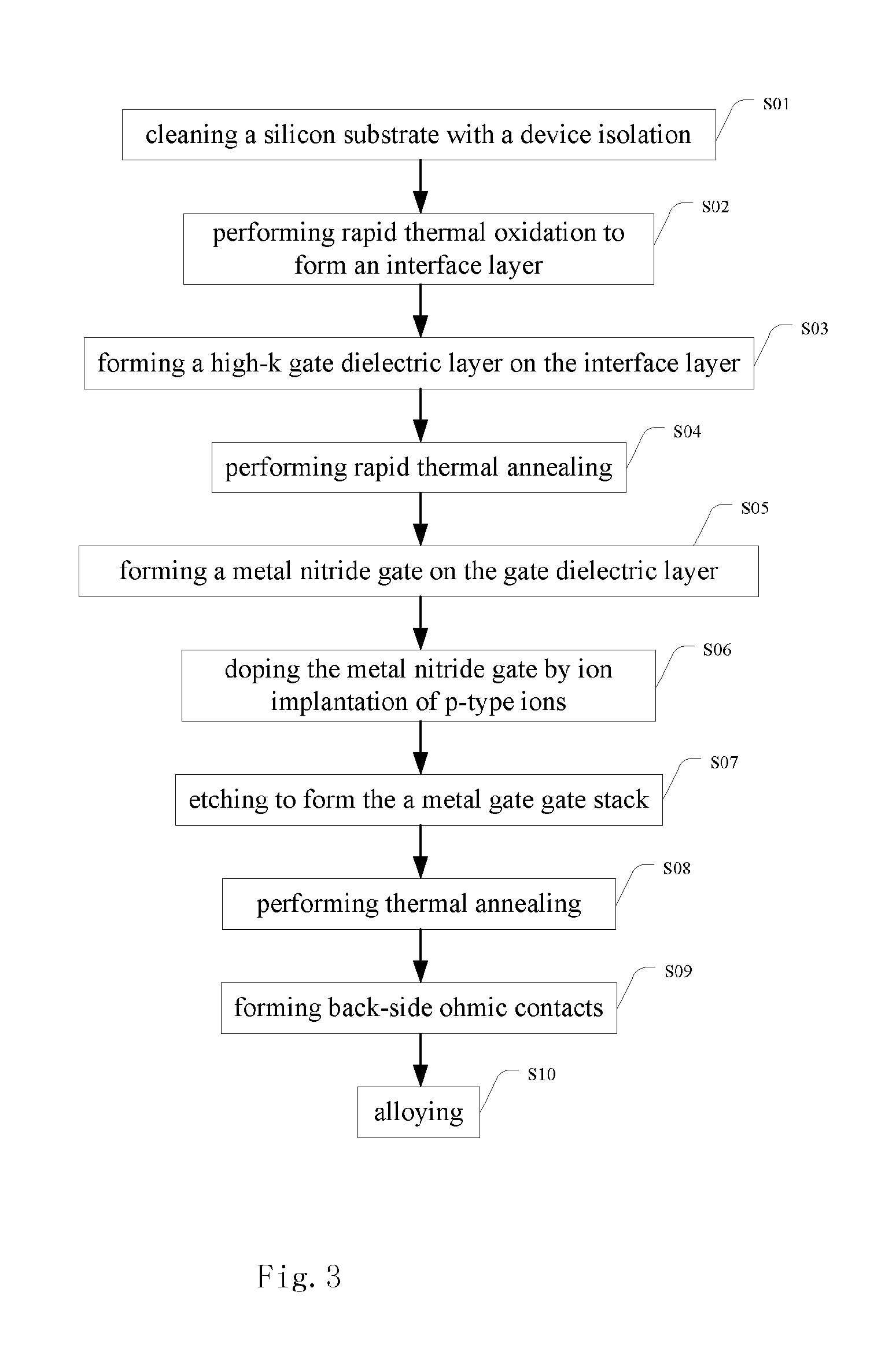

Method for tuning the work function of a metal gate of the pmos device

ActiveUS20110256701A1The process is simple and convenientImprove thermal stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesInterfacial reactionGate dielectric

The present application discloses a method for tuning the work function of a metal gate of the PMOS device, comprising the steps of depositing a layer of metal nitride or a metal on a layer of high-k gate dielectric by physical vapor deposition (PVD), as a metal gate; doping the metal gate with dopants such as Al, Pt, Ru, Ga, Ir by ion implantation; and driving the doped metal ions to the interface between the high-k gate dielectric and interfacial SiO2 by high-temperature annealing so that the doped metal ions accumulate at the interface or generate dipoles by interfacial reaction, which in turn tunes the work function of the metal gate. The inventive method can be widely used and its process is simple and convenient, has a better ability of tuning the work function of the metal gate, and is compatible with the conventional CMOS process.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

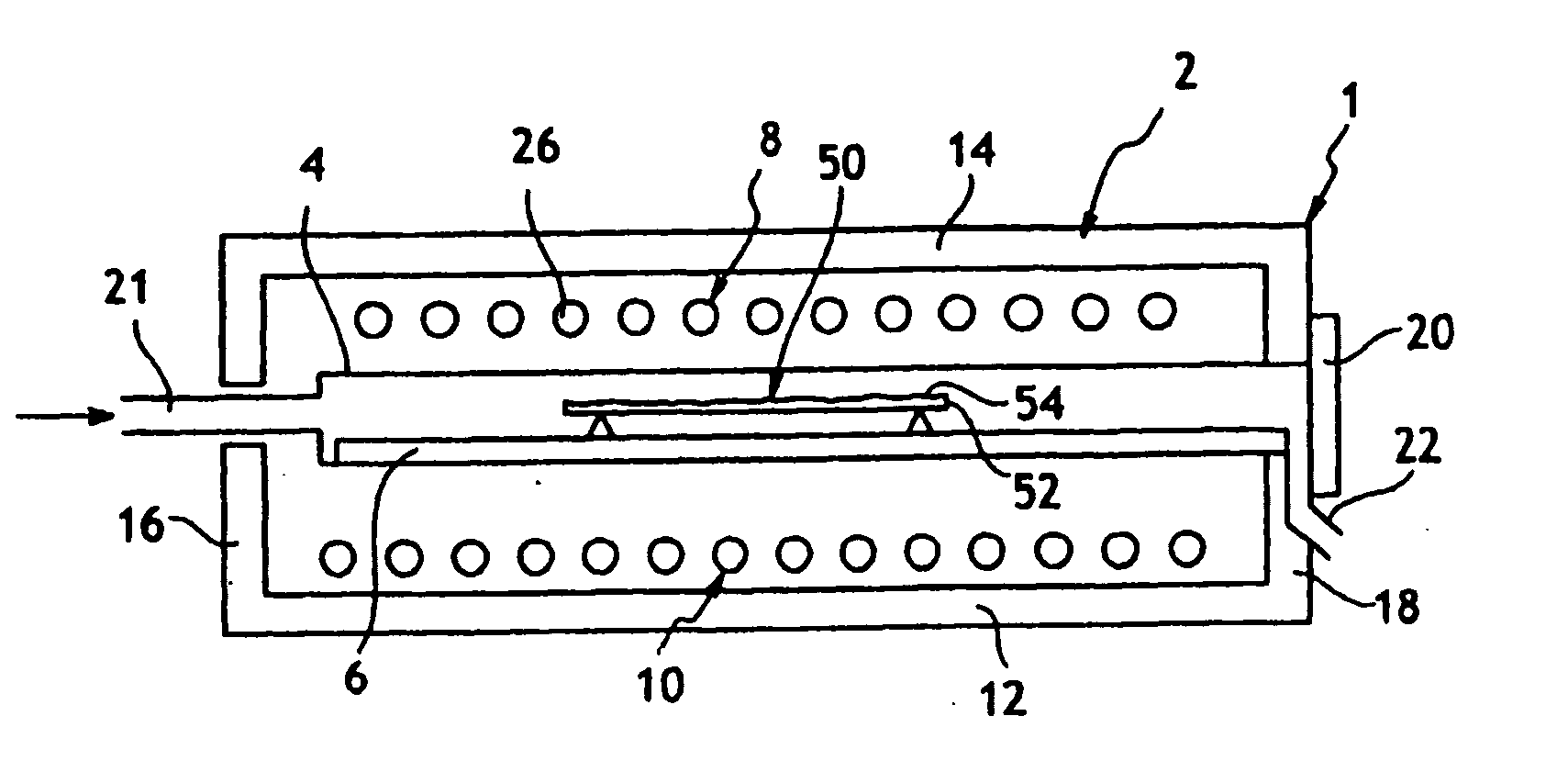

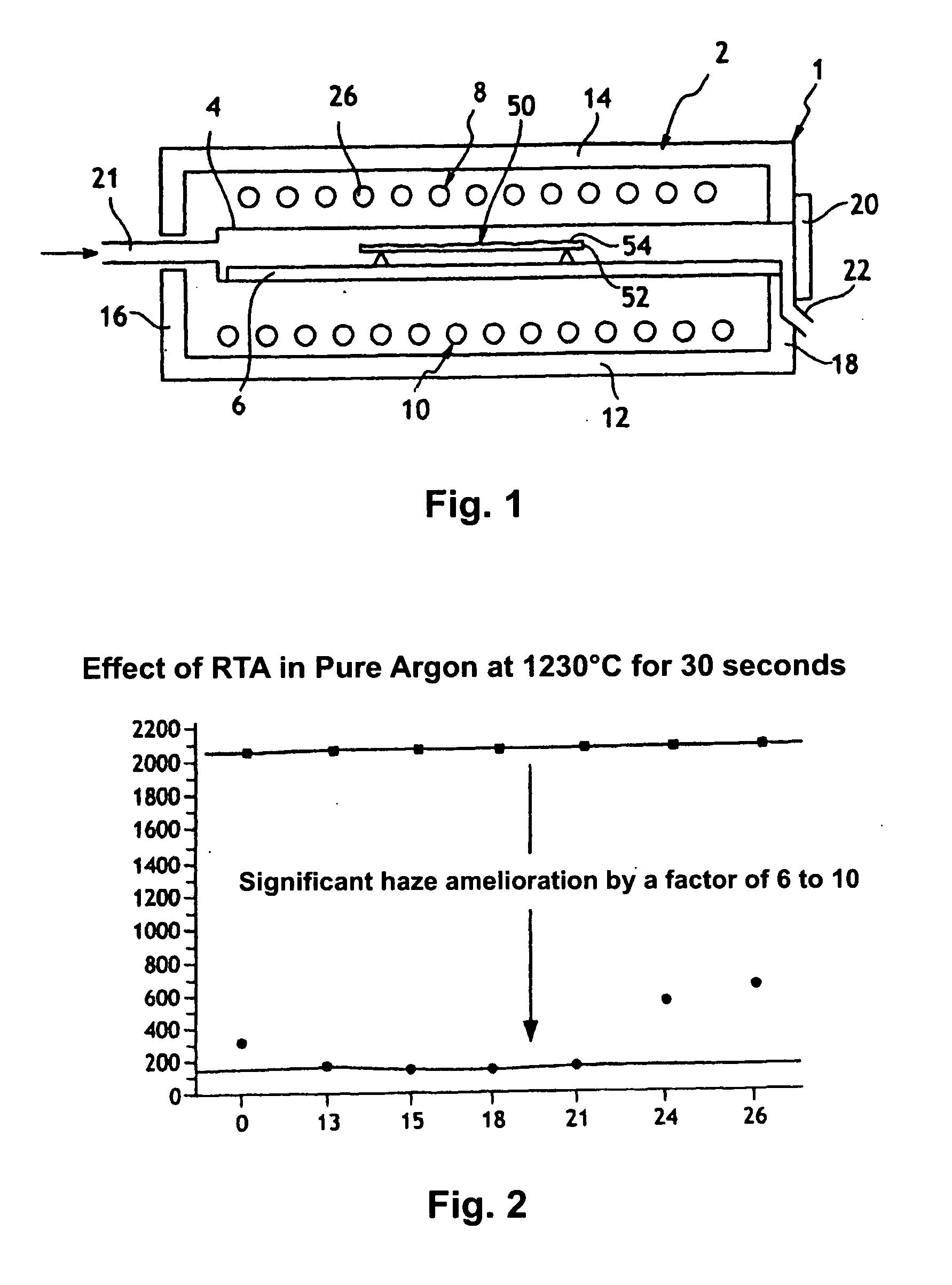

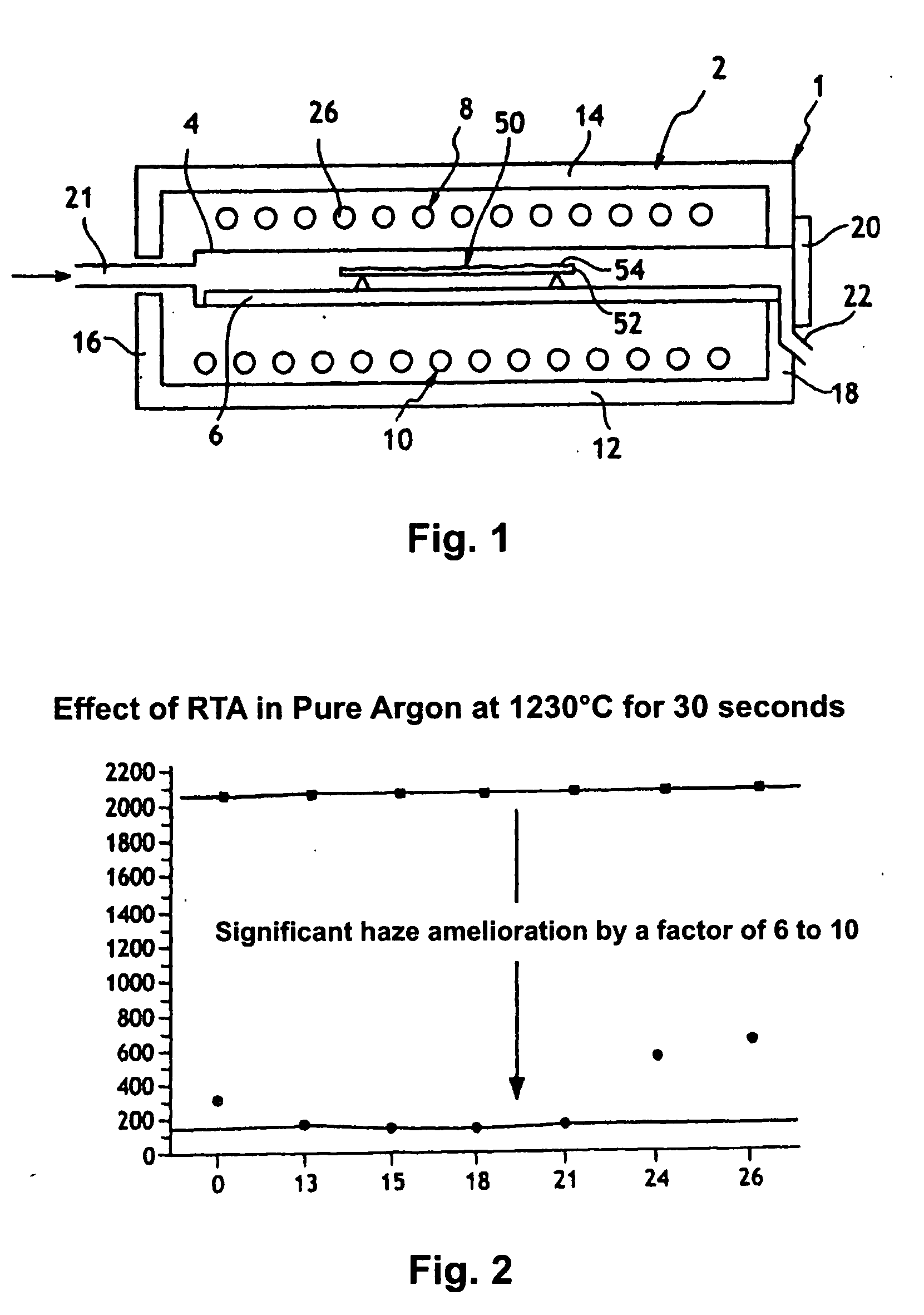

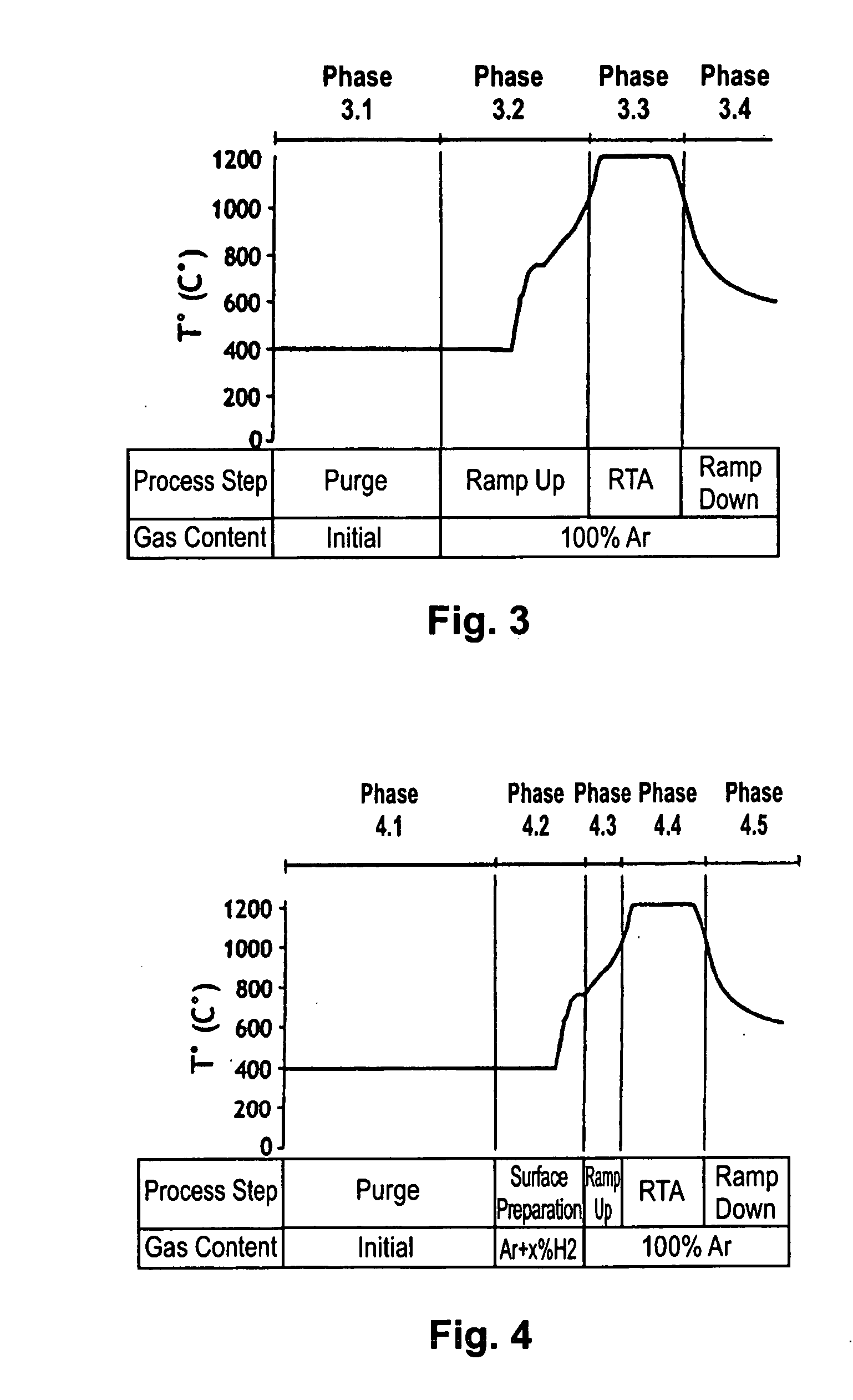

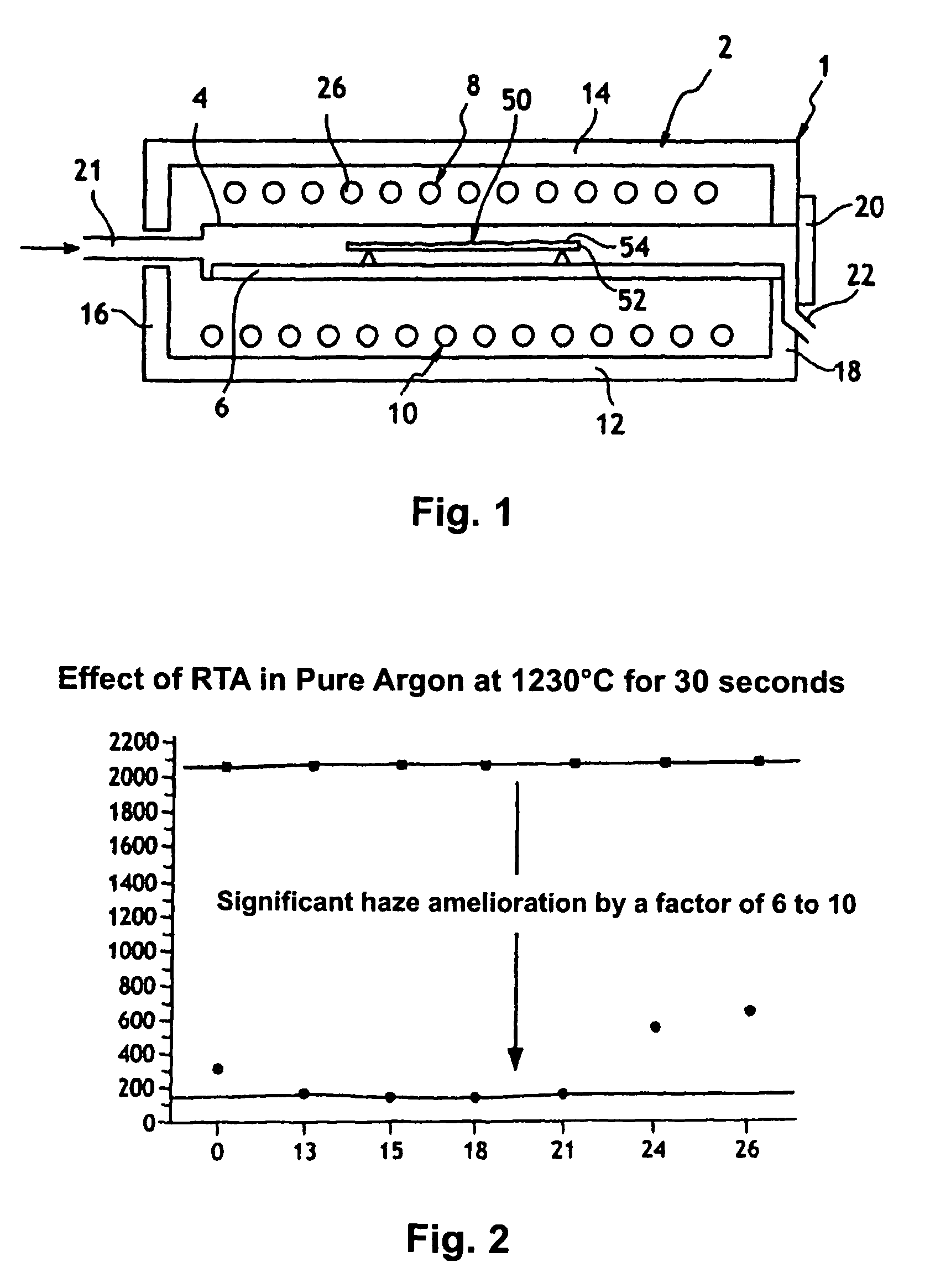

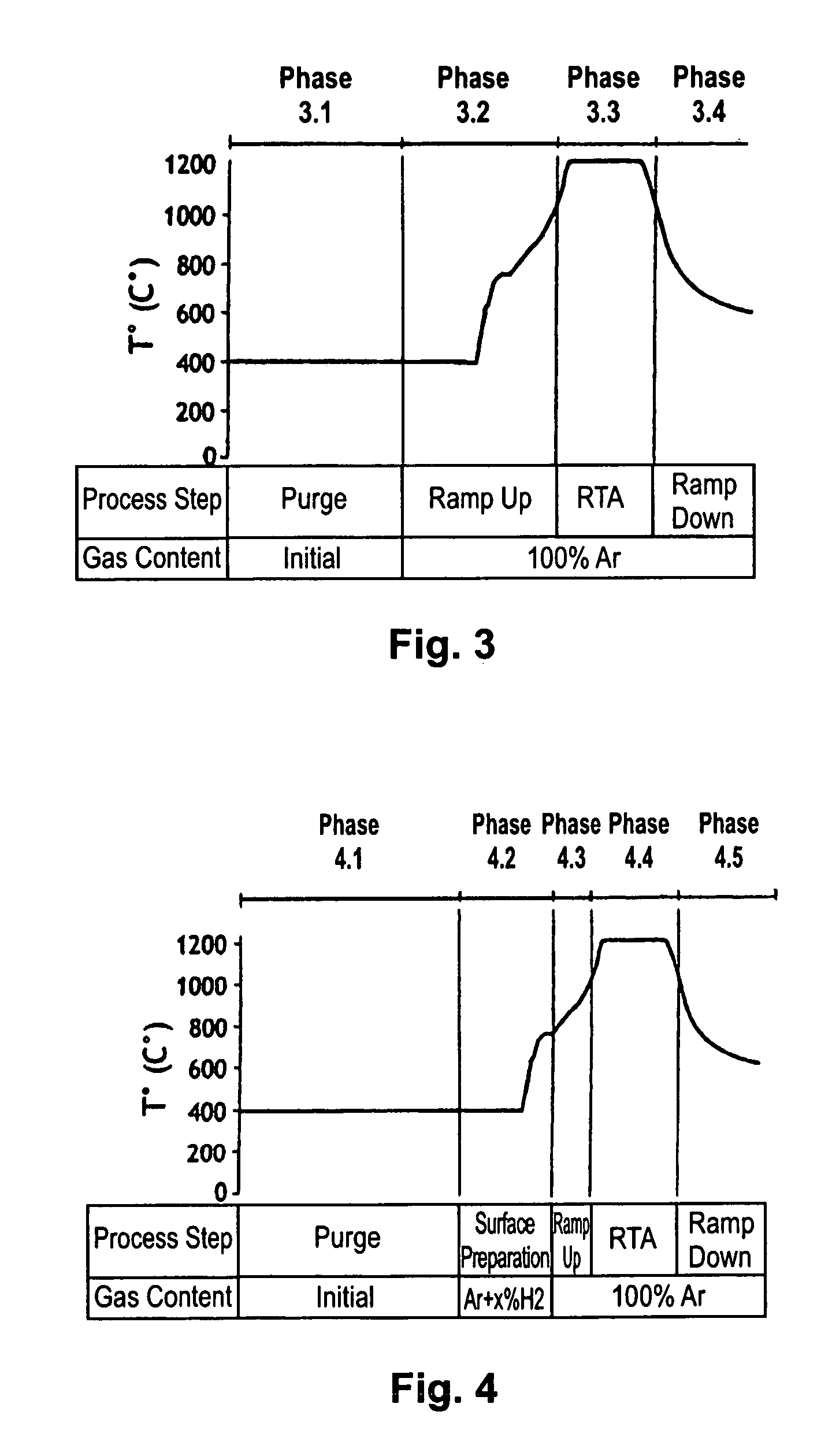

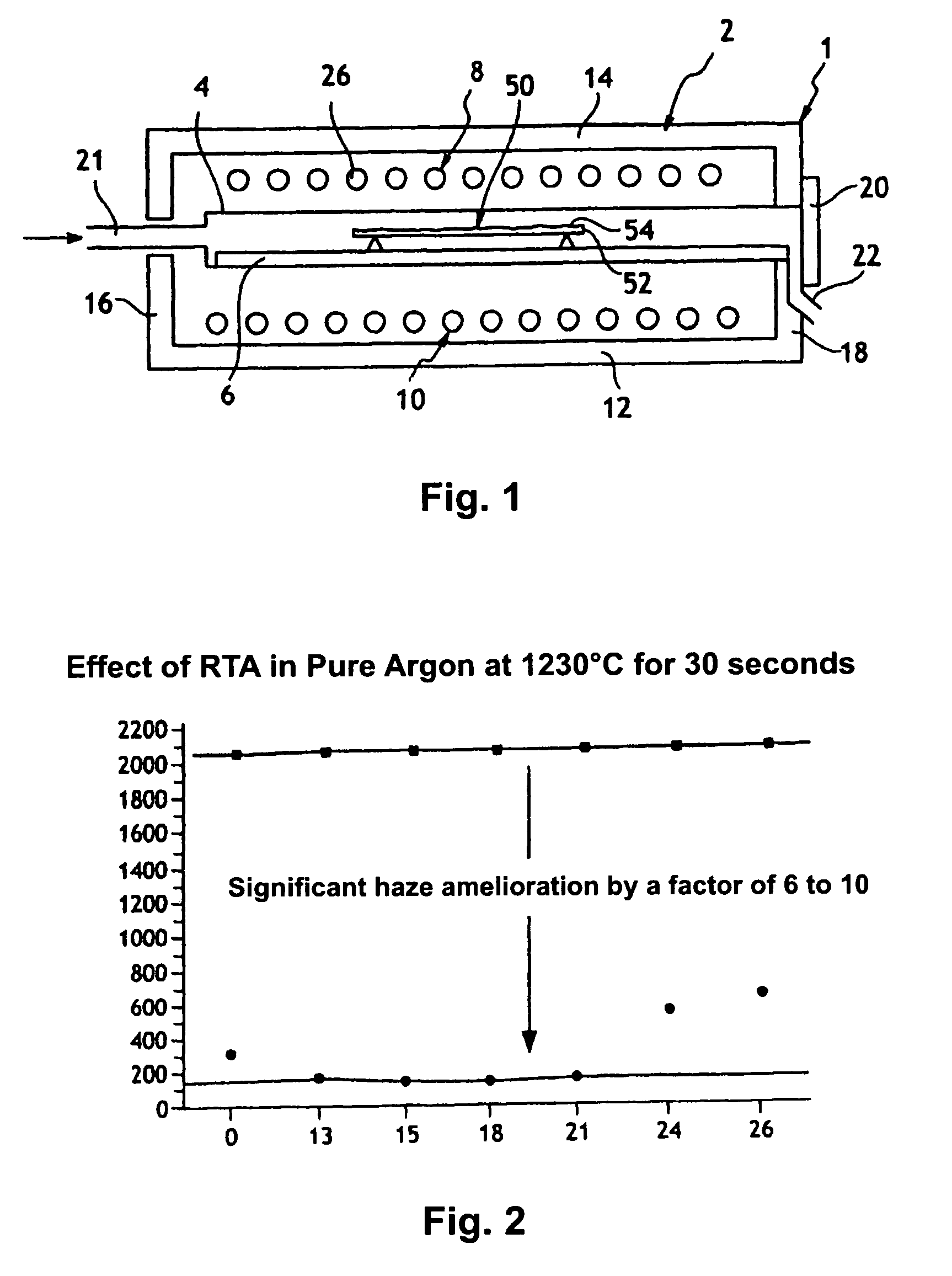

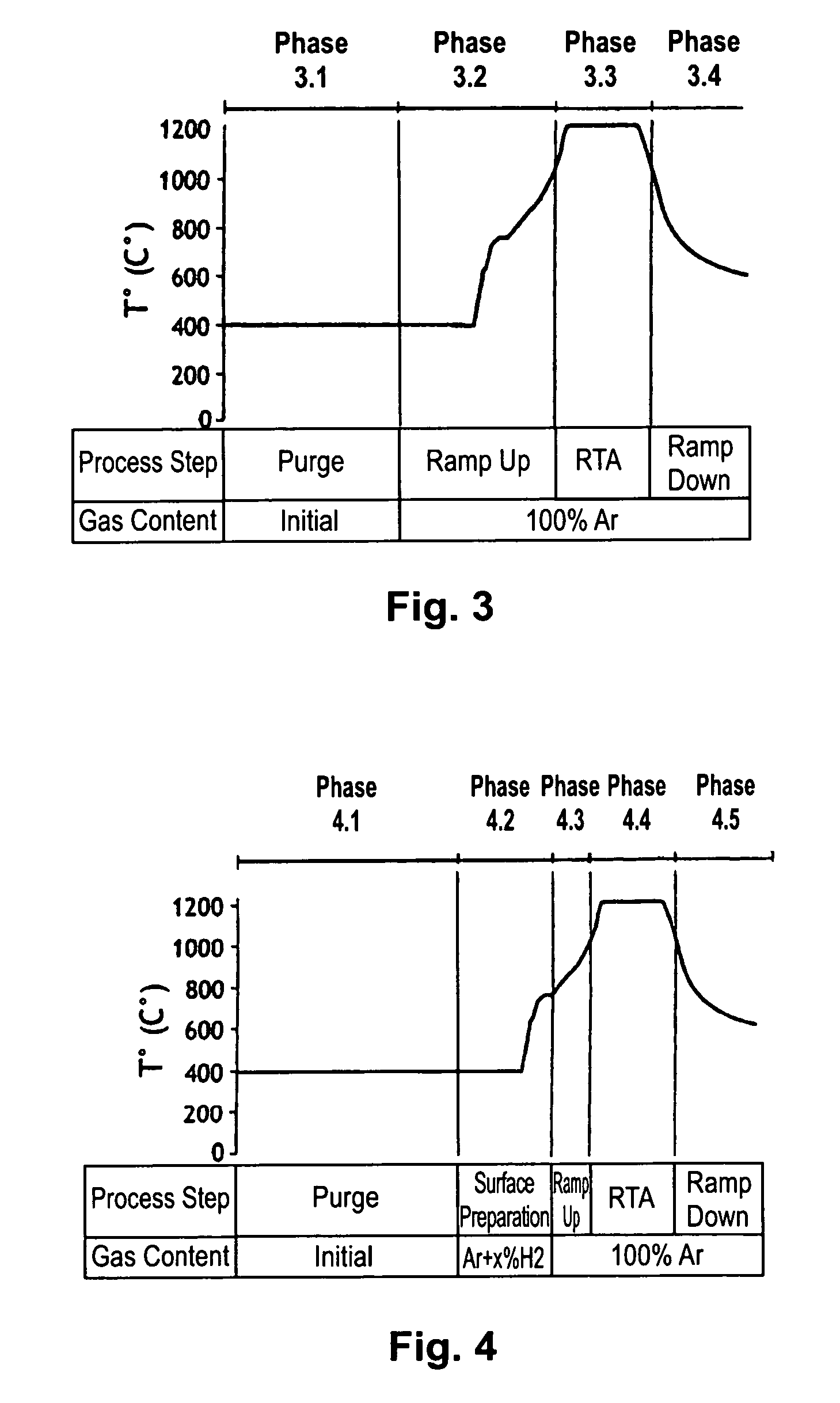

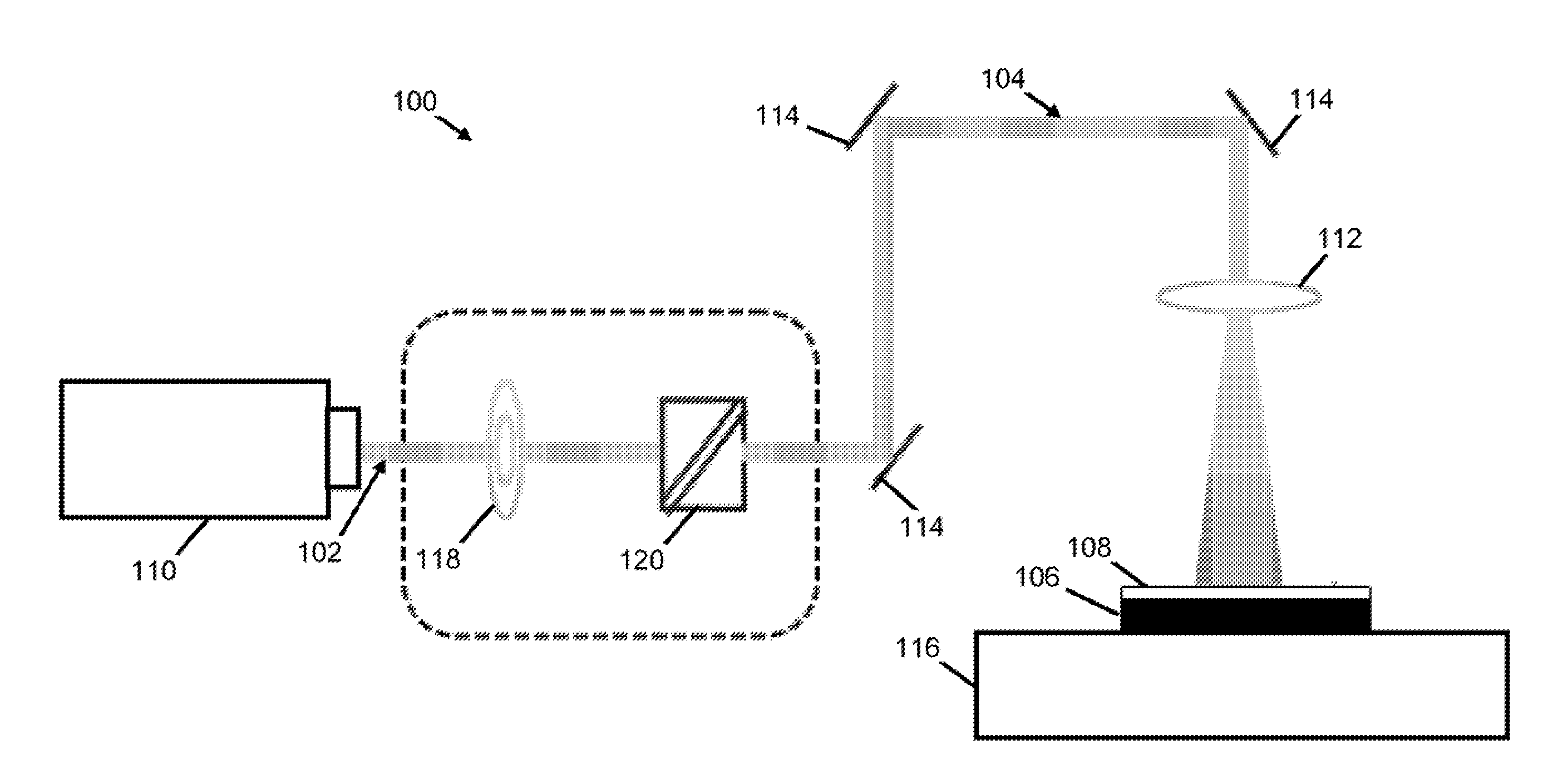

Method of reducing the surface roughness of a semiconductor wafer

ActiveUS20060035445A1Reduce surface roughnessSimple methodSemiconductor/solid-state device manufacturingMaterial removalArgon atmosphere

The invention provides a method for reducing the roughness of a free surface of a semiconductor wafer that includes removing material from the free surface of the wafer to provide a treated wafer, and performing a first rapid thermal annealing on the treated wafer in a pure argon atmosphere to substantially reduce the roughness of the free surface of the treated wafer. The material removal is selected and conducted to improve the effectiveness of the subsequent rapid thermal annealing in reducing the roughness of the free surface of the treated wafer.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

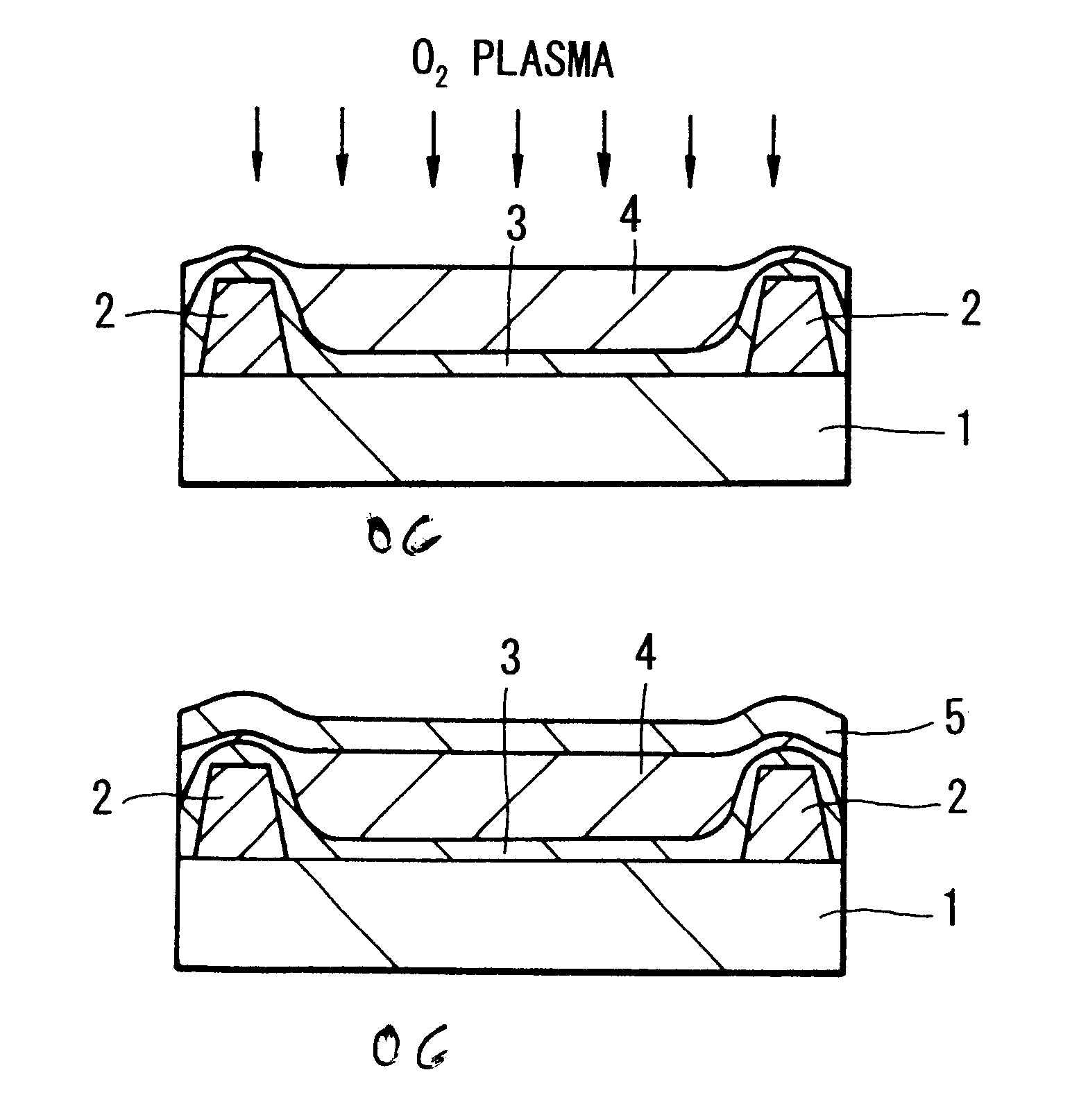

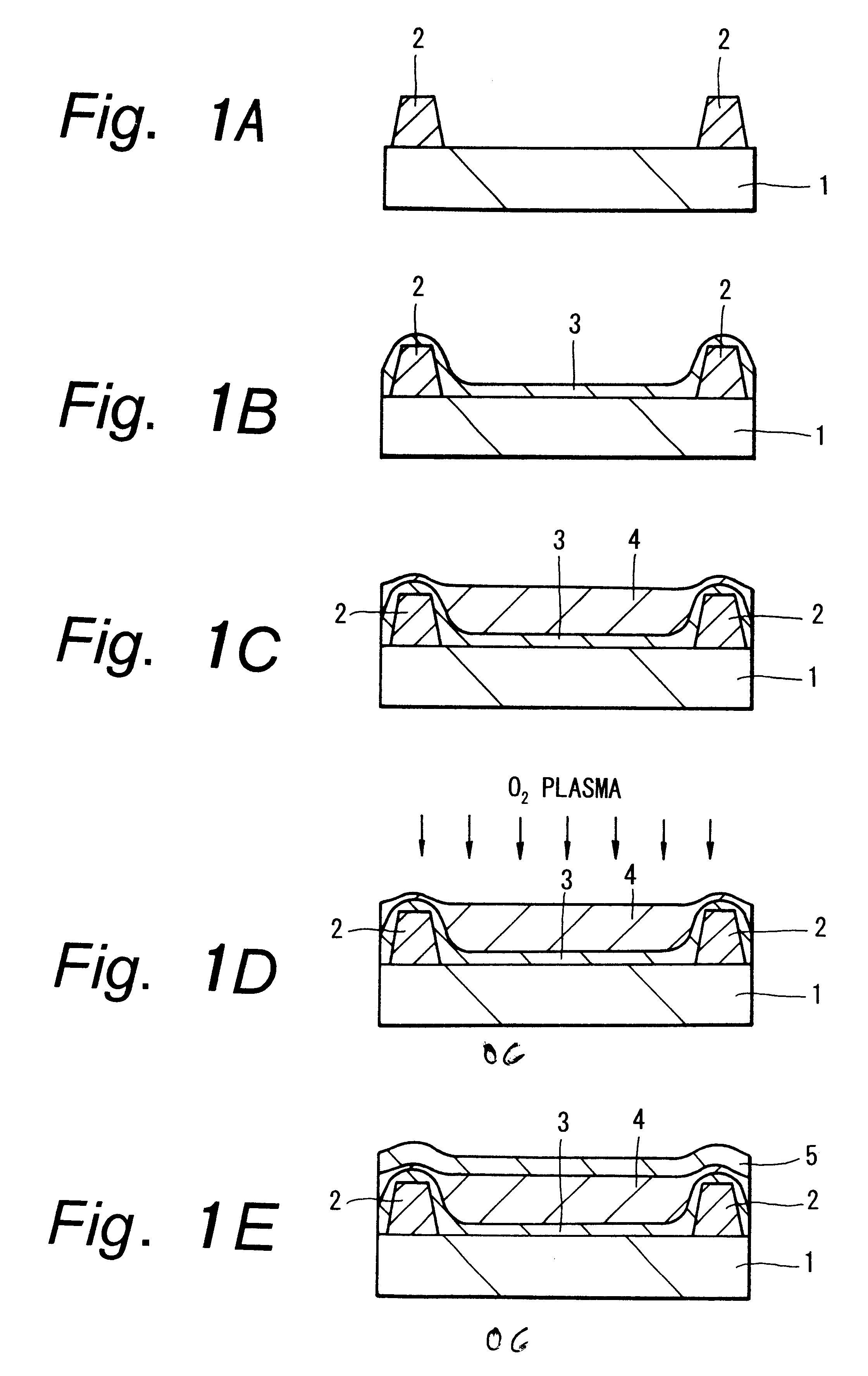

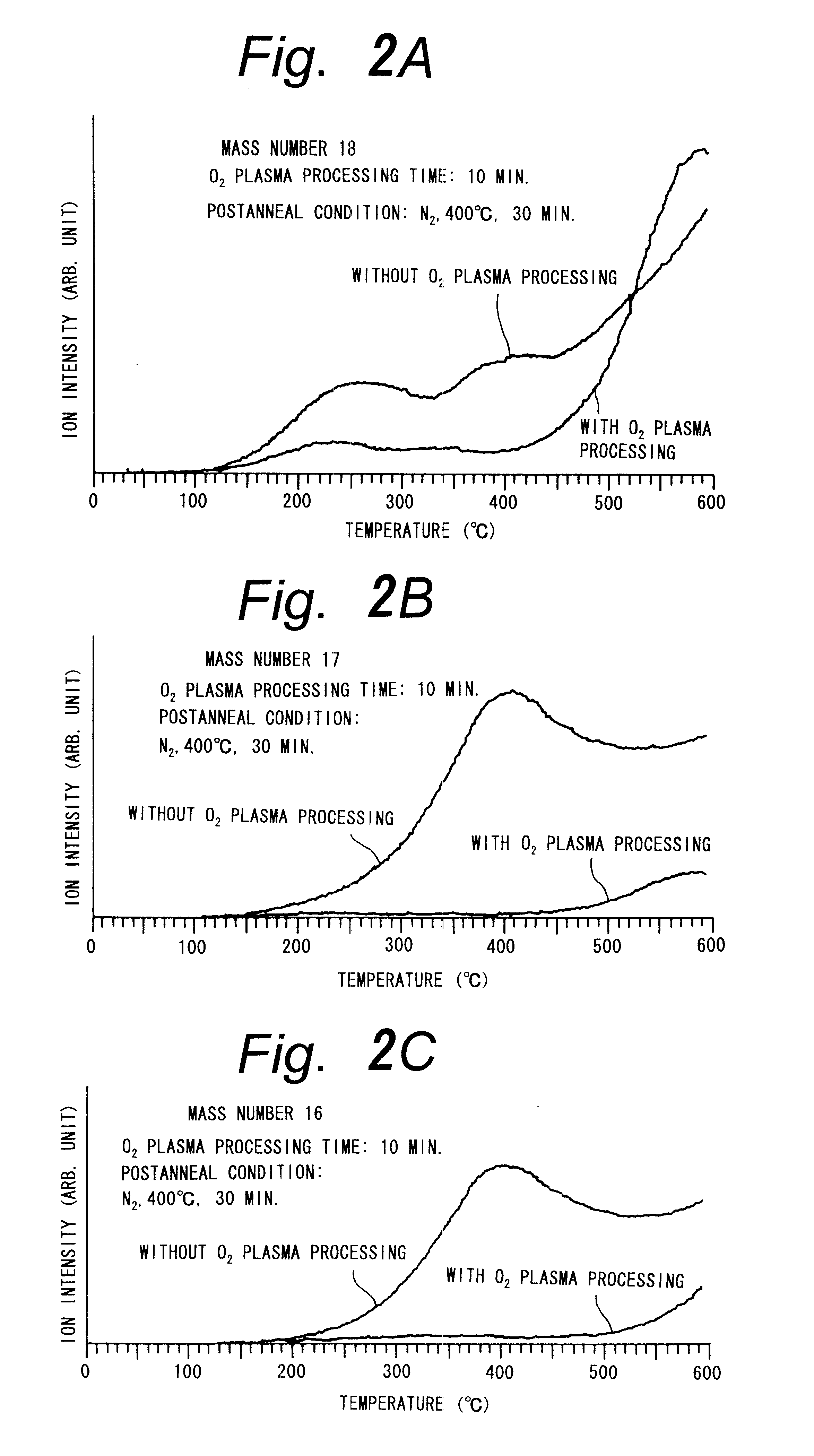

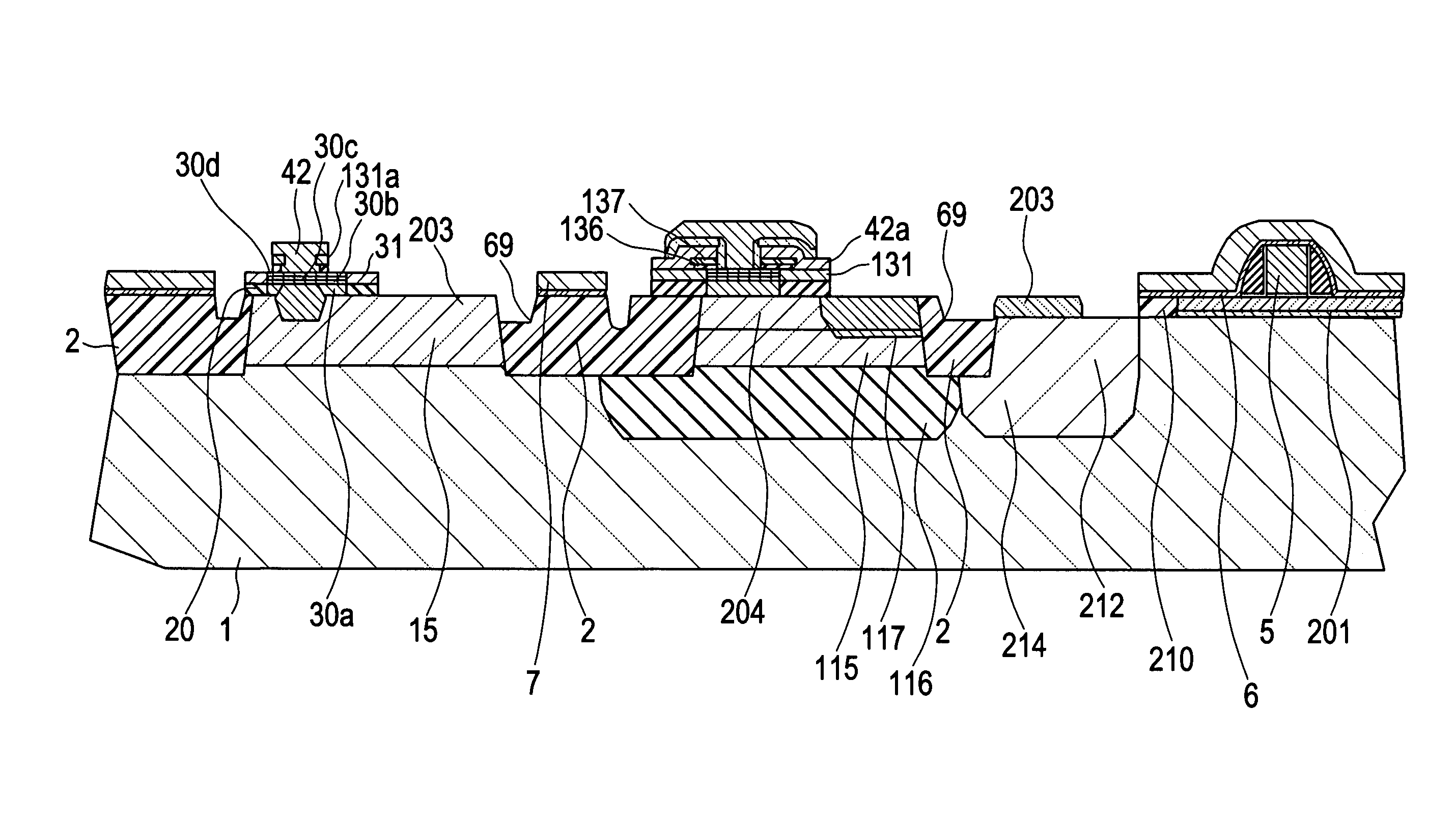

Method for making an insulating film

InactiveUS6429147B2Rapid thermal annealingAvoid problemsSemiconductor/solid-state device detailsSolid-state devicesInter layerSource material

In a method for manufacturing an insulating film using a fluid source material without inviting corrosion of metal wiring or the problem of poisoned via, after making a SiO2 film as a base layer on an Si substrate defining an uneven surface with an Al alloy wiring by plasma CVD using SiH4 and N2O, and further making an inter-layer insualting film having a fluidity on the SiO2 film by low pressure CVD using SiH4 or organosilane and H2O2, O2 plasma processing is applied to the inter-layer insulating film. After that, a SiO2 film as a cap layer is made on the inter-layer insulating film by plasma CVD using SiH4 and N2O. Rapid thermal annealing using lamp heating or O3 annealing may be done in lieu of O2 plasma processing.

Owner:SONY CORP

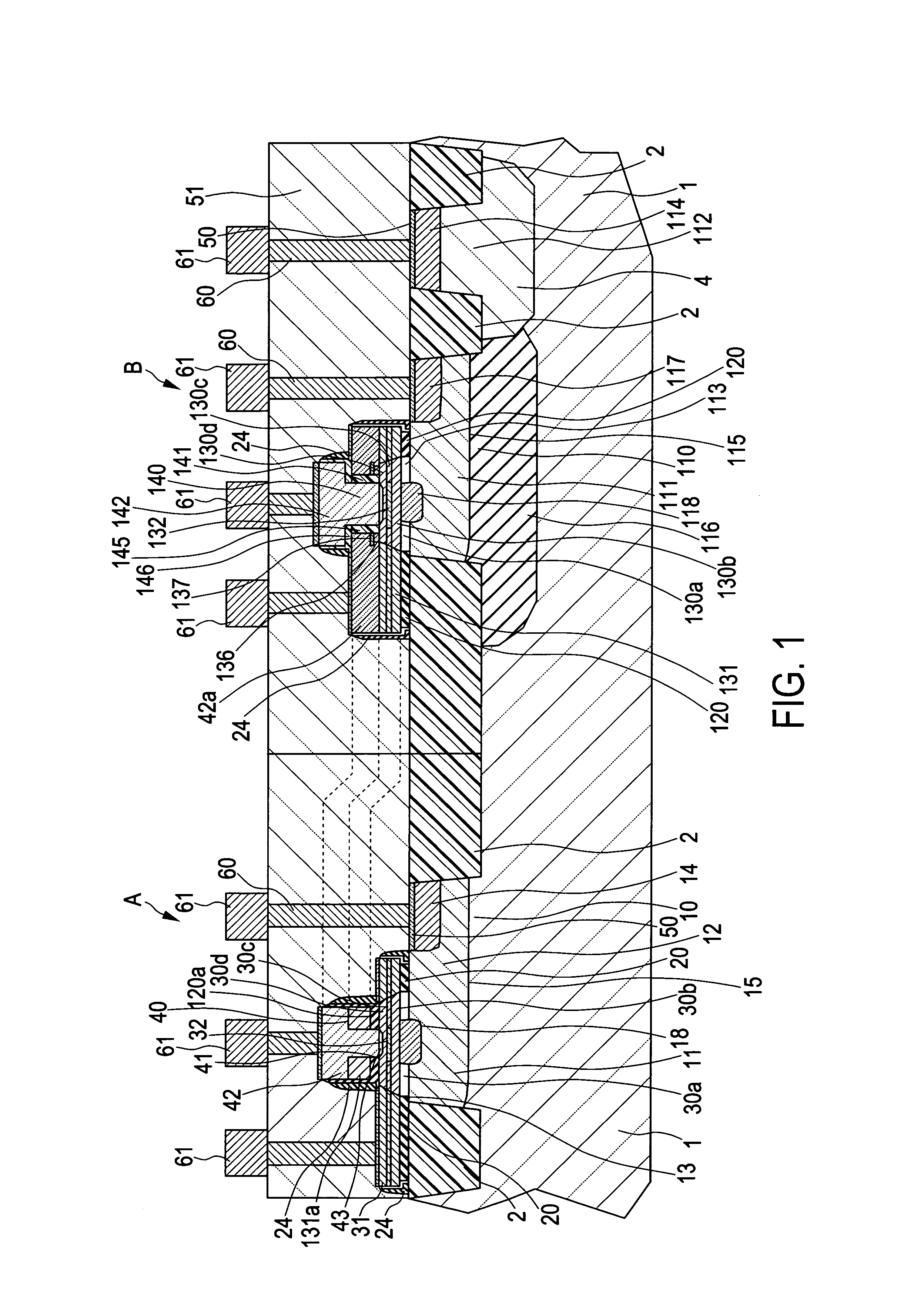

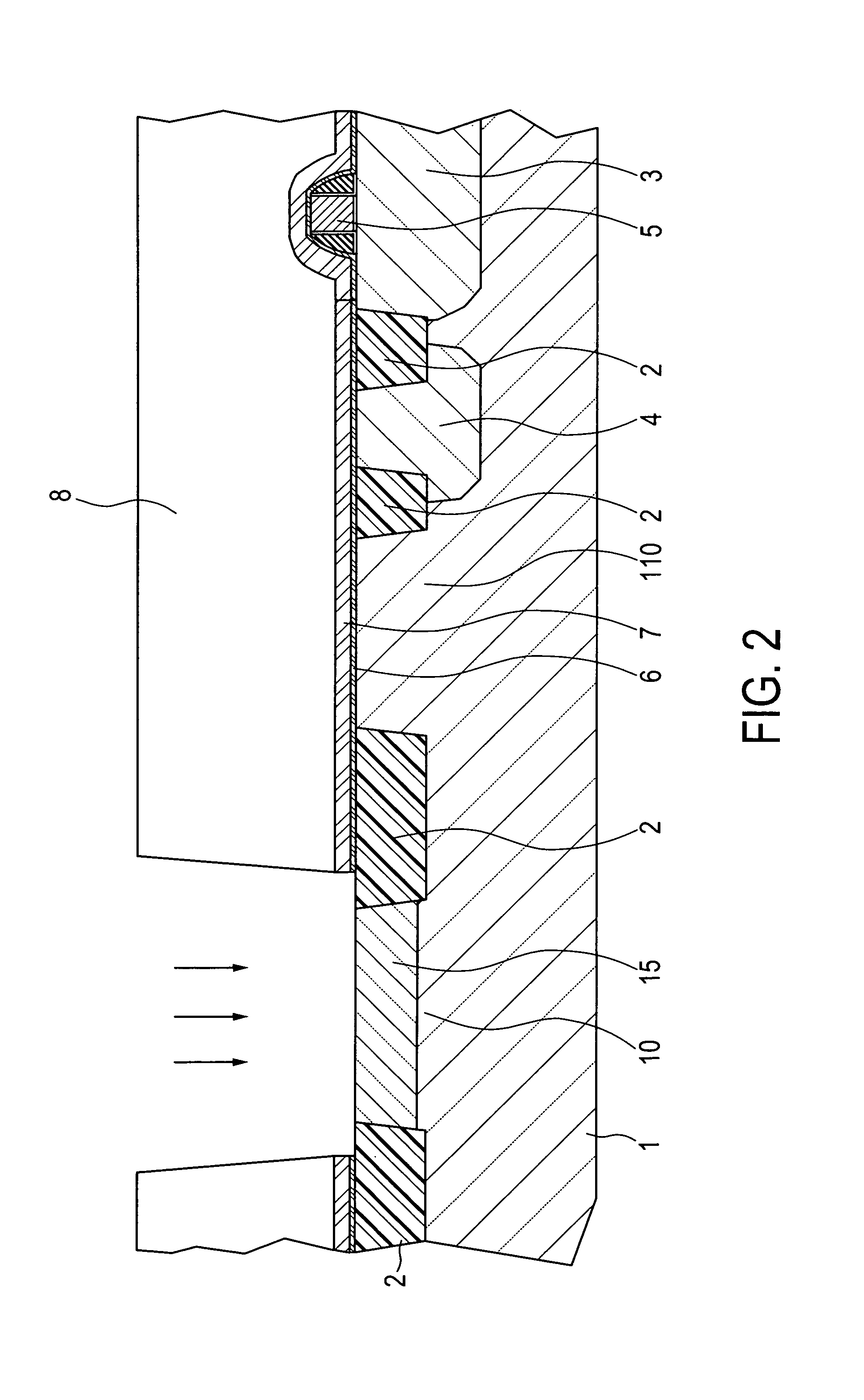

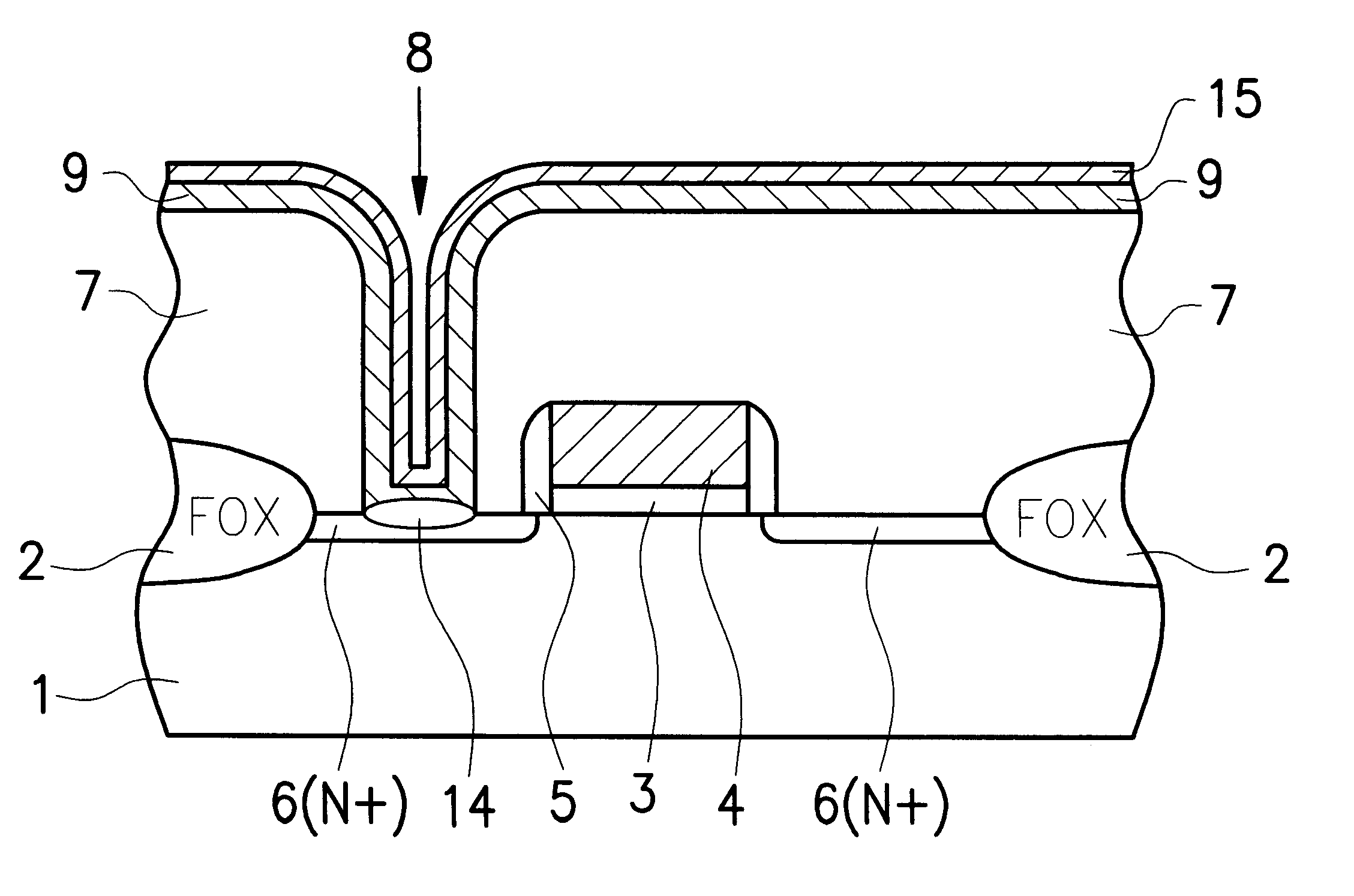

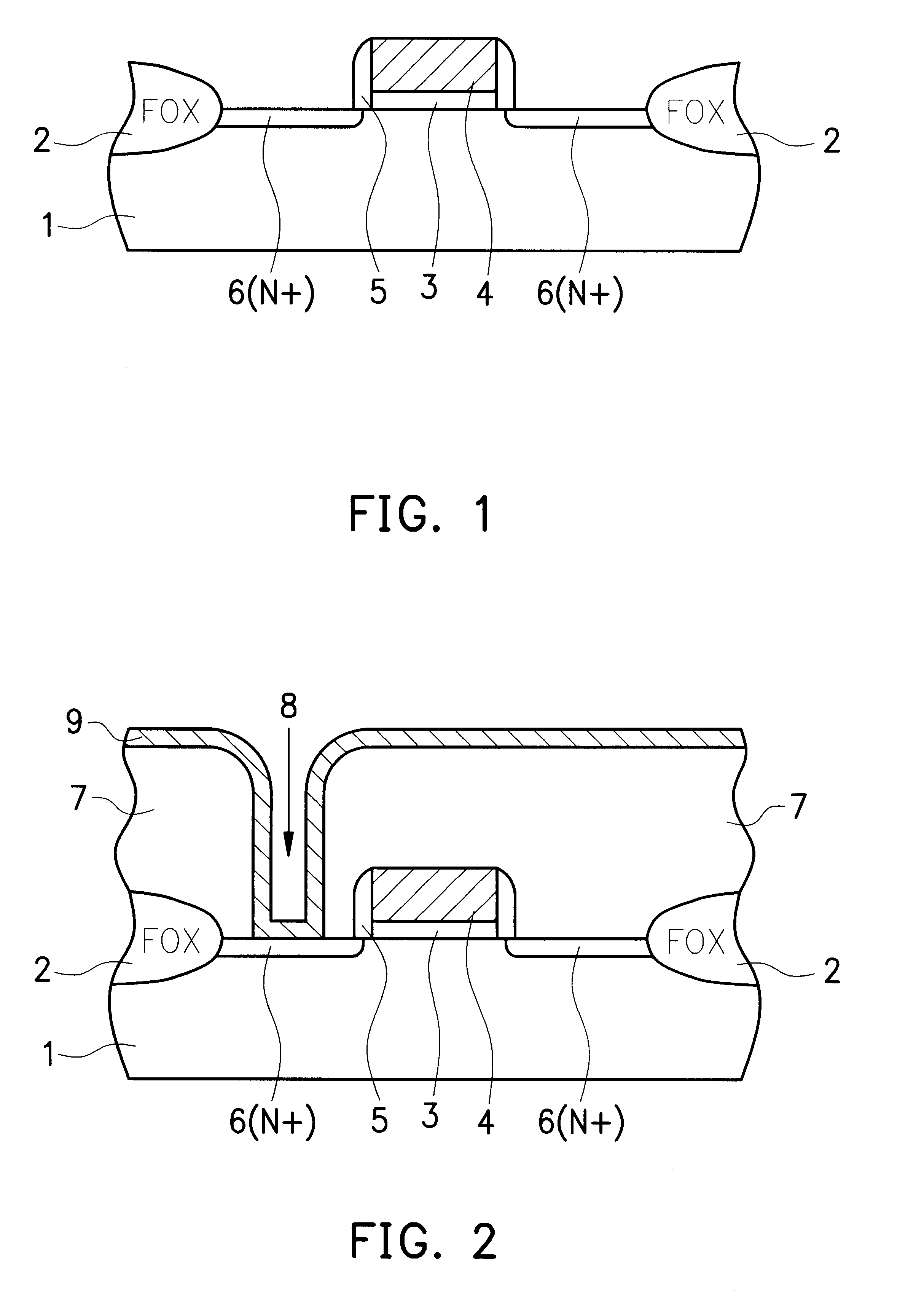

Bipolar complementary semiconductor device

ActiveUS7855404B2Reduce resistanceHigh-frequency propertyTransistorSolid-state devicesBiCMOSEngineering

A complementary BiCMOS semiconductor device comprises a substrate of a first conductivity type and a number of active regions which are provided therein and which are delimited in the lateral direction by shallow field insulation regions, in which vertical npn-bipolar transistors with an epitaxial base are arranged in a first subnumber of the active regions and vertical pnp-bipolar transistors with an epitaxial base are arranged in a second subnumber of the active regions, wherein either one transistor type or both transistor types have both a collector region and also a collector contact region in one and the same respective active region. To improve the high-frequency properties exclusively in a first transistor type in which the conductivity type of the substrate is identical to that of the collector region, an insulation doping region is provided between the collector region and the substrate.

Owner:IHP GMBH INNOVATIONS FOR HIGH PERFORMANCE MICROELECTRONICS LEIBNIZ INST FUR INNOVATIVE

Diffusion barrier enhancement for sub-micron aluminum-silicon contacts

InactiveUS6225222B1Enhance layeringEliminate or reduce aluminum-silicon interdiffusionSemiconductor/solid-state device manufacturingTitanium nitrideOxygen

Methods for enhancing the effectiveness of barrier layers, needed to prevent interaction between overlying aluminum interconnect metallizations, and underlying silicon device regions, has been developed. One method consists of using dual layers of titanium nitride, on titanium disilicide. The first titanium nitride layer is obtained via rapid thermal annealing of an underlying titanium layer, in a nitrogen containing ambient, also resulting in the formation of the underlying titanium disilicide layer. The second titanium nitride layer is deposited using reactive sputtering. A second method, used to create an enhanced barrier layer, is to reactively sputter titanium nitride, directly on an underlying titanium layer. Rapid thermal annealing, in an ammonia and oxygen ambient, results in an oxygen containing titanium nitride barrier layer. The rapid thermal anneal cycle also converts the underlying titanium layer, to the desired titanium disilicide layer. The barriers produced by these methods have demonstrated barrier effectiveness, in terms of preventing aluminum penetration, when compared to counterparts, fabricated without the use of the processes, described in this invention.

Owner:UNITED MICROELECTRONICS CORP

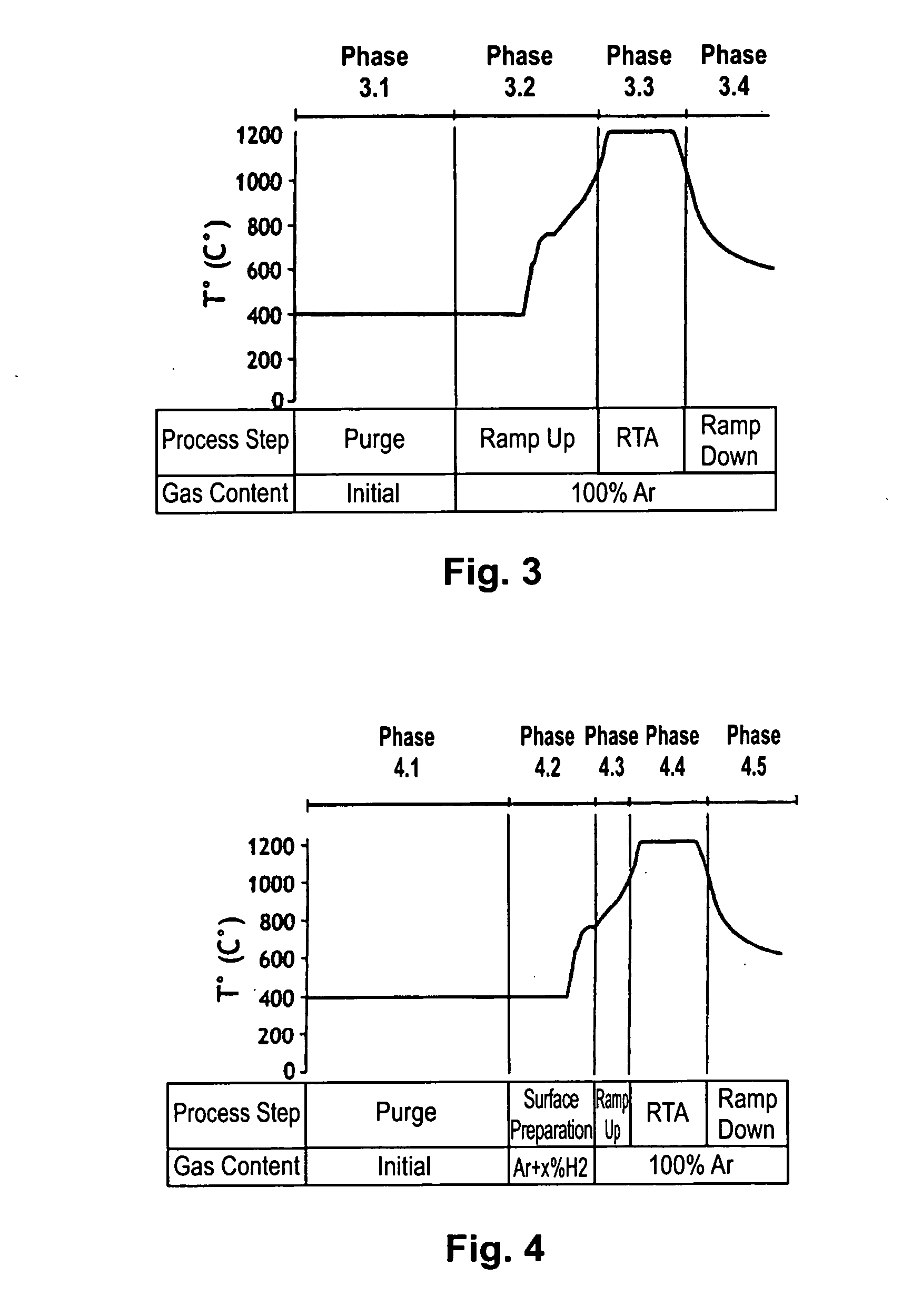

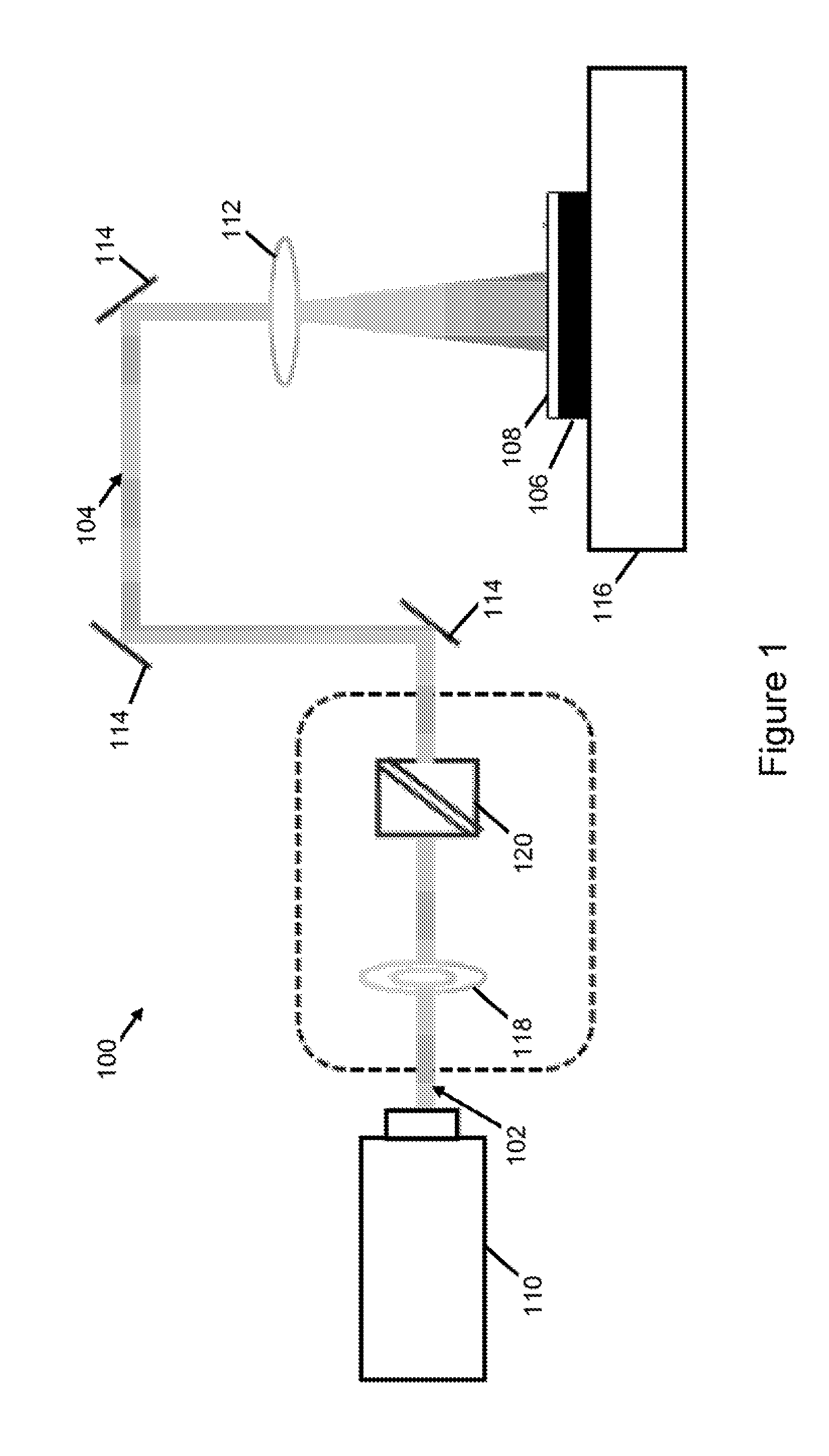

Method of reducing the surface roughness of a semiconductor wafer

InactiveUS20060024908A1Reduce surface roughnessSimple methodDecorative surface effectsSolid-state devicesMetallurgySurface roughness

A method for reducing the roughness of a free surface of a semiconductor wafer that includes establishing a first atmosphere in an annealing chamber, replacing the first atmosphere with a second atmosphere that includes a gas selected to and in an amount to substantially eliminate or reduce pollutants on a wafer, and exposing the free surface of the wafer to the second atmosphere to substantially eliminate or reduce pollutants thereon. The second atmosphere is then replaced with a third atmosphere that includes pure, and rapid thermal annealing is performed on the wafer exposed to the third atmosphere in the annealing chamber to substantially reduce the roughness of the free surface of the wafer.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

Method For Manufacturing Silicon Single Crystal Wafer

InactiveUS20090000535A1Increase productionIncrease costPolycrystalline material growthAfter-treatment detailsDiffusionSurface layer

Owner:SHIN-ETSU HANDOTAI CO LTD

Method for tuning the work function of a metal gate of the PMOS device

ActiveUS8367558B2Ability to tune work functionThe process is simple and convenientSemiconductor/solid-state device manufacturingSemiconductor devicesInterfacial reactionGate dielectric

A method for tuning the work function of a metal gate of the PMOS device is disclosed. The method comprises depositing a layer of metal nitride or a metal on a layer of high-k gate dielectric by physical vapor deposition (PVD), as a metal gate; doping the metal gate with dopants such as Al, Pt, Ru, Ga, Ir by ion implantation; and driving the doped metal ions to the interface between the high-k gate dielectric and interfacial SiO2 by high-temperature annealing so that the doped metal ions accumulate at the interface or generate dipoles by interfacial reaction, which in turn tunes the work function of the metal gate. The method can be widely used and its process is simple and convenient, has a better ability of tuning the work function of the metal gate, and is compatible with the conventional CMOS process.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

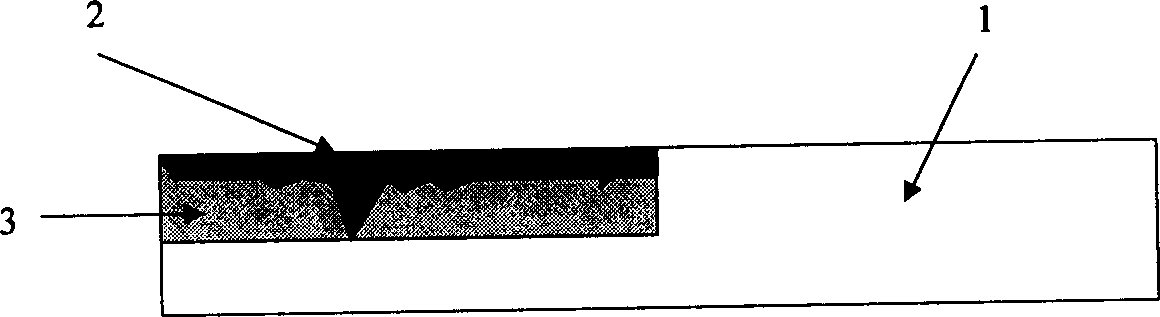

Structure and manufacturing method of semiconductor device

InactiveCN103035837ARapid thermal annealingImproved resistance characteristicsSolid-state devicesSemiconductor devicesMetal-insulator-metalEngineering

The invention discloses a structure of semiconductor device. The structure of the semiconductor device comprises a medal mounted on a lower layer, an anti-reflection layer and a medal insulator formed in sequence on the upper surface of the medal mounted on the lower layer. Medal as a lower electrode is deposited in a through-hole of the medal insulator and a medal oxide layer is formed on the upper end of the lower electrode. A barrier layer made of medals is arranged among the lower electrode, the medal oxide layer, and the side wall of the through-hole. The structure of the semiconductor device is characterized in that a medal aluminum layer deposited on the upper end of the medal insulator and the upper end of the medal oxide layer is further included, the medal aluminum layer is an upper electrode, and medal-insulator-medal is finally formed by the lower electrode, the medal oxide layer, and the medal aluminum layer. The invention further discloses a manufacturing method of semiconductor. Initial resistance can be significantly improved, and the structure and manufacturing method of the semiconductor device has good characteristics of variable resistance.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Image sensors including impurity layer adjacent isolation region

ActiveUS7586170B2Reduce dark currentRapid thermal annealingSolid-state devicesRadiation controlled devicesEngineeringImpurity

Owner:SAMSUNG ELECTRONICS CO LTD

Method for producing high-resistance simox wafer

InactiveUS20100022066A1Low resistivityReduce diffuseSemiconductor/solid-state device manufacturingHigh resistanceOxygen

A method for producing a high-resistance SIMOX wafer wherein oxygen diffused inside of a wafer by the heat treatment at a high temperature in an oxidizing atmosphere can be reduced to suppress the occurrence of thermal donor. In one embodiment, a heating-rapid cooling treatment is conducted after the heat treatment at a high temperature in an oxidizing atmosphere to implant vacancies from a surface of a wafer into an interior thereof to thereby easily precipitate oxygen diffused inside the wafer during the heat treatment.

Owner:SUMCO CORP

Method for producing semi-conductor device

InactiveCN1361551AControl and reduce concentrationImprove the crystallization effectTransistorPolycrystalline material growthAmorphous siliconMetal silicide

A method of manufacturing a semiconductor device which has a crystalline silicon film comprises the steps of forming crystal nuclei in a surface region of an amorphous silicon film and then growing the crystals from the nuclei by a laser light. Typically the crystal nuclei are silicon crystals or metal suicides having an equivalent structure as silicon crystal.

Owner:SEMICON ENERGY LAB CO LTD

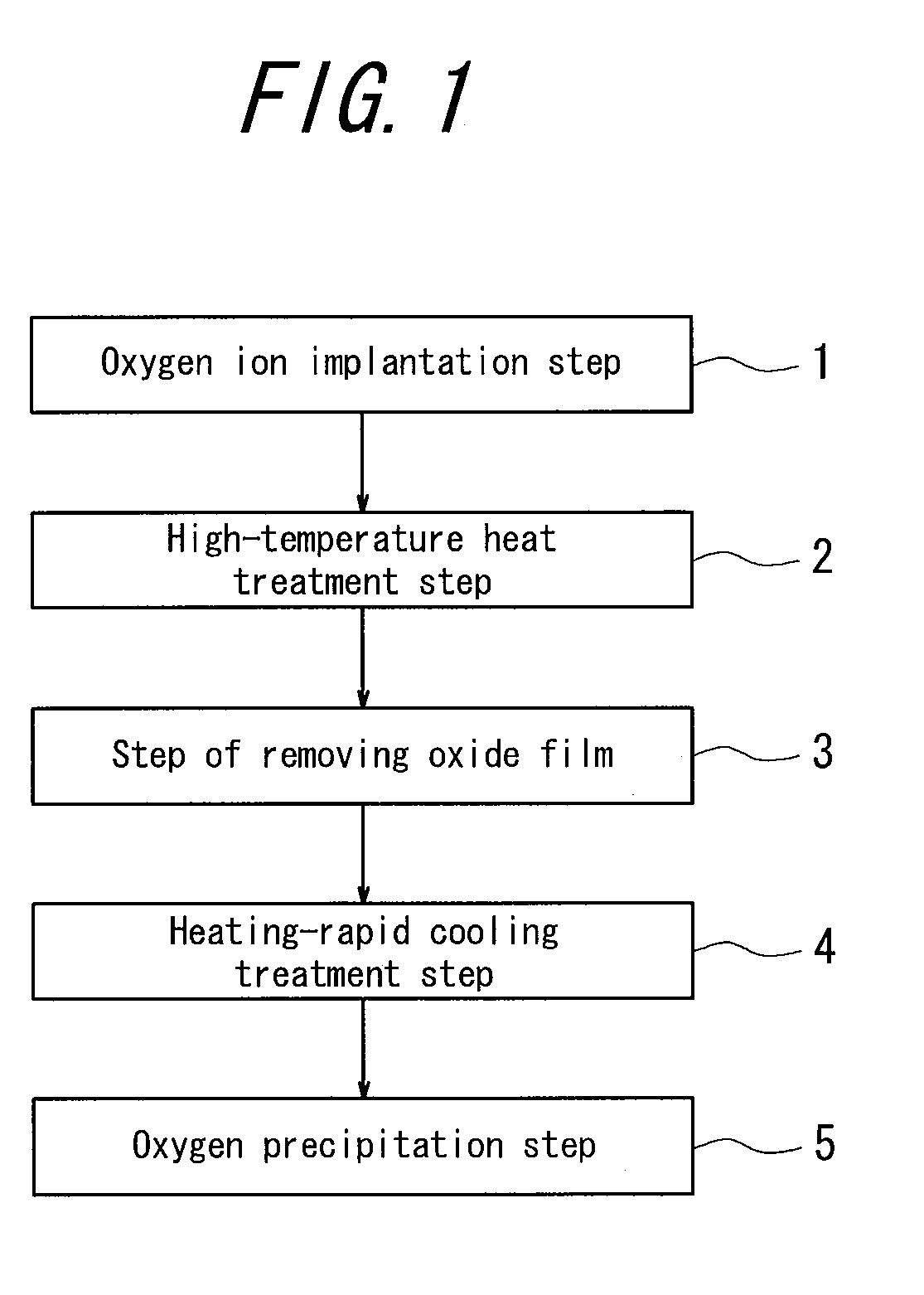

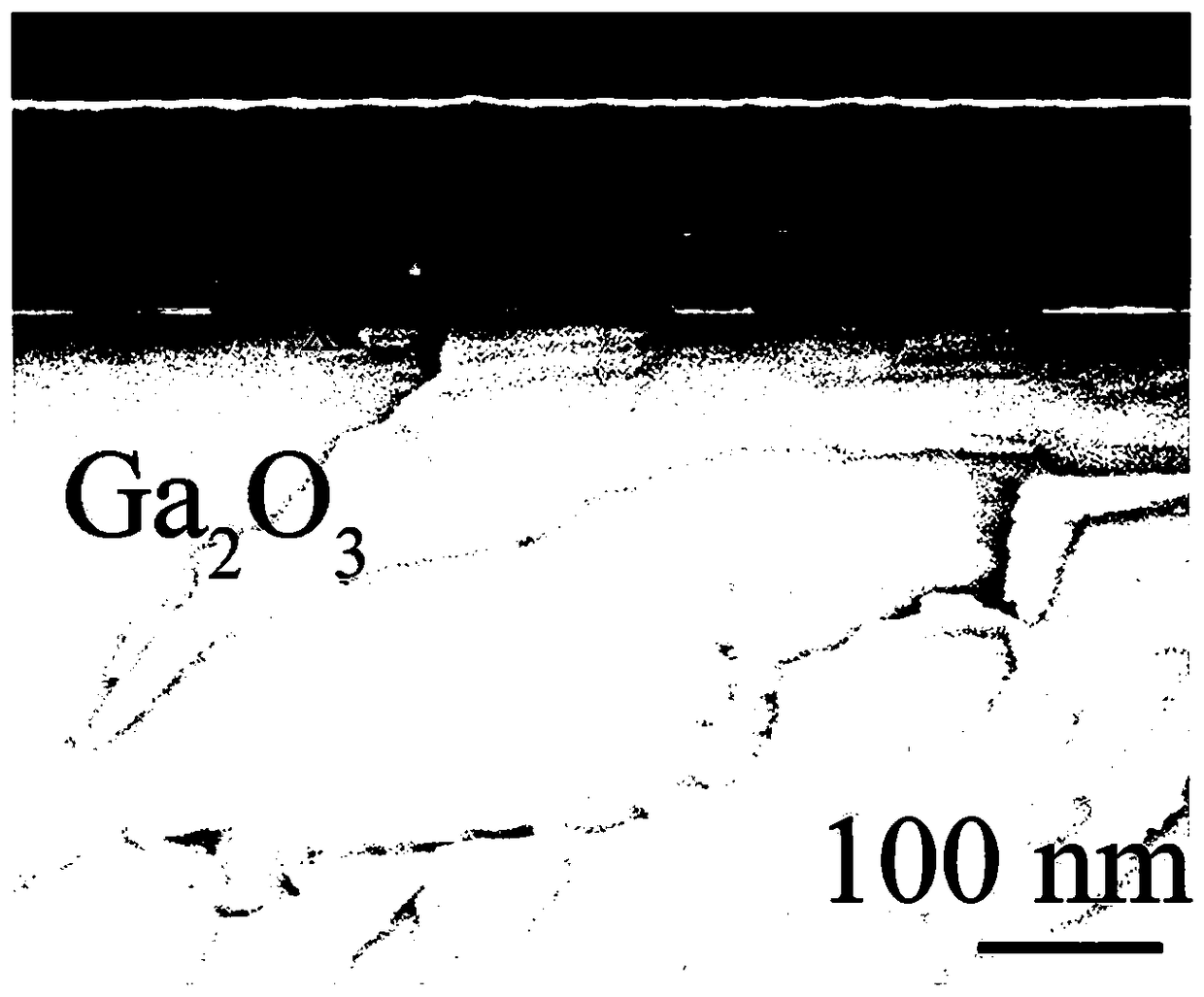

Gallium oxide semiconductor Schottky diode and manufacturing method thereof

PendingCN109449214AExcellent performanceReduced levels of hypoxia-related deficienciesSemiconductor/solid-state device manufacturingSemiconductor devicesOxideMetal

The invention discloses a gallium oxide (Ga2O3) semiconductor Schottky diode. The Ga2O3 semiconductor Schottky diode comprises a semiconductor layer, an anode electrode and a cathode electrode; the semiconductor layer is Ga2O3 film, the anode electrode is oxide of stannum (SnOx). The manufacturing method of the Schottky diode disclosed by the invention comprises the following steps: a) preparing aGa2O3 sheet; b) cleaning the sheet; c) etching the Ga2O3 sheet; d) preparing cathode and metal contact point layer; e) performing annealing treatment; f) preparing the SnOx film; and g) preparing ananode metal contact point layer. An ideal factor of the Ga2O3 semiconductor Schottky diode is 1.02 and extremely close to 1, the barrier height is 1.17eV, and the switch ratio exceeds 1010; and the acquired Schottky diode is excellent in performance. Through the manufacturing method of the Schottky diode disclosed by the invention, the SnOx is used as the Schottky contact electrode, and then the high-performance Ga2O3 Schottky diode is obtained.

Owner:SHANDONG UNIV

Method of reducing the surface roughness of a semiconductor wafer

InactiveUS7883628B2Reduce roughnessEliminate and reduce pollutantDecorative surface effectsSolid-state devicesMetallurgySurface roughness

A method for reducing the roughness of a free surface of a semiconductor wafer that includes establishing a first atmosphere in an annealing chamber, replacing the first atmosphere with a second atmosphere that includes a gas selected to and in an amount to substantially eliminate or reduce pollutants on a wafer, and exposing the free surface of the wafer to the second atmosphere to substantially eliminate or reduce pollutants thereon. The second atmosphere is then replaced with a third atmosphere that includes pure, and rapid thermal annealing is performed on the wafer exposed to the third atmosphere in the annealing chamber to substantially reduce the roughness of the free surface of the wafer.

Owner:SOITEC SA

Integration of rare-earth doped amplifiers into semiconductor structures and uses of same

InactiveUS7440180B2Improve stability and reliabilityStable and reliableExcitation process/apparatusActive medium materialAudio power amplifierSemiconductor structure

An integrated device is disclosed which has a substrate and a Rare-Earth Doped Semiconductor layer (REDS layer) integrated with the substrate. The REDS layer is patterned to define one or more optically amplifying structures each having a first I / O port for receiving or outputting a first optical signal, and at least one pump energy receiving port for receiving pumping energy in the form of at least one of electrical pump energy and / or optical pump energy. In one particular set of embodiments, at least one of the optical amplifying structures is a Raman type amplifier where a corresponding pump energy receiving port is structured for receiving Raman type pumping energy having an effective frequency which is about one optical phonon frequency higher than a signal frequency of an optical signal supplied at a corresponding I / O port. Methods are disclosed for fabricating Rare-Earth Doped Semiconductor layers, including providing such layers in semiconductor-on-insulator (SOI) structures and for enhancing the effective, long-term concentrations of incorporated, rare earth atoms. Additionally, non-parallel pumping techniques are disclosed.

Owner:TANG YIN S

Method for implantation of high dopant concentrations in wide band gap materials

InactiveUS7589004B2Increase concentrationMinimizing defect concentrationSemiconductor/solid-state device manufacturingDopantHigh concentration

A method that combines alternate low / medium ion dose implantation with rapid thermal annealing at relatively low temperatures. At least one dopant is implanted in one of a single crystal and an epitaxial film of the wide band gap compound by a plurality of implantation cycles. The number of implantation cycles is sufficient to implant a predetermined concentration of the dopant in one of the single crystal and the epitaxial film. Each of the implantation cycles includes the steps of: implanting a portion of the predetermined concentration of the one dopant in one of the single crystal and the epitaxial film; annealing one of the single crystal and the epitaxial film and implanted portion at a predetermined temperature for a predetermined time to repair damage to one of the single crystal and the epitaxial film caused by implantation and activates the implanted dopant; and cooling the annealed single crystal and implanted portion to a temperature of less than about 100° C. This combination produces high concentrations of dopants, while minimizing the defect concentration.

Owner:LOS ALAMOS NATIONAL SECURITY

Method of reducing the surface roughness of a semiconductor wafer

ActiveUS7749910B2Reduce roughnessImprove efficiencySemiconductor/solid-state device manufacturingMaterial removalArgon atmosphere

The invention provides a method for reducing the roughness of a free surface of a semiconductor wafer that includes removing material from the free surface of the wafer to provide a treated wafer, and performing a first rapid thermal annealing on the treated wafer in a pure argon atmosphere to substantially reduce the roughness of the free surface of the treated wafer. The material removal is selected and conducted to improve the effectiveness of the subsequent rapid thermal annealing in reducing the roughness of the free surface of the treated wafer.

Owner:SOITEC SA

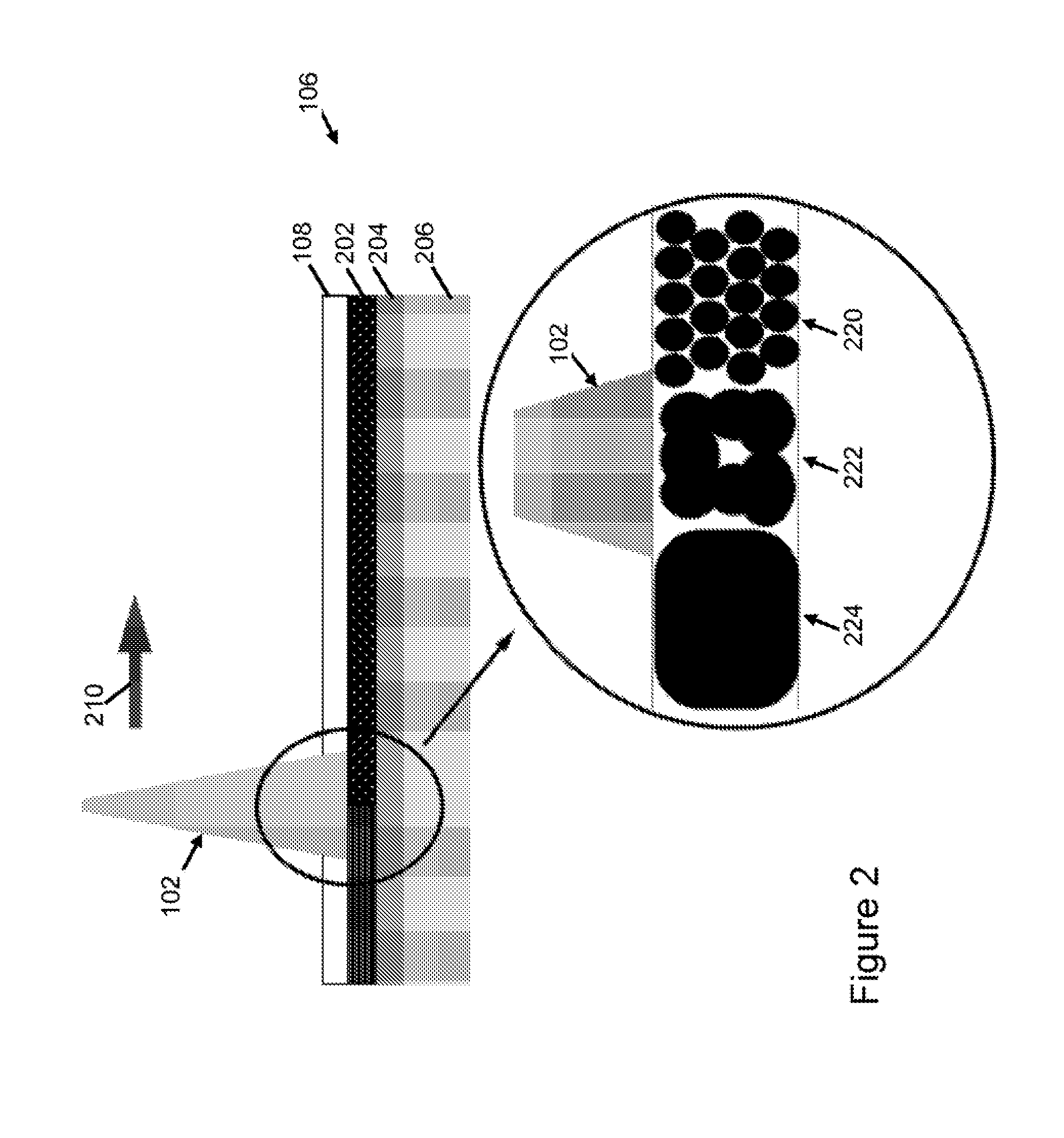

High speed laser crystallization of particles of photovoltaic solar cells

InactiveUS20130092664A1Low costFast processing methodFinal product manufacturePhotovoltaic energy generationLaser crystallizationHigh pressure

A system and method for enhancing the conversion efficiency of thin film photovoltaics. The thin film structure includes a photovoltaic absorbent layer covered by a confinement layer. A laser beam passes through the confinement layer and hits the photovoltaic absorbent layer. The laser can be pulsed to create localized rapid heating and cooling of the photovoltaic absorbent layer. The confinement layer confines the laser induced plasma plume creating a localized high-pressure condition for the photovoltaic absorbent layer. The laser beam can be scanned across specific regions of the thin film structure. The laser beam can be pulsed as a series of short pulses. The photovoltaic absorbent layer can be made of various materials including copper indium diselenide, gallium arsenide, and cadmium telluride. The photovoltaic absorbent layer can be sandwiched between a substrate and the confinement layer, and a molybdenum layer can be between the substrate and the photovoltaic absorbent layer.

Owner:PURDUE RES FOUND INC

Method to thin a silicon-on-insulator substrate

ActiveUS8962492B2Rapid thermal annealingDecorative surface effectsSemiconductor/solid-state device manufacturingSurface layerEtching

A method to thin an initial silicon-on-insulator substrate that has a layer of silicon oxide buried between a silicon carrier substrate and a silicon surface layer. This method is noteworthy in that it includes conducting a thermal oxidation treatment of the initial substrate to cause oxidation of part of the silicon surface layer and form a thermal oxide thereon; conducting a first cycle of etching followed by cleaning of the silicon surface layer after the thermal oxidation treatment, wherein the etching of the first cycle is conducted so as to fully remove the thermal oxide from the silicon surface layer to thin it and lift off all unstable parts of the initial substrate at edges thereof to form a thinned substrate; conducting, after the first cycle, a second cycle of etching followed by cleaning of the silicon surface layer, wherein the etching of the second cycle is conducted to remove from the surface of the thinned substrate, polluting particles formed during the first etching cycle and that have deposited thereupon, in order to obtain a final SOI substrate having a thinned surface layer that forms an active layer for the substrate.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

Method for forming shallow junction

InactiveCN1385880AEvenly distributedReduce processSemiconductor/solid-state device manufacturingSalicidePeak value

Present silicide is prepared after insert source / drain and anneal excited to form junctions with the reliability problem mainly on electric drain which influences the final performance of transistors. This ivnention is to form silicide first, then inject in impurities and anneal to junction. The distributed peak value of inserted impurities lies under the silicide avoiding the problem brought with the diffusion of silicide in which the junction is easy to be controlled, high impurities concentration and repeatability, reducing the procedure of taking oxide as the injection mask.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com