Method for forming shallow junction

A shallow junction and integrated circuit technology, applied in the field of forming drain-source shallow junctions, can solve problems such as elimination, and achieve the effects of stable distribution of impurity concentration, reduction of processes, and easy control of junction depth.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

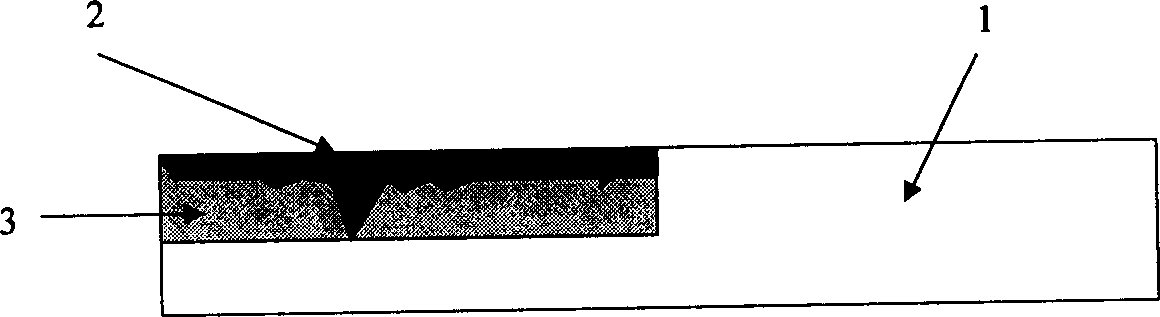

[0021] Implementation steps of the present invention are as follows:

[0022] 1. Clean the wafer surface with diluted hydrofluoric acid

[0023] 2. Deposit the metal required to form silicide on the surface of the silicon wafer by PVD method, such as Co (cobalt) / Ti (titanium)

[0024] 3. Using rapid thermal annealing method, at a lower temperature, such as 550 degrees, to form a high-resistance silicide, such as CoSi

[0025] 4. Corrosion away unnecessary and unreacted metals, such as Co or Ti metals.

[0026] 5. Through rapid thermal annealing at a higher temperature, such as 850 degrees, to form a low-resistance silicide, such as CoSi 2

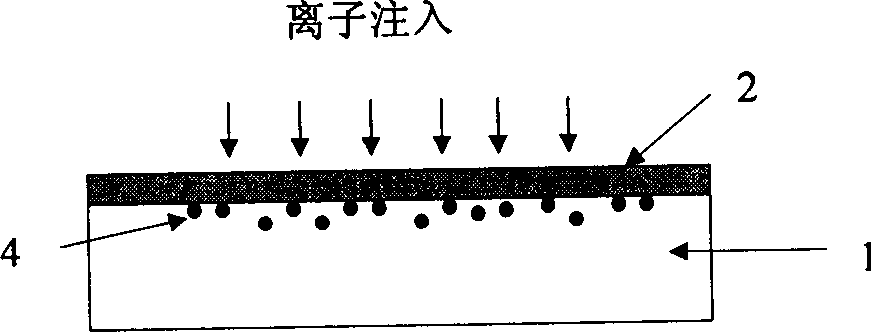

[0027] 6. Using silicide as an implant mask, such as CoSi 2 , to complete the implantation of the source / drain junction and the gate dose, the peak of the impurity concentration is just below the silicide, such as about 5nm

[0028] 7. Use SPIKE annealing or IMPULSE annealing to form a shallow junction.

[0029] The shallow junction p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com