Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

119results about How to "Extended test time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

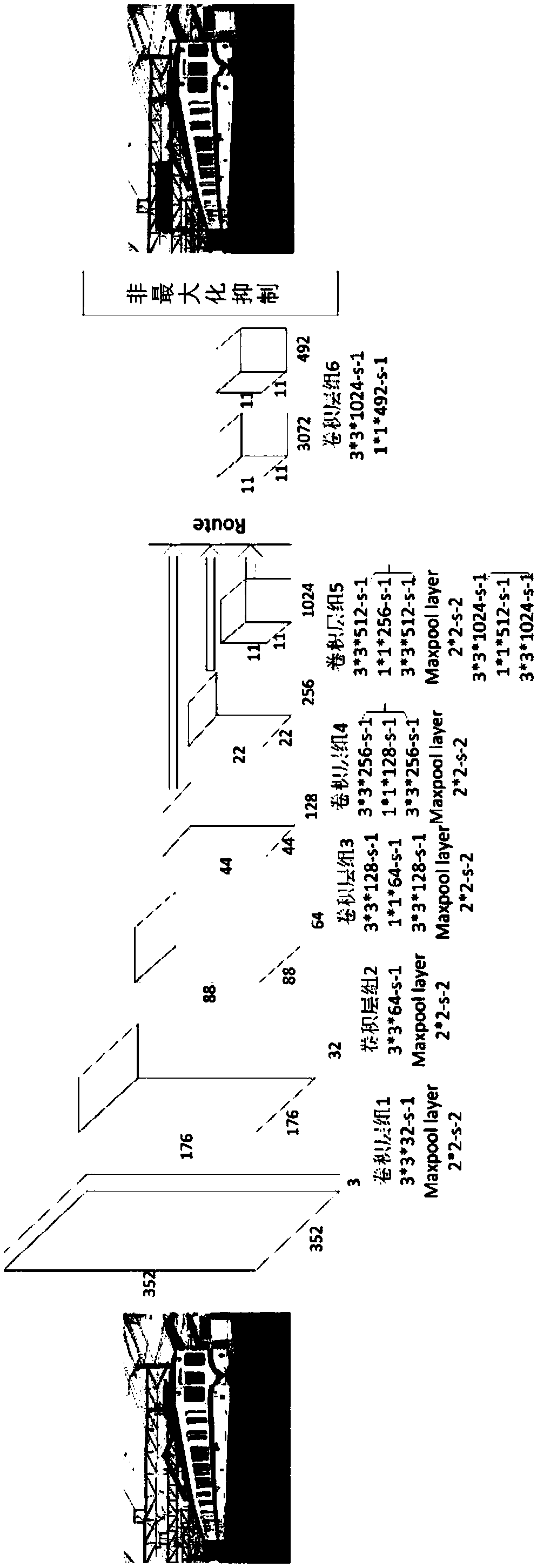

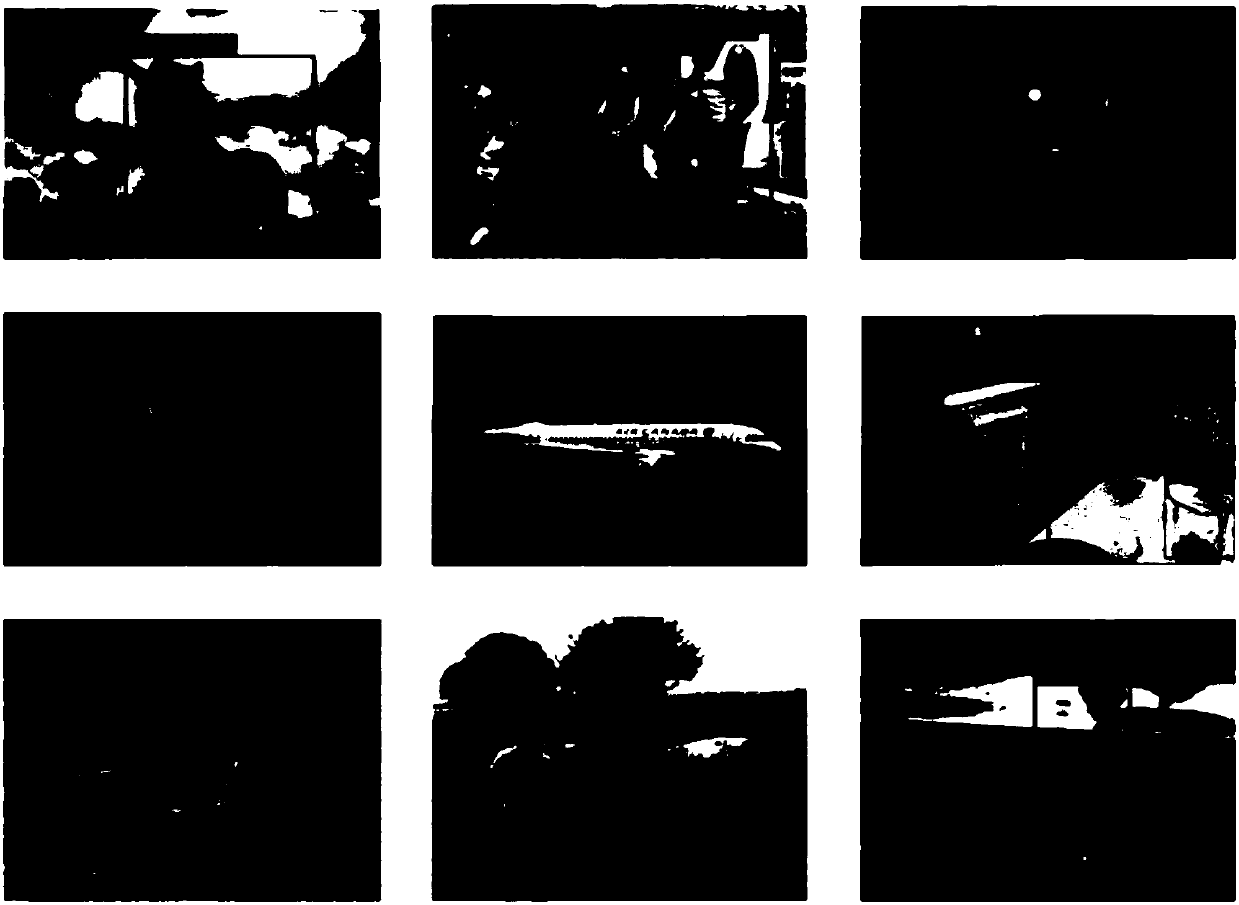

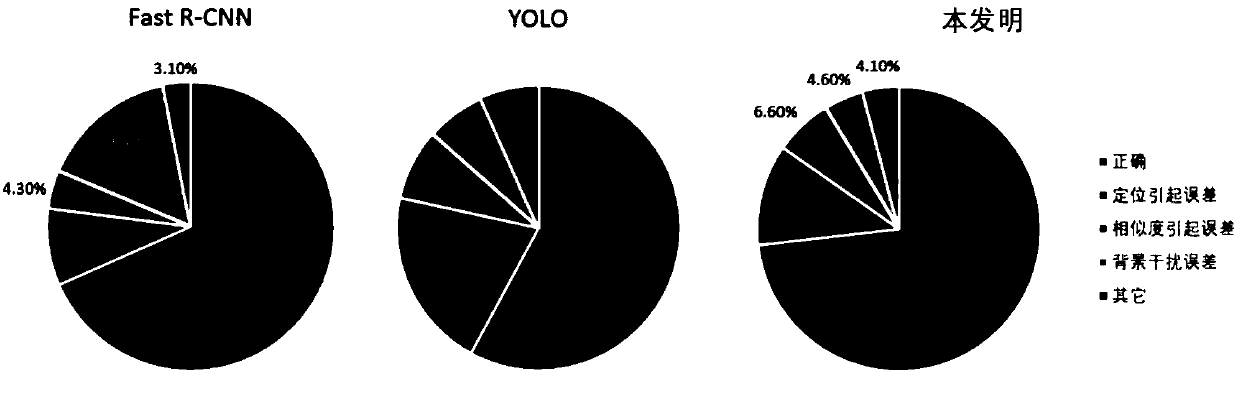

Target detection method based on multi-feature fusion of full convolutional network

ActiveCN107563381AIncrease training timeExtended test timeCharacter and pattern recognitionNeural learning methodsImaging FeatureConvolution

The invention designs a target detection method based on multi-feature fusion of a full convolutional network. The main technical features are that constructing a full convolutional neural network having six convolutional layer groups; using the first five groups of convolutional layers of the convolutional neural network to extract image features, and outputting the image features to be fused toform a fusion feature chart; performing convolutional processing on the fused feature map to directly generate a fixed number of target frames of different sizes; and calculating a classification error and positioning error between the target frames generated by the convolutional neural network and real frames, utilizing a random gradient descent method to reduce a training error to obtain parameters of a final training model, and finally carrying out a test to obtain a target detection result. The target detection method based on multi-feature fusion of the full convolutional network utilizesa powerful capability of representing a target of a deep convolutional network, constructs the full convolutional neural network used for target detection, proposes a new fusion feature method, improves detection speed and precision of an algorithm, and obtains a good target detection result.

Owner:ACADEMY OF BROADCASTING SCI STATE ADMINISTATION OF PRESS PUBLICATION RADIO FILM & TELEVISION +1

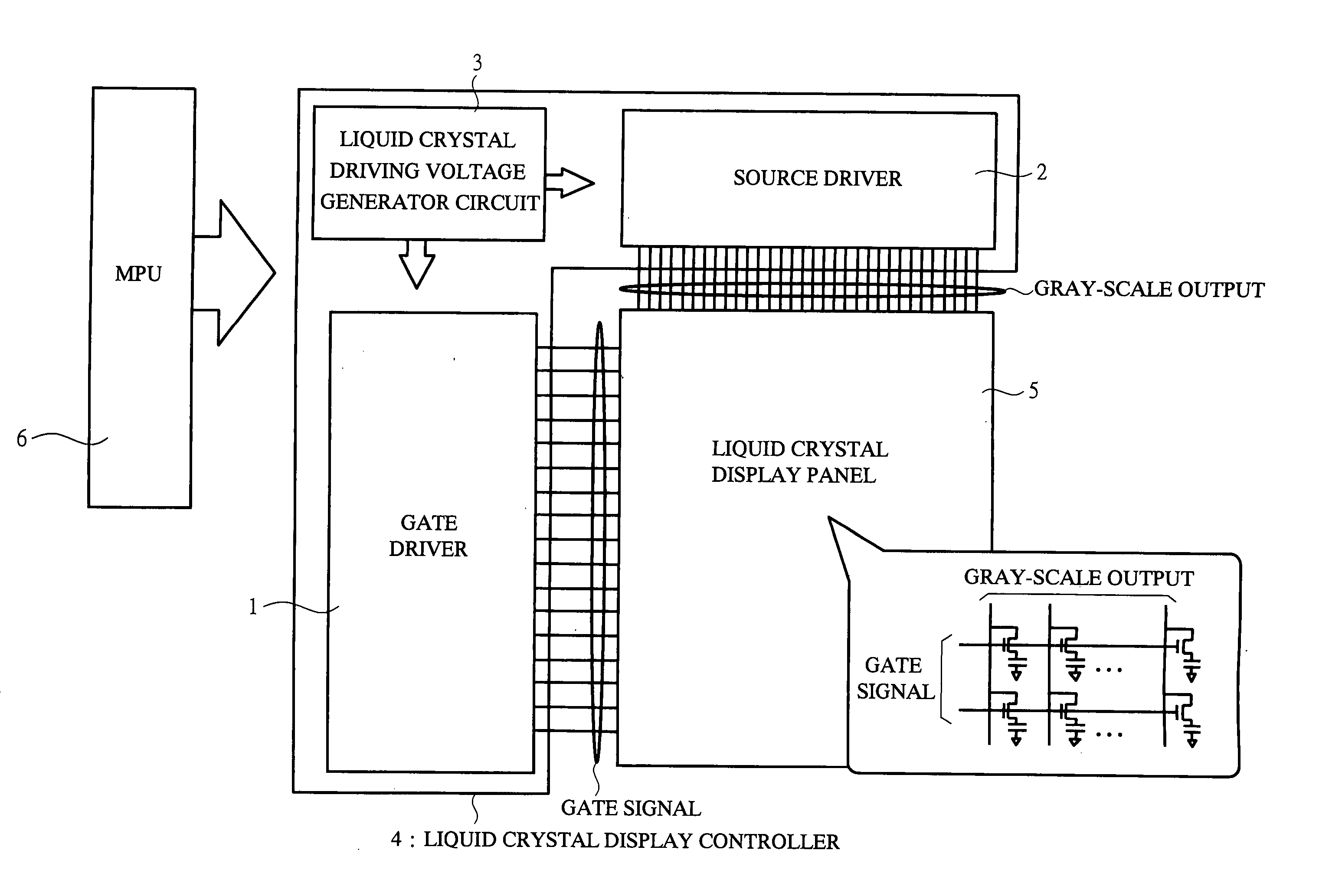

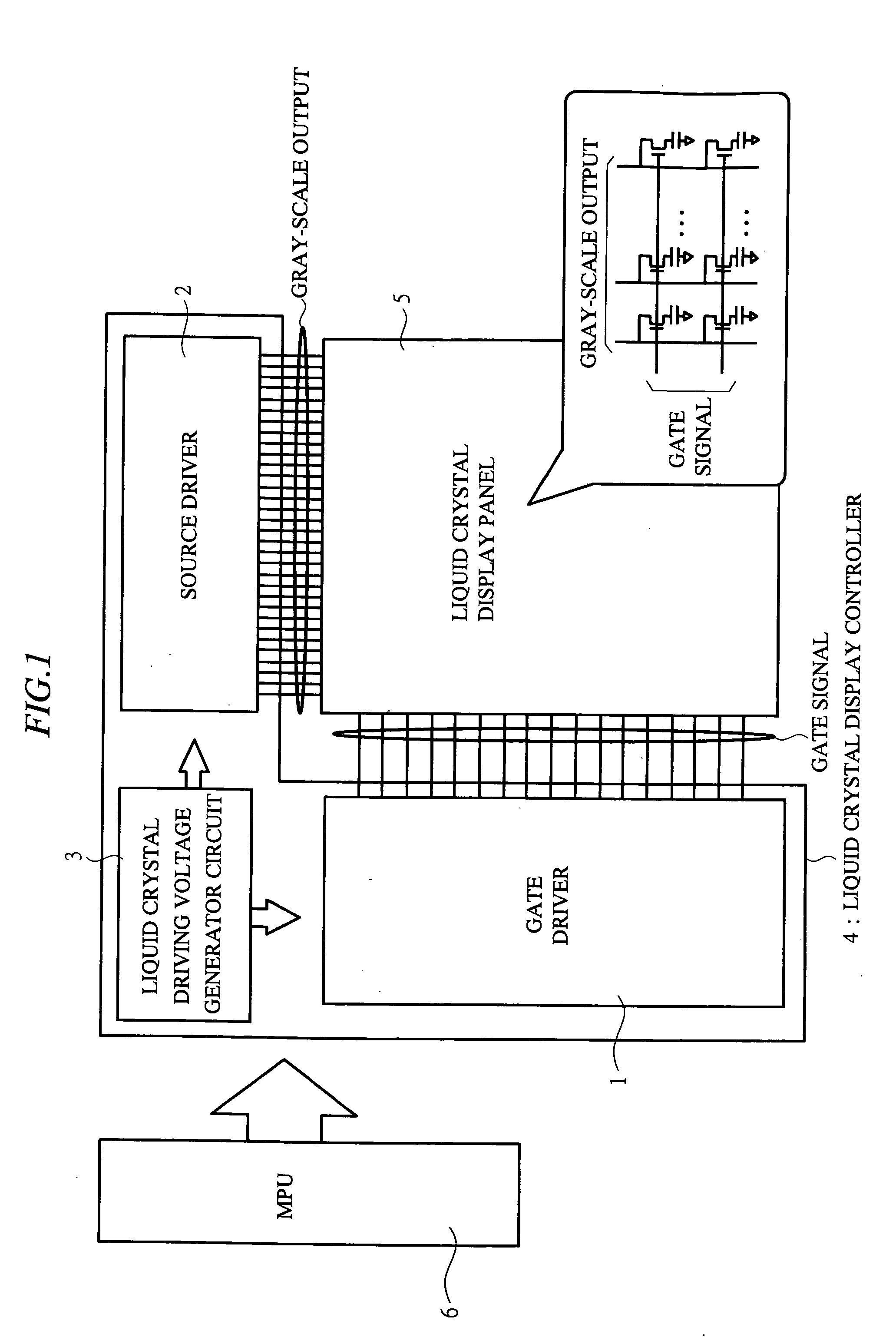

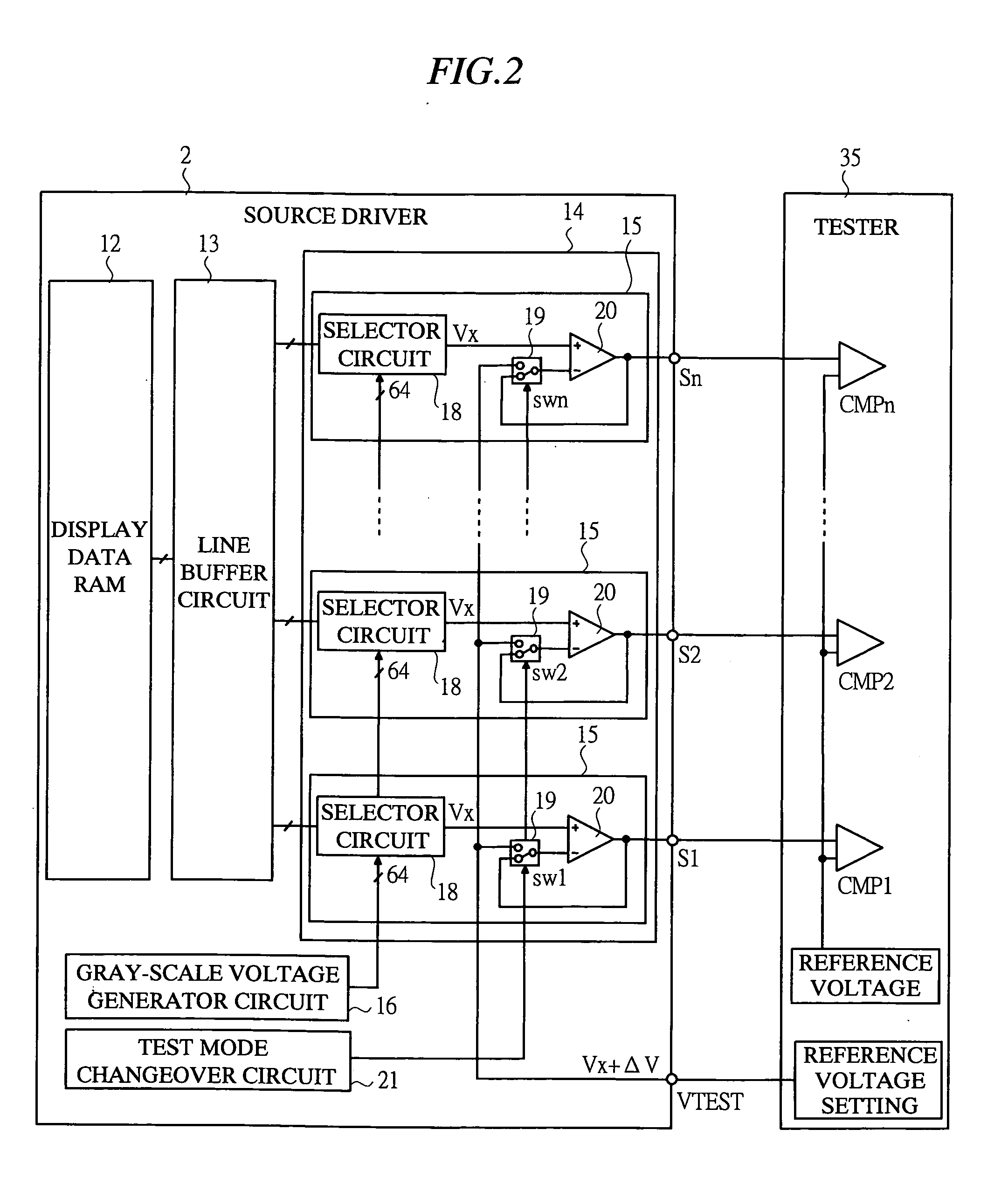

Semiconductor device and testing method thereof

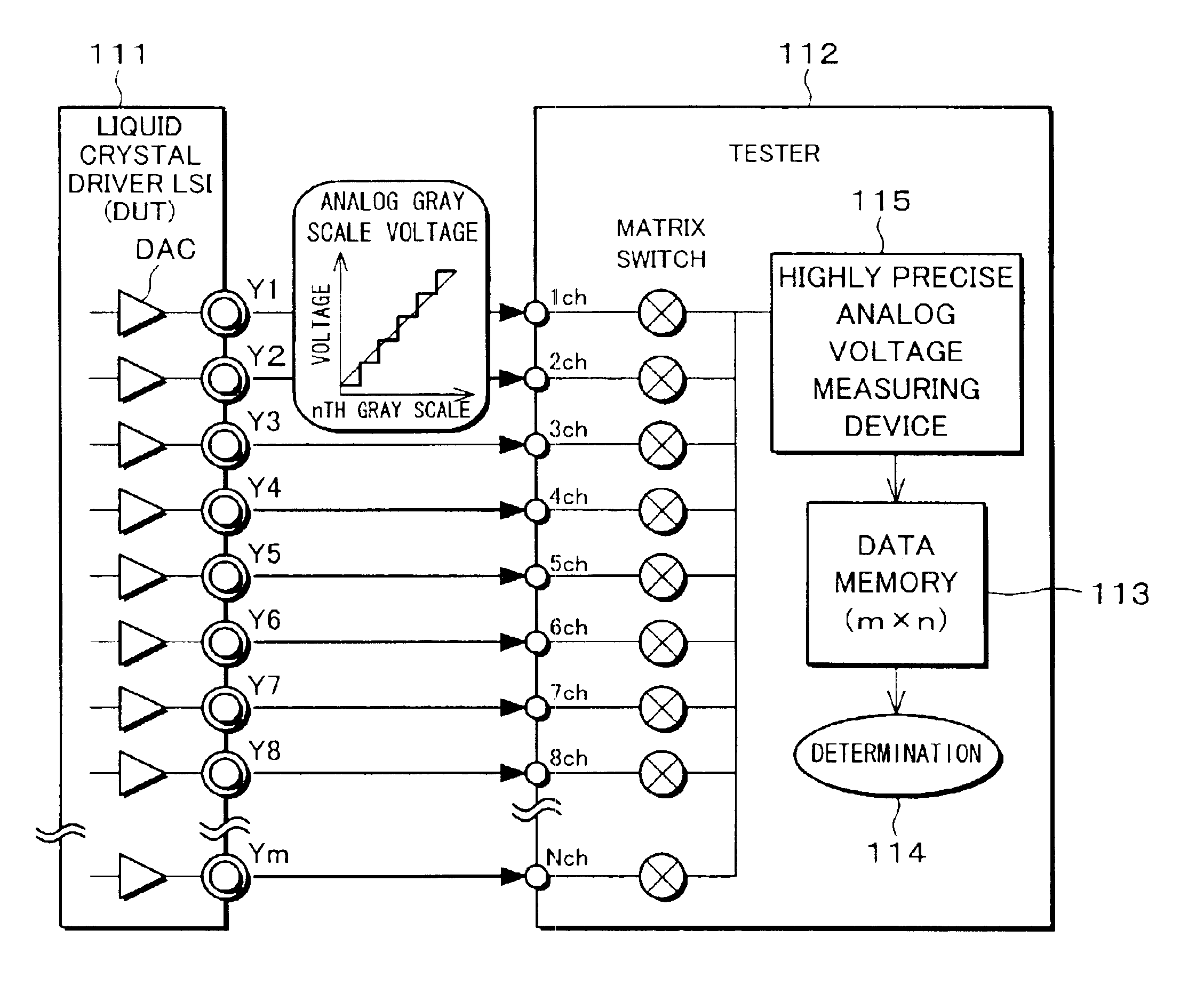

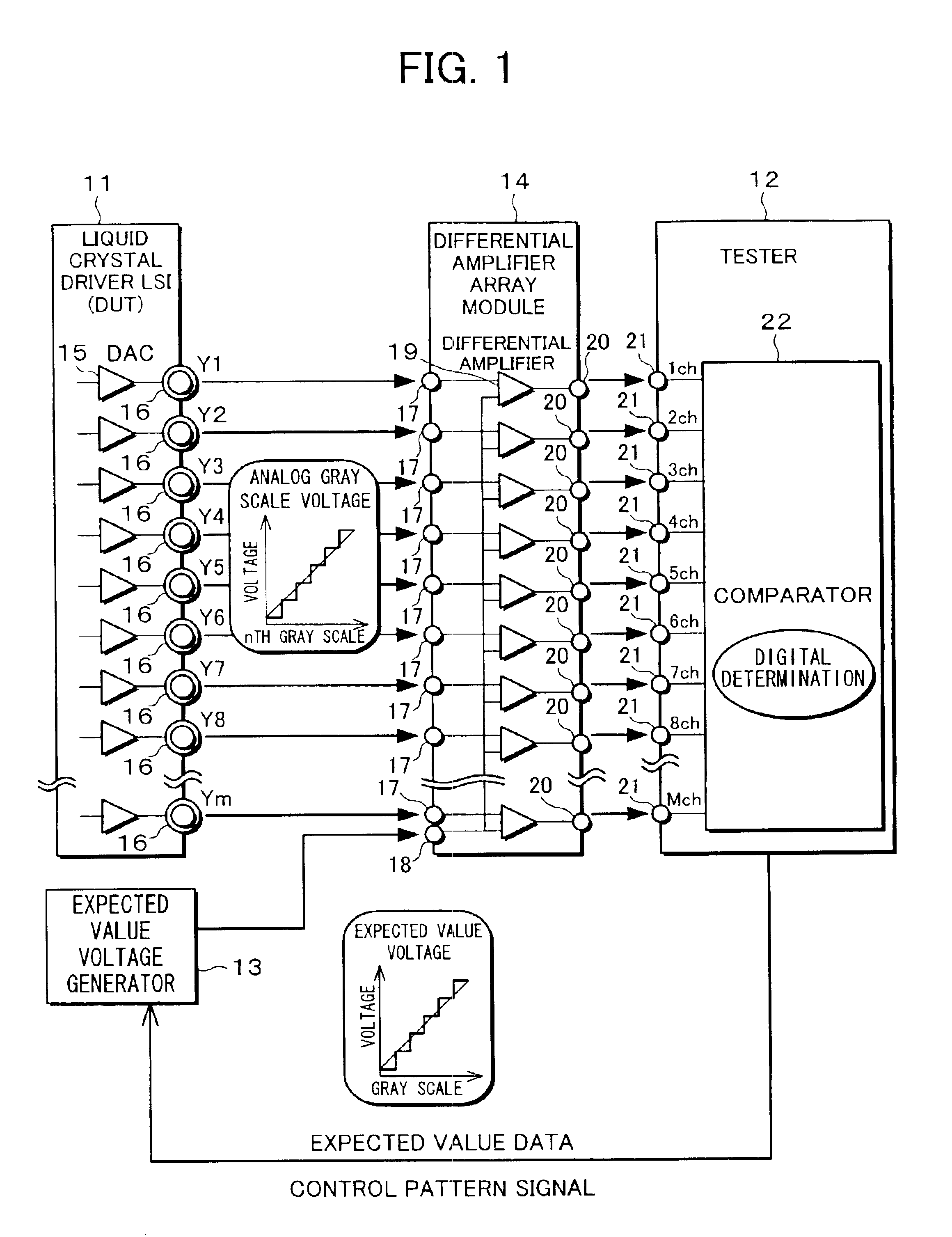

InactiveUS20050122300A1Extended test timeShorten the timeAnalog circuit testingSolid-state devicesDriver circuitVoltage generator

A semiconductor device according to the present invention has a liquid crystal driver circuit, and when gray-scale voltage thereof is tested, the gray-scale voltage (Vx) generated in a gray-scale voltage generator circuit provided therein is compared with reference voltage (e.g., Vx+ΔV) generated for testing the gray-scale voltage and the test result is output as binarized voltage from external terminals of the semiconductor device. This can speed up the gray-scale voltage test even in the case of higher gray scale in the liquid crystal driver circuit or increased number of output terminals of the semiconductor device. Therefore, it becomes possible to reduce the time and cost required for the test.

Owner:RENESAS ELECTRONICS CORP

Halogen-free resin composition and application thereof

ActiveCN105542394AExtended dip soldering resistanceLow water absorptionElectrical equipmentCircuit susbtrate materialsEpoxyHeat resistance

The invention discloses a halogen-free resin composition which is prepared from the following components in parts by weight: 15 to 30 parts of epoxy resin with a large epoxy equivalent, 20 to 55 parts of epoxy resin with a small epoxy equivalent, 10 to 45 parts of a curing agent, and 0.03 to 2.0 parts of a curing accelerant, wherein the equivalent of the epoxy resin with the large epoxy equivalent is 300 to 800g / eq, and the equivalent of the epoxy resin with the small epoxy equivalent is 170 to 280g / eq; the degree of functionality of the epoxy resin is 2 to 4. The effect of improving the heat resistance and the wet resistance of a copper foil layer-covered pressing plate prepared by the composition disclosed by the invention is outstanding; the problems that a copper foil layer-covered pressing plate CEM-1 is easy to crack and layer under a high-temperature condition and easily absorbs water under a wet condition are solved; the reliability of the CEM-1 under the wet and hot environments is enhanced; furthermore, the halogen-free resin composition is halogen-free and environment-friendly.

Owner:SHAANXI SHENGYI TECH

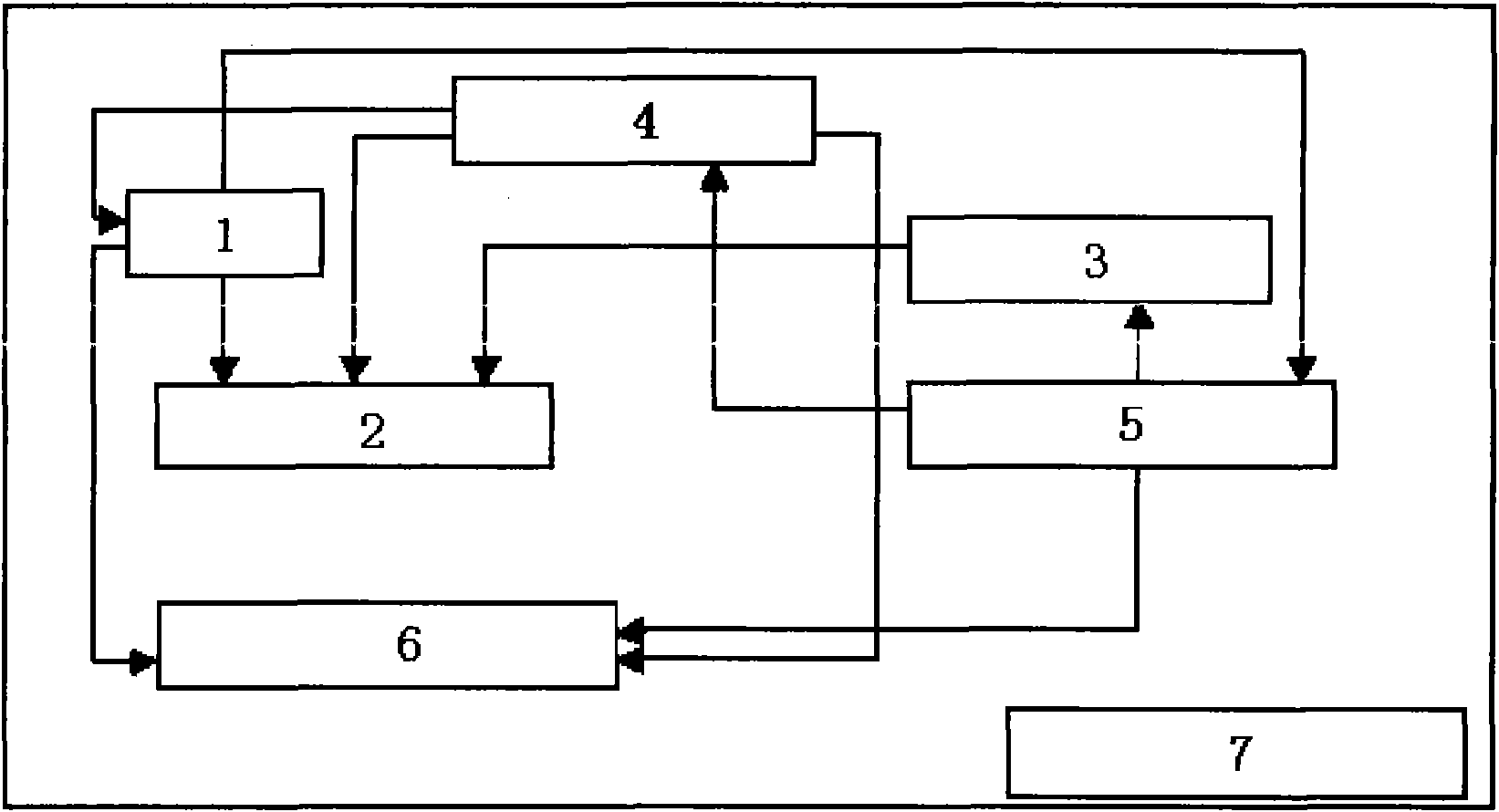

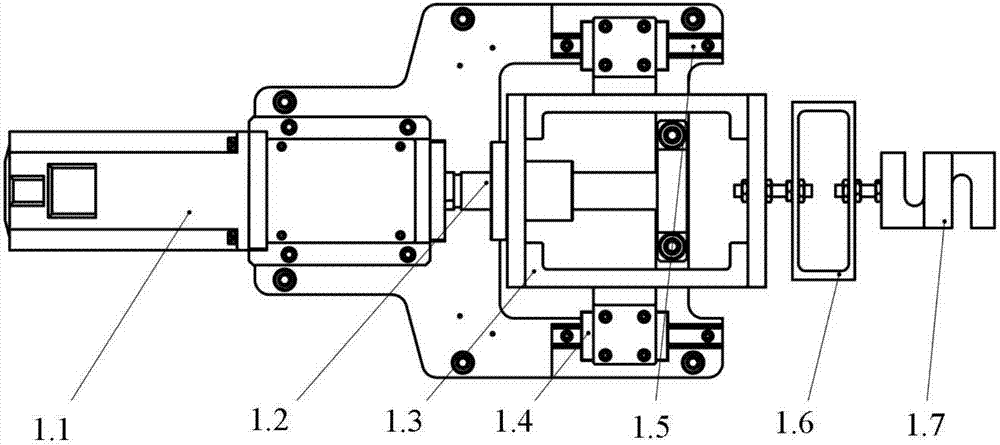

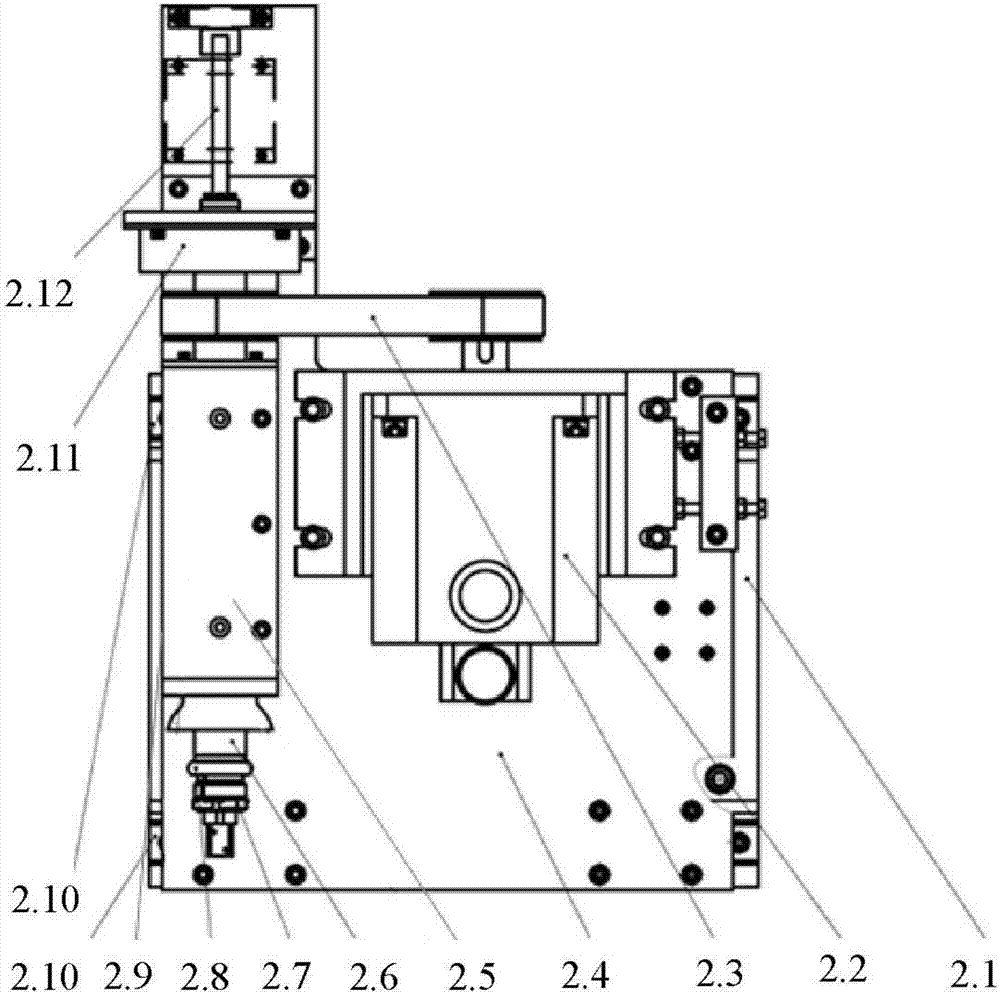

Simulation test method and simulation test system for unmanned aerial vehicle (UAV) system

InactiveCN102109418AReduce flight riskAvoid flying risksStructural/machines measurementBackground informationReal time display

The invention discloses a simulation test method and a simulation test system for an unmanned aerial vehicle (UAV) system. The method comprises the following steps of: arranging the UAV system on a multi-latitude motion platform system, and providing the multidimensional motion of the UAV system by using the multi-latitude motion platform system; providing signal data of simulated motion for the UAV system by using a signal source simulation system; providing a control logic process of motion simulation, platform motion amount closed loop measurement and the corresponding measurement of the UAV system by using a control and measurement system; and providing a drive source required by the motion of the multi-latitude motion platform system by using a motion servo system, and providing a parameter record, real-time display and superposed background information by using a simulation parameter recording and displaying system. By the method and the system, the UAV system can be subjected to dynamic test check and simulation on the ground, and actual flight is replaced, so that actual flight risk is obviously reduced, a test verification period is shortened, and cost is saved.

Owner:贵州贵航无人机有限责任公司

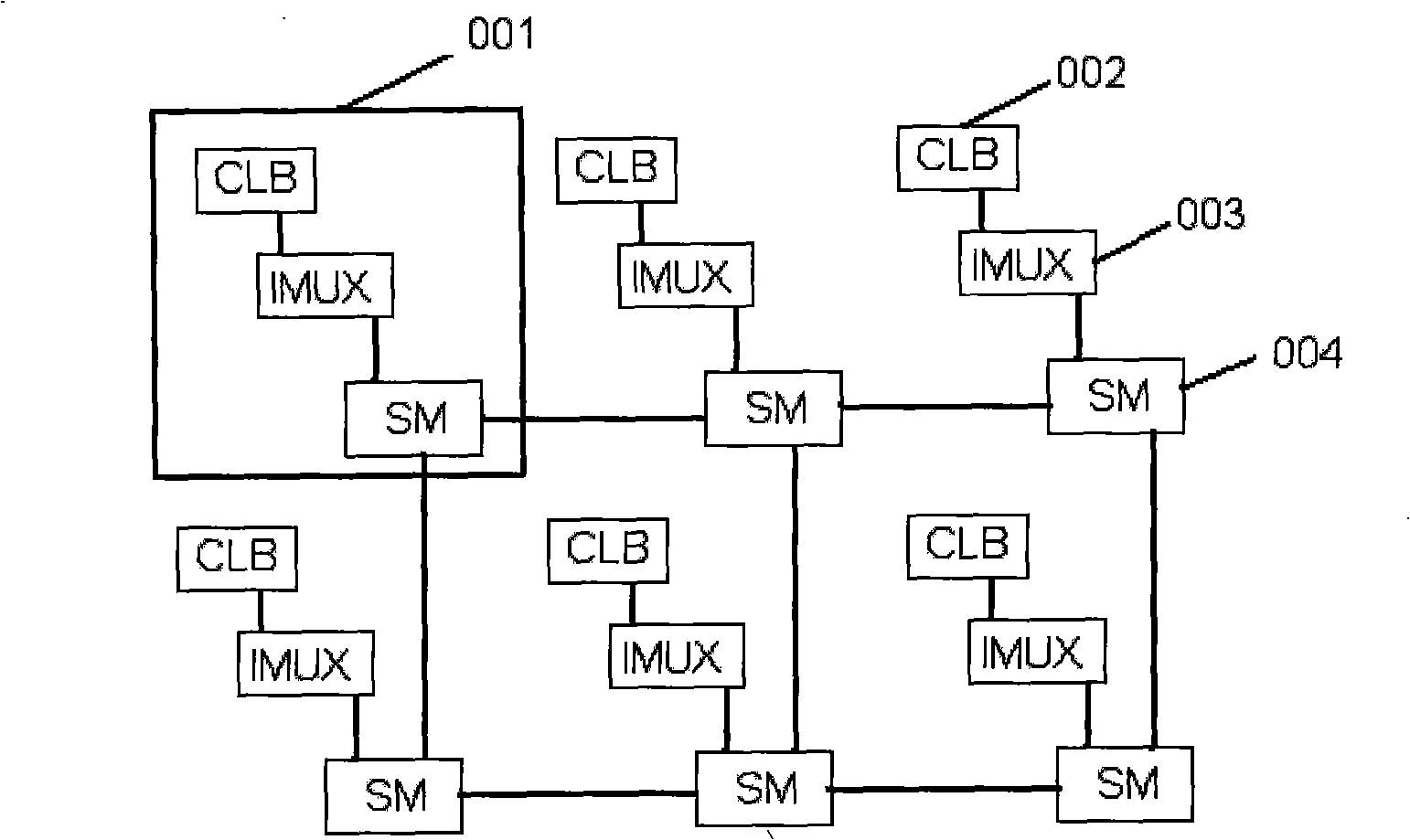

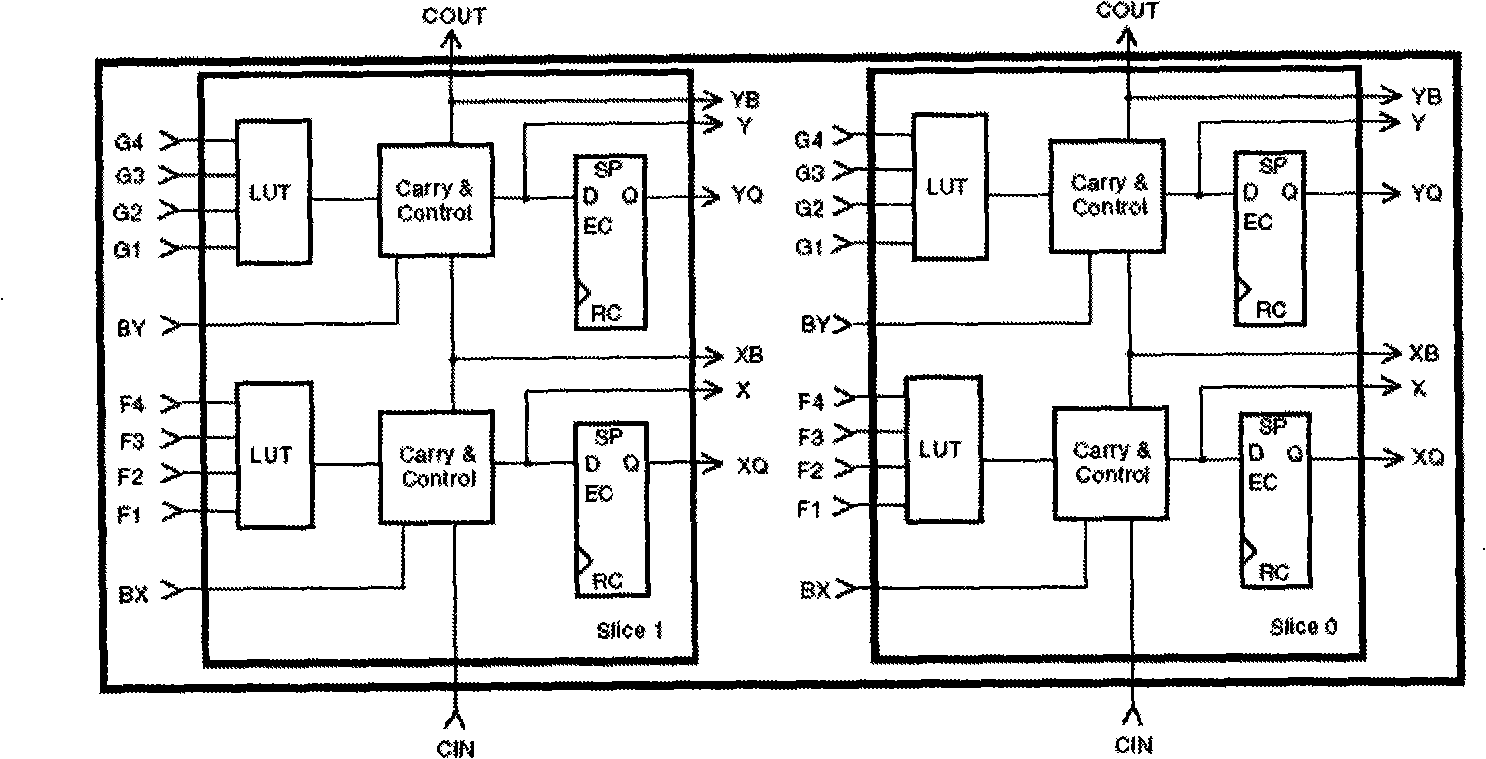

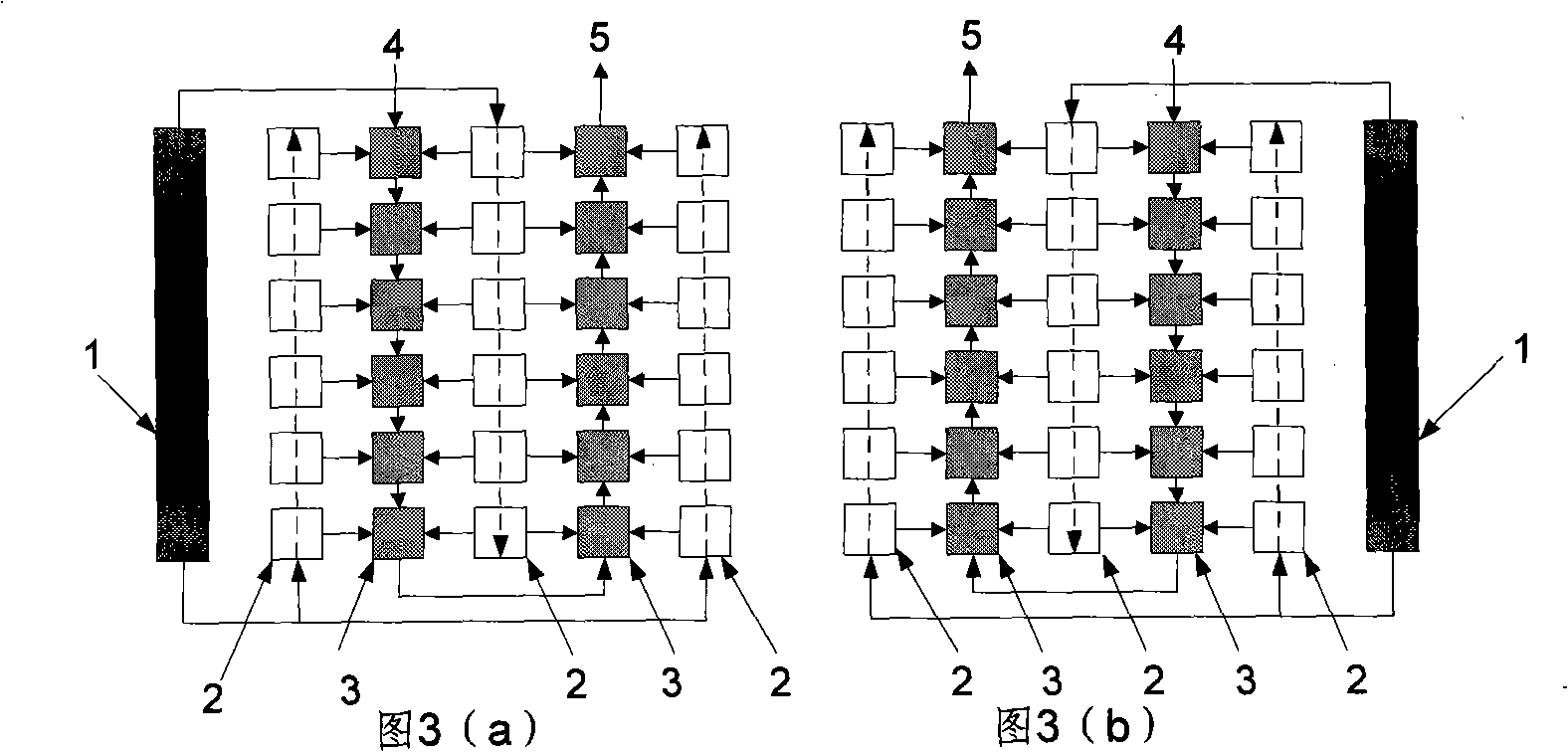

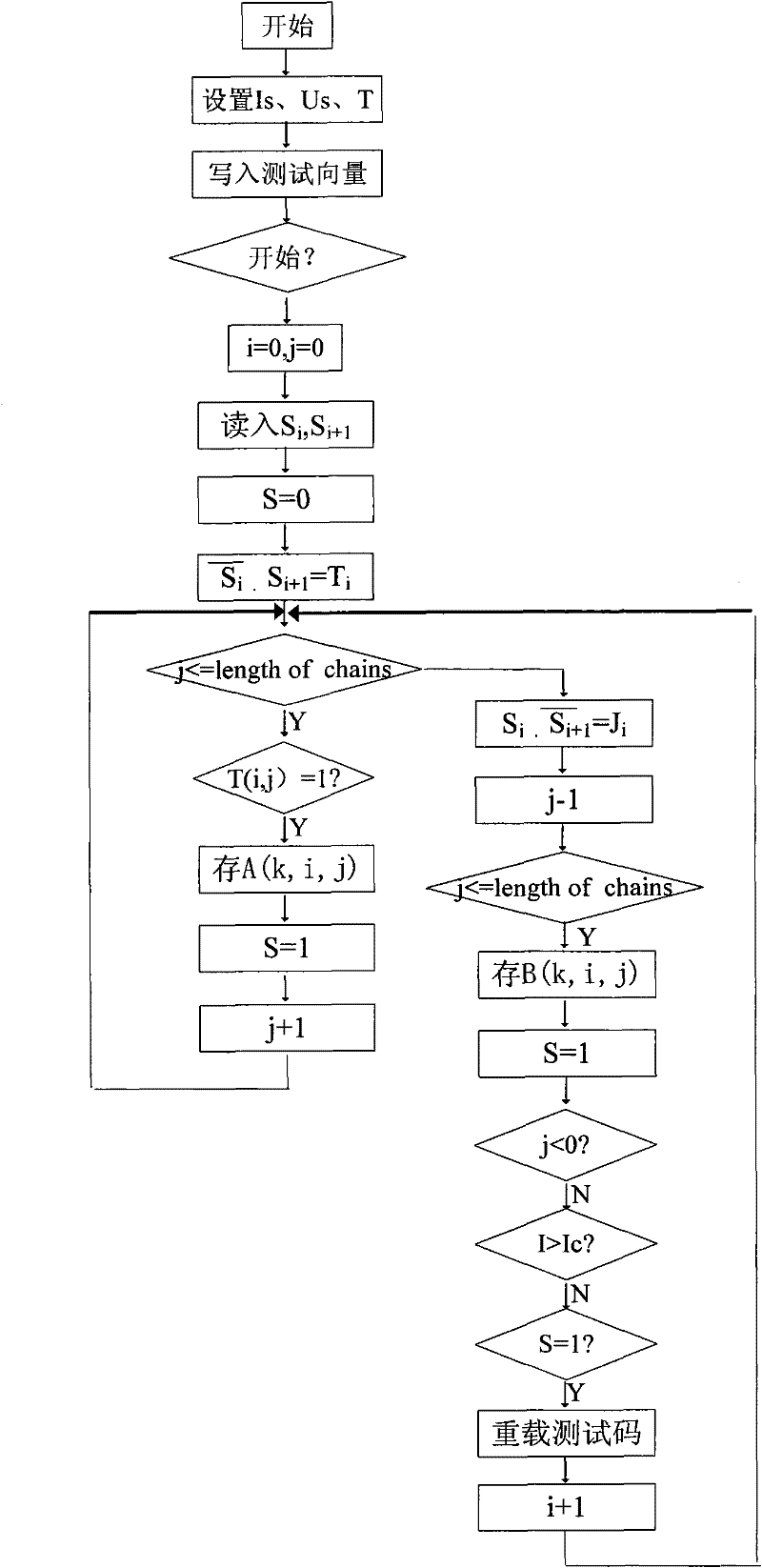

Built-in self-test method of FPGA logical resource

ActiveCN101515020ASimple configuration structureDifficult to designElectrical testingTest efficiencyLeft half

The invention provides a built-in self-test method of FPGA logical resource. The internal logical module of FPGA is alternately divided into a left half part and a right half part according to row. In the test process, the logical module array of the right half part is firstly configured as a to-be-tested circuit, and the rest logical module arrays are configured as a test vector generating circuit and an output response analyzing circuit, and then the logical module array of the left half part is configured as the to-be-tested circuit, and the rest logical module arrays are configured as the test vector generating circuit and the output response analyzing circuit. The circuit structure is not changed in each process. The logical resource is covered by multiple configurations and the test result is output by a built-in scan register chain. All configurations in the invention are as follows: all logical modules configured as the response analyzing circuits are in cascade connection end to end according to one-dimensional array, so as to simplify the self-test result retrieval manner. Provided that the test coverage is 100%, the built-in self-test method reduces times of the configurations of FPGA logical resource, reduces test cost and increases test flexibility, so as to improve test efficiency.

Owner:BEIJING MXTRONICS CORP +1

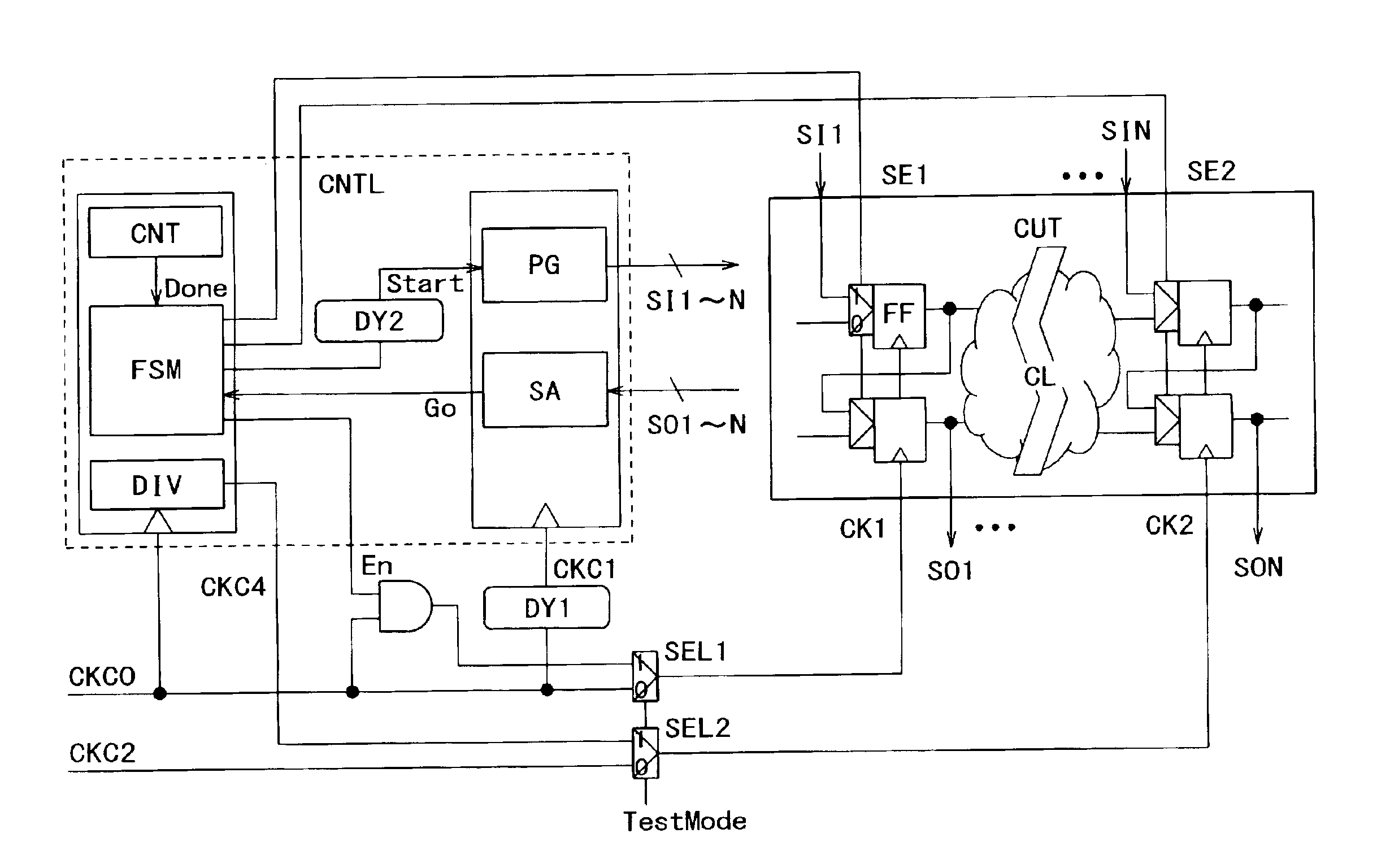

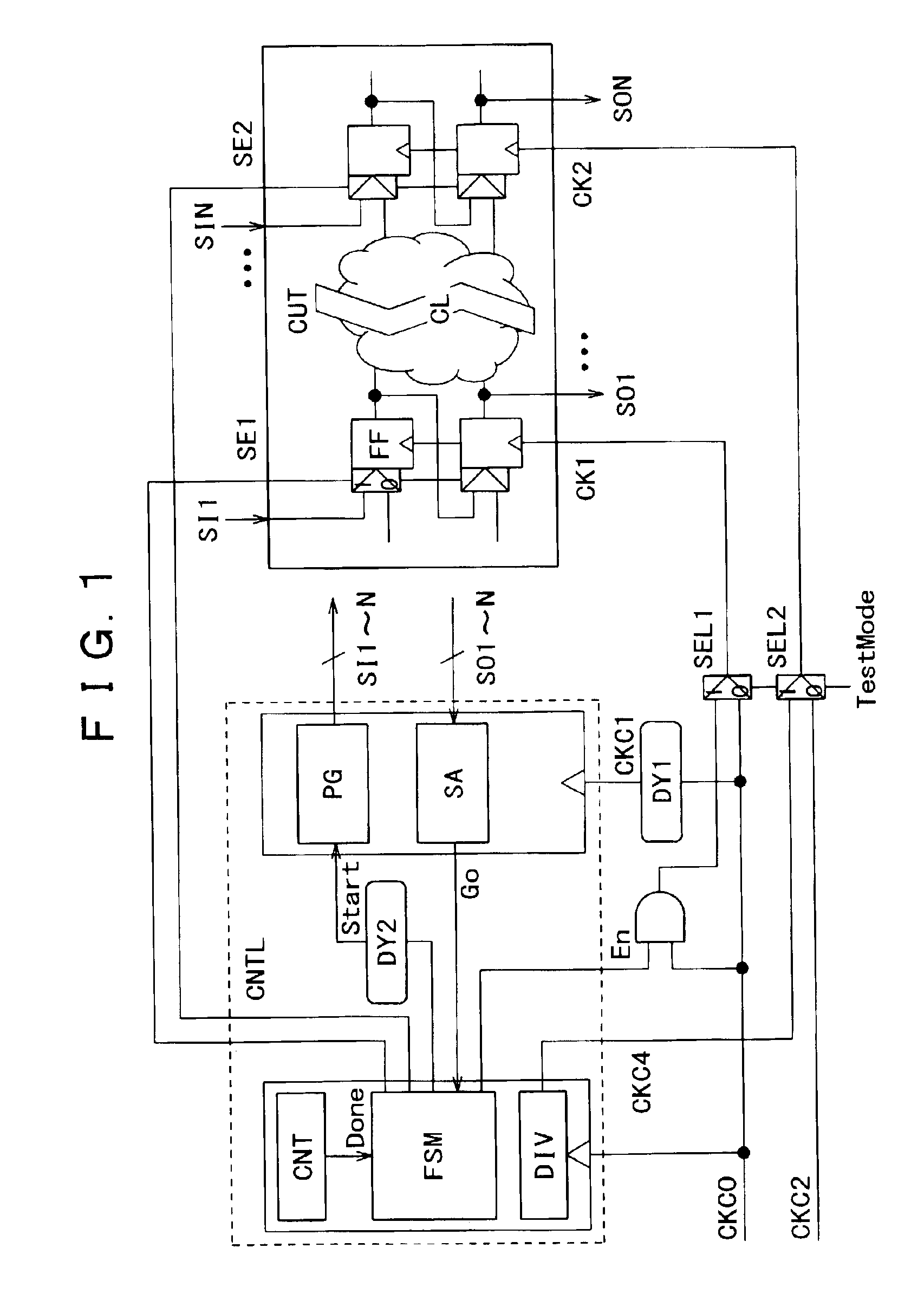

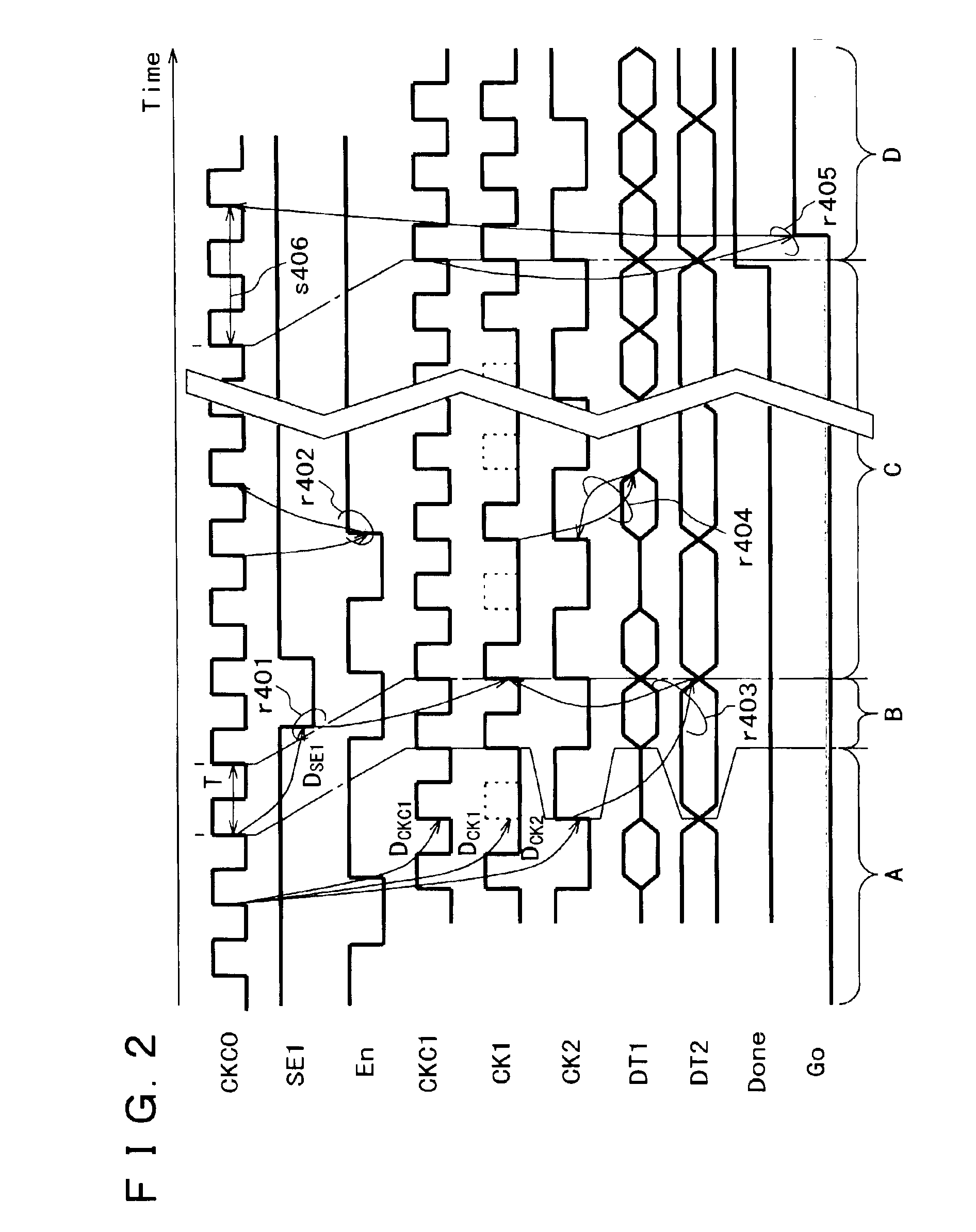

Semiconductor integrated circuit and its design methodology

ActiveUS6907585B2Reduce differenceWithout increasing test timeElectronic circuit testingDetecting faulty computer hardwareIntegrated circuitIt design

A method and device are provided for applying logic BIST at speed for large-scale and high-performance logic circuits without increasing test time, and decreasing test costs as a result. In one example, a logic BIST controller is divided into two portions. A clock signal having a small delay is used to drive a partial circuit that supplies a user circuit with a scan enable signal and a clock signal. A clock signal having a large delay is used to drive a partial circuit that supplies the user circuit with a test pattern and collects a test result.

Owner:RENESAS ELECTRONICS CORP

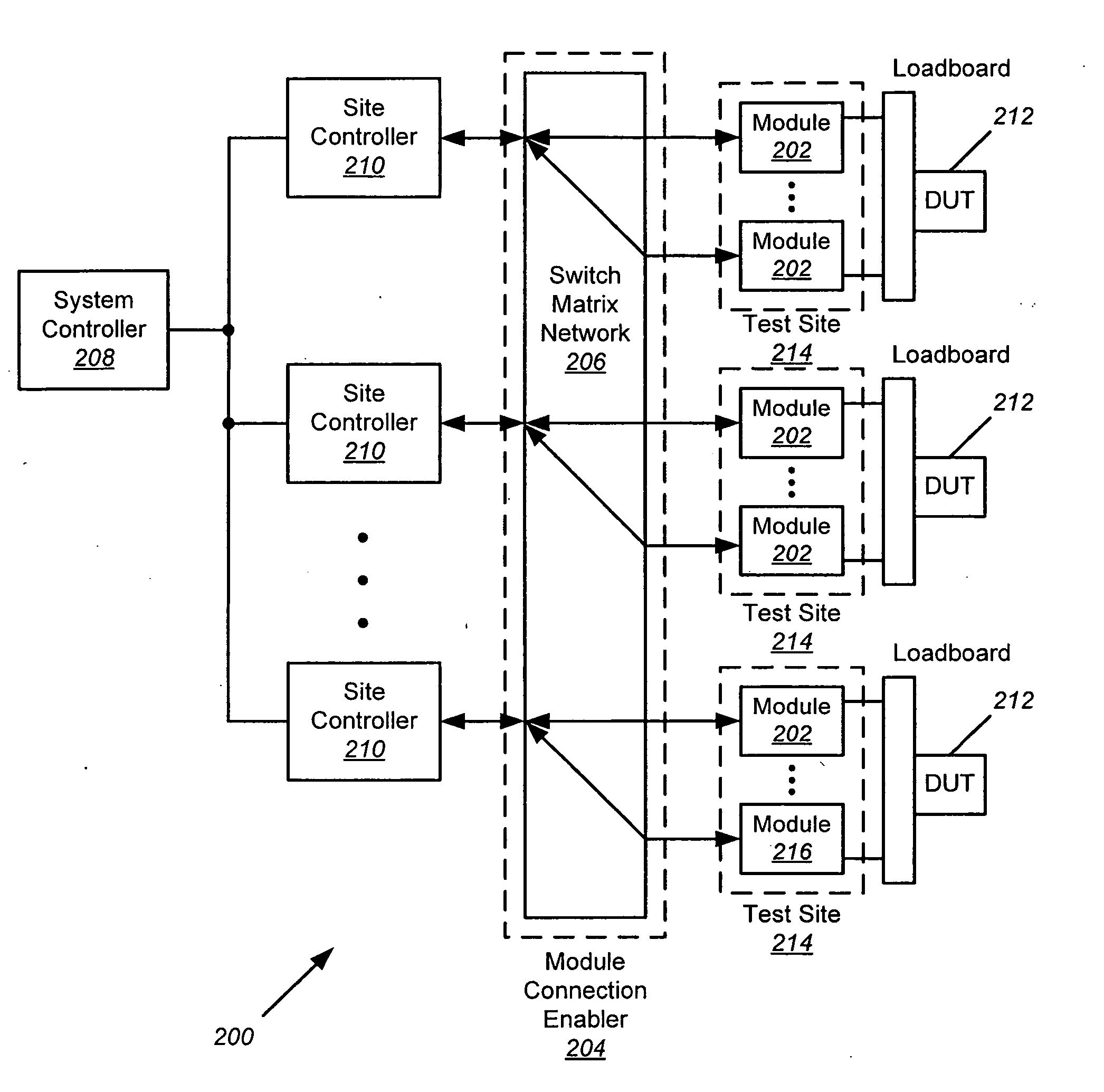

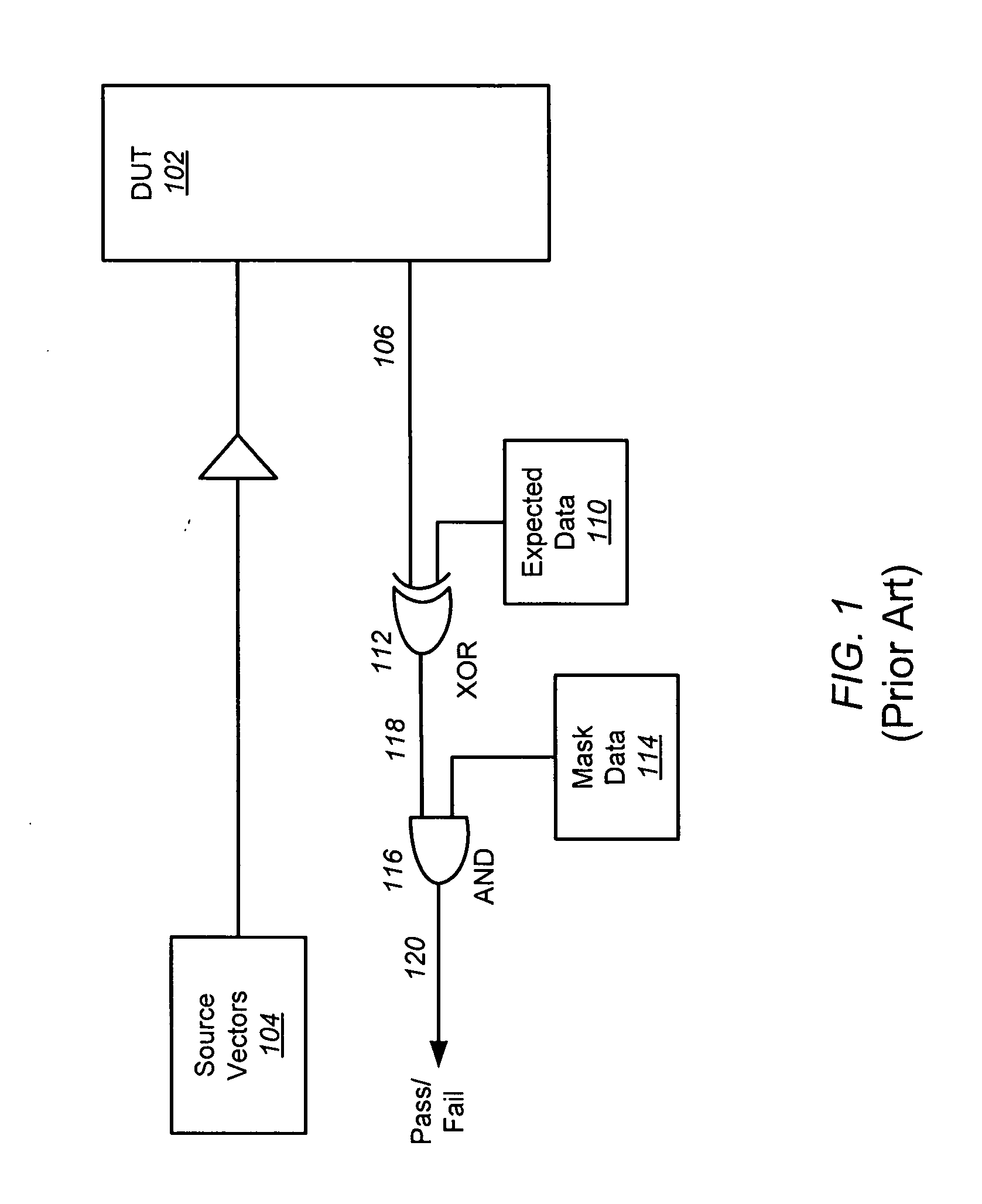

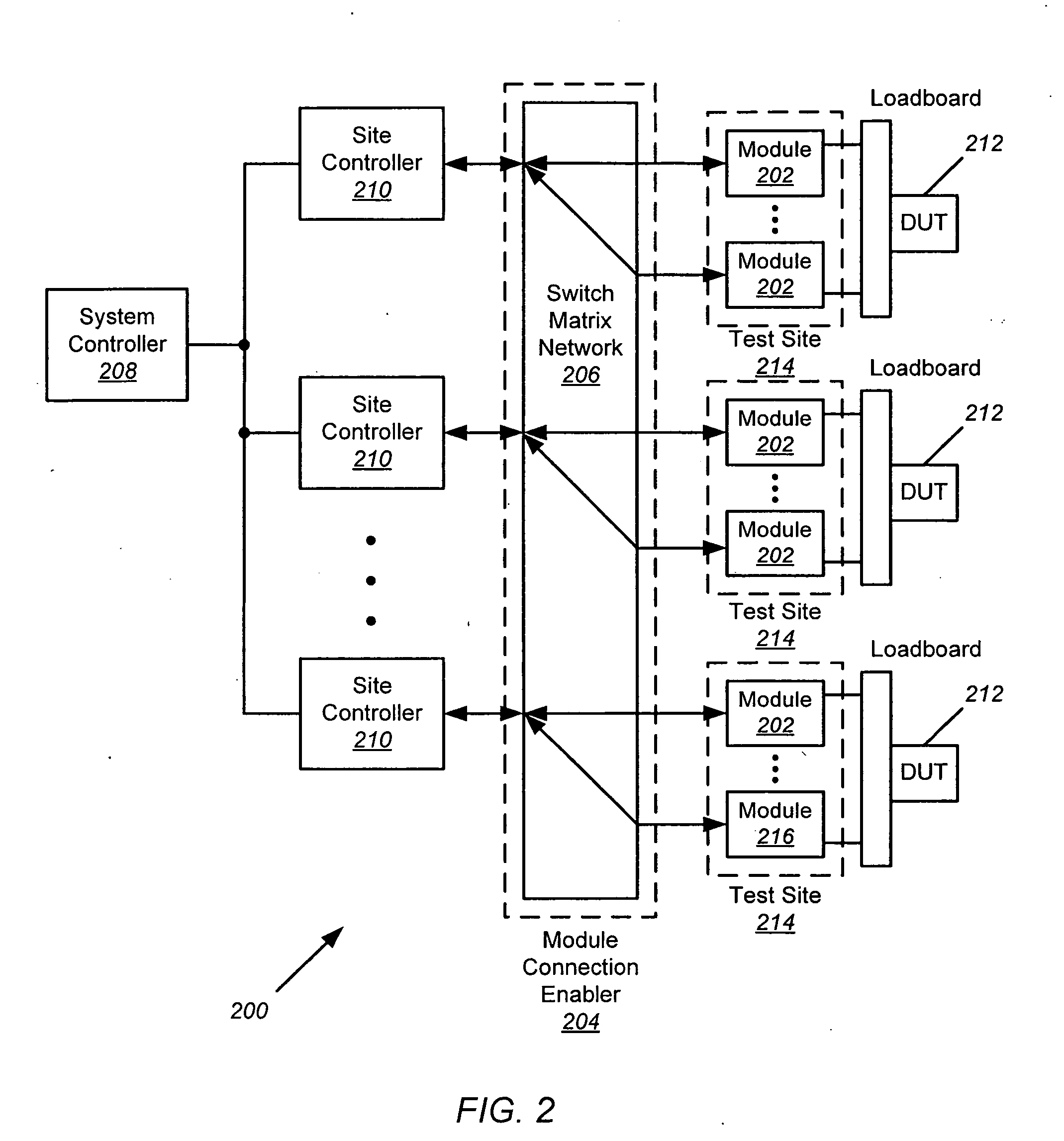

Pattern controlled, full speed ATE compare capability for deterministic & non-deterministic IC data

InactiveUS20080126899A1Guaranteed to workExtended test timeDigital circuit testingSemiconductor/solid-state device testing/measurementData compressionData stream

Pattern controllable LFSRs or MISRs are disclosed that are able to mask indeterminate states while performing tests on DUT outputs. At appropriate times, the MISRs or the LFSRs will mask the data being input to the MISRs or the LFSRs so that indeterminate states are not received. This allows fast / complex ATE Rx memory to be replaced by slower and smaller MISR pattern memory. At the end of a test period, the LFSRs or MISRs generate signatures which are then compared to a set of possible valid signatures for non-deterministic data. A pass / fail result is produced. By masking indeterminate states, fewer valid signatures need to be stored. Masking of the MISRs or LFSRs may be based on the fact that indeterminate states and good data in a serial output data stream tend to occur in predictable patterns, or that good data may follow alignment characters. MISR or LFSR output signatures may also be employed to test individual pattern segments instead of the entire input test pattern. This expected DUT Rx data compression implementation works for one signature (deterministic) data as well.

Owner:ADVANTEST CORP

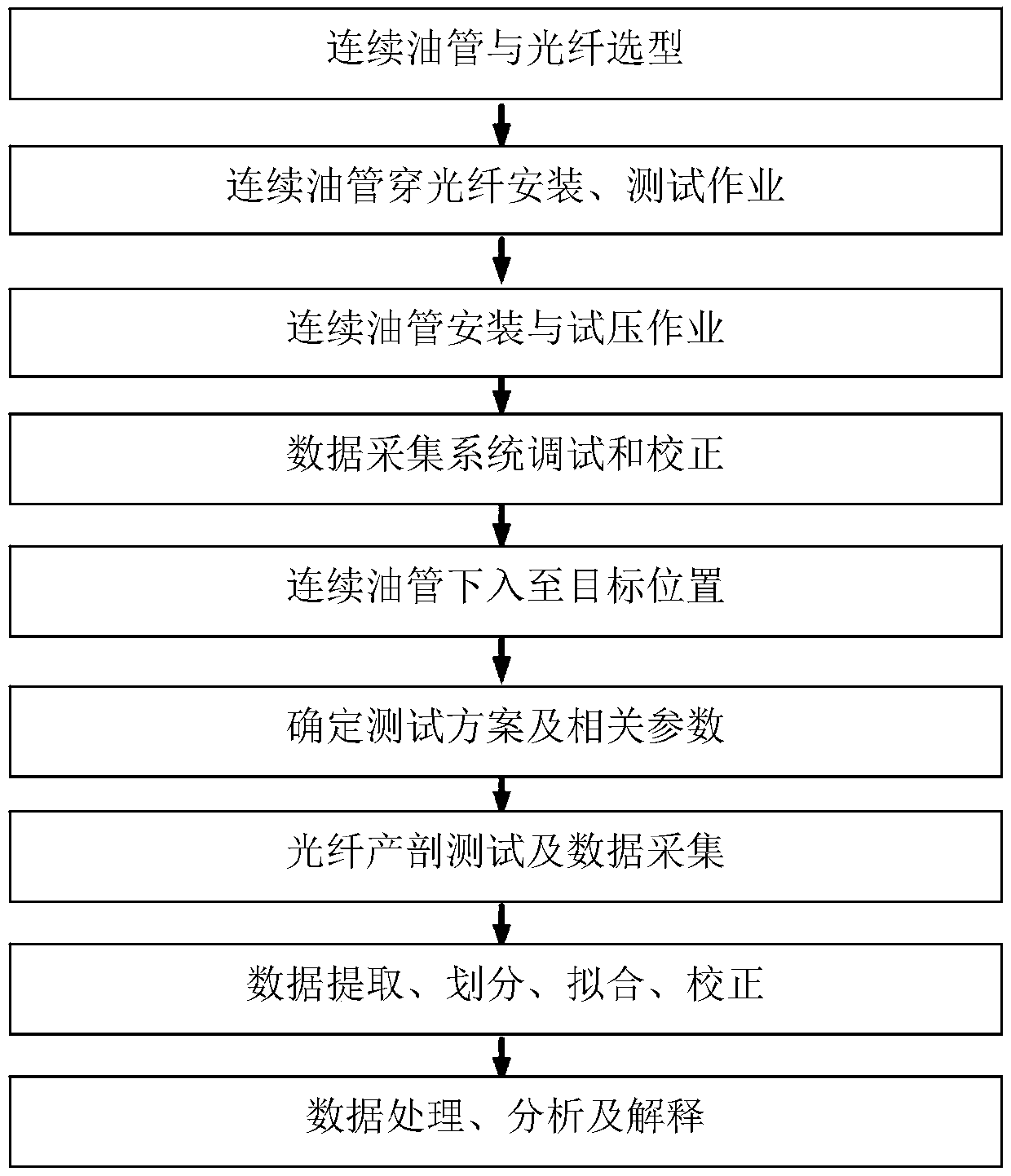

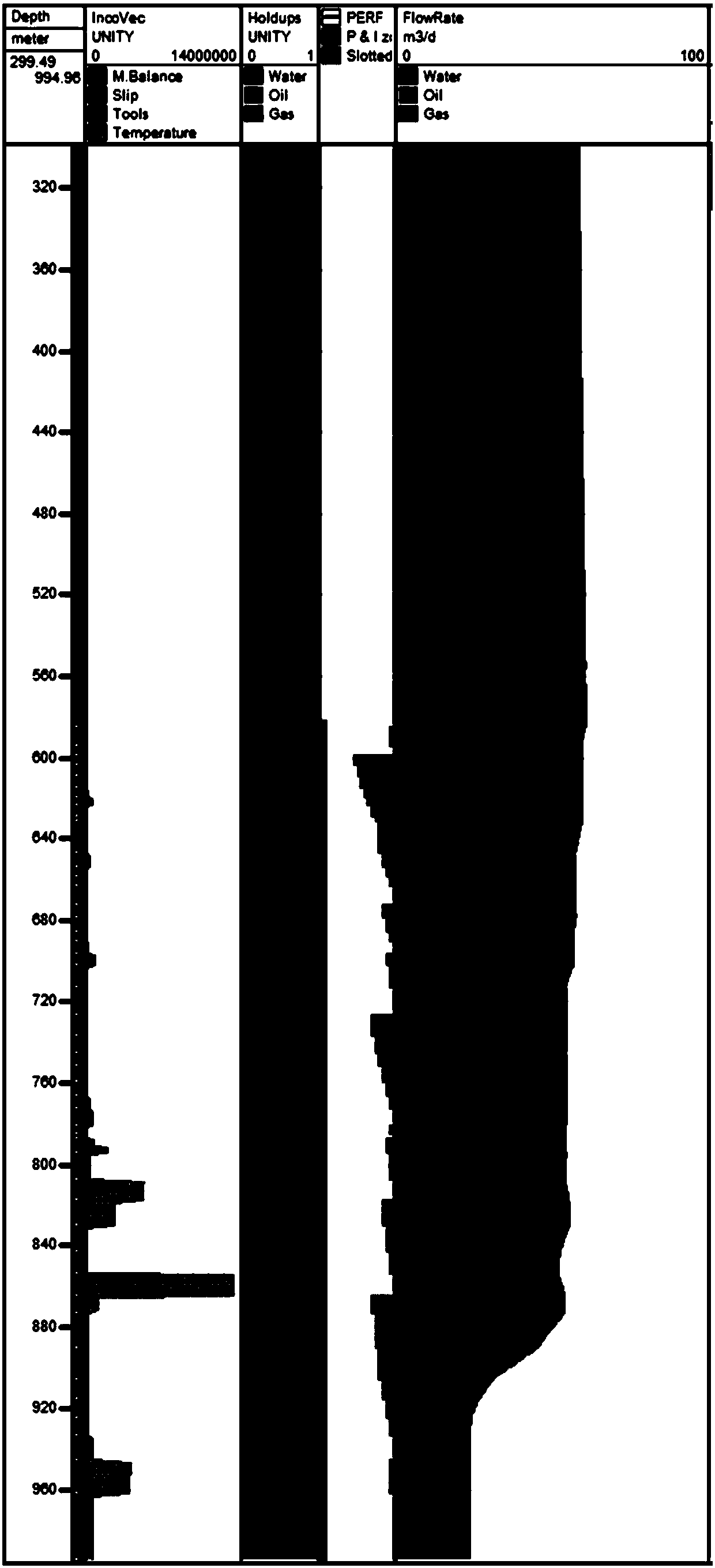

Method for testing producing profiles of horizontal well through coiled tubing optical fiber technology

The invention provides a method for testing producing profiles of a horizontal well through a coiled tubing optical fiber technology. The method comprises the following steps of type selection of coiled tubings and optical fibers, mounting of the optical fibers penetrating through the coiled tubings, testing operation, mounting and pressure testing operation of the continuous oil pipes, debuggingand rectifying of a data collecting system, putting down of the continuous oil pipes to target positions, determining of testing schemes and relevant parameters, testing of the optical fiber producingprofiles and collecting of data, extracting, dividing, fitting, rectifying and treatment of the data, and analyzing and explaining of the data. According to the method provided by the invention, no logging instrument is arranged, the continuous oil pipes are applied to put down the testing optical fibers to target layers, real-time monitoring of a whole shaft for 24 h is achieved accordingly, theproducing profiles of all tested well sections of the horizontal well and the producing contribution of all the producing layers are obtained, the well diameter limitation of putting down of producing oil pipes or large-drift-diameter bridge plugs in the well shaft can be overcome, or the problem of large construction difficulty of testing of the producing profiles of the large-slope horizontal well is solved.

Owner:ORIENT BAOLIN TECH DEV BEIJING

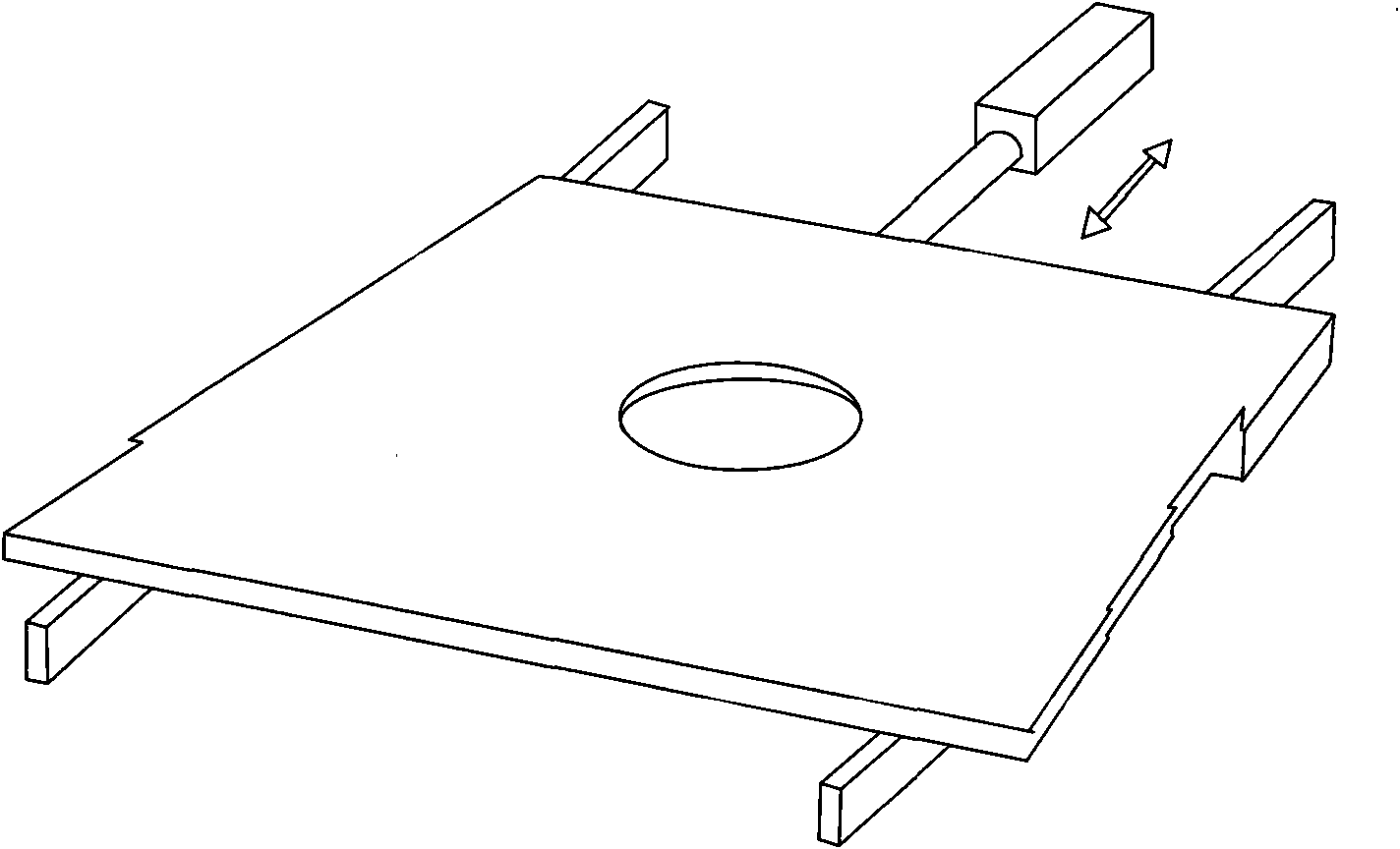

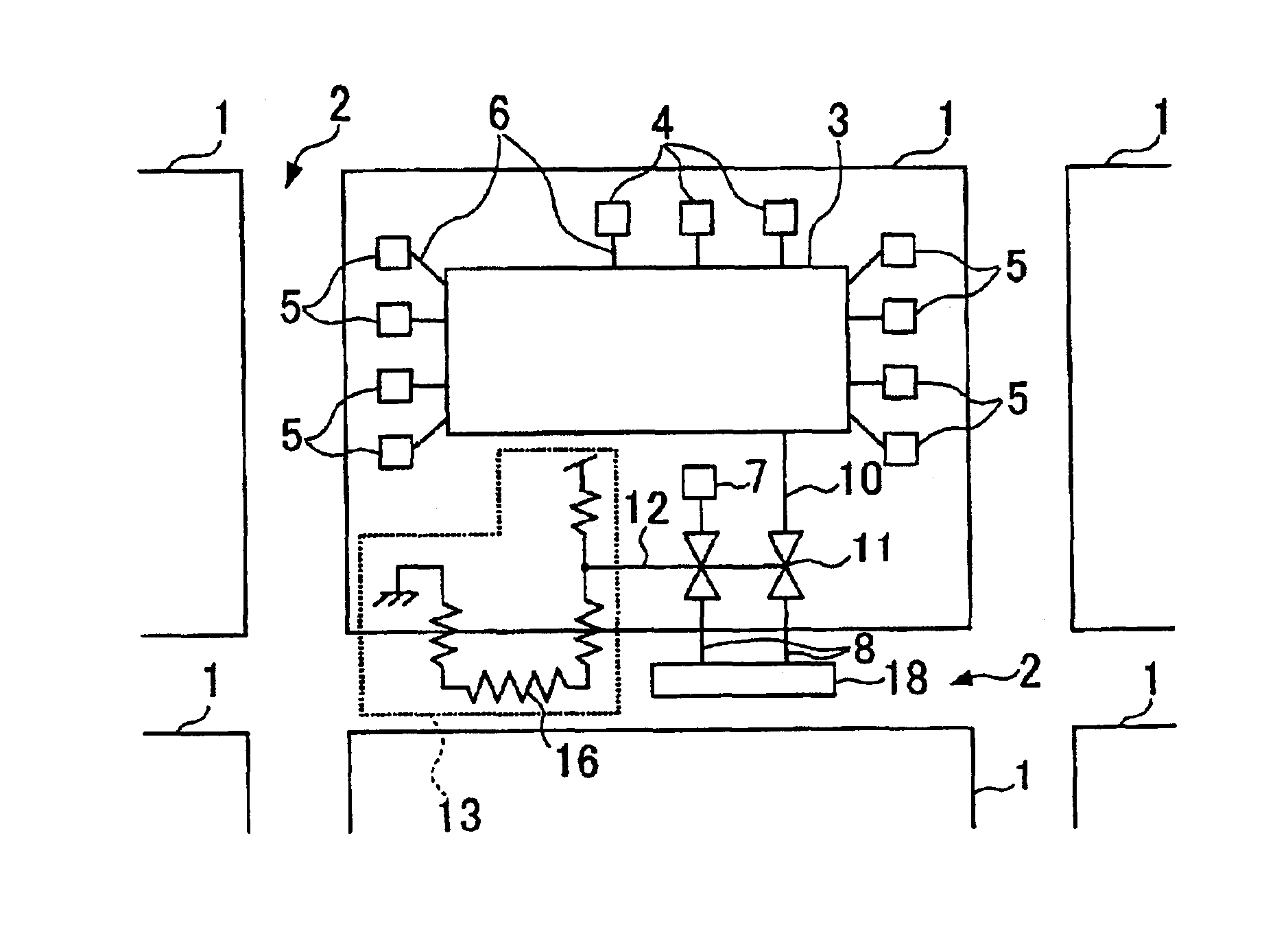

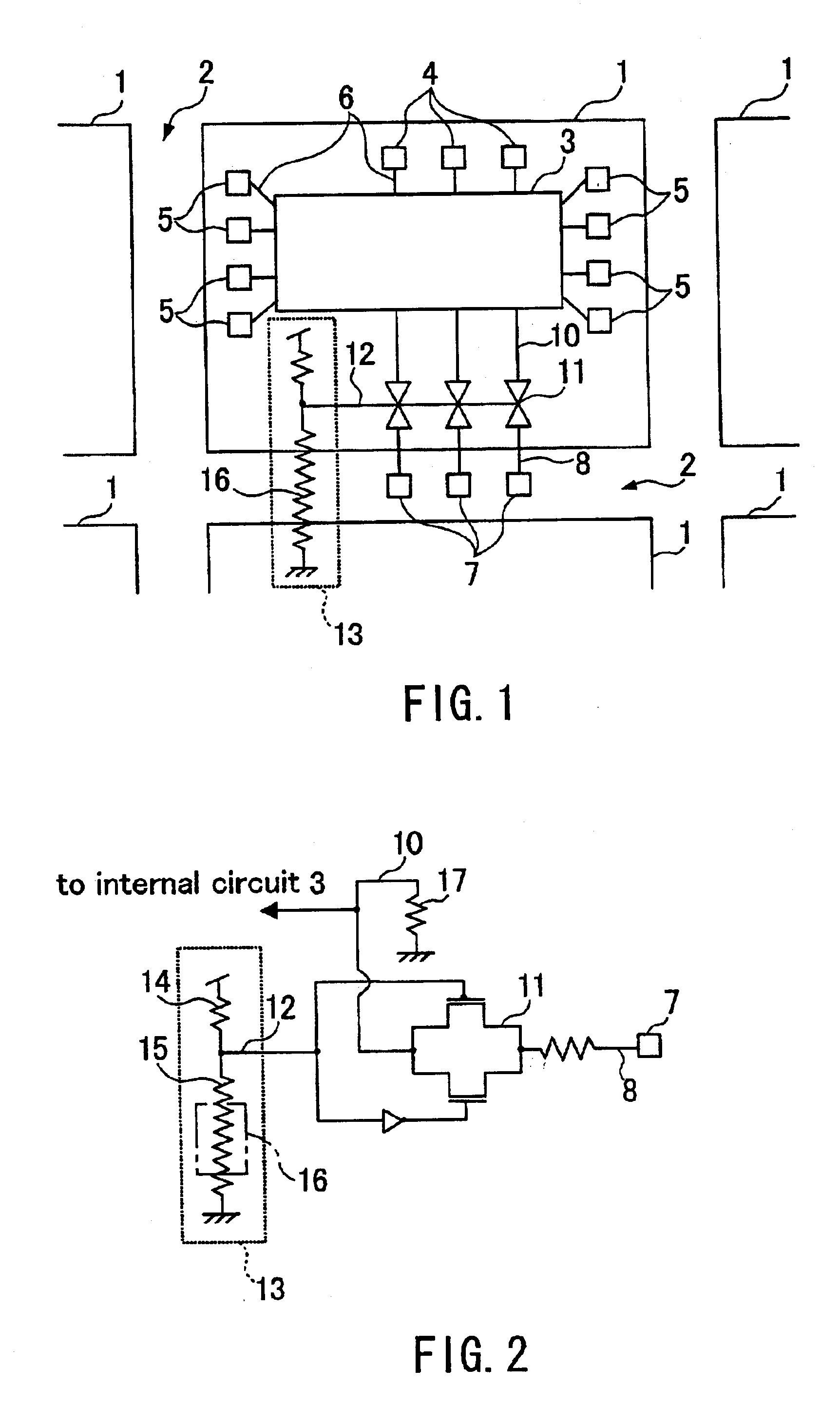

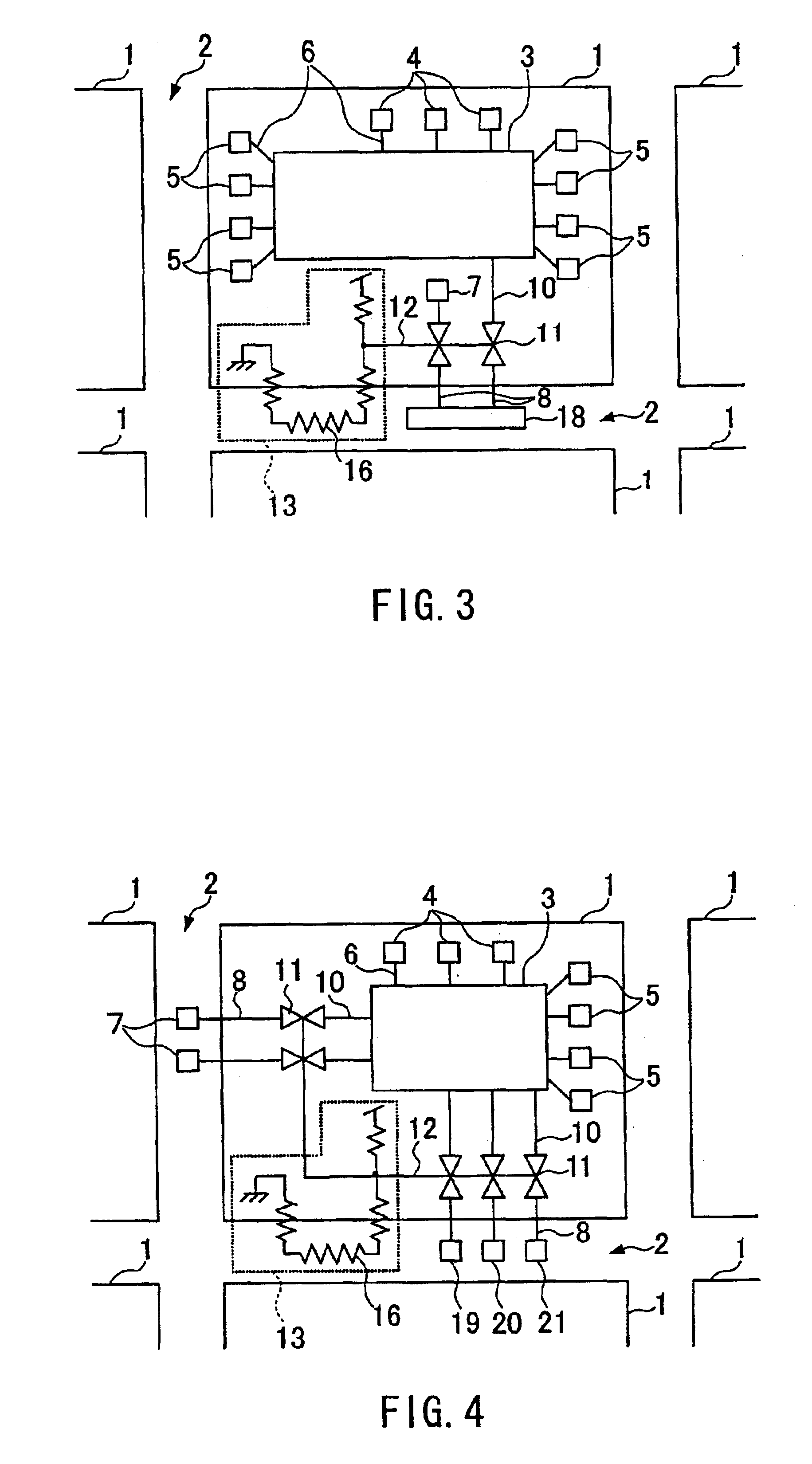

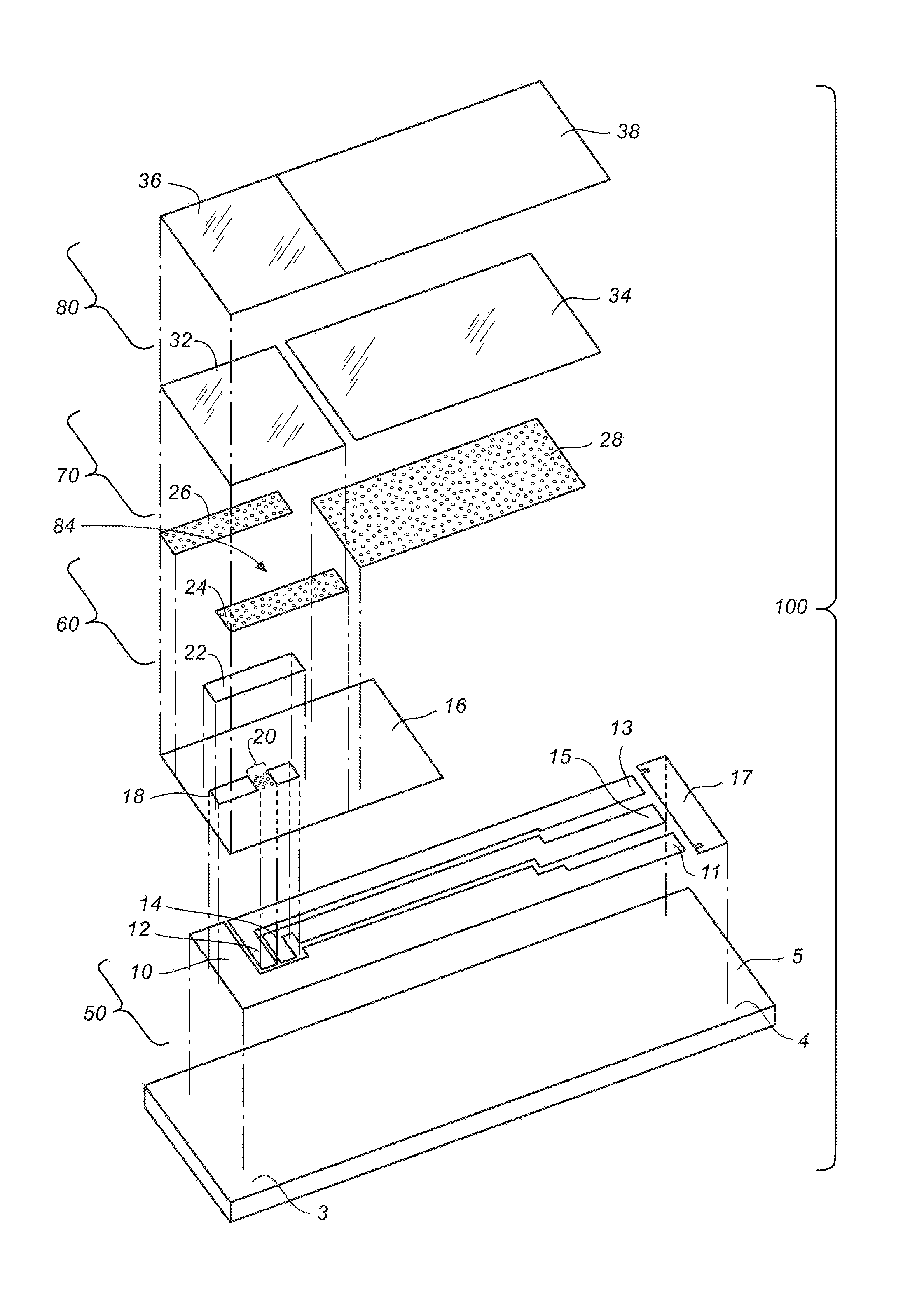

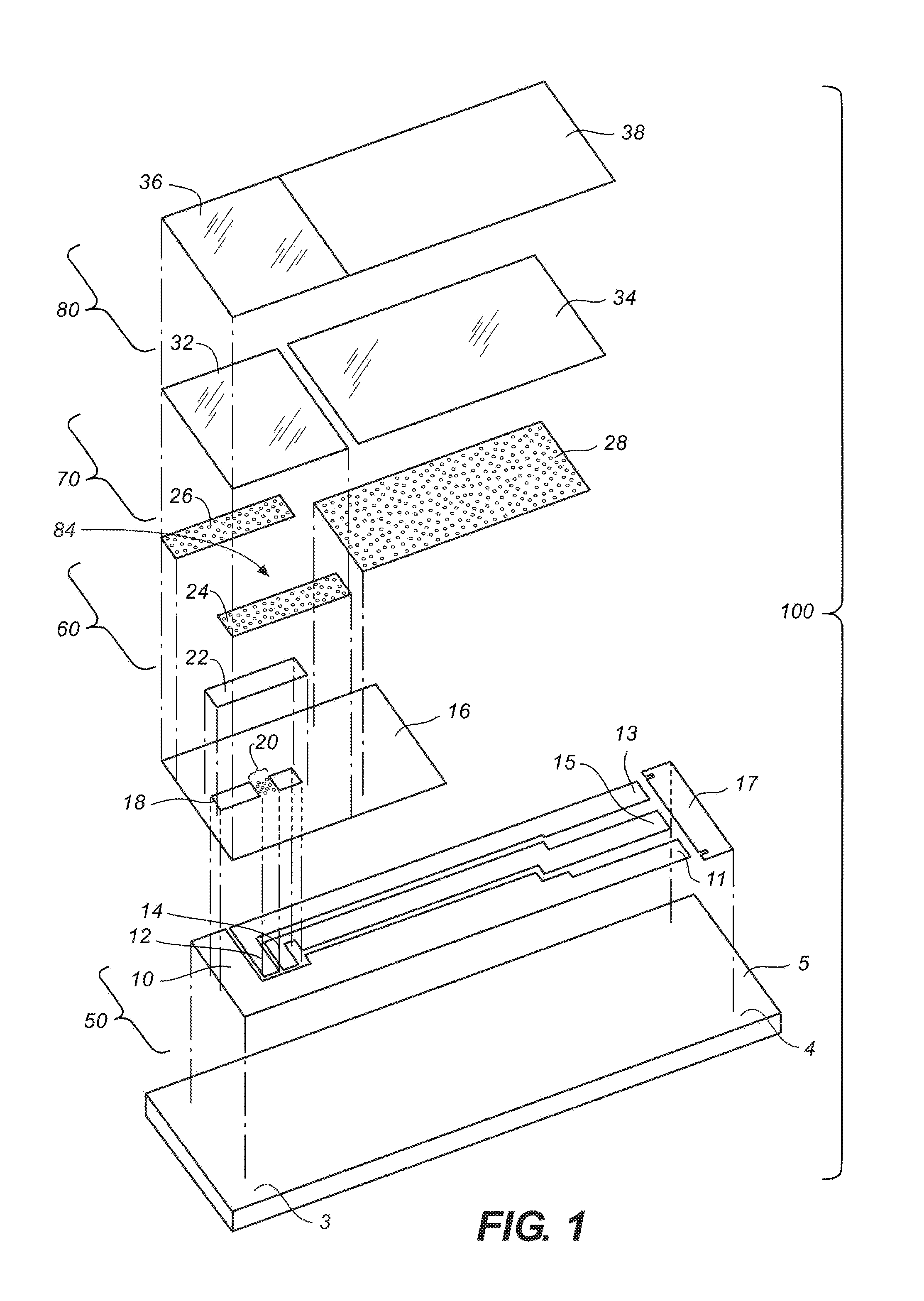

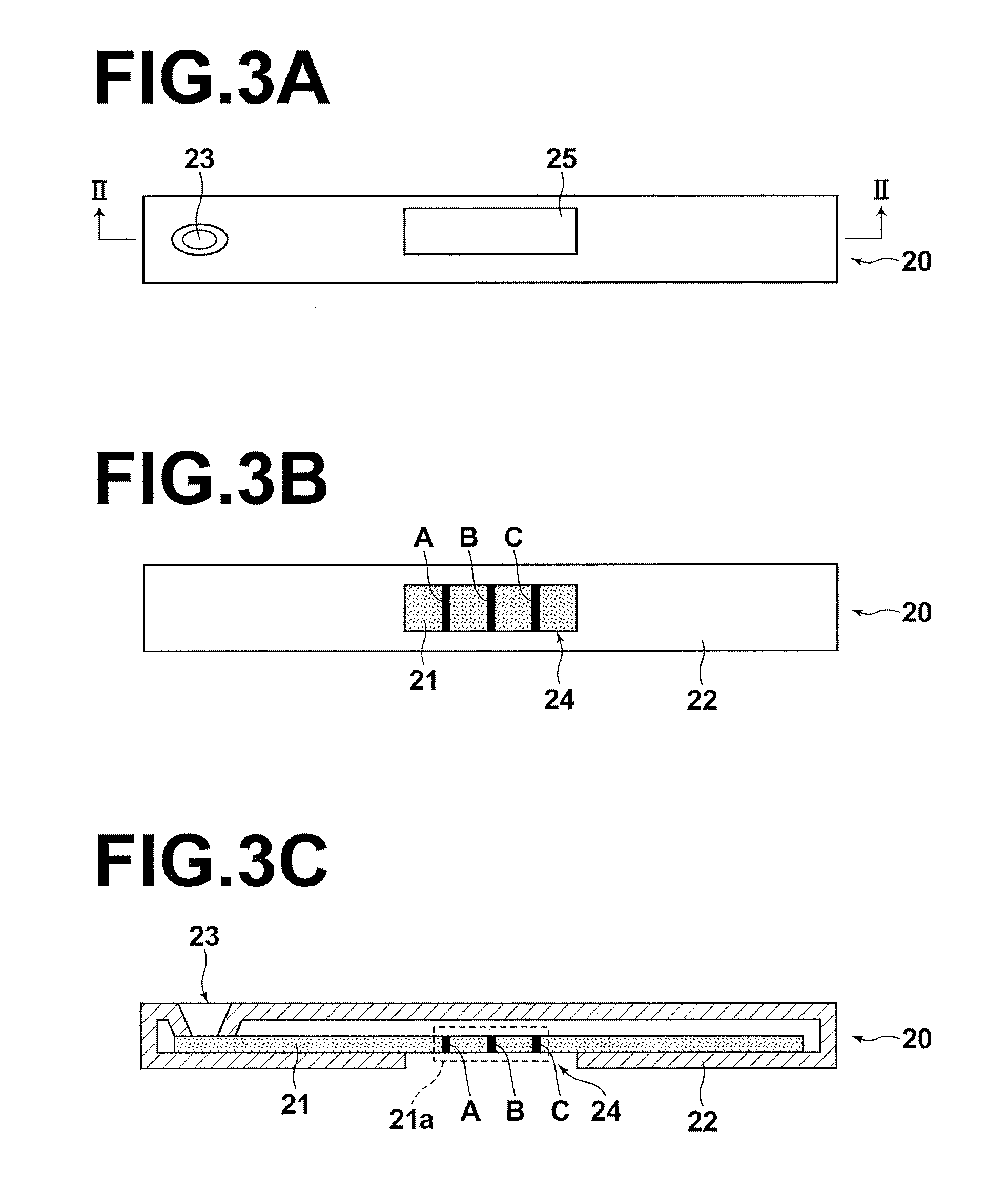

Semiconductor device

InactiveUS6838891B2Extended test timeInternal circuit is preventedSemiconductor/solid-state device testing/measurementElectronic circuit testingEngineeringSemiconductor

A semiconductor device includes a plurality of semiconductor integrated circuits formed on a semiconductor wafer; an testing pad for inputting and outputting a signal to and from an internal circuit of the semiconductor integrated circuit; a switch for switching a state of a connection between the semiconductor integrated circuit and the testing pad; and a wiring pattern formed on a parting line around the semiconductor integrated circuit and connected to an input terminal of the switch. When the semiconductor integrated circuits are separated, cutting off of the wiring pattern causes the switch to be turned off, so that the internal circuit is prevented from being affected by the influence of the cutting plane.

Owner:PANASONIC CORP

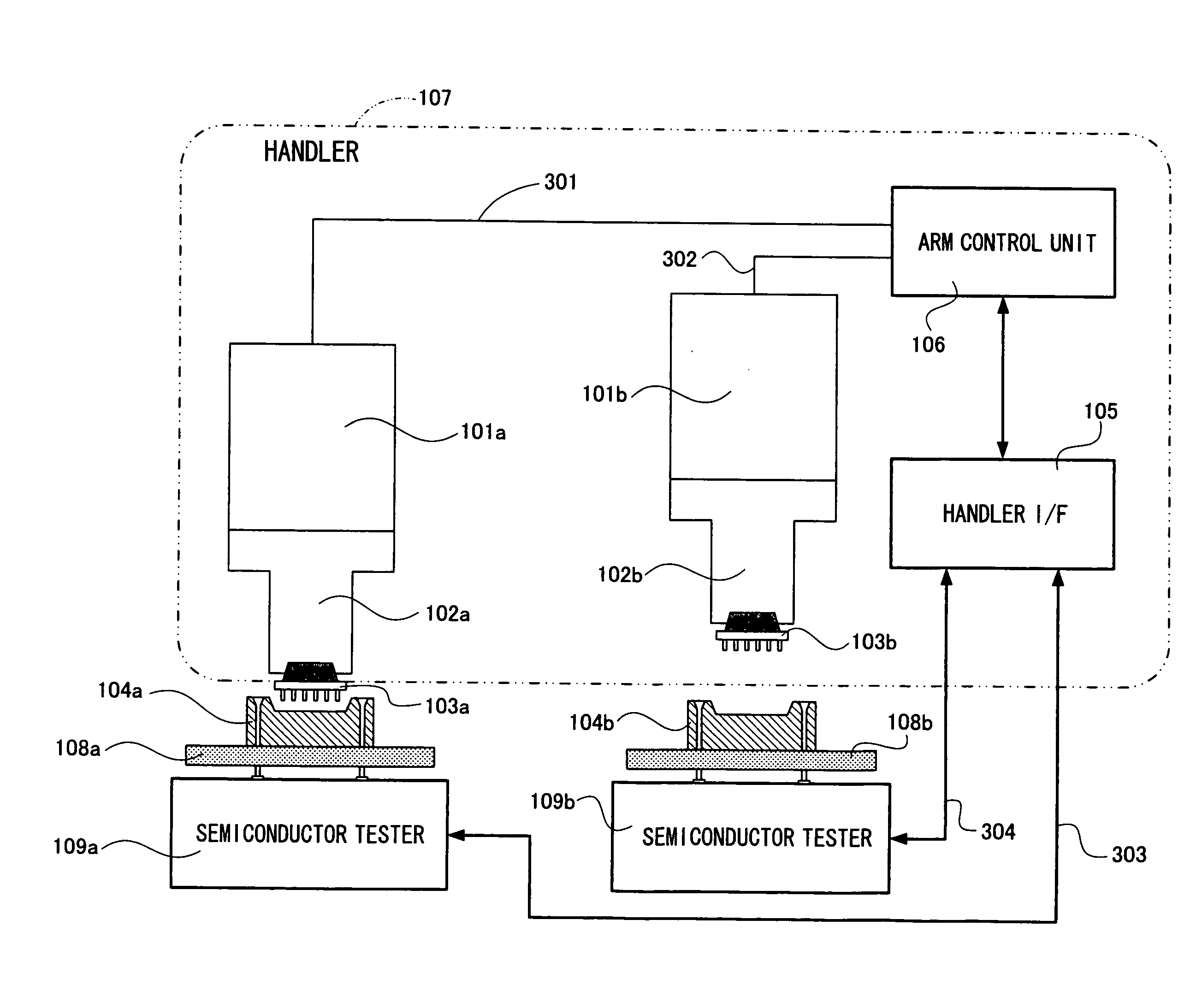

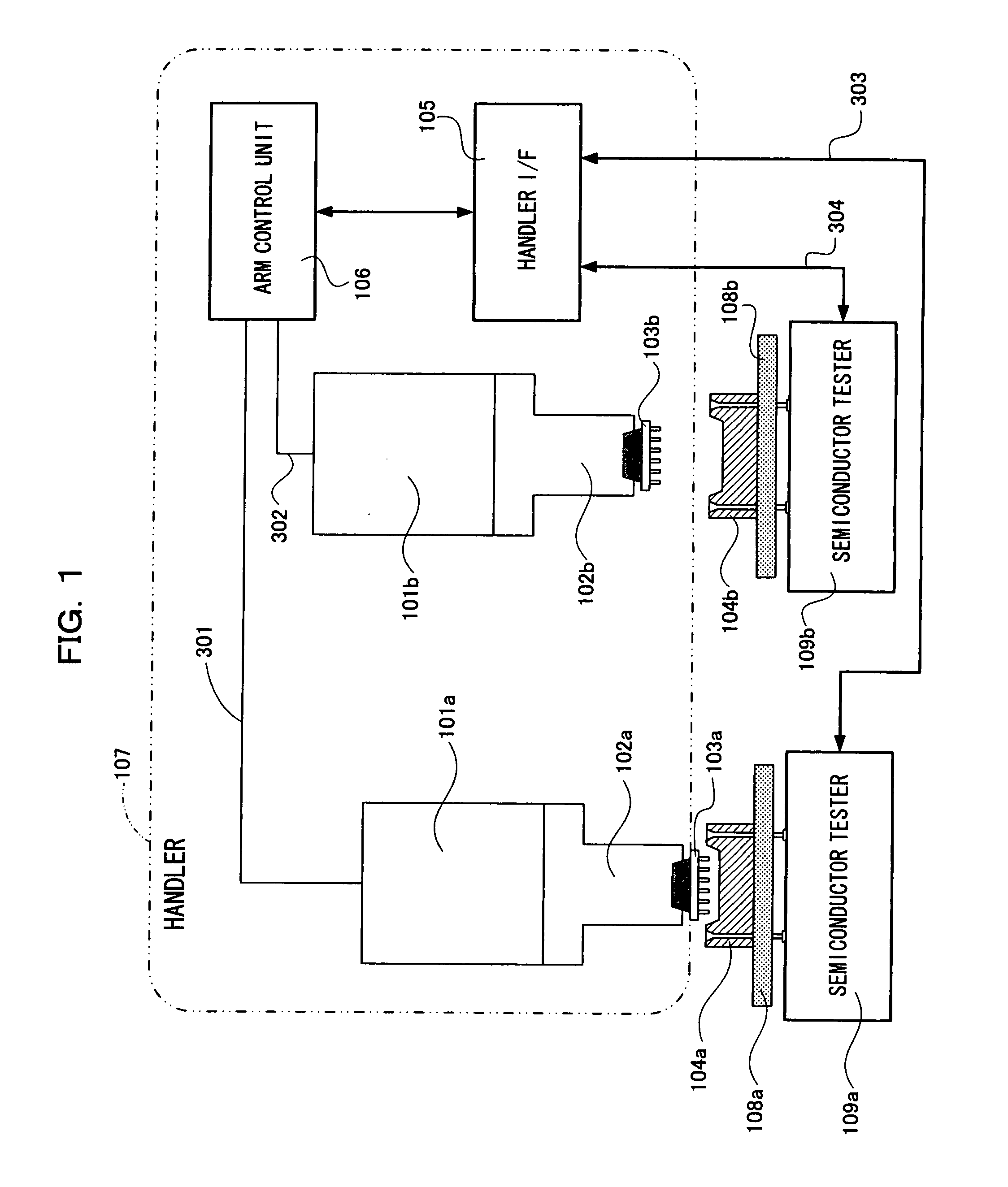

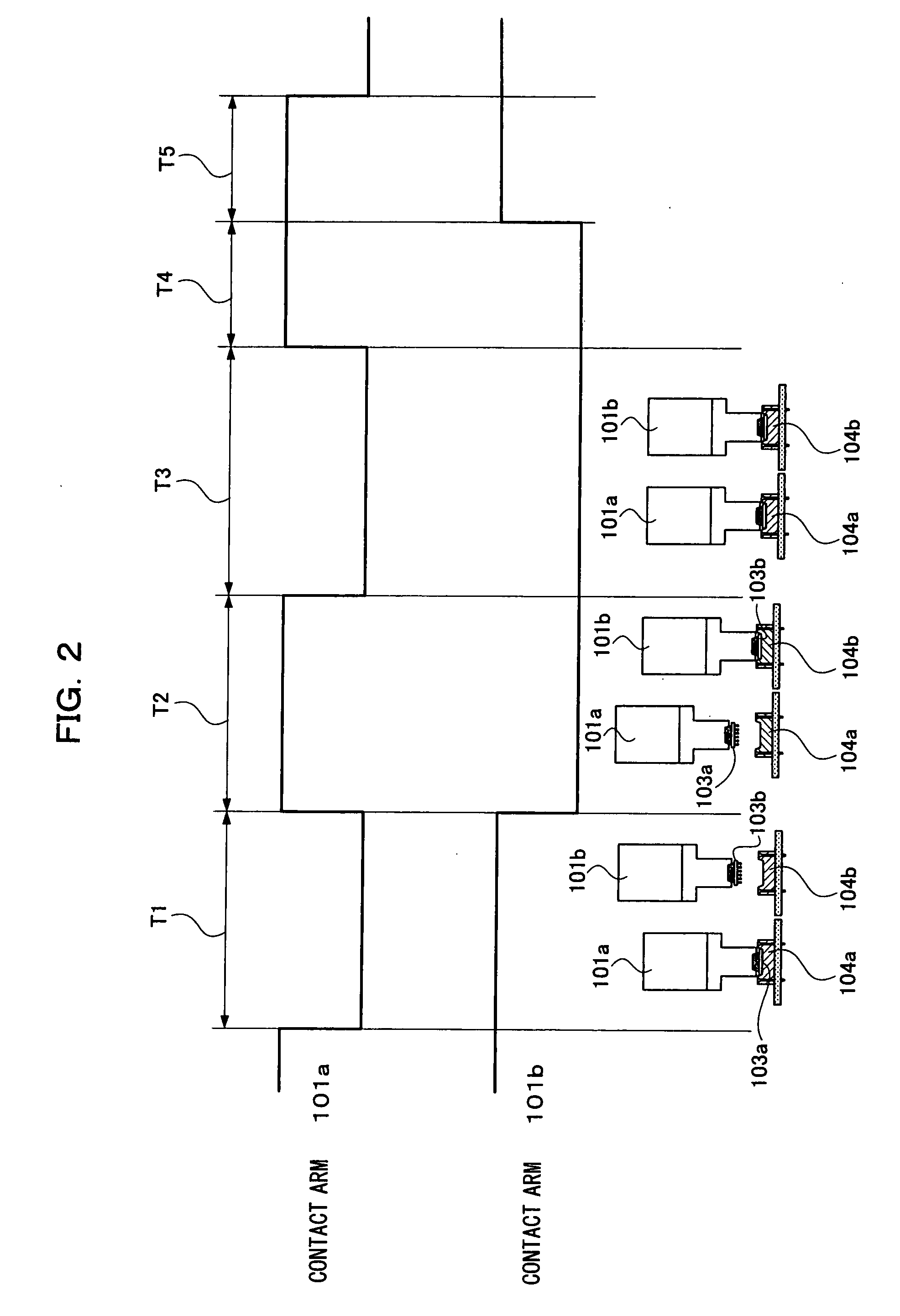

Handler and method of testing semiconductor device by means of the handler

InactiveUS20080007285A1Extended test timeReduce test efficiencyIndividual semiconductor device testingTest boardSemiconductor

An object of the present invention is to provide a handler and a testing method thereof which enable efficient measurements on a plurality of semiconductor devices. An arm control unit 106 controls, for each of contact arms 101a and 101b, the timing of control for performing contact control for bringing semiconductor devices 103a and 103b to be tested to one of a contact state and a non-contact state with test boards 108a and 108b connected to semiconductor testers 109a and 109b. The plurality of semiconductor devices are simultaneously measured using the handler 107, so that when a “defective item” is found on a specific measurement part, only the defective item on the measurement part can be replaced with another untested item and thus tests can be efficiently conducted.

Owner:PANASONIC CORP

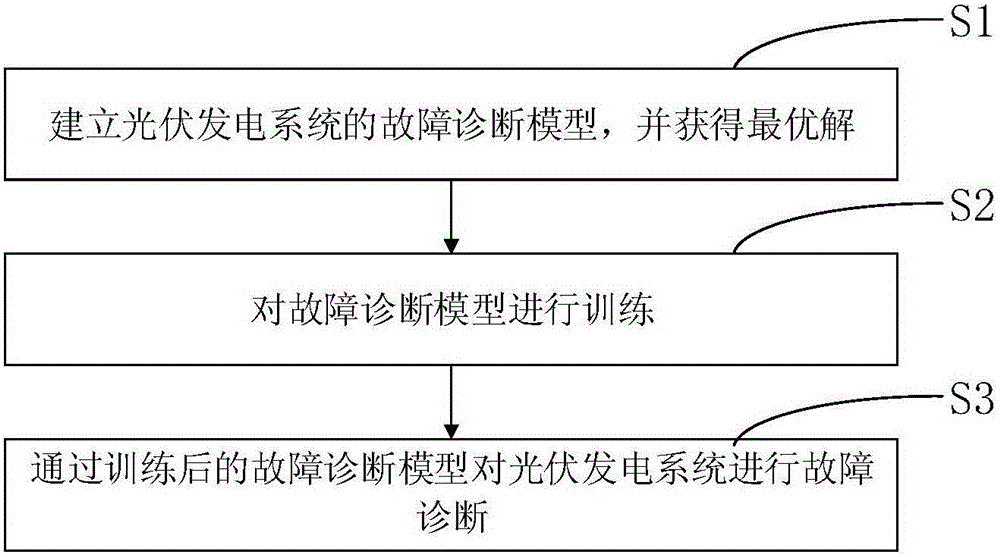

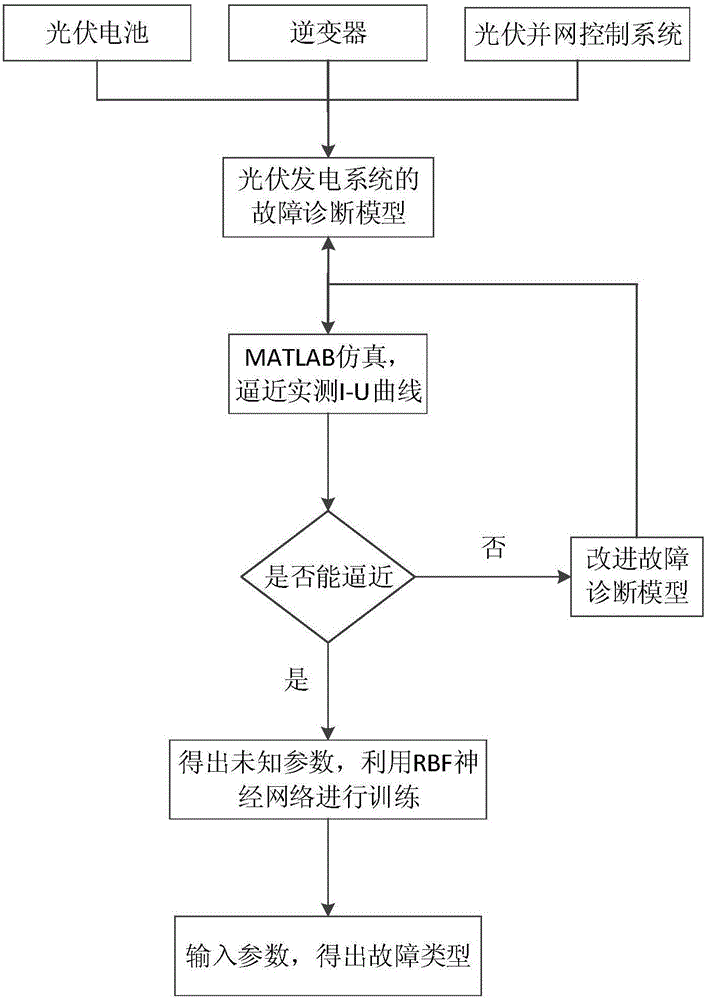

Parameter identification-based photovoltaic power generation system fault diagnosis method and system

InactiveCN106067758AExtended power generation timeImprove power generation efficiencyPhotovoltaic monitoringPhotovoltaic energy generationDiagnosis methodsControl system

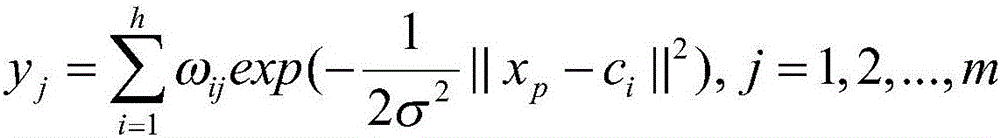

The invention relates to a parameter identification-based photovoltaic power generation system fault diagnosis method and a parameter identification-based photovoltaic power generation system fault diagnosis system. The parameter identification-based photovoltaic power generation system fault diagnosis method includes the following steps that: the fault diagnosis model of a photovoltaic power generation system is built, and the optimal solutions of the fault diagnosis model are obtained; the fault diagnosis model is trained; and fault diagnosis is carried out on the photovoltaic power system based on the trained fault diagnosis model. According to the parameter identification-based photovoltaic power generation system fault diagnosis method of the invention, according to problems which easily appear in the photovoltaic power generation system, namely, open-circuiting and short-circuiting of a photovoltaic battery assembly, the overload of an inverter and the failure of a control system, the parameter identification-based photovoltaic power generation system fault diagnosis model under a mismatch condition is built; an I-U curve is obtained according to the data of a photovoltaic power plant in different working conditions; analog simulation is carried out on the actually-measured I-U curve, so that the optimal solutions of the parameters of the model are obtained; an RBF neural network is utilized to train the model, so that the trained fault diagnosis model is obtained; and test samples or real-time samples of the photovoltaic power plant are inputted to the model, so that fault diagnosis can be carried out.

Owner:HOHAI UNIV CHANGZHOU

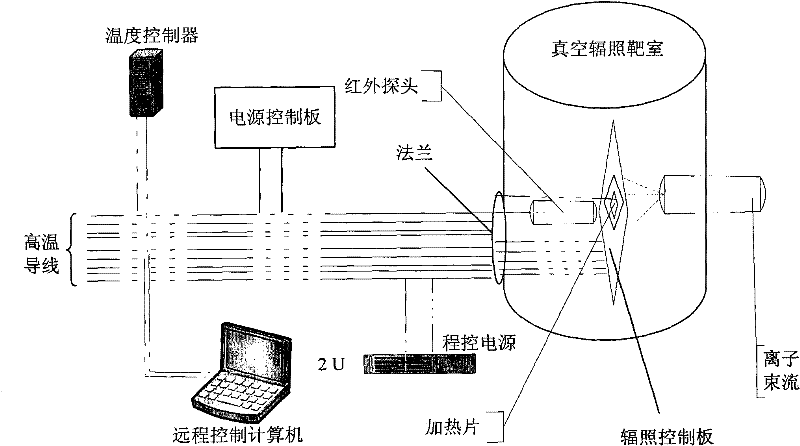

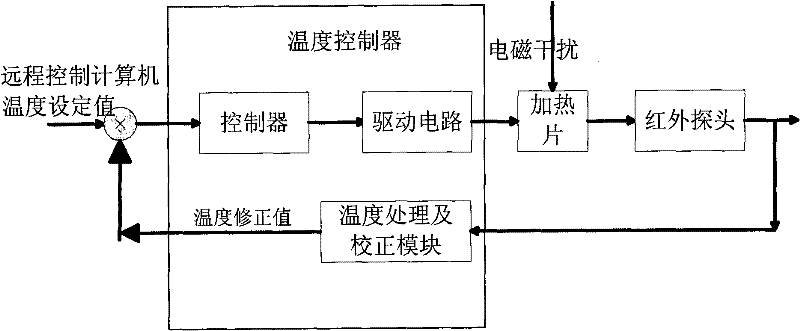

Temperature control system and method for performing single event effect test under same

InactiveCN102243502AAdapt to the needs of developmentIncreased flexibility of useTemperatue controlContactless circuit testingTemperature controlAnti jamming

The invention relates to a method for performing a single event effect test under the same. The temperature control system comprises a remote control computer, a temperature controller, a heating plate, an infrared probe and a high-temperature conducting wire, wherein the temperature controller is respectively connected with the infrared probe and the heating plate through the high-temperature conducting wire and is connected with the remote control computer, the remote control computer sends a temperature control instruction to the temperature controller, the temperature controller controls the heating of the heating plate according to the temperature control instruction, the infrared probe acquires the heating temperature value of the heating plate and feeds the heating temperature value back to the temperature controller, and the temperature controller modifies and regulates the heating temperature of the heating plate according to the fed-back heating temperature value so as to ensure that the heating temperature is identical to a preset temperature value. The temperature control system can be used for remote automatic calibration, has the advantages of accuracy and stability for measurement, strong anti-jamming capability, high reliability, self-protection capability and strong compatibility, and can meet the requirements of the single event effect test under different temperatures.

Owner:BEIJING MXTRONICS CORP +1

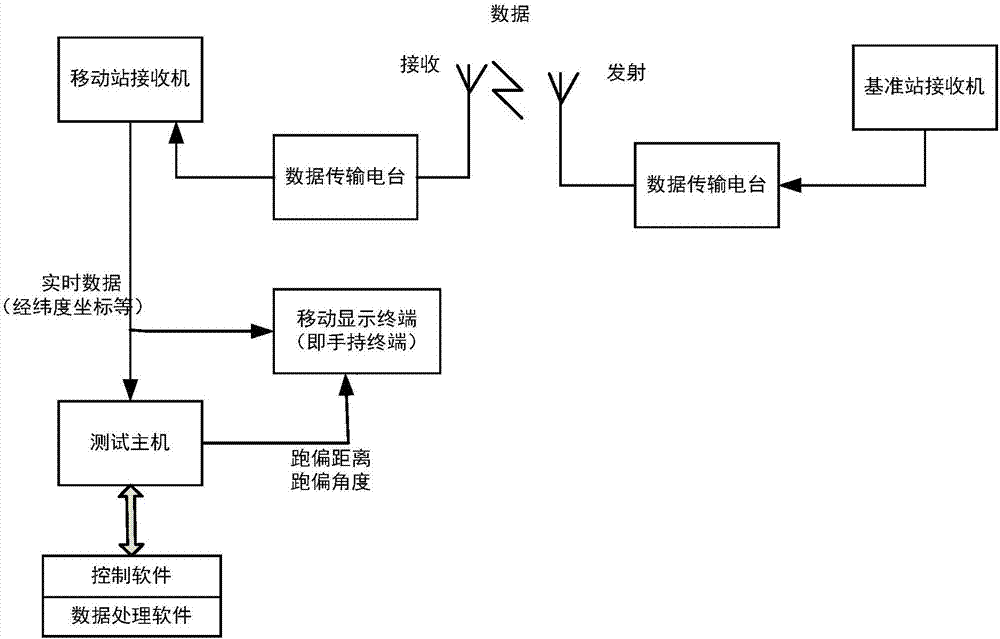

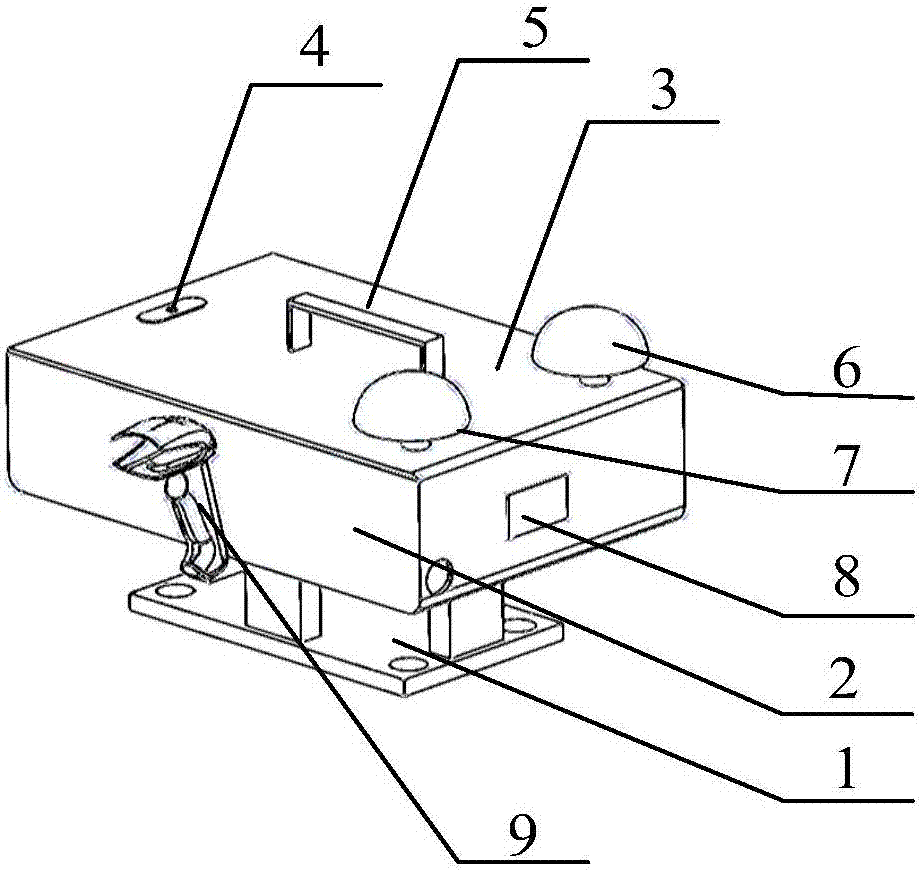

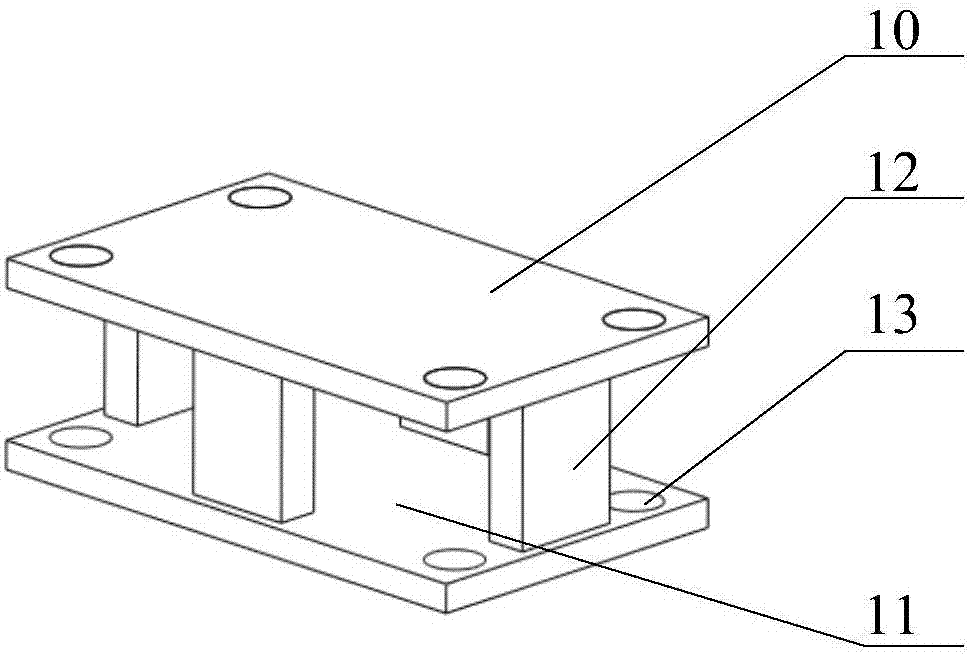

Vehicle-mounted vehicle driving deviation detection apparatus and detection method

InactiveCN107255566AExtended test timeEasy to operateVehicle testingMicrocontrollerCar manufacturing

The invention discloses a vehicle-mounted vehicle driving deviation detection apparatus and detection method. The vehicle-mounted vehicle driving deviation detection apparatus includes a magnetic attraction seat, a vehicle terminal, and a wireless laser bar code scanner. The vehicle terminal is composed of a GPS positioning module, a single-chip microcomputer main control module, a data transmission and display module, an interface module, an alarm module and a power module. The host of a mobile station acquires the vehicle trajectory information in real time and sends the information to a reference station via a radio station in the host, a differential algorithm is formed in the system to obtain the high-precision mobile station coordinate, the deviation amount of the vehicle to be measured is processed and calculated through the main control chip of the single-chip microcomputer main control module, the result of the deviation amount is displayed on a four-bit digital display screen after the testing is finished, and the vehicle speed is displayed in the testing process in real time. The apparatus is simple in structure and convenient to detach, and can realize the display of the deviation amount and the vehicle speed, is suitable for automobile manufacture enterprises to do streamline test, and has wide market potential and application prospect.

Owner:WUHAN UNIV OF SCI & TECH

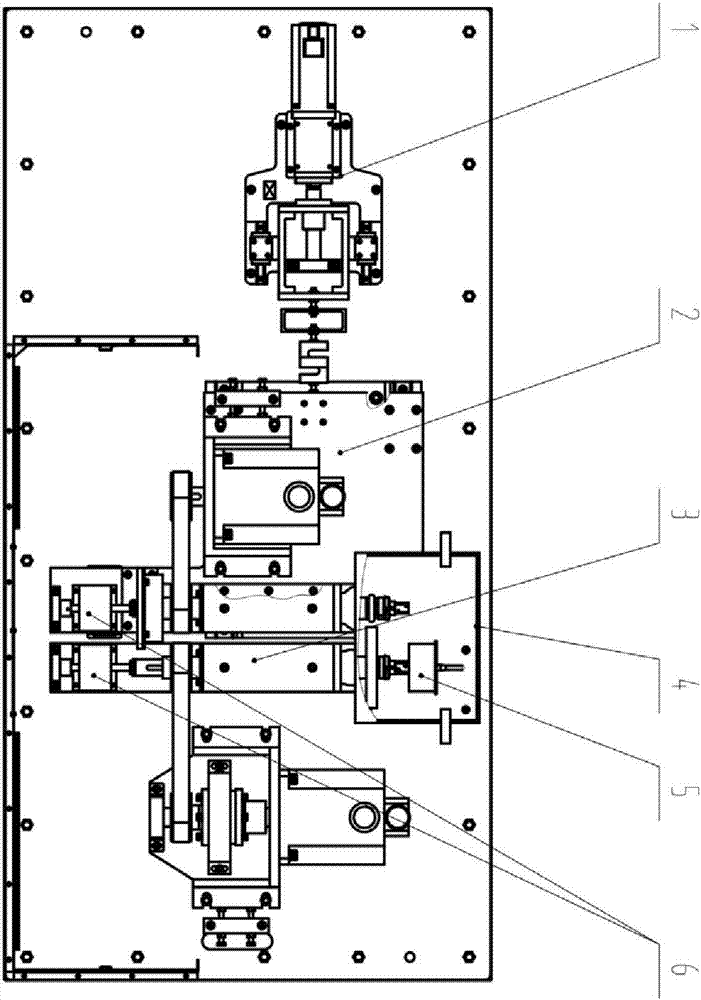

Rolling current-carrying friction abrasion tester

ActiveCN107014708AIncrease temperatureAccurate and controllable loading currentInvestigating abrasion/wear resistanceReal-time dataPower flow

The invention discloses a rolling current-carrying friction abrasion tester which comprises a normal loading component, a moving-axis rolling platform, a fixed-axis rolling component, a liquid conductive component, a wireless temperature measuring component, a cooling and lubricating system and an atmosphere box. By adopting a servo motor as a power source, normal loading closed-loop control is provided and normal loading is accurately controlled; rotating shafts are controlled to rotate by the servo motor and the rotating speeds of the two rotating shafts can be accurately controlled separately; an all-insulation design is adopted by a rotating assembly and current is loaded to a friction pair by adopting a liquid conductive technology and the loaded current is accurately controllable; the cooling and lubricating system is arranged, so that over-high temperature of the rotating shafts is prevented and the experiment testing time is effectively prolonged; the atmosphere box is arranged, so that different experiment environments can be simulated. All real-time data are collected and stored by adopting a lower computer, various data changes in the experiment process can be accurately analyzed through cooperation with a synchronous high-speed video camera, and the mechanism of current-carrying friction is researched.

Owner:NANJING BIO INSPIRED INTELLIGENT TECH +1

Apparatus and method for reading out defect information items from an integrated chip

InactiveUS7038956B2Simple calculationReduce testingElectrical testingDigital storageBit lineMemory chip

One embodiment of the invention provides a method for providing defect information from an integrated memory chip having dynamic memory cells arranged on word lines and bit lines, wherein a word line group having a number of word lines may be replaced by a redundant word line group and wherein a bit line may be replaced by a redundant bit line to replace defective memory cells, wherein test data are written to the memory cells of the memory chip for the purpose of testing the memory cells, the written data being read out and compared with the previously written test data to generate first defect information items depending on the result of the comparison, the first defect information item indicating a defect if the written test data and the read-out data are different, the memory cells along one of the bit lines being read successively, the first defect information item in each case being generated for each of the read memory cells, the first defect information items being buffer-stored during the testing of the memory cells on the word line group, a second defect information item being generated, the second defect information item indicating a defect if at least one of the first defect information items indicates a defect, the second defect information item being output after the end of the read-out of the memory cells of the word line group along the bit line.

Owner:POLARIS INNOVATIONS LTD

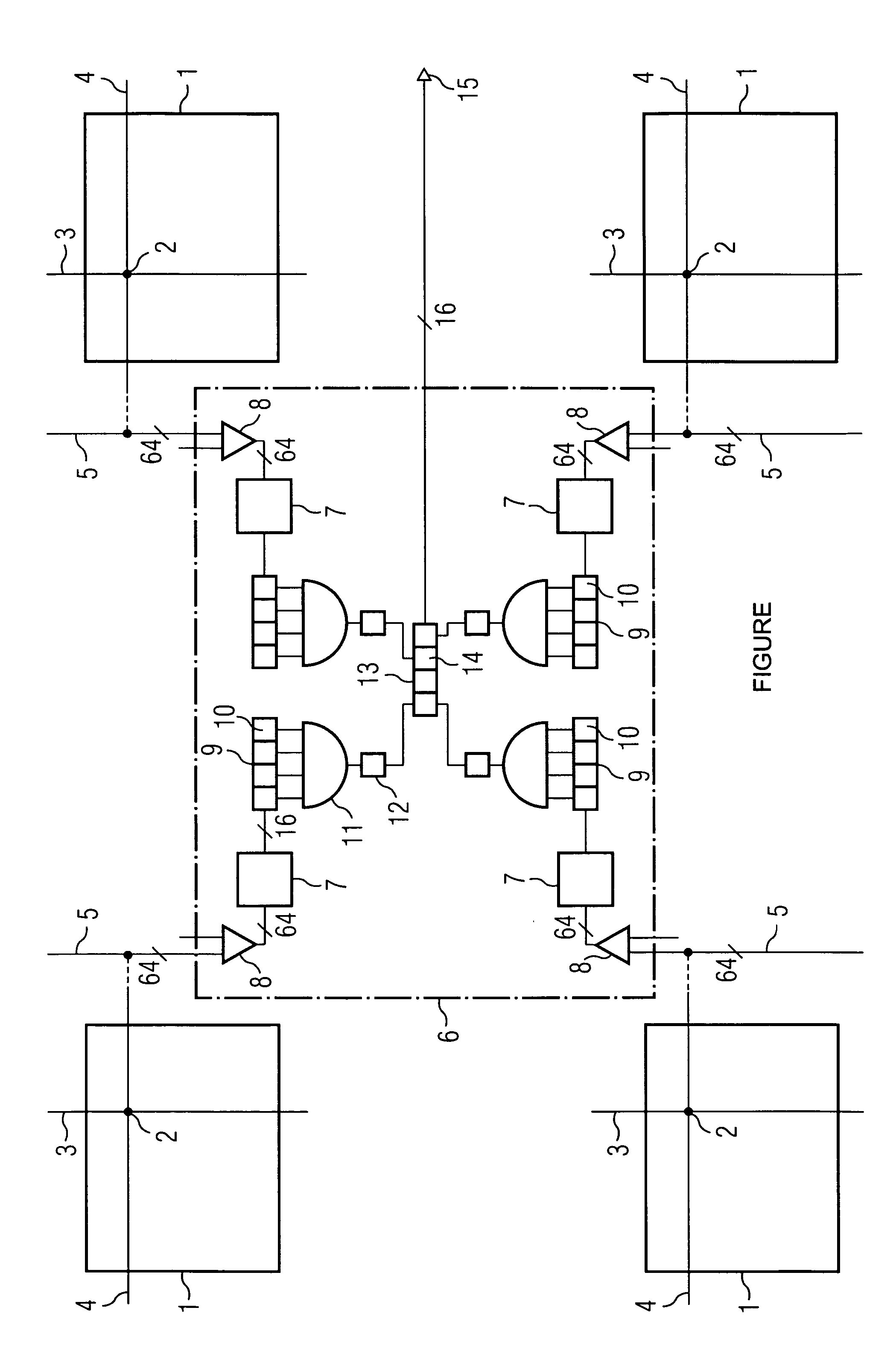

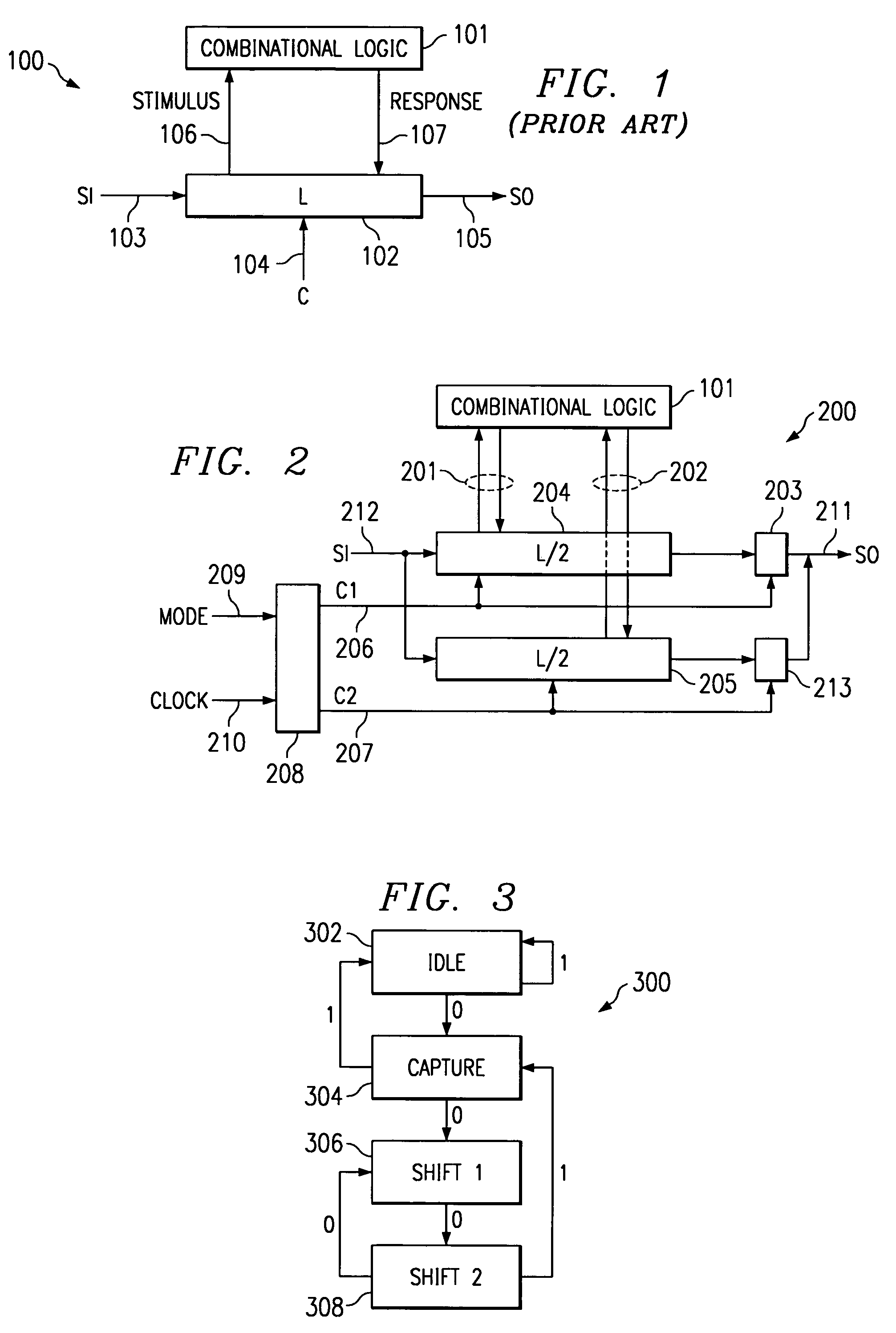

IC with separate scan paths and shift states

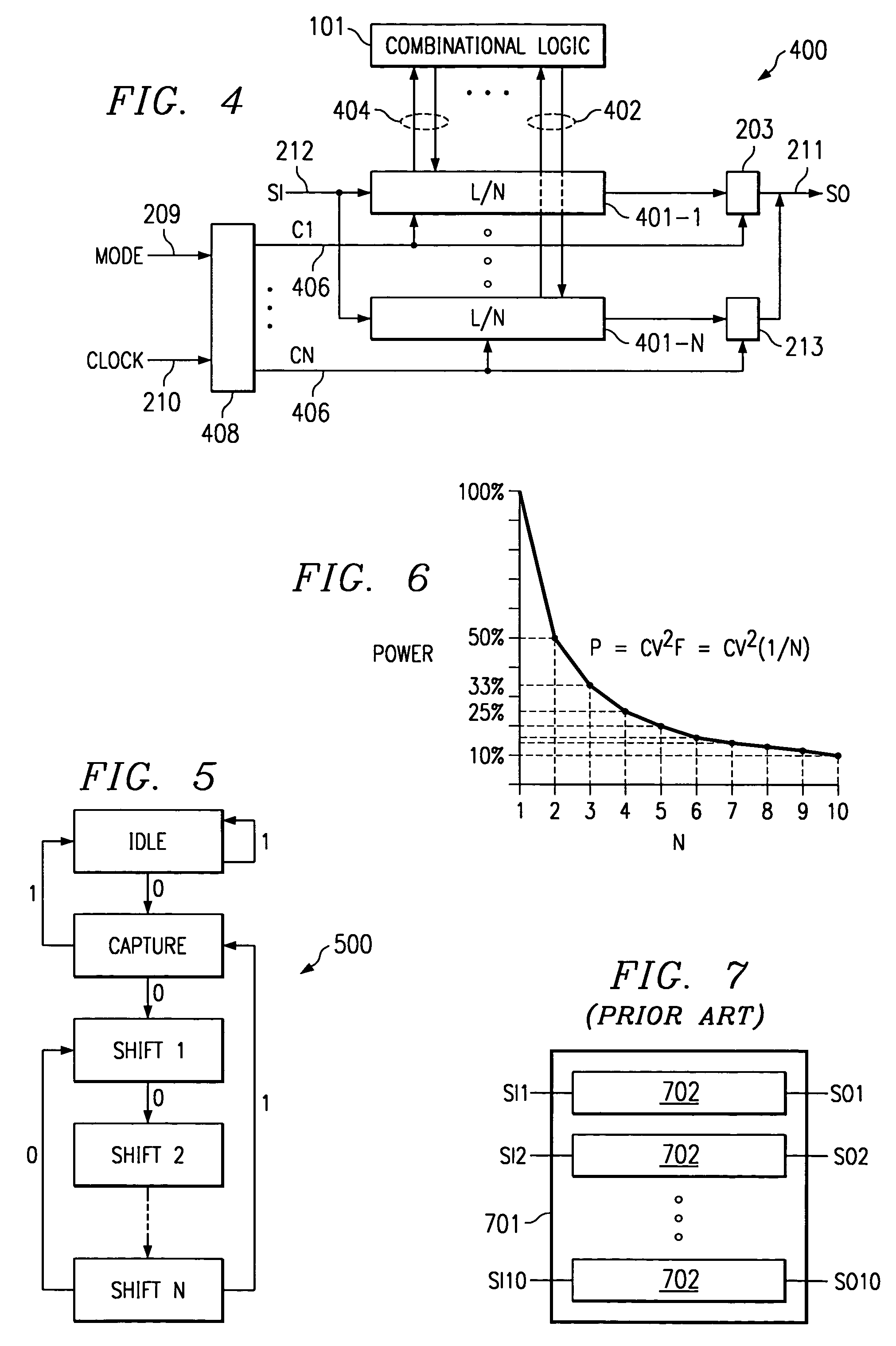

InactiveUS7155650B2Extended test timeReduce operating powerDigital circuit testingError detection/correctionCapacitanceCombinational logic

Plural scan test paths (401) are provided to reduce power consumed during testing such as combinational logic (101). A state machine (408) operates according to plural shift states (500) to control each scan path in capturing data from response outputs of the combinational logic and then shifting one bit at a time to reduce the capacitive and constant state power consumed by shifting the scan paths.

Owner:TEXAS INSTR INC

Testing structure and testing method for hot carrier effect of MOS (Metal Oxide Semiconductor) device

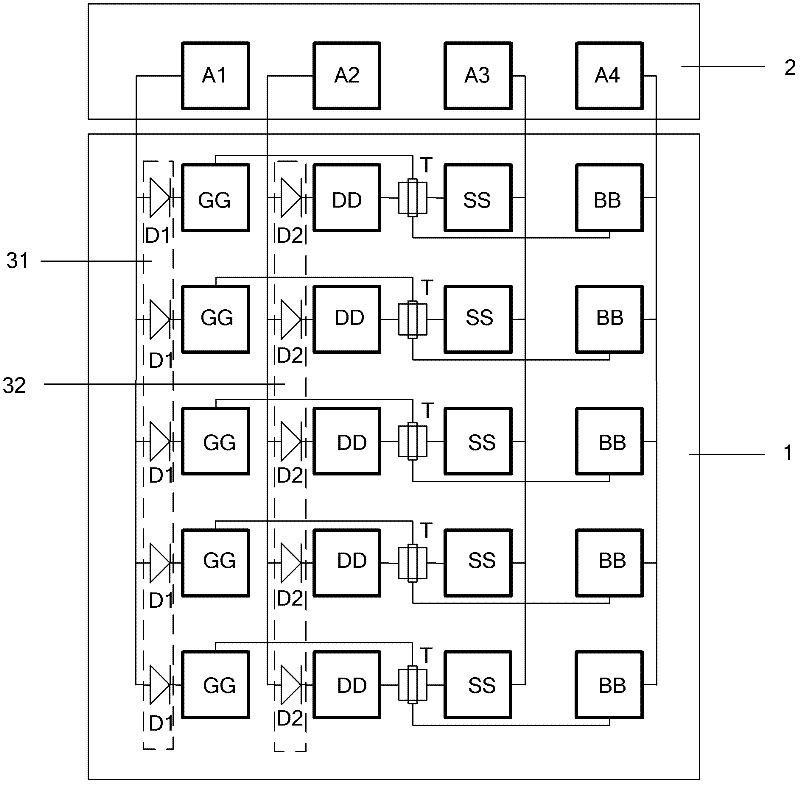

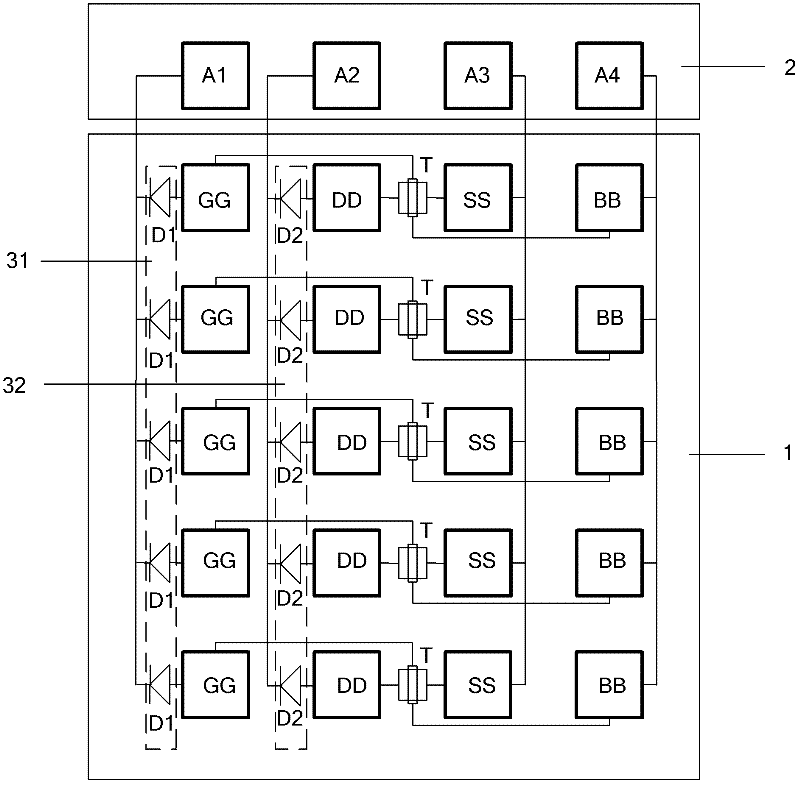

ActiveCN102253324ASave stress loading timeExtended test timeIndividual semiconductor device testingOxide semiconductorHot carrier effect

The invention discloses a testing structure for a hot carrier effect of an MOS (Metal Oxide Semiconductor) device. The structure comprises at least two groups of arrayed test structure units (1), wherein a grid bonding pad (GG) of each group of the test structure unit (1) is connected with a first bonding pad (A1) through a first diode (D1); a drain bonding pad (DD) is connected with a second bonding pad (A2) through a second diode (D2); and a source bonding pad (SS) and a substrate bonding pad (BB) are connected with a third bonding pad (A3) and a fourth bonding pad (A4) respectively. The invention also discloses a method for testing the hot carrier effect by applying the parallel testing structure, and the method comprises the following steps: S1, testing a single device; S2, testing stress loading; S3, repeating tests of the step S1 and the step S2 alternately, and comparing electrical performance parameters of multiple measurements. By adopting the method, the testing efficiency of the hot carrier of the MOS device can be improved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

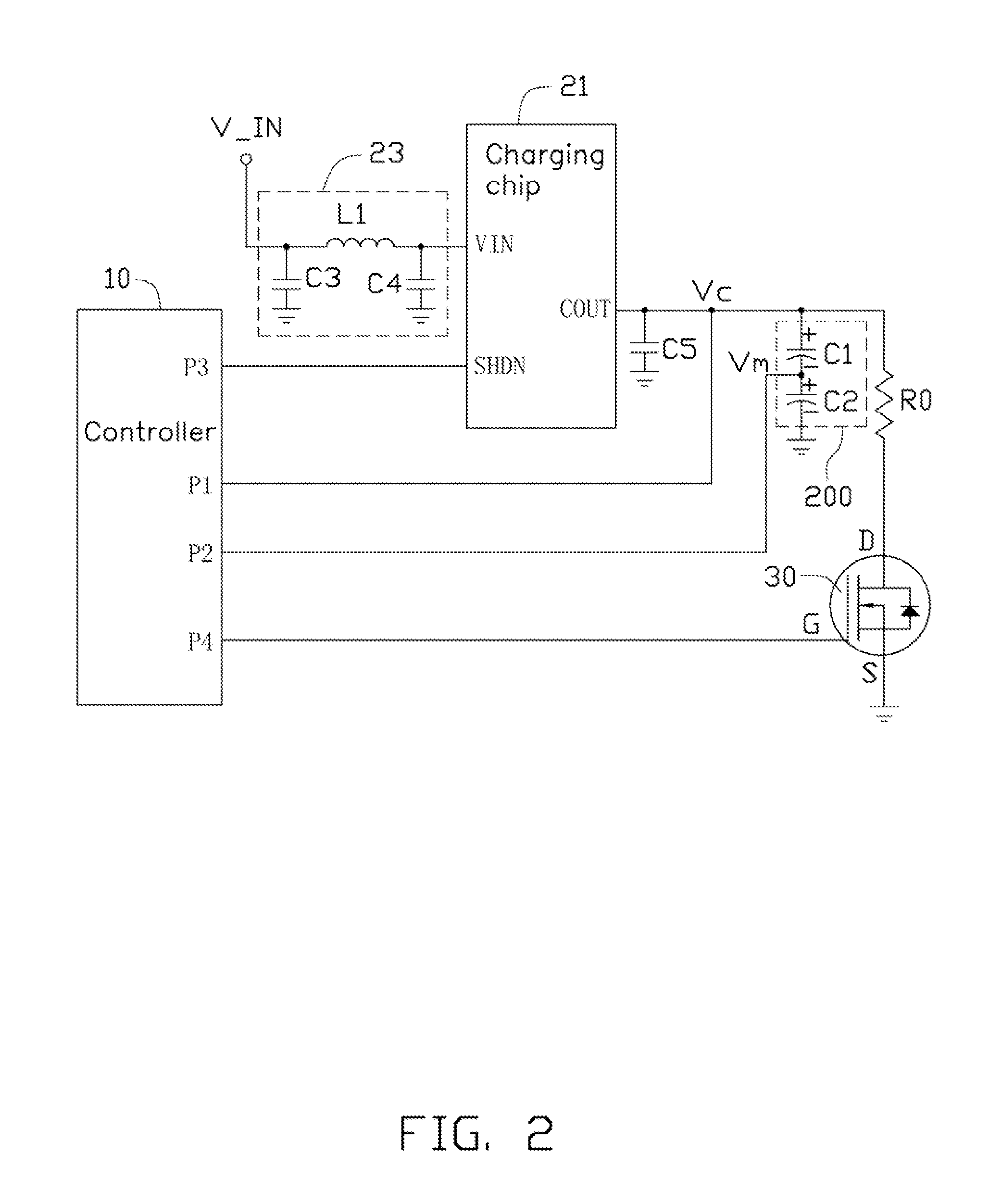

Balancing resistor testing apparatus

InactiveUS20130049778A1Reduce the differenceExtended test timeCircuit monitoring/indicationCharge equalisation circuitElectricityElectrical resistance and conductance

A balancing resistor testing apparatus is configured for acquiring a resistance of a balancing resistor electronically connected to a supercapacitor of a series supercapacitor assembly in parallel. The balancing resistor testing apparatus includes a controller and a digital potentiometer. The controller detects a voltage across each supercapacitor of the series supercapacitor. The digital potentiometer comprising a plurality of variable resistors each of which is electronically connected to a supercapacitor in parallel, the controller controls the digital potentiometer to continuously adjust the effective resistance of each potentiometer until the controller detects that each supercapacitor has the same or very similar voltage.

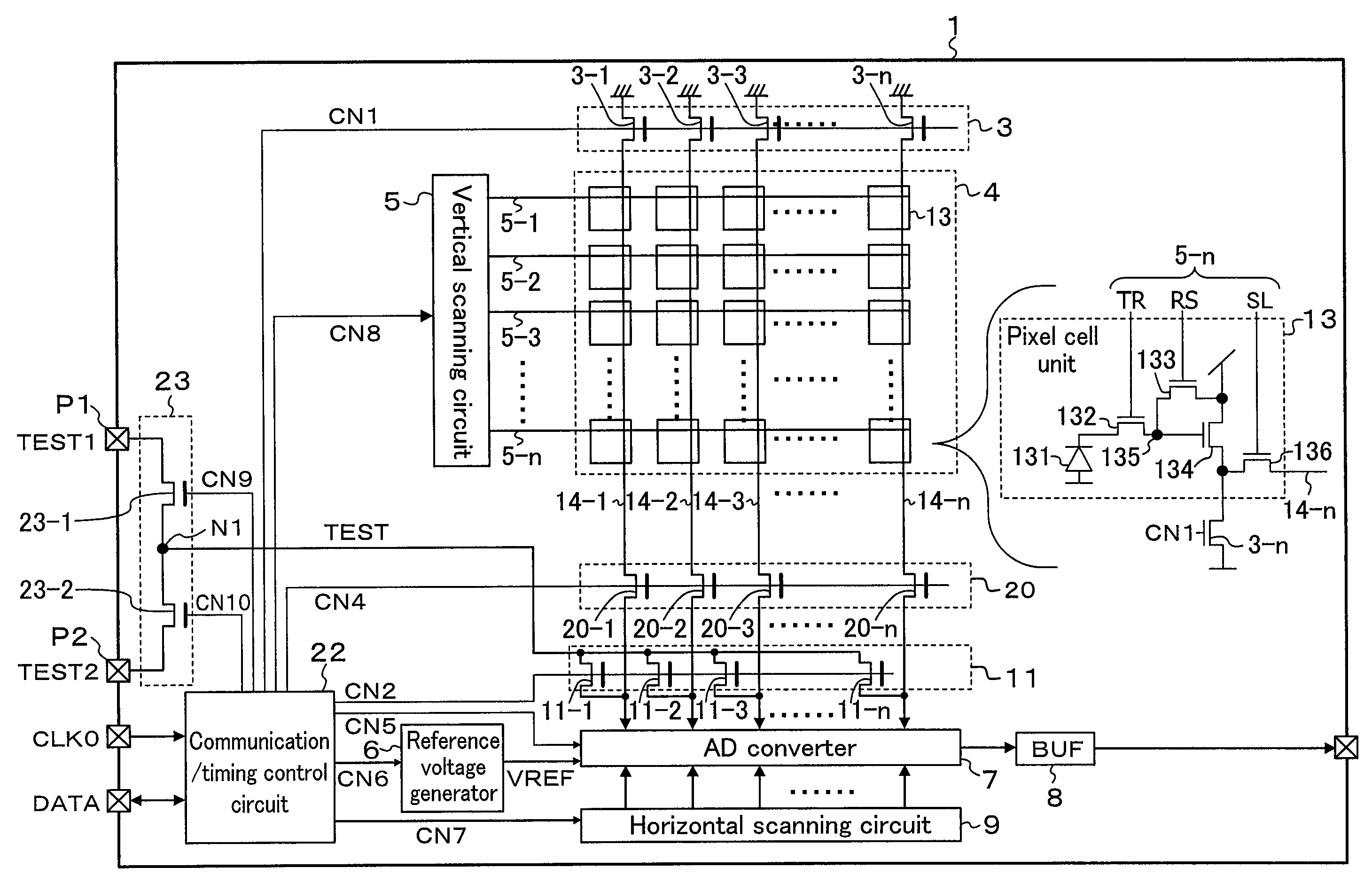

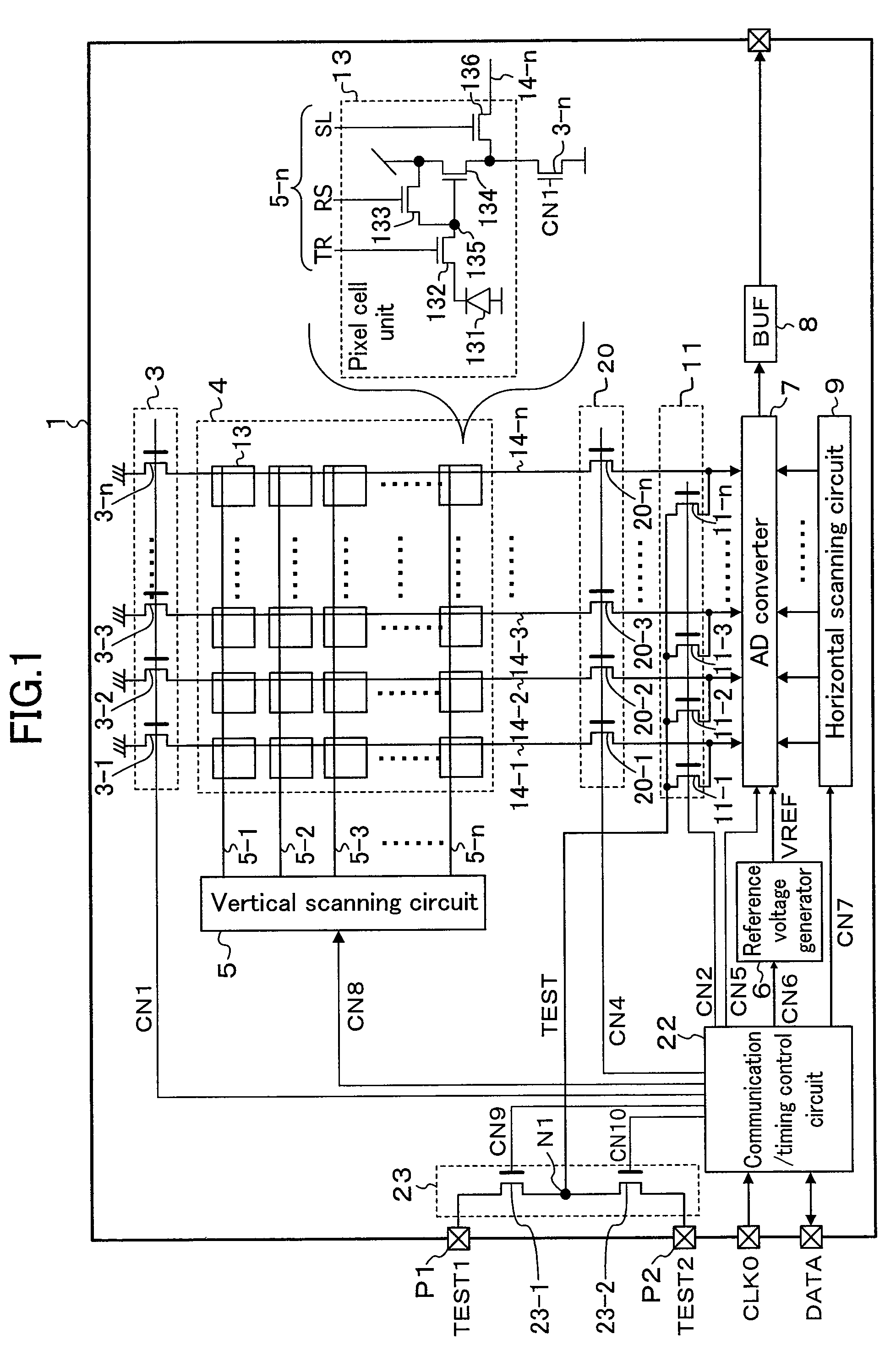

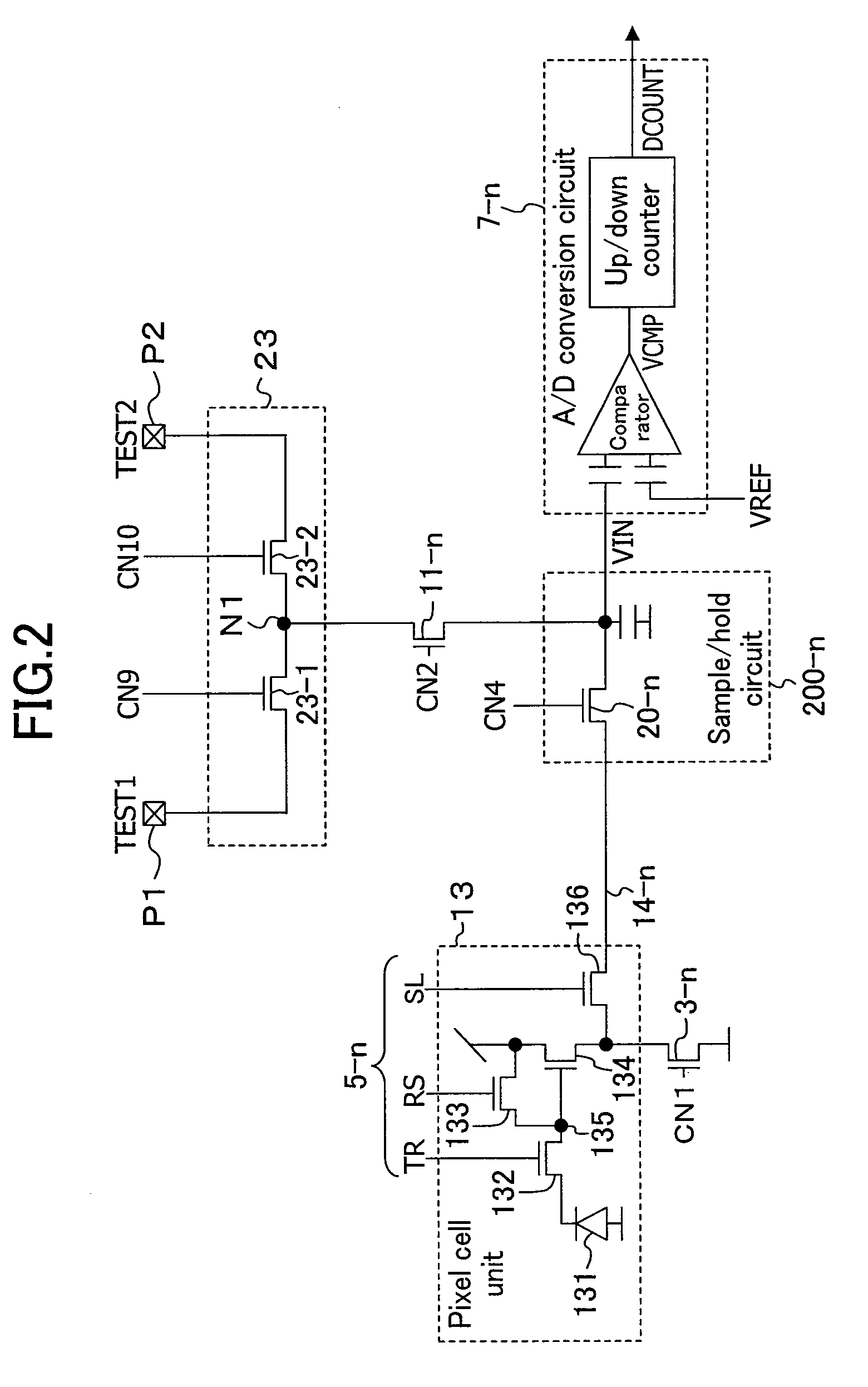

A/d converter-incorporated solid-state imaging device

InactiveUS20090284629A1Extended test timeReduce necessityTelevision system detailsElectric signal transmission systemsA d converterSignal selection

The solid-state imaging device includes: a first node for receiving a first signal from outside the solid-state imaging device; a second node for receiving a second signal from outside the solid-state imaging device; a test signal selection circuit for outputting the first signal received at the first node and the second signal received at the second node as a test signal by switching between the first and second signals at desired timing; and a test signal input circuit for supplying the test signal from the test signal selection circuit to an input of the A / D converter.

Owner:PANASONIC CORP

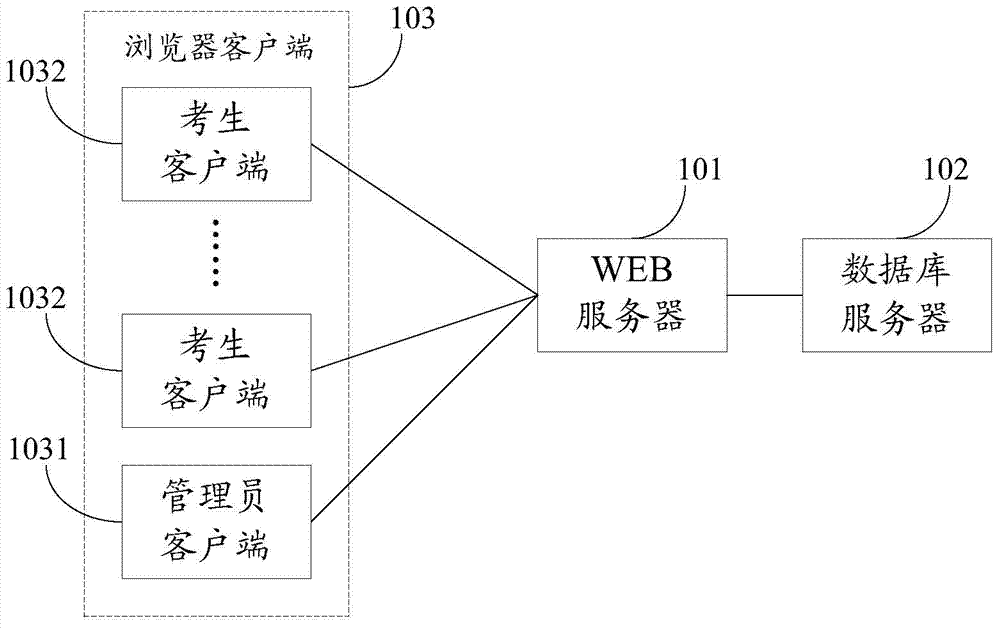

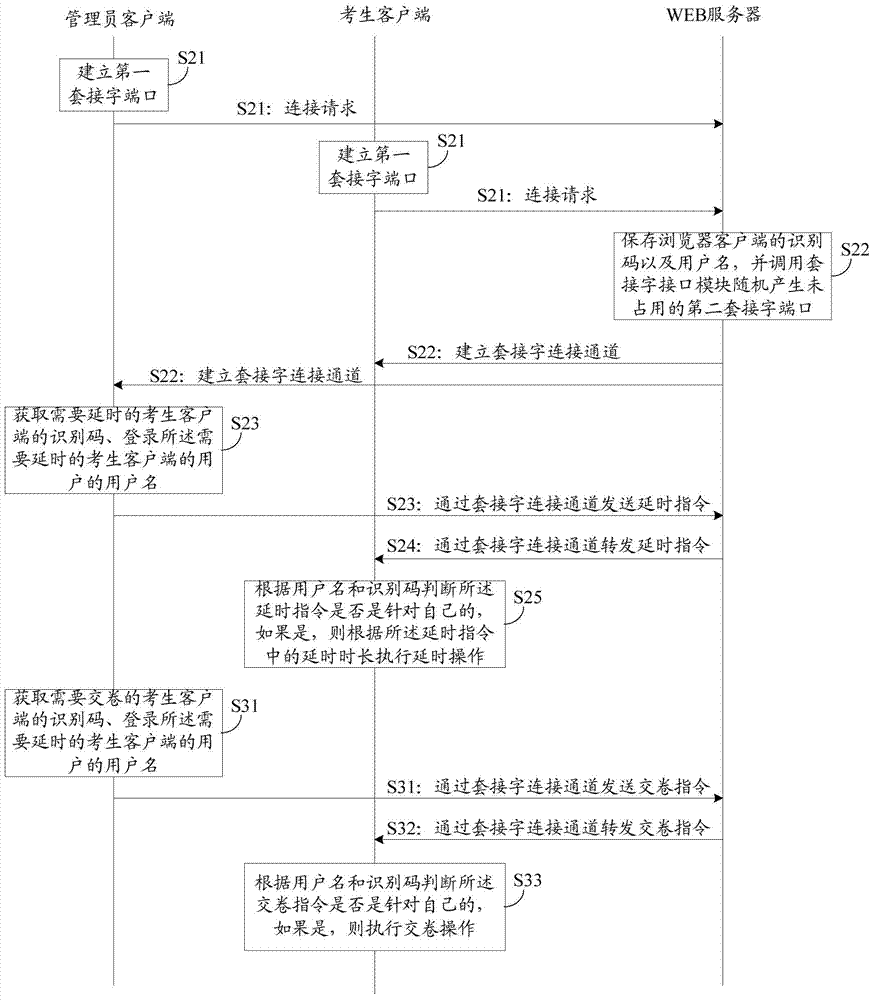

Online examination system and information processing method applied to online examination system

ActiveCN103685555AExtended test timeReduce the impactData switching networksElectrical appliancesClient-sideWeb server

The invention discloses an information processing method applied to an online examination system. After a user logs in to the online examination system through a browser client, the browser client sends connecting requests to a WEB server, the WEB server establishes a socket connecting channel with a browser server after receiving the connecting requests, and the socket connecting channel is a real-time duplex communication channel; when an examinee client needs to perform time delay operation, an administrator client sends time delay instructions carrying an identification code of the examinee client needing time delay, a user name of the user logging in to the examinee client needing time delay and time delay duration to the WEB server, the WEB server forwards the time delay instructions to the examinee client through the socket connecting channel, the examinee client judges whether the time delay instructions aim at the examinee client after receiving the time delay instructions, the time delay operation is performed if the time delay instructions aim at the examinee client, and a function of prolonging examination time for examinees is achieved.

Owner:BEIJING GUODIANTONG NETWORK TECH CO LTD +1

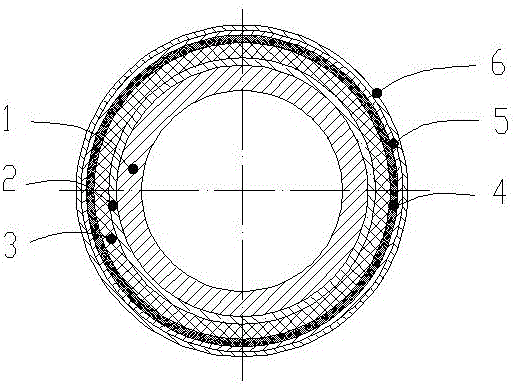

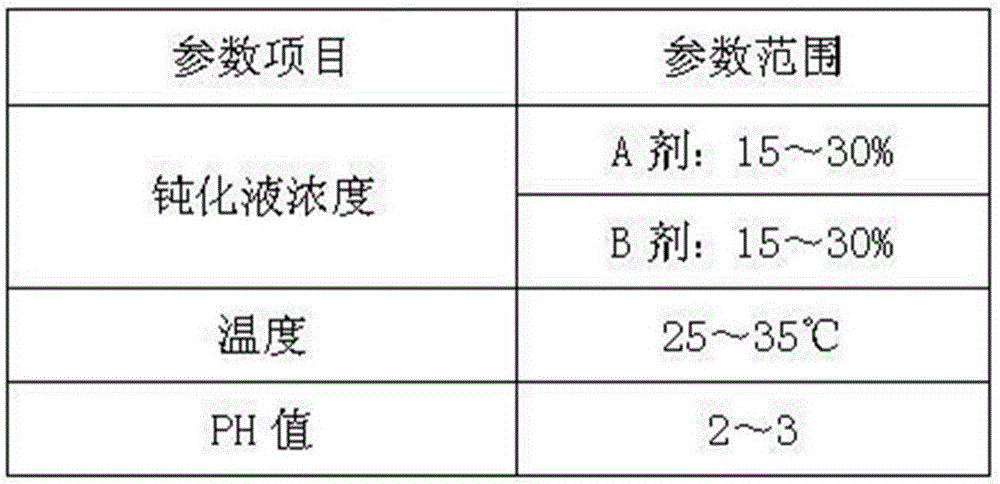

Composite galvanized army green steel pipe for refrigeration and manufacturing method of composite galvanized army green steel pipe

InactiveCN106544490AUniform thicknessImprove bindingHot-dipping/immersion processesFurnace typesZincWear resistance

The invention discloses a composite galvanized army green steel pipe for refrigeration and a manufacturing method of the composite galvanized army green steel pipe. The composite galvanized army green steel pipe comprises a steel pipe positioned on the innermost layer and is characterized in that a zinc-iron alloy layer is arranged on the outer surface of the steel pipe; a pure zinc layer is arranged on the outer surface of the zinc-iron alloy layer; an army green passivation layer is arranged on the outer surface of the pure zinc layer; a first closing layer and a second closing layer are separately arranged outside the army green passivation layer; and a product is obtained by the steps of carrying out deoiling, thermal treatment, composite galvanization, preheating, burnishing, washing with water, colored passivation, drying, closing for two time and drying. The composite galvanized army green steel pipe has a good binding force; a passivation bonding force among layers is high and weather fastness of the passivation layer is high; a finished product of the steel pipe has excellent wear resistance; the composite galvanized army green steel pipe has the advantages of good bright line, smoothness, anti-tarnishing property, rigorous process and high stability of the finished product; and when a condenser and a dew removable tube are manufactured, a protective heat shrink tube does not need to be added, so the working procedure is simple.

Owner:ZHEJIANG KANGSHENG CO LTD

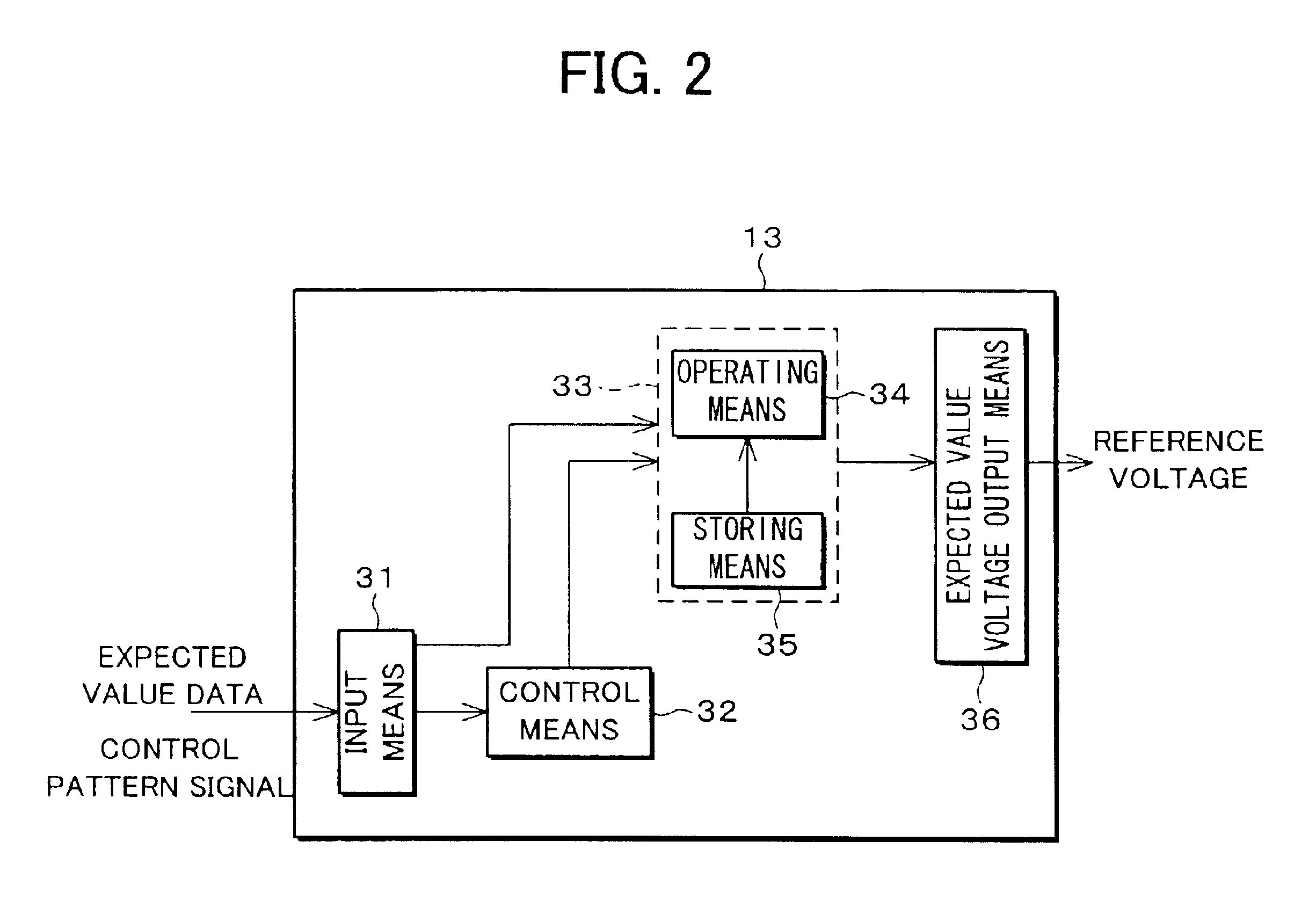

Reference voltage generating device, semiconductor integrated circuit including the same, and testing device and method for semiconductor integrated circuit

InactiveUS6850085B2Test accurateIncrease volumeAnalog circuit testingStatic indicating devicesVoltage generatorComputer module

A testing device for a semiconductor integrated circuit of the present invention includes a differential amplifier array module and tester which determine whether an output voltage of a liquid crystal driver LSI is at a proper level and an expected value voltage generator which generates an expected value voltage in accordance with expected value data to output it to the differential amplifier array module. The expected value voltage generator produces expected value data by interpolation in accordance with incoming expected value data fewer in number than the expected value voltage to be generated, so as to be equal in number to the expected value voltage. This makes it possible to carry out an extremely short time and highly accurate test for output voltages of a device under test (liquid crystal driver LSI).

Owner:SHARP KK

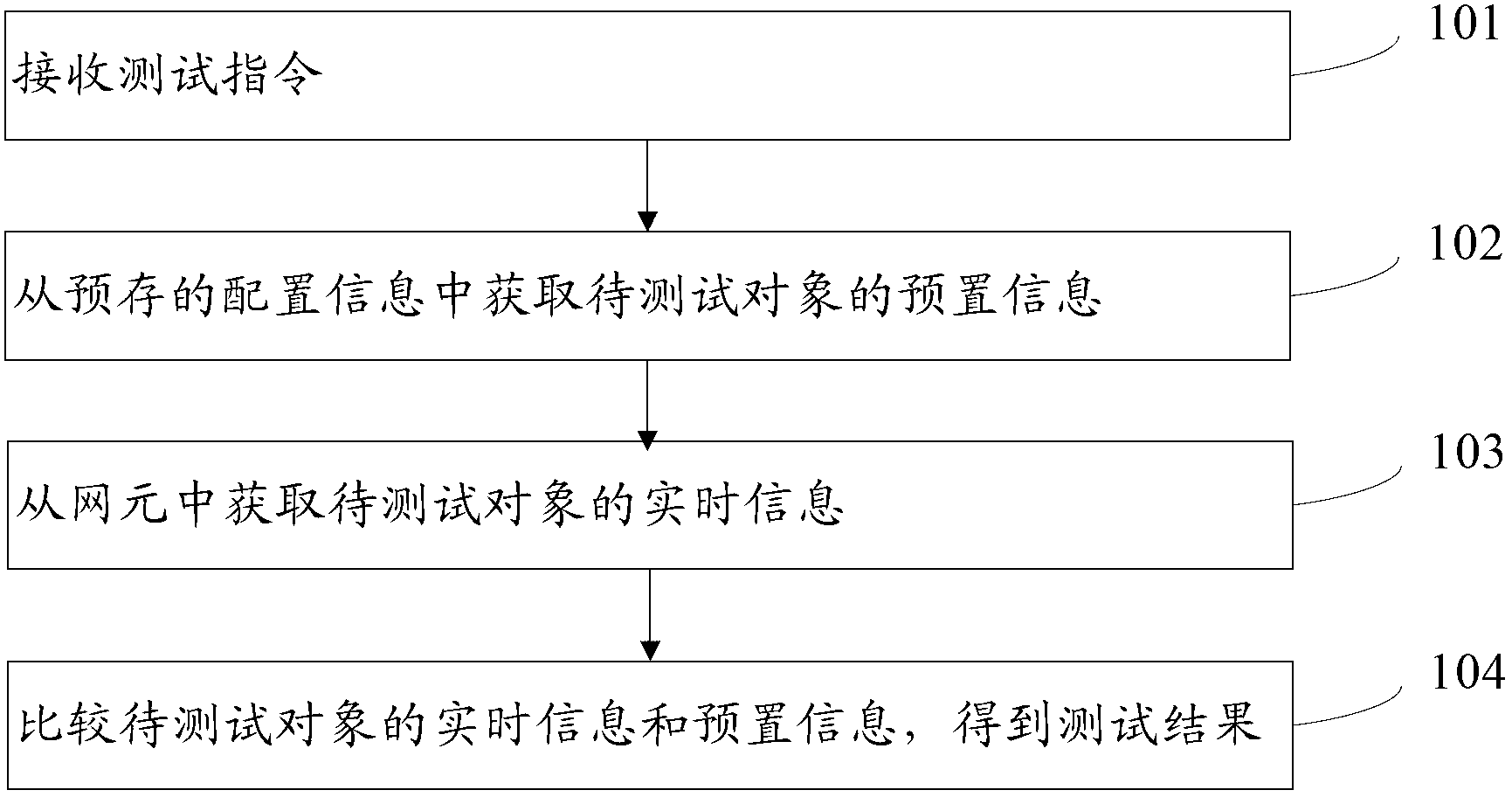

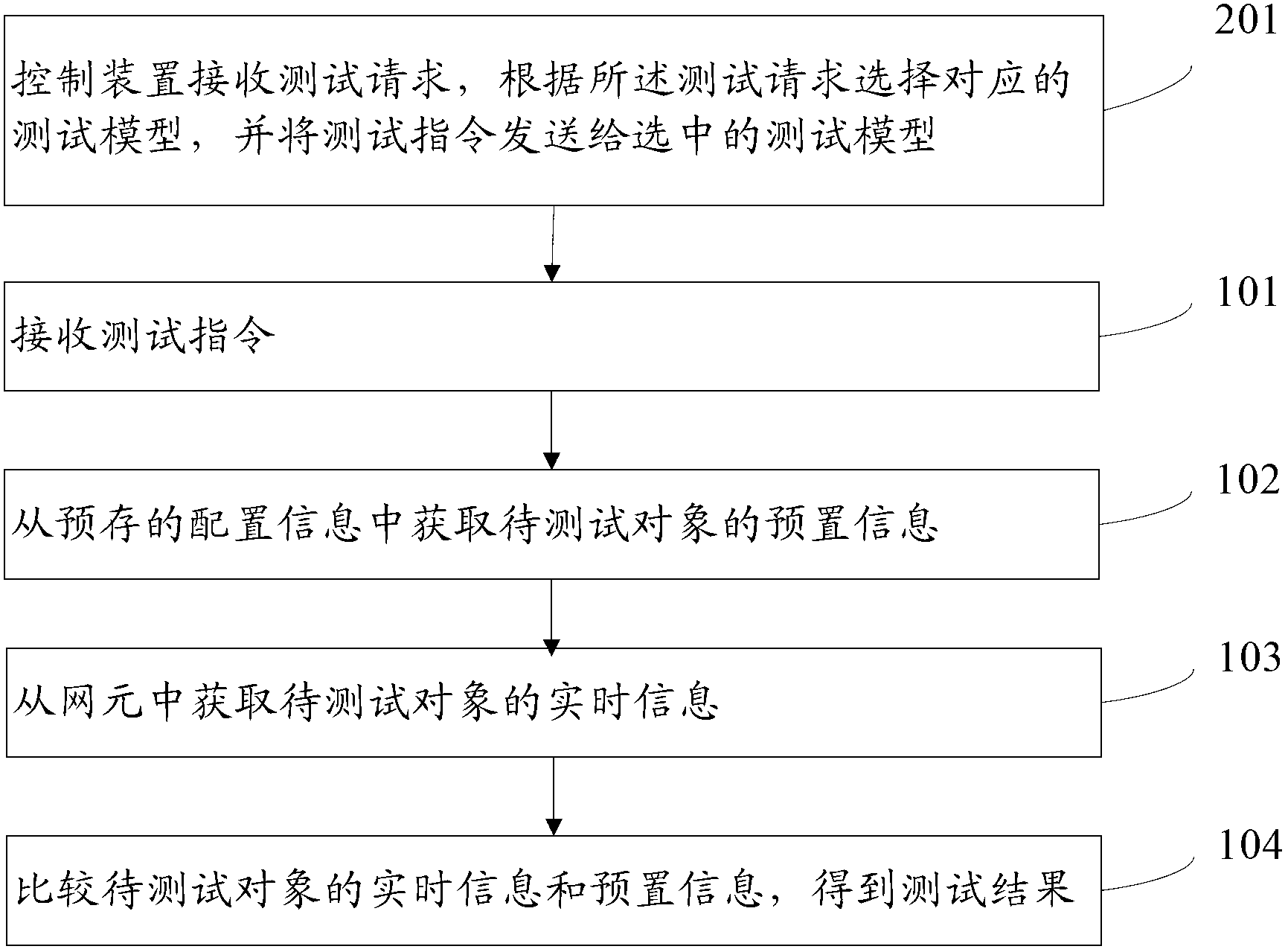

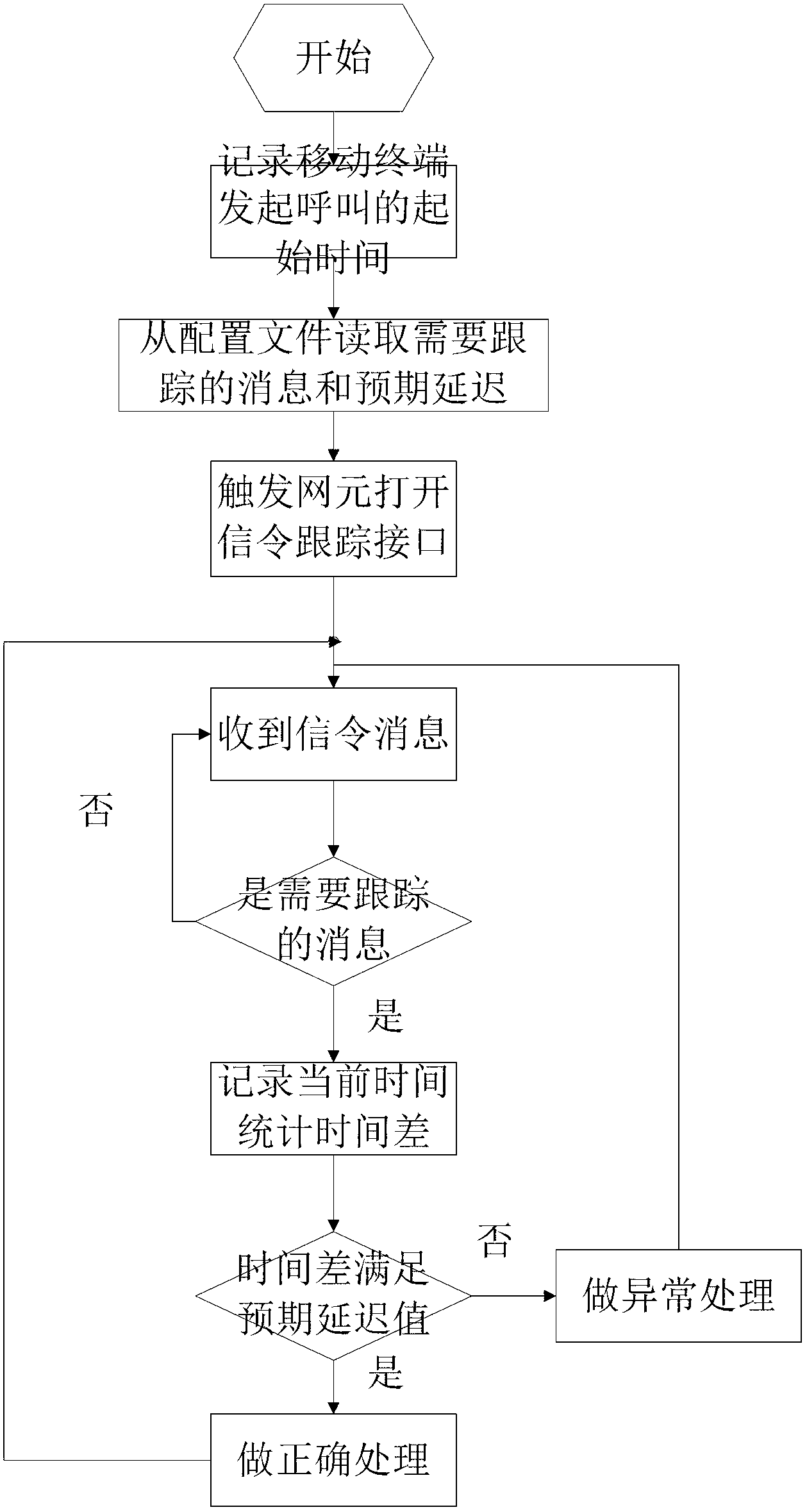

Automatic network communication quality automatic testing method and automatic network communication quality testing system

ActiveCN103024790AExtended test timeReduce testing costsWireless communicationTest efficiencyTime information

The invention provides an automatic network communication quality testing method comprising the following steps of: receiving a testing command; obtaining preset information of an under-test object from pre-stored configuration information; obtaining real-time information of the under-test object from a network element; and comparing the real-time information with the preset information of the under-test object to get the testing result. The invention further provides a network communication quality automatic testing system for realizing the method. The network communication quality automatic testing method and the network communication quality automatic testing system can be used for realizing automatic test on the network communication quality, improving the testing efficiency and lowering the testing cost.

Owner:DATANG MOBILE COMM EQUIP CO LTD

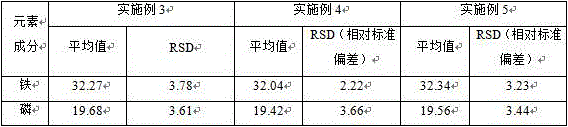

Fluorescence analysis method for measuring element content of lithium iron phosphate

InactiveCN105842266AFast detection methodEasy to operateMaterial analysis using wave/particle radiationEnvironmental resistanceX-ray

The invention discloses a fluorescence analysis method for measuring element content of lithium iron phosphate. The method comprises the following steps: equally dividing a lithium iron phosphate sample into three parts; processing a first part of the lithium iron phosphate sample by the use of hydrochloric acid, filtering and carrying out standard solution titration with potassium dichromate, and measuring content of iron element; processing the second part of the lithium iron phosphate sample by the use of hydrochloric acid, filtering and measuring content of phosphorus element by an ammonium phosphomolybdate volumetric method; preparing six standard samples with different contents from the third part of the lithium iron phosphate sample; respectively compressing into flaky pieces, and measuring fluorescence intensity of iron and phosphorus elements in each flaky standard sample by X-ray fluorescence spectrometry; drawing an XRF standard curve; compressing the lithium iron phosphate sample to be measured into flaky pieces, and measuring fluorescence intensity; and obtaining iron and phosphorus contents through the XRF standard curve. The method of combining a wet chemistry method and an X-ray fluorescent spectrometry is fast and high-speed, is simple to operate, has little error and long consumption time, and is environmentally friendly.

Owner:HEFEI GUOXUAN HIGH TECH POWER ENERGY

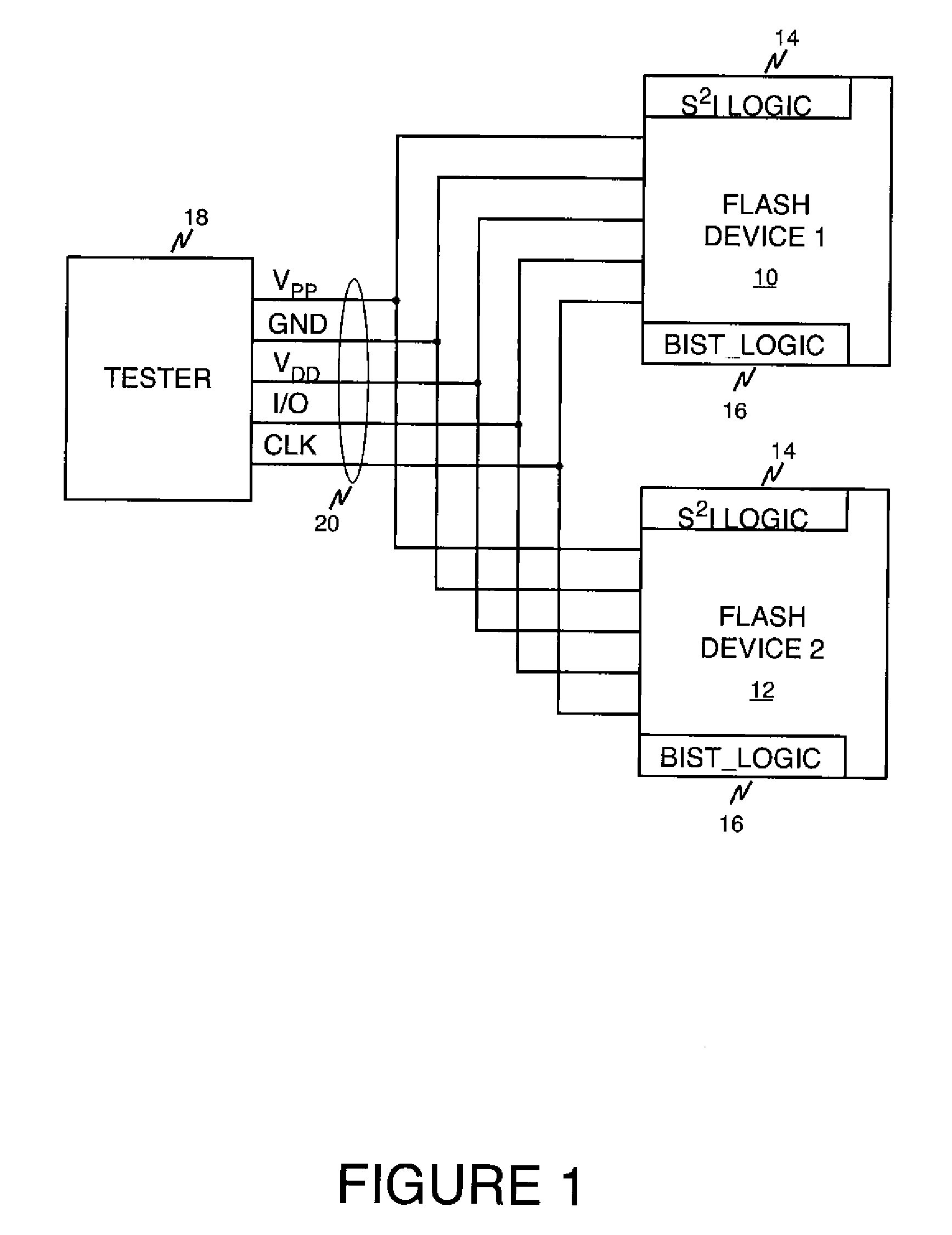

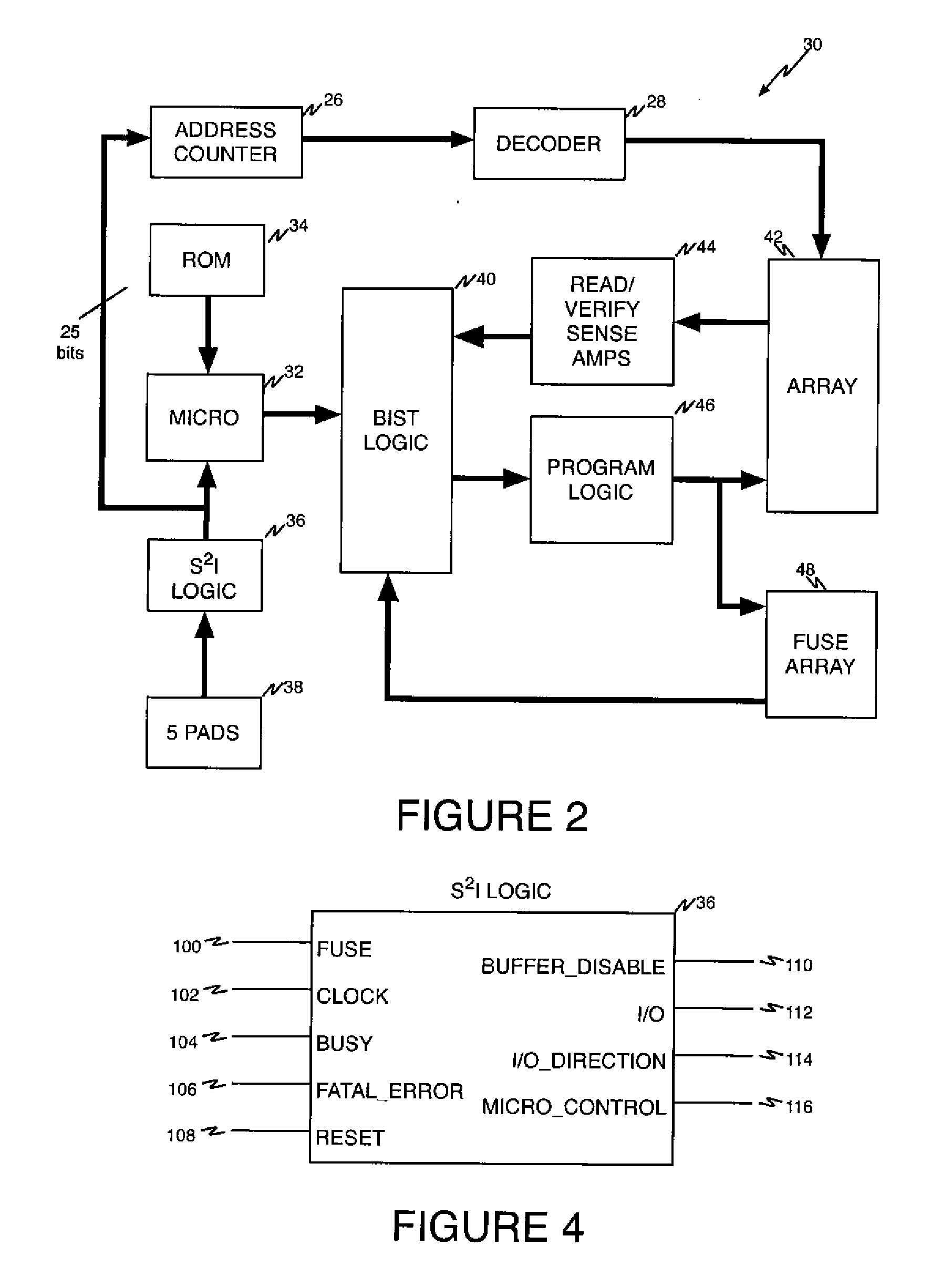

Embedded architecture with serial interface for testing flash memories

InactiveUS20080201623A1Shorten test timeSpeedElectronic circuit testingError detection/correctionArray data structureSerial port

A flash memory device includes a flash memory array, a set of non-volatile redundancy registers, a serial interface, and testing logic coupled to the serial interface, the testing logic configured to accept a set of serial commands from an external tester; erase the array; program the array with a test pattern; read the array and compare the results with expected results to identify errors; determine whether the errors can be repaired by substituting a redundant row or column of the array, and if so, generate redundancy information; and program the redundancy information into the non-volatile redundancy registers.

Owner:ATMEL CORP

Method for determining hematocrit corrected analyte concentrations

InactiveUS20130240375A1Reduce probabilityLess producedWeather/light/corrosion resistanceMicrobiological testing/measurementAnalyteLinear regression

The method includes: providing a test strip comprising a reference electrode and a working electrode coated with a reagent layer; applying a fluid sample to the test strip for a reaction period; applying a test voltage between the reference electrode and the working electrode; measuring a test current as a function of time; measuring a steady state current value when the test current has reached an equilibrium; calculating a ratio of the test current to the steady state current value; plotting the ratio of the test current to the steady state current value as a function of the inverse square root of time; calculating an effective diffusion coefficient from the slope of the linearly regressed plot of the ratio of the test current to the steady state current value as a function of the inverse square root of time; and calculating a hematocrit-corrected concentration of analyte.

Owner:LIFESCAN IP HLDG LLC

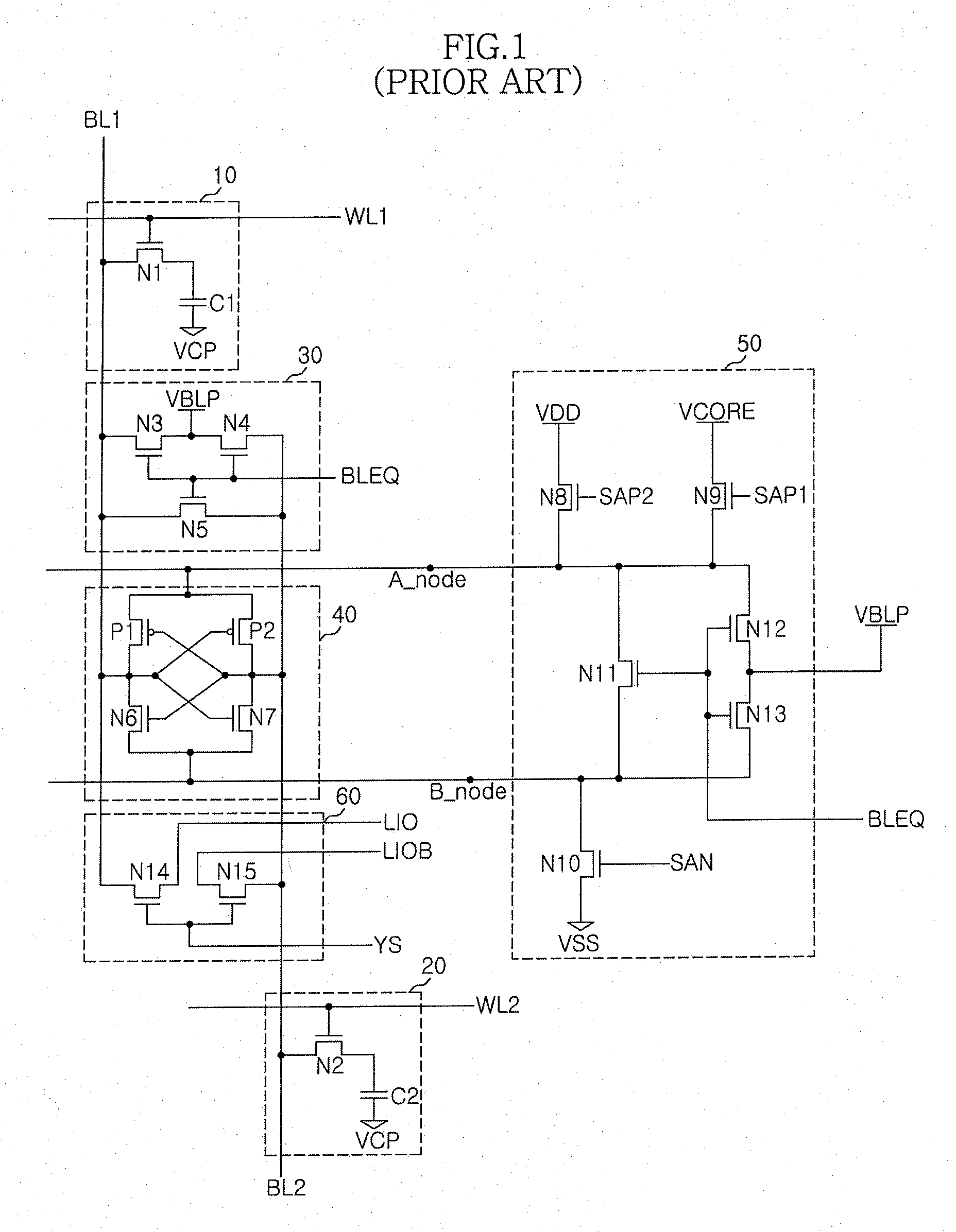

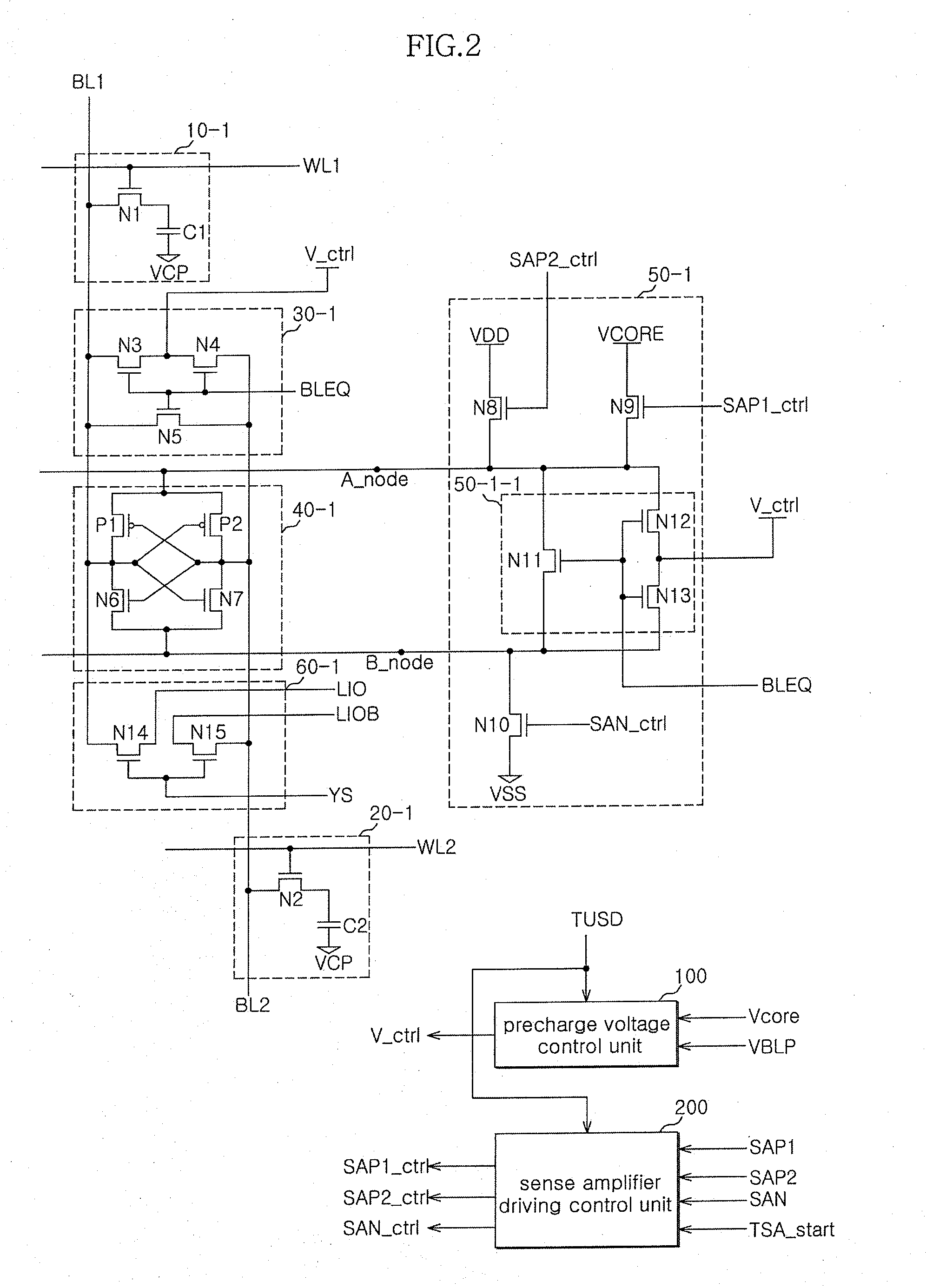

Semiconductor memory apparatus and test method using the same

ActiveUS20110075498A1Increases test timeExtended test timeDigital storageSense amplifierCharge voltage

A semiconductor memory apparatus includes: a precharge voltage control unit configured to selectively output a bit line precharge voltage or a core voltage as a control voltage in response to a test signal; a bit line equalization unit configured to precharge a bit line to the control voltage; a sense amplifier driving control unit configured to generate a first voltage supply control signal, a second voltage supply control signal and a third voltage supply control signal in response to the test signal, a sense amplifier enable test signal, a first voltage supply signal, a second voltage supply signal and a third voltage supply signal; and a voltage supply unit configured to provide the core voltage, an external voltage and a ground voltage to a sense amplifier with an open bit line structure in response to the first to third voltage supply control signals.

Owner:SK HYNIX INC

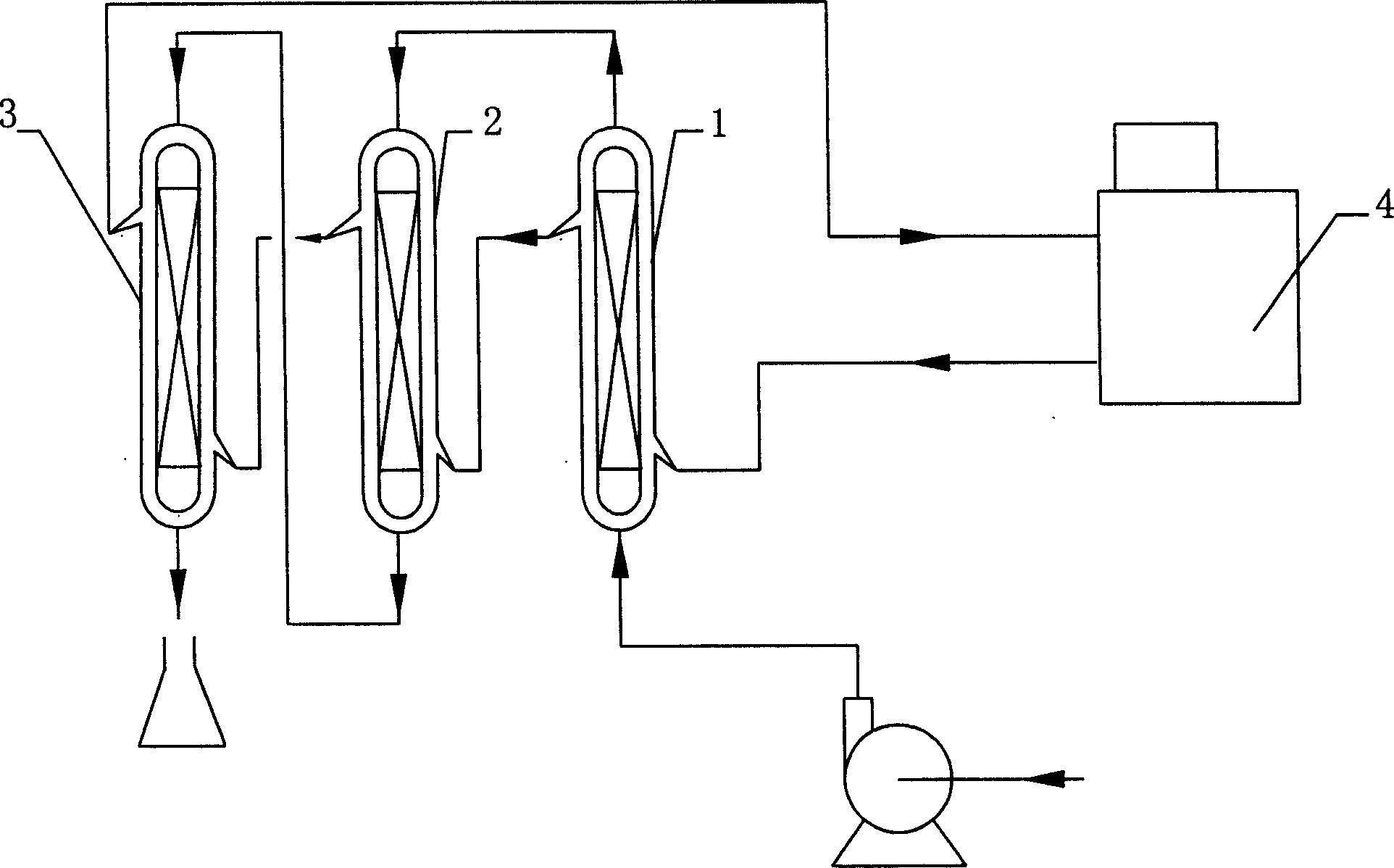

Acetic acid refining method for improving acetic acid potassium permanganate test time

ActiveCN1634843AExtended test timeThe method is simpleCarboxylic compound separation/purificationAcetic acidTested time

The invention relates to a method for removing the reducing impurity in acetic acid and improving the test time of potassium permanganate of acetic acid, characterized by filling acetic acid -insoluble solid strong oxidizer in adsorption column 1, acetic acid passing the oxidizer for removing the reducing impurity in acetic acid, then acetic acid passing adsorption column 2 filled with alumina and adsorption column 3 filled with active carbon for refining acetic acid again and removing water and unsaturated aldehydes in acetic acid. Potassium permanganate test is done for obtaining high quality of acetic acid with good potassium permanganate test time.

Owner:SHANGHAI HUAYI ENERGY CHEM

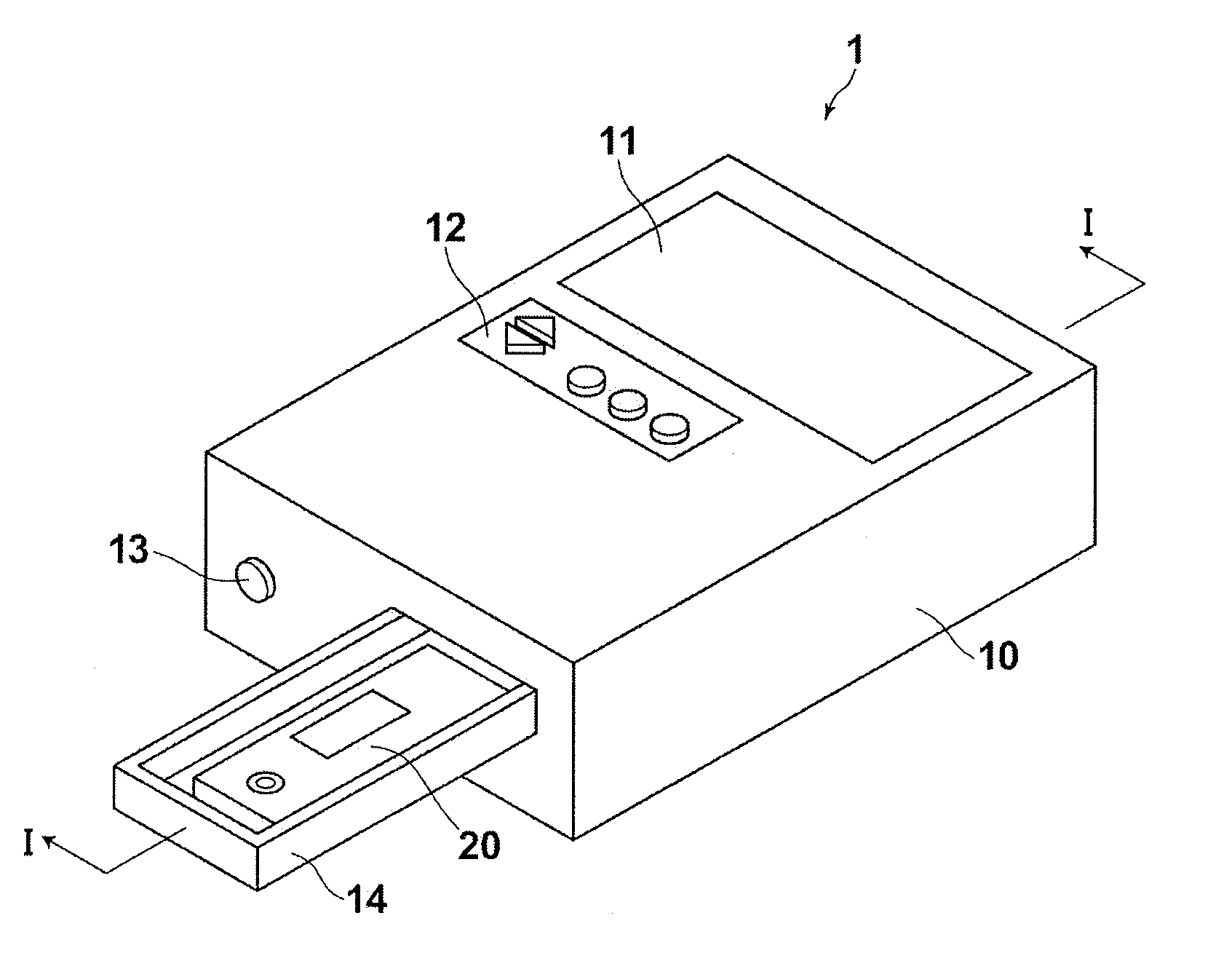

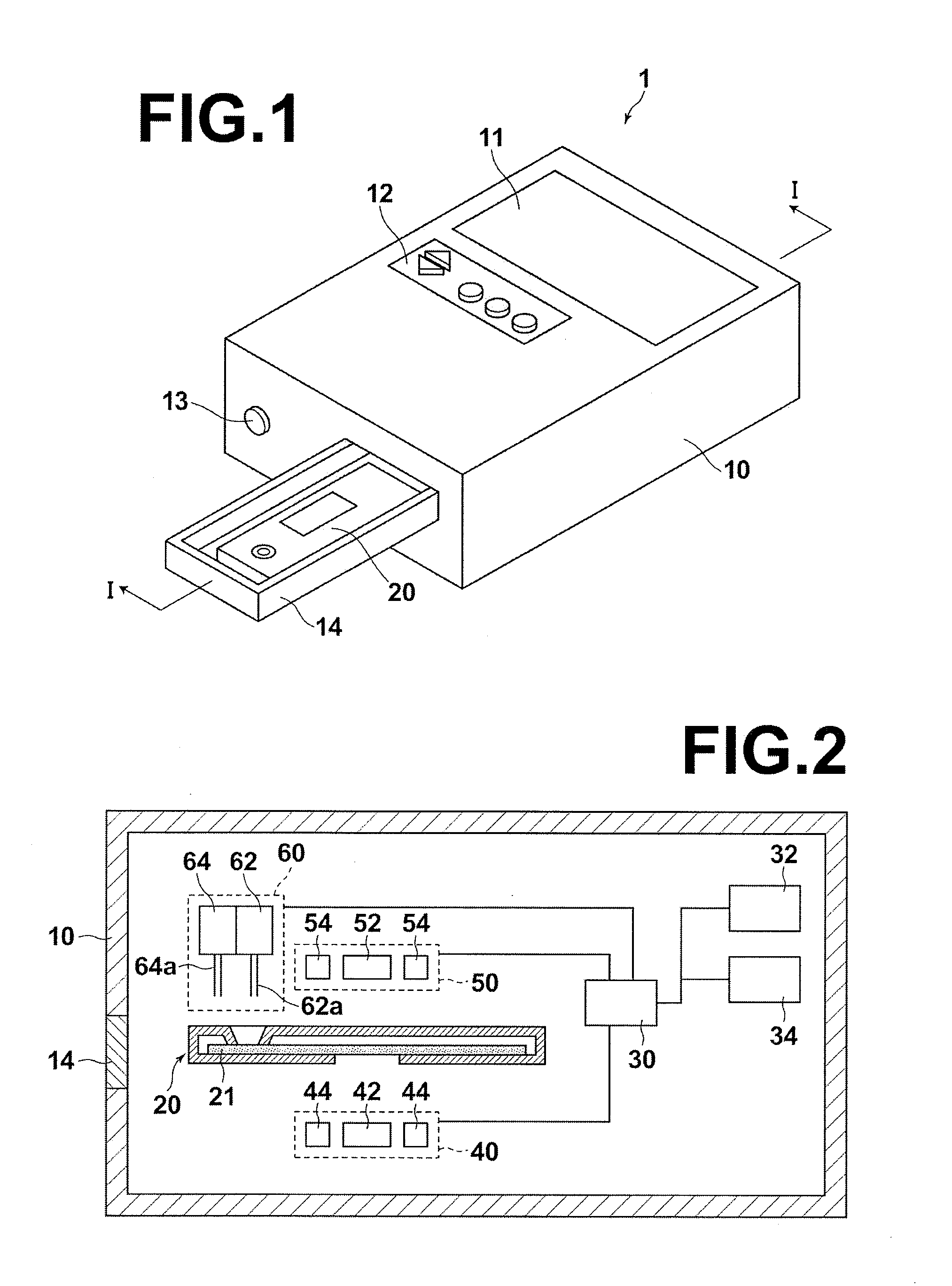

Chromatographic measurement apparatus

ActiveUS20110072885A1Increase test timeReliable test resultMaterial analysis by observing effect on chemical indicatorComponent separationTest articleChromatographic measurement

A chromatographic measurement apparatus for measuring a color development state of an insoluble carrier with a sample solution and a label solution developed thereon to test a test article, the insoluble carrier including a test detection area where a material that binds specifically to a test article is immobilized and a control detection area used for determining an end of measurement. The chromatographic measurement apparatus includes: a determining unit for carrying out determination of validity and determination of necessity of amplification of a test result of the test article; and an amplifying unit for amplifying the color development state according to the result of the determination of necessity of amplification by the determining unit. The amplification is carried out only when it is determined that amplification is necessary.

Owner:FUJIFILM CORP

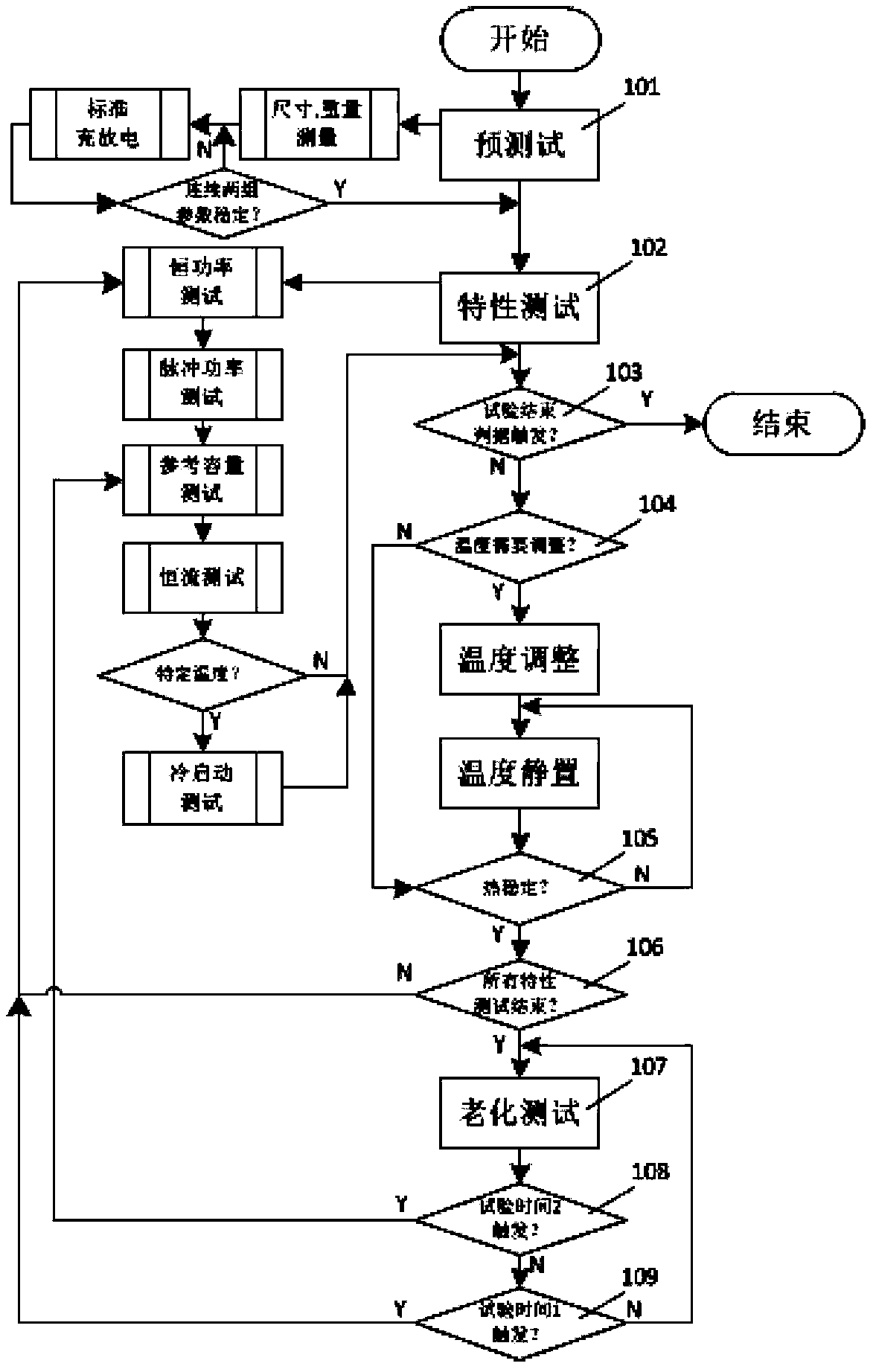

Characteristic testing method and device applied to different aging stages of super capacitors

ActiveCN104297576AImprove universalityImprove reliabilityElectrical testingTemperature controlPower grid

The invention relates to a characteristic testing method and device applied to different aging stages of super capacitors. The method includes the steps such as pre-testing, characteristic testing, temperature adjustment, temperature standing and aging testing. The device comprises power grid input, a power conversion device, a transitional super capacitor, a DC / DC converter, a temperature control box, a tested super capacitor and a host computer. Compared with the prior art, the characteristic testing method and device of the invention have advantages of a wide covering range, small characteristic influence, highly targeted performance, short consumed time and the like.

Owner:智车上海实业有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com