Built-in self-test method of FPGA logical resource

A technology of built-in self-test and logic resources, applied in the field of built-in self-test based on scan register FPGA logic resources, it can solve the problem of lack of in-depth introduction, and achieve the goal of simplifying the retrieval method, simplifying the configuration structure, and improving the test efficiency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

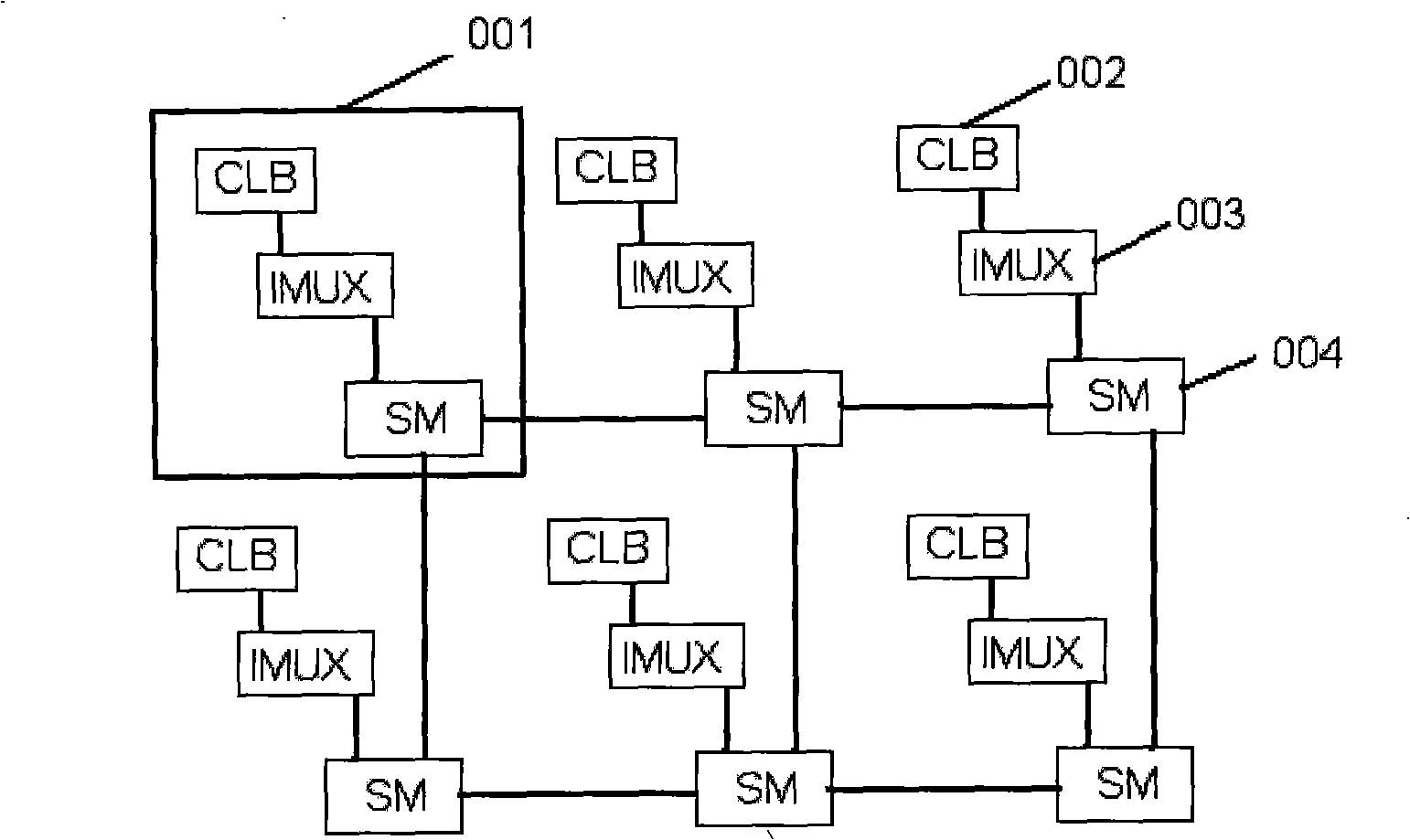

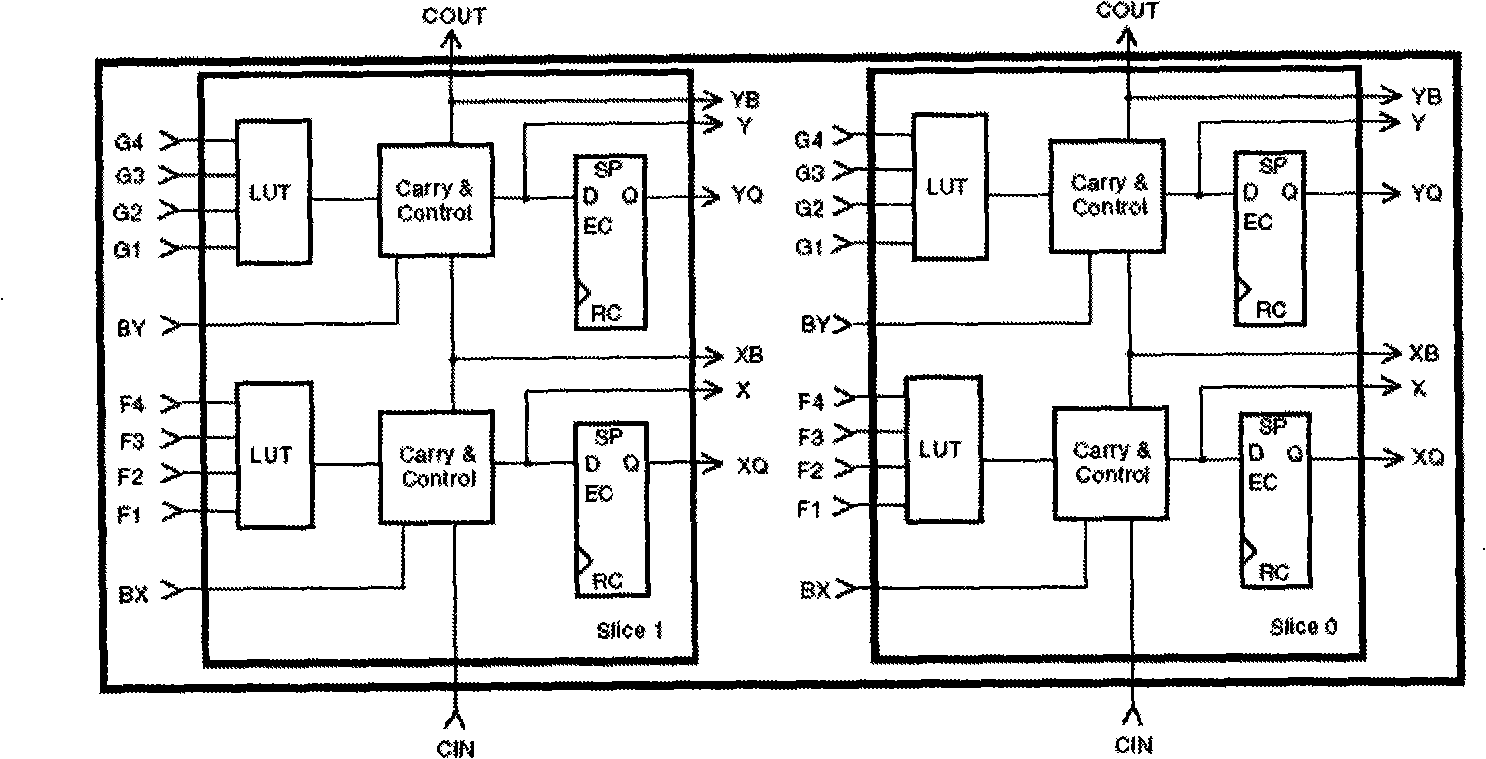

[0030] FPGA basic circuit structure such as figure 1 As shown, it is mainly composed of TITLE array 001 and input and output module 005. Programmable logic module 002 is a logic unit in one of TITLE array 001, and it realizes interconnection with surrounding programmable logic modules through IMUX003 and switch matrix 004 , users can flexibly implement various functions by configuring the programmable logic module 002. The configurable logic module 002 is the logical unit in the TITLE array 001, such as figure 2 The configurable logic module 002 shown is mainly composed of two identical SLICE units. It realizes the interconnection with the surrounding programmable logic modules through the IMUX003 and the switch matrix 004, and the user can flexibly realize it by configuring the configurable logic module 002 various functions.

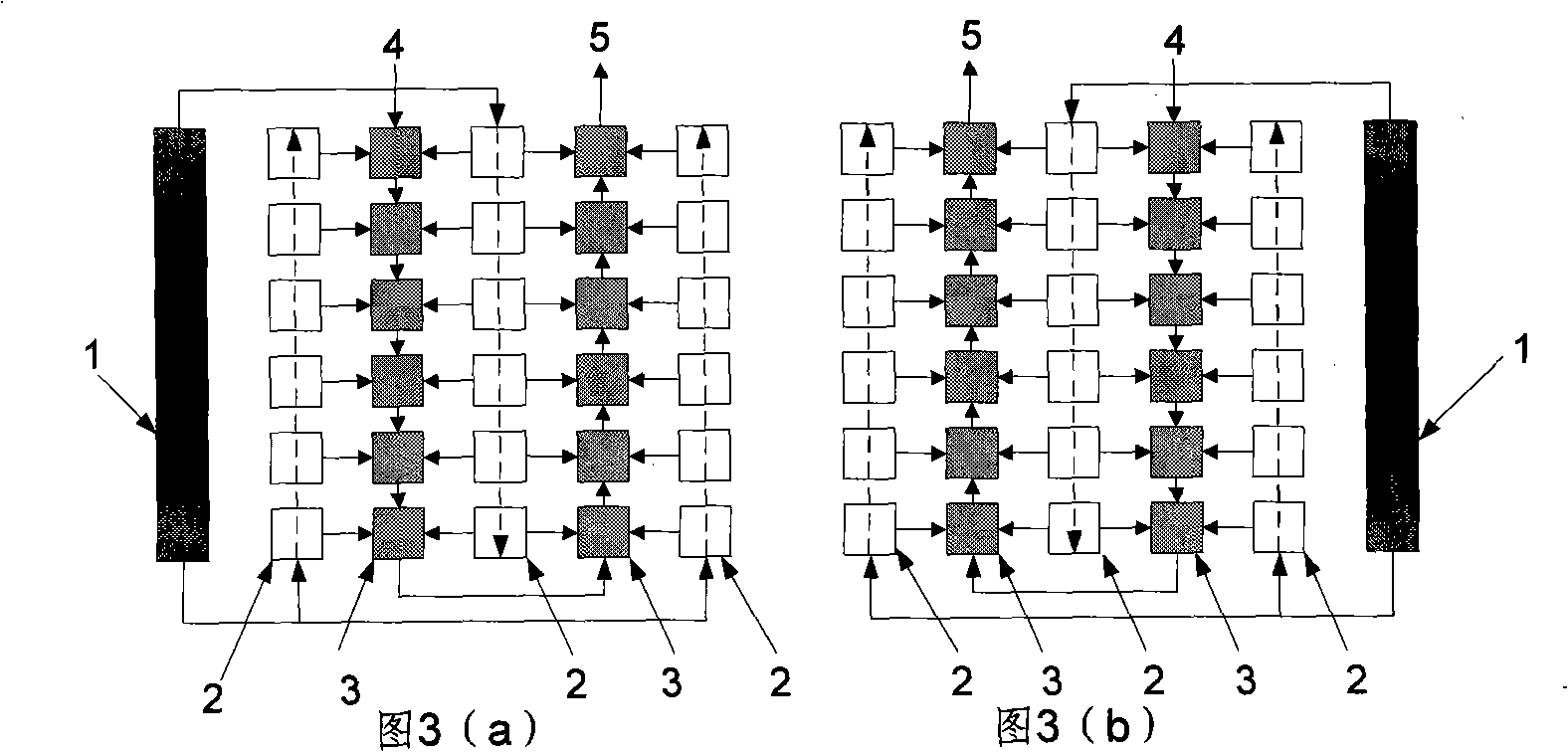

[0031] The built-in self-test structure of the present invention is as image 3 As shown, the built-in self-test process is as follows:

[0032] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com