Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

59 results about "Principal clock" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In telecommunications, the principal clock of a set of redundant clocks, is the clock that is selected for normal use. The principal clock may be selected because of a property, e.g. superior accuracy, that makes it a unique member of the set.

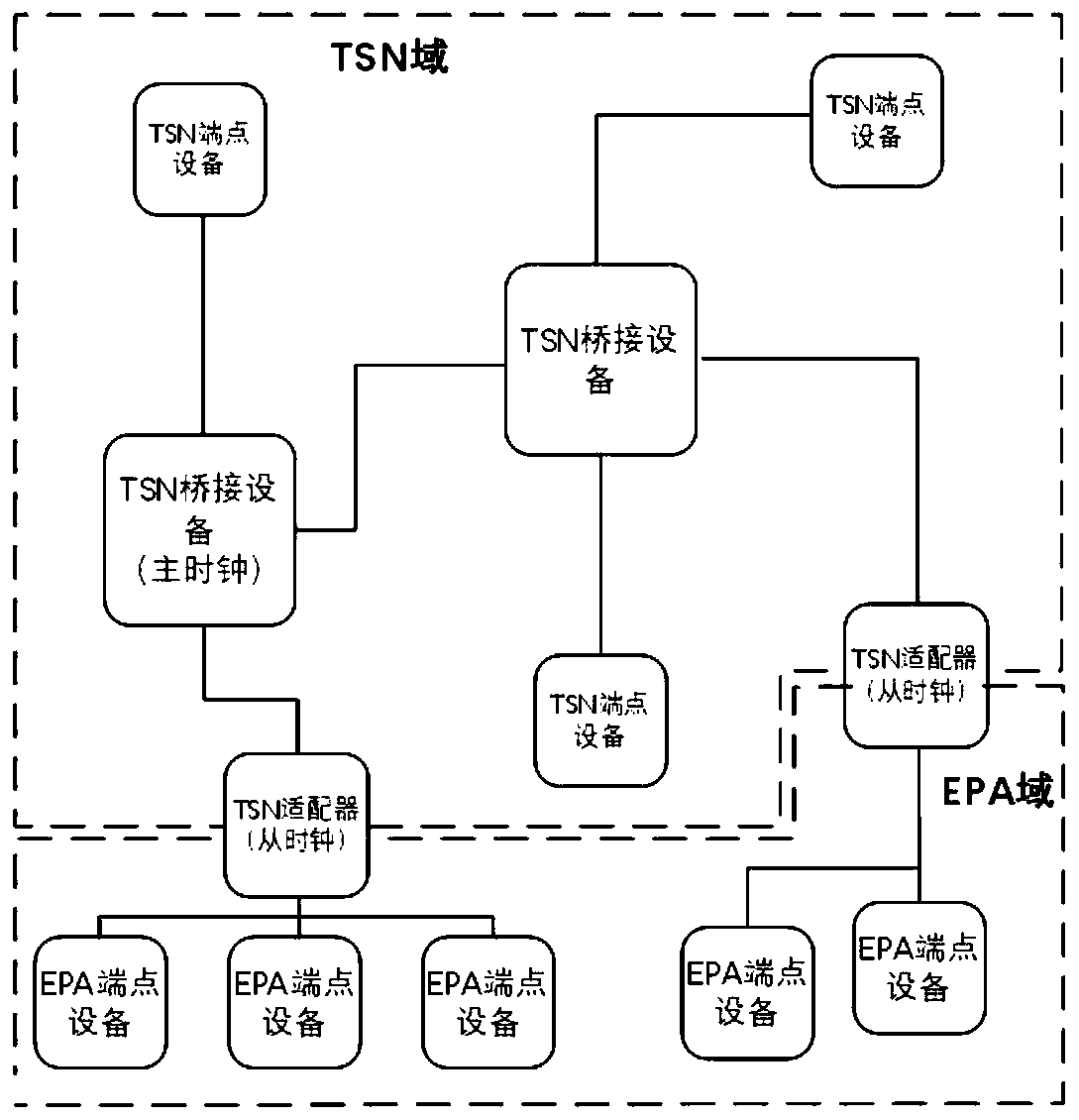

EPA industrial bus and time sensitive network adaptation system and method

ActiveCN110943899AProtect normal transmissionEfficient use ofTime-division multiplexNetworks interconnectionLow jitterLow delay

The invention relates to an EPA industrial bus and time sensitive network adaptation system and method, solves the technical problem that an EPA Ethernet cannot be connected with a time sensitive network in real time to construct a fast channel, and comprises an EPA endpoint device and a TSN endpoint device. The EPA endpoint device is in communication connection with a TSN bridging device througha TSN adapter, and the TSN bridging device is connected with the TSN endpoint device; the TSN adapter receives the time data issued by the main clock from the TSN bridging device, and adds a timestampin the process of receiving or transmitting the clock synchronization data to complete clock synchronization; and the TSN bridging device is used for providing time synchronization, low delay, low jitter and flow bandwidth guarantee, so that the problem is better solved, and the method can be applied to the EPA industrial technology.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

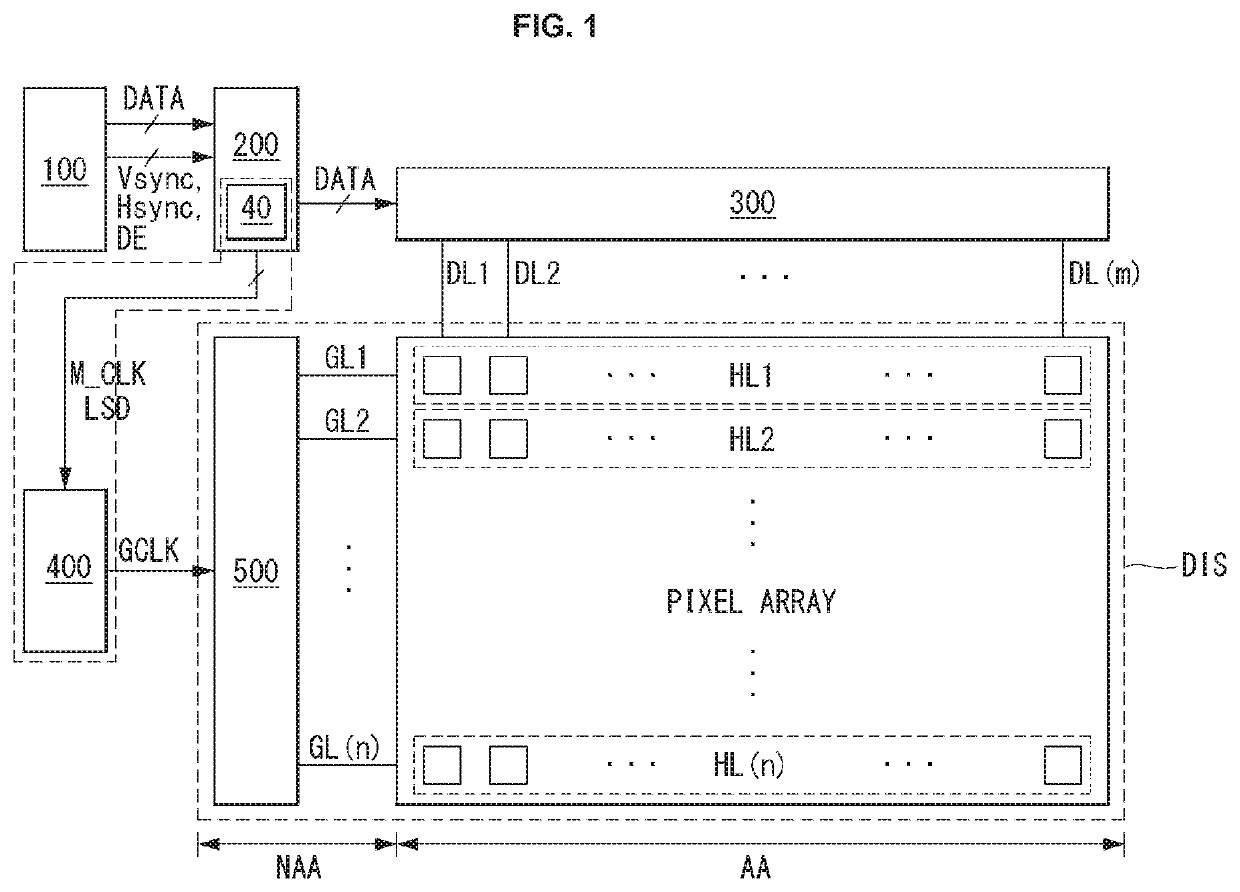

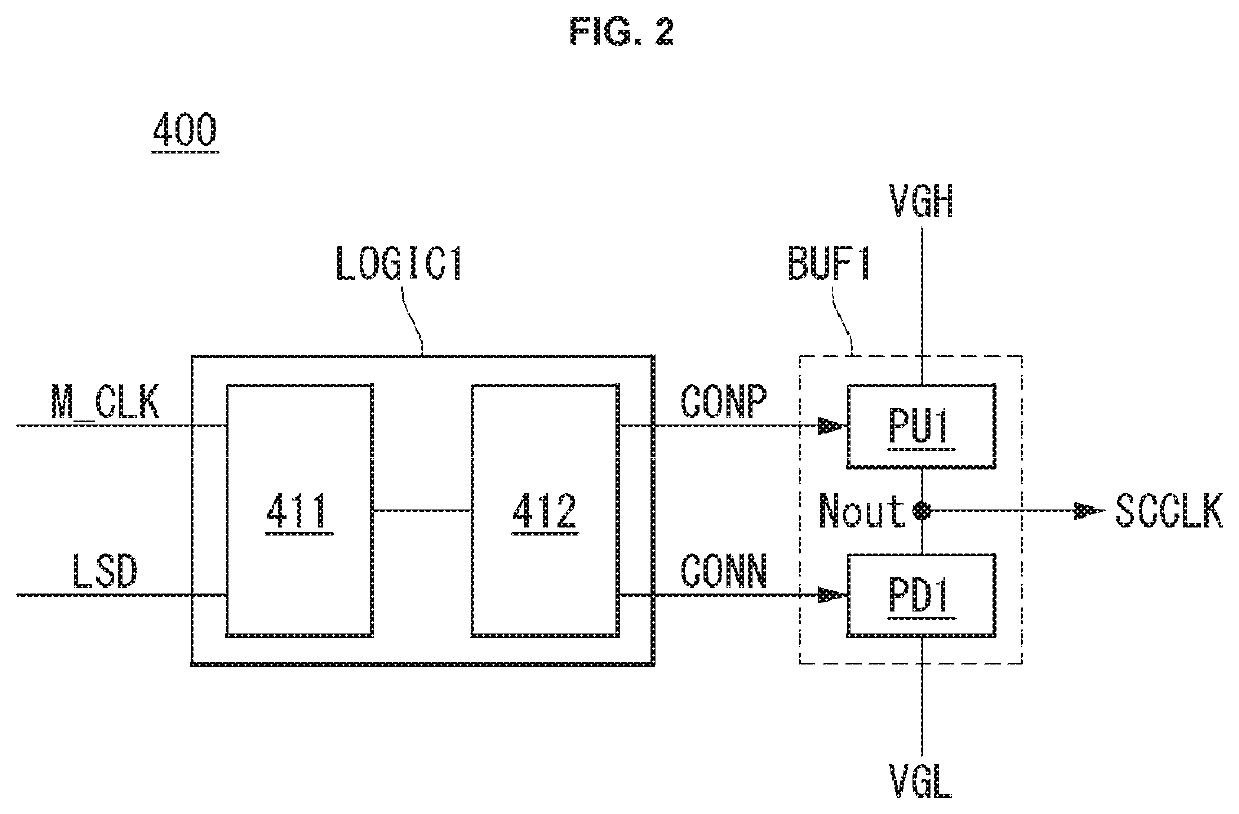

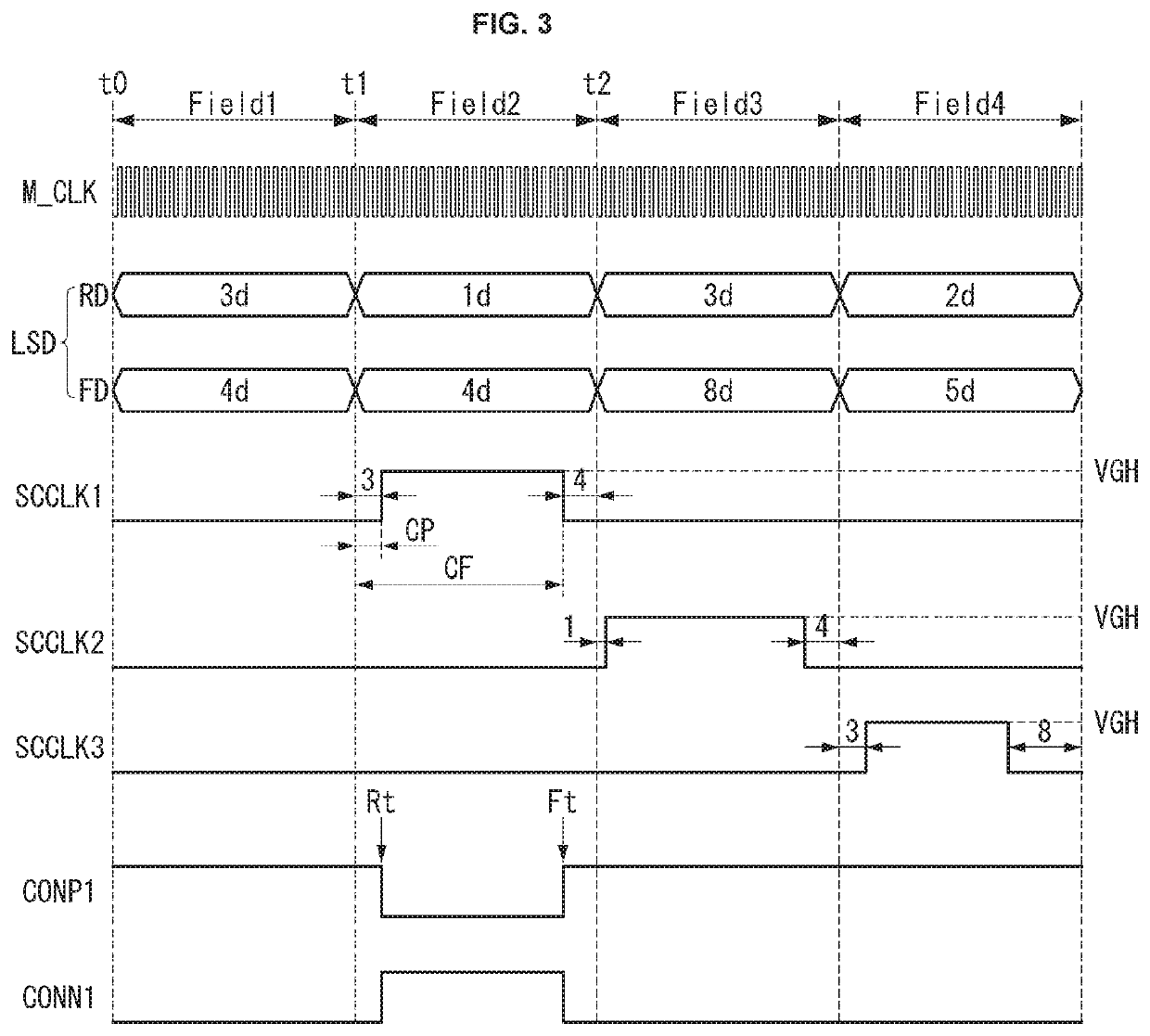

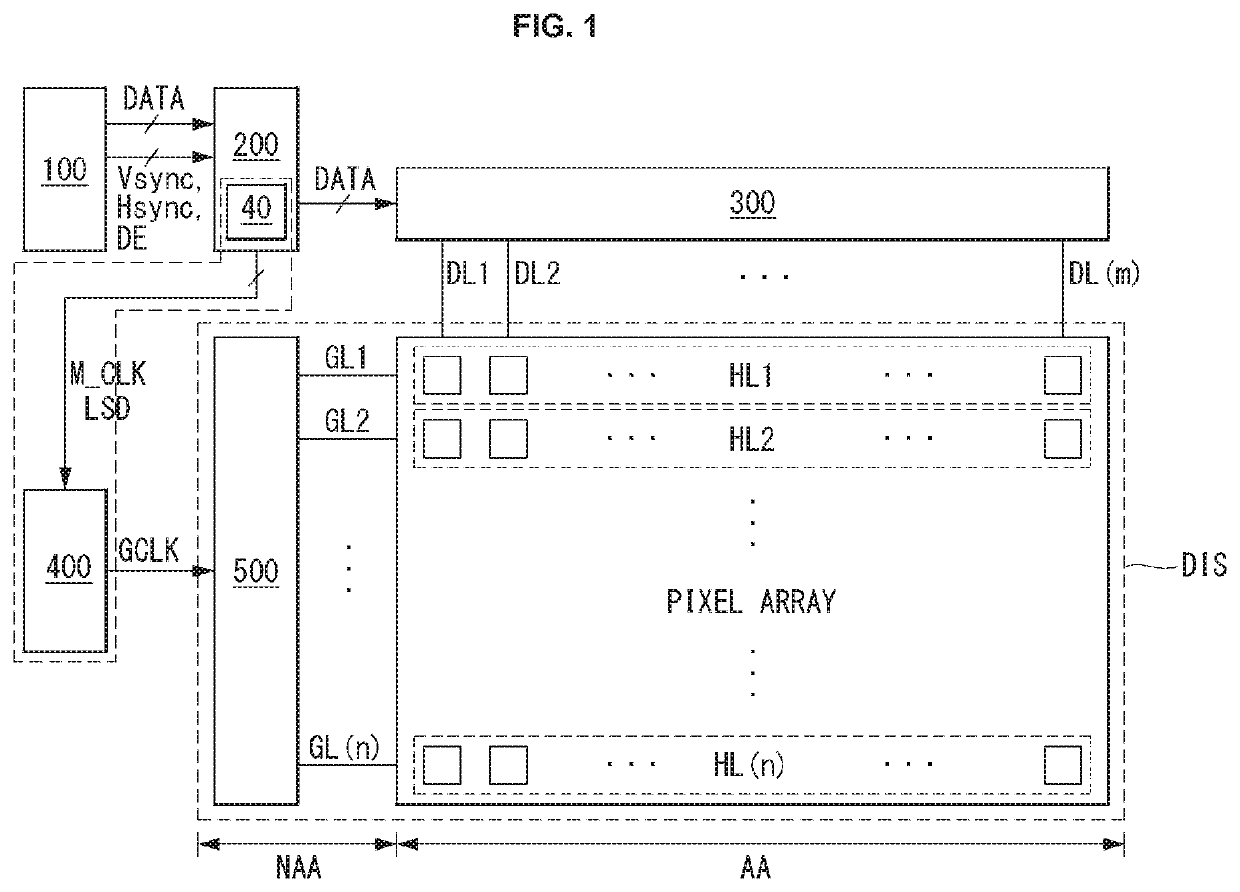

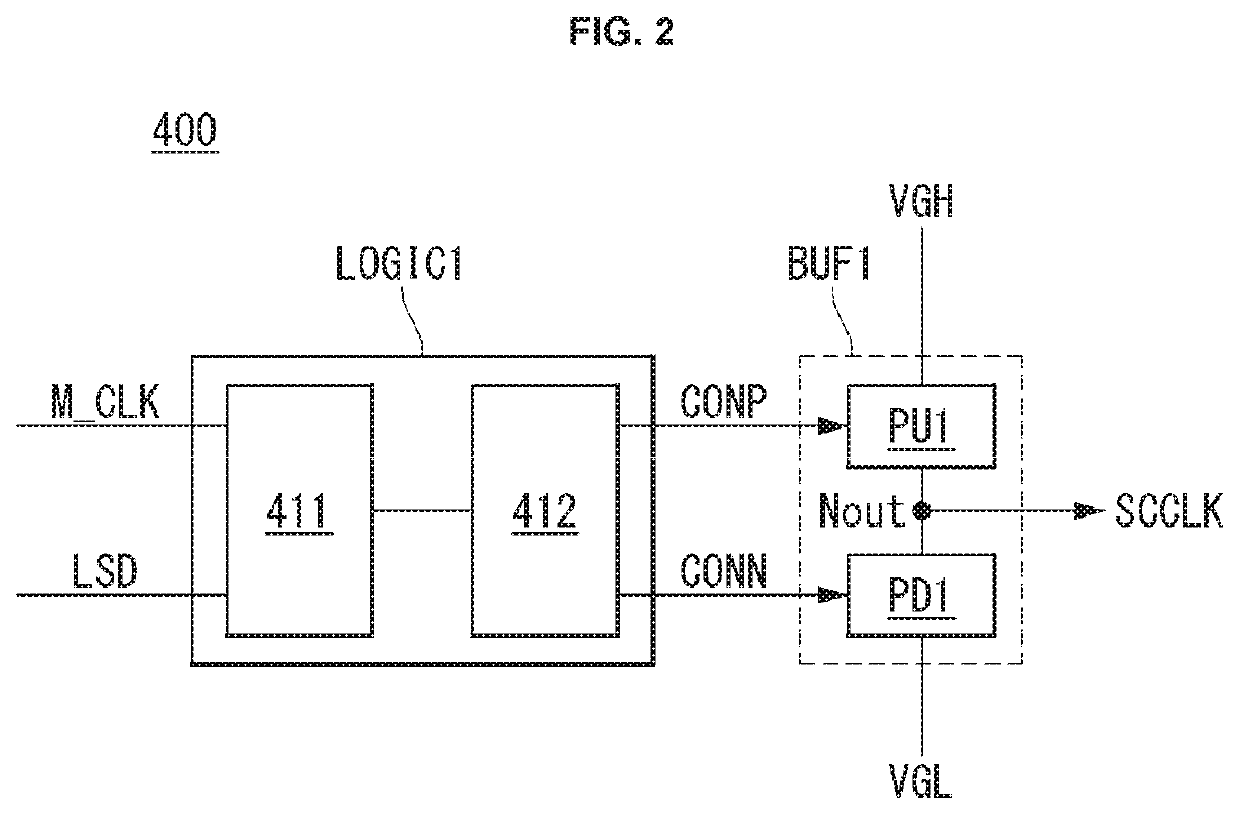

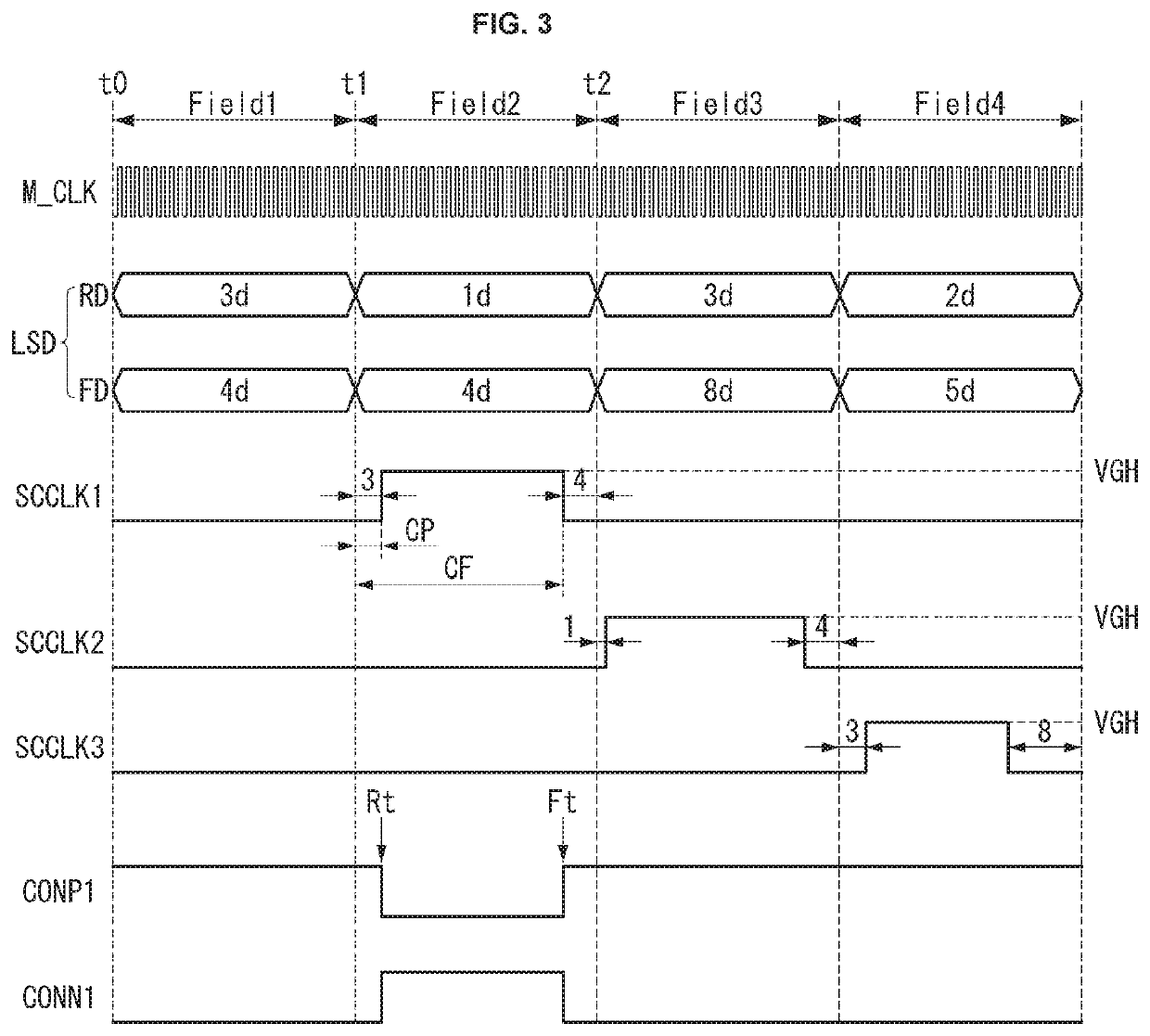

Gate clock generator and display device having the same

The present disclosure provides a gate clock generator including a counter, a buffer control signal generator, and an output unit. The counter receives control data having rising timing information and falling timing information and a main clock. The counter generates a first output when a value is obtained by counting the main clock from a preset reference time point reaches rising data. The counter further generates a second output when a value is obtained by counting the main clock from the reference time point reaches falling data. The buffer control signal generator generates a first buffer control signal of a gate ON voltage from a timing of the first output to a timing of the second output. The output unit outputs a gate ON voltage of a gate clock during an output period of the gate ON voltage of the first buffer control signal.

Owner:LG DISPLAY CO LTD

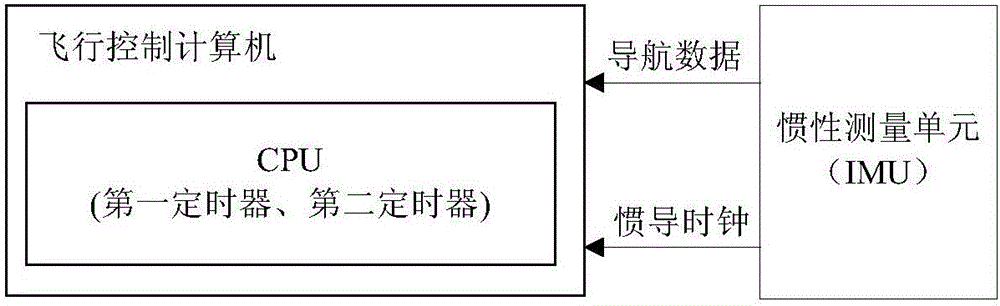

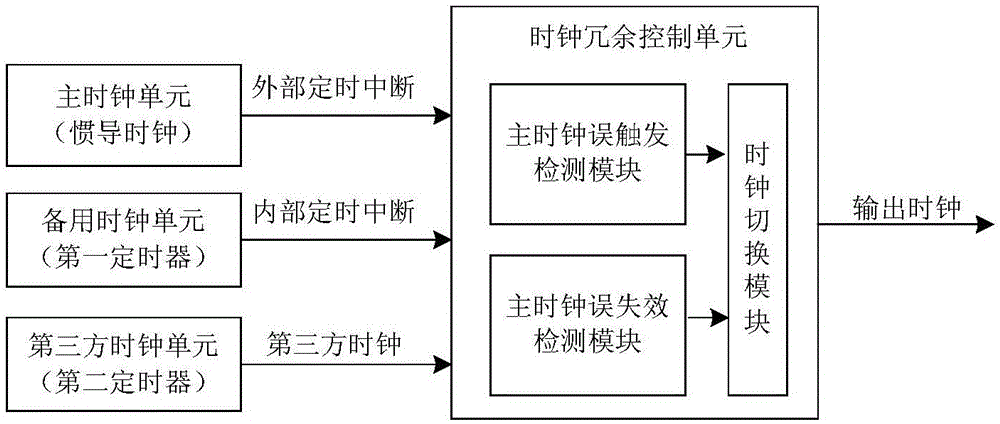

Satellite-borne clock redundant system and method

ActiveCN106154824ARealize clock redundancy functionImprove reliabilitySafety arrangmentsThird partyControl system

The invention provides a satellite-borne clock redundant system and method. The satellite-borne clock redundant system and method are used for providing a system clock for a spaceflight control system. According to the system and method, an external high-accuracy clock and two internal clocks sources of which are not the same serve as a main clock, a backup clock and a third-party clock respectively, the third-party clock can be adopted for arbitration only when the main clock and the backup clock are inconsistent, single-redundancy faults of the clock can be allowed, the tri-redundancy aim is achieved, implementation is simple, and cost is low. According to the satellite-borne clock redundant system and method, the clock redundancy function of a control system is achieved through the high-accuracy clock of an inertia unit and the two clocks in a flight control computer, the high-accuracy clock of the inertia unit is sufficiently used, influences of faults of the clock on running of the control system are avoided, the reliability and the safety of the control system can be improved, and the satellite-borne clock redundant system and method have the advantages of being low in implementation cost and facilitating engineering realization.

Owner:BEIJING AEROSPACE AUTOMATIC CONTROL RES INST +1

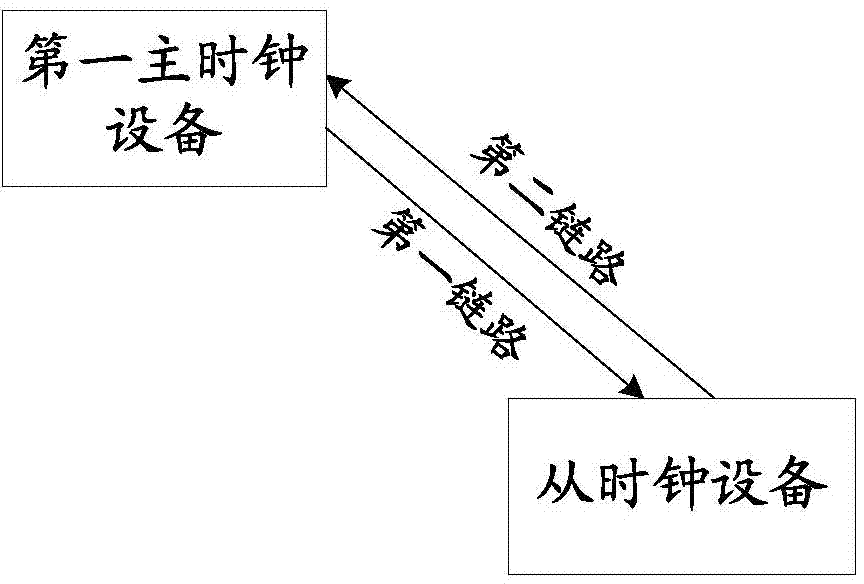

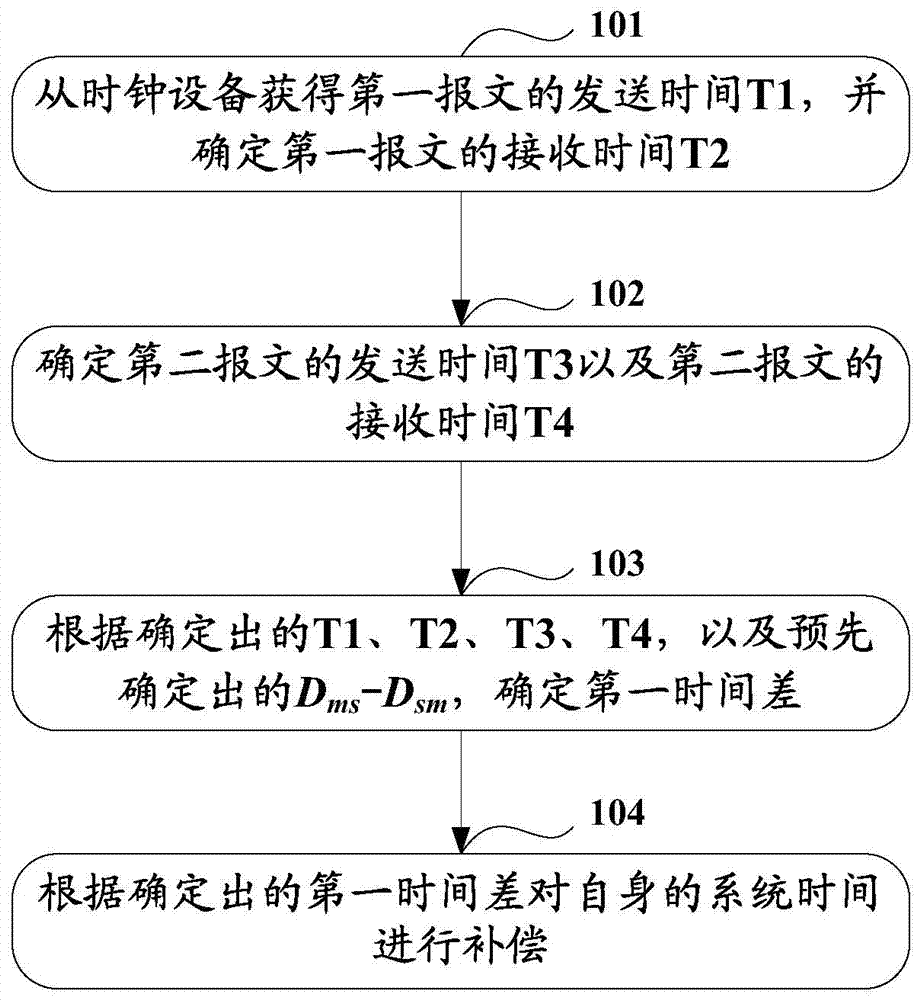

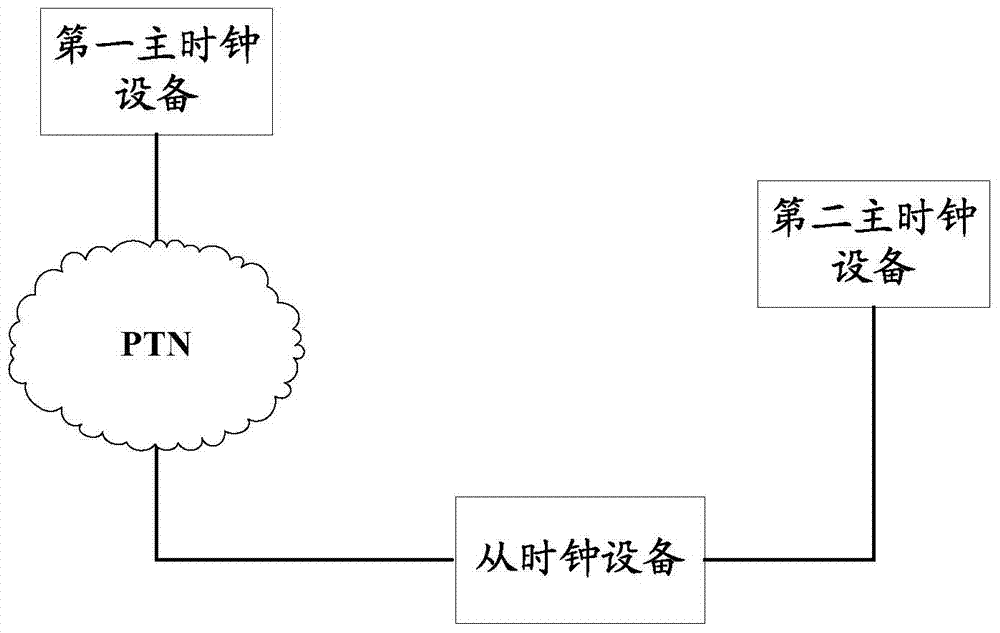

Method and device for compensating system time

The invention discloses a method and a device for compensating system time. The method specifically includes that difference value of transmission delay produced by a first link and transmission delay produced by a second link is determined according to a second time difference of system time of a subordinate clock device and system time of a second principal clock device, so that a first time difference of current system time of the subordinate clock device and system time of a first principal clock device is determined according to the determined difference value, the system time of the subordinate clock device can be compensated when the subordinate clock device fails to output PPS (pulse per second)signals.

Owner:RAISECOM TECH

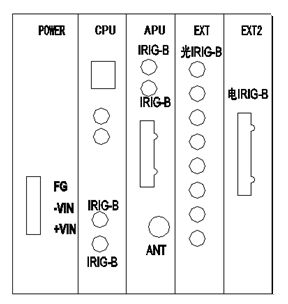

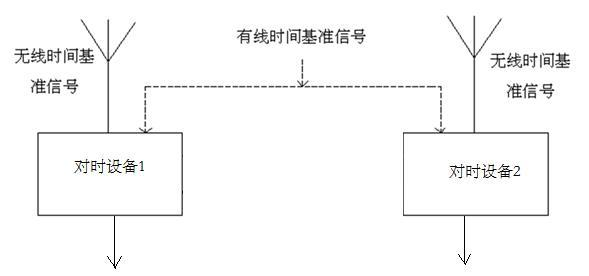

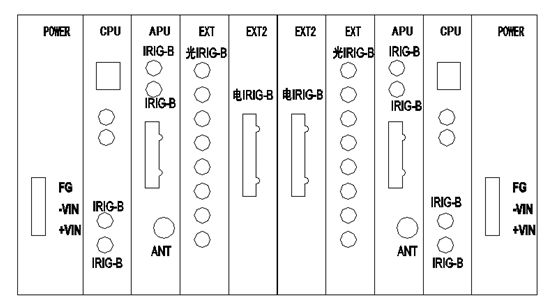

Mutual inspection method for mutually backup double clock, and time comparing device

InactiveCN102591195AImprove stabilityRealize autonomous switchingSynchronous motors for clocksSetting time indicationComputer hardwareHardware structure

The invention relates to a mutual inspection method for a mutually backup double clock, and a time comparing device. The mutual inspection method for the double clock, which is provided by the invention, can inspect whether IRIG-B code information of the mutually backup double clock is normal or not, and can realize automatic switching and alarming functions, so as to improve the stability of a synchronous system. One time comparing device integrates two main clocks, the hardware structure of each clock is the same as the current clock, IRIG-B input and output ports of the two clocks (CPU plug-ins) are connected correspondingly, and one main clock can receive the information from the other main clock for mutual inspection and mutual backup. One time comparing device can realize the functions of two time comparing devices originally, so that the cost is saved, and the occupied space is saved as well.

Owner:河南森海电气有限公司

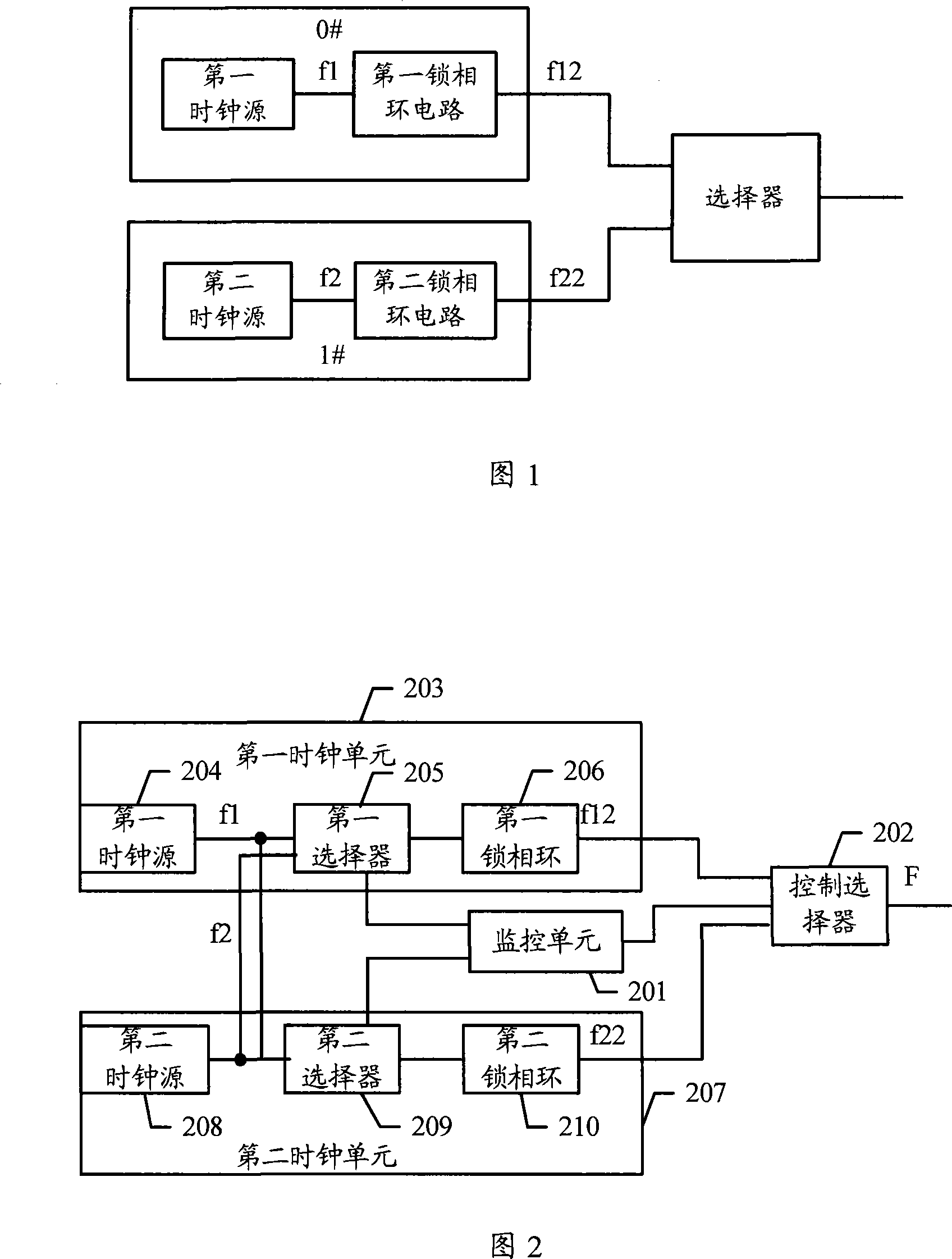

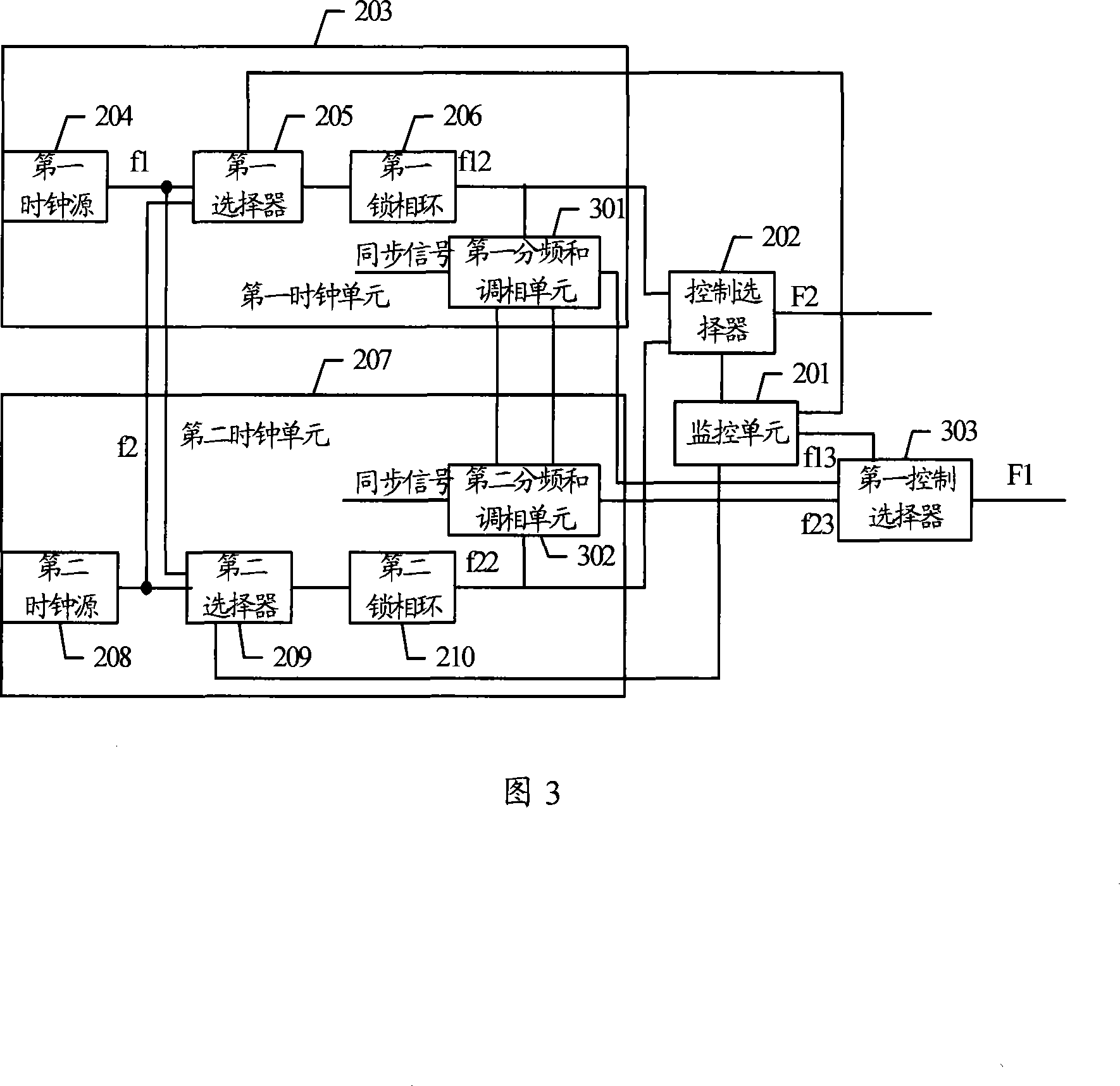

Clock synchronization device and method

InactiveCN101197650AStability is not affectedGood synchronizationError preventionRedundant hardware error correctionNetwork serviceComputer science

The invention, relating to the network service technical field, discloses a clock synchronization device and a method. The device comprises a first clock unit and a second clock unit, wherein, the first clock unit is used for choosing a clock signal and smoothing processing the phase jump generated by the chosen clock signal; the second clock unit is used for choosing the clock signal the same as the first clock unit chooses and smoothing processing the phase jump generated by the chosen clock signal to ensure that the signal outputted by the second clock unit is synchronized with the signal outputted by the first clock unit. The invention ensures that the signals outputted by the two clocks have good synchronization effect; therefore, the stability of the operation of a post-stage circuit is not affected when a principal clock and an auxiliary clock are rearranged.

Owner:SHANGHAI HUAWEI TECH CO LTD

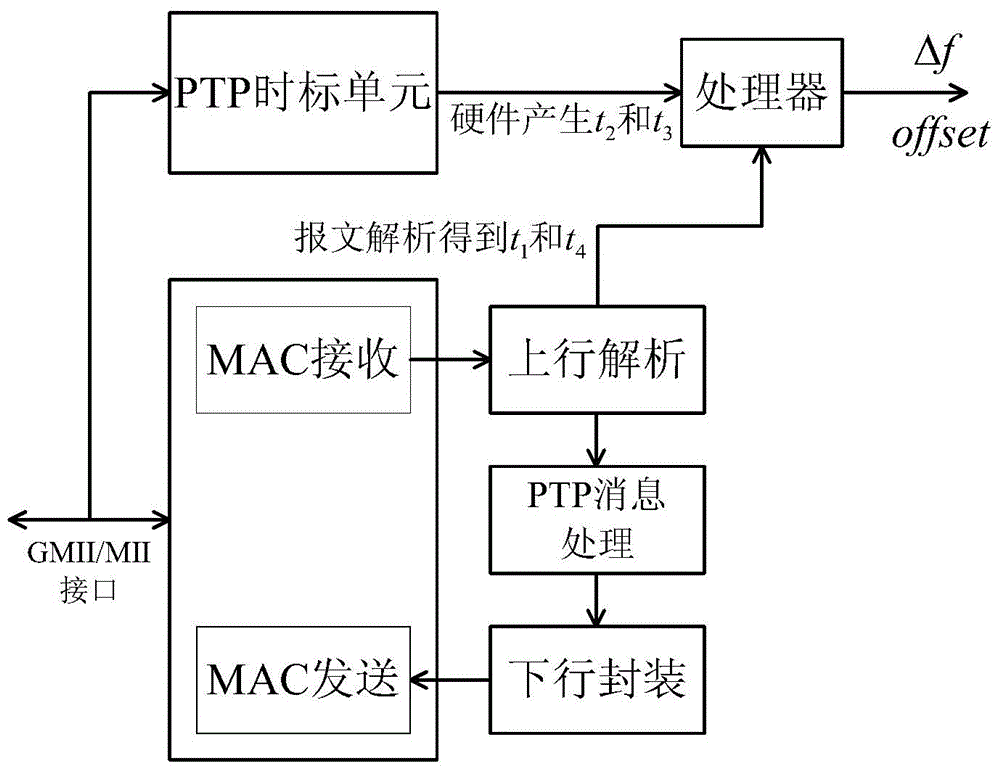

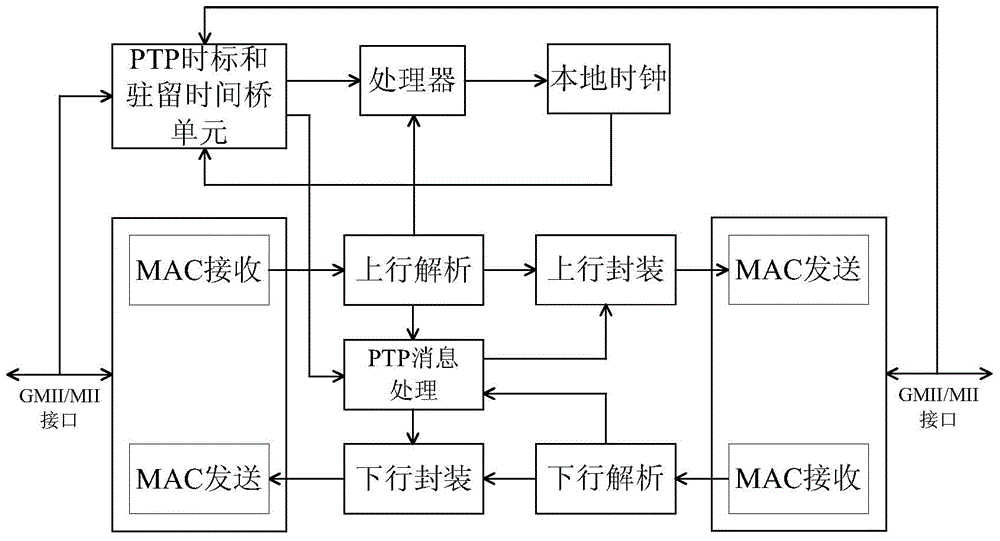

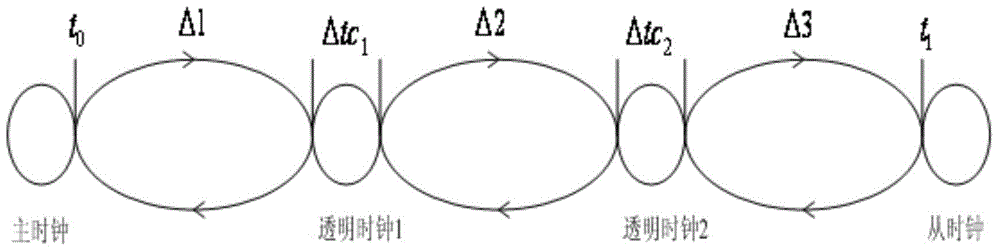

Airborne network IEEE1588 protocol transparent clock port synchronization method

The invention provides an airborne network IEEE1588 protocol transparent clock port synchronization method. An IEEE1588 protocol transparent clock comprises an uplink analysis unit, an uplink packaging unit, a PTP message processing unit, a downlink packaging unit, a downlink analysis unit, a PTP time mark and residence time bridge unit, a processor, a local clock unit, and an MAC hardcore. The method is characterized in that the method comprises the following steps: (1), the MAC hardcore receives a synchronization message transmitted by a main clock point in a local PTP domain to a local side, and the PTP time mark unit records a time stamp t2 when the synchronization message reaches a GMII / MII interface, and uploads the time stamp t2 to a processor unit in a local control module.

Owner:CHINESE FLIGHT TEST ESTAB

Method for reducing current consumption in a mobile communication terminal

InactiveUS6973584B2Total current dropExtend standby timeEnergy efficient ICTVolume/mass flow measurementMobile endCurrent consumption

A method for reducing current consumption of a mobile terminal is provided. The method includes setting a task as an initial idle task of the mobile terminal for performing a simple infinite loop in a state where all of the effective tasks performed by a program of the mobile terminal are blocked, counting global variable values of the idle task for a predetermined time according to a timer interrupt signal generated by the timer at regular intervals and storing the global variable values of the idle task as a reference value of an idle task of a program of the mobile terminal, resetting the counted value, measuring by counting the global variable values of the idle task where an effective task occupies the idle task for a predetermined time and storing the global variable values of the idle task as an idle value of the effective task according to a timer interrupt generated every predetermined time by the timer when the program of the mobile terminal performs the effective task, dividing the measured idle value of the effective task by the reference value of the idle task, to thus calculate a program idle rate of the mobile terminal, and storing the program idle rate, and changing a PLL value according to the program idle rate of the mobile terminal and varying a main clock frequency of a CPU of the mobile communication terminal.

Owner:SAMSUNG ELECTRONICS CO LTD

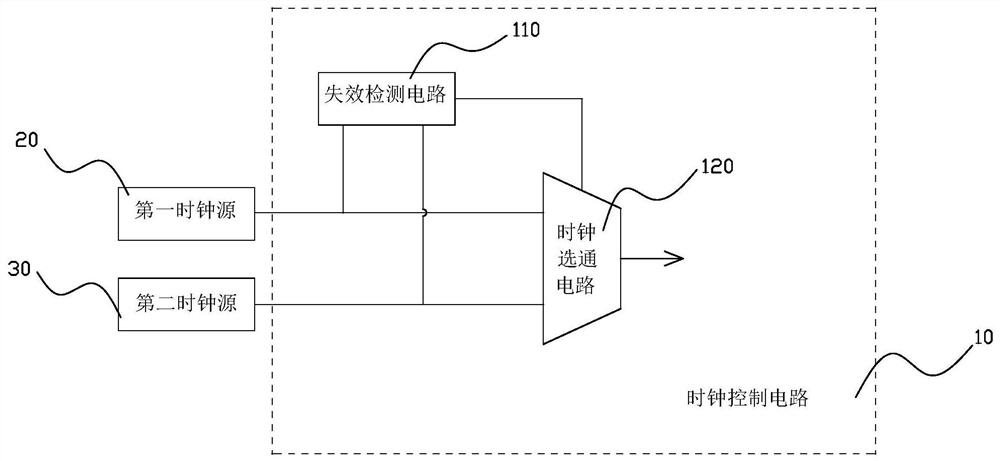

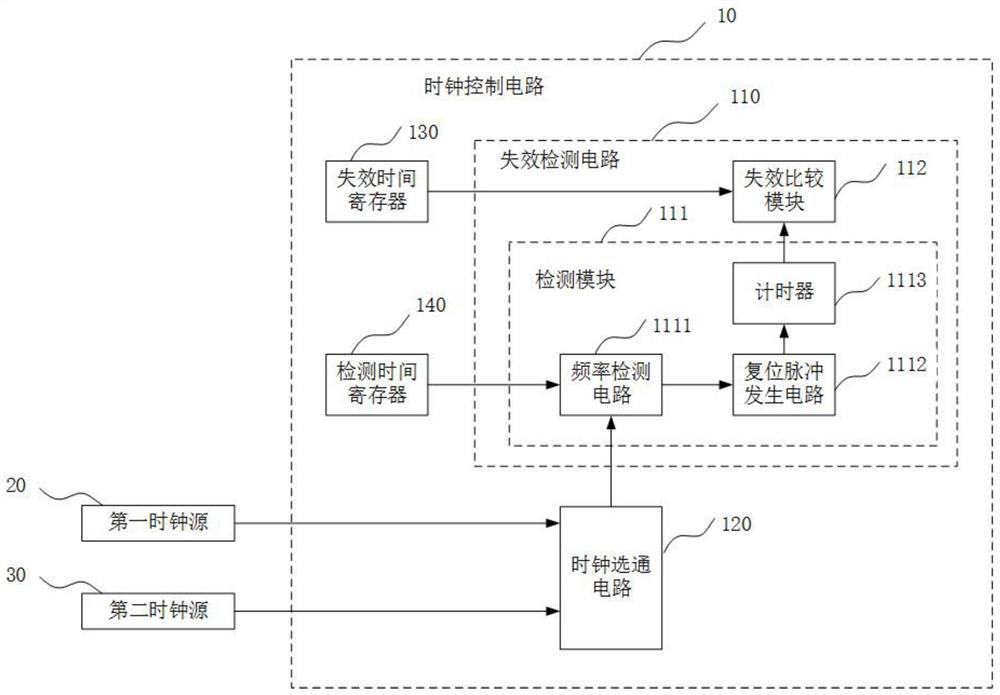

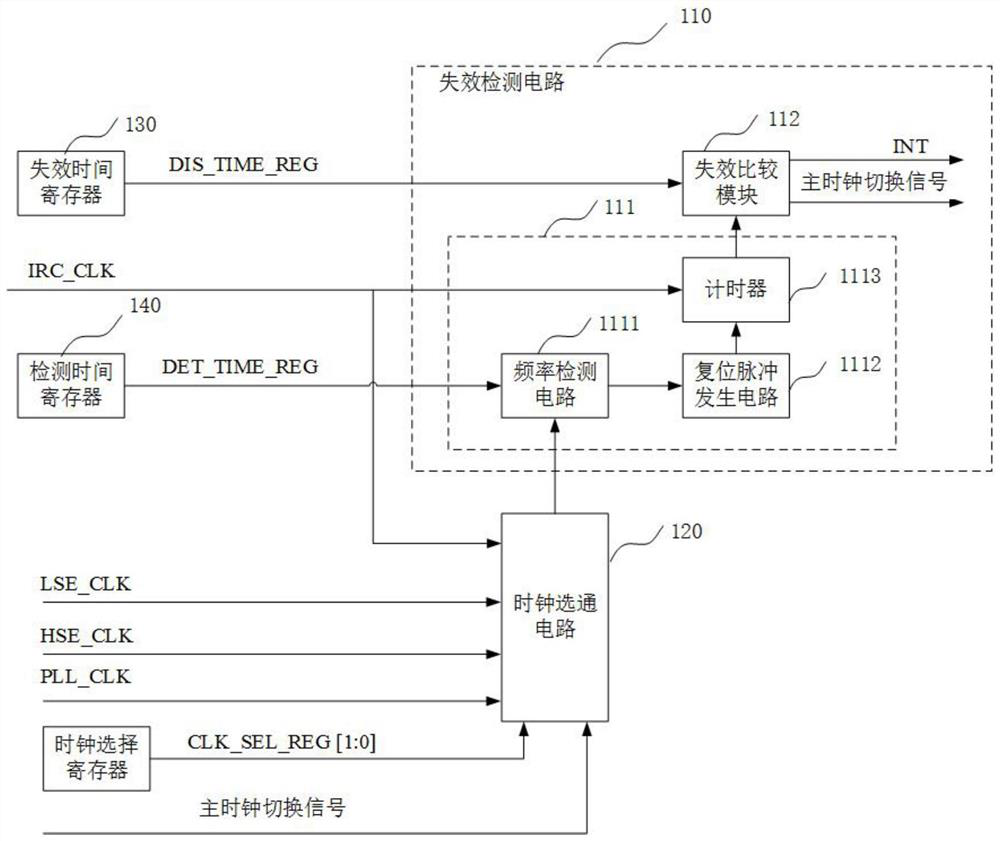

Clock control circuit, chip and clock control method

PendingCN112083755AImprove adaptabilitySave extra spaceGenerating/distributing signalsArchitecture with single central processing unitComputer hardwareHemt circuits

The invention discloses a chip with a clock control circuit, a clock control method and the clock control circuit, the clock control circuit is applied to the chip, a first clock source is arranged inthe chip, and the clock control circuit comprises a failure detection circuit and a clock gating circuit; the failure detection circuit is connected with the first clock source and a preset second clock source, the failure detection circuit is used for detecting whether a main clock source of the chip fails or not, and the main clock source of the chip is the first clock source or the second clock source; and the clock gating circuit is connected with the failure detection circuit, the first clock source and the second clock source, and the clock gating circuit is used for switching the mainclock source of the chip when the main clock source of the chip fails according to the output signal of the failure detection circuit. According to the chip, different clock sources are selected as chip clocks according to requirements, clock source switching can be carried out in time through the clock control circuit, and enough safety guarantee measures are provided for a chip system.

Owner:HEFEI CHIPSEA ELECTRONICS TECH CO LTD

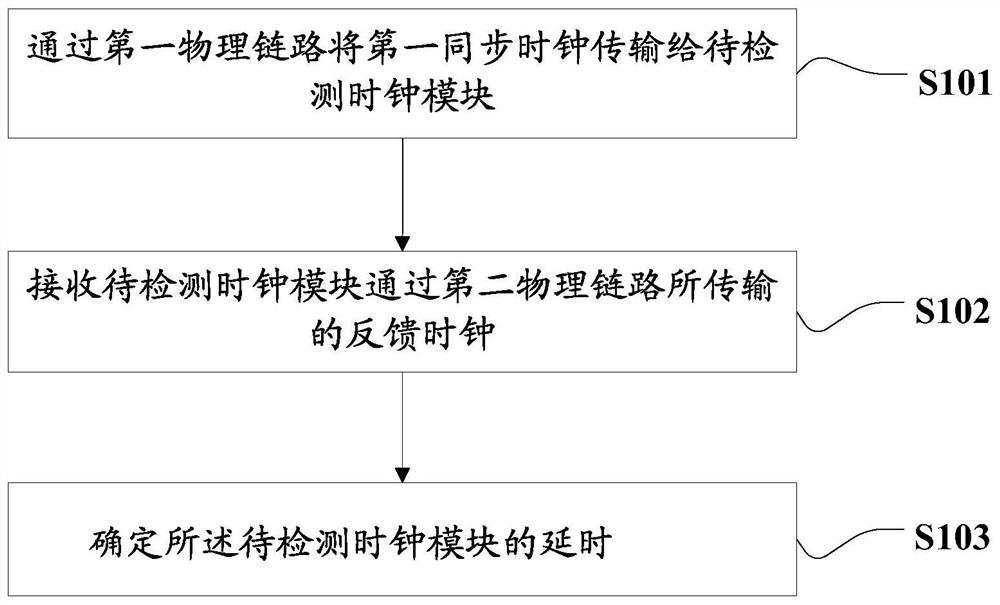

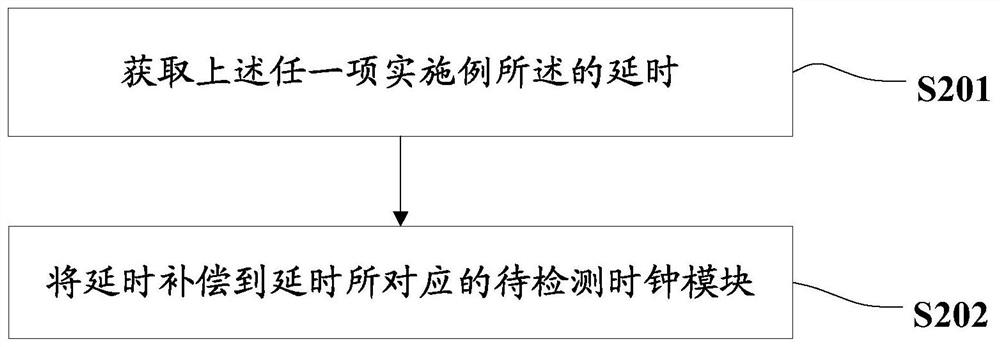

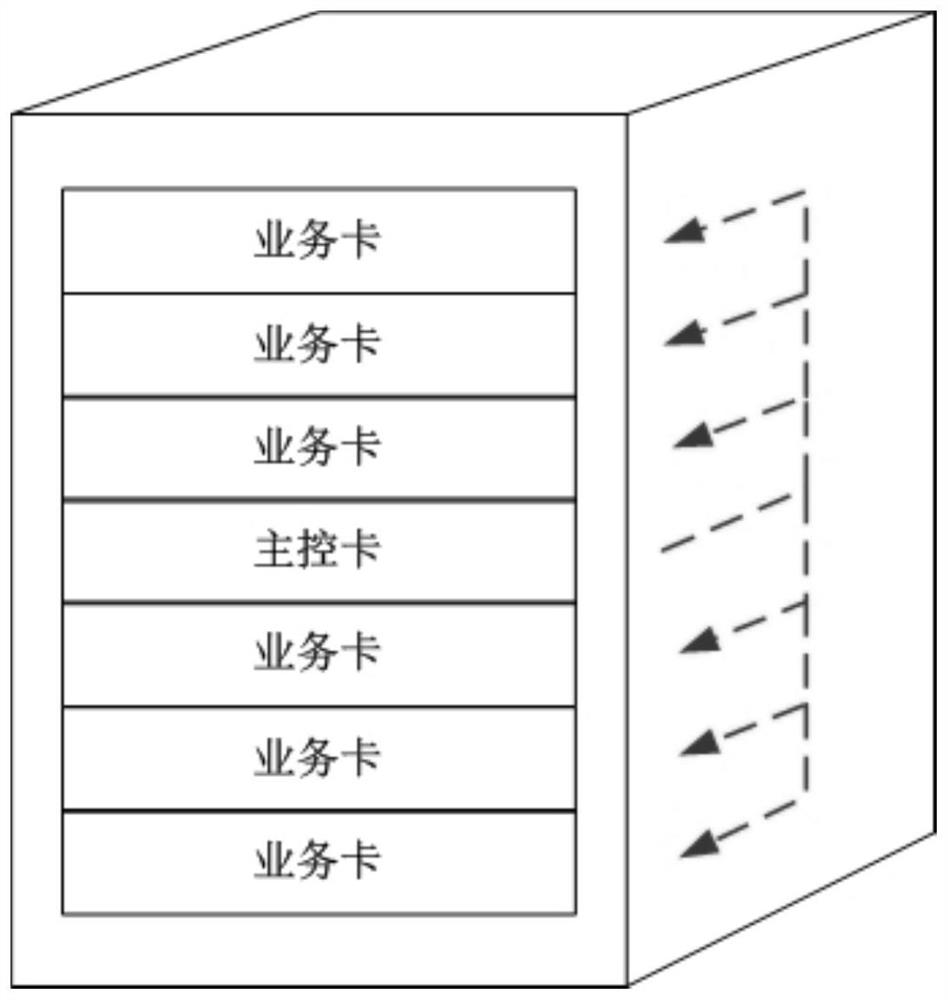

Clock delay detection method and device, clock delay compensation method and device, terminal and readable storage medium

PendingCN112486246AReduce mistakesHigh precisionTime-division multiplexGenerating/distributing signalsComputer hardwareClock time

The embodiment of the invention provides clock delay detection and compensation methods and devices, a terminal and a readable storage medium, and the clock delay detection method comprises the steps:transmitting a first synchronous clock to a to-be-detected clock module through a first physical link; receiving a feedback clock which is transmitted by the to-be-detected clock module through a second physical link and is adjusted according to the phase of the first synchronous clock, and determining the delay of the to-be-detected clock module according to the feedback clock, the self-return clock, the delay parameter corresponding to the first physical link and the delay parameter corresponding to the second physical link. The invention also provides the clock delay detection and compensation methods and devices, the terminal and the readable storage medium. By calculating the delay of a main clock module and the delay caused by the physical characteristics of a first physical link and a second physical link, the error of time delay caused by detecting clock distribution of switch equipment can be further reduced, so that the precision of clock time delay detection is improved.

Owner:ZTE CORP

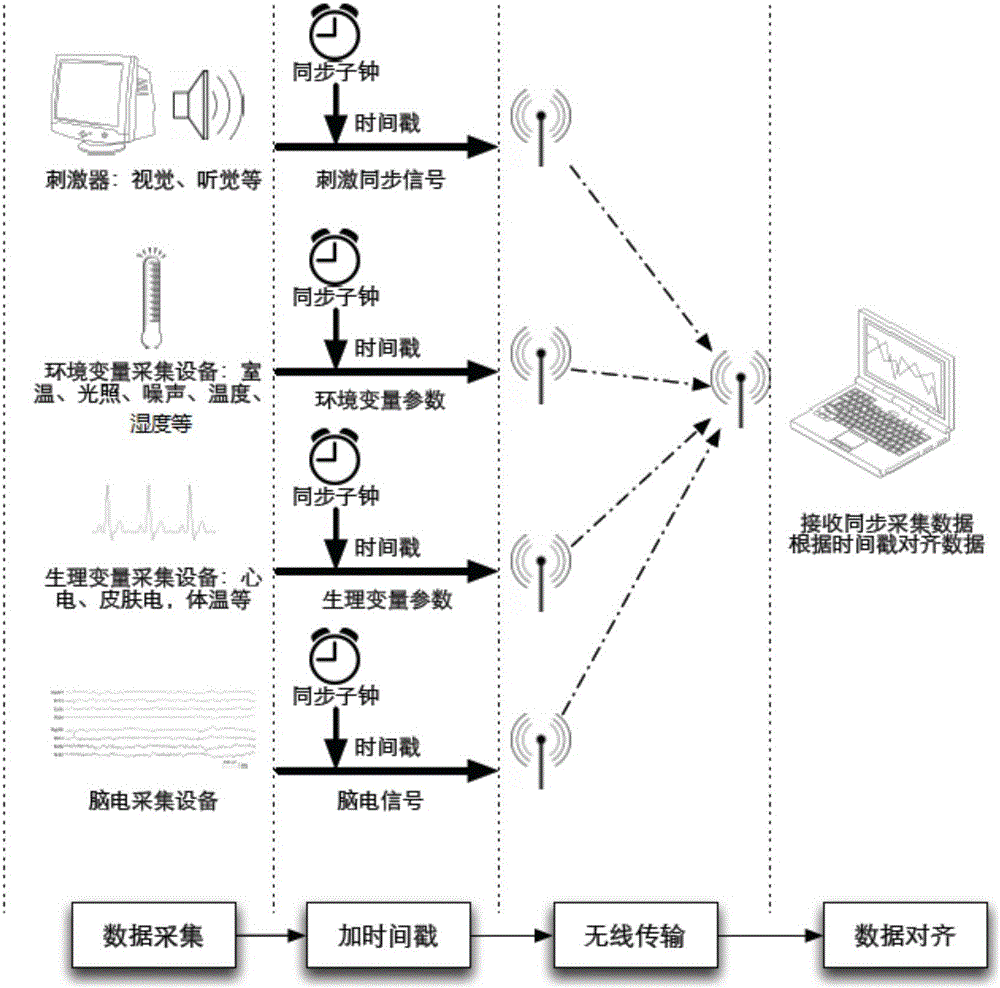

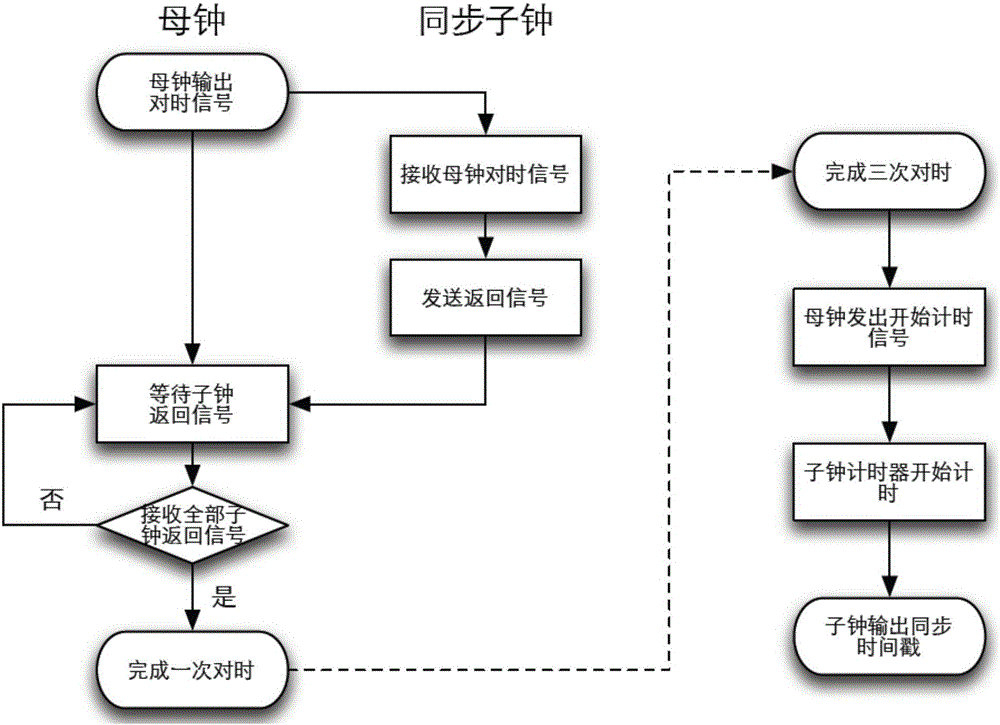

Method for precisely synchronizing wireless data of electroencephalogram device

InactiveCN106332268AAchieve wireless synchronizationStimulus synchronizationSynchronisation arrangementWireless network protocolsConnectionless communicationTimestamp

The invention provides a method for precisely synchronizing wireless data of electroencephalogram device. The electroencephalogram device comprises a central processing system and at least one acquisition subsystem. A principal clock of the central processing system completes synchronous timing among secondary clocks of the acquisition subsystems through a method of performing multiple times of time synchronization. Each time of time synchronization comprises the steps that the central processing system sends synchronization data wirelessly to the secondary clocks of all acquisition subsystems through a first communication protocol; the acquisition subsystem resets a timestamp of the corresponding acquisition secondary clocks after receiving the synchronization data; the synchronized secondary clocks add the timestamp to each data packet and send the timestamp to the central processing system through a second communication protocol along with data information; and the central processing system performs data alignment and processing by combining the received data information according to actual requirements. The first communication protocol is a connectionless communication protocol, and the second communication protocol is a connection-oriented communication protocol.

Owner:NEURACLE TECH CHANGZHOU CO LTD

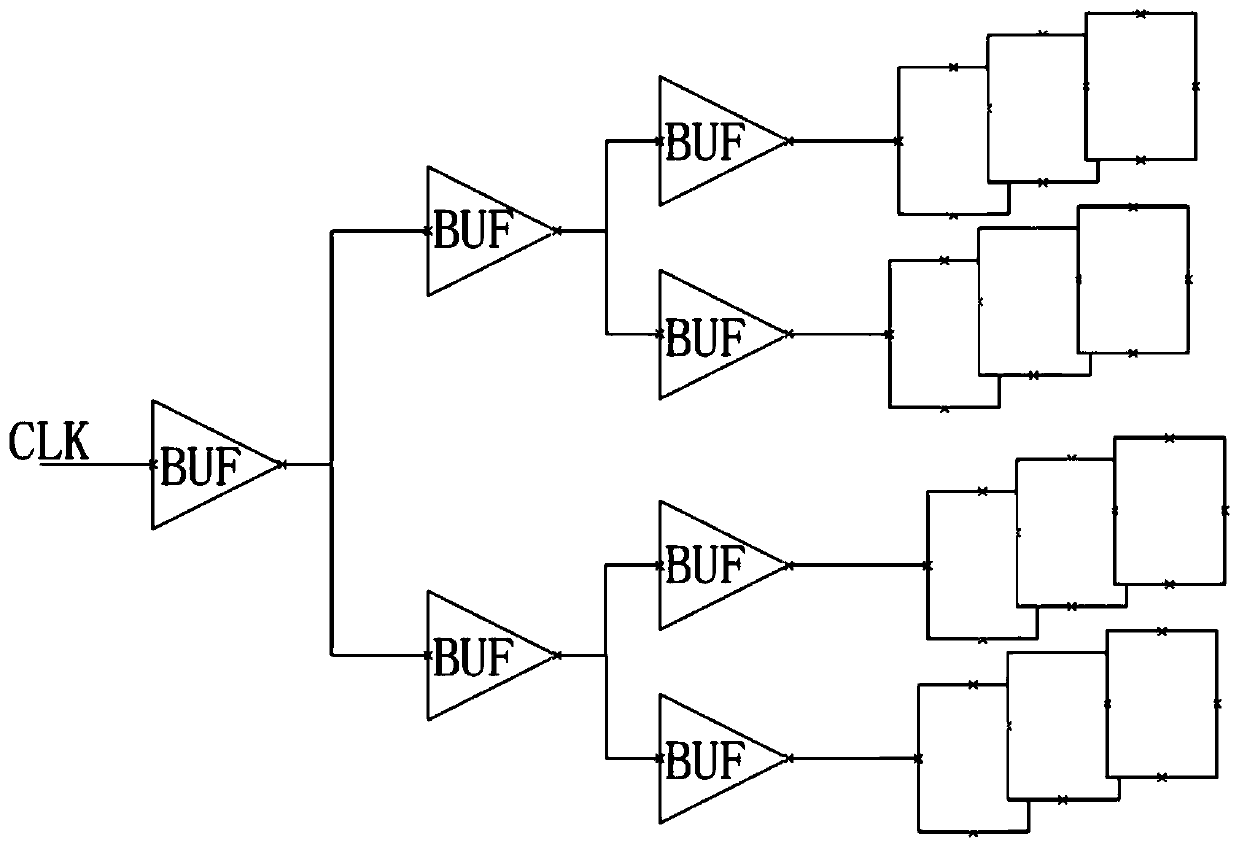

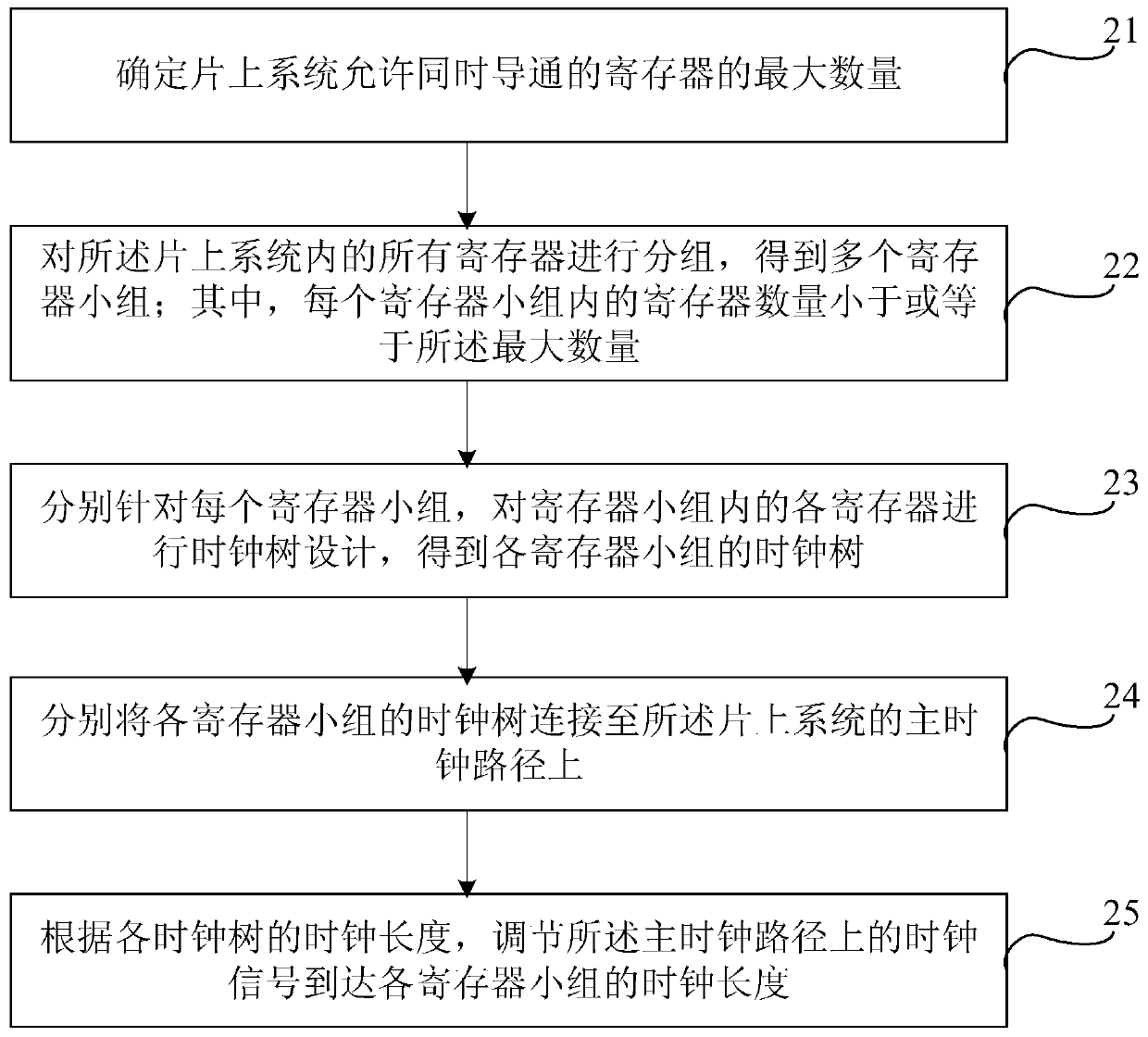

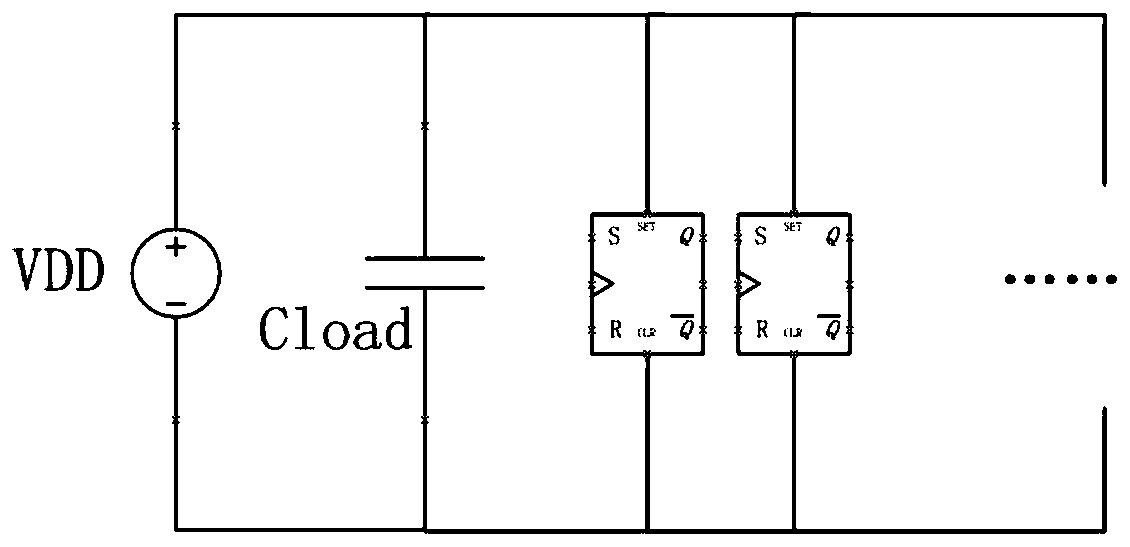

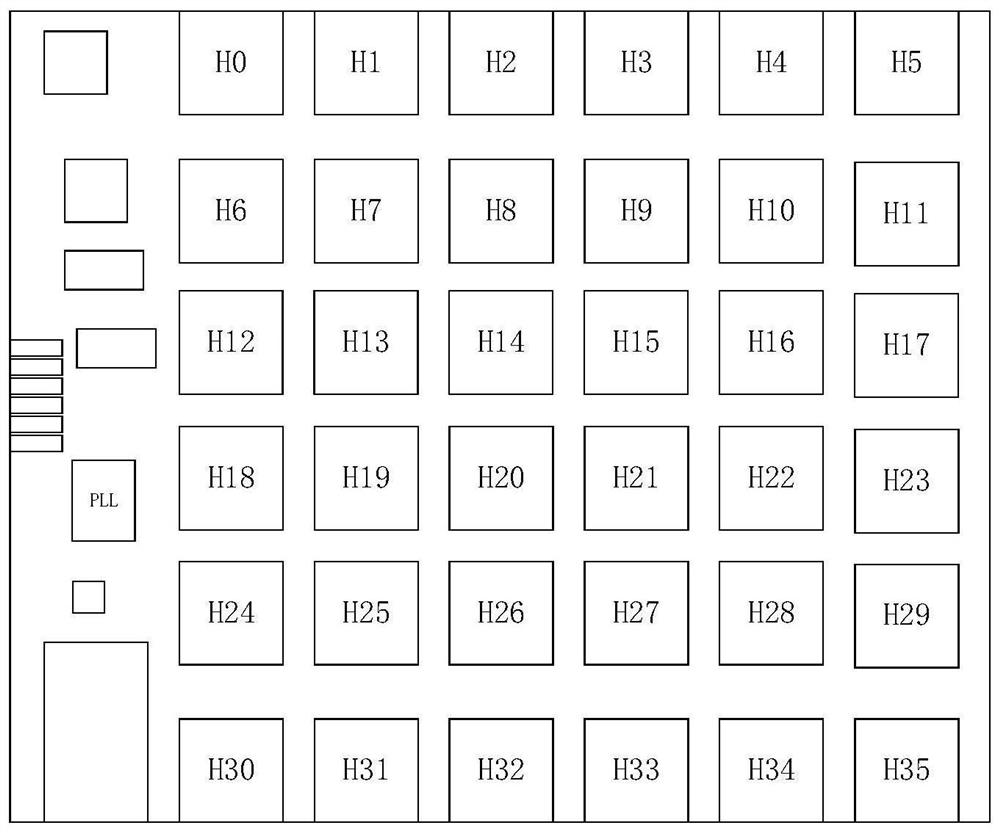

Design method and device for clock tree structure of system on chip, equipment and medium

ActiveCN110825210AReduce instantaneous power consumptionReduce in quantityGenerating/distributing signalsEnergy efficient computingClock treeEmbedded system

The invention provides a design method and device for a clock tree structure of a system on chip, equipment and a medium. The design method comprises the following steps: determining the maximum number of registers which are allowed to be conducted simultaneously by the system on chip; grouping all registers in the system on chip to obtain a plurality of register groups; wherein the number of registers in each register group is smaller than or equal to the maximum number; for each register group, performing clock tree design on each register in the register group to obtain a clock tree of eachregister group; respectively connecting the clock tree of each register group to a main clock path of the system-on-chip; according to the clock length of each clock tree, adjusting the clock lengthof the clock signal on the main clock path reaching each register group; wherein the clock lengths of the clock signals reaching the register groups are different from each other. According to the invention, the number of registers which are overturned simultaneously can be reduced, the instantaneous power consumption of the system-on-chip is effectively reduced, and the impact on a power supply is reduced.

Owner:PHYTIUM TECH CO LTD

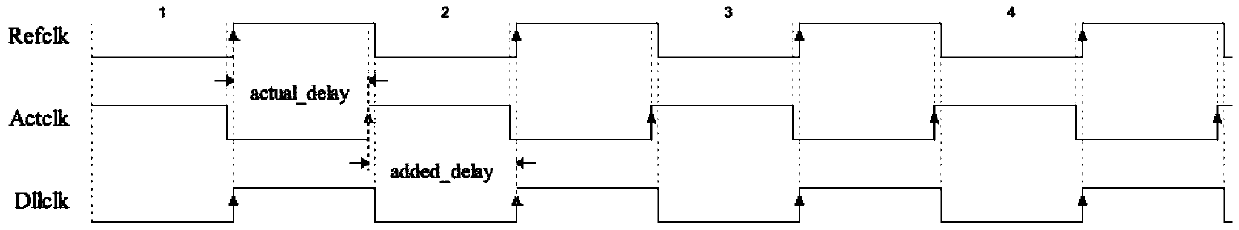

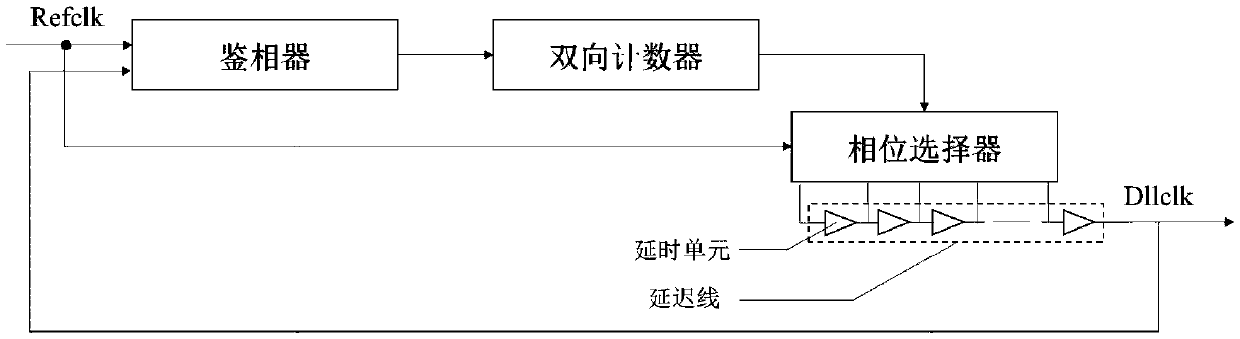

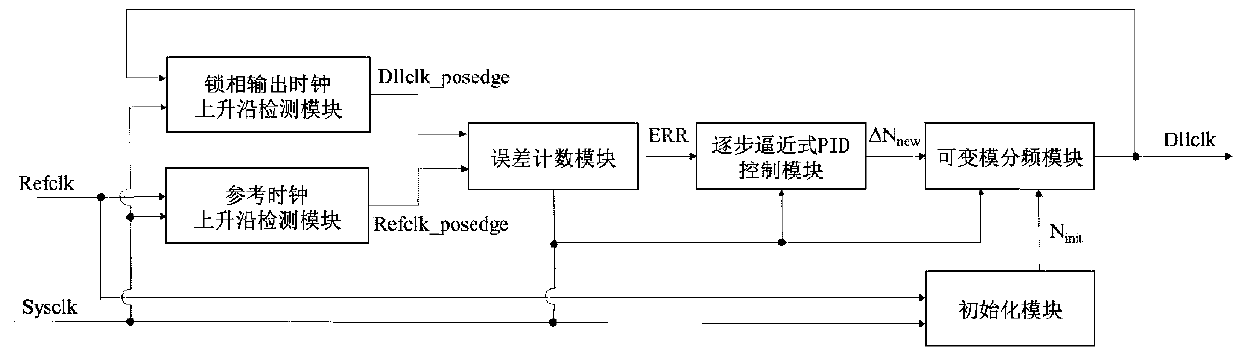

DLL system based on successive approximation PID control algorithm

ActiveCN110750048ASolve the real problemReduce areaPulse automatic controlControllers with particular characteristicsLow frequency bandEngineering

The invention provides a DLL system based on a successive approximation PID control algorithm. The system comprises: a phase-locked output clock rising edge detection module, a reference clock risingedge detection module, an error counting module, a successive approximation PID control module, and a variable mode frequency division module and an initialization module, furthermore, a system clockis the main clock of the entire system, a reference clock is a clock signal that needs to be locked, a phase-locked output clock is a locked clock signal, the system continuously and circularly adjusts the phase-locked output clock and finally outputs a clock signal with a fixed phase difference with the reference clock after a plurality of cycles The reference clock of the system can not only work at a high frequency band, but also can work at a low frequency band; no delay line is required, so that the area can be reduced, and the power consumption can be reduced; the problem of inconsistentdelay times of delay units is avoided; and the design complexity is low, and the design can be easily implemented on FPGA and ASIC.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

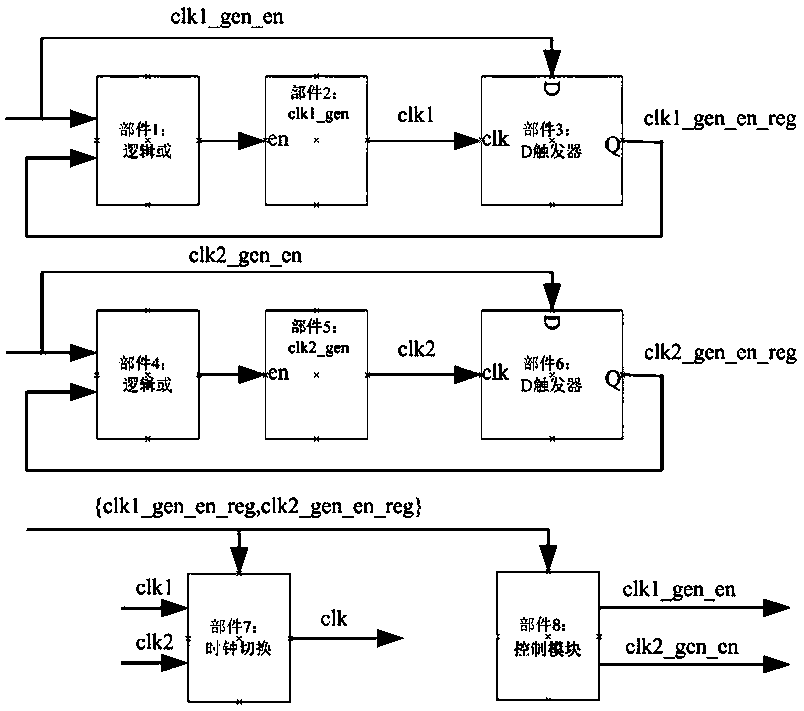

Chip clock circuit and control method thereof

ActiveCN110413041AImprove reliabilityLower power consumption levelsGenerating/distributing signalsComputer moduleCondition monitoring

The invention provides a chip clock circuit and a control method thereof. The chip clock circuit comprises a plurality of clocks, a clock switching module and a control module, the clocks comprise a logic OR module, a clock generation module and a trigger module, clock clk signals generated by the clocks are obtained through the input end of the clock switching module, and one clock is selected asa main clock to be output; and the control module monitors the state of each clock and controls the closing or opening of each clock. The state of a chip clock signal is monitored in real time through the control module; according to the real-time monitoring result, the clock signals are switched in time, high reliability of the clock signals of the chip is ensured, the chip is in a stable and reliable working state, the chip system can be ensured to run at a low power consumption level through a computer readable storage program, one more clock signal can be provided for the system selectively, and the flexibility of the clock of the chip system is improved.

Owner:EDGELESS SEMICON CO LTD OF ZHUHAI +1

Gate clock generator and display device having the same

The present disclosure provides a gate clock generator including a counter, a buffer control signal generator, and an output unit. The counter receives control data having rising timing information and falling timing information and a main clock. The counter generates a first output when a value is obtained by counting the main clock from a preset reference time point reaches rising data. The counter further generates a second output when a value is obtained by counting the main clock from the reference time point reaches falling data. The buffer control signal generator generates a first buffer control signal of a gate ON voltage from a timing of the first output to a timing of the second output. The output unit outputs a gate ON voltage of a gate clock during an output period of the gate ON voltage of the first buffer control signal.

Owner:LG DISPLAY CO LTD

Message expansion circuit of secure hash algorithm

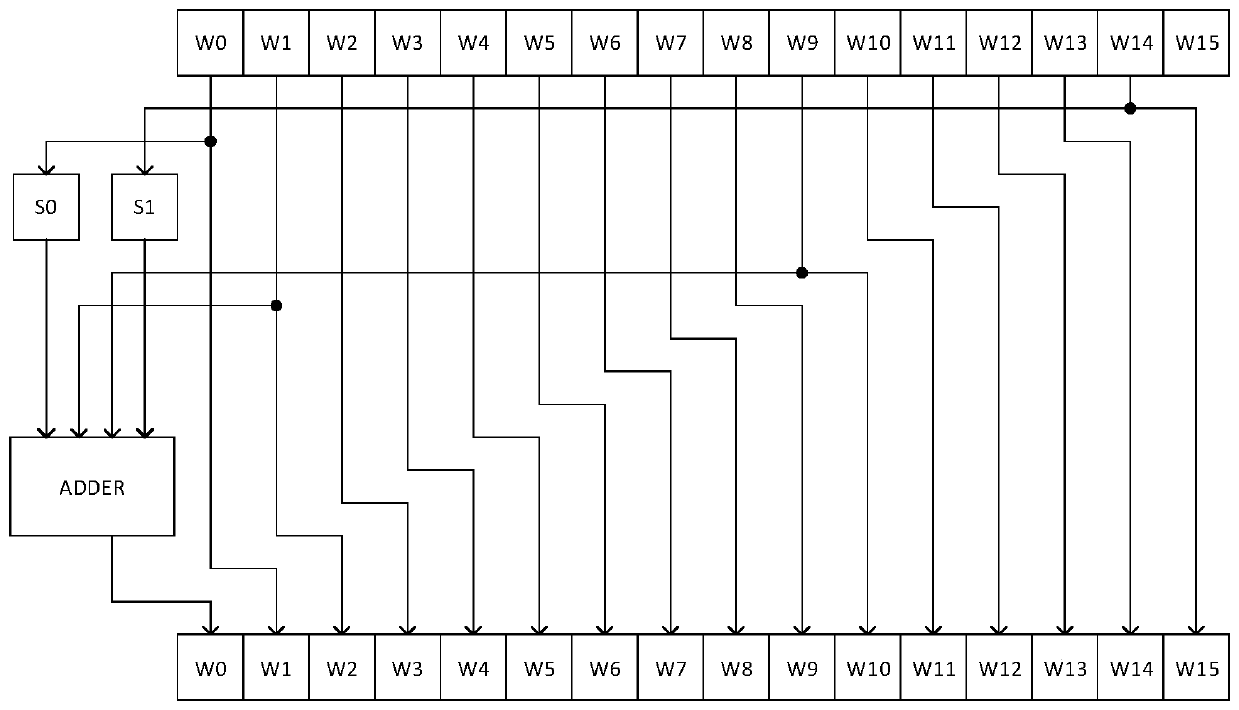

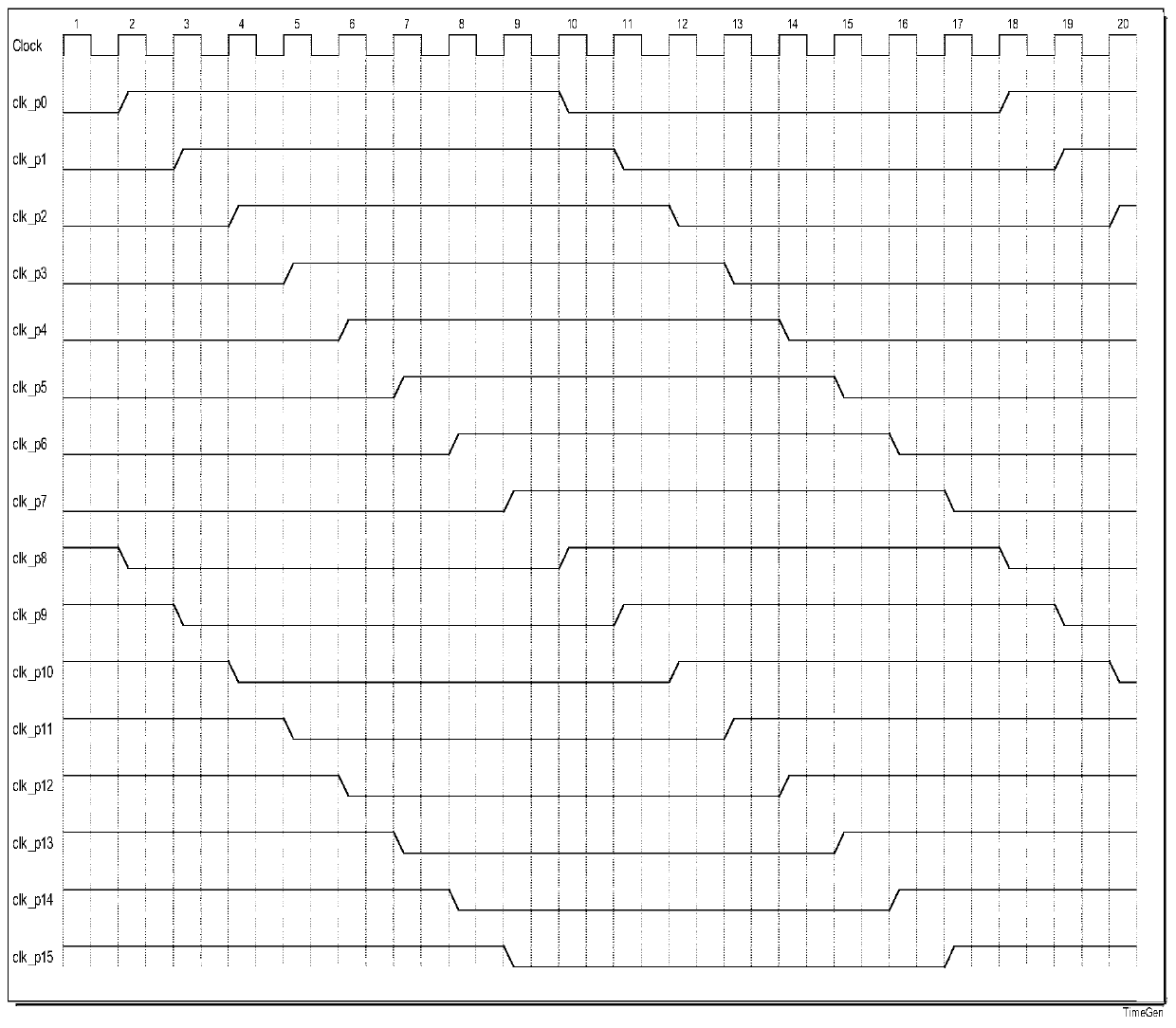

ActiveCN111488627AReduce power consumptionInternal/peripheral component protectionEnergy efficient computingClock rateSequential logic

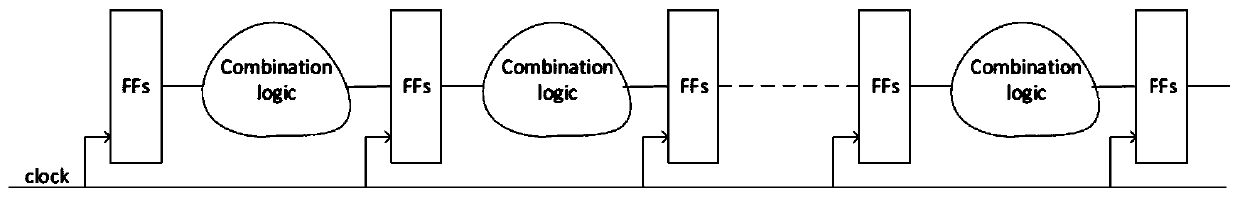

The invention discloses a message expansion circuit of a secure hash algorithm. The message expansion circuit comprises 64 stages of pipeline circuits, and each stage of pipeline circuit comprises 16groups of latches and a combinational logic circuit; the combinational logic circuit comprises four selectors, two shift XOR circuits and an adder. Each stage of pipeline circuit comprises a main clock; 16 groups of frequency division clocks with the phase difference of 1 in sequence are also generated, the 16 groups of frequency division clocks are respectively used as trigger clocks of 16 groupsof latches, and the clock frequency of the frequency division clocks is 1 / 16 of that of the main clock, i.e., the frequency division clocks respectively trigger the corresponding latches at the moments of 0-15 of the main clock; and the clock phase difference of the same group of latches in two adjacent stages of pipeline circuits is kept at 15. According to the message expansion circuit of the secure hash algorithm, the clock and flip rate of a sequential logic circuit are reduced to 1 / 16 of those of a traditional implementation, and the power consumption of the SHA256 message expansion circuit can be greatly reduced.

Owner:杭州德旺信息技术有限公司

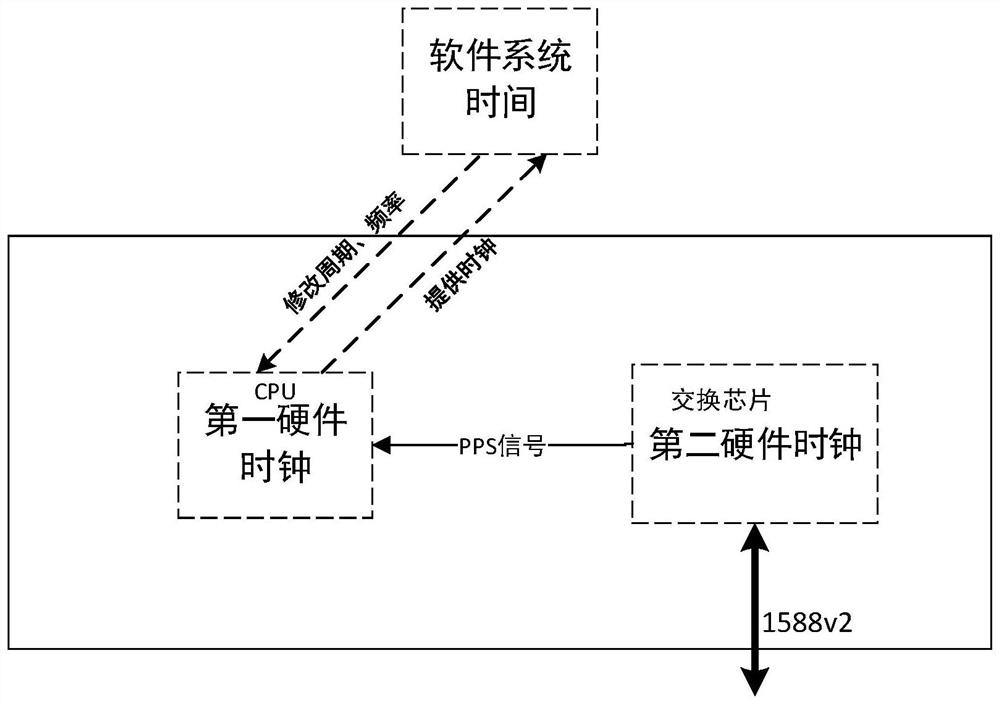

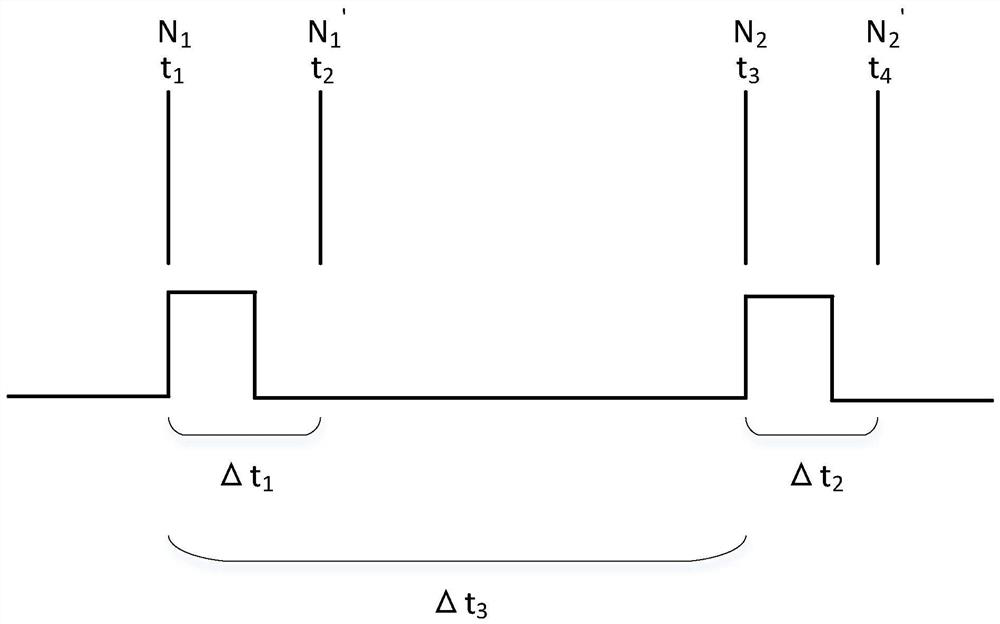

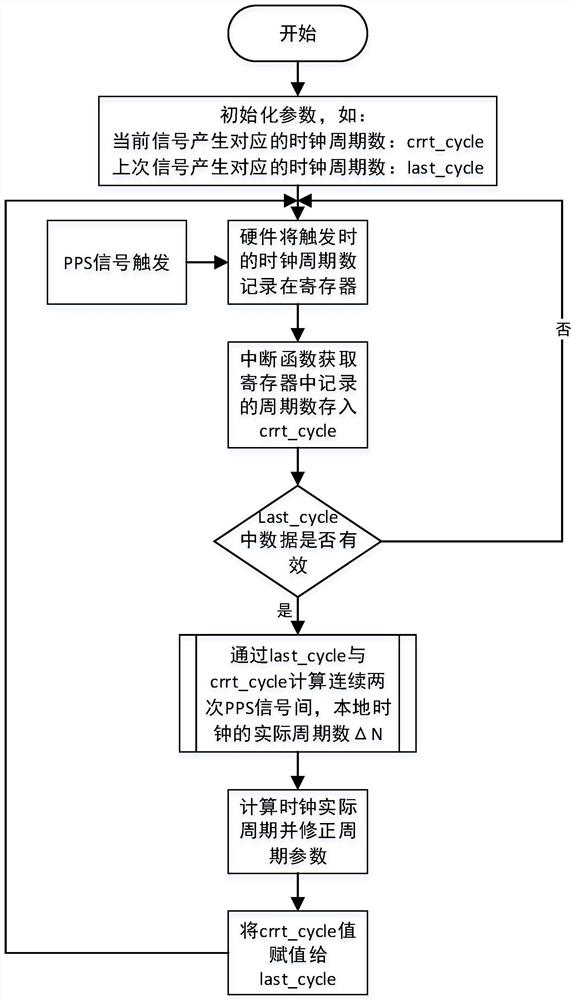

Method and device for improving synchronization precision among multiple clocks

ActiveCN111614428AHigh synchronization accuracyTime-division multiplexComputer hardwareSignal source

The invention discloses a method and a device for improving the synchronization precision among multiple clocks, and the device comprises multi-source clock equipment which comprises a plurality of hardware clocks. The method comprises the following steps: based on a precise synchronous clock protocol, synchronizing a certain hardware clock in multi-source clock equipment with main clock equipmentin a network; configuring the synchronized hardware clock, triggering a PPS signal, and providing a clock synchronization signal source for other hardware clock sources in the multi-source clock device; obtaining counting information of a synchronized hardware clock source when the PPS signal is generated, and calculating real characteristics of the synchronized hardware clock source; and correcting the synchronized hardware clock source in the multi-source clock equipment so as to achieve clock synchronization among multiple clocks in the equipment. According to the method, the defect that time is obtained through CPU interruption traditionally is overcome, a hardware mode is adopted, nanosecond-level synchronization is achieved among multiple clocks in the equipment, and the synchronization precision is high.

Owner:CETC AVIONICS

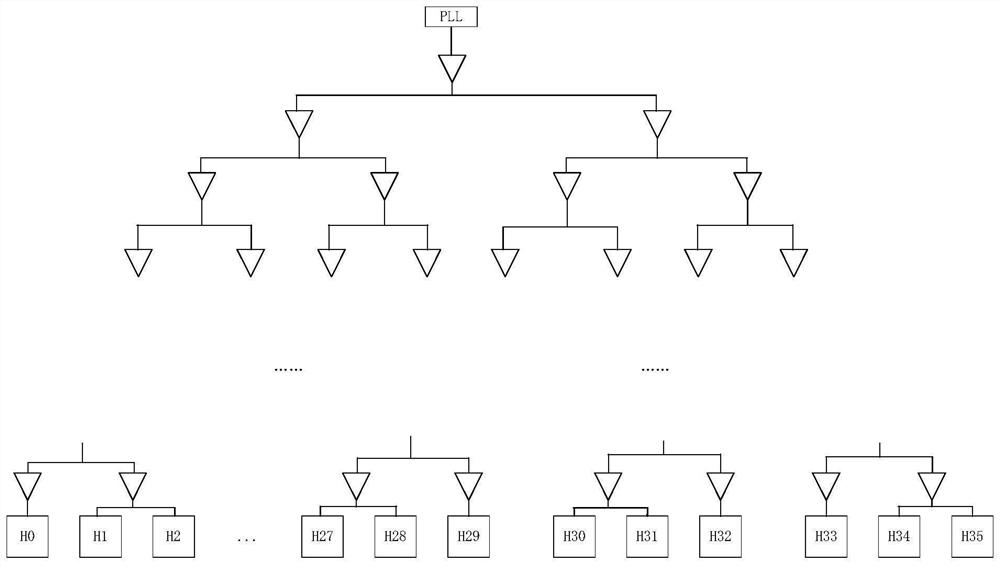

Fishbone-shaped clock tree and implementation method

ActiveCN113723046AReduce buffer unitReduce power consumptionComputer aided designEnergy efficient computingComputer architectureParallel computing

The invention belongs to the technical field of clock trees, and discloses a fishbone-shaped clock tree and an implementation method. The fishbone-shaped clock tree comprises: a main clock tree and a plurality of sub-clock trees, wherein the main clock tree is led out from a PLL, the sub-clock trees are led out from the main clock tree, and each sub-clock tree is provided with a plurality of clock branch points; each clock branch point is used as a source of a traditional clock tree to establish the traditional clock tree. The fishbone-shaped clock tree and the implementation method have the beneficial effects that a fishbone-shaped clock tree structure is established by establishing the main clock tree and the sub-clock trees, so that buffer units between a PLL and a chip sub-module are reduced, and the power consumption of chips is reduced; in addition, the main clock tree and the sub-clock trees also play a role of a common path, the OCV occupies a few clock cycles, and the final time sequence convergence is easy.

Owner:广芯微电子(广州)股份有限公司

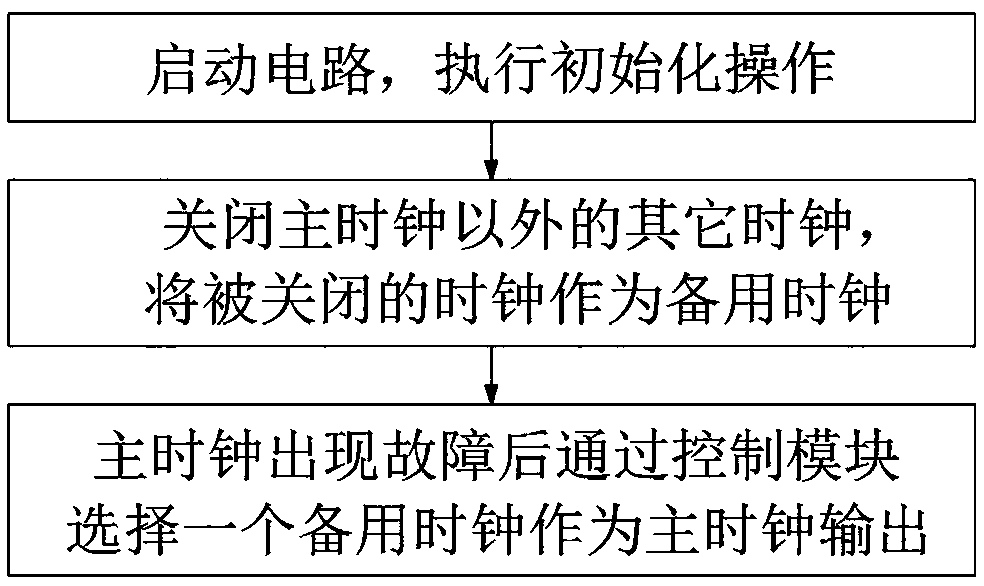

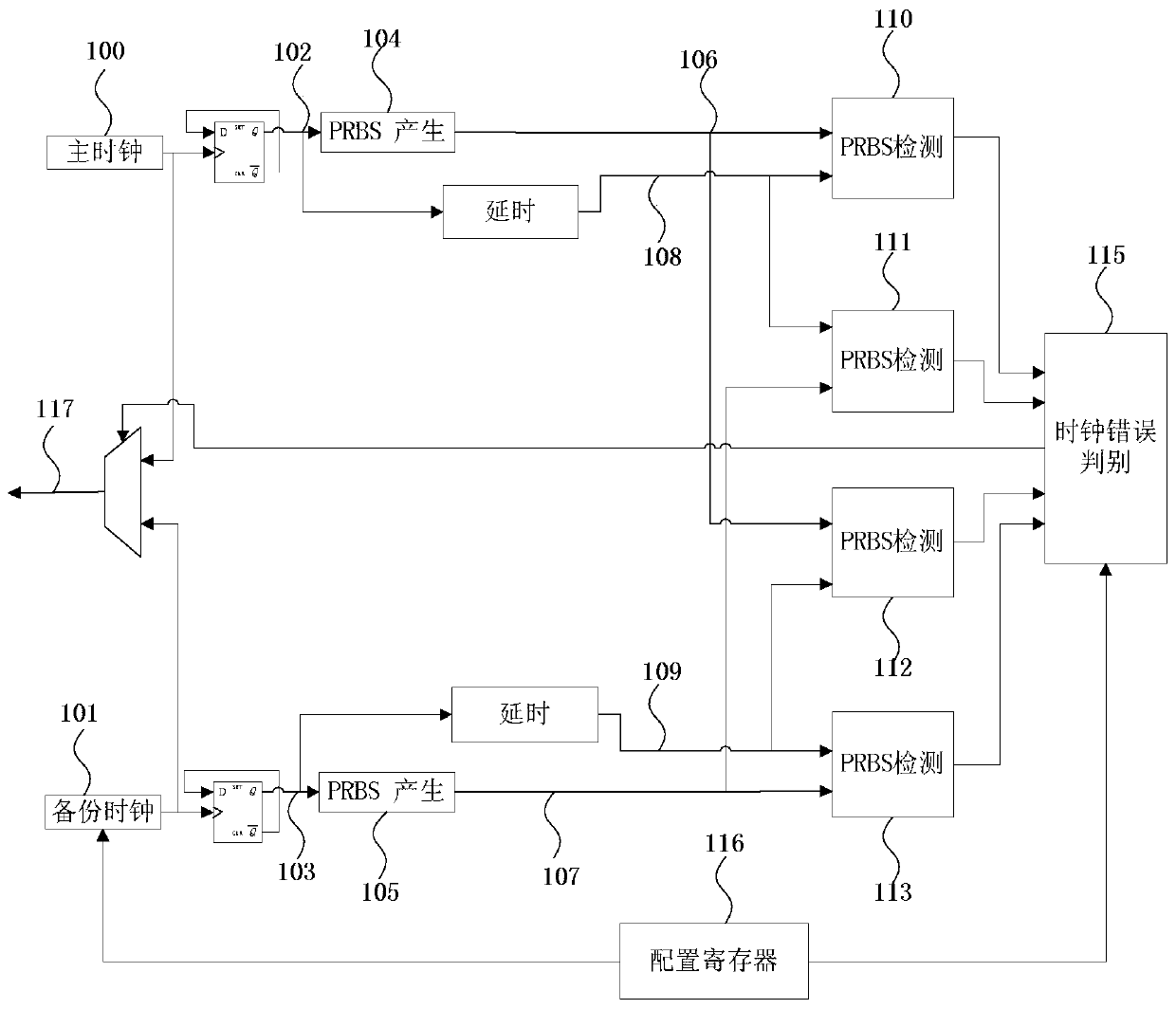

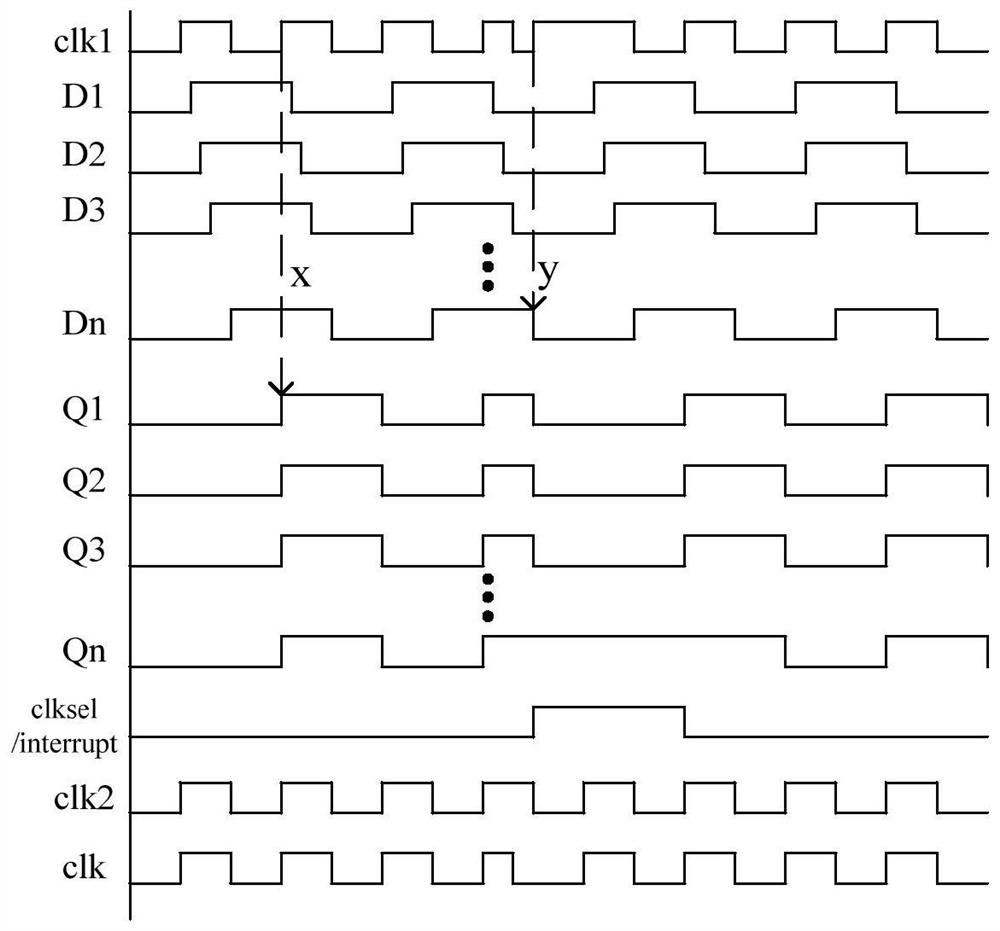

Multi-clock automatic switching method

PendingCN110795289AReal-time transmissionGuaranteed to workGenerating/distributing signalsRedundant hardware error correctionComputer hardwareEmbedded system

The invention relates to a multi-clock automatic switching method, comprising the following steps: monitoring whether a main clock has an error or not; judging whether the working frequency of a backup clock is normal or not; monitoring whether the main clock is lost; judging whether the backup clock is lost or not through the main clock; determining whether the clock is switched or not: countingmaster clock detection errors according to a configuration register counter value, and if the count value reaches the configuration register value and the master clock has errors, needing to be switched; if the master clock has a clock error and the backup clock is normal and switching conditions are met, determining the backup clock which is correspondingly switched according to the priority of the backup clock of the configuration register; and if the backup clock needing to be switched also has an error, switching to the clock with the secondary priority according to the priority of the backup clock of the register.

Owner:BEIJING INST OF COMP TECH & APPL

Time synchronization monitoring test device and method

ActiveCN110855395ASolving testing challengesGuaranteed uptimeCircuit arrangementsTime-division multiplexInteroperabilityMonitoring system

The invention discloses a time synchronization monitoring test device and method. The device comprises a configuration module, an IEC 61850 client simulation module, an IEC 61850 server simulation module, a monitored equipment simulation module, a model verification module, an automatic mapping module, a dynamic operation verification module, a dynamic operation alarm module, a message monitoringmodule and a background flow generation module. The method can be used for testing the functional performance of the time synchronization monitoring system, checking whether various functions and performance indexes of the time synchronization monitoring system meet the standard requirements or not, checking the interoperability of communication between the time synchronization monitoring management and control platform and the main clock device, and providing technical support for the time synchronization monitoring system to access a power grid and reliably operate.

Owner:STATE GRID JIANGSU ELECTRIC POWER CO ELECTRIC POWER RES INST +3

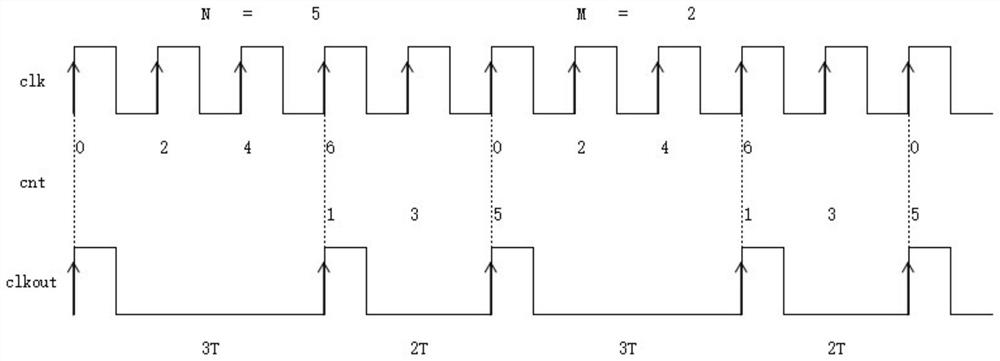

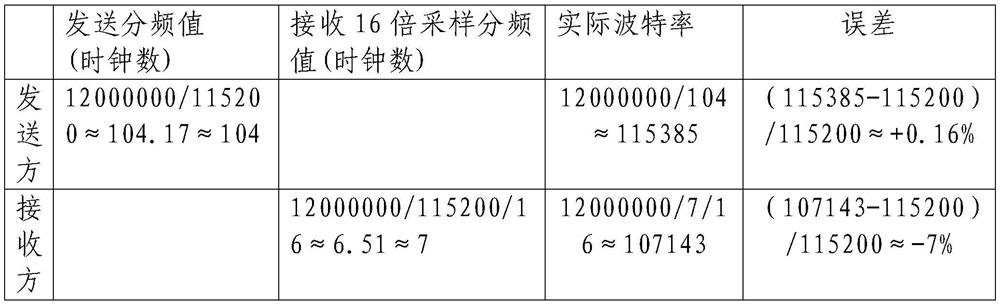

Method for arbitrary fractional frequency division of digital circuit clock

PendingCN113271084AEliminate cumulative errorsAchieve optimal processingPulse generation by differential amplifiersTelecommunicationsModular design

The invention relates to a method for any fractional frequency division of a digital circuit clock, and belongs to the field of digital circuits. The method comprises the following steps: S1, setting a counter with an initial value of 0; S2, performing counting under a main clock with the frequency of N, and adding M to each clock counter value; S3, judging a numerical value obtained by adding M to the counter value, and if the numerical value is smaller than N, returning to the step S2; if not, executing the step S4; S4, when the counter value+M is greater than or equal to N, generating a pulse, and setting the counter value as the counter value+M-N; and S5, repeating the steps S2, S3 and S4, wherein the generated pulses form a target clock with the frequency of M. The method is simple and accurate, and has no accumulative error; for any main clock and target clock, human intervention is not needed, the frequency division counting process is controlled, good adaptability is achieved, and modular design is facilitated.

Owner:中国人民解放军93216部队

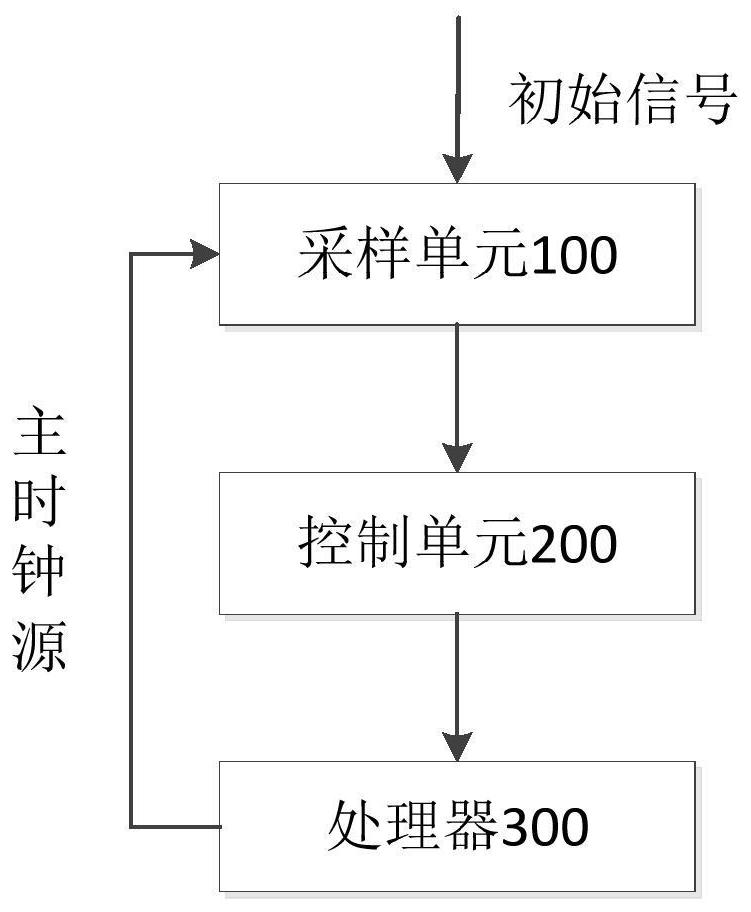

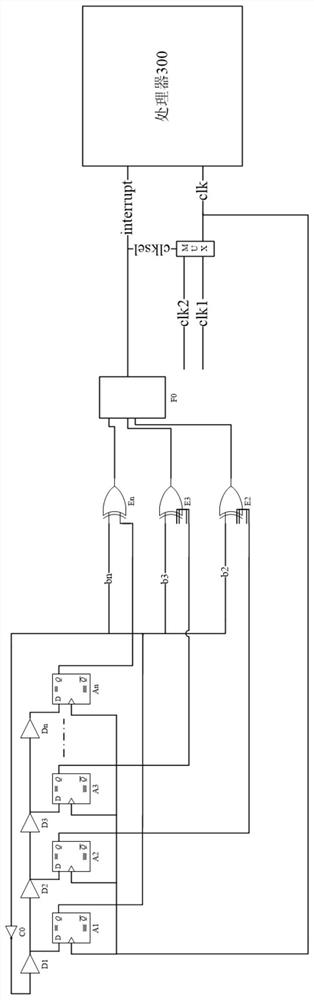

Control circuit

ActiveCN112286083ARealize real-time controlProgramme controlComputer controlControl signalControl cell

The invention relates to a control circuit. The control circuit comprises a sampling unit and a control unit, wherein the sampling unit is connected to the main clock source and used for setting a sampling period according to a clock signal output by the main clock source and sampling a group of sample signals according to the sampling period, and the control unit is connected to the sampling unitand used for generating a control signal according to a sampling result of the sampling unit and transmitting the control signal to the processor. Therefore, the processor can control the abnormal condition of the main clock source according to the control signal. According to the invention, the main clock source of the processor is used as the sampling clock of the control circuit, the sample signal is sampled according to the sampling clock, the control signal is output to the processor according to the sample result, and the processor processes the abnormal condition of the main clock source according to the control signal, so that the real-time control of the main clock source is realized.

Owner:EDGELESS SEMICON CO LTD OF ZHUHAI +1

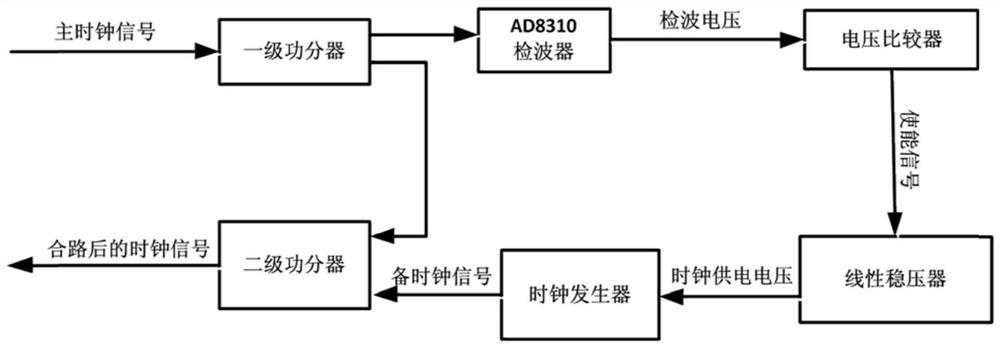

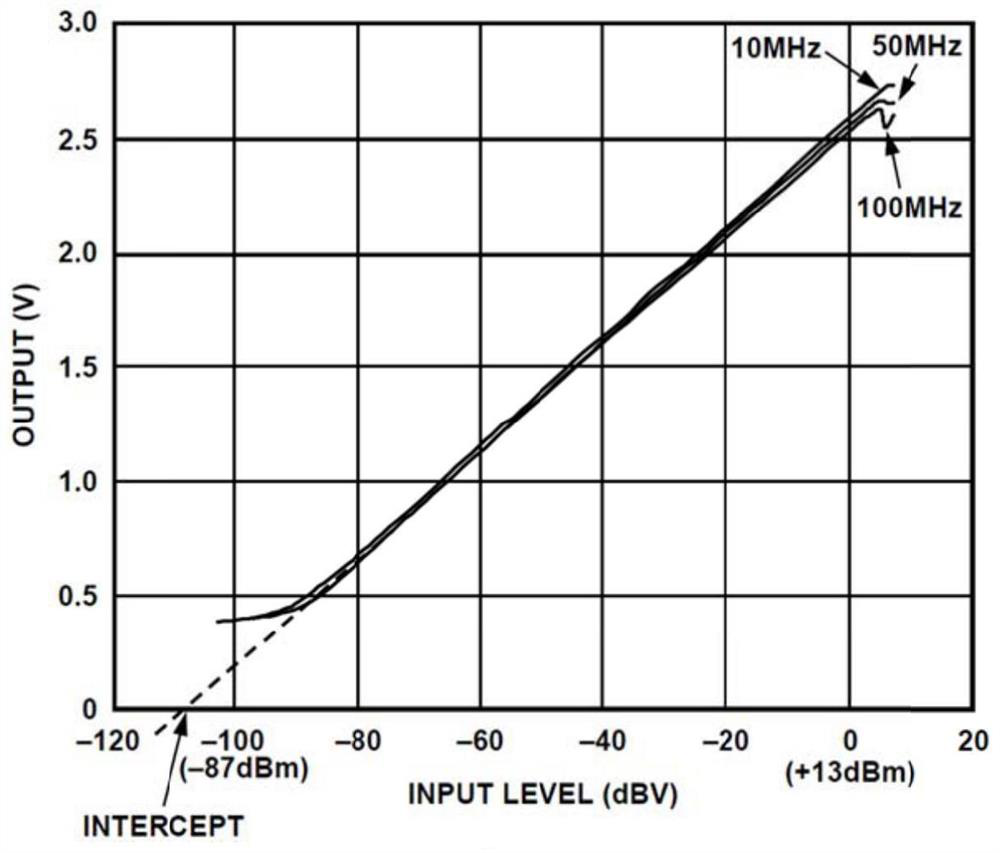

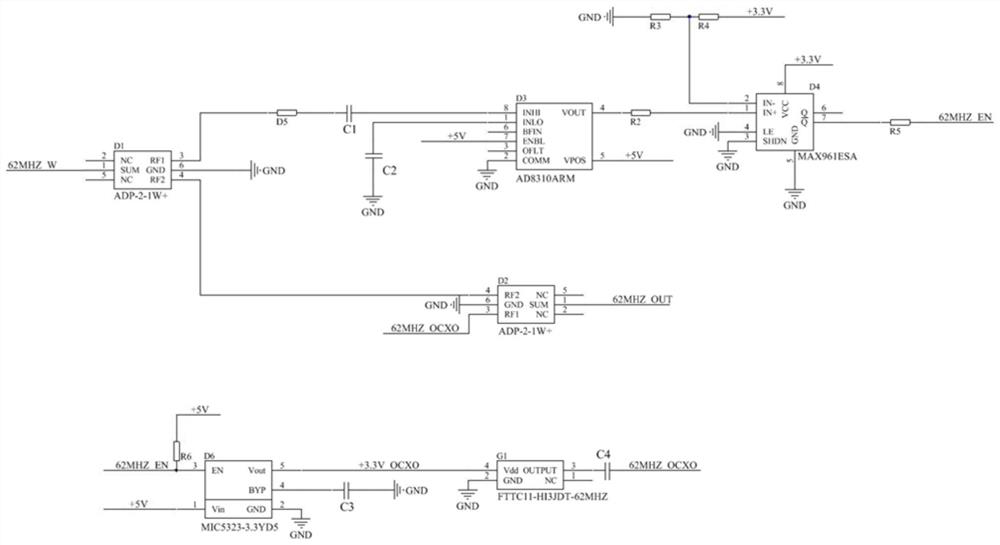

A clock self-test circuit based on ad8310 detector

ActiveCN110988931BReduce power consumptionImprove performancePulse automatic controlSatellite radio beaconingLinear regulatorOvervoltage

A clock self-inspection circuit based on an AD8310 wave detector belongs to the technical field of navigation. The invention integrates a primary power divider, a secondary power divider, an AD8310 detector, a voltage comparator, a linear voltage regulator, and a clock generator in one design; realizes the switching function of the main clock signal and the standby clock signal; adopts a The method of using the first-stage power divider and the second-level power divider in series improves the isolation between the main clock signal and the standby clock signal, and avoids the problem that the standby clock signal cannot be turned on due to the wrong interpretation of the voltage comparator when the main clock signal is turned off. The clock self-inspection circuit proposed by the present invention converts the power of the main clock signal into a voltage value by using a logarithmic detector, judges the on-off of the main clock signal, and passes the voltage comparator to realize the control of the enable signal of the linear voltage regulator , can accurately self-test the main clock signal. The invention has high reliability, light weight, low power consumption and strong practical value.

Owner:BEIJING RES INST OF TELEMETRY +1

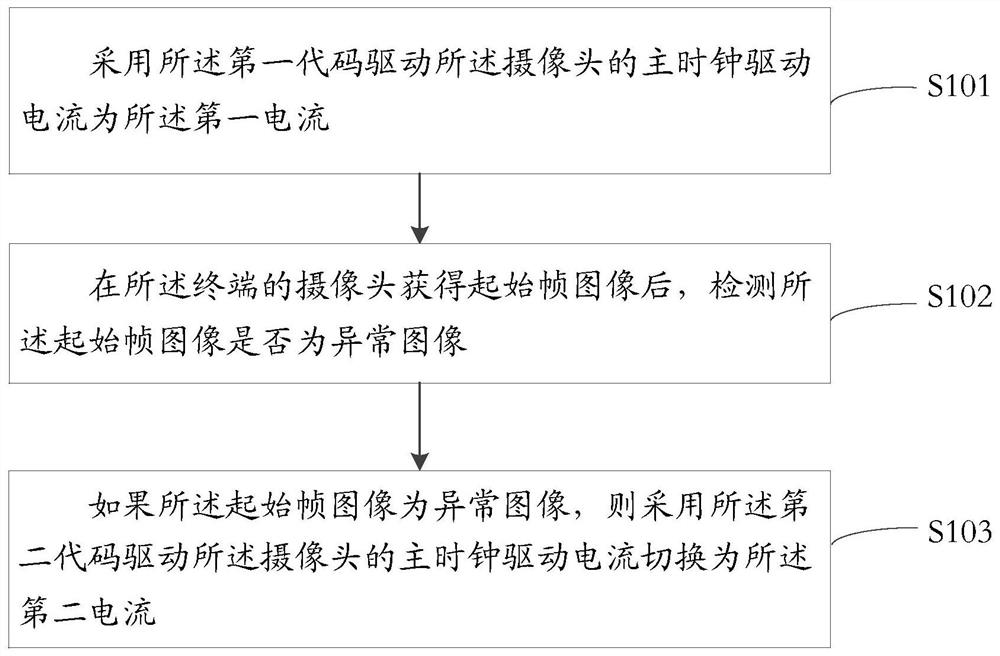

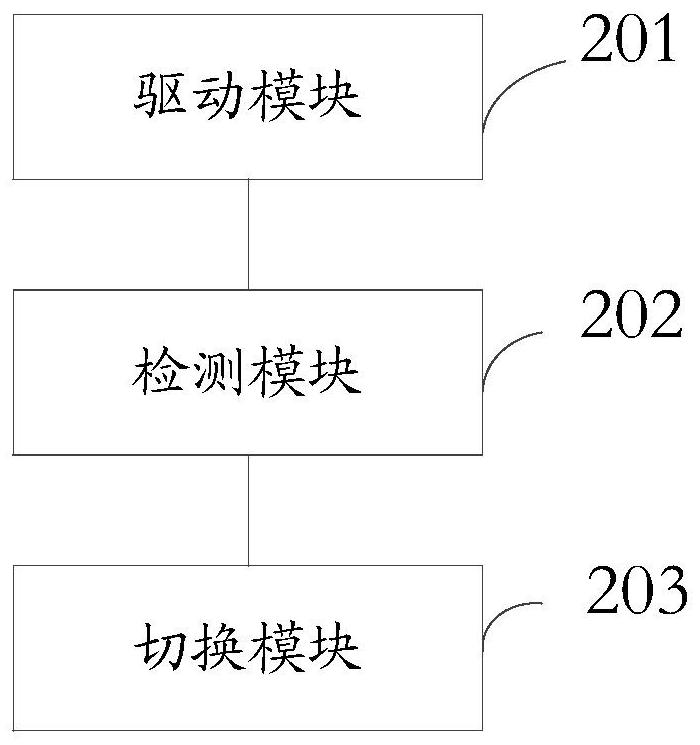

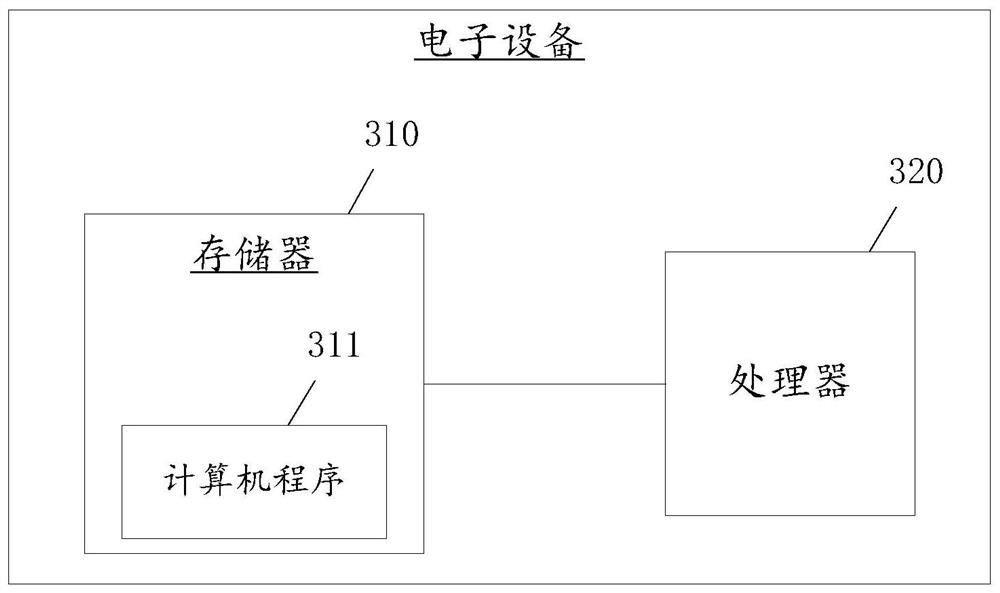

A terminal camera control method, device, electronic equipment and medium

ActiveCN111225203BGuaranteed battery lifeGuaranteed image qualityTelevision system detailsColor television detailsComputer hardwareCamera control

The invention discloses a camera control method, device, electronic device and medium of a terminal. The terminal pre-stores a first code whose main clock driving current for driving the camera is the first current and the main clock driving current used for driving the camera is the first current. The second code of two currents, the first current is smaller than the second current, and the method includes: using the first code to drive the main clock driving current of the camera to be the first current; after the camera of the terminal obtains the starting frame image, detecting the starting frame image Whether the frame image is an abnormal image; if the initial frame image is an abnormal image, the main clock driving current that uses the second code to drive the camera is switched to the second current. The method, device, electronic device and medium provided by the present invention are used to solve the technical problem in the prior art that the battery life of the mobile phone and the shooting quality of the camera cannot be taken into account, and the technical effect of taking into account the battery life of the mobile phone and the shooting quality of the camera is achieved.

Owner:KUNSHAN Q TECH CO LTD

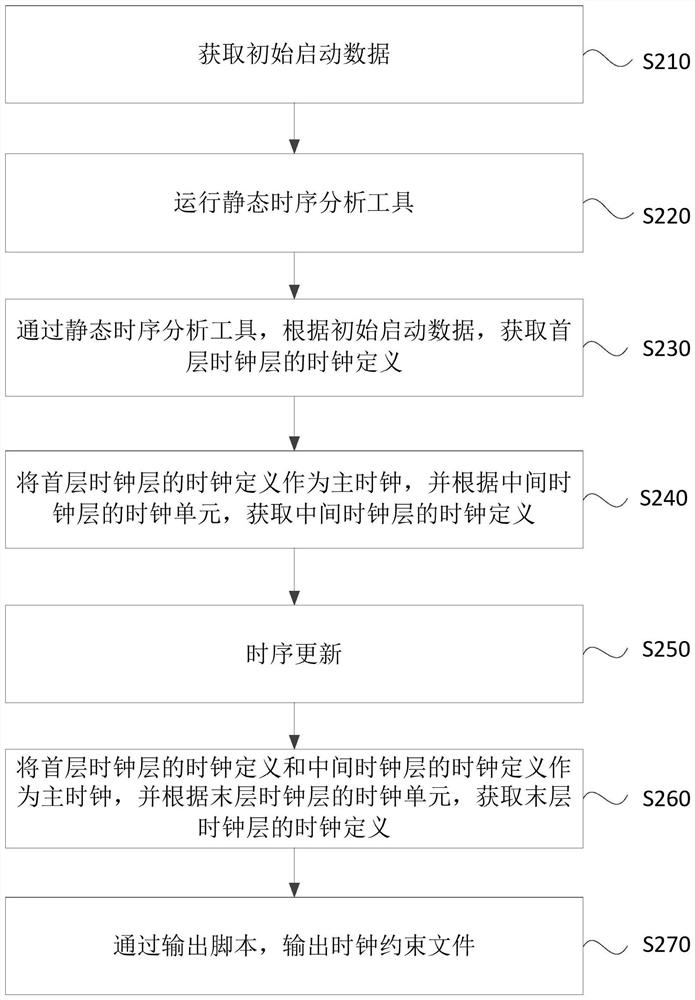

Clock constraint file collection method, device, equipment and storage medium

PendingCN112861452AShorten the development cycleImprove accuracyCAD circuit designComputer hardwareClock constraint

The embodiment of the invention discloses a clock constraint file collection method, a device, equipment and a storage medium. The method comprises the steps of obtaining a clock architecture of a chip, wherein the clock architecture comprises a plurality of clock layers, and each clock layer comprises at least one clock unit; according to the layer sequence of the clock architecture, obtaining clock definitions of all the clock layers in sequence; and obtaining a clock constraint file according to the clock definition of each clock layer. According to the technical scheme provided by the embodiment of the invention, the clock definitions of all the clock layers of which the layer sequence is located before the current clock layer are taken as the main clock of the current clock layer, and the clock definitions of all the clock layers are sequentially collected, so that the clock constraint file is collected according to the clock definitions of all the clock layers, automatic generation of the clock constraint file is realized, and the generation efficiency is improved. The writing time is saved, the development efficiency is improved, the research and development cycle of the chip is shortened. Meanwhile, the accuracy and reliability of writing the clock constraint file are improved.

Owner:SANECHIPS TECH CO LTD

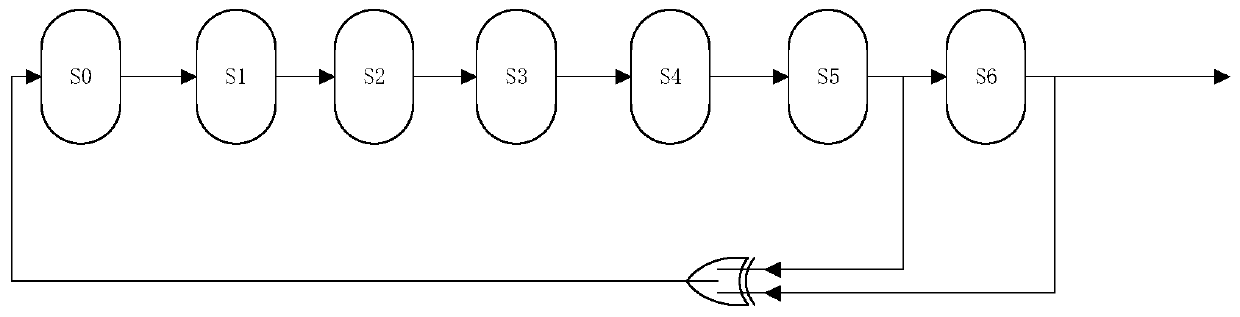

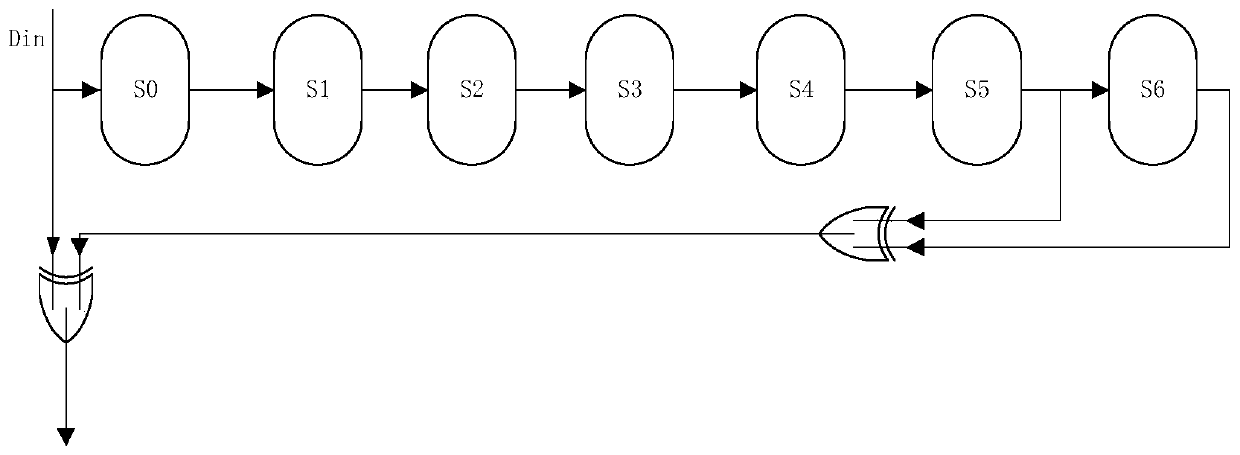

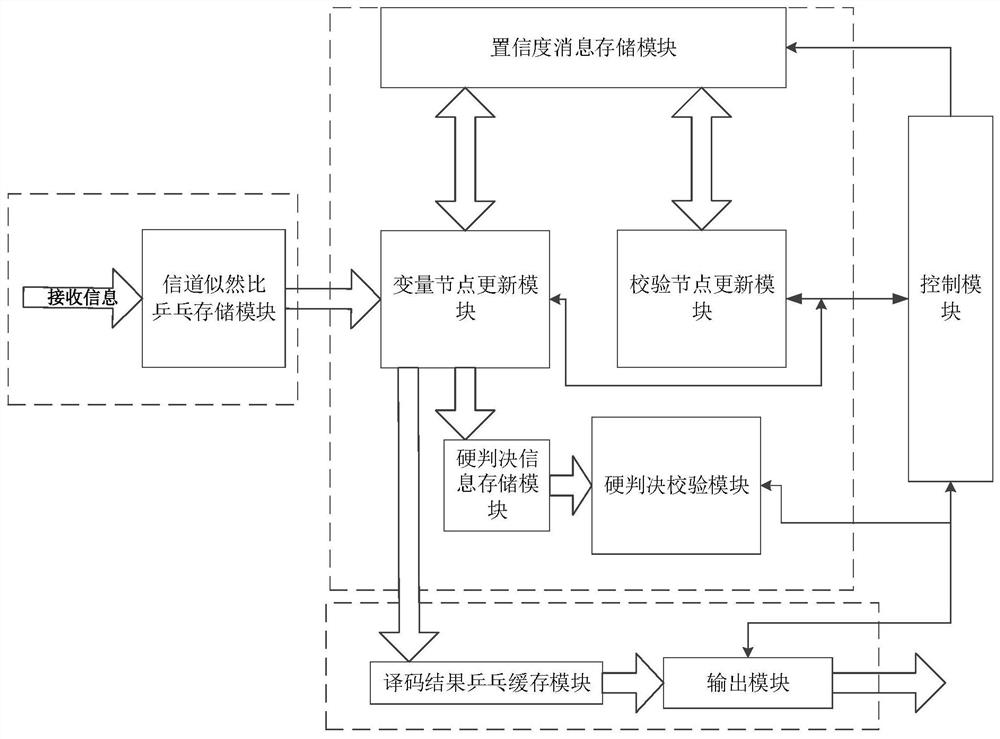

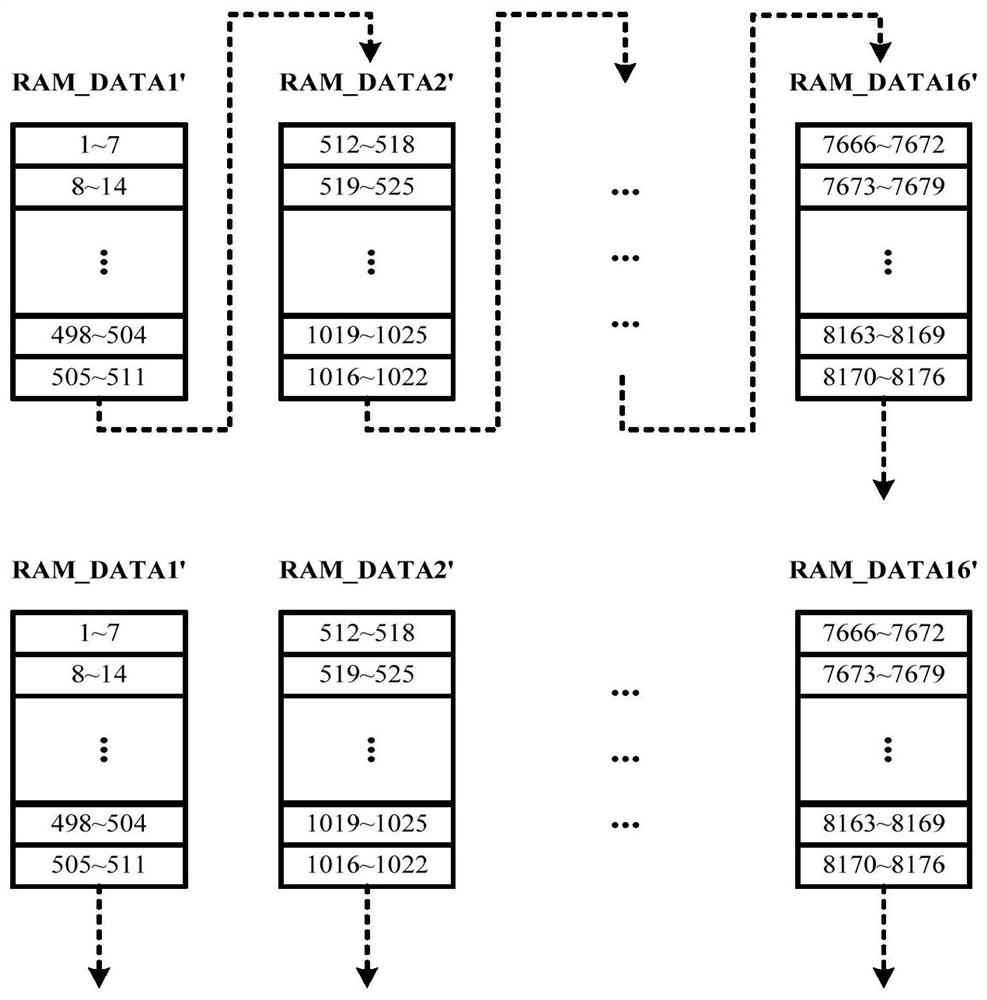

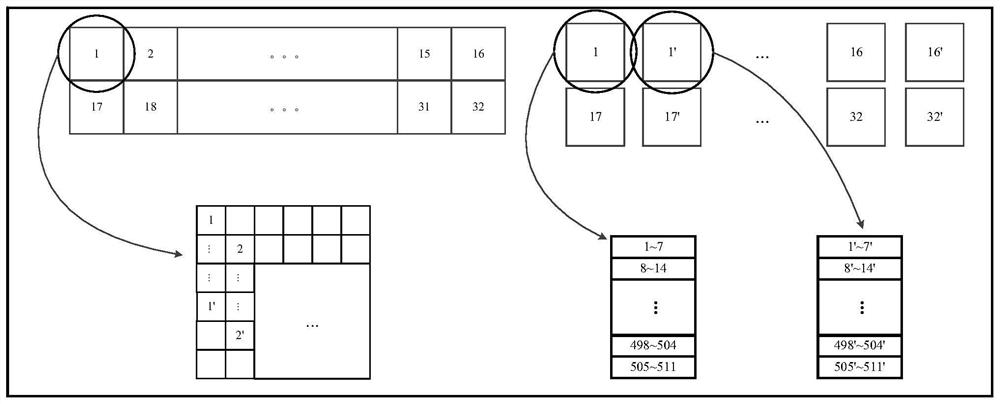

A kind of ldpc decoder and decoding method based on fpga

ActiveCN109495115BGuaranteed inflow and outflowSolve conflictsError correction/detection using multiple parity bitsCode conversionShift registerDegree of parallelism

An FPGA-based LDPC decoder and a decoding method belong to the technical field of channel coding in the communication field. The invention solves the problem of how to improve the throughput rate of the LDPC decoder while reducing the hardware resource overhead. The present invention separates the serial circuit from the parallel part by using the method of ping-pong buffering, and each part adopts independent clocks to ensure the inflow and outflow of continuous data streams and high throughput; and the present invention adopts a new circular storage method to The problem of address conflict is solved, the use of the barrel shift register or the connection network is avoided, and the occupancy rate of hardware resources of the decoding circuit is reduced at the same time. When the partial parallel decoding structure of the present invention is adopted, the parallel degree is 7, the main clock frequency is 110MHz, the code rate is 7 / 8, the sub-matrix dimension is 511, the number of iterations is 15, and the average number of variable node update clocks is 1.008, the throughput rate The maximum achieved was about 356.48Mbps. The present invention can be applied to the technical field of channel coding in the communication field.

Owner:HARBIN INST OF TECH

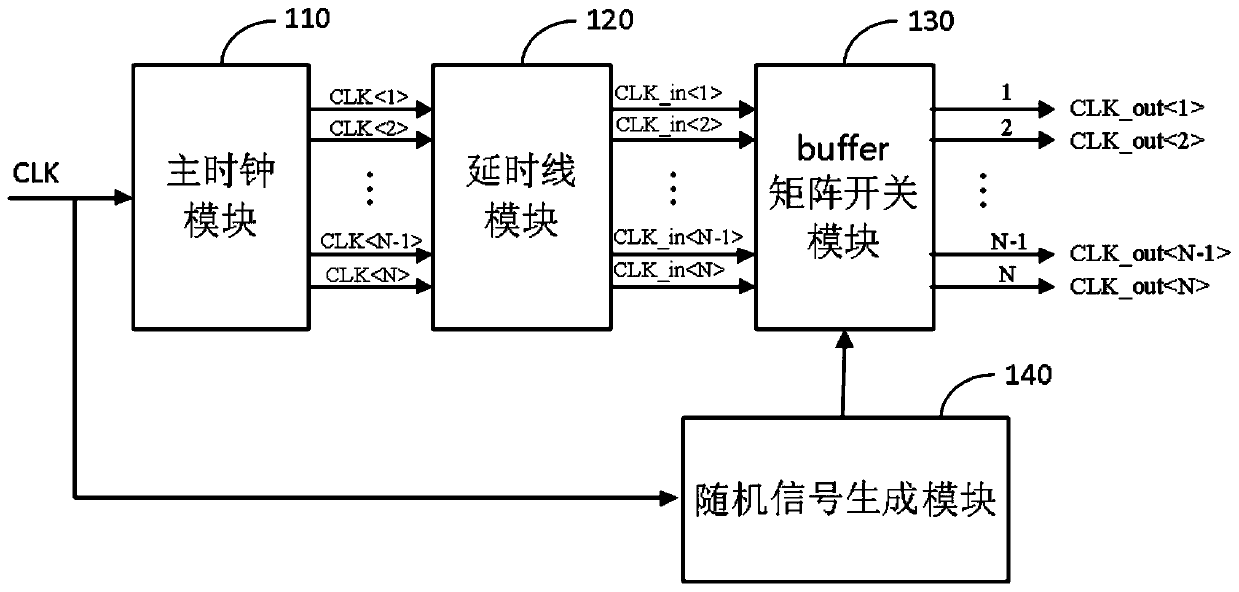

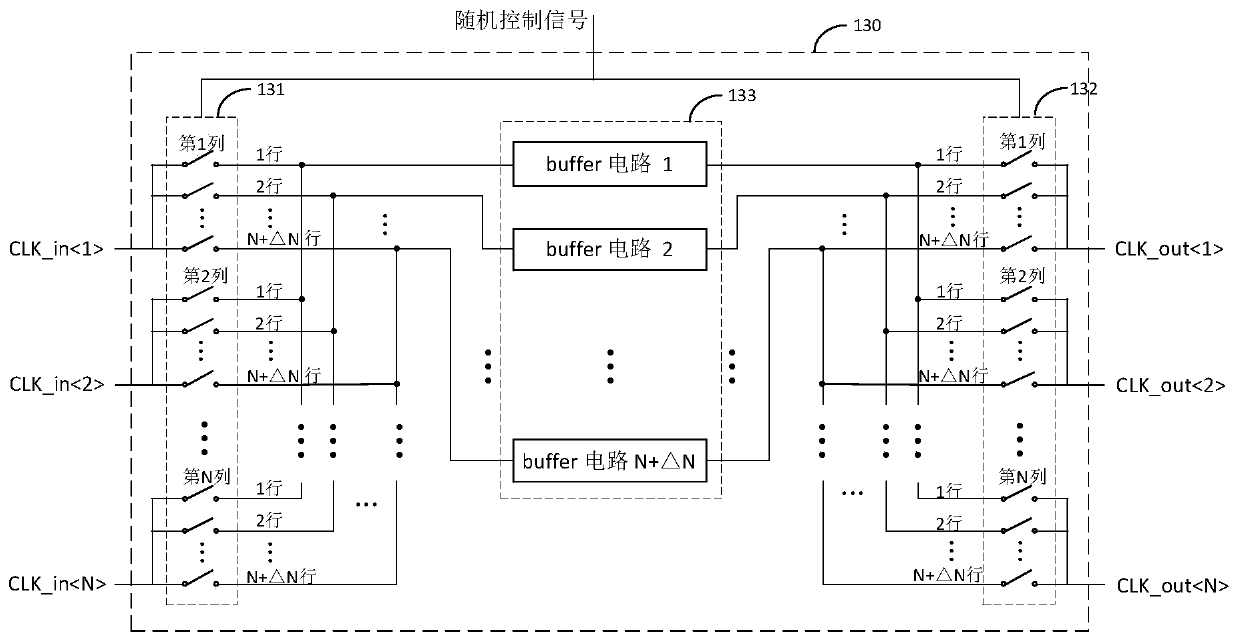

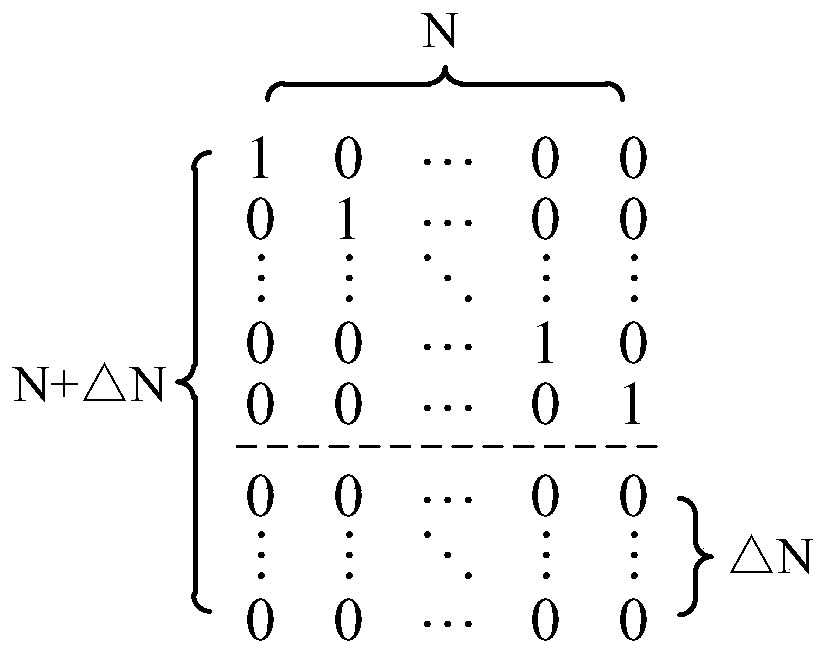

A Multi-phase Clock Generation Circuit Adding Random Disturbance

ActiveCN109101074BEliminate the effects of high precision TIADC performanceImprove stabilityAnalogue/digital conversionGenerating/distributing signalsControl signalHemt circuits

The invention discloses a multiphase clock generation circuit with random disturbance added, the clock generation circuit includes a main clock module, a random signal generation module and a buffer matrix switch module; the main clock module is used to generate N multiphase clock signals; The buffer matrix switch module is used to randomly switch the input transmission paths of the N multi-phase clock signals under the control of the random control signal output by the random signal generation module, and output N multi-phase clock signals with random disturbance added. clock signal. The present invention whitens the clock phase error by adding random disturbance, and only loses a small amount of signal-to-noise ratio, which can eliminate the influence of multi-phase clock phase error on the performance of high-precision TI ADC in real time, and can track and eliminate the clock phase error as the working environment changes. The impact of changing fluctuations can whiten the error spurious components at a fixed frequency into the noise floor, without interrupting the normal operation of TI ADC, the design is simple to implement, and the stability is high.

Owner:NO 24 RES INST OF CETC

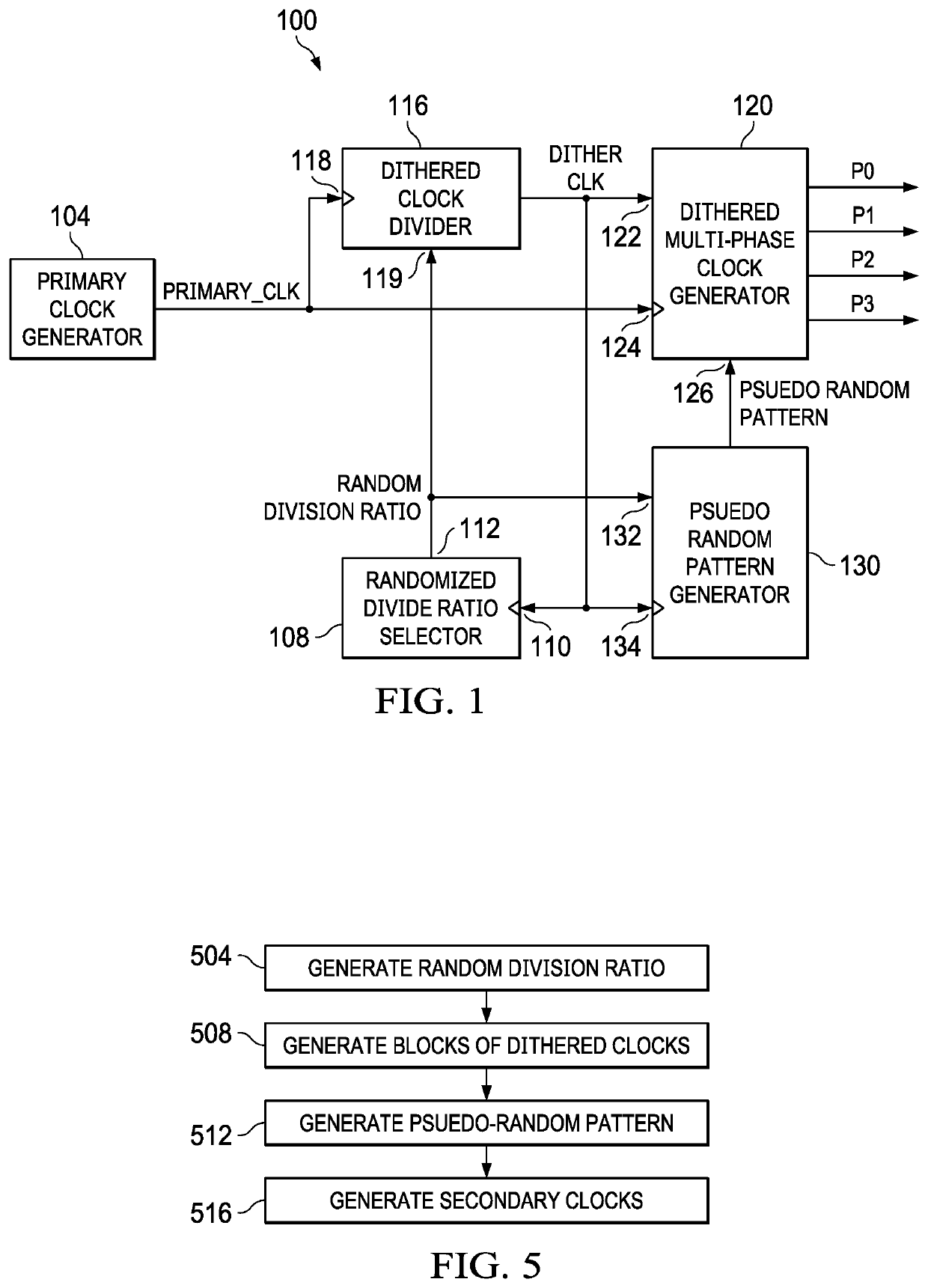

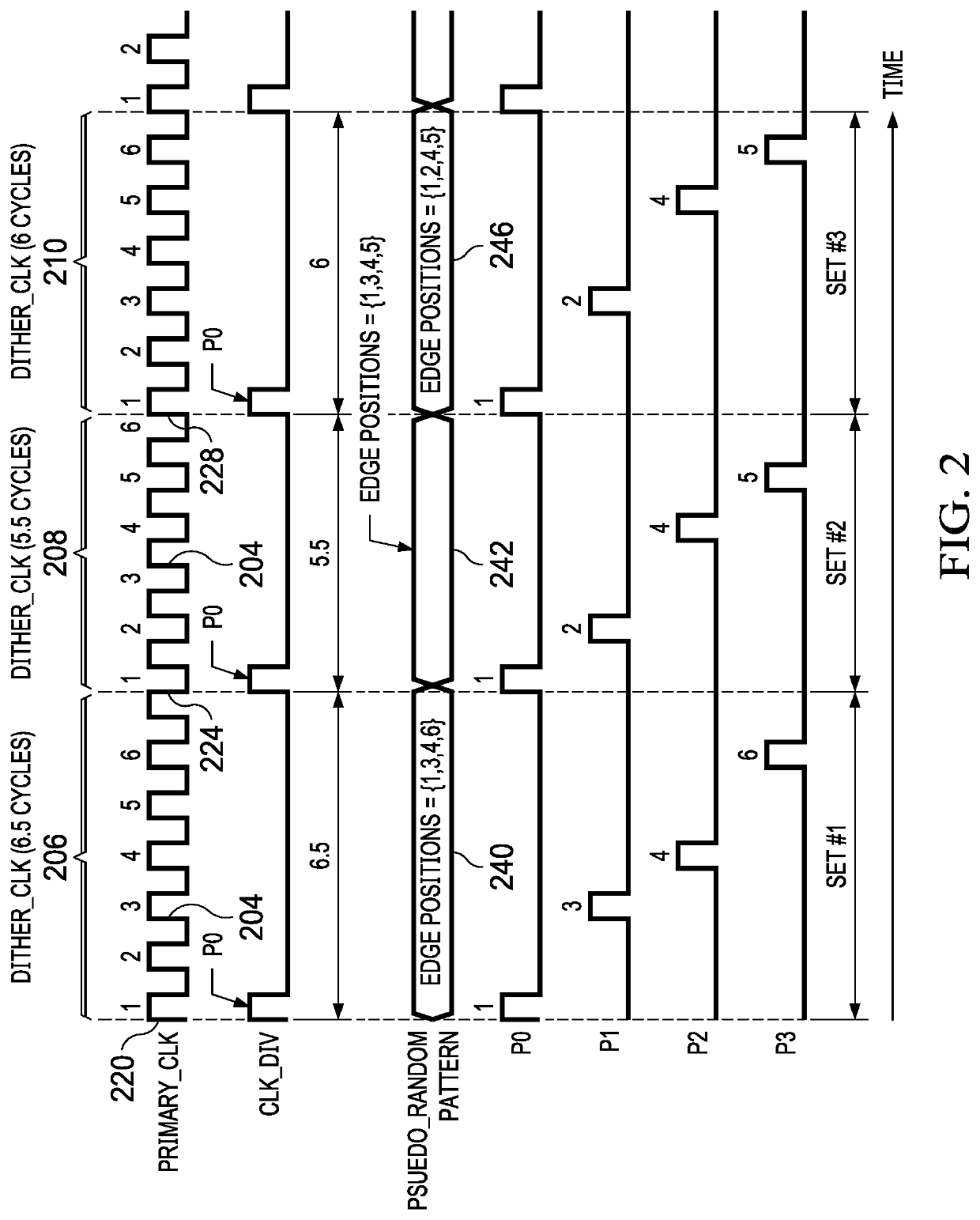

Methods and Systems for Generation of Balanced Secondary Clocks from Root Clock

A system for generating secondary clock signals from a primary clock signal includes a dithered clock divider which has a first input adapted to receive the primary clock signal and a second input adapted to receive a random division ratio. The dithered clock divider provides a dithered clock signal. The system includes a multi-phase clock generator which has a first input adapted to receive the primary clock signal, a second input adapted to receive the dithered clock signal, and a third input adapted to receive a pseudo-random pattern. The multi-phase clock generator provides the secondary clock signals from multiple phases of the dithered clock signal. The system includes a pseuodo-random pattern generator which provides the pseudo-random pattern.

Owner:TEXAS INSTR INC

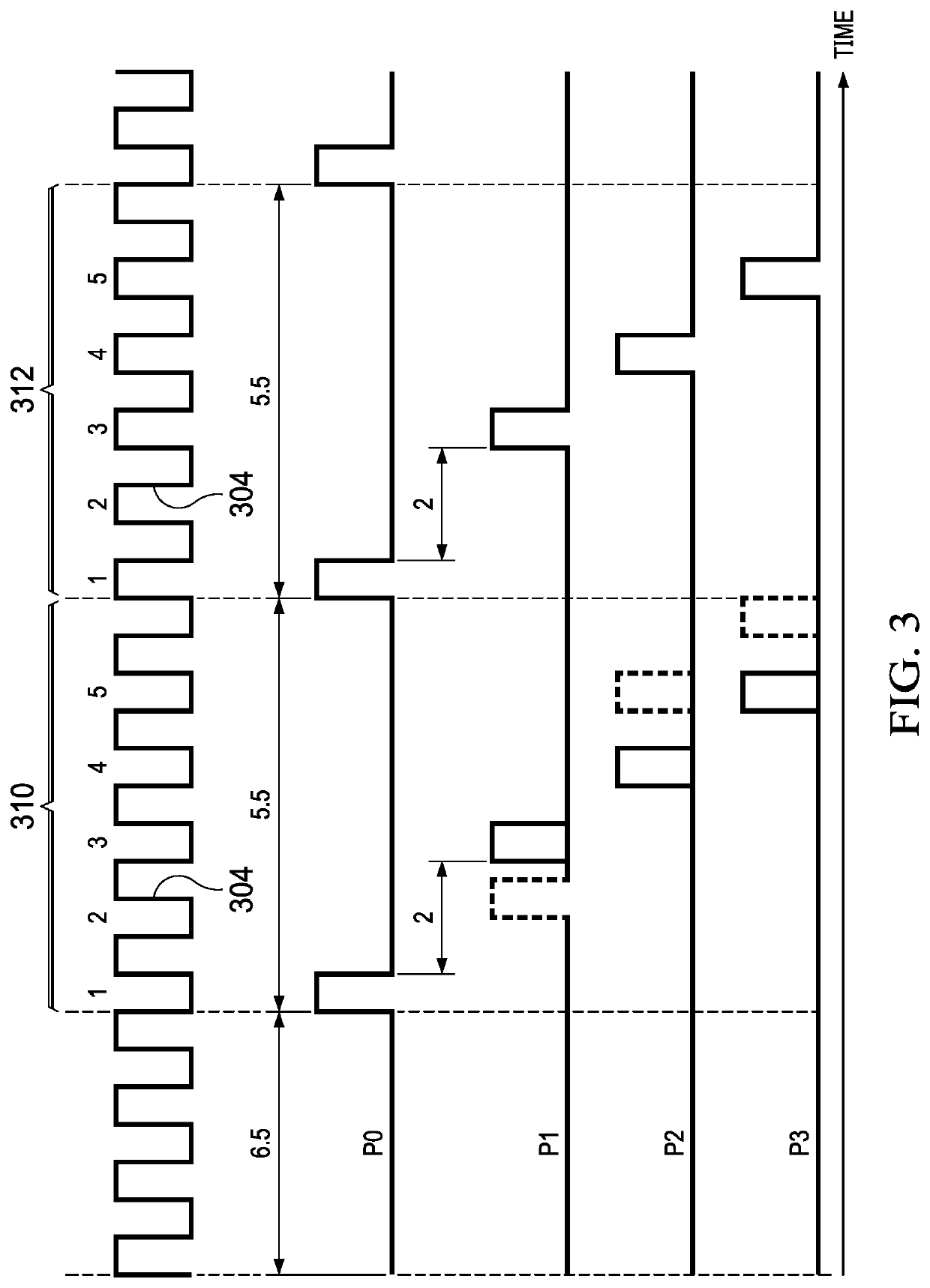

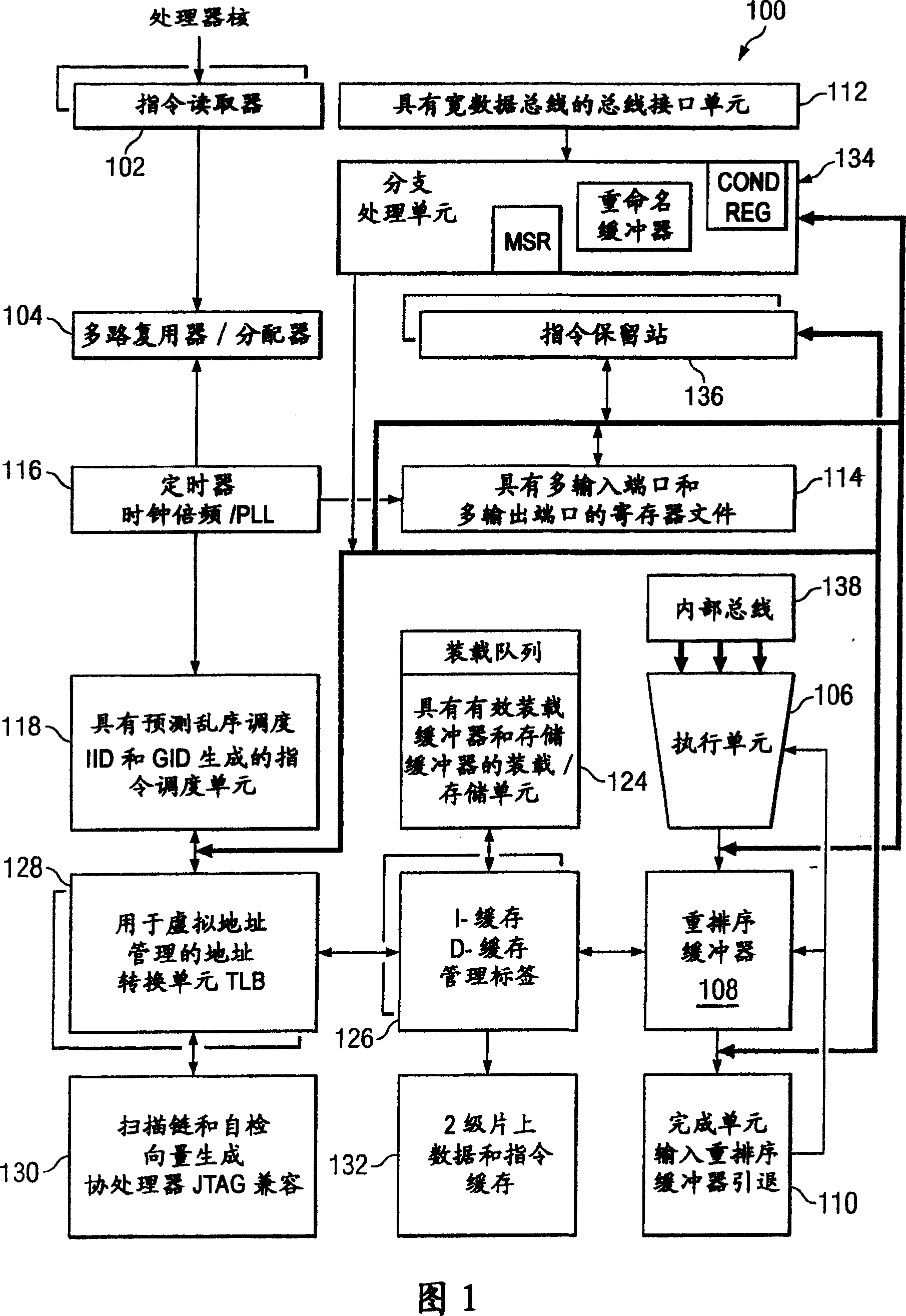

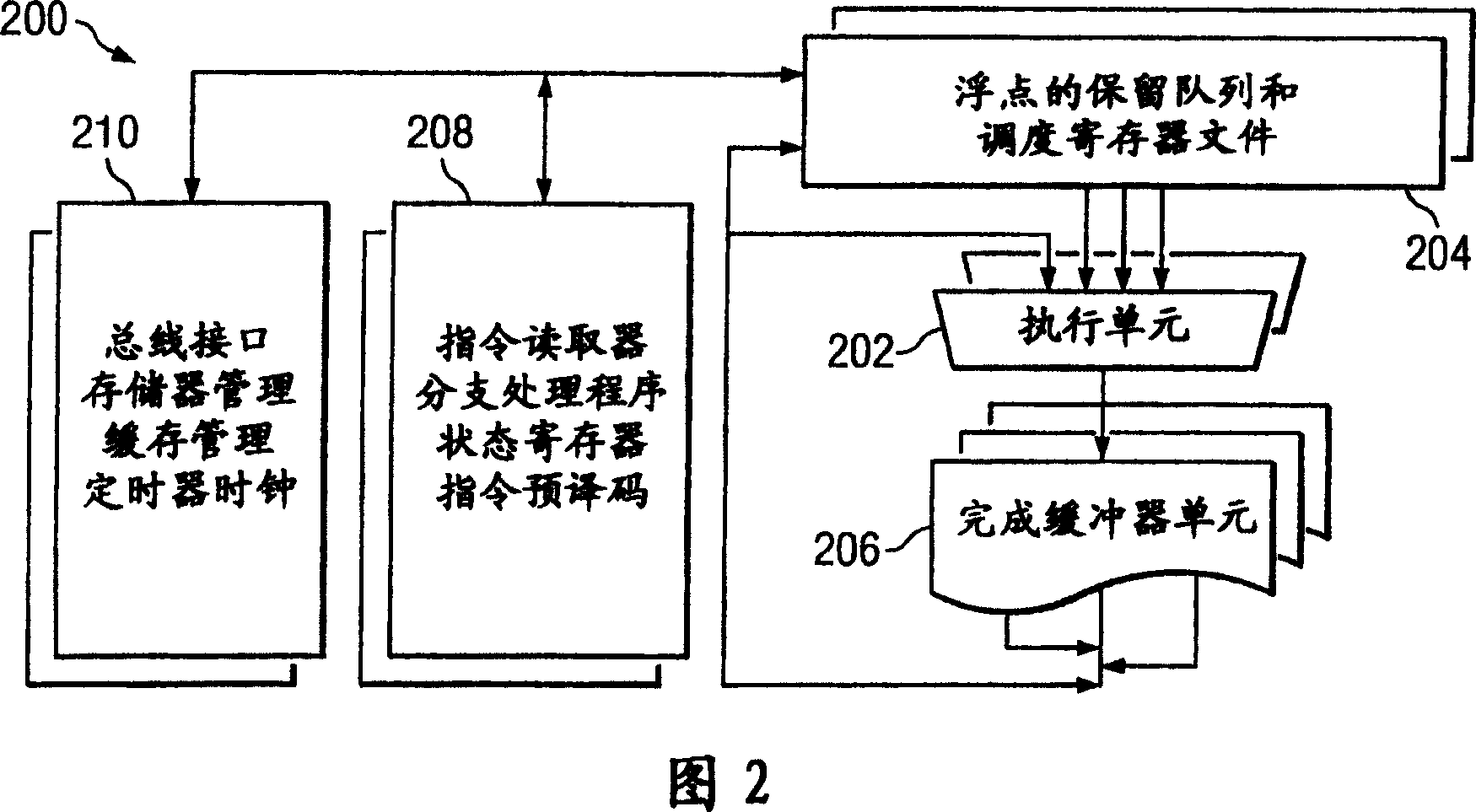

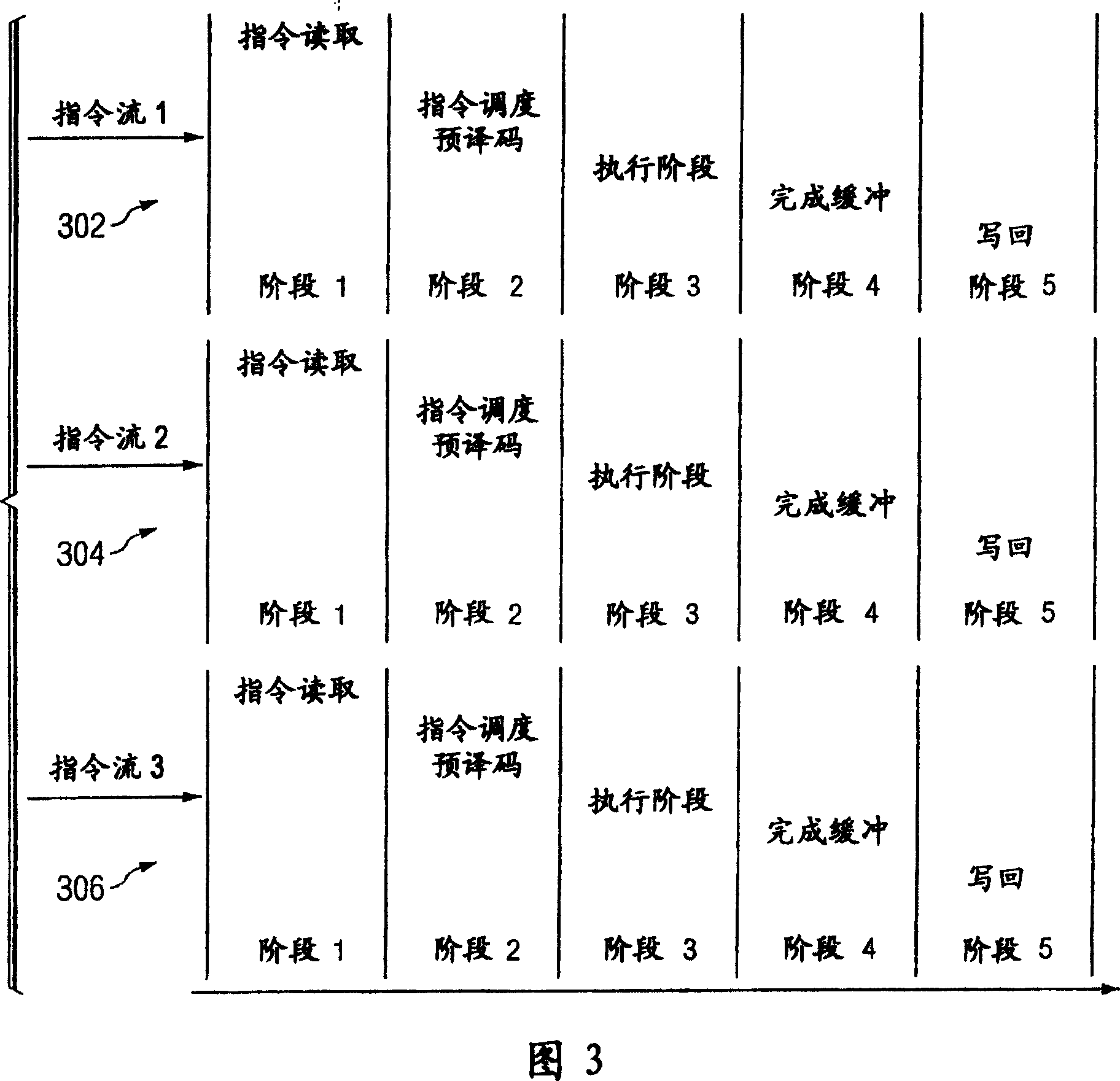

Method and apparatus for modeling multiple concurrently dispatched instruction streams in super scalar CPU

InactiveCN100345104CConcurrent instruction executionArchitecture with multiple processing unitsProcessing InstructionModelSim

A method is provided, wherein a virtual internal master clock is used in connection with a RISC CPU. The RISC CPU comprises a number of concurrently operating function units, wherein each unit runs according to its own clocks, including multiple-stage totally unsynchronized clocks, in order to process a stream of instructions. The method includes the steps of generating a virtual model master clock having a clock cycle, and initializing each of the function units at the beginning of respectively corresponding processing cycles. The method further includes operating each function unit during a respectively corresponding processing cycle to carry out a task with respect to one of the instructions, in order to produce a result. Respective results are all evaluated in synchronization, by means of the master clock. This enables the instruction processing operation to be modeled using a sequential computer language, such as C or C++.

Owner:INT BUSINESS MASCH CORP

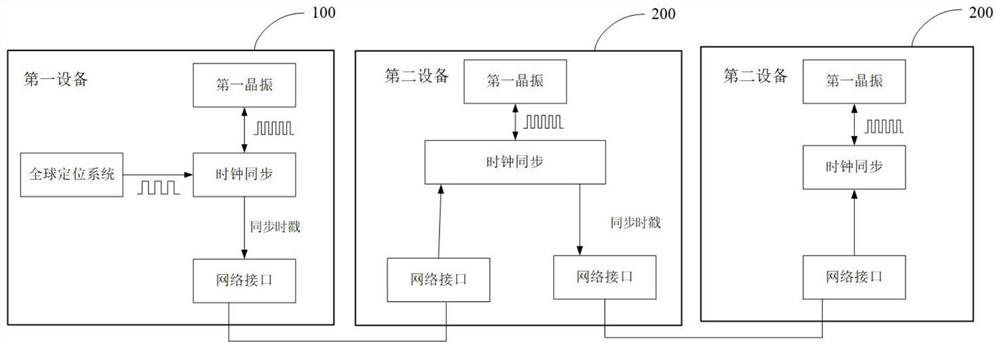

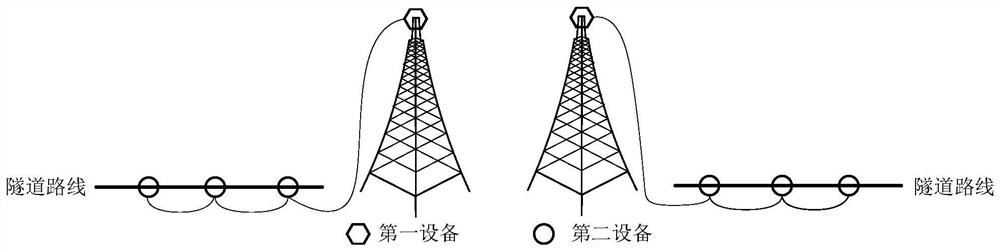

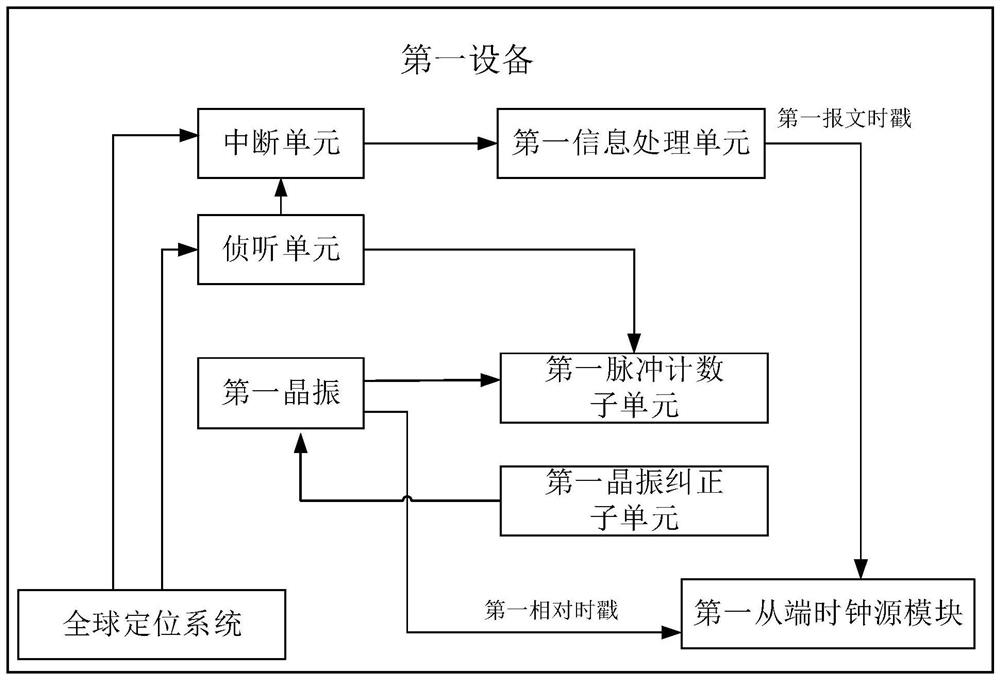

Clock synchronization system

The invention relates to a clock synchronization system. The clock synchronization system comprises: at least one first device configured to perform clock synchronization through using a global positioning system and a time synchronization protocol; and at least one second device configured to perform clock synchronization through using a time synchronization protocol; wherein the at least one first device is sequentially connected with the at least one second device through a network interface, the first device performs clock synchronization through the global positioning system, and the second device connected with the first device takes a clock synchronized by the first device as a main clock source; and when the at least one second device is connected behind the second device, each second device performs clock synchronization by taking the clock synchronized by the previous second device as a main clock source until the clock synchronization of all the second device is completed. By adopting the clock synchronization system, a high-precision clock synchronization mode of the devices can be realized step by step.

Owner:SUZHOU GUANGGE EQUIP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com