Method and apparatus for modeling multiple concurrently dispatched instruction streams in super scalar CPU

一种指令流、指令的技术,应用在并发指令执行、具有多个处理单元的架构、机器执行装置等方向,能够解决不能CPU操作建模等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

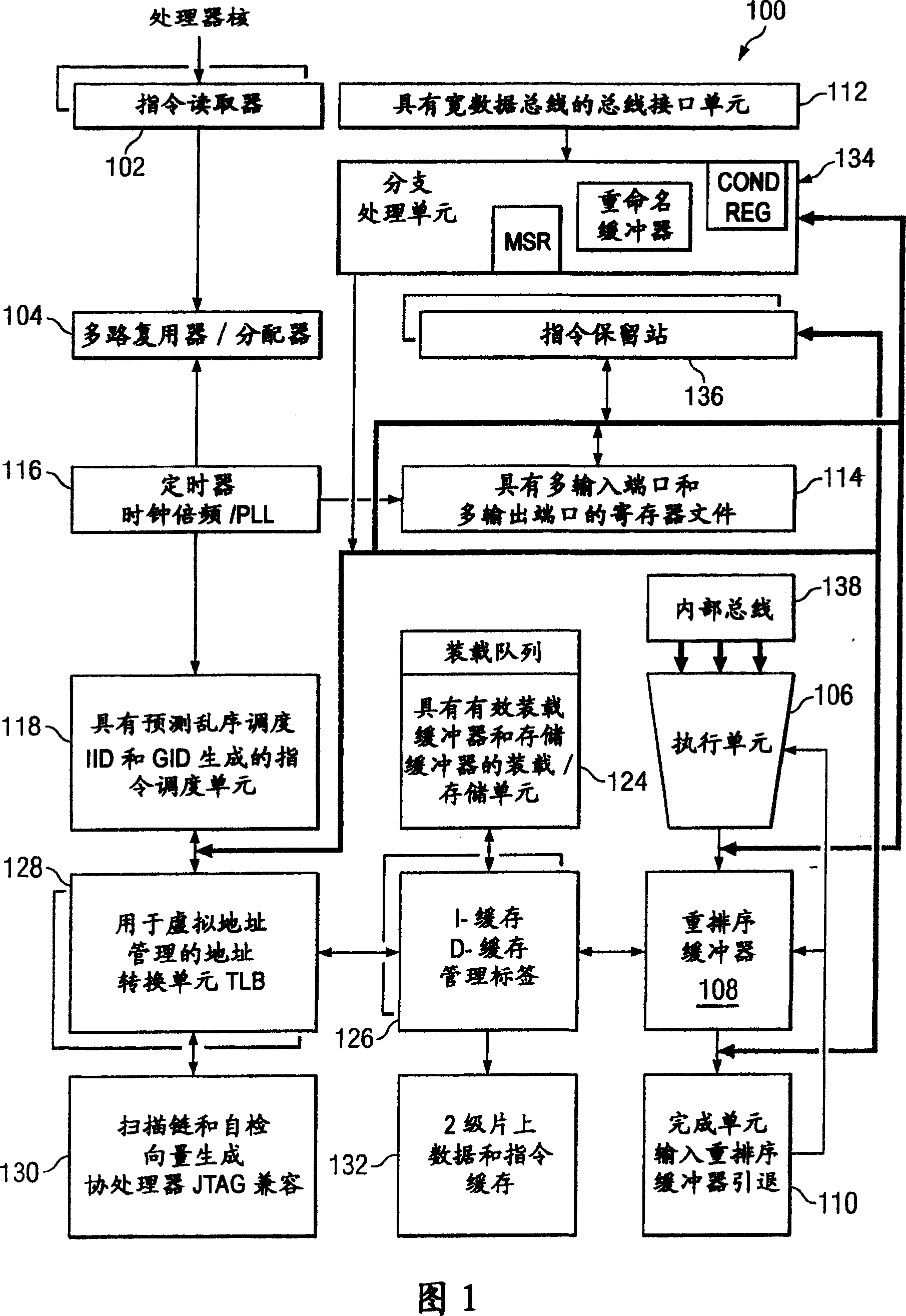

[0012] Referring to FIG. 1, there is shown a superscalar RISC CPU 100 implemented as an arrangement of concurrently operating functional blocks or functional units. The functional units include an instruction reader 102 , a multiplexer / distributor 104 and an execution unit 106 . Reorder buffer 108 and completion unit input reorder buffer 110 collectively function as a completion buffer. The interaction between the functional units 102-110 in FIG. 1, together with the bus interface unit 112 and the register file 114, will be described in detail later.

[0013] Referring further to FIG. 1, there is shown a timer 116 and an instruction dispatch unit 118, connected to the multiplexer 104, for dispatching instructions. Also shown is load / store unit 124 , interconnected with instruction cache / data cache 126 , and address translation unit 128 , as well as coprocessor 130 and cache 132 . RISC CPU 100 further includes a branch processing unit 134 , an instruction reservation station ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com