A kind of ldpc decoder and decoding method based on fpga

A decoder and decoding technology, applied in the field of LDPC decoder and decoding, to achieve the effect of reducing hardware resource occupancy rate, avoiding use, and high throughput rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

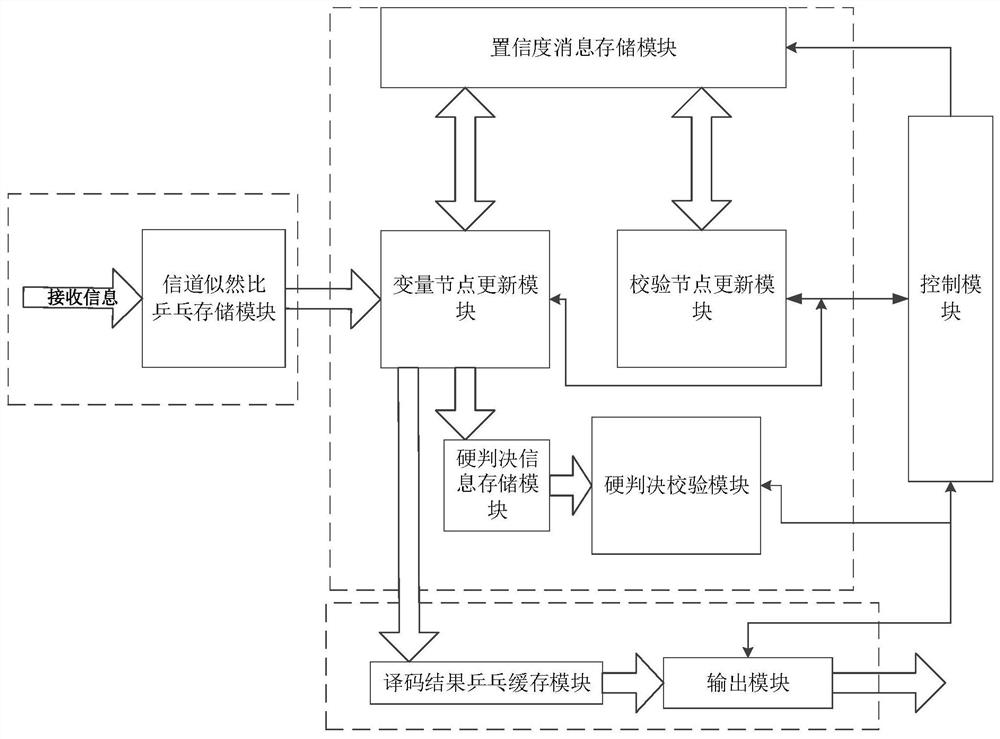

[0040] Specific implementation one: as figure 1 As shown, an FPGA-based LDPC decoder described in this embodiment, the LDPC decoder includes a channel likelihood ratio ping-pong storage module, a confidence message storage module, a hard decision information storage module, and a decoding result. Ping-pong cache module, check node update module, variable node update module, hard decision check module, control module and output module;

[0041] The channel likelihood ratio ping-pong storage module is configured to receive and store the channel log likelihood ratio information input to the decoder, and provide the channel log likelihood ratio information to the variable node update module;

[0042] The confidence message storage module is used to store the confidence message calculated by the check node update module and the variable node update module;

[0043] The check node update module is used to complete the calculation of the confidence message from the check node to the...

specific Embodiment approach 2

[0059] Embodiment 2: This embodiment is different from Embodiment 1 in that the channel likelihood ratio ping-pong storage module is a ping-pong storage pair structure.

specific Embodiment approach 3

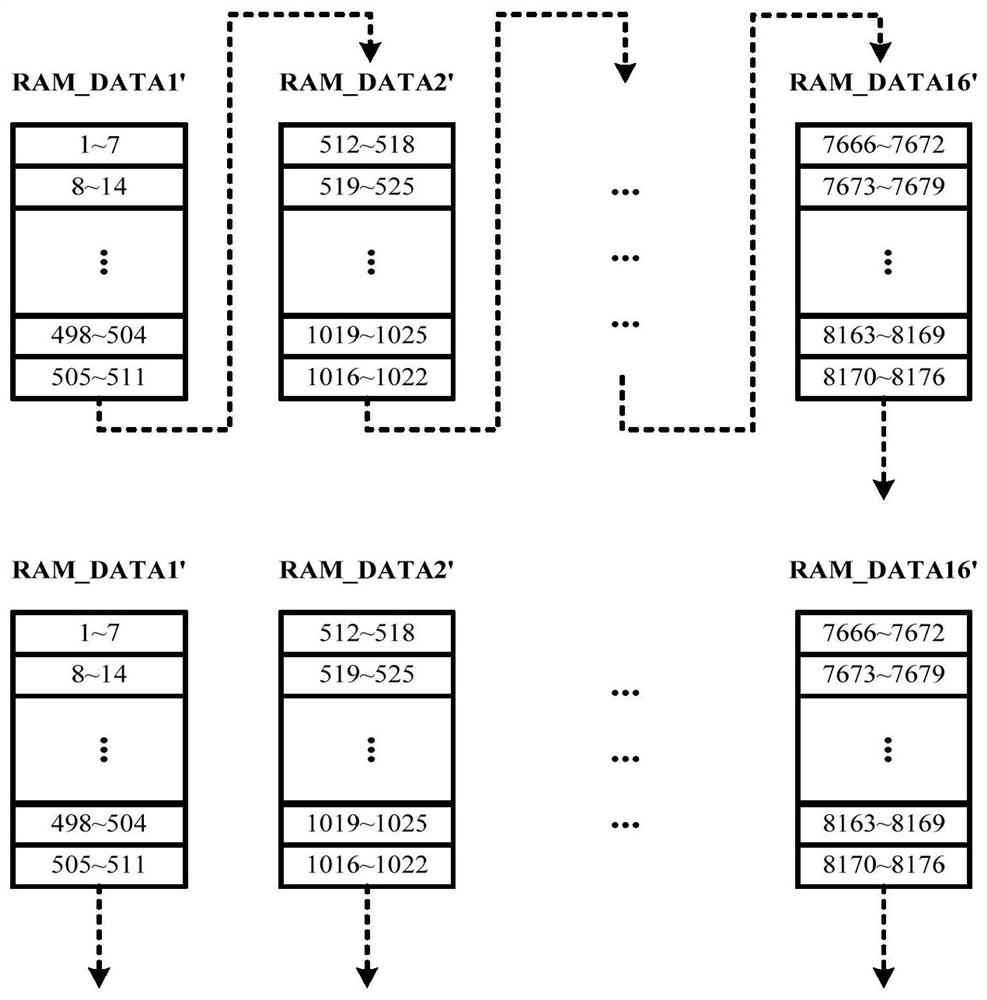

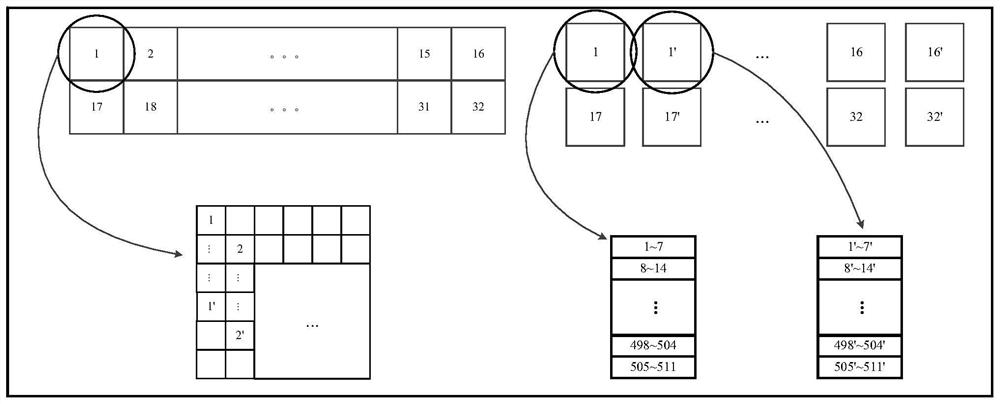

[0060] Embodiment 3: This embodiment is different from Embodiment 2 in that the channel likelihood ratio ping-pong storage module includes 16 pairs of RAMs with a bit width of P×8 and a depth of 511 / P, where P is the confidence message storage The number of data bits per address of the module.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com