DLL system based on successive approximation PID control algorithm

A technology of step-by-step approximation and control algorithm, applied in the field of DLL system, can solve the problems of large area, long delay line, increased power consumption, etc., to achieve the effect of low design complexity, simple implementation, and reduced power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention.

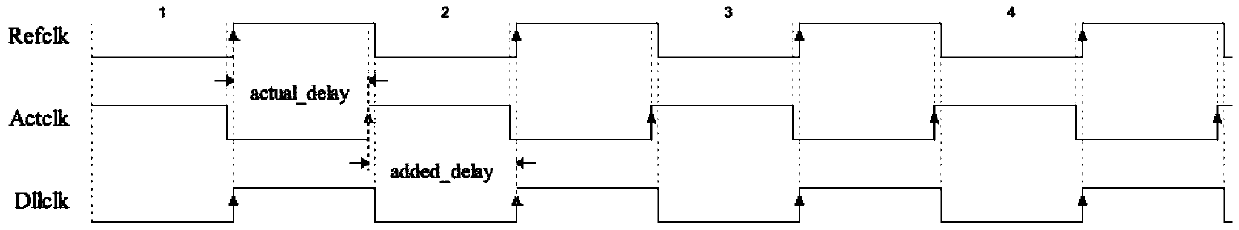

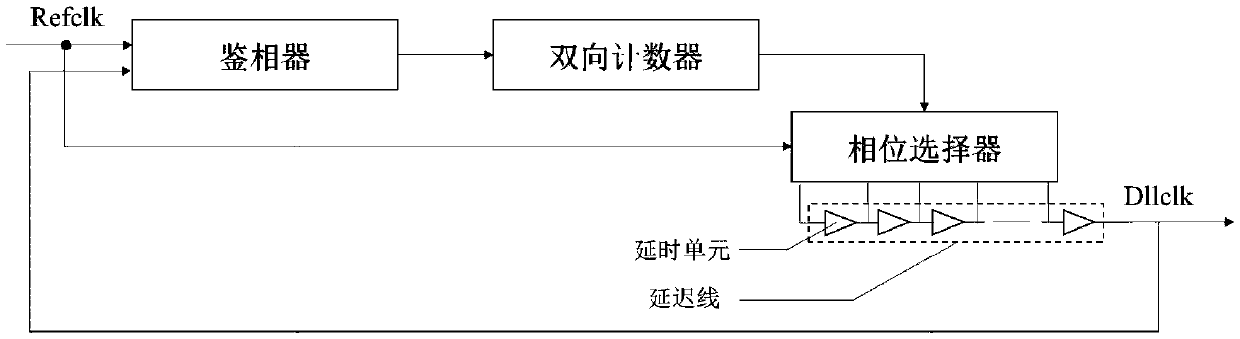

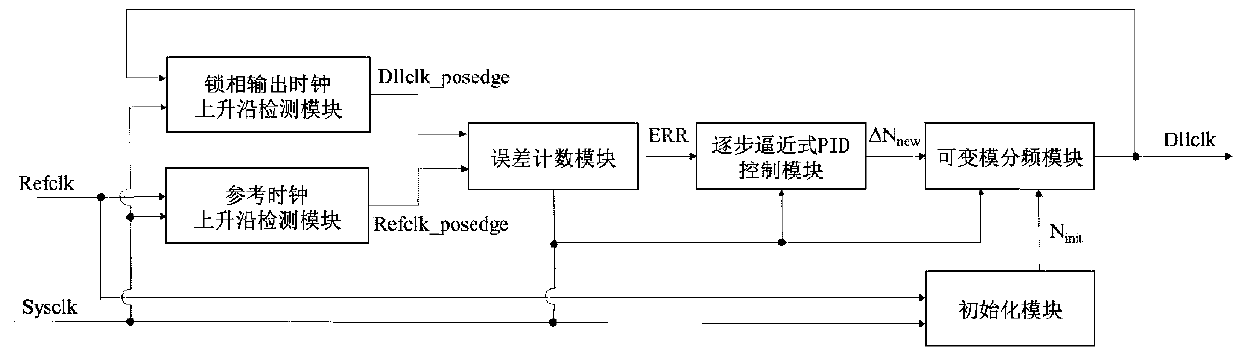

[0020] The invention is a DLL system based on a step-by-step approximation PID control algorithm, image 3 It is a structural block diagram of the DLL system proposed by the present invention. The whole system consists of [phase-locked output clock rising edge detection module], [reference clock rising edge detection module], [error counting module], [stepwise approximation PID control module], [variable mode frequency division module] and [initialization module 】composition. The system clock (Sysclk) is the main clock of the whole system, the reference clock (Refclk) is the clock signal to be locked, and the phase-locked output clock (Dllclk) is the locked clock si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com