Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

458 results about "Sequential logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

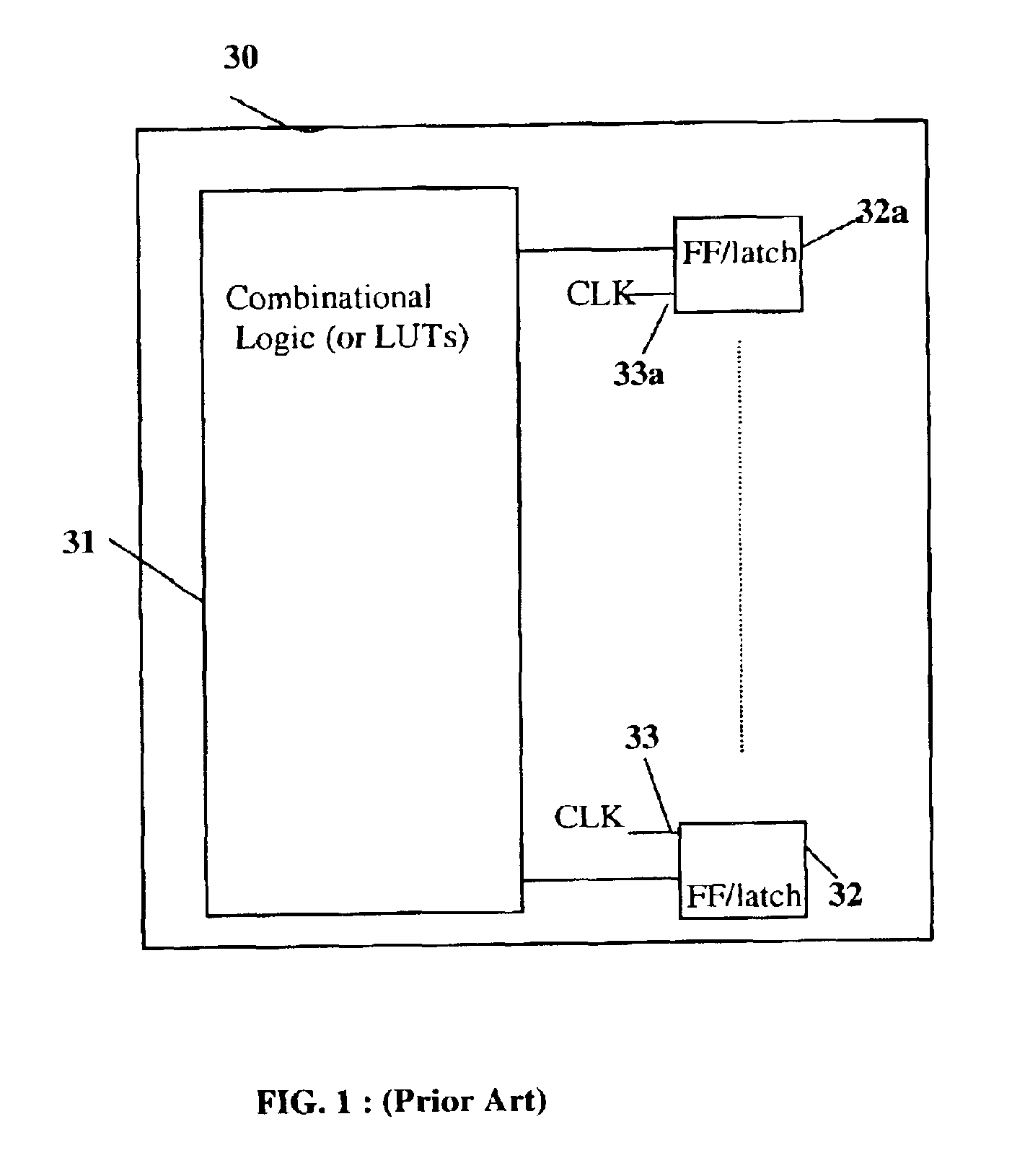

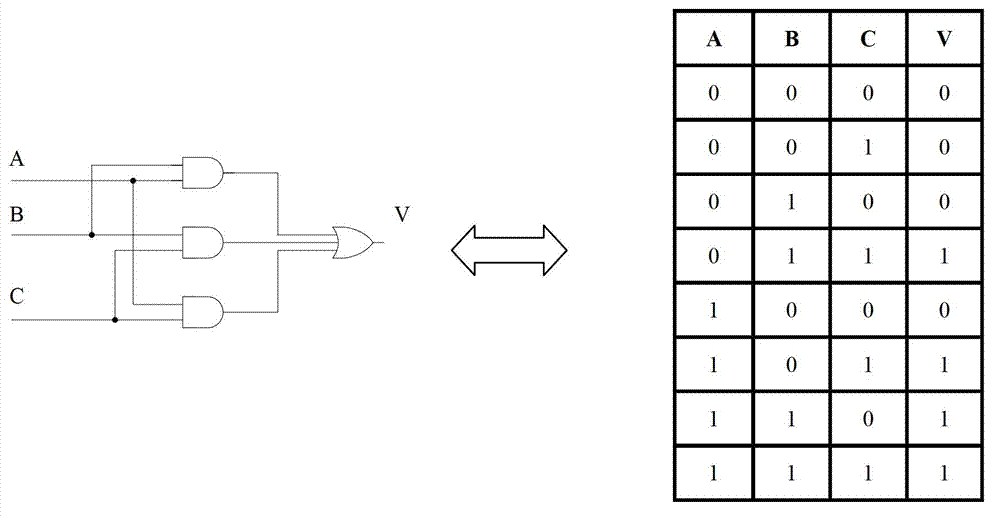

In digital circuit theory, sequential logic is a type of logic circuit whose output depends not only on the present value of its input signals but on the sequence of past inputs, the input history as well. This is in contrast to combinational logic, whose output is a function of only the present input. That is, sequential logic has state (memory) while combinational logic does not.

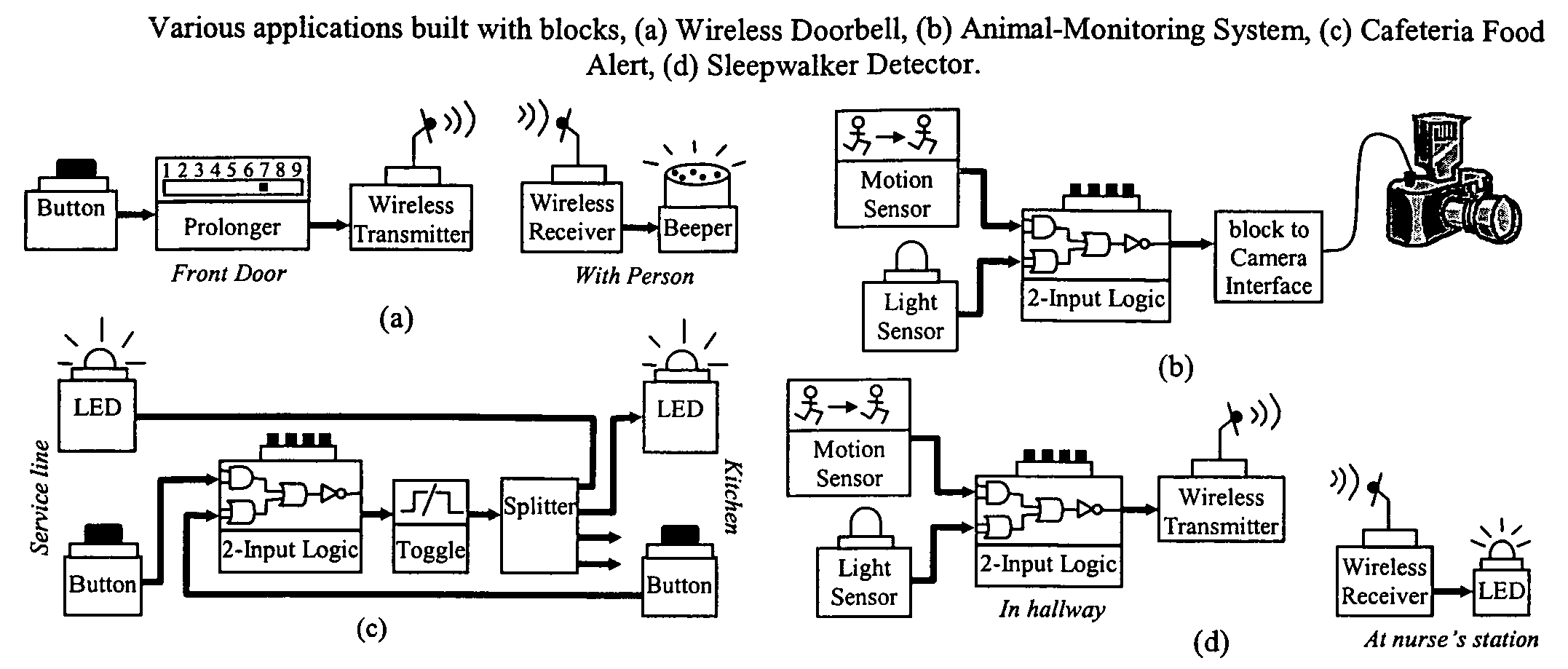

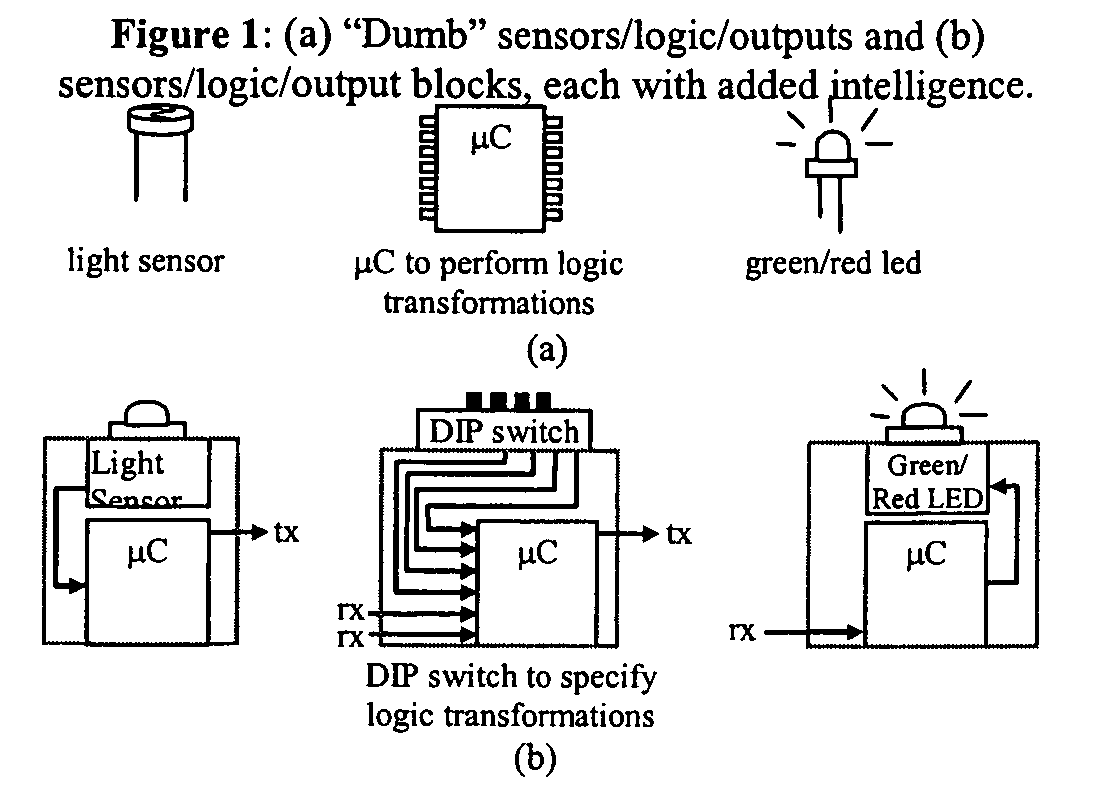

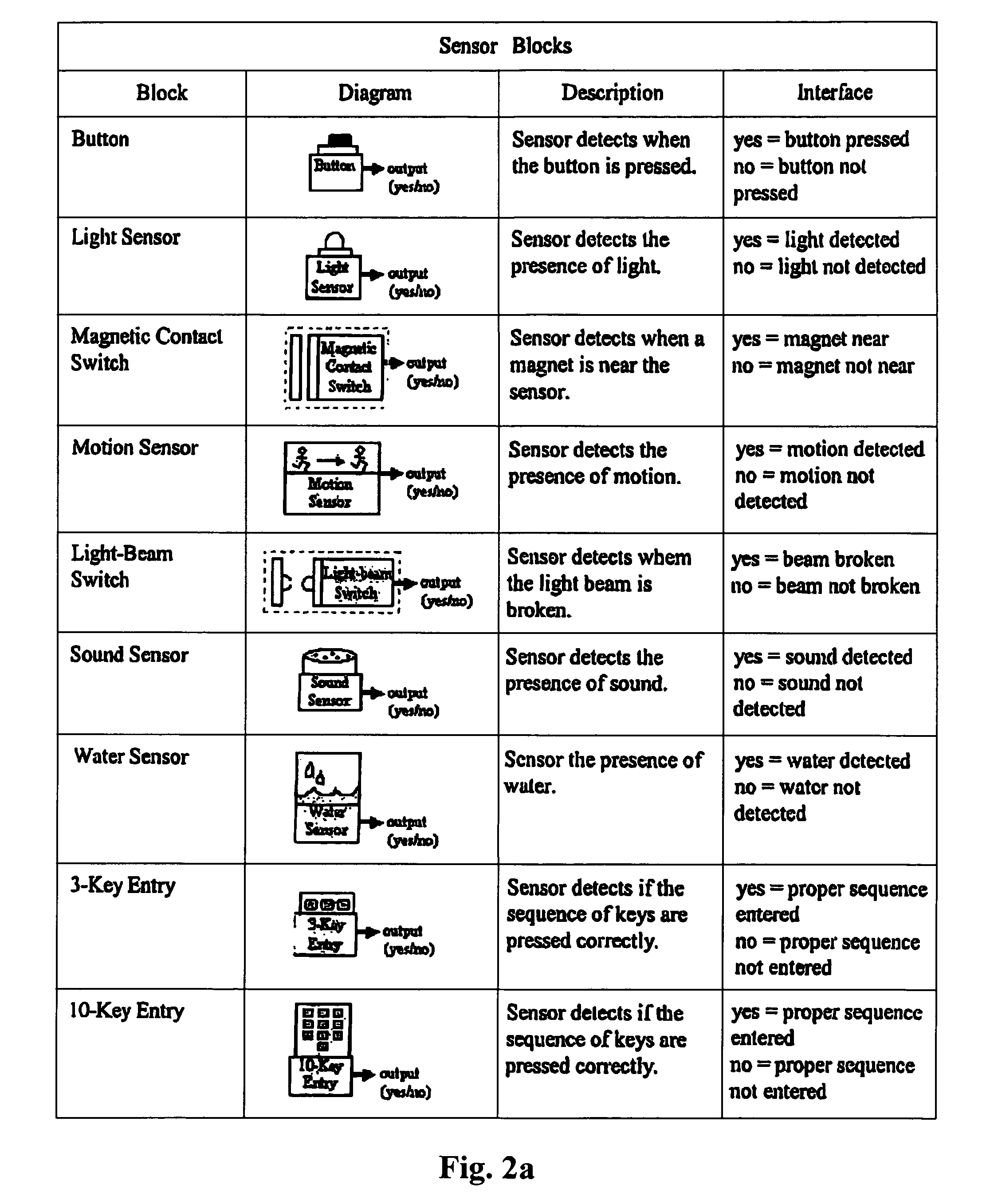

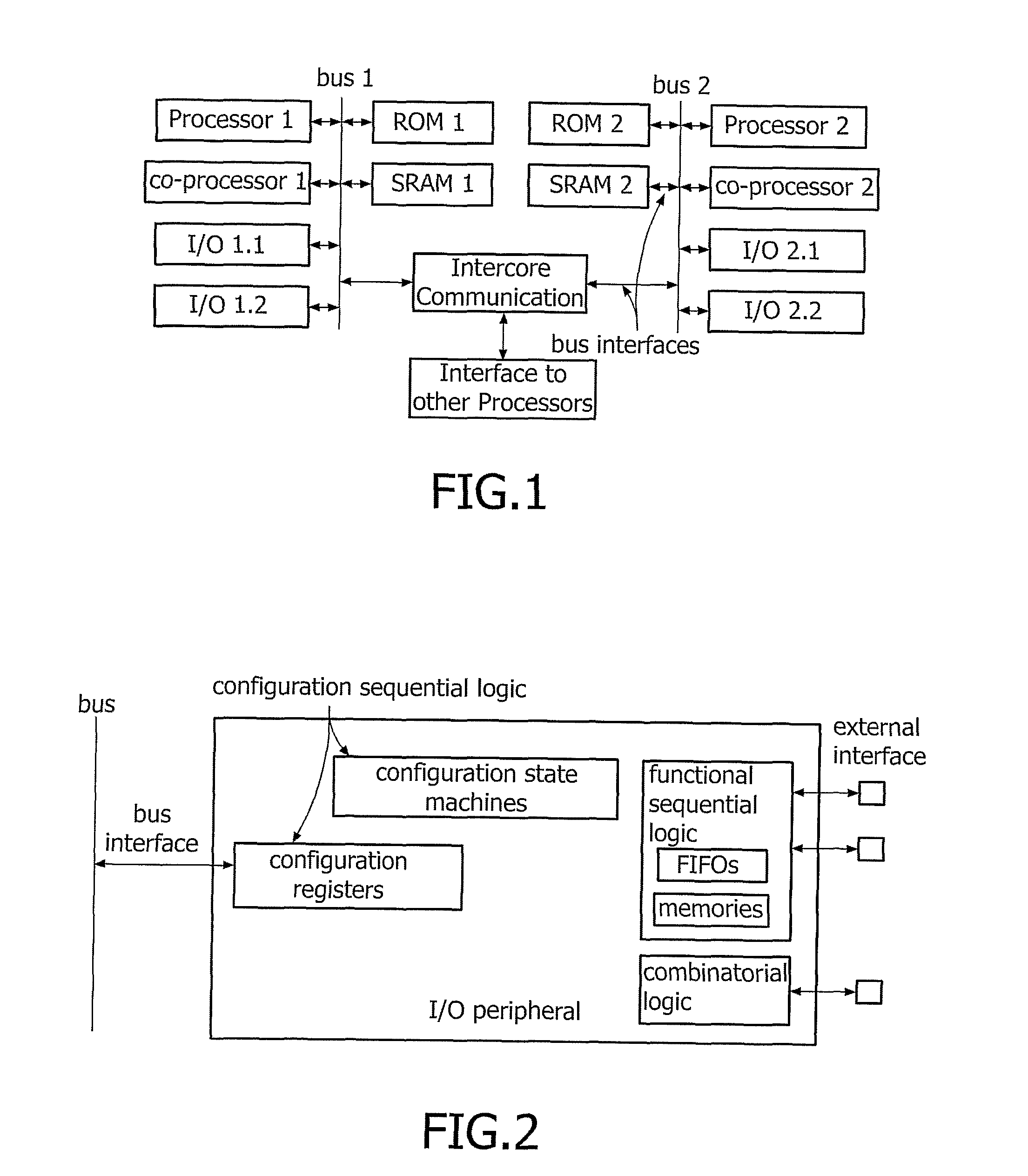

Embedded electronics building blocks for user-configurable monitor/control networks

InactiveUS7555658B2Not draining powerReduce in quantityTelemetry/telecontrol selection arrangementsVolume/mass flow measurementPower sensorControl system

Stand-alone modules or blocks for use in creating low-power sensor-based monitor / control systems. Each module performs a pre-defined function, and when included in a monitor / control network operates as a node on the network and automatically communicates with one or more connected nodes using a uni-directional packet-based protocol. One class of such predefined nodes communicates Boolean values, for example, with input sensor nodes detecting the presence or absence of environmental phenomena (e.g., motion, light, sound, water, button presses, etc.), intermediate nodes transforming those Boolean values using combinational or sequential logic, and output nodes converting the resulting Boolean values to environmental phenomena (e.g., beeping, light, electric relay activation, etc.) or to data for further processing by a computer. Another class of nodes communicates integer or number values.

Owner:RGT UNIV OF CALIFORNIA

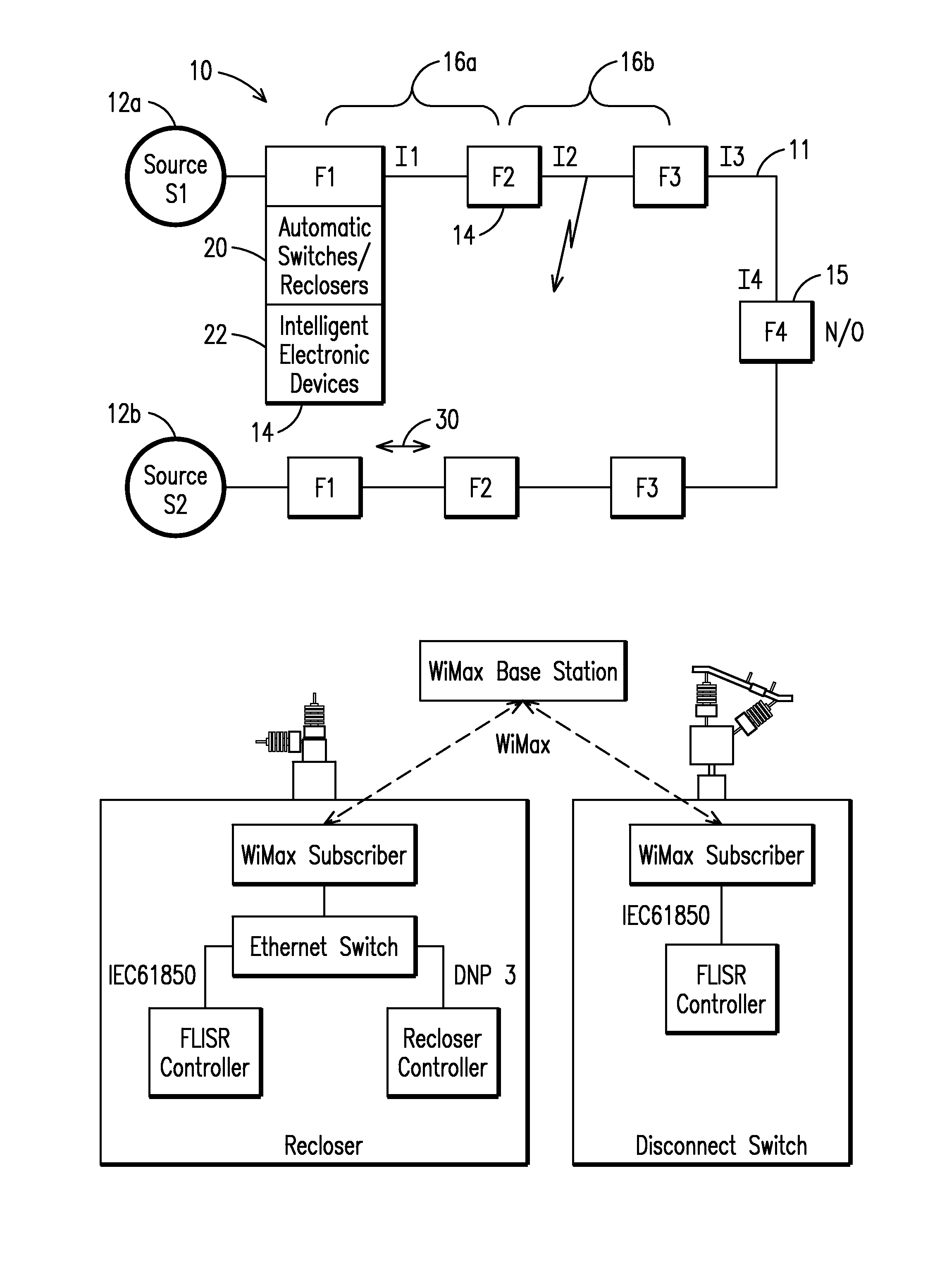

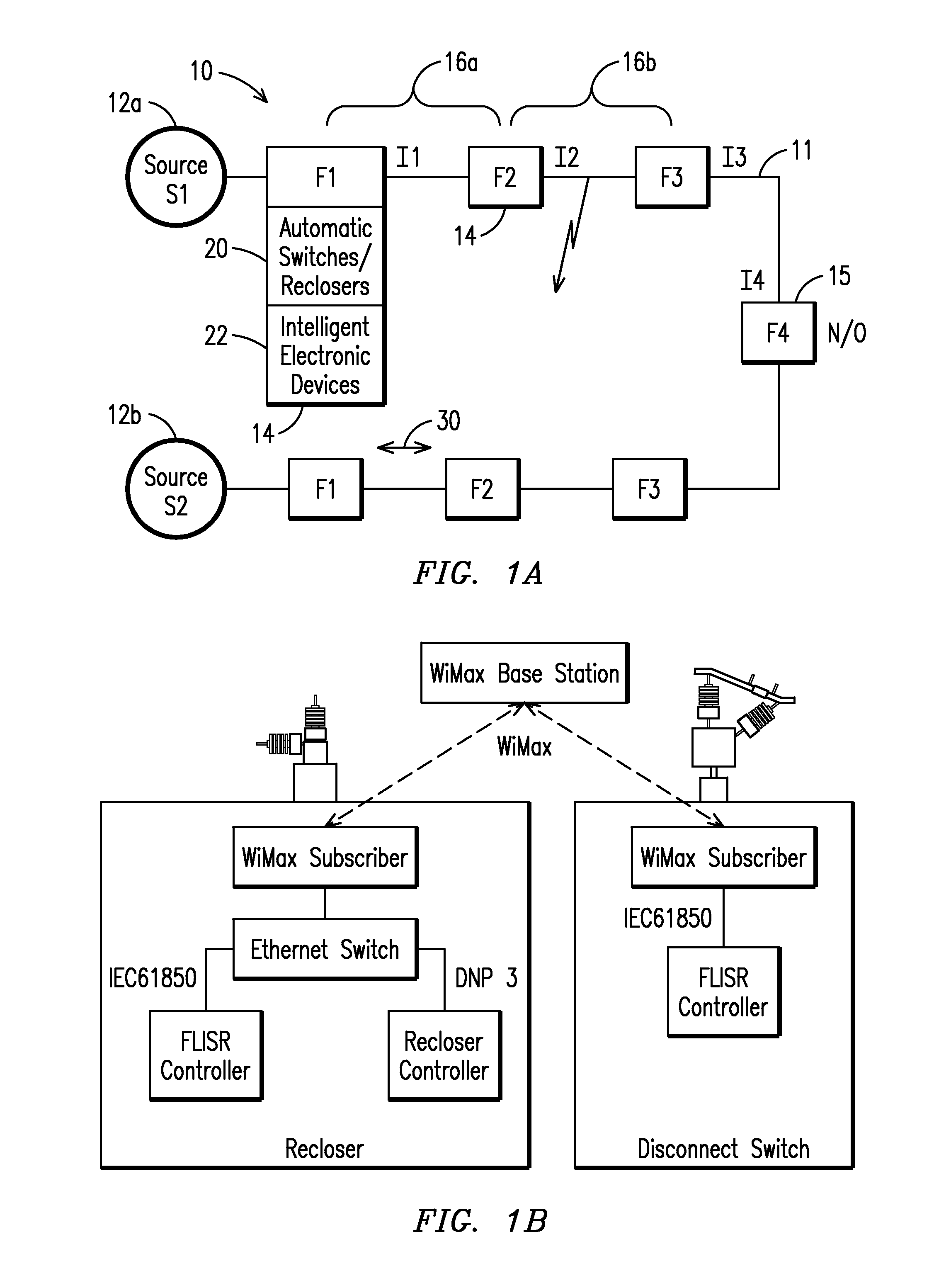

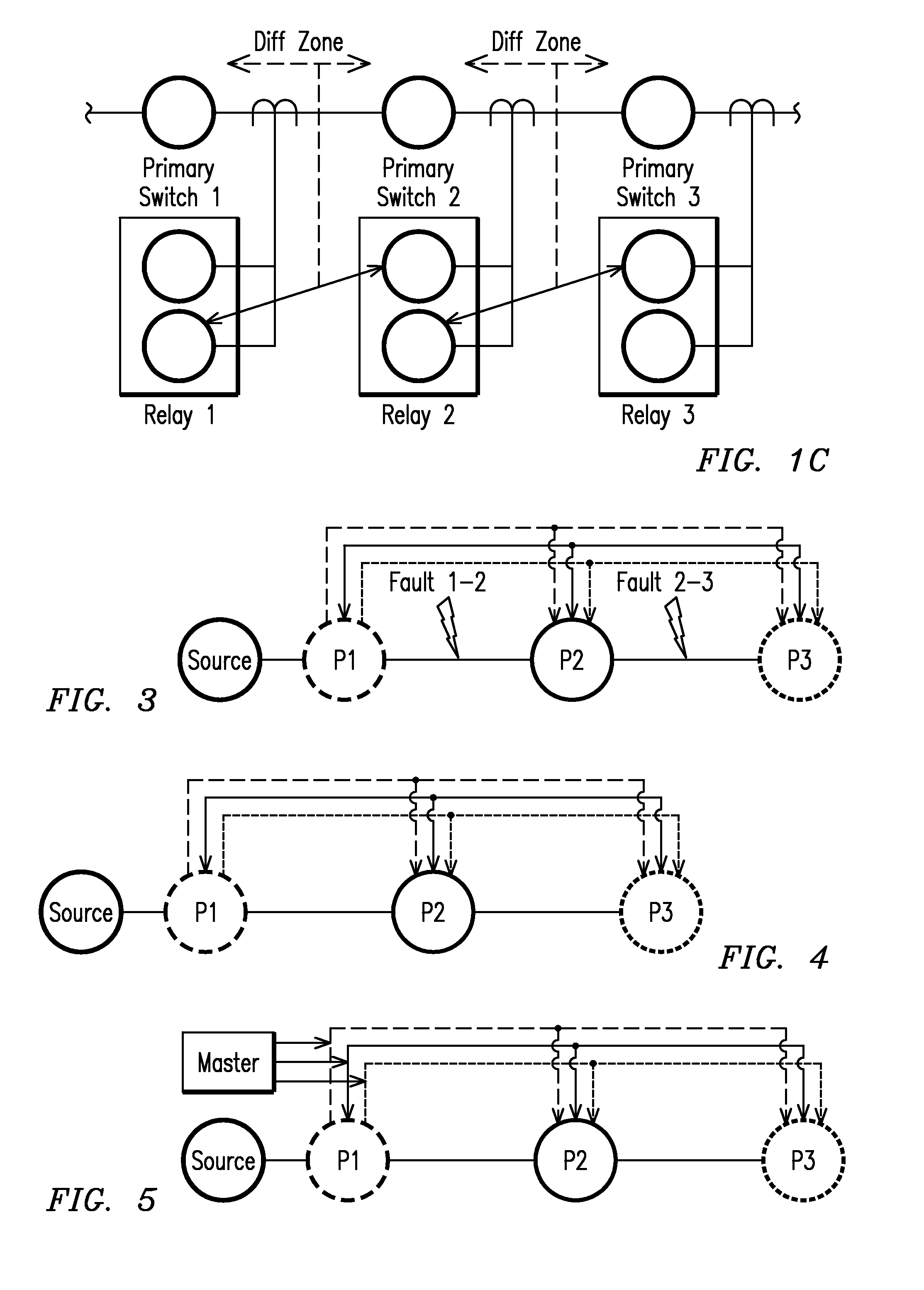

Method and system for programming and implementing automated fault isolation and restoration using sequential logic

ActiveUS20120265360A1Avoid excessive impactIncrease the number ofMechanical power/torque controlLevel controlCommunications systemDistribution power system

A method and system for programming and implementing automated fault isolation and restoration of high-speed fault detection of circuits in power distribution networks using sequential logic and peer-to-peer communication is provided. High-speed fault detection of circuits in power distribution networks uses protective relay devices (14) segmenting a distribution line (11) having Intelligent Electronic Devices (IED) (22) associated with switching devices (20) communicating peer-to-peer via a communication system (30) to provide fast and accurate fault location information in distribution systems with sequential logic.

Owner:SIEMENS IND INC

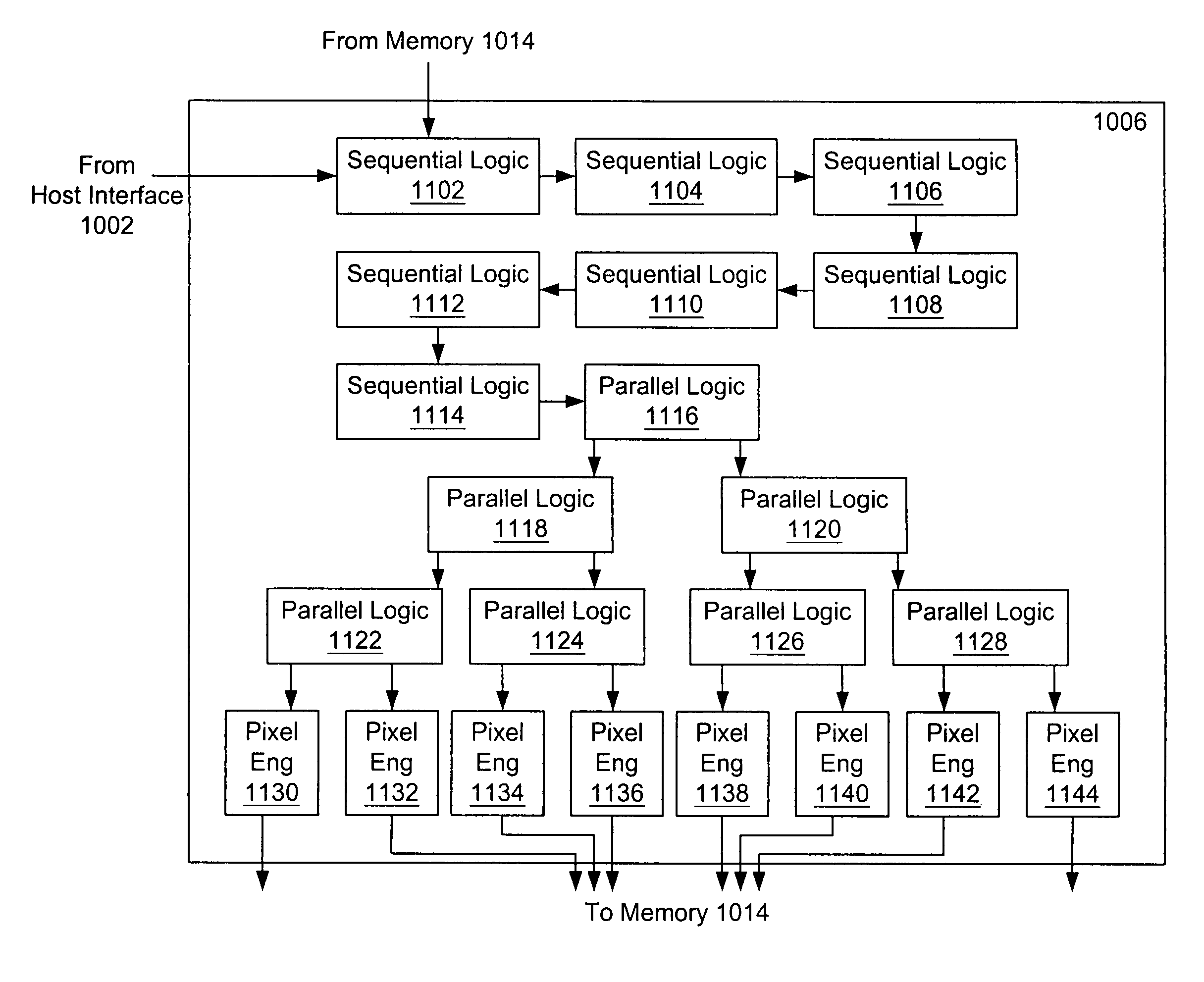

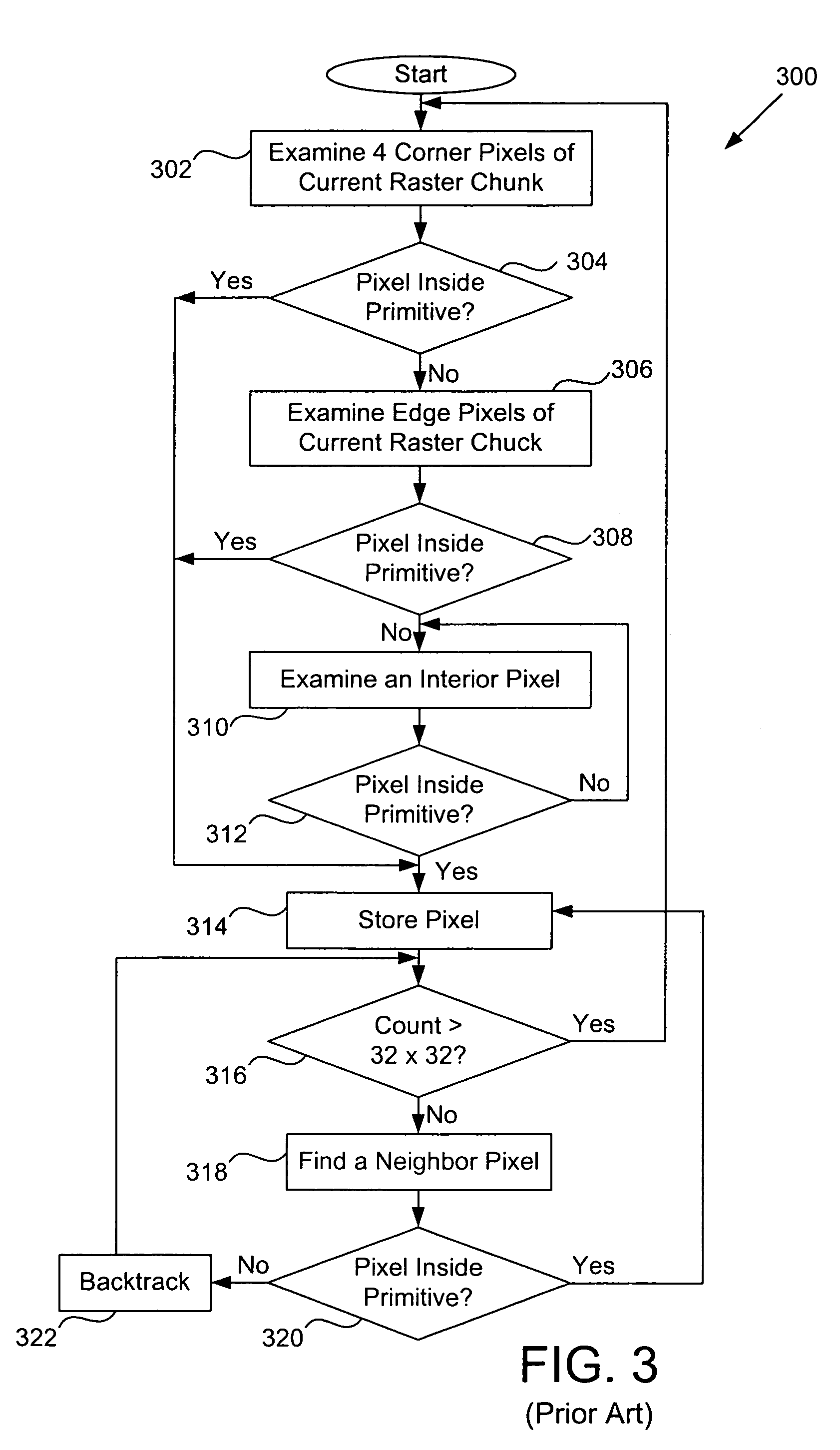

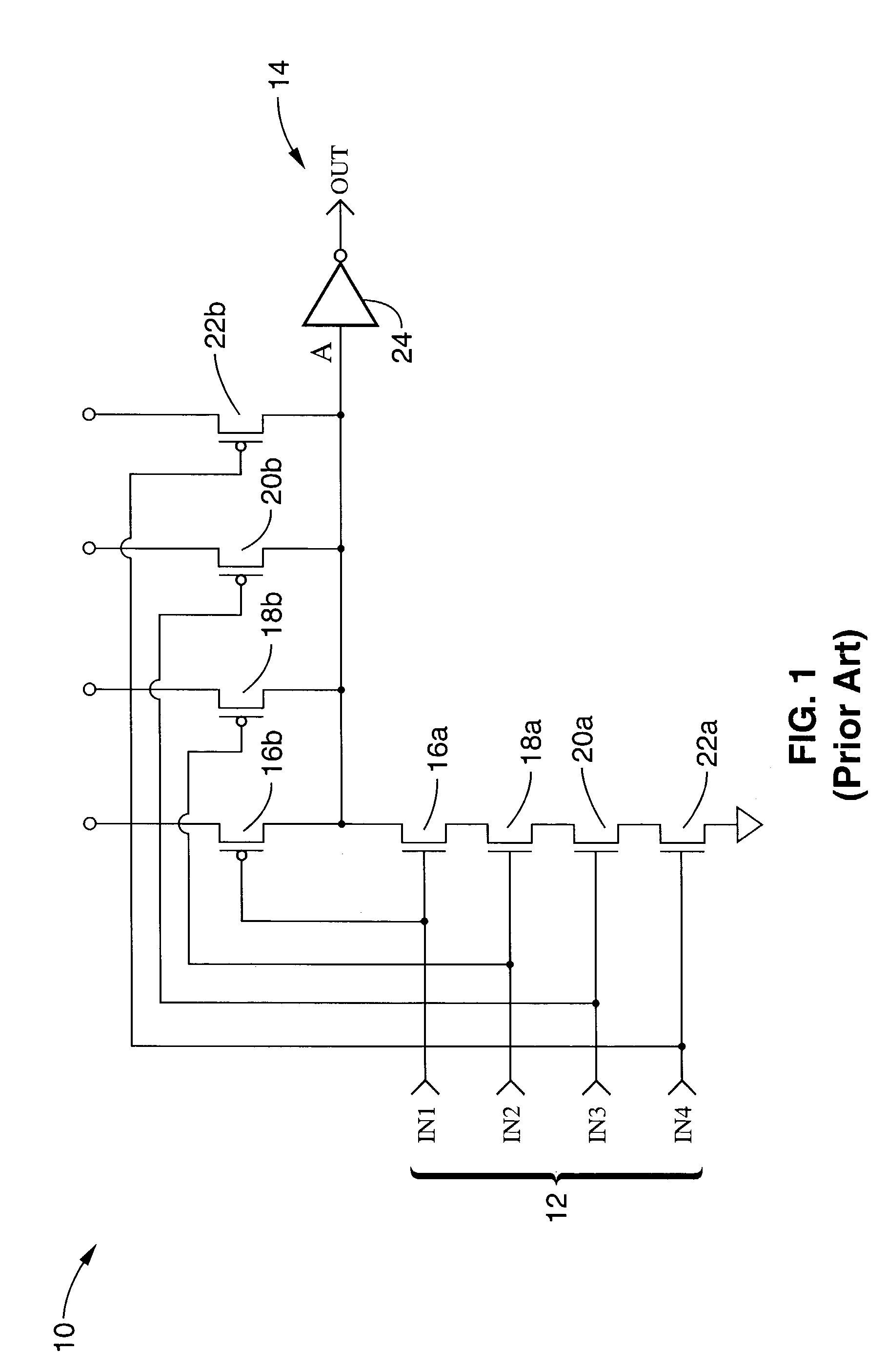

Parallel architecture for graphics primitive decomposition

InactiveUS7119809B1Efficient decompositionProcessor architectures/configurationFilling planer surface with attributesGraphicsDecomposition

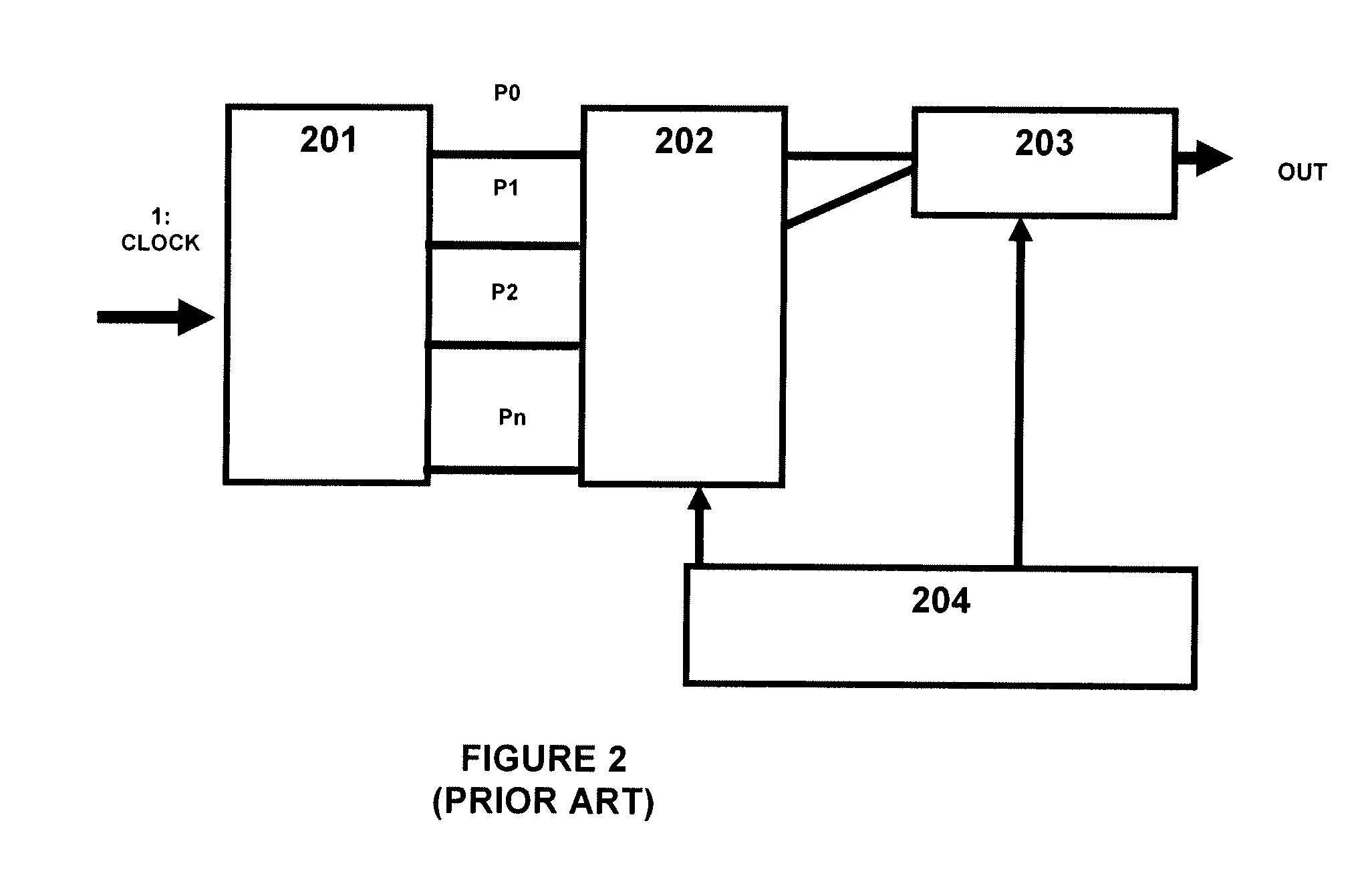

A parallel architecture for determining pixels inside a graphics primitive is provided. The architecture is a pipeline structure having a predetermined number of sequential logic circuits connected in series followed by a predetermined number of parallel logic circuits arranged in a pyramid structure. Each sequential logic circuit uses arithmetic edge functions corresponding to edges of a graphics primitive to determine whether a polygonal portion of a raster image is inside the graphics primitive. If the polygonal portion is at least partly inside the graphics primitive, the sequential logic circuit divides the polygonal portion into a predetermined number of subportions and computes descriptors (e.g., vertices and translated edge functions) for each subportion sequentially. Descriptors are then transferred sequentially to the next stage. Each parallel logic circuit performs the same functions as that of a sequential logic circuit except that a parallel logic circuit computes descriptors of the subportions in parallel and transfers them to the next stage in parallel.

Owner:S3 GRAPHICS

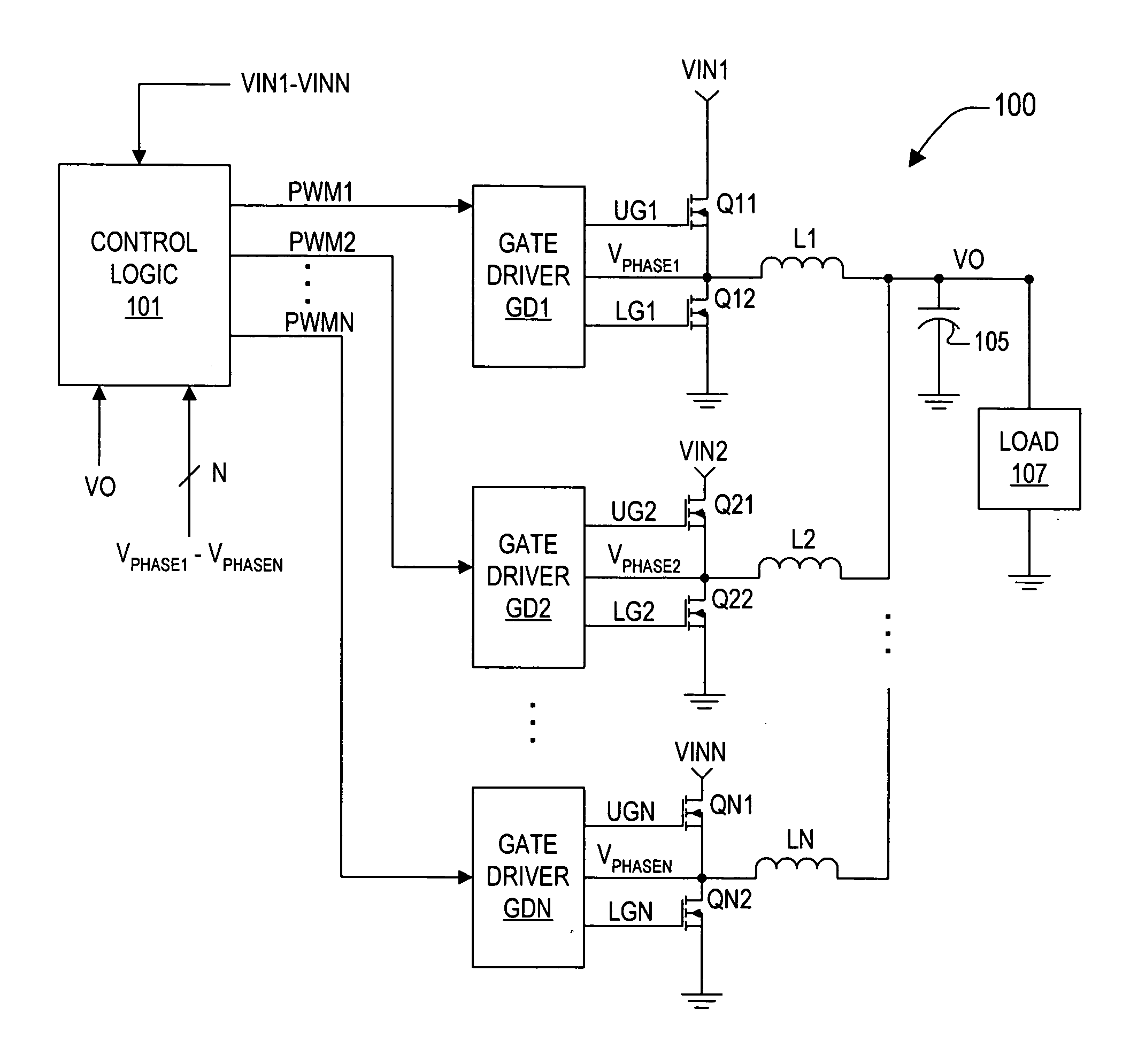

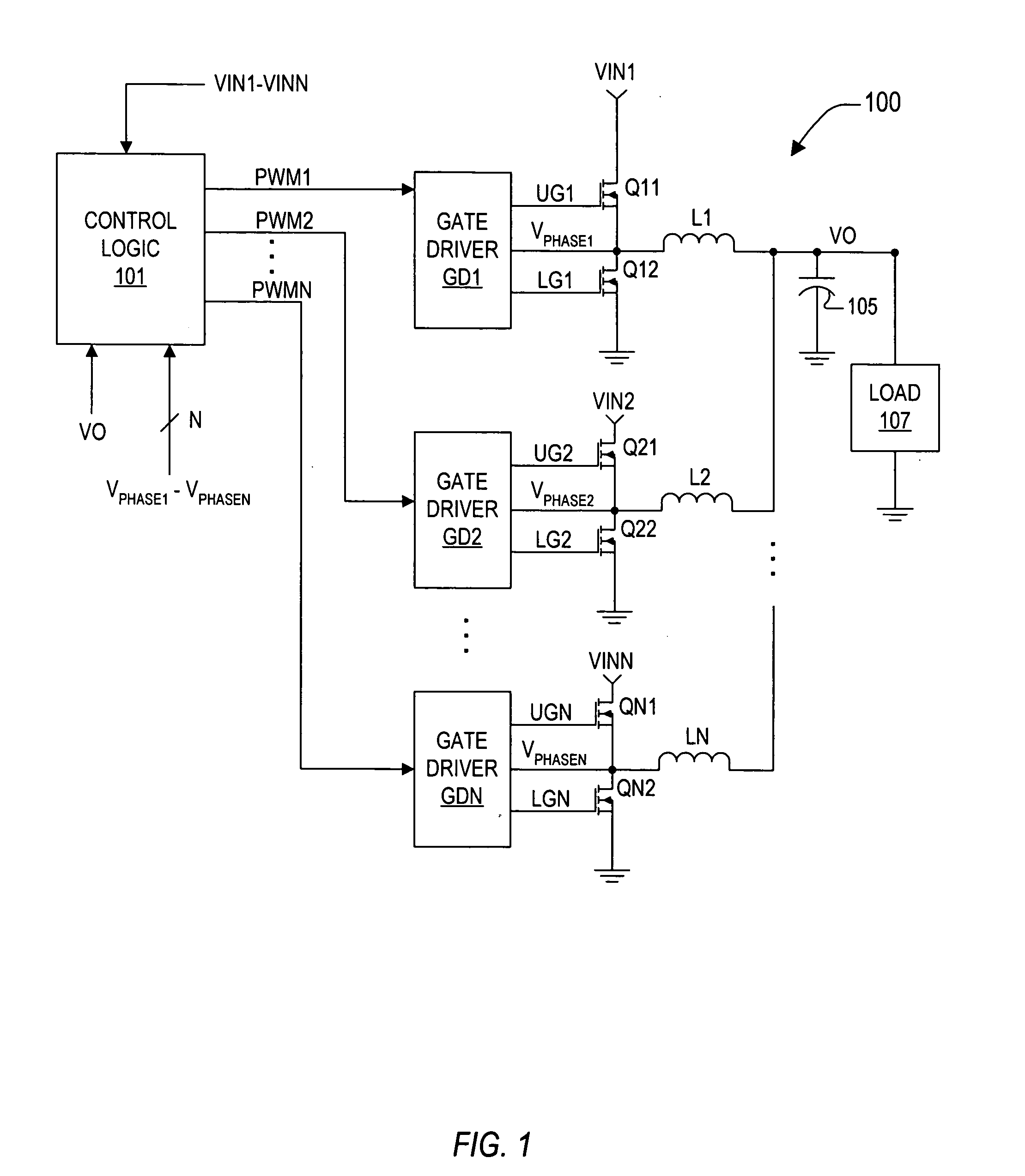

Synchronization of multiphase synthetic ripple voltage regulator

InactiveUS20050001597A1Dc-dc conversionDc source parallel operationVoltage generatorAudio power amplifier

A multiphase synthetic ripple voltage generator for a multiphase DC-DC regulator including a master clock circuit that generates a master clock signal, sequence logic and a ripple regulator for each phase. The DC-DC regulator includes multiple switching circuits, each responsive to a corresponding PWM signal to switch input voltages via a phase node through an output inductor to develop an output voltage. The sequence logic sets each PWM signal in sequential order based on the master clock signal. Each ripple generator includes a transconductance amplifier, a ripple capacitor and a comparator. The transconductance amplifier has an input coupled to a corresponding output inductor and an output coupled to a corresponding ripple capacitor. The comparator has a first input coupled to the ripple capacitor, a second input receiving an error voltage, and an output coupled to the sequence logic for resetting a corresponding PWM signal.

Owner:INTERSIL INC

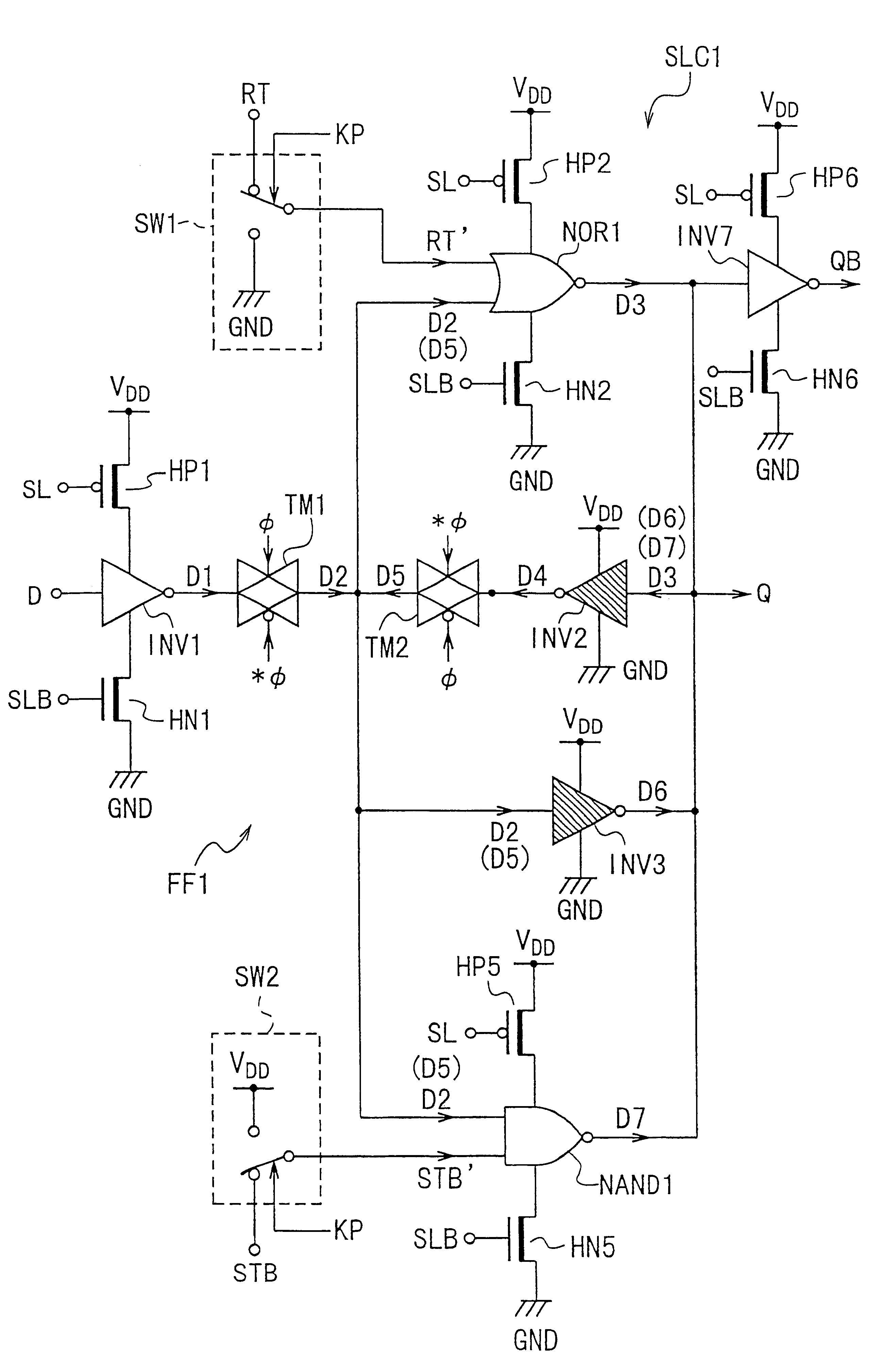

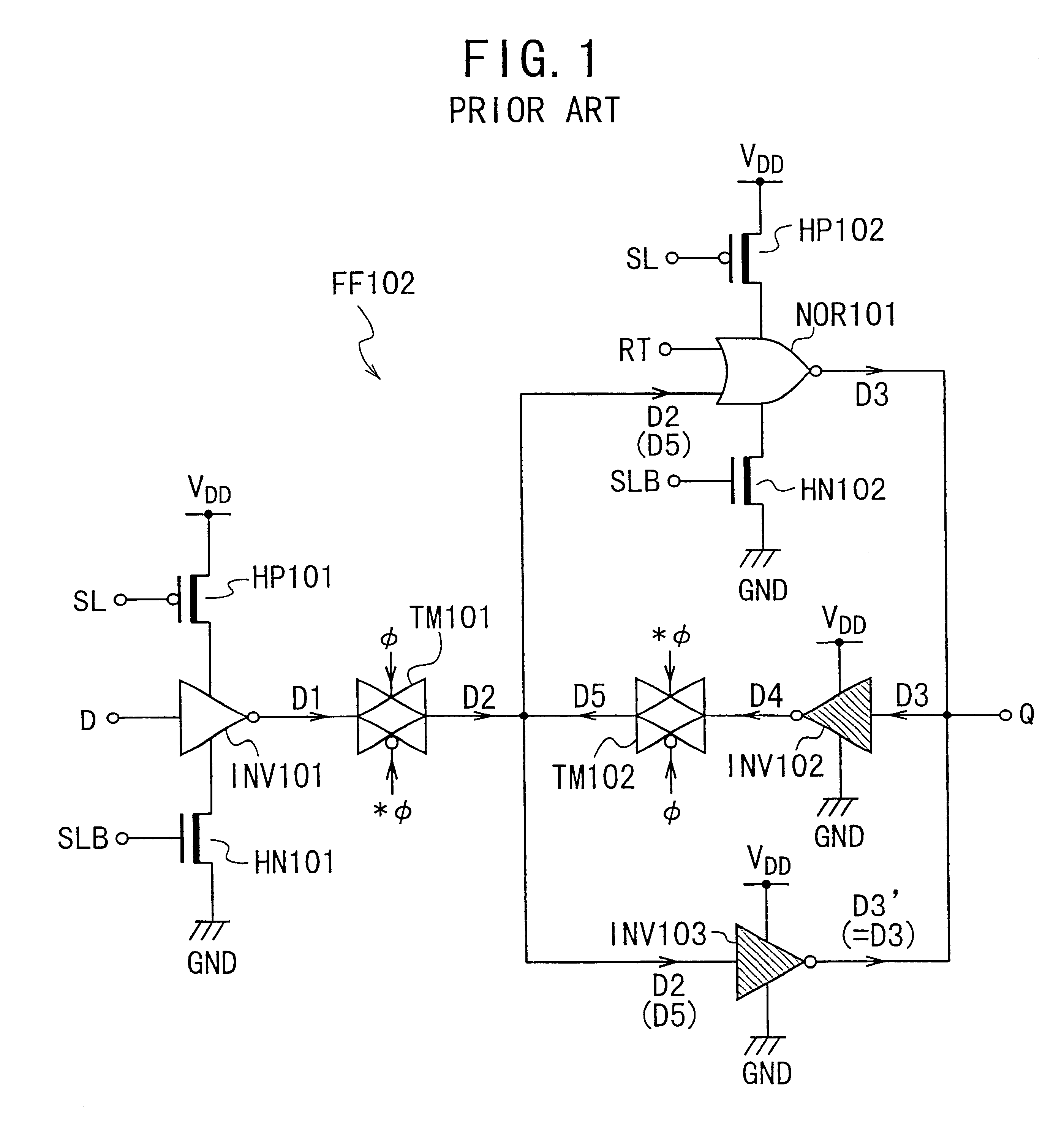

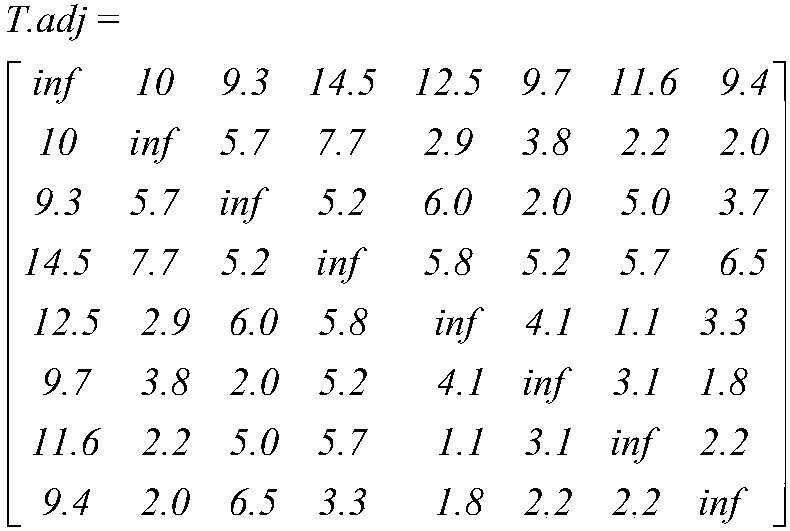

Sequential logic circuit with active and sleep modes

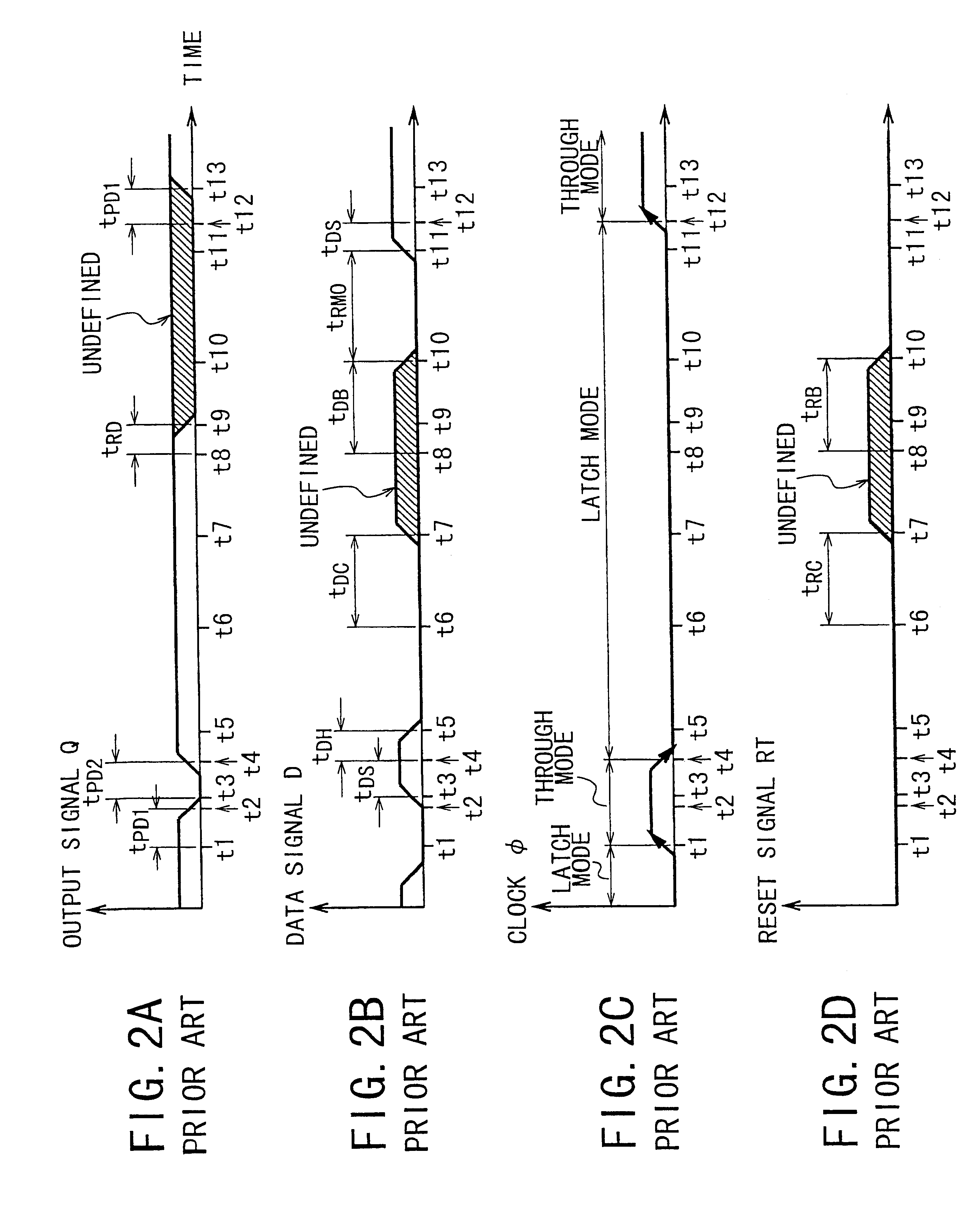

InactiveUS6310491B1Logic circuits characterised by logic functionData resettingLogic stateSequential logic

A sequential logic circuit having active and sleep modes prevents stored information from being lost immediately after the transition from a sleep mode to an active mode. This sequential logic circuit includes a latch circuit having an input terminal to which an input signal is applied, an output terminal from which and output signal is derived, and a set and / or reset terminal to which a set and / or reset signal is applied. The latch circuit has an active mode where a latch function is operable and a sleep mode where the latch function is inoperable, one of which is alternatively selected. The output signal is set or reset to have a specific logic state by the set or reset signal having a specific logic level applied to the set or reset terminal in the active mode. The sequential logic circuit further includes circuitry for preventing the set or reset signal from being applied to the set or reset terminal in the sleep mode, thereby avoiding loss of information or data latched in the latch circuit prior to transition to the sleep mode from the active mode. Thus, the information-latch operation in both of the modes is ensured.

Owner:NEC ELECTRONICS CORP

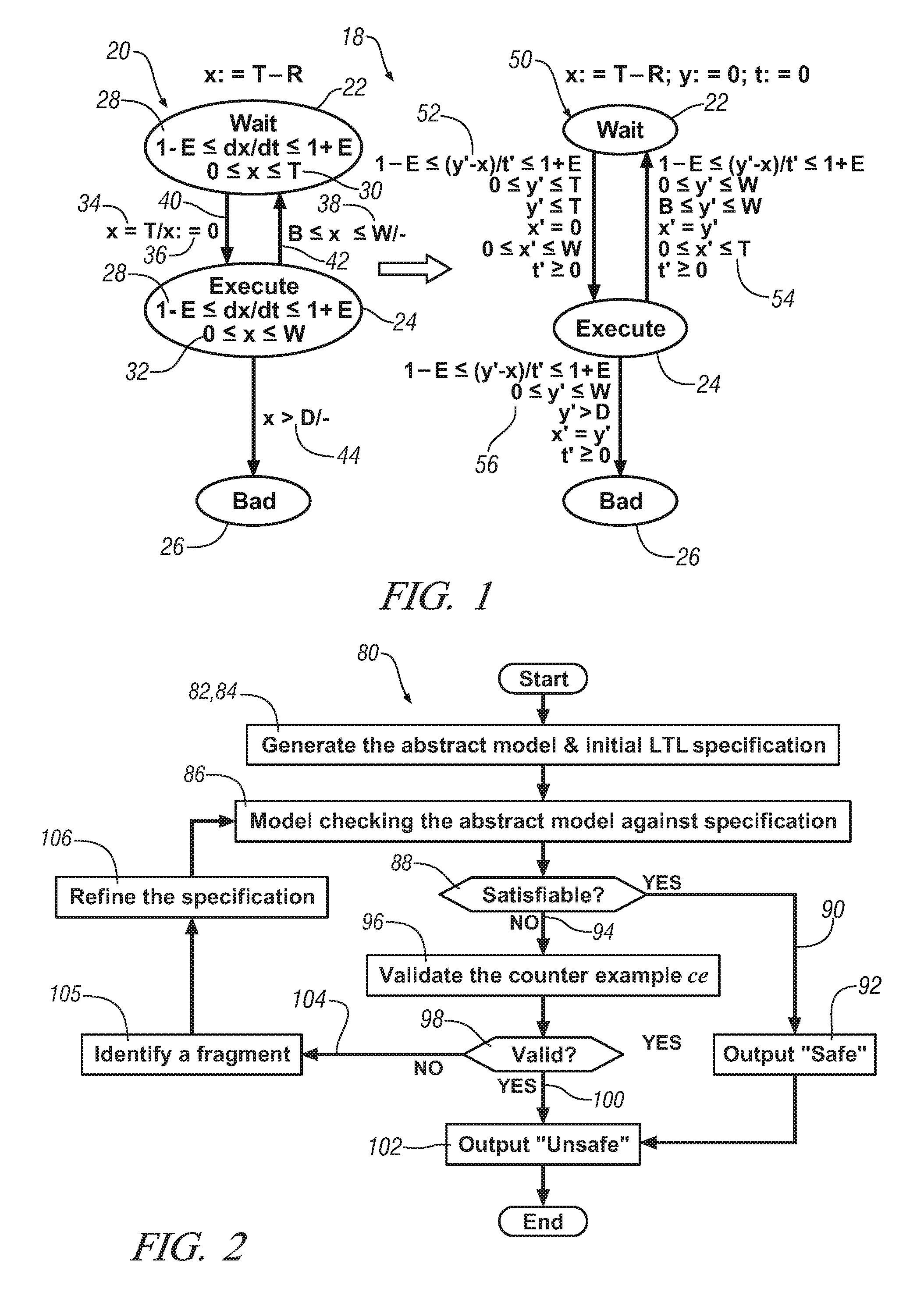

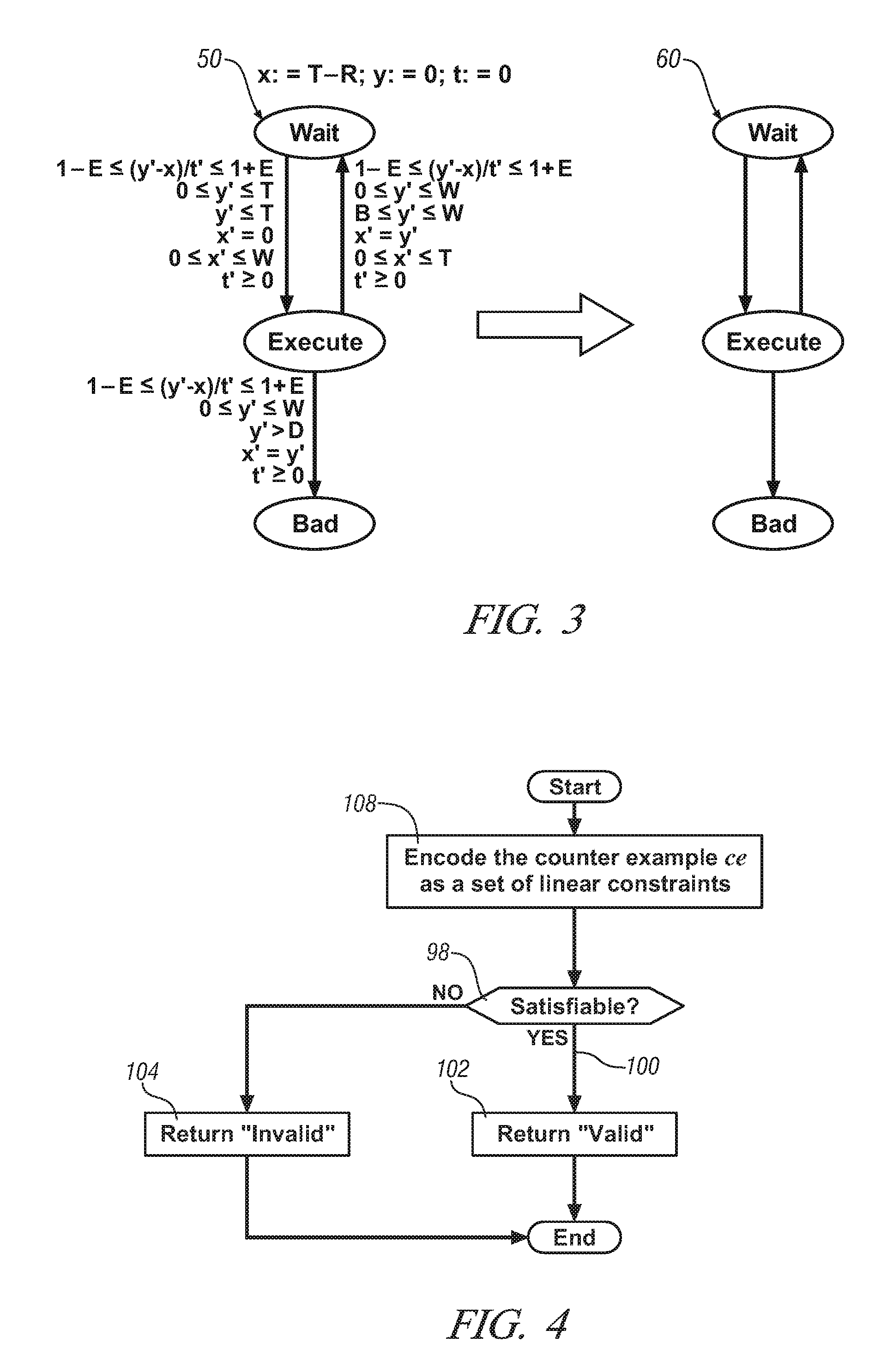

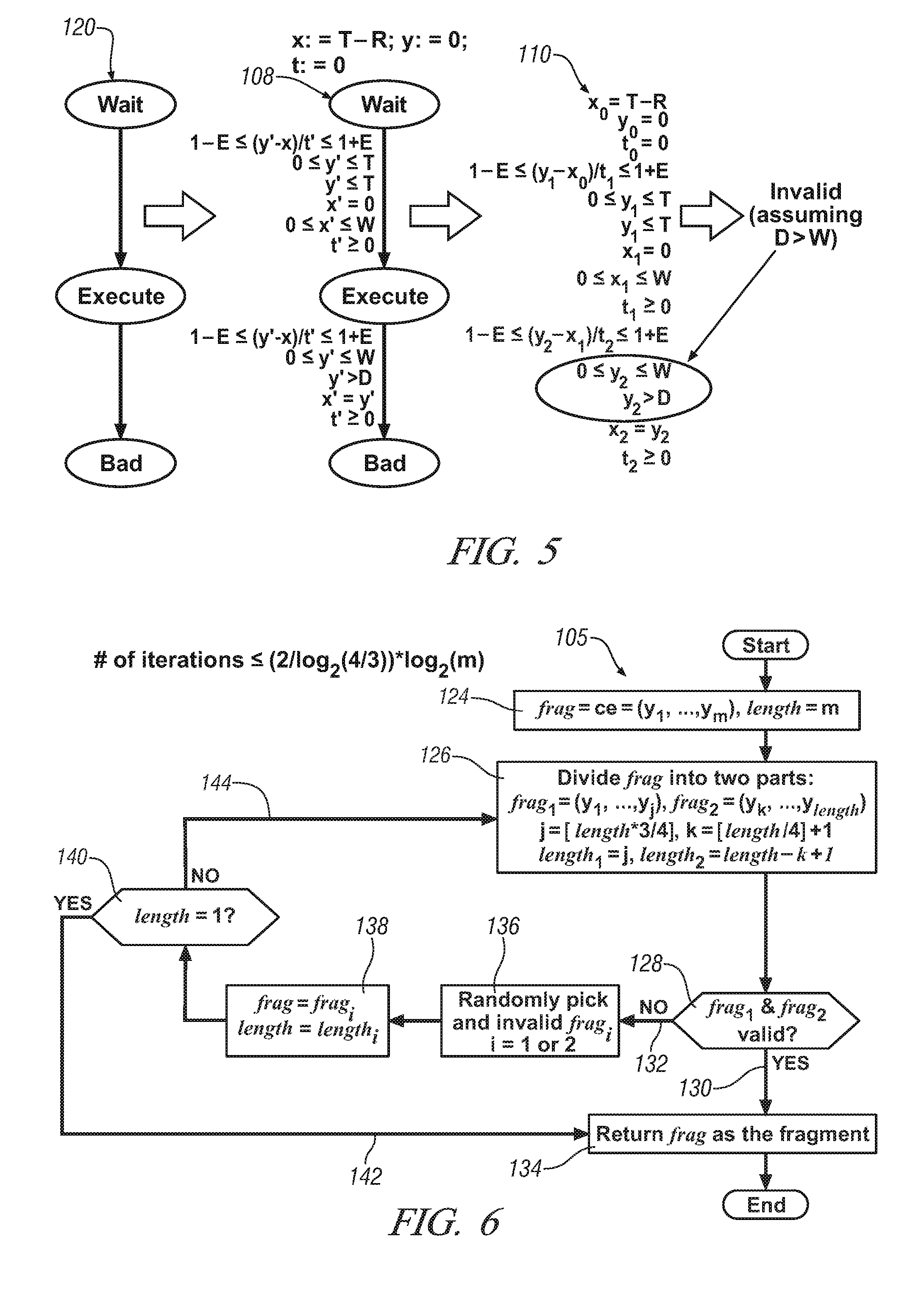

Verification of Linear Hybrid Automaton

The present invention provides a method for verification of linear hybrid automaton by generation an initial abstract model based on an original Linear-Time Temporal Logic (LTL) specification, validating a counterexample using an approach of linear constraints, identifying a fragment in the counterexample by iteratively applying an approach of linear constraints satisfaction in a limited number of times, and refining the original LTL specification based on the fragment derived.

Owner:GM GLOBAL TECH OPERATIONS LLC

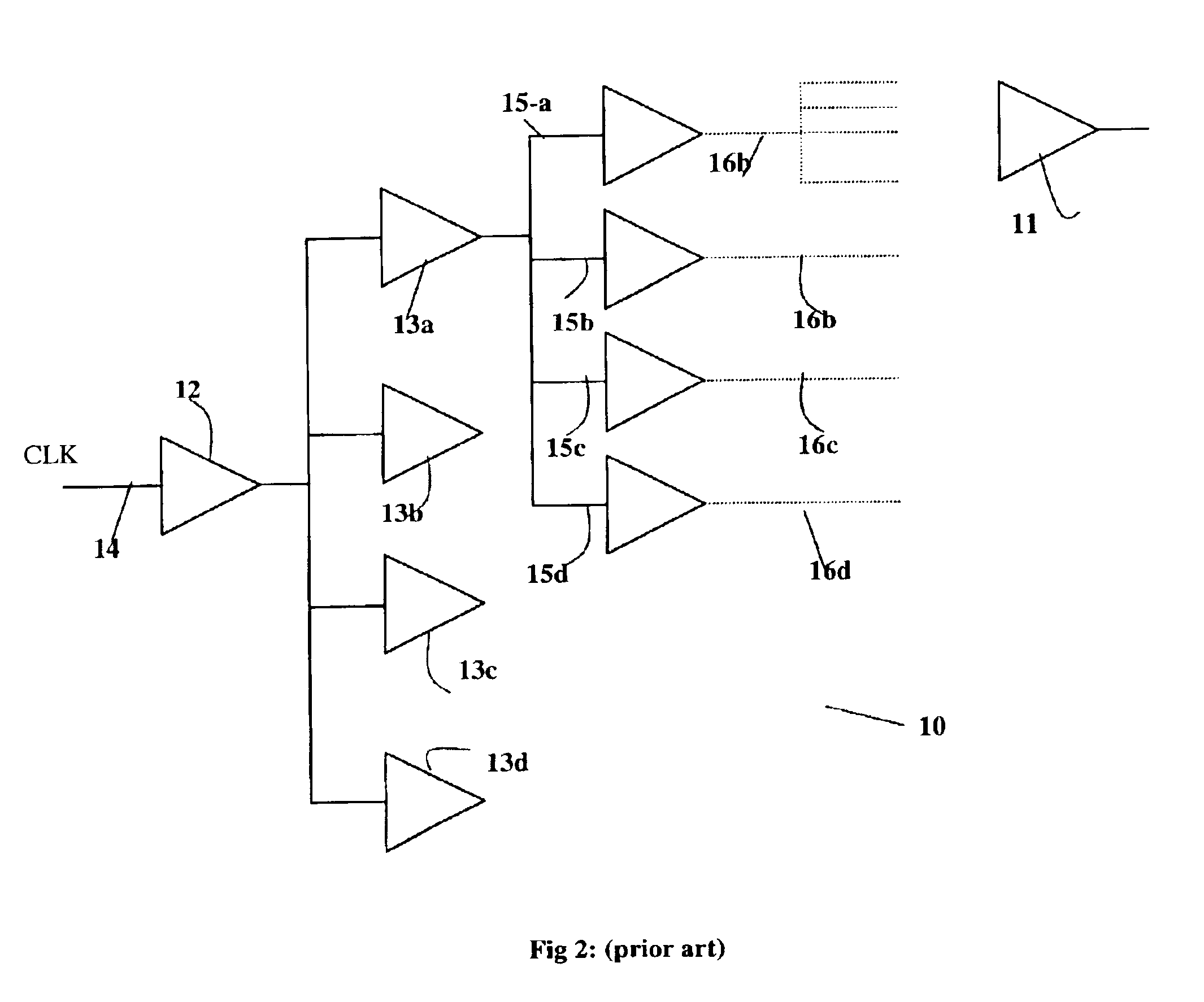

Low power clock distribution scheme

InactiveUS6879185B2Reduce power consumptionPulse automatic controlSolid-state devicesIdentification deviceSequential logic

An electronic circuit containing one or more digital synchronous sequential logic blocks at least one of which is either selected or deselected during operation. The electronic circuit includes an improved clock distribution scheme that reduces power consumption, comprising identifying means for determining the select / deselect state of each said deselectable synchronous sequential logic block, coupled to disabling means for disabling the clock input to each deselected synchronous sequential logic block.

Owner:MINERAL LASSEN

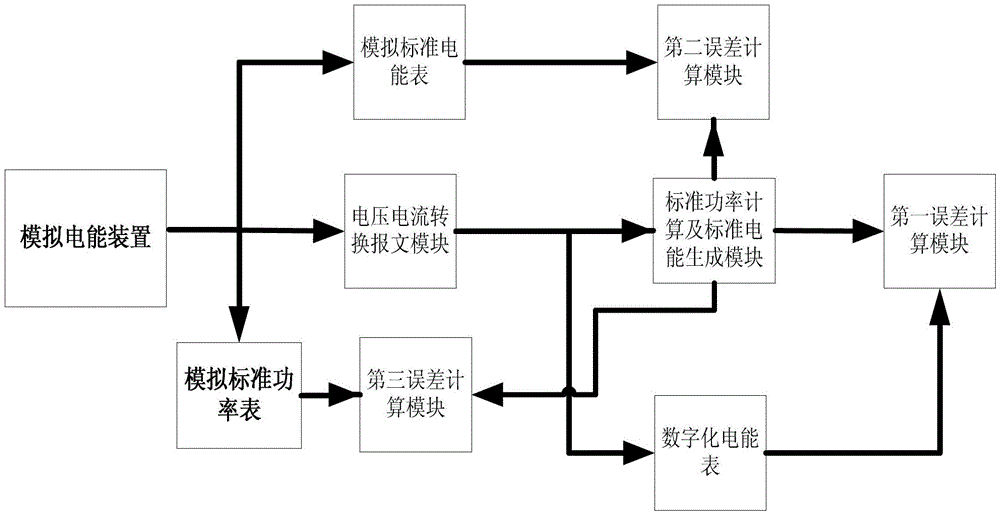

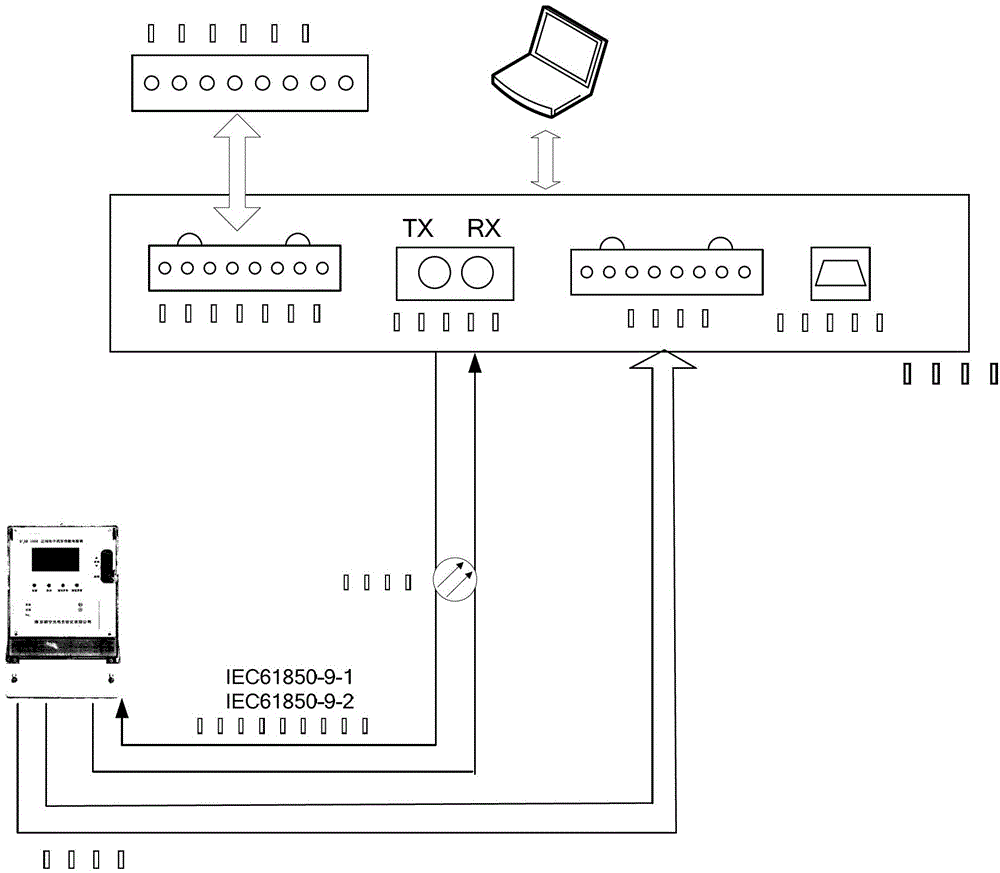

Digital electric energy meter quantity value tracing system based on analog quantity detection and digital electric energy meter quantity value tracing method based analog quantity detection

ActiveCN103336264AOvercome the technical problem that digital quantities are not easily traceableElectrical measurementsElectricitySimulation based

The invention relates to a complete digital electric energy meter quantity value tracing system based on analog quantity detection and a digital electric energy meter quantity value tracing method based the analog quantity detection. The digital electric energy meter quantity value tracing system based on the analog quantity detection includes an analog electric energy device, an analog standard electric energy meter, an analog standard power meter, a voltage and current conversion message module, a standard power calculation and standard electric energy generation module, and three error calculation modules; the voltage and current conversion message module samples voltage and current parameters of the analog electric energy device, and transmits an IEC61850 message under sequential logic control; and the standard power calculation and standard electric energy generation module samples the content of the IEC61850 message, computes the power of the IEC61850 message real time, and generates electric energy, and performs display and pulse output. With the digital electric energy meter quantity value tracing system based on the analog quantity detection of the invention adopted, quantity values of digital electric energy meters can be traced back to analog quantity measurement standards through an improved method, and the technical problem of difficult tracing of the digital quantity of the digital electric energy meters can be solved, and an improved solution is provided for the tracing of the quantity values of the digital electric energy meters.

Owner:STATE GRID CORP OF CHINA +2

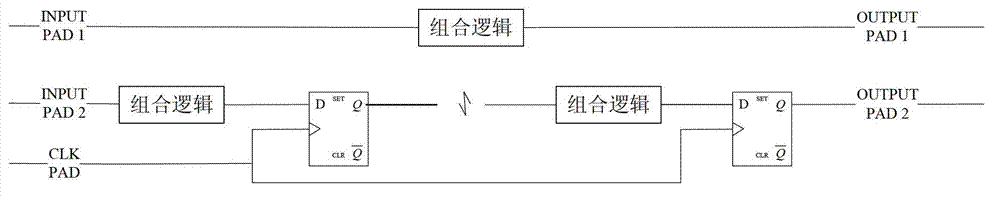

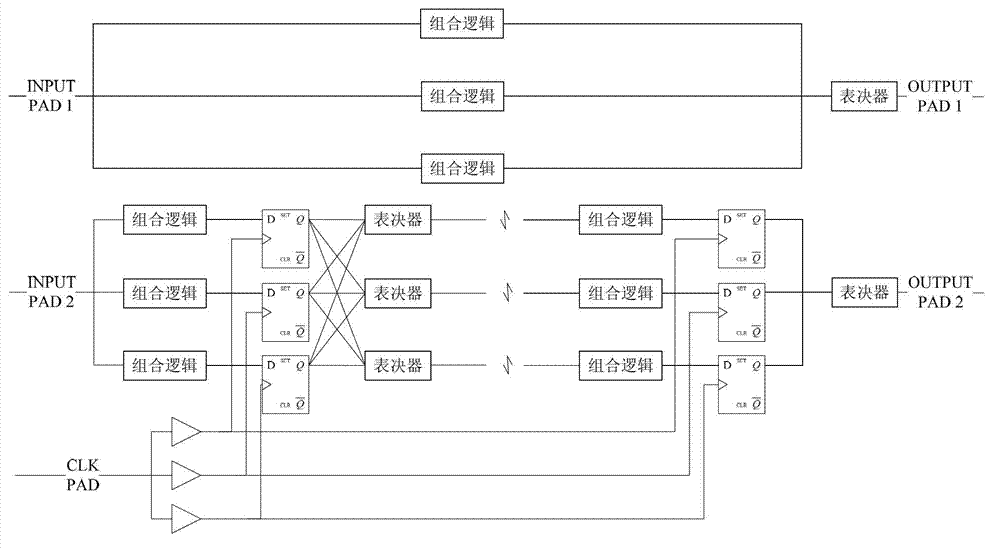

Radiation-proof triple-modular redundancy circuit structure

InactiveCN102820879AImprove design efficiencyImprove radiation resistanceReliability increasing modificationsSequential logicTriple modular redundancy

The invention provides a radiation-proof triple-modular redundancy circuit structure, which is characterized in that a combined logic circuit and a time sequence logic circuit of the circuit are tripled, and a voter is added behind the three time sequence logic circuits, so that each section of route of the circuit is tripled. In addition, a voter is added respectively in each section of route, so that single-particle fault is eliminated in each section of route through a structure consisting of a redundancy route and the voter. The radiation-proof triple-modular redundancy circuit structure has the advantages that a redundancy module is used for shielding the influence of the fault on the entire circuit. The triple-modular redundancy circuit structure can be generated through relevant scripts, so that the design efficiency of the circuit is improved, and meanwhile, the radiation-proof performance of the entire circuit is greatly improved.

Owner:58TH RES INST OF CETC

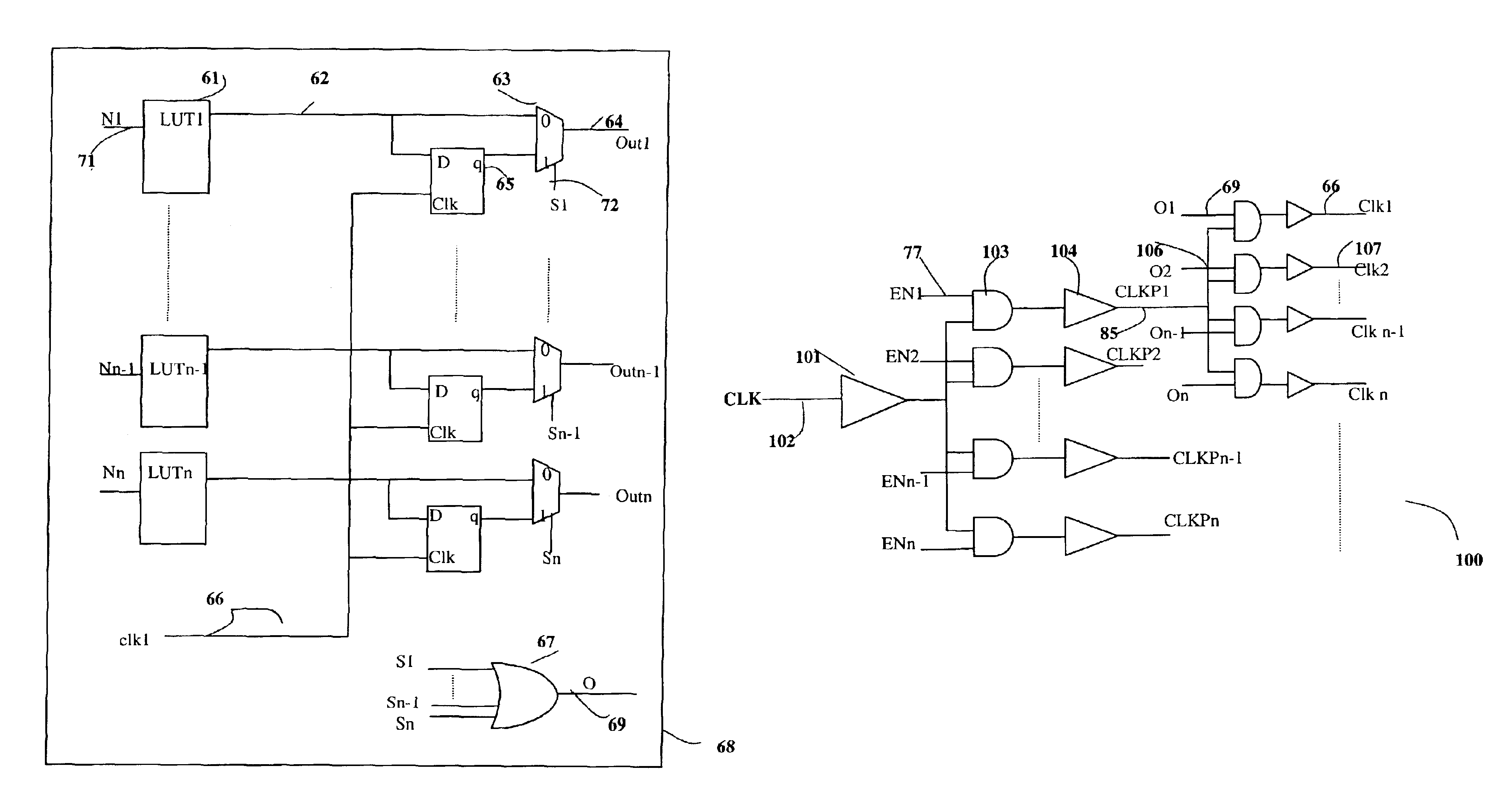

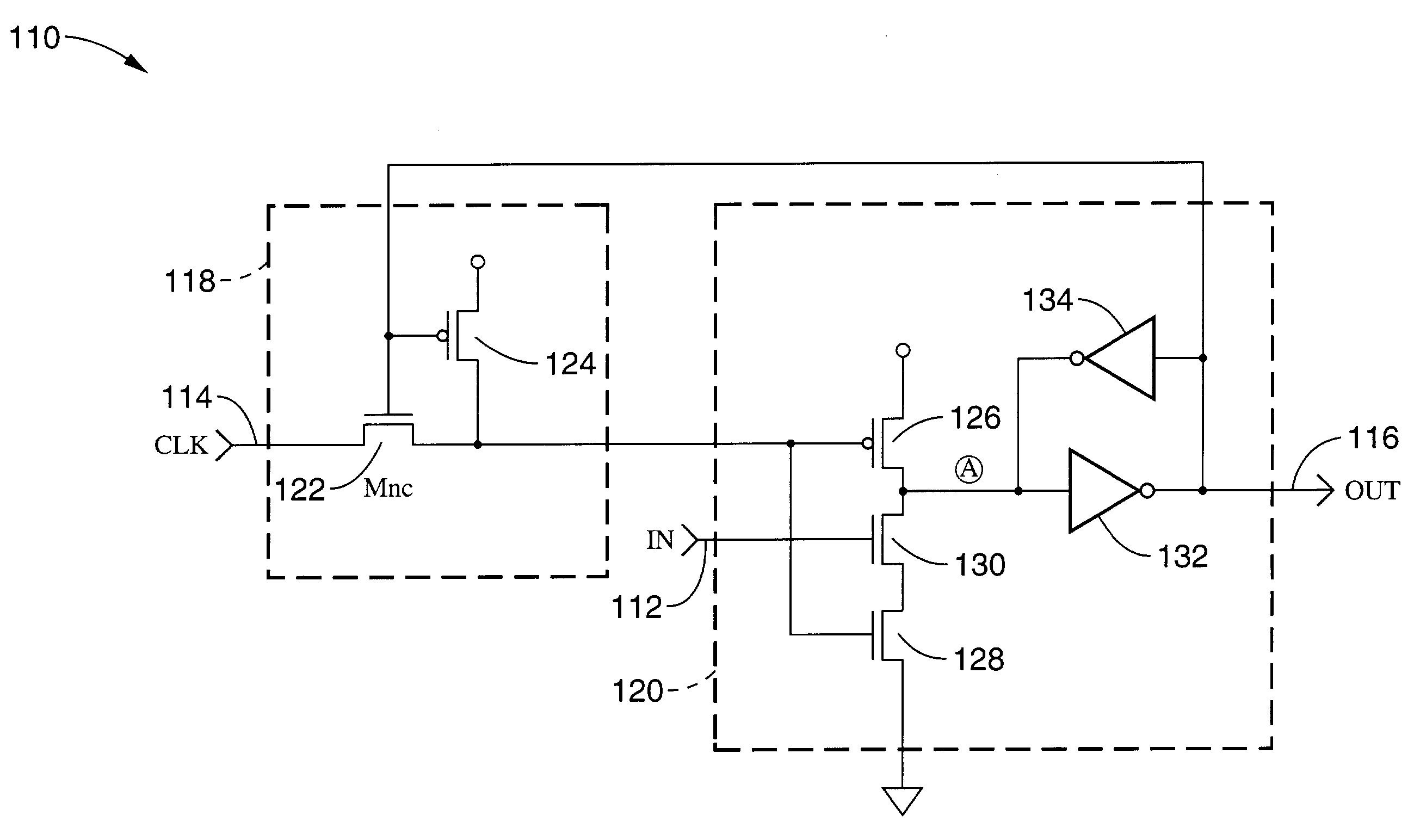

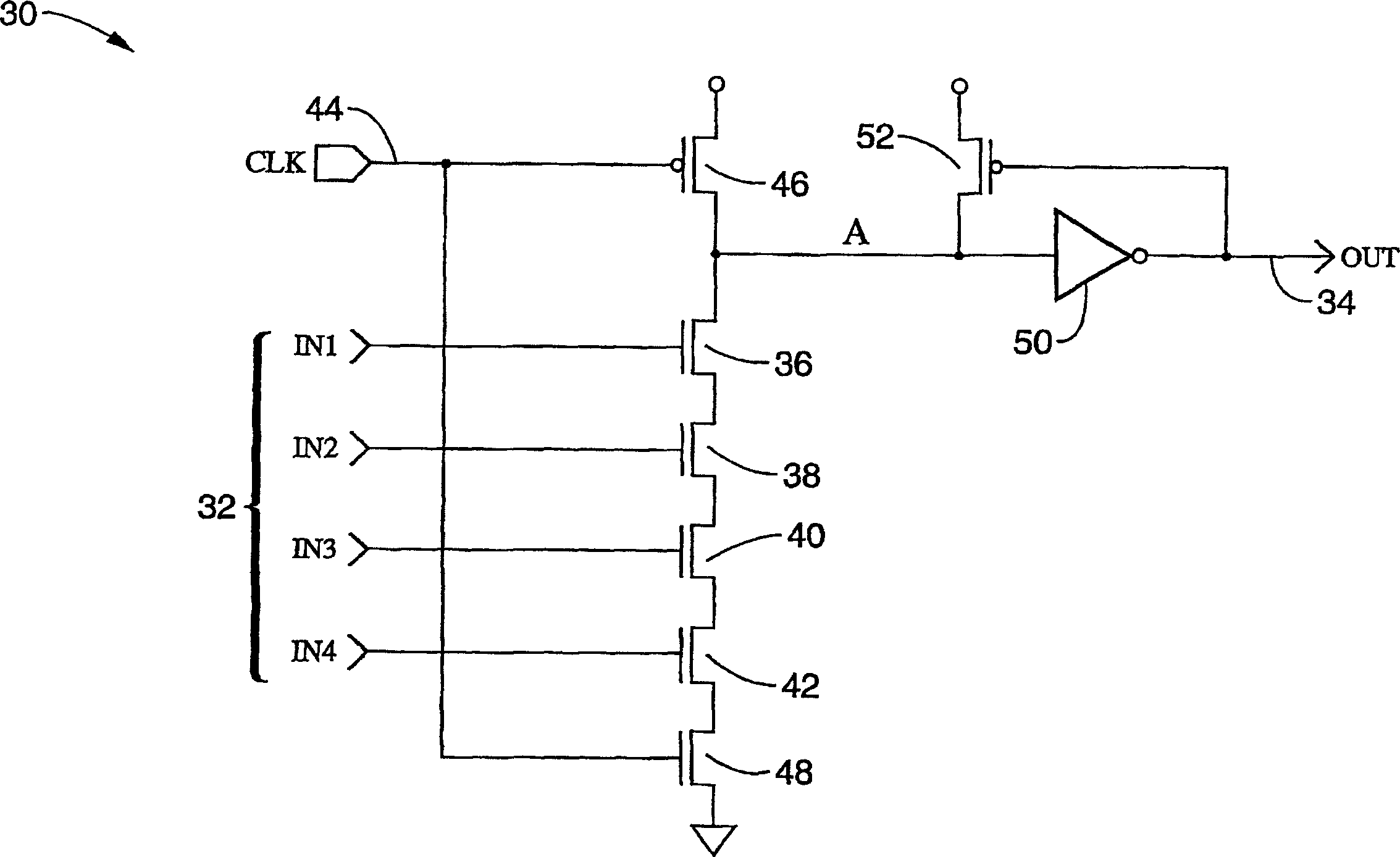

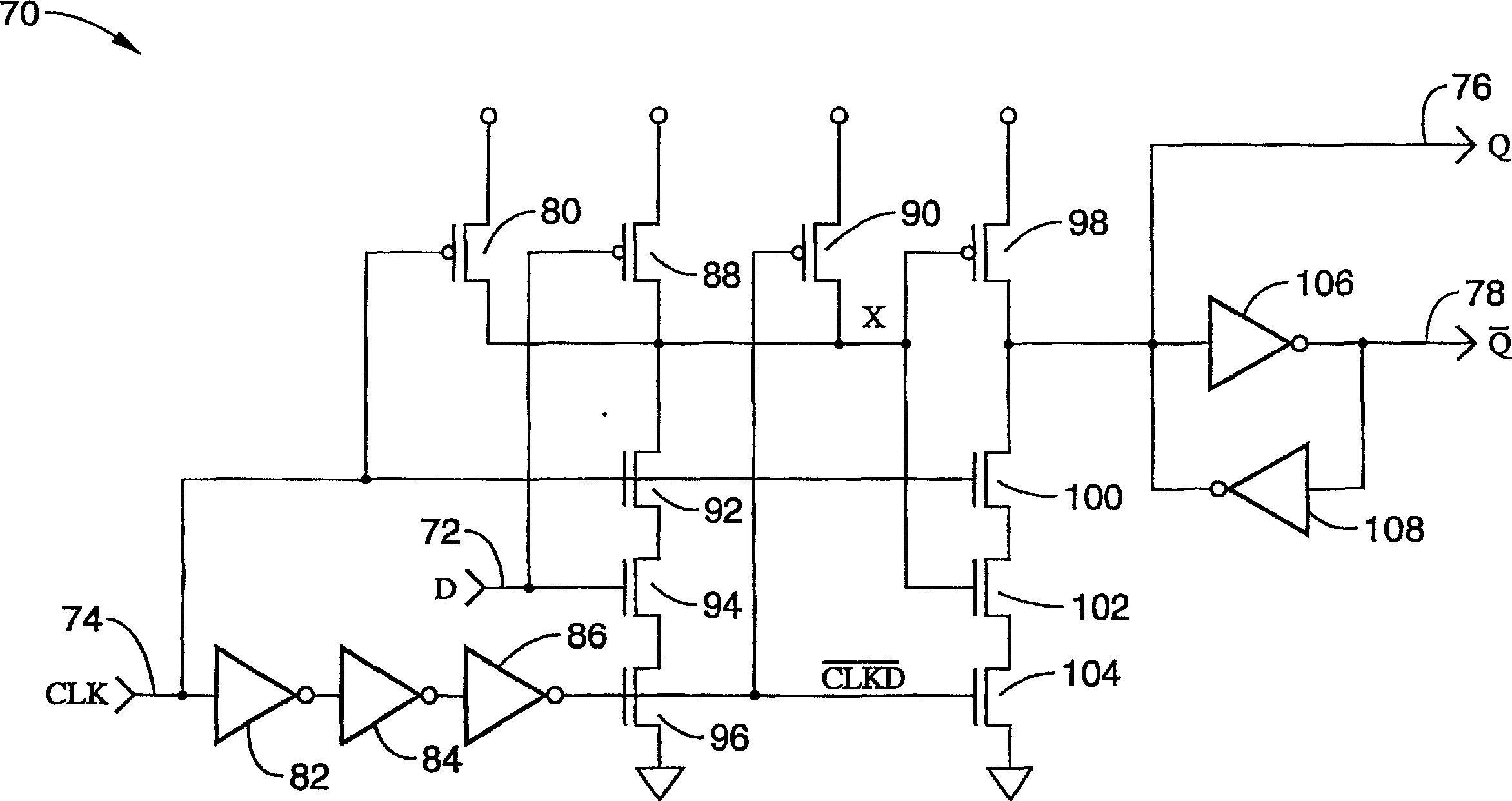

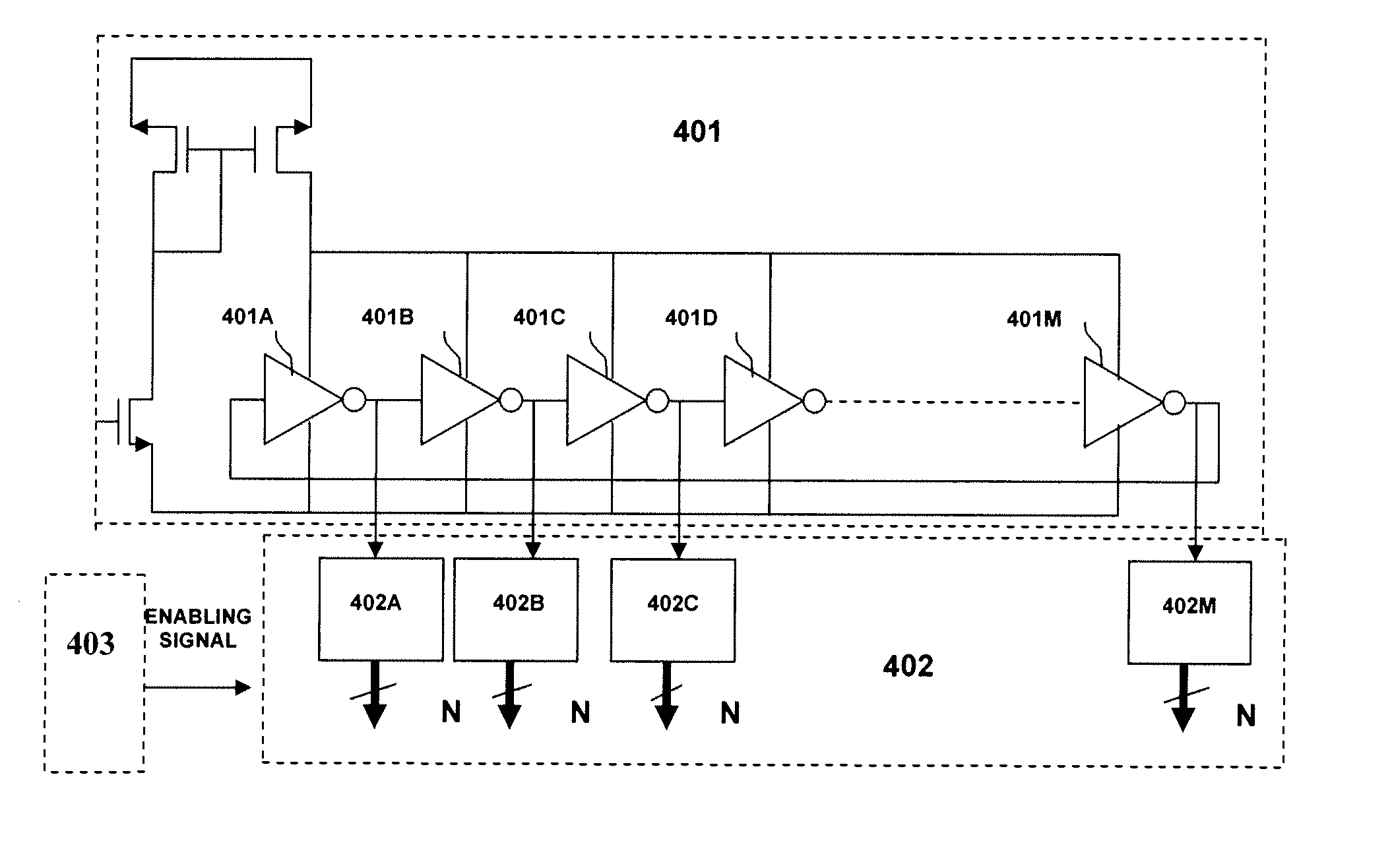

Event driven dynamic logic for reducing power consumption

InactiveUS6977528B2Reduce power consumptionReduce capacitive loadReliability increasing modificationsPower reduction by control/clock signalCapacitanceState variation

Methods and circuits are described for reducing power consumption within digital logic circuits by blocking the passage of clock signal transitions to the logic circuits when the clock signal would not produce a desired change of state within the logic circuit, such as at inputs, intermediary nodes, outputs, or combinations. By way of example, the incoming clock is blocked if a given set of logic inputs will not result in an output change of state if a clock signal transition were to be received. By way of further example, the incoming clock is blocked in a data flip-flop if the input signal matches the output signal, such that receipt of a clock transition would not produce a desired change of state in the latched output. The invention may be utilized for creating lower power combinatorial and / or sequential logic circuit stages subject to less unproductive charging and discharging of gate capacitances.

Owner:RGT UNIV OF CALIFORNIA

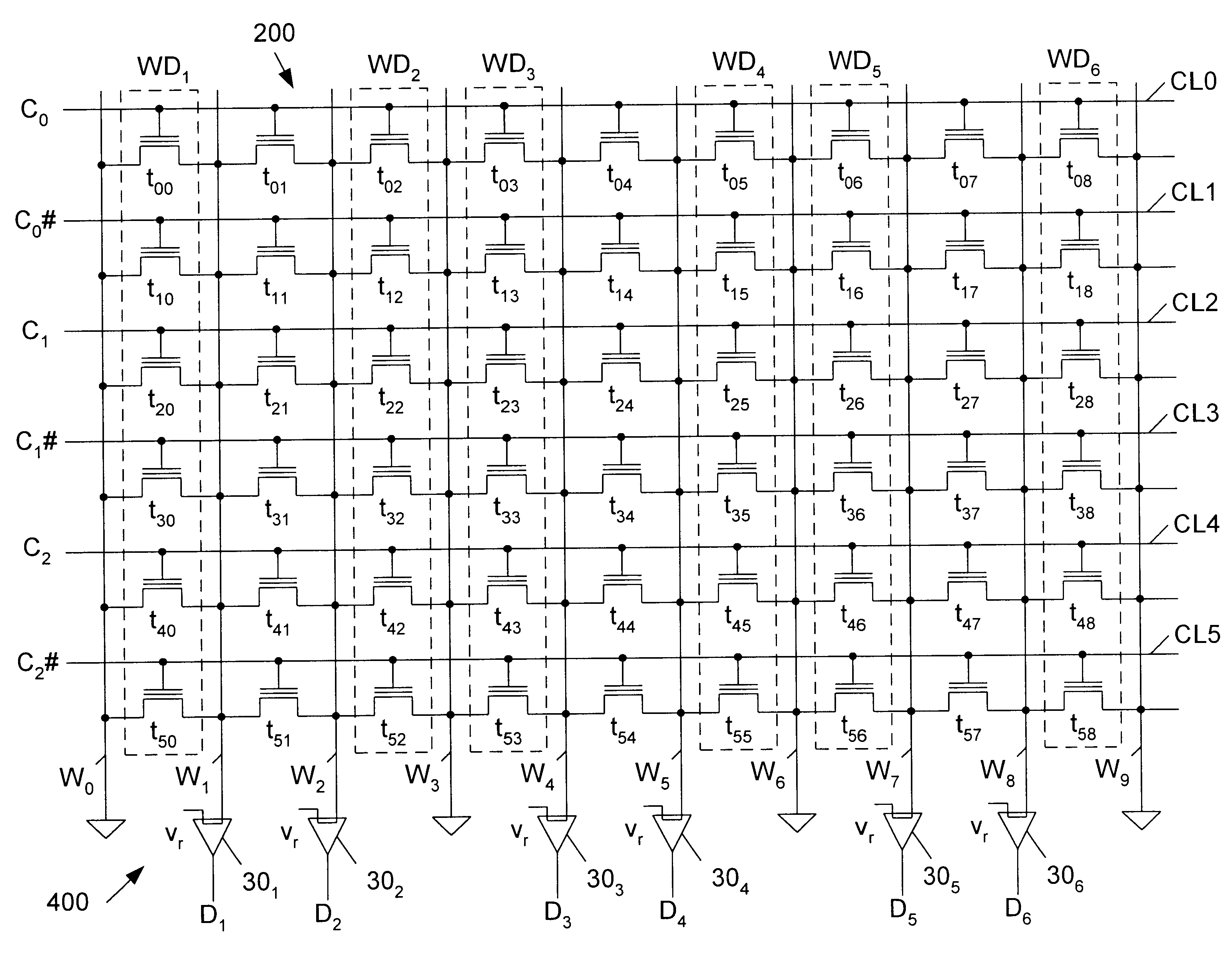

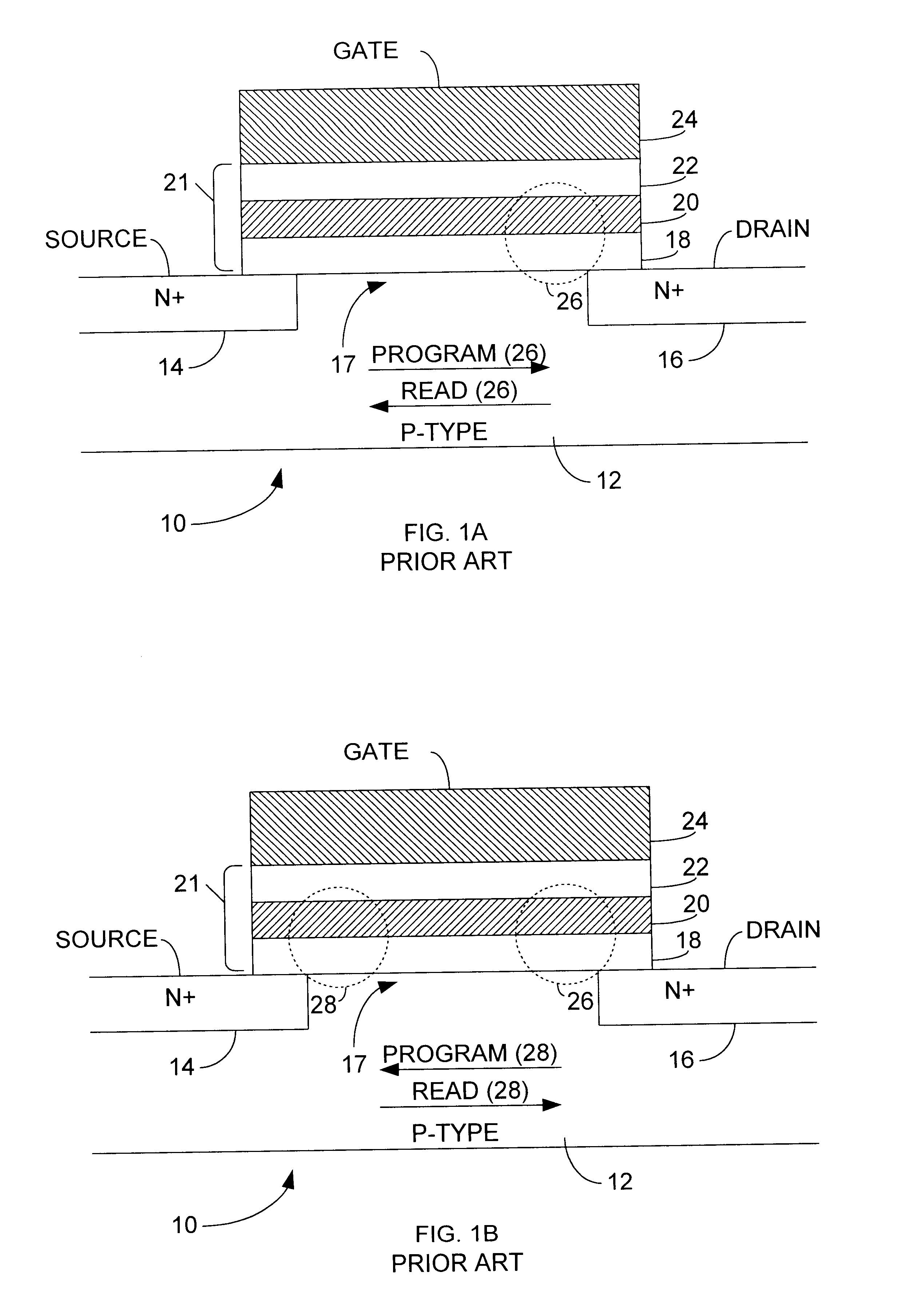

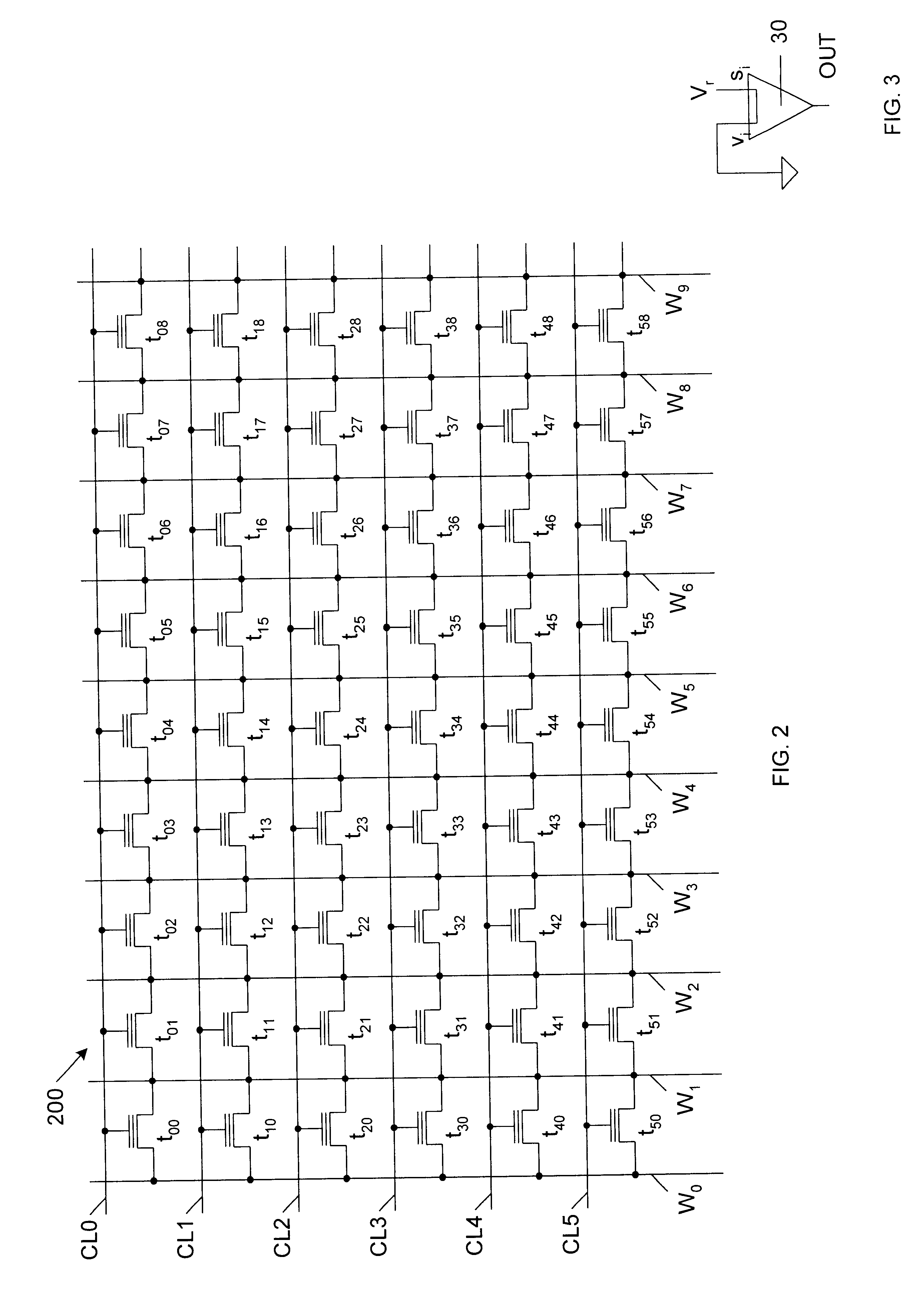

Content-addressable memory for virtual ground flash architectures

InactiveUS6339540B1Easy to useSolid-state devicesRead-only memoriesAudio power amplifierSequential logic

Five architectures for the implementation of virtual ground non-volatile content-addressable memory are provided. Three of the architectures are applicable to 2-bit non-volatile memory transistors having separate programming capability for two current directions (i.e., drain-to-source and source-to-drain. Another architecture is applicable to any floating gate memory transistor, including 1-bit and 2-bit non-volatile memory transistors. In general, an array of non-volatile memory transistors is arranged in a plurality of horizontal rows and vertical columns. Words are stored in selected columns of the array. Horizontal compare lines are coupled to receive a comparand word, with each compare line being coupled to the gates of the memory transistors in a row of the array. The vertically aligned source / drain regions of the memory transistors are coupled to form word lines. Sense amplifiers are coupled to selected word lines. Switches can be coupled to the sense amplifiers and / or word lines, thereby enabling program and compare operations to be performed in two different directions when 2-bit non-volatile memory transistors are used. Compare operations can be performed over two or more phases when 2-bit non-volatile memory transistors are used. Sequential logic circuits can also be coupled to the sense amplifiers, and used to store the results of different compare phases.

Owner:LONGITUDE LICENSING LTD

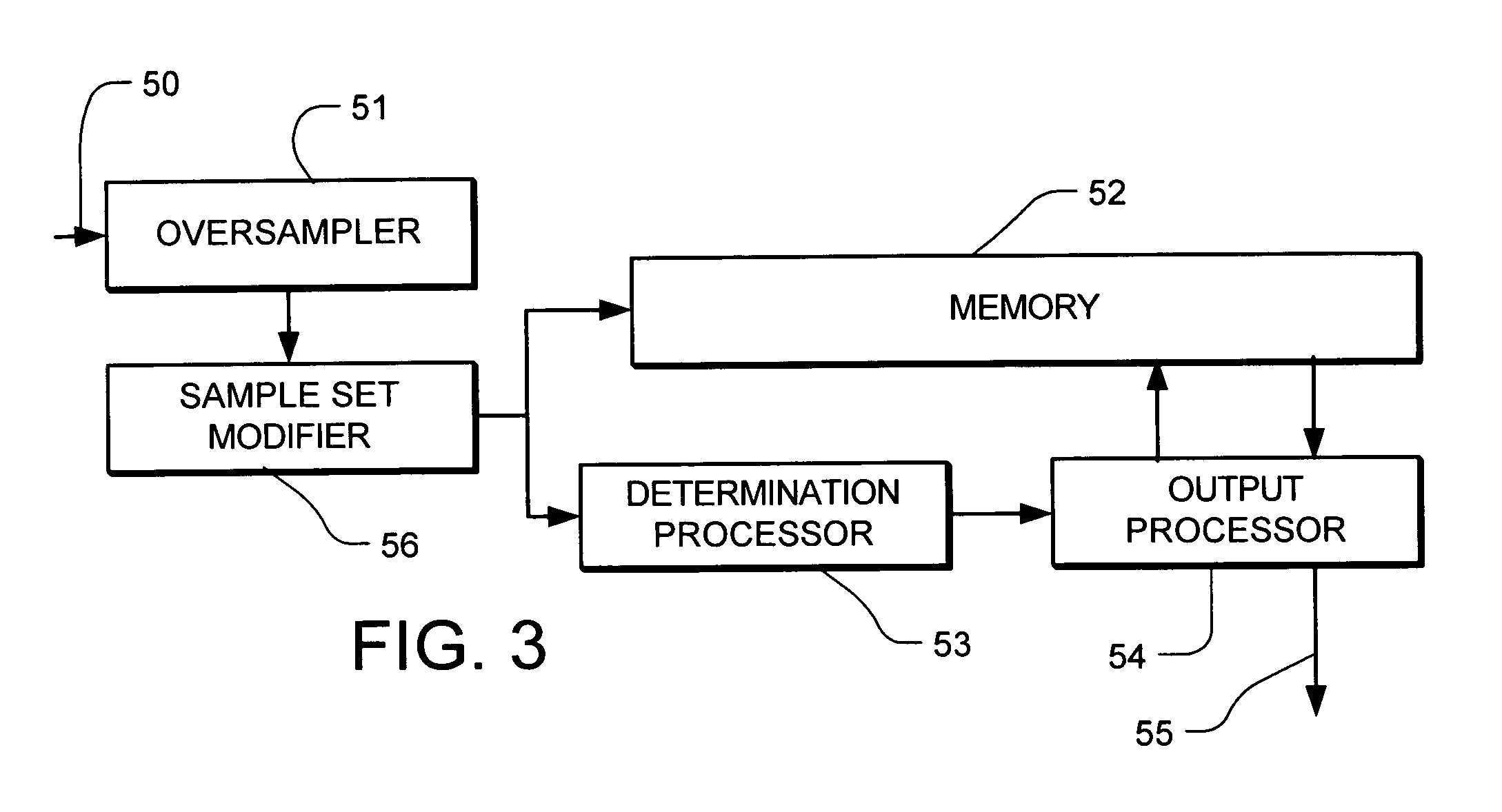

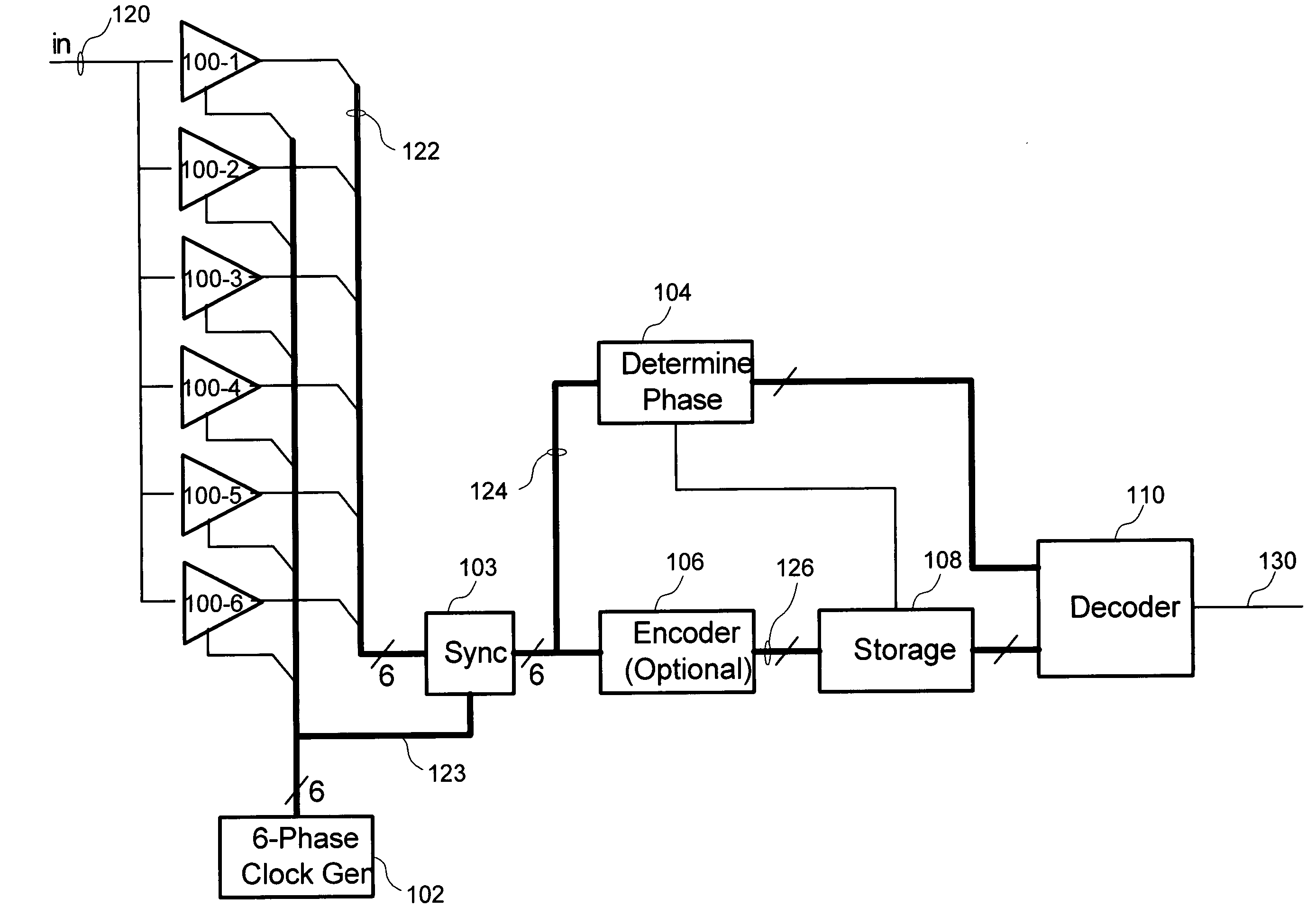

Method and apparatus for data recovery

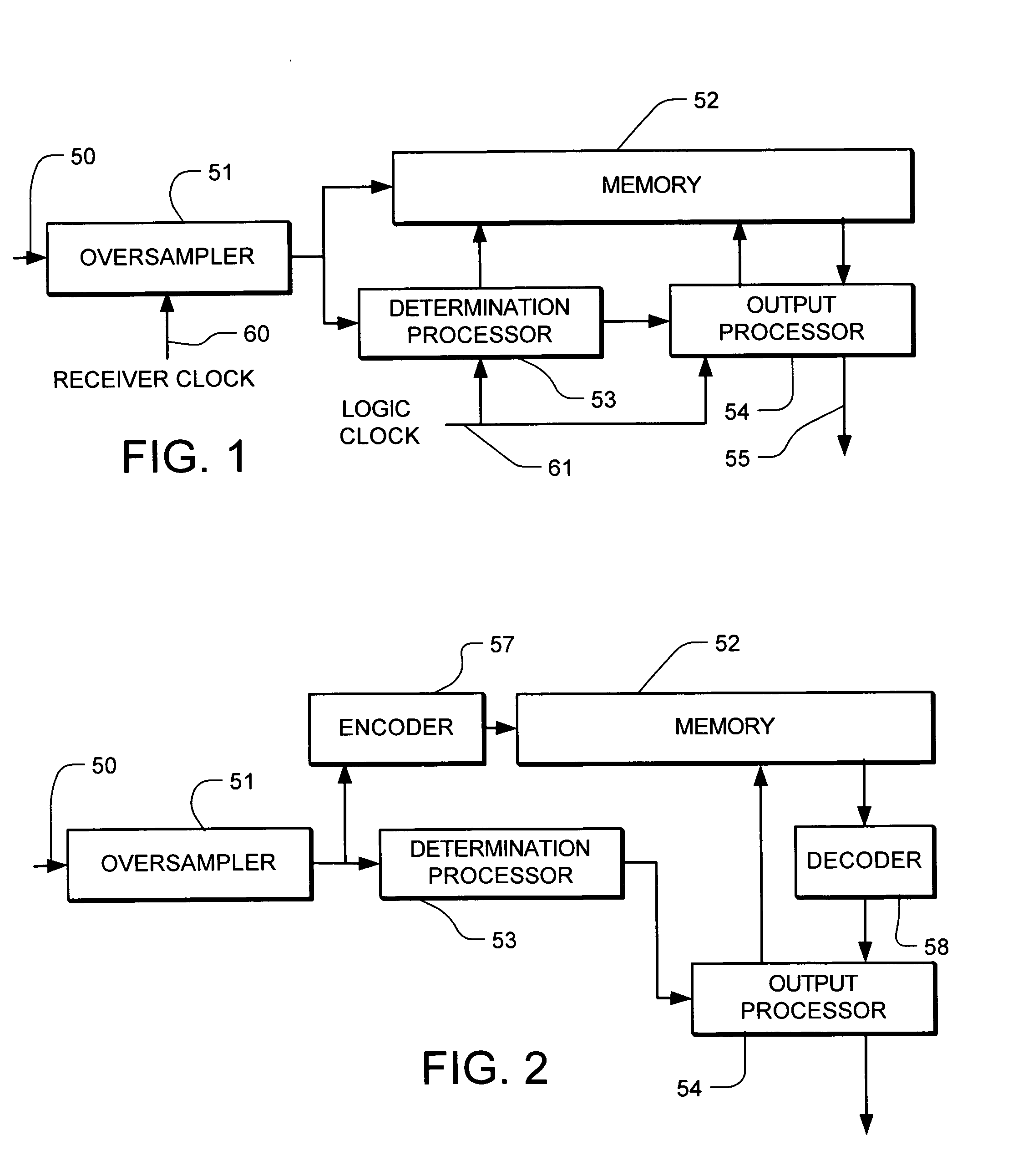

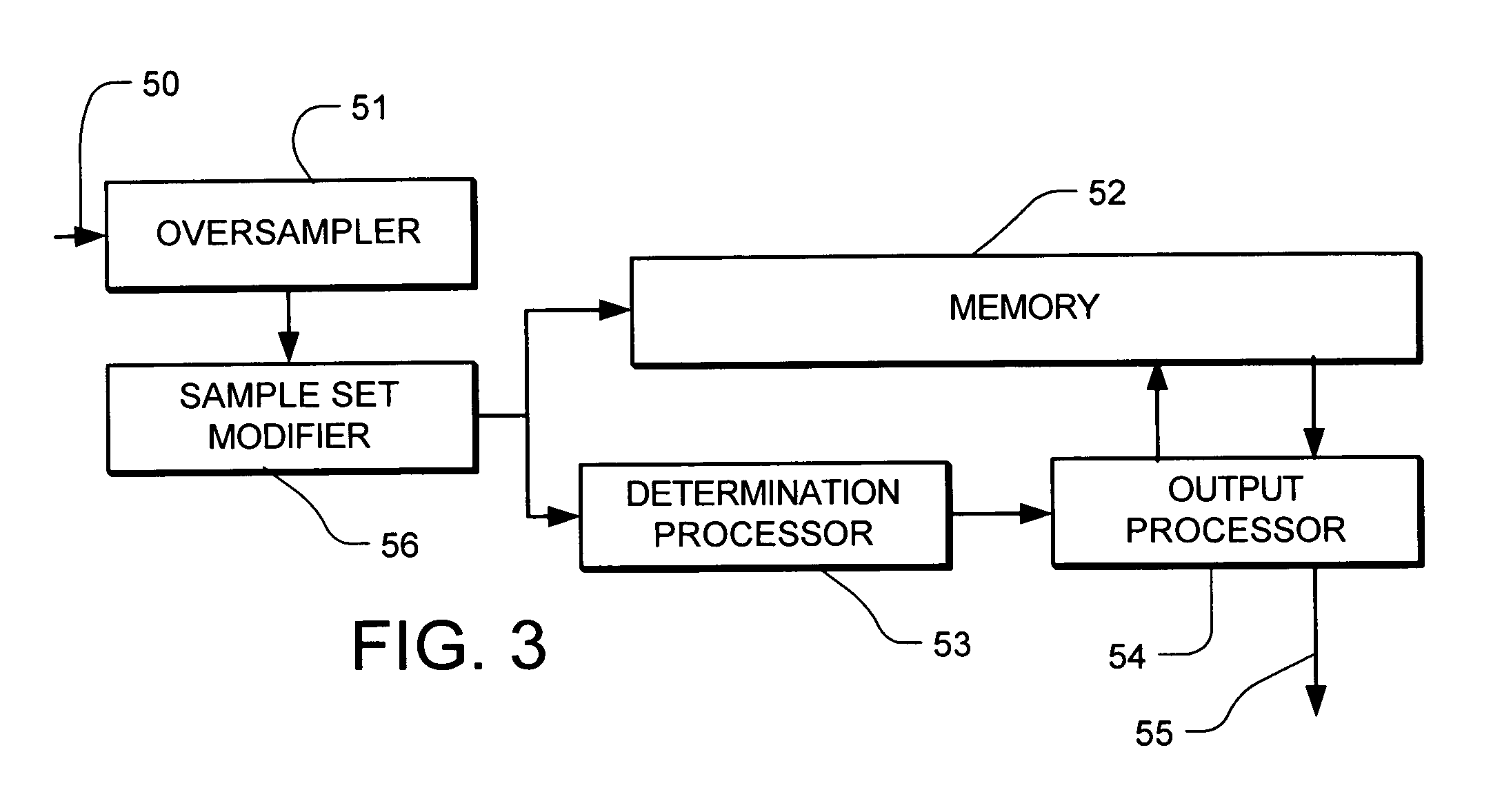

ActiveUS7489739B2Continuously circulated pulse countersModulated-carrier systemsData compressionData signal

A method for recovering data includes oversampling an input data signal to provide sample sets, and storing a plurality of sample sets in addressable memory. The sample sets are processed, using sequential logic to make determinations of respective samples suitable for use in data recovery from corresponding sample sets. One function applied for the determination, includes taking a first mean transition position in a first group of sample sets, taking a second mean transition position in a second group of sample sets, computing a slope value for change in transition position, and making the determination based on the order of the plurality of samples, the first and second means, and the slope. The determined samples are obtained and data recovery is achieved. Sample sets can be modified according to equalization functions. Other modifications include encoding the sample sets for data compression.

Owner:RAMBUS INC

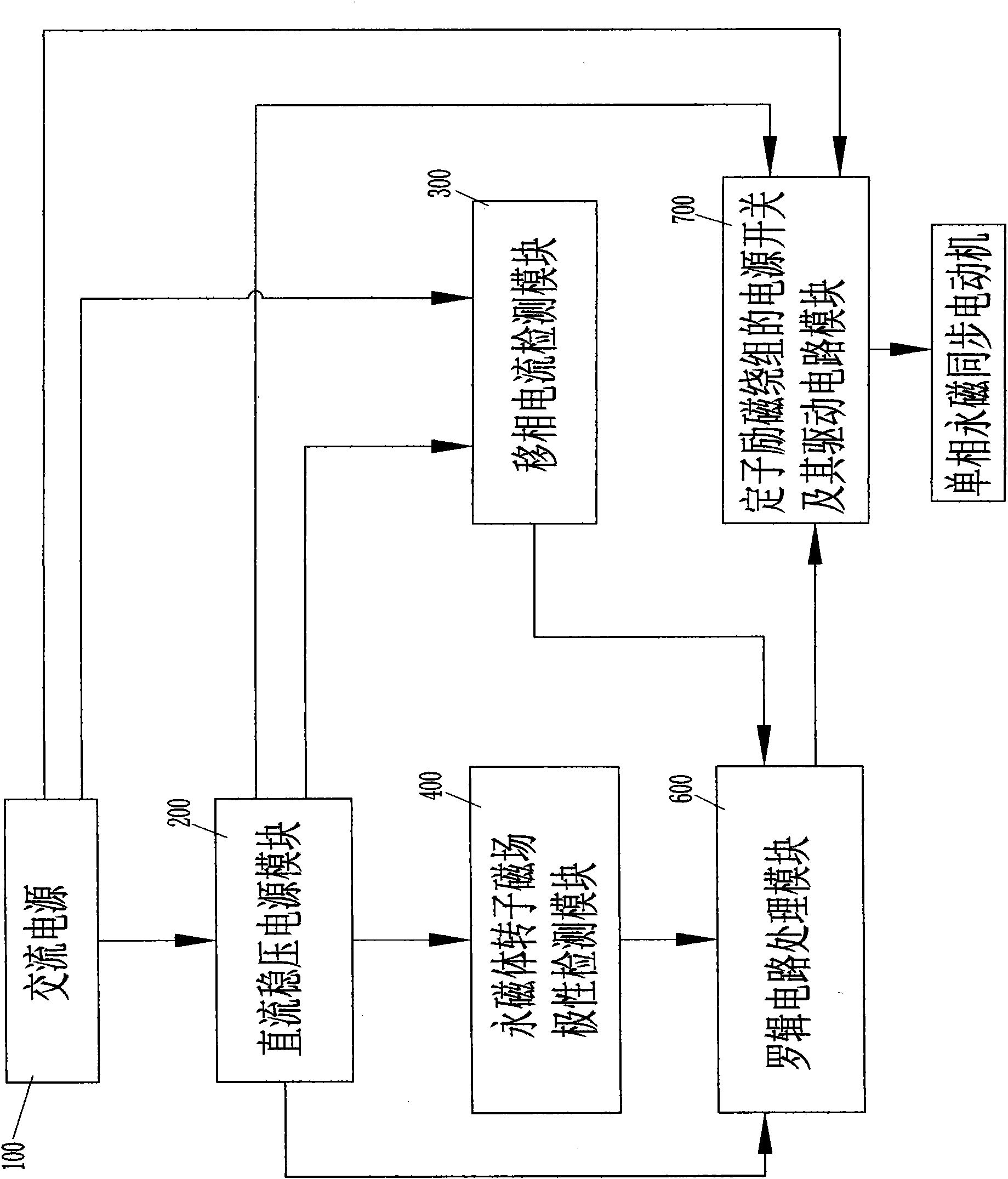

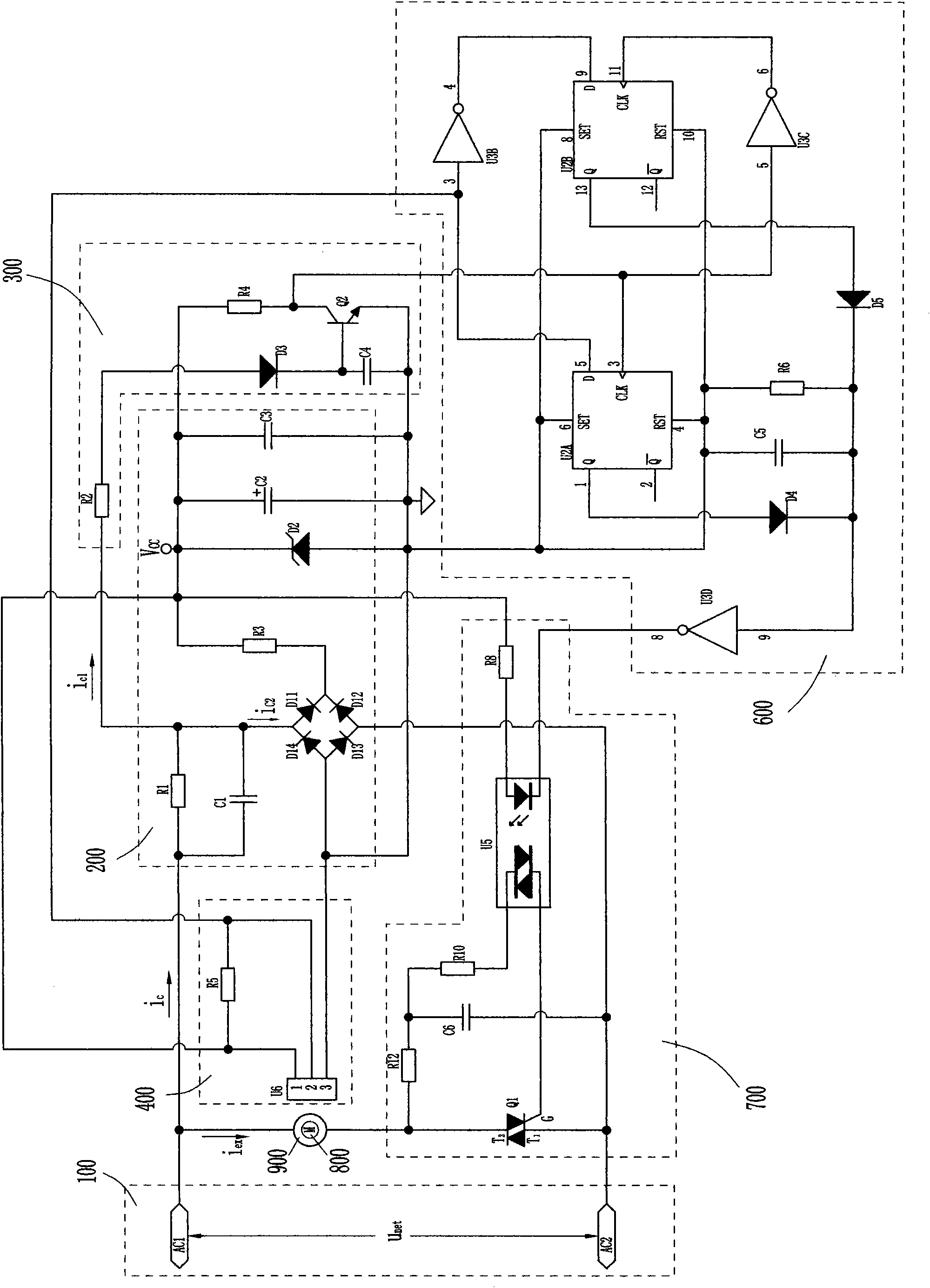

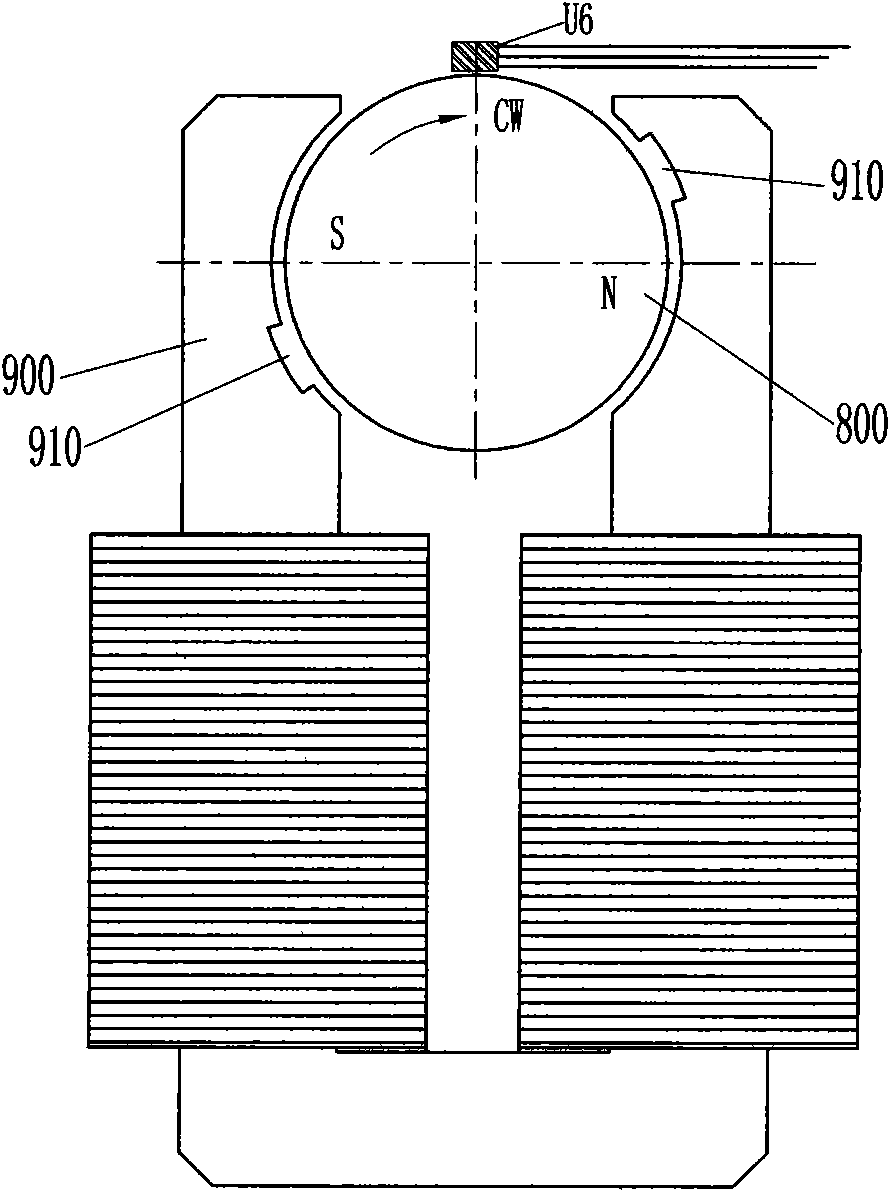

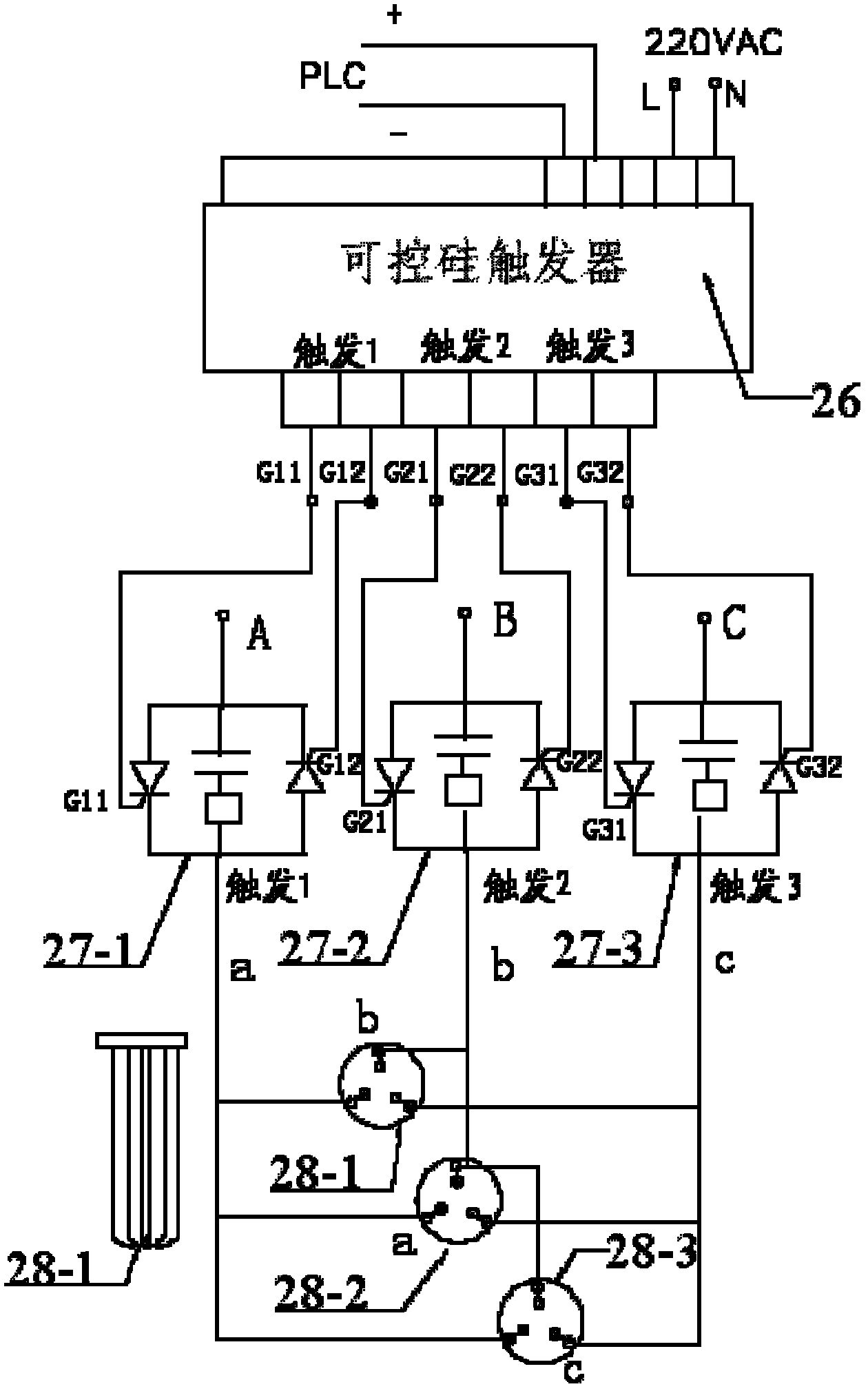

Convenient method for controlling direction of rotation of synchronous motor of single-phase permanent magnet and motor using same

InactiveCN102075130ASimple control methodGuaranteed uptimeDynamo-electric machinesElectronic commutatorsPermanent magnet rotorSynchronous motor

The invention provides a convenient method for controlling direction of rotation of a synchronous motor of a single-phase permanent magnet. The method comprises the following steps: A. arranging a power switch of stator exciting current and ensuring the power switch to conform to the following requirements: when a rotor of the permanent magnet is motionless, the power switch is conducted after the power voltage is connected, or after the rotor of the permanent magnet rotates, the power switch is conducted if the direction of rotation conforms to the set requirement, or after the rotor of the permanent magnet rotates, the power switch is turned off if the direction of rotation is opposite to the set requirement, and when the rotor of the permanent magnet only shakes or wriggles, the power switch is conducted; B. arranging a permanent magnet rotor field polarity sensing device obtaining the real-time field polarity of the permanent magnet rotor in designated position; and C. using the simplest sequential logical circuit to complete each judgment in the step A, thus implementing control of the direction of rotation of the rotor of the permanent magnet. The invention has the advantages of simple and practical control method, simple control circuit, low cost, high reliability, strong interference resistance, capability of effectively reducing the noises of thyristor switches, etc.

Owner:艾如菊

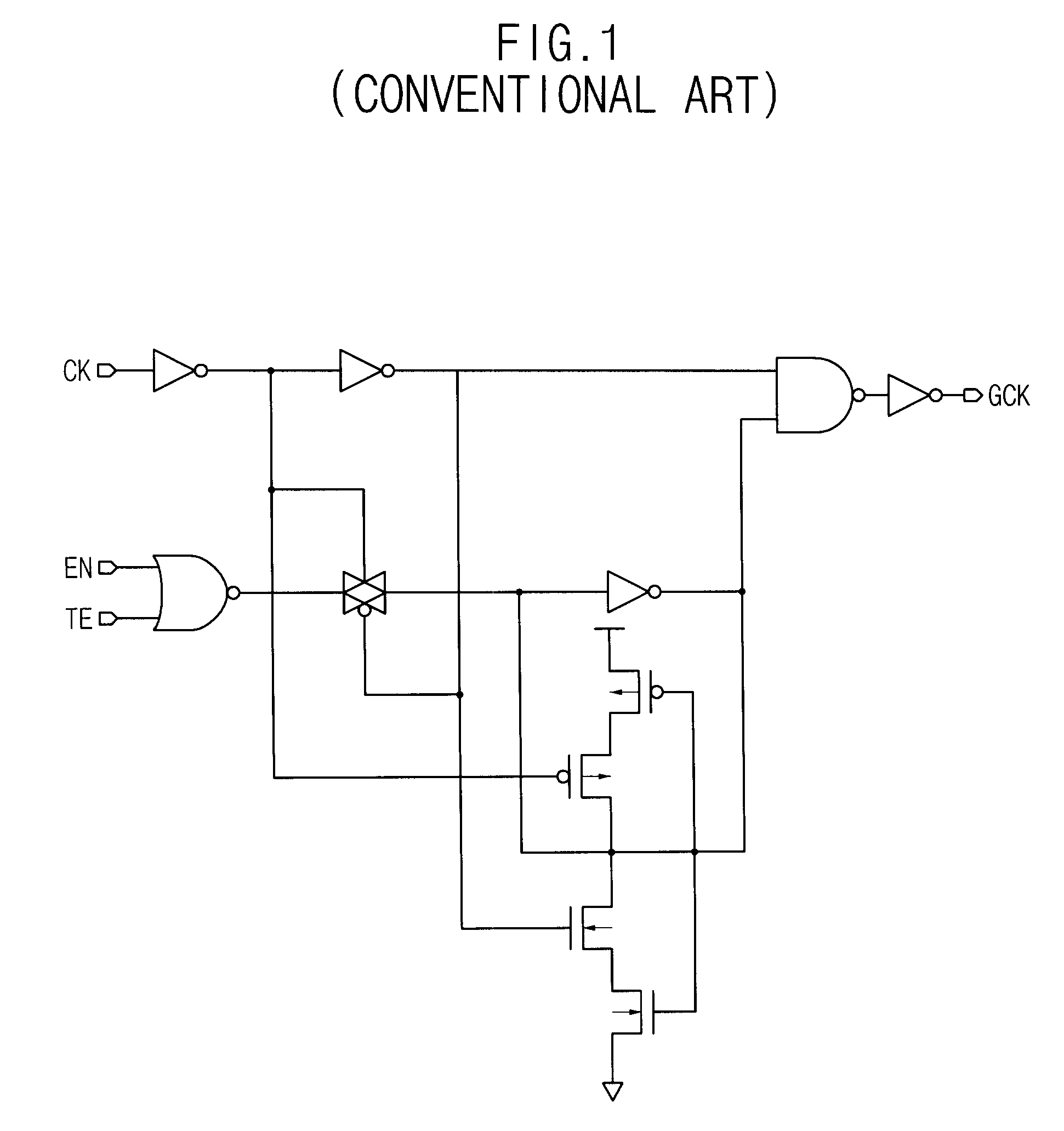

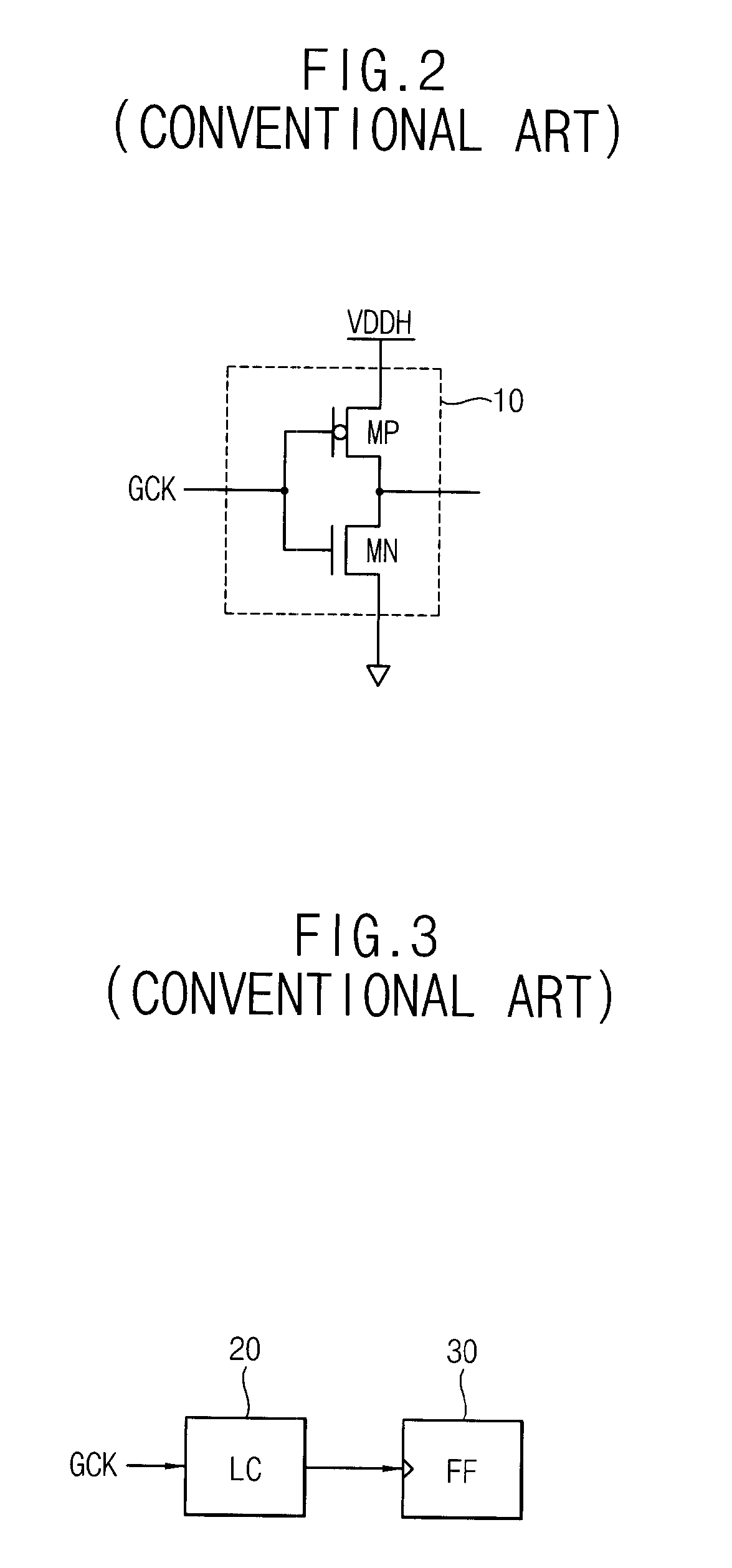

Level-converted and clock-gated latch and sequential logic circuit having the same

A level-converted and clock-gated latch includes a pulse generator, a level converting unit, and a latch circuit. The pulse generator is provided with a first power-supply voltage and generates a pulse signal having a first voltage level, in response to a clock signal. The level converting unit is provided with a second power-supply voltage and generates an intermediate clock signal having a second voltage level, in response to an inverted clock signal, the clock signal and an enable signal. The latch circuit is provided with the second power-supply voltage, latches the intermediate clock signal, and provides a gated clock signal having the second voltage level. An activation interval of the gated clock signal is controlled based on the enable signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and apparatus for data recovery

ActiveUS20060062327A1Phase-modulated carrier systemsSynchronising arrangementData compressionData signal

A method for recovering data includes oversampling an input data signal to provide sample sets, and storing a plurality of sample sets in addressable memory. The sample sets are processed, using sequential logic to make determinations of respective samples suitable for use in data recovery from corresponding sample sets. One function applied for the determination, includes taking a first mean transition position in a first group of sample sets, taking a second mean transition position in a second group of sample sets, computing a slope value for change in transition position, and making the determination based on the order of the plurality of samples, the first and second means, and the slope. The determined samples are obtained and data recovery is achieved. Sample sets can be modified according to equalization functions. Other modifications include encoding the sample sets for data compression.

Owner:RAMBUS INC

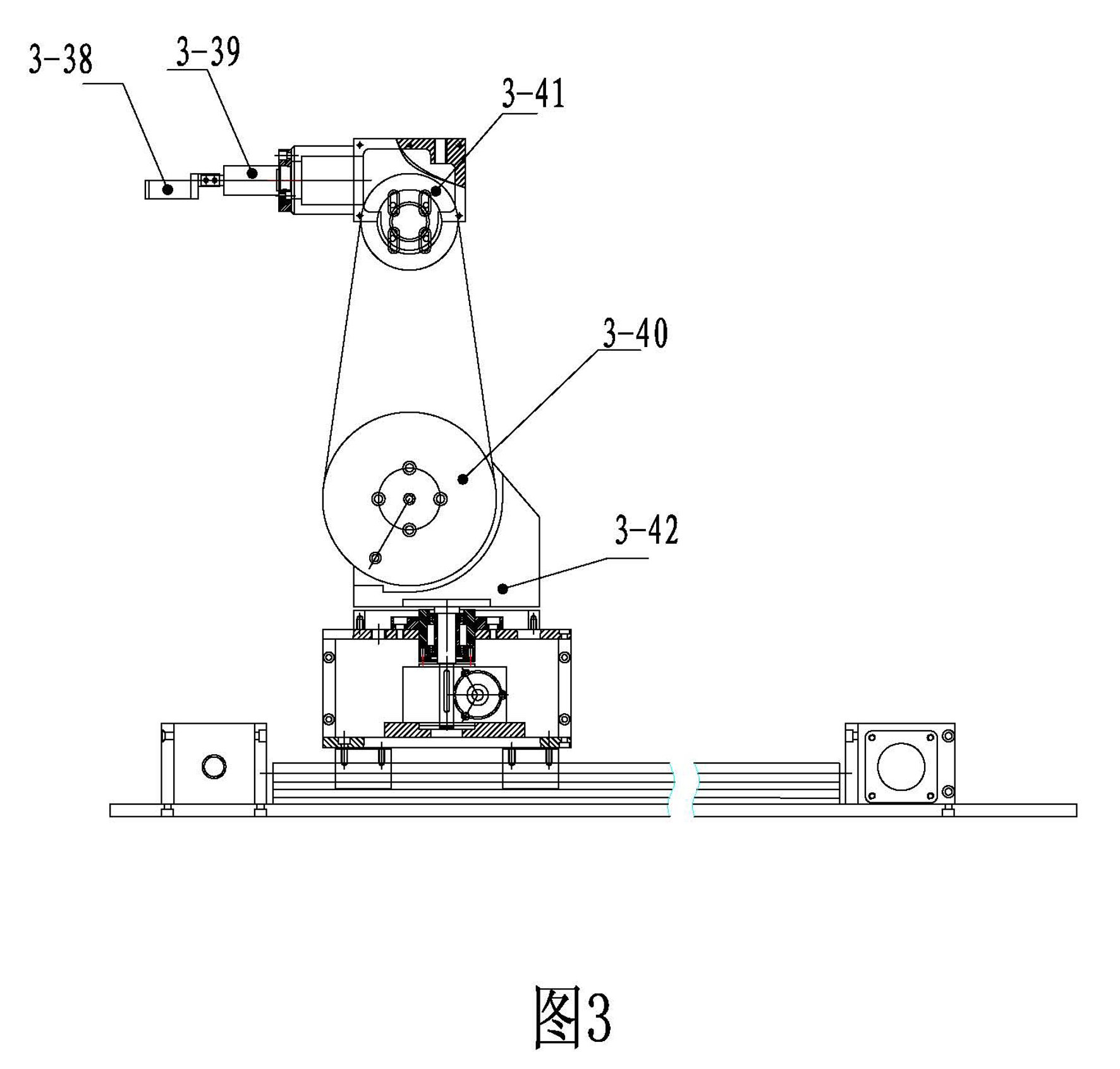

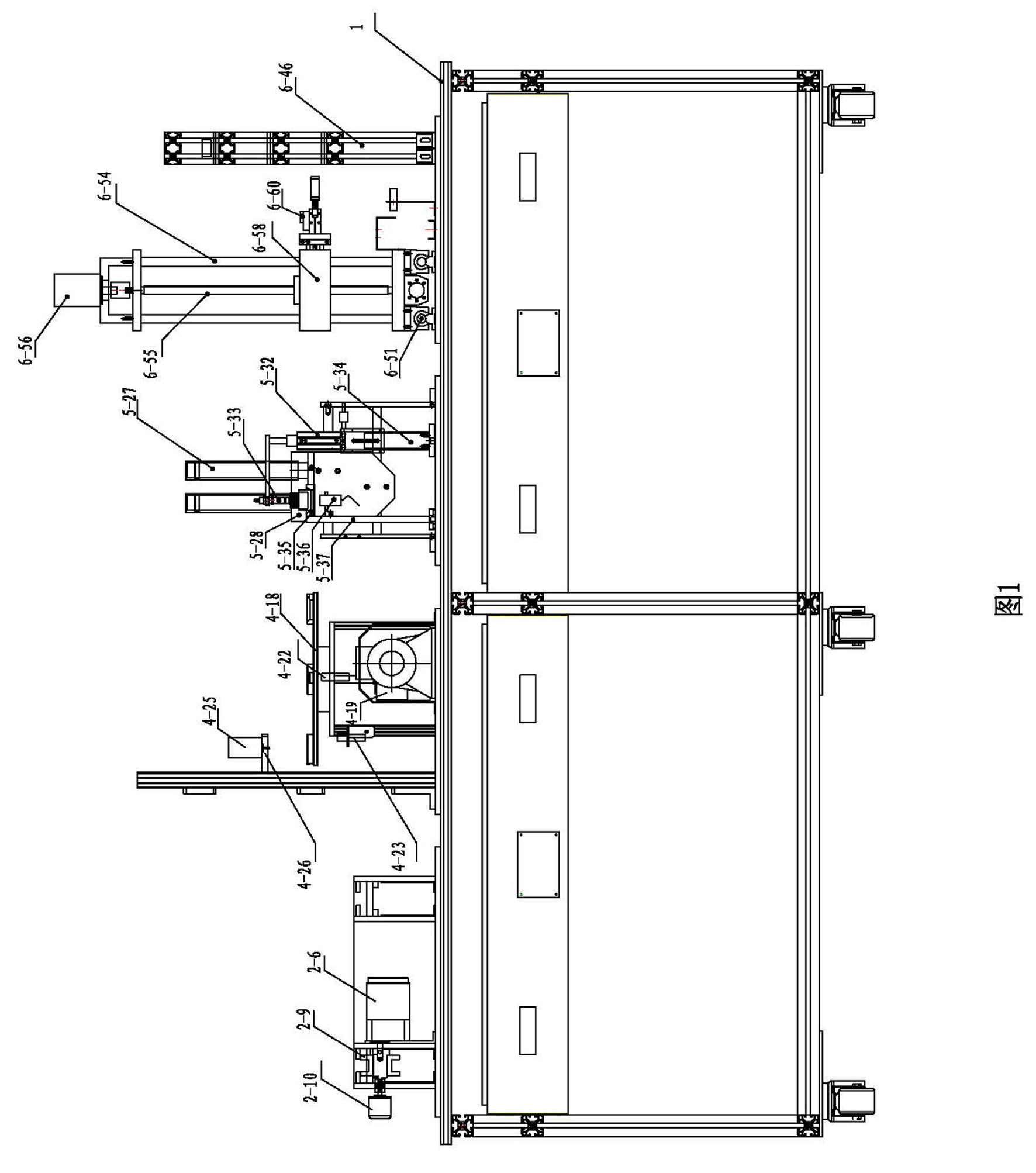

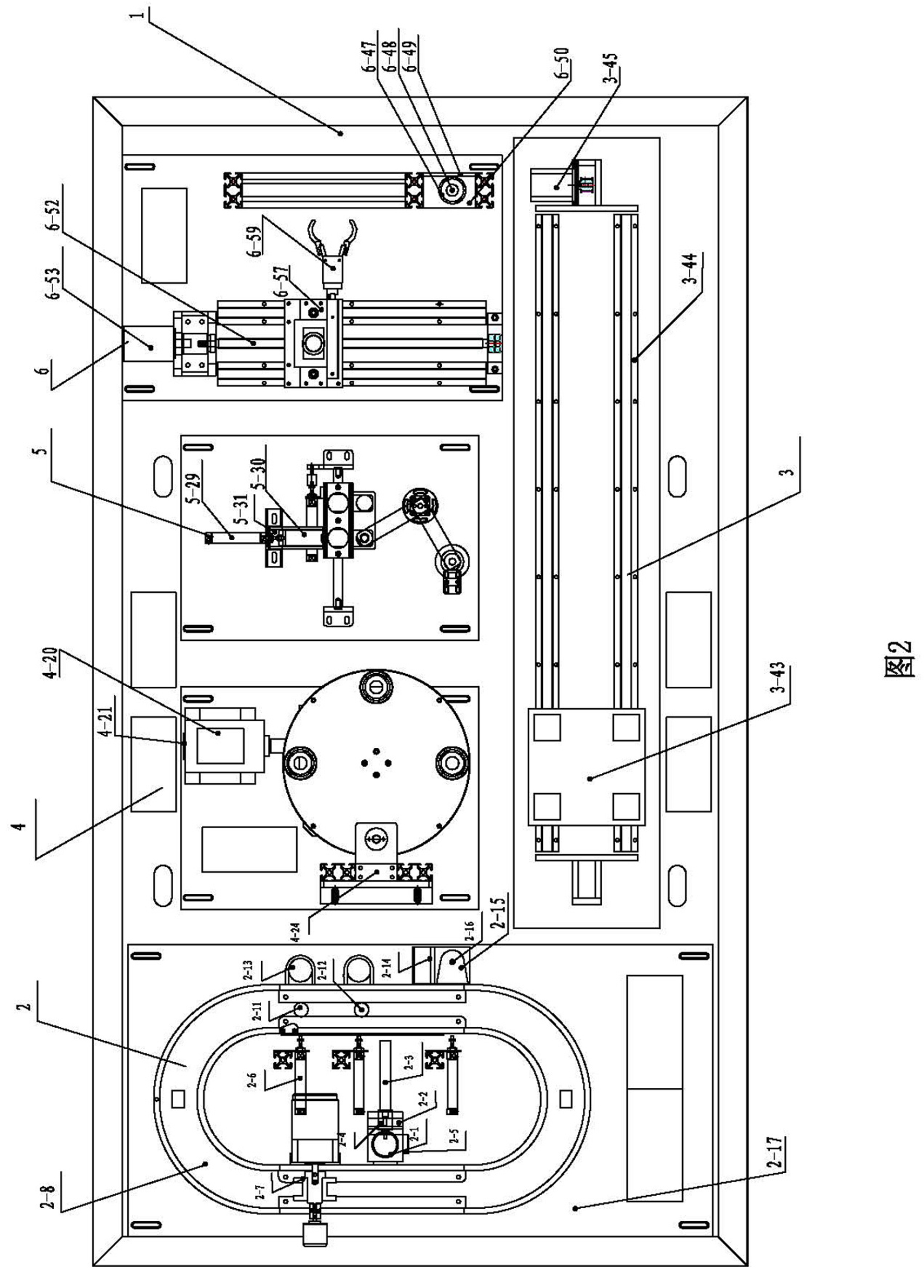

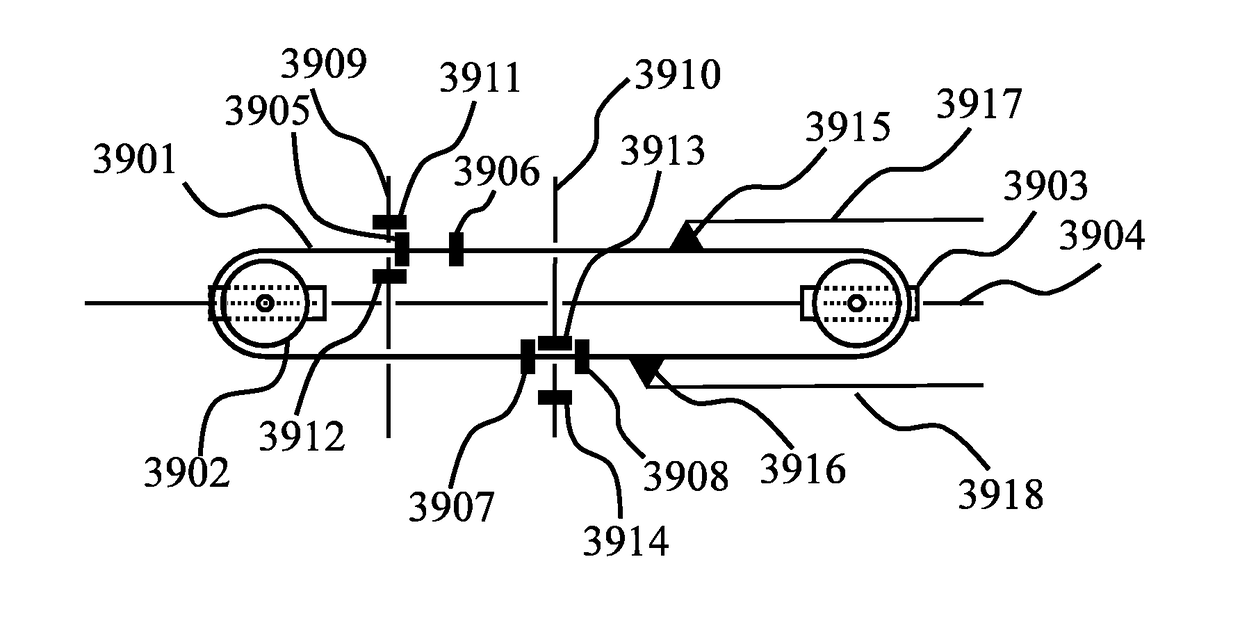

Electromechanical integrated comprehensive training assessment device

ActiveCN101976530AConvenient teachingUnderstand the workflowEducational modelsProduction lineTraining assessment

The invention relates to an electromechanical integrated comprehensive training assessment device which comprises an execution unit, a control unit and an operating platform, wherein, the execution unit comprises an annular conveying and sorting unit, a movable four-degree-of-freedom mechanical arm unit for sorting and transferring workpieces from the annular conveying and sorting unit, a constant-speed processing unit for processing materials, an assembly unit for assembling the workpieces, and a warehouse access unit for accessing the workpieces; the control unit comprises a processor for carrying out sequential logic control on the execution unit through a circuit and a gas circuit; and the execution unit and the control unit are arranged on the operating platform. By adopting the electromechanical integrated comprehensive training assessment device, a student can more deeply and perceptively understand the workflow of an automatic production line in industrial production and complete study which needs to be finished in the actual operating site in a training room.

Owner:ZHEJIANG TIANHUANG TECH INDAL

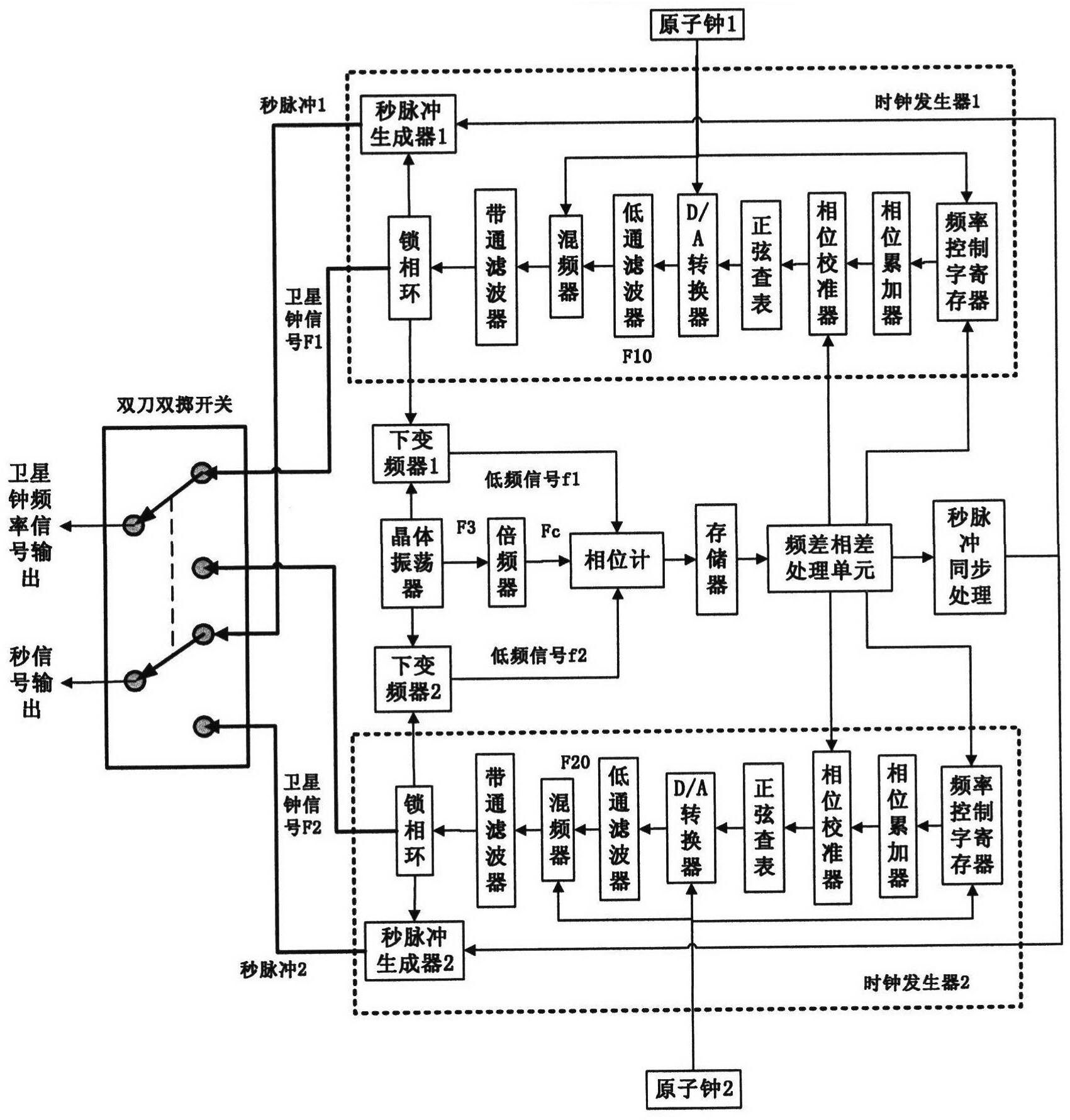

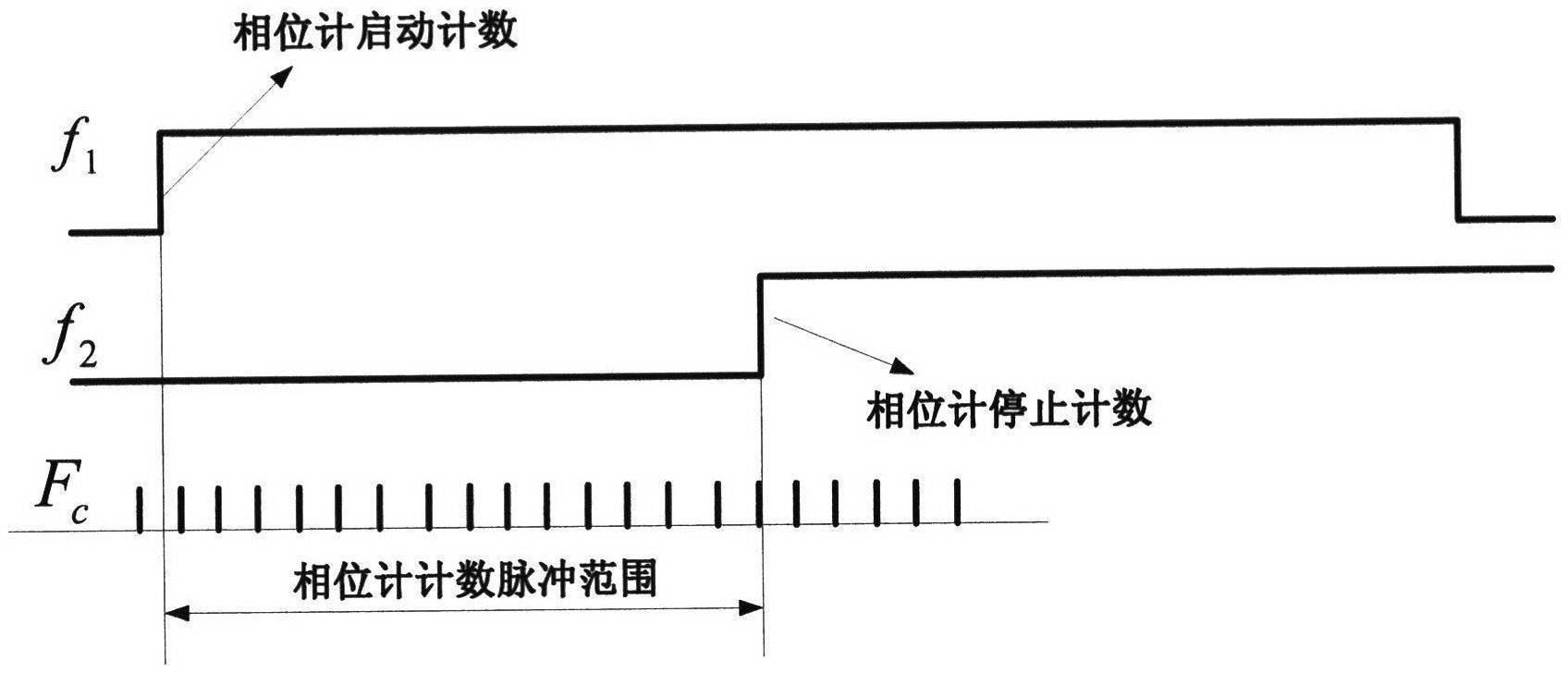

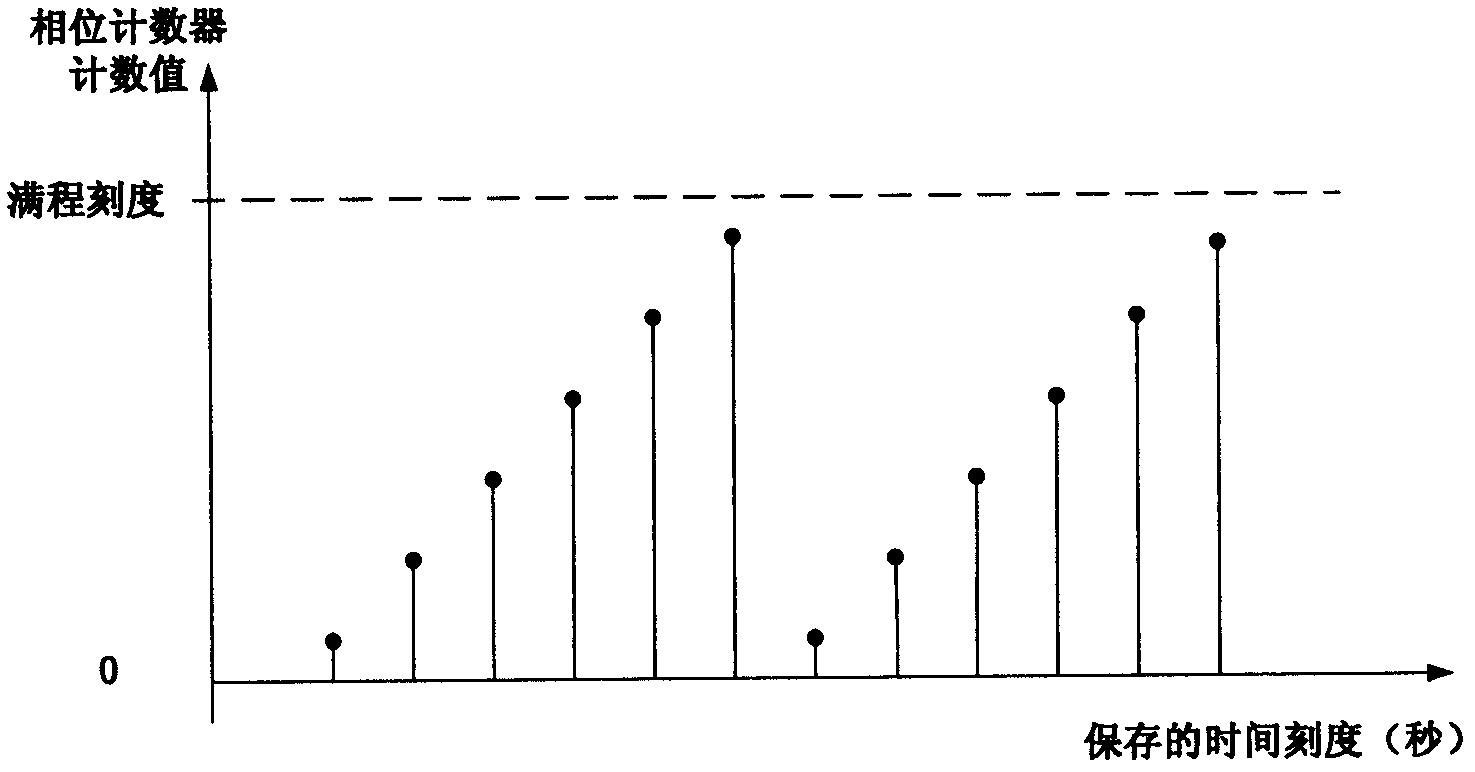

Seamless switching method for master and slave satellite clocks of navigation satellite

The invention discloses a seamless switching method for master and slave satellite clocks of a navigation satellite. The method comprises the following steps of: performing dual mixer time difference measurement on master and slave satellite clock signals, keeping values of a phase difference counter in a memory according to a certain frequency, and performing frequency difference processing, phase difference processing and second pulse synchronous processing on data in the memory in a time division mode under sequential logic control. In the frequency difference processing time period, synchronization of master and slave clock signal frequencies is finished. In the phase difference processing period, synchronization of master and slave clock signal phases is finished. In the second pulsesynchronous processing period, the second pulse initial change edge generated by the slave clock is synchronized with the second pulse initial change edge of the main clock. Both the master and slaveclocks generate satellite clock frequency signals and second pulse signals; and when the master and slave clocks are switched, the outputs of the satellite clock frequency signals and the second pulse signals are simultaneously switched. When the master and slave working clocks are switched by adopting the method, the master and slave satellite clock difference is low, the second pulse signals are continuous, and the requirement for continuous use of navigation signals is not affected during master and slave switching of the satellite clocks.

Owner:BEIJING INST OF SPACECRAFT SYST ENG

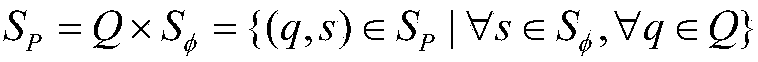

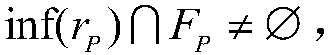

Linear sequential logic-based mobile terminal express delivery path planning method

ActiveCN107169591AExpand the scope of deliveryGuaranteed optimalityForecastingLogisticsMobile endThe Internet

Disclosed is a linear sequential logic theory-based mobile terminal express delivery path planning method. A weighted transition system which satisfies an actual delivery environment is established by a baidu map software development kit on a smart phone platform with an Android system; meanwhile, a multi-point delivery task is described by linear sequential logic language, and the task is converted into a Buchi automat; next, the transition system is fused with the delivery task to establish a task feasible network topology; the optimal path is searched on the task feasible network topology through a Dijkstra algorithm; next, the path is mapped back to the baidu map to obtain the optimal discrete path; and finally, continuation of the discrete path is realized by the positioning and navigating function of the baidu map software development kit. By virtue of the linear sequential logic theory-based mobile terminal express delivery path planning method, the problem of limitation in multi-point delivery task and the delivery region is solved, the optimality of the delivery path of couriers can be ensured, the delivery efficiency of couriers can be improved, and intelligent delivery based on Internet plus is realized.

Owner:ZHEJIANG UNIV OF TECH

Event driven dynamic logic for reducing power consumption

InactiveCN1679237AReduced power dissipation levelsReduce power lossPower reduction by control/clock signalLogic circuits characterised by logic functionCapacitanceState variation

Methods and circuits are described for reducing power consumption within digital logic circuits by blocking the passage of clock signal transitions to the logic circuits when the clock signal would not produce a desired change of state within the logic circuit, such as at inputs, intermediary nodes, outputs, or combinations. By way of example, the incoming clock is blocked if a given set of logic inputs will not result in an output change of state if a clock signal transition were to be received. By way of further example, the incoming clock is blocked in a data flip-flop if the input signal matches the output signal, such that receipt of a clock transition would not produce a desired change of state in the latched output. The invention may be utilized for creating lower power combinatorial and / or sequential logic circuit stages subject to less unproductive charging and discharging of gate capacitances.

Owner:RGT UNIV OF CALIFORNIA

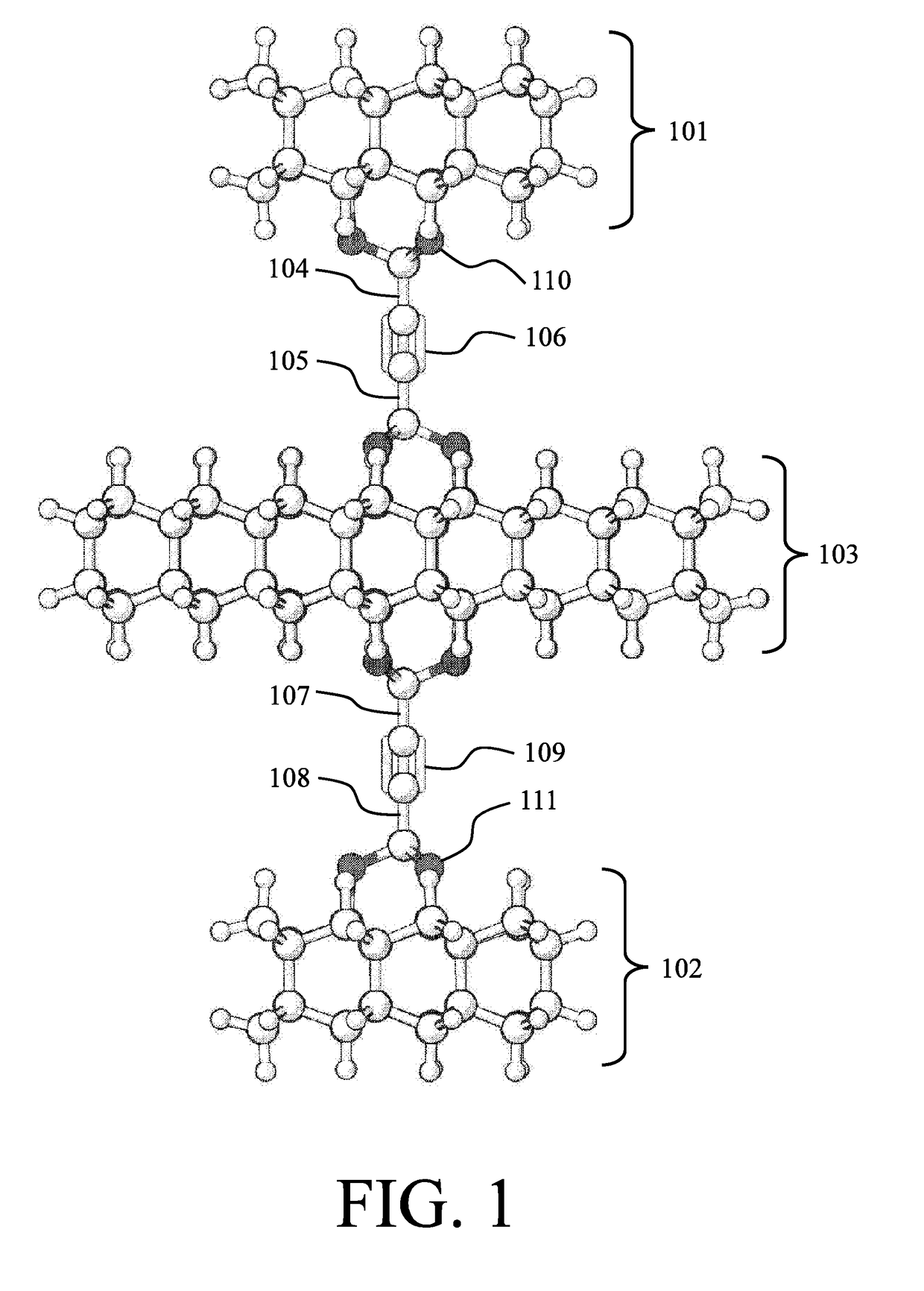

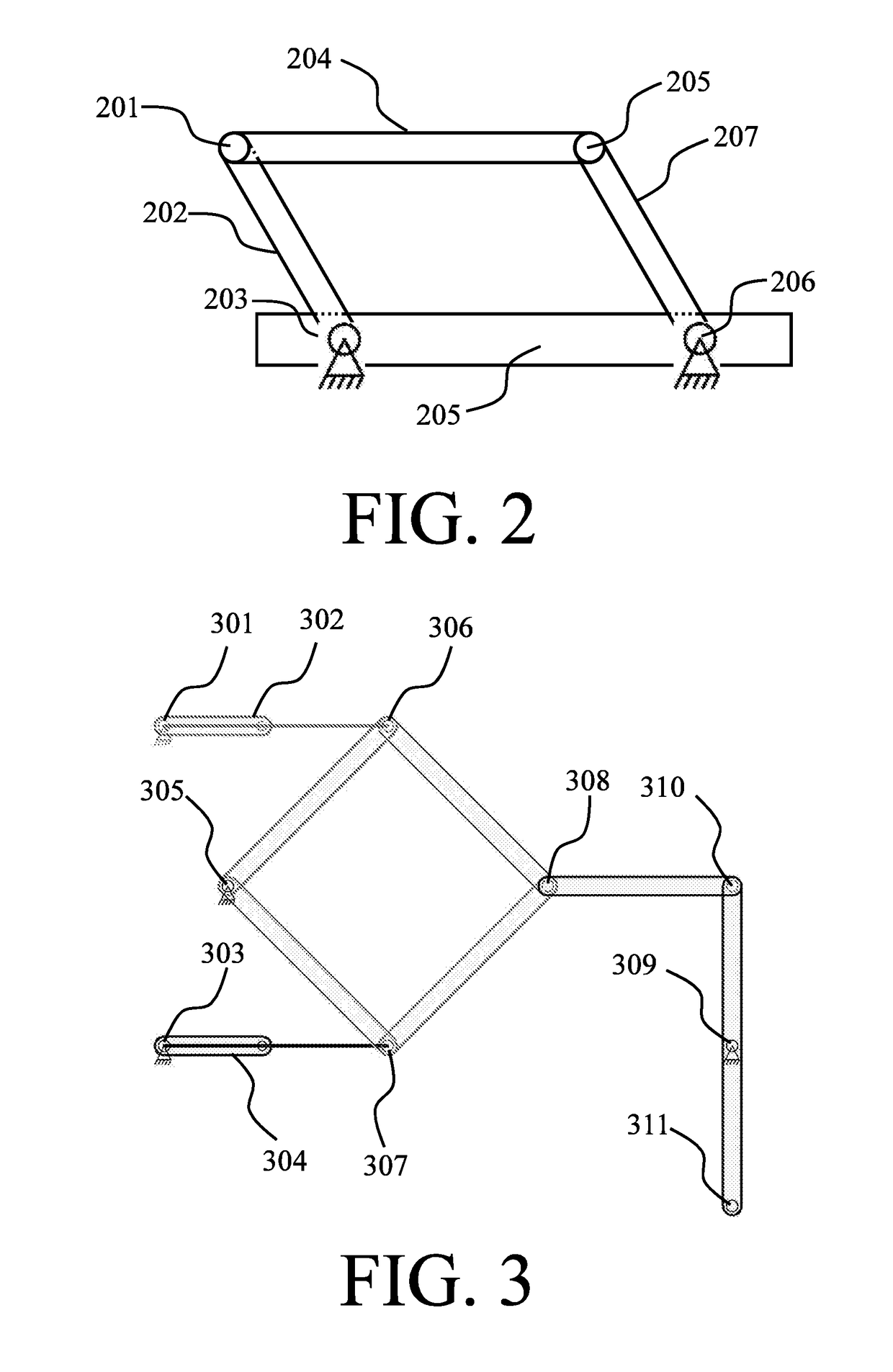

Mechanical Computing Systems

ActiveUS20170192748A1Reduce energy consumptionReduce the numberComputations using multiple devicesLogic circuits characterised by logic functionMechanical computerTheoretical computer science

Systems and methods for creating mechanical computing mechanisms and Turing-complete systems which include combinatorial logic and sequential logic, and are energy-efficient.

Owner:CBN NANO TECH INC

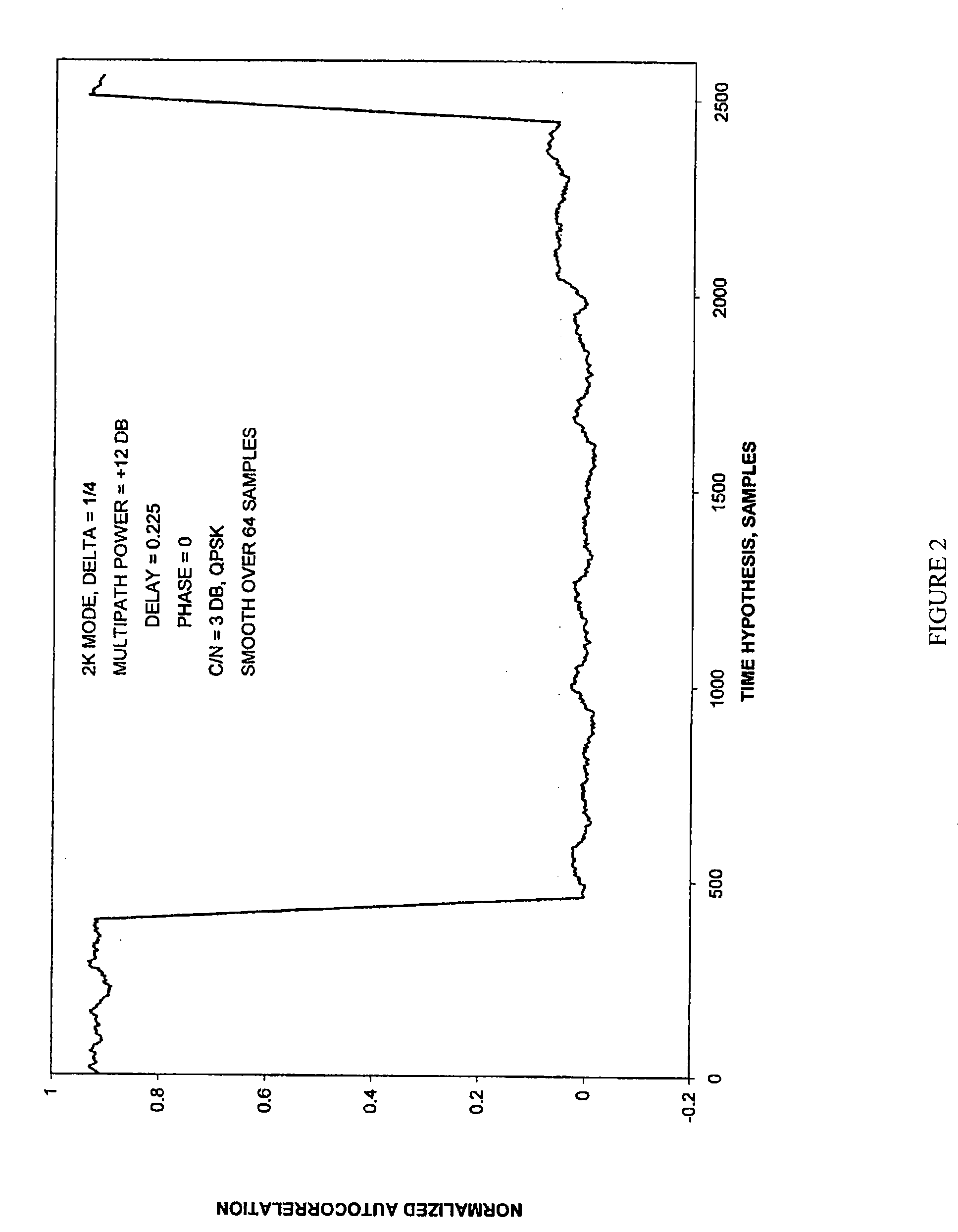

Apparatus and method for tracking symbol timing of OFDM modulation in a multi-path channel

InactiveUS20070092013A1Amplitude-modulated carrier systemsSecret communicationEngineeringSequential logic

Methods and Systems for tracking symbol timing of an OFDM signal are disclosed. In one embodiment, a wireless receiver includes signal tracking and timing logic to facilitate the timing of a demodulation operation such that the demodulation operation occurs on the proper symbol boundary, particularly when the OFDM signal has multipath components and the second component has greater power than the first.

Owner:CSR TECH INC

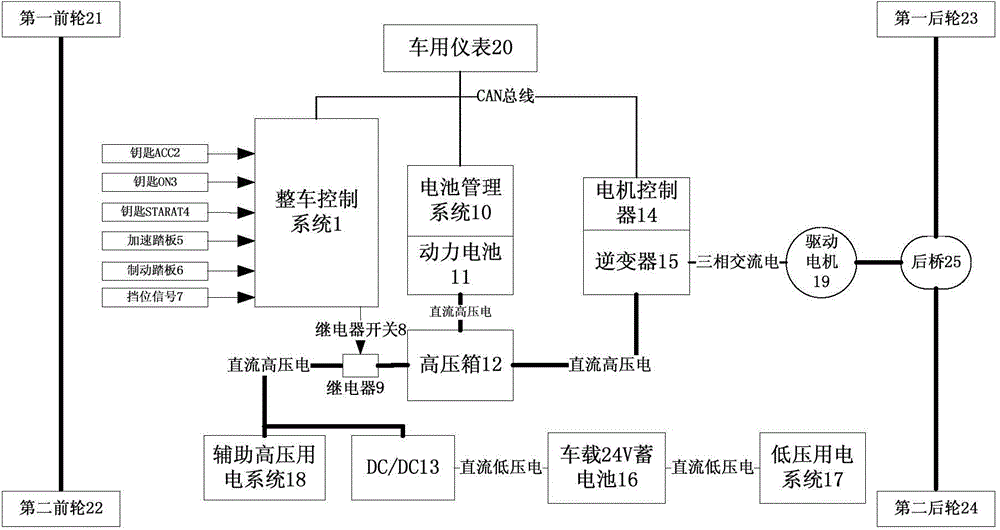

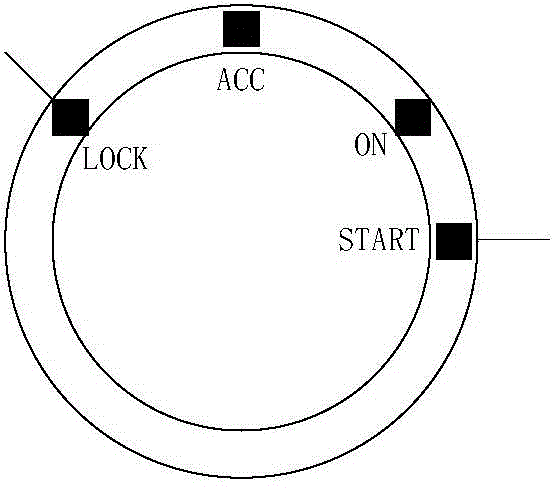

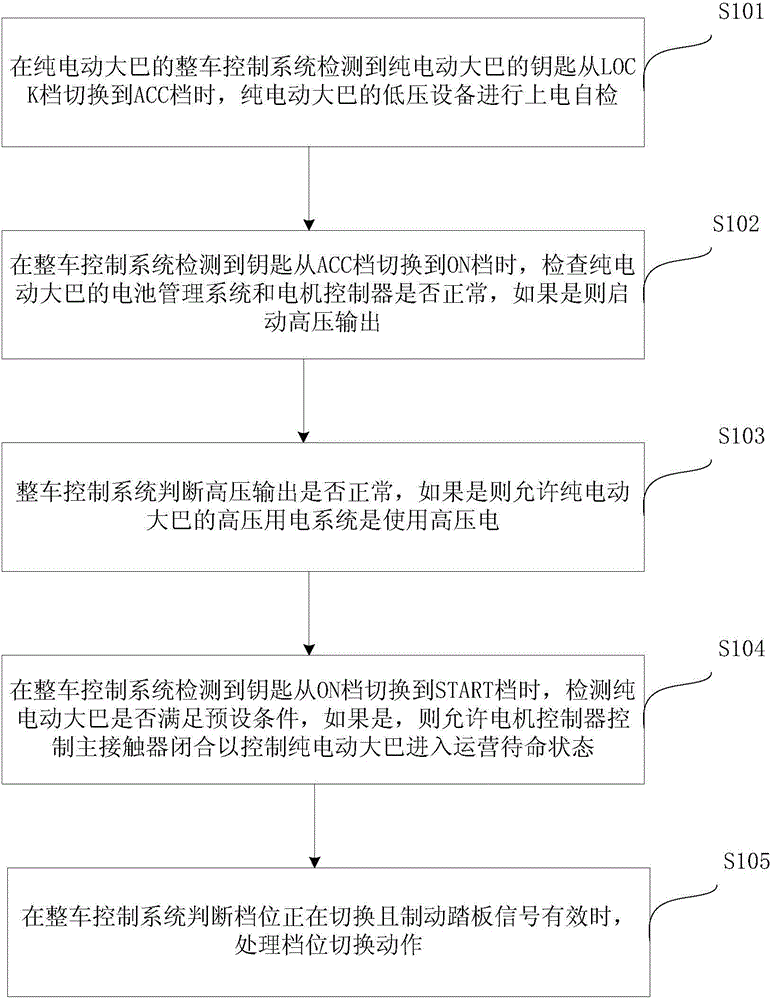

Pure-electric-coach safety start sequential logic control method

InactiveCN103600667AEasy to operateEnsure safetySpeed controllerElectric/fluid circuitLow voltageEngineering

The invention provides a pure-electric-coach safety start sequential logic control method. The method includes when detecting that a key of a pure electric coach is switched from the LOCK gear to the ACC (acceleration) gear, performing a power-on self-test on lower-voltage equipment of the pure electric coach; when detecting that the key is switched from the ACC gear to the ON gear, detecting whether a battery management system and a motor controller of the pure electric coach are in a normal state or not; if yes, starting high-voltage output; judging whether the high-voltage output is normal or not; if yes, allowing high-voltage power to be utilized by a high-voltage power consumption system of the pure electric coach; when detecting that the key is switched from the ON gear to the START gear, detecting whether the pure electric coach meets preset conditions or not; if yes, allowing the motor controller to control a main contactor to be closed to control the pure electric coach to enter an operational standby state; when judging that the gears are switched currently and a brake pedal signal is effective, processing gear switching operation. By the method, the high-voltage output can be safely started during starting of the pure electric coach, and safety of the electric coach, electric equipment and passengers is guaranteed.

Owner:SINOEV TECH

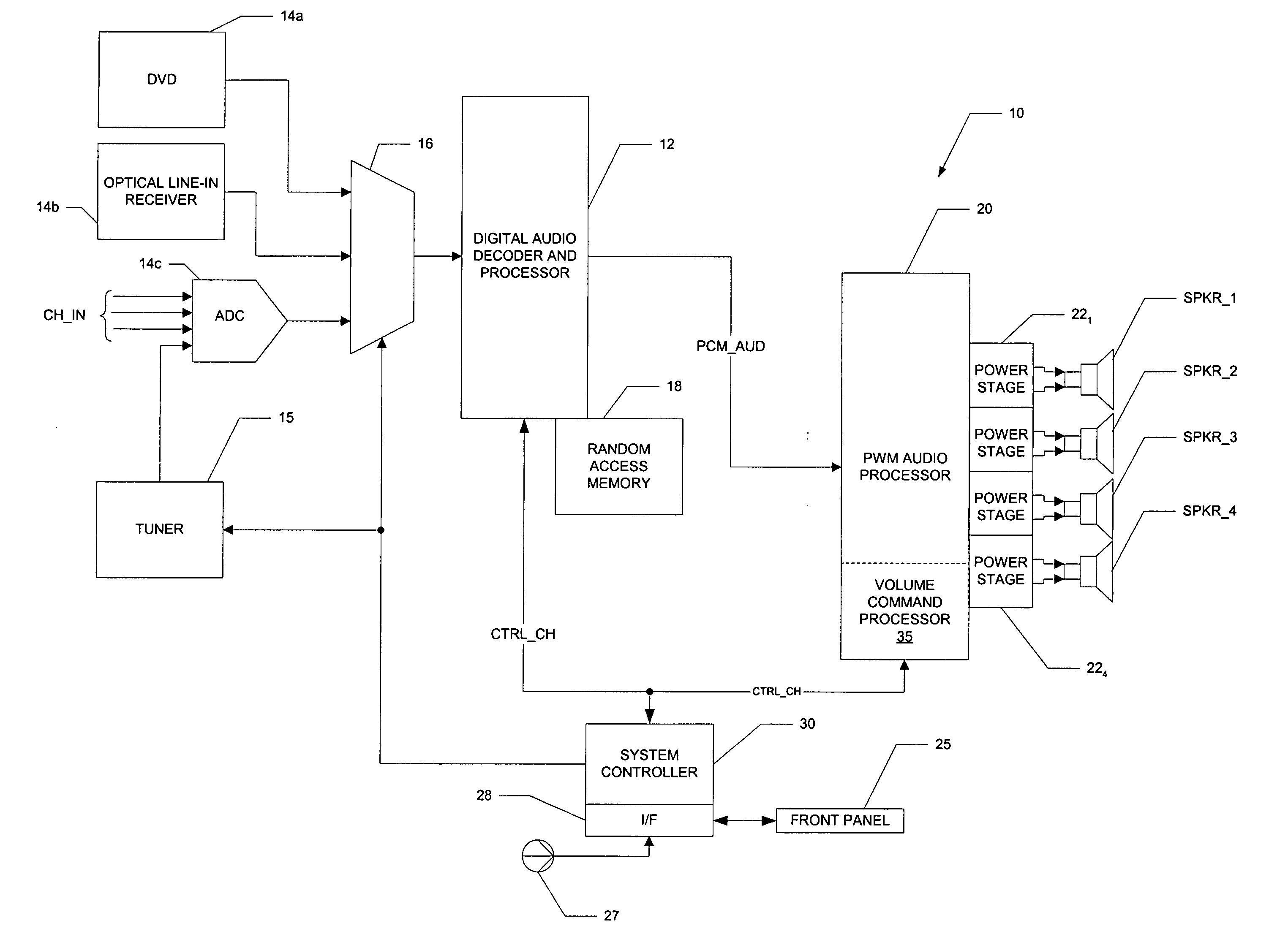

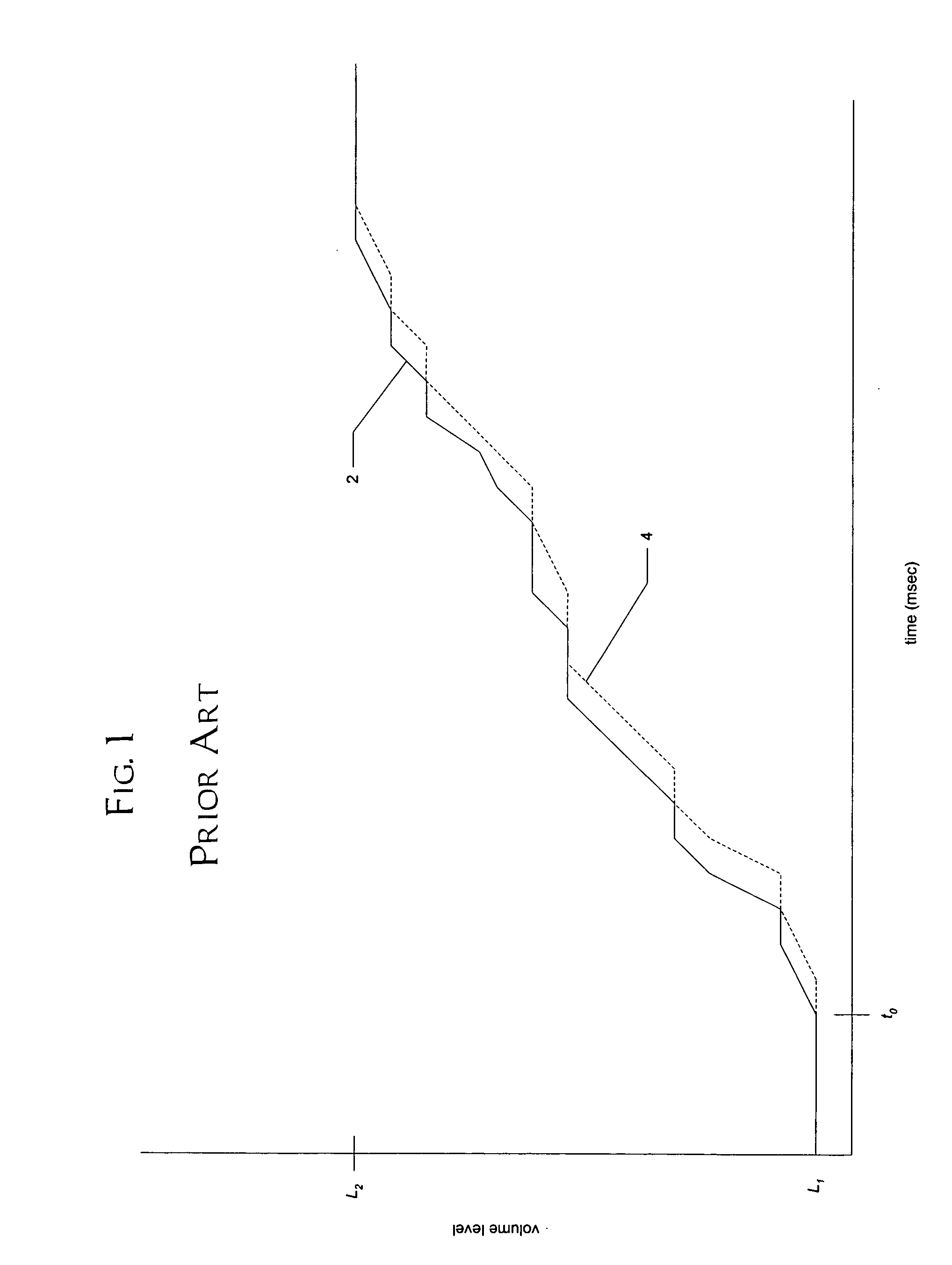

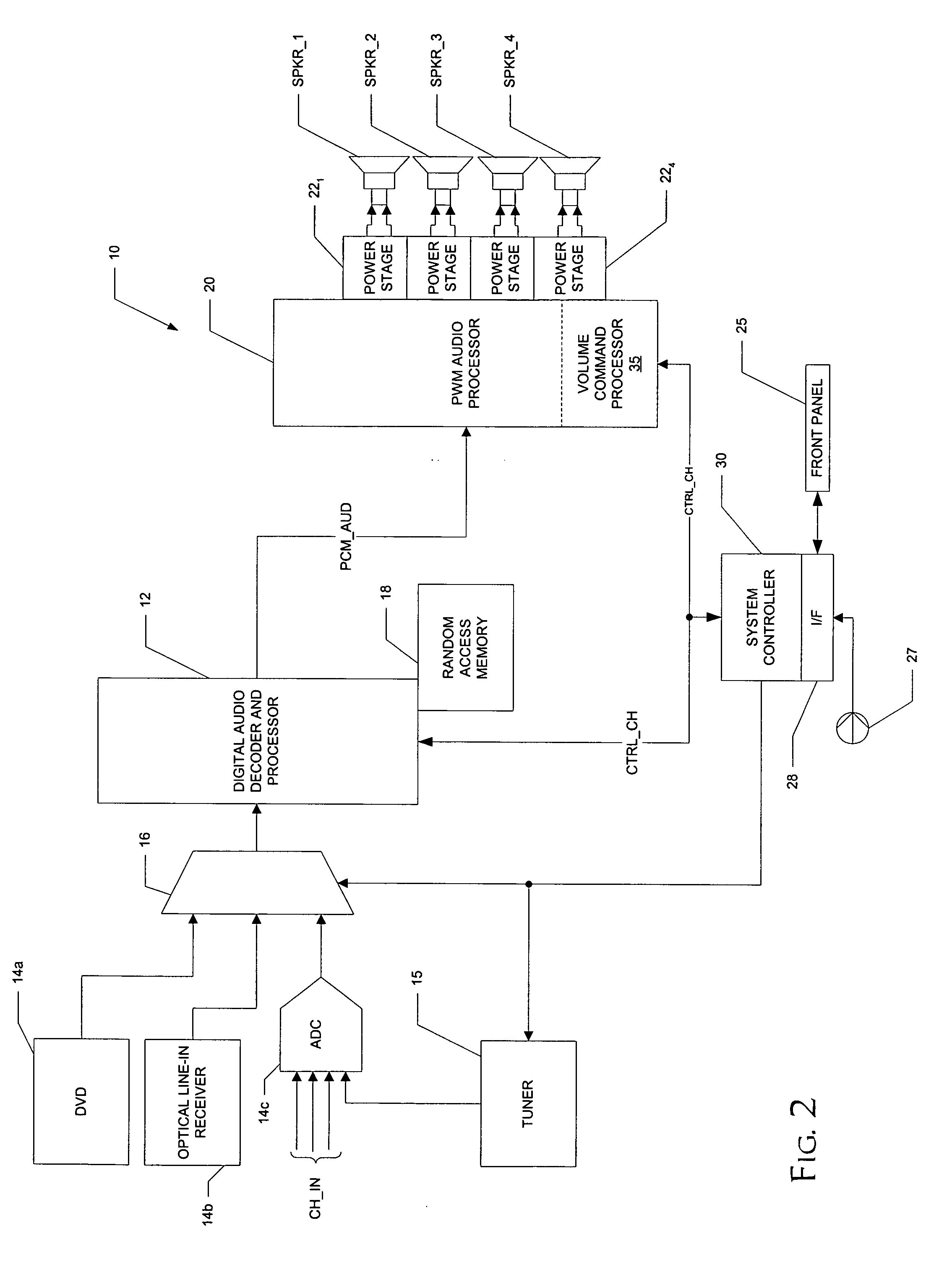

Batch processing control of volume events in a digital amplifier environment

InactiveUS20060247811A1Efficiently effectedAvoid artifactsDigital/coded signal controlAmplifier with semiconductor-devices/discharge-tubesBatch processingRemote control

A digital audio-visual receiver (10) with improved digital control of audio volume is disclosed. Upon receipt of a user volume command, via a front panel (25) or a remote control and infrared receiver (27), sequential logic (36) in a volume command processor (35) in a PWM audio processor (20) of the receiver (10) initiates a timer (38), which measures or counts a selected interval. If additional volume commands are received during the interval, sequential logic (36) resets and restarts the timer (38). Upon the timer (38) interval elapsing without another volume command, the volume command processor (35) generates a ramping volume output signal to reach the volume level of the last received volume command over a selected time duration. Audible artifacts during changes in audio volume are thus avoided.

Owner:TEXAS INSTR INC

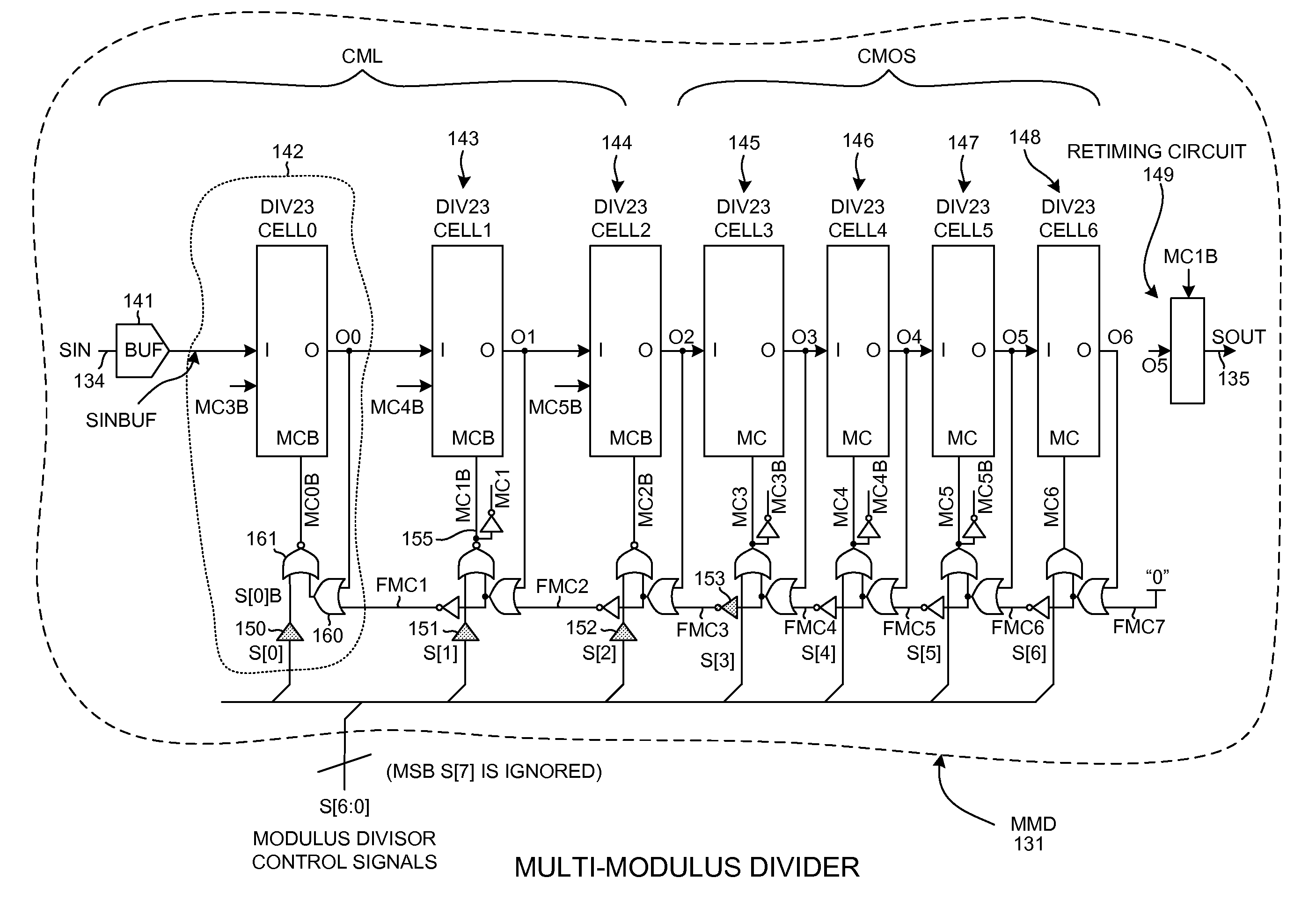

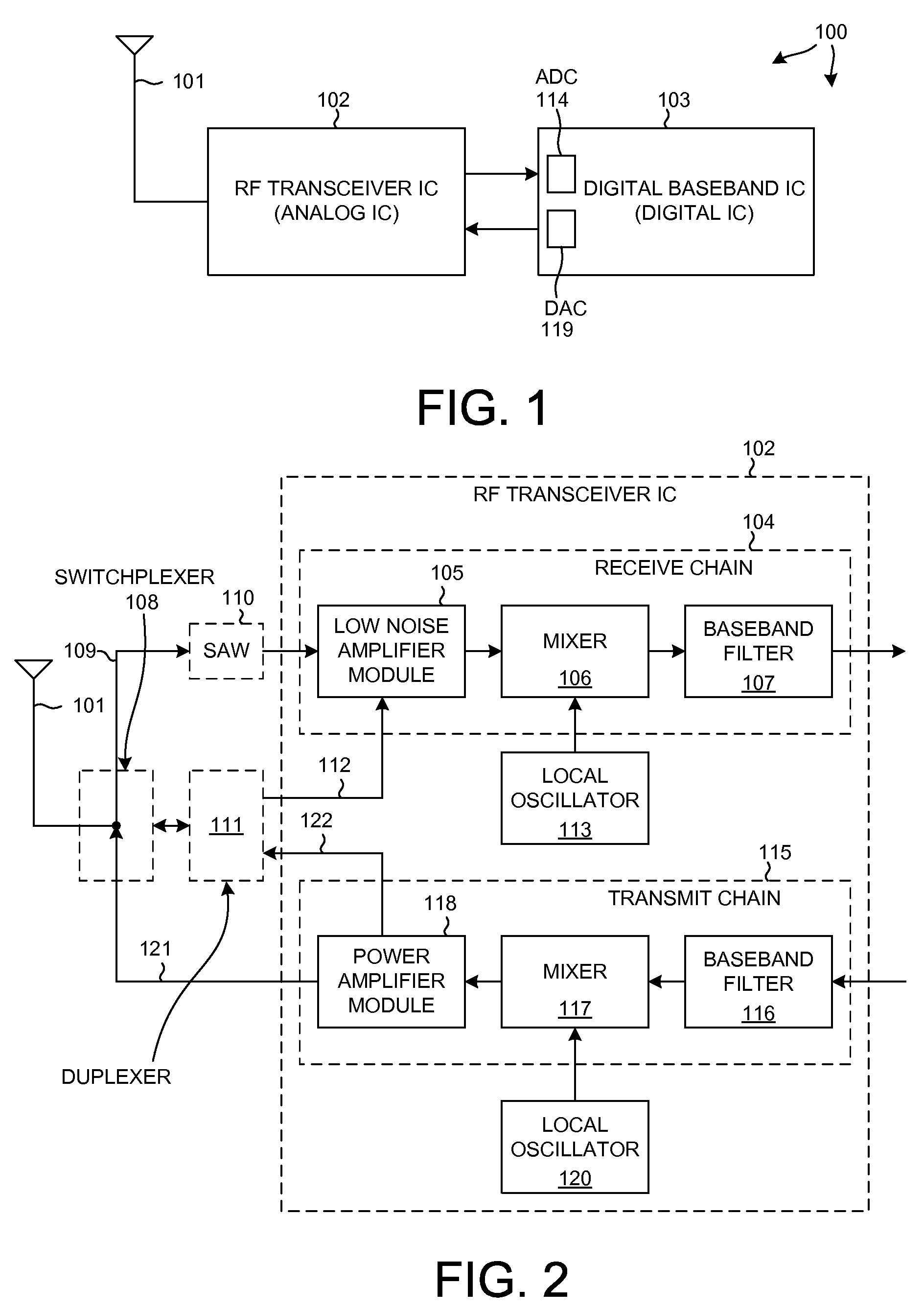

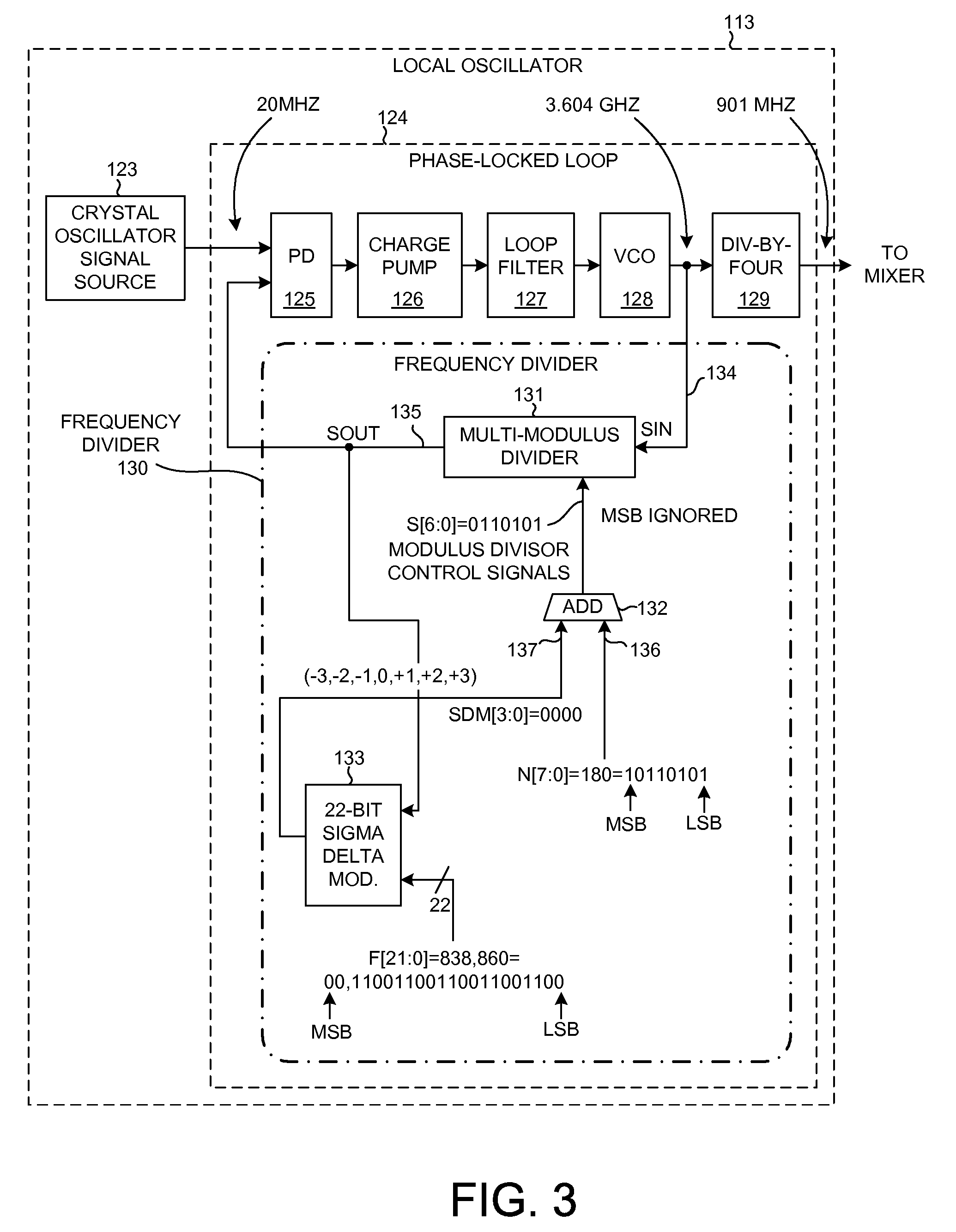

Multi-modulus divider retiming circuit

A multi-modulus divider (MMD) receives an MMD input signal and outputs an MMD output signal SOUT. The MMD includes a chain of modulus divider stages (MDSs). Each MDS receives an input signal, divides it by either two or three, and outputs the result as an output signal. Each MDS responds to its own modulus control signal that controls whether it divides by two or three. In one example, a sequential logic element outputs SOUT. The low jitter modulus control signal of one of the first MDS stages of the chain is used to place a sequential logic element into a first state. The output signal of one of the MDS stages in the middle of the chain is used to place the sequential logic element into a second state. Power consumption is low because the sequential logic element is not clocked at the high frequency of the MMD input signal.

Owner:QUALCOMM INC

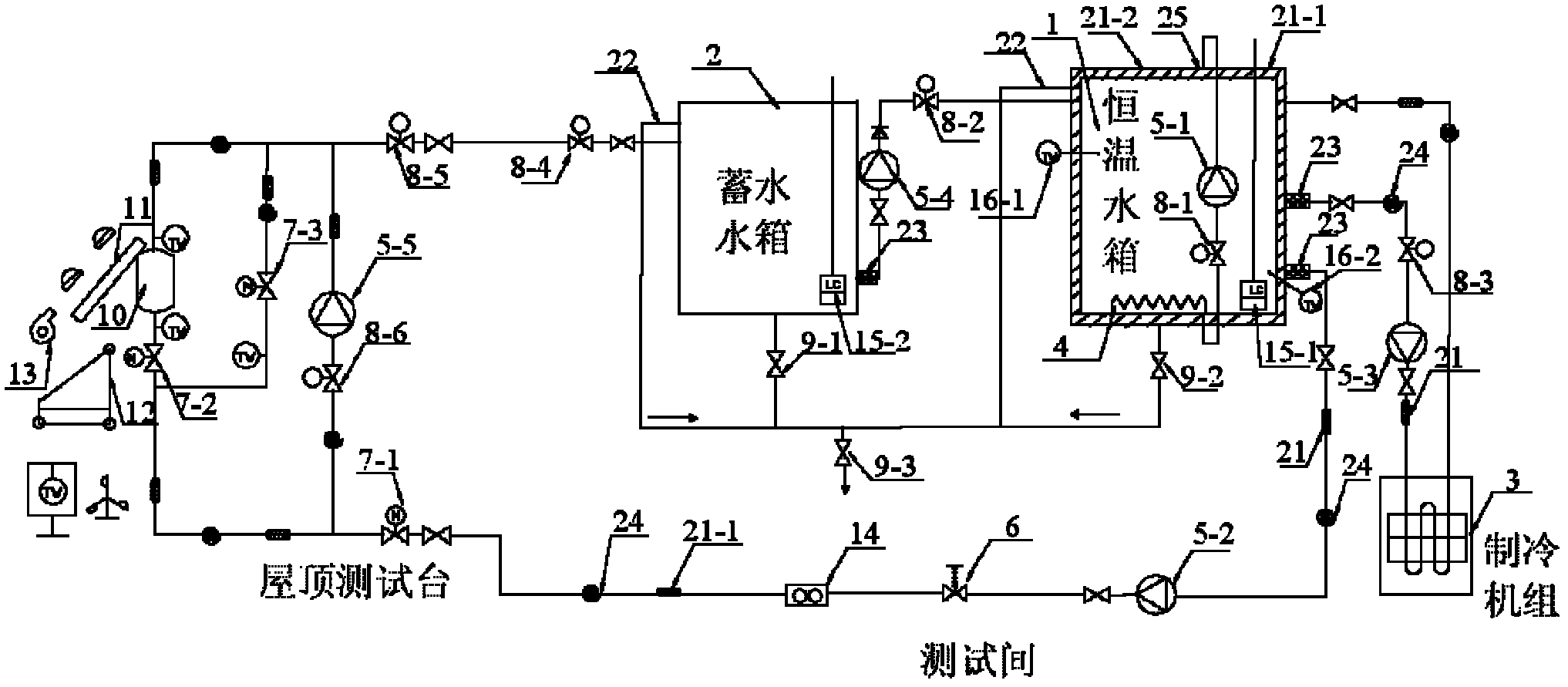

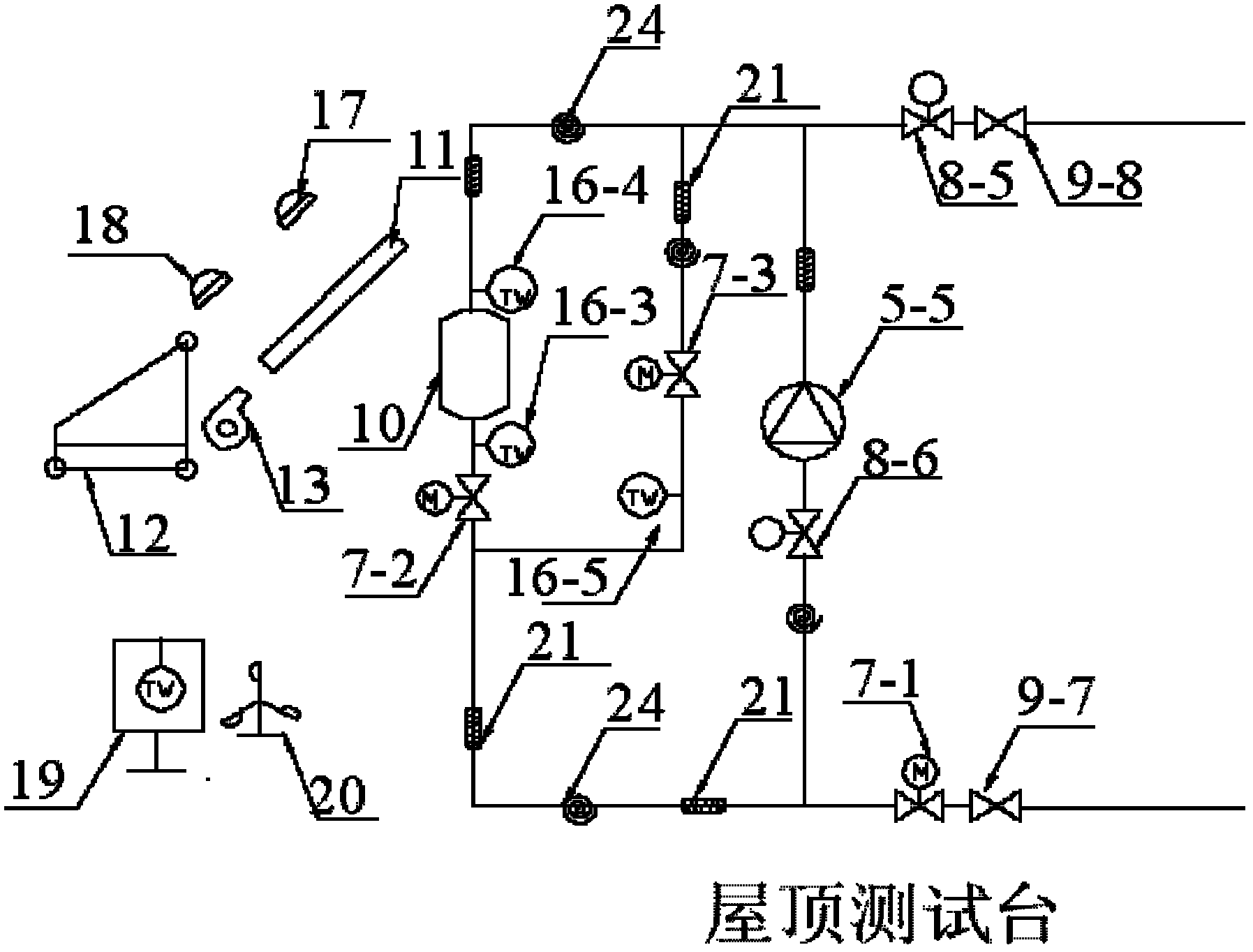

Thermal performance test system of solar water heater

InactiveCN102564783APrevent backflowRealize fully automatic intelligent controlStructural/machines measurementWater storageData acquisition

The invention discloses a thermal performance test system of a solar water heater. The thermal performance test system comprises a pipeline system, a test rack and a full-automatic intelligent control system. The pipeline system comprises a constant-temperature water tank (1), a refrigeration system connected with the constant-temperature water tank (1), a self-circulation system positioned outside the constant-temperature water tank (1), and an electric heating device arranged at the bottom of the constant-temperature water tank; the pipeline system is connected with a thermal storage water tank (10) in a test rack system of the solar water heater; and the pipeline system, the constant-temperature water tank and a water storage water tank form a loop. The full-automatic intelligent control system realizes data acquisition, sequential logic control and real-time regulation and control of temperature and flow by adopting a programmable controller (PLC).

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

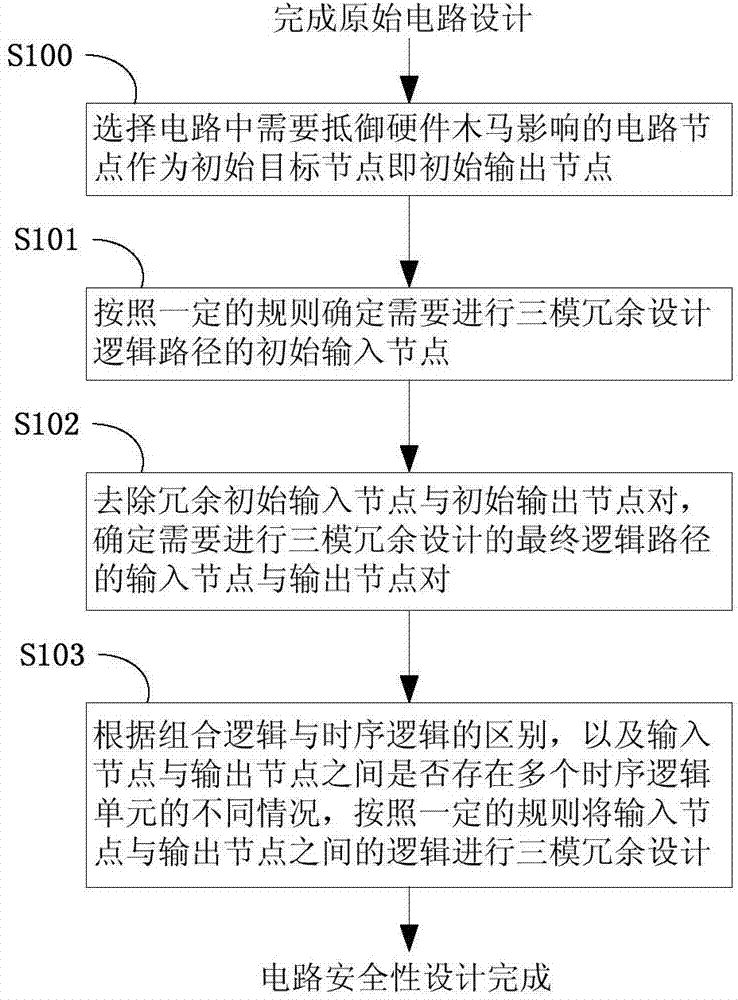

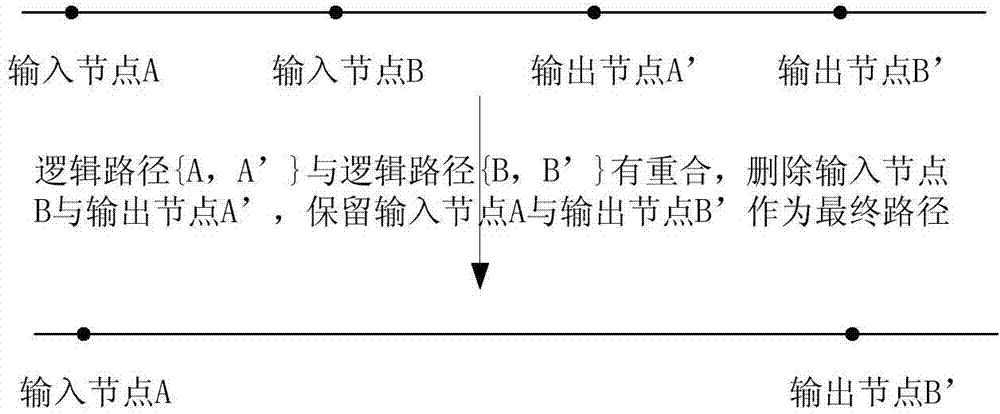

Circuit safety design method for defending against threat of hardware Trojan horse based on triple modular redundancy

ActiveCN104715121ADefend against potential threatsGuaranteed to be correctInternal/peripheral component protectionSpecial data processing applicationsNODALSequential logic

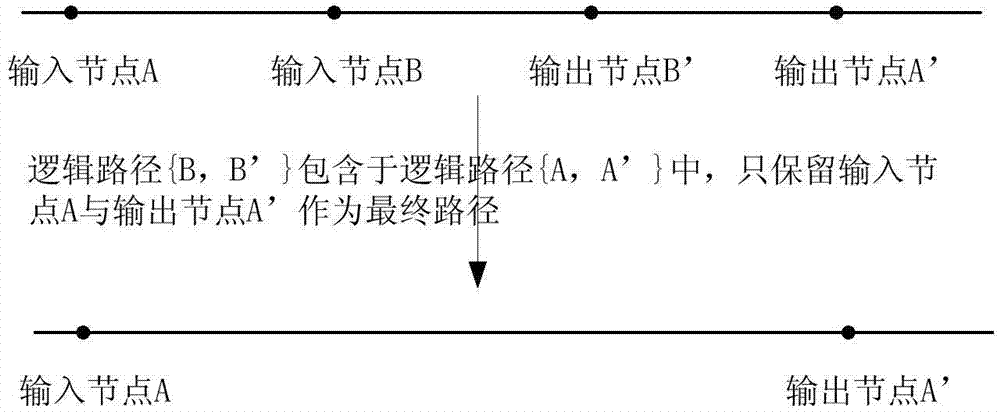

The invention provides a circuit safety design method which utilizes triple modular redundancy to guarantee that an original circuit can work stably even if a hardware Trojan horse is maliciously embedded in the original circuit. The circuit safety design method comprises the following steps: firstly, after finishing the design and verification of the original circuit, selecting logical nodes which can not be covered by all conventional testing methods, and taking the logical nodes as output nodes; secondly, backtracking the output nodes as terminal points in a fan-in direction, and determining input nodes according to certain rules; and finally, performing the triple modular redundancy design of paths between the input nodes and the output nodes respectively according to the difference between combinatorial logic and sequential logic. Through the circuit safety design method, final output cannot be affected even after the logic value of a circuit node, which cannot be tested or has high risk, is changed under the influence of a hardware Trojan horse, and the original function of the circuit is kept.

Owner:58TH RES INST OF CETC

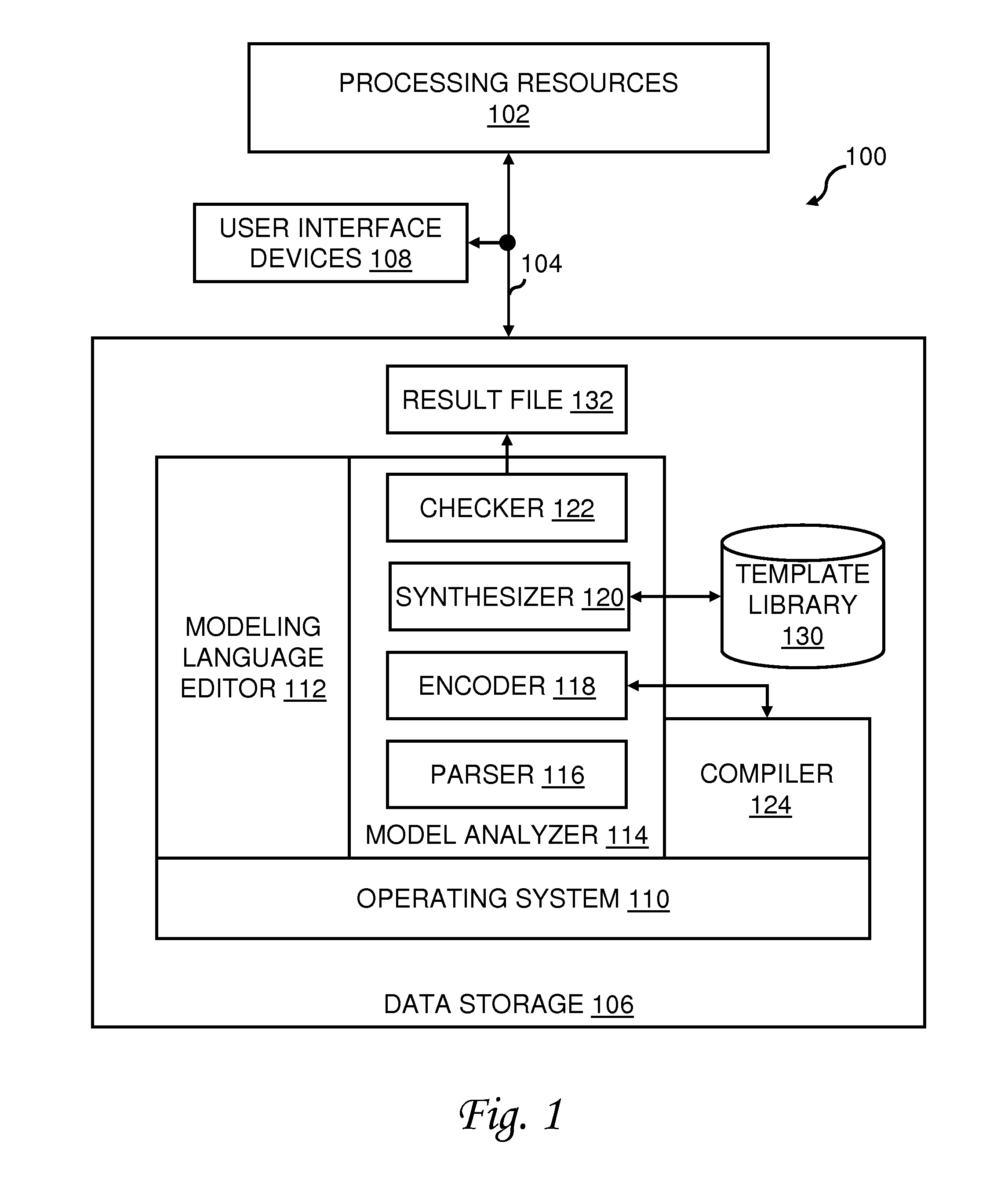

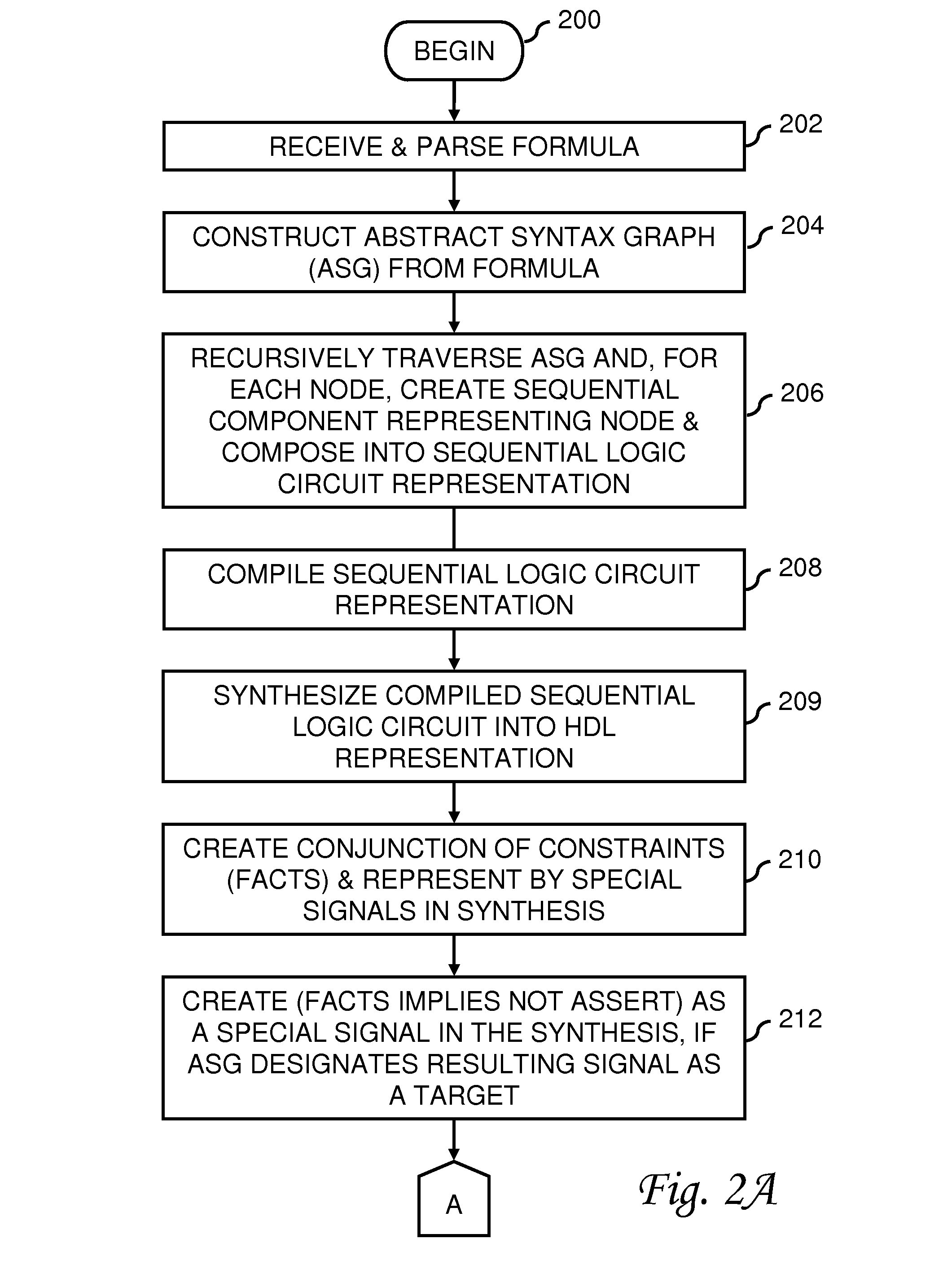

Method, System and Program Product Supporting Sequential Encoding for Relational Analysis (SERA) of a Software Model

InactiveUS20080209389A1Software simulation/interpretation/emulationSpecial data processing applicationsSoftware systemHigh level modeling

A method of verifying a software system includes receiving a description of a software system described utilizing a high-level modeling language, and responsive thereto, parsing the description and constructing an abstract syntax graph. The abstract syntax graph is transformed into a sequential logic representation of the software system, and following the transforming, the software system is verified based upon the sequential logic representation. Following verification, results of verification of the software system are output.

Owner:GLOBALFOUNDRIES INC

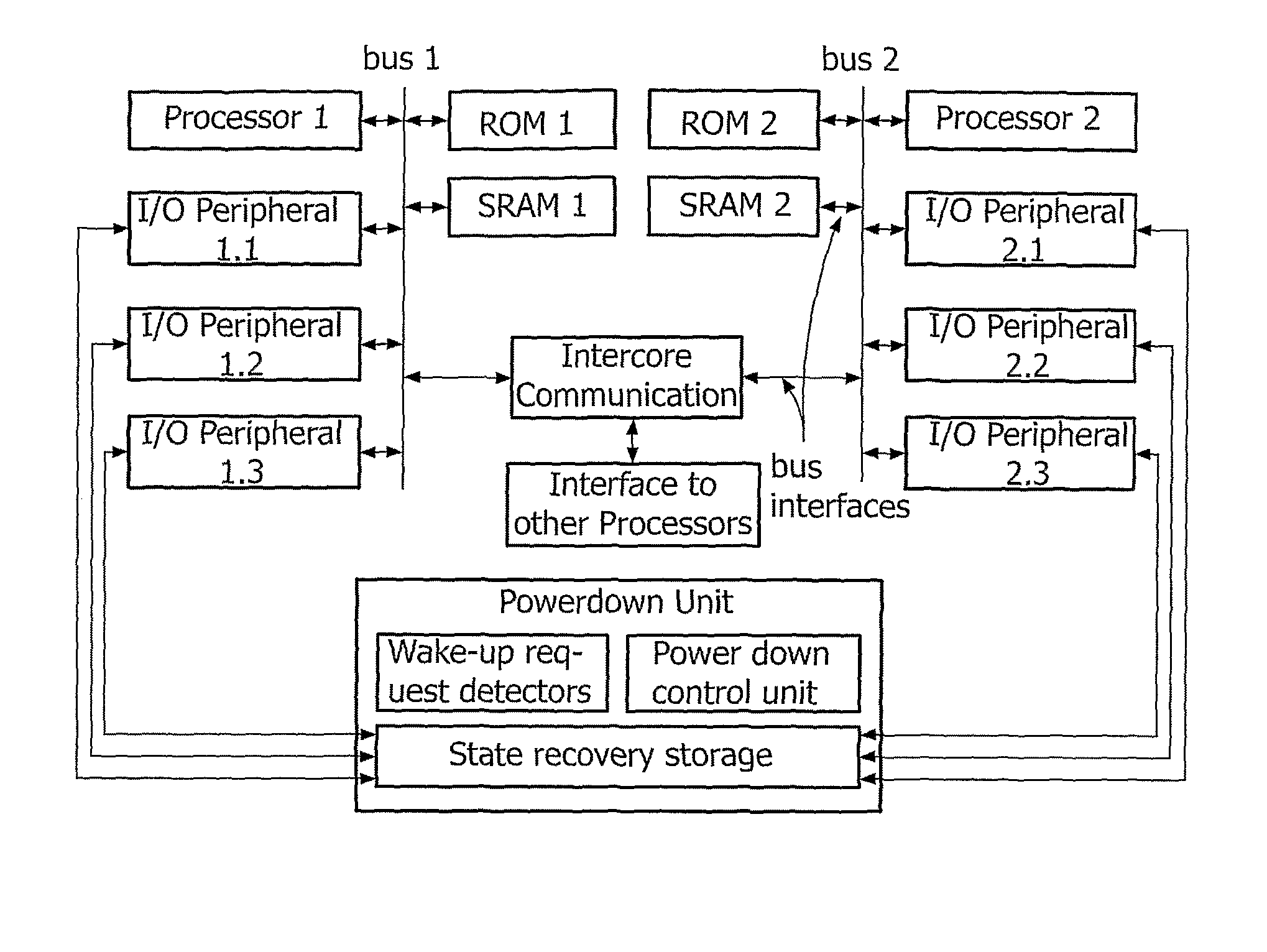

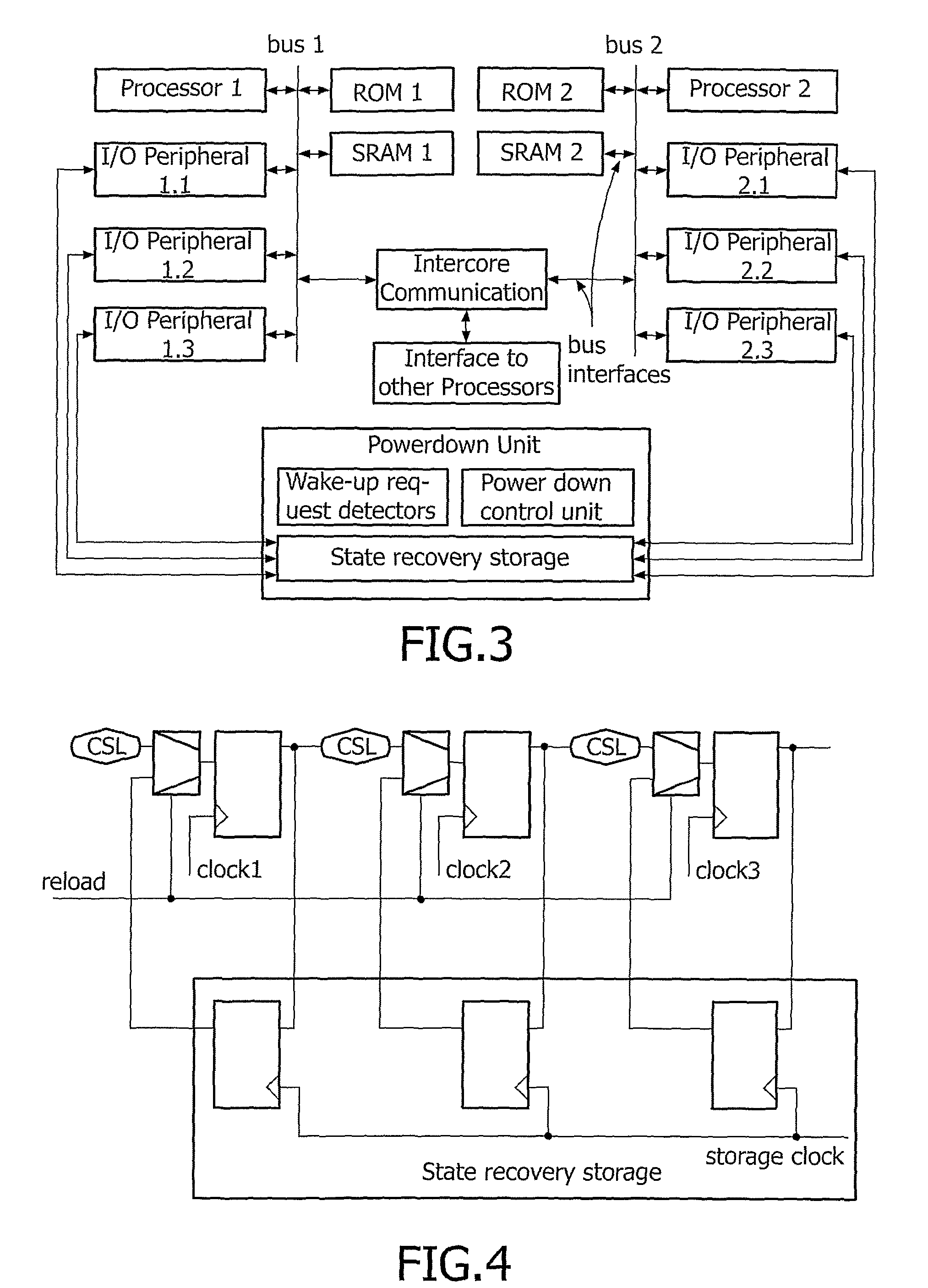

Method apparatus comprising integrated circuit and method of powering down such circuit

ActiveUS7848718B2Total current dropMinimizing leakage currentAnalogue computers for vehiclesResonant long antennasLow leakageEngineering

The present invention relates to a mobile apparatus comprising an integrated circuit to operate predefined functions, which integrated circuit is susceptible to be set in a standby operating mode wherein which said circuit can resume operation within a predefined delay. The circuit comprises configuration sequential logic having defined states that need to be stored before the circuit enters in standby mode. The mobile apparatus further comprises a power down unit for storing the states of the configuration sequential logic into a low leakage storage area during standby mode that reduces standby current considerably.

Owner:SNAPTRACK

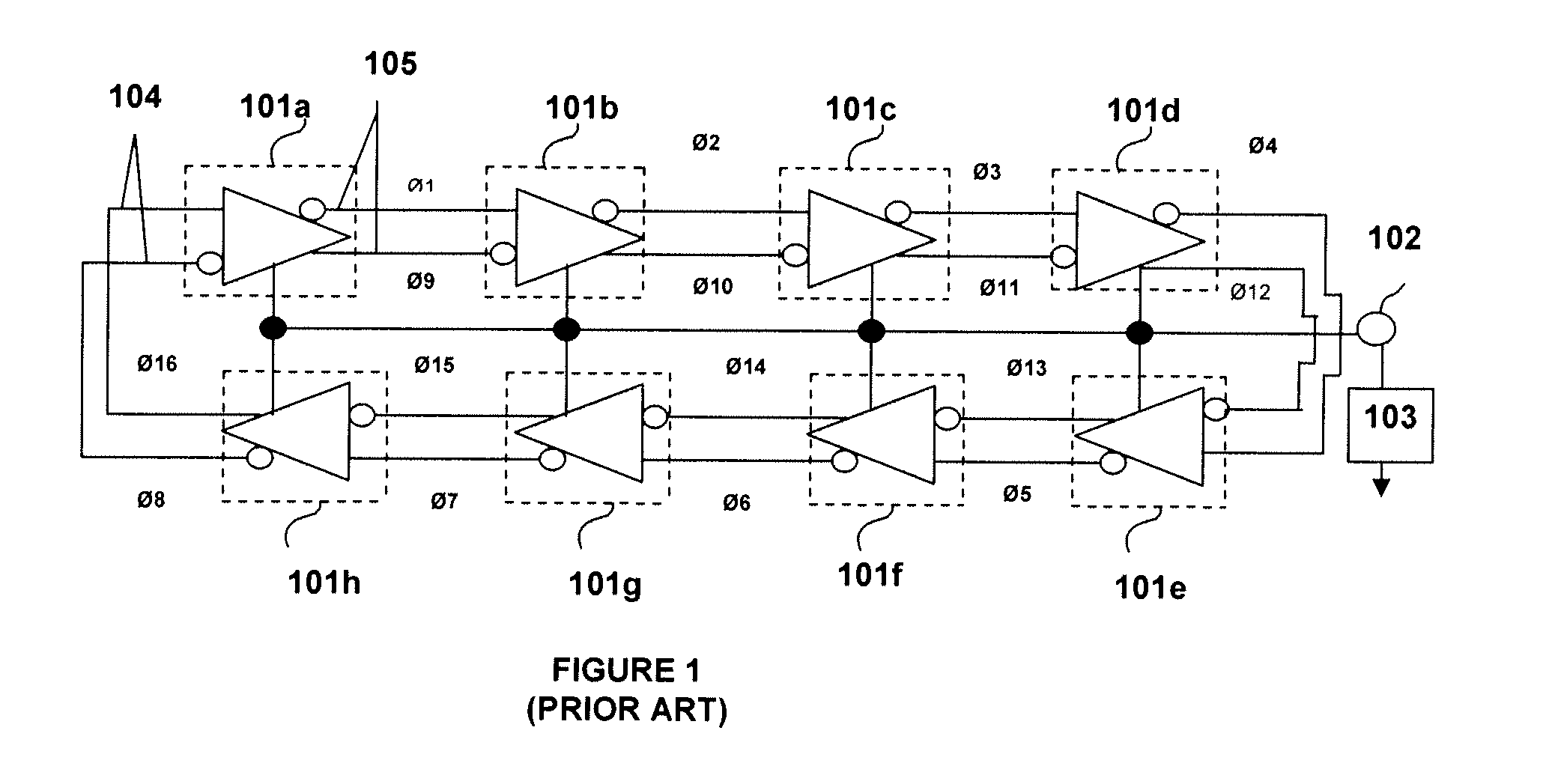

System and method for multiple-phase clock generation

ActiveUS20070200641A1Simple processPulse automatic controlPulse generation by logic circuitsSequential logicMulti phase

A multiple phase clock circuit includes a multiple stage voltage controlled oscillator (VCO) and multiple clock dividers. The VCO is operative at a frequency ‘N’ times higher than the required output frequency and generates ‘M’ equally spaced outputs having different phases but same frequency which are sent to multiple clock dividers. A modified Johnson counter is used as a clock divider. Each counter divides the frequency of the clock signal by N. As a result, each of the M outputs of the VCO are divided into N outputs, thereby making a total of ‘M×N’ equally spaced outputs. These output clock pulses have same frequency but different phases. A sequential logic is provided within the device for enabling the Johnson counters as soon as the VCO starts giving output, thus maintaining the sequence of the output of the Johnson counters.

Owner:STMICROELECTRONICS PVT LTD

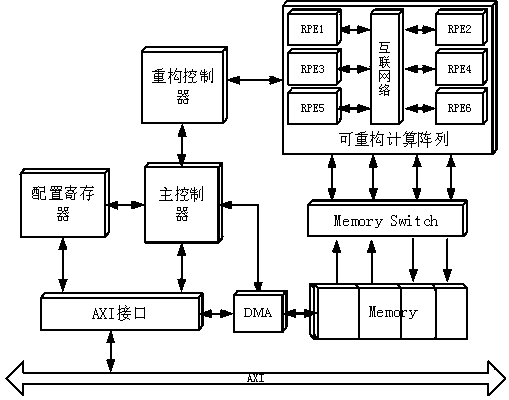

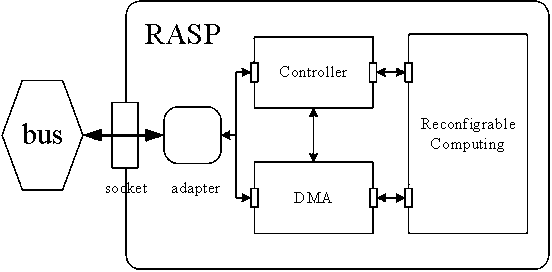

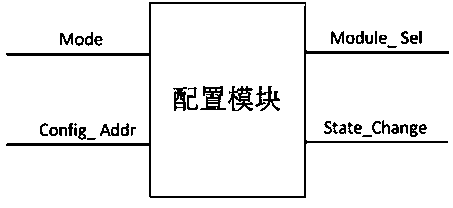

Accurate-period simulation model for reconfigurable special processor core and hardware architecture thereof

InactiveCN103927219AGood software and hardware interfaceSimulate sequential logicSoftware simulation/interpretation/emulationSpecial data processing applicationsHardware architectureComputer module

The invention relates to an accurate-period simulation model for a reconfigurable special processor core on the basis of a SystemC accurate-period model. The accurate-period simulation model comprises a control module, a transmission module and an operation module. The control module sends out configuration parameters and is used for controlling interaction with the exterior of the model and the working conditions of all modules in the model. The transmission module is used for receiving the configuration parameters sent by the control module and used for data transmission outside the special processor core and inside the special processor core. The operation modules are used for receiving the configuration parameters sent by the control module and carrying out operation according to the received configuration parameters and the set algorithm. The accurate-period simulation model has the advantages that a good soft hardware interface is provided on the basis of SystemC language modeling; sequential logic of hardware can be well simulated due to the fact that the model is accurate in period, and the problems can be found fast; compared with other simulation tools and verification platforms, a verification platform of the model is easy to set up, and the simulation velocity is high.

Owner:NANJING UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com