Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

36 results about "High level modeling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Standards-compliant model-based video encoding and decoding

ActiveUS20130230099A1Reduce the impactAvoid problemsColor television with pulse code modulationColor television with bandwidth reductionHigh level modelingVideo encoding

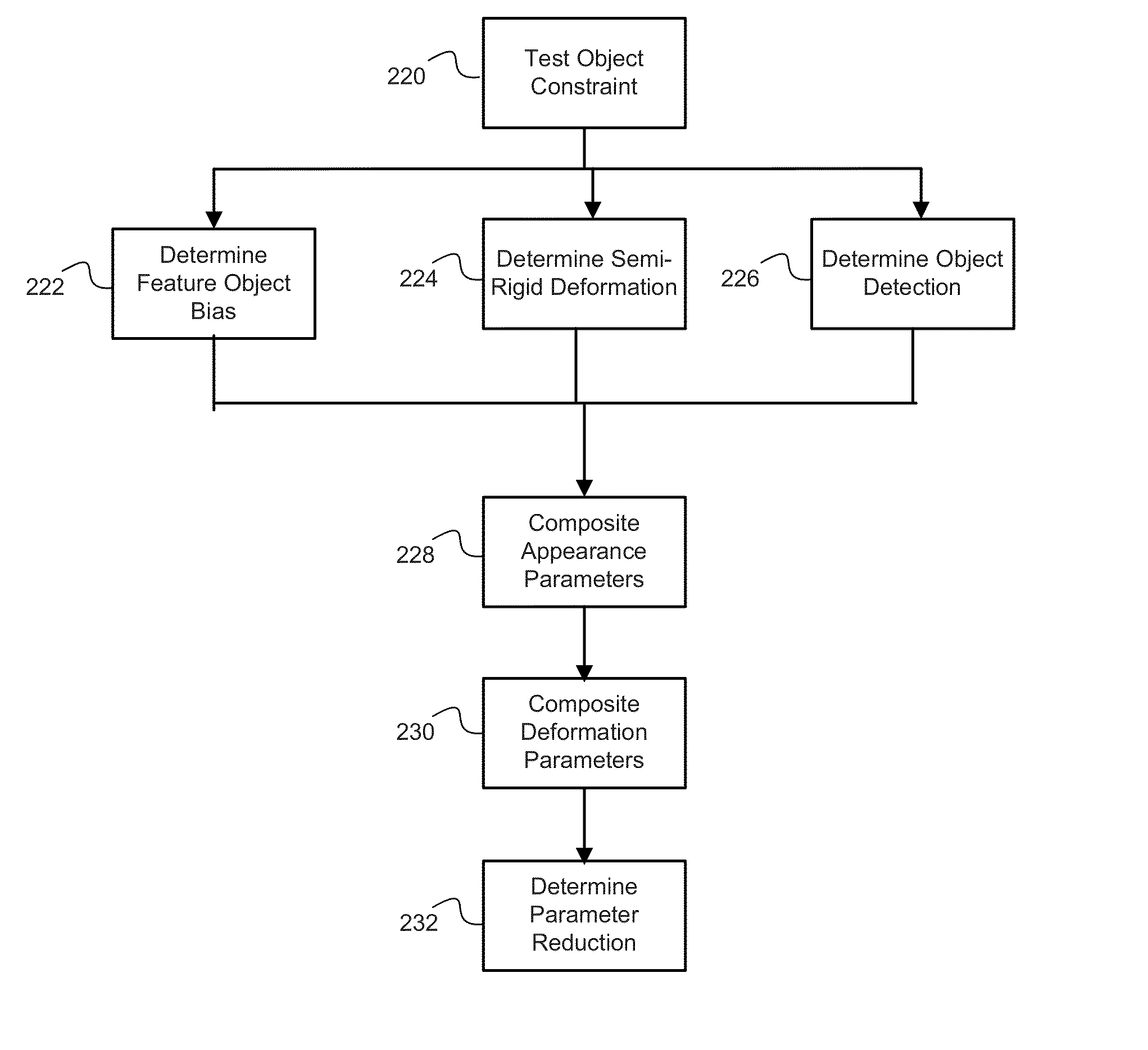

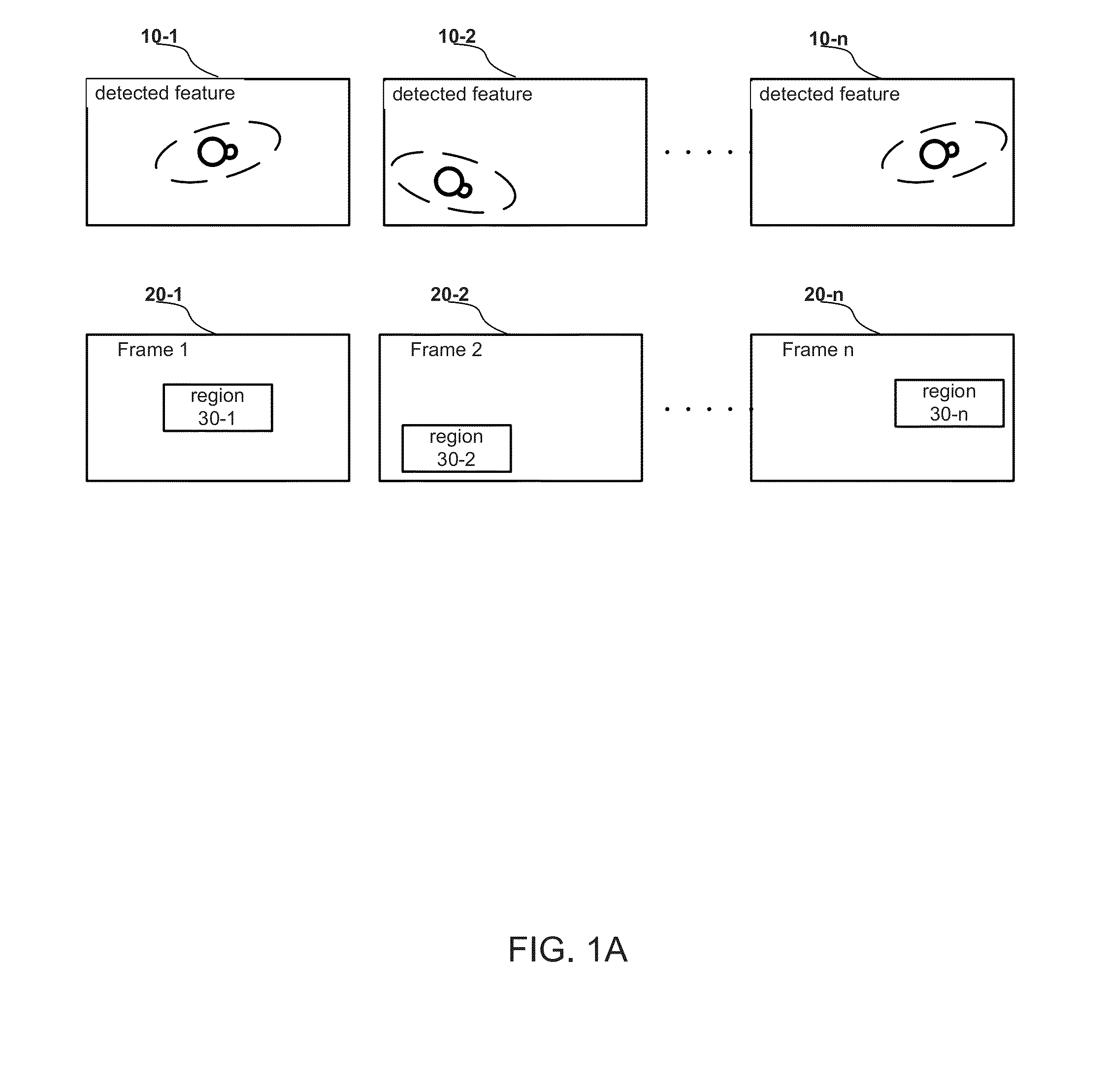

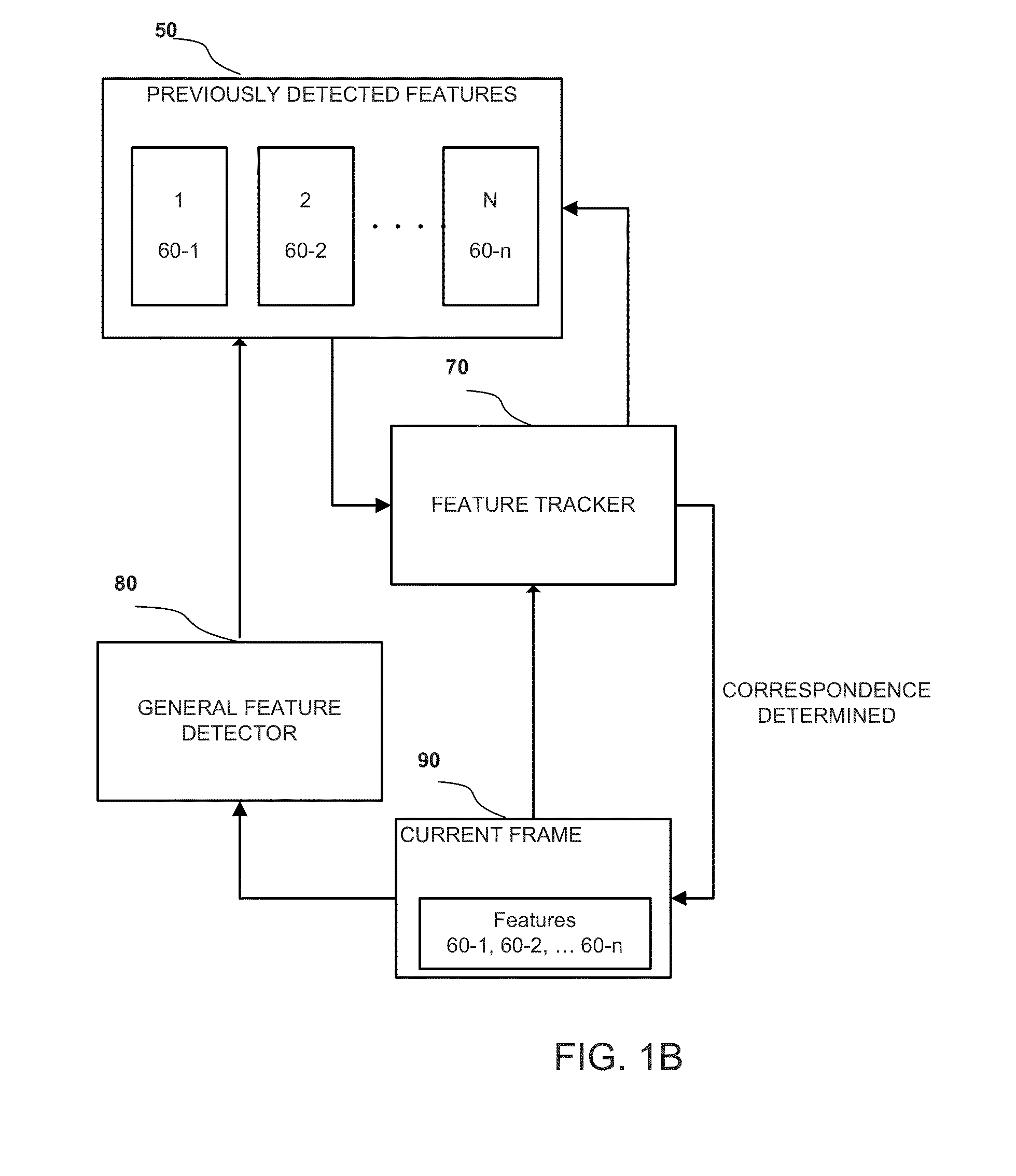

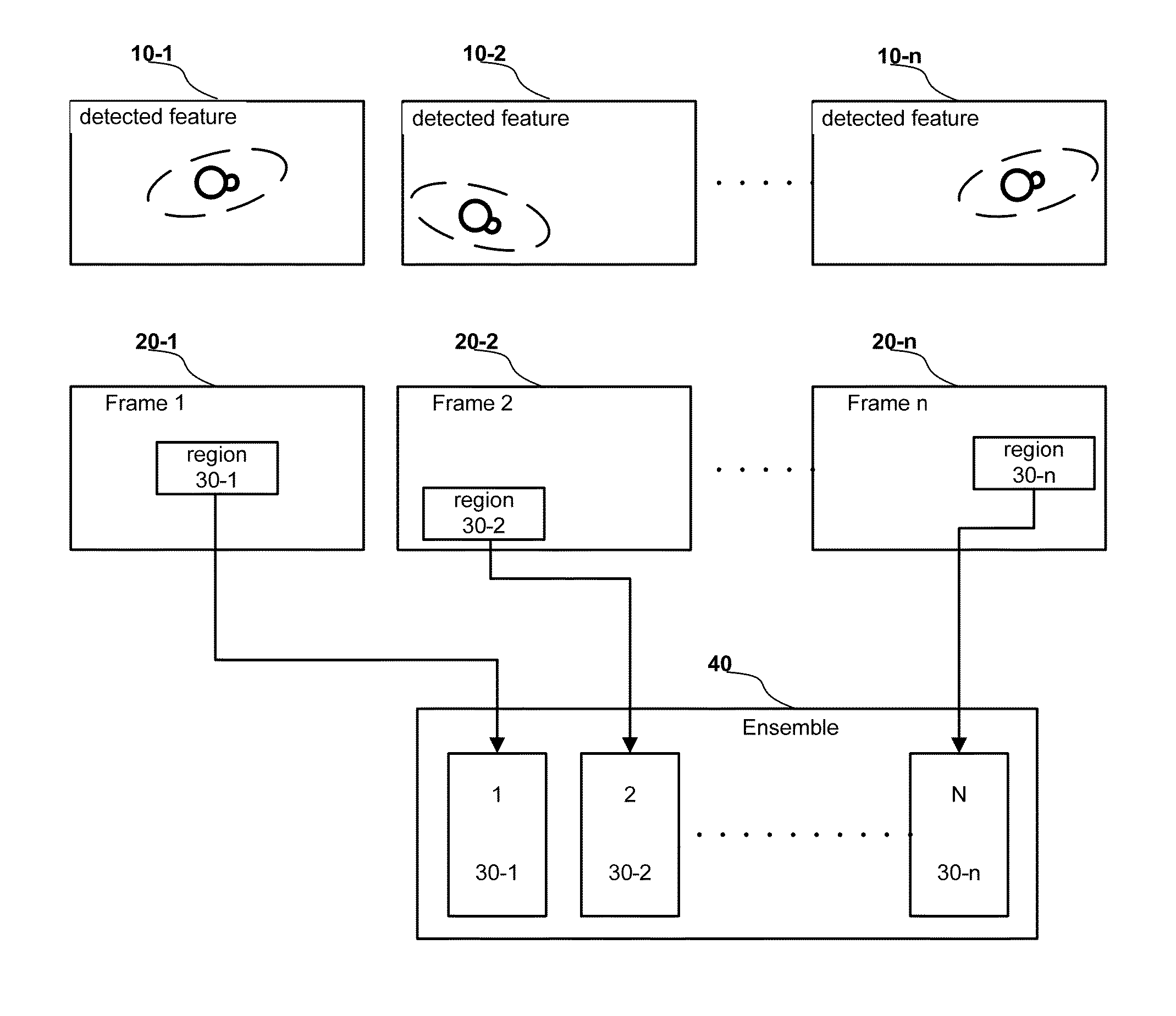

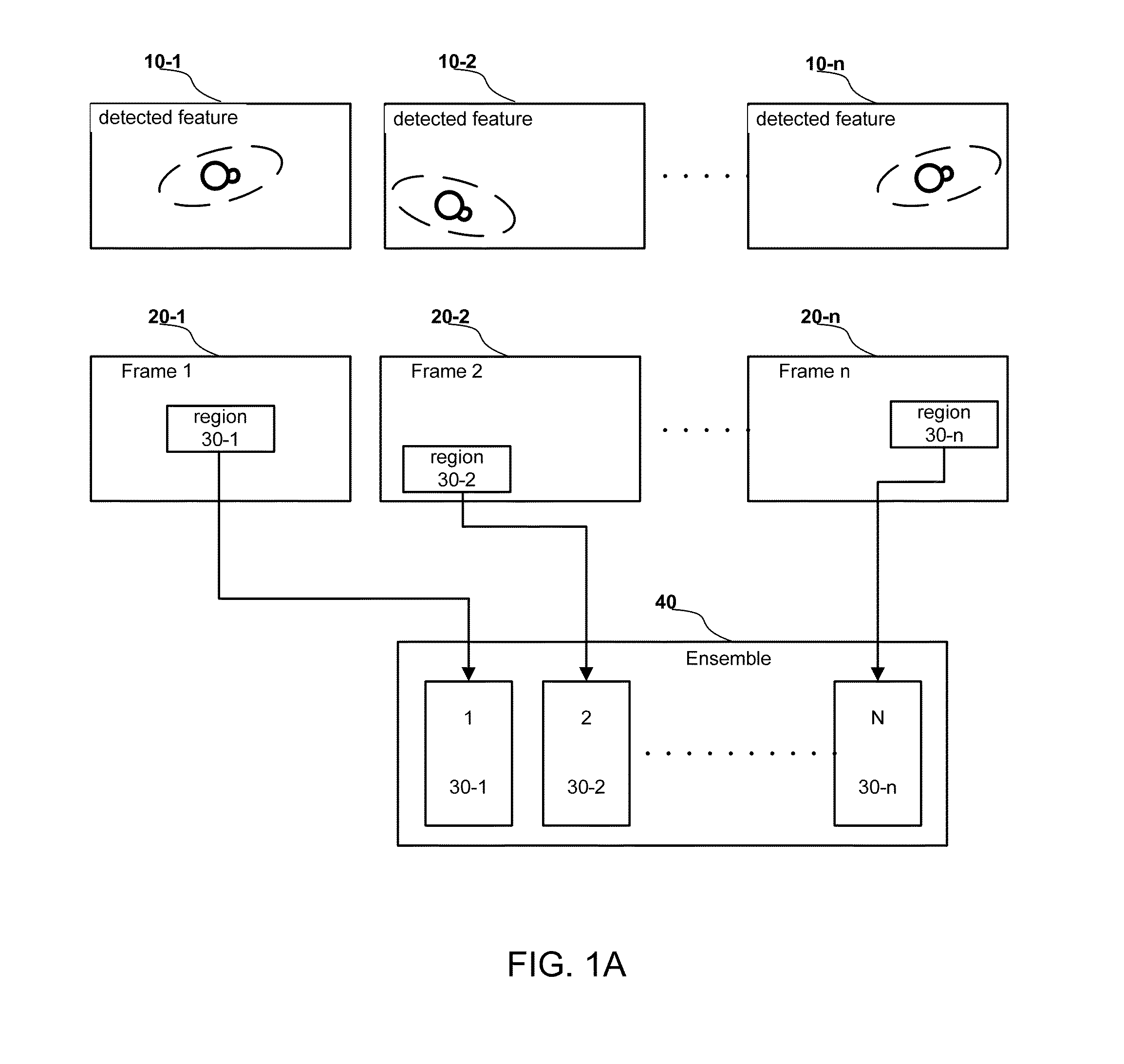

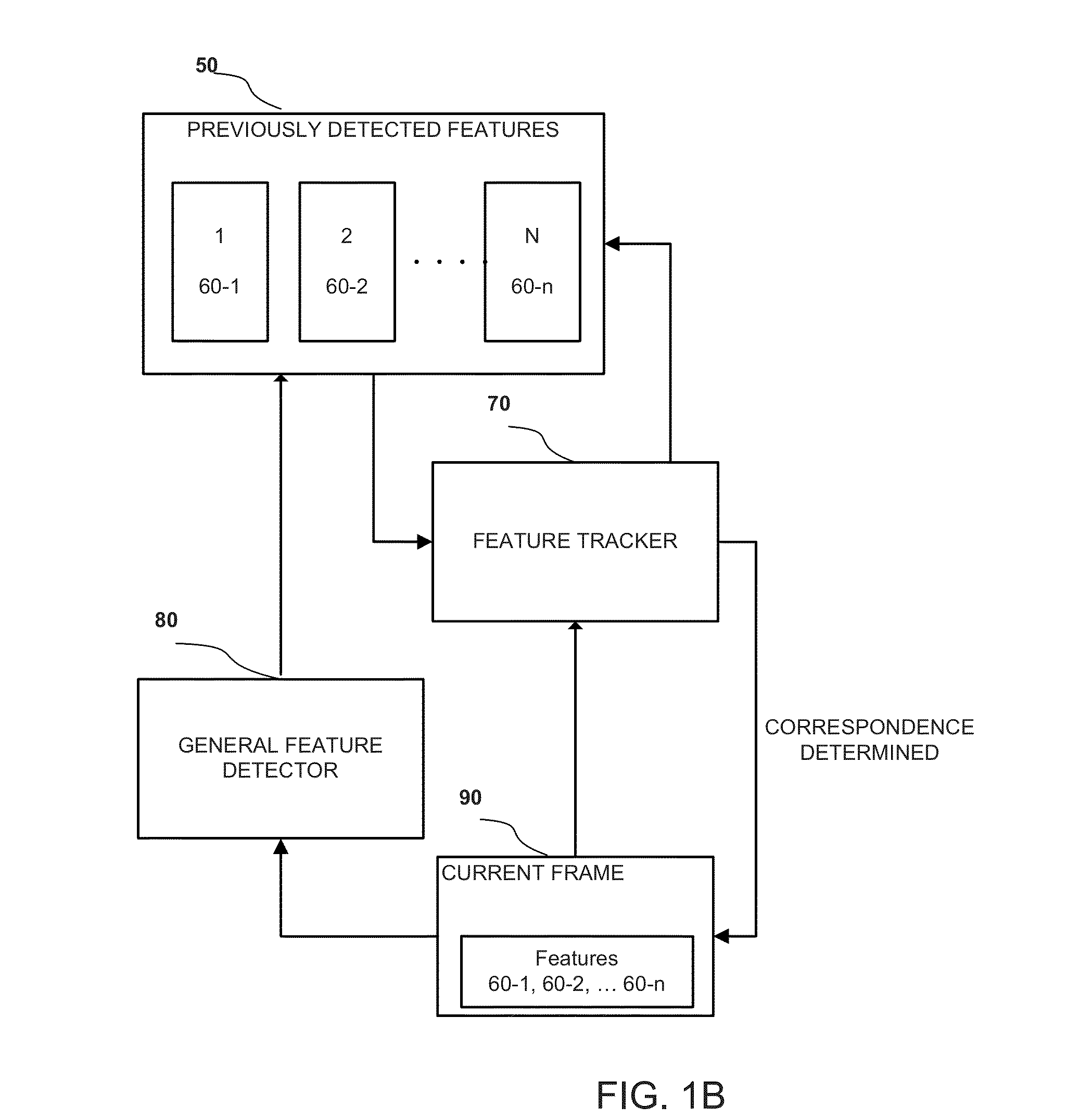

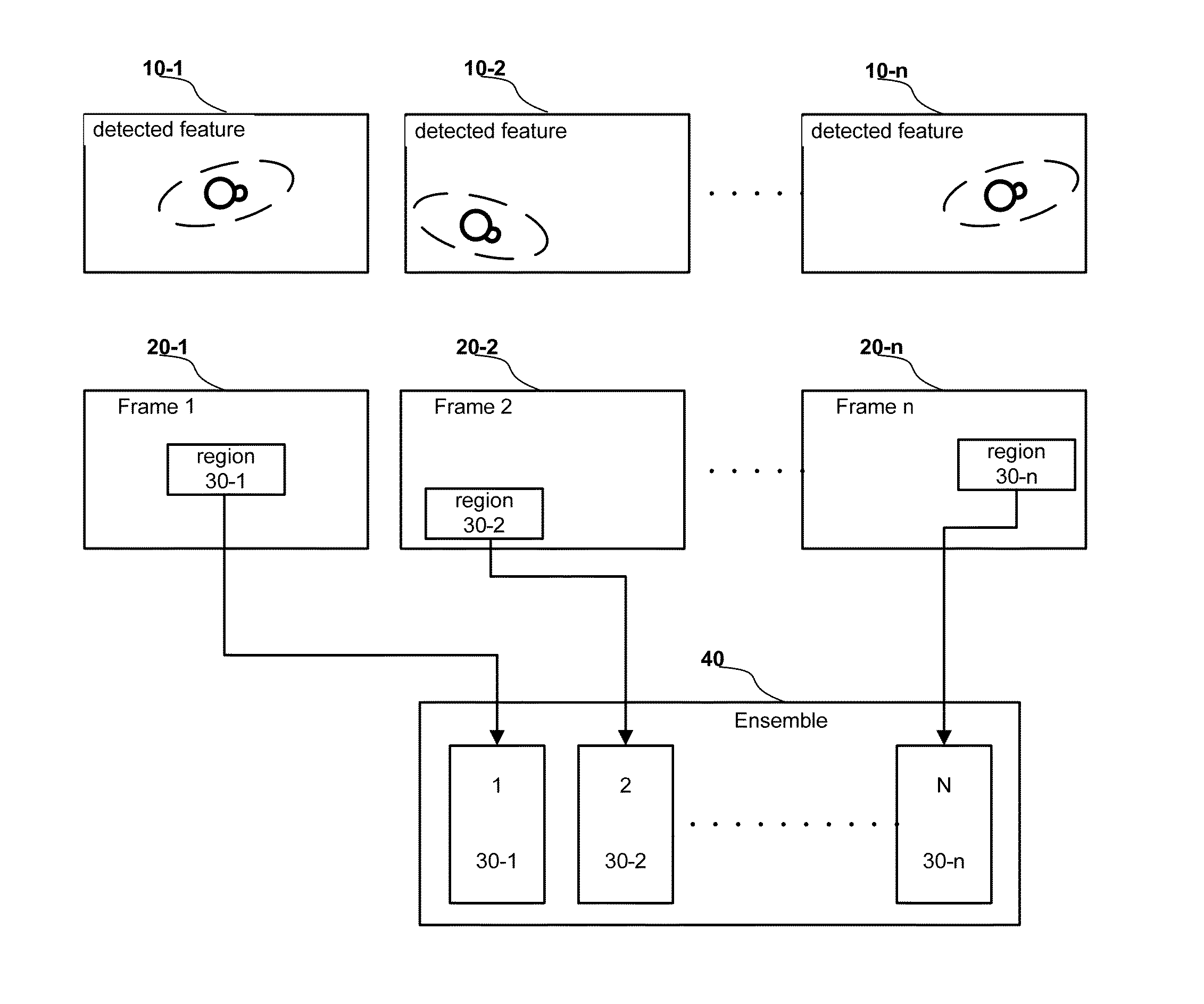

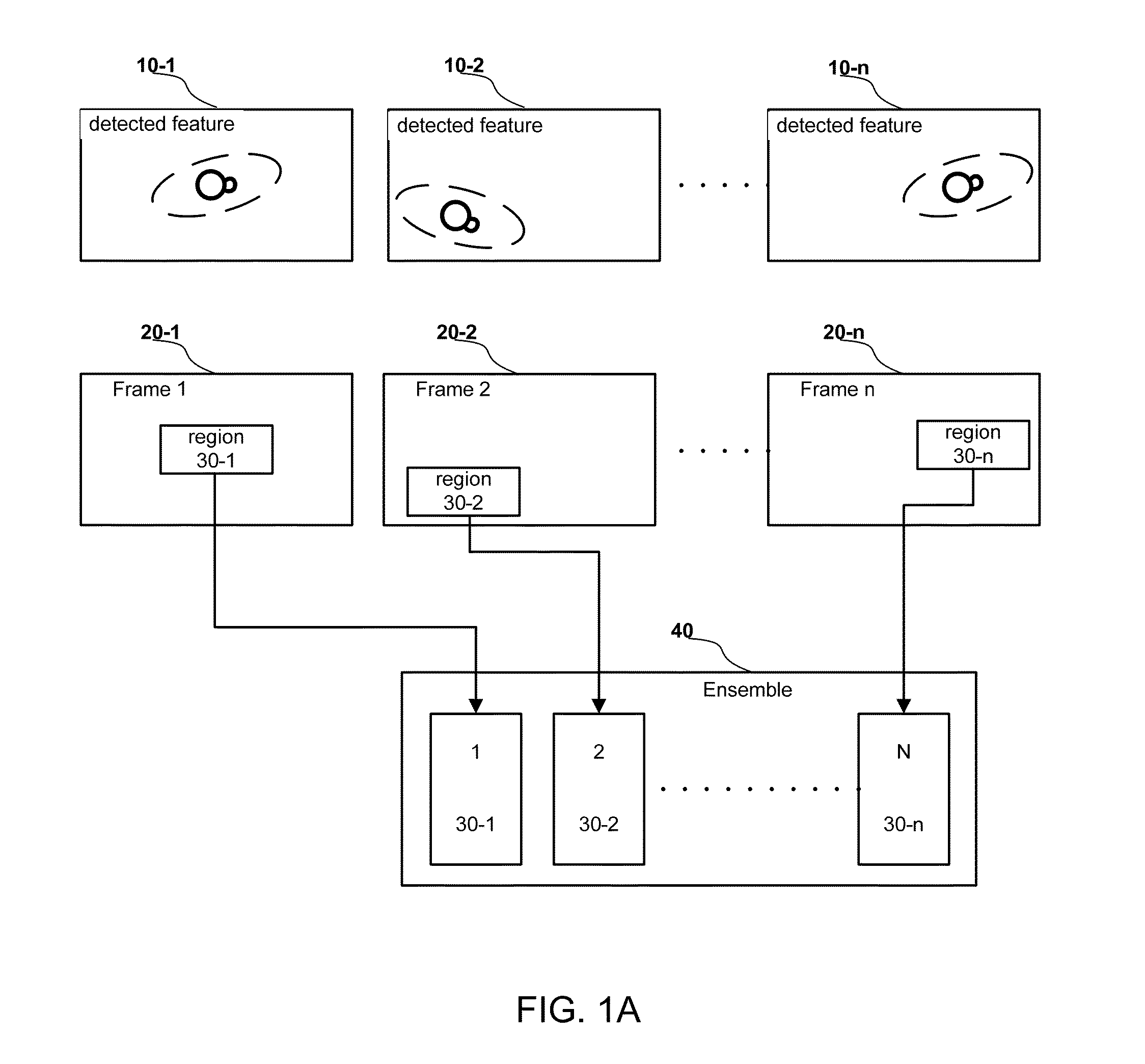

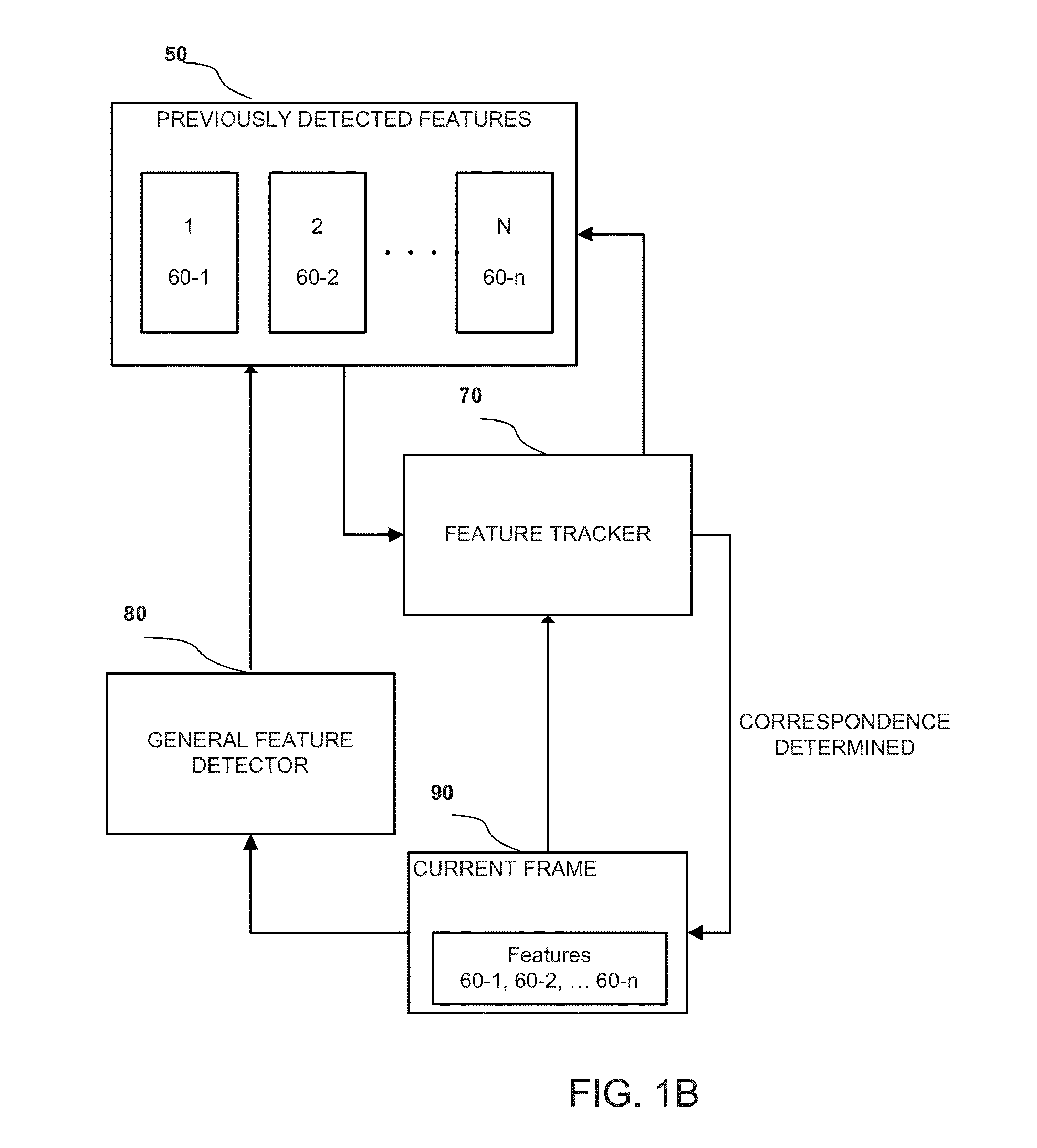

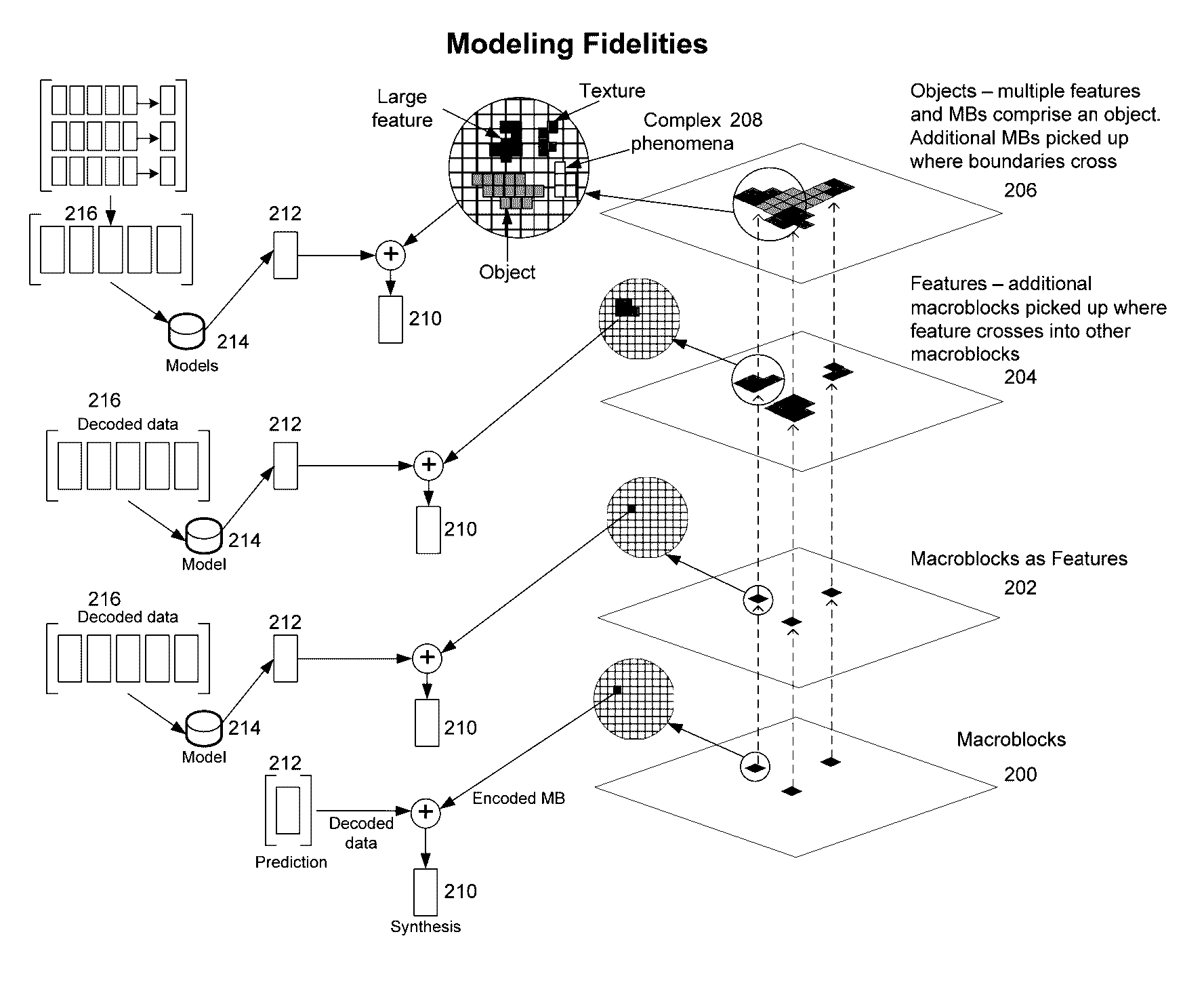

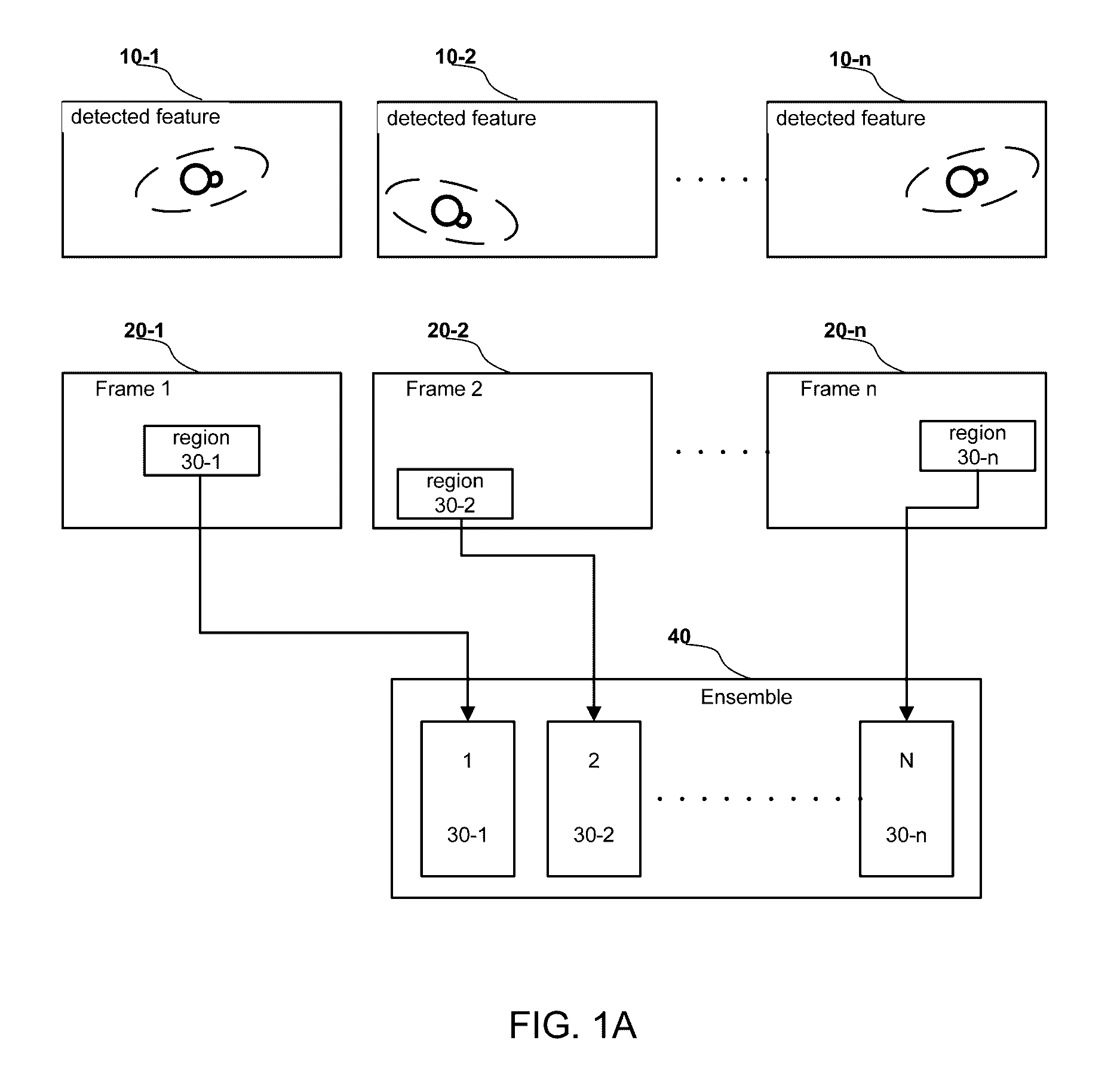

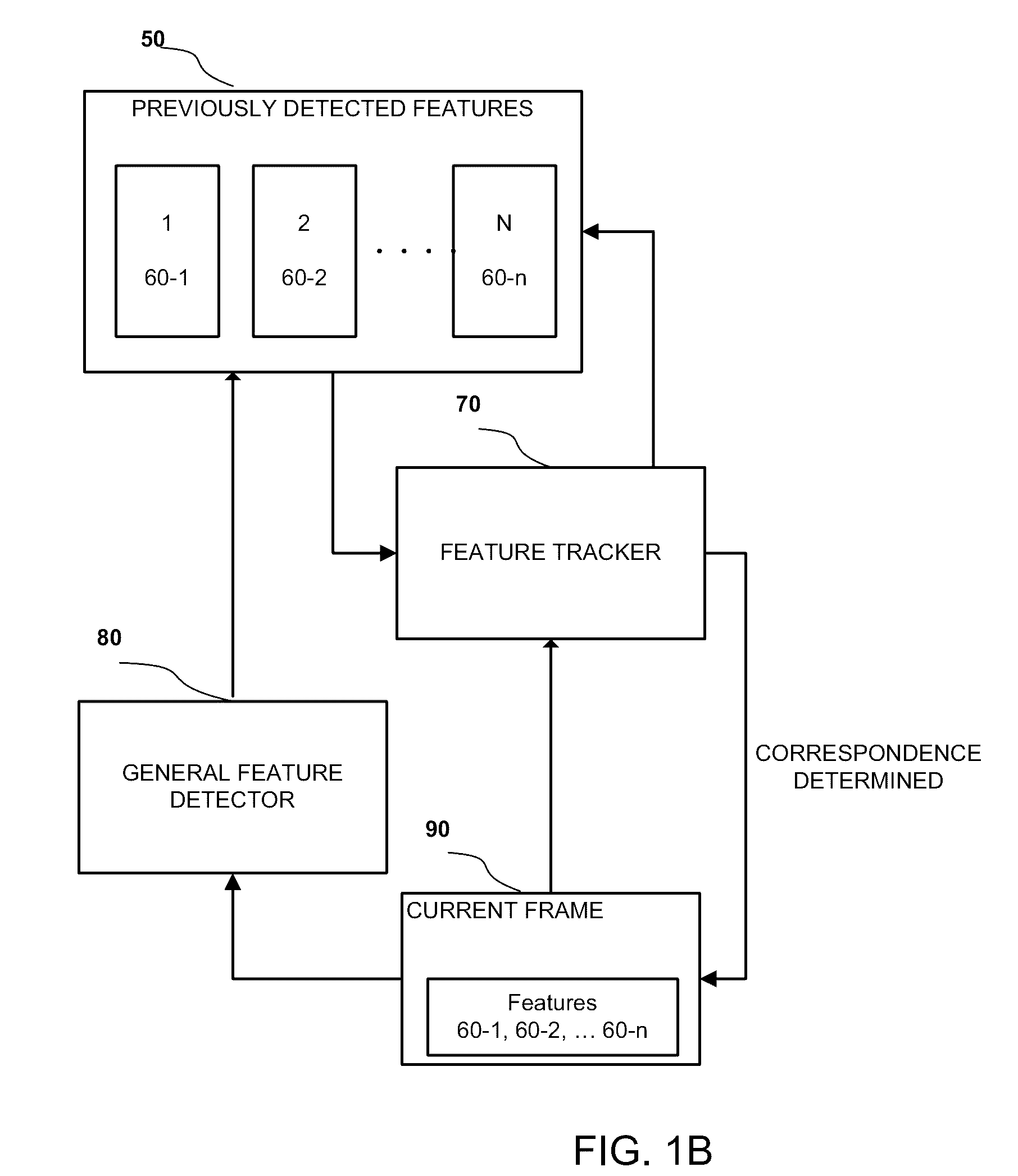

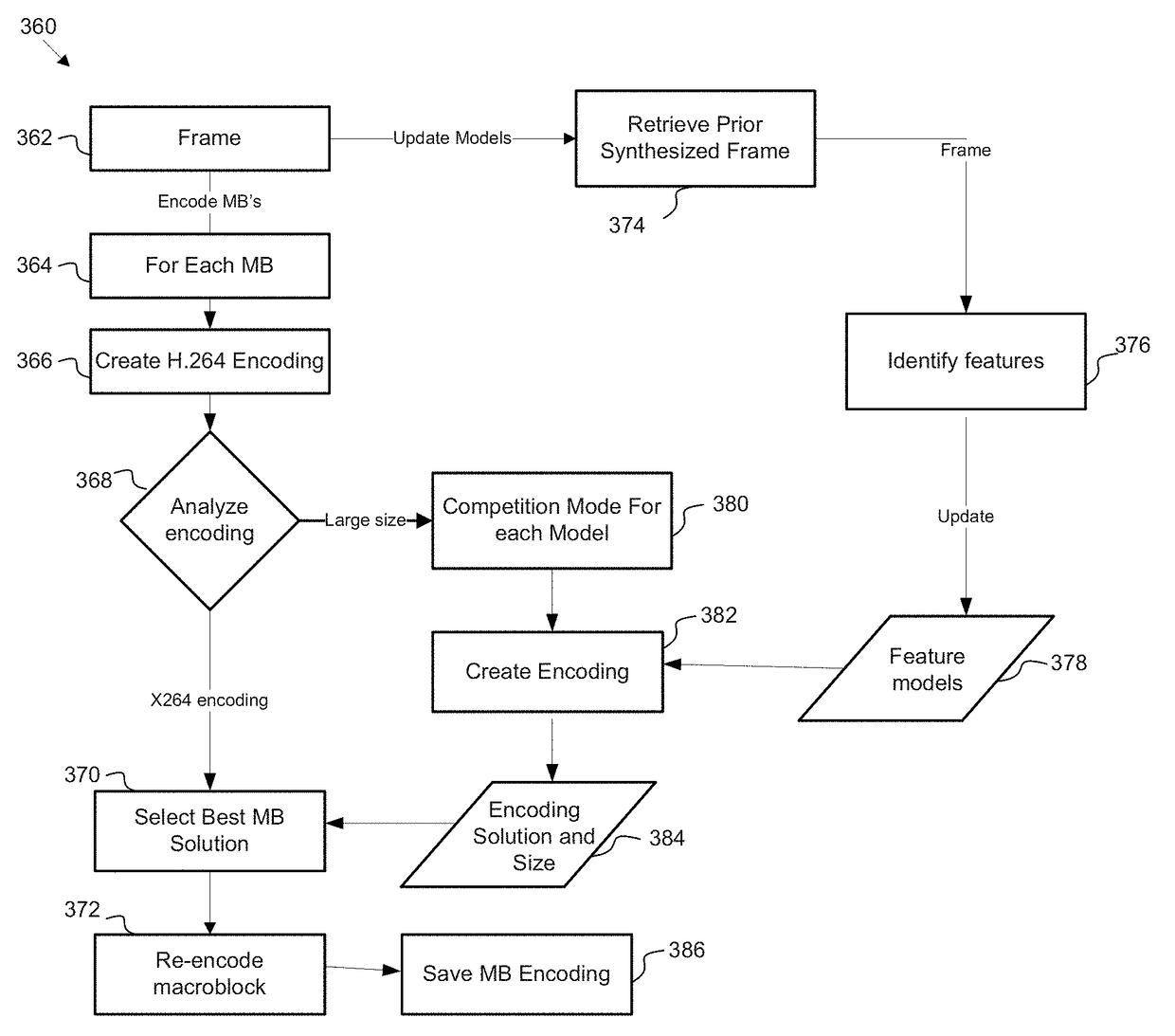

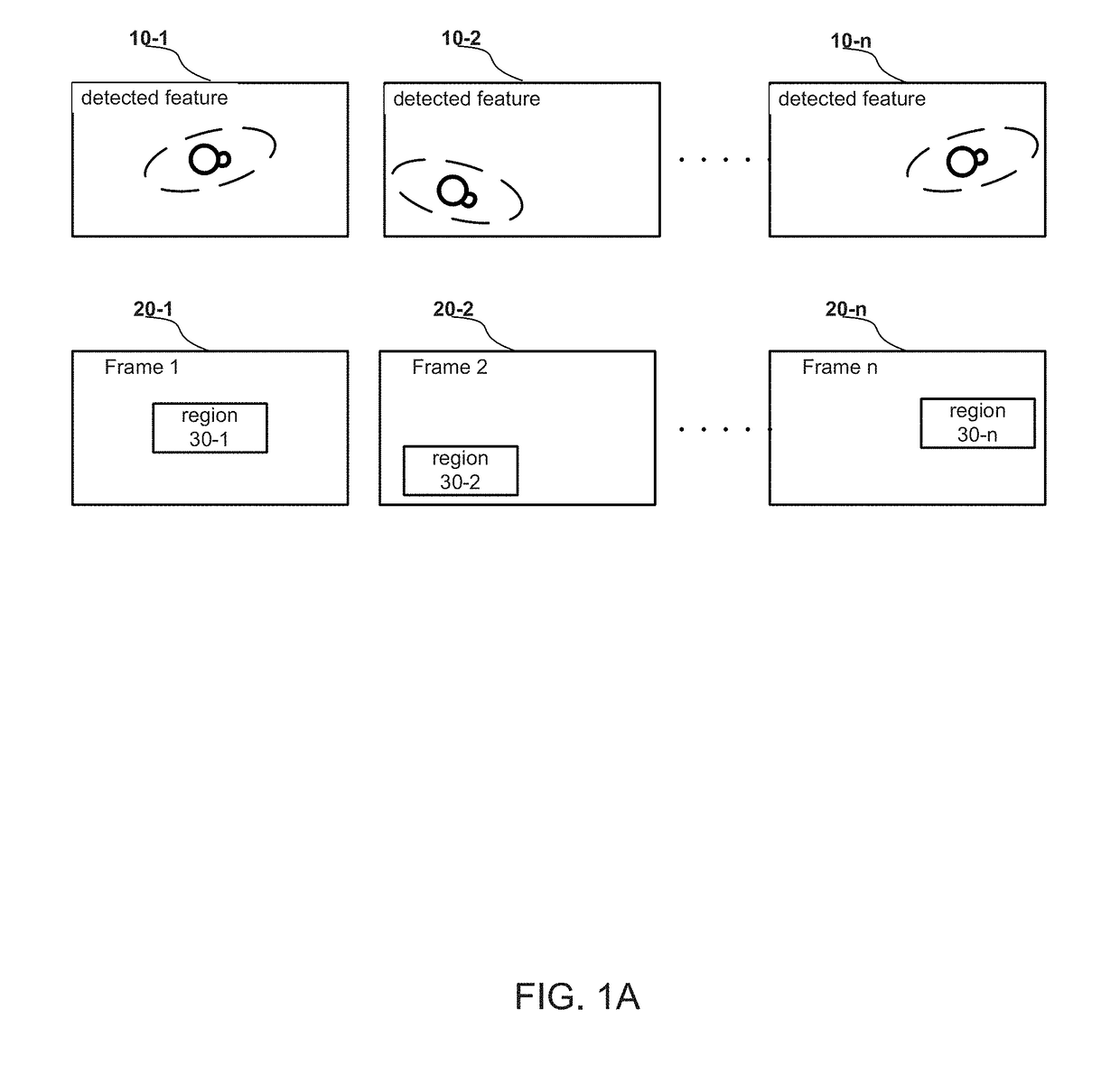

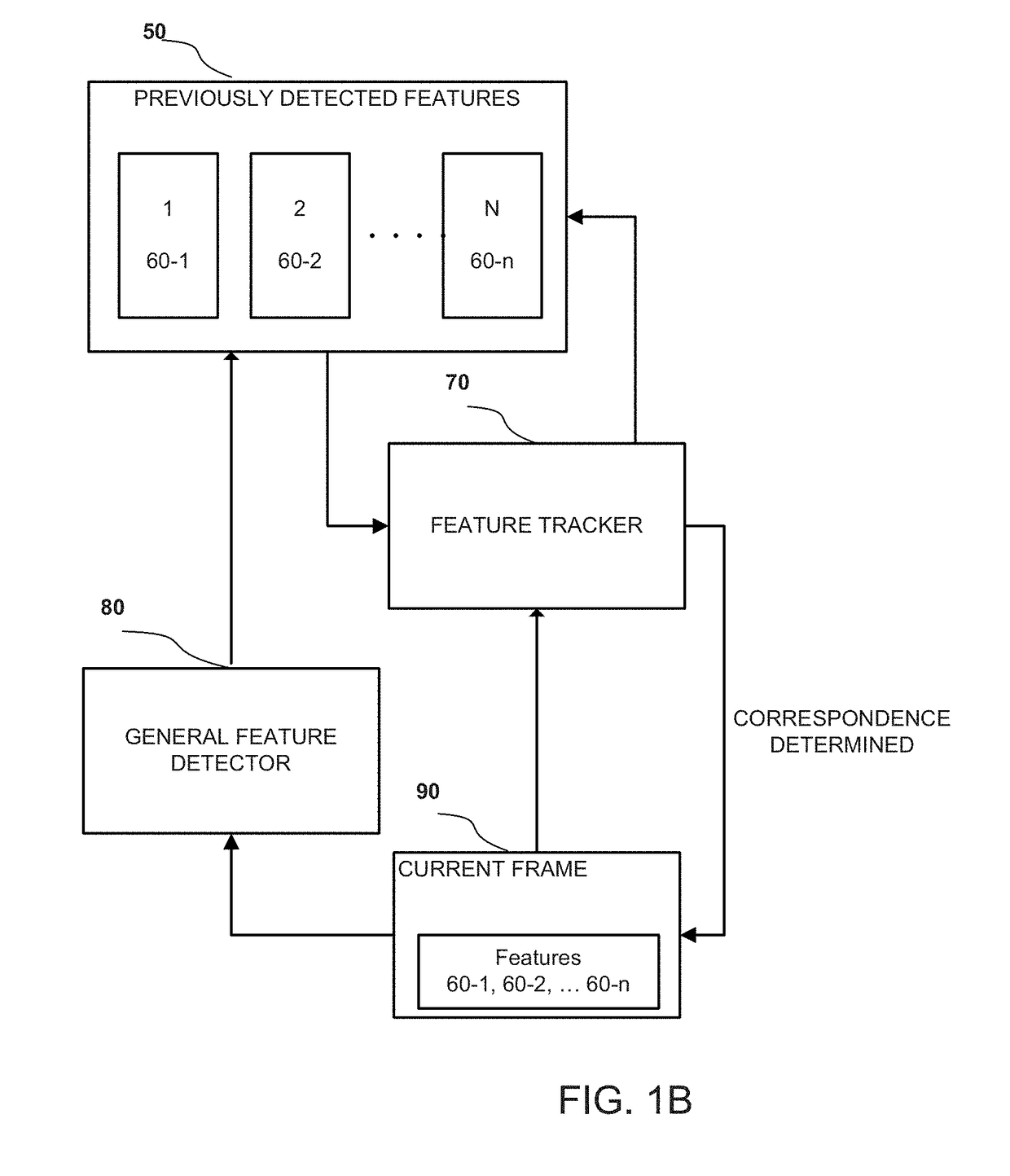

A model-based compression codec applies higher-level modeling to produce better predictions than can be found through conventional block-based motion estimation and compensation. Computer-vision-based feature and object detection algorithms identify regions of interest throughout the video datacube. The detected features and objects are modeled with a compact set of parameters, and similar feature / object instances are associated across frames. Associated features / objects are formed into tracks and related to specific blocks of video data to be encoded. The tracking information is used to produce model-based predictions for those blocks of data, enabling more efficient navigation of the prediction search space than is typically achievable through conventional motion estimation methods. A hybrid framework enables modeling of data at multiple fidelities and selects the appropriate level of modeling for each portion of video data. A compliant-stream version of the model-based compression codec uses the modeling information indirectly to improve compression while producing bitstreams that can be interpreted by standard decoders.

Owner:EUCLID DISCOVERIES LLC

Context Based Video Encoding and Decoding

ActiveUS20130107948A1Efficient codingEfficient storageColor television with pulse code modulationColor television with bandwidth reductionHigh level modelingVideo encoding

A model-based compression codec applies higher-level modeling to produce better predictions than can be found through conventional block-based motion estimation and compensation. Computer-vision-based feature and object detection algorithms identify regions of interest throughout the video datacube. The detected features and objects are modeled with a compact set of parameters, and similar feature / object instances are associated across frames. Associated features / objects are formed into tracks and related to specific blocks of video data to be encoded. The tracking information is used to produce model-based predictions for those blocks of data, enabling more efficient navigation of the prediction search space than is typically achievable through conventional motion estimation methods. A hybrid framework enables modeling of data at multiple fidelities and selects the appropriate level of modeling for each portion of video data.

Owner:EUCLID DISCOVERIES LLC

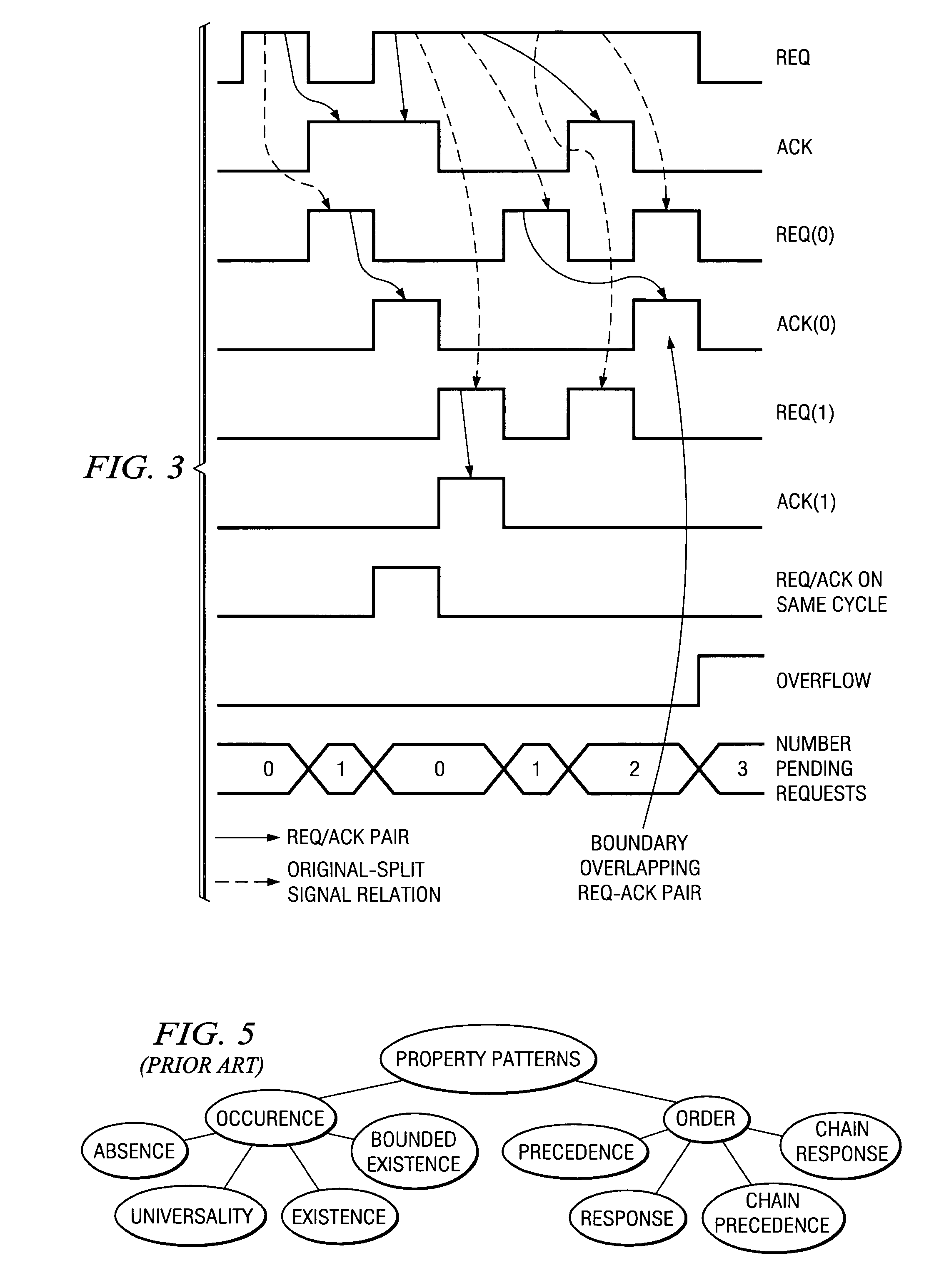

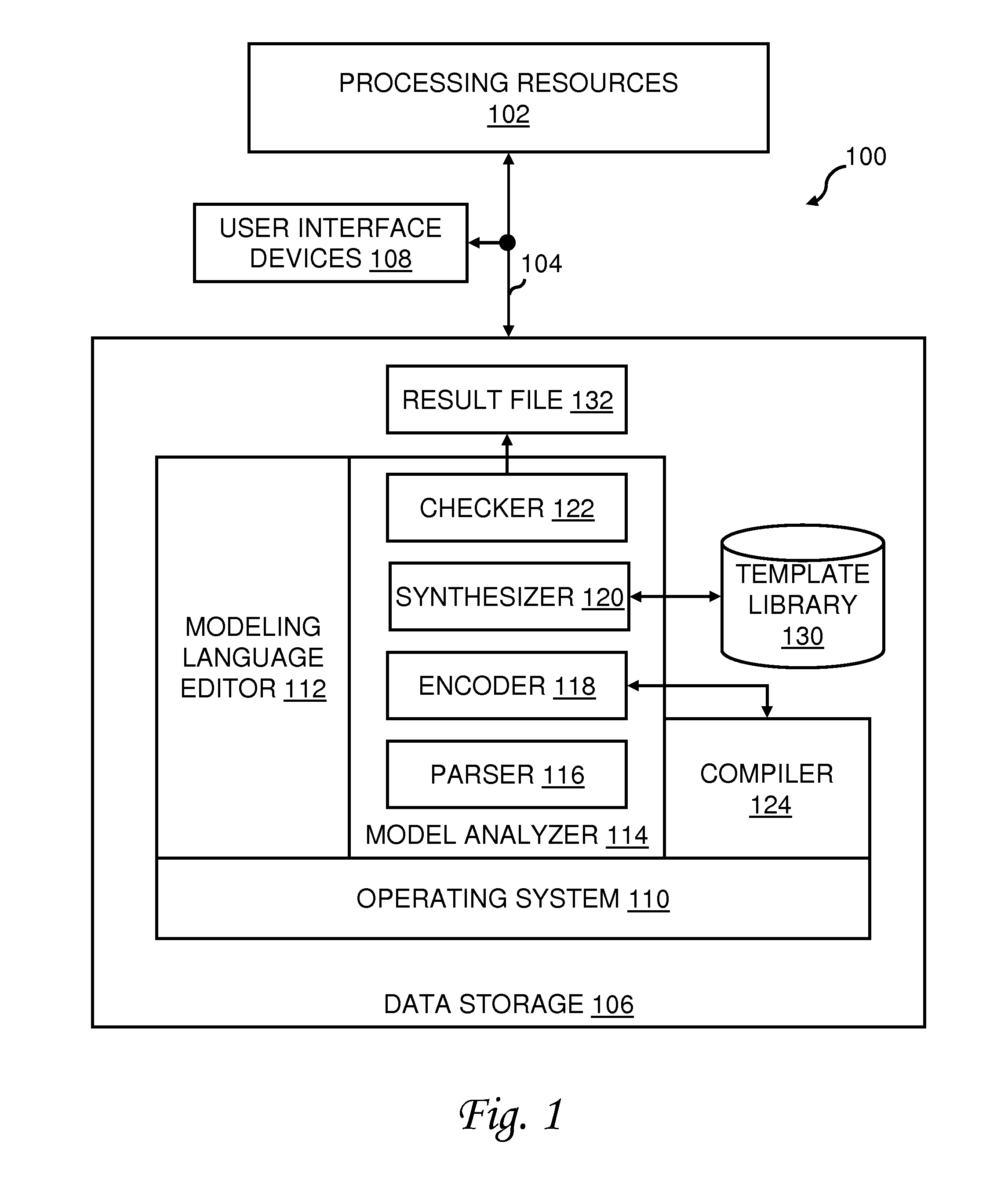

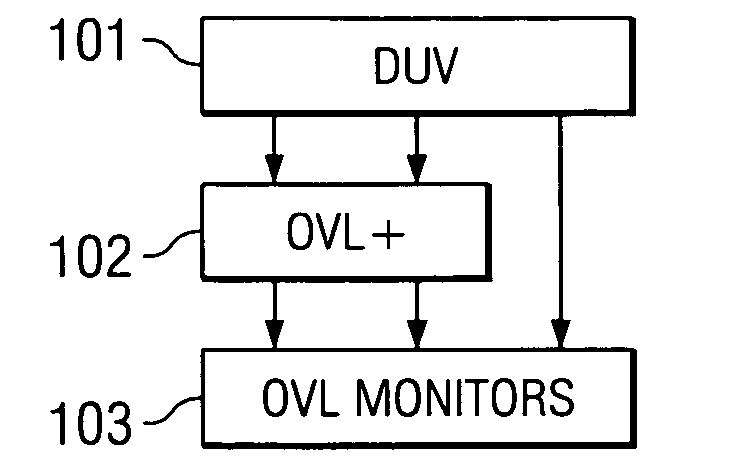

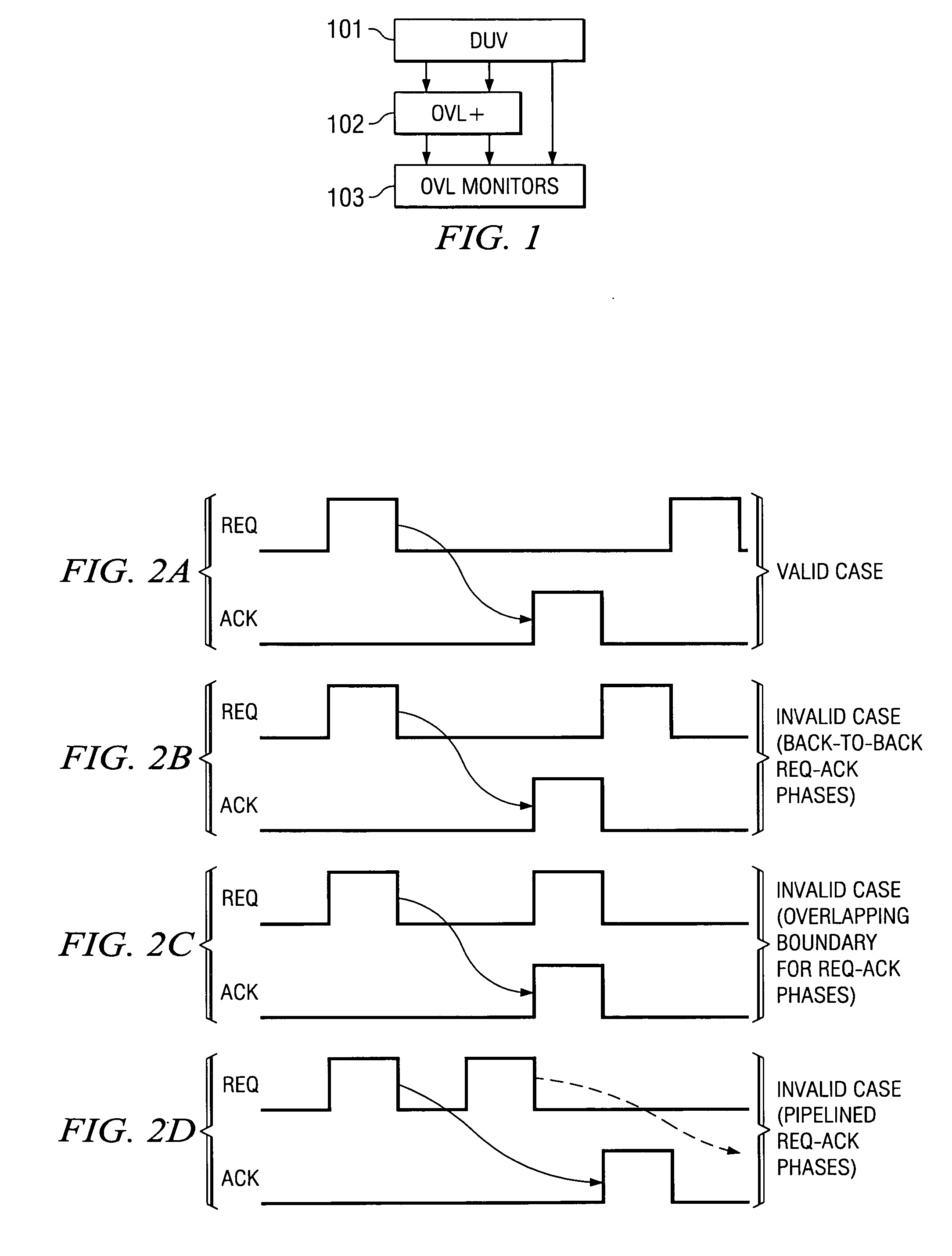

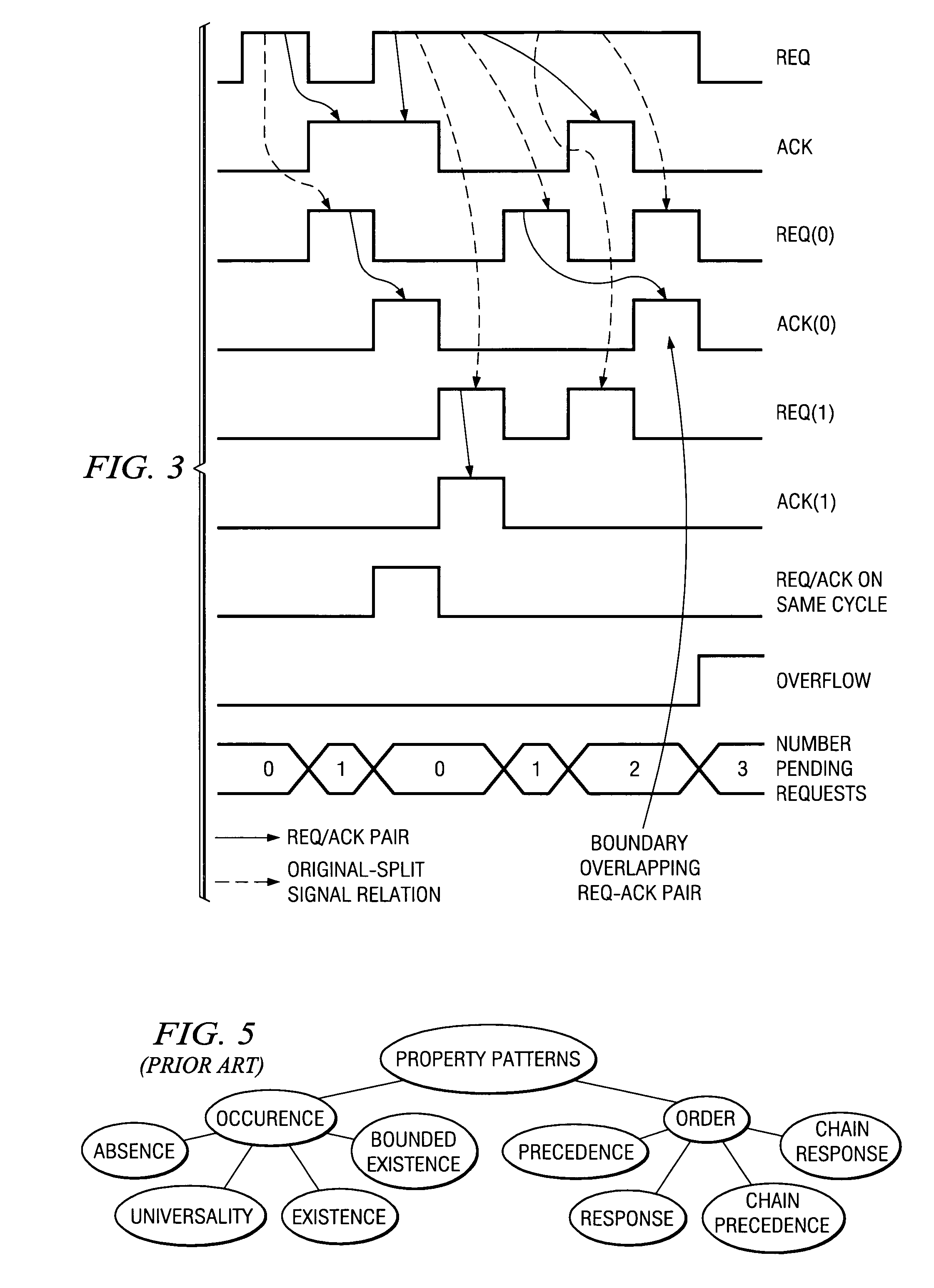

Using patterns for high-level modeling and specification of properties for hardware systems

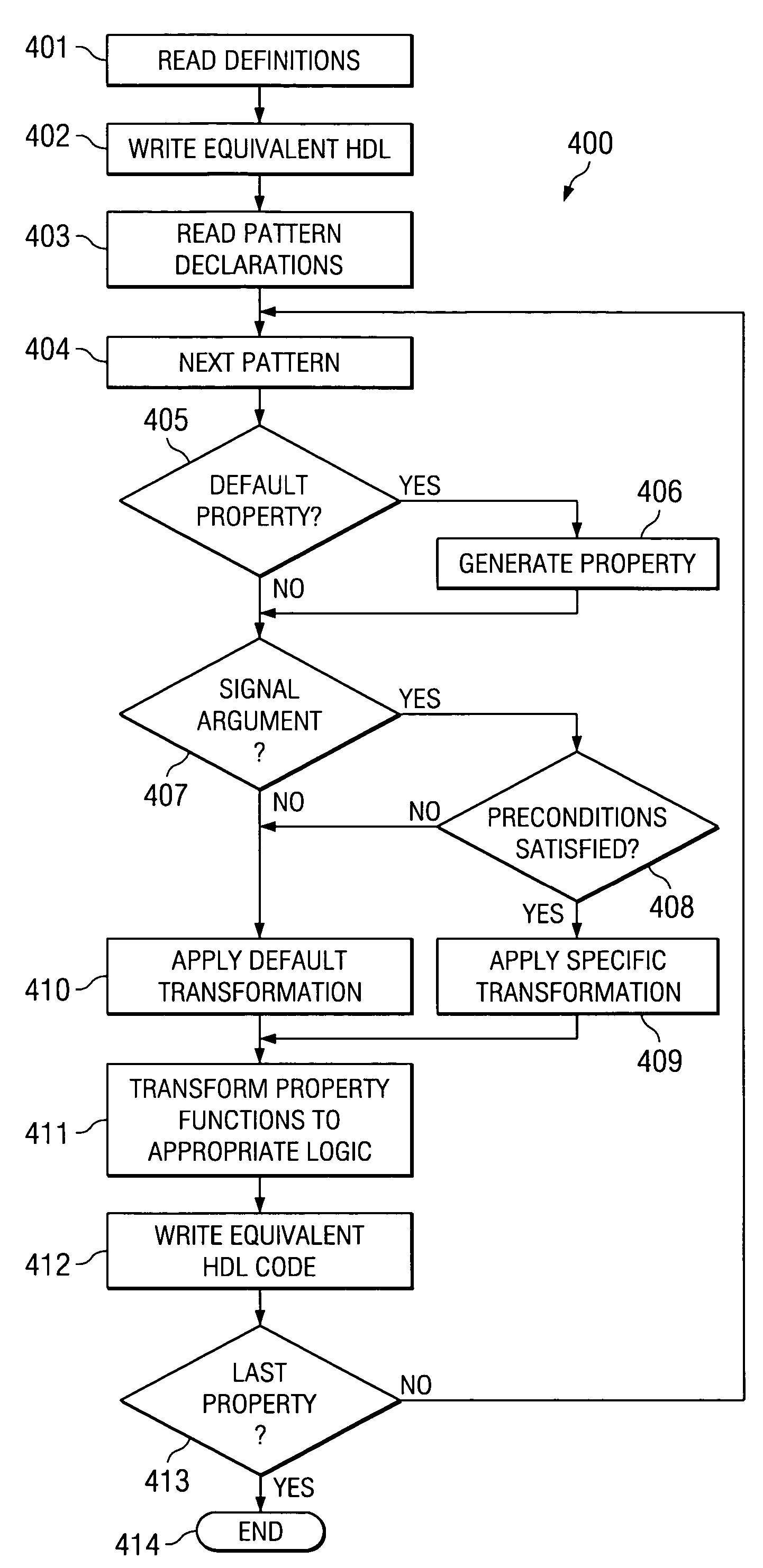

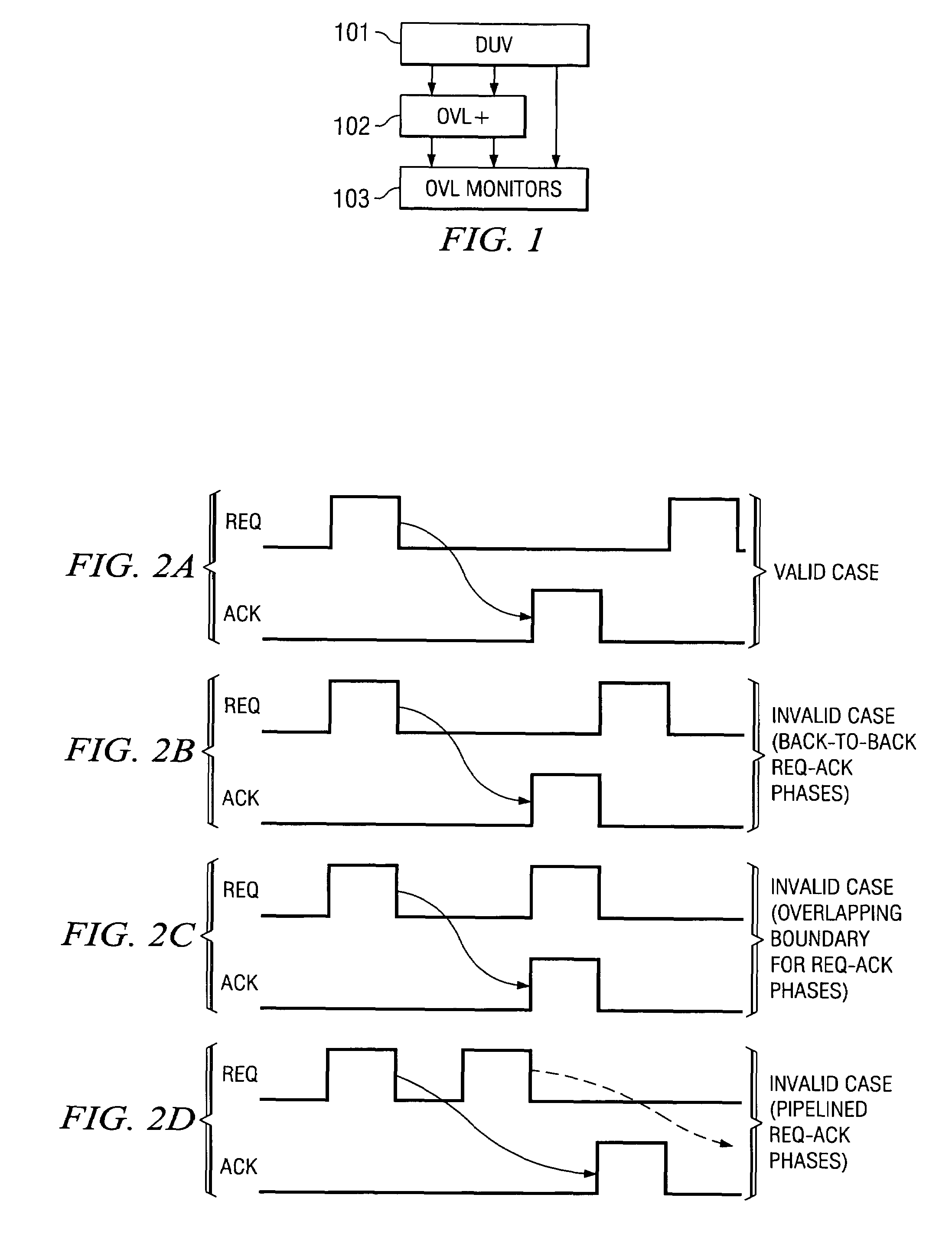

ActiveUS7325209B2Simplify writingSimplifies taskElectronic circuit testingError detection/correctionElectronic systemsHigh level modeling

This invention is a high-level language to specify electronic system design patterns for functional verification. This invention includes automatic translation of the high-level language specification into assertion code from these patterns and temporal properties for design verification. This eliminates the need to code extra RTL to handle features such as pipelines and bus priorities. Such common features are specified only in high-level patterns and temporal properties to be verified. This is advantageous because less verification code to be written, automated synthesis of assertions enforces monitor-style of writing assertions rather than generator-style, and the high-level code can be seamlessly migrated to another verification tool by producing another code generator for the new assertion language.

Owner:TEXAS INSTR INC

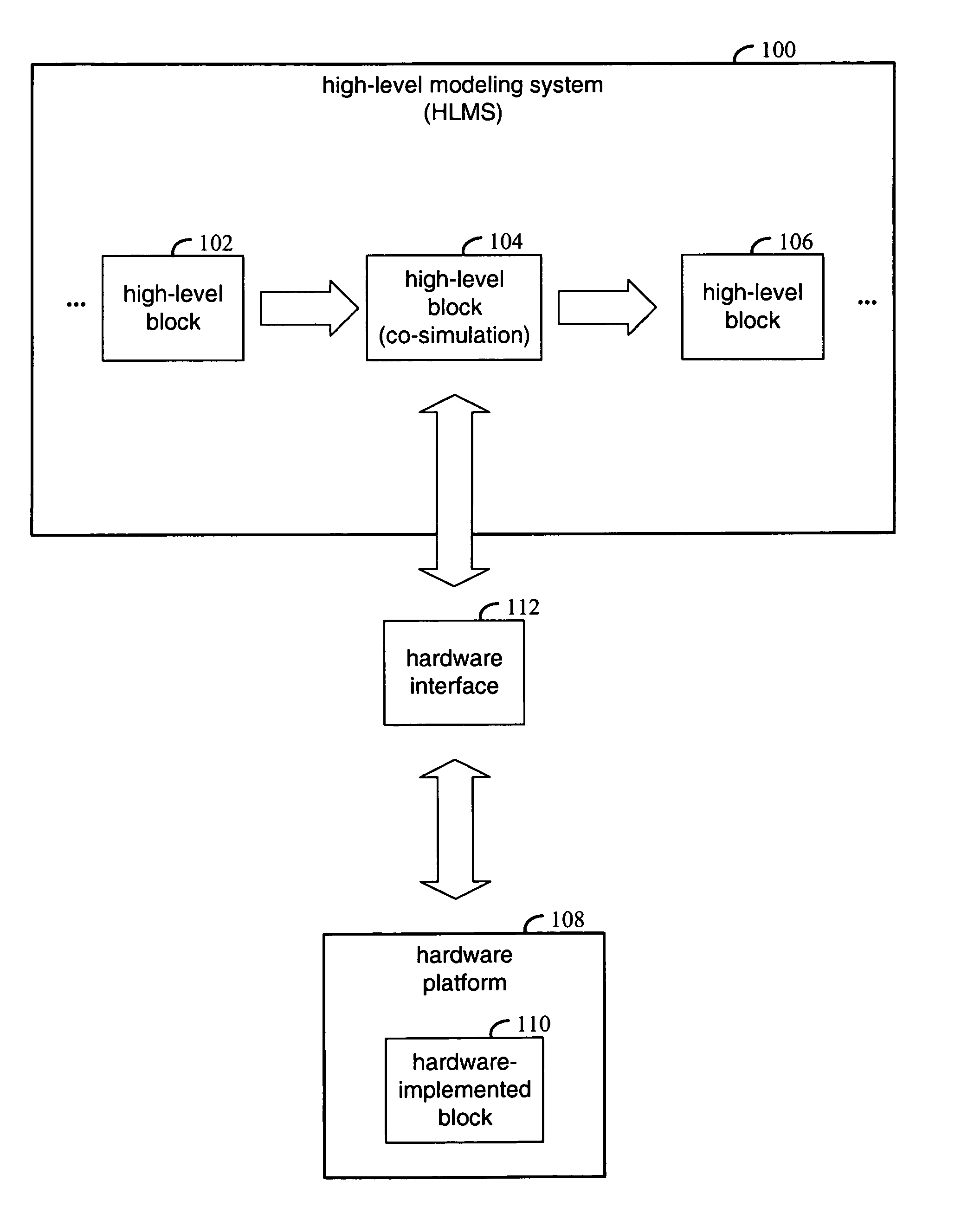

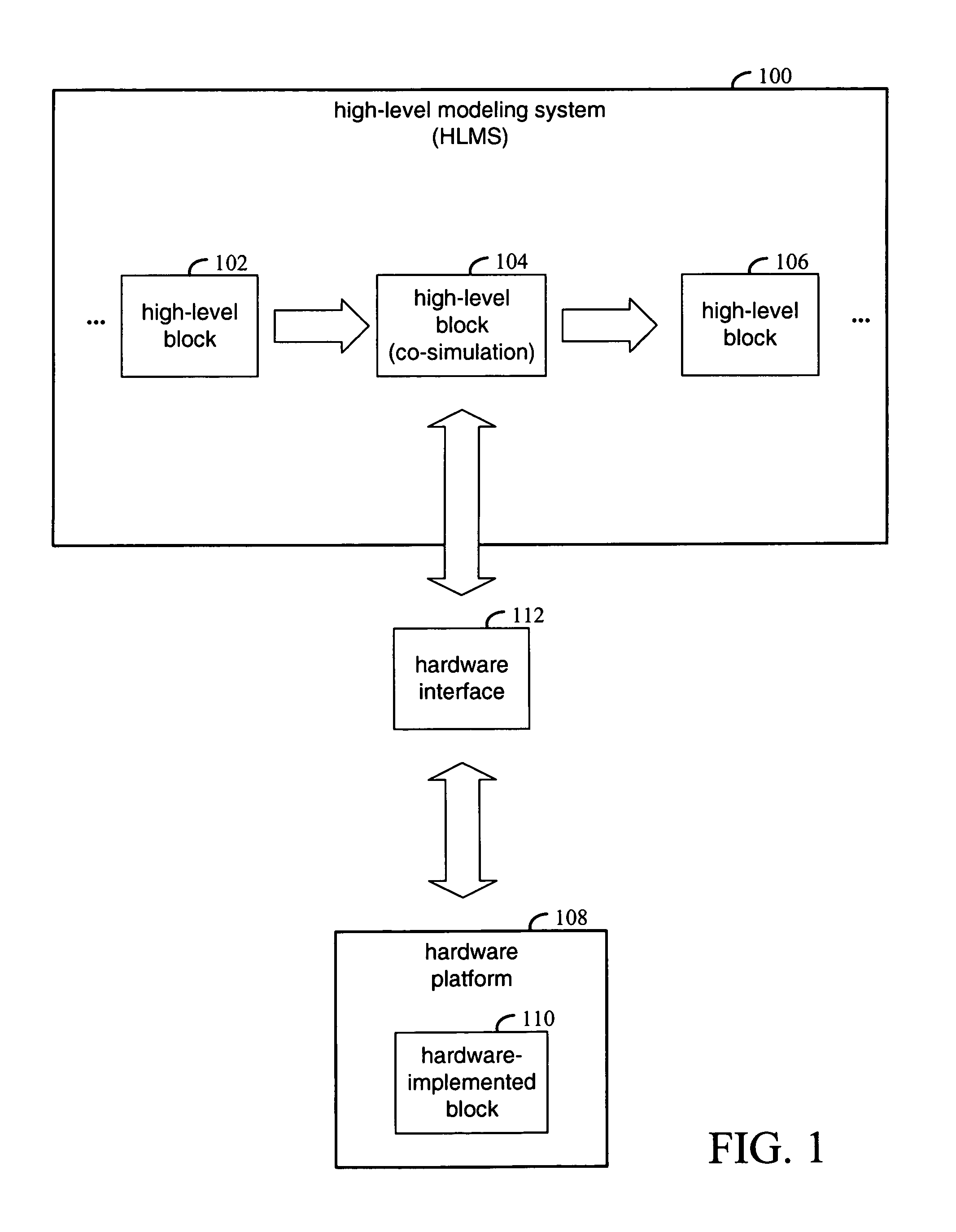

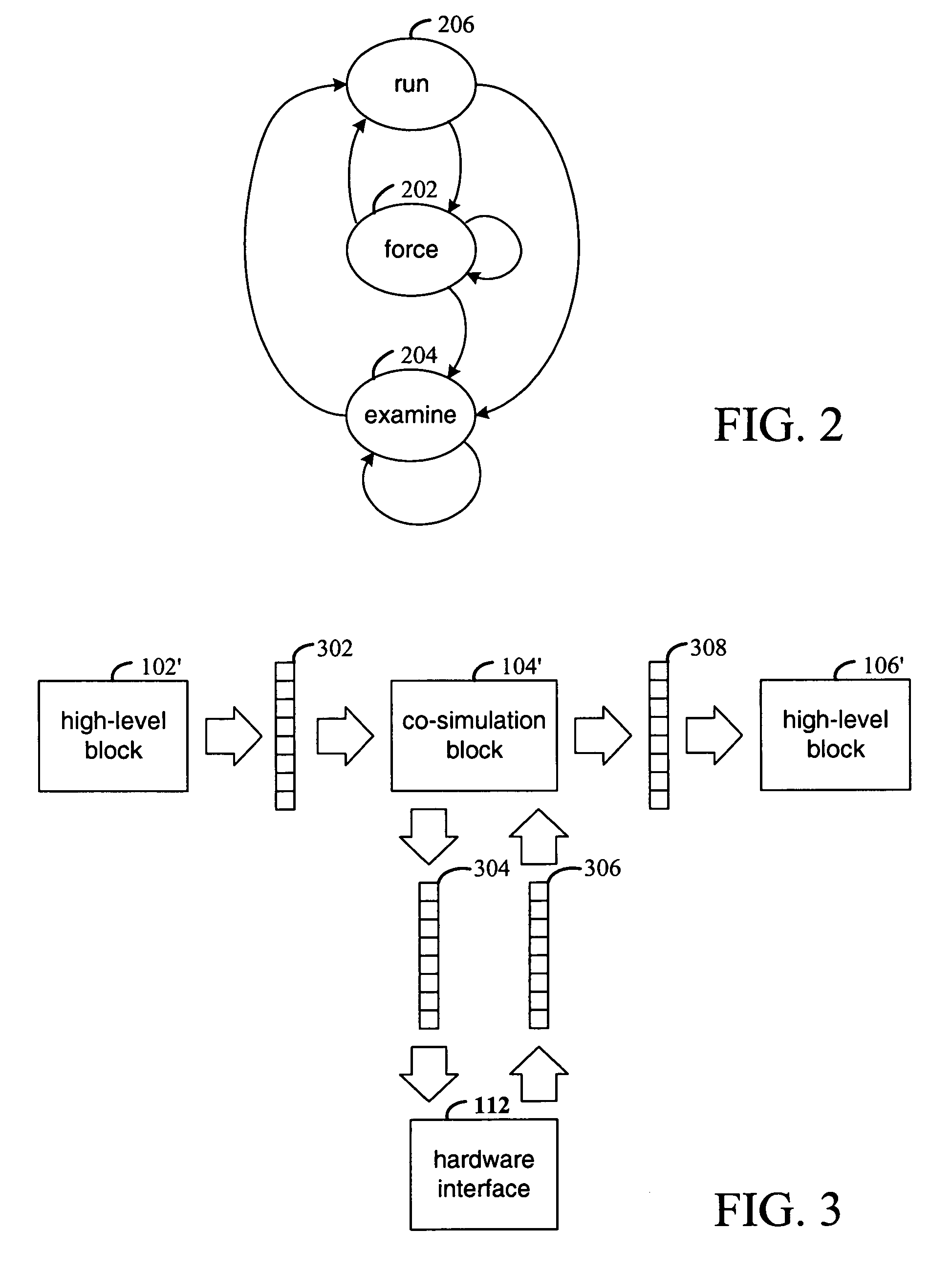

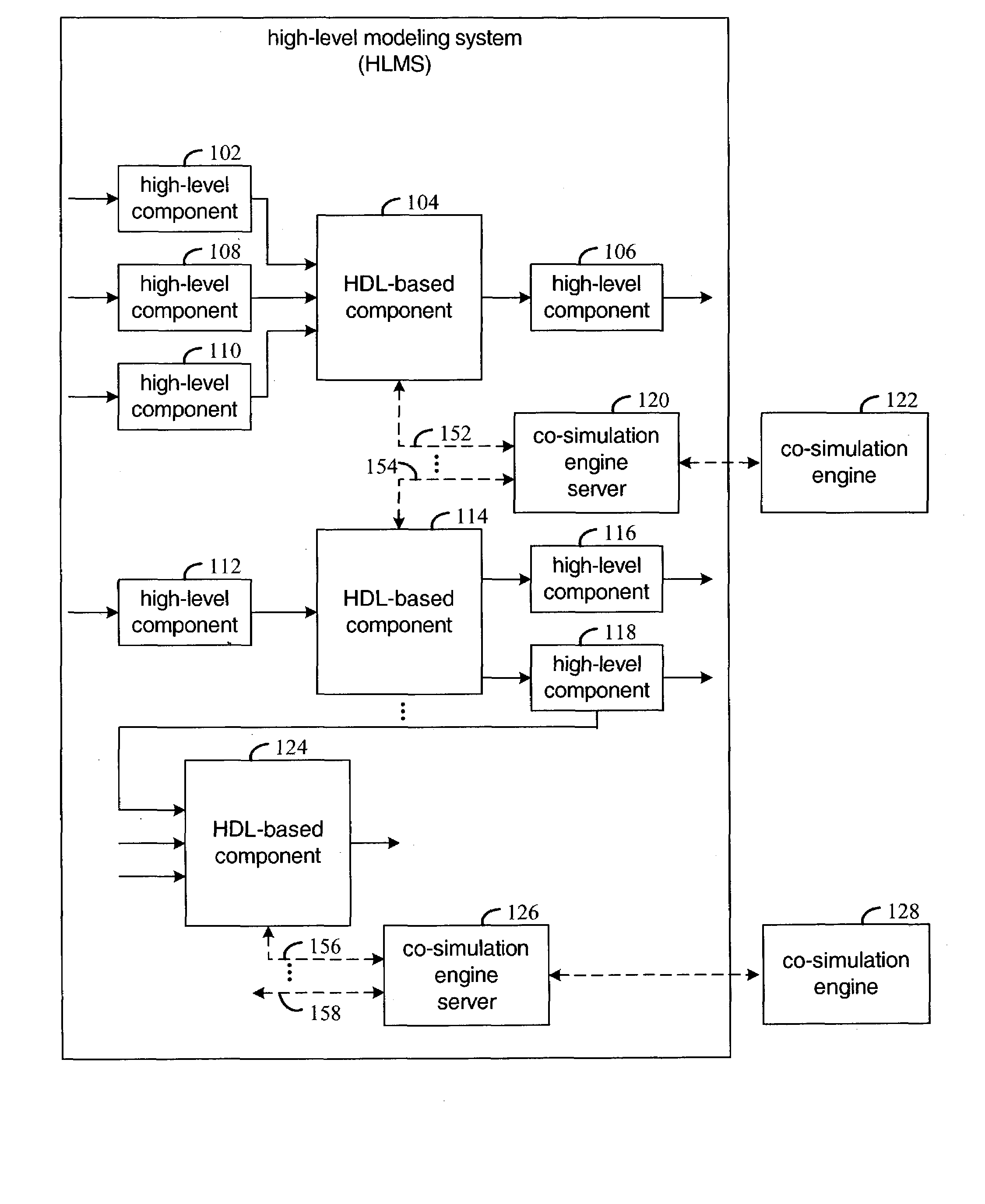

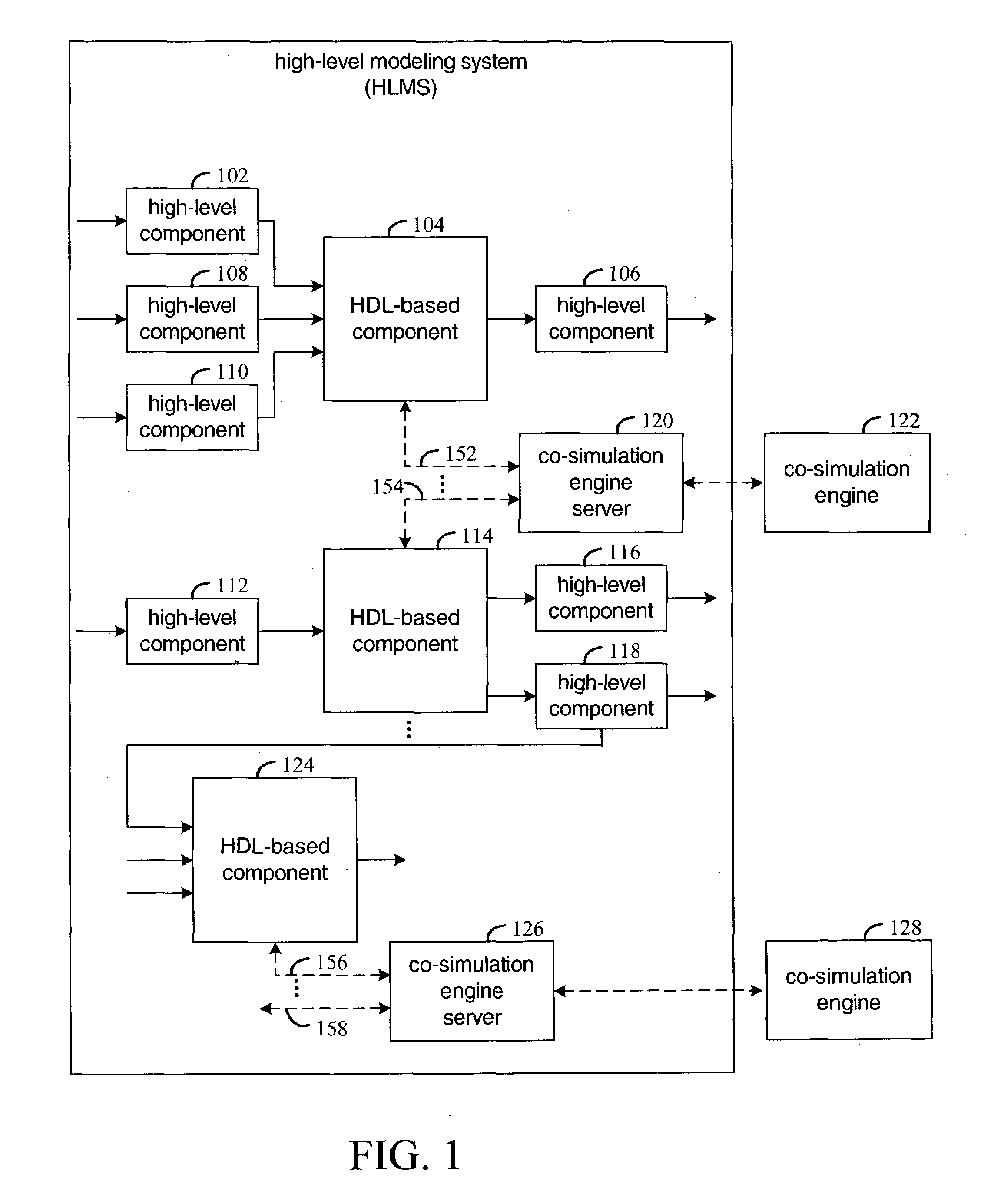

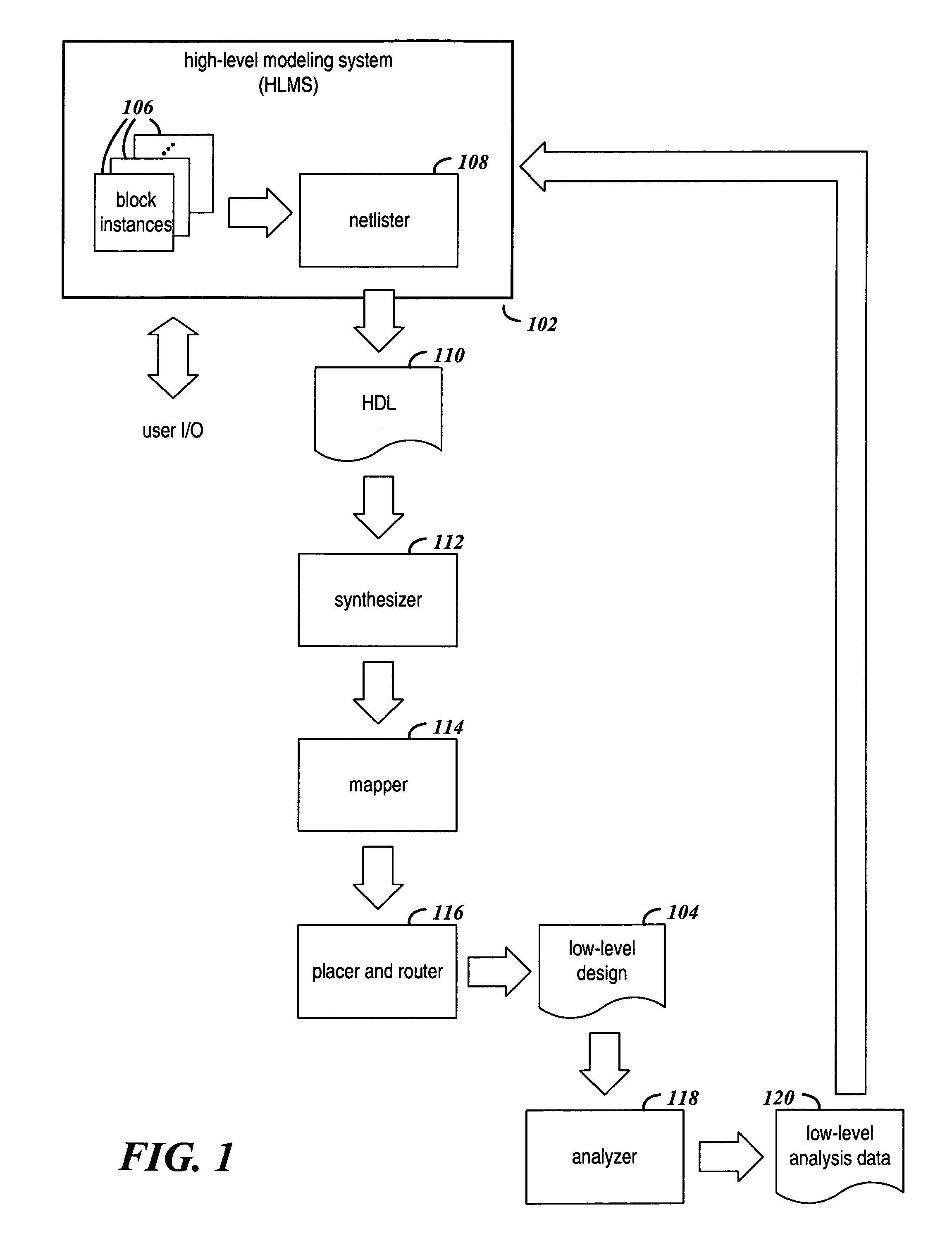

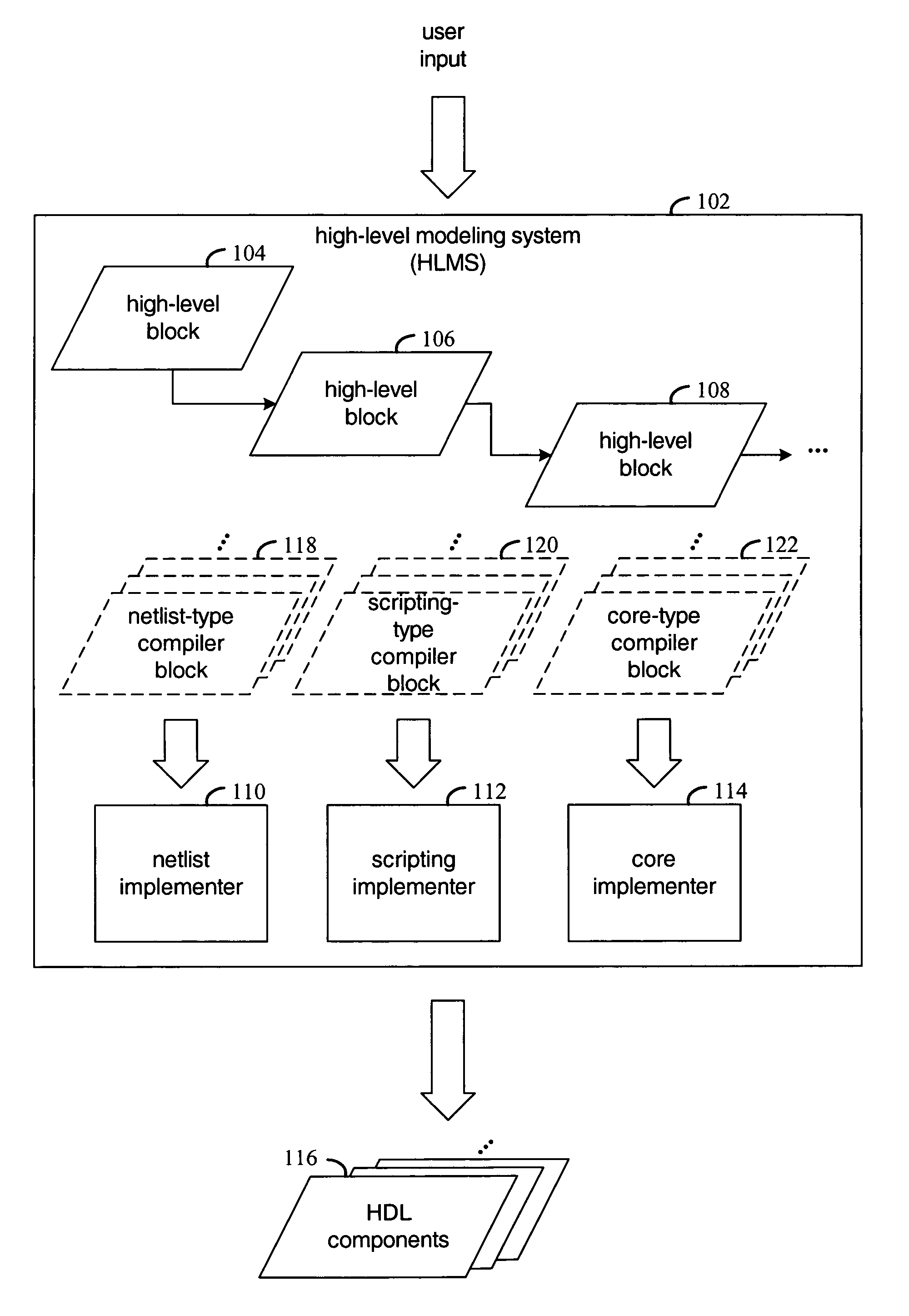

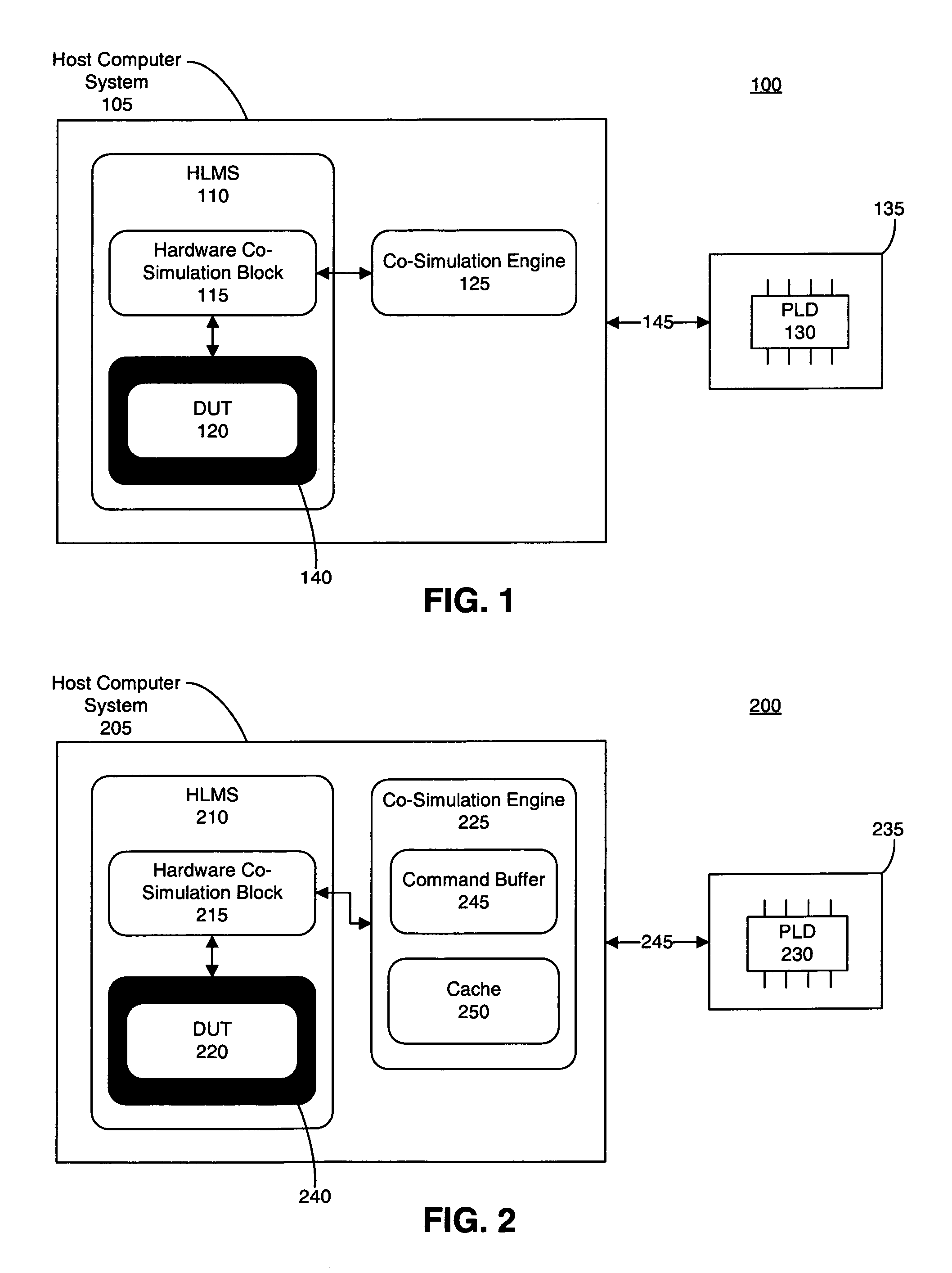

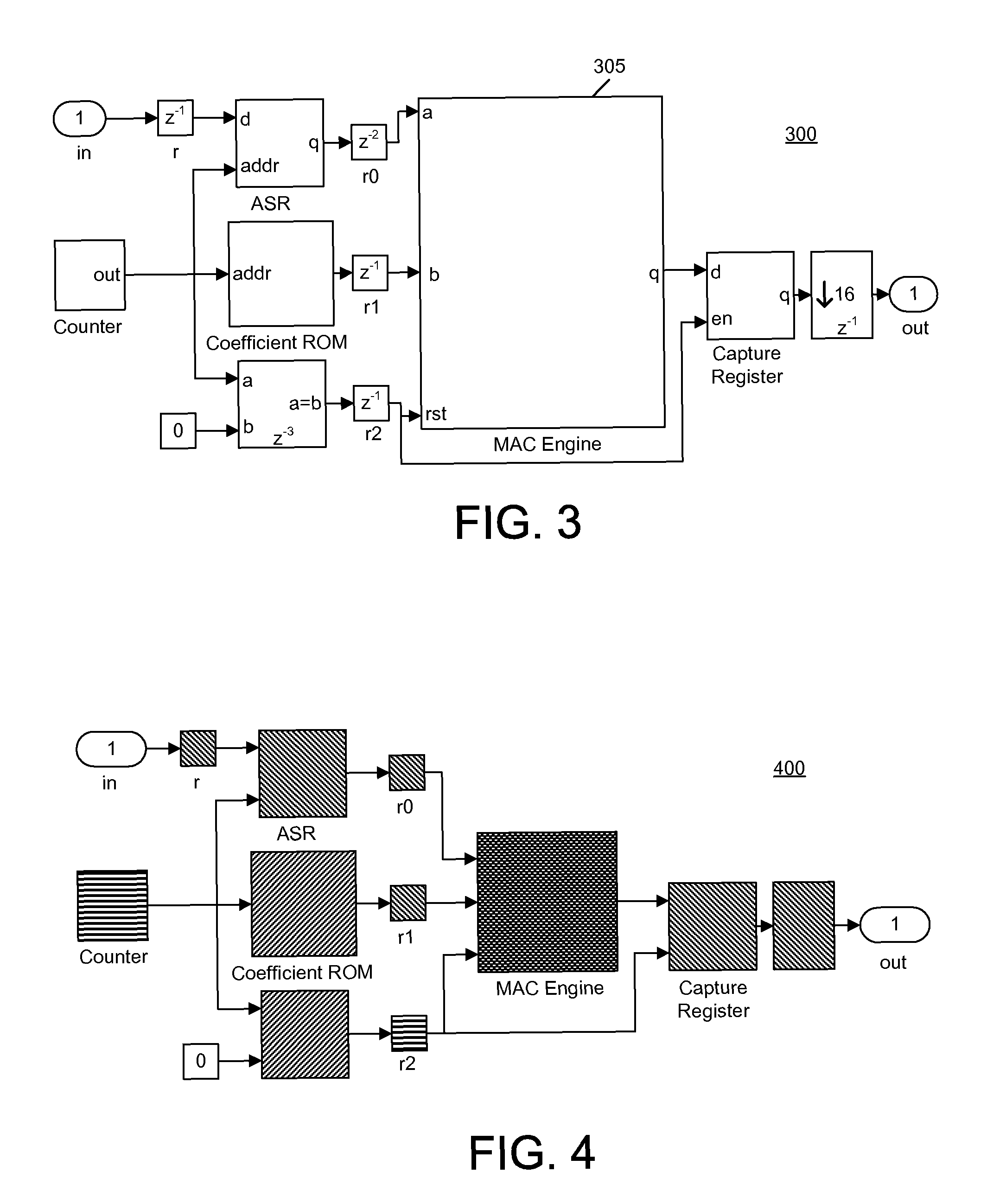

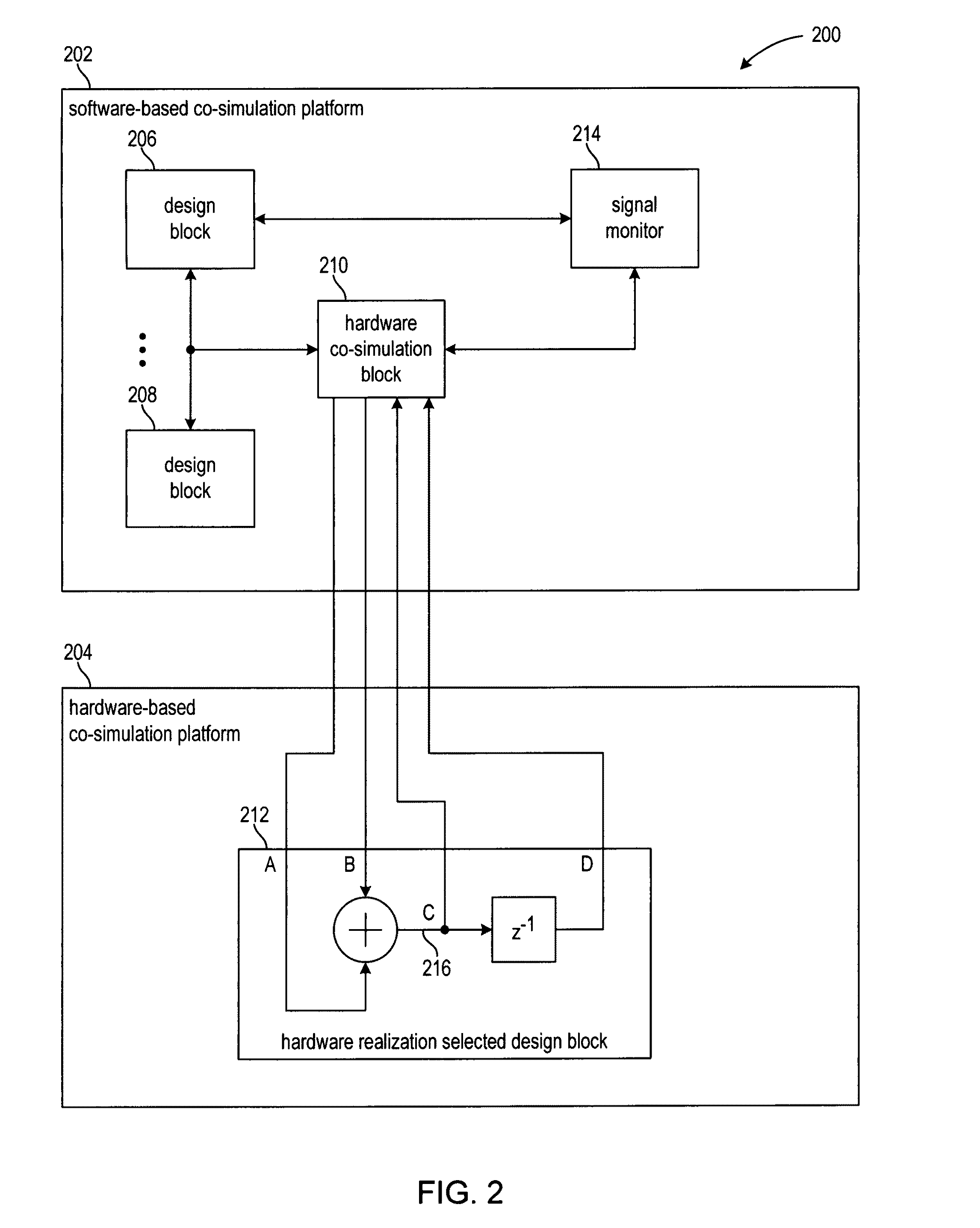

Vector transfer during co-simulation

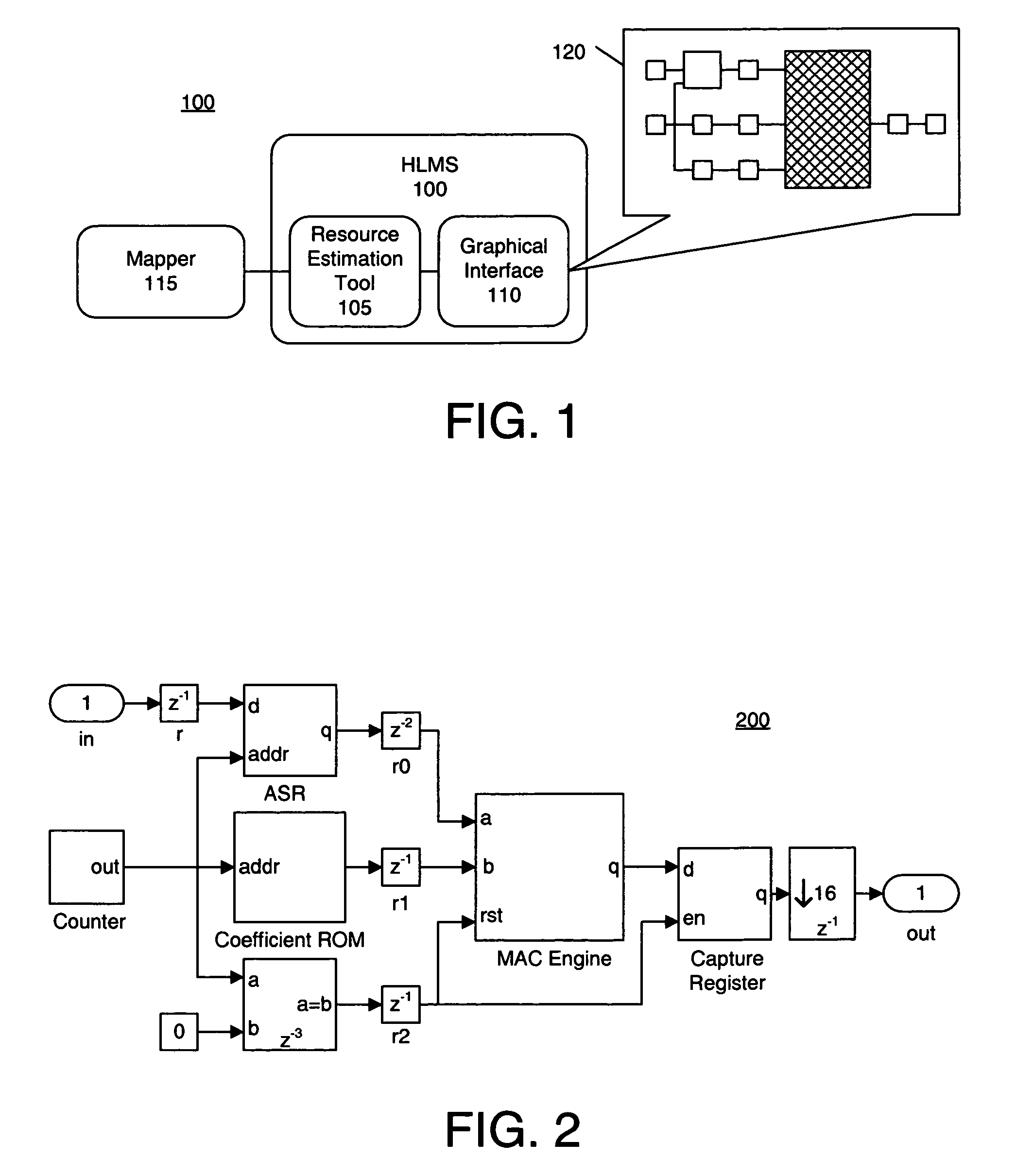

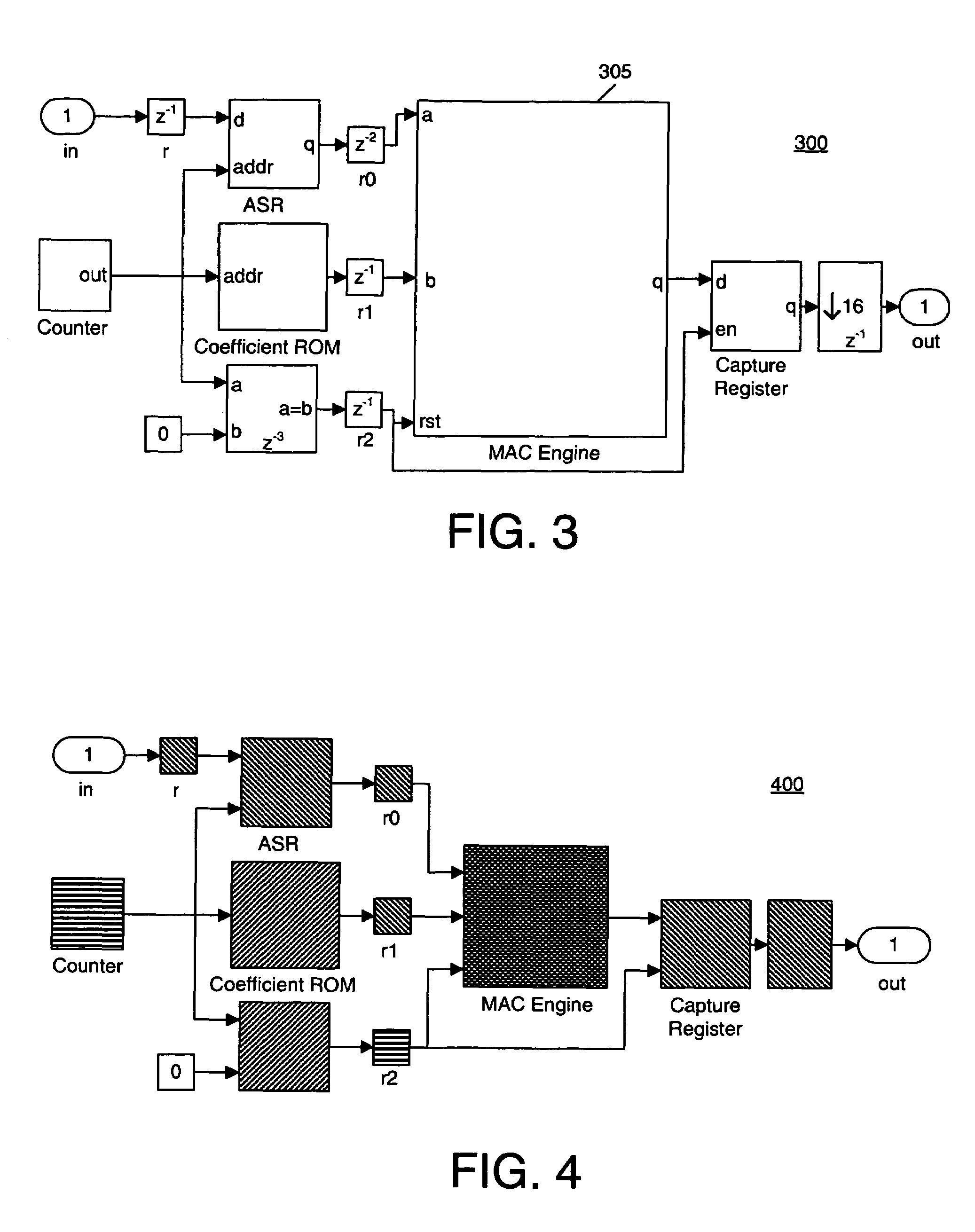

ActiveUS7376544B1Detecting faulty computer hardwareCAD circuit designHigh level modelingParallel computing

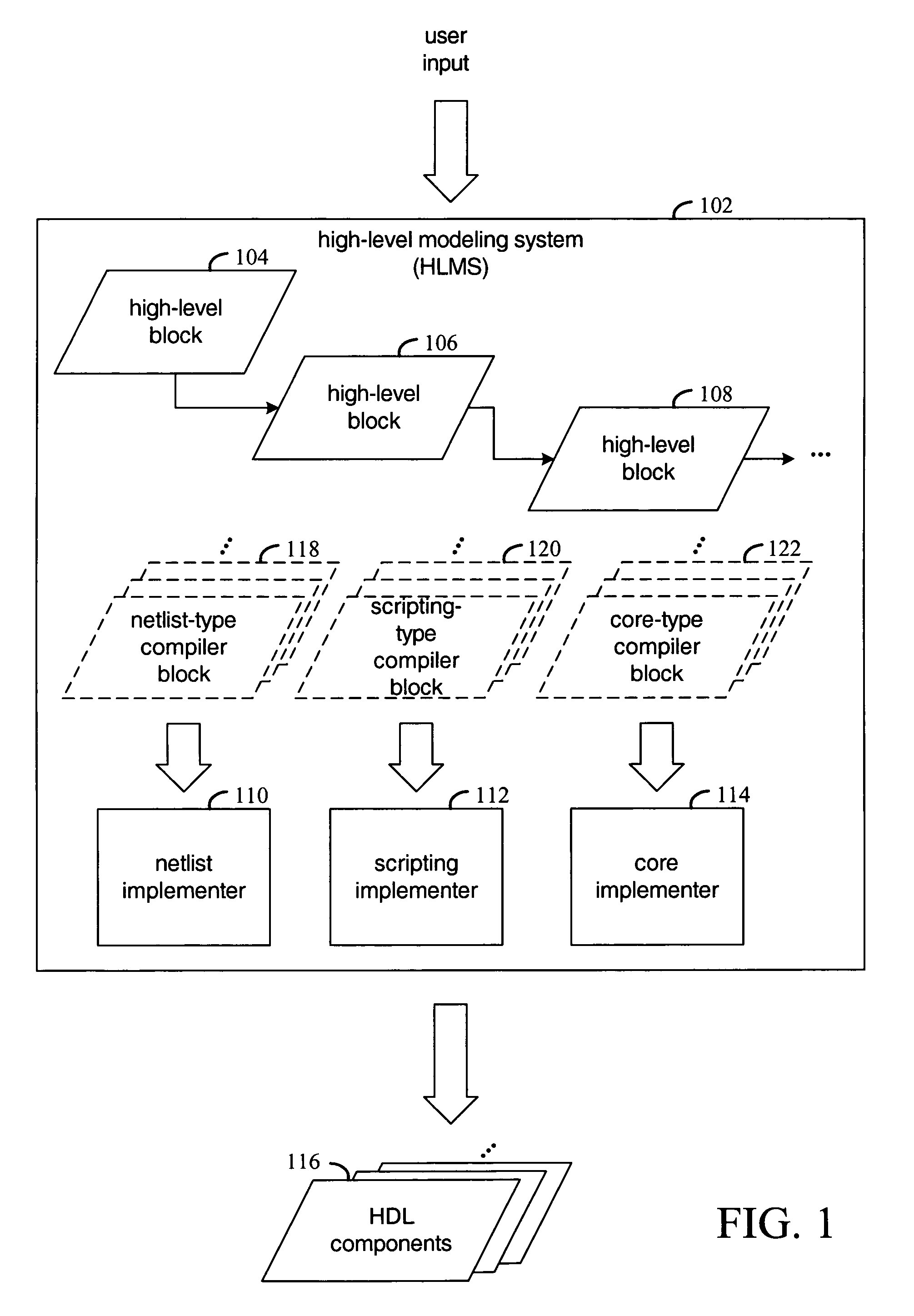

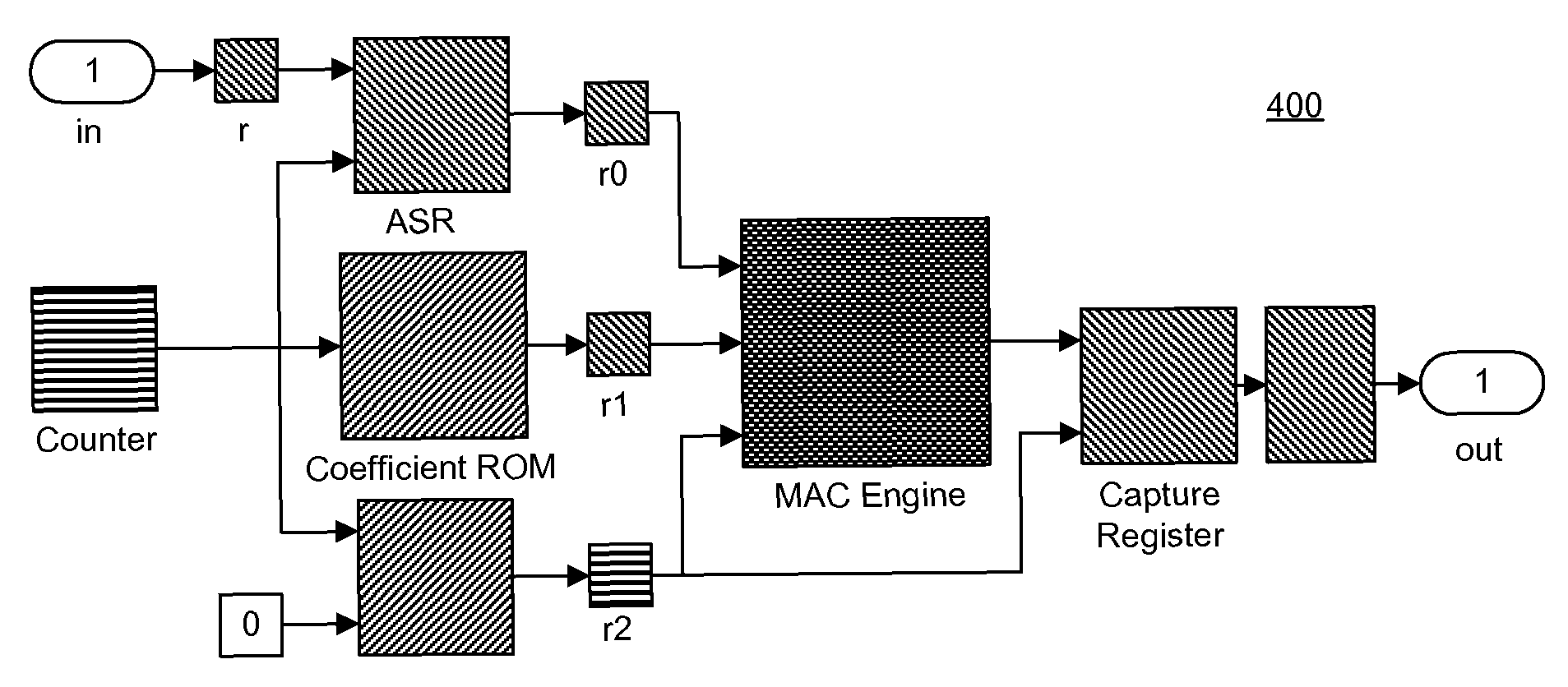

Various embodiments are disclosed for transferring data between blocks in a design during simulation. Operation of at least one high-level block in the design is simulated in a high-level modeling system (HLMS). A hardware-implemented block in the design is co-simulated on a hardware simulation platform. A first vector of data received by a co-simulation block is transferred to the simulated hardware-implemented block via a transfer function.

Owner:XILINX INC

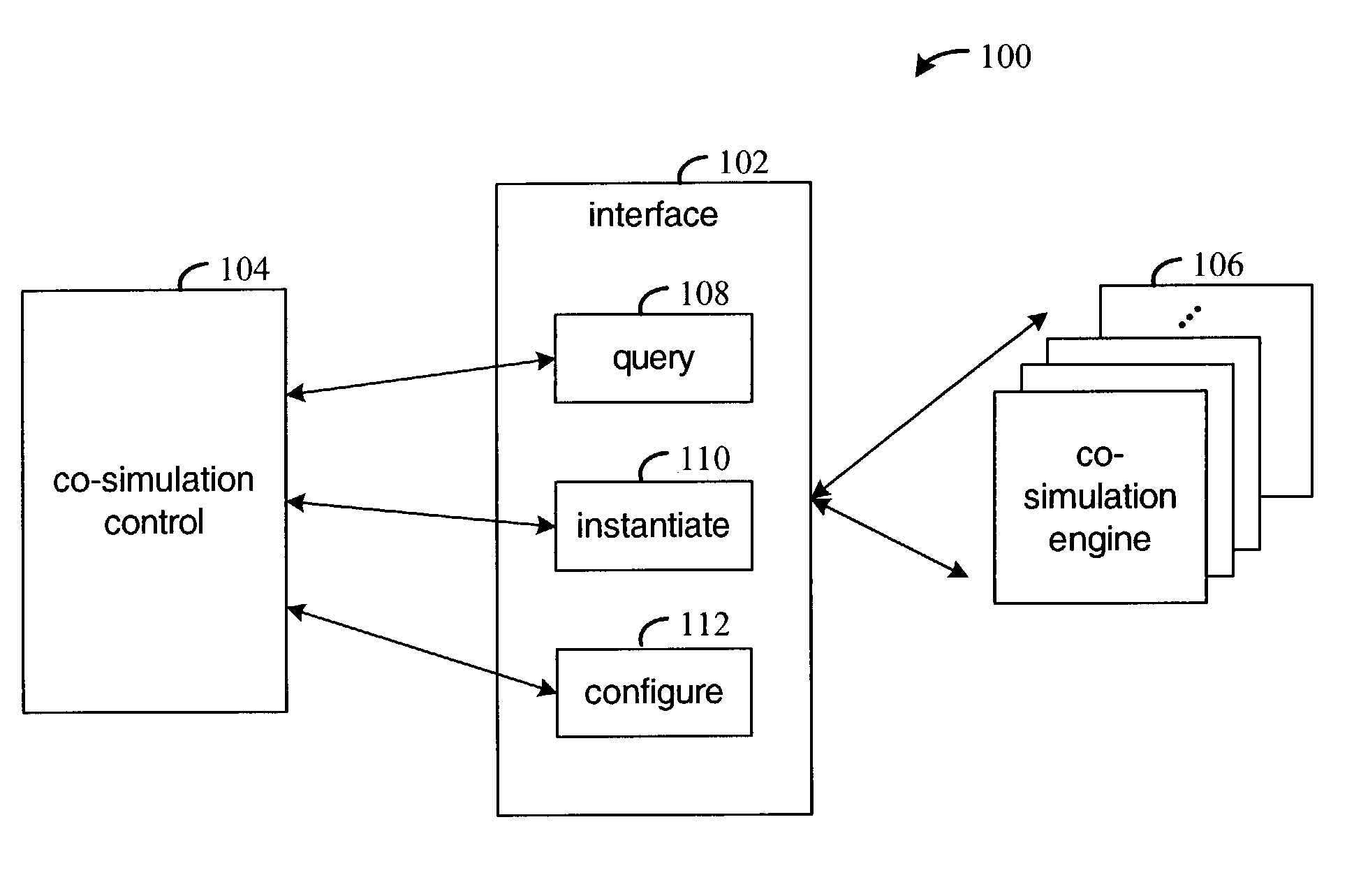

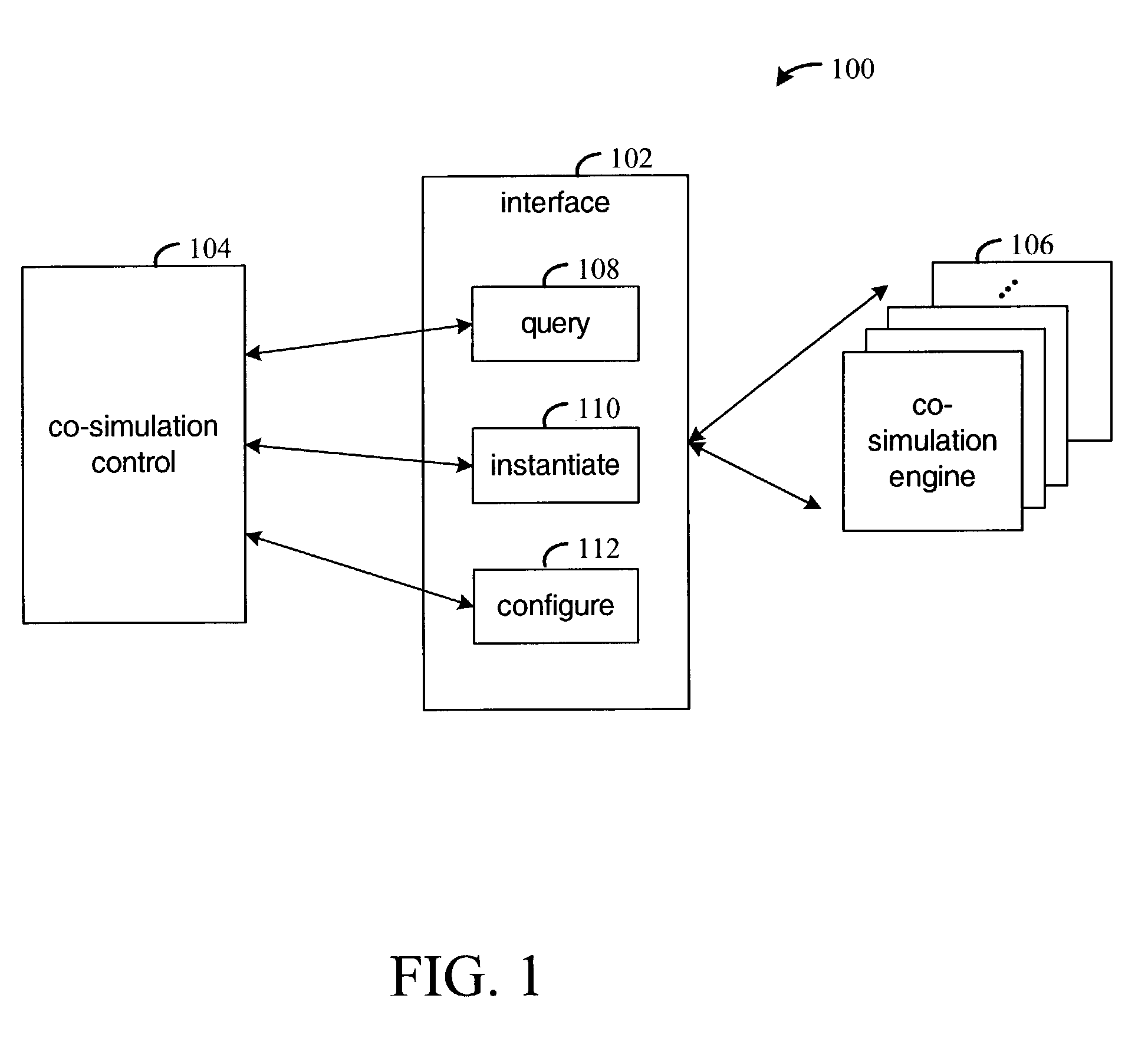

Design partitioning for co-stimulation

InactiveUS7143369B1CAD circuit designSoftware simulation/interpretation/emulationHigh level modelingEngineering

Method and apparatus for simulating operations of a circuit design that includes high-level components and HDL components. Groups of HDL components are associated with different co-simulation engines. The high-level components of the design are simulated in a high-level modeling system (HLMS), and the HDL components in each group are simulated on the associated co-simulation engine.

Owner:XILINX INC

Context Based Video Encoding and Decoding

InactiveUS20130114703A1Efficient storageEfficient codingColor television with pulse code modulationColor television with bandwidth reductionVideo encodingHigh level modeling

A model-based compression codec applies higher-level modeling to produce better predictions than can be found through conventional block-based motion estimation and compensation. Computer-vision-based feature and object detection algorithms identify regions of interest throughout the video datacube. The detected features and objects are modeled with a compact set of parameters, and similar feature / object instances are associated across frames. Associated features / objects are formed into tracks and related to specific blocks of video data to be encoded. The tracking information is used to produce model-based predictions for those blocks of data, enabling more efficient navigation of the prediction search space than is typically achievable through conventional motion estimation methods. A hybrid framework enables modeling of data at multiple fidelities and selects the appropriate level of modeling for each portion of video data.

Owner:EUCLID DISCOVERIES LLC

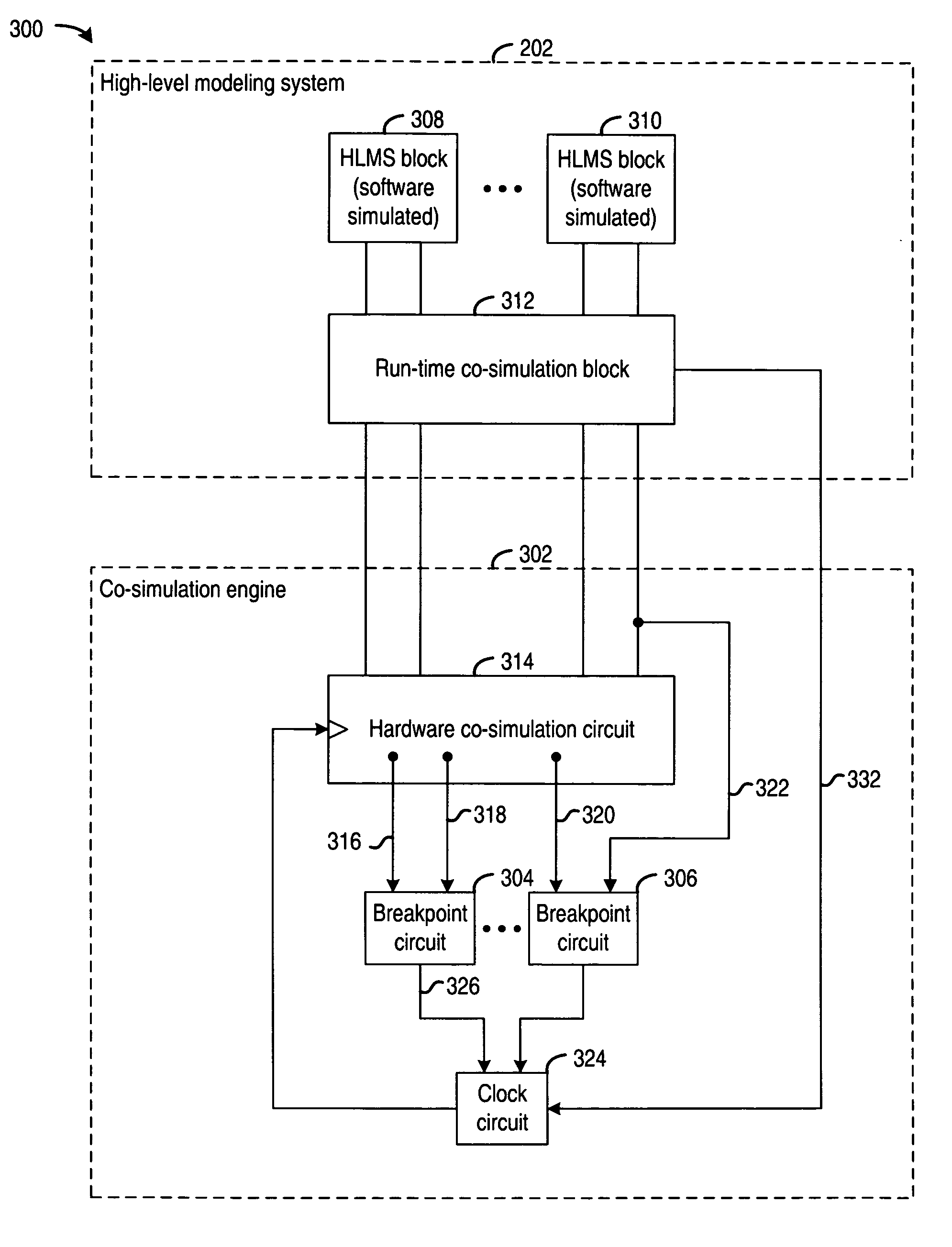

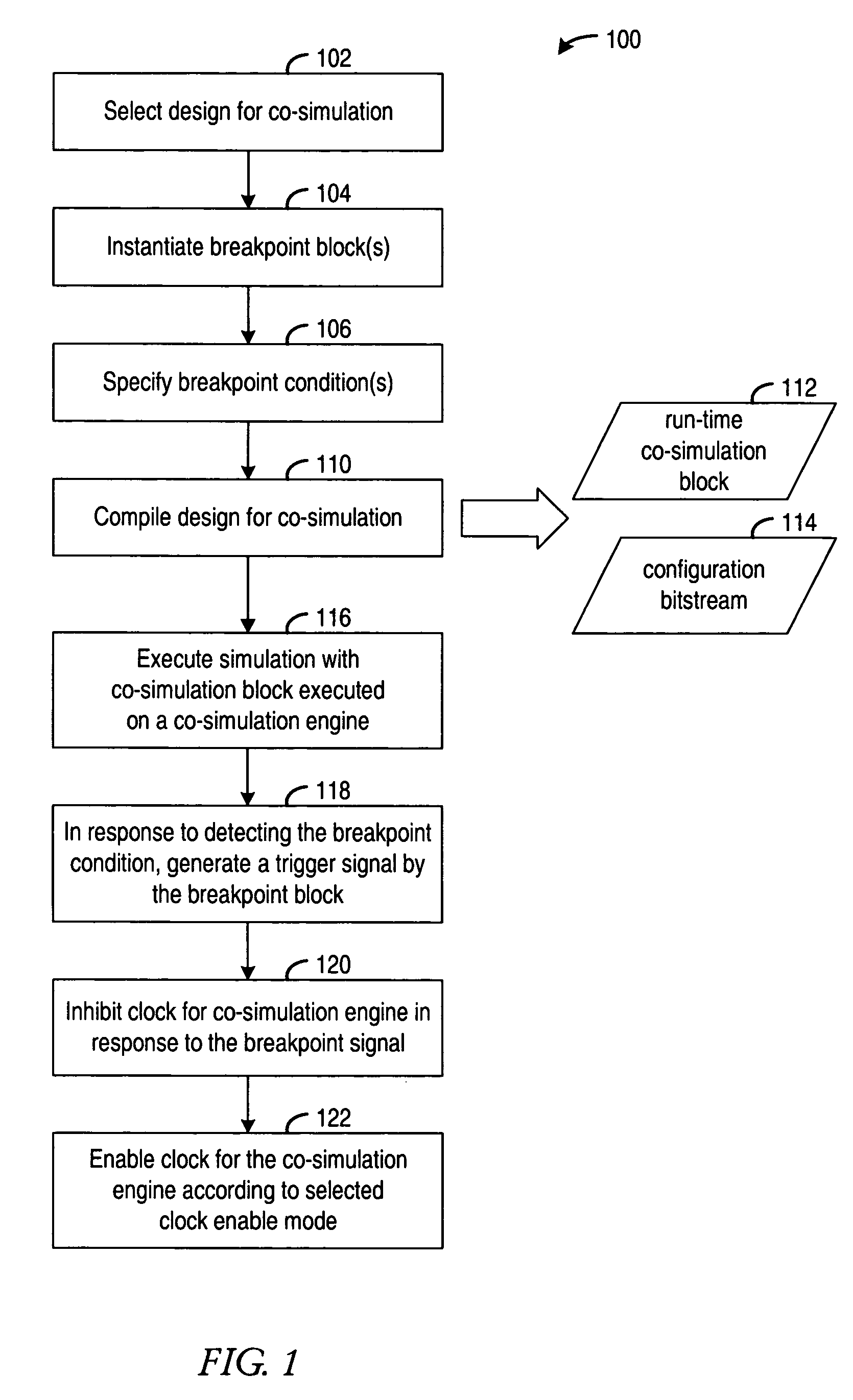

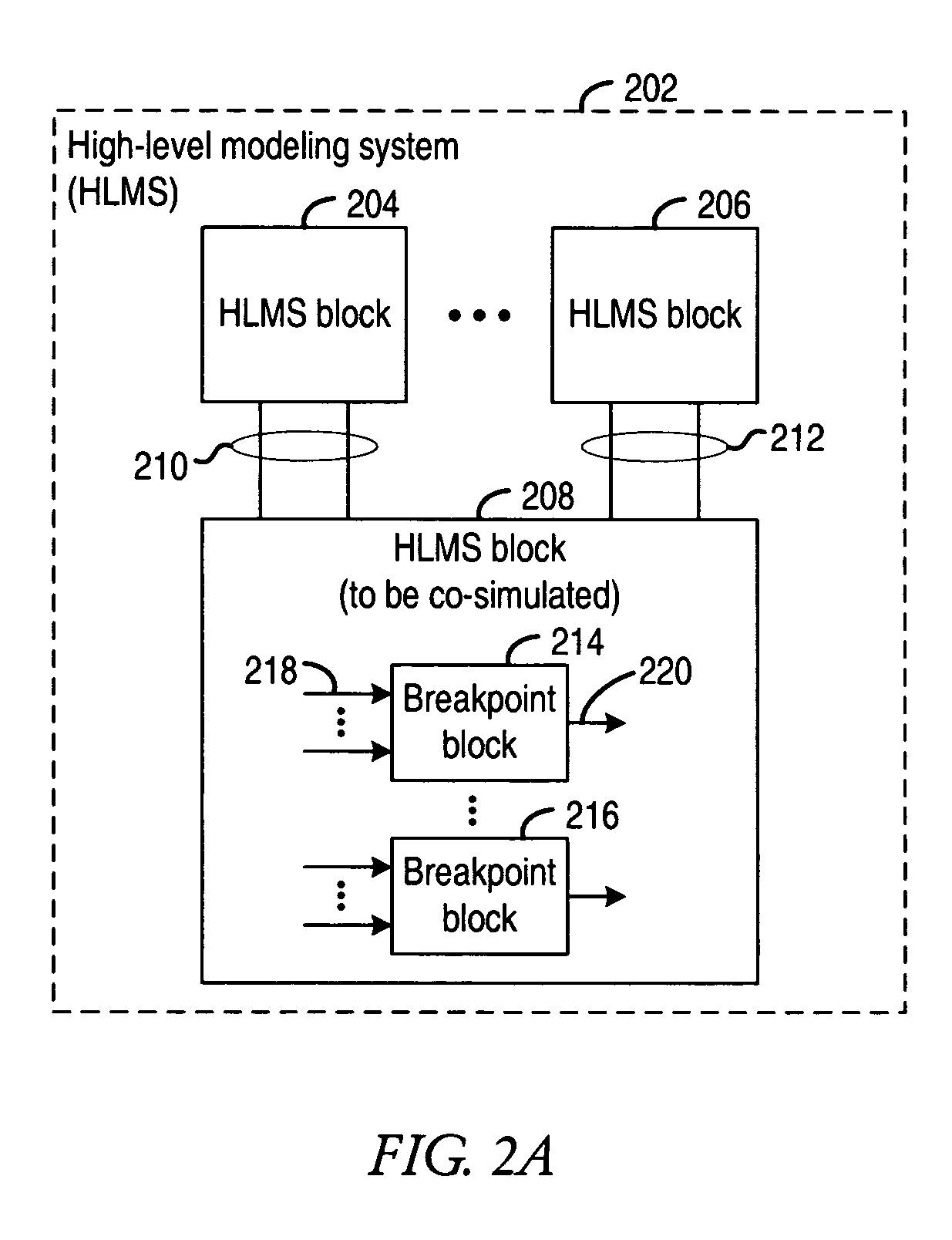

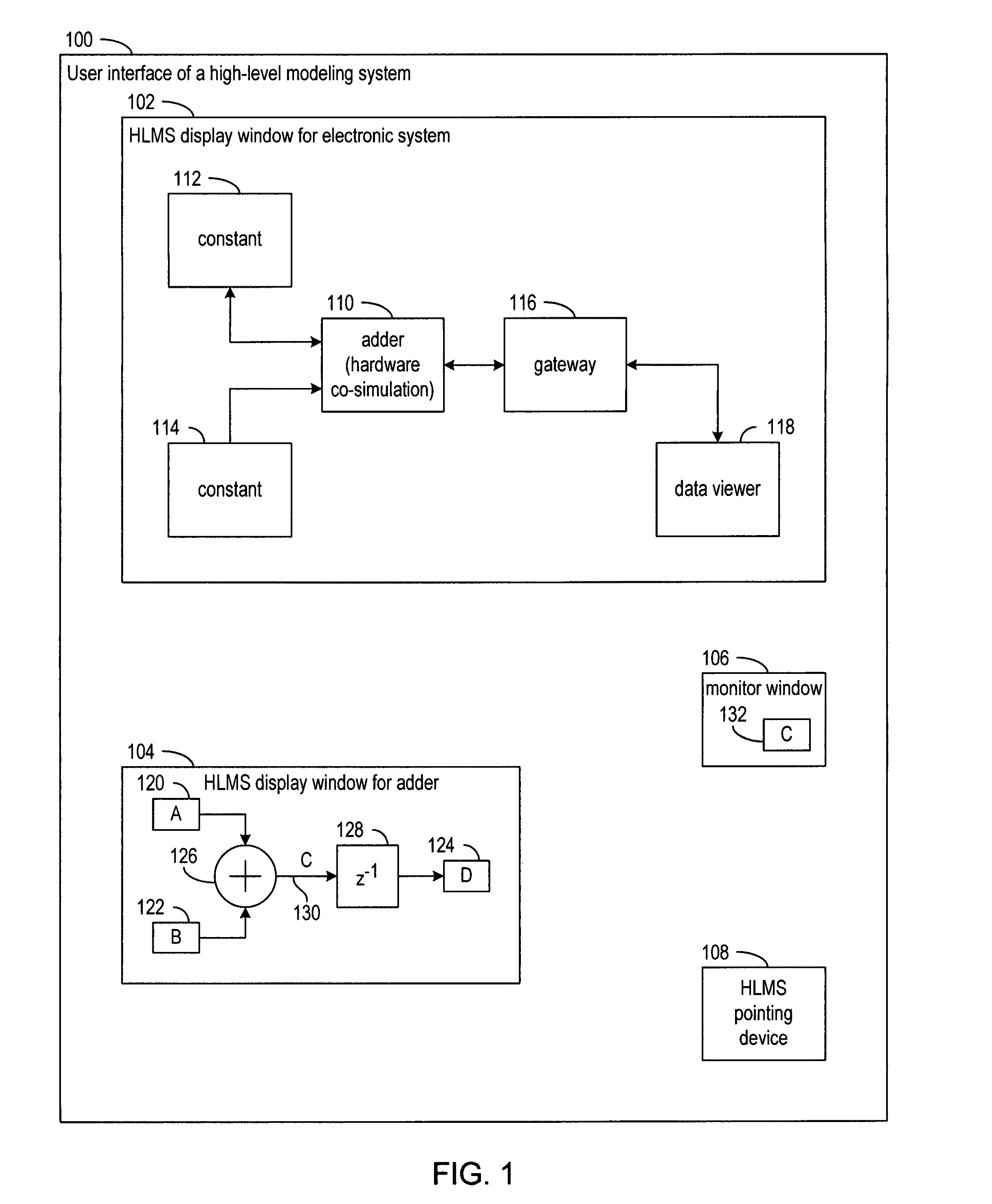

Hardware co-simulation breakpoints in a high-level modeling system

ActiveUS7346481B1Design optimisation/simulationCAD circuit designElectronic systemsHigh level modeling

Various approaches for controlling simulation of an electronic system are disclosed. In one approach, at least one breakpoint block is instantiated in a high-level design. The breakpoint block has an associated breakpoint condition driven by at least one signal of the design, and the design further includes at least one simulation block and at least one co-simulation block. The simulation block is simulated on a software-based simulation platform, and the co-simulation block and the breakpoint block are co-simulated on a hardware-based co-simulation platform. Advancement of a clock signal to the co-simulation block on the hardware-based co-simulation platform is inhibited in response to satisfaction of the breakpoint condition. After inhibiting the clock signal, advancement of steps of the clock signal is controlled on the co-simulation platform in one of a plurality of user-selectable clock advancement modes.

Owner:XILINX INC

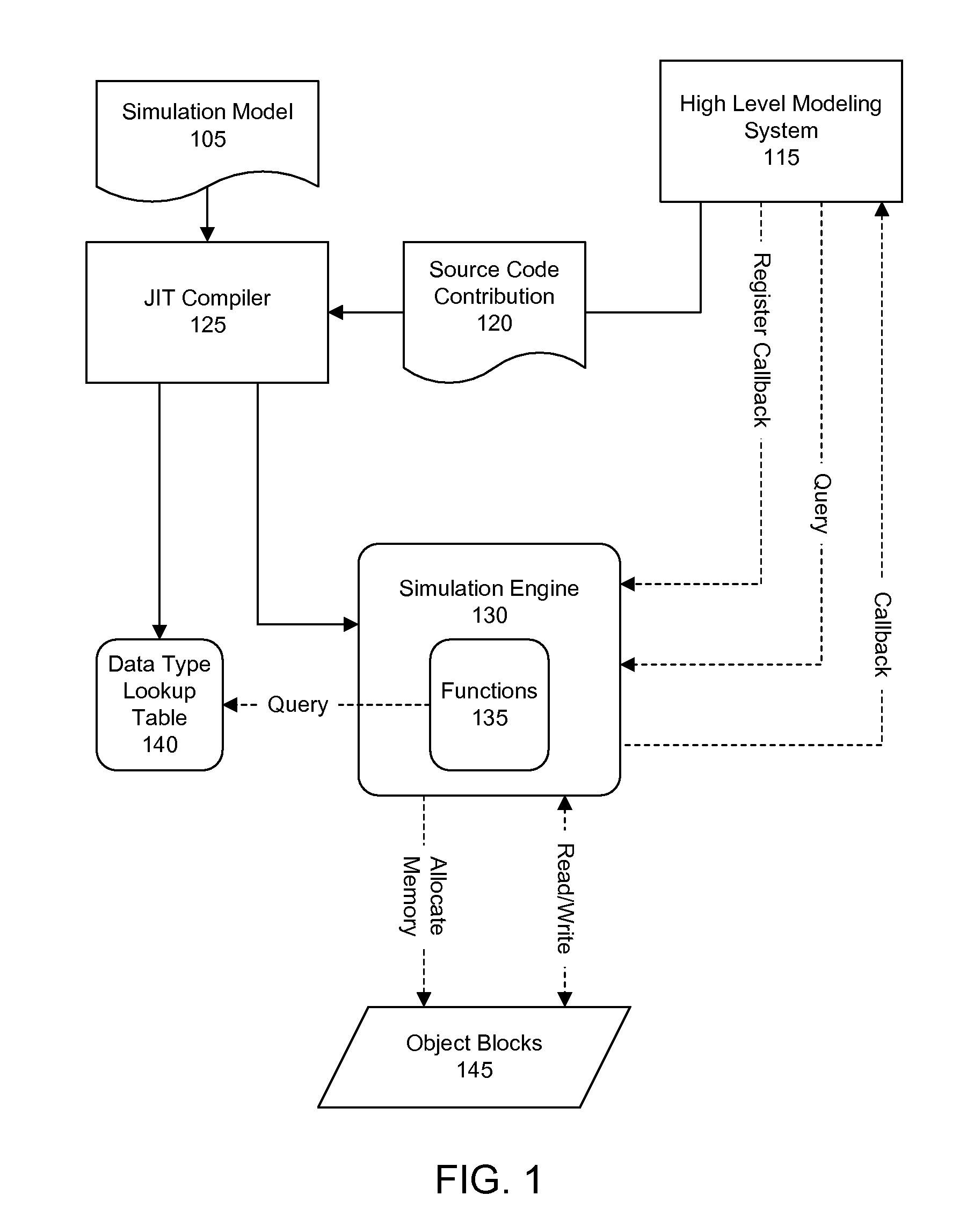

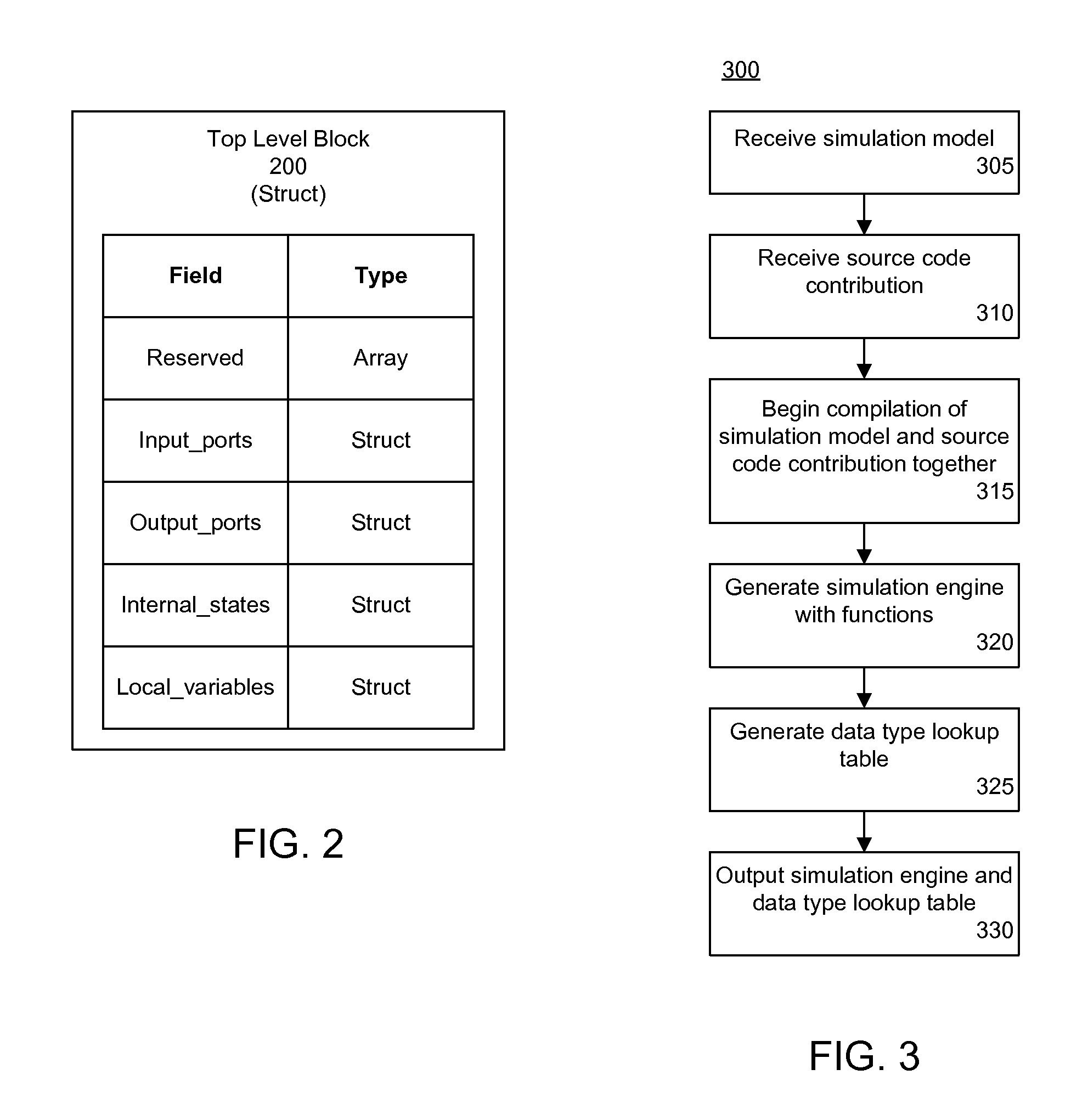

Reloadable just-in-time compilation simulation engine for high level modeling systems

ActiveUS8352229B1Analogue computers for electric apparatusProgram controlAnalog circuit designJust-in-time compilation

A computer-implemented method of creating a simulation engine for simulating a circuit design can include receiving a source code contribution from a high level modeling system and receiving a simulation model specified in an interpretive language that specifies the circuit design. The source code contribution can be compiled together with the simulation model using a Just-In-Time compiler. A simulation engine, specified in native machine code, can be output as a single, integrated software component formed from the source code contribution and the simulation model.

Owner:XILINX INC

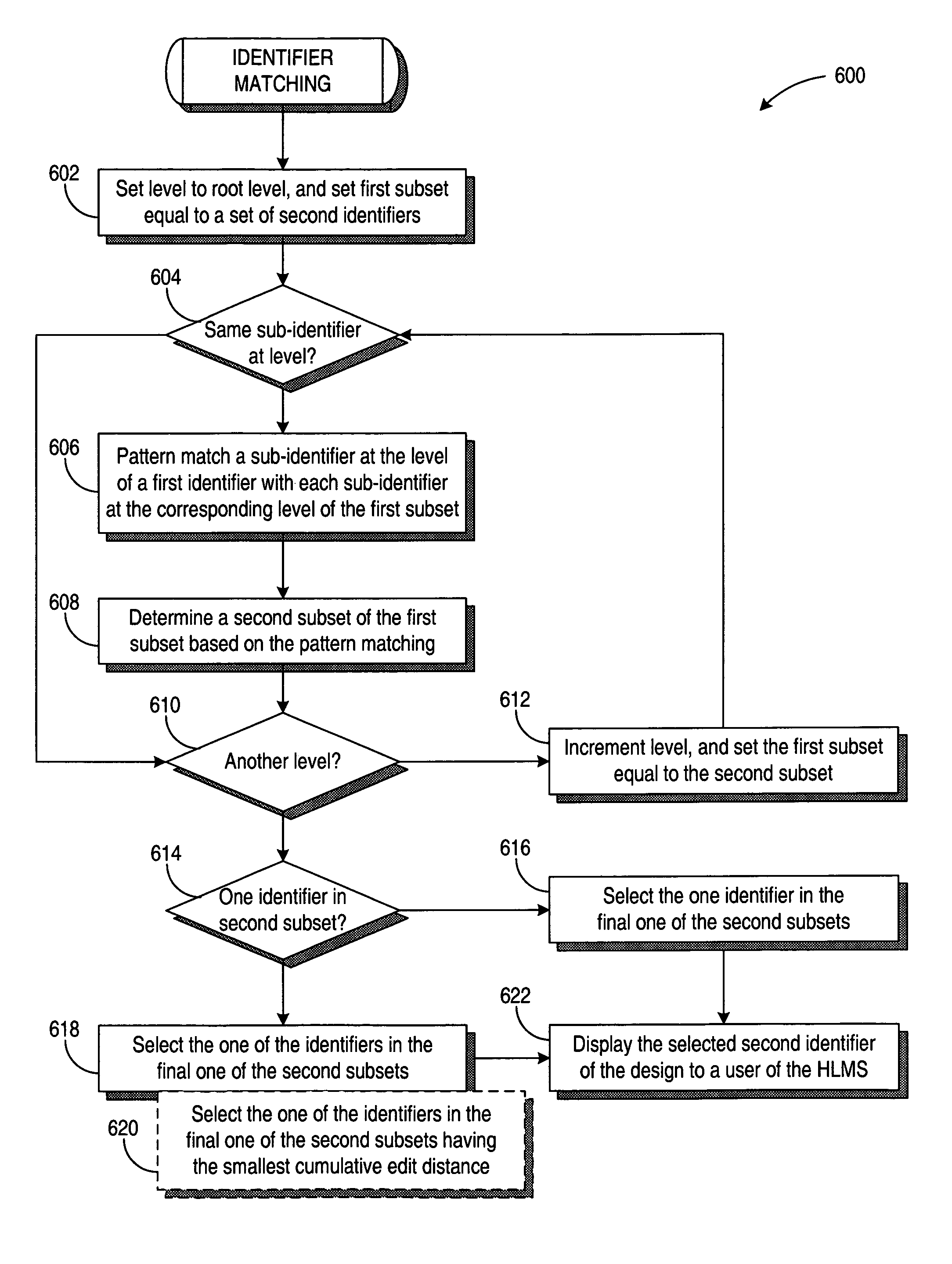

Method and system for matching a hierarchical identifier

ActiveUS7363599B1Computer aided designSpecial data processing applicationsHigh level modelingPattern matching

A first hierarchical identifier is efficiently matched with a particular hierarchical identifier from a set of second hierarchical identifiers of a design in a high level modeling system. The matching tolerates name changes and additional design details in the hierarchical identifiers. A first sub-identifier at each level of the first hierarchical identifier is pattern matched with each second sub-identifier at a corresponding level of at least one second hierarchical identifier in a respective first subset of the second hierarchical identifiers. The pattern matching may include determining an edit distance between the first and second sub-identifiers. For each of the levels, a respective second subset of the respective first subset is determined in response to the pattern matching. The particular hierarchical identifier is selected from an intersection of all of the second subsets. The particular hierarchical identifier of the design is displayed on a user interface of the high-level modeling system.

Owner:XILINX INC

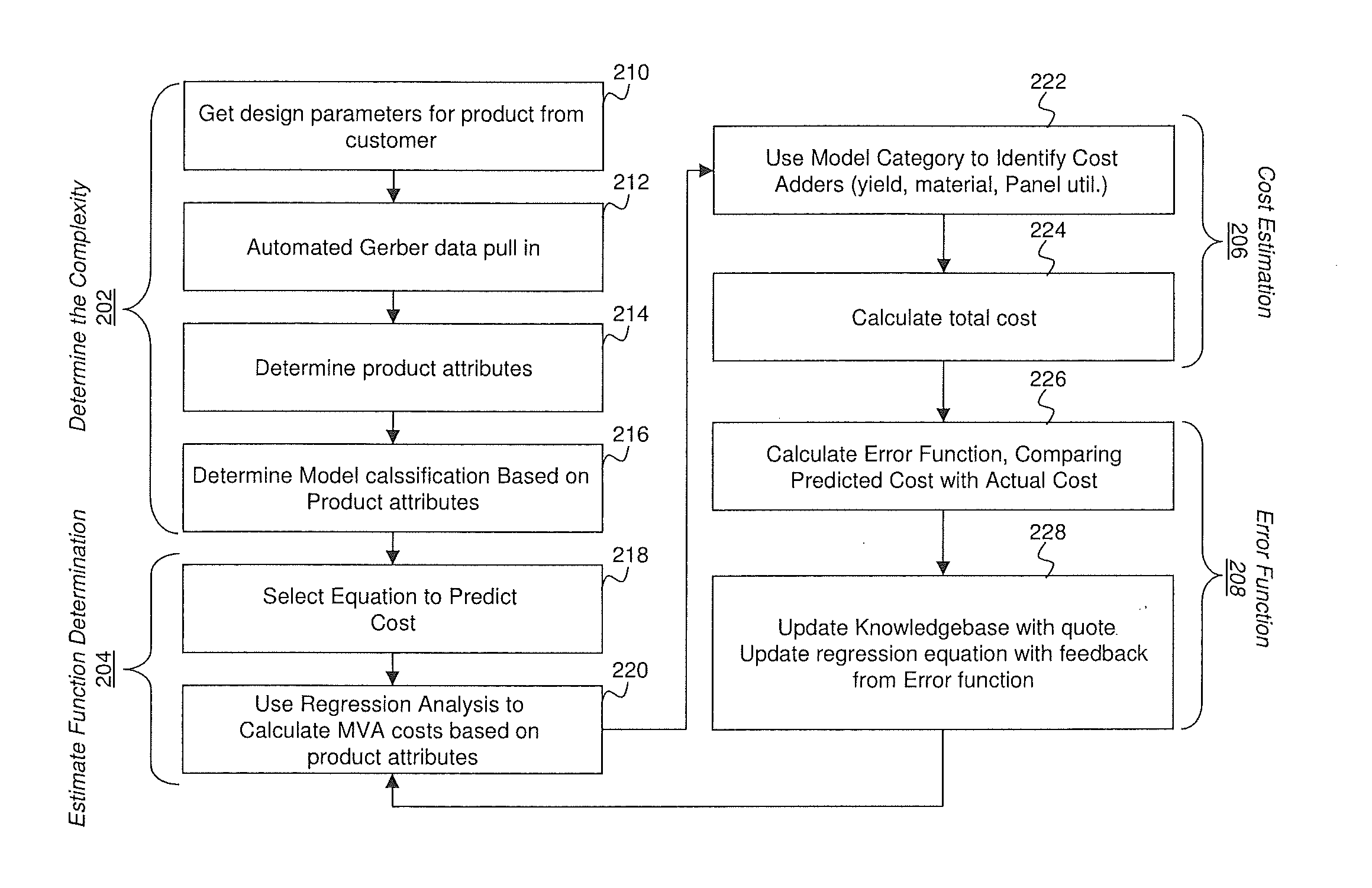

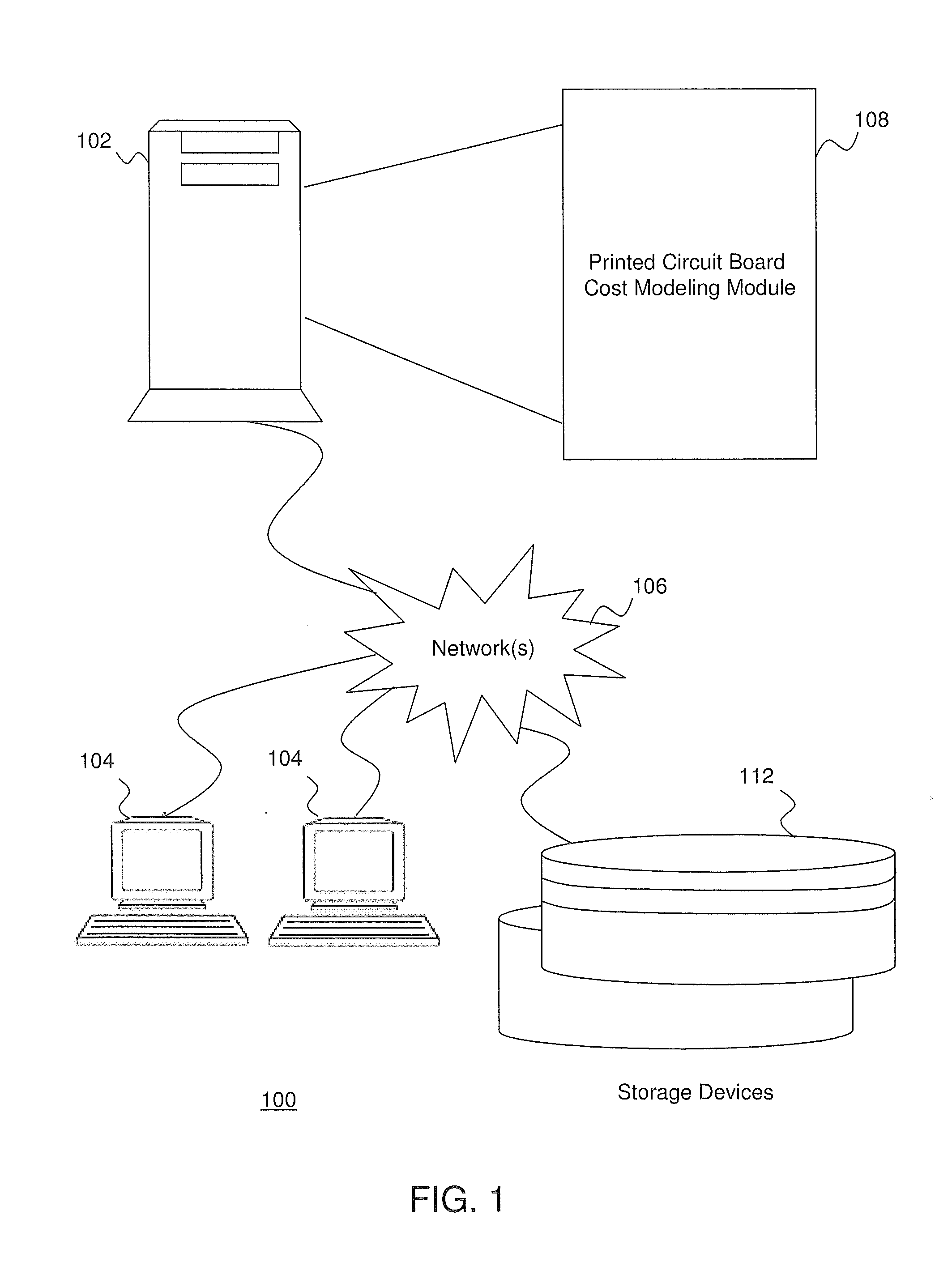

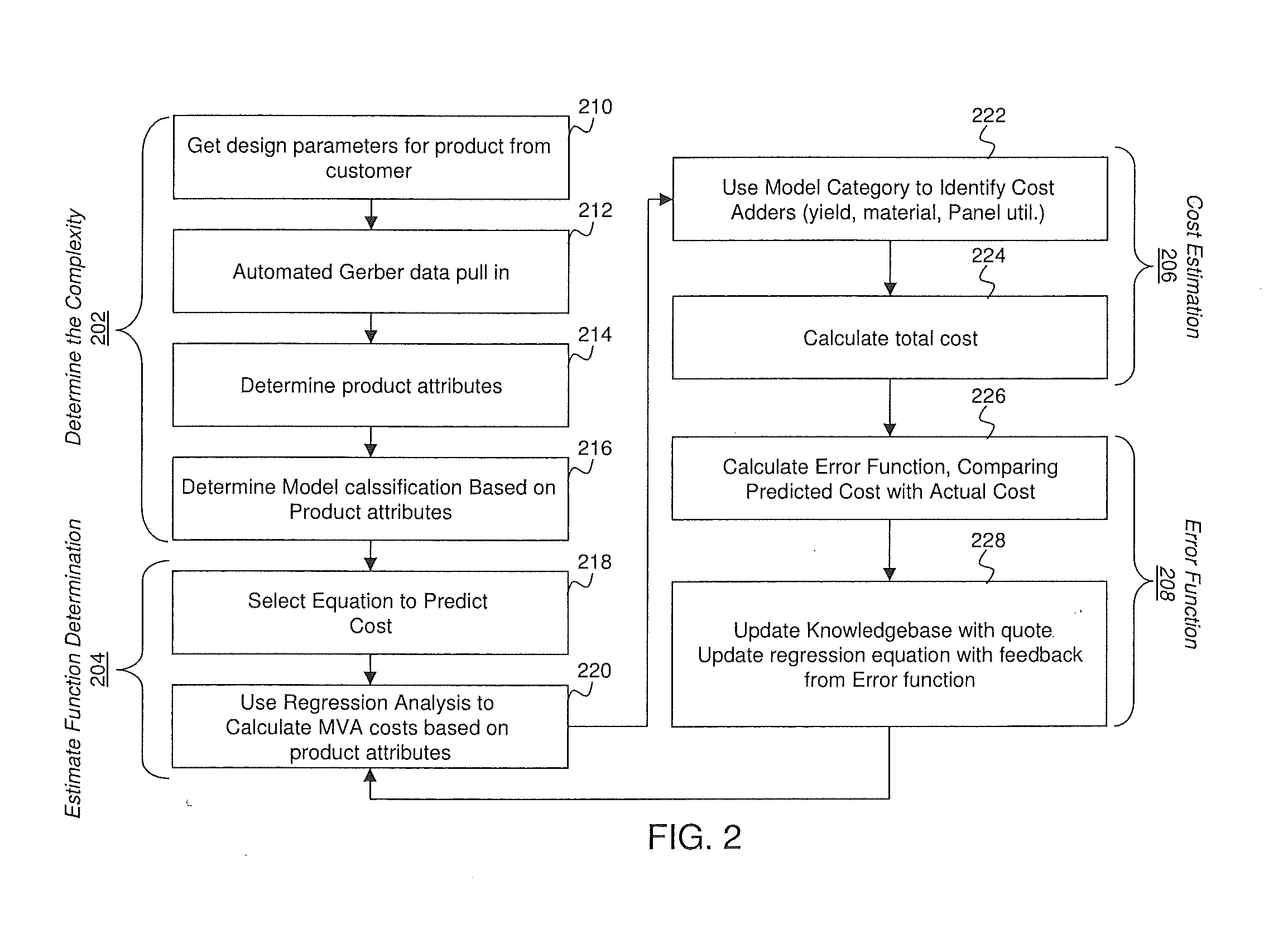

Advanced modeling of printed circuit board costs

InactiveUS20130024400A1CAD circuit designElectric/magnetic computingHigh level modelingRegression analysis

A total cost estimate is calculated based on a set of printed circuit board (PCB) design parameters. The set of PCB design parameters are received, and PCB attributes are extracted from them. Based on the PCB attributes the PCB is classified and a cost equation is calculated. The cost equation is calculated based on a regression analysis of one or more of the PCB attributes. Once the cost equation is calculated, the total cost is computed based on the cost equation.

Owner:IBM CORP

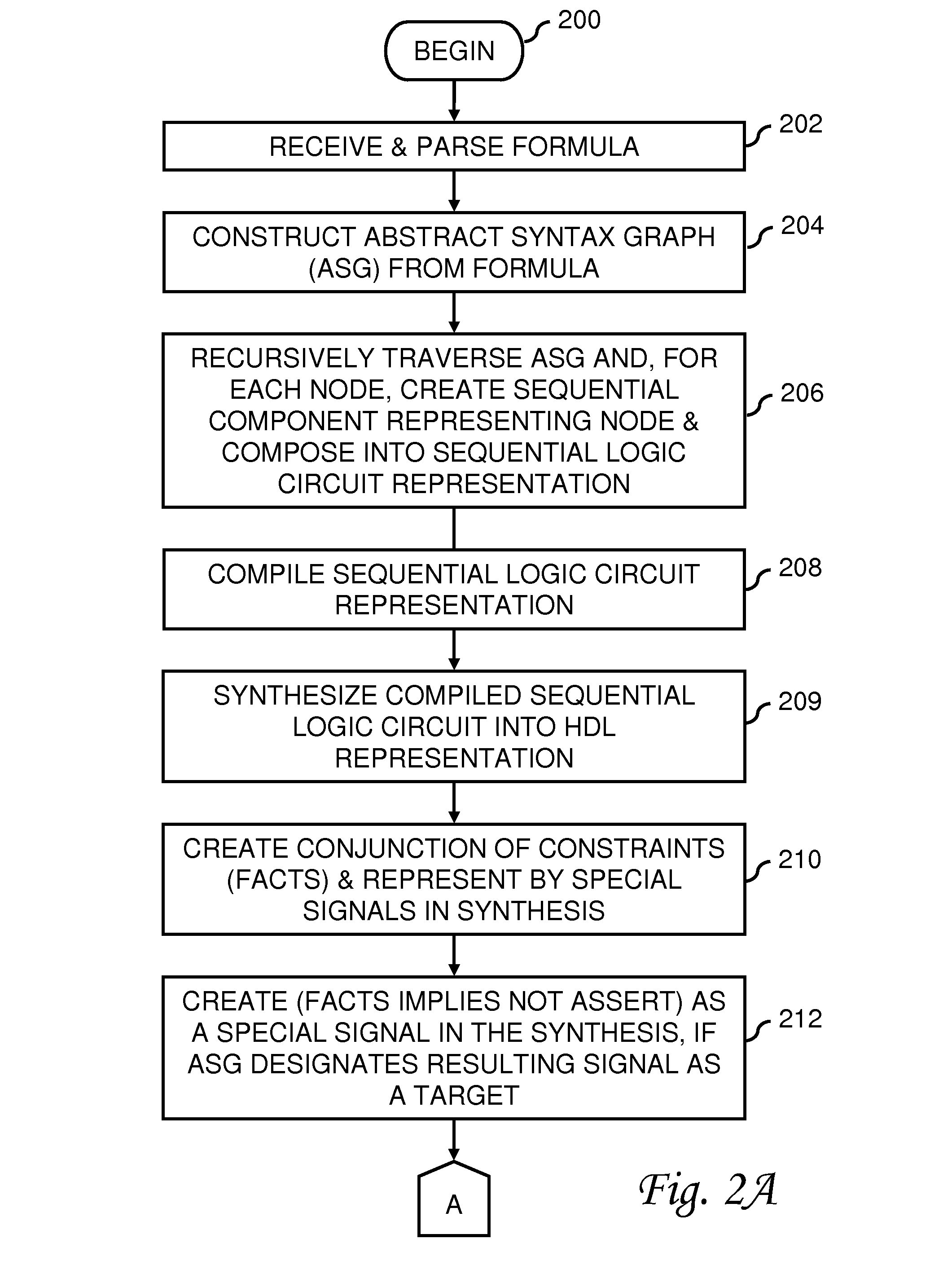

Method, System and Program Product Supporting Sequential Encoding for Relational Analysis (SERA) of a Software Model

InactiveUS20080209389A1Software simulation/interpretation/emulationSpecial data processing applicationsSoftware systemHigh level modeling

A method of verifying a software system includes receiving a description of a software system described utilizing a high-level modeling language, and responsive thereto, parsing the description and constructing an abstract syntax graph. The abstract syntax graph is transformed into a sequential logic representation of the software system, and following the transforming, the software system is verified based upon the sequential logic representation. Following verification, results of verification of the software system are output.

Owner:GLOBALFOUNDRIES INC

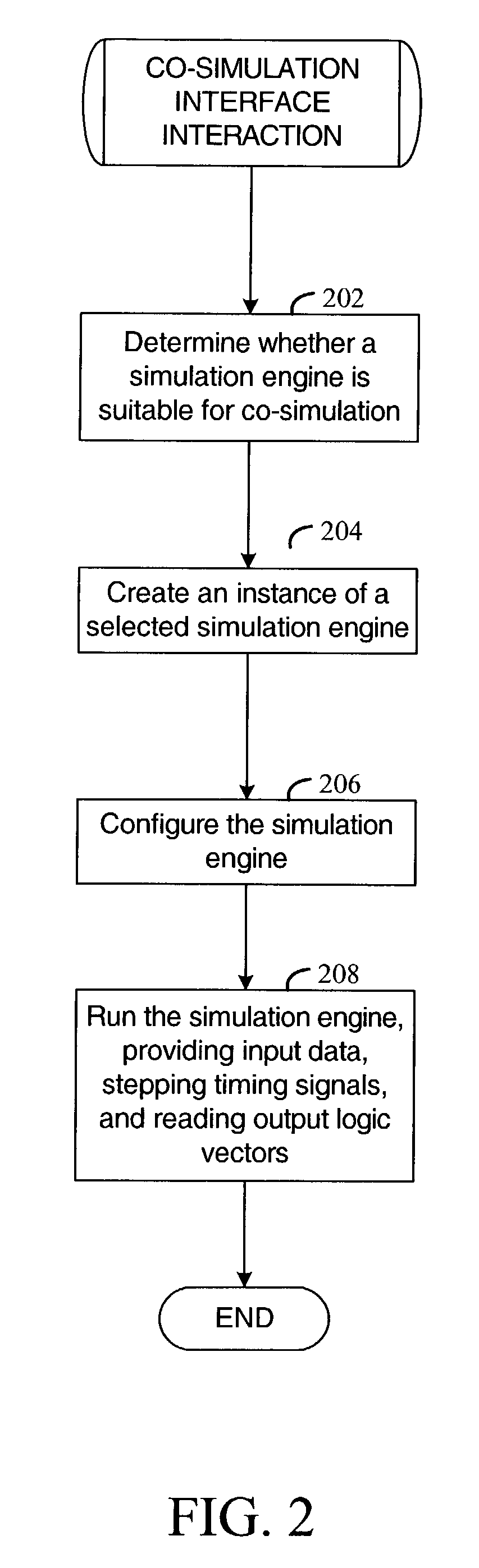

Co-simulation interface

ActiveUS7366651B1Program control using stored programsElectronic circuit testingHigh level modelingEngineering

Method and apparatus for interfacing between a high-level modeling system and a hardware description language (HDL) co-simulation engine. A plurality of HDL co-simulation engine libraries are queried as to the capabilities of the engines. A co-simulation engine is selected based on the capabilities, and an instance of the engine is created. The selected co-simulation engine is configured, input logic vectors are provided to the selected HDL co-simulation engine, and the co-simulation engine is executed accordingly.

Owner:XILINX INC

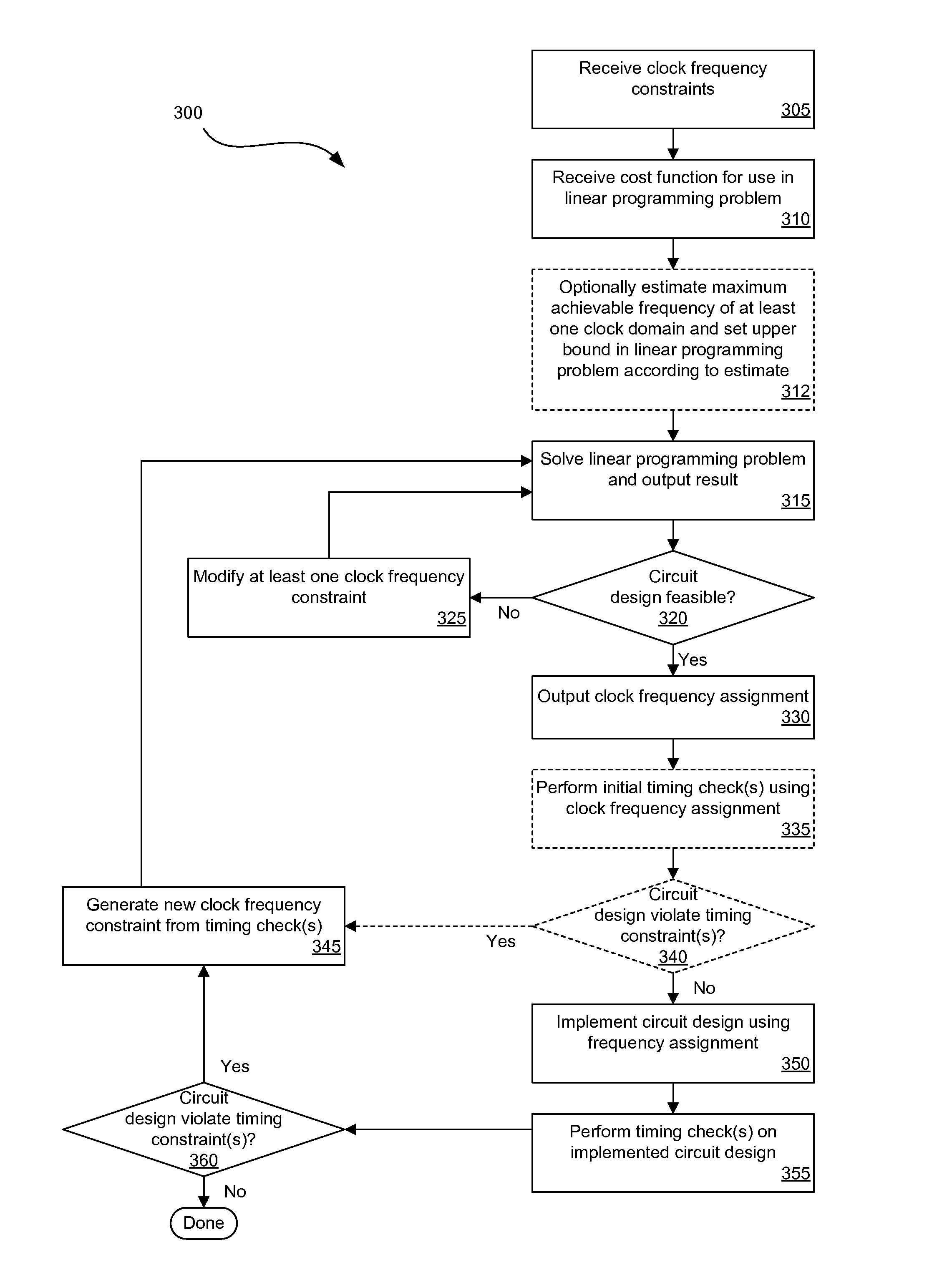

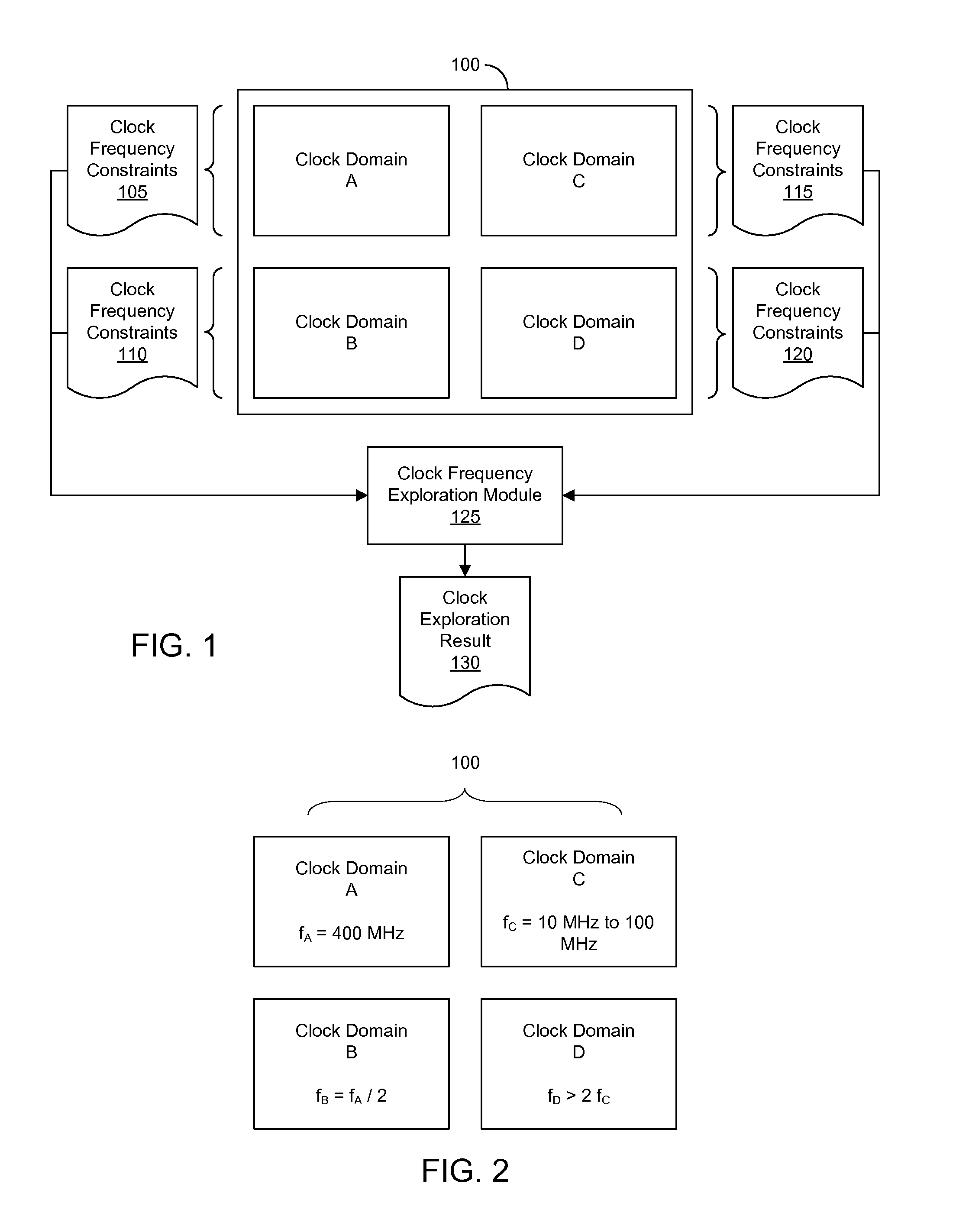

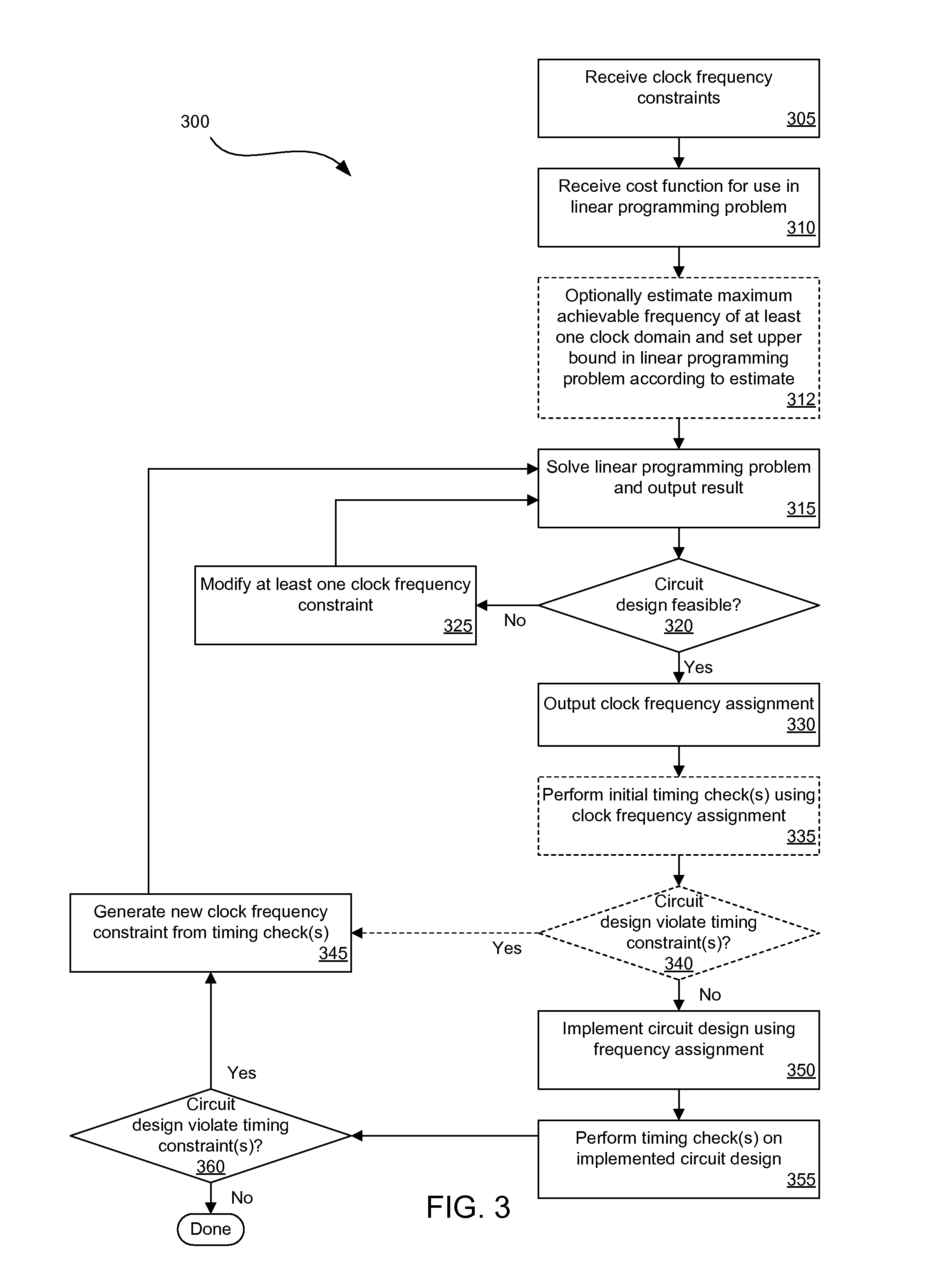

Clock frequency exploration for circuit designs having multiple clock domains

ActiveUS8020127B1Minimize cost functionCAD circuit designSoftware simulation/interpretation/emulationClock rateHigh level modeling

A computer-implemented method of circuit design can include receiving clock frequency constraints defining relationships between clock frequencies of a plurality of clock domains of a circuit design specified within a high-level modeling system (305) and receiving a cost function that is dependent upon the clock frequencies of the plurality of clock domains (310). A feasibility result can be determined according to the clock frequency constraints and the cost function (315). The feasibility result can indicate whether a clock frequency assignment exists that specifies a clock frequency for each of the plurality of clock domains that does not violate any clock frequency constraint. The feasibility result can be output (315).

Owner:XILINX INC

Using patterns for high-level modeling and specification of properties for hardware systems

ActiveUS20060156145A1Simplify writingSimple taskElectronic circuit testingError detection/correctionElectronic systemsHigh level modeling

This invention is a high-level language to specify electronic system design patterns for functional verification. This invention includes automatic translation of the high-level language specification into assertion code from these patterns and temporal properties for design verification. This eliminates the need to code extra RTL to handle features such as pipelines and bus priorities. Such common features are specified only in high-level patterns and temporal properties to be verified. This is advantageous because less verification code to be written, automated synthesis of assertions enforces monitor-style of writing assertions rather than generator-style, and the high-level code can be seamlessly migrated to another verification tool by producing another code generator for the new assertion language.

Owner:TEXAS INSTR INC

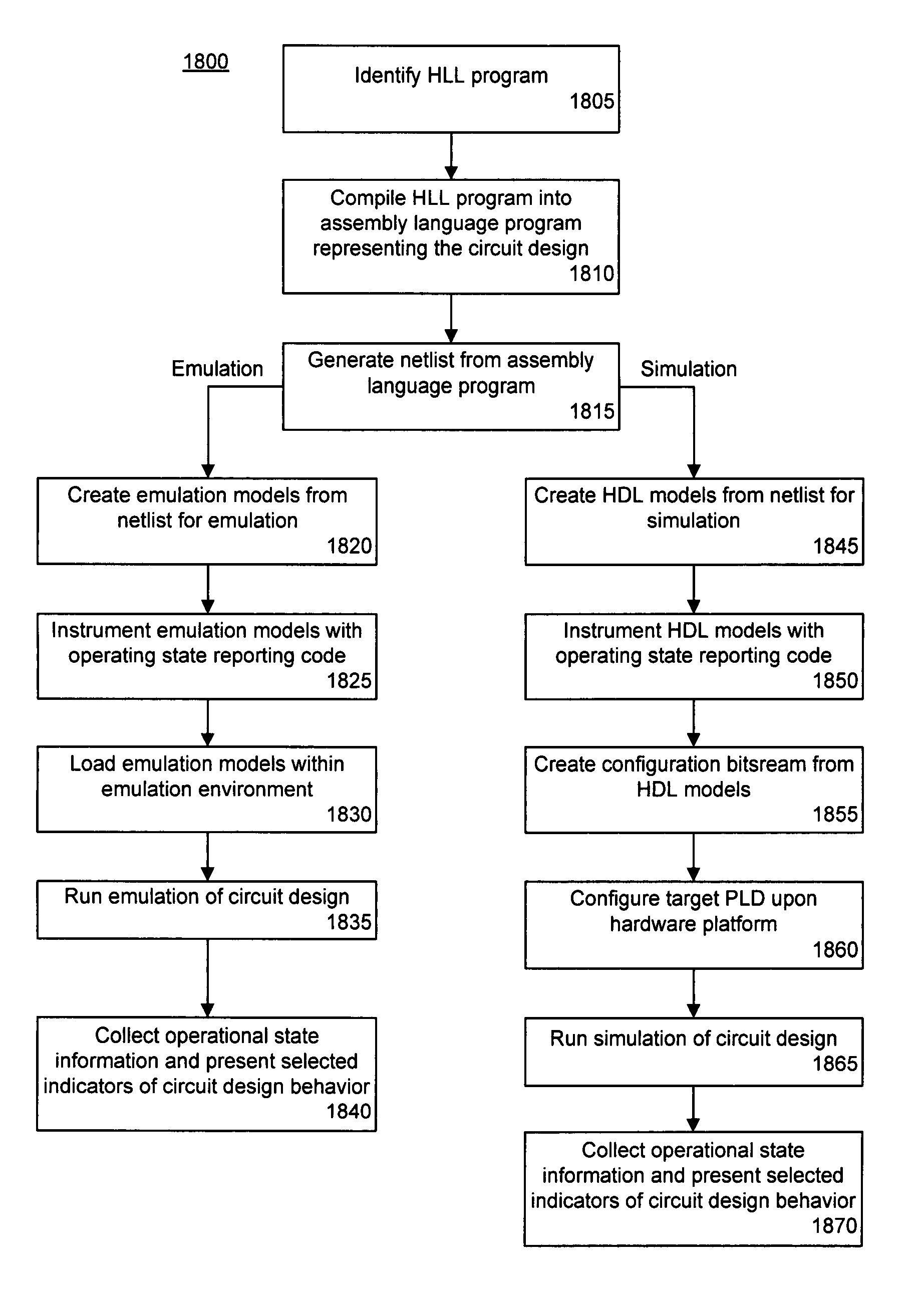

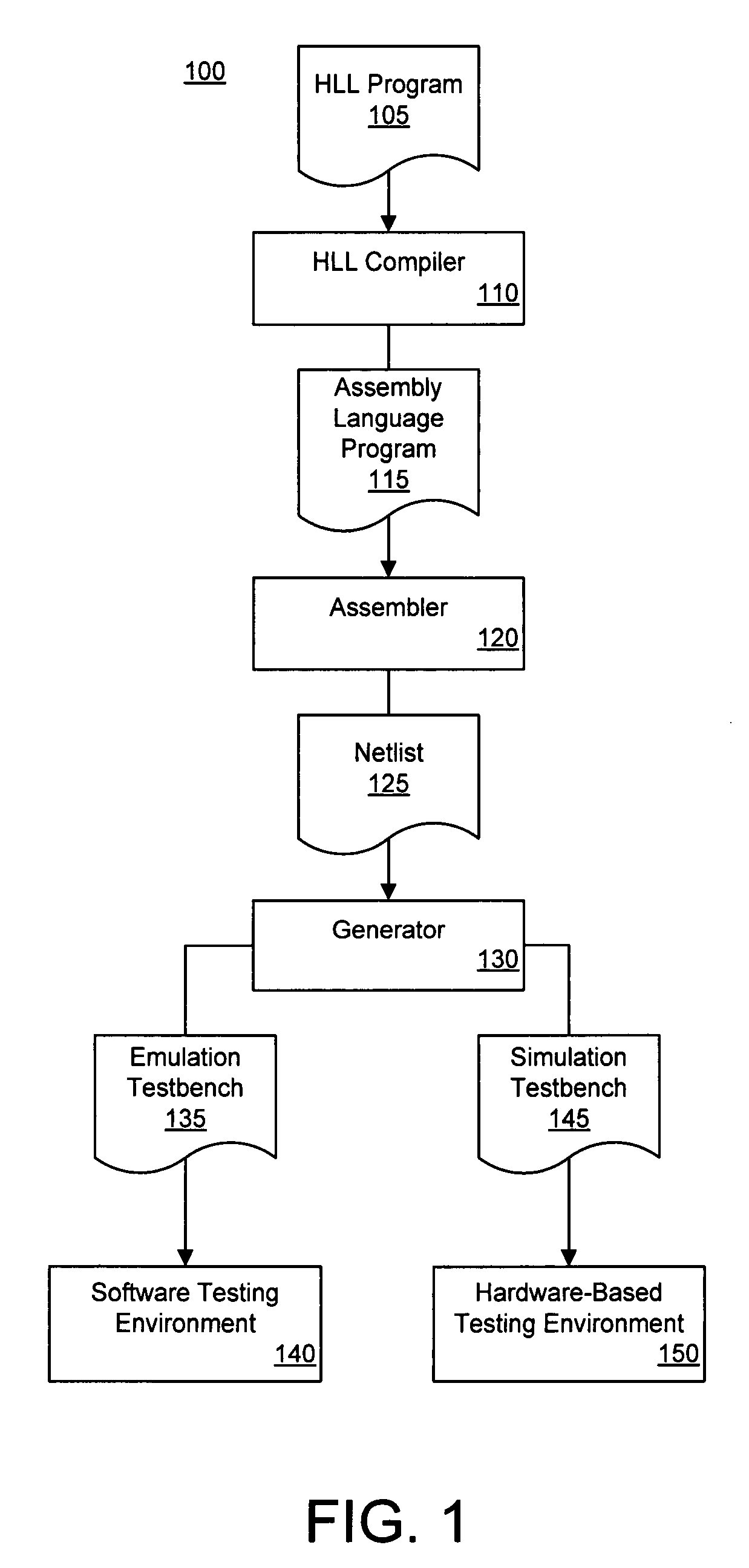

Profiling a hardware system generated by compiling a high level language onto a programmable logic device

A method of profiling a hardware system can include compiling a high level language program into an assembly language representation of the hardware system and translating instructions of the assembly language representation of the hardware system into a plurality of executable, software models. The models can be implemented using a high level modeling language for use with cycle accurate emulation. The method also can include instrumenting at least one of the plurality of models with code that, when executed, provides operating state information relating to the model as output and indicating expected behavior of the circuit by executing the models in an emulation environment.

Owner:XILINX INC

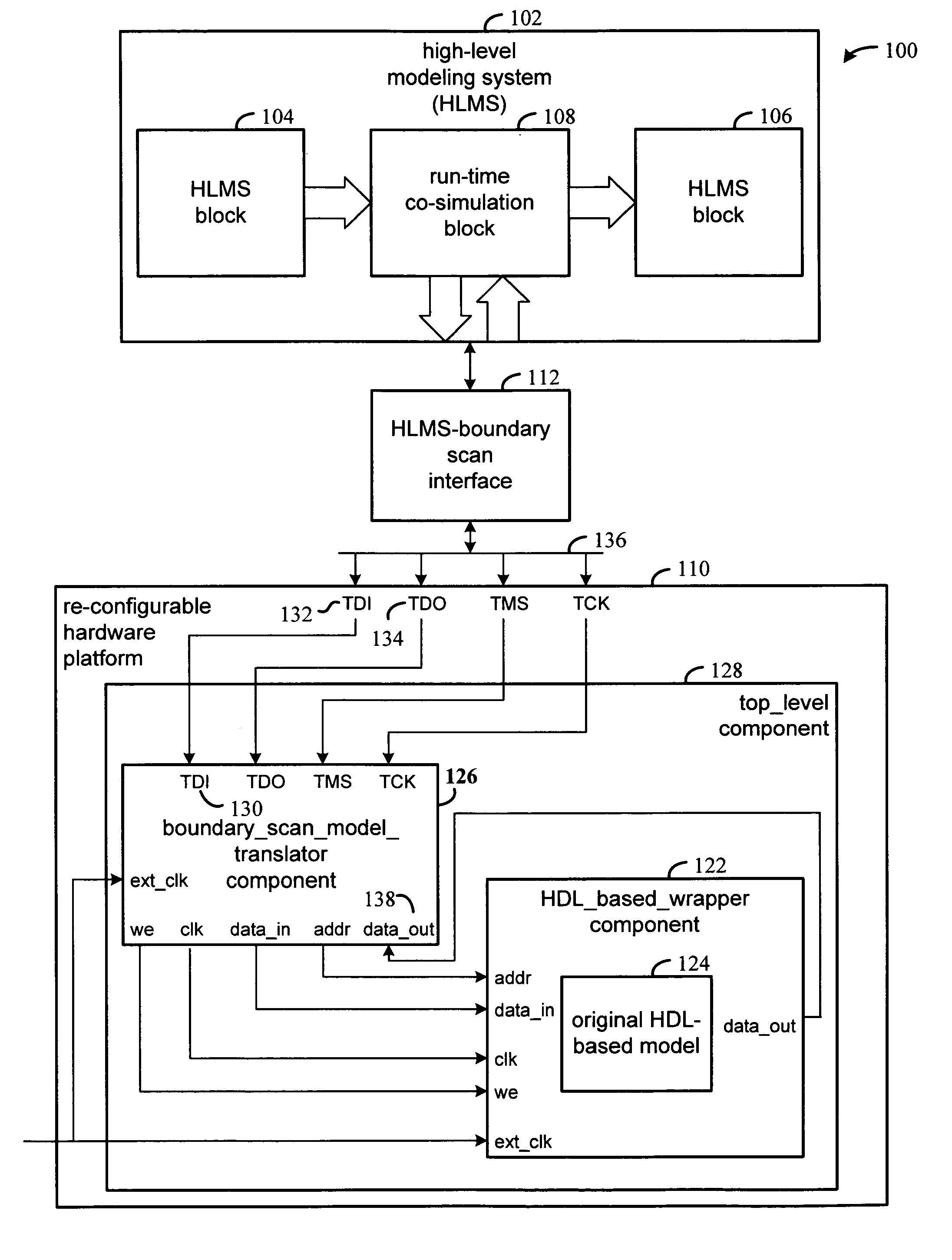

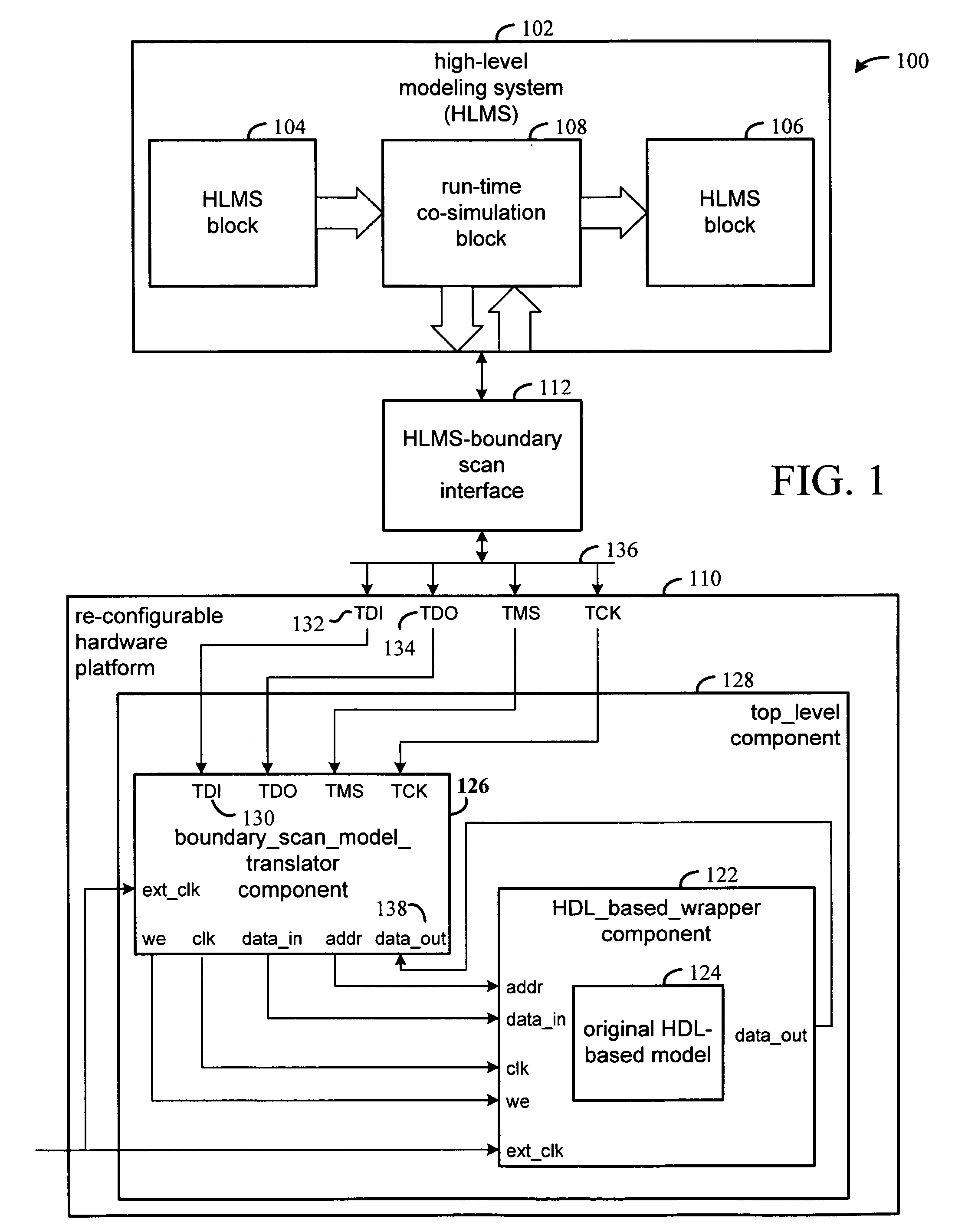

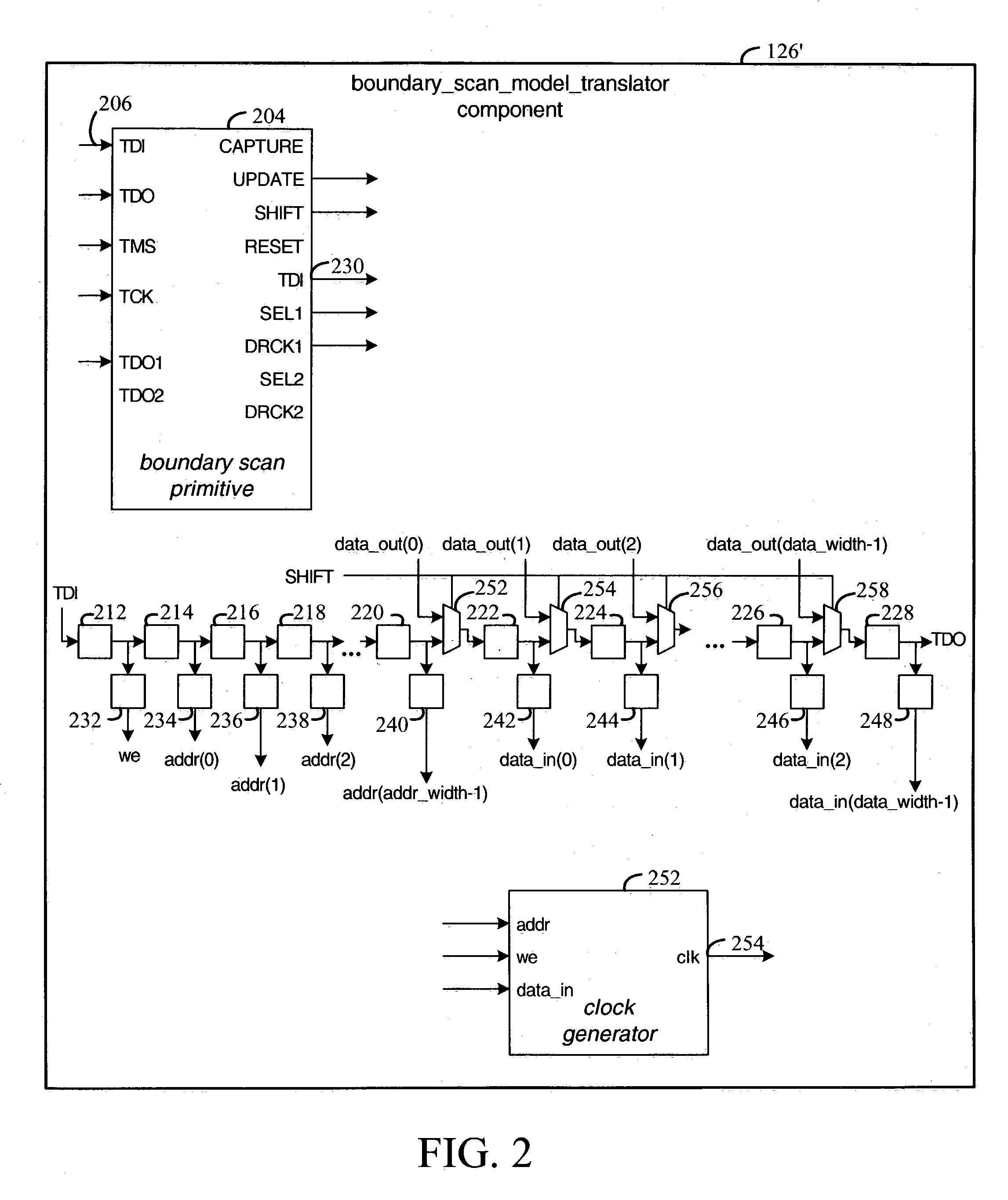

Co-simulation via boundary scan interface

ActiveUS7184946B2Detecting faulty computer hardwareCAD circuit designComputer architectureHigh level modeling

Method and apparatus for interfacing a high-level modeling system (HLMS) with a reconfigurable hardware platform for co-simulation. In one embodiment a boundary-scan interface is coupled to the HLMS and is configured to translate HLMS-issued commands to signals generally compliant with a boundary-scan protocol, and translate signals generally compliant with a boundary-scan protocol to data compatible with the HLMS. A translator and a wrapper are implemented for configuration of the hardware platform. The translator translates between signals that generally compliant with the boundary-scan protocol and signals that are compliant with a second protocol. A component to be co-simulated is instantiated within the wrapper, and the wrapper transfers signals between the translator and the component.

Owner:XILINX INC

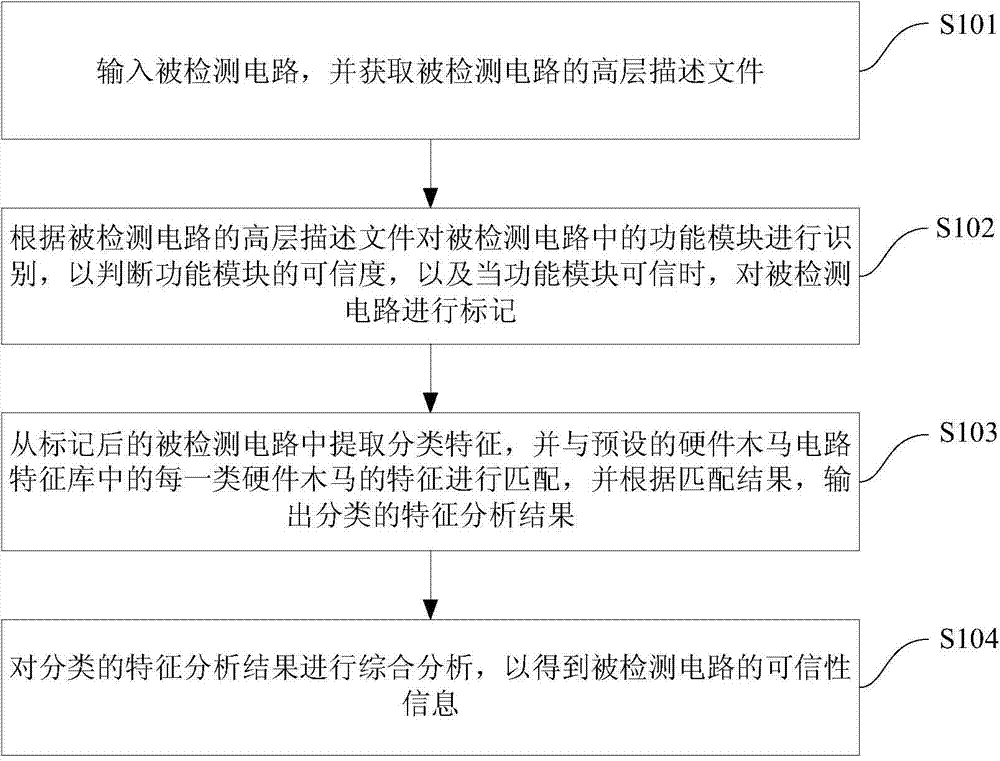

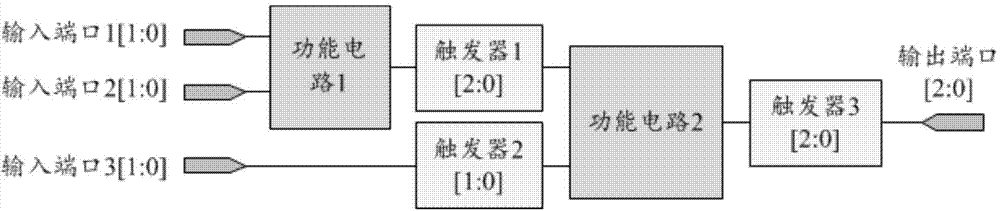

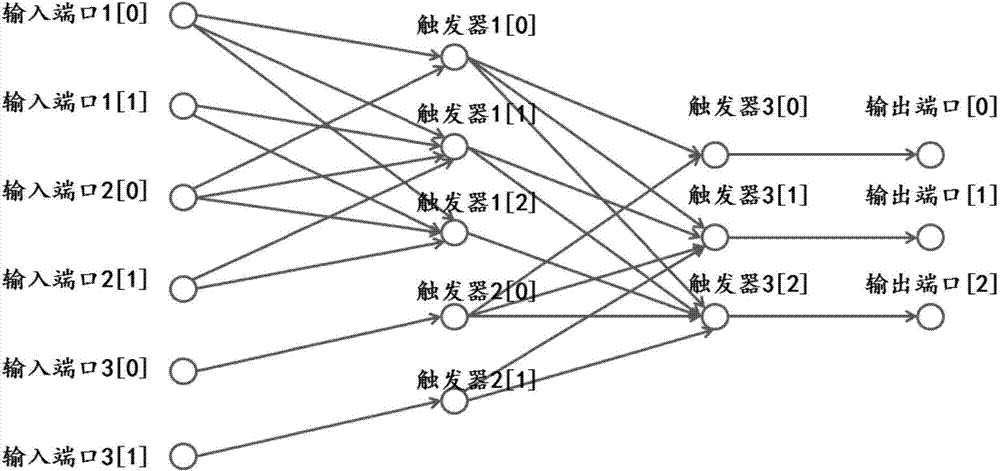

Hardware Trojan detecting method based on circuit characteristic analysis

ActiveCN104850804AReduce running timeLess impact on the design processInternal/peripheral component protectionHardware TrojanHigh level modeling

The invention provides a hardware Trojan detecting method based on circuit characteristic analysis. The hardware Trojan detecting method includes steps of inputting a detected circuit and acquiring a high-level modeling file of the detected circuit; identifying functional modules in the detected circuit according to the high-level modeling file of the circuit to be detected so as to judge reliability of the functional modules, and marking the detected circuit when the functional modules are reliable; extracting classification features from the marked detected circuit, matching each type of hardware Trojan characteristics in a preset hardware Trojan circuit characteristic database and outputting characteristic analysis results of classes according to the matching results; comprehensively analyzing the characteristic analysis results of classes so as to obtain reliability information of the detected circuit. By the hardware Trojan detecting method, hardware Trojan detecting speed is effectively increased as well as discrimination degree of the detecting area of different types of hardware Trojan, and detection effect of hardware Trojan in the time sequencing circuit is effectively improved.

Owner:TSINGHUA UNIV

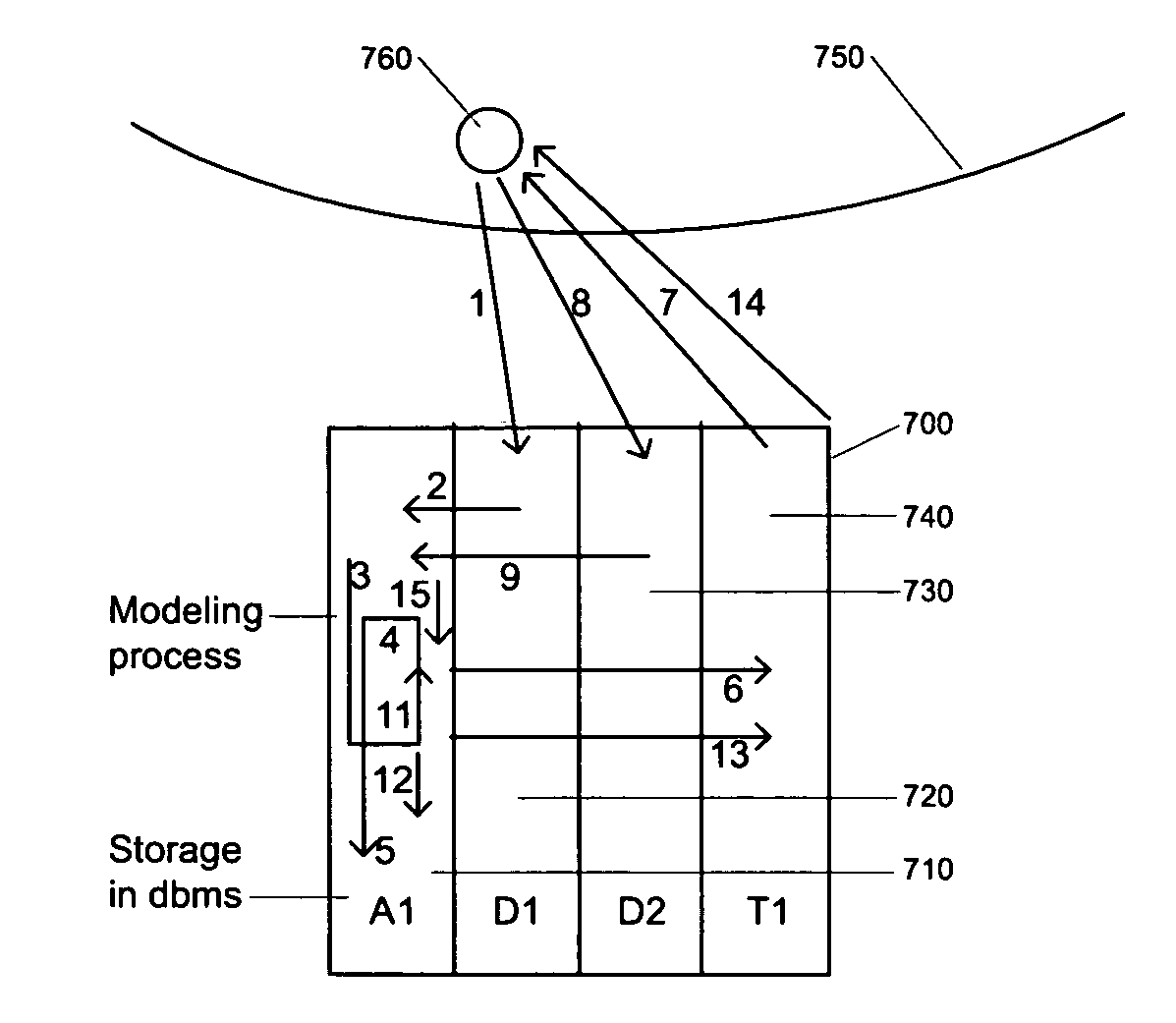

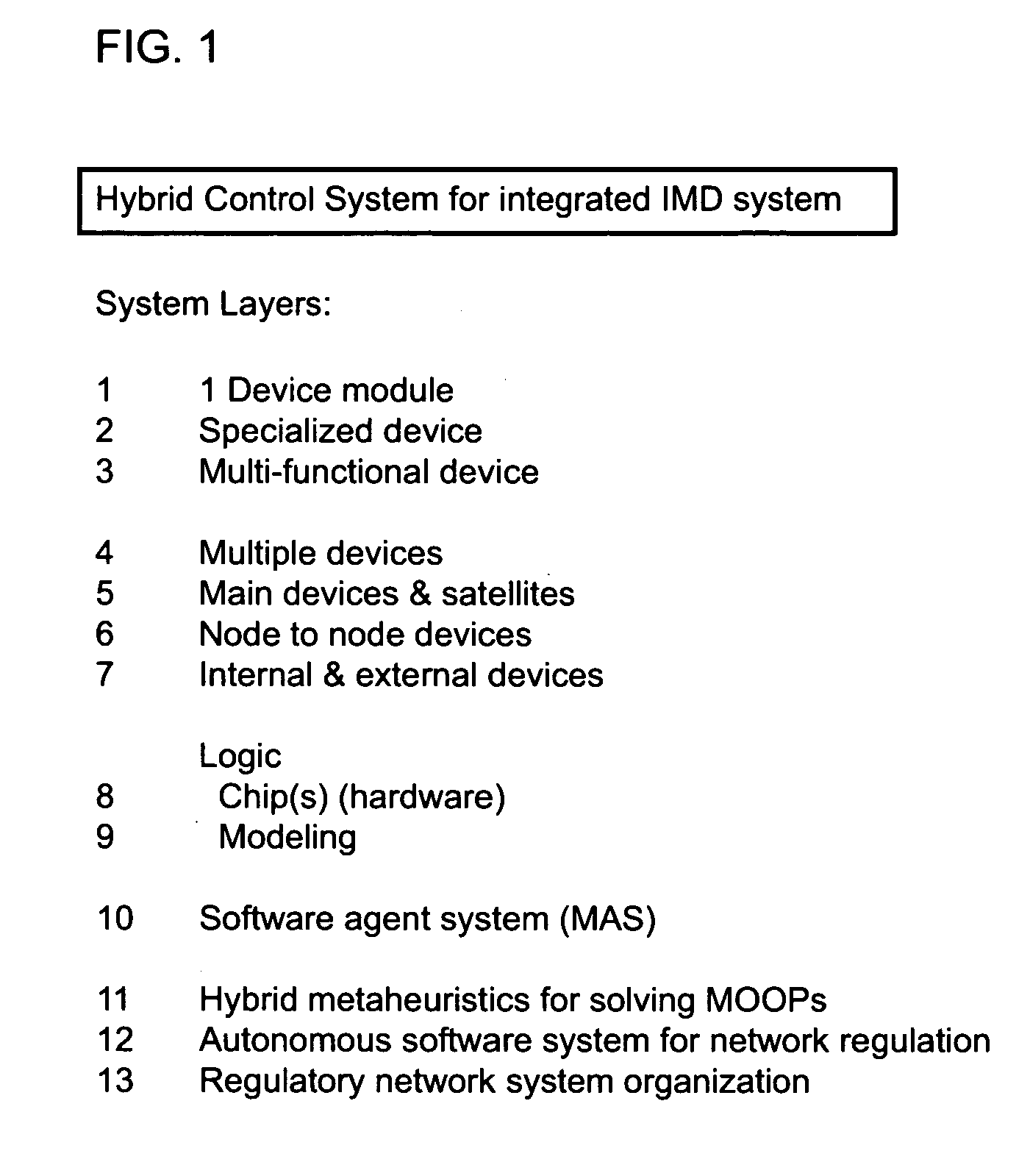

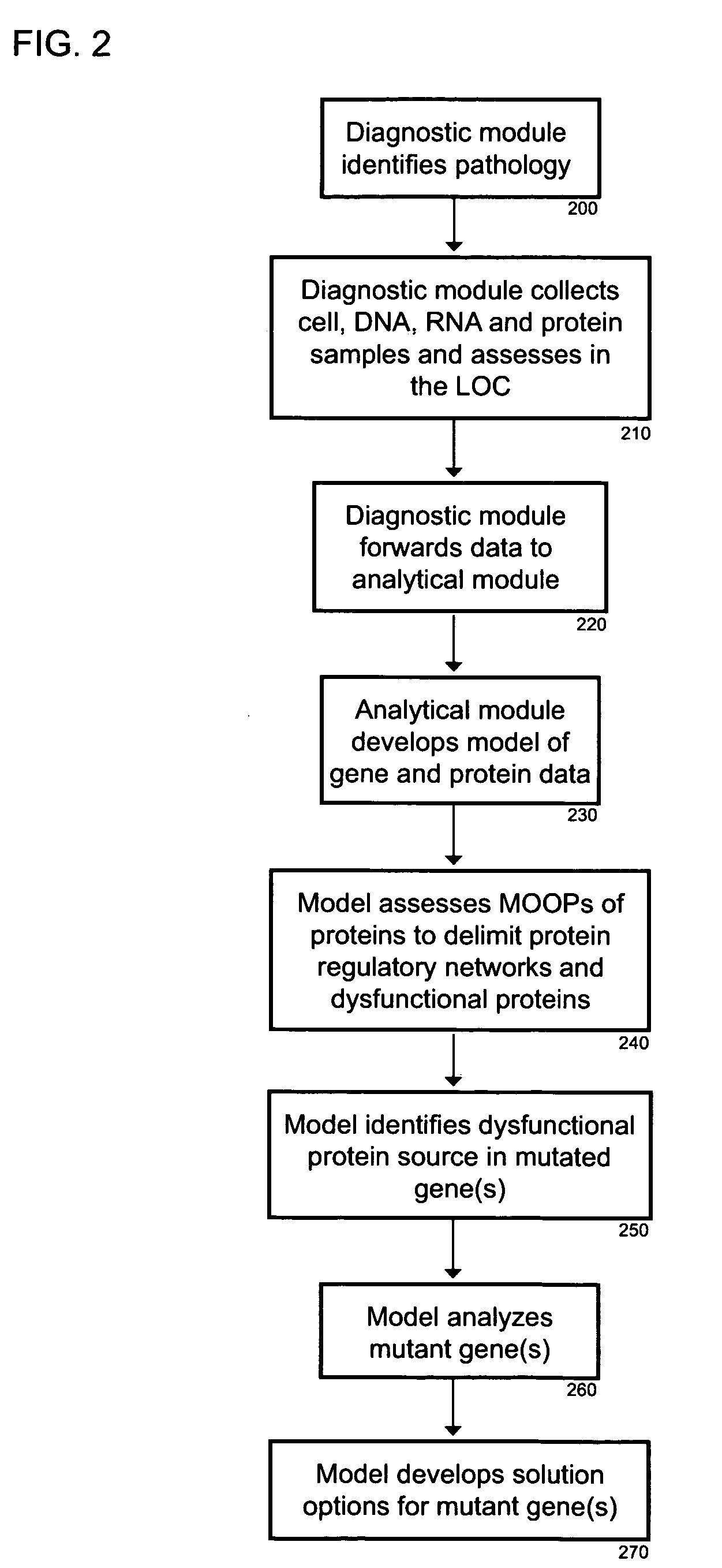

Intelligent medical device system dynamics for biological network regulation

InactiveUS20100069832A1Improve efficiencyEfficient managementMedical simulationLocal control/monitoringHigh level modelingSystem usage

The intelligent medical device (iMD) system coordinates the dynamics of hardware and software components in a self-organizing autonomous system. The iMD system uses advanced modeling and metaheuristics to solve complex optimization problems involving the customization of medical therapies. The system uses evolvable hardware and reprogrammable features to coordinate the diagnostic and therapeutic functions of the iMDs.

Owner:SOLOMON NEAL

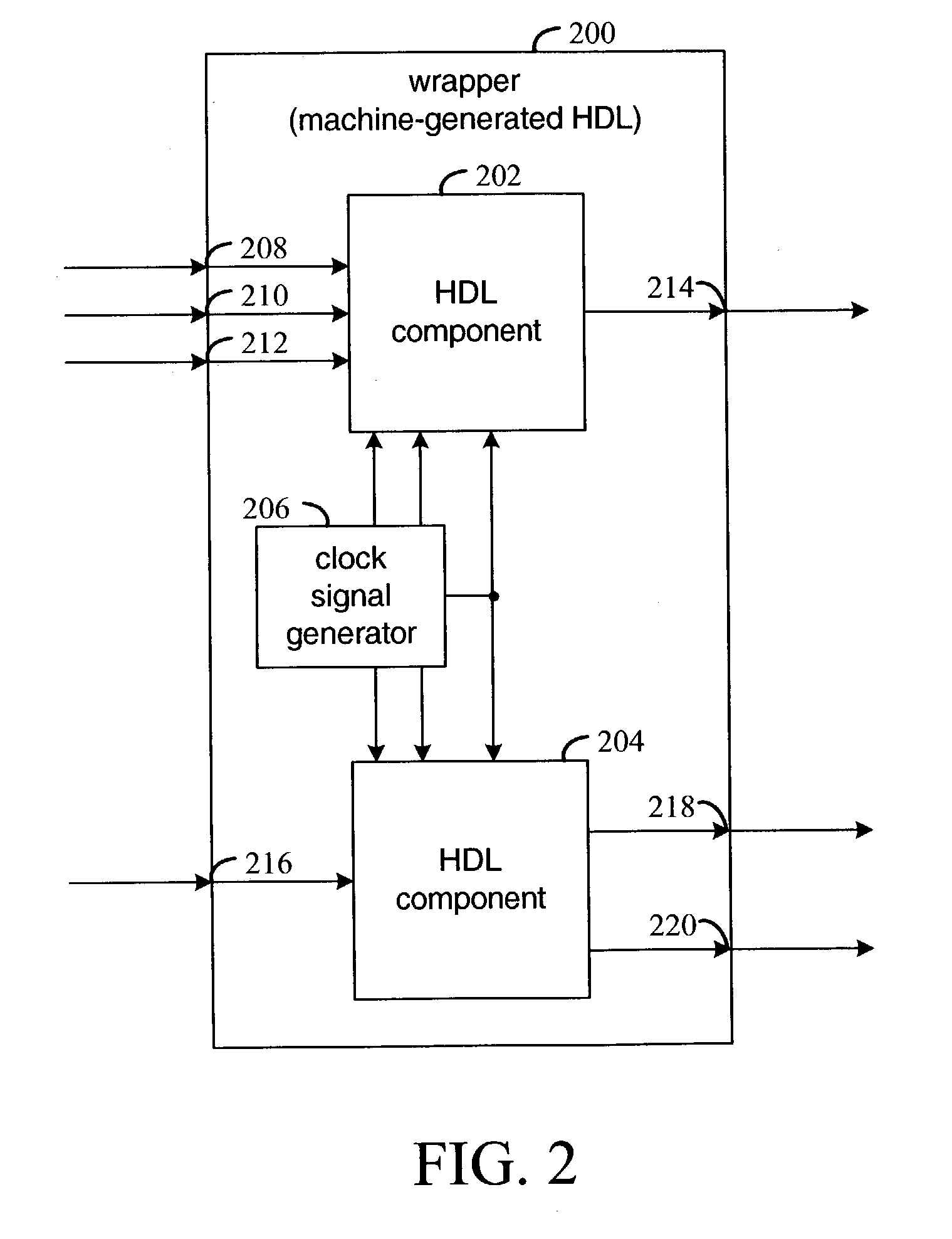

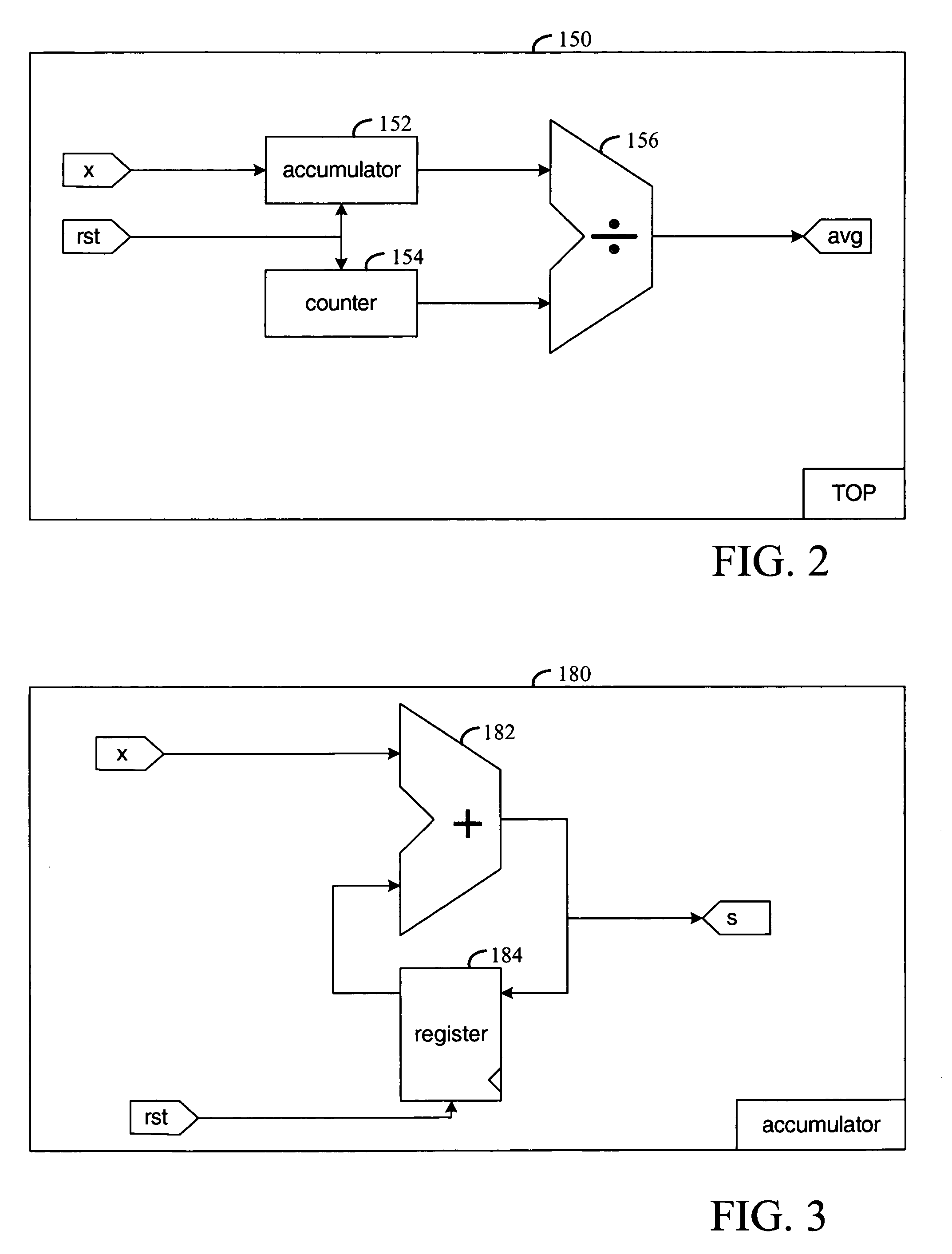

Compilation in a high-level modeling system

Methods and apparatus are disclosed for compiling high-level blocks of an electronic hardware design in a high-level modeling system (HLMS) into hardware description language (HDL) components. Clock requirements are established, along with (optionally) explicit connections from implicit connections between the high-level blocks. In one pass through the high-level blocks, HDL components are generated that are consistent with the clock requirements and explicit connections, if any.

Owner:XILINX INC

Model-based video encoding and decoding

ActiveUS9578345B2Efficient storageEfficient codingDigital video signal modificationHigh level modelingVideo encoding

A model-based compression codec applies higher-level modeling to produce better predictions than can be found through conventional block-based motion estimation and compensation. Computer-vision-based feature and object detection algorithms identify regions of interest throughout the video datacube. The detected features and objects are modeled with a compact set of parameters, and similar feature / object instances are associated across frames. Associated features / objects are formed into tracks and related to specific blocks of video data to be encoded. The tracking information is used to produce model-based predictions for those blocks of data, enabling more efficient navigation of the prediction search space than is typically achievable through conventional motion estimation methods. A hybrid framework enables modeling of data at multiple fidelities and selects the appropriate level of modeling for each portion of video data.

Owner:EUCLID DISCOVERIES LLC

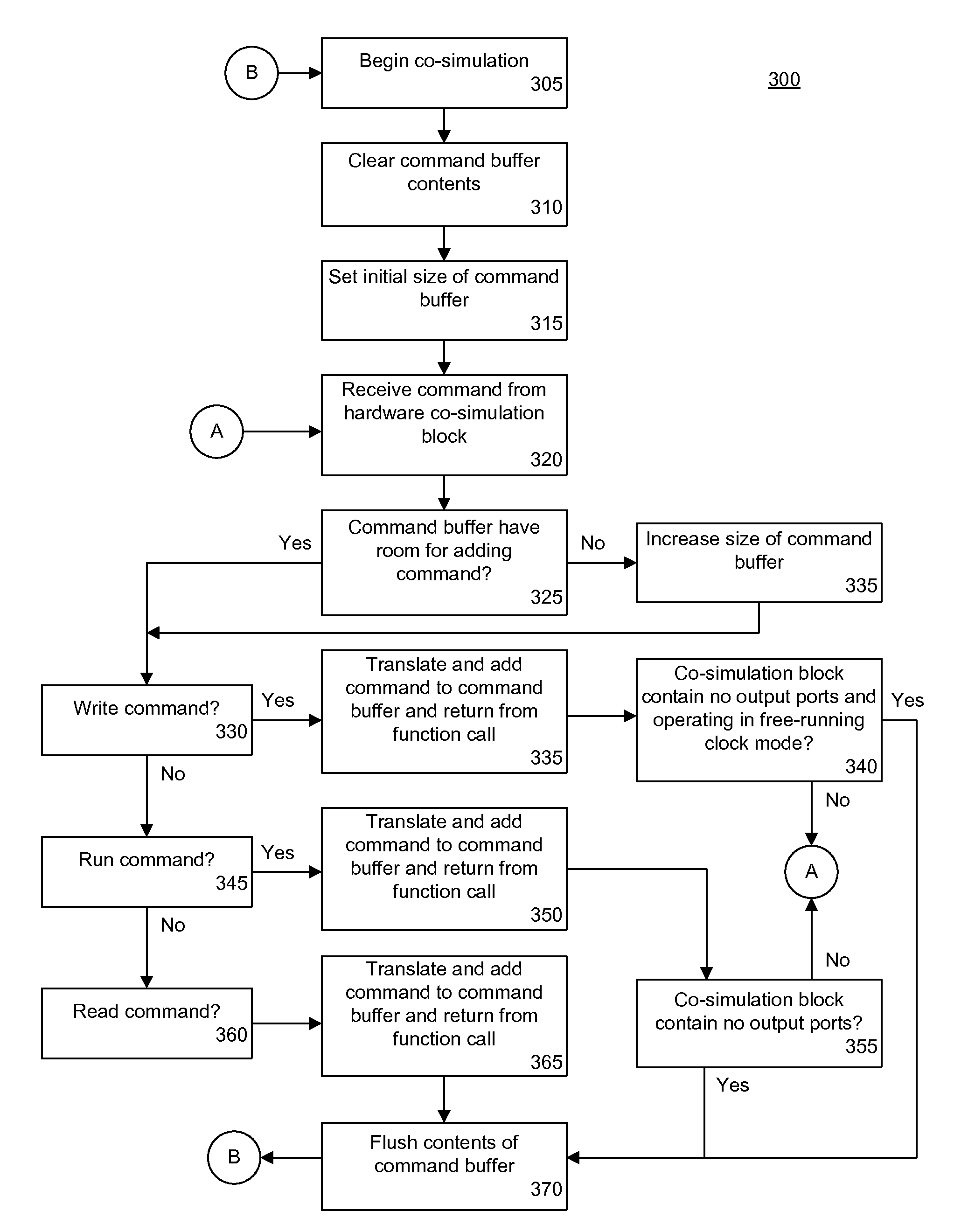

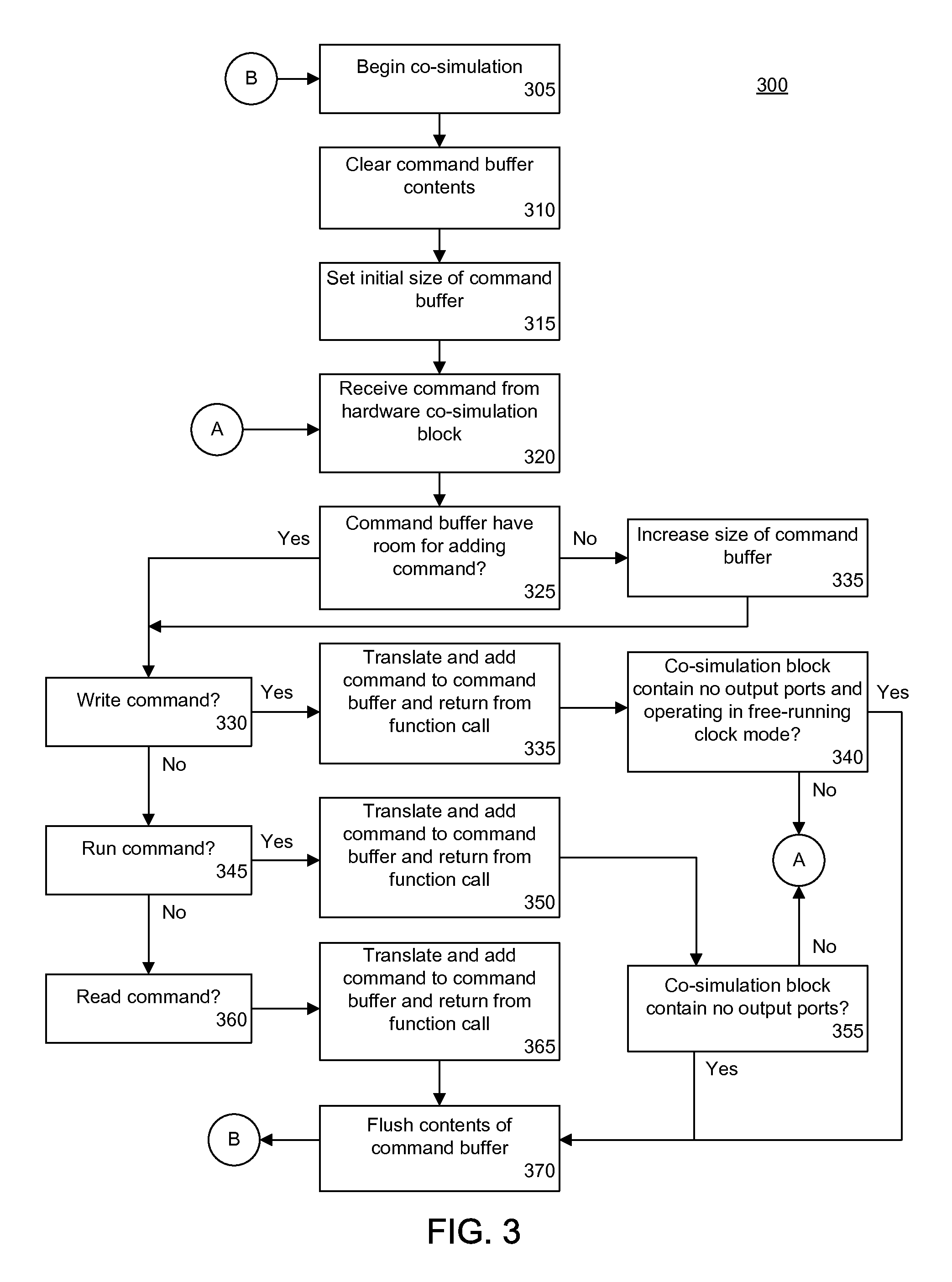

Command buffering for hardware co-simulation

ActiveUS7707019B1Analogue computers for electric apparatusCAD circuit designHigh level modelingProgrammable logic device

A method of co-simulation involving a high level modeling system and an integrated circuit such as, e.g., a programmable logic device (PLD) can include, when writing to at least one input port of the PLD, storing a plurality of commands from a co-simulation engine within a command buffer and, responsive to a send condition, sending the plurality of commands to the PLD as a single transaction. When reading from at least one output port of the PLD, selectively reading from a cache external to the PLD or a memory of the PLD according to a state of cache coherency.

Owner:XILINX INC

Standards-compliant model-based video encoding and decoding

ActiveUS9743078B2Efficient storageReduce impactDigital video signal modificationHigh level modelingVideo encoding

A model-based compression codec applies higher-level modeling to produce better predictions than can be found through conventional block-based motion estimation and compensation. Computer-vision-based feature and object detection algorithms identify regions of interest throughout the video datacube. The detected features and objects are modeled with a compact set of parameters, and similar feature / object instances are associated across frames. Associated features / objects are formed into tracks and related to specific blocks of video data to be encoded. The tracking information is used to produce model-based predictions for those blocks of data, enabling more efficient navigation of the prediction search space than is typically achievable through conventional motion estimation methods. A hybrid framework enables modeling of data at multiple fidelities and selects the appropriate level of modeling for each portion of video data. A compliant-stream version of the model-based compression codec uses the modeling information indirectly to improve compression while producing bitstreams that can be interpreted by standard decoders.

Owner:EUCLID DISCOVERIES LLC

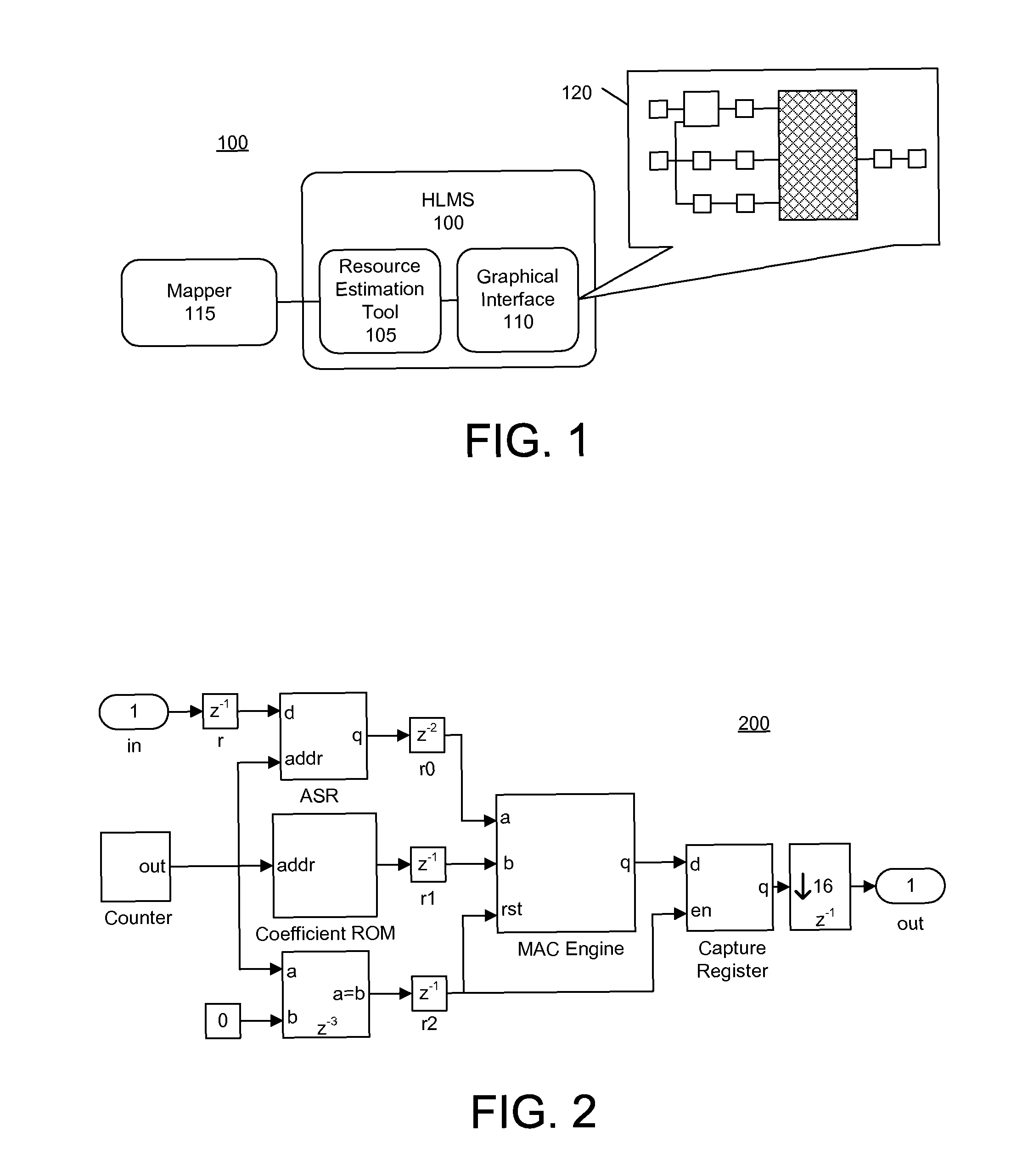

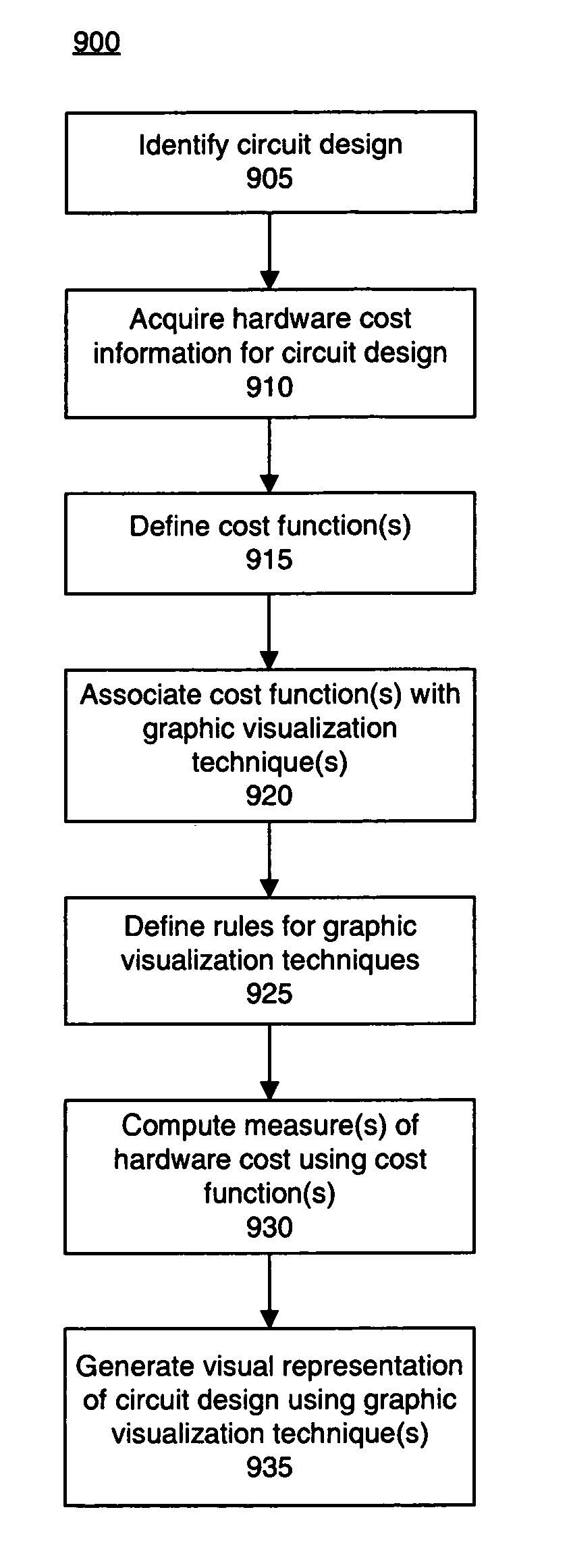

Visualizing hardware cost in high level modeling systems

ActiveUS7913217B1Reduce measurementCAD circuit designSpecial data processing applicationsGraphicsHigh level modeling

Within a high level modeling system (HLMS), a method of visualizing a circuit design can include identifying the circuit design and reading hardware cost information for the circuit design. The method also can include presenting a graphical representation of the circuit design having at least one visual characteristic which can be varied according to the hardware cost information.

Owner:XILINX INC

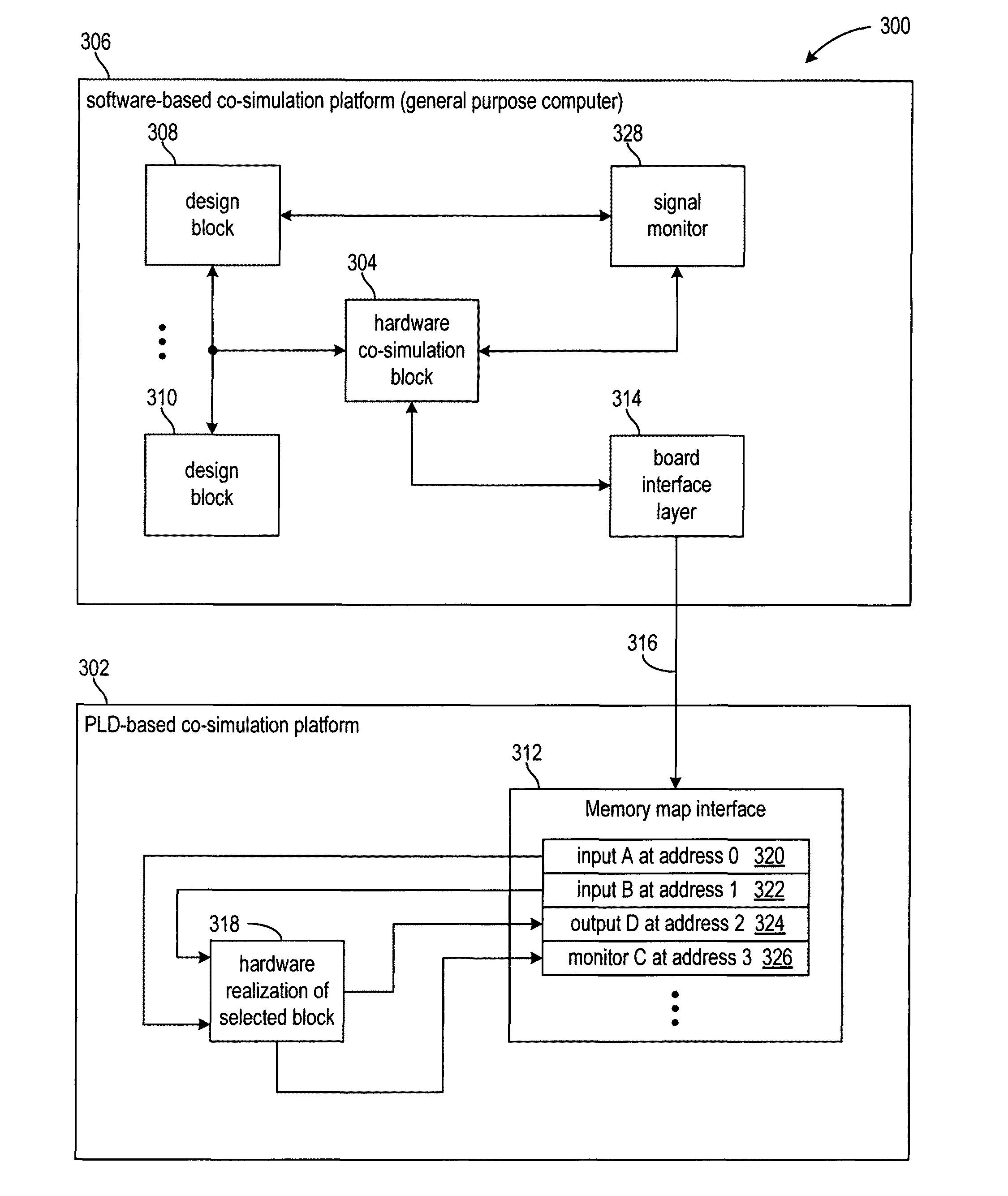

Displaying signals of a design block emulated in hardware co-simulation

ActiveUS8082139B1Electric/magnetic detection for well-loggingAnalogue computers for electric apparatusElectronic systemsHigh level modeling

Methods and systems for simulating an electronic system in a high level modeling system (HLMS). A design block and certain signals of the electronic system are selected. The selected signals include internal signals of the design block that are not ports of the design block. The electronic system is simulated in the HLMS, which includes a hardware-based co-simulation platform and a software-based co-simulation platform. A hardware realization of the design block is automatically generated and the design block is emulated in the hardware based co-simulation platform using the hardware realization of the design block. A sequence of values is displayed for the selected signals of the electronic system. During the simulation of the electronic system in the HLMS, the sequence of values for the internal signals of the design block and another sequence of values for the ports of the design block are transferred between the co-simulation platforms.

Owner:XILINX INC

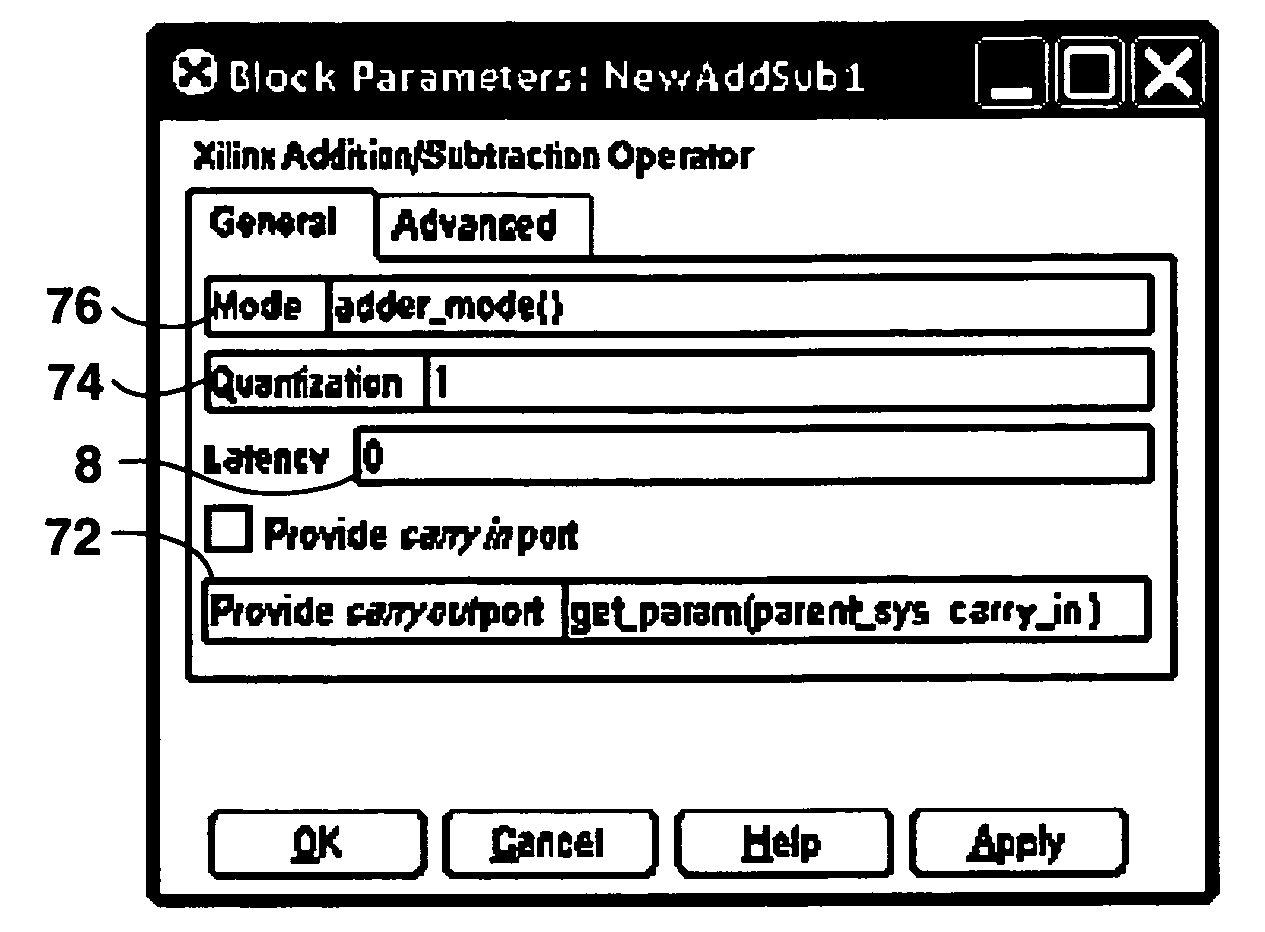

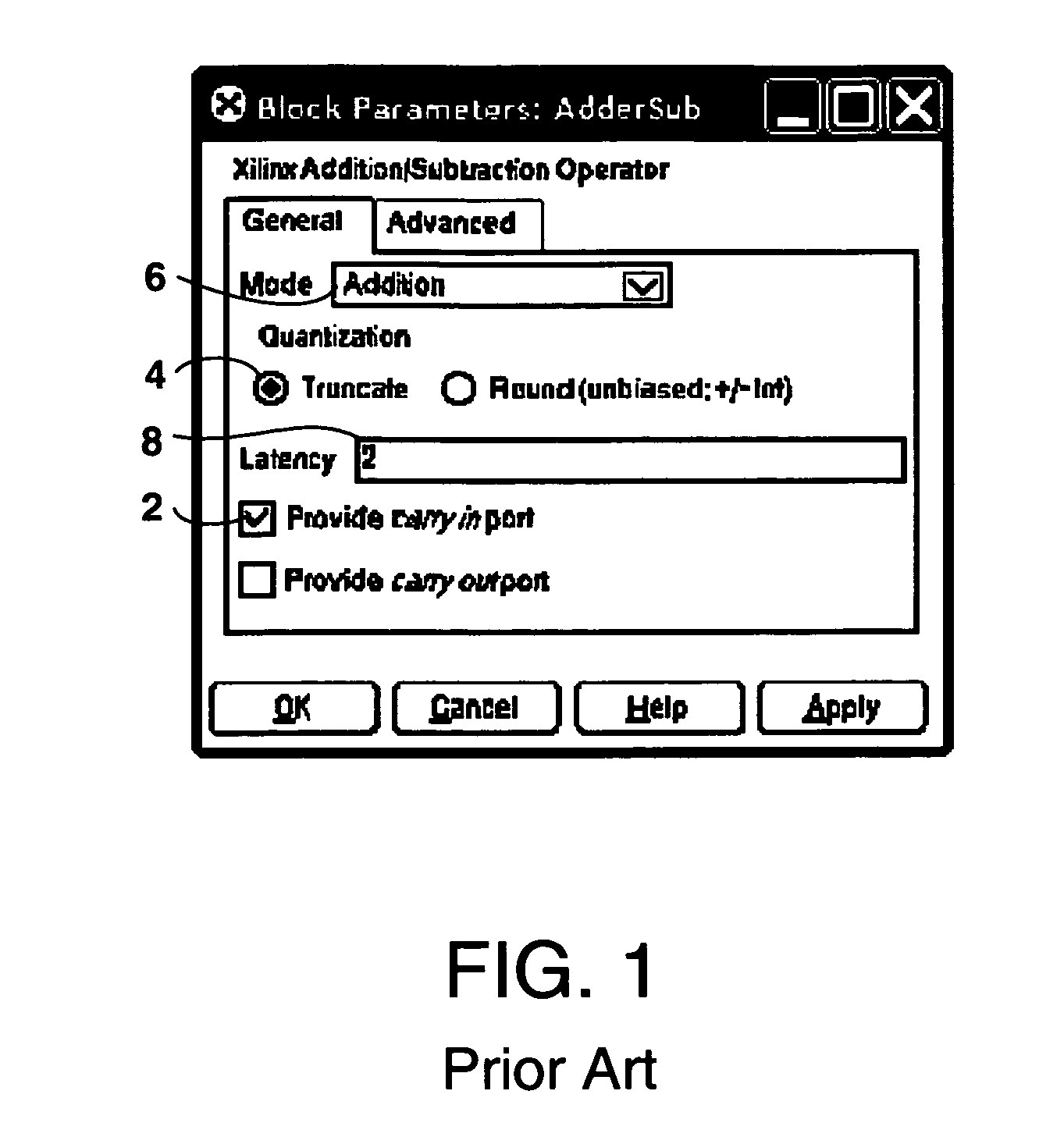

Programmatically specifying the state of graphical user interface (GUI) controls

ActiveUS7512890B1Simple interfaceEasy mappingSoftware engineeringDigital computer detailsGraphicsRadio button

A graphical user interface (GUI) is provided with a specifiable edit control field that is accessed in conjunction with a non-edit field, the non-edit field for example being a check box, or radio buttons. The specifiable edit field can be accessed for example by right clicking or double clicking on the non-edit field or overall GUI. The specifiable edit field allows changing parameters of the non-edit field via entry of a programmatic expression that evaluates to an valid input to the non-edit field. For example in a high-level modeling program that enables modeling modules of a Field Programmable Gate Array (FPGA), when a normal editing field can modify only one module at a time, the specifiable editing field can allow modifying a plurality of modules at one time that are hierarchically linked together by the associated non-edit field, such as a check box.

Owner:XILINX INC

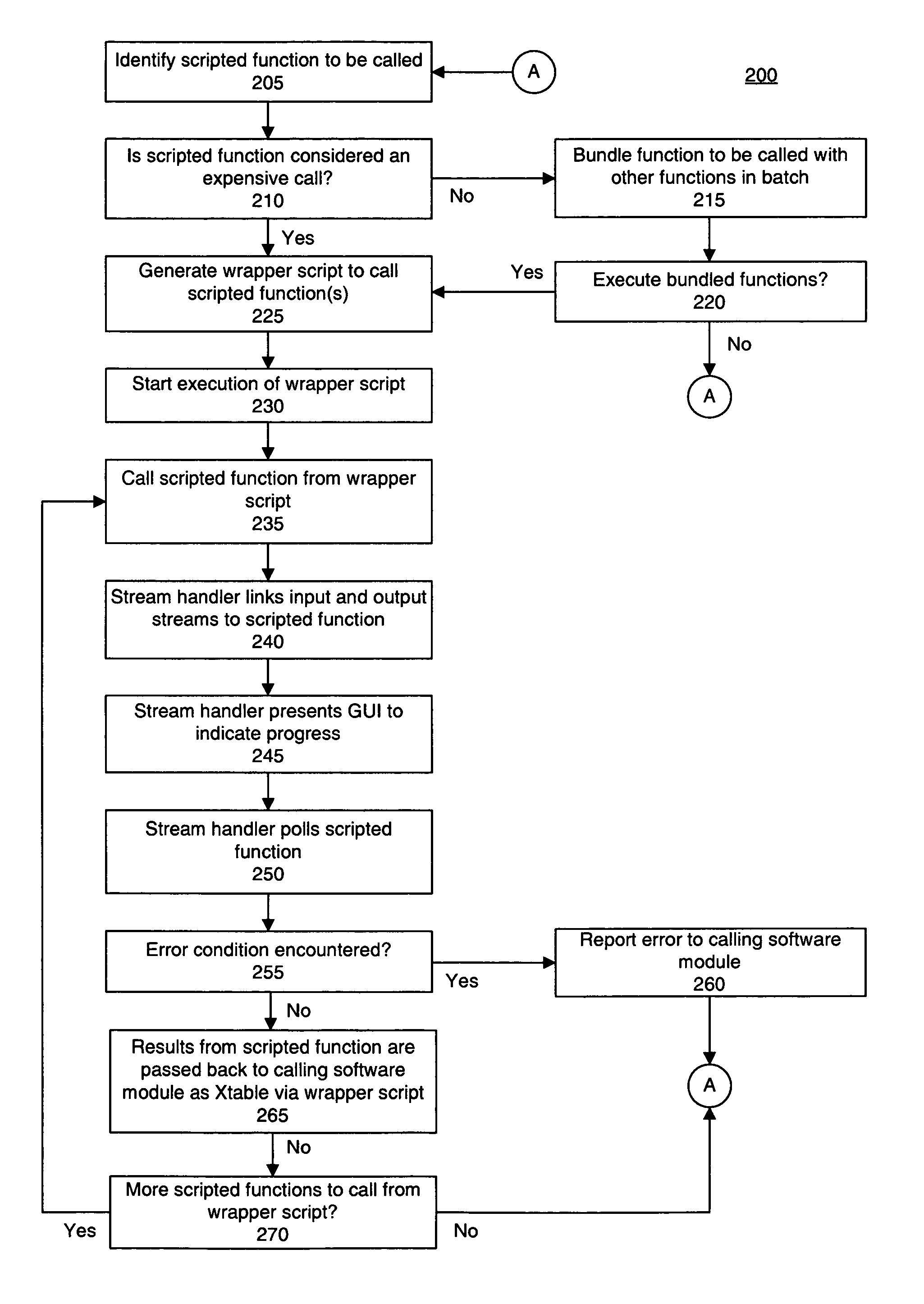

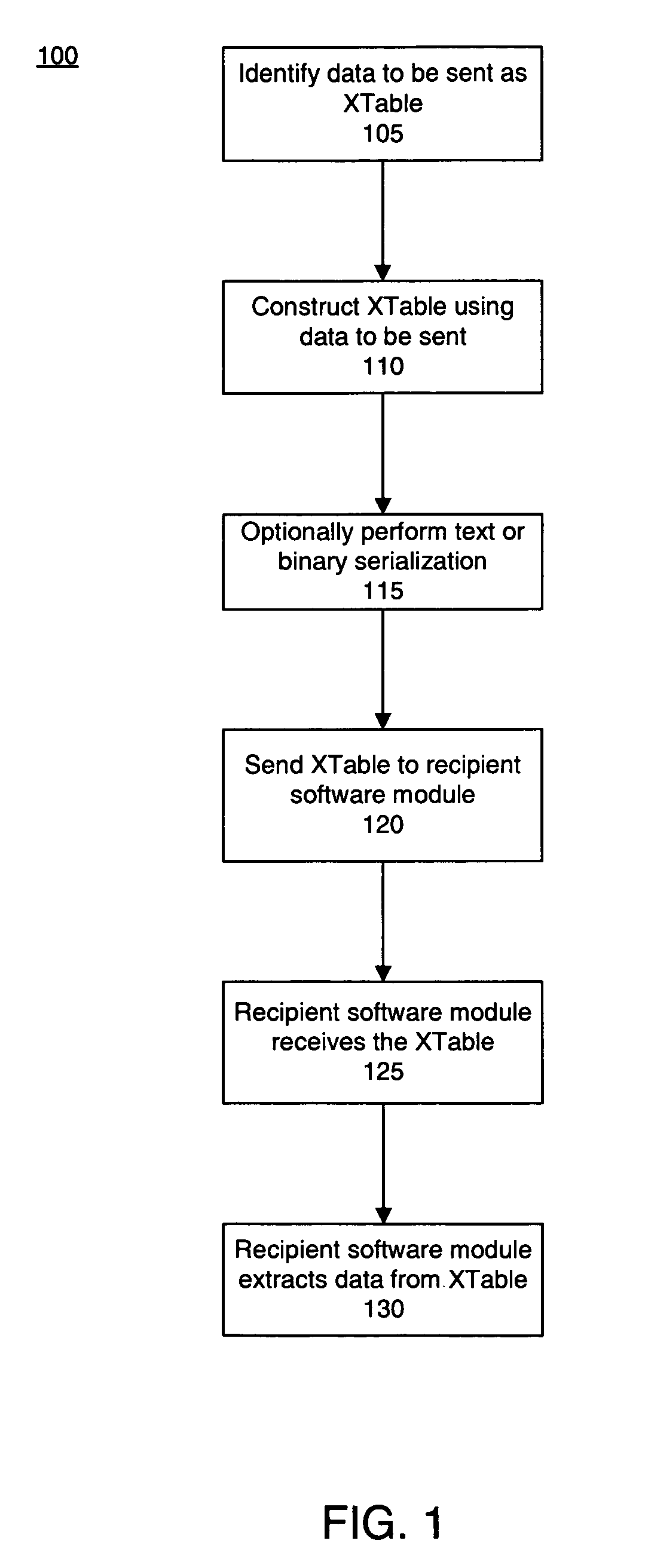

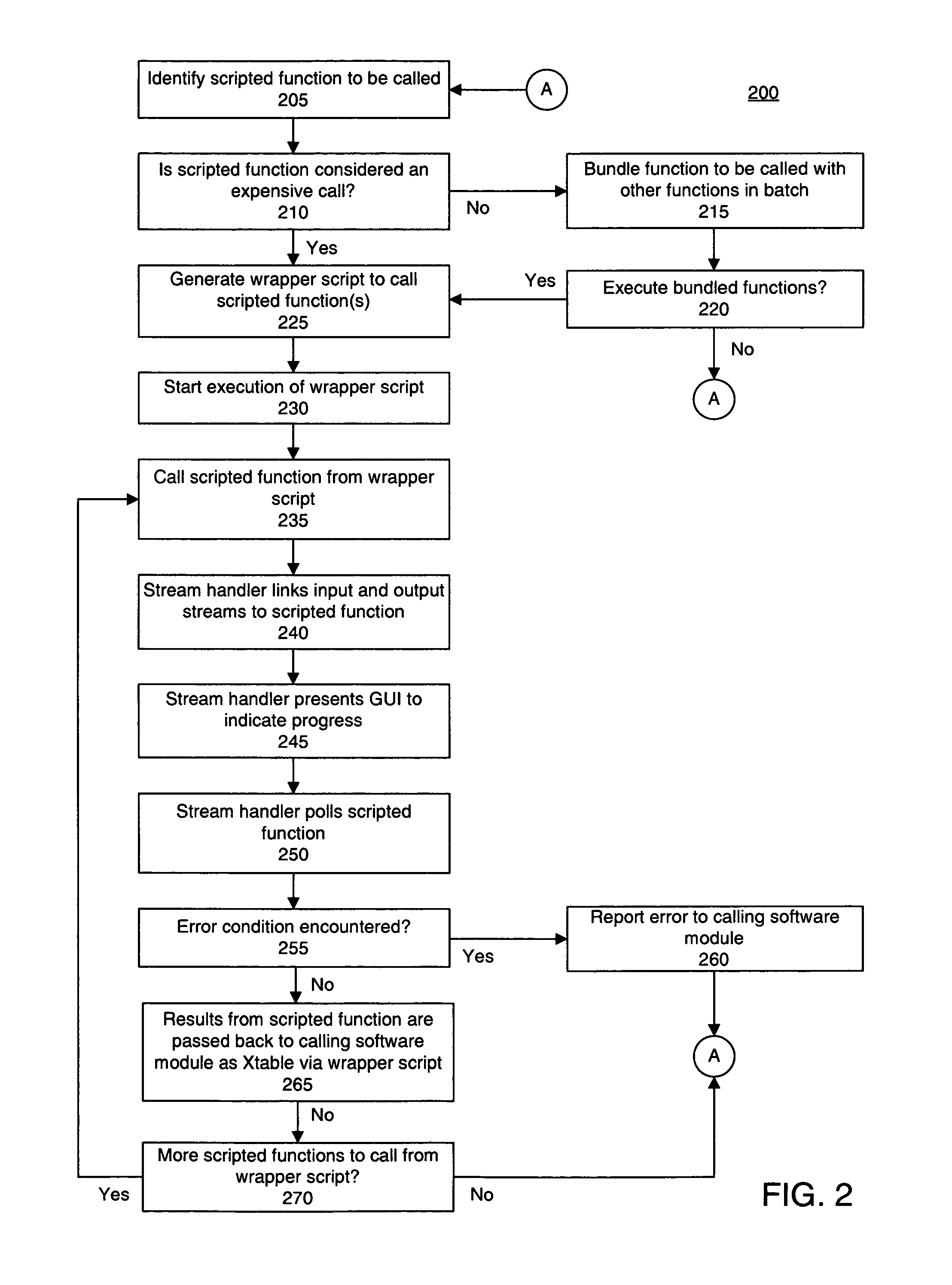

Using scripts for netlisting in a high-level modeling system

ActiveUS7797677B1Costly for callCAD circuit designSoftware simulation/interpretation/emulationSoftware systemHigh level modeling

A method of passing data among modules of a heterogeneous software system can include identifying a scripted function to be executed within the heterogeneous software system and building a wrapper script by embedding a call to the scripted function and an XTable object associated with the scripted function within the wrapper script. The method further can include executing the wrapper script thereby causing the scripted function to execute and receiving a result from execution of the scripted function.

Owner:XILINX INC

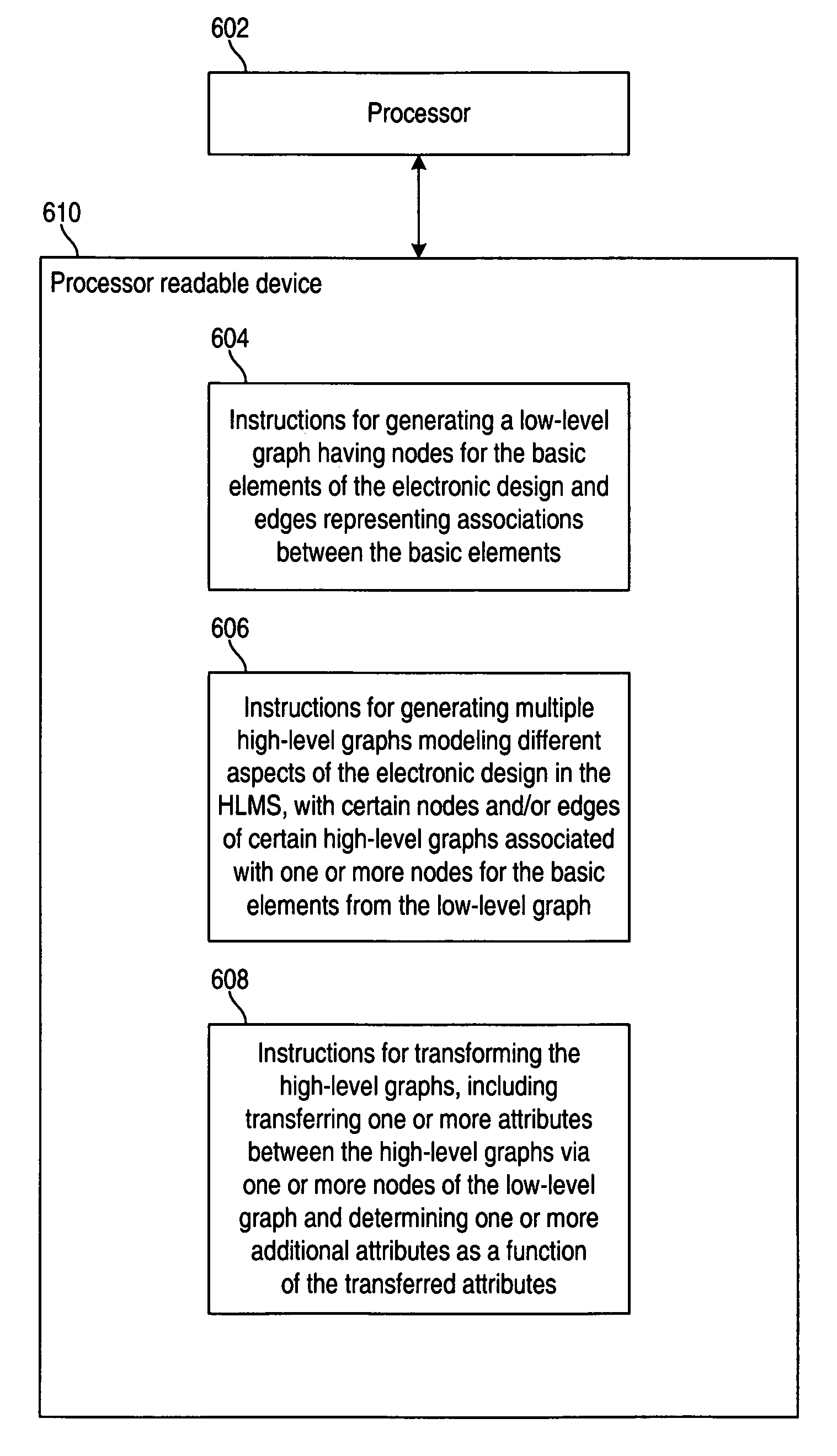

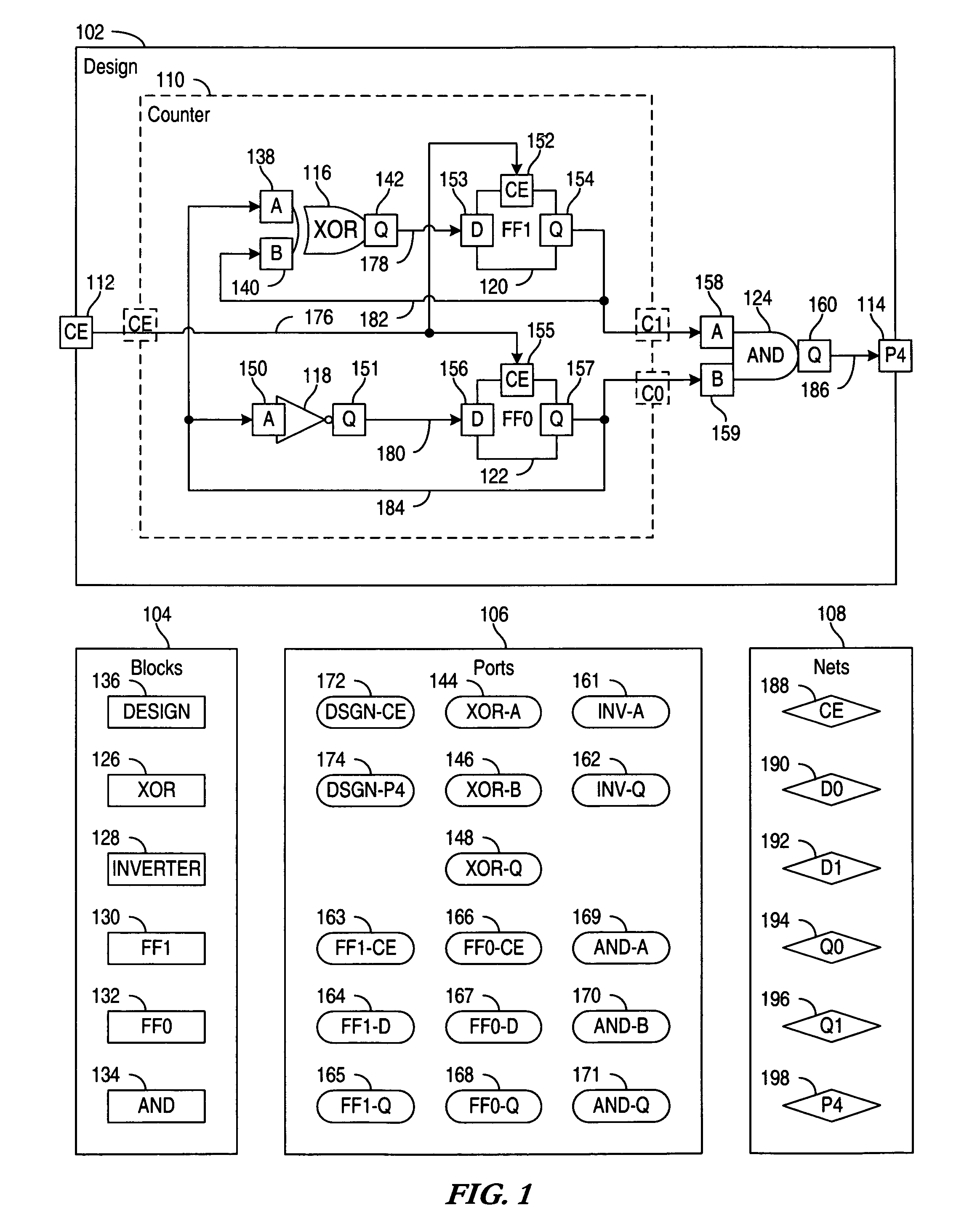

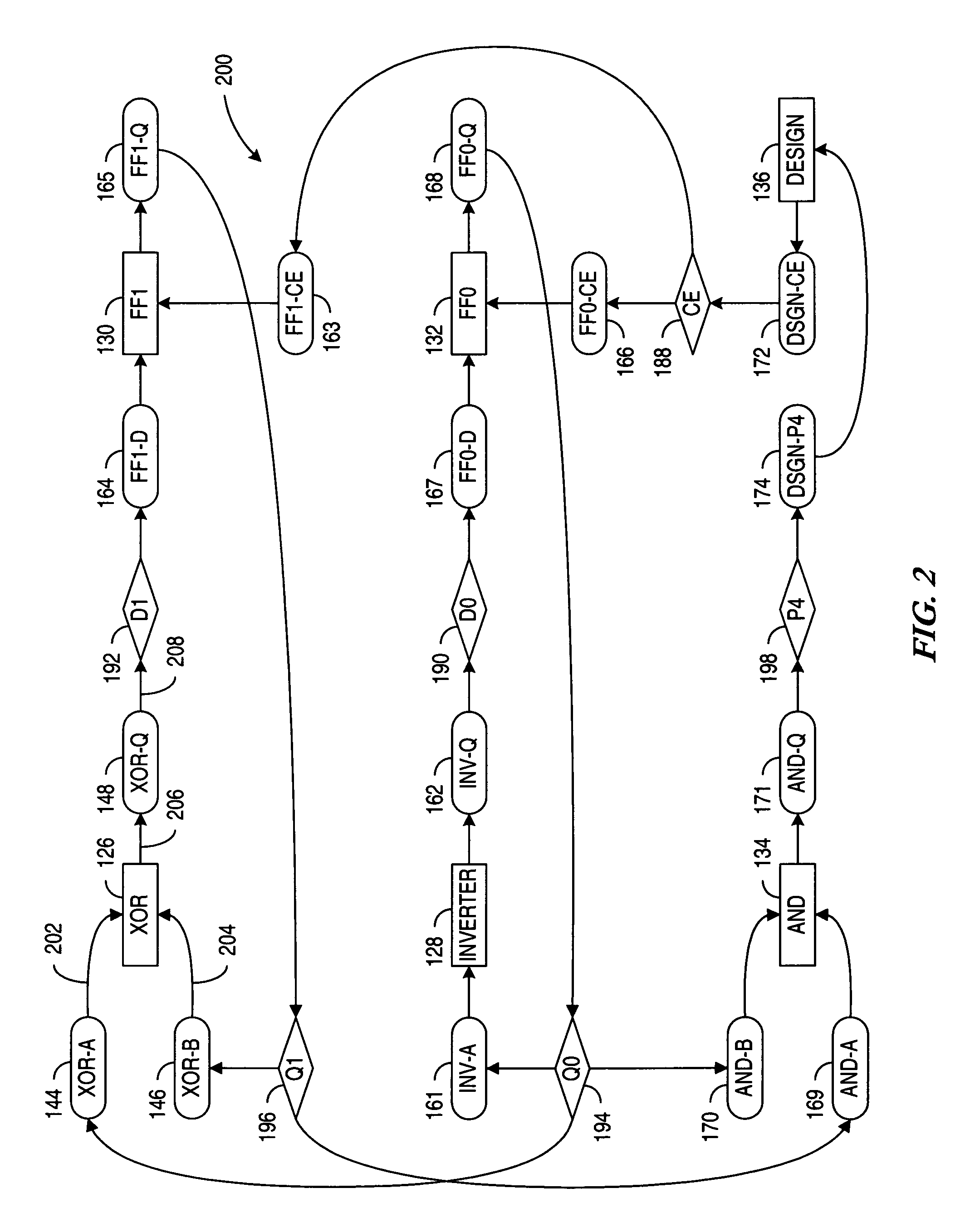

Transformation of graphs representing an electronic design in a high modeling system

Methods and apparatus are provided for processing an electronic design in a high level modeling system. A first graph is generated, with the nodes representing basic elements of the electronic design and including a shared node representing the basic element of a block, a port, or a network of the electronic design. Multiple second graphs are generated modeling different aspects of the electronic design. A first and second member of the nodes and edges of respective ones of the second graphs are each associated with the shared node of the first graph. The different aspects of the electronic design of the second-type graphs transformed, with a first attribute of one of the second graphs written to the shared node using the first member, and a second attribute of another of the second graphs determined as a function of the first attribute read from the shared node using the second member.

Owner:XILINX INC

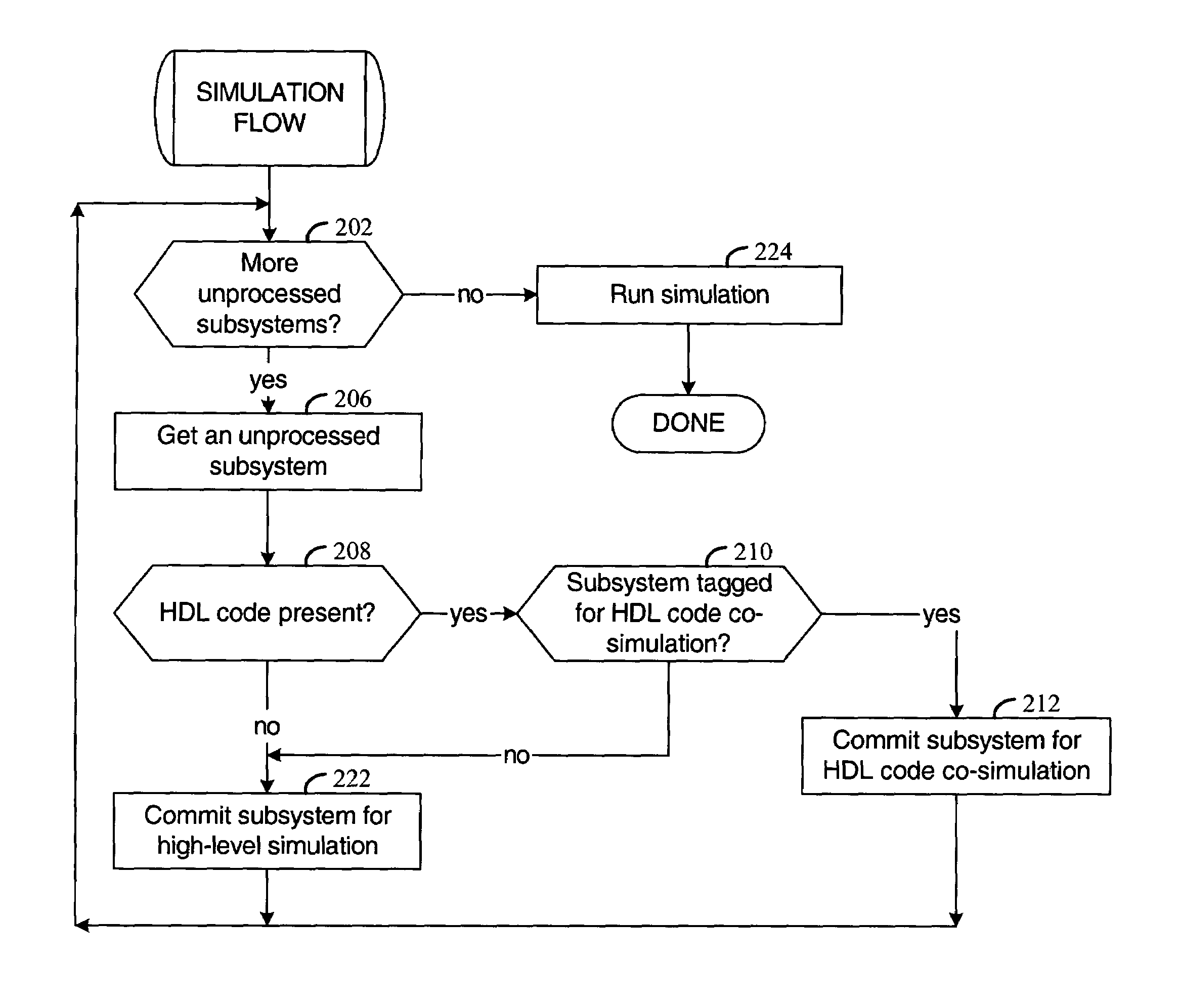

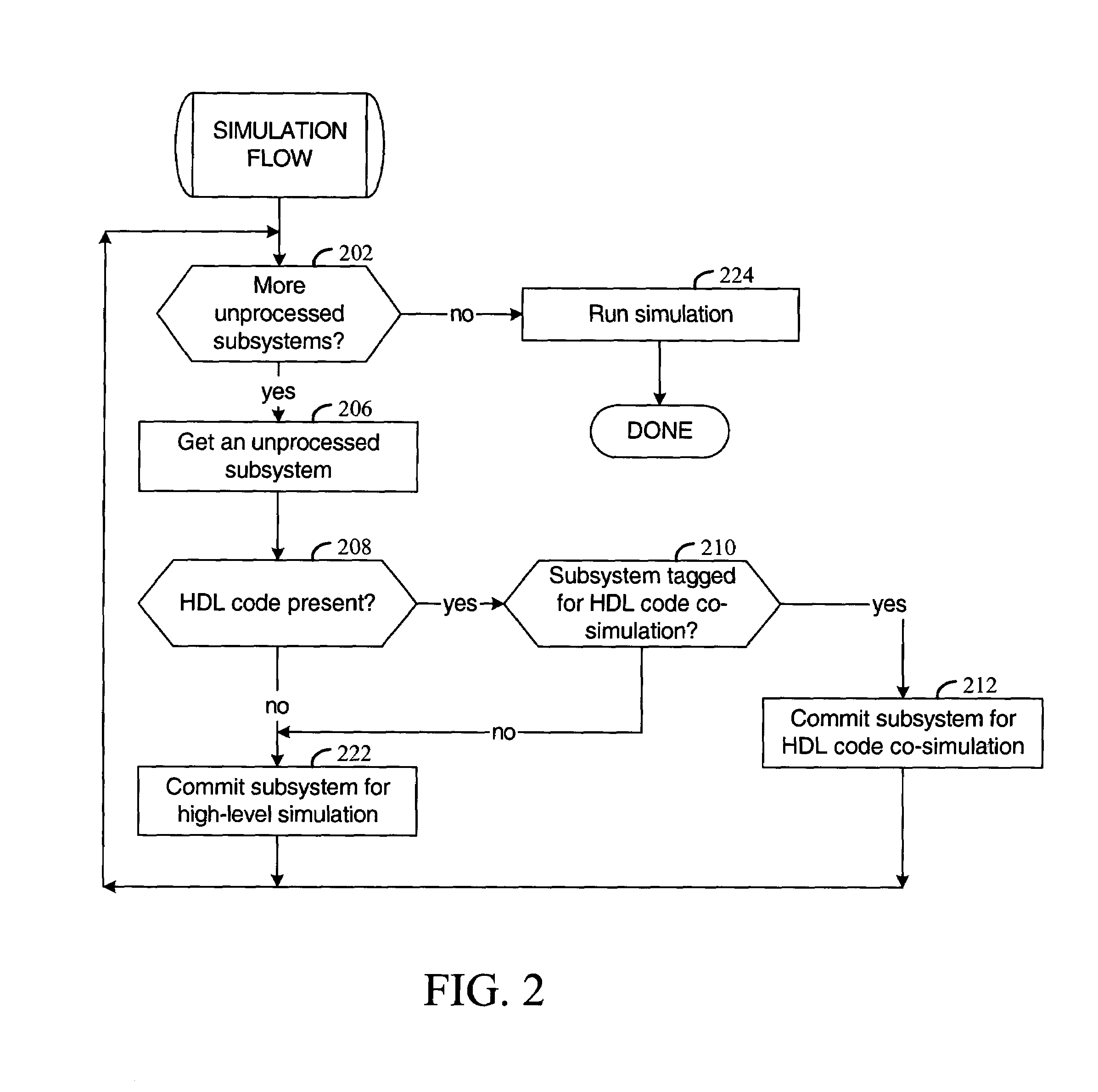

Incremental netlisting

ActiveUS7086030B1CAD circuit designSoftware simulation/interpretation/emulationProgramming languageHigh level modeling

Method and apparatus for preparing a design in a high-level modeling system. Hardware description language (HDL) code is generated for one or more of a plurality of high-level subsystems in a high-level design tagged by the user for HDL code generation. Previously generated HDL code may be reused instead of generating new HDL code for each subsystem tagged by the user for HDL code reuse.

Owner:XILINX INC

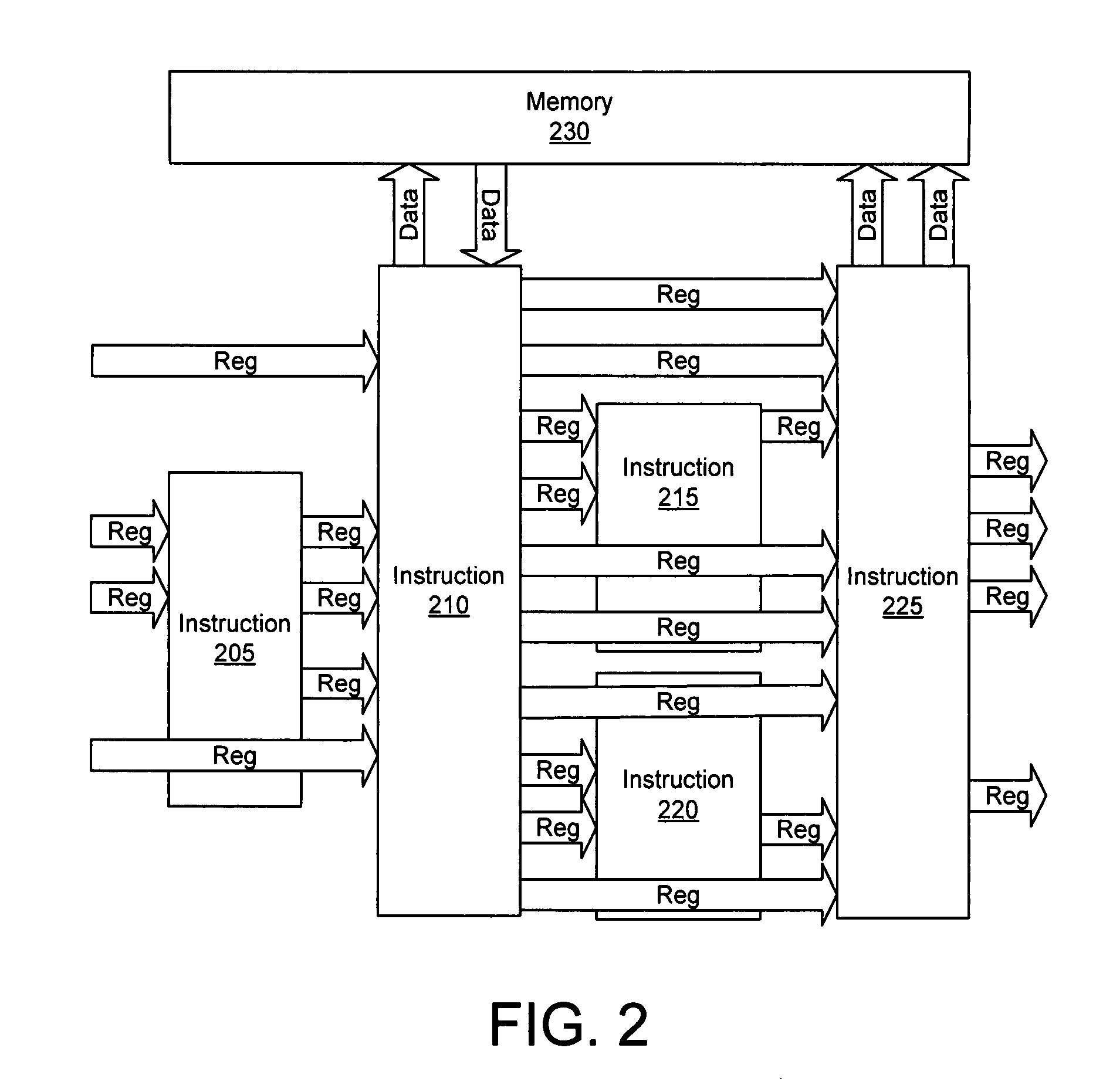

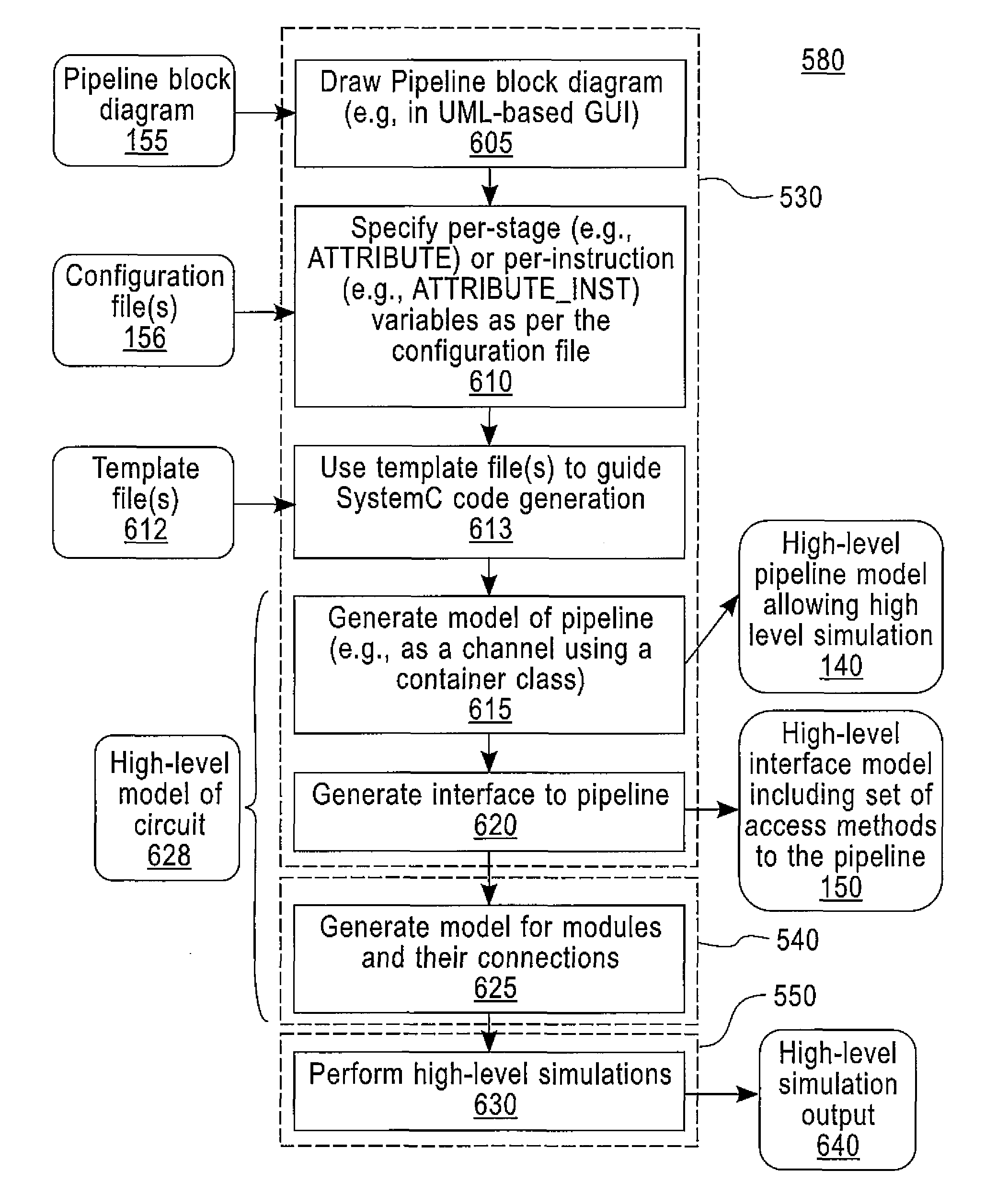

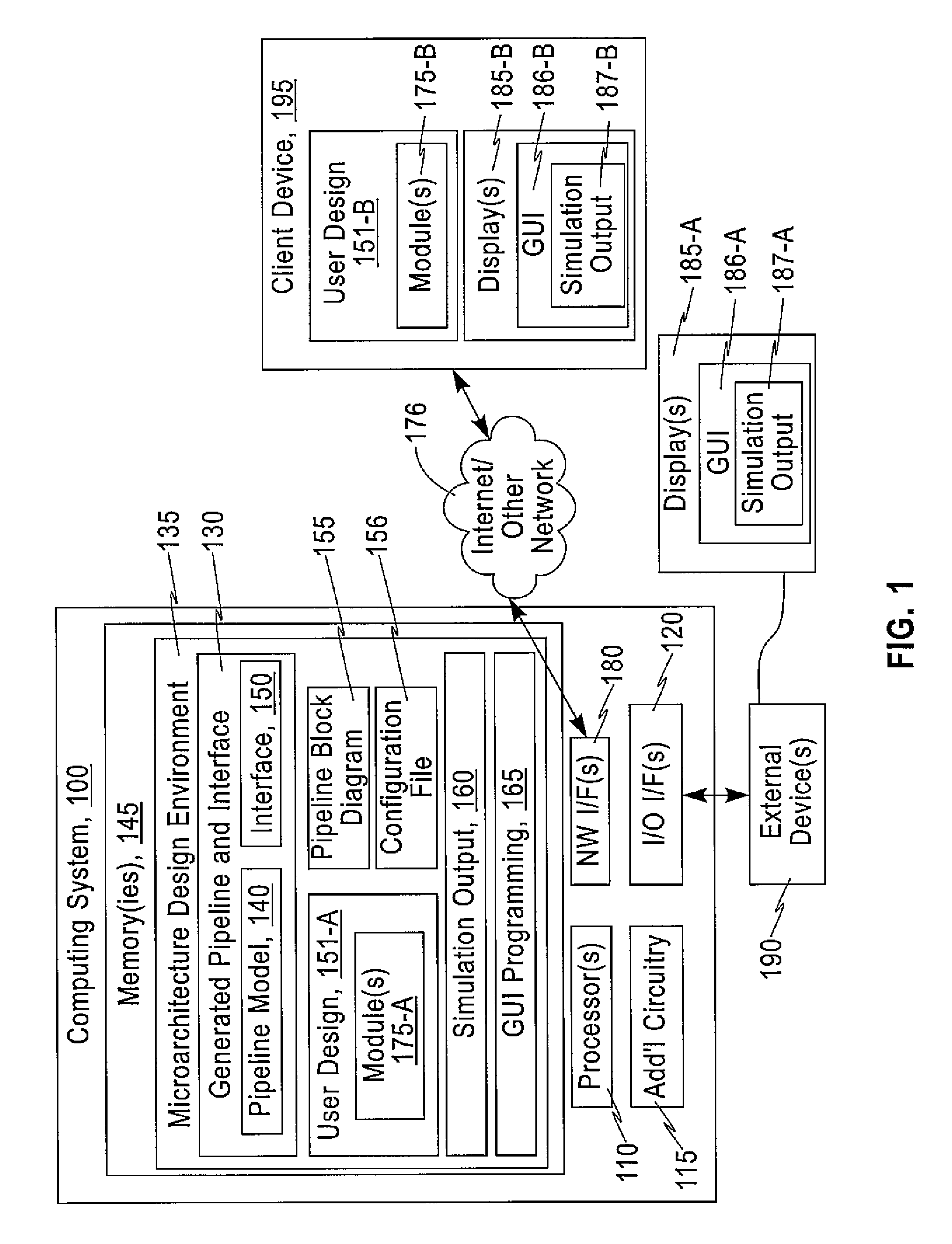

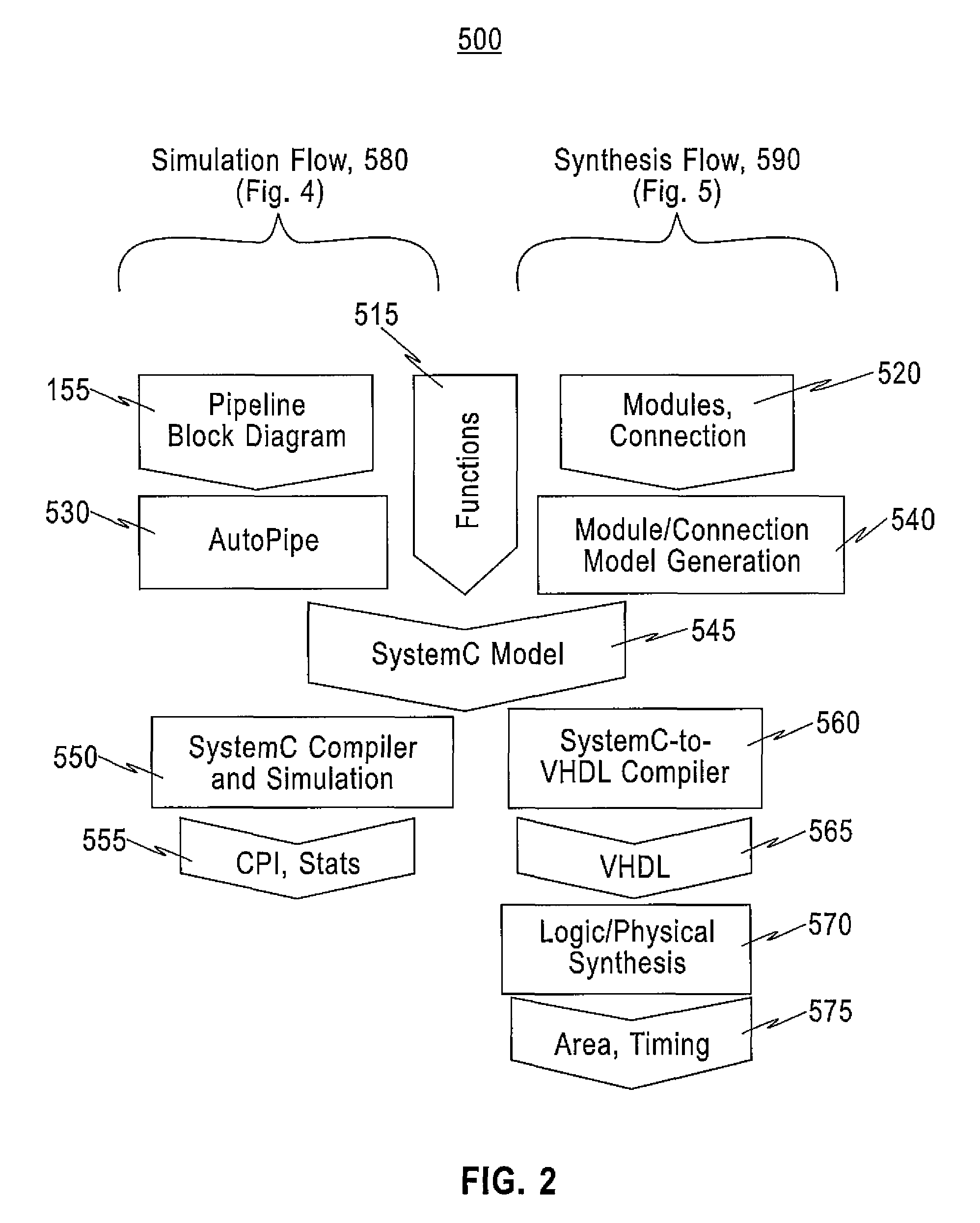

Automating a microarchitecture design exploration environment

InactiveUS9405866B1Design optimisation/simulationCAD circuit designComputer architectureAccess method

In a computing system running an environment for designing operation of circuitry, at least the following are performed for providing simulations and evaluations of one or more user-defined modules of circuitry including one or more pipeline stages in a pipeline. A model of the pipeline is automatically generated by using a pipeline block diagram, where the model is generated in a high-level modeling language able to perform simulations of circuitry with the pipeline. An interface is automatically generated between the one or more user-defined modules and the generated model of the pipeline, the interface including a set of access methods to the pipeline. Evaluation is performed of the one or more user-defined modules using the automatically generated model of the pipeline and the automatically generated interface. Methods, apparatus, and computer program products are disclosed.

Owner:IBM CORP

Visualizing hardware cost in high level modeling systems

ActiveUS7444610B1Reduce measurementCAD circuit designSpecial data processing applicationsGraphicsHigh level modeling

Within a high level modeling system (HLMS), a method of visualizing a circuit design can include identifying the circuit design and reading hardware cost information for the circuit design. The method also can include presenting a graphical representation of the circuit design having at least one visual characteristic which can be varied according to the hardware cost information.

Owner:XILINX INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com