Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

452results about How to "Efficient coding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

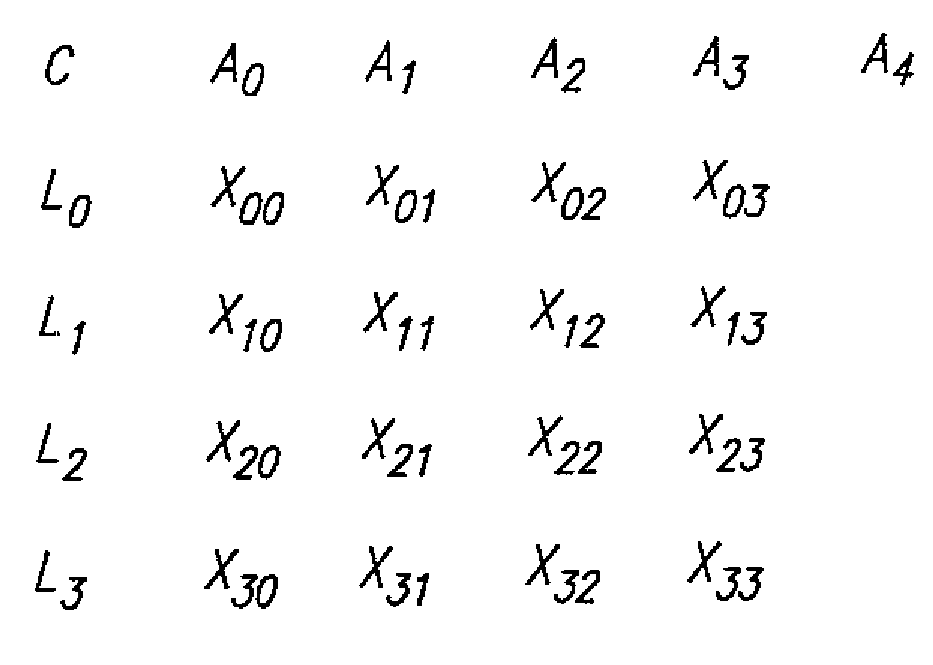

Visual and interactive wrapper generation, automated information extraction from web pages, and translation into xml

InactiveUS20050022115A1Data efficientEfficient codingDigital computer detailsSemi-structured data indexingData transformationEngineering

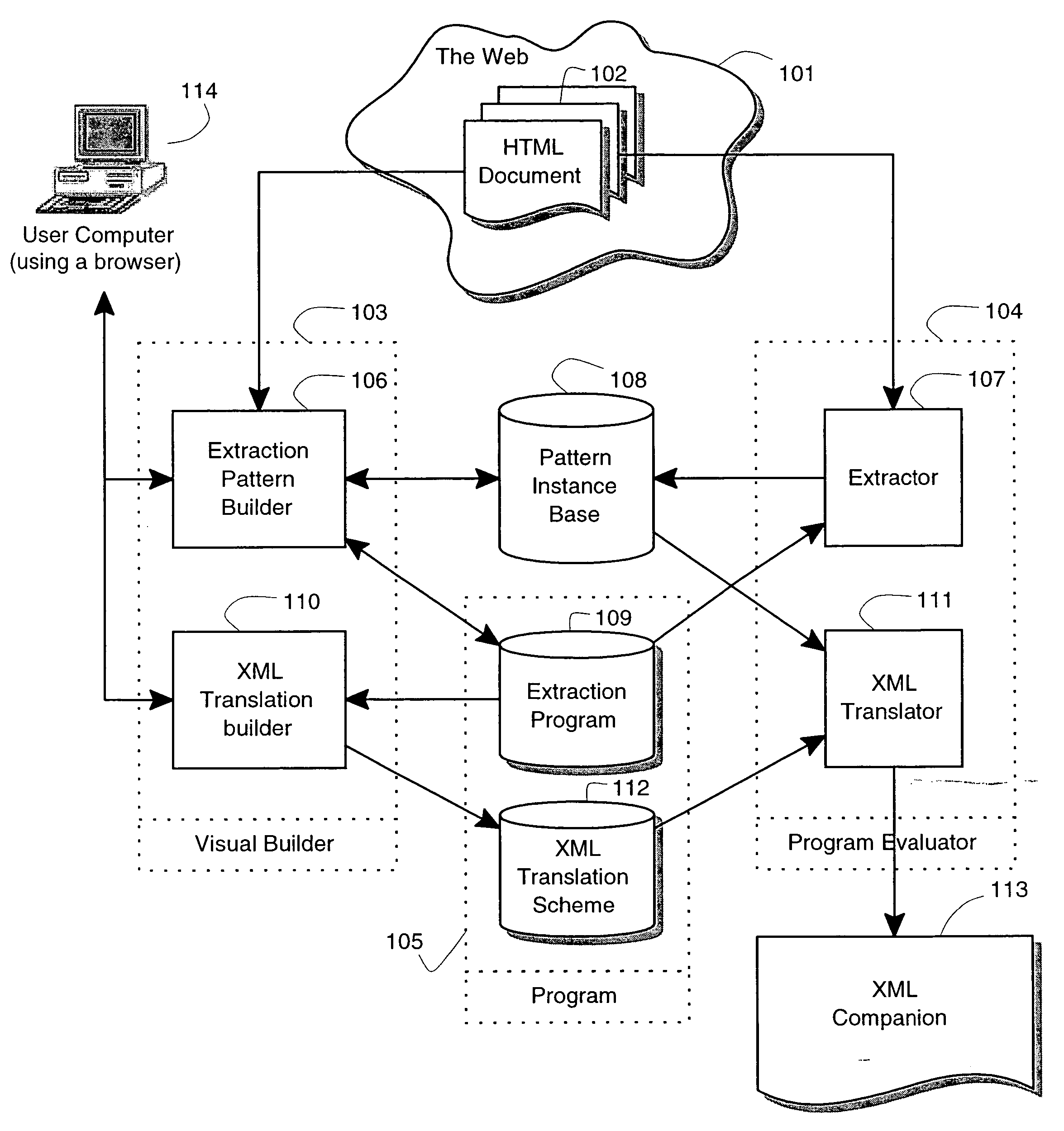

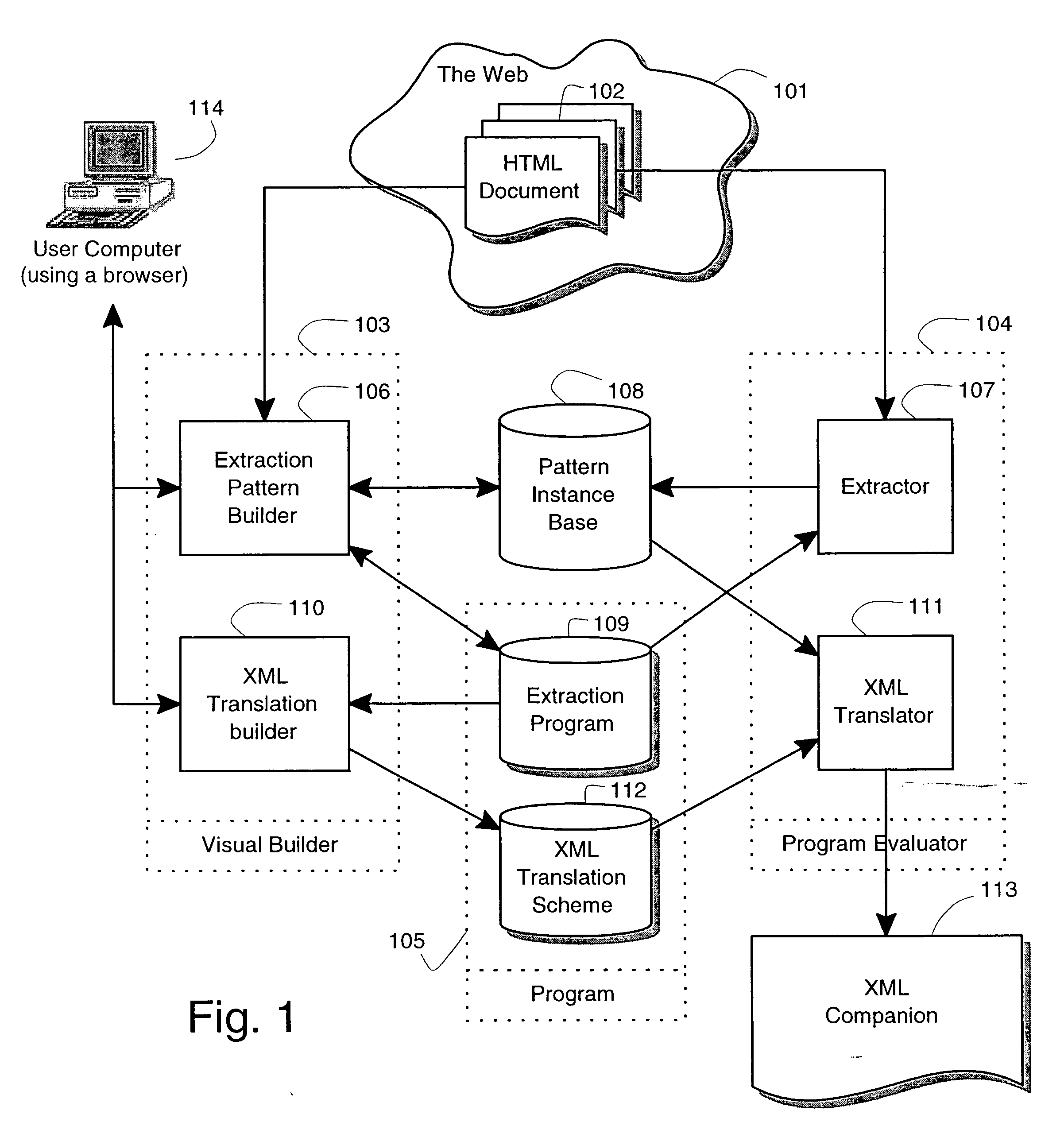

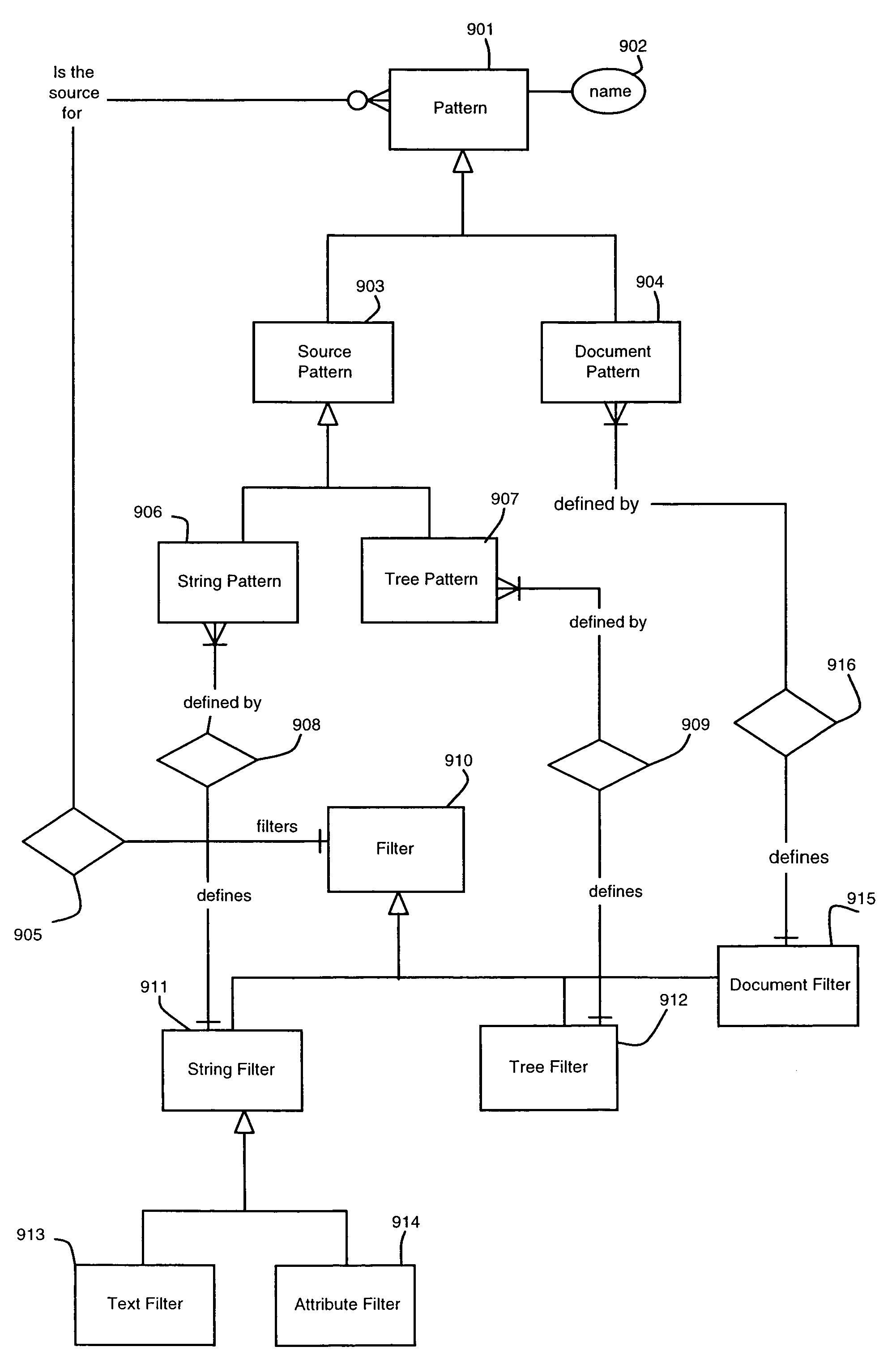

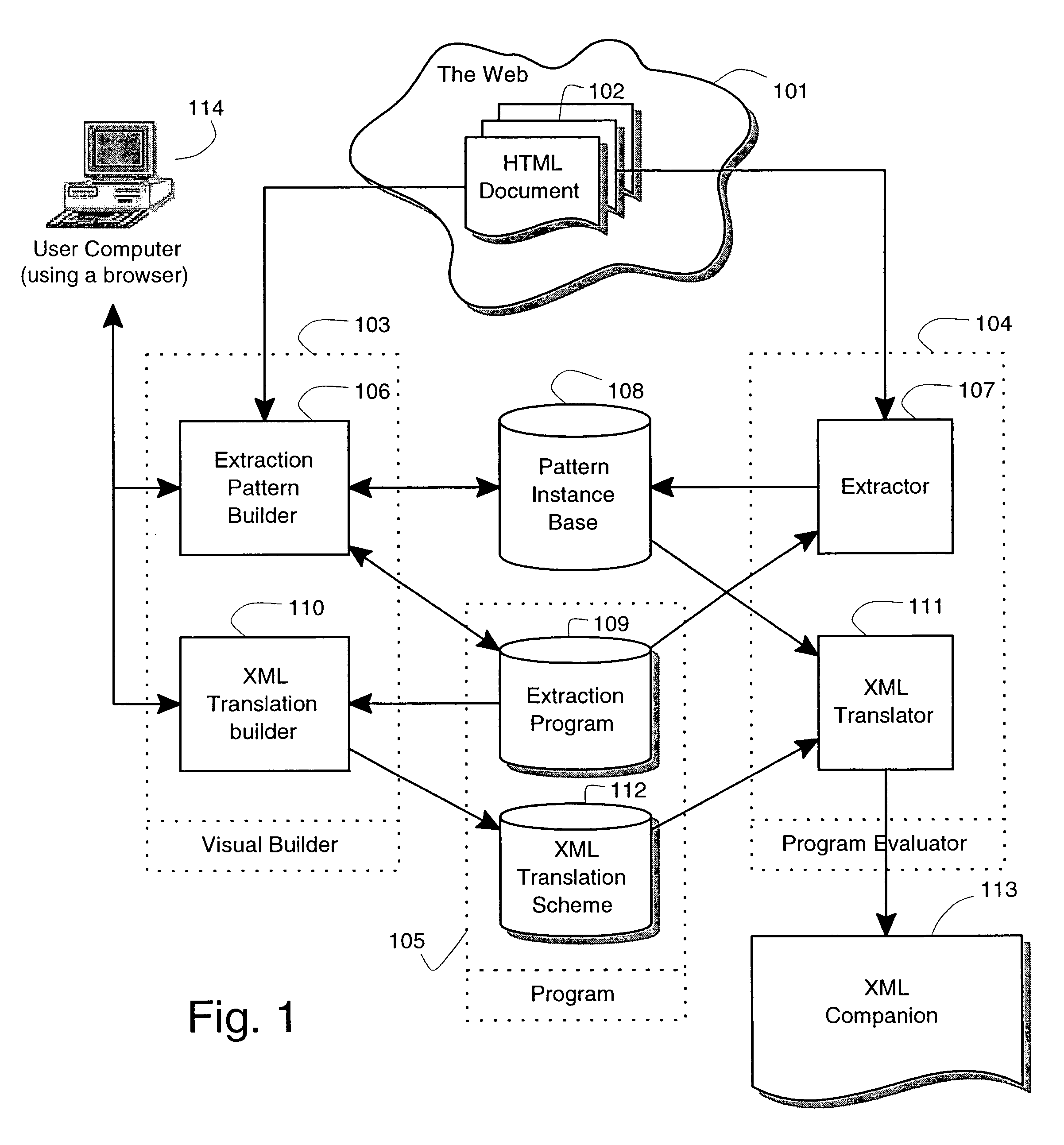

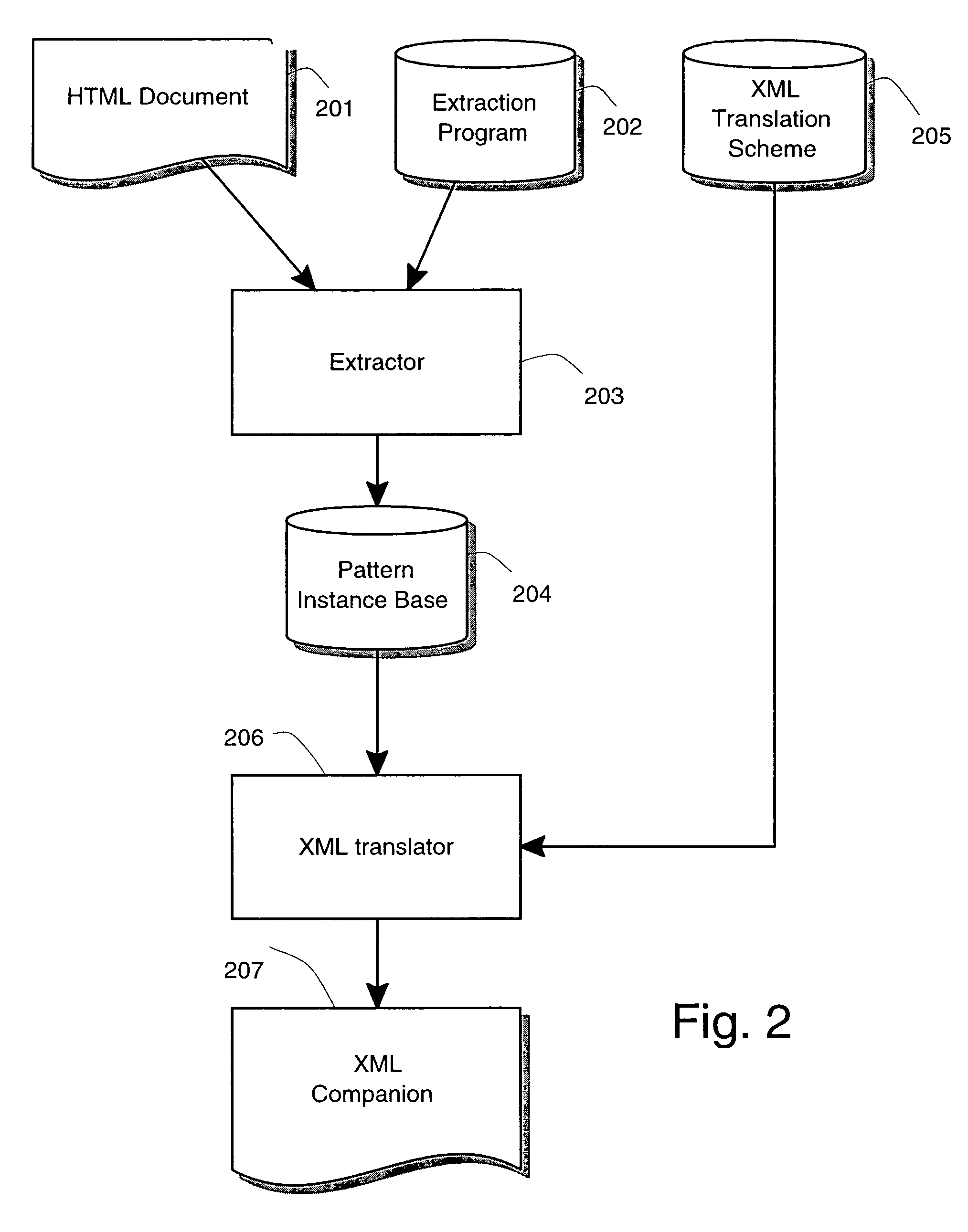

A method and a system for information extraction from Web pages formatted with markup languages such as HTML [8]. A method and system for interactively and visually describing information patterns of interest based on visualized sample Web pages [5,6,16-29]. A method and data structure for representing and storing these patterns [1]. A method and system for extracting information corresponding to a set of previously defined patterns from Web pages [2], and a method for transforming the extracted data into XML is described. Each pattern is defined via the (interactive) specification of one or more filters. Two or more filters for the same pattern contribute disjunctively to the pattern definition [3], that is, an actual pattern describes the set of all targets specified by any of its filters. A method and for extracting relevant elements from Web pages by interpreting and executing a previously defined wrapper program of the above form on an input Web page [9-14] and producing as output the extracted elements represented in a suitable data structure. A method and system for automatically translating said output into XML format by exploiting the hierarchical structure of the patterns and by using pattern names as XML tags is described.

Owner:LIXTO SOFTWARE

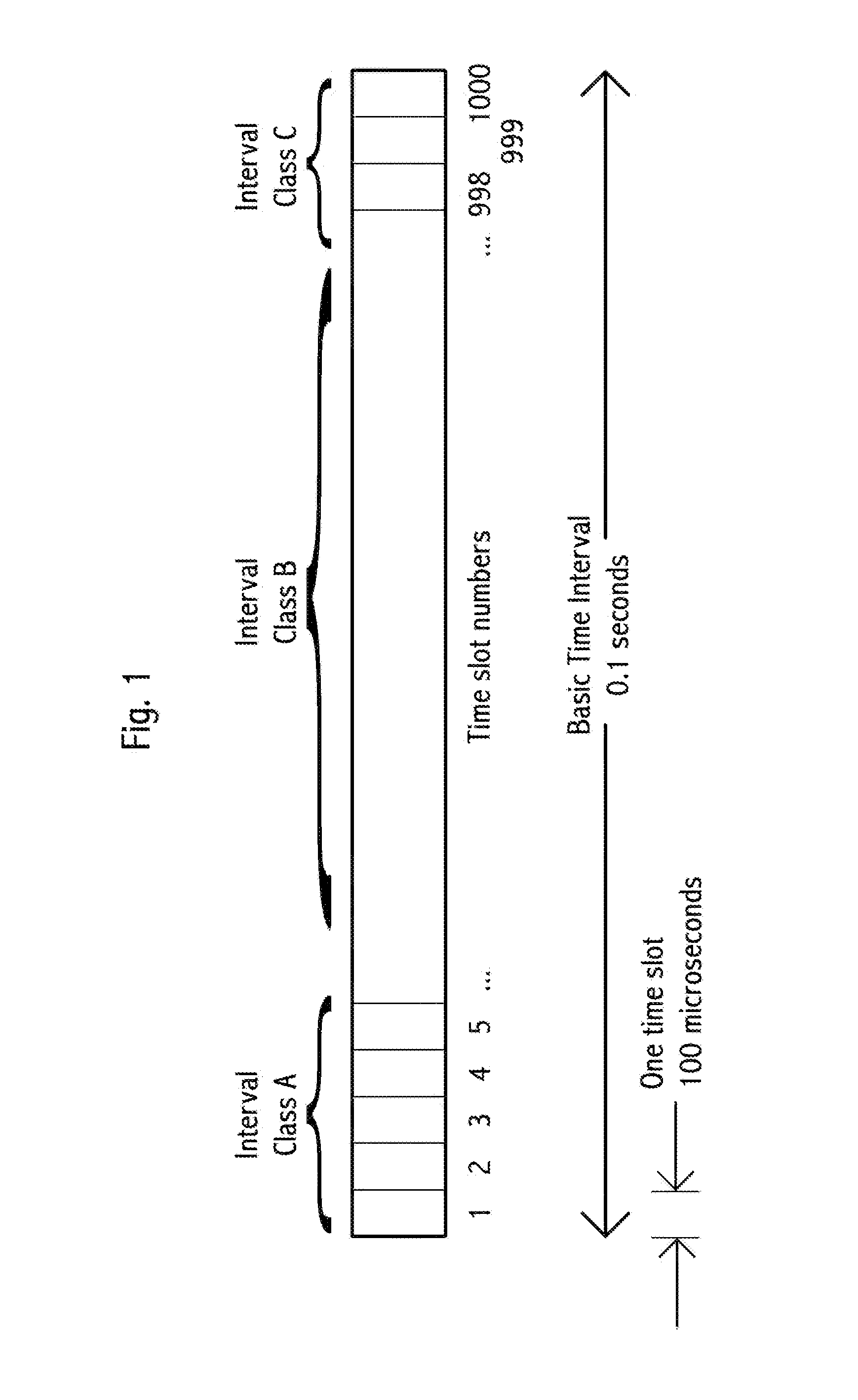

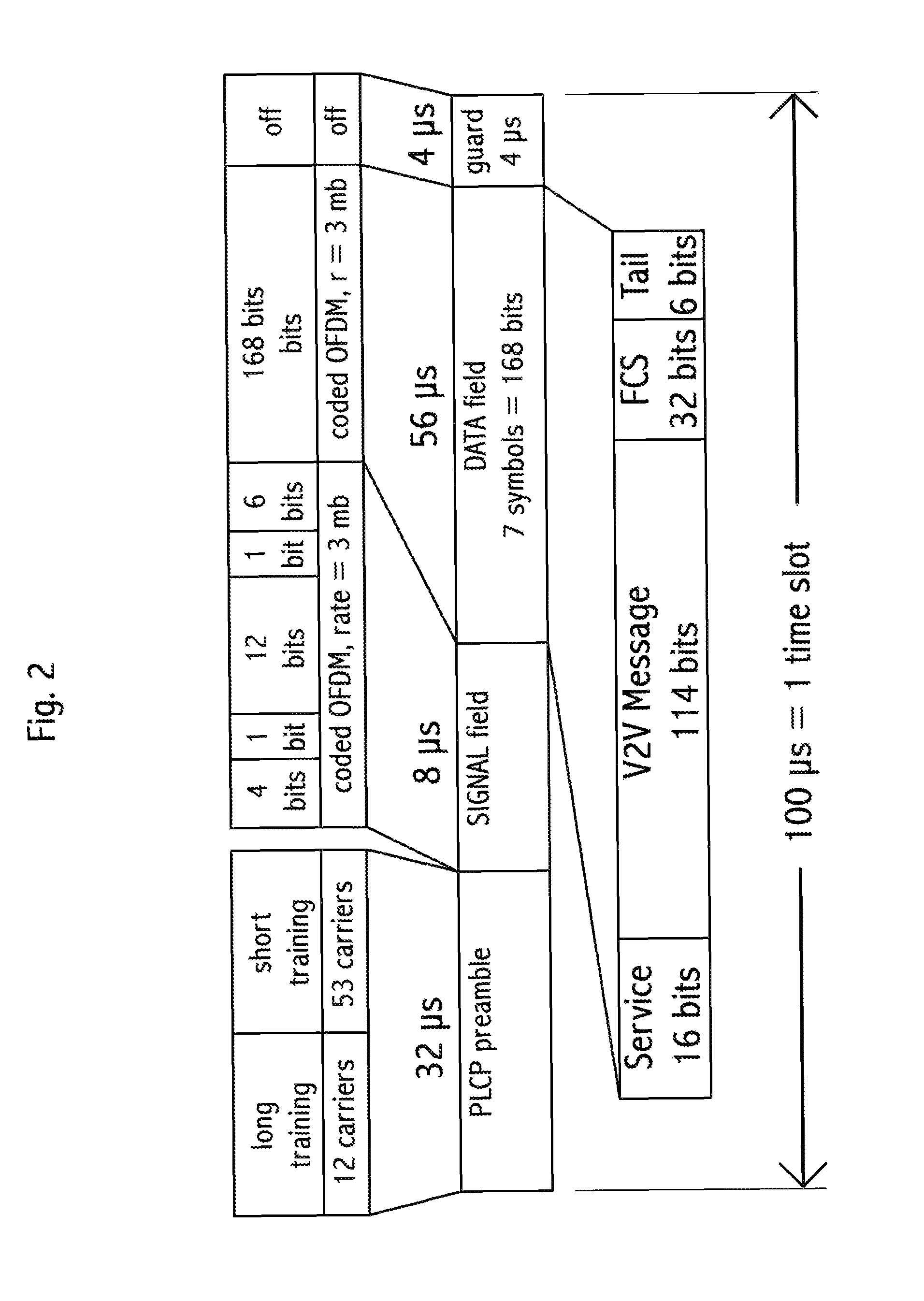

Time-slot-based system and method of inter-vehicle communication

ActiveUS8520695B1Efficient communicationEfficient codingInstruments for road network navigationArrangements for variable traffic instructionsWireless transmissionCommunications system

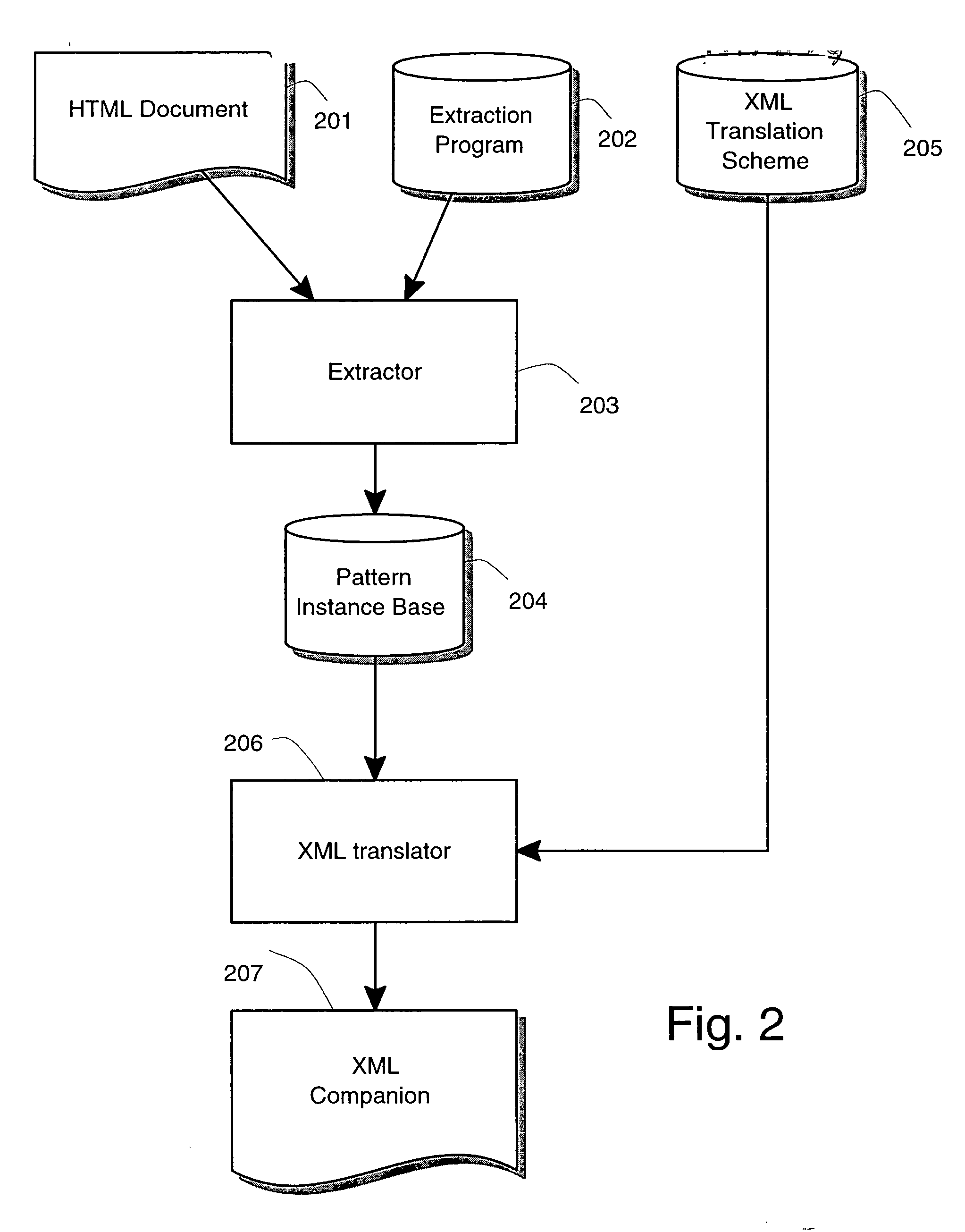

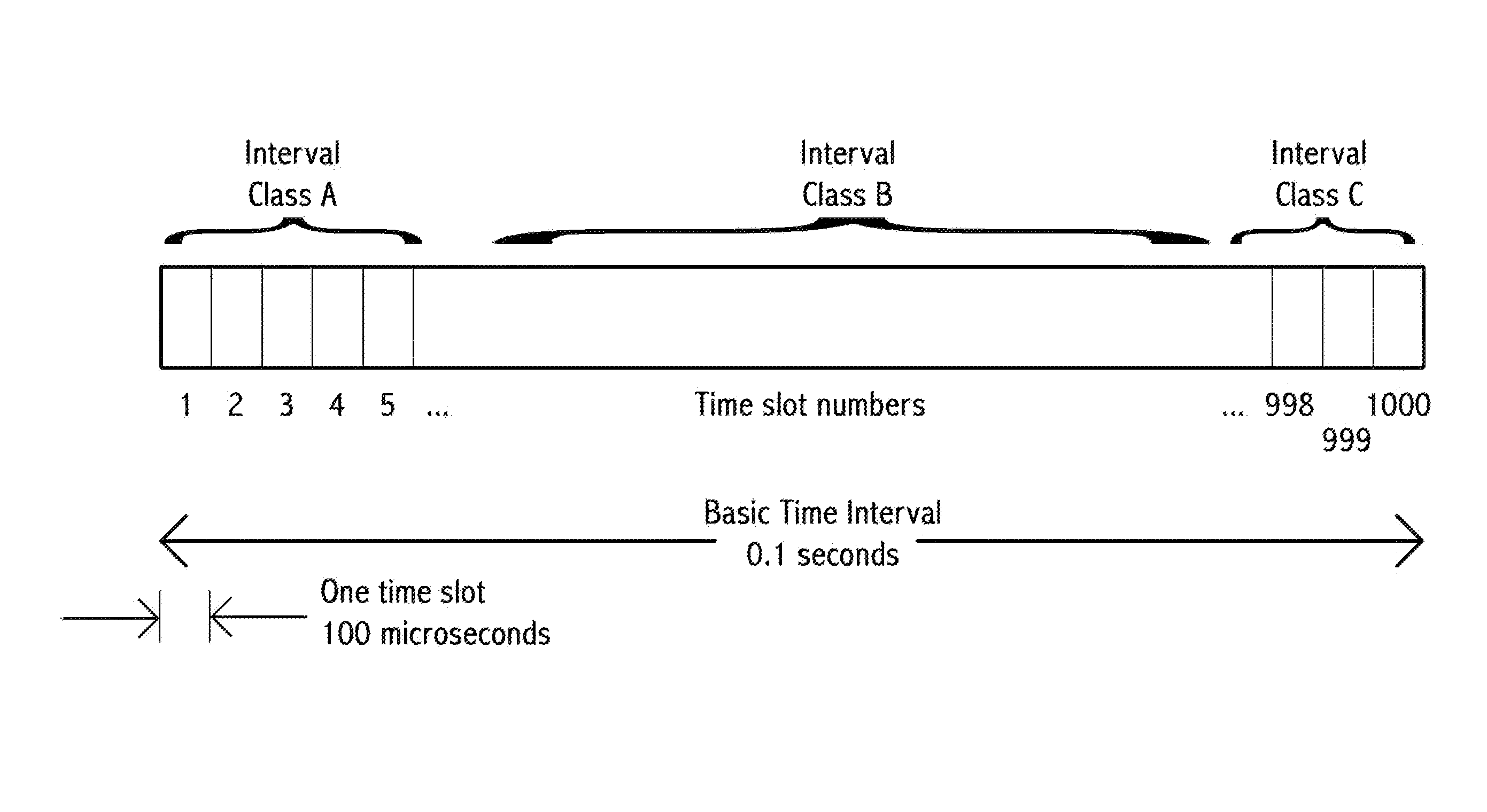

Device, system and method, in a vehicle communication system, to transmit wirelessly a message comprising the position, heading and speed of a vehicle or other moving object, wherein the transmission is repeated at regular intervals in a temporarily fixed time slot within a predetermined basic time interval. In a key embodiment the message duration is equal to or less than a predetermined time slot duration. Embodiments use generally the same time slot in a contiguous sequence of basic time intervals. Algorithms are described to resolve wireless interference within a time slot. Embodiments divide the basic time interval in multiple durations, “class regions,” for different message classes. Embodiments use different wireless bandwidth allocation algorithms for the class regions.

Owner:ZETTA RES & DEV - FORC SERIES

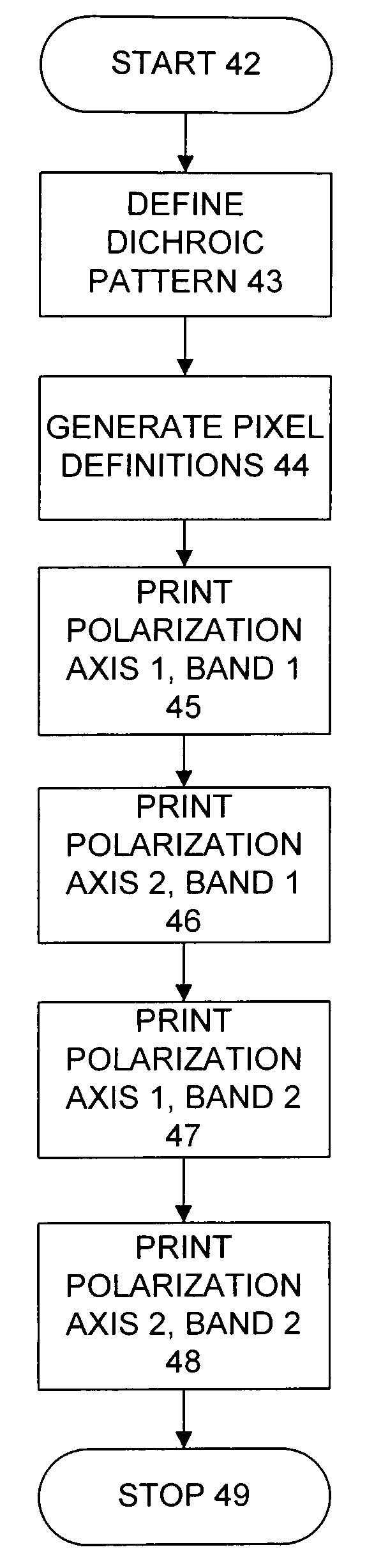

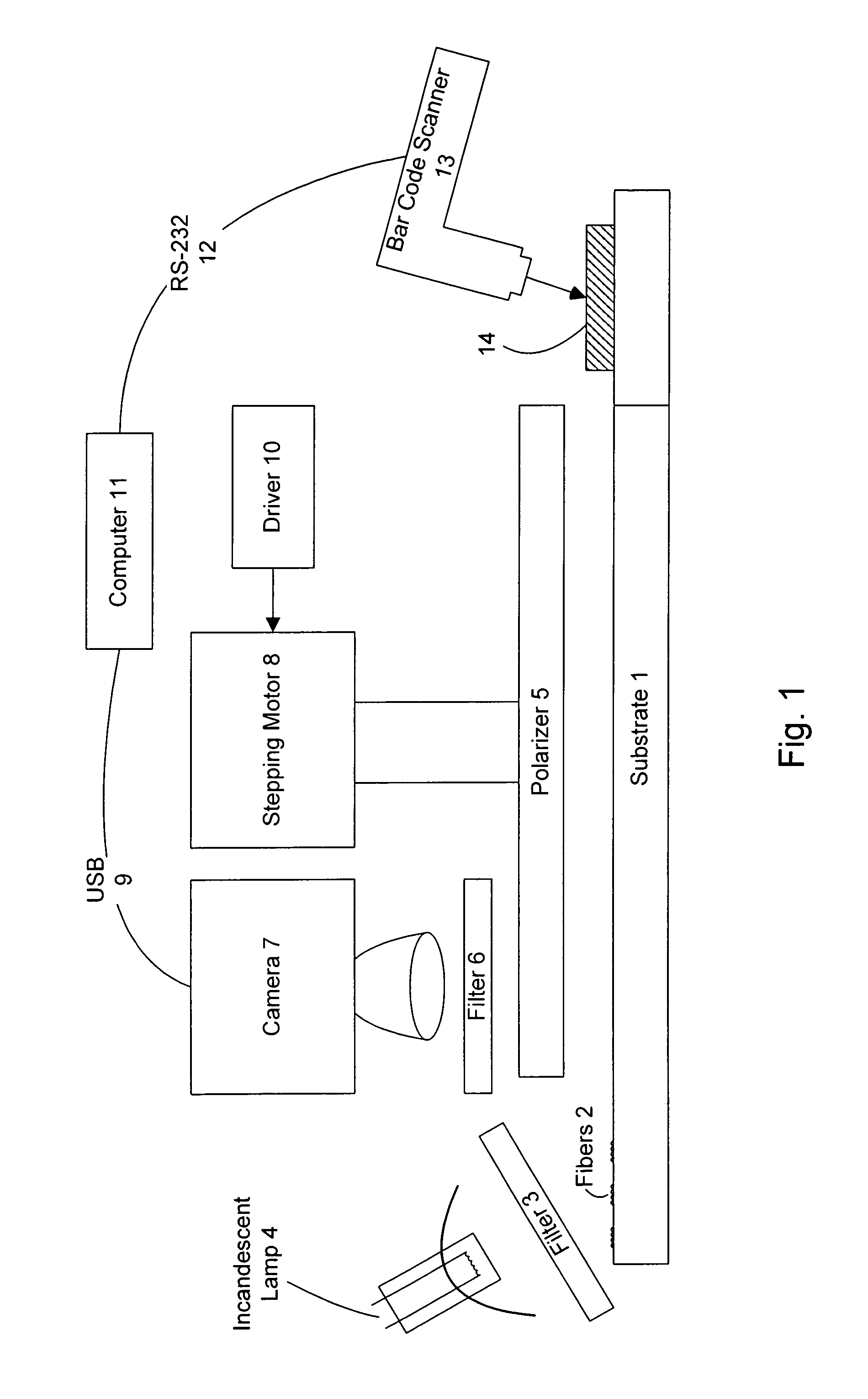

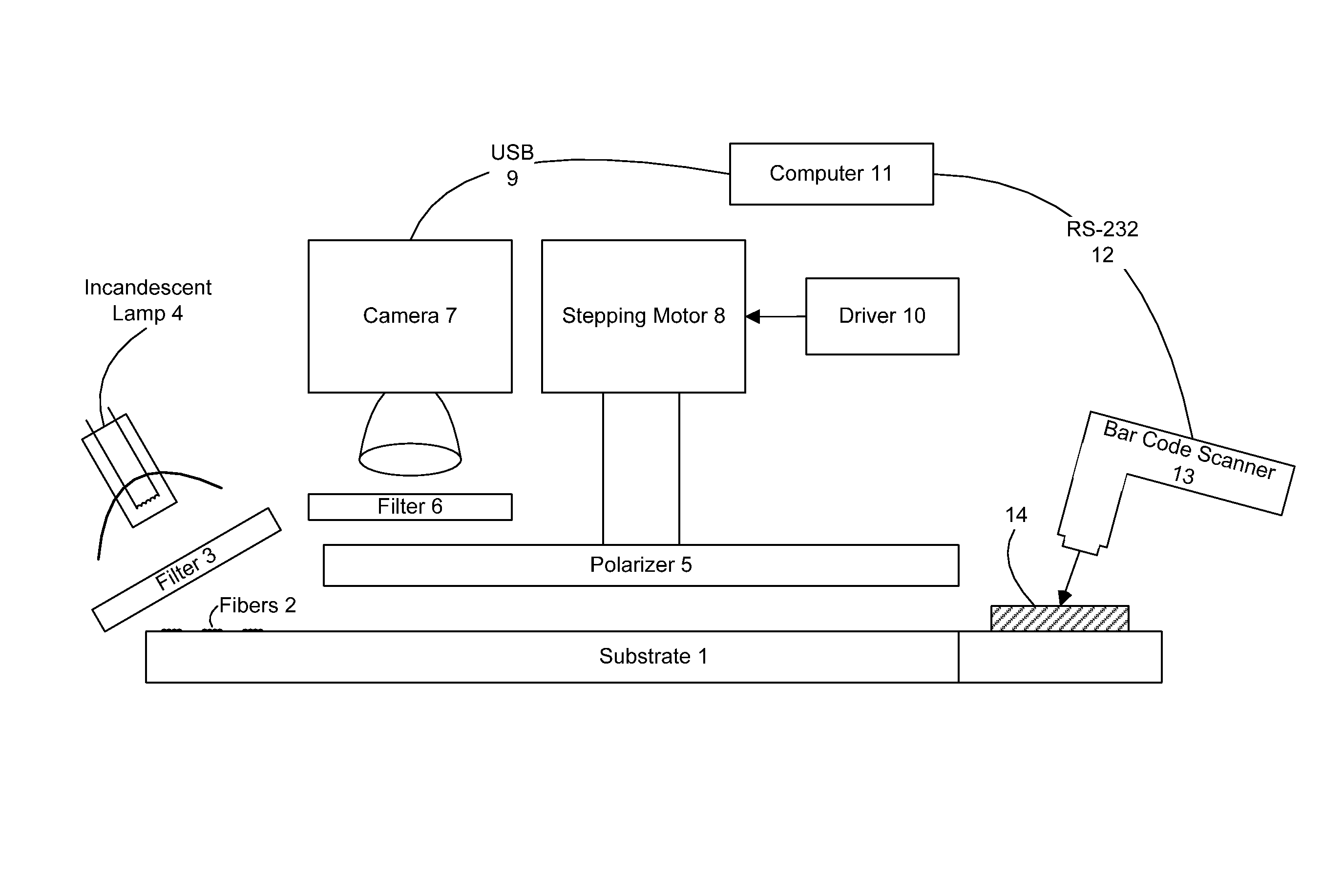

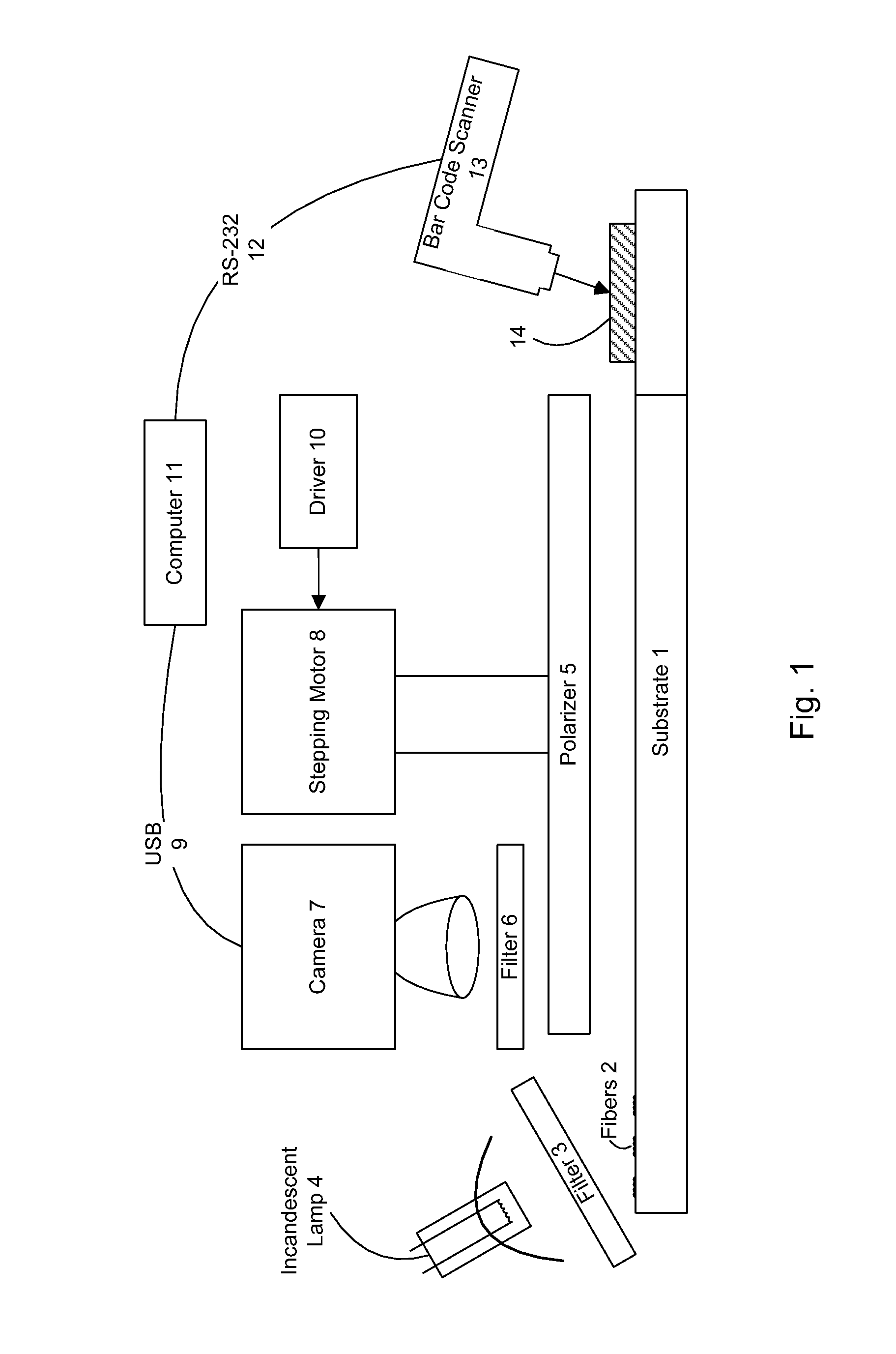

Authentication method and system

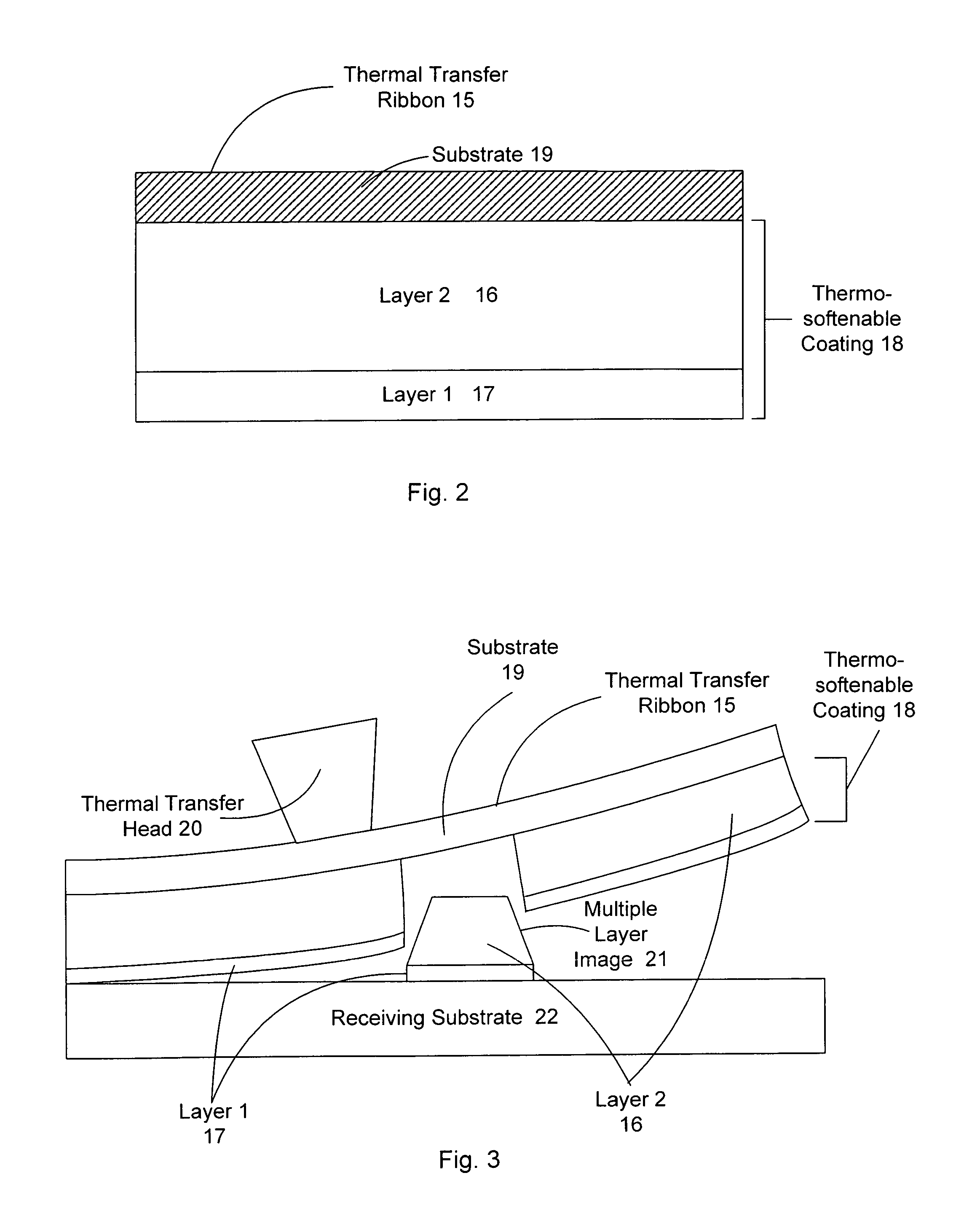

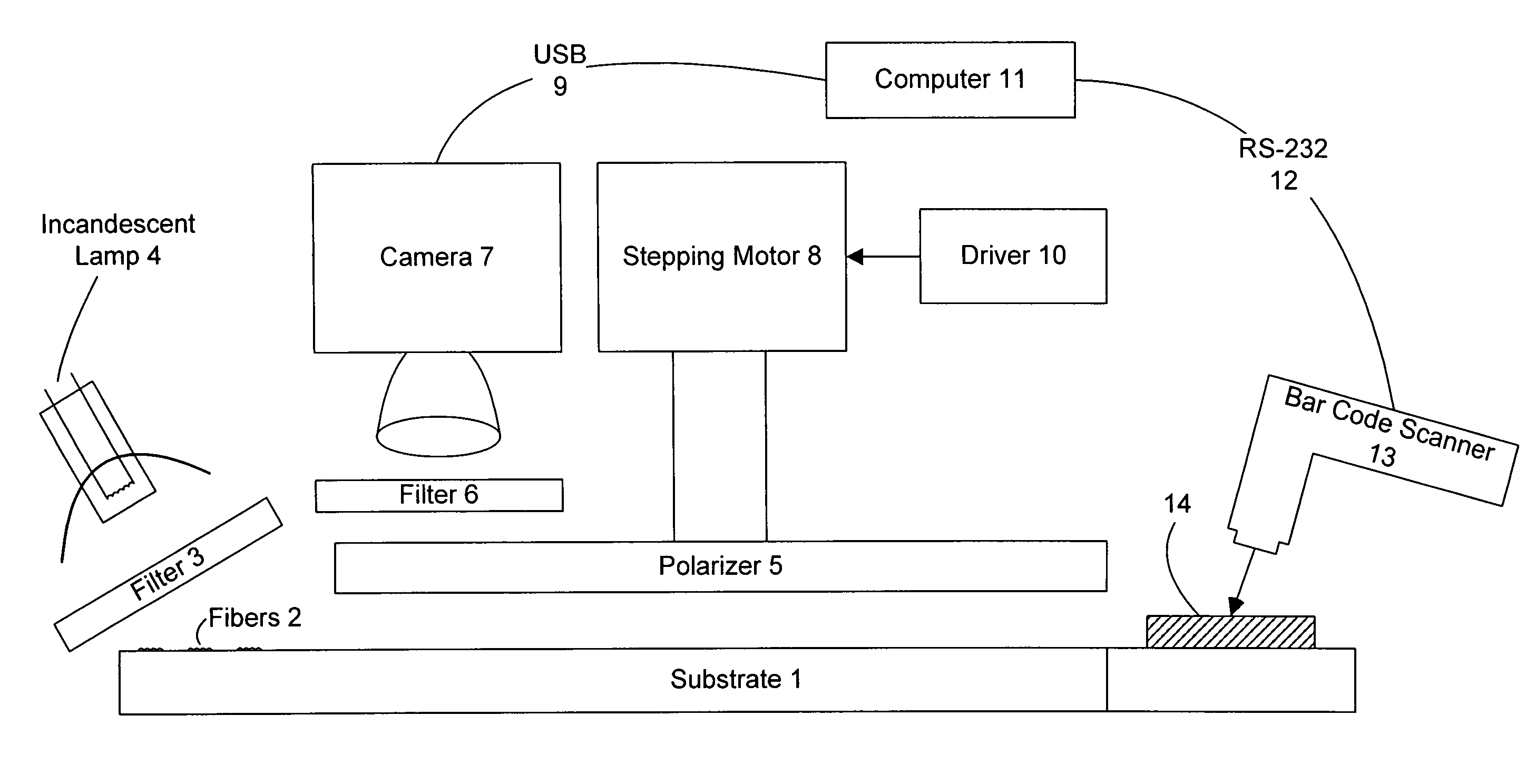

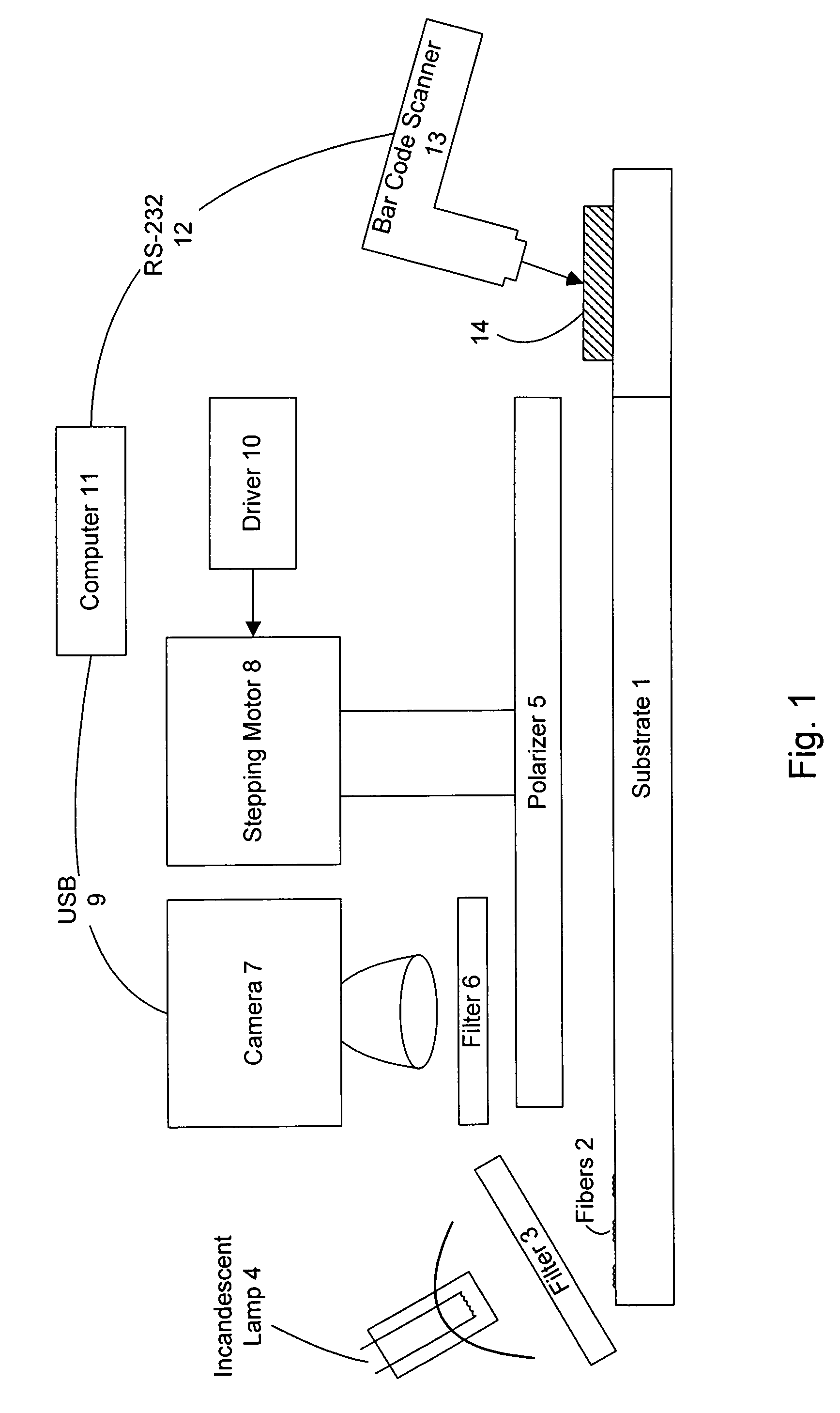

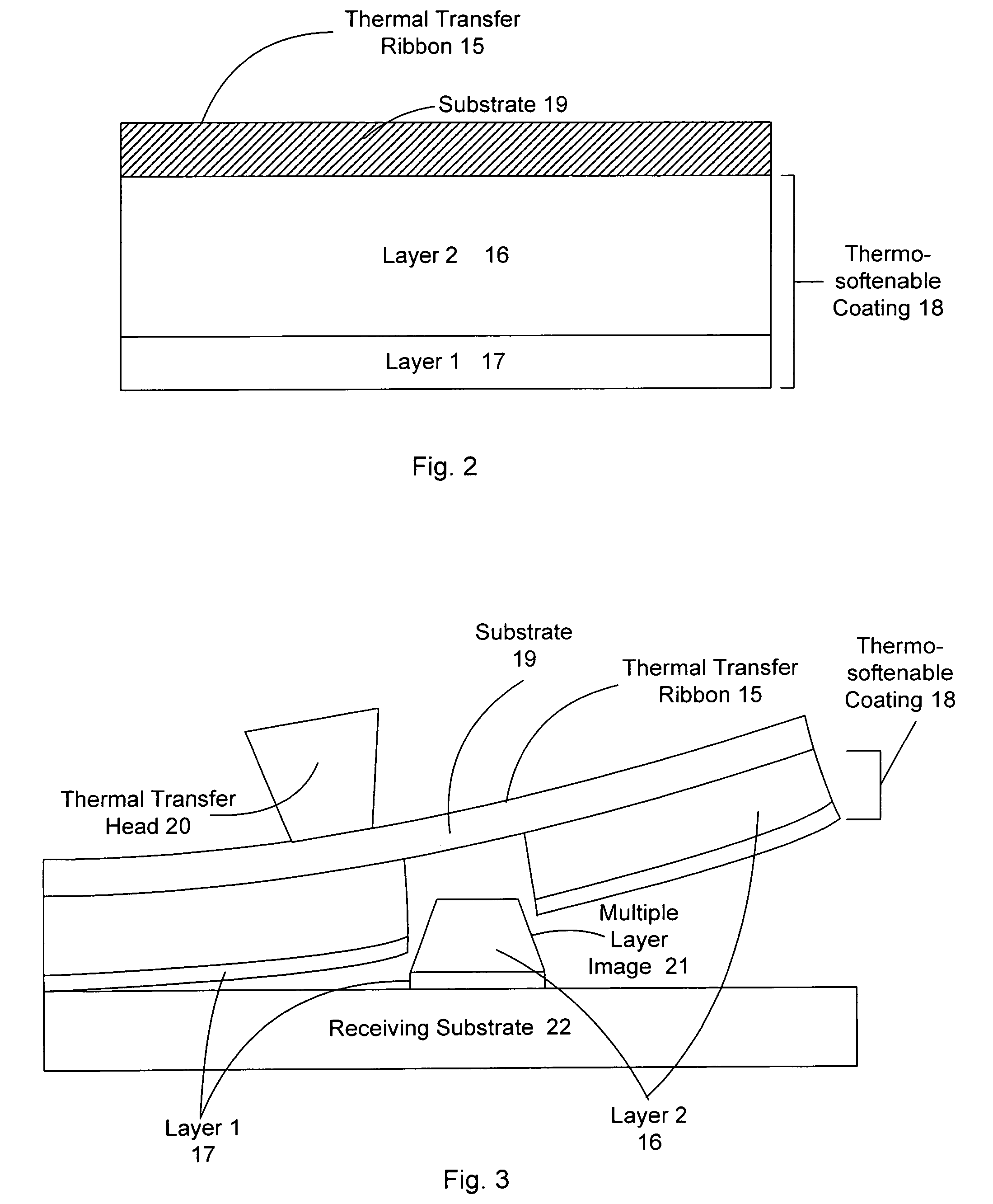

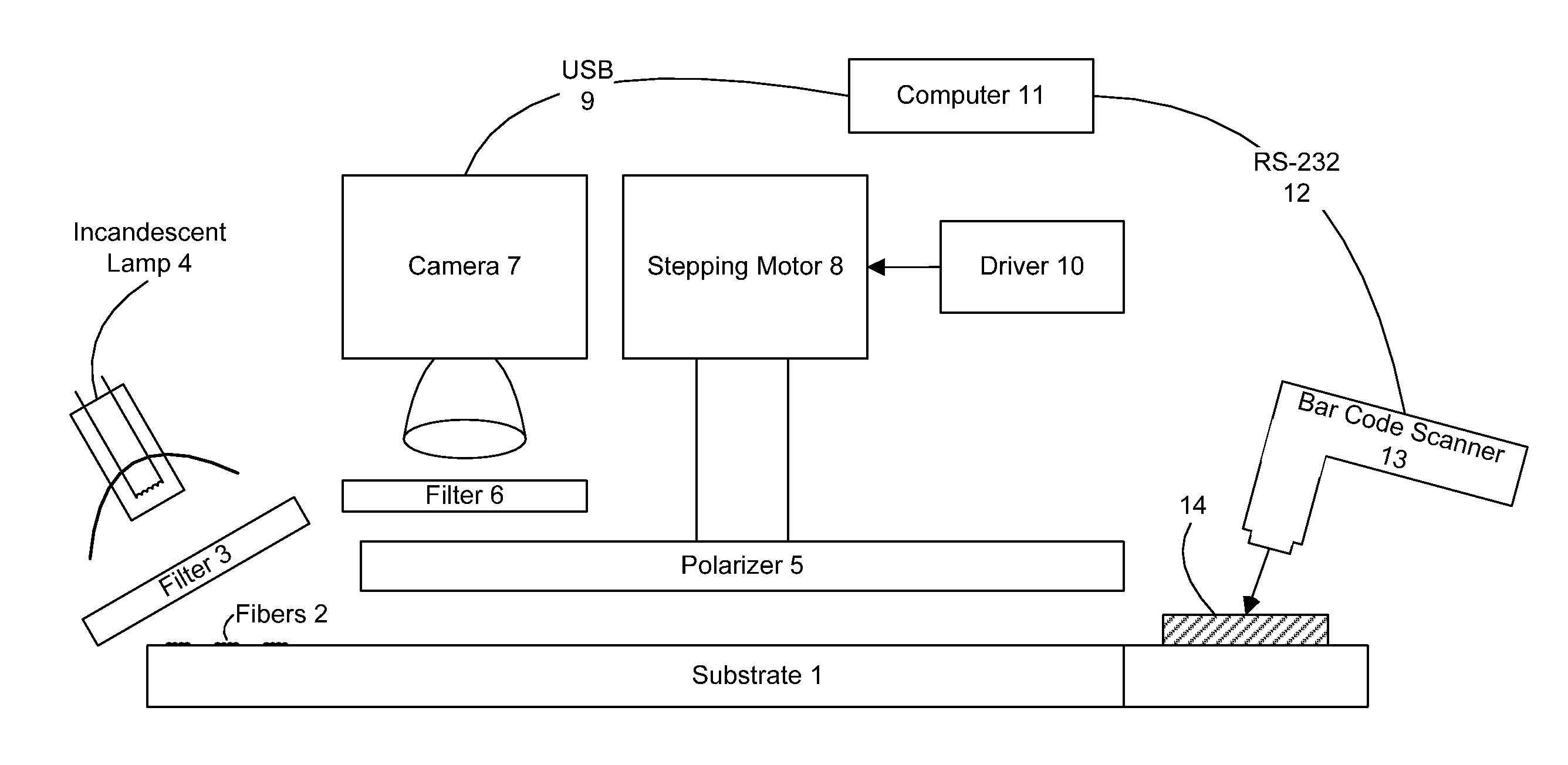

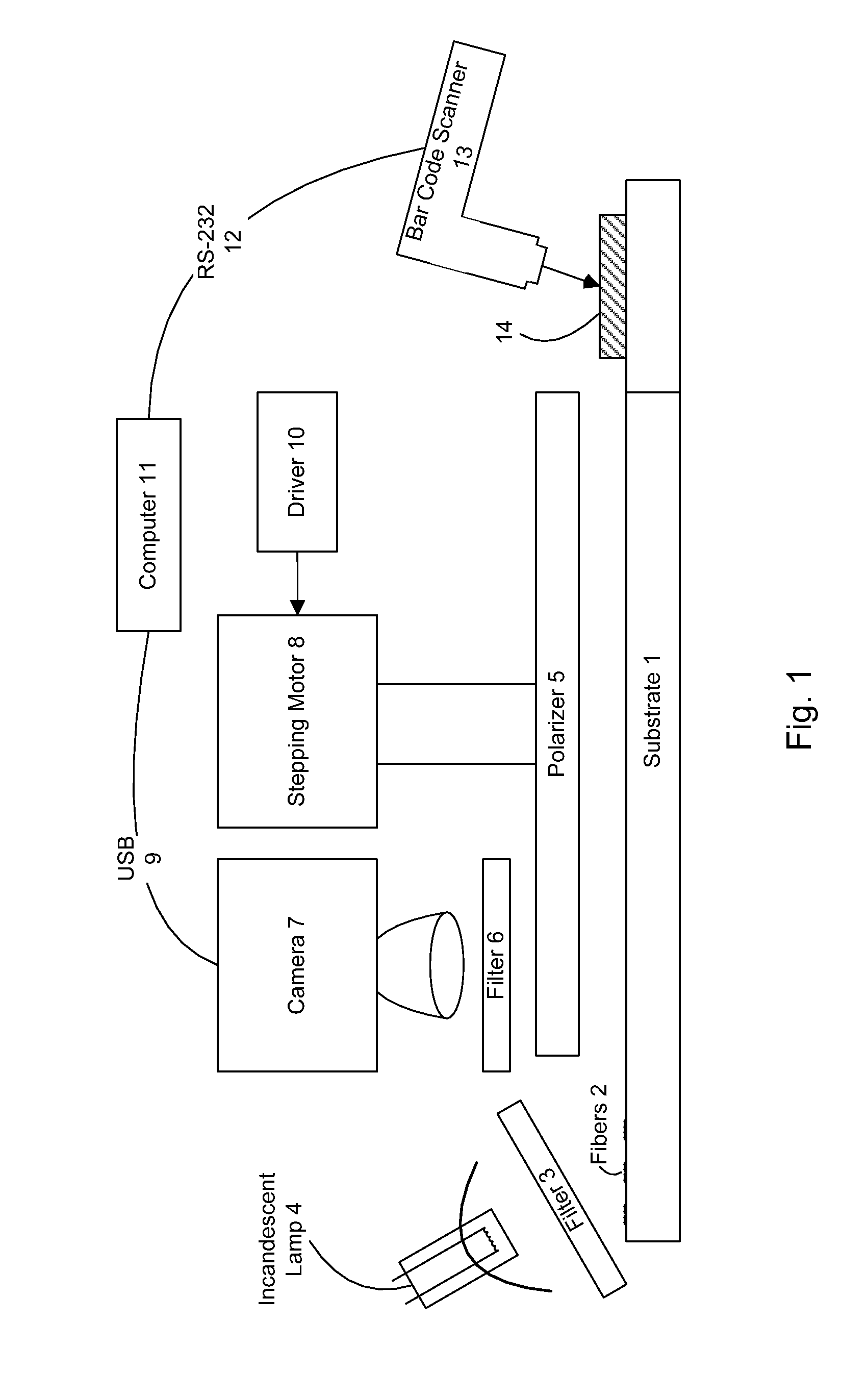

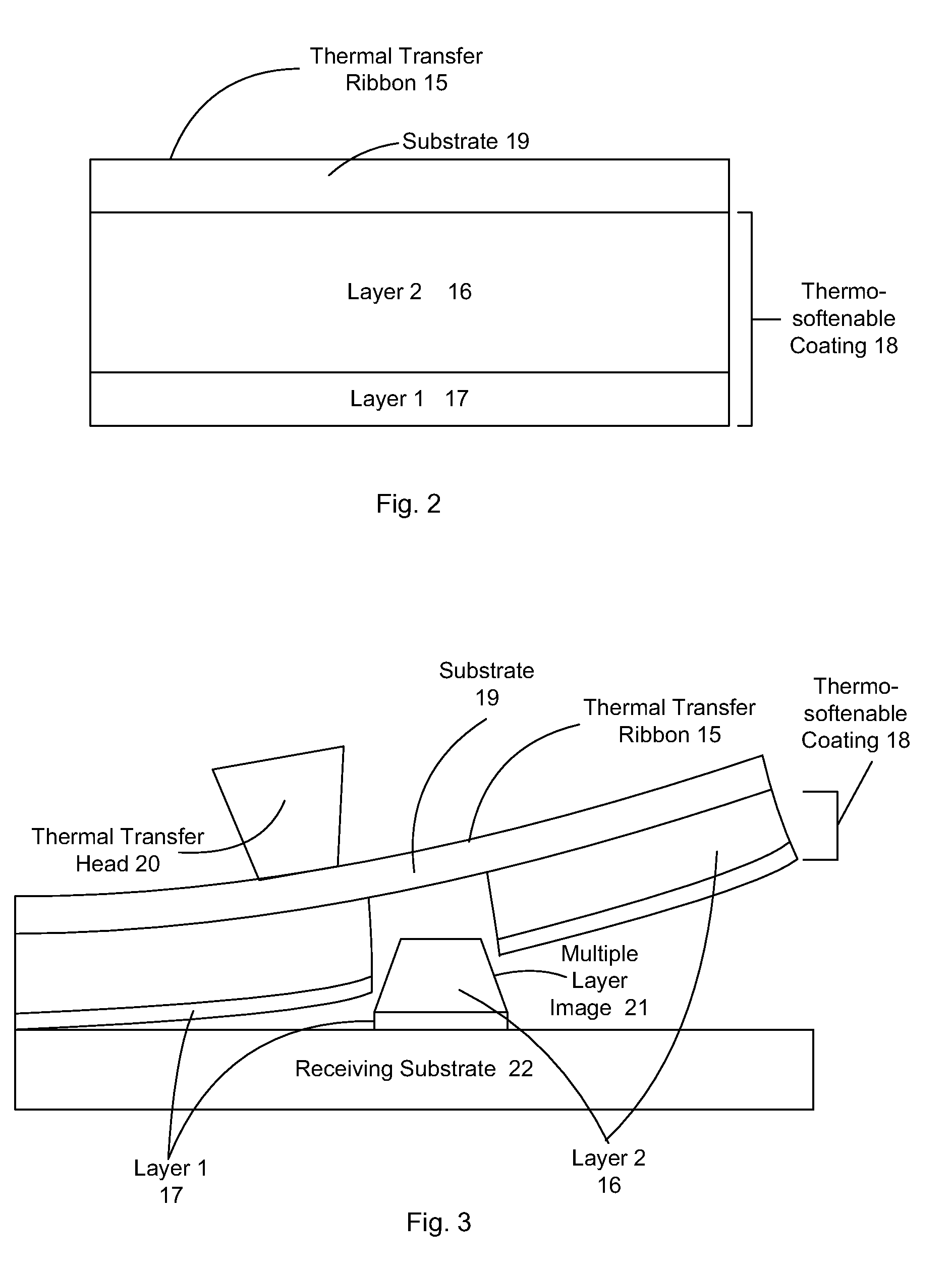

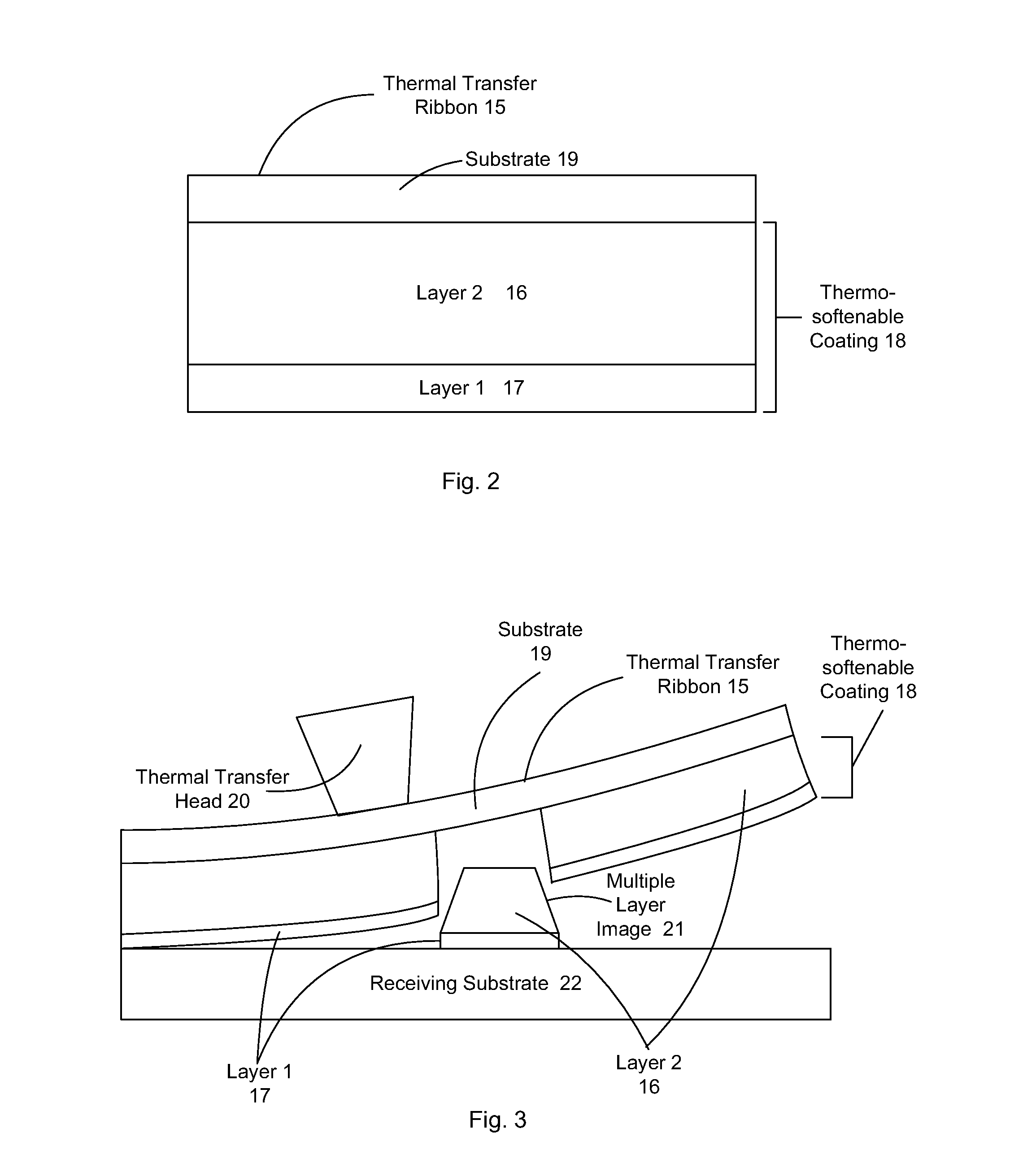

InactiveUS7089420B1Great difficultyEfficient codingOther printing matterUser identity/authority verificationComputer hardwareOptical property

The present invention provides a method and apparatus for the production and labeling of objects in a manner suitable for the prevention and detection of counterfeiting. Thus, the system incorporates a variety of features that make unauthorized reproduction difficult. In addition, the present invention provides an efficient means for the production of labels and verification of authenticity, whereby a recording apparatus which includes a recording medium, having anisotrophic optical domains, along with a means for transferring a portion of the recording medium to a carrier, wherein a bulk portion of the recording medium has macroscopically detectable anisotrophic optical properties and the detecting apparatus thereon.

Owner:COPILOT VENTURES FUND III

Authentication method and system

InactiveUS7162035B1Great difficultyEfficient codingUser identity/authority verificationComputer security arrangementsComputer hardwareOptical property

The present invention provides a method and apparatus for the production and labeling of objects in a manner suitable for the prevention and detection of counterfeiting. Thus, the system incorporates a variety of features that make unauthorized reproduction difficult. In addition, the present invention provides an efficient means for the production of labels and verification of authenticity, whereby a recording apparatus which includes a recording medium, having anisotrophic optical domains, along with a means for transferring a portion of the recording medium to a carrier, wherein a bulk portion of the recording medium has macroscopically detectable anisotrophic optical properties and the detecting apparatus thereon.

Owner:COPILOT VENTURES FUND III

Authentication method and system

InactiveUS7773749B1Great difficultyEfficient codingDigital data processing detailsAnalogue secracy/subscription systemsComputer hardwareOptical property

The present invention provides a method and apparatus for the production and labeling of objects in a manner suitable for the prevention and detection of counterfeiting. Thus, the system incorporates a variety of features that make unauthorized reproduction difficult. In addition, the present invention provides an efficient means for the production of labels and verification of authenticity, whereby a recording apparatus which includes a recording medium, having anisotrophic optical domains, along with a means for transferring a portion of the recording medium to a carrier, wherein a bulk portion of the recording medium has macroscopically detectable anisotrophic optical properties and the detecting apparatus thereon.

Owner:COPILOT VENTURES FUND III

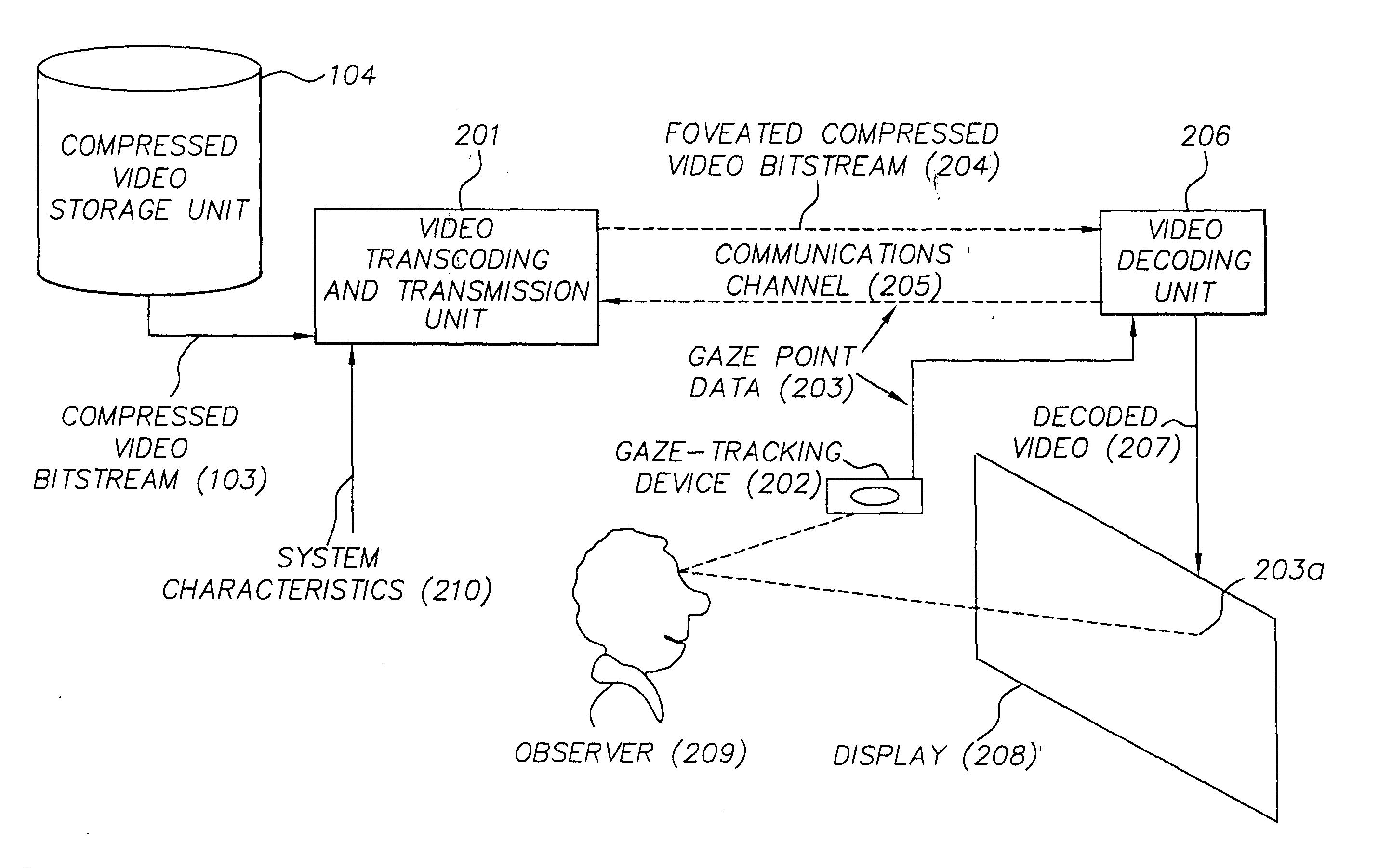

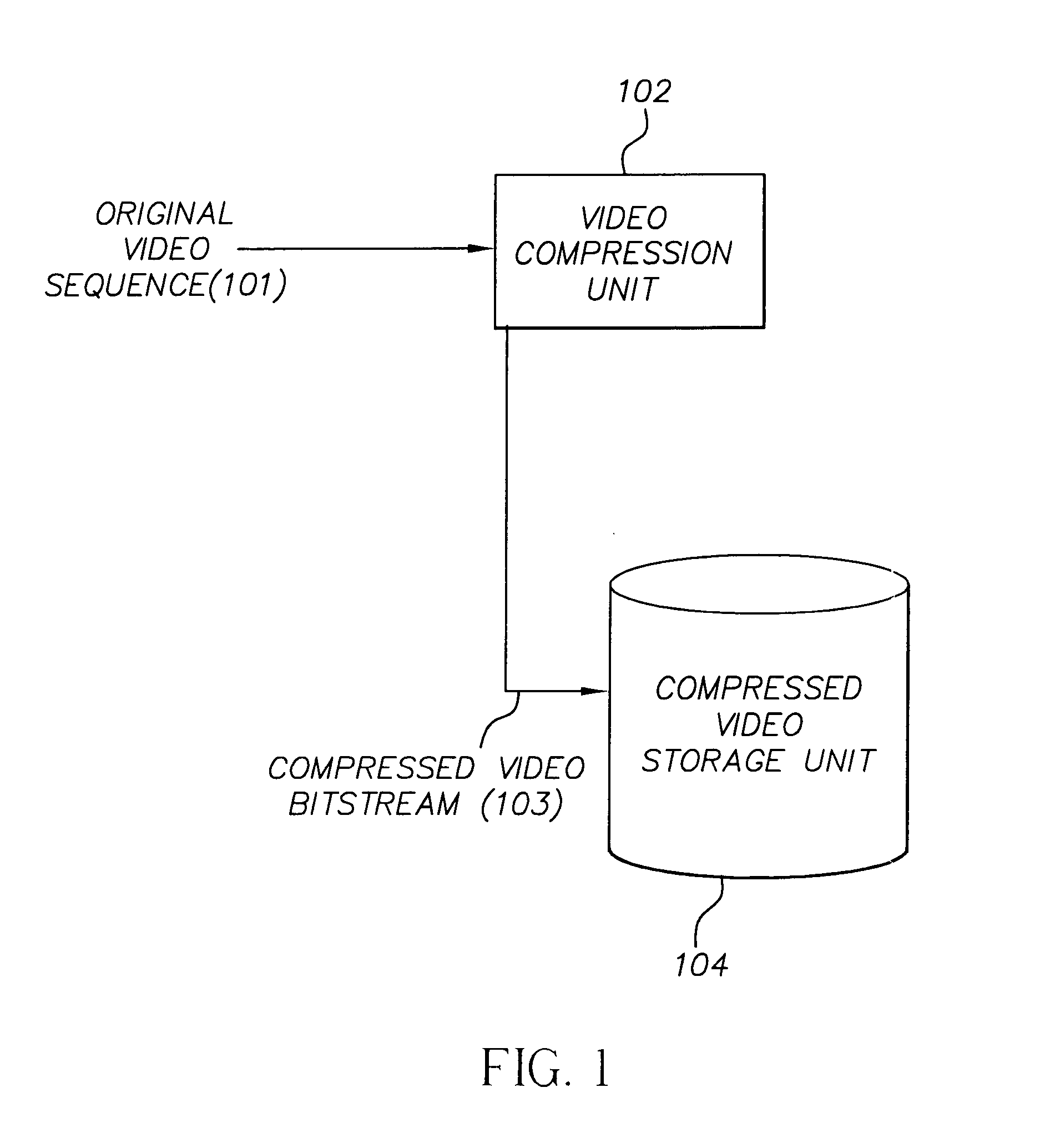

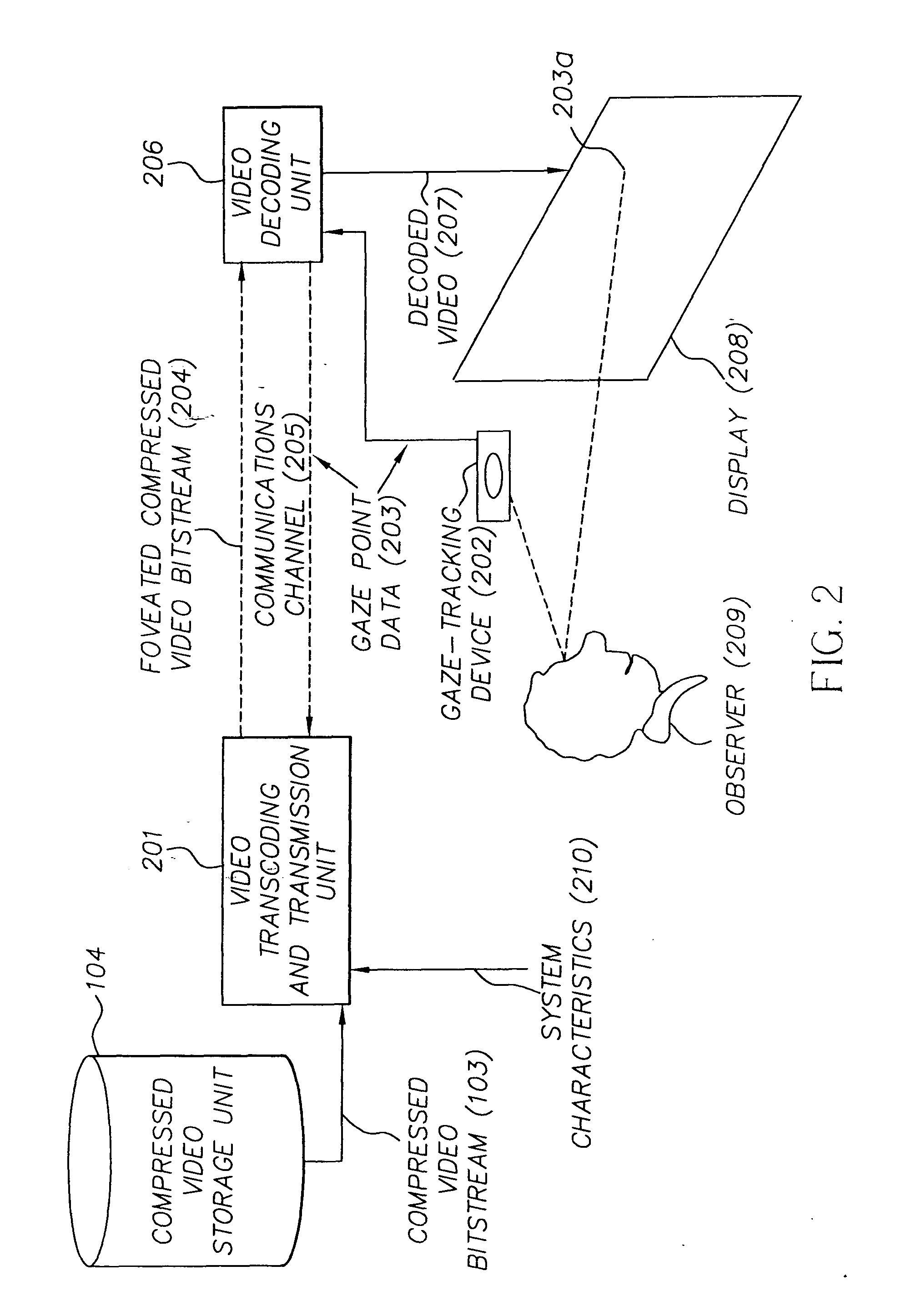

Foveated video coding system and method

InactiveUS20050018911A1Reduce bandwidth requirementsAttenuation bandwidthCharacter and pattern recognitionTelevision systemsDigital videoDisplay device

In transcoding a frequency transform-encoded digital video signal representing a sequence of video frames, a foveated, compressed digital video signal is produced and transmitted over a limited bandwidth communication channel to a display according to the following method: First, a frequency transform-encoded digital video signal having encoded frequency coefficients representing a sequence of video frames is provided, wherein the encoding removes temporal redundancies from the video signal and encodes the frequency coefficients as base layer frequency coefficients in a base layer and as residual frequency coefficients in an enhancement layer. Then, an observer's gaze point is identified on the display. The encoded digital video signal is partially decoded to recover the frequency coefficients, and the residual frequency coefficients are adjusted to reduce the high frequency content of the video signal in regions away from the gaze point. The frequency coefficients, including the adjusted residual frequency coefficients, are then recoded to produce a foveated, transcoded digital video signal, and the foveated, transcoded digital video signal is displayed to the observer.

Owner:EASTMAN KODAK CO

Authentication method and system

InactiveUS8270603B1Great difficultyEfficient codingComputer security arrangementsCoding/ciphering apparatusComputer hardwareOptical property

The present invention provides a method and apparatus for the production and labeling of objects in a manner suitable for the prevention and detection of counterfeiting. Thus, the system incorporates a variety of features that make unauthorized reproduction difficult. In addition, the present invention provides an efficient means for the production of labels and verification of authenticity, whereby a recording apparatus which includes a recording medium, having anisotrophic optical domains, along with a means for transferring a portion of the recording medium to a carrier, wherein a bulk portion of the recording medium has macroscopically detectable anisotrophic optical properties and the detecting apparatus thereon.

Owner:COPILOT VENTURES FUND III

Encoder and method

ActiveUS20140140359A1Quality lossEfficient codingTime-division multiplexDigital video signal modificationTheoretical computer scienceEncoder

An encoder includes data processing hardware which is operable: to divide input data into a plurality of blocks or packets; to apply a plurality of transformations to content of the blocks or packets to generate corresponding transformed data; to check a quality of representation of the transformed data prior to application of the transformations to determine whether or not the quality of representation of the transformed data satisfies one or more quality criteria; if the quality of representation of the transformed data does not satisfy the one or more quality criteria, to sub-divide and / or to combine the one or more blocks or packets further and repeating the transformation step; and if the quality of representation of the transformed data satisfies the one or more quality criteria, to output the transformed data to provide encoded output data representative of the input data to be encoded.

Owner:GURULOGIC MICROSYST

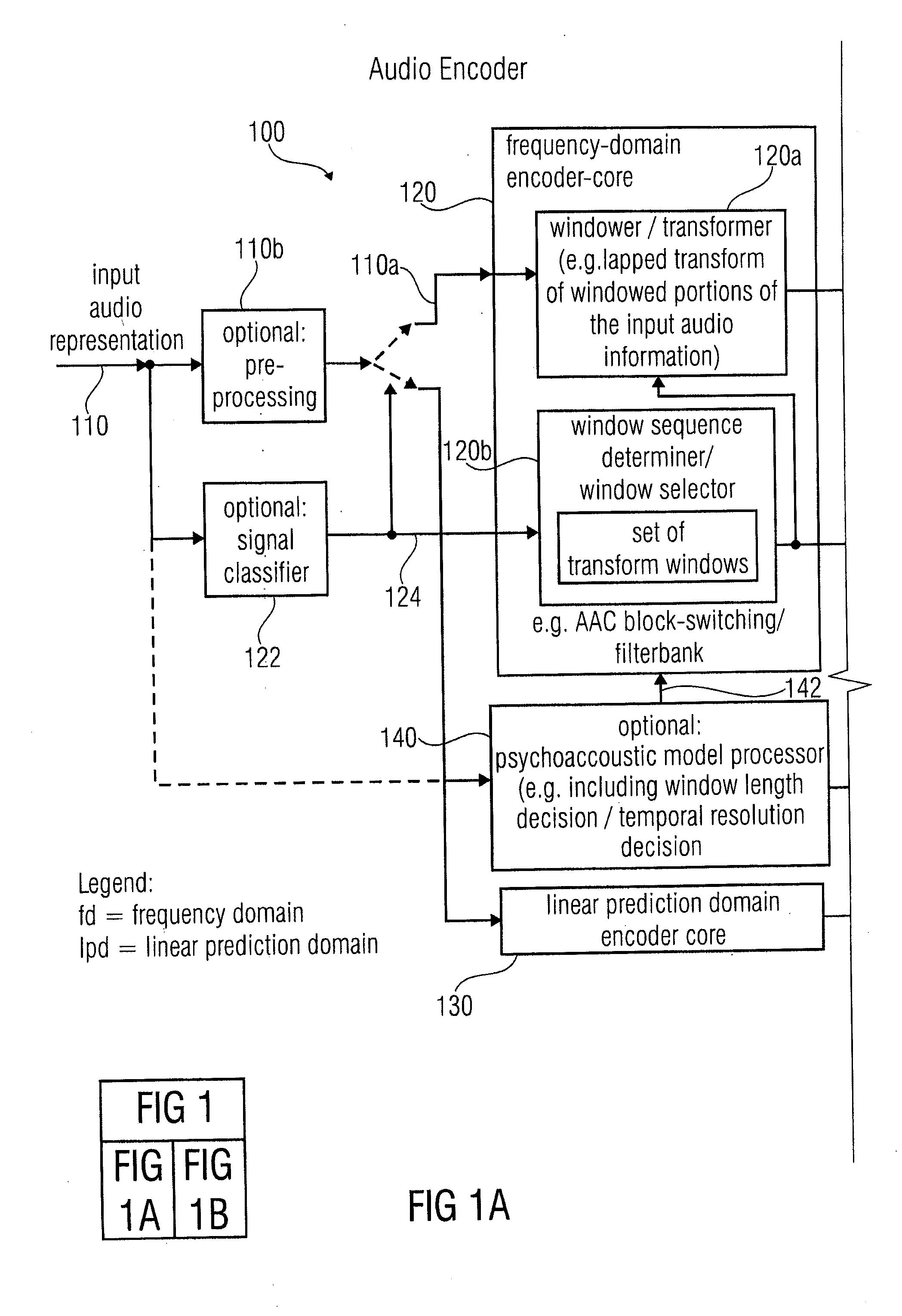

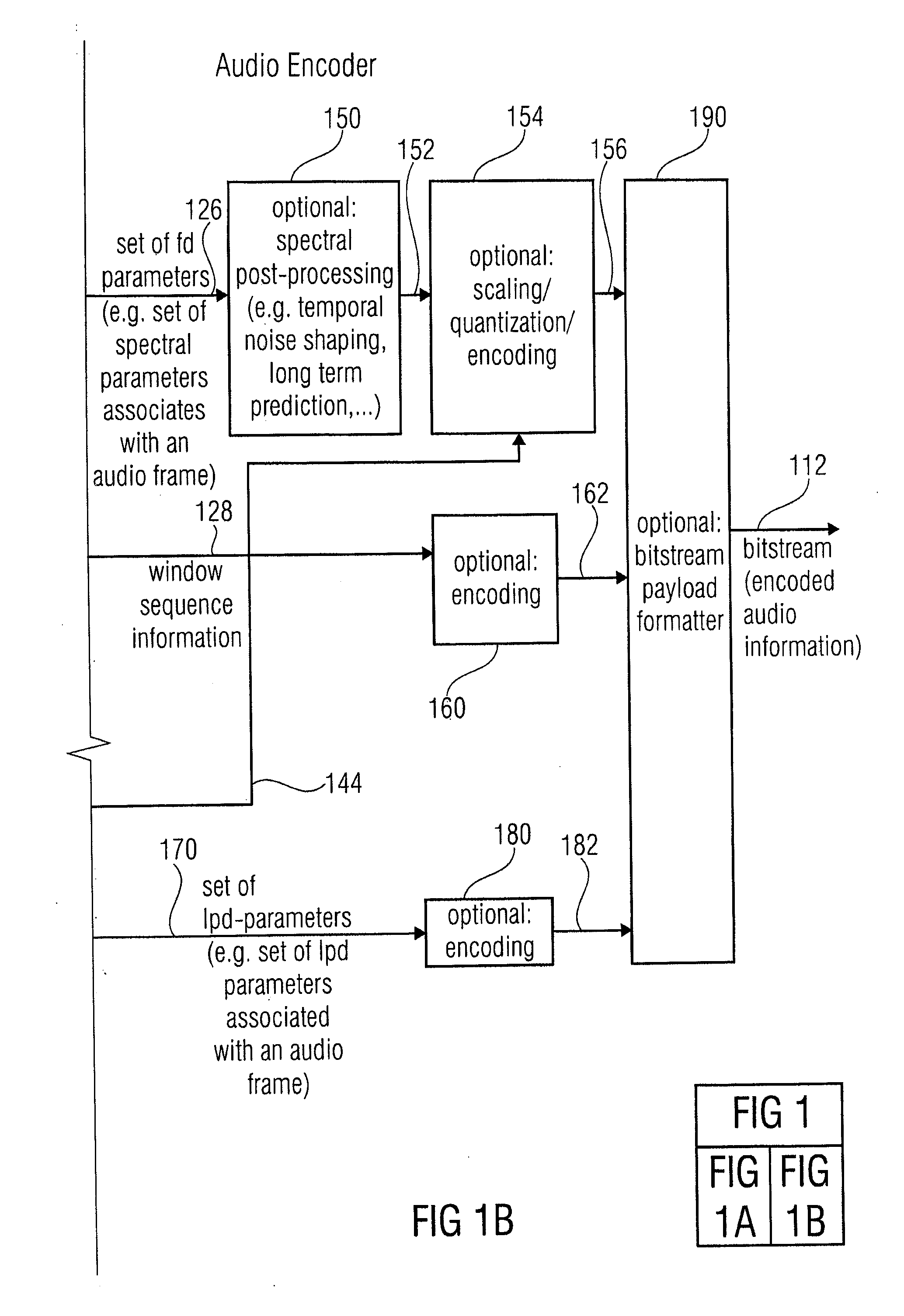

Audio Decoder, Audio Encoder, Methods for Decoding and Encoding an Audio Signal and Computer Program

ActiveUS20100217607A1Good bitrate efficiencyImproves encoding accuracySpeech analysisTransmissionTime domainLinear prediction

An audio decoder for providing a decoded representation of an audio content on the basis of an encoded representation of the audio content comprises a linear-prediction-domain decoder core configured to provide a time-domain representation of an audio frame on the basis of a set of linear-prediction domain parameters associated with the audio frame and a frequency-domain decoder core configured to provide a time-domain representation of an audio frame on the basis of a set of frequency-domain parameters, taking into account a transform window out of a set comprising a plurality of different transform windows. The audio decoder comprises a signal combiner configured to overlap-and-add-time-domain representations of subsequent audio frames encoded in different domains, in order to smoothen a transition between the time-domain representations of the subsequent frames. The set of transform windows comprises one or more windows specifically adapted for a transition between a frequency-domain core mode and a linear-prediction-domain core mode.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

Video compression and encoding method

ActiveUS7499492B1Efficient codingPulse modulation television signal transmissionPicture reproducers using cathode ray tubesData transmissionMotion vector

A method of compressing video data having at least one frame having at least one block and each block having an array of pixels is provided. The method transforms the pixels of each block into coefficients and creates an optimal transmission order of the coefficients. The method also optimizes the speed of processing compressed video data by partitioning the data bitstream and coding each partition independently. The method also predicts fractional pixel motion by selecting an interpolation method for each given plurality or block of pixels depending upon at least one metric related to each given block and varies the method from block to block. The method also enhances error recovery for a current frame using a frame prior to the frame immediately before the current frame as the only reference frame for lessening quality loss during data transmission. Enhanced motion vector coding is also provided.

Owner:GOOGLE LLC

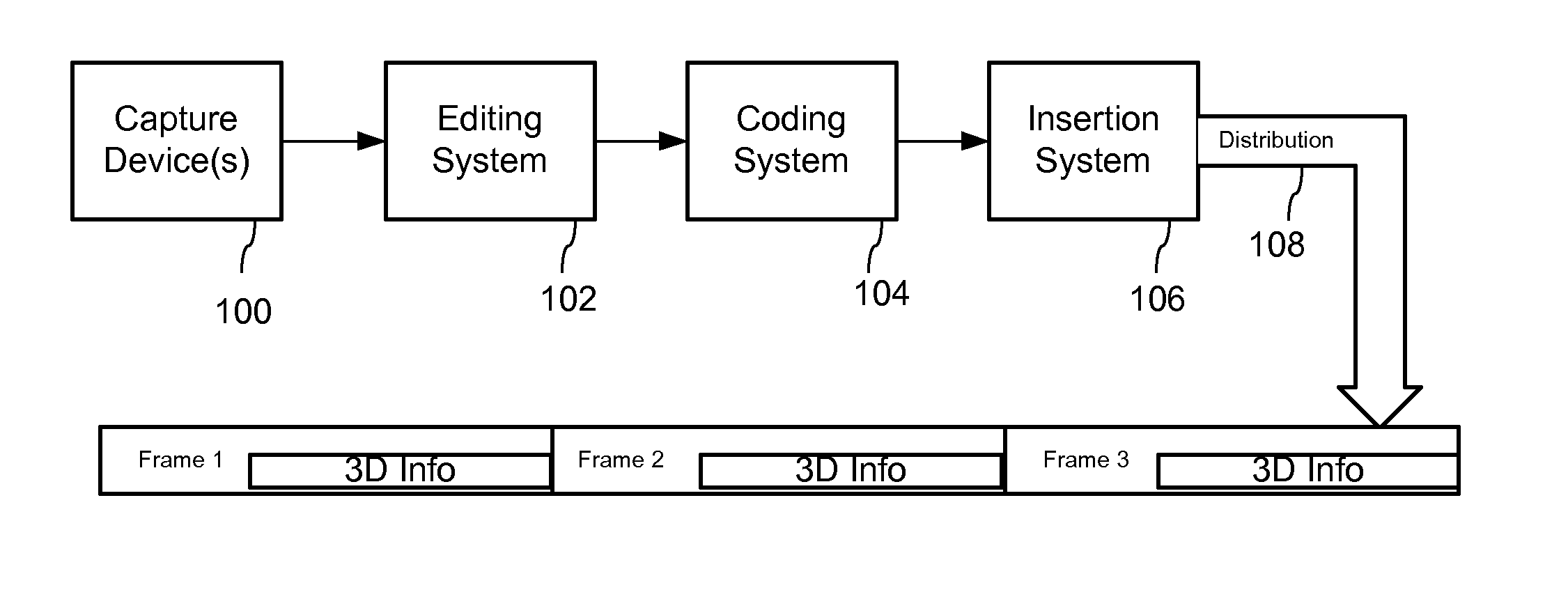

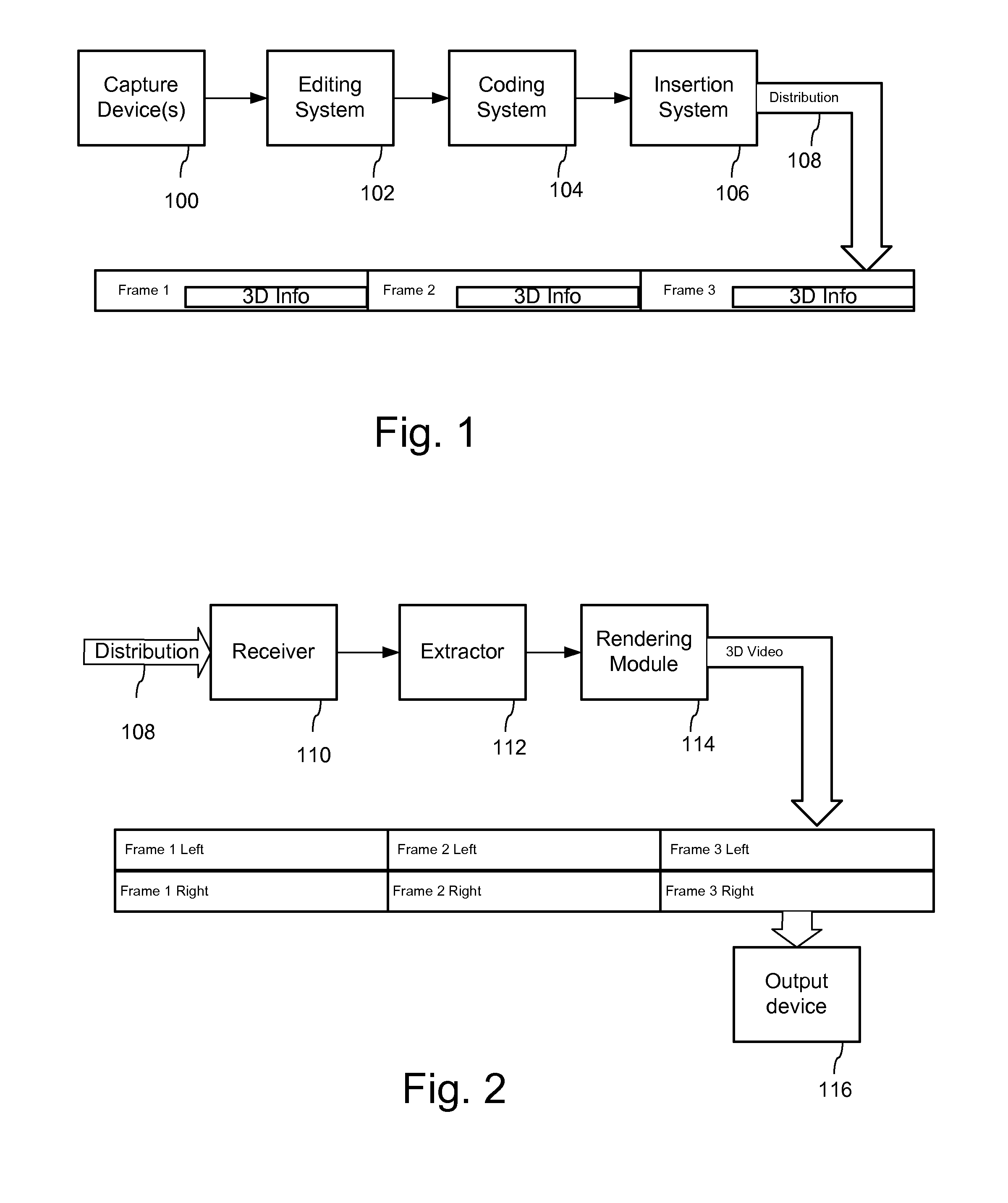

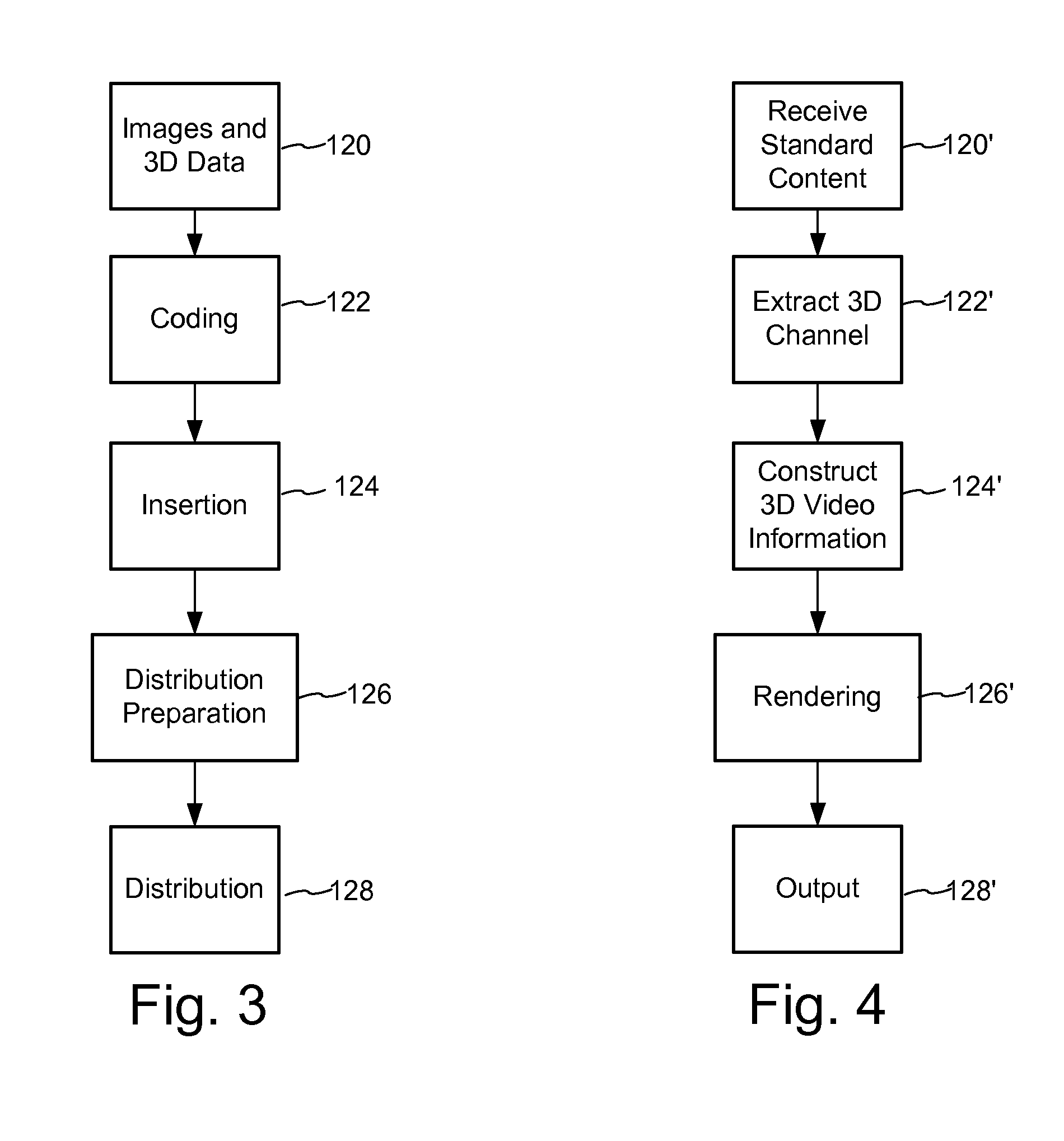

3D Data Representation, Conveyance, and Use

InactiveUS20100309287A1Efficient codingImprove experienceDigital video signal modificationSteroscopic systemsParallaxMotion vector

3D video can be transmitted in a legacy 2D video format by conveying 3rd dimension parameters within a steganographic channel of the perceptual video signal, e.g., DCT coefficients, video samples (luminance, chrominance values), etc. The 3rd dimension parameters can be coded as depth values, disparity, displacement, difference, or parallax values, including depth that is converted into X-Y shifts for adjustment to motion vectors in coded video sequence. To limit the amount of information for the steganographic channel, the 3rd dimension information can be quantized relative to the depth from viewer and other prioritization parameters that limit the need for 3rd dimension information to only aspects of the scene that are deemed important to create a desired 3D effect.

Owner:DIGIMARC CORP

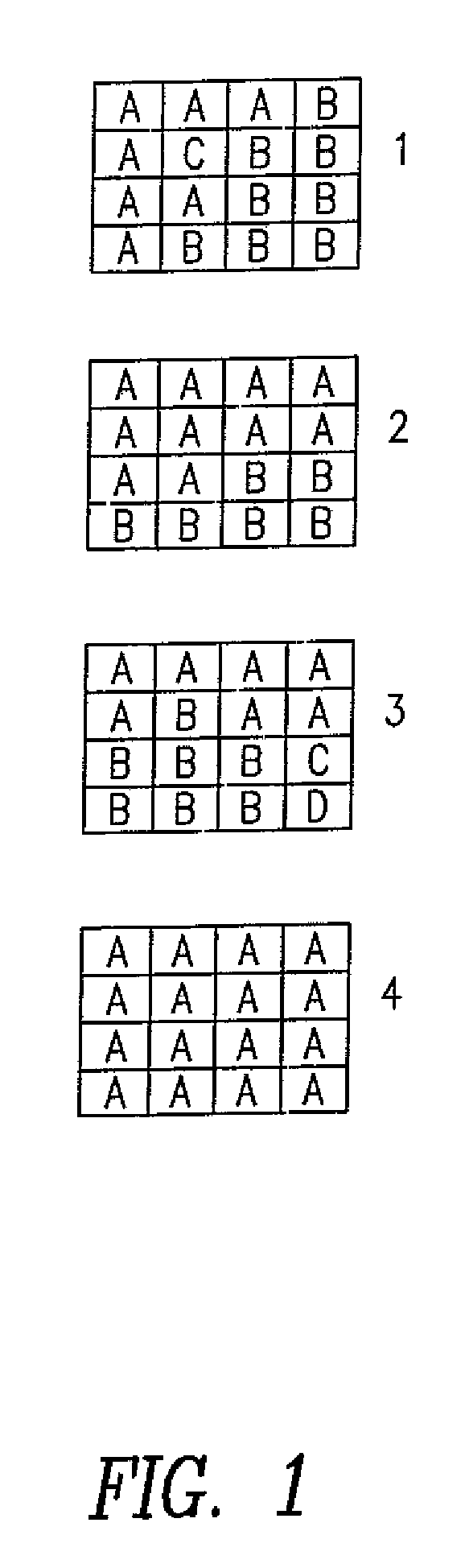

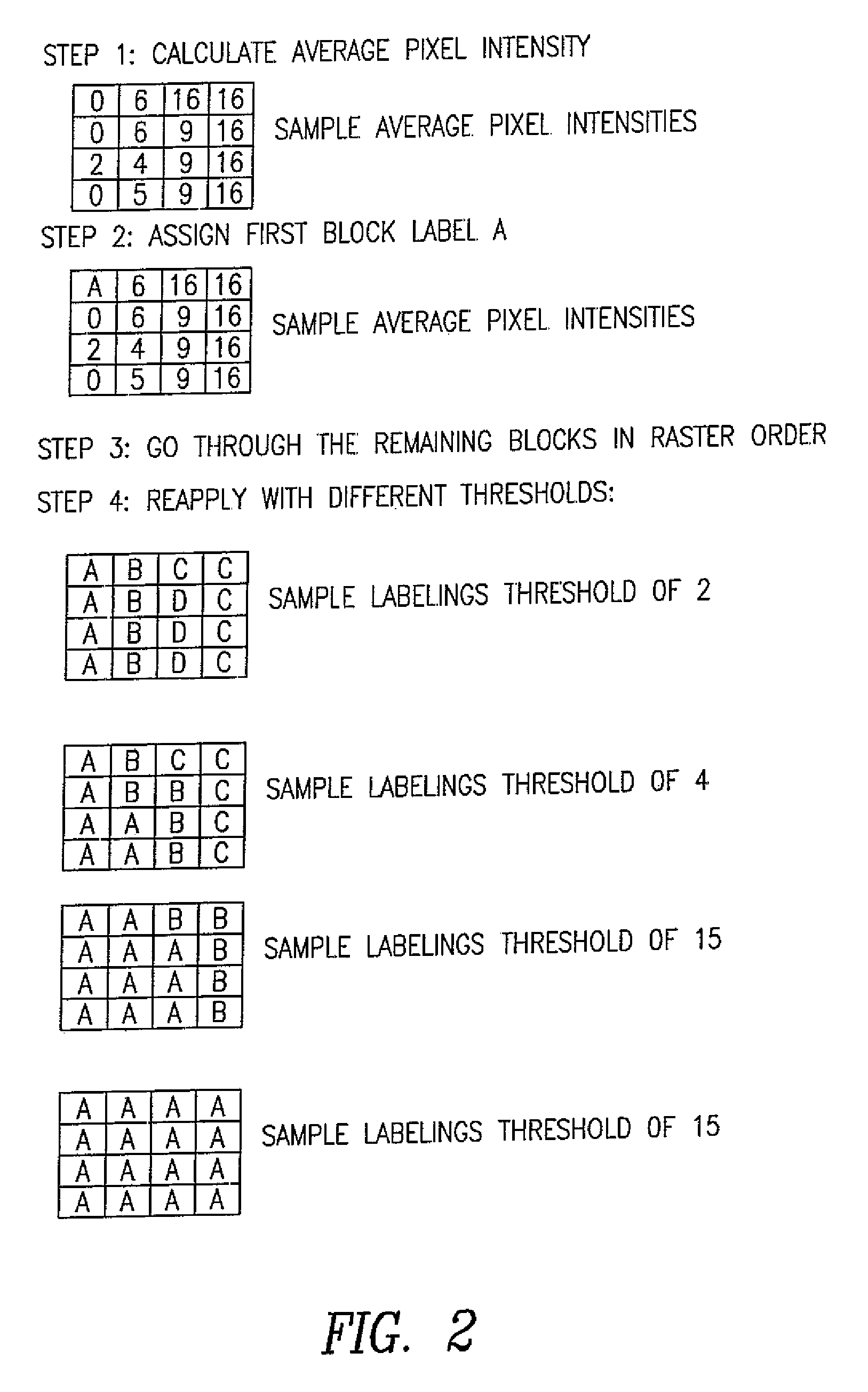

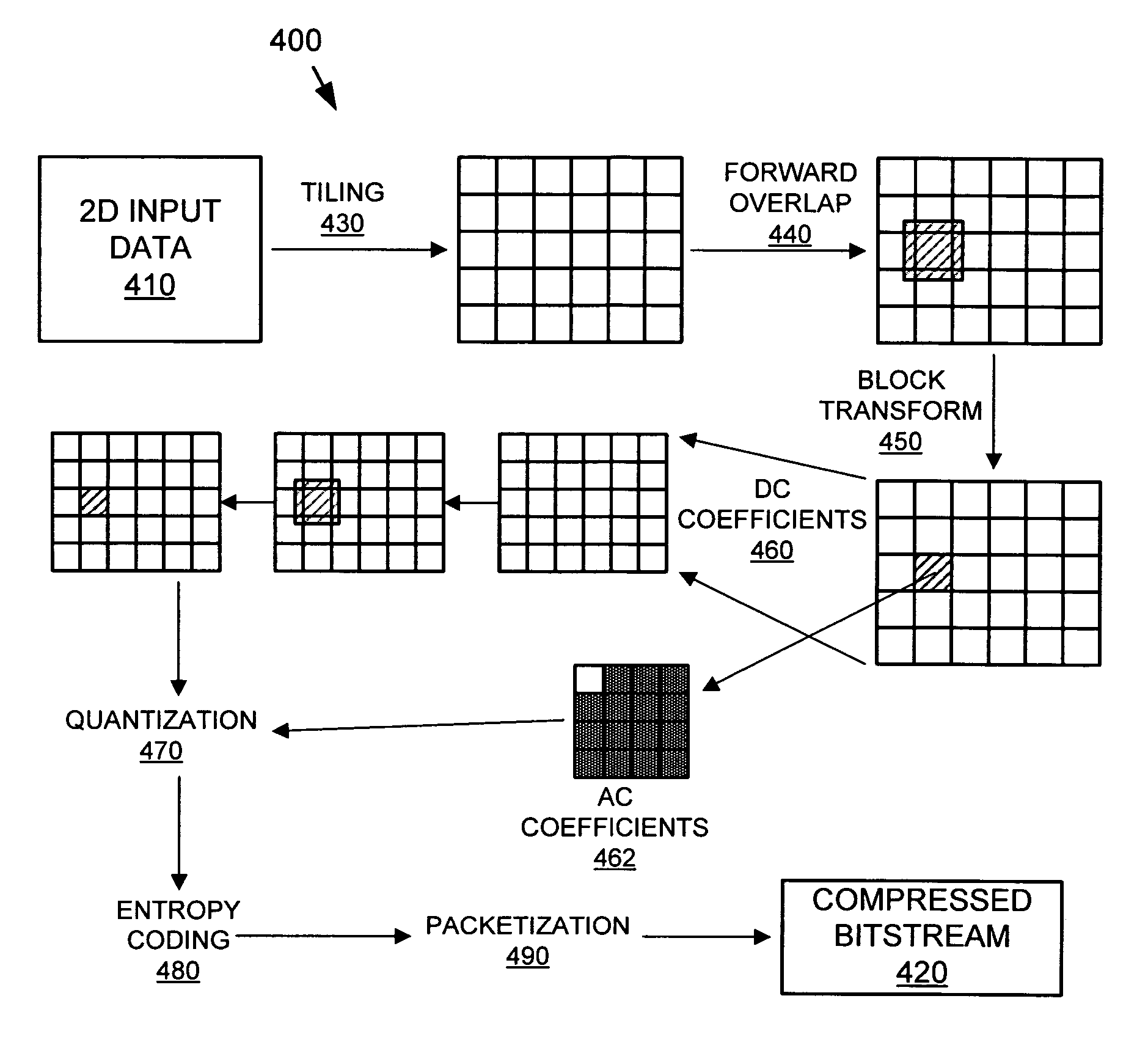

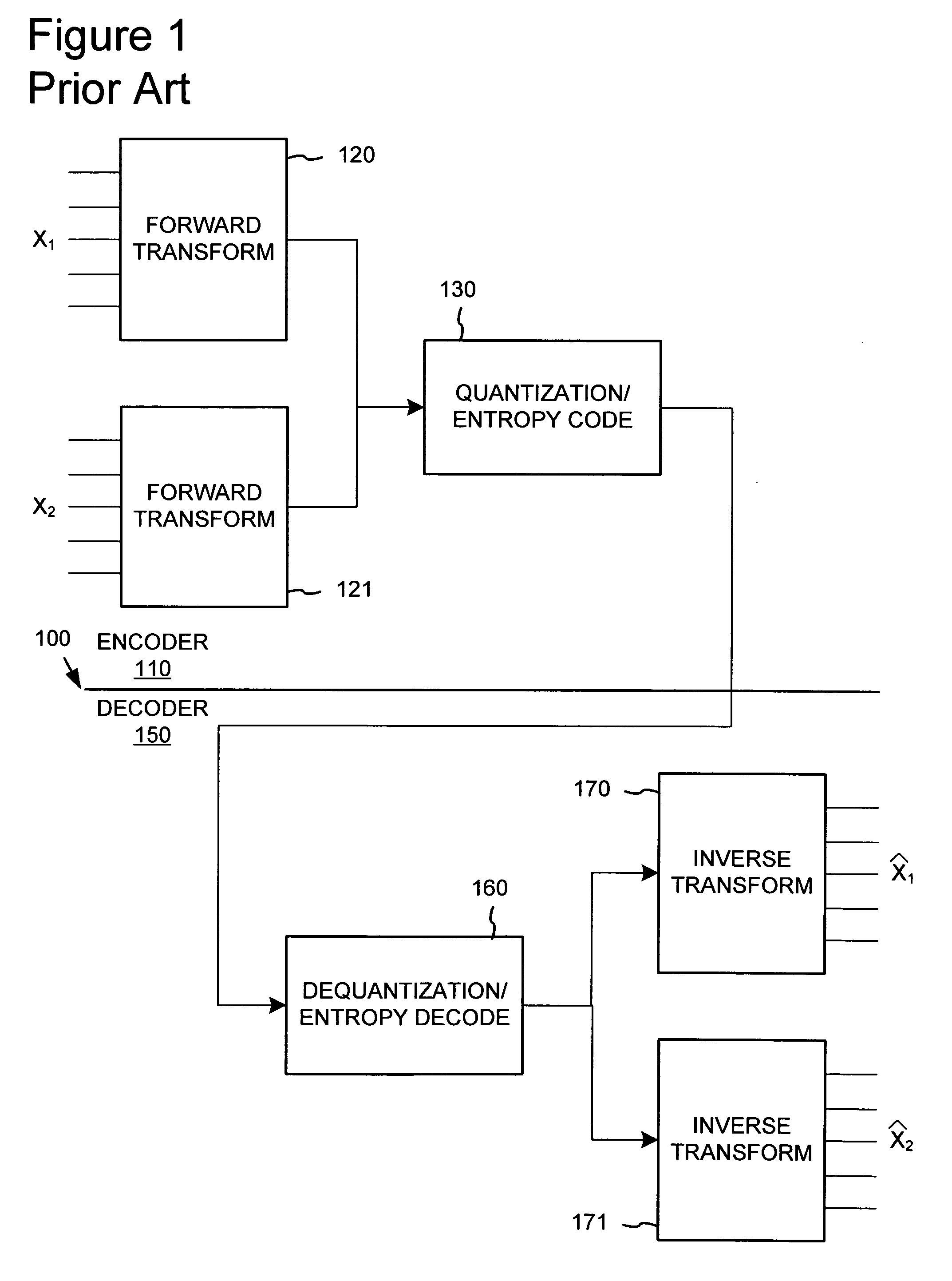

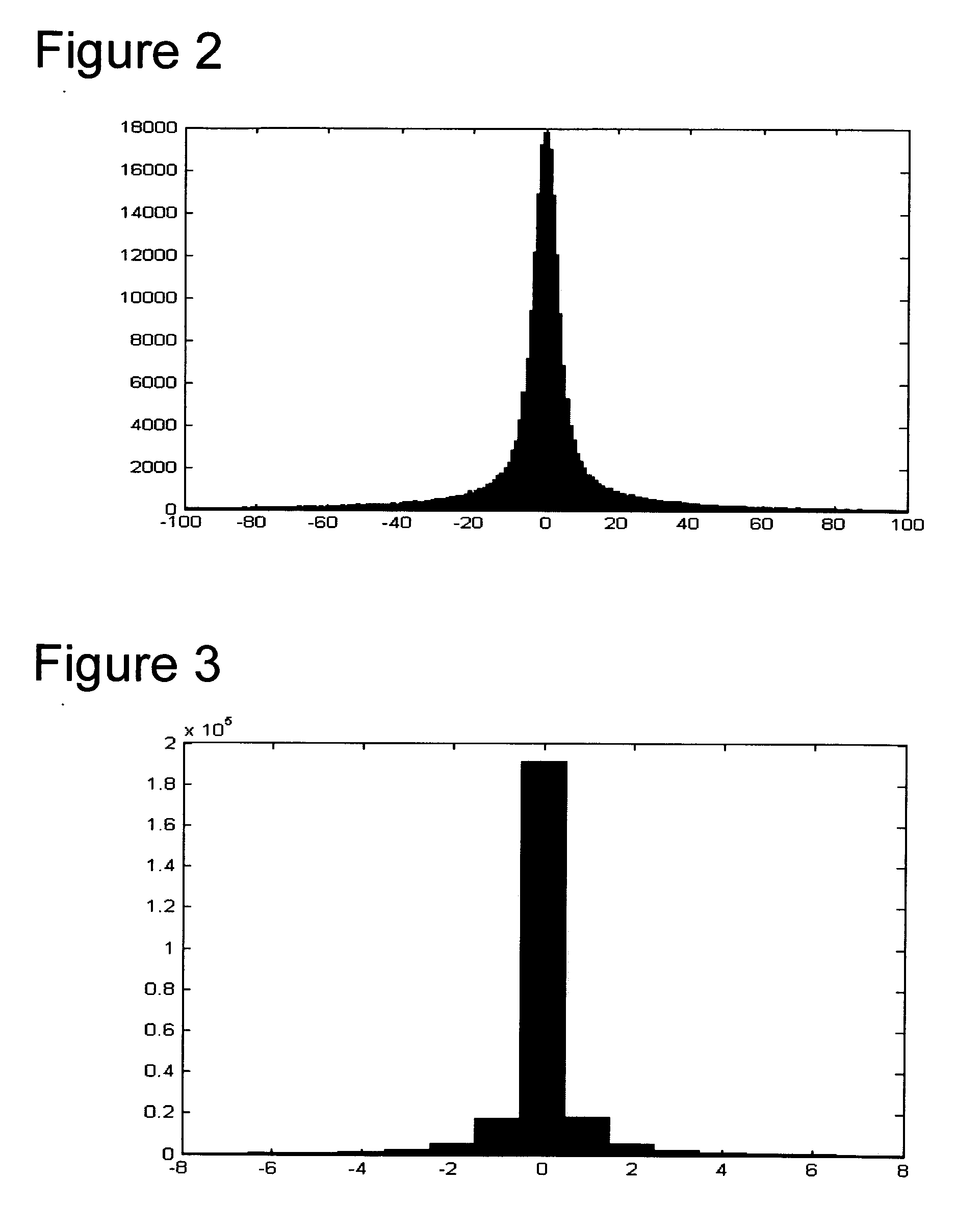

Efficient coding and decoding of transform blocks

ActiveUS20070036223A1Efficient compressionEfficient codingColor television with pulse code modulationColor television with bandwidth reductionNonzero coefficientsBlock transform

A block transform-based digital media codec more efficiently encodes transform coefficients by jointly-coding non-zero coefficients along with succeeding runs of zero-value coefficients. When a non-zero coefficient is the last in its block, a last indicator is substituted for the run value in the symbol for that coefficient. Initial non-zero coefficients are indicated in a special symbol which jointly-codes the non-zero coefficient along with initial and subsequent runs of zeroes. The codec allows for multiple coding contexts by recognizing breaks in runs of non-zero coefficients and coding non-zero coefficients on either side of such a break separately. The codec also reduces code table size by indicating in each symbol whether a non-zero coefficient has absolute value greater than 1 and whether runs of zeros have positive value, and separately encodes the level of the coefficients and the length of the runs outside of the symbols.

Owner:MICROSOFT TECH LICENSING LLC

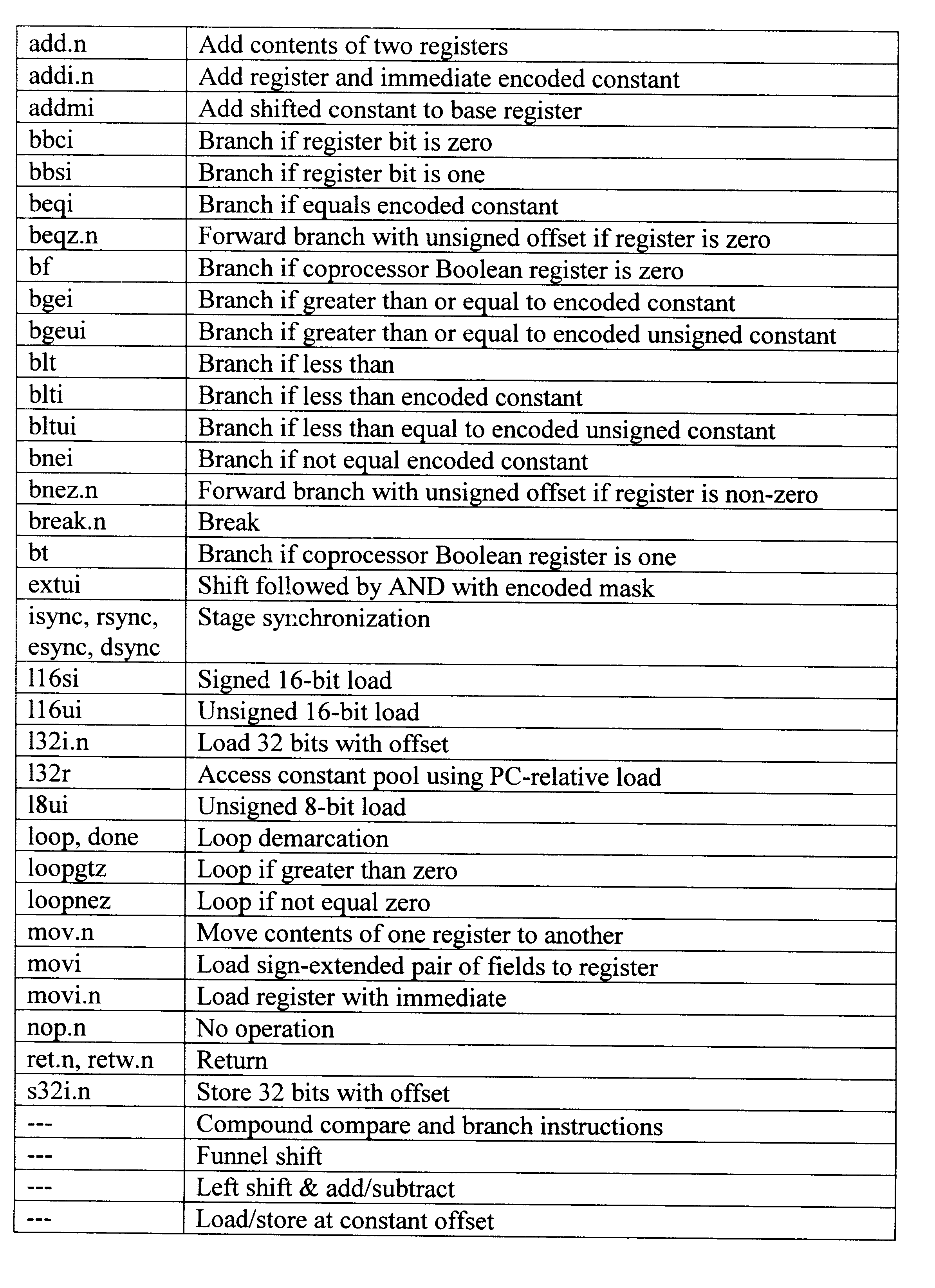

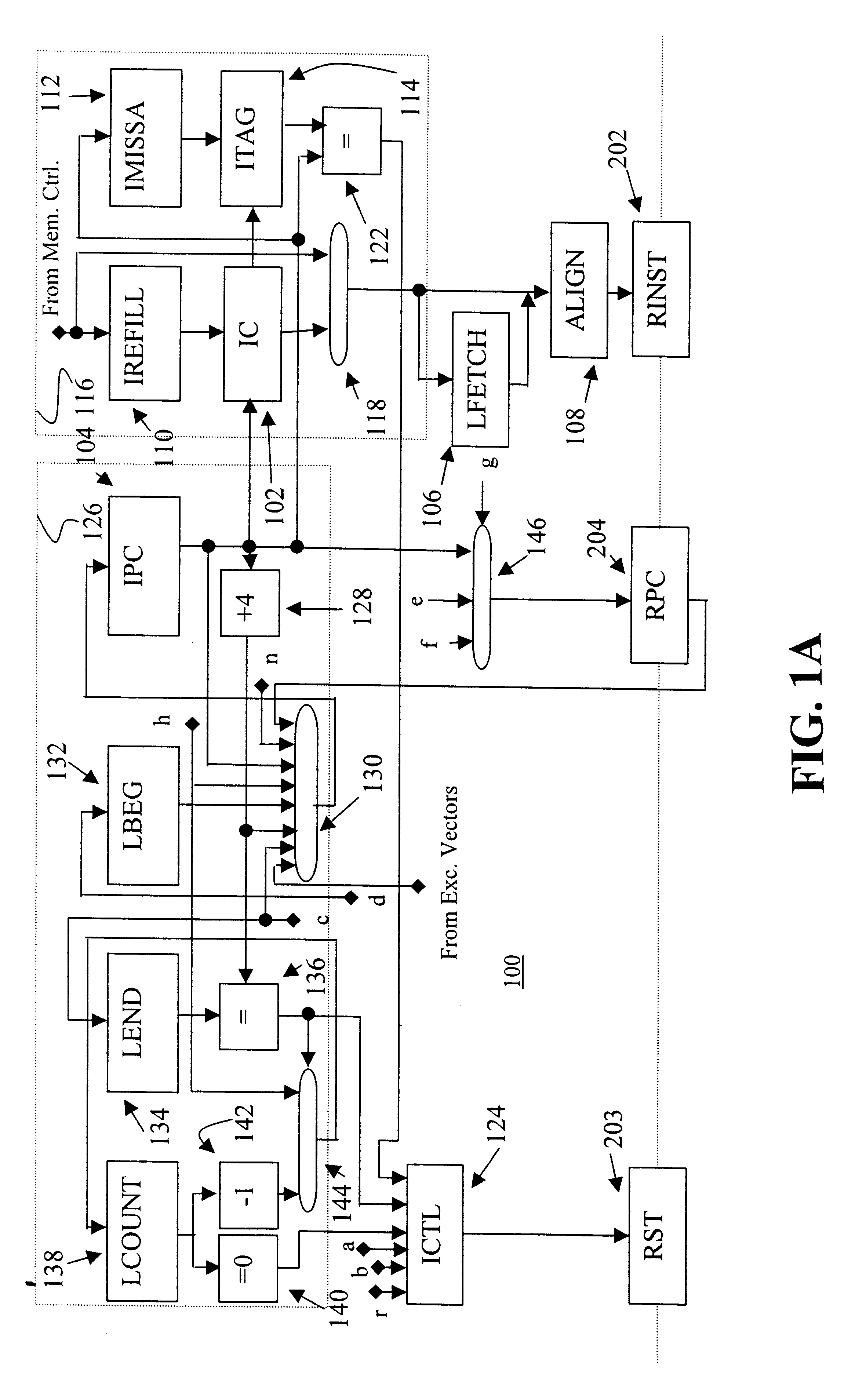

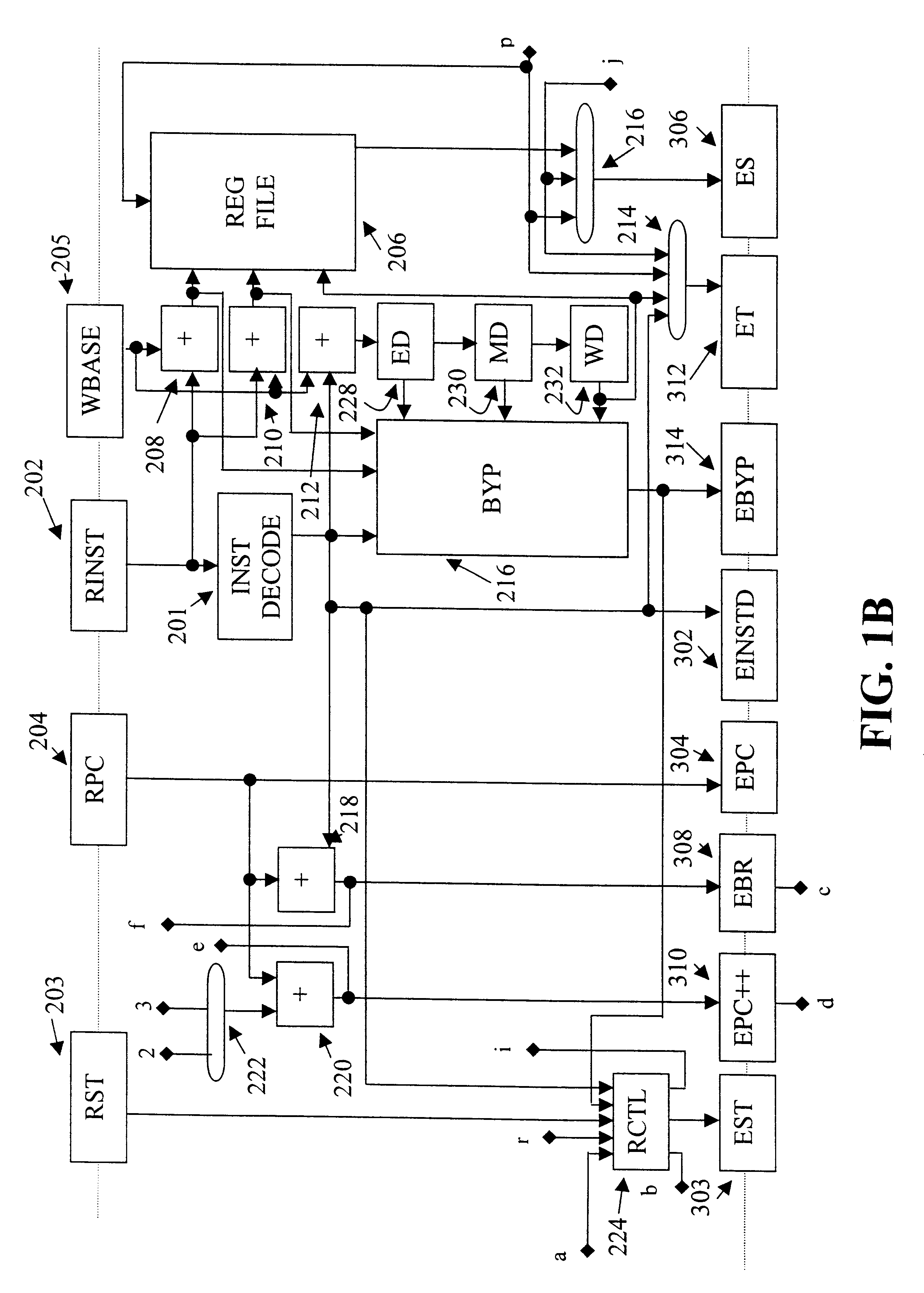

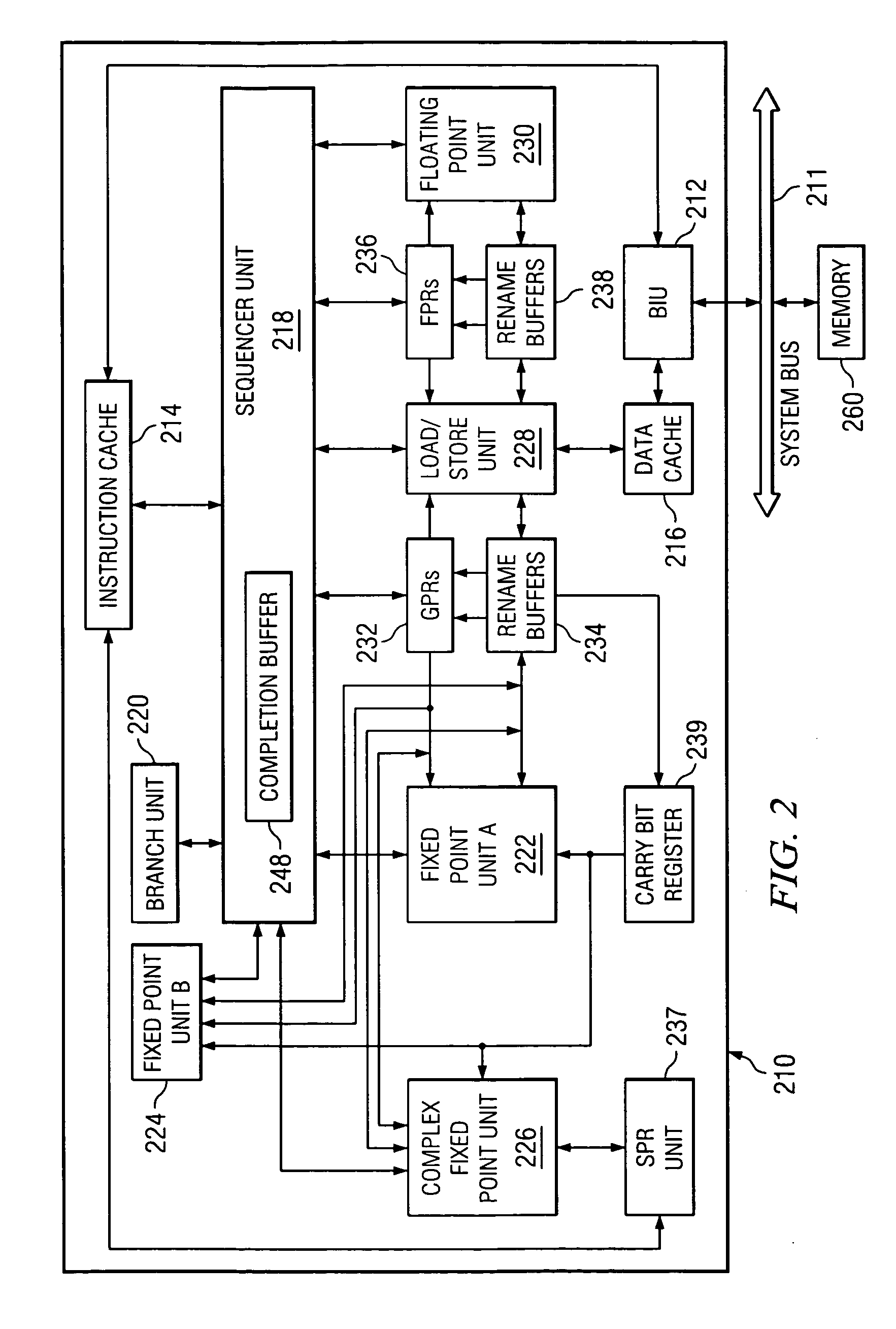

High data density RISC processor

InactiveUS6282633B1High densityIncrease in CPIInstruction analysisDigital computer detailsProgram instructionProcessor register

A RISC processor implements an instruction set which, in addition to optimizing a relationship between the number of instructions required for execution of a program, clock period and average number of clocks per instruction, also is designed to optimize the equation S=IS * BI, where S is the size of program instructions in bits, IS is the static number of instructions required to represent the program (not the number required by an execution) and BI is the average number of bits per instruction. Compared to conventional RISC architectures, this processor lowers both BI and IS with minimal increases in clock period and average number of clocks per instruction. The processor provides good code density in a fixed-length high-performance encoding based on RISC principles, including a general register with load / store architecture. Further, the processor implements a simple variable-length encoding that maintains high performance.

Owner:TENSILICA

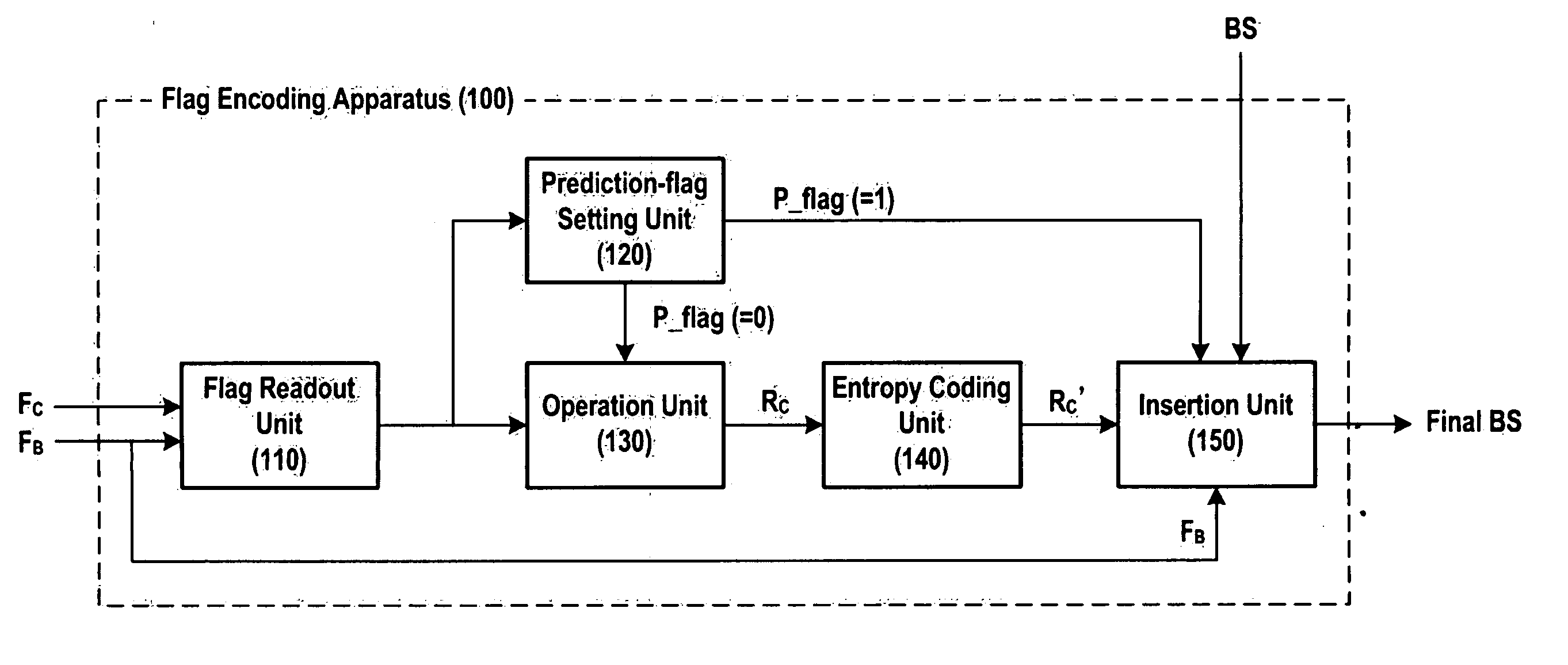

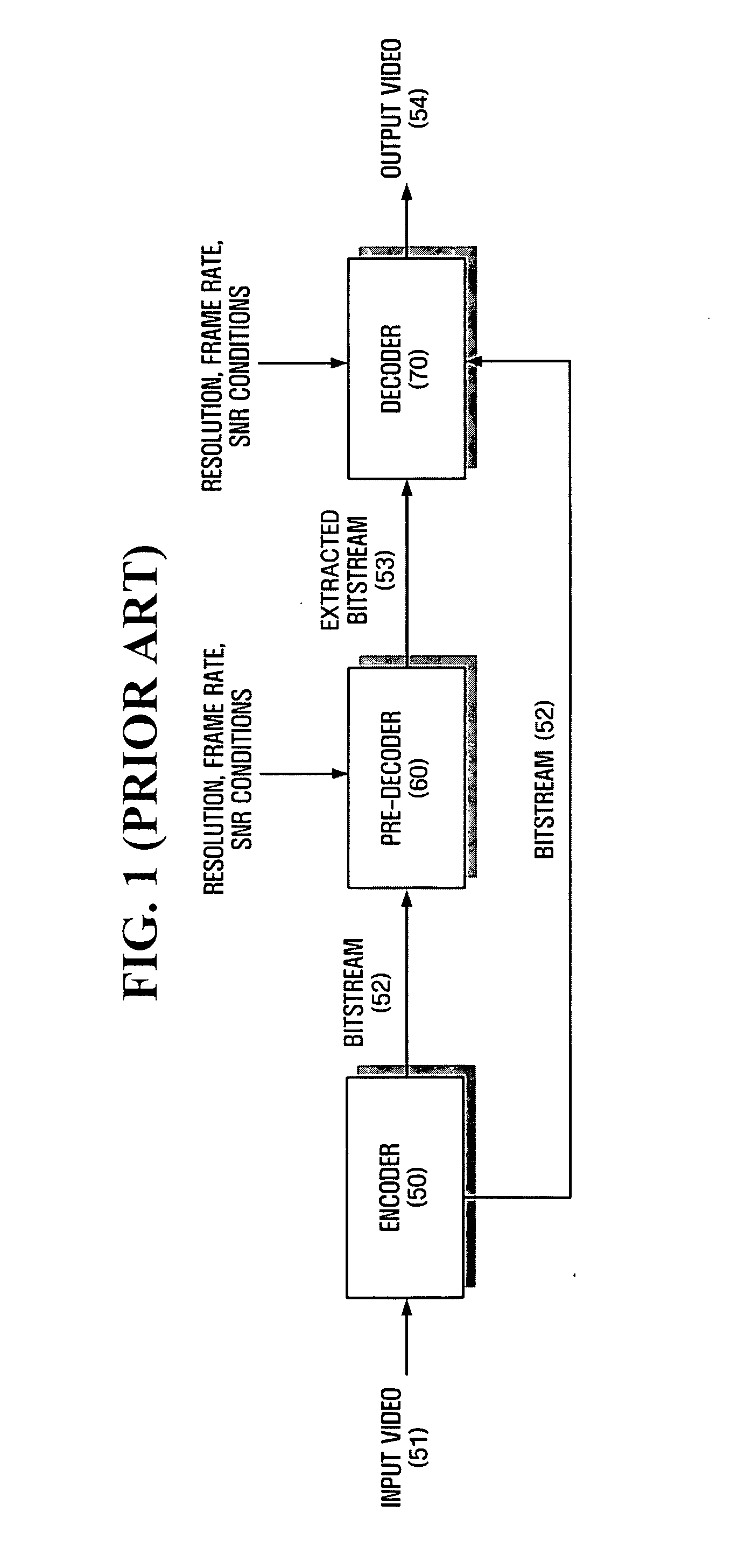

Method of encoding flags in layer using inter-layer correlation, method and apparatus for decoding coded flags

InactiveUS20070086516A1Efficient codingPulse modulation television signal transmissionPicture reproducers using cathode ray tubesInter layerComputer science

A method and apparatus for efficiently encoding diverse flags being used in a multilayer-based scalable video codec, based on an inter-layer correlation. The encoding method includes judging whether flags of a current layer included in a specified unit area are all equal to flags of a base layer, setting a specified prediction flag according to the result of judgment, and if it is judged that the flags of the current layer are equal to the flags of the base layer, skipping the flags of the current layer and inserting the flags of the base layer and the prediction flag into a bitstream.

Owner:SAMSUNG ELECTRONICS CO LTD

Visual and interactive wrapper generation, automated information extraction from Web pages, and translation into XML

A method and a system for information extraction from Web pages formatted with markup languages such as HTML [8]. A method and system for interactively and visually describing information patterns of interest based on visualized sample Web pages [5,6,16-29]. A method and data structure for representing and storing these patterns [1]. A method and system for extracting information corresponding to a set of previously defined patterns from Web pages [2], and a method for transforming the extracted data into XML is described. Each pattern is defined via the (interactive) specification of one or more filters. Two or more filters for the same pattern contribute disjunctively to the pattern definition [3], that is, an actual pattern describes the set of all targets specified by any of its filters. A method and for extracting relevant elements from Web pages by interpreting and executing a previously defined wrapper program of the above form on an input Web page [9-14] and producing as output the extracted elements represented in a suitable data structure. A method and system for automatically translating said output into XML format by exploiting the hierarchical structure of the patterns and by using pattern names as XML tags is described.

Owner:LIXTO SOFTWARE

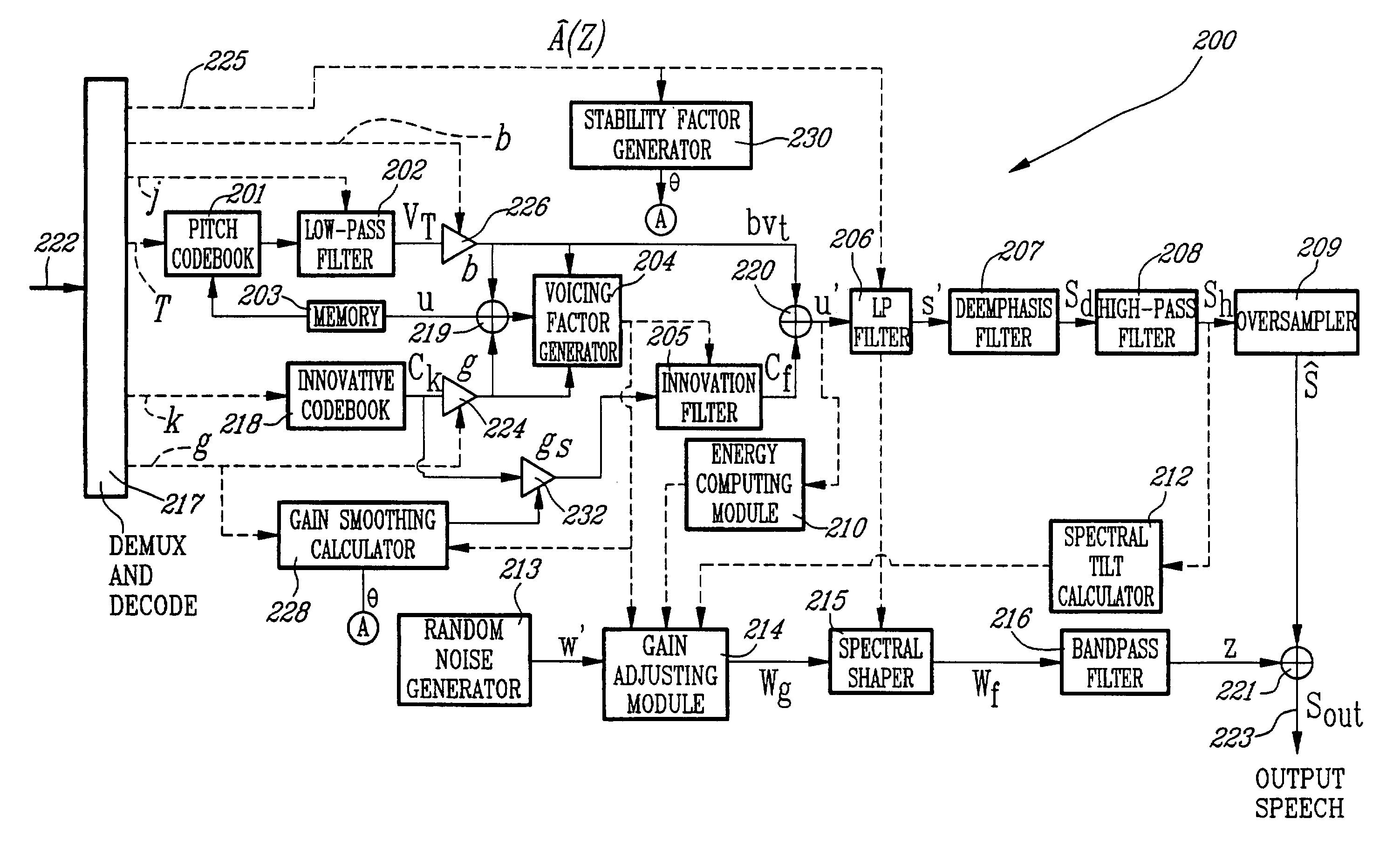

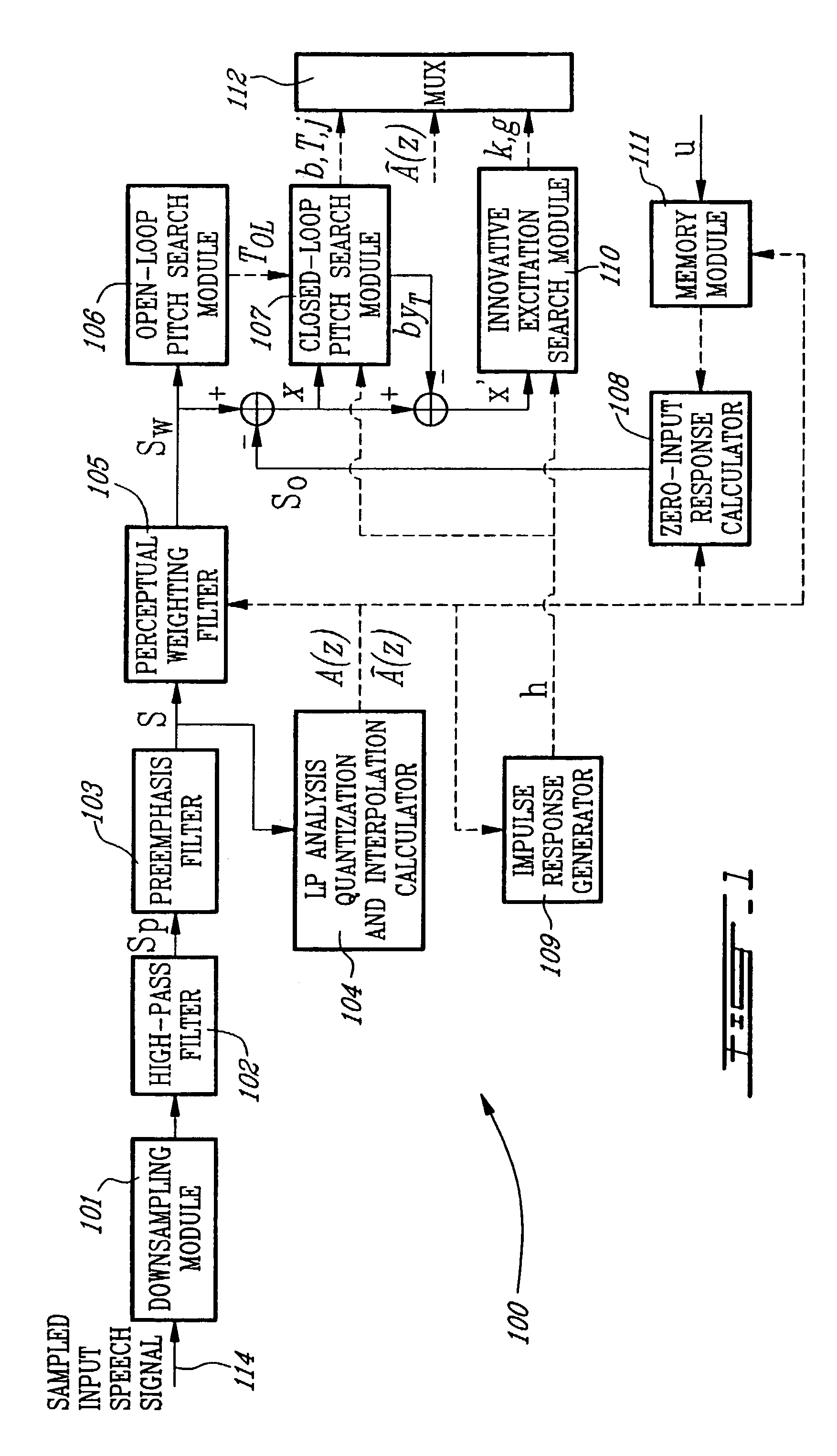

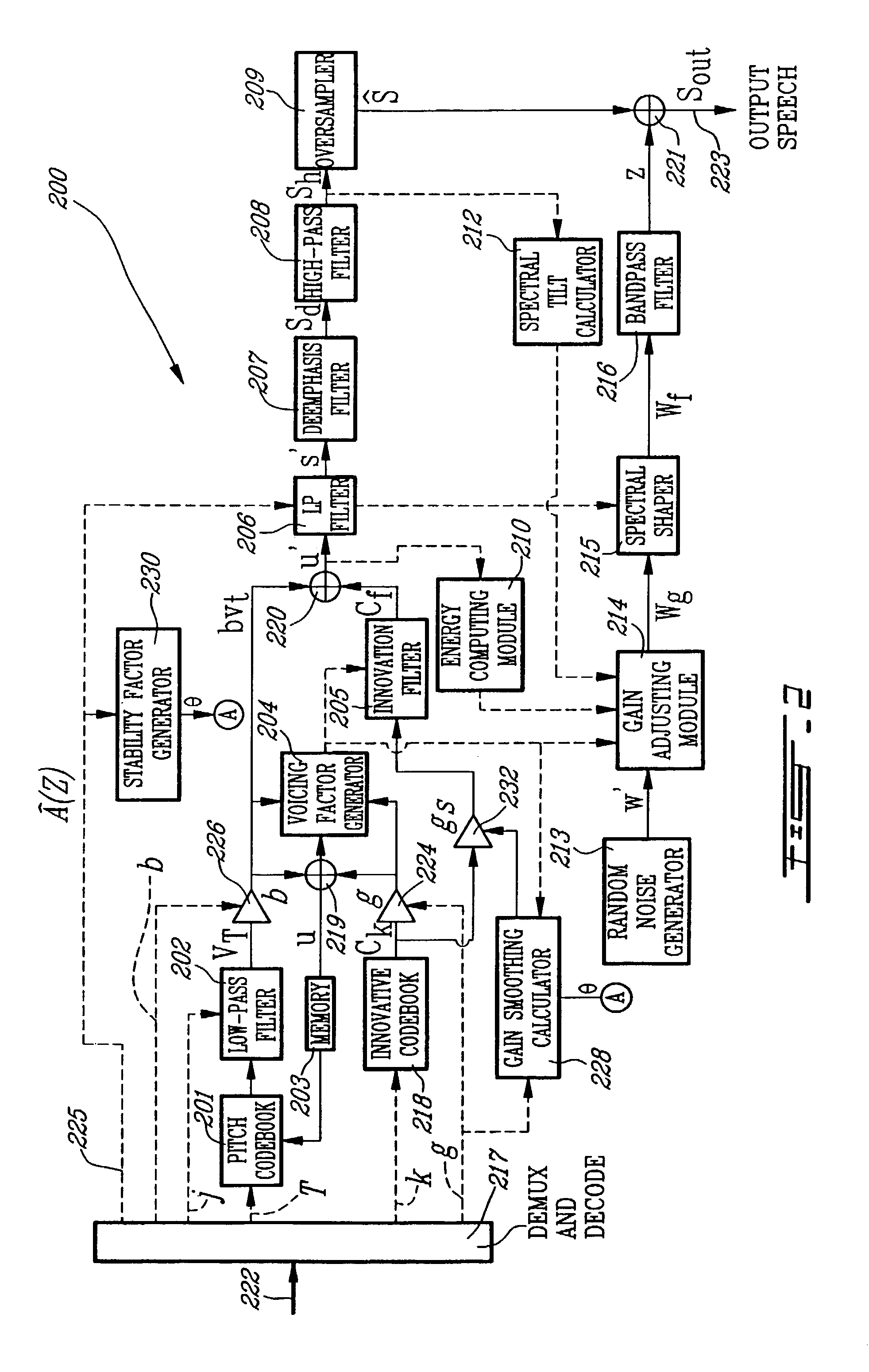

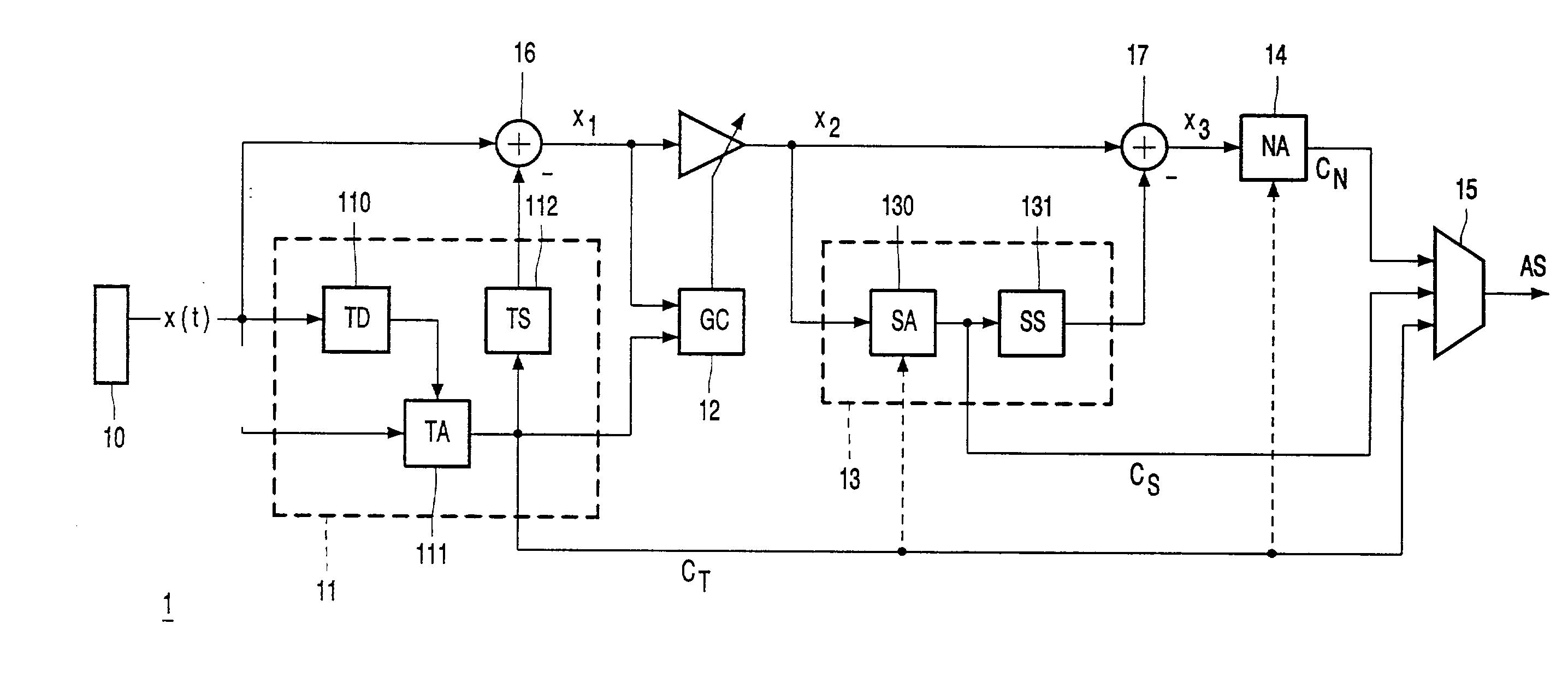

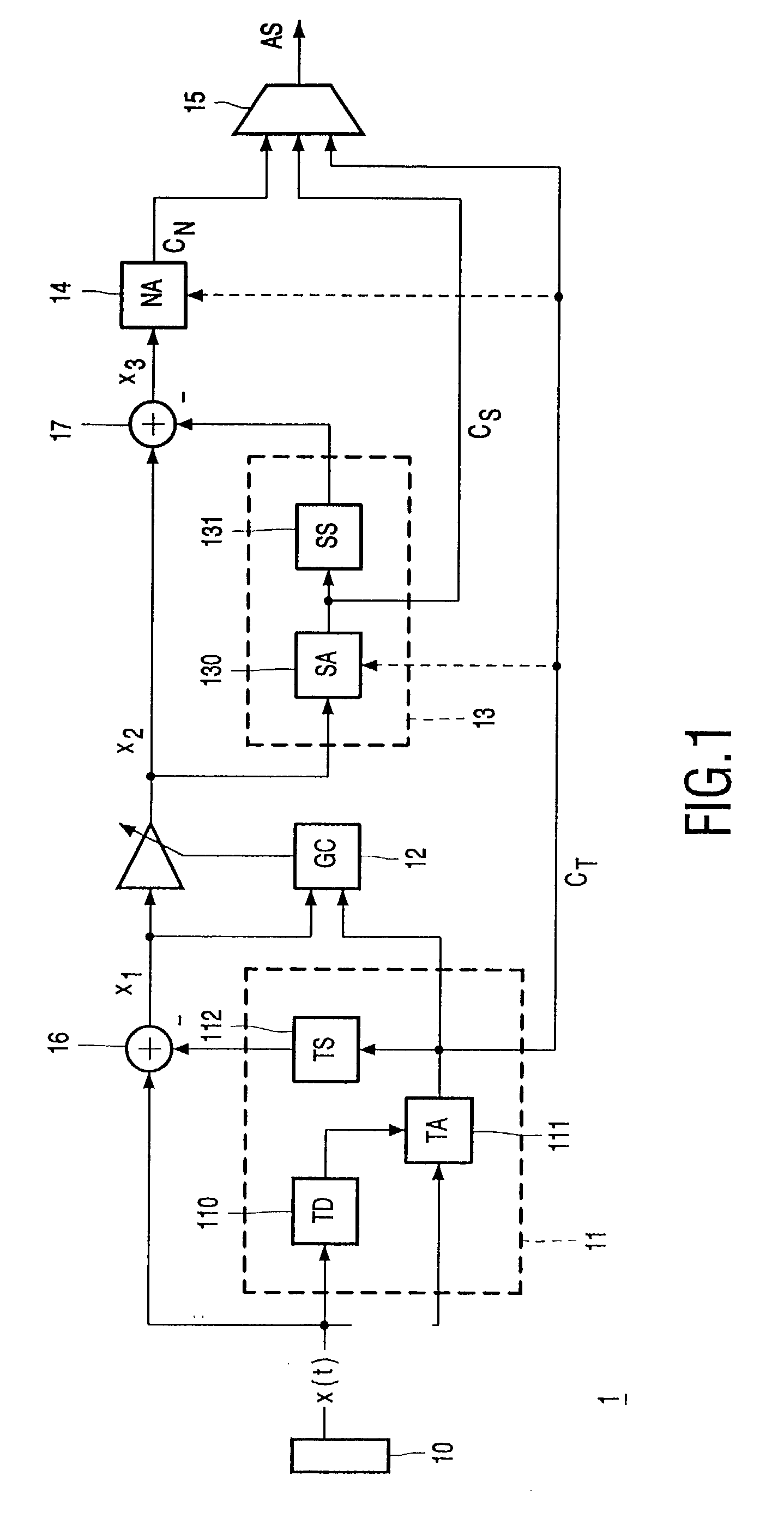

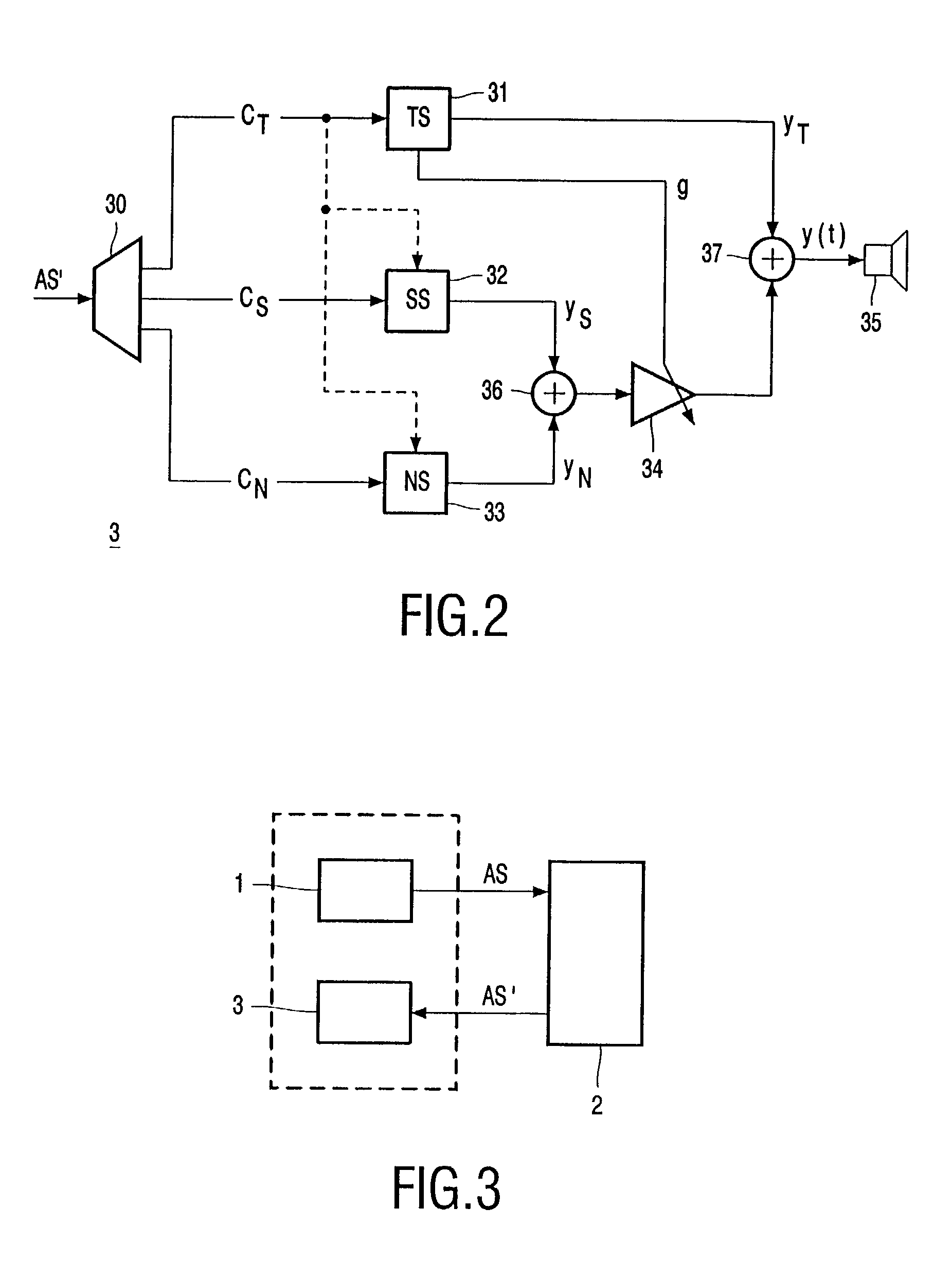

Gain-smoothing in wideband speech and audio signal decoder

InactiveUS7191123B1Quality improvementEfficient codingInformation formatSpeech analysisAudio power amplifierLinearity

The gain smoothing method and device modify the amplitude of an innovative codevector in relation to background noise present in a previously sampled wideband signal. The gain smoothing device comprises a gain smoothing calculator for calculating a smoothing gain in response to a factor representative of voicing in the sampled wideband signal, a factor representative of the stability of a set of linear prediction filter coefficients, and an innovative codebook gain. The gain smoothing device also comprises an amplifier for amplifying the innovative codevector with the smoothing gain to thereby produce a gain-smoothed innovative codevector. The function of the gain-smoothing device improves the perceived synthesized signal when background noise is present in the sampled wideband signal.

Owner:SAINT LAWRENCE COMM

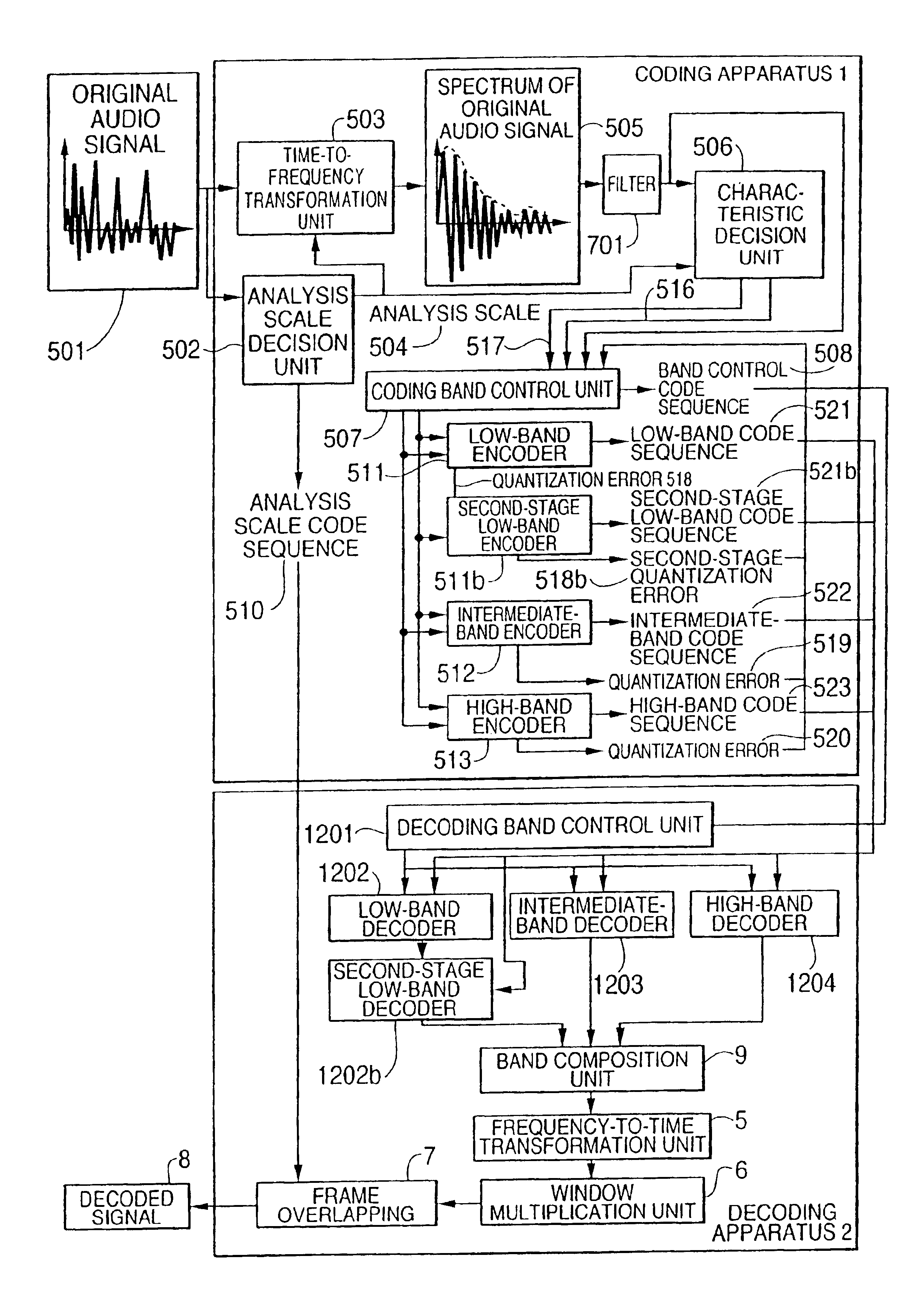

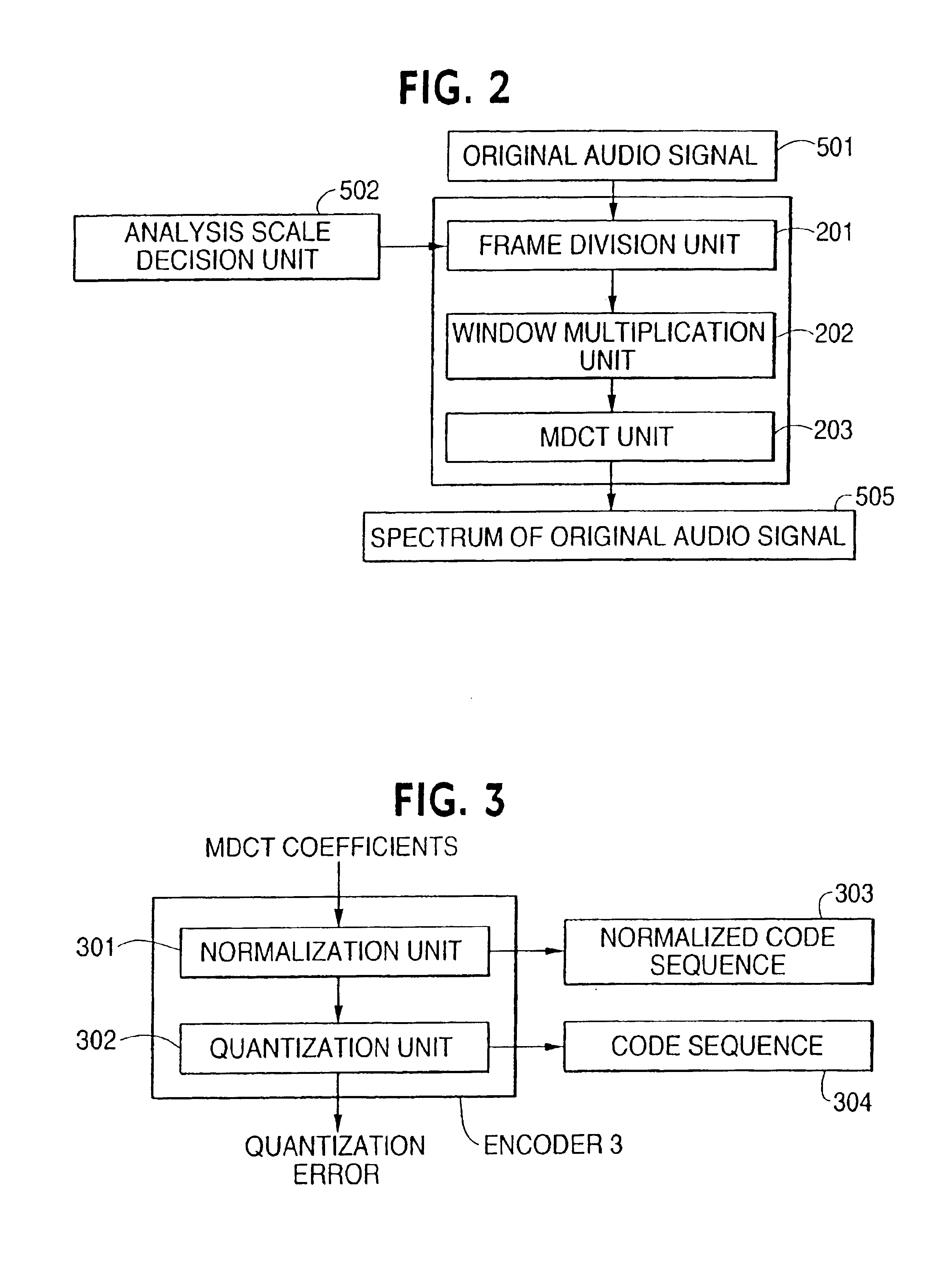

Audio signal coding apparatus, audio signal decoding apparatus, and audio signal coding and decoding apparatus

InactiveUS6871106B1Scalable and adaptableImprove coding efficiencySpeech analysisCode conversionAudio signal flowAudio frequency

An audio signal coding apparatus includes a first-stage encoder for quantizing the time-to-frequency transformed audio signal and second-and-subsequent-stages of encoders each for quantizing a quantization error output from the previous-stage encoder A characteristic decision unit is provided which decides the frequency band of an audio signal to be quantized by each encoder of multiple-stage encoders, and a coding band control unit receives the frequency band decided by the characteristic decision unit and the time-to-frequency transformed audio signal, decides the order of connecting the respective encoders, and transforms the quantization bands of the encoders and the connecting order to code sequences. Therefore, it is possible to provide an audio signal coding apparatus performing adaptive scalable coding, which exhibits sufficient performance when coding various audio signals.

Owner:PANASONIC CORP

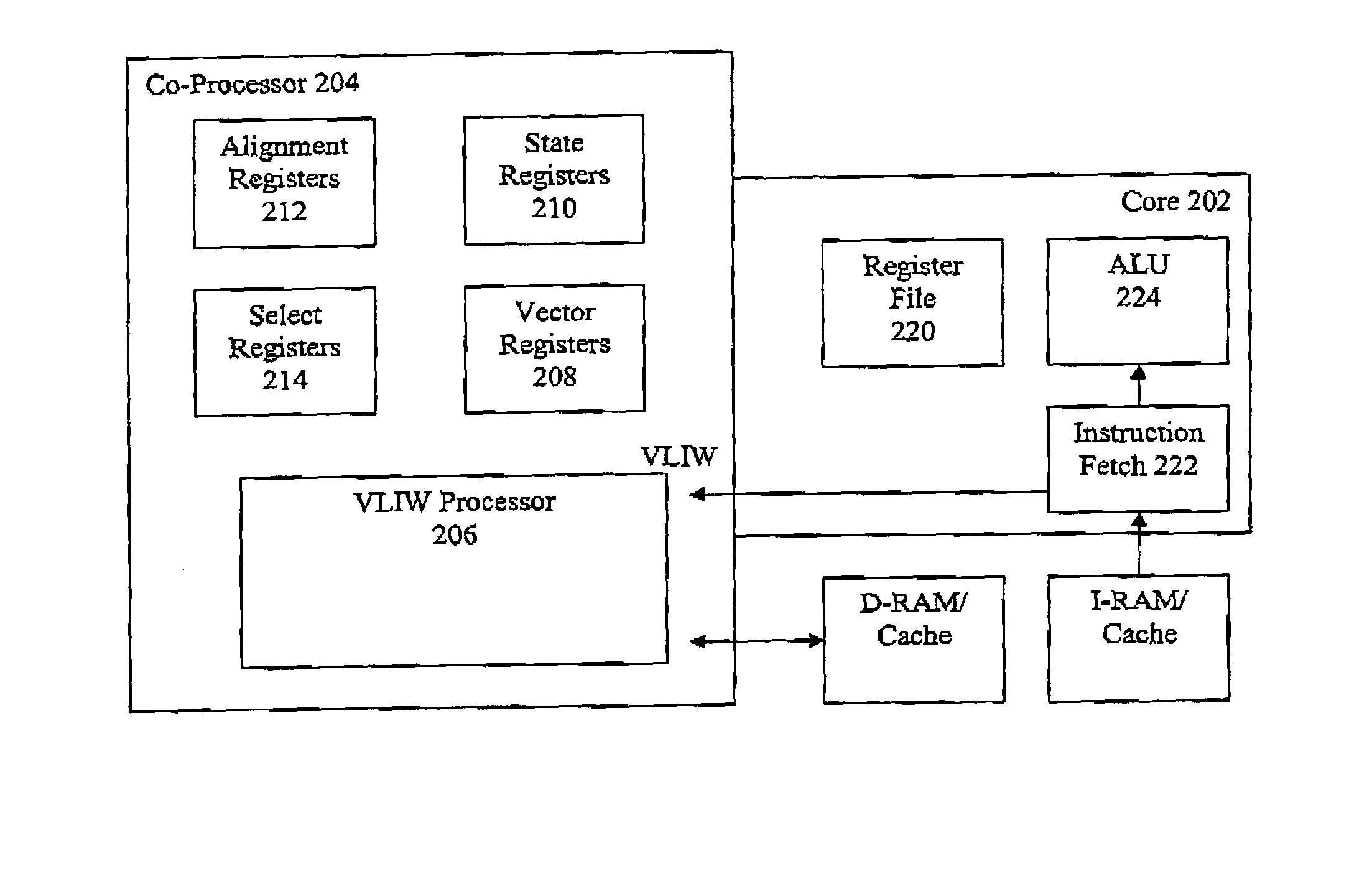

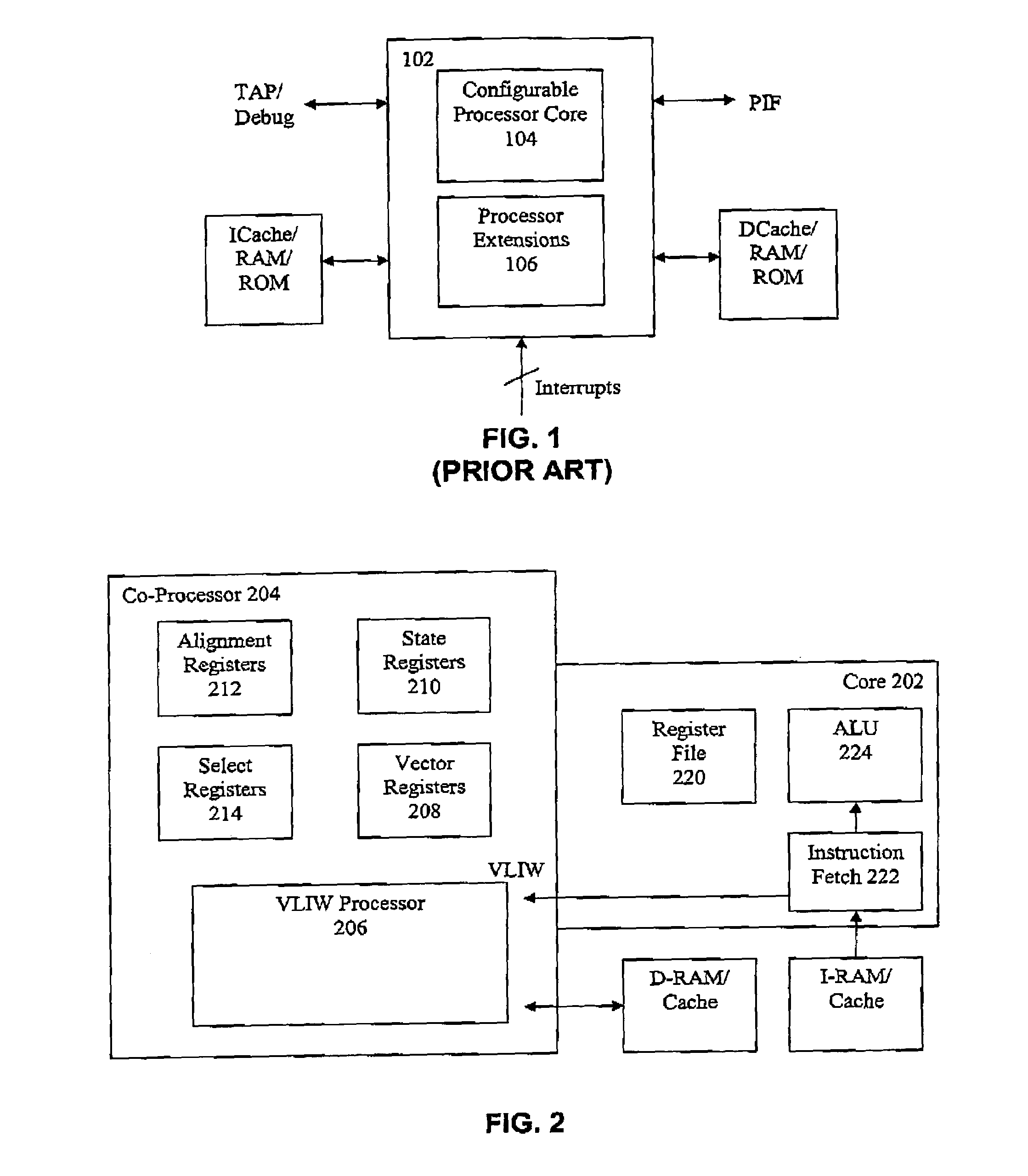

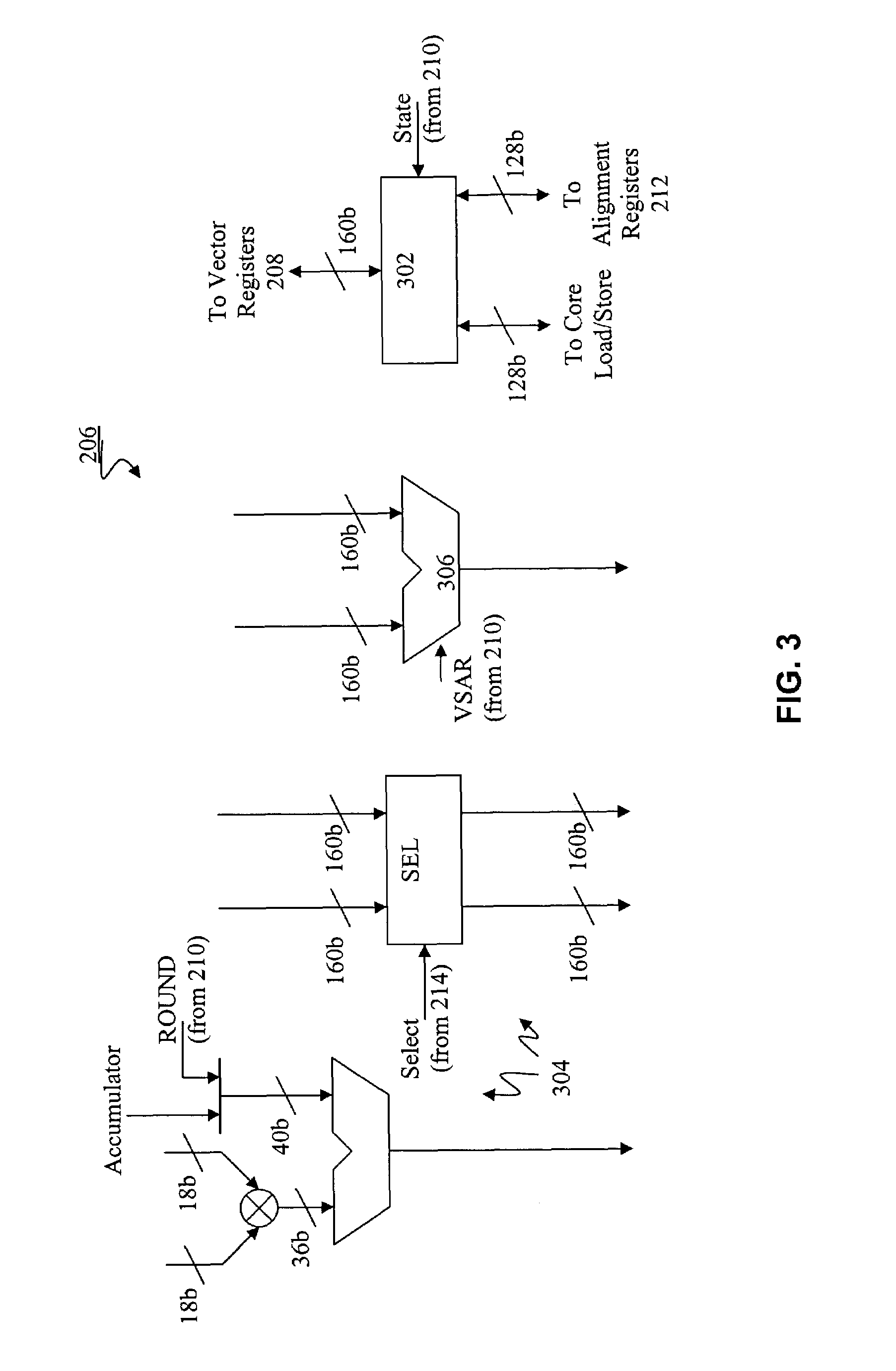

Vector co-processor for configurable and extensible processor architecture

ActiveUS7376812B1High coding densityImprove performanceInstruction analysisGeneral purpose stored program computerDigital signal processingCritical section

A processor can achieve high code density while allowing higher performance than existing architectures, particularly for Digital Signal Processing (DSP) applications. In accordance with one aspect, the processor supports three possible instruction sizes while maintaining the simplicity of programming and allowing efficient physical implementation. Most of the application code can be encoded using two sets of narrow size instructions to achieve high code density. Adding a third (and larger, i.e. VLIW) instruction size allows the architecture to encode multiple operations per instruction for the performance critical section of the code. Further, each operation of the VLIW format instruction can optionally be a SIMD operation that operates upon vector data. A scheme for the optimal utilization (highest achievable performance for the given amount of hardware) of multiply-accumulate (MAC) hardware is also provided.

Owner:TENSILICA

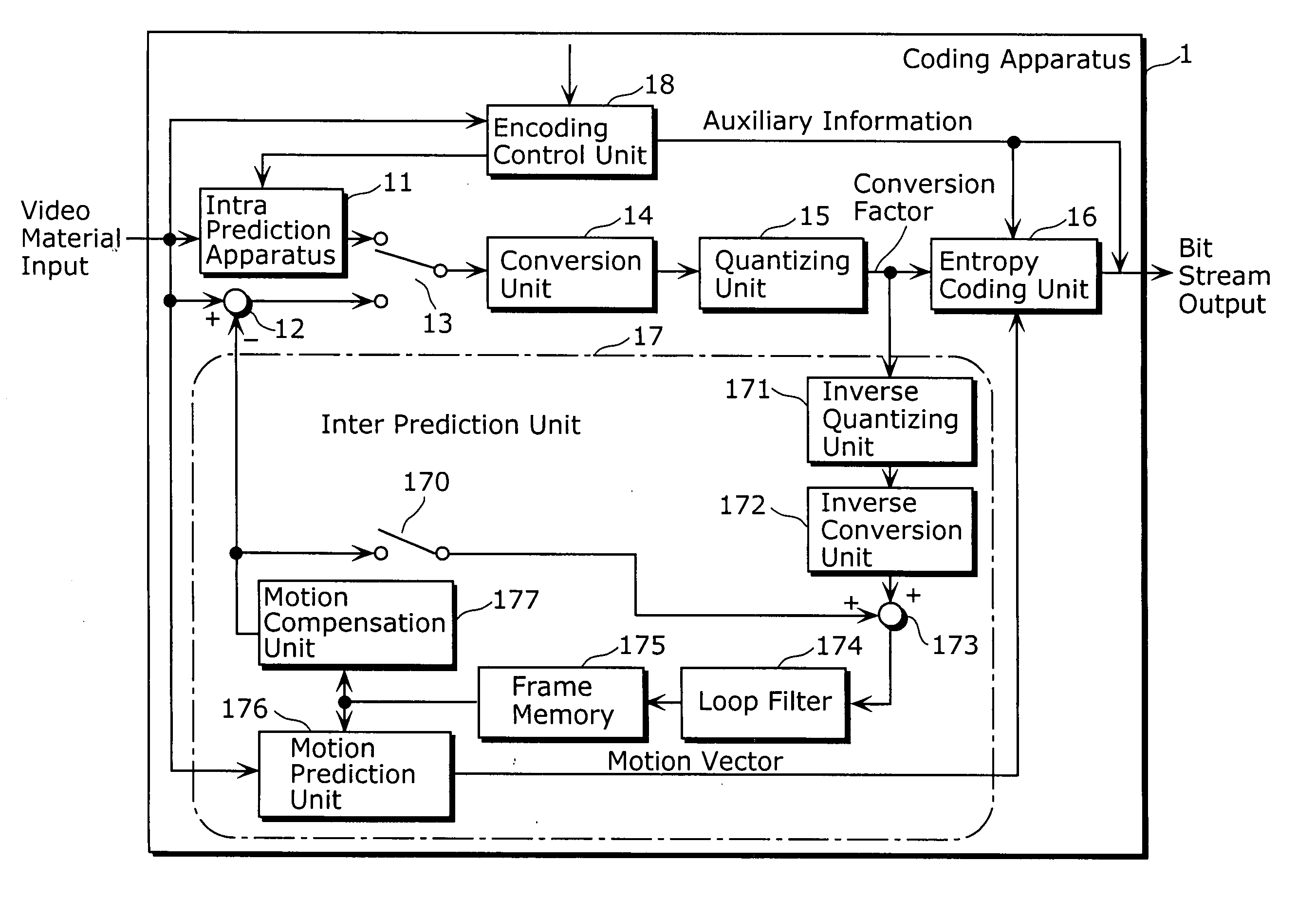

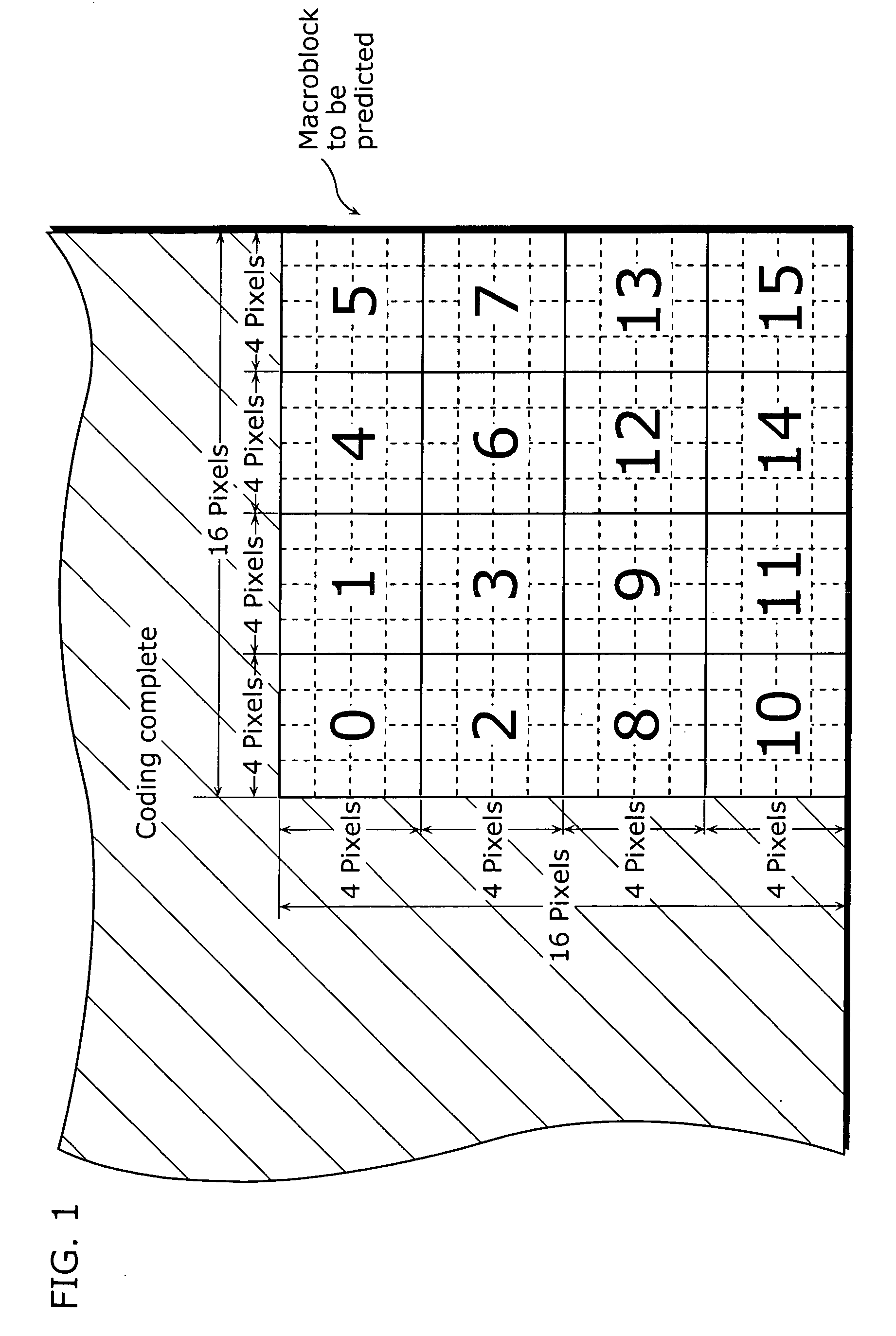

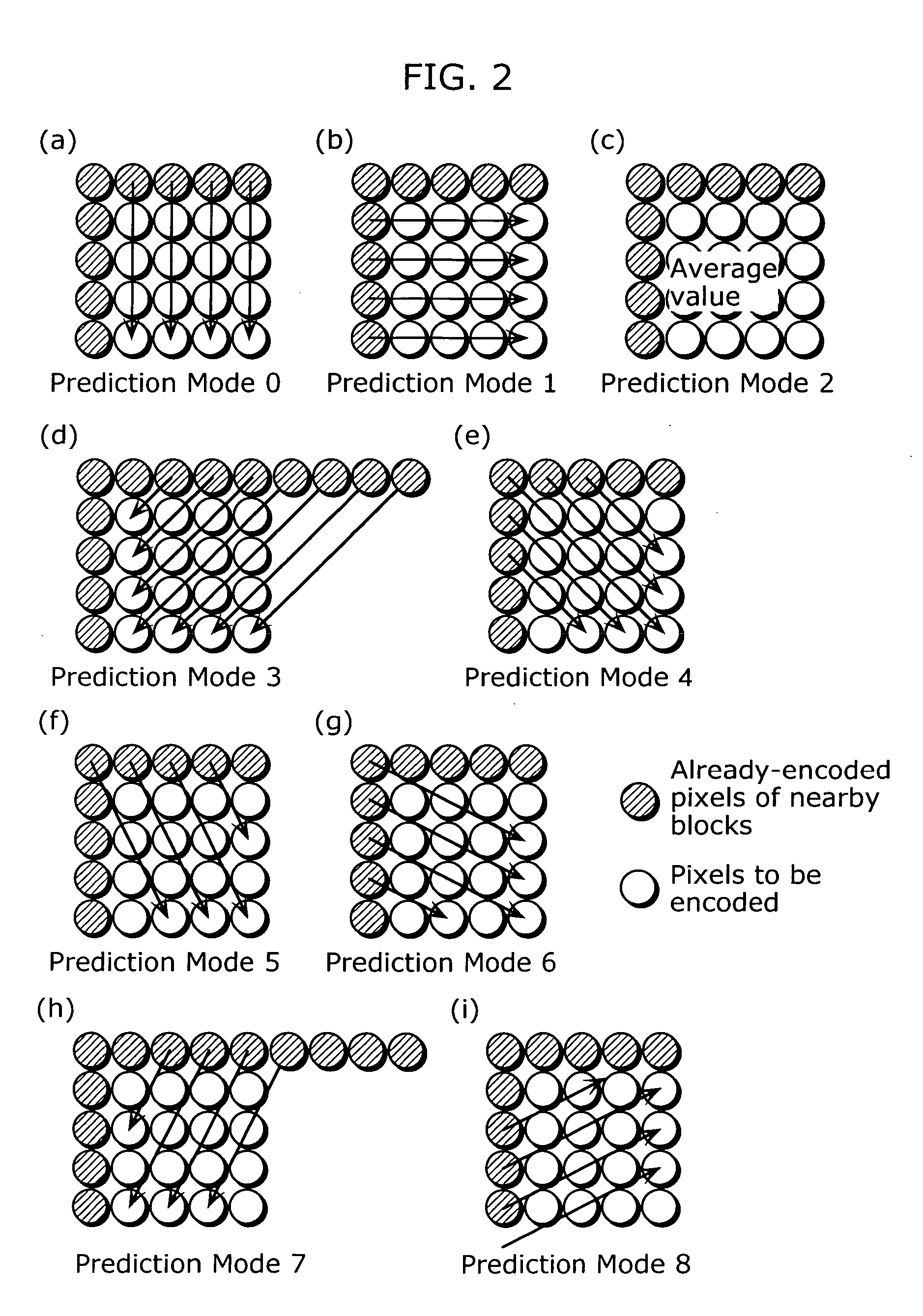

Intra prediction apparatus

InactiveUS20060120456A1Improve efficiencyImprove picture qualityColor television with pulse code modulationColor television with bandwidth reductionParallel computingExecution unit

An intra prediction apparatus includes: a candidate narrowing-down unit which narrows down, from a plurality of intra prediction directions, an intra prediction direction candidate which is applied to a block of multiple pixels that constitutes a video in accordance with a characteristic of the video; and an intra prediction execution unit which executes intra prediction in the intra prediction direction narrowed down by said candidate narrowing-down unit. Through this, computational load can be lightened while contributing to improvement in picture quality and encoding efficiency.

Owner:GK BRIDGE 1

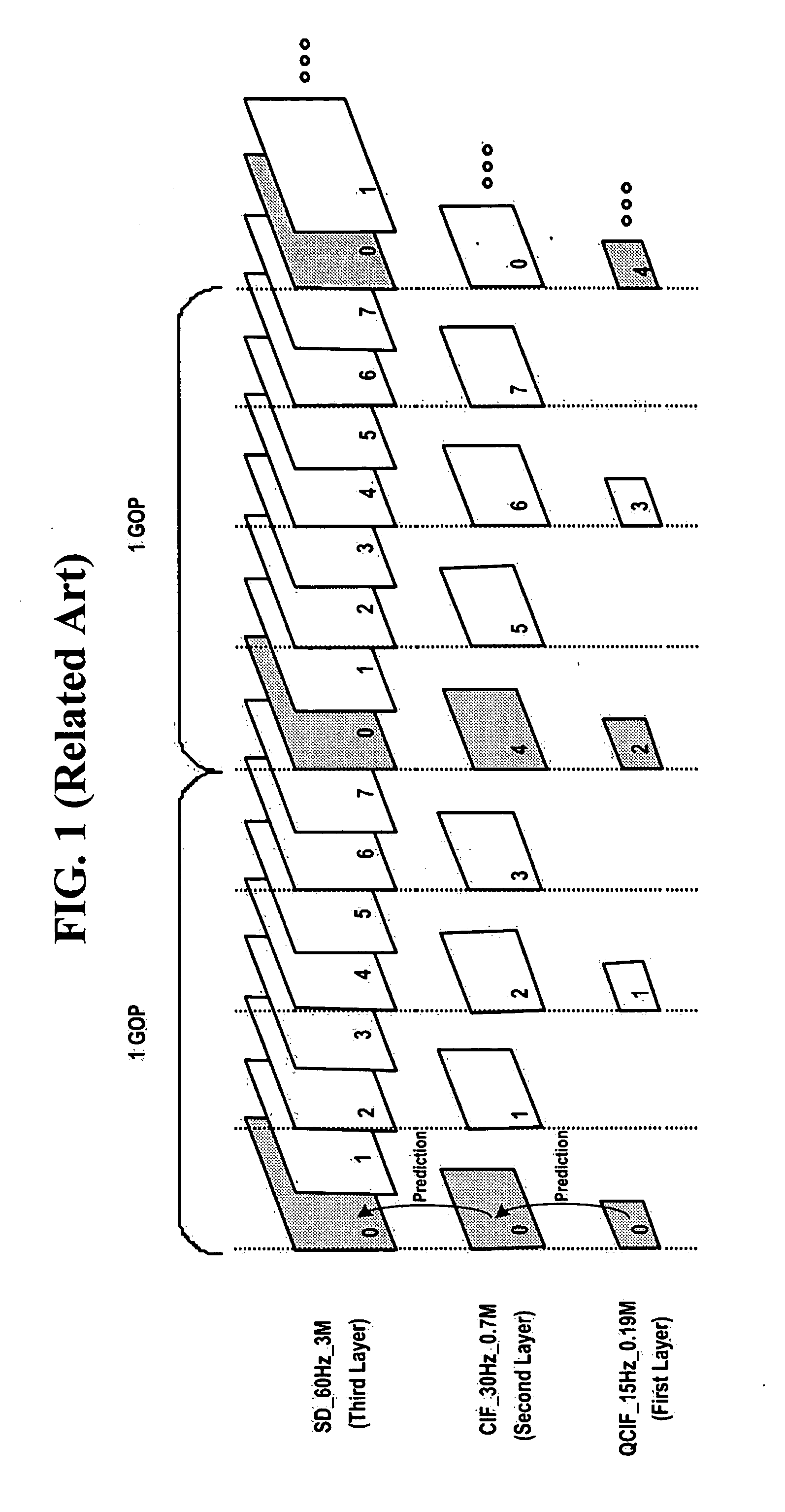

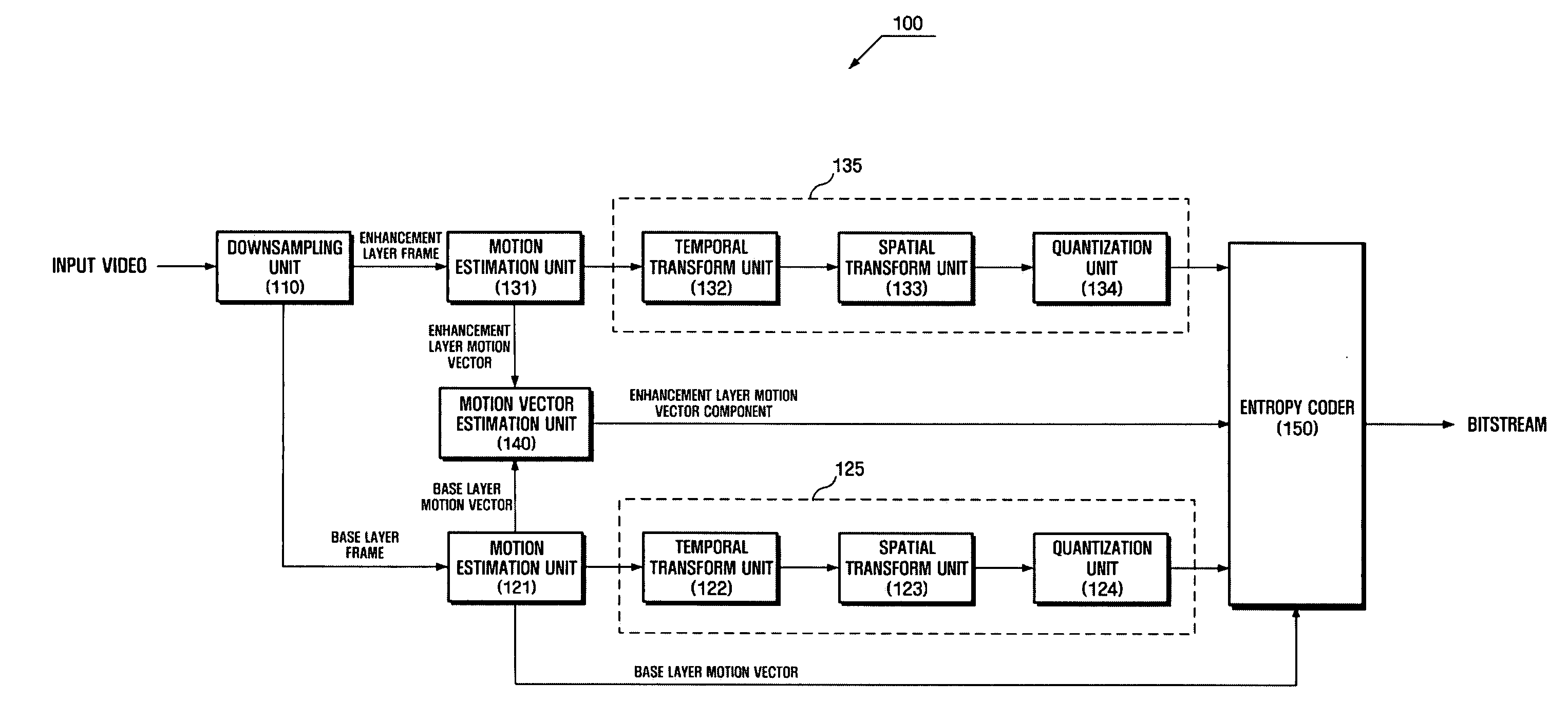

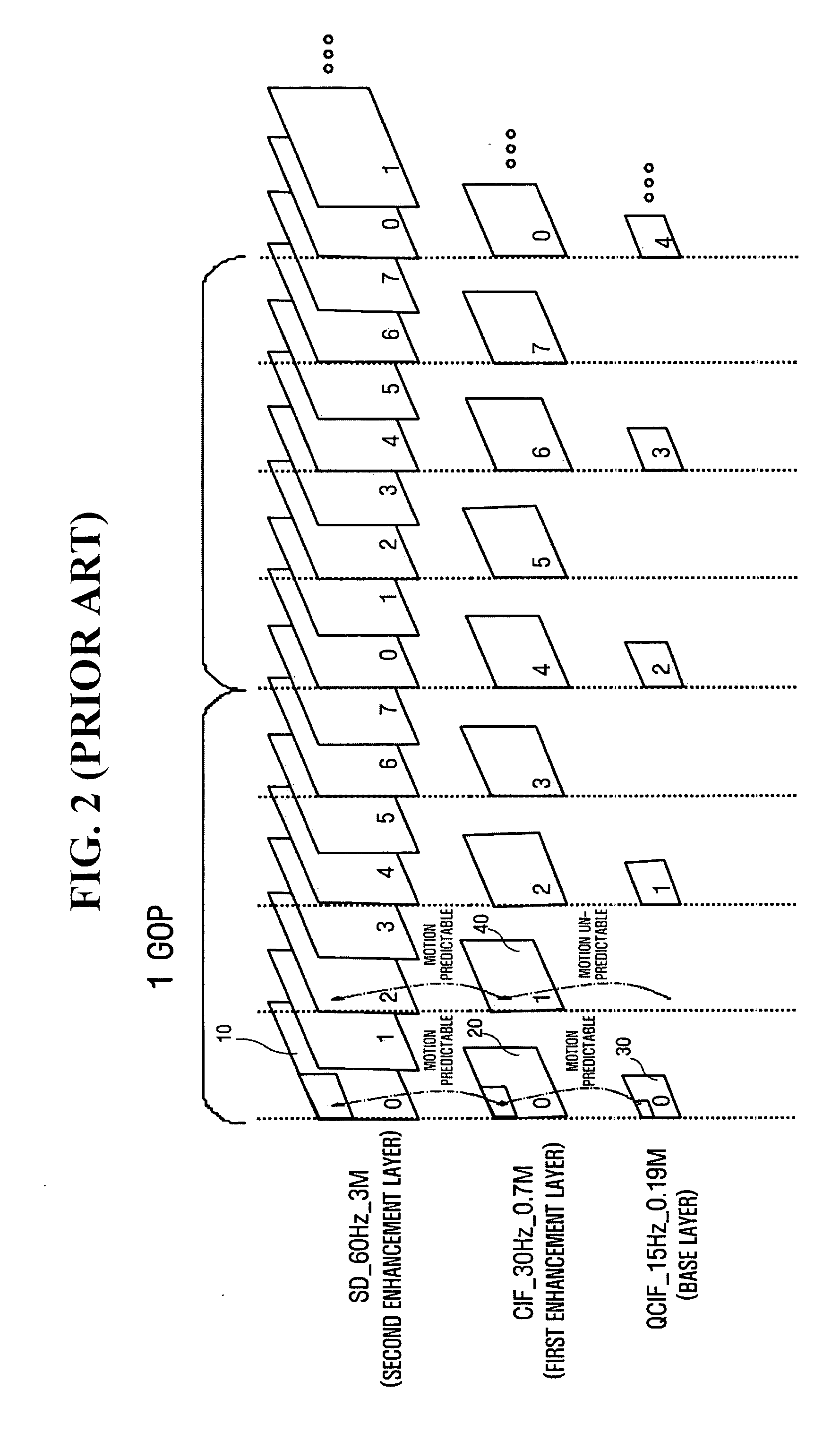

Method and apparatus for effectively compressing motion vectors in video coder based on multi-layer

InactiveUS20060088101A1Effective predictionEfficiently compressing multi-layered motion vectorsColor television with pulse code modulationColor television with bandwidth reductionMotion vectorComputer science

A method and apparatus of improving the compression efficiency of a motion vector by efficiently predicting a motion vector in an enhancement layer from a motion vector in a base layer in a video coding method using a multi-layer are provided. The method includes obtaining a motion vector in a base layer frame having a first frame rate from an input frame, obtaining a motion vector in a first enhancement layer frame having a second frame rate from the input frame, the second frame rate being greater than the first frame rate, generating a predicted motion vector by referring to a motion vector for at least one frame among base layer frames present immediately before and after the same temporal position as the first enhancement layer frame if there is no base layer frame at the same temporal position as the first enhancement layer frame, and coding a difference between the motion vector in the first enhancement layer frame and the generated predicted motion vector, and the obtained motion vector in the base layer.

Owner:SAMSUNG ELECTRONICS CO LTD

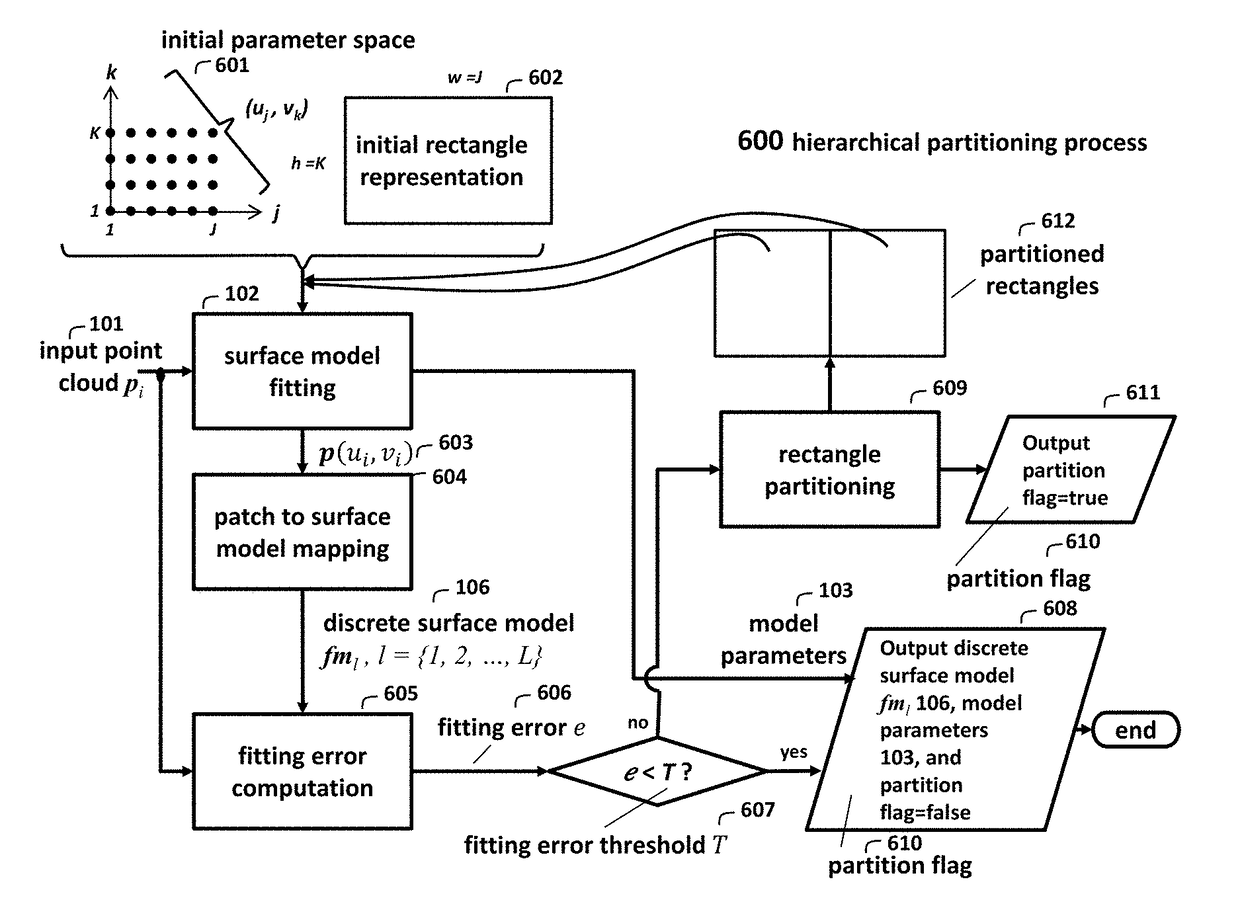

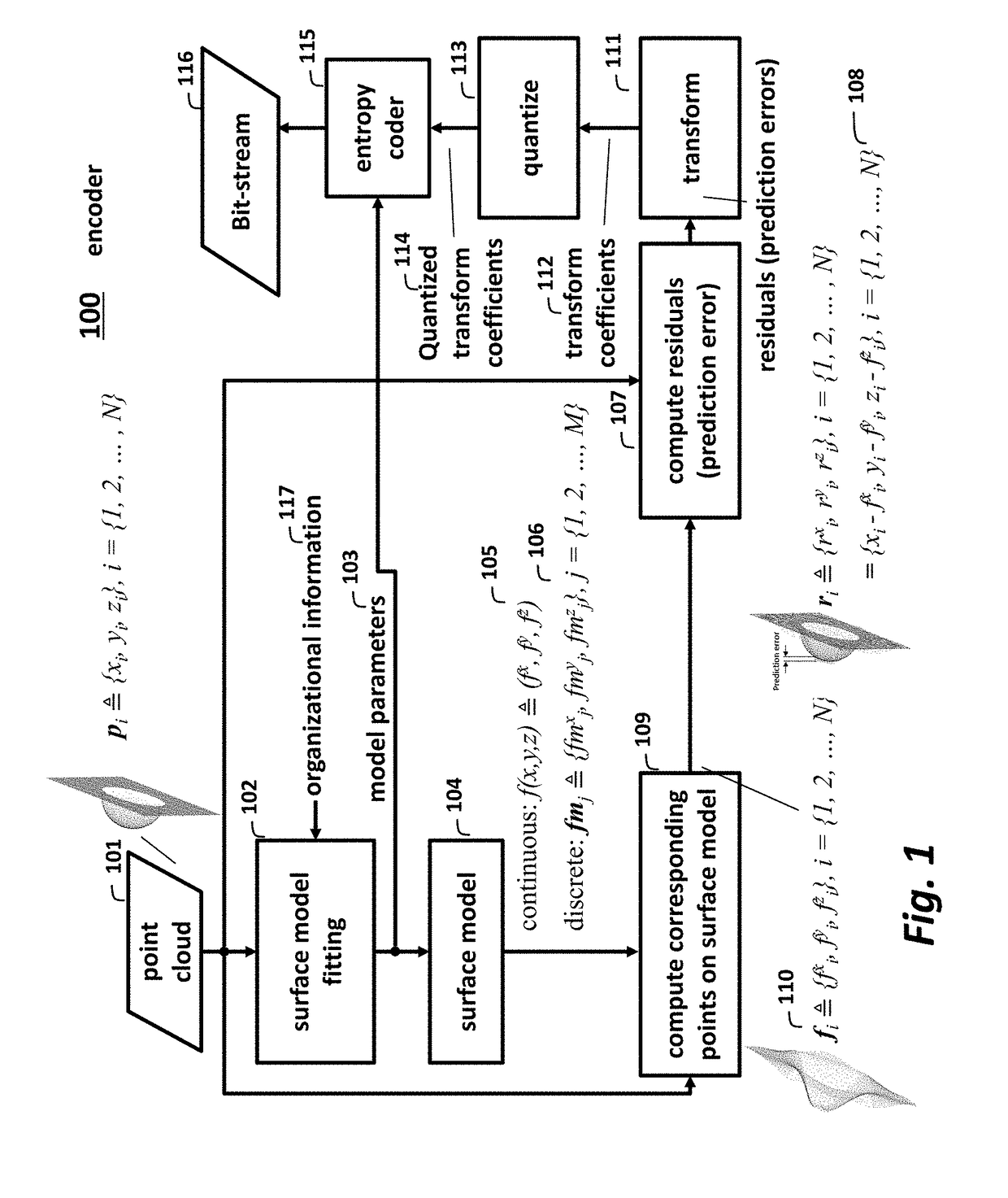

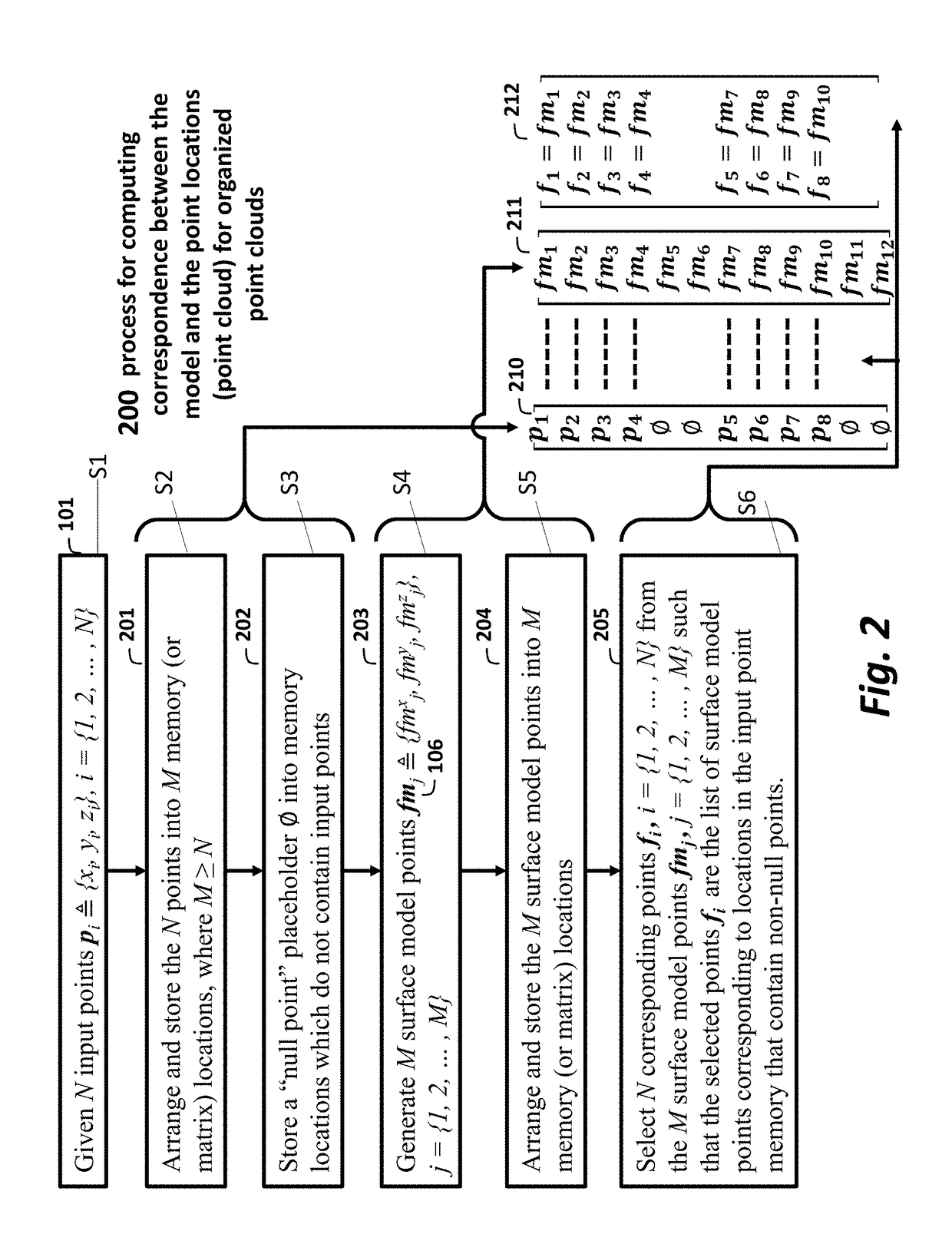

Method for Predictive Coding of Point Cloud Geometries

InactiveUS20180053324A1Efficient decodingEfficient codingDetails involving 3D image dataImage codingPoint cloudThree-dimensional space

A method for encoding a point cloud representing a scene using an encoder including a processor in communication with a memory includes steps of fitting a parameterized surface onto the point cloud having input points representing locations in a three-dimensional space, generating model parameters from the parameterized surface, computing corresponding points from the parameterized surface, wherein the corresponding points correspond to the input points, computing residual data based on the corresponding points and the input points of the point cloud, compressing the model parameters and residual data to yield coded model parameters and coded residual data, respectively, and producing a bit-stream from the coded model parameters of the parameterized surface and the coded residual data.

Owner:MITSUBISHI ELECTRIC RES LAB INC

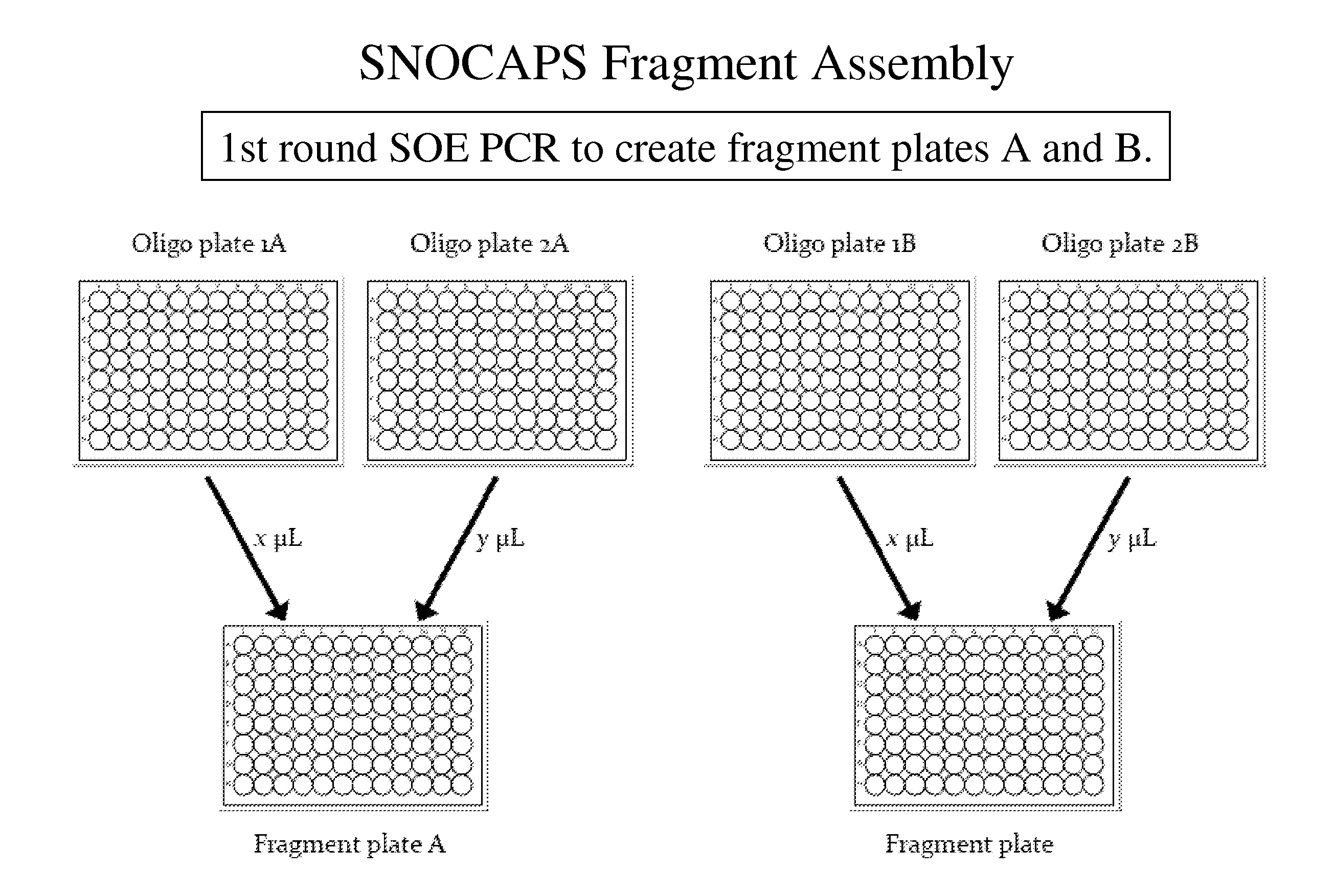

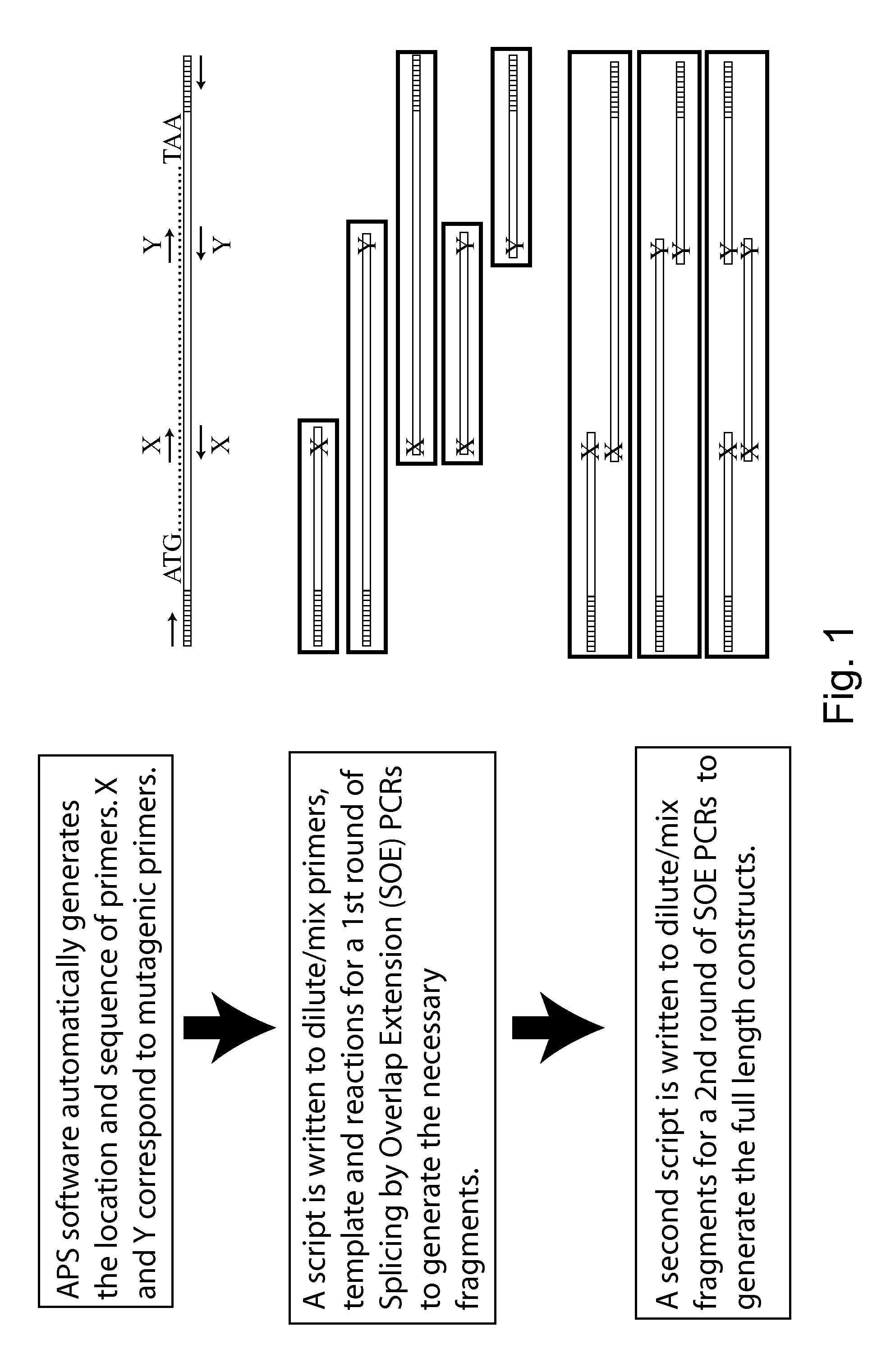

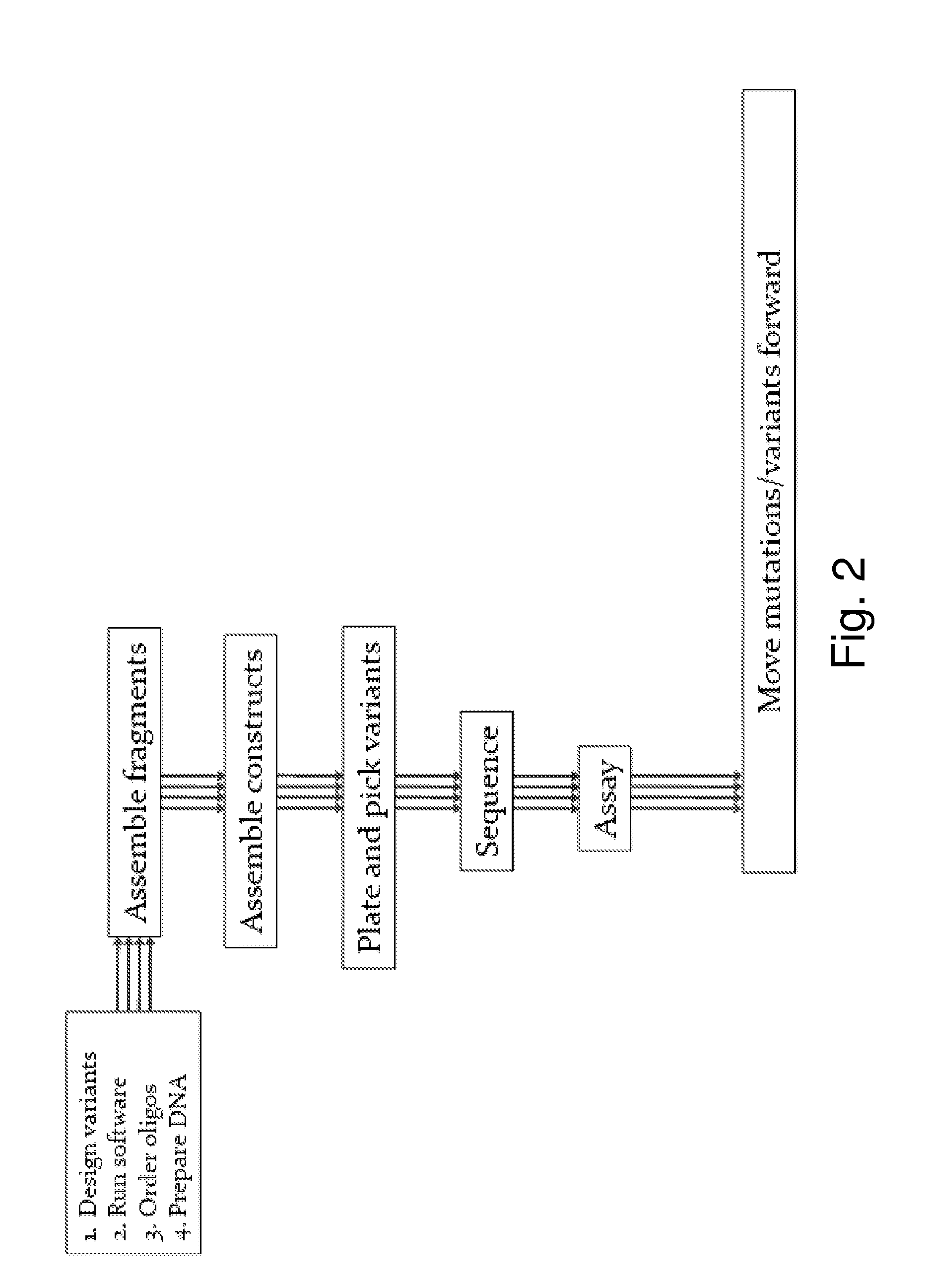

Reduced codon mutagenesis

InactiveUS20110082055A1Reduce complexityImprove screening efficiencyLibrary creationProtein nucleotide librariesOversamplingDegenerate oligonucleotide

Methods and compositions that reduce complexity of libraries of variant biological molecules, that reduce oversampling of these libraries during screening and that improve screening efficiency are provided. Sets of efficient degenerate codon sets are provided that efficiently encode all, or nearly all canonical amino acids. Degenerate oligonucleotides comprising these codons are provided, as are polynucleotide variants. Variant pooling strategies are used during library construction. Logical filtering is applied to select codon sites for mutagenesis, or to select amino acid sets to be incorporated at such sites. Methods for reducing non-optimal oversampling during screening are provided.

Owner:CODEXIS INC

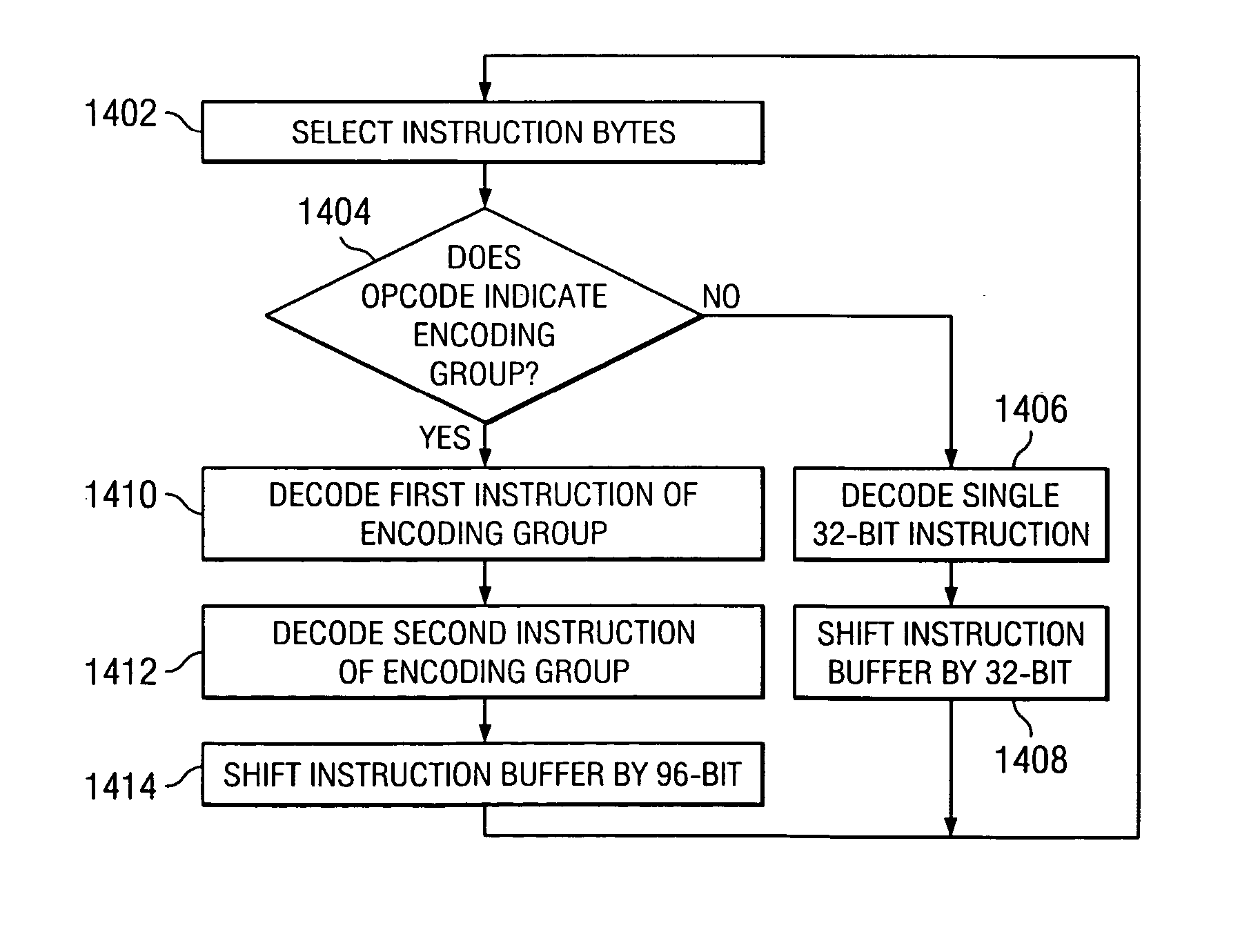

Method and apparatus for embedding wide instruction words in a fixed-length instruction set architecture

InactiveUS20060174089A1Control freedomEfficient codingInstruction analysisGeneral purpose stored program computerInstruction setInstruction stream

A method, system, and computer program product for mixing of conventional and augmented instructions within an instruction stream, wherein control may be directly transferred, without operating system intervention, between one type of instruction to another. Extra instruction word bits are added in a manner that is designed to minimally interfere with the encoding, decoding, and instruction processing environment in a manner compatible with existing conventional fixed instruction width code. A plurality of instruction words are inserted into an instruction word oriented architecture to form an encoding group of instruction words. The instruction words in the encoding group are dispatched and executed either independently or in parallel based on a specific microprocessor implementation. The encoding group does not indicate any form of required parallelism or sequentiality. One or more indicators for the encoding group are created, wherein one indicator is used to indicate presence of the encoding group.

Owner:IBM CORP

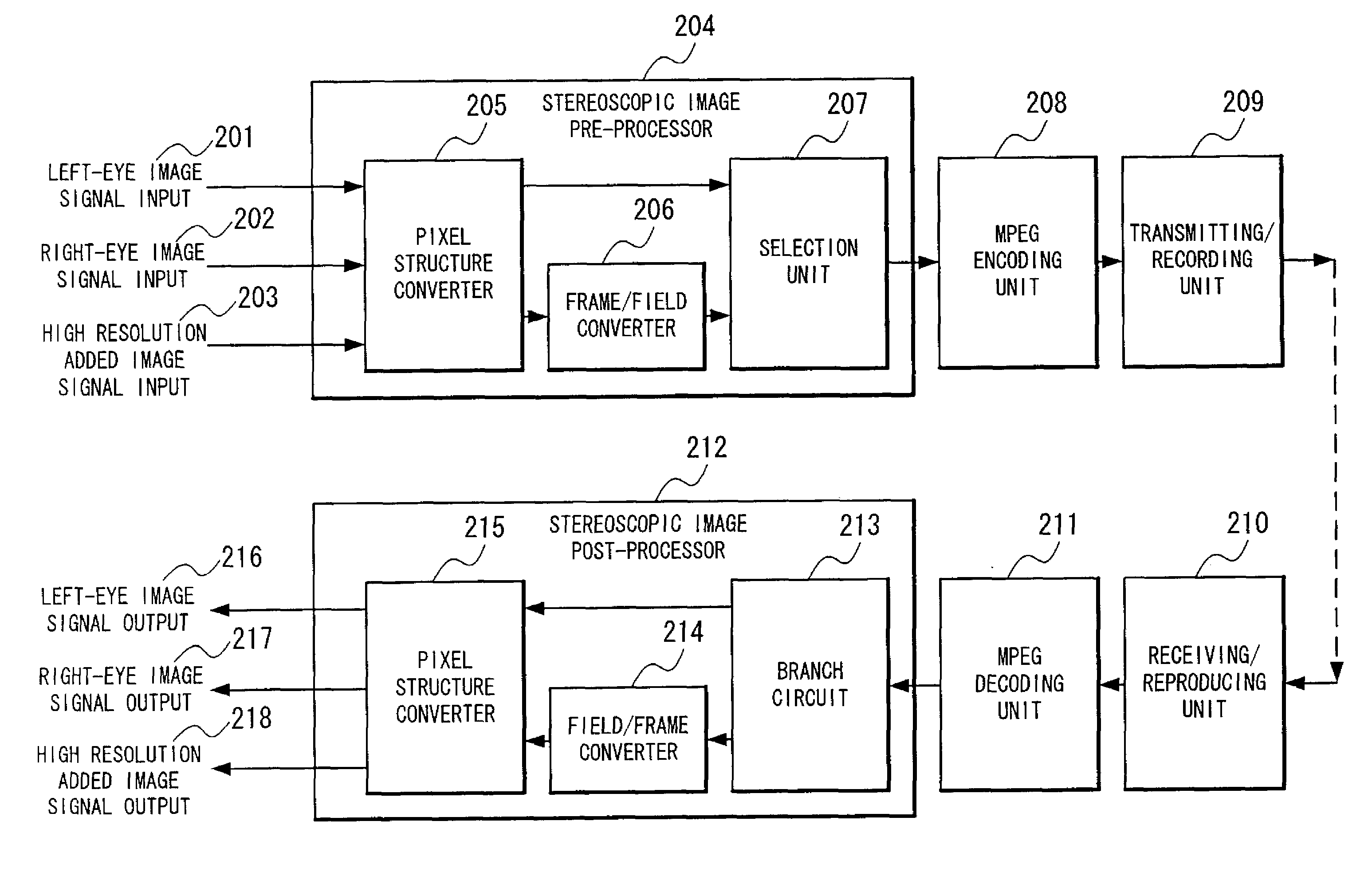

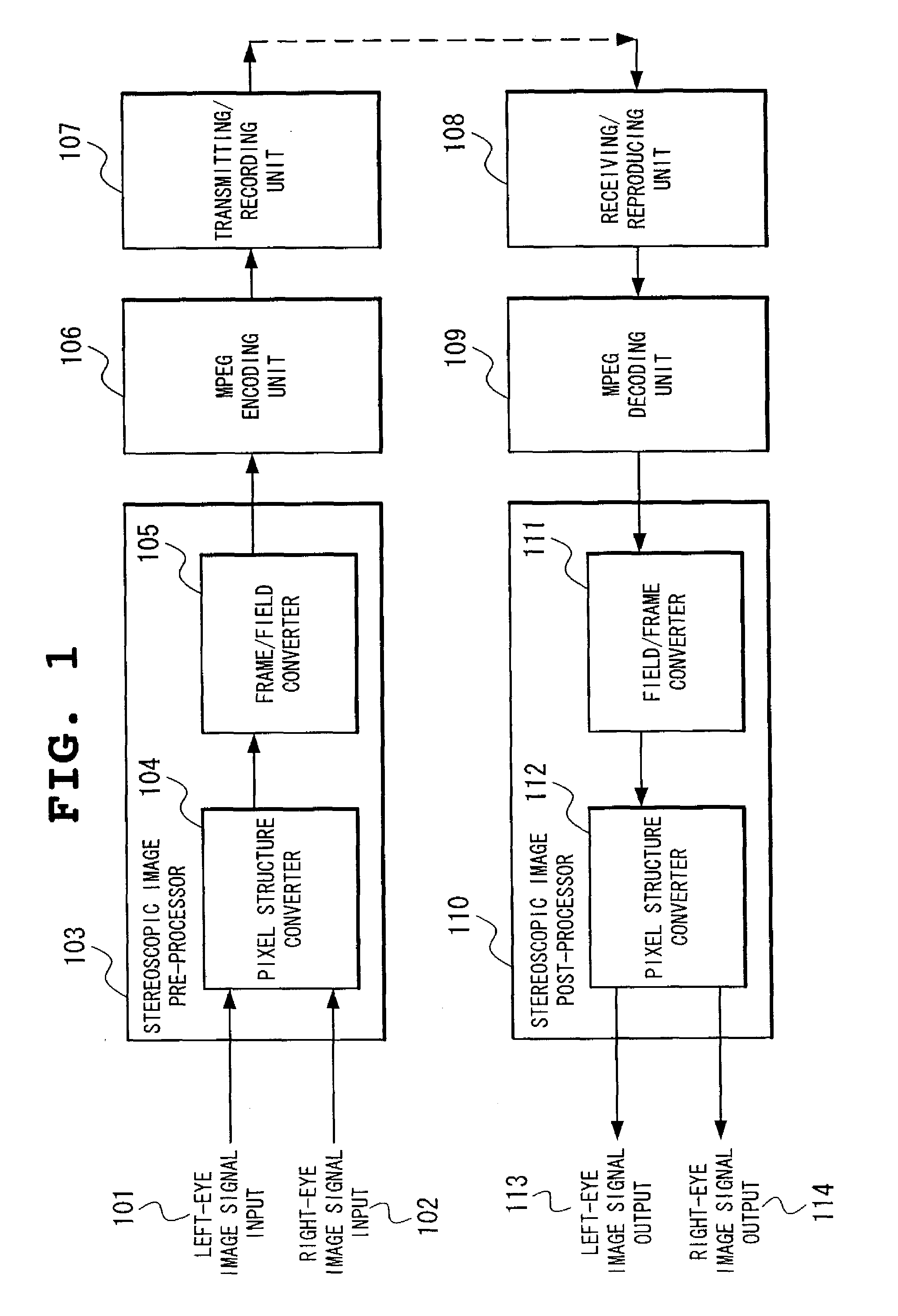

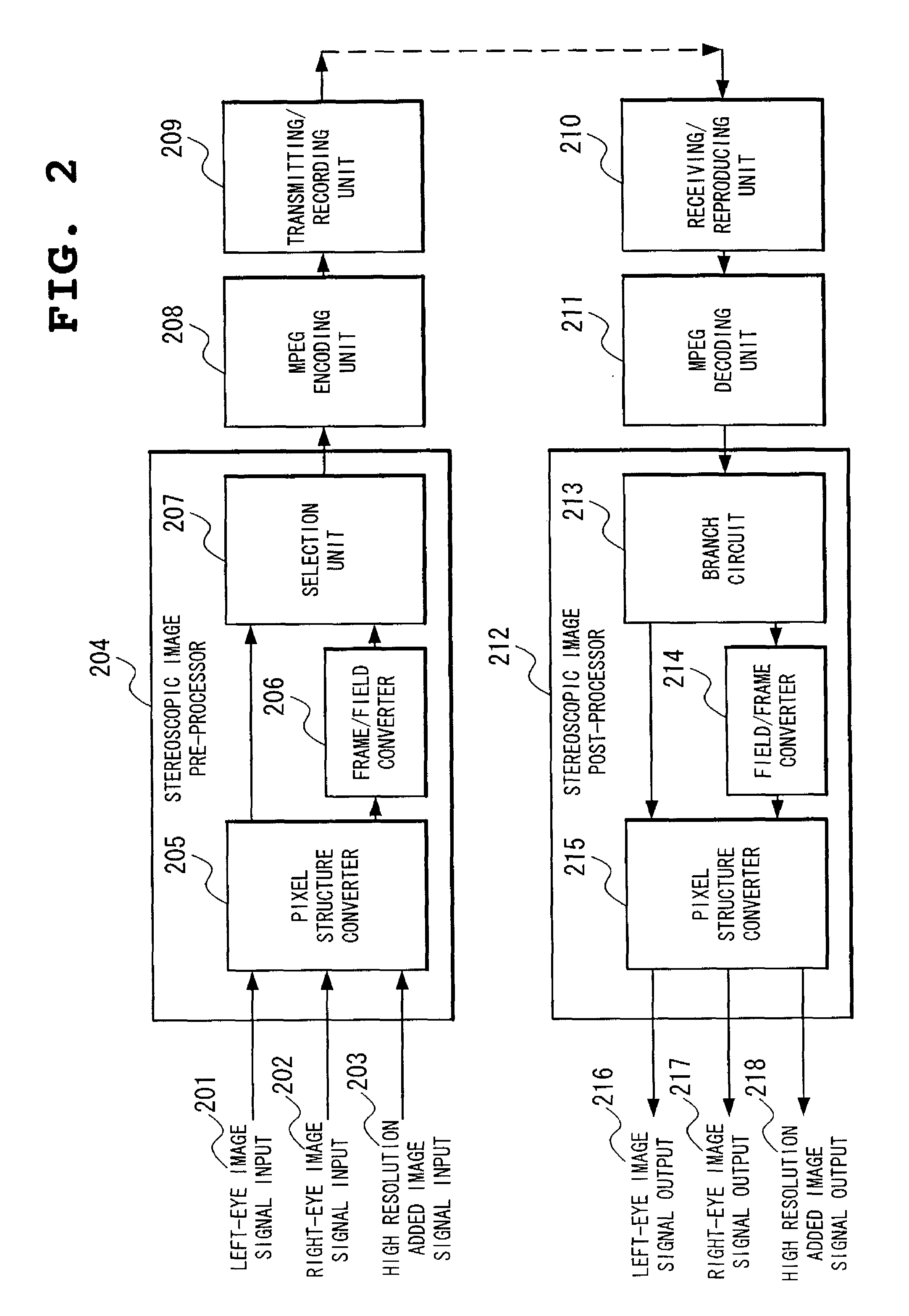

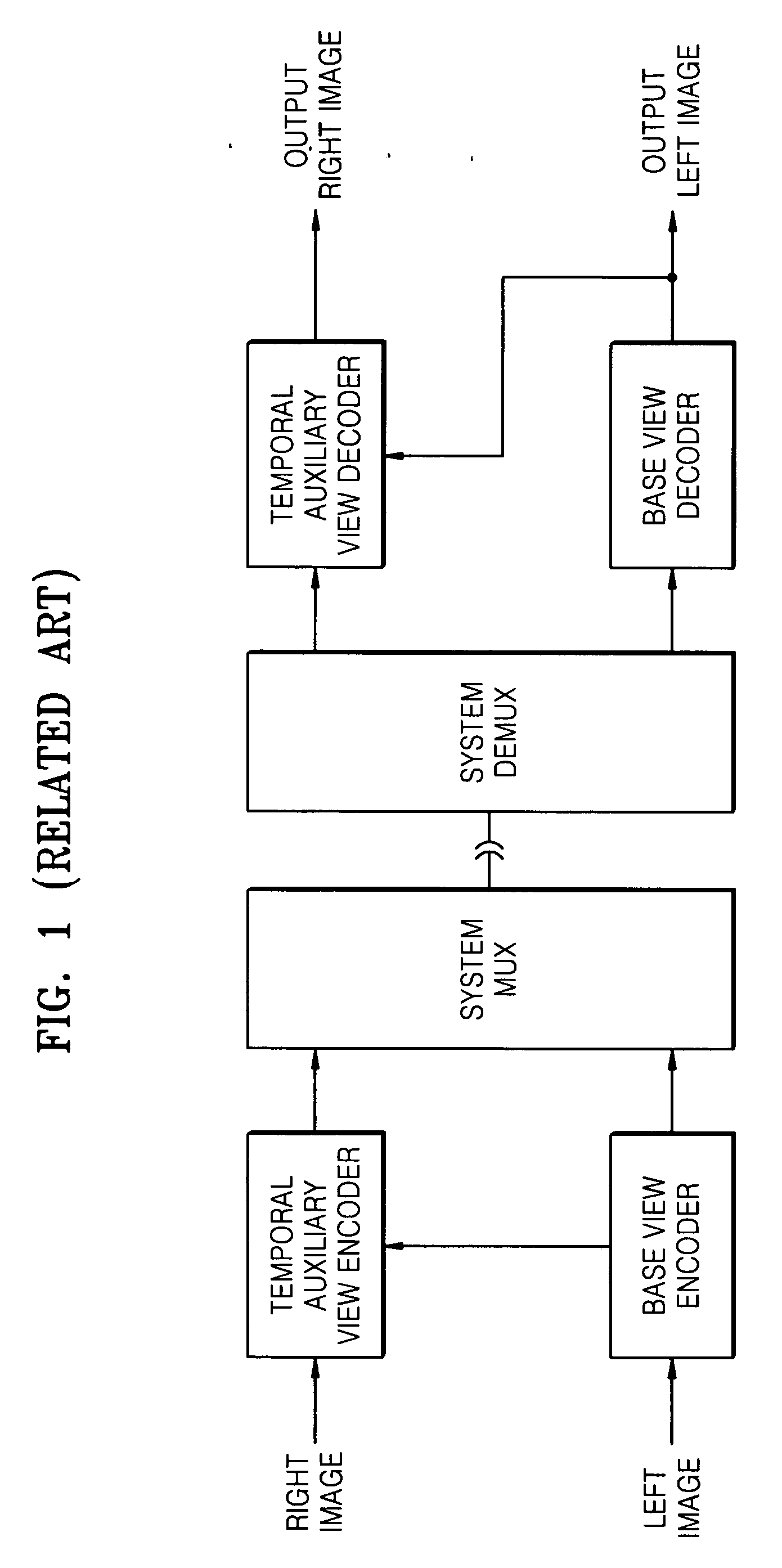

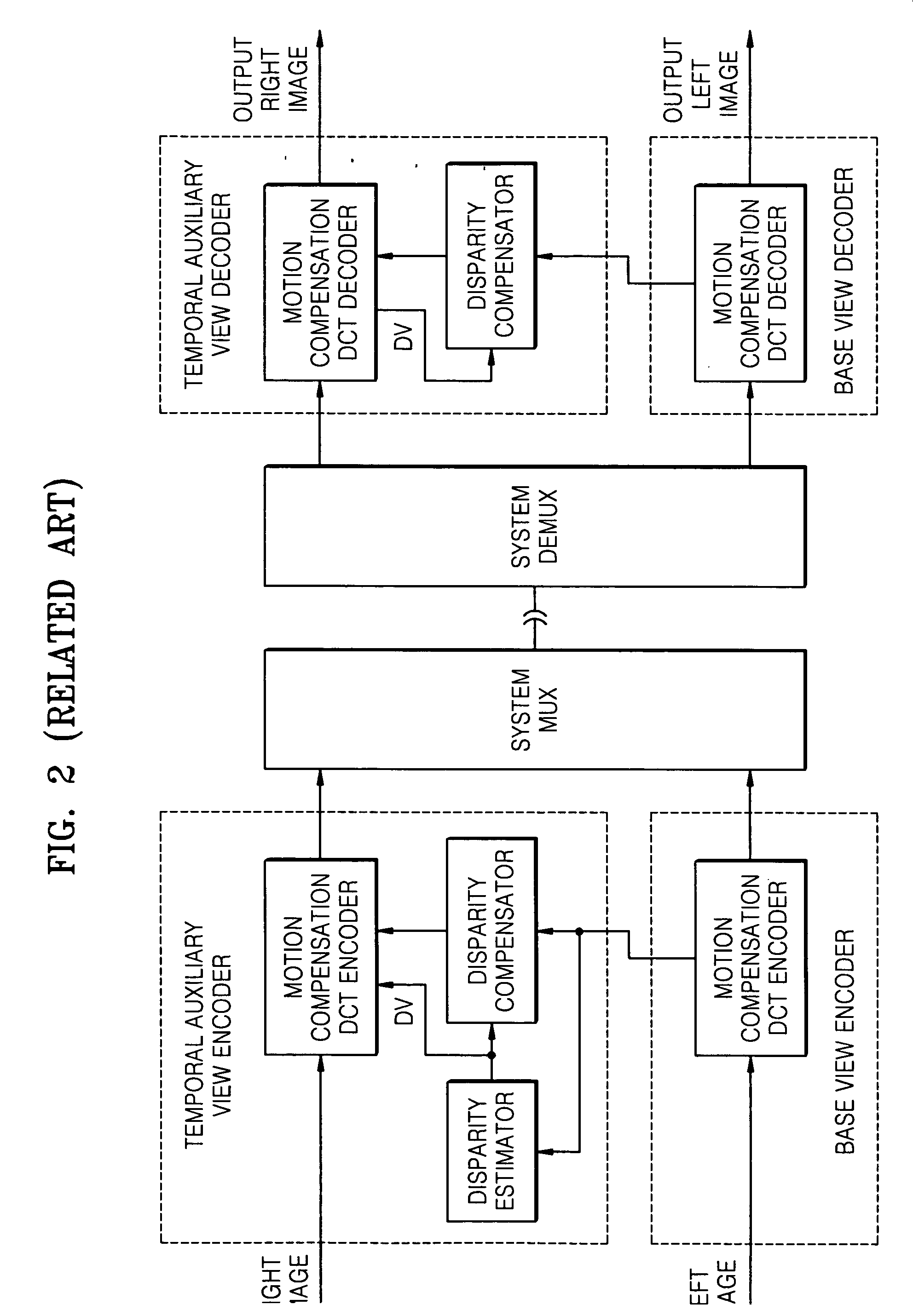

Stereoscopic image encoding and decoding device multiplexing high resolution added images

InactiveUS20080152241A1Efficiently encoding and transferring image dataEfficient codingCharacter and pattern recognitionImage codingMultiplexingComputer graphics (images)

A left-eye image signal and a right-eye image signal are supplied to a pixel structure converter of a stereoscopic image pre-processor, and multiplexed, so to form one image, an interlace image is formed by a frame / field converter, encoded in an MPEG format by an MPEG encoding unit, stored into a storage and transmitted outward by a transmitting / recording unit. The encoded stereoscopic image signal received from the outward and reproduced from the storage is decoded by am MPEG decoding unit after going through a receiving / reproducing unit, the interlace image is reproduced, returned to the frame image by a field / frame converter of a stereoscopic image post-processor, and reproduced as the left-eye image signal and the right-eye image signal and output by the pixel structure converter.

Owner:NEC CORP

Audio coding based on frequency variations of sinusoidal components

InactiveUS7146324B2Improve coding efficiencyGood for continuationSpeech analysisCode conversionContinuationAudio frequency

Coding of an audio signal is provided where an indicator of the frequency variation of sinusoidal components of the signal is used in the tracking algorithm of a sinusoidal coder where sinusoidal parameters from appropriate sinusoids from consecutive segments are linked. By applying an indicator such as a warp factor or polynomial fitting, more accurate tracks are obtained. As a result, the sinusoids can be encoded more efficiently. Furthermore, a better audio quality can be obtained by improved phase continuation.

Owner:PENDRAGON WIRELESS LLC

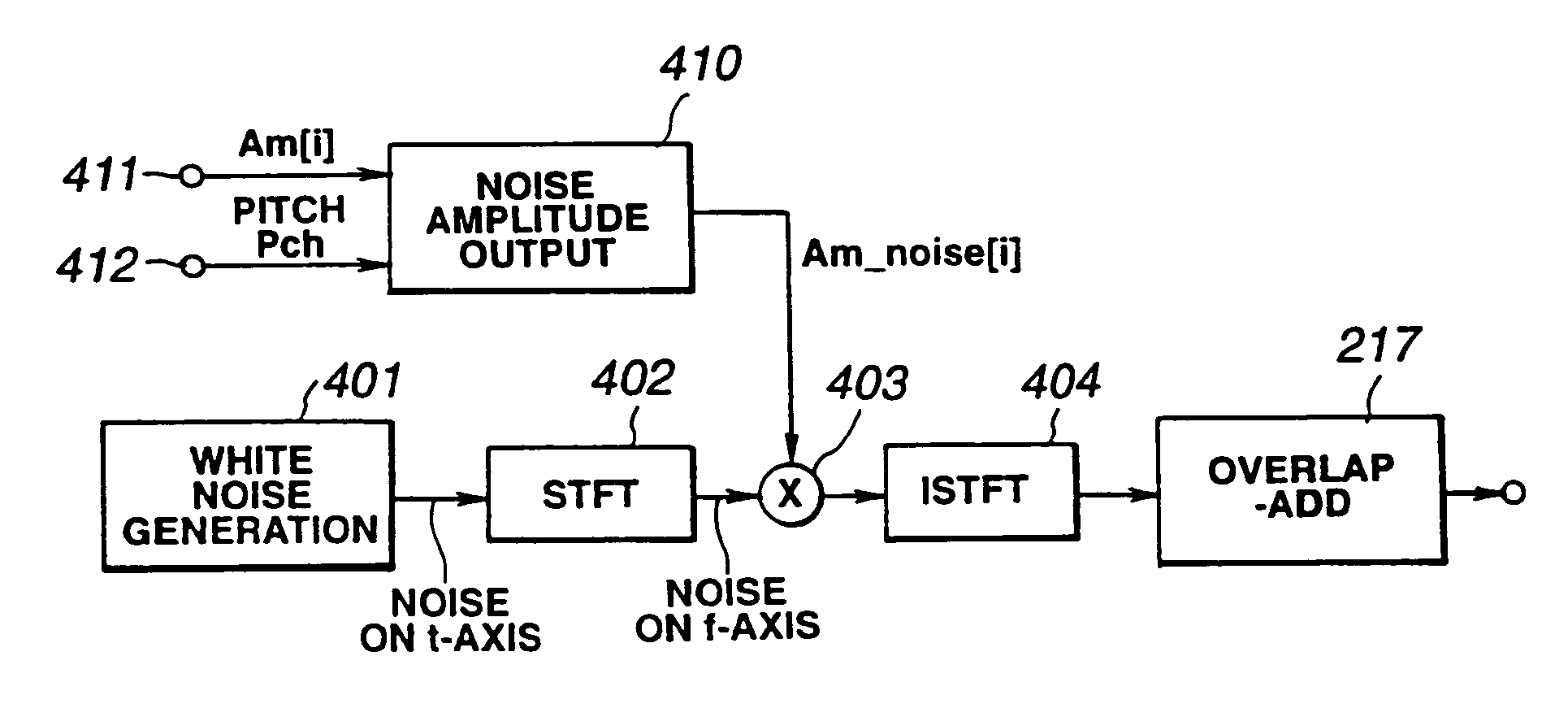

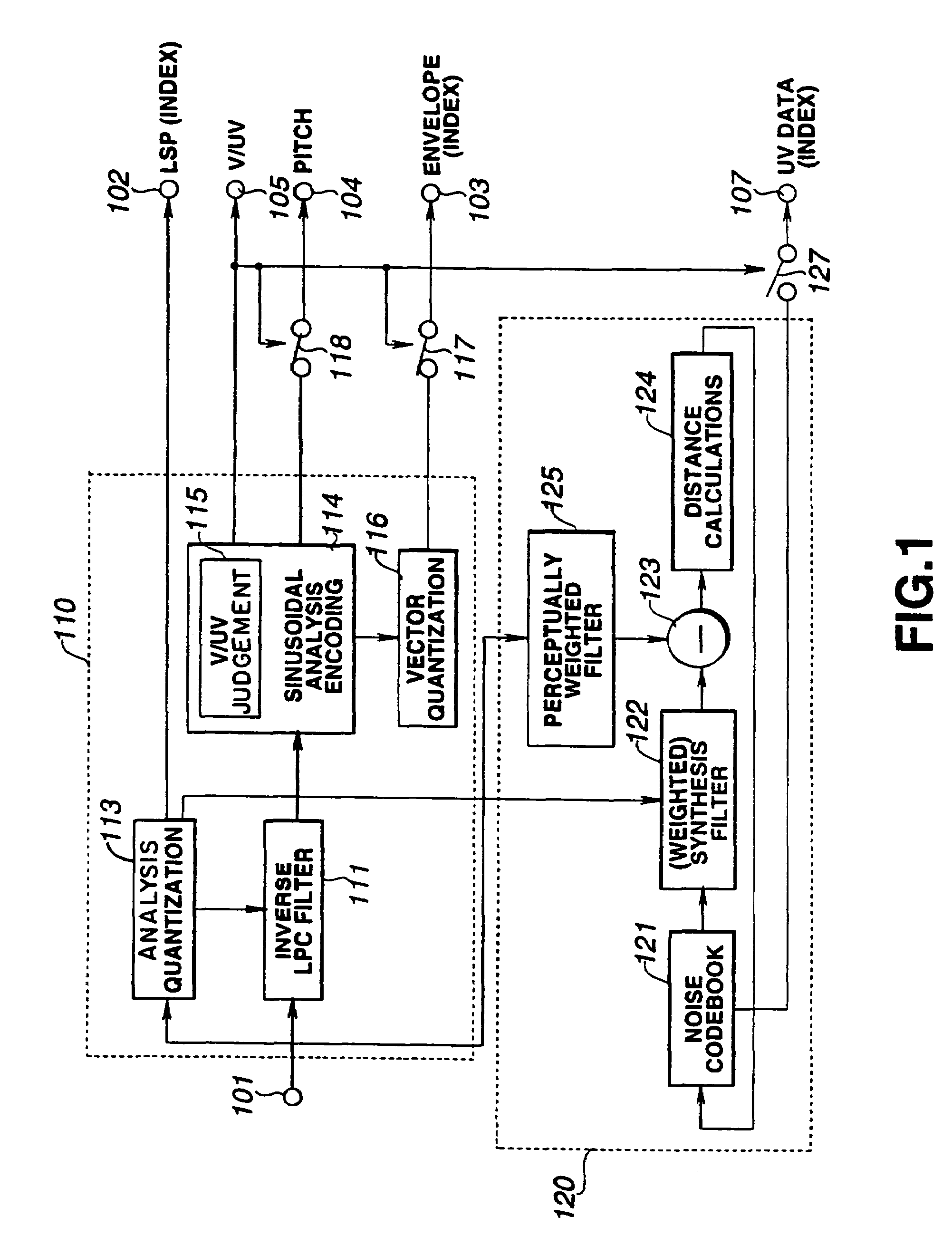

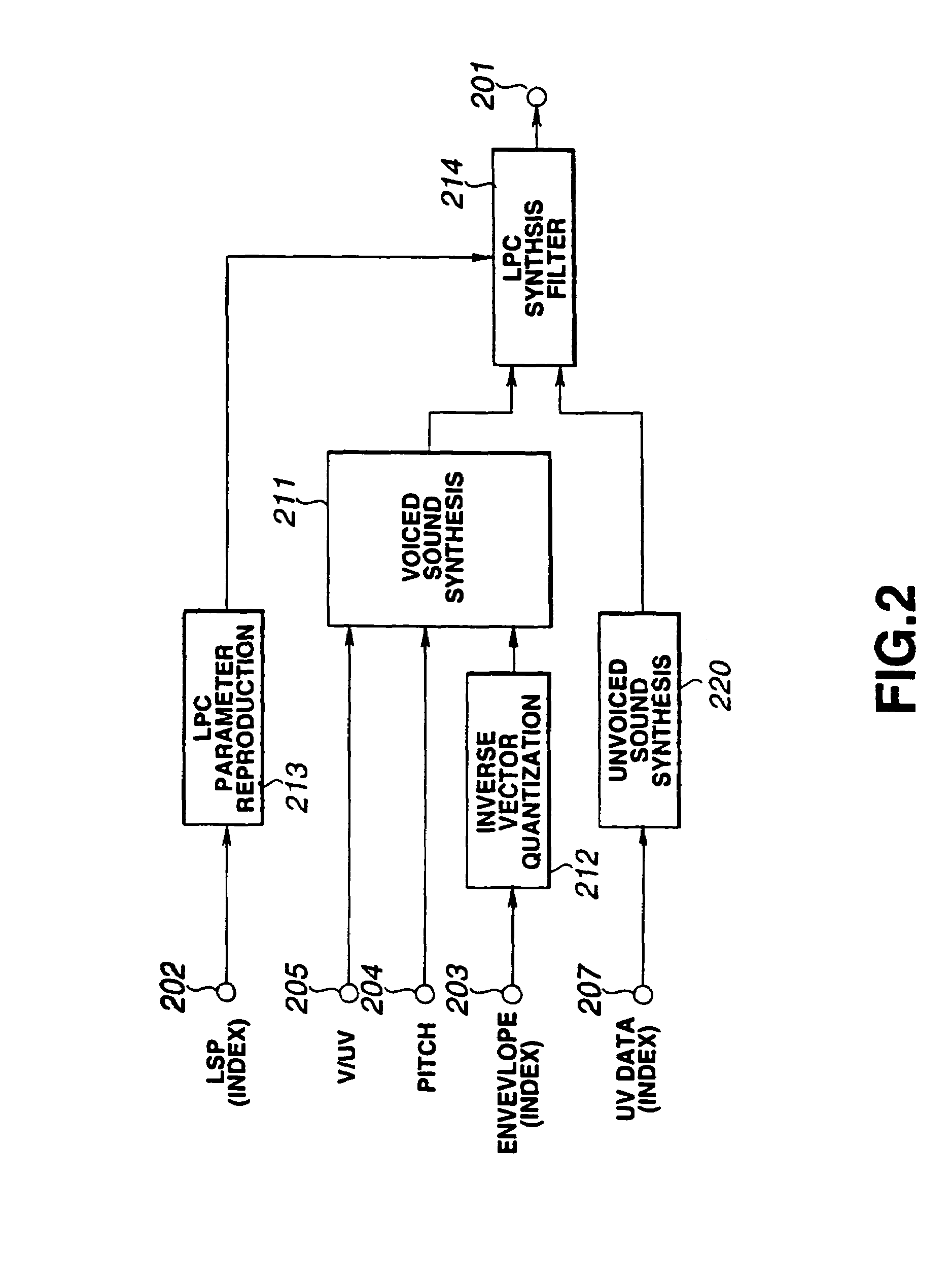

Method and apparatus for speech encoding and decoding by sinusoidal analysis and waveform encoding with phase reproducibility

InactiveUS7454330B1Efficient codingImprove expressivenessSpeech analysisCode conversionUltrasound attenuationCode-excited linear prediction

A speech encoding method and apparatus in which an input speech signal is divided in terms of blocks or frames as encoding units and encoded in terms of the encoding units, whereby explosive and fricative consonants can be impeccably reproduced, while there is an attenuation of the occurrence of foreign sounds being generated at a transient portion between voiced (V) and unvoiced (UV) portions, so that the speech with high clarity devoid of “stuffed” feeling may be produced. The encoding apparatus includes a first encoding unit for finding residuals of linear predictive coding (LPC) of an input speech signal for performing harmonic coding and a second encoding unit for encoding the input speech signal by waveform coding. The first encoding unit and the second encoding unit are used for encoding a voiced (V) portion and an unvoiced (UV) portion of the input signal, respectively. Code excited linear prediction (CELP) encoding employing vector quantization by a closed loop search of an optimum vector using an analysis-by-synthesis method is used for the second encoding unit. A corresponding decoding method and apparatus is also provided.

Owner:SONY CORP

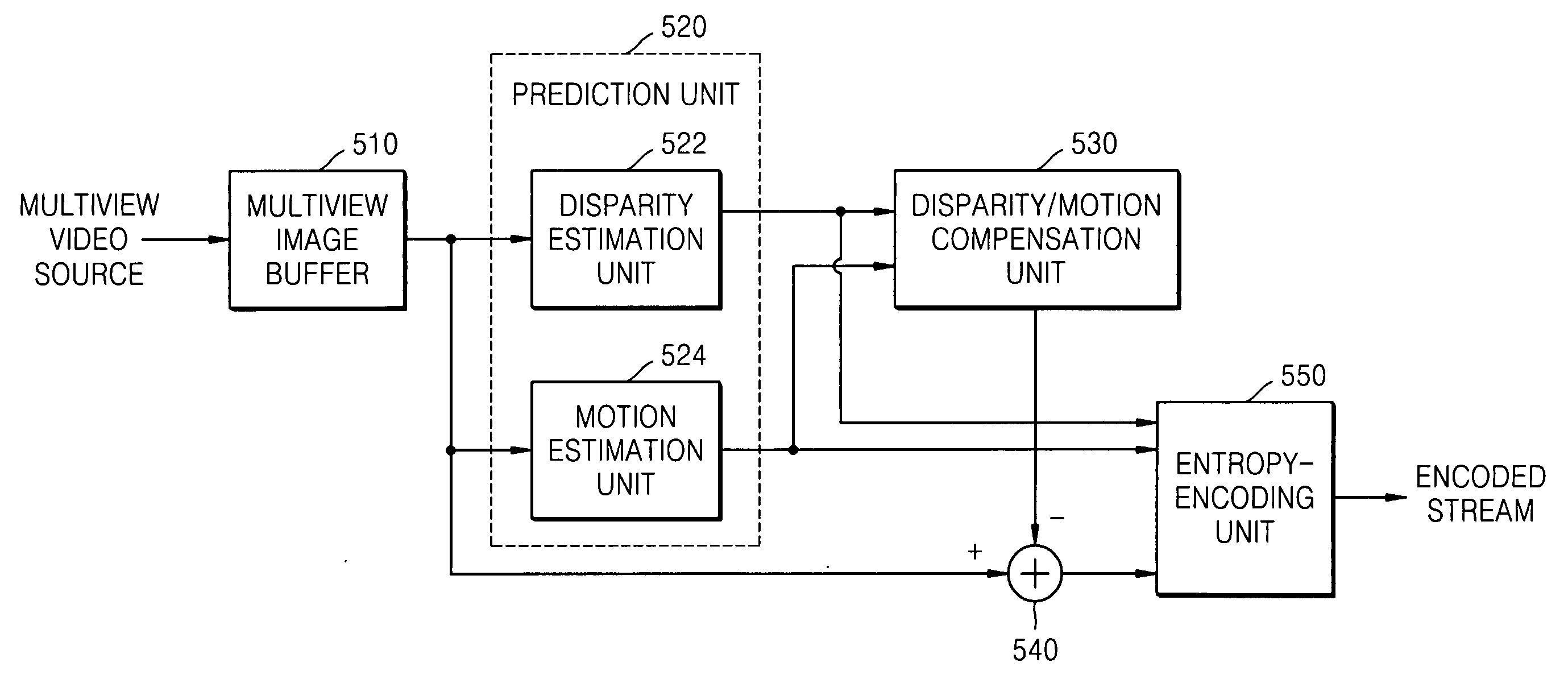

Method and apparatus for encoding multiview video

InactiveUS20070041443A1Efficient codingColor television with pulse code modulationColor television with bandwidth reductionPattern recognition

Owner:SAMSUNG ELECTRONICS CO LTD

Video compression and encoding method

ActiveUS7606310B1Efficient codingPulse modulation television signal transmissionPicture reproducers using cathode ray tubesPattern recognitionMotion vector

A method of compressing video data having at least one frame having at least one block and each block having an array of pixels is provided. The method transforms the pixels of each block into coefficients and creates an optimal transmission order of the coefficients. The method also optimizes the speed of processing compressed video data by partitioning the data bitstream and coding each partition independently. The method also predicts fractional pixel motion by selecting an interpolation method for each given plurality or block of pixels depending upon at least one metric related to each given block and varies the method from block to block. The method also enhances error recovery for a current frame using a frame prior to the frame immediately before the current frame as the only reference frame for lessening quality loss during data transmission. Enhanced motion vector coding is also provided.

Owner:GOOGLE LLC

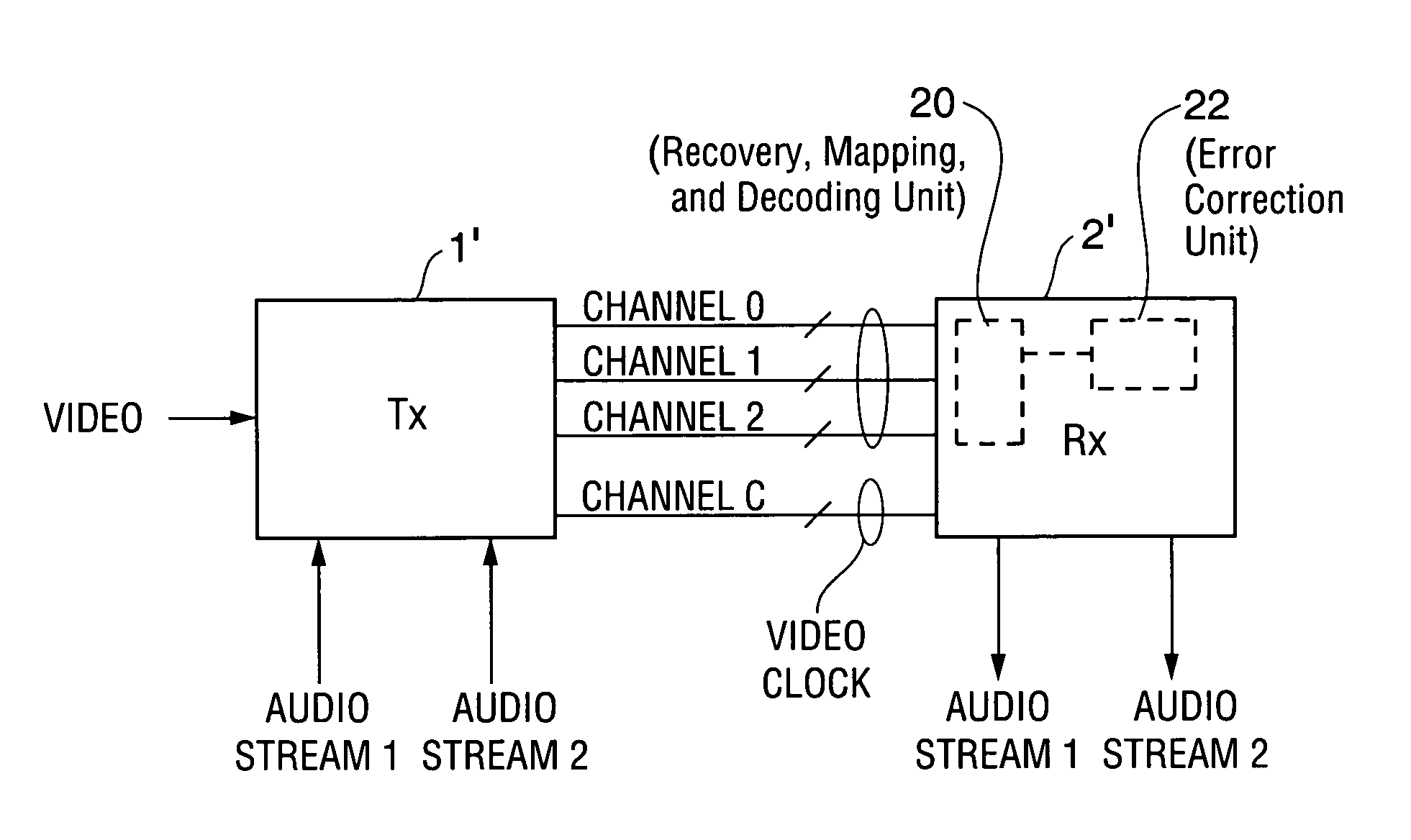

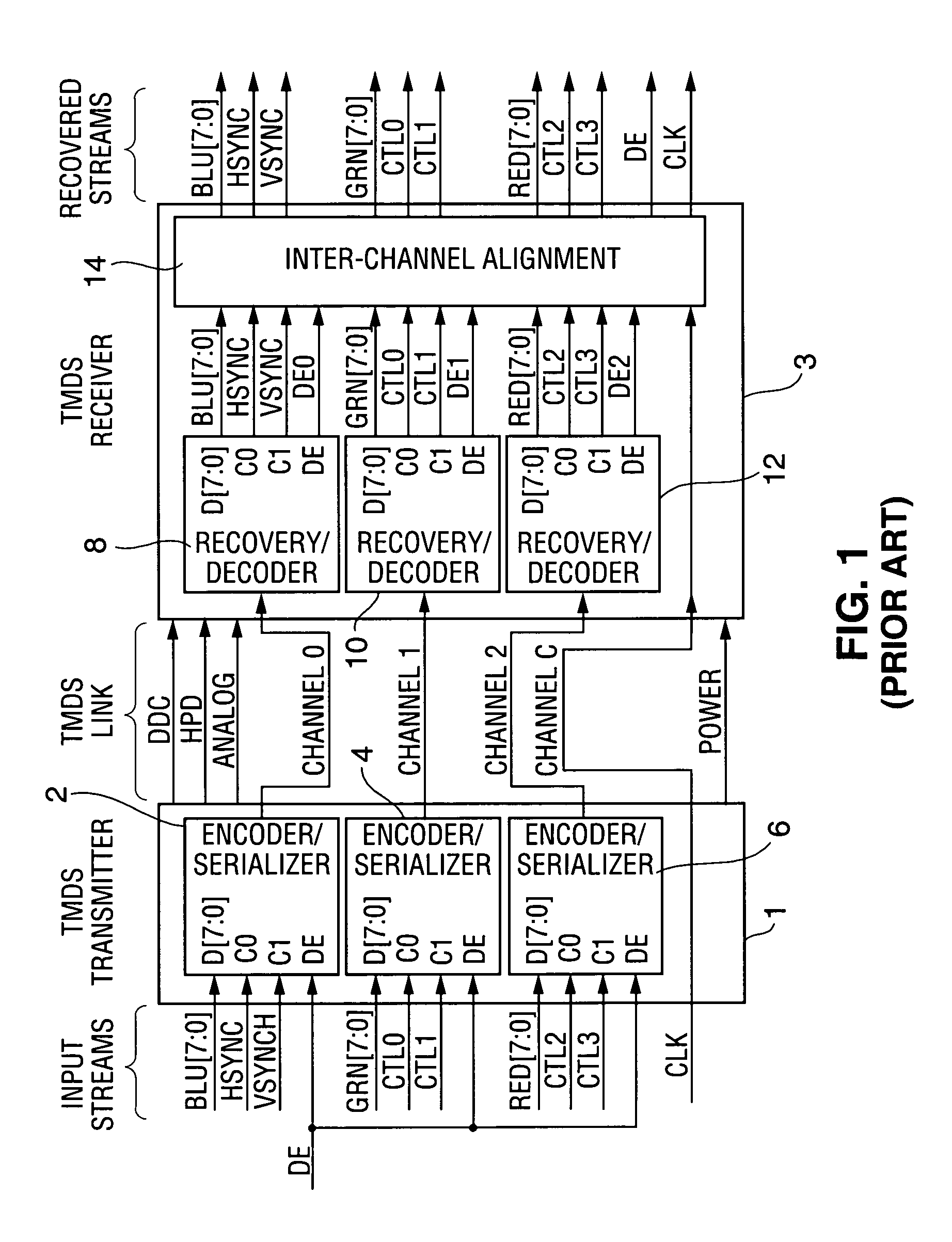

Method and system for reducing inter-symbol interference effects in transmission over a serial link with mapping of each word in a cluster of received words to a single transmitted word

InactiveUS7257163B2Reduce bit error rateIncreased source data transmission rateError detection/prevention using signal quality detectorPicture reproducers using cathode ray tubesSymbol of a differential operatorComputer science

A system in which encoded data (e.g., encoded video and auxiliary data) are transmitted over a serial link. Other aspects of the invention are transmitters for use in encoding data for transmission over a serial link, receivers for receiving such data, and methods for sending encoded data over a serial link. Source data to be transmitted are encoded using a subset of a full set of code words. The subset consists of preferred code words. Disjoint clusters of code words in the full set are predetermined. Each cluster includes one or more of the preferred words, and optionally also at least one additional code word that is similar to a preferred word of the cluster in the sense that it is likely to be generated as a result of probable bit errors in transmission, or transmission and decoding, of such preferred word. Each preferred word of a cluster is indicative of a single source data value. Each received code word in a cluster is mapped to the source data value determined by each preferred word of the cluster.

Owner:KONINKLJIJKE PHILIPS NV

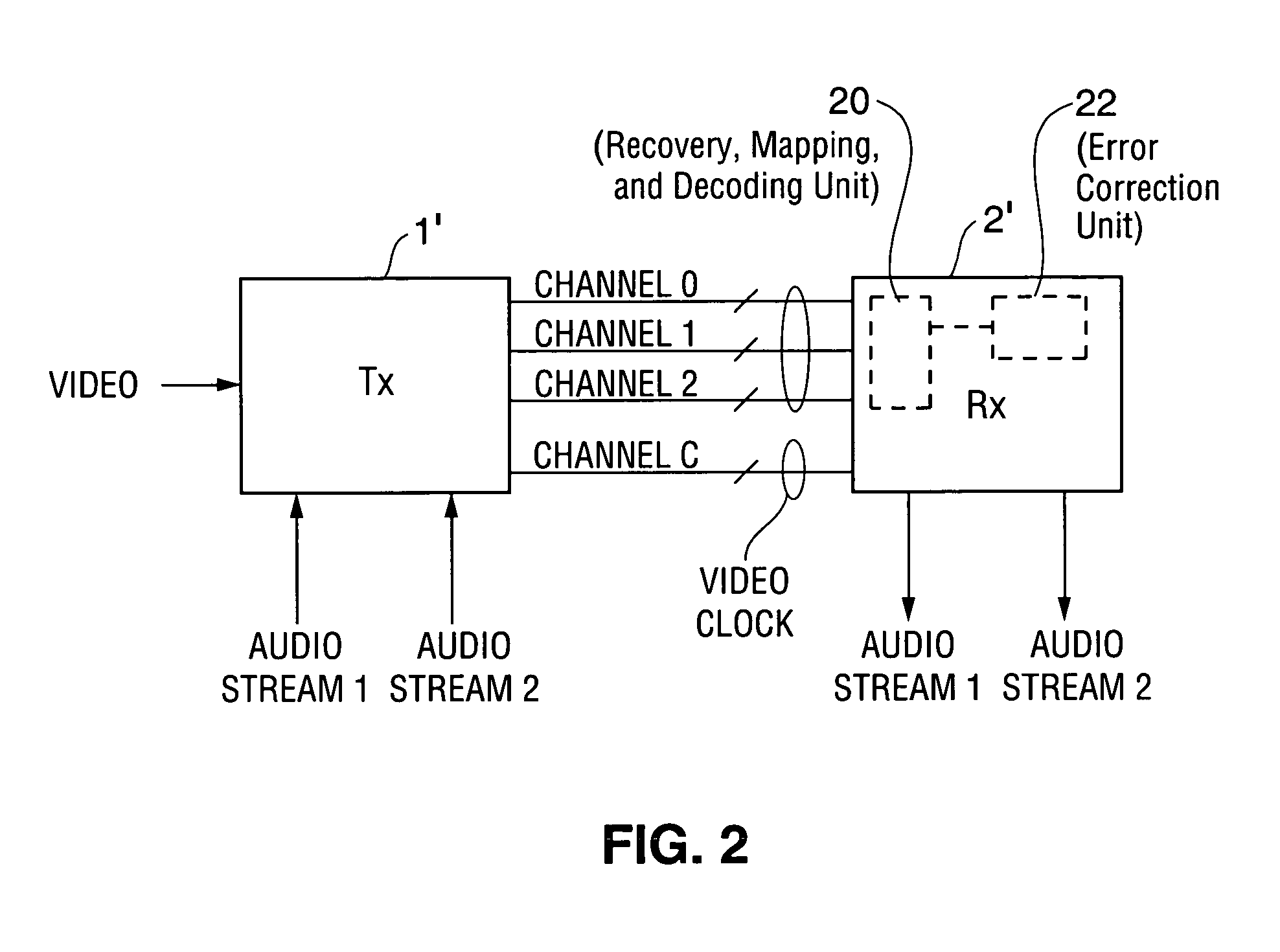

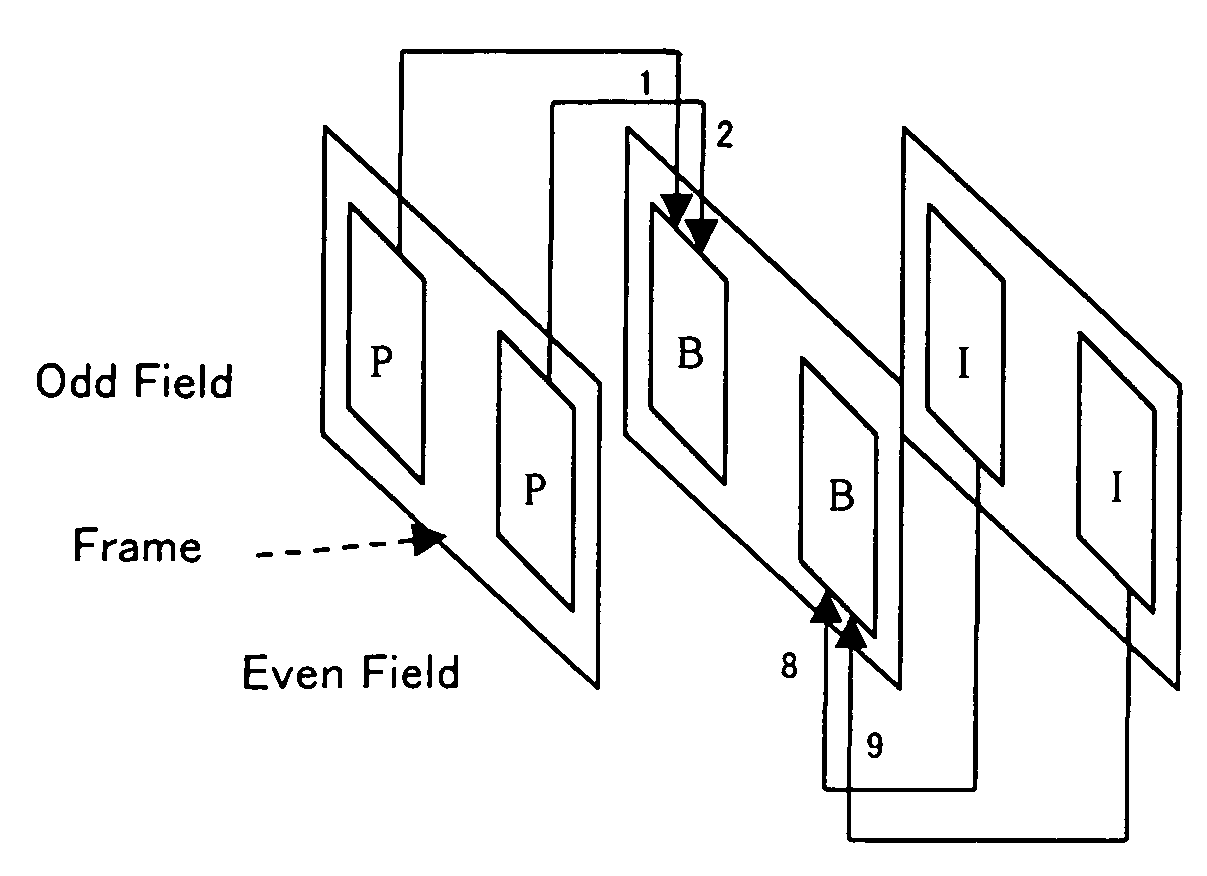

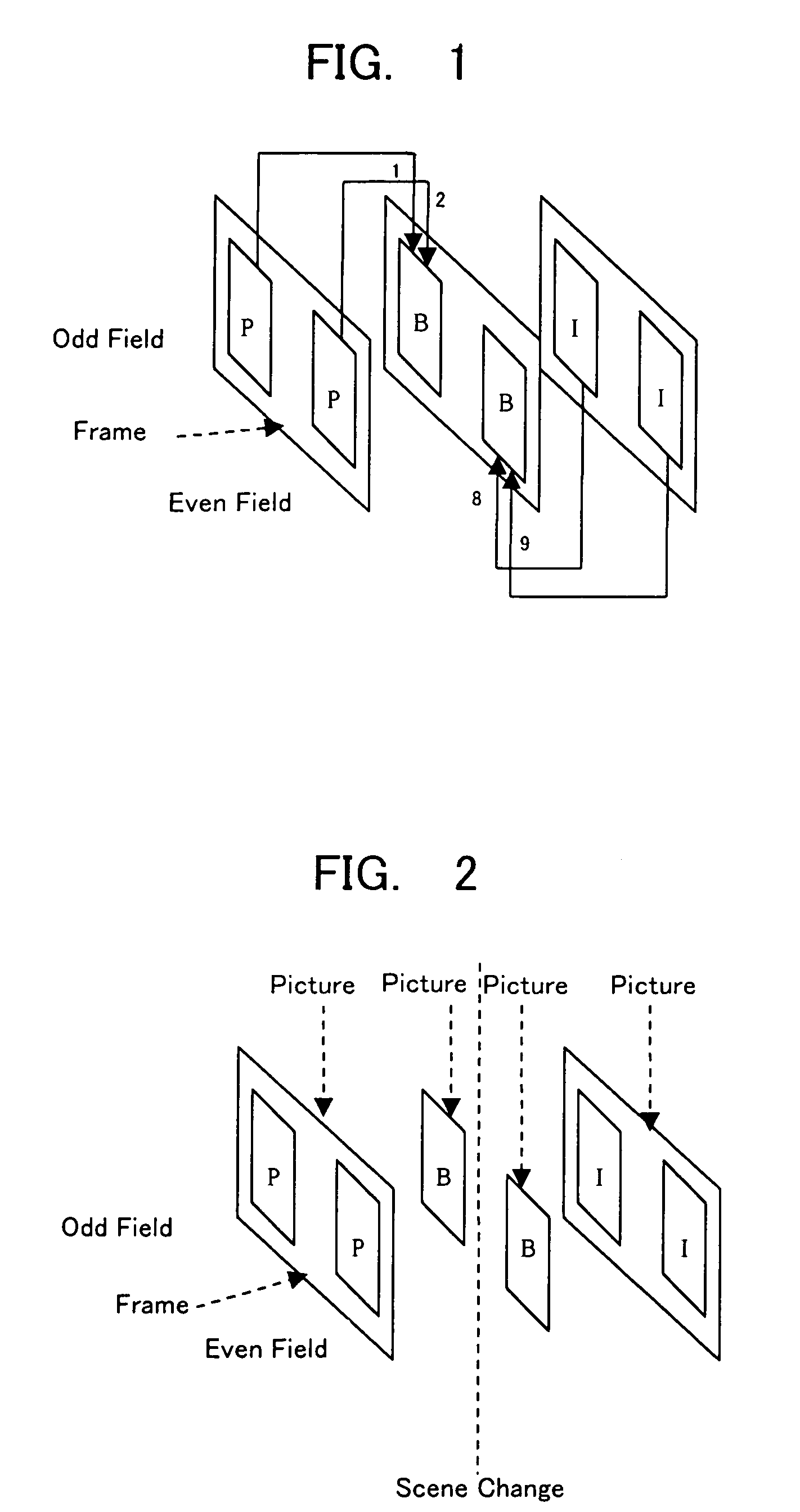

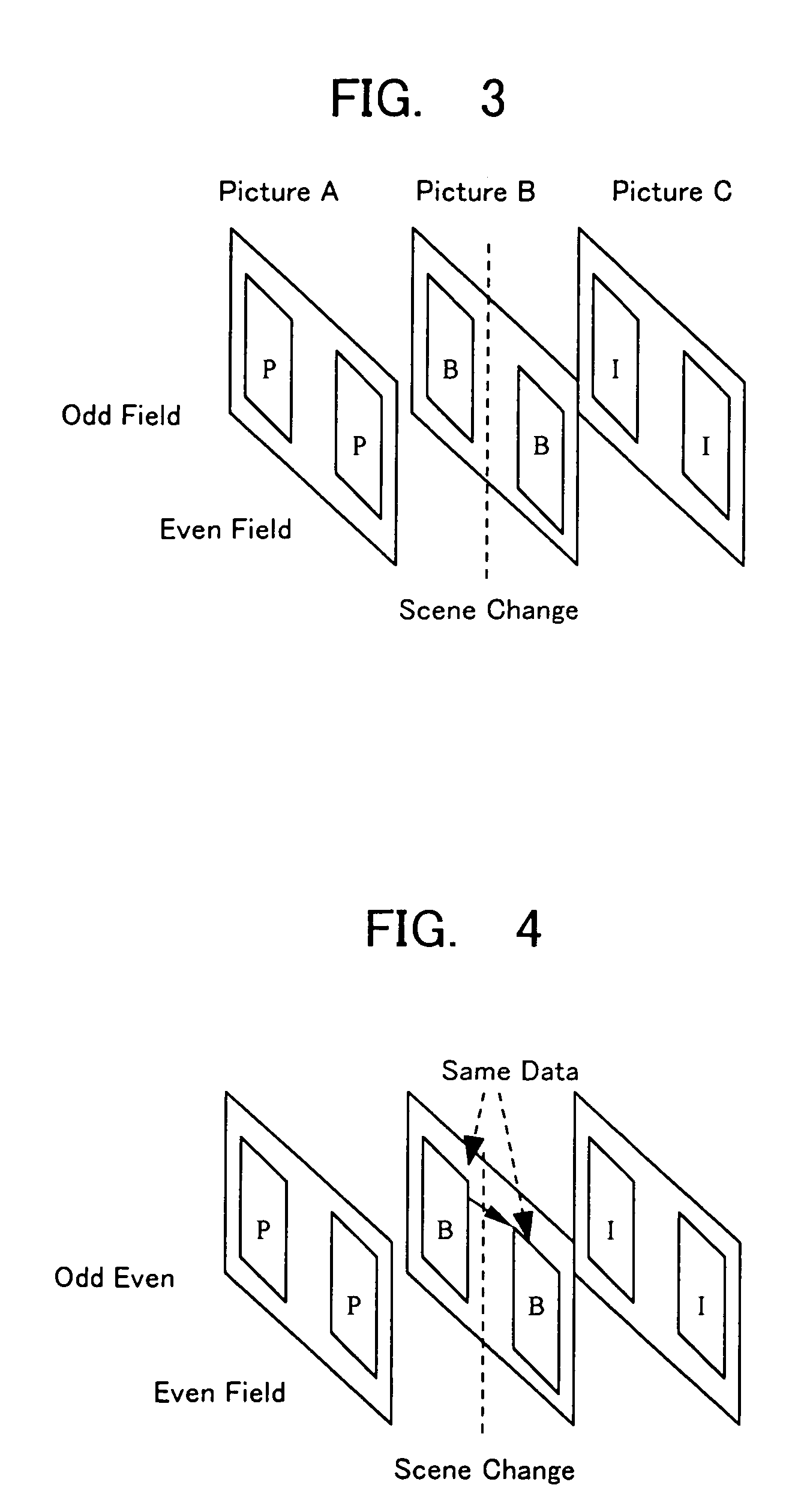

Moving pictures encoding method and apparatus for detecting a scene change between fields of an interlaced image

InactiveUS7453941B1Good picture quality encodingEfficient codingColor television with pulse code modulationColor television with bandwidth reductionPattern recognitionInterlaced video

An encoding method, which achieves encoding efficiency, and good picture quality encoding even when there exists a picture in which a scene change occurs within an interlaced frame, is provided. A moving pictures encoding method treats a frame of interlaced image input signals as a picture, and performs prediction and encoding for this picture in macro-block units from a picture of both a forward picture, which is temporally in the past, and a backward picture, which is in the future. When performing encoding in accordance with the above-mentioned bi-directional picture, the method performs inter-field motion prediction, which treats as a unit a field, which divides each picture in macro-blocks into either odd numbers or even numbers of pixel scanning lines of this frame, and as a prediction mode, selectively switches in picture units between using prediction from a forward field motion vector for one field, and using prediction from a backward field motion vector for the other field, generates a predictive picture corresponding to the selected prediction mode, and encodes the input signal using the generated predictive picture.

Owner:FUJITSU LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com