Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

180 results about "Triple modular redundancy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

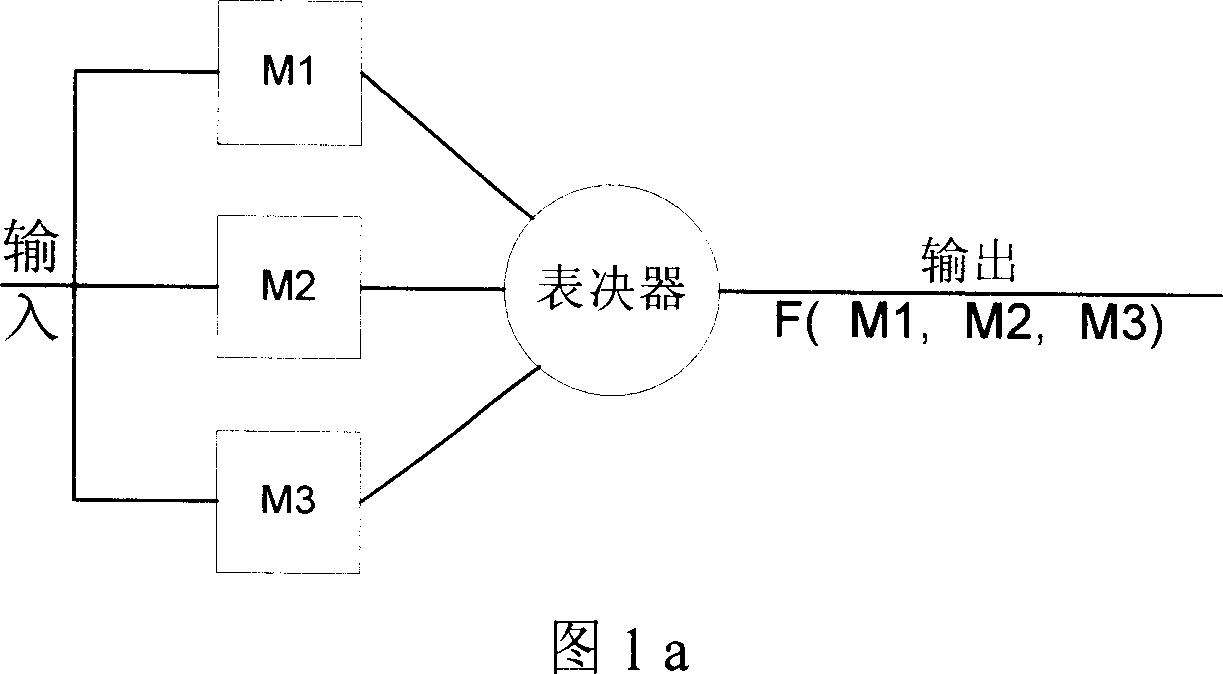

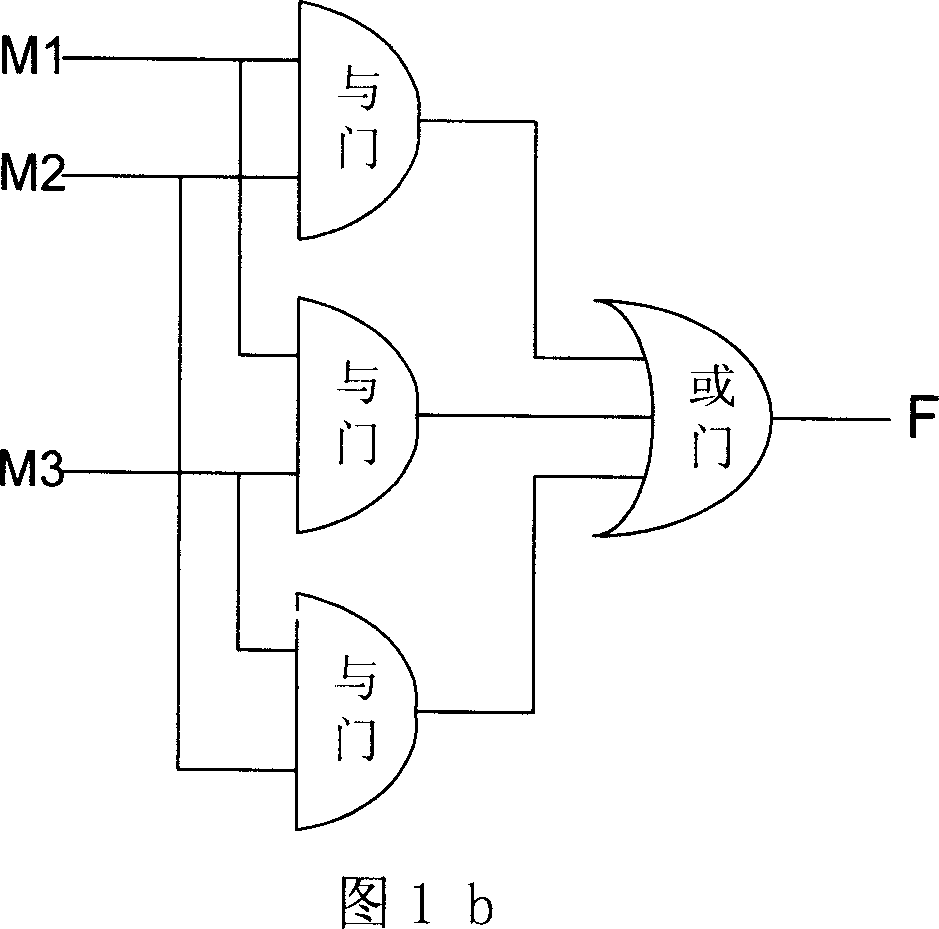

In computing, triple modular redundancy, sometimes called triple-mode redundancy, (TMR) is a fault-tolerant form of N-modular redundancy, in which three systems perform a process and that result is processed by a majority-voting system to produce a single output. If any one of the three systems fails, the other two systems can correct and mask the fault.

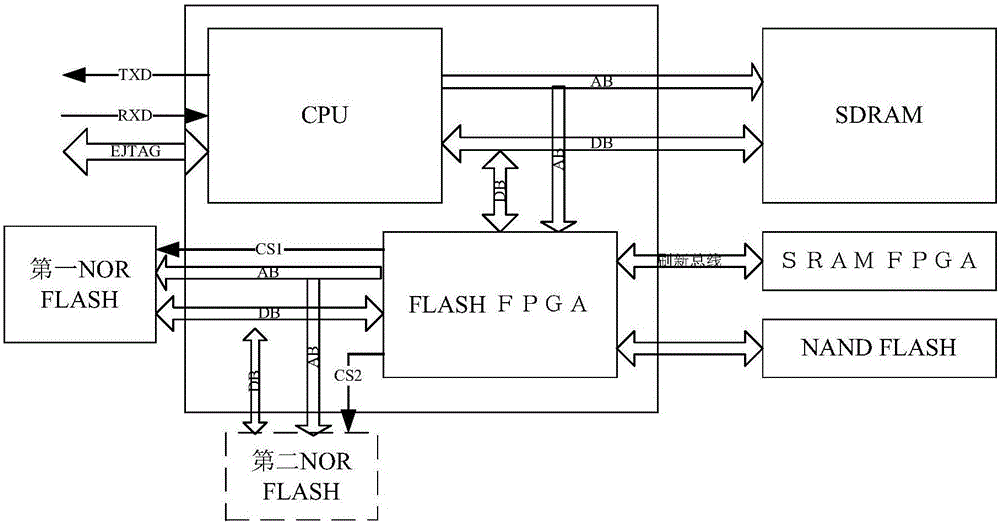

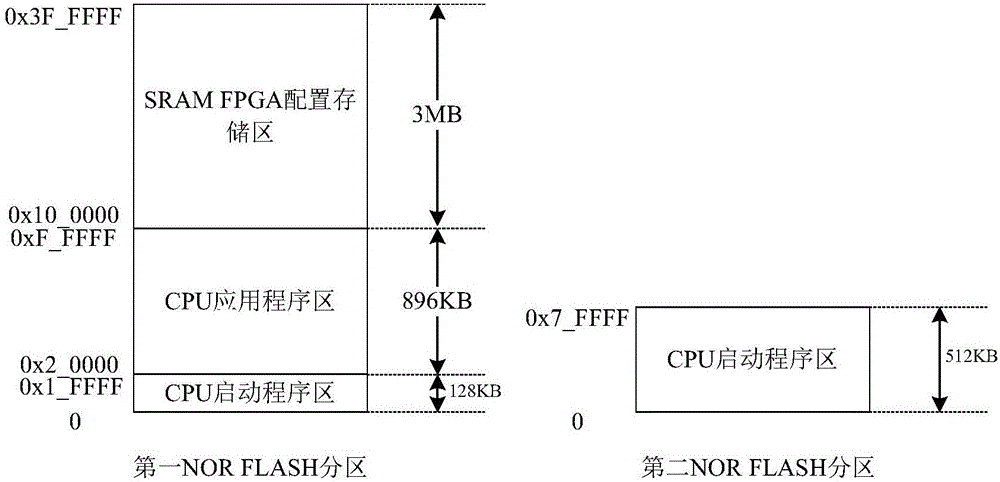

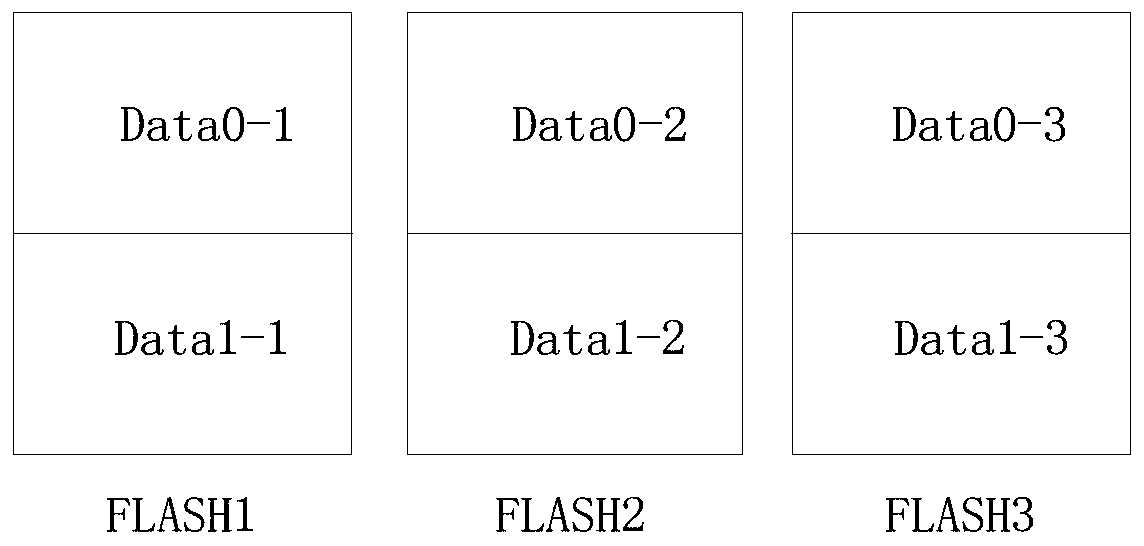

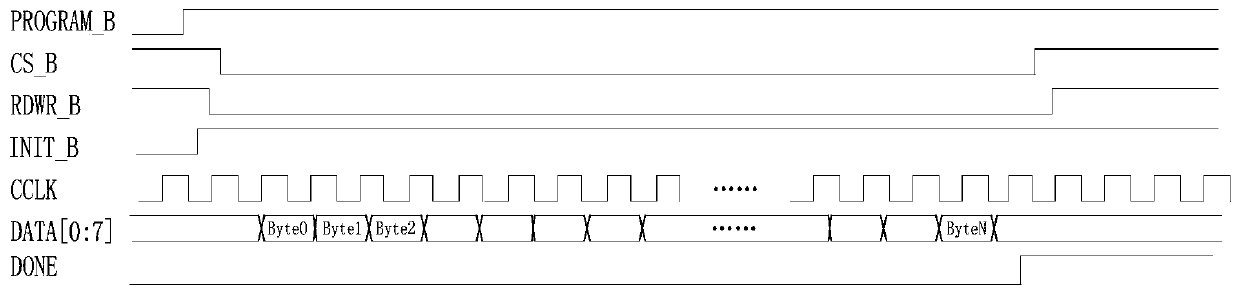

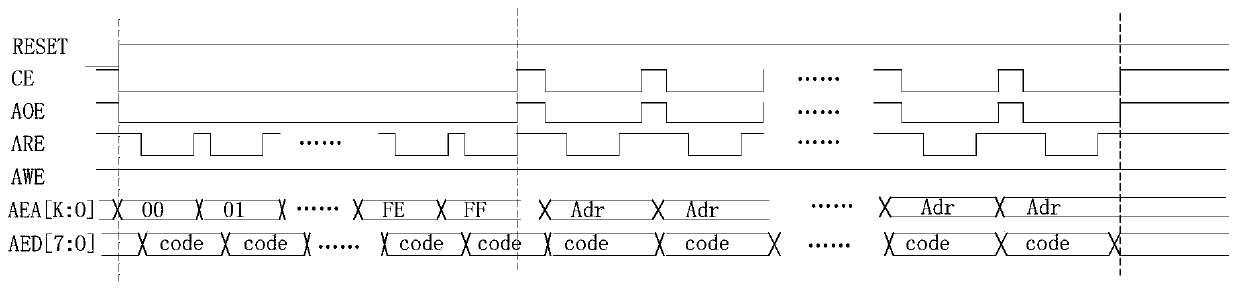

Configuration method and system used for satellite-bone SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array) working on track for long time

InactiveCN102779079AAvoid misconfigurationsReduce switching timesFault responseStatic random-access memoryUninterruptible power supply

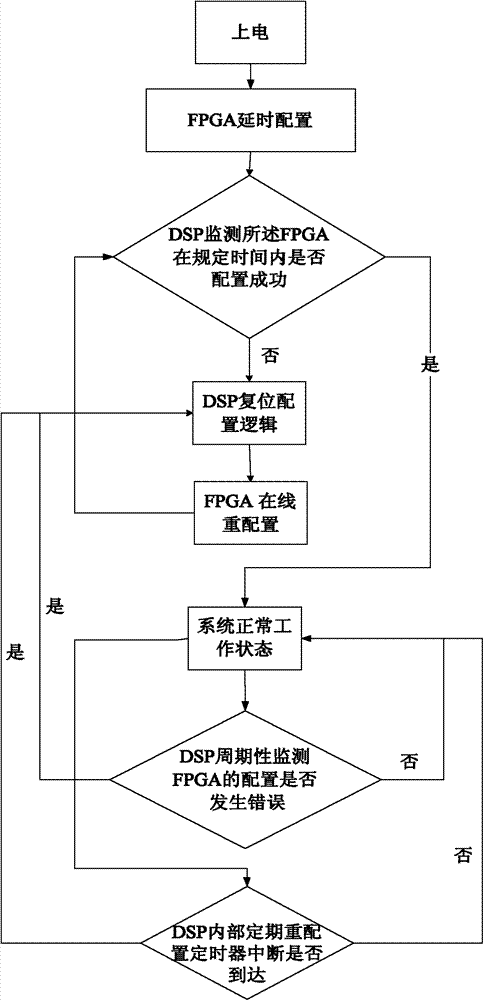

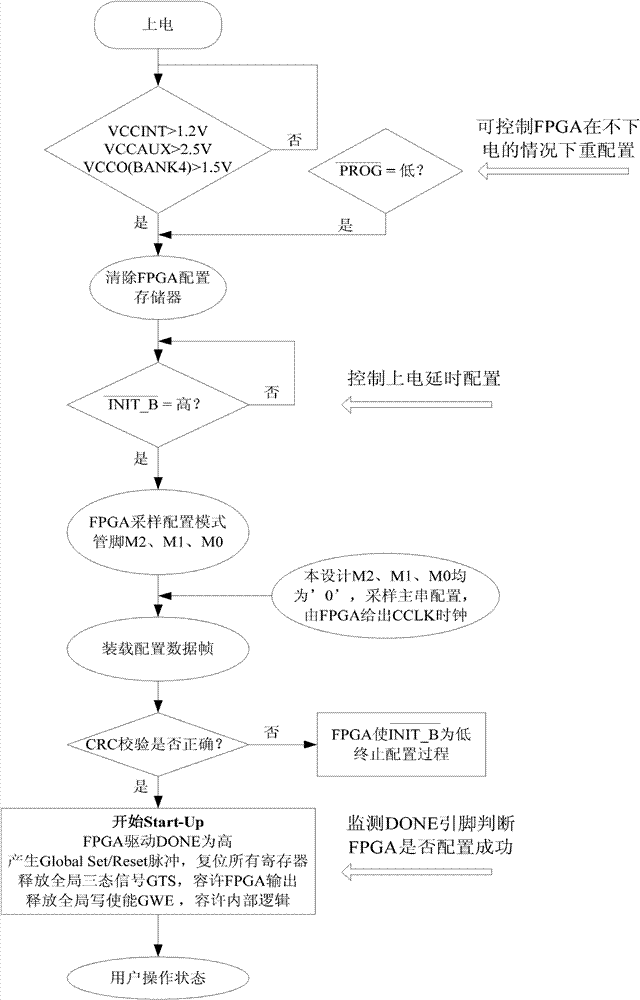

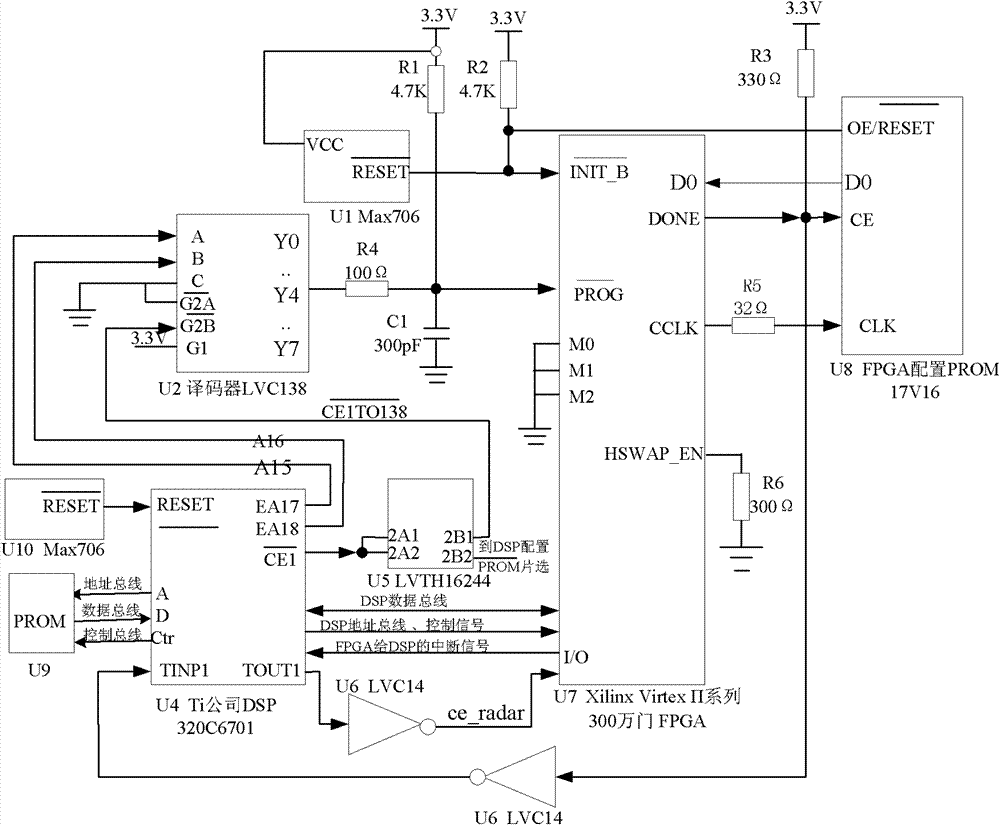

The invention relates to a configuration method and system used for a satellite-bone SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array) working on track for a long time. The method comprises the following steps: electrification: a delay configuration strategy is adopted for the FPGA to avoid configuration errors caused by power supply fluctuation generated at the moment of the boot; configuration process monitoring: the configuration condition of the FPGA is monitored by a DSP (Digital Signal Processor), and when the configuration of the FPGA is monitored to be normally completed, the FPGA is informed of entering a normal measurement state by the DSP, and an on-line reconfiguration step is started if the configuration of the FPGA is monitored to be not completed in time; reconfiguration: a low-level pulse larger than 300ns is controlled to be applied to a configuration reset pin of the FPGA by the DSP under the condition of uninterruptible power supply, and then the configuration process is automatically completed by the FPGA; normal working process monitoring: whether the configuration of the FPGA is correct or not is monitored regularly by the DSP in a normal working process, and FPGA on-line reconfiguration is started by the DSP if the configuration of the FPGA is wrong; and regular reconfiguration: a triple modular redundancy design is adopted for the FPGA, and is matched with the regular reconfiguration to improve the reliability of the FPGA.

Owner:NAT SPACE SCI CENT CAS

Single event upset-resistant satellite-borne data processing system and method

ActiveCN106557346AReduce areaLow costProgram loading/initiatingRedundant data error correctionData processing systemData treatment

Owner:NAT SPACE SCI CENT CAS

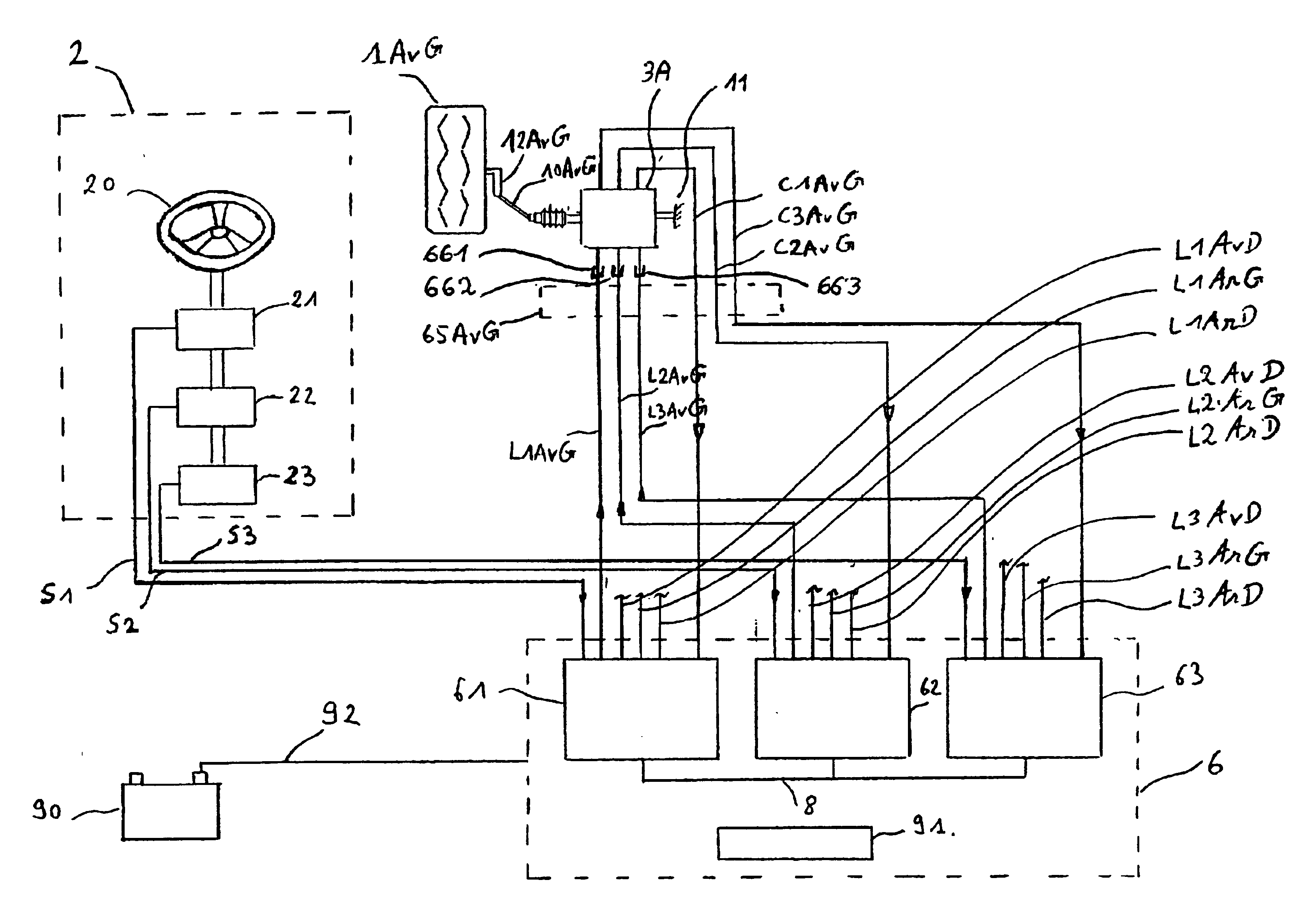

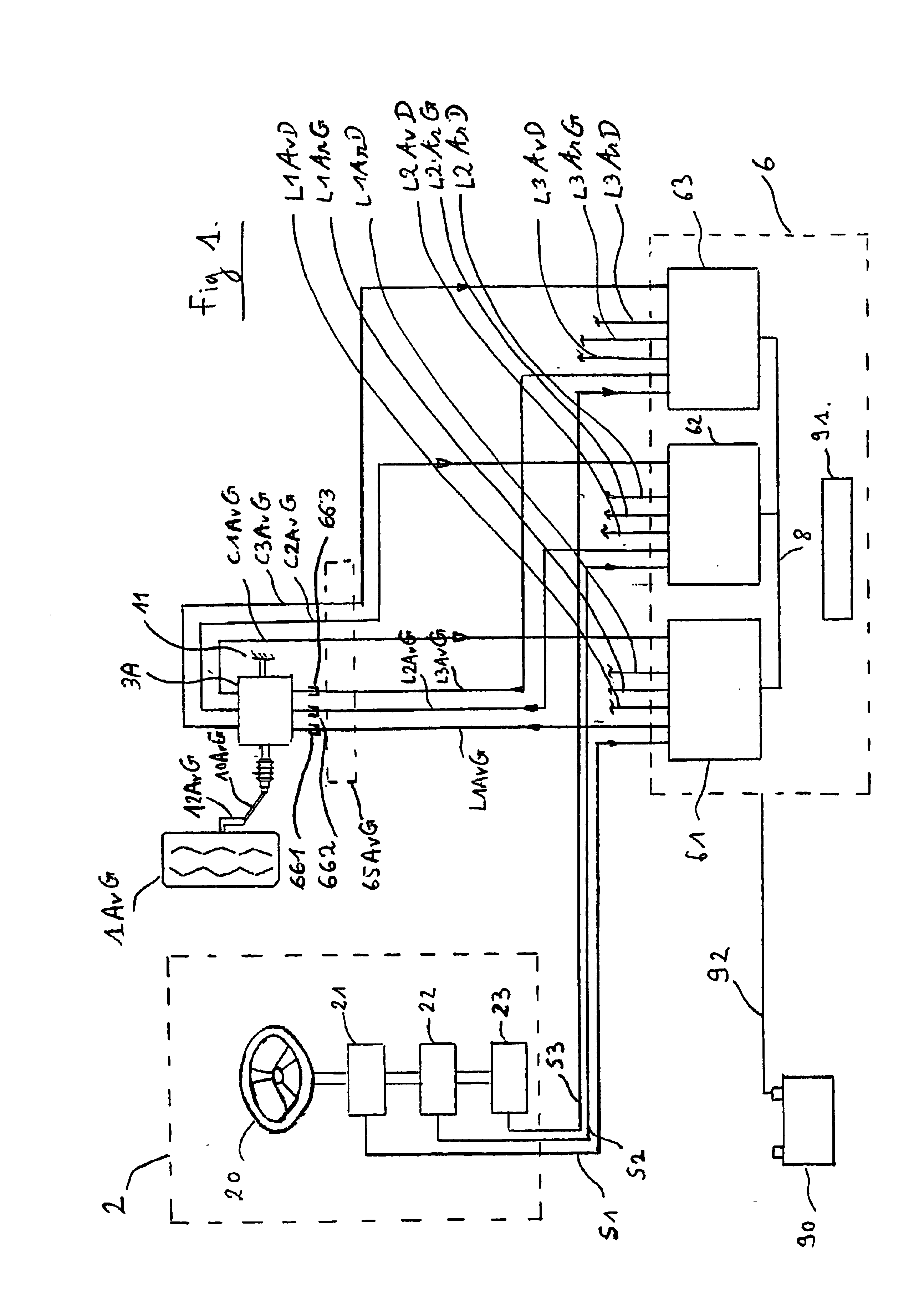

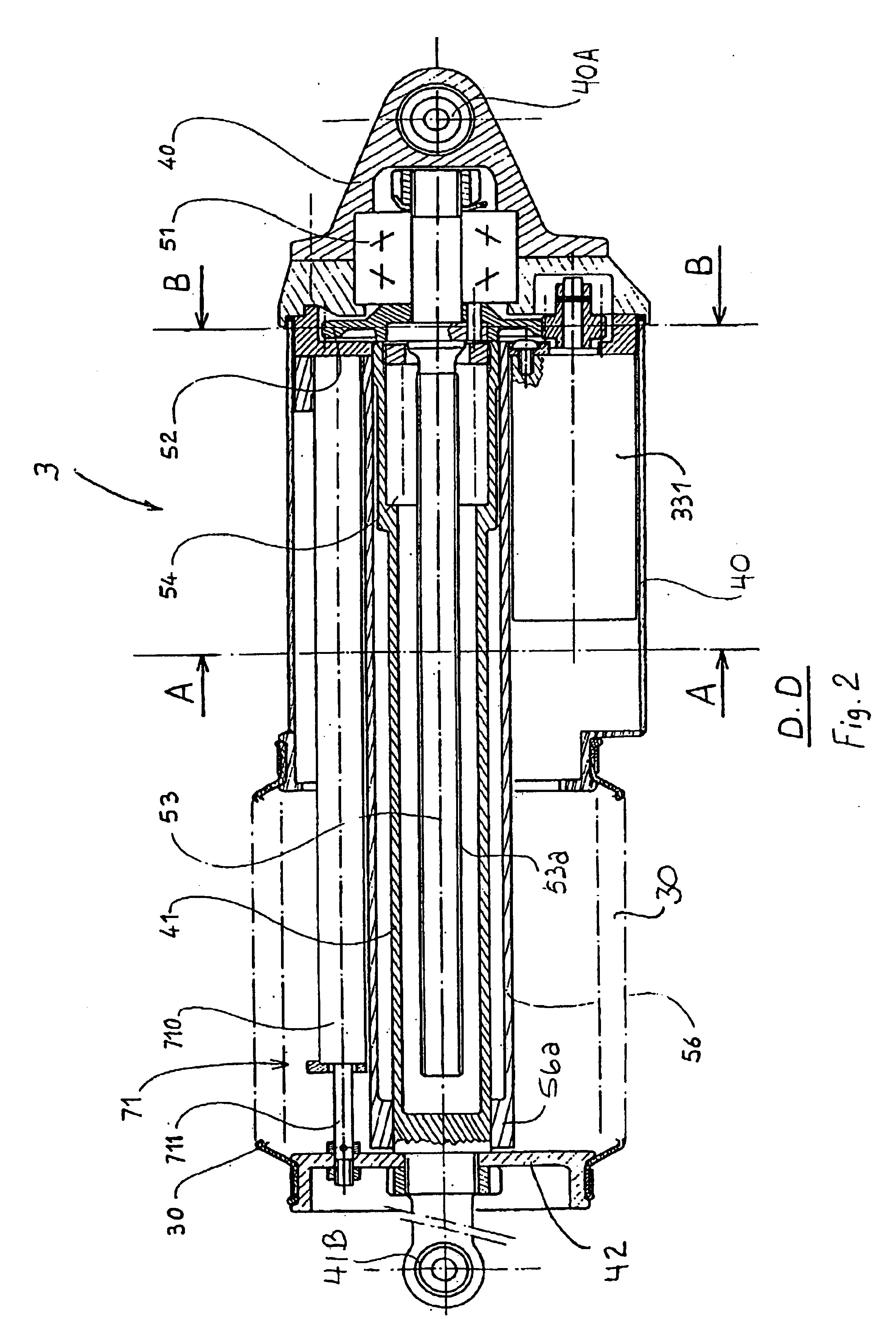

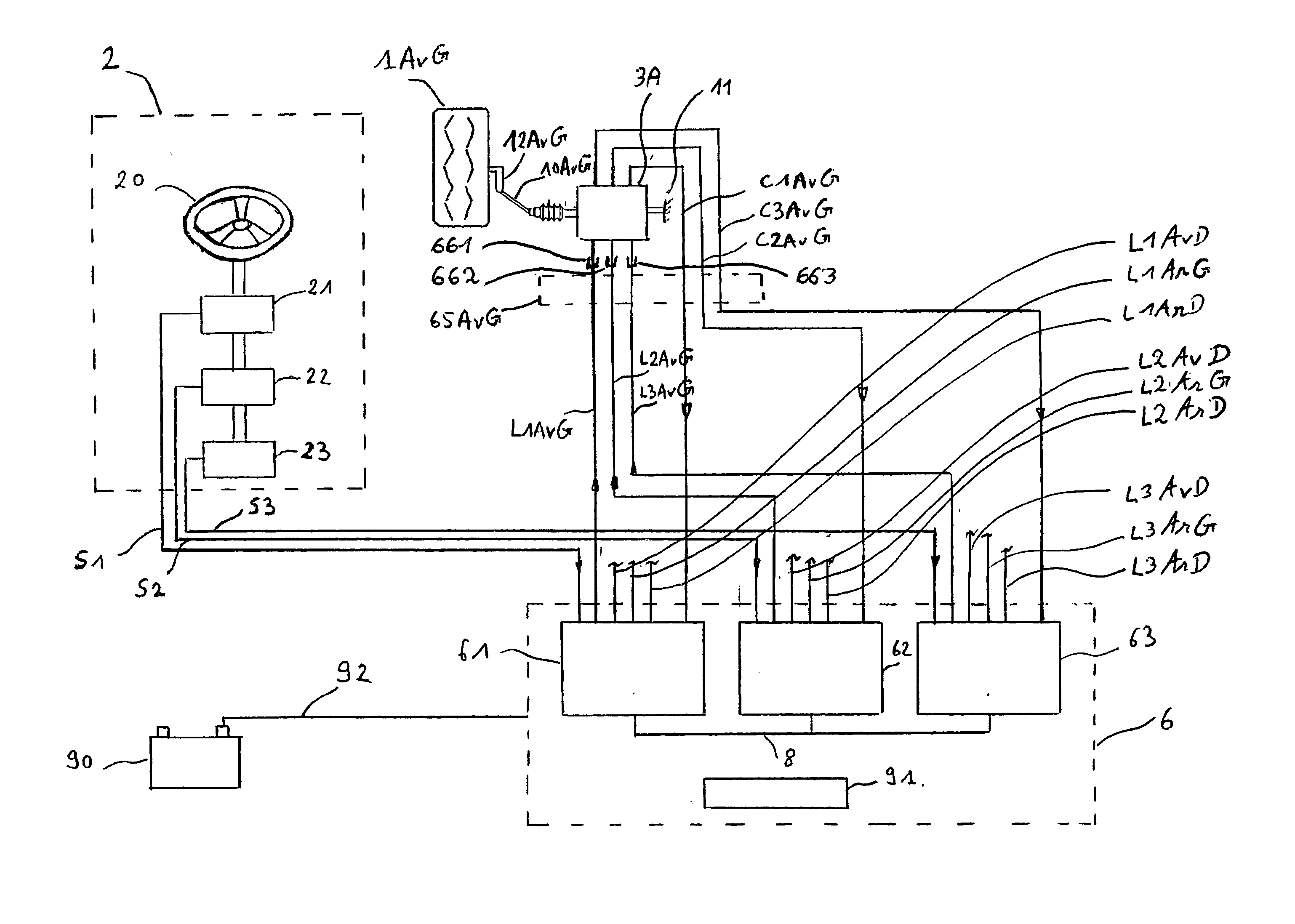

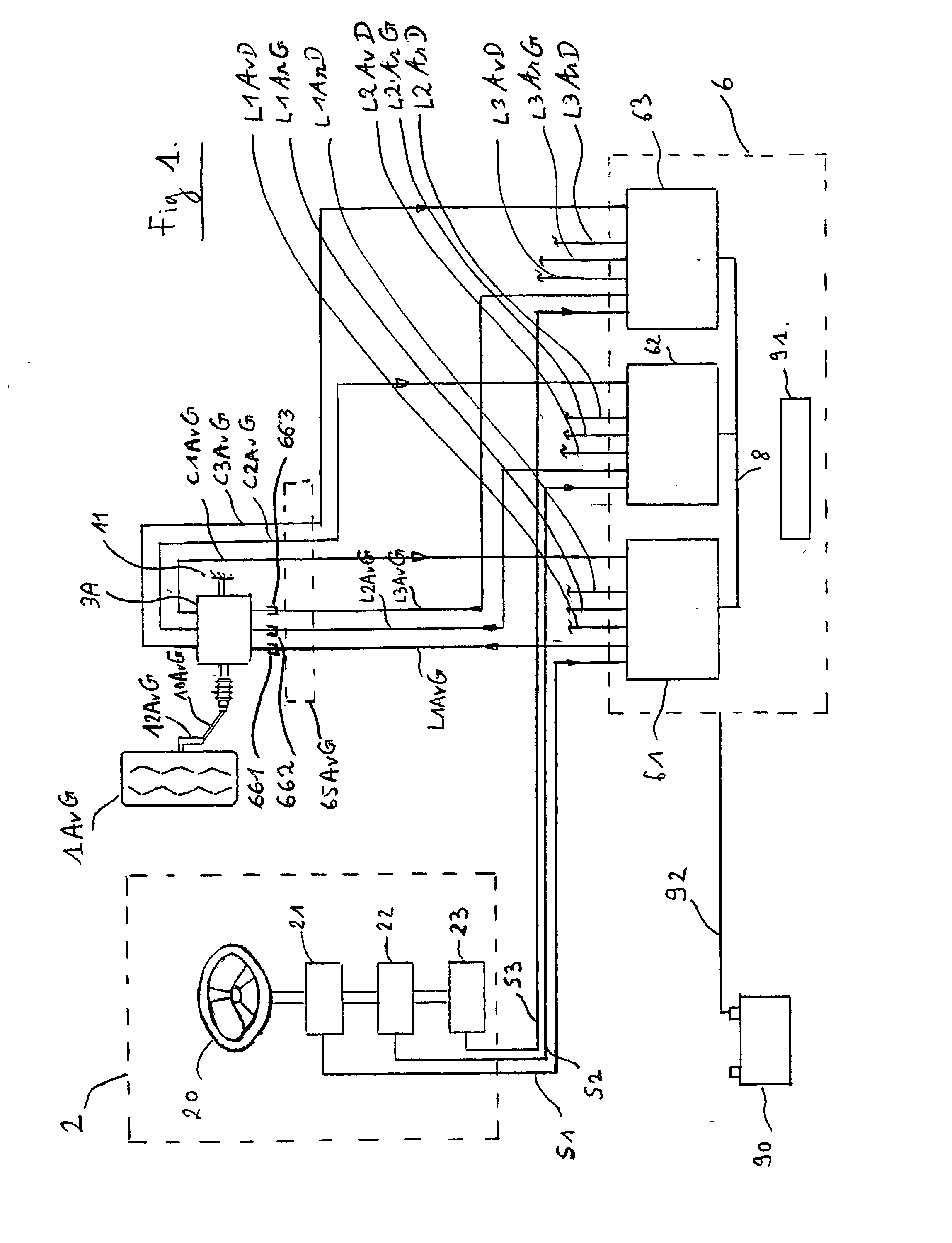

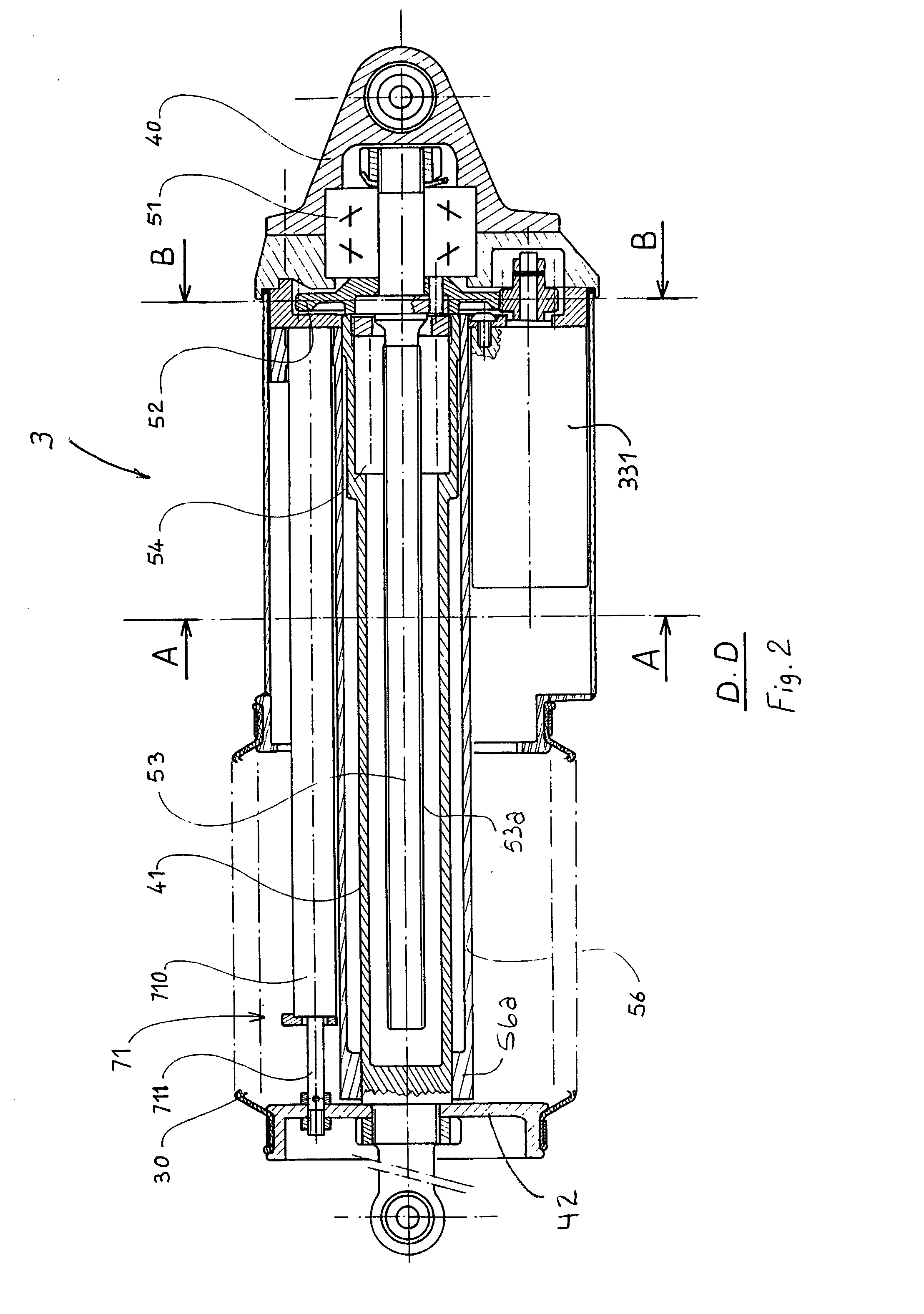

Electrical steering for vehicle, with triple redundancy

A steering system for a vehicle includes a steerable wheel 1 capable of being steered, a steering wheel 20, and an electrical actuator 3 for altering the steering angle of the steerable wheel. The electrical actuator 3 has three electric motors 31, 32, 33 which act in parallel and three controllers 61, 62, 63 which operate in parallel, each forming part of an electrical control channel for the steering angle. The controller of each electrical channel receives one of the three electrical signals in the control channels and is connected to one of the position sensors and drives one of the electric motors in order to set the said steering angle. The torques delivered by the respective motors are added together in normal operation. The system also includes an interconnection bus 8 for the three electrical control channels, and means for detecting a discrepancy in the status of one electrical channel with respect to the other two, in order to give a malfunction warning and maintain operation in a downgraded mode in the event of a discrepancy.

Owner:CONCEPTION & DEV MICHELIN SA

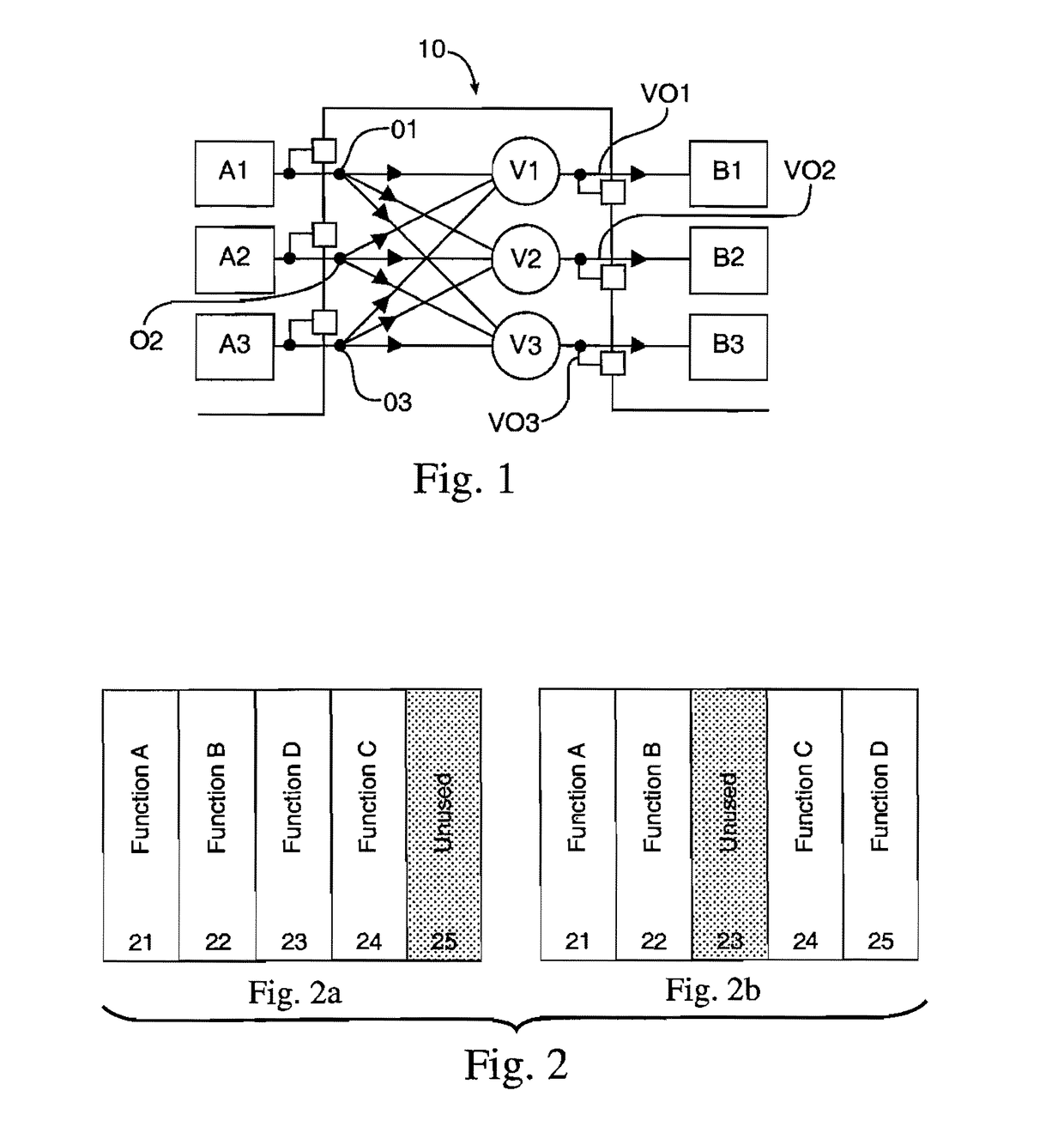

Relocatable field programmable gate array bitstreams for fault tolerance

InactiveUS7906984B1Reliability increasing modificationsSolid-state devicesTriple modular redundancyMicroprocessor

A Field Programmable Gate Array (FPGA) circuit capable of operating through at least one fault. The FPGA circuit includes a configuration memory and an embedded microprocessor. The embedded microprocessor having access to the configuration memory, static modules, at least one relocatable module, and at least one spare module. The relocatable module being relocatable from a first target area to a second target area. The relocatable module being relocatable by manipulating a partial bitstream with the embedded microprocessor. The microprocessor calculating a plurality of bitstream changes, to relocate the at least one relocatable module using at least triple modular redundancy (TMR).

Owner:AIR FORCE US SEC THE THE

Electrical steering for vehicle, with triple redundancy

A steering system for a vehicle includes a steerable wheel 1 capable of being steered, a steering wheel 20, and an electrical actuator 3 for altering the steering angle of the steerable wheel. The electrical actuator 3 has three electric motors 31, 32, 33 which act in parallel and three controllers 61, 62, 63 which operate in parallel, each forming part of an electrical control channel for the steering angle. The controller of each electrical channel receives one of the three electrical signals in the control channels and is connected to one of the position sensors and drives one of the electric motors in order to set the said steering angle. The torques delivered by the respective motors are added together in normal operation. The system also includes an interconnection bus 8 for the three electrical control channels, and means for detecting a discrepancy in the status of one electrical channel with respect to the other two, in order to give a malfunction warning and maintain operation in a downgraded mode in the event of a discrepancy.

Owner:CONCEPTION & DEV MICHELIN SA

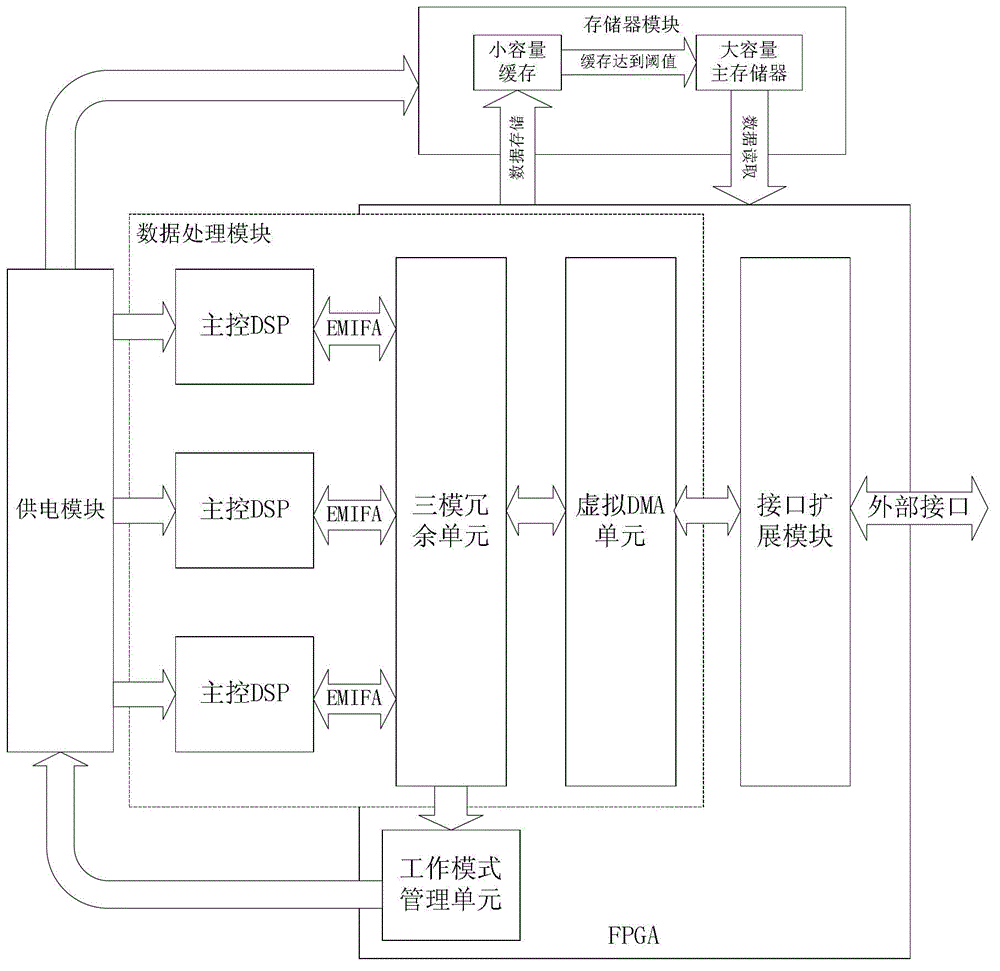

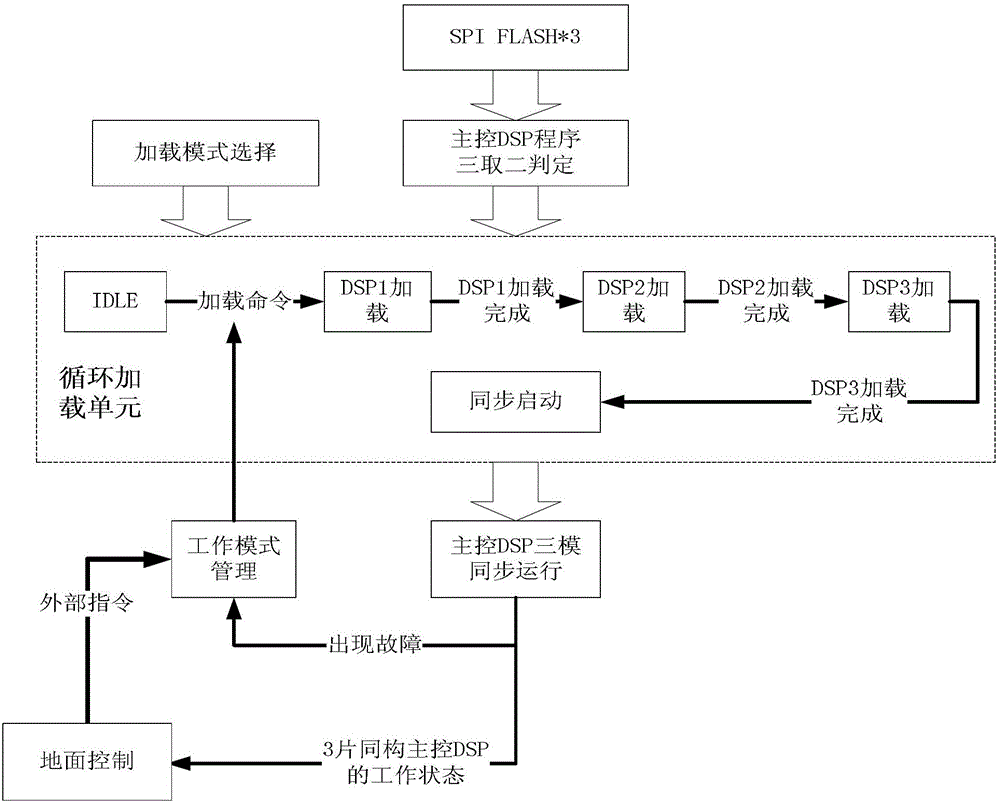

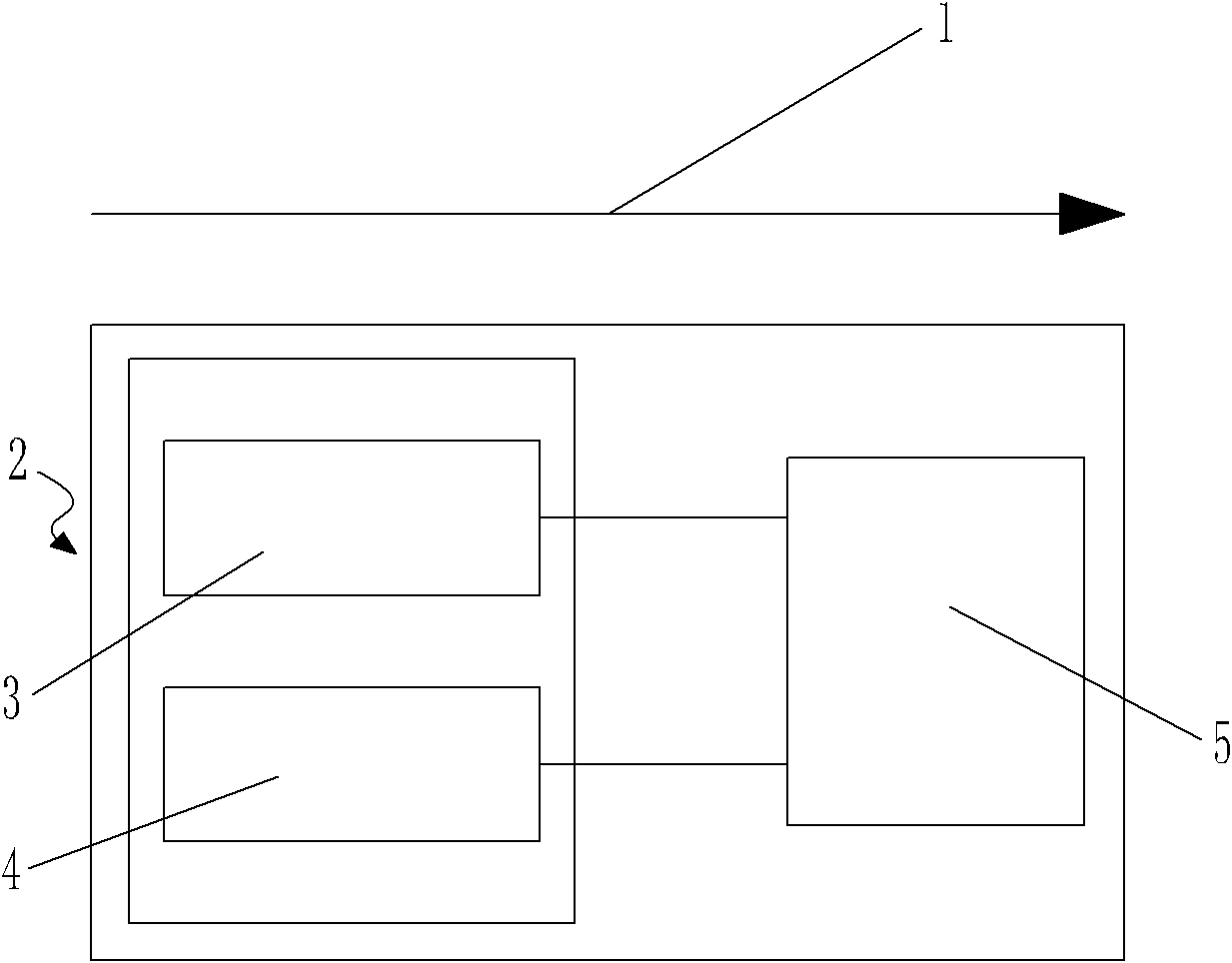

Triple modular redundancy based satellite-borne comprehensive electronic system

ActiveCN102945217AImprove reliabilityExtend your lifeElectric digital data processingProcess moduleData memory

The invention discloses a triple modular redundancy based satellite-borne comprehensive electronic system used for data processing and data storage of a pico-satellite. The triple modular redundancy based satellite-borne comprehensive electronic system comprises a data processing module, a data memory module, an interface extension module and a power supply module, wherein the data processing module is connected with the interface extension module, and is connected with the data memory module; and the output of the power supply module is respectively connected with the input of the data processing module and the input of the data memory module. The data processing module fuses the principle of triple modular redundancy, so as to have high reliability, and avoid influence due to random errors to a certain extent; the data memory module adopts a cache and main memory combined manner, so as to realize high-capacity and long-life targets of a memory module based on the low cost; and the virtue DMA (direct memory access) principle is fused between the data processing module and the interface extension module, so as to simply and effectively solve the problem that the processing capability of the data processing module is wasted because the speed of an external interface of the data processing module is faster than that of an extension interface.

Owner:ZHEJIANG UNIV

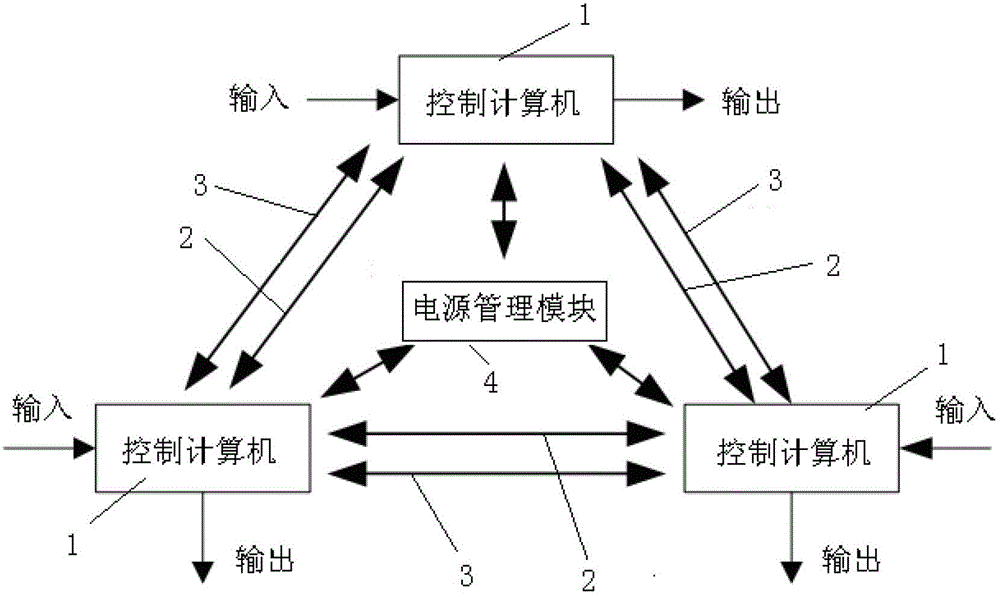

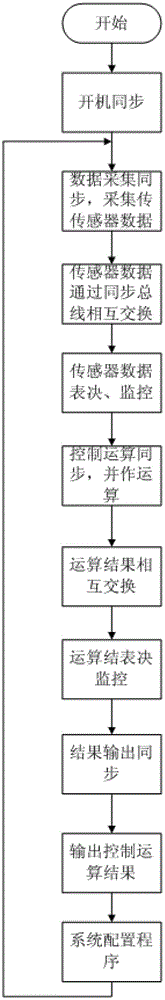

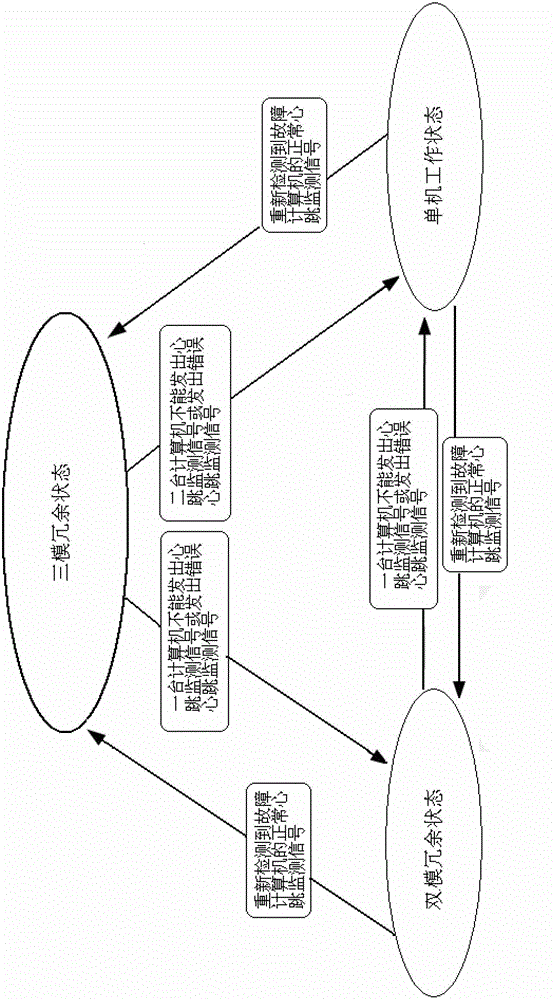

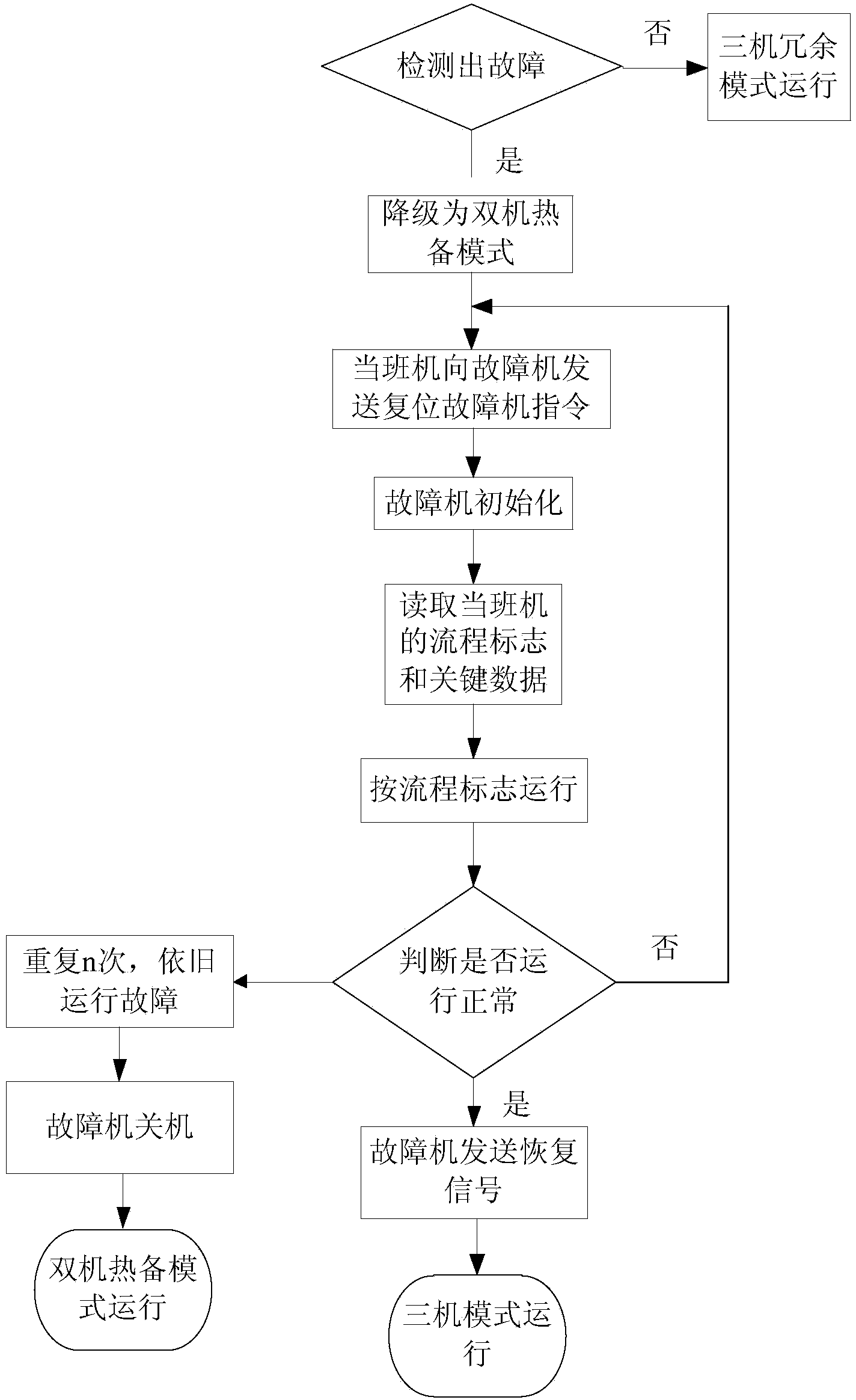

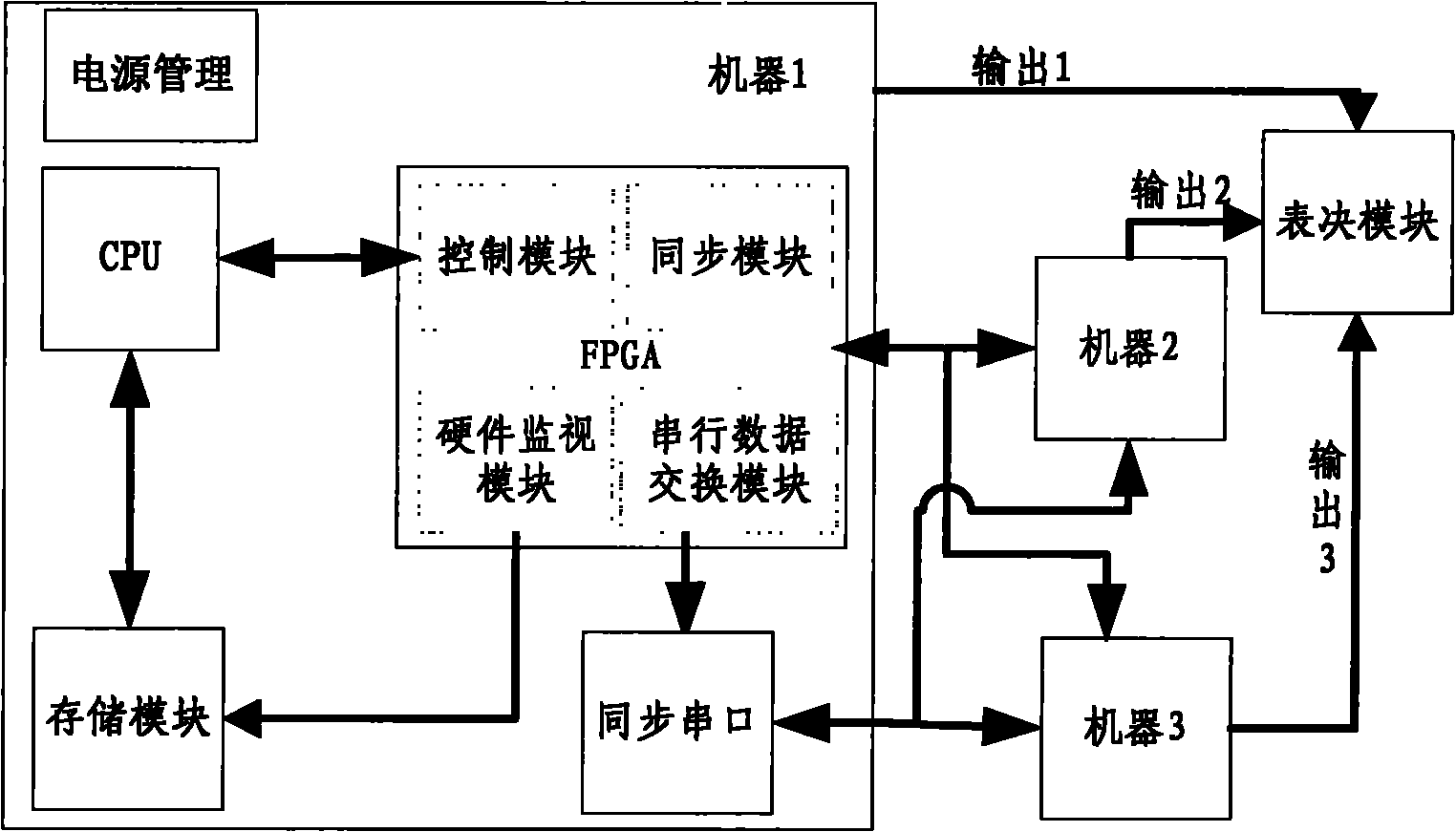

Degradable triple-modular redundancy computer system based on software synchronization

InactiveCN102724083AAuto complete refactoringRealize synchronous acquisitionData switching networksComputer control systemData interchange

The invention discloses a degradable triple-modular redundancy computer system based on software synchronization, relates to a triple-modular redundancy computer control system, and solves the problem that the conventional triple-modular redundancy system is complicated due to addition of an arbitration module. The degradable triple-modular redundancy computer system consists of three same control computers, communication buses, high-speed communication buses and a power management module, wherein the synchronization information transfer and data exchange of the control computers are finished through the communication buses which are connected two by two; the control computers vote for sensor data and control operation results by using a 2-out-of-3 voting algorithm; high-frequency heartbeat monitoring signals of the computers are transferred by interconnecting the high-speed communication buses two by two, and real-time state mutual monitoring of the control computers is realized; the three control computers operate degradation programs, so the degradation operation of a redundancy system is realized; and the three control computers operate reconstruction programs, so the reconstruction operation of the redundancy system is realized. The arbitration module is not required to be added.

Owner:HARBIN ENG UNIV

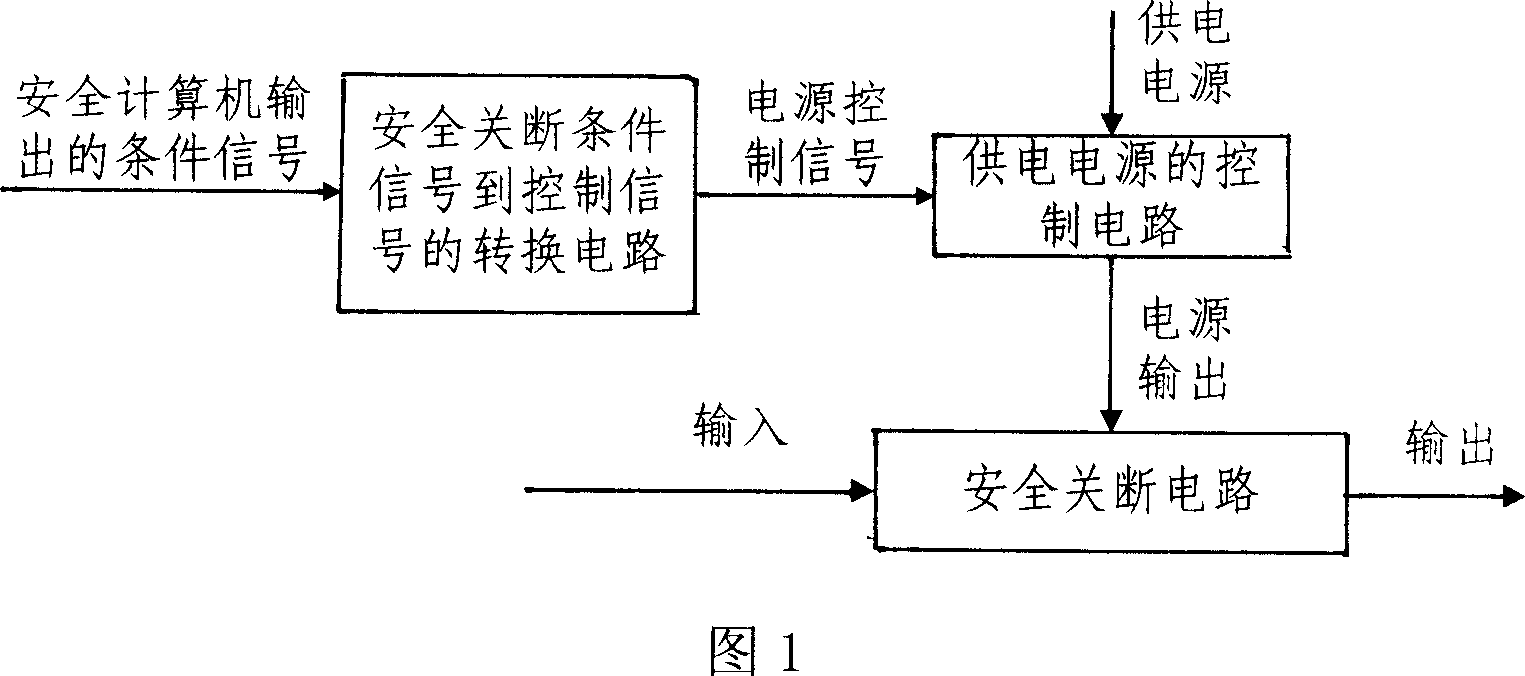

Safety cut-off method and device for output in three-mould redundancy safety computer

ActiveCN101046678AImprove reliabilityImprove securitySafety arrangmentsRedundant hardware error correctionEngineeringTriple modular redundancy

The present invention discloses a safe turn-off method for output in triple modular redundancy safety computer. Said invention mainly utilizes the safe turn-off condition signal outputted by triple modular redundancy safety computer to make judgement, and utilizes several groups of safe turn-off condition signals to make decision and judge that it has need of making safe turn-off or not. It is characterized by that said invention utilizes a change-over circuit from dynamic signal to level signal to generate turn-off signal, and can directly control the power supply of modular output safe turn-off circuit so as to implement safe turn-off output.

Owner:TRAFFIC CONTROL TECH CO LTD

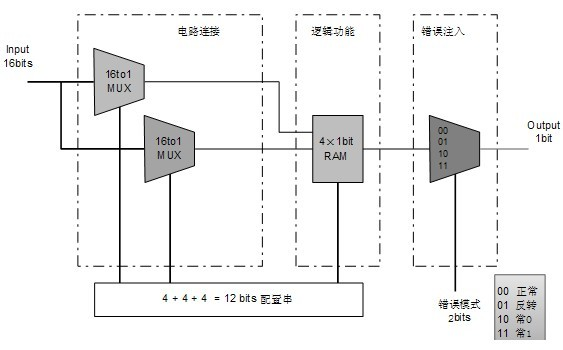

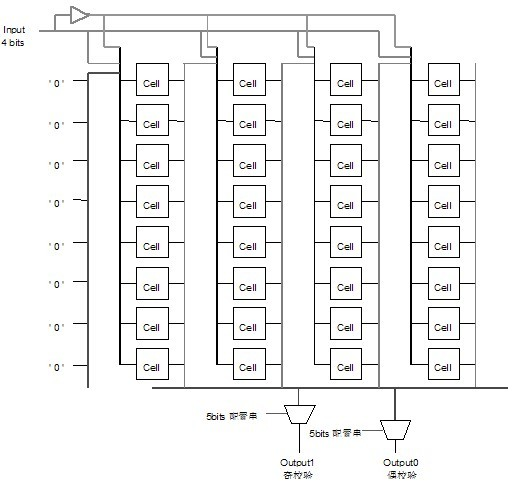

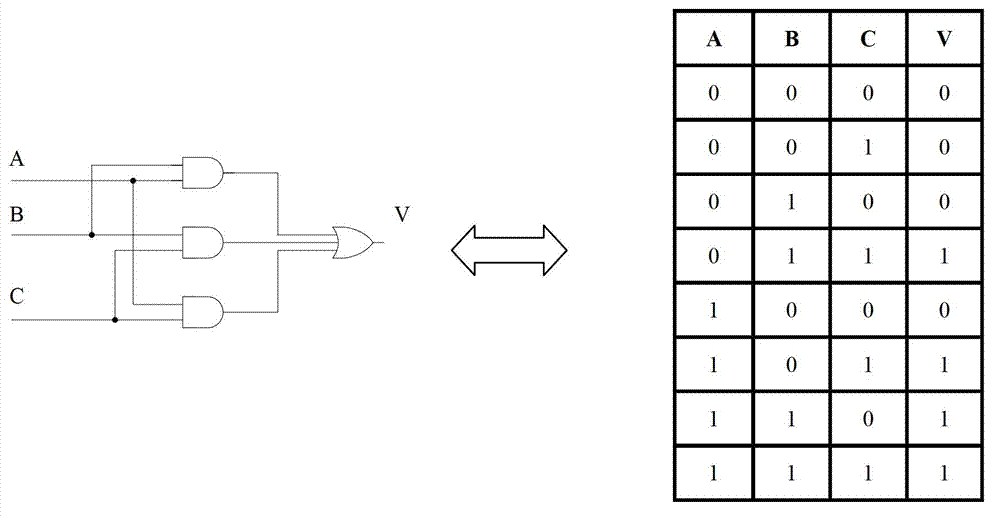

Isomerous triple modular redundancy fault-tolerant method based on LUT (Look-up Table) evolvable hardware

InactiveCN102135928ACorrectness monitoringRich diversityRedundant hardware error correctionLogic cellComputer module

The invention relates to the technical field of evolvable hardware and fault tolerance, especially to an isomerous triple modular redundancy fault-tolerant method based on LUT (Look-up Table) evolvable hardware. In the invention, basic logic units implemented based on LUT are constructed and constitute a virtual reconfigurable circuit; a software / hardware cooperative genetic algorithm is used forautomatically searching for three configuration strings meeting conditions; data is continuously input to three target circuits through an excitation signal generated inside hardware so that an isomerous triple modular redundancy module is under the state of running inside hardware; and some faults are input to the virtual reconfigurable circuit in an analog manner in the form of key interruptionin order to observe fault detection, fault tolerance and self-repairing procedure of the system. The method provided by the invention has excellent expandability, and can enrich the diversity of the target circuit and improve the fault-tolerant capability of the entire redundancy fault-tolerant system.

Owner:WUHAN UNIV

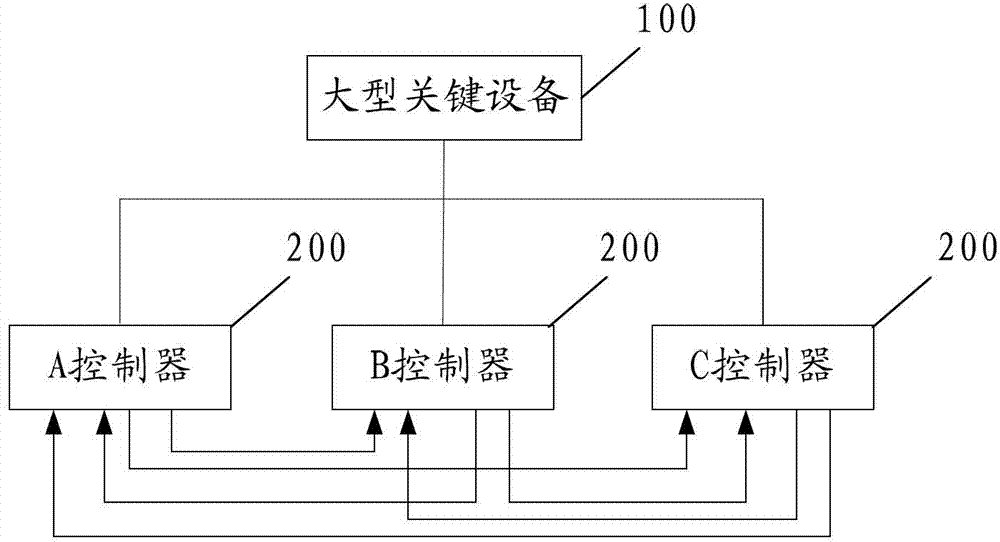

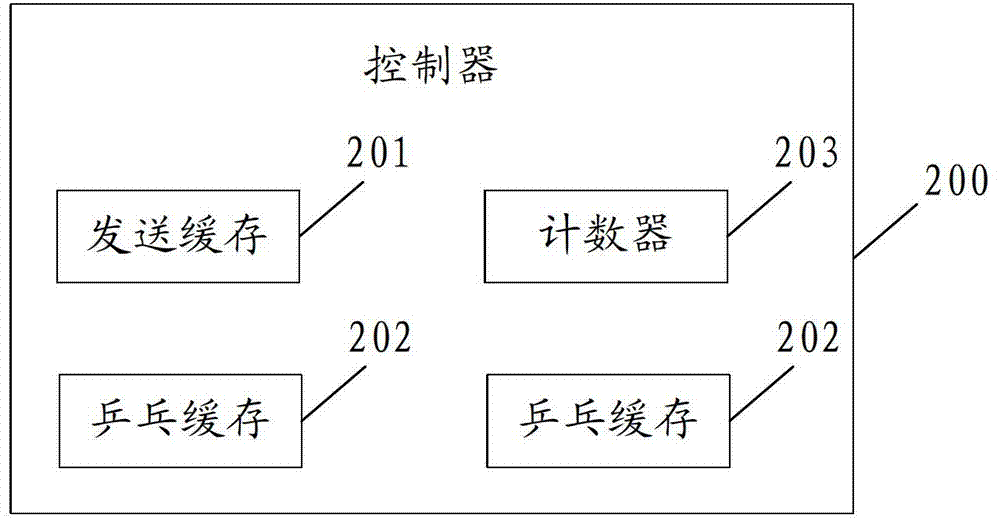

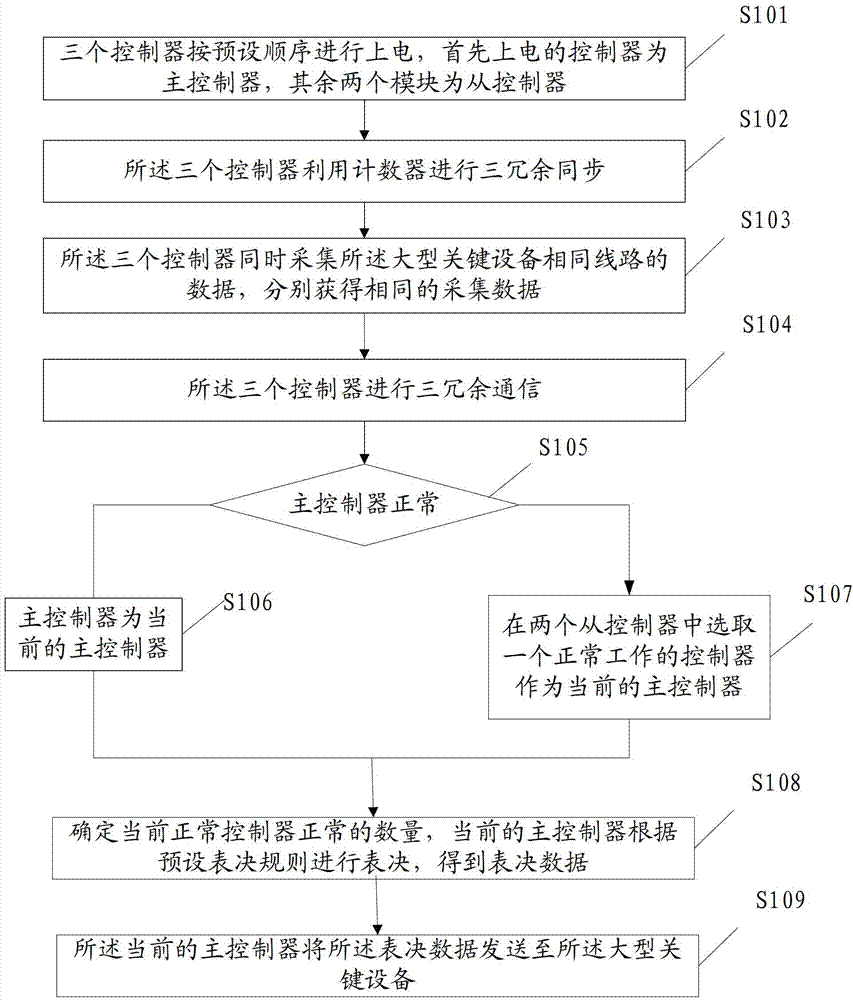

Method and system for controlling triple redundancy

ActiveCN103399546AMeet increasing demandsTotal factory controlProgramme total factory controlFailure probabilityDevice failure

The invention provides a method and a system for controlling triple redundancy. The system comprises large equipment and three controllers connected with the large equipment. With the three controllers, data interaction with the large critical equipment is performed, the same collected data is processed by the three controllers, the collected data of the three controllers is voted by the three controllers after triple redundancy communication, and the voted data are fed back to the large critical equipment. When the controller with high fault-tolerant capability is selected, the probability that one controller is in failure is reduced, and the probability that the three controllers are in failure at the same time is lower, thus the three controllers process the data of the large critical equipment at the same time so that the failure probability of the large critical equipment is reduced as much as possible and the increasing requirement of a client on the large critical equipment is met.

Owner:HANGZHOU HOLLYSYS AUTOMATION +1

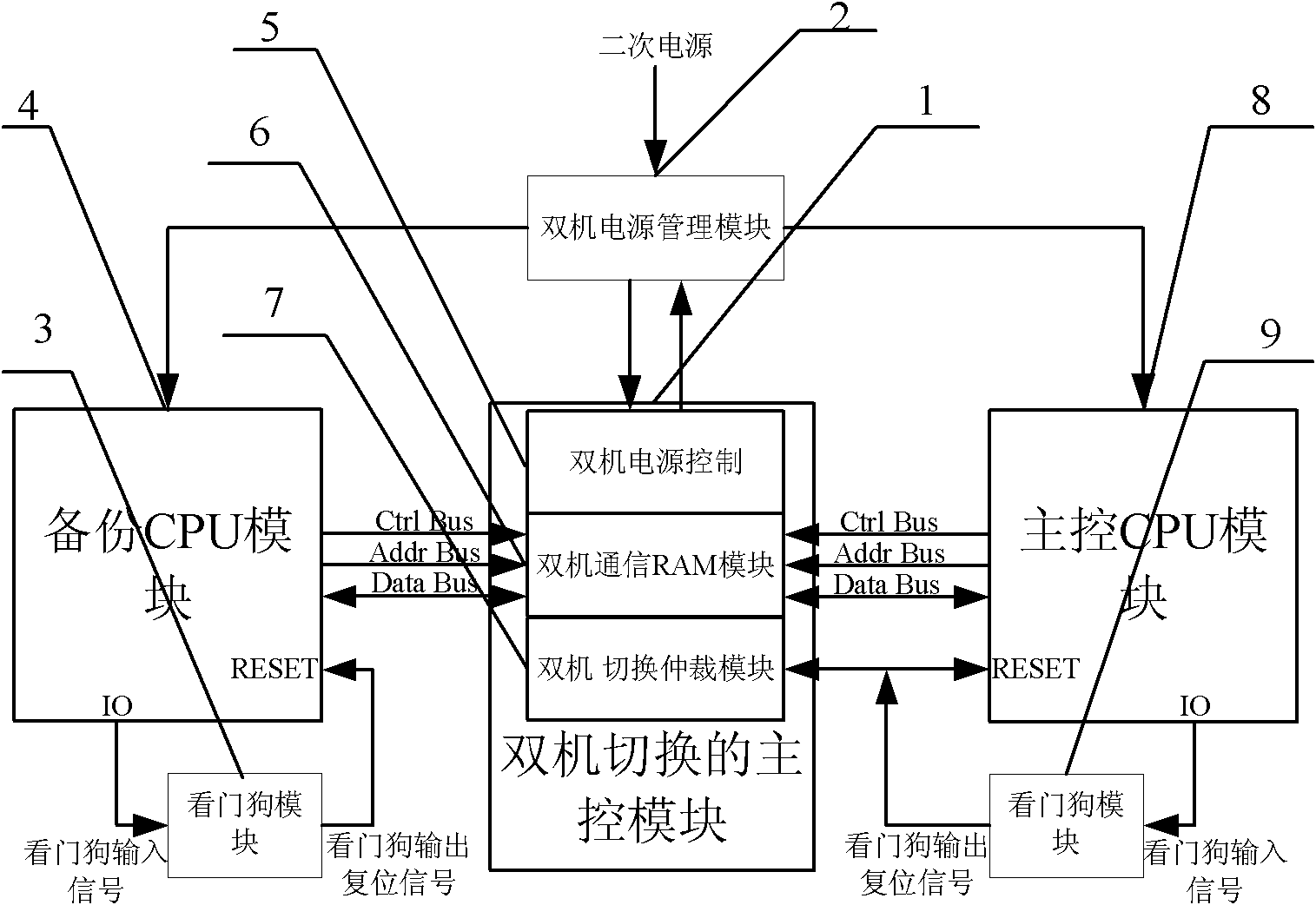

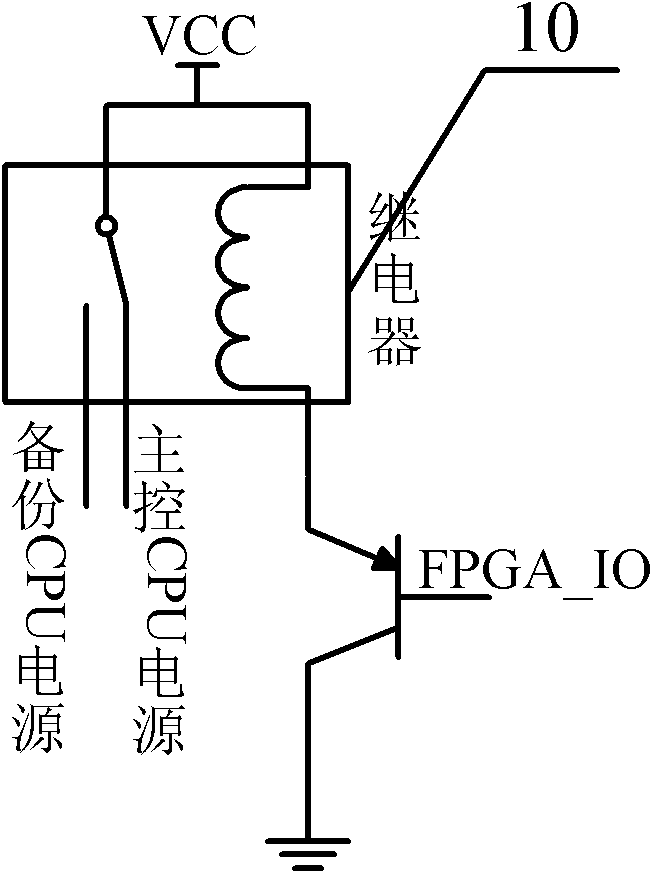

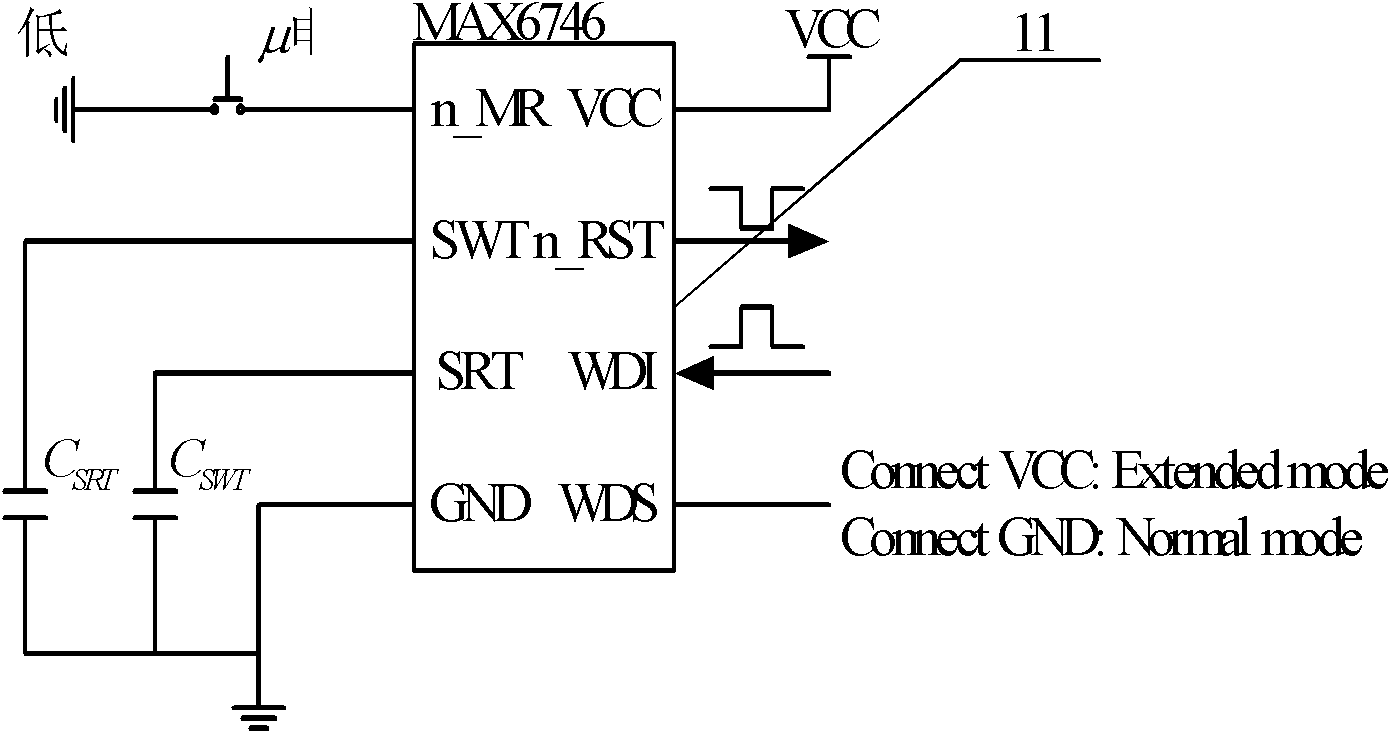

Dual-computer cold-standby system of attitude and orbit control computer

InactiveCN102331786AReduce power consumptionImprove stabilityAttitude controlRedundant hardware error correctionCold standbyStatic random-access memory

The invention discloses a dual-computer cold-standby system of an attitude and orbit control computer. The dual-computer cold-standby system comprises a dual-computer switched main control module, a dual-computer power management module, central processing unit (CPU) modules and watchdog modules, wherein two CPU modules are totally identical and have the respective watchdog modules; and the CPU modules are reset during software runaway. The CPU modules adopt an architecture of combination of an advanced reduced instruction set computer (RISC) machine (ARM) and a field programmable gate array (FPGA), and a triple modular redundancy (TMR) voting module in the FPGA performs voting correction on a signal in a static random access memory (SRAM), so the reliability of the ARM during program running is improved. In a normal mode, a standby CPU module is in a non-energizing state; the dual-computer switched main control module performs fault detection on a main control CPU module; when an irreversible fault of the main control CPU module is determined, computer switching operation is performed; with the dual-computer power management module, power switching between the main control CPU module and the standby CPU module is realized; relevant parameters of the field information and a running application program, which are stored by a dual-computer communication random access memory (RAM) module in real time, of the main control CPU module are used by the standby CPU module, so the inheritance of a control process is realized.

Owner:BEIHANG UNIV

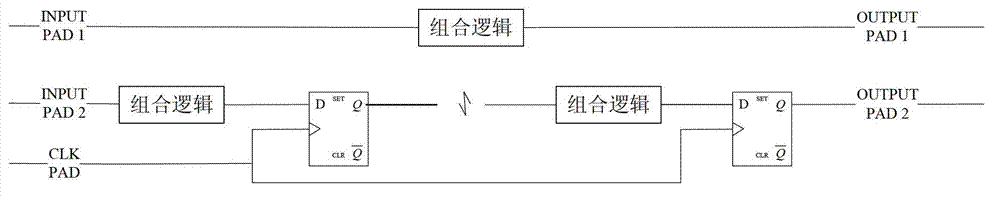

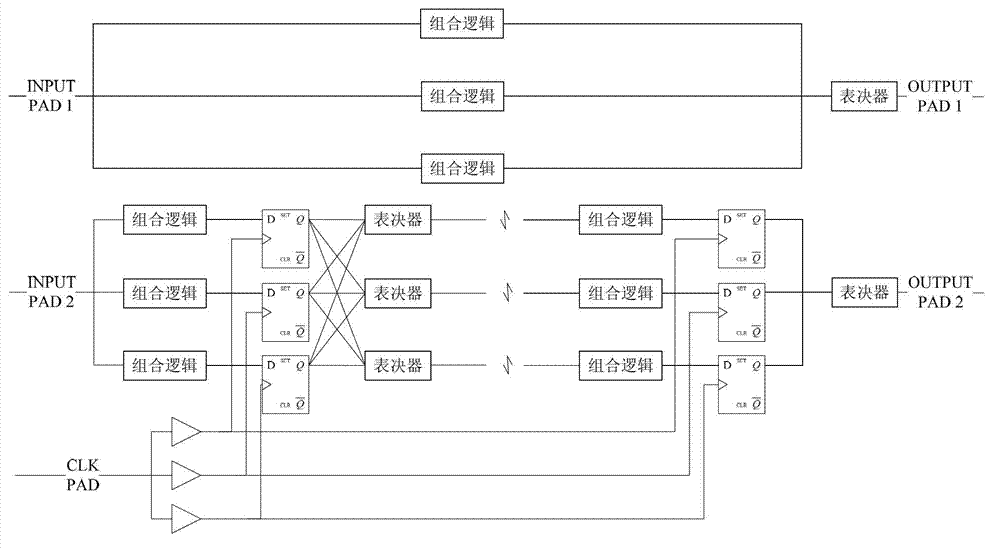

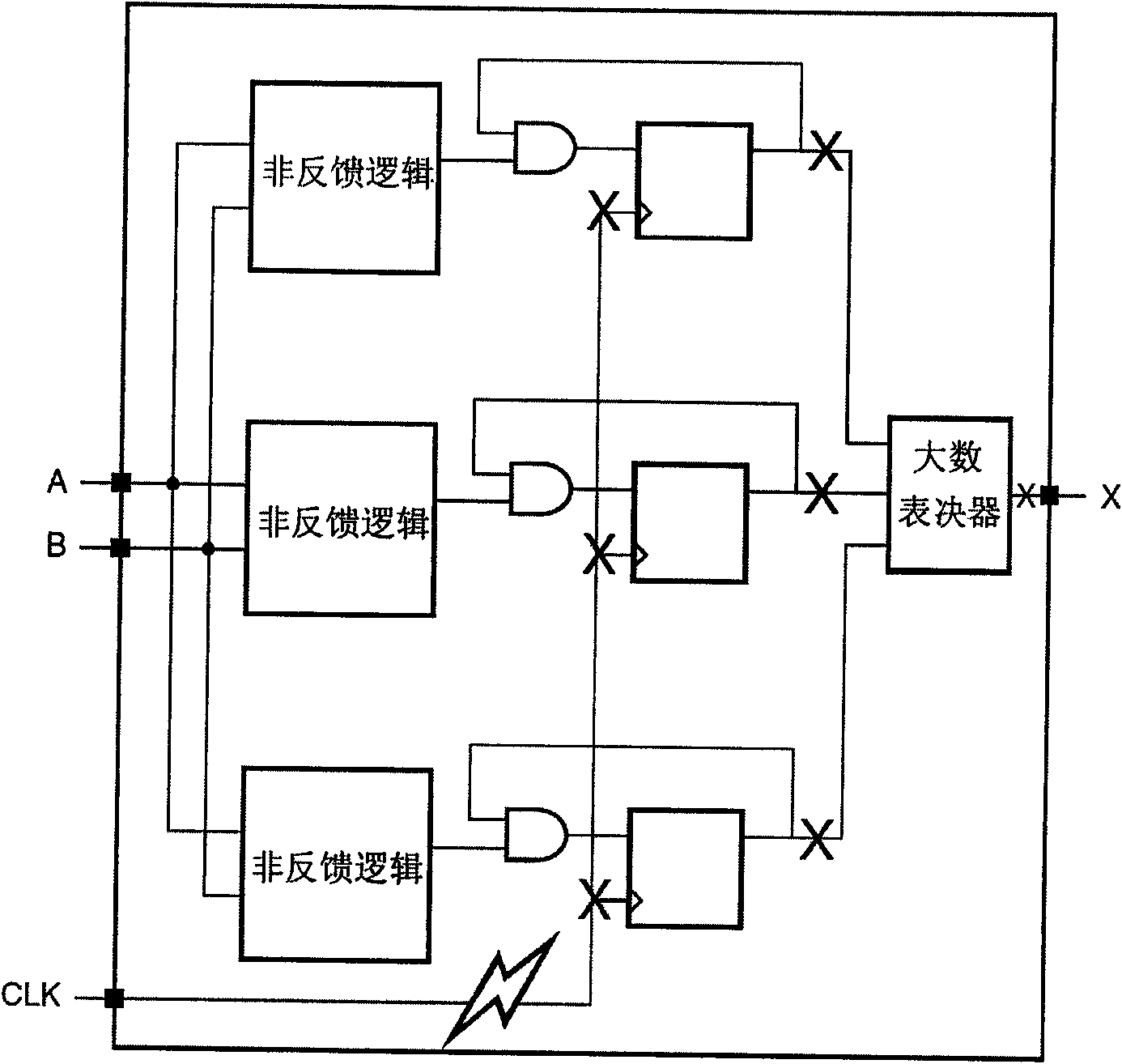

Radiation-proof triple-modular redundancy circuit structure

InactiveCN102820879AImprove design efficiencyImprove radiation resistanceReliability increasing modificationsSequential logicTriple modular redundancy

The invention provides a radiation-proof triple-modular redundancy circuit structure, which is characterized in that a combined logic circuit and a time sequence logic circuit of the circuit are tripled, and a voter is added behind the three time sequence logic circuits, so that each section of route of the circuit is tripled. In addition, a voter is added respectively in each section of route, so that single-particle fault is eliminated in each section of route through a structure consisting of a redundancy route and the voter. The radiation-proof triple-modular redundancy circuit structure has the advantages that a redundancy module is used for shielding the influence of the fault on the entire circuit. The triple-modular redundancy circuit structure can be generated through relevant scripts, so that the design efficiency of the circuit is improved, and meanwhile, the radiation-proof performance of the entire circuit is greatly improved.

Owner:58TH RES INST OF CETC

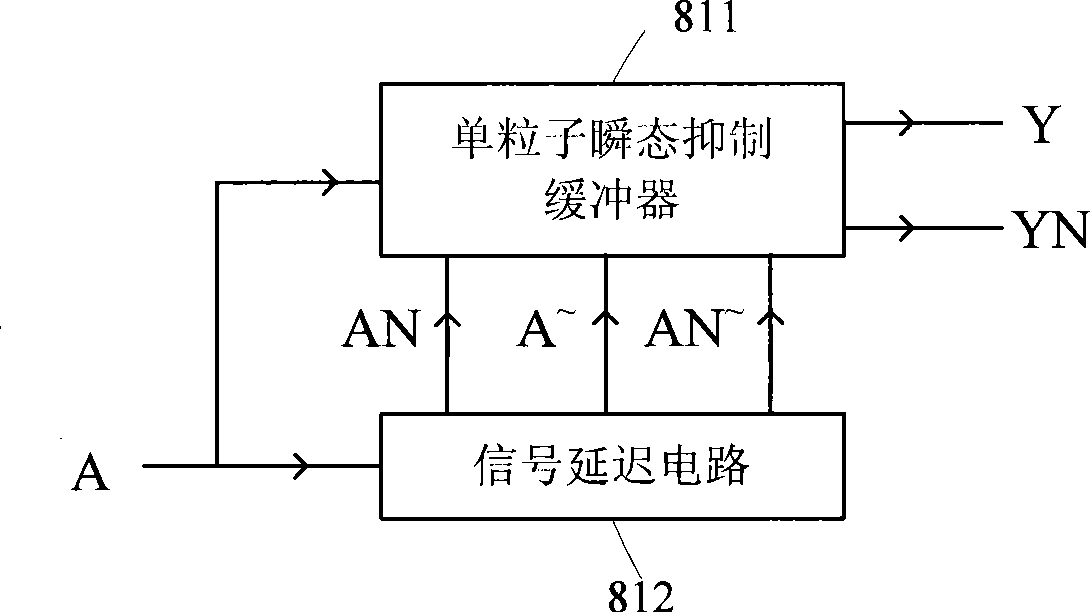

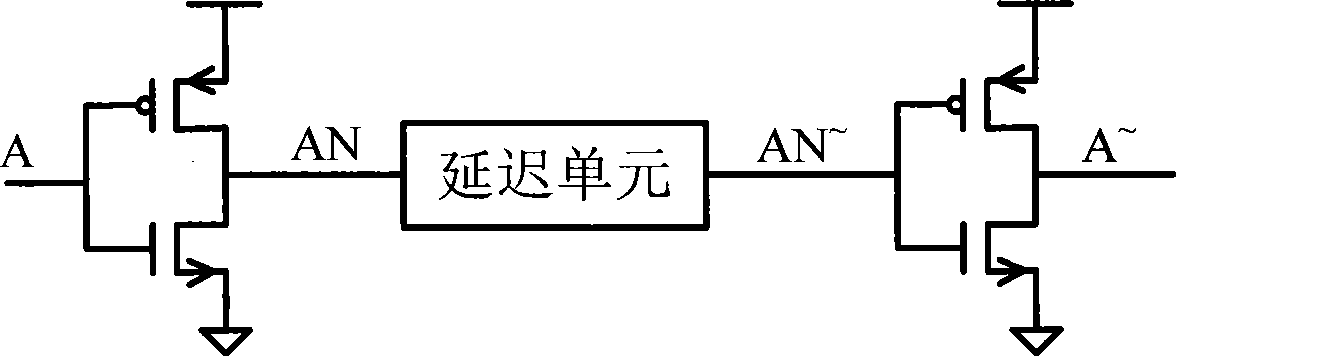

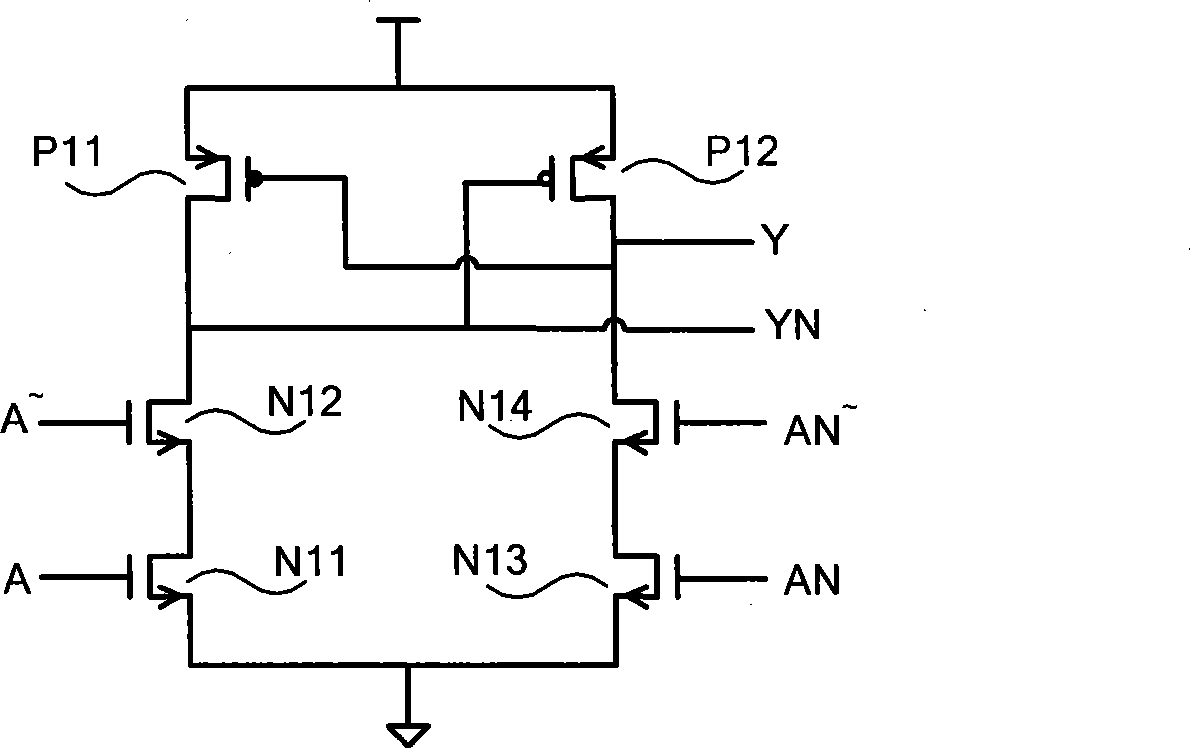

Buffer cell circuit for resisting single-particle transient state

InactiveCN101447786AAbility to suppress transient pulsesEliminate the effects ofLogic circuits coupling/interface using field-effect transistorsTransient stateDelayed time

The invention relates to a buffer cell circuit for resisting the single-particle transient state which mainly consists of a single-particle transient-suppression buffer circuit and a signal-delay circuit, wherein, the signal-delay circuit consists of an inverter and a delay unit, the single-particle transient-suppression buffer circuit is an N-shaped single-particle transient-suppression buffer circuit or a P-shaped single-particle transient-suppression buffer circuit. With the adoption of the buffer circuit of the invention, the single-particle transient pulse which is generated on an input signal and provided with a pulse width smaller than the delay time internally set in a buffer, is eliminated, and key signals such as a clock, a reset, data, and the like, are effectively protected. At the same time, the buffer also possesses the strong ability for resisting single-particle transient state. In addition, The design for a circuit resisting single-particle is reinforced by adopting the buffer cell circuit for resisting the single-particle transient state, so that the area caused by the reinforcement of single-particle resistance and the power consumption are remarkably reduced compared with the common reinforcing methods, such as the triple modular redundancy, and the like.

Owner:BEIJING MXTRONICS CORP +1

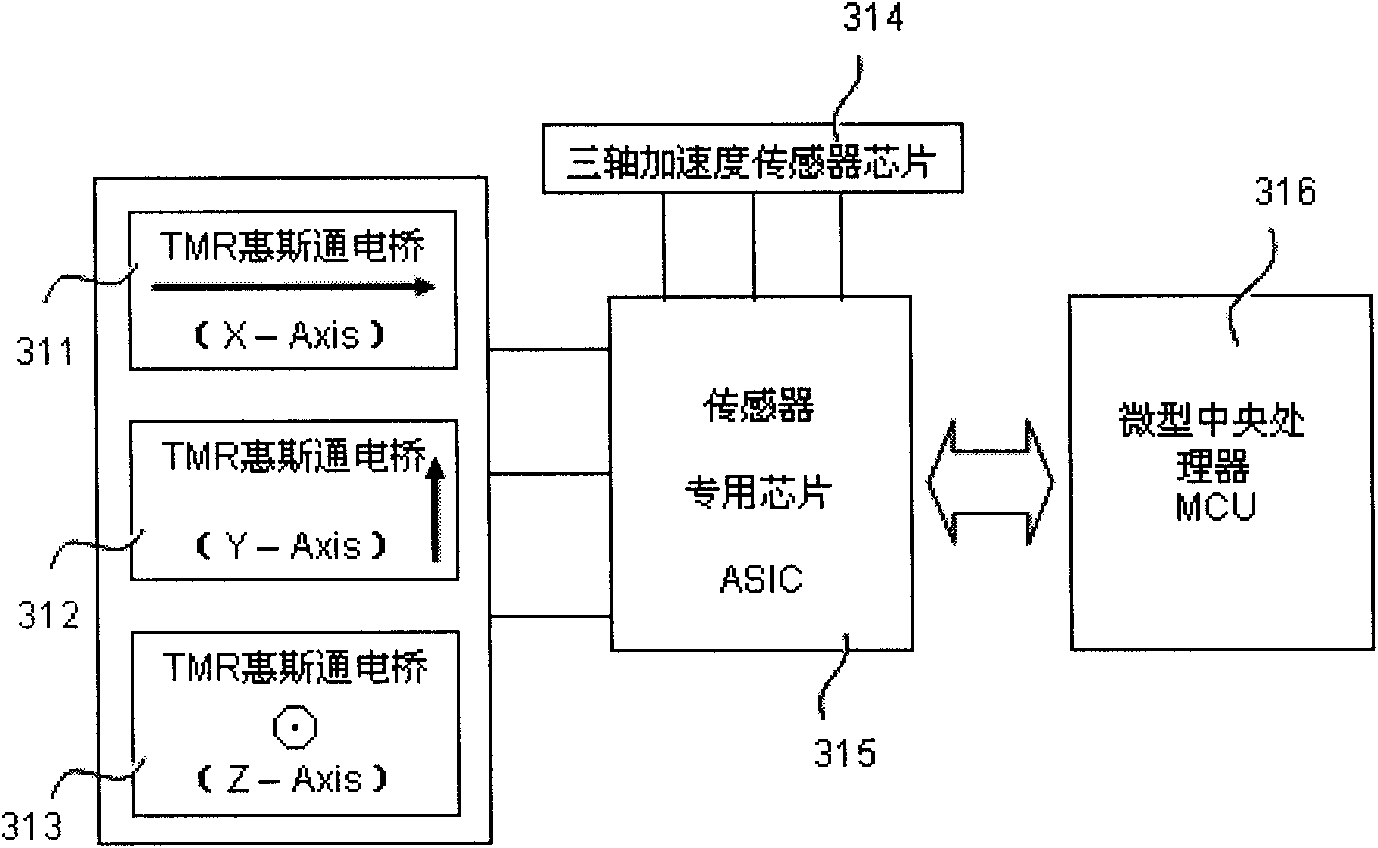

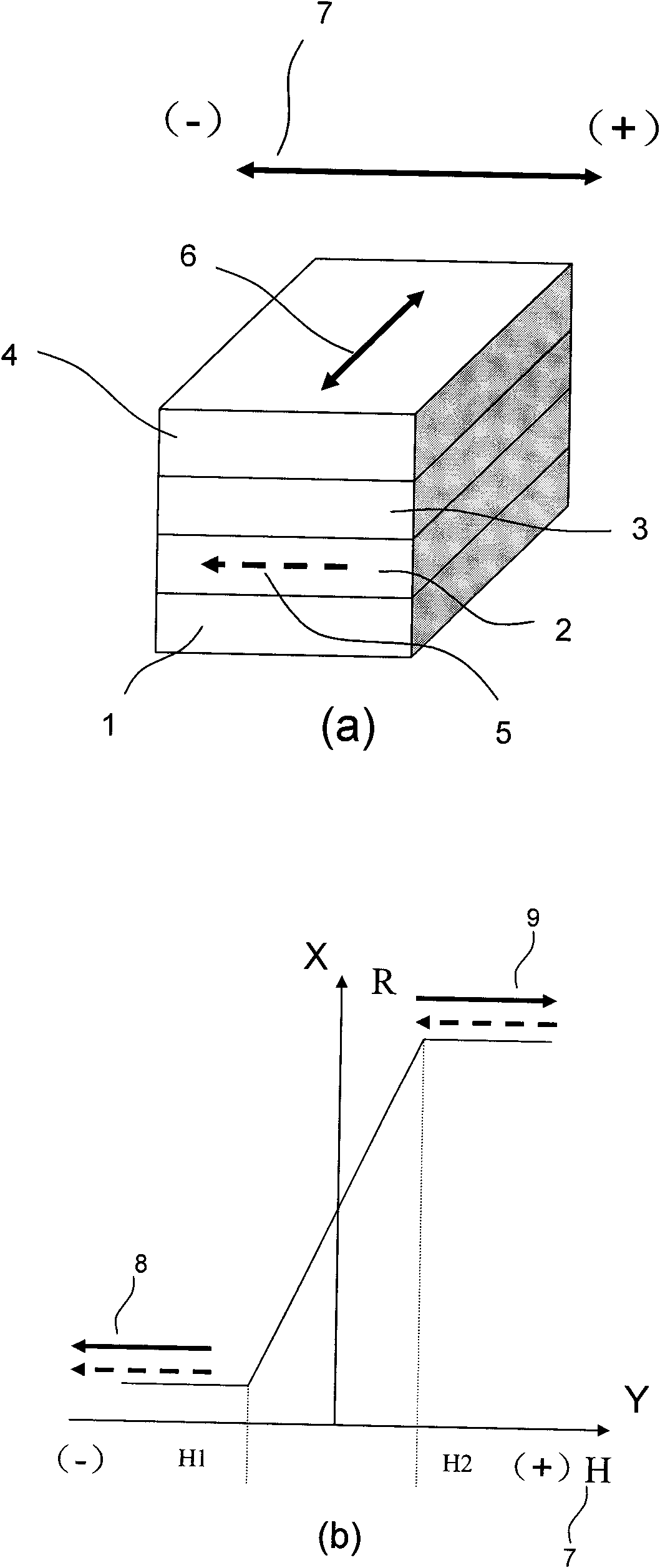

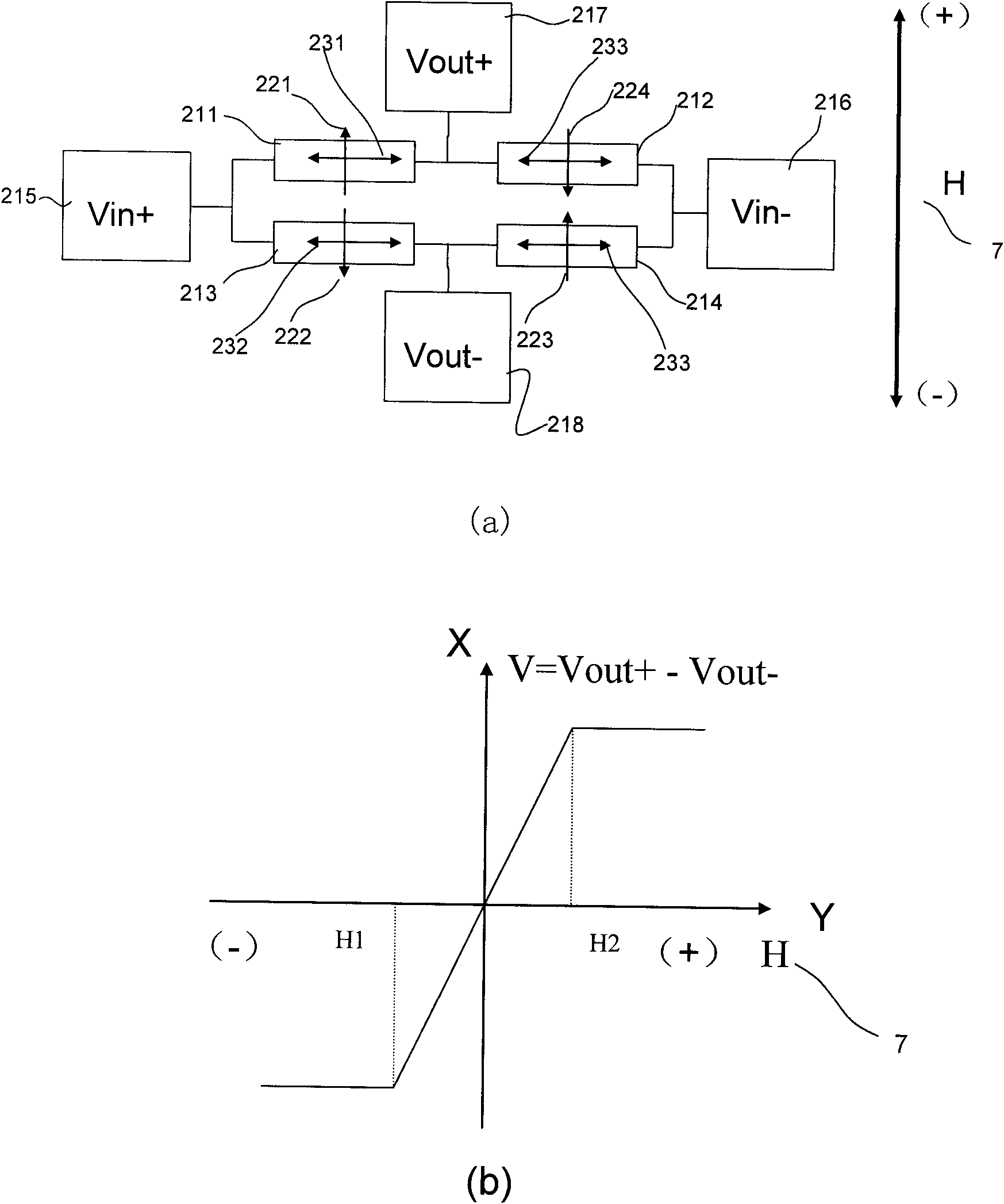

TMR (Triple Modular Redundancy) electronic compass

ActiveCN101813479ALarge dynamic rangeHigh measurement accuracyCompassesResponse FrequencyWide dynamic range

The invention relates to a TMR (Triple Modular Redundancy) electronic compass utilizing a tunnel junction magneto-resistance effect. The TMR electronic compass comprises a TMR Wheatstone bridge sensor, a huge Hall effect magnetic sensor, a triaxial acceleration sensor chip, a sensor ASIC (Application Specific Integrated Circuit) chip and a micro central processing unit, wherein the TMR Wheatstone bridge sensor is used for measuring magnetic fields in an X direction and a Y direction; and a magnetic field in a Z direction can be measured by using the TMR Wheatstone bridge sensor and also be measured by using the huge Hall effect magnetic sensor, and in the invention, both the two design schemes are proposed. The TMR electronic compass has the following characteristics of wide dynamic range, high measuring precision, small packaging size, good temperature characteristic, high response frequency, low cost and strong anti-interference performance.

Owner:王建国 +1

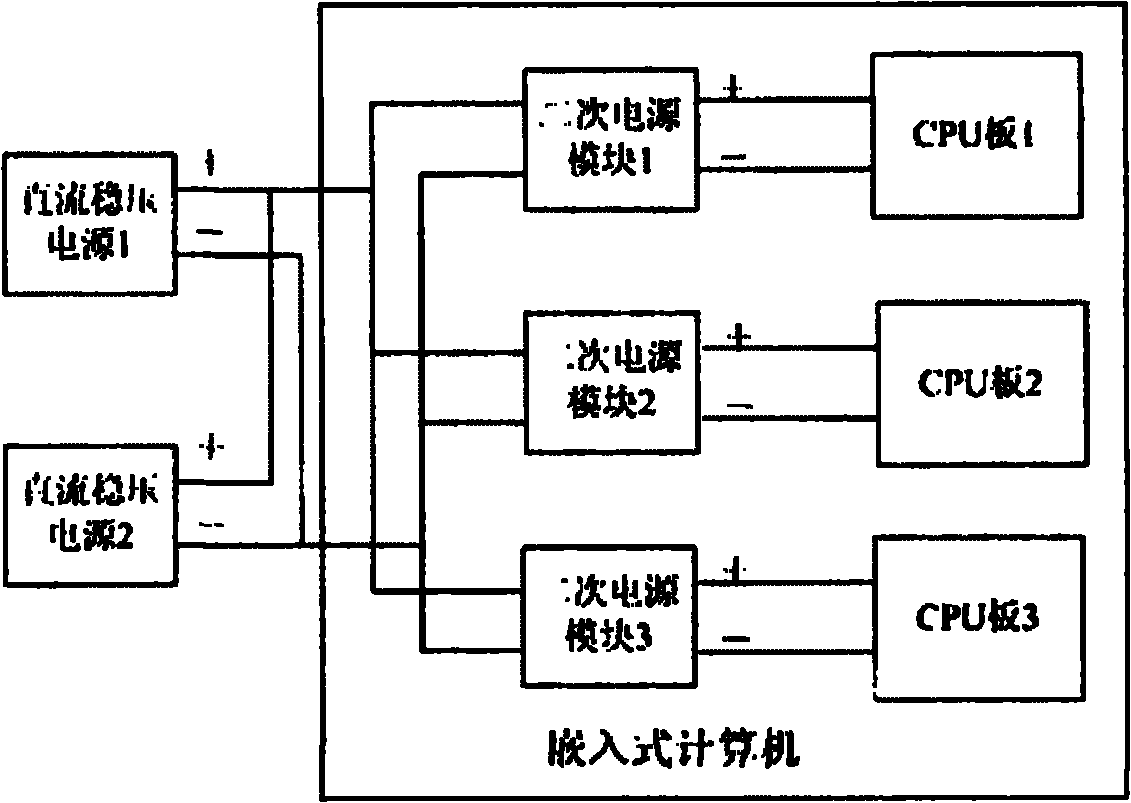

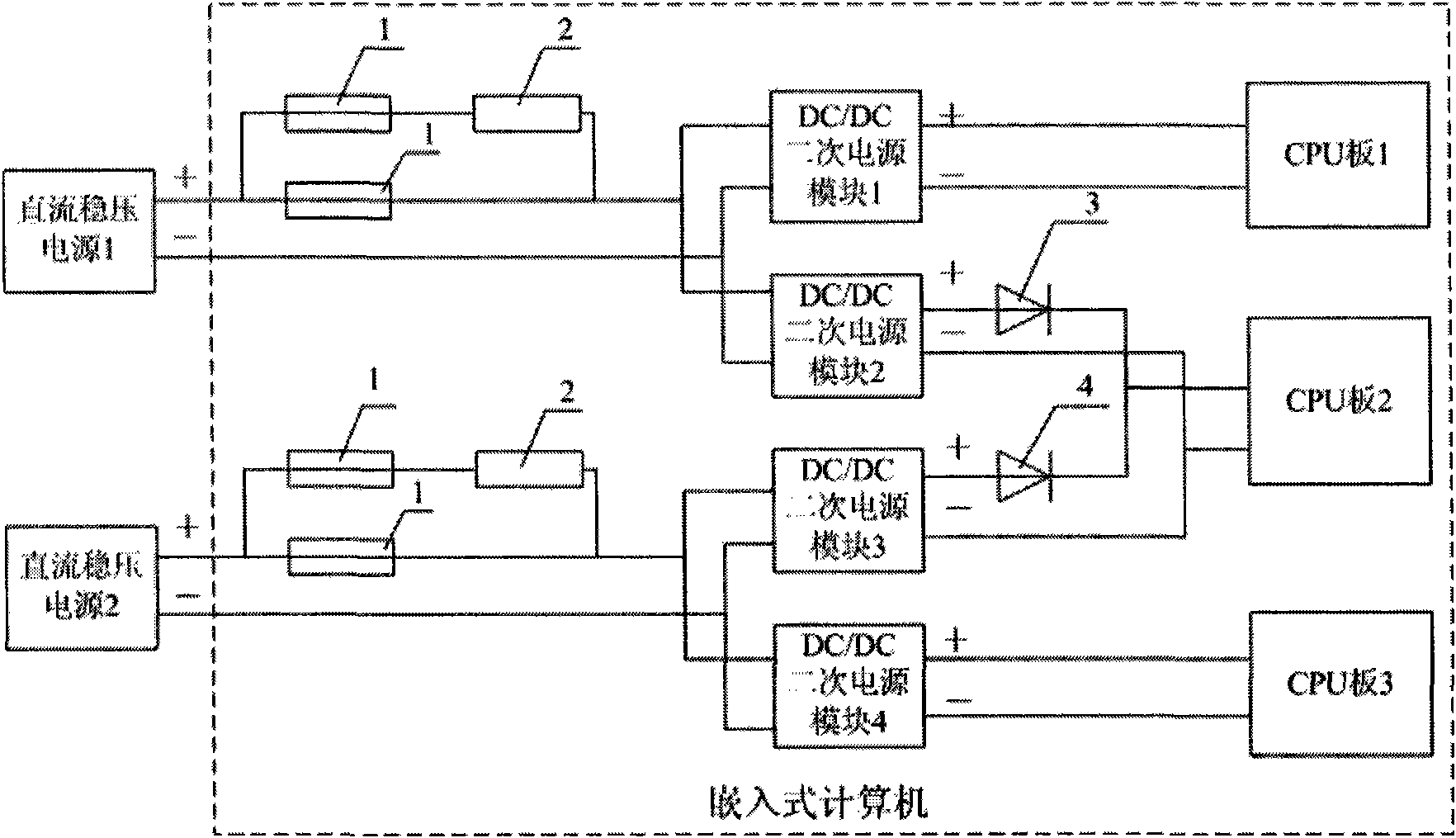

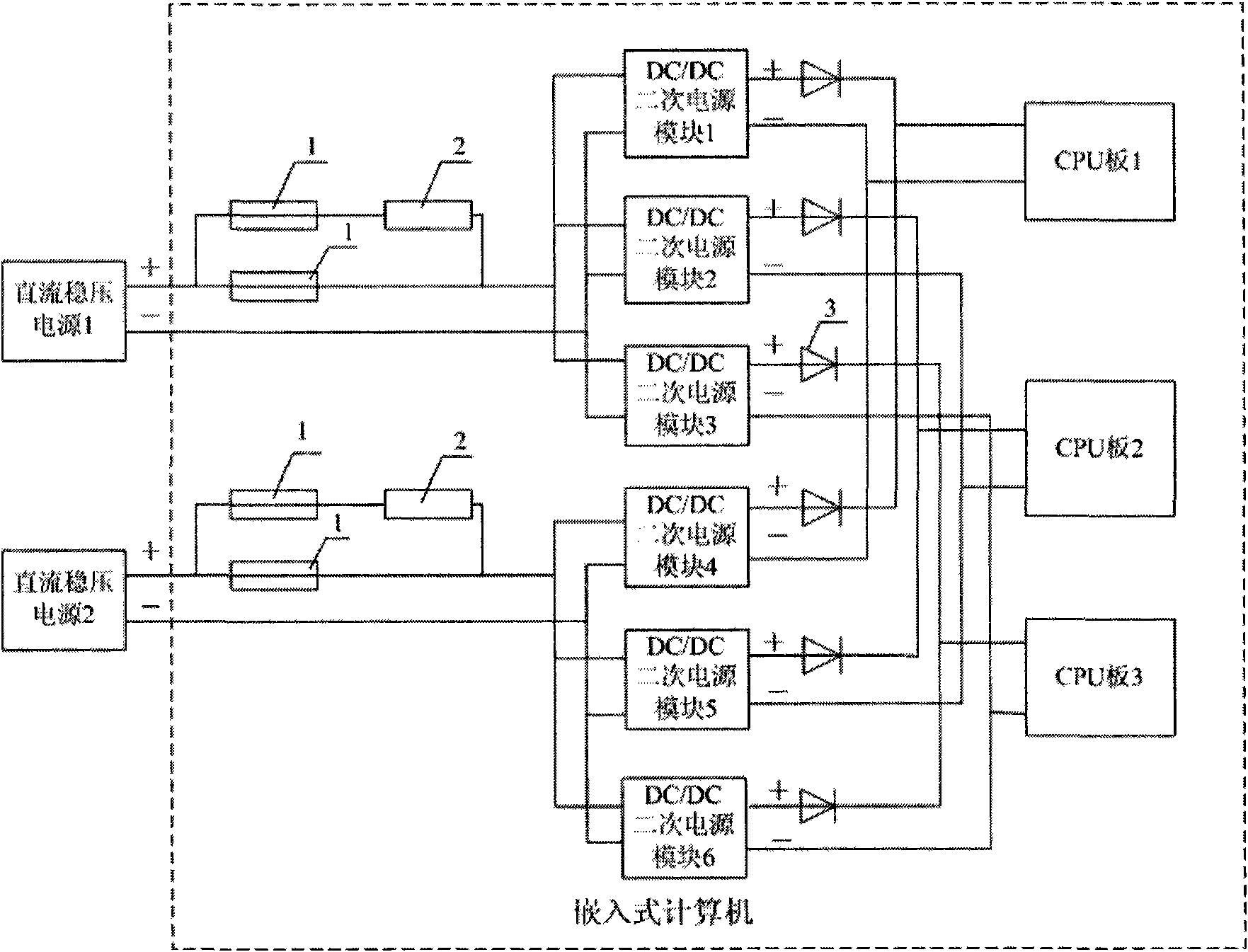

Reliable power supply circuit of triple redundancy embedded computer system

ActiveCN101777790AImprove power supply reliabilityEliminate failed failure modesEmergency protective circuit arrangementsEmergency power supply arrangementsComputerized systemShort circuit protection

The invention relates to a reliable power supply circuit of a triple redundancy embedded computer system, in which a fuse is connected with an output end of a positive bus bar of each DC stabilized power source after being connected with a resistor in series and then connected with a fuse in parallel so as to carry out short circuit protection on the bus bar, each DC stabilized power source is divided into two paths after short circuit protection to supply power for two DC / DC secondary power source modules, two DC / DC secondary power source modules for which power is supplied by different DC stabilized power sources are selected, the output ends of the two selected DC / DC secondary power source modules are respectively connected with a diode in series and then are connected together in parallel to supply power for a CPU board, and the other two DC / DC secondary power source modules respectively supply power for another two CPU boards. The invention solves the problem of reliability of the power supply circuit of the triple redundancy embedded computer and eliminates the single point failure mode of system failure caused by open circuit or short circuit failure.

Owner:BEIJING INST OF ASTRONAUTICAL SYST ENG

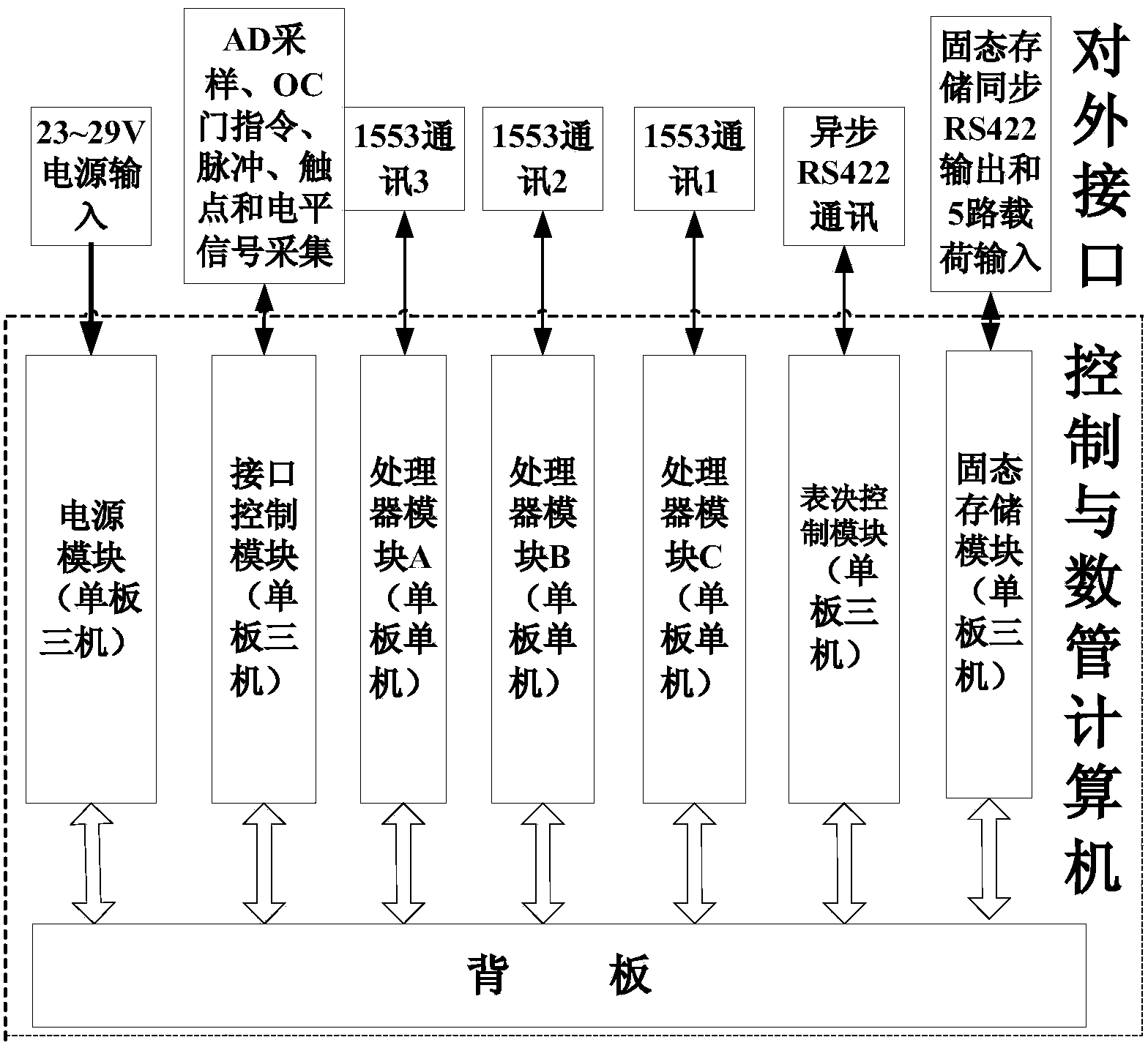

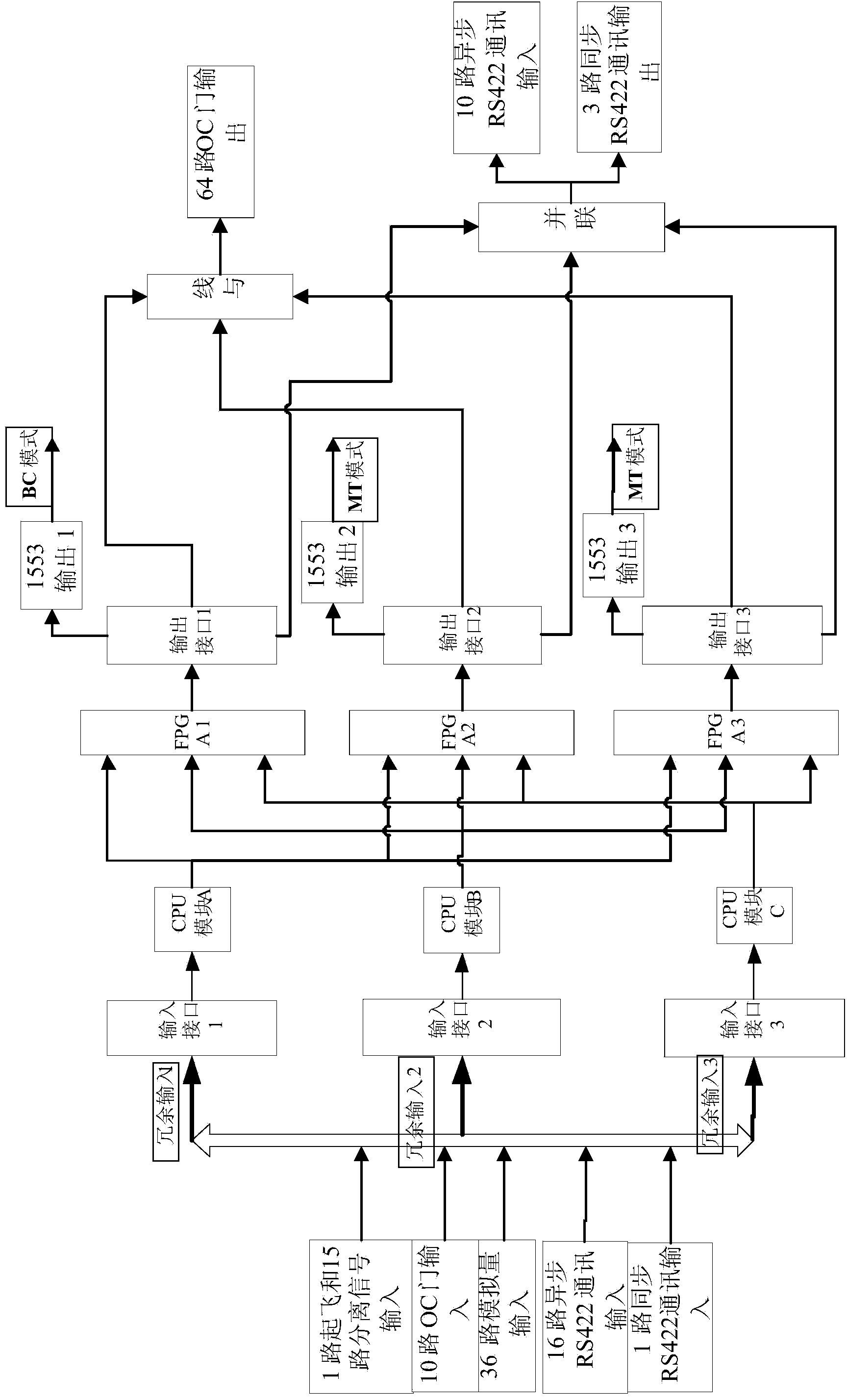

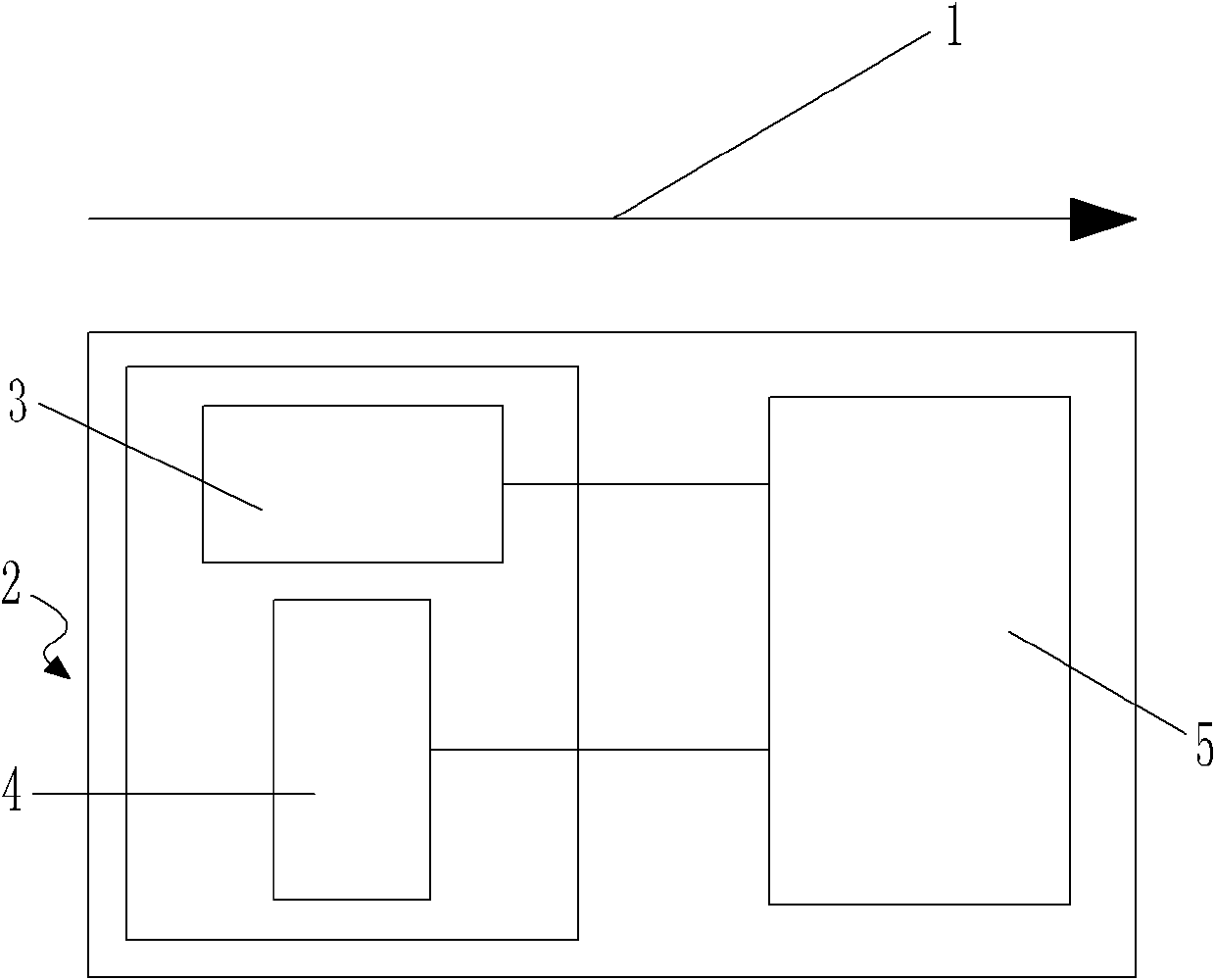

Triple modular redundancy control and data management computer and using method thereof

InactiveCN104182305AImprove reliabilityLow costRedundant hardware error correctionSolid-state storageComputer module

The invention provides a triple modular redundancy control and data management computer and a using method thereof which are highly reliable. The computer comprises a power supply module, a solid storage module, a voting control module, an interface control module and three processor modules. The power supply module comprises three power supply units supplying power for three processors respectively so as to supply power for the solid storage module, the voting control module and the interface control module; the solid storage module comprises three solid data storage units, and the signal communication is implemented between the three solid data storage units and the three processors and between the three solid data storage units and a ground test and control communicator; the voting control module comprises three voting control units, and the signal communication is implemented between each voting control unit and the three processor modules; the output interface of the voting control module comprises a 1553B bus output interface, an OC gate output interface and a RS422 communicating output interface.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

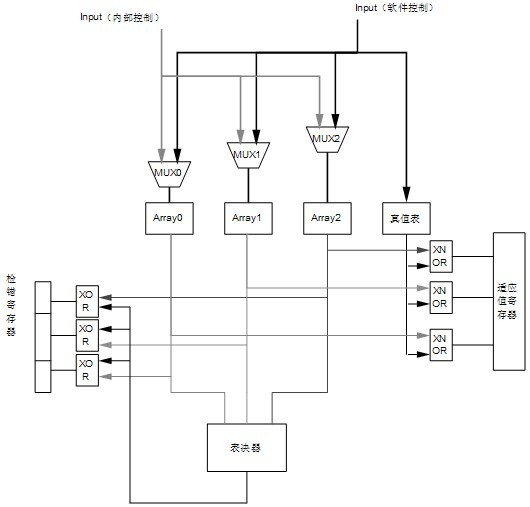

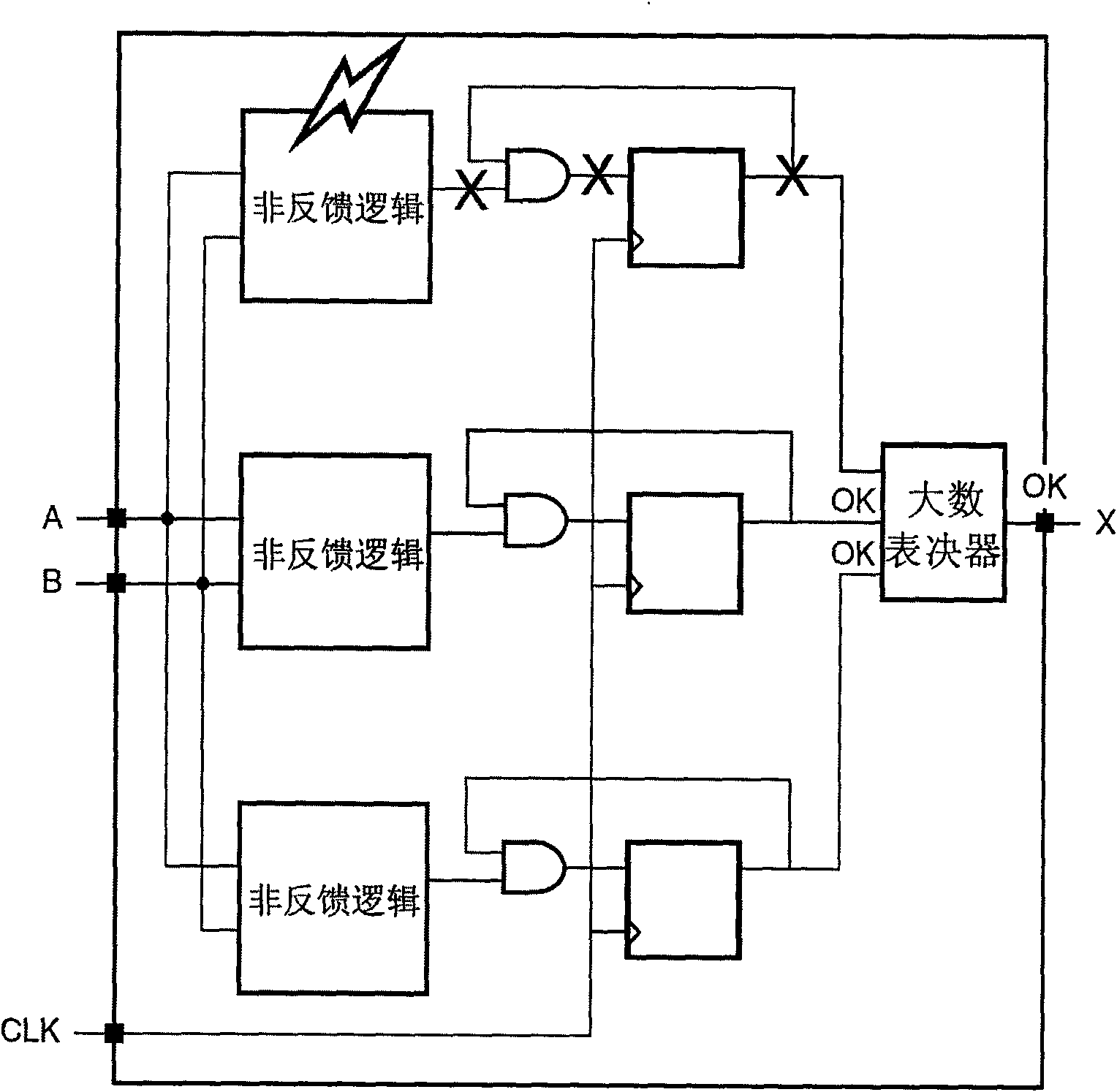

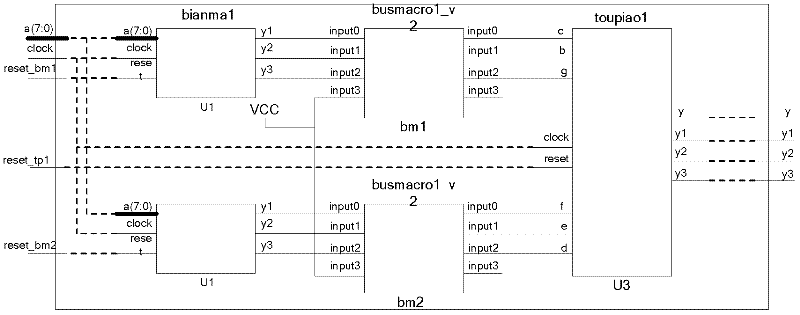

Method for applying commercial on-spot programmable device to triple-modular redundancy anti-irradiation in irradiation environment

InactiveCN101615211ABroad representationPracticalitySpecial data processing applicationsRedundant hardware error correctionLookup tableFpga chip

The invention relates to a method for applying a commercial on-spot programmable device to triple-modular redundancy anti-irradiation in an irradiation environment based on lookup table structure and a generic algorithm thereof, aiming at easing the problem that commercial FPGA chips are prone to cause overturning of programming point single particle in the irradiation environment due to irradiation energy energetic particles in the space. The method carries out classification according to user circuit logical type; the first type is input logic, the second type is non-feedback logic and the third type is feedback logic, the fourth type is output logic. In the method of the invention, different triple-modular redundancy anti-irradiation processing methods are proposed with regards to the 4 types of logic. The method of the invention is a universal method through which various user circuits are mapped to the commercial FPGA, features widespread representativeness, generality and practicability.

Owner:FUDAN UNIV

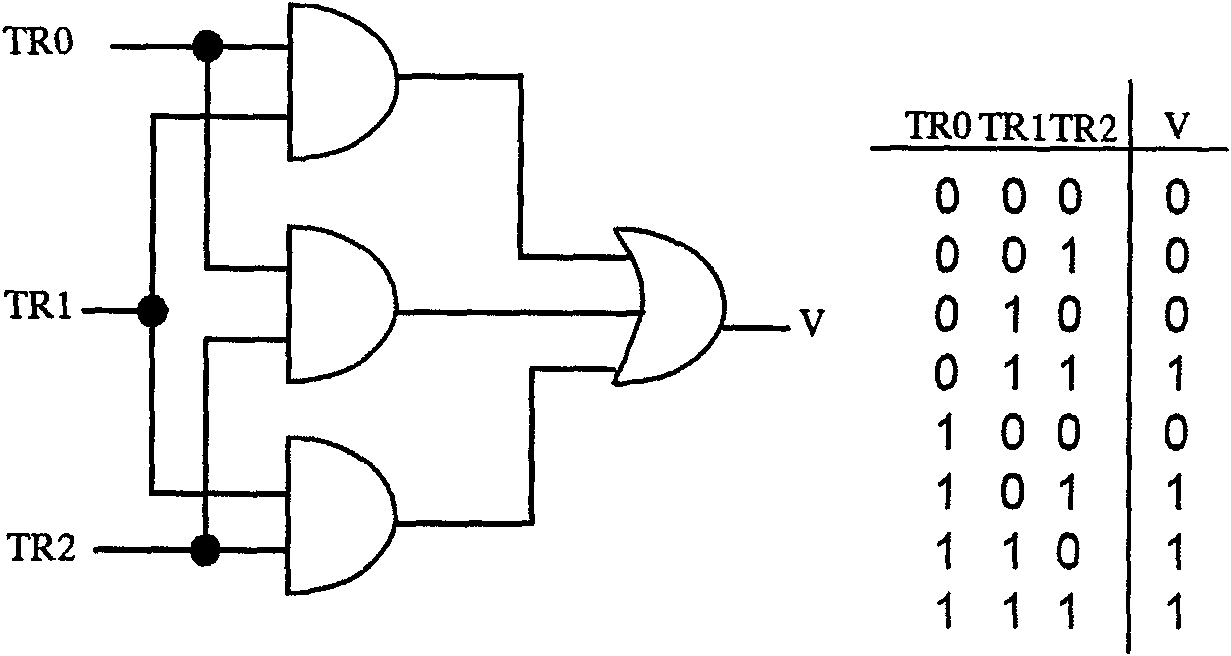

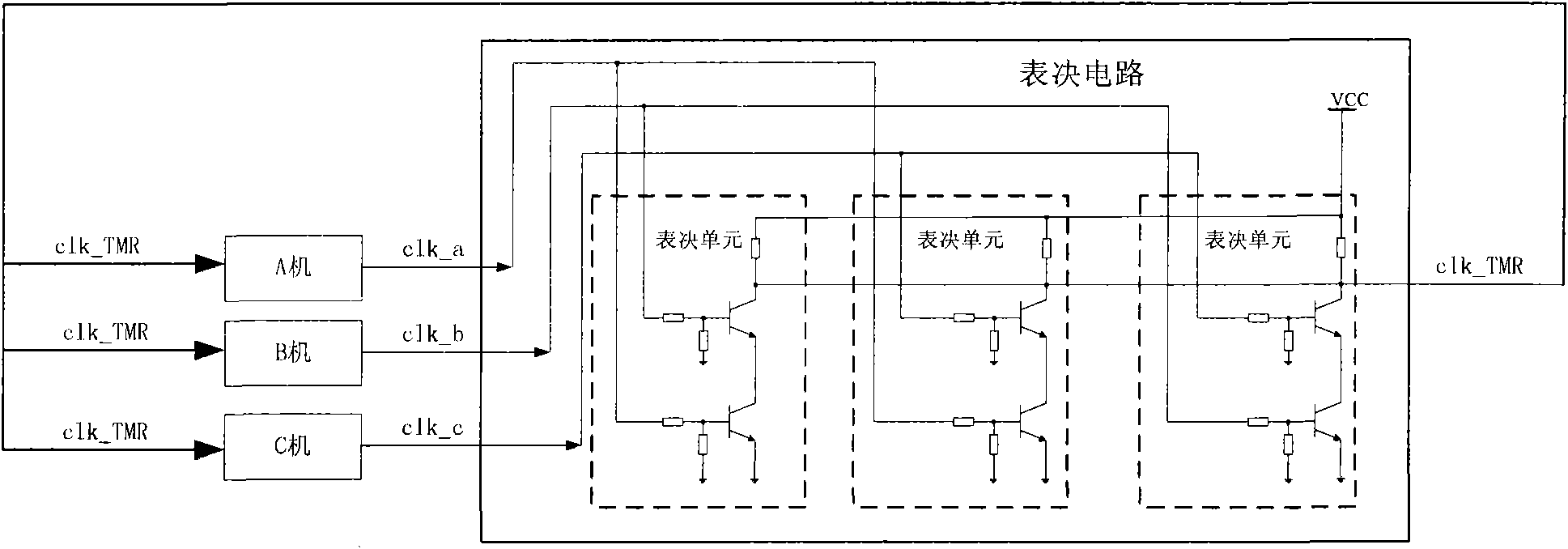

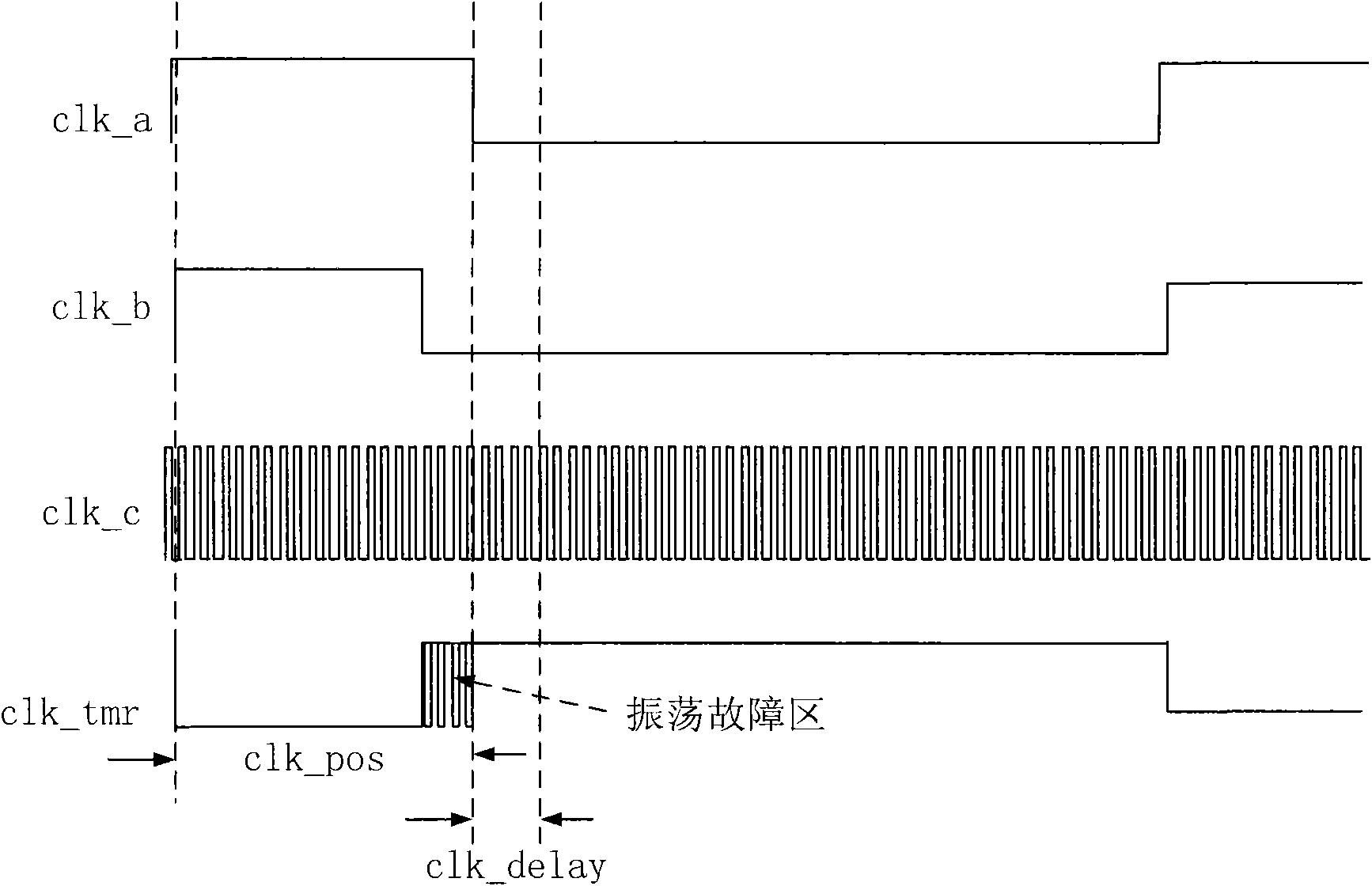

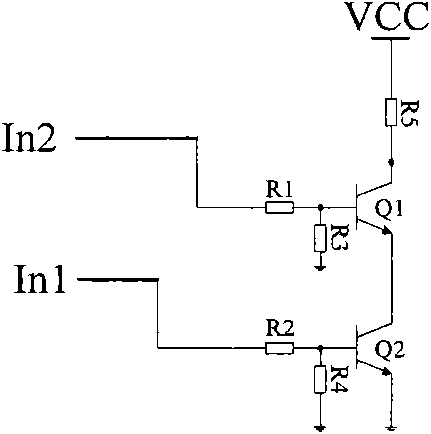

Control cycle synchronizer of triple-modular redundancy fault-tolerant computer

ActiveCN102053883ASimple designReduce hardware sizeRedundant hardware error correctionClock driftTime delays

The invention relates to a control cycle synchronizer of a triple-modular redundancy fault-tolerant computer, which comprises single machines A, B and C, a voting circuit and control cycle interruption management modules arranged in the A, B and C, wherein the single machines A, B and C simultaneously input respective control cycle clocks to the voting circuit; the voting circuit uses an internal voting unit and wired-and logic to carry out a 2-out-of-3 vote on the input control cycles so as to produce a unified control cycle clock; the single machines A, B and C use the unified control cycle clock to response to control cycle interruption; and the control cycle interruption management modules turn off the control cycle interruption after the control cycle interruption is started, and turn on the control cycle interruption of the single machines A, B and C again after a certain time delay. By using the simple circuit design scheme, in the invention, the high-reliability control cycle synchronization control on the triple-modular redundancy fault-tolerant computer is realized, and all simplex fault modes including normally-0 or normally-1 faults as well as clock drift faults (including high-frequency oscillation and frequency downshift) can be tolerated.

Owner:BEIJING INST OF CONTROL ENG

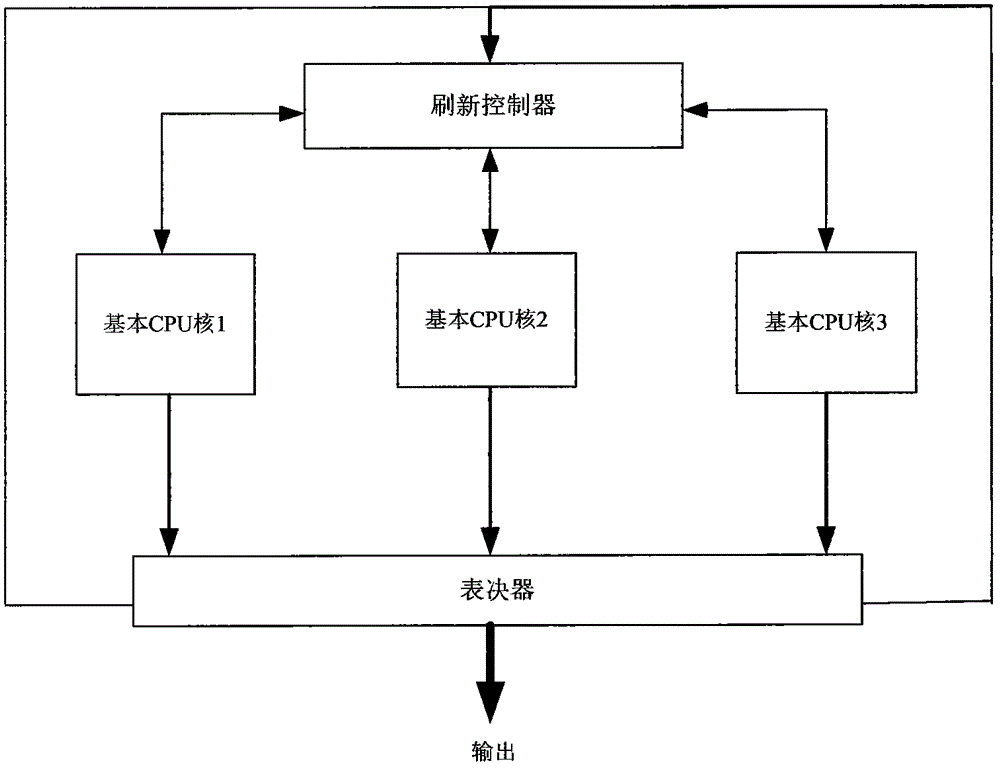

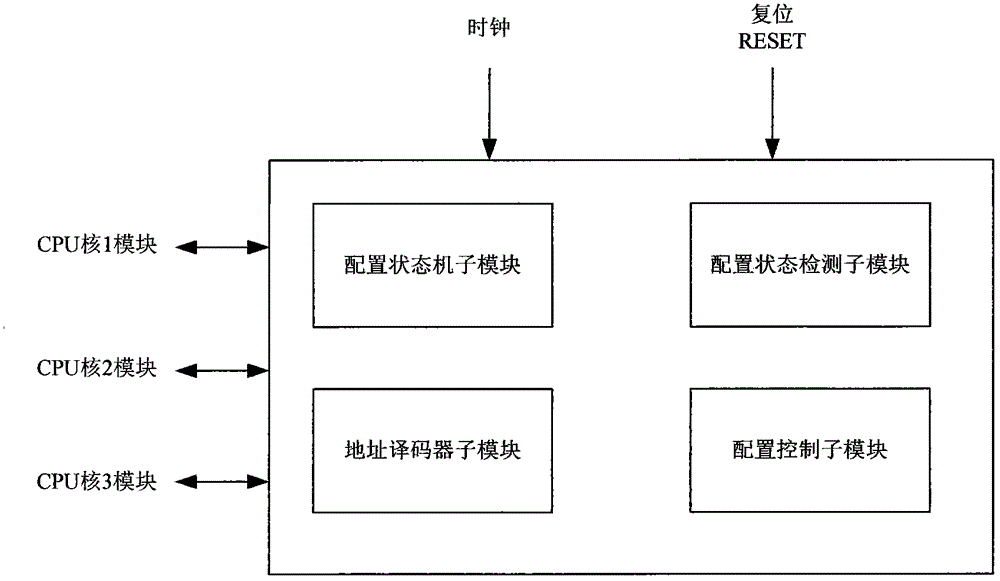

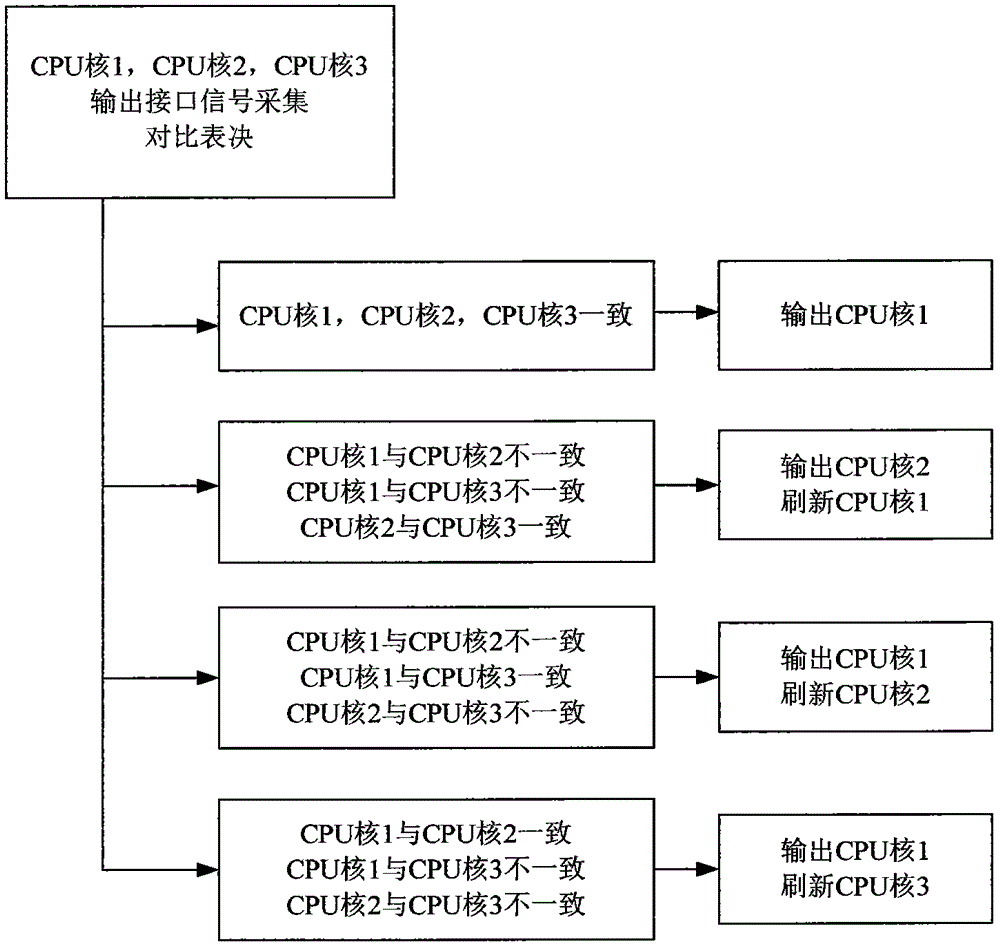

Method for designing triple-modular redundancy type fault-tolerant computer IP core with fault spontaneous restoration function

InactiveCN105279049AGuaranteed correctnessResource usage is reasonableRedundant hardware error correctionSingle point of failureComputer science

The invention designs a triple-modular redundancy type fault-tolerant computer core consisting of three basic CPU cores, namely, three same basic CPU cores are combined into one fault-tolerant computer core, a triple-modular redundancy mode is adopted, and when any one basic CPU core has a fault, the correctness of computer calculation continues to be kept and the fault is spontaneously corrected. According to the computer core, the correct basic CPU core refreshes the basic CPU core with the fault by adopting an automatic refreshing technology, so that the fault is eliminated and a normal working state is recovered. A designed IP core is an independent fault-tolerant computer core in the form of a soft core and used for automatically detecting a single-point fault caused by a single-particle effect, automatically obtaining a correct result and spontaneously correcting the fault. The technical scheme of the invention solves the problem in design of the fault-tolerant computer IP core by adopting the triple-modular redundancy technology, and can be used for FPGA application development and integrated circuit design.

Owner:KANGYUXING TECH BEIJING

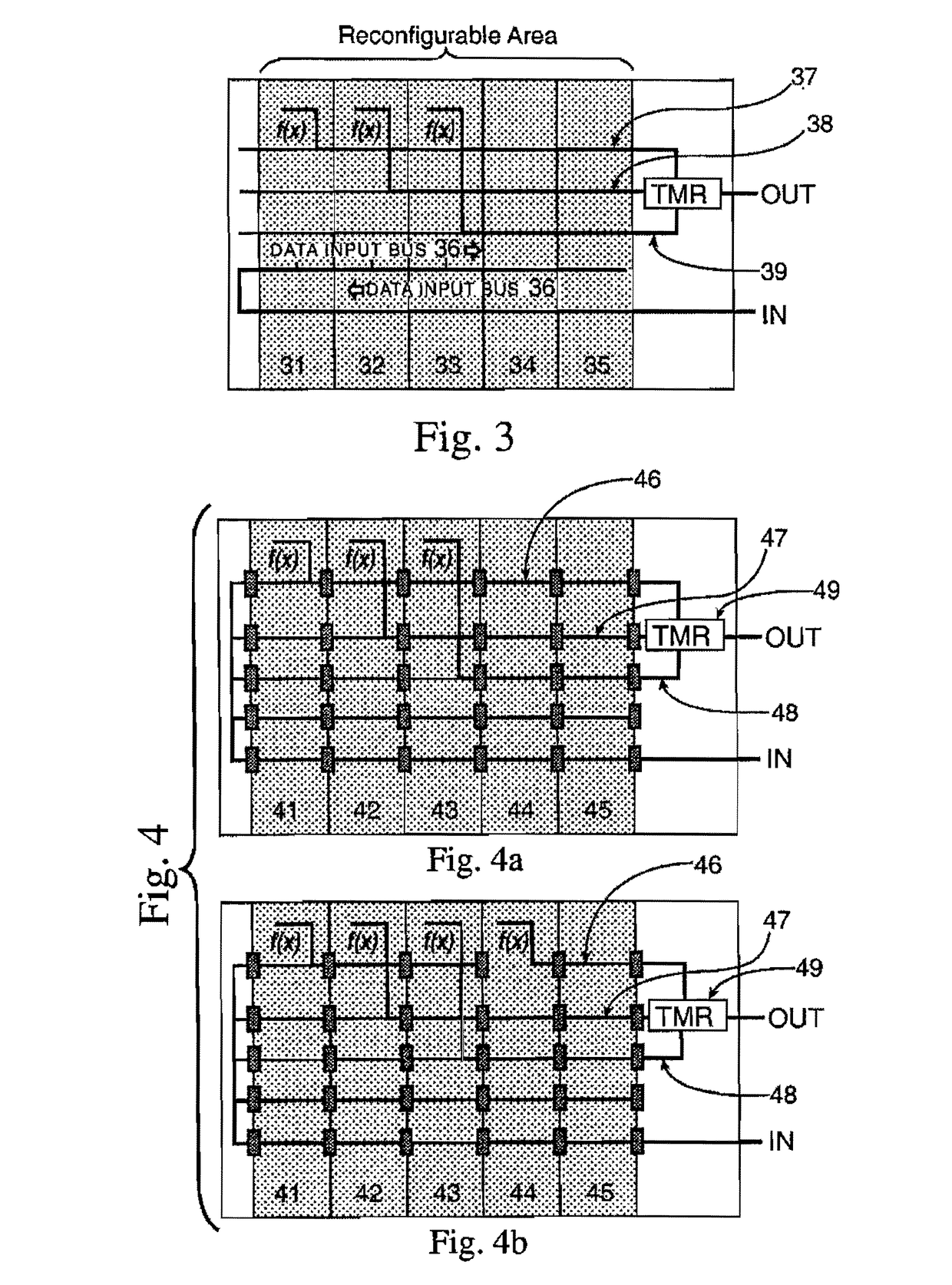

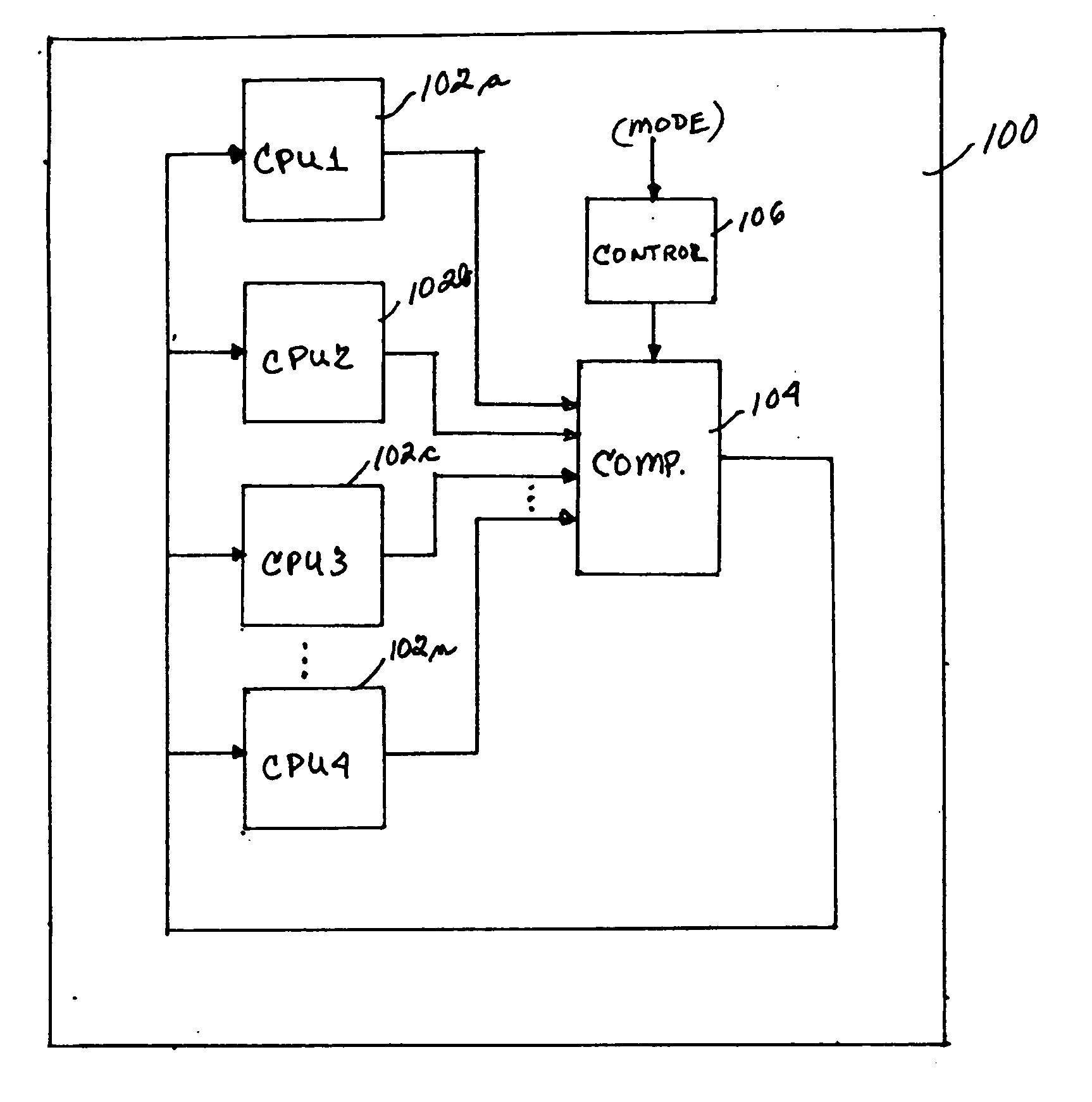

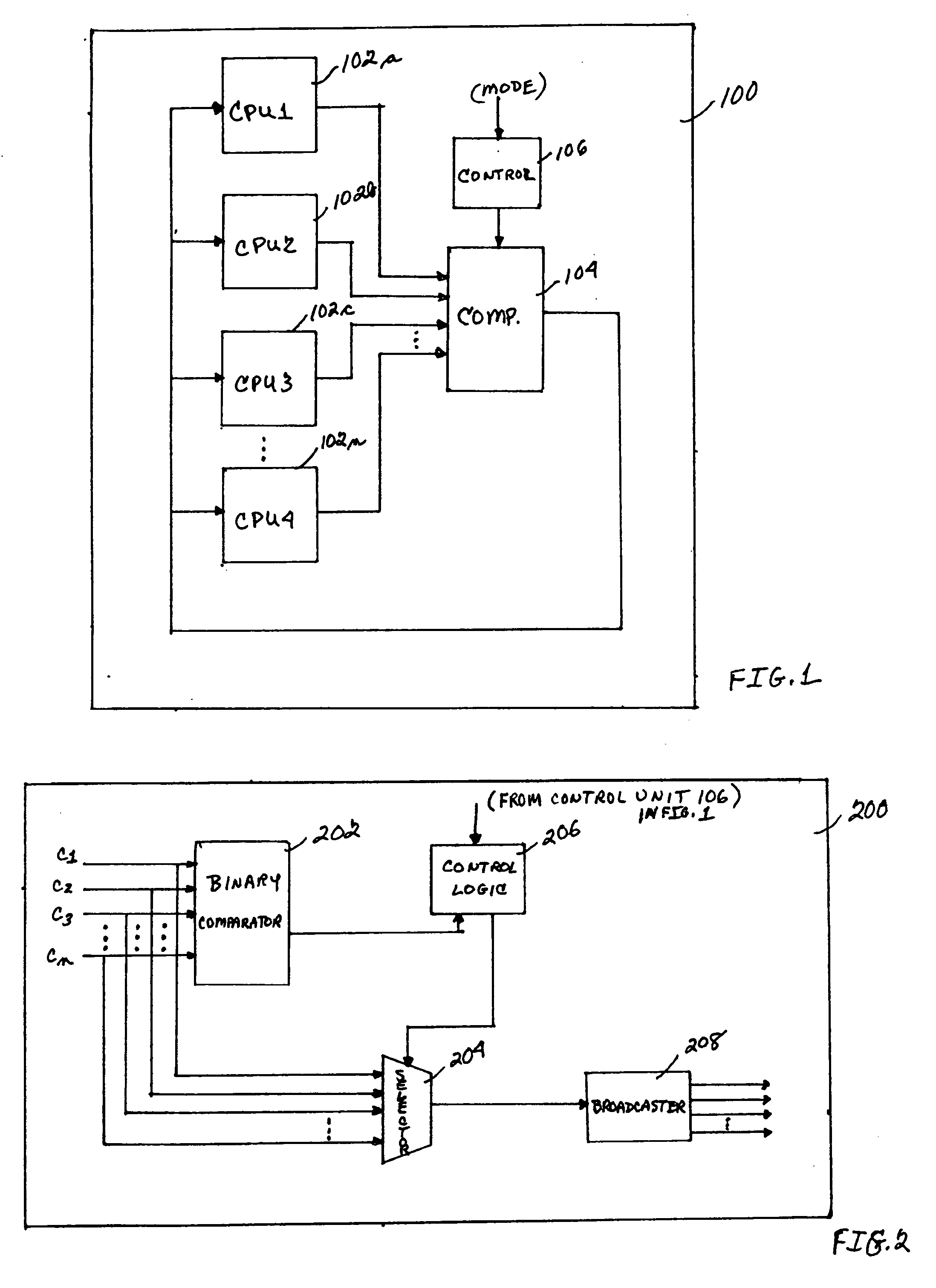

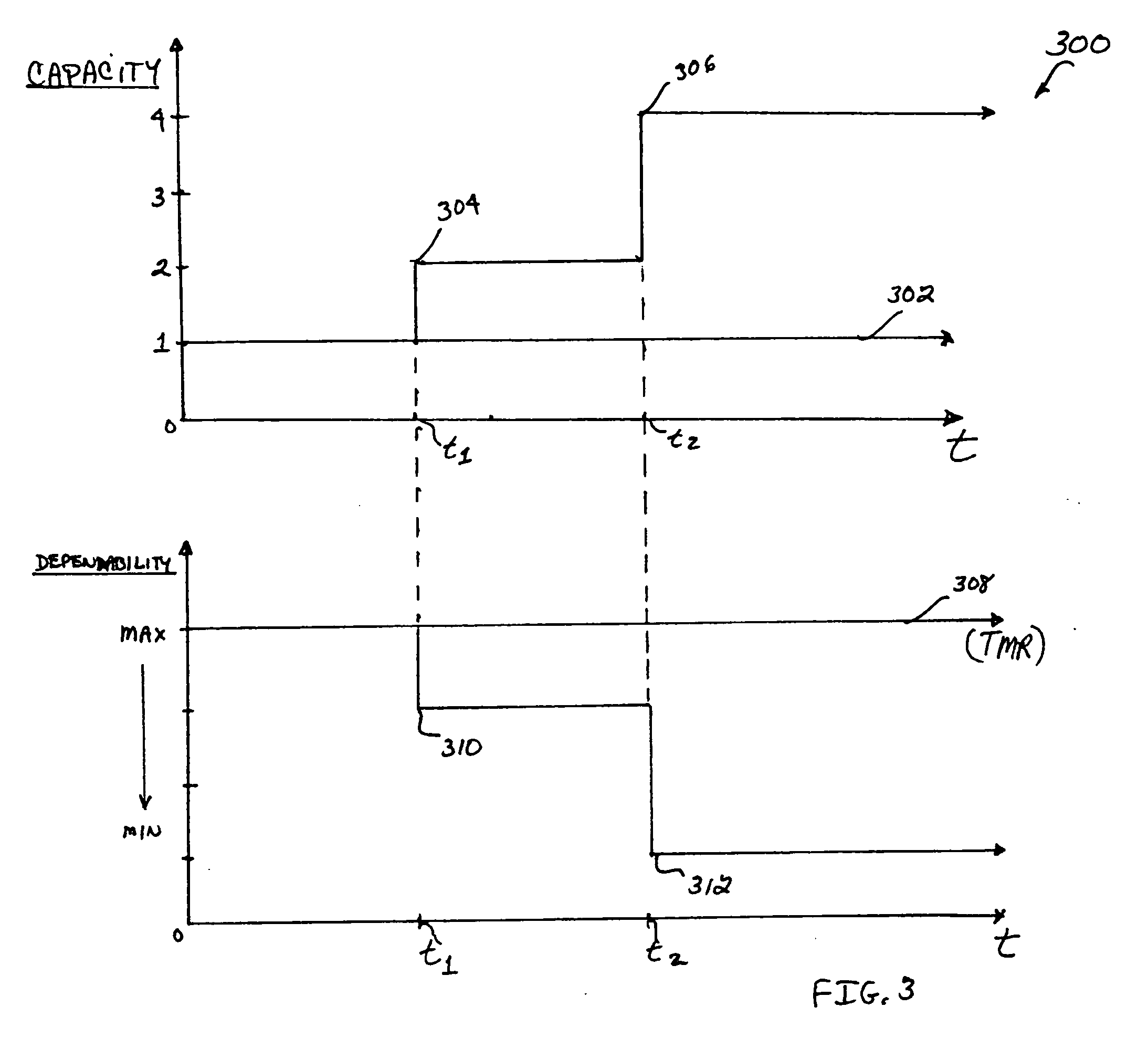

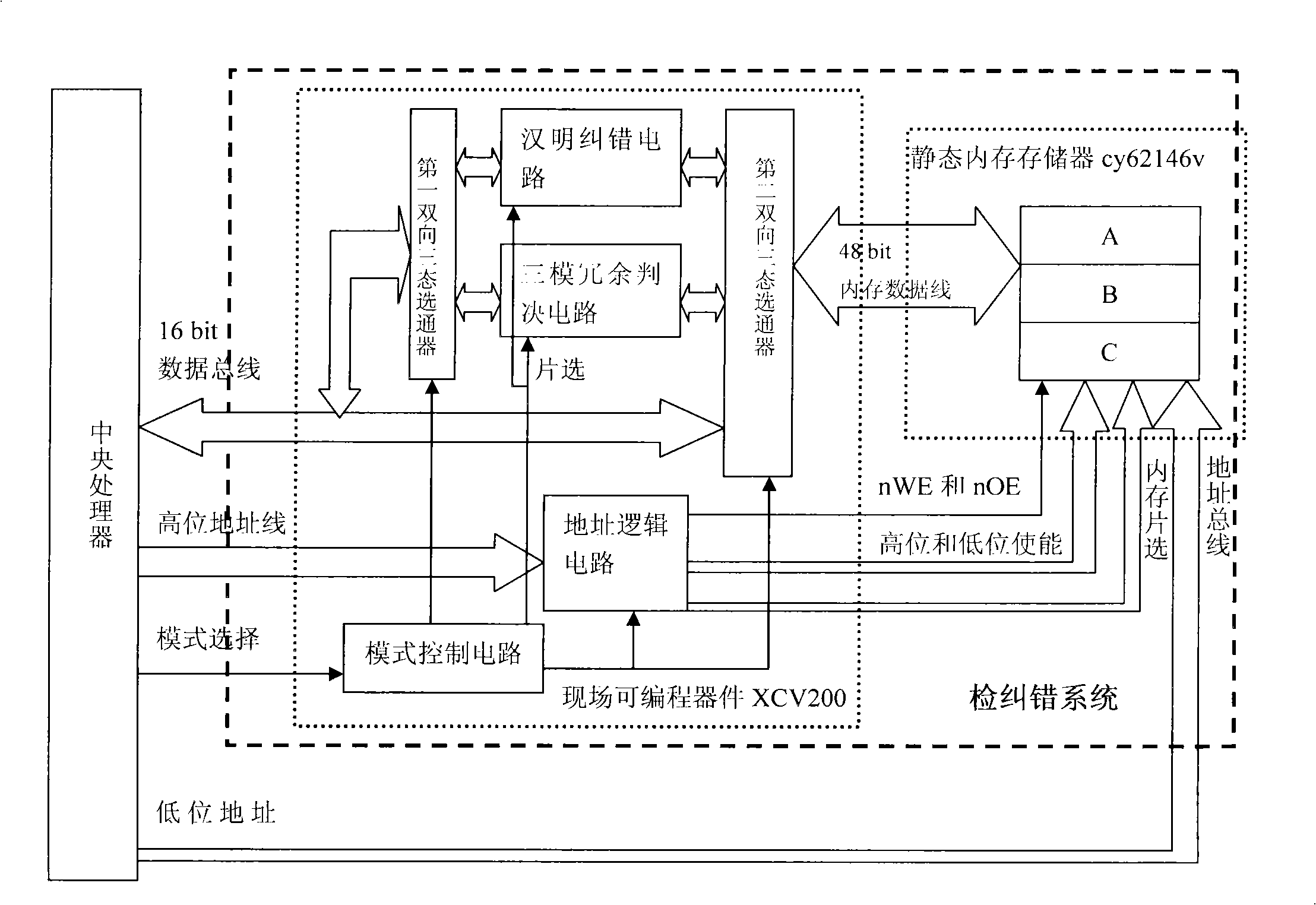

System and method for dynamically optimizing performance and reliability of redundant processing systems

InactiveUS20060236168A1Improve performanceReduced level of dependabilityElectronic circuit testingError detection/correctionGeneral purposeDynamical optimization

An improved system and method for dynamically optimizing the performance and reliability of redundant processing systems (e.g., for use in space applications) are disclosed. As one example, a Field Programmable Gate Array (FPGA) that includes a plurality of processors is disclosed. Based on mission specific modes or environmental conditions, the processing system can dynamically and safely transition between the high performance of, for example, a general purpose, quad Symmetric Multiprocessor (SMP) and the high reliability of a redundant set of processors (e.g., Triple Modular Redundancy system). This architecture allows the use of a single FPGA with multiple processors to take advantage of the maximum processing throughput available when sufficient mission conditions are met, and can also safely transition to a lower throughput, high reliability mode when needed. In other words, at particular points during a mission, high processing capacity and throughput can be obtained at the expense of reliability or dependability as the mission conditions allow. If the mission conditions can support a reduced level of dependability at a particular point in time, then the processors can be adapted to run in a single string (e.g., triple or quad string) to produce three to four times the processing capacity of the redundant set.

Owner:HONEYWELL INT INC

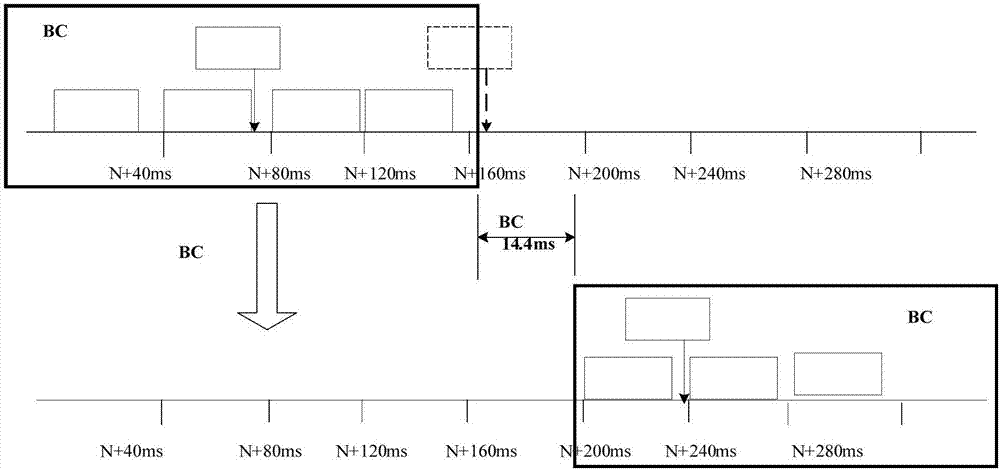

Error detecting and error correcting system for tiny satellite star load computer data storage

InactiveCN101354666AIncrease flexibilityTake advantage ofRedundant data error correctionMode controlData store

An error detection and correction system for the data storage of a miniature satellite onboard spacecraft computer belongs to the technical field of the computer storage in a miniature satellite in the space technology. The system is characterized in that the system comprises a static memory storage unit assembly and a field programmable device FPGA, wherein the FPGA comprises a Hamming error correcting circuit, a triple modular redundancy decision circuit, two both-way tristate gates, an address logic circuit and a mode control circuit; according to the address contents of an external central processing unit, the mode control circuit selects any of the three modes of Hamming error correction, triple modular redundancy decision and error-free control; and according to the storage space configured by the address logic circuit controlled by the mode control circuit, the storage unit assembly consisting of 12 static memory storage units carries out the read-write operation of the data signal inputted by the central processing unit through the two both-way tristate gates. As the system respectively separates the memory space of the memory storage unit assembly into flexible and adjustable groups according to the three modes, the memory can be flexibly distributed according to the error correcting modes so as to be fully utilized.

Owner:TSINGHUA UNIV

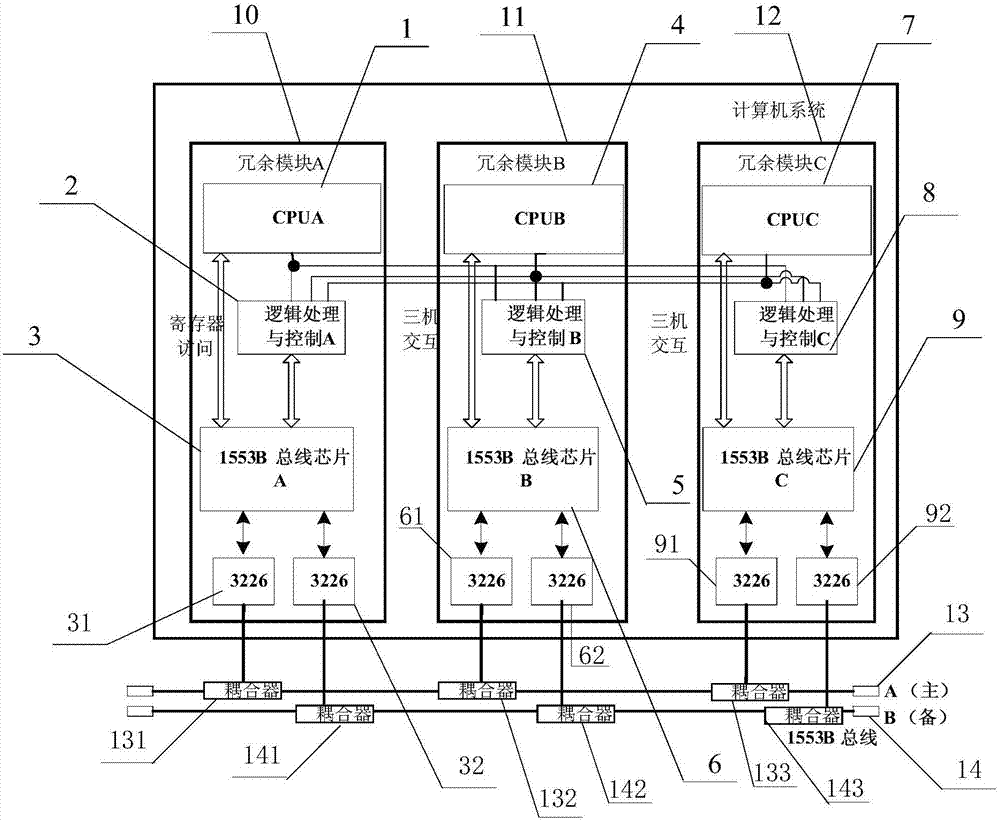

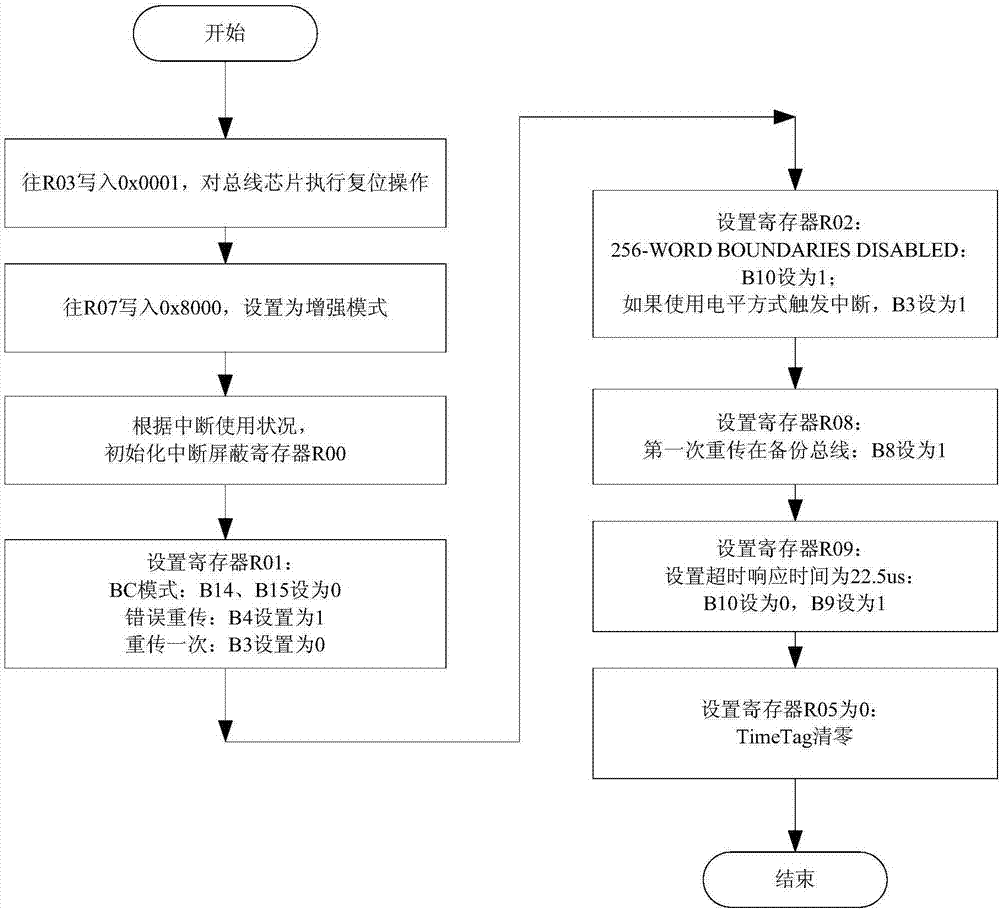

Triple-redundancy 1553B bus dynamic switching method

ActiveCN107347018AImplement fault diagnosisImplement failoverBus networksElectricityDiagnosis methods

The invention provides a triple-redundancy 1553B bus dynamic switching method, which includes the following steps: S1, a triple-modular redundancy bus network computer system architecture is built; S2, a redundancy bus configuration method is designed, a bus A for communication is a main bus by default, a first redundancy module is a on-duty module by default when the computer system is powered on, a first bus chip is configured in a BC mode, and a second bus chip and a third bus chip are configured in an MT mode; S3, a bus fault diagnosis method is designed for triple-modular bus real-time fault identification; and S4, a triple-redundancy bus mode composed of a BC mode and two MT modes is reestablished according to the on-duty module switching principle. A spacecraft computer requiring high real-time performance and reliability can determine a triple-redundancy bus fault by using the serial timing characteristic and the information monitoring function of buses. The method is easy to implement, runs reliably, is not affected by the external environment, is quick, and can be easily used in engineering.

Owner:SHANGHAI AEROSPACE CONTROL TECH INST

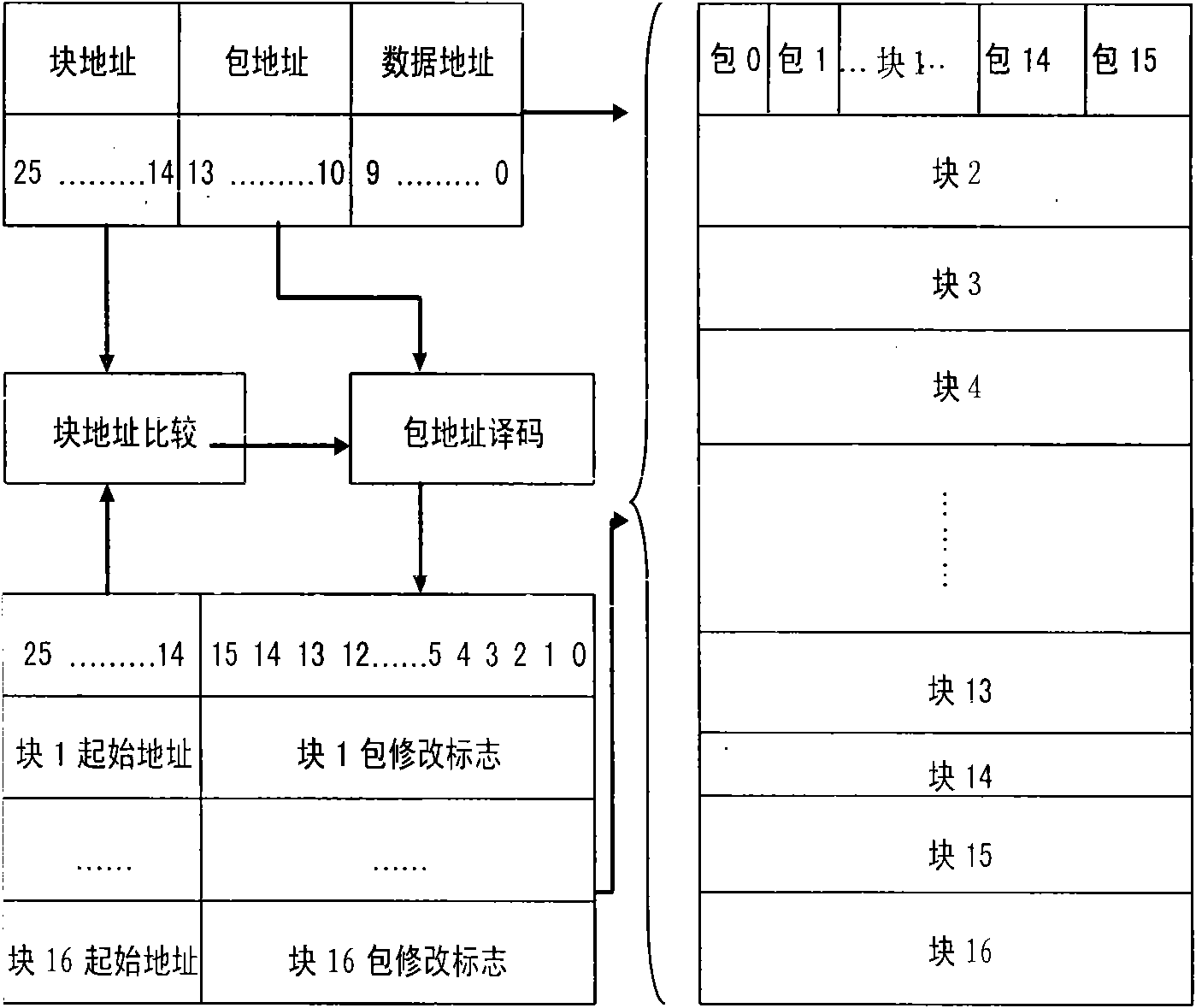

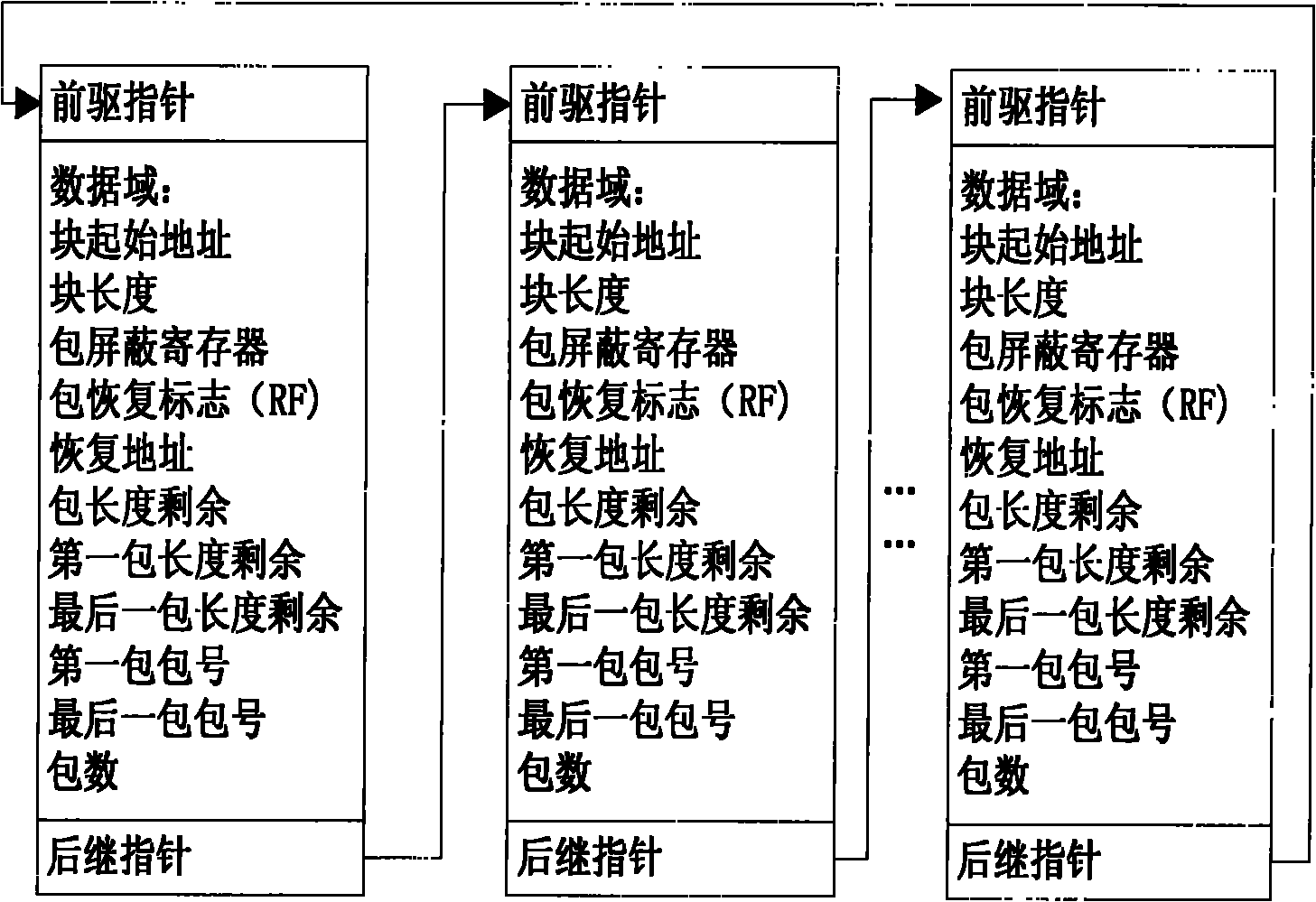

Hardware monitoring and micro-packet protocol-based key data restoration method

InactiveCN102012850AGuaranteed continuityEnsure consistencyRedundant operation error correctionRestoration methodComputerized system

The invention discloses a hardware monitoring and micro-packet protocol-based key data restoration method in a triple modular redundancy fault-tolerant computer system. The method is characterized by comprising the following steps of: dividing to-be-restored key data into hardware data blocks with equal size and dividing each hardware data block into monitoring packets with the same size; meanwhile, setting a monitor on hardware aiming at each hardware data block, wherein the number of the monitoring packets which can be monitored by the monitor is equal to that of the monitoring packets obtained by dividing each hardware data block; forming a basis for retransmitting a data region of the hardware data block once the condition that the monitoring packet is updated or amended is discovered; and retransmitting data with packet as a unit so as to reduce retransmitted data quantity.

Owner:CAPITAL NORMAL UNIVERSITY

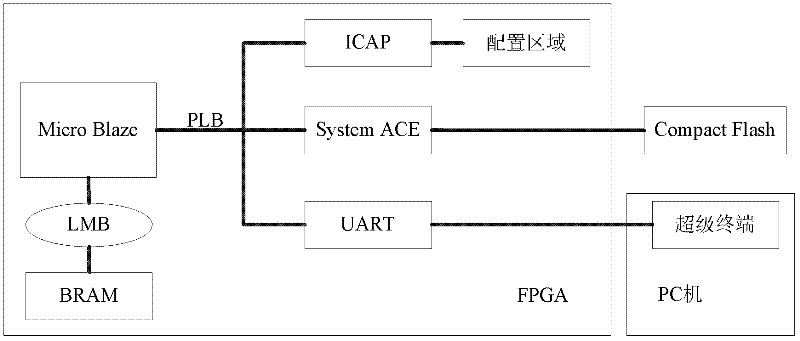

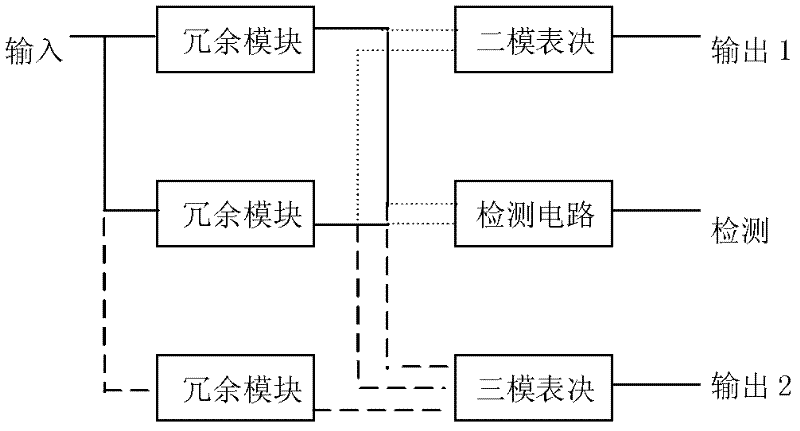

Self-reconfigurable D/TMR (Dual/Triple Modular Redundancy) system based on FPGA (Field Programmable Gate Array) and fault-tolerant design method thereof

InactiveCN102541698AReduce areaReduce power consumptionRedundant hardware error correctionResource utilizationError-tolerant design

The invention discloses a fault-tolerant design method of a self-reconfigurable D / TMR (Dual / Triple Modular Redundancy) system based on an FPGA (Field Programmable Gate Array), comprising the following work steps: (a) utilizing a DMR bit stream to configure a dynamic reconfigurable area; (b) detecting the state of a DMR system through a detection circuit and judging whether faults exit; if not, keeping a DMR state of the dynamic reconfigurable area; otherwise, reading a configuration TMR bit stream on a CF (Collaborative Filtering) card; and configuring the dynamic reconfigurable area into a TMR state. The fault-tolerant design method provided by the invention can overcome the disadvantages of a fault-tolerant mechanism, has the advantages of higher resource utilization rate, high fault-tolerant capability and high reliability, and can realize rapid self-repairing of faults. The invention further discloses the self-reconfigurable D / TMR system based on the FPGA.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Single event upset characteristic testing method for partially triple modular redundancy reinforced SRAM (static random access memory) type FPGA (field programmable gate array)

The invention provides a single event upset characteristic testing method for partially triple modular redundancy reinforced SRAM (static random access memory) type FPGA (field programmable gate array). The method comprises the following steps: irradiating a tested device at a set fluence rate, recording a single event error for once when the output characteristic of the device is not correct and the functions of the device do not return to normal within time T1 after the particle irradiation stops, and repeating the above steps for multiple times and then calculating a single even error section; reducing the particle fluence rate continuously till the single even error section becomes stable; and repeating the above steps under at least five different LET values in total.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

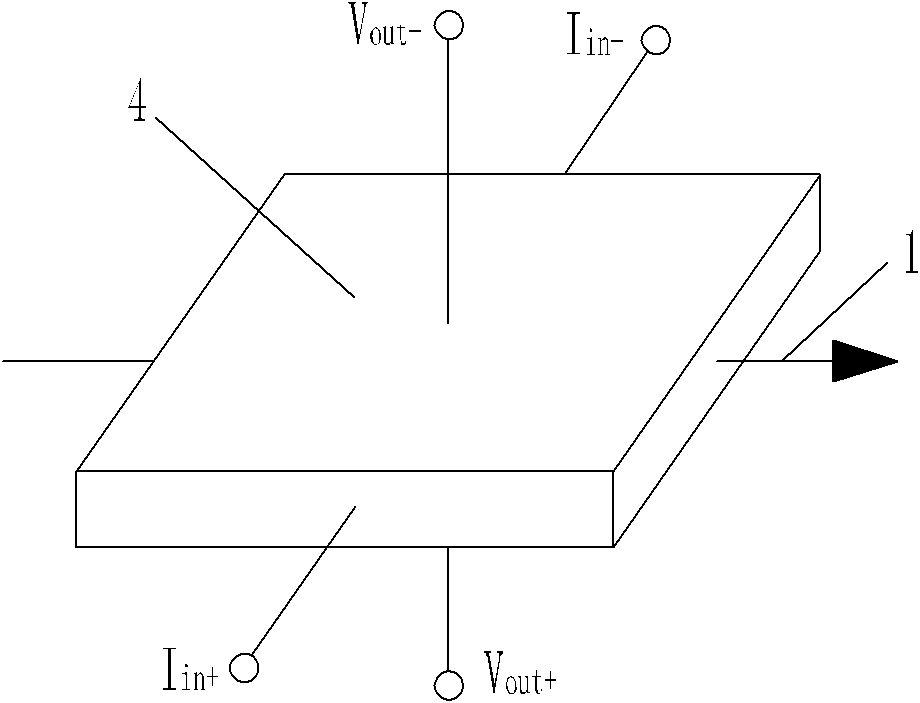

Current measurement device

ActiveCN102169133AWide linear measurement rangeHigh sensitivityCurrent/voltage measurementVoltage/current isolationMeasurement deviceResponse Frequency

The invention discloses a current measurement device, which is used for measuring current in a powered-on lead wire. The current measurement device comprises a plurality of measurement units; each of the measurement units comprises a first sensor and a second sensor, wherein the first sensor is arranged along a tangent direction parallel to a magnetic field around the powered-on lead wire and used for measuring a current value within a low measurement range, and the second sensor is arranged in a manner of forming an angle with the tangent direction of the magnetic field around the powered-onlead wire and used for measuring a current value within a high measurement range; and the first sensor and the second sensor are located in the same plane vertical to a straight line where the powered-on lead wire is placed and connected with a sensor special application specific integrated circuit (ASIC) chip. By using the advantages that a triple modular redundancy (TMR) sensor is high in sensitivity and a hall sensor is wide in linear measurement range or measuring a component of the magnetic field around the powered-on lead wire by using the inclined TMR sensor, the current measurement device is high in sensitivity and wide in linear measurement range, and has the advantages of high temperature characteristic and response frequency, low power consumption and small volume.

Owner:MULTIDIMENSION TECH CO LTD

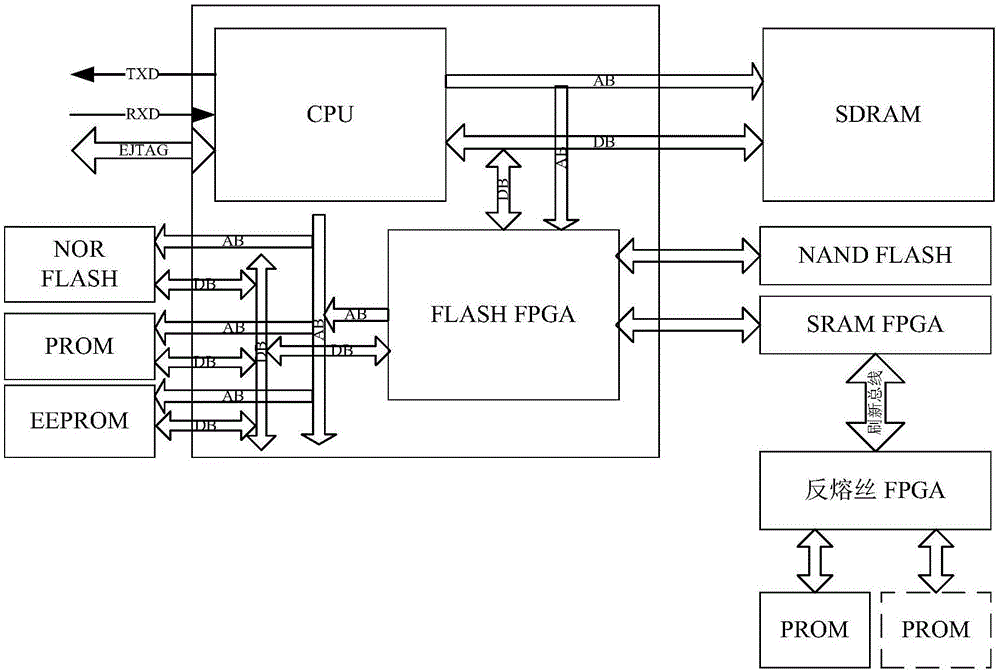

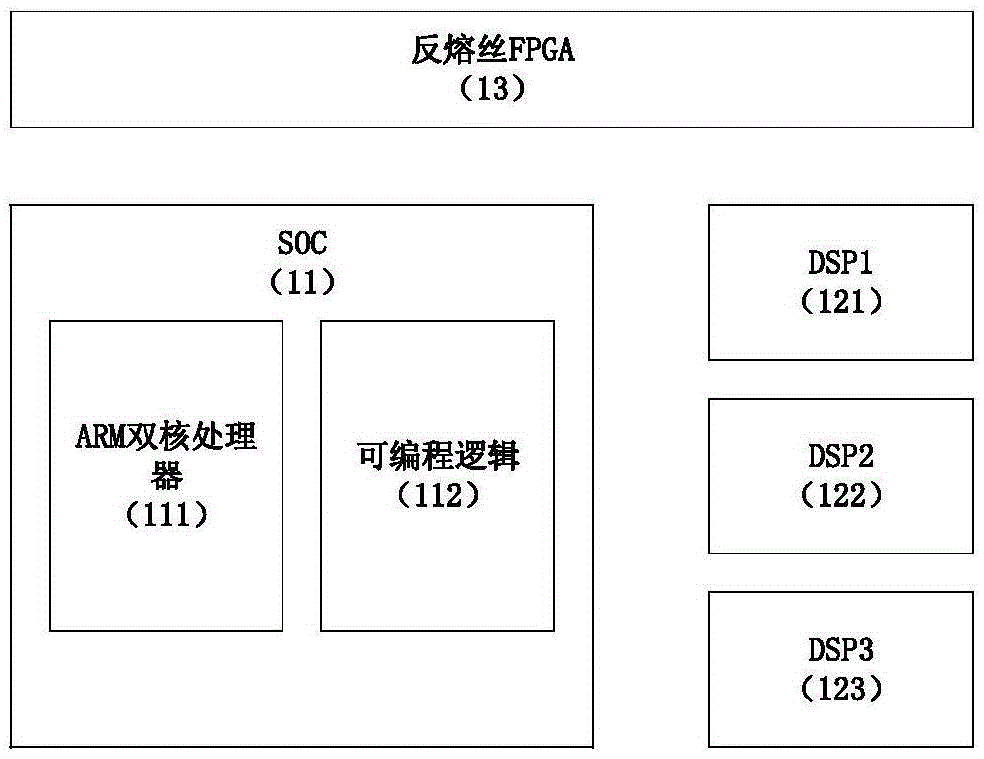

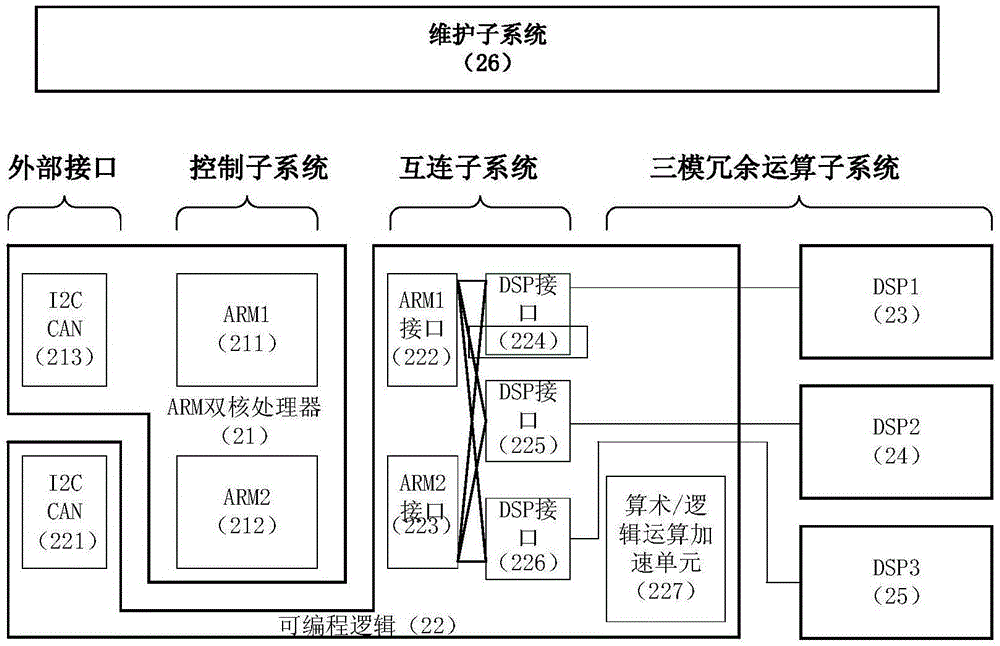

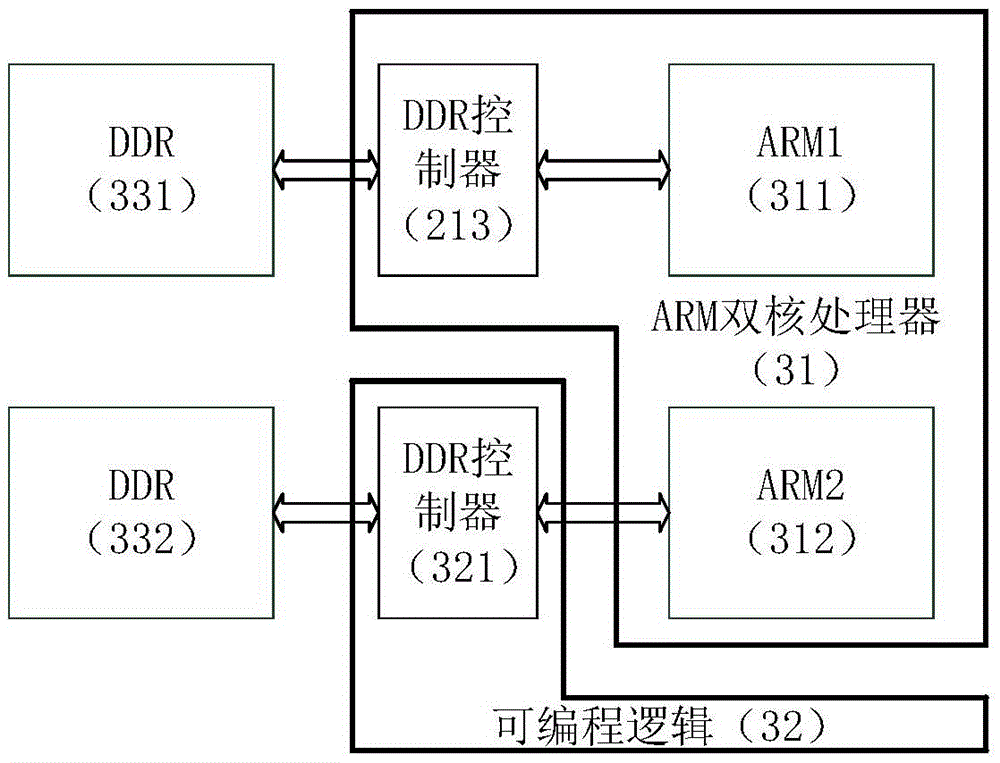

Aerospace computer

ActiveCN105550074ARealize dual machine backupImprove reliabilityRedundant hardware error correctionDual coreSystem maintenance

The invention provides an aerospace computer. The aerospace computer comprises an anti-fuse FPGA (Field Programmable Gate Array), a commercial SOC (System On Chip) and three DSPs (Digital Signal Processors), which achieve a system maintenance function. According to the aerospace computer provided by the invention, on the anti-fuse FPGA, not only is a state of each hardware unit module monitored, but also a state of each logic function operating on each hardware unit module is monitored, so that on the basis, the computer is dynamically loaded when necessary to guarantee a system to flexibly, reliably and uninterruptedly operate; the commercial SOC device adopted by the aerospace computer internally comprises an ARM dual-core processor used as a center control processor and a high-capacity programmable logic (PL) used for arithmetical logic operation acceleration, so that when a high integration level of the system is ensured, dual-computer backup of the center control processor is achieved by two cores of the ARM dual-core processor, hardware backup of a data channel and an interface is achieved by designing internal data association and an external interface on the PL, and a triple-modular redundancy voting mechanism of DSP interfaces is achieved by respectively designing the DSP interfaces; and according to the invention, the aerospace computer which is high in integration level, high in reliability and high in performance, is miniaturized and is flexible in configuration can be achieved.

Owner:CHINA JILIANG UNIV

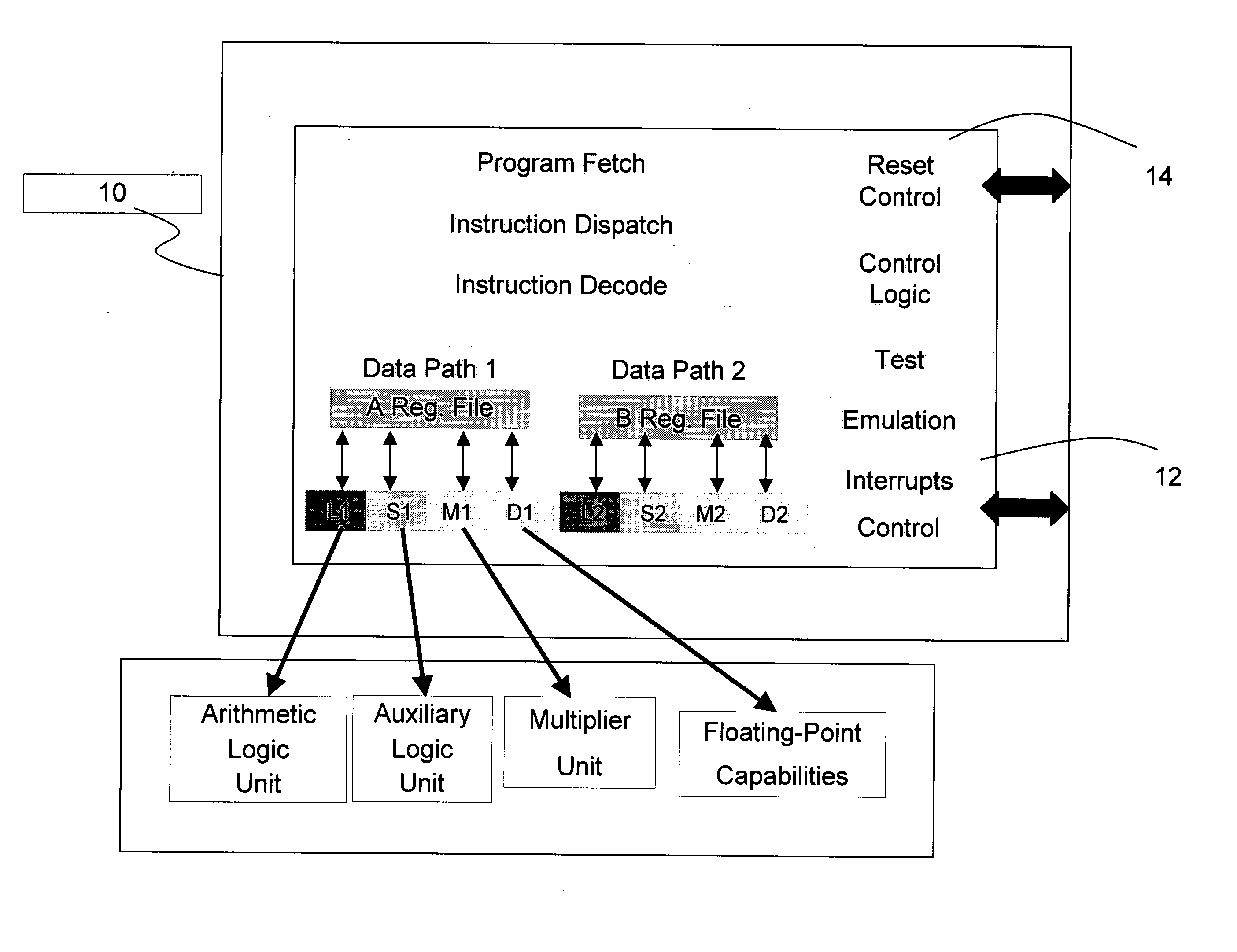

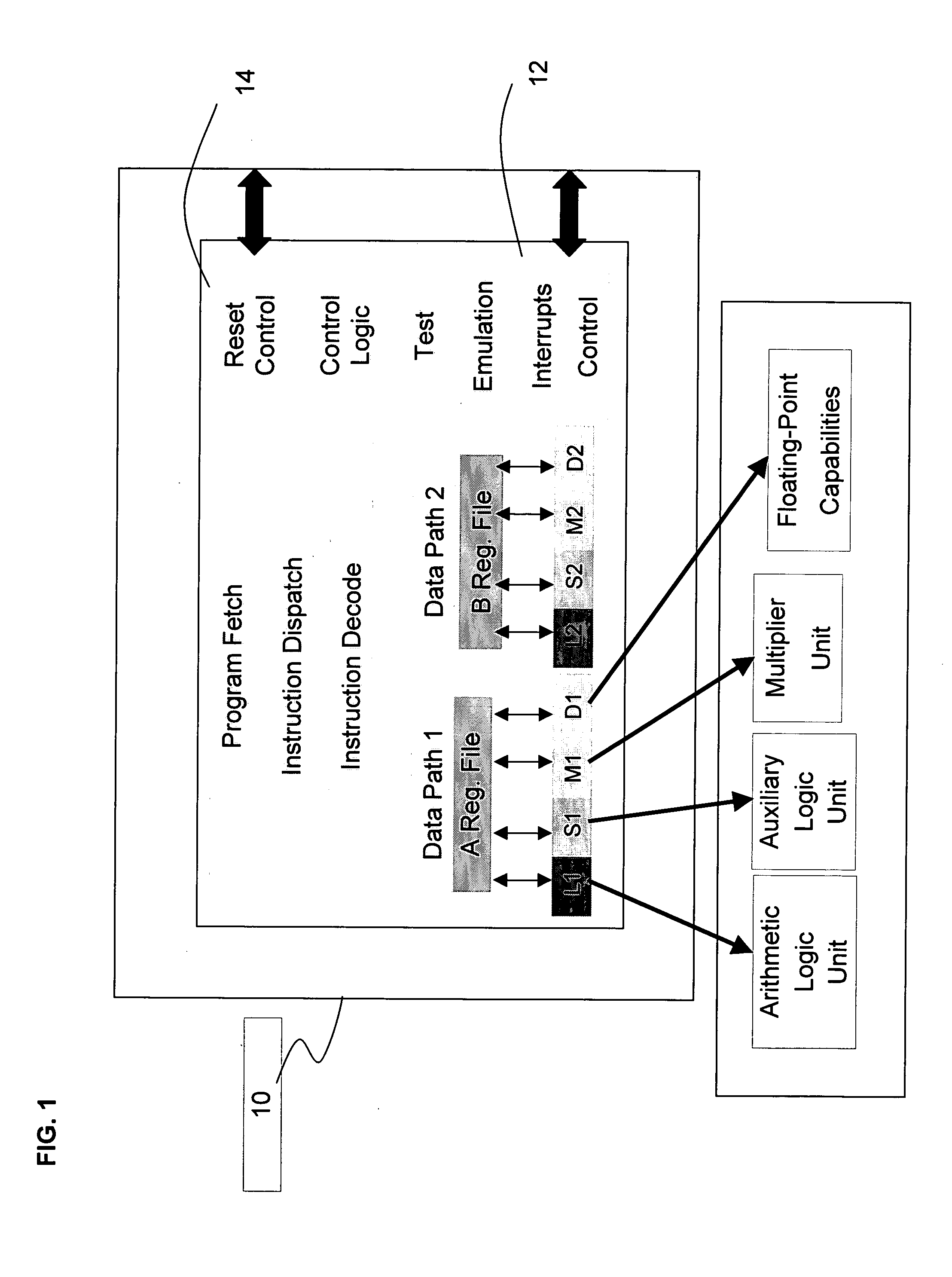

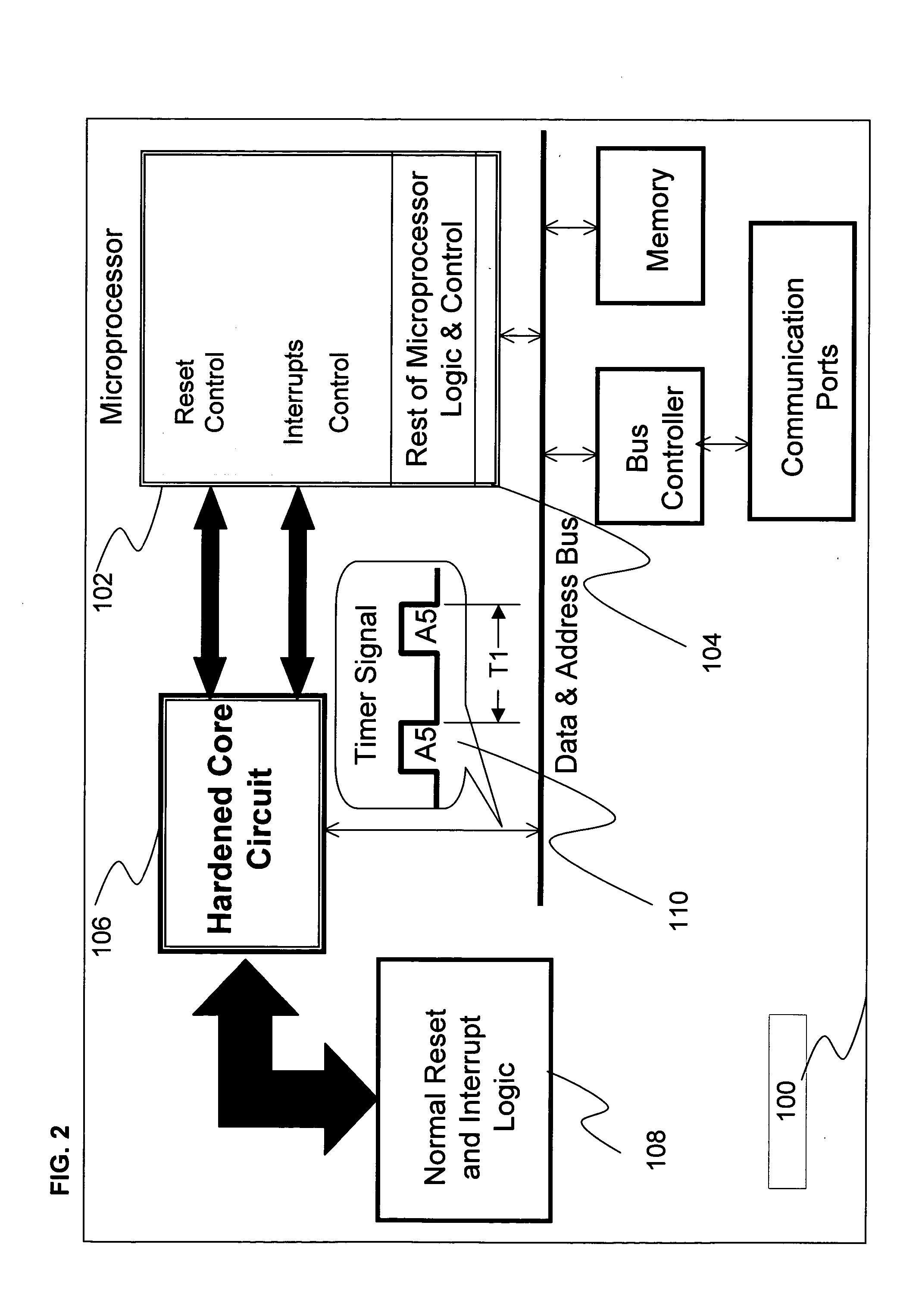

Functional interrupt mitigation for fault tolerant computer

A new method for the detection and correction of environmentally induced functional interrupts (or “hangs”) induced in computers or microprocessors caused by external sources of single event upsets (SEU) which propagate into the internal control functions, or circuits, of the microprocessor. This method is named Hardened Core (or H-Core) and is based upon the addition of an environmentally hardened circuit added into the computer system and connected to the microprocessor to provide monitoring and interrupt or reset to the microprocessor when a functional interrupt occurs. The Hardened Core method can be combined with another method for the detection and correction of single bit errors or faults induced in a computer or microprocessor caused by external sources SEUs. This method is named Time-Triple Modular Redundancy (TTMR) and is based upon the idea that very long instruction word (VLIW) style microprocessors provide externally controllable parallel computing elements which can be used to combine time redundant and spatially redundant fault error detection and correction techniques. This method is completed in a single microprocessor, which substitute for the traditional multi-processor redundancy techniques, such as Triple Modular Redundancy (TMR).

Owner:CZAJKOWSKI DAVID +1

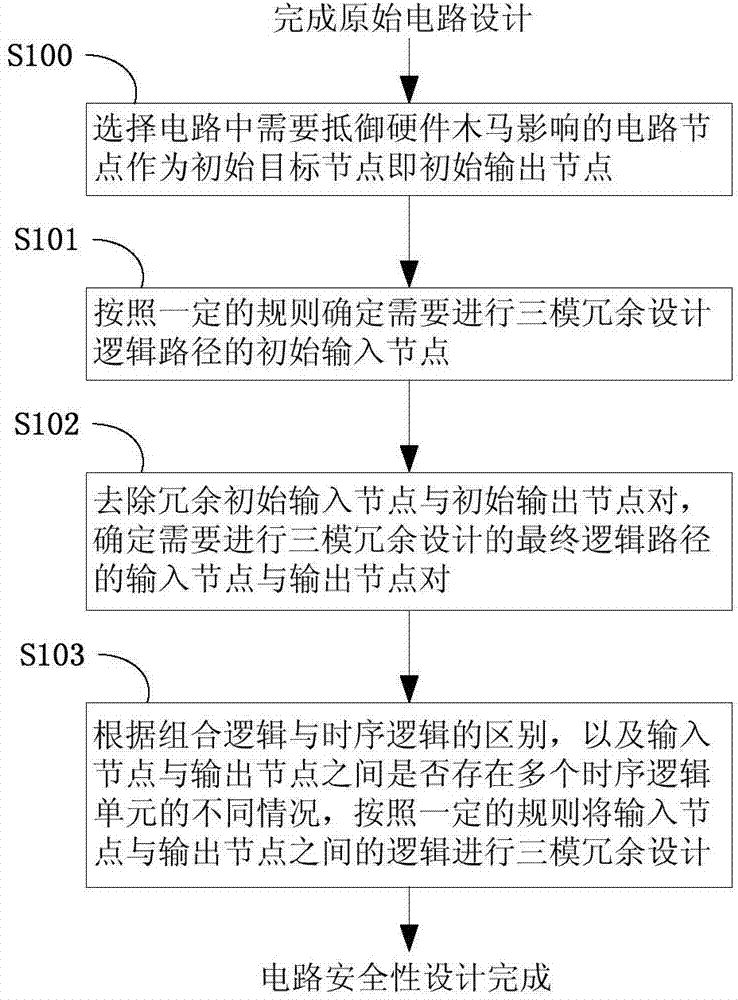

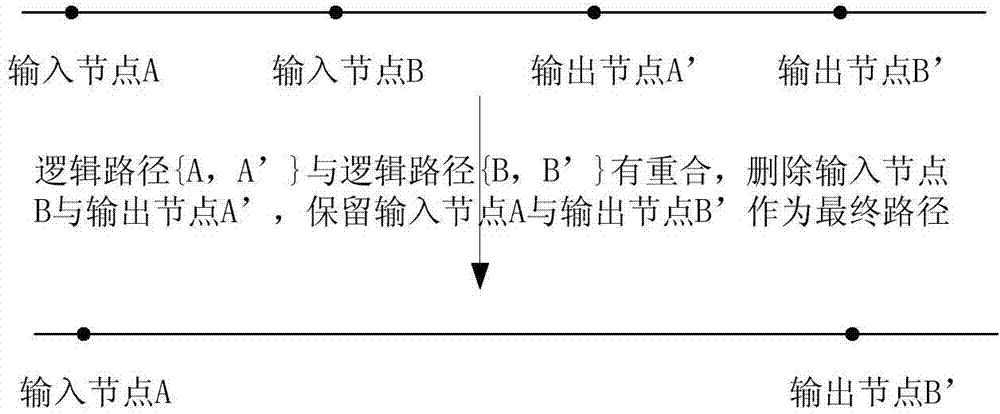

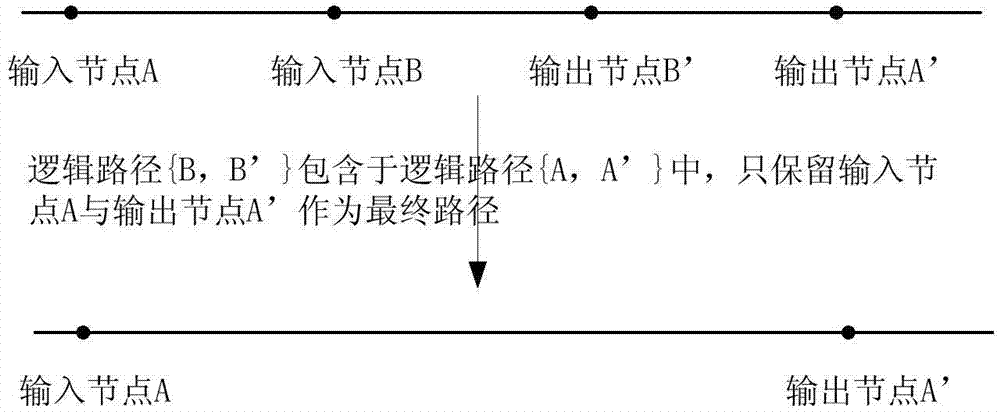

Circuit safety design method for defending against threat of hardware Trojan horse based on triple modular redundancy

ActiveCN104715121ADefend against potential threatsGuaranteed to be correctInternal/peripheral component protectionSpecial data processing applicationsNODALSequential logic

The invention provides a circuit safety design method which utilizes triple modular redundancy to guarantee that an original circuit can work stably even if a hardware Trojan horse is maliciously embedded in the original circuit. The circuit safety design method comprises the following steps: firstly, after finishing the design and verification of the original circuit, selecting logical nodes which can not be covered by all conventional testing methods, and taking the logical nodes as output nodes; secondly, backtracking the output nodes as terminal points in a fan-in direction, and determining input nodes according to certain rules; and finally, performing the triple modular redundancy design of paths between the input nodes and the output nodes respectively according to the difference between combinatorial logic and sequential logic. Through the circuit safety design method, final output cannot be affected even after the logic value of a circuit node, which cannot be tested or has high risk, is changed under the influence of a hardware Trojan horse, and the original function of the circuit is kept.

Owner:58TH RES INST OF CETC

Program on-orbit loading refreshing method based on triple modular redundancy

PendingCN111176908AAvoid bit errorsProperly configure program contentRedundant hardware error correctionEnergy efficient computingDsp architectureDependability

The invention relates to the technical field of satellite loads, in particular to a program on-orbit loading refreshing method based on triple modular redundancy. According to the method, the reliability of on-orbit operation of the space load is remarkably improved, the single-bit overturning phenomenon caused by the space single event phenomenon and the like is avoided to a great extent, and thecontinuous reliability of on-orbit operation of the space load based on the SRAM type FPGA + DSP architecture is improved. The method is simple to implement, and can meet the reliability requirementof long-time on-orbit continuous operation of the space load digital circuit part under the condition of consuming less resources.

Owner:BEIJING RES INST OF TELEMETRY +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com