Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

52 results about "Error-tolerant design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An error-tolerant design (also: human-error-tolerant design) is one that does not unduly penalize user or human errors. It is the human equivalent of fault tolerant design that allows equipment to continue functioning in the presence of hardware faults, such as a "limp-in" mode for an automobile electronics unit that would be employed if something like the oxygen sensor failed.

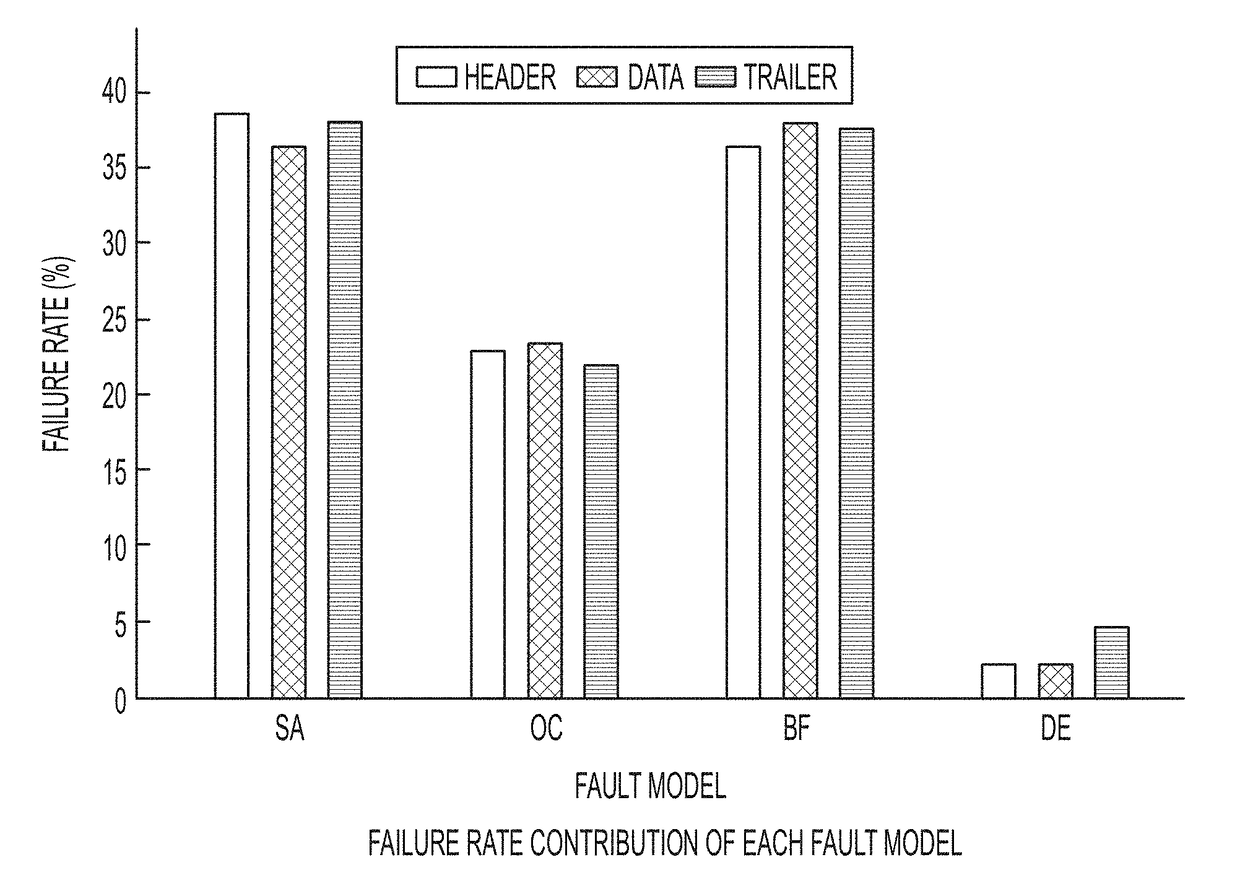

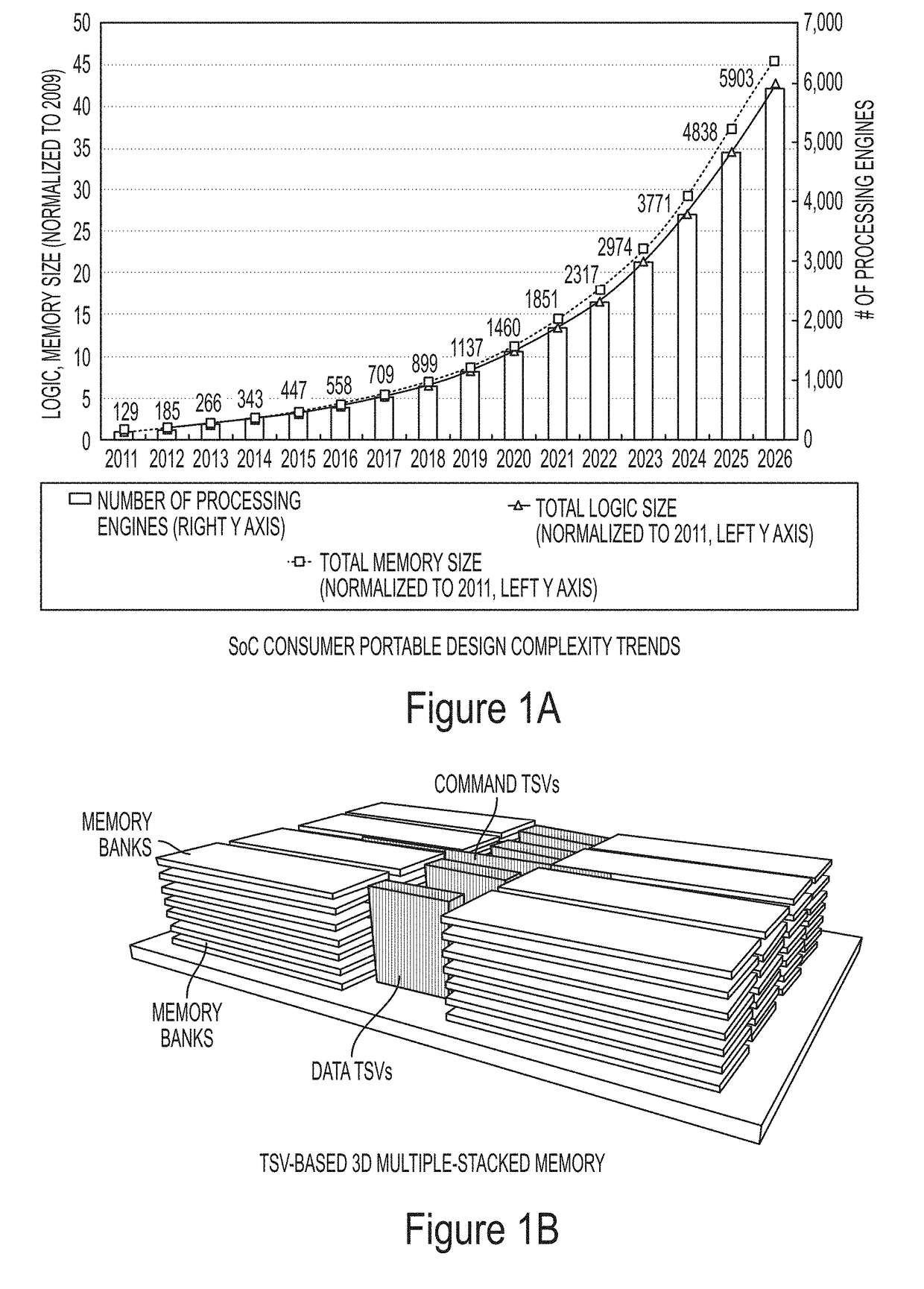

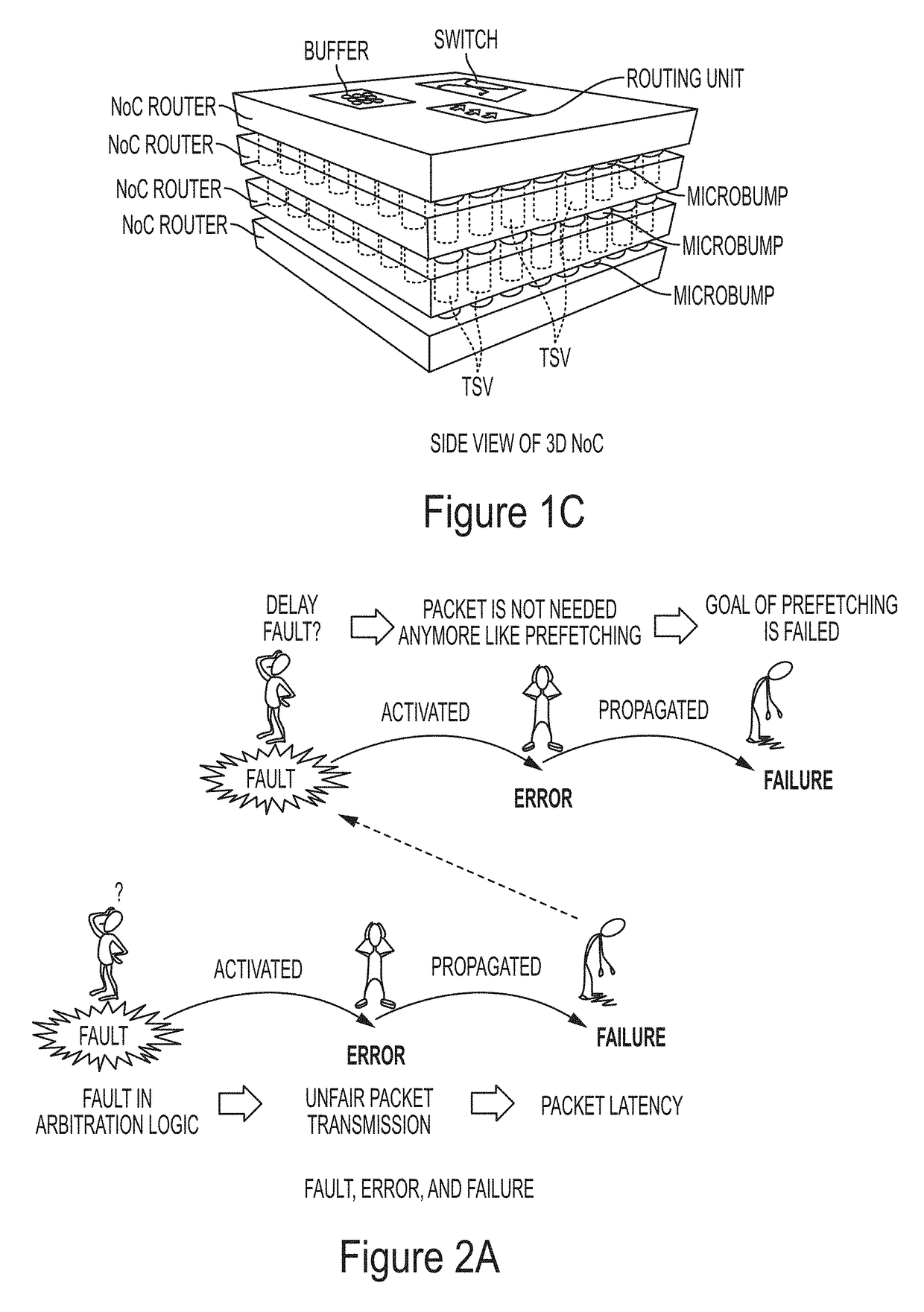

THREE-DIMENSIONAL NoC RELIABILITY EVALUATION

Methods, storage mediums, and apparatuses for evaluating the reliability of Three-Dimensional (3D) Network-on-Chip (NoC) designs are described. The described embodiments provide a 3D NoC specific fault-injector tool which is able to model logic-level fault models of 3D NoC specific physical faults in 3D-NoC platform. These embodiments automate the whole process of static and dynamic fault injection base on the user preference and reports the specific reliability metrics for 3D NoC platform as a single tool. The described embodiments can be used for the reliability evaluation and effectiveness of fault-tolerant designs in any of the 3D-many core designs such as manycore systems in different ranges of application from embedded systems in cellphones to larger systems which can be used in next generation of autonomous cars or hypercube memory cells.

Owner:SYNOPSYS INC

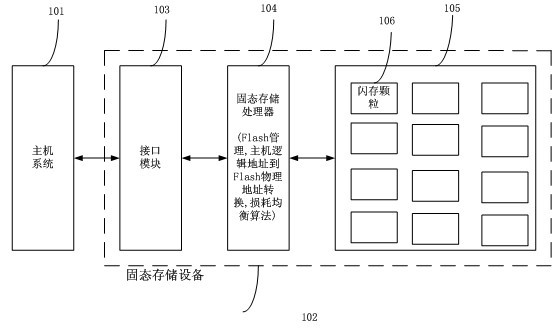

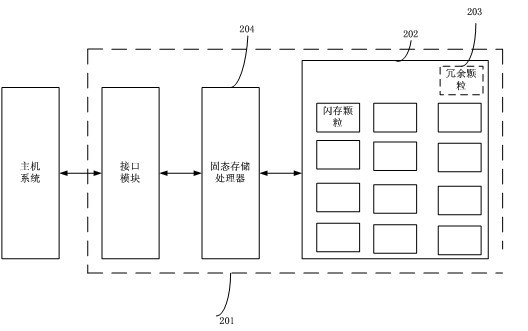

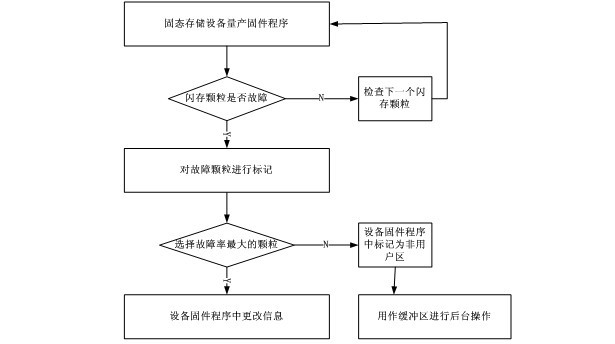

Fault tolerance design method for solid-state memory device

ActiveCN102043689AWill not affect the excellent rateExtended service lifeRedundant hardware error correctionSolid-state storageError-tolerant design

The invention discloses a fault tolerance design method for a solid-state memory device, in which standby redundant memory particles are additionally added in design of a circuit board of a memory device, when the device has flash memory fault in production back-end test or usage, the failed particles are substituted by the redundant memory particles, thereby ensuring that excellent rate of production of the memory device cannot be influenced even encapsulation test is not performed on the particles; simultaneously, service life of the device is effectively prolonged by adding the redundant memory particles in the method, when the flash memory particles in the device reach certain service life, the flash memory particles are substituted by the redundant particles or idle particles, so that the service life of the device is effectively prolonged through the continuous substitution. The method can be implemented in process of device production test and / or usage.

Owner:WUHAN SOLIC CZECHOSIOVAKIA DATA SCI & TECH +1

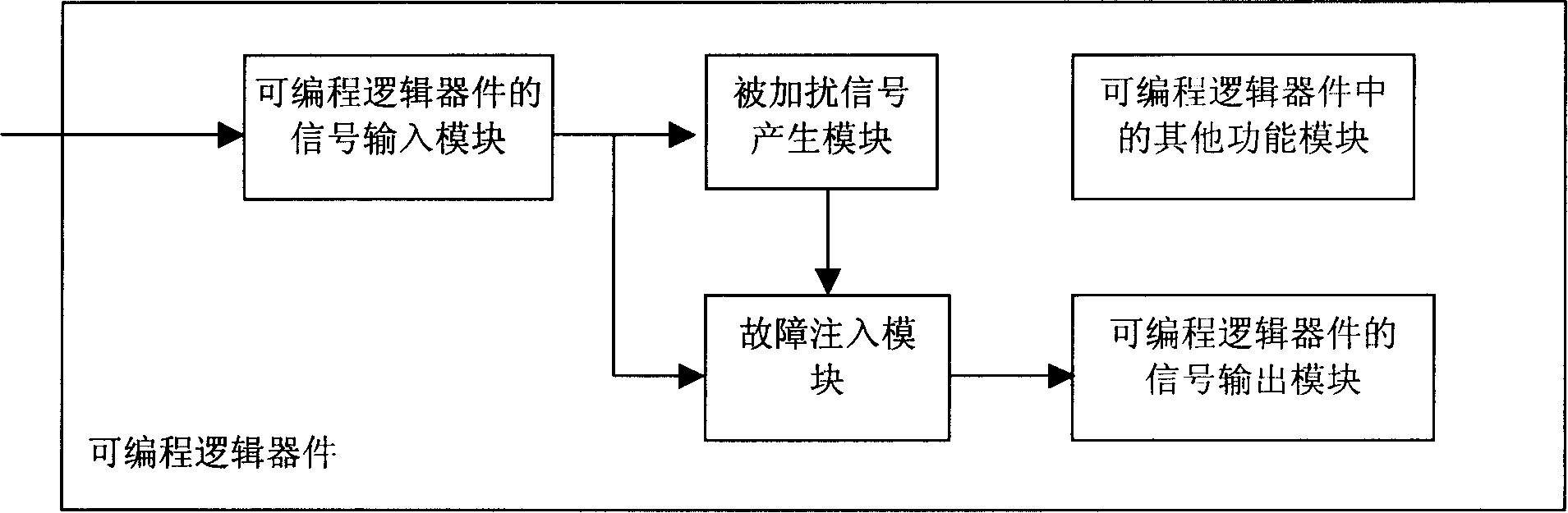

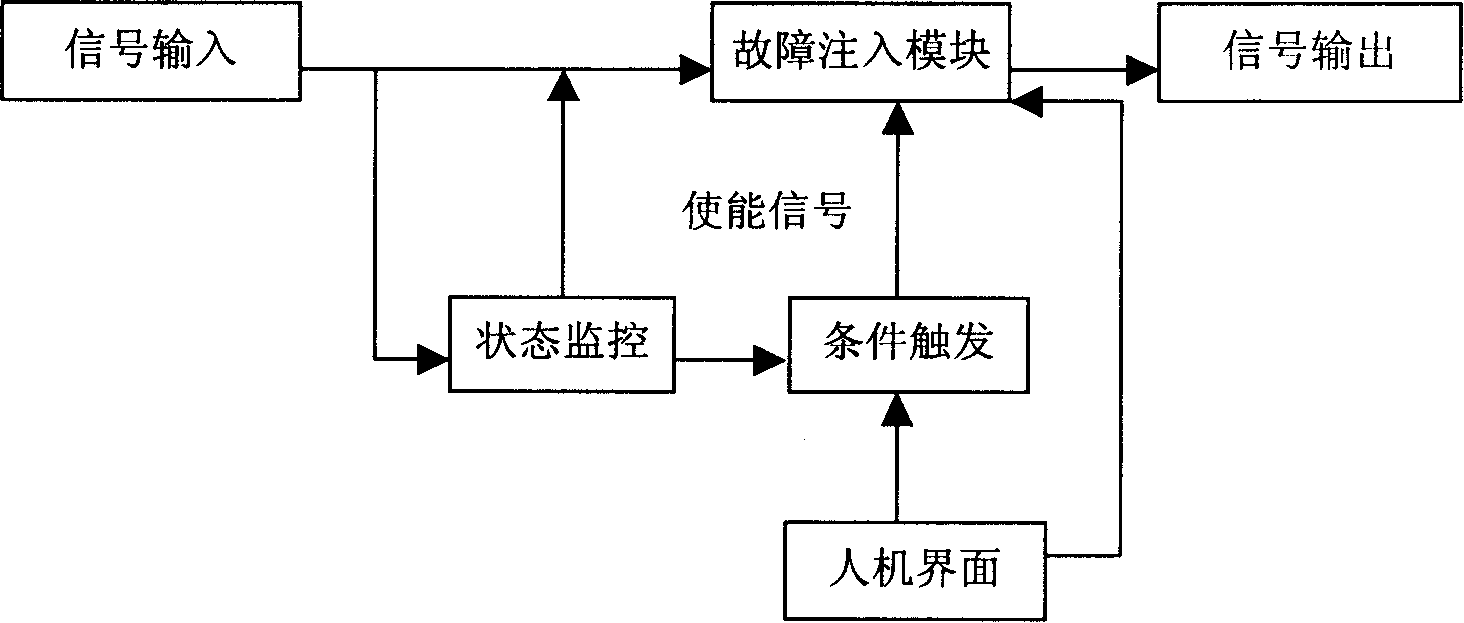

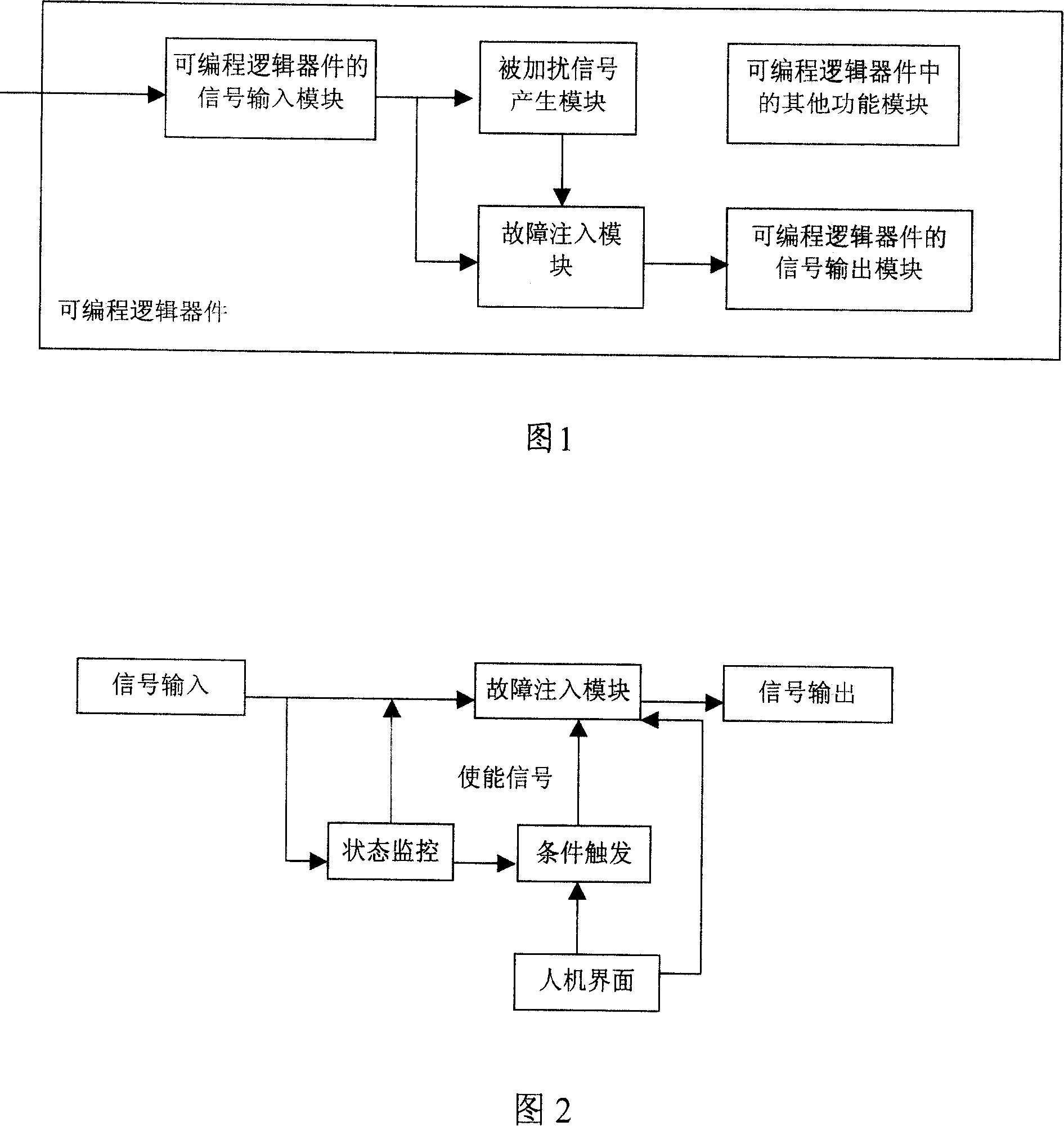

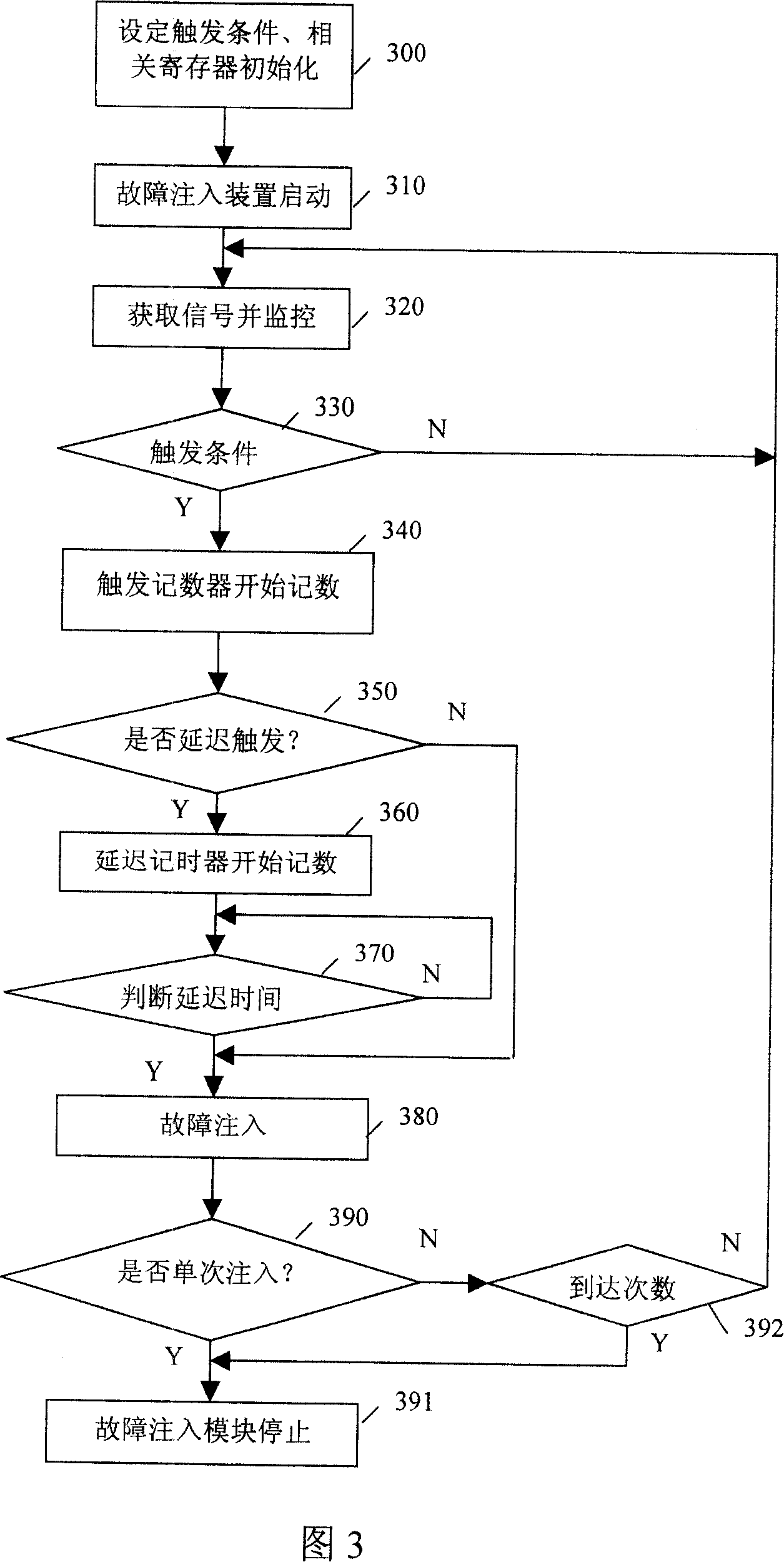

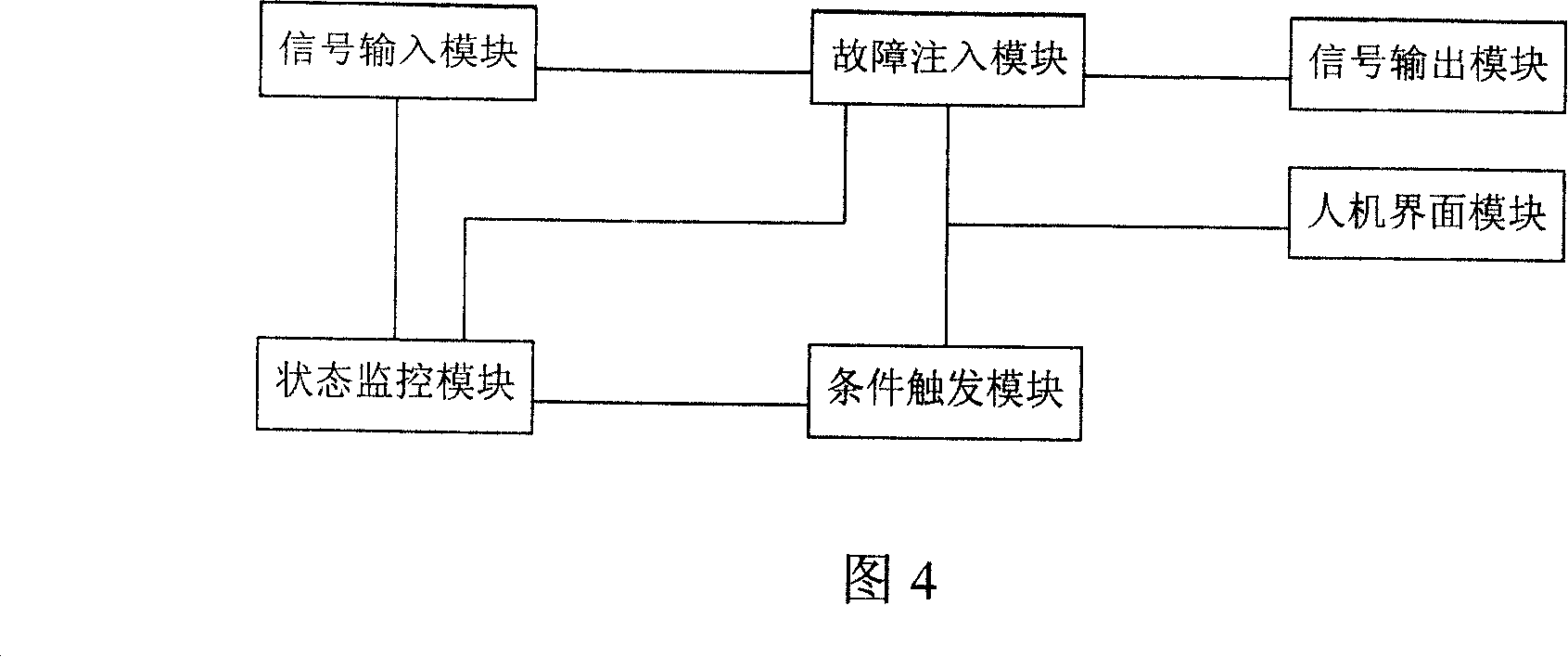

Fault filling method and apparatus based on programmable logical device

InactiveCN1740980AAvoid the phenomenon of electrical damageAvoid missing detectionFault responseProgrammable logic deviceEngineering

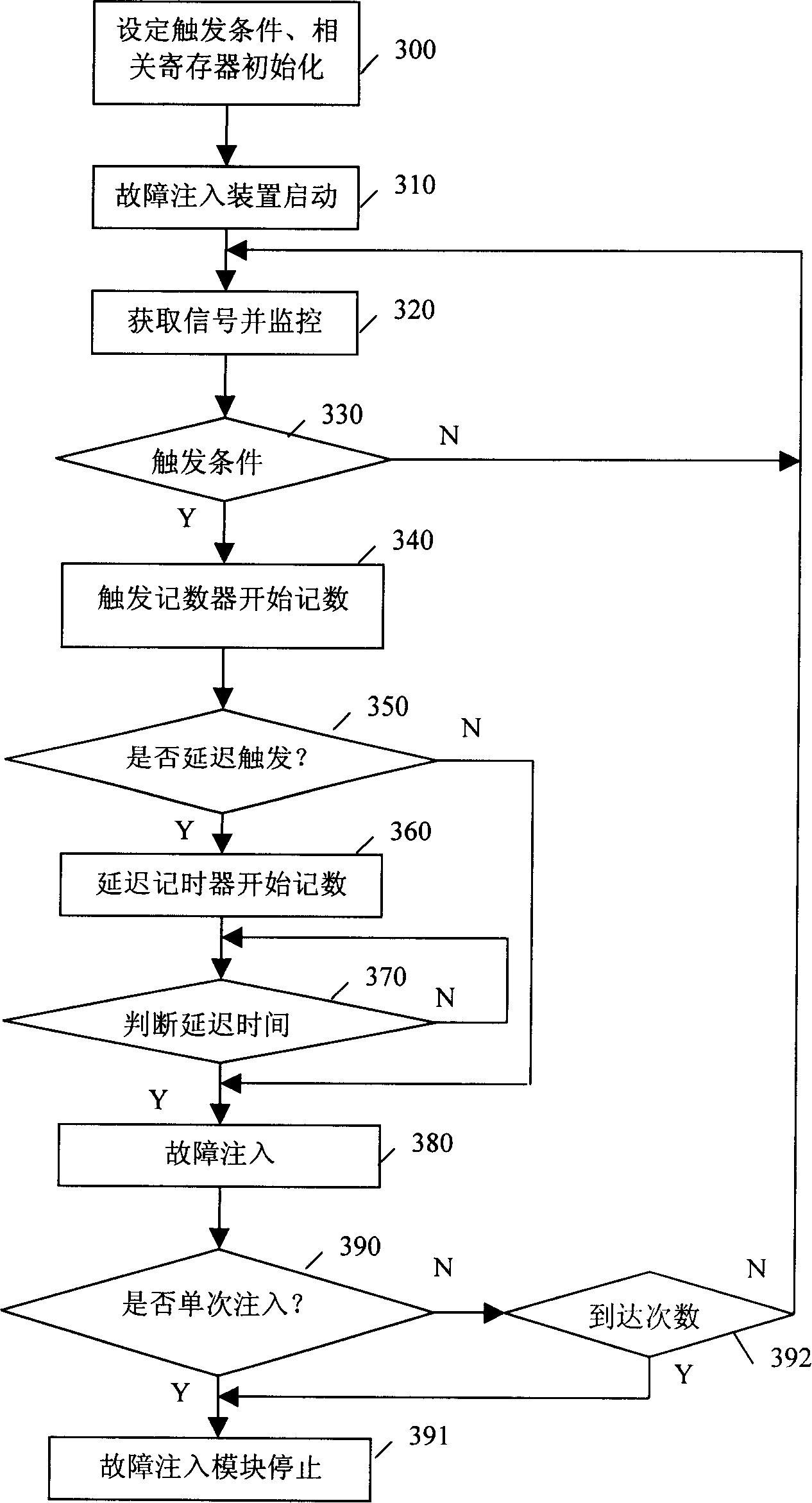

The present invention provides a fault injection method based on programmable logic device and its device. Its kernel lies in that a fault injection module is set in the interior of programmable logic device having need of making fault injection to obtain the signal of the described programmable logic device, the described fault injection module can inject the correspondent fault into the obtained signal and can output the signal in which the fault is injected. Said invention has no need of external fault injection equipment or scrambling equipment, and can utilize the fault injection module set in the interior of programmable logic device to make fault injection process have no need of manual intervention and do not damage the programmable logic device.

Owner:HUAWEI TECH CO LTD

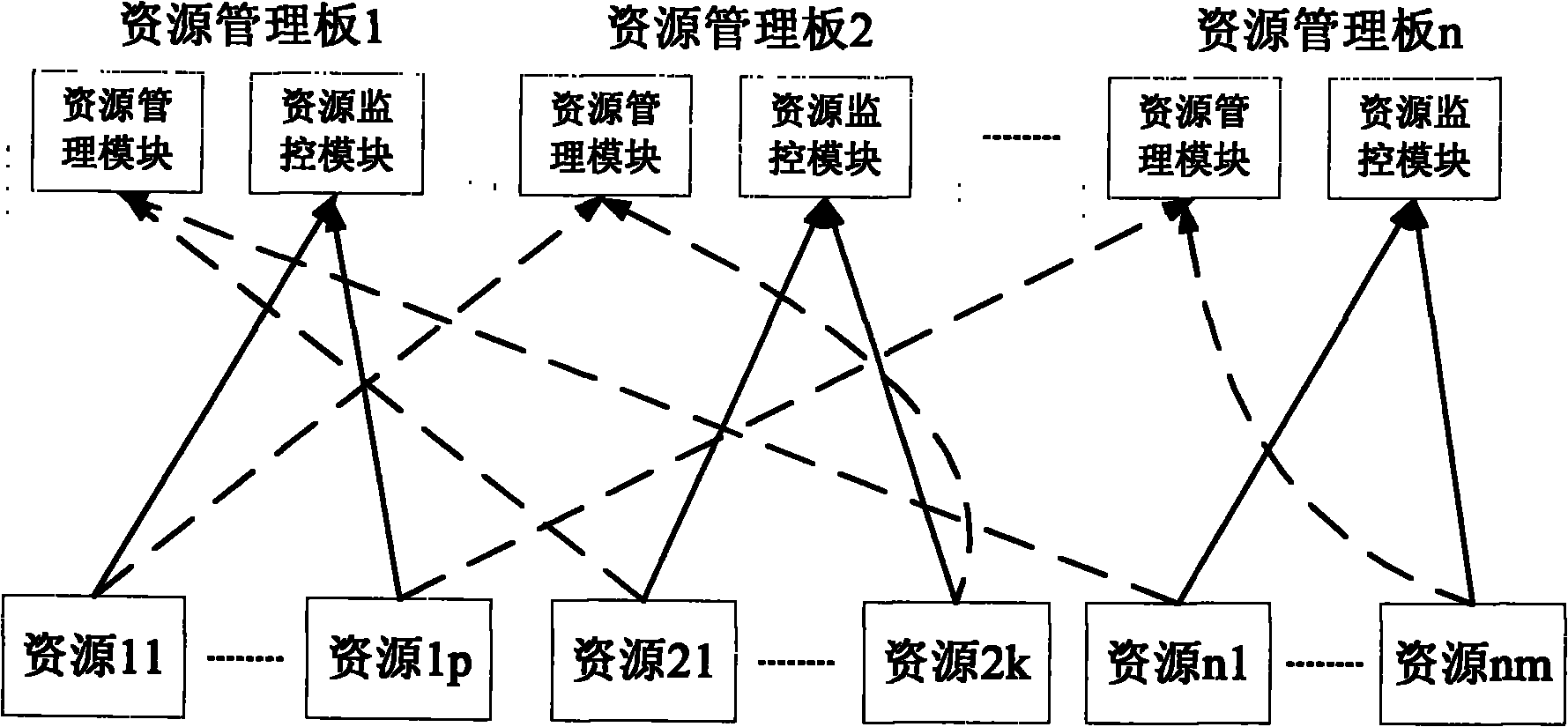

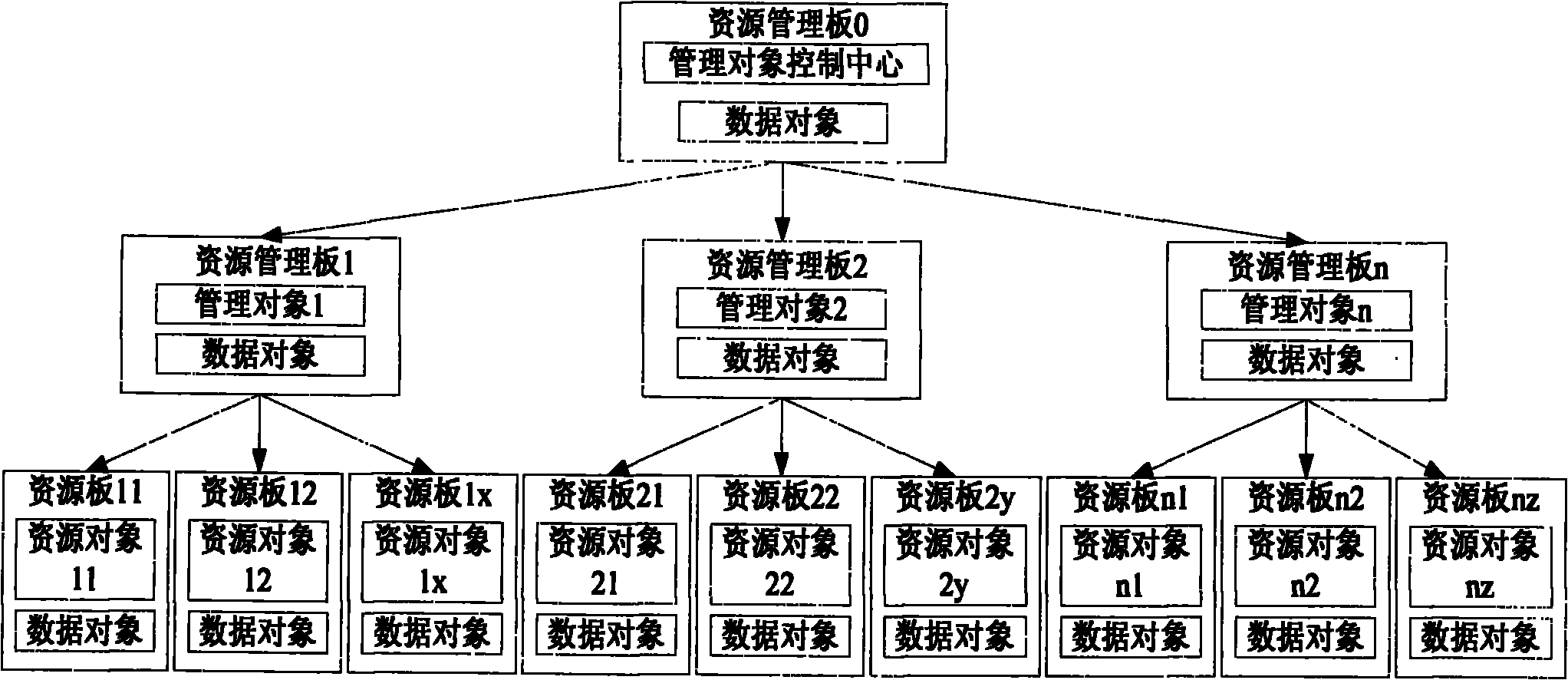

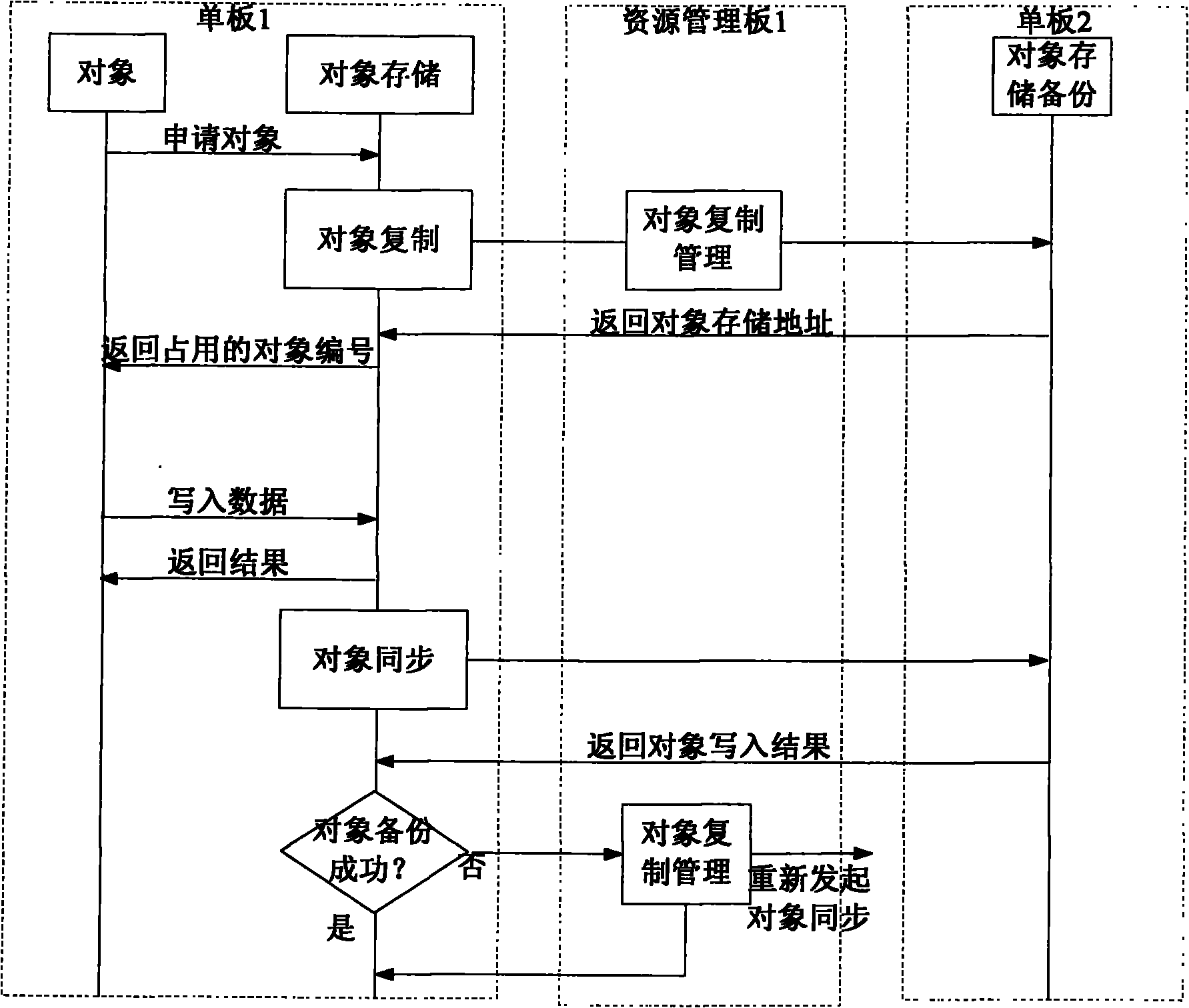

Method and system for managing distributed resources

InactiveCN101996094AMultiprogramming arrangementsData switching networksManagement objectResource information

The invention relates to a method and system for managing distributed resources. The system comprises resource objects, data objects, management objects and a control center, wherein the control center is used for configuring the service functions and the backup modes of all resource objects in the system and allocating management tasks for all management objects; the management objects are used for taking charge of the resource management of managed recourse objects according to the management tasks allocated by the control center and providing a query and control service aiming at the managed recourse objects; the resource objects are used for completing corresponding logic functions under the control of the management objects; and the data objects are used for storing the resource information in the resource objects and the resource control information in the management objects. The invention increases the efficiency of resource utilization and simplifies the resource management process by adopting grading object management and effective fault-tolerant design and ensures fast recovery capability and mechanism under the condition that various errors occur in the resource.

Owner:ZTE CORP

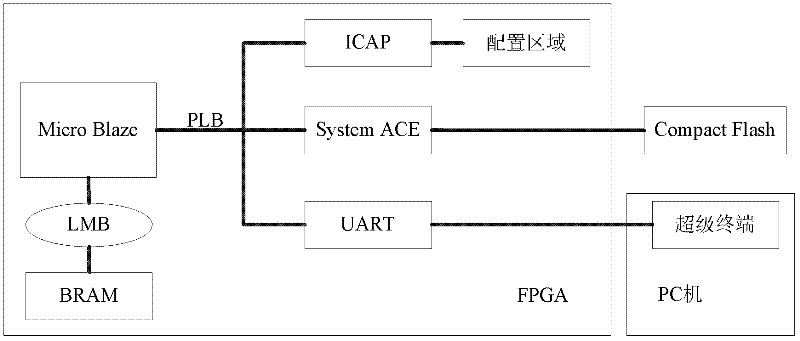

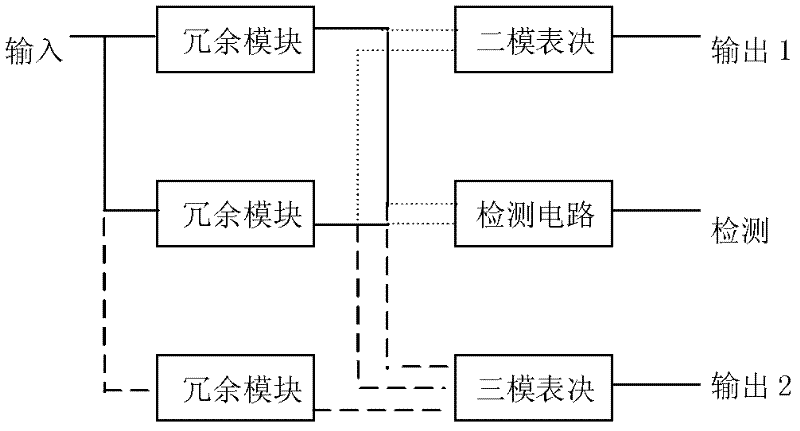

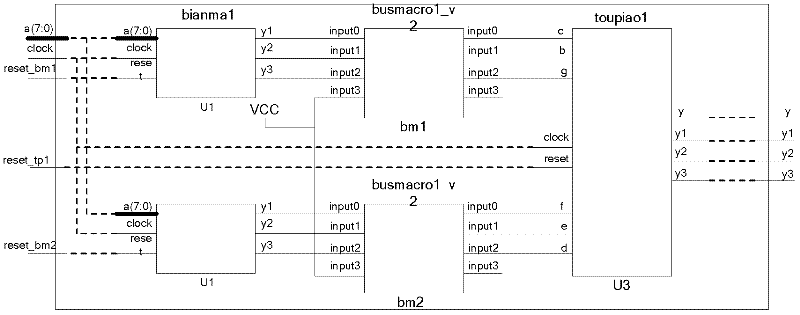

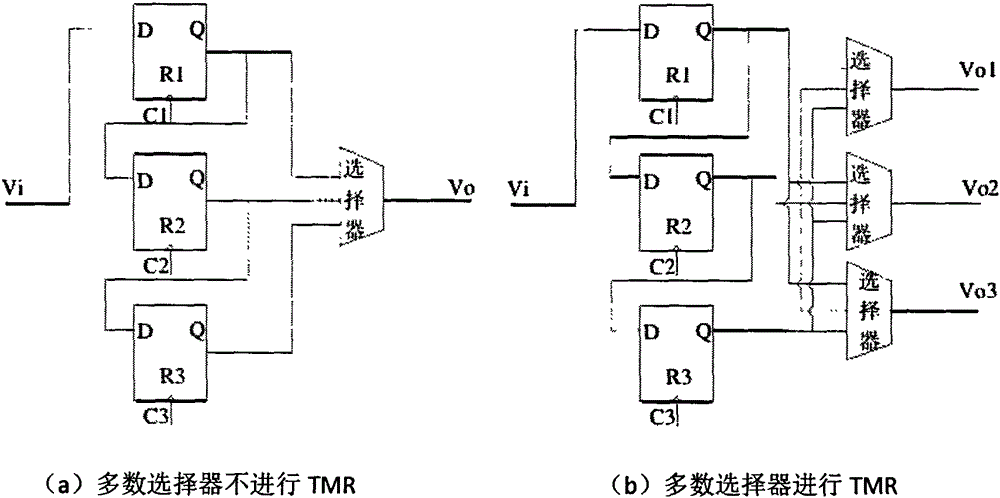

Self-reconfigurable D/TMR (Dual/Triple Modular Redundancy) system based on FPGA (Field Programmable Gate Array) and fault-tolerant design method thereof

InactiveCN102541698AReduce areaReduce power consumptionRedundant hardware error correctionResource utilizationError-tolerant design

The invention discloses a fault-tolerant design method of a self-reconfigurable D / TMR (Dual / Triple Modular Redundancy) system based on an FPGA (Field Programmable Gate Array), comprising the following work steps: (a) utilizing a DMR bit stream to configure a dynamic reconfigurable area; (b) detecting the state of a DMR system through a detection circuit and judging whether faults exit; if not, keeping a DMR state of the dynamic reconfigurable area; otherwise, reading a configuration TMR bit stream on a CF (Collaborative Filtering) card; and configuring the dynamic reconfigurable area into a TMR state. The fault-tolerant design method provided by the invention can overcome the disadvantages of a fault-tolerant mechanism, has the advantages of higher resource utilization rate, high fault-tolerant capability and high reliability, and can realize rapid self-repairing of faults. The invention further discloses the self-reconfigurable D / TMR system based on the FPGA.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

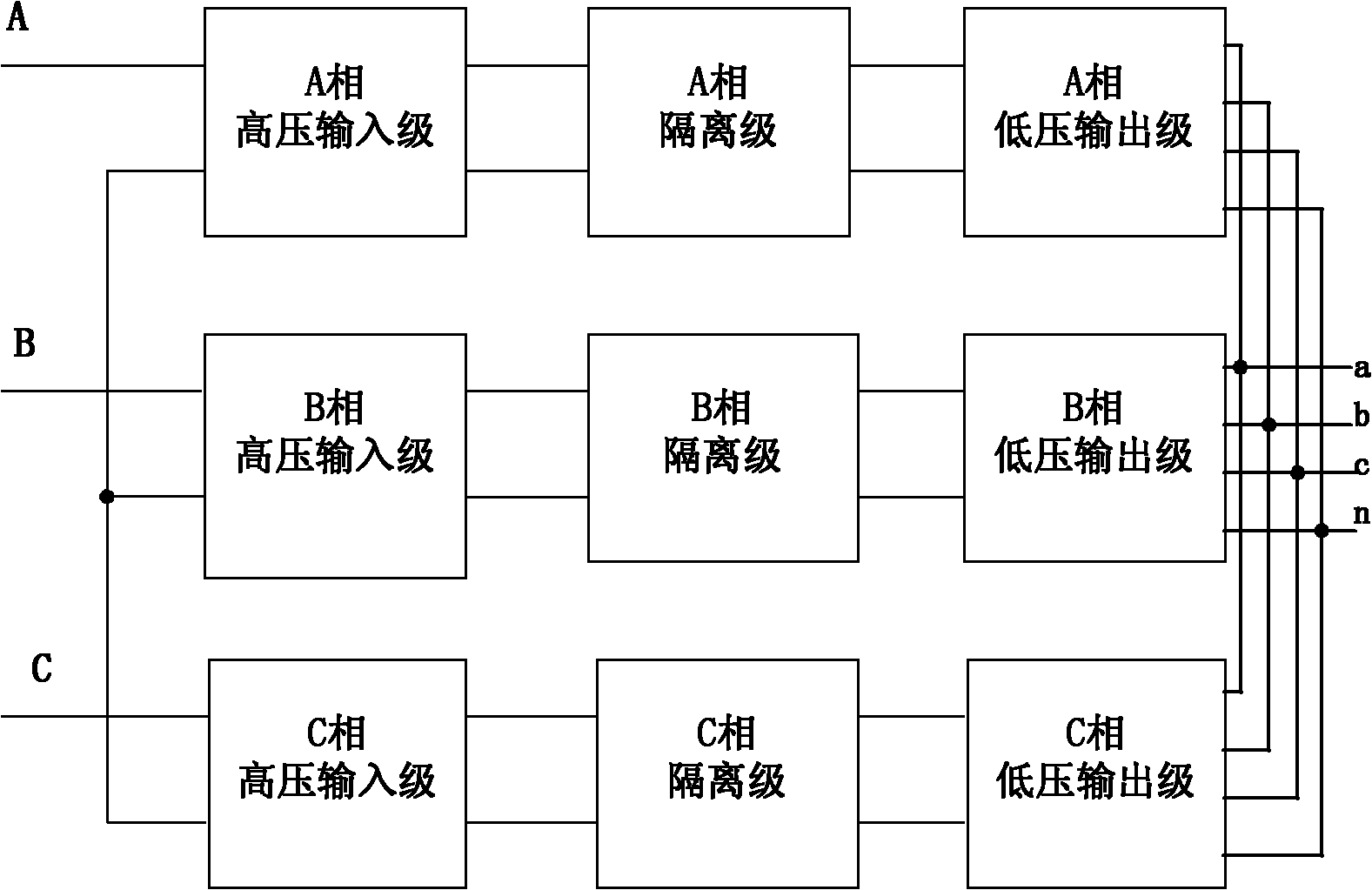

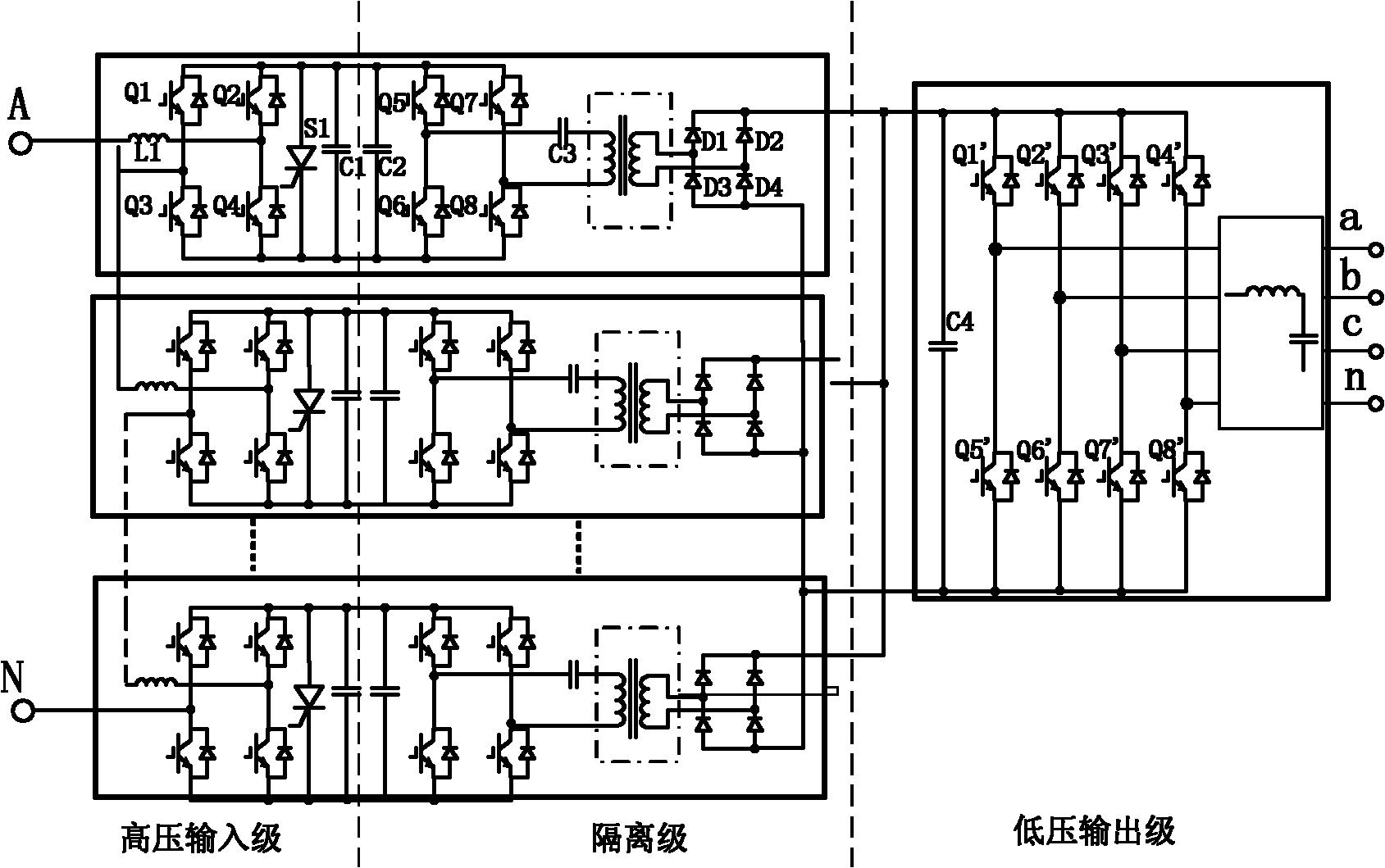

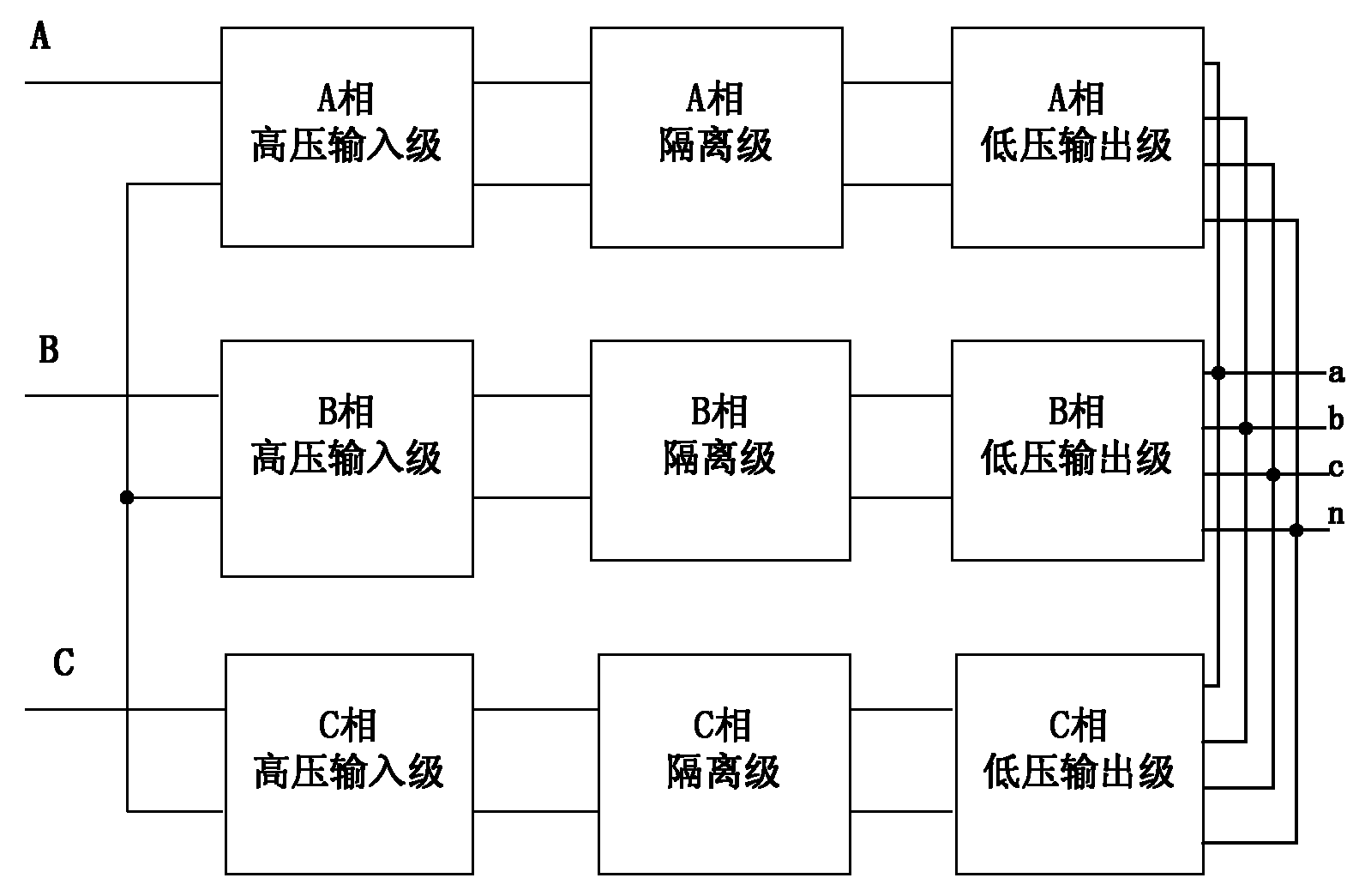

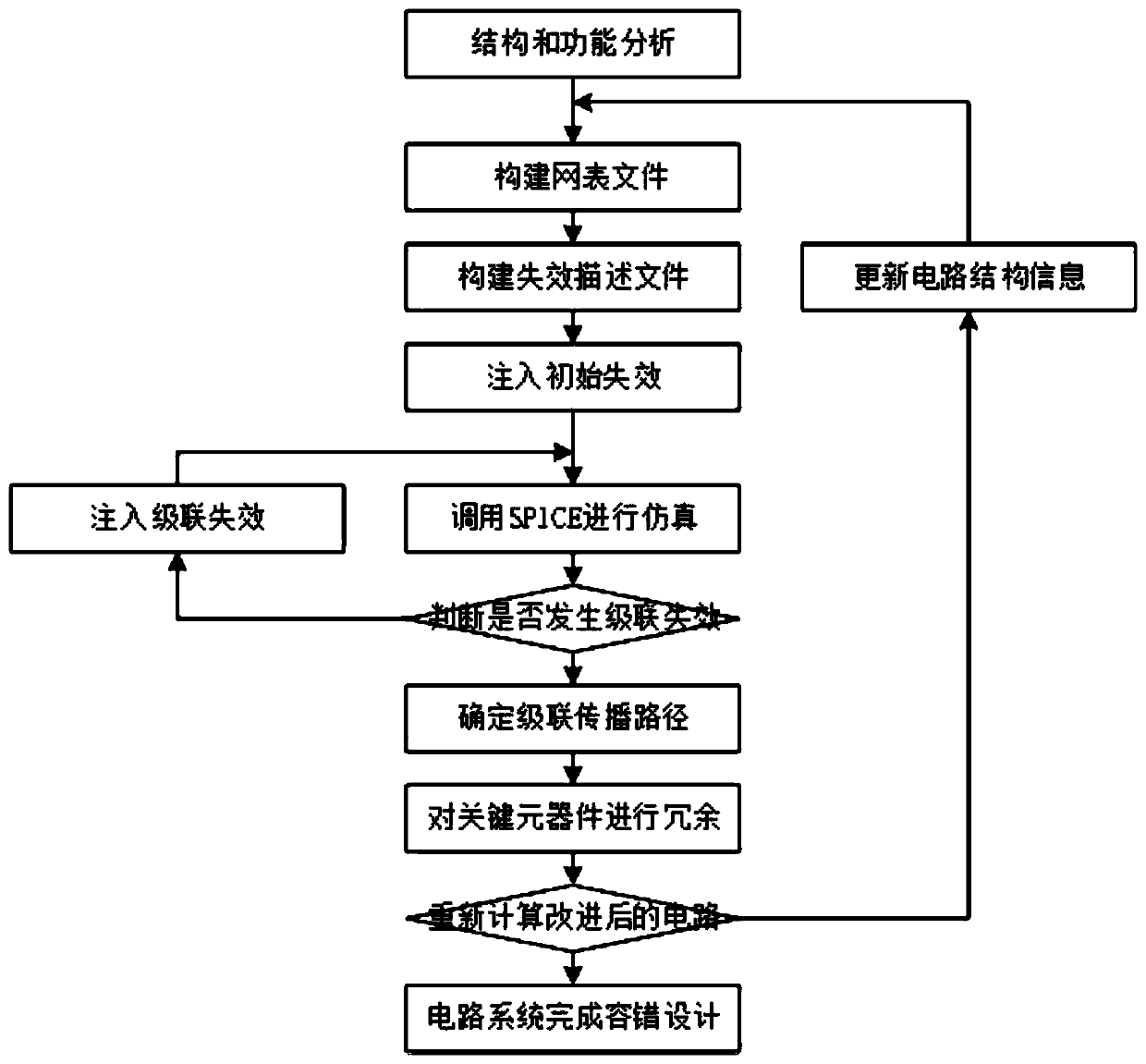

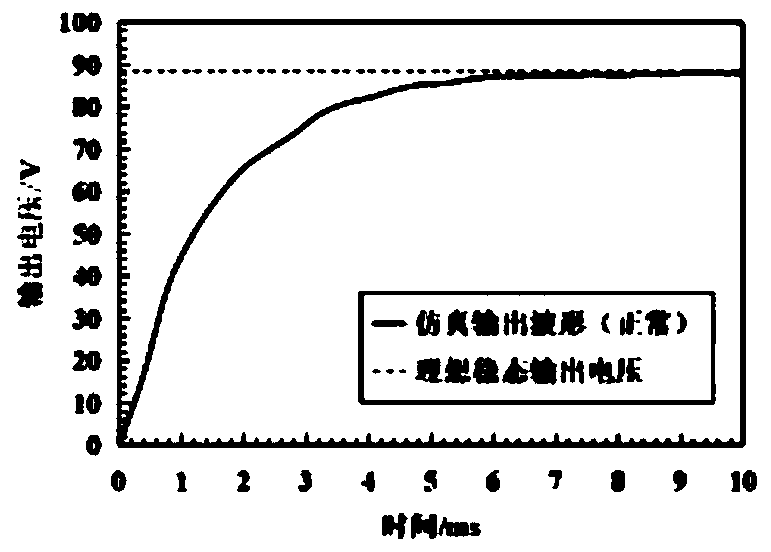

Fault tolerance design-based high-power power electronic transformer

InactiveCN102075096AAchieve self-balancingEffect on the other side when resolving an unbalanced faultDc-dc conversionAc-ac conversionOvervoltageLow voltage

The invention discloses a fault tolerance design-based high-power power electronic transformer. The input end of the power electronic transformer adopts a three-phase star structure for access; each single phase of the input end of the power electronic transformer is connected with the input end of a high-voltage input module, the output end of the high-voltage input module is connected with the primary circuit of an insulation module corresponding to the high-voltage input module, and the secondary circuit of the isolation module is connected with the input end of a low-voltage output modulein the single phase; and the output ends of the low-voltage output modules in the single phases adopt three-phase four-wire output and are connected in parallel to be led out as the output end of thepower electronic transformer. The fault tolerance design-based high-power power electronic transformer can replace the conventional power electronic transformer to realize voltage transformation, energy transmission and electrical isolation, and can stabilize output voltage and solve voltage quality problems of wires, such as voltage dip, voltage rise, voltage flicker, overvoltage, undervoltage and the like, through corresponding control policies.

Owner:SOUTHEAST UNIV +1

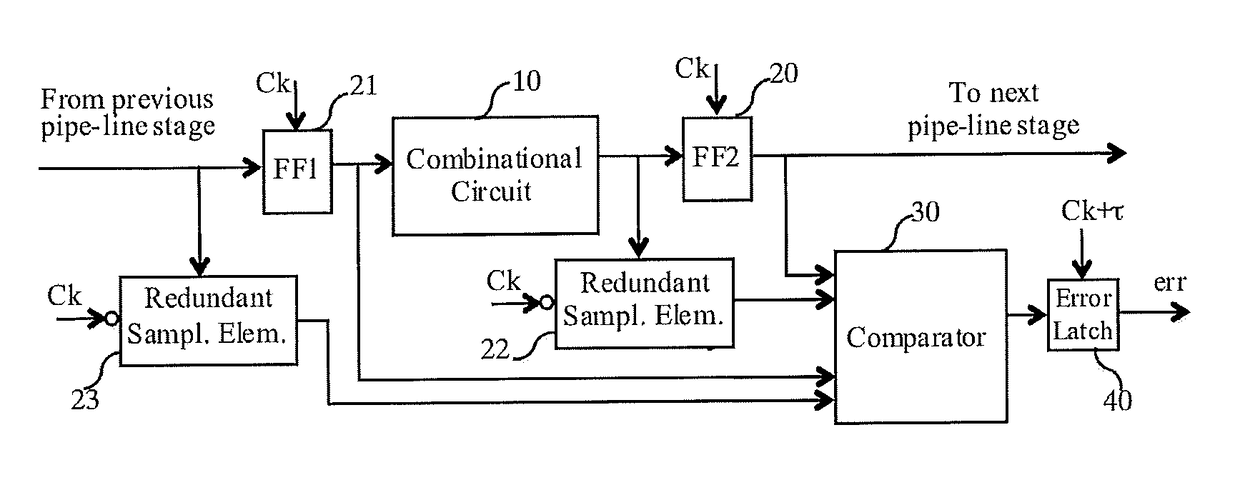

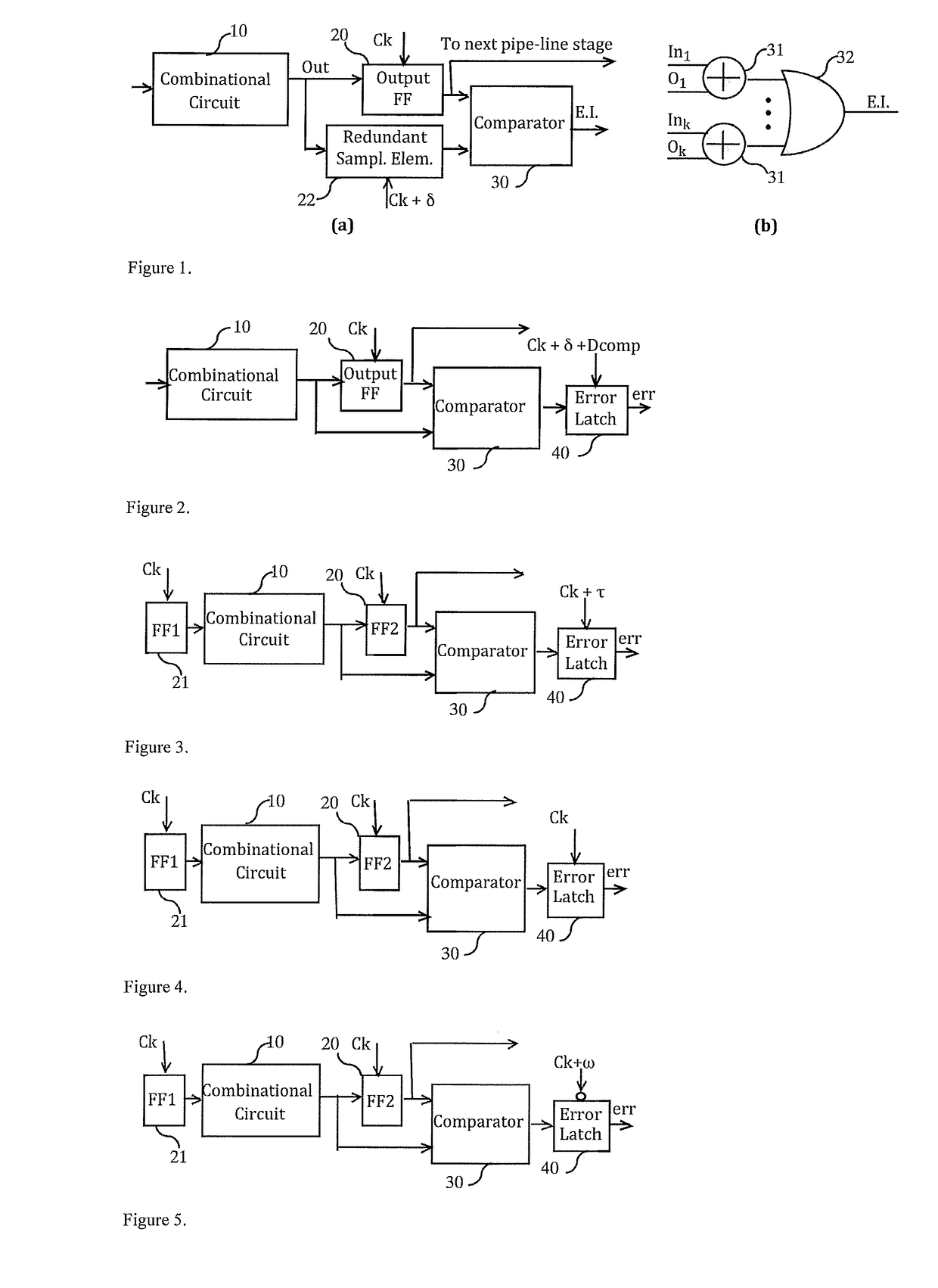

Highly efficient double-sampling architectures

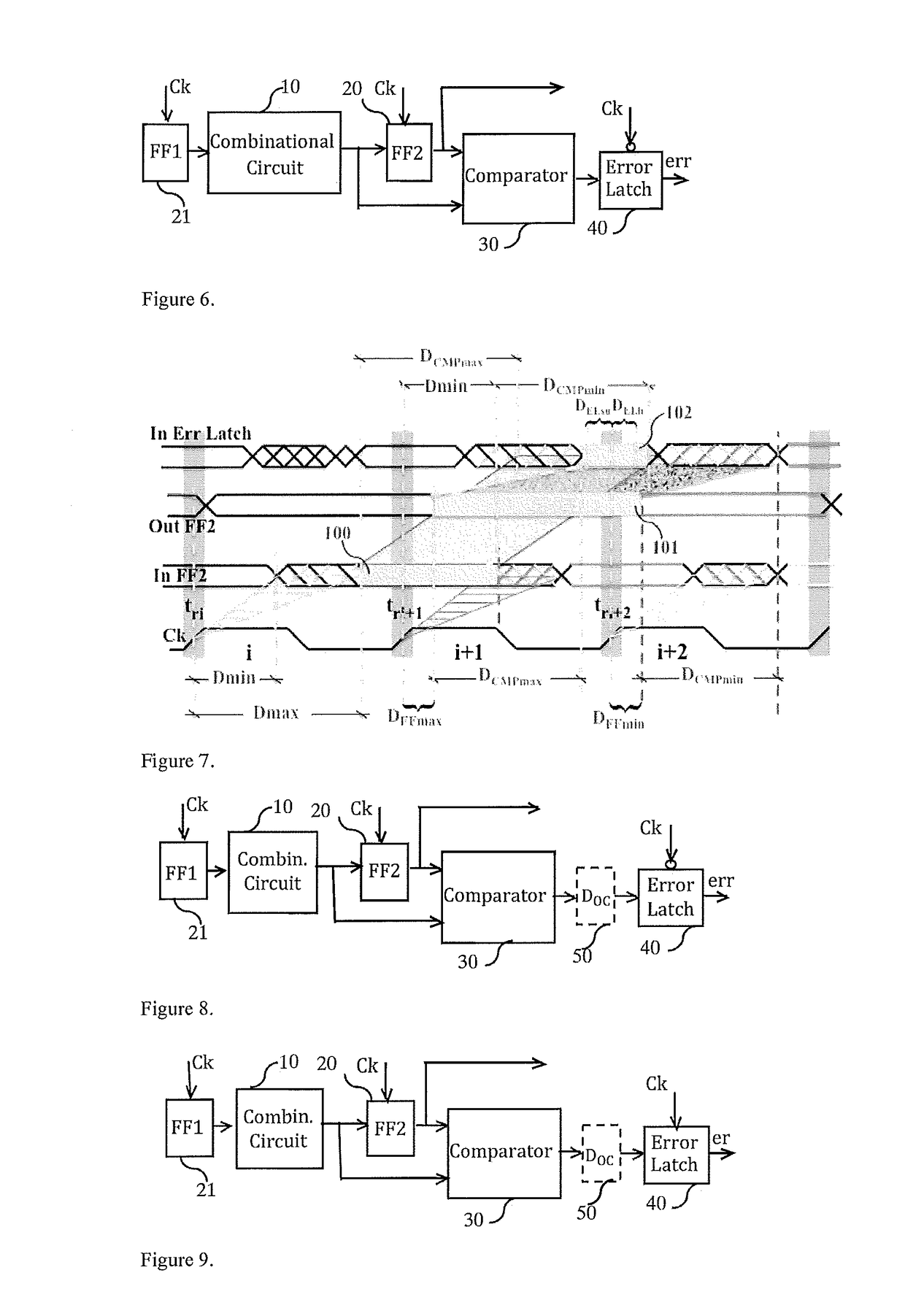

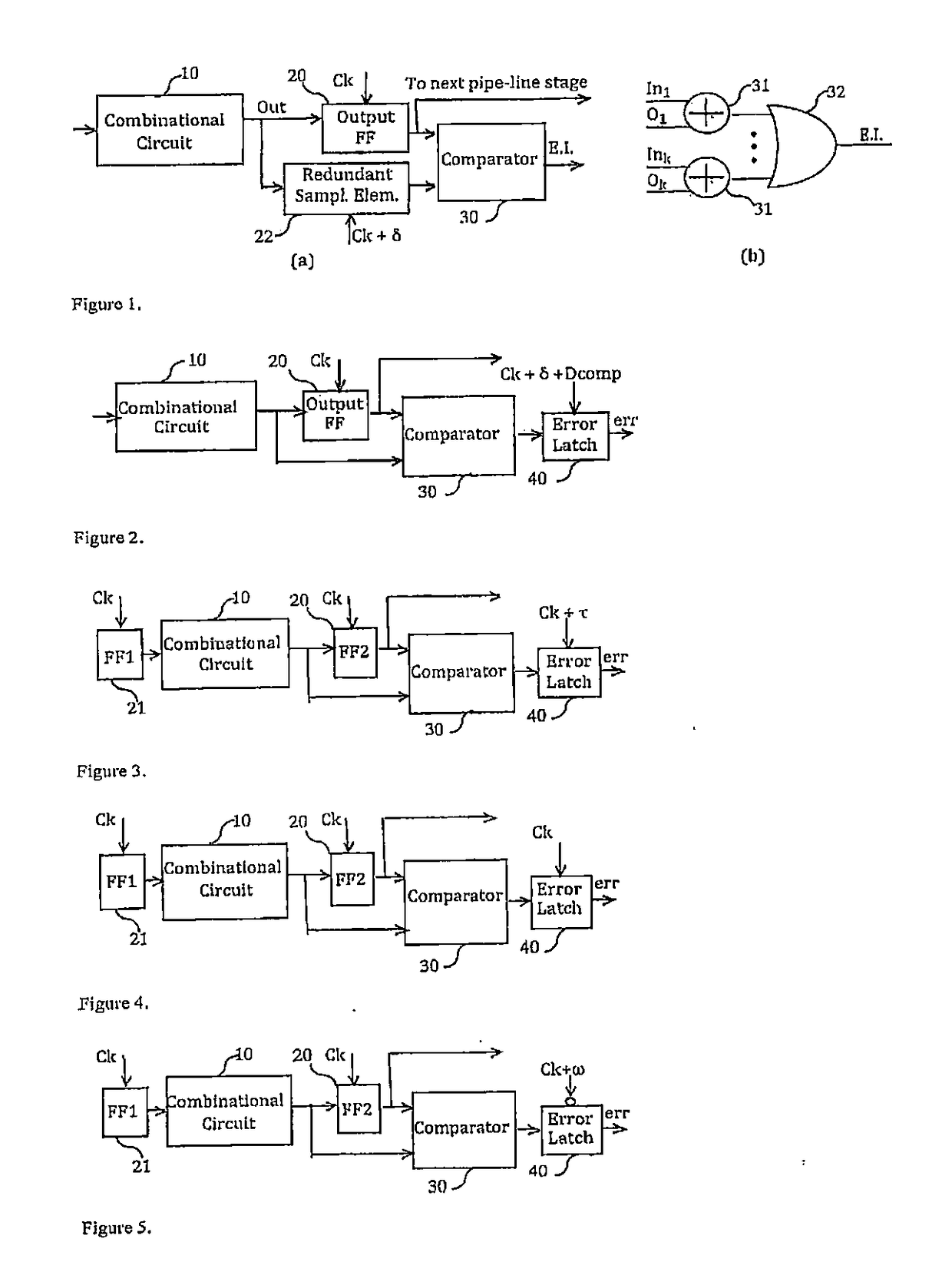

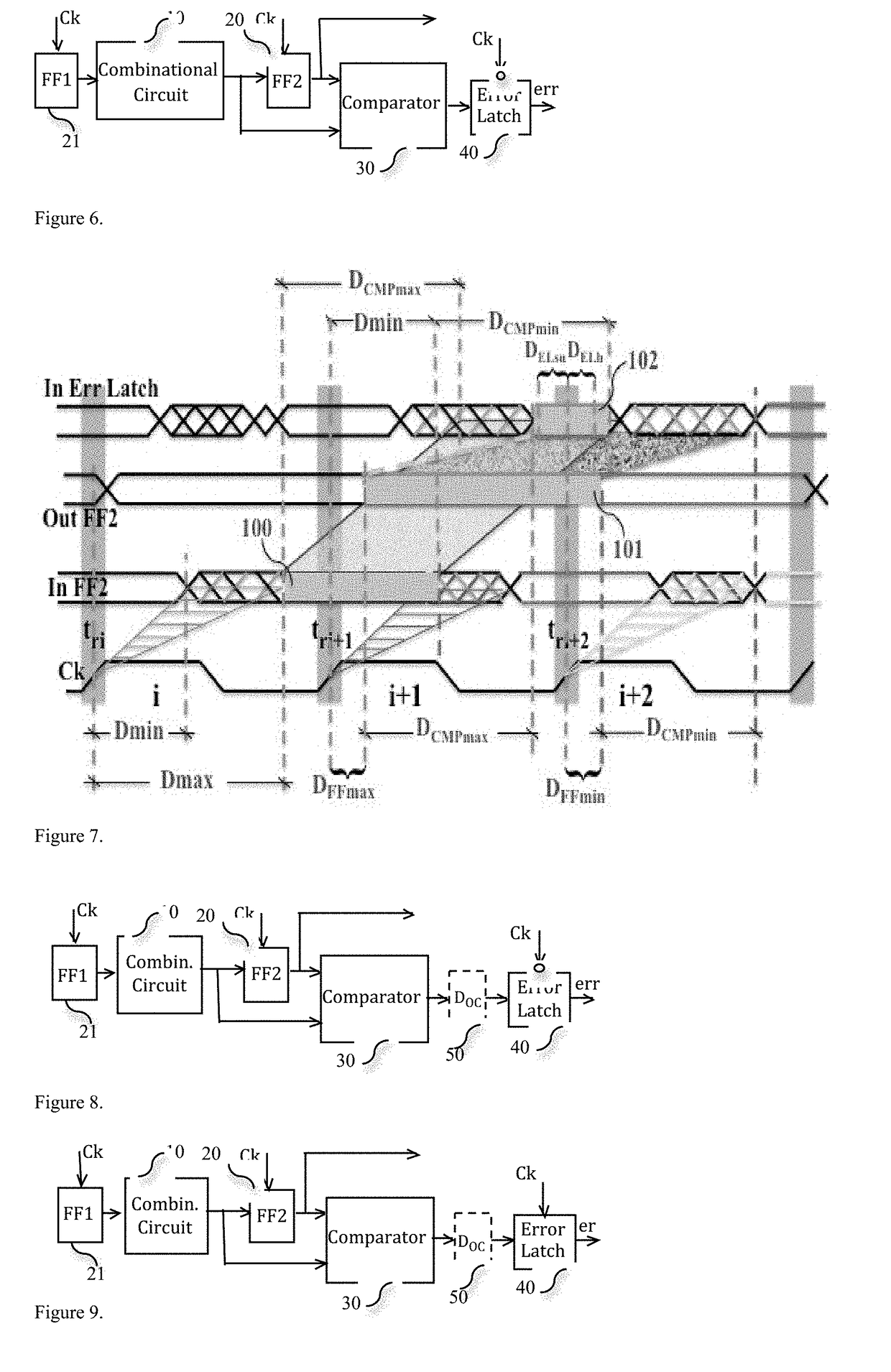

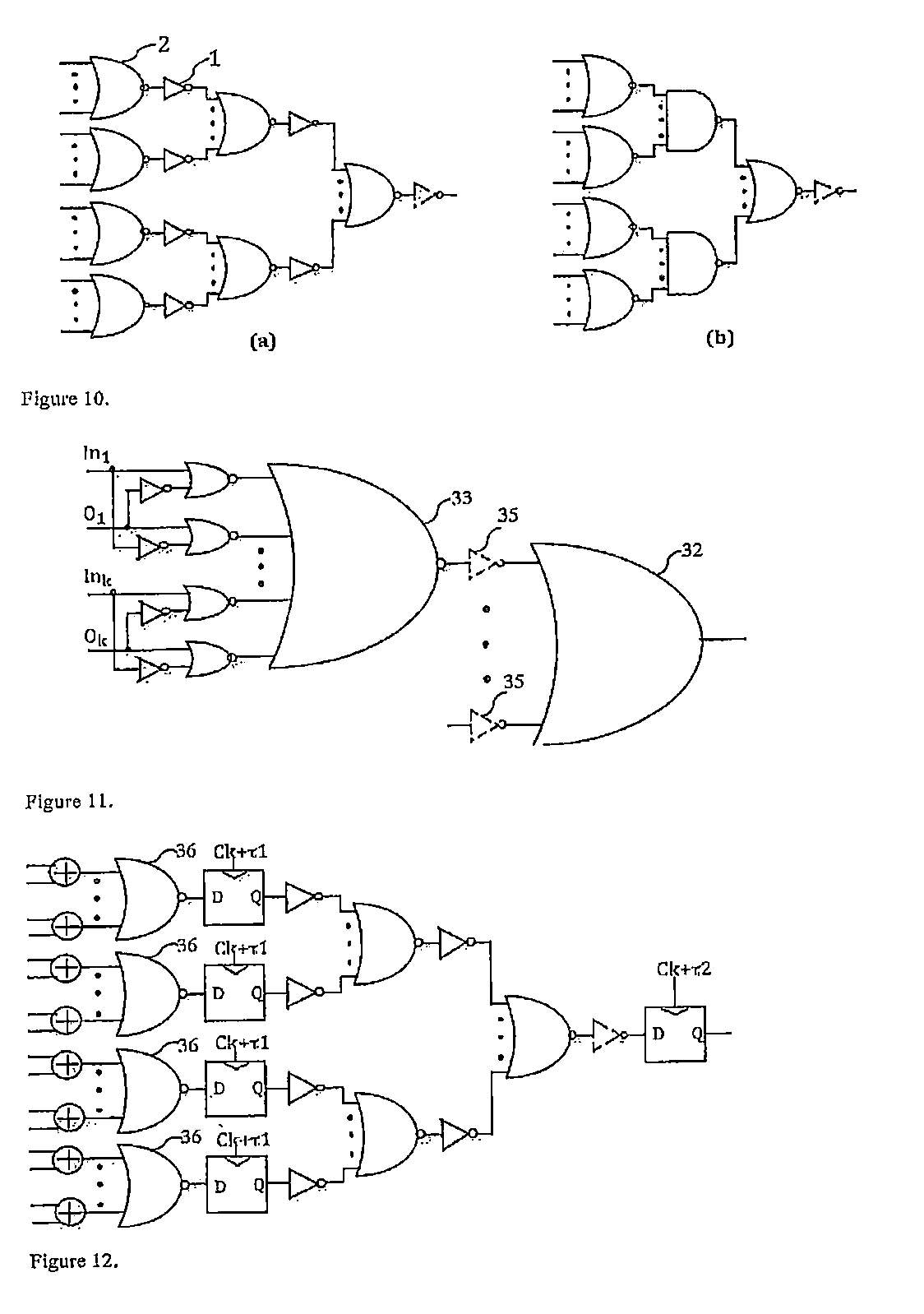

InactiveUS20170184664A1Designs.-Cost reductionImprove efficiencyReliability increasing modificationsDigital circuit testingDependabilityComputer science

Aggressive technology scaling impacts parametric yield, life span, and reliability of circuits fabricated in advanced nanometric nodes. These issues may become showstoppers when scaling deeper to the sub-10 nm domain. To mitigate them various approaches have been proposed including increasing guard-bands, fault-tolerant design, and canary circuits. Each of them is subject to several of the following drawbacks; large area, power, or performance penalty; false positives; false negatives; and in sufficient coverage of the failures encountered in the deep nanometric domain. The invention presents a highly efficient double-sampling architecture, which allow mitigating all these failures at low area and performance penalties, and also enable significant power reduction.

Owner:NICOLAIDIS MICHEL

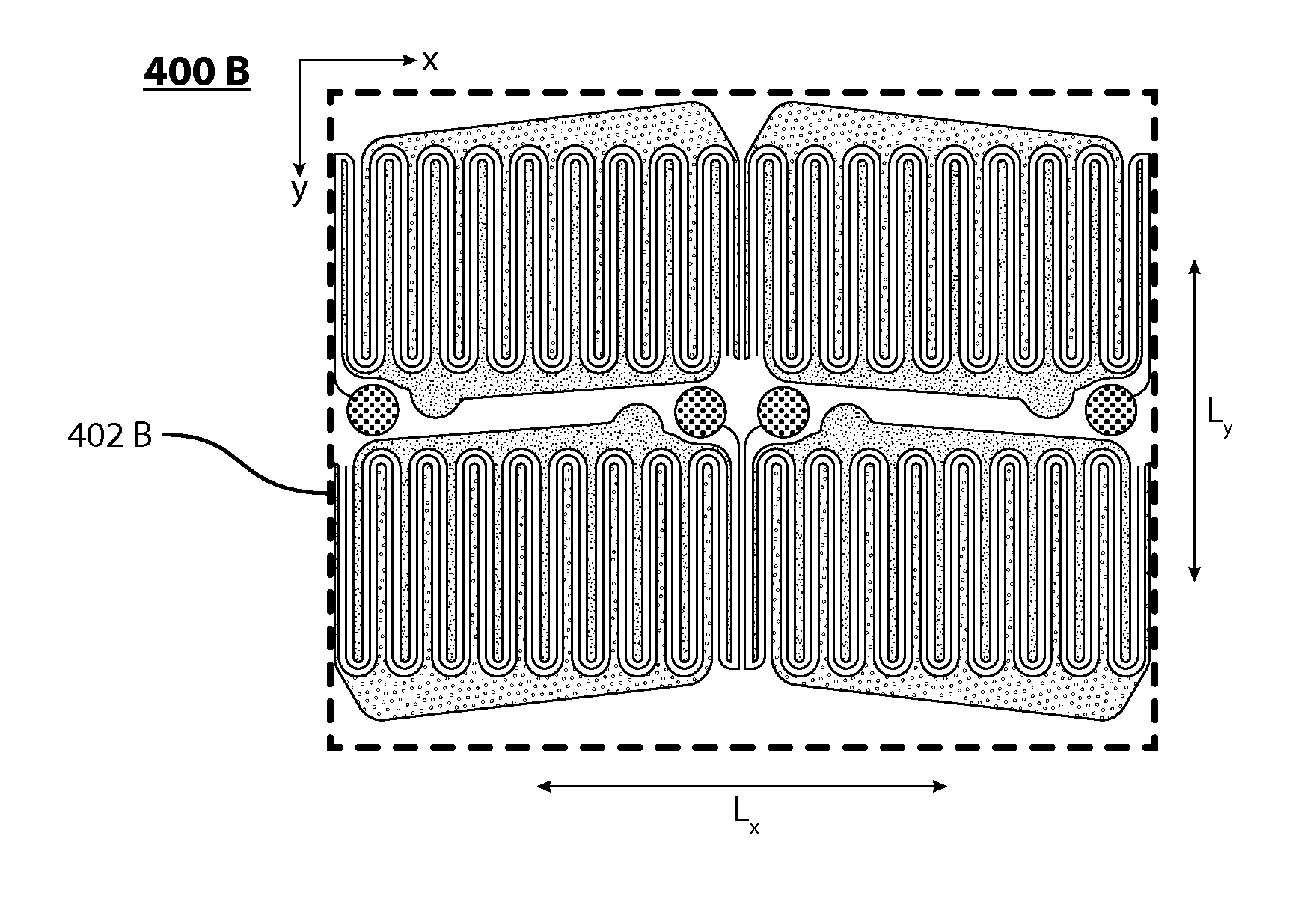

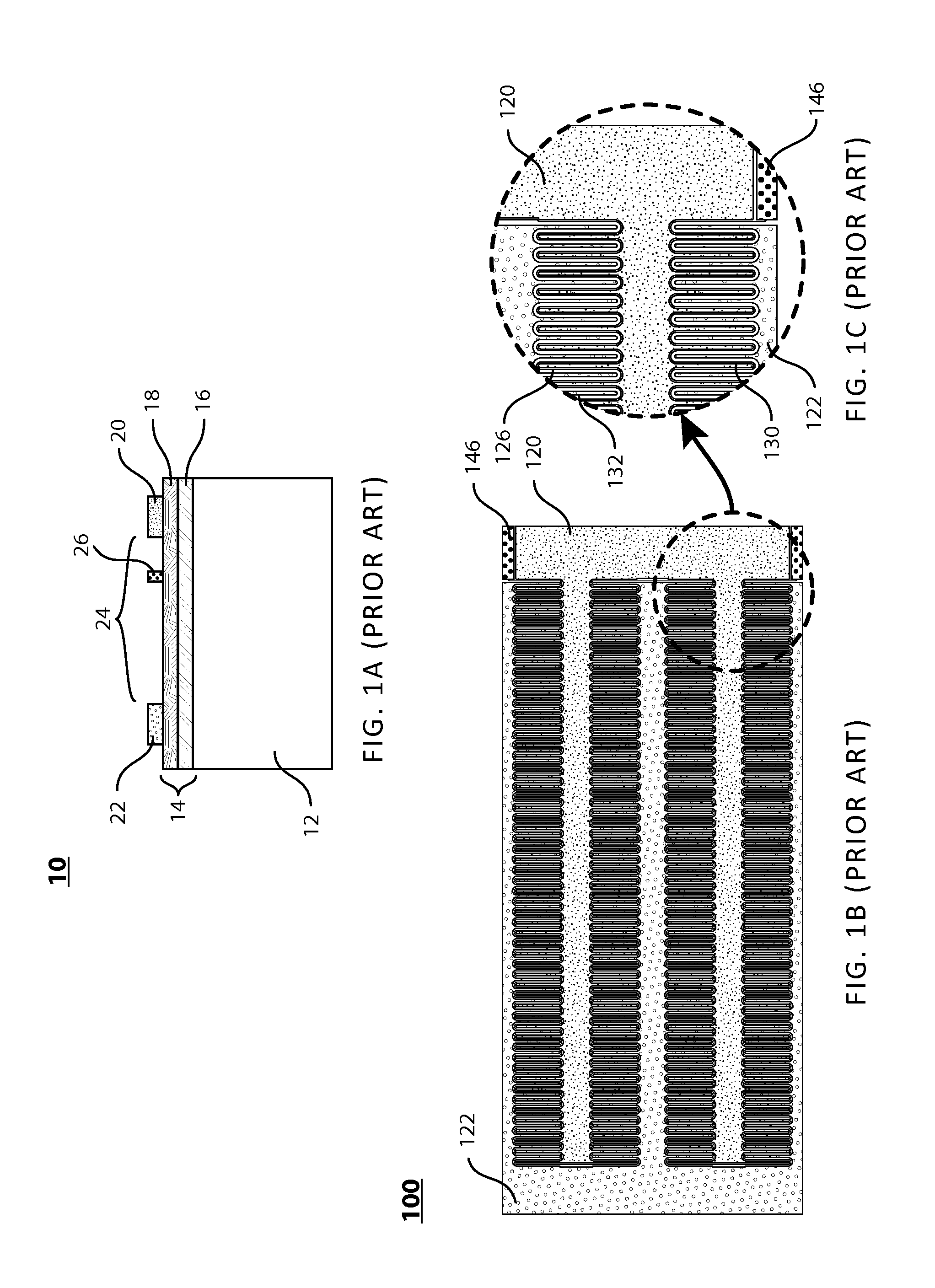

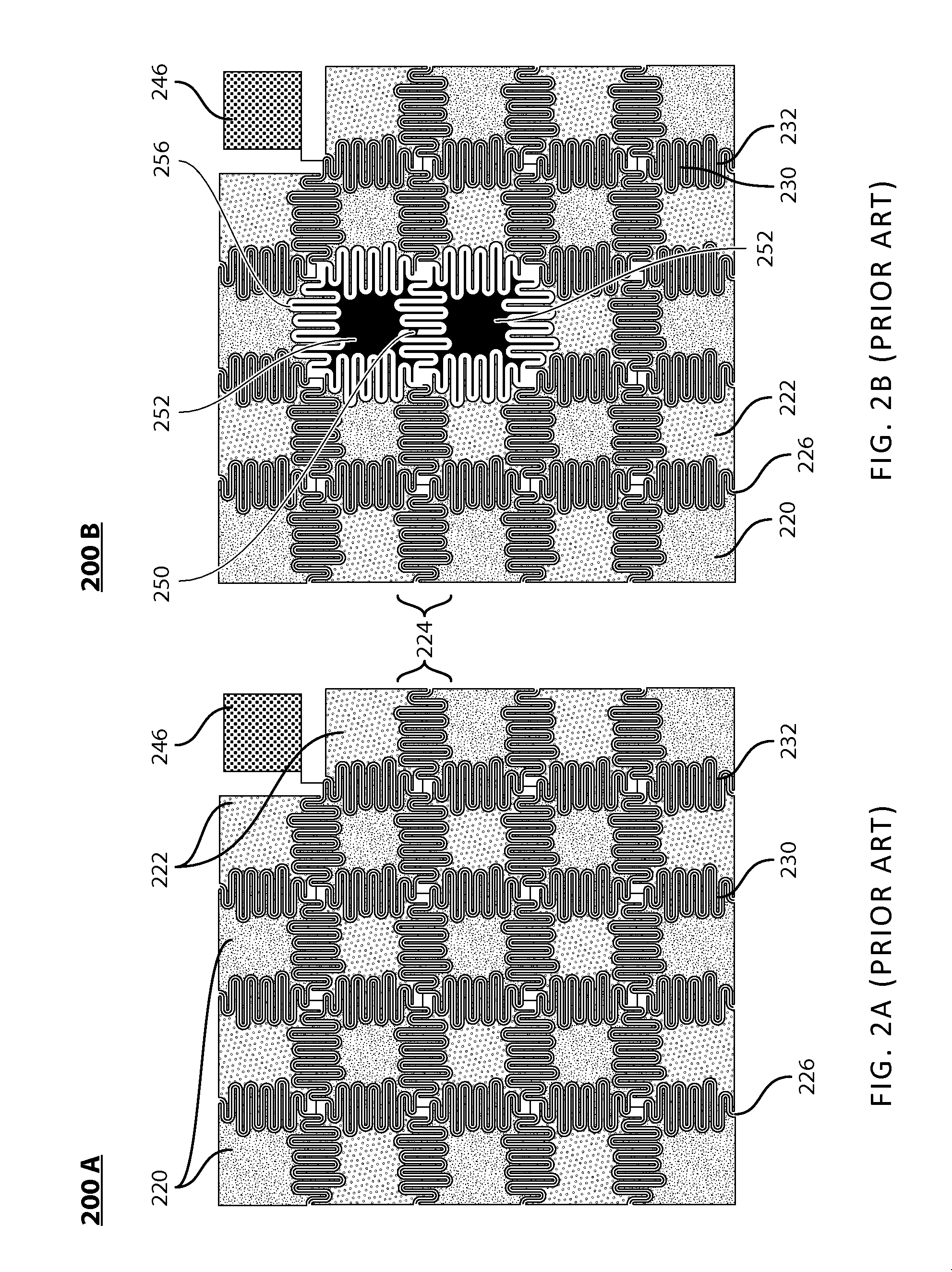

Fault tolerant design for large area nitride semiconductor devices

ActiveUS20150162252A1Improve fault toleranceImprove isolationTransistorSemiconductor/solid-state device testing/measurementContact padElectrical connection

A fault tolerant design for large area nitride semiconductor devices is provided, which facilitates testing and isolation of defective areas. A transistor comprises an array of a plurality of islands, each island comprising an active region, source and drain electrodes, and a gate electrode. Electrodes of each island are electrically isolated from electrodes of neighboring islands in at least one direction of the array. Source, drain and gate contact pads are provided to enable electrical testing of each island. After electrical testing of islands to identify defective islands, overlying electrical connections are formed to interconnect source electrodes in parallel, drain electrodes in parallel, and to interconnect gate electrodes to form a common gate electrode of large gate width Wg. Interconnections are provided selectively to good islands, while electrically isolating defective islands. This approach makes it economically feasible to fabricate large area GaN devices, including hybrid devices.

Owner:GAN SYST

Dynamic Reconfiguration Modeling of Avionics System Based on AltaRica

ActiveCN109214140ASolve unsolvable problemsImprove accuracyDesign optimisation/simulationSpecial data processing applicationsElectricityFinite-state machine

The invention relates to an avionics system dynamic reconfiguration modeling method based on AltaRica, which is used for avionics system task reliability modeling. On the basis of analyzing the characteristics of the avionics system, the invention proposes that the task reliability of the system is modeled based on the AltaRica model with the finite state machine as the theoretical basis. This method can realize the integrated modeling of system function and fault logic. Through the extended definitions of fault state and trigger event, it can describe the jump and influence relationship of each component working state under the condition of fault occurrence and fault-tolerant design, and truly reflect the design characteristics of avionics system. The invention models the complex dynamicreconstruction process, facilitates the analysis of the task reliability of the dynamic reconstruction process, combines the AltaRica model with the dynamic reconstruction process of the avionics system, and creates a new process modeling method.

Owner:CHINA AERO POLYTECH ESTAB

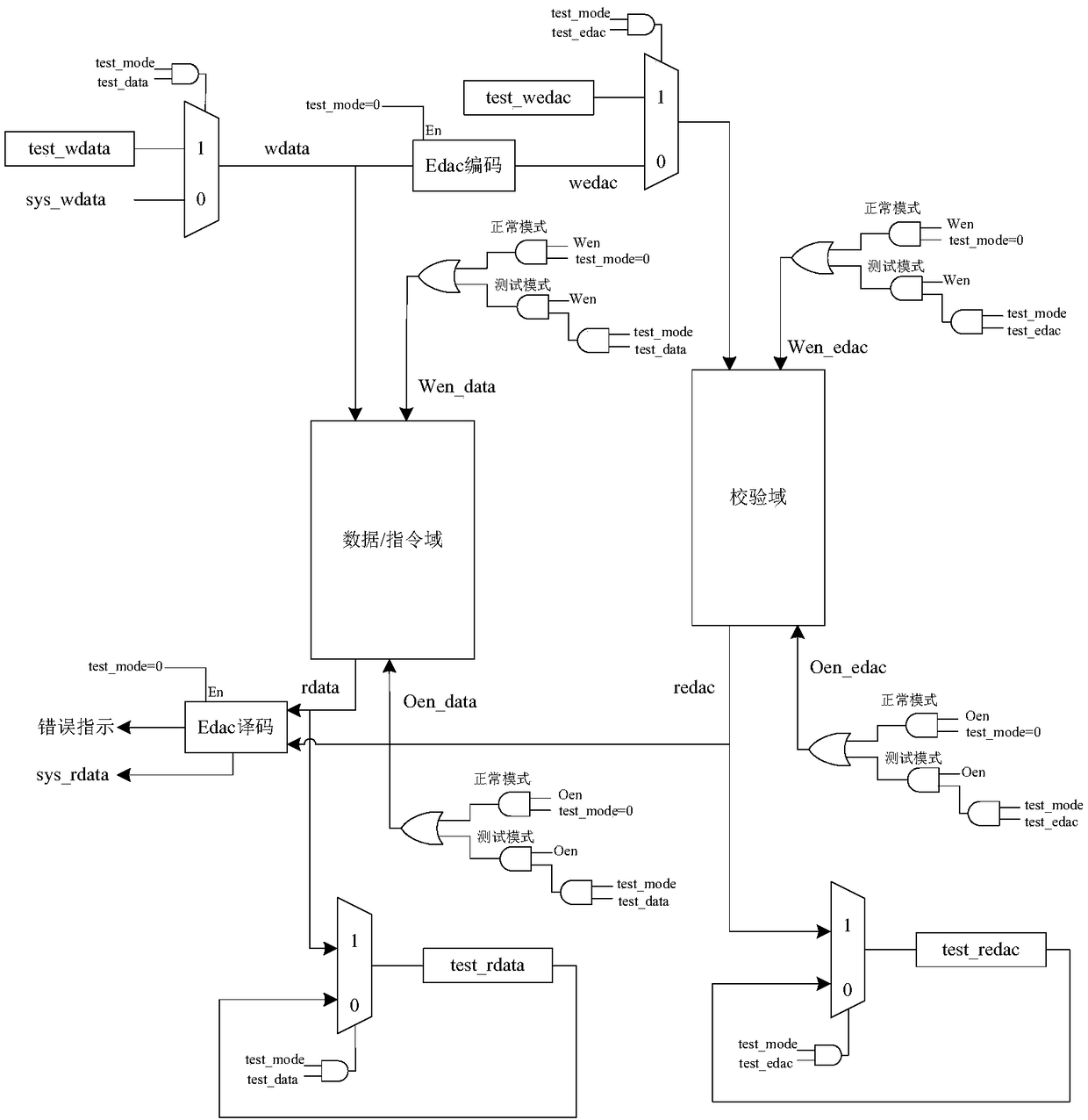

Fault injection design and verification method of memory with EDAC error tolerance

ActiveCN108766501AEnsure consistencyFault injection is simple and straightforwardStatic storageArchitecture with single central processing unitComputer architectureControl signal

The invention discloses a fault injection design and verification method of a memory with EDAC error tolerance. Reading and writing access of a data / instruction domain and a check domain is controlleddifferently according to working modes, in the test mode, during reading operation of the data / instruction domain, a control signal of the reading operation of the data / instruction domain is only effective, and test reading access of the data / instruction domain is realized; during reading operation of the check domain, a control signal of the reading operation of the check domain is only effective, and test reading access of the check domain is realized; during fault injection of the data / instruction domain, a control signal of the writing operation of the data / instruction domain is only effective; during fault injection of the check domain, a control signal of writing operation of the check domain is only effective, and any fault injection of the data / instruction domain and the check domain is realized. Independent reading and writing access of the data / instruction domain and the check domain is realzied, and testability of the memory after error tolerance design is guaranteed.

Owner:XIAN MICROELECTRONICS TECH INST

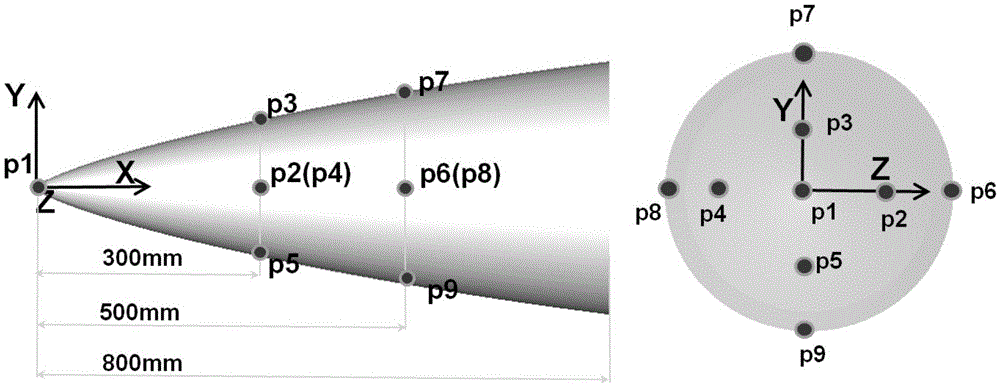

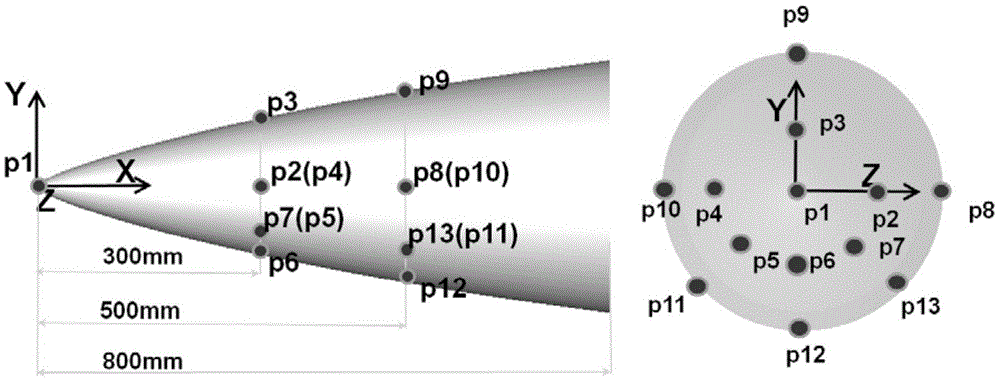

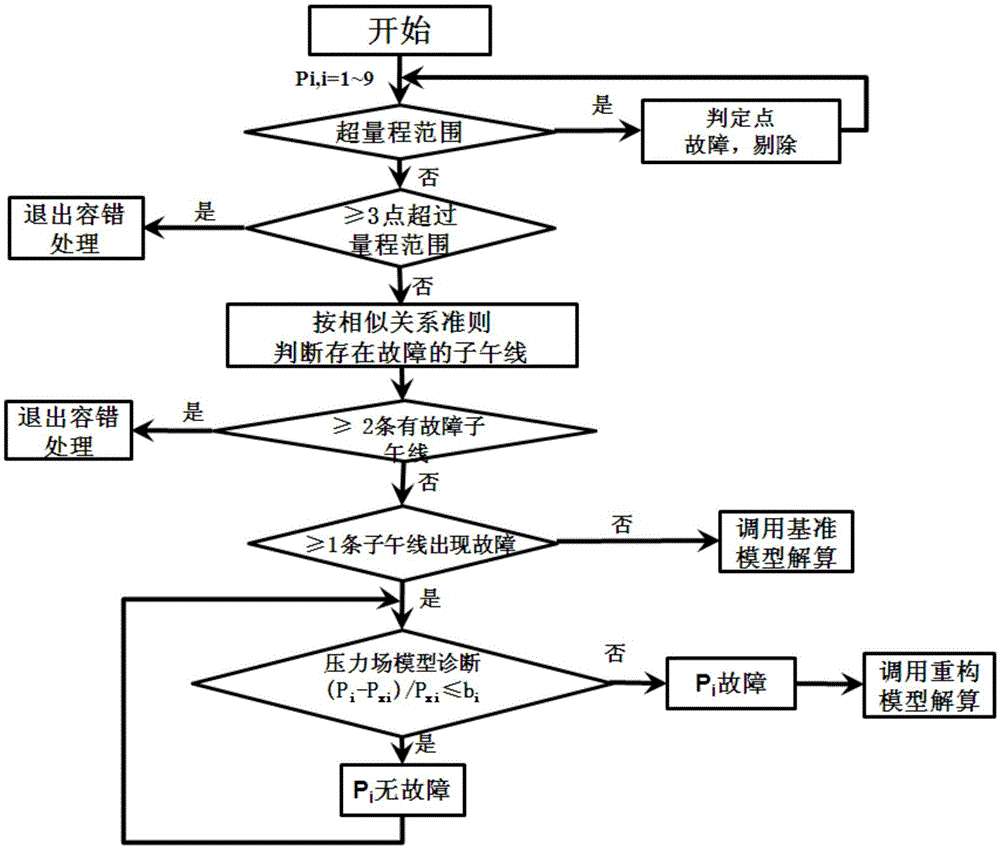

Active fault tolerant design method of FADS (flush air data sensing) system

InactiveCN105574271AAccurate diagnosisImprove efficiencyDesign optimisation/simulationCAD circuit designReference modelActive fault

The invention relates to an active fault tolerant design method of an FADS (flush air data sensing) system and belongs to the technical field of FADS. According to the active fault tolerant design method, a hierarchical diagnosis strategy is adopted, a pressure sensing point array is mounted on an aircraft to measure pressure at pressure sensing points, then whether faults occur to a meridian is judged according to a similarity relation matrix, a pressure filed fault diagnosis model is used for diagnosing a specific faulted point on the meridian, and whether a reference model or a reconstruction model is called for atmospheric parameter calculation is determined according to the fault condition. The method is accurate in diagnosis, high in efficiency, high in fault tolerant capacity and high in reliability.

Owner:CHINA ACAD OF AEROSPACE AERODYNAMICS

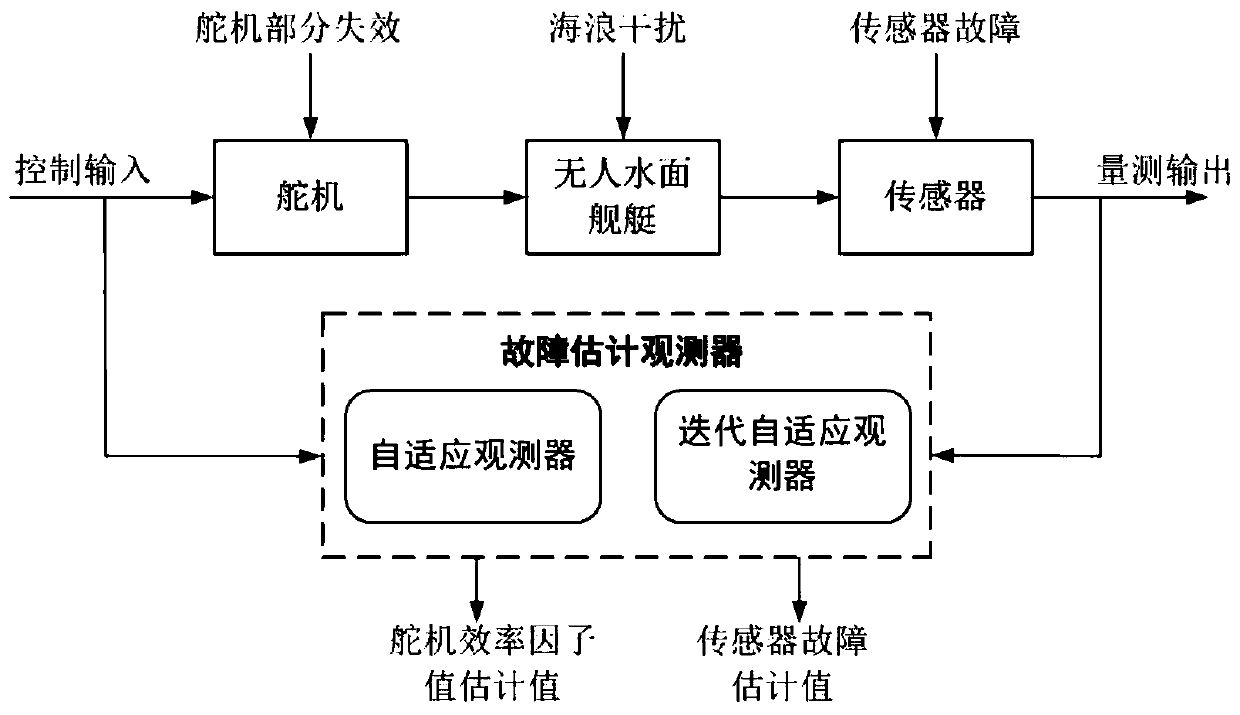

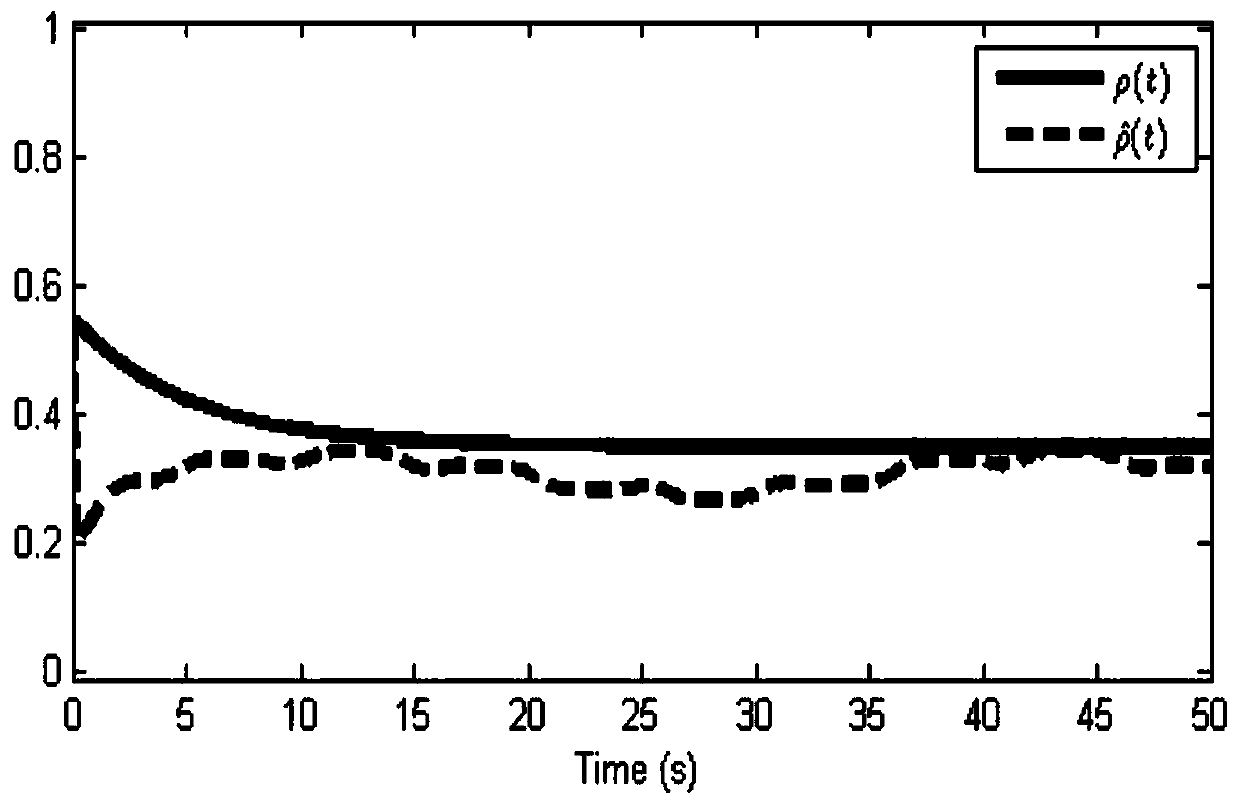

Unmanned ship fault estimation method based on iterative adaptive observer

PendingCN110989563AImprove reliabilityReduce constructionProgramme controlElectric testing/monitoringEngine efficiencyControl engineering

The invention, which belongs to the technical field of unmanned ship control, relates to an unmanned ship fault estimation method based on an iterative adaptive observer. The method comprises the steps: decomposing an unmanned surface vessel model containing steering engine failures and sensor failures into two subsystems simultaneously through coordinate transformation, enabling subsystem 1 to only contain steering engine failures and the subsystem 2 to only contain sensor failures; for the subsystem 1, designing an adaptive fault observer to estimate a steering engine efficiency factor; forthe subsystem 2, designing an iterative adaptive fault observer to estimate a sensor fault; and establishing an error equation of the subsystem 1 and the subsystem 2, and judging the stability of theerror system. According to the inbvention, accurate estimation of the fault condition of the unmanned ship system can be realized, and information such as the fault occurrence time, the development process and the severity degree of the fault is given, so that the safety of the unmanned ship can be conveniently monitored by an operation center; the steering engine failure condition and the sensorfailure condition of the unmanned ship can be estimated at the same time, so that the cost of fault-tolerant design is reduced.

Owner:HARBIN ENG UNIV

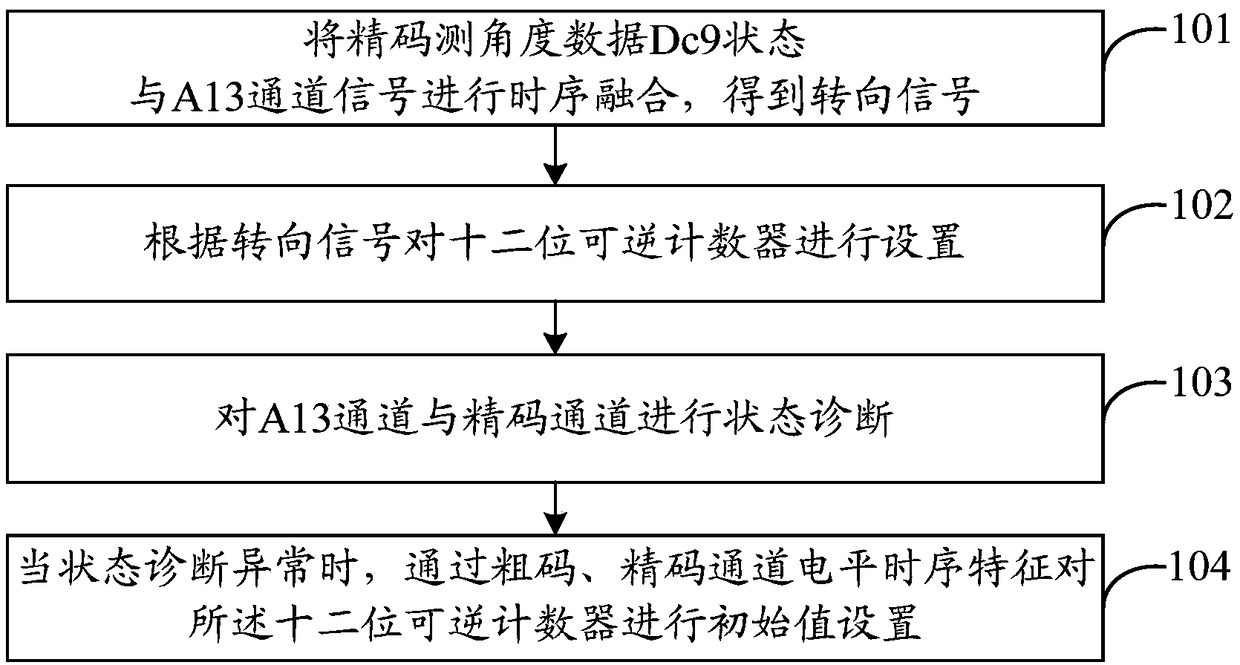

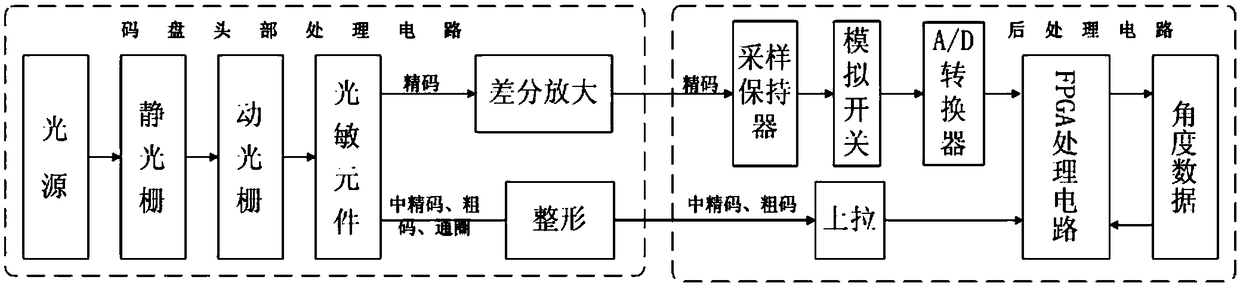

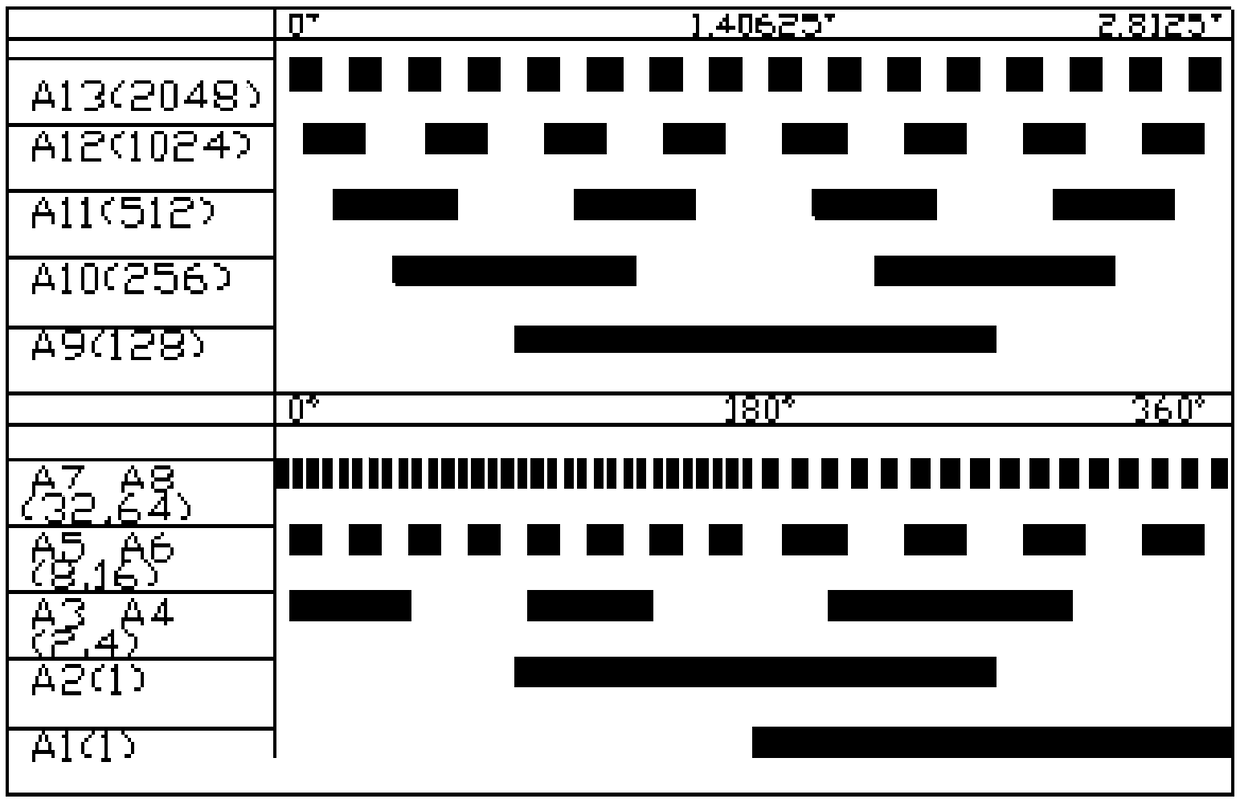

Fault-tolerant design method of an absolute photoelectric encoder measuring channel

ActiveCN108981765AImprove reliabilityAutomatically correct the valueConverting sensor outputError-tolerant designComputer science

The invention discloses a fault-tolerant design method of an absolute photoelectric encoder measuring channel. The method comprises: subjecting a fine code angle data Dc9 state and with an A13 channelsignal to timing sequence fusion obtain a turning signal; setting a twelve-bit reversible counter according to the turning signal; performing state diagnosis on the A13 channel and the fine code channel; and in case of abnormal state diagnosis, setting the initial value of the twelve-bit reversible counter by coarse code and fine code channel level timing sequence features. When fine code channels J1 and J2 and a medium code channel A13 are normal, and at least one of A1 to A8 channels is normal, the method can automatically correct errors within one round at the initial power up, outputs correct angle data, and greatly improves reliability.

Owner:SHANGHAI AEROSPACE CONTROL TECH INST

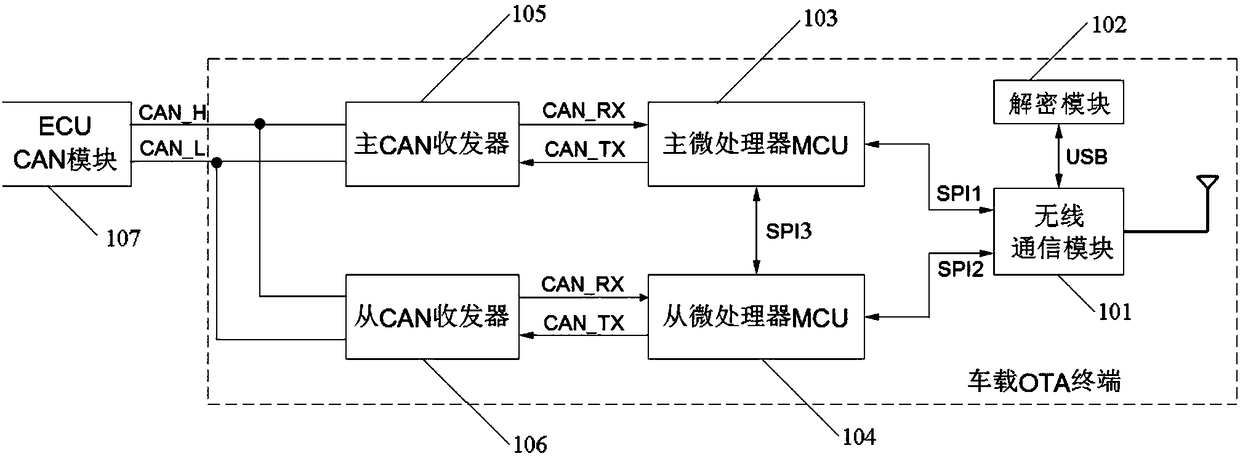

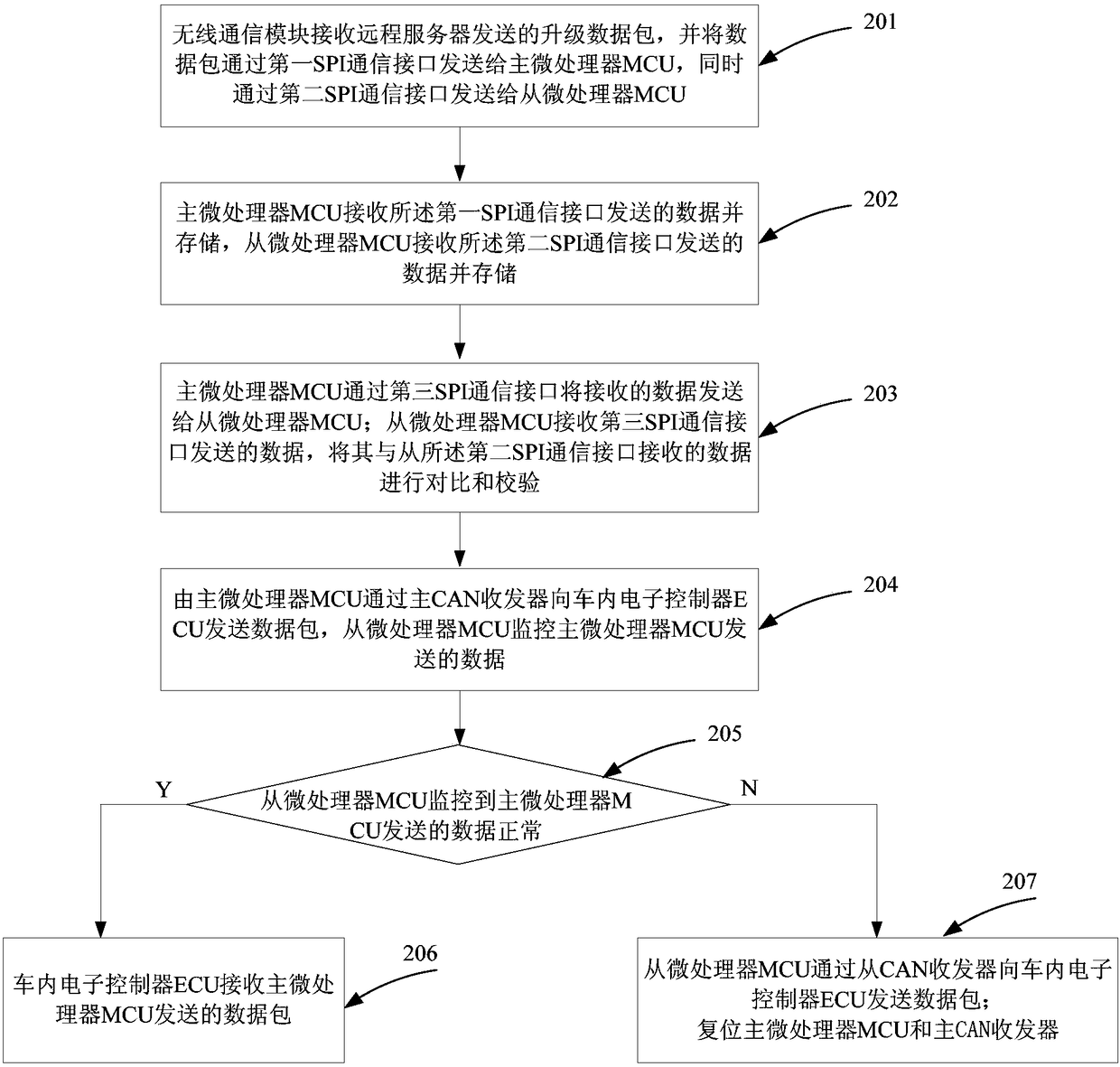

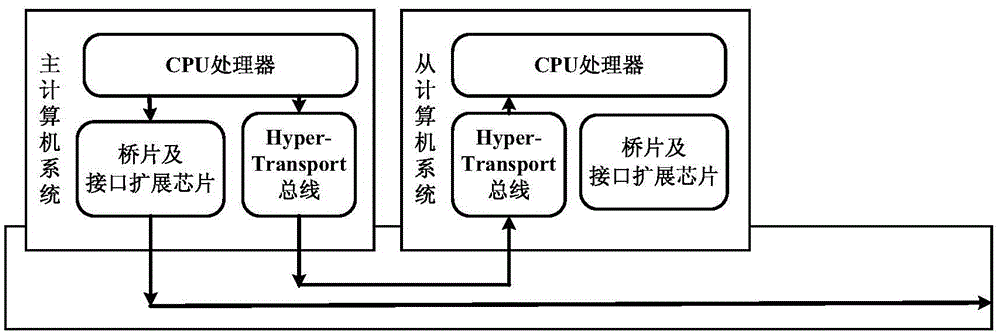

Upgrading method based on on-board OTA terminal fault-tolerance design

The invention discloses an upgrading method based on on-board OTA terminal fault-tolerance design. The upgrading method comprises steps that a main micro-processing unit MCU and a slave micro-processing unit MCU are used to run the same program, and are used to receive data transmitted by a wireless communication module via an SPI communication interface at the same time; mutual-data verificationis carried out by the SPI communication interface between the main micro-processing unit MCU and the slave micro-processing unit MCU, and then the normal data communication of the SPI communication interface is guaranteed; the main micro-processing unit MCU and the slave micro-processing unit MCU are used to carry out internal judgement of issued CAN data packets, and are used to determine that the main micro-processing unit MCU is used to transmit upgrading data packets to an internal electronic control unit ECU by a main CAN transceiver, and the slave micro-processing unit MCU is used to monitor the transmitted data. The upgrading method based on the on-board OTA terminal fault-tolerance design is advantageous in that by adopting an isomorphic double-core architecture, the fault-tolerance design related to sudden faults occurred during the working of the on-board OTA terminal is realized, and then the accuracy of the firmware upgrading of the internal electronic control unit ECU is guaranteed.

Owner:XIAMEN YAXON NETWORKS CO LTD

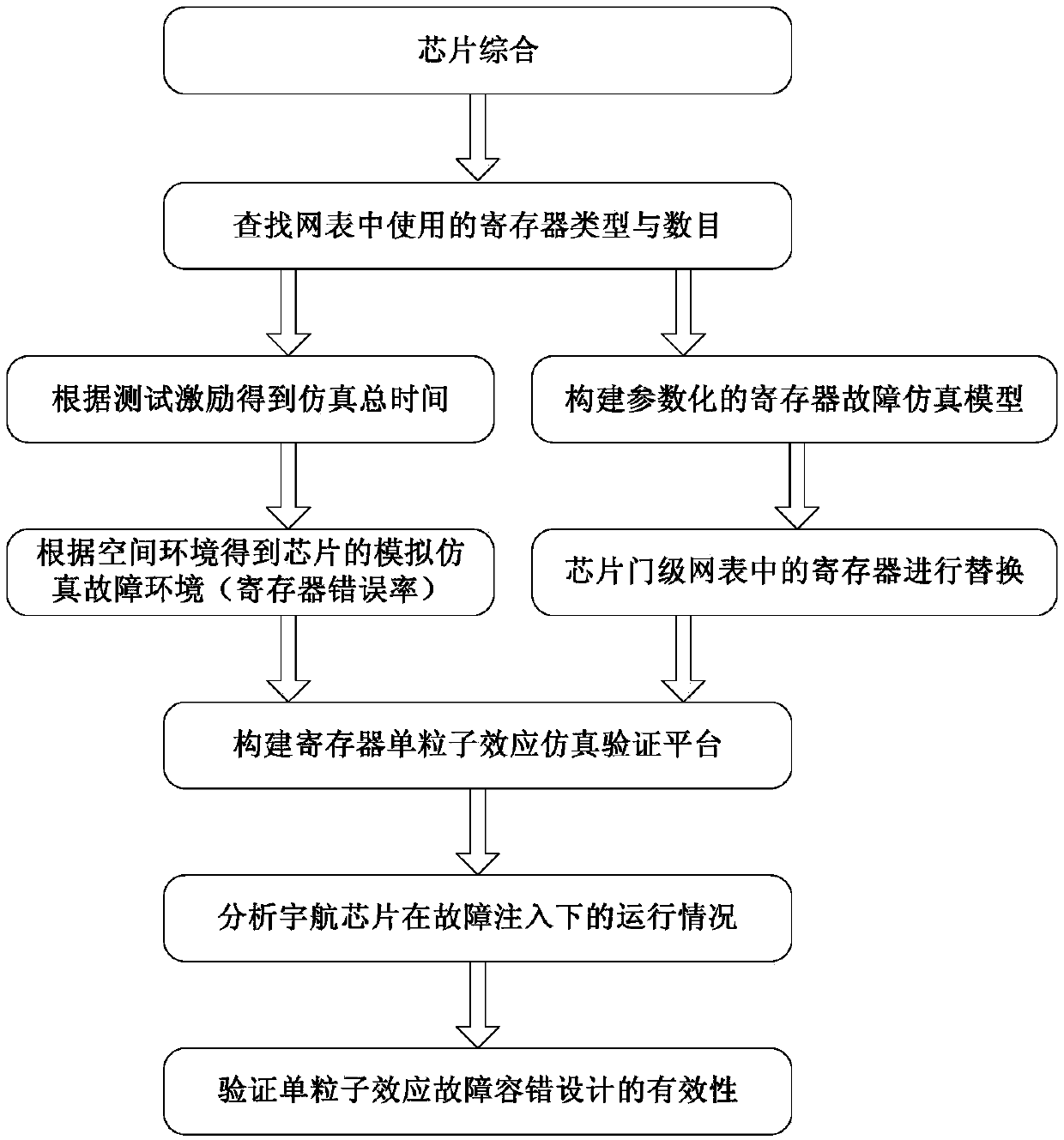

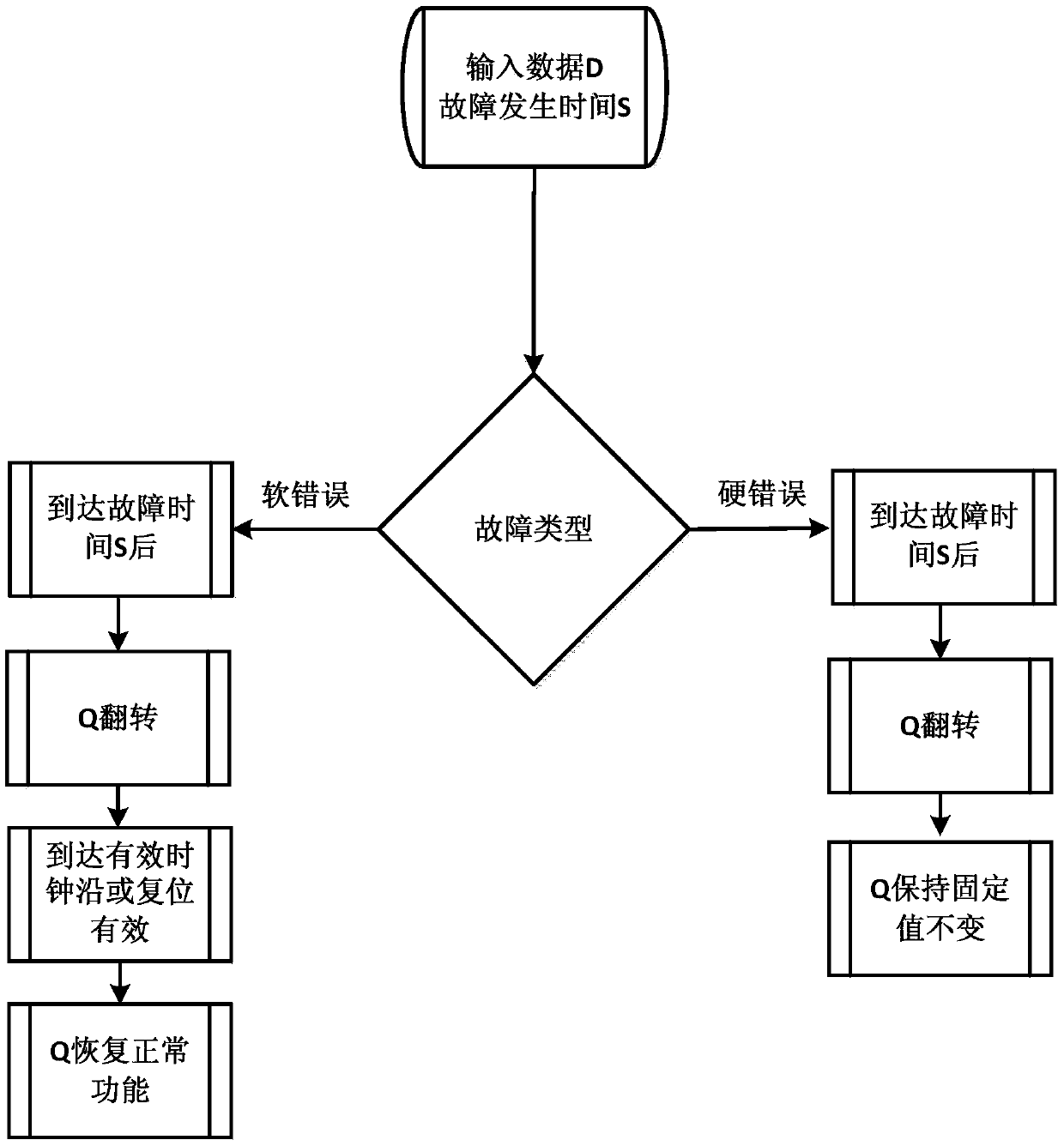

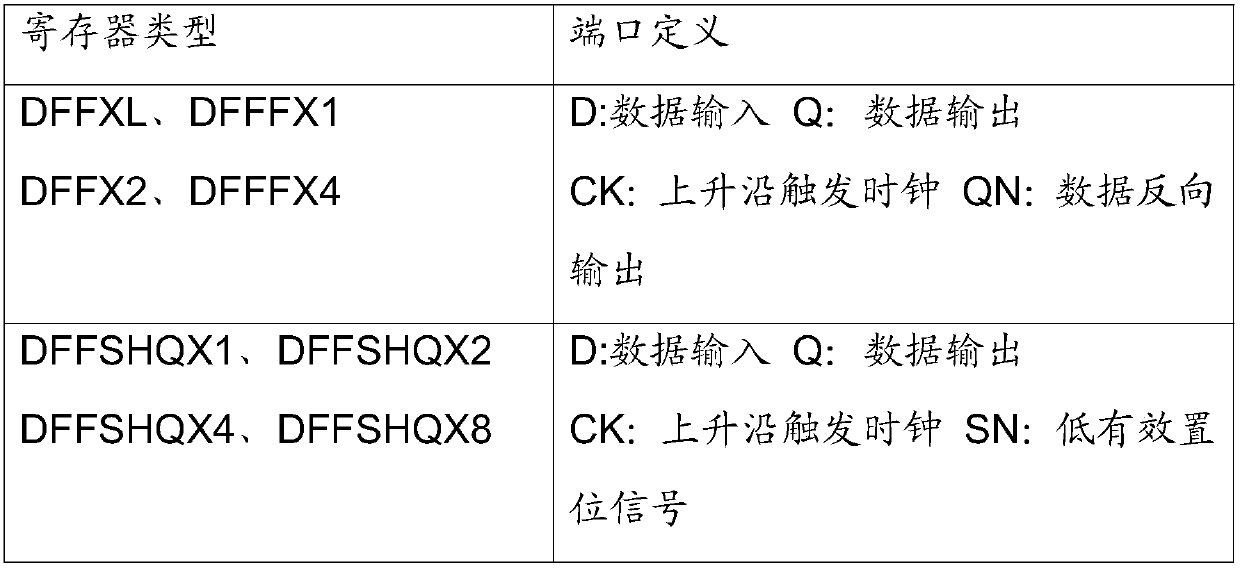

A register single event effect analog simulation method for an aerospace chip

ActiveCN109558649AVerify validityDoes not affect the verification processDesign optimisation/simulationSpecial data processing applicationsHigh energySimulation

The invention discloses a register single event effect analog simulation method for an aerospace chip. The method comprises the steps of constructing a parameterized register fault simulation model; randomly replacing the normal register simulation model in the chip netlist with a register fault simulation model, wherein the replacement number is determined by the error turnover rate of the spacenavigation chip set in the space environment and the total number of registers in the chip, the error occurrence time of the registers is randomly selected from 0 to the maximum simulation time, simulating the simulation fault module behavior through a simulation tool, and then verifying the effectiveness of the chip-level register fault-tolerant strategy. According to the method, the single eventeffect soft error can be simulated and the hard error formed by the high-energy single event effect can be simulated without analyzing codes and independently designing a test case. The method can support the aerospace radiation reinforcement research and can be applied to verification and analysis of fault-tolerant design of the single event effect fault.

Owner:BEIJING INST OF CONTROL ENG

Remote control decoding and fault tolerance method

ActiveCN101193194AImprove reliabilityAvoid misuseTelevision system detailsNon-electrical signal transmission systemsKey pressingRemote control

The invention discloses a remote control decoding fault-tolerance method. When the received remote control key-pressing code is a repeated key-pressing code, a tolerance value is given. When the code error rate of the remote control decoding is lower than the tolerance value, the key-pressing value with code error is set as the key-pressing value corresponding to the last key-pressing. When the code error rate of the remote control decoding is higher than the tolerance value, the key-pressing value with code error is set as the key-pressing value corresponding to no operation of key-pressing. Thus false action of the TV set can be prevented. In the invention, the fault-tolerance design is added to the remote control decoding software, namely, certain tolerance for code error is provided. When the code error rate is lower than the tolerance value, the key-pressing is considered as repeated; when the code error rate is higher than the tolerance value, no key-pressing is believed to occur until the key is released. The tolerance value is determined according to the light or electromagnetic wave disturbance degree in the environment, thus the remote control reliability of the TV set is effectively improved and false action of the TV set is prevented, which is good for promoting the whole quality of the TV set.

Owner:HISENSE VISUAL TECH CO LTD

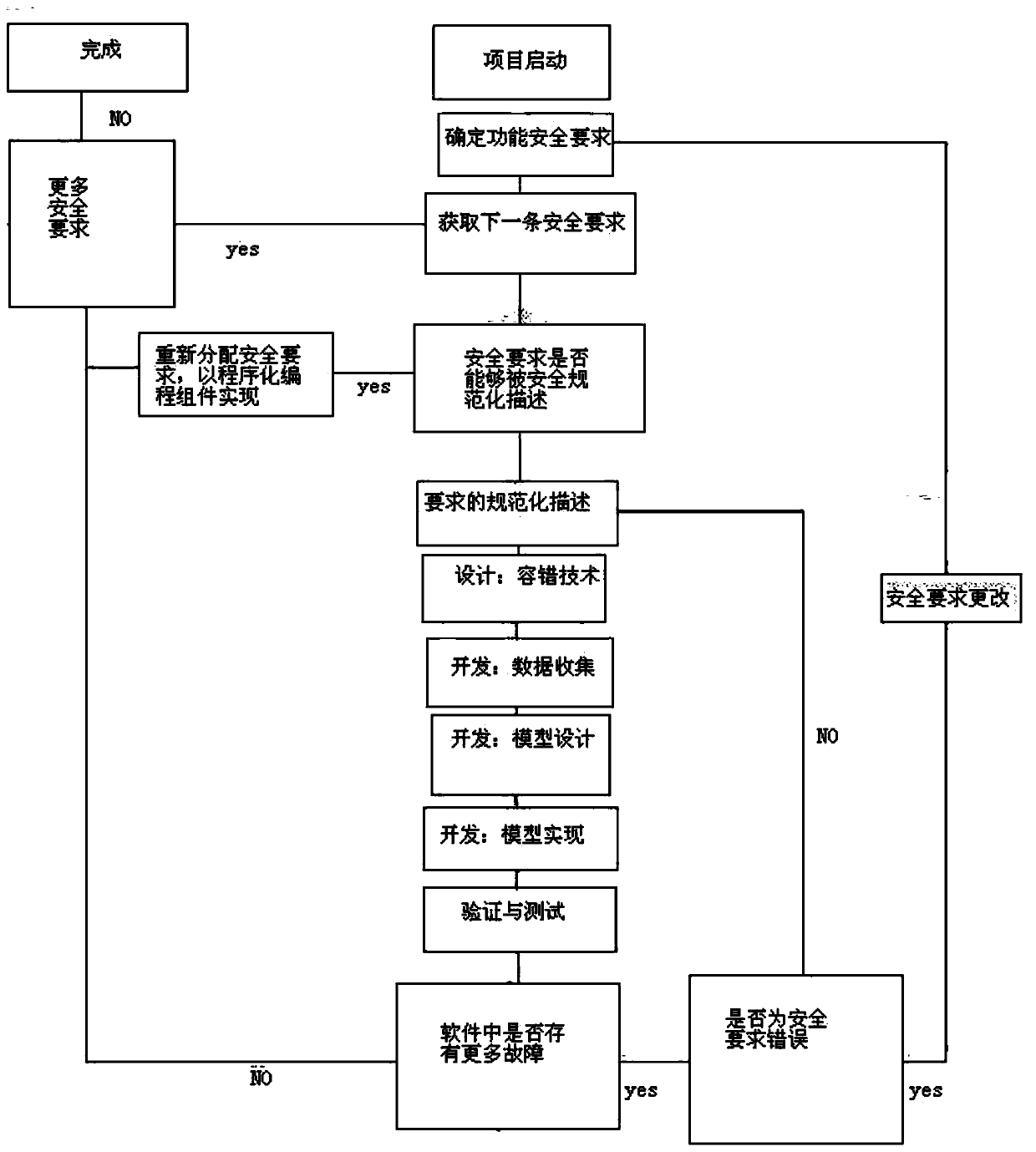

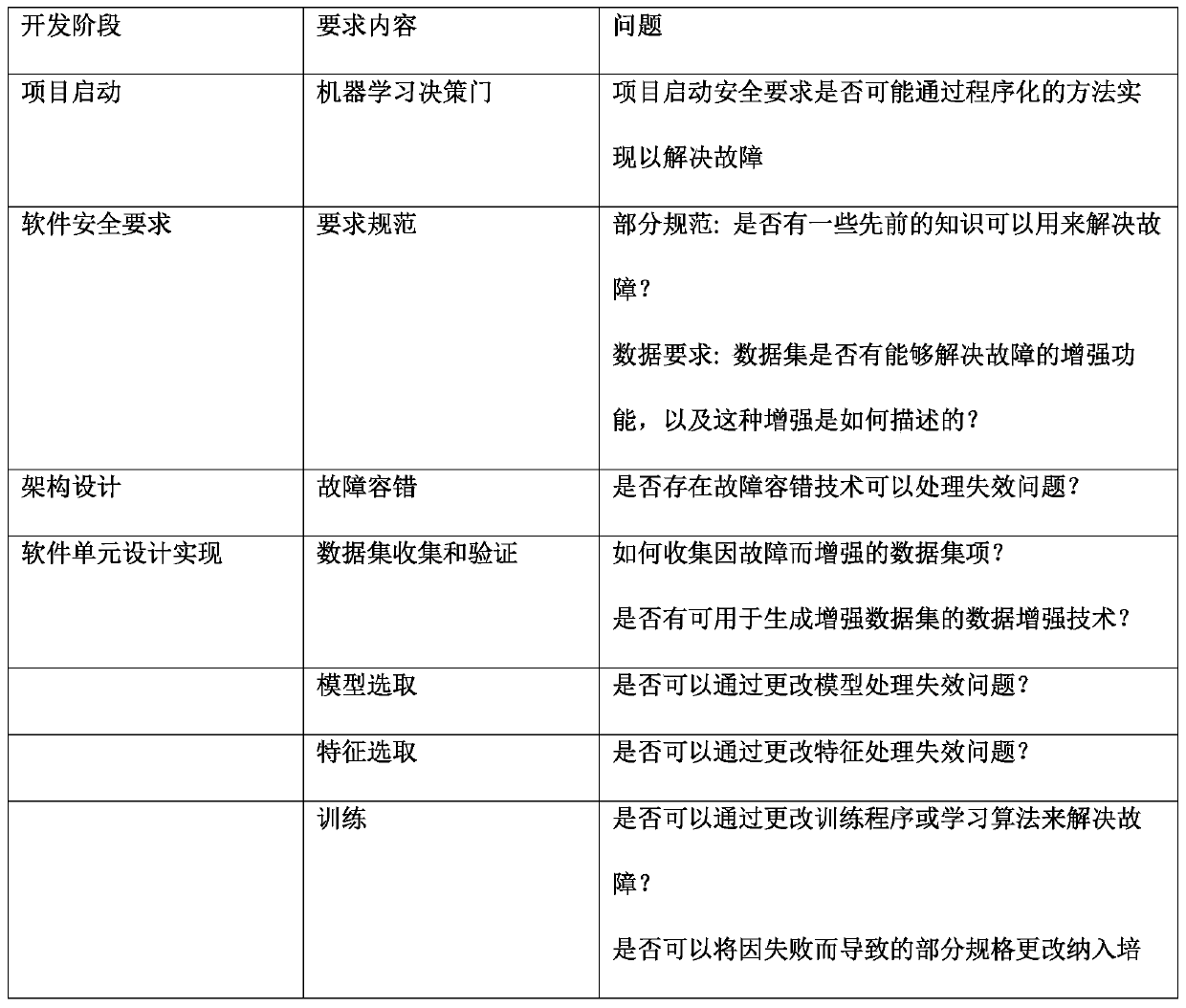

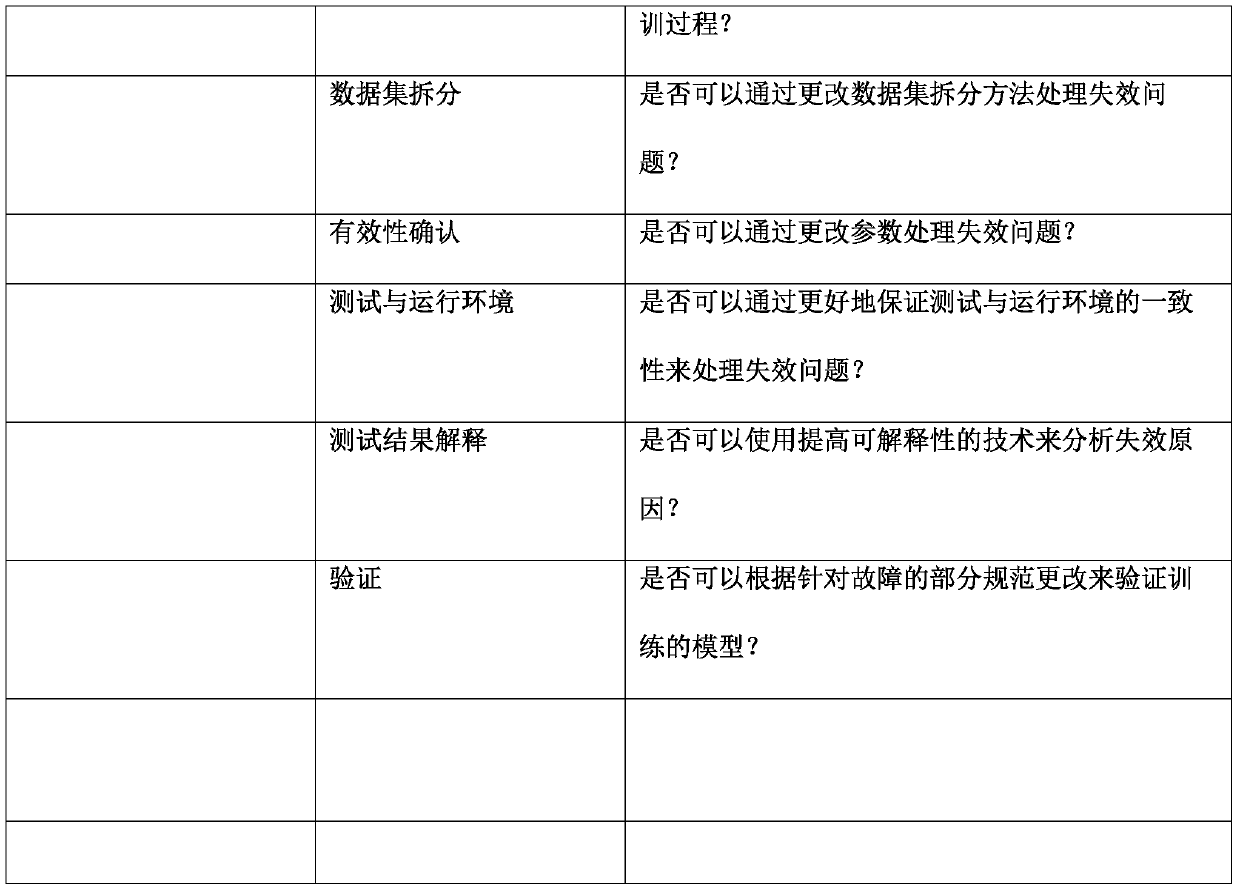

Process method for applying a machine learning algorithm to automobile software development function safety

PendingCN109933309AImprove development efficiencyImprove securitySoftware testing/debuggingSoftware designModel selectionSoftware architecture

A process method for applying a machine learning algorithm to automobile software development function safety comprises the following seven steps: step 1, a project starting stage: adopting a machinelearning decision-making door; 2, a software security requirement stage: standardizing and describing security requirements; Step 3, a software architecture design stage: adopting a fault-tolerant design method; 4, a software development stage: collecting data; 5, a software development stage and model selection; 6, a software development stage and model implementation are carried out; And 7, a software integration stage, verification and testing. According to the method, in the development process of automobile electronic software, the property of partial standardized description is clear, analgorithm feature selection model based on various machine learning is facilitated, and then the development efficiency and safety are improved. Based on the above, the method has a good applicationprospect.

Owner:上海工业控制安全创新科技有限公司

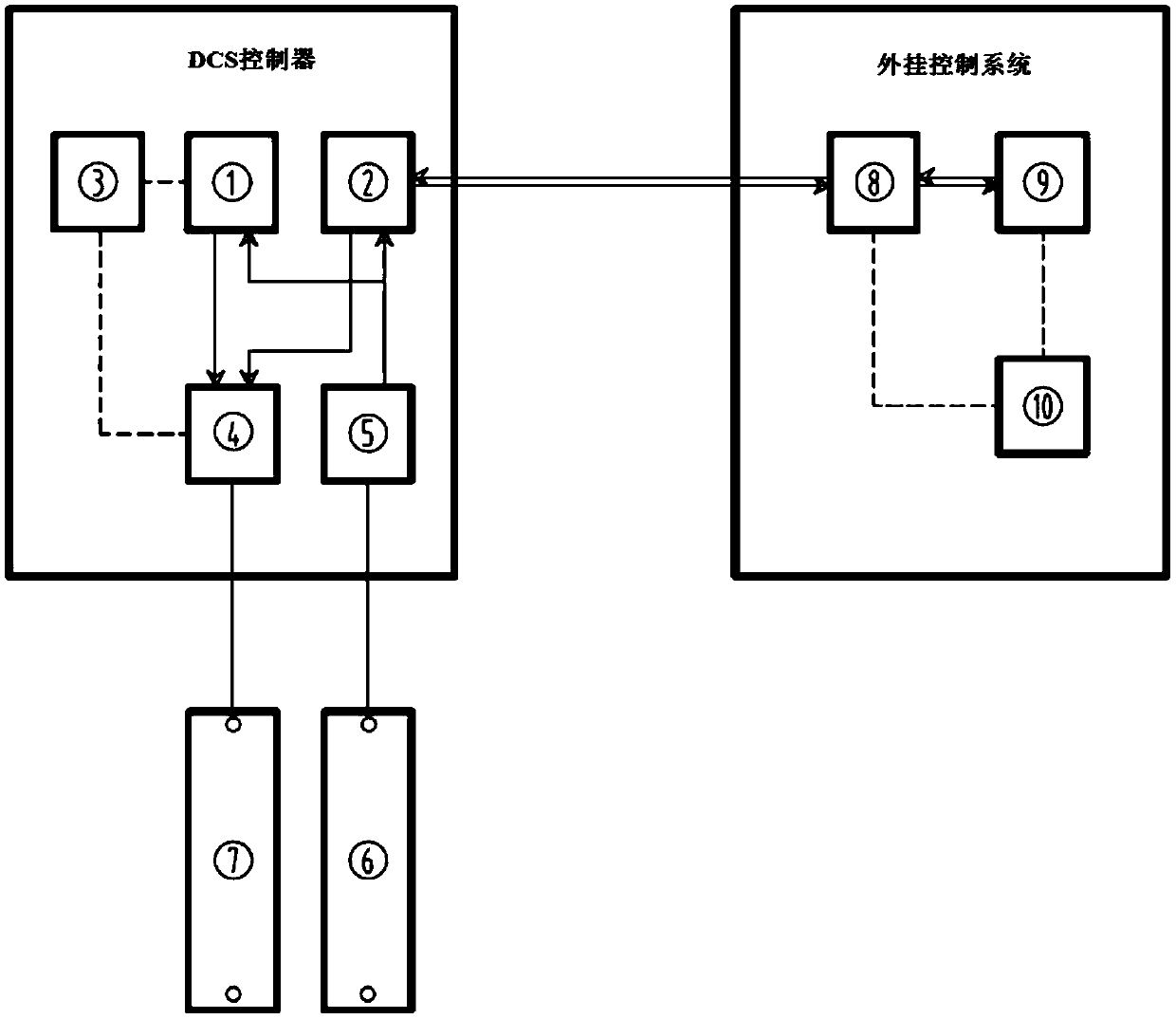

DCS external-mounting intelligent control system and method based on fault-tolerant design

PendingCN109521746AAddress reliabilitySolve quality problemsTotal factory controlProgramme total factory controlModbusAutomatic control

The invention discloses a DCS external-mounting intelligent control system and method based on the fault-tolerant design. The system is characterized in that a signal input module, a signal processingmodule and a DCS automatic control module are sequentially connected; the DCS automatic control module, an automatic tracking undisturbed switching module and a signal output module are sequentiallyconnected; the signal processing module, a DCS Modbus communication module, an external-mounting Modbus communication module and an external-mounting control module are sequentially connected, a fault-tolerant control module is connected with the DCS automatic control module and the automatic tracking undisturbed switching module, and a communication verification and fault tolerance module is connected with the Modbus communication module and the external-mounting control module. The system and method disclosed by the invention can effectively solve a problem of poor reliability of the DCS external-mounting control system.

Owner:XIAN TPRI BOILER ENVIRONMENTAL PROTECTION ENG CO LTD +1

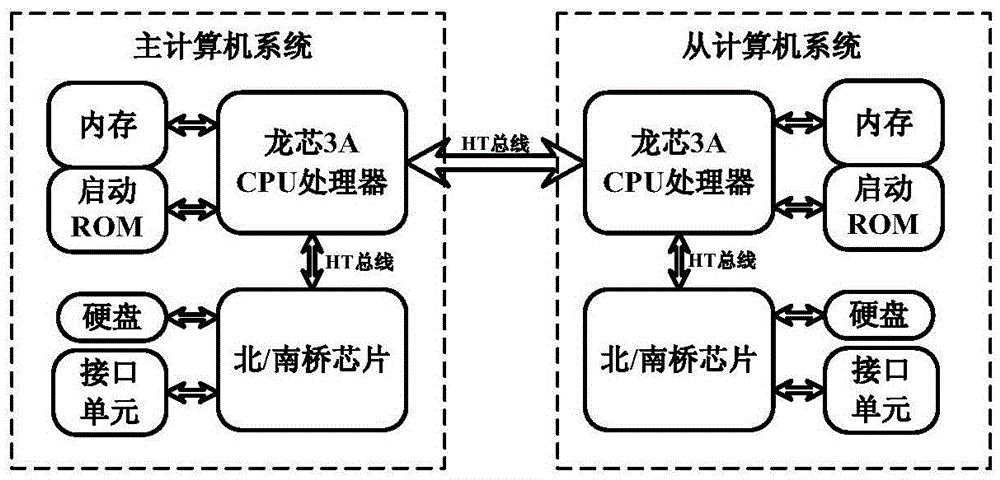

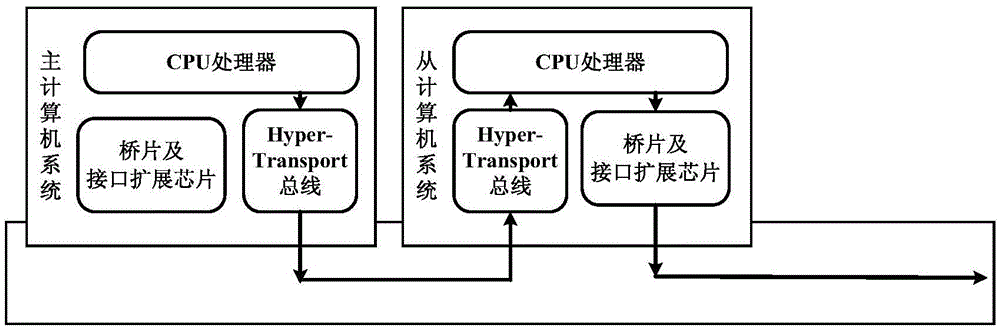

Computer fault-tolerant device based on domestic Loongson processor connection

ActiveCN106815093AImprove securityImprove reliabilityRedundant operation error correctionResource developmentS system

The invention relates to the technical field of main control units of ground core information control devices, in particular to a computer fault-tolerant device based on domestic Loongson processor connection. According to the computer fault-tolerant device in the technical scheme, fault detection of dual-computer-data-state-shared synchronous consistency and handshake mutual inspection is achieved through a specific interstage-connection interface of a domestic Loongson 3A multi-core processor and the specific high-speed bi-direction technology, the specific serial point-to-point technology, the specific packet switching technology, the specific virtual channel technology, the specific out-of-order execution technology and the like of a HT bus. According to the computer fault-tolerant device, the defects of the reliability and resource development of a domestic general processor are effectively overcome; according to redundant backup and fault tolerance design of s system function, the safety, the reliability and the testing performance of a core main control unit in an information system are fully improved, and the workability and the applicability after the information system is subjected to domestication construction are powerfully guaranteed.

Owner:BEIJING INST OF ASTRONAUTICAL SYST ENG +1

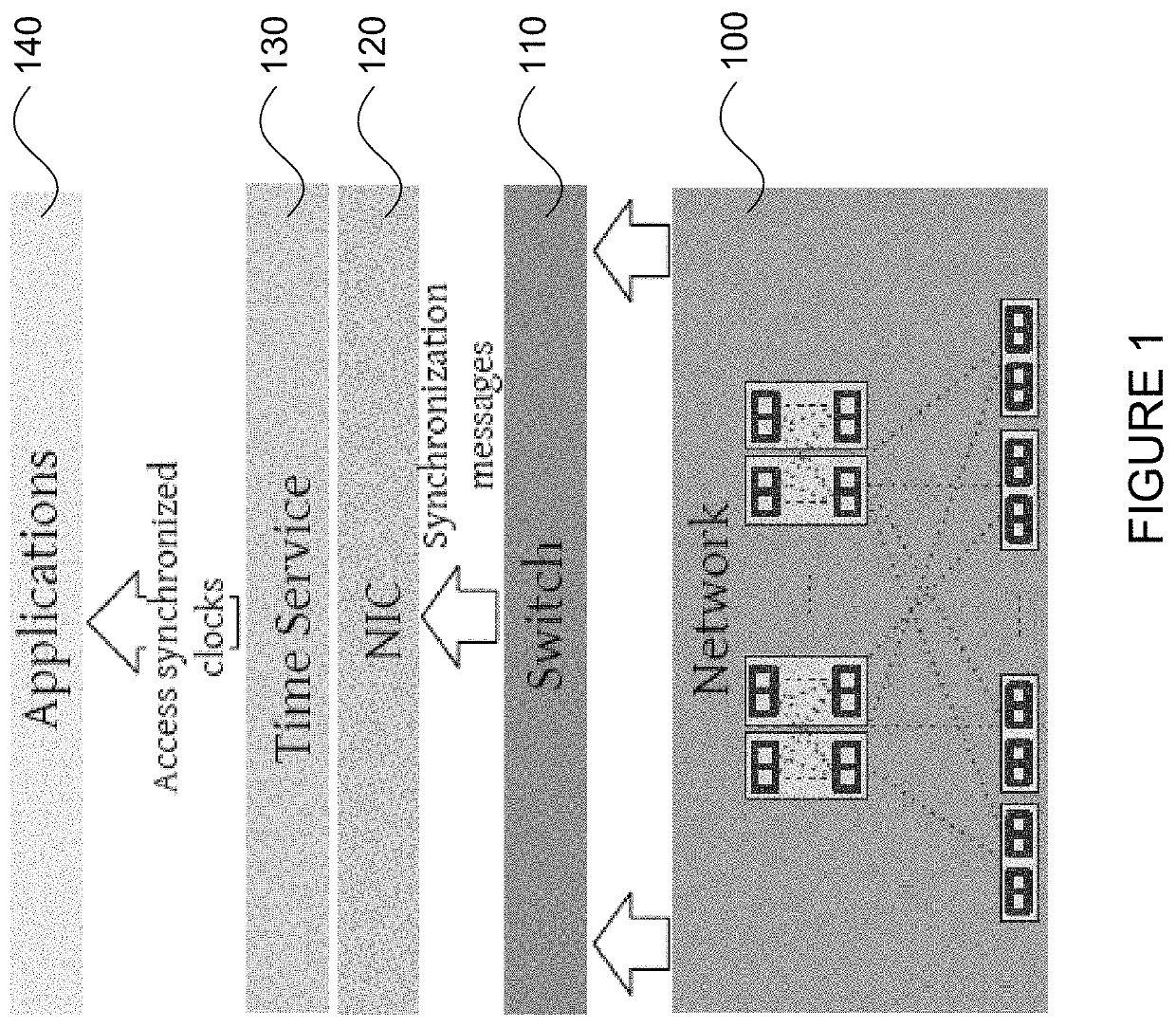

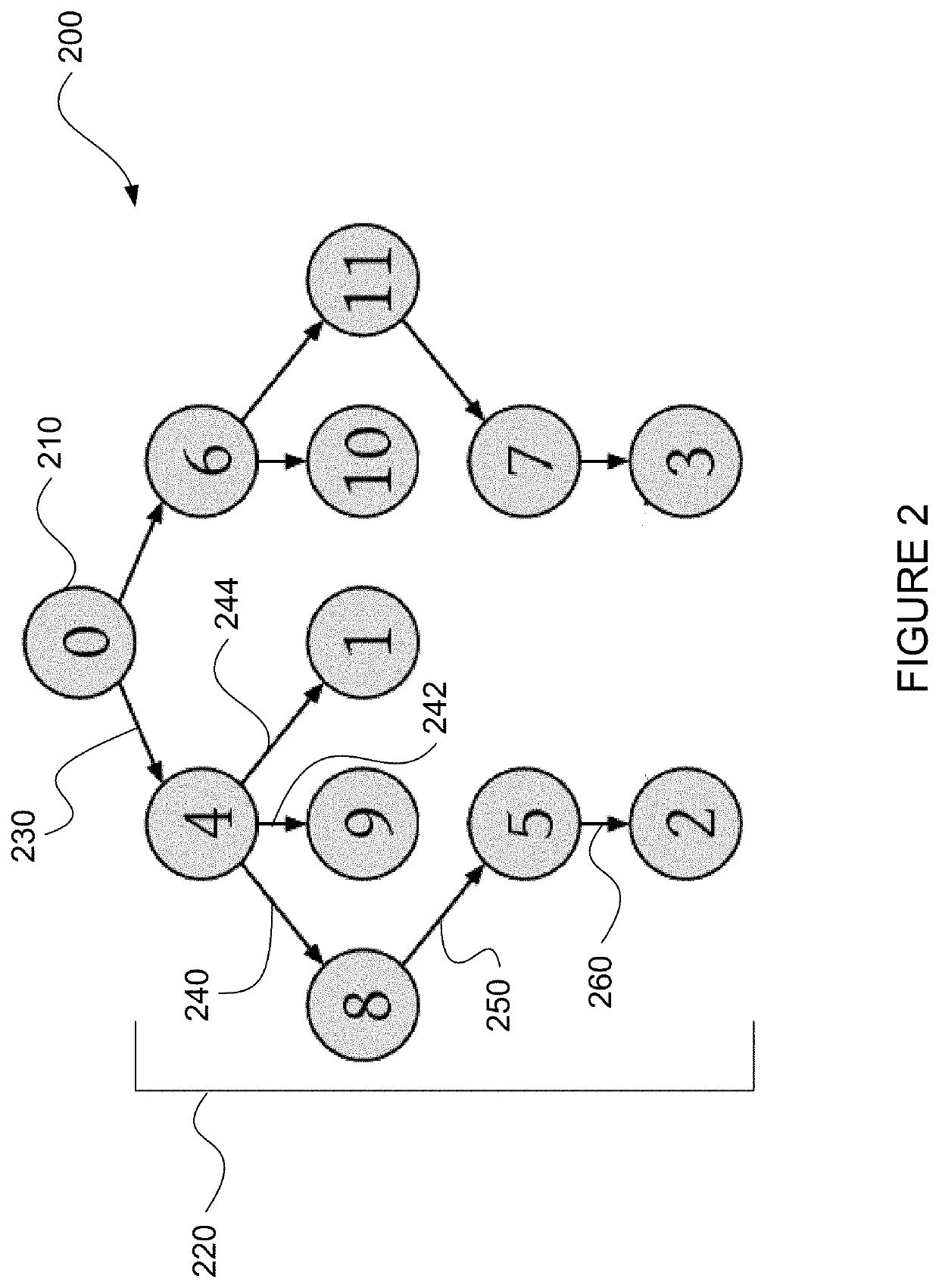

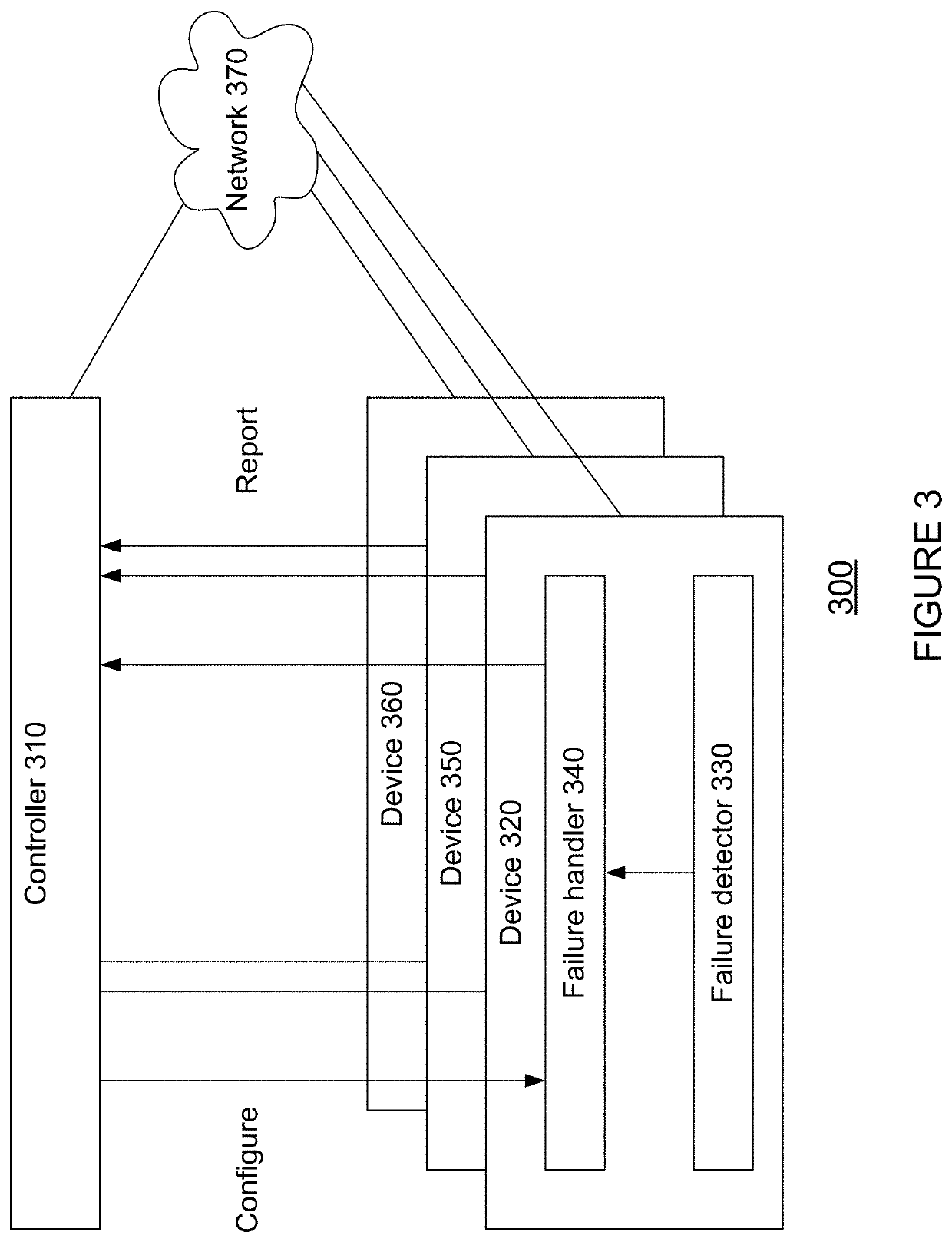

Fault Tolerant Design For Clock-Synchronization Systems

ActiveUS20210320736A1Synchronisation error correctionError detection/correctionComputer networkSystem reconfiguration

A system is provided for synchronizing clocks. The system includes a plurality of devices in a network, each device having a local clock. The system is configured to synchronize the local clocks according to a primary spanning tree, where the primary spanning tree has a plurality of nodes connected through a plurality of primary links, each node of the plurality of nodes representing a respective device of the plurality of devices. The system is also configured to compute a backup spanning tree before a failure is detected in the primary spanning tree, wherein the backup spanning tree includes one or more backup links that are different from the primary links. As such, upon detection of a failure in the primary spanning tree, the system reconfigures the plurality of devices such that clock synchronization is performed according to the backup spanning tree.

Owner:GOOGLE LLC

Highly efficient double-sampling architectures

InactiveUS20190011499A1Improve efficiencyError detection efficiencyReliability increasing modificationsDigital circuit testingDependabilityError-tolerant design

Aggressive technology scaling impacts parametric yield, life span, and reliability of circuits fabricated in advanced nanometric nodes. These issues may become showstoppers when scaling deeper to the sub-10nm domain. To mitigate them various approaches have been proposed including increasing guard-bands, fault-tolerant design, and canary circuits. Each of them is subject to several of the following drawbacks; large area, power, or performance penalty; false positives; false negatives; and in sufficient coverage of the failures encountered in the deep nanometric domain. The invention presents a highly efficient double-sampling architecture, which allow mitigating all these failures at low area and performance penalties, and also enable significant power reduction.

Owner:NICOLAIDIS MICHEL

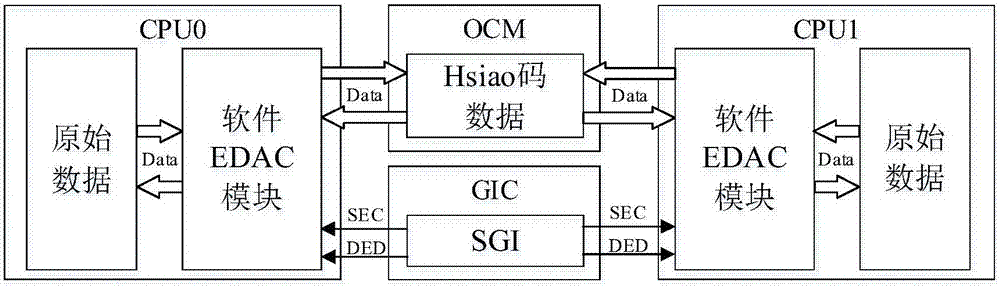

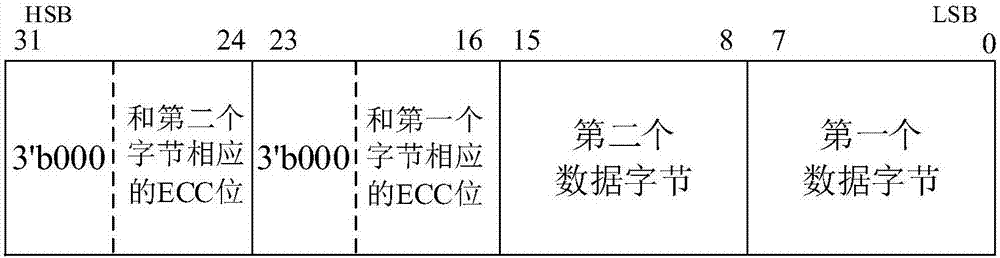

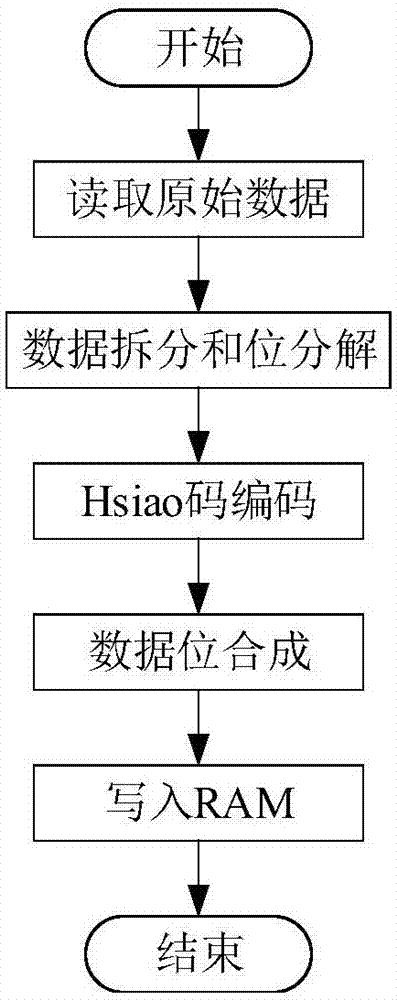

Zynq-7000-based scratch-pad memory single event upset protection method

ActiveCN107291570ASolve the problem of repeatedly reading wrong dataAvoid confictRedundant hardware error correctionMemory faultsSpace environment

The invention relates to a Zynq-7000-based scratch-pad memory single event upset protection method which is applied to a memory fault-tolerant design of Zynq-7000SoC in a space environment, and aims to solve the problems that single event upset affects data reliability of a memory on an internal pad of a Zynq-7000 chip in a space environment. Correct communication between dual-core processors in the Zynq-7000 chip is guaranteed. On the basis of resource characteristics of the Zynq-7000 chip, data reinforcing operation of communication between the dual-core processors and the scratch-pad memory is realized by a software EDAC method, state tags of a single-bit error and a dual-bit error and dual-core synchronous write-back operation of the single-bit error are realized by a software interruption mode, and functions of single-error-correcting and double-error-detecting and data write-back of data are fulfilled in an ARM processor, therefore, the single event upset resistance of the memory on the internal pad of Zynq-7000 is improved, and an important means is provided for reliability of data communication between the dual-core processes in Zynq-7000 SoC.

Owner:HARBIN INST OF TECH

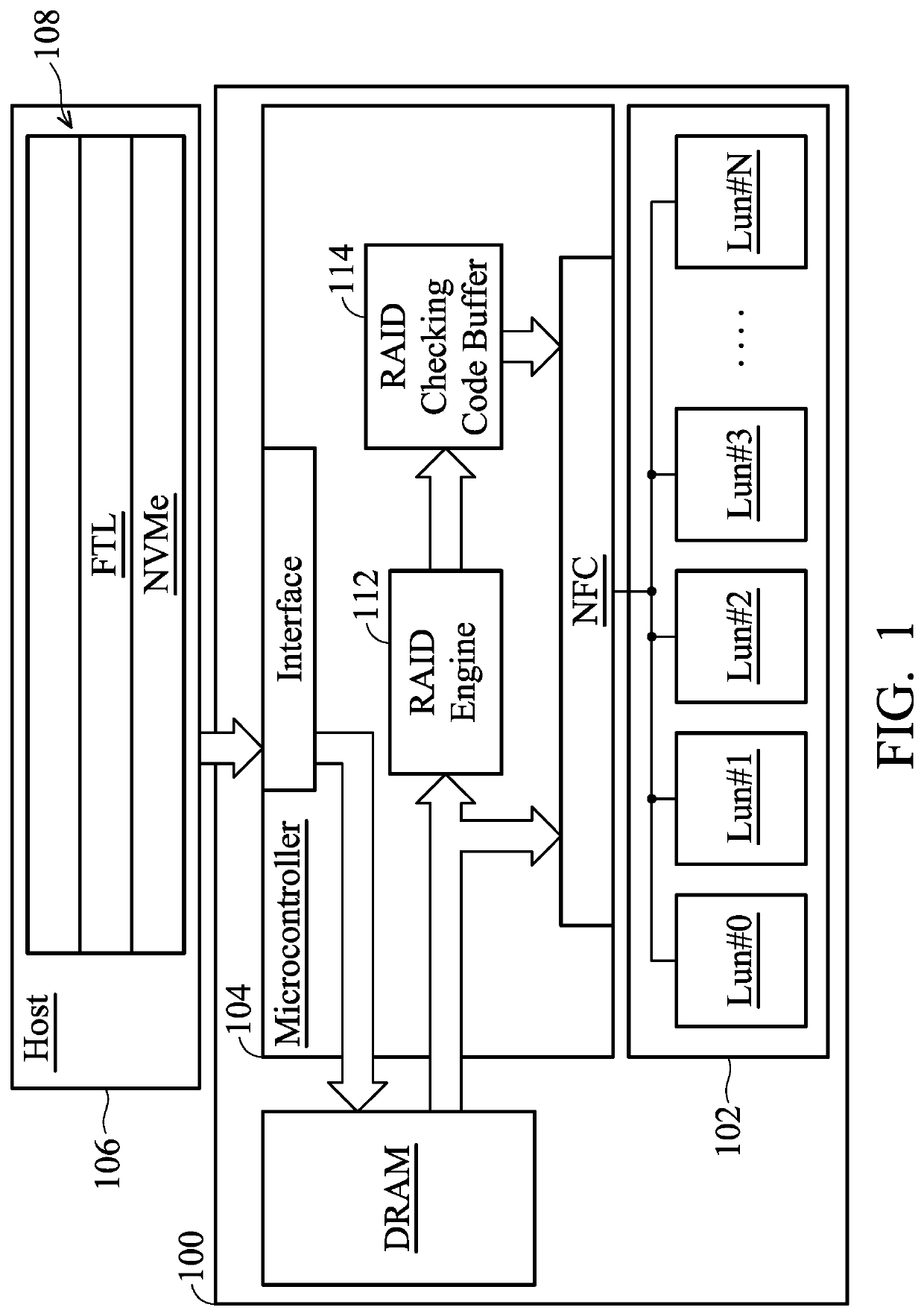

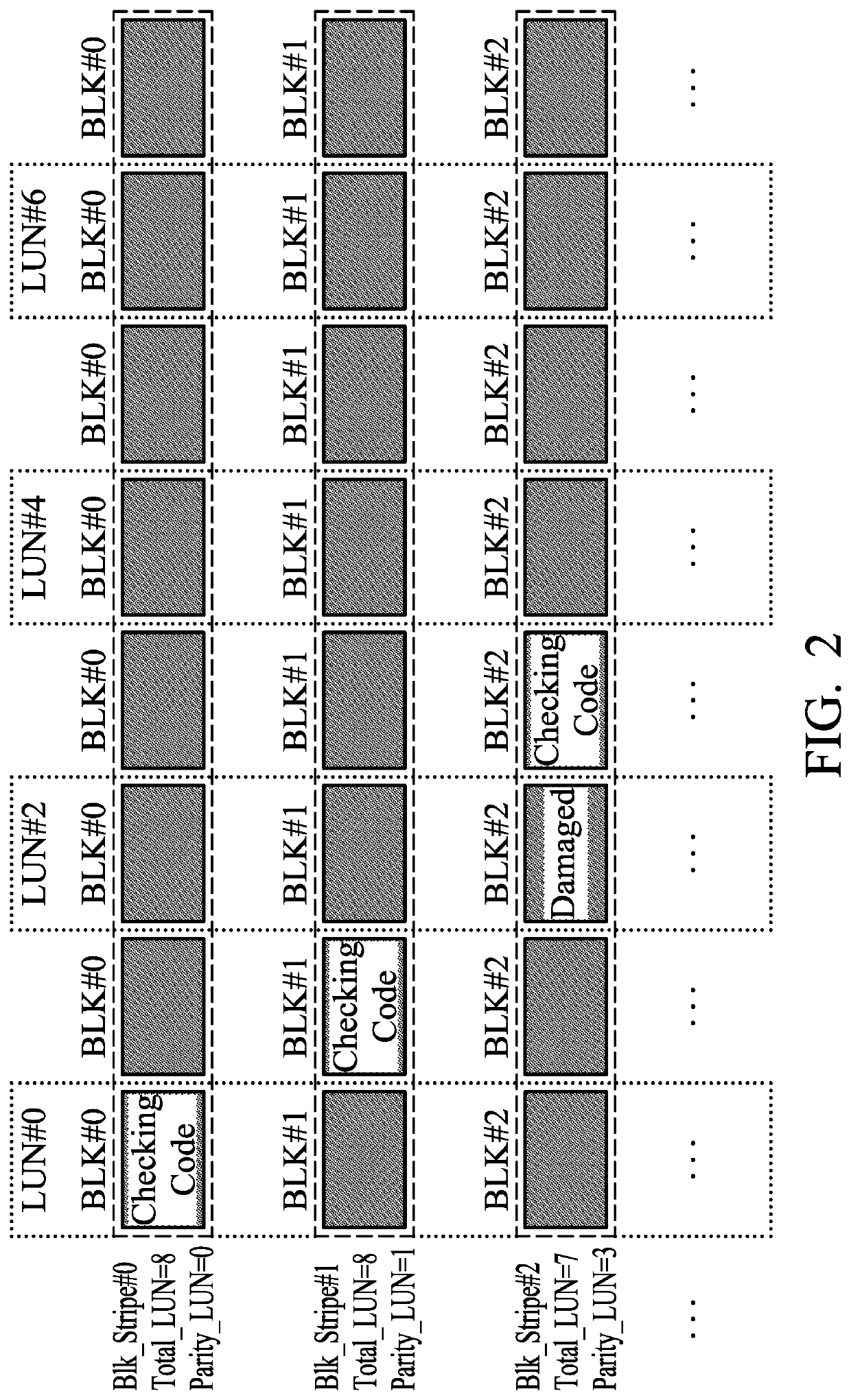

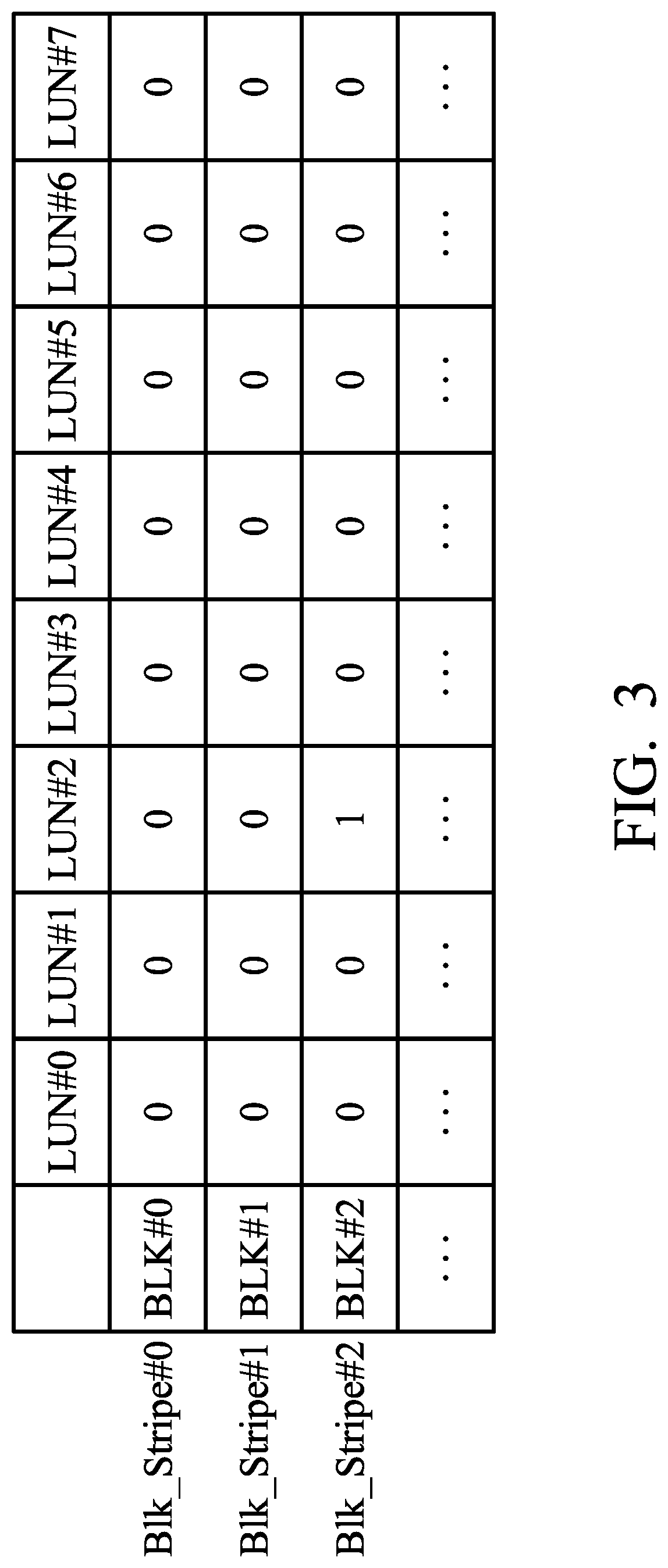

Data storage device, host device for data storage device operations, and data writing method

ActiveUS10783037B2Memory architecture accessing/allocationRedundant data error correctionRAIDPhysical address

A data storage device with fault-tolerant design. The data storage device has a RAID (Redundant Array of Independent Disks) engine that generates RAID checking code for user data requested in a write command. The user data is programmed to a non-volatile memory according to a target physical address indicated in the write command. The RAID checking code is programmed to the non-volatile memory according to a reserved physical address. The user data and the RAID checking code are programmed to a stripe of pages within a stripe of blocks.

Owner:SILICON MOTION INC (TW)

Fault filling method and apparatus based on programmable logical device

InactiveCN100371901CAvoid the phenomenon of electrical damageAvoid missing detectionFault responseProgrammable logic deviceError-tolerant design

The present invention provides a fault injection method based on programmable logic device and its device. Its kernel lies in that a fault injection module is set in the interior of programmable logic device having need of making fault injection to obtain the signal of the described programmable logic device, the described fault injection module can inject the correspondent fault into the obtained signal and can output the signal in which the fault is injected. Said invention has no need of external fault injection equipment or scrambling equipment, and can utilize the fault injection module set in the interior of programmable logic device to make fault injection process have no need of manual intervention and do not damage the programmable logic device.

Owner:HUAWEI TECH CO LTD

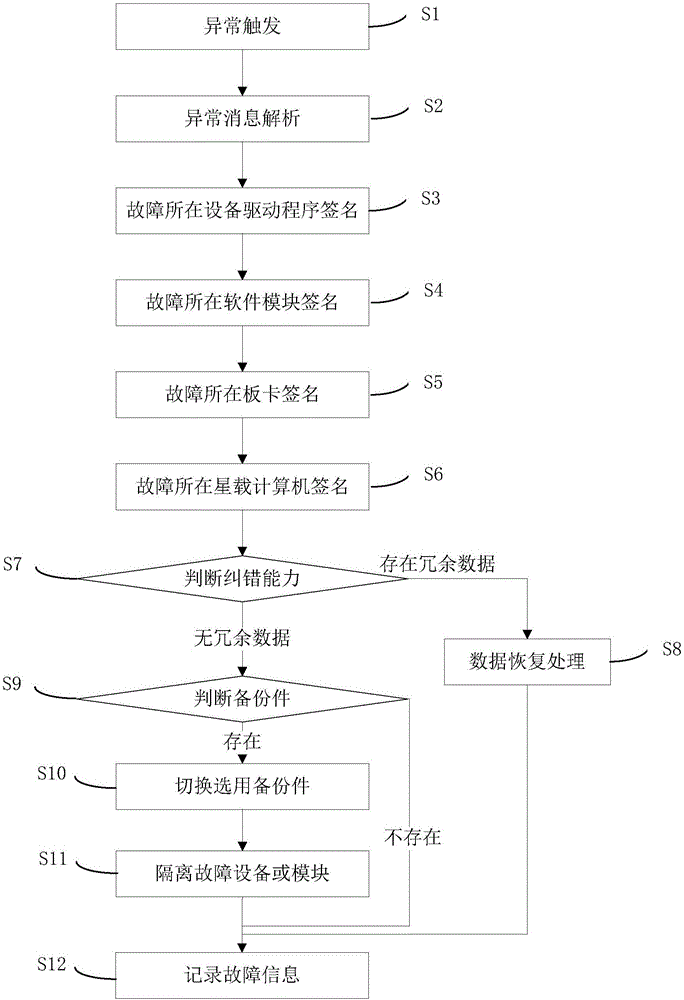

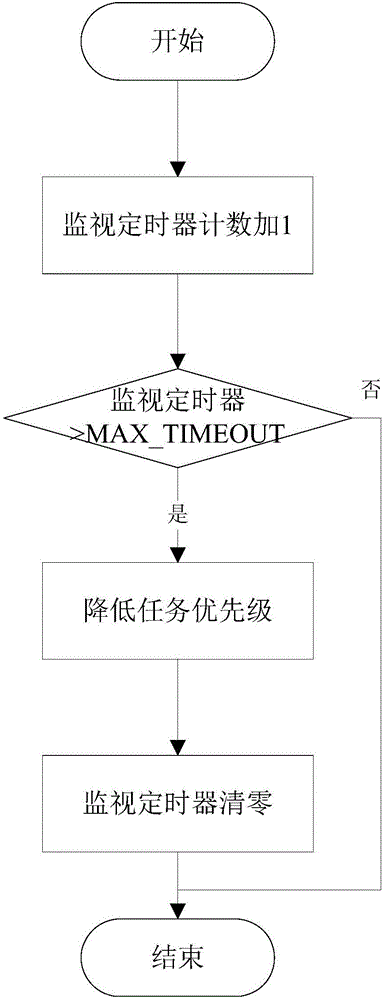

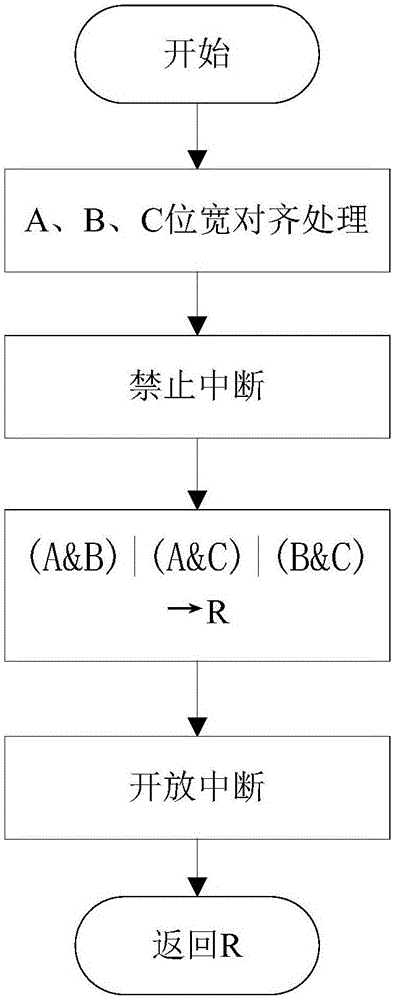

Fault-tolerant method for plug-and-play supported satellite-borne software

InactiveCN106407046AImprove development efficiencyImprove reliabilityRedundant operation error correctionInformation analysisMulti platform

The invention relates to a fault-tolerant method for satellite-borne software under a multi-platform environment, and discloses a fault-tolerant method for a plug-and play supported satellite-borne software. The fault-tolerant method comprises the steps of abnormity triggering, abnormal information analysis, signature of an equipment driving program where a fault occurs, signature of a software module where the fault occurs, signature of a board card where the fault occurs, signature of a satellite-borne computer where the fault occurs, judgment of error correction capability, data recovery processing, judgment of a backup file, switching and selection of the backup file, fault equipment or module isolation and fault information recording. By the method, the problem of difficulty in extension and compatibility during the adoption of a fault-tolerant design on satellite-borne software of a multiprocessor and hardware equipment under a complicated application environment is solved, and the beneficial effects of improving rapid development capability and reliability of software and supporting plug-and-play of equipment are achieved.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

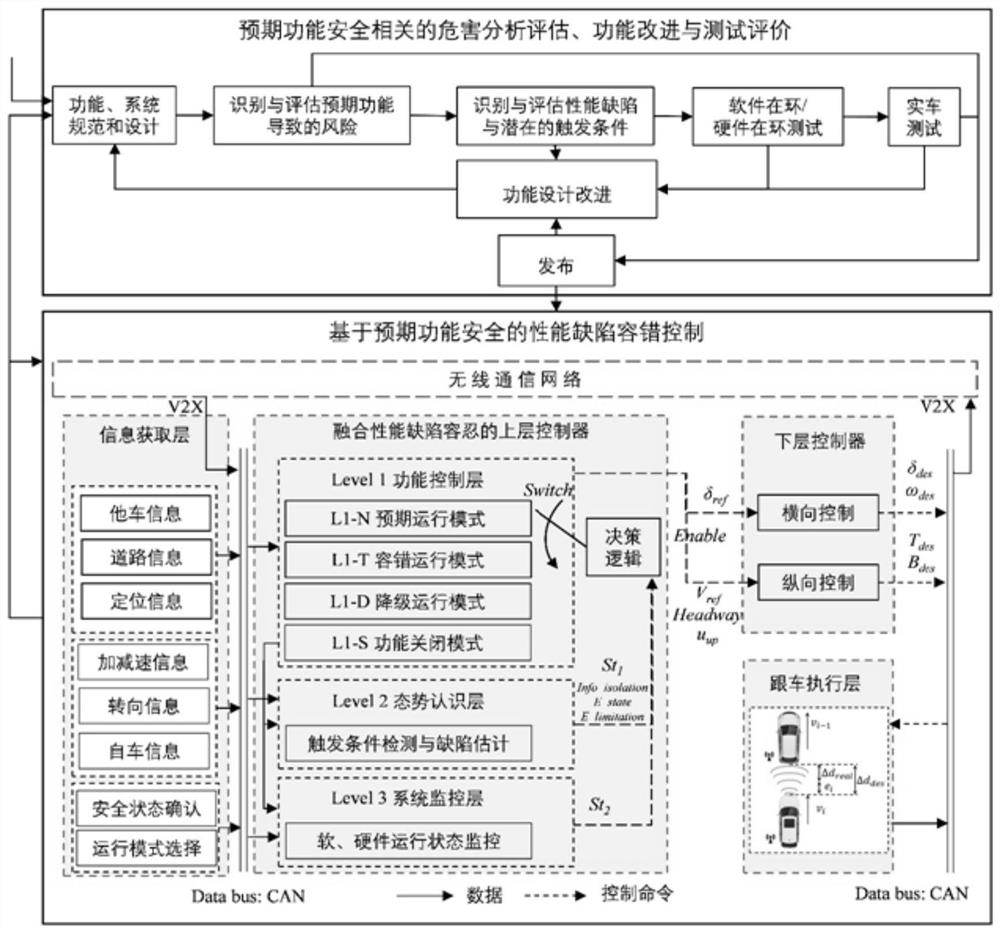

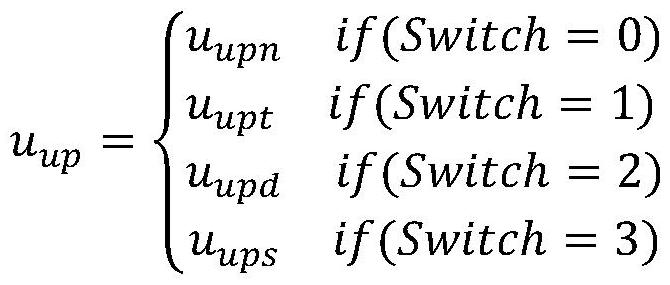

Cooperative adaptive cruise control fault-tolerant design system based on expected function security

ActiveCN113110494AReduce riskAnticipated Functional AssuranceInternal combustion piston enginesPosition/course control in two dimensionsIntelligent NetworkControl engineering

The invention discloses a cooperative self-adaptive cruise control fault-tolerant design system based on expected function safety, and aims at cooperative self-adaptive cruise control of an intelligent network connection automobile technology to carry out fault-tolerant design based on the expected function safety. The system includes two parts of: hazard analysis and evaluation based on expected function safety, function improvement and test evaluation and performance defect fault-tolerant control based on the expected function safety. wherein the performance defect fault-tolerant control based on expected function safety comprises an information acquisition layer, an upper-layer controller fusing performance defect tolerance, decision logic, a CACC fault-tolerant lower-layer controller and a car following execution layer. The invention aims to provide a cooperative self-adaptive cruise control fault-tolerant design architecture based on expected function safety, which is used for solving the problem of vehicle damage caused by insufficient design and functional defects of the existing cooperative self-adaptive cruise control function, and ensuring the driving safety in a cooperative self-adaptive cruise control function mode.

Owner:TSINGHUA UNIV

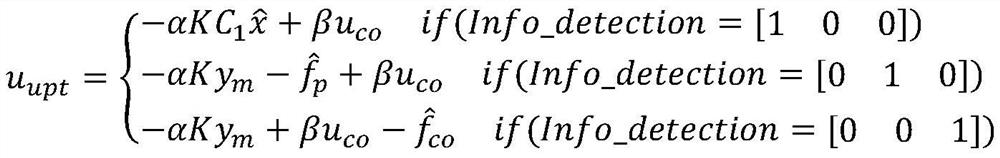

A circuit system fault-tolerant capability simulation analysis method considering cascade failure

ActiveCN109948256AAccurate calculationAccurate cascading failure propagation pathsSpecial data processing applicationsCascading failureStructure and function

The invention provides a circuit system fault-tolerant capability simulation analysis method considering cascade failure. The circuit system fault-tolerant capability simulation analysis method comprises the steps of S1, realizing structure and function analysis; S2, constructing a netlist file; S3, constructing a failure description file; S4, carrying out initial injection failure; S5, calling the SPICE for simulation; S6, judging whether cascade failure occurs or not, if the cascade failure occurs, updating the circuit structure information and returning to the step S2, and if the cascade failure does not occur, considering that the cascade failure process is stopped; S7, collecting relevant data of a cascade failure propagation path; S8, carrying out redundancy backup on the key components according to a cascade failure analysis result in the step S7; and S9, updating the circuit structure, and recalculating the improvement degree of the fault-tolerant capability of the improved anddesigned circuit. Simulation calculation analysis is carried out based on SPICE simulation software, cascade failure propagation behaviors of the circuit system can be analyzed from the perspective of the system, fault-tolerant design of the circuit system is guided, and method support is provided for circuit internal structure optimization and reconstruction.

Owner:BEIHANG UNIV +1

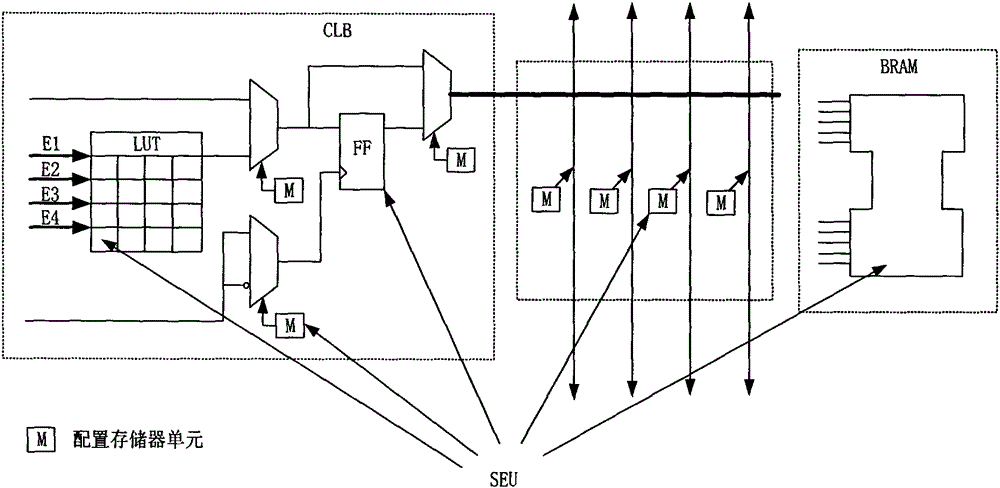

SEU fault tolerance technology applied to FPGA

InactiveCN106469096ASmall scaleImprove reliabilityError detection/correctionError-tolerant designComputer science

The invention discloses an SEU fault tolerance design applied to an FPGA. An idea of a reconfigurable technology is used for SEU fault tolerance in the FPGA to improve the operation reliability of a system. Switching of a logic function is achieved by a reconfigurable region A through dynamically loading a configuration file A1.bit or A2.bit.

Owner:汪鹏

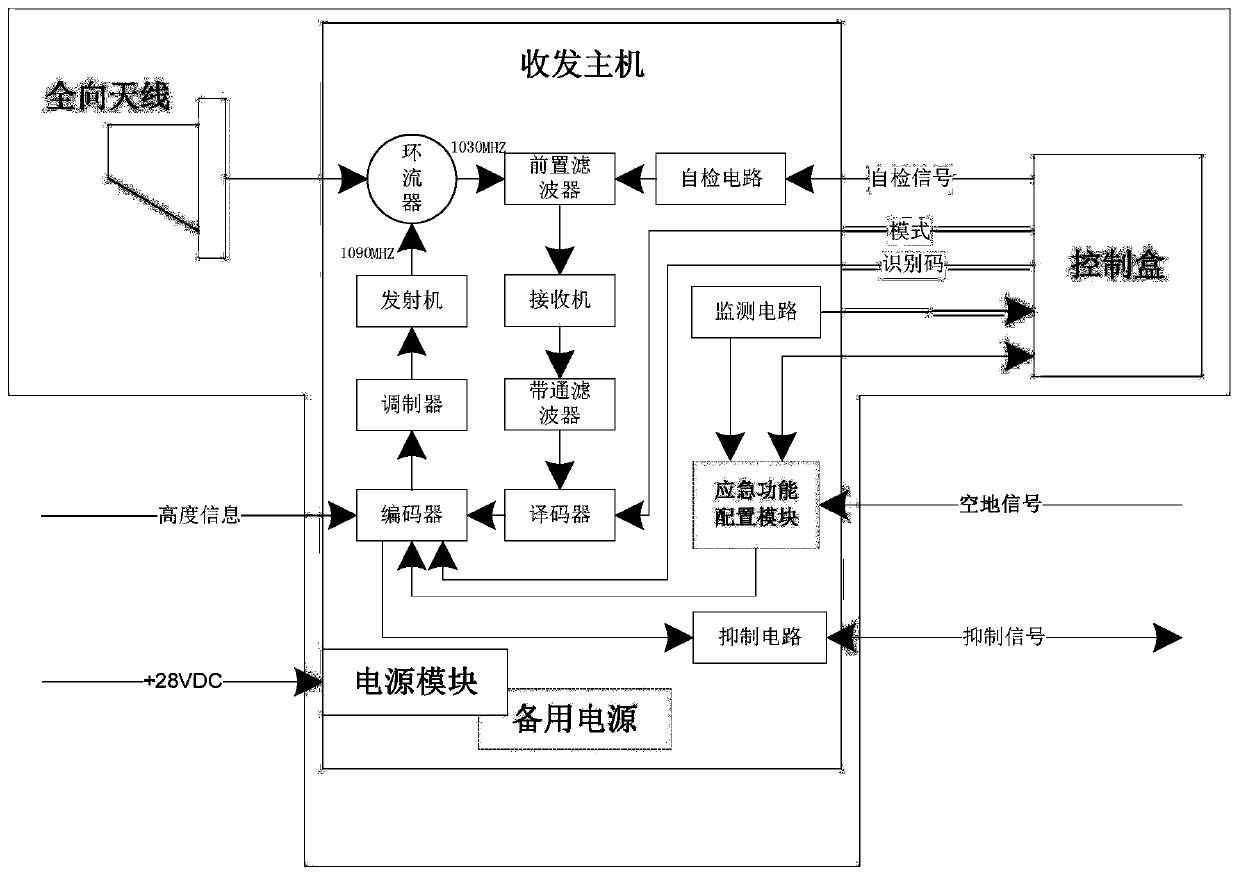

A/C-mode responder system with anti-human error function

InactiveCN110379208AReduce failureReduce human operation authorityMultiple aircraft traffic managementOmnidirectional antennaTransceiver

The invention discloses an A / C-mode responder system with the anti-human error function. The system comprises three LRUs: a transceiver host, a control box and an omnidirectional antenna. The transceiver host mainly completes processing of a transceiving signal, protocol processing, interface adaptation, and emergency identification and management and is capable of monitoring the system state to identify an external operation so as to select a working mode. The control box is used for completing setting of the system working mode and parameter setting by the flight personnel according to setting permission of opening working modes and parameters of the system and aircraft flight state provided by the transceiver host. The omnidirectional antenna is used for receiving an interrogation signal sent by a ground secondary radar. According to the system, the human operation authority is minimized; for the necessary manual operations, an error-proof operation and anti-error operation design is made for avoiding the false operation and the violation operation, so that the equipment and system failures caused by human factors are reduced effectively and the system redundancy is improved substantially and thus the continuous and effective ground monitoring is supported.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

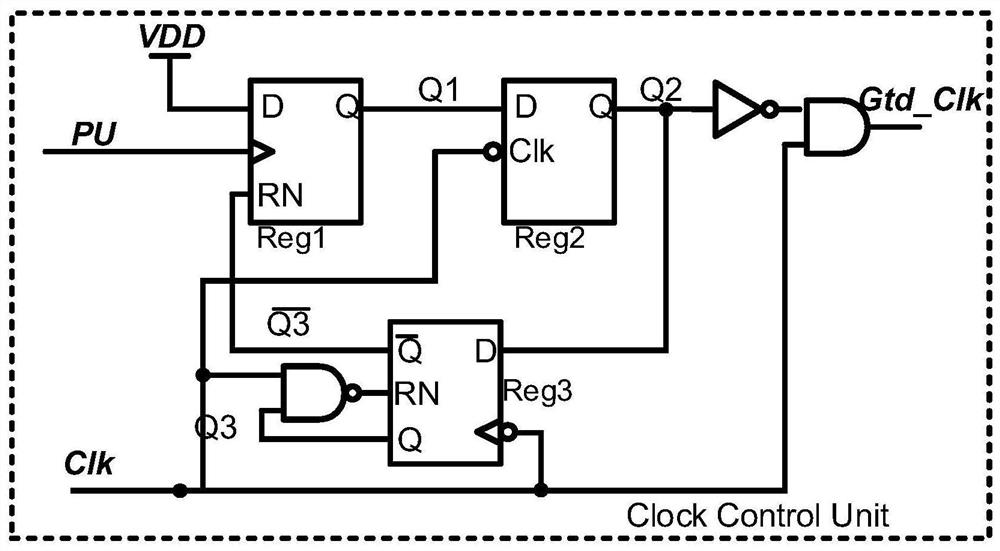

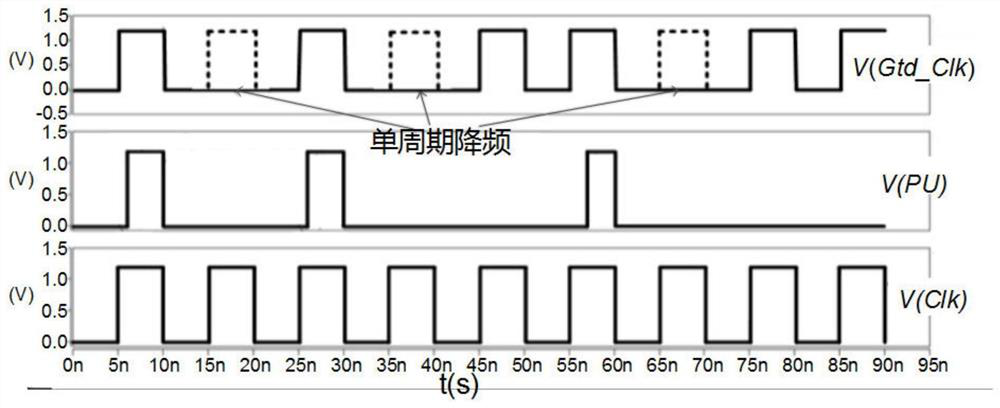

Sub-threshold single-cycle clock frequency reduction control circuit

ActiveCN112019166ASimple clock signalMulti-frequency-changing modulation transferenceEnergy efficient computingControl signalControl engineering

The invention relates to a sub-threshold single-cycle clock frequency reduction control circuit. The control circuit comprises two input ports; one output port, the input end port inputs a clock signal and an input pulse signal respectively; and the output port outputs the clock down-conversion signal after frequency reduction, and based on the sub-threshold single-cycle clock down-conversion control circuit provided by the invention, the clock down-conversion signal after frequency reduction is output by controlling the level states of the input pulse signal and the clock signal, so that single-cycle clock down-conversion control is realized. The sub-threshold single-cycle clock frequency reduction control circuit provided by the invention is simple in control signal and suitable for being applied to fault-tolerant design, error correction control and circuits with single-cycle clock frequency reduction requirements.

Owner:北京中科芯蕊科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com