Self-reconfigurable D/TMR (Dual/Triple Modular Redundancy) system based on FPGA (Field Programmable Gate Array) and fault-tolerant design method thereof

A fault-tolerant design and self-reconfiguration technology, applied to hardware redundancy for data error detection and response error generation, can solve problems such as low utilization of FPGA resources and weak system fault tolerance, and achieve low The effect of power consumption, high resource utilization, and fast self-healing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings.

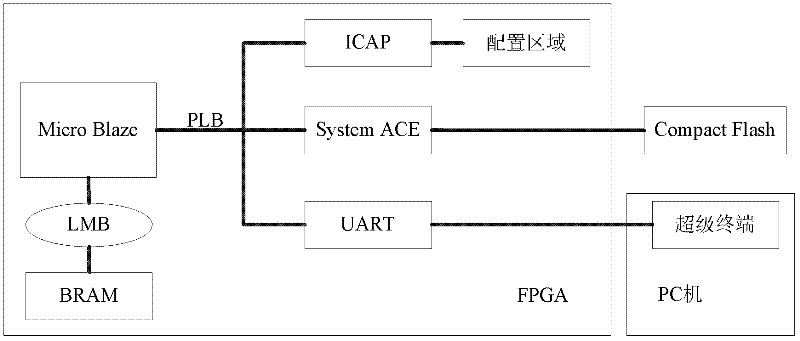

[0015] Such as figure 1 As shown, the present invention provides a self-reconfiguration D / TMR system based on FPGA, including self-reconfiguration controller (realized by Micro Blaze soft core), ICAP (Internet Content Adaptation) interface, configuration area module, System ACE (System Advanced Configuration Environment) interface, UART (Universal Asynchronous Receiver / Transmitter) interface and CF (Compact Flash) card, among them, self-reconfiguration controller, configuration area module, System ACE interface and ICAP interface are all implemented on FPGA, and UART is set The interface is used to realize the communication with the HyperTerminal on the PC, and the ICAP interface, System ACE interface, UART interface and reconfiguration area module are connected to the PLB bus as peripherals, and the external CF card is used to store the b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com