Event driven dynamic logic for reducing power consumption

A technology of power consumption and logic circuit, applied in the direction of logic circuit, power consumption reduction, logic circuit with logic function, etc., can solve the problem of power consumption of circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

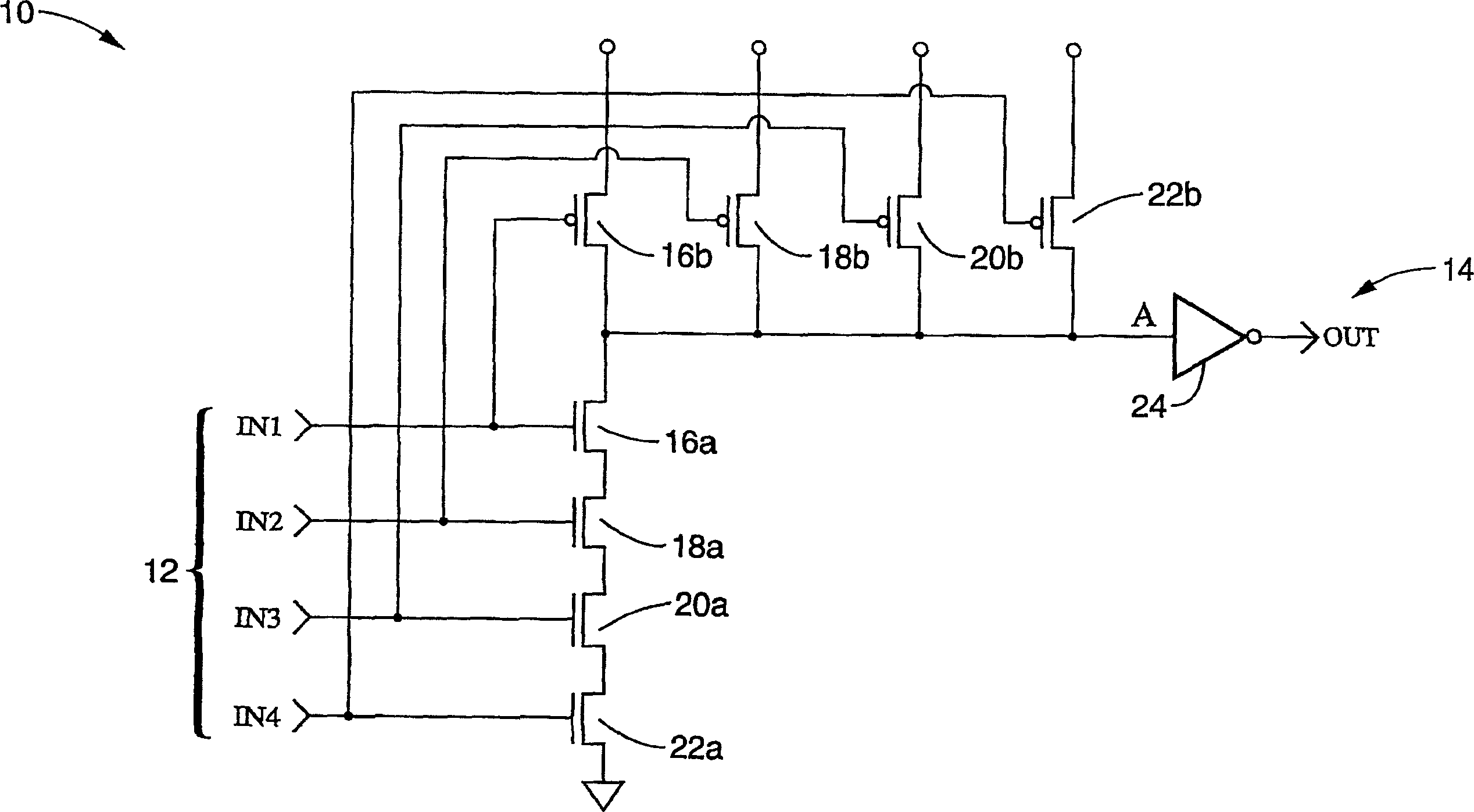

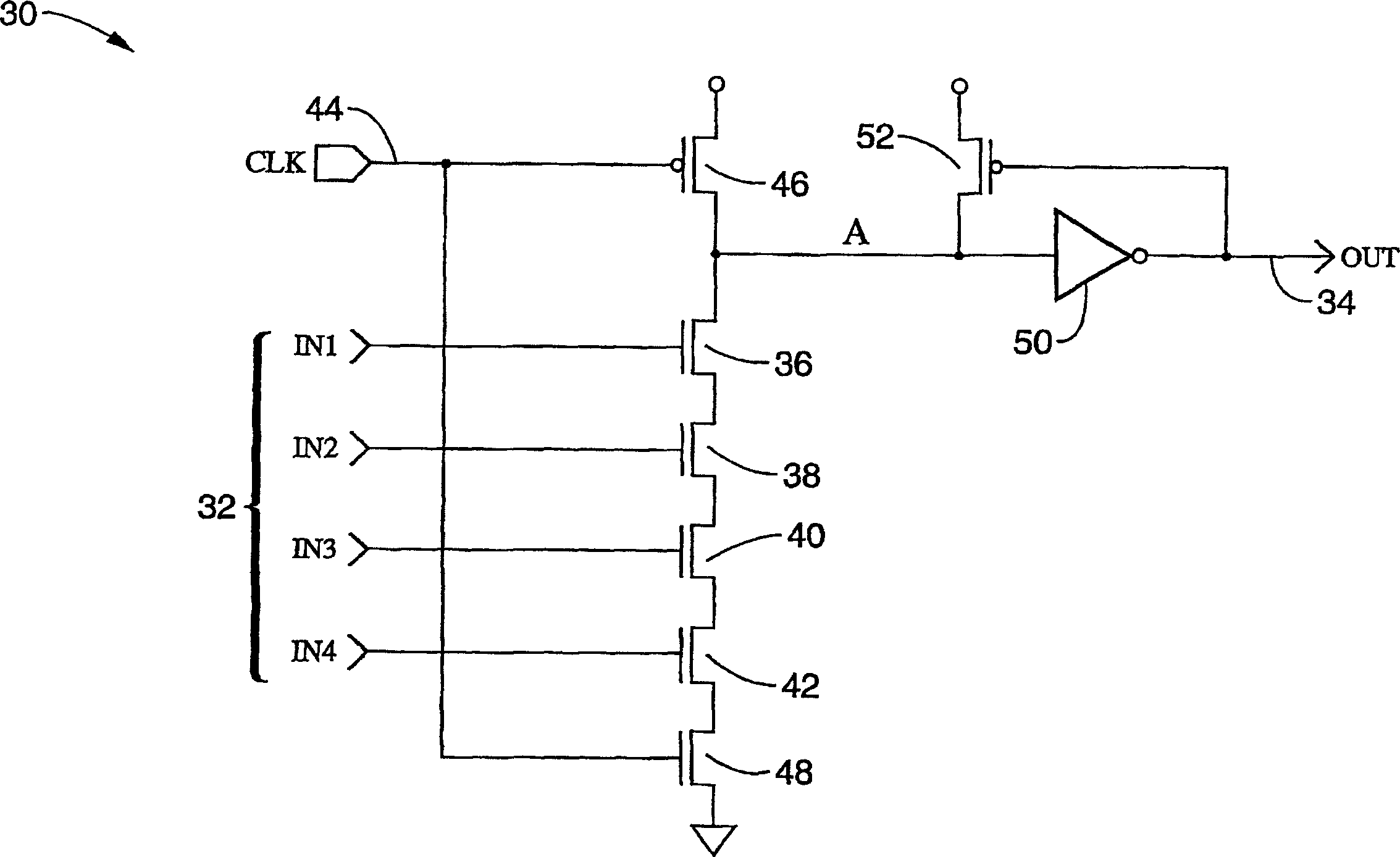

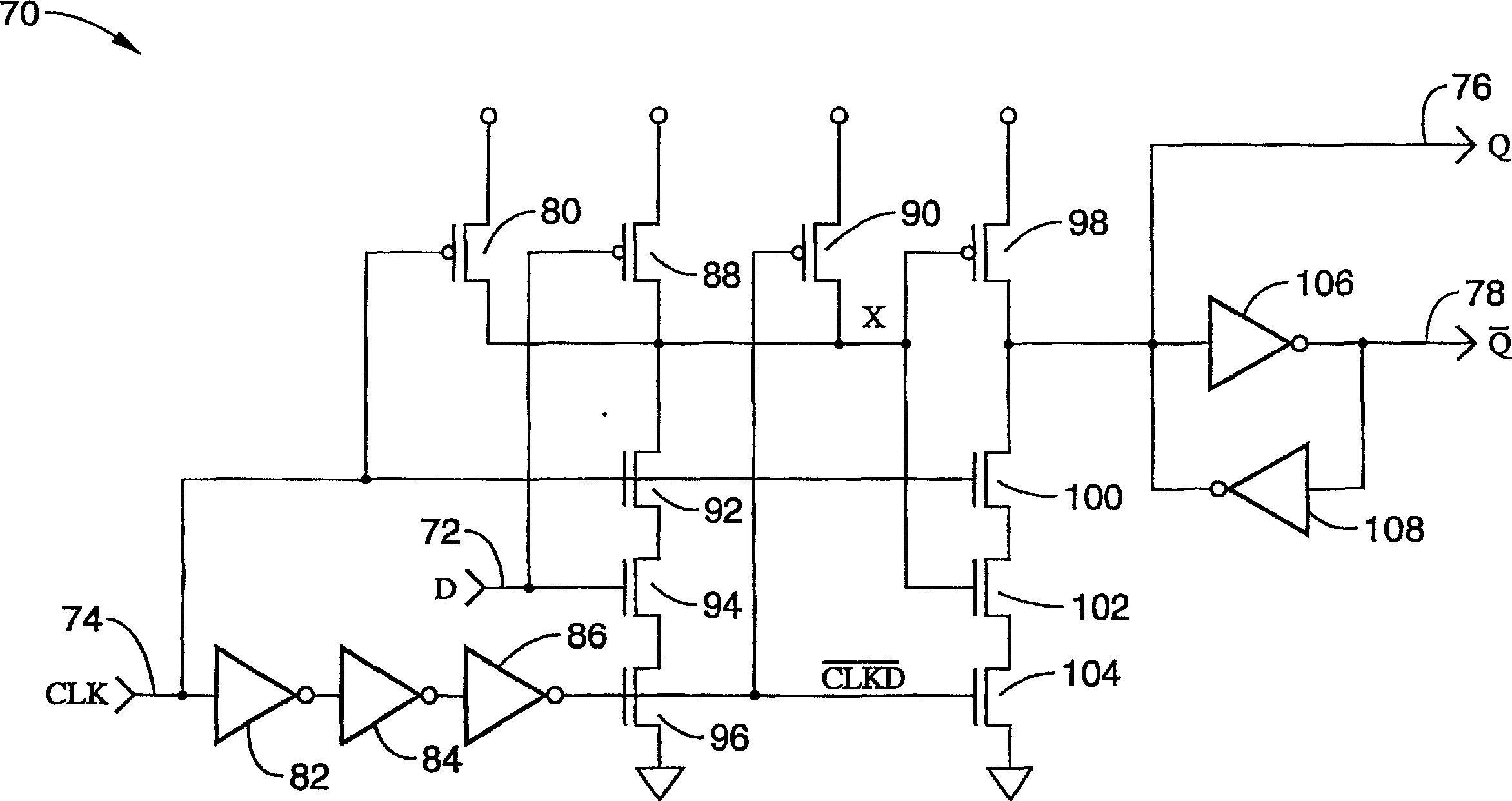

[0057] With more particular reference to the drawings, for illustrative purposes, the present invention is presented in Figure 4 to Figure 9 implemented in the apparatus outlined in . It will be understood that the apparatus may vary in configuration and part details, and that the method may vary in specific steps and sequences, without departing from the basic concept as disclosed herein.

[0058] Figure 4 A single-input event-driven logic circuit 110 is illustrated, which is similar to the four-input AND domino combinational logic circuit shown in FIG. 2 . Logic circuit 110 has logic input 112 , clock input 114 and output 116 . Clock path control circuitry 118 is shown for selectively blocking the clock signal through conventional combined dynamic logic circuitry 120 in response to a true logic evaluation.

[0059] The general operation of the invention involves cycling logic circuits through clock phases including precharge and evaluation phases while receiving an activ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com