Method for arbitrary fractional frequency division of digital circuit clock

A digital circuit and fractional frequency division technology, applied in the direction of electric pulse generator circuit, differential amplifier to generate pulses, etc., can solve the problems of error periodicity, jitter, etc., and achieve no cumulative error, good adaptability, and easy modular design Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the purpose, content and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0028] The invention relates to the field of clock frequency division methods and the field of digital circuits, in particular to a method for frequency division of arbitrary decimals.

[0029] The content of the present invention is to propose a method for arbitrary frequency division of the clock. The clock frequency obtained by frequency division is accurate and has no cumulative error; it is self-adaptive to any frequency division value, does not require human intervention, and is convenient for modular design; The jitter performance of the resulting target clock can be optimized.

[0030] Frequency division method of the present invention is as follows:

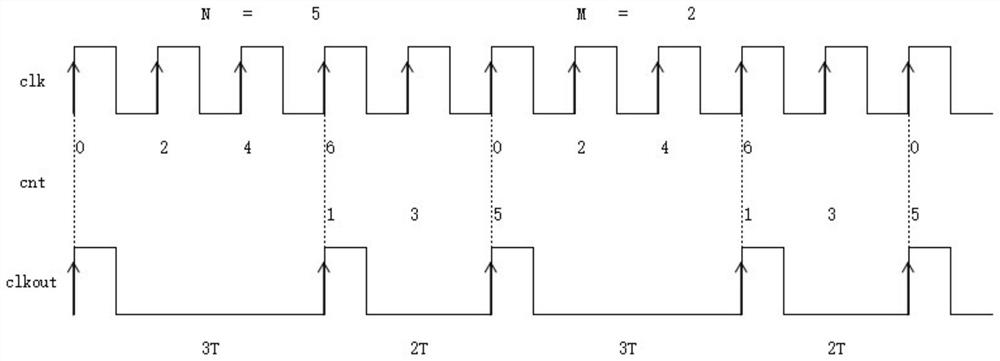

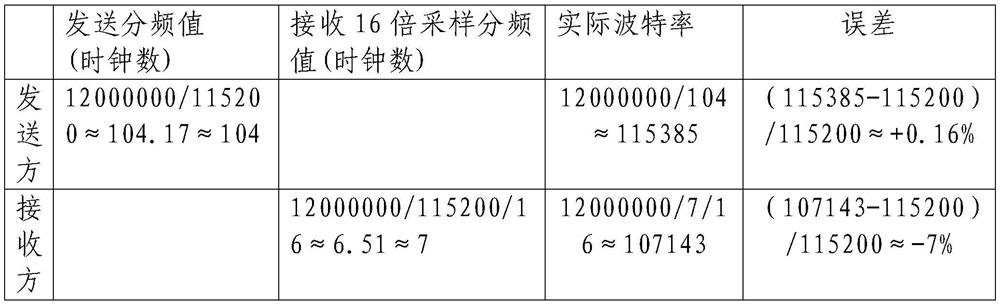

[0031] Let the master clock frequency be N, the target cloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com