Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

199 results about "Atomic nucleus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The atomic nucleus is the small, dense region consisting of protons and neutrons at the center of an atom, discovered in 1911 by Ernest Rutherford based on the 1909 Geiger–Marsden gold foil experiment. After the discovery of the neutron in 1932, models for a nucleus composed of protons and neutrons were quickly developed by Dmitri Ivanenko and Werner Heisenberg. An atom is composed of a positively-charged nucleus, with a cloud of negatively-charged electrons surrounding it, bound together by electrostatic force. Almost all of the mass of an atom is located in the nucleus, with a very small contribution from the electron cloud. Protons and neutrons are bound together to form a nucleus by the nuclear force.

Lithium ion battery silicon carbide composite anode material and preparation method thereof

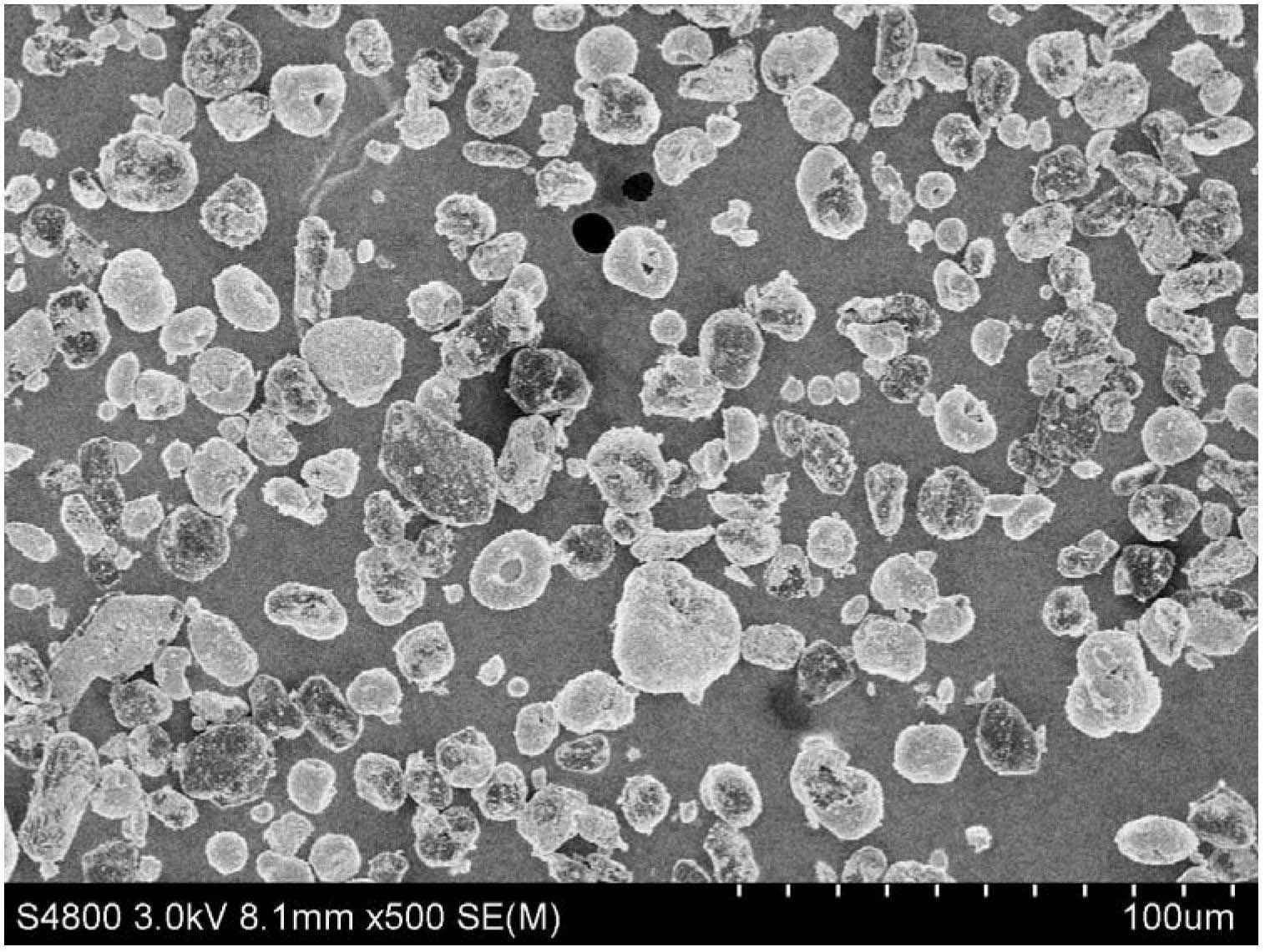

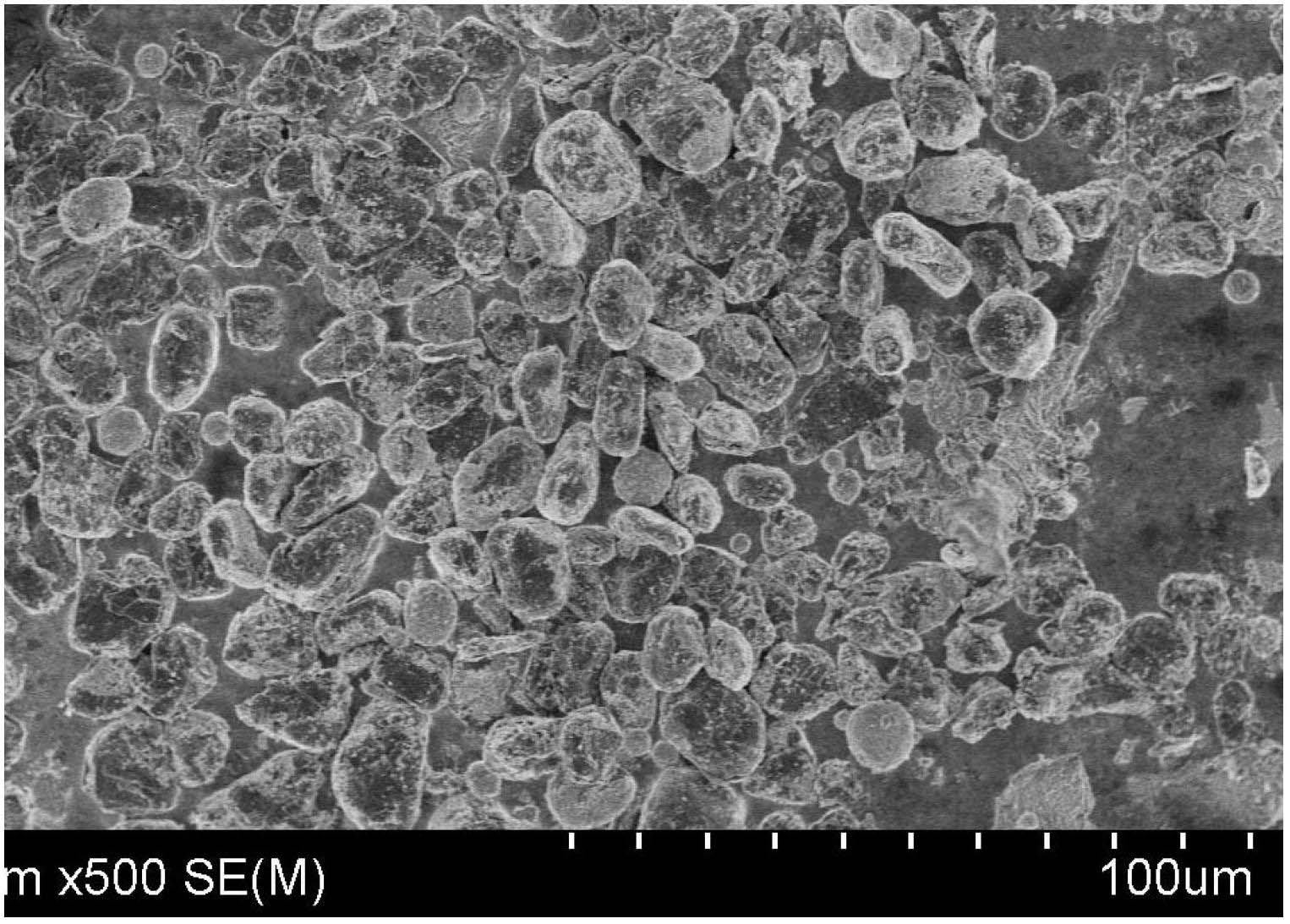

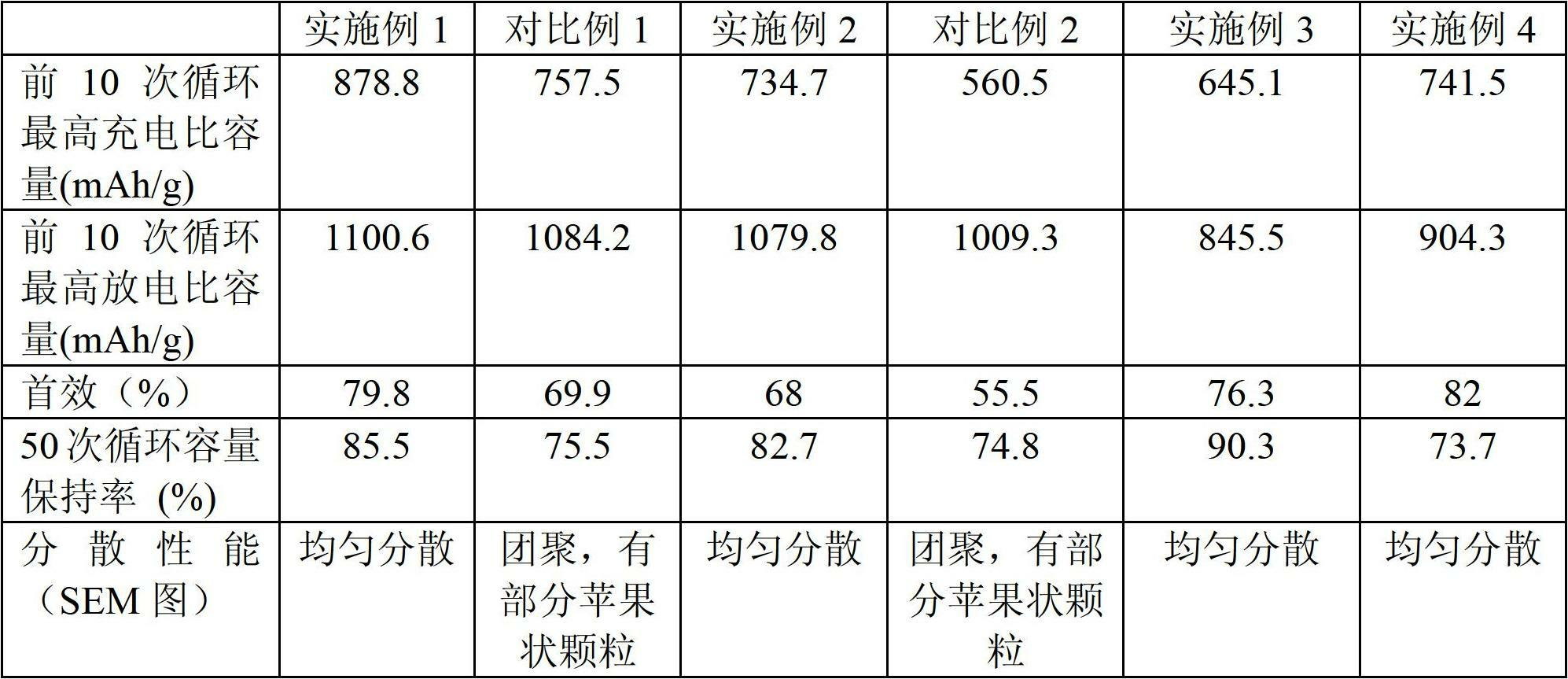

The invention discloses a lithium ion battery silicon carbide composite anode material and a preparation method thereof and aims to solve the technical problem of improving the cycling stability of a silicon carbide cathode. The lithium ion battery silicon carbide composite anode material consists of the following components in percentage by mass: 85 to 75 percent of graphite and 15 to 25 percent of silica particles, wherein the nano silica particles are dispersed on a graphite carrier to form a nuclear shell structure and are 5 to 16 mum in granularity. The preparation method comprises the following steps of: preparing a graphite dispersing agent and a silicon grinding dispersing agent; adding the silicon grinding dispersing agent into the graphite dispersing agent; and performing thermal treatment. When the method is compared with the prior art, silicon atoms are dispersed on a graphite atomic nucleus by a cation-anion charge absorption method, so that the silicon atoms can uniformly wrap the surface of the graphite, the dispersity of silicon is effectively improved in a silicon carbide composite material preparing process, the initial efficiency and the cycling stability of the silicon carbide composite anode material are improved, and a battery using the material as an anode material has relatively high safety, multiplying power performance and cycle performance.

Owner:BTR NEW MATERIAL GRP CO LTD

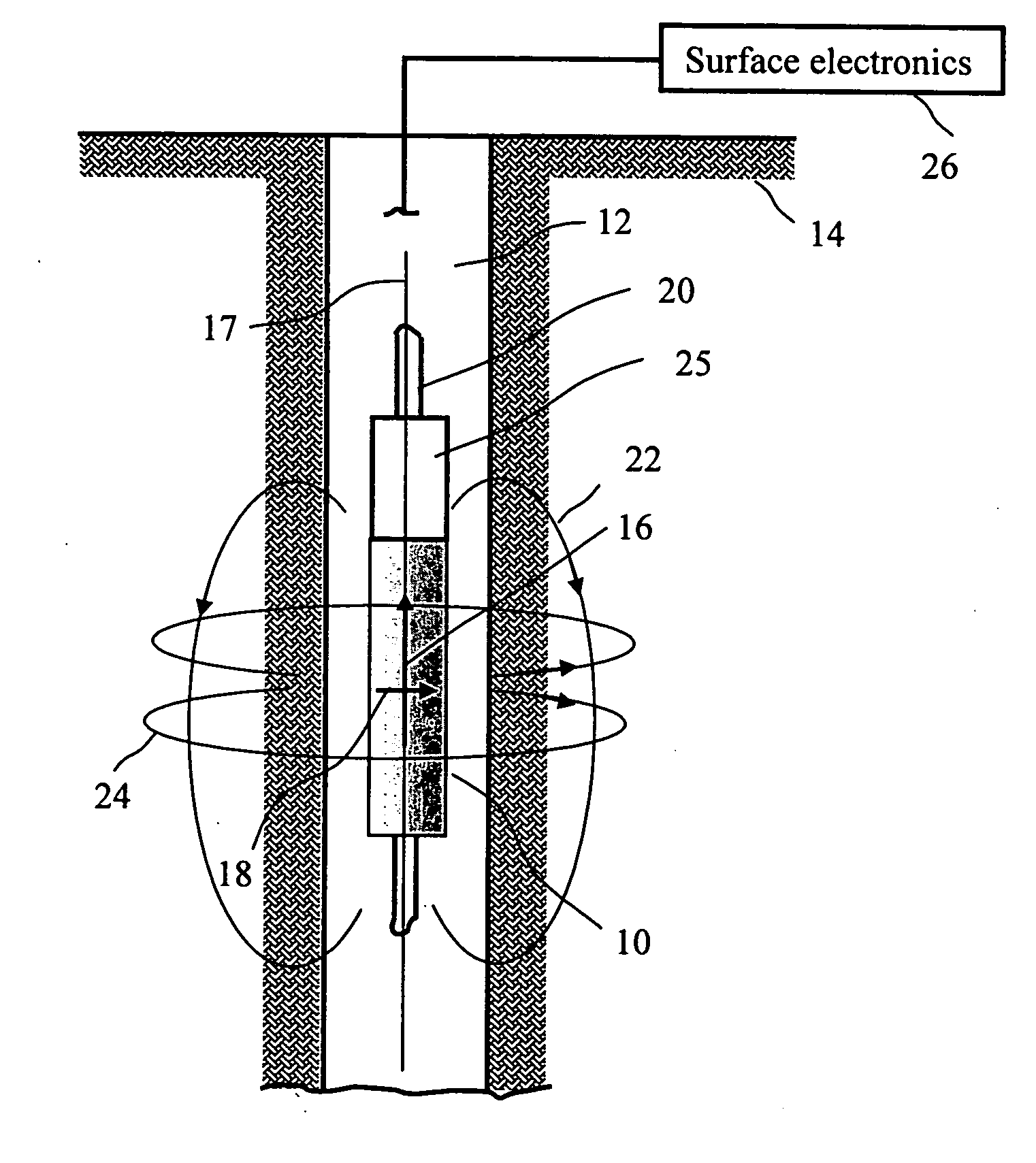

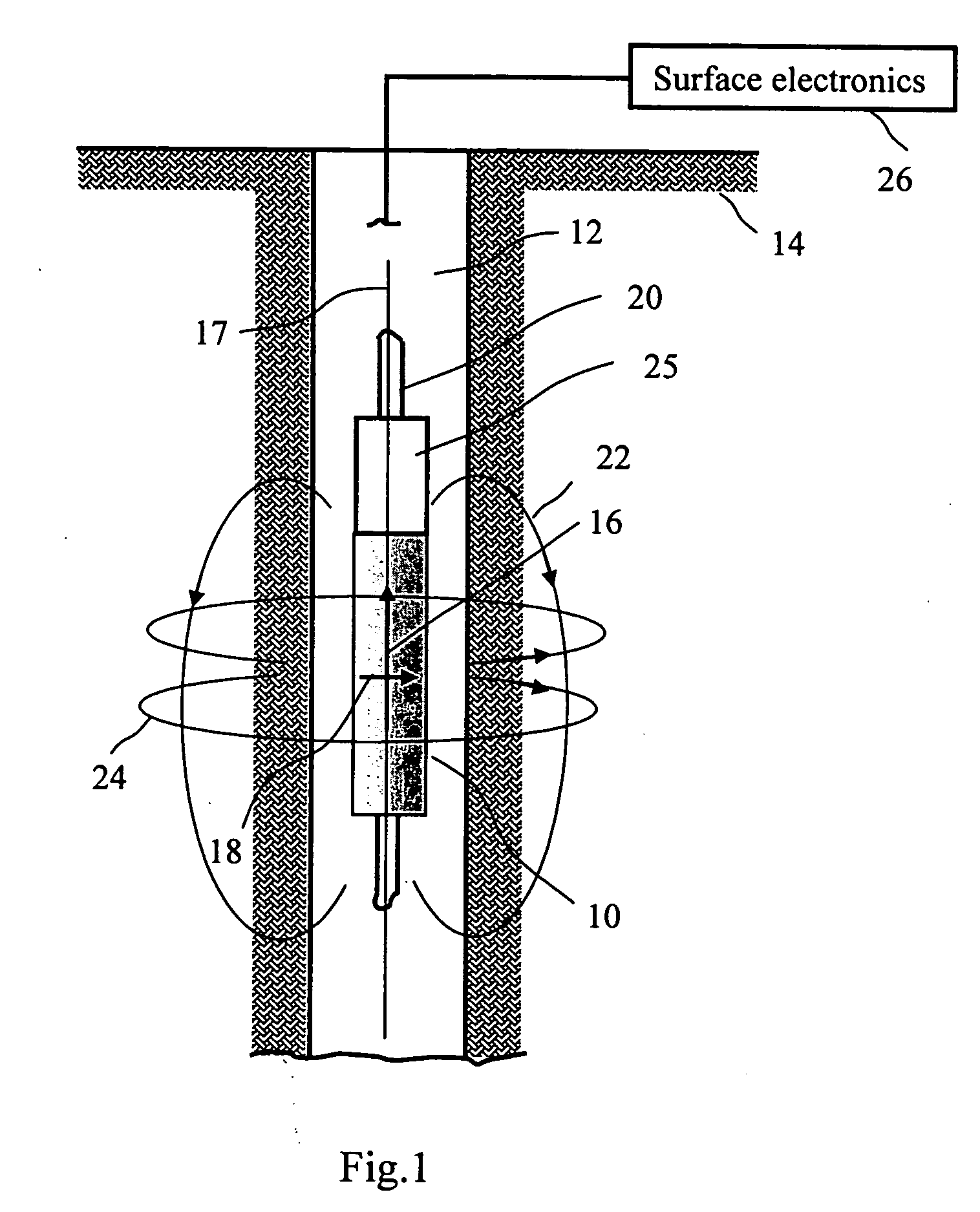

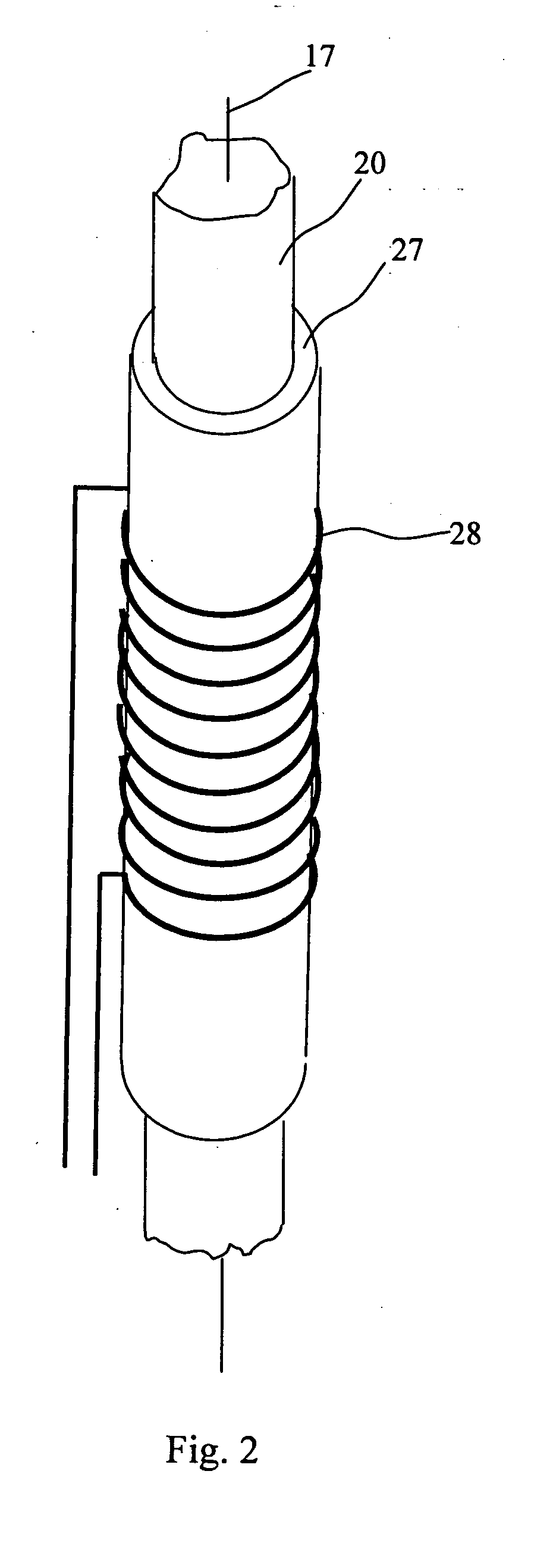

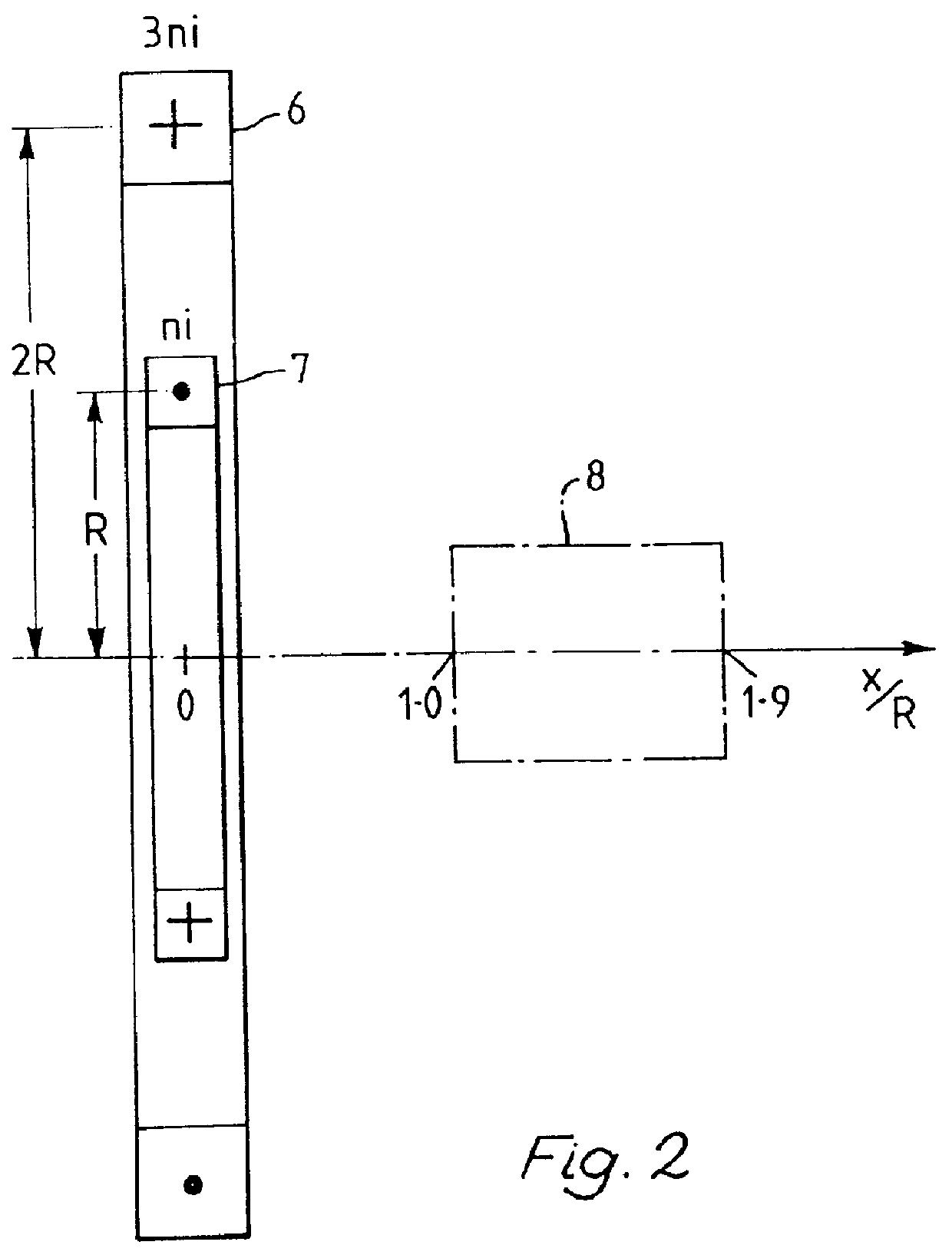

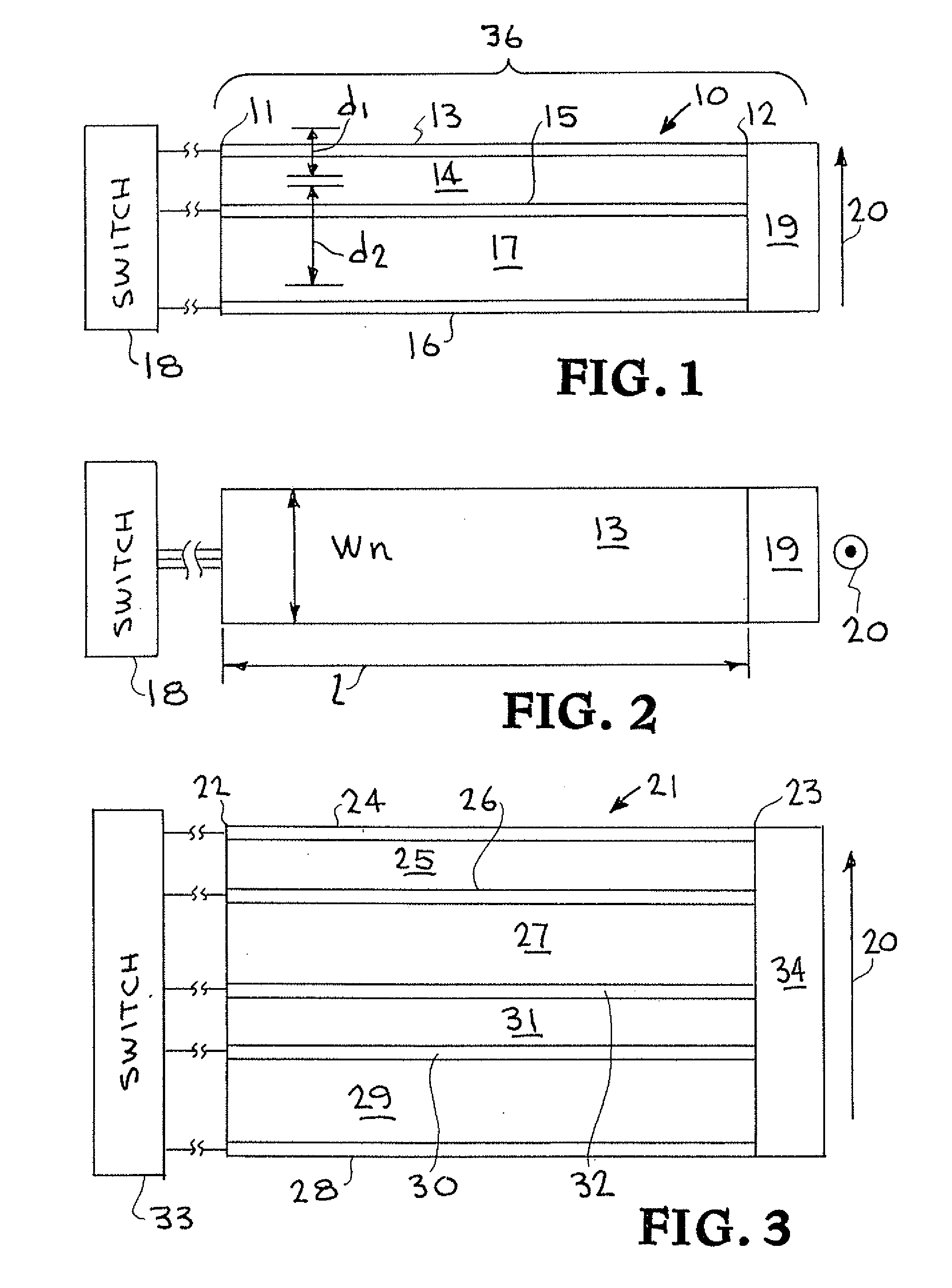

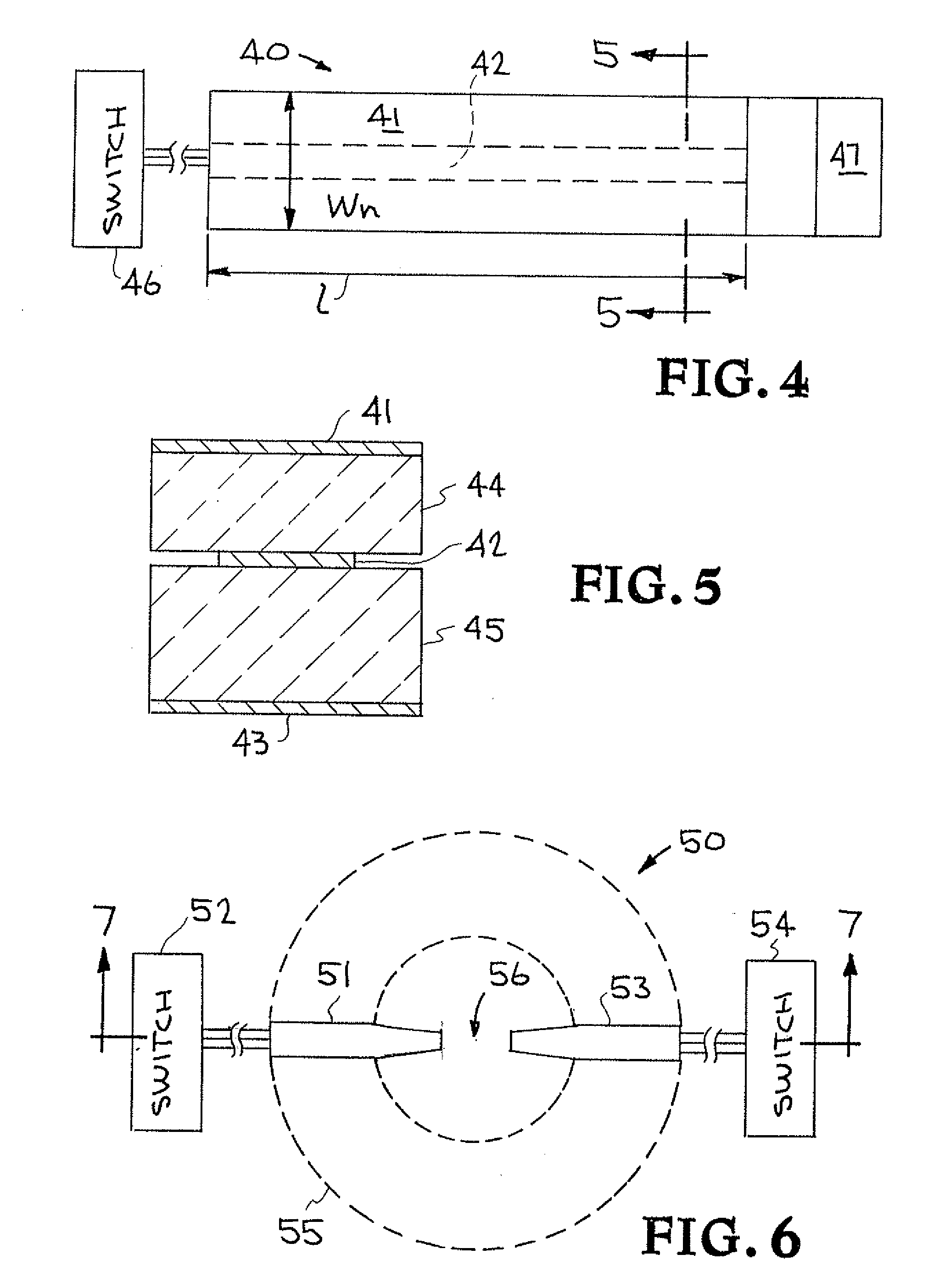

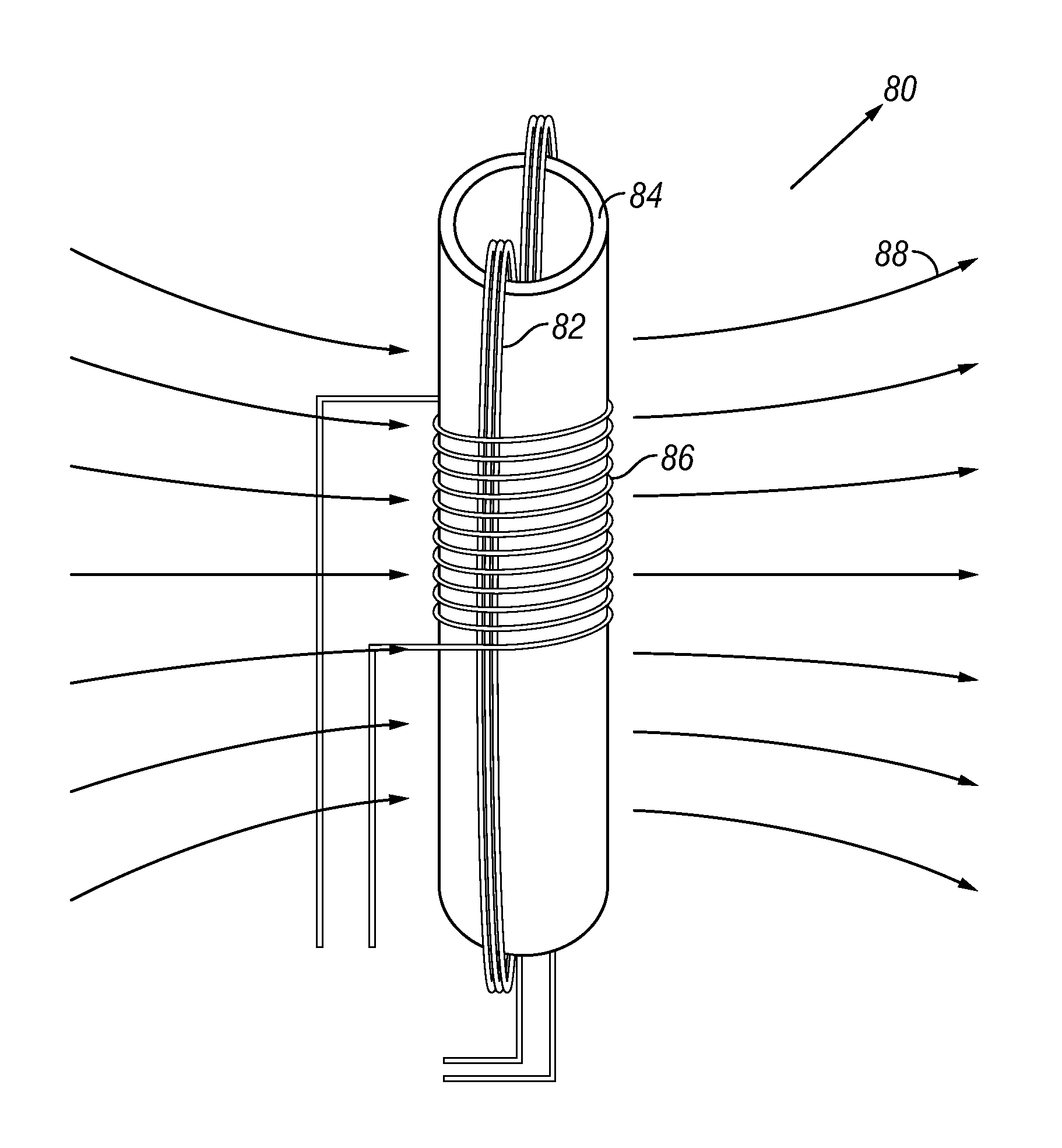

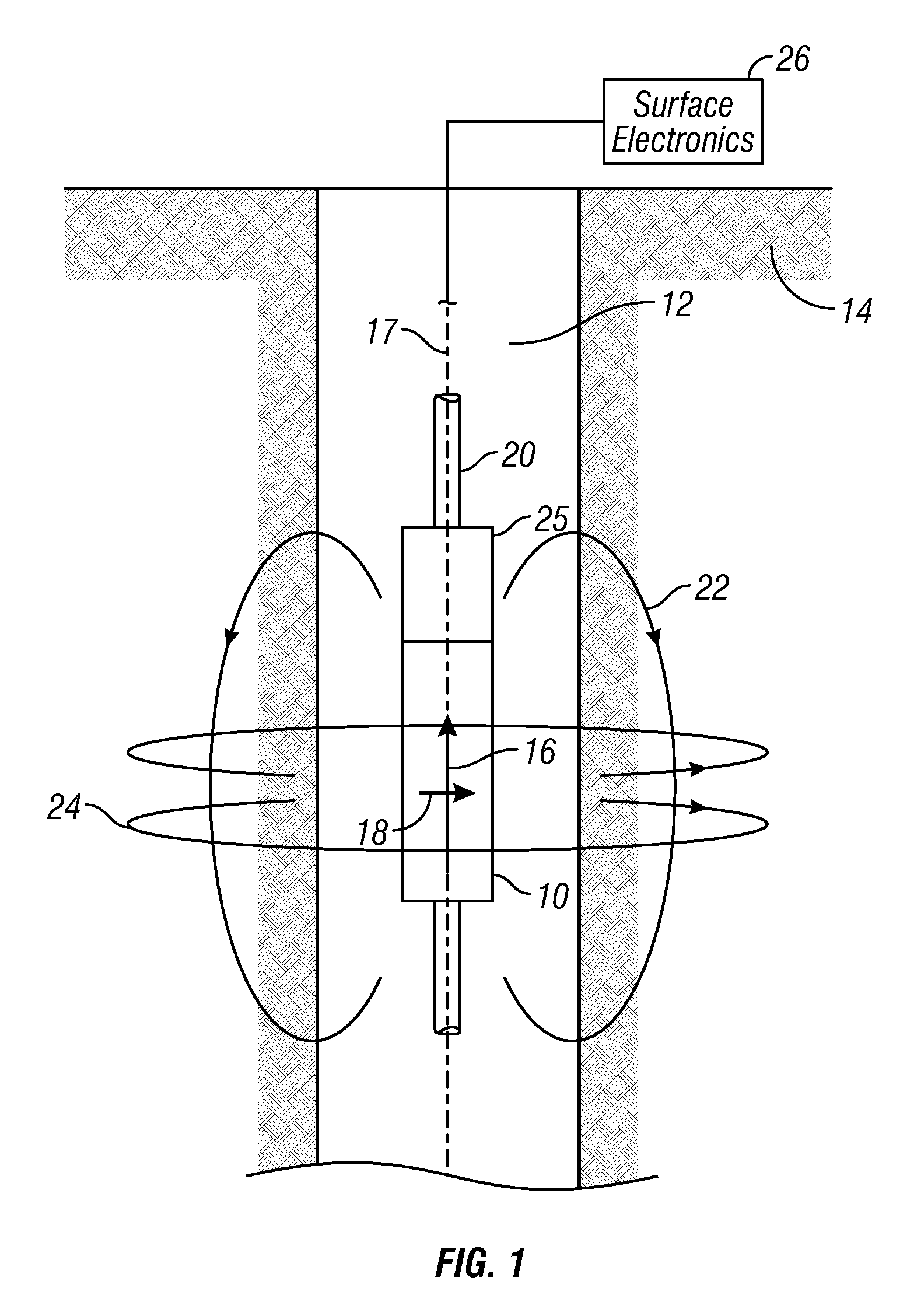

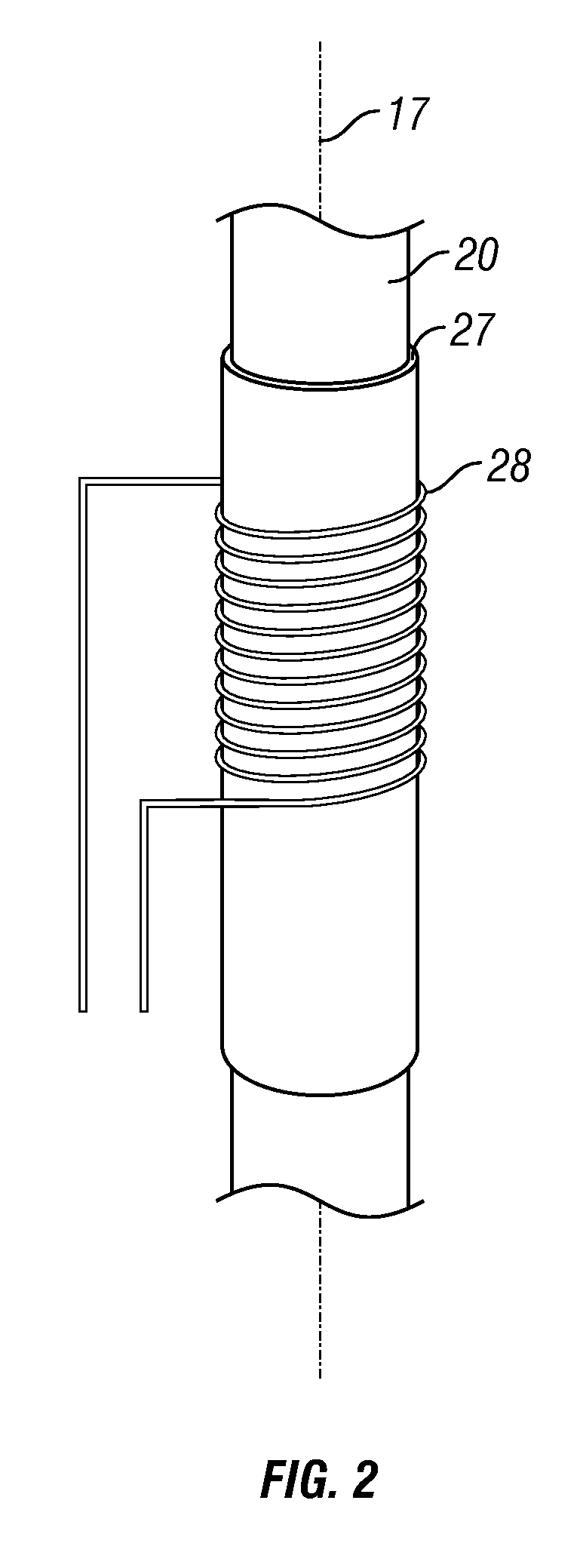

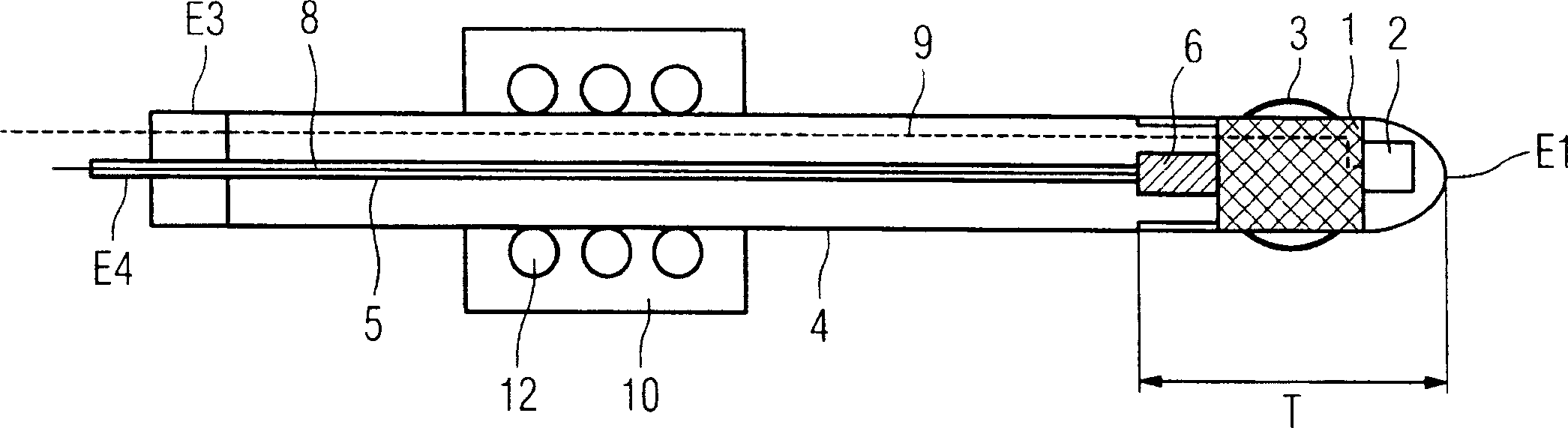

Nuclear magnetic resonance tool using switchable source of static magnetic field

ActiveUS20060255799A1Effective permeability of magneticElectric/magnetic detection for well-loggingMaterial analysis by using resonanceSolid-state nuclear magnetic resonanceSpin magnetic moment

A nuclear magnetic resonance sensing apparatus and method for operating in an earth borehole comprises a source of switchable magnetic field to polarize nuclei in the region of interest, said source comprising a coil wound on a magnetic core having controllable residual magnetization. Maintaining the magnetization of the core during a polarization interval does not require steady current in the coil. Switching intensity and polarity of magnetization of the core causes precession of spin magnetic moments of the nuclei; the precession induces a signal indicative of nuclear magnetic resonance properties of earth formations.

Owner:BAKER HUGHES INC

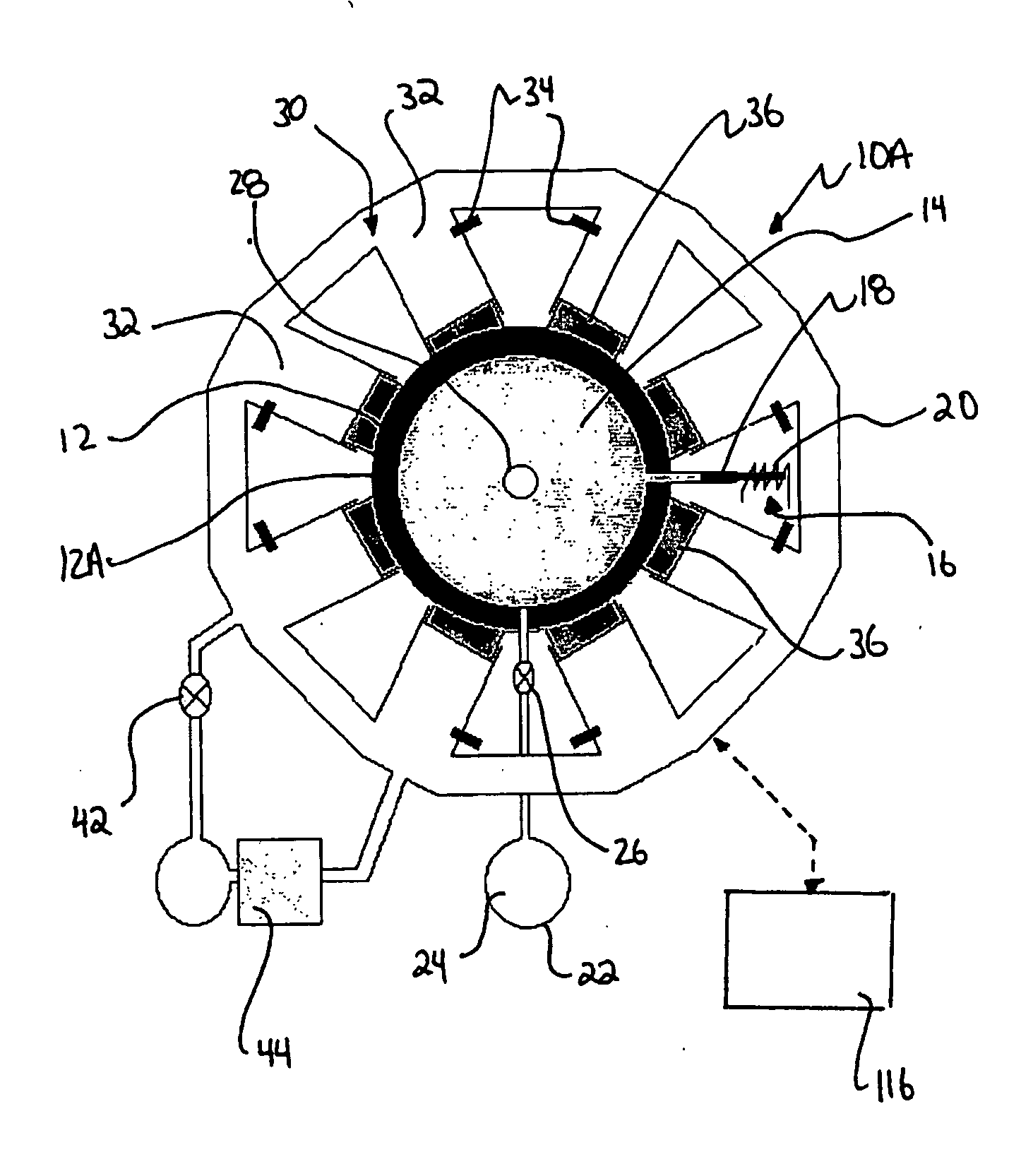

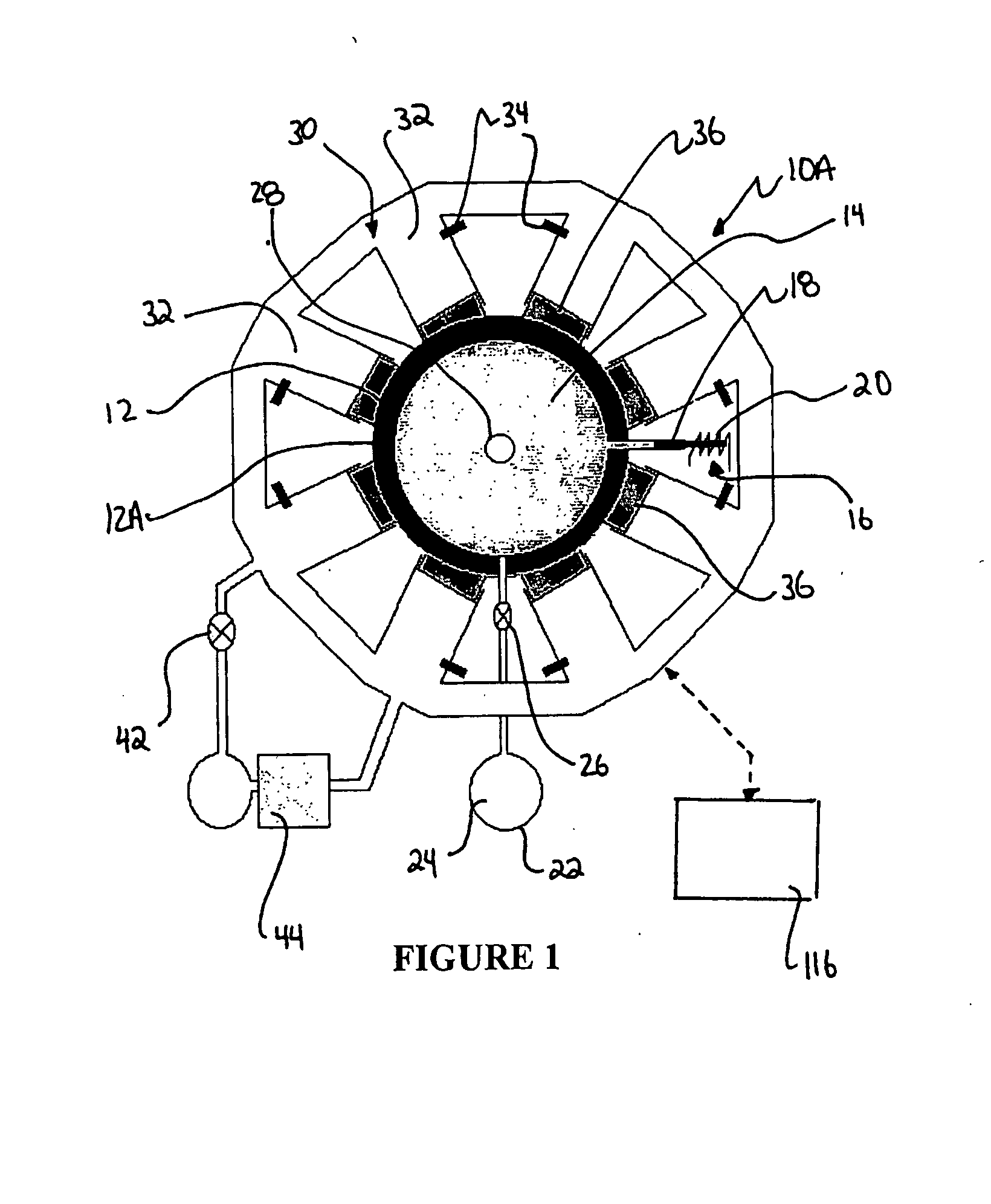

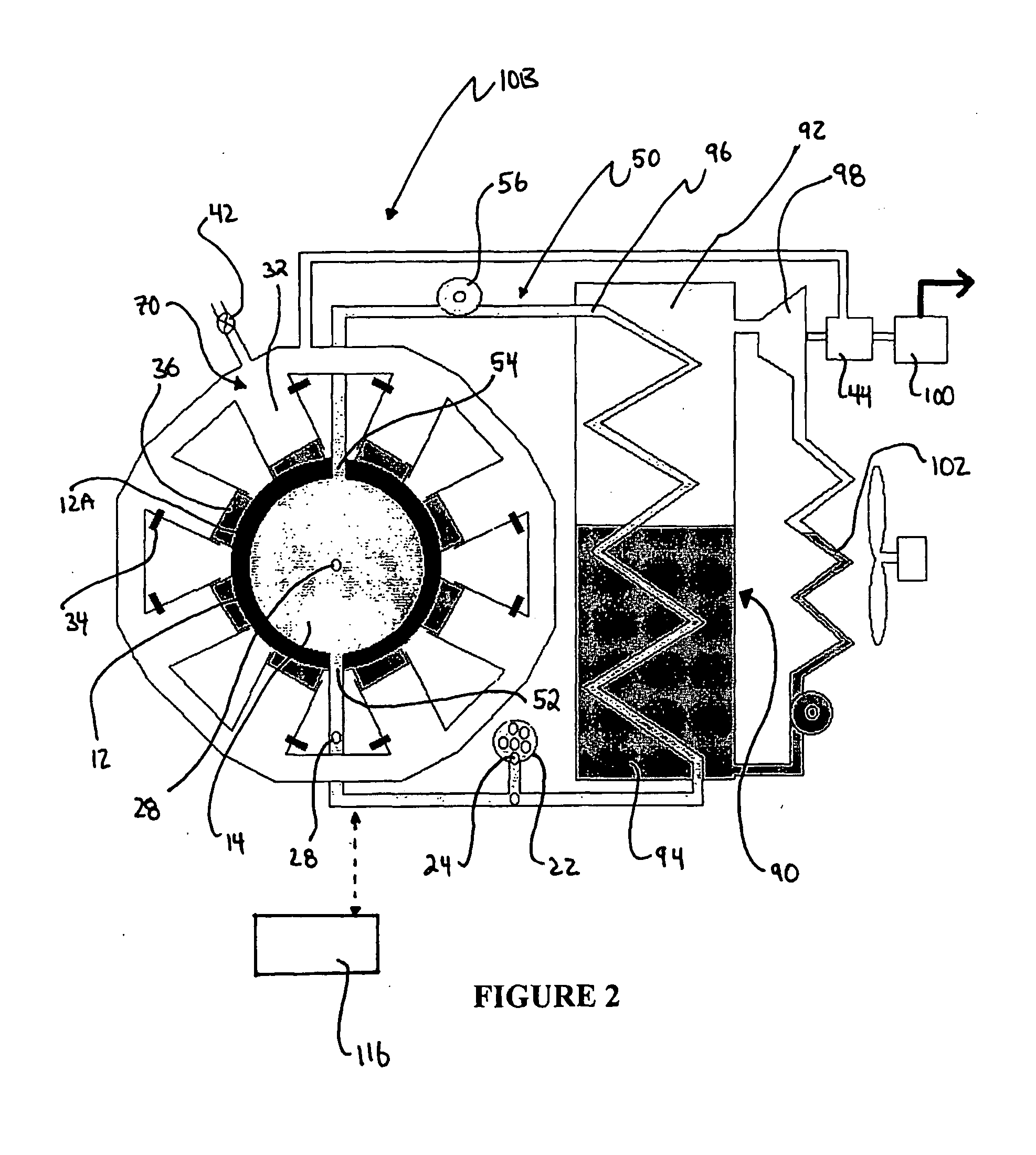

Apparatus and method for fusion reactor

InactiveUS20050129161A1Nuclear energy generationDirect voltage acceleratorsNuclear fusionAtomic nucleus

A method for inducing nuclear fusion and a reactor for inducing nuclear fusion involve positioning a bubble containing fusionable nuclei at the center of a liquid filled spherical vessel and generating a spherically symmetric positive acoustic pulse in the liquid. The acoustic pulse surrounds and converges toward the center of the vessel to compress the bubble, thereby providing energy to and inducing nuclear fusion of the atomic nuclei.

Owner:GENERAL FUSION INC

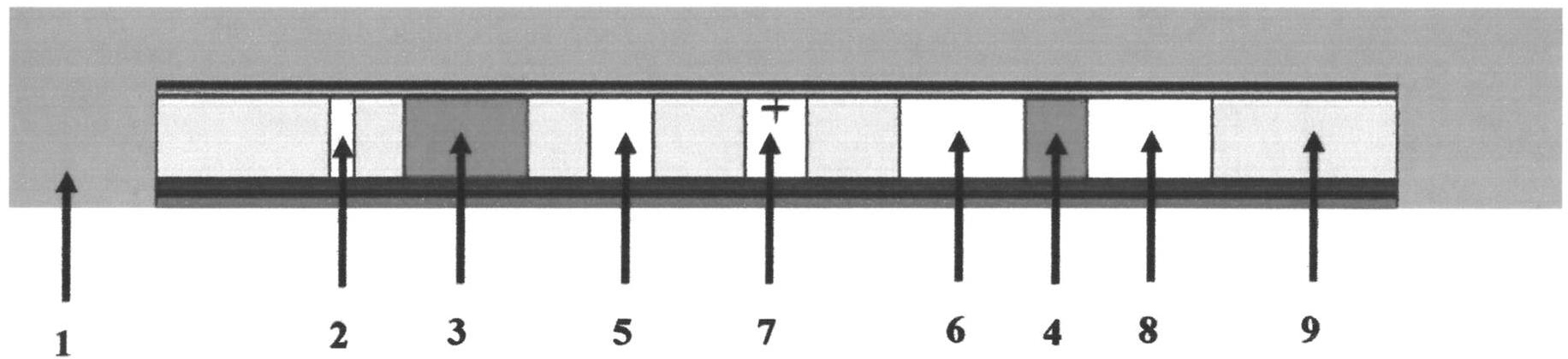

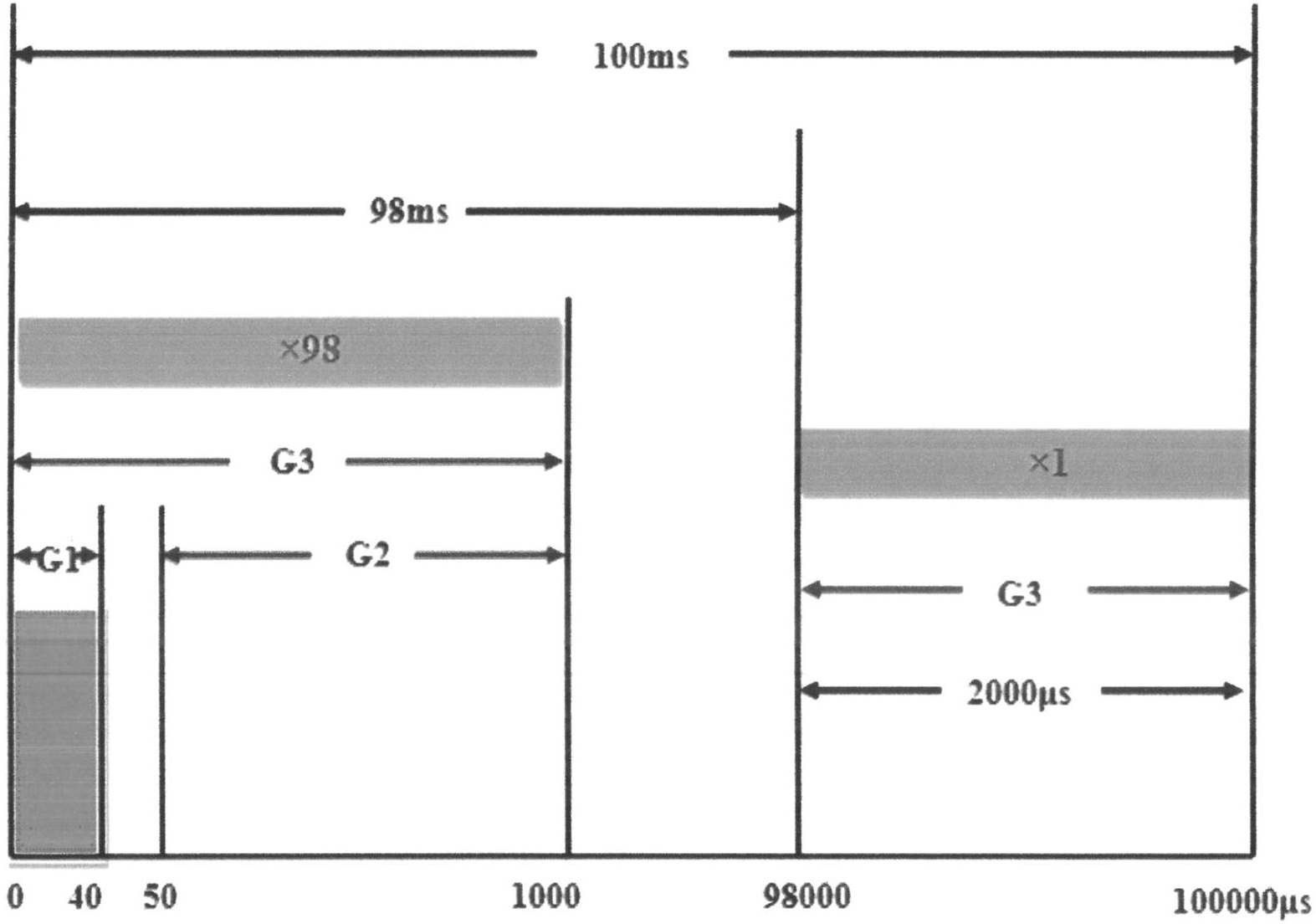

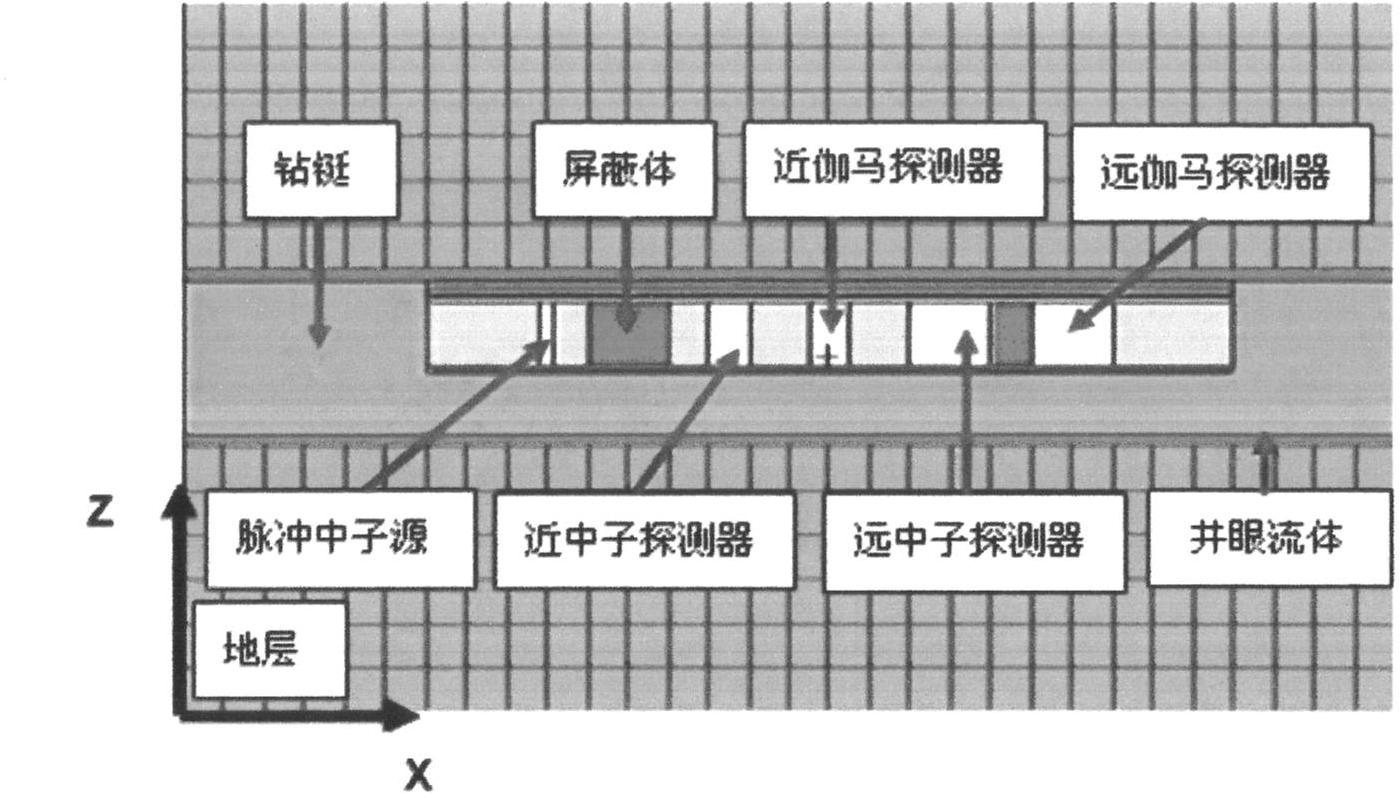

Multi-parameter logging method while drilling based on controllable neutron source

ActiveCN102518431AShorten the lengthSimple structureBorehole/well accessoriesNuclear radiation detectionSequence designLithology

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

Biological retarder anti-cancer technology

In order to solve the high-speed cancer excited state problem, a biological retarder is needed. Cancer energy is converted into intramolecular transfer or other vibrational state transfer through collision. By means of the nucleus retarder principle, a neutron and a retarder atomic nucleus are subjected to collision so that the speed can be decreased, and the retarder which does not absorb neutrons and does not react with neutrons is selected. An important task of the cancer biology and even the natural science is that which material can bear a cancer nuclear fission biological retarder. According to repeated experiments, various safety factors are synthesized, and finally a biological moderator is correctly selected through a successful experiment. Bifidobacterium is free of toxicity and harm to a body, and the biological retarder can be ideal for treating a cancer. In the future, more microorganism retarders will be produced, the biological retarder is used for decelerating tumors, a proper amount of deceleration molecular nuclear energy can be used as senile cell addition nuclear energy, and the biological retarder gives power to biological science and will play an indispensable critical role.

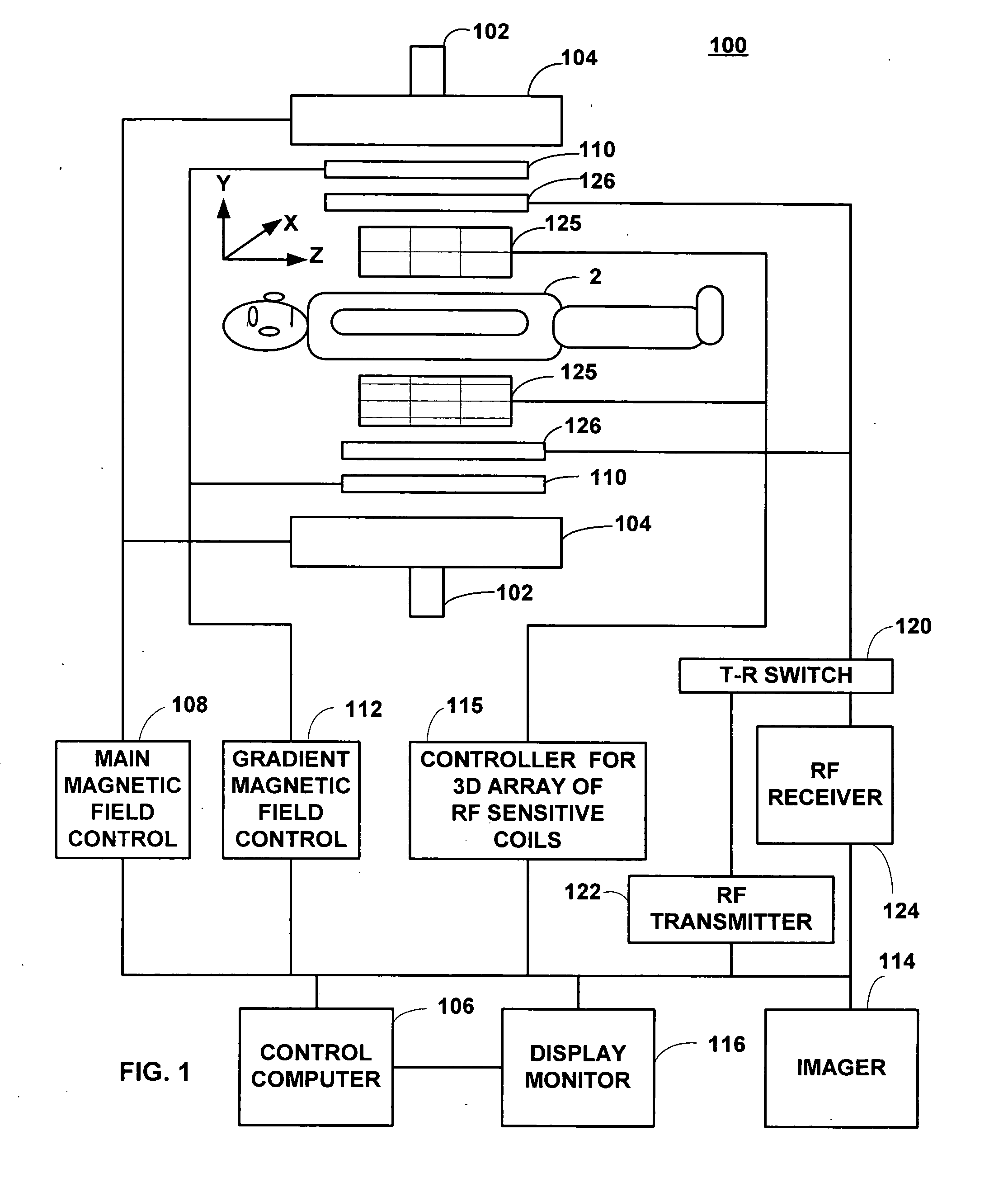

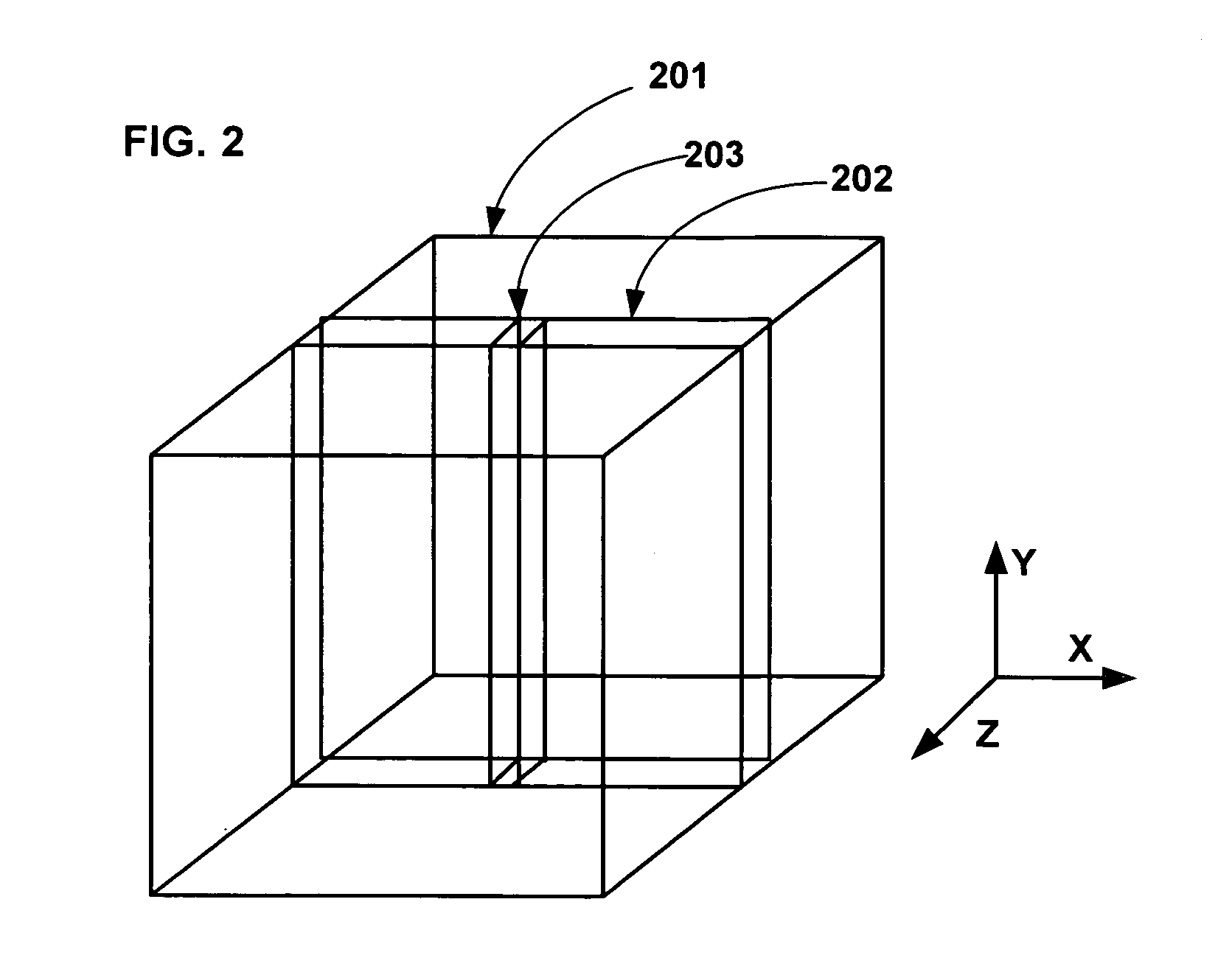

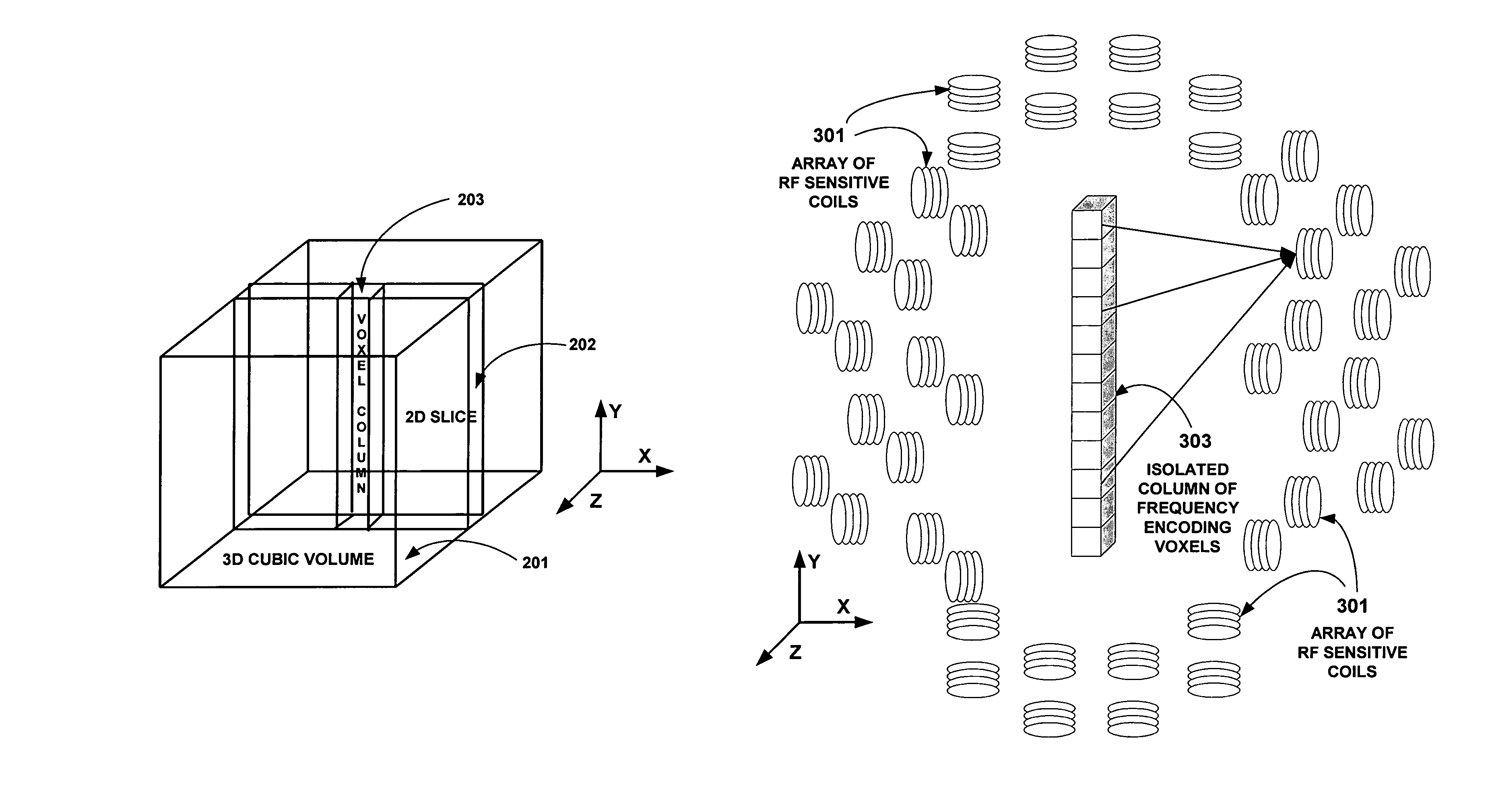

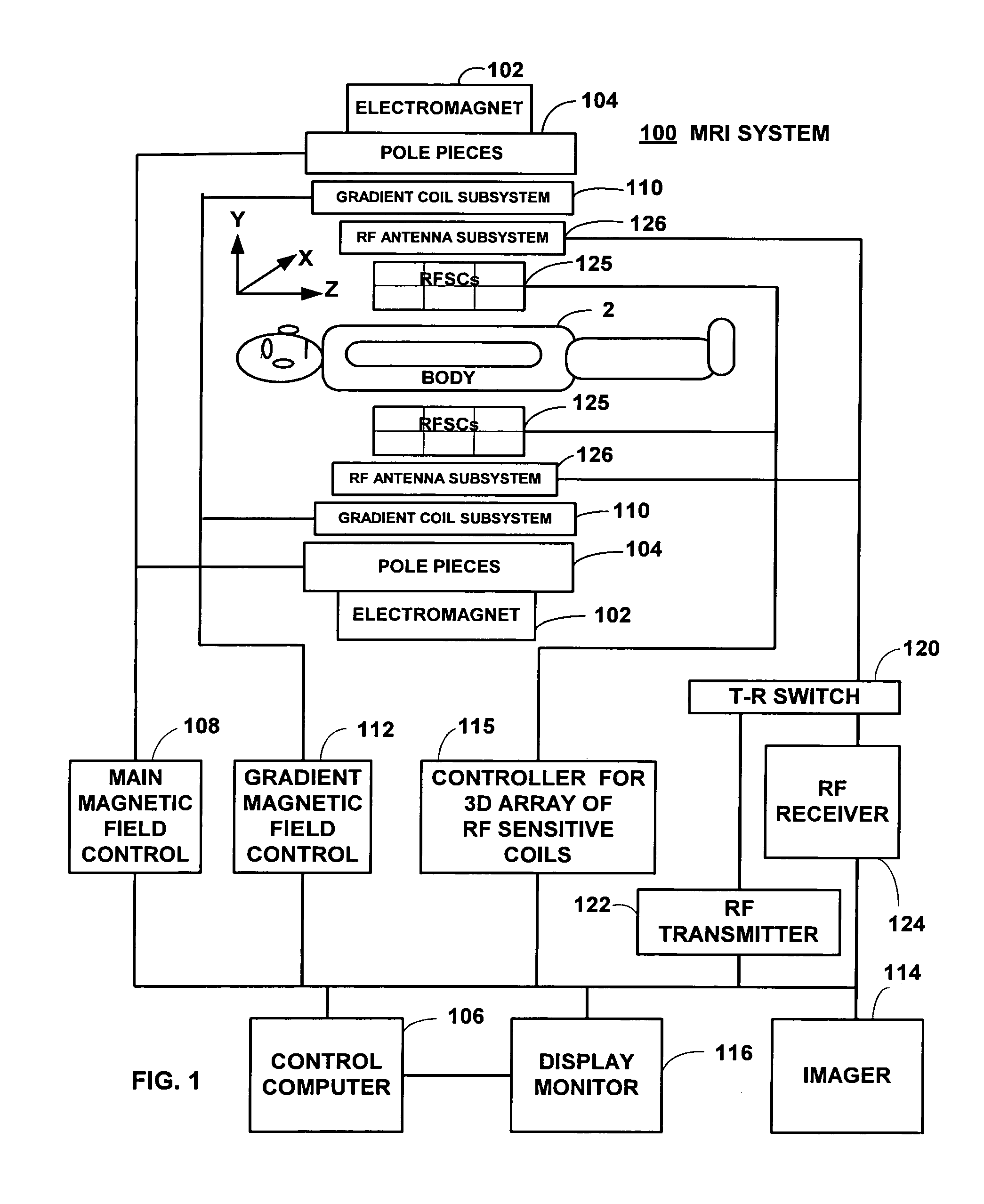

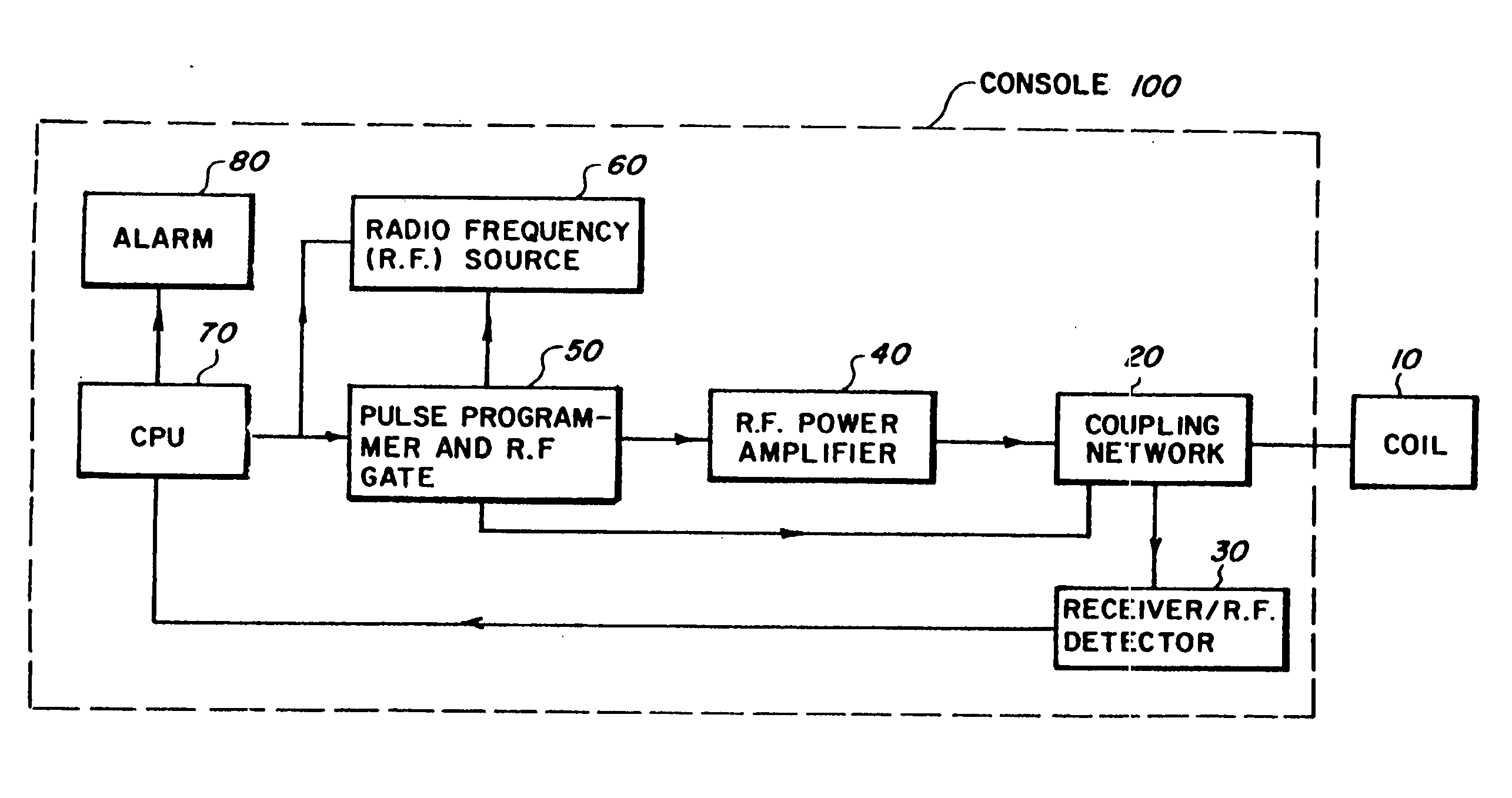

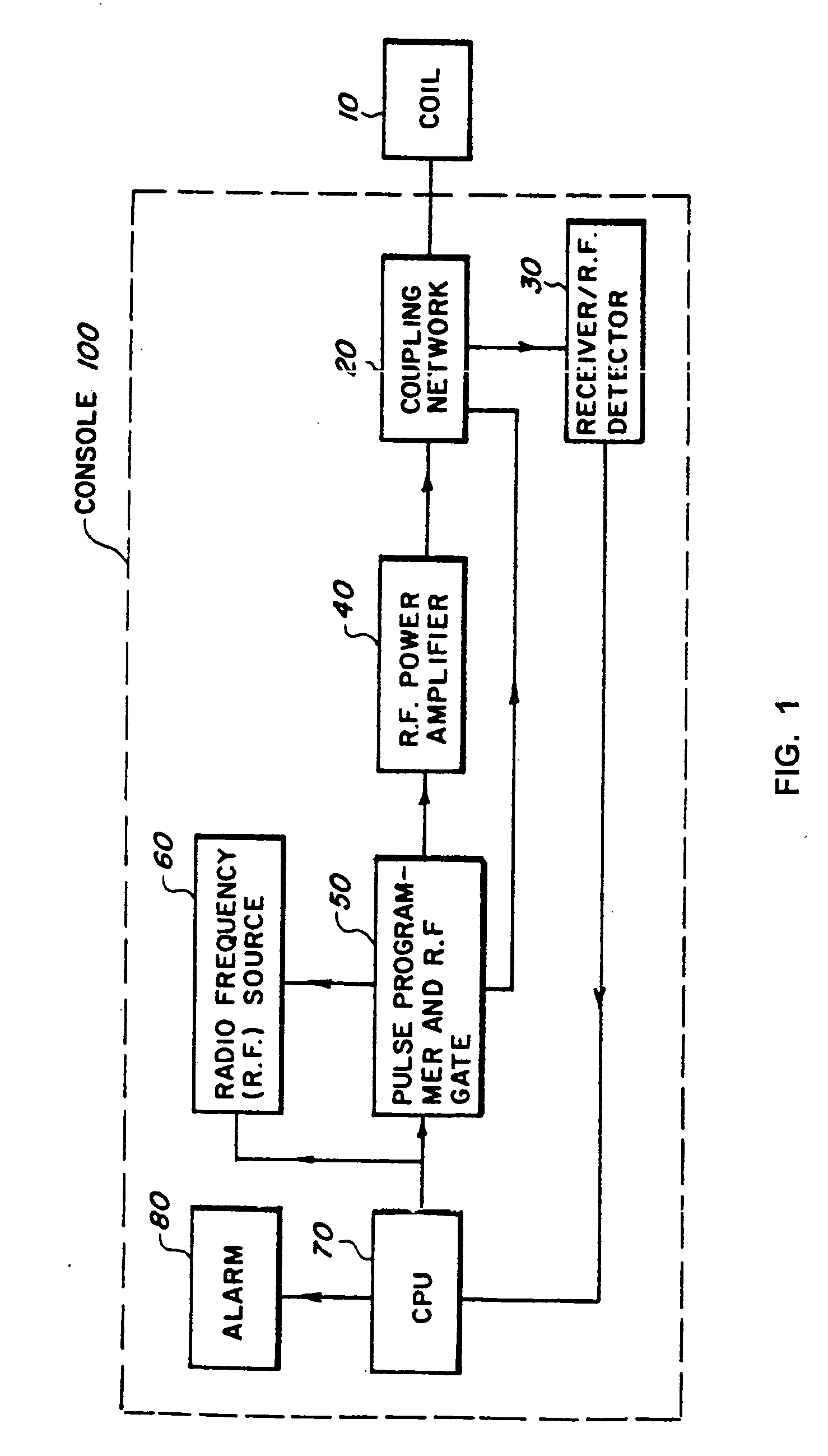

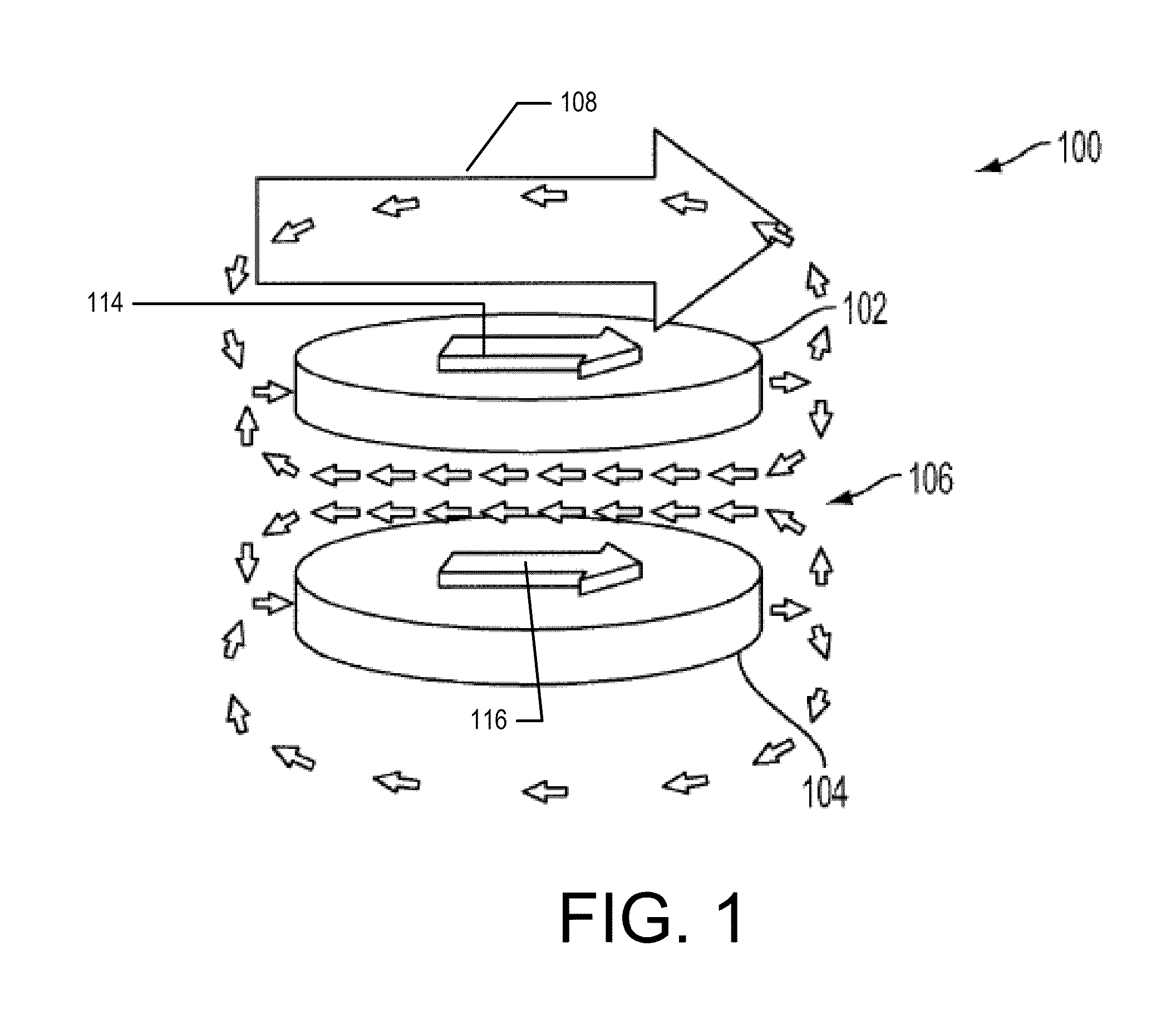

Field image tomography for magnetic resonance imaging

InactiveUS20110115485A1Shorten the length of timeReduce usageMeasurements using NMR imaging systemsElectric/magnetic detectionObject basedSystem matrix

Field Image Tomography (FIT) is a fundamental new theory for determining the three-dimensional (3D) spatial density distribution of field emitting sources. The field can be the intensity of any type of field including (i) Radio Frequency (RF) waves in Magnetic Resonance Imaging (MRI), (ii) Gamma radiation in SPECT / PET, and (iii) gravitational field of earth, moon, etc. FIT exploits the property that field intensity decreases with increasing radial distance from the field source and the field intensity distribution measured in an extended 3D volume space can be used to determine the 3D spatial density distribution of the emitting source elements. A method and apparatus are disclosed for MRI of target objects based on FIT. Spinning atomic nuclei of a target object in a magnetic field are excited by beaming a suitable Radio Frequency (RF) pulse. These excited nuclei emit RF radiation while returning to their normal state. The intensity or amplitude distribution of the RF emission field g is measured in a 3D volume space that may extend substantially along the radial direction around the emission source. g is related to the 3D tomography f through a system matrix H that depends on the MRI apparatus, and noise n through the vector equation g=Hf+n. This equation is solved to obtain the tomographic image f of the target object by a method that reduces the effect of noise.

Owner:SUBBARAO MURALIDHARA

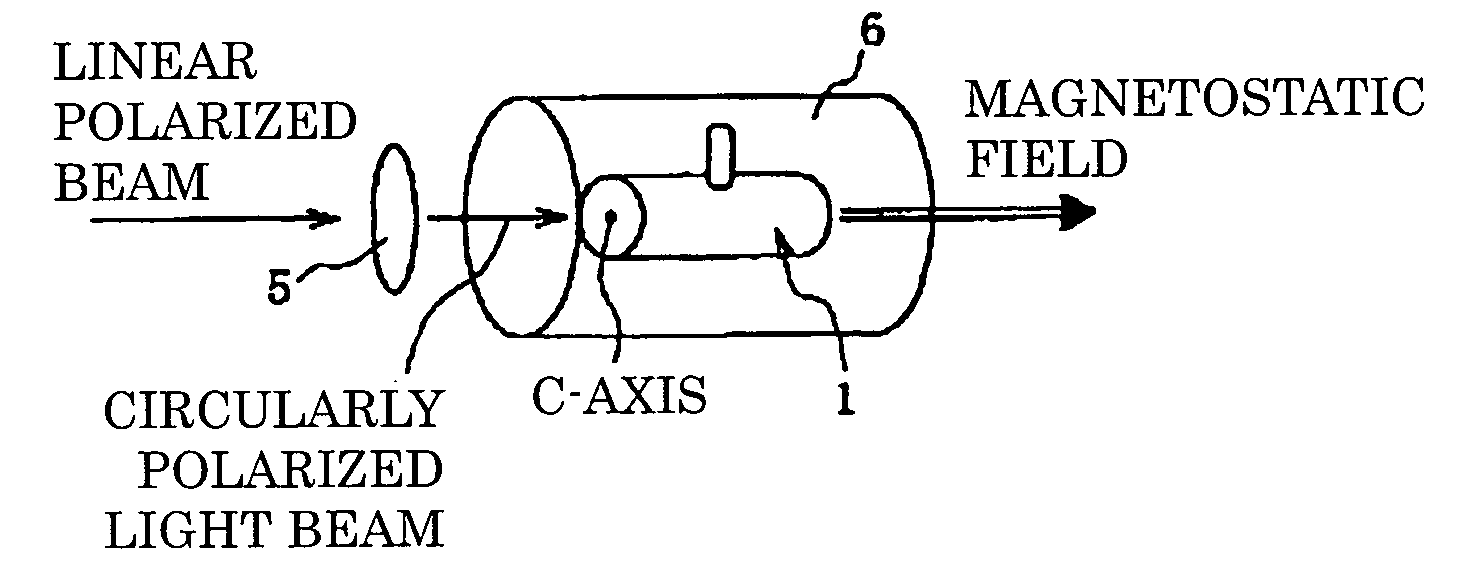

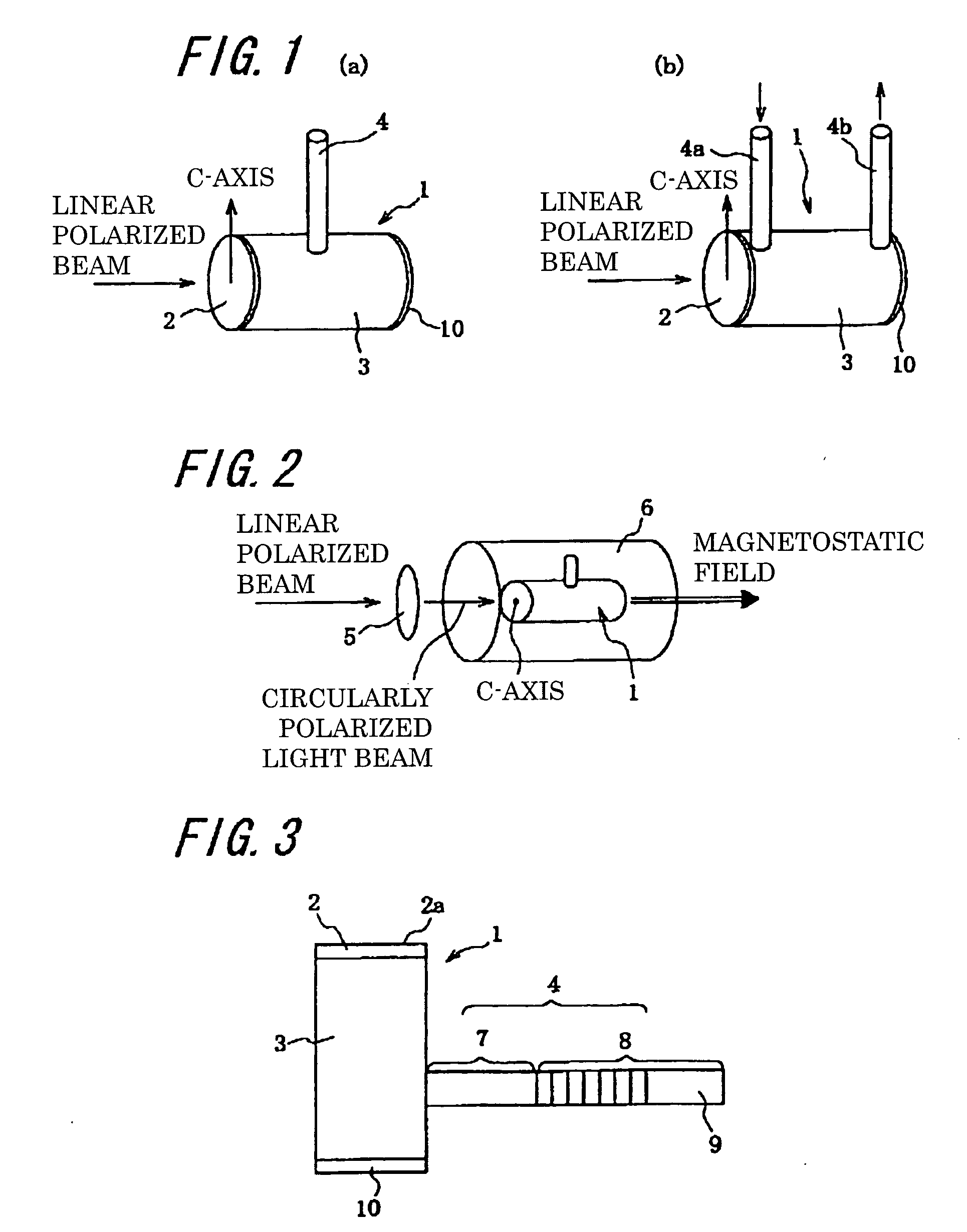

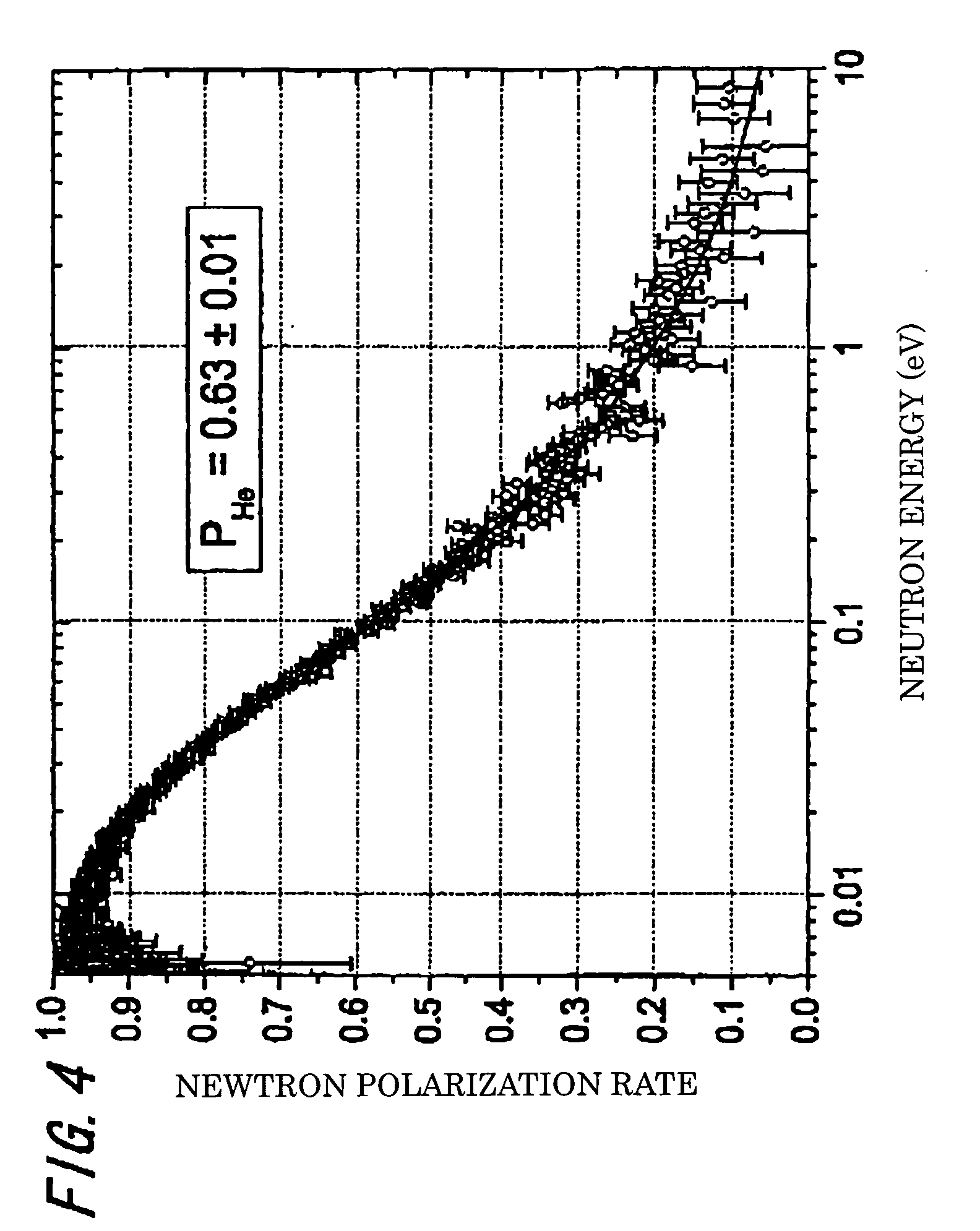

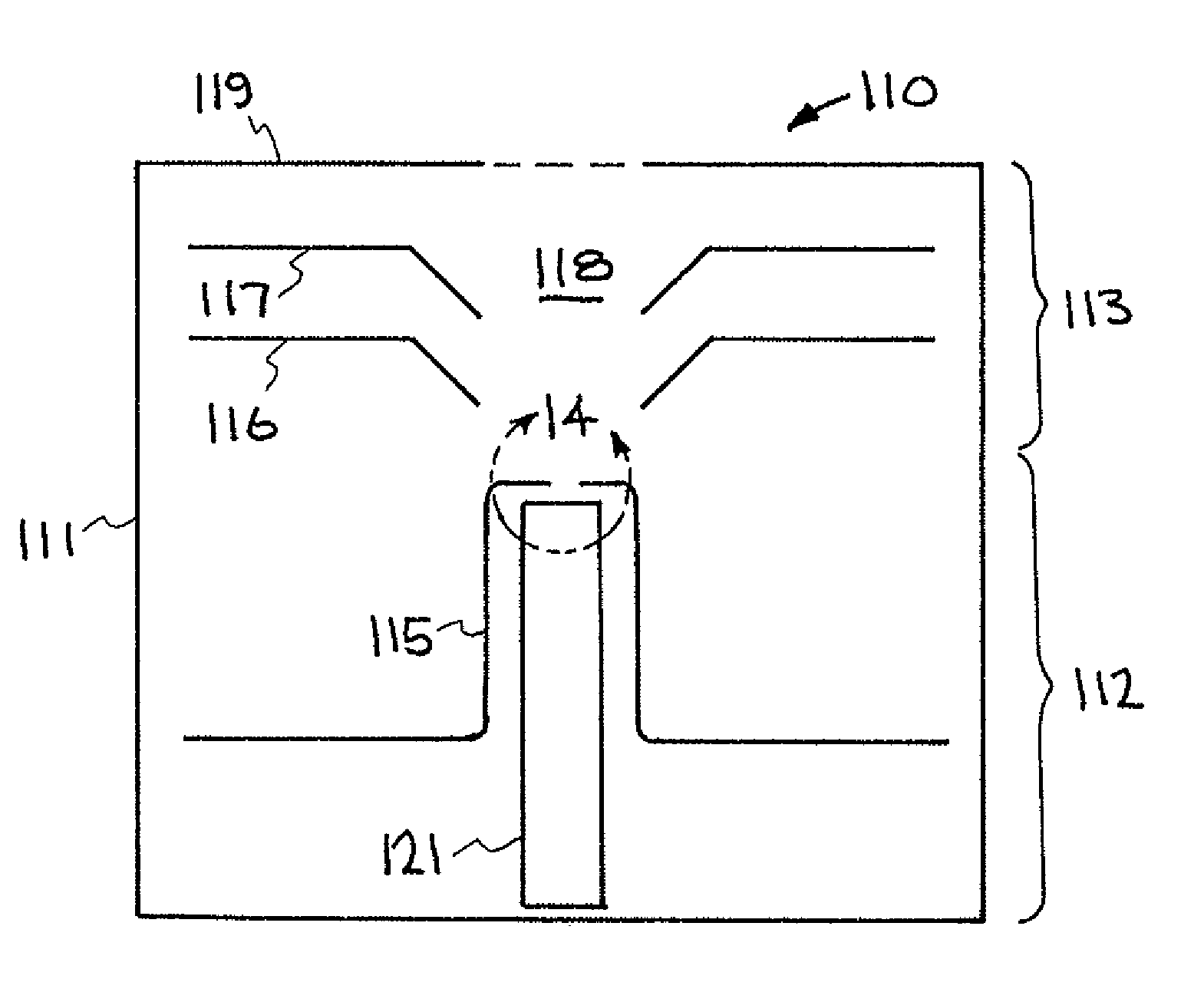

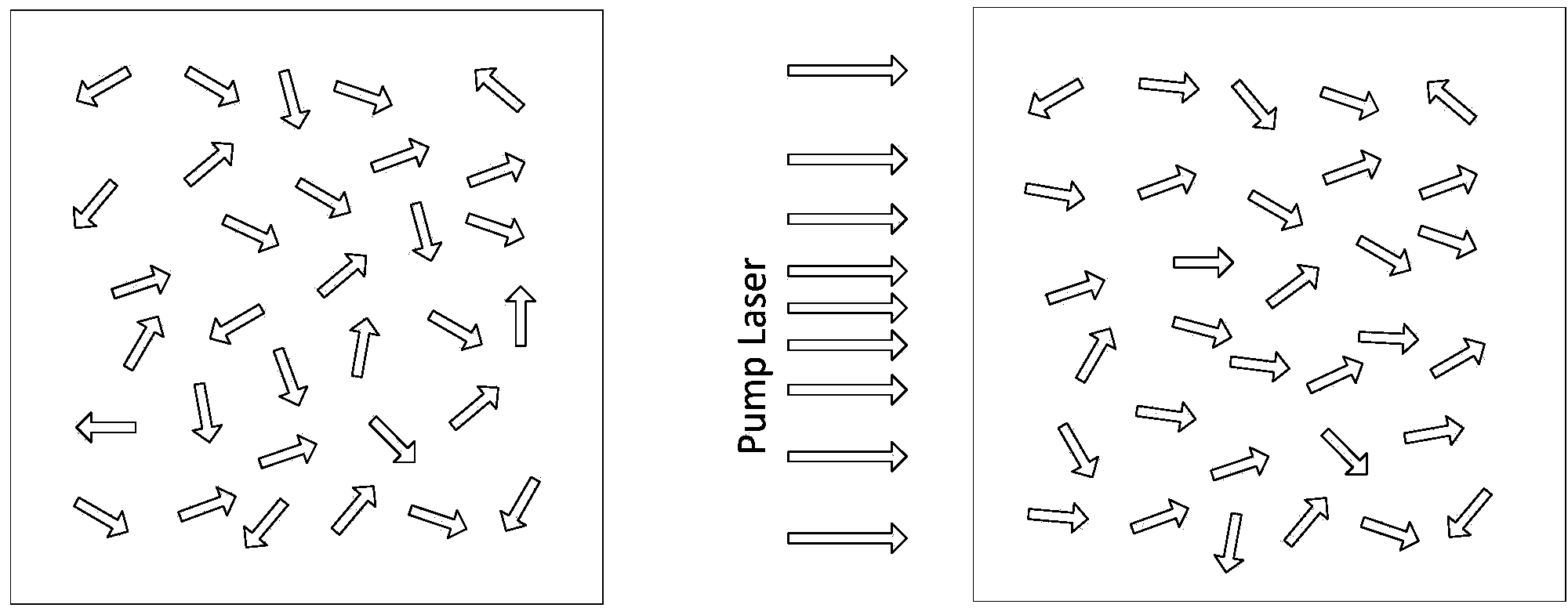

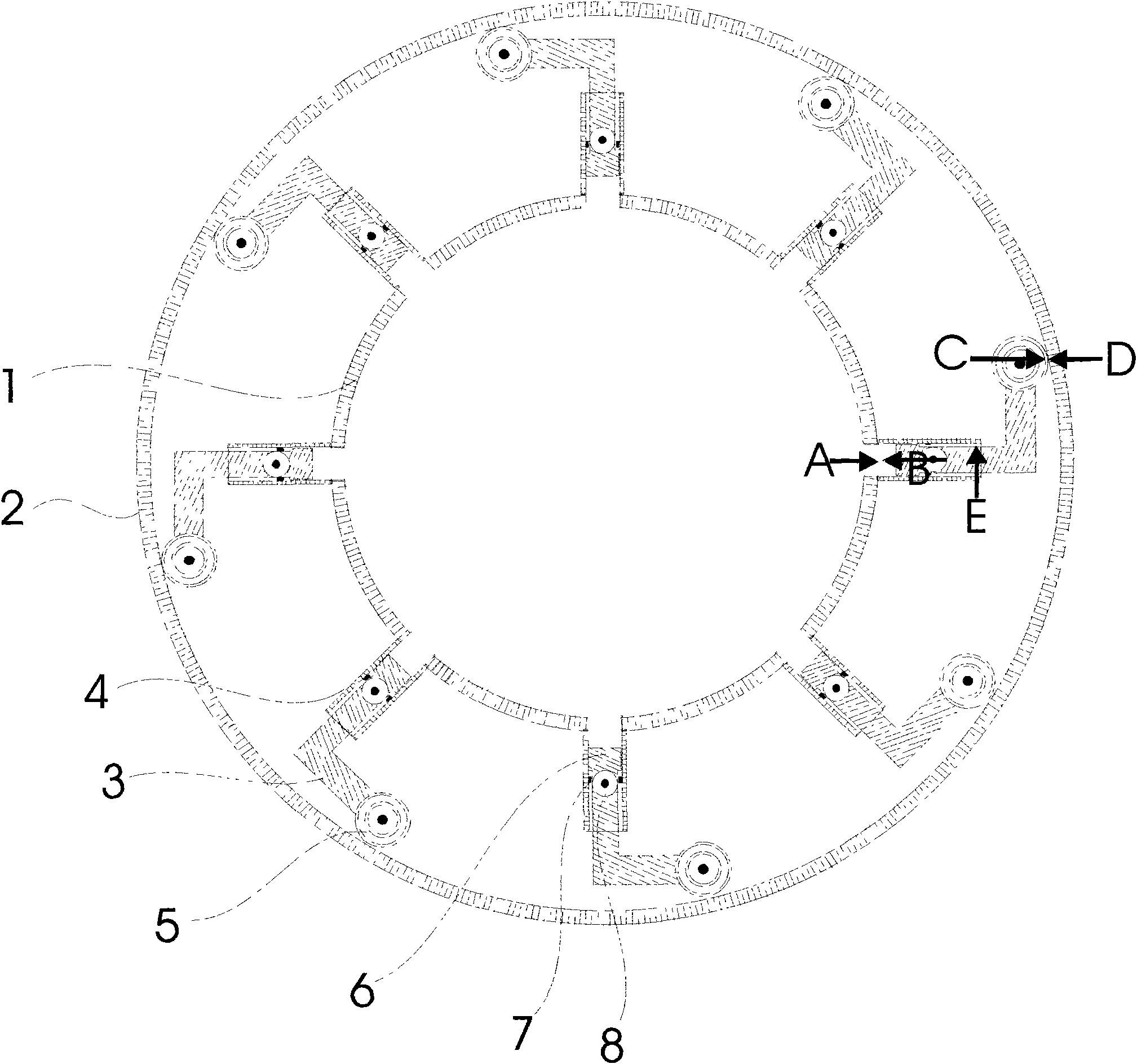

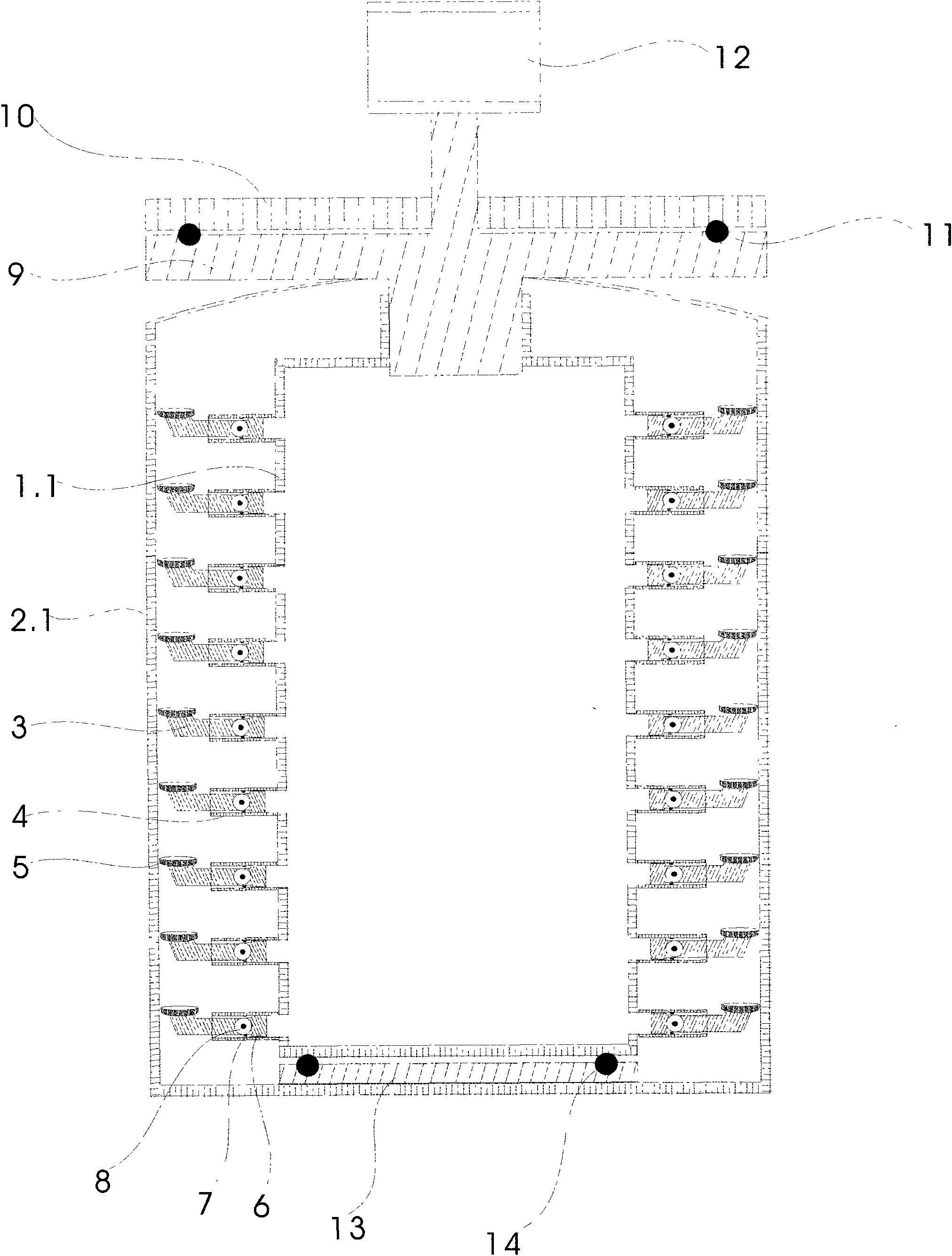

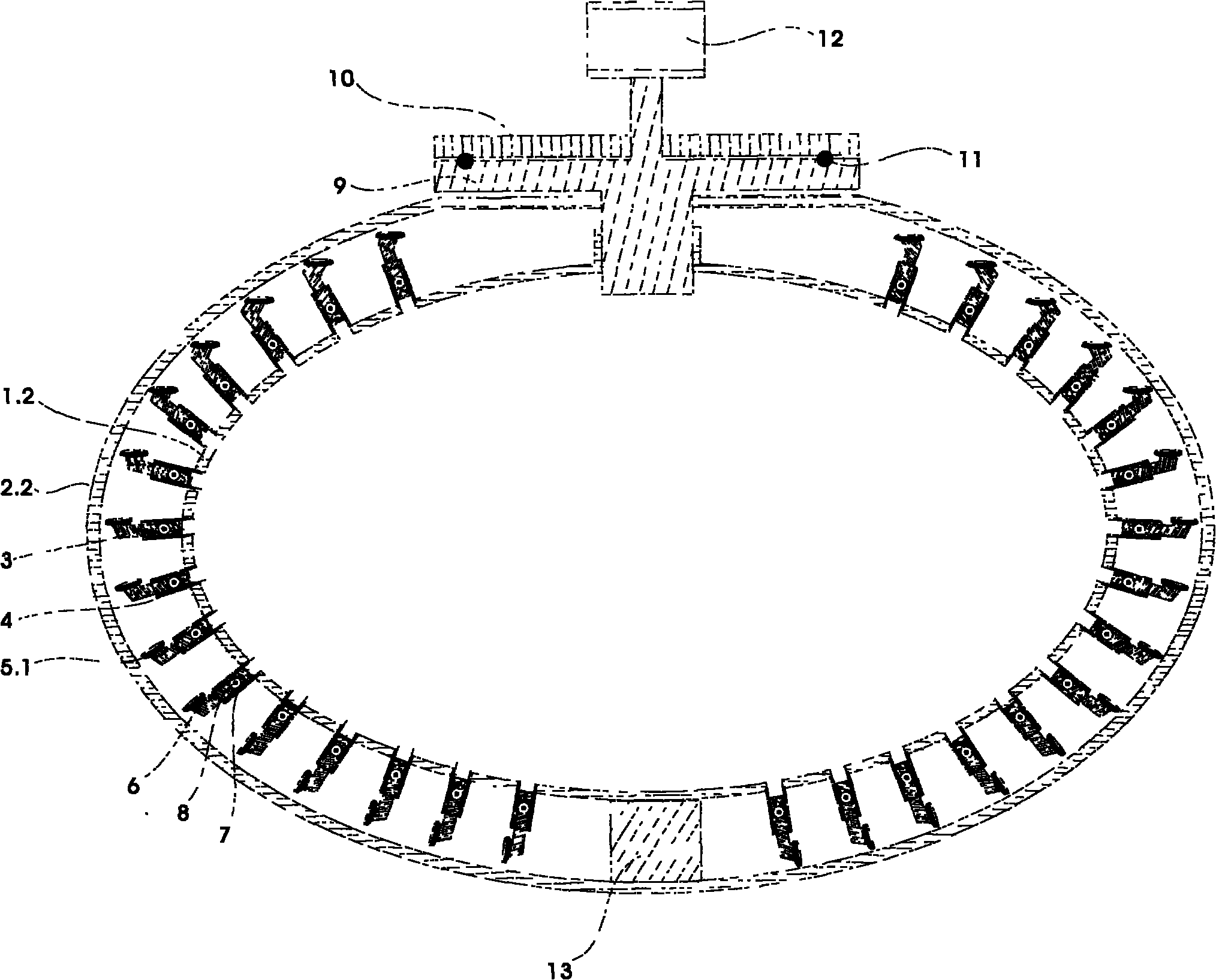

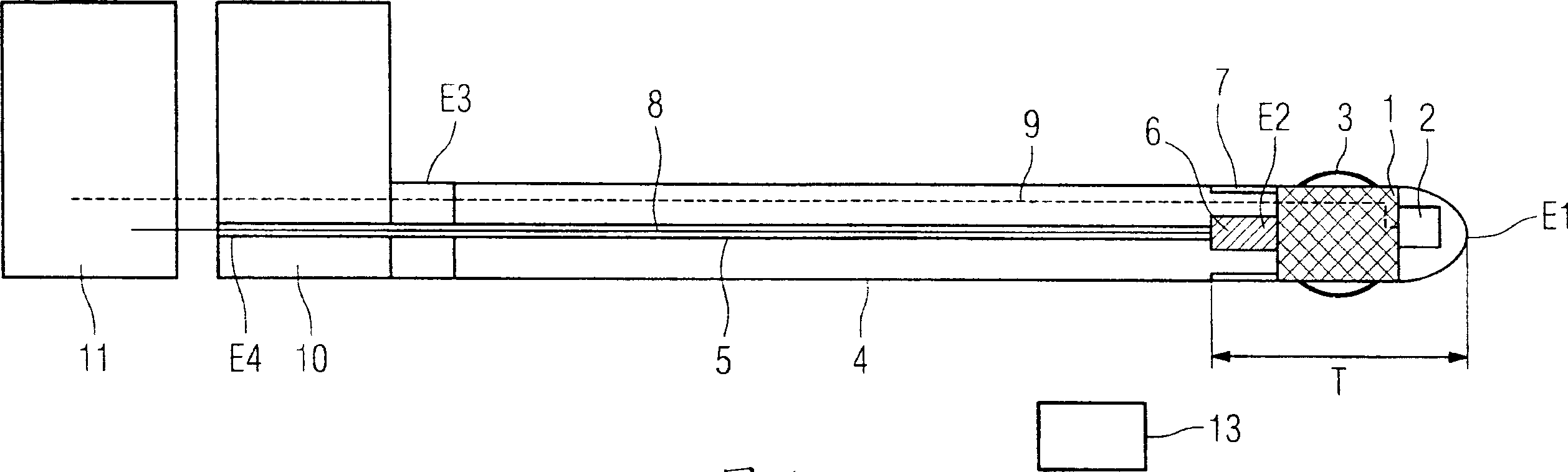

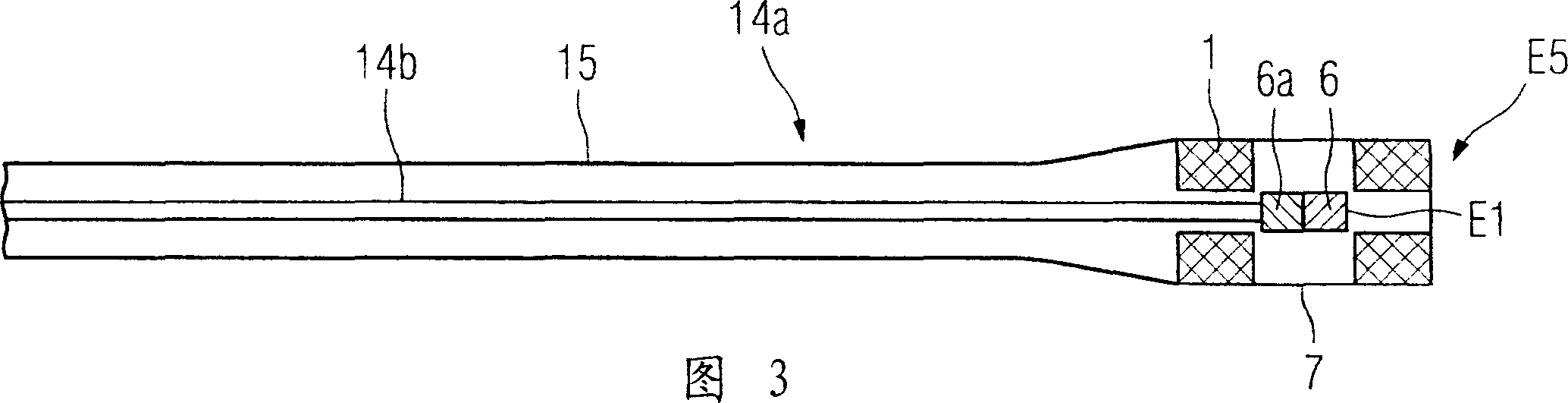

Vessel for Rare Gas Filling, and Method for Polarization of Rare Gas Atomic Nucleus Using Said Vessel

InactiveUS20090101806A1Accurate thicknessImprove polarizationOther accessoriesMasersNoble gasNeutron scattering

A vessel for rare-gas filling is provided, where almost complete light circular polarization is realized, which has a light incident window of a single crystal material whose thickness and crystal axis orientation are optimized, and a polarization method of rare gas nuclei in the vessel is also provided. In addition, embodiments of the vessel is provided, which is impervious to alkali metal, and sustains high pressure, and shows no permeability for 3He gas, and has negligibly small neutron absorption so as to be suitable for application to basic science, for example, neutron scattering, and the polarization method in the vessel is also provided.The vessel for rare-gas filling of the present invention comprises a vessel body 3, and a pipe 4, which is connected to the vessel body 3 and introduces a rare-gas containing gas and an alkali metal into the vessel body 3. A light incident window 2 made of a single-crystal material, which has proper thickness and proper crystal axis orientation, is attached to the vessel body 3. The vessel for rare-gas filling is preferably made of sapphire or the like.

Owner:HIGH ENERGY ACCELERATOR RESEARCH ORGANIZATION

Field image tomography for magnetic resonance imaging

InactiveUS8378682B2Measurements using NMR imaging systemsElectric/magnetic detectionObject basedSystem matrix

Field Image Tomography (FIT) is a fundamental new theory for determining the three-dimensional (3D) spatial density distribution of field emitting sources. The field can be the intensity of any type of field including (i) Radio Frequency (RF) waves in Magnetic Resonance Imaging (MRI), (ii) Gamma radiation in SPECT / PET, and (iii) gravitational field of earth, moon, etc. FIT exploits the property that field intensity decreases with increasing radial distance from the field source and the field intensity distribution measured in an extended 3D volume space can be used to determine the 3D spatial density distribution of the emitting source elements. A method and apparatus are disclosed for MRI of target objects based on FIT. Spinning atomic nuclei of a target object in a magnetic field are excited by beaming a suitable Radio Frequency (RF) pulse. These excited nuclei emit RF radiation while returning to their normal state. The intensity or amplitude distribution of the RF emission field g is measured in a 3D volume space that may extend substantially along the radial direction around the emission source. g is related to the 3D tomography f through a system matrix H that depends on the MRI apparatus, and noise n through the vector equation g=Hf+n. This equation is solved to obtain the tomographic image f of the target object by a method that reduces the effect of noise.

Owner:SUBBARAO MURALIDHARA

Methods and apparatus for NQR testing

InactiveUS6100688AEasy to distinguishImprove signal-to-noise ratioThermometerDiagnostic recording/measuringMagnetic field gradientResonance

A method and apparatus for imaging within a sample space an object containing quadrupolar nuclei comprises irradiating the object to excite nuclear quadrupole resonance, applying to the object a magnetic field gradient having a profile Bo(x) such that the square of the profile (Bo(x))2 varies linearly with distance (x), detecting resonance response signals from the nuclei, and deriving an image from the response signals. A method of and apparatus for nuclear quadrupole resonance testing an object, and a method of and apparatus for detecting the presence of a particular substance containing a given species of quadrupolar nucleus, are also disclosed.

Owner:BTG INT LTD

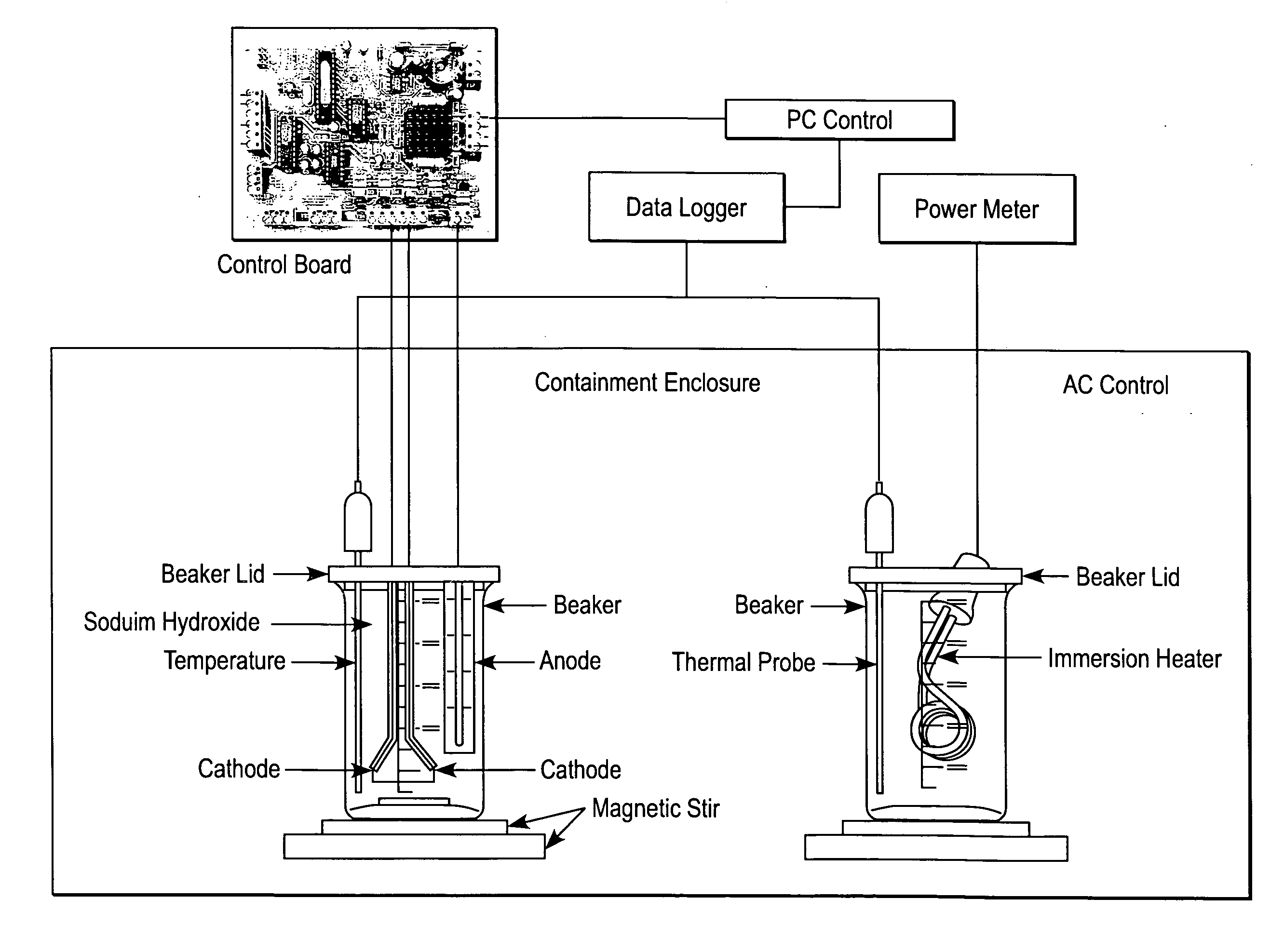

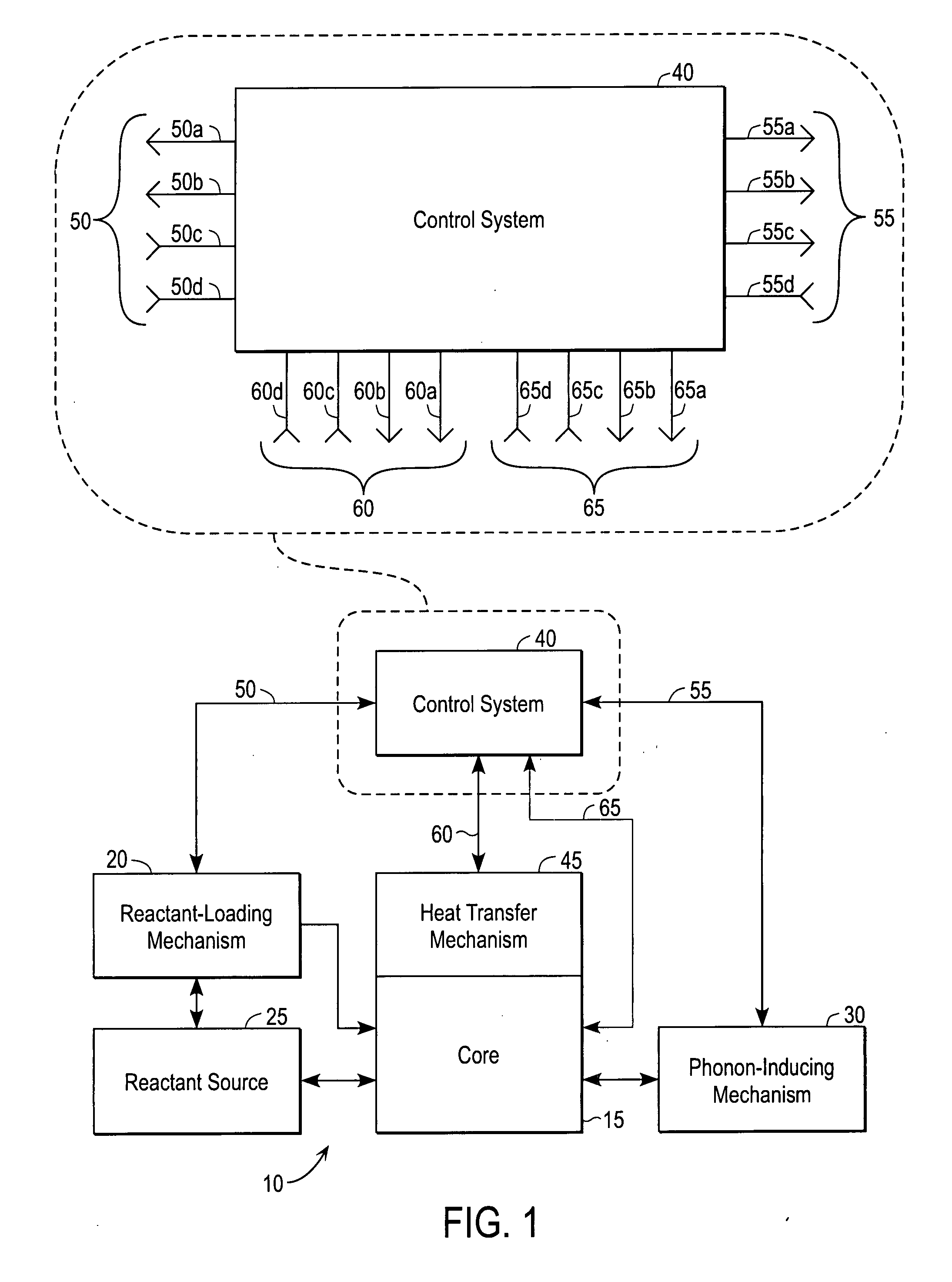

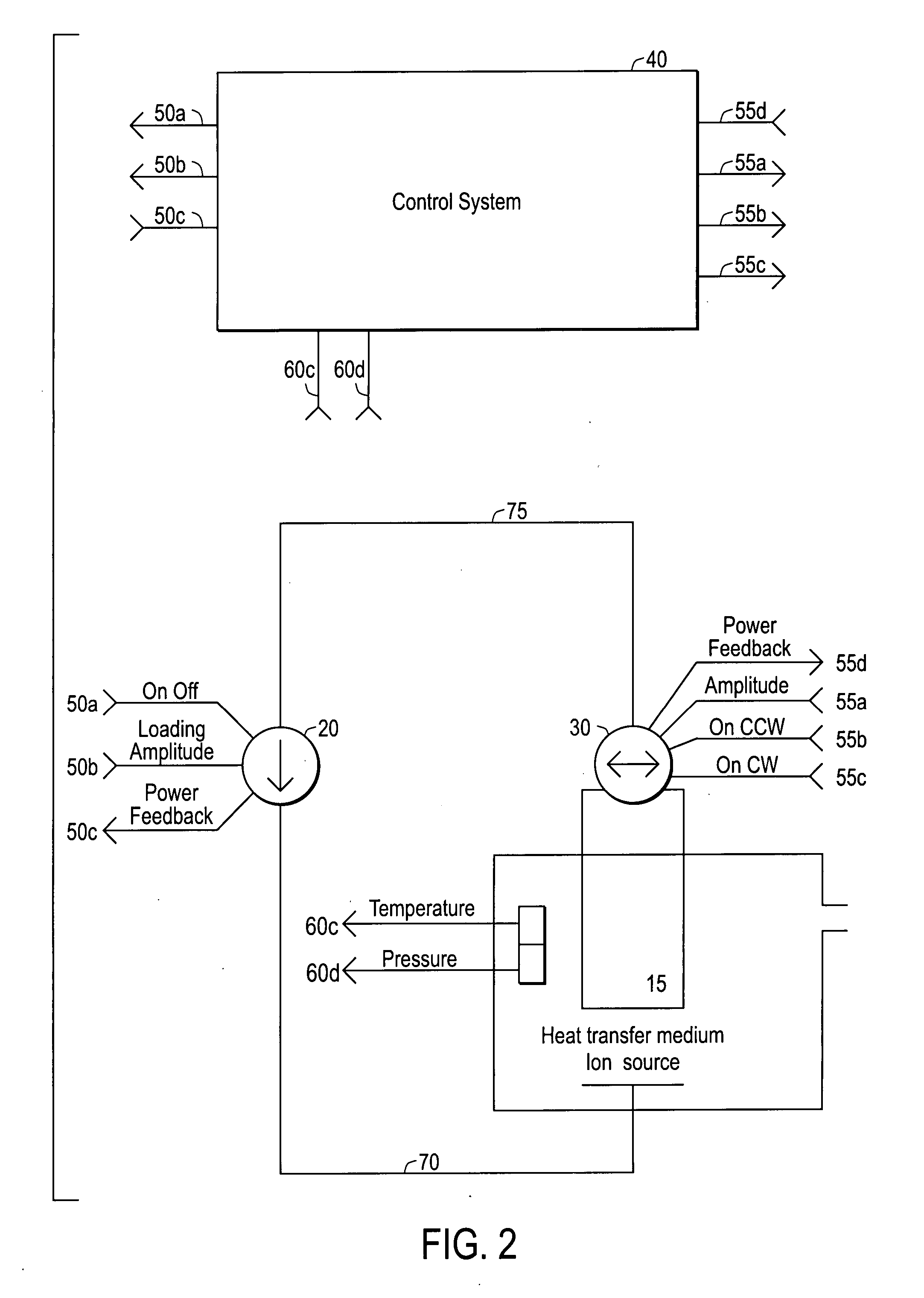

Energy generation apparatus and method

InactiveUS20070206715A1Avoid destructionConsume energyNuclear energy generationLow temperature fusion reactorEngineeringElectron

A practical technique for inducing and controlling the fusion of nuclei within a solid lattice. A reactor includes a loading source to provide the light nuclei which are to be fused, a lattice which can absorb the light nuclei, a source of phonon energy, and a control mechanism to start and stop stimulation of phonon energy and / or the loading of reactants. The lattice transmits phonon energy sufficient to affect electron-nucleus collapse. By controlling the stimulation of phonon energy and controlling the loading of light nuclei into the lattice, energy released by the fusion reactions is allowed to dissipate before it builds to the point that it causes destruction of the reaction lattice.

Owner:BRILLOUIN ENERGY CORP

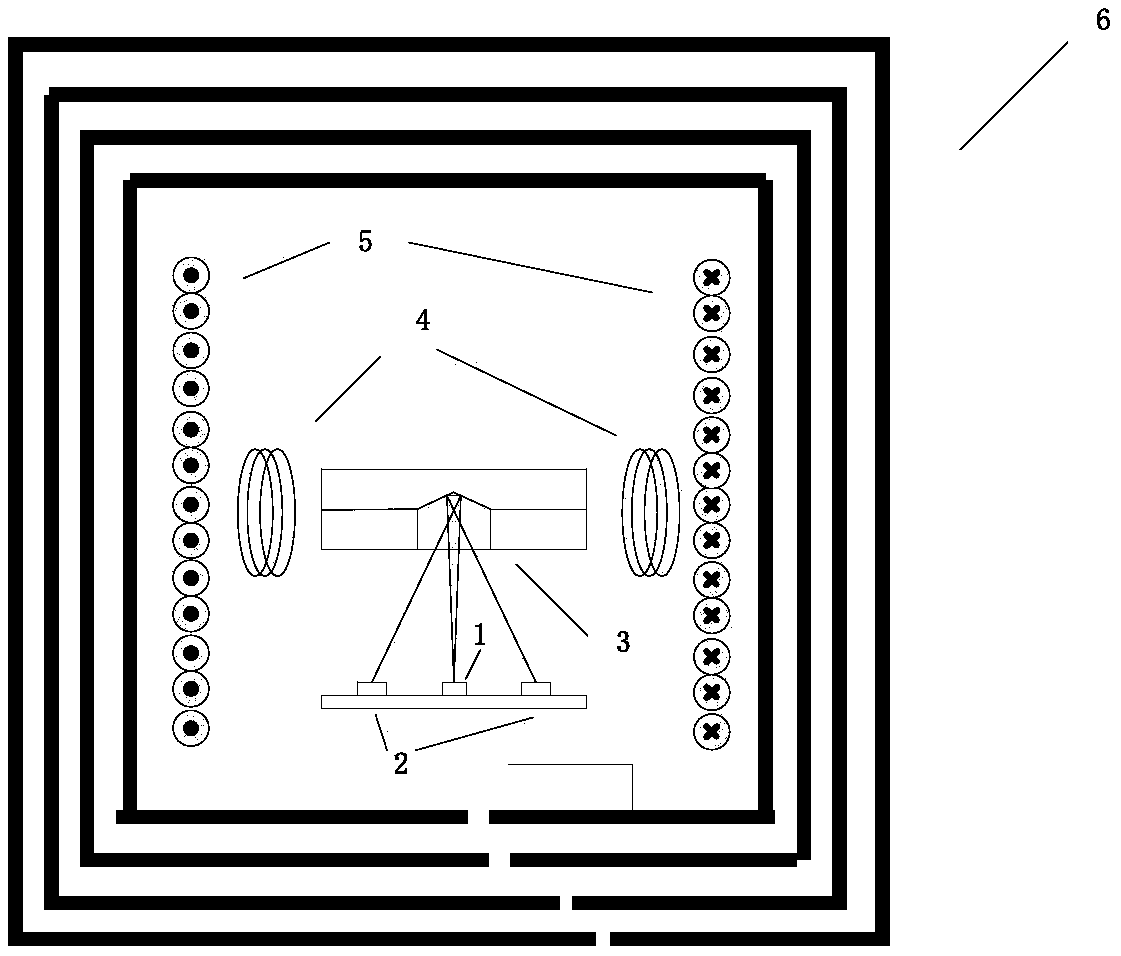

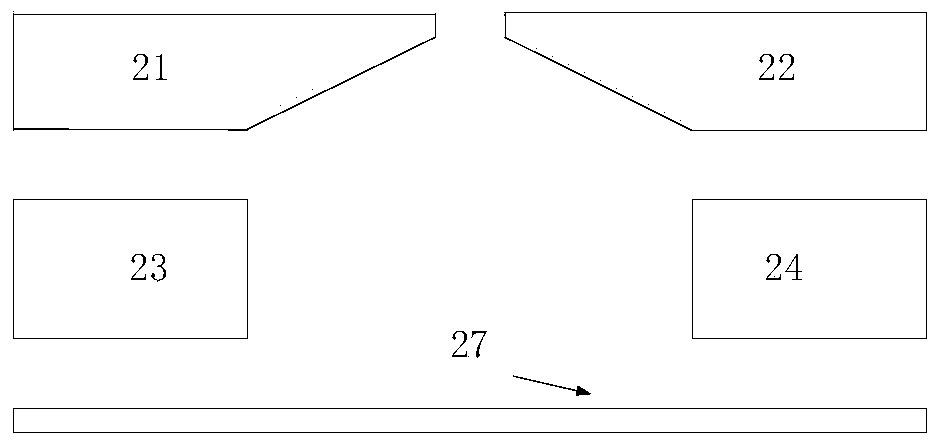

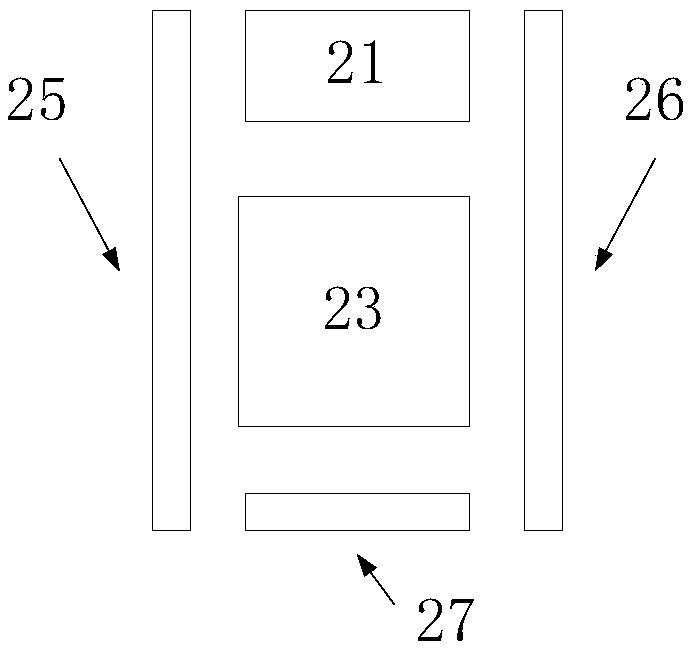

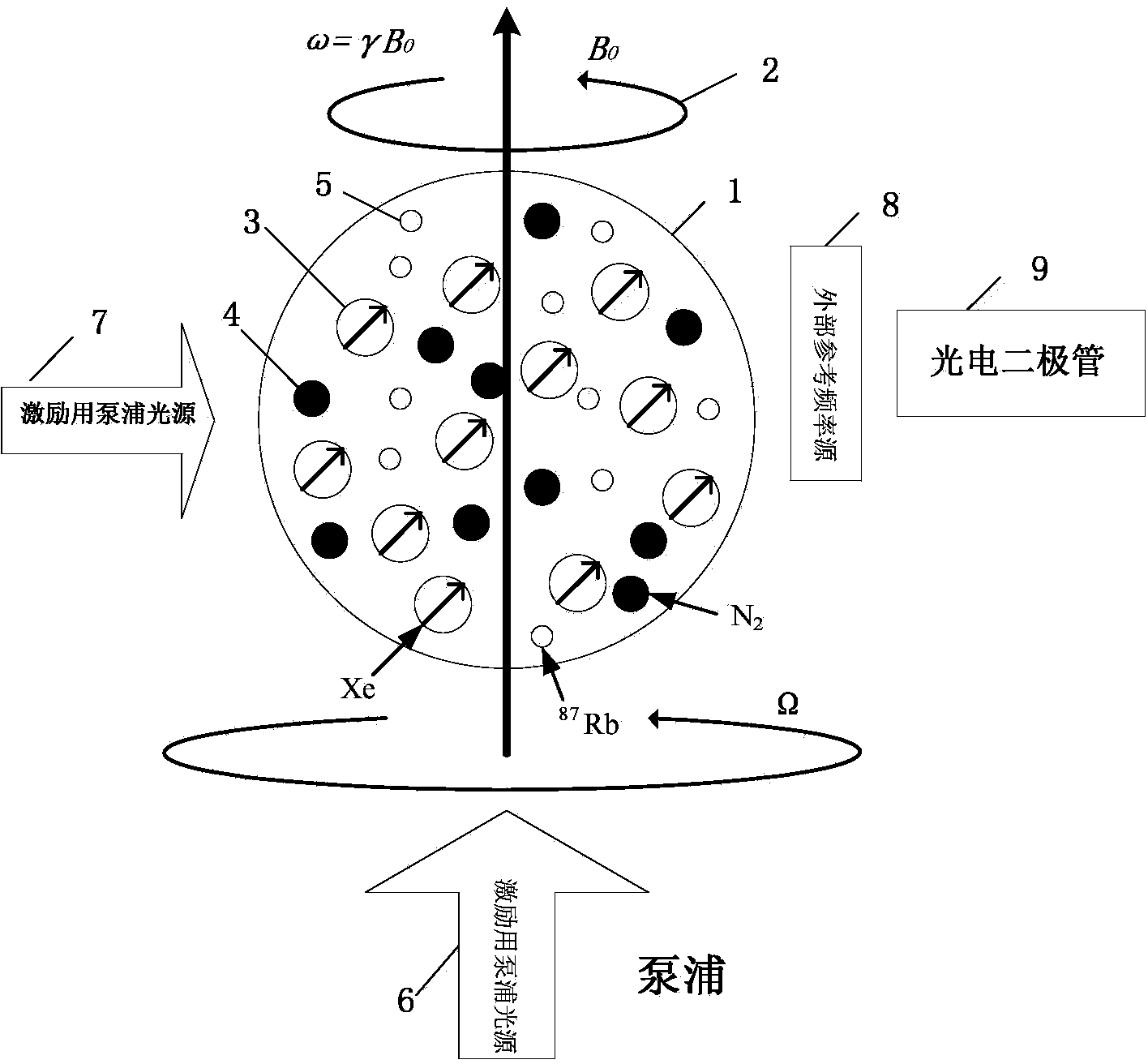

Miniature nuclear magnetic resonance gyroscope

The invention belongs to a gyroscope device in the field of inertia measurement and relates to a miniature nuclear magnetic resonance atomic gyroscope. The miniature nuclear magnetic resonance atomic gyroscope comprises a vacuum room filled with alkali metal and a gas mixture of inert gases. The inside of the top of the vacuum room is plated with a reflective film. A laser for releasing light beam used for pumping and detection is arranged at the bottom of the vacuum room. Two detectors are symmetrically arranged at two sides of the laser and are used for detecting rotation speed signals. Helmholtz coils used for generating a transverse oscillating magnetic field are arranged at two sides of the vacuum room. Solenoid coils used for generating a static magnetic field required by Larmor precession of atomic nucleus surround an optical system composed of the vacuum room, the laser and the Helmholtz coils. The outside of the solenoid coils adopts a shielding structure for magnetic shielding. Volume of the gyroscope is reduced, influence of jitter due to light intensity on precision of the gyroscope is effectively lowered, and precision of the gyroscope is enhanced.

Owner:FLIGHT AUTOMATIC CONTROL RES INST

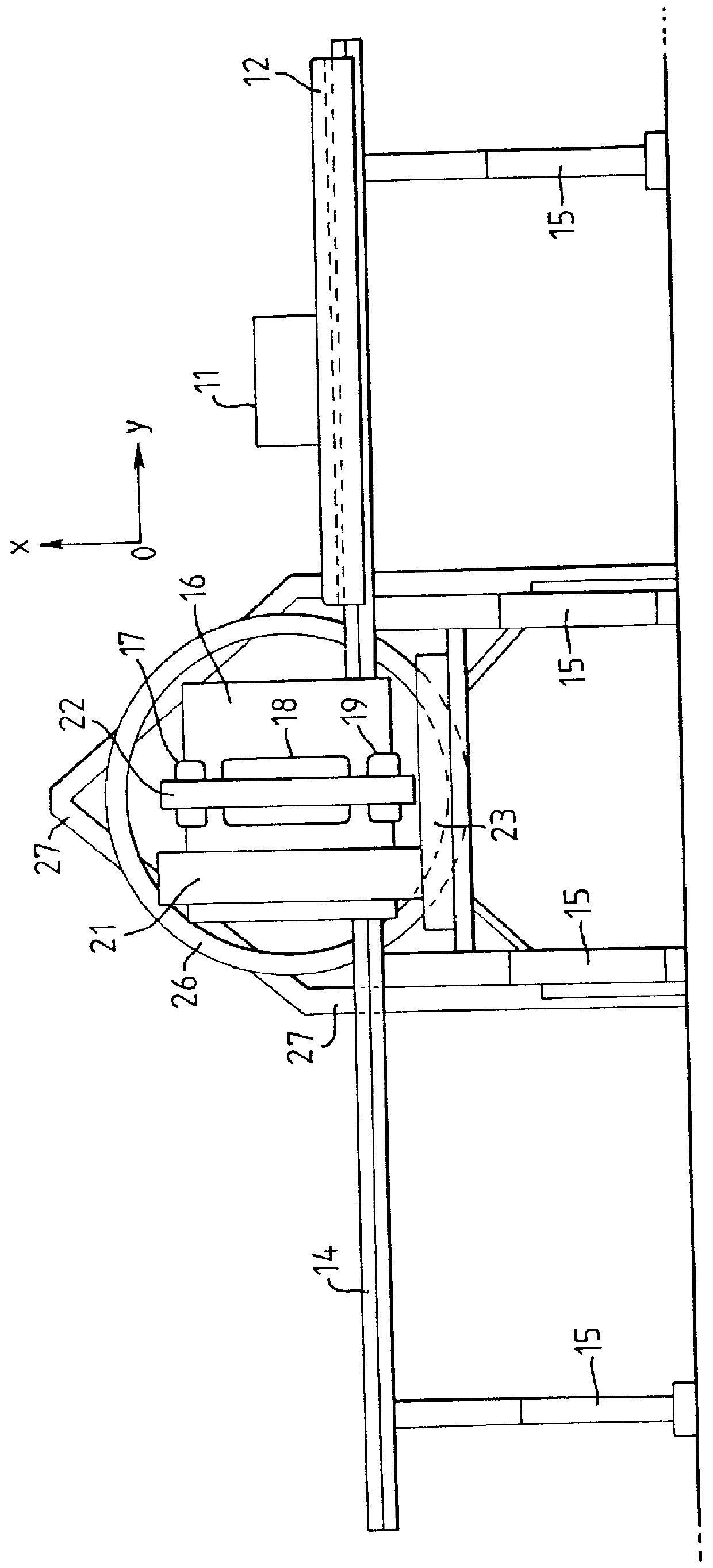

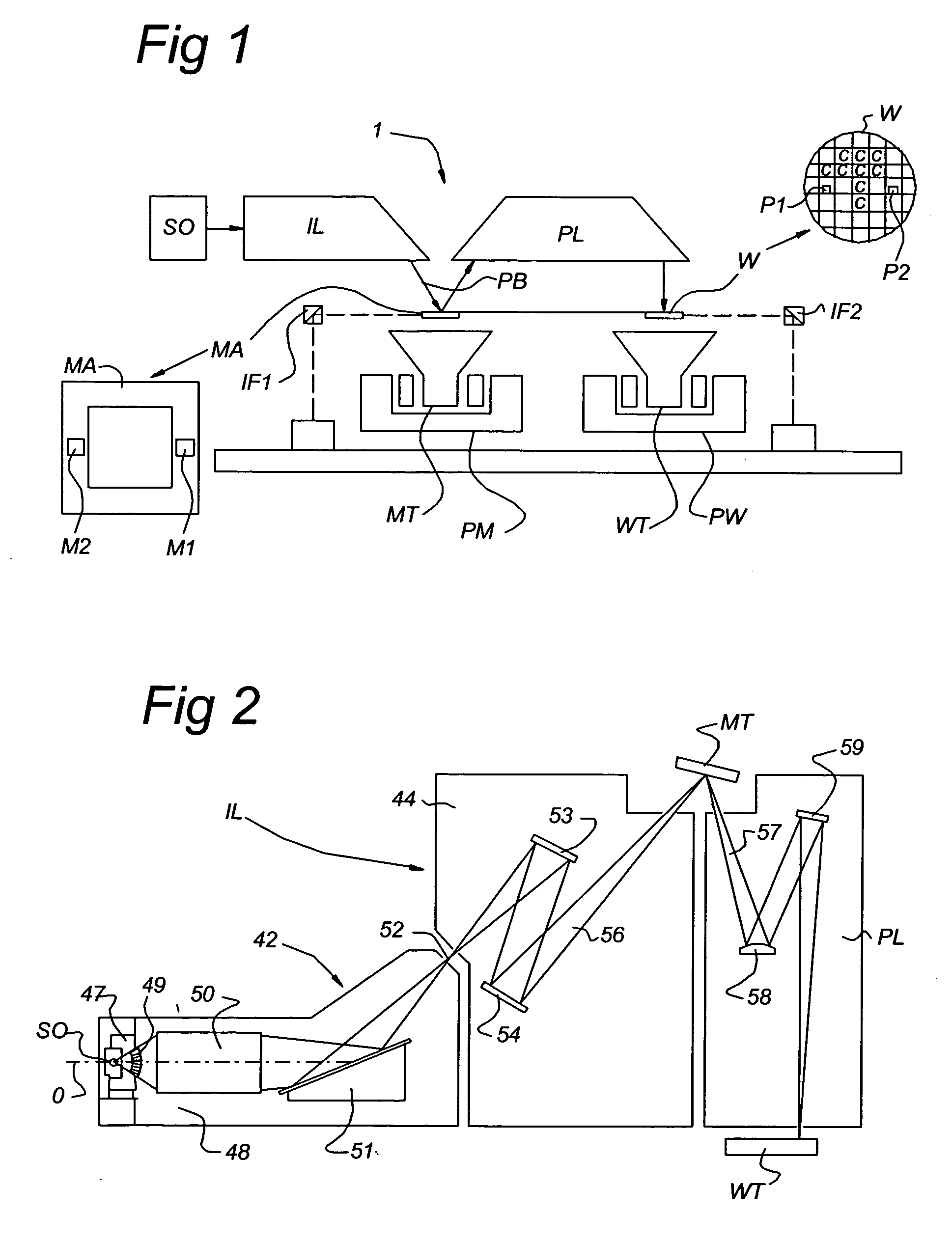

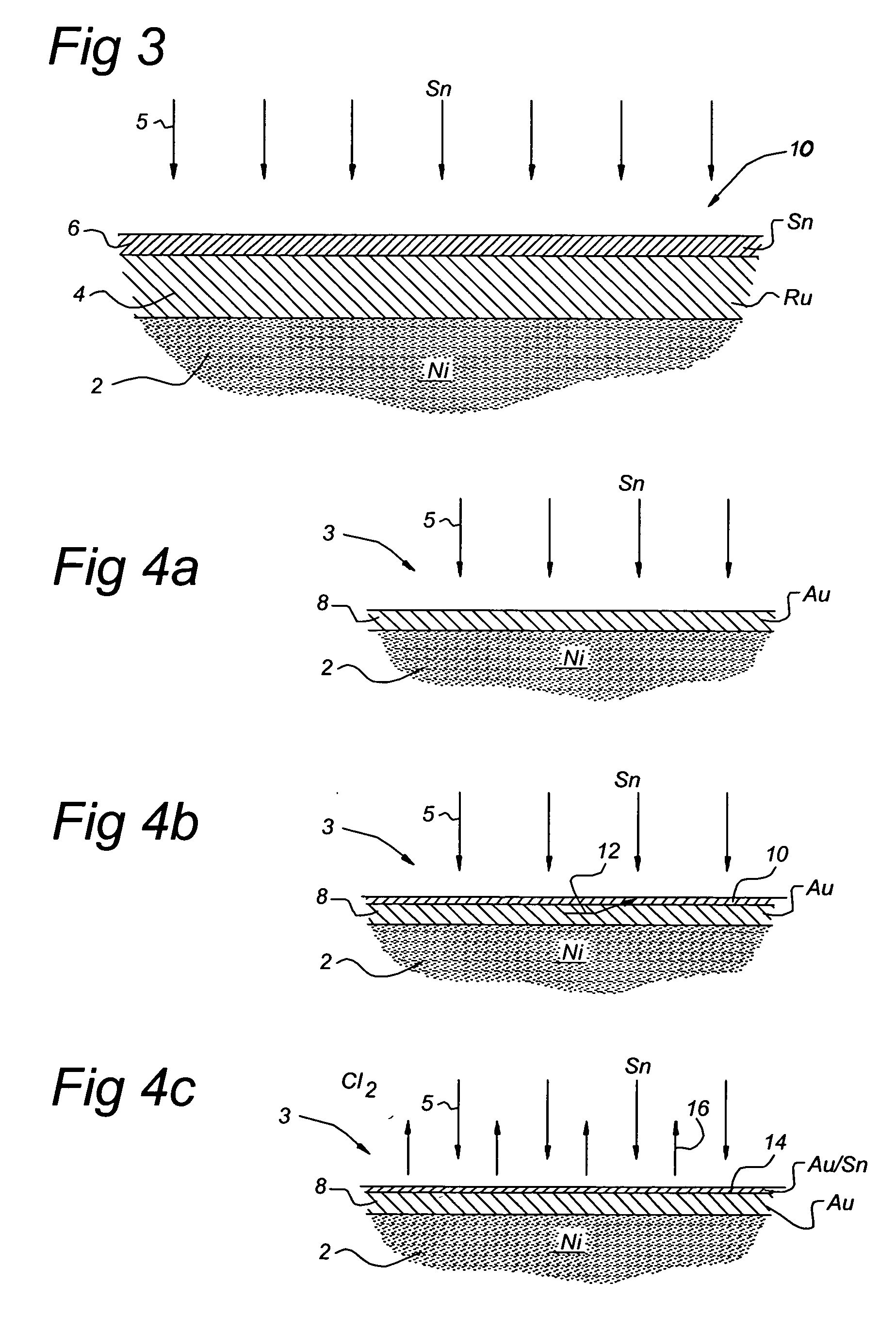

Mirror for use in a lithographic apparatus, lithographic apparatus, device manufacturing method, and device manufactured thereby

InactiveUS20050111080A1Improve surface mobilityEasy to evaporateMirrorsNanoinformaticsAlloyMetal particle

A top layer of a predetermined metal is provided on a mirror for use in a lithographic apparatus having source to provide radiation of a desired wavelength. The source generates a stream of undesired metal particles that are deposited to form smaller and larger nuclei on the mirror. The top layer may interdiffuse in a predetermined temperature range with nuclei of the metal deposition. An additional layer of an alloy of the metal particles and the metal of the top layer is formed that has a higher reflectivity than a layer only comprising the metal particles would have.

Owner:ASML NETHERLANDS BV

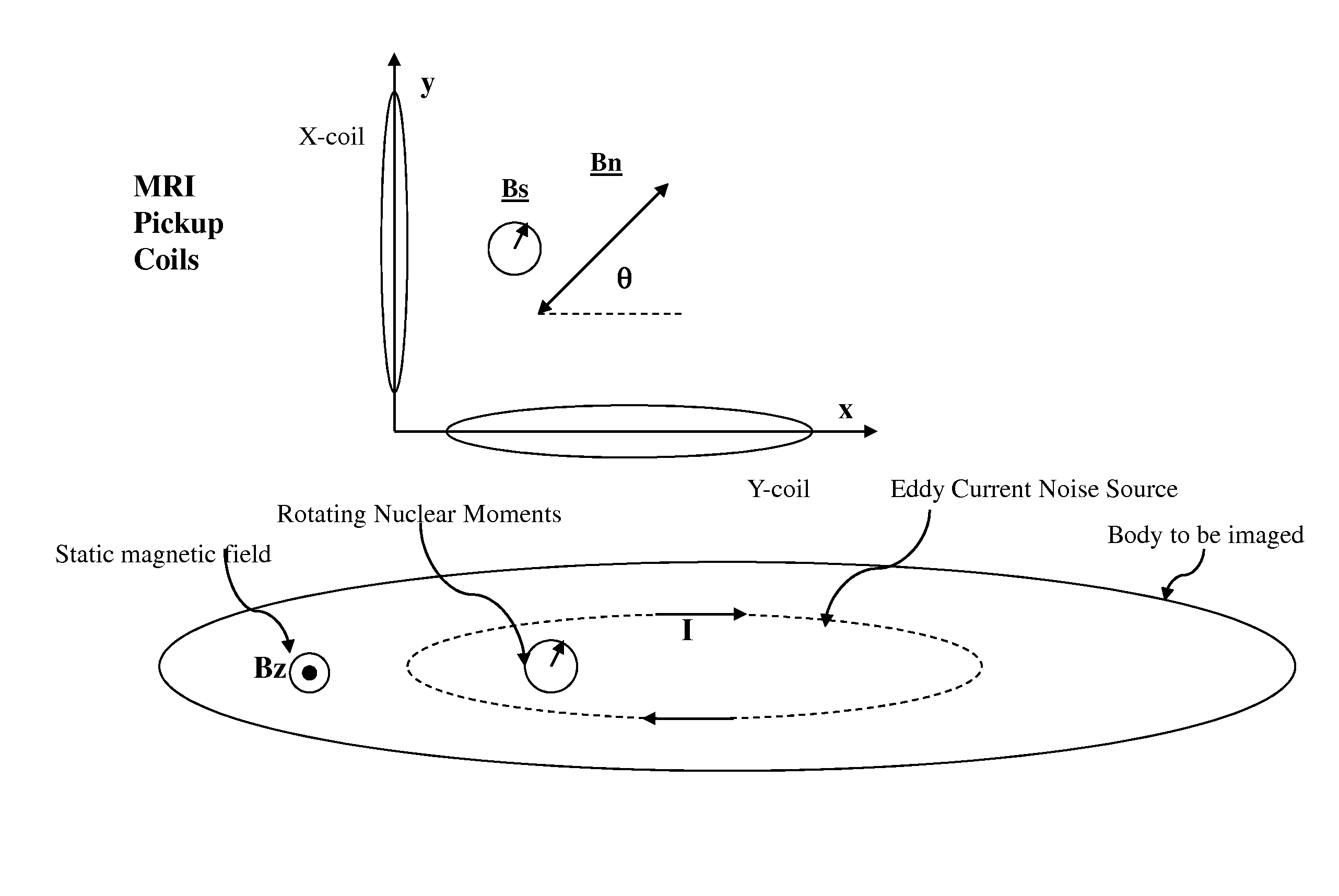

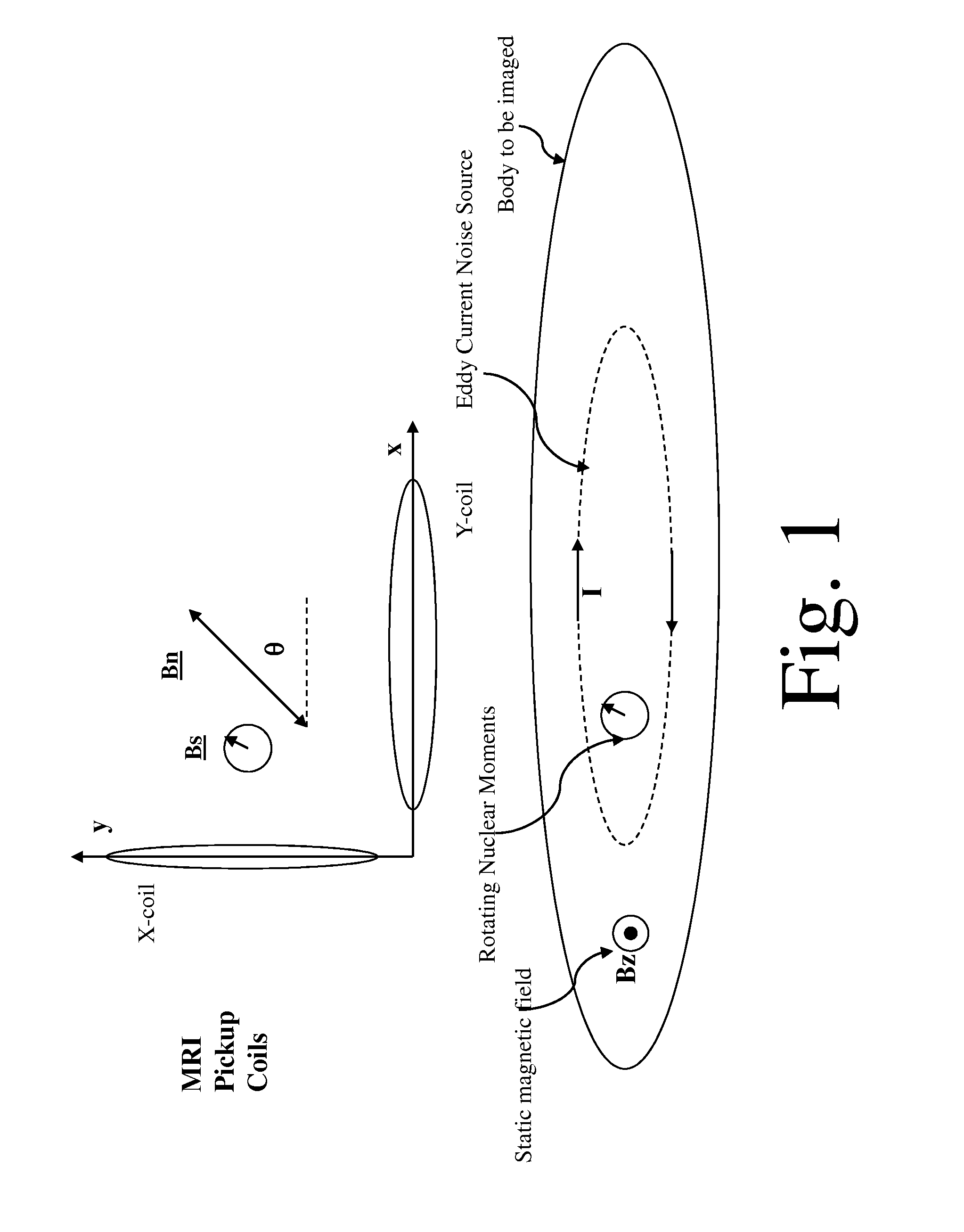

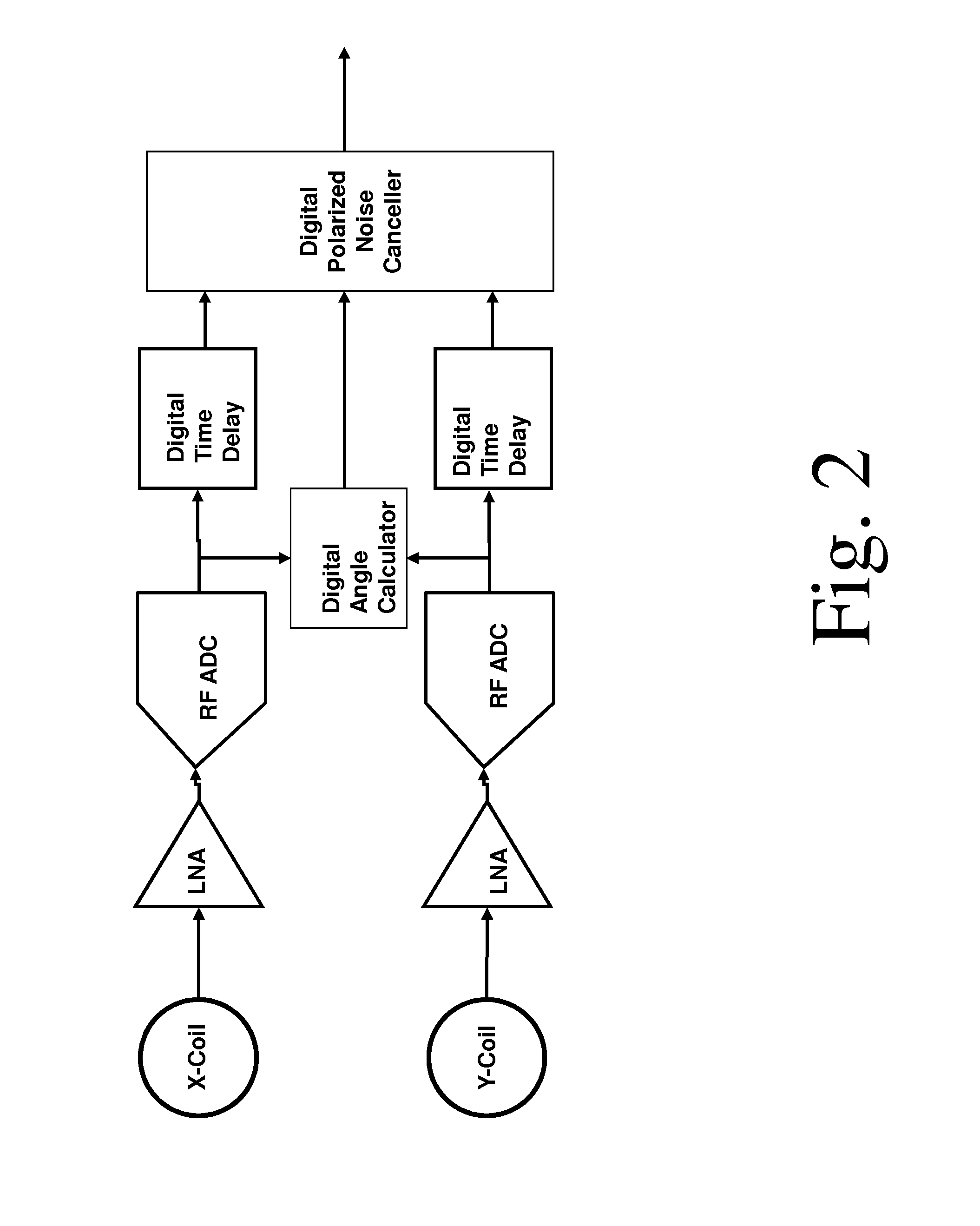

System and method for noise reduction in magnetic resonance imaging

ActiveUS8970217B1Improve noiseSignificant signal processingMeasurements using NMR imaging systemsElectric/magnetic detectionNoise reductionSignal-to-quantization-noise ratio

Signals of interest in magnetic resonance imaging (MRI) systems comprise narrowband, circularly polarized (CP) radio-frequency magnetic fields from rotating atomic nuclei. Background “body noise” may comprise broadband, linearly polarized (LP) magnetic fields from thermally-activated eddy currents, and may exceed the signal in a band of interest, limiting the imaging resolution and requiring excessive averaging times. Noise may be selectively detected and substantially suppressed, while enhancing the signal of interest, using appropriate digital time-domain algorithms. At least two quadrature receiving antennas may be employed to distinguish and separate the LP noise from the CP signal. At least one broadband receiver may be used to identify and localize fast noise sources and to digitally filter the representation of their radio-frequency magnetic fields in the signal. Selective body noise reduction may allow enhanced signal-to-noise ratio of the system, leading to improved imaging resolution and shorter scan time.

Owner:THE JOHNSON REVOCABLE TRUST DATED 6 25 2003

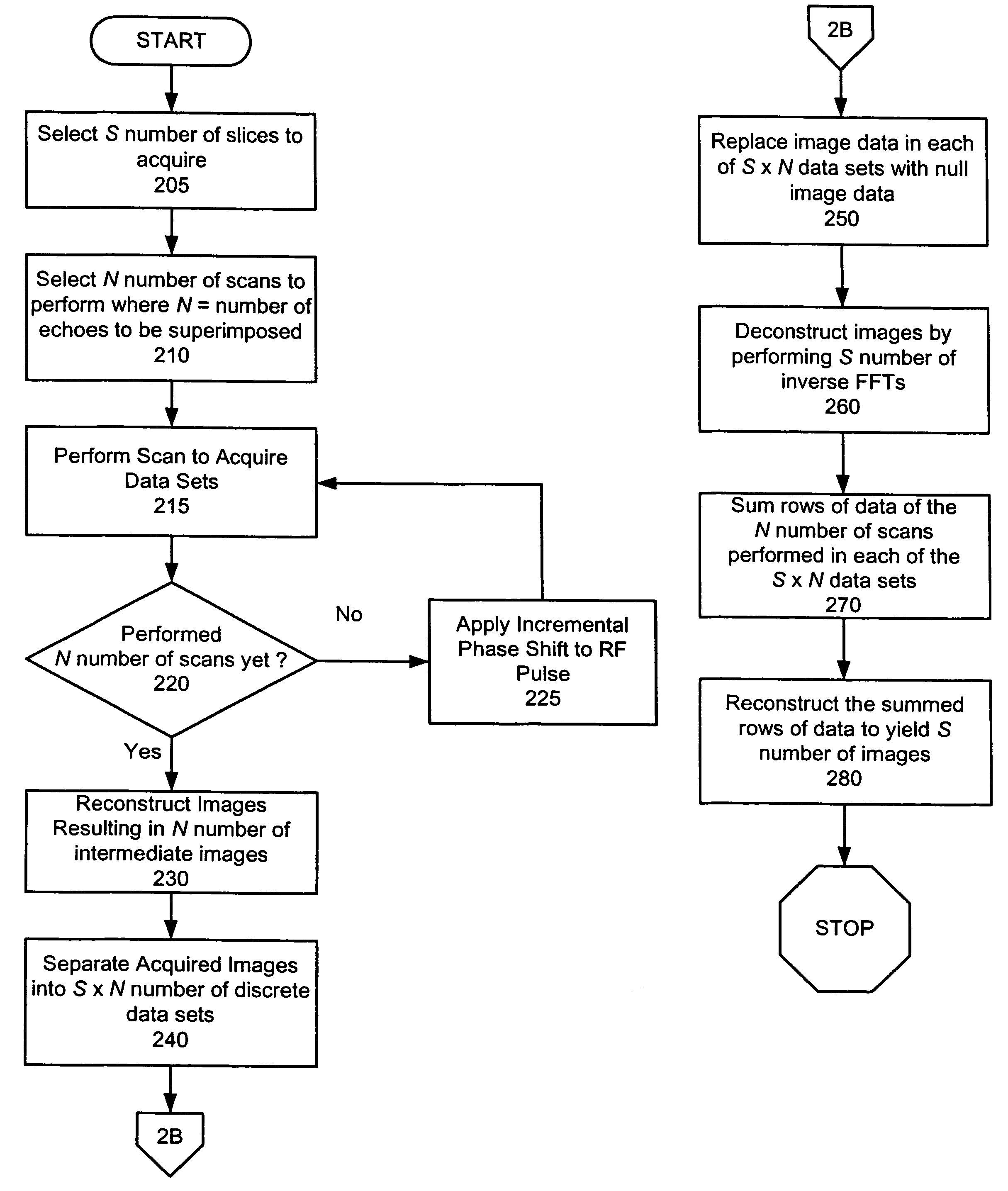

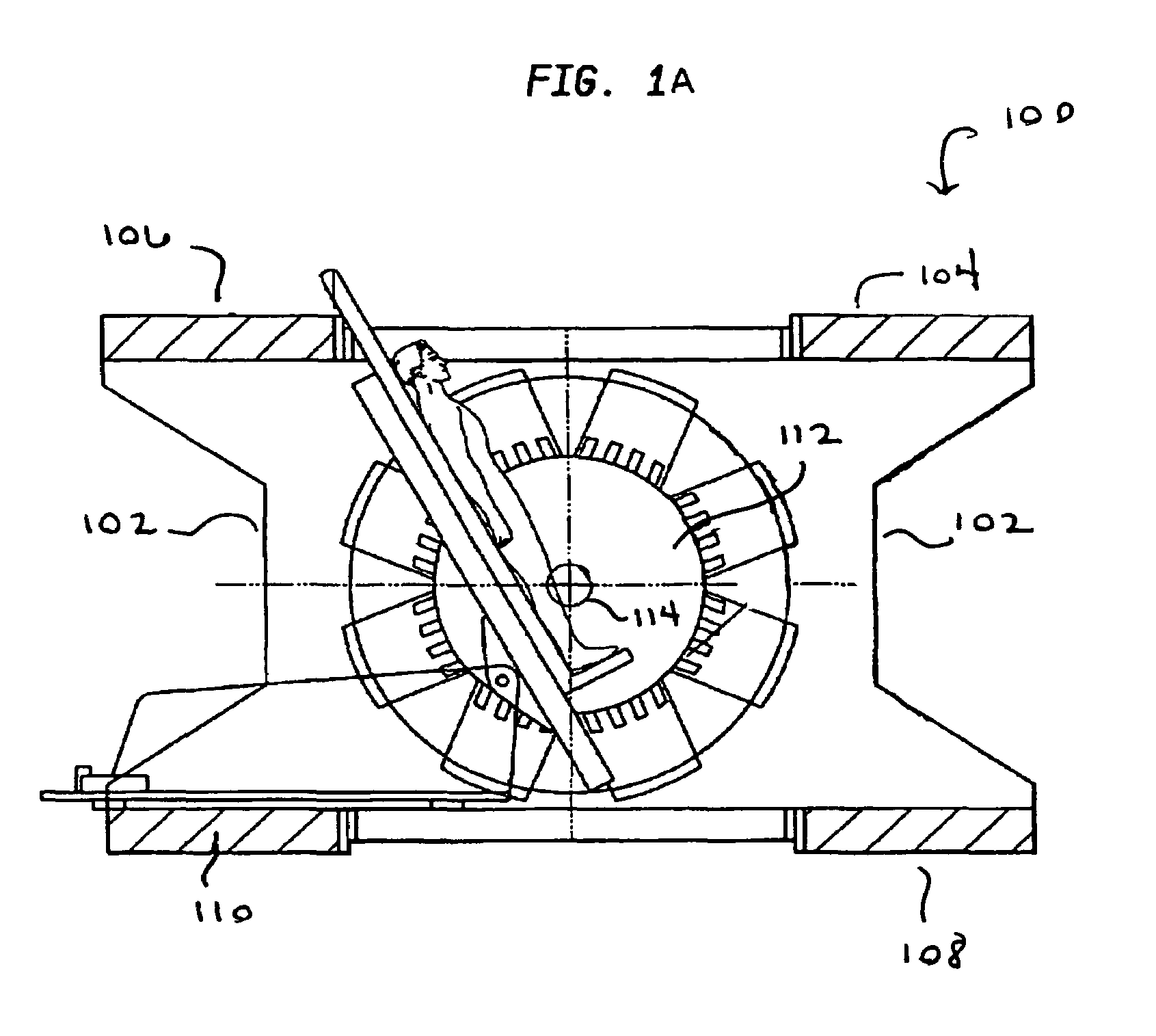

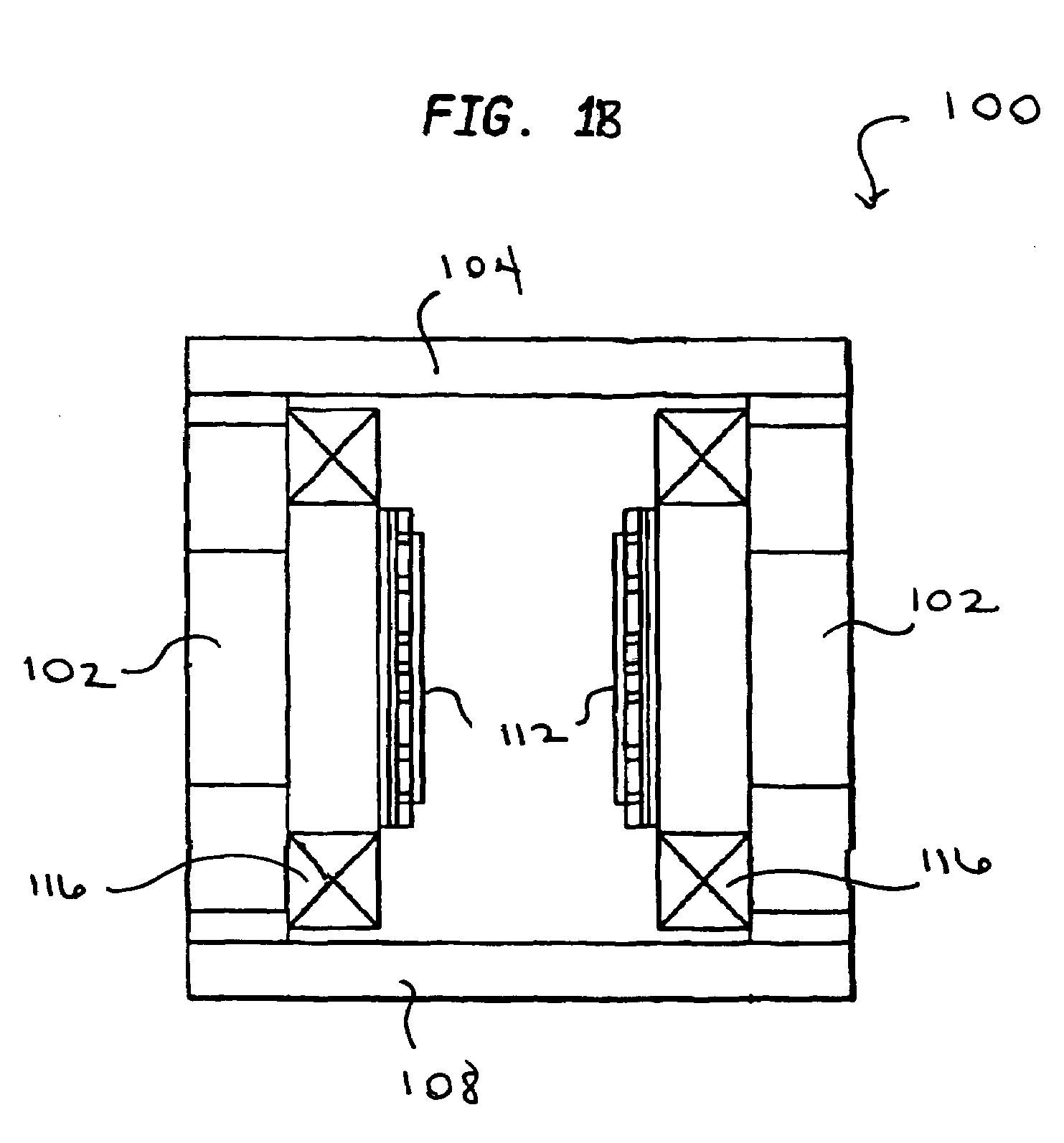

Magnetic resonance imaging

ActiveUS7230424B1Improve magnetic efficiencyImprove signal-to-noise ratioMagnetic measurementsElectric/magnetic detectionRapid imagingSignal-to-noise ratio (imaging)

Through advancing the phase of radio frequency (RF) excitation with each phase-encoding level, a method and apparatus increases the effectiveness of a Magnetic Resonance Imaging (MRI) device by correcting for main magnetic field inhomogeneities without noticeably decreasing the signal-to-noise ratio. The present invention also increases the effectiveness of fast imaging with steady precession (FISP) scans and allows FISP scans to image multiple slices. In an MRI device, a patient is subjected to a constant magnetic field, and RF pulses are used to excite the nuclei in the patient's body. The nuclei release a corresponding RF signal as the nuclei relax, which can be measured and mapped into a visual display. The RF pulses used to excite the nuclei in the body cooperate with a slice select gradient and a phase-encoding gradient. When the RF pulse is phase shifted with each phase-encoding gradient level, improved signal-to-noise ratios are observed.

Owner:FONAR

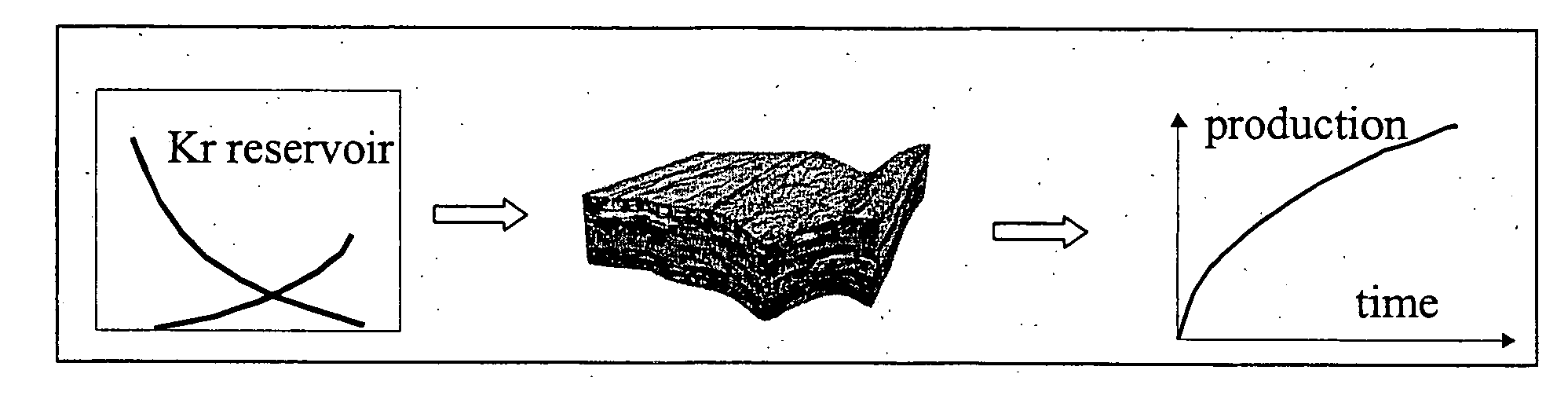

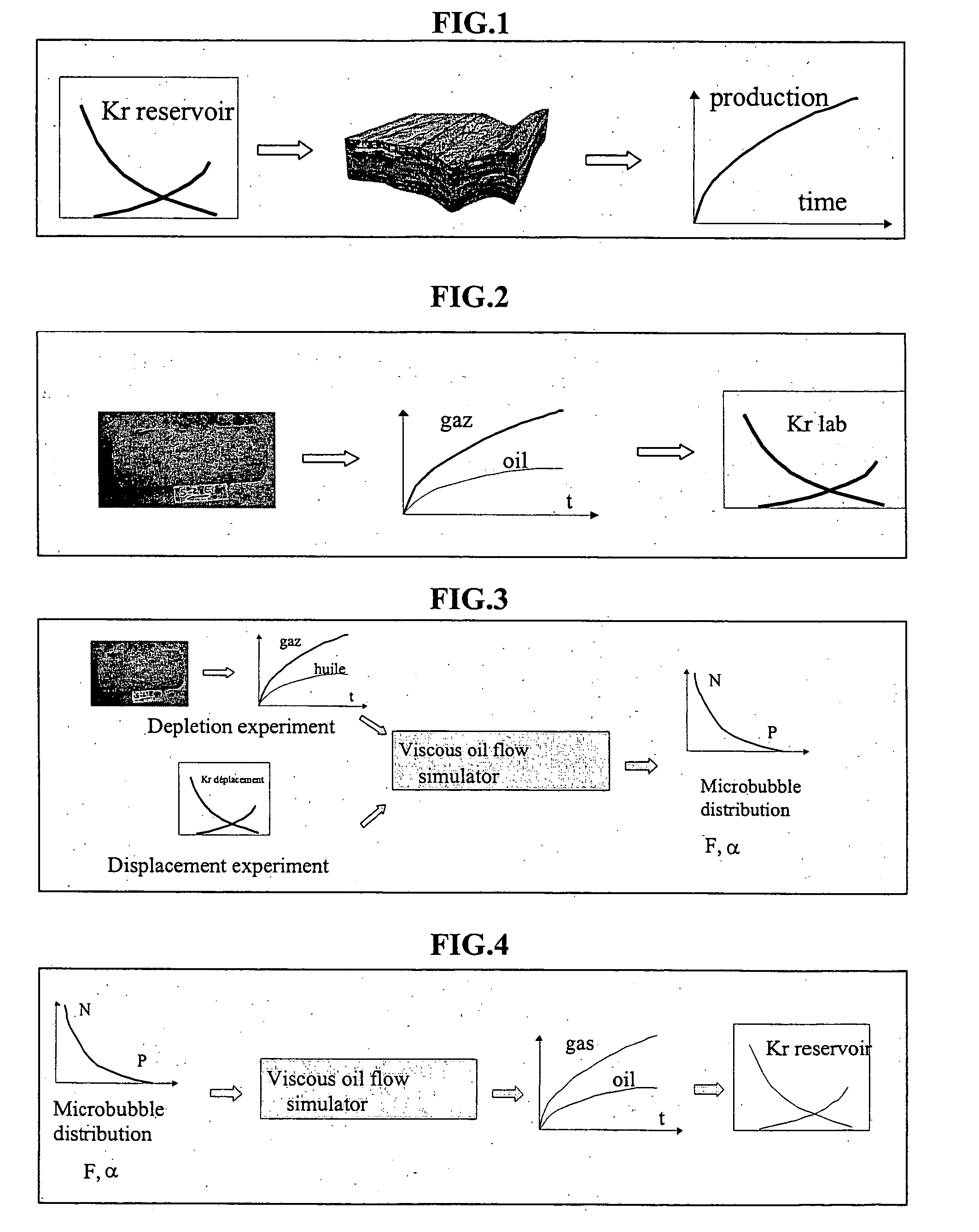

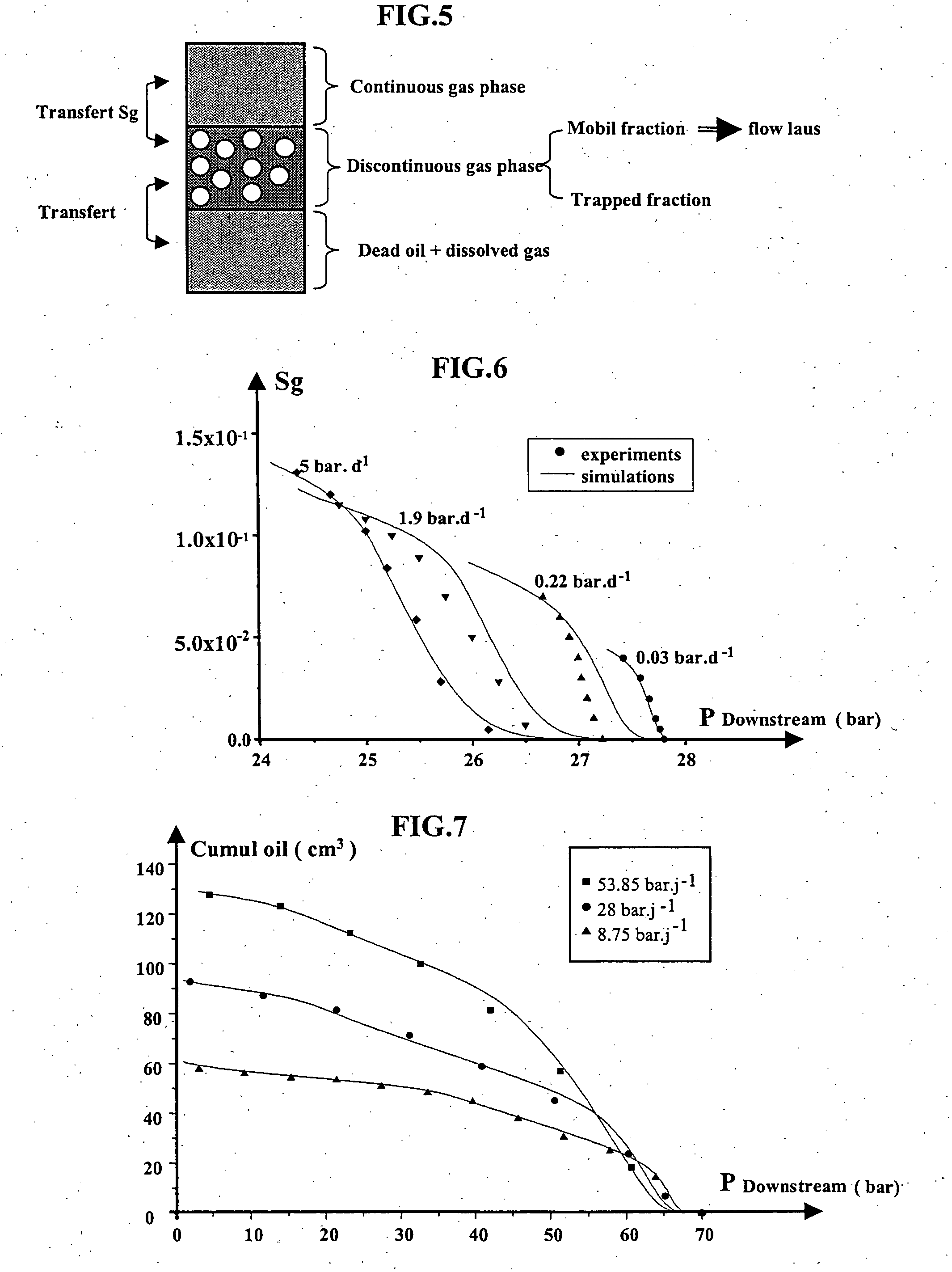

Method for modelling the production of hydrocarbons by a subsurface deposit which are subject to depletion

ActiveUS20050165593A1Realistic representationElectric/magnetic detection for well-loggingPermeability/surface area analysisHydrocotyle bowlesioidesRock sample

A method for forming a model simulating production, by an underground reservoir subject to depletion, of hydrocarbons comprising notably relatively high-viscosity oils. From laboratory measurements of the respective volumes of oil and gas produced by rock samples from the reservoir subject to depletion, and the relative permeabilities (Kr) of rock samples to hydrocarbons, a model of the formation and flow of the gas fraction is used to determine a volume transfer coefficient (hv) by means of an empirical function representing the distribution of nuclei that can be activated at a pressure P (function N(P)) which is calibrated with reference to the previous measurements. Considering that the nuclei distribution N(P) in the reservoir rocks is the same as the distribution measured in the laboratory, the numerical transfer coefficient corresponding thereto in the reservoir at selected depletion rates is determined using the gas fraction formation and flow model, which allows predicting the relative permeabilities in the reservoir and the production thereof which is useful for reservoir engineering. Method for forming a model allowing to simulate the production, by an underground reservoir subjected to depletion, of hydrocarbons comprising notably relatively high-viscosity oils. From laboratory measurements of the respective volumes of oil and gas produced by rock samples from the reservoir and subjected to depletion, and the relative permeabilities (Kr) of rock samples to hydrocarbons, a model of the formation and flow of the gas fraction is used to determine a volume transfer coefficient (hv) by means of an empirical function representing the distribution of nuclei that can be activated at a pressure P (function N(P)) which is calibrated with reference to the previous measurements. Considering that the nuclei distribution N(P) in the reservoir rocks is the same as the distribution measured in the laboratory, the numerical transfer coefficient corresponding thereto in the reservoir at selected depletion rates is determined using the gas fraction formation and flow model, which allows to predict the relative permeabilities in the reservoir and the production thereof. Applications notably reservoir engineering.

Owner:INST FR DU PETROLE

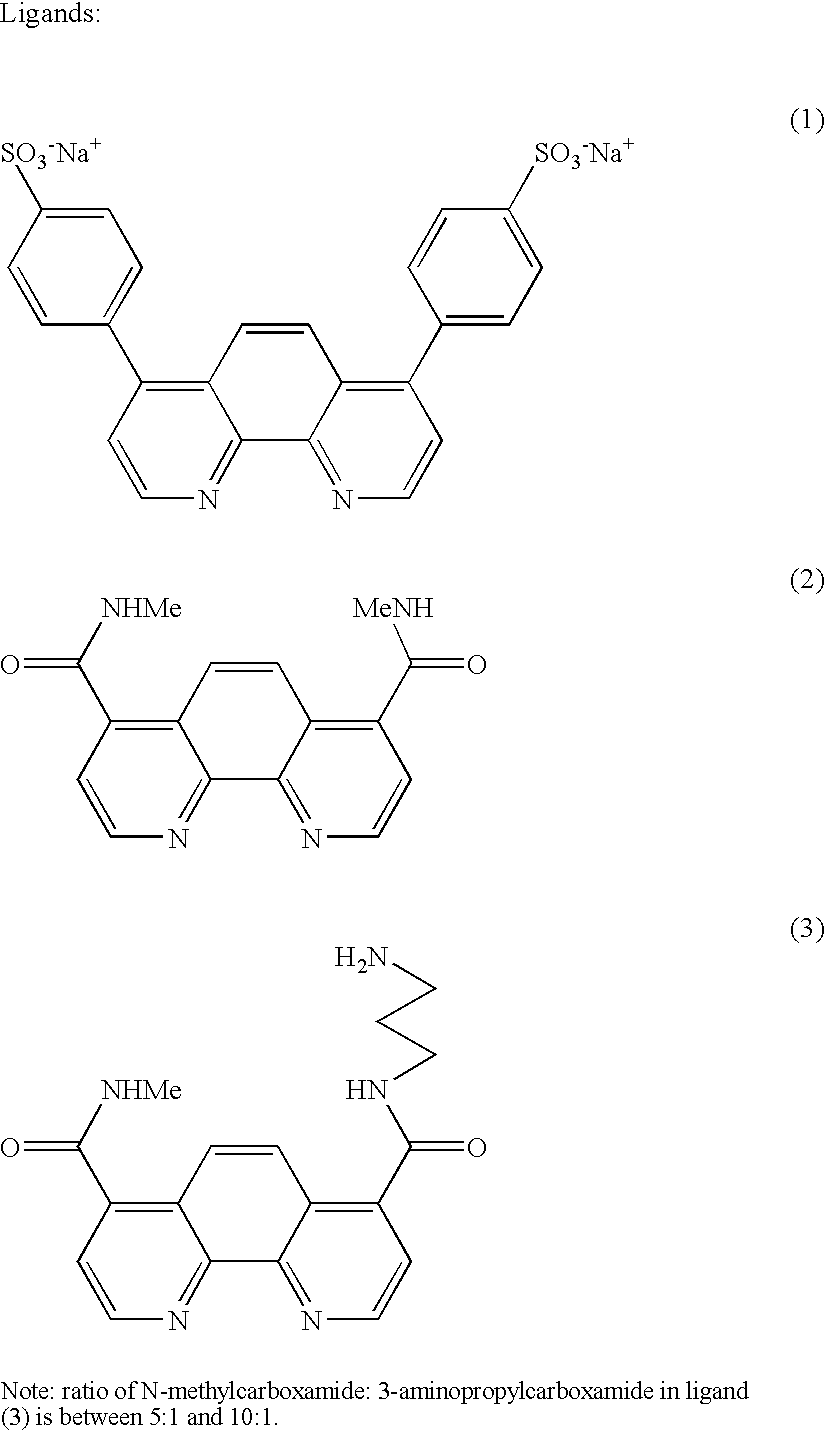

Small organometallic probes

InactiveUS20050130207A1Group 1/11 organic compounds without C-metal linkagesPowder deliveryPlatinumFluorescein

Small organometallic probes comprise a core of metal atoms bonded to organic moieties. The metal atoms are gold, silver, platinum, palladium, or combinations thereof. In one embodiment, a multifunctional organometallic probe comprises a core of metal atoms surrounded by a shell of organic moieties covalently attached to the metal atoms, a fluorescent molecule, e.g., fluorescein, covalently attached to one of the organic moieties, and a targeting molecule, e.g., an antibody, covalently attached to another of the organic moieties.

Owner:HAINFELD JAMES F +2

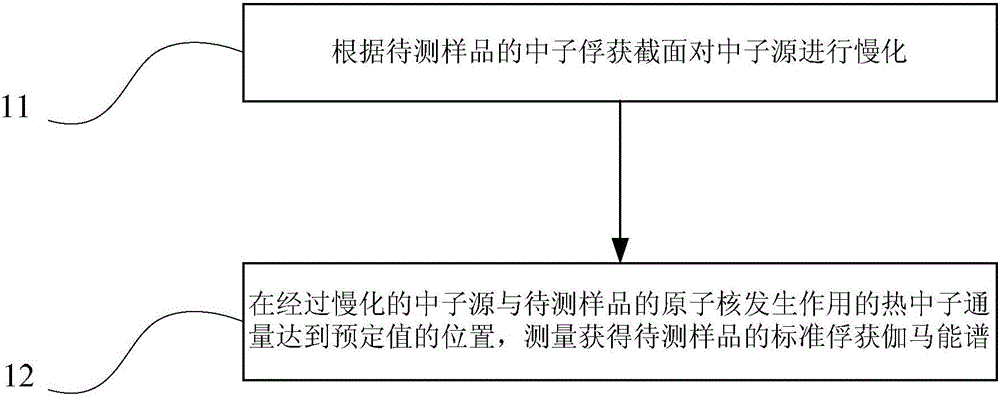

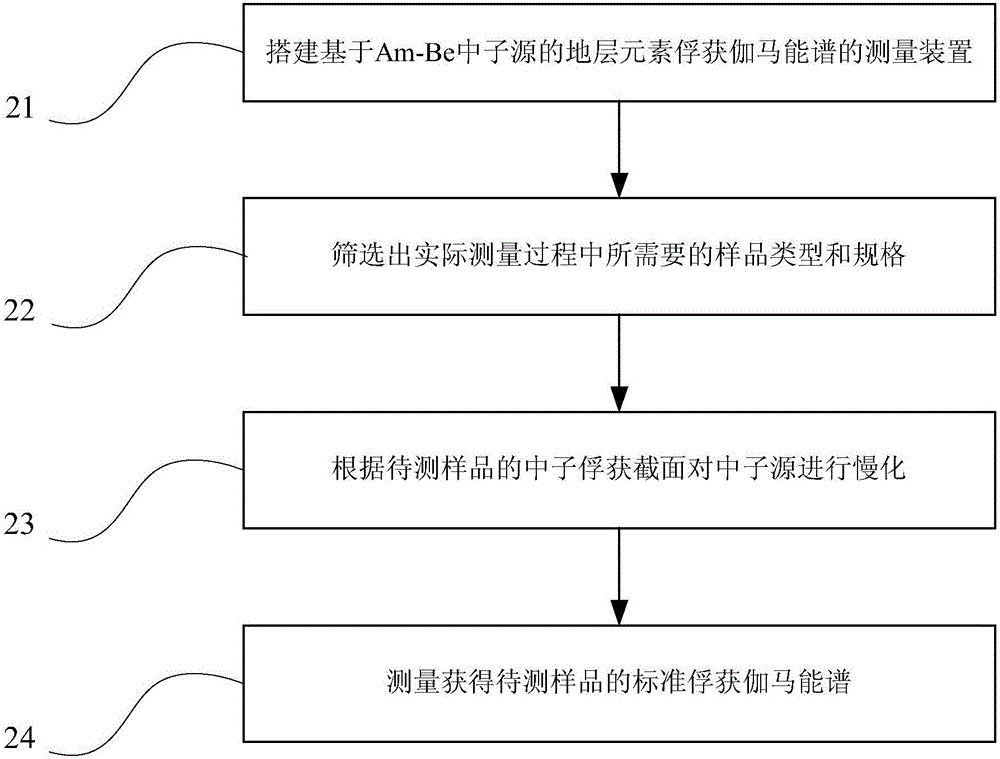

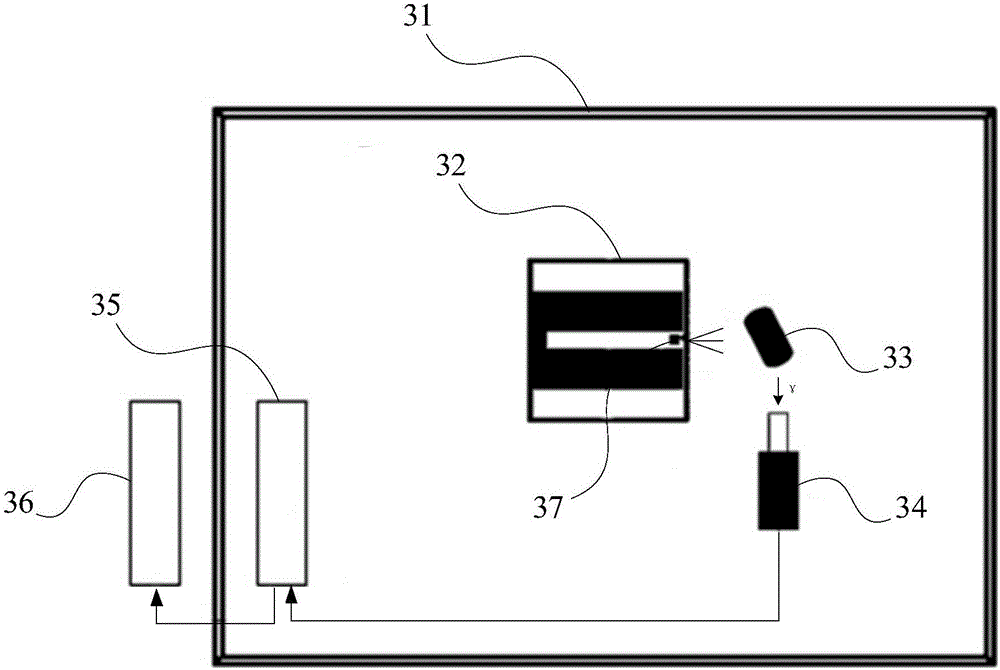

Formation element capture gamma-ray spectra measurement method and device

ActiveCN105093343AImprove accuracyMaterial analysis using wave/particle radiationNuclear radiation detectionThermal neutron fluxNeutron capture

The invention provides a formation element capture gamma-ray spectra measurement method and device, and belongs to the technical field of oil-gas exploration logging. The method comprises the steps that a neutron source is slowed down according to the neutron capture cross section of samples to be measured; and standard capture gamma-ray spectra of the samples to be measured can be acquired through measurement when thermal neutron flux of reaction of the neutron source through slowing down and the atomic nucleus of the samples to be measured reaches the position of the preset value. The neutron source is slowed down according to the neutron capture cross section of different samples to be measured so that the element capture gamma-ray spectra of the samples to be measured can be acquired through measurement, and multiple types of formation element capture gamma-ray spectra with higher accuracy can be acquired.

Owner:PETROCHINA CO LTD

Compact Accelerator For Medical Therapy

InactiveUS20100032580A1Stability-of-path spectrometersBeam/ray focussing/reflecting arrangementsBending magnetsParticle beam

A compact accelerator system having an integrated particle generator-linear accelerator with a compact, small-scale construction capable of producing an energetic (˜70-250 MeV) proton beam or other nuclei and transporting the beam direction to a medical therapy patient without the need for bending magnets or other hardware often required for remote beam transport. The integrated particle generator-accelerator is actuable as a unitary body on a support structure to enable scanning of a particle beam by direction actuation of the particle generator-accelerator.

Owner:LAWRENCE LIVERMORE NAT SECURITY LLC

Method for measuring rotating angle of aircraft based on nuclear magnetic resonance

The invention provides a method for measuring the rotating angle of an aircraft based on nuclear magnetic resonance. The method is characterized in that two isotope nucleuses with the same element and different gyromagnetic ratios serve as a measurement carrier of an aircraft rotating angle measurement gyroscope; an alkali metal element is added into a cylindrical glass sealed cavity in a nuclear magnetic resonance resonant cavity of the aircraft rotating angle measurement gyroscope based on a spin polarization exchange mechanism; electron spin polarization of alkali metal atoms is transferred to two isotopic atoms serving as the rotating speed measurement carrier of the gyroscope to cause net nucleus spin polarization of the two isotopic atoms. Therefore, the magnetic polarization strength of the isotopic measurement carrier can be improved, and a signal to noise ratio of a detected signal can be improved.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

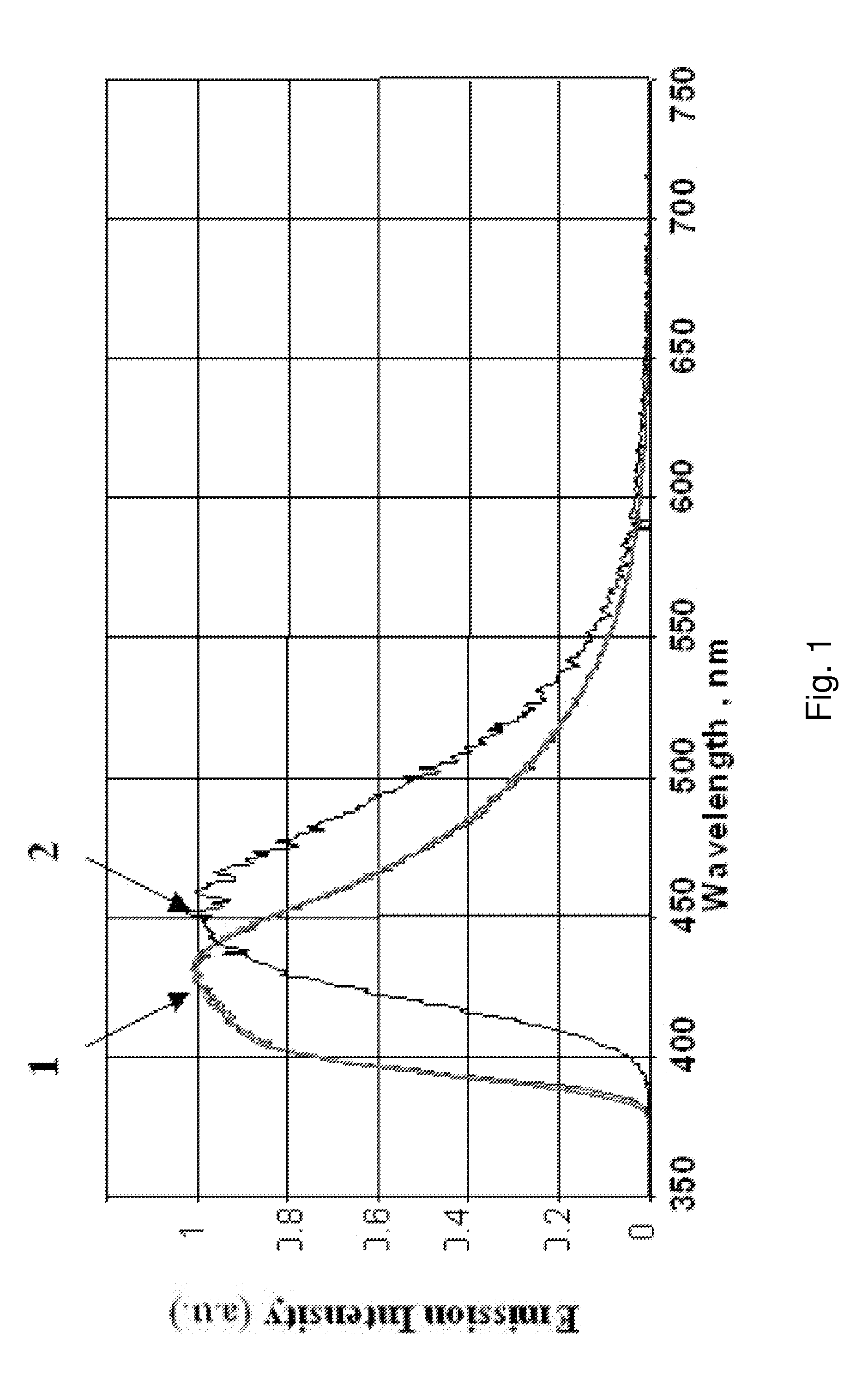

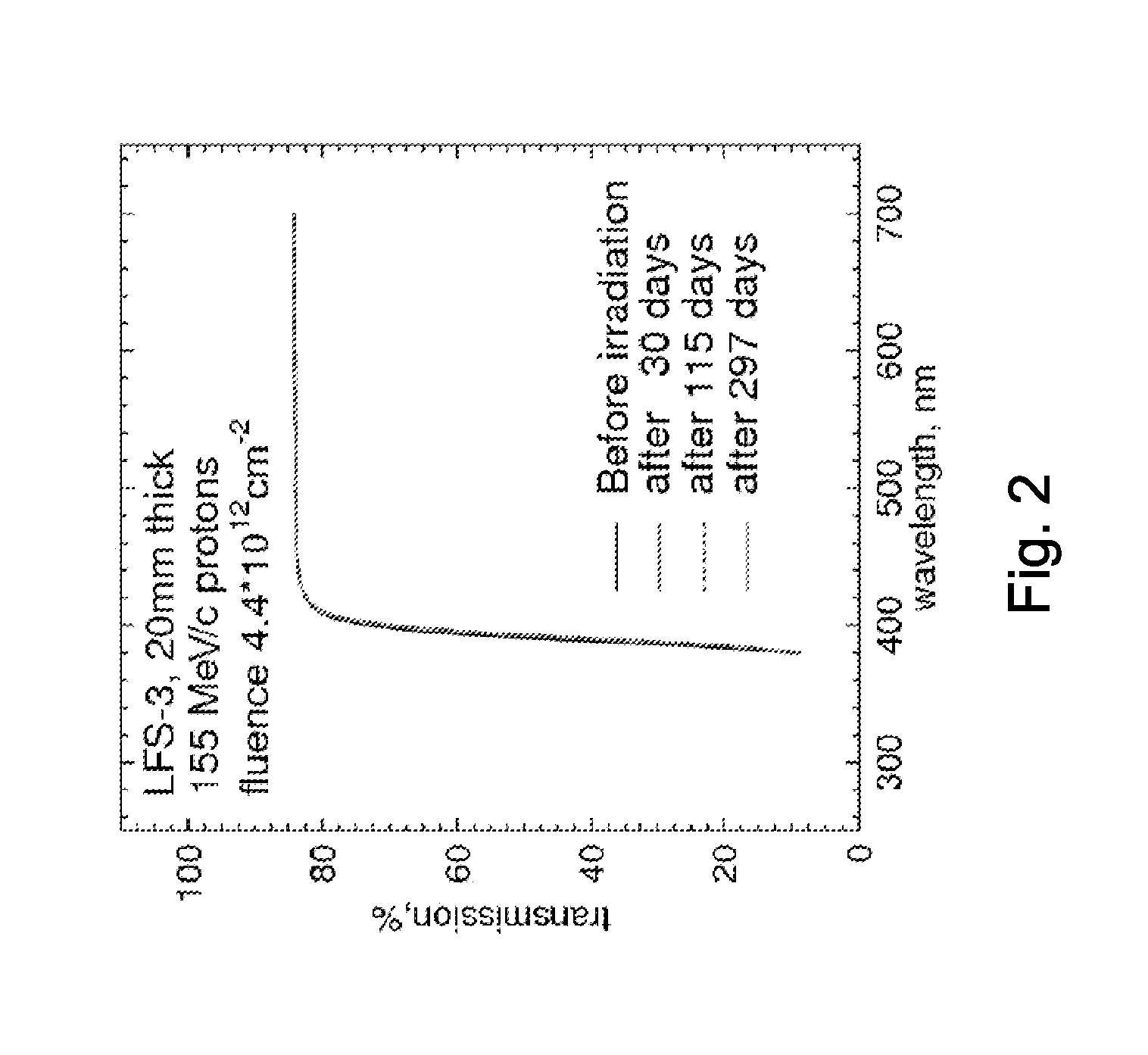

Multi-doped lutetium based oxyorthosilicate scintillators having improved photonic properties

InactiveUS20140061537A1Short decay timeGood energy resolutionPolycrystalline material growthAfter-treatment detailsLutetiumHigh energy

The present invention relates to a set of multi-doped cerium-activated scintillation materials of the solid solutions on the basis of the rare earth silicate, comprising lutetium and having compositions represented by the chemical formulas: (Lu2−w−x+2yAwCexSi1−y)1−zMexJjOq and (Lu2−w−x−2yAwCexSi1+y)1−zMezJjOq. The invention is useful for detection of elementary particles and nuclei in high-energy physics, nuclear industry; medicine, Positron Emission Tomography (TOF PET and DOI PET scanners) and Single Photon Emission Computed Tomography (SPECT), Positron Emission Tomography with Magnetic Resonance imaging (PET / MR); X-ray computer fluorography; non-destructive testing of solid state structure, including airport security systems, the Gamma-ray systems for the inspection of trucks and cargo containers.

Owner:ZECOTEK IMAGING SYST SINGAPORE

Nuclear magnetic resonance tool using switchable source of static magnetic field

ActiveUS7859260B2Electric/magnetic detection for well-loggingMaterial analysis by using resonanceSolid-state nuclear magnetic resonanceSpin magnetic moment

A nuclear magnetic resonance sensing apparatus and method for operating in an earth borehole comprises a source of switchable magnetic field to polarize nuclei in the region of interest, said source comprising a coil wound on a magnetic core having controllable residual magnetization. Maintaining the magnetization of the core during a polarization interval does not require steady current in the coil. Switching intensity and polarity of magnetization of the core causes precession of spin magnetic moments of the nuclei; the precession induces a signal indicative of nuclear magnetic resonance properties of earth formations.

Owner:BAKER HUGHES INC

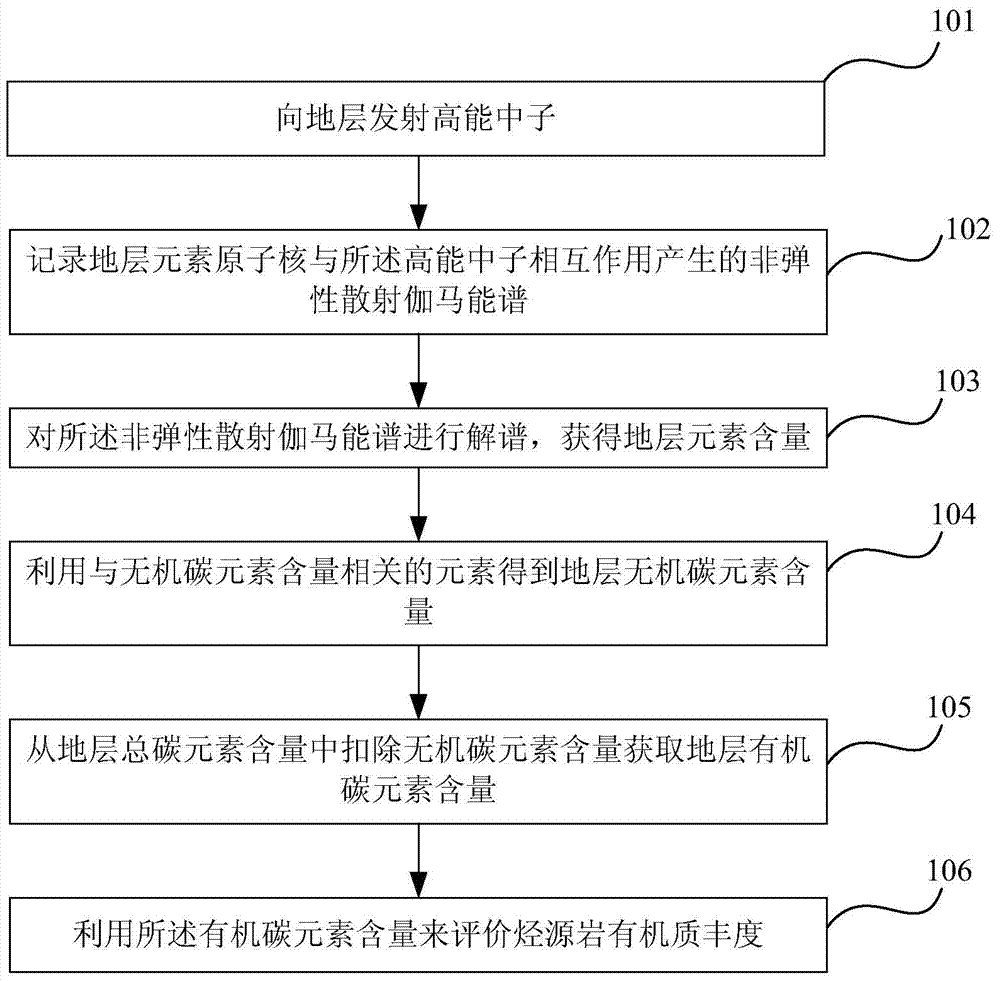

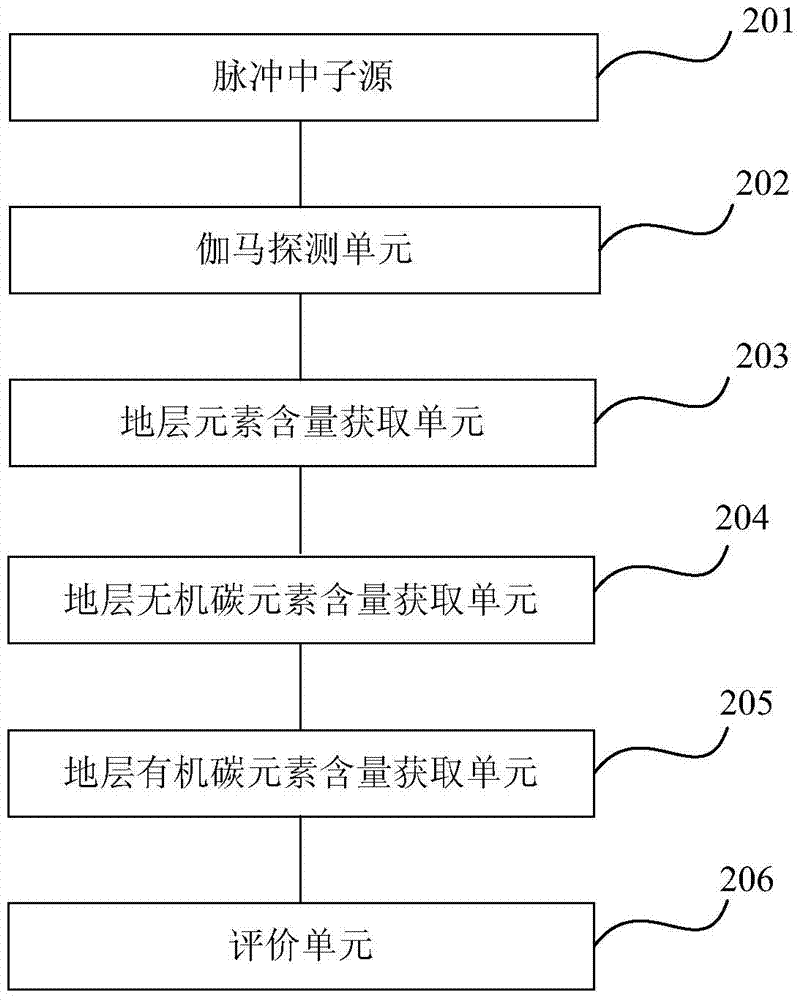

Method and device for evaluating abundance of organic matter of hydrocarbon source rock

InactiveCN103760182ASolve the technical status of evaluating organic carbon elementsMeet the needs of direct evaluation of organic matter abundance in source rocksMaterial analysis using wave/particle radiationInelastic scatteringSoil organic matter

The invention provides a method and a device for evaluating abundance of organic matter of a hydrocarbon source rock, wherein the method comprises the following steps: emitting high-energy neutron to a stratum; recording an inelastic scattering gamma-ray spectra generated by the interaction of nucleus of elements in the stratum and the high-energy neutron; analyzing the inelastic scattering gamma-ray spectra, to obtain the content of elements in the stratum; obtaining the content of inorganic carbon in the stratum by using the elements associated with the content of the inorganic carbon; deducting the content of the inorganic carbon from the total carbon content of the stratum, so as to obtain the content of the organic carbon in the stratum; evaluating the abundance of organic matter of the hydrocarbon source rock by using the content of the organic carbon element.

Owner:PETROCHINA CO LTD

Cancellation of ringing in magnetic resonance utilizing a composite pulse

InactiveUS20050030029A1Eliminating or canceling acoustic ringingCoil ringdown and piezoelectric ringing are also substantially reducedMaterial analysis by using resonanceElectric/magnetic detectionSpinsPulse sequence

A magnetic resonance detection apparatus is provided that is not susceptible to acoustic ringing, and a method is provided for eliminating or canceling acoustic ringing from a detected magnetic resonance signal. Specifically, a composite pulse is utilized that allows for both efficient reduction of acoustic ringing signals and the detection of true NQR signals. The composite pulse can be used in any of the common NQR pulse sequences currently utilized simply via substitution of the original single pulses with the composite pulse. Furthermore, although a preferred application involves the spin-1 nucleus 14N and NQR, the composite pulse will be useful for the NQR of other nuclei such as 35Cl and 39K and in NMR applications and involving half-integer quadrupolar nuclei and spin-½ nuclei. In addition, coil ringdown and piezoelectric ringing are also substantially reduced.

Owner:NAVY USA REPRESENTED BY THE SEC OF THE

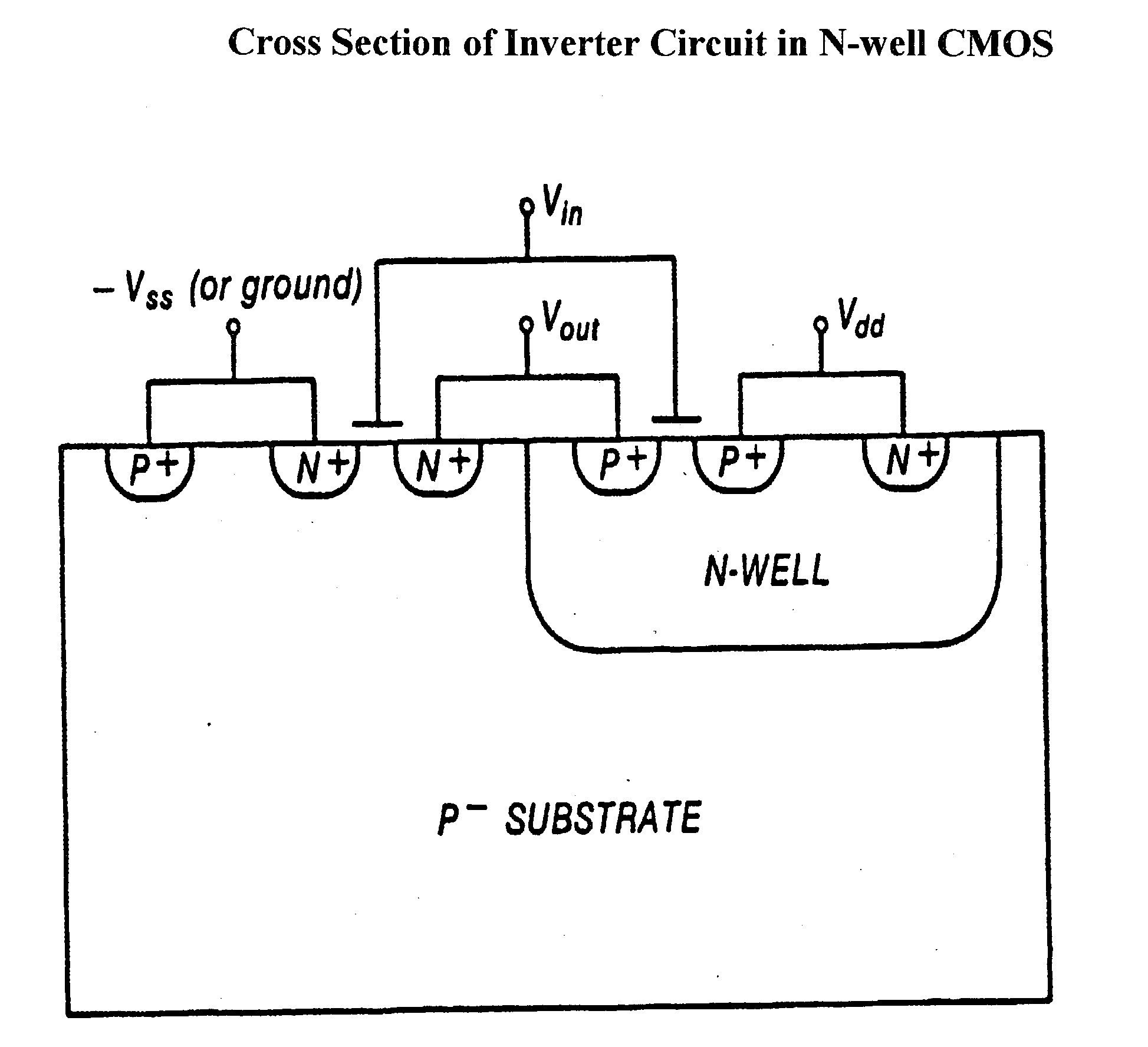

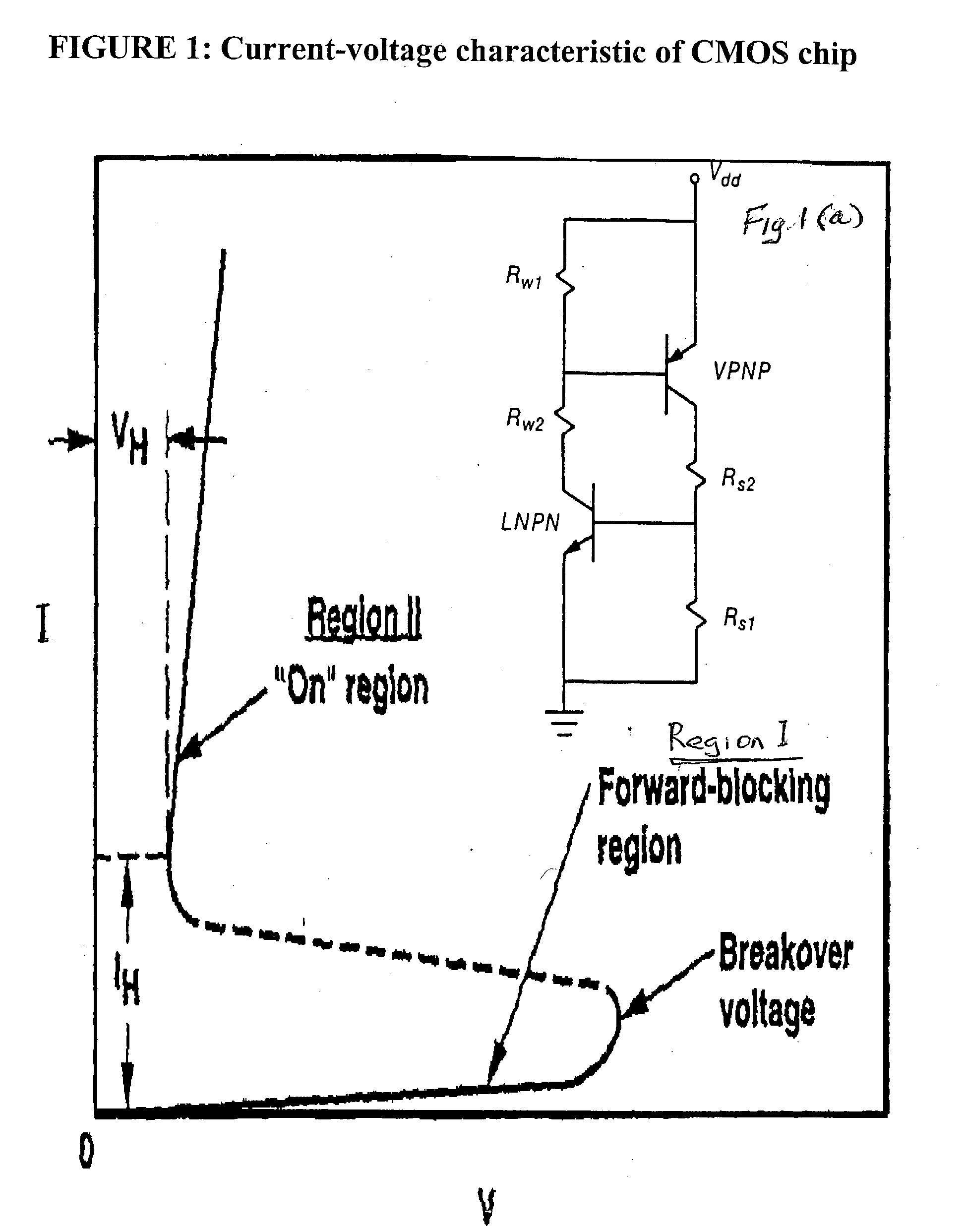

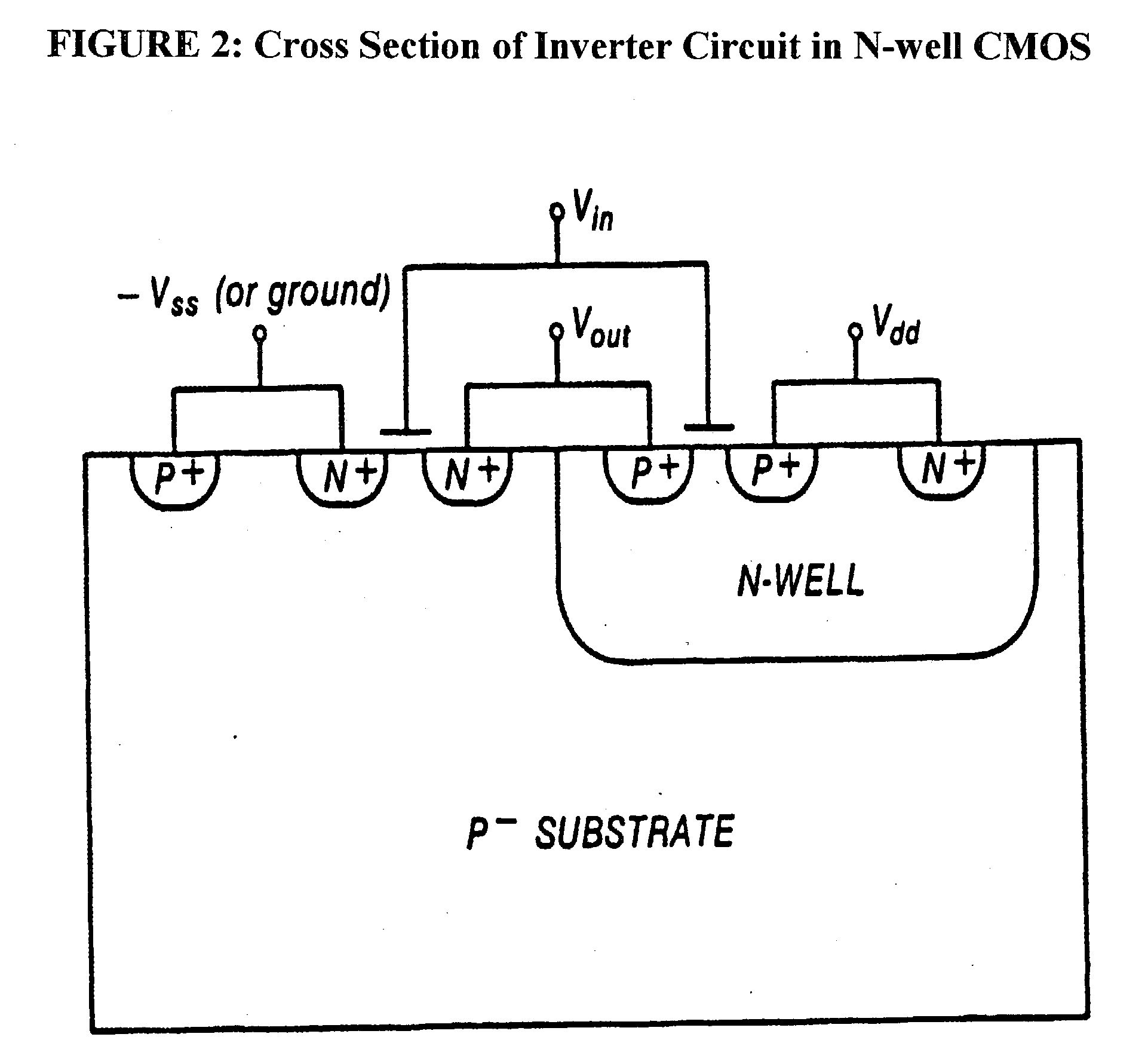

Technique for suppression of latchup in integrated circuits (ICS)

InactiveUS20040147080A1Improve abilitiesImprove reliabilityTransistorSemiconductor/solid-state device detailsHigh energySingle crystal

The present invention relates to a technique that can be used to reduce the sensitivity of integrated circuits to a failure mechanism to which some integrated circuits (ICs) are susceptible, known as latchup. The present invention relates to a scheme for suppressing latchup sensitivity by a step to be performed after the IC has been manufactured, rather than being a step in the normal production process. The process involves exposing silicon, either in wafer or die form, to energetic ions, such as protons (hydrogen nuclei) or heavier nuclei (e.g. argon, copper, gold, etc.), having energy sufficient to penetrate the silicon from the back of the wafer or die to within a well-defined distance from the surface of the silicon on which the integrated circuit has been formed (the front surface). The ions will enter the silicon through the surface of the silicon opposite to the surface onto which the integrated circuit has been formed (the back surface), will travel through the silicon, and will be completely stopped within a narrow, controlled distance from the front surface. This very high energy ion implantation will change the properties of silicon in such a way that the process or processes responsible for latchup are inhibited, either from the structural damage done to the single crystal, or from changes in the electrical properties of the silicon due to the chemical properties of the implanted ions, or both. Since the implanted ions all stop within a narrow region, spaced away from the region in which the components of the integrated circuit are located, the functionality and parameters of the IC are not degraded. Consequently, the procedure of the present invention is a method of processing silicon wafers or die so that the sensitivity of the ICs on this wafer or die to latchup is reduced or eliminated.

Owner:FULL CIRCLE RES

Environment-friendly aqueous road paint and manufacturing method thereof

The invention discloses environment-friendly aqueous road paint and manufacturing method thereof. Components such as water, a dispersing agent, inorganic salt fillers, diatomite, a wetting agent, rutile type titanium white powder, photocatalyst, acrylic emulsion, a pH regulating agent, a defoaming agent, a thickening agent, a film forming aid, and the like are sufficiently mixed according to a certain process flow. By utilizing the strong adsorptive capacity of the diatomite, harmful substances in vehicle exhausts are absorbed in a coating containing the photocatalyst, and the photocatalyst absorbs optical energy amount to below bandgap energy under the irradiation of light so as to ensure that electrons of the photocatalyst obtain certain energy to separate from the constraints of atomic nucleuses and electron orbits and become free electrons, thus various harmful gases in the vehicle exhausts, such as carbon monoxide, hydrocarbons, nitric oxides and the like can be oxidized and decomposed to finally form carbon dioxide, water and other innocuous substances having no harm to the human body so as to achieve the purpose of degrading the vehicle exhausts, thereby reducing photochemical smog phenomena.

Owner:CHINA PAINT MFG CO SHENZHEN

Atomic motion simulator

The invention relates to a power system, in particular to an atomic motion simulator for automatically making circumferential rotation motion without external energy or power. The known structure of an atom comprises an atomic nucleus, protons, electrons, neutrons, and the like, but the real structure inside the atom and perpetual generating mechanism inside the atomic nucleus cannot be known. The atomic motion simulator can help human beings to know the perpetual mechanism inside the atom and provide new methods for acquiring infinite clean energy and power.

Owner:李贵祥

Magnetic microstructures for magnetic resonance imaging

The present invention relates to a magnetic resonance structure with a cavity or a reserved space that provides contrast and the additional ability to frequency-shift the spectral signature of the NMR-susceptible nuclei such as water protons by a discrete and controllable characteristic frequency shift that is unique to each MRS design. The invention also relates to nearly uniform solid magnetic resonance T2* contrast agents that have a significantly higher magnetic moment compared to similarly-sized existing MRI contrast agents.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE COMMERCE +1

Method for separate imaging of water and fat based on inversion recovery technology and system

ActiveCN101518445ALarge signal amplitudeImprove signal-to-noise ratioDiagnostic recording/measuringMeasurements using NMR imaging systemsSignal-to-noise ratio (imaging)Hydrogen

The invention discloses a method for separate imaging of water and fat based on inversion recovery technology, which includes the following steps of: determining a first inversion recovery time when the longitudinal magnetization component of hydrogen atomic nucleus in fat or water is zero; respectively selecting a second inversion recovery time and a third inversion time before and after the first inversion recovery time; during the second and the third inversion recovery time, respectively using a scanning sequence to excite a detected object and obtaining two images simultaneously including a pure water image and a pure fat image; synthesizing the two obtained images; and when the synthesis removes the pure fat image included in the two images, obtaining a pure water image, when the synthesis removes the pure water image included in the two images, obtaining a pure fat image. By the use of the invention, the pure water image and the pure fat image can be obtained at one time by using the scanning sequence to excite the detected object and the signal-to-noise ratio of the images is relatively high.

Owner:SIEMENS HEALTHINEERS LTD

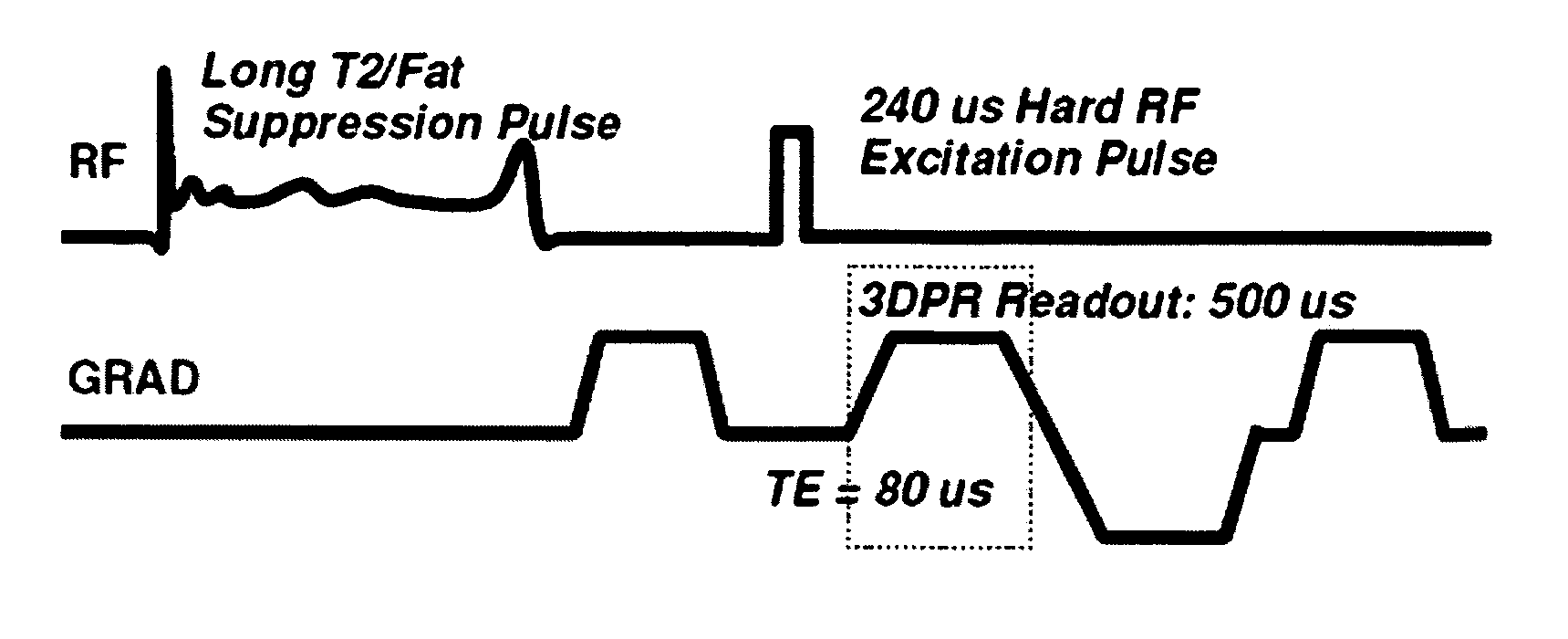

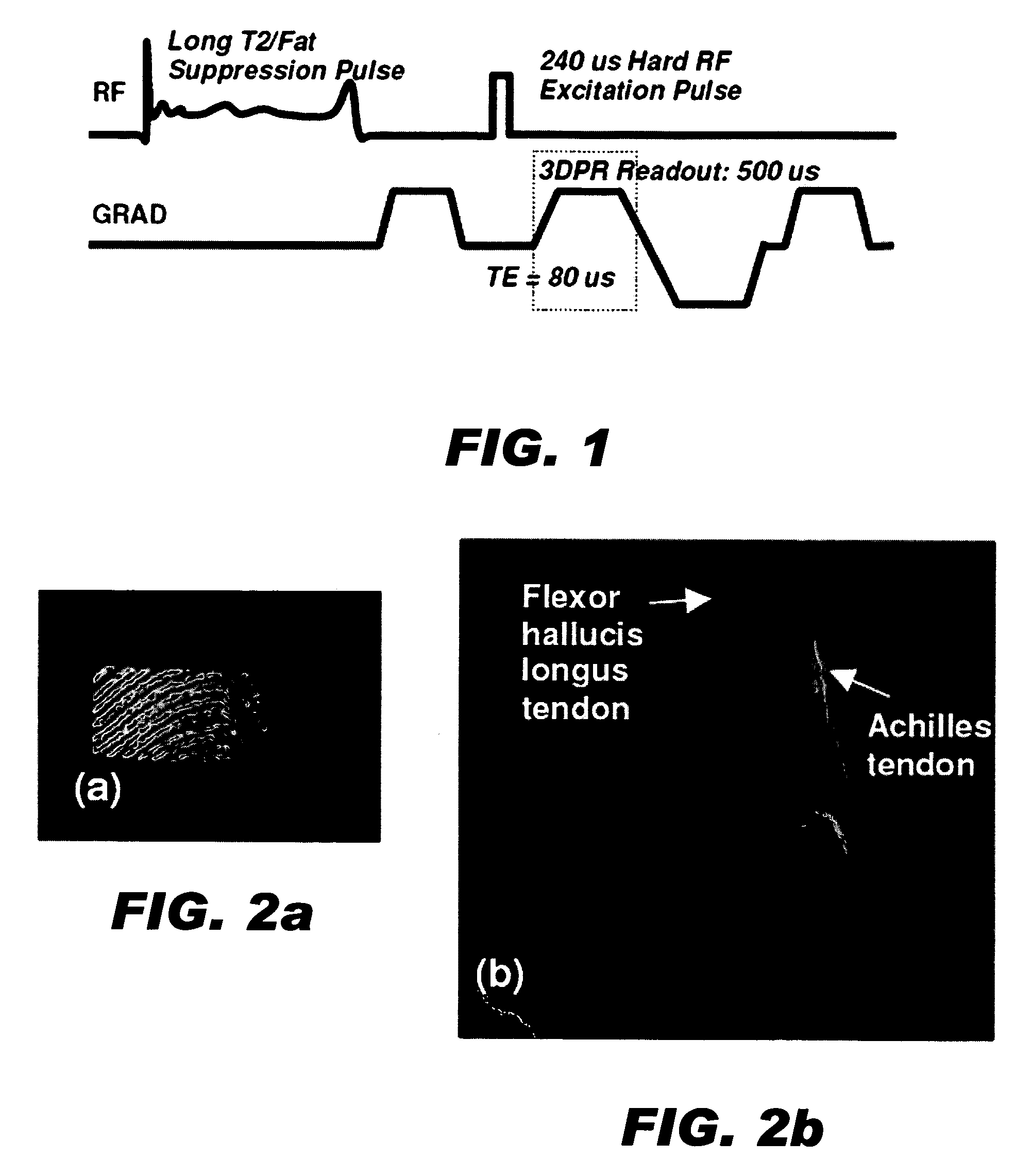

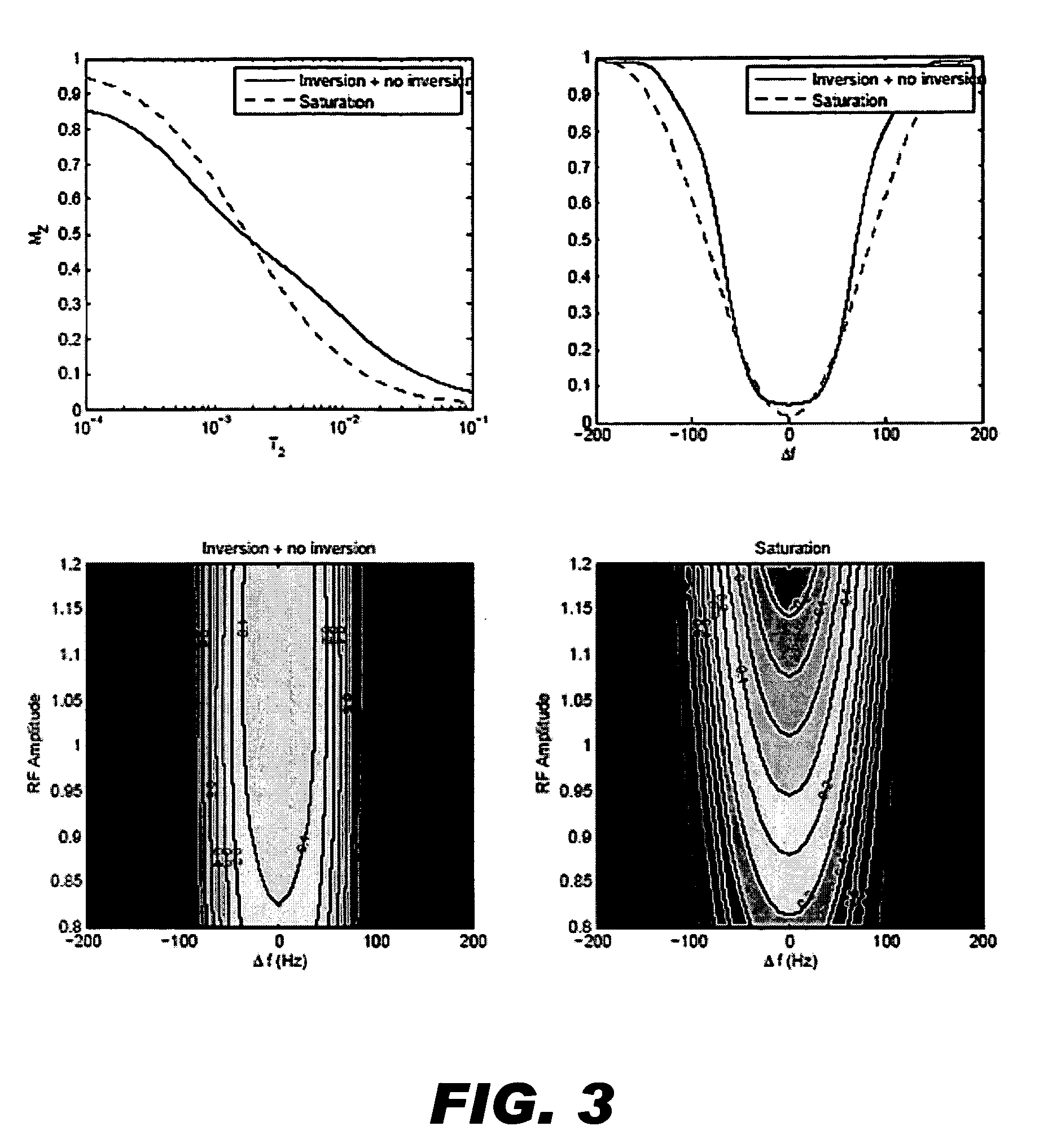

RF pulses for long T2 suppression in MRI

ActiveUS7288936B2Minimal interferenceMagnetic measurementsElectric/magnetic detectionTransverse planePulse sequence

In imaging a first species having a short T2 magnetic resonance parameter in the presence of a second and third species having longer T2 parameters, a method of suppressing signals from the longer T2 species comprises the steps of: a) applying a RF saturation pulse with multiple suppression bands for the second and third species to excite nuclei spins of the longer T2 species with the magnitude of the RF pulse being sufficiently low so as not to excite nuclei spins of the short T2 species, the RF saturation pulse being sufficiently long to rotate the longer T2 species nuclei spins into a transverse plane, and b) dephasing the longer T2 species nuclei spins in the transverse plane. An imaging pulse sequence is then applied to image the short T2 species. Alternatively, the method can comprise the steps of a) applying a first inversion pulse for selective inverting species of the second longer T2 species, b) obtaining first image signals after step a, c) applying a second inversion pulse for selectively inverting species of the third longer T2 species, d) obtaining second image signals after step c), and e) combining the first image signals and the second image signal to image the first short T2 species with the longer second and third species cancelling in the combination. In each of these methods, either the second or third longer T2 species can be suppressed without suppressing the other by applying the RF saturation or inversion pulse only to the species to be suppressed.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com