Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

34results about How to "Improve performance and yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Integrated scheme for yield improvement by self-consistent minimization of IC design and process interactions

InactiveUS20050114822A1Improve performanceHigh yieldCAD circuit designOriginals for photomechanical treatmentEngineeringSensitivity analyses

A method for performing self-consistent minimization of IC design and process interactions is disclosed. This method is based on calculating the amount of design-process interaction based on the information derived from circuit sensitivity analysis and process characterization. Optical proximity correction is subsequently performed in such a way that a) ensures that desired circuit performance is achieved in a given manufacturing environment if at all possible and b) also limits the increase in mask complexity to a realistic minimum.

Owner:AXELRAD VALERY +2

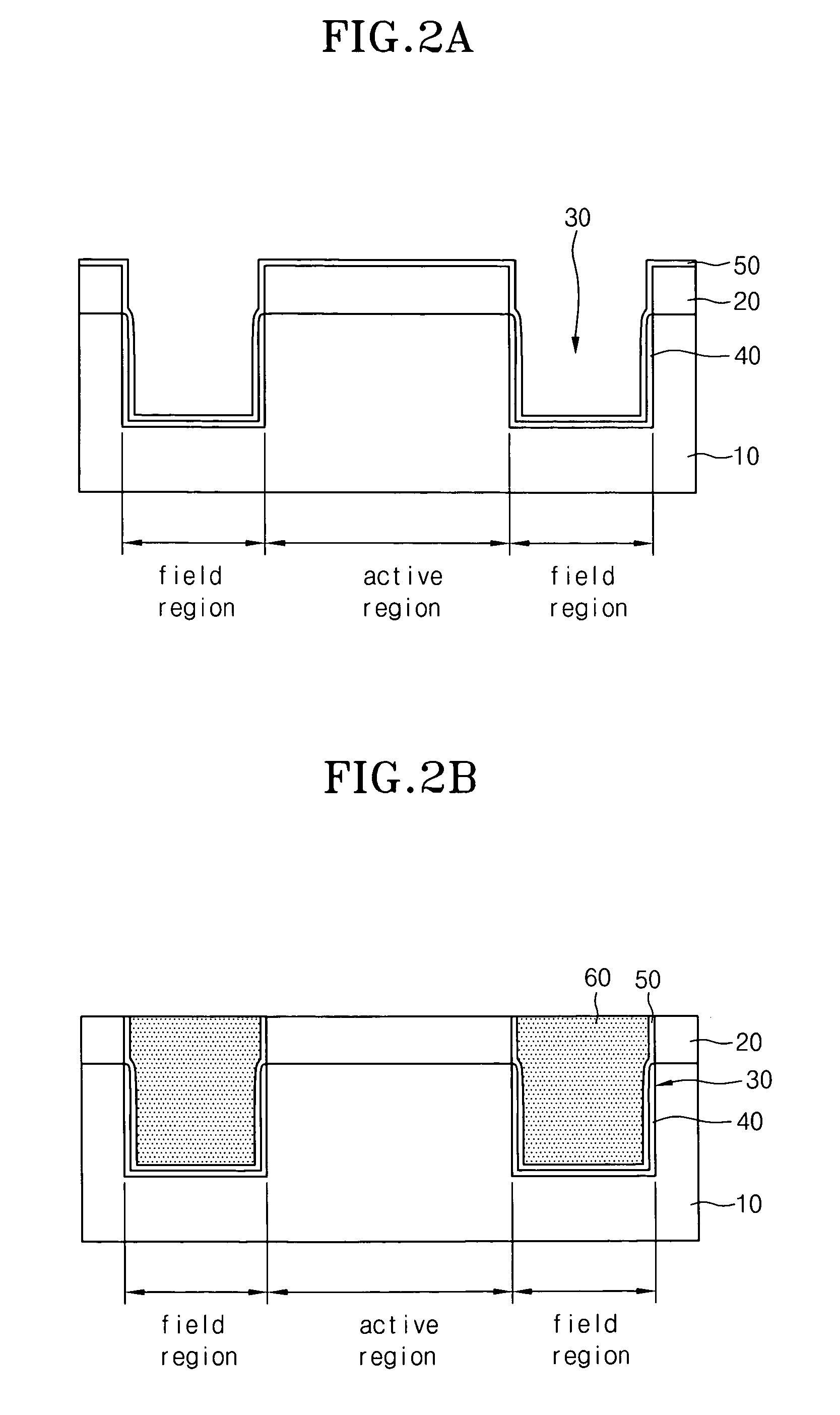

Method for forming shallow trench isolation in semiconductor device

InactiveUS20060145287A1Insulation performance be improveImprove insulation performanceSemiconductor/solid-state device manufacturingEtchingBiomedical engineering

A method for forming shallow trench isolation in a semiconductor device. The method includes forming a trench in a predetermined depth on a semiconductor substrate, filling the trench with a first filing oxide, injecting an impurity into a portion of the first filling oxide inside the trench, removing the portion of the first filling oxide by wet etching, and filling the trench with a second filling oxide.

Owner:DONGBU ELECTRONICS CO LTD

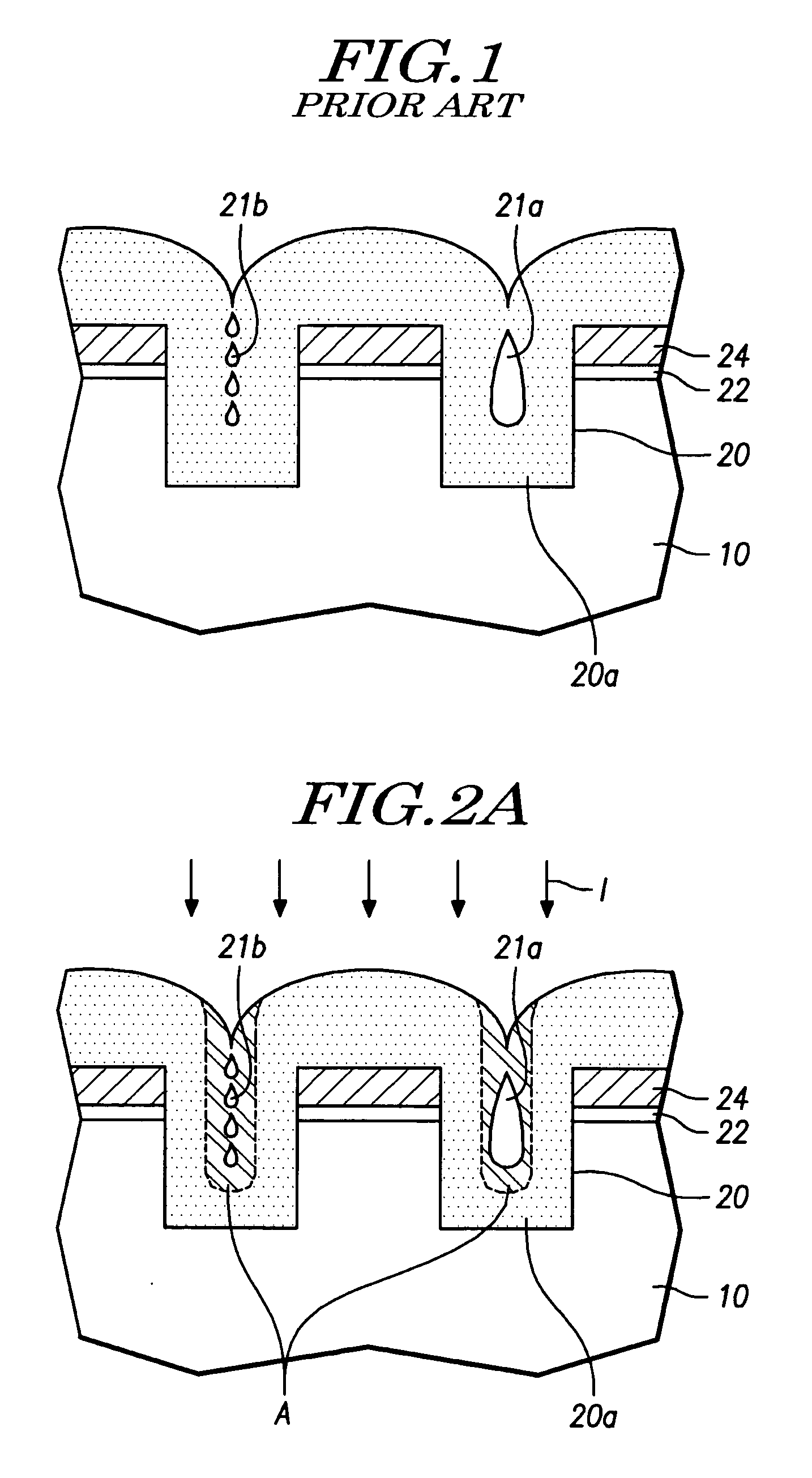

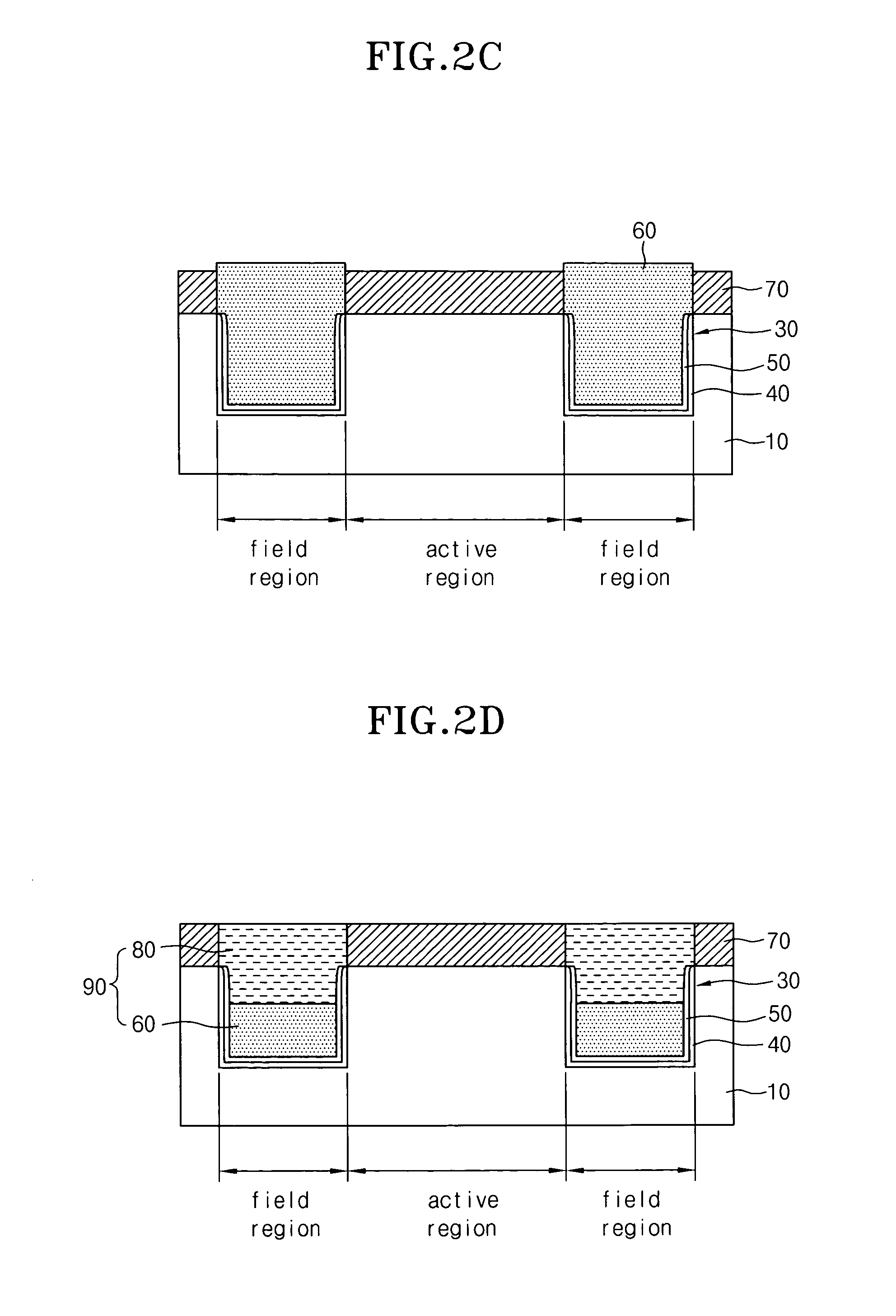

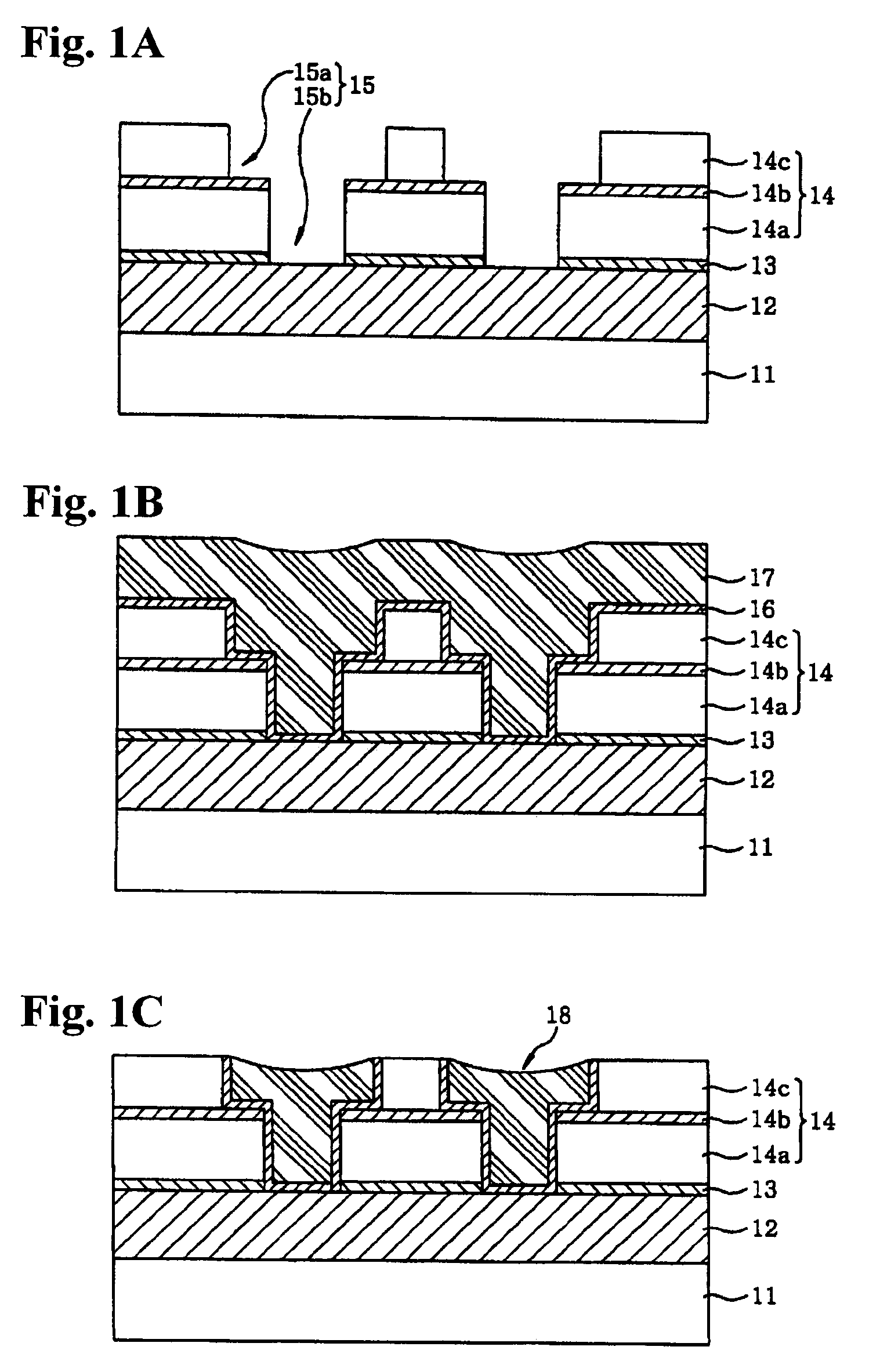

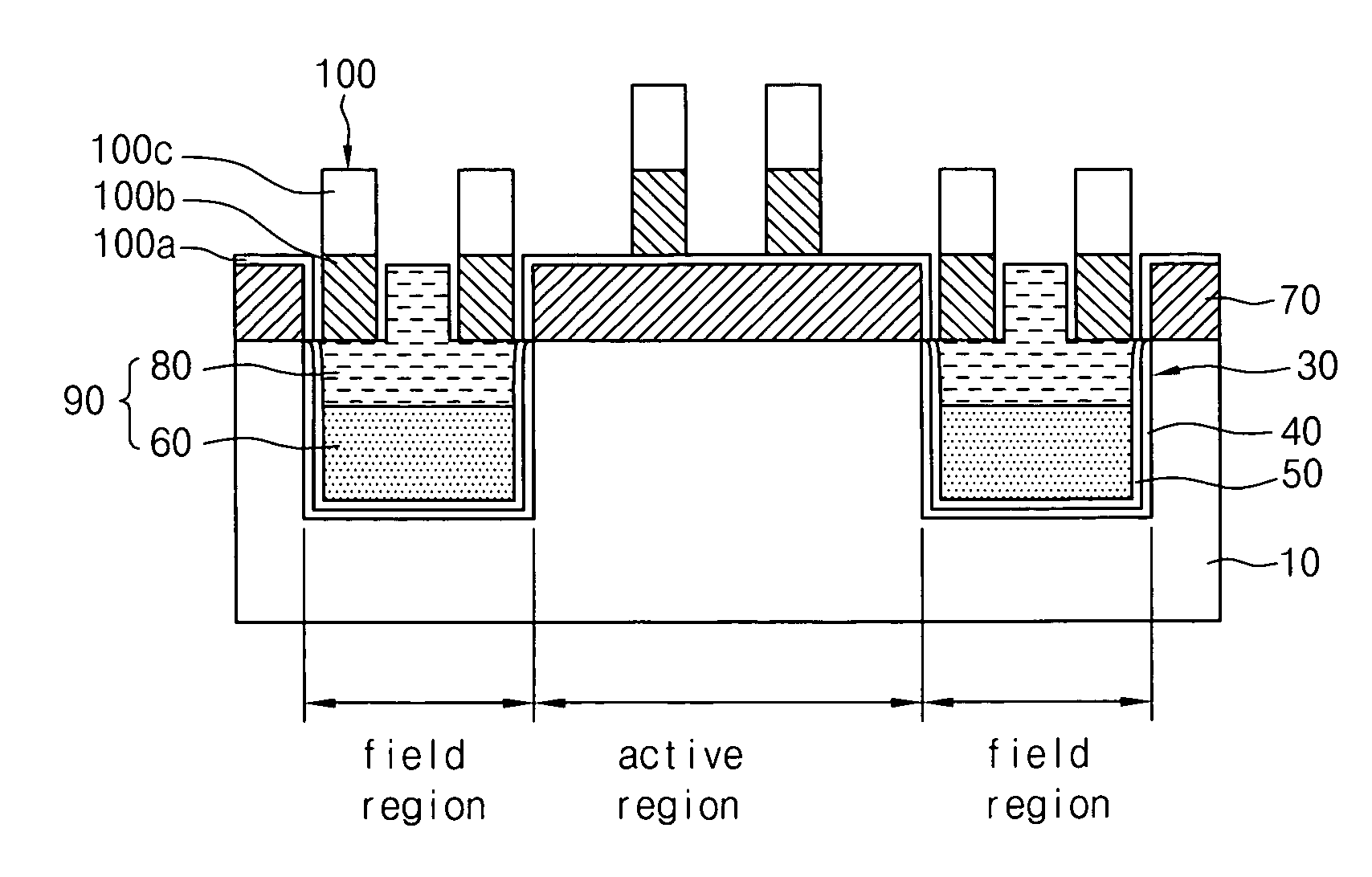

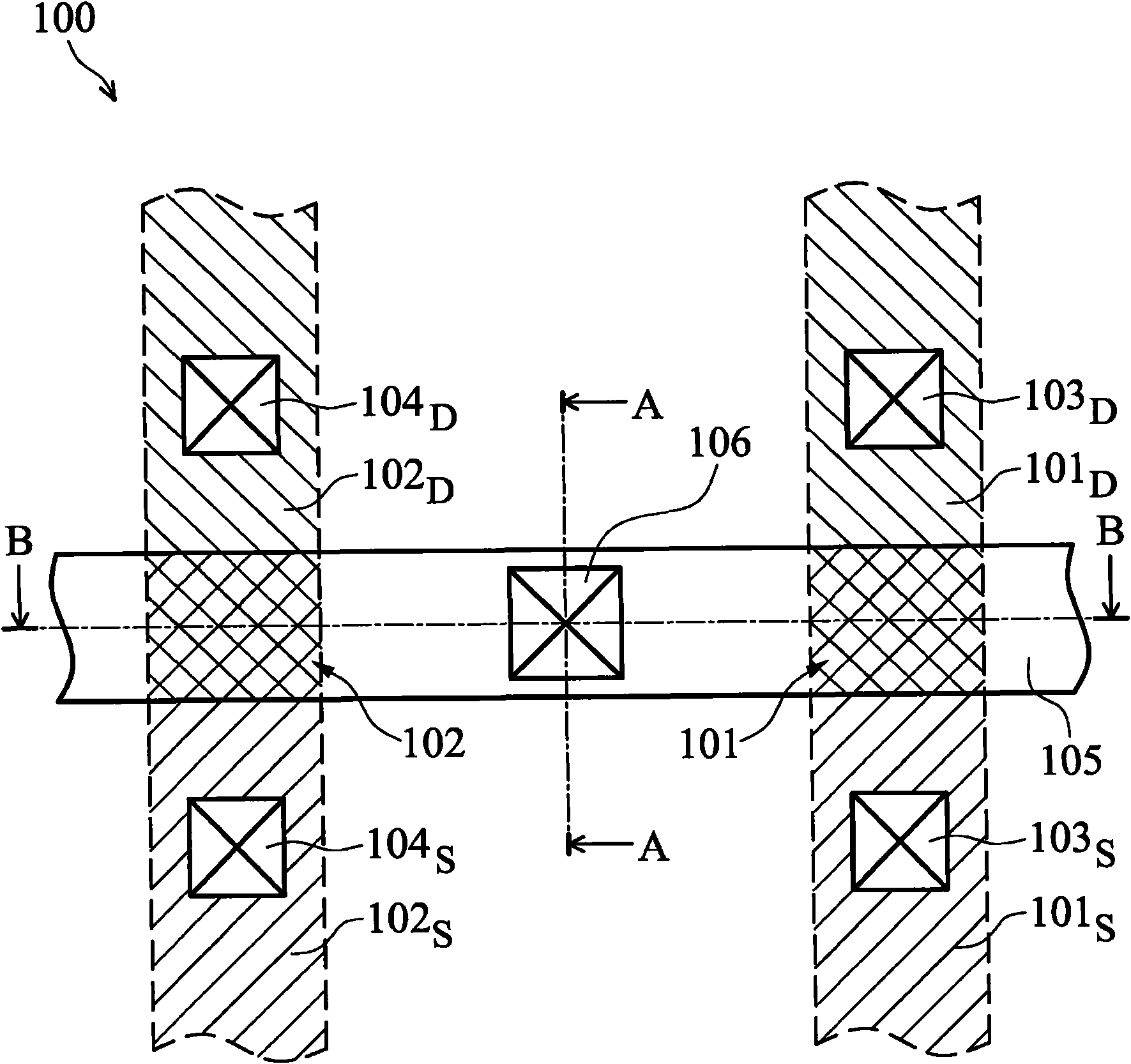

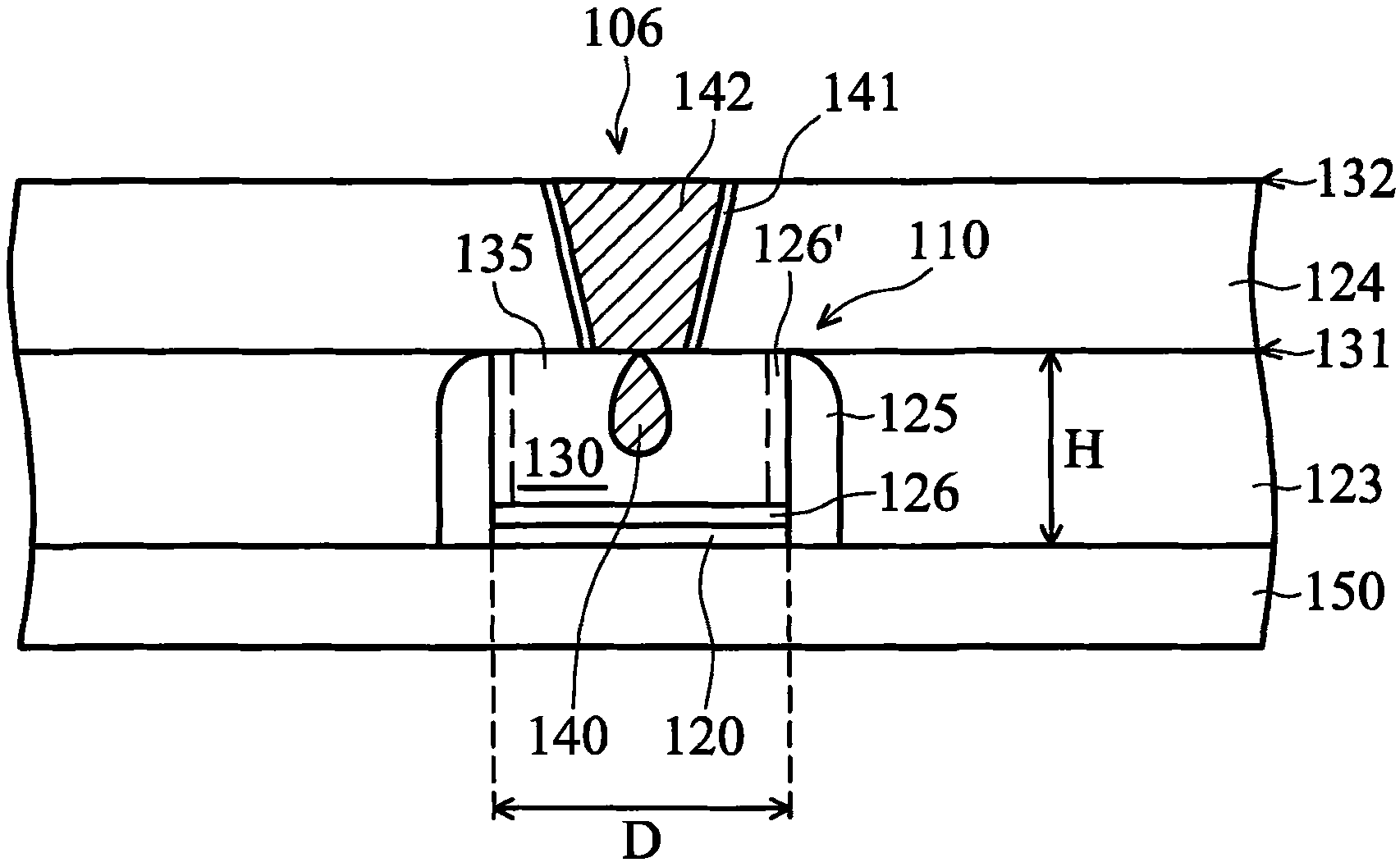

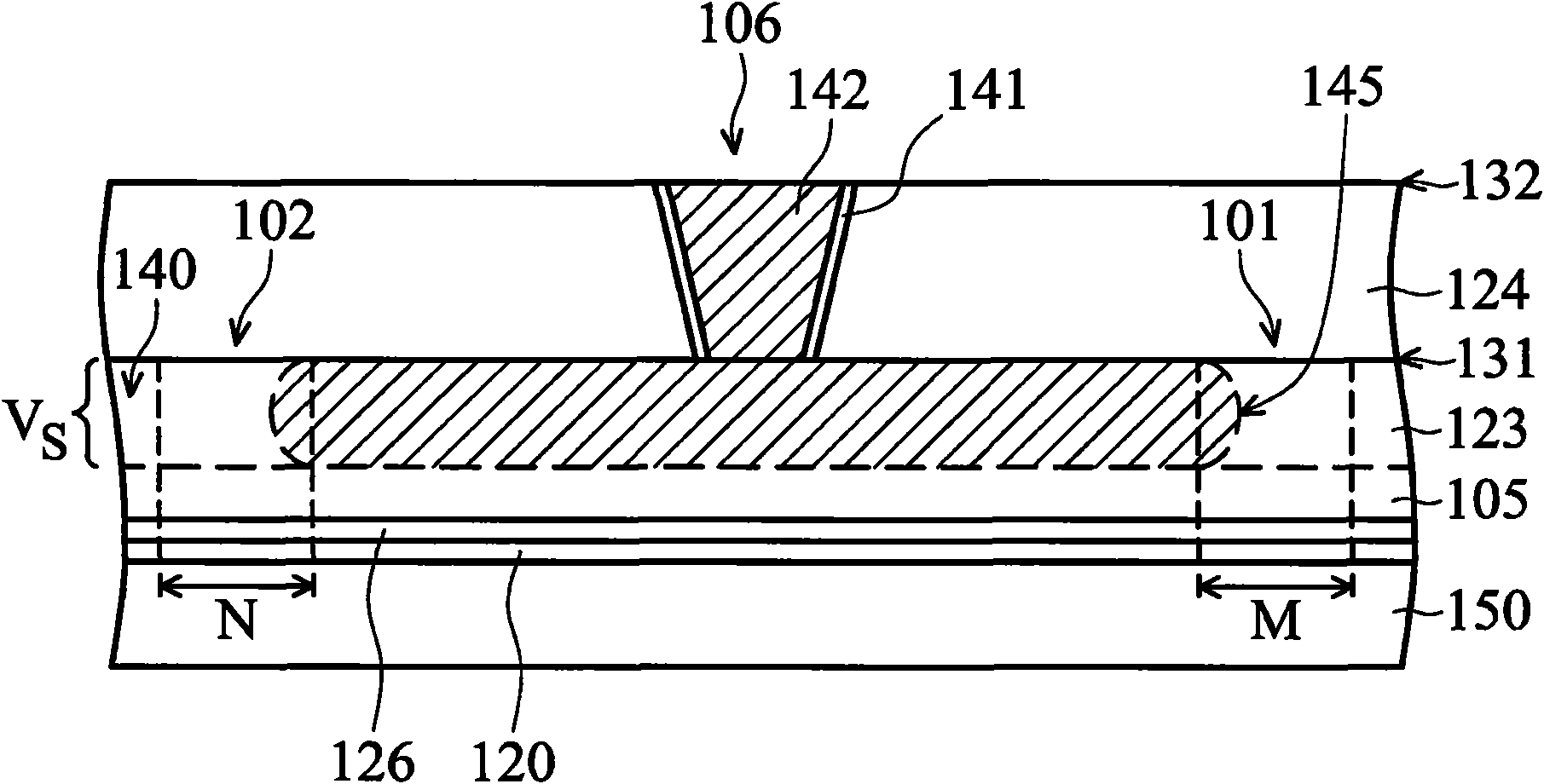

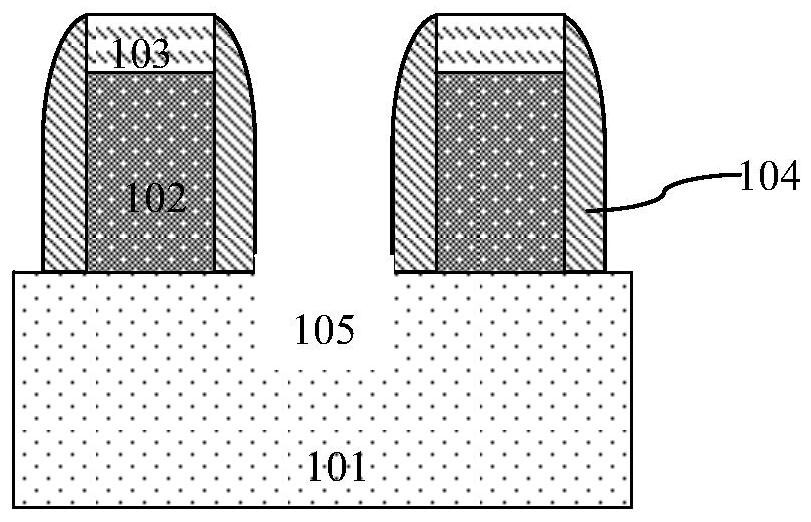

Method of forming fin transistor

InactiveUS20070148840A1Avoid layeringImprove performance and yieldSemiconductor/solid-state device manufacturingSemiconductor devicesSiliconHard mask

A fin transistor is formed by forming a hard mask layer on a substrate having an active region and a field region. The hard mask layer is etched to expose the field region. A trench is formed by etching the exposed field region. The trench is filled with an SOG layer. The hard mask layer is removed to expose the active region. An epi-silicon layer is formed on the exposed active region. The SOG layer is then partially etched from the upper end of the trench, thus filling a lower portion of the trench. A HDP oxide layer is deposited on the etched SOG layer filling the trench, thereby forming a field oxide layer composed of the SOG layer and the HDP oxide. The HDP oxide layer in the field oxide layer is etched to expose both side surfaces of the epi-silicon layer. A gate is then formed on the epi-silicon layer of which both side surfaces are exposed and the field oxide layer.

Owner:SK HYNIX INC

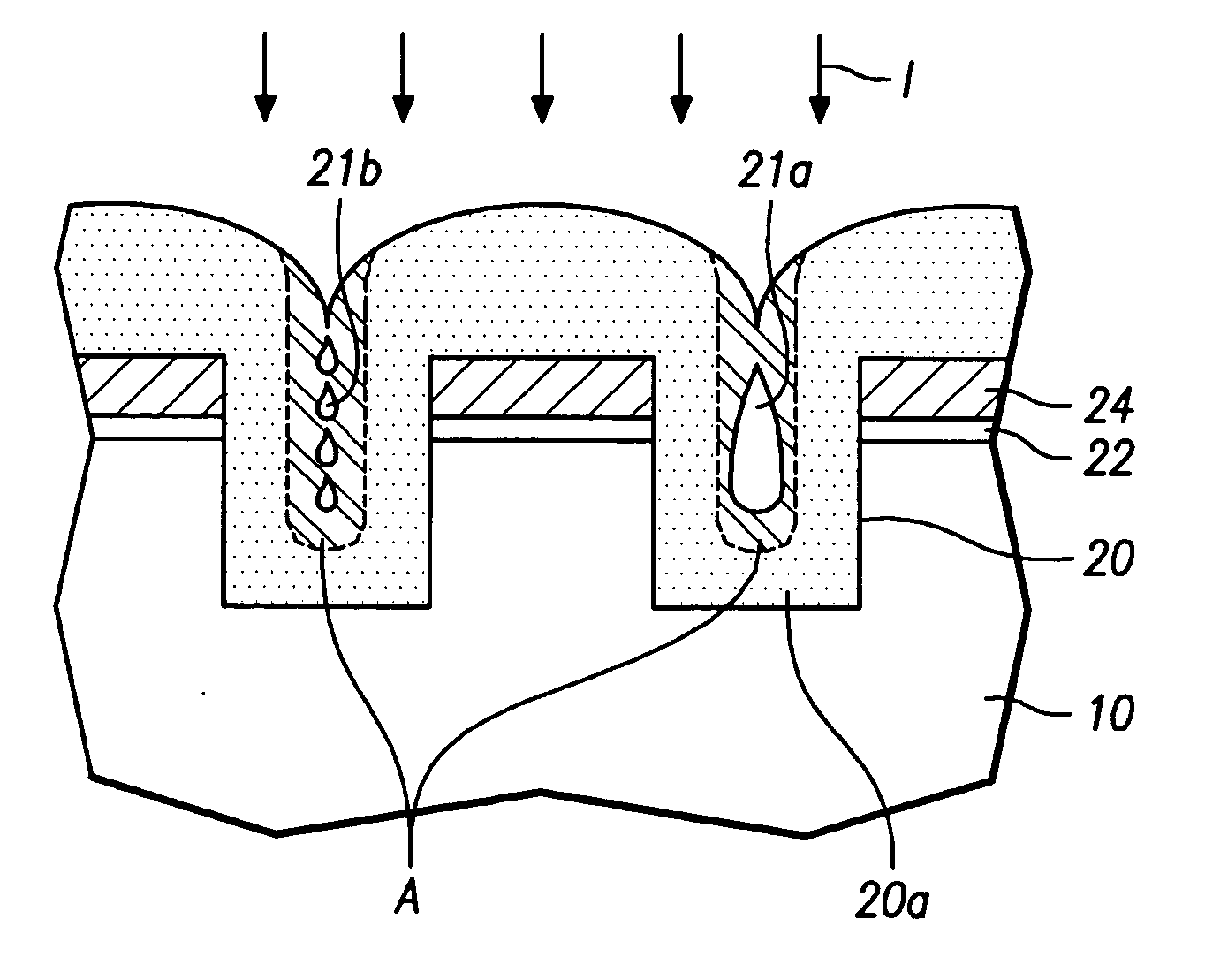

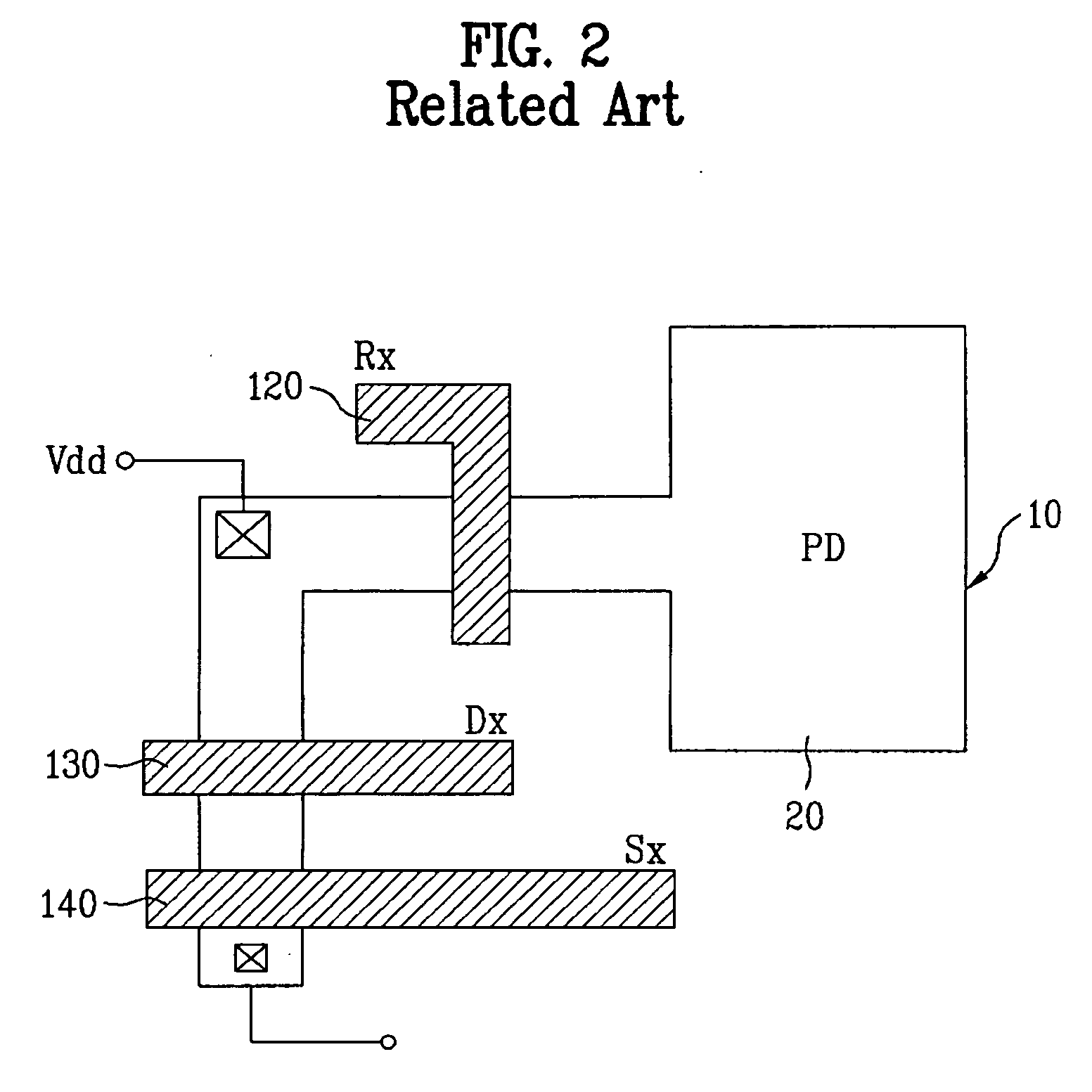

Method for fabricating a CMOS image sensor

InactiveUS20060141654A1Improve performance and yieldSolid-state devicesSemiconductor/solid-state device manufacturingCMOSElectron

A method for fabricating a CMOS image sensor in which an electron shower is performed for microlenses whose surfaces are charged to a positive potential, so as to neutralize the positive potential, thereby improving performance and yield of the image sensor.

Owner:DONGBU ELECTRONICS CO LTD

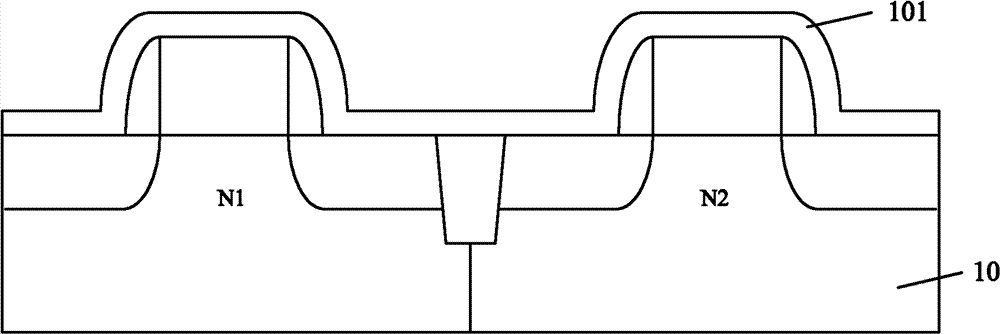

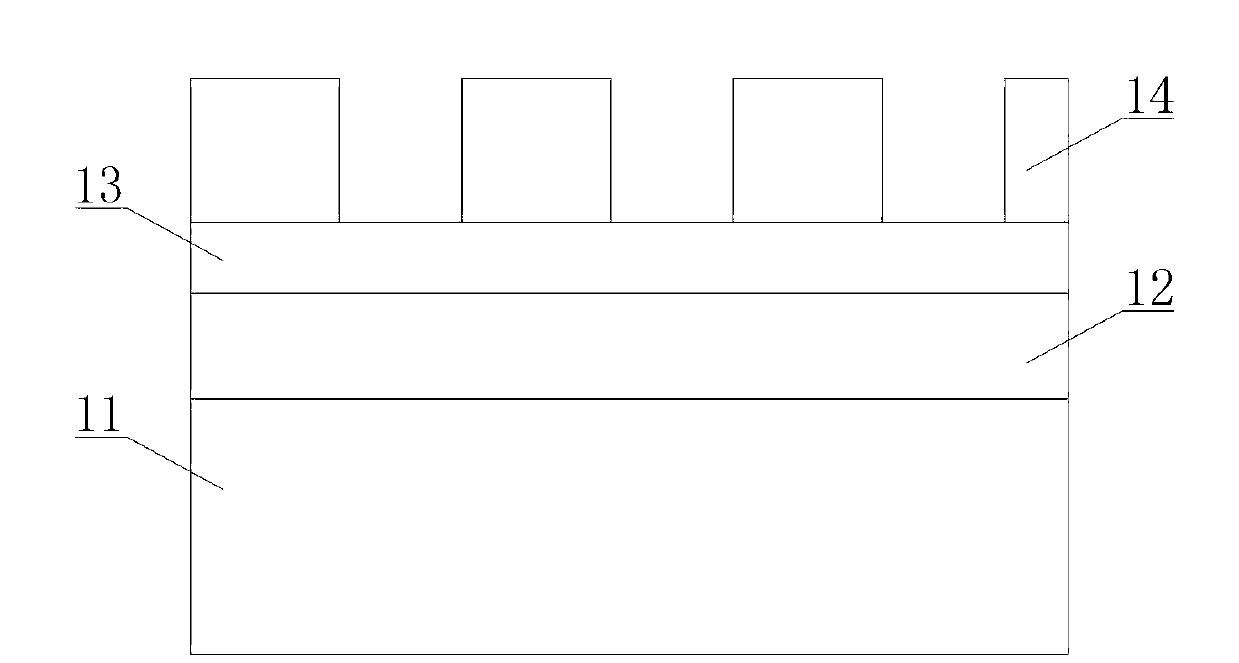

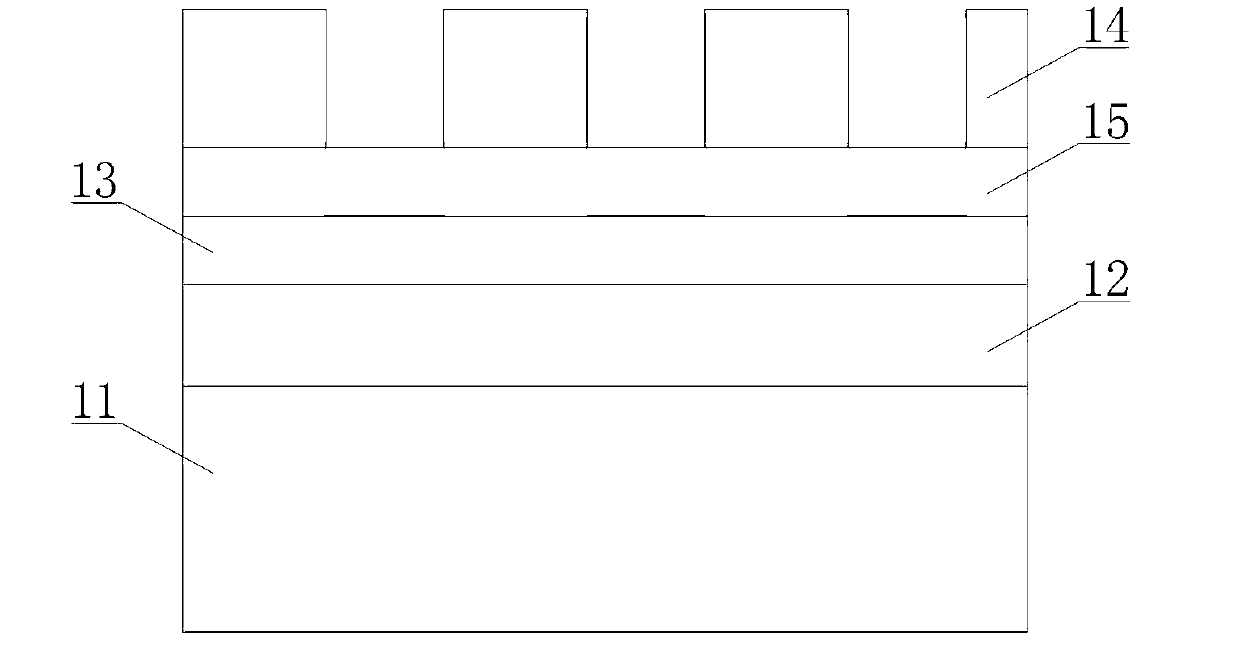

Fabrication method of CMOS (complementary metal-oxide-semiconductor transistor) transistor

ActiveCN102790013AImprove performance and yieldEvenly distributedSemiconductor/solid-state device manufacturingOxide semiconductorLaser annealing

The invention discloses a fabrication method of a CMOS (complementary metal-oxide-semiconductor transistor) transistor. The fabrication method comprises the steps of: providing a semiconductor structure, wherein the semiconductor structure comprises a semiconductor substrate, an NMOS (negative channel metal oxide semiconductor) transistor and a PMOS (positive channel metal oxide semiconductor) transistor formed on the semiconductor substrate; forming a strain layer on the surface of the NMOS transistor; etching the strain layer; exposing the PMOS transistor; carrying out a laser annealing process after carrying out primary peak annealing process; and carrying out secondary peak annealing process to restore damage generated by laser annealing, and removing the strain layer on the surface of the NMOS transistor. The damage generated by the semiconductor substrate is avoided, so that the performance and the yield of a semiconductor apparatus are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

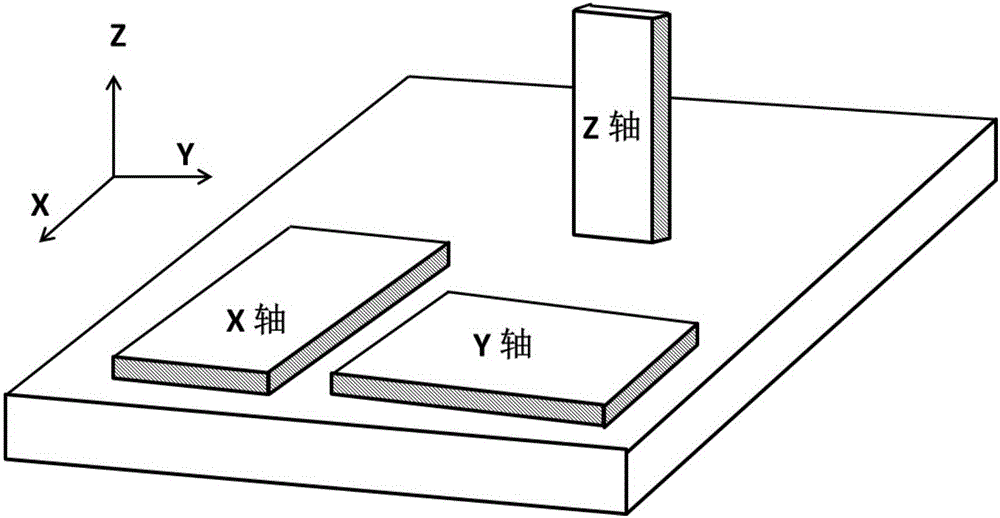

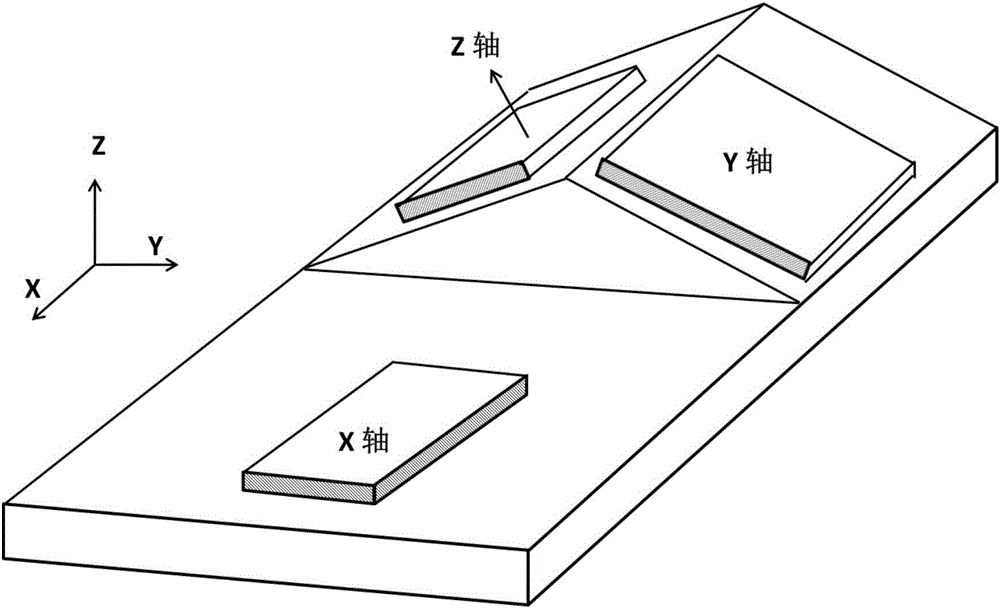

Single-chip three-axis magnetic sensor

InactiveCN106249181AImprove performance and yieldHigh precisionMagnetic measurementsMeasurement precisionElectrical conductor

The invention discloses a single-chip three-axis magnetic sensor. The three-axis magnetic sensor includes: an X-axis magnetic sensor, a Y-axis magnetic sensor, and a Z-axis magnetic sensor; the X-axis magnetic sensor and the Y-axis magnetic sensor are located in a plane , the Z-axis magnetic sensor adjusts the initial magnetization direction of the Z-axis magnetoresistive sensing unit, the orientation of the conductor unit and the magnetic The position of the resistive sensing unit and the conductor unit on the slope achieves a Z-axis magnetic sensor that only senses the magnetic field in the vertical direction but not the magnetic field in the horizontal direction. The single-chip three-axis magnetic sensor proposed by the invention can improve measurement accuracy and reduce production cost.

Owner:QST CORP

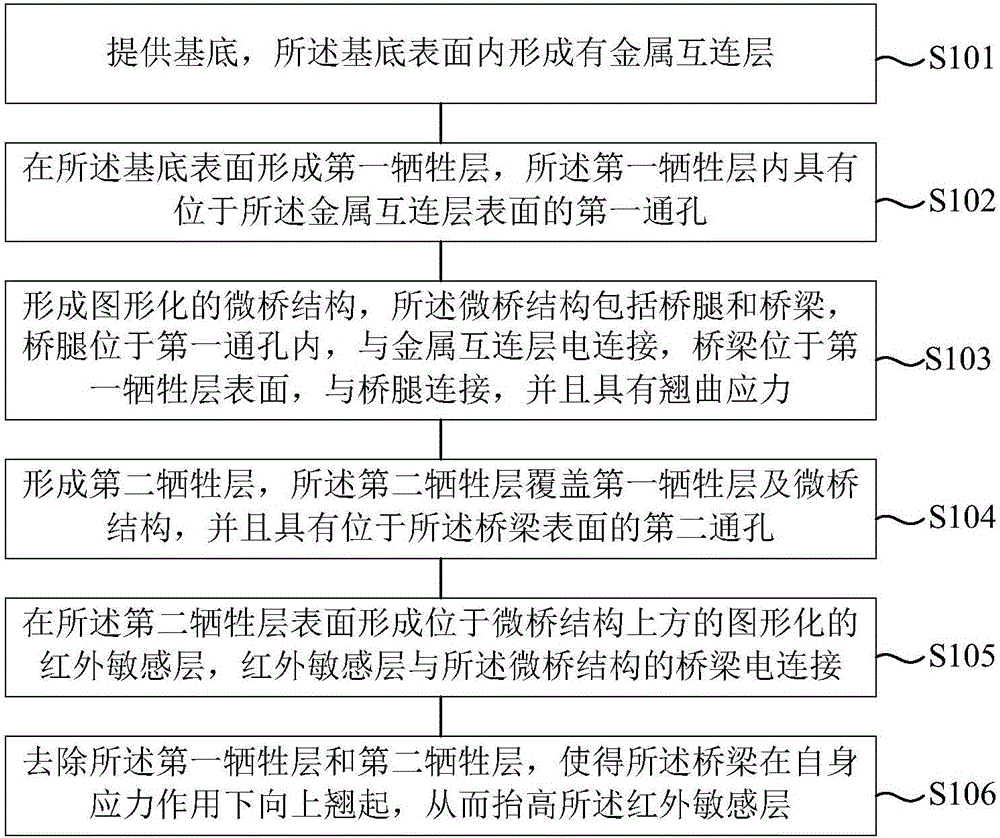

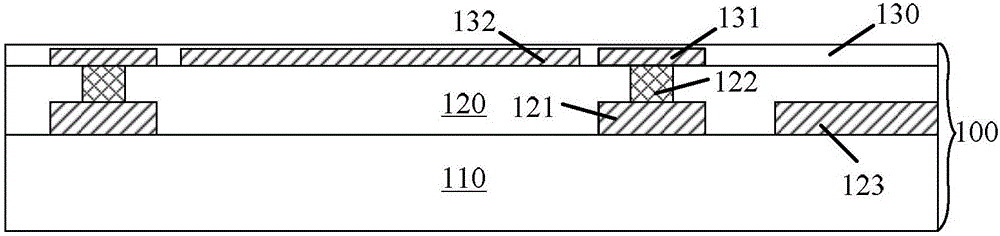

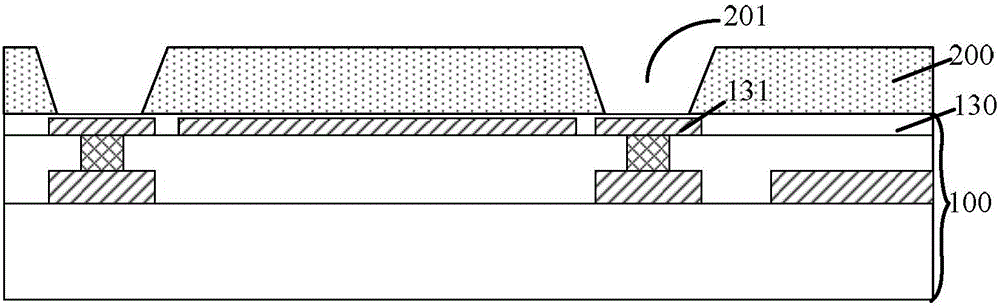

Infrared detector with microbridge structure and production method thereof

ActiveCN106629578AIncreasing the thicknessImprove performance and yieldTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesOptoelectronicsInfrared detector

The invention provides an infrared detector with microbridge structures and a production method thereof. The infrared detector comprises a base, wherein metal interconnection layers are formed in the surface of the base; the graphical microbridge structures which are partially suspended above the base, wherein the microbridge structures comprises bridge legs and bridge beams, the support beams are electrically connected with the metal interconnection layers, and the bridge beams are suspended and tilt upwards; and graphical infrared sensitive layers which are partially suspended above the microbridge structures, wherein the infrared sensitive layers are electrically connected with the bridge beams of the microbridge structures and are supported by the bridge beams. The yield of the infrared detector is improved and the relatively high performance is achieved.

Owner:ZHEJIANG DALI TECH +1

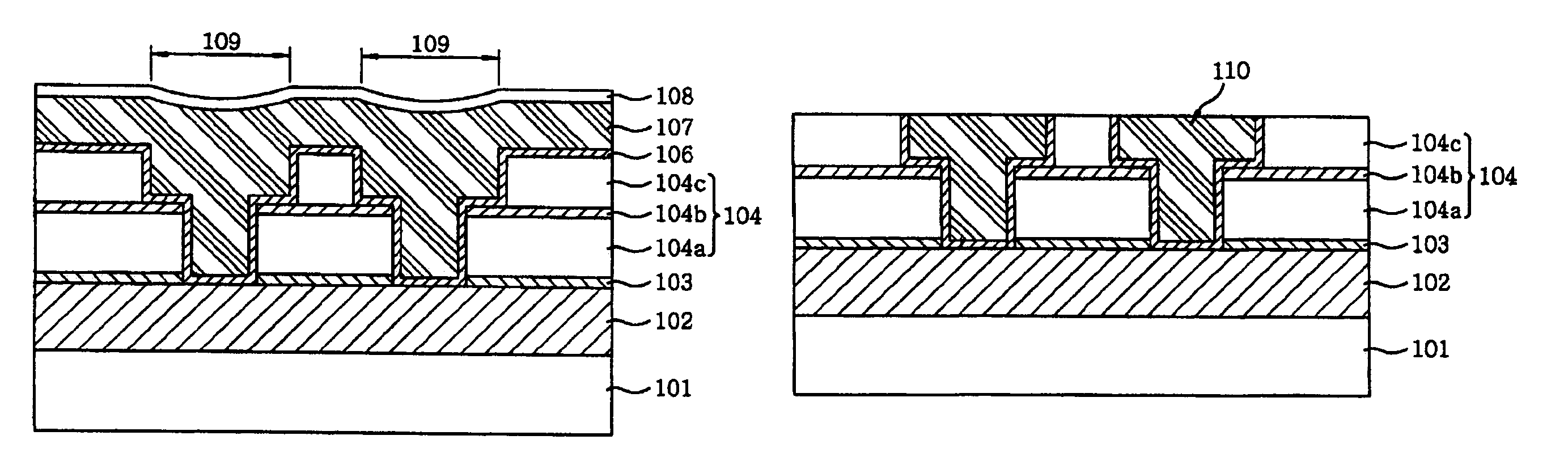

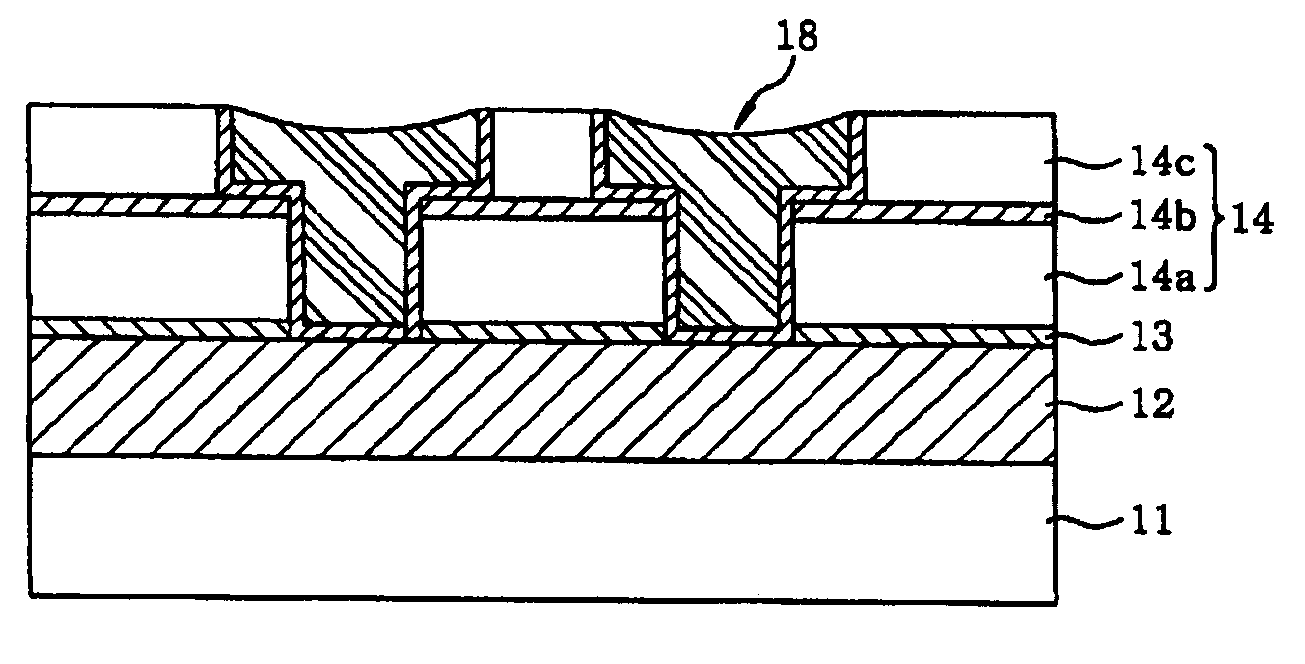

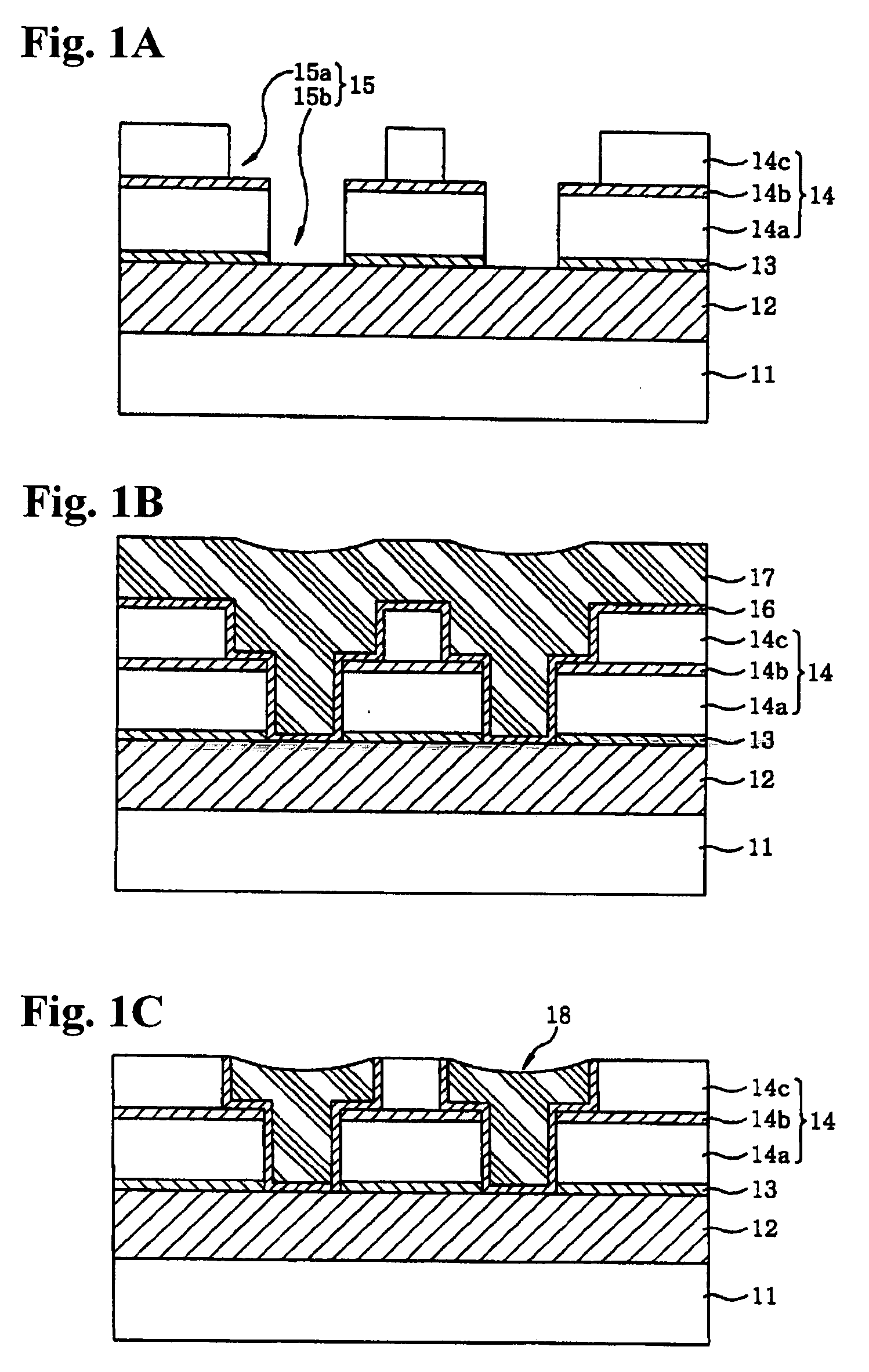

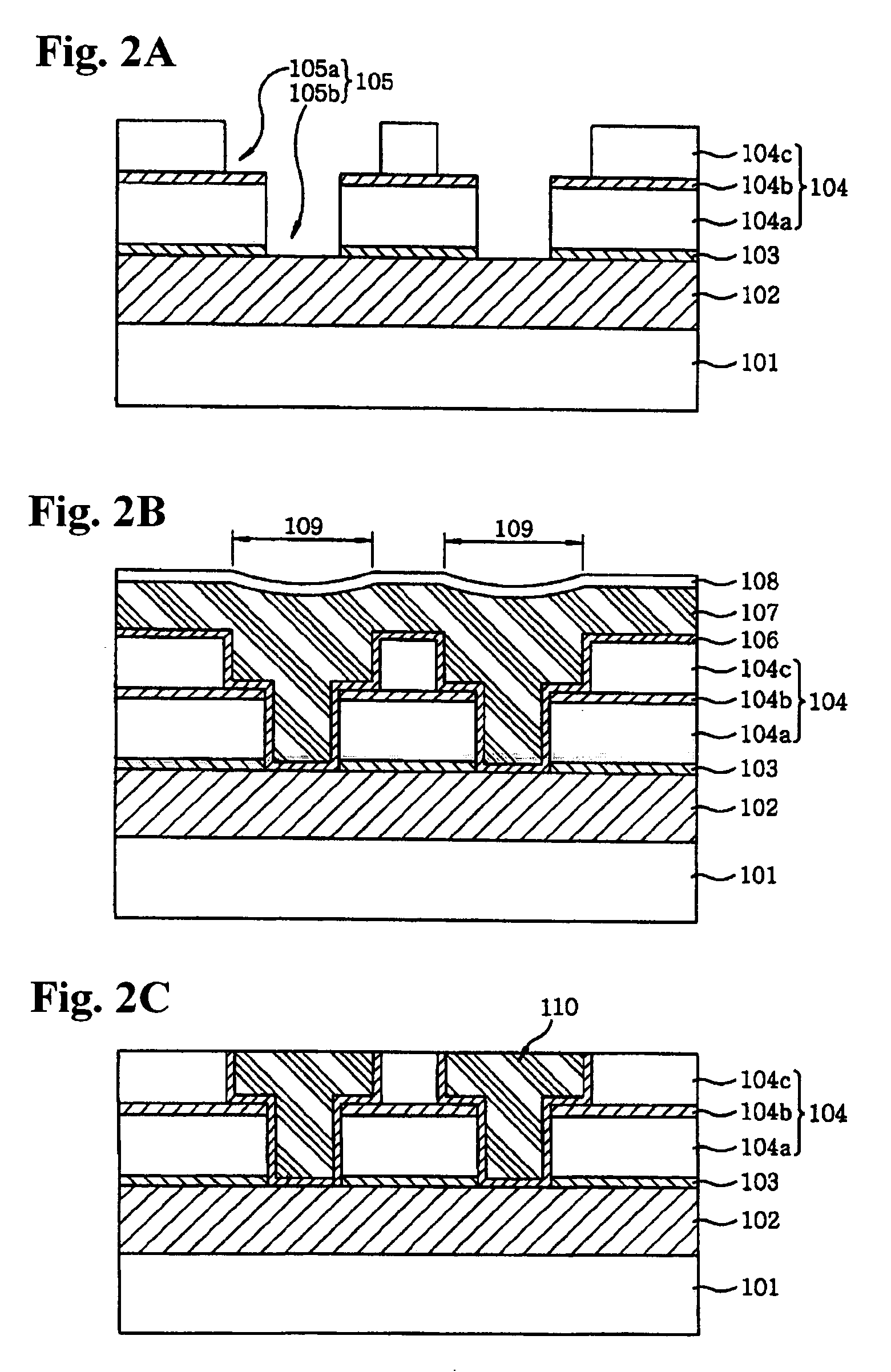

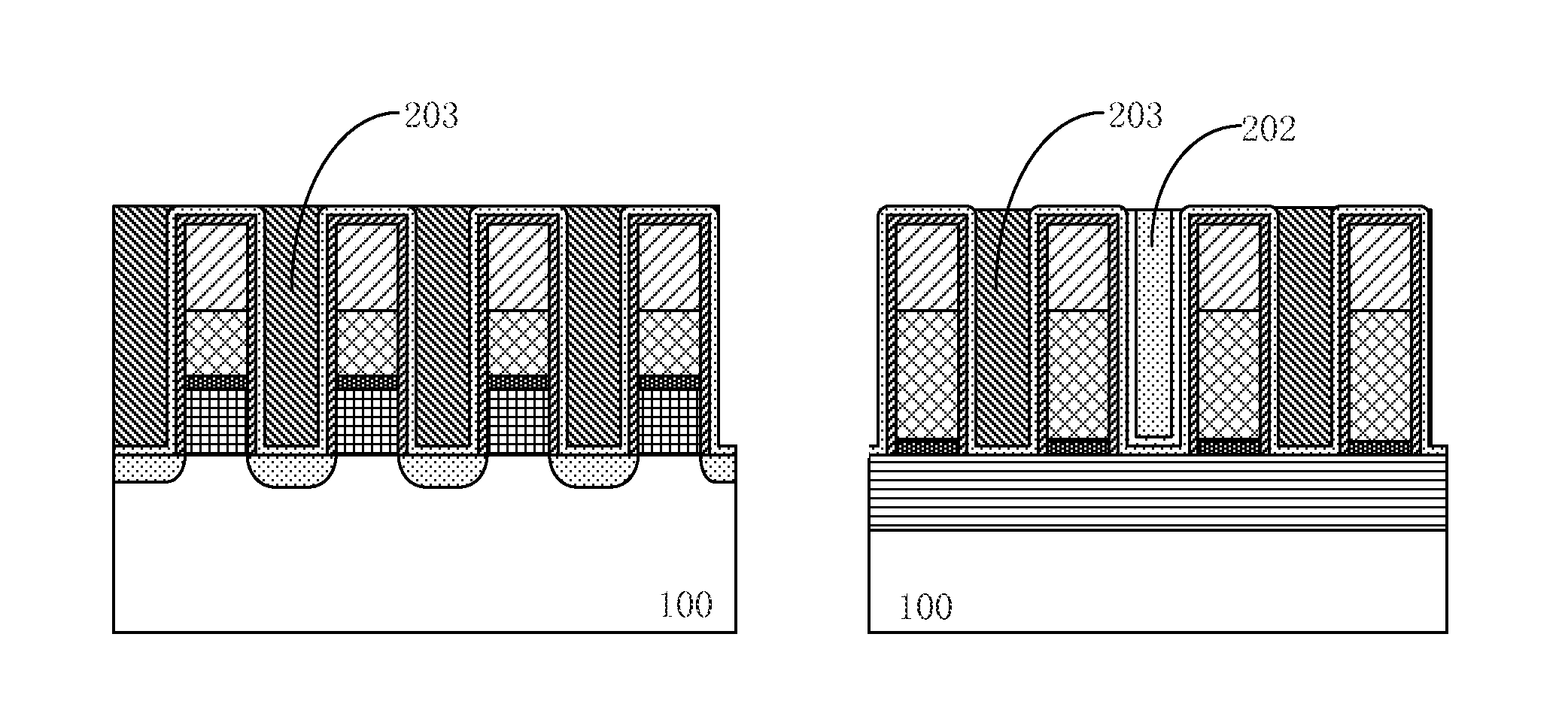

Method for fabricating metal line in a semiconductor

ActiveUS7300866B2Improve performance and yieldImprove flatnessSemiconductor/solid-state device manufacturingOxidation resistantSemiconductor

A metal line is fabricated in a semiconductor device by a method including: forming an etch stop layer on a substrate; forming an interlayer insulating layer on the etch stop layer, the interlayer insulating layer including dual damascene patterns, each respectively having a trench and a via contact hole; forming a barrier metal layer and a line metal layer on the interlayer insulating layer and in the dual damascene patterns; forming an anti-oxidation layer on above the line metal layer; and forming a metal line in the dual damascene patterns by planarizing an entire surface of the anti-oxidation layer.

Owner:MARVELL ASIA PTE LTD +1

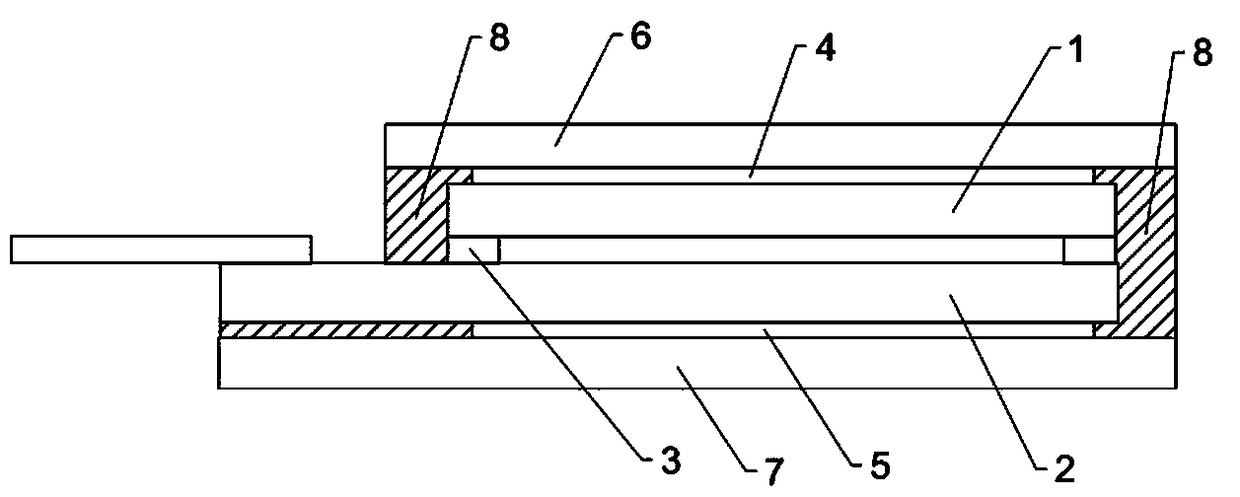

Packaging structure and method for flexible liquid crystal display panels

InactiveCN109164619AImprove performance and yieldLow manufacturing costNon-linear opticsPolarizerSealing wax

The invention discloses a packaging structure for flexible liquid crystal display panels. The packaging structure comprises a first substrate, a second substrate, a box sealing adhesive, a first polarizer, a second polarizer and a sealant, wherein the box sealing adhesive is located between the first substrate and the second substrate and is used for adhering the first substrate and the second substrate; the first polarizer is arranged on the outer surface of the first substrate; the second polarizer is arranged on the outer surface of the second substrate; the sealant is located between the first substrate and the second substrate and located at the outer side of the box sealing adhesive; and both the first polarizer and the second polarizer are polarizers with low water vapor permeability. According to the packaging structure, barrier membranes conventionally arranged on polarizers are saved, and the barrier membranes are integrated in the polarizers to obtain polarizers with low water vapor permeability; and meanwhile, a sealing wax layer is arranged at the outer side of the box sealing adhesive, and the polarizers with low water vapor permeability can effectively block the water vapor through being flush with two sides of the substrates, so that the performance and yield of the packaging structure are improved and the manufacturing cost is saved.

Owner:TRULY SEMICON

Method of forming fin transistor

InactiveUS7655534B2Avoid layeringImprove performance and yieldSemiconductor/solid-state device manufacturingSemiconductor devicesSiliconHard mask

A fin transistor is formed by forming a hard mask layer on a substrate having an active region and a field region. The hard mask layer is etched to expose the field region. A trench is formed by etching the exposed field region. The trench is filled with an SOG layer. The hard mask layer is removed to expose the active region. An epi-silicon layer is formed on the exposed active region. The SOG layer is then partially etched from the upper end of the trench, thus filling a lower portion of the trench. A HDP oxide layer is deposited on the etched SOG layer filling the trench, thereby forming a field oxide layer composed of the SOG layer and the HDP oxide. The HDP oxide layer in the field oxide layer is etched to expose both side surfaces of the epi-silicon layer. A gate is then formed on the epi-silicon layer of which both side surfaces are exposed and the field oxide layer.

Owner:SK HYNIX INC

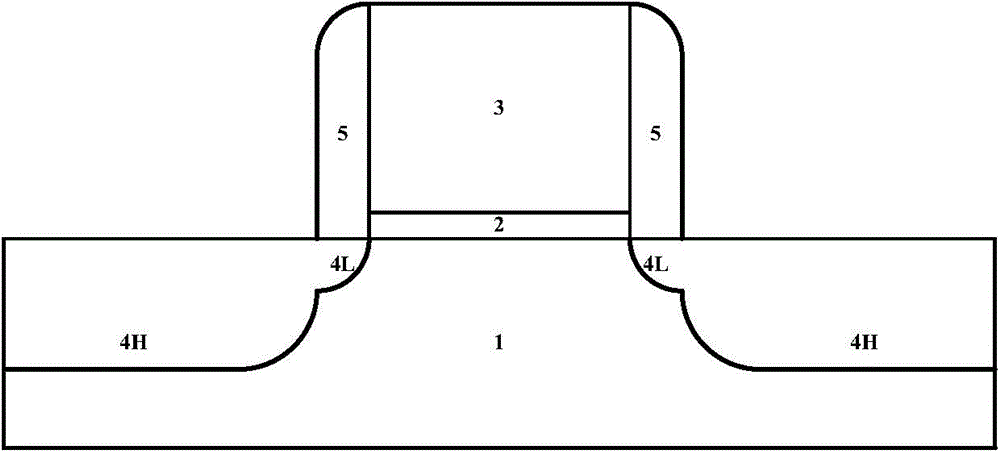

Integrated circuit structure and method to stop contact metal from extruding into gate

ActiveCN102169829AImprove performance and yieldImprove pass rateSolid-state devicesSemiconductor/solid-state device manufacturingWork functionCoverage function

The invention provides an integrated circuit structure and method to methods and structures used to prevent protrusion of contact metal (such as W) horizontally into gate stacks of neighboring devices to affect the work functions of these neighboring devices. A metal gate below a contact plug is defined by a work function layer with good sidewall coverage function and used as a gasket layer of the metal gate, wherein the contact plug is the neighboring device and in common use with (or connected to) the metal gate and the work function layer has good ladder coverage function to prevent the contact metal extruding into the gate stacks of the neighboring devices. Only modification to the mask layout for the photomask(s) used for removing dummy polysilicon is involved. No additional lithographical operation or mask is needed. Therefore, no modification to the manufacturing processes or additional substrate processing steps (or operations) is involved or required. The benefits of using the methods and structures described above may include increased device yield and performance.

Owner:TAIWAN SEMICON MFG CO LTD

Method for fabricating metal line in a semiconductor

ActiveUS20060009037A1Improve performanceHigh yieldSemiconductor/solid-state device manufacturingDevice materialOxidation resistant

A metal line is fabricated in a semiconductor device by a method including: forming an etch stop layer on a substrate; forming an interlayer insulating layer on the etch stop layer, the interlayer insulating layer including dual damascene patterns, each respectively having a trench and a via contact hole; forming a barrier metal layer and a line metal layer on the interlayer insulating layer and in the dual damascene patterns; forming an anti-oxidation layer on above the line metal layer; and forming a metal line in the dual damascene patterns by planarizing an entire surface of the anti-oxidation layer.

Owner:MARVELL ASIA PTE LTD +1

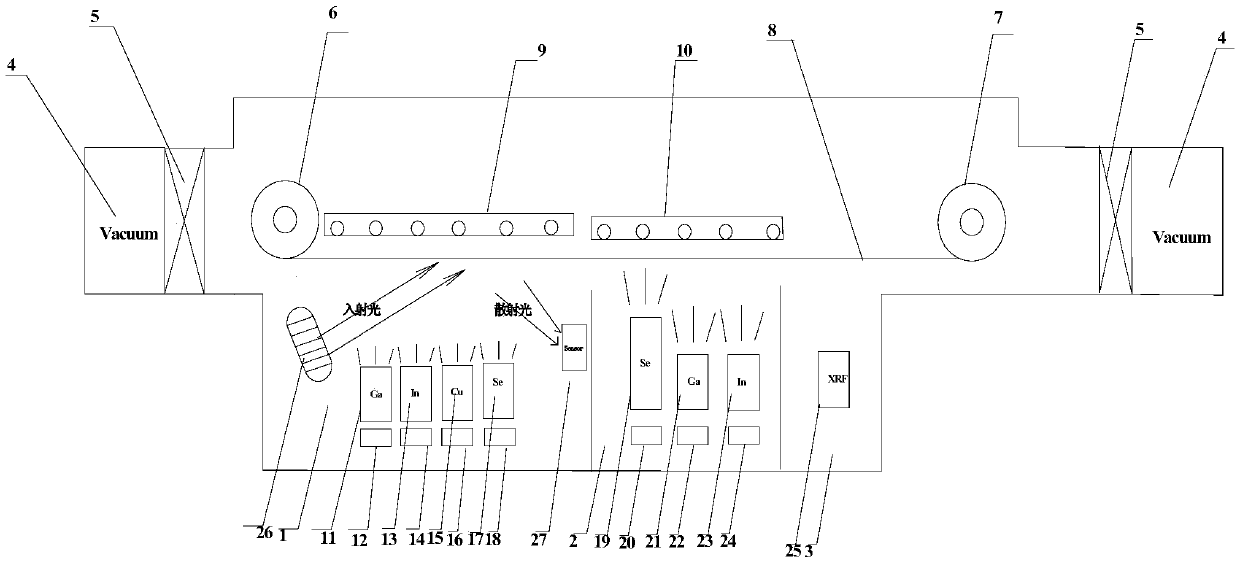

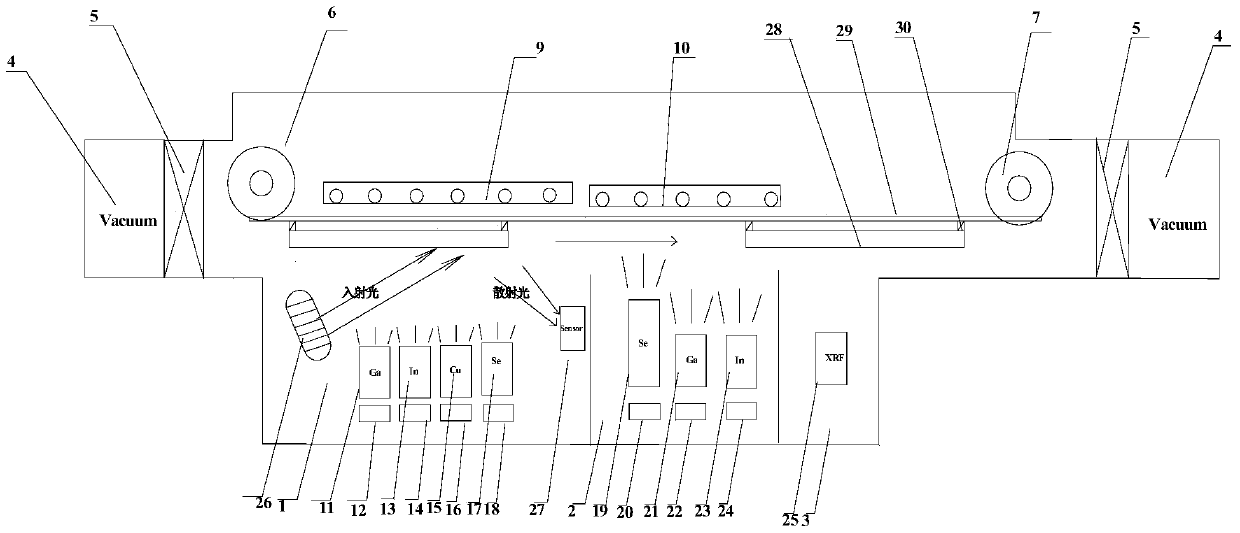

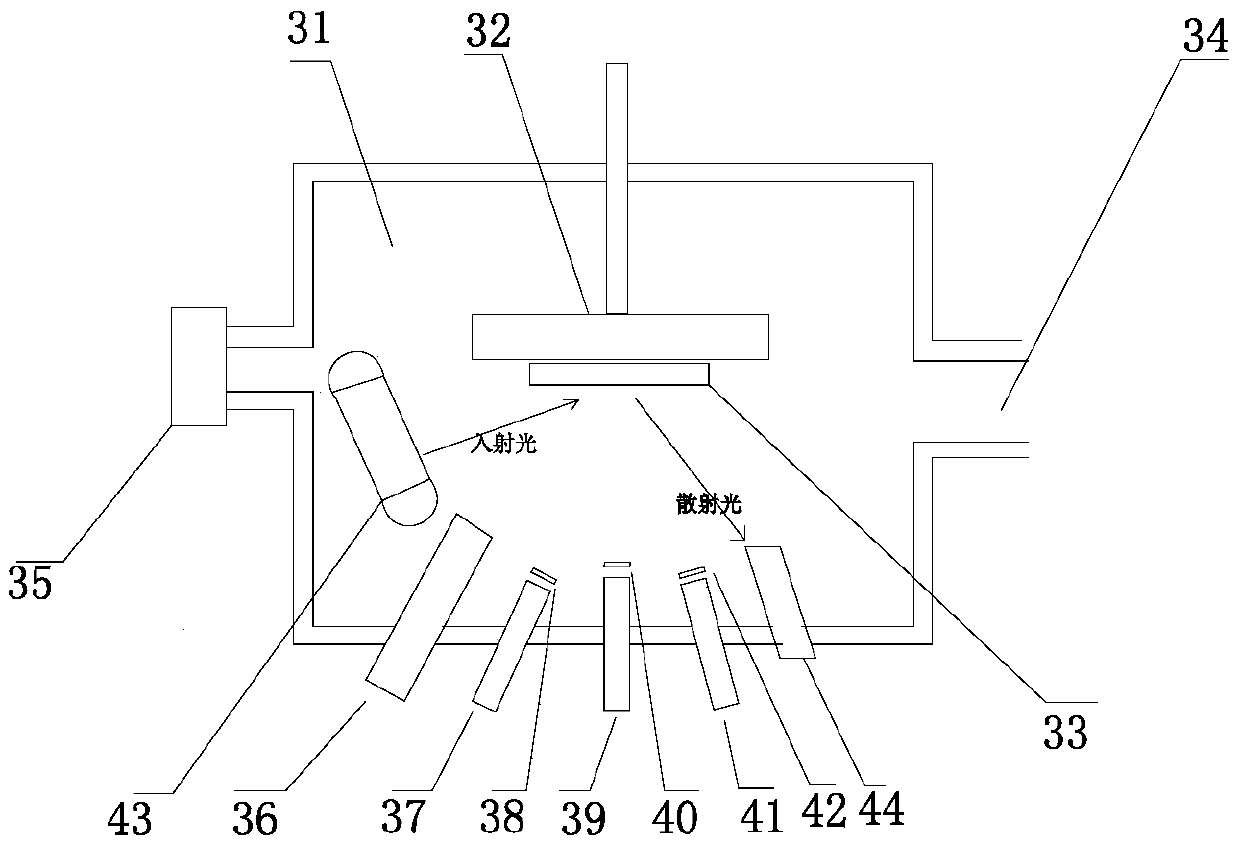

Method for on-line monitoring of preparation of copper indium gallium selenide absorption layer

ActiveCN105514218AImprove crystal qualityImprove performance and yieldFinal product manufacturePhotovoltaic energy generationCopper indium gallium selenide solar cellsScattered light

The invention discloses a method for on-line monitoring of preparation of a copper indium gallium selenide (CIGS) absorption layer. In a growing process of the CIGS absorption layer, an incandescent lamp is adopted to irradiate a surface of a substrate all the time, a change of the intensity of scattered light from the surface of the substrate is detected through a photosensitive sensor, a change of crystal quality of a surface of a CIGS thin film can be easily monitored on line, not limited by the area of the absorption layer, a transition point of a thin film component from poor copper to rich copper can be judged timely and accurately, the component proportion (Cu / (In+Ga)) in a process of deposition of the CIGS absorption layer is indirectly monitored and controlled, the CIGS absorption layer which is uniform and has relatively high crystal quality is prepared, and the performance and rate of finished products of CIGS thin film solar cells are improved. The CIGS absorption layer can be prepared on a rigid or flexible substrate, and the method provided by the invention can be applied to a laboratory deposition process of the CIGS absorption layer, and can also be used for preparation of a large-area CIGS thin film.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 18 RES INST

Producing and processing technology of superplastic pure iron material

The invention discloses a producing and processing technology of a superplastic pure iron material. The producing and processing technology comprises the following steps: (1) selecting a material: selecting a material which is produced in China and of which the type is CH1T as a base material; (2) performing drawing: drawing the material by a roller die drawing technique to obtain steel wires; and (3) performing annealing: using an isothermal recrystallization annealing technology, placing the steel wires in a heat treatment furnace, inflating the heat treatment furnace with inert gas, increasing the temperature in the heat treatment furnace to 660- 680 DEG C, keeping the temperature for 1- 2 hours, then performing cooling to 580-600 DEG C at a cooling rate of 15-20 DEG C / h keeping the temperature for 2-3 hours, and then performing cooling to room temperature at a cooling rate of 30-50 DEG C / h. The wire obtained by the processing of the producing and processing technology disclosed by the invention is high in plasticity, the wire does not crack after cold heading tests of deformation of 1 / 4 or above, and the wire has high elongation which is greater than or equal to 90%, ultra low hardness HV which is less than or equal to 90, refined grains with an average grain size level being greater than or equal to 11, uniform grain size, equiaxed grains and grain area difference being less than or equal to 5%.

Owner:DONGGUAN KELEE STEEL WIRE

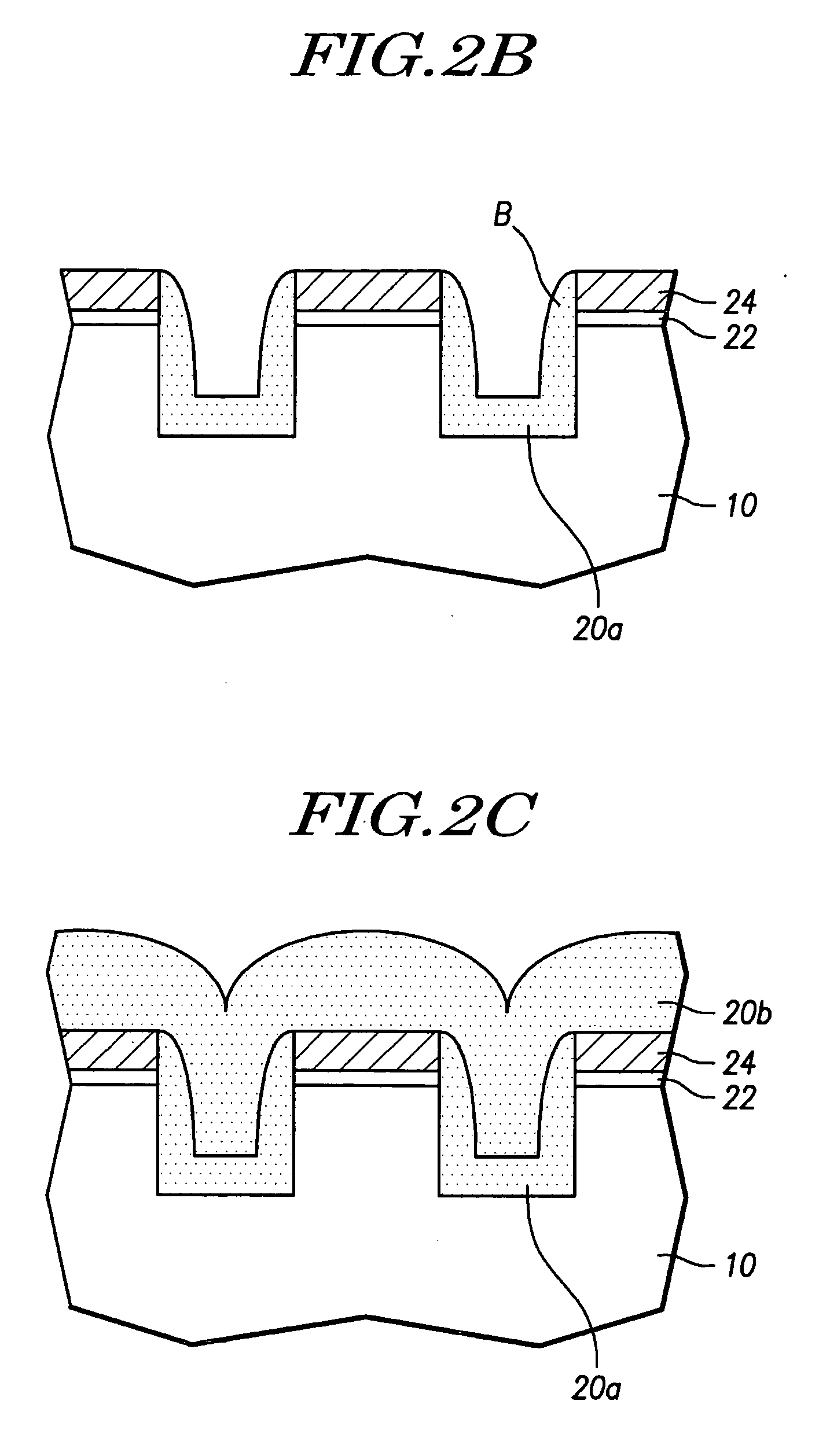

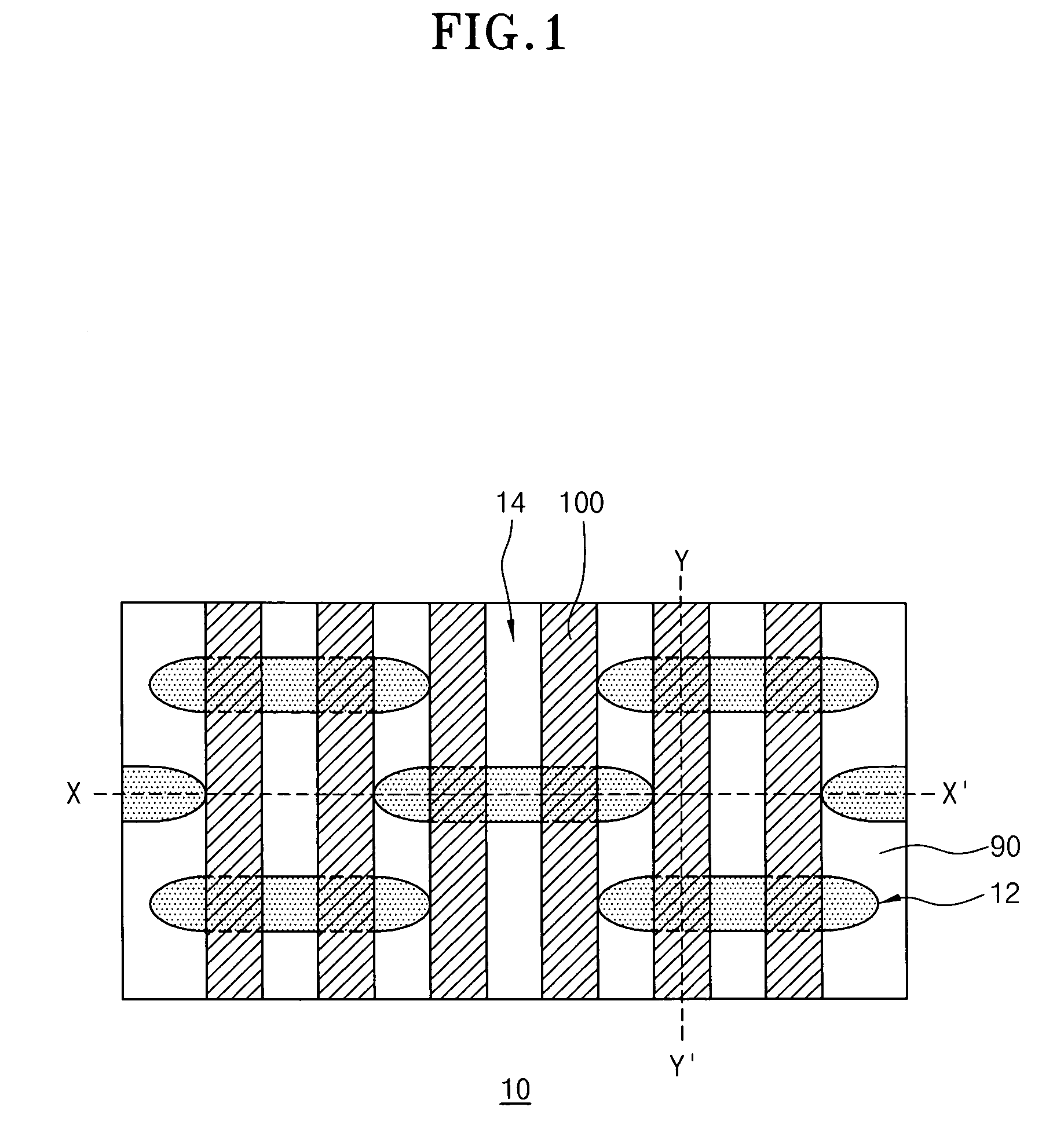

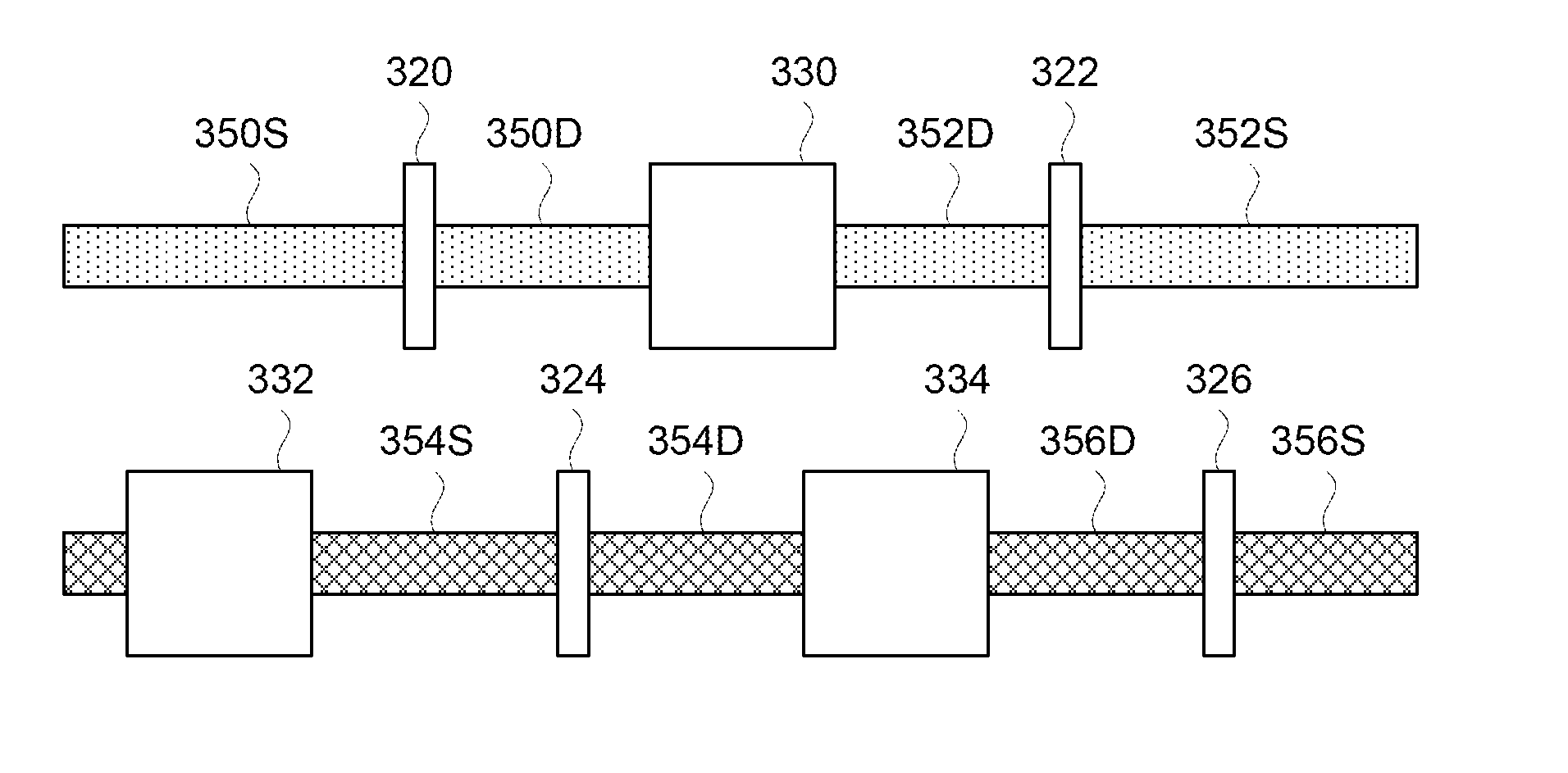

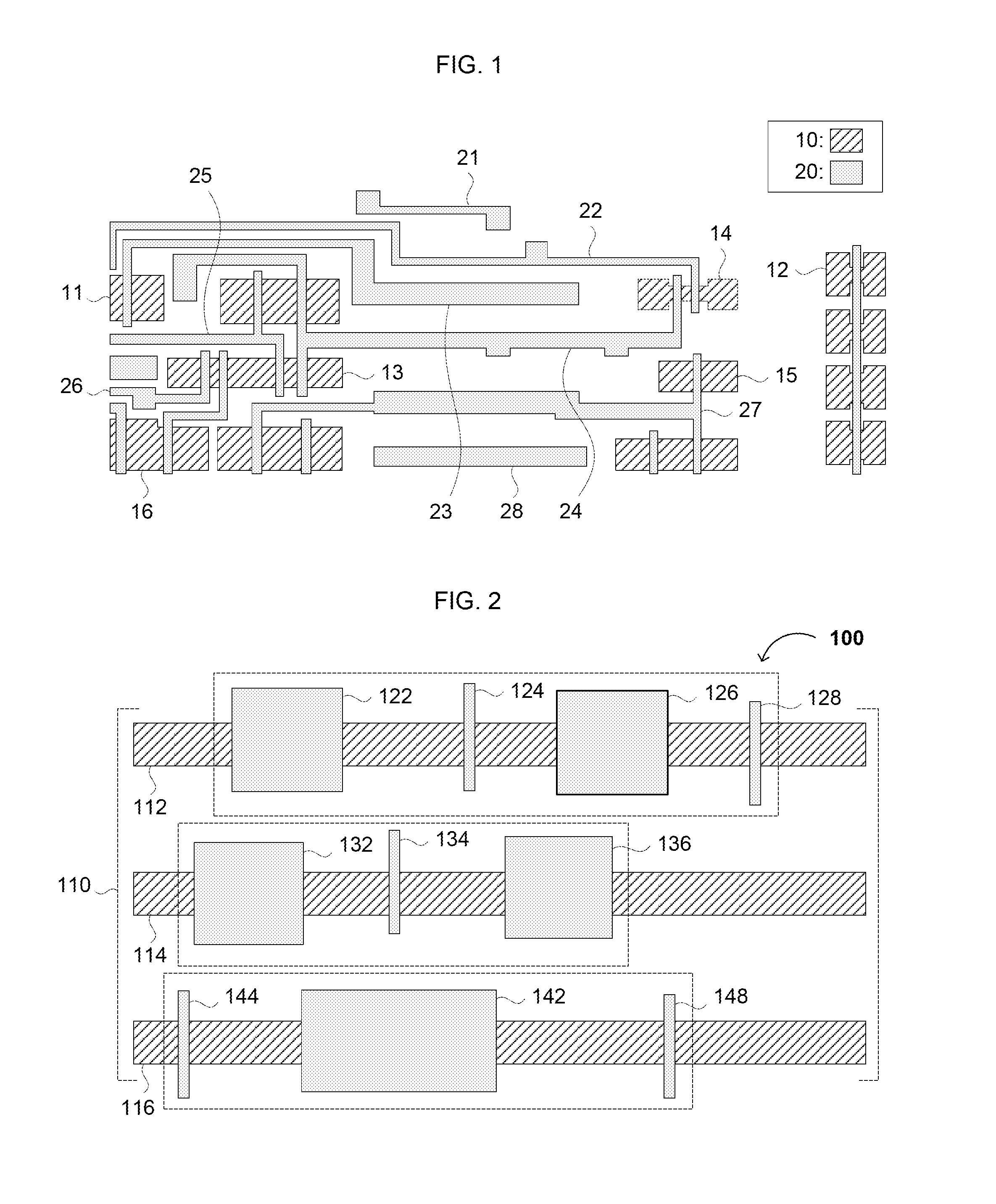

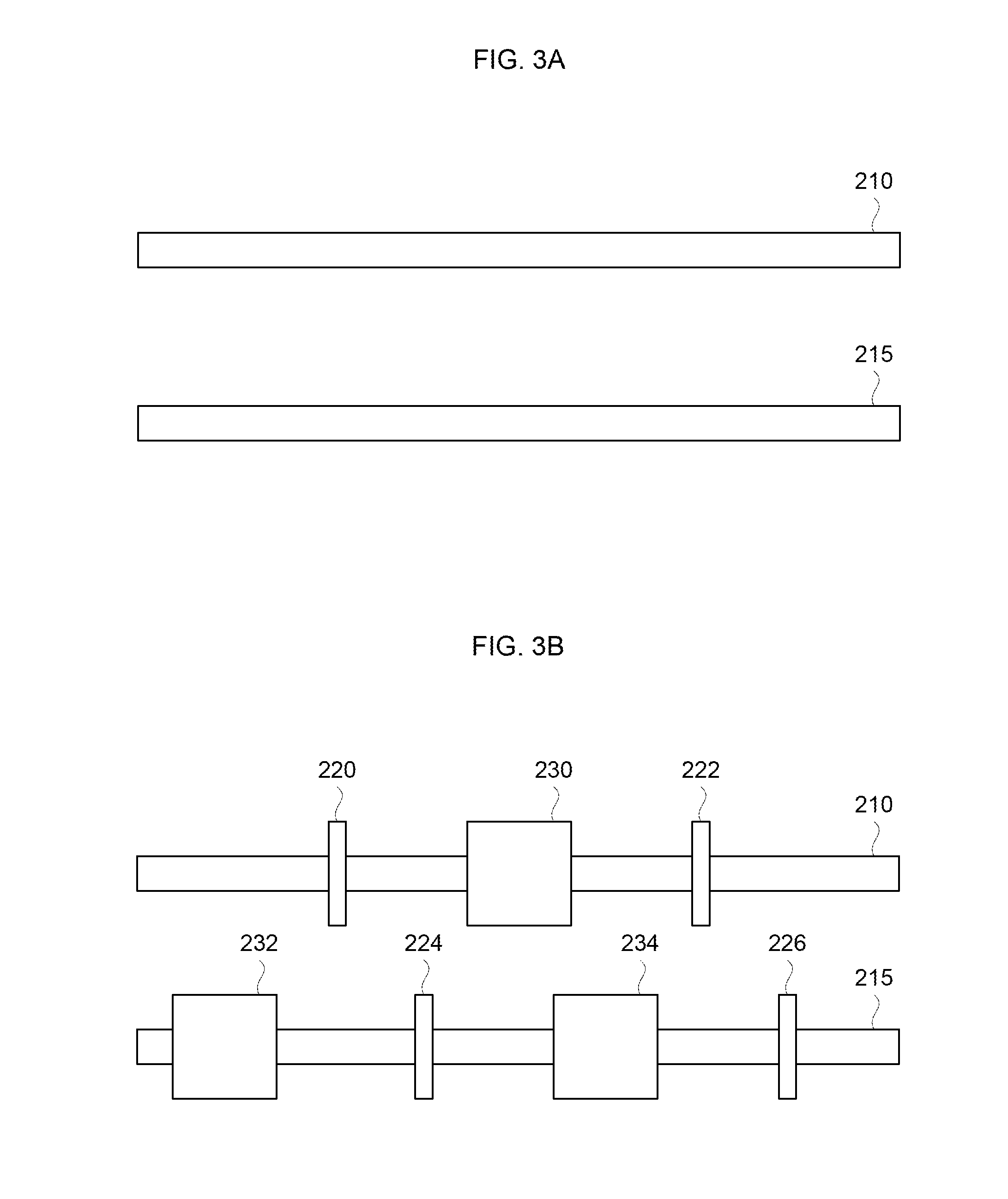

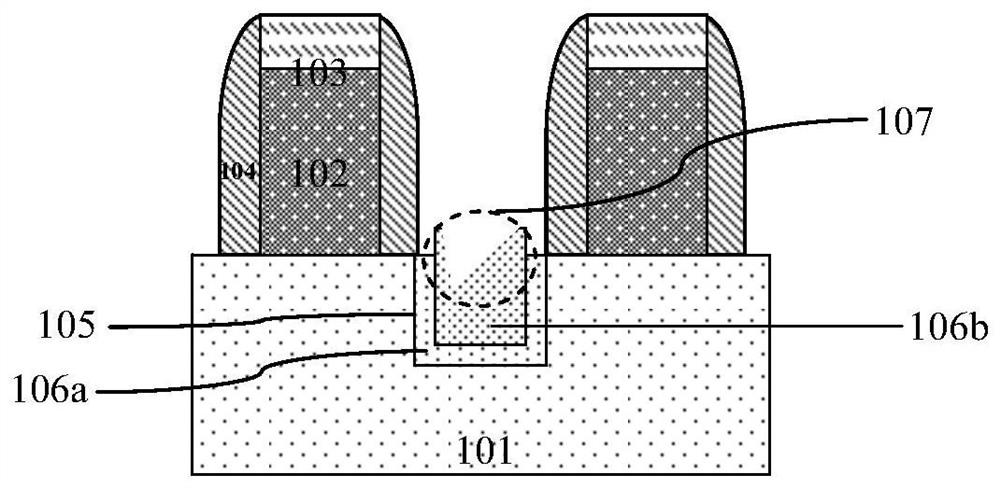

Printed Compatible Designs and Layout Schemes for Printed Electronics

ActiveUS20110186333A1Adequate spacingImprove performance and yieldPrinted circuit liquid treatmentSemiconductor/solid-state device detailsPhotolithographyPrinted electronics

Owner:ENSURGE MICROPOWER ASA

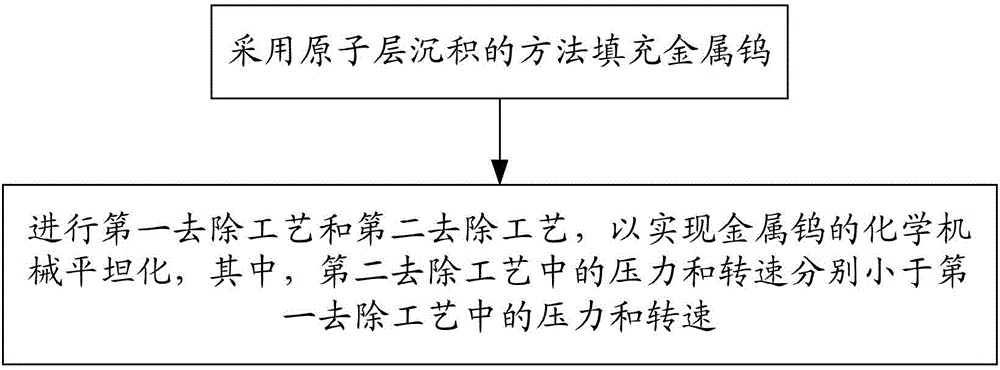

Chemical machinery planarization process method

ActiveCN104979277AReduce metal lossImprove performance and yieldSemiconductor/solid-state device manufacturingTungstenMetal

The invention provides a chemical machinery planarization process method. The method comprises the following steps: filling metallic tungsten by use of an atomic layer deposition method; carrying out a first removal process and a second removal process so as to realize chemical machinery planarization of the metallic tungsten, wherein the pressure and the rotating speed in the second removal process are respectively smaller than the pressure and the rotating speed in the first removal process. According to the invention, the chemical machinery planarization of the metallic tungsten is realized by use of a two-step removal process, and the pressure and the rotating speed in the later removal process are reduced, such that the mechanical effect in a grinding process is reduced in the second removal process, metal loss at the top of a metal gate can be reduced, and the performance and the yield of a device are improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for chemical mechanical polishing of high-K metal gate structures

ActiveUS9337104B1Improve performance and yieldTransistorSemiconductor/solid-state device manufacturingReactive gasCompound (substance)

A method for manufacturing a semiconductor device includes providing a substrate, a dielectric layer on the substrate, a first hard mask layer on the substrate, and a second hard mask layer on the first hard mask layer. The method also includes removing the first hard mask layer using a reactive gas that does not cause damage to the dielectric layer to improve the performance and yield of the semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

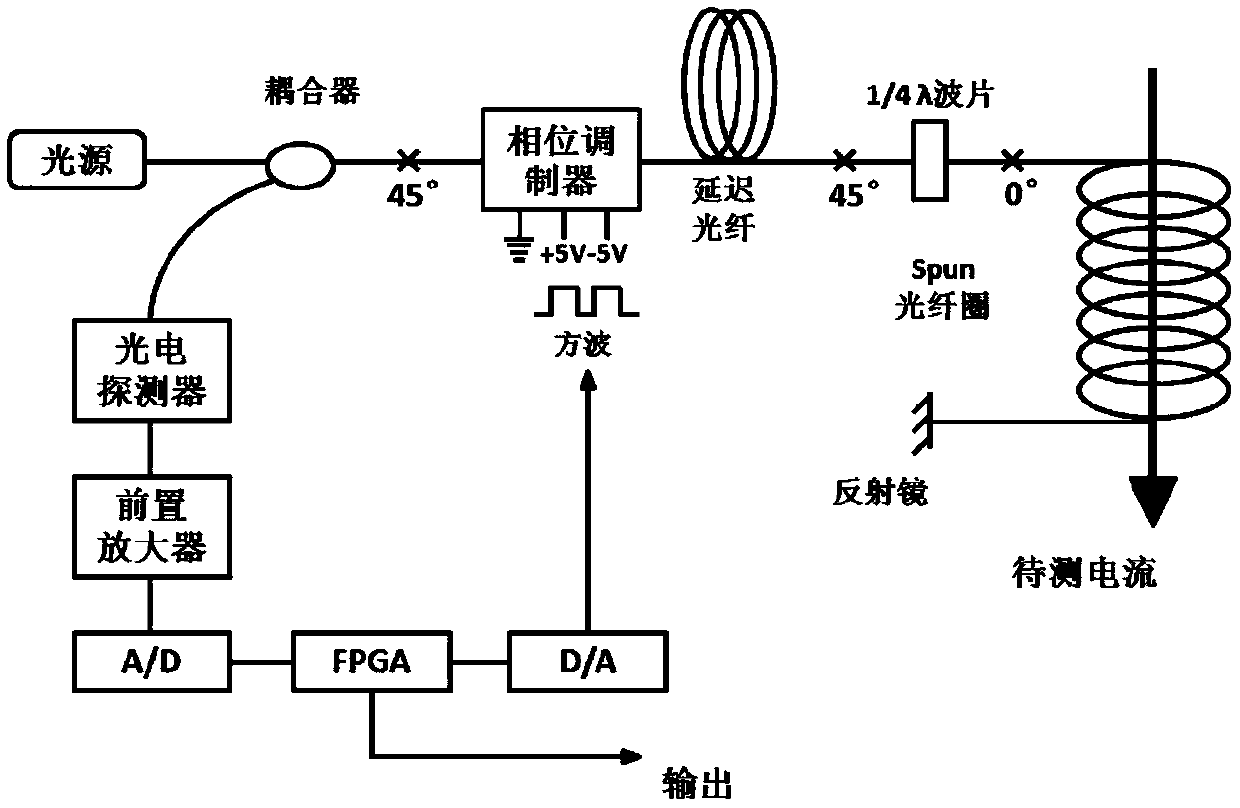

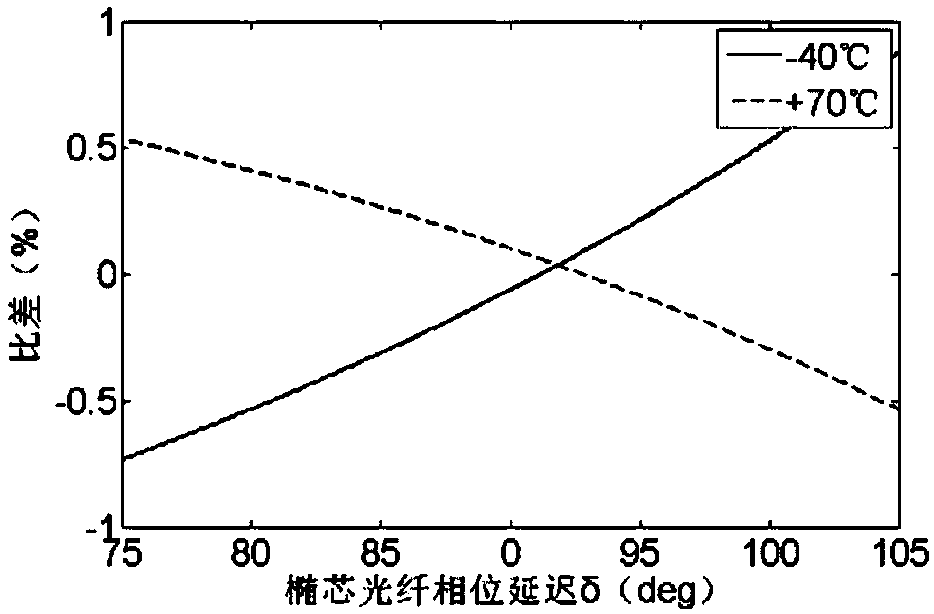

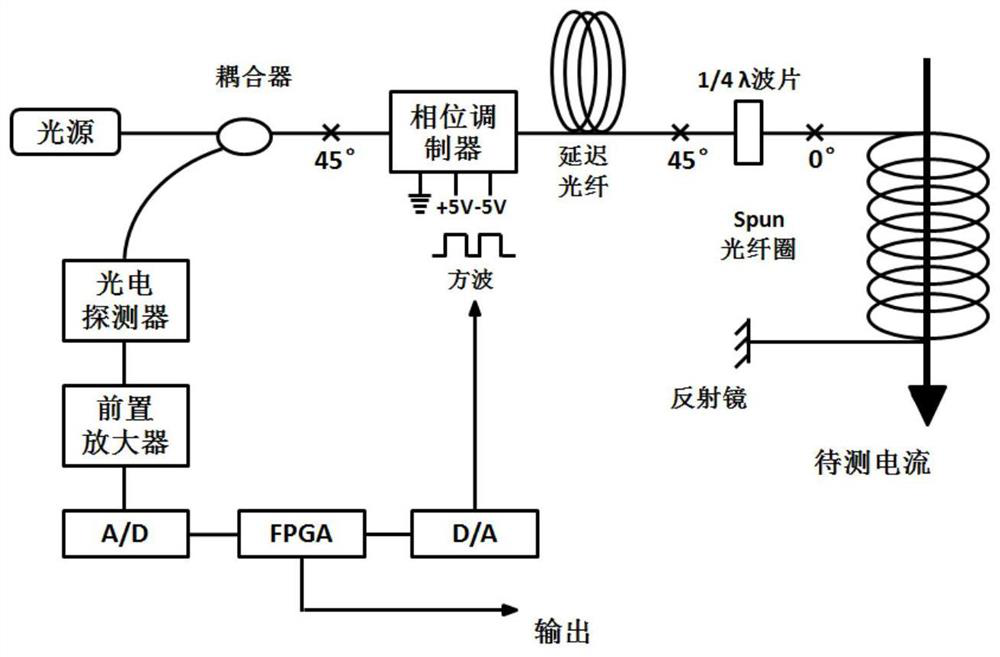

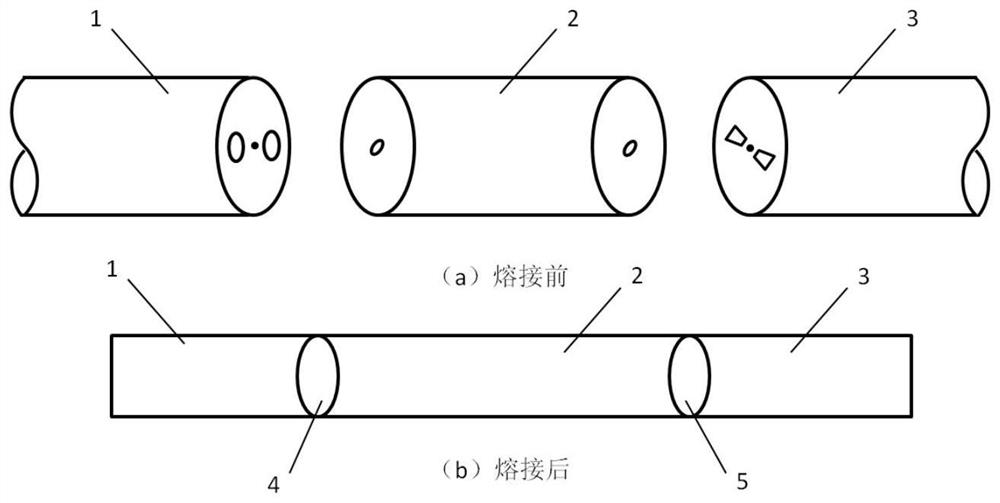

Manufacturing method of quarter-wave plate for temperature compensation

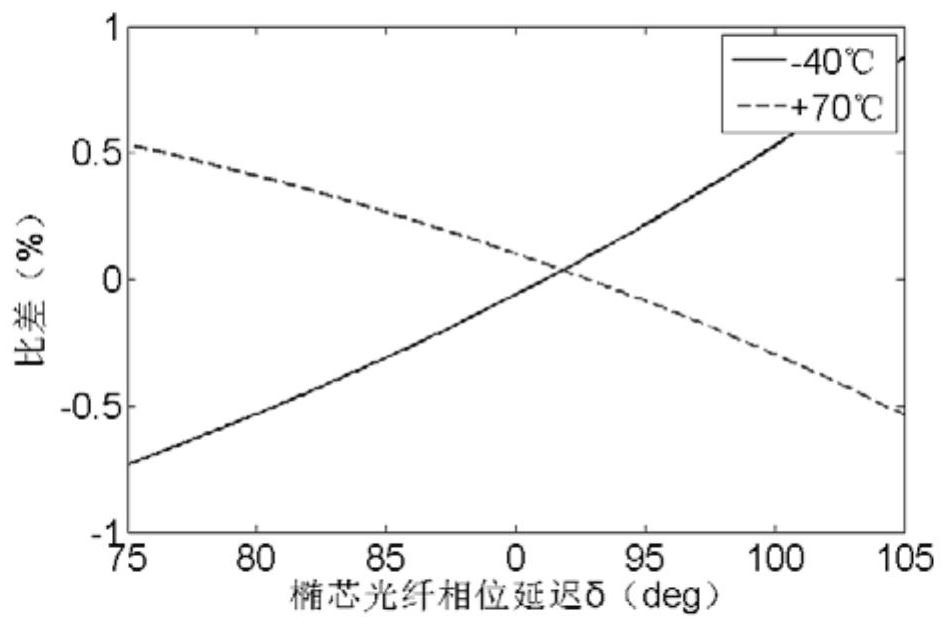

ActiveCN111175968AAchieving Stability and ConsistencyImprove performance and yieldPolarising elementsVoltage/current isolationPhysicsBatch production

The invention discloses a manufacturing method of a quarter-wave plate for temperature compensation of an optical fiber current transformer, which can realize stability and consistency of a current ratio difference of the optical fiber current transformer in a full-temperature range in a batch production process, reduce a reject ratio of products and ensure long-term working accuracy and stabilityof the optical fiber current transformer. The method comprises the following steps: (1) establishing an optical fiber current transformer mathematical model; (2) measuring phase retardation of an elliptical core optical fiber; and (3) carrying out a quarter-wave plate manufacturing process. The method have advantages that a manufacturing process scheme of the quarter-wave plate is stable and consistent, and the stability and consistency of the current ratio difference of an optical fiber current transformer system in the full-temperature range can be realized so that performance and a yield of the optical fiber current transformer system are improved.

Owner:BEIJING AUTOMATION CONTROL EQUIP INST

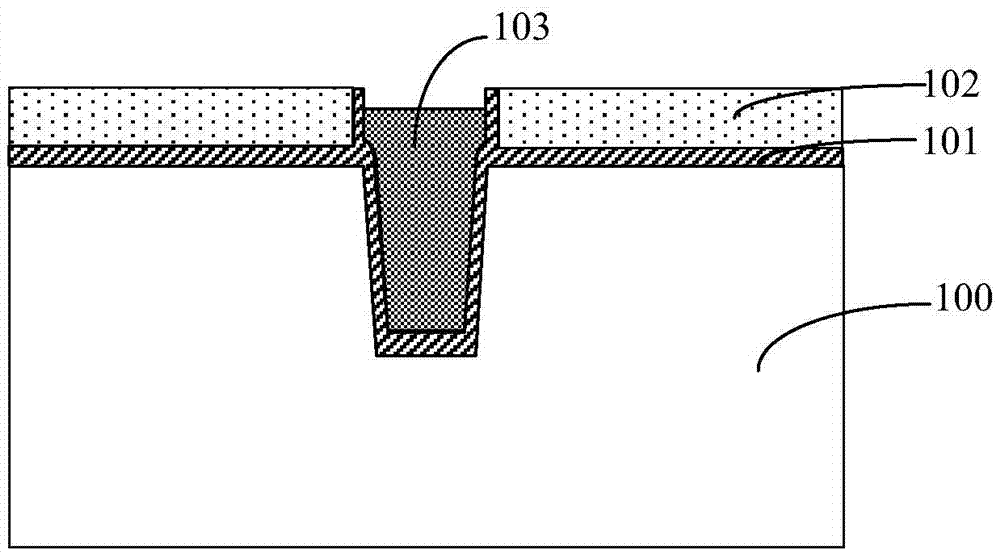

Method for forming contact holes in a semiconductor device

ActiveUS20160104641A1Improve breakdown voltageIncrease overall performance and yieldTransistorSemiconductor/solid-state device detailsResistCompound (substance)

Owner:SEMICON MFG INT (SHANGHAI) CORP

Photoresist reworking etching process

ActiveCN103345130ASimple processImprove performance and yieldSemiconductor/solid-state device manufacturingPhotosensitive material processingPhotoresistChemistry

The invention relates to the technical field of integrated circuits, and in particular relates to a photoresist reworking etching process. According to the photoresist reworking etching process disclosed by the invention, in an etching process manufacturing procedure, a photoresist needing to be reworked and a non-nitrogen bottom anti-reflecting layer are sequentially removed, a new non-nitrogen bottom anti-reflecting layer is re-deposited, and the photoresist is continuously coated for performing a subsequent photoetching process so as to complete a photoresist reworking process. Therefore, during the photoetching process, preparation of a protection layer on the non-nitrogen bottom anti-reflecting layer for preventing optical parameters or surface properties of the non-nitrogen bottom anti-reflecting layer from being influenced during subsequent photoetching reworking is eliminated, so that the flow of the whole photoetching process is simplified; meanwhile, by the adoption of the photoresist reworking etching process, the accuracy of a product subjected to photoresist reworking in a subsequent photoetching process remains unchanged, and the performance and yield of the product are further improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

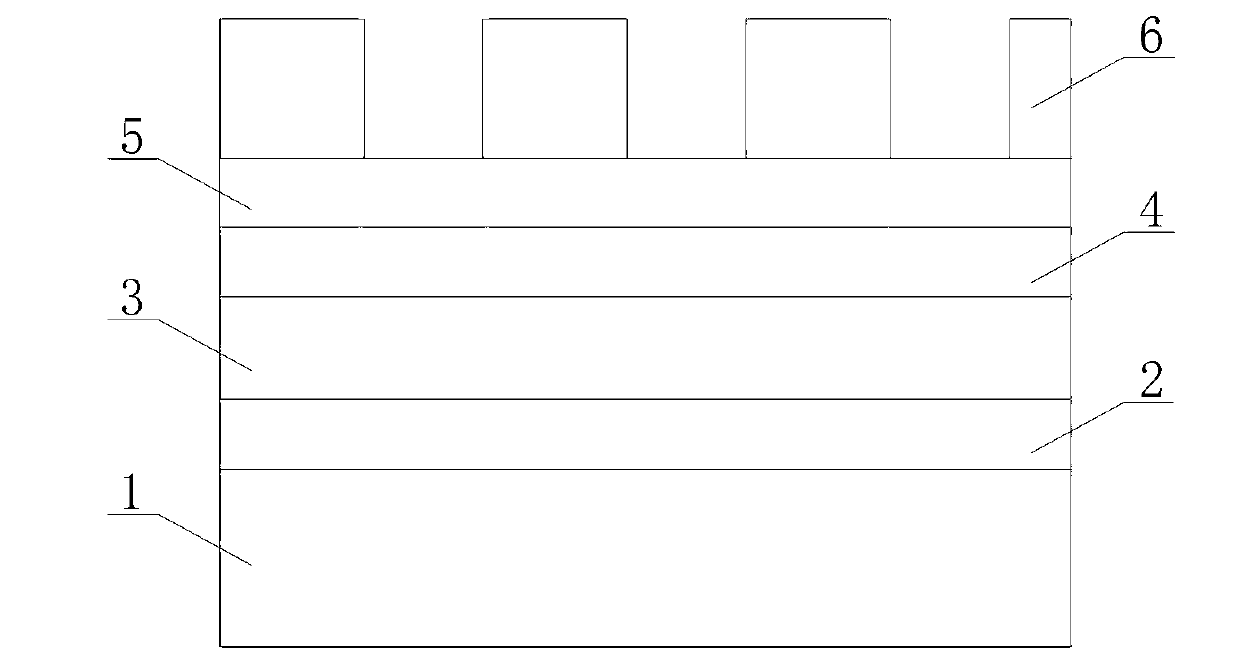

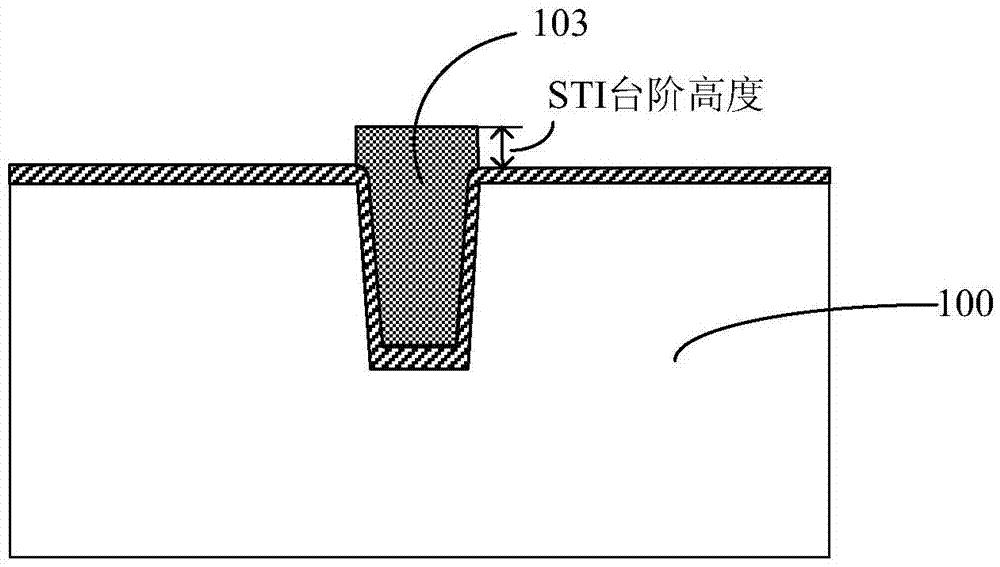

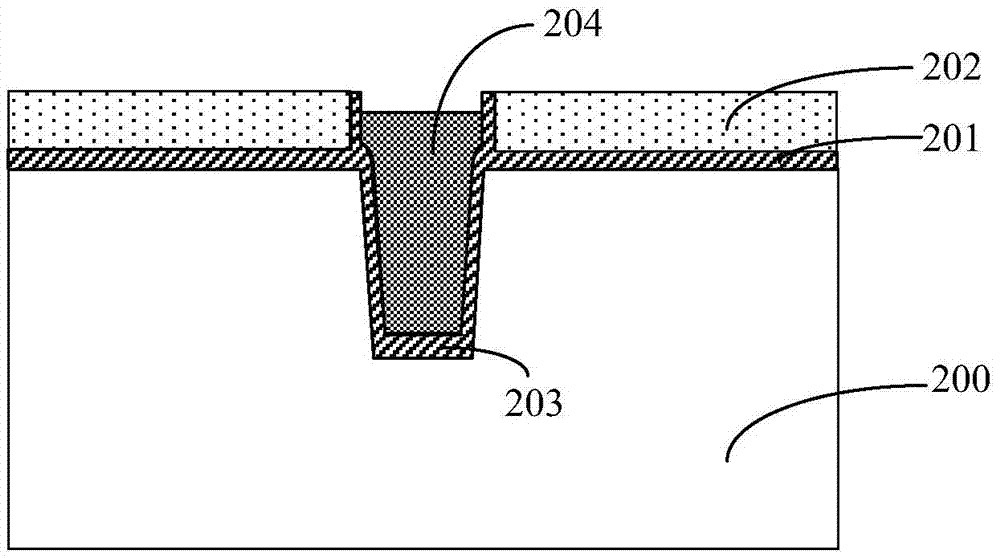

Manufacturing method for semiconductor device

InactiveCN106910707ASmall fluctuations in step heightImprove performance and yieldSemiconductor/solid-state device manufacturingEngineeringSemiconductor

The invention provides a manufacturing method for a semiconductor device, and relates to the technical field of semiconductors. The manufacturing method comprise providing a semiconductor substrate, and forming a hard mask layer defining the pattern of a shallow trench isolation structure on the surface of the semiconductor substrate; forming a shallow trench isolation structure in the semiconductor substrate with the surface of the shallow trench isolation structure being lower than that of the hard mask layer and higher than that of the semiconductor substrate; forming a protective layer on the surface of the shallow trench isolation structure through deposition; removing the hard mask layer; and removing the protective layer. According to the invention, by forming the protective layer on the shallow trench isolation structure, the surface of the shallow trench isolation structure can be effectively prevented from being etched and damaged during the wet method etching removal process of the hard mask layer, furthermore the STI step height fluctuation is small, and therefore the performance and the yield rate of the device are increased.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

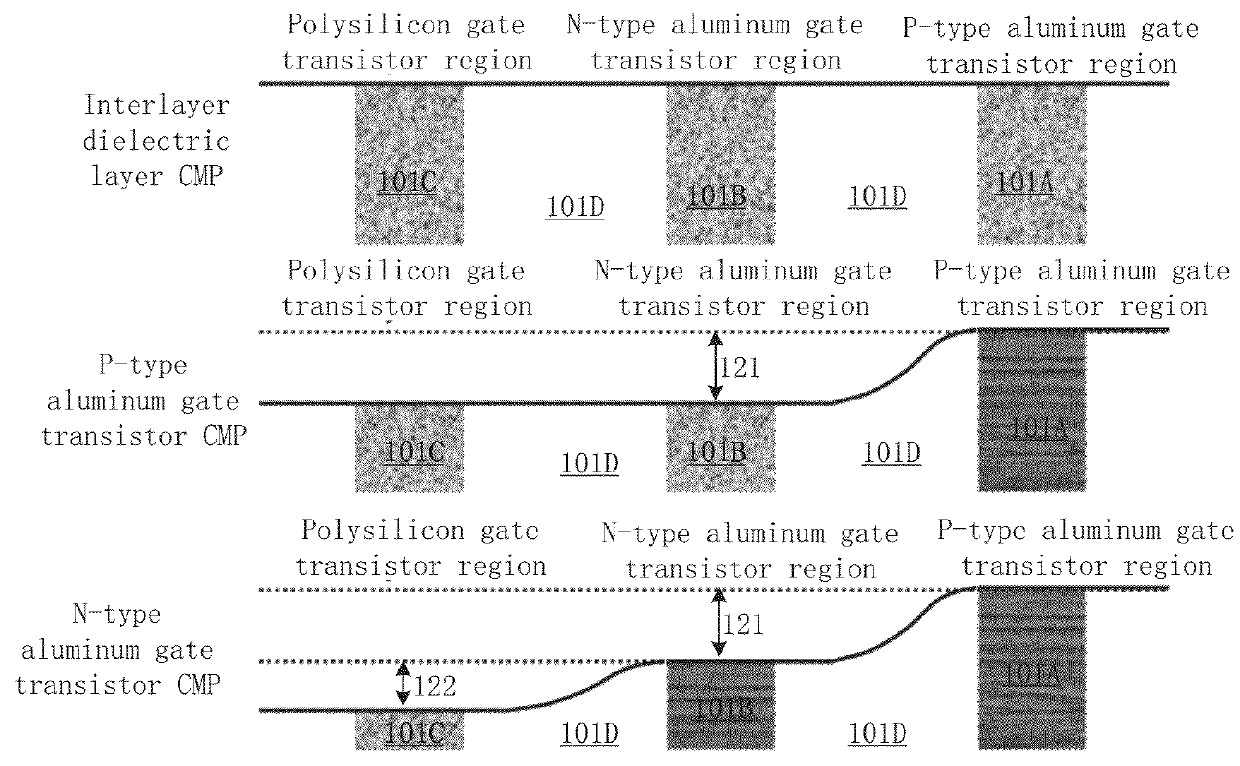

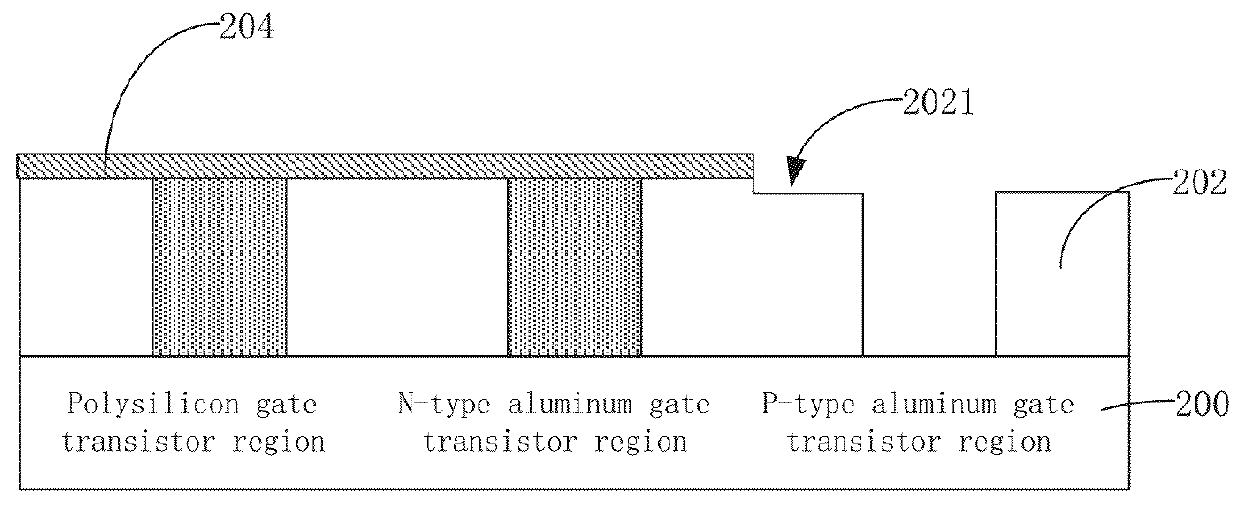

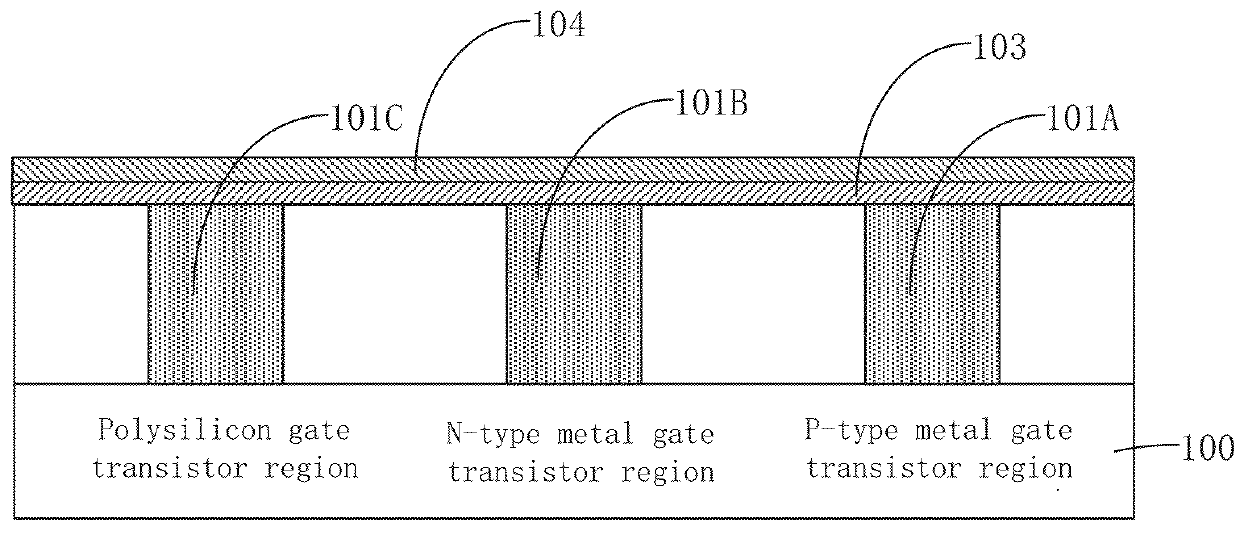

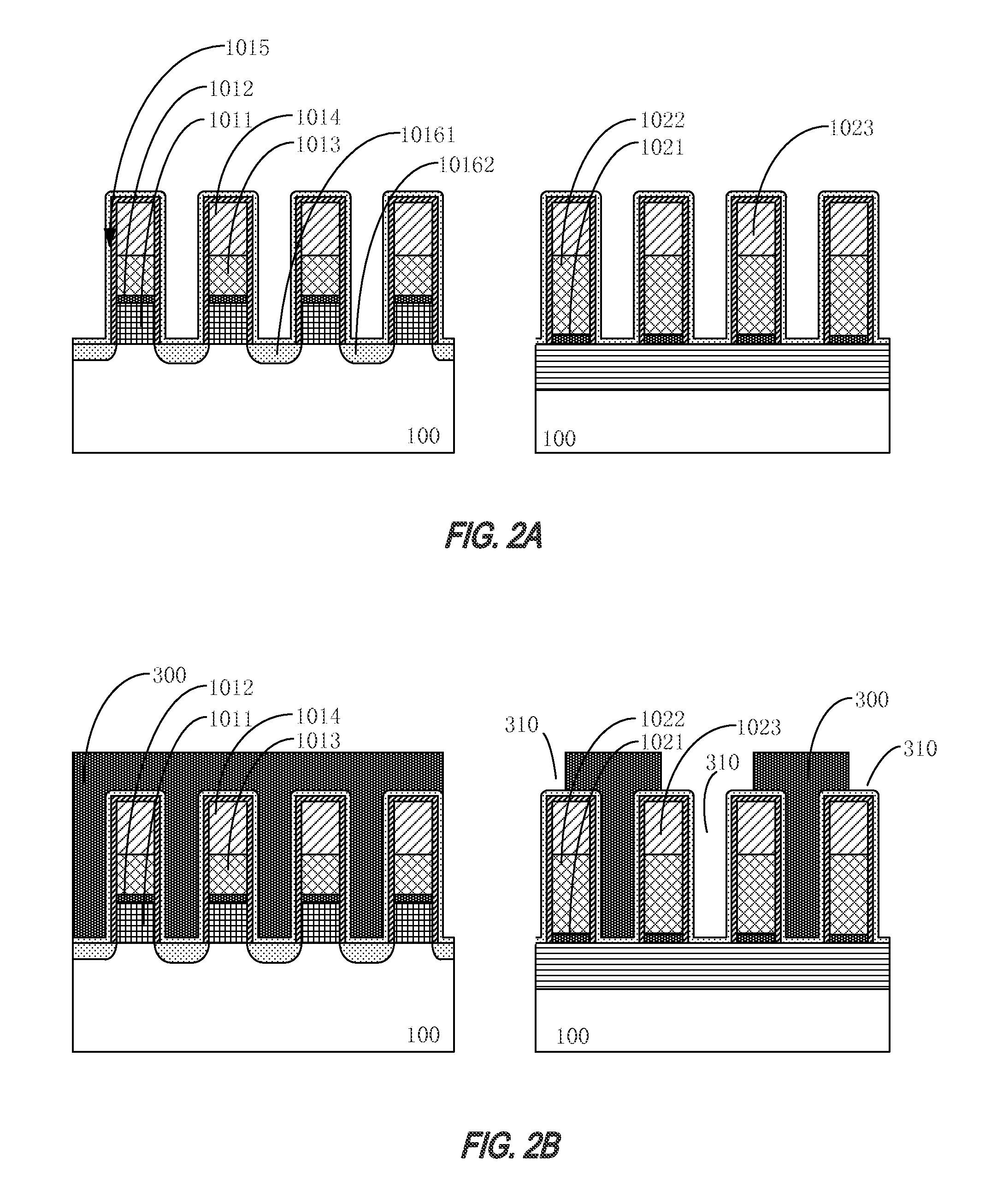

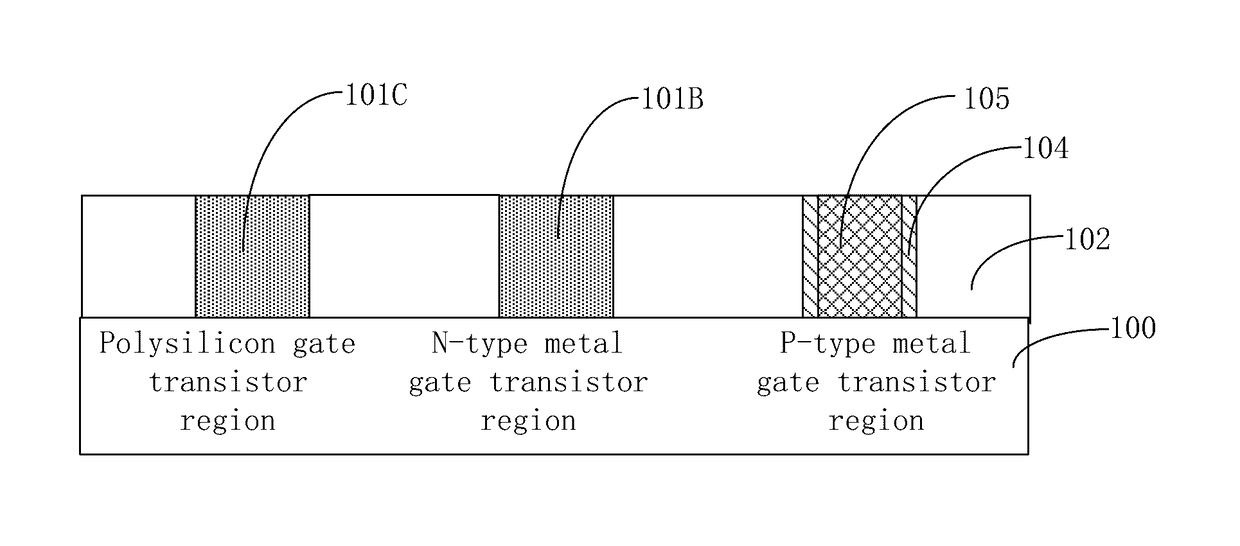

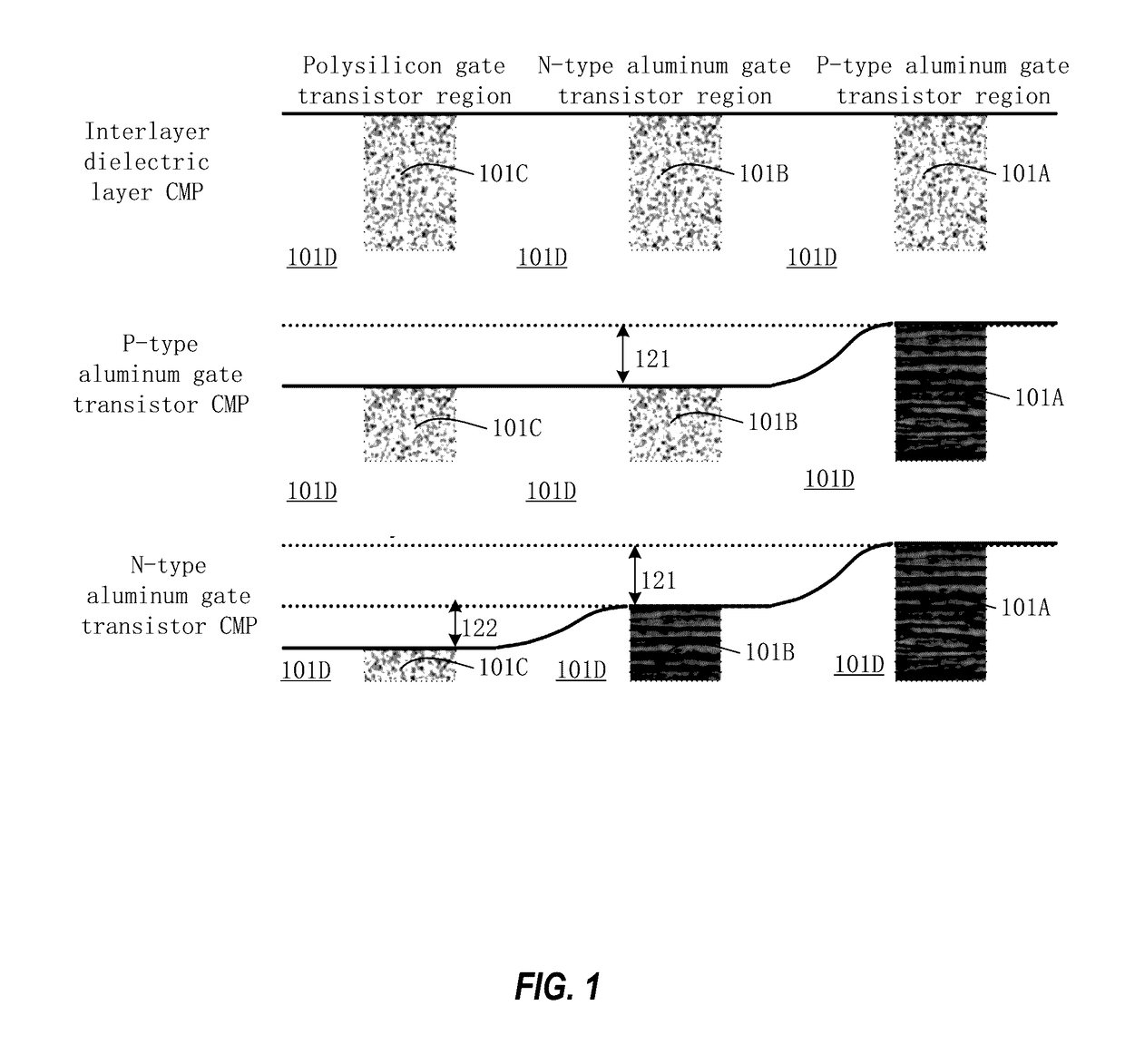

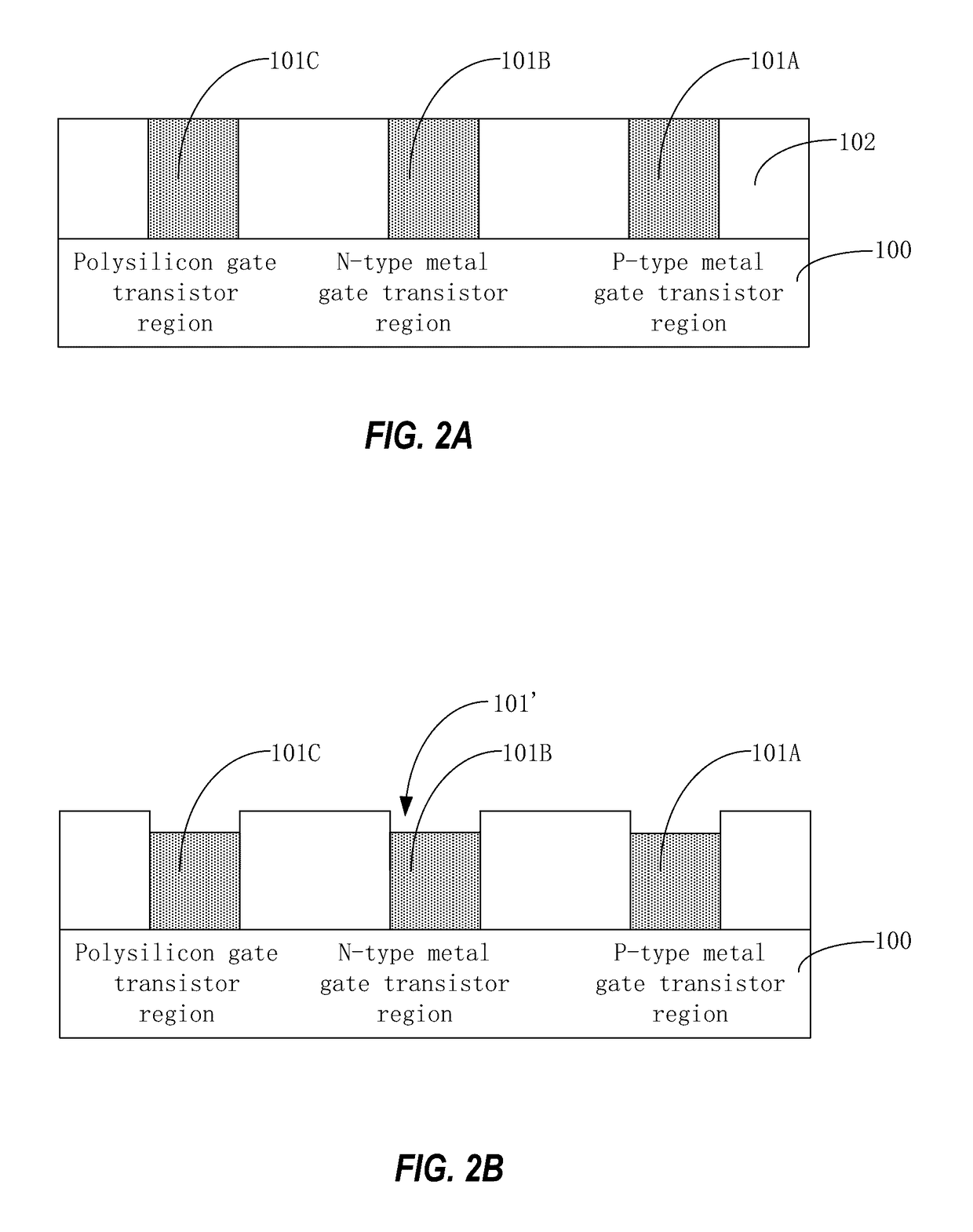

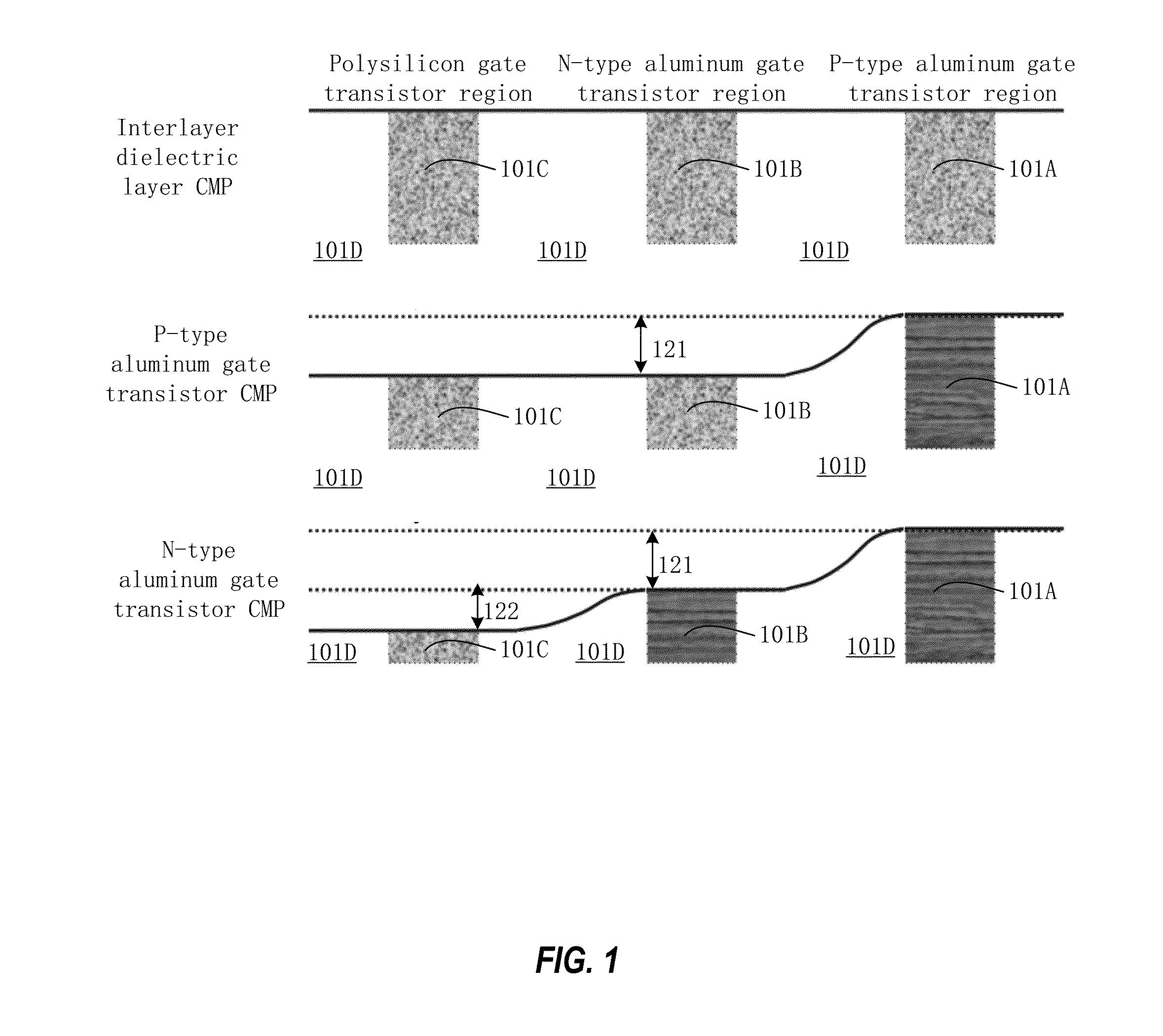

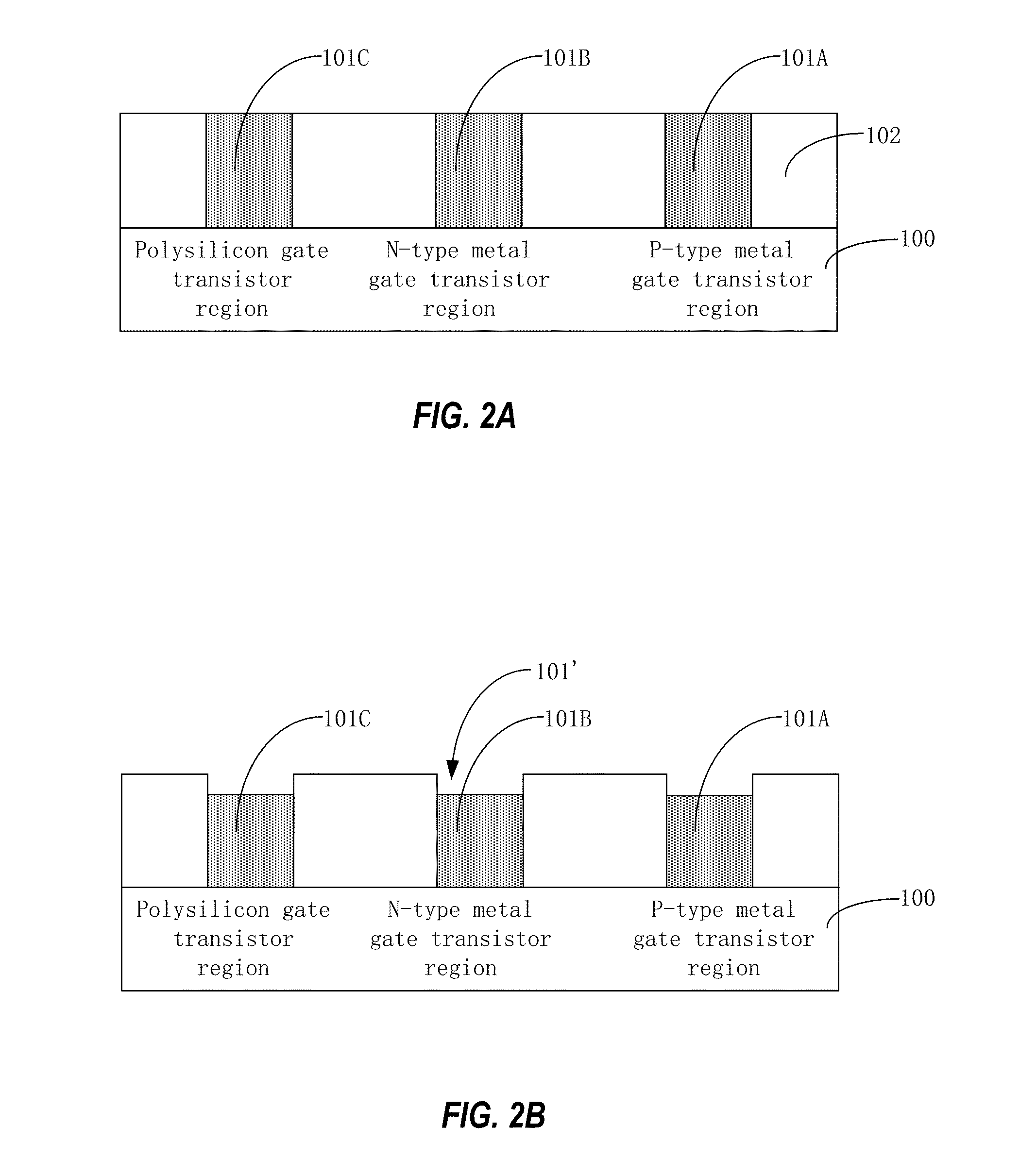

Method for CMP of high-K metal gate structures

ActiveUS9646840B2Improve performance and yieldPrevent over-polishingSemiconductor/solid-state device manufacturingSemiconductor devicesPolysilicon gateDielectric layer

A method for manufacturing a semiconductor device includes providing a substrate containing a front-end device and forming a dielectric layer on the substrate. The front-end device includes a first dummy gate in a first type metal gate transistor region, a second dummy gate in a second type metal gate transistor region, and a polysilicon gate in a polysilicon gate region. The method also includes removing a thickness of the first, second, and polysilicon gates and forming a protective layer on the polysilicon layer to protect the polysilicon layer during a CMP process, thereby improving the performance and yield of the semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for cmp of high-k metal gate structures

ActiveUS20150340451A1Improve performance and yieldPrevent over-polishingSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A method for manufacturing a semiconductor device includes providing a substrate containing a front-end device and forming a dielectric layer on the substrate. The front-end device includes a first dummy gate in a first type metal gate transistor region, a second dummy gate in a second type metal gate transistor region, and a polysilicon gate in a polysilicon gate region. The method also includes removing a thickness of the first, second, and polysilicon gates and forming a protective layer on the polysilicon layer to protect the polysilicon layer during a CMP process, thereby improving the performance and yield of the semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

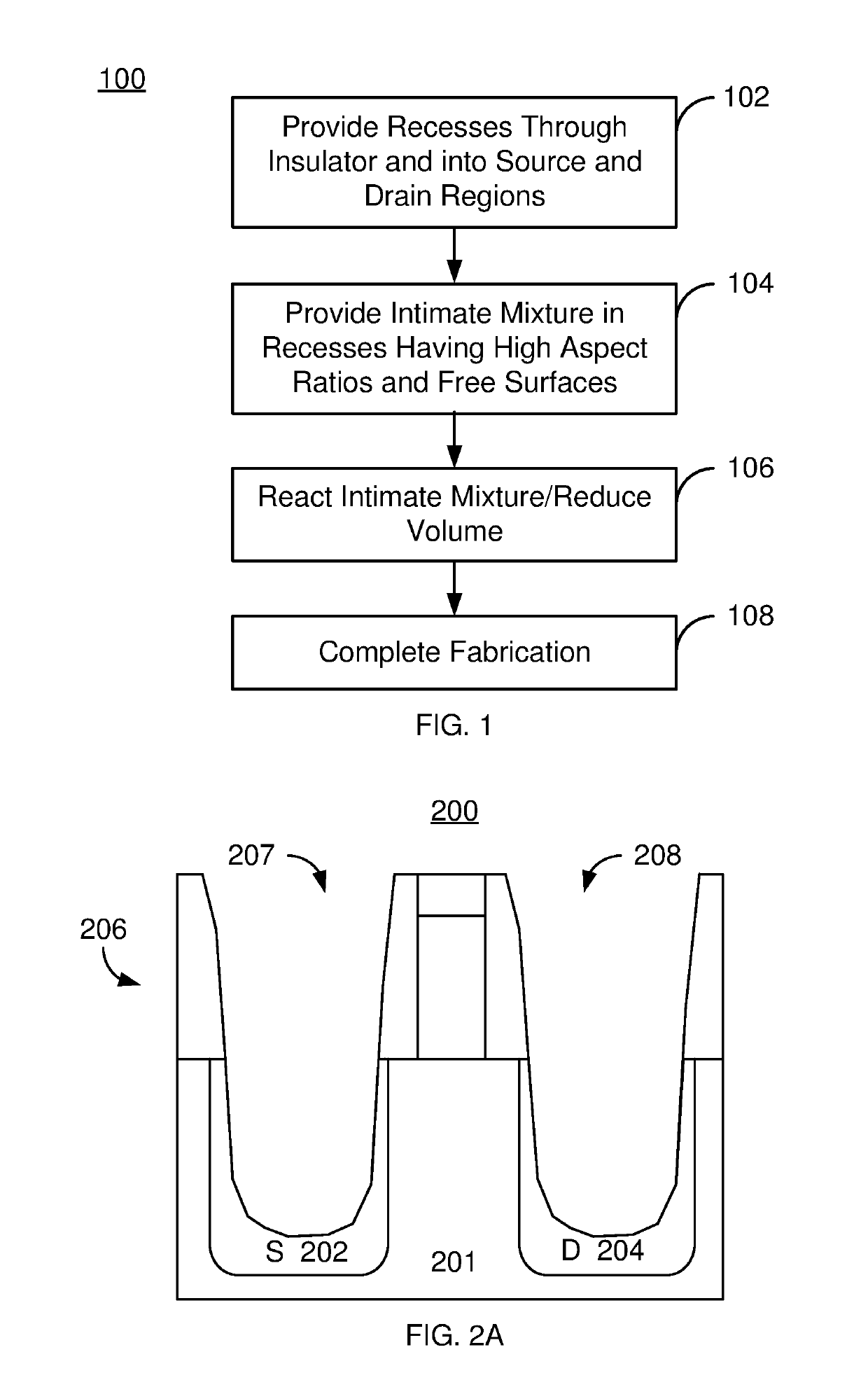

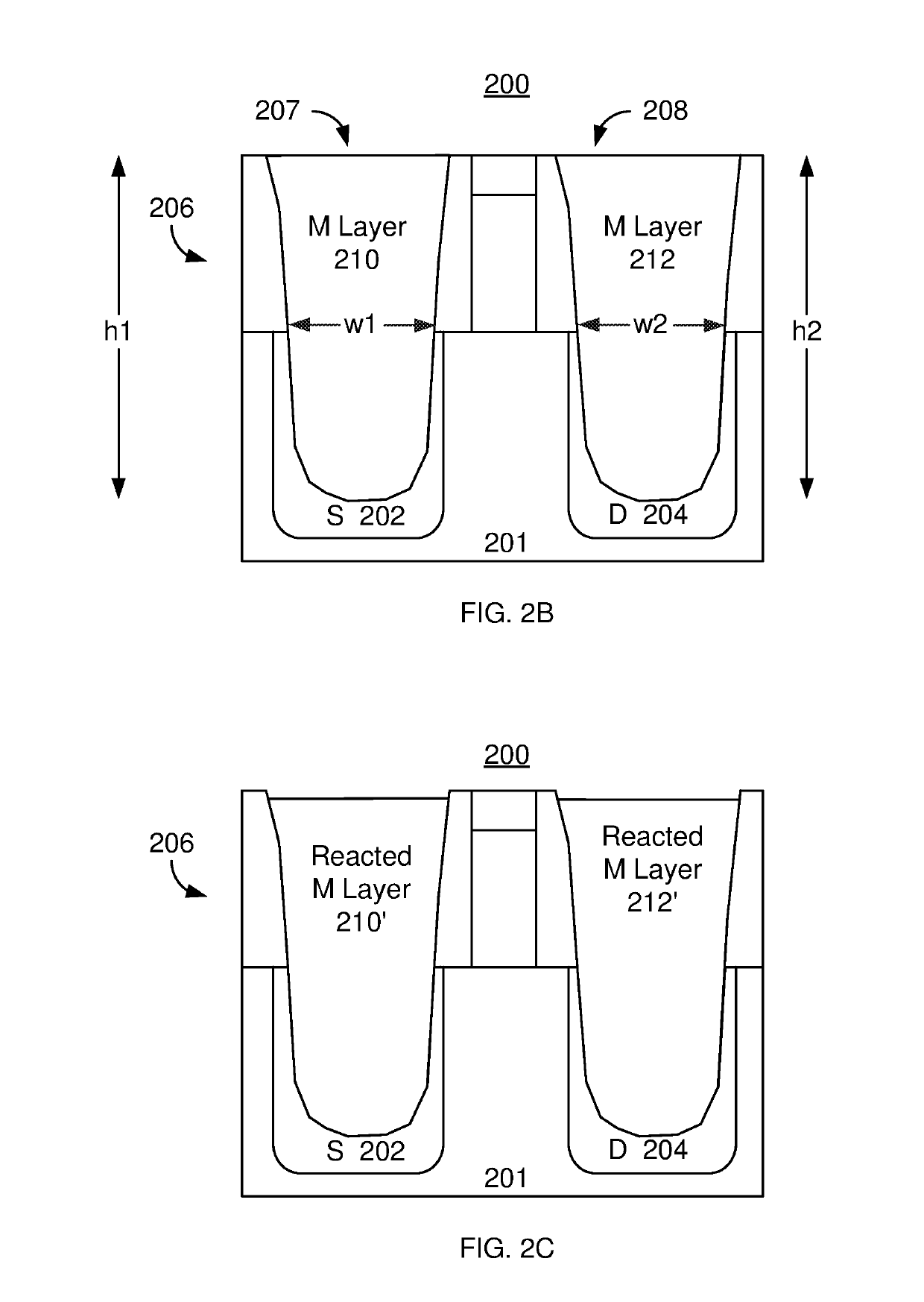

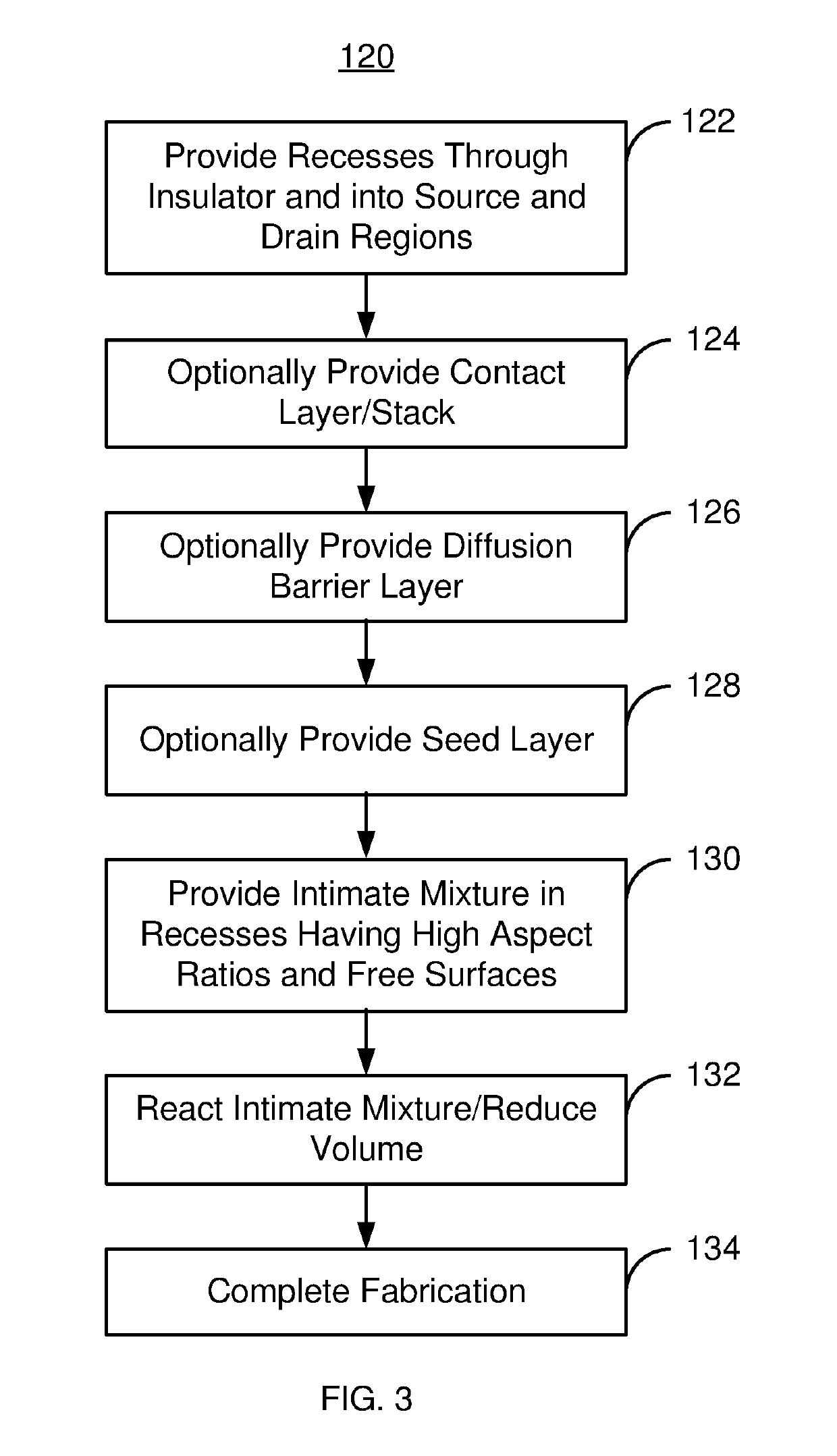

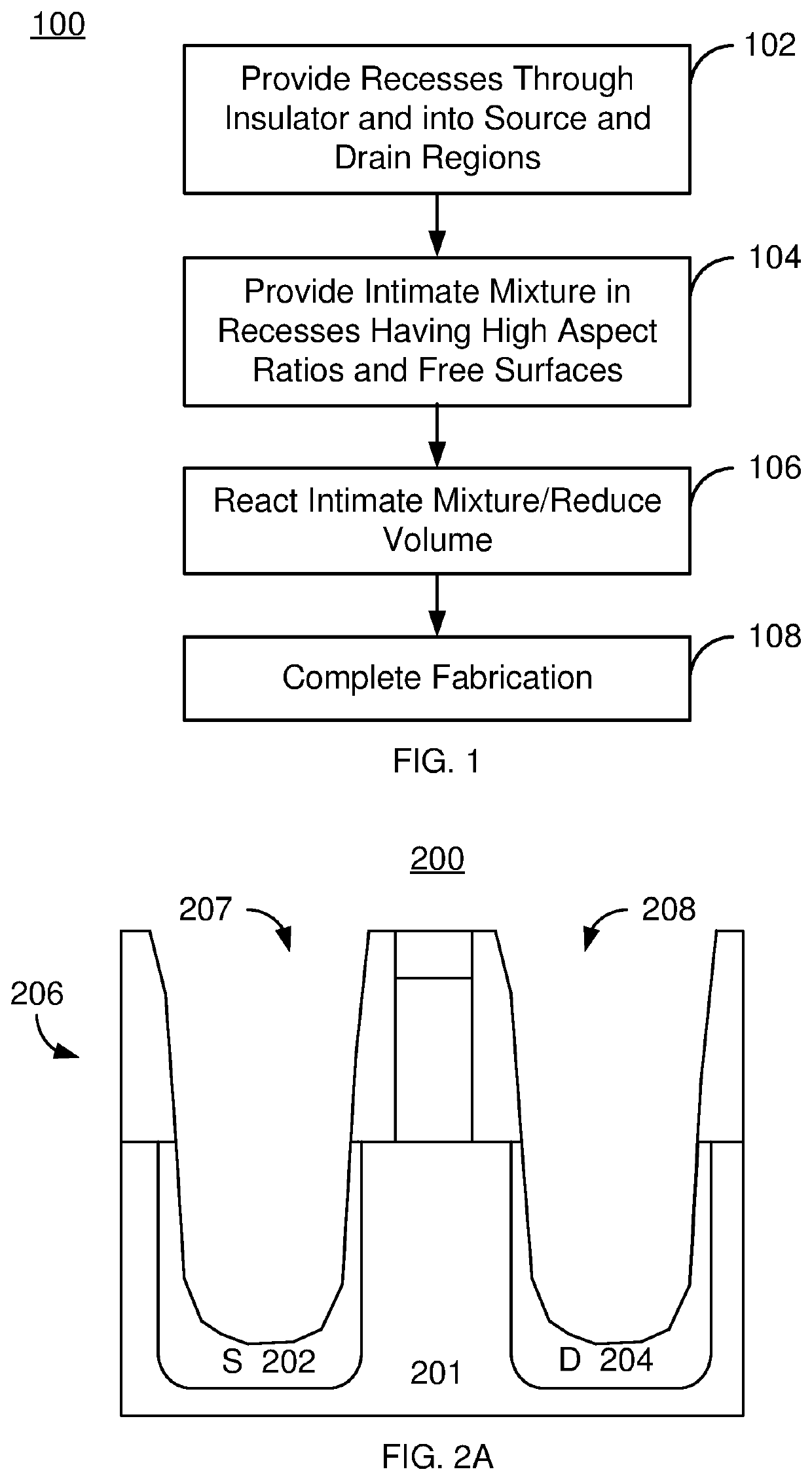

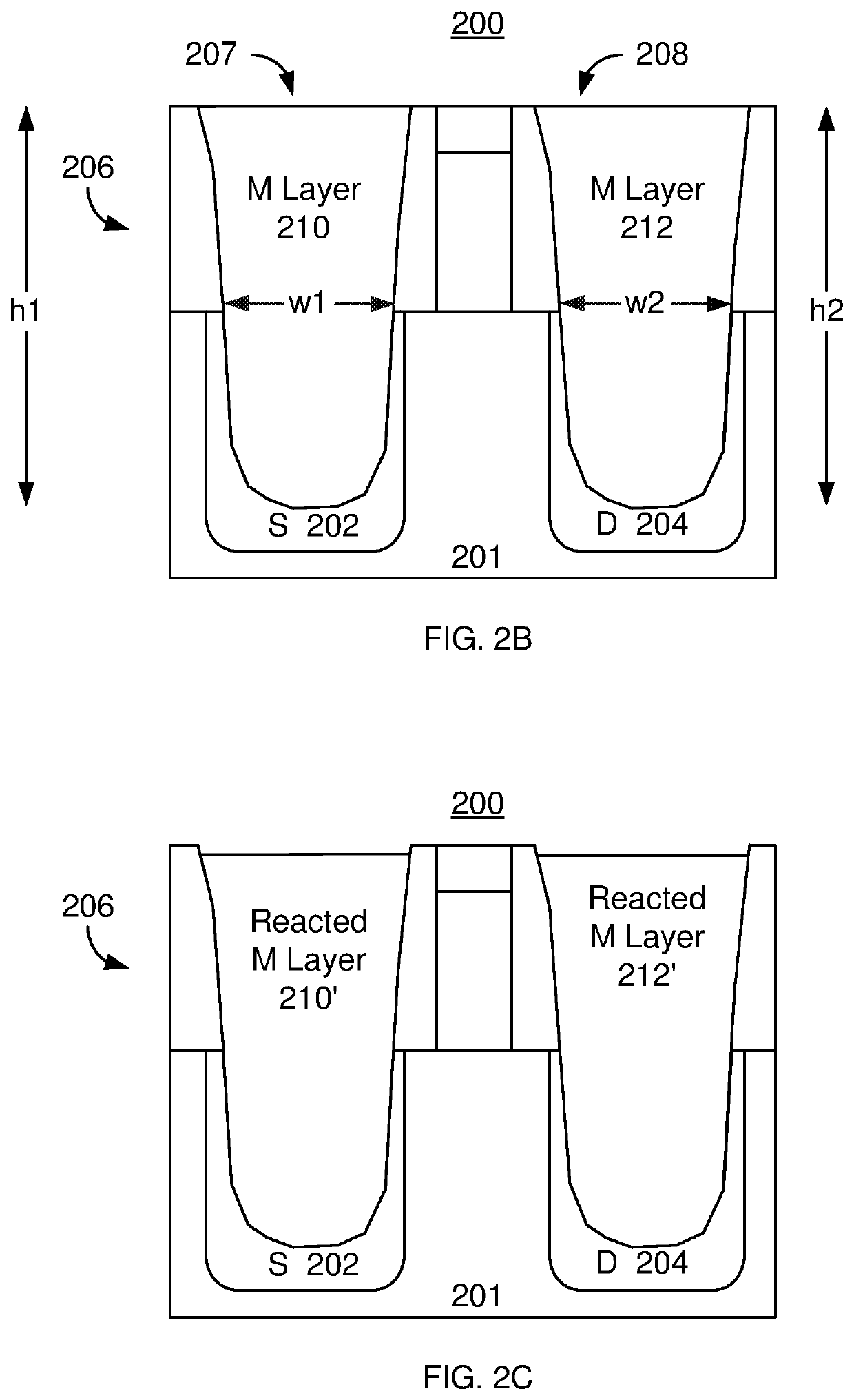

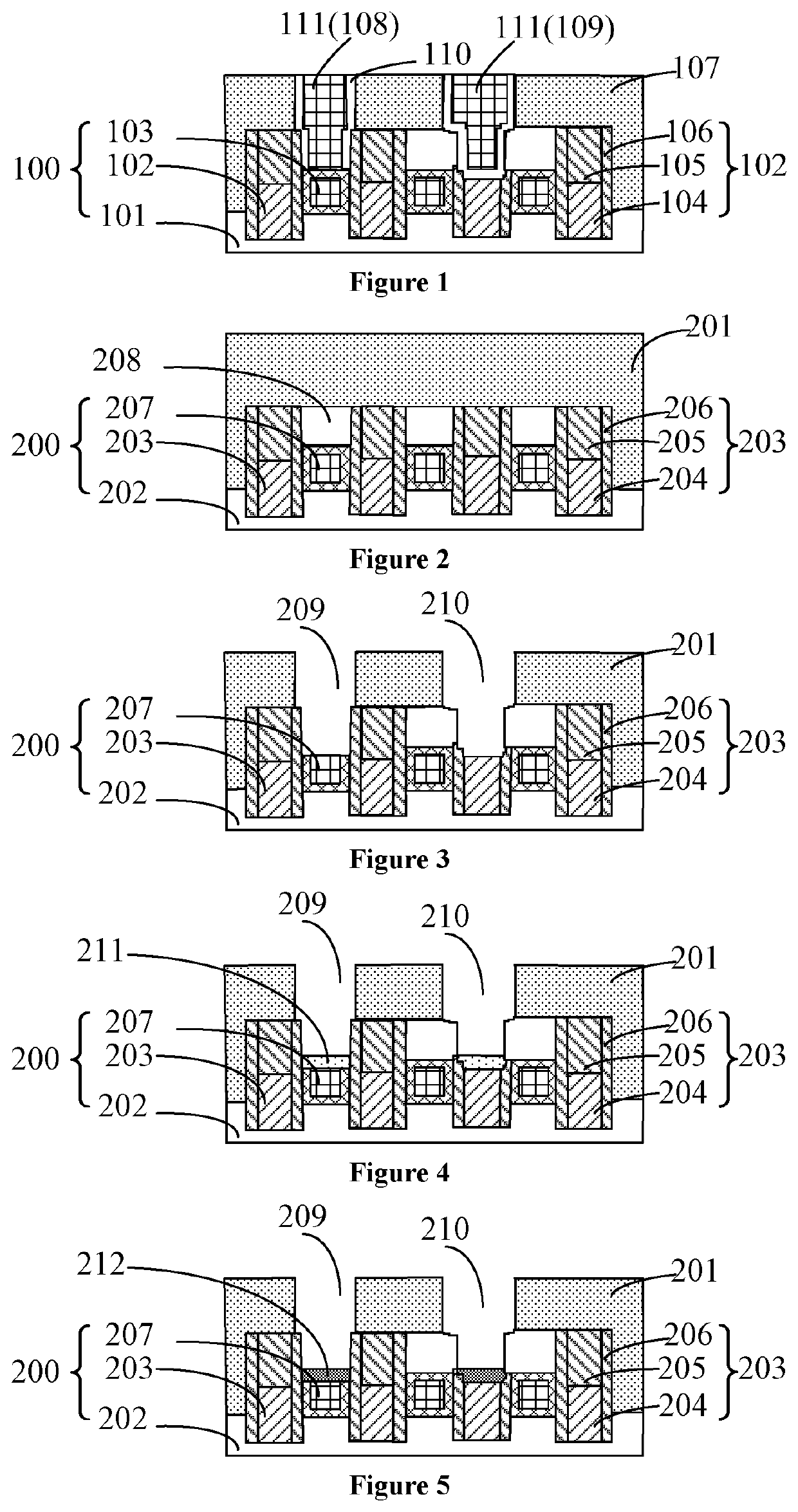

Method of providing reacted metal source-drain stressors for tensile channel stress

ActiveUS20190131451A1Reduce contact resistivityImprove performanceSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingCompound aStressor

A method provides a source-drain stressor for a semiconductor device including source and drain regions. Recesses are formed in the source and drain regions. An insulating layer covers the source and drain regions. The recesses extend through the insulating layer above the source and drain regions. An intimate mixture layer of materials A and B is provided. Portions of the intimate mixture layer are in the recesses. The portions of the intimate mixture layer have a height and a width. The height divided by the width is greater than three. A top surface of the portions of the intimate mixture layer in the recesses is free. The intimate mixture layer is reacted to form a reacted intimate mixture layer including a compound AxBy. The compound AxBy occupies less volume than a corresponding portion of the intimate mixture layer.

Owner:SAMSUNG ELECTRONICS CO LTD

A kind of manufacturing method of quarter wave plate for temperature compensation

ActiveCN111175968BImprove performance and yieldAchieve stabilityPolarising elementsVoltage/current isolationMathematical modelEngineering

The invention discloses a manufacturing method of a quarter wave plate used for temperature compensation of an optical fiber current transformer, which can realize the stable and consistent current ratio difference of the optical fiber current transformer in the whole temperature range in the mass production process, Reduce the defect rate of products and ensure the long-term working accuracy and stability of the fiber optic current transformer. The method includes the following steps: (1) establishing a mathematical model of the optical fiber current transformer; (2) measuring the phase delay of the elliptical core optical fiber; (3) manufacturing a quarter-wave plate. The advantages of the present invention are that the manufacturing process scheme of the quarter-wave plate is stable and consistent, and the stability and consistency of the current ratio difference of the optical fiber current transformer system in the full temperature range can be realized, thereby improving the optical fiber current mutual inductance. performance and yield of the system.

Owner:BEIJING AUTOMATION CONTROL EQUIP INST

Method of providing reacted metal source-drain stressors for tensile channel stress

ActiveUS10510886B2Improve performance and yieldReduce contact resistivitySemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingCompound aDevice material

A method provides a source-drain stressor for a semiconductor device including source and drain regions. Recesses are formed in the source and drain regions. An insulating layer covers the source and drain regions. The recesses extend through the insulating layer above the source and drain regions. An intimate mixture layer of materials A and B is provided. Portions of the intimate mixture layer are in the recesses. The portions of the intimate mixture layer have a height and a width. The height divided by the width is greater than three. A top surface of the portions of the intimate mixture layer in the recesses is free. The intimate mixture layer is reacted to form a reacted intimate mixture layer including a compound AxBy. The compound AxBy occupies less volume than a corresponding portion of the intimate mixture layer.

Owner:SAMSUNG ELECTRONICS CO LTD

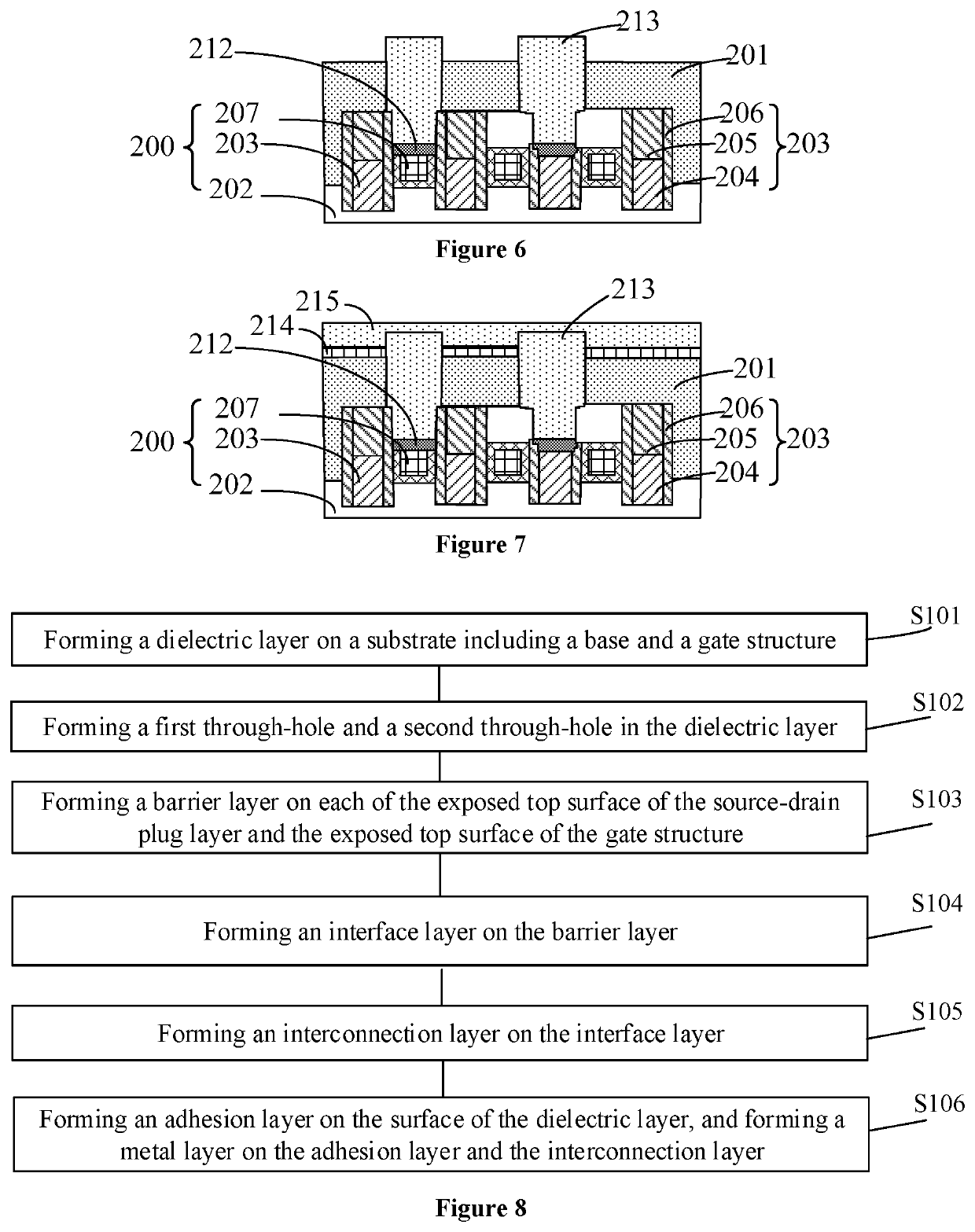

Semiconductor device and fabrication method thereof

PendingUS20220076997A1Quality improvementImprove performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterface layer

A semiconductor device and a fabrication method of the semiconductor device are provided. The semiconductor device includes a substrate, a source-drain plug layer in the substrate, a gate structure in the substrate, and a dielectric layer disposed over the substrate and covering the gate structure and the source-drain plug layer. The dielectric layer contains a first through-hole having a bottom exposing a top surface of the source-drain plug layer, and a second through-hole having a bottom exposing a top surface of the gate structure. Further, the semiconductor device includes an interface layer disposed on each of the top surface of the source-drain plug layer exposed by the first through-hole and the top surface of the gate structure exposed by the second through-hole.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

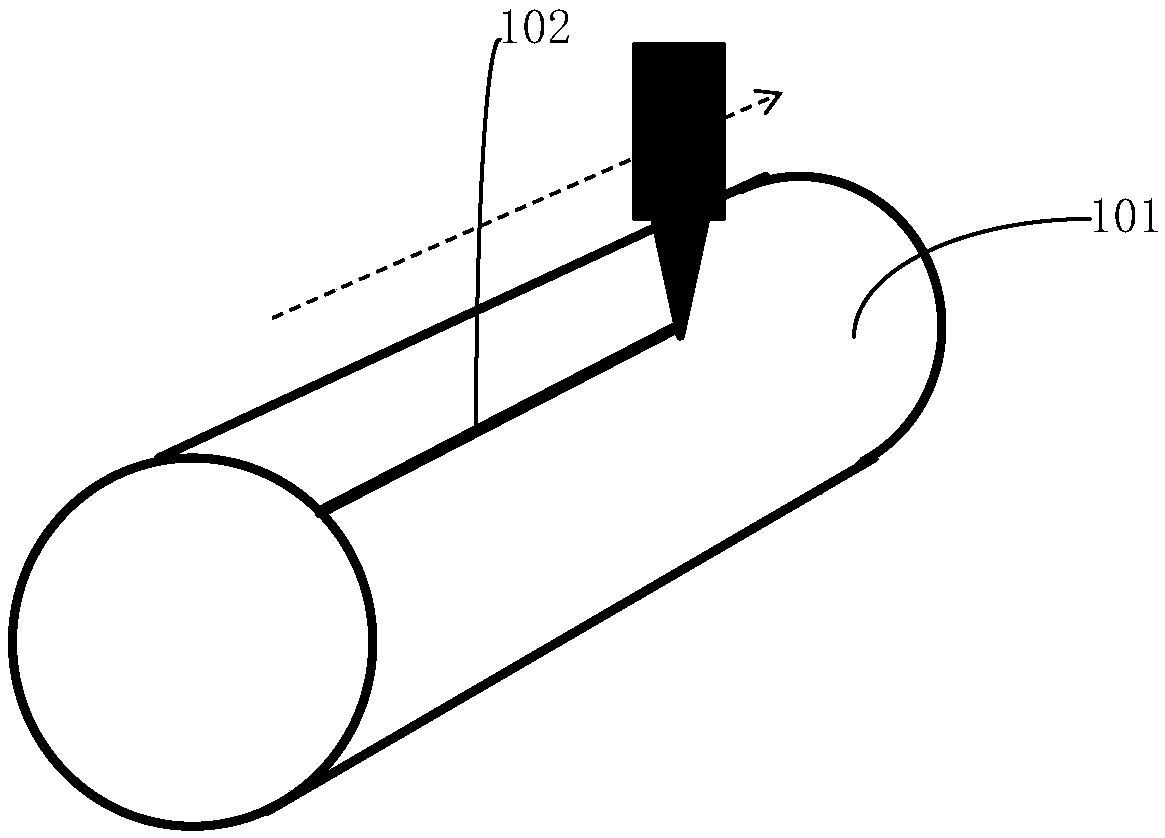

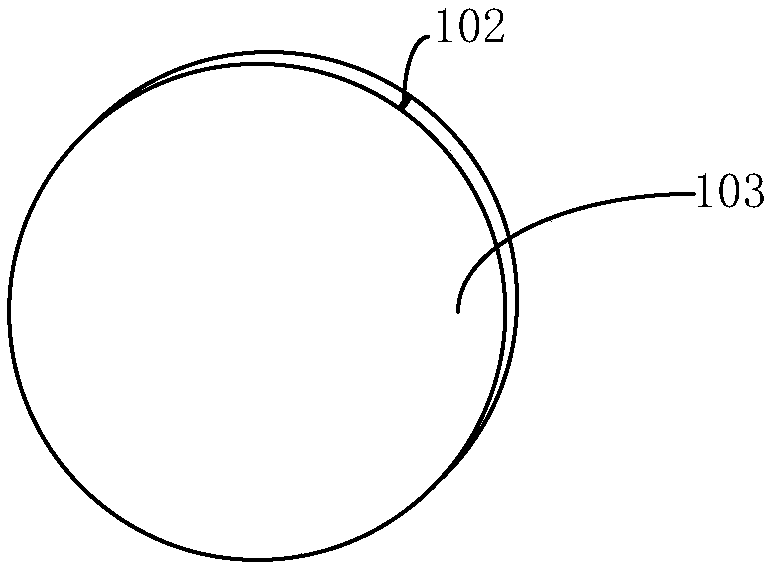

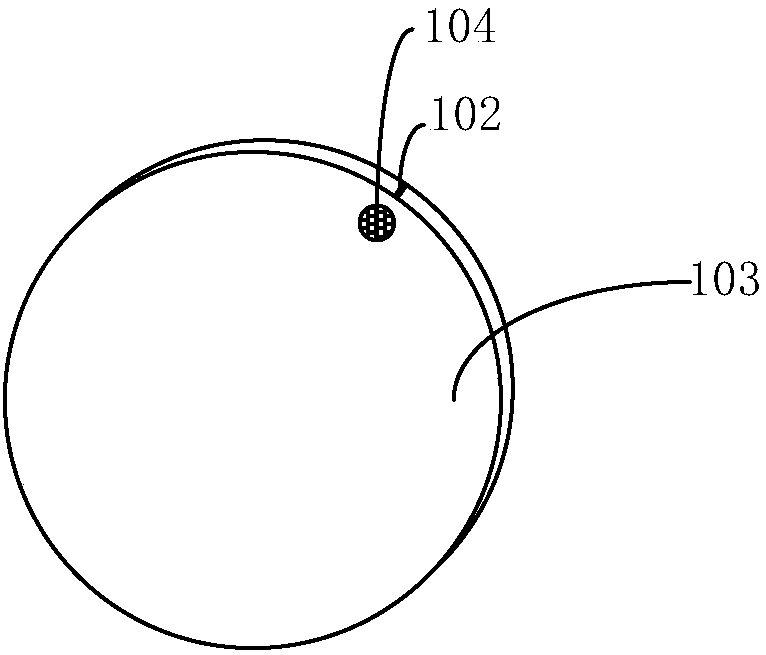

Wafer and manufacturing method thereof, and electronic device

ActiveCN109427614AImprove performance and yieldAvoid chippingSemiconductor/solid-state device manufacturingCrystal orientationLaser

The invention provides a wafer and a manufacturing method thereof and an electronic device. The method comprises the steps of providing a silicon ingot; forming a linear film layer marker for markinga crystal orientation of the silicon ingot on a side surface of the silicon ingot; slicing the silicon ingot to form a silicon wafer; forming a laser marker for marking the crystal orientation of thesilicon ingot on any of upper and lower bottom surfaces of the silicon wafer with the linear film layer marker as a reference; and removing the linear film layer marker. With the method, not only themarker can be accurately formed on the surface of the wafer, but also the cracking of the wafer during the marker manufacturing process or after manufacturing of the marker and the problem of contamination of the wafer during the marker preparation process can be avoided since no etching step exists in the whole preparation process, and thus the performance and yield of the wafer are further improved.

Owner:ZING SEMICON CORP

Manufacturing method of embedded epitaxial layer

PendingCN113140462APrevent collapseImprove performance and yieldSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsEngineering

The invention discloses a manufacturing method of an embedded epitaxial layer. The method comprises the following steps of: step 1, etching a silicon substrate to form a groove; and step 2, filling the groove with an embedded epitaxial layer: step 21, forming a buffer layer; step 22, forming a main body layer on the surface of the buffer layer; doping the main body layer in silicon to provide stress for the silicon substrate at the two sides of the groove, wherein the doping concentration of the main body layer is gradually varied in the epitaxial growth process to eliminate the fault defect and further prevent the main body layer from collapsing; step 23, forming a cap layer, and superposing the buffer layer, the main body layer and the cap layer to form an embedded epitaxial layer; wherein the buffer layer, the main body layer and the cap layer are made of the same material, and the doping concentration of the buffer layer and the cap layer is smaller than or equal to the minimum doping concentration of the main body layer. According to the invention, the main body layer of the embedded epitaxial layer can be prevented from collapsing, so that the performance and the yield of a product can be improved.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

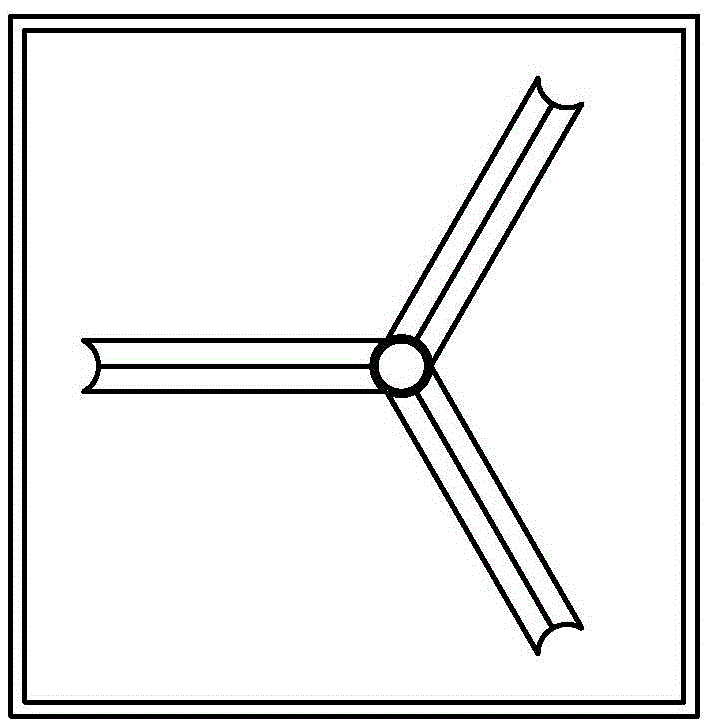

Printed compatible designs and layout schemes for printed electronics

ActiveUS8383952B2Improve performance and yieldIncrease surface tensionPrinted circuit liquid treatmentSemiconductor/solid-state device detailsPhotolithographyPrinted electronics

Embodiments of the present invention relate to circuit layouts that are compatible with printing electronic inks, printed circuits formed by printing an electronic ink or a combination of printing and conventional blanket deposition and photolithography, and methods of forming circuits by printing electronic inks onto structures having print-compatible shapes. The layouts include features having (i) a print-compatible shape and (ii) an orientation that is either orthogonal or parallel to the orientation of every other feature in the layout.

Owner:ENSURGE MICROPOWER ASA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com