Manufacturing method for semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as yield loss, material loss, and difficulty in step height of shallow trench isolation structures, so as to improve performance and yield, The effect of small fluctuations in the height of the steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

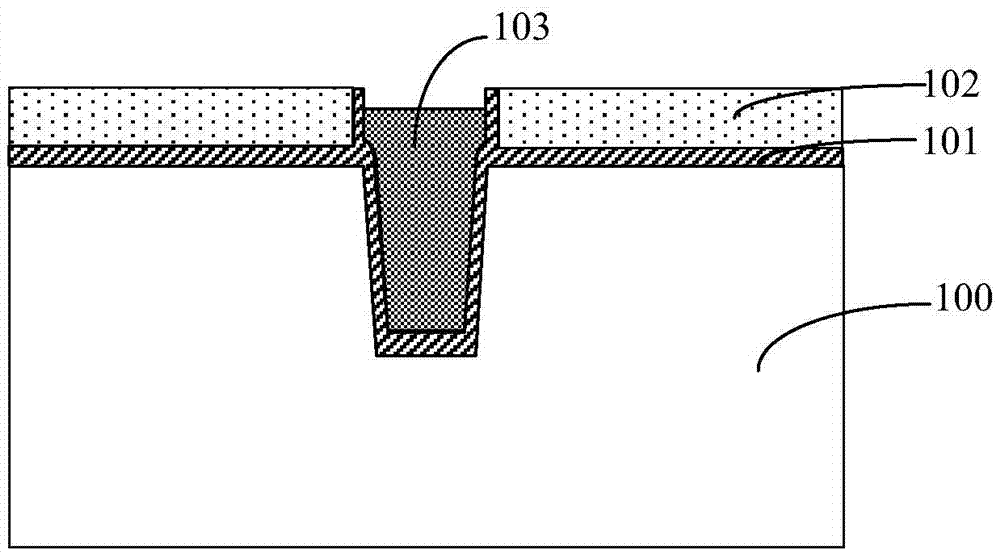

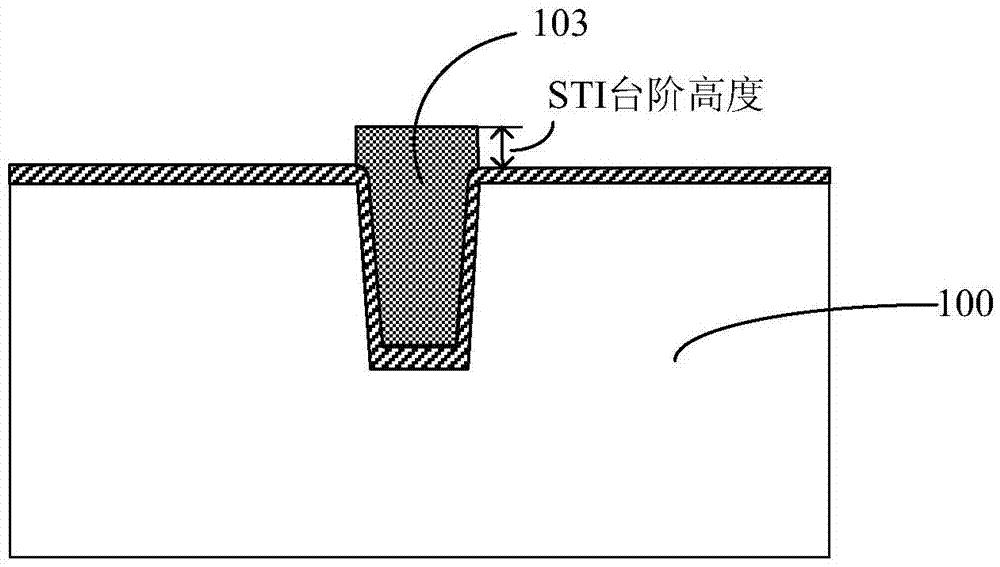

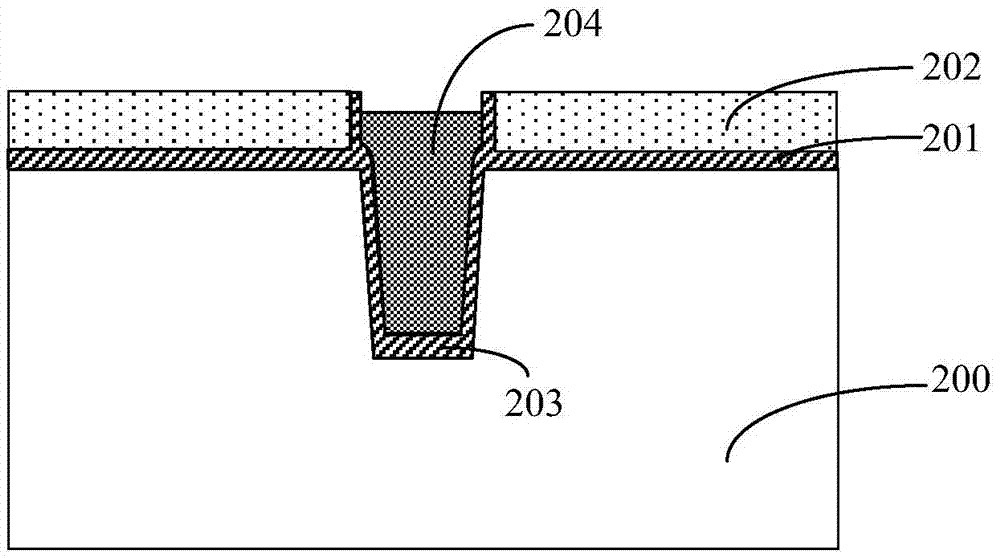

[0038] Below, refer to Figure 2A to Figure 2E as well as image 3 The detailed steps of an exemplary method of the semiconductor device manufacturing method proposed by the embodiment of the present invention will be described. Among them, 2A to Figure 2E A cross-sectional view of a structure formed in related steps of a method for manufacturing a semiconductor device according to an embodiment of the present invention; image 3 It is a schematic flowchart of a method for manufacturing a semiconductor device according to an embodiment of the present invention.

[0039] As an example, the method for manufacturing a semiconductor device in this embodiment specifically includes the following steps:

[0040] Firstly, step S301 is performed to provide a semiconductor substrate, and a hard mask layer defining a pattern of a shallow trench isolation structure is formed on the surface of the semiconductor substrate.

[0041] Specifically, such as Figure 2AAs shown, the constit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com