Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

35results about How to "Avoid etch residue" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

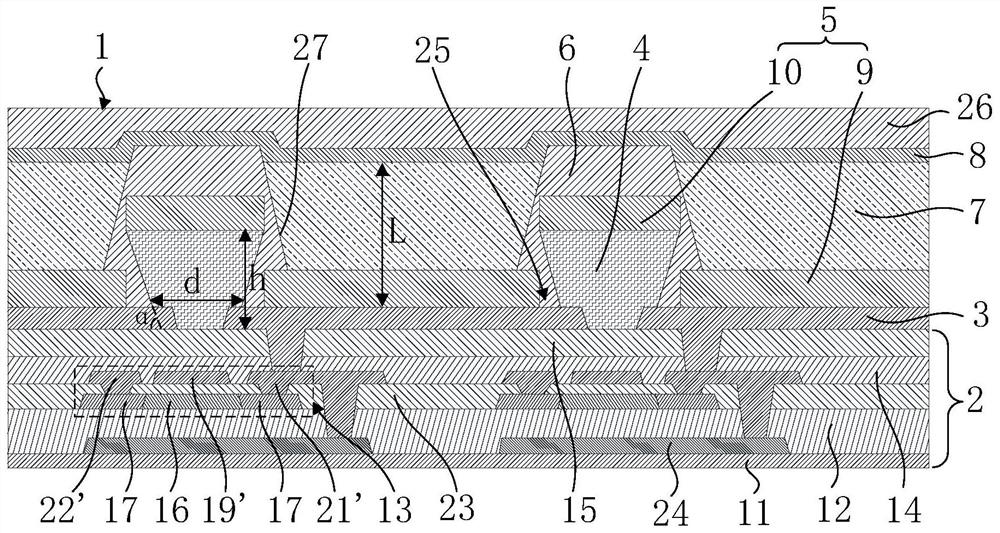

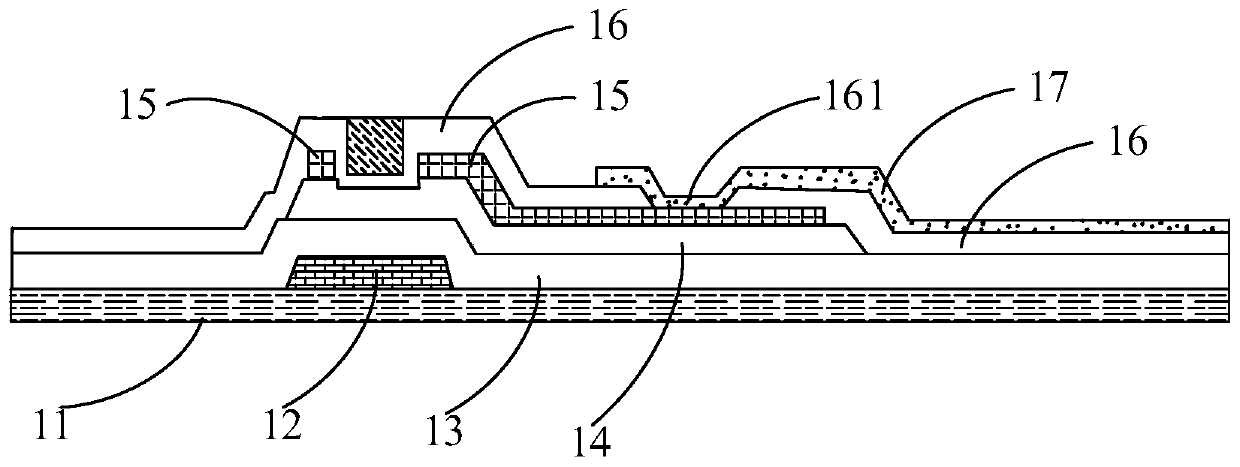

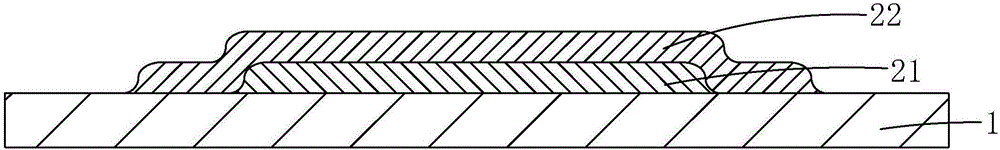

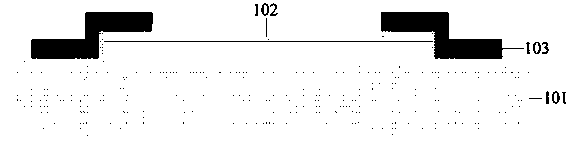

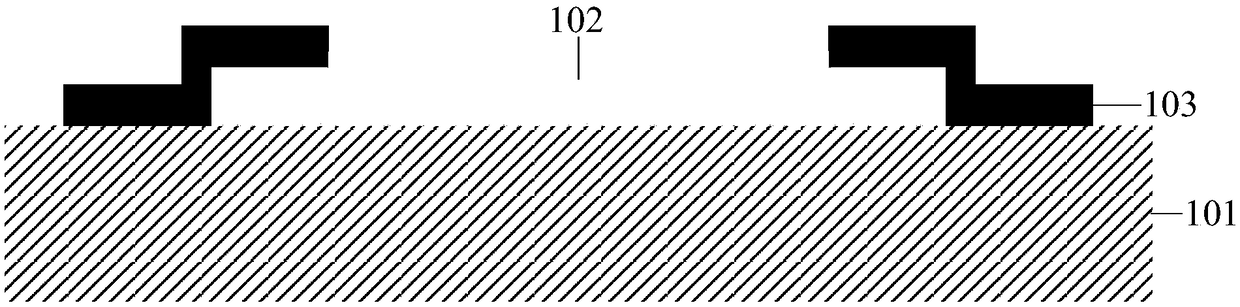

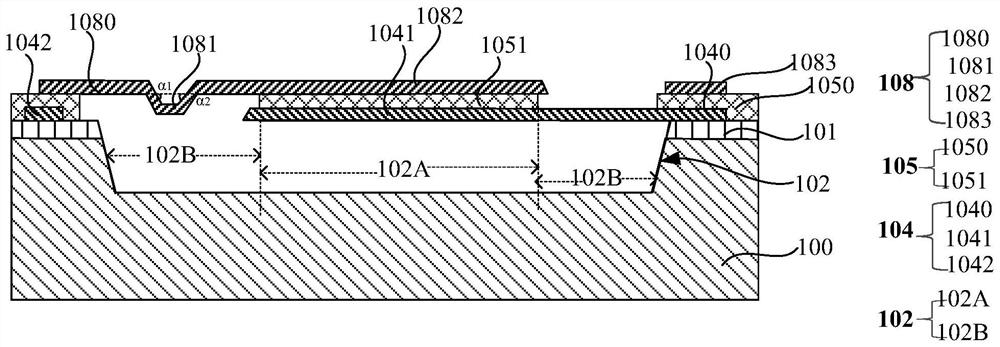

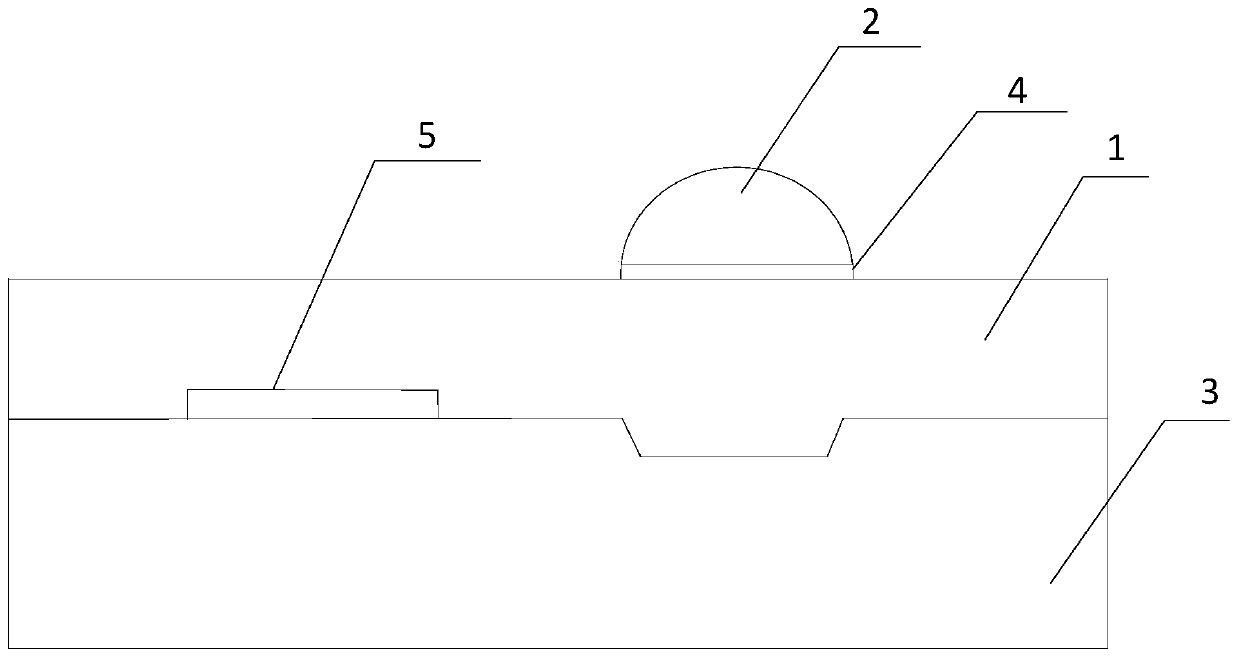

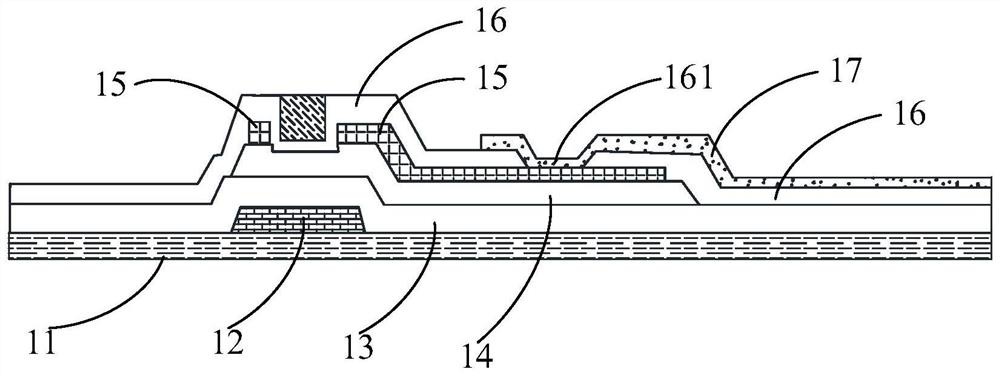

Array substrate, preparation method thereof and display panel

ActiveCN110911424AImprove job stabilityAvoid display unevennessTransistorSolid-state devicesPhysicsThin membrane

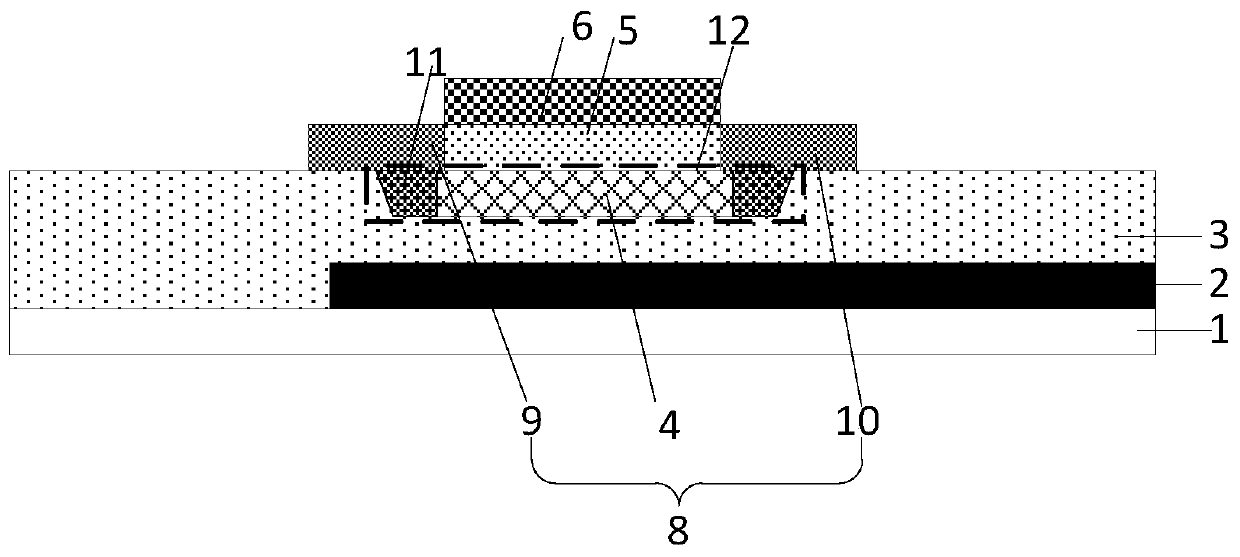

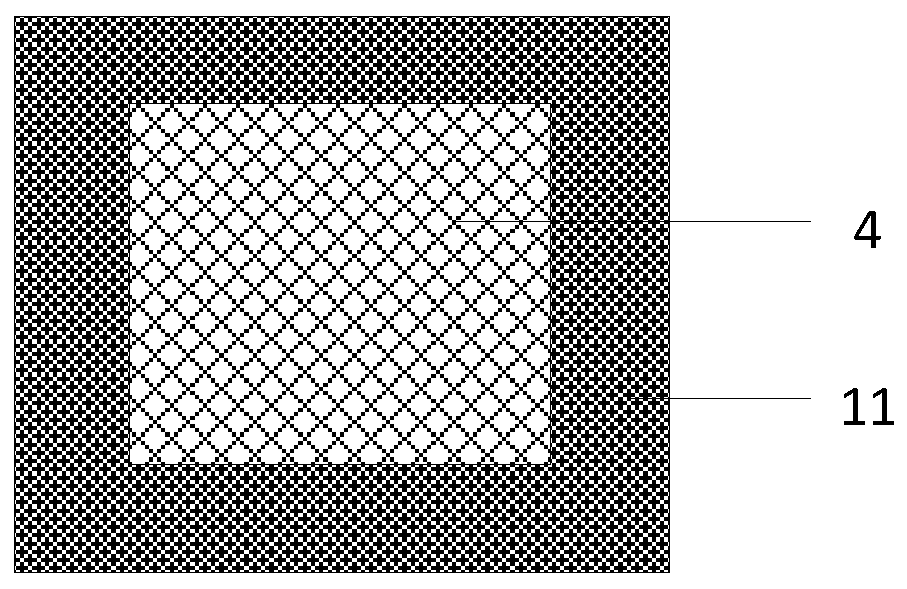

The invention discloses an array substrate, a preparation method thereof and a display panel, which are used for preventing a semiconductor region of an active layer of a thin film transistor from being illuminated, improving the working stability of the thin film transistor, avoiding uneven display pictures and improving the display effect. The array substrate comprises a substrate body, a shading layer located on the substrate body, a buffer layer located on the shading layer, an active layer located on the buffer layer and a shading part. The buffer layer is provided with a groove. The active layer includes a semiconductor region, and a first conductive region and a second conductive region connected to the semiconductor region. The semiconductor region and the shading part fill the groove. The orthographic projection of the shading part on the substrate is annular, the side surface of the semiconductor region is completely surrounded by the shading part, and the first conductor region and the second conductor region are located above the shading part and the semiconductor region. The orthographic projection of the shading layer on the substrate covers the orthographic projection of the semiconductor region on the substrate.

Owner:BOE TECH GRP CO LTD +1

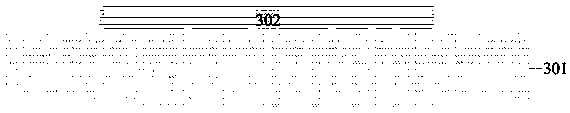

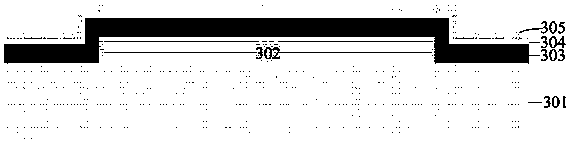

Touch display panel, manufacturing method thereof and touch display device

PendingCN111352531AImprove flexibilityReduce breakageInput/output processes for data processingPhysicsComposite material

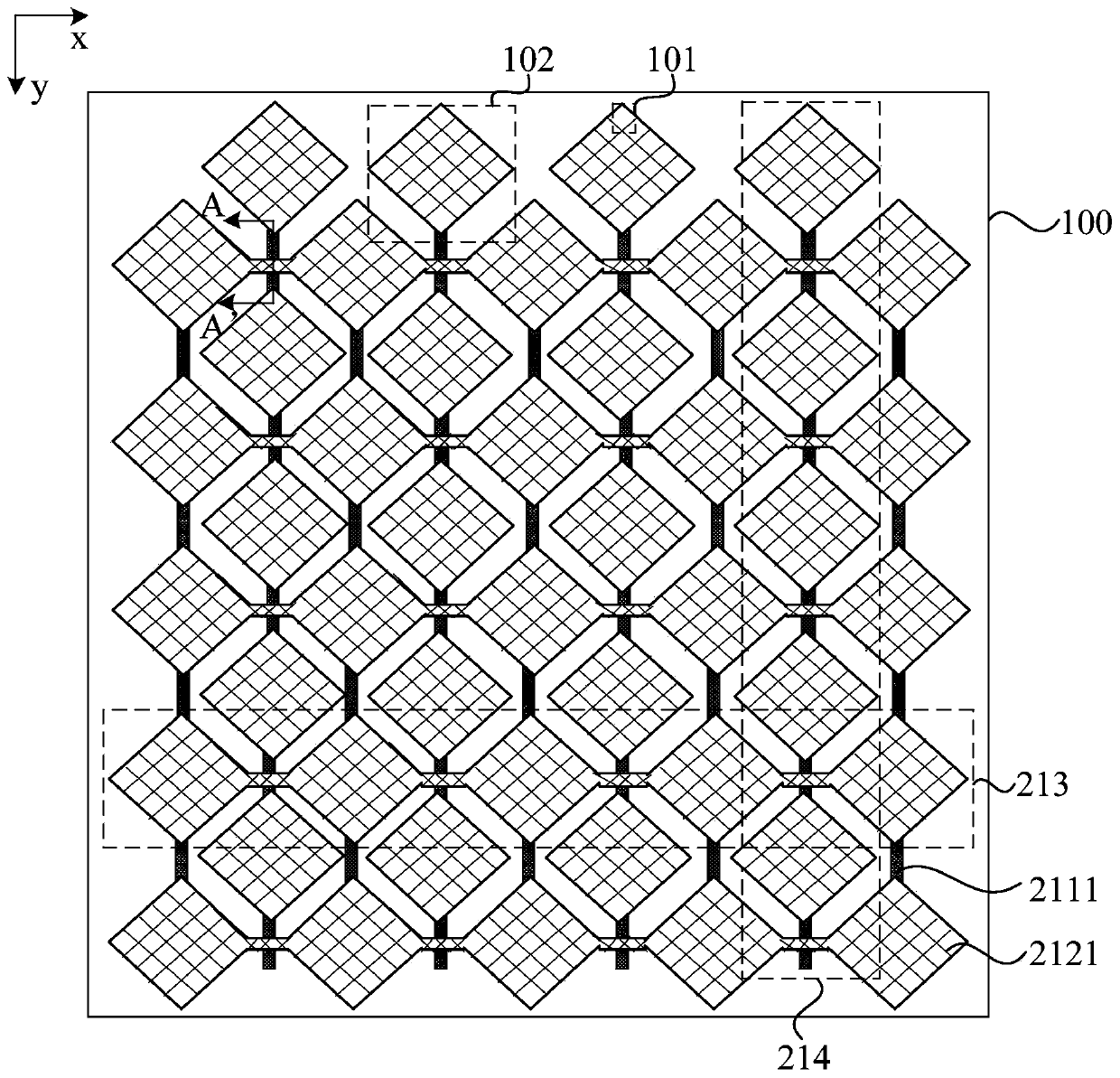

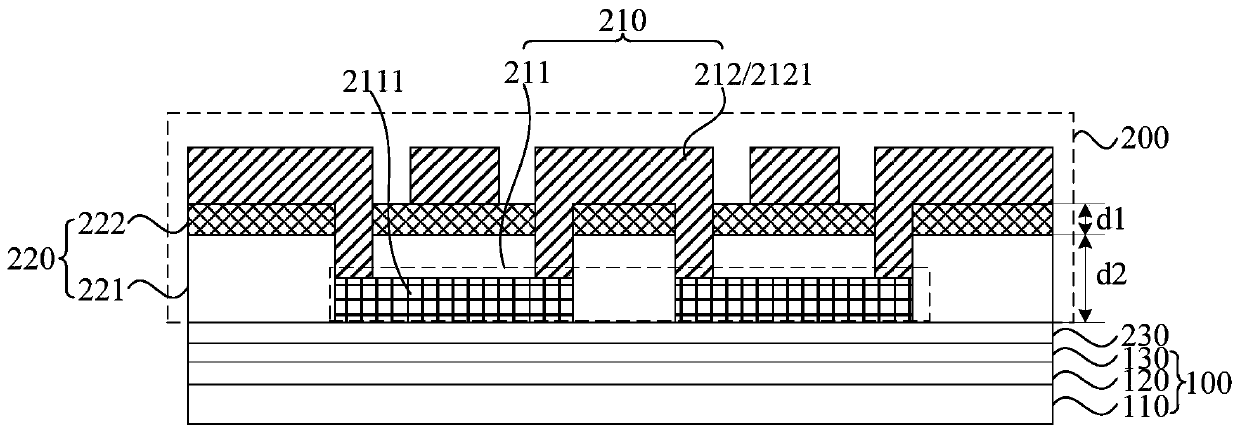

The embodiment of the invention discloses a touch display panel, a manufacturing method thereof and a display device. The touch display panel comprises a touch function layer, wherein the touch function layer comprises a touch electrode layer, and the touch electrode layer comprises at least one metal layer used for forming touch electrodes; the touch function layer further comprises insulating layers in one-to-one correspondence with the metal layers, wherein the insulating layers are adjacent film layers on the sides, close to the display function layer, of the corresponding metal layers, atleast one insulating layer is an insulating layer of a laminated structure, and the insulating layer of the laminated structure comprises an organic insulating layer and an inorganic insulating layerwhich are arranged in a laminated mode in the direction from the display function layer to the corresponding metal layer; the thickness of the inorganic insulating layers can be correspondingly reduced, so the flexibility of the touch display panel can be improved; moreover, etching residues caused by metal oxide generated by water vapor reaction in the metal layer and the organic insulating layer can be avoided, and etching residues caused by metal ions entering the organic insulating layer when the metal layer is formed can also be avoided, so that short circuit is avoided.

Owner:YUNGU GUAN TECH CO LTD

Thin film transistor and manufacturing method thereof

InactiveCN102709329ARaise the threshold voltageReduce contact resistanceTransistorSemiconductor/solid-state device manufacturingInsulation layerOxide thin-film transistor

The invention provides a thin film transistor and a manufacturing method thereof. The method comprises the following steps: forming a grid electrode, a grid insulation layer, a semiconductor layer and a doped semiconductor layer on a base plate; nitriding by using plasma, so that Si-N weak bonding on the surface of the doped semiconductor layer; depositing a second metal layer; and etching to form a source electrode and a drain electrode and exposing the semiconductor layer between the source electrode and the drain electrode. The Si-N weak bonding is formed on the doped semiconductor layer before the second metal layer is deposited, so silicon atoms between the second metal layer and the doped semiconductor layer are prevented from forming bonding, contact resistance is reduced, and etching residue caused by reduced etching speed is avoided.

Owner:CENTURY DISPLAY (SHENZHEN) CO LTD

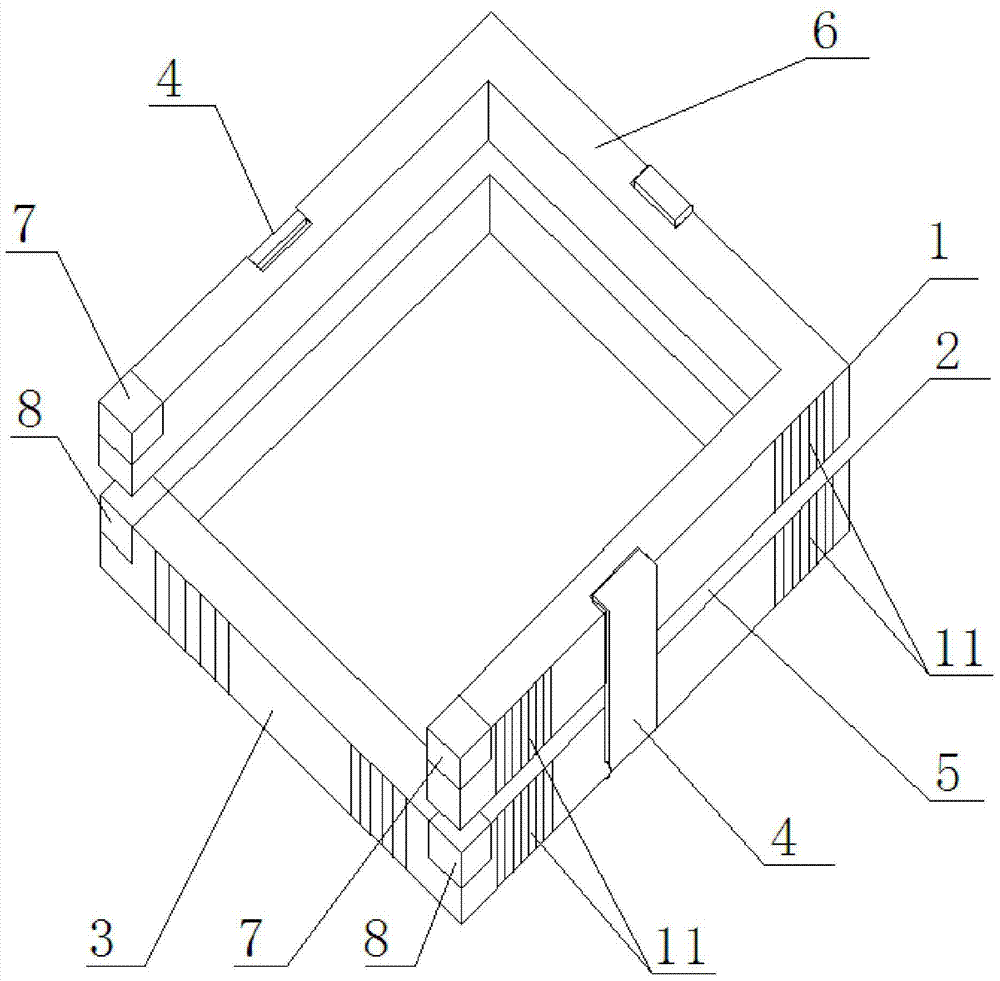

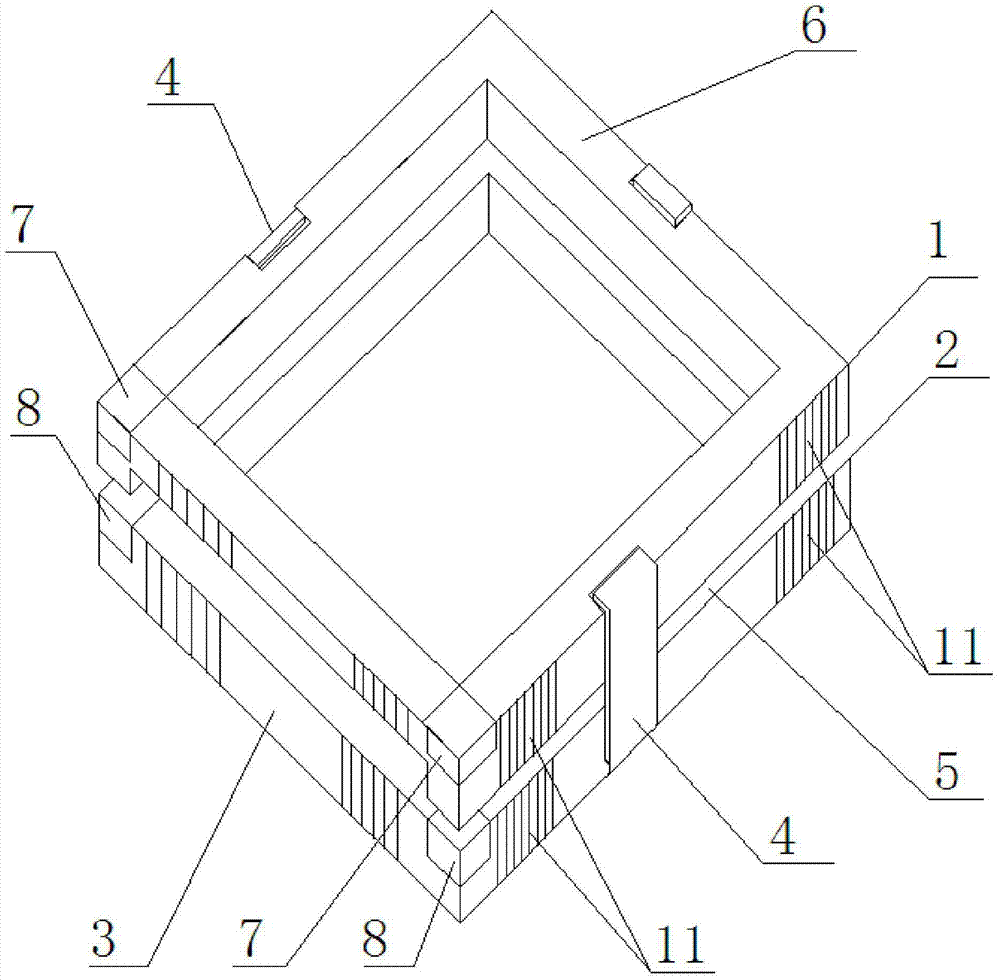

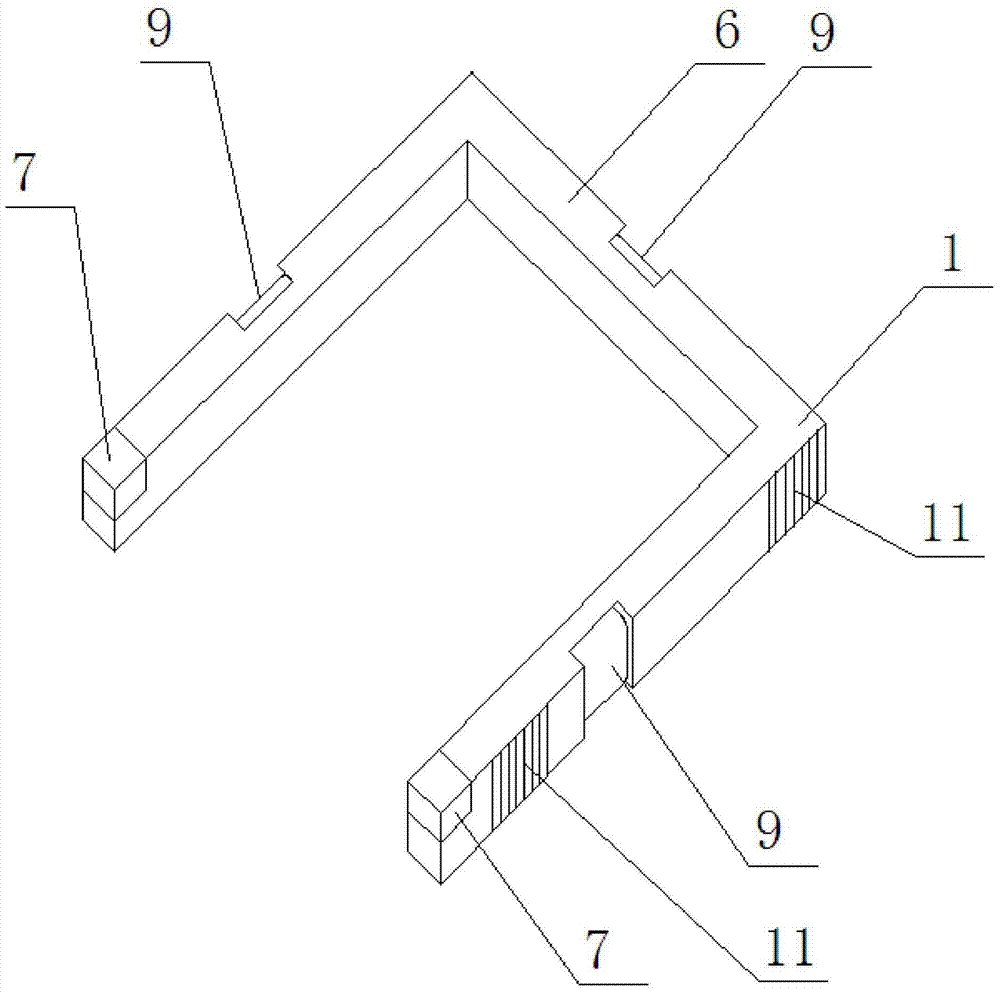

Device and method for protecting graphene film in etching and transfer

ActiveCN104332395AEasy transferAvoid damageGrapheneSemiconductor/solid-state device manufacturingFastenerEngineering

The invention relates to the technical field of graphene manufacture, in particular to a device and a method for protecting a graphene film in etching and transfer. The device comprises a first fixture and a second fixture, the first fixture is of a square frame structure comprising first fixture columns, the second fixture is of a square frame structure comprising four second fixture columns, the square size of the first fixture is as same as that of the second fixture, the first fixture is arranged above the second fixture and connected with the second fixture through movable fasteners, and a fixture gap is reserved between the first fixture and the second fixture. The device and the method have the advantages that a graphene sheet is clamped before etching by the aid of a transfer device comprising the first fixture and the second fixture, the graphene sheet can be conveniently transferred and can also be protected in etching, and damage to the graphene film due to the fact that the graphene sheet touches the bottom of an etchant trough is avoided.

Owner:CHONGQING GRAPHENE TECH +1

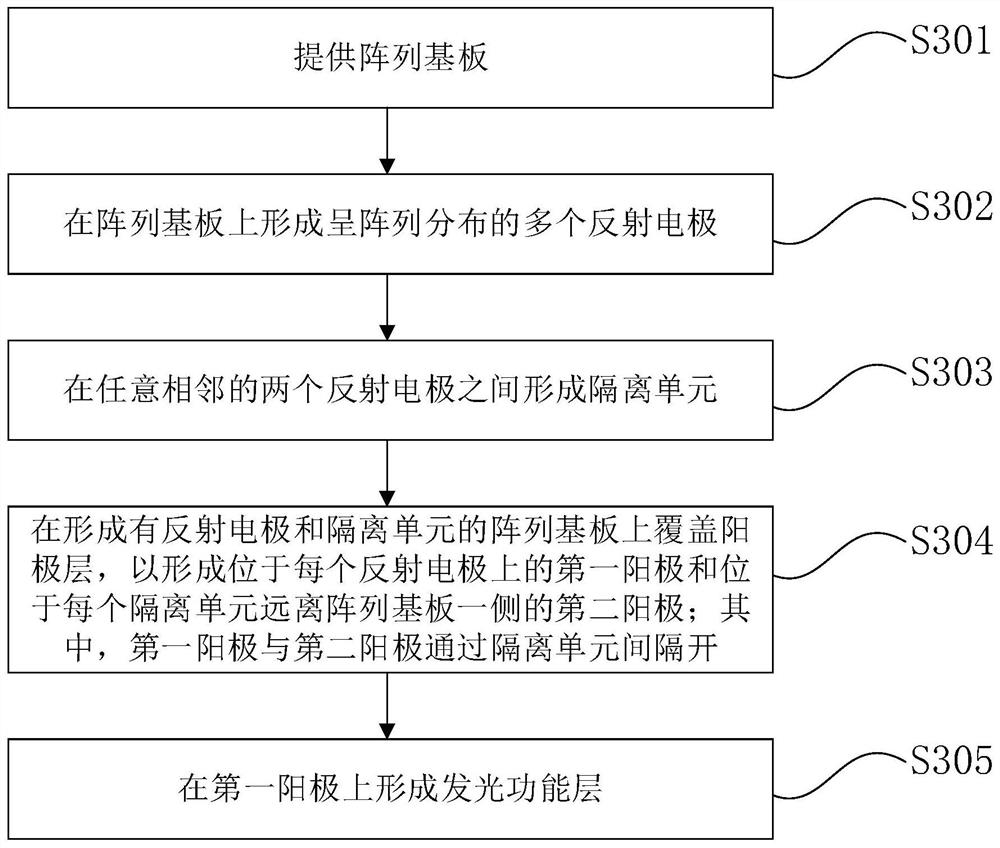

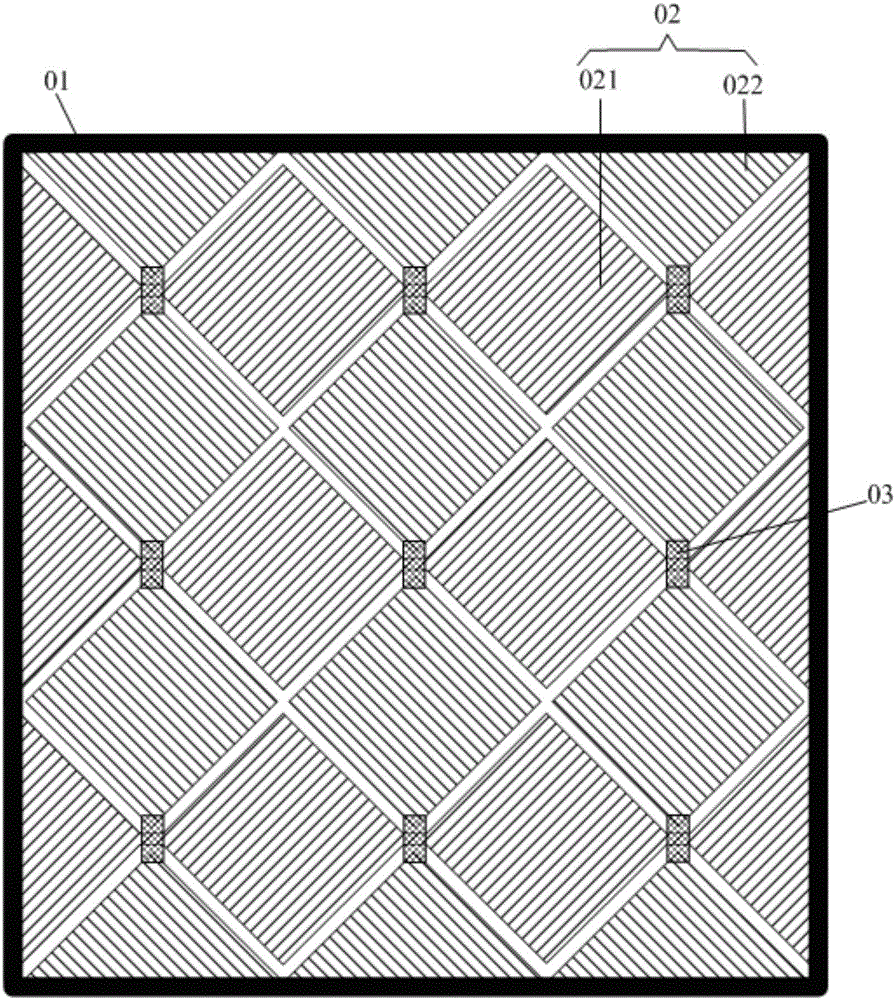

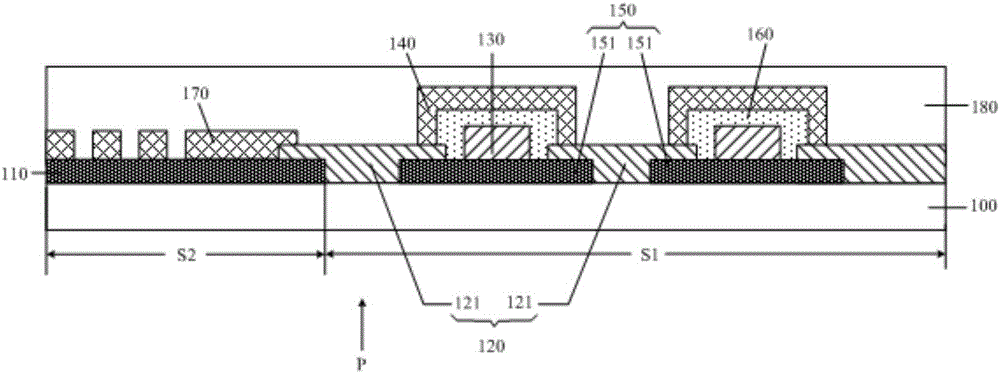

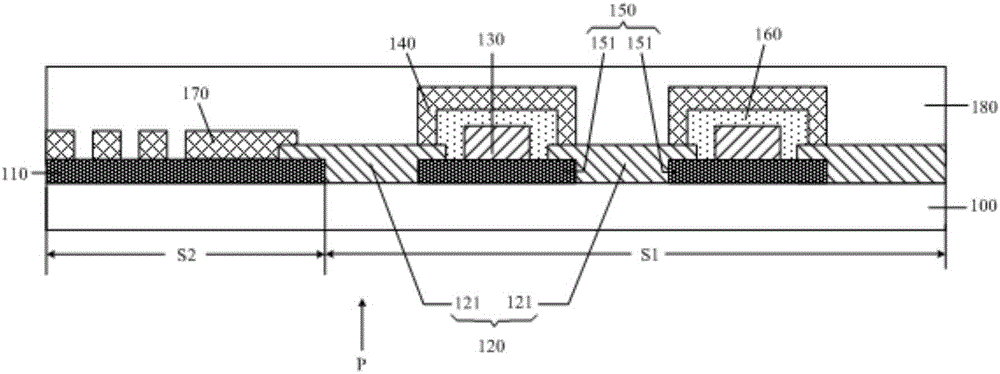

Display panel and manufacturing method thereof

InactiveCN111900194AImprove overall lifespanGood for mass productionSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringMaterials science

The invention discloses a display panel and a manufacturing method thereof. The display panel comprises an array substrate, a plurality of reflecting electrodes, a plurality of isolation units, an anode layer and a light-emitting function layer. The plurality of reflecting electrodes are positioned on the array substrate and are distributed in an array manner; one isolation unit is arranged between any two adjacent reflecting electrodes; the anode layer comprises a first anode located on each reflecting electrode and a second anode located on the side, away from the array substrate, of each isolation unit, and each first anode and the adjacent second anode are spaced through the corresponding isolation unit; and the light-emitting function layer is located on the first anodes. According tothe invention, two adjacent first anodes can be naturally disconnected through the isolation unit, and the cavity length of the device can be adjusted through the thickness of the first anodes.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Touch screen, manufacture method thereof, and display apparatus

InactiveCN106249952AReduce reflectivityAvoid etch residueInput/output processes for data processingReflectivityEngineering

The invention discloses a touch screen, its manufacturing method and a display device. By setting the bottom layer as the same layer and the same material as the black matrix layer, it is not necessary to increase the additional process and cost for preparing the bottom layer, and only need to replace the original black matrix layer. The composition pattern of the layer can be deformed to obtain the black matrix layer and the bottom pattern at the same time, and generally the material of the black matrix layer is a black material and its reflectivity is generally less than 10%, so compared with the prior art, the bridging line can be reduced. The reflectivity of the area, and the problem of etch residue can be avoided.

Owner:BOE TECH GRP CO LTD +1

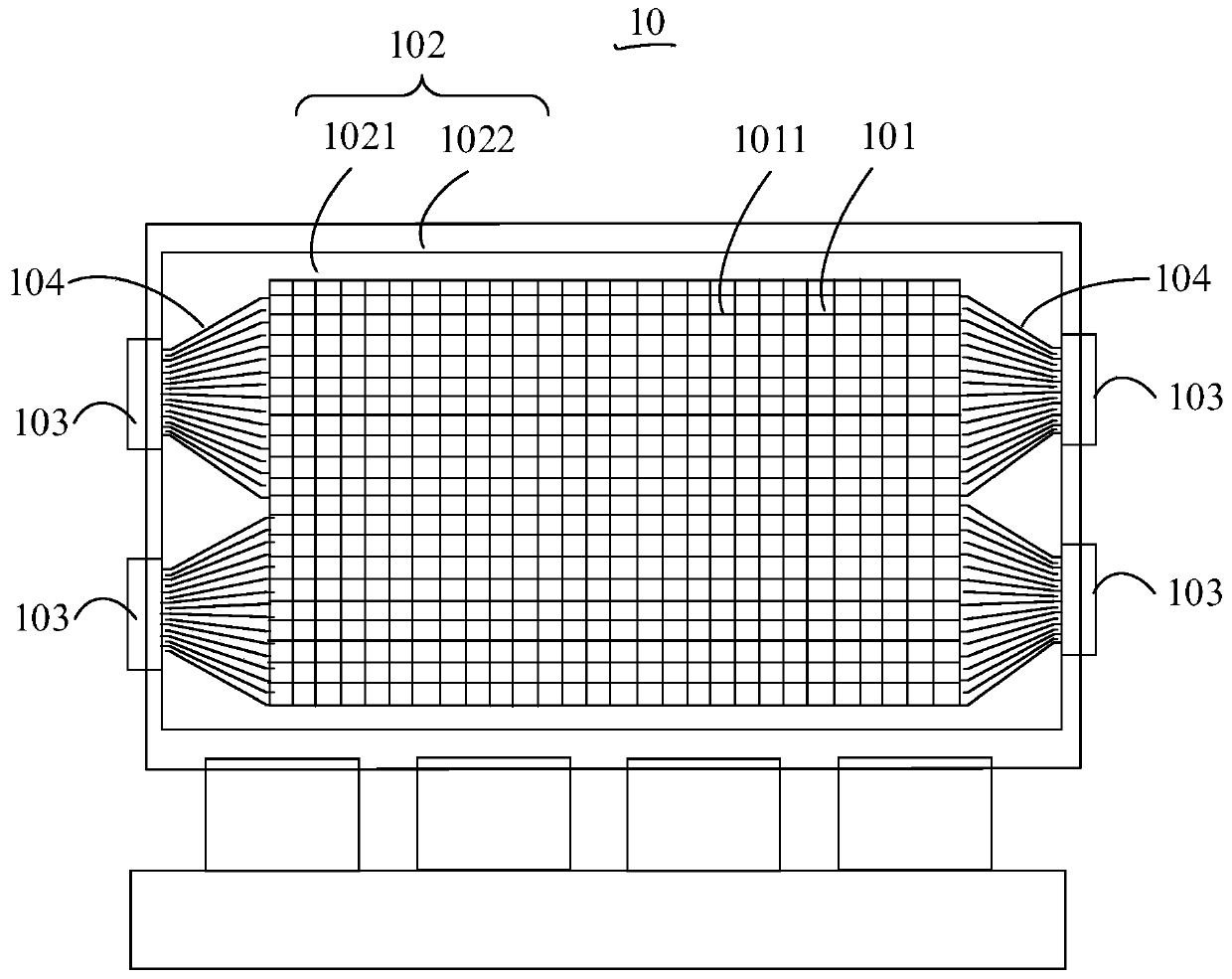

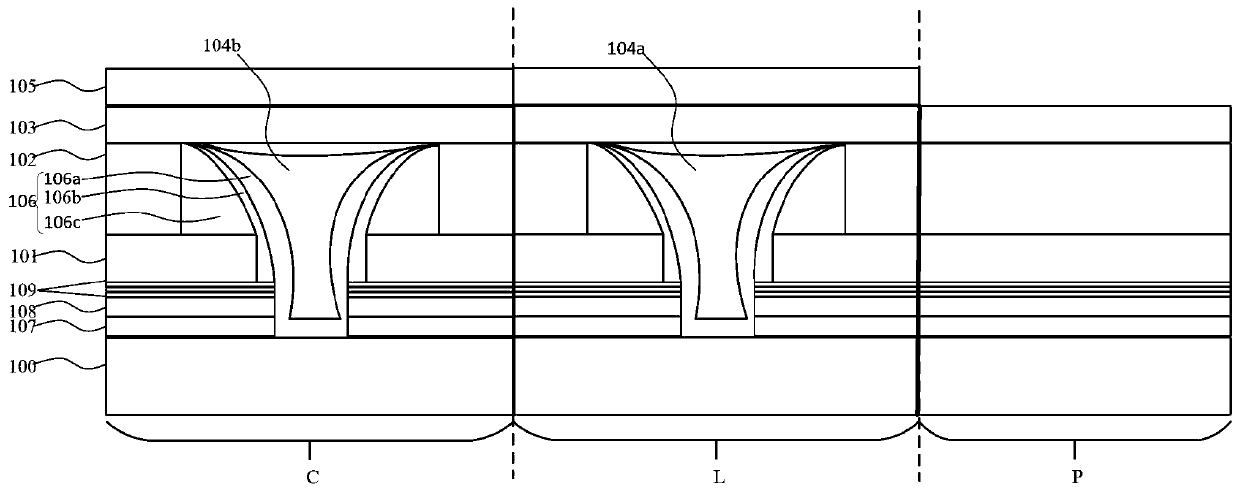

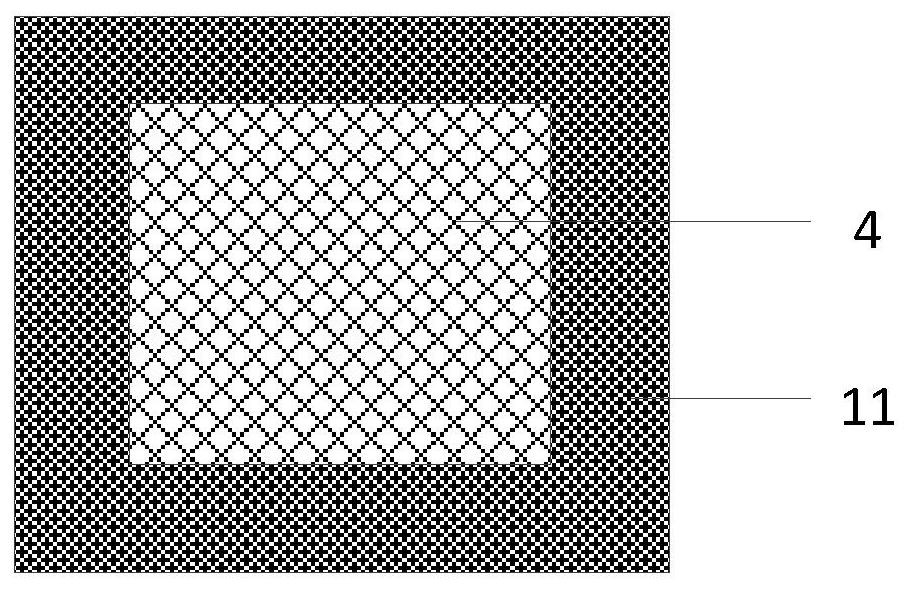

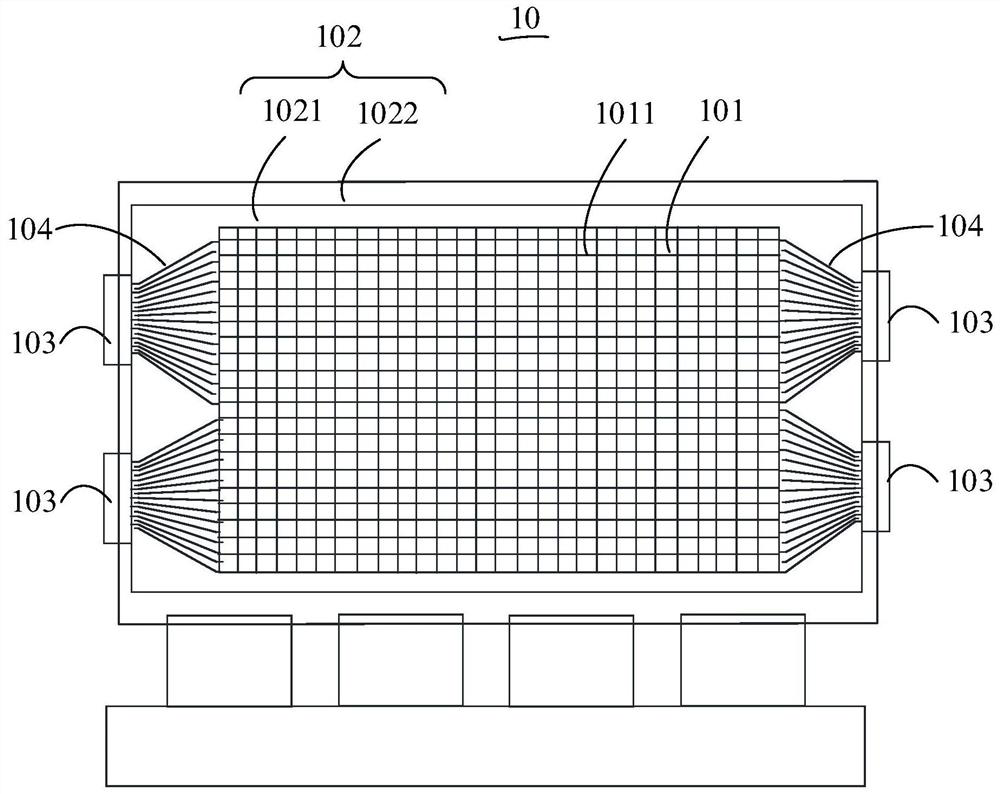

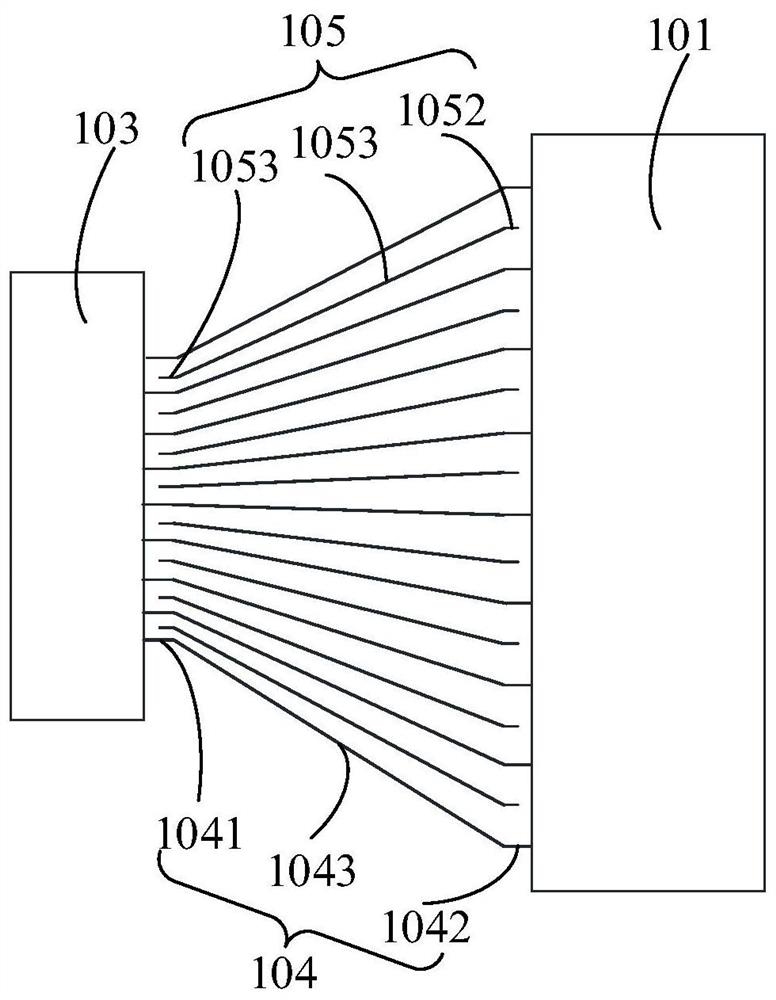

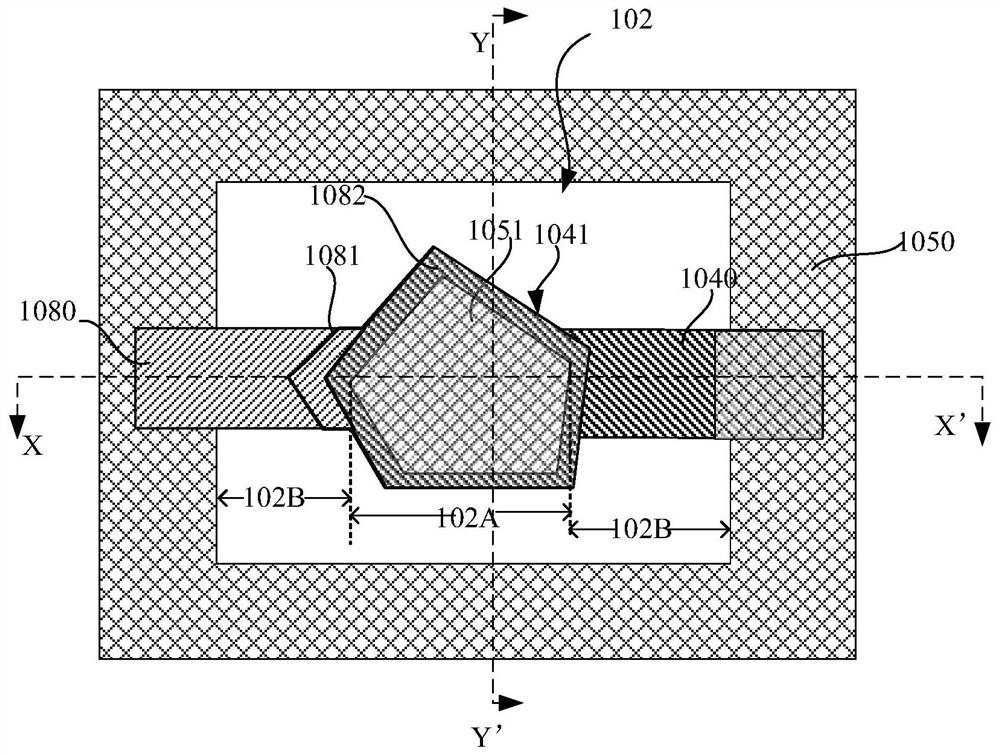

Array substrate and display panel

ActiveCN110333633AReduction of etch residueAvoid etch residueNon-linear opticsOptoelectronicsActive layer

The present invention discloses an array substrate and a display panel. The array substrate includes a glass substrate having a display area and a frame area around the display area, wherein the glasssubstrate is sequentially provided a metal layer, an insulating layer, an active layer, a second metal layer, a protective layer and a transparent conductive film layer in a cascading arrangement; adriving chip disposed on the frame area, wherein a plurality of fan-out traces are connected between the driving chip and the display area; a plurality of suspended traces formed on the transparent conductive film layer, wherein the suspended traces have suspended ends and the projections of the suspended traces and the fan-out traces on the glass substrate are alternative and staggered. The arraysubstrate of the invention has the advantage of avoiding the occurrence of etch residues.

Owner:CHONGQING HKC OPTOELECTRONICS TECH CO LTD +1

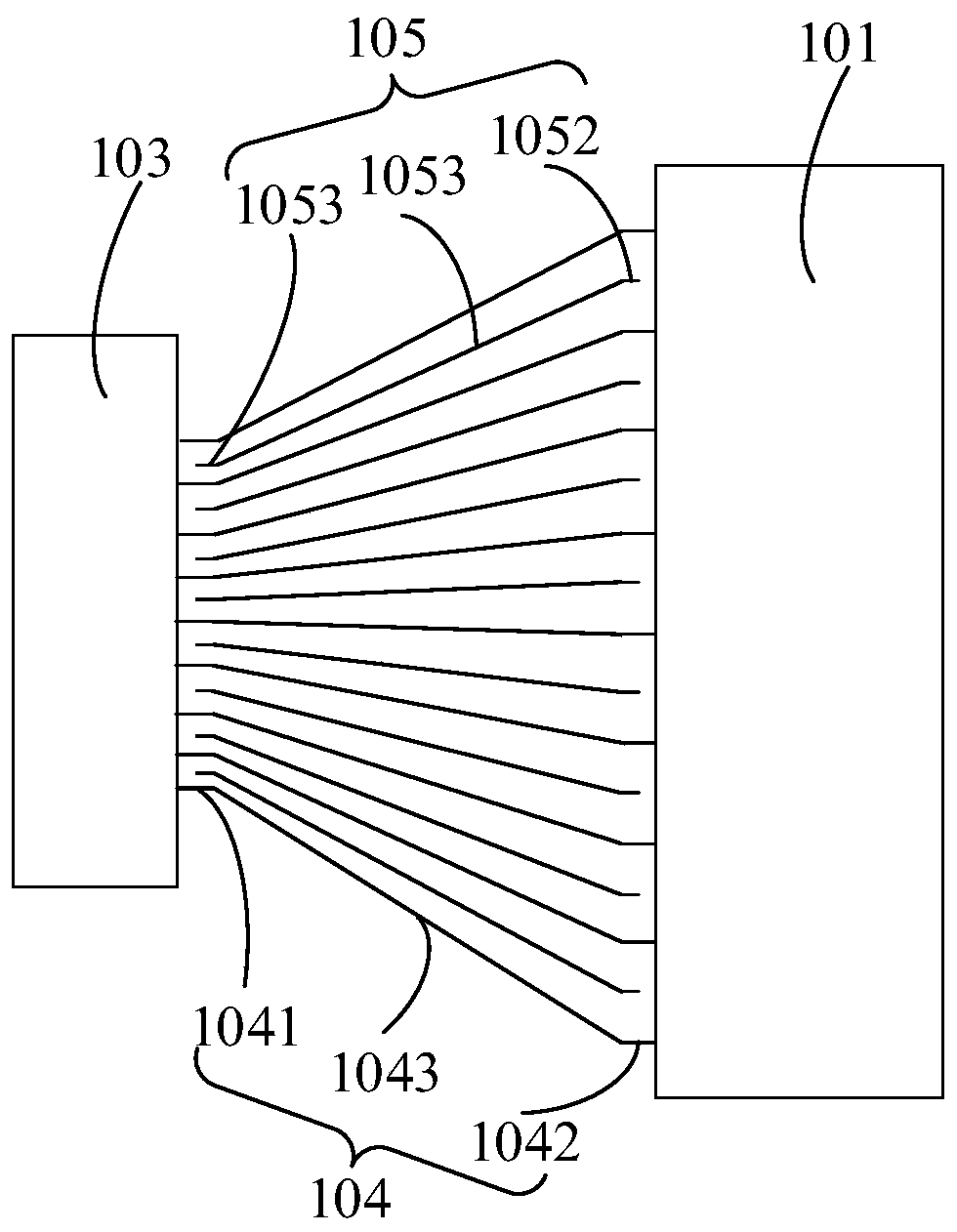

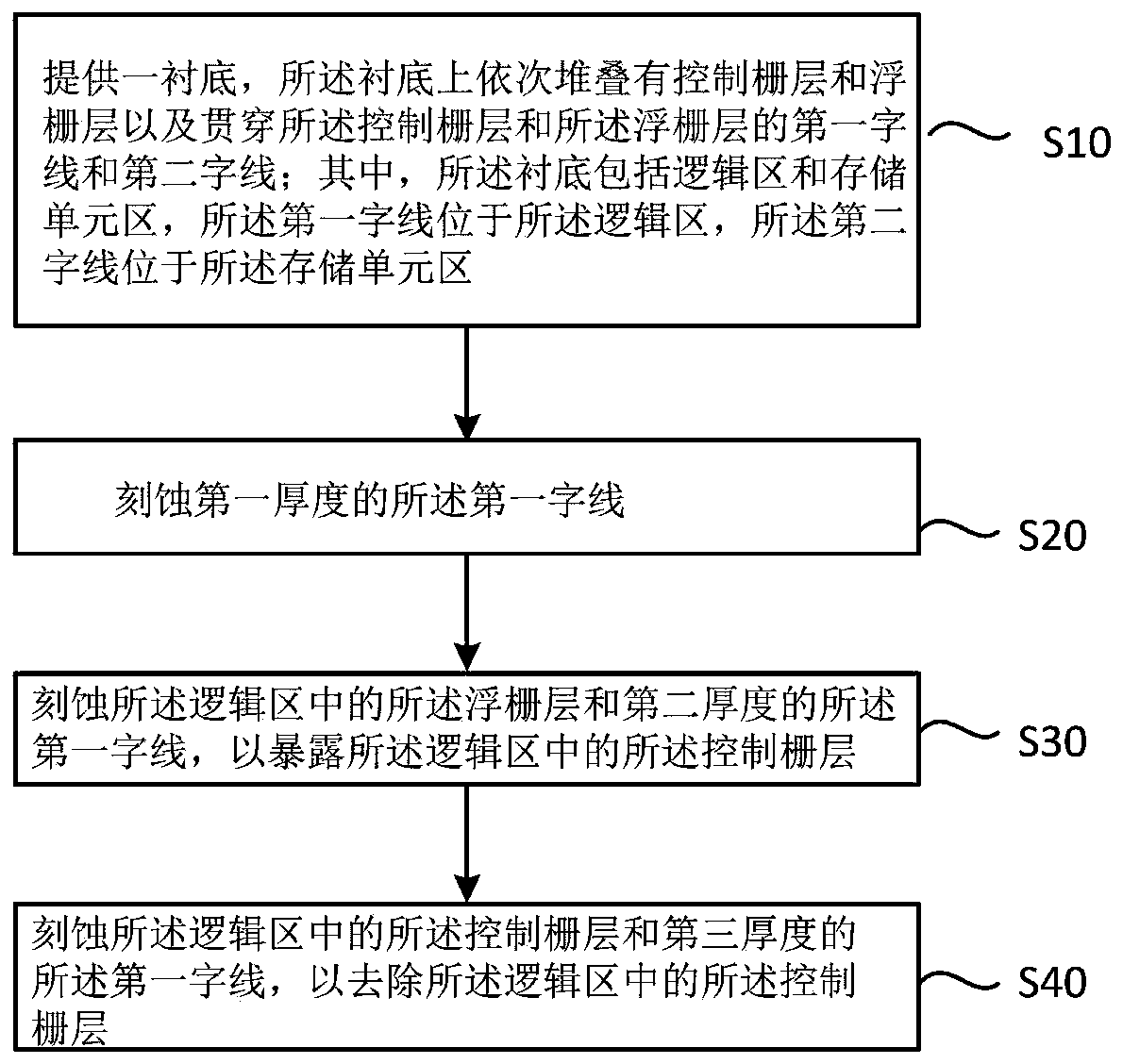

Etching method

ActiveCN111326416AAvoid etch residueSolve etch residueSolid-state devicesSemiconductor/solid-state device manufacturingMemory cellEngineering

The invention provides an etching method, and the etching method comprises the steps: providing a substrate, and sequentially stacking a control gate layer, a floating gate layer, a first word line and a second word line on the substrate, wherein the first word line and the second word line penetrate through the control gate layer and the floating gate layer, the first word line is located in a logic region, and the second word line is located in a memory cell region; etching the first word line with the first thickness; etching the floating gate layer in the logic region and the first word line with the second thickness so as to expose the control gate layer in the logic region; and etching the control gate layer in the logic region and the first word line with the third thickness so as to remove the control gate layer in the logic region. In the logic region etching process, the first word line with the first thickness is etched firstly, and then the first word line, the floating gate layer and the control gate layer are etched synchronously, so that etching residues caused by the low etching rate of the first word line are avoided. Therefore, the etching method can solve the problem that etching residues are generated due to etching selection ratio, the process effect is guaranteed, and the process time is saved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

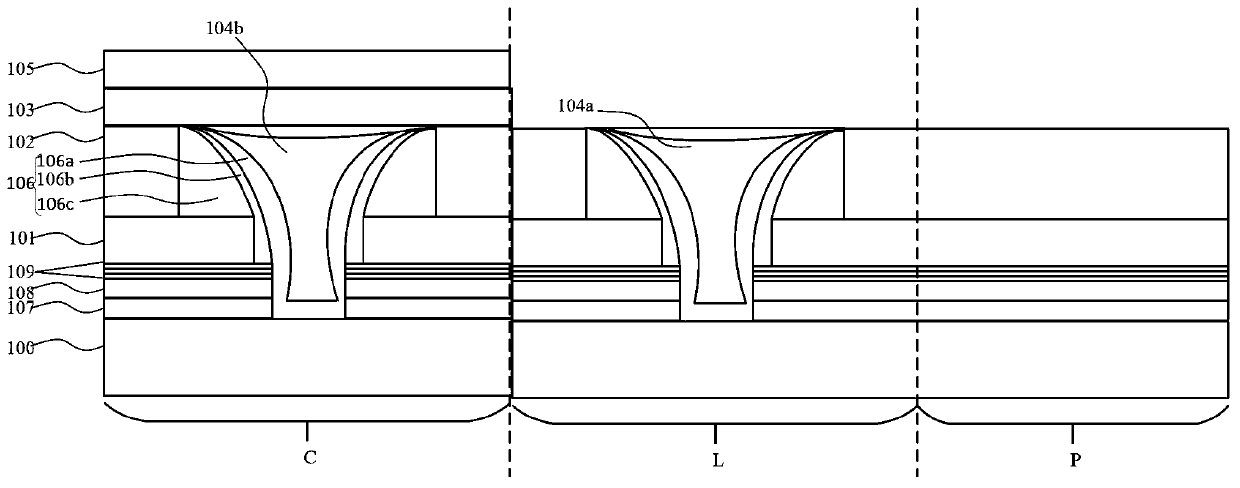

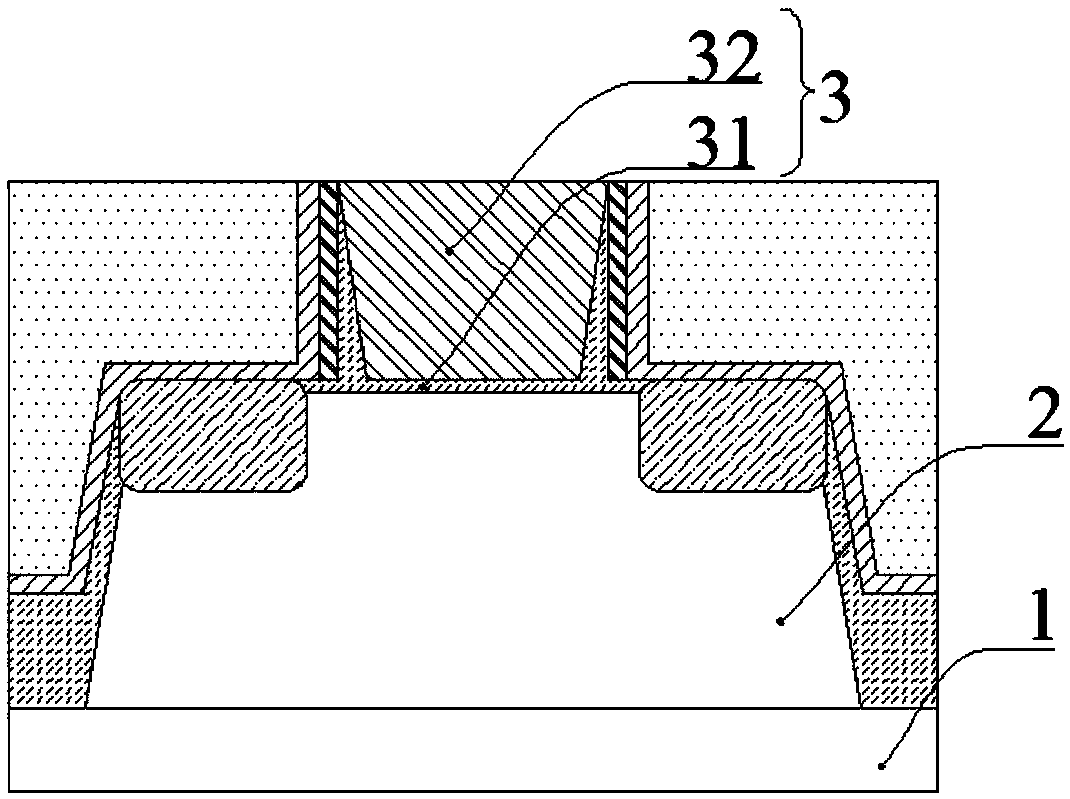

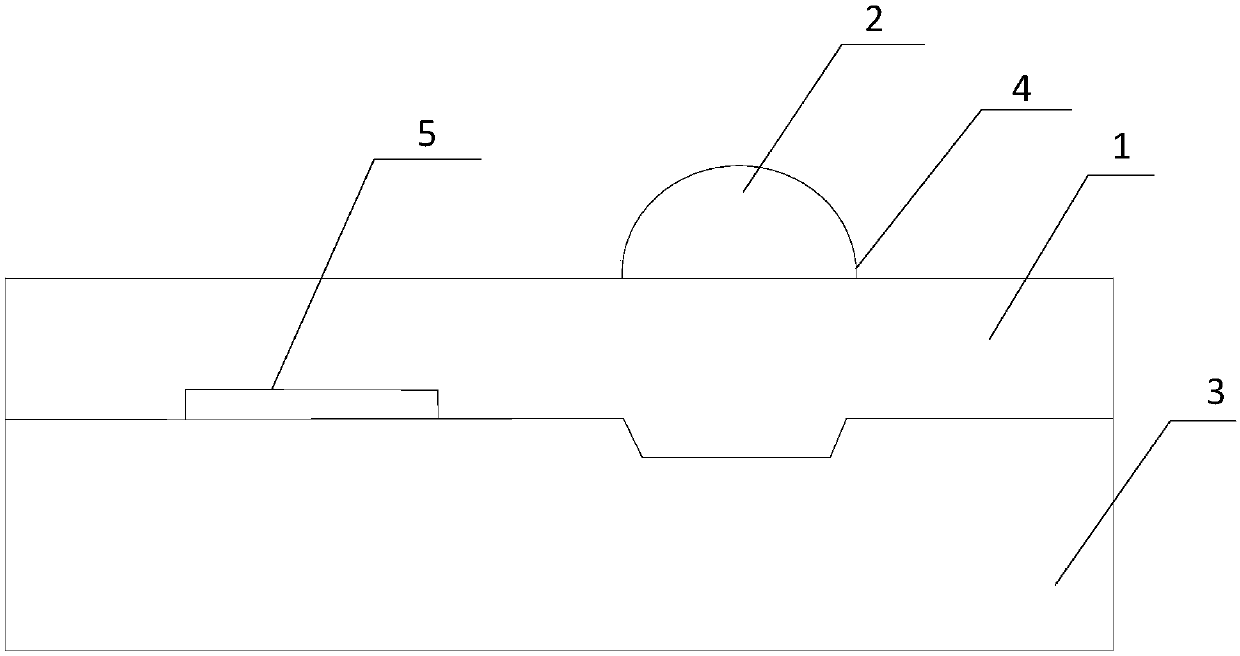

Flexible substrate and manufacturing method thereof

InactiveCN106601771AReduce thicknessReduce warpageFinal product manufactureSolid-state devicesTransmittanceEngineering

The invention provides a flexible substrate and a manufacturing method thereof. The flexible substrate is divided into a first organic material layer (21) and a second organic material layer (22), the coverage area of the second organic material layer (22) on a carrier substrate (1) is larger than the coverage area of the first organic material layer (21) on the carrier substrate (1), the long edge of the second organic material layer (22) surrounds the long edge of the first organic material layer (21), so that the thickness of the edge of the flexible substrate is reduced, the etching residue at the edge can be avoided, the coverage area of the organic material on the carrier substrate is reduced, and the warpage of the flexible substrate is reduced. In addition, an aligning mark (3) is arranged on the second organic material layer (22) between the long edge of the second organic material layer (22) and the long edge of the first organic material layer (21), so that the aligning precision of the subsequent vapor plating processes can be guaranteed, and because only one layer of organic material is arranged at the aligning mark (3), the light transmittance is increased and the aligning success rate is improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

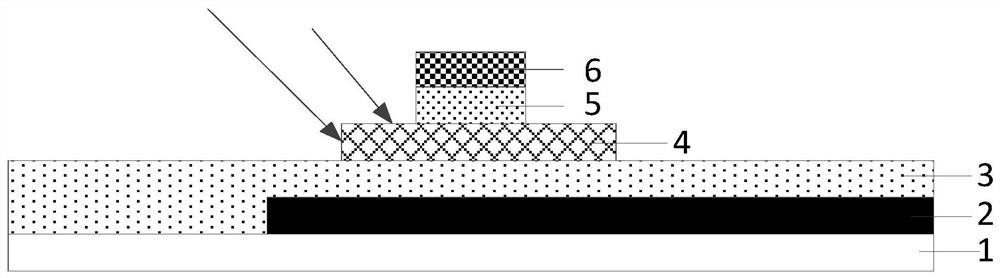

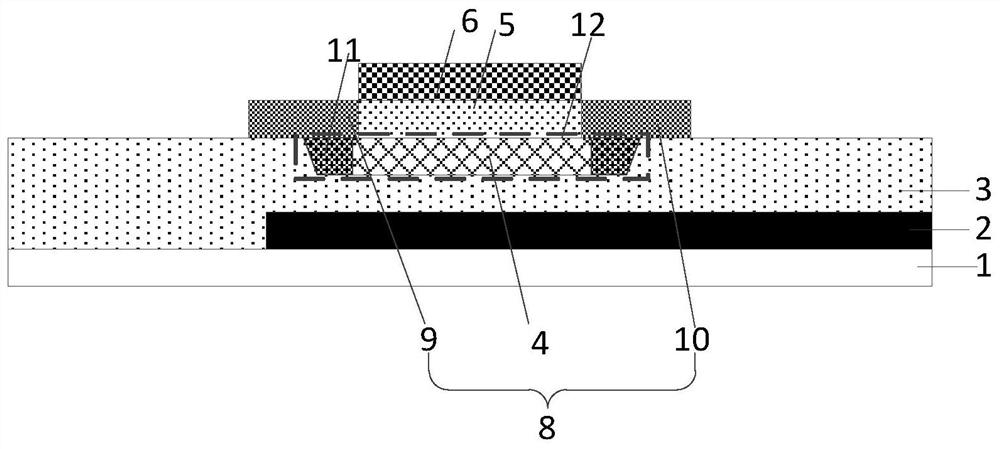

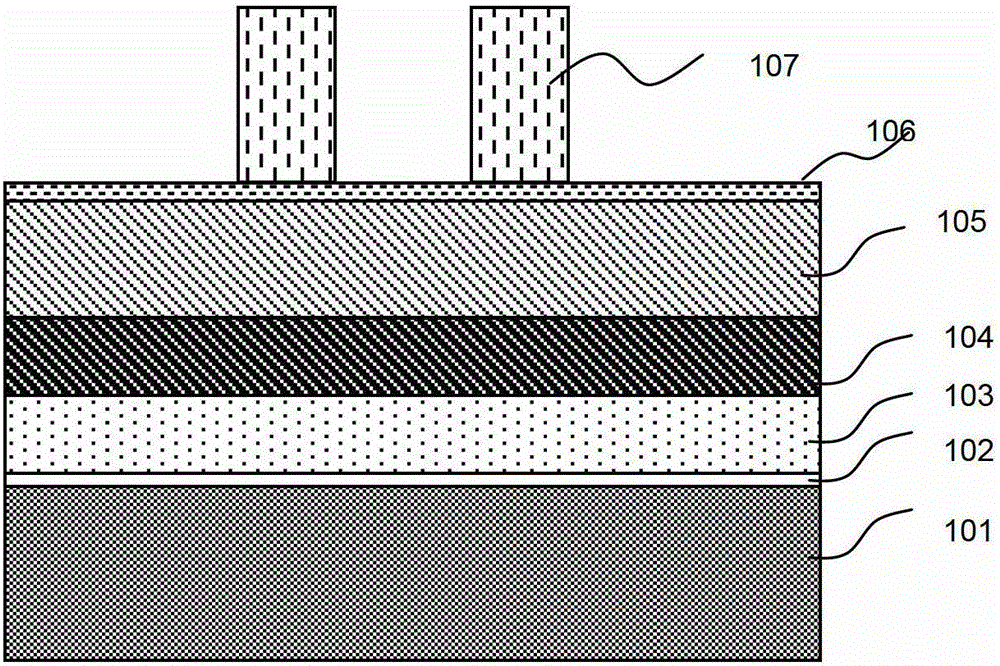

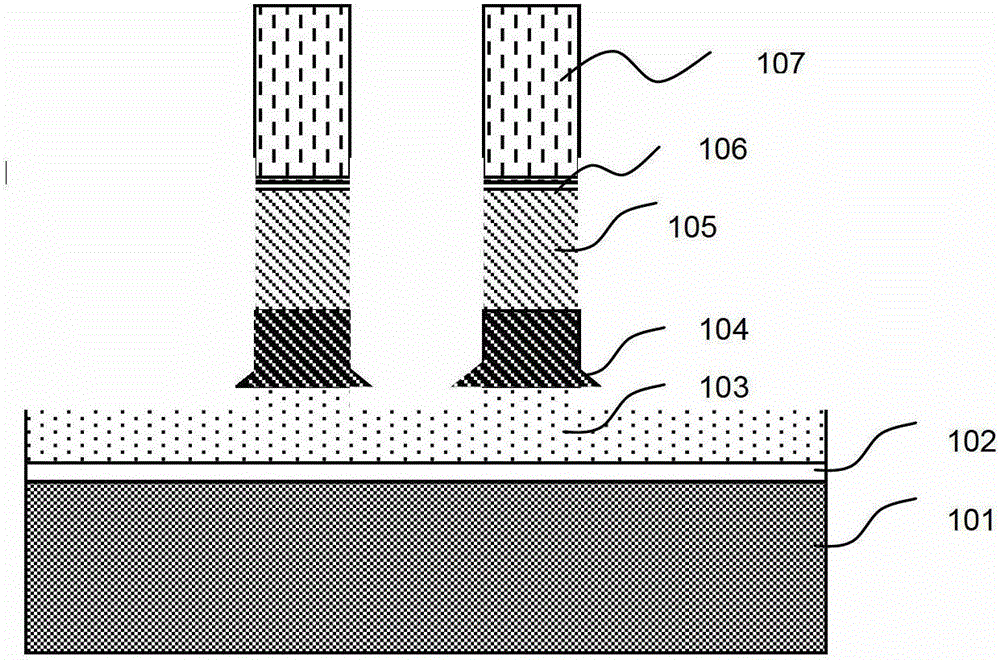

Bulk acoustic wave resonator, manufacturing method thereof, filter and radio frequency communication system

PendingCN111786651AHigh quality factorImprove performanceImpedence networksCommunications systemPiezoelectric resonance

The invention provides a bulk acoustic wave resonator, a manufacturing method thereof, a filter and a radio frequency communication system. A bottom electrode concave part formed on the periphery of apiezoelectric resonance layer and suspended above a cavity can prevent transverse waves generated by the piezoelectric resonance layer from being transmitted to the periphery of the cavity and reflect the transverse waves back to an effective working area, so that the sound wave loss is reduced, the quality factor of the resonator is improved, and finally, the performance of a device can be improved. Furthermore, the overlapping parts of a bottom electrode overlapping part and the cavity and the overlapping parts of a top electrode overlapping part and the cavity are suspended, and the bottomelectrode overlapping part and the top electrode overlapping part are mutually staggered, so that a parasitic parameter can be greatly reduced, the problems of electric leakage, short circuit and thelike can be avoided, and the reliability of the device can be improved.

Owner:NINGBO SEMICON INT CORP

Manufacture method for thin-film resistor

InactiveCN109904145AAvoid over etchingHigh precisionSemiconductor/solid-state device detailsSolid-state devicesEtchingMetal electrodes

The invention discloses a manufacture method for a thin-film resistor. The manufacture method comprises the following steps that: S01: providing a substrate of which the surface is coated with an insulating layer; S02: depositing a thin film resistor material on the substrate, and carrying out graphics on the film resistor material; S03: depositing a metal electrode material, an etching stop layerand a hard mask in sequence on the substrate and the thin film resistor material; S04: adopting first-type dry method etching to carry out graphics on the hard mask, and removing photoresist; S05: adopting second-type dry method etching to continuously carry out graphics on the etching stop layer; and S06: adopting wet method etching to continuously carry out graphics on the metal electrode material to form the thin-film resistor. By use of the manufacture method, the problem of the over etching of the thin-film resistor and the etching residue of the metal electrode can be avoided, and the accuracy and the reliability of the thin-film resistor can be improved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

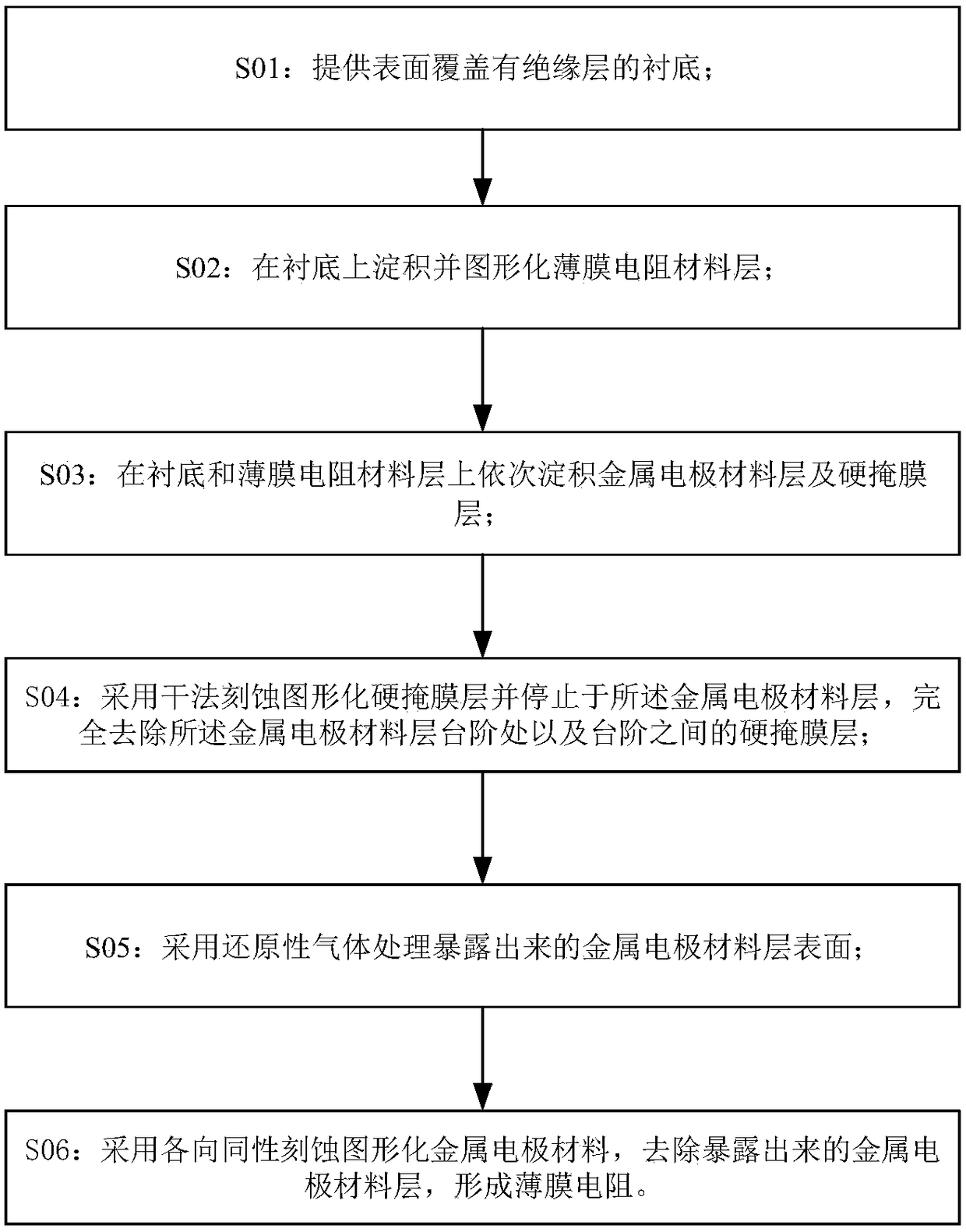

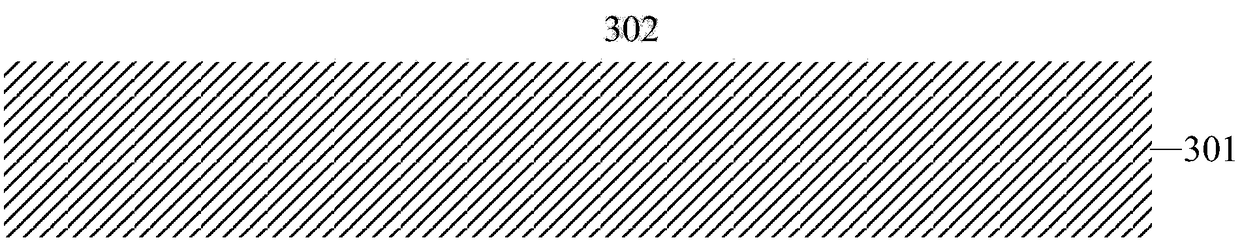

Preparation method of thin-film resistor

InactiveCN108598259AHigh precisionImprove reliabilitySolid-state devicesResistorsInsulation layerMetal electrodes

The present invention discloses a preparation method of a thin-film resistor. The method comprises the following steps: S01 providing a substrate, wherein the surface of the substrate is covered withan insulation layer; S02 depositing and graphing a thin-film resistor material layer on the substrate; S03 depositing a metal electrode material layer and a hard mask layer on the substrate and the thin-film resistor material layer successively; S04 graphing the hard mask layer by adopting dry etching, stopping on the metal electrode material layer, and removing the hard mask layer at the steps ofthe metal electrode material layer and the hard mask layer between the steps of the metal electrode material layer completely; S05 processing the surface of the exposed metal electrode material layerby adopting reducing gas(es); and S06 graphing the metal electrode material by adopting isotropic etching, and removing the exposed metal electrode material layer to form the thin-film resistor. Thepreparation method of the thin-film resistor can avoid the problems of over-etching of the thin-film resistor and etching residue of the metal electrode and improve the accuracy and the reliability ofthe thin-film resistor.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

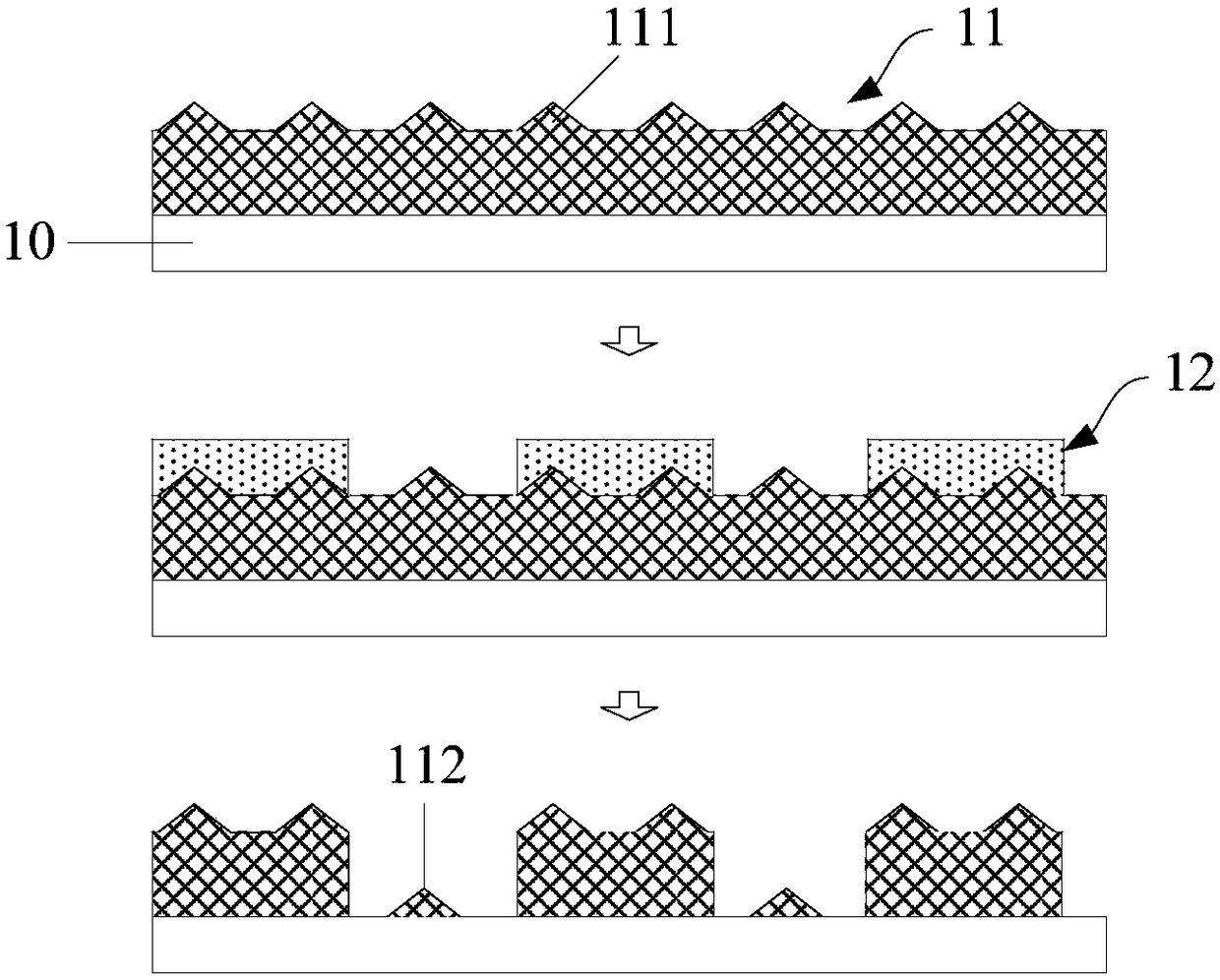

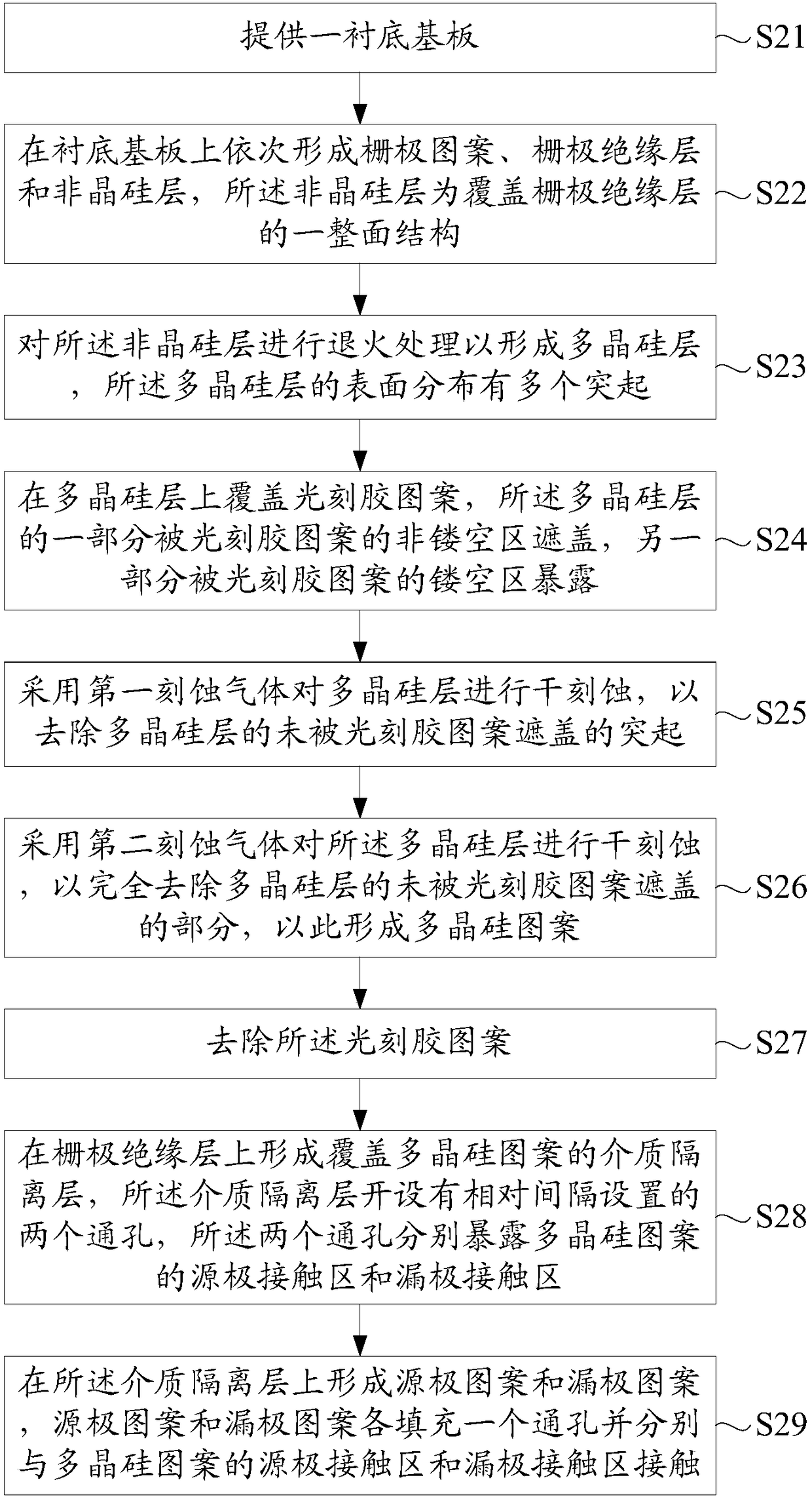

TFT manufacturing method and TFT substrate

InactiveCN108257873AGood removal effectAvoid etch residueSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringPhotoresist

The invention discloses a TFT manufacturing method and a TFT substrate. In the process of etching to form a polysilicon pattern, one part of a polysilicon layer is covered by a non-hollowed region ofa photoresist pattern, the other part is exposed by a hollowed-out region of the photoresist pattern, secondly, dry etching of the polysilicon layer is carried out through employing the first etchinggas to remove protrusion of the polysilicon layer not covered by the photoresist pattern, and dry etching of the polysilicon layer is carried out through employing the second etching gas to remove thepart of the polysilicon layer not covered by the photoresist pattern. The method is advantaged in that complete etching can be facilitated to remove the polysilicon layer not covered by the photoresist pattern, and etching residue is avoided.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Bulk acoustic wave resonator, manufacturing method thereof, filter and radio frequency communication system

PendingCN111786650AHigh quality factorImprove performanceImpedence networksCommunications systemEngineering

The invention provides a bulk acoustic wave resonator, a manufacturing method thereof, a filter and a radio frequency communication system. A top electrode concave part formed on the periphery of a piezoelectric resonance layer and suspended above a cavity can prevent transverse waves generated by the piezoelectric resonance layer from being transmitted to the periphery of the cavity and reflect the transverse waves back to an effective working area, so that the sound wave loss is reduced, the quality factor of the resonator is improved, and finally, the performance of a device can be improved. Furthermore, the overlapping parts of a bottom electrode overlapping part and the cavity and the overlapping parts of a top electrode overlapping part and the cavity are suspended, and the bottom electrode overlapping part and the top electrode overlapping part are mutually staggered, so that a parasitic parameter can be greatly reduced, the problems of electric leakage, short circuit and the like can be avoided, and the reliability of the device can be improved.

Owner:NINGBO SEMICON INT CORP

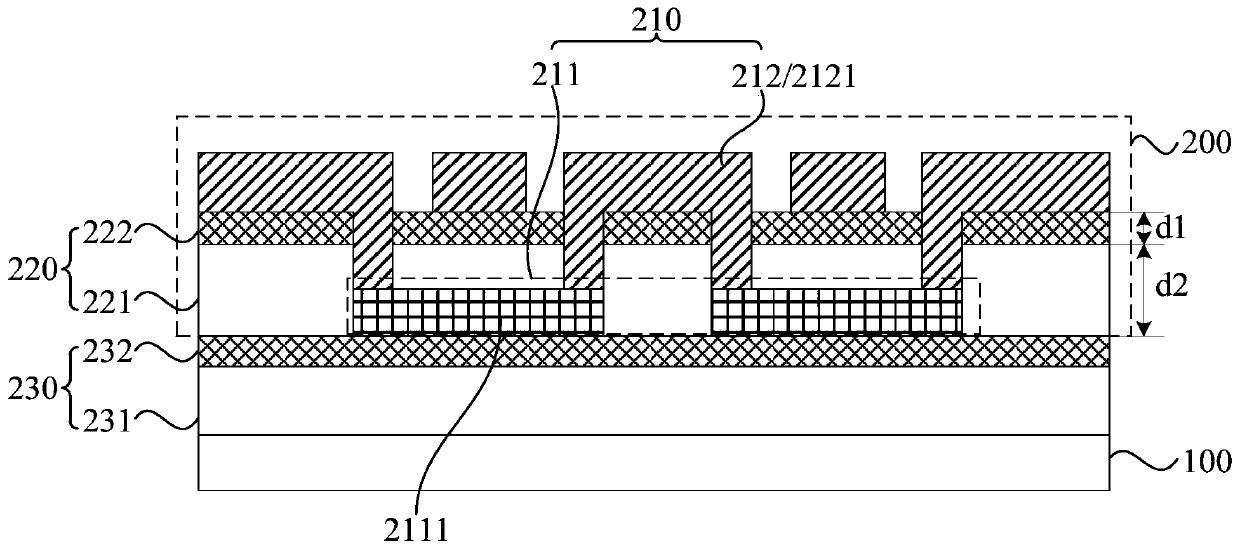

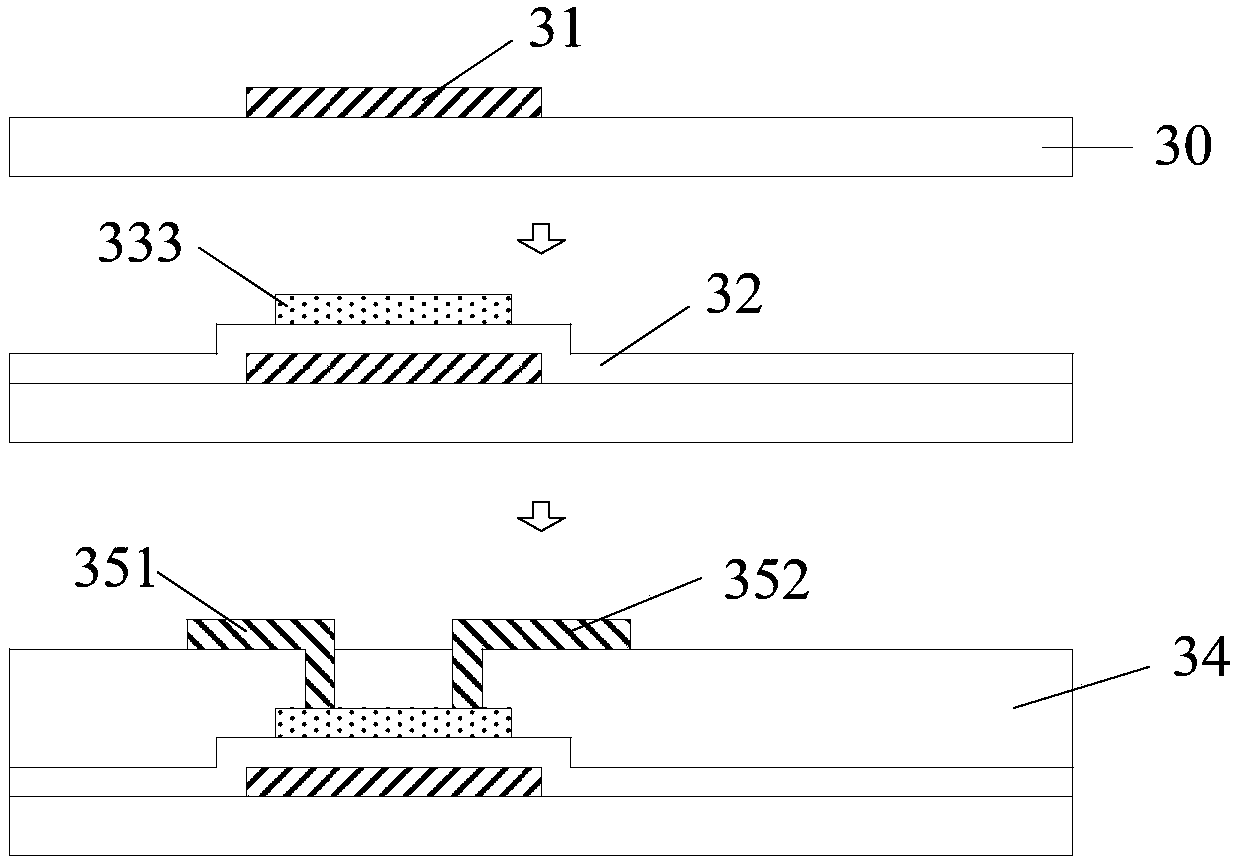

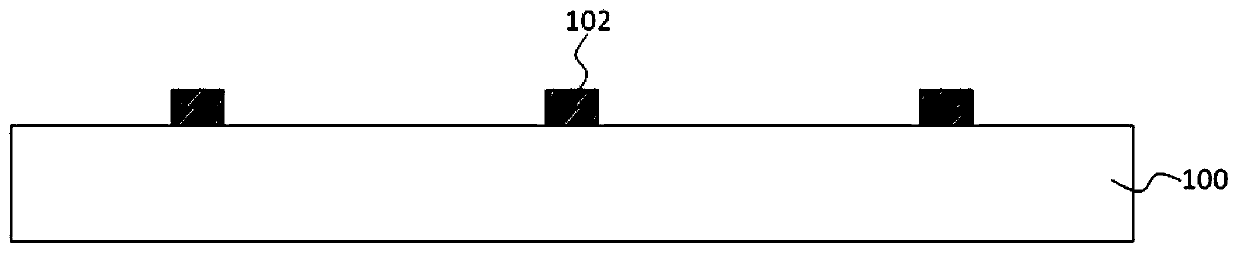

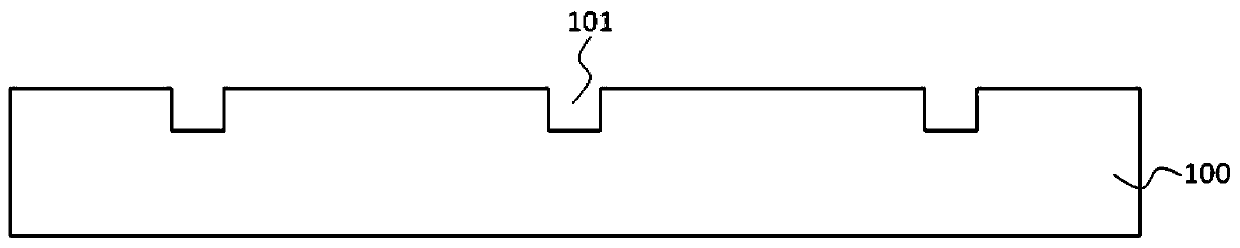

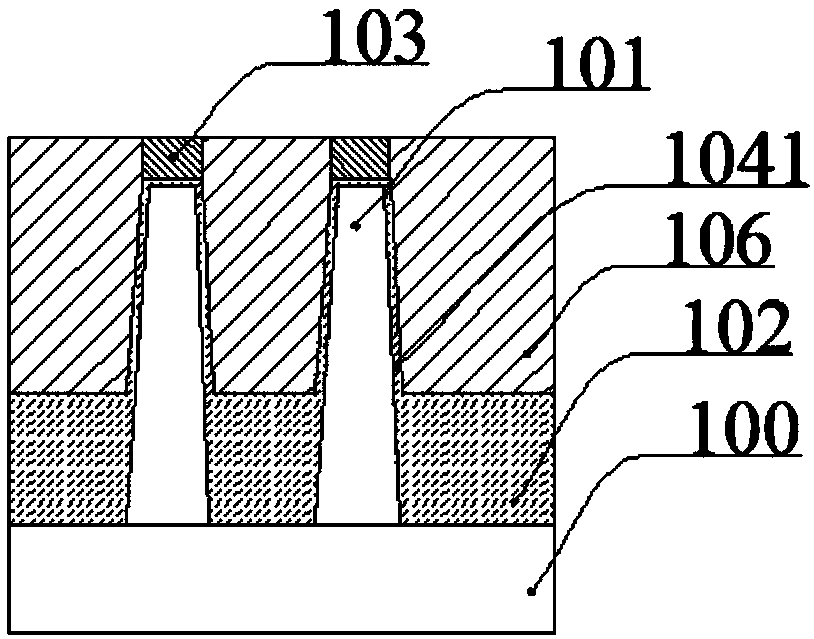

Array substrate and preparation method thereof, and display panel

ActiveCN110911424BAvoid etch residueAvoid dark spotsTransistorSolid-state devicesEngineeringActive layer

Owner:BOE TECH GRP CO LTD +1

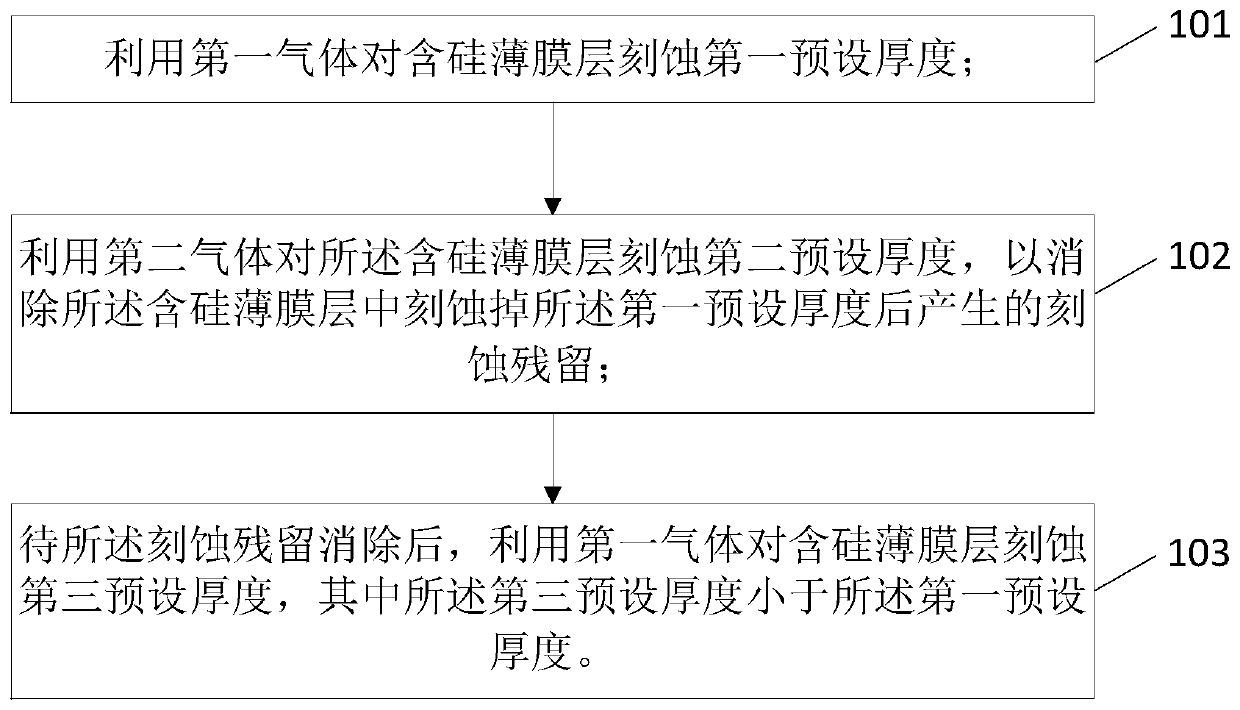

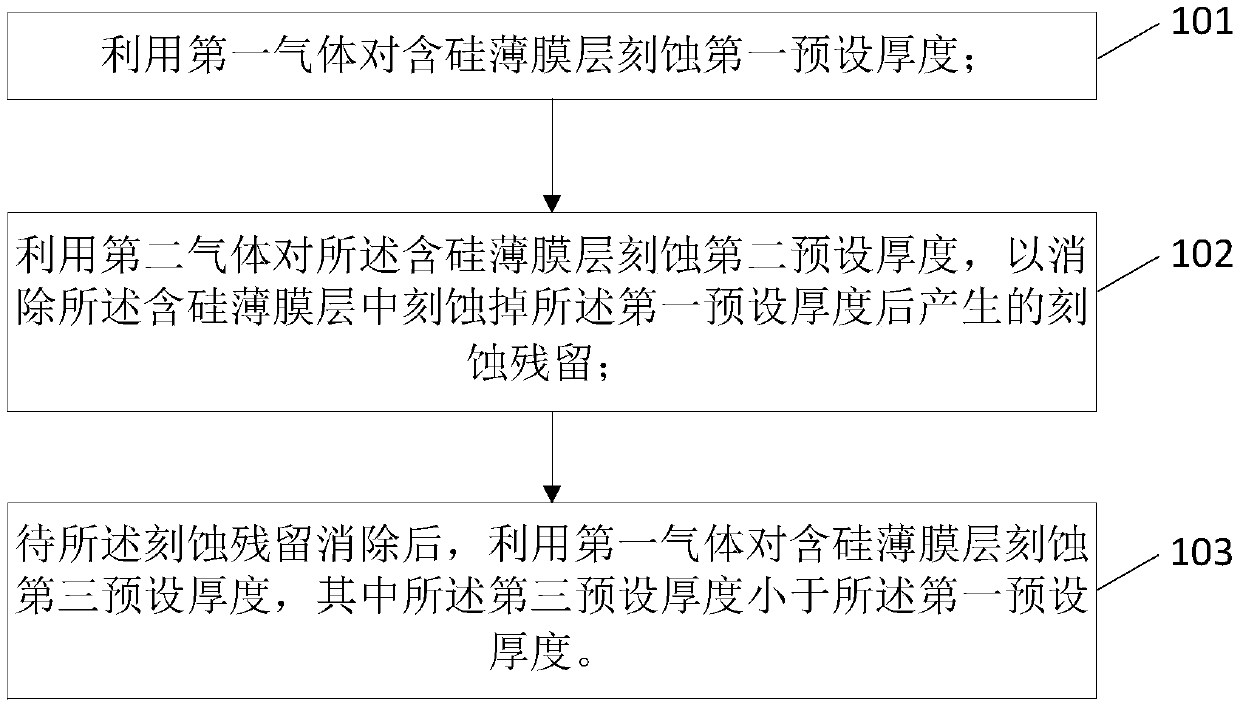

dry etching method

InactiveCN107634007BAvoid etch damageAvoid damageTransistorSemiconductor/solid-state device manufacturingFluorideDry etching

The invention discloses a dry etching method, which relates to the technical field of etching technology. The main purpose is to not only remove etching residues but also reduce damage to other thin film layers during the etching process of silicon-containing thin film layers. Improve etch quality. The main technical solution of the present invention is: a dry etching method, comprising: using a first gas to etch the silicon-containing thin film layer to a first preset thickness; using a second gas to etch the silicon-containing thin film layer to a second predetermined thickness; Set the thickness to eliminate the etching residue generated after etching the first preset thickness in the silicon-containing thin film layer; after the etching residue is eliminated, use the first gas to etch the silicon-containing thin film layer Three preset thicknesses, so that the third preset thickness is smaller than the first preset thickness; wherein, the first gas includes chlorine gas, and the second gas includes fluoride gas. The invention is mainly used for etching the thin film transistor substrate.

Owner:BOE TECH GRP CO LTD

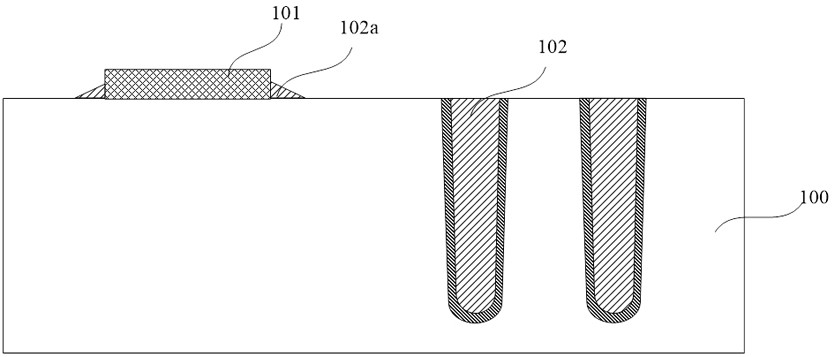

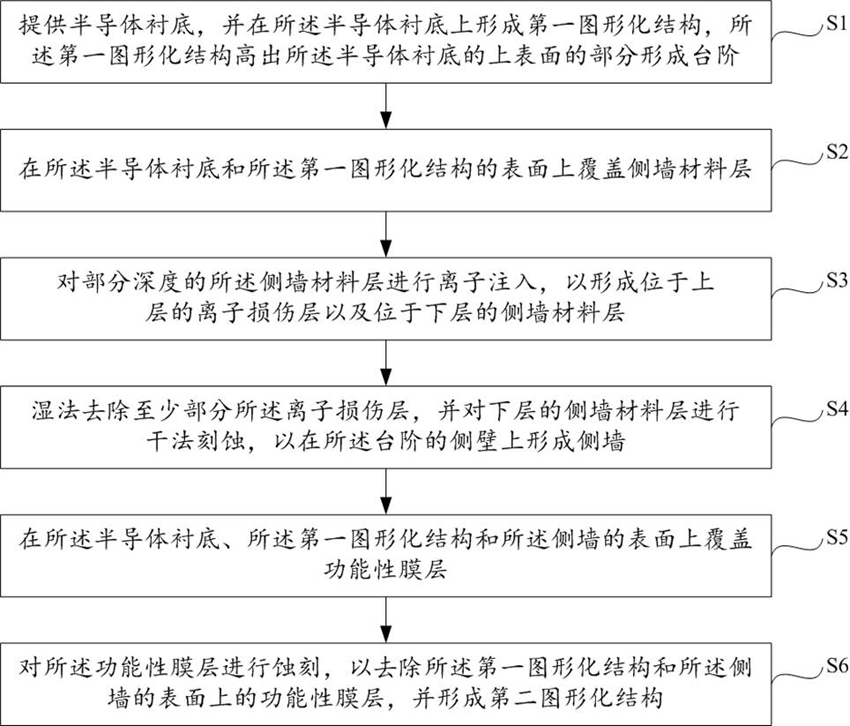

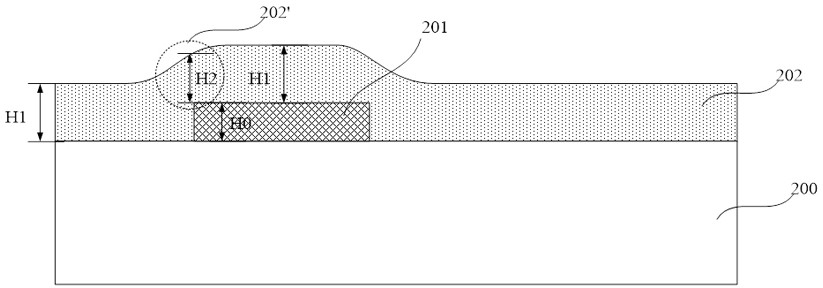

Manufacturing method of semiconductor device

ActiveCN111799225BReduce aspect ratioFacilitate etching and removalSemiconductor/solid-state device manufacturingDevice materialEngineering physics

The invention provides a method for manufacturing a semiconductor device, which converts the upper layer of the side wall material layer into an ion damage layer by ion implantation, and the ion implantation dose at the top corner of the step is lower than that at other plane positions during ion implantation, so that After removing at least part of the ion damage layer by wet method, a relatively thick sidewall material layer can be retained on the top corner of the step, and after dry etching the remaining sidewall material layer, the sidewall formed on the sidewall of the step can be made The wall, while having a required height at its top, has a maximum width at its bottom extending along the surface of the semiconductor substrate, thereby reducing the aspect ratio of the formed sidewall. And because the aspect ratio of the formed sidewall is slower, it is more conducive to the etching and removal of the redundant film layer formed at the step in the subsequent process, avoiding the problem of etching residues formed on the sidewall of the step in the subsequent process, and thus improving the process caused by etching. The phenomenon of short-circuit failure of the device caused by the residue.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP

Array substrate and display panel

ActiveCN110333633BReduction of etch residueAvoid etch residueNon-linear opticsThin membraneActive layer

The present application discloses an array substrate and a display panel. The array substrate includes: a glass substrate, the glass substrate has a display area and a frame area around the display area, and the glass substrate is sequentially stacked with a second A metal layer, an insulating layer, an active layer, a second metal layer, a protective layer and a transparent conductive film layer; a driving chip, the driving chip is arranged on the frame area, and the connection between the driving chip and the display area There are multiple fan-out wirings connected between them; multiple floating wirings, the floating wirings are formed on the transparent conductive film layer, the two ends of the floating wirings are suspended in the air, and the multiple floating wirings are connected with the multiple The projections of the fan-out traces on the glass substrate are arranged alternately and staggered. This application has the advantage of avoiding etch residues.

Owner:CHONGQING HKC OPTOELECTRONICS TECH CO LTD +1

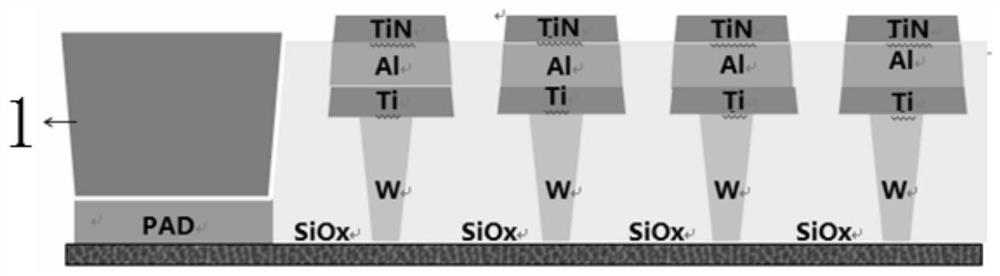

Method for Improving Edge Roughness of Tungsten Silicide Double Gate of Self-Aligned Contact Hole

ActiveCN103824763BIncrease roughnessAvoid etch residueSemiconductor/solid-state device manufacturingSemiconductor devicesResistGrid pattern

The invention discloses a method for improving tungsten silicide bigrid edge roughness of a self-aligning contact hole. The method comprises the following steps: 1.1 a tungsten silicide grid pattern is formed; 1.2 first time of grid etching is performed on tungsten silicide grid; 1.3 photo-resist is removed by adopting dry etching with a function of modifying morphology of the side wall of tungsten silicide, and then cleaning is performed by adding pure water to rinse; 1.4 dielectric film silicon nitride is deposited; and 1.5 second time of grid etching is performed and residual polycrystalline silicon is etched. In the step of photo-resist removing after completion of first time of etching, a special step of photo-resist removing with carbon tetrafluoride, which is different from a conventional step of photo-resist removing by oxygen, is adopted, and rinsing processing is performed by adding pure water. Partial side wall of tungsten silicide can be etched by the special step of photo-resist removing with carbon tetrafluoride, and the side wall of the tungsten silicide film layer can be modified to be vertical in morphology so that a small dielectric film blocking wall is difficult to form in the subsequent dielectric film deposition and second step of etching, and thus residual in polycrystalline silicon etching can be avoided.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

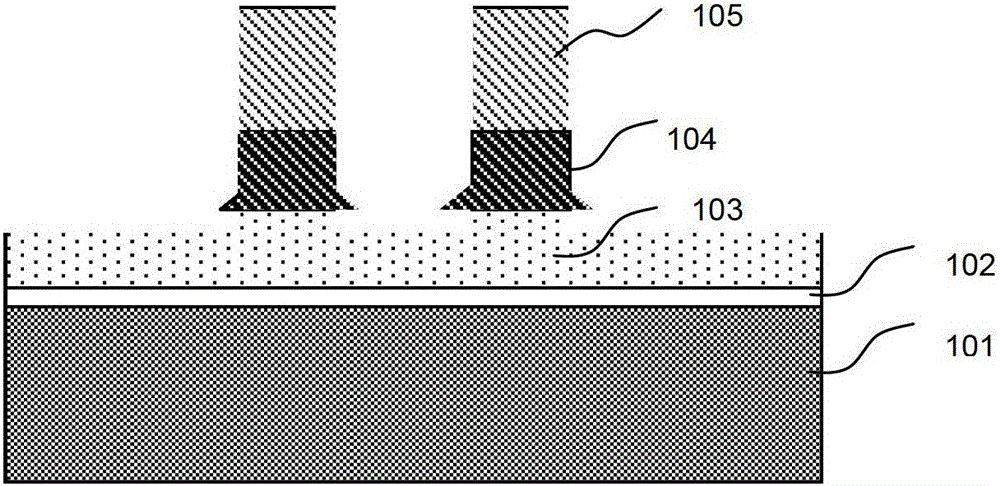

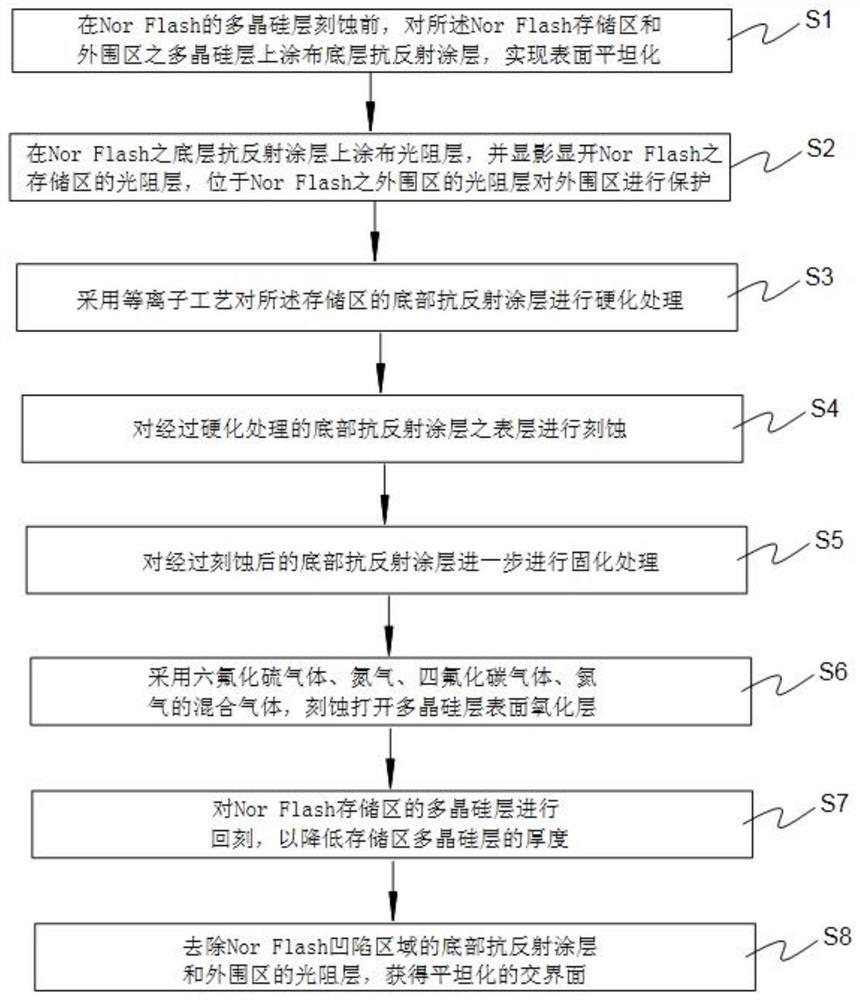

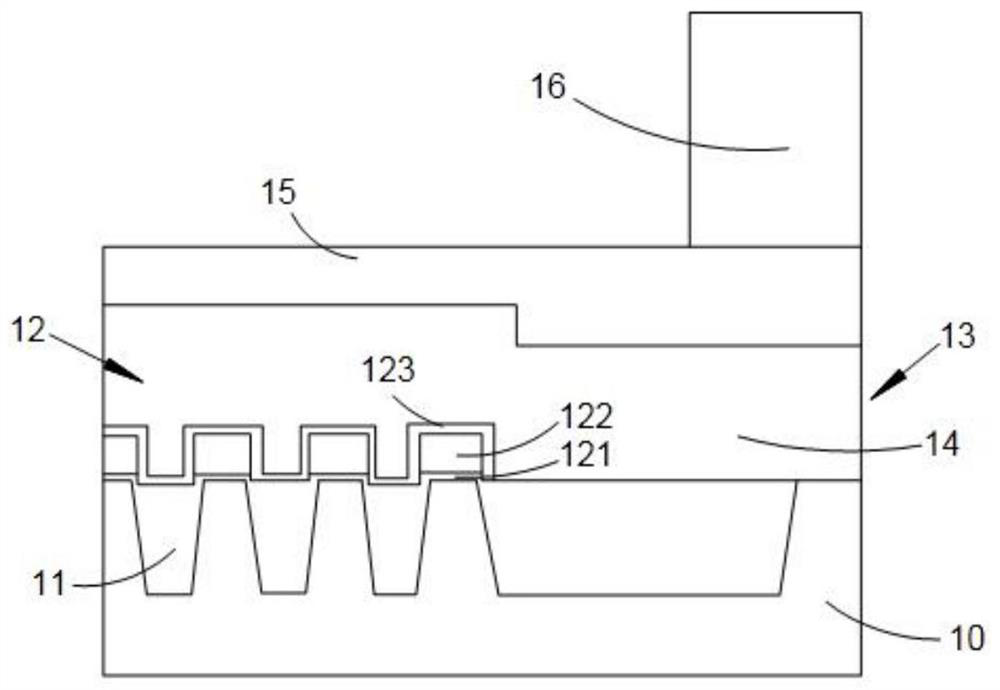

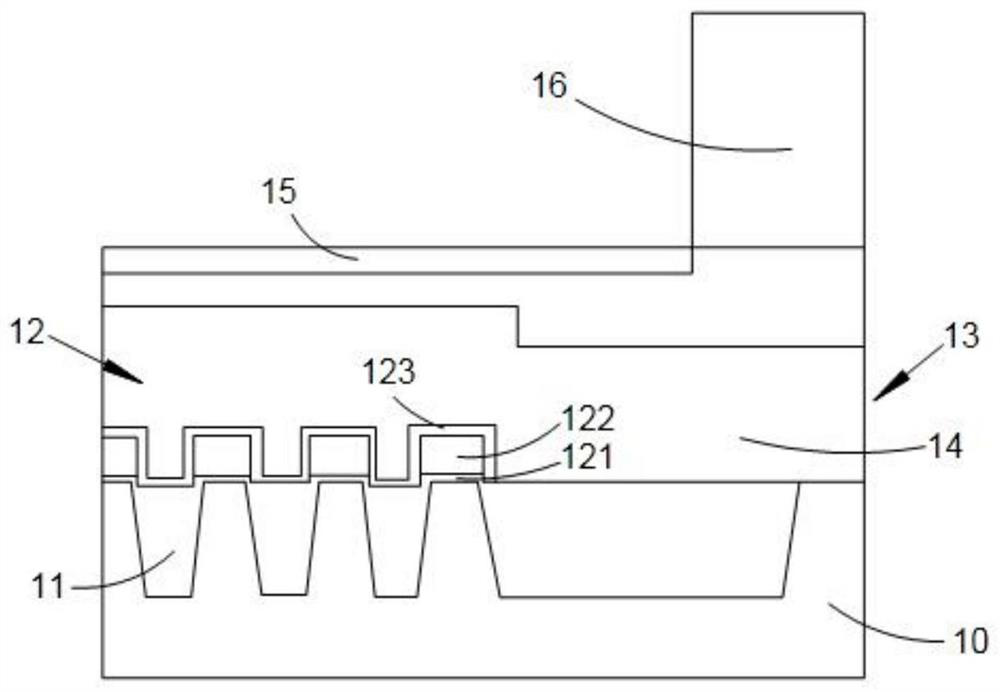

Method for improving Nor Flash polycrystalline silicon etching and dielectric layer filling process window

PendingCN114141780AReduce height differenceAvoid etch residueSolid-state devicesSemiconductor devicesEtchingPhysical chemistry

The invention relates to a method for lifting a Nor Flash polycrystalline silicon etching and dielectric layer filling process window, which comprises the following steps of: coating a bottom anti-reflection coating before etching a polycrystalline silicon layer, and lowering the polycrystalline silicon layer in a Nor Flash storage area by adopting an etchback process, so as to improve the Nor Flash polycrystalline silicon etching and dielectric layer filling process window, thereby improving the Nor Flash polycrystalline silicon etching and dielectric layer filling process window. And meanwhile, the height difference at the junction of the Nor Flash storage area and the peripheral area is reduced. According to the method, the bottom anti-reflection coating is coated before the polycrystalline silicon layer is etched, the polycrystalline silicon layer of the Nor Flash storage area is reduced by adopting the back-etching process, and meanwhile, the height difference of the junction of the Nor Flash storage area and the peripheral area is reduced, so that polycrystalline silicon etching residues and etching process window expansion caused by overlarge height difference during etching of the polycrystalline silicon layer can be avoided, and the yield of the Nor Flash storage area is improved. And the depth-to-width ratio between the control gates is also reduced due to the reduction of the height of the control gates (CG), and a dielectric layer filling process window is expanded.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

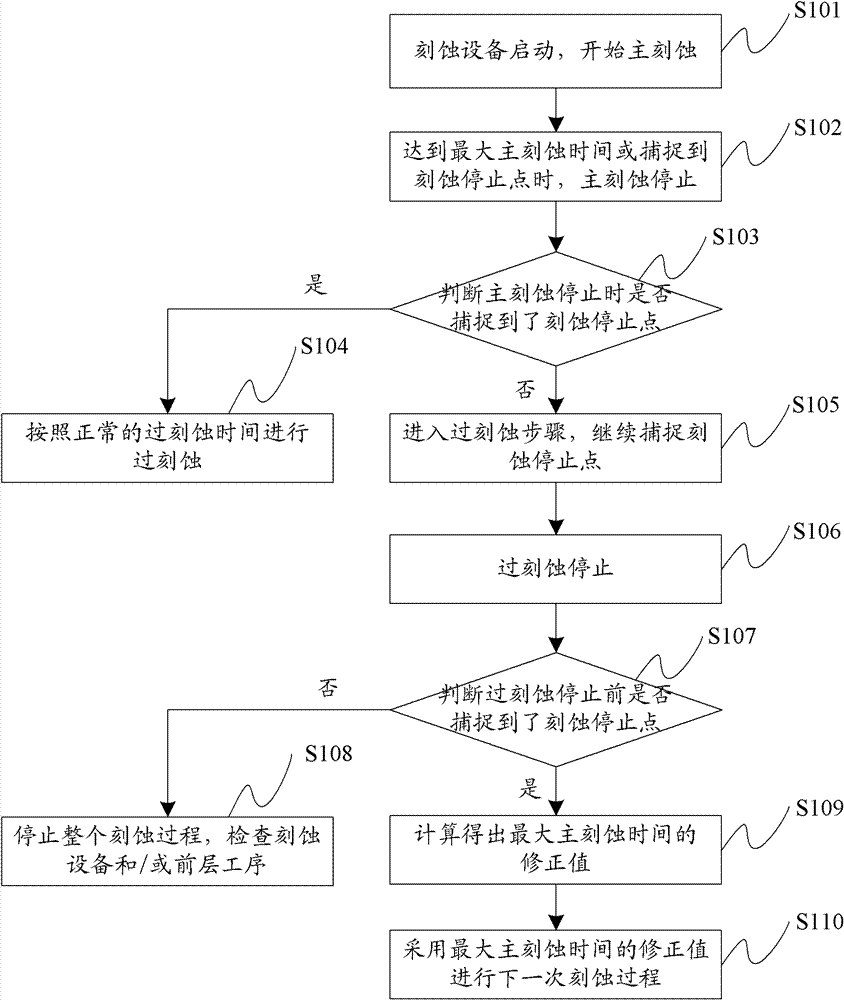

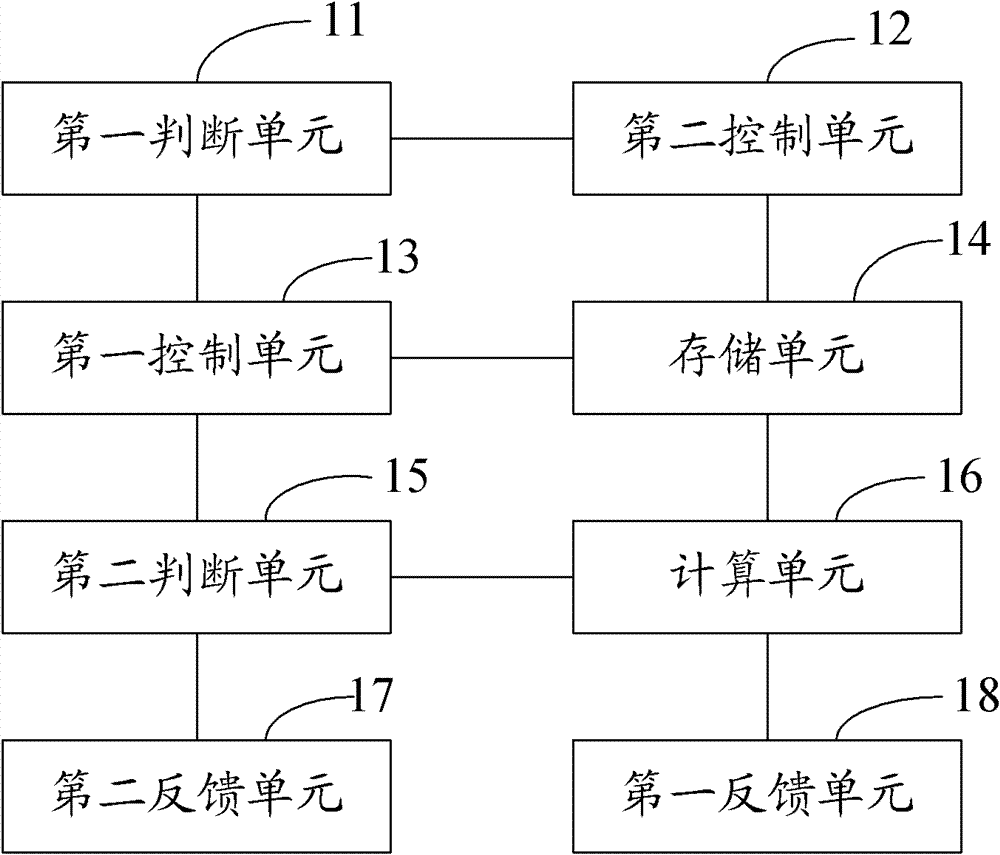

Etching method and system

ActiveCN102486987BThickness exceedsAvoid problems such as etch residueSemiconductor/solid-state device manufacturingEtchingEarly stopping

The invention discloses an etching method and an etching system, wherein the method comprises the following steps of: after main etching is stopped, judging whether etching stopping points are caught when the main etching is stopped, and if not, entering an over-etching step for continuously catching the etching stopping points; when the over-etching step reaches the preset maximum over-etching time, after the etching stopping points are caught and normal over-etching time is passed, automatically stopping; after the over etching is stopped, judging whether etching stopping points are caught or not before the over etching is stopped, and if so, obtaining a correction value of the maximum main etching time according to the etching thickness and the maximum main etching time; and adopting the correction value of the maximum main etching time to carry out next-time etching process. According to the embodiment of the invention, by the introduction of a judgment mechanism and a time feedback mechanism and control for the etching mode of etching equipment, the problems of the etching residual and slightly-large device CDs (Compact Discs) and the like after over-etching due to over-early stopping of the main etching in the prior art are solved.

Owner:CSMC TECH FAB2 CO LTD

Planar gate device structure having high switching speed and manufacturing method thereof

PendingCN110429131AFast switching speedImprove flatnessSemiconductor devicesPower semiconductor deviceCapacitance

The invention discloses a planar gate device structure having a high switching speed and a manufacturing method thereof. The planar gate device structure comprises a semiconductor substrate or an epitaxial layer, and a set of planar gates are arranged on the semiconductor substrate or the epitaxial layer, each planar gate comprises a first gate electrode insulation layer arranged at the middle position, a second gate electrode insulation layer extended from the first gate electrode insulation layer to the two sides, and a gate electrode arranged on the first gate electrode insulation layer andthe second gate electrode insulation layer, wherein the thickness of the first gate electrode insulation layer is larger than the thickness of the second gate electrode insulation layer. The manufacturing method of the planar gate is simple and easy to achieve, the device having the planar gate structure has lower gate and drain capacitance, the faster switching speed and the lower switching loss, and can be widely applied to the power semiconductor device fields such as MOSFET, IGBT and MCT.

Owner:ANHUI PROVINCE QIMEN COUNTY HUANGSHAN ELECTRIC APPLIANCE

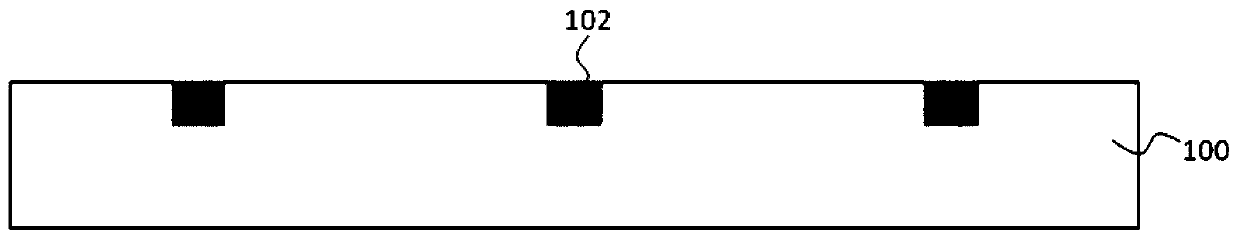

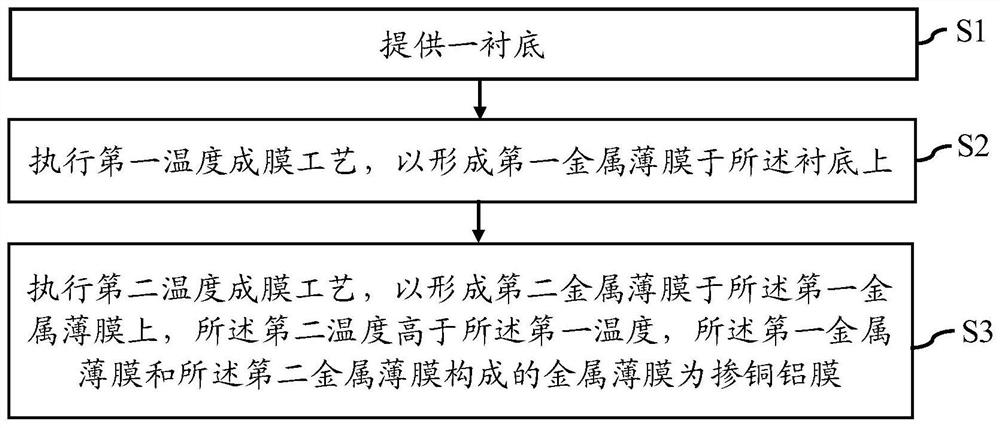

Manufacturing method of metal thin film and manufacturing method of semiconductor device

PendingCN113436962APrevent precipitationShorten the timeSemiconductor/solid-state device manufacturingMetallurgyDevice material

The invention provides a manufacturing method of a metal film and a manufacturing method of a semiconductor device. The manufacturing method of the metal film comprises the following steps: providing a substrate; executing a first temperature film forming process to form a first metal film on the substrate; and executing a second temperature film forming process to form a second metal film on the first metal film, wherein the second temperature is higher than the first temperature, and a metal film formed by the first metal film and the second metal film is a copper-doped aluminum film. According to the technical scheme, the problem of copper precipitation of the metal film can be avoided, so that etching residues are avoided when the metal film is etched.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP

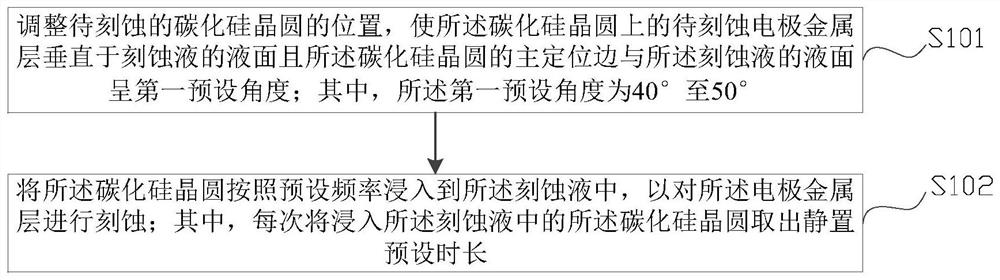

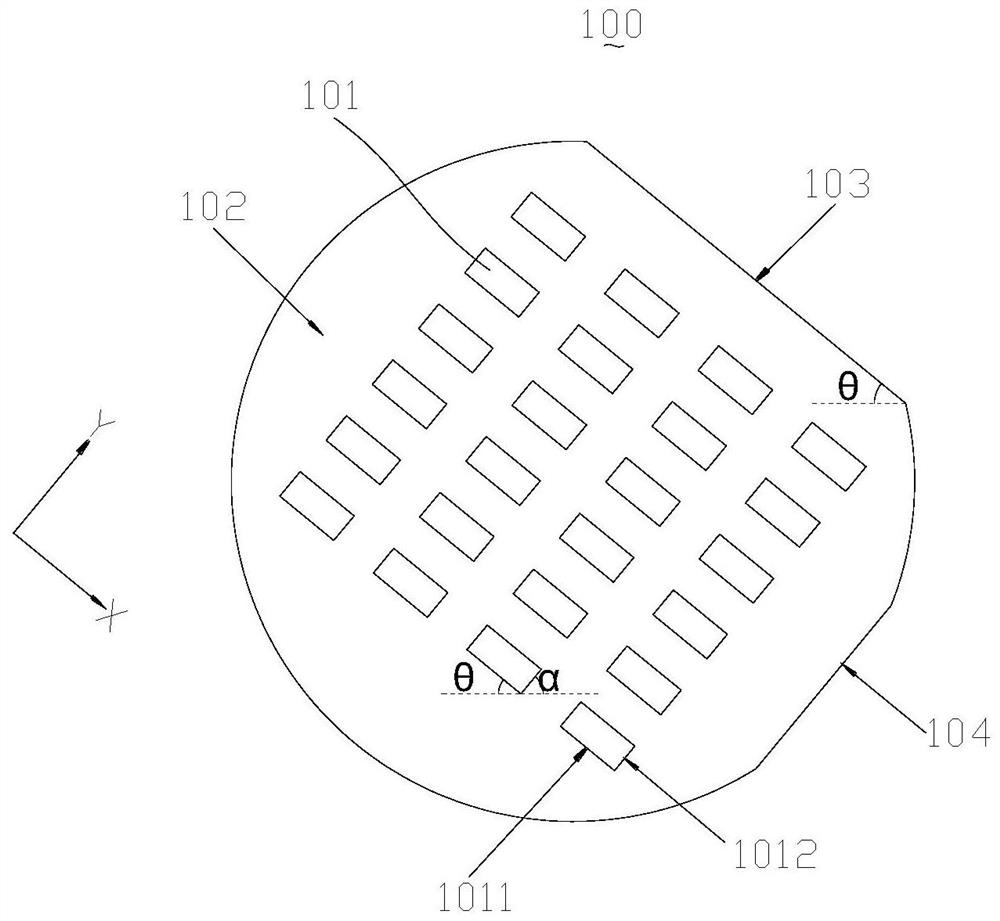

Wet etching method for electrode metal layer of silicon carbide device

PendingCN113130304AImprove etch uniformityShorten etch process timeSemiconductor/solid-state device manufacturingCarbide siliconEtching

The invention provides a wet etching method for an electrode metal layer of a silicon carbide device. The method comprises the steps that the position of a silicon carbide wafer to be etched is adjusted, so that an electrode metal layer to be etched on the silicon carbide wafer is perpendicular to the liquid level of etching liquid, and a first preset angle is formed between the main positioning edge of the silicon carbide wafer and the liquid level of the etching liquid, and the first preset angle ranges from 40 degrees to 50 degrees; the silicon carbide wafer is immersed into the etching liquid according to a preset frequency so as to etch the electrode metal layer; wherein each time the silicon carbide wafer immersed in the etching liquid is taken out, the silicon carbide wafer is subjected to standing for a preset period of time. The etching difference of each tube core in the longitudinal direction and the transverse direction in the etching process of the electrode metal layer can be eliminated, hydrogen bubbles which are generated in the etching process of the electrode metal layer and are attached to the surface of the electrode metal layer can be eliminated, and etching residues are avoided. The electrical property and the yield of the device are improved, and the manufacturing cost is saved.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

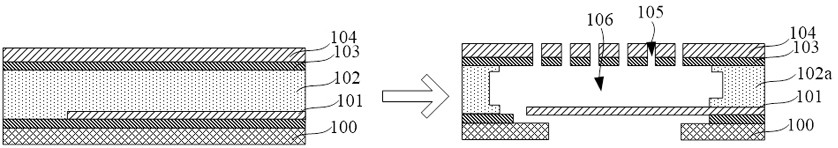

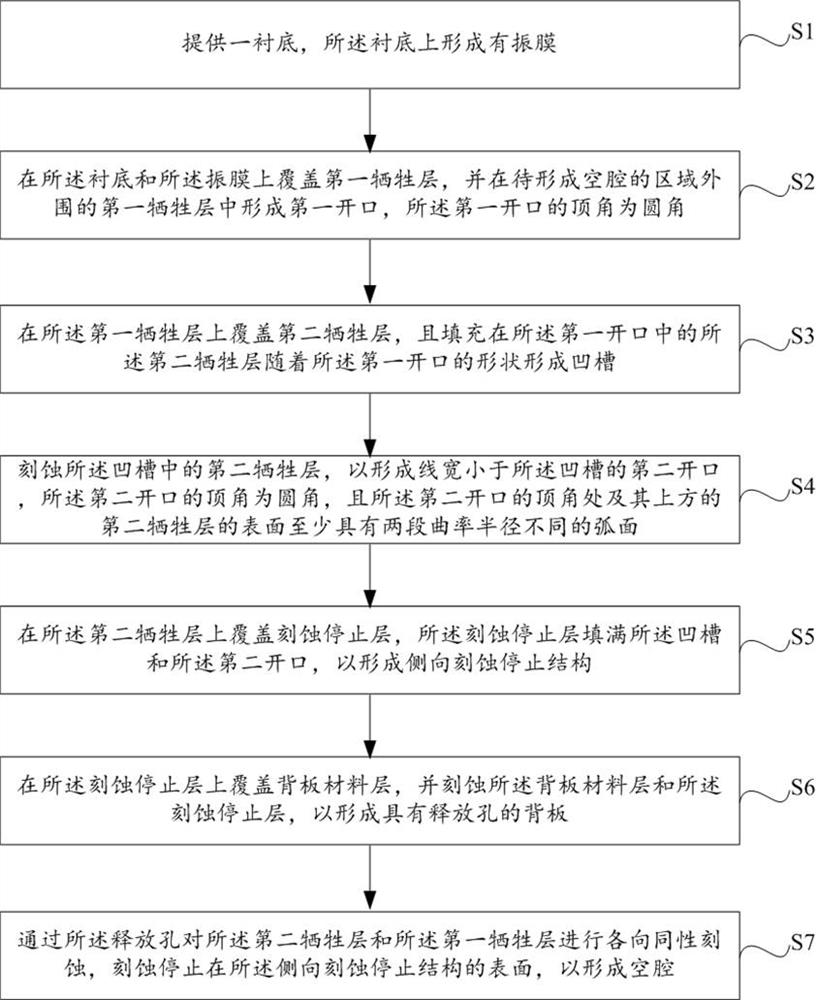

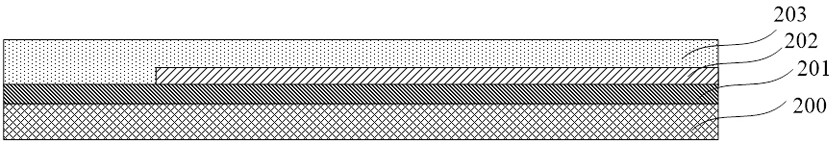

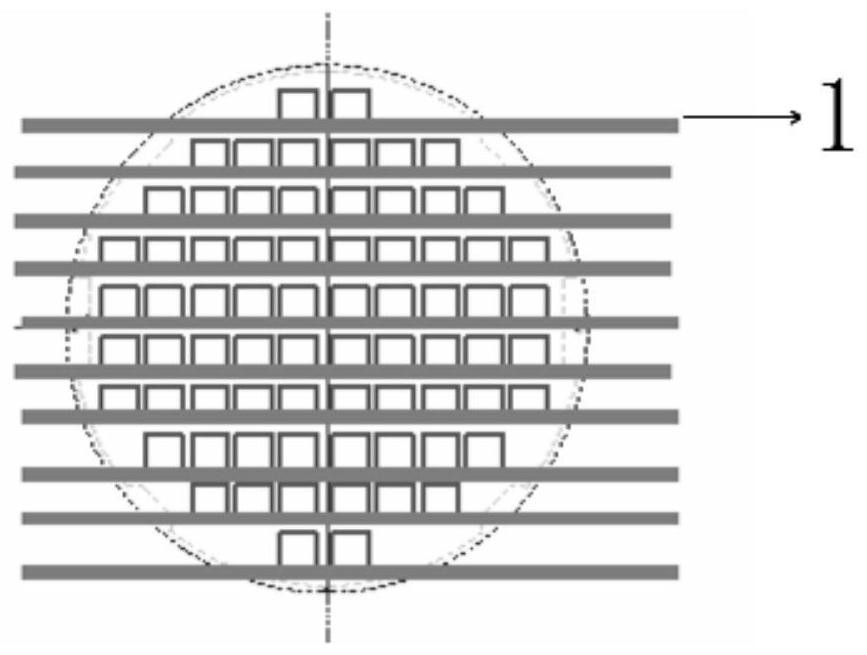

Microphone and its manufacturing method

ActiveCN112995885BImprove performanceControllable side draw distanceSemiconductor electrostatic transducersElectrostatic transducer microphonesMechanical reliabilityMechanical engineering

The present invention provides a microphone and its manufacturing method. Because the first opening of the first sacrificial layer makes the second sacrificial layer conformally form a groove, and then forms the second opening in the groove, then the second opening can be The etch stop layer is filled in the middle to form a lateral stop structure, whereby the first sacrificial layer and the second sacrificial layer are isotropically etched through the release hole to form the diaphragm and the back plate of the microphone. When the cavity is hollow, the etching can be stopped on the surface of the lateral stop structure, which realizes the effect of controllable undercut distance between the first sacrificial layer and the second sacrificial layer, and reduces the limitation on the isotropic etching process. After the cavity is formed, a more stable support column can be formed, which improves the mechanical reliability of the microphone.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP

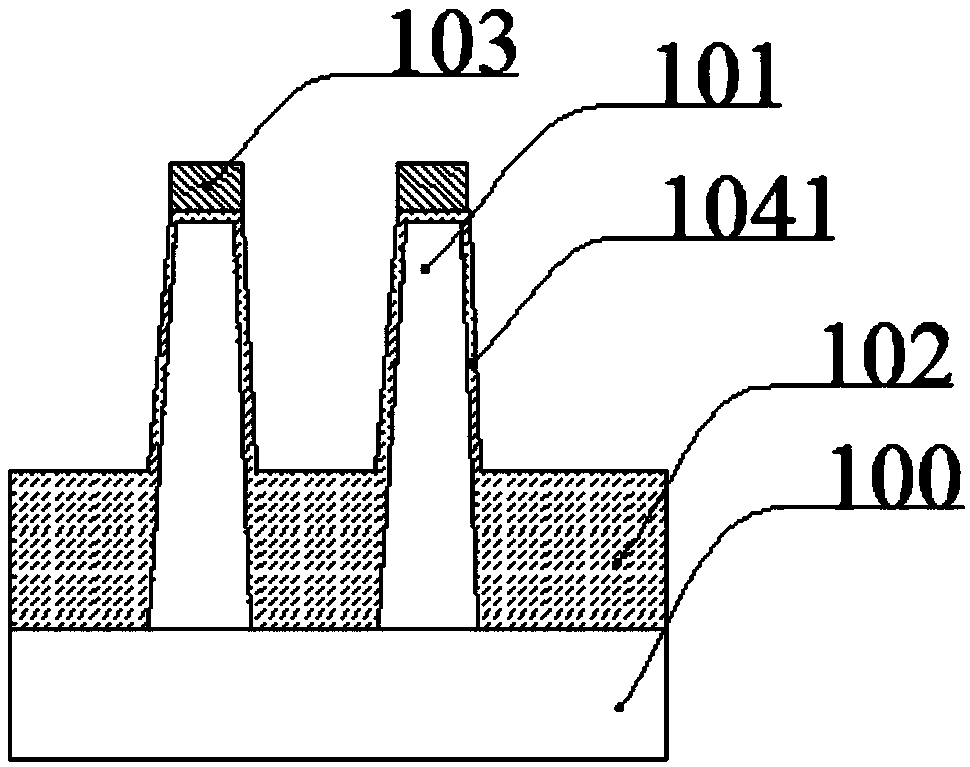

Method for opening terminal area of high-efficiency silicon-based micro display device

PendingCN112928231AAvoid badAvoid uncleannessSolid-state devicesSemiconductor/solid-state device manufacturingSilicon chipThin membrane

The invention discloses a method for opening a terminal area of a high-efficiency silicon-based micro-display device. The method comprises the following steps: 1, pasting a PET adhesive tape: pasting the PET adhesive tape on a PAD area after a previous process is completed; 2, packaging operation: carrying out OLED and thin film packaging operation on a piece attached with the PET adhesive tape; 3, PET adhesive tape removal: conducting PET adhesive tape removal on the piece having been subjected to OLED and thin film packaging so as to enable a PAD area to be exposed; and 4, cleaning: cleaning the silicon wafer obtained in the step 3, and completing a terminal area opening process. According to the method, poor patterns caused by coating, exposure and development can be avoided, etching residues and poor over-etching caused by dry etching are avoided, incomplete and poor wet photoresist removal is avoided, and the requirement for the liquid chemical tolerance of a TFE film layer is lowered; and on the other hand, a technological process is shortened, cost is greatly saved, and productivity is improved.

Owner:ANHUI SEMICON INTEGRATED DISPLAY TECH CO LTD

Bulk acoustic wave resonator, manufacturing method thereof, filter and radio frequency communication system

PendingCN111786648AHigh quality factorImprove performanceImpedence networksCommunications systemEngineering

The invention provides a bulk acoustic wave resonator, a manufacturing method thereof, a filter and a radio frequency communication system. A top electrode protruding part formed on the periphery of apiezoelectric resonance layer and suspended above a cavity can prevent transverse waves generated by the piezoelectric resonance layer from being transmitted to the periphery of the cavity and reflect the transverse waves back to an effective working area, so that the sound wave loss is reduced, the quality factor of the resonator is improved, and finally the performance of a device can be improved. Furthermore, the overlapping parts of a bottom electrode overlapping part and the cavity and the overlapping parts of a top electrode overlapping part and the cavity are suspended, and the bottomelectrode overlapping part and the top electrode overlapping part are mutually staggered, so that a parasitic parameter can be greatly reduced, the problems of electric leakage, short circuit and thelike can be avoided, and the reliability of the device can be improved.

Owner:NINGBO SEMICON INT CORP

Semiconductor structure and forming method thereof

PendingCN111048417AAvoid etch residueGood removal effectSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

The invention relates to a semiconductor structure and a forming method thereof. The forming method comprises the steps of providing a base, wherein the base comprises a substrate and discrete fins arranged on the substrate in a protruding manner; forming a pseudo gate structure stretching across the fins, wherein the pseudo gate structure comprises a first pseudo gate layer and a second pseudo gate layer located on the first pseudo gate layer, the width of the first pseudo gate layer is gradually increased from bottom to top, and the side wall of the second pseudo gate layer is perpendicularto the top surface of the substrate; forming a source-drain doping layer in the fins on the two sides of the pseudo gate structure; forming a dielectric layer on the source-drain doping layer, whereinthe dielectric layer exposes the top of the pseudo gate structure; removing the pseudo gate structure, and forming an opening in the dielectric layer; and forming a metal gate structure filling the opening. The included angle between the side wall of the first pseudo gate layer and the top wall of the fin is less than 90 degrees, so that the process space for subsequently removing the first pseudo gate layer is large, and the first pseudo gate layer is not prone to being left. On the basis, the side wall of the second pseudo gate layer is perpendicular to the top surface of the substrate, sothat the transverse space of the top surface of the fin is saved, the further reduction of the device size is facilitated, and the performance of the semiconductor structure is optimized.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Dry etching method

InactiveCN107634007AAvoid etch damageAvoid damageTransistorSemiconductor/solid-state device manufacturingDry etchingSilicon

Owner:BOE TECH GRP CO LTD

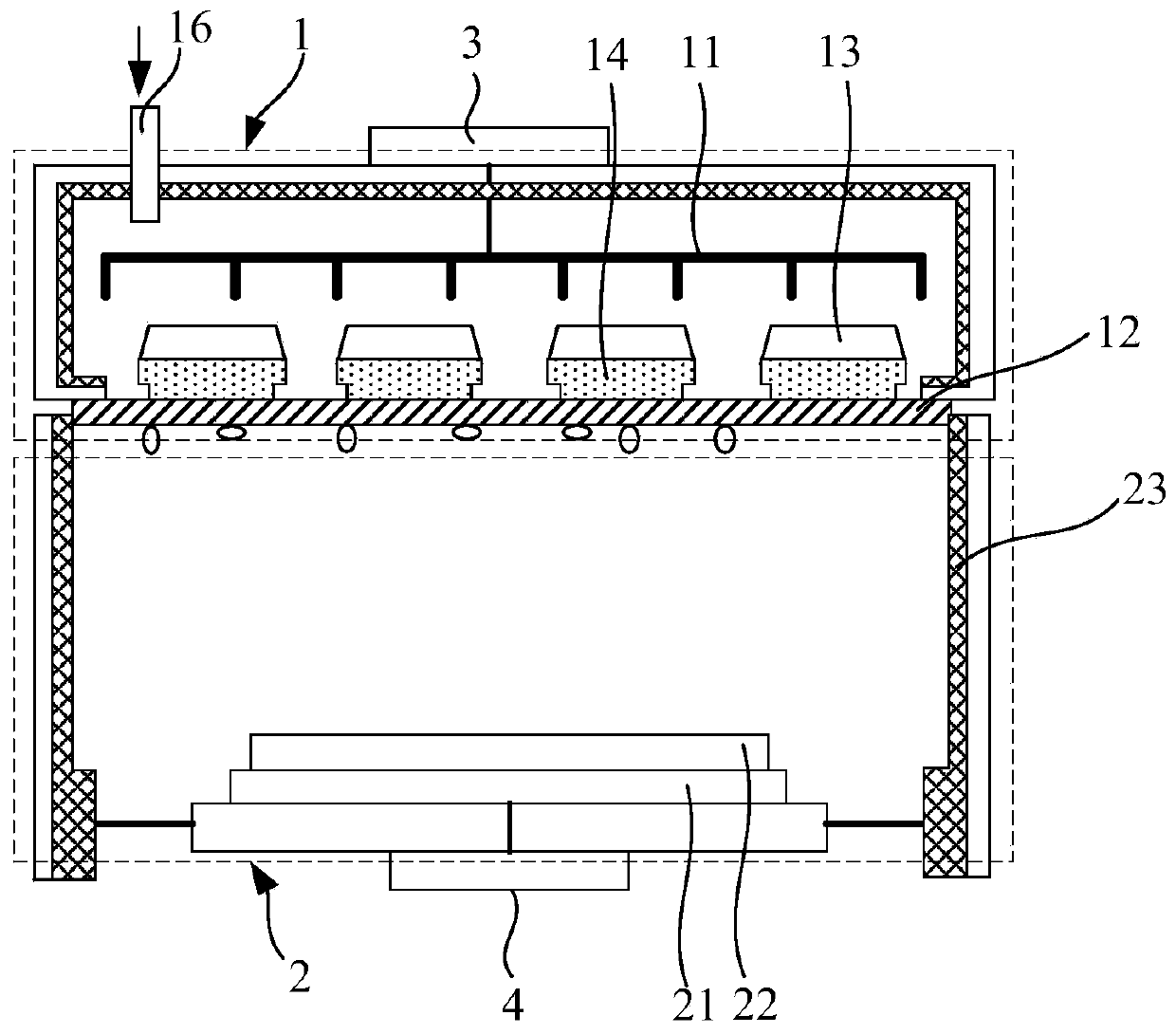

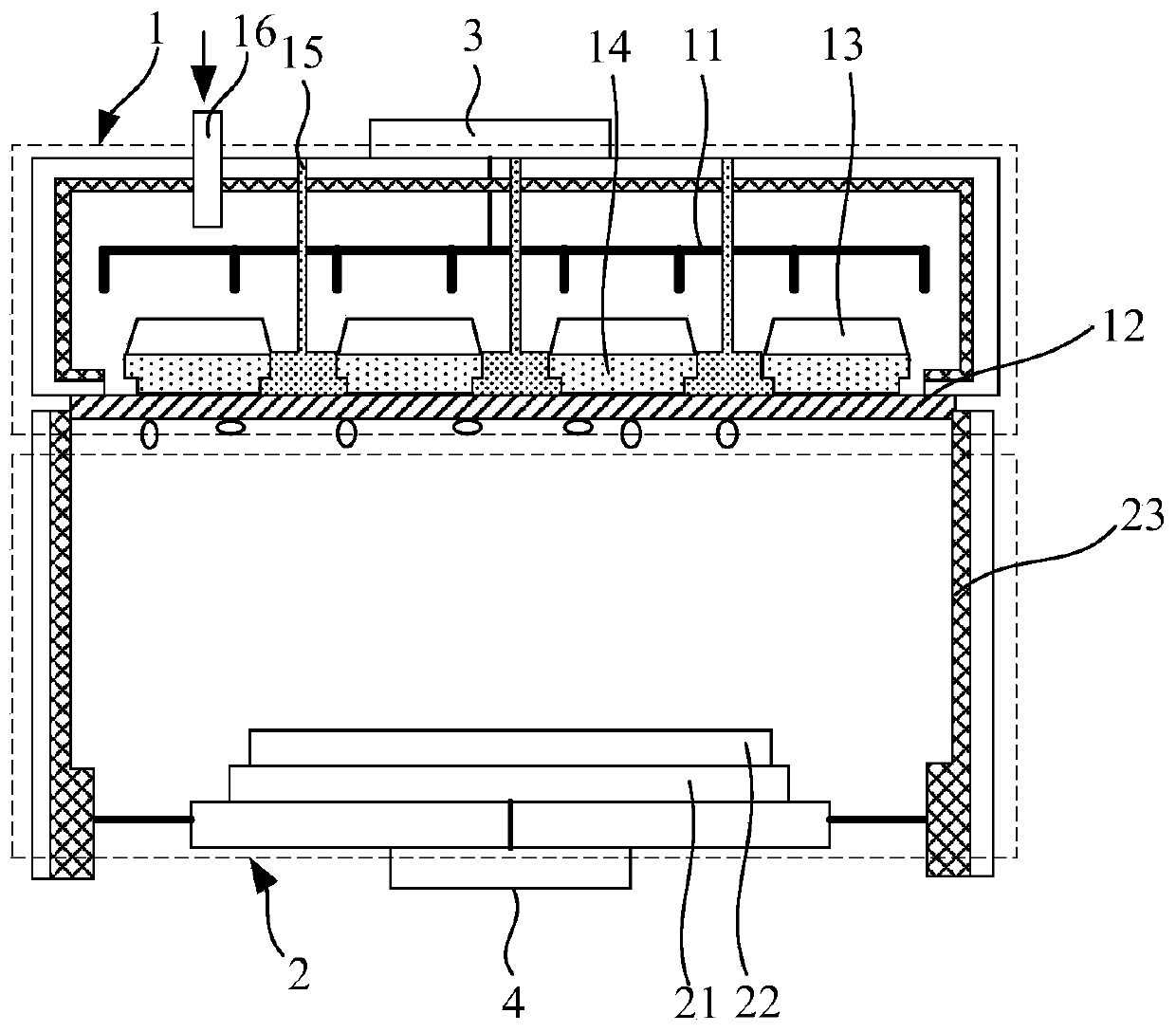

Etching device

ActiveCN111584338AAvoid etch residueRapid temperature controlElectric discharge tubesSemiconductor/solid-state device manufacturingMechanical engineeringDry etching

The invention discloses an etching device, which comprises an upper cavity and a lower cavity, and is characterized in that the lower cavity is used for carrying out an etching process on a device. The upper cavity comprises a coil, which is used for bearing alternating current, and an electromagnetic field is generated by the alternating current; electricity inducers which are arranged under thecoil at intervals and used for transmitting the electromagnetic field generated by the coil to the lower cavity; an insulating plate which is arranged at the bottom of the upper cavity and used for preventing plasmas formed by the electromagnetic field from making direct contact with the electricity inducers, and preventing causing corrosion to the electricity inducers and generating arc discharge; and a heating component which is arranged between the insulating plate and the electricity inducers and is used for controlling the temperature of the electricity inducers and the insulating plate.The etching device provided by the embodiment of the invention is used for solving the problem of etching residues caused by adhesion of products in a dry etching process.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com