Array substrate and preparation method thereof, and display panel

An array substrate and substrate substrate technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as uneven display screen, poor TFT stability, and start-up voltage drift.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

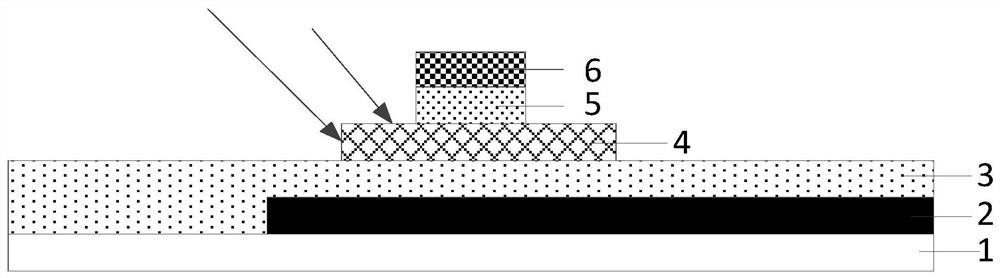

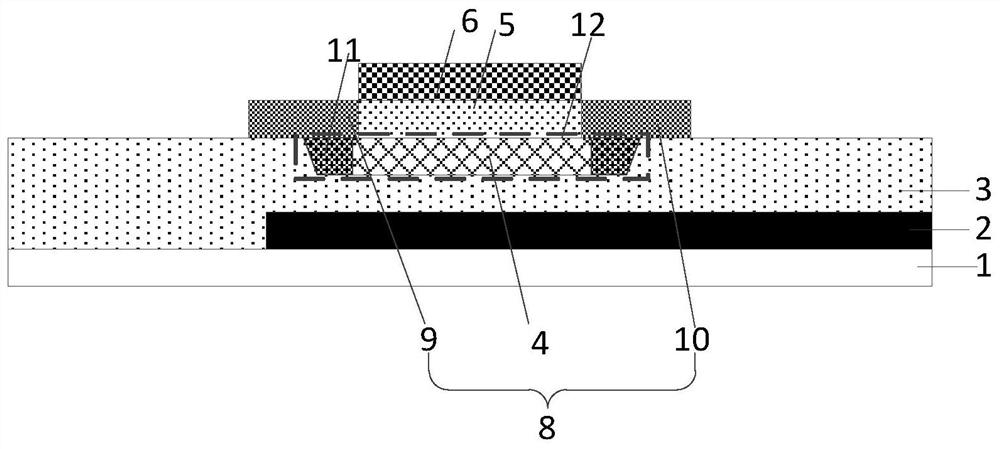

[0063] The embodiments of the present application provide an array substrate, such as figure 2 As shown, the array substrate includes: a base substrate 1, a light shielding layer 2 located on the base substrate 1, a buffer layer 3 located on the light shielding layer 2, and a buffer layer 3 located on the buffer layer 3 The source layer 8, and the light shielding part 11; the buffer layer 3 has a groove 12;

[0064] The active layer 8 includes: a semiconductor region 4, and a first conductive region 9 and a second conductive region 10 of the semiconductor region 4;

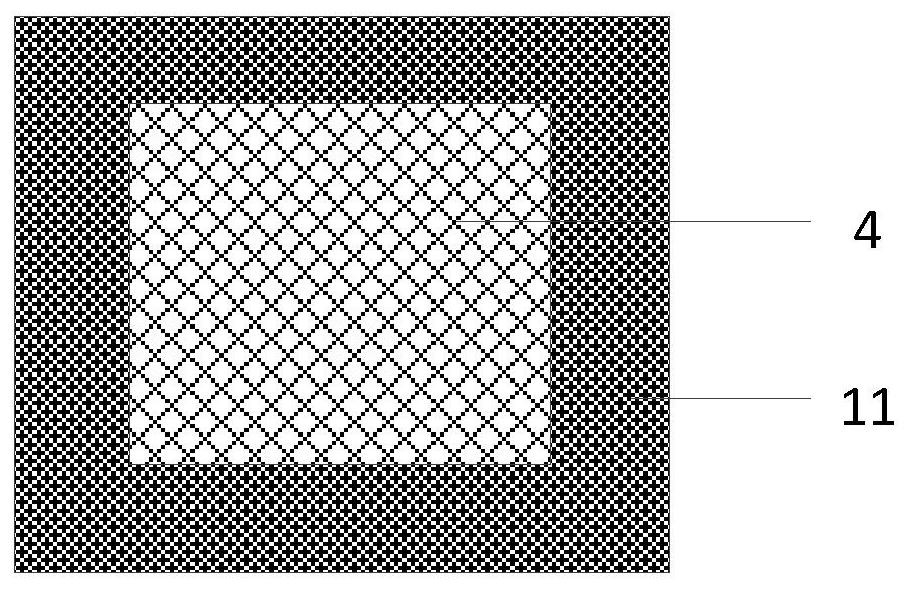

[0065] The semiconductor region 4 and the light shielding portion 11 fill the groove 12; such as image 3 As shown, the shape of the orthographic projection of the light shielding portion 11 on the base substrate 1 is annular, the side surface of the semiconductor region 4 is completely surrounded by the light shielding portion 11, the first conductive region 9 and the The second conductive region 10 is located...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com