Method for improving Nor Flash polycrystalline silicon etching and dielectric layer filling process window

A process window, polysilicon layer technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of insufficient filling capacity of the dielectric layer, incomplete etching, easy formation of voids, etc., to avoid polysilicon etching residues, expansion, etc. The effect of etching the process window and enlarging the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to illustrate the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

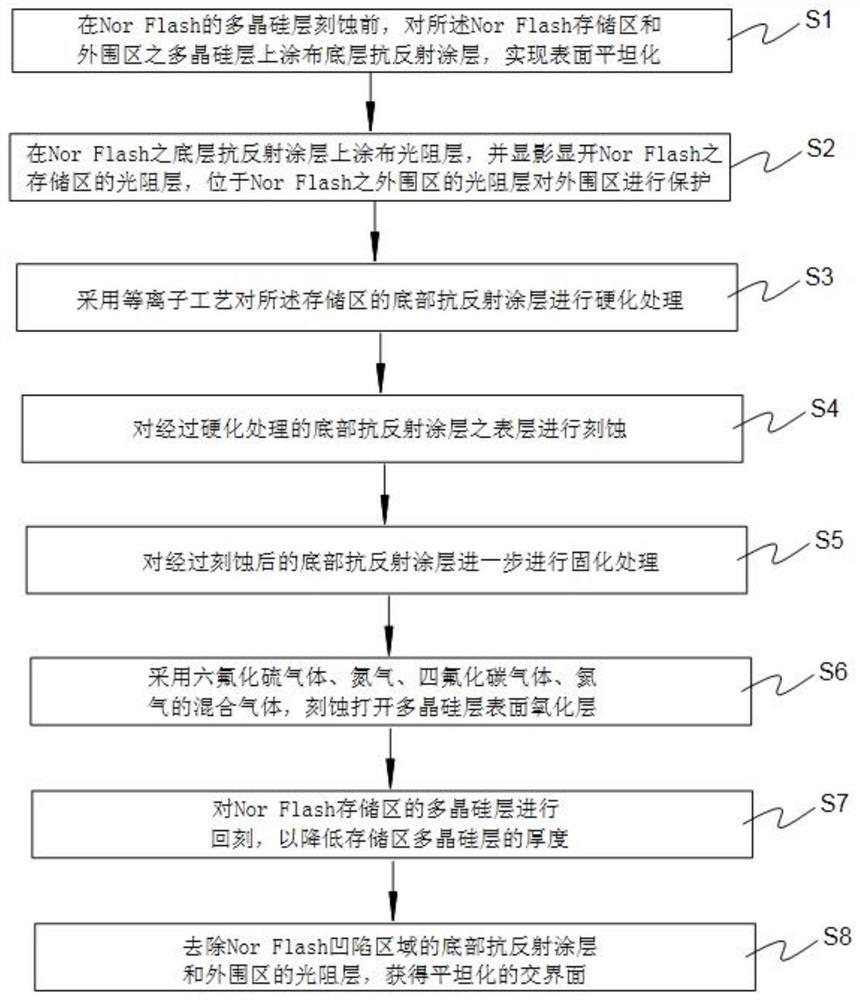

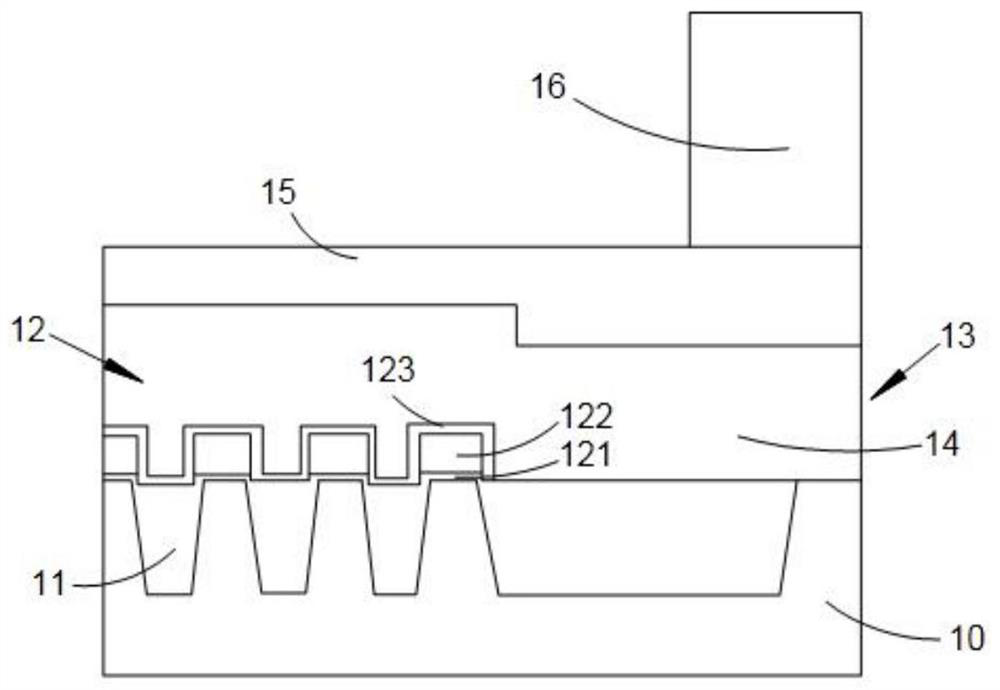

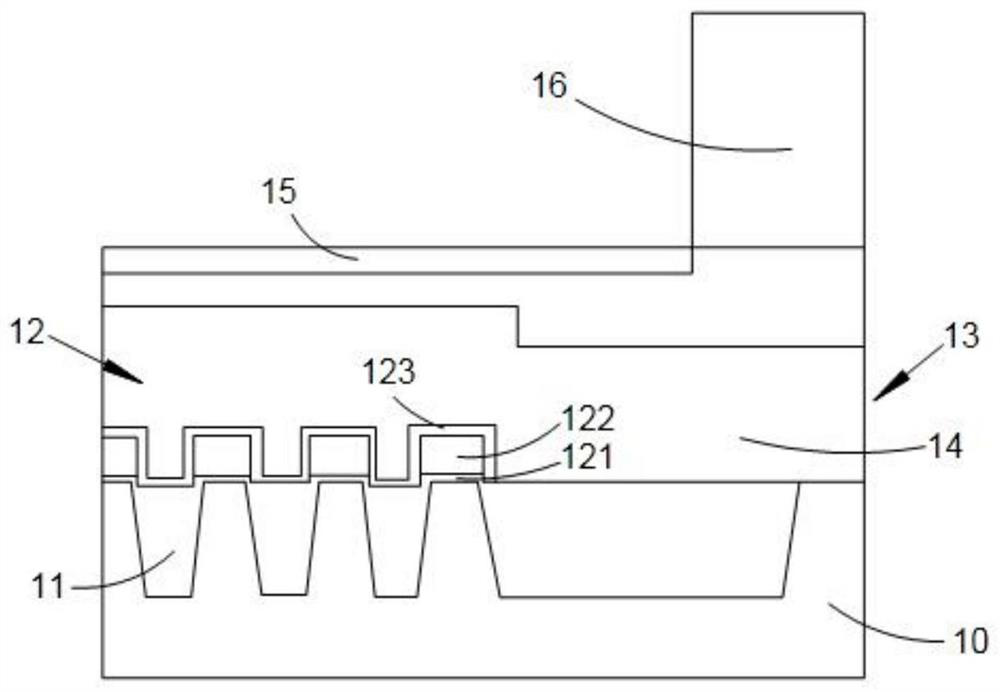

[0029] see figure 1 , figure 1 Shown is the flow chart of the method for improving the process window of Nor Flash polysilicon etching and dielectric layer filling in the present invention. In the present invention, the method for promoting the Nor Flash polysilicon etching and dielectric layer filling process window, by coating the bottom anti-reflective coating before the polysilicon layer etching, and adopting the etching-back process to reduce the area of the Nor Flash storage area polysilicon layer, and reduce the height difference between the Nor Flash storage area and the peripheral area at the same time. Obviously, after using the etch-back process to reduce the thickness of the polysilicon layer in the Nor Flash storage ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com