Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

249results about How to "Improve etch uniformity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

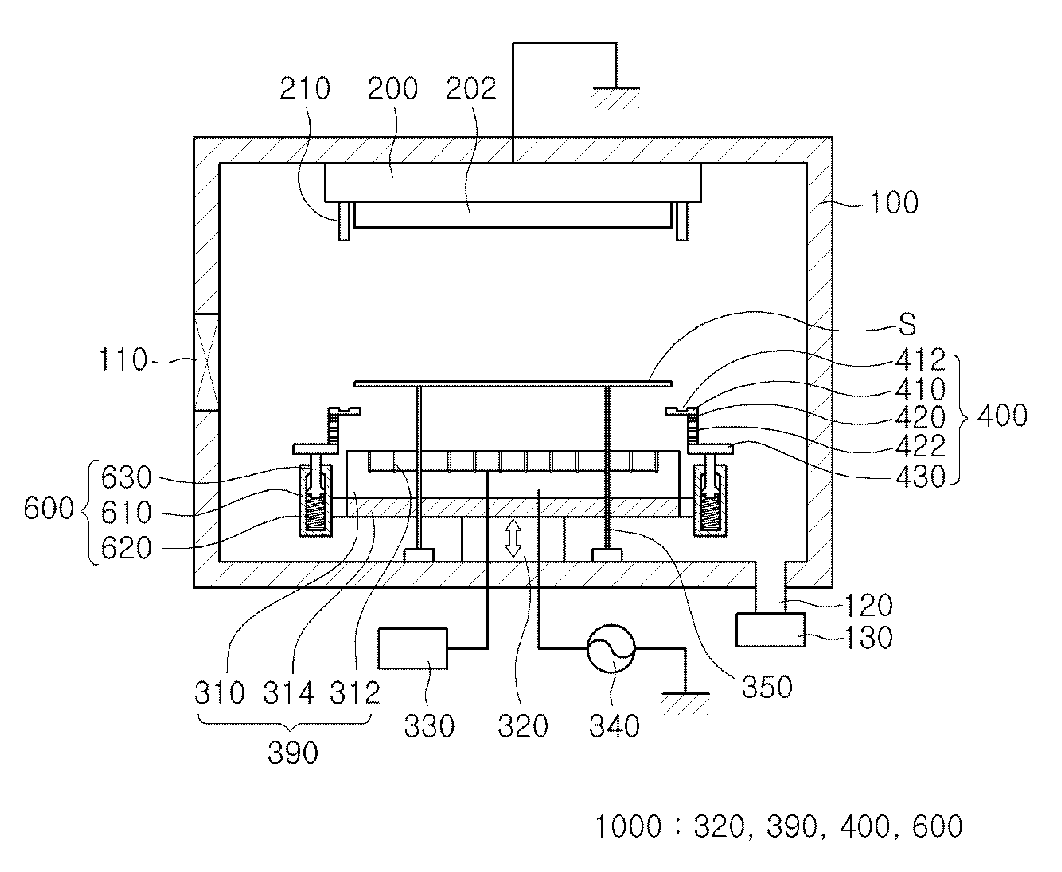

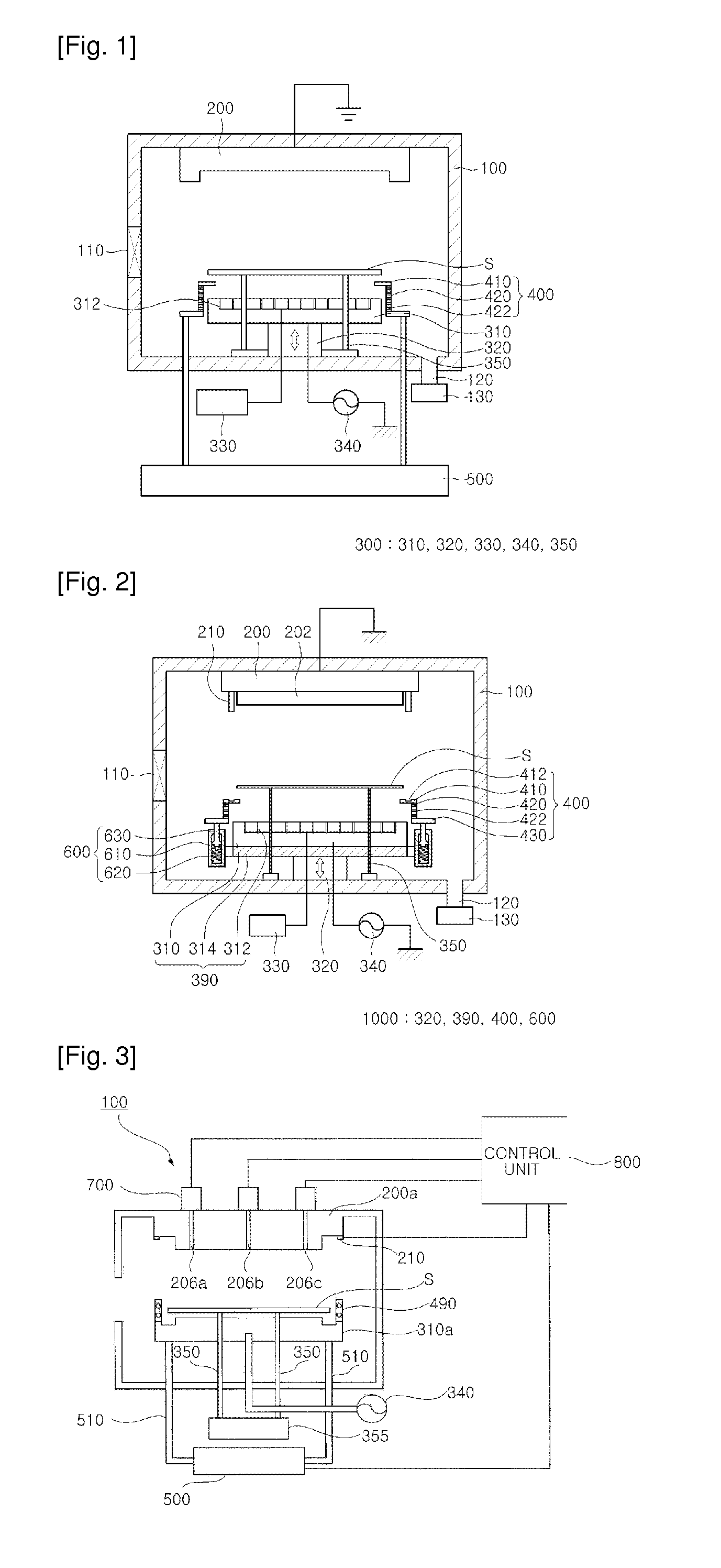

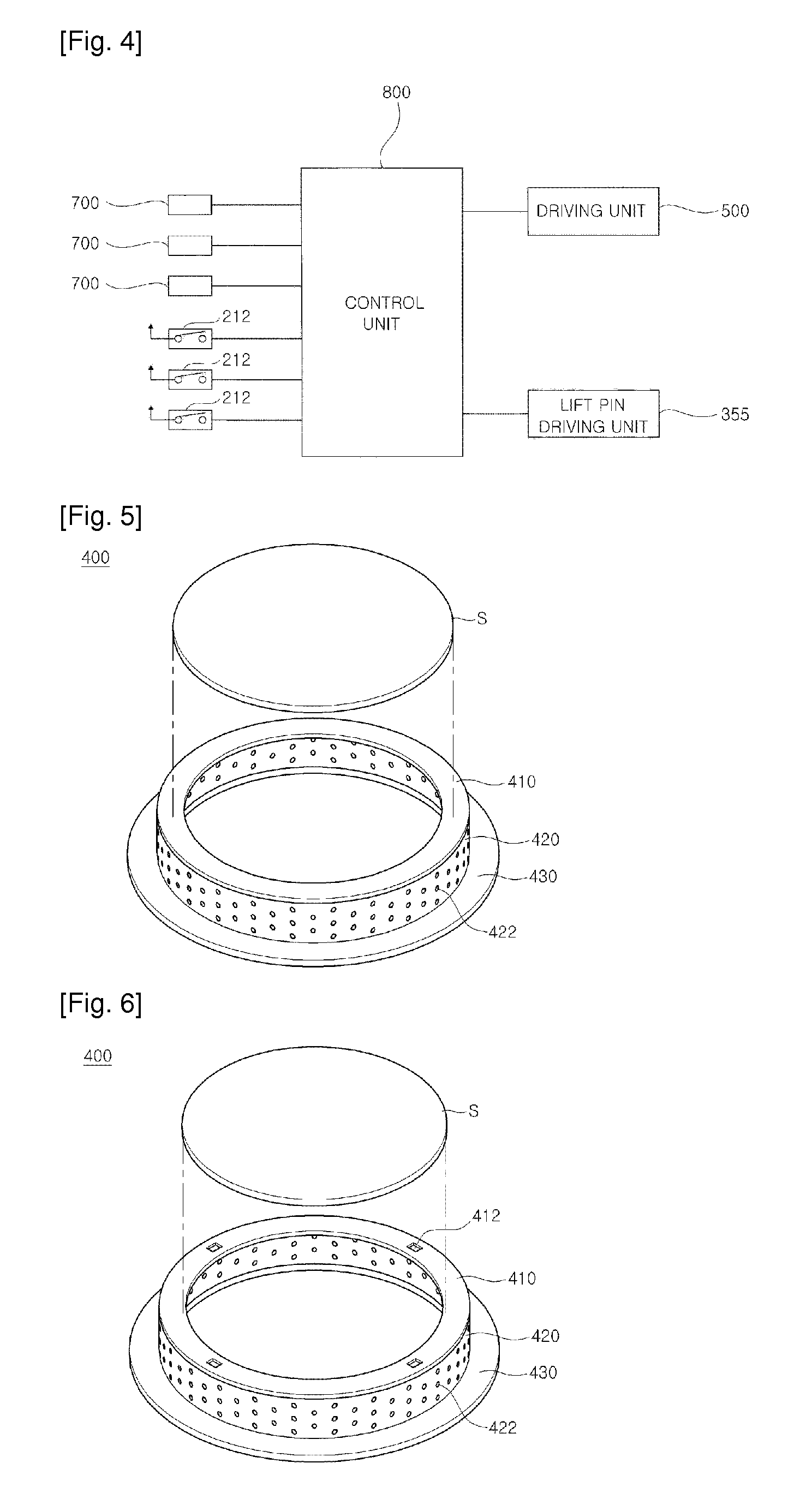

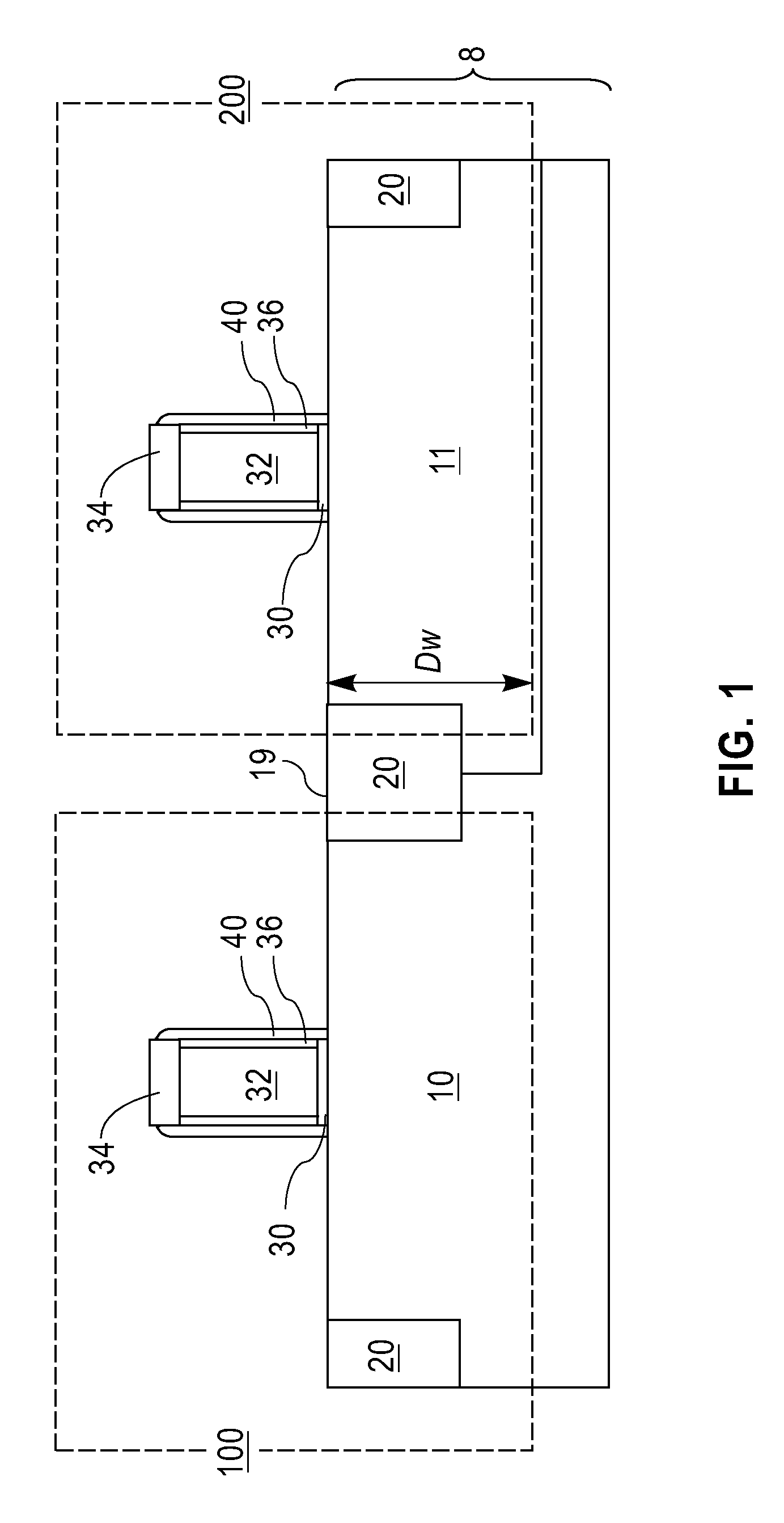

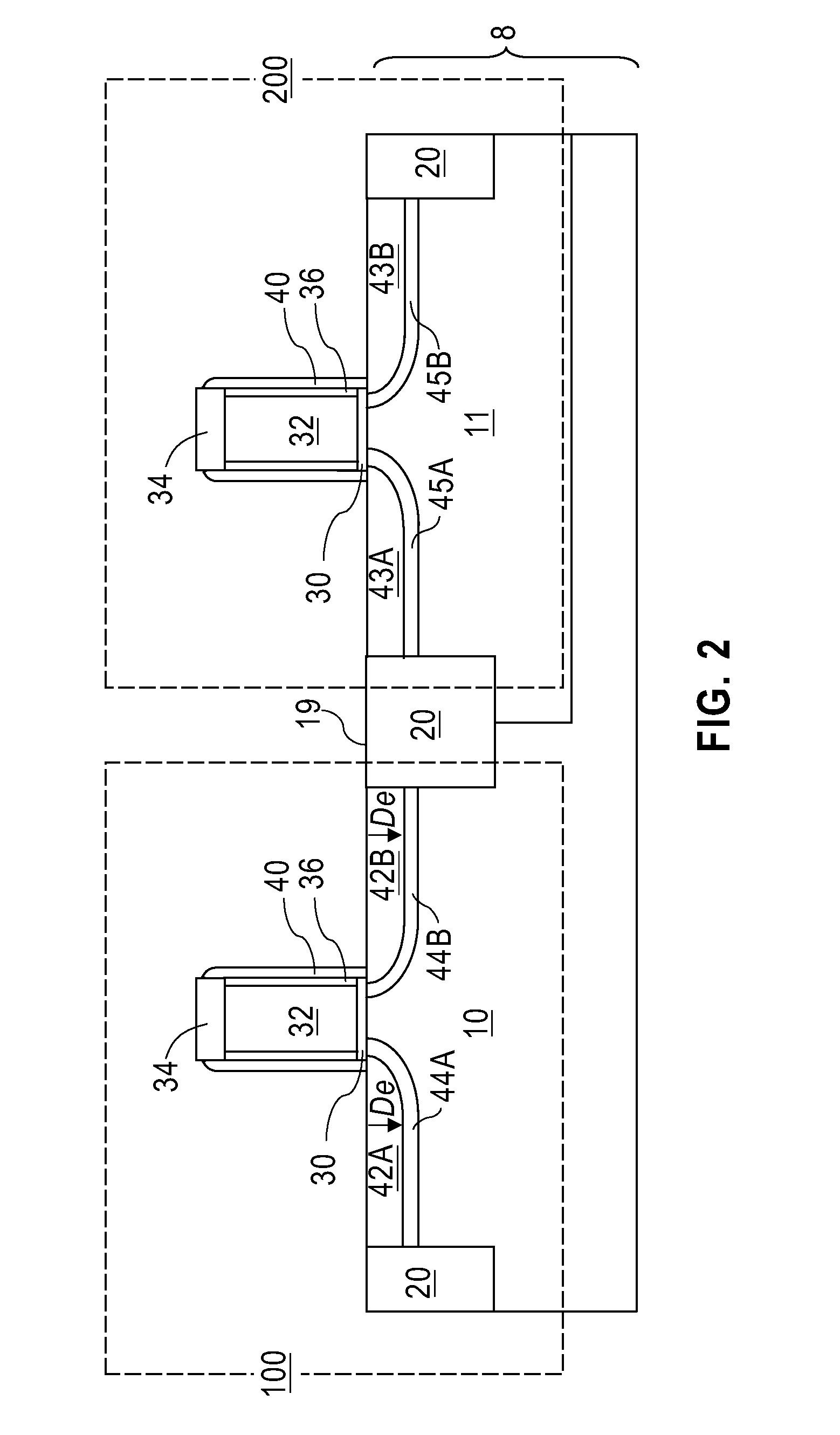

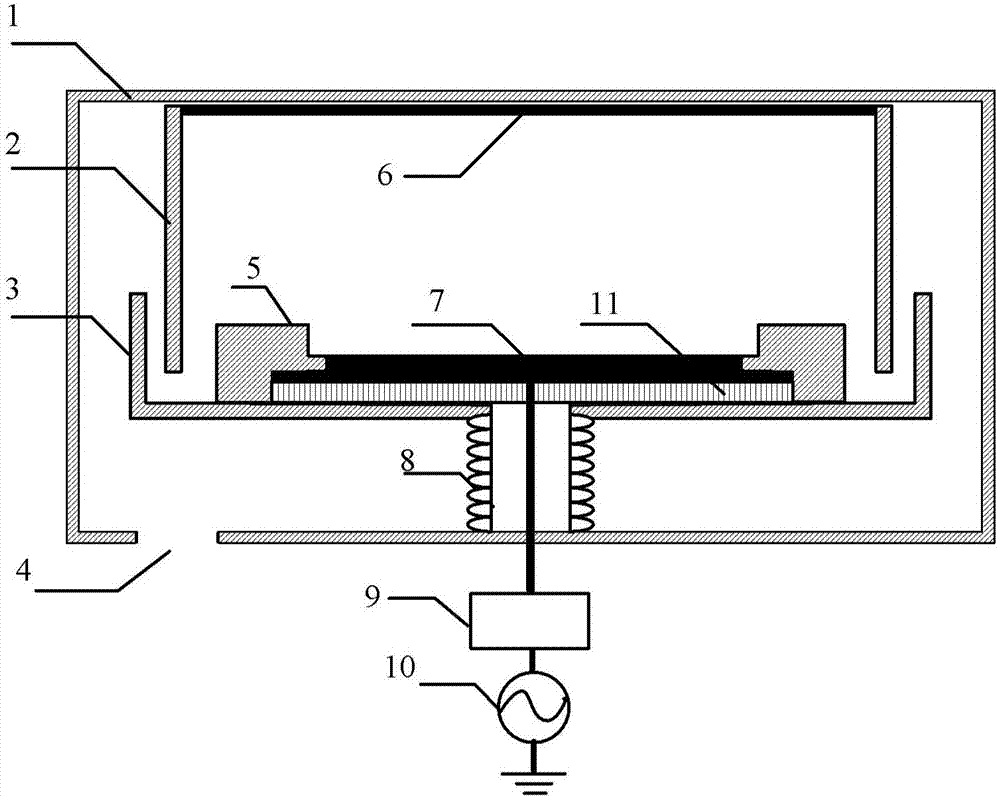

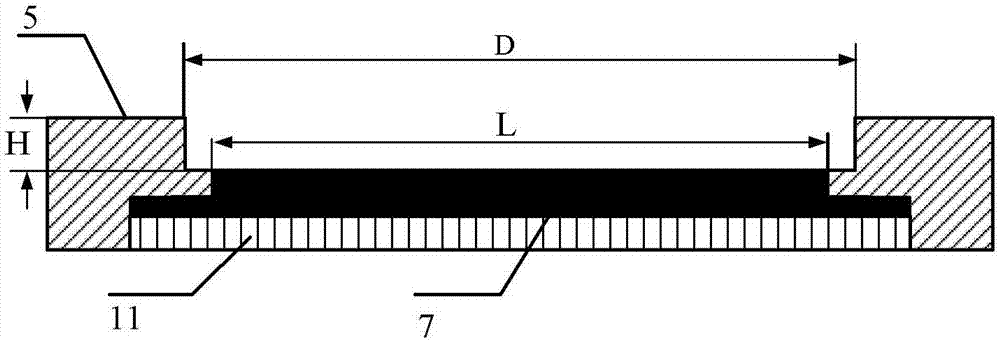

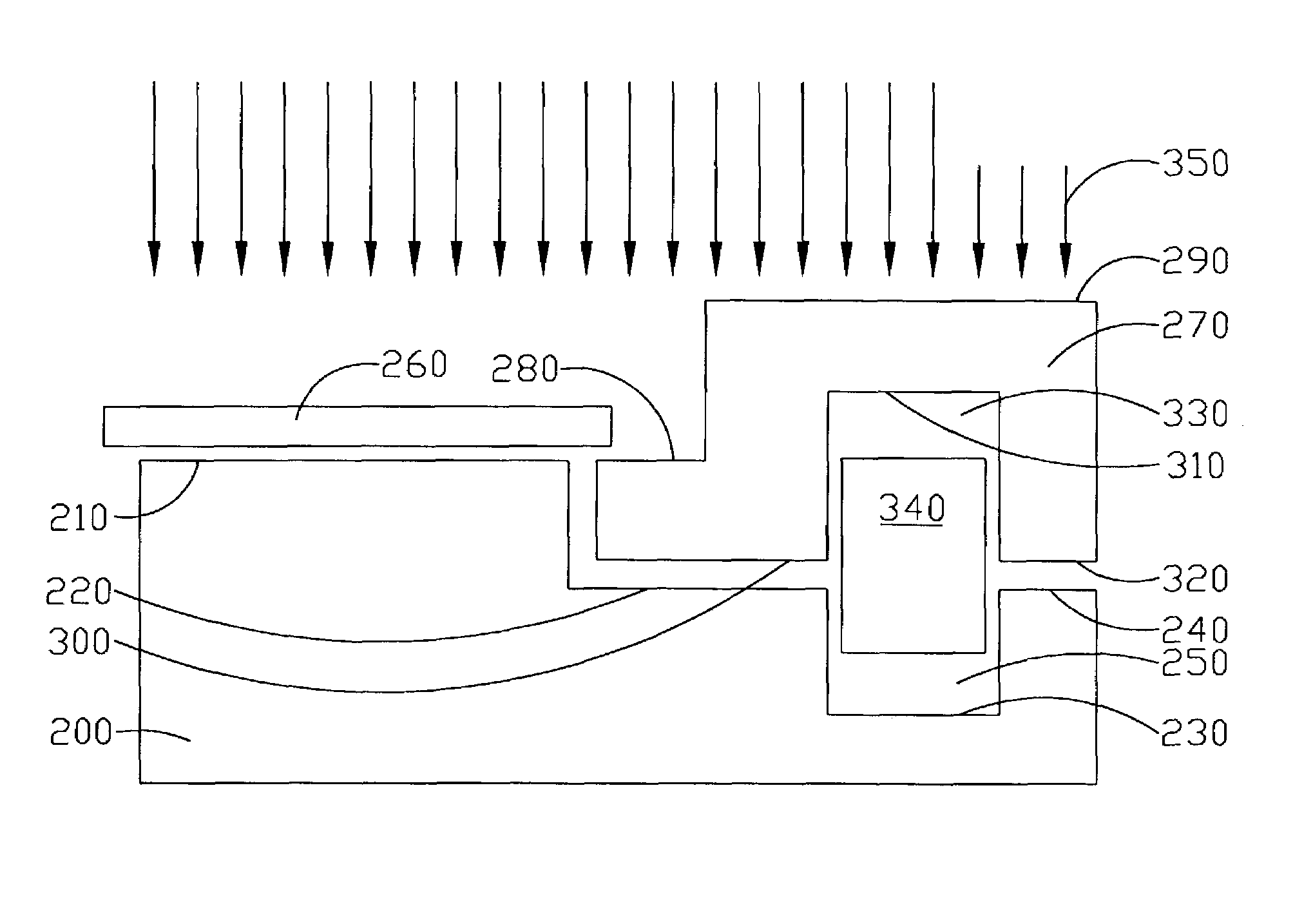

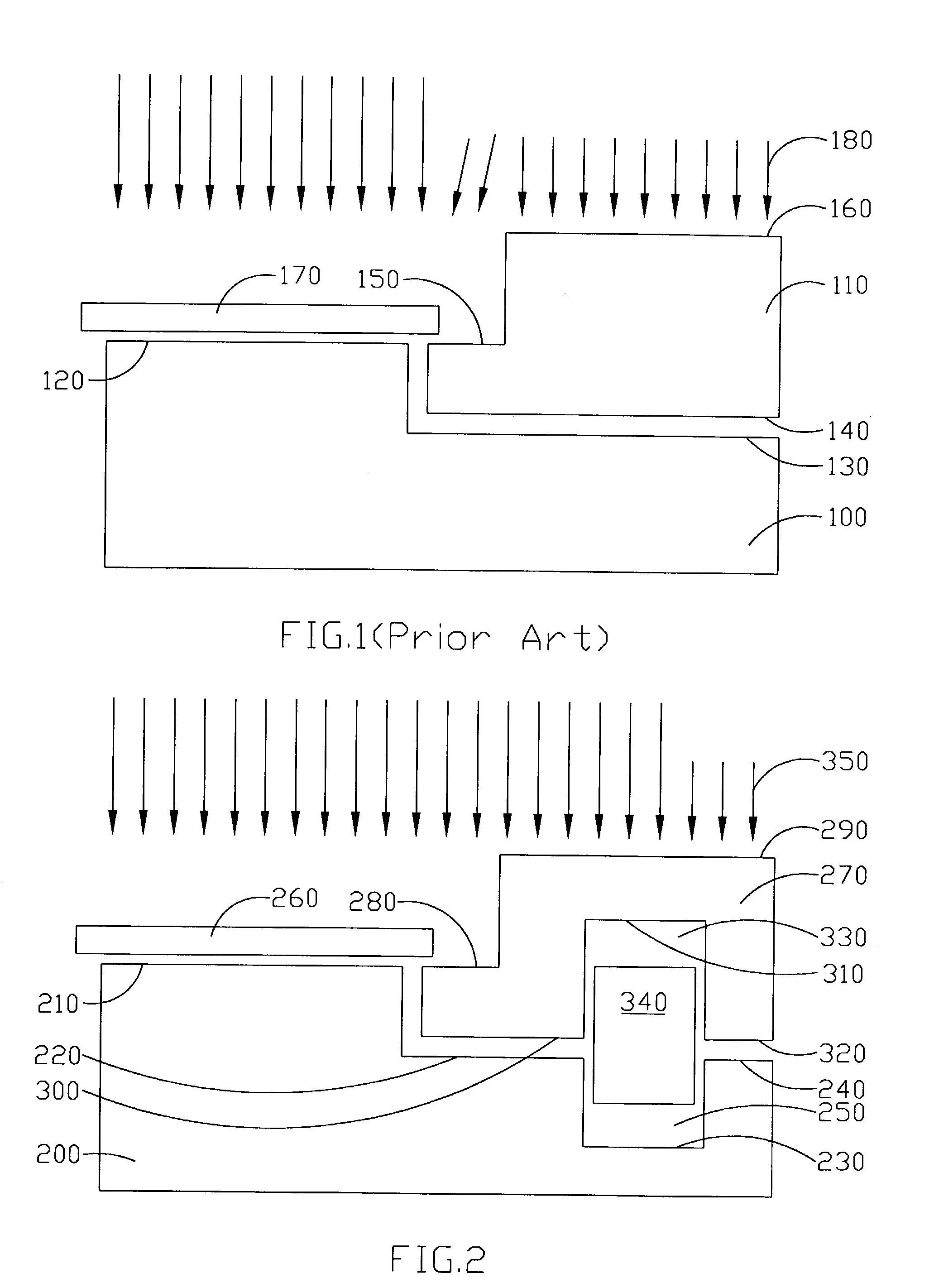

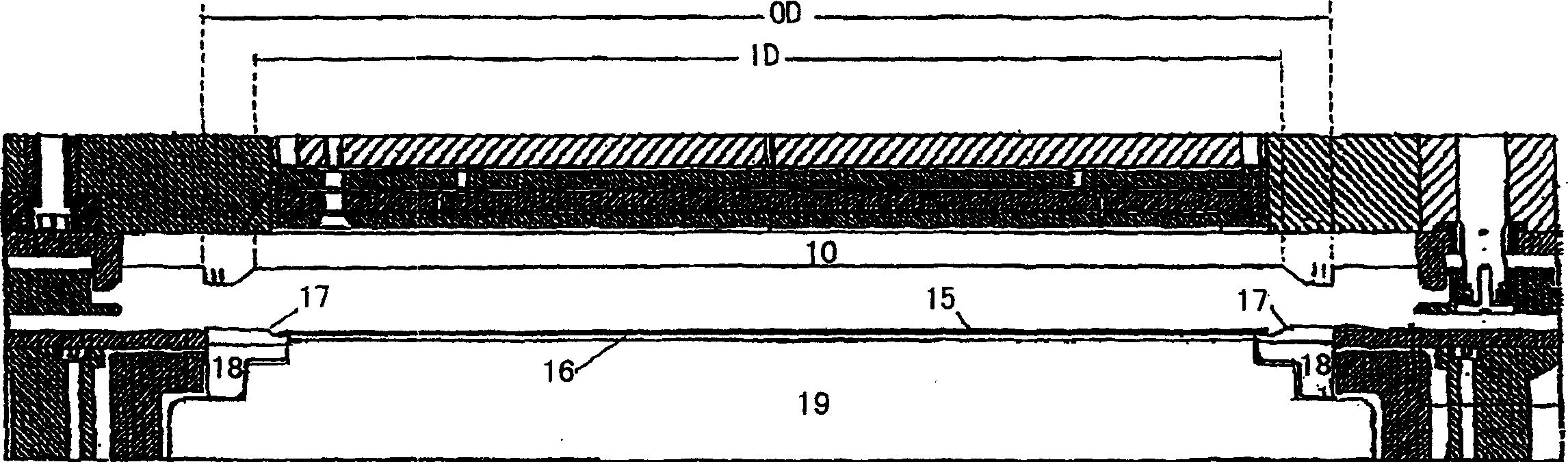

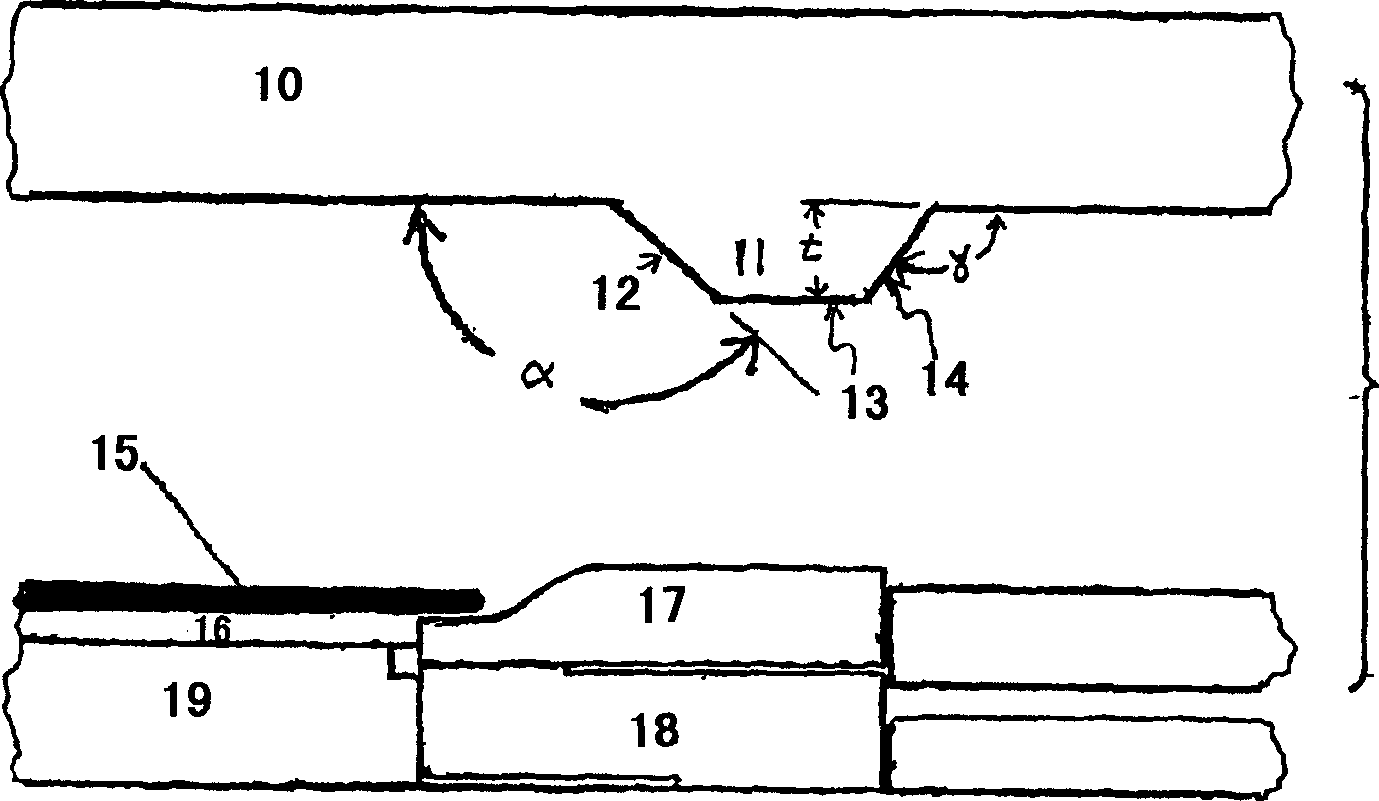

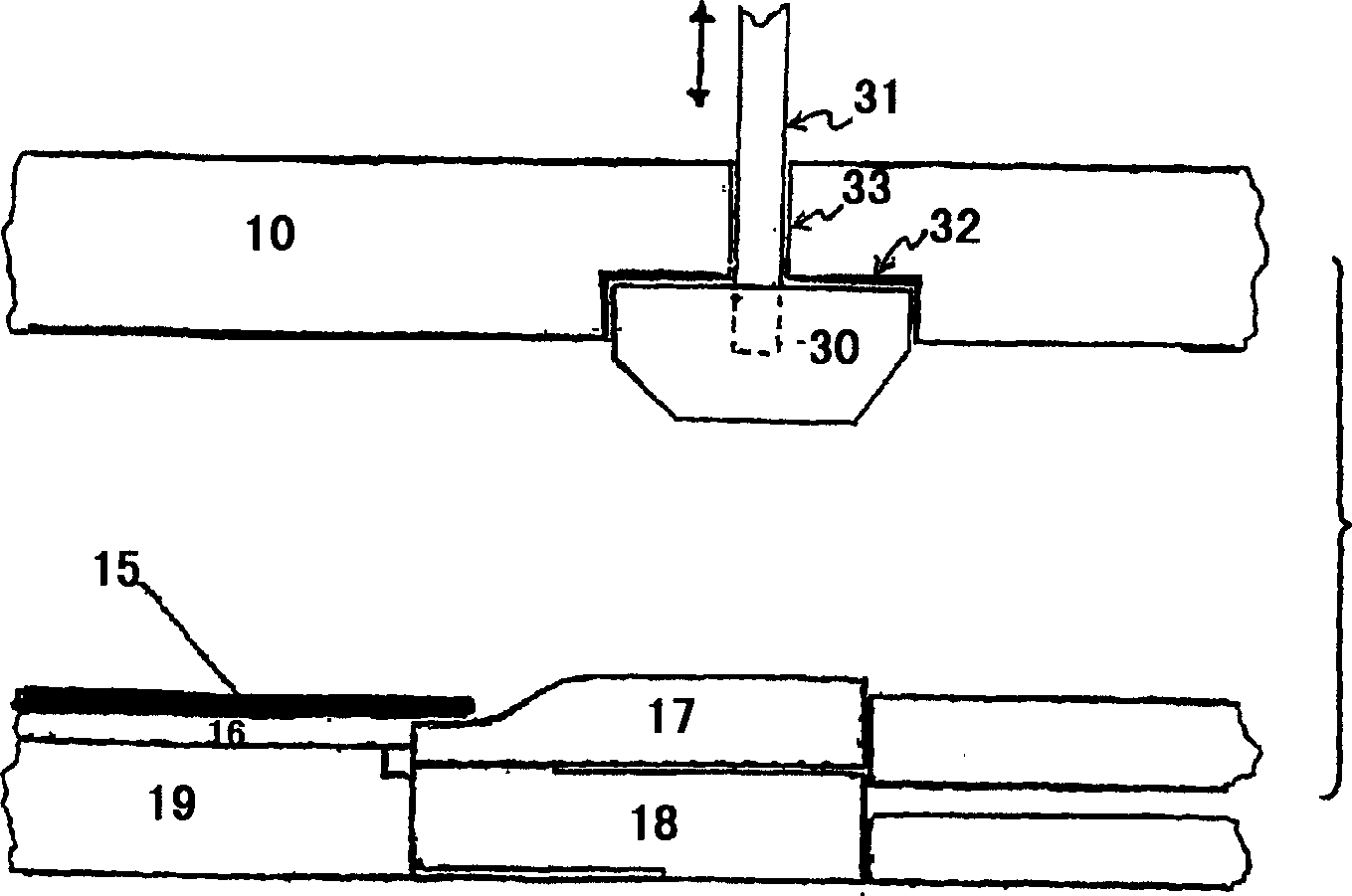

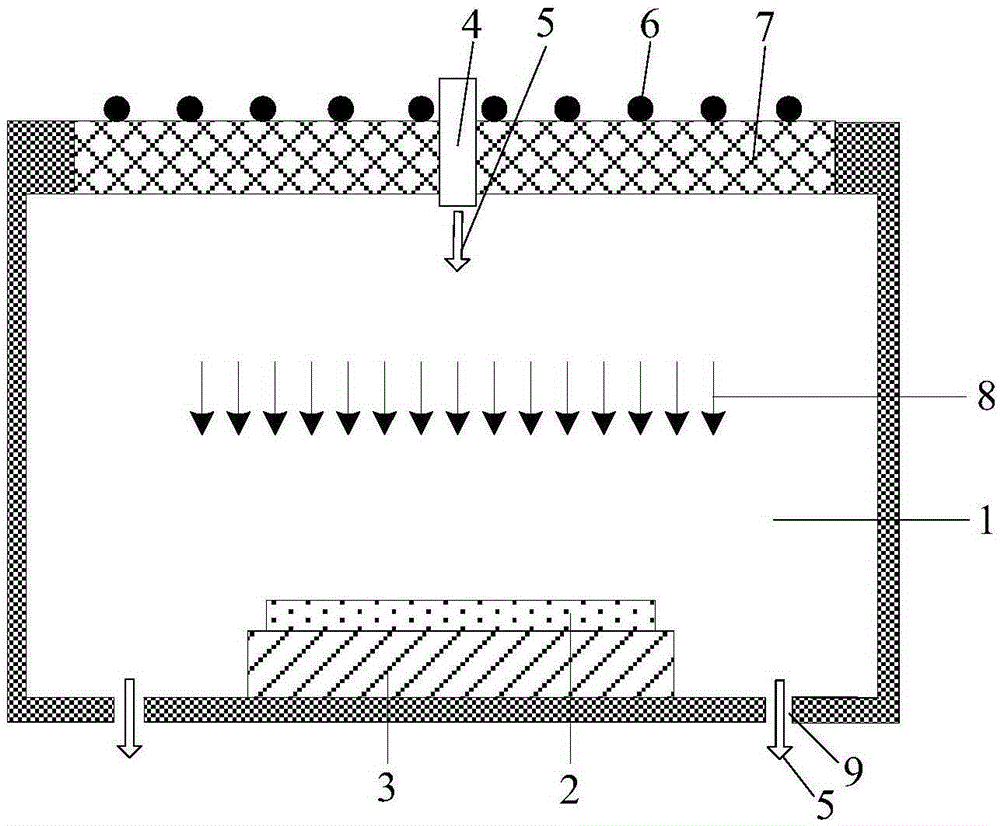

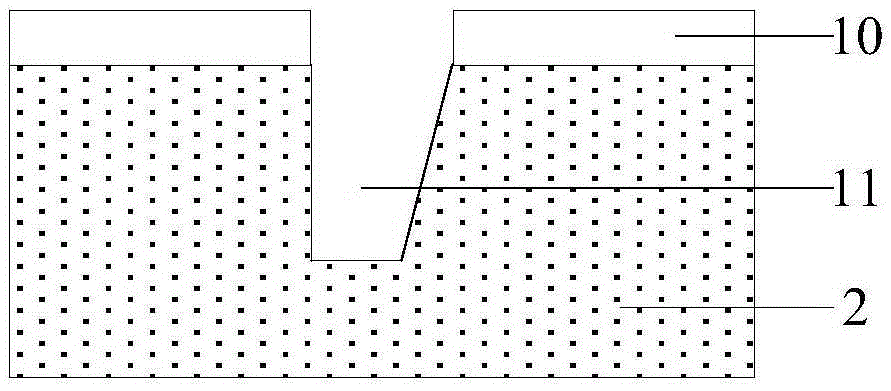

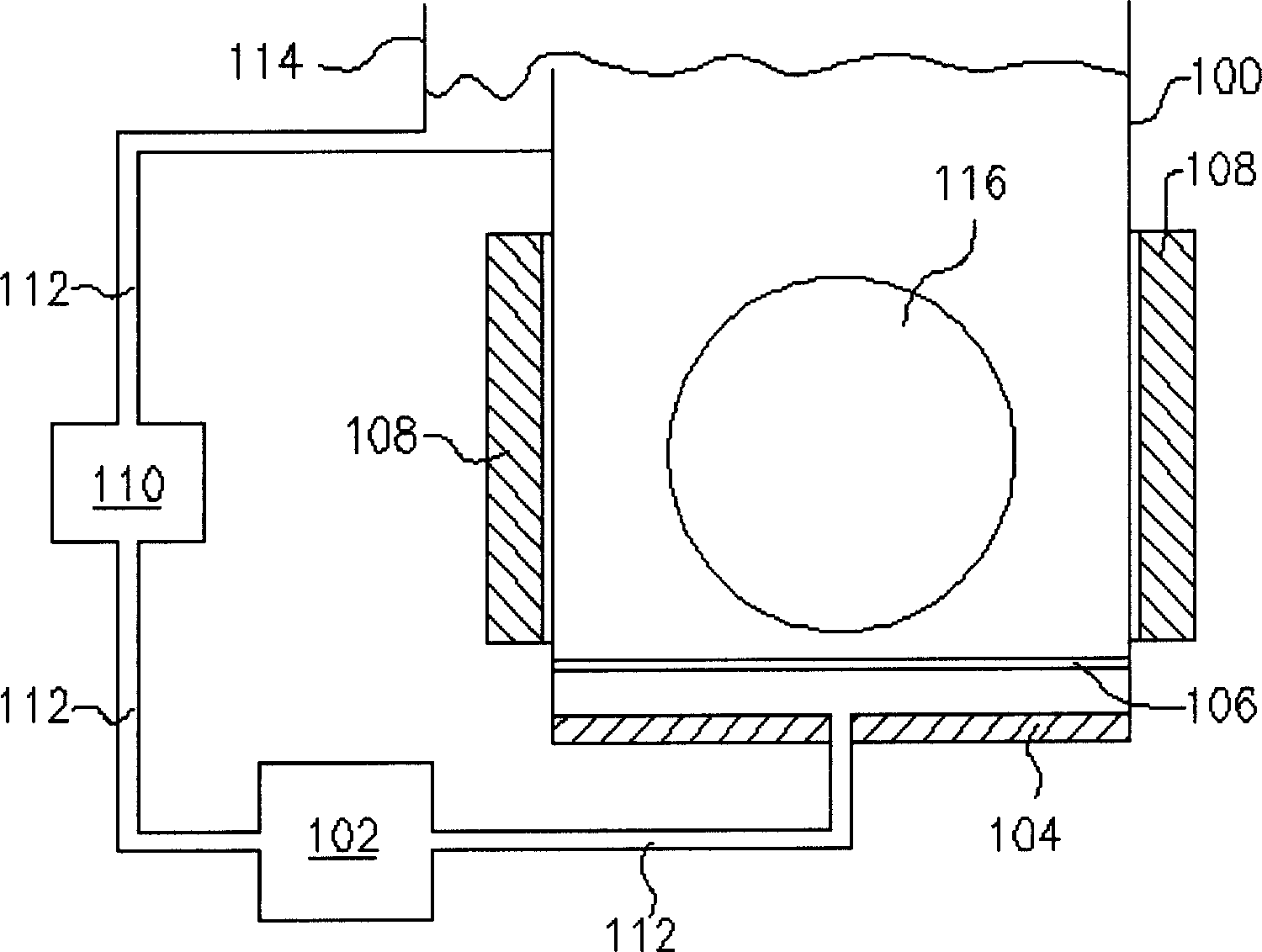

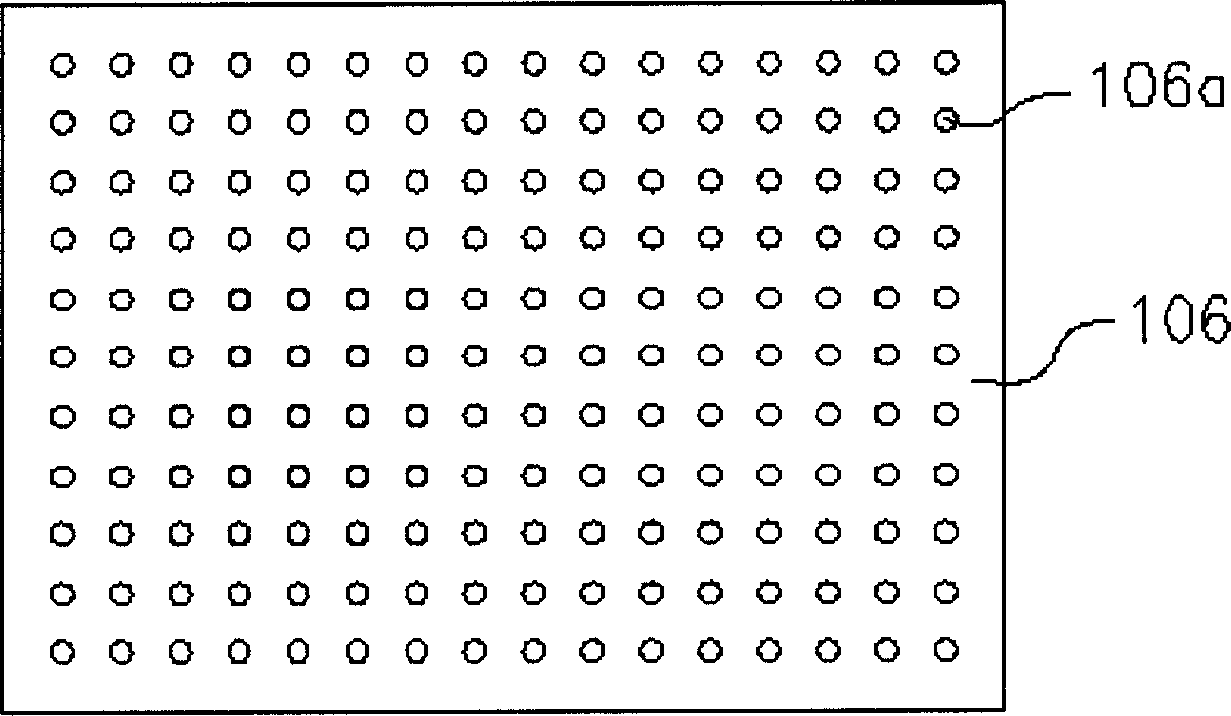

Substrate holder, substrate supporting apparatus, substrate processing apparatus, and substrate processing method using the same

InactiveUS20110049100A1Improve etch uniformityPrevent leakageElectric discharge tubesDecorative surface effectsEngineeringProcess efficiency

Provided are a substrate holder, a substrate supporting apparatus, a substrate processing apparatus, and a substrate processing method. Particularly, there are provided a substrate holder, a substrate supporting apparatus, a substrate processing apparatus, and a substrate processing method that are adapted to improve process efficiency and etch uniformity at the back surface of a substrate.

Owner:CHARM ENG CO LTD

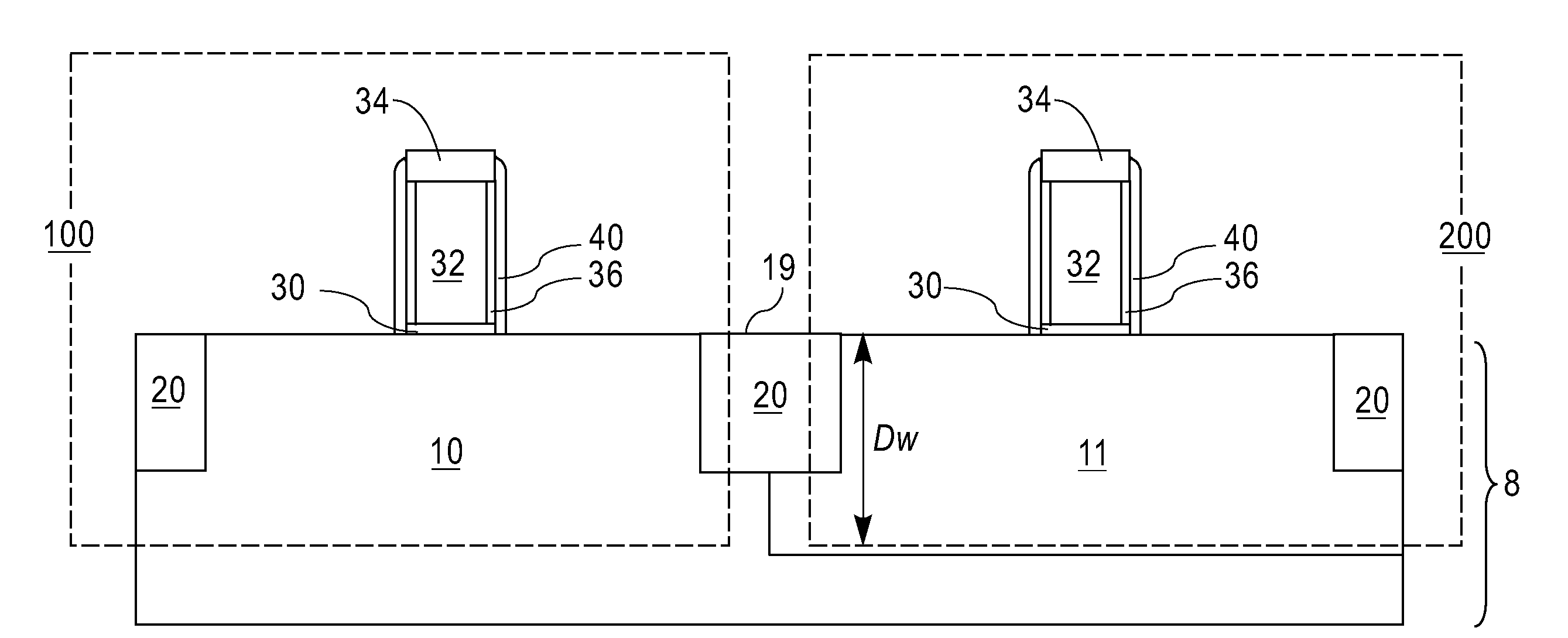

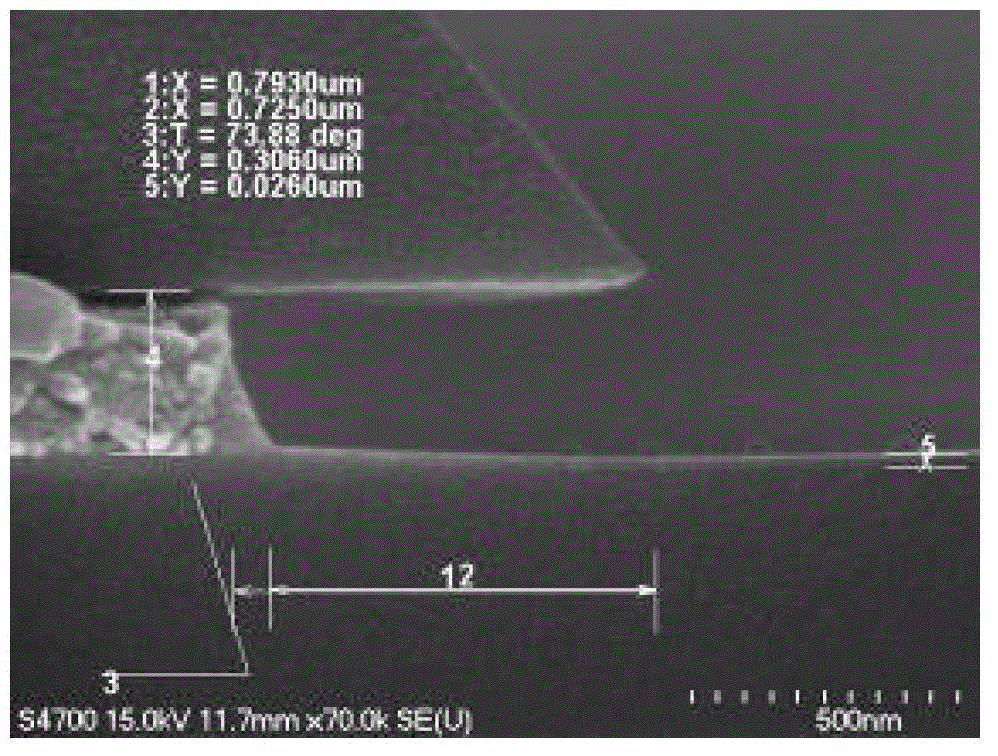

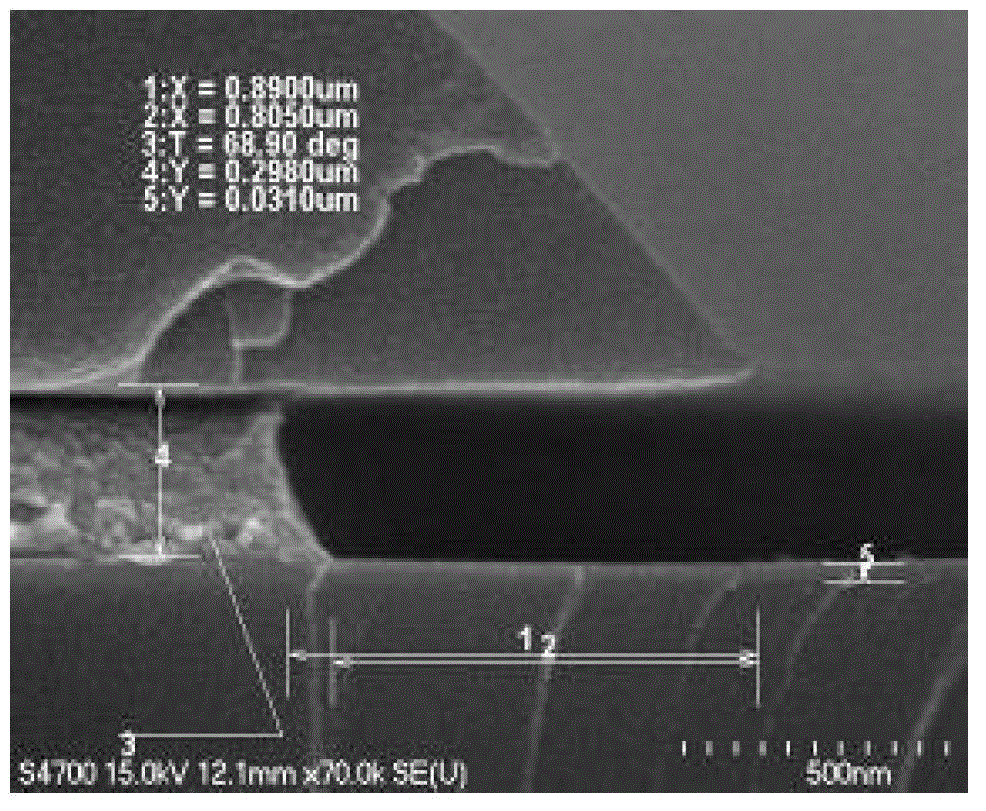

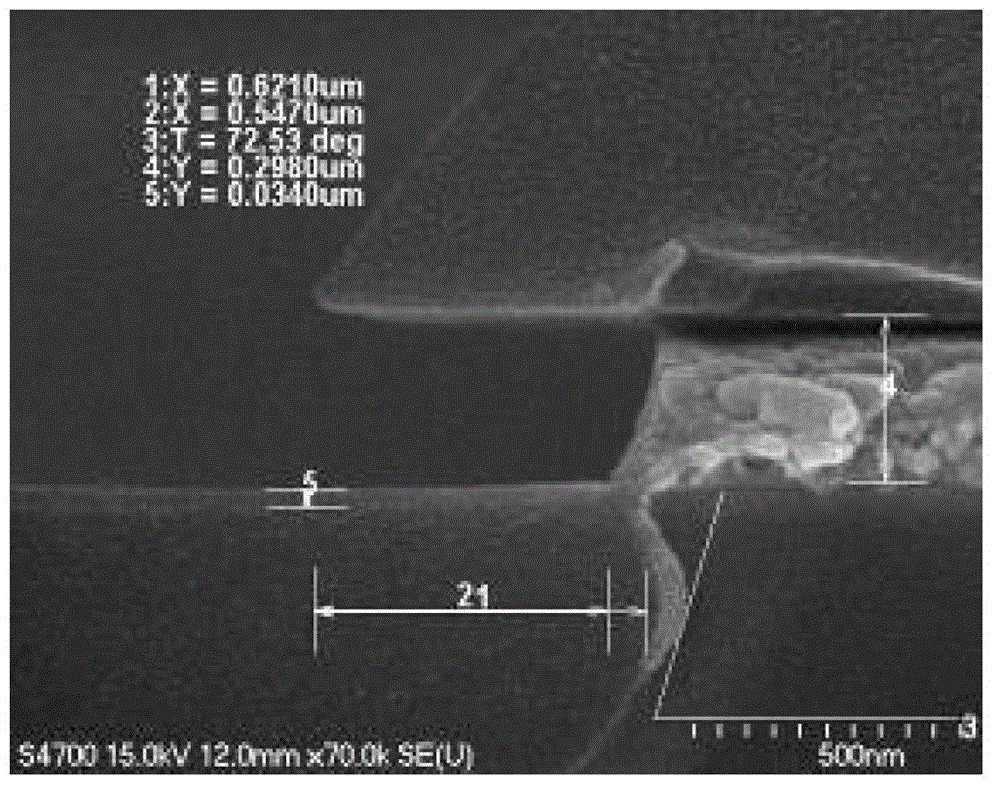

Mosfet having a high stress in the channel region

InactiveUS20090174002A1Improve etch uniformityEasy to controlTransistorSemiconductor/solid-state device manufacturingDopantMOSFET

Source and drain extension regions are selectively removed by a dopant concentration dependent etch or a doping type dependent etch, and an embedded stress-generating material such as SiGe alloy or a Si:C alloy in the source and drain extension regions is grown on a semiconductor substrate. The embedded stress-generating material may be grown only in the source and drain extension regions, or in the source and drain extension regions and in deep source and drain regions. In one embodiment, an etch process that removes doped semiconductor regions of one conductivity type selective to doped semiconductor regions of another conductivity type may be employed. In another embodiment, a dopant concentration dependent etch process that removes doped semiconductor regions irrespective of the conductivity type selective to undoped semiconductor regions may be employed.

Owner:GLOBALFOUNDRIES INC

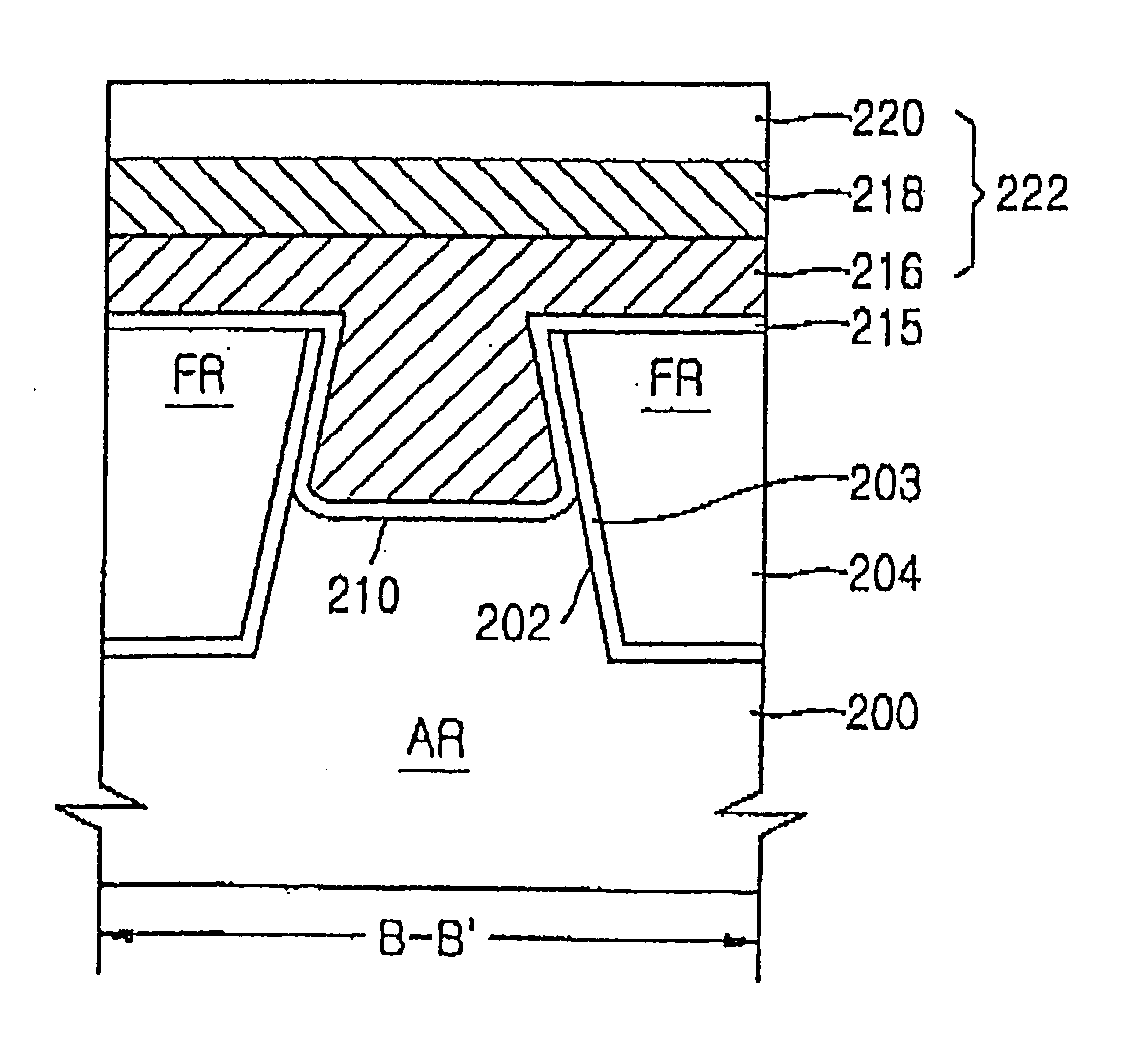

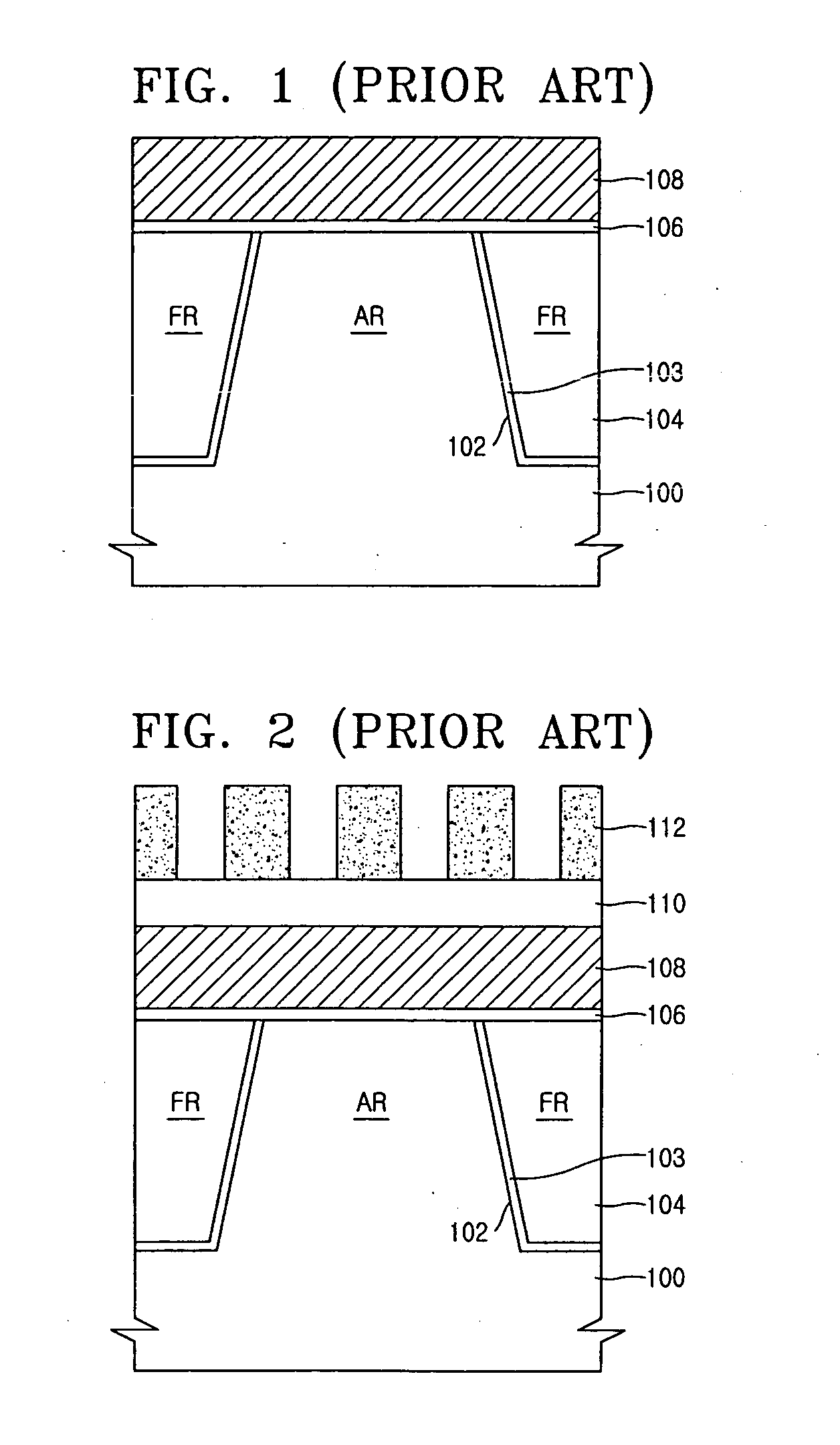

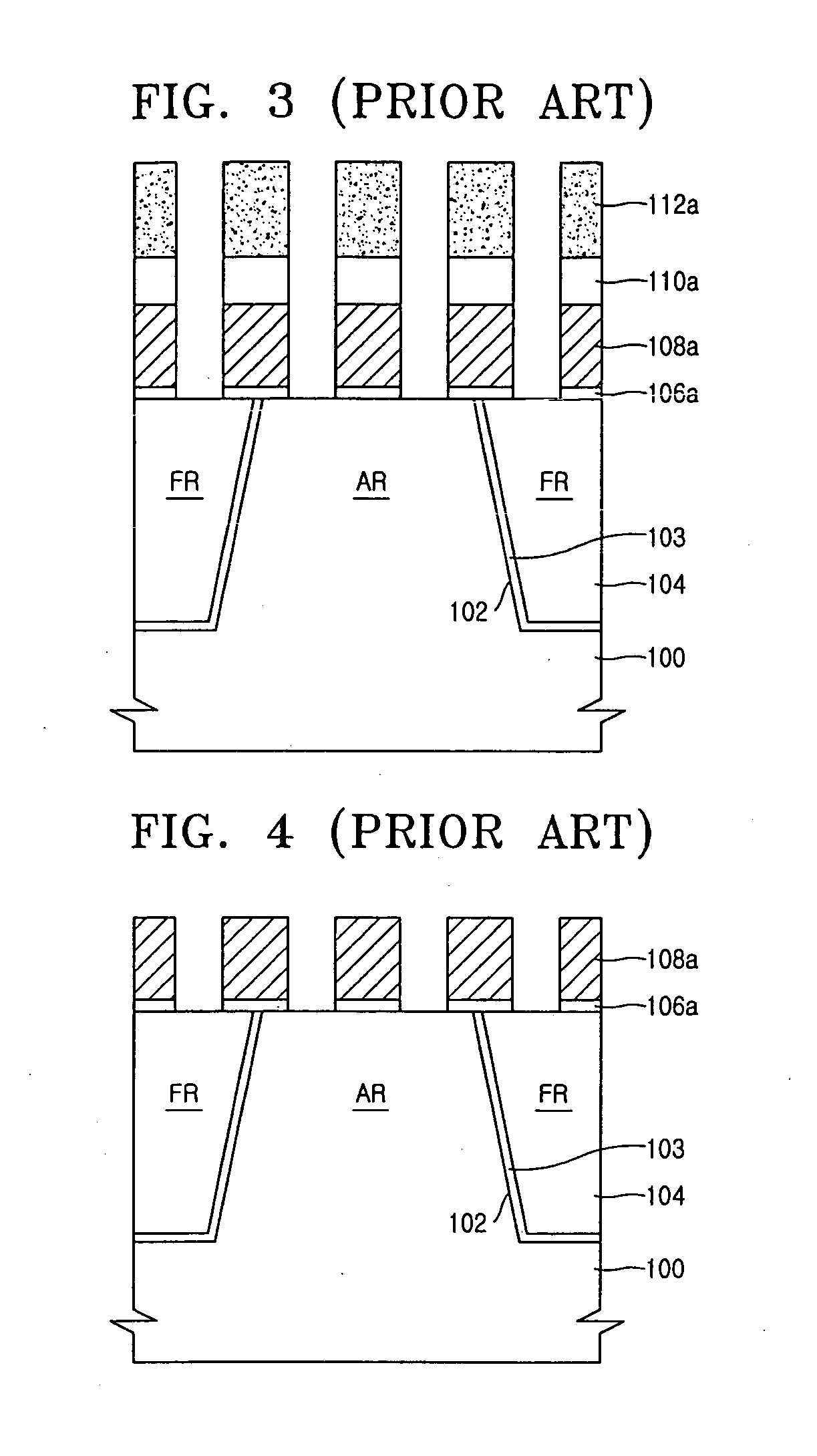

Method of fabricating a recess channel array transistor using a mask layer with a high etch selectivity with respect to a silicon substrate

ActiveUS20050136616A1Easily controlGood etch uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsEtching selectivity

A method of fabricating a recess channel array transistor. Using a mask layer pattern having a high etch selectivity with respect to a silicon substrate, the silicon substrate and an isolation insulating layer are etched to form a recess channel trench. After forming a gate insulating layer and a recess gate stack on the recess channel trench, a source and a drain are formed in the silicon substrate adjacent to both sidewalls of the recess gate stack, thereby completing the recess channel array transistor. Because the mask layer pattern having the high etch selectivity with respect to the silicon substrate is used, a depth of the recess channel trench is easily controlled while good etching uniformity of the silicon substrate is obtained.

Owner:SAMSUNG ELECTRONICS CO LTD

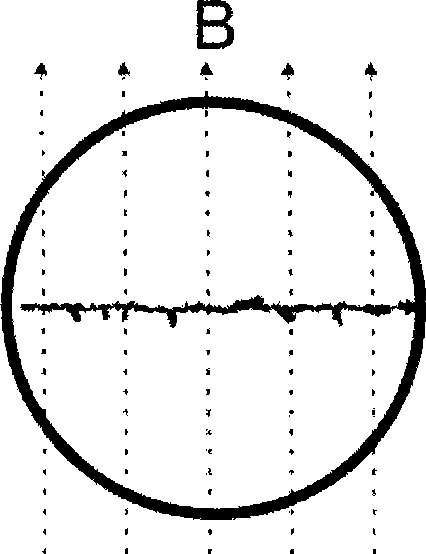

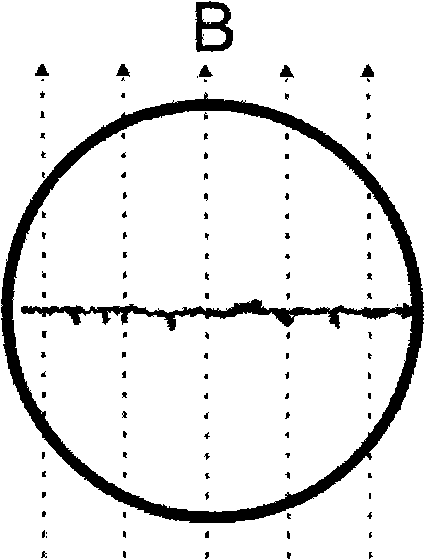

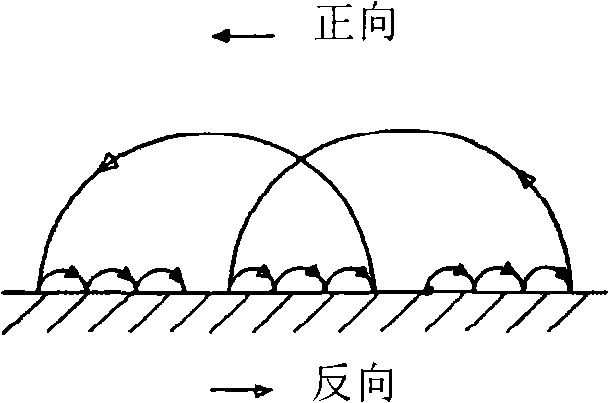

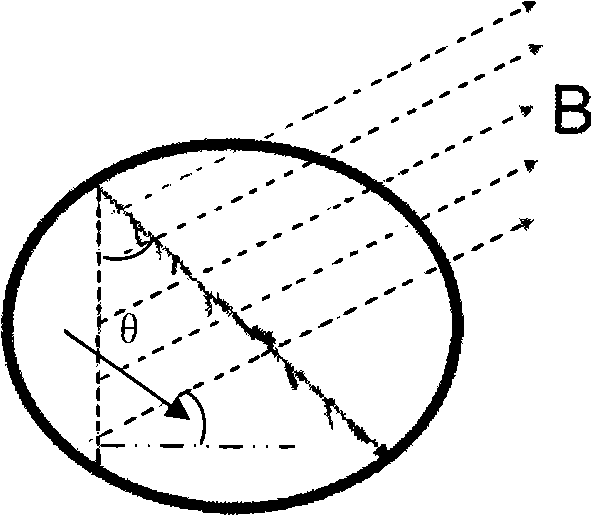

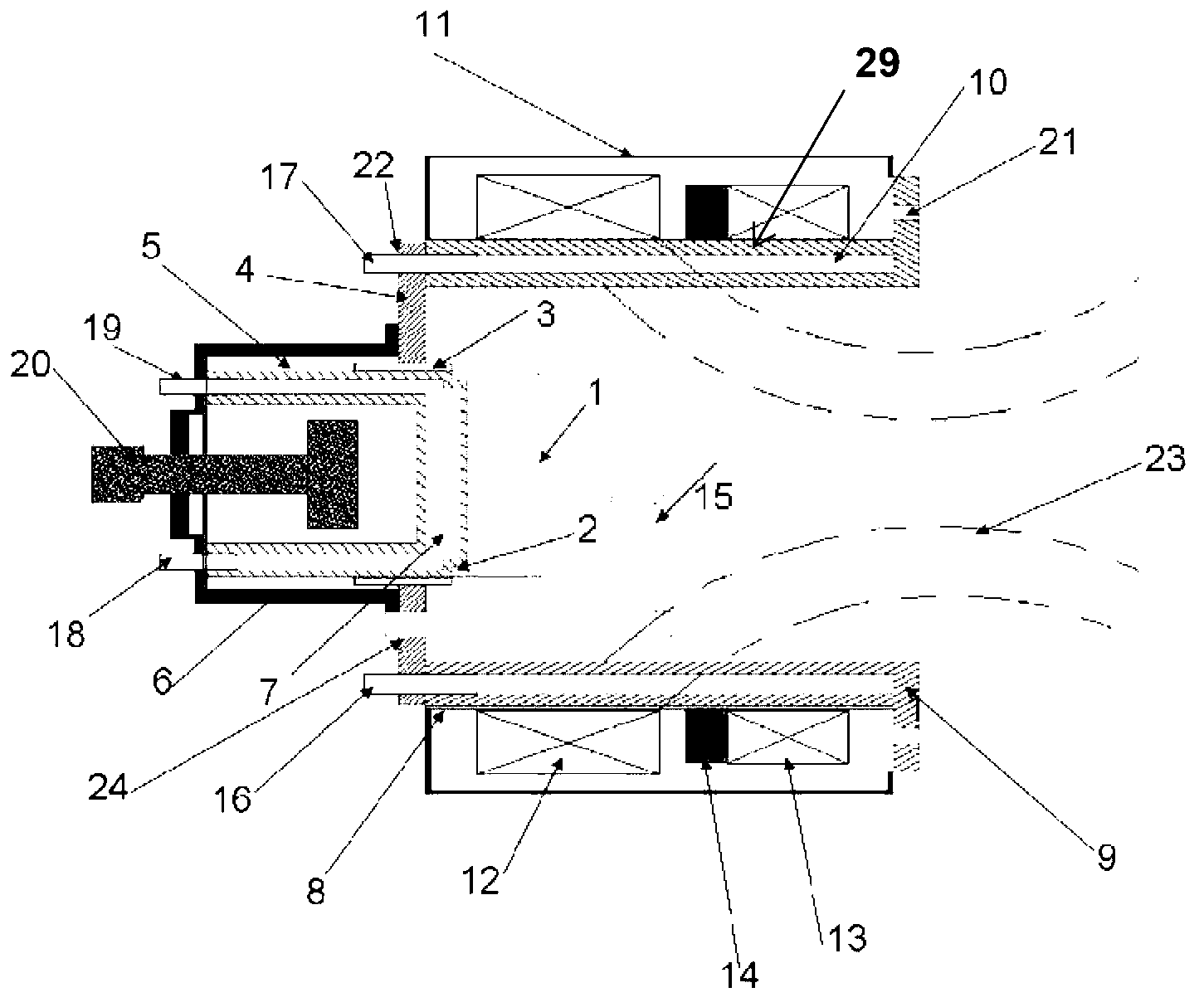

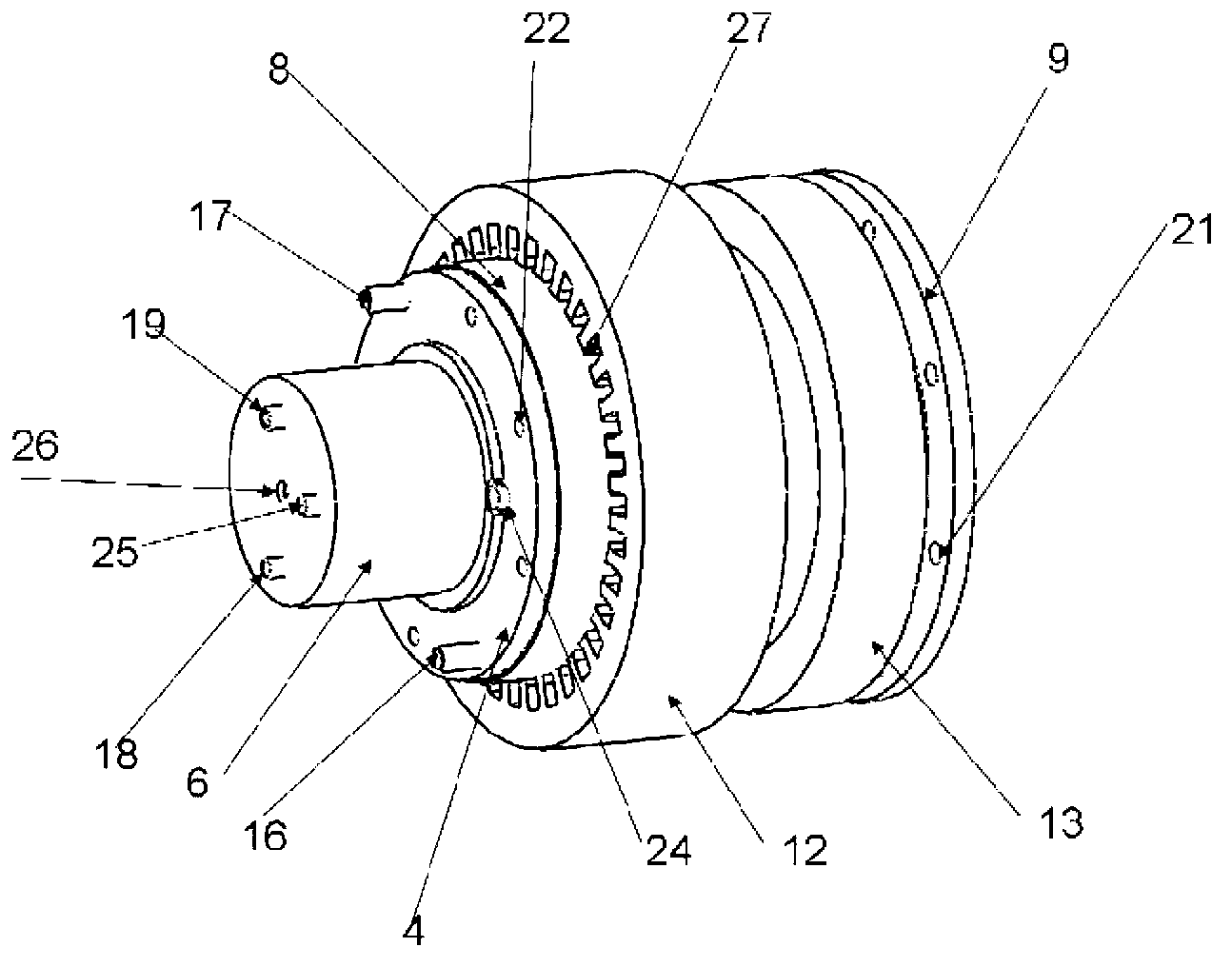

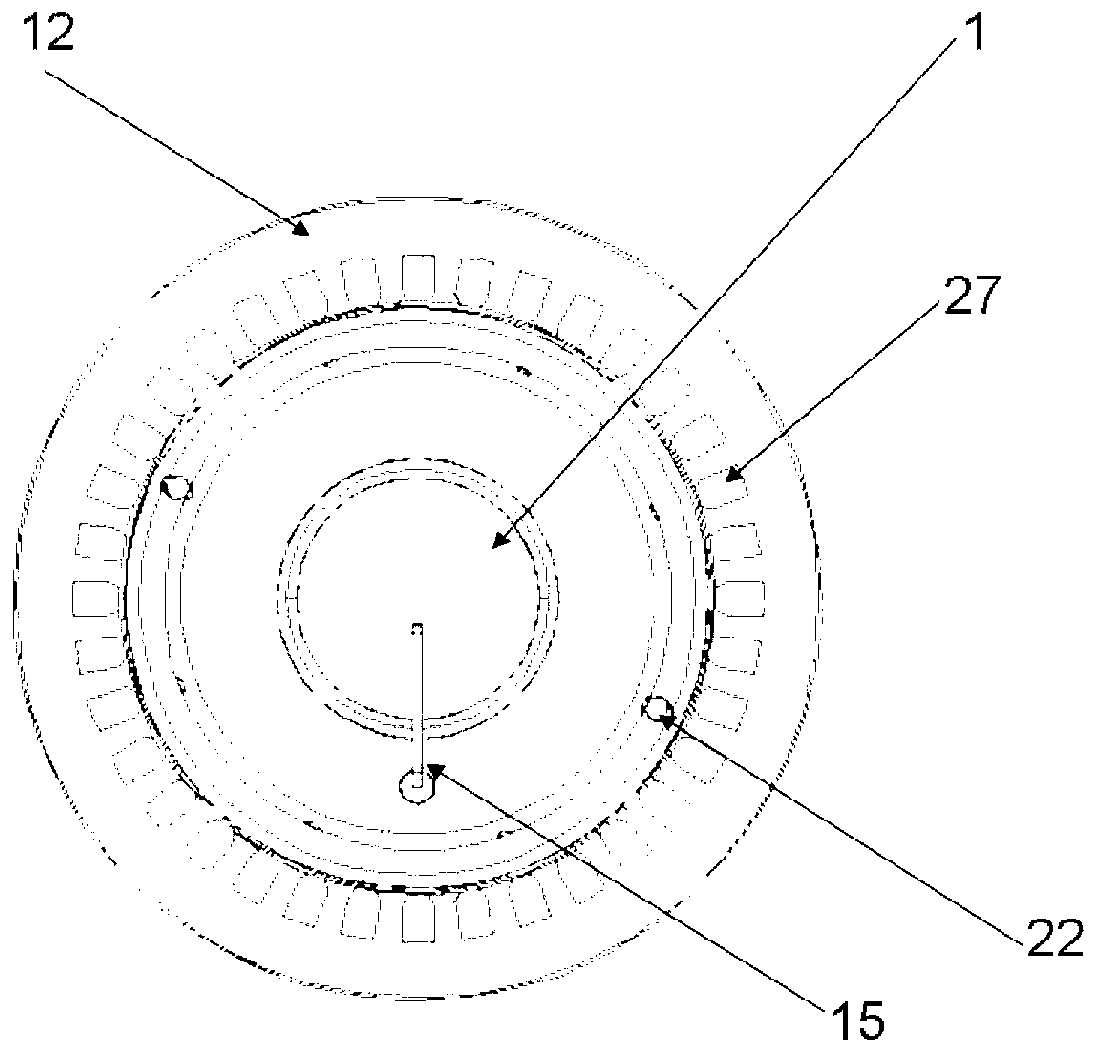

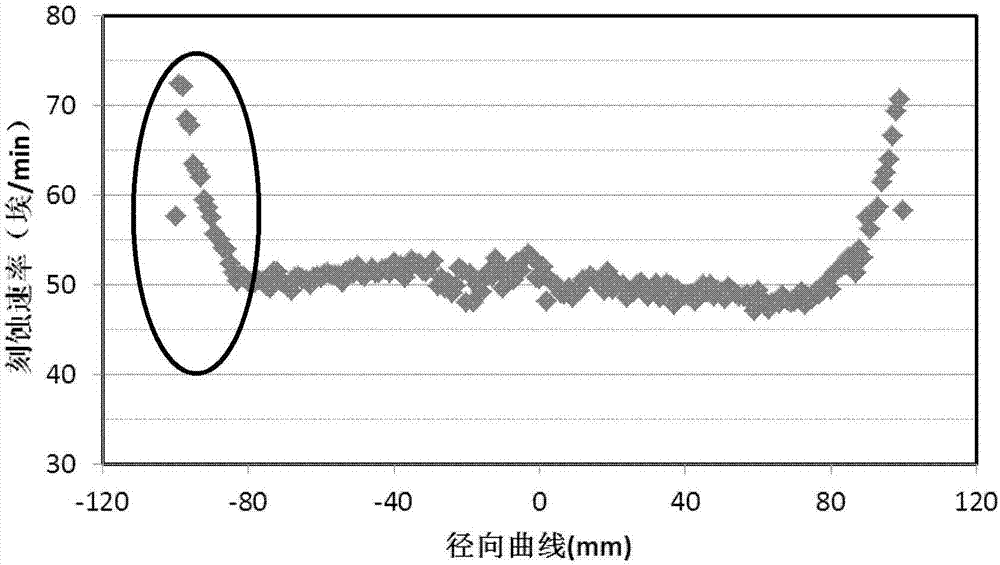

Multi-mode programmable arc ion plating apparatus controlled by rotary lateral magnetic field

InactiveCN101363116AControl speedImprove job stabilityVacuum evaporation coatingSputtering coatingPhysicsElectromagnetic coil

The invention relates to the field of film preparation, in particular to an arc ion plating device which controls arc point movement by a rotary magnetic field and is controlled by a rotary transverse magnetic field with the multi-mode programmable modulation. The device is provided with a target material, a rotary magnetic field generating device, an electromagnetic coil, an insulating bush, a flange, a vacuum chamber and a matrix holder, wherein, the matrix holder and the target material are arranged inside the vacuum chamber, the front face of the target material is opposite to the matrix holder, the back of the target material is provided with electromagnetic coils, the rotary magnetic field generating device arranged outside the vacuum chamber is sheathed on a flange sleeve or an furnace body tube around the target material, and insulation is used for protection between the rotary magnetic field generating device and the flange sleeve or the furnace body tube. By controlling the arc point movement by the rotary transverse magnetic field with the multi-mode programmable modulation, the arc ion plating device can improve the discharge mode and the operating stability of the arc point, improve the etching uniformity and the utilization rate of the target material and reduce the large particle emission of the target material. The arc ion plating device is used for preparing high-quality films and functional films and expanding the application range of the arc ion plating.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

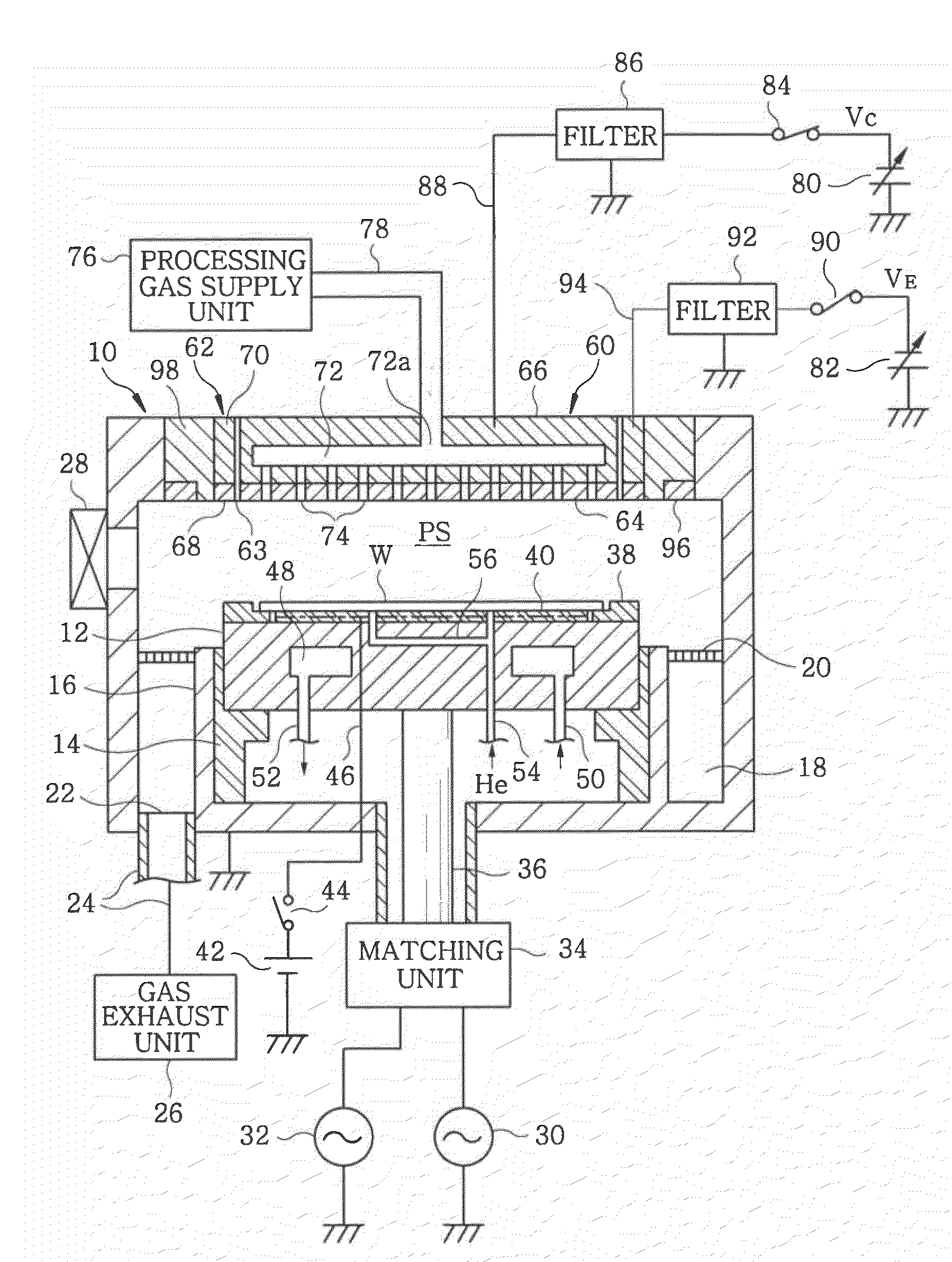

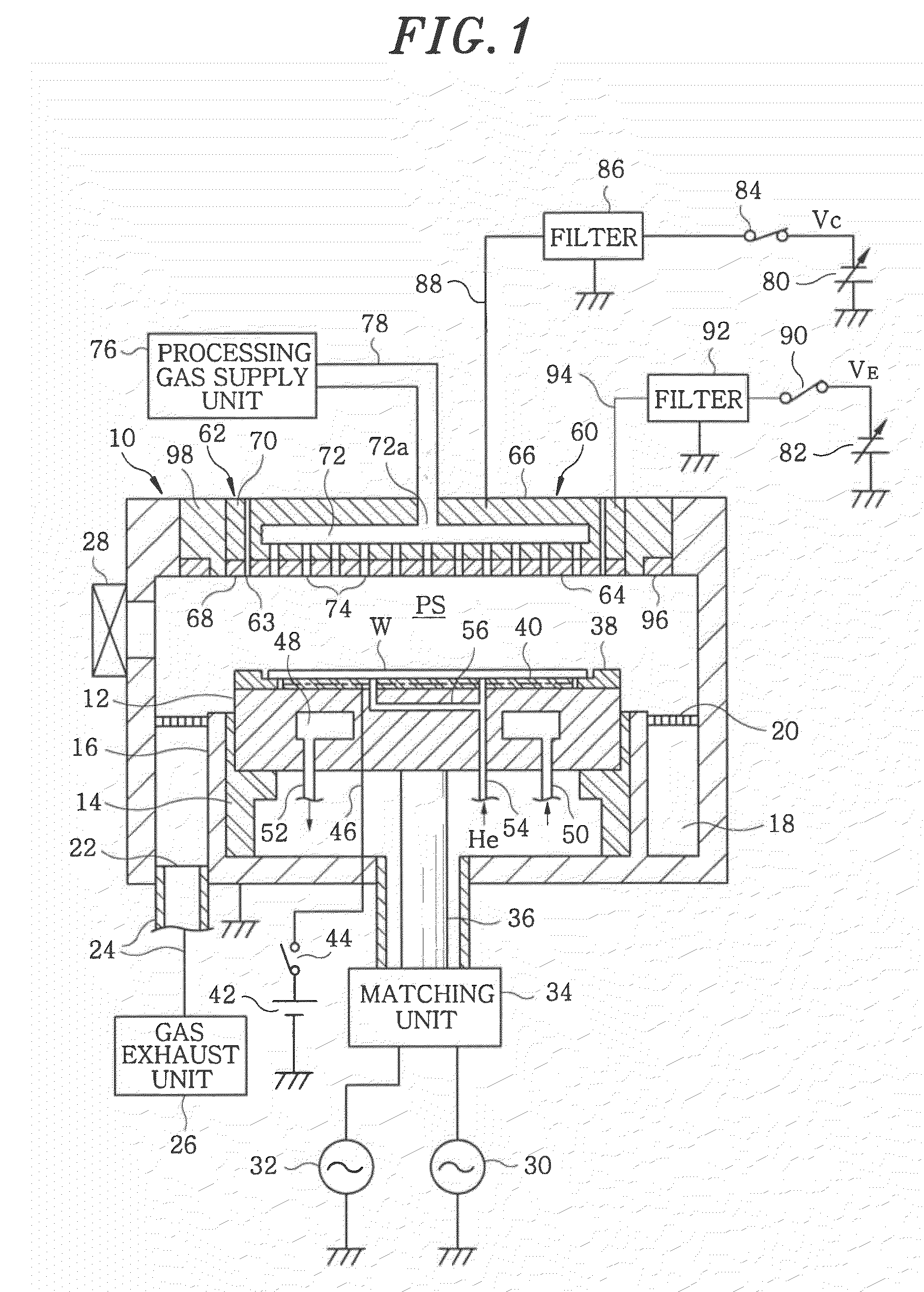

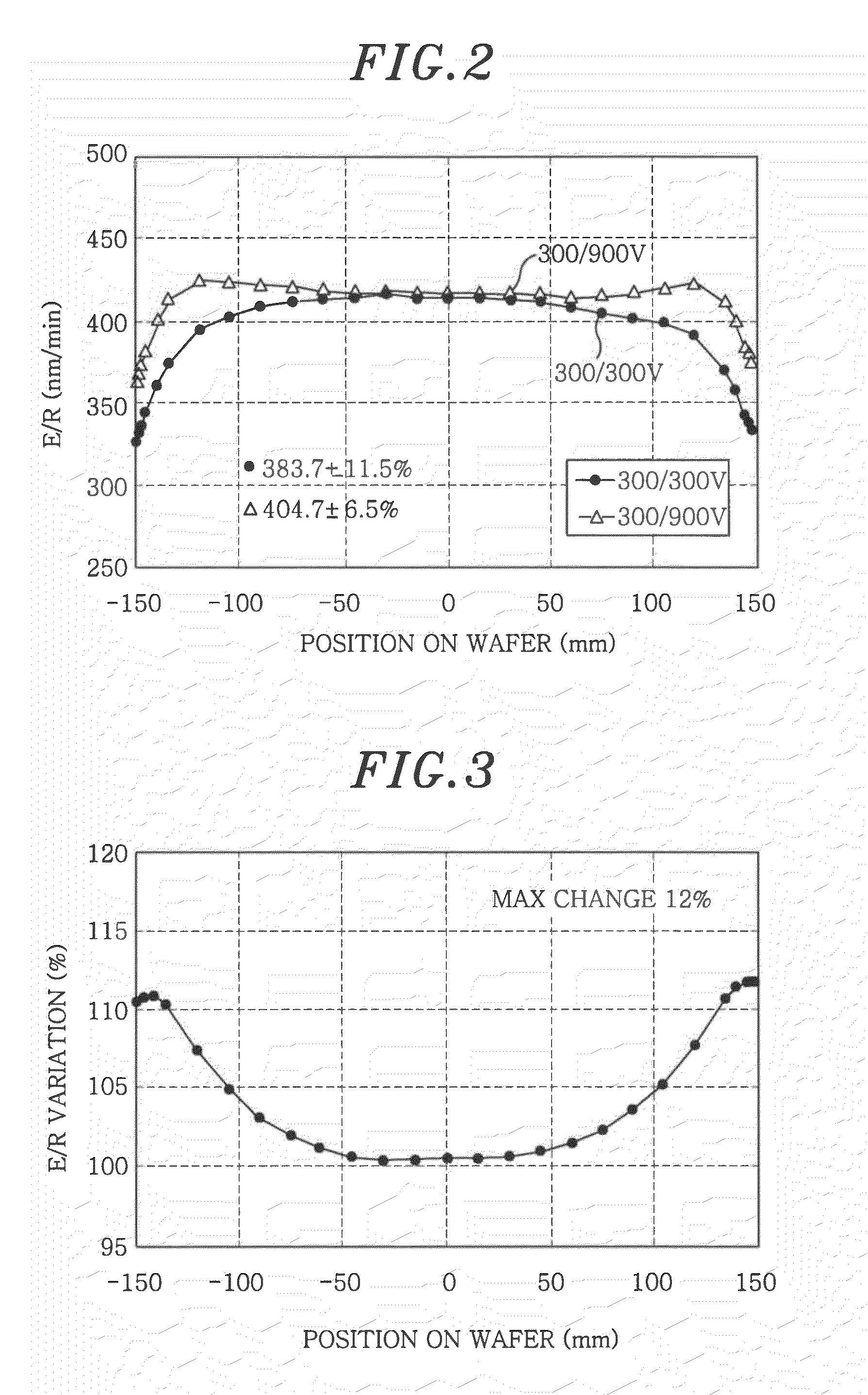

Plasma processing apparatus and plasma etching method

ActiveUS20090242515A1Improve uniformityImprove etch uniformityElectric discharge tubesDecorative surface effectsRf dischargeRadio frequency

A plasma processing apparatus includes an inner upper electrode provided to face a lower electrode mounting thereon a substrate, an outer upper electrode provided in a ring shape at a radially outside of the inner upper electrode and electrically isolated from the inner upper electrode in a vacuum evacuable processing chamber and a processing gas supply unit for supplying a processing gas into a processing space between the inner and the outer upper electrode and the lower electrode. A radio frequency (RF) power supply unit is also provide to apply a RF power to the lower electrode or the inner and the outer upper electrode to generate a plasma of the processing gas by RF discharge. A first and a second DC power supply unit are provided to apply a first and a second variable DC voltage to the inner upper electrode, respectively.

Owner:TOKYO ELECTRON LTD

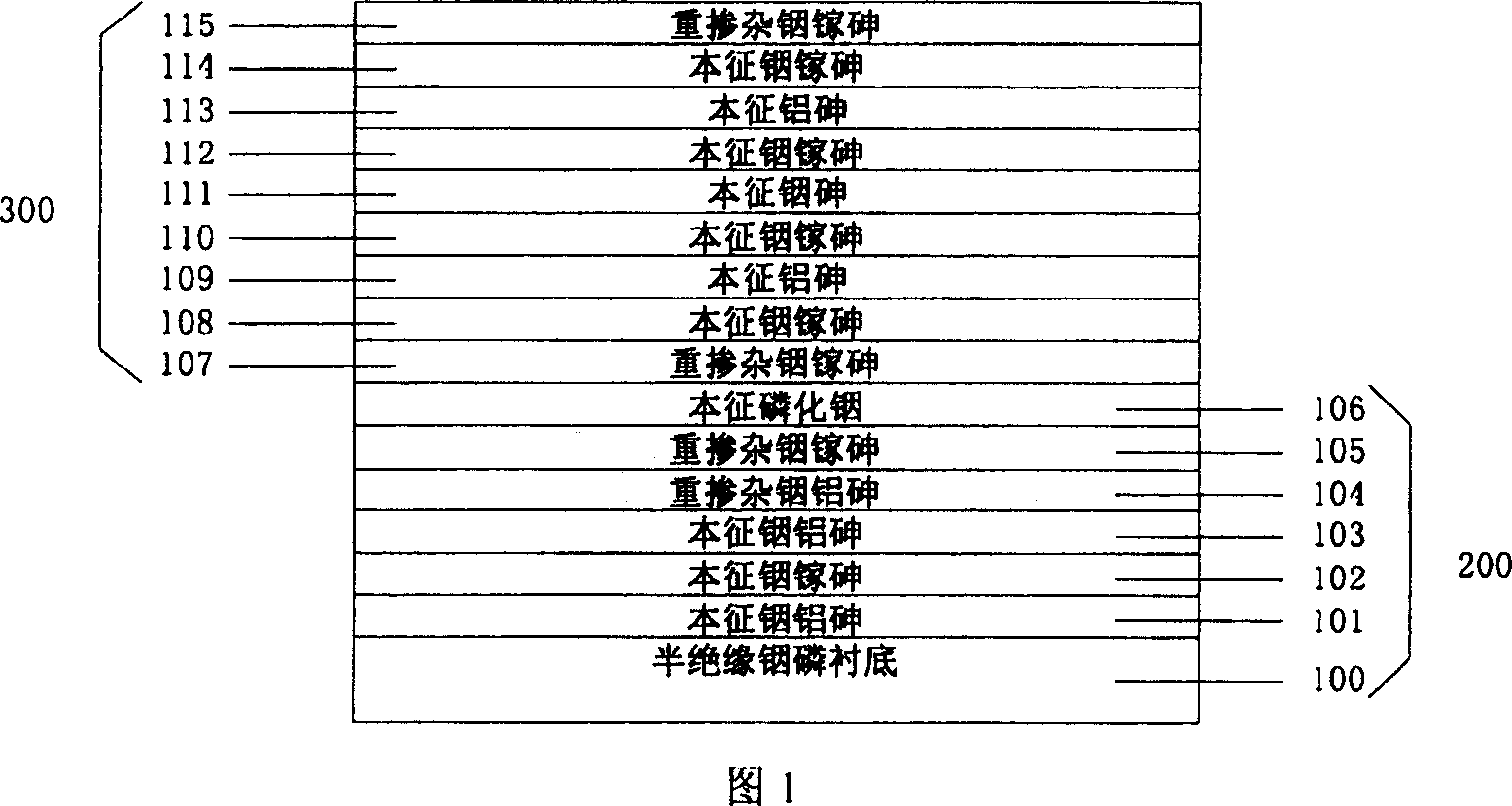

Method for realizing RTD and HEMT single chip integration using dry etching technology

InactiveCN101064275AAvoid damageRaise the threshold voltageSemiconductor/solid-state device manufacturingSource areaMetal electrodes

A method of realizing integrating of RTD and HEMT using dry etching technique includes: Vegetating typical HEMT material structure and RTD material structure on the underlay; photoengraving the pattern of RTD emitting area to produce AuGeNi metal layer to form RTD metal emitting pole; photoengraving to form source area; photoengraving the source electrode and drain electrode of HEMT; anneal in high temperature; photoengraving the HEMT bar pattern to corrode part of the adulteration hat layer; a layer of passivation medium is deposited on surface of device; photoengraving the HEMT gate electrode pattern to generate TiPtAu metal as the gate electrode of HEMT element; photoengraving the down-lead hole; photoengraving the down-lead interlinkage area, vaporizing or sputtering thick TiAlTiAu metal electrode, and then it is peeled off.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

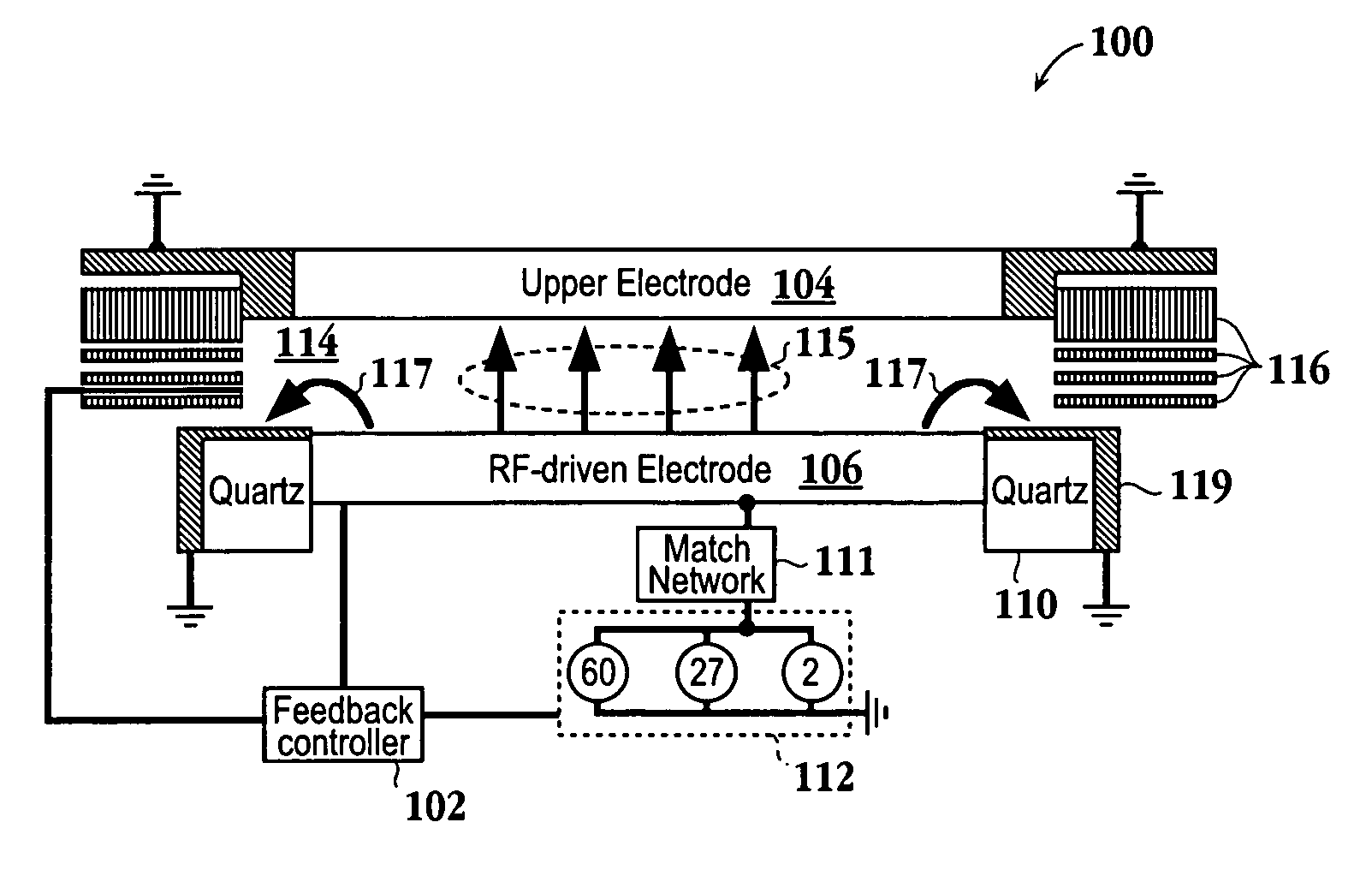

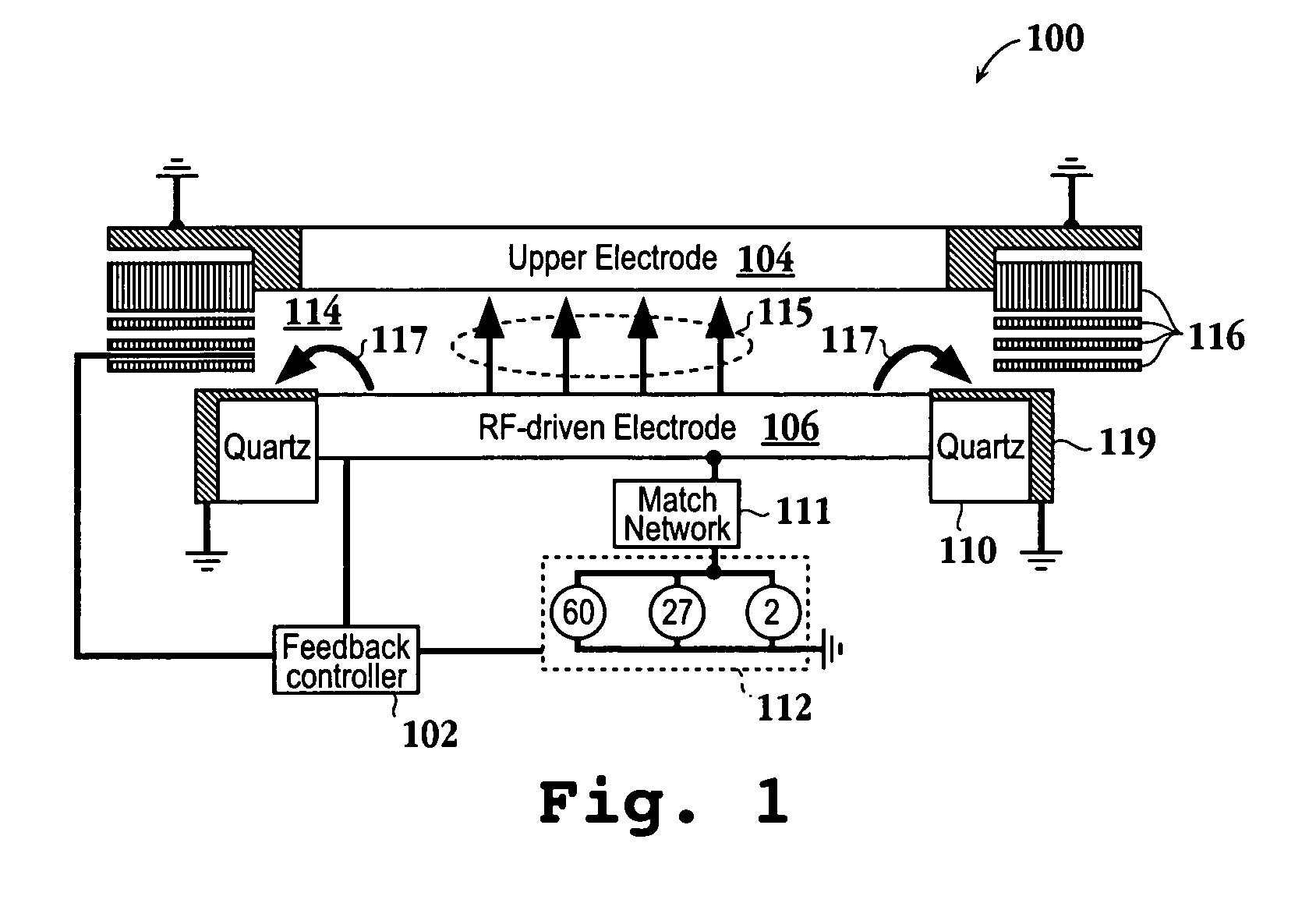

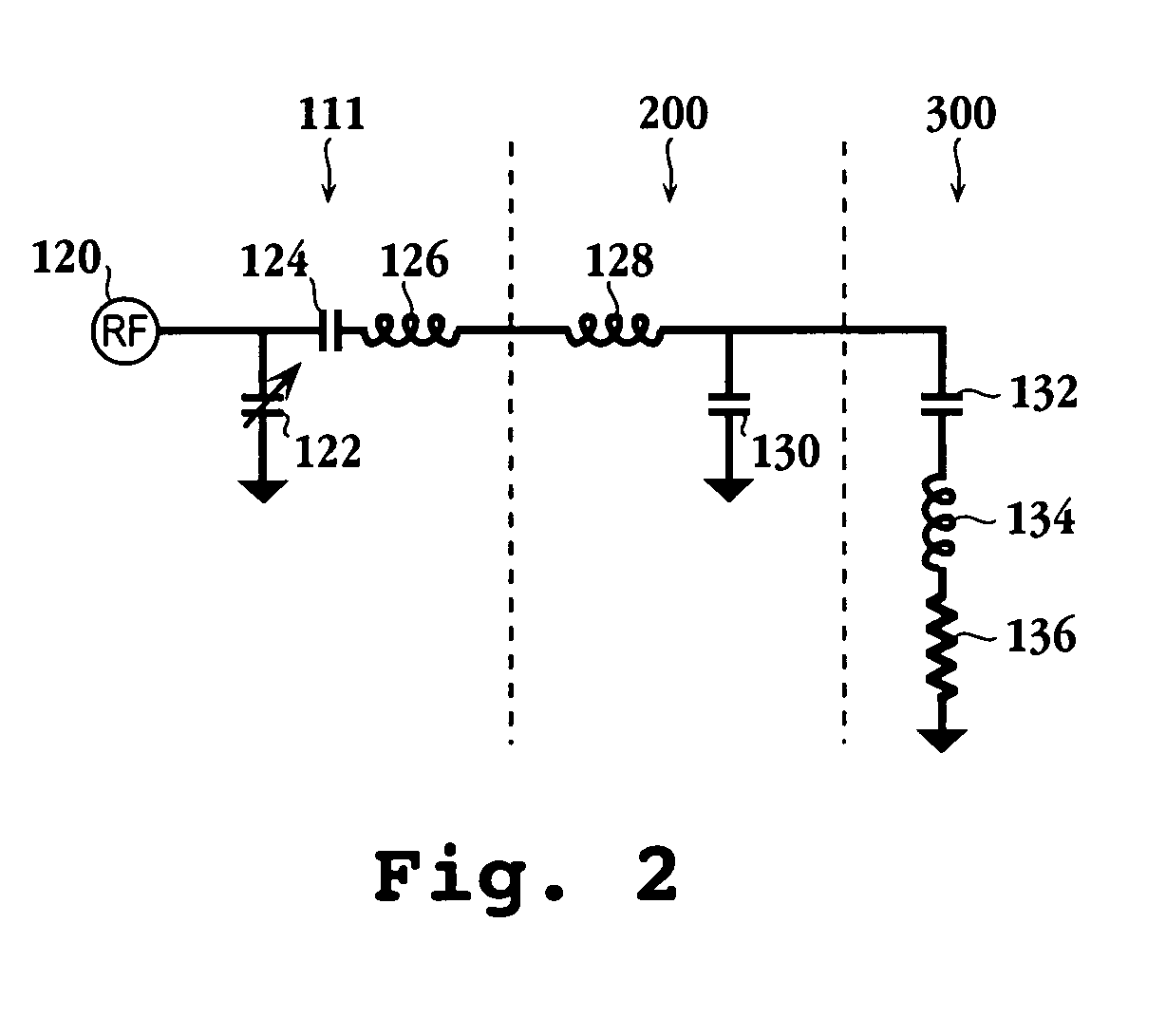

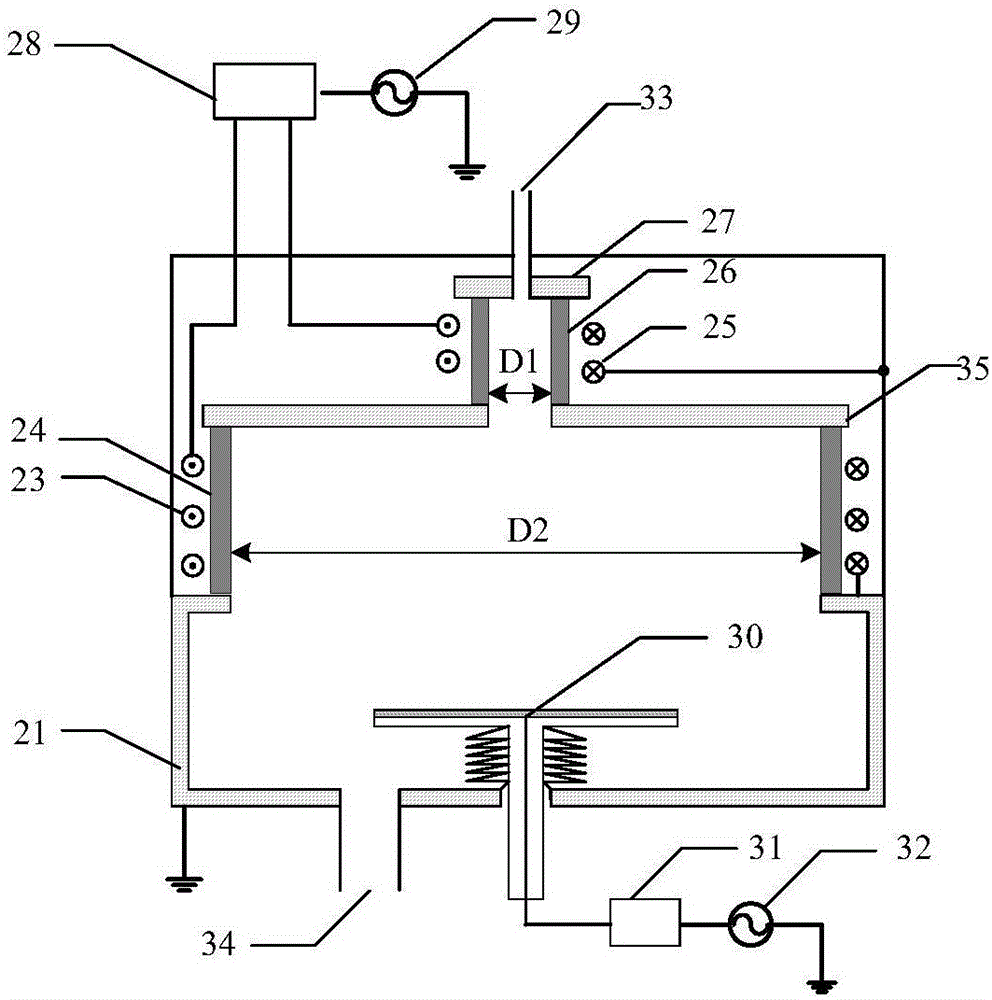

Apparatus and method for controlling etch uniformity

ActiveUS8674255B1Improve etch uniformityElectric discharge tubesElectric arc lampsRadio frequencyPlasma processing

A plasma processing system is provided. The plasma processing system includes a radio frequency (RF) power generator configured to have a tunable frequency power output, the frequency output being adjustable within a range. A processing chamber having a bottom electrode and a top electrode is included. A plasma region being defined between the bottom and top electrodes and the processing chamber receives RF power from the RF power generator. A match network is coupled between the RF power generator and the processing chamber. The match network has a first tunable element and a second tunable element. The first tunable element adjusts a split between a first grounding pathway defined within an inner region of the plasma region and a second grounding pathway defined within an outer region of the plasma region. The second tunable element adjusts a load delivered to the processing chamber from the power generator.

Owner:LAM RES CORP

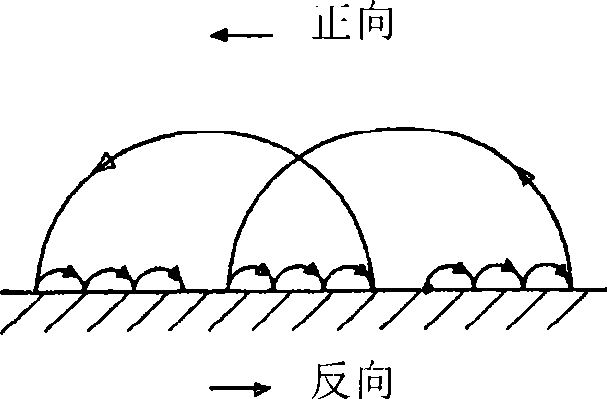

Arc source of dynamic controlled arc ion plating

InactiveCN101358328AImprove discharge formImprove job stabilityVacuum evaporation coatingSputtering coatingTarget surfaceIon plating

The invention relates to the field of film preparation, in particular to an arc ion plating arc source which controls the movement of arc pit with dynamic magnetic field. The dynamic controlled arc ion plating arc source is provided with a dynamic control magnetic field generator, a target and a target base; the target is arranged on the target base; the dynamic control magnetic field generator consists of a main control magnetic field generator and an auxiliary magnetic field generator; the main control magnetic field generator is arranged behind the target and is coaxial with the target; the auxiliary magnetic field generator is arranged around the main control magnetic field generator. In the invention, arc-shaped magnetic fields which are dynamically distributed are formed on the target surface with the help of the cooperation of the two magnetic field generators, so as to improve the discharge form and work stability of the arc pit, control the movement track of the arc pit, improve the erosion evenness and target utility rate of the target, reduce the emission of large target particles and prepare high-quality film.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

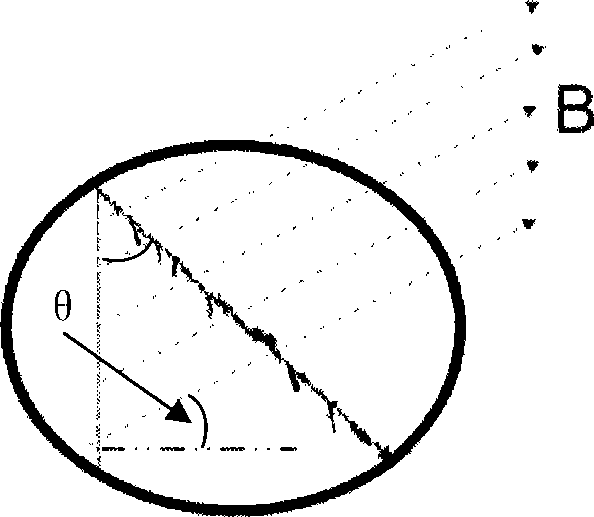

Compact and efficient cold cathode arc source of quasi diffusion arc

ActiveCN102936717AFast movementShort stayVacuum evaporation coatingSputtering coatingPhysicsSource structure

The invention relates to the technical field of preparation of films and coatings, particularly to a compact and efficient cold cathode arc source of a quasi diffusion arc. The cold cathode arc source is composed of an arc source head and a control magnetic field group, wherein the arc source head comprises a target, a target base, a target base shielding cover, a target base plate, an arc striking device and a permanent magnet device; the control magnetic field group comprises a flange sleeve, a flange sleeve insulating bush, a dipolar radial rotating magnetic filed generating device, an axial focusing guiding magnetic field generating device, a coaxial focusing magnetic field magnetic yoke and a flange sleeve shielding cover; and the arc source head is connected with the bottom of the flange sleeve through the target base plate to form a whole arc source structure, and connected with a finance through a flange arranged in front of the flange sleeve. Arc spots are distributed on the whole target surface under the comprehensive action of a certain magnetic field intensity and rotary frequency, the power density of the arc spots is reduced, the quasi diffusion arc state is achieved, launch of large grains is reduced, simultaneously, purified high-density plasmas are extracted through the axial focusing guiding magnetic field, and the transmission efficiency is improved.

Owner:WENZHOU POLYTECHNIC

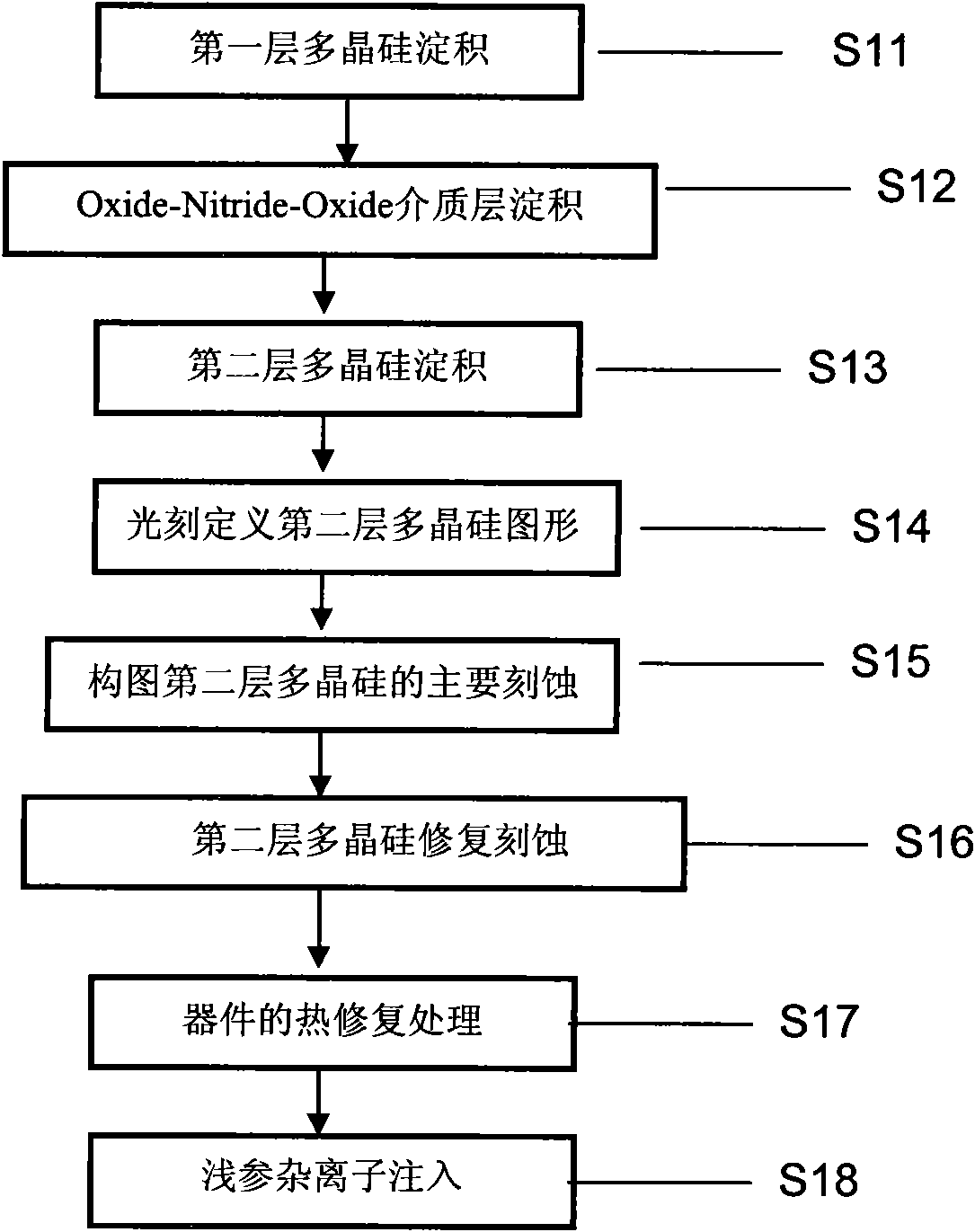

Method for repairing and etching polysilicon

InactiveCN101667542AGuaranteed reliabilityImprove yieldSemiconductor/solid-state device manufacturingMicroelectronicsPhysics

The invention discloses a method for repairing and etching polysilicon, which belongs to the technical field of microelectronics manufacturing. The method provided by the invention is used for repairing and etching the polysilicon forming a control grid in an EEPROM and is characterized by only adopting a mixed chemical gas of O2 and CF4 for plasma etching. The etching method is a chemical etchingand has a extremely low substrate silicon etching speed, thereby avoiding damaging a pn junction between a source electrode and a substrate and a pn junction between a drain electrode and the substrate and consequently ensuring the reliability of the EEPEOM device and improving the yield of product.

Owner:SEMICON MFG INT (SHANGHAI) CORP

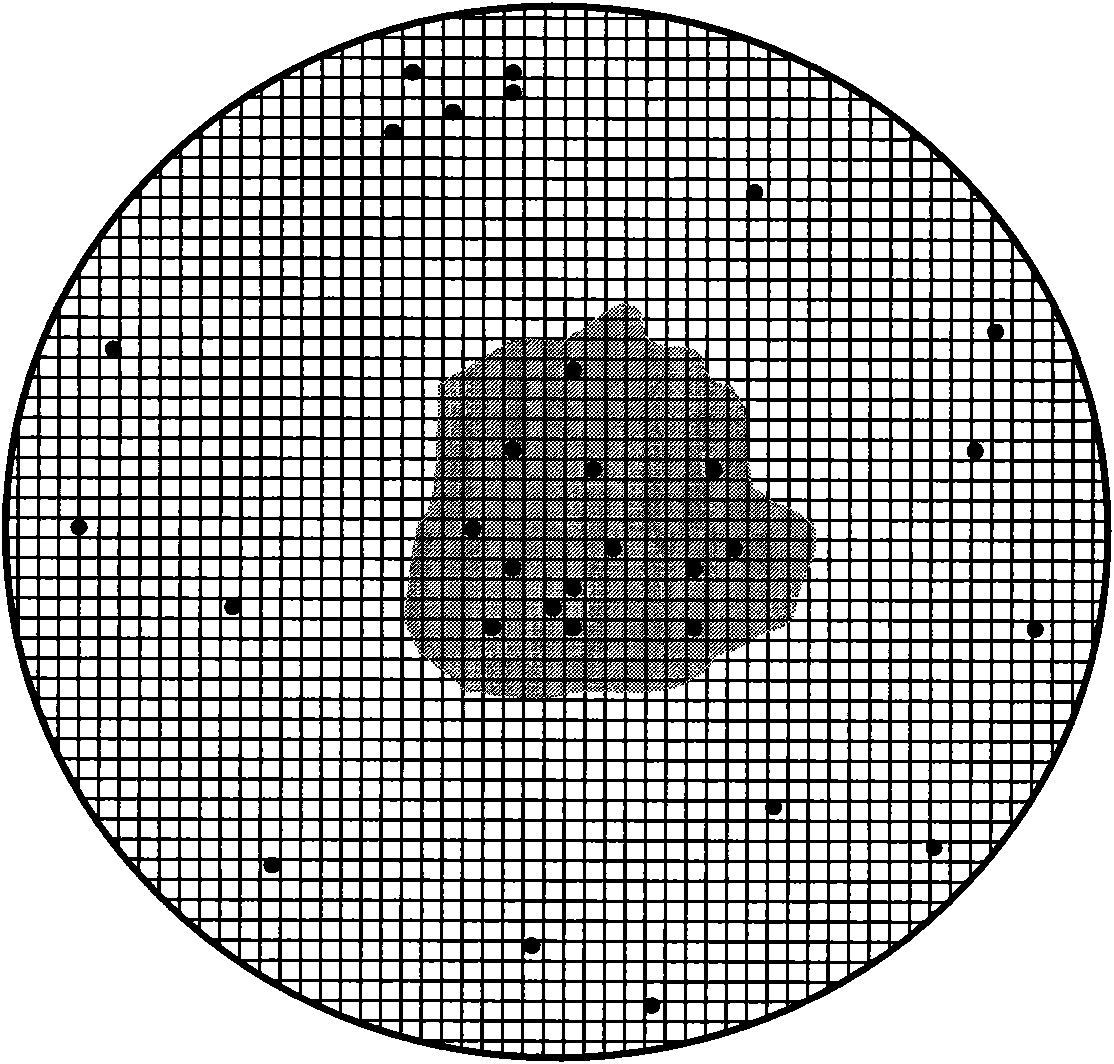

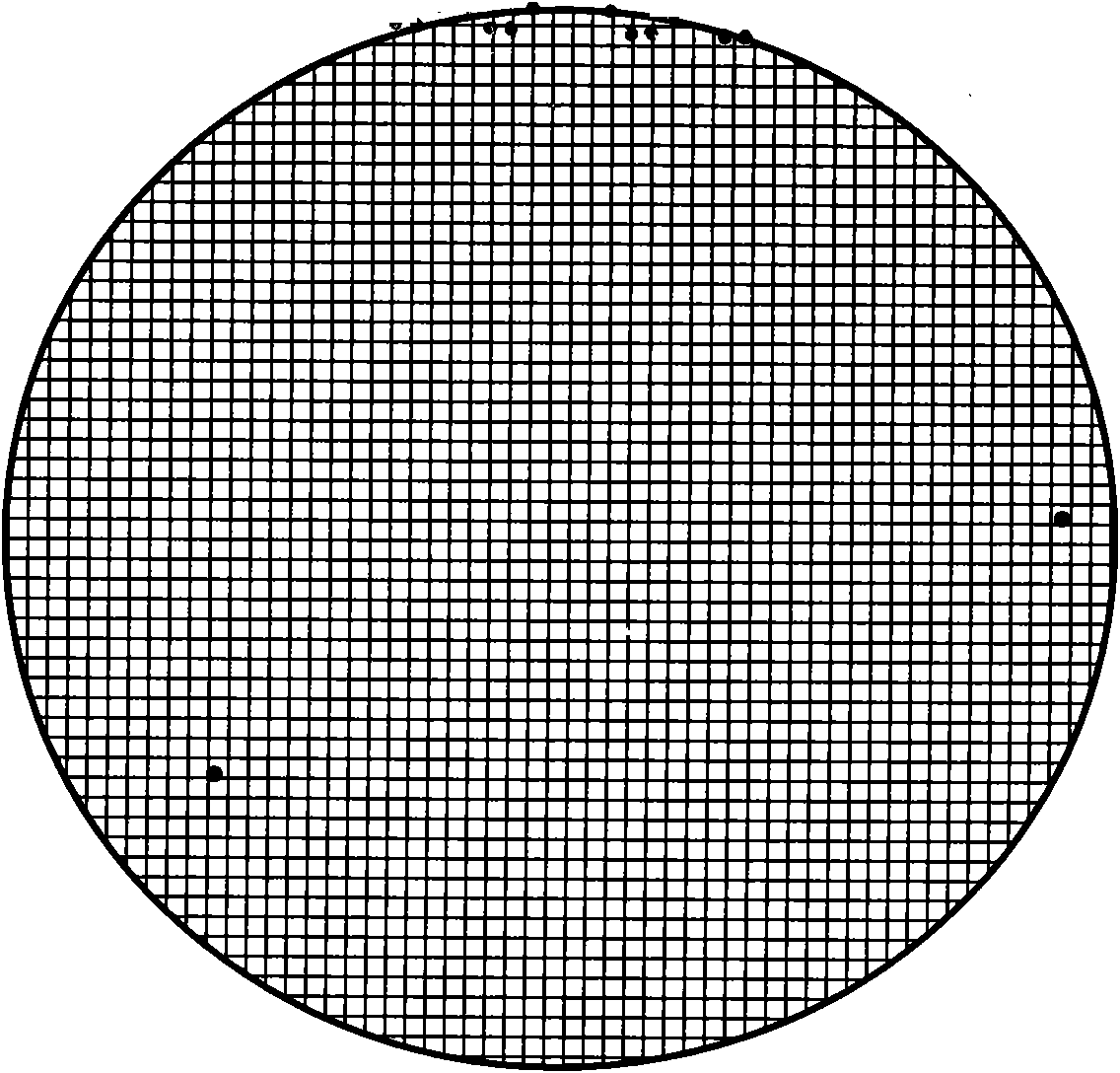

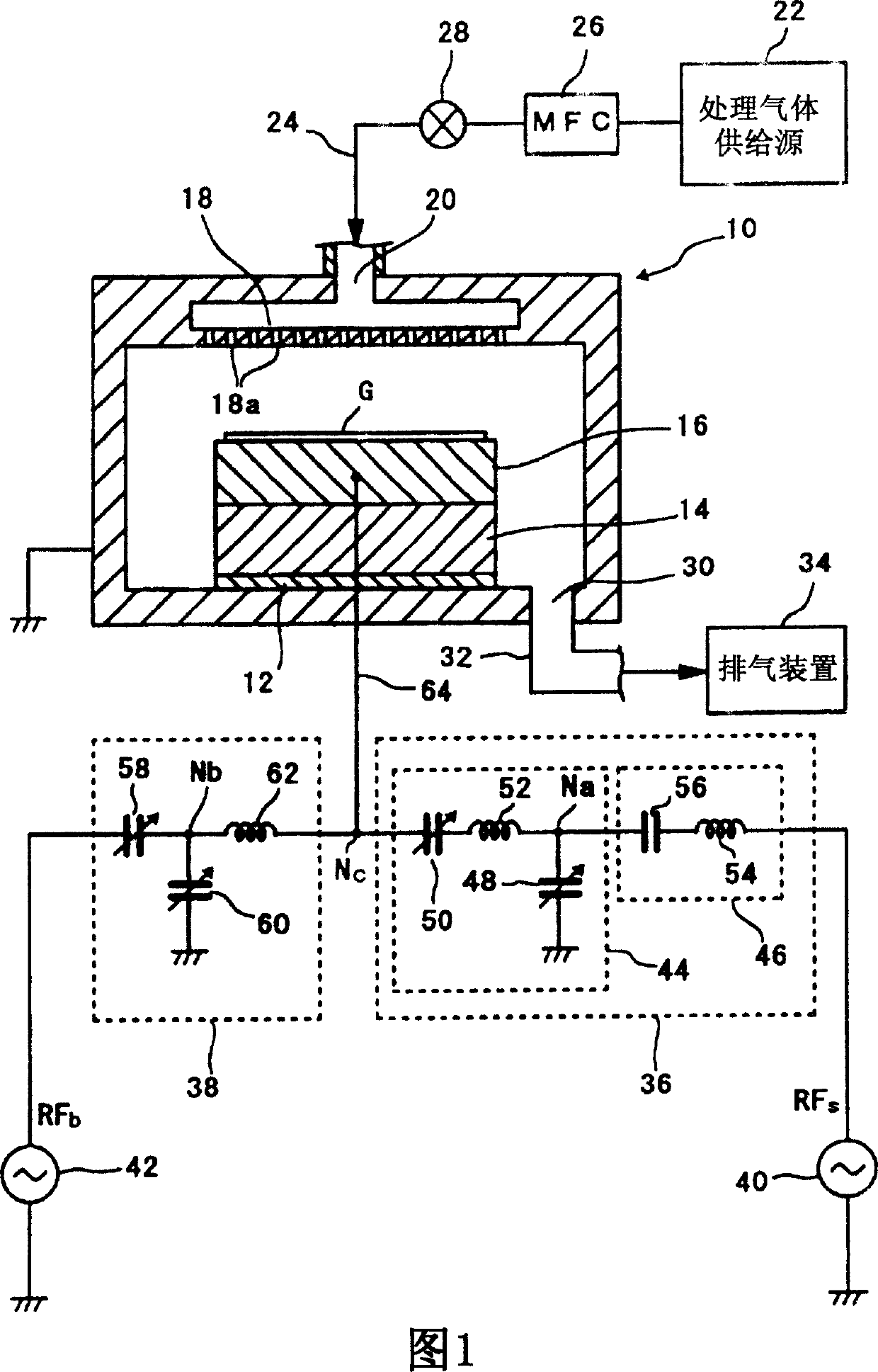

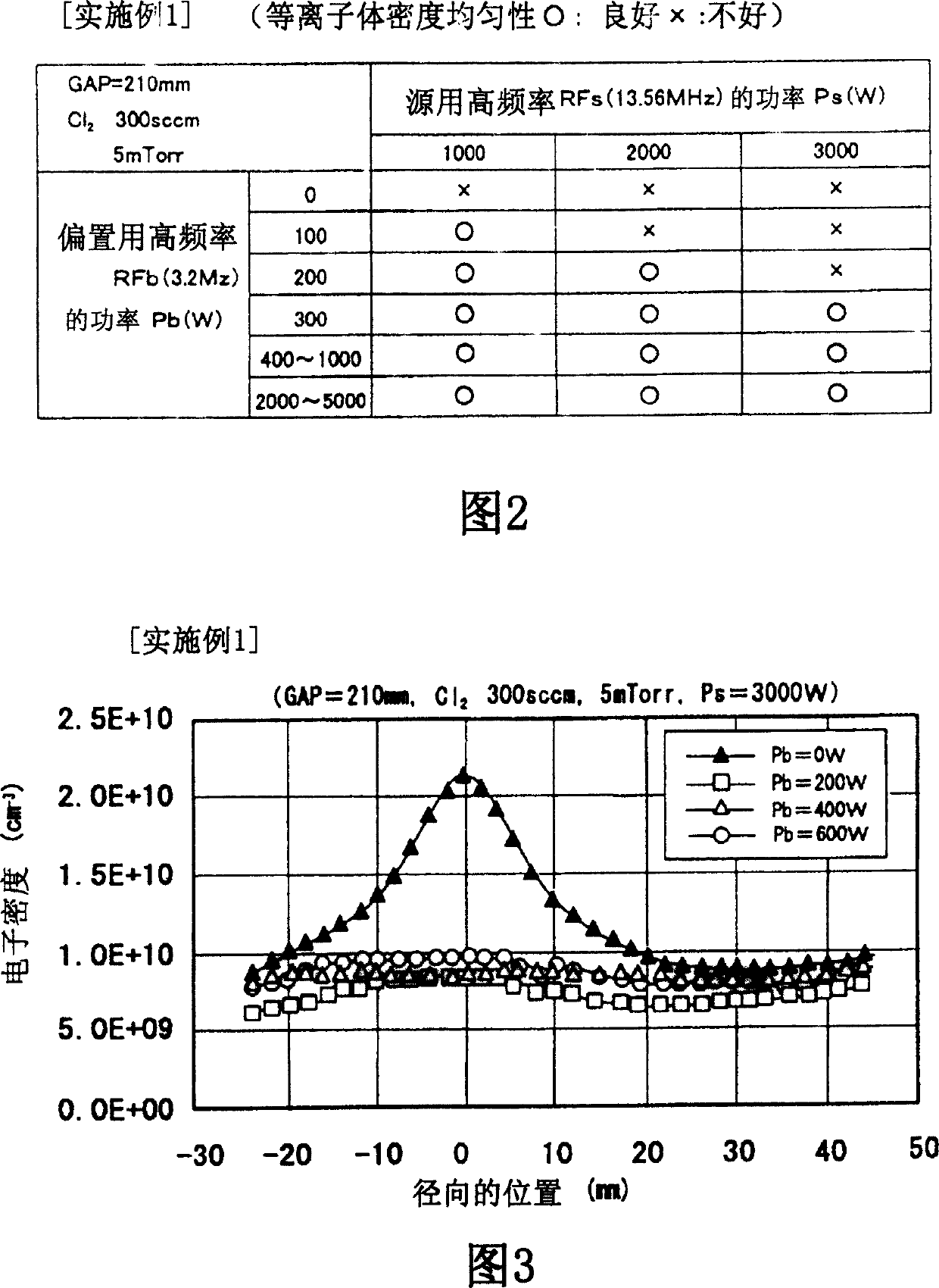

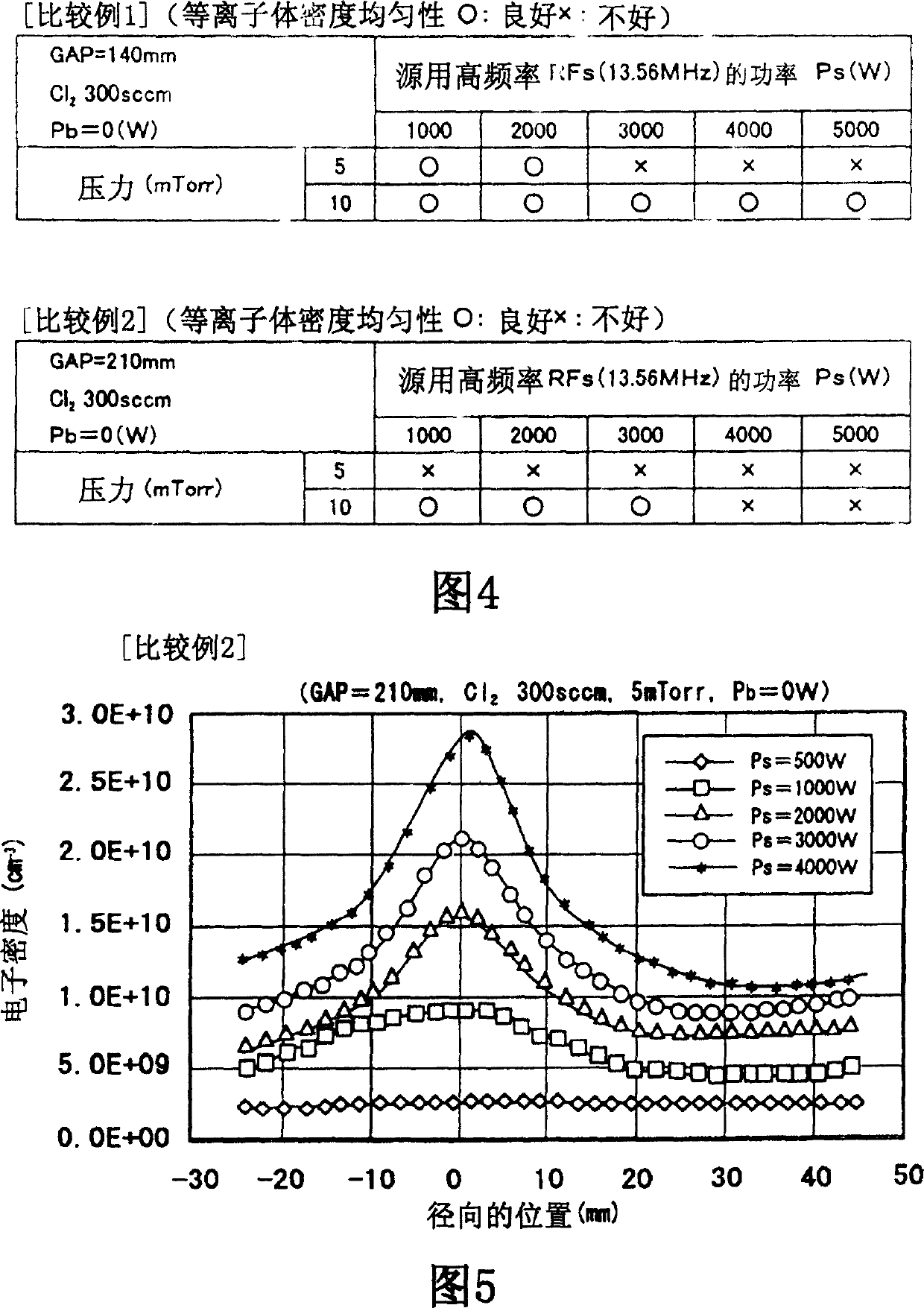

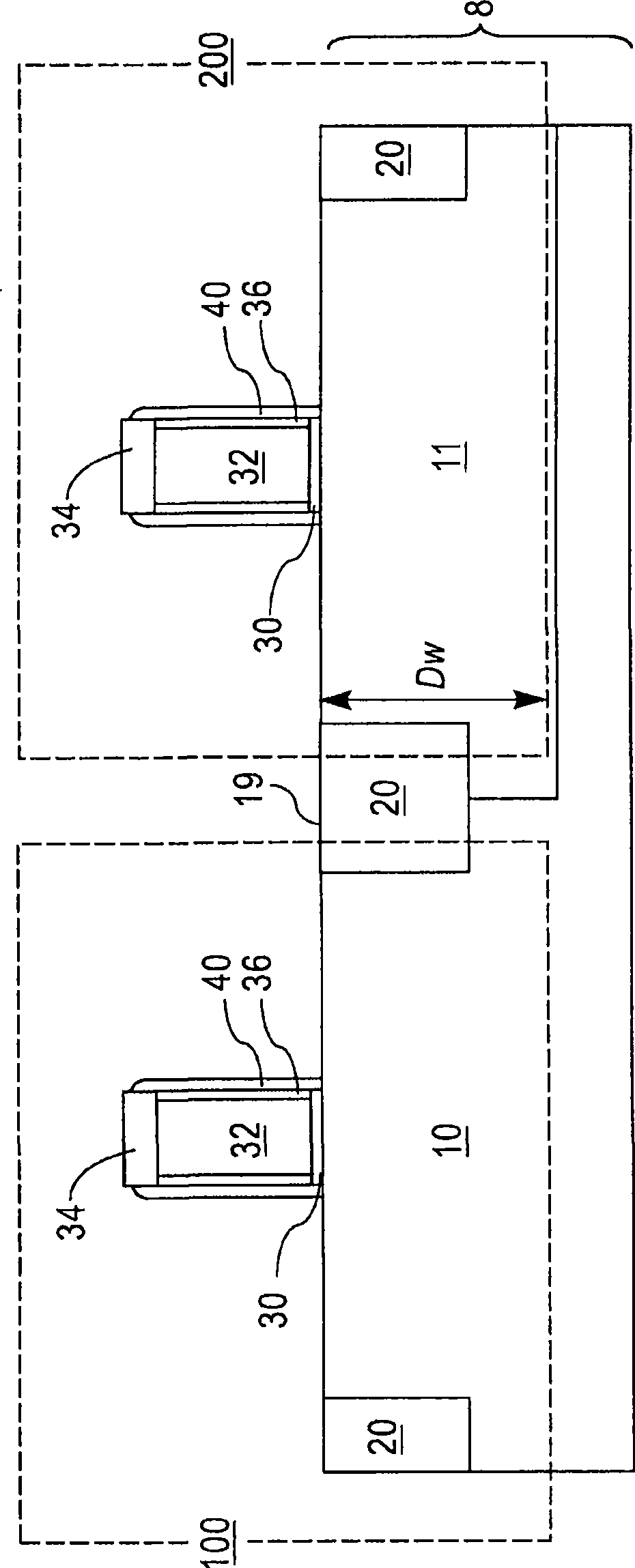

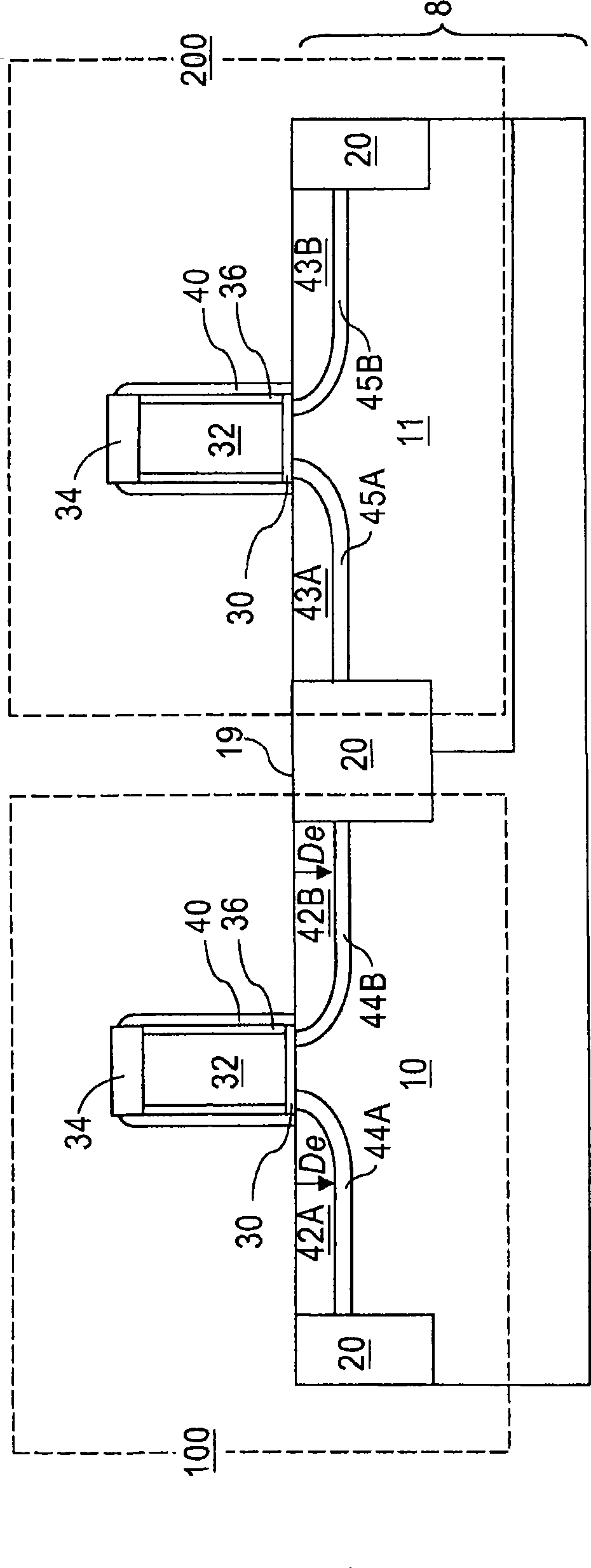

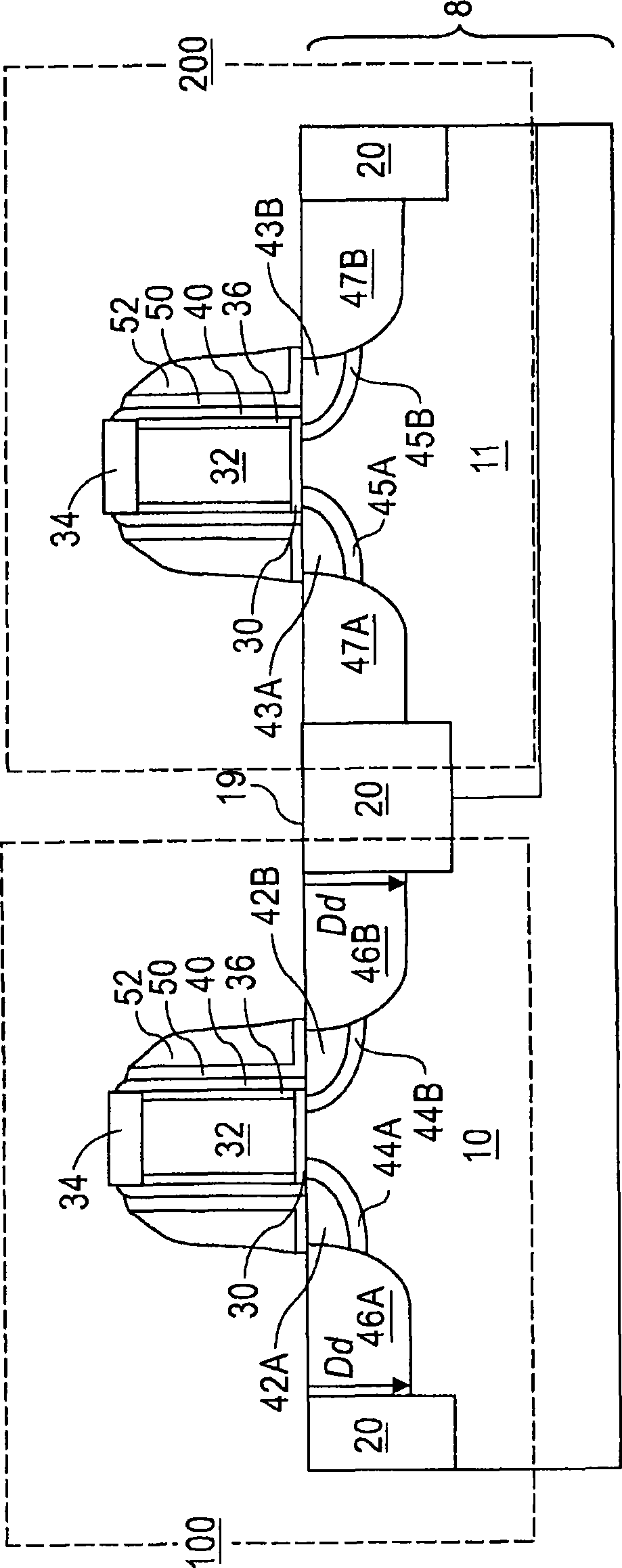

Plasma etching method and plasma treatment apparatus

ActiveCN1581445AIncrease etch rateImprove uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingRadio frequencyPhysics

To realize reduction in size and low cost of a matching circuit in the double-frequency superimposing and impressing system. In this plasma etching apparatus, an upper electrode 18 is connected (grounded) to the ground potential via a chamber 10, while a lower electrode 16 is electrically connected to a first radio frequency power source 40 (for example, 13.56 MHz) and a second radio frequency power source 42 (for example, 3.2 MHz) via a first matching unit 36 and a second matching unit 38. The second matching unit 38 in the lower frequency side is formed of a T-type circuit in which a coil 62 is provided in the final output stage and the coil 62 is also operated as a high-cut filter for shielding the radio frequency (13.56 MHz) from the first radio frequency power source 40.

Owner:TOKYO ELECTRON LTD

MOSFET having a high stress in the channel region and fabricating method thereof

InactiveCN101483190AControl etch profileLoad effect minimizationTransistorSemiconductor/solid-state device manufacturingDopantMOSFET

Source and drain extension regions are selectively removed by a dopant concentration dependent etch or a doping type dependent etch, and an embedded stress-generating material such as SiGe alloy or a Si:C alloy in the source and drain extension regions is grown on a semiconductor substrate. The embedded stress-generating material may be grown only in the source and drain extension regions, or in the source and drain extension regions and in deep source and drain regions. In one embodiment, an etch process that removes doped semiconductor regions of one conductivity type selective to doped semiconductor regions of another conductivity type may be employed. In another embodiment, a dopant concentration dependent etch process that removes doped semiconductor regions irrespective of the conductivity type selective to undoped semiconductor regions may be employed.

Owner:INT BUSINESS MASCH CORP

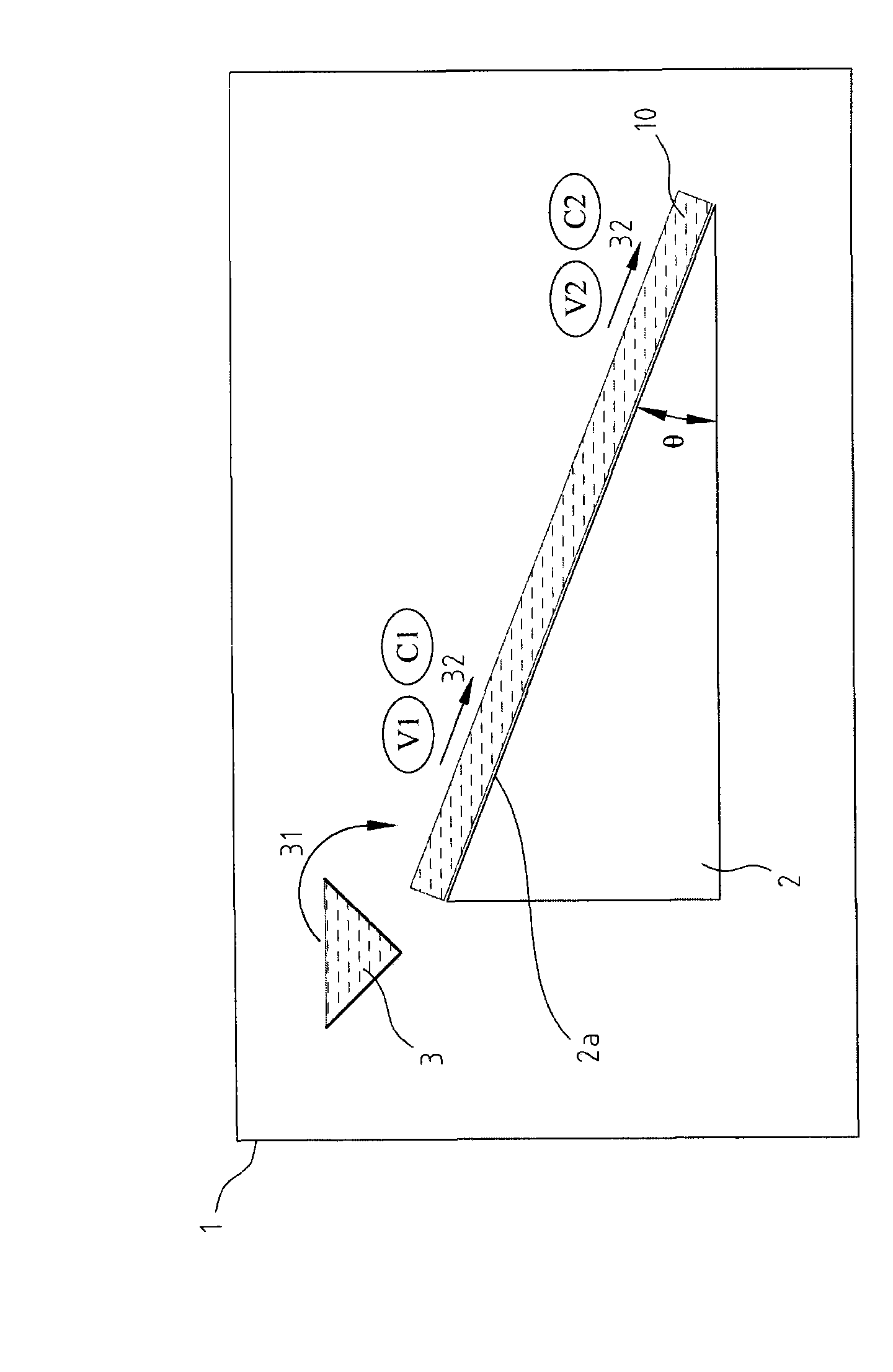

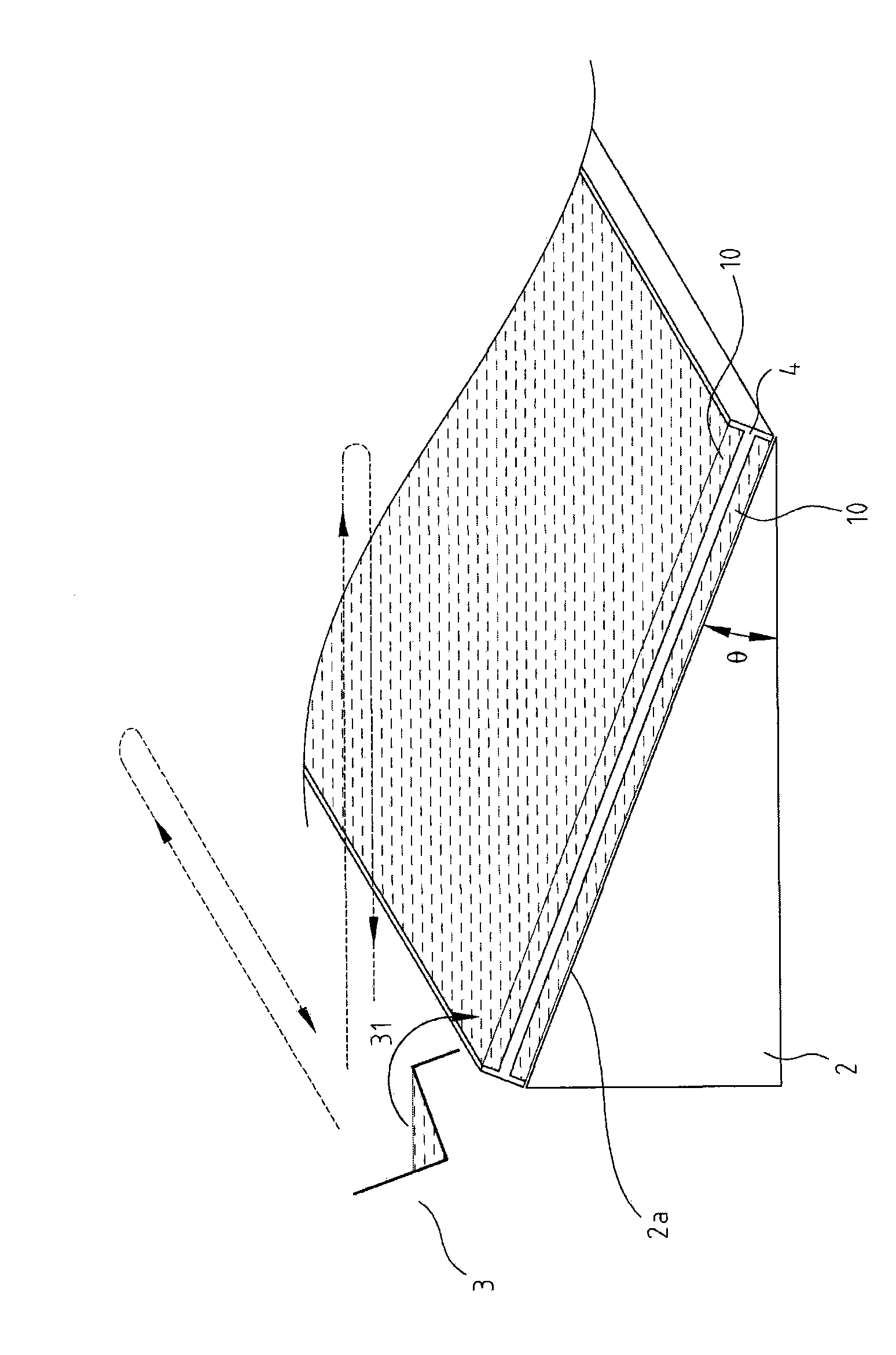

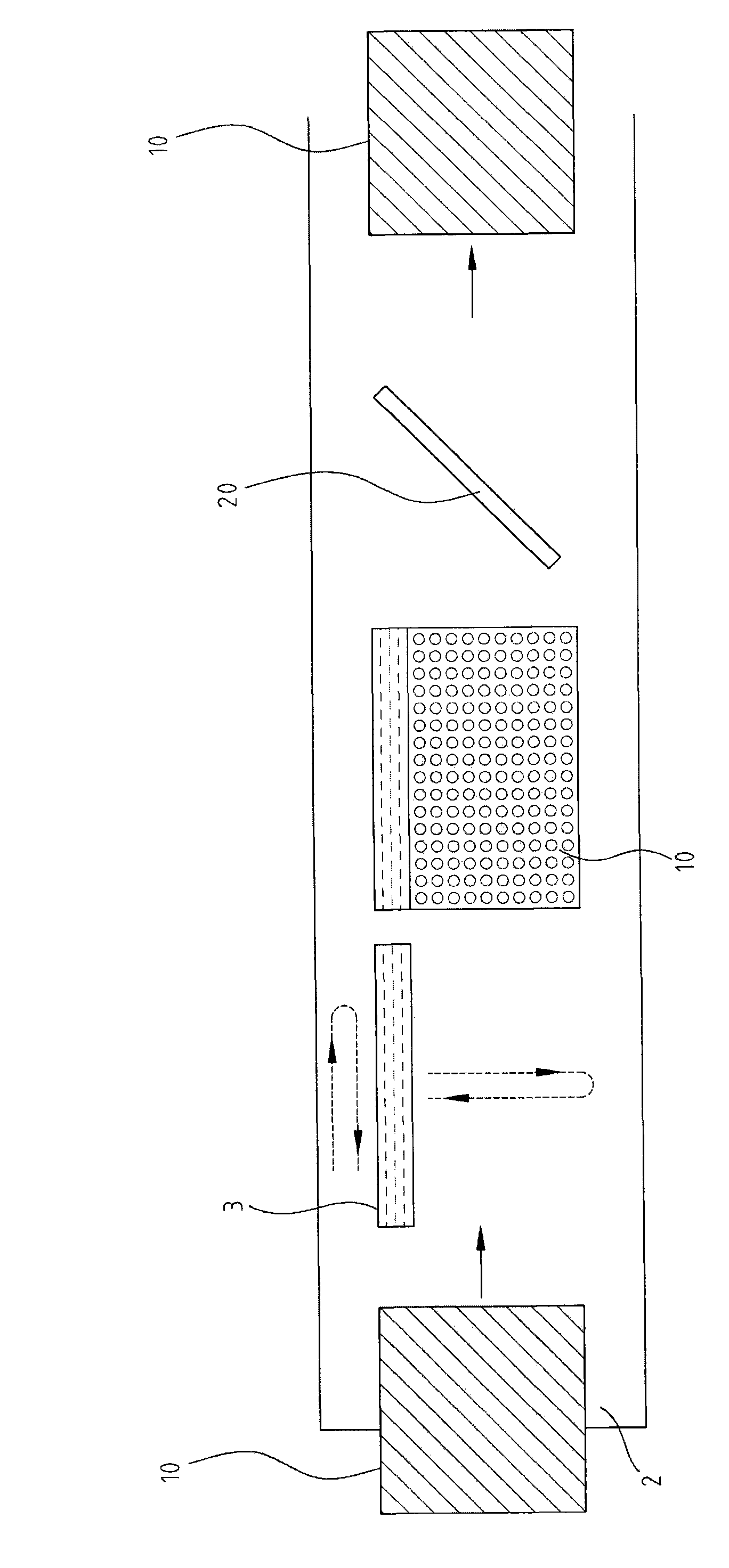

Device and method for etching optical glass

The invention discloses a device and a method for etching optical glass. When the glass of large size is etched and / or thinned, the device and the method are used for uniformly etching and / or thinning the optical glass in a driveline mode with inclination to reduce the stress of the optical glass and uniformly releasing an etching solution by adopting a scan-type waterfall layer sulfuric acid solution coating mode and a moving mode of scanning back and forth and / or left and right from the upside of the optical glass so as to uniformly etch and thin the optical glass. When the optical glass etching device of the invention is used for carrying out the optical glass etching method, because the optical glass is inclined, the limitation of the mechanical strength and the physical properties of the glass are reduced in conveying and transmission and the problems caused when the glass is vertically conveyed and transmitted are avoided; and due to the fact that the optical glass is coated with the sulfuric acid solution in a way of scanning type waterfall layer, the etching speed can be increased and the etching uniformity of the optical glass can be enhanced.

Owner:PHOTO JET INT

Method for forming metal wire harness

The invention provides a method for forming a wire harness for a copper-based metal film through an etching liquid compound, so that in a double layer coating of a metallic oxide layer and a copper layer, erosion of the metallic oxide at a lower part is minimized and only the copper layer at an upper part is eroded. In addition, the etching liquid compound for the copper-based metal film is provided.

Owner:DONGWOO FINE CHEM CO LTD

Reaction chamber and capacitive coupling plasma device

PendingCN107578977AReduce etch rateImprove etch uniformityElectric discharge tubesCapacitanceCapacitive coupling

The invention provides a reaction chamber and a capacitive coupling plasma device. The reaction chamber comprises a bottom wall, a lining, a supporting assembly and a magnetic assembly. The lining isarranged in a chamber body and comprises a bottom lining located above the bottom wall of the chamber body. The supporting assembly is arranged in the process area surrounded by the bottom lining andused for supporting a wafer. The magnetic assembly is arranged outside the process area and used for forming a magnetic field so that the difference of the etching speeds of the edge area and the central area of the wafer can be reduced.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

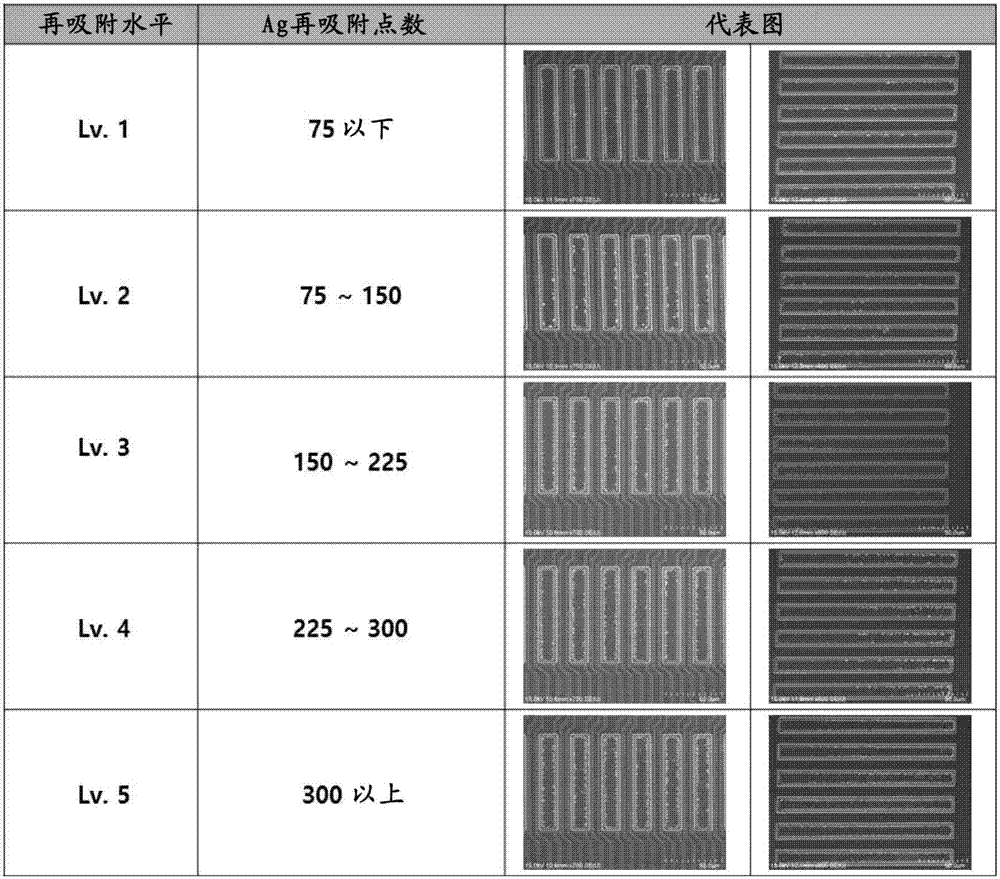

Etching solution composition for silver-containing layer and a display substrate using the same

InactiveCN107419270APrevent resorptionMaintain etch uniformityNon-linear opticsSurface treatment compositionsPhosphoric acidSolution composition

The invention relates to the etchant composition and display substrate using the same of the argentiferous thin film, more specifically, the phosphoric acid 45 about the total weight of composition, through 55 weight%, the nitric acid 2 through 9 weight%, the acetic acid 5 through 15 weight%, and the potassium nitrate 1 through 5 weight%, the etchant composition of the argentiferous thin film including the residual water, and the display substrate using the same.

Owner:DONGWOO FINE CHEM CO LTD

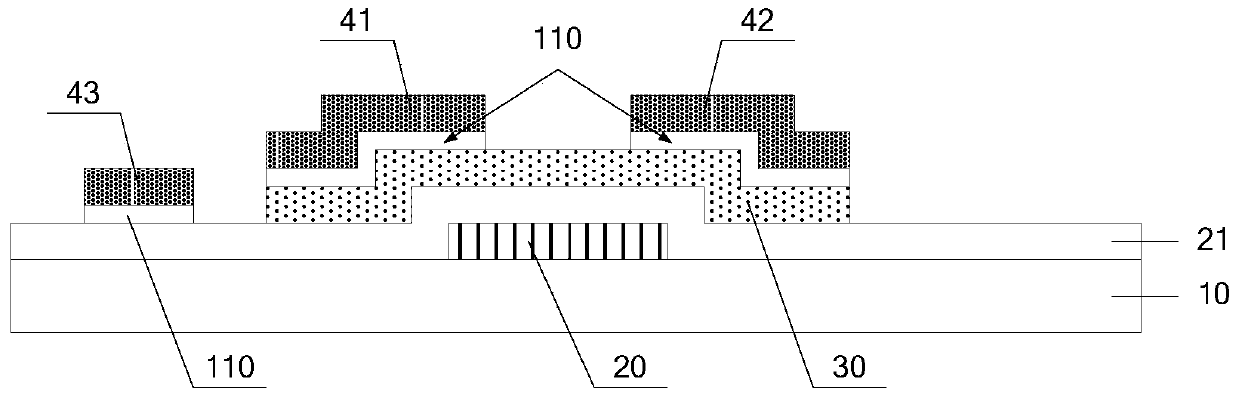

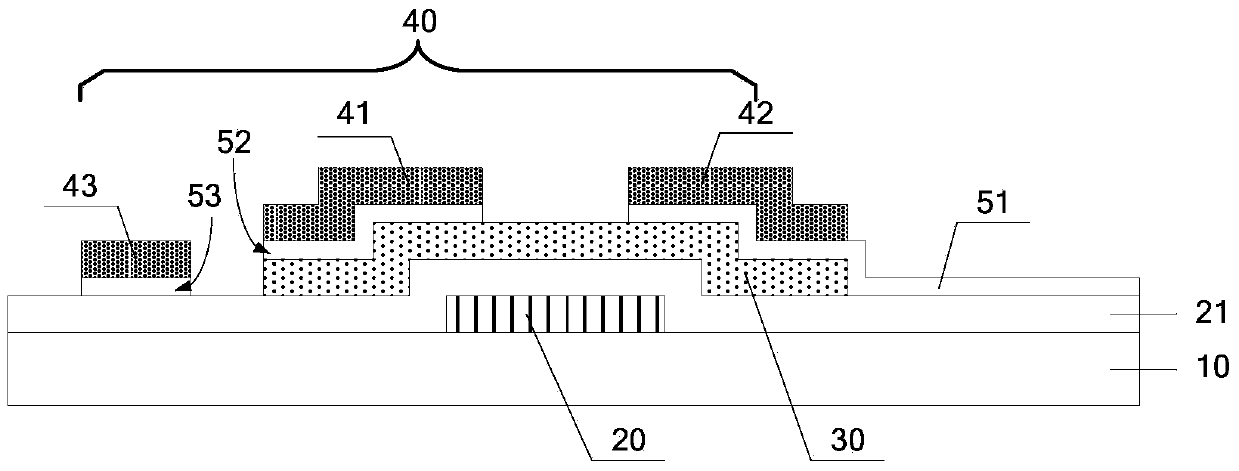

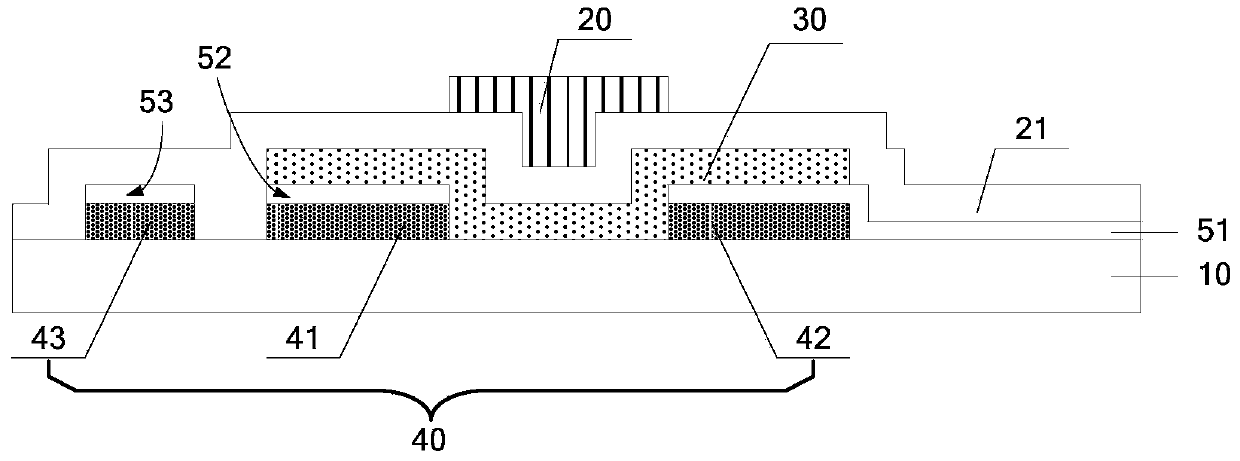

Array substrate and preparation method thereof, and display device

ActiveCN104183603AImprove yield rateAffect normal displaySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOptoelectronics

The embodiment of the invention provides an array substrate and a preparation method thereof, and a display device, and relates to the technical field of display so that poor size uniformity of a gap between a source electrode and a drain electrode when barrier layers are formed is prevented and the cost of the barrier layers is reduced and a problem of metal loss and signal discontinuity is solved. The array substrate includes a grid metal layer which is on an underlayer substrate and includes a grid electrode and a grid line; a grid insulating layer; an active layer; a source and drain metal layer which includes the source electrode, the drain electrode, and a data line, wherein the source and drain metal layer includes a copper metal layer and / or a copper alloy layer; and a pixel electrode layer which includes a pixel electrode directly contacting the drain electrode, a first pixel electrode reservation pattern directly contacting the source electrode, and a second pixel electrode reservation pattern directly contacting the data line, wherein an area of the pixel electrode, directly contacting the drain electrode, and the first pixel electrode reservation pattern are located between the active layer and the source and drain metal layer, and an area of the pixel electrode, not directly contacting the drain electrode, and the second pixel electrode reservation pattern are located on / beneath the grid insulating layer. The preparation method is used for preparation of the array substrate.

Owner:BOE TECH GRP CO LTD +1

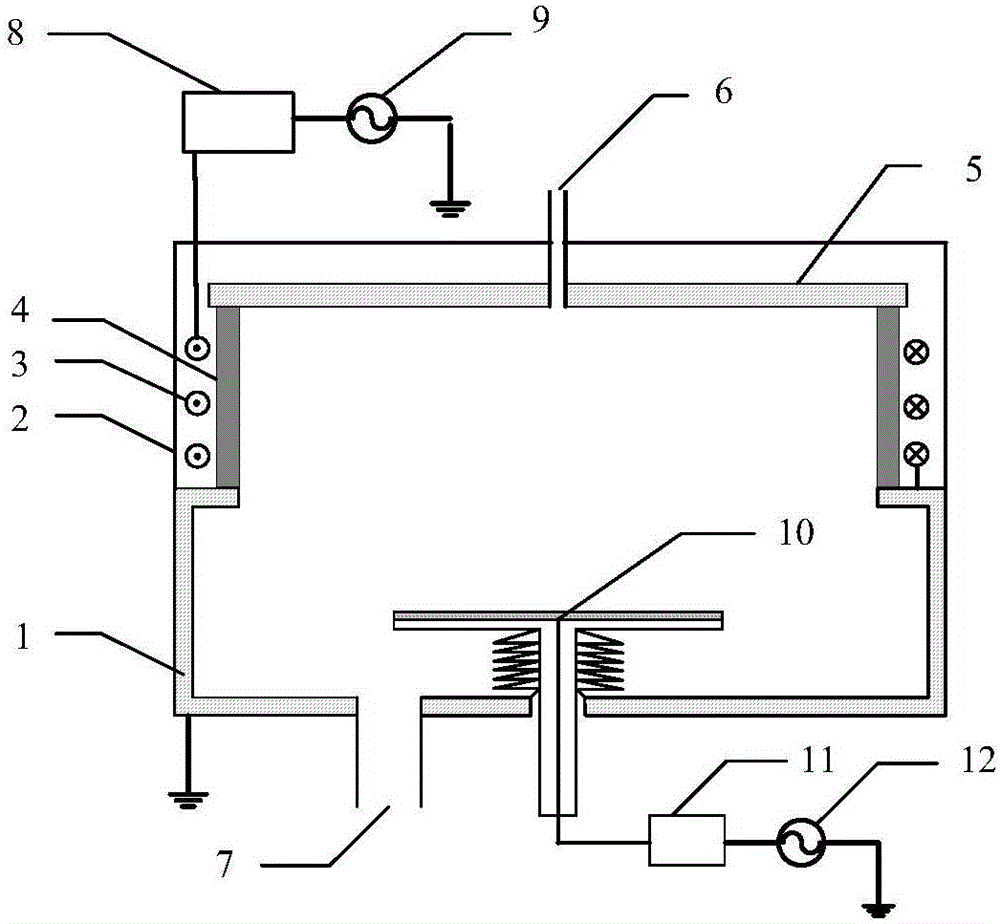

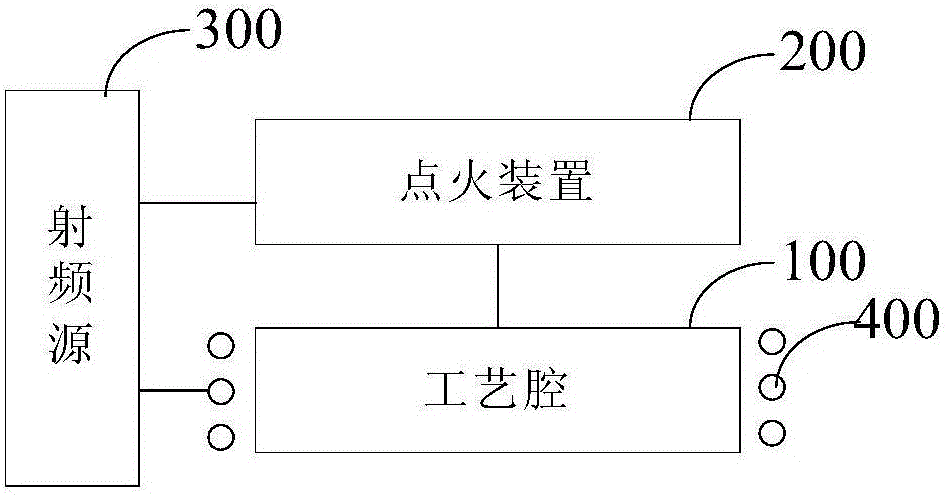

Reaction cavity and semiconductor processing device

InactiveCN106298422AImprove stabilityImprove etch uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingRadio frequencyEngineering

The invention provides a reaction cavity and a semiconductor processing device. The reaction cavity comprises a technical cavity for generating plasmas, an ignition device arranged at the top of the technical cavity and an RF source; the ignition device starts the plasmas positioned in part of the ignition device; and the RF source provides an RF energy to a first RF coil and the ignition device, adjusts distribution of the RF energy obtained by the first RF coil and the ignition device, and starts the plasmas in part of the ignition device and in the technical cavity sequentially. The reaction cavity provided by the invention ensure smooth starting, keeps the technical air pressure in the technical cavity constant, and thus, improves the total technical stability. In the starting process, the technical air pressure in the technical cavity is relatively low, the etching uniformity can be improved, and a substrate is prevented from damage caused by relatively high starting voltage.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

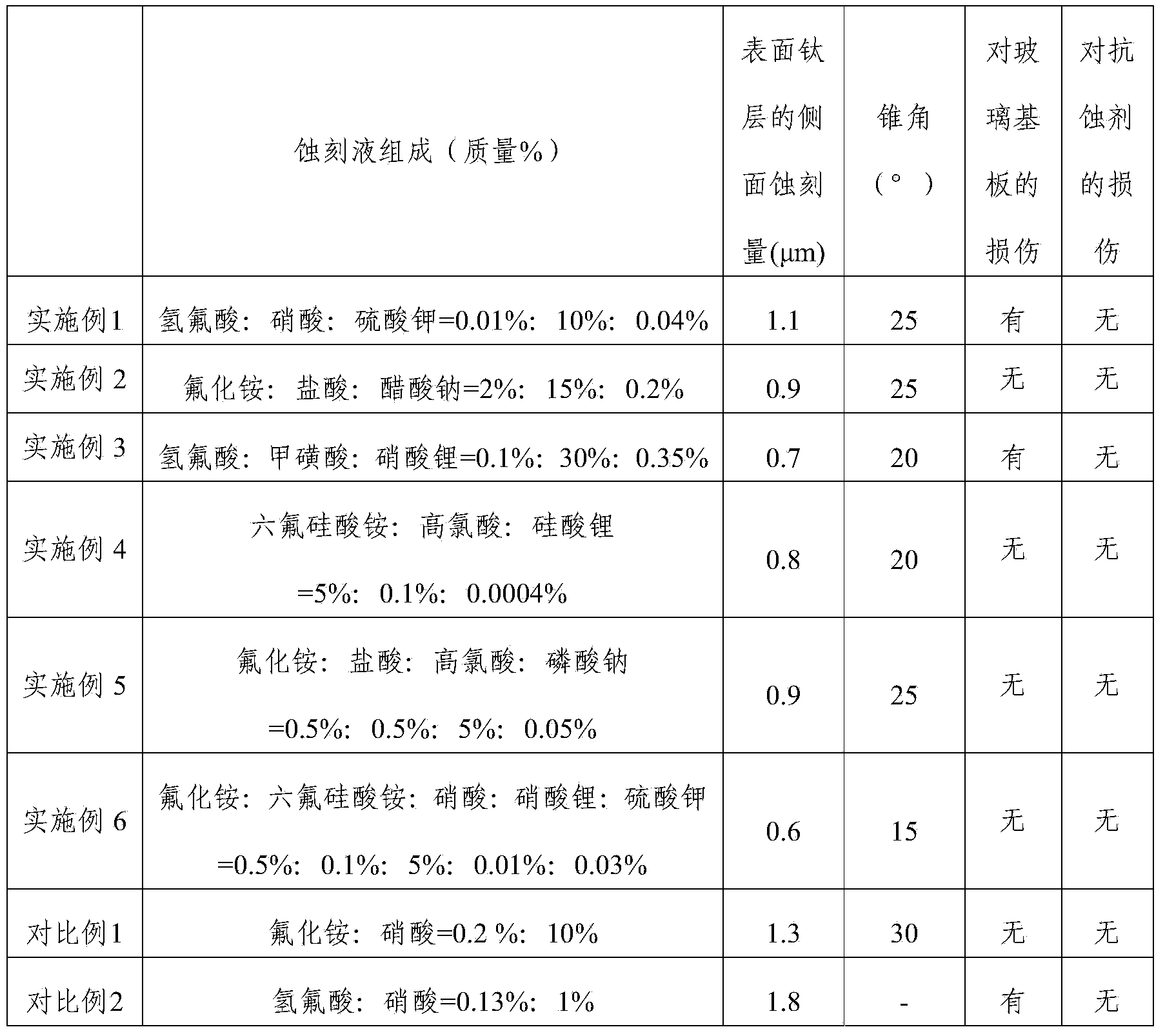

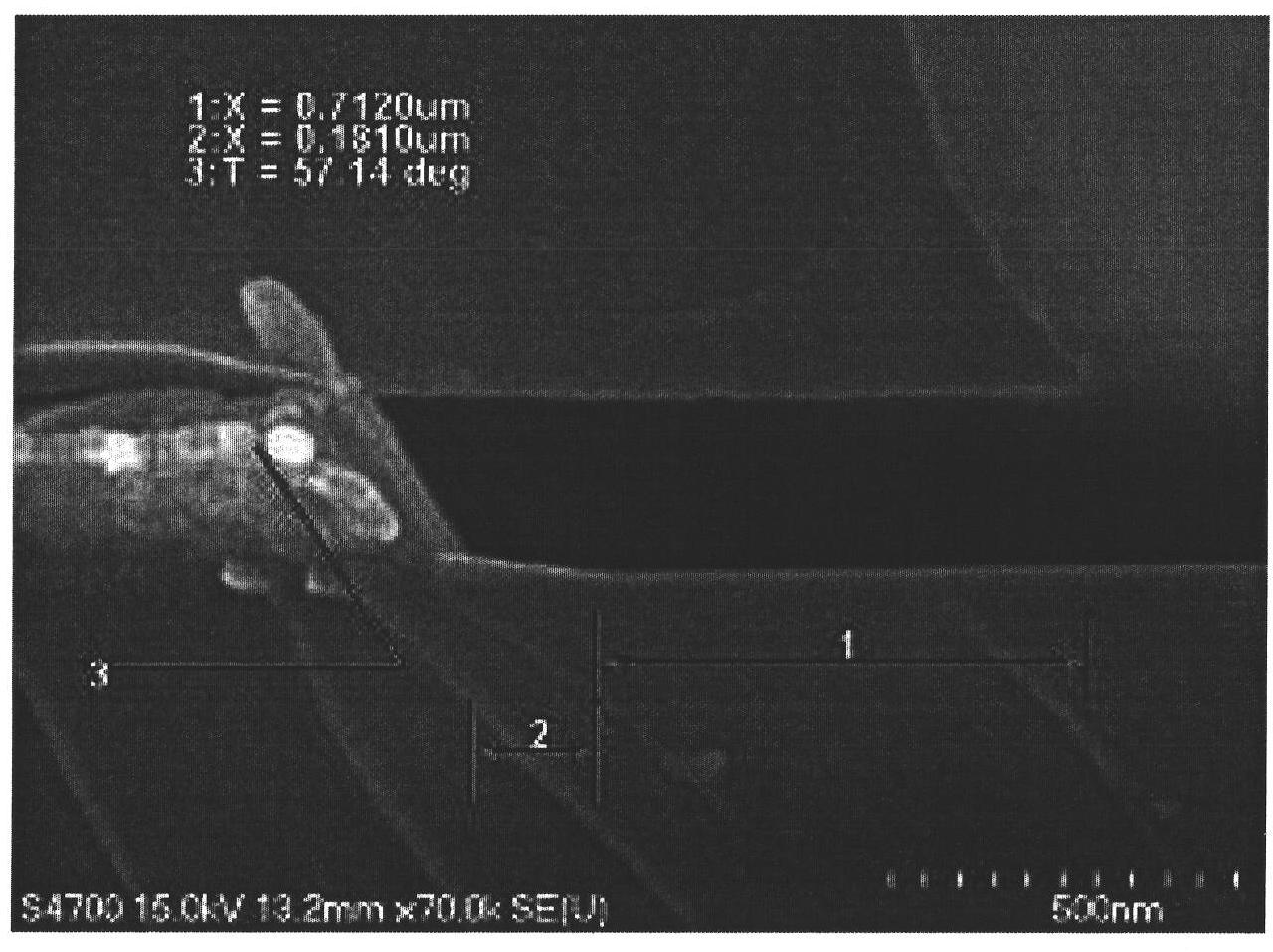

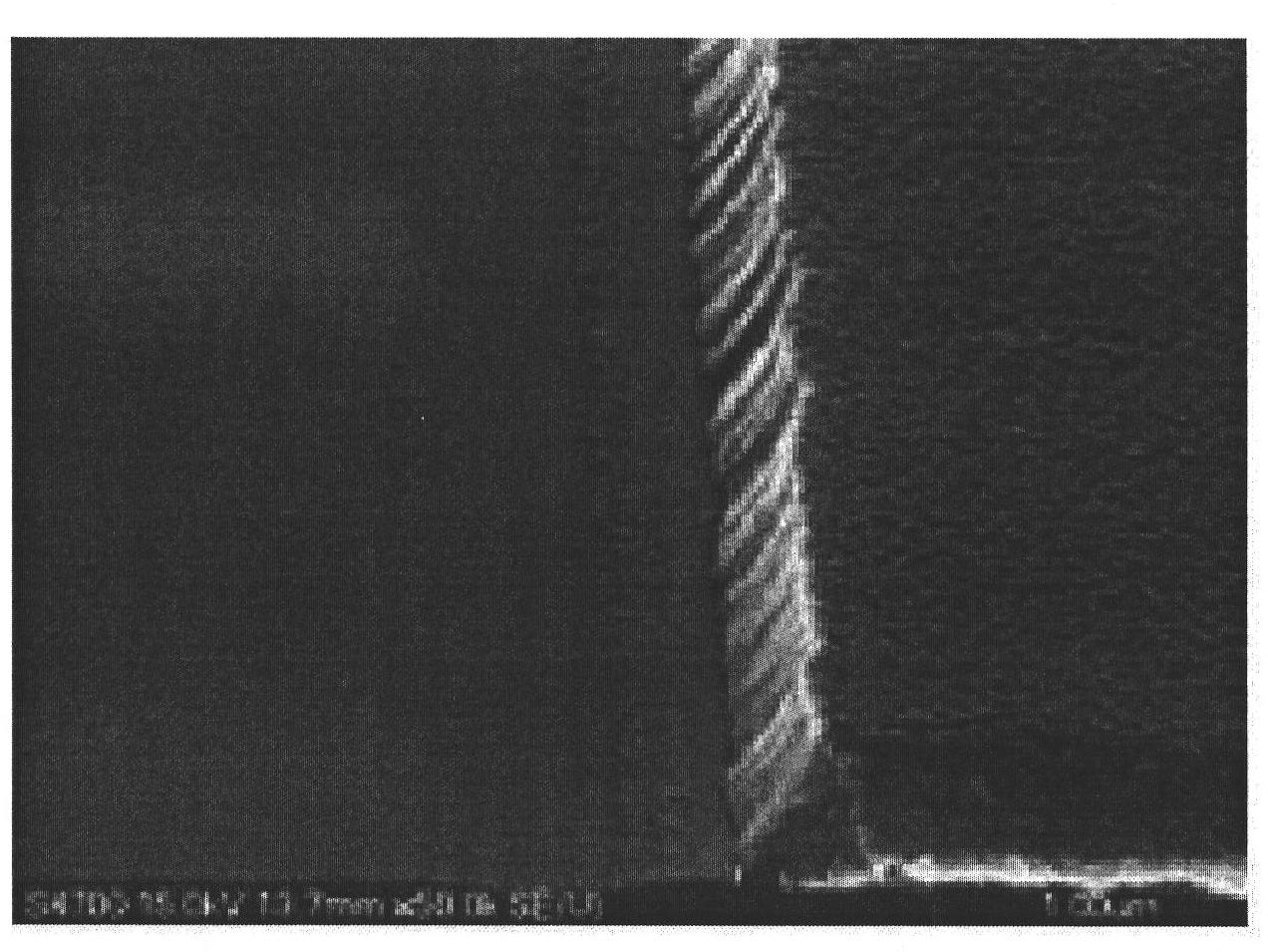

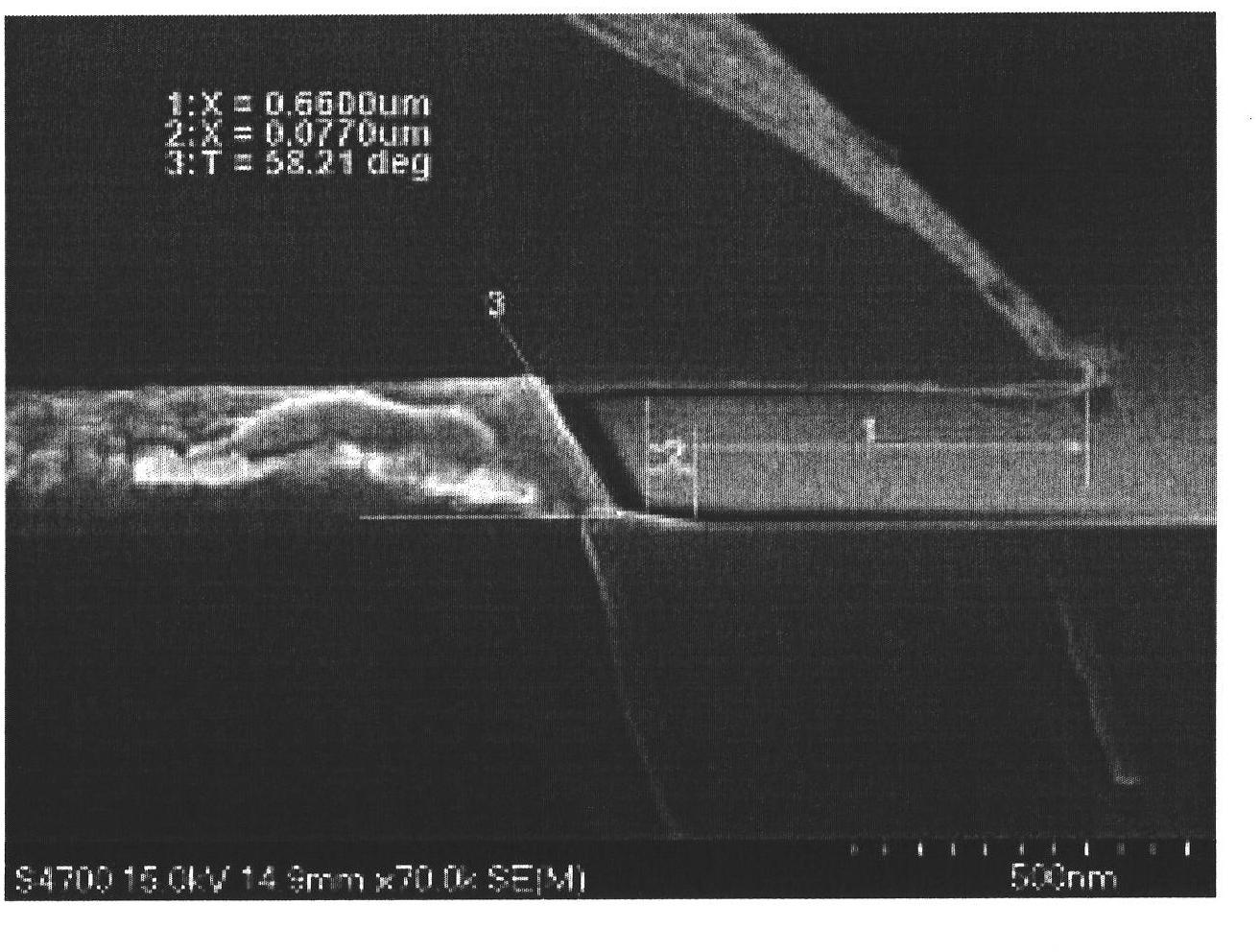

Etching solution composition for titanium-aluminum-titanium metal laminated membrane

The invention relates to an etching solution composition for a titanium-aluminum-titanium metal laminated membrane consisting of a titanium metal membrane, an aluminum metal membrane and a titanium metal membrane. The composition consists of fluorides, oxidizing acid, non-oxidizing alkali metal salt and water, wherein the non-oxidizing alkali metal salt is preferentially at least one of water-soluble lithium, potassium and sodium salts; the mass percent concentration of the fluorides, the oxidizing acid and the non-oxidizing alkali metal salt are 0.01-5 percent, 0.1-30 percent and 0.0004-0.35 percent, respectively. Compared with the prior art, the etching solution composition has the advantages that the three laminated metal membranes can be etched together, the lateral erosion amount can be effectively reduced, the etching uniformity is improved, and the obtained taper angle is 25 degrees below. In addition, the etching solution composition adopts low-price non-oxidizing salts or mixtures thereof instead of high-price salt-type auxiliary oxidants, so that the production cost is reduced, and the balance between the cost and performance is achieved.

Owner:JIANGYIN JIANGHUA MICROELECTRONICS MATERIAL

Method of fabricating array substrate for liquid crystal display

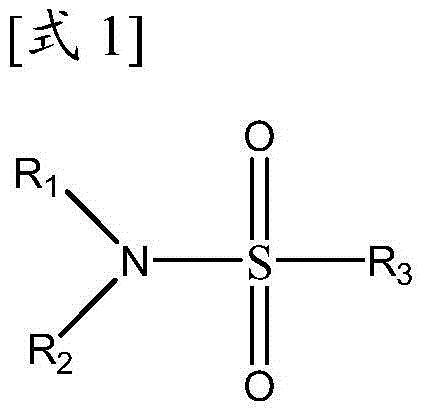

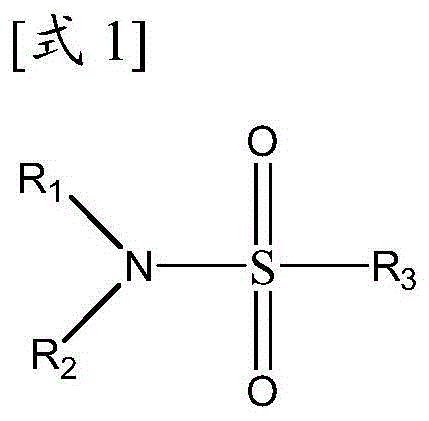

ActiveCN102576170AImprove etch uniformityImprove linearitySolid-state devicesNon-linear opticsPhosphonic acid derivativesLiquid-crystal display

Disclosed is a method of fabricating an array substrate for a liquid crystal display, including forming a copper-based metal layer on a substrate and etching the copper-based metal layer using an etchant composition thus forming gate wiring, and forming a copper-based metal layer on a semiconductor layer and etching the copper-based metal layer using the etchant composition thus forming source / drain electrodes, the etchant composition including based on the total weight of the composition, A) 5.0 ~ 25 wt% of hydrogen peroxide (H2O2), B) 0.01 ~ 1.0 wt% of a fluorine-containing compound, C) 0.1 ~ 5.0 wt% of an azole compound, D) 0.1 ~ 10.0 wt% of one or more compounds selected from among phosphonic acid derivatives and salts thereof, and E) a remainder of water.

Owner:DONGWOO FINE CHEM CO LTD

Etching solution for silicon wafer

InactiveCN109321253AReduce uniformityGuaranteed uniformitySurface treatment compositionsReaction ratePhosphoric acid

The invention discloses an etching solution for a silicon wafer. The etching solution is mainly prepared from electronic-grade nitric acid, electronic-grade hydrofluoric acid, electronic-grade sulfuric acid, electronic-grade phosphoric acid, electronic-grade acetic acid, a surfactant and ultrapure water, wherein the nitric acid serves as an oxidizing agent and can oxidize silicon into silicon oxide, the hydrofluoric acid serves as a dissolving agent and can dissolve and remove the silicon oxide so as to realize etching of the silicon wafer, the sulfuric acid can improve the viscosity of the solution, stabilize the reaction rate, not change the etching morphology and improve the etching uniformity, the phosphoric acid can also improve the viscosity of the solution, improve the mass transferresistance, decrease the etching rate and not change the etching morphology, the acetic acid serves as a diluent and can reduce the ionization degree of the nitric acid, inhibit the oxidation capacity of the nitric acid, decrease the reaction rate and influence the surface morphology after etching, and the surfactant can reduce the surface tension of the solution and improve the surface morphology of the etched silicon wafer. The etching solution has the advantages of being stable and controllable in etching rate and uniform and flat in etching surface.

Owner:湖北兴福电子材料股份有限公司

Chemical etching liquor for aluminium and aluminum alloy

Owner:SHENZHEN FUTAIHONG PRECISION IND CO LTD

Apparatus for supporting wafer in semiconductor process

ActiveUS7025858B2Improve foregoing drawbackImprove etch uniformityDecorative surface effectsVacuum evaporation coatingSemiconductor packageEngineering

The present invention provides an apparatus for supporting a wafer in a semiconductor process. The apparatus includes an electrostatic chuck, a focus ring and a conductive material. The electrostatic chuck has a first fillister in its periphery. When a DC power is applied to the electrostatic chuck, the wafer is attached tightly to the electrostatic chuck by electromagnetic force. The focus ring has a second fillister opposite to the first fillister, and the focus ring is fixed on the periphery of the electrostatic chuck. The conductive material is located below the focus ring, and the conductive material is moving between the first fillister and the second fillister by a drive apparatus. When the conductive material is moving close to the focus ring in semiconductor etching process, it can improve the etching uniformity of the wafer periphery.

Owner:WINBOND ELECTRONICS CORP

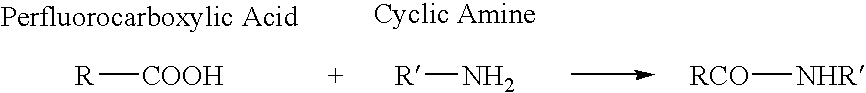

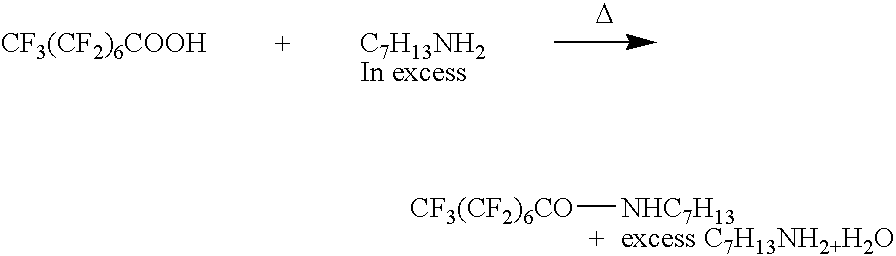

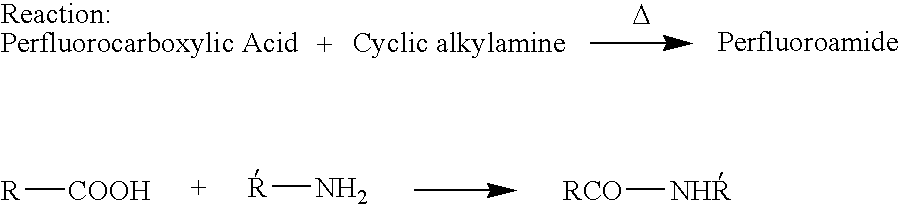

Etchants containing filterable surfactant

InactiveUS7112289B2Improve surface activityEasy to solveSemiconductor/solid-state device manufacturingSurface treatment compositionsEtchingSURFACTANT BLEND

An improved etching and cleaning composition for semiconductor devices is provided in which the etch solution incorporates a novel surfactant comprising a combination of a linear perfluorocarboxylic acid, a cyclic amine and an aliphatic alcohol.

Owner:KMG ELECTRONICS CHEM

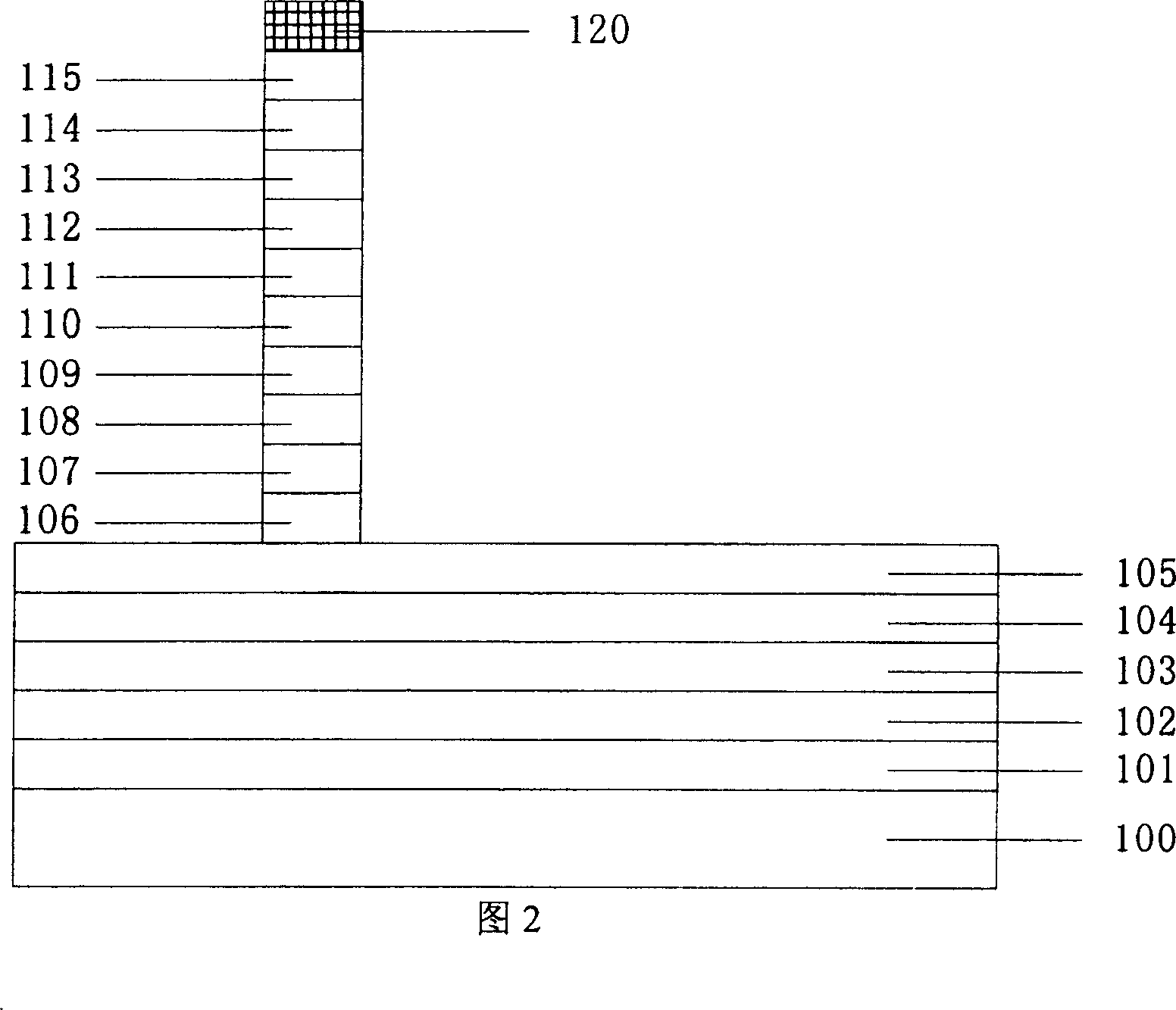

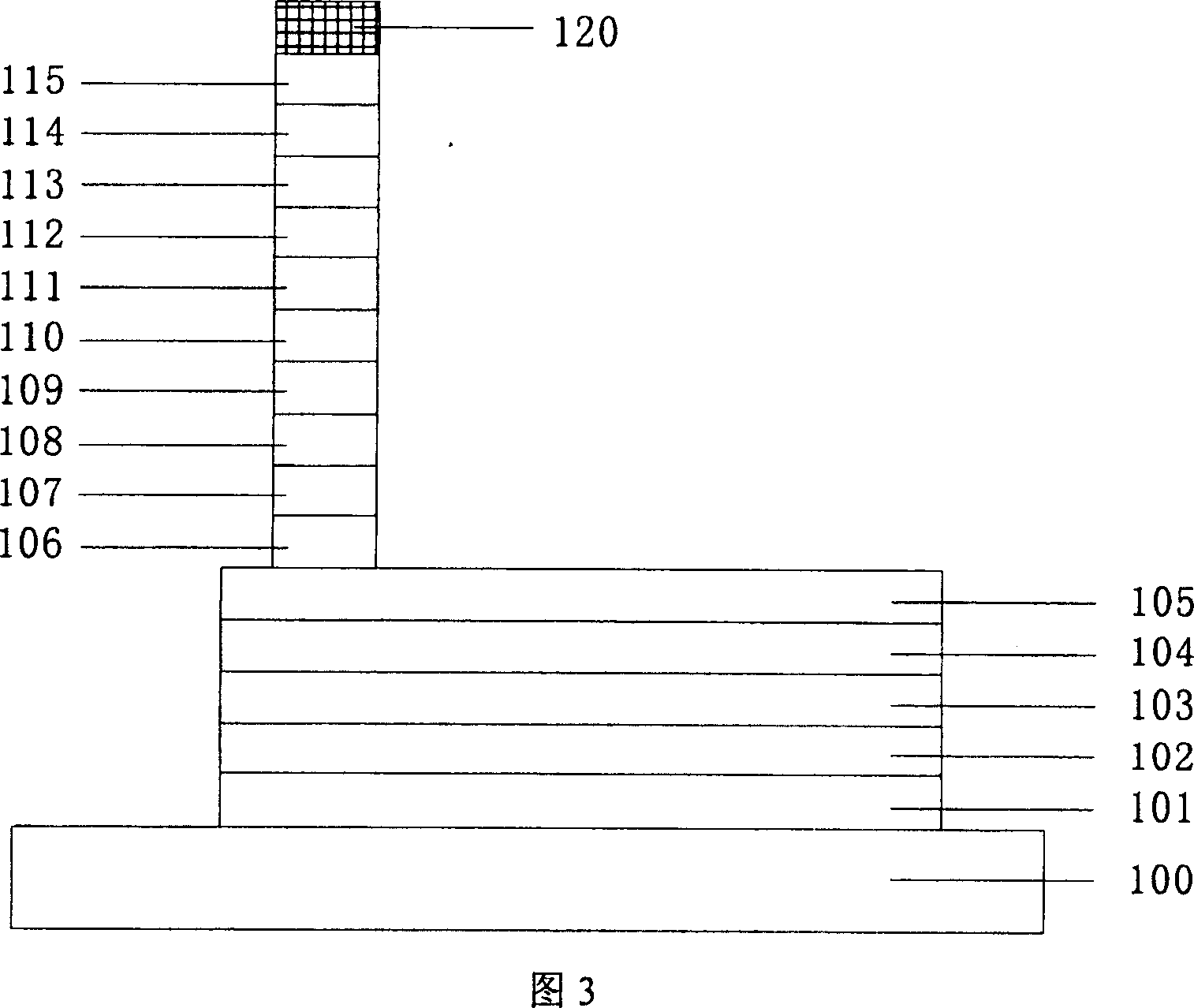

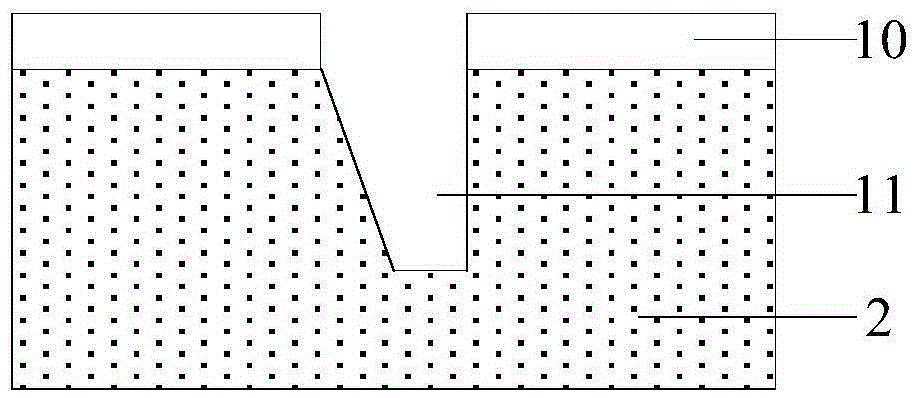

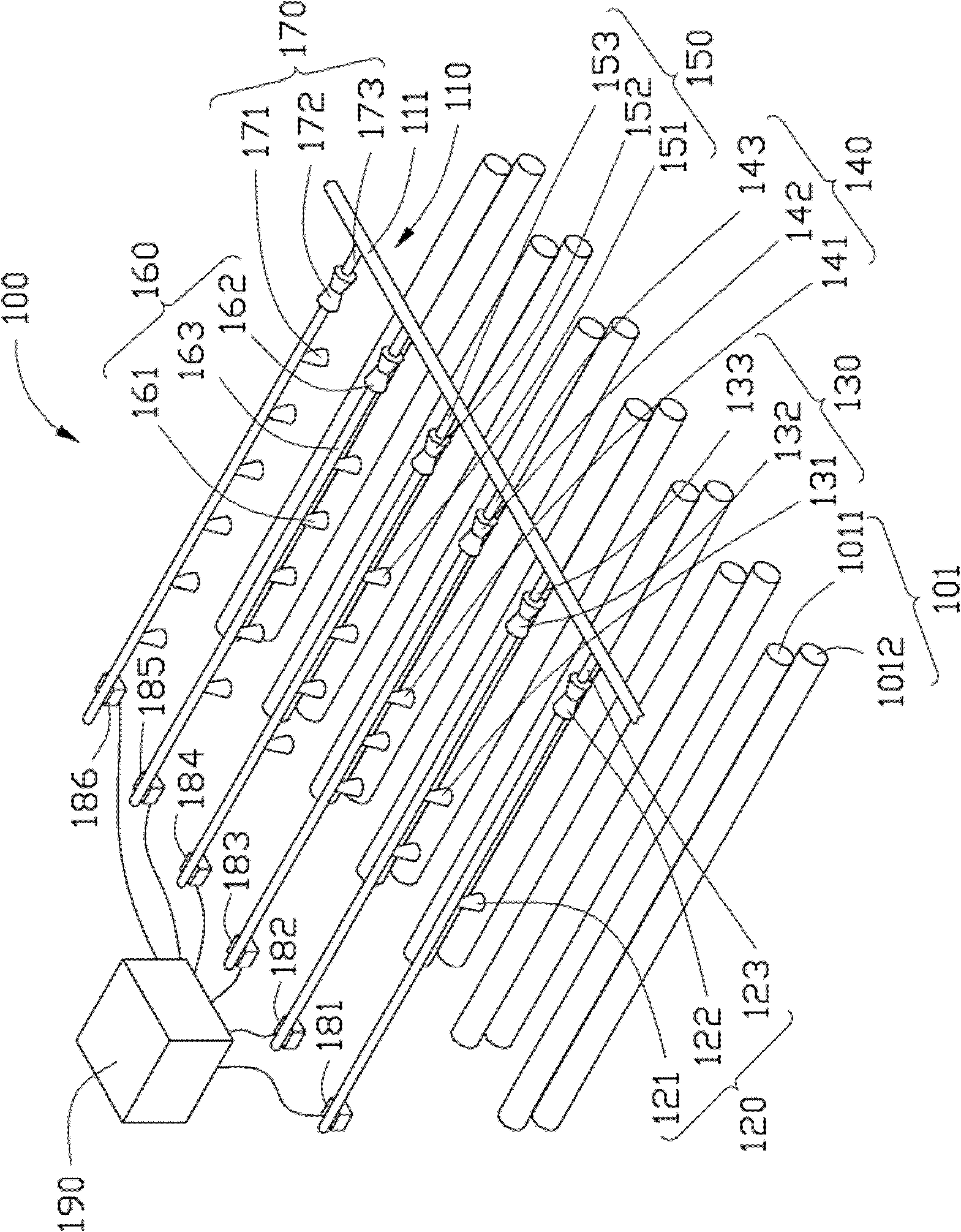

Stepped upper electrode for plasma processing uniformity

InactiveCN1723528AEasy to shapeSmall sizeElectric discharge tubesSemiconductor/solid-state device manufacturingParallel platePlasma processing

A plasma discharge electrode having a front surface with a central portion thereof including gas outlets discharging a process gas which forms a plasma and a peripheral portion substantially surrounding the gas outlets. The peripheral portion has at least one step for controlling a density of the plasma formed by the electrode. The electrode can be used as the grounded upper electrode in a parallel plate plasma processing apparatus such as a plasma etching apparatus. The geometric features of the step and of a corresponding edge ring on the lower electrode can be varied to achieve the desired etch rate profile across a wafer surface.

Owner:LAM RES CORP

Wafer etching device and method

ActiveCN106653645AImprove etch uniformityAvoid Isolation Performance Degradation IssuesSolid-state devicesSemiconductor/solid-state device manufacturingEtchingSemiconductor

The invention provides a wafer etching device and method, and relates to the technical field of semiconductors, wherein the device and method are used for improving the etching uniformity of a wafer, and improving the yield of an integrated circuit. The device comprises an etching cavity and a placement platform which is disposed in the etching cavity and can rotate. The placement platform is used for bearing the wafer, and at least rotates clockwise for one circle and anticlockwise for one circle in the etching process of the wafer. The device provided by the invention is used for the etching of the device.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

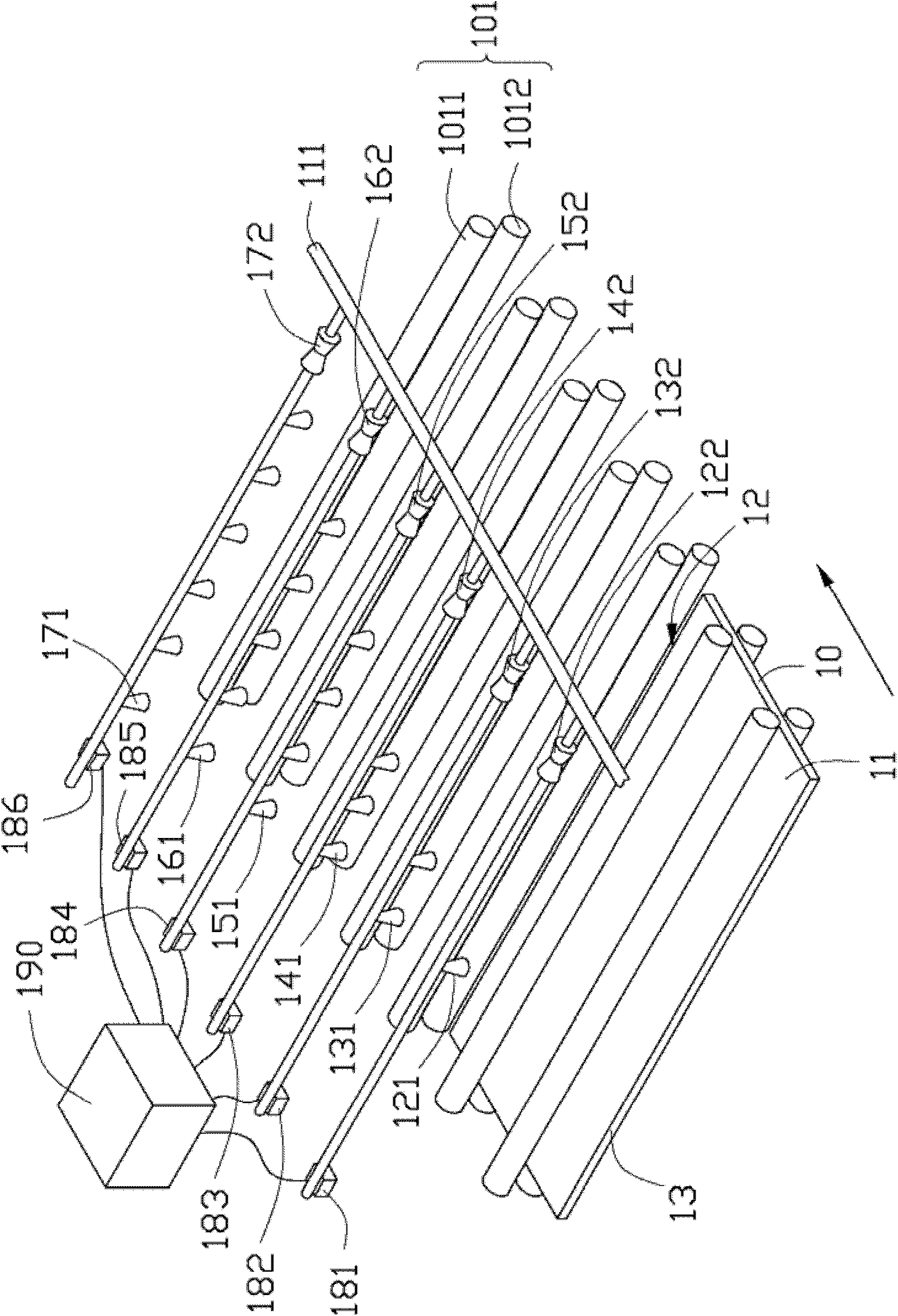

Etching device and circuit board etching method

InactiveCN102256447AImprove etch uniformityImprove uniformityPrinted circuit liquid treatmentSpraying apparatusElectricitySpray nozzle

The invention relates to an etching device which comprises a plurality of spray pipes, a plurality of sensors and a controller, wherein the spray pipes are successively arranged in parallel in a direction perpendicular to the transfer direction of a circuit board, each spray pipe comprises spray nozzles and a valve arranged on the spray pipe, the quantity of the spray nozzles on each spray pipe along the transfer direction of the circuit board is successively and gradually increased, the distances between every two adjacent spray nozzles on each spray pipe are equal, the spray nozzles on eachspray pipe are symmetrically distributed in relative to the same straight line perpendicular to the spray pipes, and the valve is used for controlling whether the spray nozzles located on the same spray pipe with the valve spray an etching liquid or not; the sensors are in one-to-one correspondence to the spray pipes and are used for sensing the position relationship between the circuit board andthe spray pipe corresponding to each sensor; and the controller is electrically connected with the sensors and the valves and is used for controlling the opening and closing of the valve corresponding to each sensor according to the sensing results so as to control whether the spray nozzles located on the same spray pipe with the valve spray the etching liquid or not. The invention also relates to a method for etching a circuit board by using the etching device.

Owner:AVARY HLDG (SHENZHEN) CO LTD +1

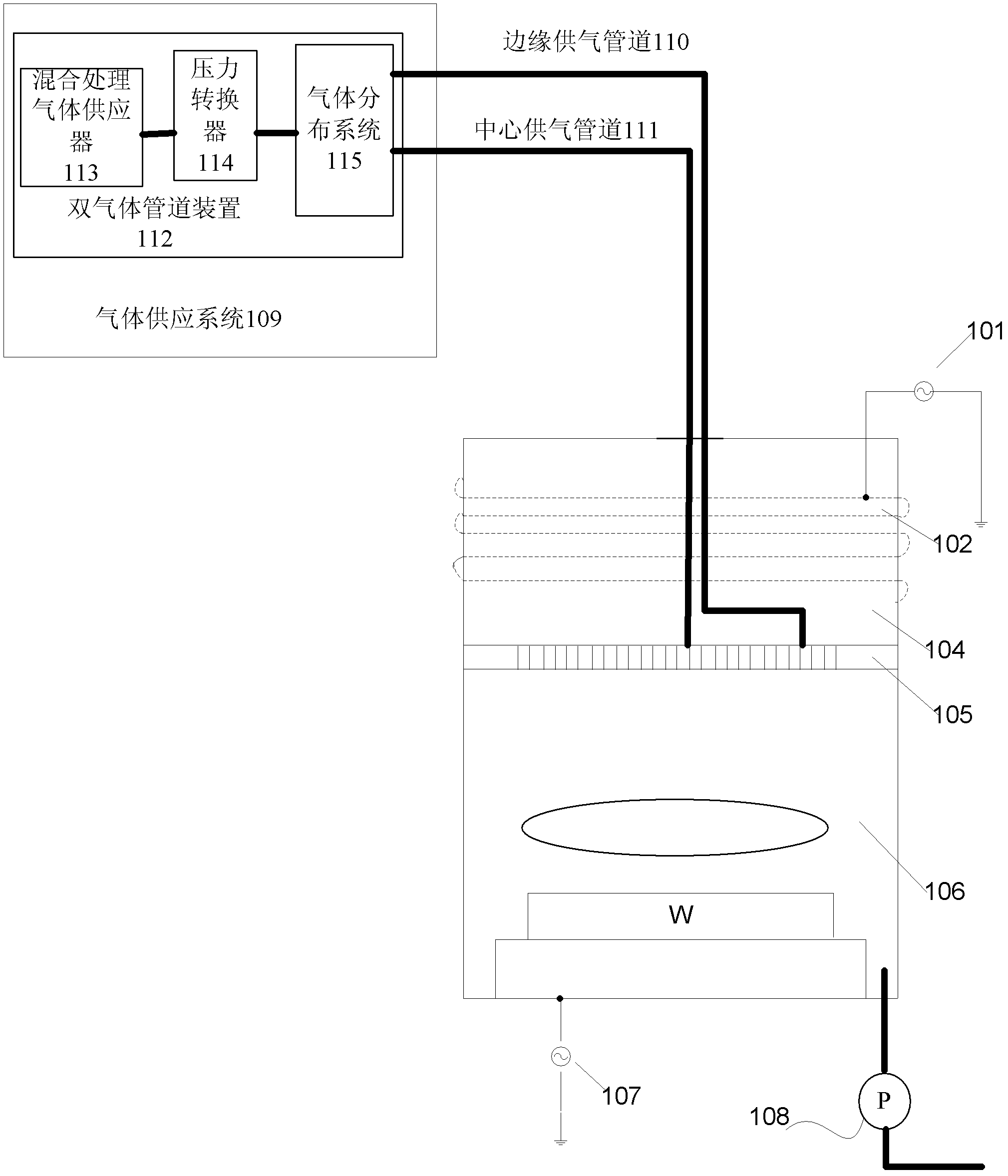

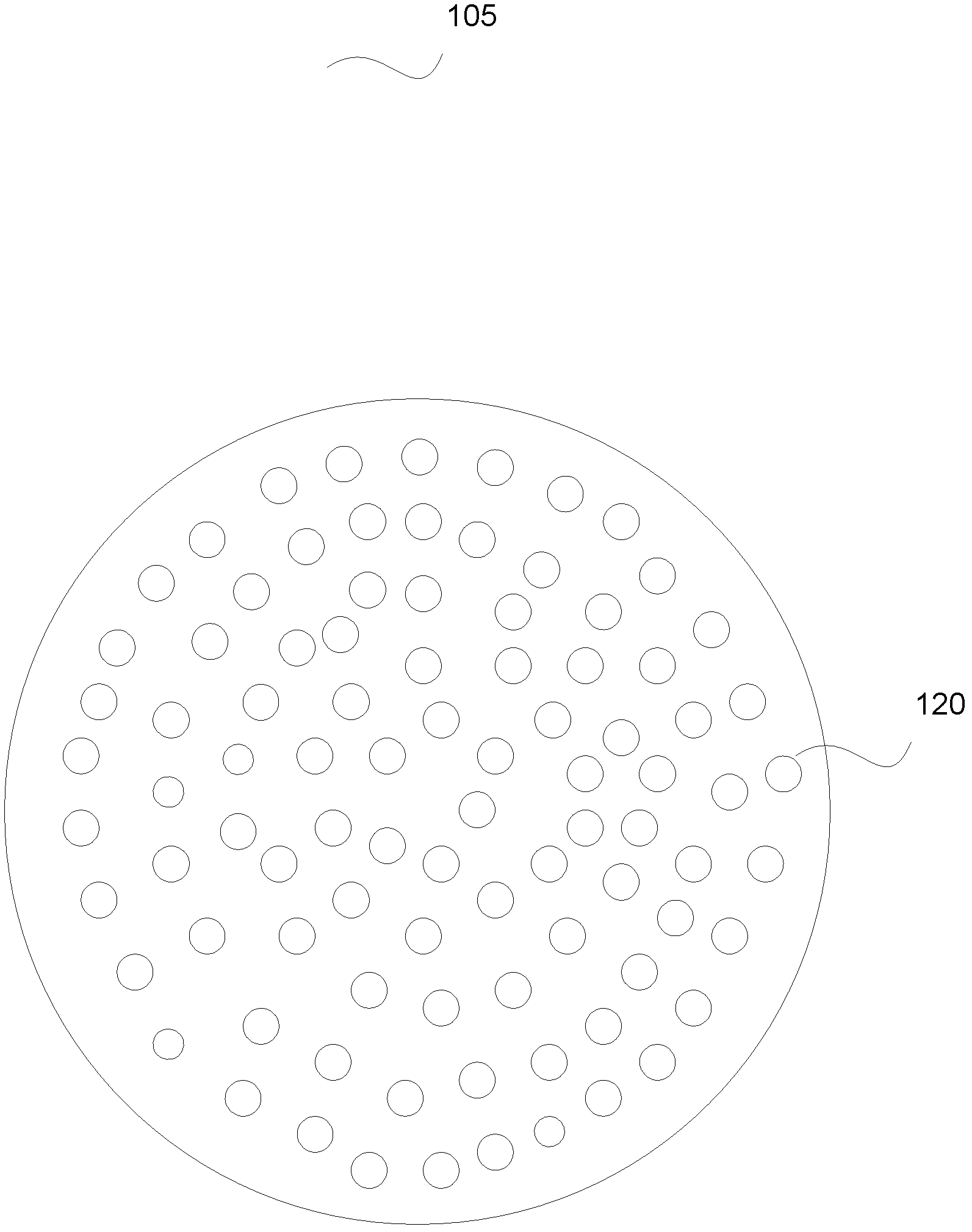

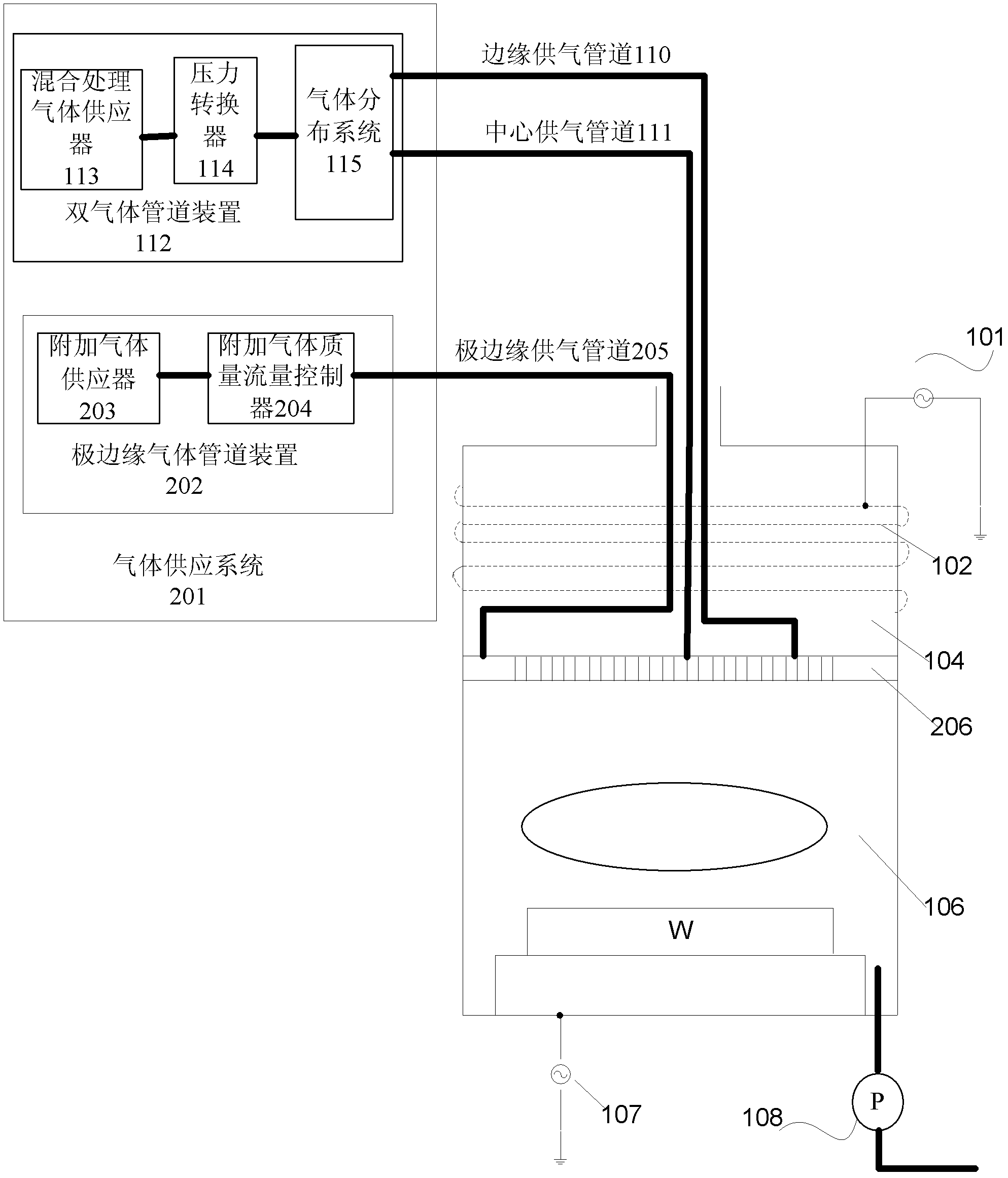

Etching device using extreme-edge gas pipeline

InactiveCN103219260AFine-tune and control activity levelsFine-tune and control limit activityElectric discharge tubesSemiconductor/solid-state device manufacturingAdditive ingredientSprayer

The invention provides an etching device which comprises a gas supply system and an etching reaction chamber. The etching reaction chamber comprises a gas sprayer which is connected with a double-gas pipeline device and an extreme-edge gas pipeline device. The gas supply system comprises the double-gas pipeline device and the extreme-edge gas pipeline device, wherein the double-gas pipeline device is used for supplying gas for the center part and the edge part of an etched wafer, and the extreme-edge gas pipeline device is used for supplying etching reaction gas for the extreme-edge of the etched wafer. In the etching process, through changes of gas ingredients and gas flow amount at the extreme-edge position of the wafer, etching evenness of the surface of the wafer is improved, and meanwhile the etching speed is delicately controlled.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Equipment and method for etching silicon nitride thin film

InactiveCN1549311AImprove mixing uniformitySmall water dropletsSemiconductor/solid-state device manufacturingPhosphoric acidOptoelectronics

The present invention relates to an equipment for etching silicon nitride film and its method. Firstly, a phosphoric acid tank is provided, and an ultrasonic wave generator is mounted on the side wall of the phosphoric acid tank, then a wafer a silicon nitride film is formed on the wafer therein, and the ultrasonic wave generator can be started so as to etch or remove the silicon nitride film on the wafer.

Owner:MACRONIX INT CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com