Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

940 results about "Etching selectivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

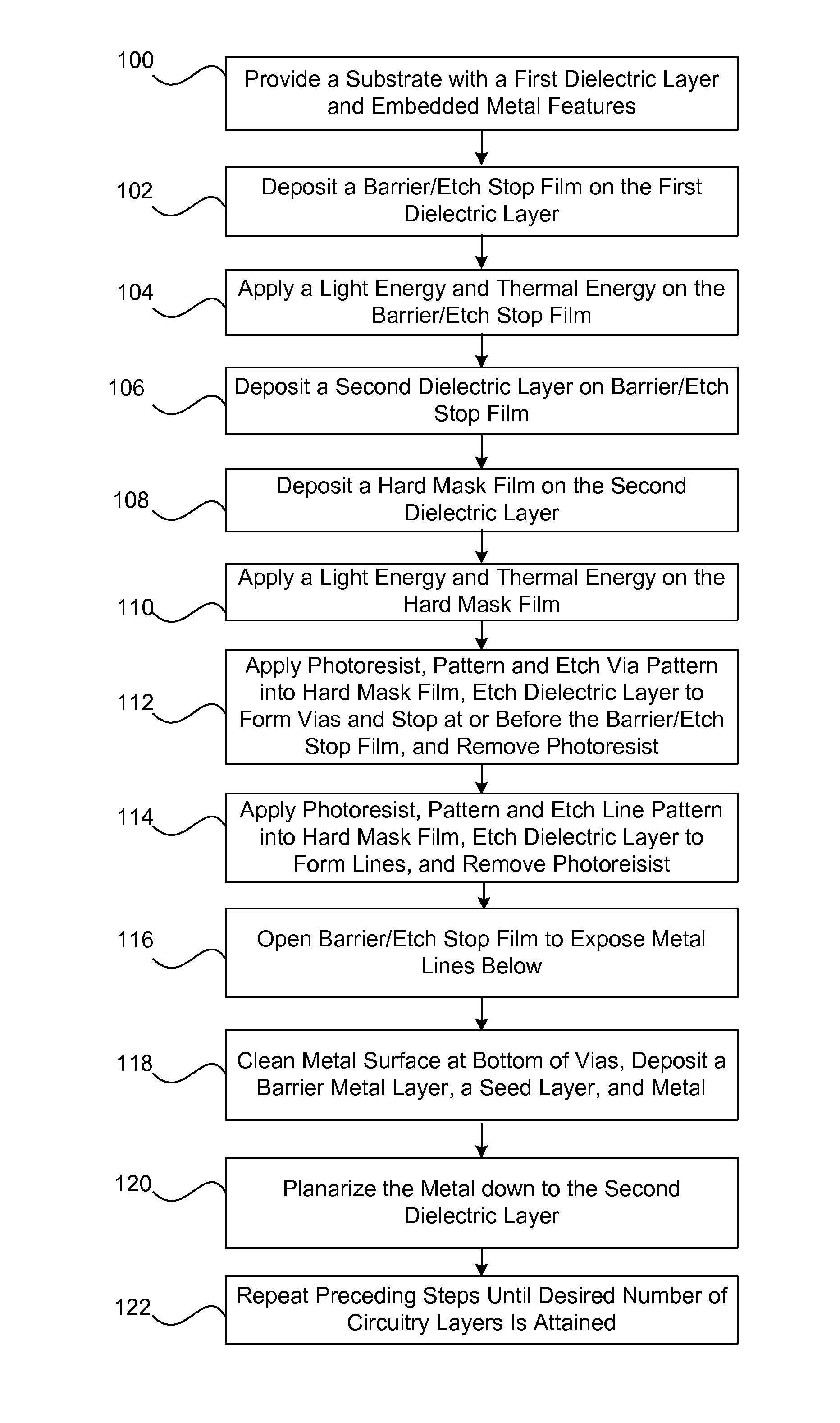

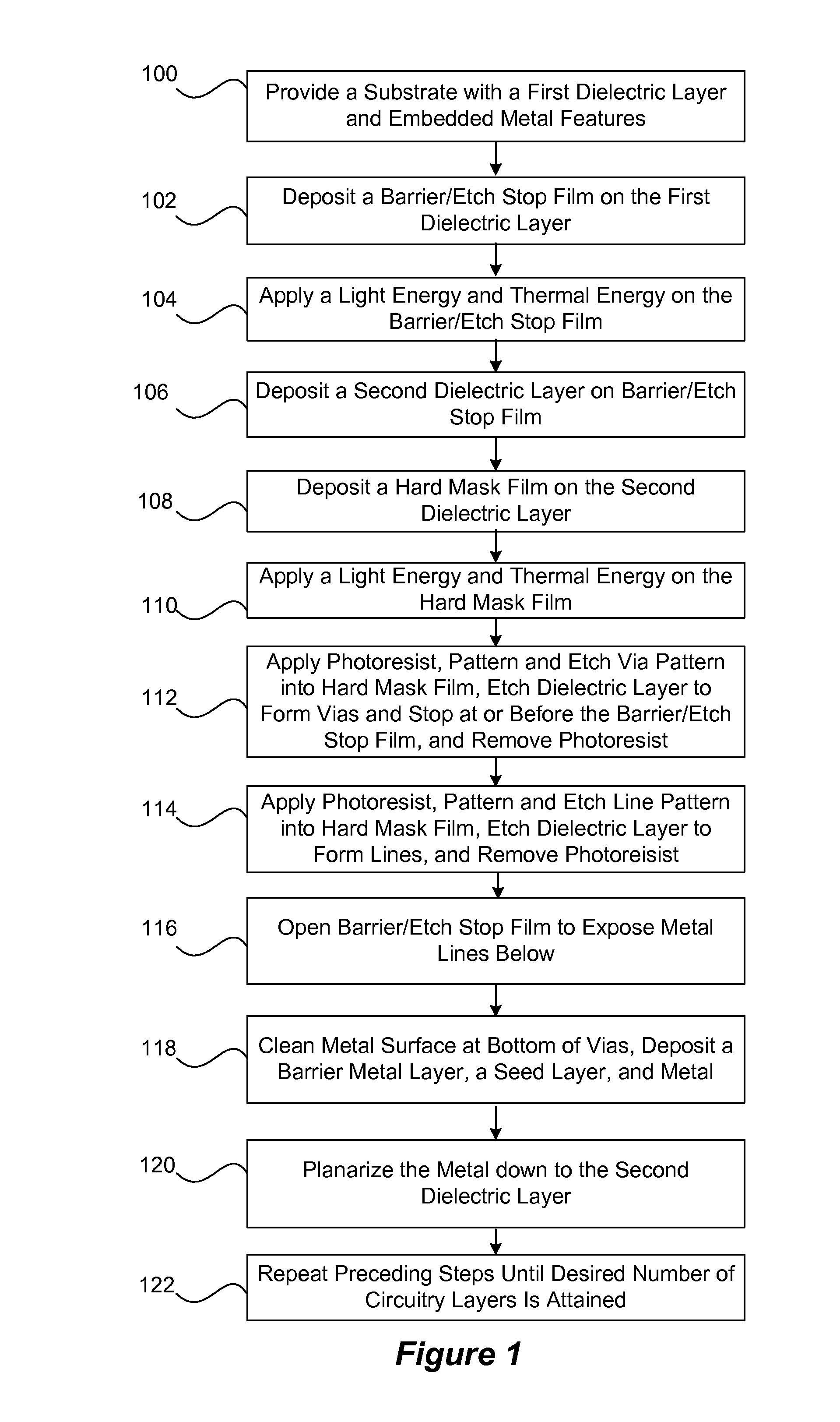

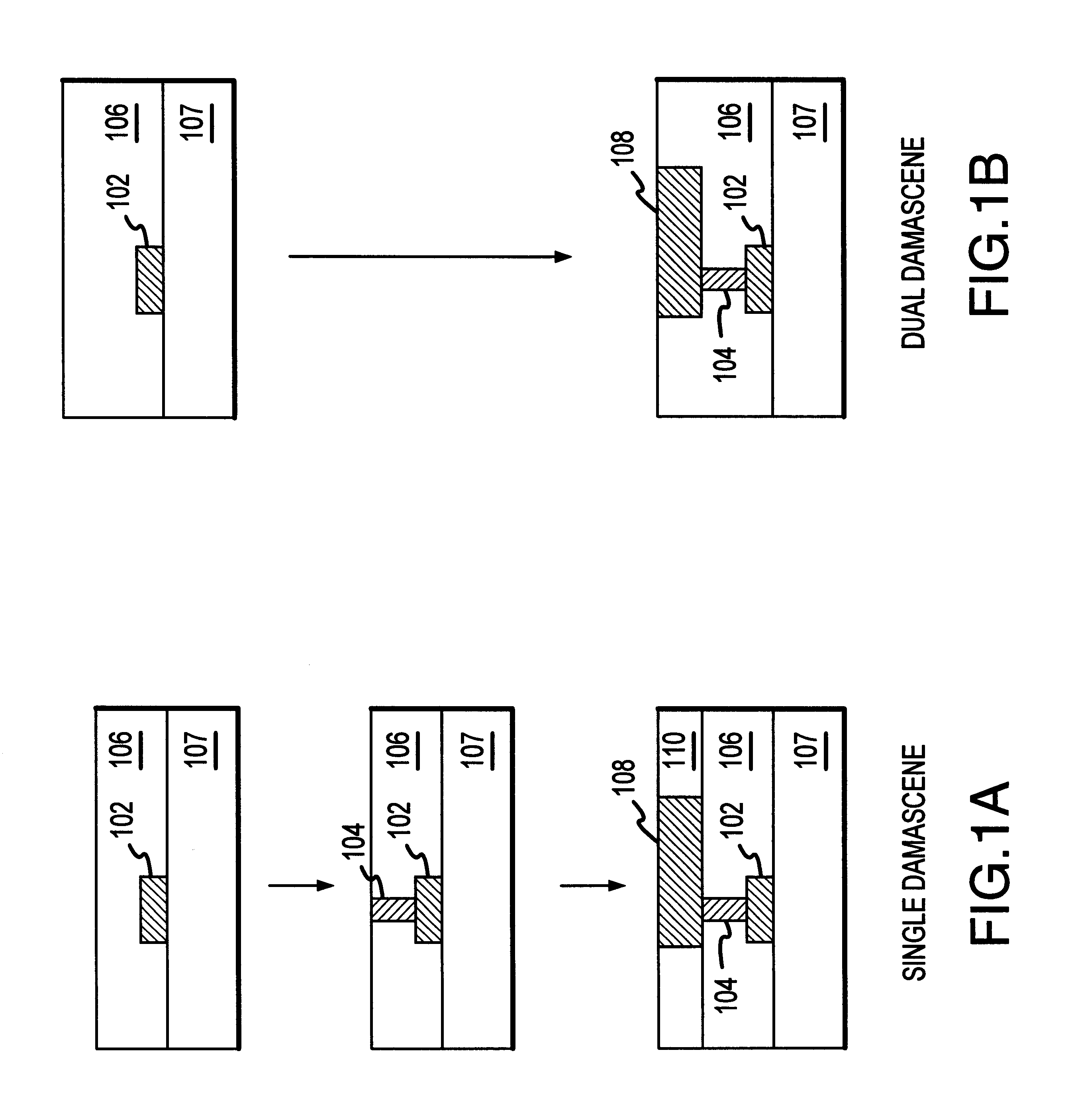

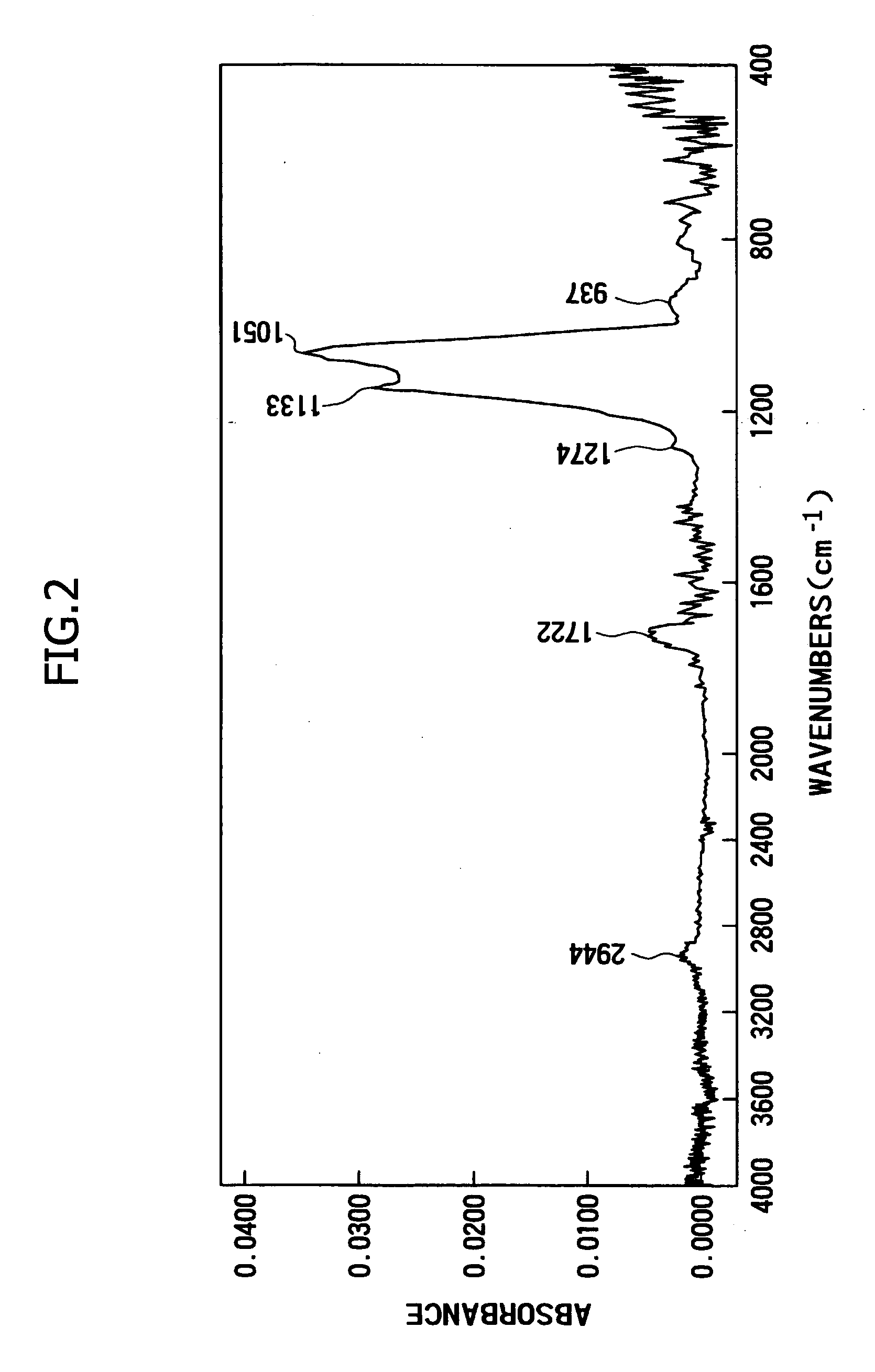

UV treatment of etch stop and hard mask films for selectivity and hermeticity enhancement

ActiveUS8242028B1Increase hermeticityHigh selectivitySemiconductor/solid-state device manufacturingThermal energyHydrogen

A method for the ultraviolet (UV) treatment of etch stop and hard mask film increases etch selectivity and hermeticity by removing hydrogen, cross-linking, and increasing density. The method is particularly applicable in the context of damascene processing. A method provides for forming a semiconductor device by depositing an etch stop film or a hard mask film on a substrate and exposing the film to UV radiation and optionally thermal energy. The UV exposure may be direct or through another dielectric layer.

Owner:NOVELLUS SYSTEMS

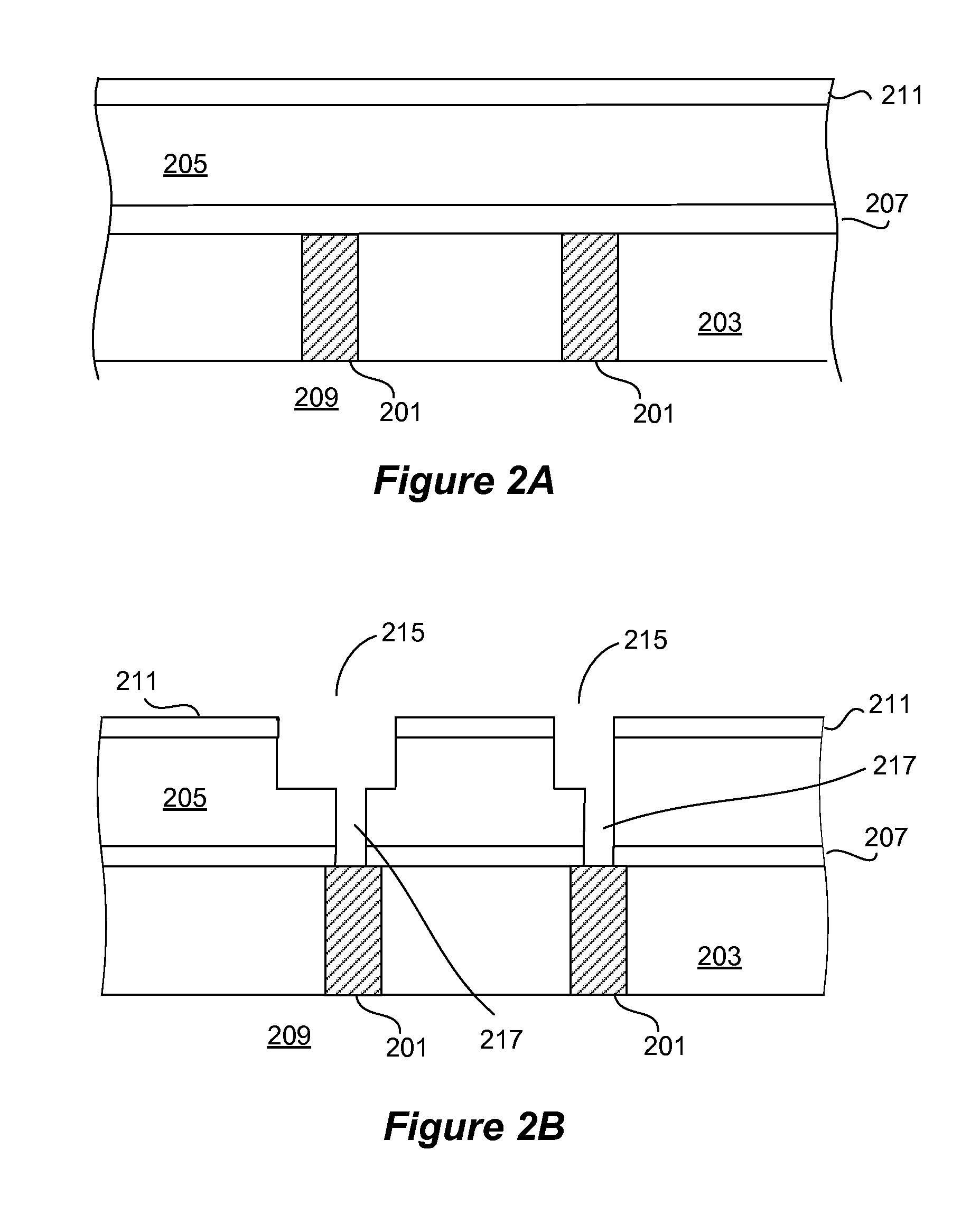

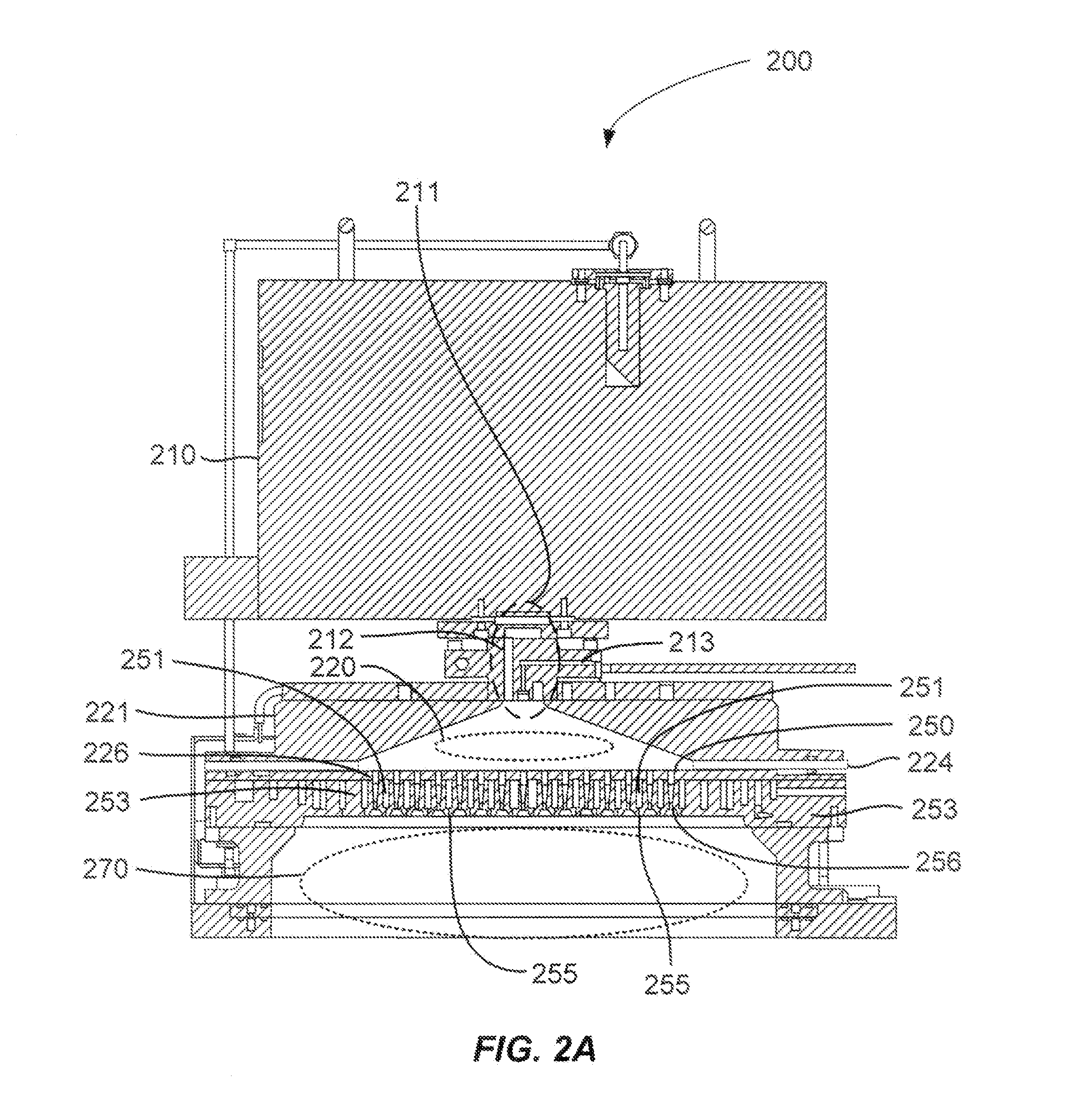

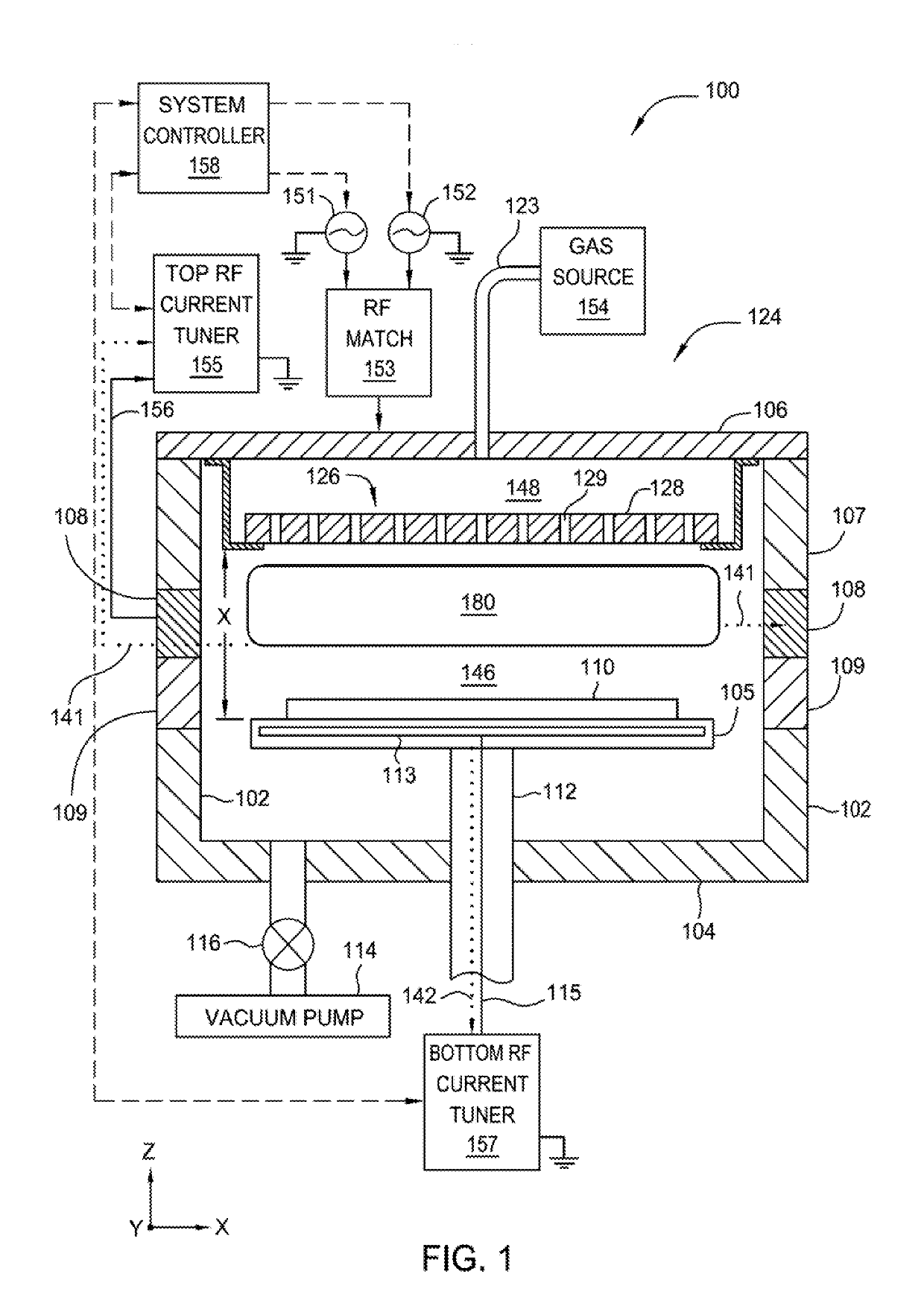

Methods and apparatus for plasma-based deposition

ActiveUS20140057454A1Reduction of overall thermal budgetImprove etch selectivityElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringPartial pressure

High-deposition rate methods for forming transparent ashable hardmasks (AHMs) that have high plasma etch selectivity to underlying layers are provided. The methods involve placing a wafer on a powered electrode such as a powered pedestal for plasma-enhanced deposition. According to various embodiments, the deposition is run at low hydrocarbon precursor partial pressures and / or low process temperatures. Also provided are ceramic wafer pedestals with multiple electrode planes embedded with the pedestal are provided. According to various embodiments, the pedestals have multiple RF mesh electrode planes that are connected together such that all the electrode planes are at the same potential.

Owner:NOVELLUS SYSTEMS

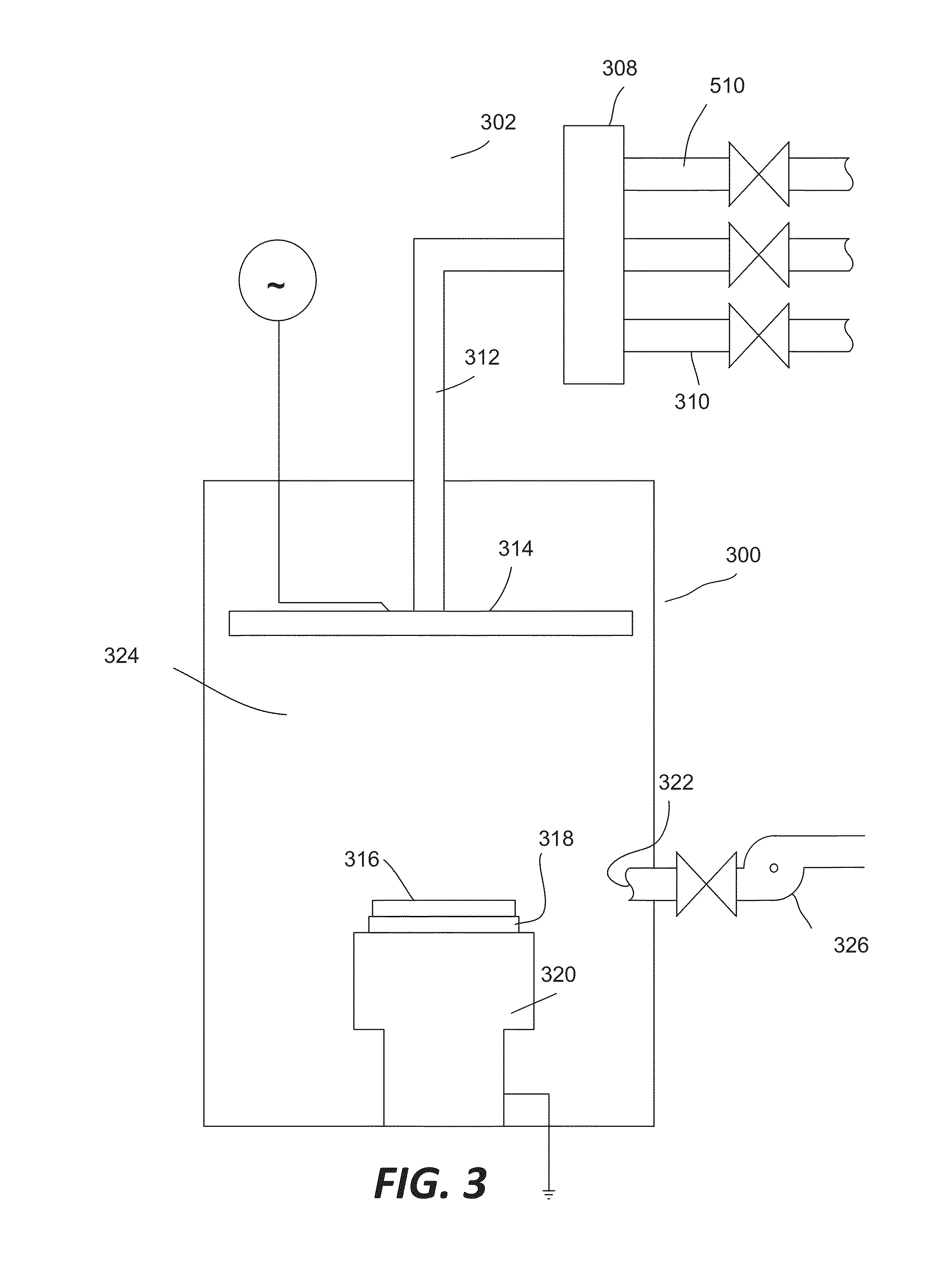

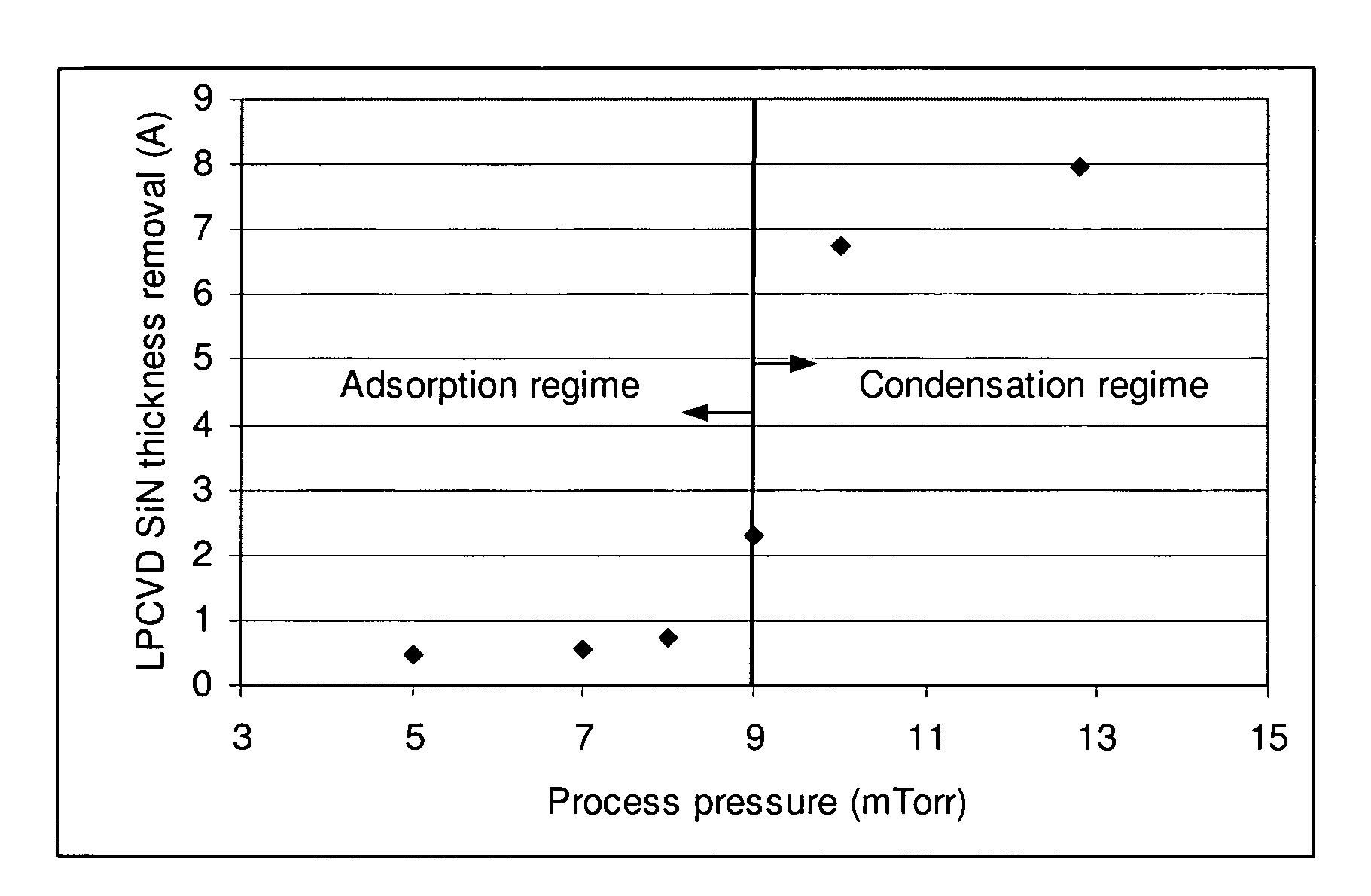

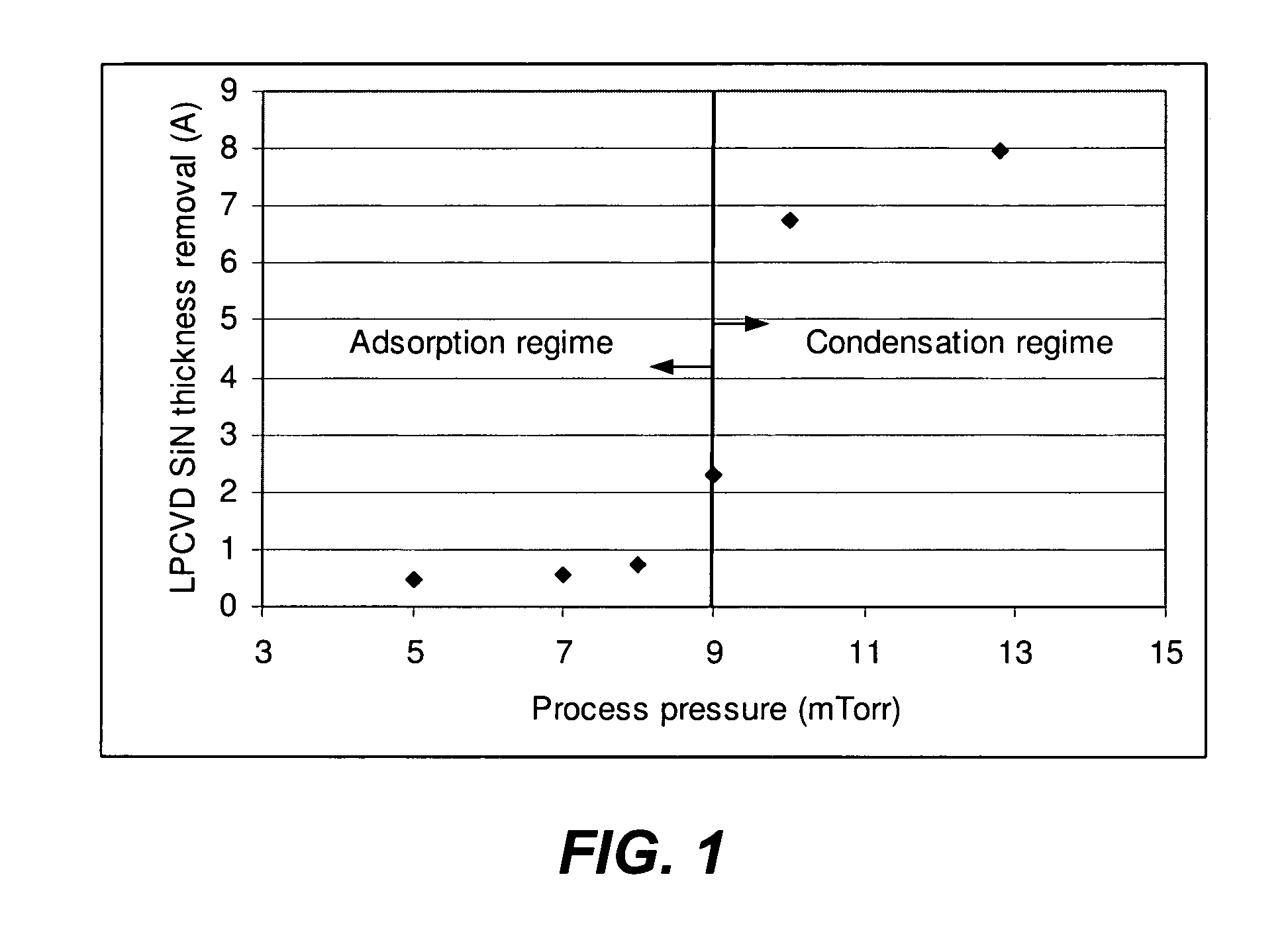

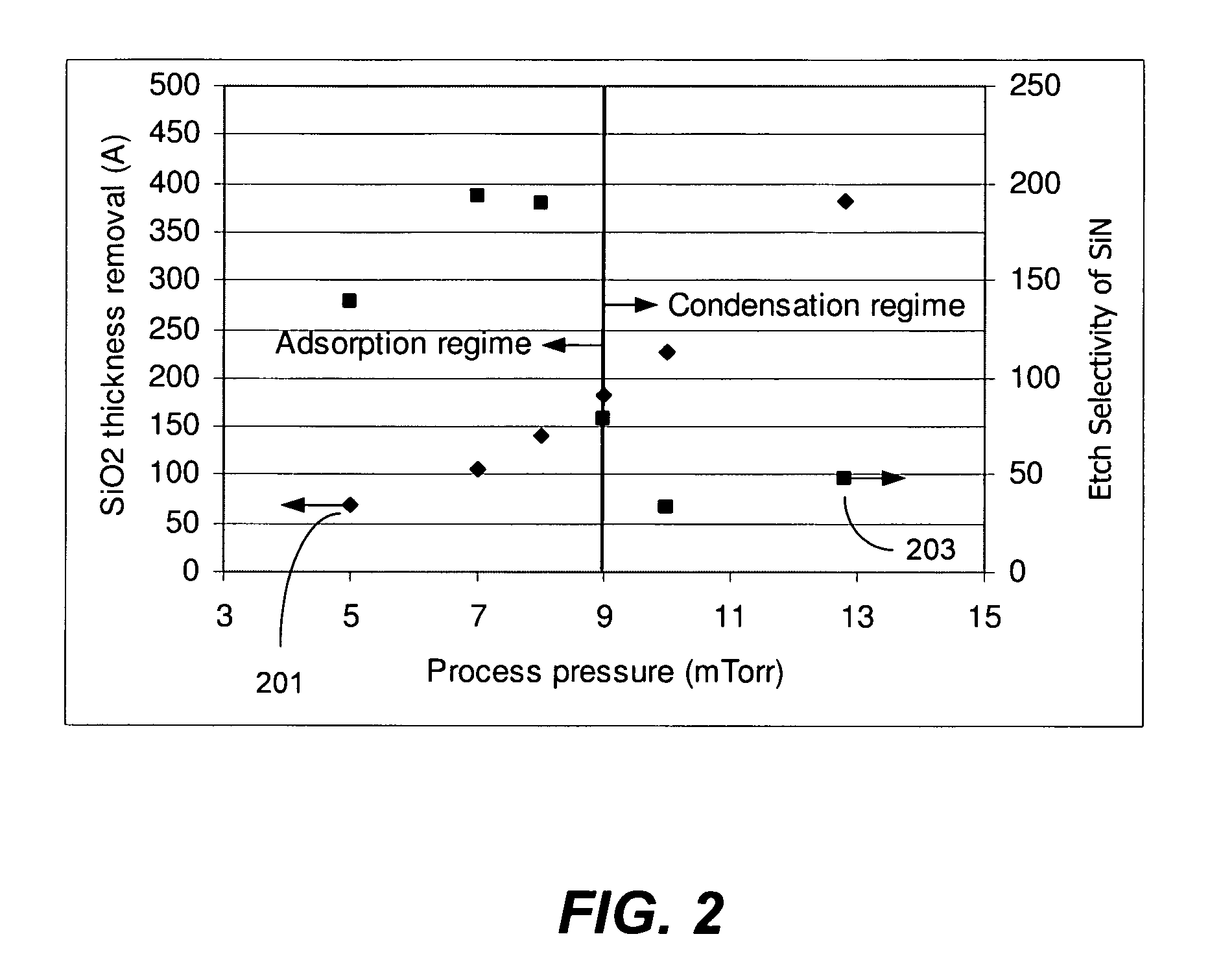

Modulating etch selectivity and etch rate of silicon nitride thin films

ActiveUS8187486B1Decorative surface effectsSemiconductor/solid-state device manufacturingNitrideMolecular physics

Etching of nitride and oxide layers with reactant gases is modulated by etching in different process regimes. High etch selectivity to silicon nitride is achieved in an adsorption regime where the partial pressure of the etchant is lower than its vapor pressure. Low etch selectivity to silicon nitride is achieved in a condensation regime where the partial pressure of the etchant is higher than its vapor pressure. By controlling partial pressure of the etchant, very high etch selectivity to silicon nitride may be achieved.

Owner:NOVELLUS SYSTEMS

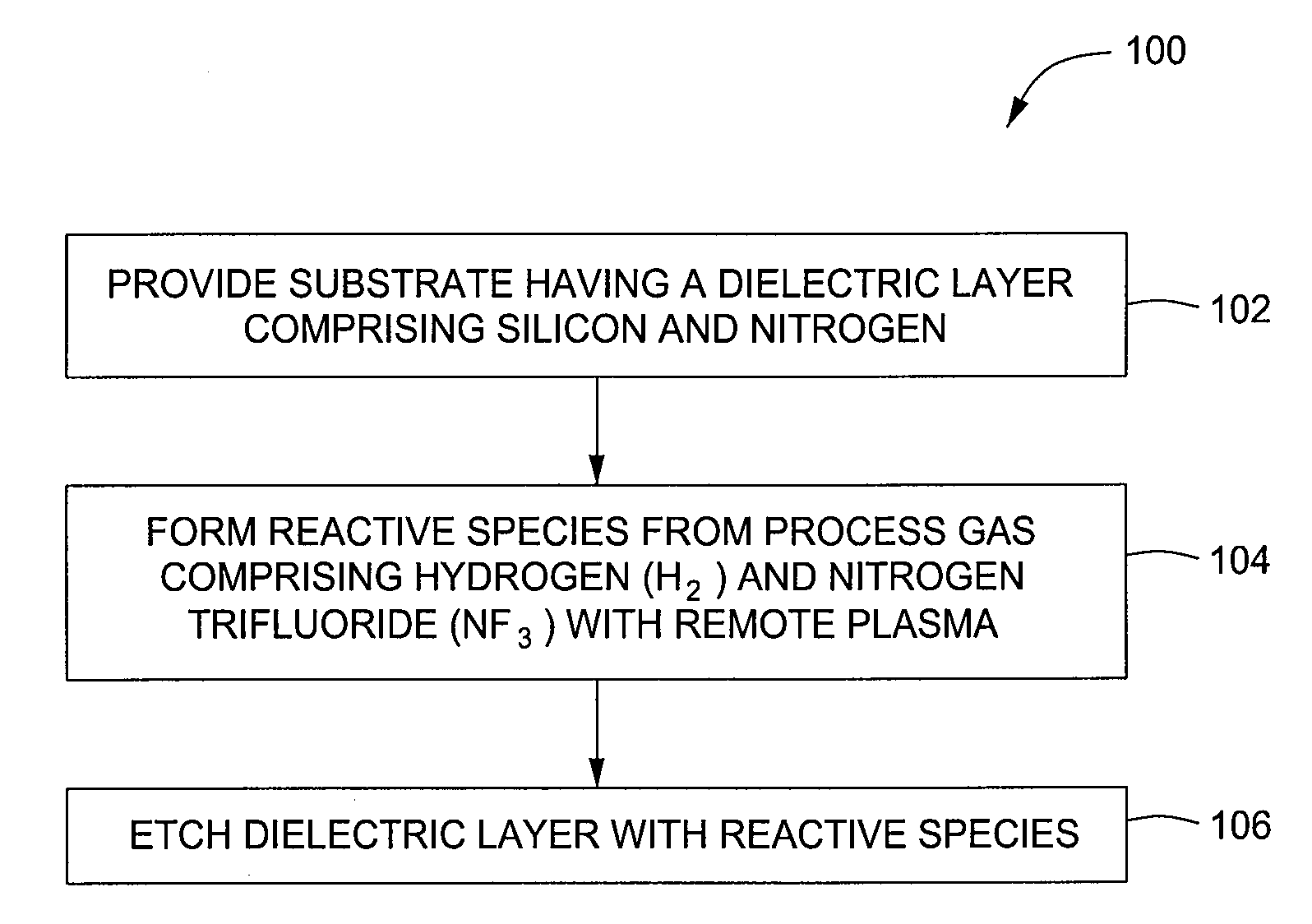

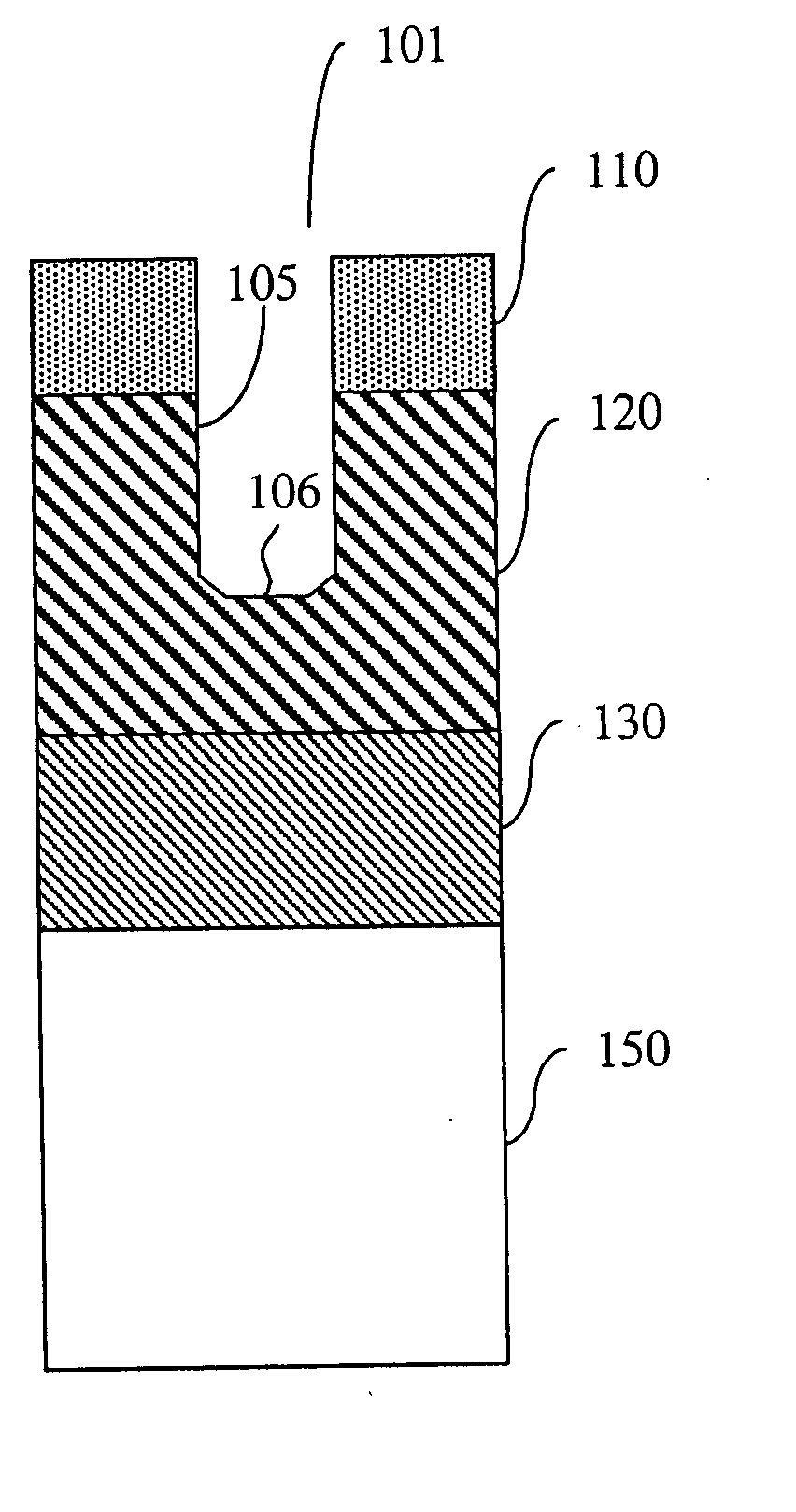

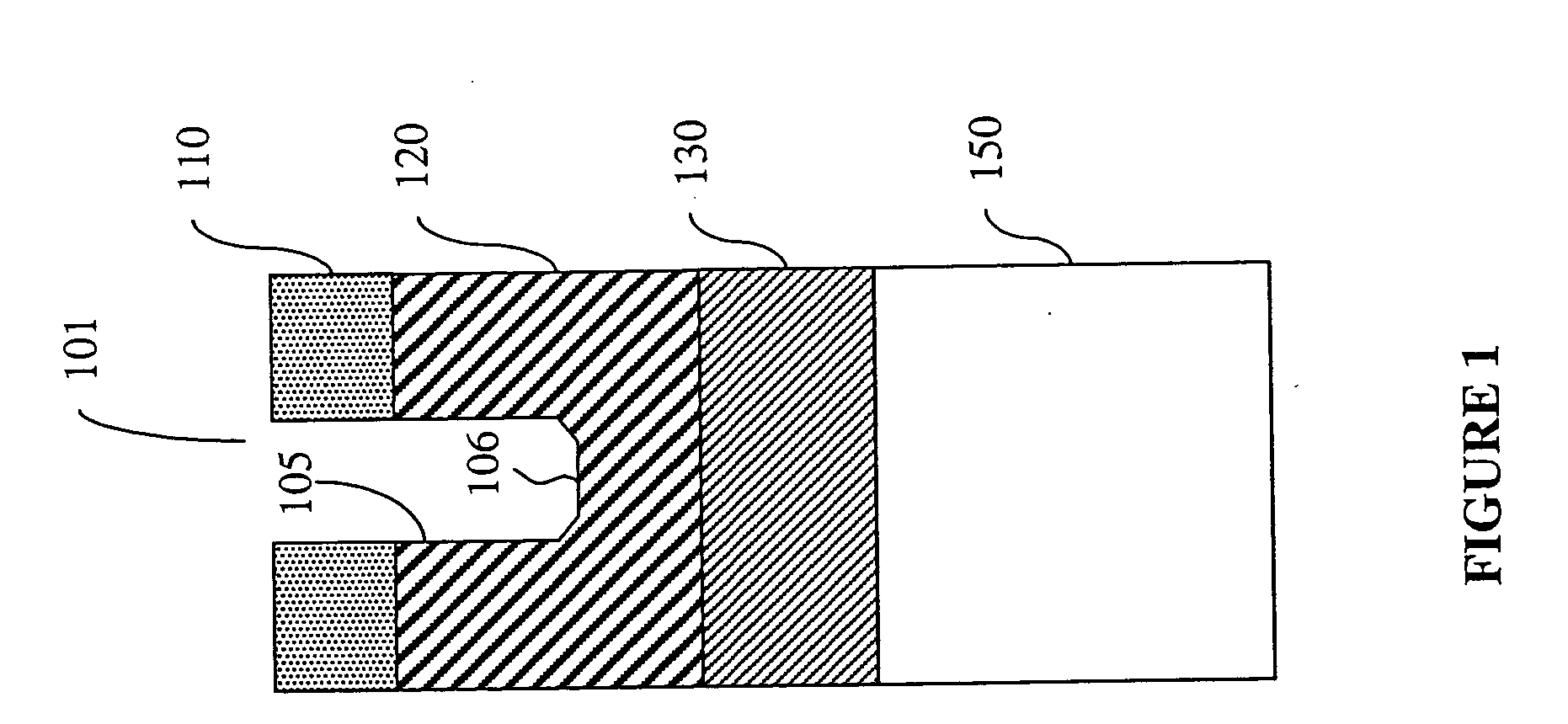

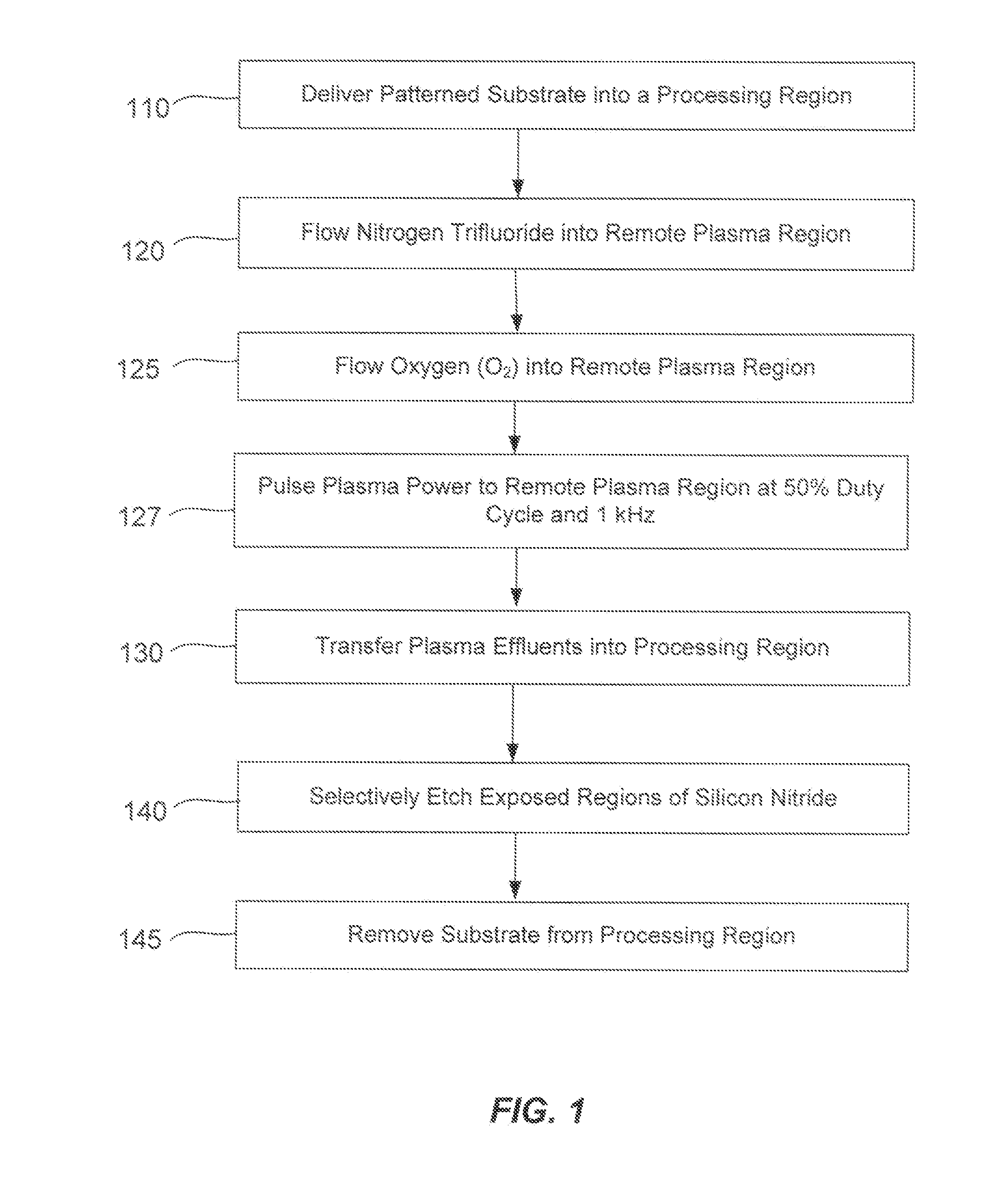

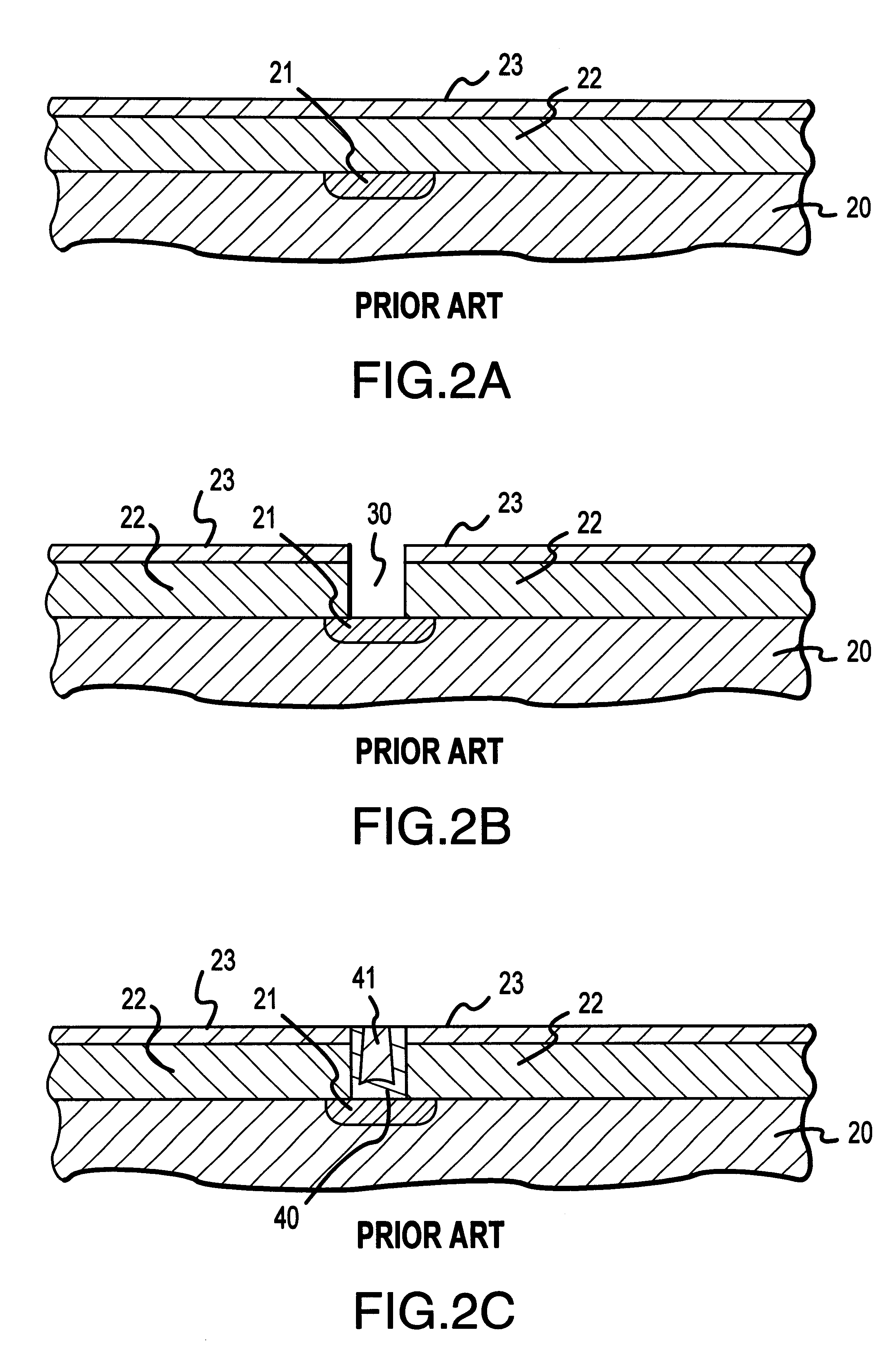

Selective etching of silicon nitride

InactiveUS20090104782A1Promotes selective oxidationSemiconductor/solid-state device manufacturingRemote plasmaHydrogen

Owner:APPLIED MATERIALS INC

Selective etching of carbon-doped low-k dielectrics

InactiveUS20050026430A1High selectivityReducing micro-loadingDecorative surface effectsVacuum evaporation coatingPlasma etchingChemistry

The present invention includes a process for selectively etching a low-k dielectric material formed on a substrate using a plasma of a gas mixture in a plasma etch chamber. The gas mixture comprises a fluorine-rich fluorocarbon or hydrofluorocarbon gas, a nitrogen-containing gas, and one or more additive gases, such as a hydrogen-rich hydrofluorocarbon gas, an inert gas and / or a carbon-oxygen gas. The process provides a low-k dielectric to a photoresist mask etching selectivity ratio greater than about 5:1, a low-k dielectric to a barrier / liner layer etching selectivity ratio greater about 10:1, and a low-k dielectric etch rate higher than about 4000 Å / min.

Owner:APPLIED MATERIALS INC

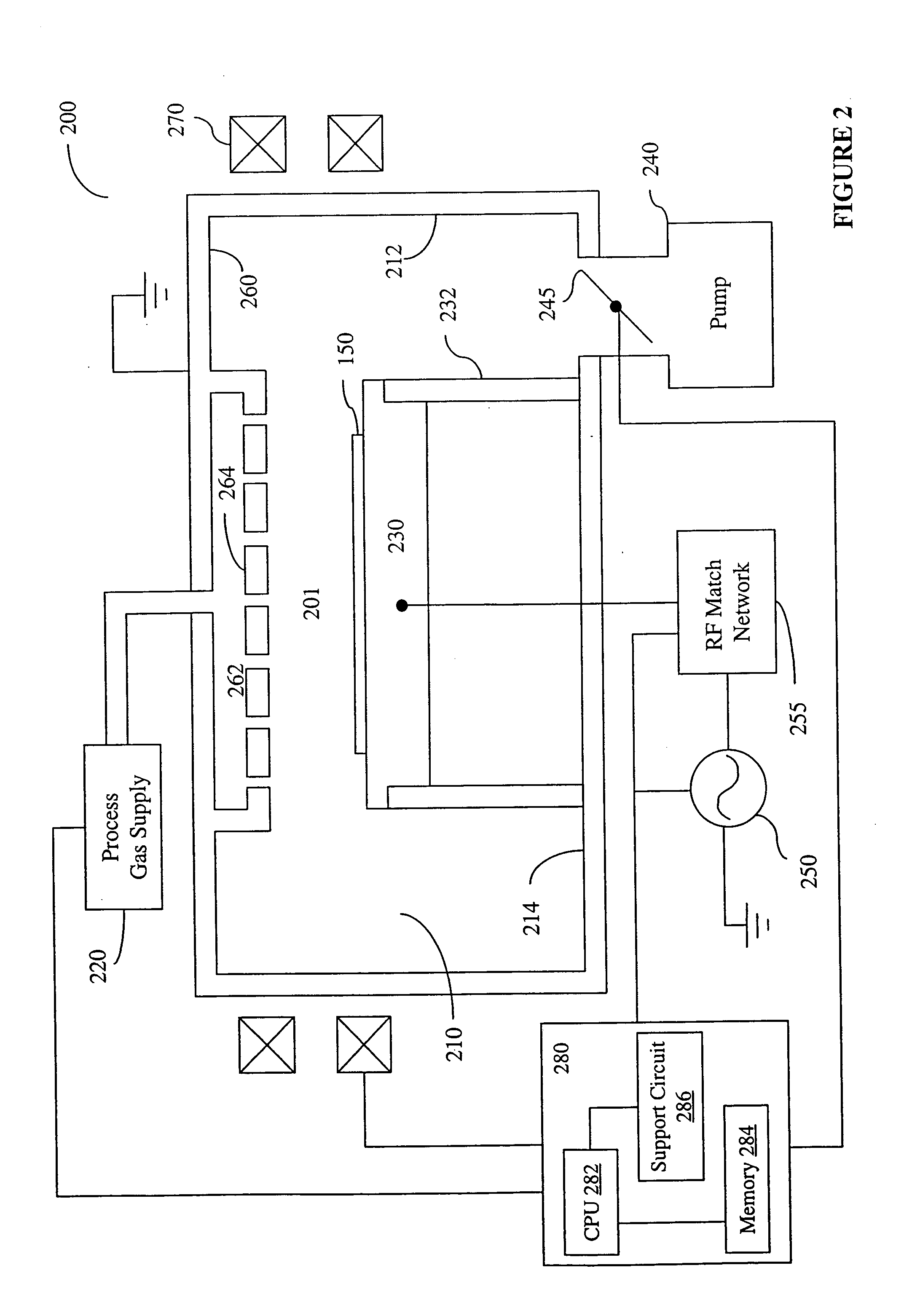

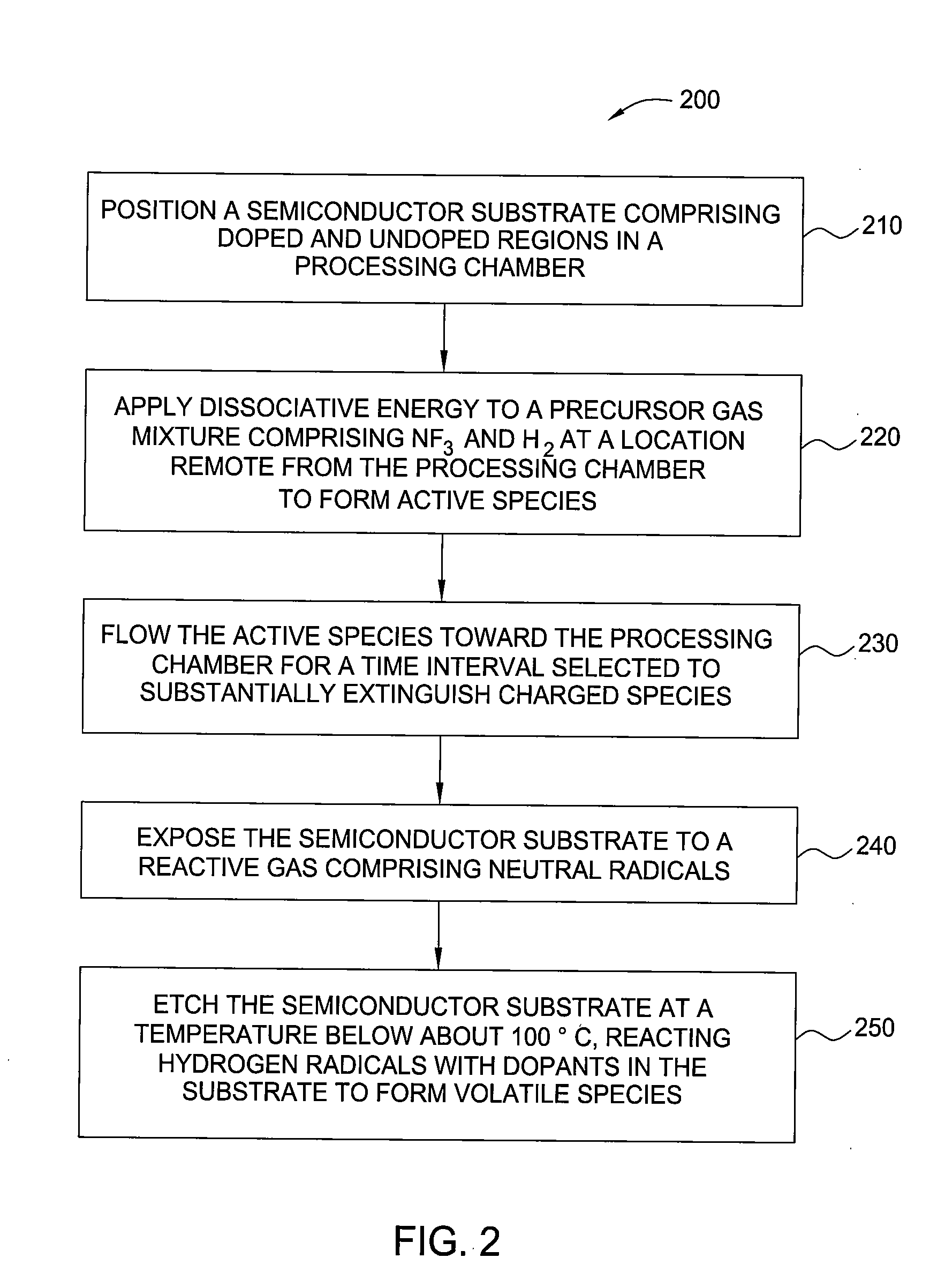

Nf3/h2 remote plasma process with high etch selectivity of psg/bpsg over thermal oxide and low density surface defects

InactiveUS20100099263A1Fast etchElectric discharge tubesSemiconductor/solid-state device manufacturingHydrogenRemote plasma

A method and apparatus for selectively etching doped semiconductor oxides faster than undoped oxides. The method comprises applying dissociative energy to a mixture of nitrogen trifluoride and hydrogen gas remotely, flowing the activated gas toward a processing chamber to allow time for charged species to be extinguished, and applying the activated gas to the substrate. Reducing the ratio of hydrogen to nitrogen trifluoride increases etch selectivity. A similar process may be used to smooth surface defects in a silicon surface.

Owner:APPLIED MATERIALS INC

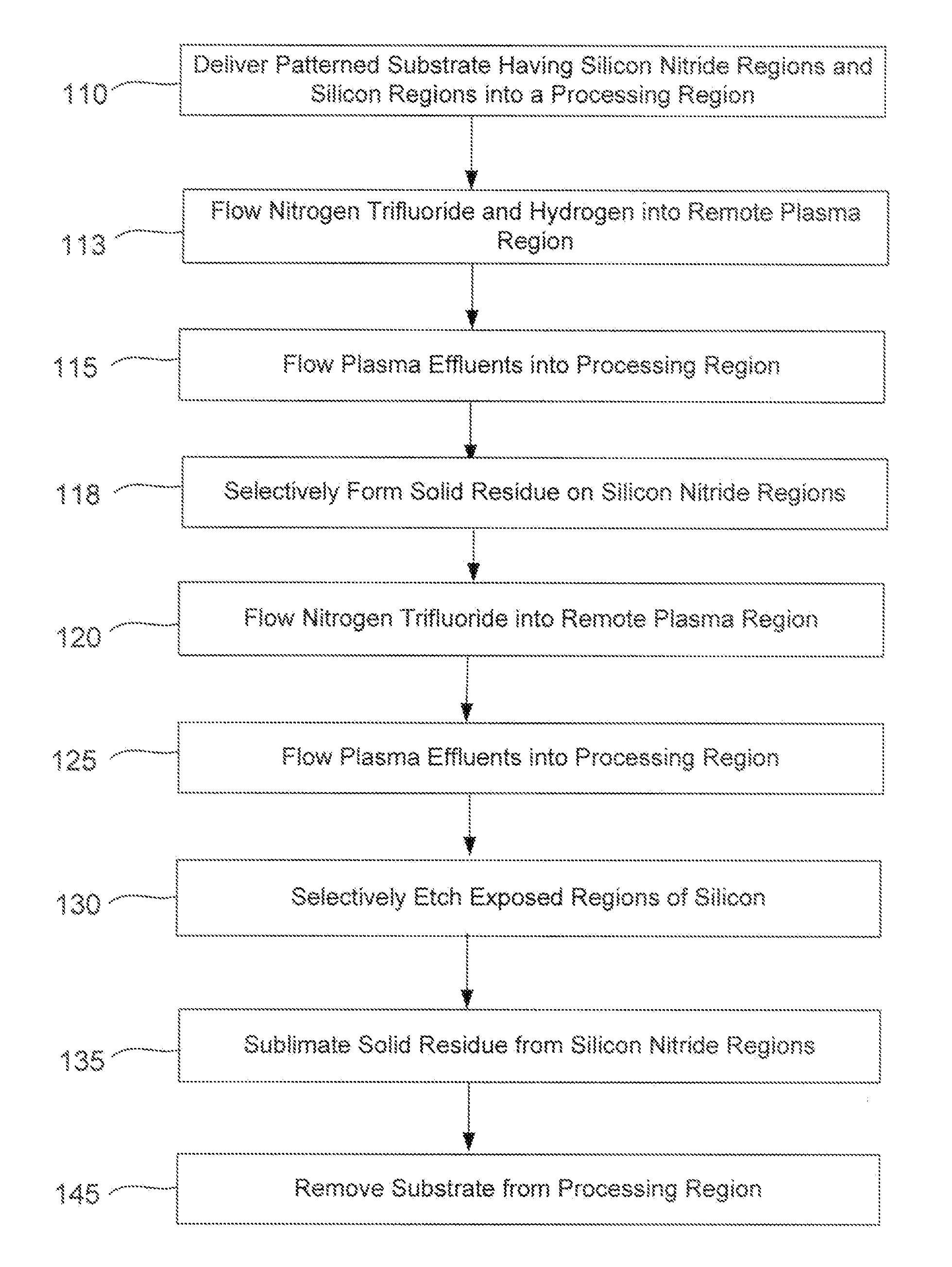

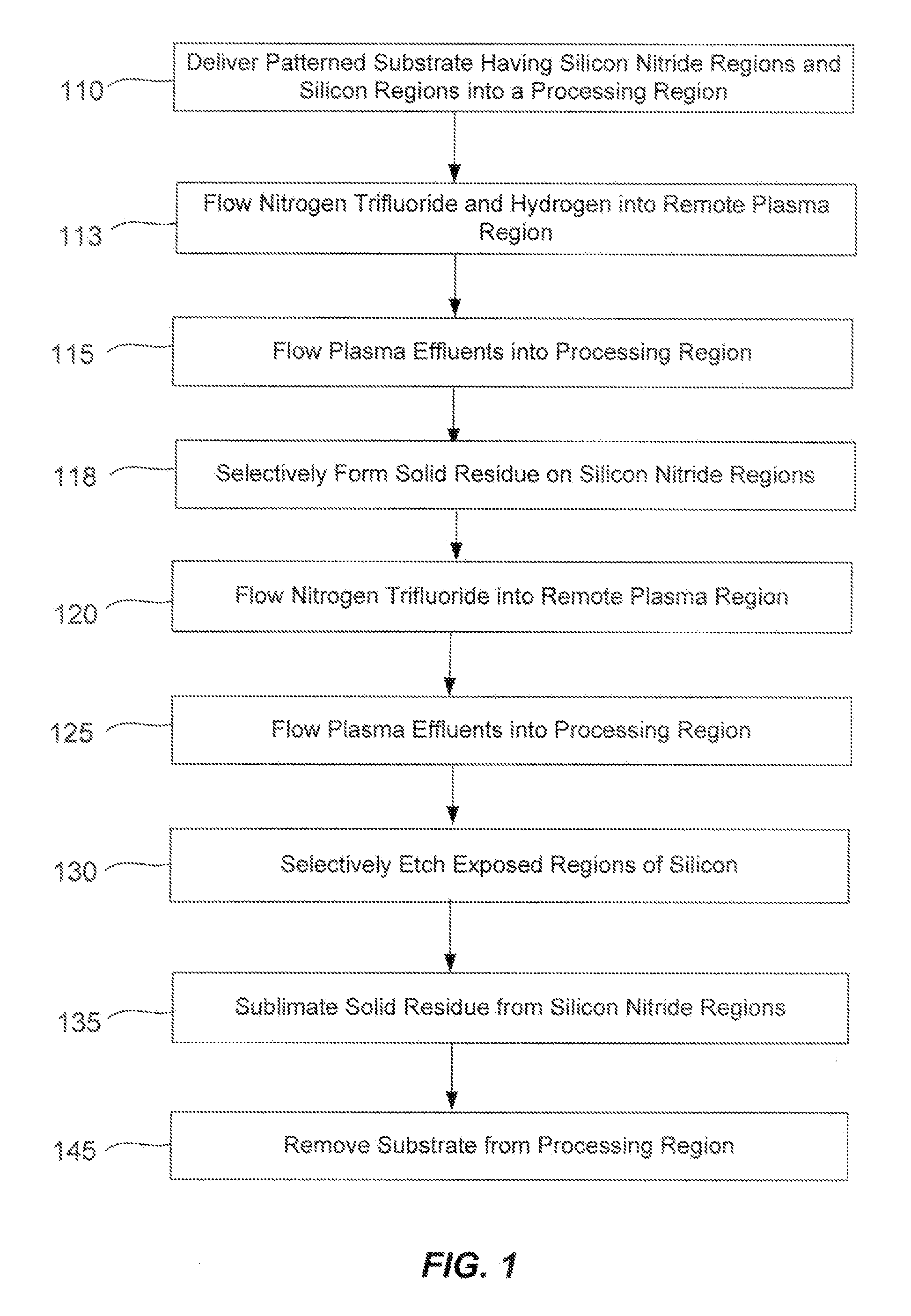

Selective suppression of dry-etch rate of materials containing both silicon and nitrogen

InactiveUS20130059440A1Inhibit etch rateImprove etch selectivityElectric discharge tubesSemiconductor/solid-state device manufacturingRemote plasmaHydrogen

A method of suppressing the etch rate for exposed silicon-and-nitrogen-containing material on patterned heterogeneous structures is described and includes a two stage remote plasma etch. The etch selectivity of silicon relative to silicon nitride and other silicon-and-nitrogen-containing material is increased using the method. The first stage of the remote plasma etch reacts plasma effluents with the patterned heterogeneous structures to form protective solid by-product on the silicon-and-nitrogen-containing material. The plasma effluents of the first stage are formed from a remote plasma of a combination of precursors, including nitrogen trifluoride and hydrogen (H2). The second stage of the remote plasma etch also reacts plasma effluents with the patterned heterogeneous structures to selectively remove material which lacks the protective solid by-product. The plasma effluents of the second stage are formed from a remote plasma of a fluorine-containing precursor.

Owner:APPLIED MATERIALS INC

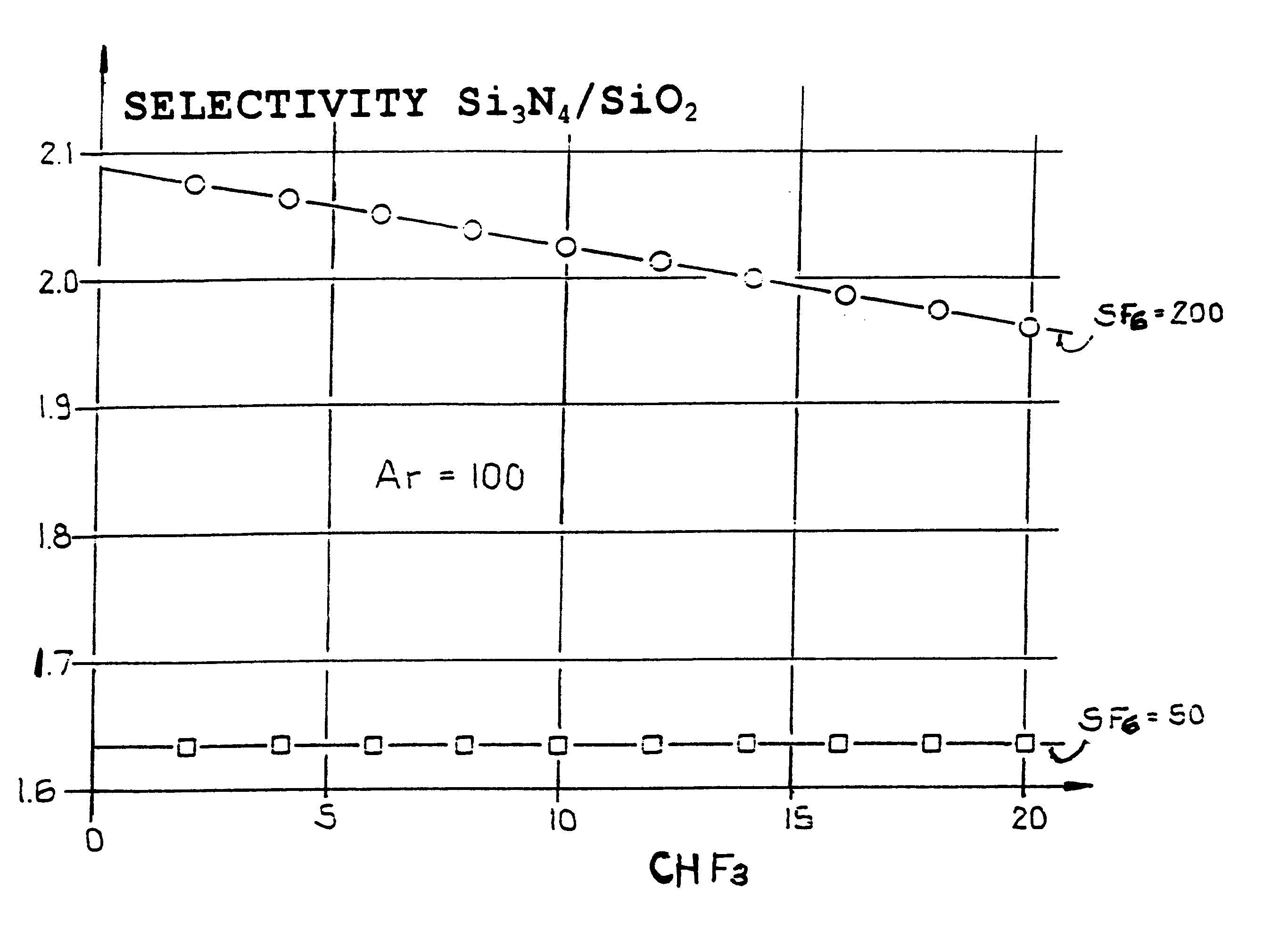

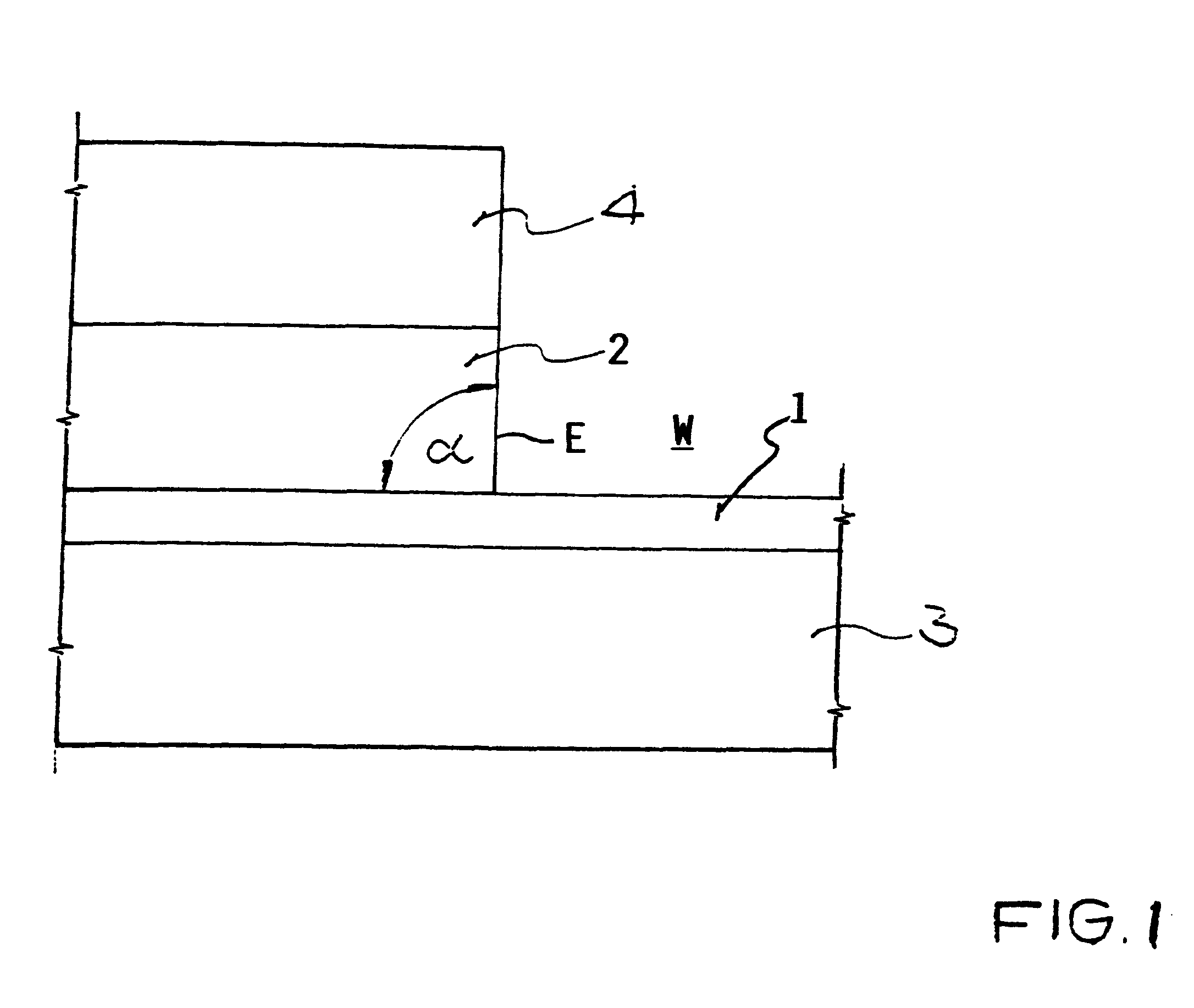

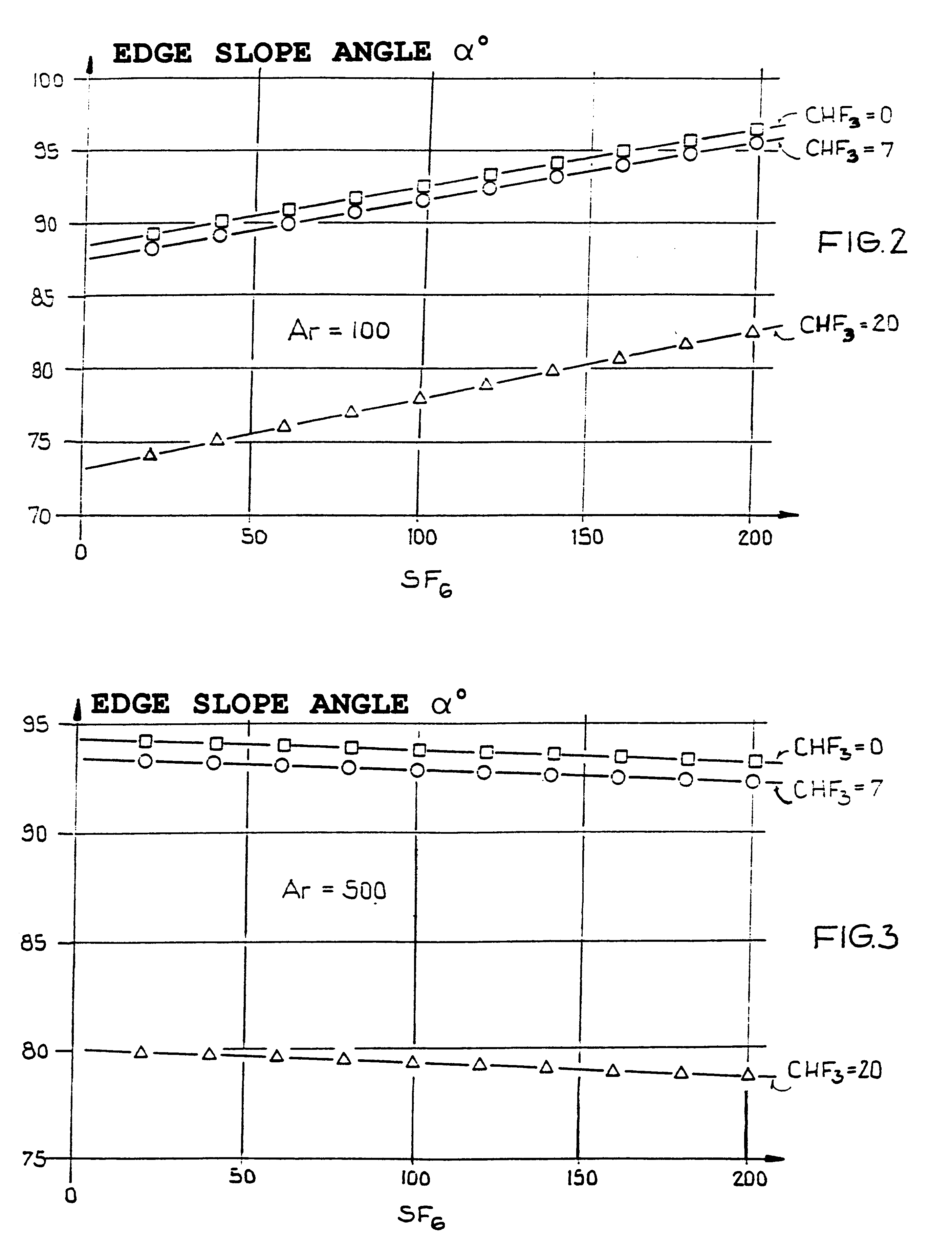

Method for anisotropic plasma-chemical dry etching of silicon nitride layers using a gas mixture containing fluorine

InactiveUS6569773B1Improve uniformityHigh atomic weightSemiconductor/solid-state device manufacturingSilicon oxideOxygen

An etching gas mixture containing CHF3, SF6 and a non-oxidizing gas such as Ar is used as an etching gas mixture for the anisotropic plasma-chemical dry-etching of a silicon nitride layer differentially or selectively relative to a silicon oxide layer. The gas mixture does not contain oxygen, chlorine, bromine, iodine or halides in addition to the above mentioned constituents, so that the process can be carried out in reactor systems equipped with oxidizable electrodes. By adjusting the gas flow rates or composition ratios of CHF3, SF6, and argon in the etching gas mixture, it is possible to adjust the resulting etching selectivity of silicon nitride relative to silicon oxide, and the particular edge slope angle of the etched edge of the remaining silicon nitride layer. A high etch rate for the silicon nitride is simultaneously achieved.

Owner:ATMEL CORP +1

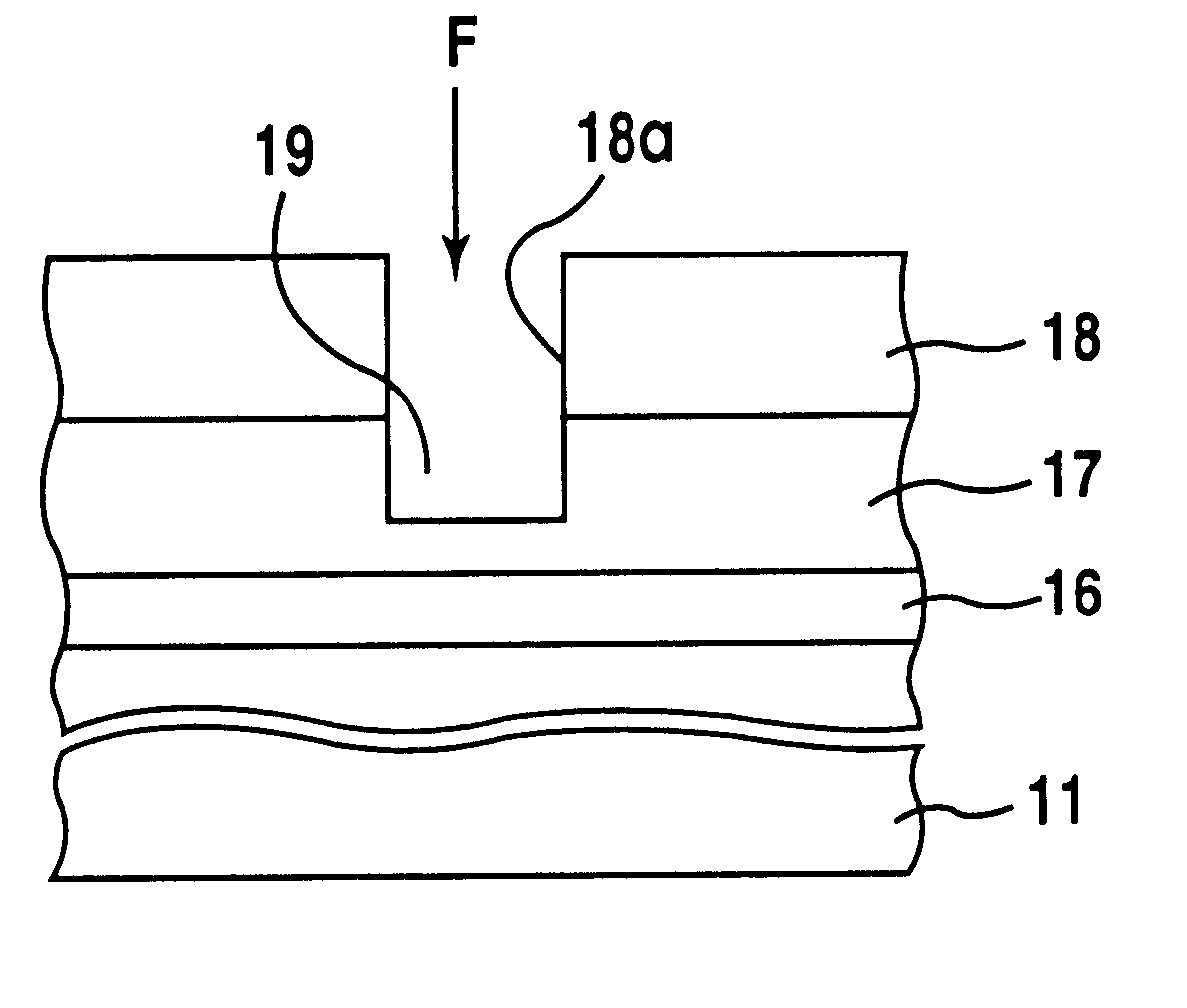

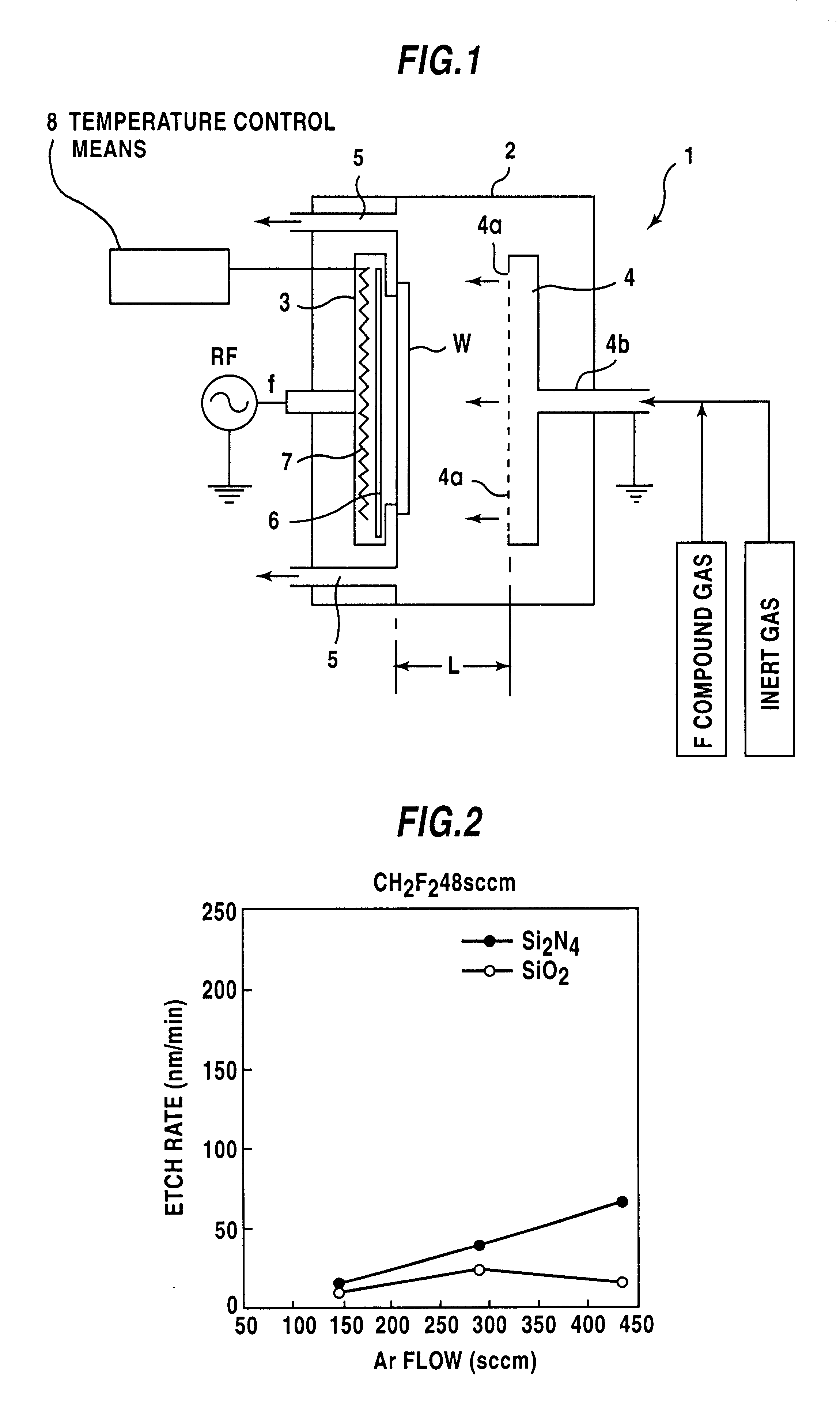

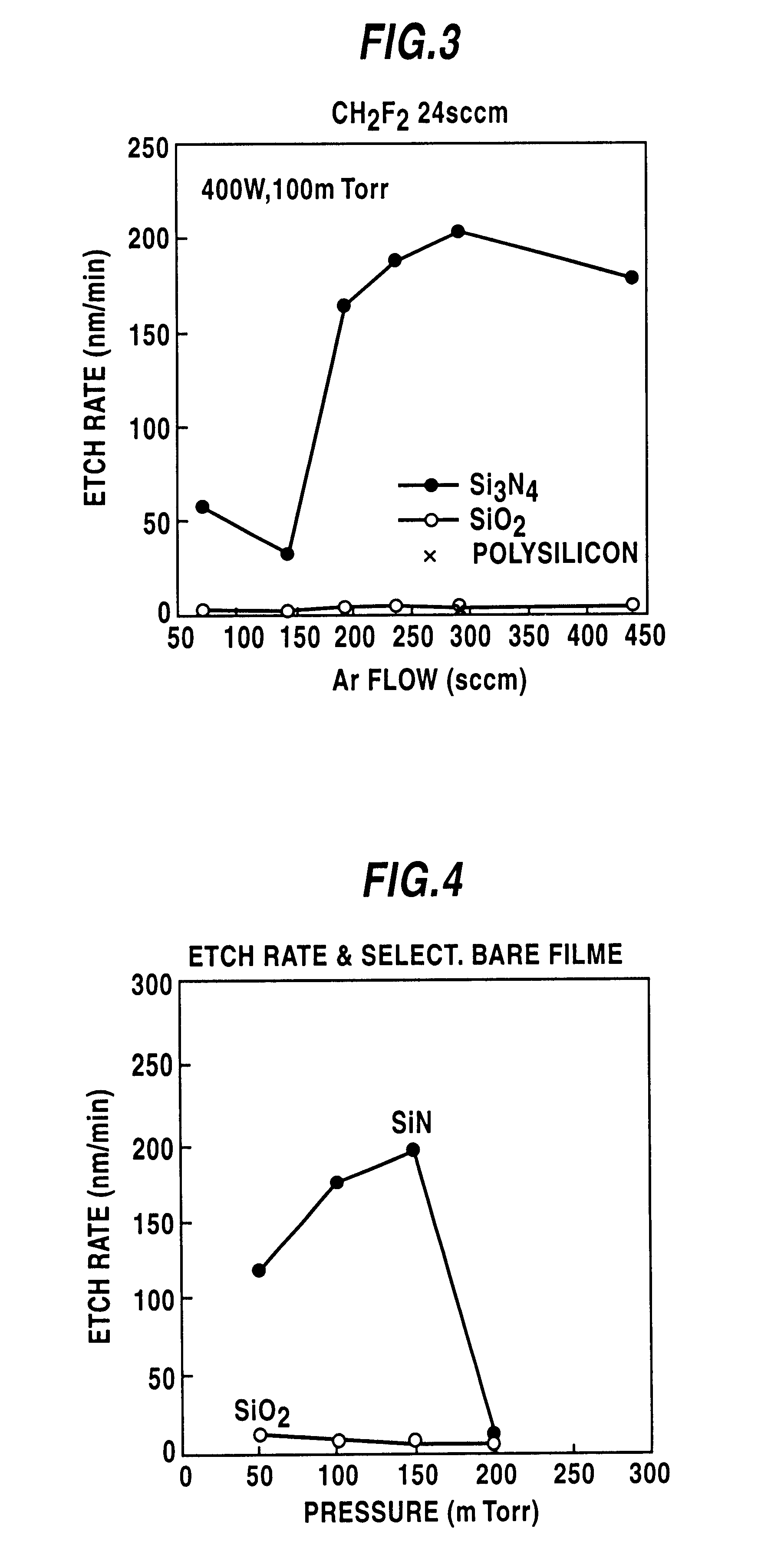

Method of etching silicon nitride by a mixture of CH2 F2, CH3F or CHF3 and an inert gas

InactiveUS6376386B1Solid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideDry etching

There are included steps of forming a silicon nitride layer on a silicon layer or a silicon oxide layer, loading the silicon layer or the silicon oxide layer and the silicon nitride layer in a dry etching atmosphere, and selectively etching the silicon nitride layer with respect to the silicon layer or the silicon oxide layer by flowing a fluorine gas consisting of any one of CH2F2, CH3F, or CHF3 and an inert gas to the dry etching atmosphere. Hence, in the etching process of the silicon nitride layer, the etching selectivity of the silicon nitride layer to Si or SiO2 can be enhanced and also etching anisotropy can be enhanced.

Owner:FUJITSU SEMICON LTD

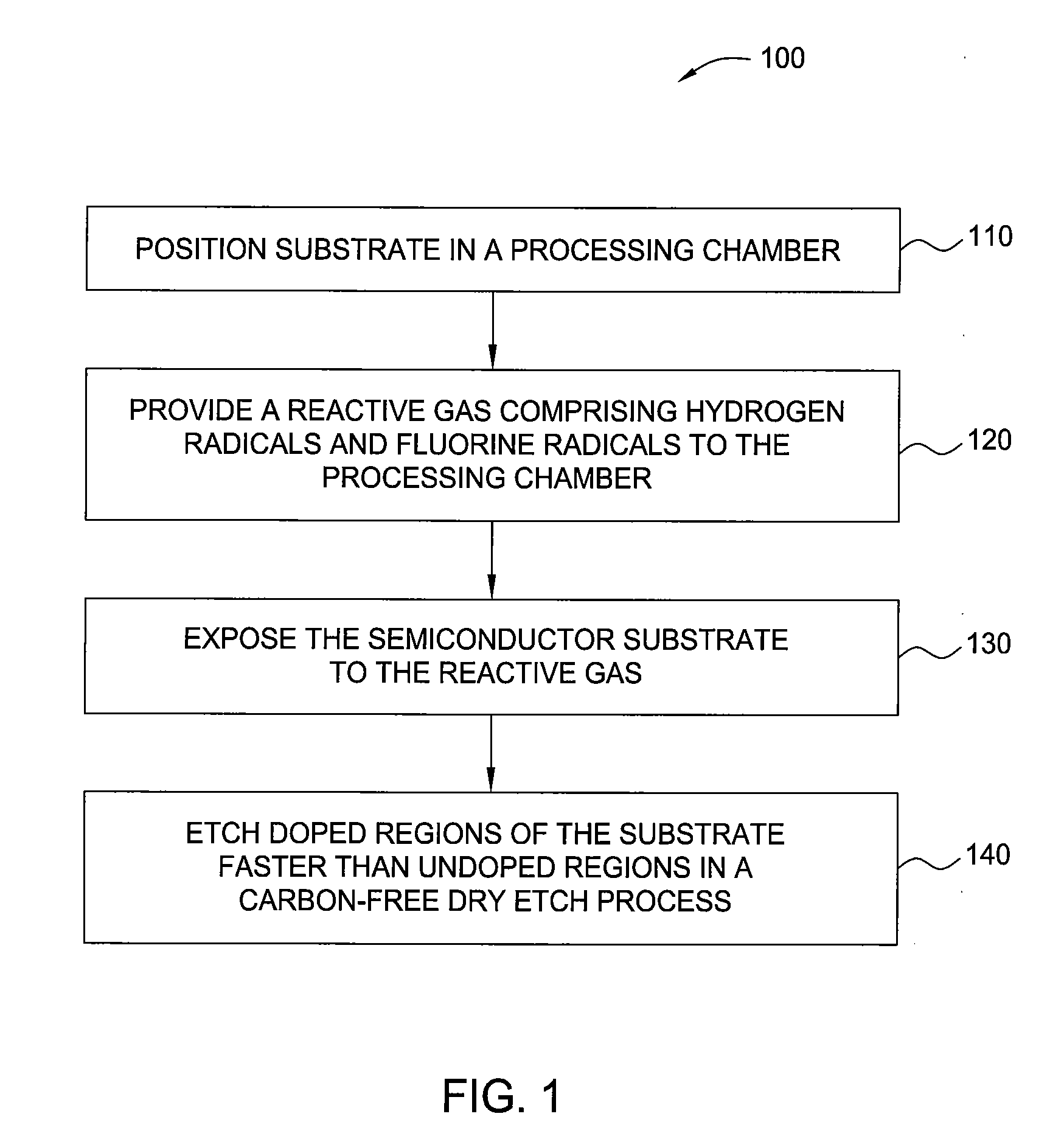

Dry-etch selectivity

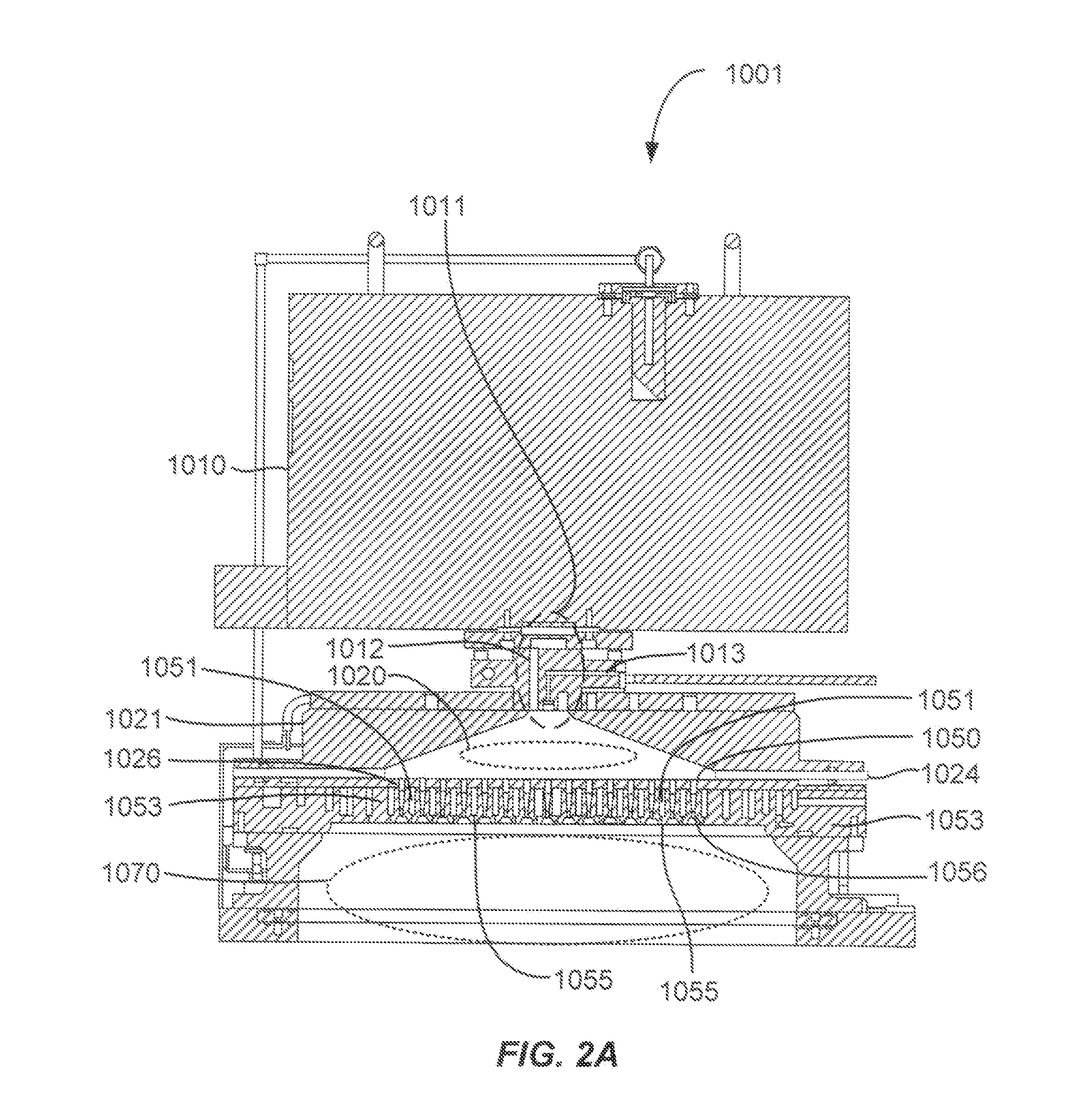

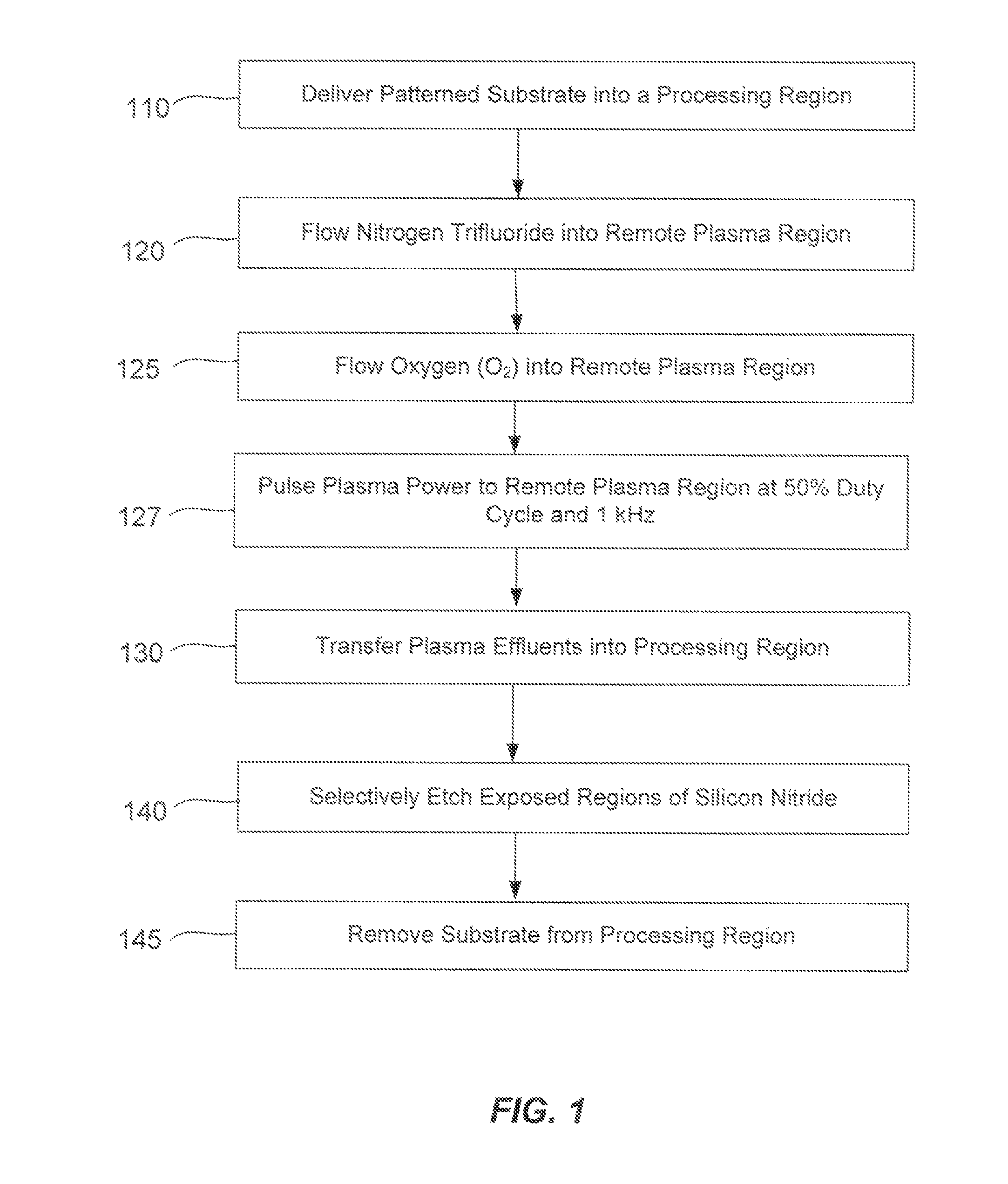

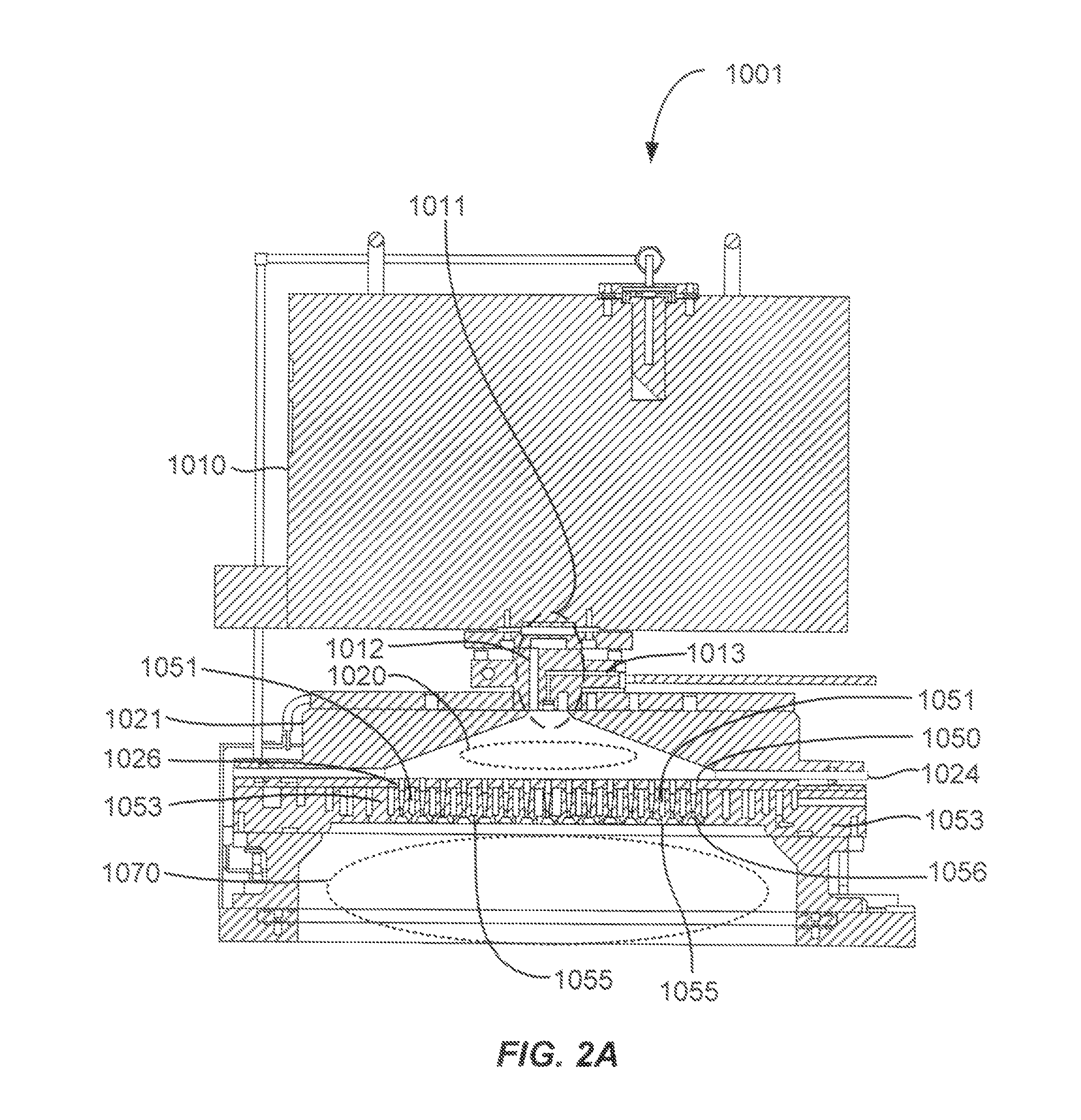

InactiveUS20140141621A1Reduce the numberElectric discharge tubesSemiconductor/solid-state device manufacturingRemote plasmaProcess region

A method of etching exposed patterned heterogeneous structures is described and includes a remote plasma etch formed from a reactive precursor. The plasma power is pulsed rather than left on continuously. Plasma effluents from the remote plasma are flowed into a substrate processing region where the plasma effluents selectively remove one material faster than another. The etch selectivity results from the pulsing of the plasma power to the remote plasma region, which has been found to suppress the number of ionically-charged species that reach the substrate. The etch selectivity may also result from the presence of an ion suppression element positioned between a portion of the remote plasma and the substrate processing region.

Owner:APPLIED MATERIALS INC

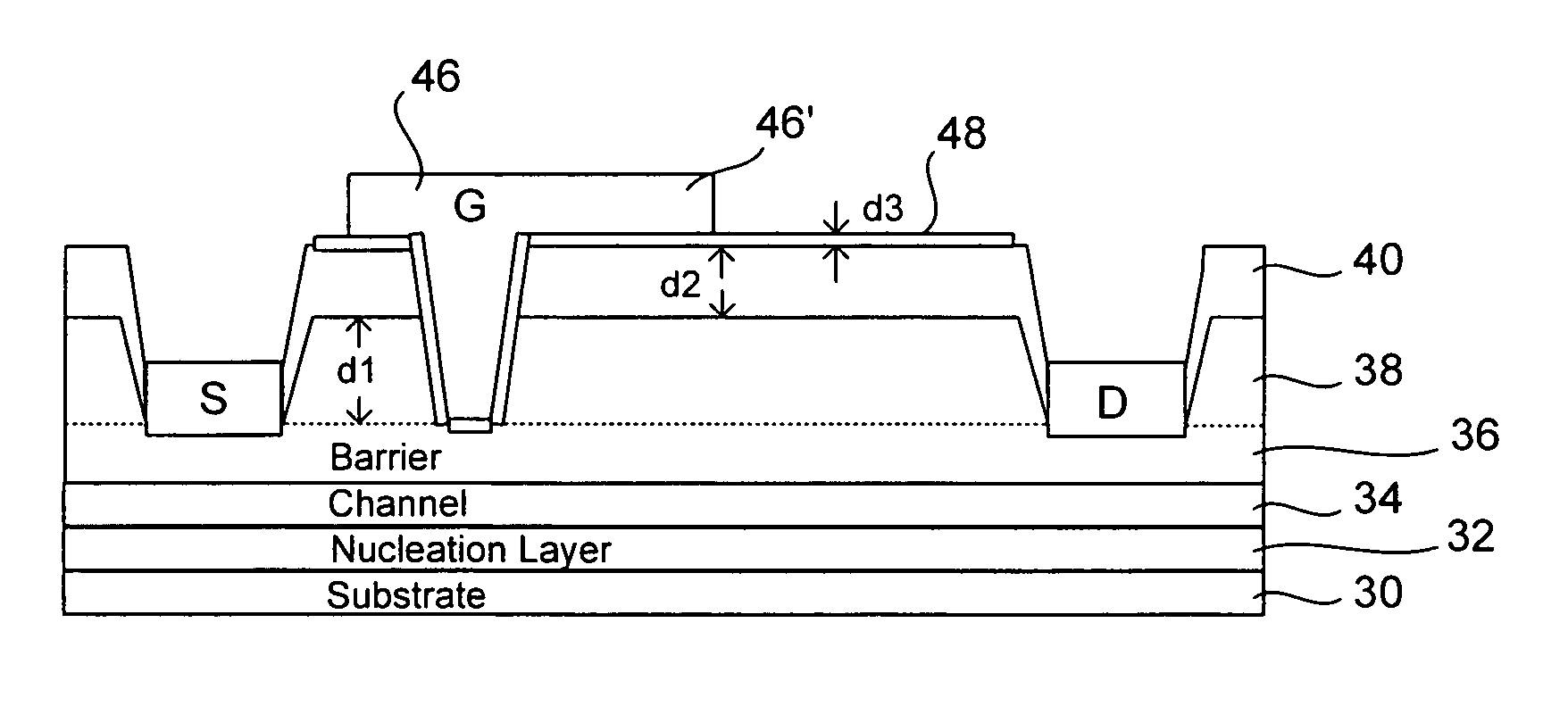

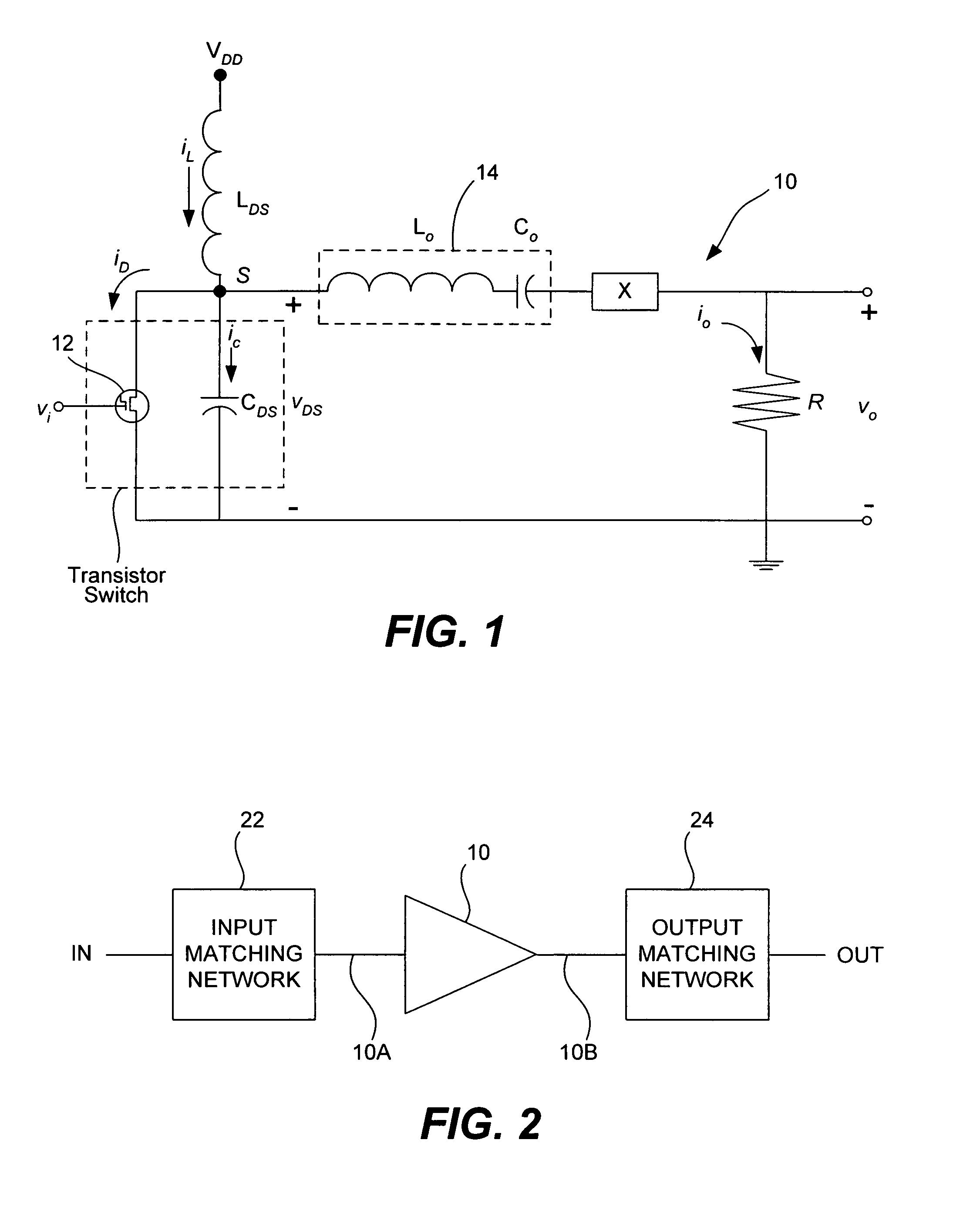

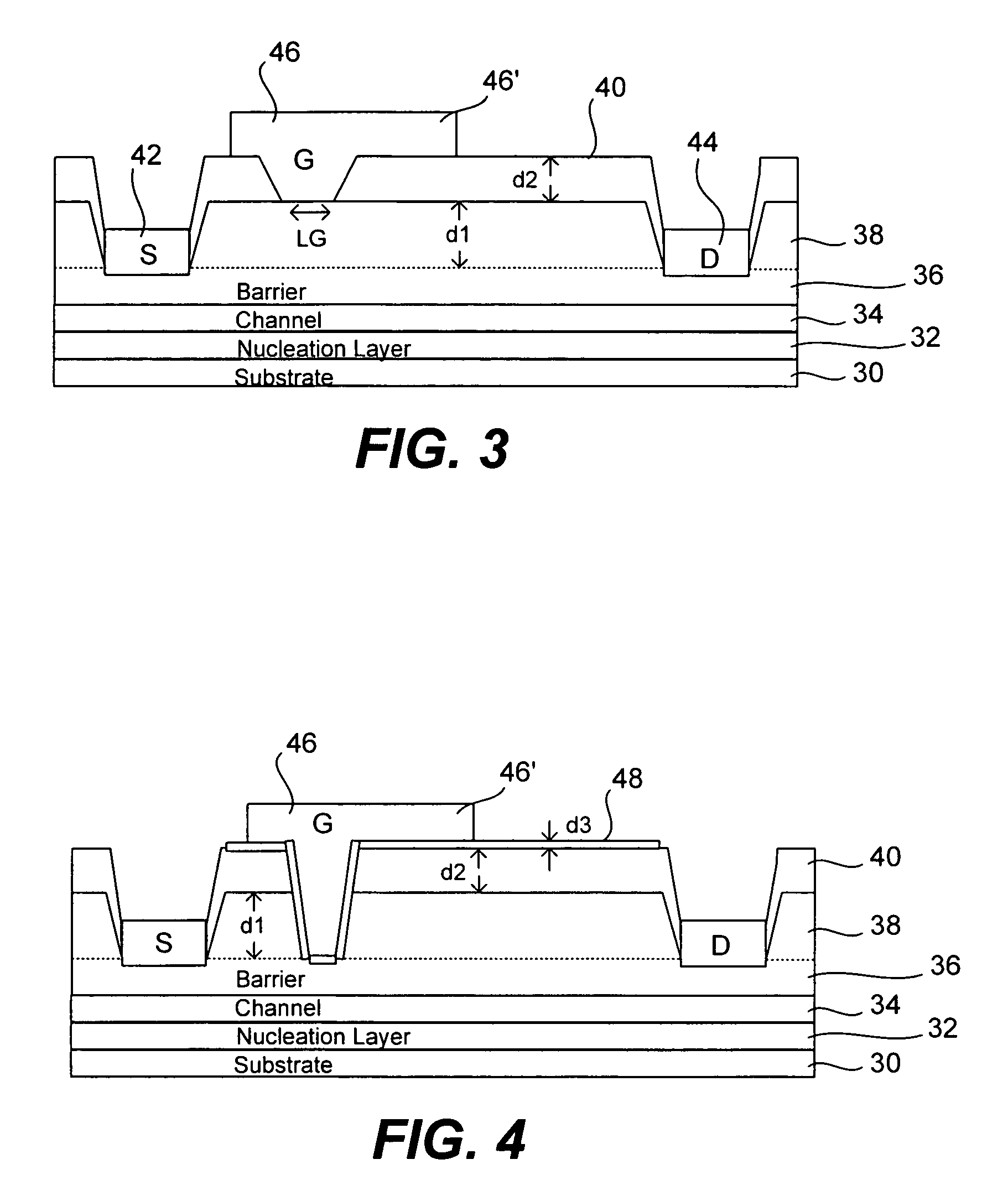

Switch mode power amplifier using MIS-HEMT with field plate extension

ActiveUS7548112B2Guaranteed uptimeIncrease heightTransistorHigh frequency amplifiersAudio power amplifierSilicon oxide

Disclosed are a switch mode power amplifier and a field effect transistor especially suitable for use in a switch mode power amplifier. The transistor is preferably a compound high electron mobility transistor (HEMT) having a source terminal and a drain terminal with a gate terminal therebetween and positioned on a dielectric material. A field plate extends from the gate terminal over at least two layers of dielectric material towards the drain. The dielectric layers preferably comprise silicon oxide and silicon nitride. A third layer of silicon oxide can be provided with the layer of silicon nitride being positioned between layers of silicon oxide. Etch selectivity is utilized in etching recesses for the gate terminal.

Owner:WOLFSPEED INC

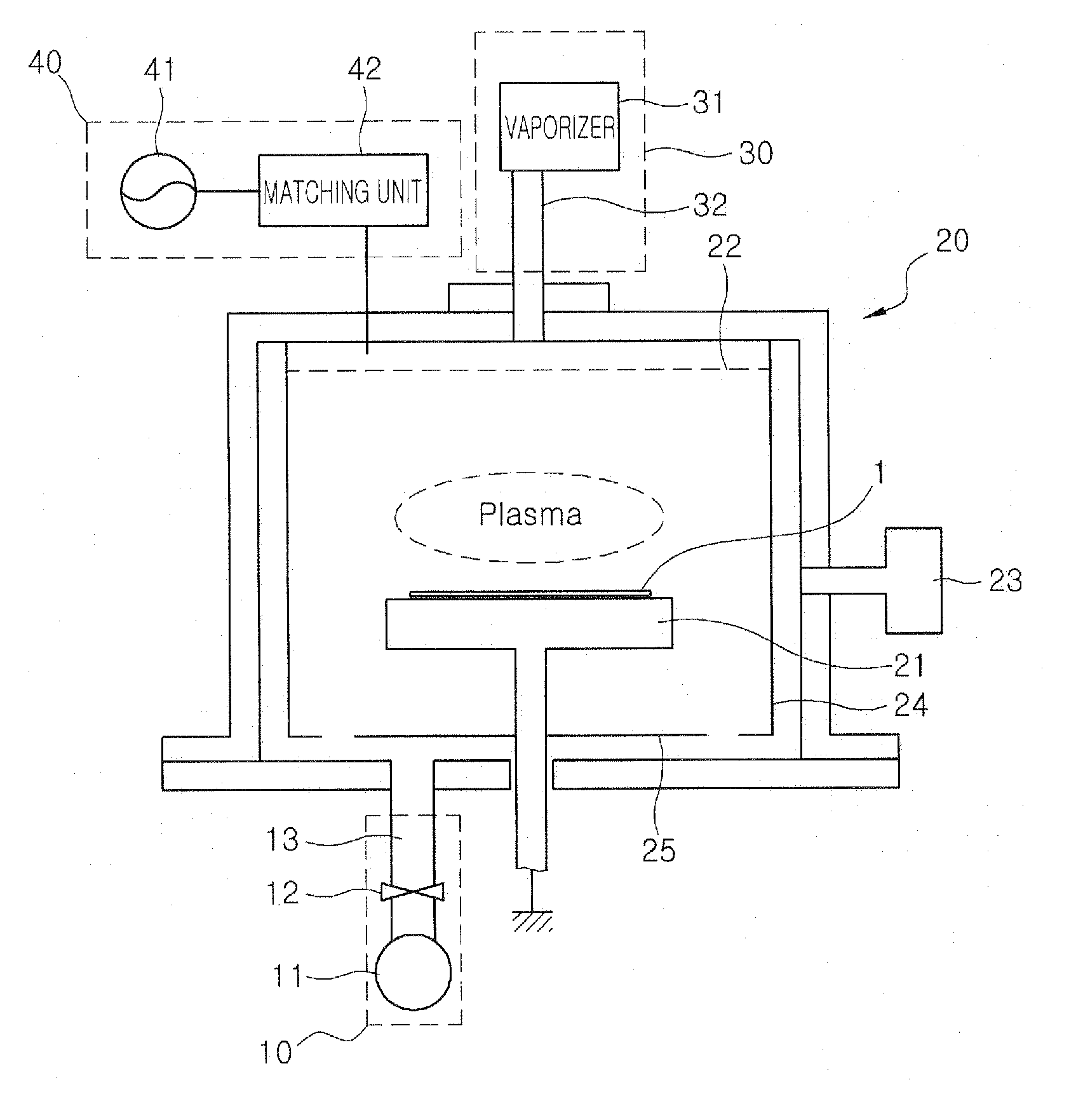

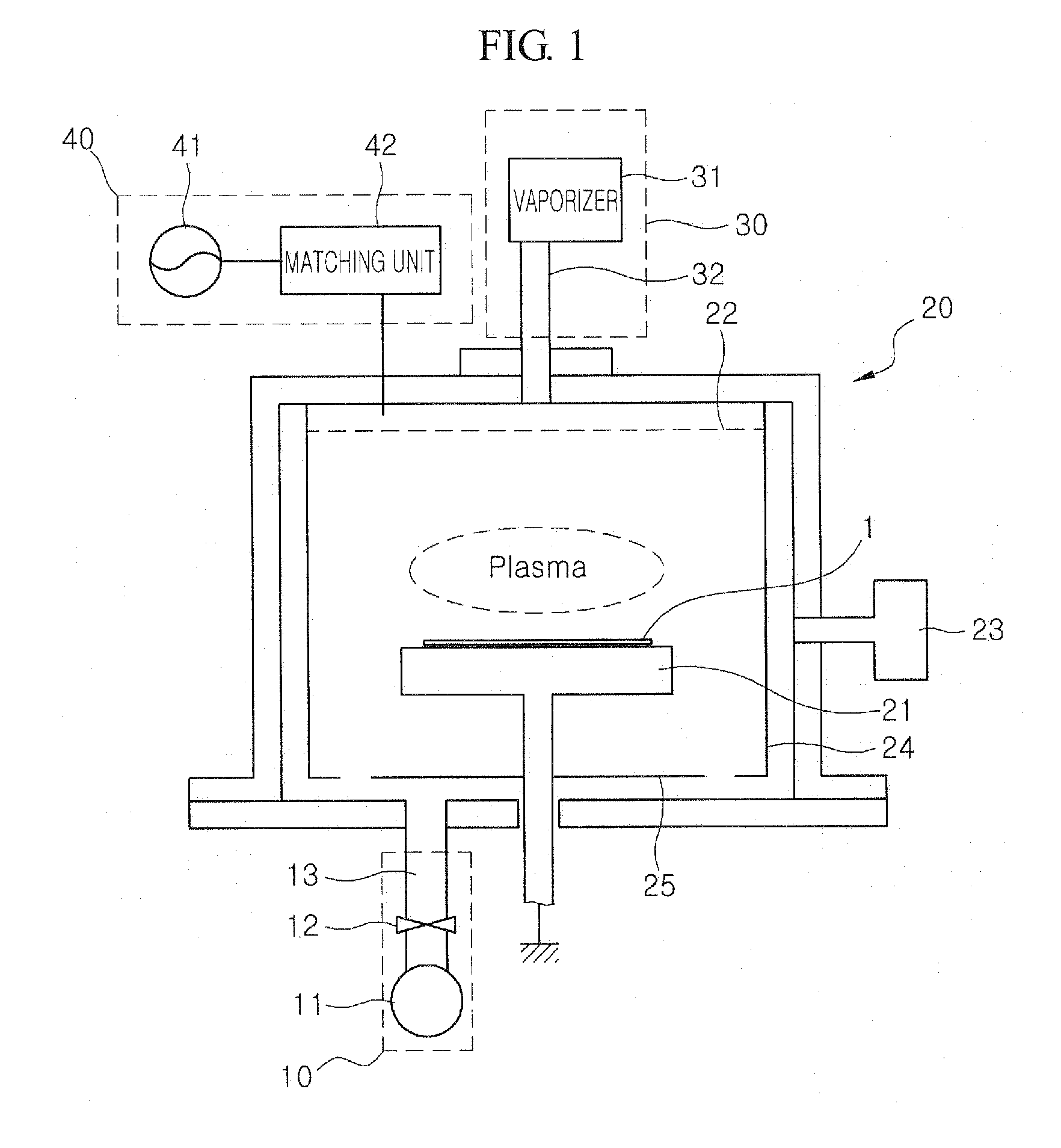

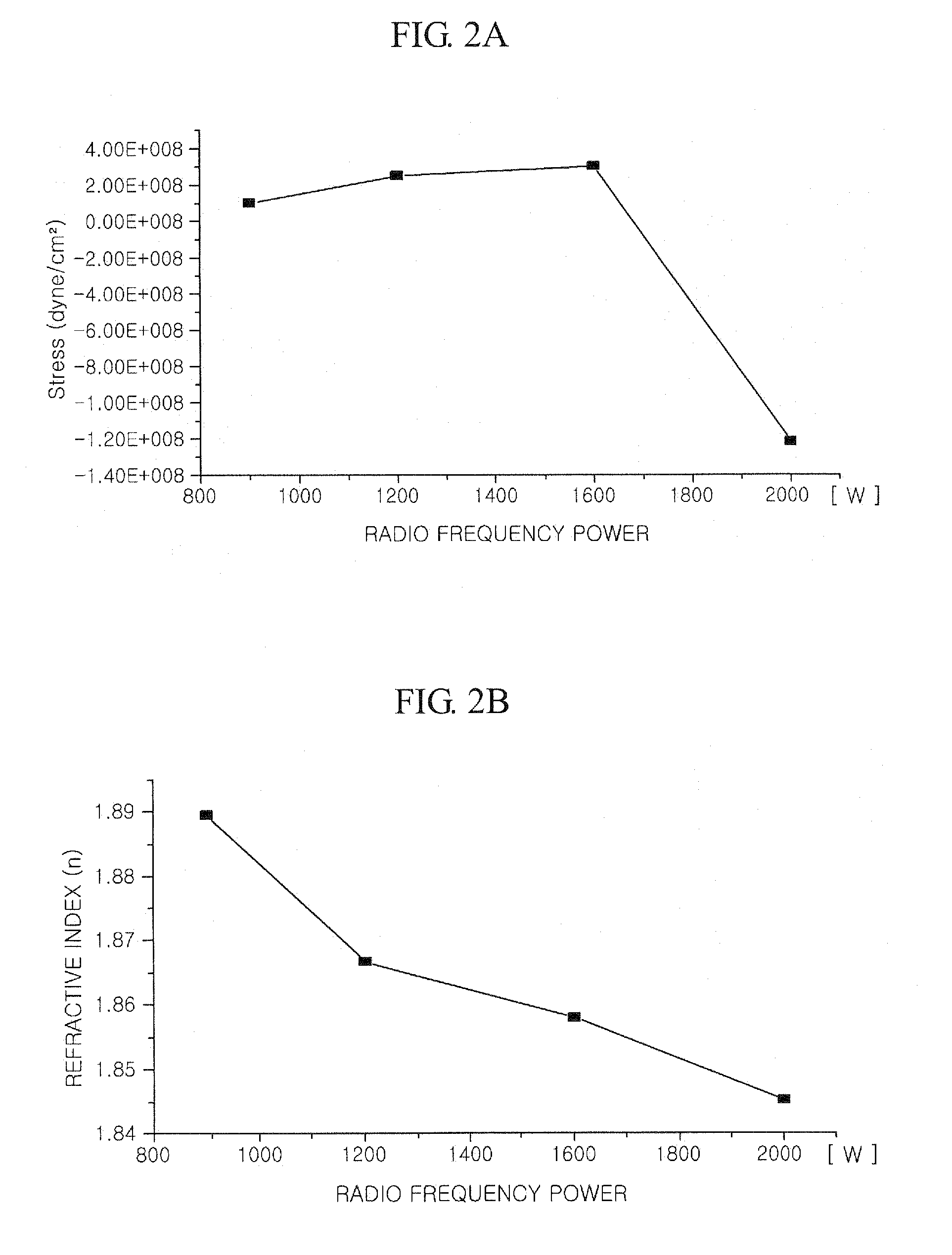

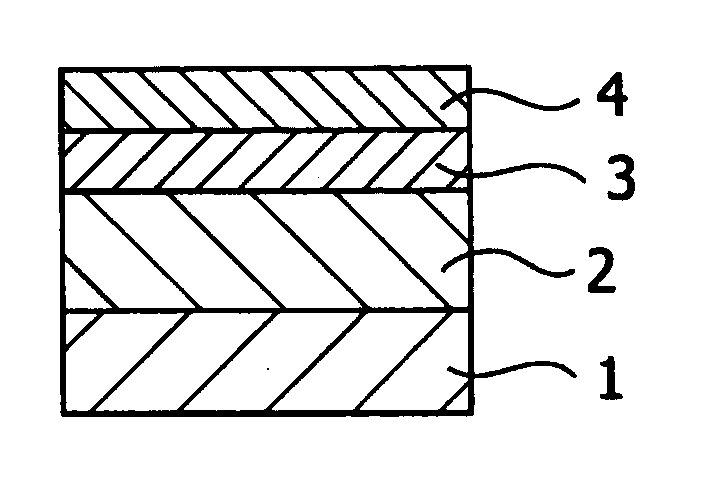

Method of forming amorphous carbon film and method of manufacturing semiconductor device using the same

InactiveUS20080293248A1Better controllableLight absorption coefficient is lowSemiconductor/solid-state device manufacturingChemical vapor deposition coatingRefractive indexDiffuse reflection

The present invention relates to a method of forming an amorphous carbon film and a method of manufacturing a semiconductor device using the method. An amorphous carbon film is formed on a substrate by vaporizing a liquid hydrocarbon compound, which has chain structure and one double bond, and supplying the compound to a chamber, and ionizing the compound. The amorphous carbon film is used as a hard mask film.It is possible to easily control characteristics of the amorphous carbon film, such as a deposition rate, an etching selectivity, a refractive index (n), a light absorption coefficient (k) and stress, so as to satisfy user's requirements. In particular, it is possible to lower the refractive index (n) and the light absorption coefficient (k). As a result, it is possible to perform a photolithography process without an antireflection film that prevents the diffuse reflection of a lower material layer.Further, a small amount of reaction by-product is generated during a deposition process, and it is possible to easily remove reaction by-products that are attached on the inner wall of a chamber. For this reason, it is possible to increase a cycle of a process for cleaning a chamber, and to increase parts changing cycles of a chamber. As a result, it is possible to save time and cost.

Owner:TES CO LTD

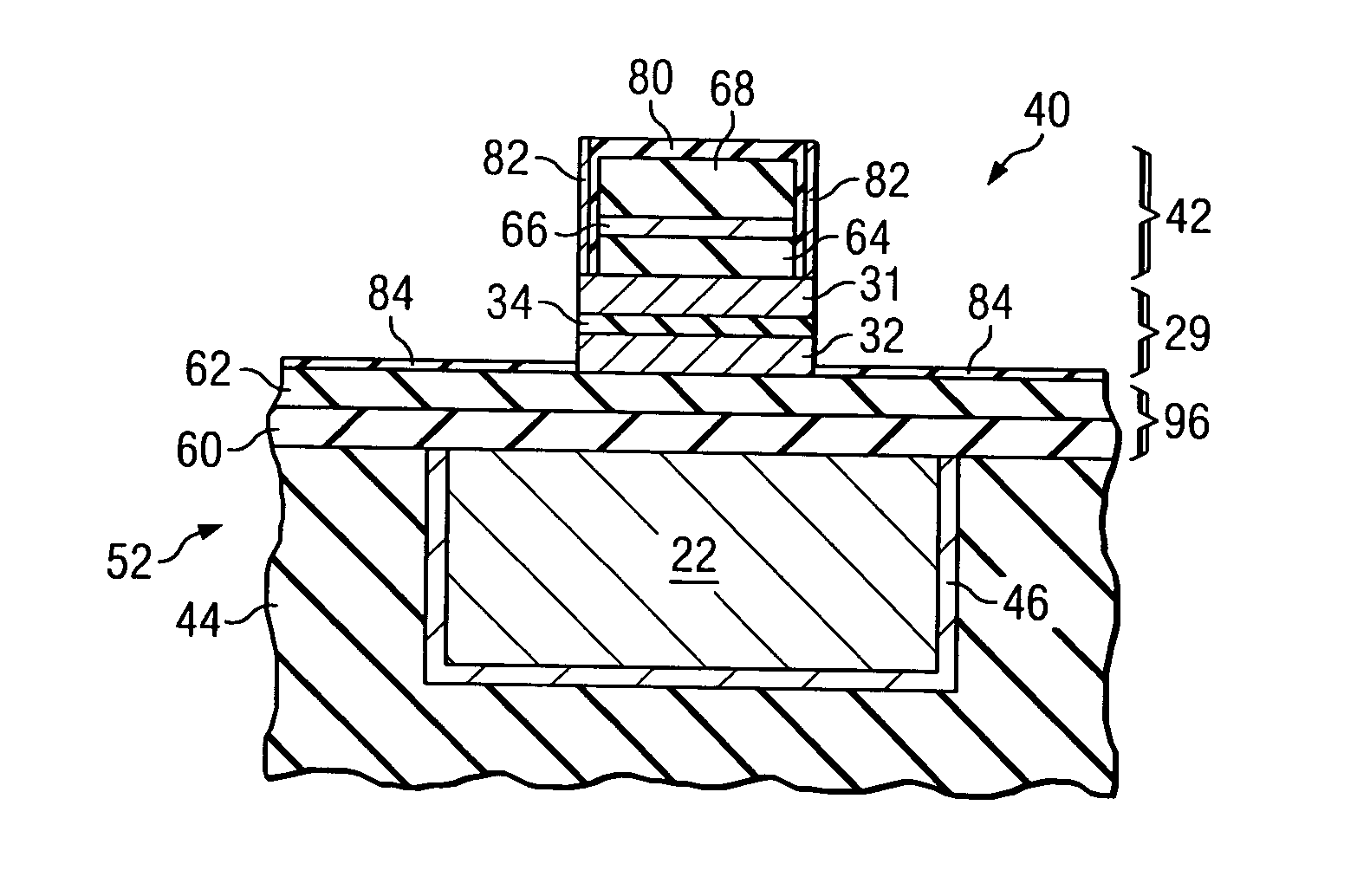

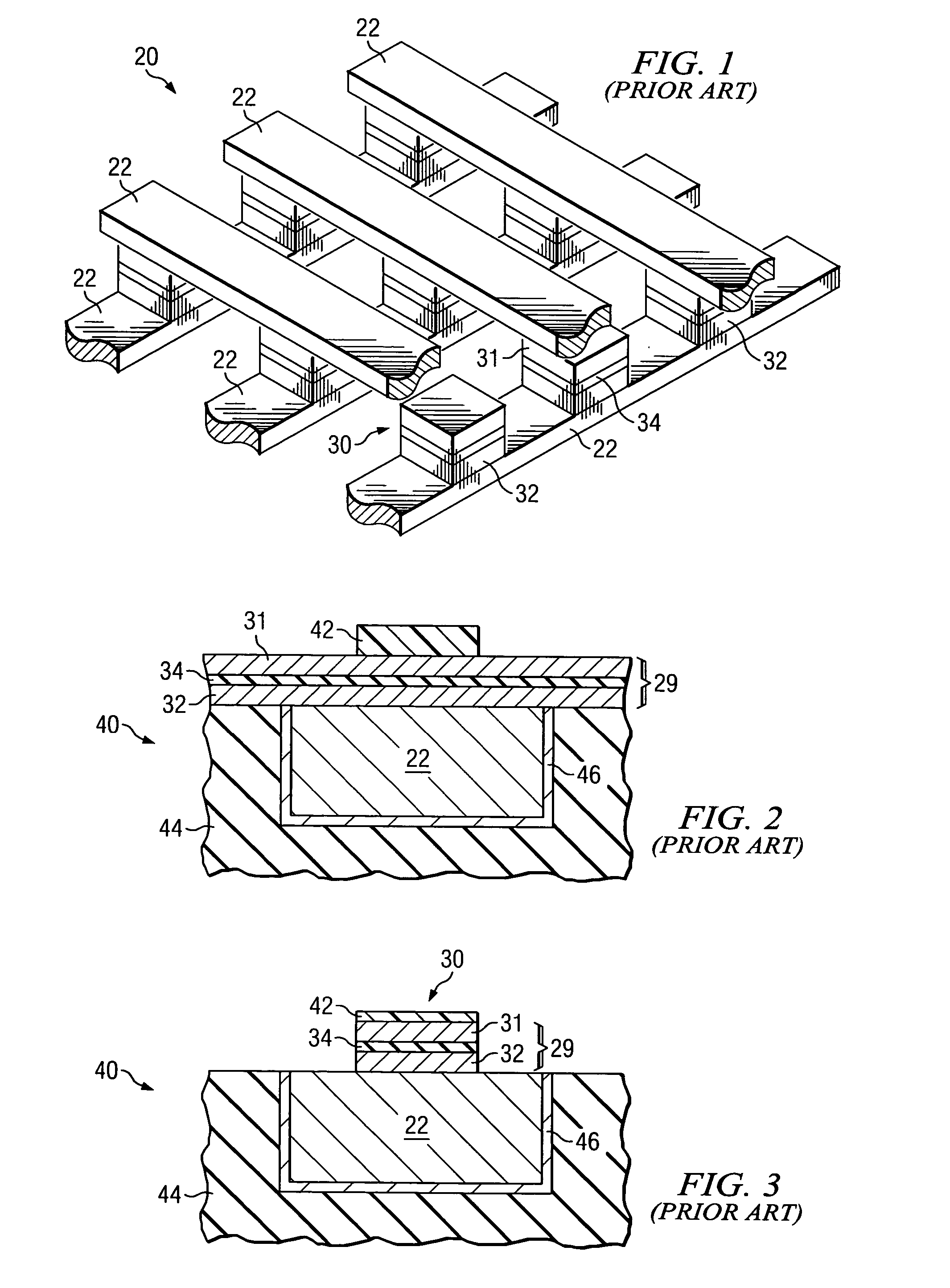

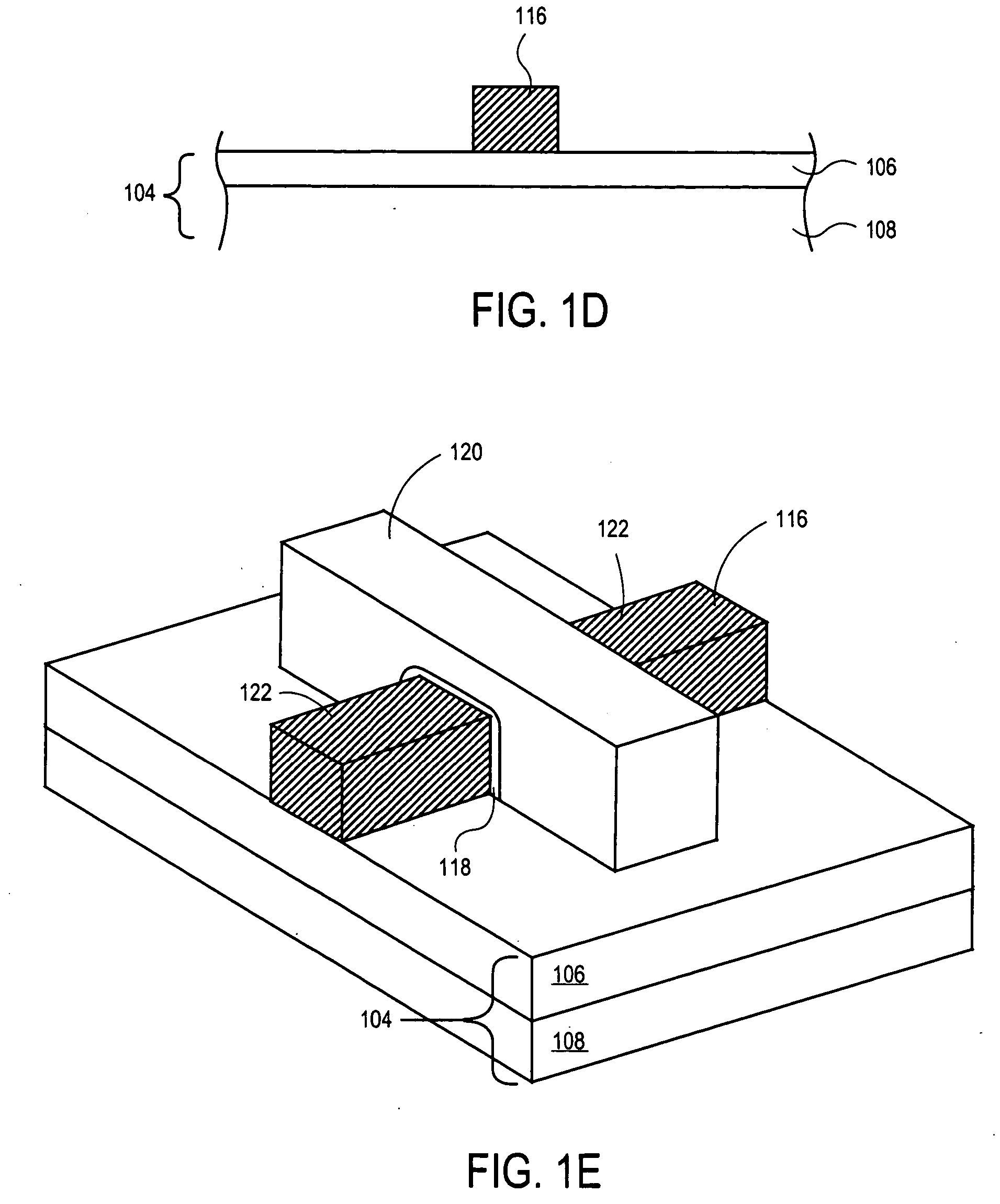

Methods of forming self-aligned contact pads using a damascene gate process

InactiveUS20010055842A1Excellent dummy gate profileImprove act coverageTransistorSemiconductor/solid-state device manufacturingContact padConductive materials

Self-aligned contacts in integrated circuits can be formed on an integrated circuit substrate having an active region. A groove can be formed in the insulating layer and a conductive material can be formed in the groove to a level that is recessed in the groove. An insulating material can be formed in the groove on the conductive material that has an etch selectivity with respect to the insulating layer. A contact that is self-aligned to the active region can be then be formed.

Owner:SAMSUNG ELECTRONICS CO LTD

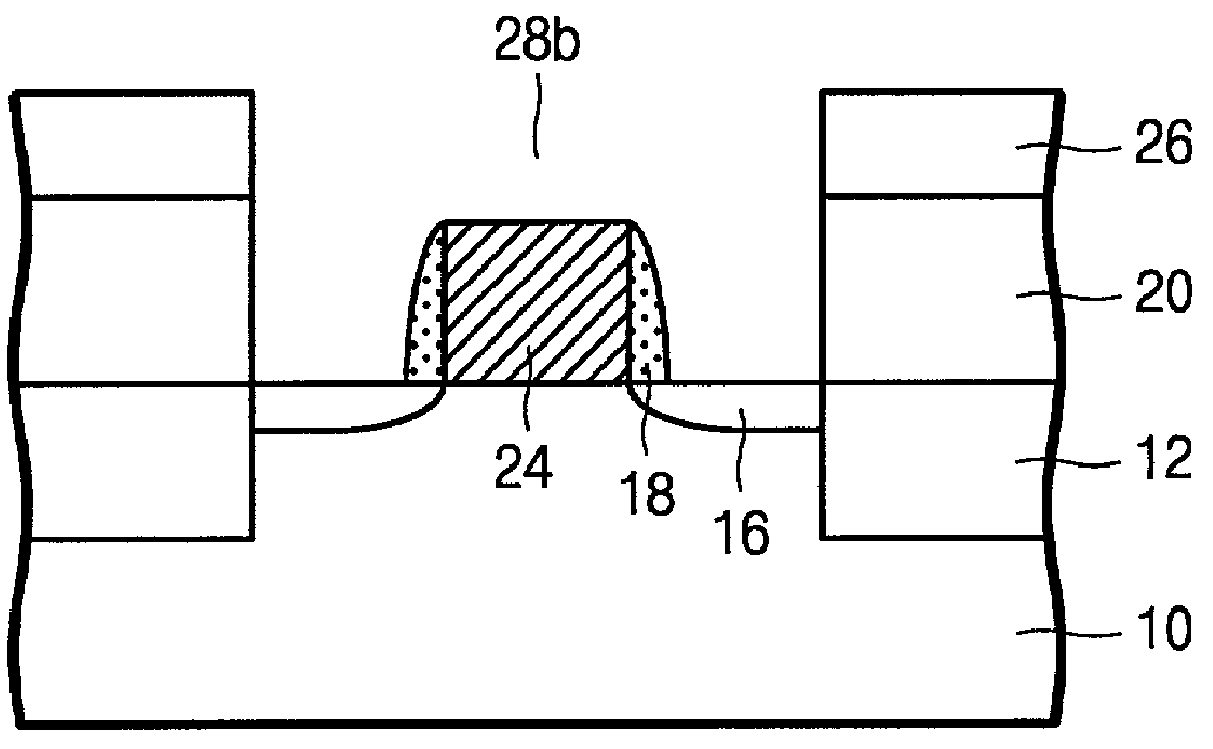

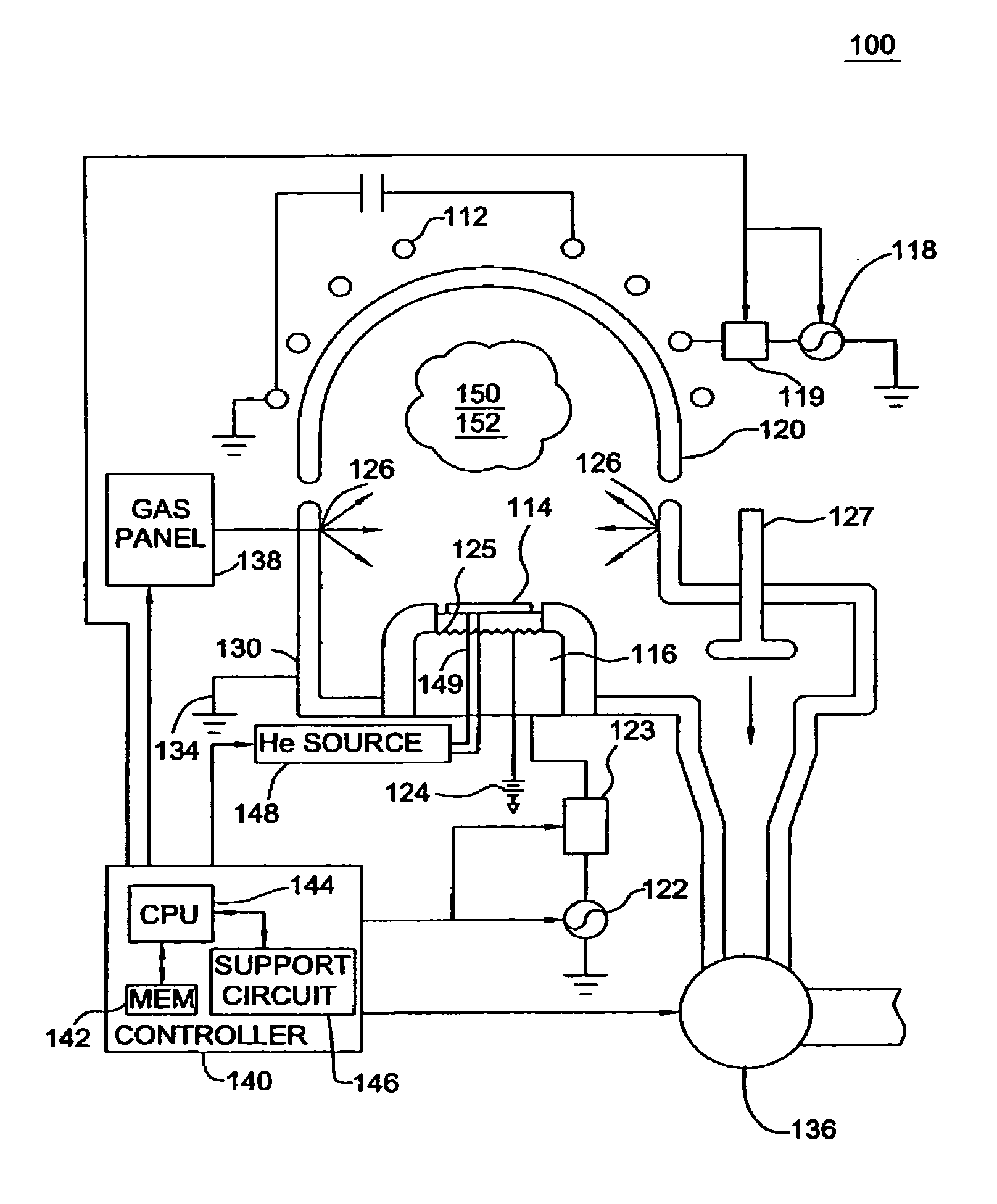

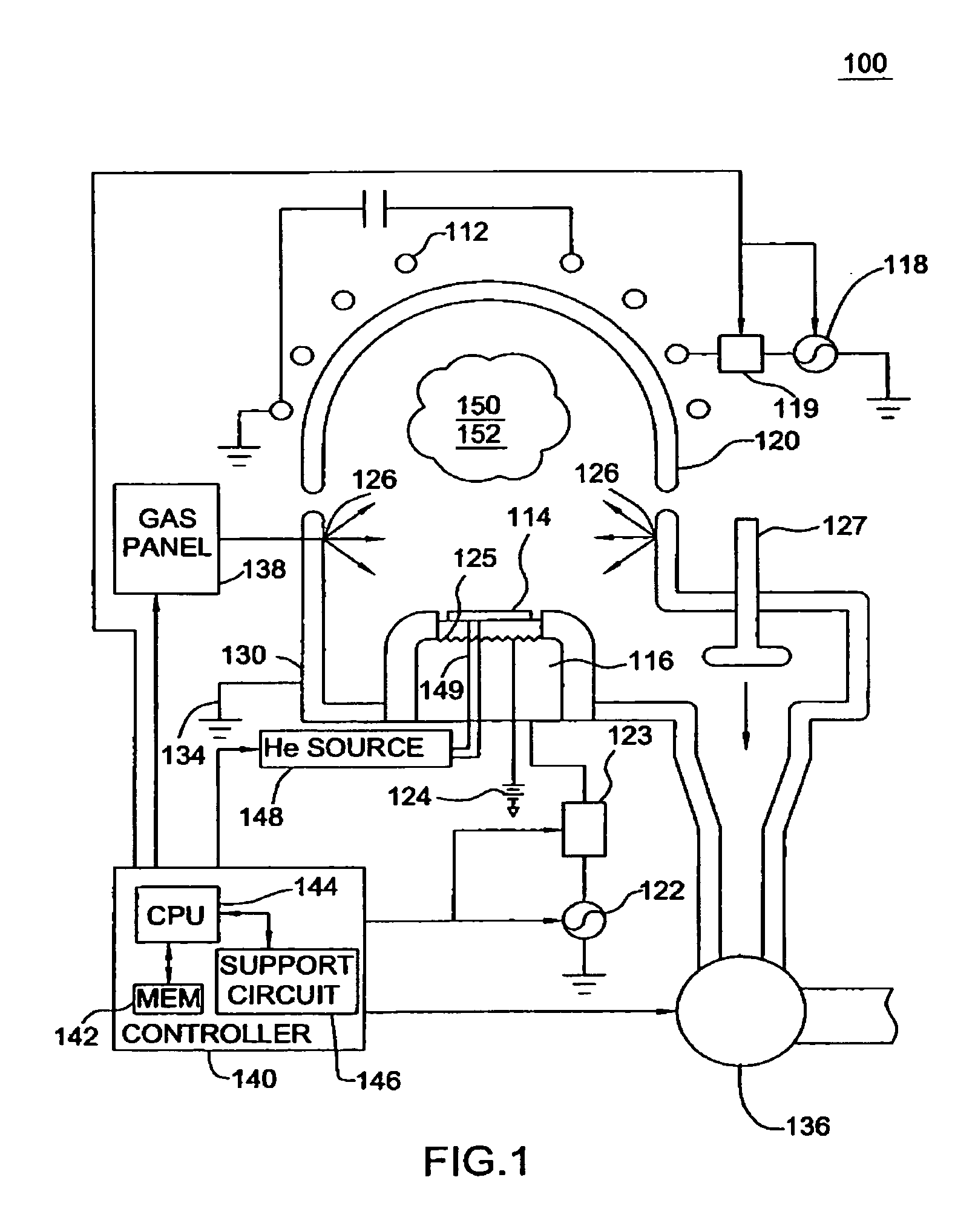

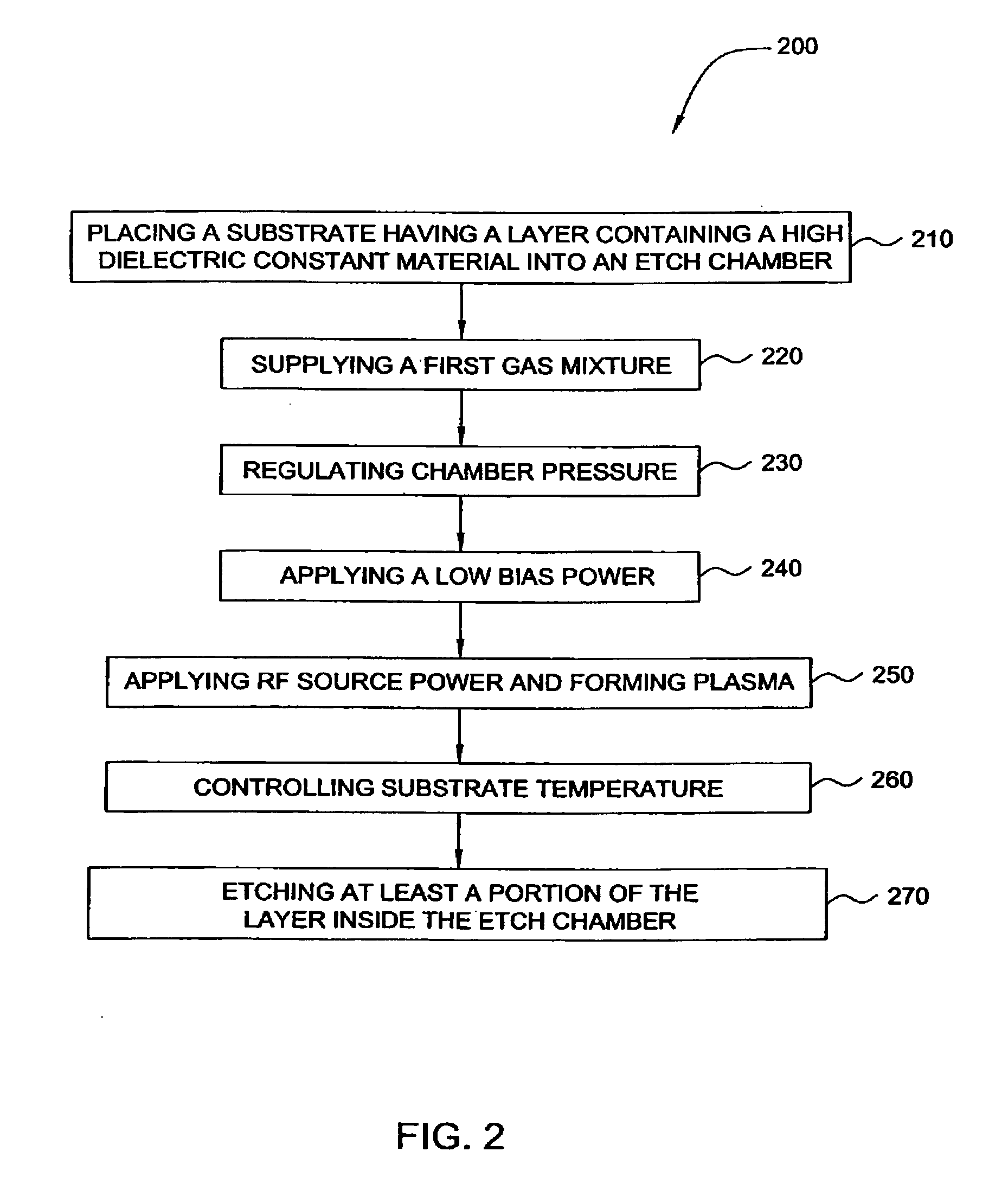

Etching high-kappa dielectric materials with good high-kappa foot control and silicon recess control

InactiveUS20060252265A1High selectivityDecorative surface effectsSemiconductor/solid-state device manufacturingDielectricHalogen

An apparatus and a method for etching high dielectric constant (high-κ) materials using halogen containing gas and reducing gas chemistries are provided. One embodiment of the method is accomplished by etching a layer using two etch gas chemistries in separate steps. The first etch gas chemistry contain no oxygen containing gas in order to break through etching of the high dielectric constant materials, to dean any residues left from previous polysilicon etch process resulting in less high-κ foot, and also to control silicon recess problem associated with an underlying silicon oxide layer. The second over-etch gas chemistry provides a high etch selectivity for high dielectric constant materials over silicon oxide materials to be combined with low source power to further reduce silicon substrate oxidation problem.

Owner:APPLIED MATERIALS INC

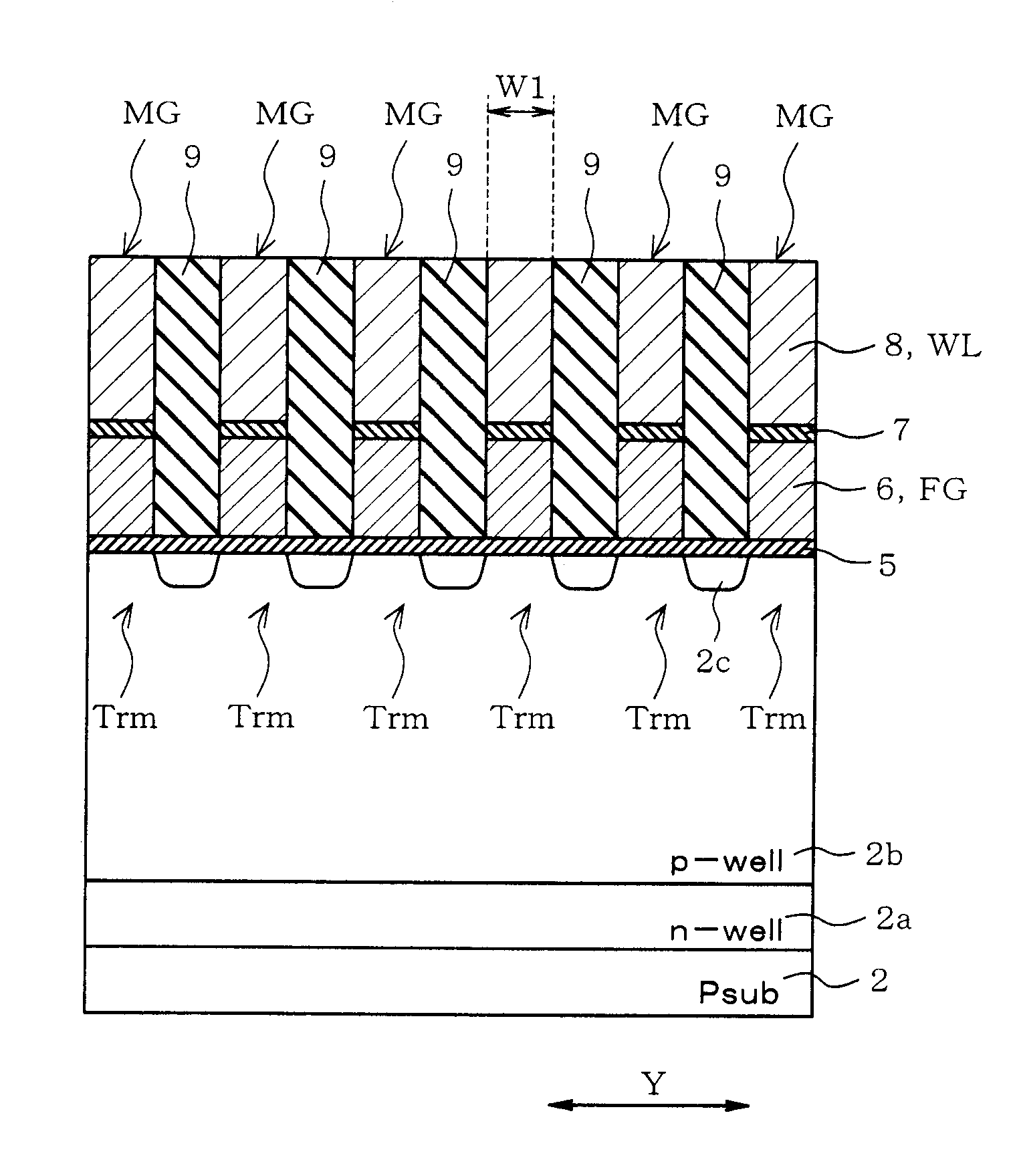

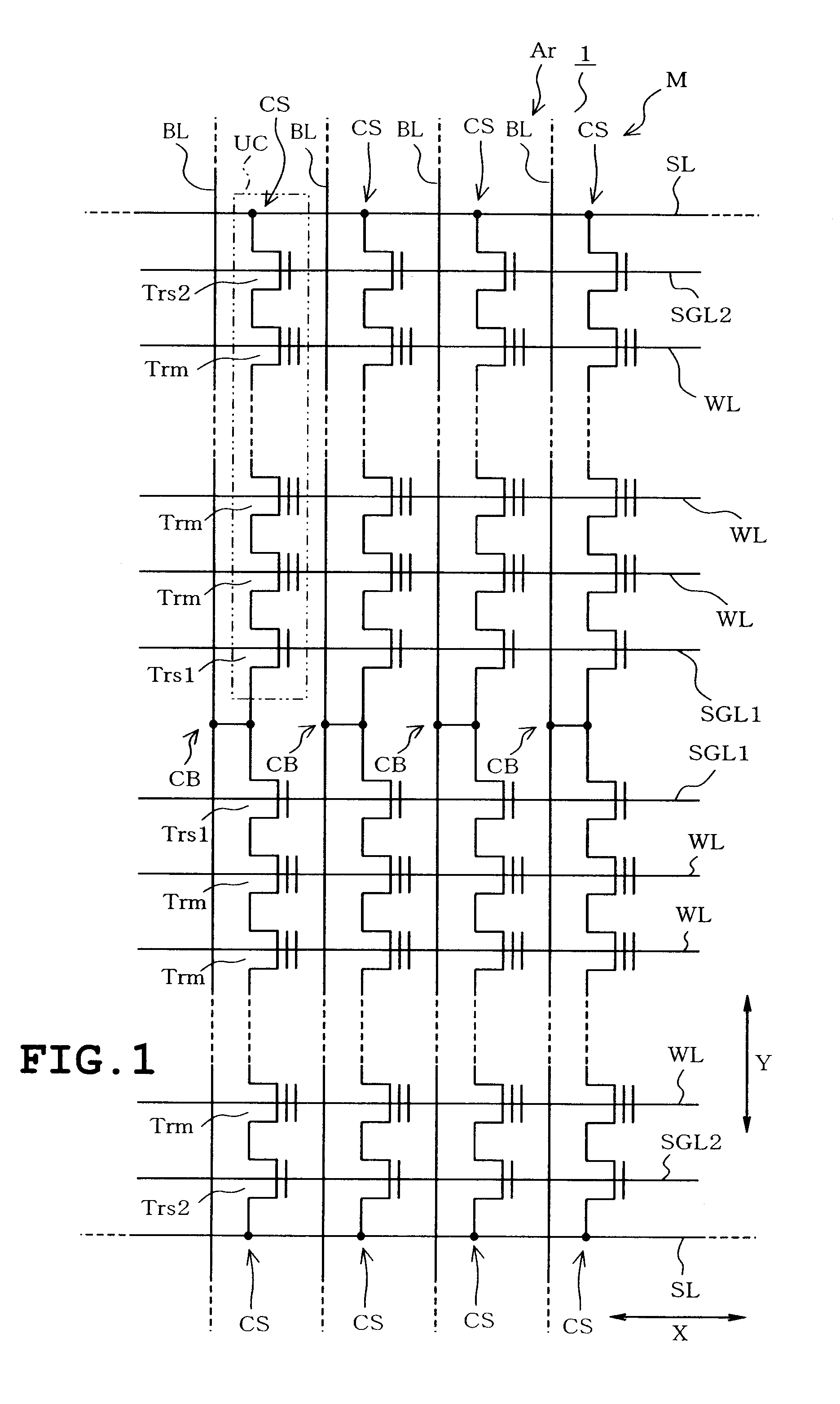

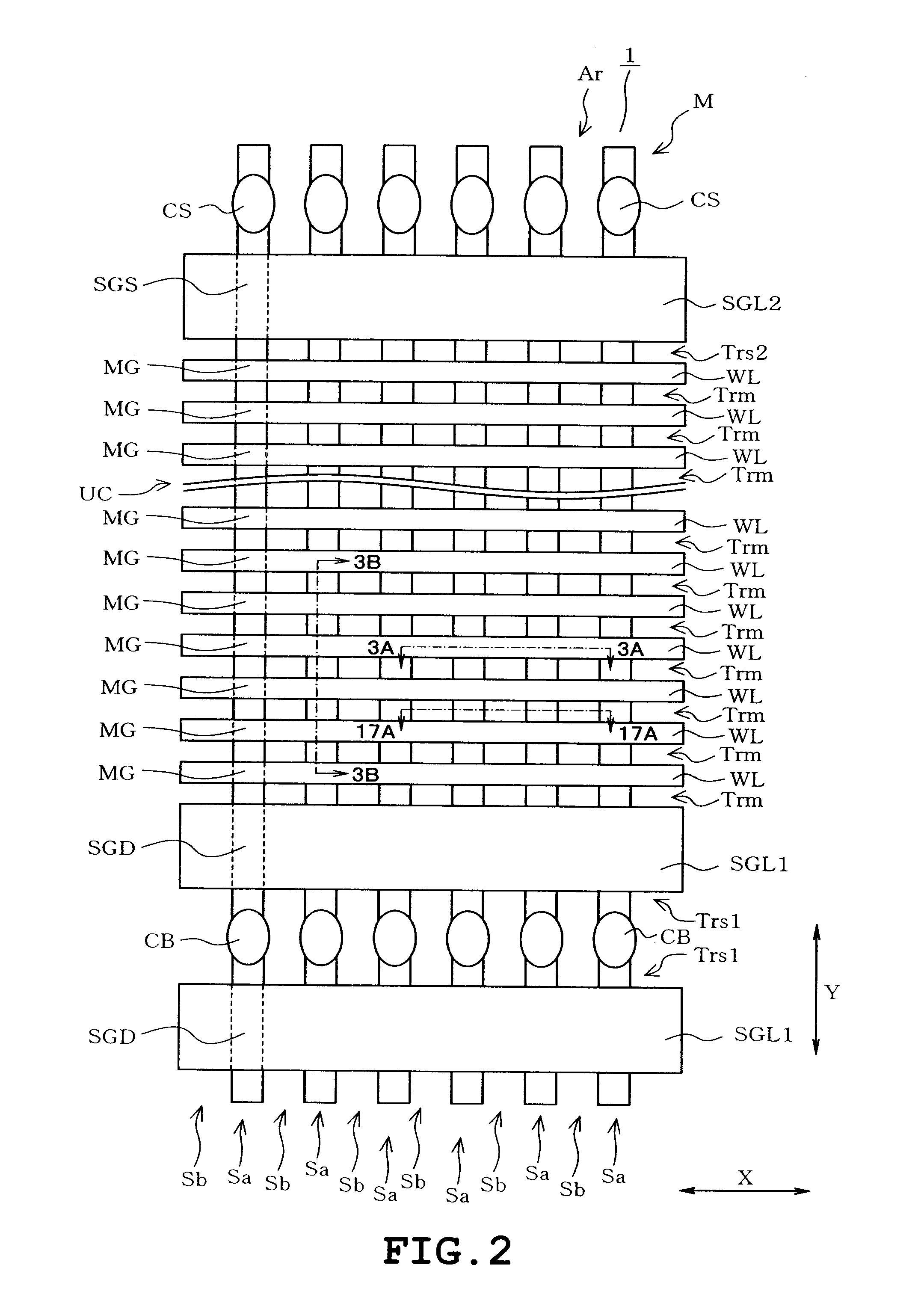

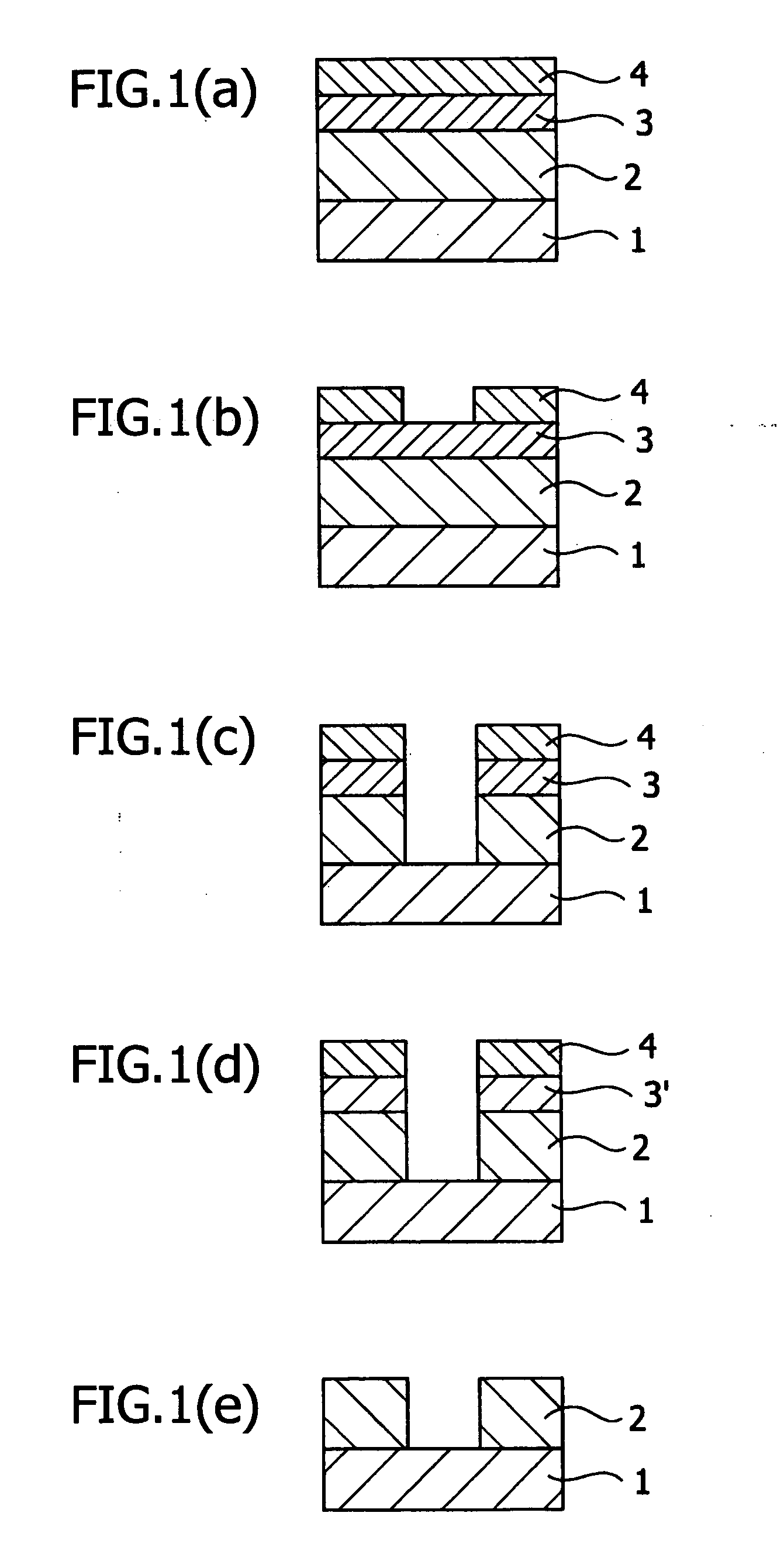

Method of fabricating semiconductor device

InactiveUS20100197107A1Improve etch selectivitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method of fabricating a semiconductor device includes forming a first film on a processed film, patterning the first film into a pattern with smaller width and a space with larger width, forming a second film along upper and side surfaces of first film and an upper surface of second film, etching the second film thereby to expose upper surfaces of first film and processed film while part of second film remains along the side surface of first film, etching the first film under the condition that the first film has higher etch selectivity than the second film, etching an upper part of second film under the condition that the second film has a higher etch selectivity than the processed film, after the first film has been etched, and etching the processed film with the second film serving as mask after the upper part of second film has been etched.

Owner:KK TOSHIBA

Dry-etch selectivity

Owner:APPLIED MATERIALS INC

Fabrication process for a magnetic tunnel junction device

InactiveUS20050051820A1Avoid shortingMagnetic-field-controlled resistorsSolid-state devicesEngineeringOxygen

A method of fabricating a magnetic tunnel junction (MTJ) device is provided. A patterned hard mask is oxidized to form a surface oxide thereon. An MTJ stack is etched in alignment with the patterned hard mask after the oxidizing of the patterned hard mask. Preferably, the MTJ stack etch recipe includes chlorine and oxygen. Etch selectivity between the hard mask and the MTJ stack is improved.

Owner:INFINEON TECH AG +1

Method for forming conductive wires of semiconductor device

InactiveUS20040161921A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductorMetal

A method is provided for forming a conductive wire of a semiconductor device using, for example, a damascene process. A conductive wire, such as a metal wire, is formed, based on a notching phenomenon which occurs when the etching selectivity between a polycrystalline silicon layer and a lower film is approximately 5 to 500:1.

Owner:KEY FOUNDRY CO LTD

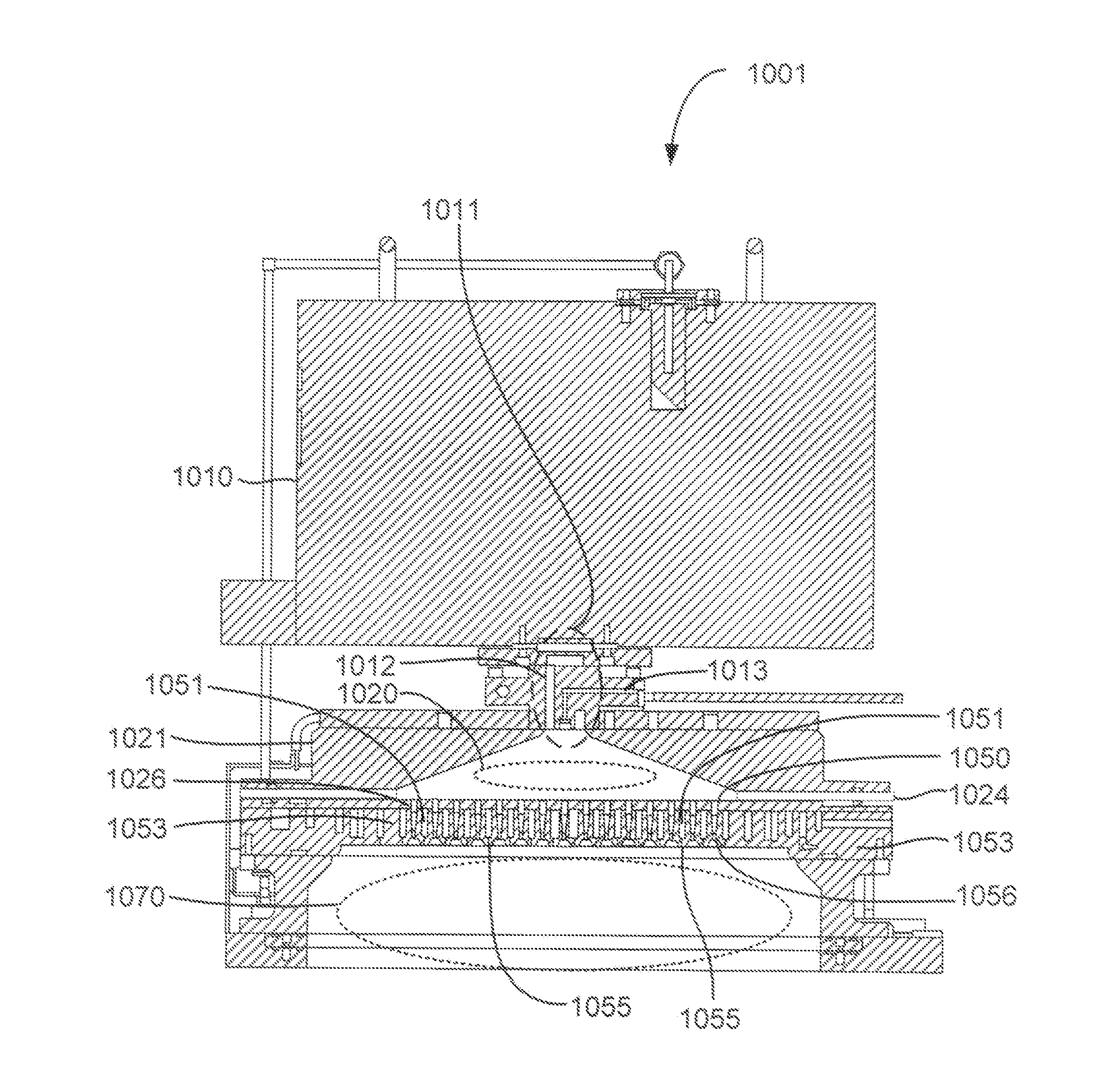

Oxide etch selectivity systems and methods

ActiveUS9349605B1Improve etch selectivityEnhance and suppress reactionElectric discharge tubesSemiconductor/solid-state device manufacturingHydrogenProcess region

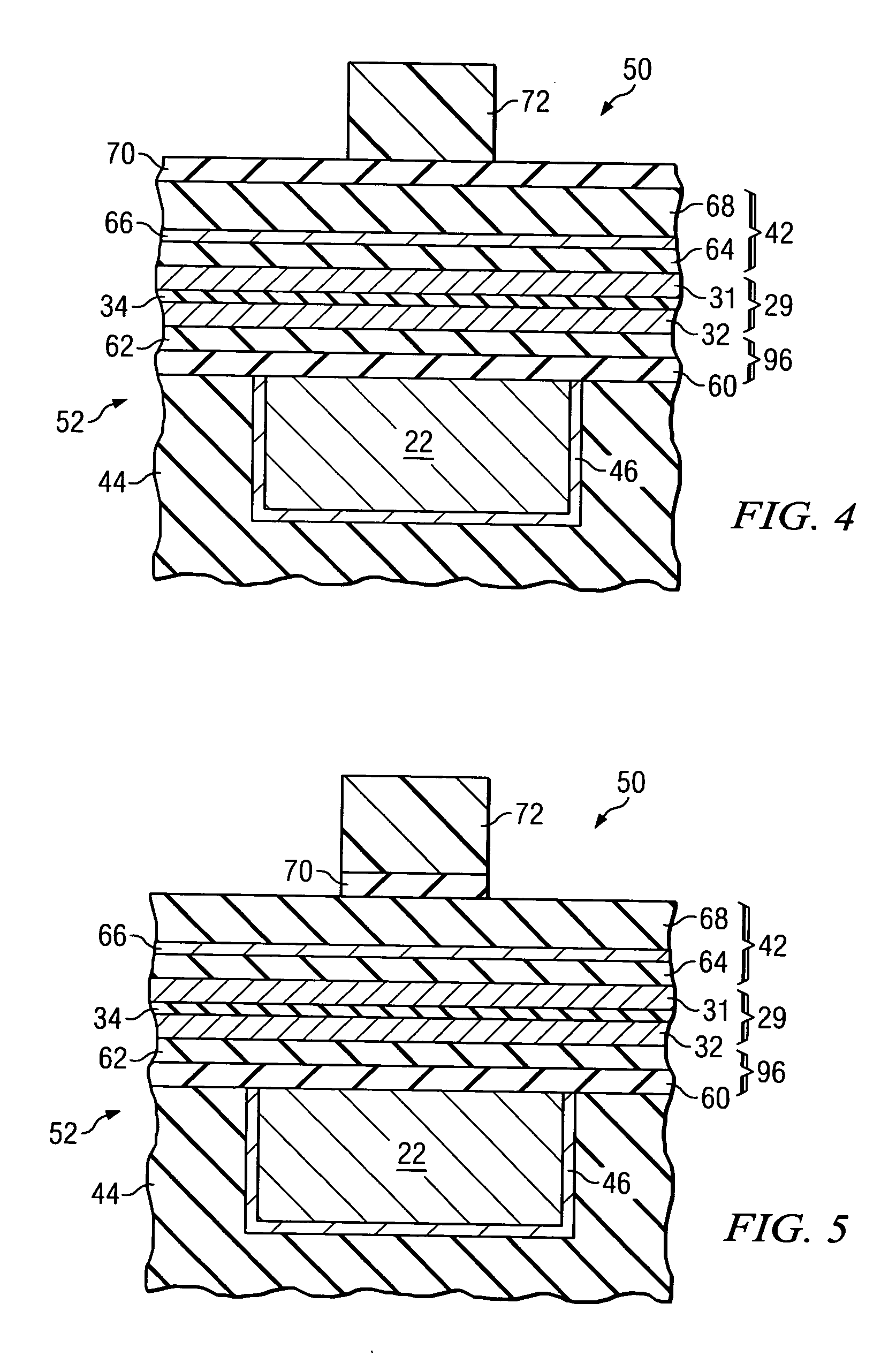

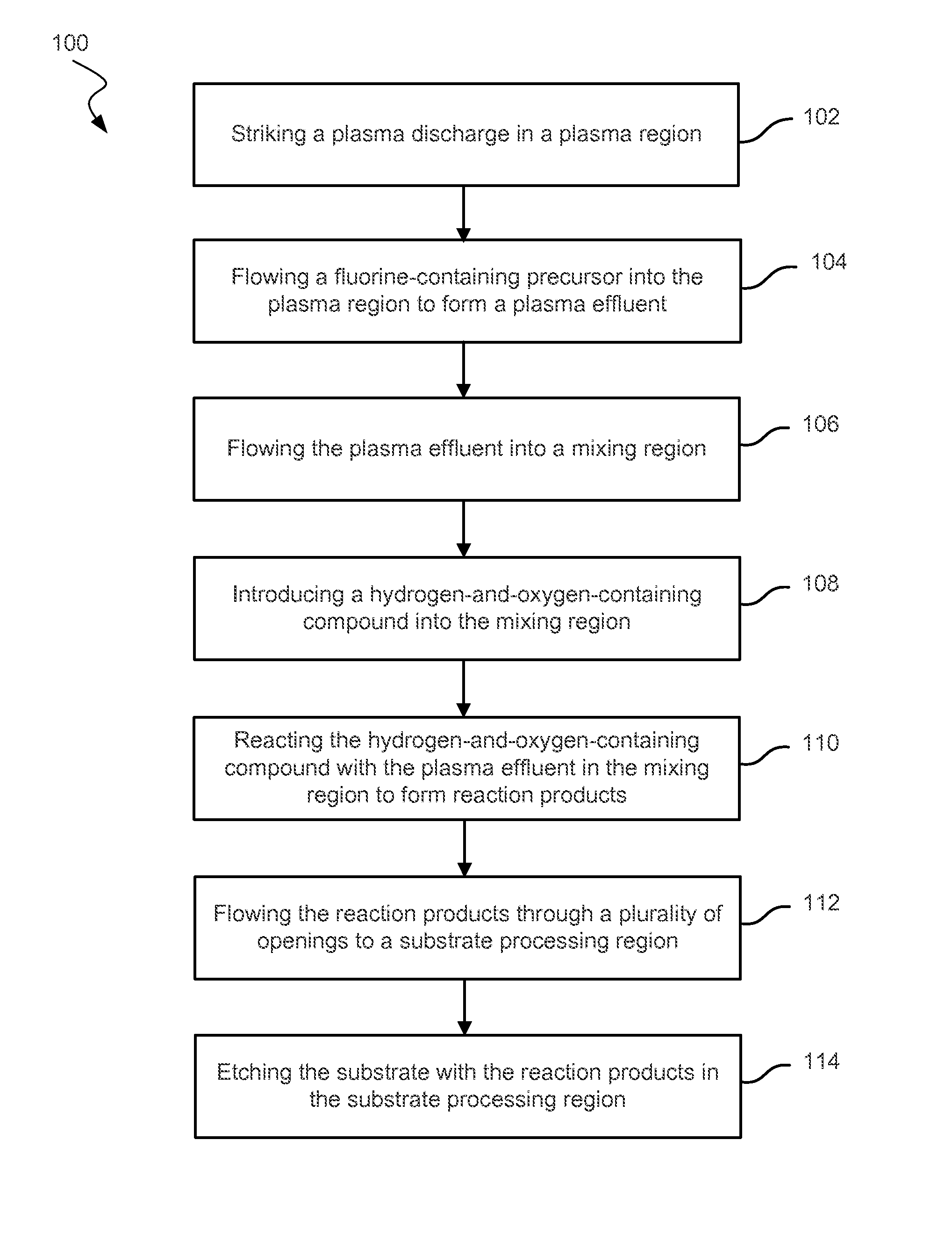

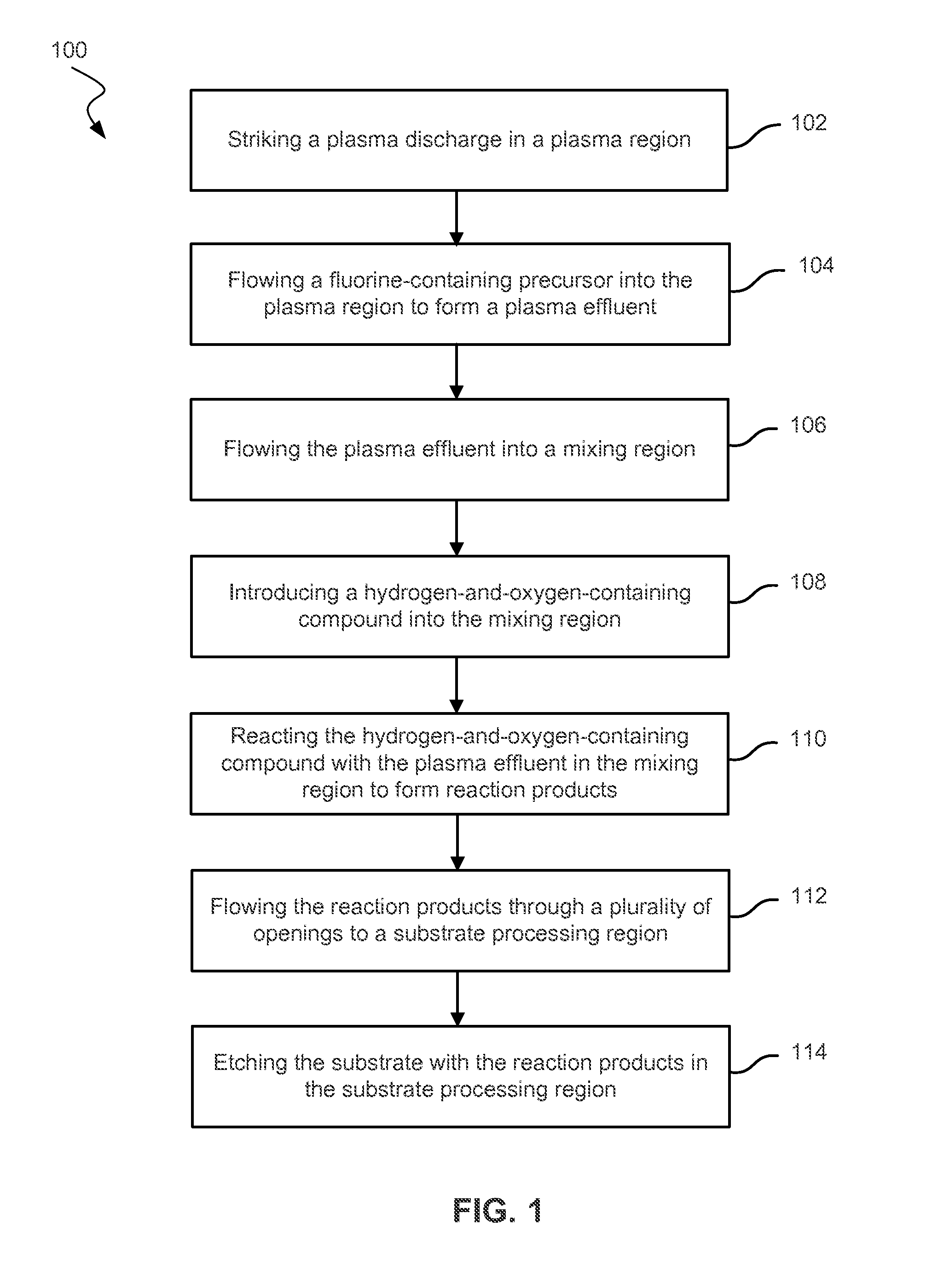

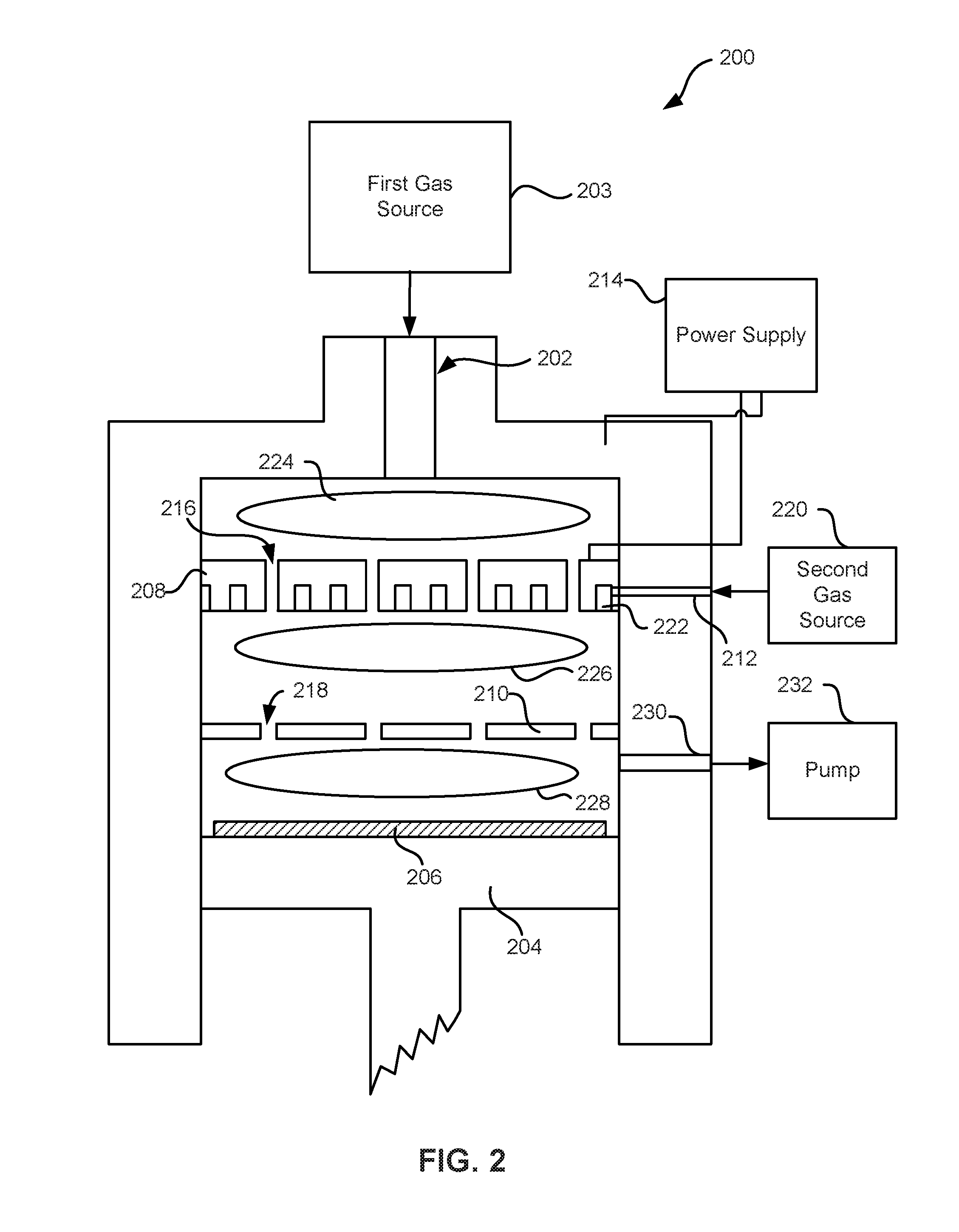

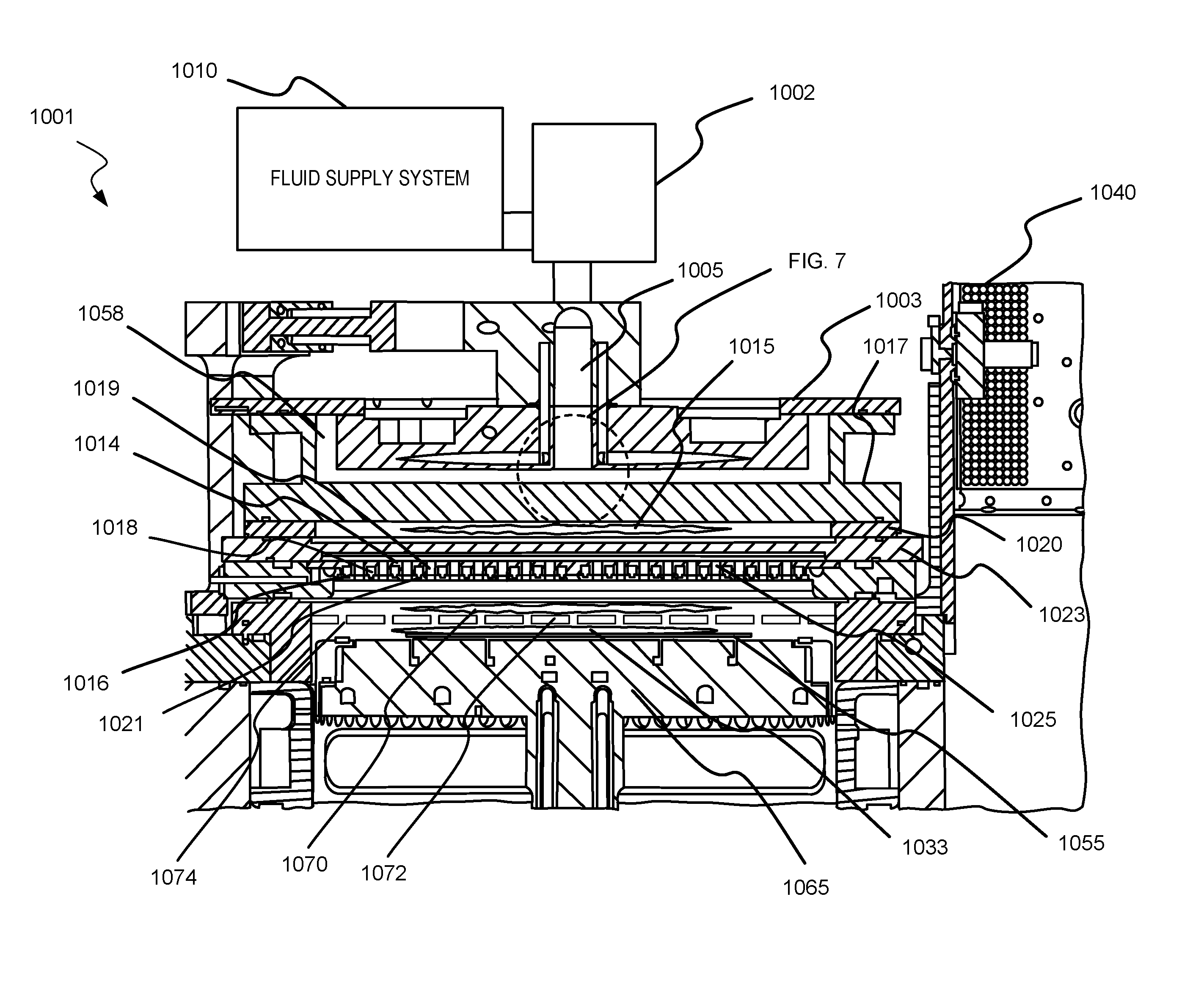

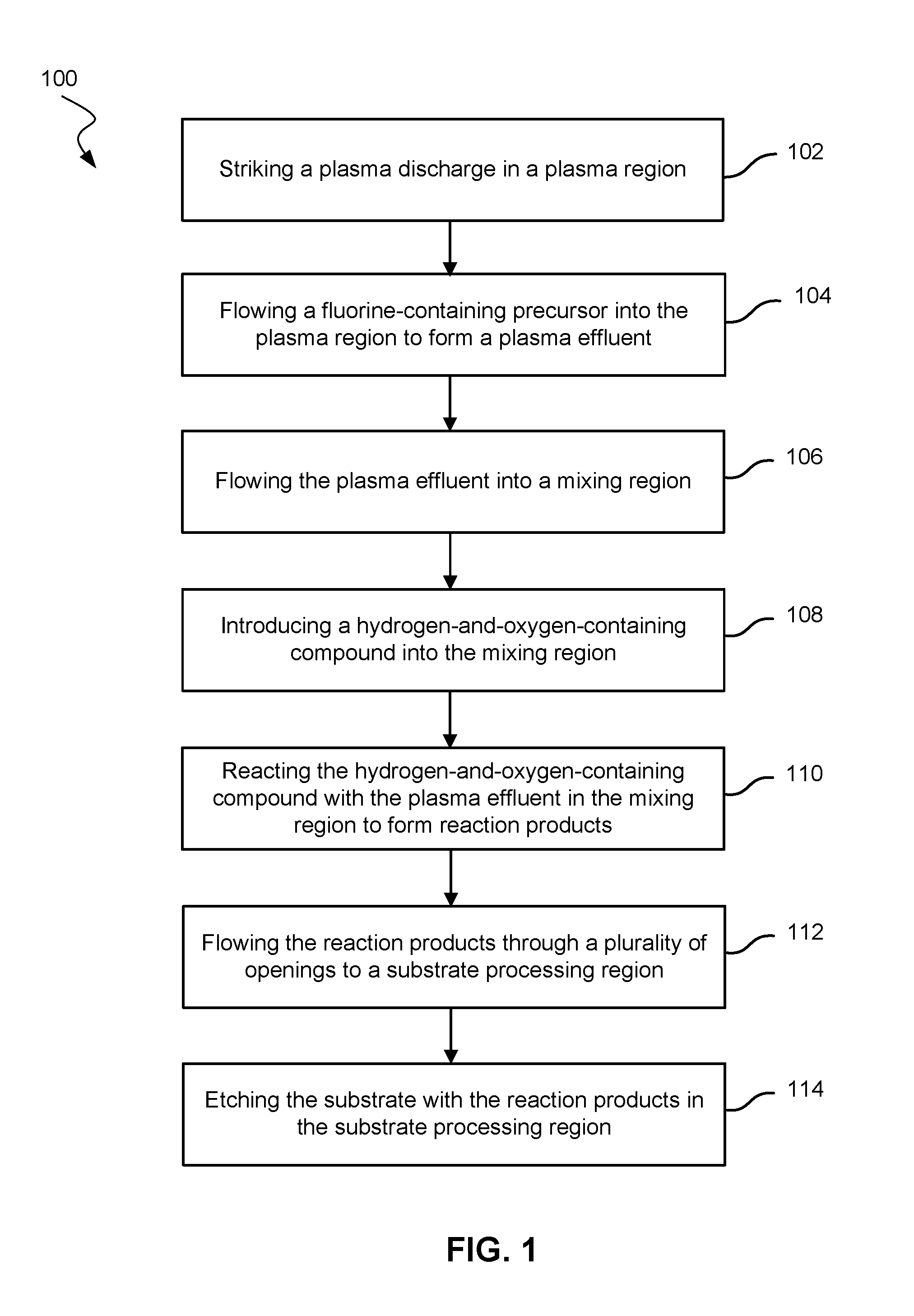

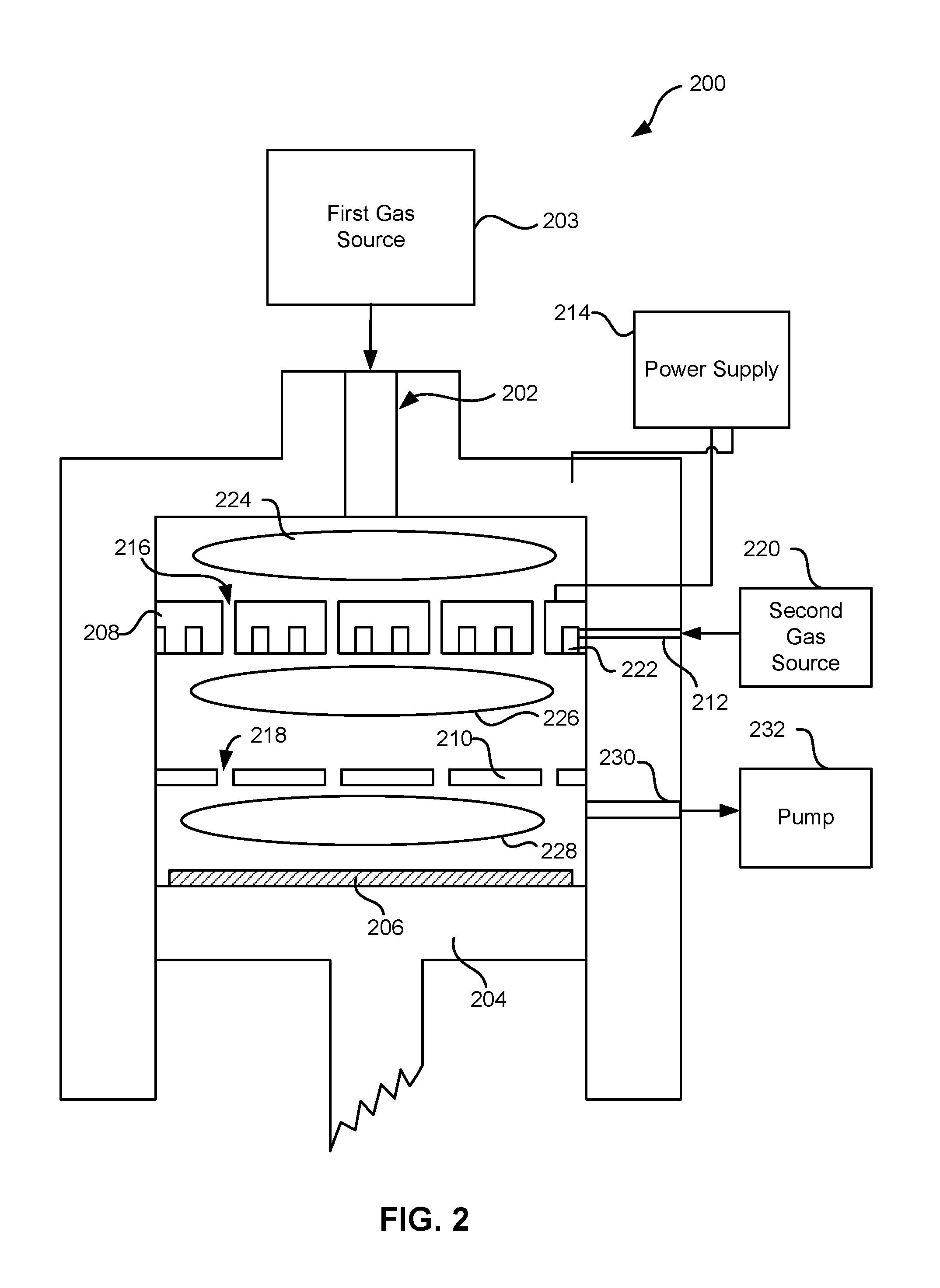

Embodiments of the present technology may include a method of etching a substrate. The method may include striking a plasma discharge in a plasma region. The method may also include flowing a fluorine-containing precursor into the plasma region to form a plasma effluent. The plasma effluent may flow into a mixing region. The method may further include introducing a hydrogen-and-oxygen-containing compound into the mixing region without first passing the hydrogen-and-oxygen-containing compound into the plasma region. Additionally, the method may include reacting the hydrogen-and-oxygen-containing compound with the plasma effluent in the mixing region to form reaction products. The reaction products may flow through a plurality of openings in a partition to a substrate processing region. The method may also include etching the substrate with the reaction products in the substrate processing region.

Owner:APPLIED MATERIALS INC

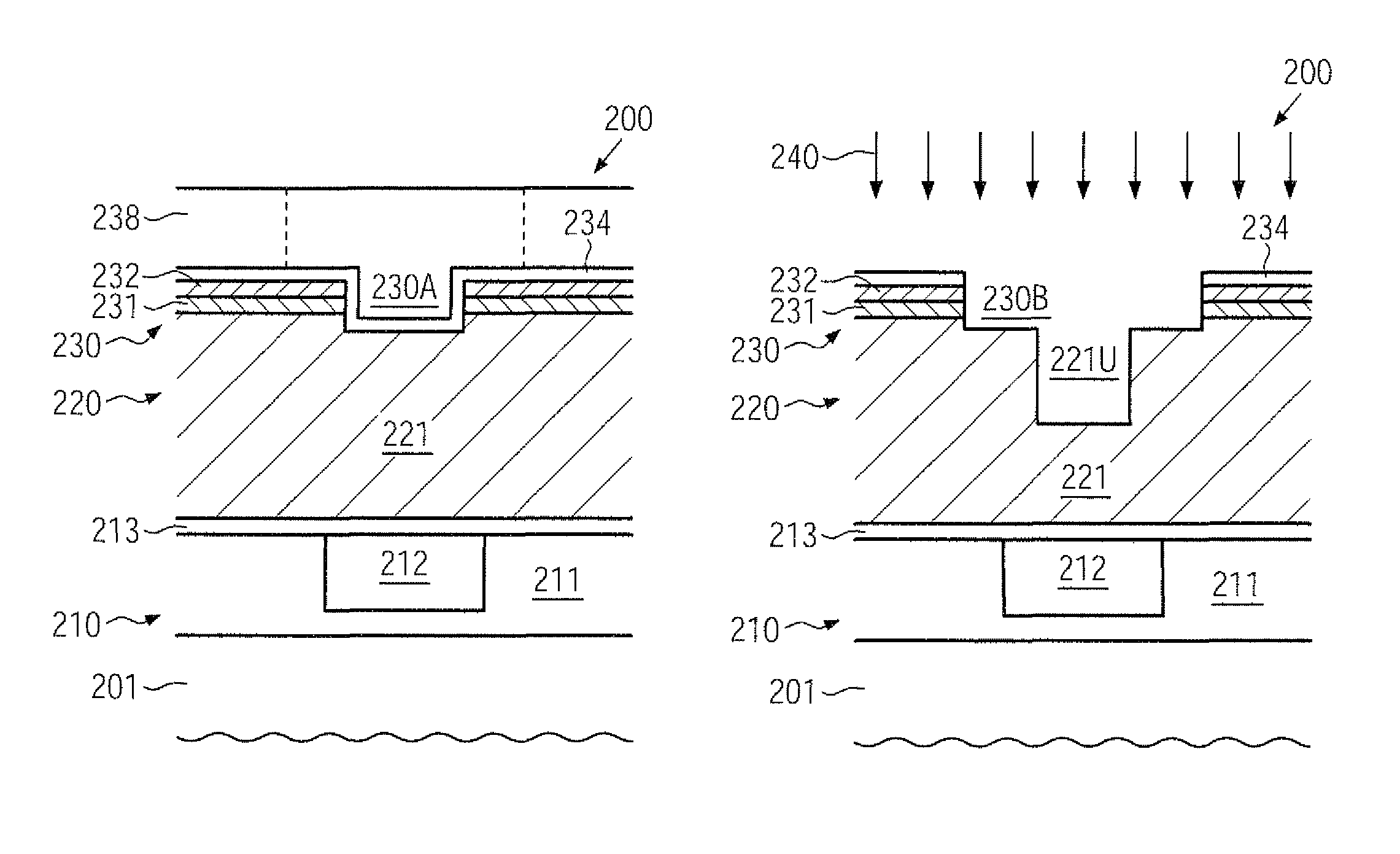

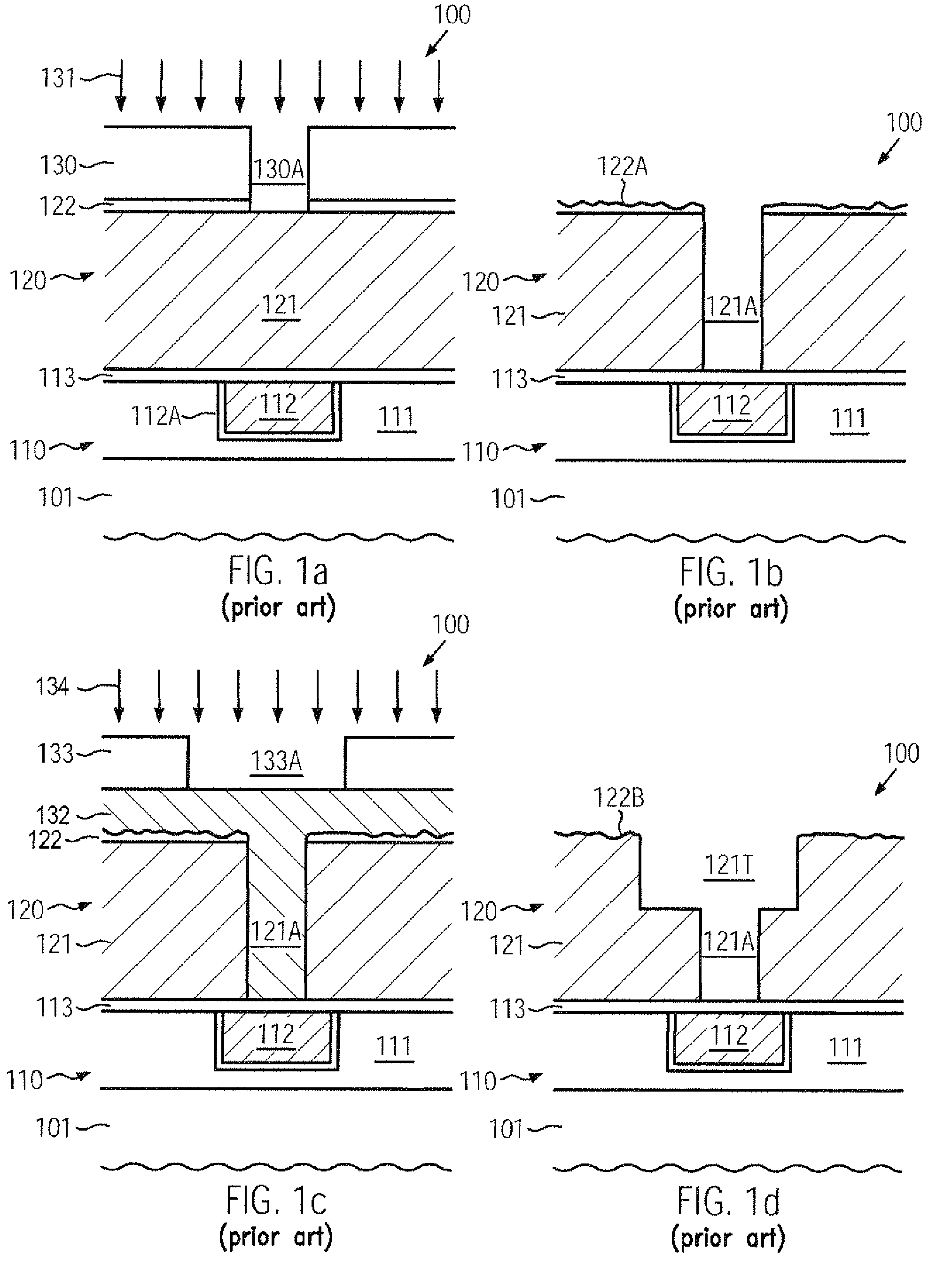

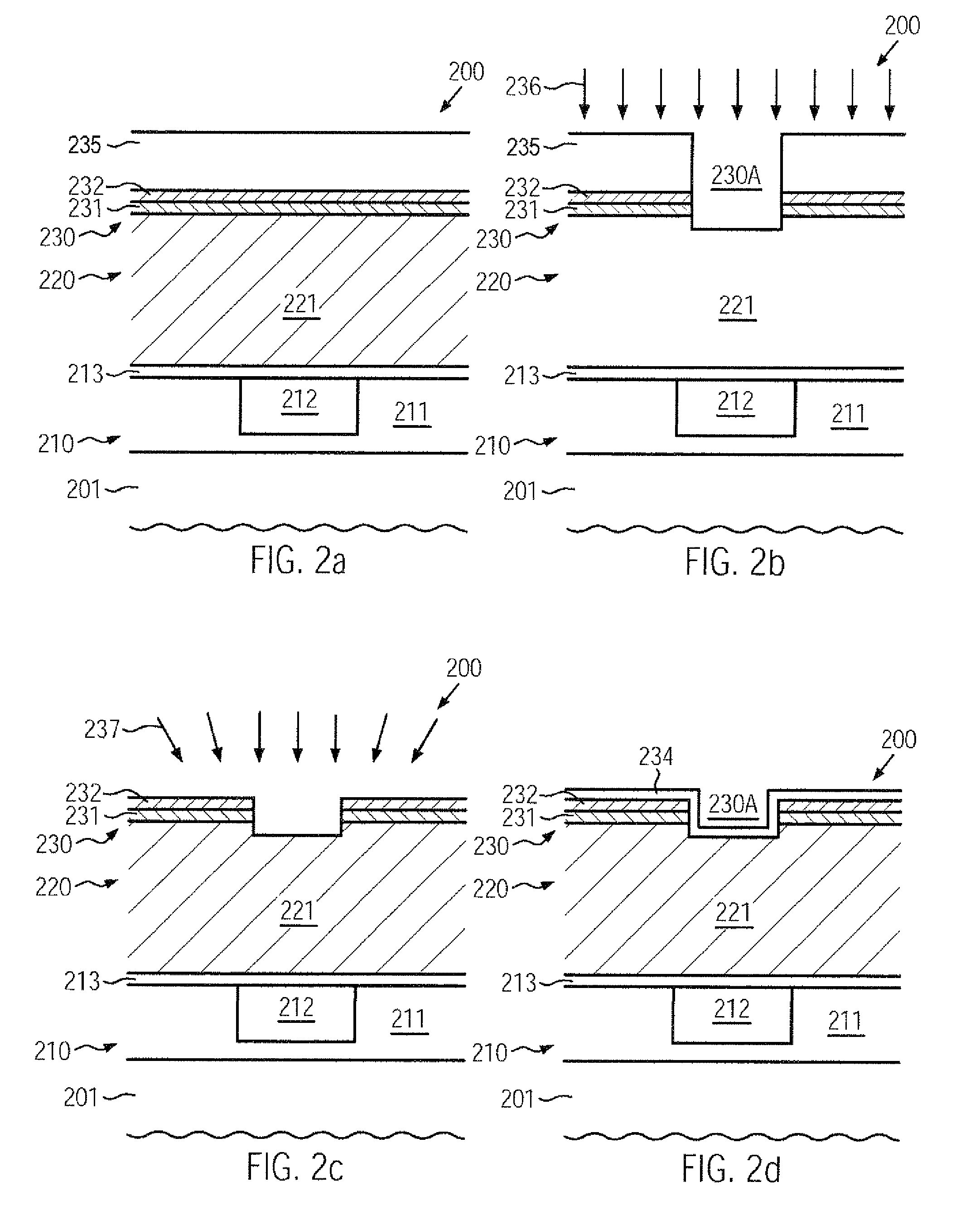

Method for patterning a metallization layer by reducing resist strip induced damage of the dielectric material

ActiveUS8048811B2Improve surface integrityReduce exposureSolid-state devicesSemiconductor/solid-state device manufacturingResistSemiconductor

By forming a hardmask layer in combination with one or more cap layers, undue exposure of a sensitive dielectric material to resist stripping etch ambients may be reduced and integrity of the hardmask may also be maintained so that the trench etch process may be performed with a high degree of etch selectivity during the patterning of openings in a metallization layer of a semiconductor device.

Owner:ADVANCED MICRO DEVICES INC

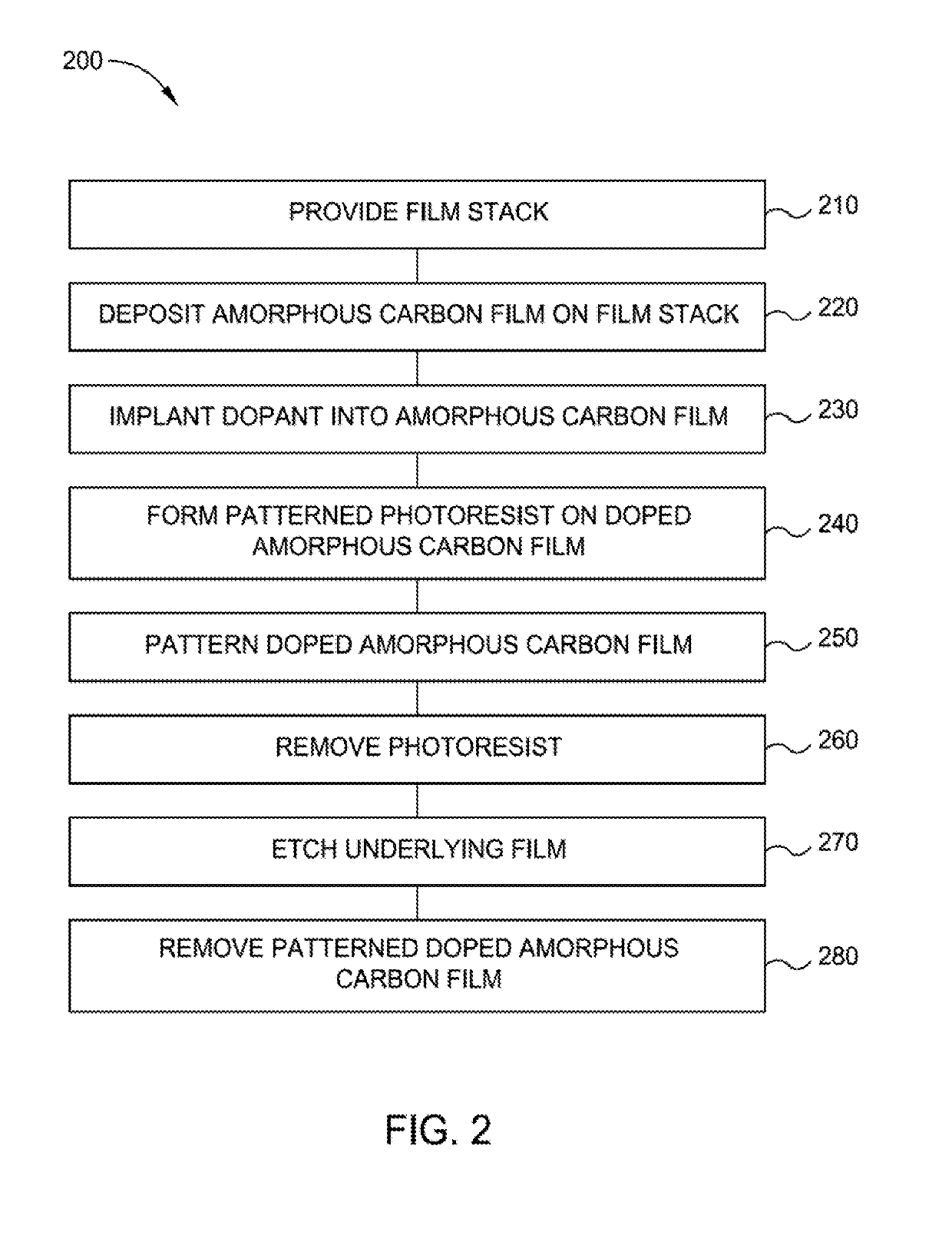

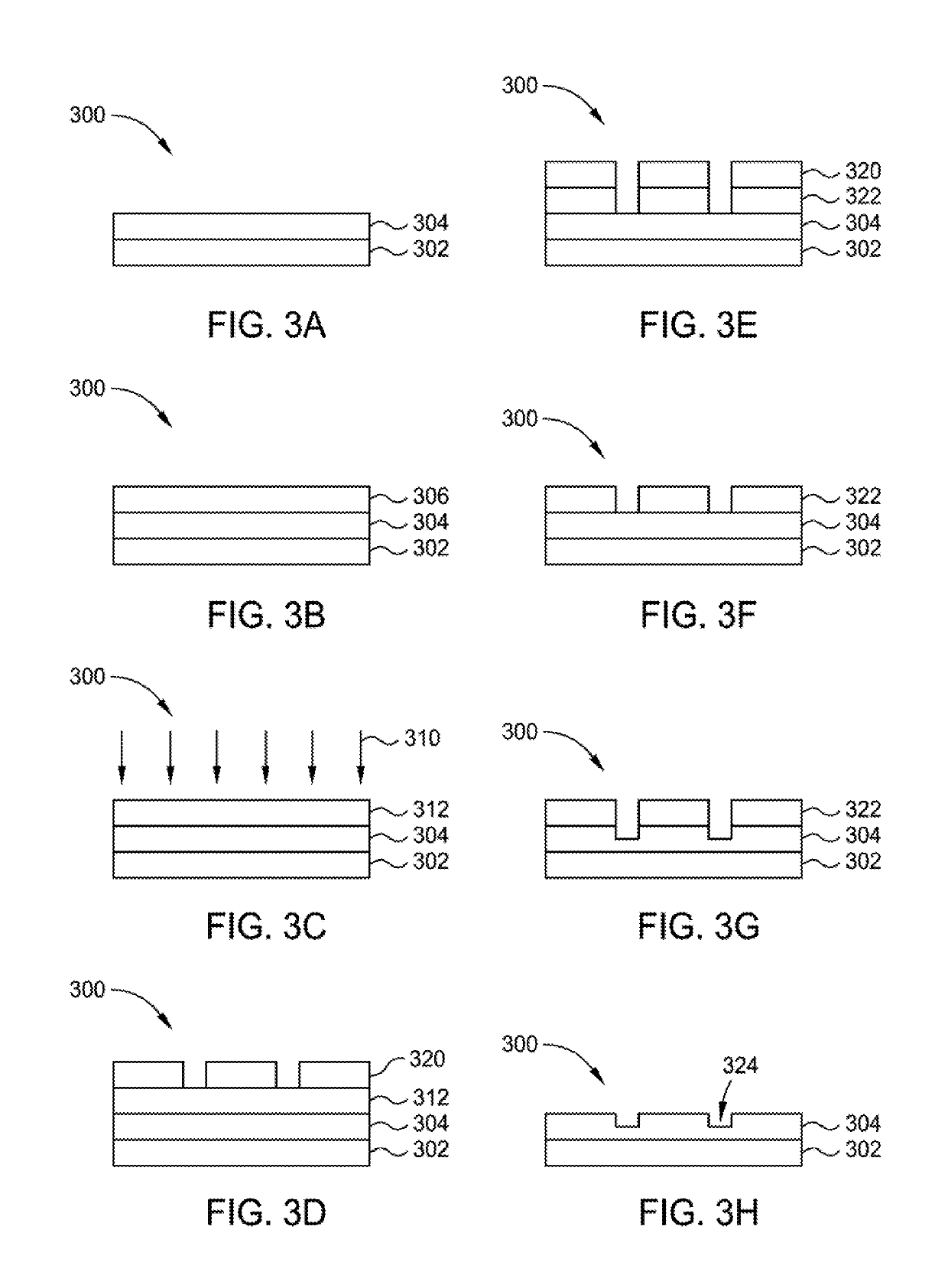

Highly etch selective amorphous carbon film

ActiveUS20190172714A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingKryptonDopant

Implementations described herein generally relate to the fabrication of integrated circuits. More particularly, the implementations described herein provide techniques for deposition of amorphous carbon films on a substrate. In one implementation, a method of forming an amorphous carbon film is provided. The method comprises depositing an amorphous carbon film on an underlayer positioned on a susceptor in a first processing region. The method further comprises implanting a dopant or inert species into the amorphous carbon film in a second processing region. The dopant or inert species is selected from carbon, boron, nitrogen, silicon, phosphorous, argon, helium, neon, krypton, xenon or combinations thereof. The method further comprises patterning the doped amorphous carbon film. The method further comprises etching the underlayer.

Owner:APPLIED MATERIALS INC

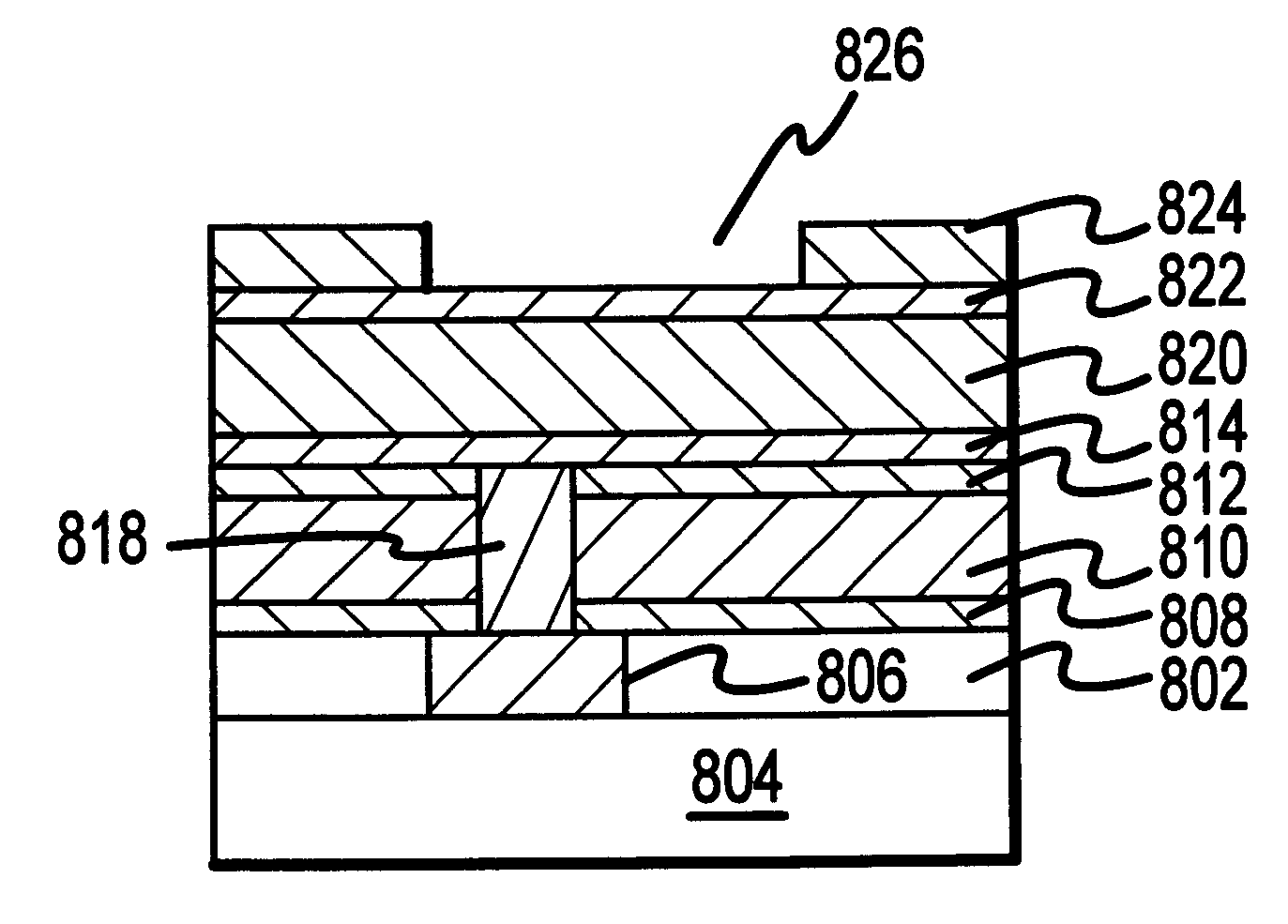

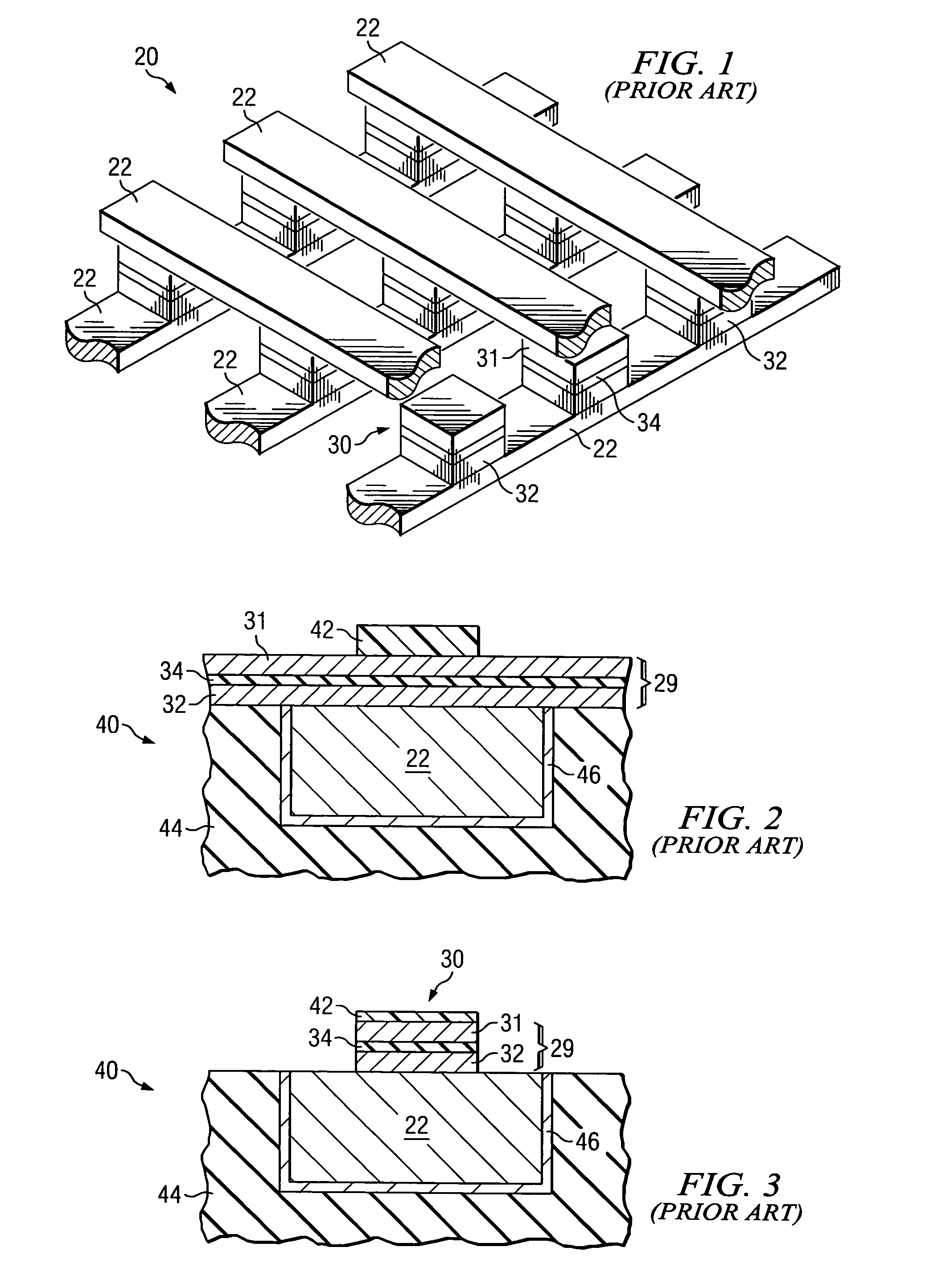

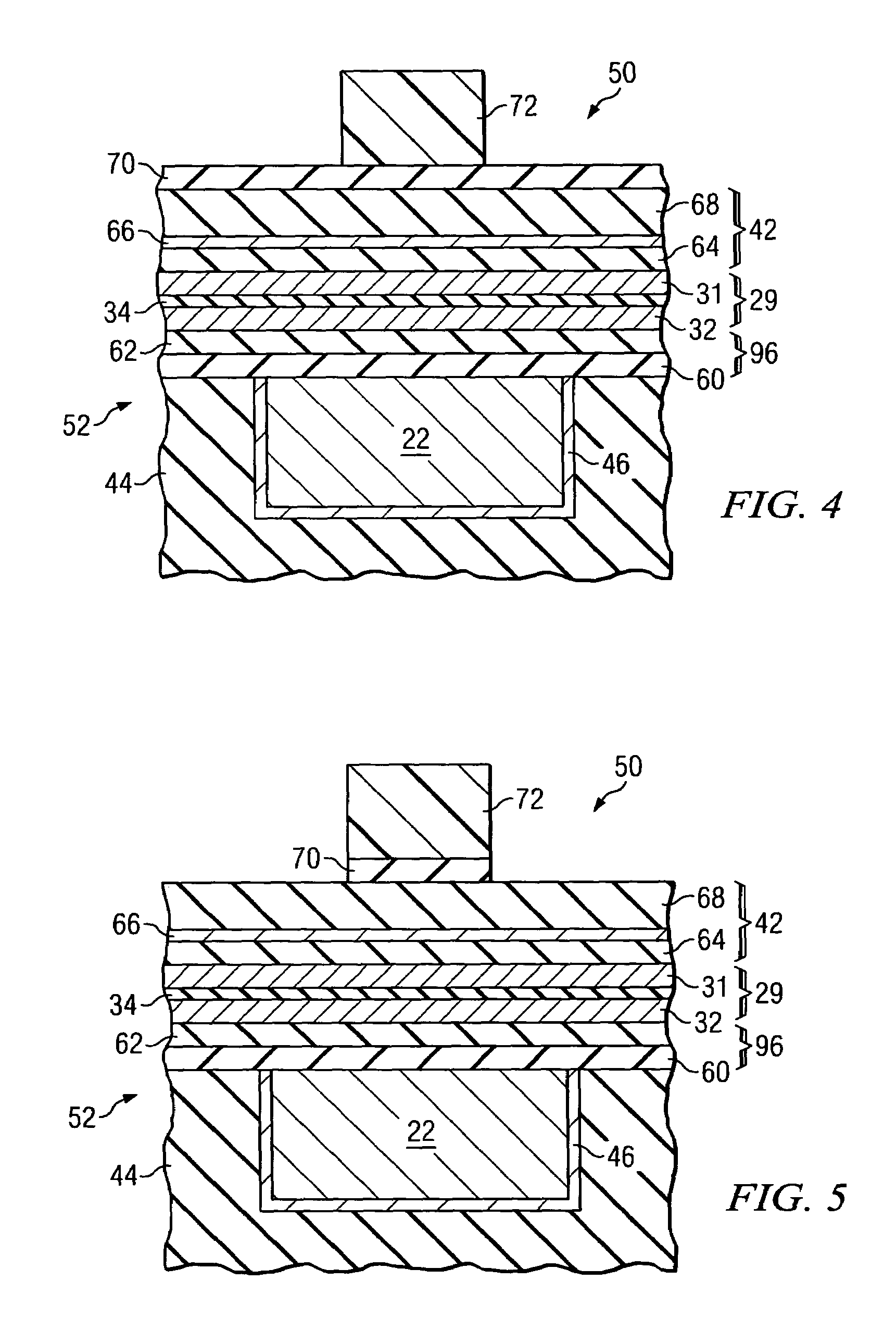

IC interconnect structures and methods for making same

Methods and structures are disclosed for advanced interconnects in sub-micron and sub-half-micron integrated circuit devices fabricated using a single damascene process. a dielectric etch-stop layer (e.g., silicon nitride) is deposited subsequent to rather than prior to CMP processing of the previous metallization layer (e.g., the conductive plug). This scheme effectively eliminates the effect of CMP-induced erosion on the etch-stop layer and therefore allows an extremely thin etch stop to be used. Moreover, a high etch-selectivity can be obtained for the trench etch, and all etch-stop material is removed from beneath the interconnect metal, thereby reducing parasitic effects. A patterned dielectric layer is used as a metal cap in place of the standard blanket silicon nitride layer, thus preventing the formation of blisters and bubbles associated with trapped moisture and gasses, and reducing interconnect capacitance.

Owner:NEWPORT FAB

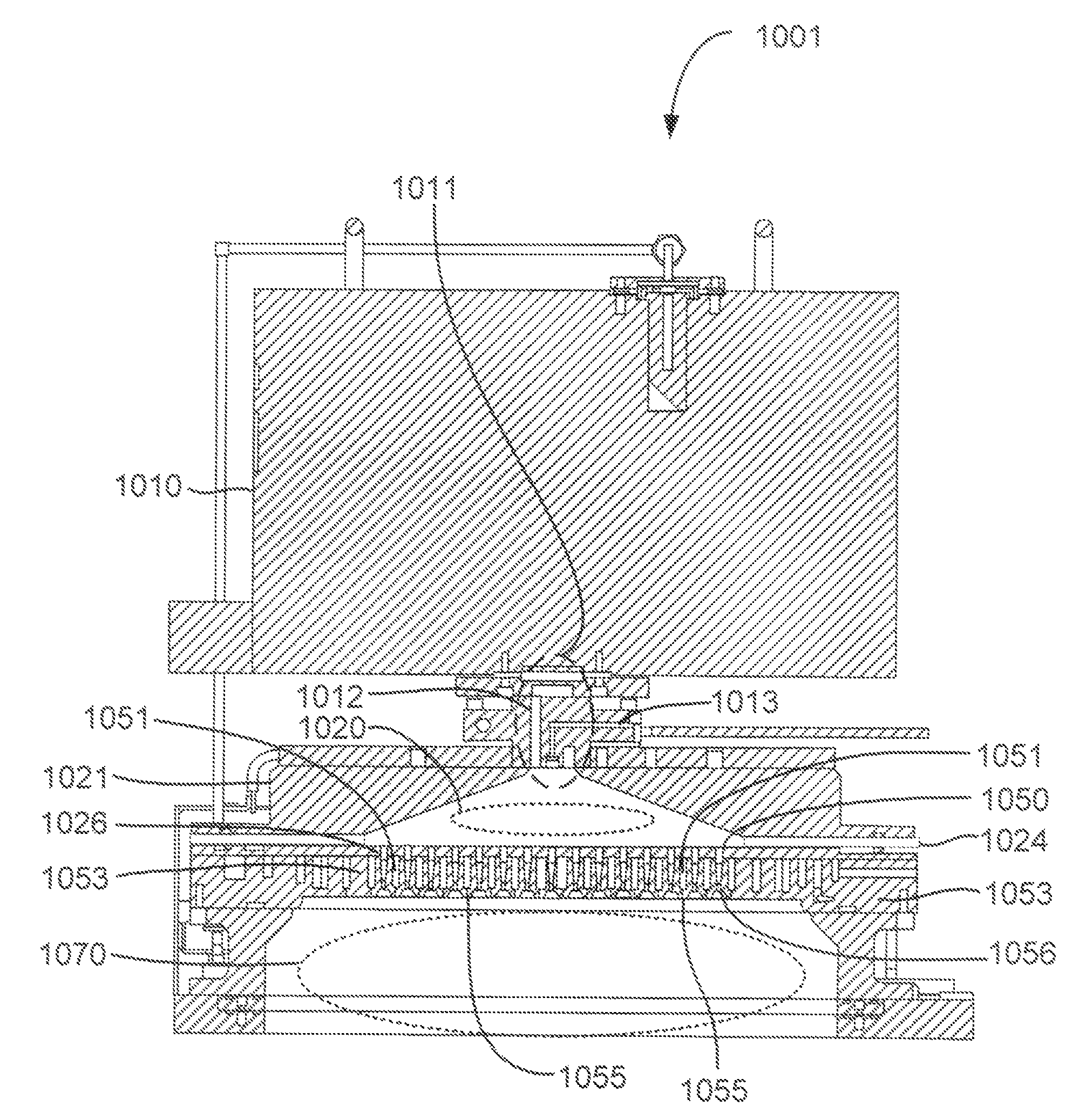

Oxide etch selectivity systems and methods

ActiveUS20170040175A1Improve etch selectivityEnhance and suppress reactionElectric discharge tubesSemiconductor/solid-state device manufacturingHydrogenProcess region

Embodiments of the present technology may include a method of etching a substrate. The method may include striking a plasma discharge in a plasma region. The method may also include flowing a fluorine-containing precursor into the plasma region to form a plasma effluent. The plasma effluent may flow into a mixing region. The method may further include introducing a hydrogen-and-oxygen-containing compound into the mixing region without first passing the hydrogen-and-oxygen-containing compound into the plasma region. Additionally, the method may include reacting the hydrogen-and-oxygen-containing compound with the plasma effluent in the mixing region to form reaction products. The reaction products may flow through a plurality of openings in a partition to a substrate processing region. The method may also include etching the substrate with the reaction products in the substrate processing region.

Owner:APPLIED MATERIALS INC

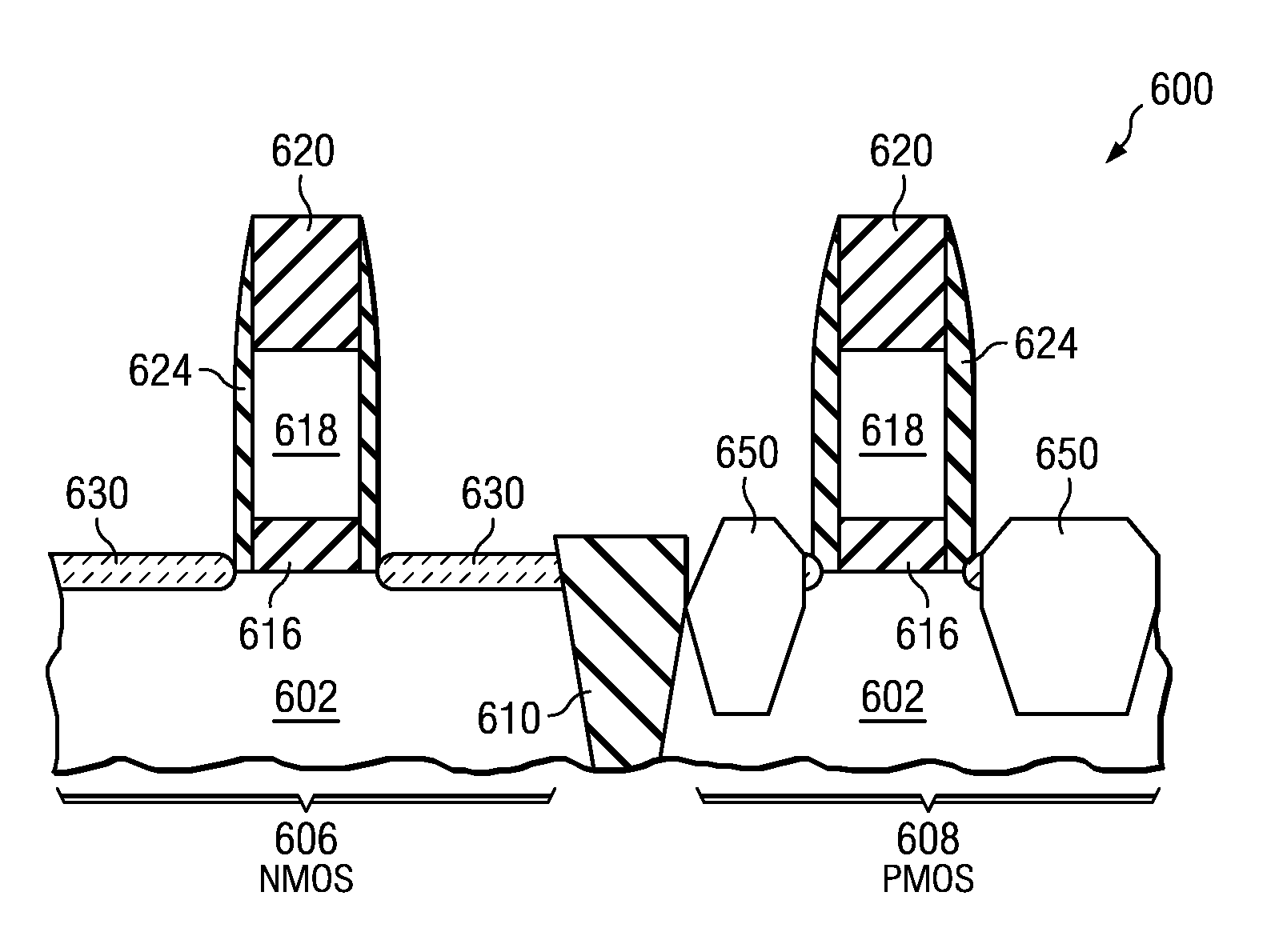

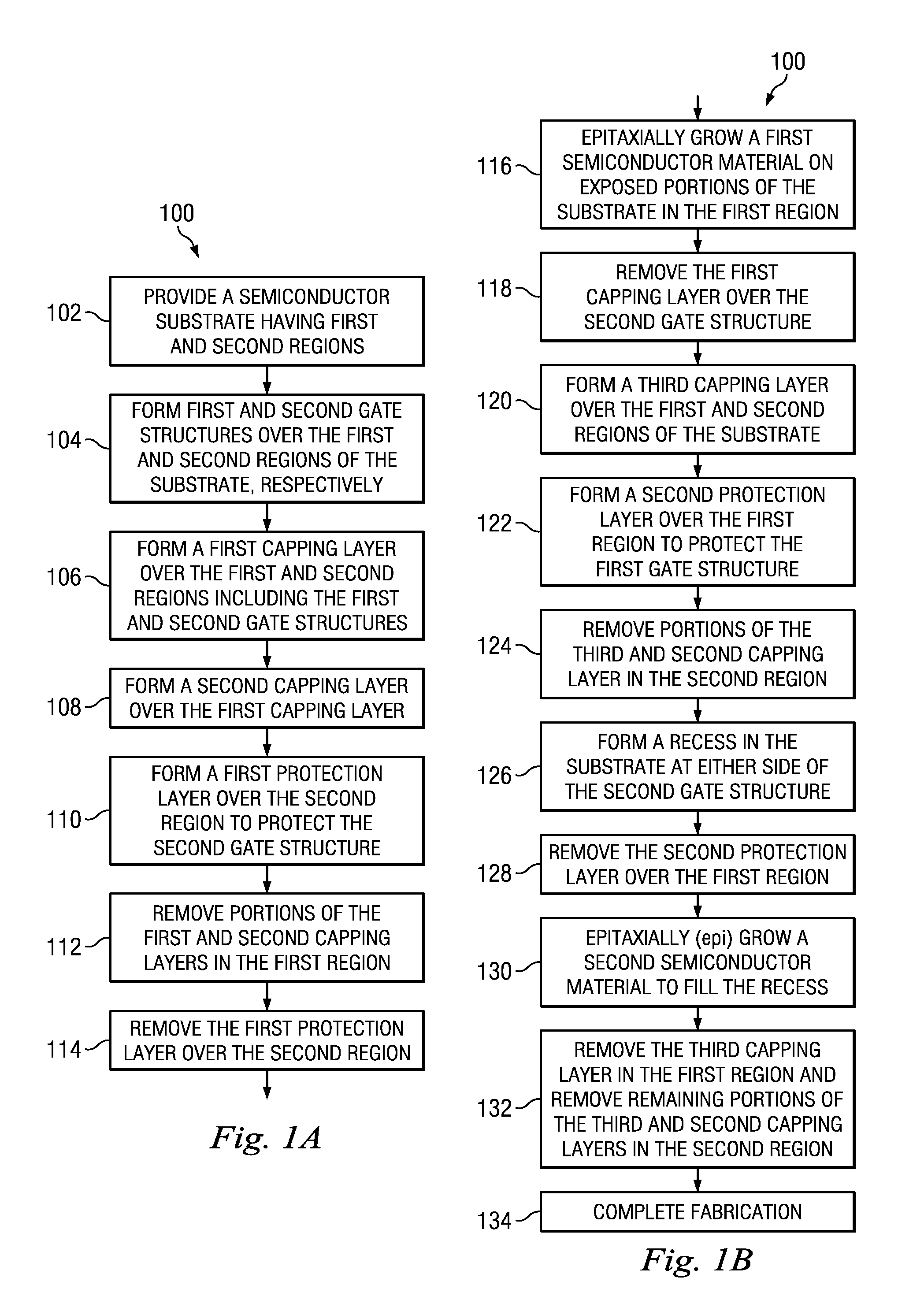

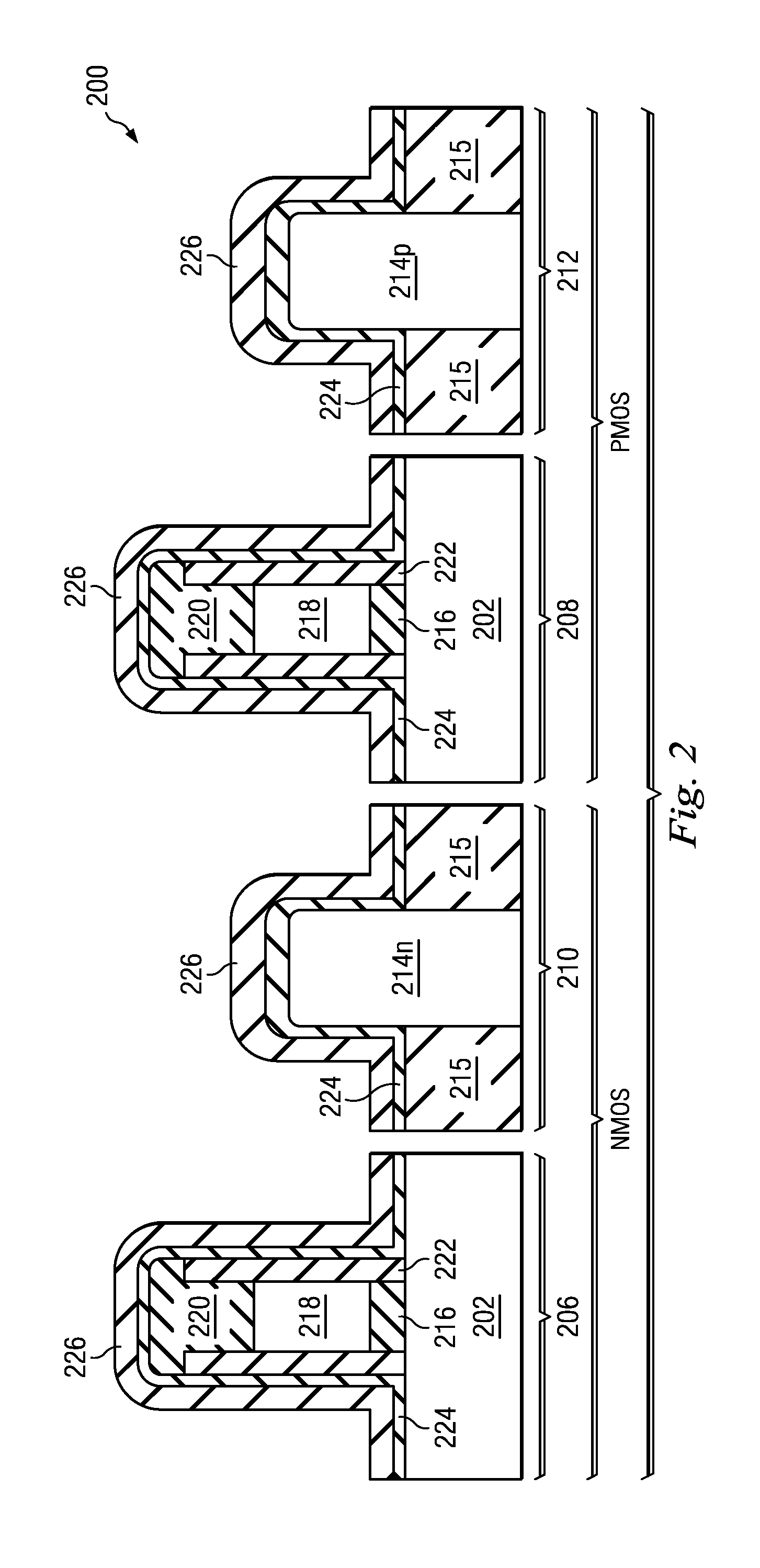

Method of Dual EPI Process For Semiconductor Device

ActiveUS20110201164A1Semiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor materials

The present disclosure provides a method of fabricating a semiconductor device that includes forming first and second gate structures over first and second regions of a substrate, respectively, forming spacers on sidewalls of the first and second gate structures, the spacers being formed of a first material, forming a capping layer over the first and second gate structures, the capping layer being formed of a second material different from the first material, forming a protection layer over the second region to protect the second gate structure, removing the capping layer over the first gate structure; removing the protection layer over the second region, epitaxially (epi) growing a semiconductor material on exposed portions of the substrate in the first region, and removing the capping layer over the second gate structure by an etching process that exhibits an etching selectivity of the second material to the first material.

Owner:TAIWAN SEMICON MFG CO LTD

Fabrication process for a magnetic tunnel junction device

A method of fabricating a magnetic tunnel junction (MTJ) device is provided. A patterned hard mask is oxidized to form a surface oxide thereon. An MTJ stack is etched in alignment with the patterned hard mask after the oxidizing of the patterned hard mask. Preferably, the MTJ stack etch recipe includes chlorine and oxygen. Etch selectivity between the hard mask and the MTJ stack is improved.

Owner:INFINEON TECH AG +1

Antireflective film-forming composition, method for manufacturing the same, and antireflective film and pattern formation method using the same

ActiveUS20050277058A1Improve etch selectivityEtching speed is fastSemiconductor/solid-state device manufacturingSilver halide emulsionsCross-linkResist

The present invention provides a material for an antireflective film characterized by high etching selectivity with respect to a resist, that is, which has a fast etching speed when compared to the resist, and in addition, can be removed without damage to a film which is to be processed. The present invention also provides a pattern formation method for forming an antireflective film layer on a substrate using this antireflective film-forming composition, and a pattern formation method that uses this antireflective film as a hard mask, and a pattern formation method that uses this antireflective film as a hard mask for processing the substrate. The present invention provides an antireflective film-forming composition comprising an organic solvent, a cross linking agent, and a polymer comprising a light absorbing group obtained by hydrolyzing and condensing more than one type of silicon compound, a crosslinking group and a non-crosslinking group.

Owner:SHIN ETSU CHEM IND CO LTD +1

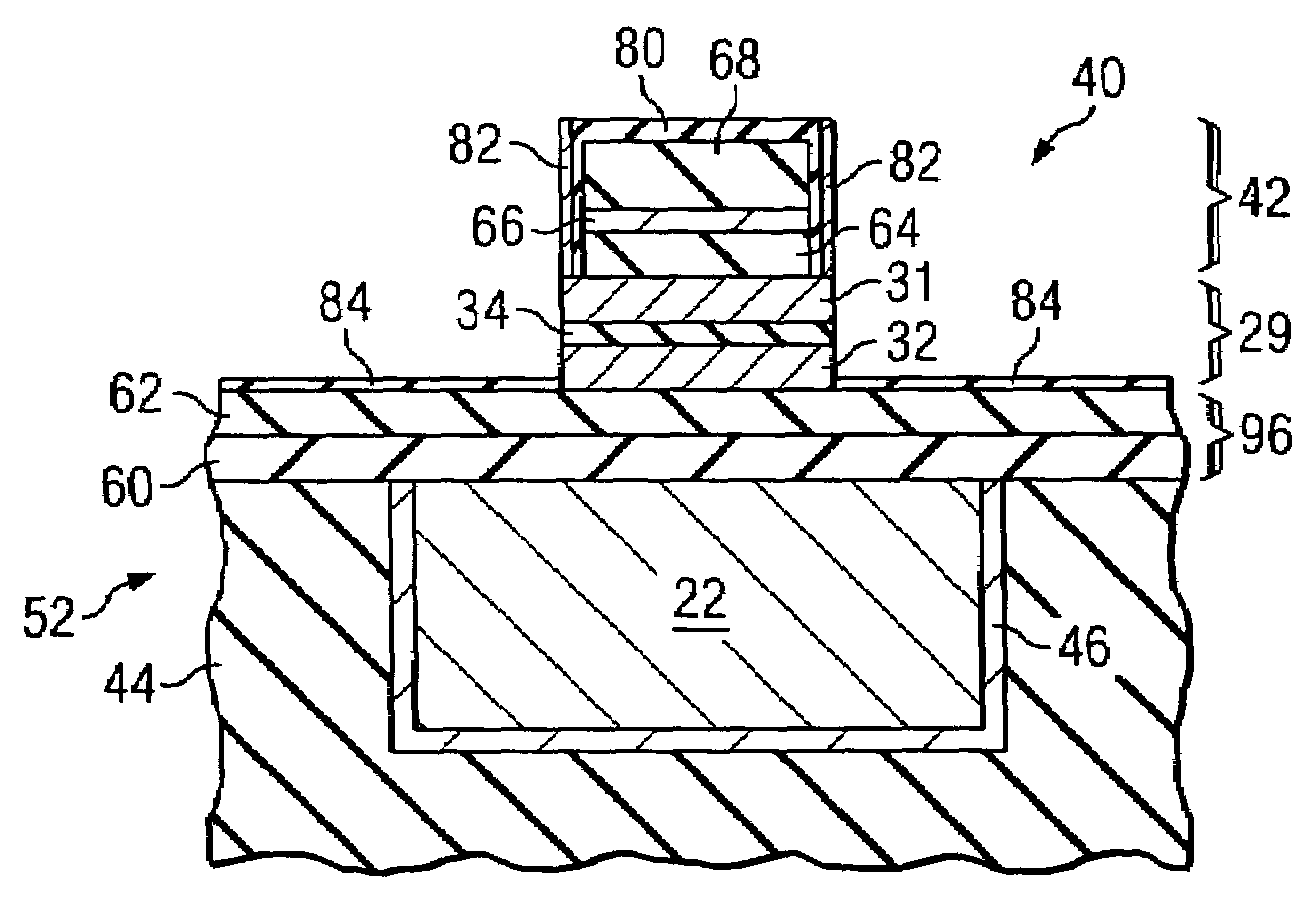

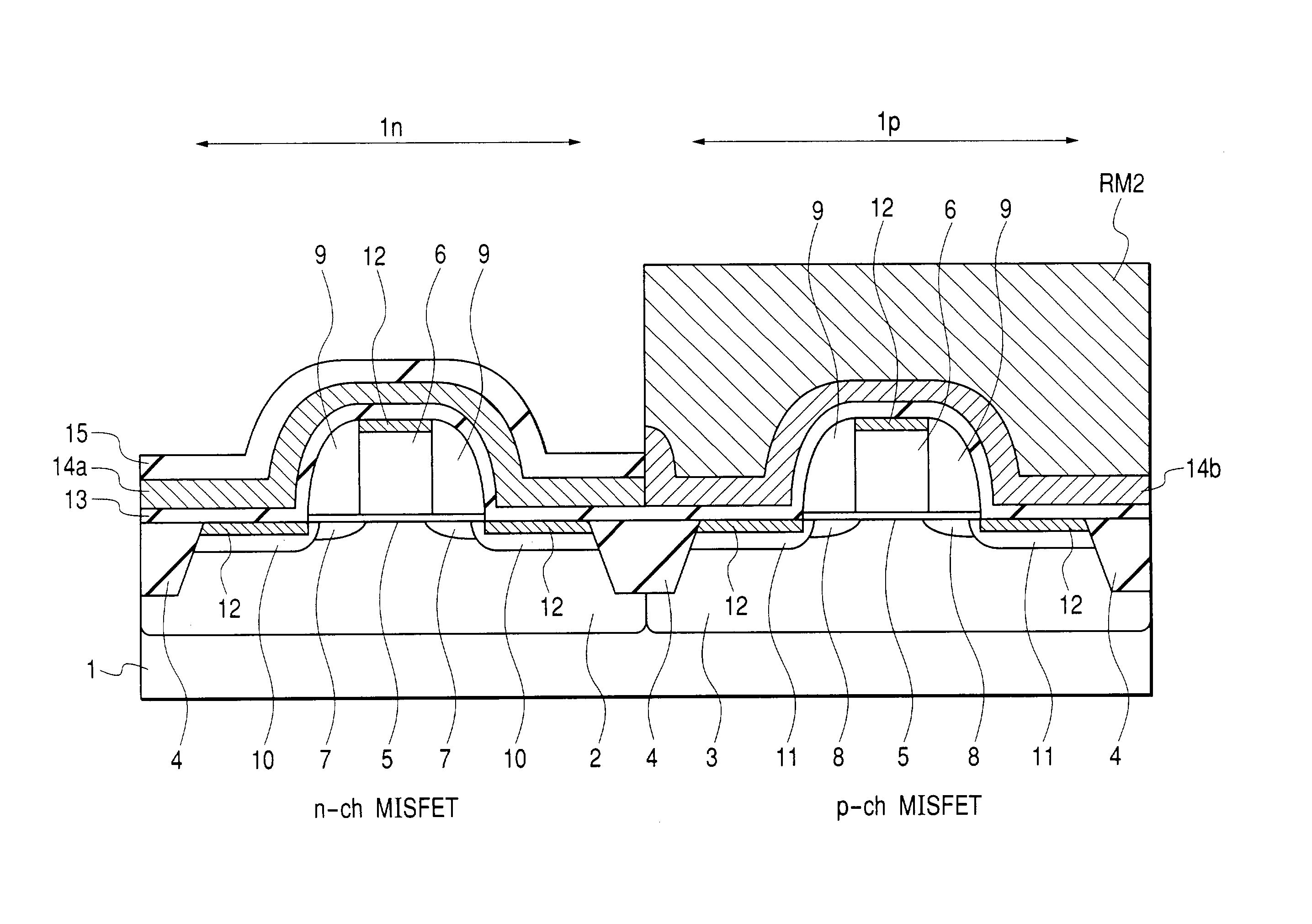

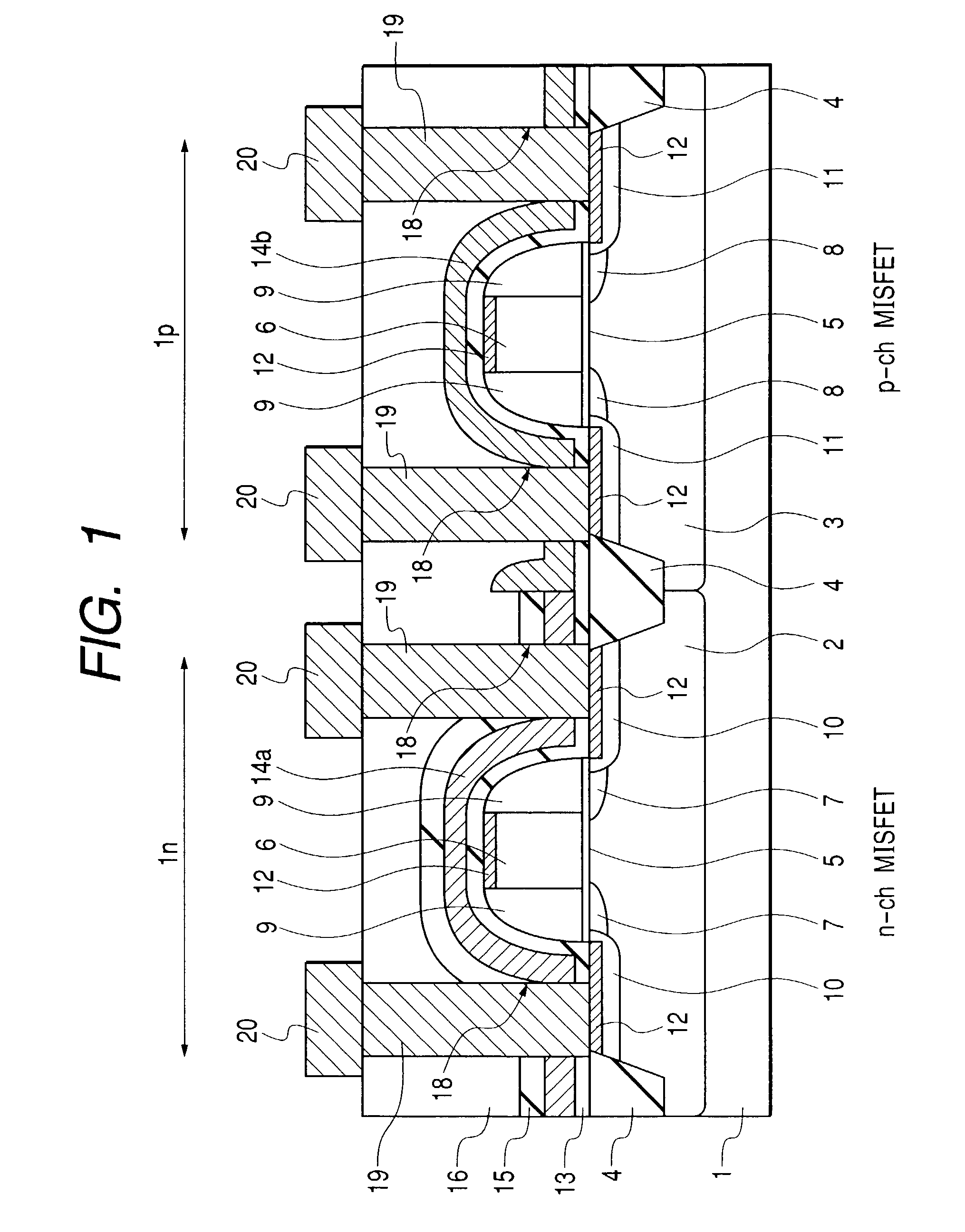

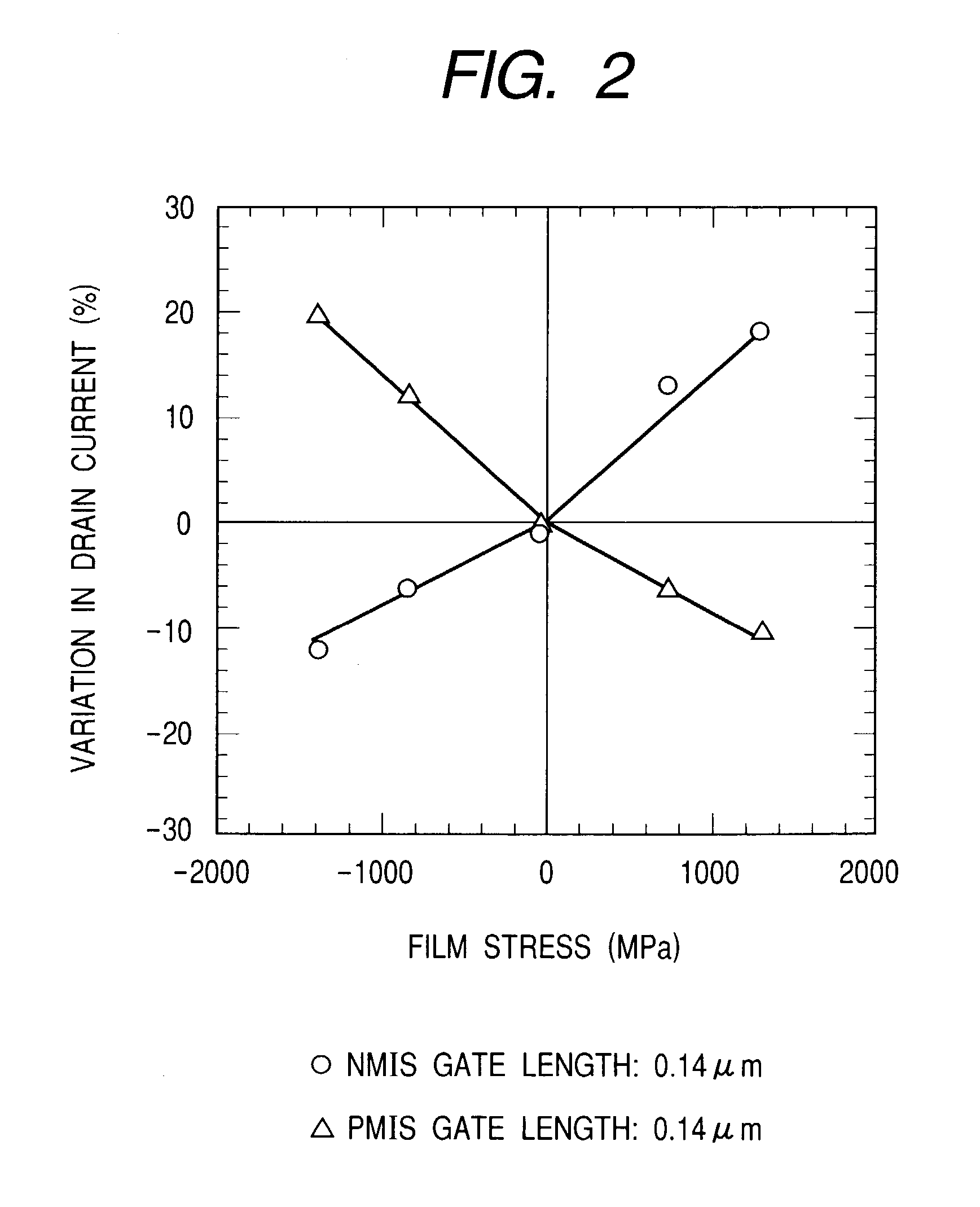

Semiconductor device and a method of manufacturing the same

InactiveUS7105394B2Relieve pressureIncrease currentTransistorSemiconductor/solid-state device manufacturingSemiconductorEtching selectivity

A method of manufacturing a semiconductor device having an n-type FET and p-type FET, each formed over a semiconductor substrate, calls for (a) forming, over the n-type FET and p-type FET, a first insulating film, for generating a tensile stress in the channel formation region of the n-type FET, to cover gate electrodes of the FETs, while covering, with an insulating film, a semiconductor region between the gate electrode of the p-type FET and an element isolation region of the semiconductor substrate; (b) selectively removing the first insulating film from the upper surface of the p-type FET by etching; (c) forming, over the n-type and p-type FETs, a second insulating film, for generating a compressive stress in the channel formation region of the p-type FET, to cover gate electrodes of the FETs; and (d) selectively removing the second insulating film from the upper surface of the n-type FET.

Owner:RENESAS ELECTRONICS CORP

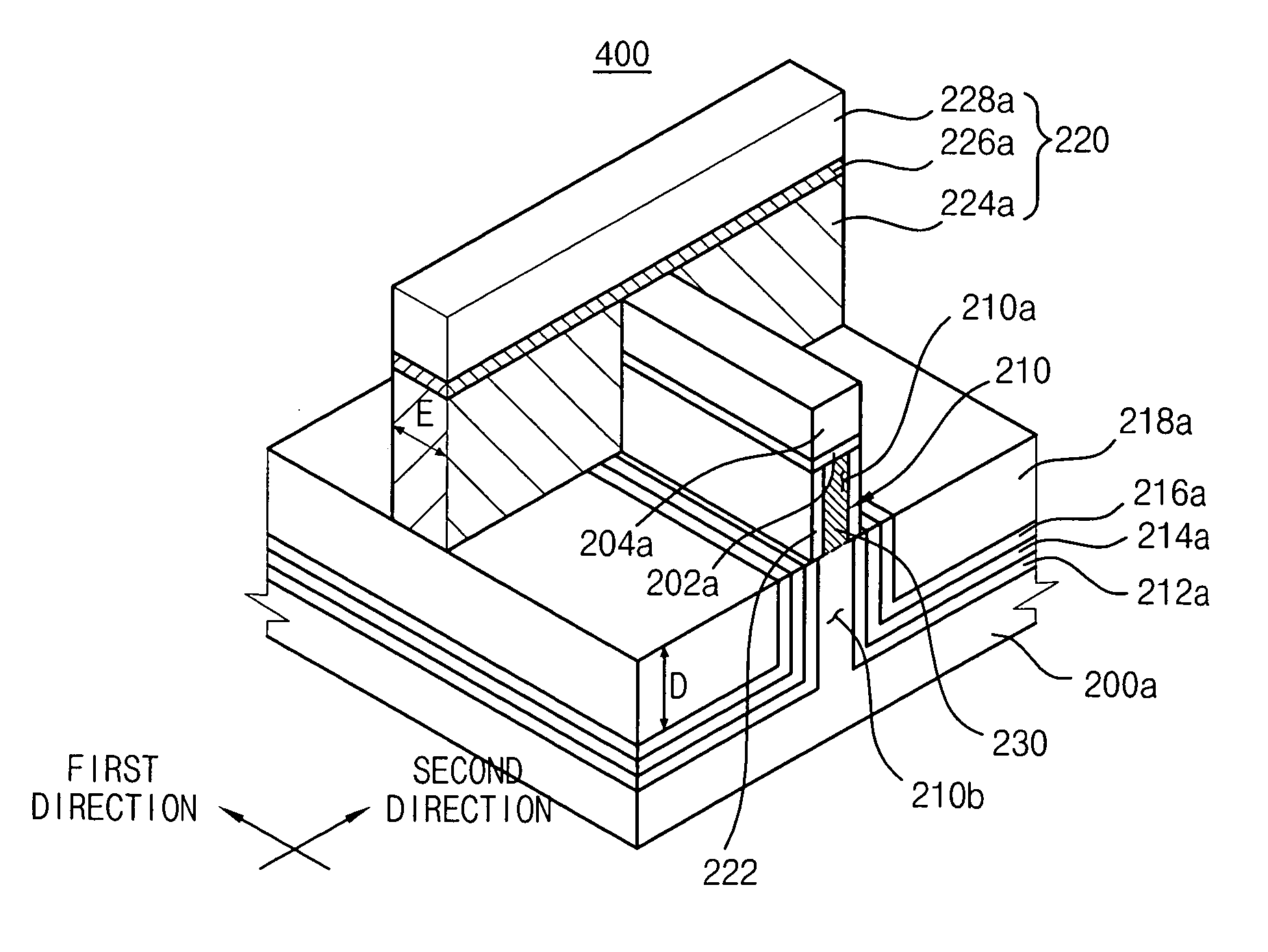

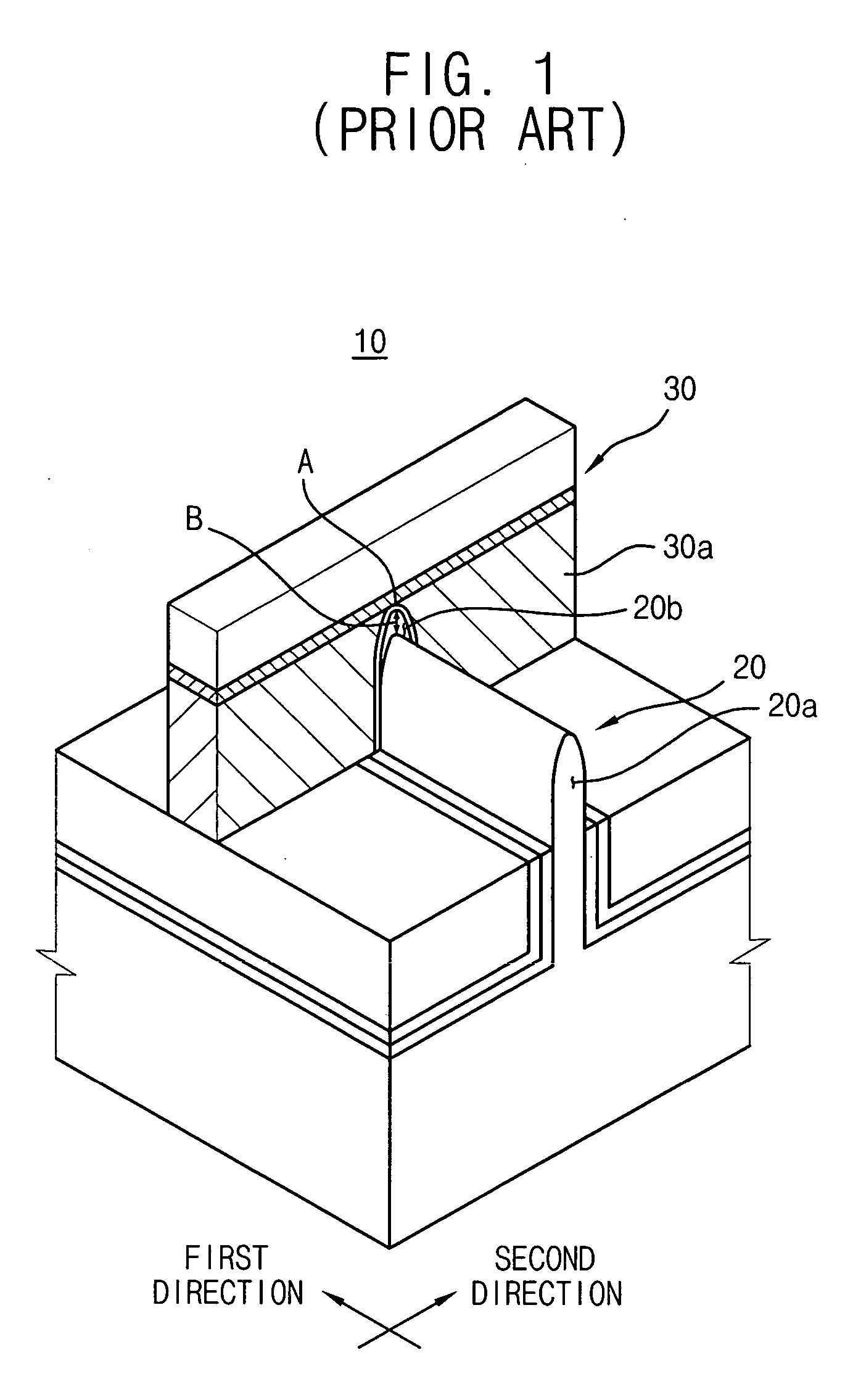

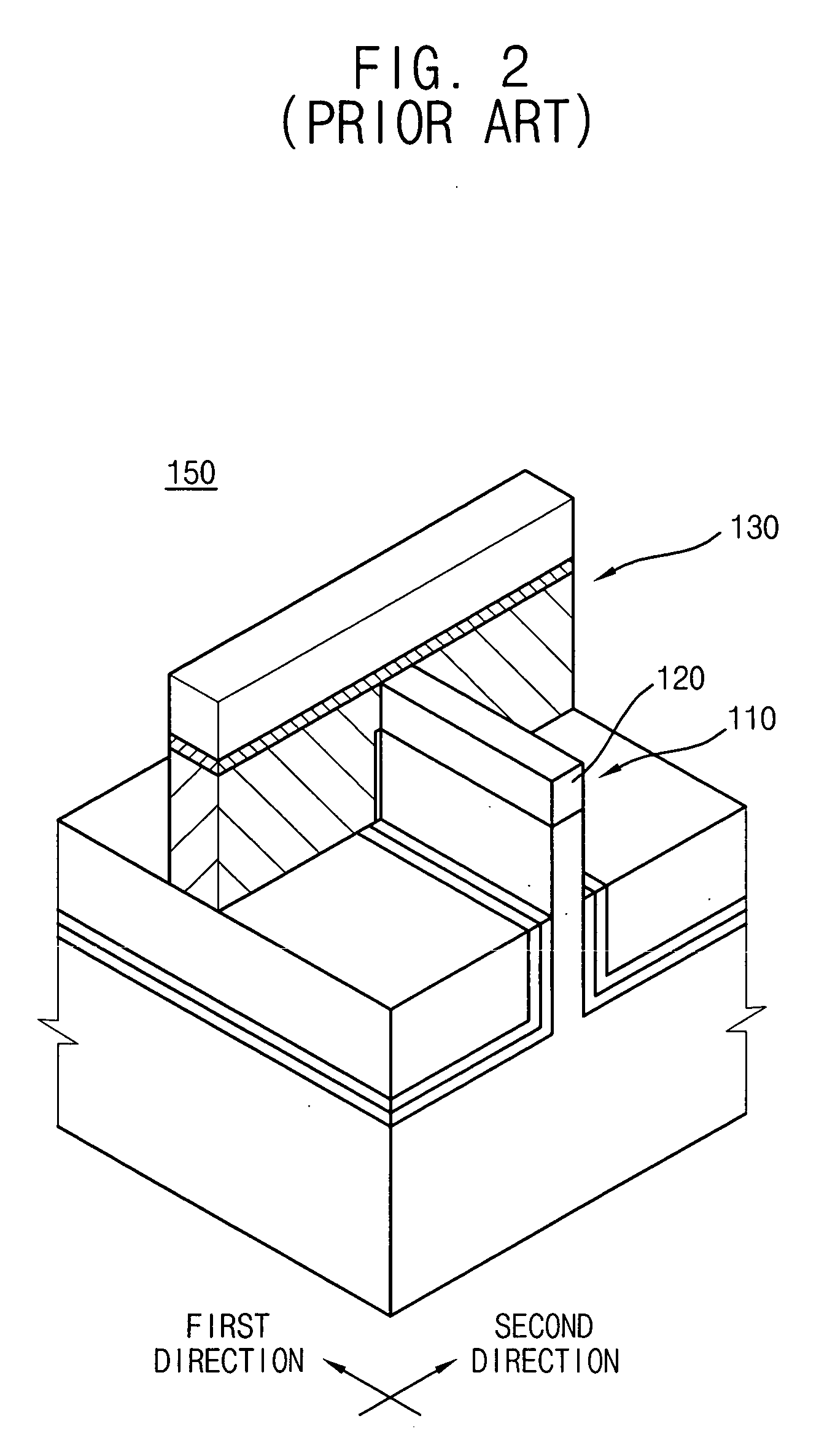

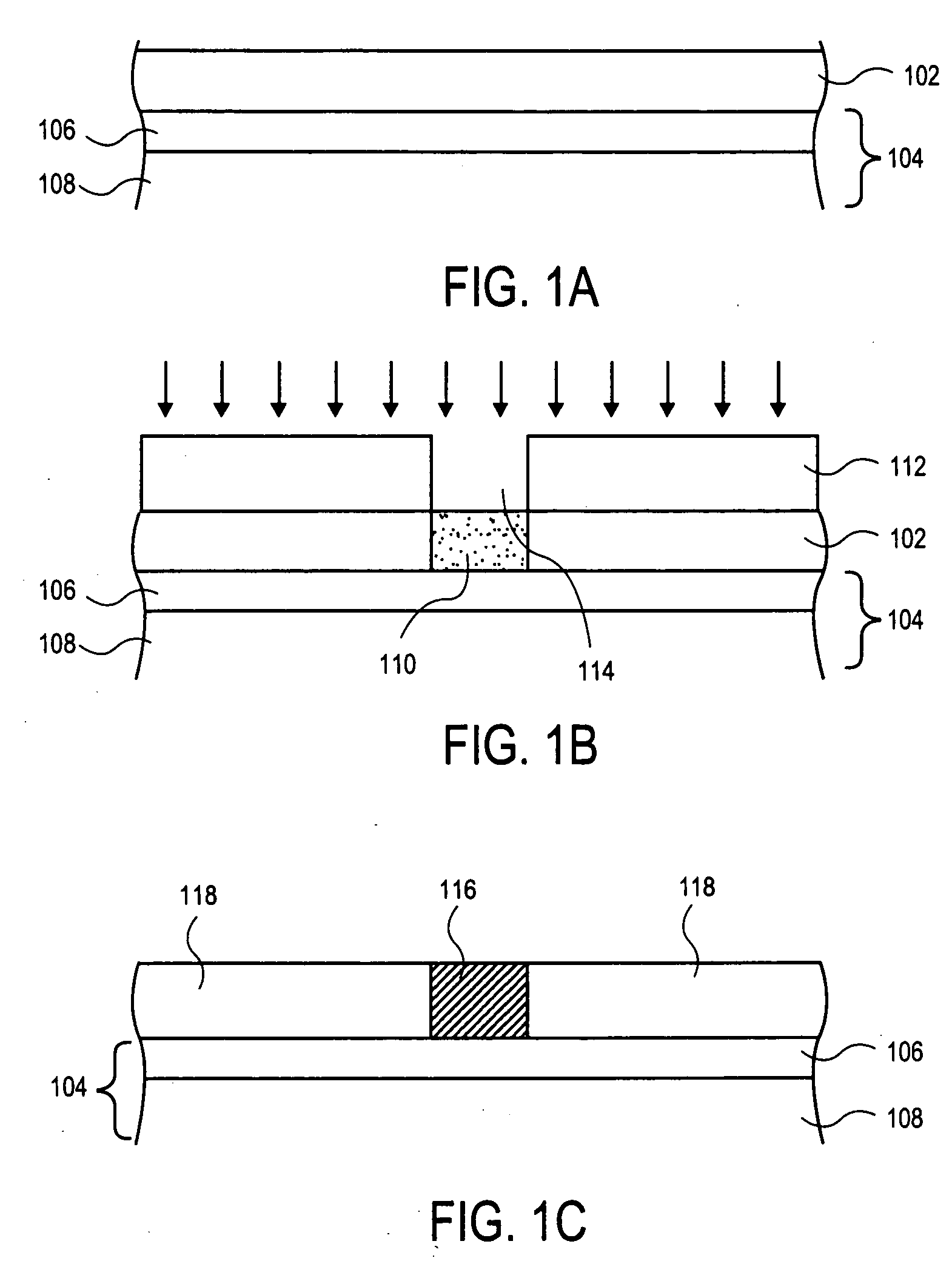

Fin field effect transistor and method of manufacturing the same

ActiveUS20060118876A1Stay in shapeAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerInternal stress

In a fin field effect transistor (FET), an active pattern protrudes in a vertical direction from a substrate and extends across the substrate in a first horizontal direction. A first silicon nitride pattern is formed on the active pattern, and a first oxide pattern and a second silicon nitride pattern are sequentially formed on the substrate and on a sidewall of a lower portion of the active pattern. A device isolation layer is formed on the second silicon nitride pattern, and a top surface of the device isolation layer is coplanar with top surfaces of the oxide pattern and the second silicon nitride pattern. A buffer pattern having an etching selectivity with respect to the second silicon nitride pattern is formed between the first oxide pattern and the second silicon nitride pattern. Internal stresses that can be generated in sidewalls of the active pattern are sufficiently released and an original shape of the first silicon nitride pattern remains unchanged, thereby improving electrical characteristics of the fin FET.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of varying etch selectivities of a film

InactiveUS20050148131A1TransistorSemiconductor/solid-state device manufacturingCrystallographyDopant

A method of patterning a crystalline film. A crystalline film having a degenerate lattice comprising first atoms in a first region and a second region is provided. Dopants are substituted for said first atoms in said first region to form a non-degenerate crystalline film in said first region. The first region and the second region are exposed to a wet etchant wherein the wet etchant etches the degenerate lattice in said second region without etching the non-degenerate lattice in the first region.

Owner:INTEL CORP

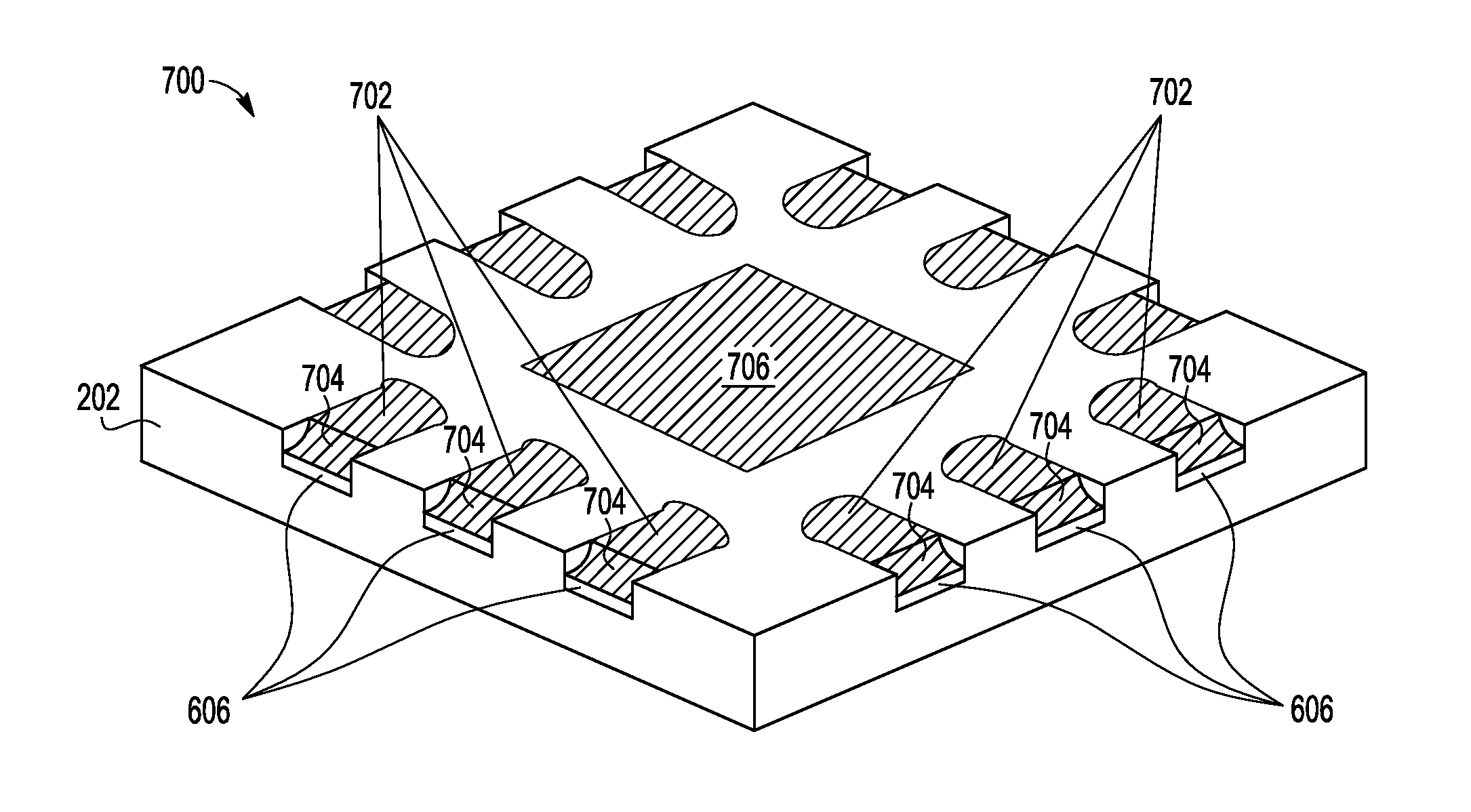

Packaging Process to Create Wettable Lead Flank During Board Assembly

ActiveUS20110244629A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringLead frame

A method and apparatus are described for fabricating a low-pin-count chip package (701) including a die pad (706) for receiving an integrated circuit device and a plurality of connection leads (702) having recessed lead ends (704) at the outer peripheral region of each contact lead. After forming the package body (202) over the integrated circuit device, unplated portions (104) of the exposed bottom surface of the selectively plated lead frame are partially etched to form recessed lead ends (302) at the outer peripheral region of each contact lead, and the recessed lead ends are subsequently re-plated (402) to provide wettable recessed lead ends at the outer peripheral region of each contact lead.

Owner:NXP USA INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com