Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

69results about How to "Reduce the amount of etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

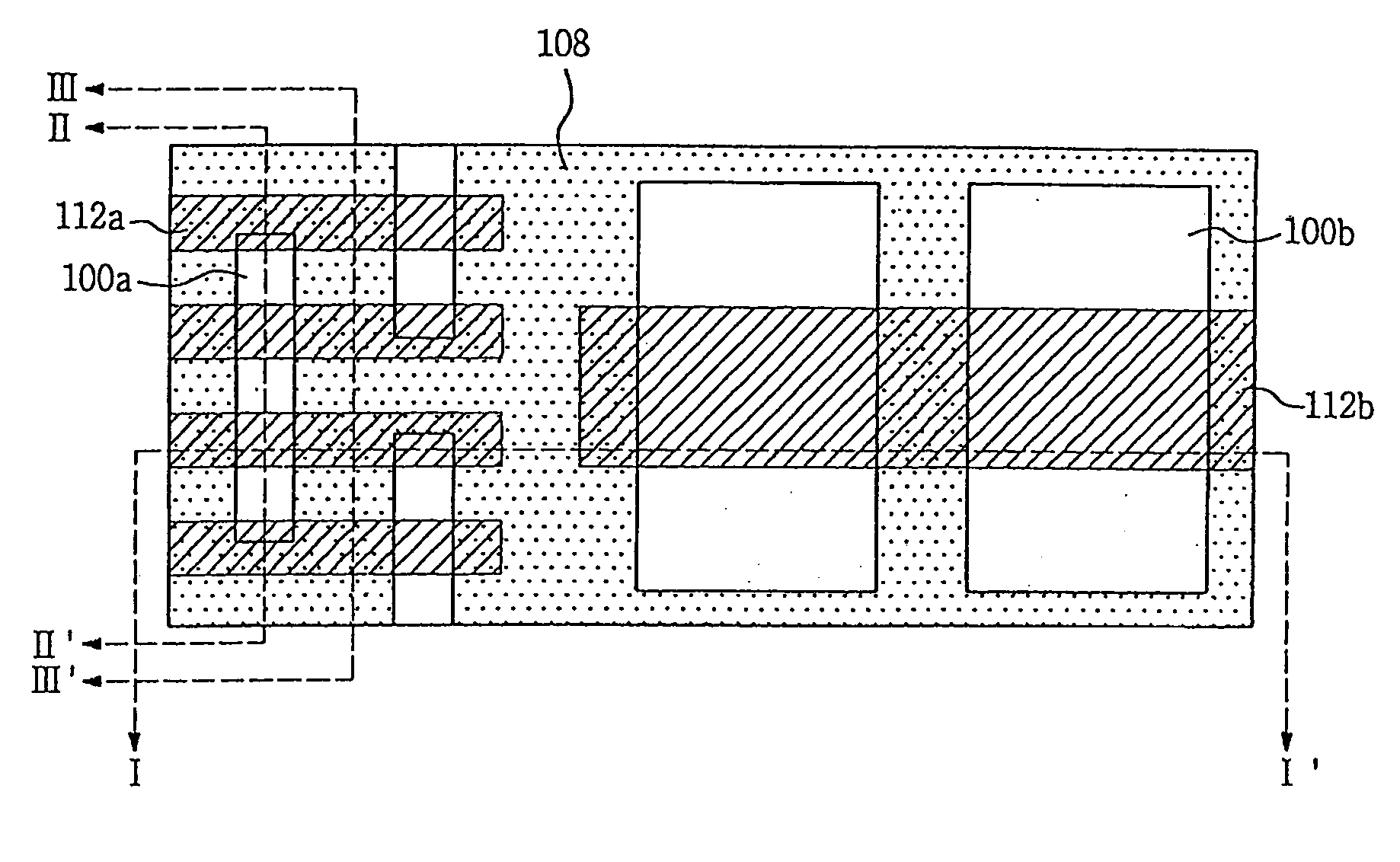

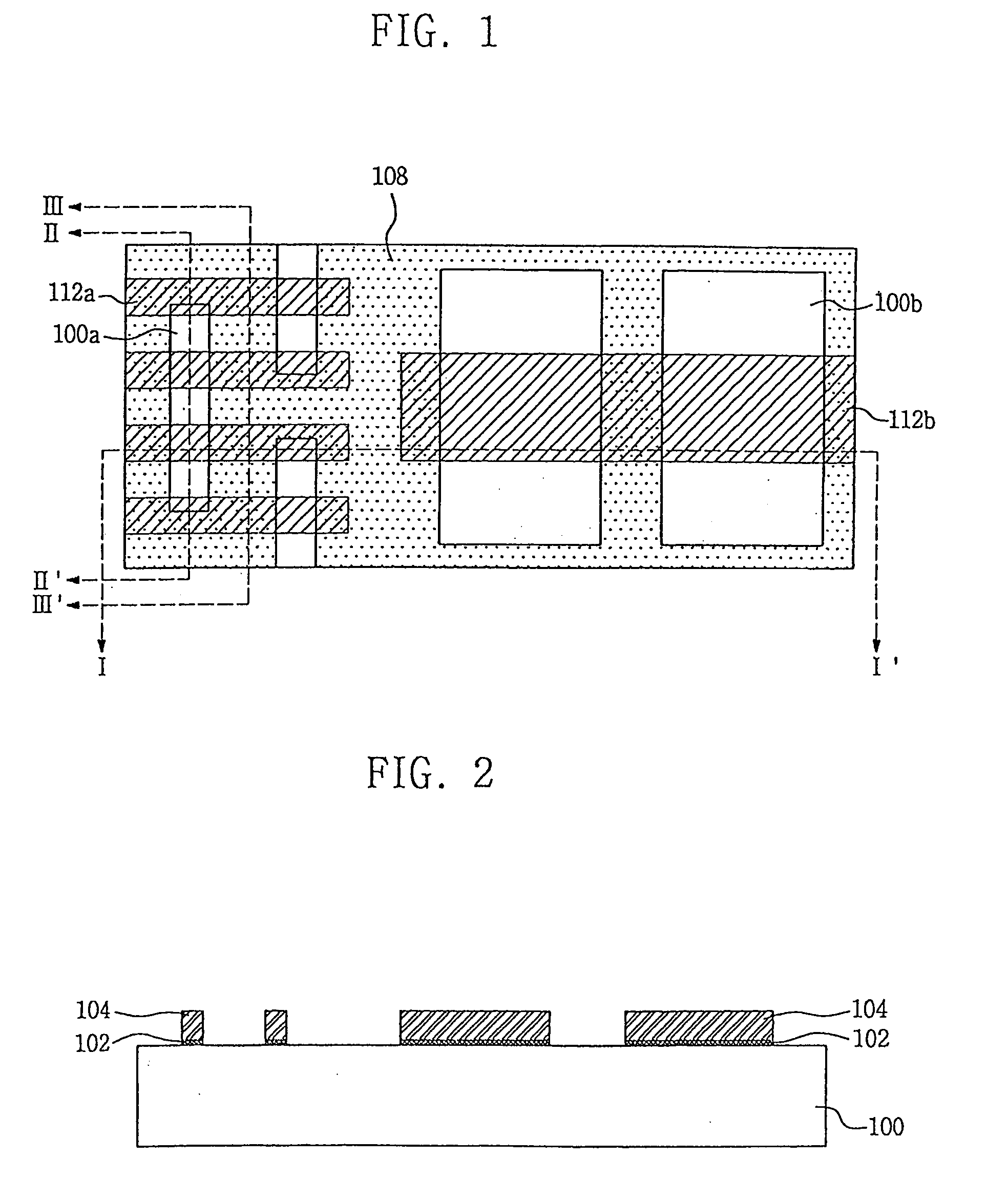

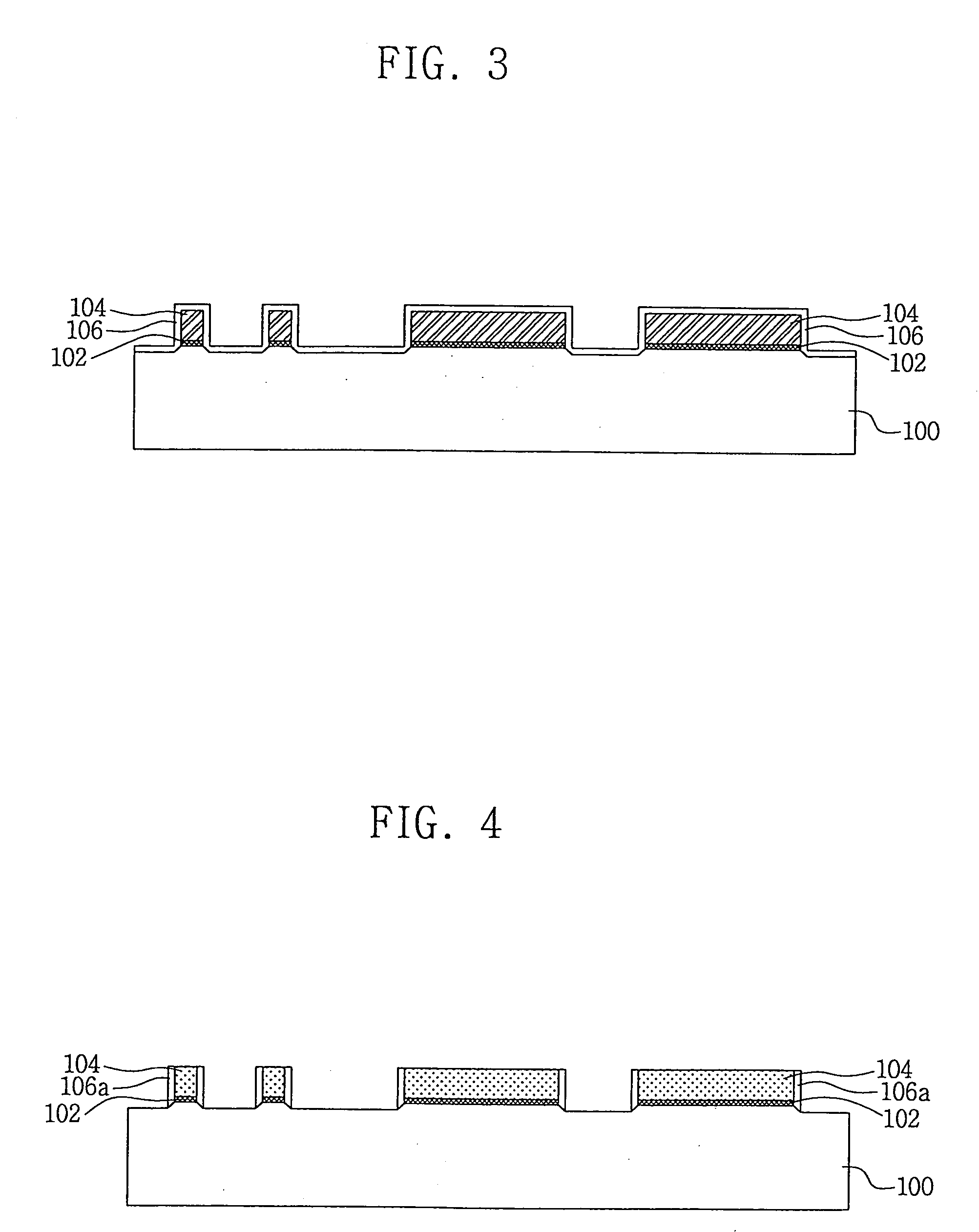

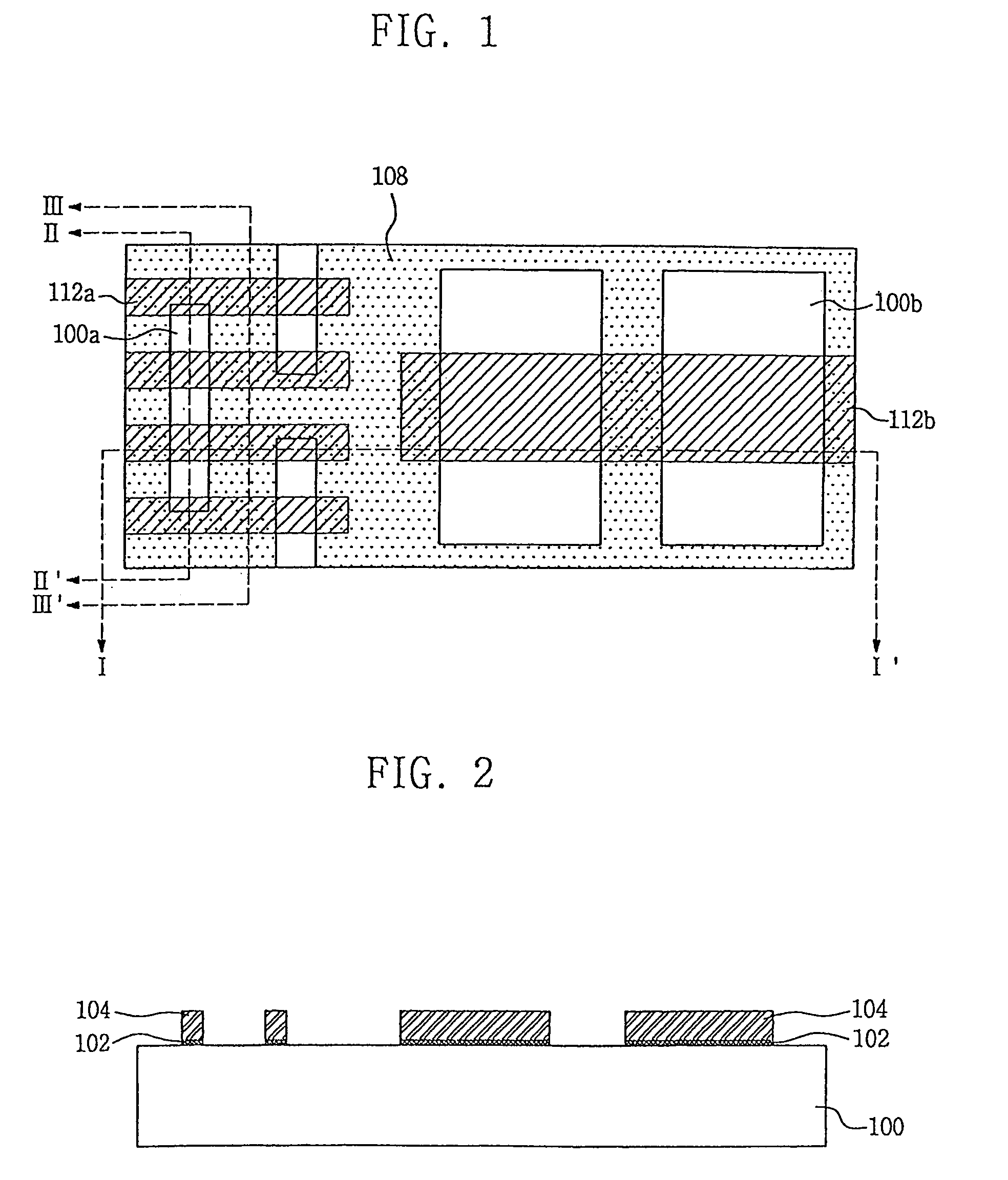

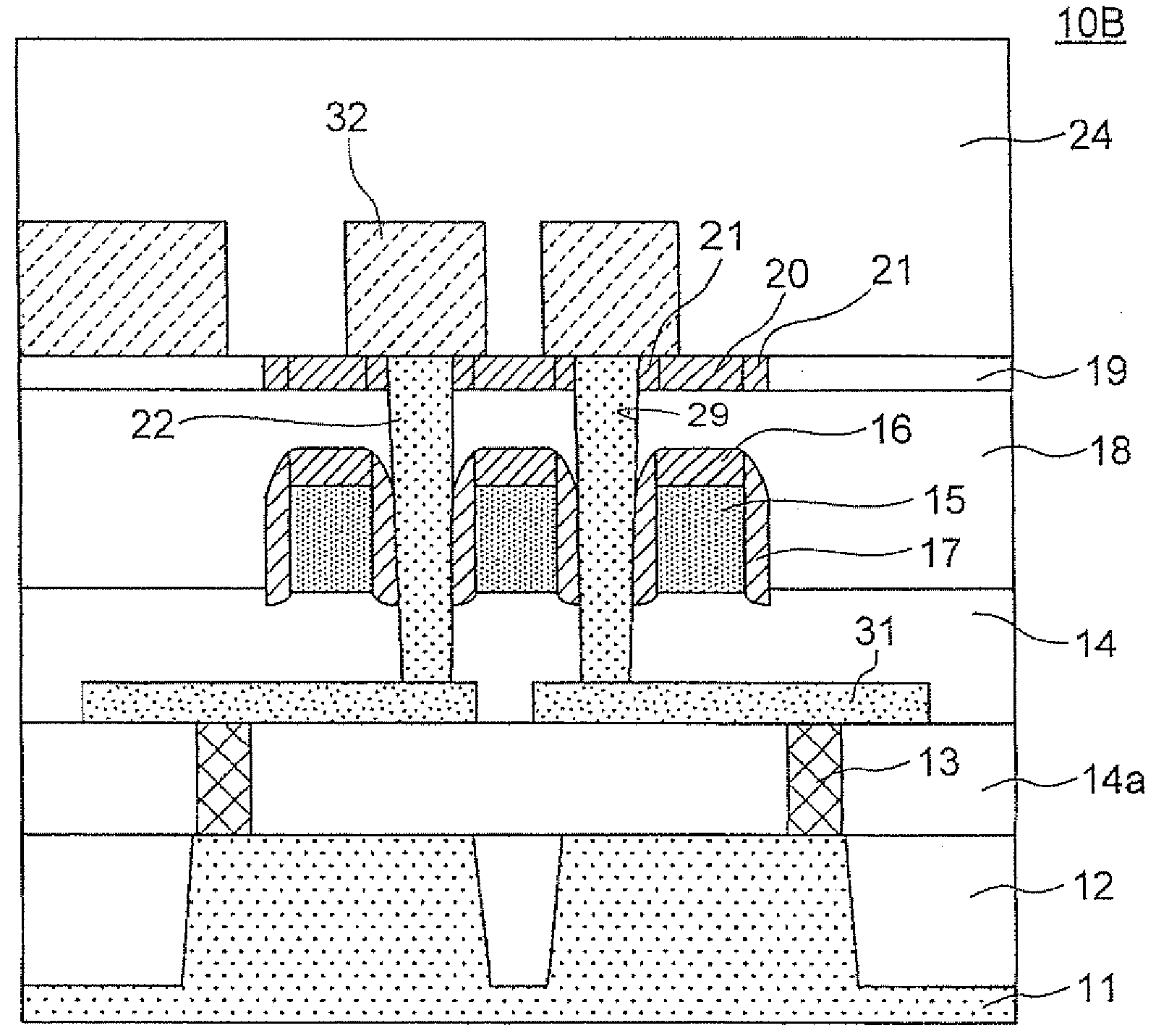

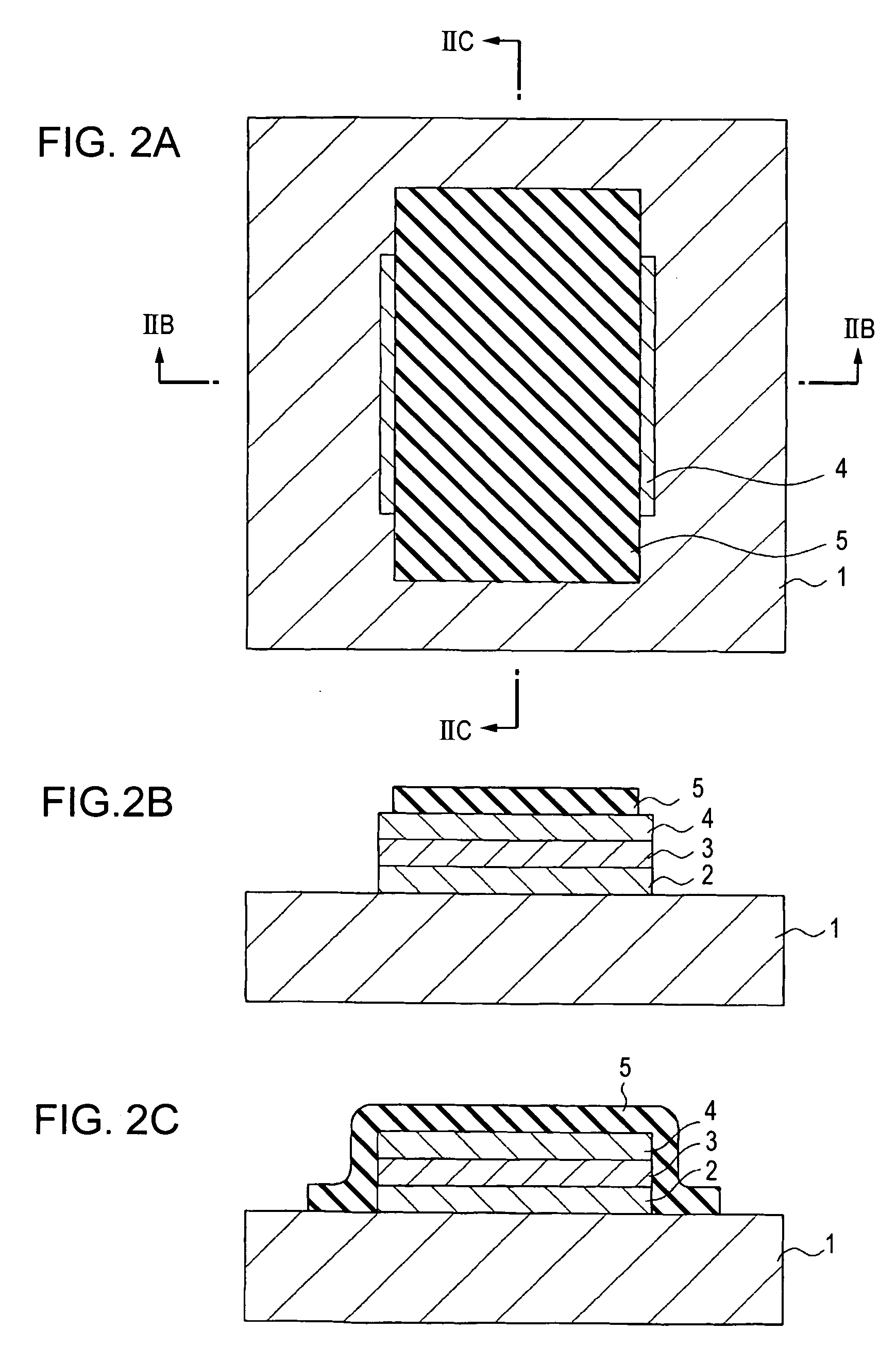

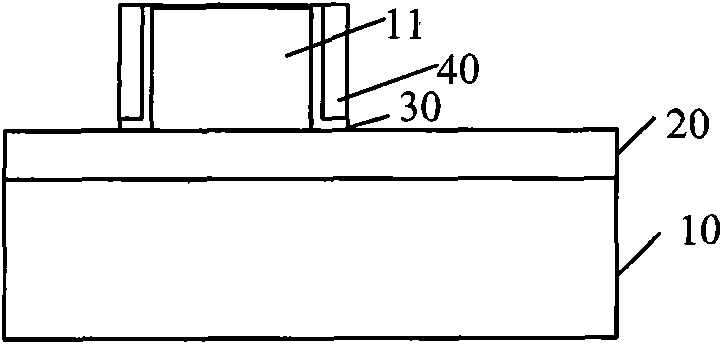

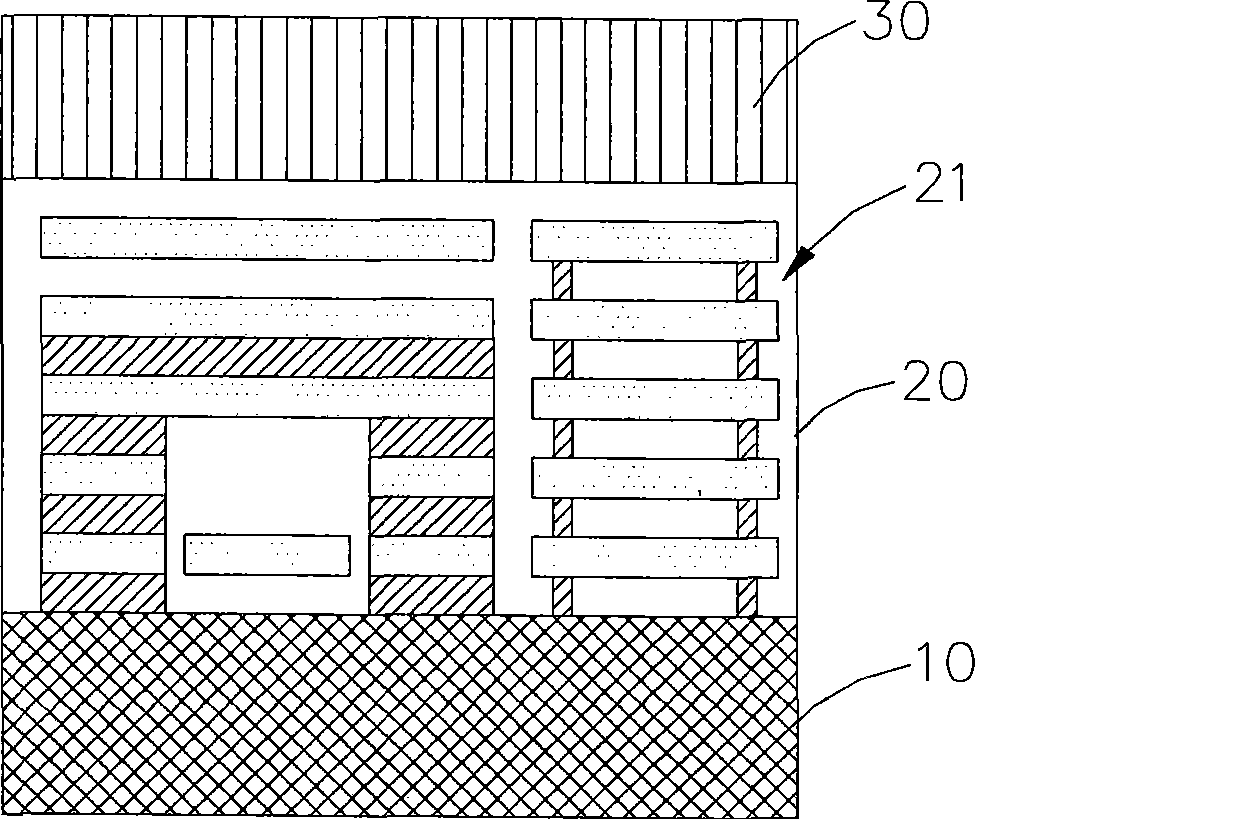

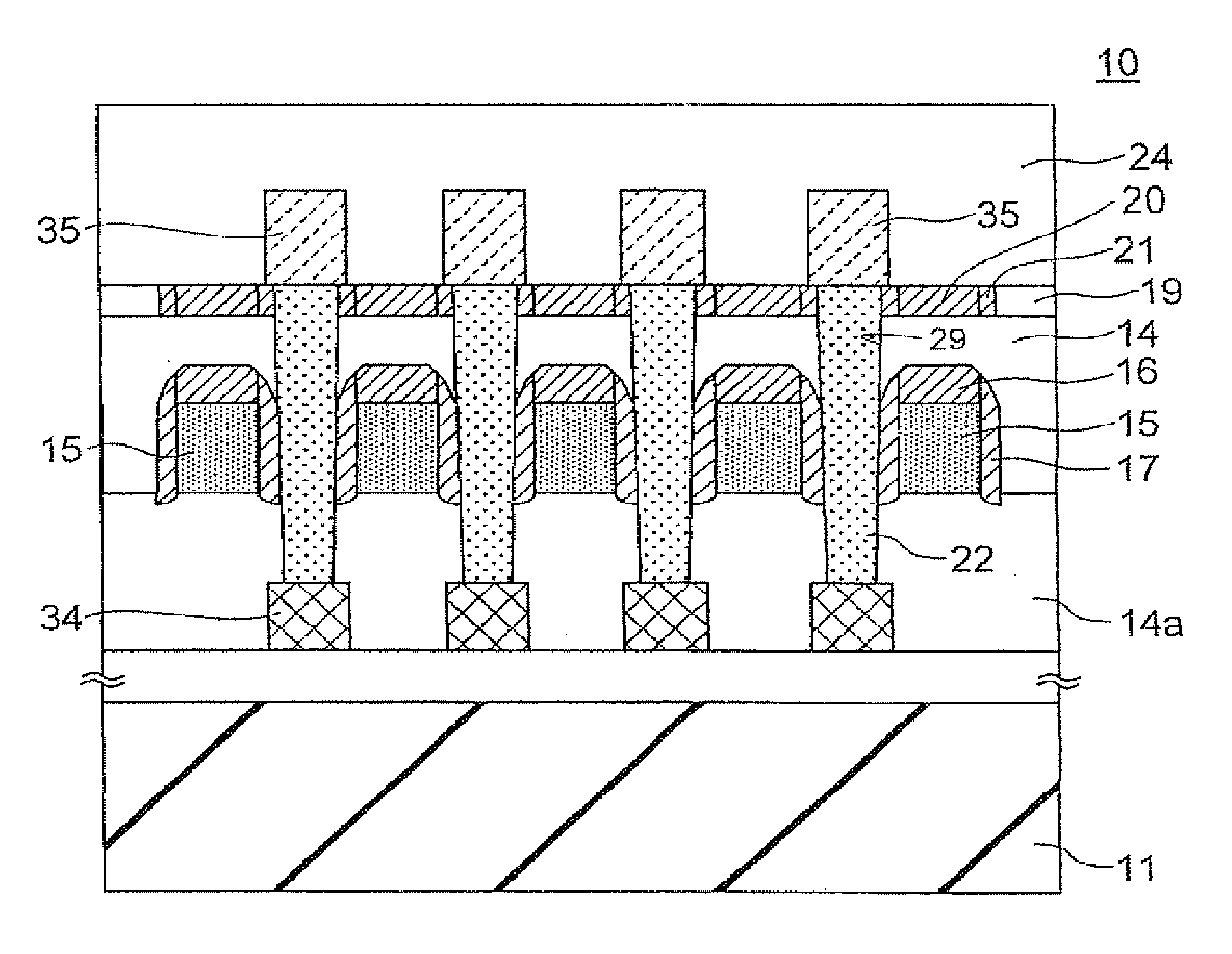

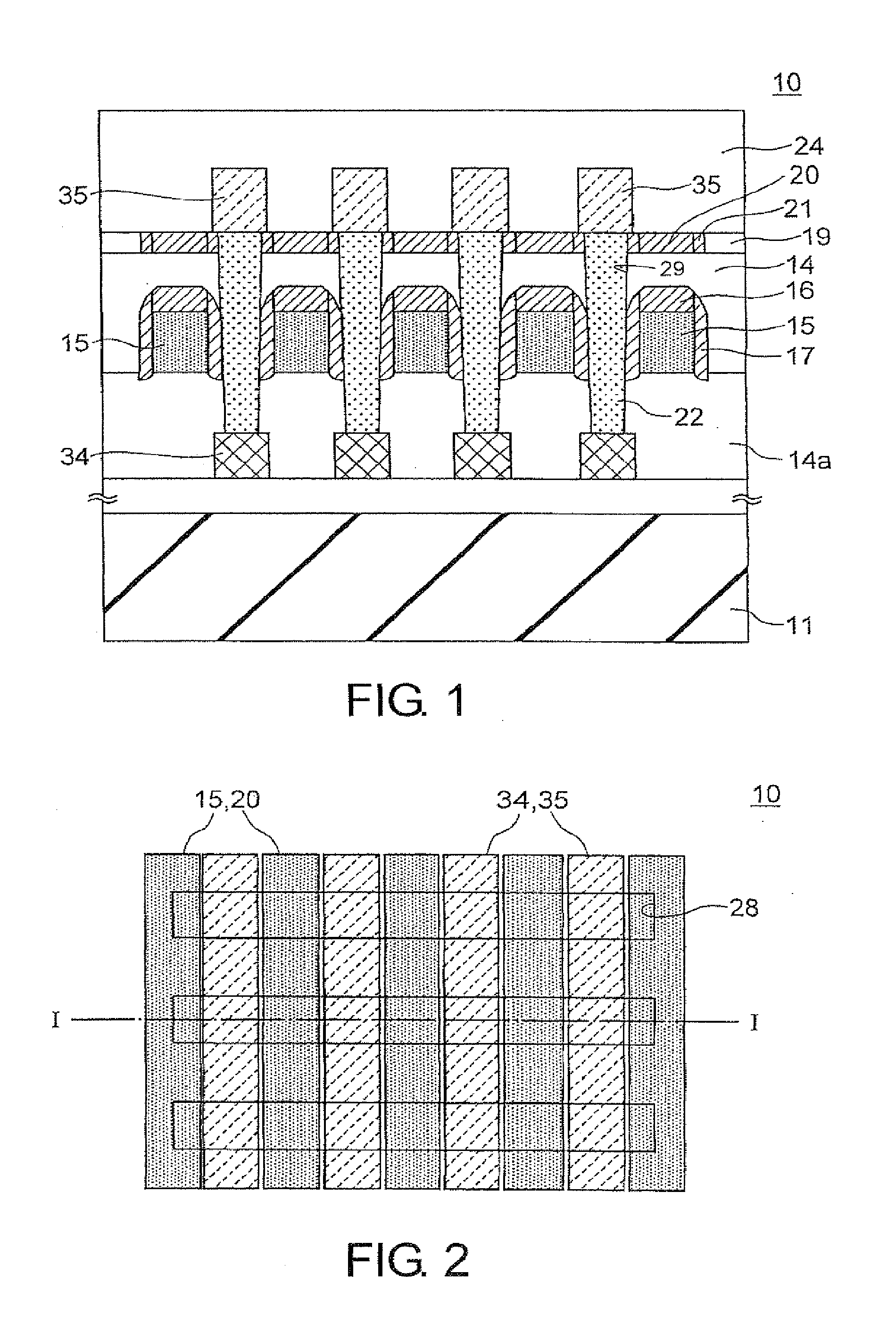

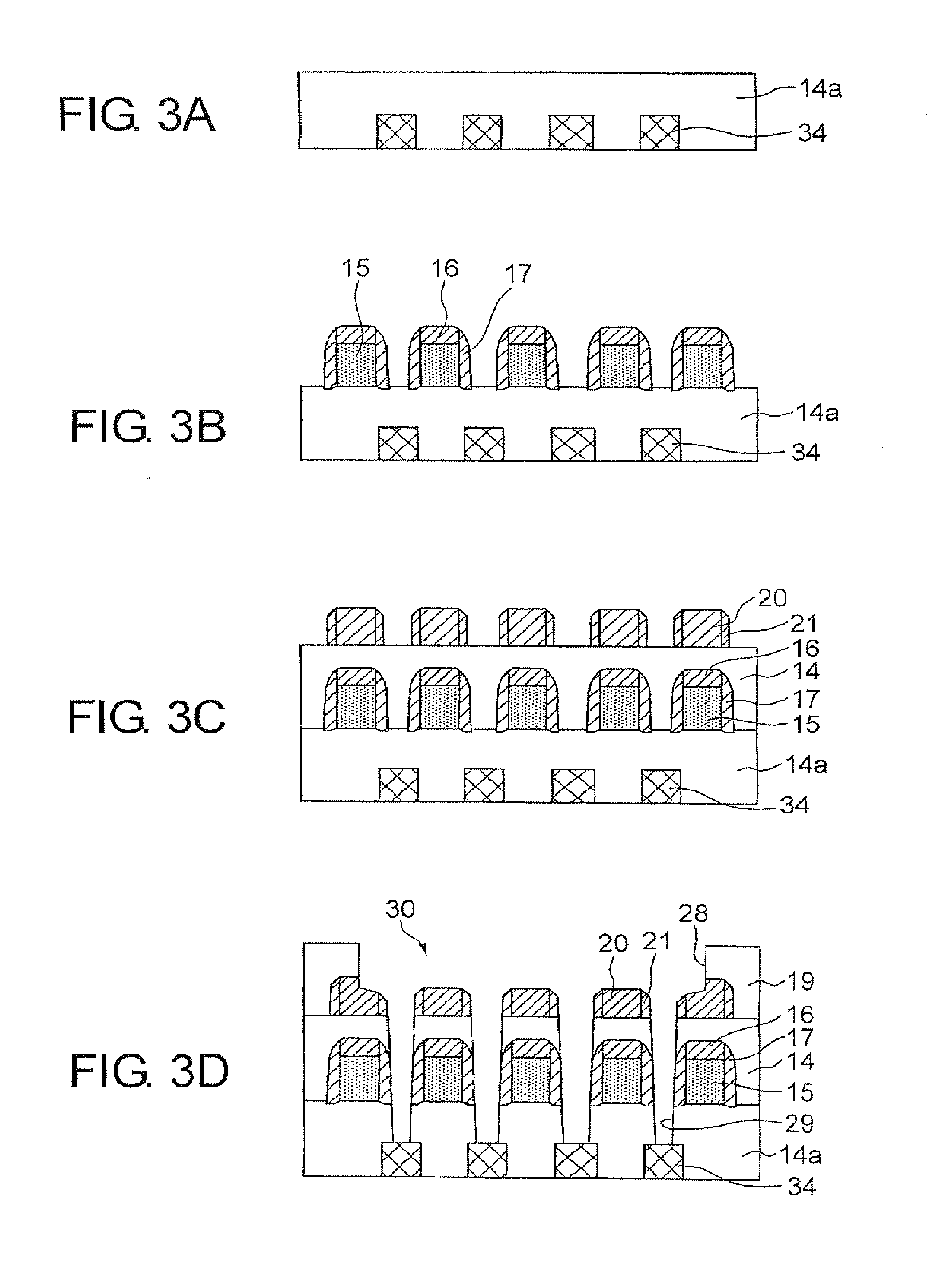

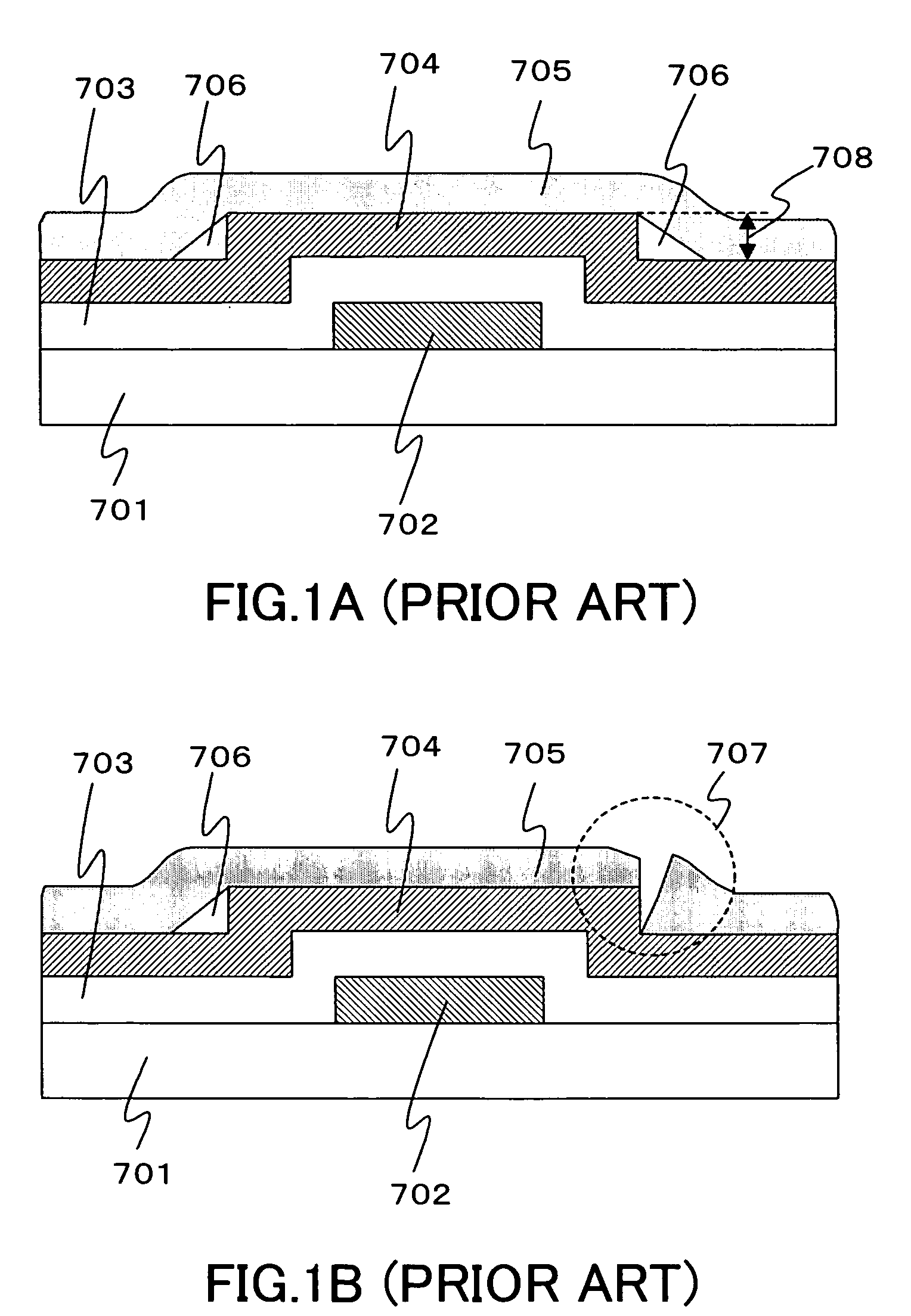

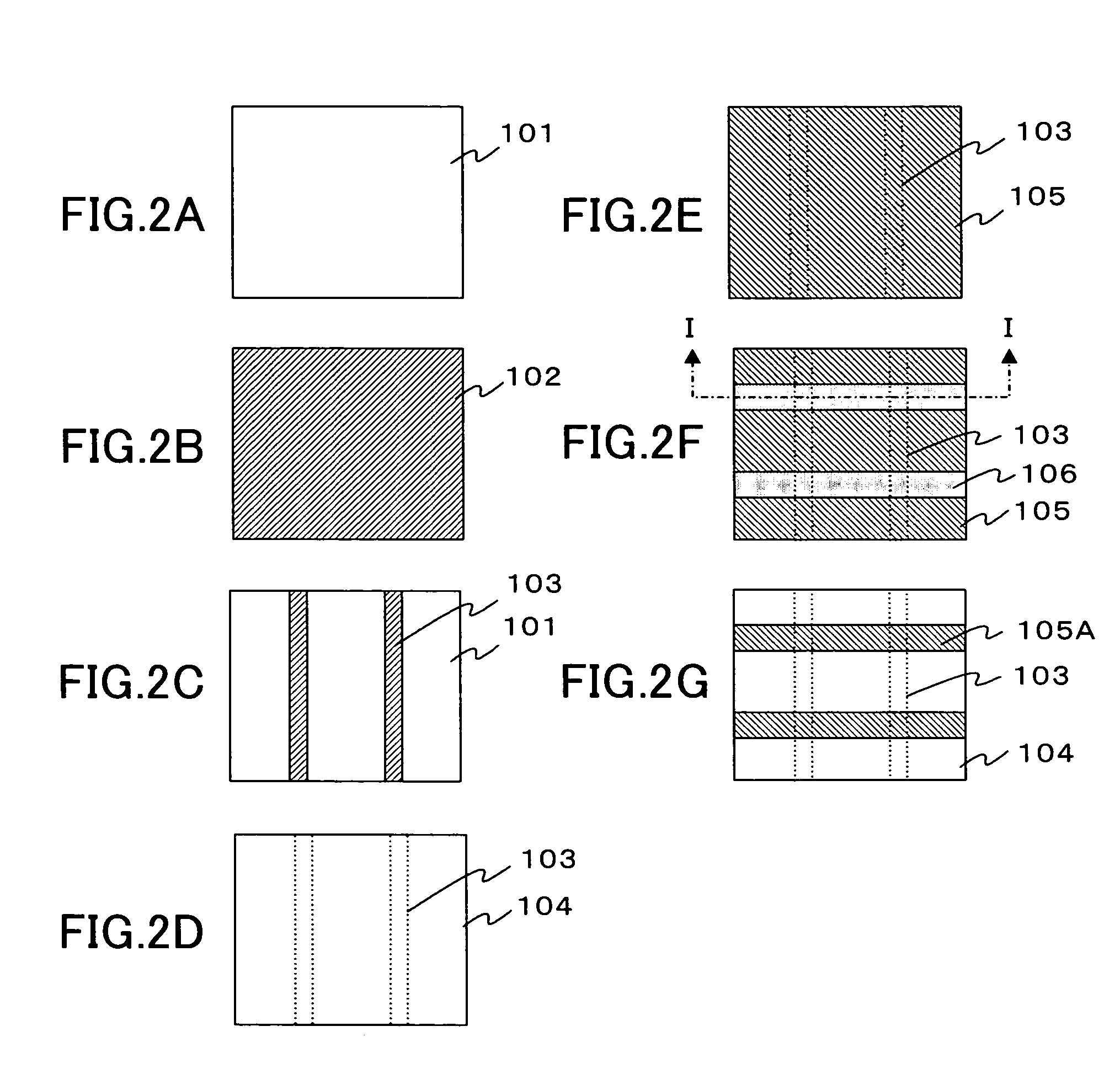

Method of forming fin field effect transistor

ActiveUS20050153490A1Prevent and substantially reduce leakage currentElectrode can be separatedTransistorSolid-state devicesInsulation layerDrain current

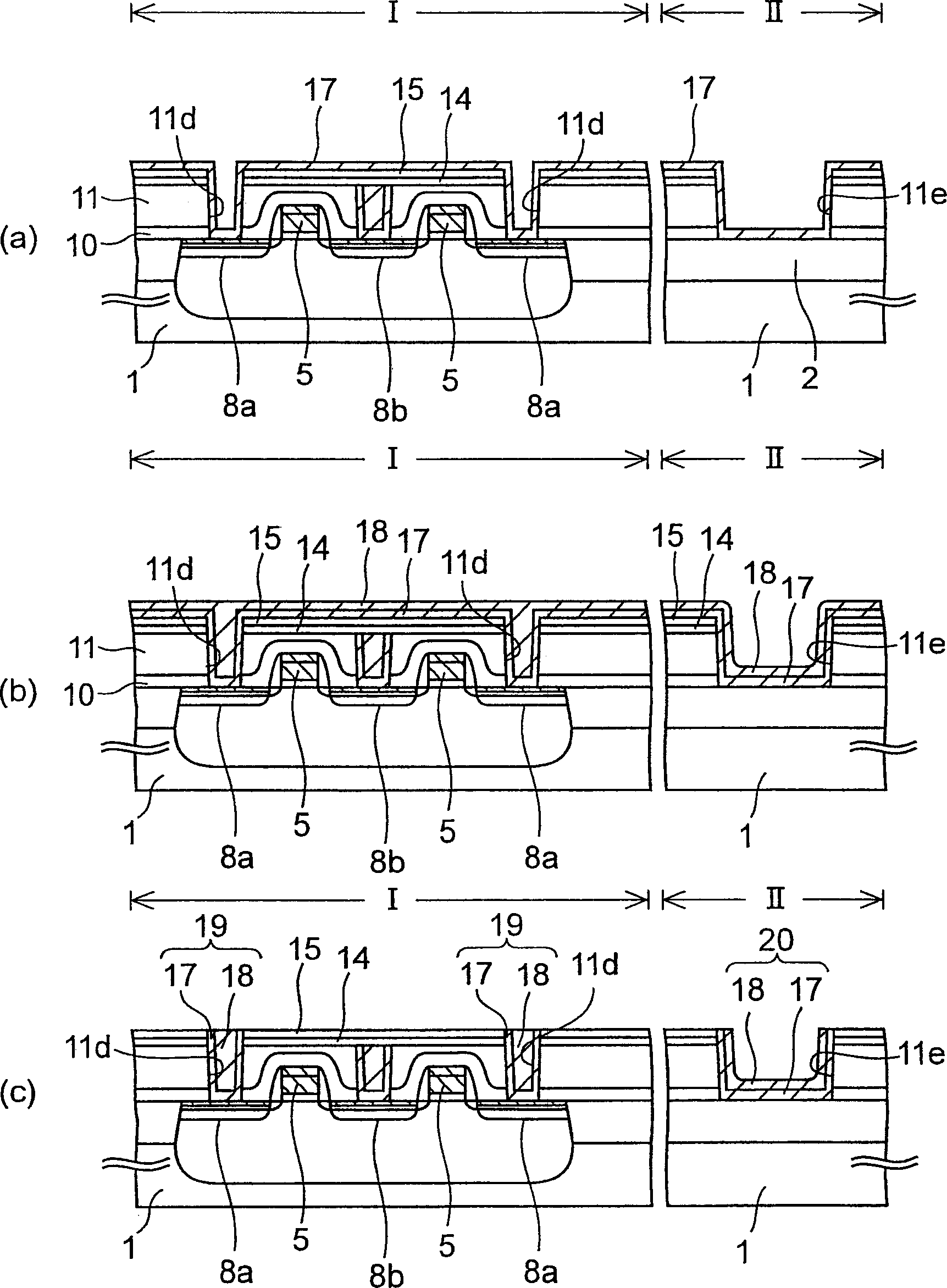

According to some embodiments, a fin type active region is formed under an exposure state of sidewalls on a semiconductor substrate. A gate insulation layer is formed on an upper part of the active region and on the sidewalls, and a device isolation film surrounds the active region to an upper height of the active region. The sidewalls are partially exposed by an opening part formed on the device isolation film. The opening part is filled with a conductive layer that partially covers the upper part of the active region, forming a gate electrode. Source and drain regions are on a portion of the active region where the gate electrode is not. The gate electrode may be easily separated and problems causable by etch by-product can be substantially reduced, and a leakage current of channel region and an electric field concentration onto an edge portion can be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of forming fin field effect transistor

ActiveUS7056781B2Prevent and substantially reduce leakage currentElectrode can be separatedTransistorSolid-state devicesInsulation layerEngineering

According to some embodiments, a fin type active region is formed under an exposure state of sidewalls on a semiconductor substrate. A gate insulation layer is formed on an upper part of the active region and on the sidewalls, and a device isolation film surrounds the active region to an upper height of the active region. The sidewalls are partially exposed by an opening part formed on the device isolation film. The opening part is filled with a conductive layer that partially covers the upper part of the active region, forming a gate electrode. Source and drain regions are on a portion of the active region where the gate electrode is not. The gate electrode may be easily separated and problems causable by etch by-product can be substantially reduced, and a leakage current of channel region and an electric field concentration onto an edge portion can be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

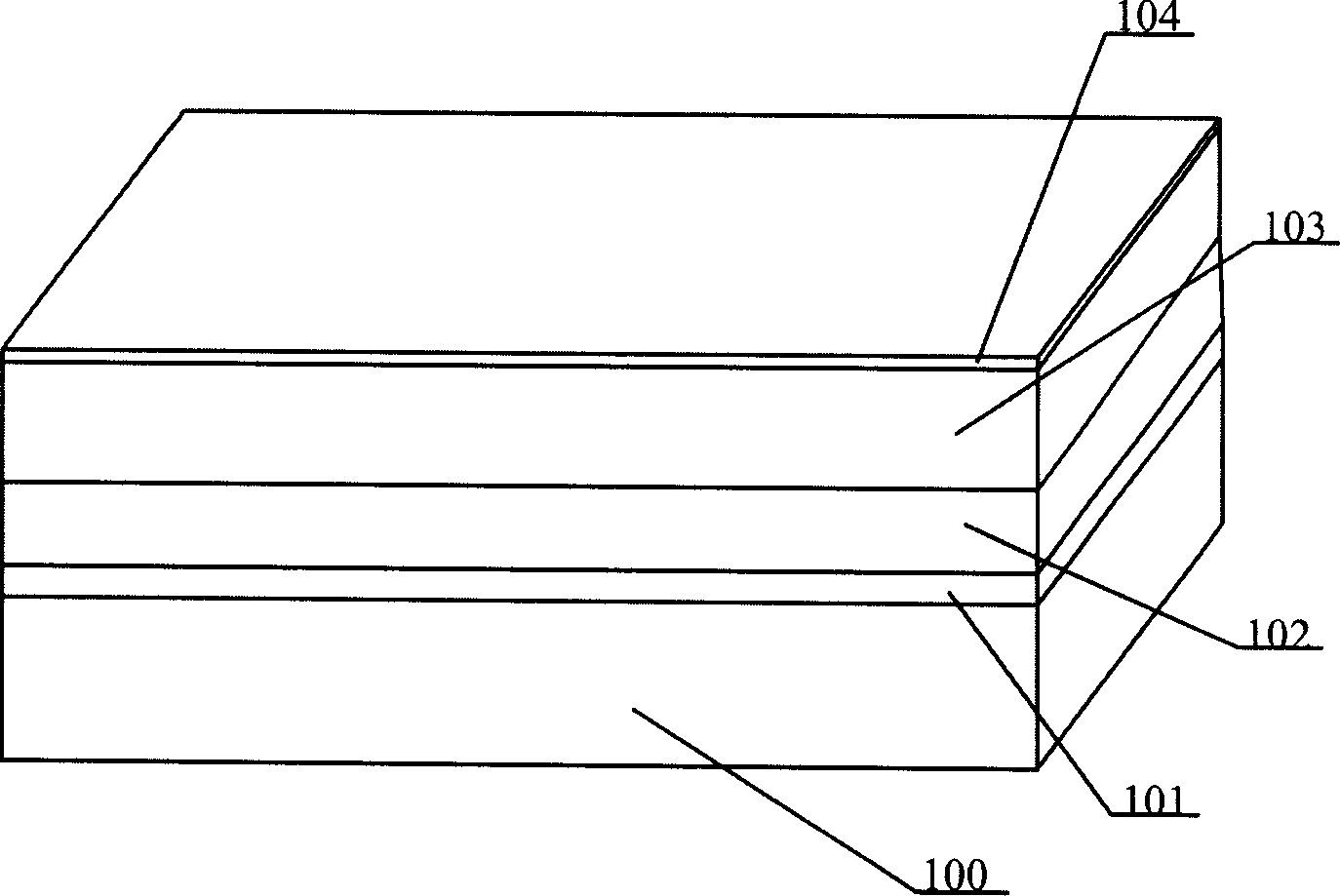

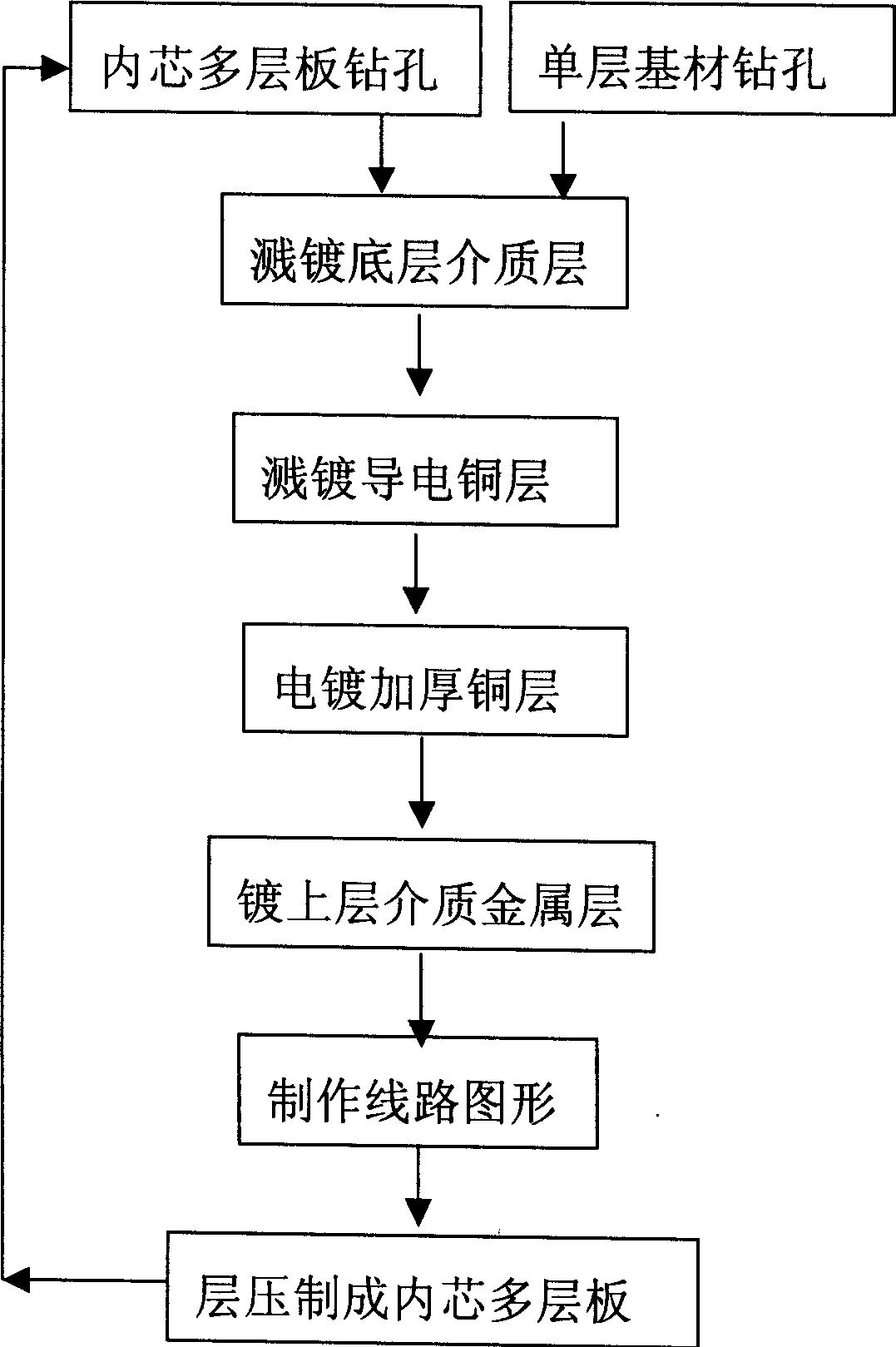

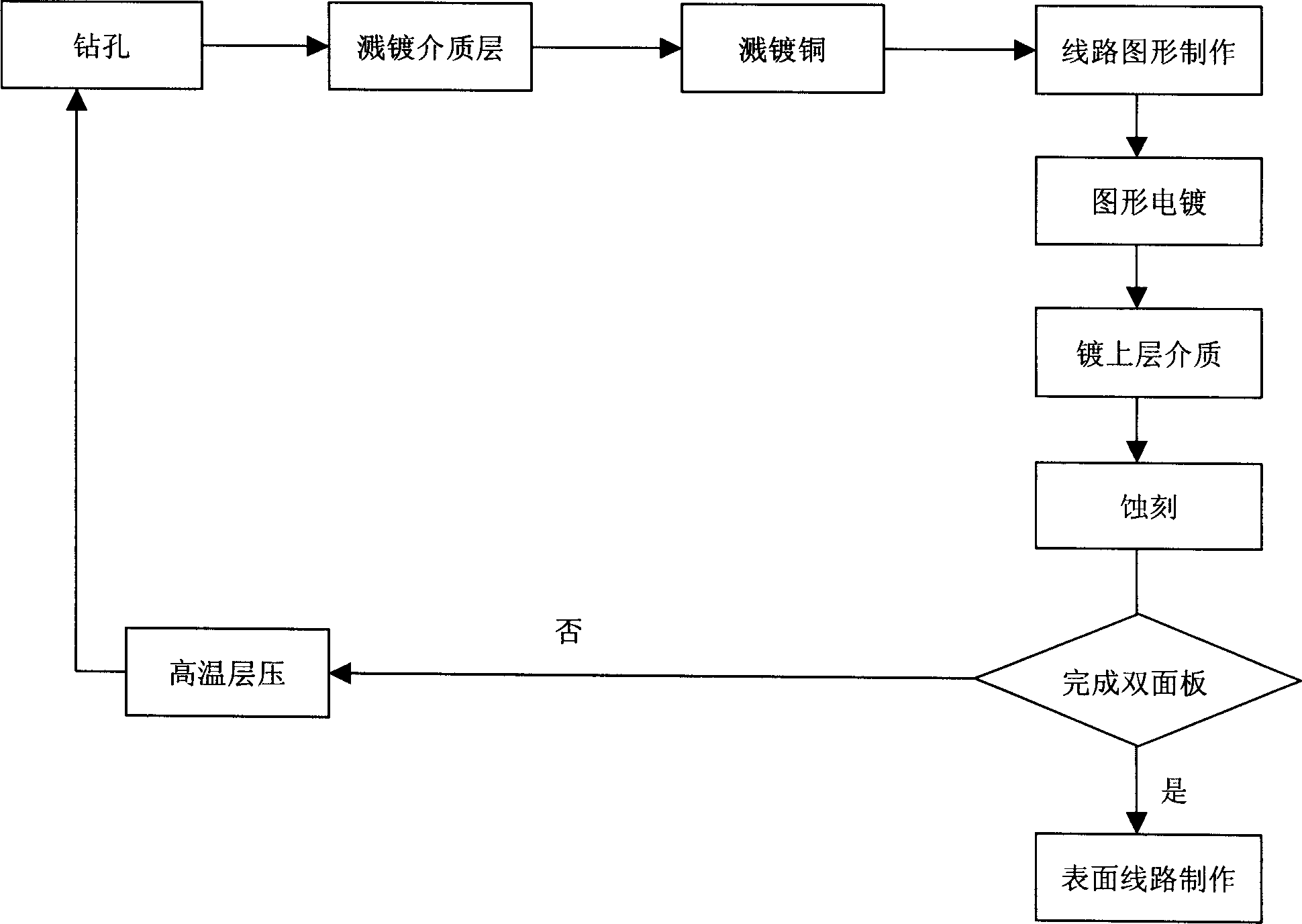

Magnetically controlled sputtering process of making printed circuit board

InactiveCN1527656AFlexible thickness controlAvoid inhomogeneityMultilayer circuit manufacturePrinted element electric connection formationCopper platingOptoelectronics

The present invention provides one kind of magnetically controlled sputtering process of making printed circuit board. The process includes the following steps: drilling holes on the single layer base material; magnetically controlled sputtering the bottom dielectric and metal layer on the drilled single layer base material; magnetically controlled sputtering conducting copper layer on the single layer base material; drilling holes on multilayer board; magnetically controlled sputtering bottom dielectric and metal layer on the drilled multilayer board; magnetically controlled sputtering conducting copper layer on the drilled multilayer board; and repeating the foregoing steps until reaching the required layer number of the printed circuit board. The present invention combines unique hole forming method and sputtering method and has raised copper-plating and hole-metallizing efficiency, raised reliability and high fine circuit making capacity.

Owner:曹波 +2

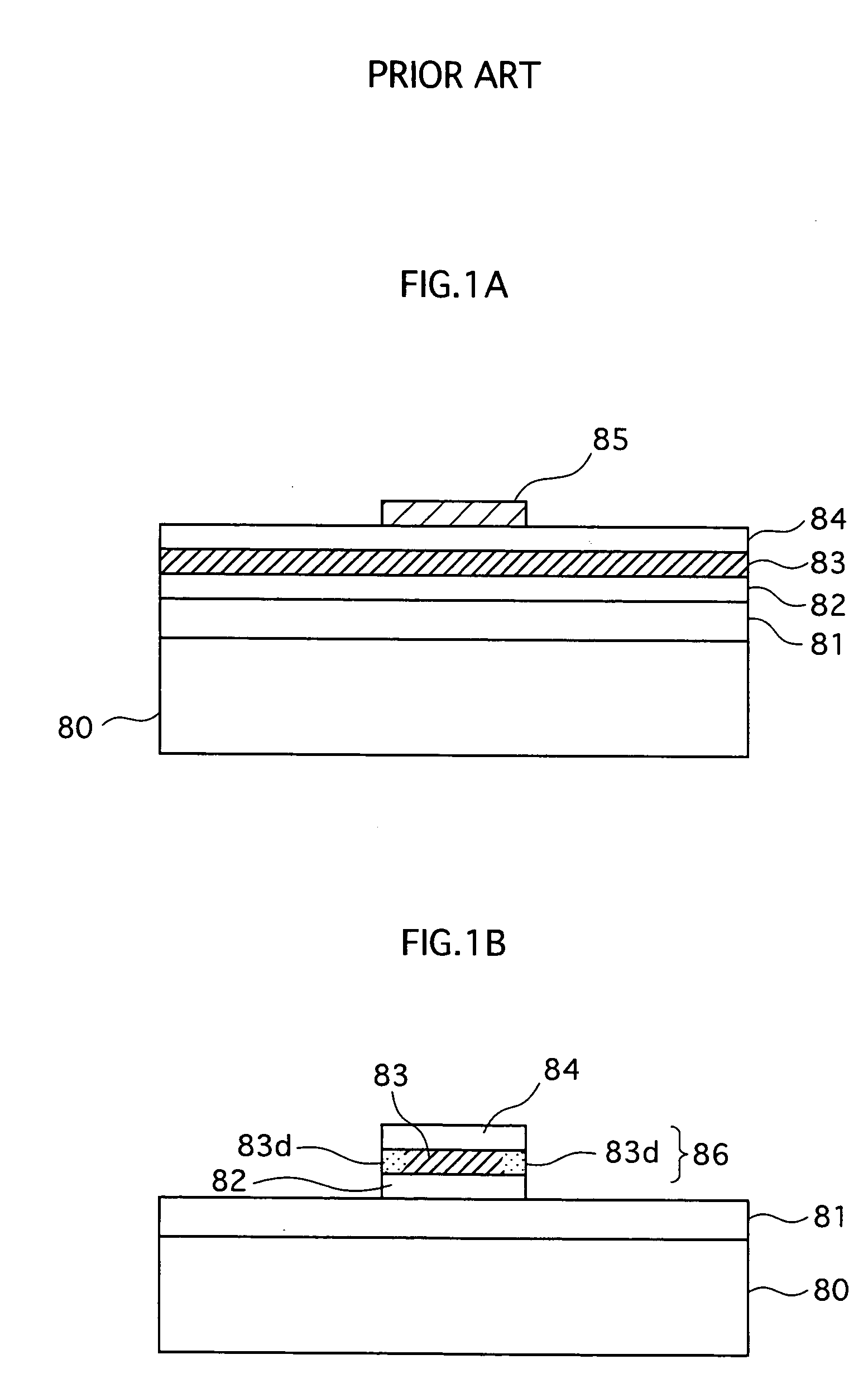

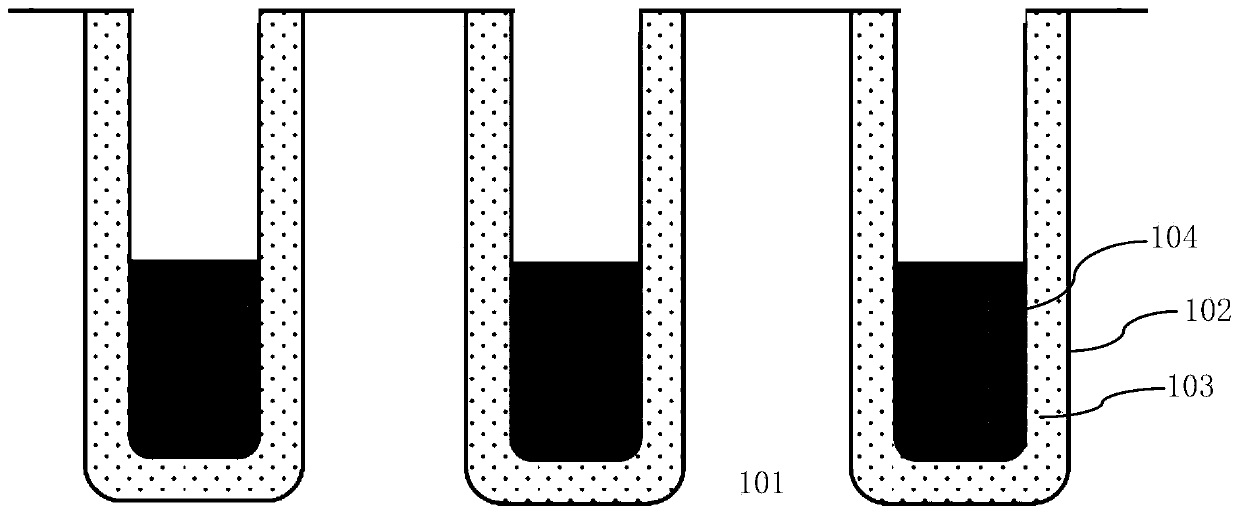

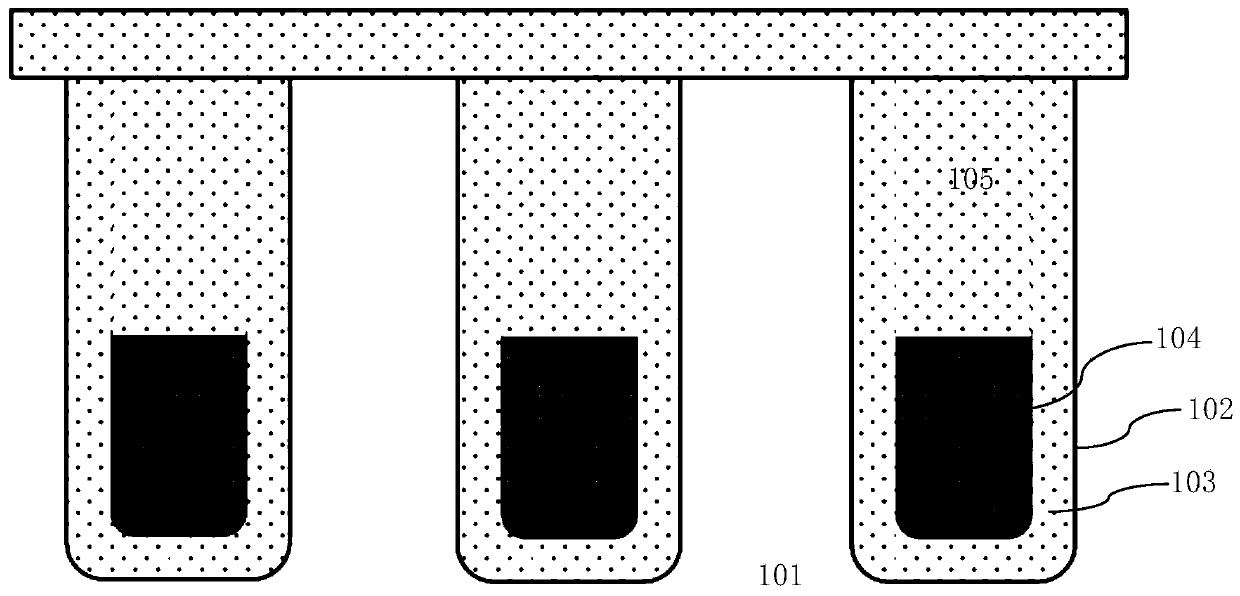

Semiconductor device and manufacturing method for the same

InactiveUS20050236691A1Excellent metal-insulator phase transition propertyEasy to readSolid-state devicesSemiconductor devicesDevice materialMetal insulator phase transition

A manufacturing method for a semiconductor device that includes a crystal of metal-insulator phase transition material as a resistor, the method having the steps of forming an electrode on a semiconductor substrate, forming an insulating film on the electrode, forming a through-hole in the insulating film so as to expose the electrode, and housing the crystal in the through-hole so as to contact the electrode.

Owner:PANASONIC CORP

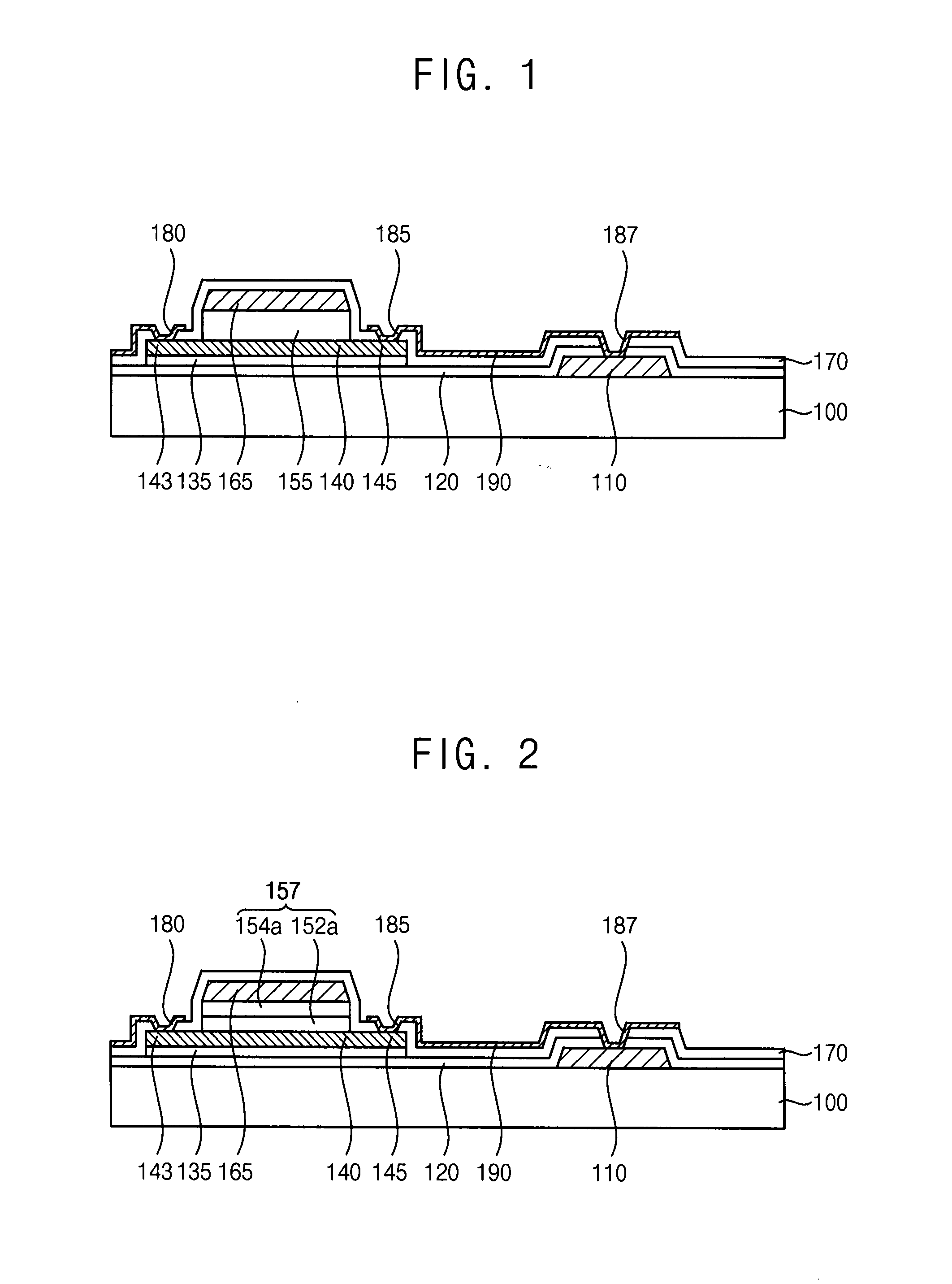

Display substrates, methods of manufacturing the same and display devices including the same

InactiveUS20150162363A1Layer thicknessReduce the amount of etchingTransistorSolid-state devicesInsulation layerDisplay device

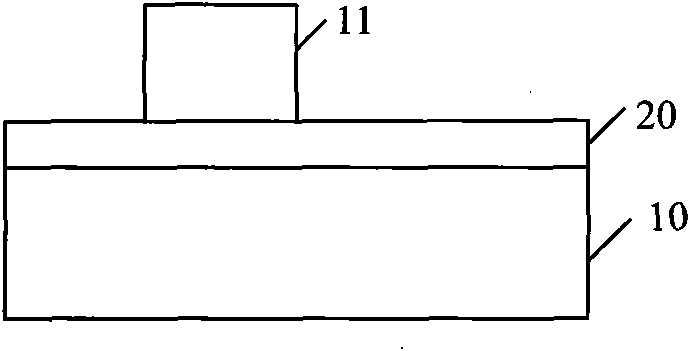

A display substrate includes a data pad on a base substrate, a first buffer layer which covers the data pad, a second buffer layer pattern which is disposed on the first buffer layer and separated from the data pad in a plan view, an active layer on the second buffer layer pattern, a gate insulation layer pattern on the active layer, both ends of the active layer exposed by the gate insulation layer pattern, and a gate electrode on the gate insulation layer pattern.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor device, manufacturing method thereof, and data processing system

InactiveUS20090256237A1Reduce insulation thicknessSufficient resolutionTransistorSemiconductor/solid-state device detailsEngineeringData processing

A miniaturized semiconductor device is provided by reducing the design thickness of a wiring line protecting film covering the surface of a wiring layer, and reducing the distance between the wiring layer and via plugs formed by a self-aligning process. Dummy mask layers extending in the same layout pattern as the wiring layer is formed above the wiring layer covered with a protecting film composed of a cap layer and side wall layers. In the self-aligning process for forming via plugs in a self-aligned manner with the wiring layer and its protecting film, the thickness of the cap layer is reduced and the design interval between the via plugs is reduced, whereby the miniaturization of the semiconductor device is achieved.

Owner:ELPIDA MEMORY INC

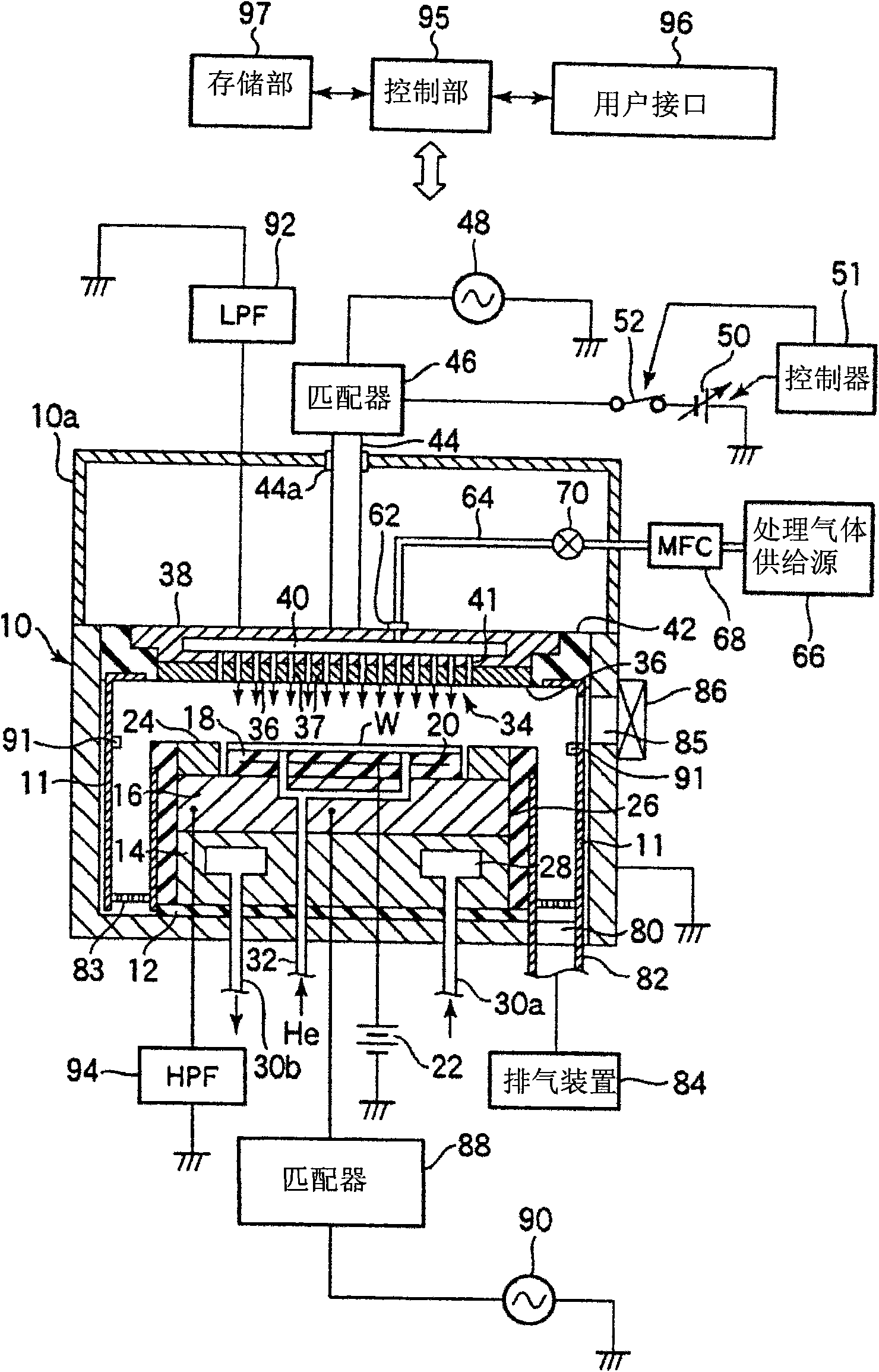

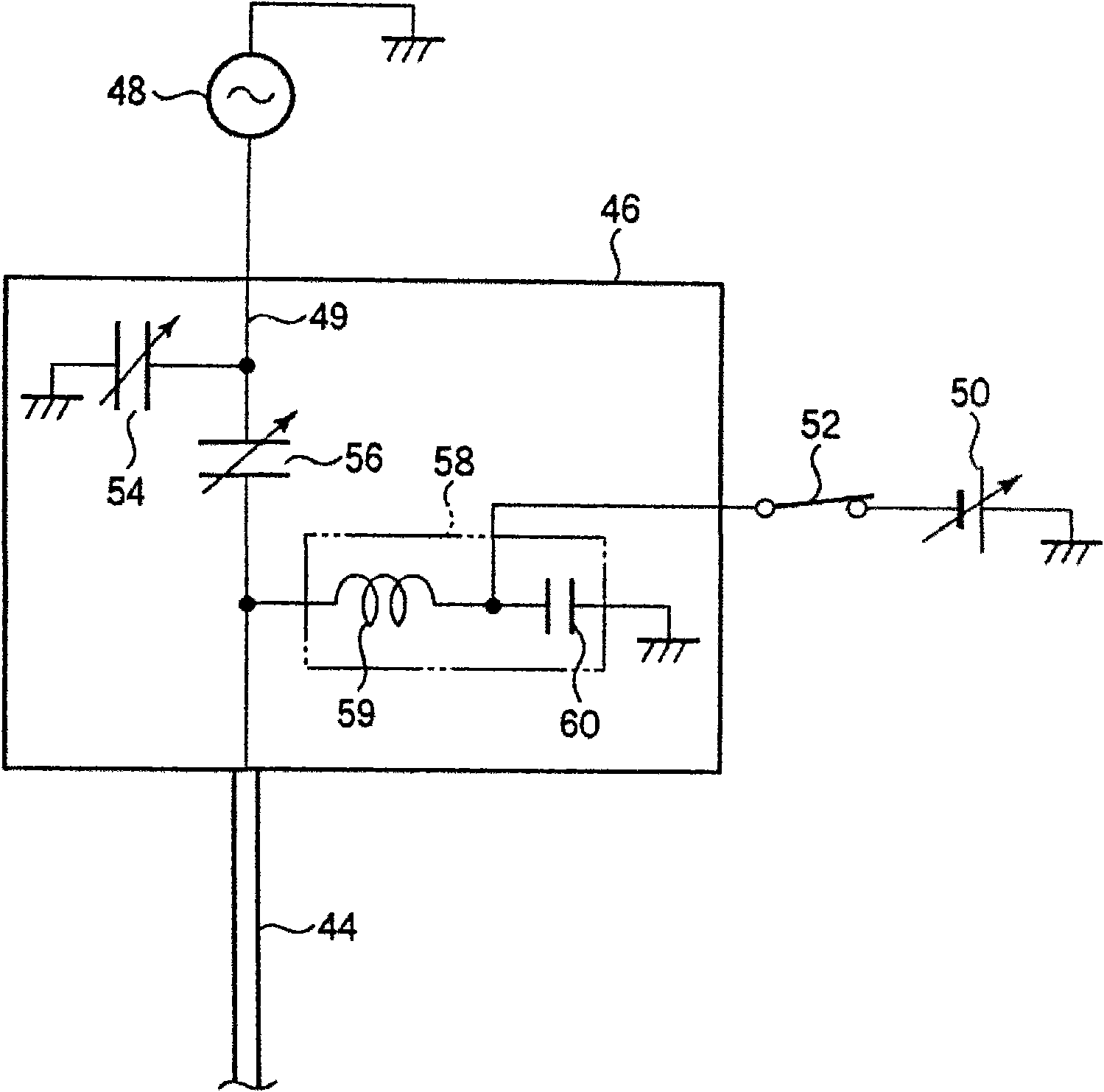

Plasma processing method and resist pattern modifying method

InactiveCN101667543AContainment damageImprove performanceElectric discharge tubesSemiconductor/solid-state device manufacturingResistNoble gas

The invention provides a plasma processing method and a modifying method of a resist pattern, which is capable of synchronously realizing excellent etching selectivity and shape performance in the process of etching fine holes with high aspect ratio on an oxidation film. The method comprises the following steps: a step of moving the oxidation film, a hard mask layer and the patterned base plate ofa photoresist, which are formed with etched objects in sequence, to a processing container (10) and loading on a lower electrode; a step of supplying a processing gas containing CxFy (wherein x is aninteger less than 3 and y is an integer less than 8), C4F8, rare gas and O2 to the processing container (10); a step of exerting a high-frequency power on an upper electrode (34) from a first high-frequency exerting unit (48) for generation of the plasmas of the processing gas; a step of exerting a high-frequency power for bias voltage on a lower electrode (16) from a second high-frequency powerexerting unit (90); and a step of exerting a direct current voltage on the upper electrode (34) from a direct current voltage exerting unit (50).

Owner:TOKYO ELECTRON LTD

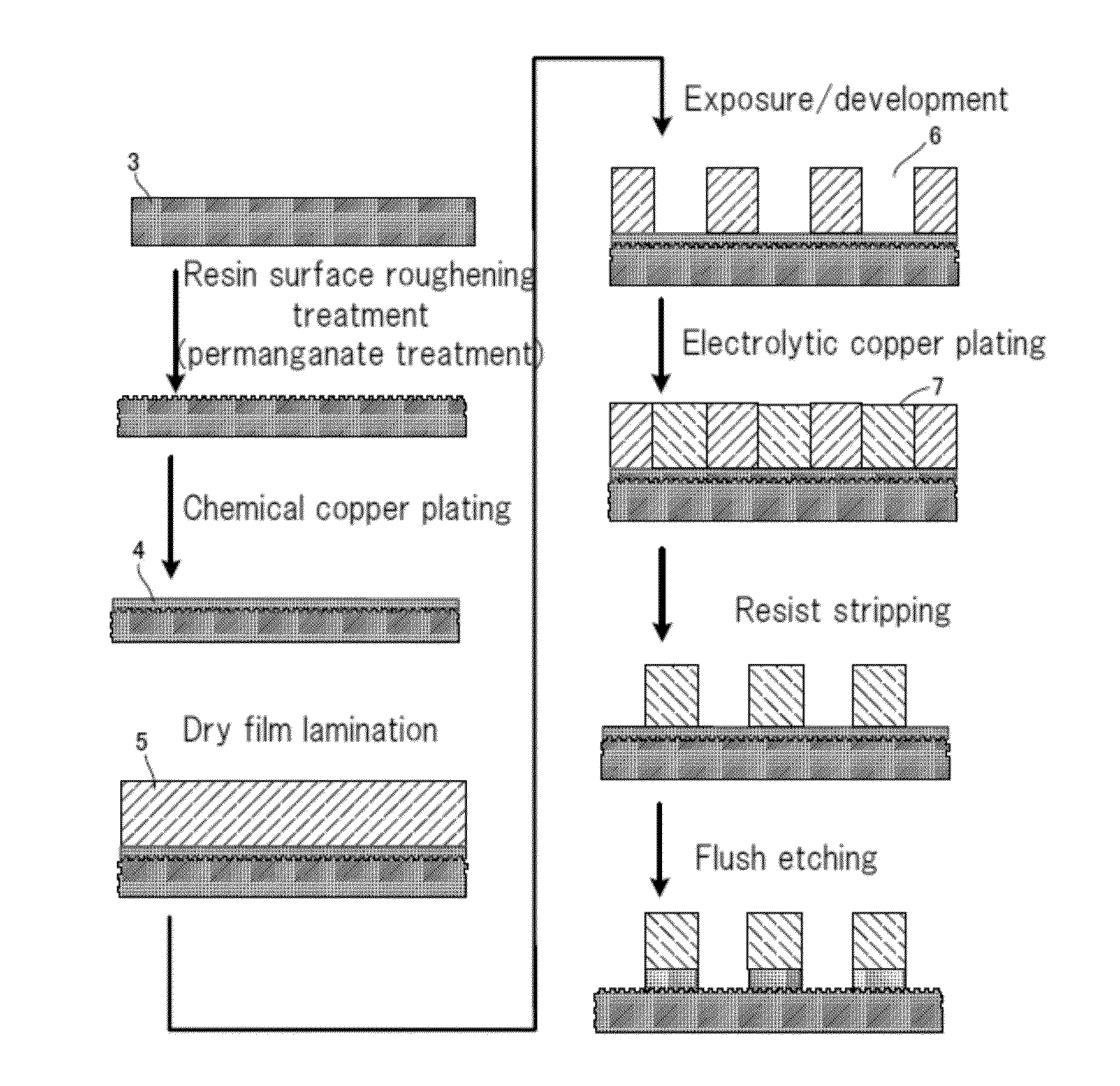

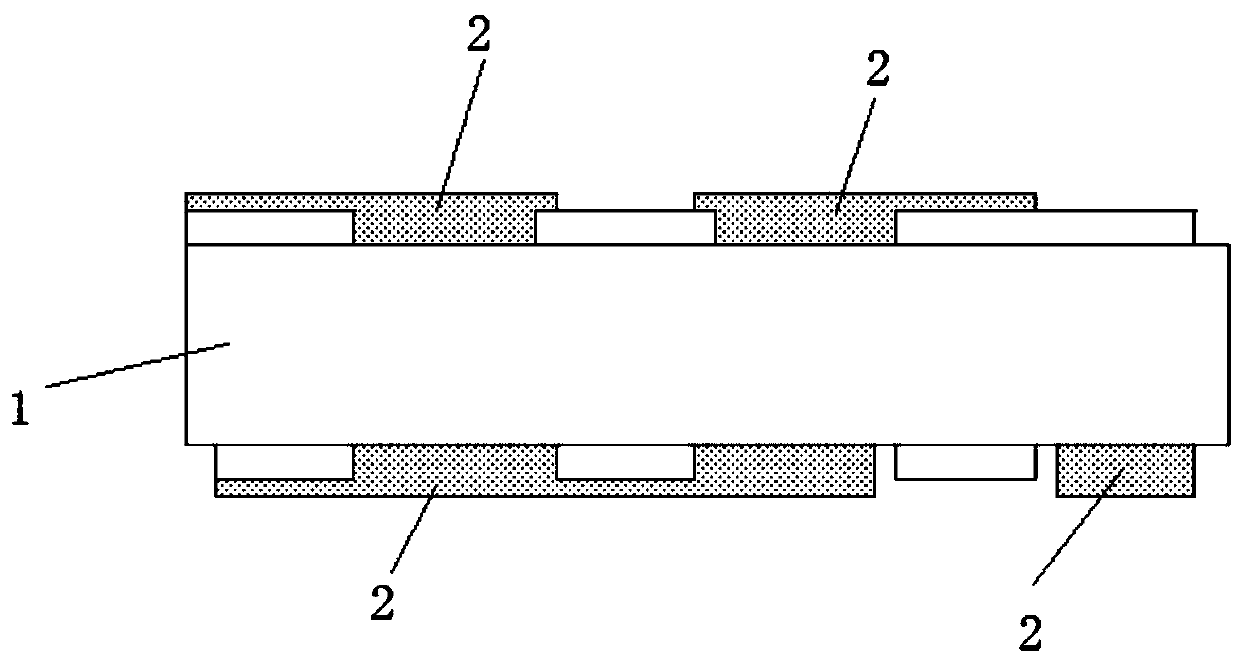

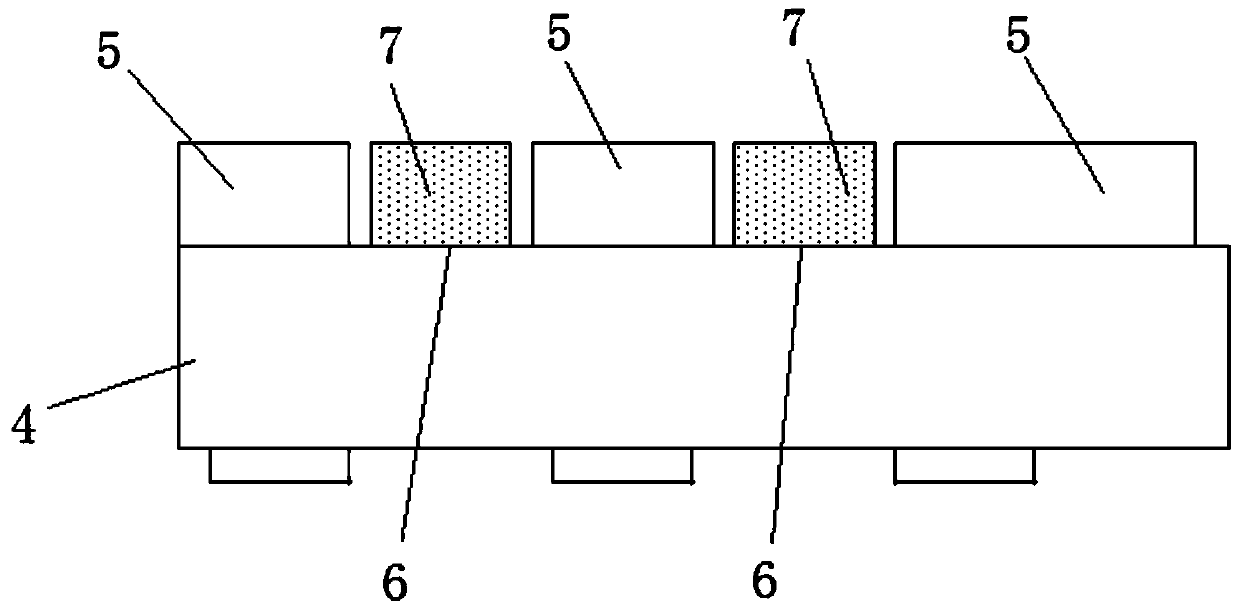

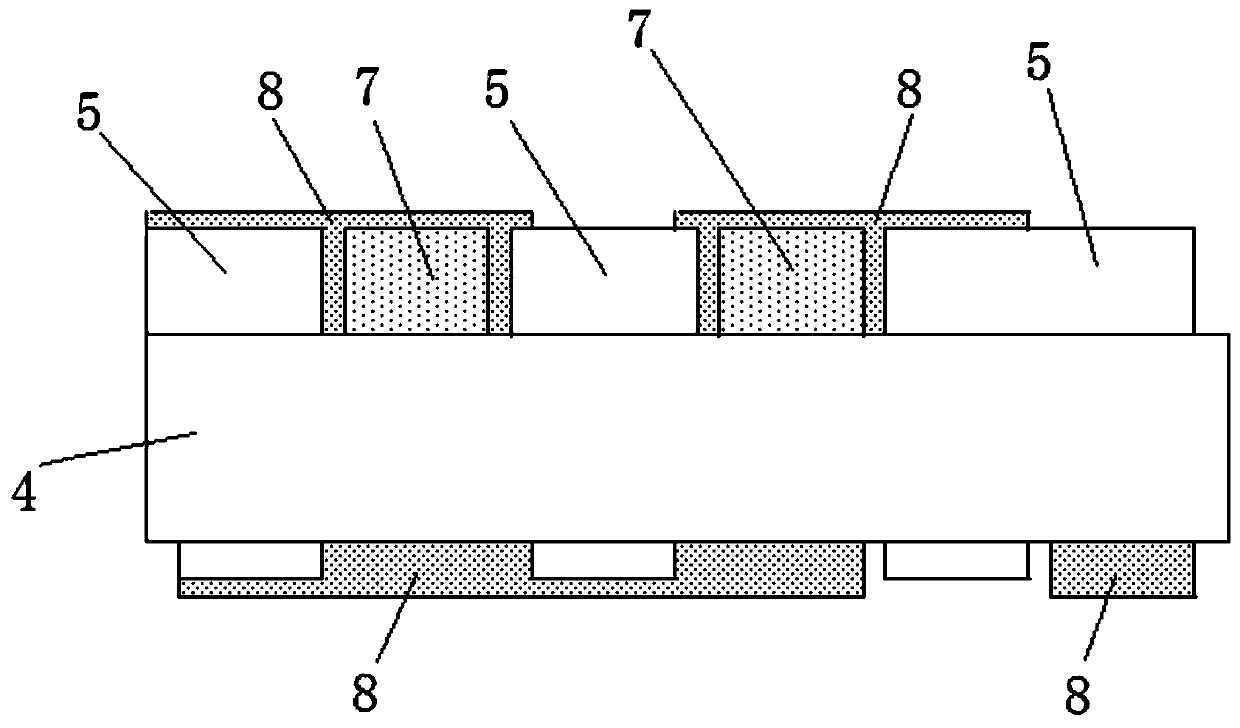

Method for producing printed-wiring board

ActiveUS20150034590A1Improve unevennessReduce the amount of etchingPhotomechanical apparatusLiquid/solution decomposition chemical coatingResistInsulation layer

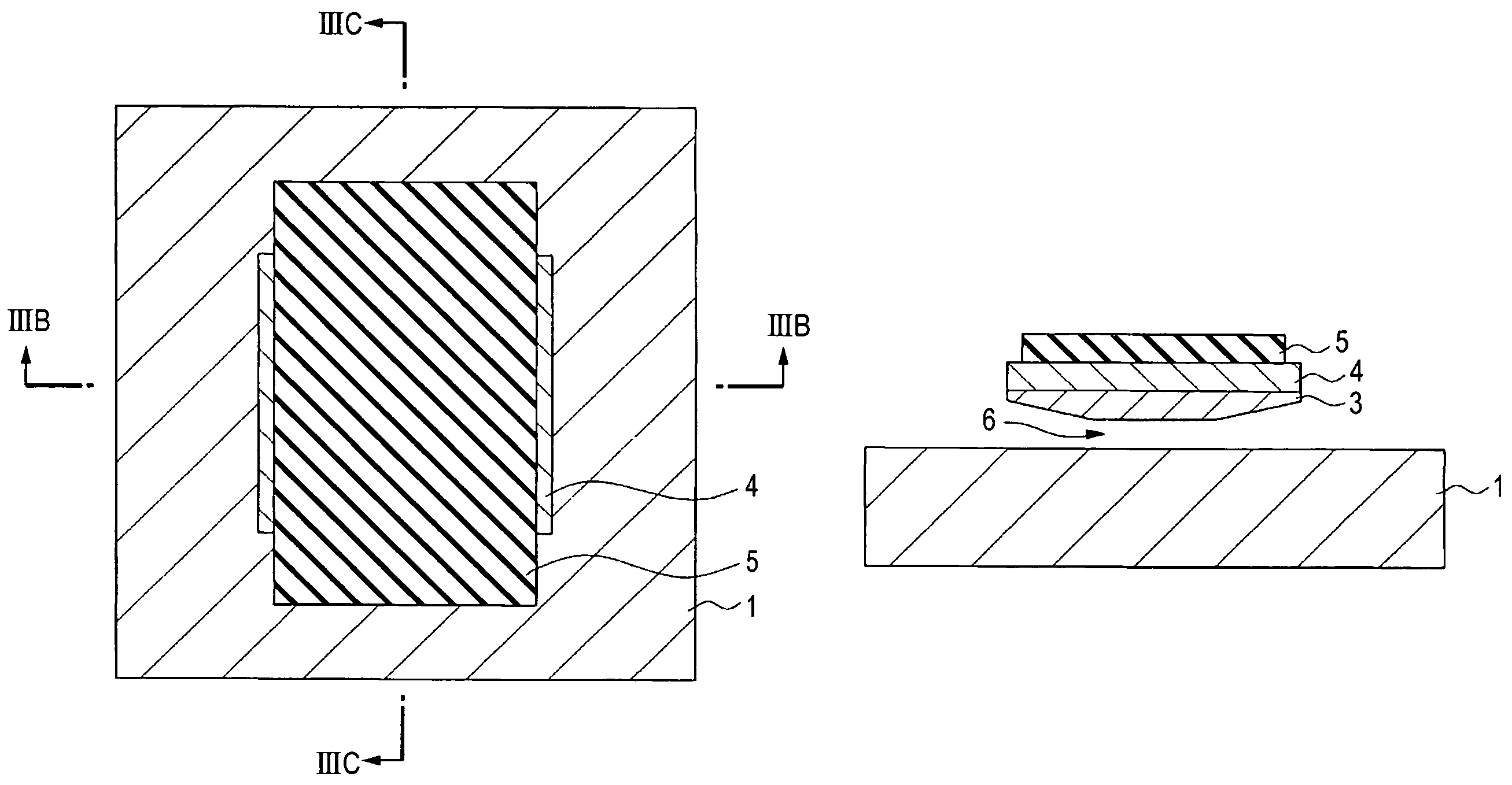

The present invention provides a method for producing a printed-wiring board in a semi-additive process, comprising the steps of: providing a chemical copper plating 4 on an insulation layer 3 or forming a copper thin film on the insulation layer 3 using a sputtering method; subjecting the obtained copper surface 4 to a roughening treatment using an etching solution containing 0.1 to 3% by mass of hydrogen peroxide, 0.3 to 5% by mass of sulfuric acid, 0.1 to 3 ppm of halogen ion and 0.003 to 0.3% by mass of tetrazoles; attaching a dry film resist 5 to the copper surface 4 after the roughening treatment to perform exposure and development and providing an electrolytic copper plating 7 to an opening 6 after the exposure; and subjecting the remaining dry film resist to a stripping treatment using a resist stripping liquid containing 0.5 to 20% by mass of monoethanolamine, 0.2 to 10% by mass of quaternary ammonium hydroxide, 0.01 to 10% by mass of ethylene glycols and 0.01 to 0.5% by mass of azoles.

Owner:MITSUBISHI GAS CHEM CO INC

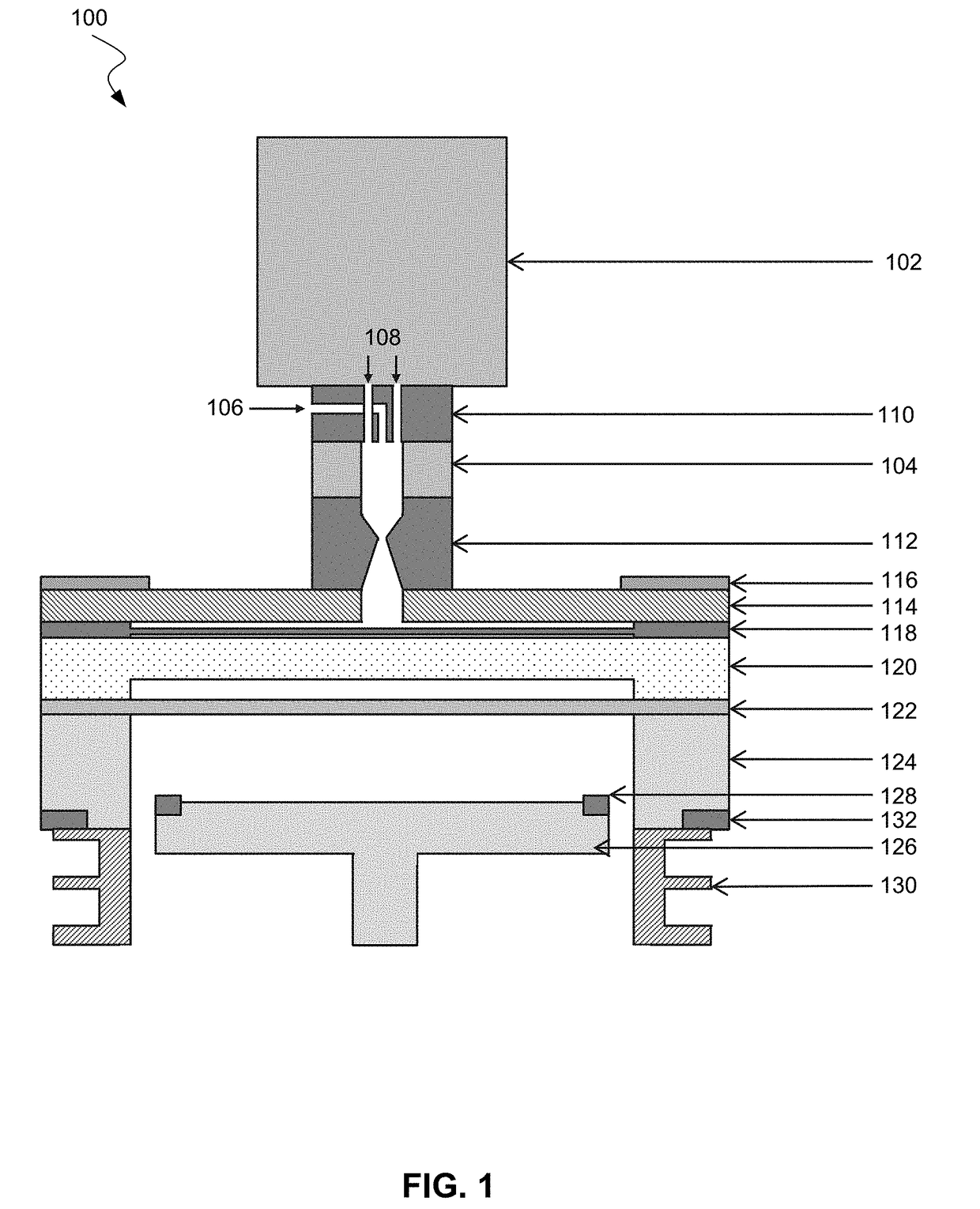

Process window widening using coated parts in plasma etch processes

ActiveUS20190043726A1Small sizeMore tolerantElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringProcess window

Embodiments of the present technology may include a method of etching. The method may include mixing plasma effluents with a gas in a first section of a chamber to form a first mixture. The method may also include flowing the first mixture to a substrate in a second section of the chamber. The first section and the second section may include nickel plated material. The method may further include reacting the first mixture with the substrate to etch a first layer selectively over a second layer. In addition, the method may include forming a second mixture including products from reacting the first mixture with the substrate.

Owner:APPLIED MATERIALS INC

Semiconductor substrate, semiconductor device, method of manufacturing semiconductor substare and method of manufacturing semiconductor device

InactiveUS20060091426A1Reduce manufacturing costIncrease speedSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A semiconductor substrate includes a semiconductor base substrate that has an oxide film selectively formed on a part thereof, the oxide film having a non-uniform thickness; and a semiconductor layer that is formed on the oxide film by epitaxial growth so as to have a non-uniform thickness.

Owner:SEIKO EPSON CORP

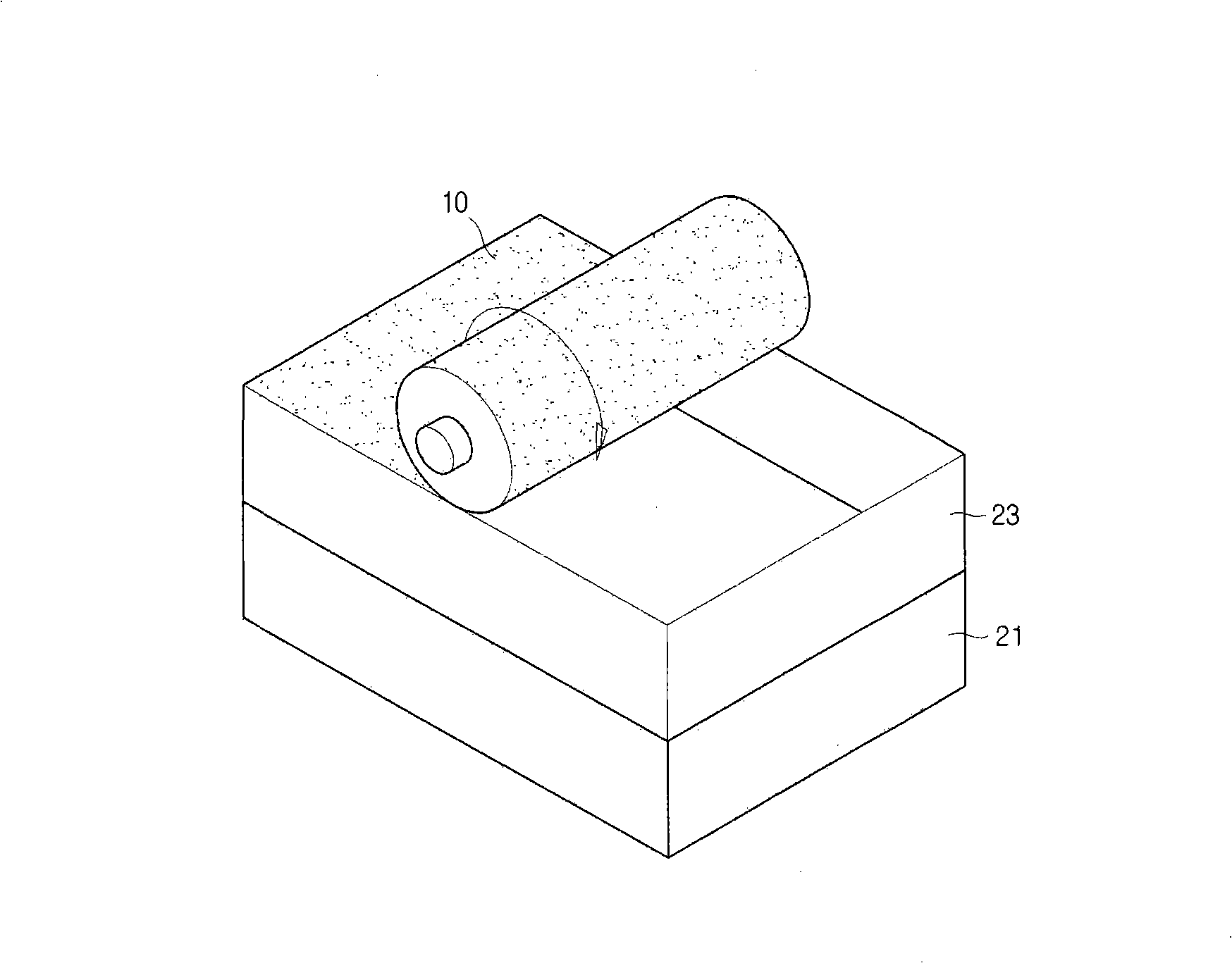

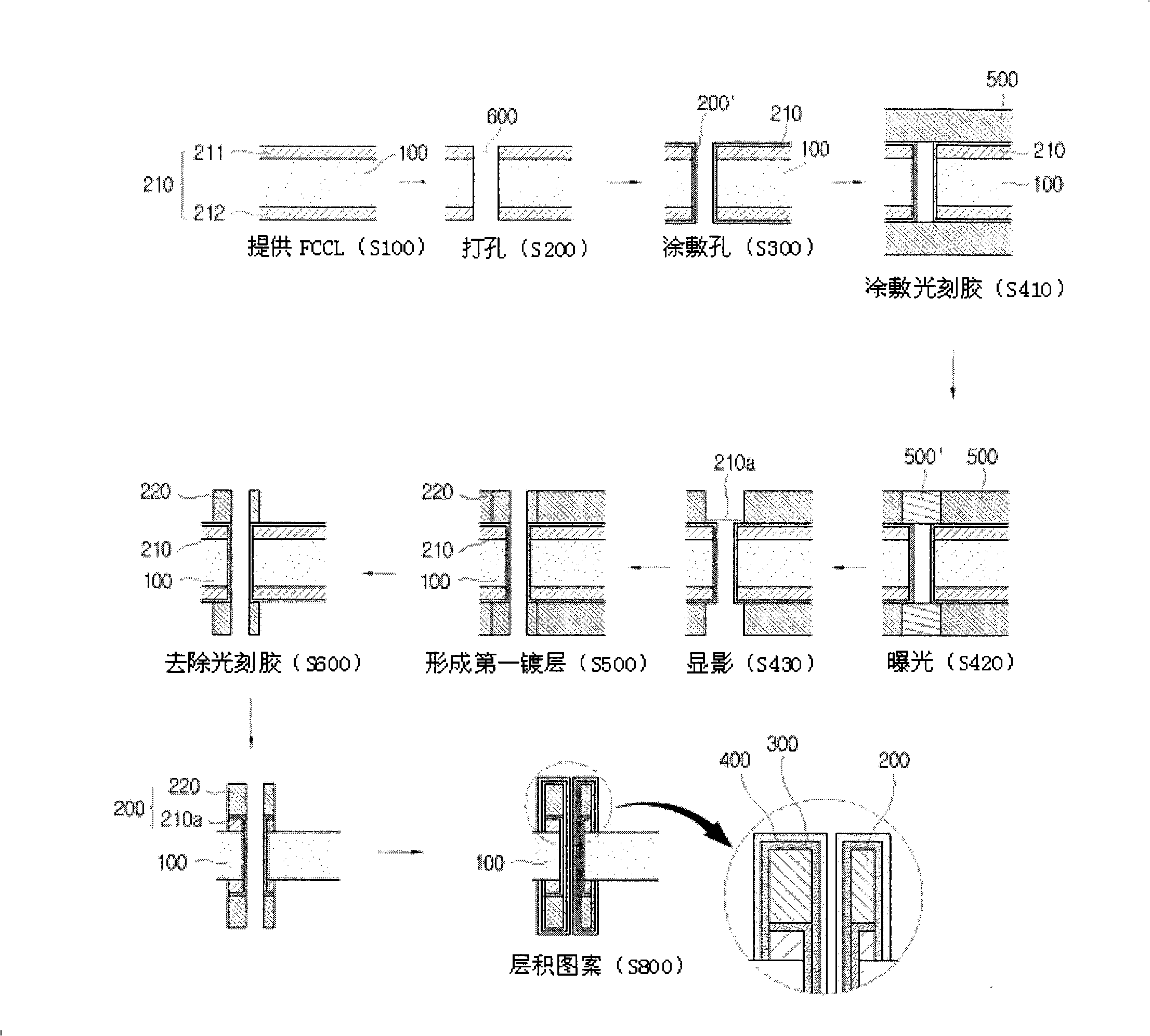

Method for manufacturing flexible printed circuit board and metallic wiring pattern of flexible printed circuit board using thereof

InactiveCN101346043AInhibition of sticking phenomenonWell formedPrinted circuit aspectsConductive material chemical/electrolytical removalSemiconductor packageCopper

The invention relates to a method for manufacturing flexible printing circuit board by half addition style, and the flexible printing circuit board metal wiring pattern manufactured therefor. The metal wiring pattern of flexible printing circuit board for tape carrier semiconductor package is formed on insulation sheet and takes on multiple stripe appearance. At least one surface of the insulation sheet is plated orderly with a first clad layer- a copper layer, a second clad layer- nickel layer, a third clad layer- gold layer, the second clad layer and the third clad layer wraps upper surface and side surface of the first clad layer. The invention also discloses a method for manufacturing single-sided and double-faced printing circuit board for manufacturing the wiring pattern.

Owner:ACQUTEK SAT

Process for improving the adhesion of polymeric materials to metal surfaces

InactiveCN1701134AImprove adhesionReduce the amount of etchingInsulating substrate metal adhesion improvementMetallic material coating processesNitro compoundTungstate

A process is described for treating metal surfaces with a composition comprising an oxidizer, an acid, a corrosion inhibitor, an unsaturated alkyl substituted with an aromatic or non-aromatic cyclic groups, and optionally but preferably a source of adhesion enhancing species selected from the group consisting of molybdates, tungstates, tantalates, niobates, vanadates, isopoly or heteropoly acids of molybdenum, tungsten, tantalum, niobium, vanadium, and combinations of any of the foregoing, an organic nitro compound, and a source of halide ions in order to increase the adhesion of polymeric materials to the metal surface.

Owner:MACDERMID INC

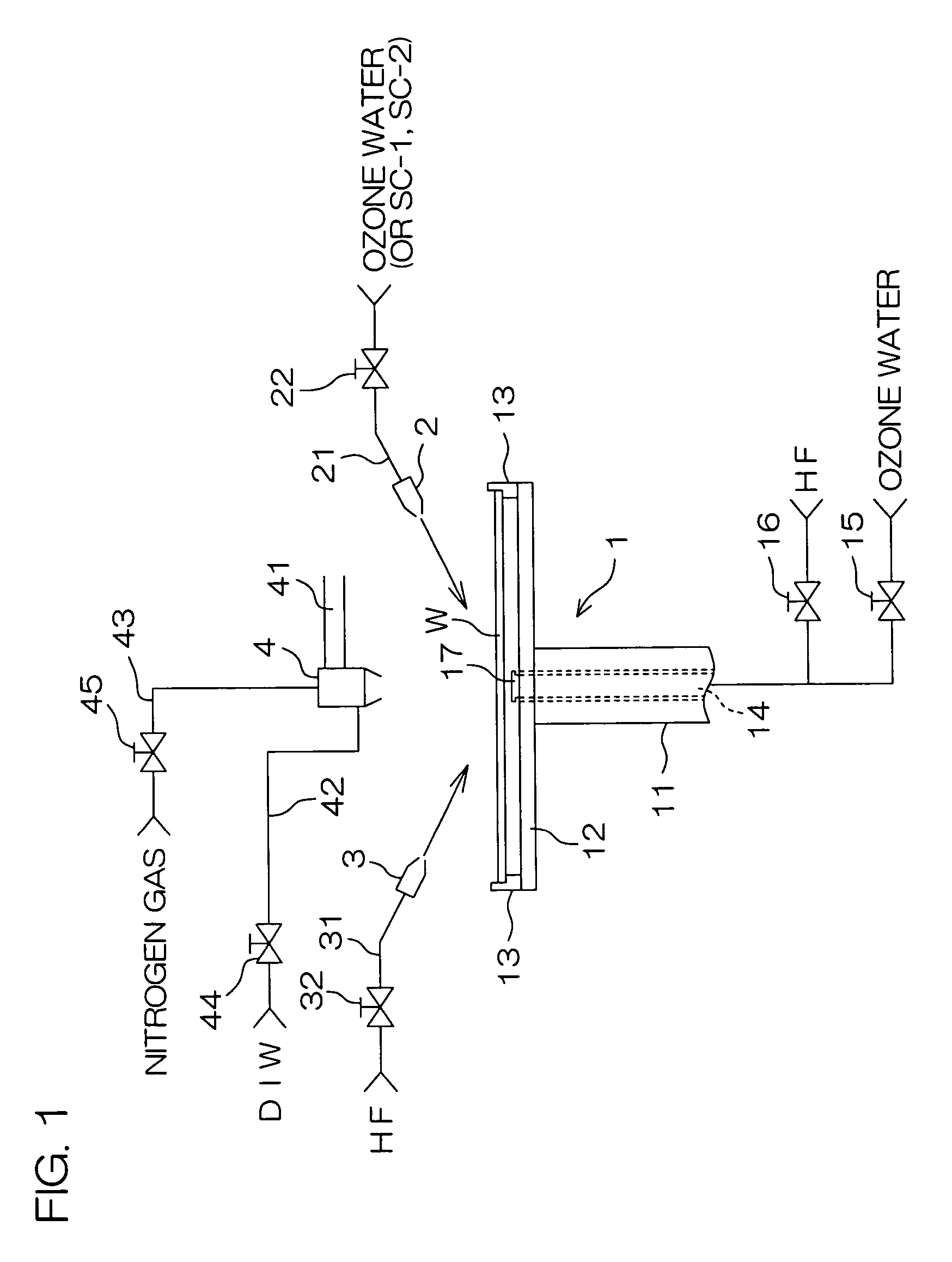

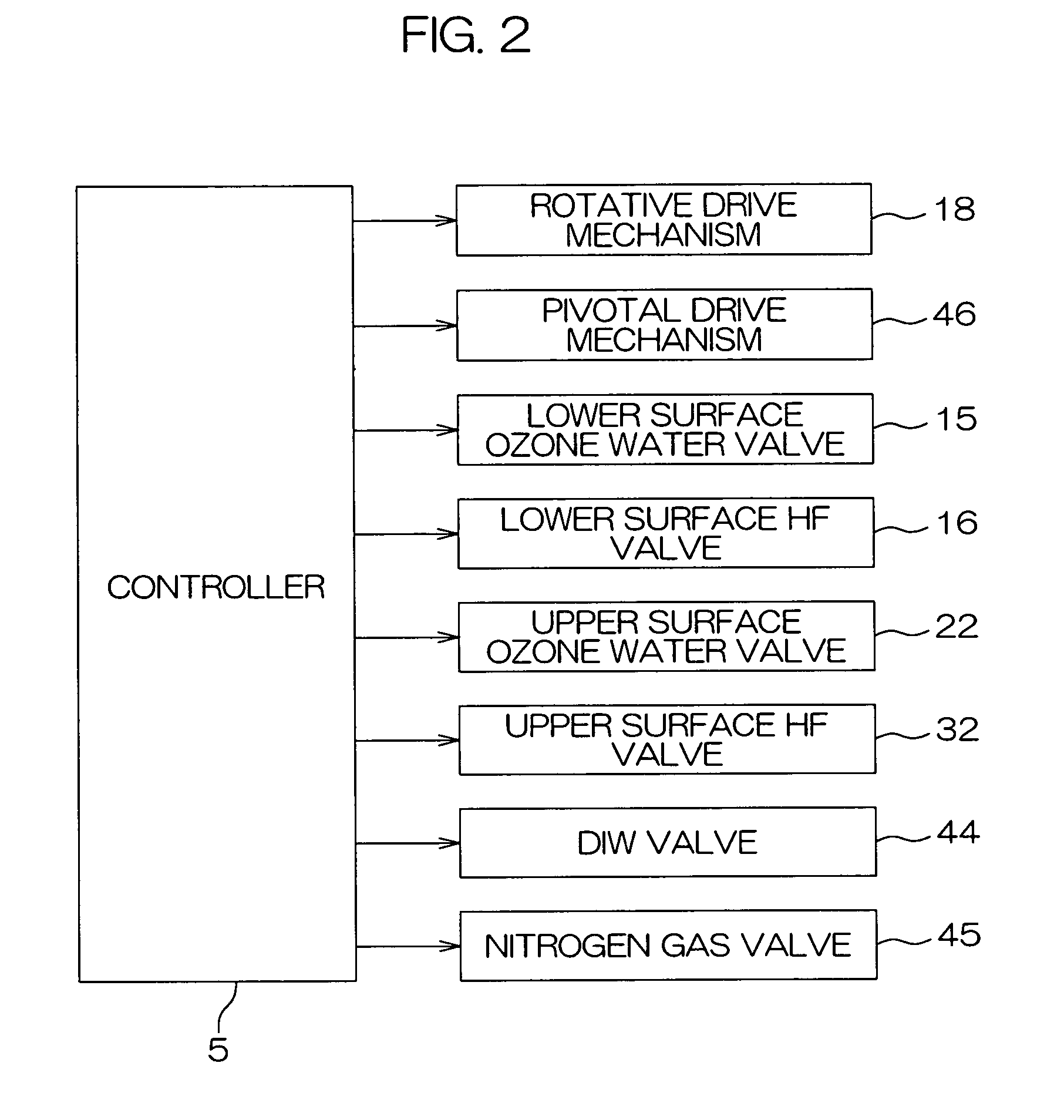

Substrate treatment apparatus and substrate treatment method

ActiveUS7494549B2Easy to cleanSubstrate surface can be preventedSemiconductor/solid-state device manufacturingElectrostatic cleaningEngineeringSubstrate surface

A substrate treatment apparatus for removing an unnecessary substance from a surface of a substrate. The apparatus is provided with: an oxidation liquid supply mechanism for supplying an oxidation liquid having an oxidative effect to the substrate surface; a physical cleaning mechanism for physically cleaning the substrate surface; and an etching liquid supply mechanism for supplying an etching liquid having an etching effect to the substrate surface. It is preferred to physically clean the substrate surface while supplying the oxidation liquid to the substrate surface.

Owner:DAINIPPON SCREEN MTG CO LTD

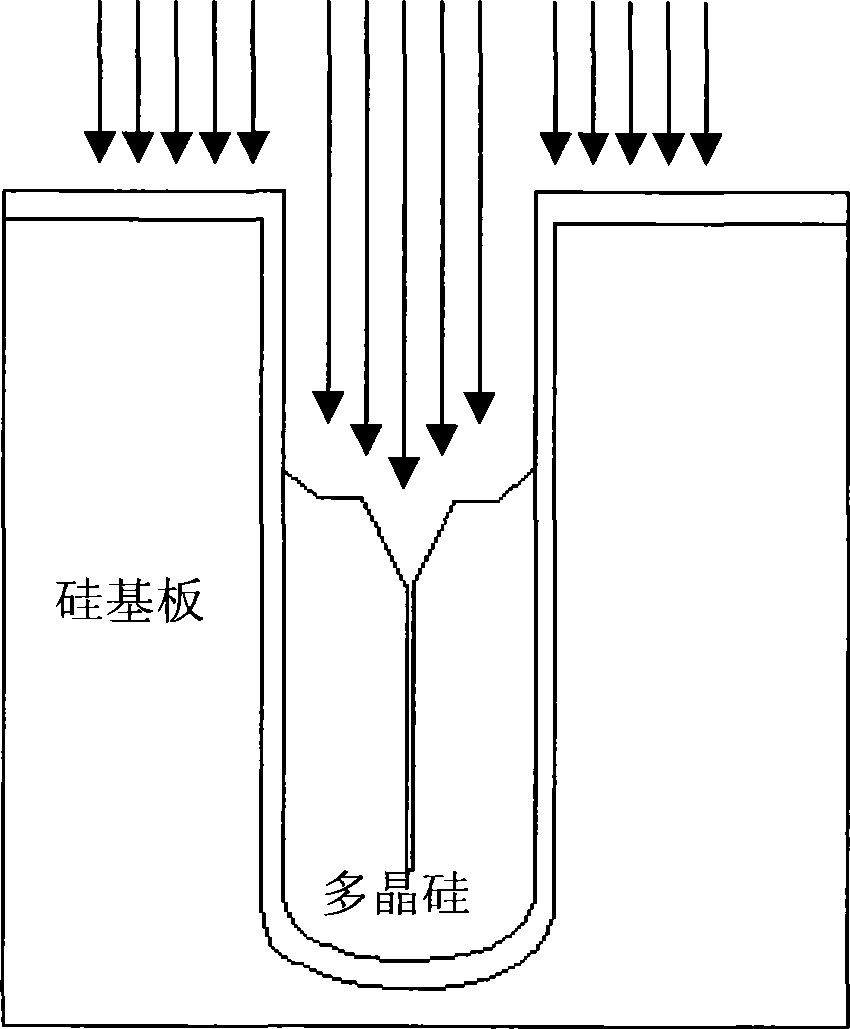

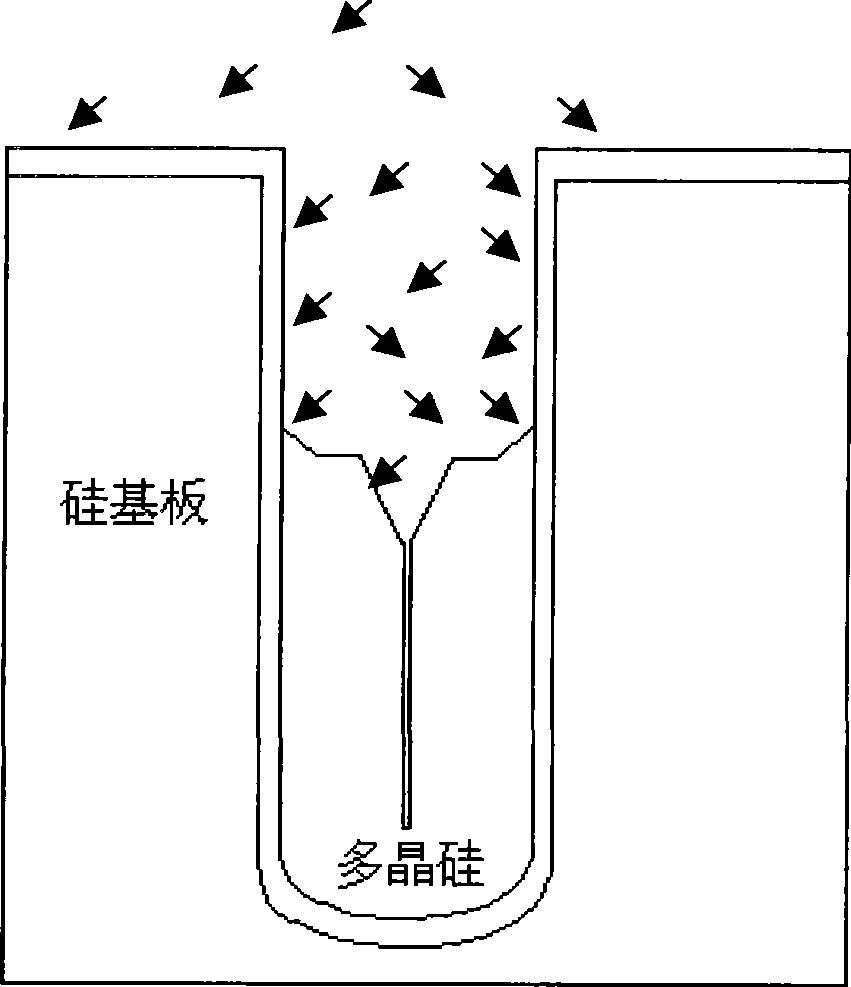

Method for dry method etching polycrystalline silicon in deep plow groove

ActiveCN101436536AReduce the amount of etchingEliminate the problem of widening gapsSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsHydrogen bromide

The invention discloses a method for dry etching for polycrystalline silicon in a deep groove, which comprises the following steps: after the dry etching for the polycrystalline silicon deposited in the deep groove by larger lower power through using chlorine, hydrogen bromide and oxygen, using carbon tetrafluoride and the chlorine as main etching gases, and using lower bias power to etch the polycrystalline silicon again approximately to each isotropic property to reduce etching amount in the vertical direction, thereby solving the problem of gap expansion, and obtaining a flat polycrystalline silicon surface simultaneously.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Dry etching method

ActiveUS20120129278A1Suppressing undesired erosionForming accuratelySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingOrganic filmAnisotropic etching

A dry etching method includes a first step and a second step. The first step includes generating a first plasma from a gas mixture, which includes an oxidation gas and a fluorine containing gas, and performing anisotropic etching with the first plasma on a silicon layer to form a recess in the silicon layer. The second step includes alternately repeating an organic film forming process whereby an organic film is deposited on the inner surface of the recess with a second plasma, and an etching process whereby the recess covered with the organic film is anisotropically etched with the first plasma. When an etching stopper layer is exposed from a part of the bottom surface of the recess formed in the first step, the first step is switched to the second step.

Owner:ULVAC INC

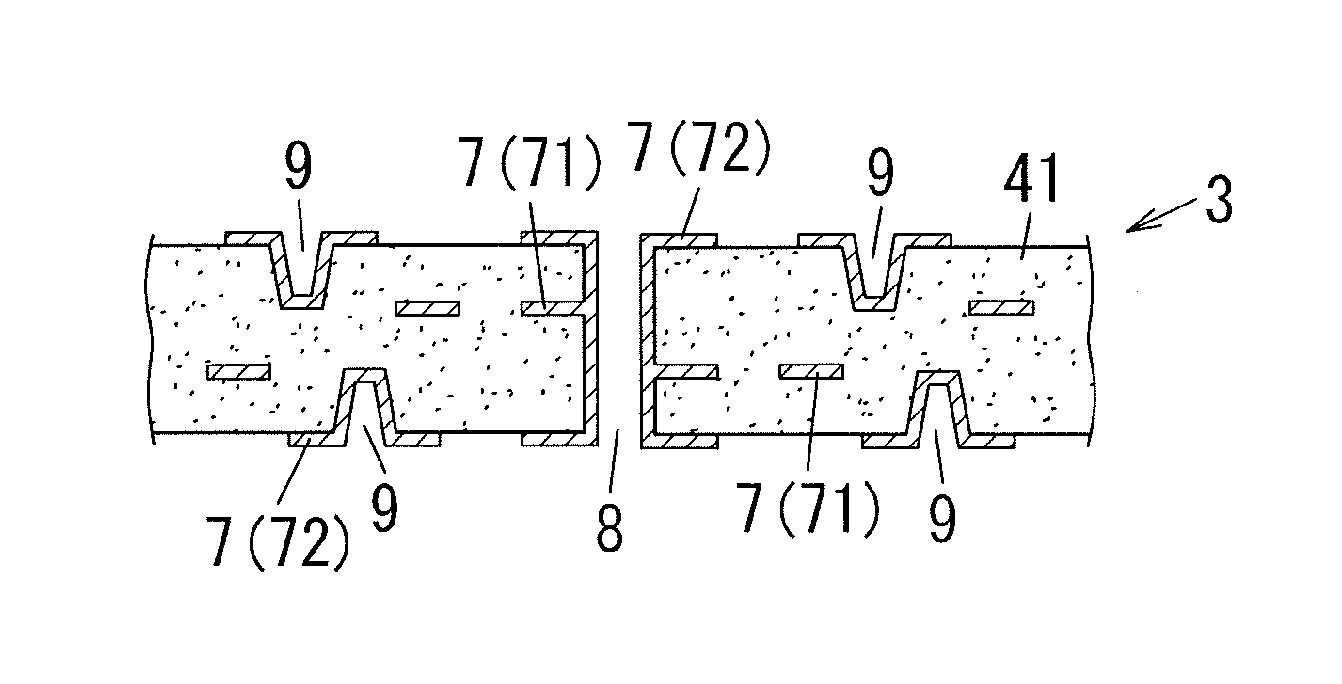

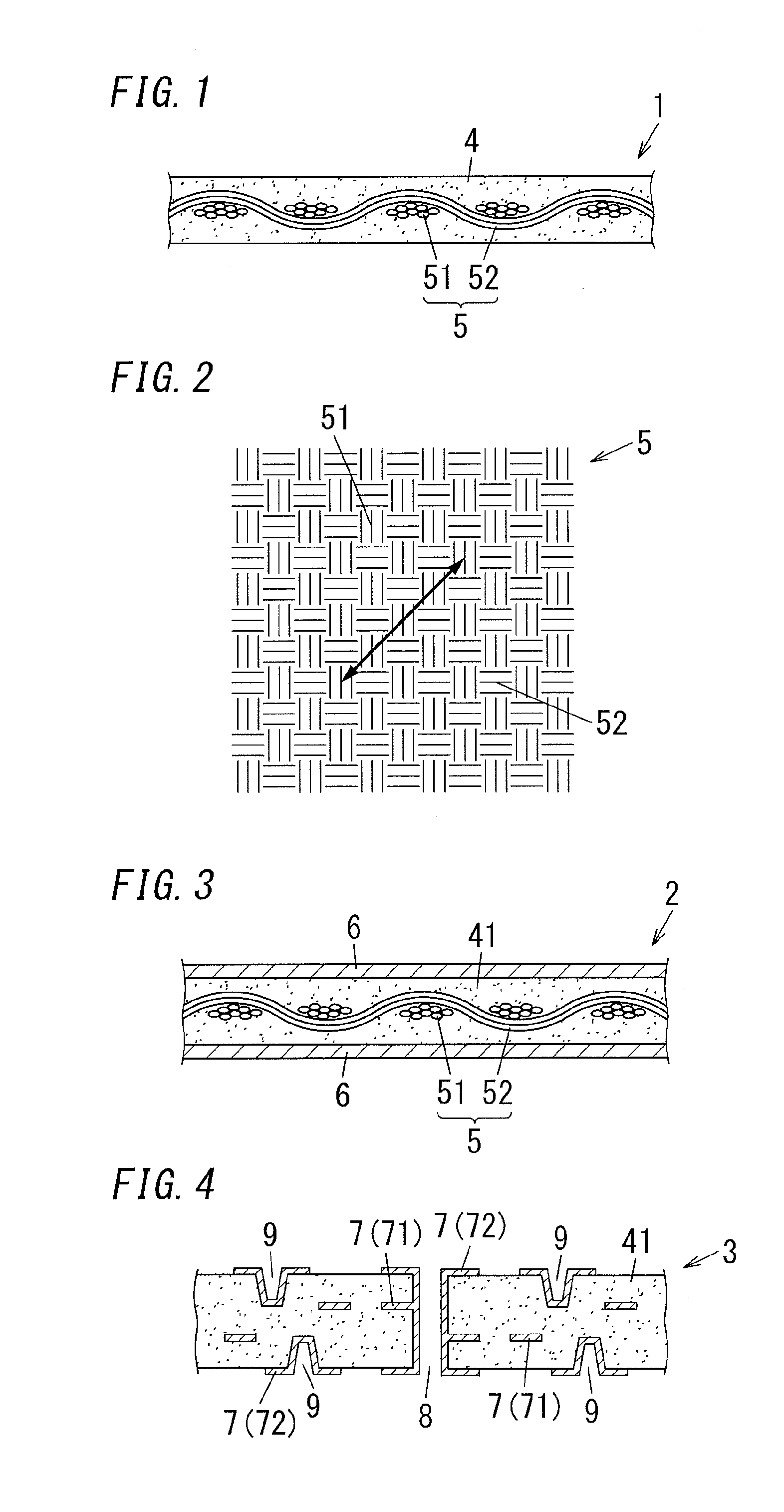

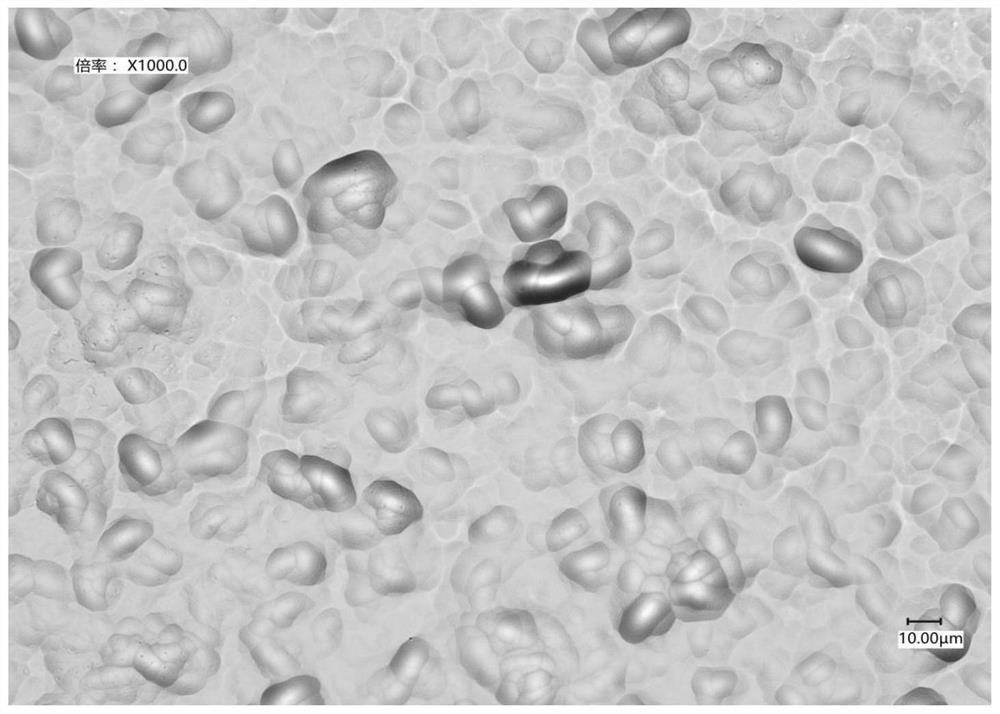

Prepreg, metal-clad laminate, and printed wiring board

InactiveUS20150282302A1Reduce warpageDecrease desmear etching amountSynthetic resin layered productsPrinted circuit aspectsEpoxyPolymer chemistry

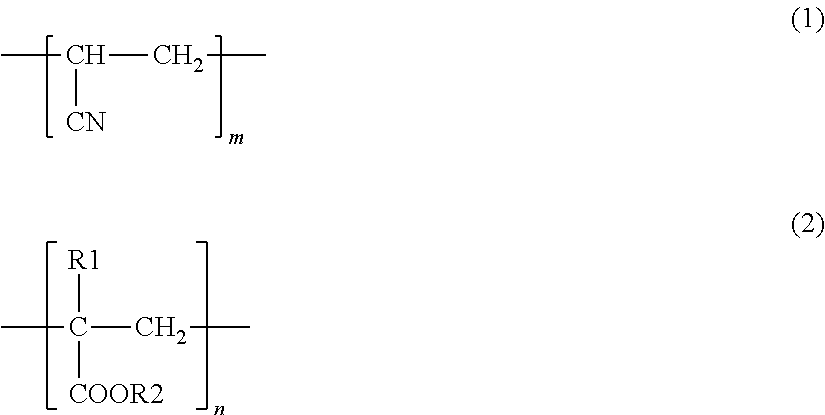

A prepreg containing: a resin composition; and a woven fabric base material. The resin composition contains: (A) at least one of an epoxy resin having a naphthalene skeleton and a phenolic curing agent having a naphthalene skeleton; (B) a high molecular weight compound having at least structures represented by formulae (1) and (2 ) or at least a structure represented by the formula (2), no unsaturated bond between carbon atoms, and a weight-average molecular weight of 250,000 to 850,000; and (C) an inorganic filler. (C) The inorganic filler is subjected to surface treatment with a silane coupling agent represented by a formula (3).

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

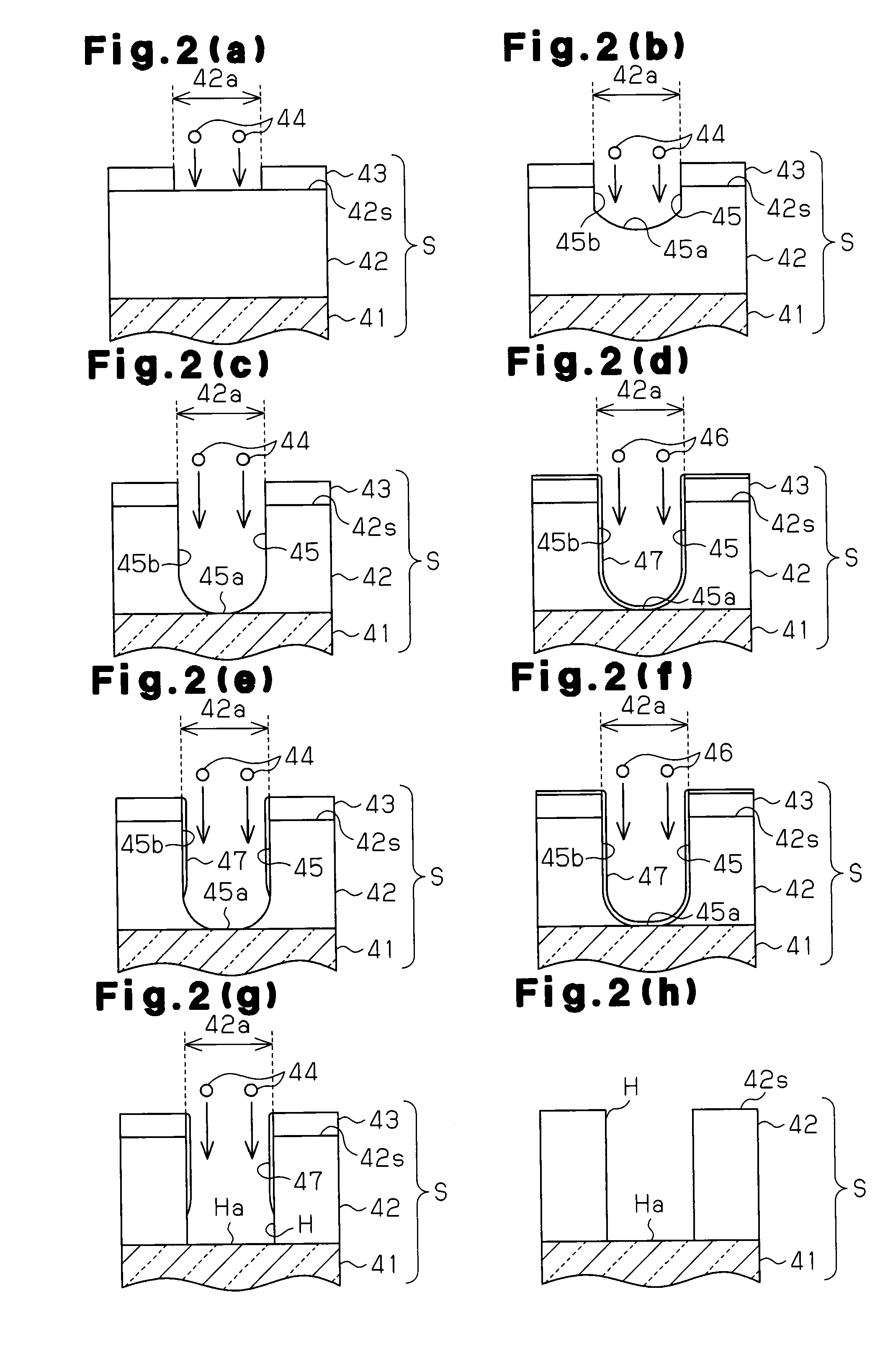

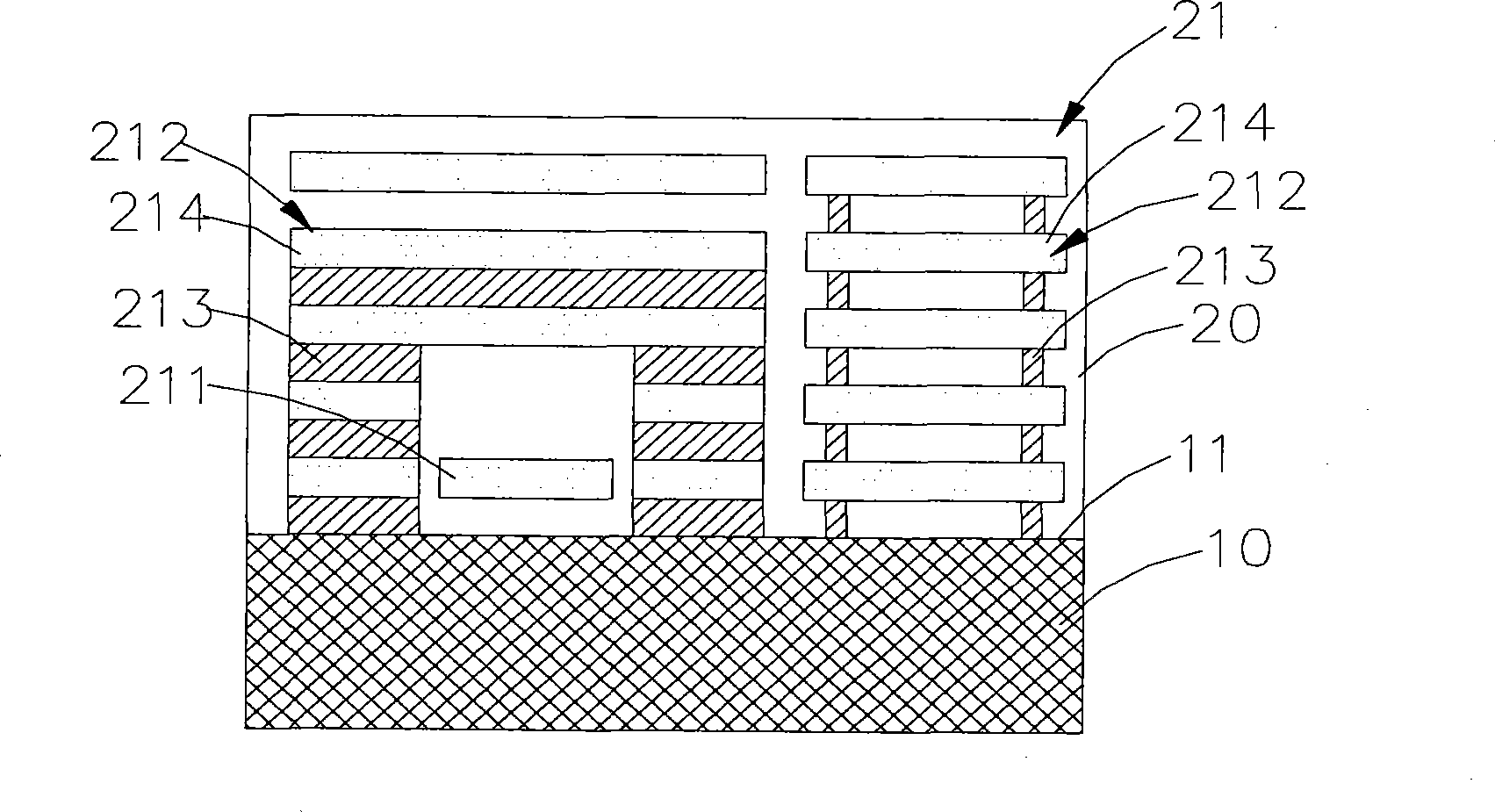

Semiconductor device and manufacturing method of the same

InactiveCN1905194AWon't get thinnerReduce the amount of etchingSemiconductor/solid-state device detailsSolid-state devicesSemiconductorCapacitor

To provide a semiconductor device capable of improving accuracy in finishing a hole in which a conductive plug right under a capacitor, and a manufacturing method of such a semiconductor device comprising the following steps: a step of forming first and second conductive plugs 32 a , 32 b in first and second holes 11 a , 11 b in a first insulating film 11; a step of forming a first opening 14 a in an oxidation preventing insulating film 14 ; a step of forming an auxiliary conductive plug 36 a in the first opening 14 a; a step of forming a capacitor Q on the auxiliary conductive plug 36 a; a step of forming third and fourth holes 41 a , 41 b in a second insulating film 41 covering the capacitor Q; a step of forming the second opening 14 b in the oxidation preventing insulating film 14 under the fourth hole 41 b; a step of forming a third conductive plug 47 a in the third hole 41 a; and a step of forming a fourth conductive plug 47 b in the third hole 41 a.

Owner:FUJITSU SEMICON LTD

Method of manufacturing semiconductor substrates and semiconductor devices

InactiveUS7553713B2Reduce manufacturing costIncrease speedTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

A semiconductor substrate includes a semiconductor base substrate that has an oxide film selectively formed on a part thereof, the oxide film having a non-uniform thickness; and a semiconductor layer that is formed on the oxide film by epitaxial growth so as to have a non-uniform thickness.

Owner:SEIKO EPSON CORP

Method for preventing gap below side wall barrier layer during self-aligning silicide process

InactiveCN101826465AAvoid gapsCreate a gapSemiconductor/solid-state device manufacturingComposite materialSalicide

The invention discloses a method for a part to prevent a gap below a side wall barrier layer during a self-aligning silicide process. The part comprises a bedding oxidation film which covers a part underlayer and a grid which is formed on the bedding oxidation film. The method comprises the following steps that: after a sacrificial layer TEOS is deposited, the sacrificial layer and the bedding oxidation film covering the part underlayer are etched until the surface of the part underalyer and the grid top part; and during the manufacturing process of the side wall barrier layer of the grid, by utilizing the self-aligning silicide way, the thickness of the oxidation layer which is deposited on the part underlayer which is etched in a wet way is more than or equal to 100 angstroms and is less than 200 angstroms. The method can prevent the gap below the barrier layer during the self-aligning process of silicide.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Solder resist layer manufacturing method, printed circuit board manufacturing method and printed circuit board

InactiveCN111050487AInhibit sheddingAvoid voidsNon-metallic protective coating applicationSolder maskPrinting ink

The invention discloses a solder resist layer manufacturing method, a printed circuit board manufacturing method and a printed circuit board. The solder resist layer manufacturing method comprises thefollowing steps: step 1, firstly, filling and leveling up a gap between thick copper on the printed circuit board by using printing ink; and step 2, performing solder resist pattern printing on the printed circuit board. The method of firstly filling and then solder resist is adopted. As the height difference between the base material area and the thick copper surface area is large, the lower base material area is firstly filled and leveled up by using solder resist ink, i.e., the height is basically equal to that of the thick copper surface, and then solder resist manufacturing is completedby using whole board ink printing so that the overall flatness of board surface ink is ensured; meanwhile, the etching amount of the ink side wall on the side of the base material area is reduced, thebinding force of the ink and the base material surface is increased, and ink falling can be prevented.

Owner:SHANGHAI MEADVILLE ELECTRONICS

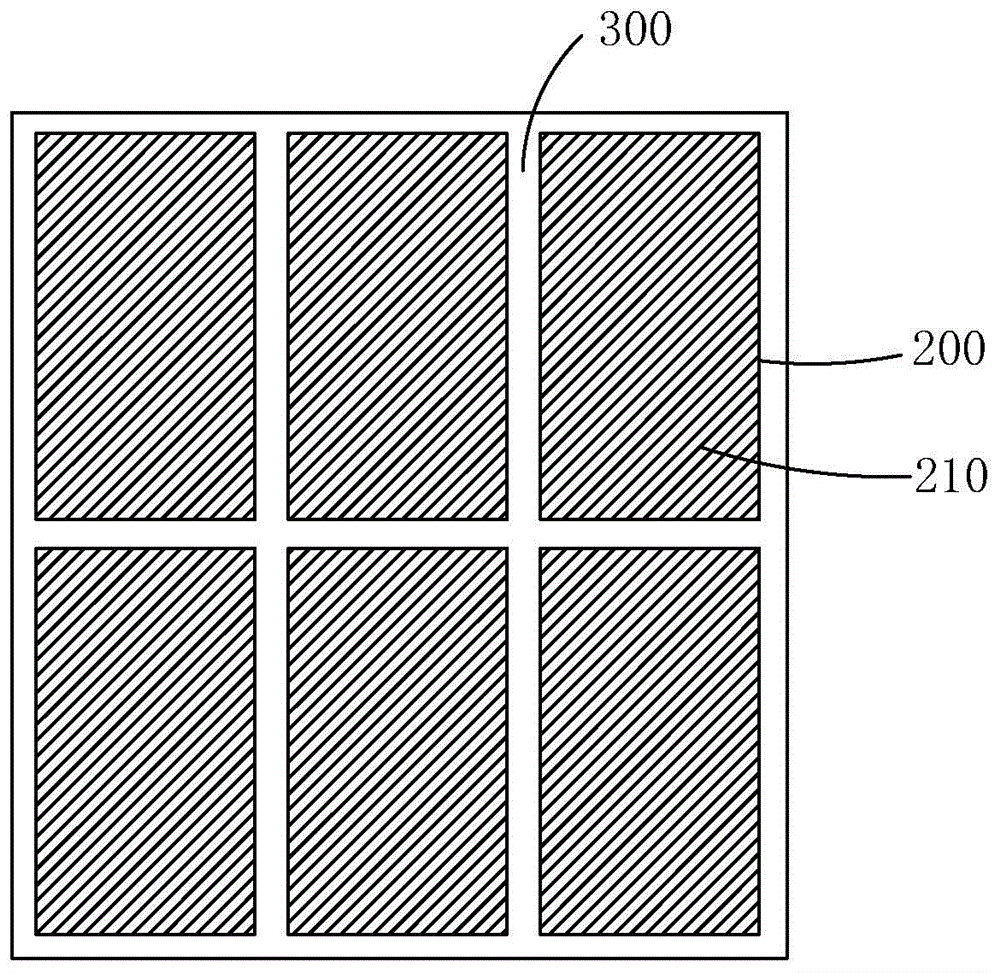

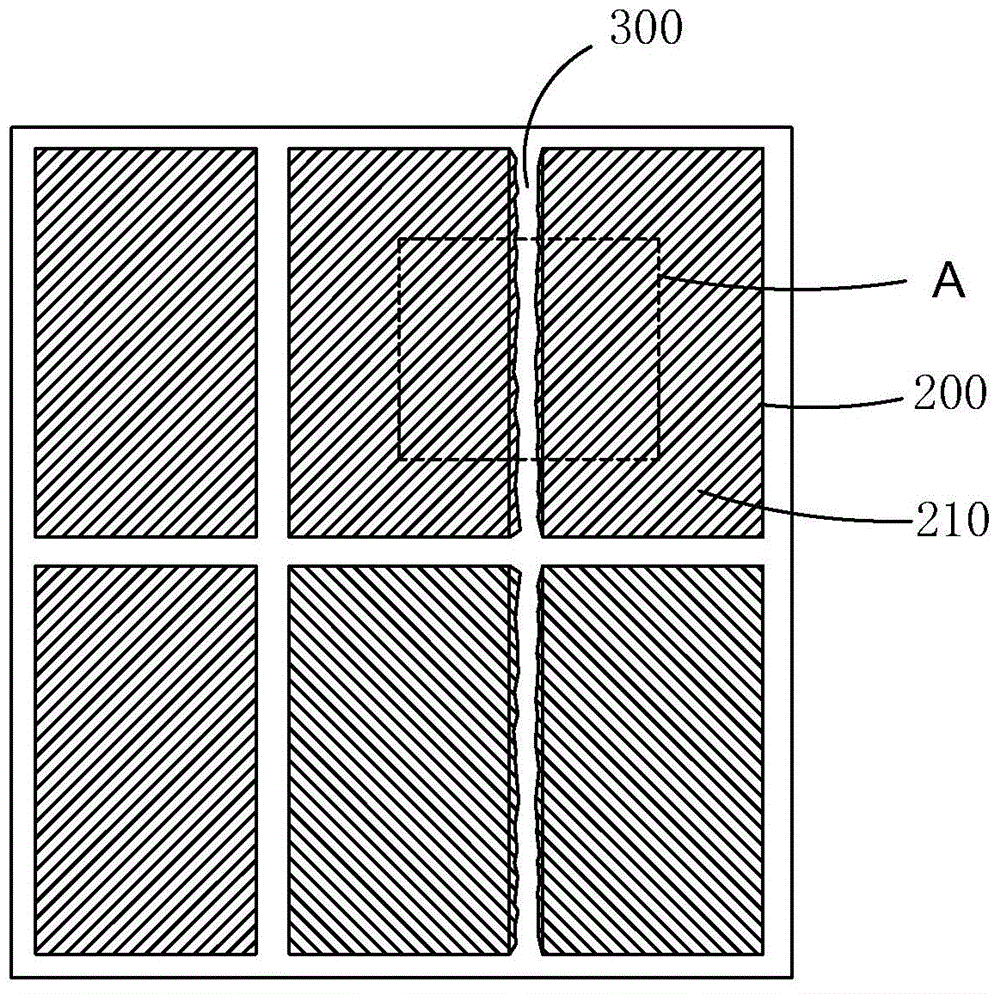

TFT substrate group and manufacturing method therefor

ActiveCN104934445AImprove the problem of endless etching on the edgeReduce concentrationSolid-state devicesSemiconductor/solid-state device manufacturingEtchingEngineering

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

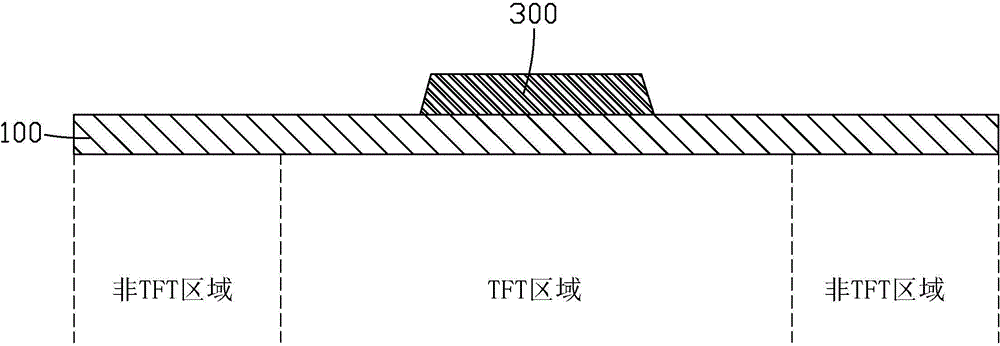

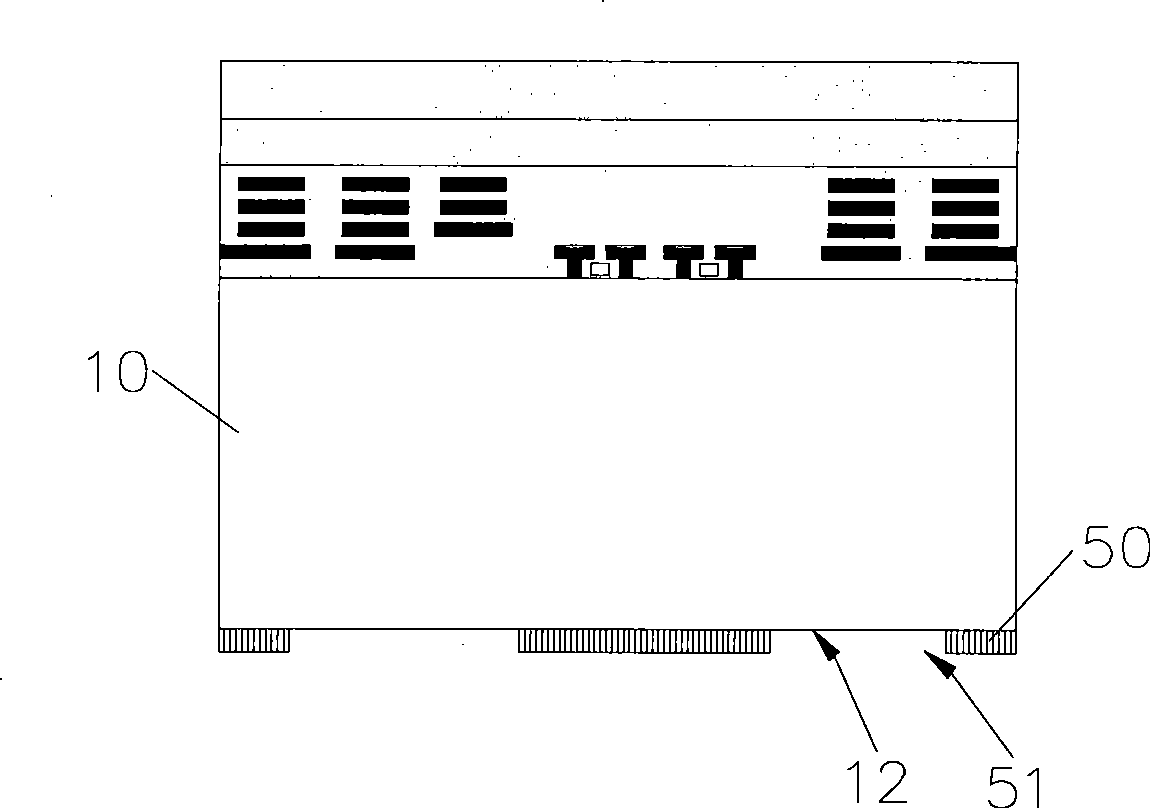

Manufacture method and structure of TFT substrate

ActiveCN104934439AImprove qualitySimple structureSolid-state devicesSemiconductor devicesLiquid-crystal displayAmorphous silicon

The invention provides a manufacture method and structure of a TFT substrate. According to the manufacture method of the TFT substrate, part, placed in a non-TFT area, of an amorphous silicon layer (51) is reserved in certain thickness in the first dry etching process, a back channel (515) is formed in the second dry etching process, the reserved amorphous silicon layer (51) in the non-TFT area, and thus, a grid insulating layer (4) is prevented from damage in the second dry etching process. The quality of the TFT substrate is improved, the risk of quality problems is reduced, the etching amount in the first dry etching process is reduced, the etching time is reduced, the production period is shortened, and the factory capacity is improved. The TFT substrate provided by the invention is simple in structure, the grid insulating layer (4) is complete without damage, and the quality of an LCD can be improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Method for manufacturing semiconductor micro electromechanical structure

InactiveCN101434375AShorten the timePrevent side erosionDecorative surface effectsChemical vapor deposition coatingEtchingSemiconductor

The invention discloses a method for manufacturing a semiconductor micro electronmechanical structure, which comprises the steps: firstly, at least one insulation circuit layer internally provided with a micro electronmechanical structure is produced on the upper surface of a silicon substrate, and a sacrifice layer and a blocking layer are sequentially produced on the upper surface of the insulation circuit layer from interior to exterior; secondly, an etching blocking layer is made on the lower backface of the silicon substrate, and deep reactive ion etching or wet etching is carried out to the lower backface of the silicon substrate so as to form a space corresponding to the micro electronmechanical structure; and finally etching is carried out to the insulation circuit layer and the sacrifice layer in sequence to lead the micro electronmechanical structure to be suspended. Therefore, lateral erosion can be effectively avoided, the probability of exposure and damage of the micro electronmechanical structure is low, and the final encapsulation cost can be reduced by being integrated with common integrated circuit packaging technologies.

Owner:MEMSMART SEMICON

Manufacturing method of trench type double-layer gate MOSFET

ActiveCN110491782AReduce process costGuaranteed shape stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEtching

The invention discloses a manufacturing method of a trench type double-layer gate MOSFET, which comprises the following steps of: forming a plurality of trenches which comprise a plurality of gate trenches and at least one source lead-out trench; forming a bottom dielectric layer and source polysilicon; forming an inter-polycrystalline silicon oxide layer by adopting an HDP CVD deposition and backetching process; forming a gate dielectric layer; performing polycrystalline silicon deposition to form a second polycrystalline silicon layer; etching back the second polycrystalline silicon layer,forming a polycrystalline silicon gate by the second polycrystalline silicon layer filled in the gate trench after etching back, and reserving the remaining second polycrystalline silicon layer on theside surface of the source lead-out trench; carrying out growth of an under-metal dielectric layer, wherein the growth thickness being greater than a target thickness, and the growth thickness of theunder-metal dielectric layer satisfying complete filling of a gap region in the source lead-out trench; carrying out wet etching to reduce the thickness of the metal lower dielectric layer to a target thickness; performing etching to form an opening of the contact hole, and filling metal. The process cost can be reduced, and the product quality can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Etching solution and etching method of general resistance silicon product

ActiveCN112608753AAdjust the corresponding ratio contentReduce generationSemiconductor/solid-state device manufacturingSurface treatment compositionsEtchingO-Phosphoric Acid

The invention relates to an etching solution for a general resistance silicon product. The etching solution is composed of ammonium bifluoride, potassium nitrate, sulfuric acid, ammonium persulfate, polyethylene glycol, phosphoric acid and a propylene glycol block polyether aqueous solution. According to the characteristics of common resistance silicon products, the traditional etching solution prepared from high-concentration and high-corrosivity hydrofluoric acid, nitric acid, acetic acid and water is improved, a certain amount of HF can be generated according to a certain rate when ammonium bifluoride and sulfuric acid are properly proportioned, and a small amount of potassium nitrate, ammonium persulfate and phosphoric acid are proportioned for etching. The spots or chromatic aberration phenomena generated in incomplete or uneven etching are reduced. The reaction is uniform and mild, the roughness is consistent with that before etching, and the roughness is not increased.

Owner:CHONGQING GENORI IND CO LTD

Method for manufacturing suspension micro electromechanical structure

InactiveCN101434376AReduce etch process timeReduce chanceDecorative surface effectsChemical vapor deposition coatingInsulation layerBlocking layer

The invention discloses a method for manufacturing a suspension micro electromechanical structure, which comprises the following steps: firstly, at least one insulation layer internally provided with a metal micro electromechanical structure is formed on the upper surface of a silicon fundus, the micro electromechanical structure comprises at least one microstructure and at least one metal sacrifice structure which are independent with each other, and the metal sacrifice structure is internally provided with metal layers and metal bolt layers connecting the metal layers; secondly, at least one blocking layer is made on the upper surface of the insulation layer; thirdly, at least one etching blocking layer is made on the lower surface of the silicon fundus; fourthly, etching is carried out to the lower surface of the silicon fundus to form a space corresponding to the inner suspension microstructure of the micro electromechanical structure; and finally, etching is carried out to the metal sacrifice structure to form the suspension of the micro electromechanical structure. The invention can effectively avoid the improper erosion of the suspension micro electromechanical structure and the surrounding insulation layer thereof, reduce the exposure rate of the suspension micro electromechanical structure, and reduce the final encapsulation cost by being integrated with common integrated circuit packaging.

Owner:MEMSMART SEMICON

3D memory device and manufacturing method thereof

ActiveCN110277407AReduce the amount of etchingImprove uniformitySolid-state devicesSemiconductor devicesInsulation layerIsolation layer

The invention discloses a 3D memory device and a manufacturing method thereof. The 3D memory device comprises a semiconductor substrate, a gate stack structure, multiple channel columns and a gate isolation structure, wherein the gate stack structure is located on the semiconductor substrate and includes gate conductor layers and interlayer insulation layers which are alternately stacked; the multiple channel columns run through the gate stack structure and is contacted with the semiconductor substrate; the gate isolation structure runs through the gate stack layer to divide a plurality of memory areas and includes a conductive channel and an isolation layer which are formed in a grid line slit, the conductive channel is contacted with the semiconductor substrate, the isolation layer mutually isolates the gate conductor layer from the conductive channel, the grid line slit is disconnected in a predetermined area to form a gap so as to enable the gate conductor layer located in different memory areas to be electrically connected at the gap, the grid line slit includes an end part close to the gap, an extension part and a connecting part used for connecting the end part and the extension part, the channel size of the connecting part close to the end part is less than the channel size thereof close to the extension part so as to limit the cavity volume of the end part, thereby improving the uniformity of the thickness of the isolation layer.

Owner:YANGTZE MEMORY TECH CO LTD

Semiconductor device manufacturing method

ActiveUS20120070978A1Reduce the overall diameterAdd depthSolid-state devicesSemiconductor/solid-state device manufacturingMiniaturizationEngineering

A miniaturized semiconductor device is provided by reducing the design thickness of a wiring line protecting film covering the surface of a wiring layer, and reducing the distance between the wiring layer and via plugs formed by a self-aligning process. Dummy mask layers extending in the same layout pattern as the wiring layer is formed above the wiring layer covered with a protecting film composed of a cap layer and side wall layers. In the self-aligning process for forming via plugs in a self-aligned manner with the wiring layer and its protecting film, the thickness of the cap layer is reduced and the design interval between the via plugs is reduced, whereby the miniaturization of the semiconductor device is achieved.

Owner:LONGITUDE LICENSING LTD

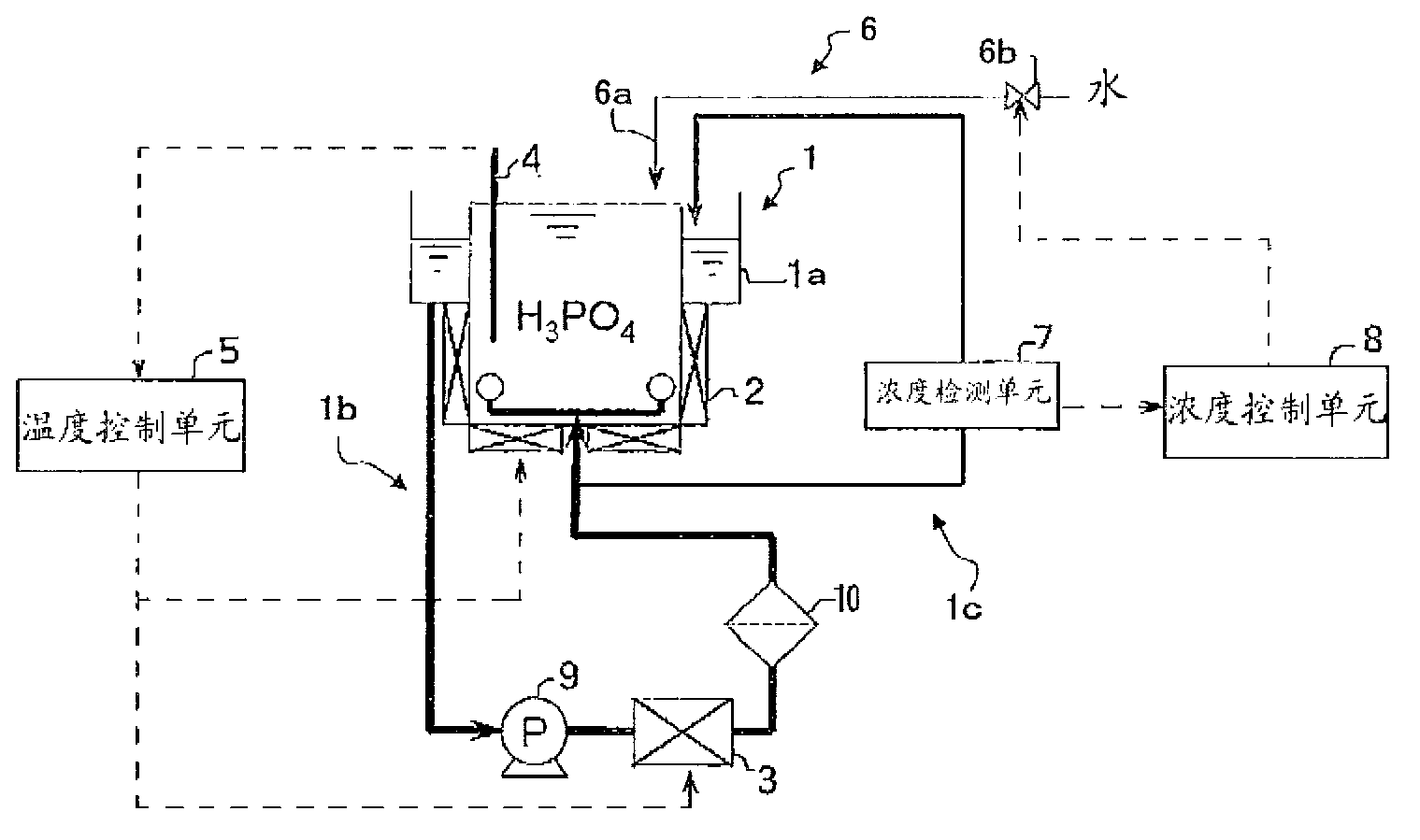

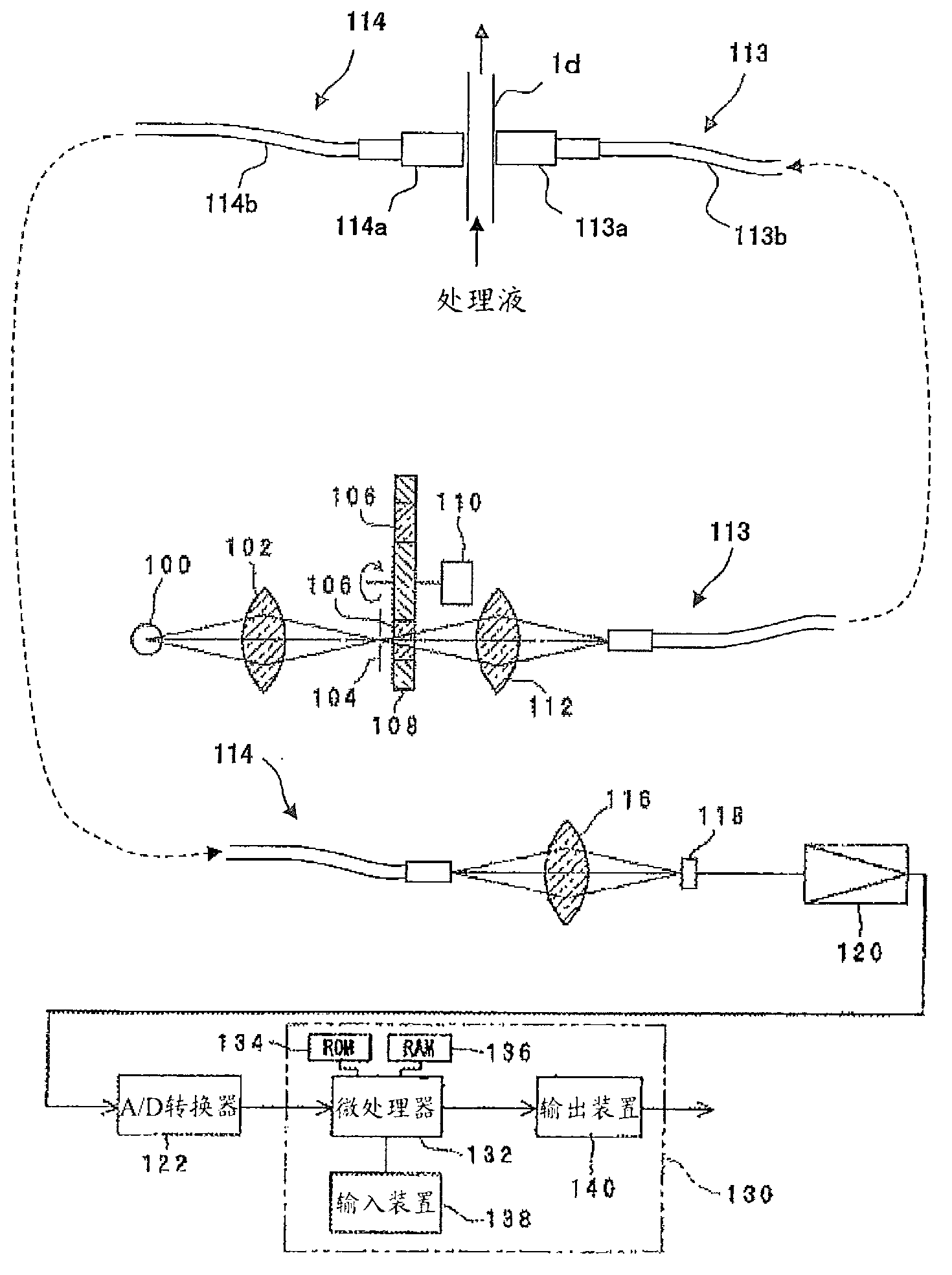

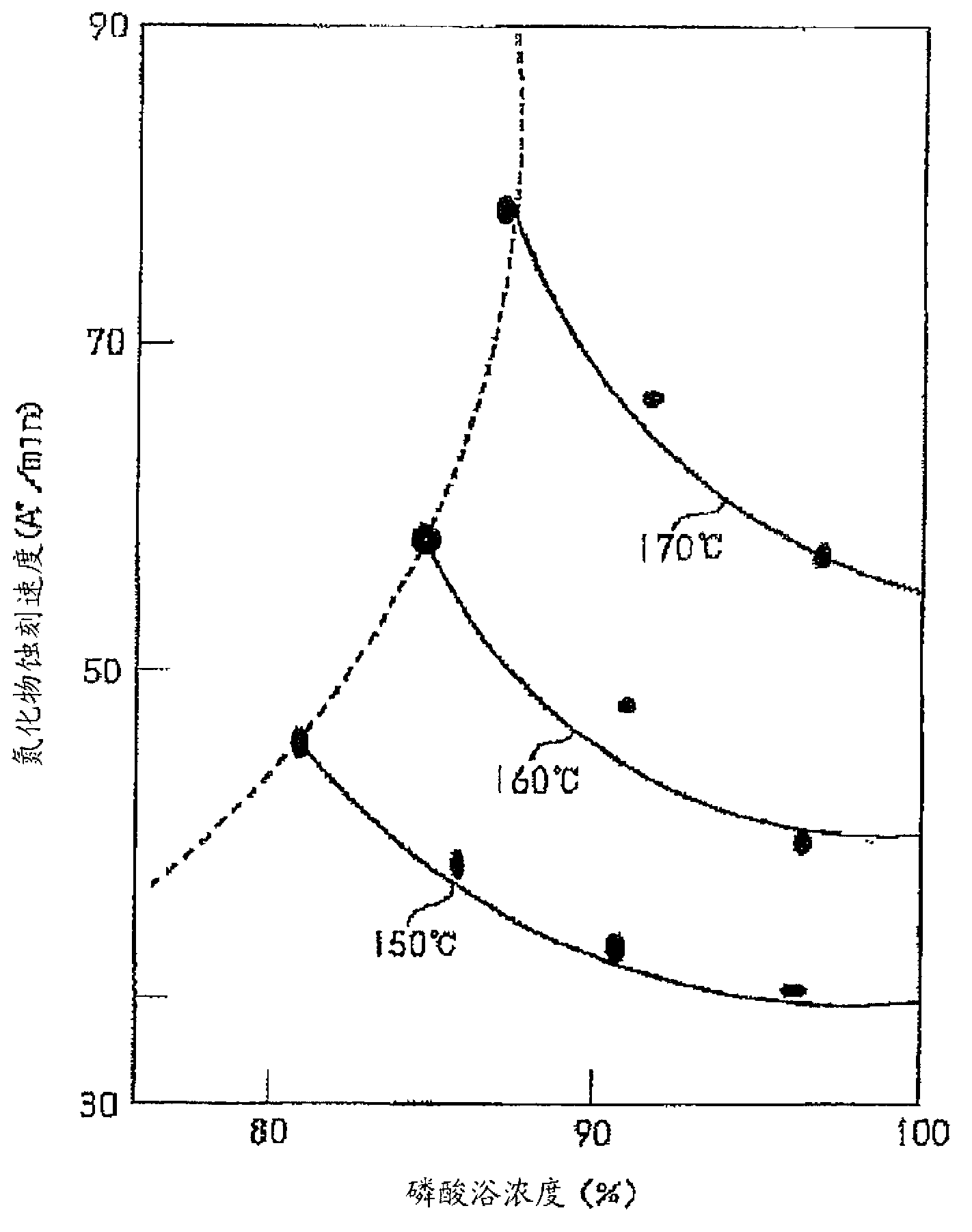

Substrate processing device

ActiveCN103155113AEtch stableReduce the amount of etchingDecorative surface effectsSemiconductor/solid-state device manufacturingCompound (substance)Engineering

Disclosed is a substrate processing device that can directly detect the concentration of a processing liquid, and thus is able to perform independent concentration control mostly without being affected by the temperature of the processing liquid, and is able to accurately perform chemical processing of a substrate. The substrate processing device, which processes by immersing the substrate in the processing liquid comprising a mixture of a chemical and a diluting liquid, is provided with: a processing tank (1) that retains the processing liquid; heating means (2, 3) that heat the processing liquid; a temperature detection means (4) that detects the temperature of the processing liquid; a temperature control means (5) that operates the aforementioned heating means (2, 3) in a manner so that the detected temperature approaches a set temperature; a replenishing means (6) that replenishes the diluting liquid in the processing liquid; a concentration detection means (7) that detects the concentration of the processing liquid by measuring the light absorption characteristics of the processing liquid; and a concentration control means (8) that operates the aforementioned replenishing means (6) in a manner so that the detected concentration approaches a set concentration.

Owner:KURASHIKI BOSEKI KK +1

Method of forming wiring pattern and method of manufacturing TFT substrate using the same

InactiveUS7718346B2Avoid it happening againReduce the amount of etchingDecorative surface effectsSolid-state devicesResistScreen printing

A method of forming a wiring pattern includes forming a first conductive film pattern, an insulating film and a second conductive film pattern intersecting with the first conductive film pattern on an insulating substrate. In the method, an etching resist pattern for forming the second conductive film pattern is formed by use of a screen printing method. Thereafter, an etching resist is softened by exposing the etching resist in an organic solvent atmosphere before hardening thereof. Thus, defects such as spaces in the etching resist are repaired. By use of the above-described method of forming a wiring pattern, a TFT substrate is manufactured.

Owner:NEC LCD TECH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com