Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

49results about How to "Reduce Interface Scattering" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

High-thermal-conductivity polyimide film prepared from core-shell structure heat-conducting filler and preparation method of film

ActiveCN110452418AShorten the heat conduction pathReduce Interface ScatteringThermal conductivityPolyimide

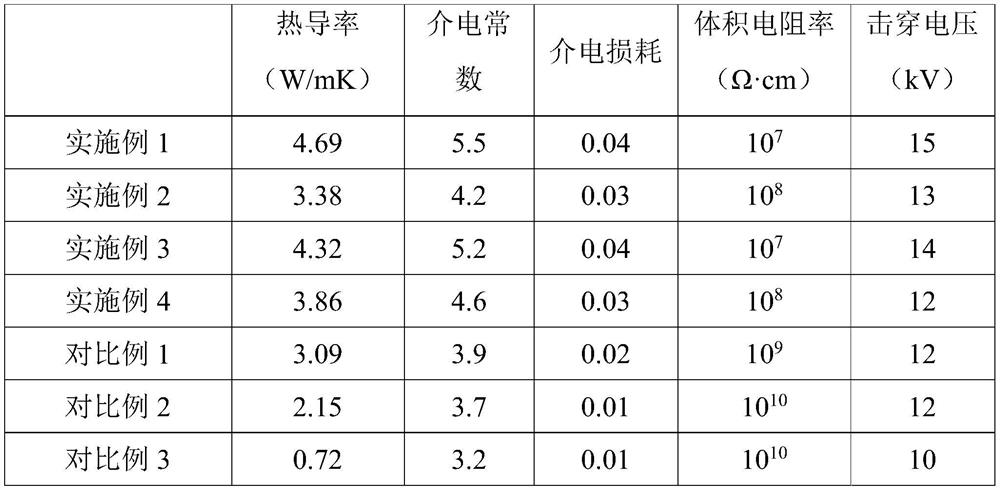

The invention discloses a high-thermal-conductivity polyimide film prepared from a core-shell structure heat-conducting filler and a preparation method of the film. The heat-conducting filler is of acore-shell structure. The film comprises, by mass, 10-50 parts of the heat-conducting filler, 1-5 parts of a modifier and 80-500 parts of a polyamide acid solution. The heat-conducting filler is a boron nitride coated aluminum oxide core-shell heat-conducting filler. The core-shell heat-conducting filler is prepared by treating aluminum oxide by using the modifier and calcining boron nitride at high temperature through an electrostatic self-assembling method. The core-shell heat-conducting filler is added into the polyamide acid solution, stirred and uniformly mixed and subjected to standing to be defoamed in vacuum, the filler is laid to form a film, programmable heating is conducted for imidization, and the high-thermal-conductivity polyimide film is prepared. The film has the main characteristics of high heat conductivity coefficient and electric insulation, the processing cost is low, the preparation process is simple, the forming period is short, and the film has wide applicationprospects in the fields of electronics, aerospace and machinery.

Owner:GUILIN UNIV OF ELECTRONIC TECH

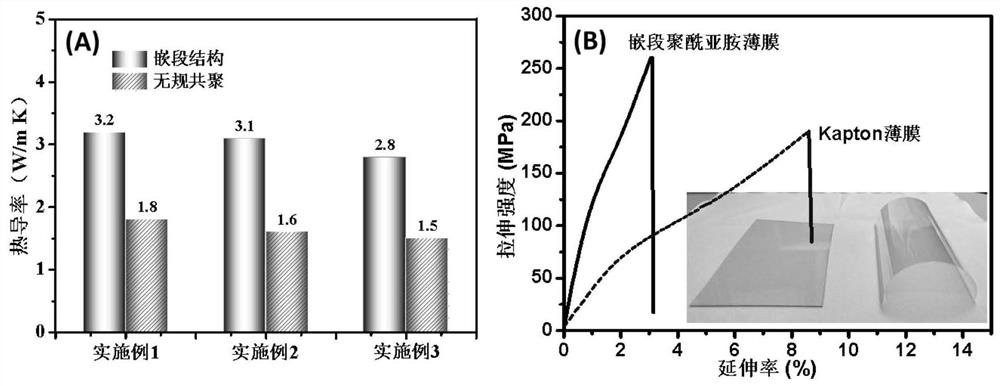

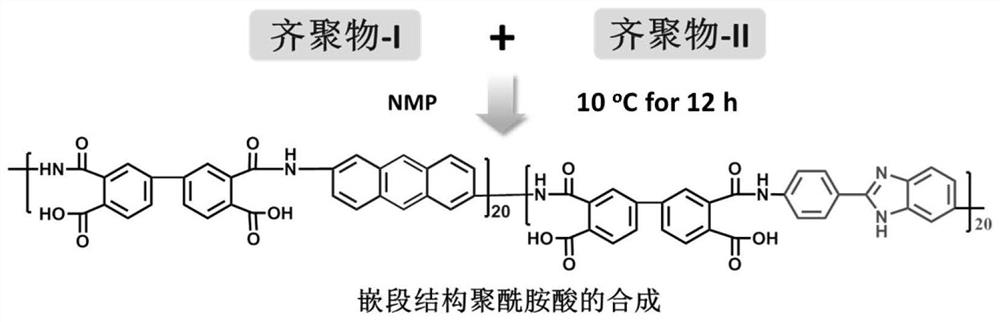

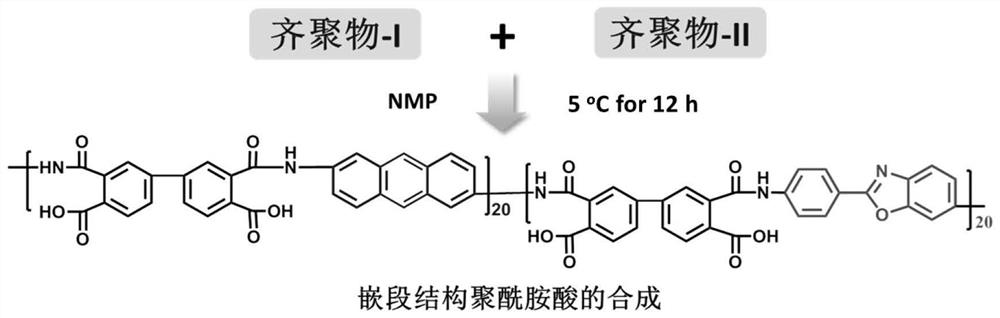

Preparation method of high-modulus high-thermal-conductivity polyimide film

ActiveCN111793207AImprove mechanical propertiesPromote disseminationSemiconductor/solid-state device detailsSolid-state devicesBenzoxazoleAnthraquinones

The invention relates to a preparation method of a high-modulus high-thermal-conductivity polyimide film. The preparation method comprises the following steps: mixing diamine containing anthryl or anthraquinone units, a dianhydride monomer and a solvent, and carrying out a polymerization reaction to obtain an anhydride structure-terminated oligomer-I solution; mixing diamine containing a benzimidazole or benzoxazole unit, a dianhydride monomer and a solvent, and carrying out a polymerization reaction to obtain a diamine-terminated oligomer-II solution; mixing the oligomer-I solution with the oligomer-II solution, carrying out a polymerization reaction, casting the obtained polyamide acid solution with a block structure to form a film, and then carrying out thermal cyclization and bidirectional stretching. The method can realize continuous preparation, is simple to operate and environment-friendly in process, is beneficial to large-scale preparation of the intrinsic high-modulus high-thermal-conductivity polyimide film, and has a good industrialization prospect.

Owner:DONGHUA UNIV

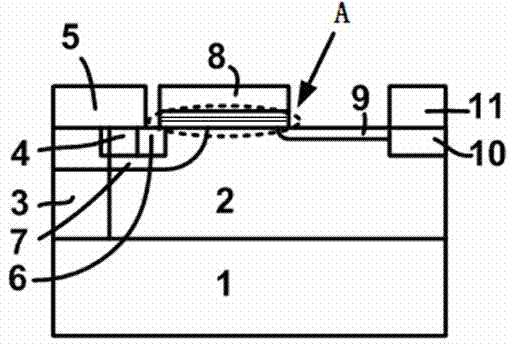

LDMOS device based on high K material

The invention discloses an LDMOS (Laterally Diffused Metal Oxide Semiconductor) device based on a high K material. The LDMOS device comprises a substrate on which a source electrode and a drain electrode are arranged; the drain electrode is connected with an N-type drift region; the source electrode and the N-type drift region are connected via a channel; a grid electrode is arranged on the channel; an insulation layer is arranged between the grid electrode and the channel. The LDMOS device is characterized in that the insulation layer comprises a high K layer made from a high K material, and sequentially comprises three layers, i.e. a SiO2 layer, a high K layer and another SiO2 layer. According to the invention, on the premise of no incensement of leakage current of a grid, the high K material with higher dielectric constant is adopted to lower thickness of the insulation layer.

Owner:KUNSHAN HUATAI ELECTRONICS TECH CO LTD

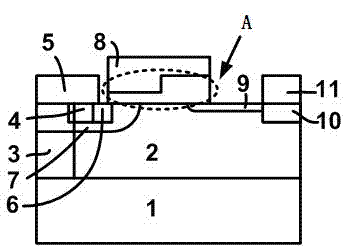

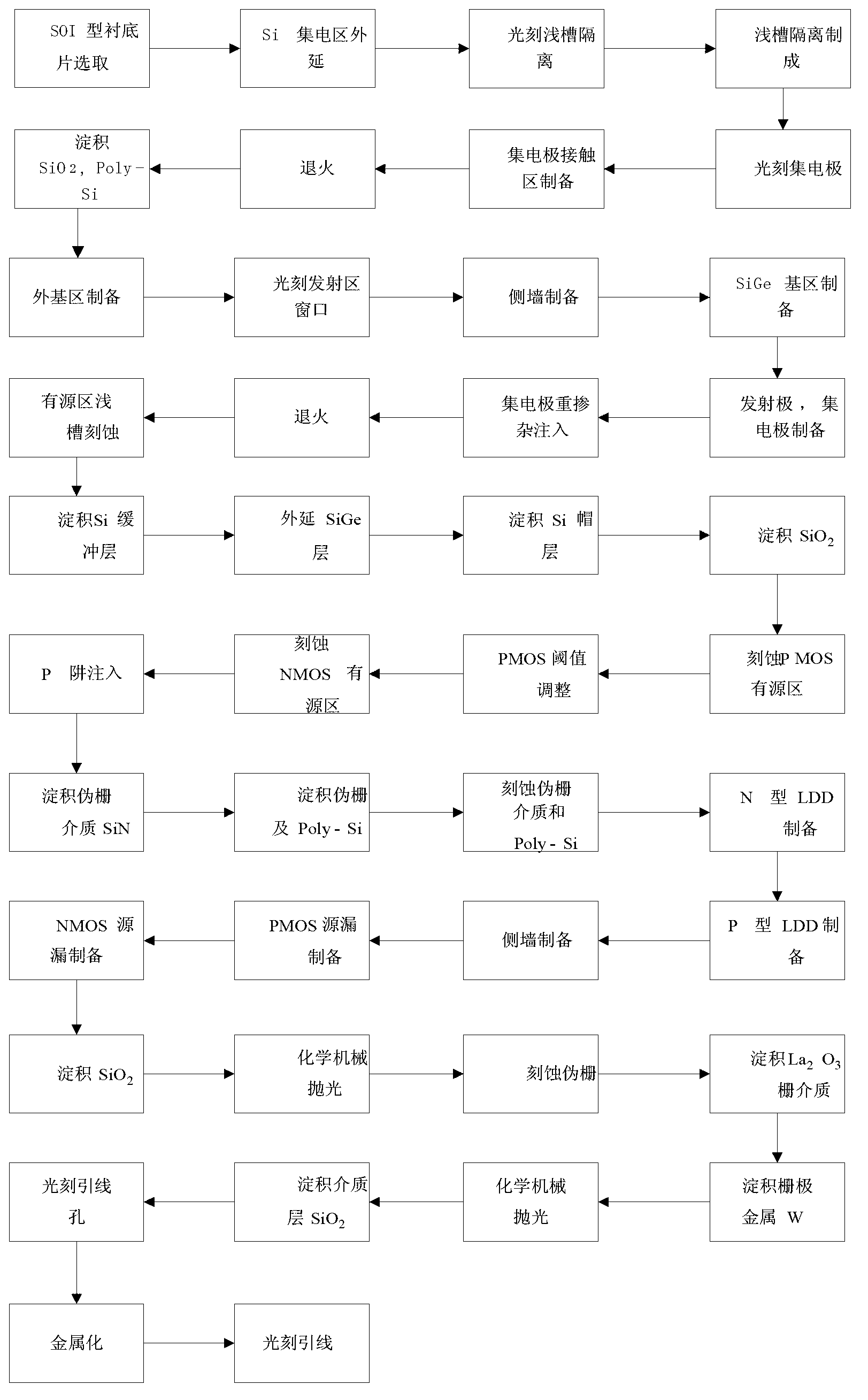

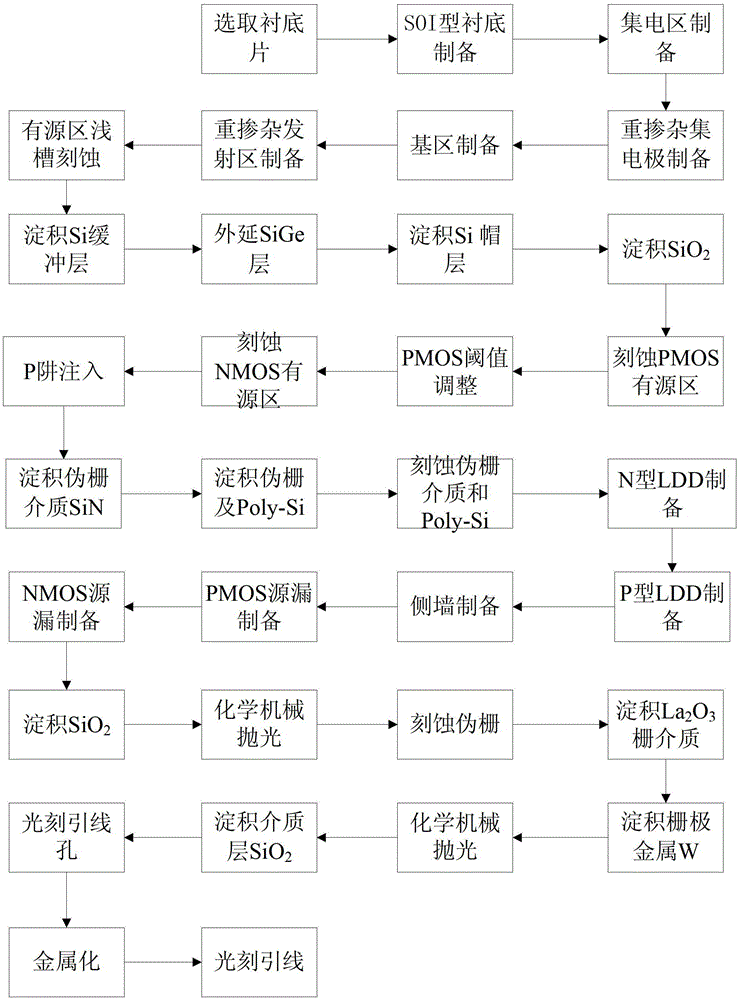

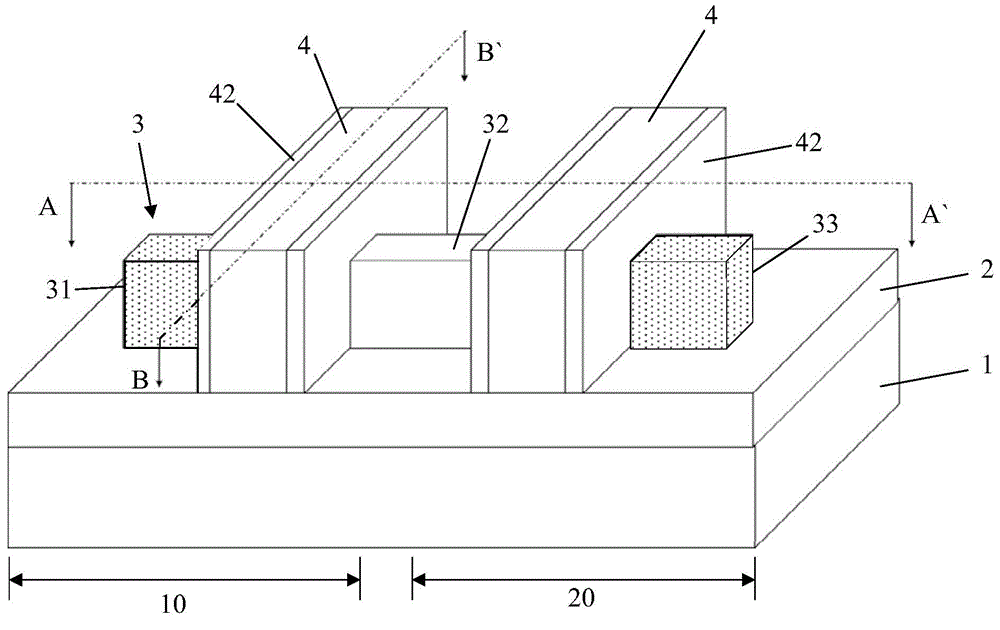

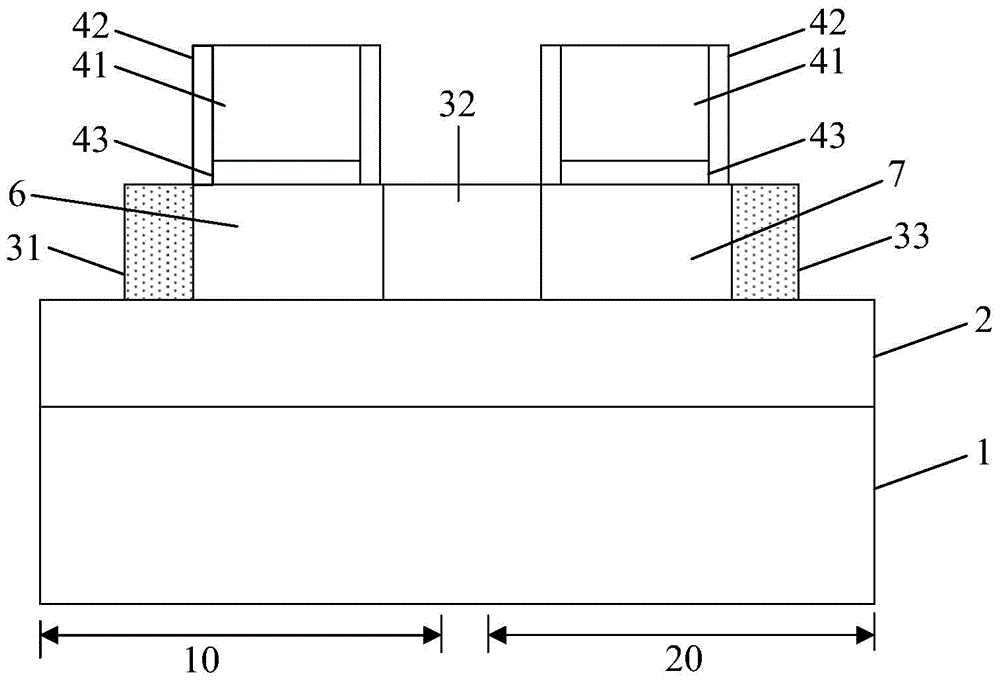

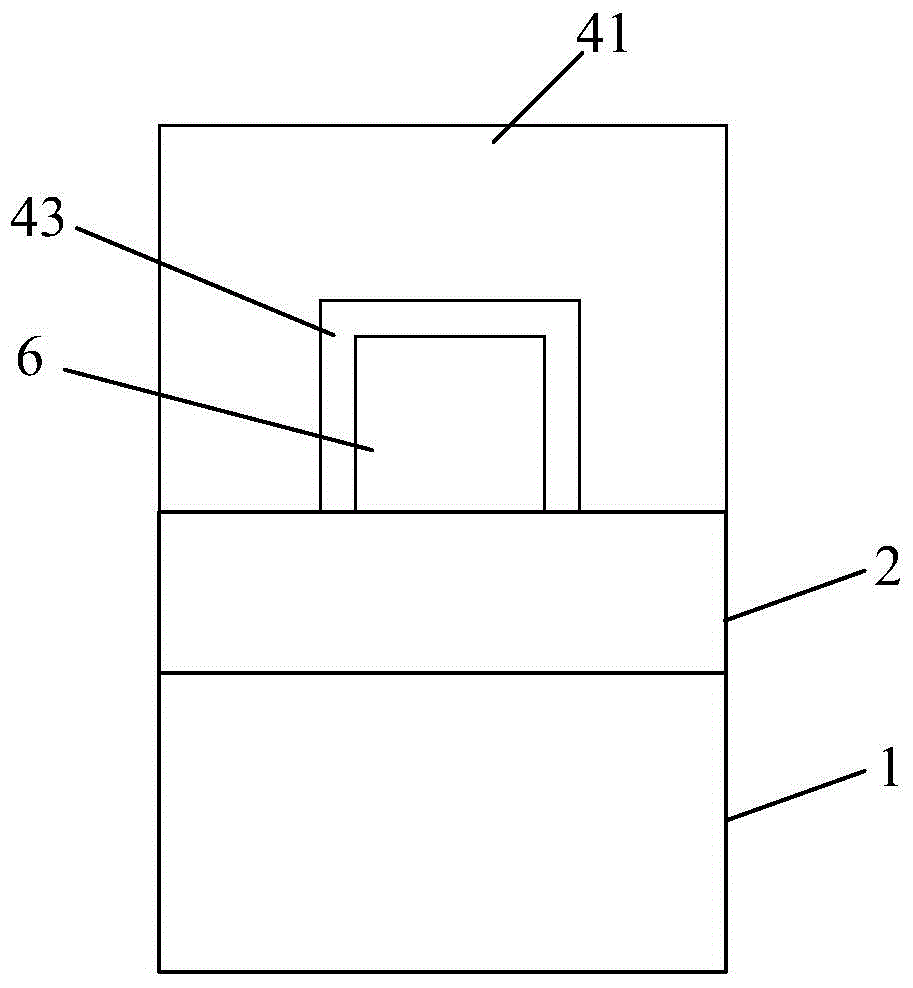

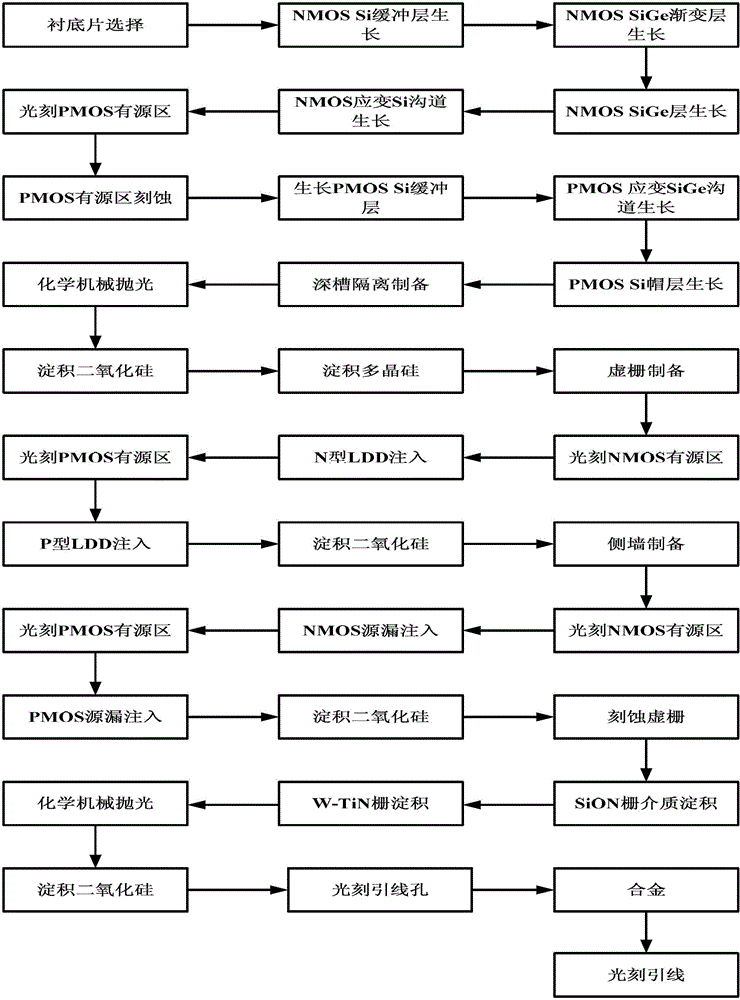

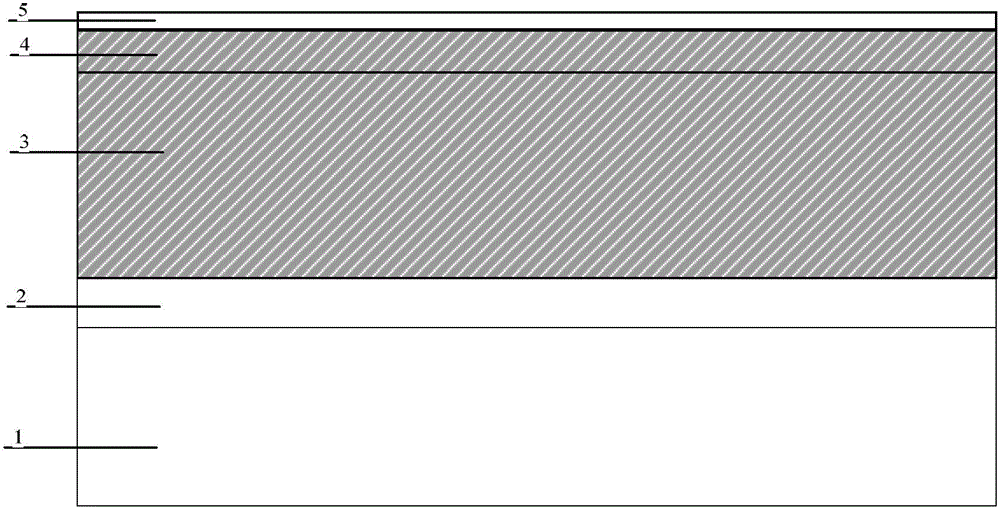

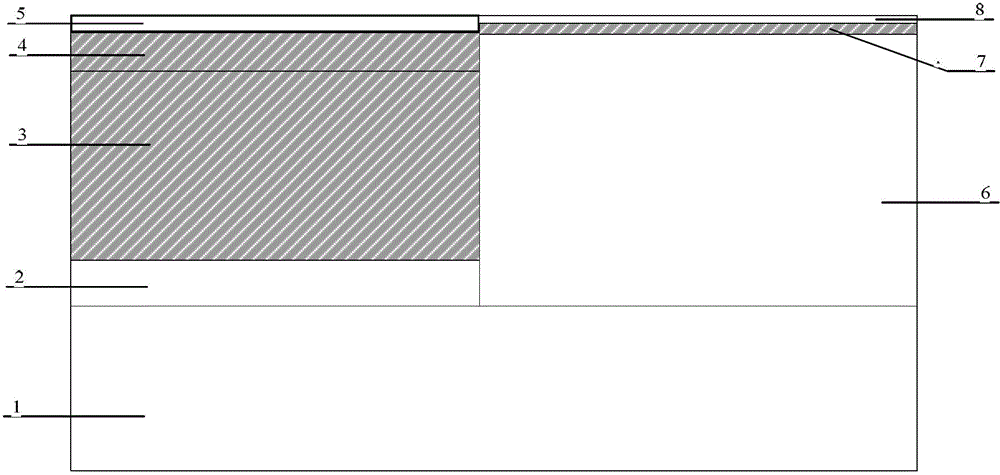

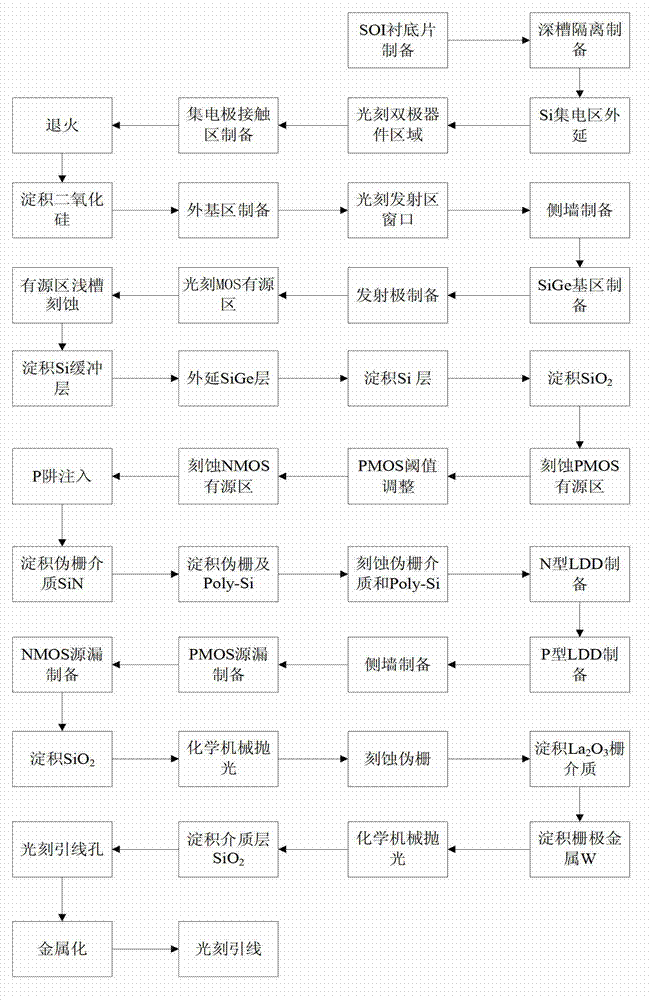

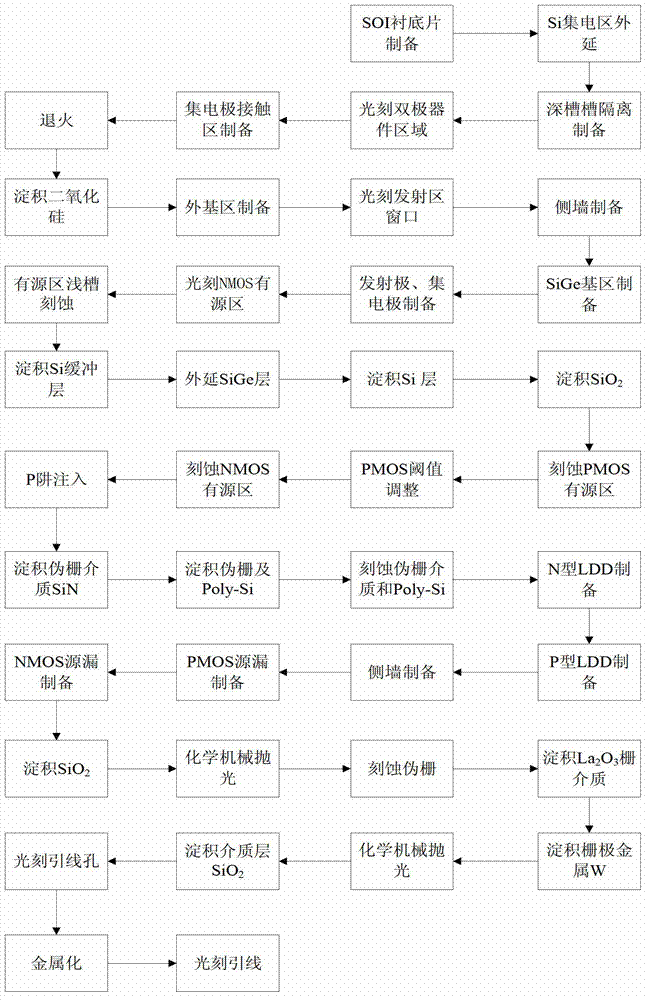

Tri-strain BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device based on SiGe HBT (Heterojunction Bipolar Transistor) and preparation method

InactiveCN102790052AImprove electrical performanceHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorHeterojunction bipolar transistor

The invention discloses a tri-strain BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device based on SiGe HBT (Heterojunction Bipolar Transistor) and a preparation method. A buried layer is prepared on a substrate, an N-Si layer, a P-SiGe layer and an N-Si layer are continuously grown, a dielectric layer is deposited, deep-groove isolation is prepared, a collector region, a base region and an emitter region are prepared, a collector electrode, base electrode and emitter electrode contact region is formed, and a SiGe HBT device is formed; active region deep grooves of an NMOS (N-channel Metal Oxide Semiconductor) device and a PMOS (P-channel Metal Oxide Semiconductor) device are etched, a P-type Si layer / a P-type SiGe gradient layer / a P-type SiGe layer / a P-type strain Si layer serving as the active region of the NMOS device and an N-type Si layer / an N-type strain SiGe layer / an N-type Si cap layer serving as the active region of the PMOS device are respectively and selectively grown in the deep grooves in an extending manner; a virtual grid electrode and a side wall are prepared, and source and drain electrodes of the NMOS and the PMOS device are formed through self-alignment; and the virtual grid is etched, a SiON grid dielectric layer and a W-TiN composite grid are deposited to form a CMOS structure, and finally the tri-stain BiCMOS integrated device and a circuit are constructed. Tensile strain Si with high electronic mobility and compressive strain SiGe with high hole mobility are sufficiently utilized as conducting channels for the NMOS device and the PMOS device, and the performance of the BiCMOS integrated circuit is effectively improved.

Owner:XIDIAN UNIV

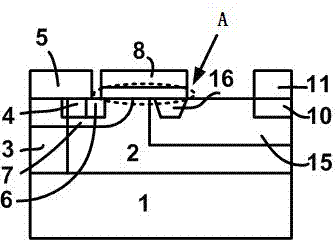

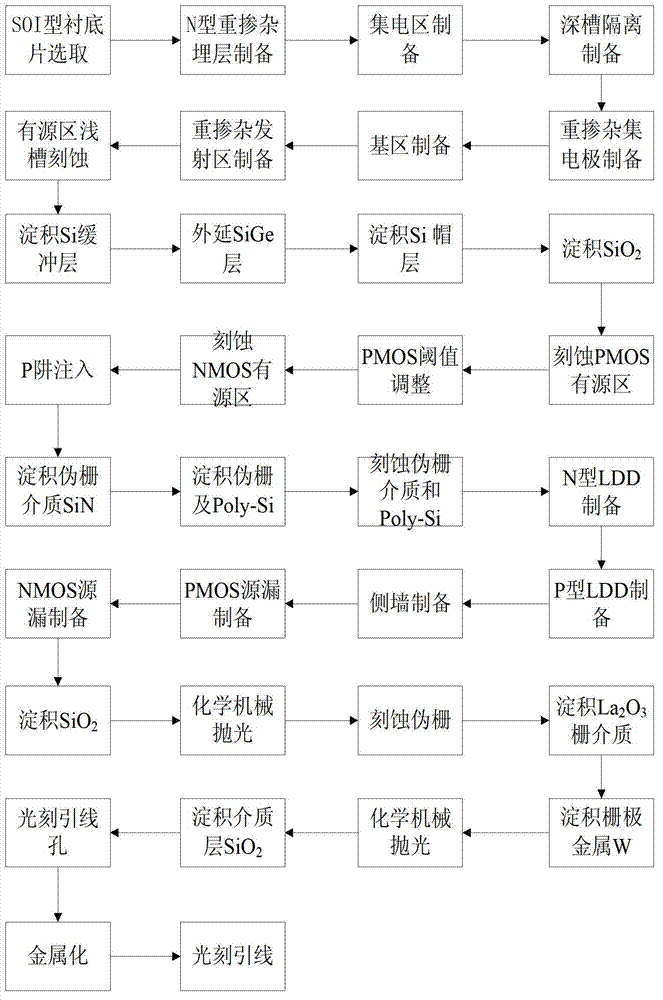

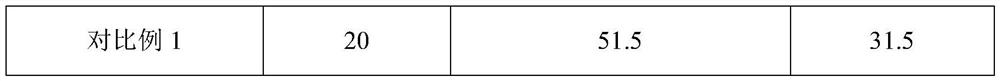

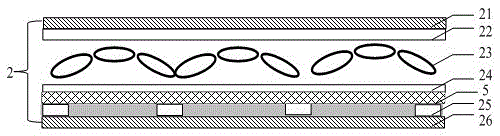

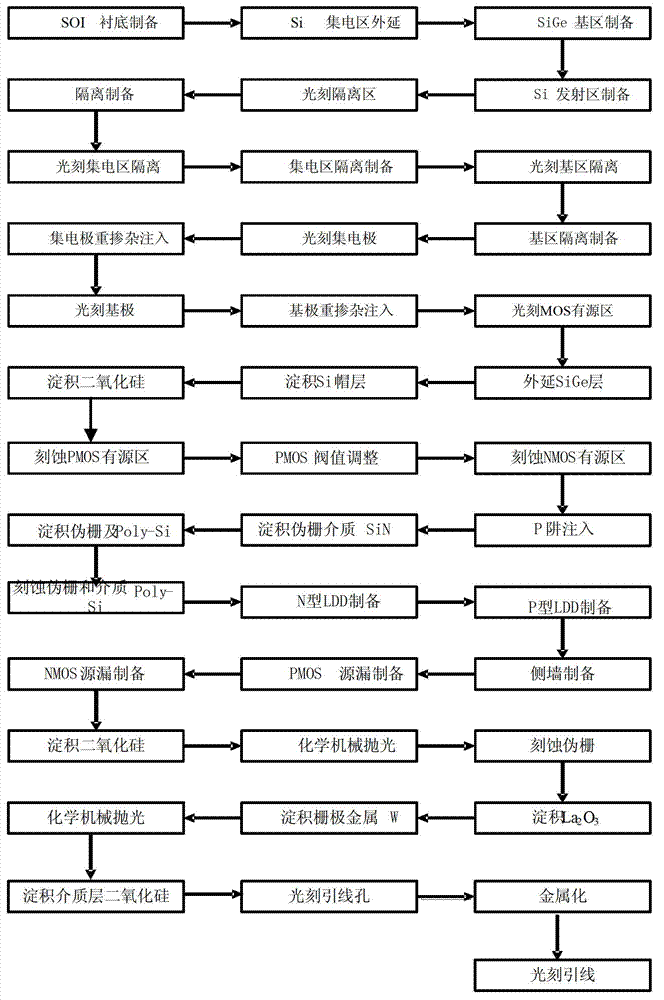

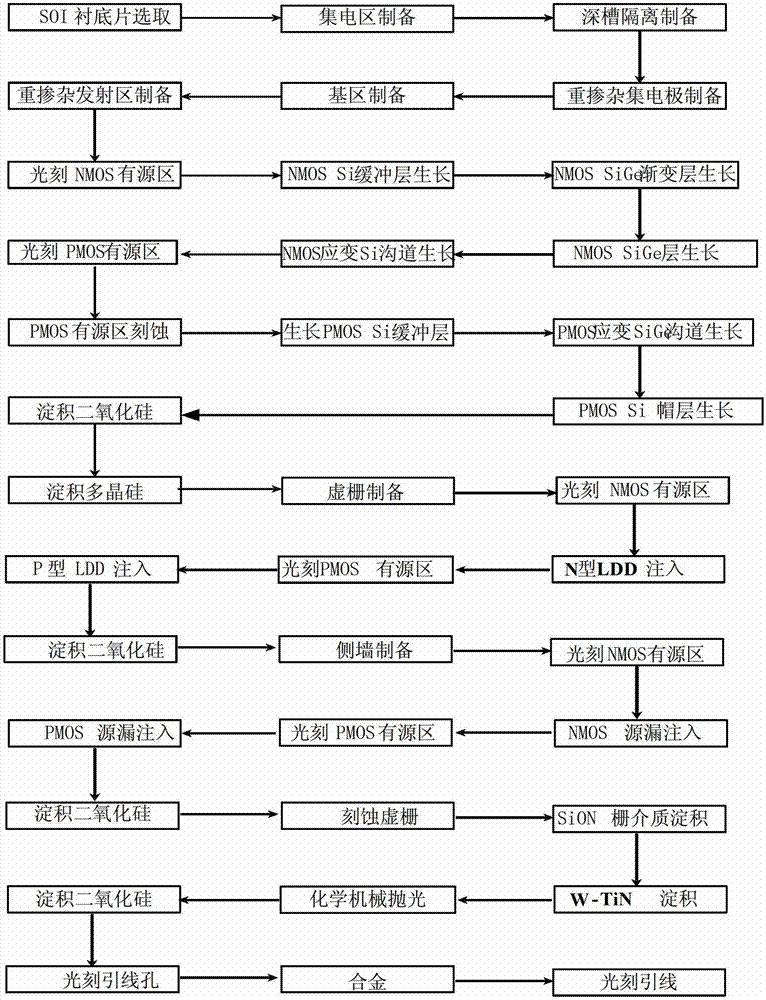

Strained SiGe BiCMOS (bipolar complementary metal oxide semiconductor) integrated device and preparation method

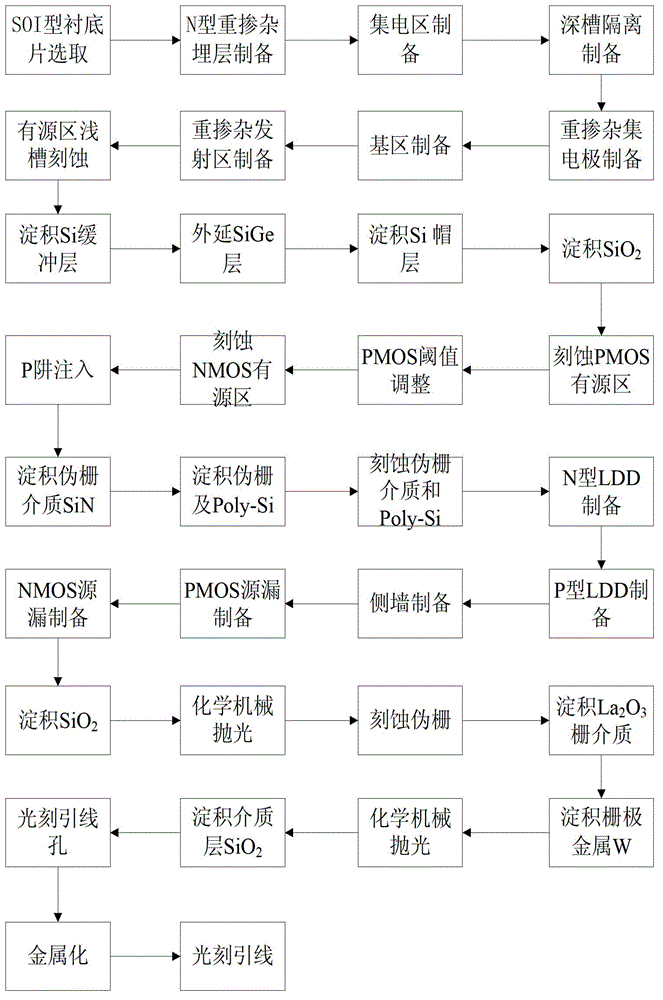

InactiveCN102738150APerformance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricIon implantation

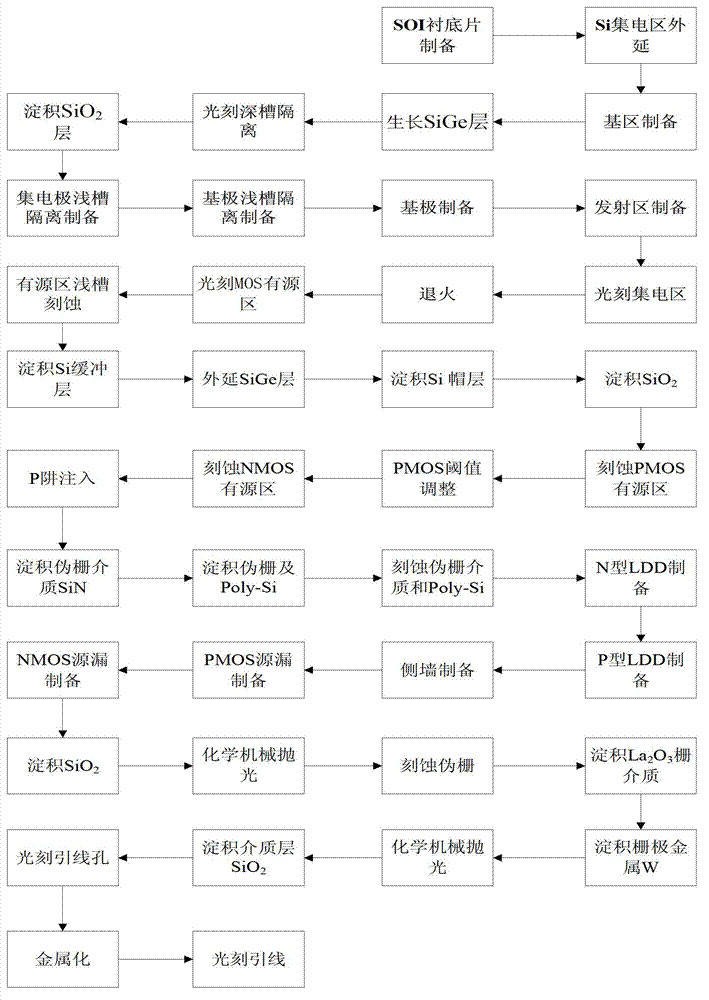

The invention discloses a strained SiGe BiCMOS (bipolar complementary metal oxide semiconductor) integrated device and a preparation method. The preparation method comprises on-chip preparing a buried layer on an SOI (silicon on insulator) substrate, growing an N-type Si epitaxy, preparing deep trench isolation, and preparing a conventional Si bipolar transistor on a bipolar device region; growing a strained SiGe material on the substrate at 600 to 800 DEG C, etching the active region of an MOS (metal oxide semiconductor) device by lithography, adjusting the threshold value of the MOS device region by ion implantation process, depositing SiO2 and polysilicon on the active region of the MOS device, etching to form a pseudo gate, preparing the source and drain region of the MOS device by self-alignment process respectively, growing a SiO2 layer on the substrate surface, removing the pseudo gate, preparing La2O3 in the impressed groove of the pseudo gate to obtain a gate dielectric, preparing a gate from the gate dielectric and tungsten (W), etching a passivation layer to form the lead holes of the drain, source and gate, metalizing, sputtering metal, and etching leads by lithography to obtain the strained SiGe BiCMOS integrated device and circuit.

Owner:XIDIAN UNIV

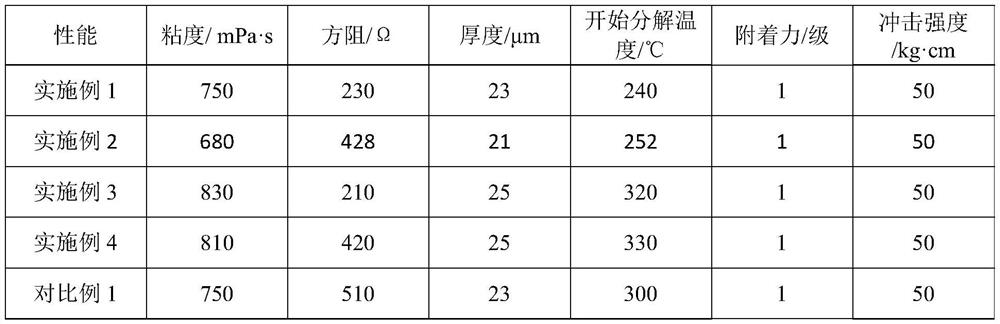

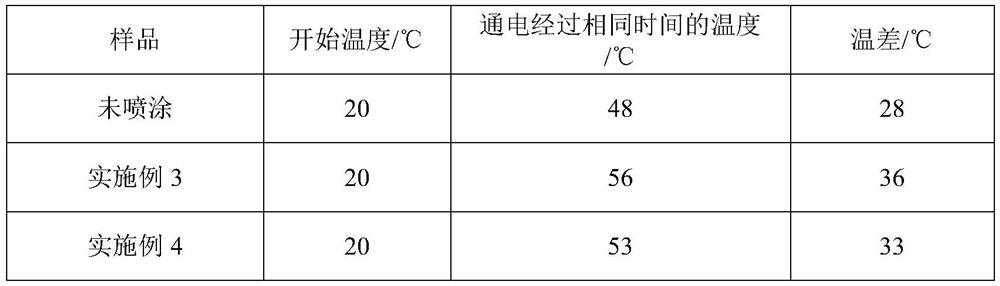

Water-based graphene heat dissipation coating as well as preparation and spraying methods thereof

PendingCN113881295AImproved ability to form thermally conductive pathwaysImprove thermal conductivityCoatingsPhysical chemistryGraphite

The invention relates to a water-based graphene heat dissipation coating. The water-based graphene heat dissipation coating comprises the following components: water-based resin, graphene dispersion slurry, deionized water, heat conduction particles, conductive carbon black, a first auxiliary agent and a second auxiliary agent, and the water-based graphene heat dissipation coating is prepared from the following components in parts by weight: 20 to 55 parts of water-based resin, 30 to 65 parts of graphene dispersion slurry, 5 to 45 parts of deionized water, 1.5 to 12 parts of heat conduction particles, 0.5 to 2 parts of conductive carbon black, 5 to 20 parts of a first auxiliary agent and 3 to 8 parts of a second auxiliary agent. The water-based graphene heat dissipation coating is low in pollution, easy to purify, non-irritant and high in safety.

Owner:BEIJING TUNGHSU CARBON ADVANCED MATERIALS TECH CO LTD +1

Junction-free field effect transistor and formation method thereof

InactiveCN105244277ALower resistanceReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorContact resistance

The invention provides a junction-free field effect transistor and a formation method thereof. The formation method comprises the steps of providing a substrate with a first region and a second region; forming a first doped region and a second doped region; removing part of the substrate so as to form a first opening and a second opening; and filling with openings with a metal containing material layer so as to form a source region and a drain region in the first opening and the second opening respectively. The invention further provides a junction-free field effect transistor, which comprises a substrate, a first doped region, a second doped region, a first gate structure, a second gate structure, a first opening and a second opening, and is characterized in that the first opening and the second opening are internally provided with metal containing material layers which act as a source region and a drain region respectively. The beneficial effects of the invention lie in that contact resistance between the source / drain region and a conductive plug is small, turn-on current is increased, and the performance of the junction-free field effect transistor is improved; and the difficulty of a doping process is simplified, and the degree of an interface scattering problem possibly occurred in the doped regions is reduced to a certain extent.

Owner:SEMICON MFG INT (SHANGHAI) CORP

High-thermal-conductivity polyimide film and preparation method thereof

The invention discloses a high-thermal-conductivity polyimide film and a preparation method thereof, and relates to the technical field of polyimides, boron nitride is subjected to high-temperature calcination, so that the surface of the boron nitride is subjected to micro-oxidation and is negatively charged, and ZIF8 is grown on the surface of the boron nitride through electrostatic interaction to obtain a composite thermal-conductivity filler; an in-situ polymerization reaction is carried out on the composite heat-conducting filler and a polymeric monomer of polyimide in a solvent to prepare polyamide acid; and finally, film casting and heat treatment are carried out to obtain the composite heat-conducting film. According to the invention, ZIF8 is loaded and grown on the surface of BN, on one hand, agglomeration of BN in a PI matrix can be inhibited, so that a good heat conduction path is formed; on the other hand, an organic ligand 2-methylimidazole of ZIF8 has good compatibility with a PI matrix, so that the interface action is inhibited, interface scattering of phonons in the PI matrix can be reduced, and the heat-conducting property of PI is improved; the prepared polyimide film is high in heat conductivity coefficient and good in mechanical property, and has very good popularization and application values.

Owner:ANHUI GUOFENG PLASTIC +1

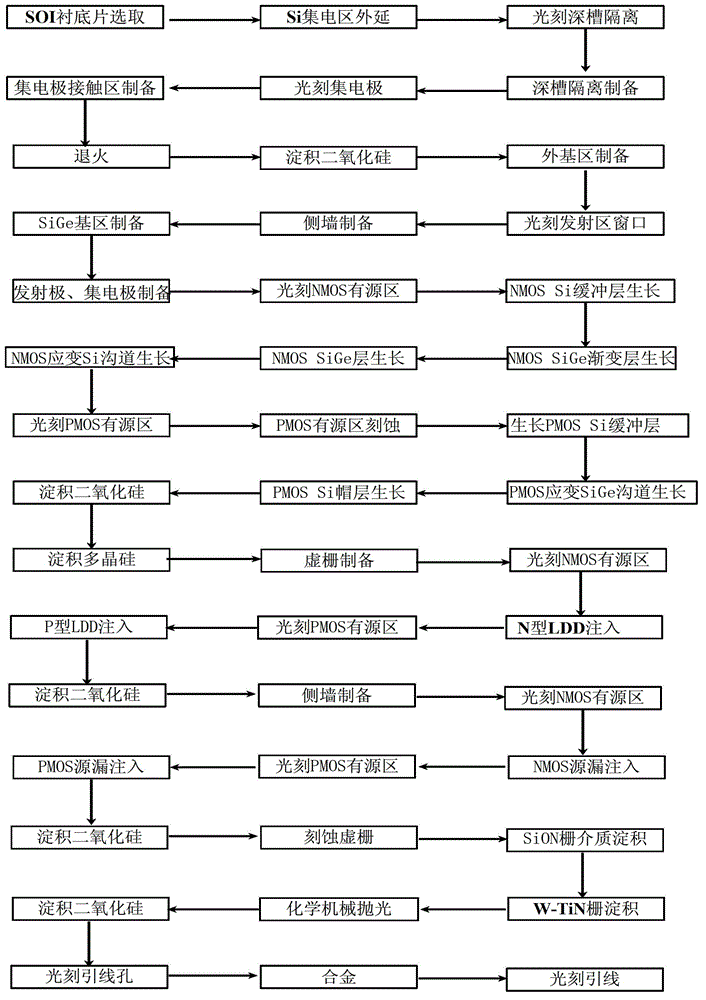

SOI (Silicon On Insulator) strain SiGe Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device and preparation method thereof

InactiveCN102723337AInhibition effectHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringP channel

The invention discloses a method for preparing an SOI (Silicon On Insulator) strain SiGe Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device and a circuit. The preparation method comprises the steps of manufacturing an SOI bipolar transistor in bipolar device area in an SOI substrate; and conducting photoetching on an MOS (Metal Oxide Semiconductor) active region in the SOI substrate, growing strain SiGe material on the active region to respectively form NMOS (N-Channel Metal Oxide Semiconductor) active region and a PMOS (P-channel Metal Oxide Semiconductor) active region, then depositing SiO2 and polycrystalline silicon in the NMOS active region and the PMOS active region, etching a virtual gird with the length being 22-350nm, conducting self alignment to generate a source-drain region of the MOS by applying a self alignment process, removing the virtual grid, preparing a grid medium and preparing wolfram (W) to be a grid electrode, conducting photoetching on a lead wire to form the integrated device with the length being 22-350nm and the circuit of the MOS device. According to the integrated device prepared by the invention, a lightly doped source drain (LDD) structure is adopted, so that the influence on the performance of the device caused by hot carriers can be inhibited effectively; and a quantum well structure is adopted in a PMOS structure, so that a hole can be limited in a SiGe layer effectively, the interface scattering is reduced, and the electric properties of frequency, current driving capability and the like of the device are improved.

Owner:XIDIAN UNIV

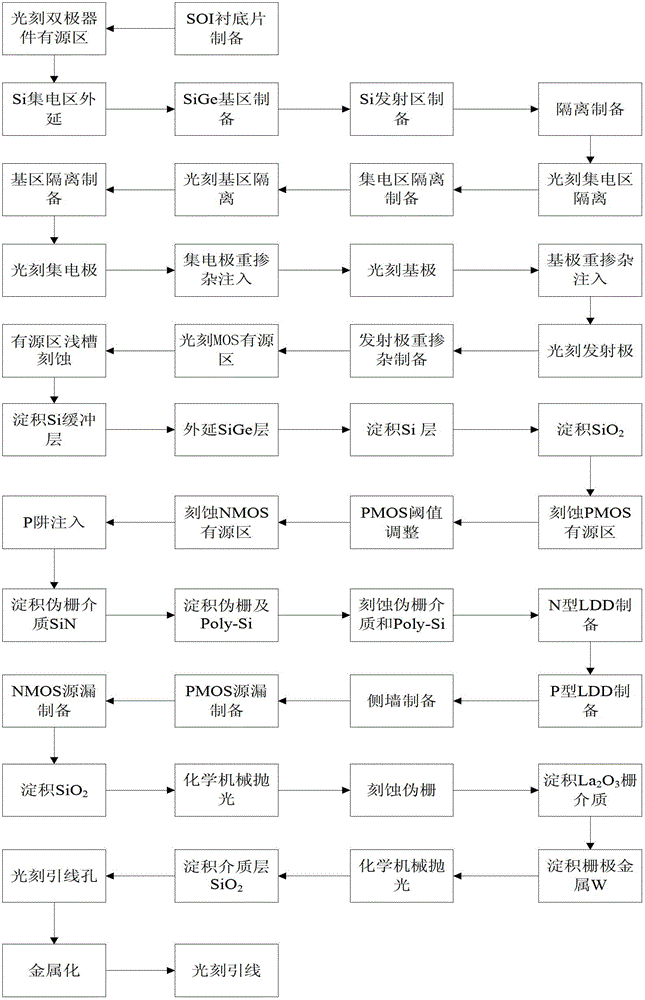

Silicon on insulator (SOI) SiGe bipolar complementary metal oxide semiconductor (BiCMOS) integrated device and preparation method thereof

InactiveCN102800681AInhibition effectHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingEtchingGate dielectric

The invention discloses a silicon on insulator (SOI) SiGe bipolar complementary metal oxide semiconductor (BiCMOS) integrated device and a preparation method of the SOI SiGe BiCMOS integrated device. The method comprises the following steps of: growing an N-type Si epitaxial layer on an SOI substrate, preparing shallow-trench isolation, forming a collector contact region, etching to form a side wall, performing wet etching to form a base region window, selectively growing a SiGe base region, photoetching a collector window, depositing an N-type Poly-Si, removing the Poly-Si, and forming a SiGe HBT device; growing a strain SiGe material on the substrate, isolating an active region of the device, photoetching an active region of an N-channel metal oxide semiconductor (NMOS) device, performing P-type ion implantation, preparing a pseudo grid, self-aligning to grow a source drain region of a metal oxide semiconductor (MOS) device, removing the pseudo grid, preparing a lanthanum oxide material to form gate dielectric and preparing metal tungsten to form a gate in a stamping groove at the pseudo grid, photoetching a lead, and preparing the integrated device and the circuit. According to the method, the characteristics of SiGe are fully utilized, and due to the prepared integrated circuit, the performance of the conventional analog and digital / analog mixed integrated circuit is greatly improved.

Owner:XIDIAN UNIV

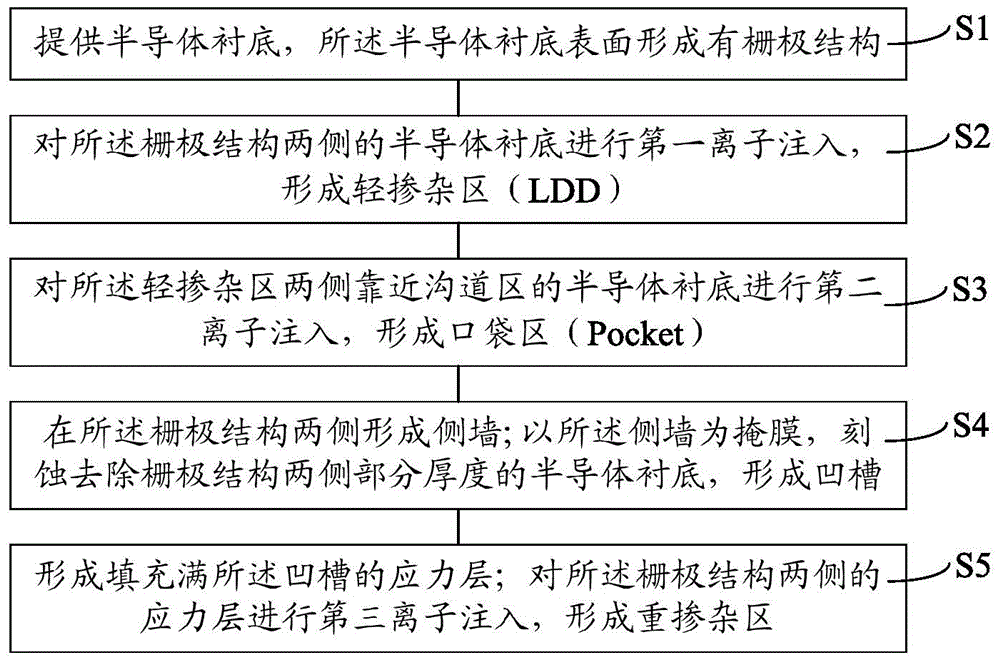

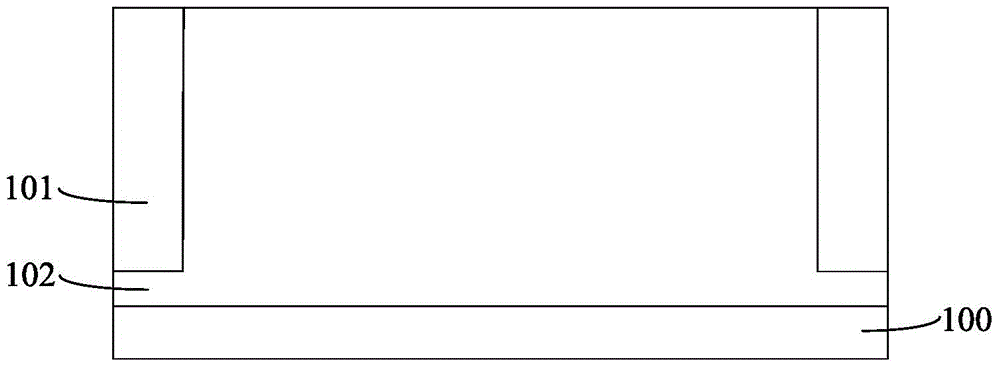

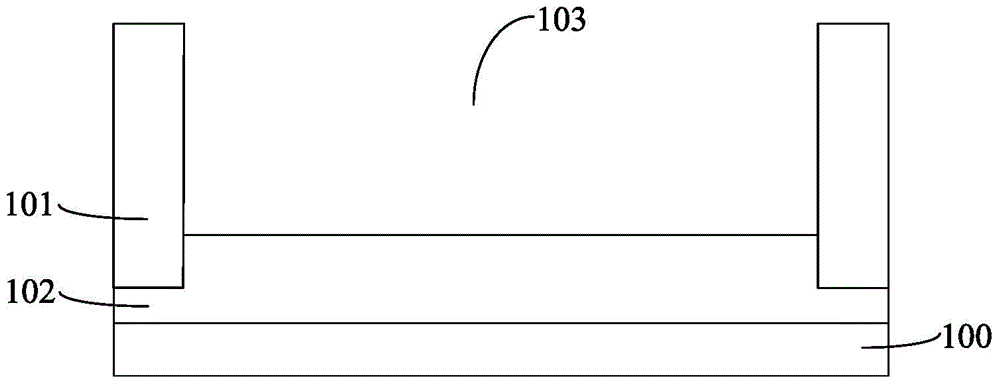

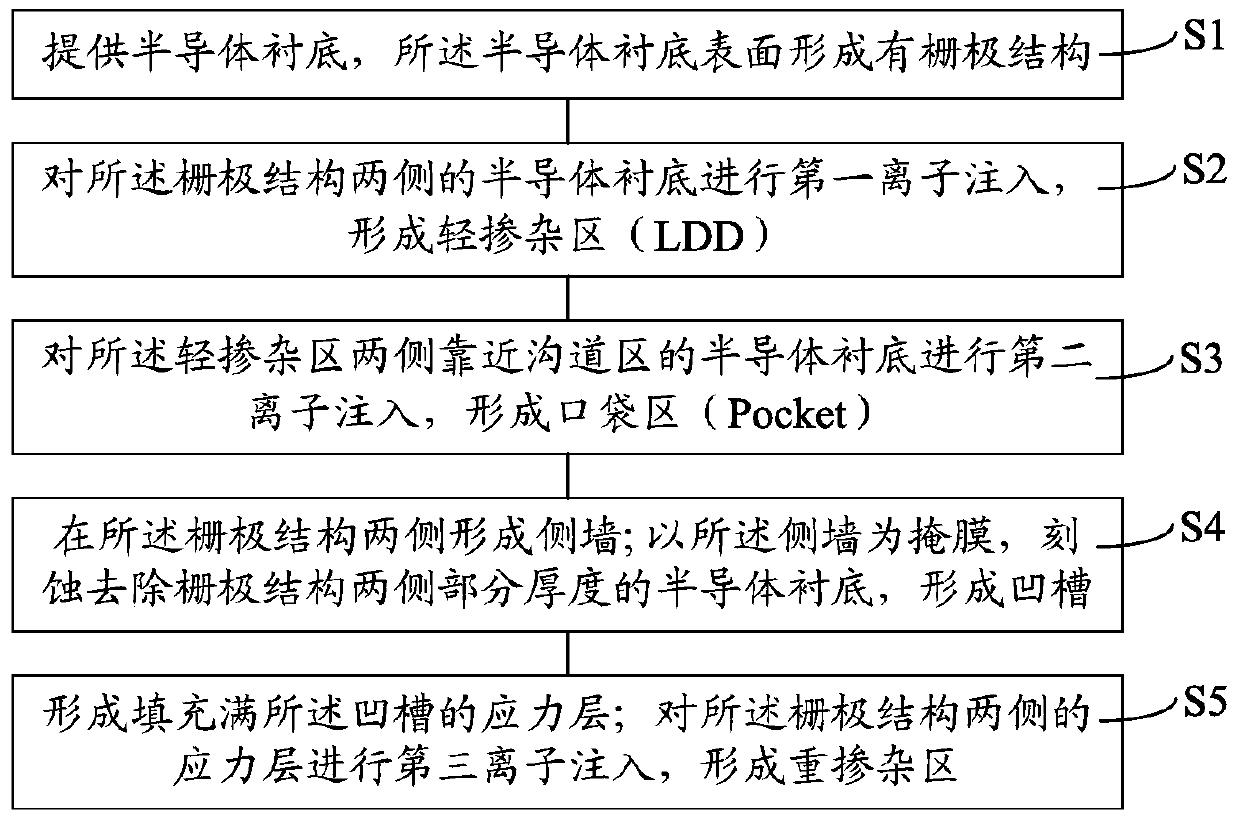

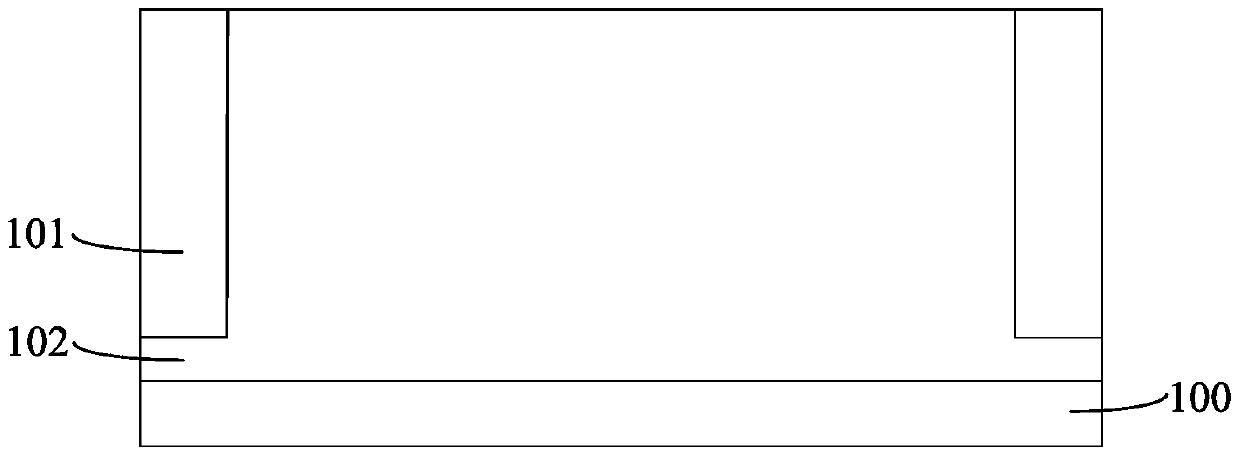

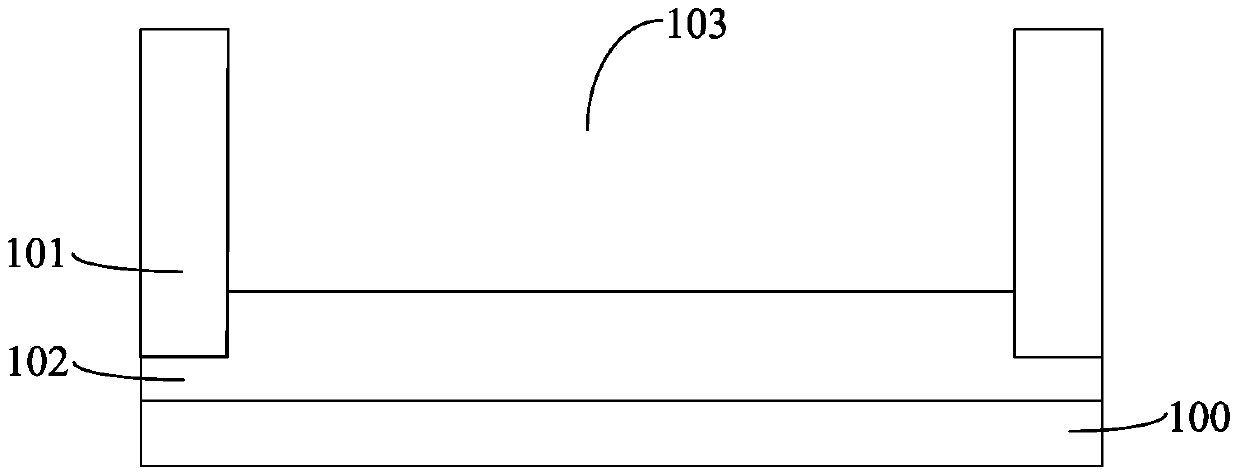

Semiconductor device and forming method thereof

ActiveCN105448727ABlock lateral diffusionImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrier mobilityLattice constant

A semiconductor device and a forming method thereof are provided. The forming method of the semiconductor device comprises the following steps: providing a substrate; forming a lamination structure covering the surface of the substrate, wherein the lamination structure includes a first stress layer disposed on the surface of the substrate, an intrinsic layer disposed on the surface of the first stress layer and a second stress layer disposed on the surface of the intrinsic layer, the lattice constant of the first stress layer is smaller than the lattice constant of the intrinsic layer, and the lattice constant of the intrinsic layer is smaller than the lattice constant of the second stress layer; forming a gate structure on the surface of the second stress layer; etching the lamination structure on the two sides of the gate structure to form grooves; and forming a third stress layer filling the grooves, wherein the lattice constant of the third stress layer is greater than the lattice constant of the first stress layer. The leakage current in the semiconductor device is reduced and the source-to-drain punch-through problem of the semiconductor device is inhibited while the carrier mobility of the semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

BiCMOS (bipolar complementary metal oxide semiconductor) integrated device based on plane-strained SiGe HBT (heterojunction bipolar transistor) device and fabrication method

InactiveCN102738149APerformance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricHemt circuits

The invention discloses a BiCMOS (bipolar complementary metal oxide semiconductor) integrated device based on plane-strained SiGe HBT (heterojunction bipolar transistor) device and a fabrication method. The fabrication method comprises preparing a SOI (silicon on insulator) substrate, etching an active region of a bipolar device, growing a collector region of the bipolar device, etching a base region by lithography, growing P-SiGe, i-Si, i-Poly-Si on the base region, preparing deep trench isolation; forming an emitter, a base and a collector, and forming the SiGe HBT device; and etching the active region of a MOS (metal oxide semiconductor) by lithography, continuously growing a Si buffer layer, a strain SiGe layer, and an intrinsic Si layer in the region, respectively forming the active region of an NMOS (N-channel metal oxide semiconductor) and PMOS (P-channel metal oxide semiconductor) device, depositing SiO2 and polysilicon on the active region of the NMOS and PMOS devices, etching to prepare a pseudo gate with a length of 22 to 350nm, forming a lightly-doped source drain and source drain of the NMOS and PMOS devices by self-alignment process, removing the pseudo gate, preparing a gate from a gate dielectric lanthanum oxide and tungsten, metalizing, and etching a lead by lithography to form the BiCMOS integrated device and the circuit. According to the BiCMOS integrated device based on plane-strained SiGe HBT device and the fabrication method provided by the invention, the lightly-doped source drain structure is adopted to effectively suppress the influences of hot carriers on the device performance so as to improve the reliability of the device.

Owner:XIDIAN UNIV

Heat-conducting polymer composite material and preparation method thereof

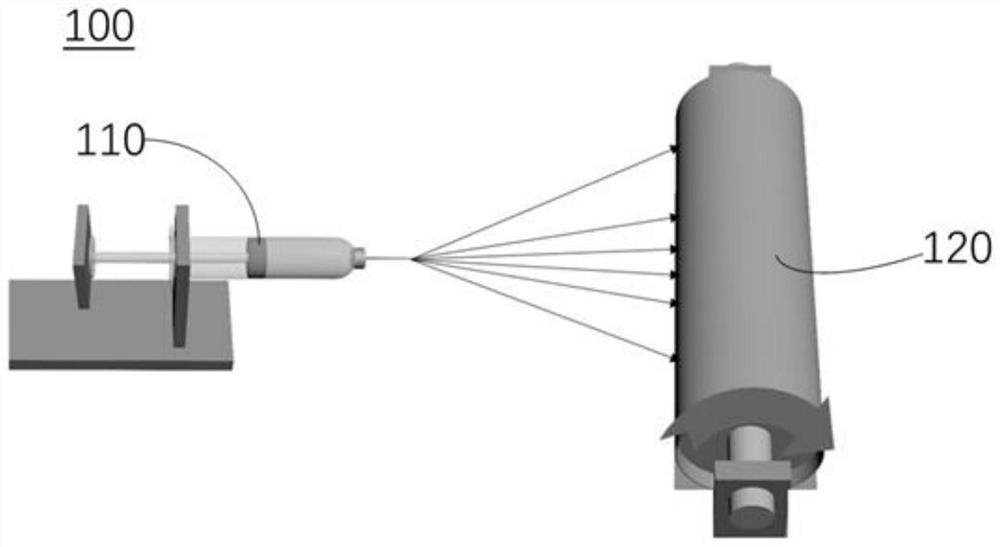

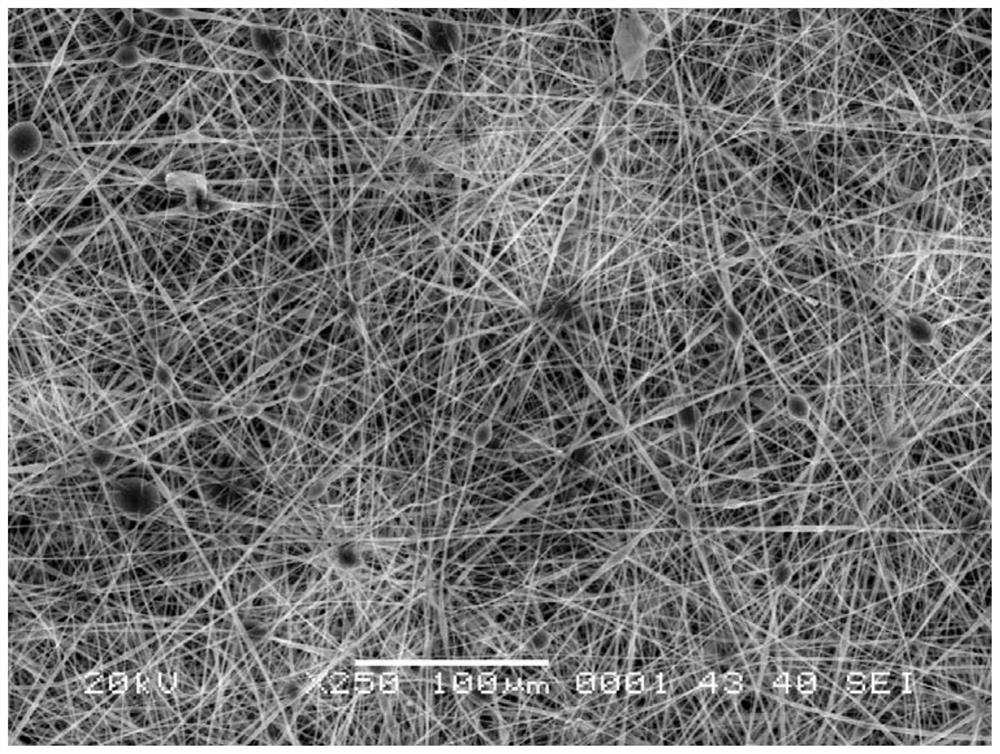

PendingCN114427145AIncrease heat conduction pathExcellent dielectric propertiesMonocomponent synthetic polymer artificial filamentNon-woven fabricsFiberSpinning

The invention relates to a preparation method of a heat-conducting polymer composite material, which comprises the following steps: mixing a coupling agent modified inorganic filler and boron nitride nanosheets in a solvent, uniformly dispersing, adding nanofibers, uniformly dispersing, adding an adhesive and an initiator, and uniformly mixing to form a mixed solution; and carrying out electrostatic spinning and curing on the mixed solution. According to the method, the heat transmission of the heat-conducting polymer composite material can be improved, the heat-conducting property is improved, and meanwhile, the heat-conducting polymer composite material prepared by the method also has good dielectric property and electrical insulation property.

Owner:SUZHOU SIDIKE NEW MATERIALS SCI & TECH +1

A kind of soi strain sige BiCMOS integrated device and preparation method

InactiveCN102723337BPerformance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringElectric properties

The invention discloses a method for preparing an SOI (Silicon On Insulator) strain SiGe Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device and a circuit. The preparation method comprises the steps of manufacturing an SOI bipolar transistor in bipolar device area in an SOI substrate; and conducting photoetching on an MOS (Metal Oxide Semiconductor) active region in the SOI substrate, growing strain SiGe material on the active region to respectively form NMOS (N-Channel Metal Oxide Semiconductor) active region and a PMOS (P-channel Metal Oxide Semiconductor) active region, then depositing SiO2 and polycrystalline silicon in the NMOS active region and the PMOS active region, etching a virtual gird with the length being 22-350nm, conducting self alignment to generate a source-drain region of the MOS by applying a self alignment process, removing the virtual grid, preparing a grid medium and preparing wolfram (W) to be a grid electrode, conducting photoetching on a lead wire to form the integrated device with the length being 22-350nm and the circuit of the MOS device. According to the integrated device prepared by the invention, a lightly doped source drain (LDD) structure is adopted, so that the influence on the performance of the device caused by hot carriers can be inhibited effectively; and a quantum well structure is adopted in a PMOS structure, so that a hole can be limited in a SiGe layer effectively, the interface scattering is reduced, and the electric properties of frequency, current driving capability and the like of the device are improved.

Owner:XIDIAN UNIV

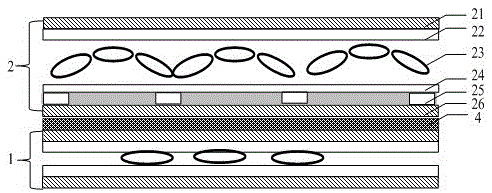

A kind of liquid crystal lens, liquid crystal display device and manufacturing method of liquid crystal lens

ActiveCN103605246BAvoid payingReduce Interface ScatteringNon-linear opticsLiquid-crystal displayTransfer procedure

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

A dual-strain bicmos integrated device based on soi substrate and its preparation method

InactiveCN102810544BSuppress performance impactInhibition effectSolid-state devicesSemiconductor/solid-state device manufacturingPhosphoniumTransmitter

The invention discloses a dual-strain bipolar complementary metal-oxide semiconductor (BiCMOS) integration device based on a silicon on insulator (SOI) substrate and a preparation method thereof. The preparation method comprises following steps that a negative-silicon (N-Si) layer, a positive-silicon germanium (P-SiGe) layer and an N-Si layer continuously grow on the SOI substrate, a deep groove isolator is prepared, a collector zone shallow groove isolator and a base zone shallow groove isolator are prepared, a collector zone is photo-etched, phosphonium ions are injected to form a collector electrode, a base electrode and a transmitter electrode, and a SiGe heterojunction bipolar transistor (HBT) device is formed; a strain SiGe material grow on the substrate, an N-channel MOS (NMOS) device active region and a P-channel MOS (PMOS) device active region are formed, a pseudo grid is prepared, a source drain region of the NMOS and the PMOS devices is respectively generated in a self-aligning way, the pseudo grid is eliminated, a lanthanum oxide (La2O3) material is prepared in a pressing groove at the pseudo grid to form a grid medium and metal tungsten (W) to form a grid electrode, a lead is photo-etched, and a dual-strain plane BiCMOS integration device and a circuit based on the SOI substrate are formed. According to the method, the characteristic that a hole mobility of the strain SiGe material is higher than that of the bulk-Si material is adequately utilized to prepare the dual-strain plane BiCMOS integration circuit based on the SOI substrate, so that the performance of the existing analog and digital-analog mixed integrated circuit is greatly improved.

Owner:XIDIAN UNIV

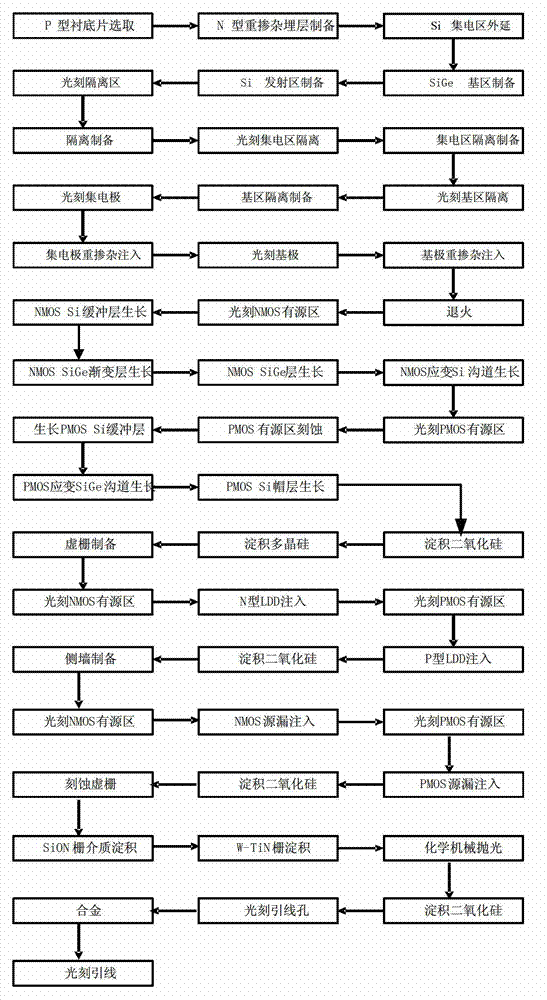

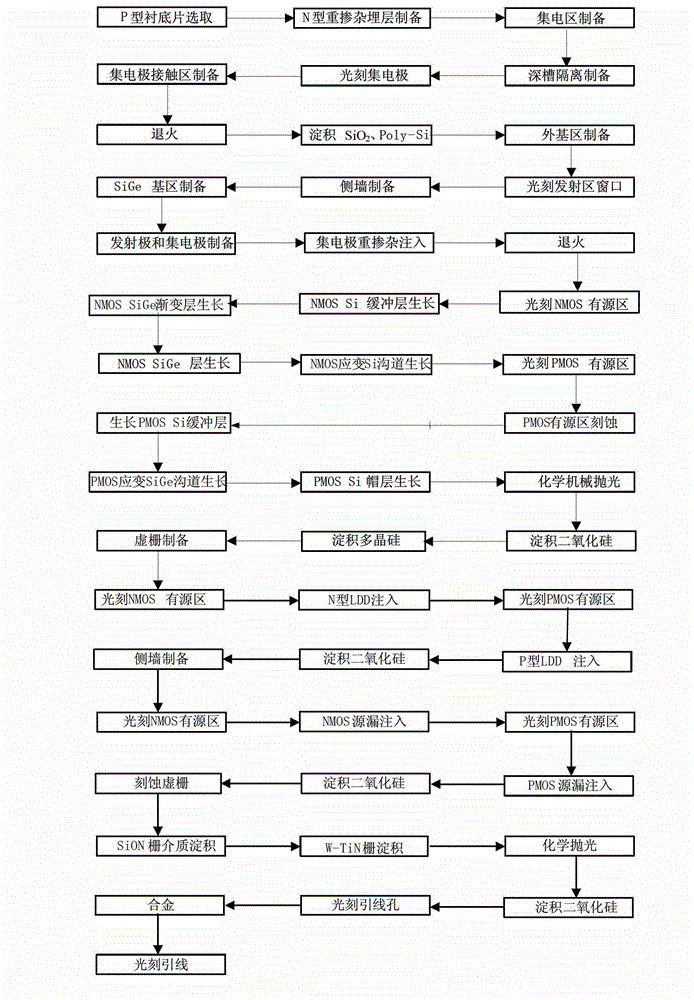

Tri-strain tri-polycrystal-plane BiCMOS (Bipolar complementary metal oxide semiconductor) integrated device and preparation method thereof

InactiveCN102867824AImprove electrical performanceHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingElectrode ContactComposite grid

The invention discloses a tri-strain tri-polycrystal-plane BiCMOS (Bipolar complementary metal oxide semiconductor) integrated device and a preparation method thereof. The method comprises the following steps: preparing an embedded layer on a substrate plate, growing N-type Si epitaxy, preparing a deep channel isolator, preparing a collecting electrode contact area, preparing a base area and a transmission area, and forming a SiGe HBT (Heterojunction bipolar transistor) device; etching deep channels in the active areas of an NMOS (N-channel metal oxide semiconductor) device and a PMOS (P-channel metal oxide semiconductor) device, selectively epitaxially growing the following layers in the channel: a P-type Si layer, a P-type SiGe gradient layer, a P-type SiGe layer, a P-type strain Si layer as the active area of the NMOS device, an N-type Si layer, an N-type strain SiGe layer, and an N-type Si cap layer as the active area of the PMOS device; preparing a virtual grid, performing MOS (Metal oxide semiconductor) device light doped source / drain (LDD) injection, preparing a spacer, and self-aligning to form an MOS device source / drain; and etching the virtual grid, and sedimentating an SiON grid dielectric layer and a W-TiN composite grid to form a CMOS structure, and finally forming a BiCMOS circuit. According to the method, a tensile strain Si with high electron mobility and a compressive strain SiGe with high hole mobility are fully utilized as the conductive channels of the NMOS device and the PMOS device respectively, thus the performances of a BiCMOS integrated circuit are effectively improved.

Owner:XIDIAN UNIV

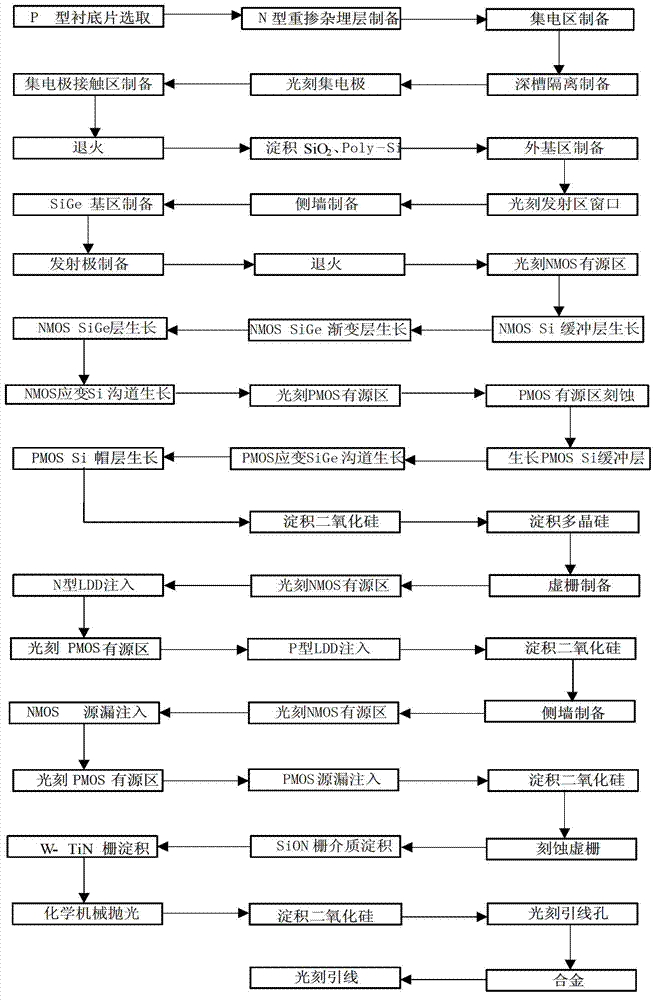

Plane strain BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor) integrated component based on self-aligned technology and preparation method thereof

InactiveCN102738164AImprove performanceImprove electrical performanceSolid-state devicesSemiconductor/solid-state device manufacturingCMOSBicmos integrated circuits

The invention discloses a plane strain BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor) integrated device based on a self-aligned technology and a preparation method thereof. The preparation method comprises the following steps: firstly preparing a buried layer on a substrate slice, growing N-type Si epitaxy, preparing a trench isolation and collector contact region, etching a base region window by using a wet method, selectively growing a SiGe base region, depositing N-type Poly-Si and removing Poly-Si outside an emitter, thus forming a SiGe HBT device; etching active region trenches of an NMOS (Negative-channel Metal Oxide Semiconductor) and a PMOS (Positive-channel Metal Oxide Semiconductor) devices; in the trenches, respectively carrying out selective epitaxial growth of a P-type Si layer, a P-type SiGe graded layer and a P-type SiGe layer serving as the active region of the NMOS device, as well as an N-type Si layer, an N-type strained SiGe layer and an N-type Si cap layer serving as the active region of the PMOS device; preparing a virtual grid and a side wall to form the source drains of the NMOS and the PMOS devices in a self-aligned manner; and preparing a grid to form a CMOS (Complementary Metal-Oxide-Semiconductor) structure so as to finally prepare a strain BiCMOS integrated device and a circuit. According to the method, tension strain Si with high electron mobility and compression strain with high hole mobility are respectively used as the conducting channels of the NMOS and the PMOS devices, thereby efficiently improving the performance of BiCMOS integrated circuit.

Owner:XIDIAN UNIV

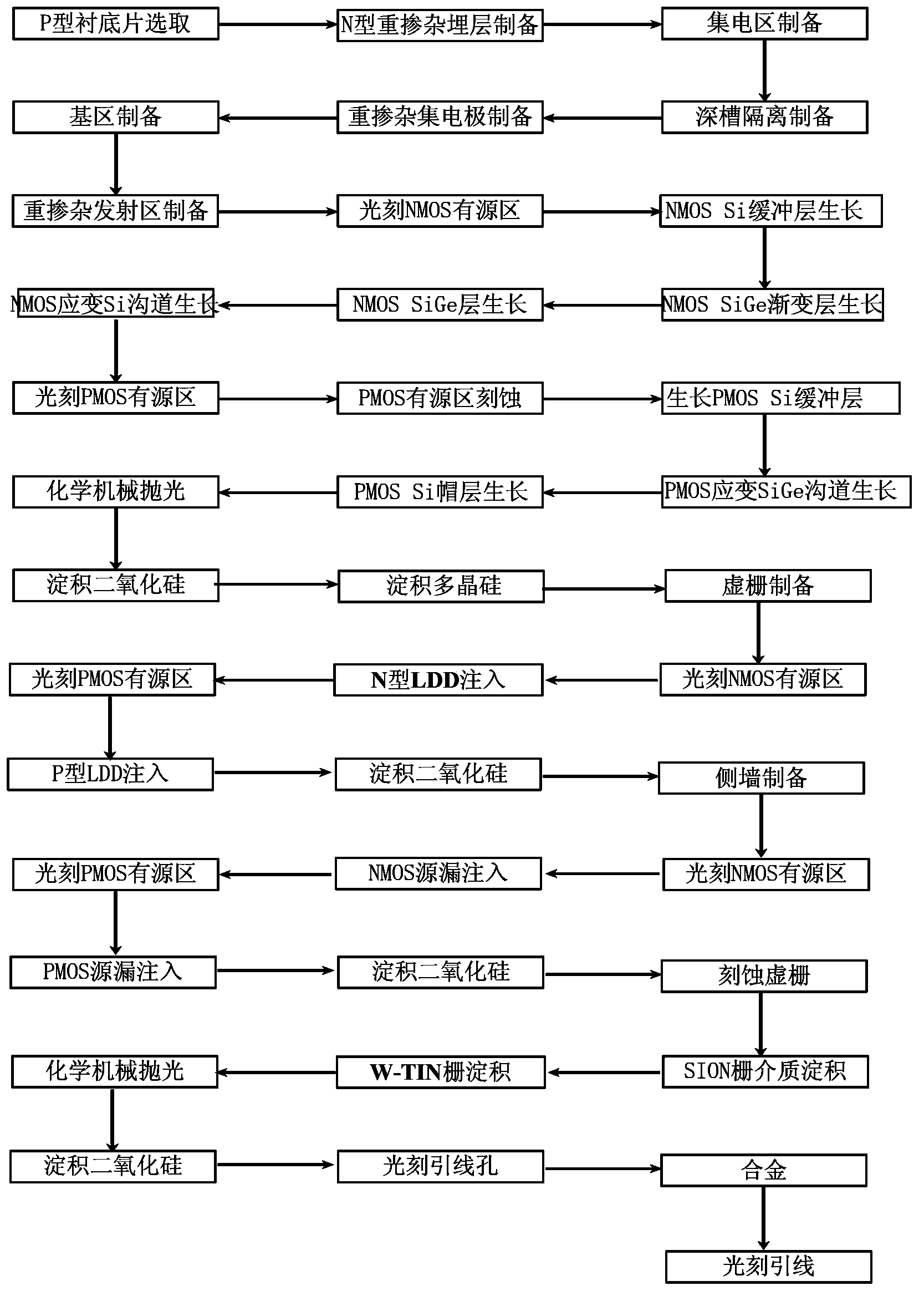

SiGe based strain BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and preparation method thereof

InactiveCN102751288APerformance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingElectrode ContactP channel

The invention discloses a SiGe based strain BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and a preparation method thereof. The preparation method comprises the steps of: first, preparing an SOI (Silicon On Insulator) substrate, continuously growing an N-Si layer, a P-SiGe layer and an N-Si layer to prepare a deep trench isolation region; respectively carrying out photo-etching on a shallow trench isolation region of a collector region and a shallow trench isolation region of a base region; carrying out ion injection to form a collecting electrode contact region, a base electrode contact region and an emitting electrode contact region, and finally forming a SiGe HBT (Heterojunction Bipolar Transistor) device; then carrying out photo-etching on an active region of an MOS (Metal Oxide Semiconductor), continuously growing a Si buffer layer, a strain SiGe layer and an intrinsic Si layer in the region to respectively form active regions of an NMOS (N-channel Metal Oxide Semiconductor) and a PMOS (P-channel Metal Oxide Semiconductor); depositing SiO2 and polycrystalline silicon in the active regions of the NMOS and the PMOS, preparing a fake grid electrode which is 22-350nm long; forming a light dope source drain electrode (LDD) and a source drain electrode of NMOS and PMOS devices by a self-aligning process, then removing the fake grid electrode, preparing grid medium lanthanum oxide (La2O3) and metal wolfram (W) to form a grid electrode; and finally metalizing, and carrying out photo-etching on a lead to form the BiCMOS integrated device and a circuit. According to the SiGe based strain BiCMOS integrated device and the preparation method of the SiGe based strain BiCMOS integrated device provided by the invention, influence of the hot carrier on the performance of the device is inhibited effectively and the reliability of the device is improved due to the adoption of the structure of the light dope source drain electrode.

Owner:XIDIAN UNIV

Double-strain plane BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and preparation method

InactiveCN102820295BImprove electrical performanceGood electrical propertiesSolid-state devicesSemiconductor/solid-state device manufacturingTensile strainBicmos integrated circuits

The invention discloses a double-strain plane BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and a preparation method. The preparation method comprises the steps of: preparing a buried layer on a substrate piece; preparing a normal Si bipolar transistor in a bipolar device area; etching a deep slot in an active area of the integrated device, and epitaxially growing a P type Si layer, an SiGe gradient layer, an SiGe layer, a strain Si layer as an active area of an NMOS (N-channel metal oxide semiconductor) device and an N type Si layer, a strain SiGe layer, and an Si cap layer as an active area of a PMOS (P-channel metal oxide semiconductor) device; preparing a virtual grid and carrying out light dope source drain injection on the device, depositing SiO2 and self-aligning to form a source drain of the device, depositing an SiON grid dielectric layer and a W-TiN composite grid, and finally forming the double-strain plane BiCMOS integrated device. The method effectively improves the performance of the BiCMOS integrated device and the circuit by using tensile strain Si with high electronic mobility and compressive strain SiGe with high hole mobility as conductive channels of the integrated device respectively.

Owner:XIDIAN UNIV

No-junction field effect transistor and manufacturing method therefor

InactiveCN105448718ALower resistanceReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductancePower flow

The invention discloses a no-junction field effect transistor and a manufacturing method therefor, and the method comprises the steps: providing a substrate; carrying out the doping so as to form a first doping region and a second doping region and to enable the doping types of the first and second doping regions to be different; forming a first grid structure and a second grid structure; removing a part of substrate, so as to form a first opening and a second opening; forming metal layers in the first and second openings; and carrying out the annealing of the metal layers and the substrate, so as to form source-drain regions. The invention also provides a no-junction field effect transistor, and the field effect transistor comprises the substrate; the first doping region and the second doping region; the first grid structure and the second grid structure; and the first and second openings, wherein the interiors of the first and second openings are provided with material layers containing metal, and the material layers serve as the source-drain regions. The beneficial effects of the invention lie in that the contact resistance between the source-drain regions and a conductive plug is smaller; the starting current is increased; the performance of the no-junction field effect transistor is improved; the technological difficulty is simplified; and the degree of interface scattering which may happen in the doping regions is reduced to some degree.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Double-strain CMOS (Complementary Metal Oxide Semiconductor) integrated device and preparation method thereof

InactiveCN102916011BImprove electrical performanceHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingComposite gridP channel

The invention discloses a double-strain CMOS (Complementary Metal Oxide Semiconductor) integrated device and a preparation method thereof. The method comprises the following steps: growing a P-type Si epitaxial layer, a P-type gradient SiGe layer and the like as NMOS (N-channel Mental Oxide Semiconductor) construction material layers continuously on a substrate, etching a PMOS (P-channel Metal Oxide Semiconductor) active area deep trench, epitaxially growing an N-type Si layer and the like as a PMOS active area selectively in the trench, and preparing the deep-trench isolator between the NMOS and the PMOS; depositing SiO2 and Poly-Si on the surface of the substrate, preparing a virtual grid electrode, depositing SiO2, preparing a side wall, and implanting N-type ions in a self-aligning manner to form the source drains of NMOS and PMOS; depositing SiO2, etching a virtual grid, depositing an SiON grid dielectric layer, and depositing a W-TiN composite grid to form the double-strain CMOS integrated device. According to the method, the tension strain Si with high electron mobility and the compression strain SiGe with high hole mobility are fully utilized as conducting channels, and the performances of the CMOS integrated device and circuits are efficiently improved.

Owner:XIDIAN UNIV

Dual polycrystalline strain SiGe plane bipolar complementary metal oxide semiconductor (BiCMOS) integrated device and preparation method

InactiveCN102738159APerformance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorHeterojunction bipolar transistor

The invention discloses a method for preparing a dual polycrystalline strain SiGe plane bipolar complementary metal oxide semiconductor (BiCMOS) integrated device. The method comprises the following steps of: preparing a silicon-on-insulator (SOI) substrate, etching a bipolar device area on the substrate, preparing a dual polycrystalline SiGe heterojunction bipolar transistor (HBT) device in the area by using a chemical vapor deposition (CVD) method and a self-aligning process, photo-etching a metal oxide semiconductor (MOS) active area, continuously growing a Si buffer layer, a strain SiGe layer and an intrinsic layer in the area, respectively forming active areas of n-channel metal oxide semiconductor (NMOS) and p-channel metal oxide semiconductor (PMOS) devices, depositing SiO2 and polycrystalline silicon in the active areas of the NMOS and PMOS devices, etching a pseudo grid with the length of 22 to 350 nanometers, forming a light doped drain (LDD) and a source drain of the NMOS and PMOS devices by adopting the self-aligning process, then removing the pseudo grid, forming grid dielectric lanthanum oxide (La2O3) and metallic tungsten (W) for forming a grid, metalizing, photo-etching leads, and thus forming a BiCMOS integrated circuit. The self-aligning process is adopted in the preparation method, and the LDD structure is adopted in the MOS structure, so that influence of hot carriers on performance of the device is efficiently inhibited, and the reliability of the device is improved.

Owner:XIDIAN UNIV

Dual-strain bipolar complementary metal-oxide semiconductor (BiCMOS) integration device based on silicon on insulator (SOI) substrate and preparation method thereof

InactiveCN102810544ASuppress performance impactInhibition effectSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorIon

The invention discloses a dual-strain bipolar complementary metal-oxide semiconductor (BiCMOS) integration device based on a silicon on insulator (SOI) substrate and a preparation method thereof. The preparation method comprises following steps that a negative-silicon (N-Si) layer, a positive-silicon germanium (P-SiGe) layer and an N-Si layer continuously grow on the SOI substrate, a deep groove isolator is prepared, a collector zone shallow groove isolator and a base zone shallow groove isolator are prepared, a collector zone is photo-etched, phosphonium ions are injected to form a collector electrode, a base electrode and a transmitter electrode, and a SiGe heterojunction bipolar transistor (HBT) device is formed; a strain SiGe material grow on the substrate, an N-channel MOS (NMOS) device active region and a P-channel MOS (PMOS) device active region are formed, a pseudo grid is prepared, a source drain region of the NMOS and the PMOS devices is respectively generated in a self-aligning way, the pseudo grid is eliminated, a lanthanum oxide (La2O3) material is prepared in a pressing groove at the pseudo grid to form a grid medium and metal tungsten (W) to form a grid electrode, a lead is photo-etched, and a dual-strain plane BiCMOS integration device and a circuit based on the SOI substrate are formed. According to the method, the characteristic that a hole mobility of the strain SiGe material is higher than that of the bulk-Si material is adequately utilized to prepare the dual-strain plane BiCMOS integration circuit based on the SOI substrate, so that the performance of the existing analog and digital-analog mixed integrated circuit is greatly improved.

Owner:XIDIAN UNIV

Semiconductor device and method of forming the same

ActiveCN105448727BRun fastImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceCharge carrier mobility

A semiconductor device and a forming method thereof are provided. The forming method of the semiconductor device comprises the following steps: providing a substrate; forming a lamination structure covering the surface of the substrate, wherein the lamination structure includes a first stress layer disposed on the surface of the substrate, an intrinsic layer disposed on the surface of the first stress layer and a second stress layer disposed on the surface of the intrinsic layer, the lattice constant of the first stress layer is smaller than the lattice constant of the intrinsic layer, and the lattice constant of the intrinsic layer is smaller than the lattice constant of the second stress layer; forming a gate structure on the surface of the second stress layer; etching the lamination structure on the two sides of the gate structure to form grooves; and forming a third stress layer filling the grooves, wherein the lattice constant of the third stress layer is greater than the lattice constant of the first stress layer. The leakage current in the semiconductor device is reduced and the source-to-drain punch-through problem of the semiconductor device is inhibited while the carrier mobility of the semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

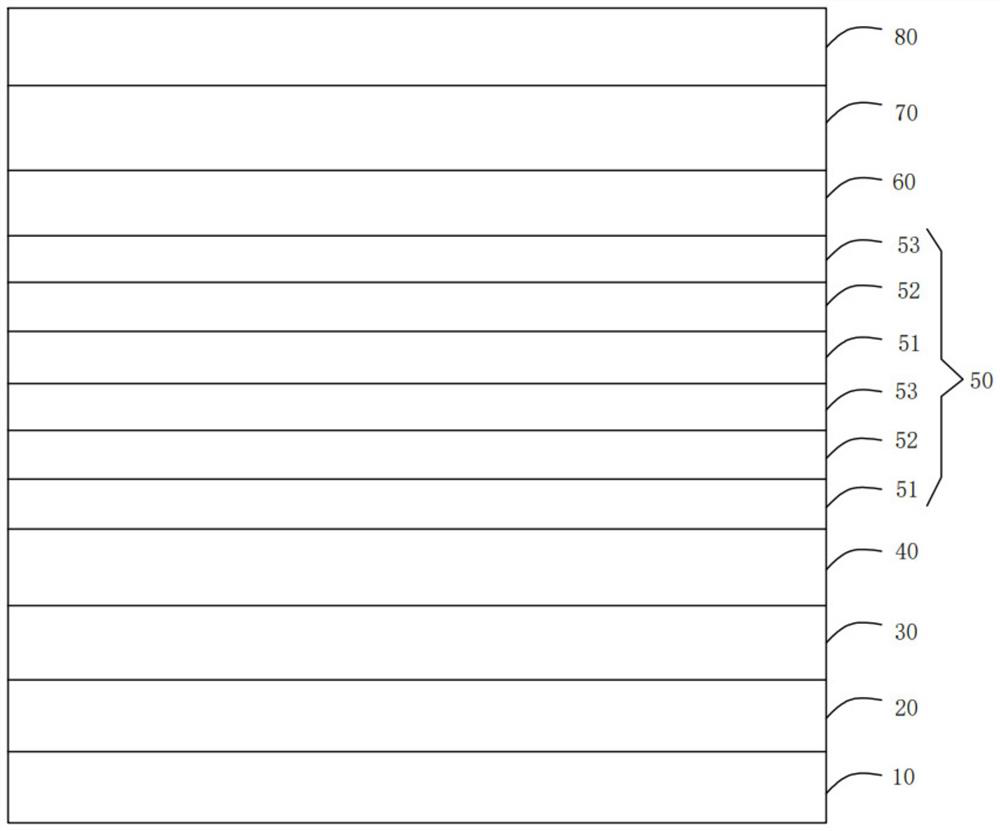

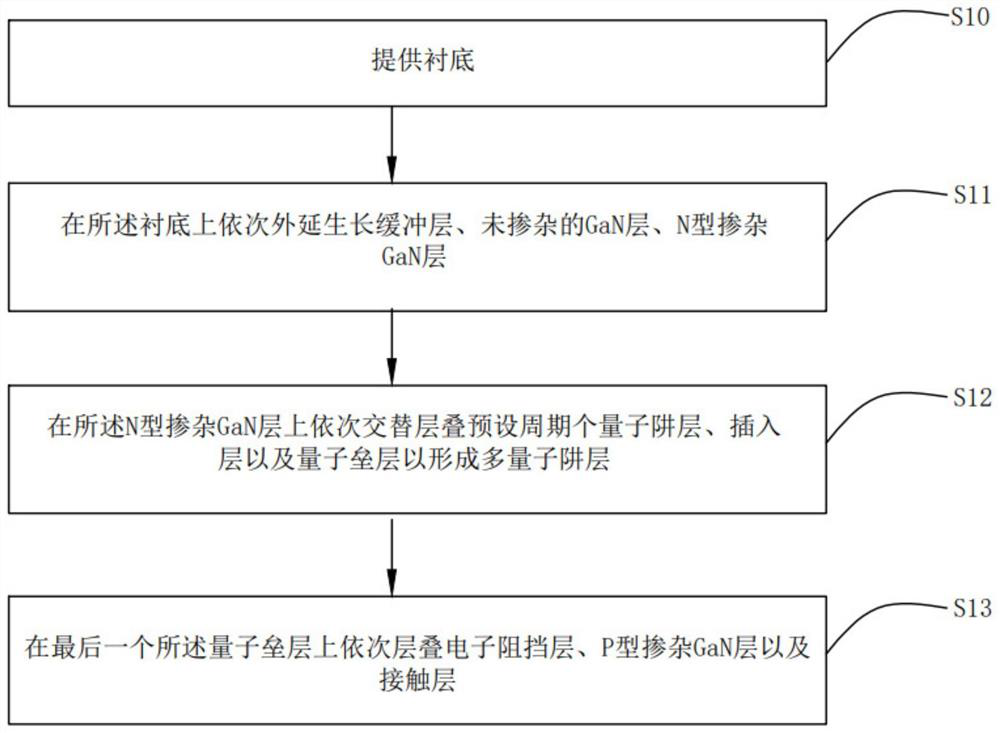

Epitaxial wafer, epitaxial wafer preparation method and blue-green light emitting diode

PendingCN114784157ARepair surface topographyAvoid direct foundationPolycrystalline material growthAfter-treatment detailsElectron holeGreen-light

The invention discloses an epitaxial wafer, an epitaxial wafer preparation method and a blue-green light emitting diode, the epitaxial wafer comprises a multi-quantum well layer, and the multi-quantum well layer comprises a quantum well layer, an insertion layer and a quantum barrier layer which are periodically, sequentially and alternately stacked; wherein the insertion layer comprises a first insertion sub-layer, a second insertion sub-layer and a third insertion sub-layer which are sequentially stacked on the quantum well layer, the quantum well layer is an InGaN layer, the quantum barrier layer is a GaN layer, the first insertion sub-layer and the third insertion sub-layer are both AlN layers, and the second insertion sub-layer is a SiN layer. According to the invention, the problem of low electron hole radiation recombination efficiency of the epitaxial wafer in the prior art is solved.

Owner:JIANGXI ZHAO CHI SEMICON CO LTD

Tri-polycrystal strain SiGe BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and preparation method

InactiveCN102820306ASuppress performance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingDielectricSoi substrate

The invention discloses a tri-polycrystal strain SiGe BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and a preparation method. The preparation method comprises the steps of: firstly, preparing an SOI (Silicon On Insulator) substrate; etching a bipolar device region; preparing a tri-polycrystal SiGe HBT (Heterojunction Bipolar Transistor) device in the region; then photoetching an MOS (Metal Oxide Semiconductor) active region; continuously growing an Si buffer layer, a strain SiGe layer and an intrinsic Si layer in the region; respectively forming active regions of an NMOS (N-channel Metal Oxide Semiconductor) device and a PMOS (P-channel Metal Oxide Semiconductor) device; depositing SiO2 and polycrystalline silicon on the active region of the MOS device; preparing a pseudo grid by etching; forming a light dope source drain and a source drain of the MOS device by a self-aligning process; then removing the pseudo grid; preparing grid dielectric lanthanum oxide and tungsten to form the grid; and finally metalizing and photoetching a lead to prepare the integrated device and a circuit. The preparation process provided by the the invention adopts the self-aligning process, and the light dope source drain structure is adopted in the MOS structure so that the influence of hot carriers on the performance of the device is effectively inhibited and the reliability of the device is improved.

Owner:XIDIAN UNIV

A kind of soi BJT dual-strain plane BiCMOS integrated device and its preparation method

InactiveCN102723340BImprove electrical performanceHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingComposite gridTin

The invention discloses an SOI (Silicon-On-Insulator)-BJT (Bipolar Junction Transistor) double-strain-plane Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device and a preparation method of the device. The preparation process is as follows: growing an N type Si epitaxial collector region on an SOI substrate sheet, preparing a deep-trench isolator, and manufacturing a conventional Si bipolar transistor in a bipolar device region; etching a deep trench in an active region of an MOS (Metal Oxide Semiconductor) device by utilizing a dry etching process, and respectively and selectively growing a P type Si layer, a P type SiGe gradual change layer, a P type SiGe layer, a P type strain Si layer which are taken as an active region of an NMOS (N-Channel Metal Oxide Semiconductor) device, an N type Si layer, an N type strain SiGe layer and an N type Si cap layer which are taken as an active region of a PMOS (P-Channel Metal Oxide Semiconductor) device in the trench in an epitaxial manner; and preparing a virtual grid electrode, respectively injecting LDD (Laser Detector Diode) of the MOS device, depositing SiO2, preparing a side wall, and conducting self alignment to form source drain of the NMOS device and the PMOS device; and etching a virtual grid, depositing a SiON grid dielectric layer and a W-TiN composite grid, and thus finally forming the Bi CMOS integrated device with the channel being 22-45nm. According to the method, the tensile strain Si with high electronic mobility and compressive strain SiGe with high hole mobility are respectively taken as conducting channels of the NMOS device and the PMOS device, so that the performances of the Bi CMOS integrated device and a circuit are improved greatly.

Owner:XIDIAN UNIV

A strained sige BiCMOS integrated device and its preparation method

InactiveCN102738150BPerformance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricIon implantation

The invention discloses a strained SiGe BiCMOS (bipolar complementary metal oxide semiconductor) integrated device and a preparation method. The preparation method comprises on-chip preparing a buried layer on an SOI (silicon on insulator) substrate, growing an N-type Si epitaxy, preparing deep trench isolation, and preparing a conventional Si bipolar transistor on a bipolar device region; growing a strained SiGe material on the substrate at 600 to 800 DEG C, etching the active region of an MOS (metal oxide semiconductor) device by lithography, adjusting the threshold value of the MOS device region by ion implantation process, depositing SiO2 and polysilicon on the active region of the MOS device, etching to form a pseudo gate, preparing the source and drain region of the MOS device by self-alignment process respectively, growing a SiO2 layer on the substrate surface, removing the pseudo gate, preparing La2O3 in the impressed groove of the pseudo gate to obtain a gate dielectric, preparing a gate from the gate dielectric and tungsten (W), etching a passivation layer to form the lead holes of the drain, source and gate, metalizing, sputtering metal, and etching leads by lithography to obtain the strained SiGe BiCMOS integrated device and circuit.

Owner:XIDIAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com