Plane strain BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor) integrated component based on self-aligned technology and preparation method thereof

A self-alignment process and integrated device technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve high cost, difficulty in preparing large-diameter single crystals, and low mobility of Si material carriers and other issues to achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

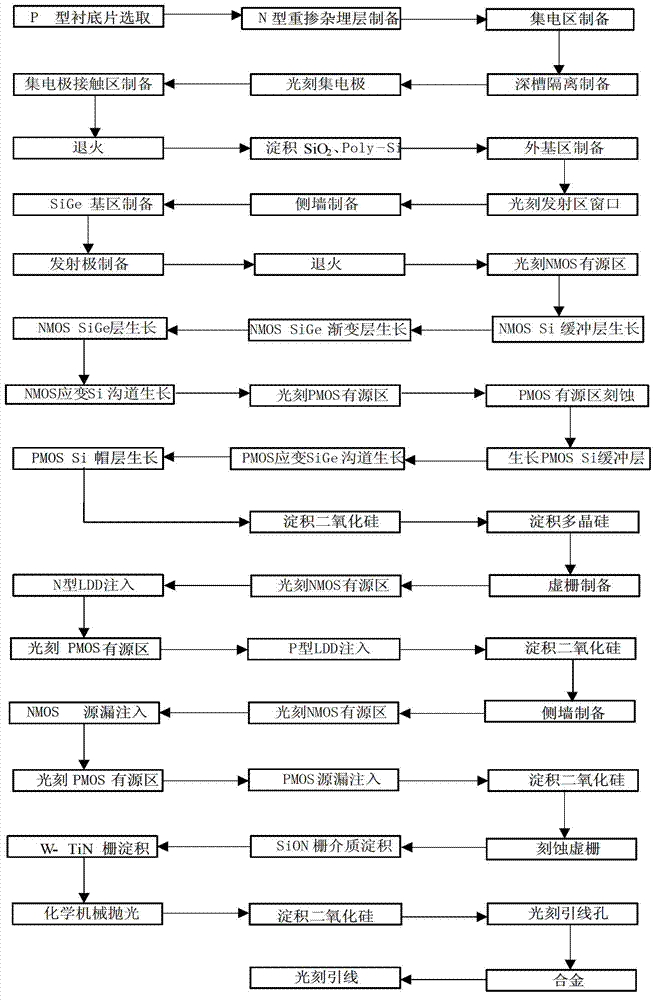

[0124] Embodiment 1: Prepare a strained BiCMOS integrated device and circuit based on a self-alignment process with a conductive channel of 45nm, and the specific steps are as follows:

[0125] Step 1, preparation of the buried layer.

[0126] (1a) Select the doping concentration to be 5×10 14 cm -3 A P-type Si sheet as a substrate;

[0127] (1b) Thermally oxidize a layer of SiO with a thickness of 300nm on the substrate surface 2 layer;

[0128] (1c) Photoetching the buried layer region, implanting N-type impurities into the buried layer region, and annealing at 800° C. for 90 minutes to activate the impurities to form an N-type heavily doped buried layer region.

[0129] Step 2, deep trench isolation preparation.

[0130] (2a) Remove the redundant oxide layer on the surface, and epitaxially grow an N-type epitaxial Si layer with a thickness of 1.5 μm as the collector region, and the doping concentration of this layer is 1×10 16 cm -3 ;

[0131] (2b) Deposit a layer o...

Embodiment 2

[0191] Embodiment 2: The plane-strained BiCMOS integrated device and circuit based on the self-alignment process are prepared with a conductive channel of 30nm, and the specific steps are as follows:

[0192] Step 1, preparation of the buried layer.

[0193] (1a) Select the doping concentration as 1×10 15 cm -3 A P-type Si sheet as a substrate;

[0194] (1b) Thermally oxidize a layer of SiO with a thickness of 400nm on the substrate surface 2 layer;

[0195] (1c) Photoetching the buried layer region, implanting N-type impurities into the buried layer region, and annealing at 900° C. for 60 minutes to activate the impurities to form an N-type heavily doped buried layer region.

[0196] Step 2, deep trench isolation preparation.

[0197] (2a) Remove the excess oxide layer on the surface, and epitaxially grow an N-type epitaxial Si layer with a thickness of 1.8 μm as the collector region, and the doping concentration of this layer is 5×10 16 cm -3 ;

[0198] (2b) Deposit ...

Embodiment 3

[0258] Embodiment 3: Prepare the strained BiCMOS integrated device and circuit based on the self-alignment process with a conductive channel of 22nm, the specific steps are as follows:

[0259] Step 1, preparation of the buried layer.

[0260] (1a) Select the doping concentration to be 5×10 15 cm -3 A P-type Si sheet as a substrate;

[0261] (1b) Thermally oxidize a layer of SiO with a thickness of 500nm on the surface of the substrate 2 layer;

[0262] (1c) Photoetching the buried layer region, implanting N-type impurities into the buried layer region, and annealing at 950° C. for 30 minutes to activate the impurities to form an N-type heavily doped buried layer region.

[0263] Step 2, deep trench isolation preparation.

[0264] (2a) Remove the excess oxide layer on the surface, and epitaxially grow an N-type epitaxial Si layer with a thickness of 2 μm, as the collector region, and the doping concentration of this layer is 1×10 17 cm -3 ;

[0265] (2b) Deposit a laye...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com