Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

77 results about "Bicmos integrated circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

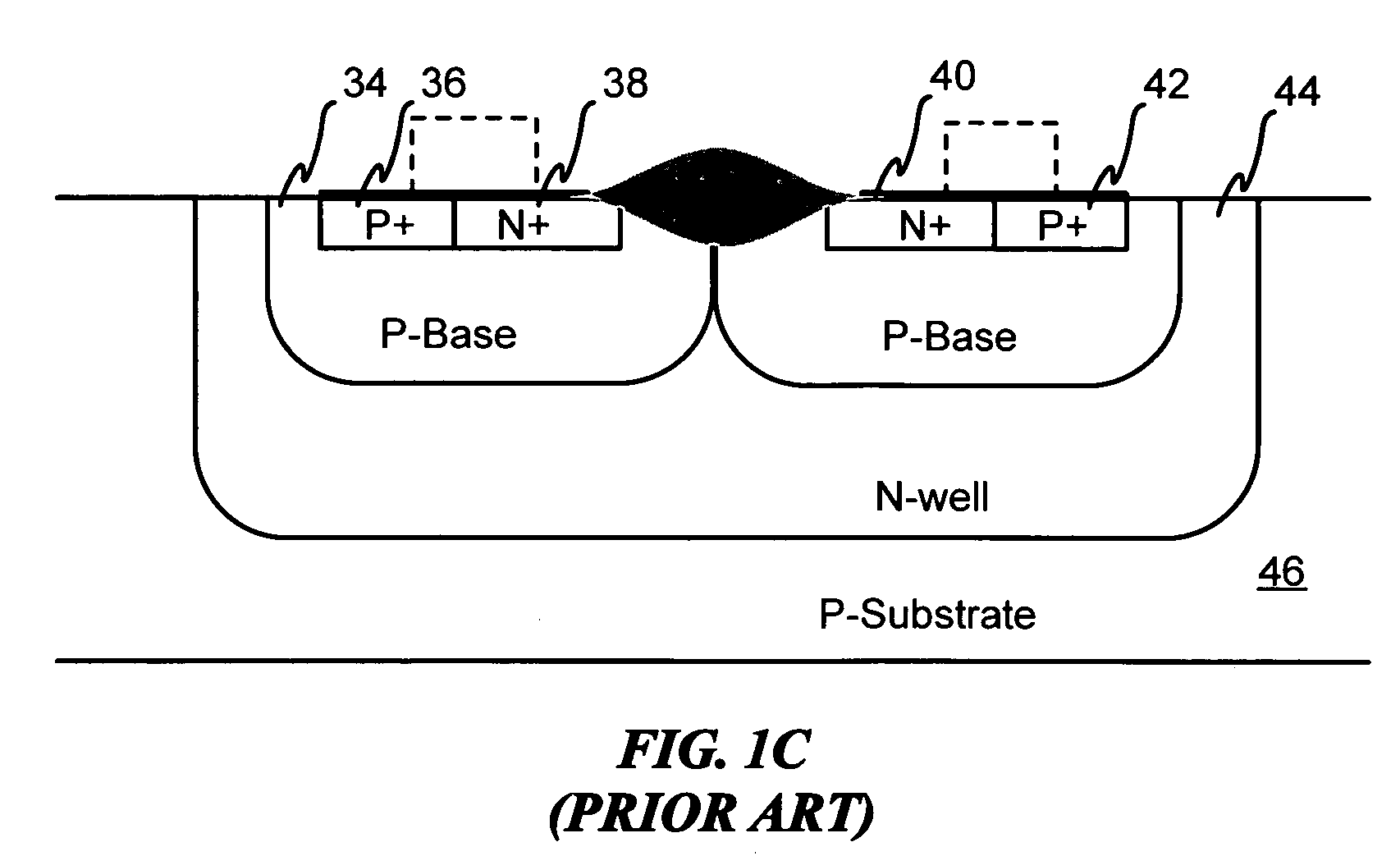

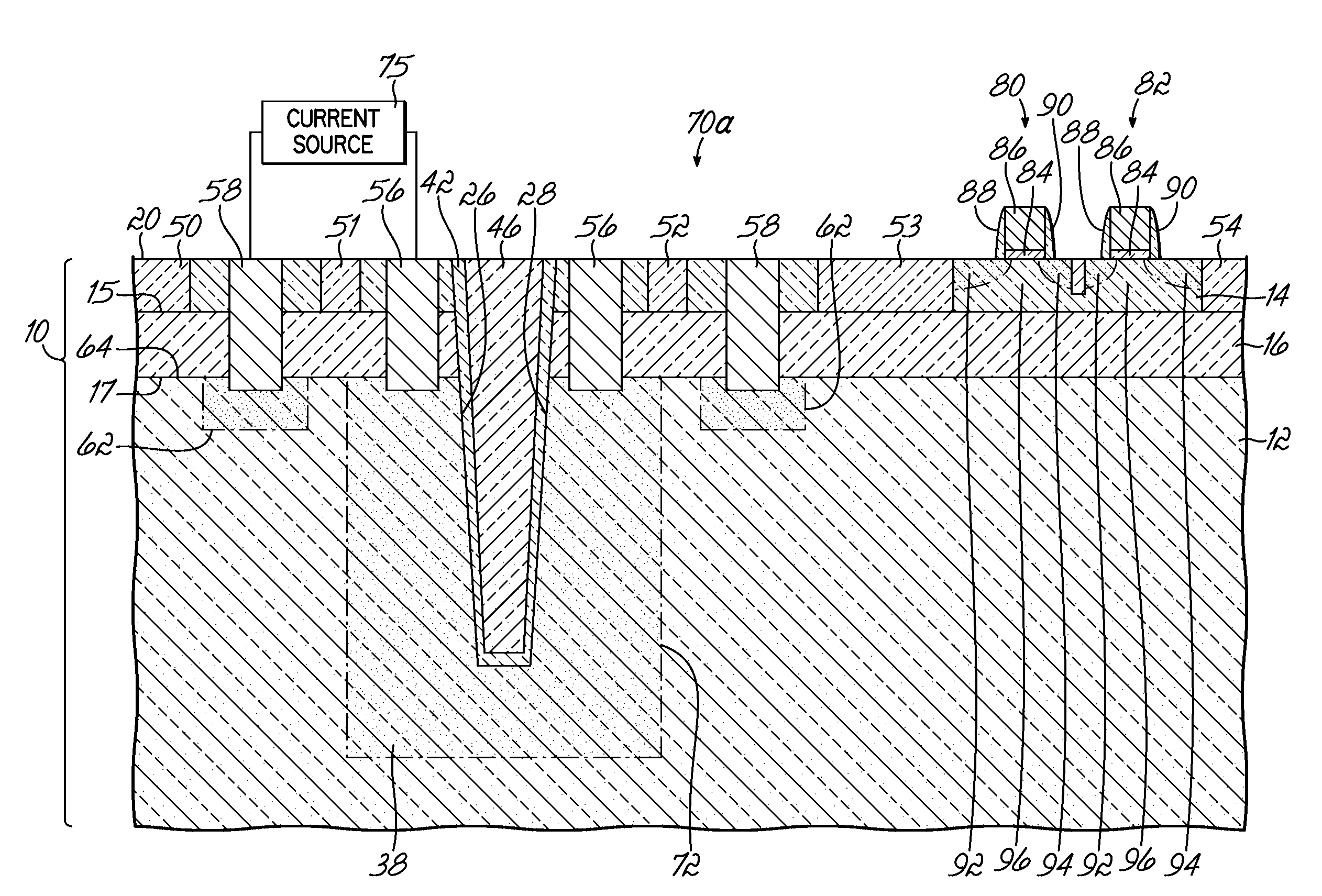

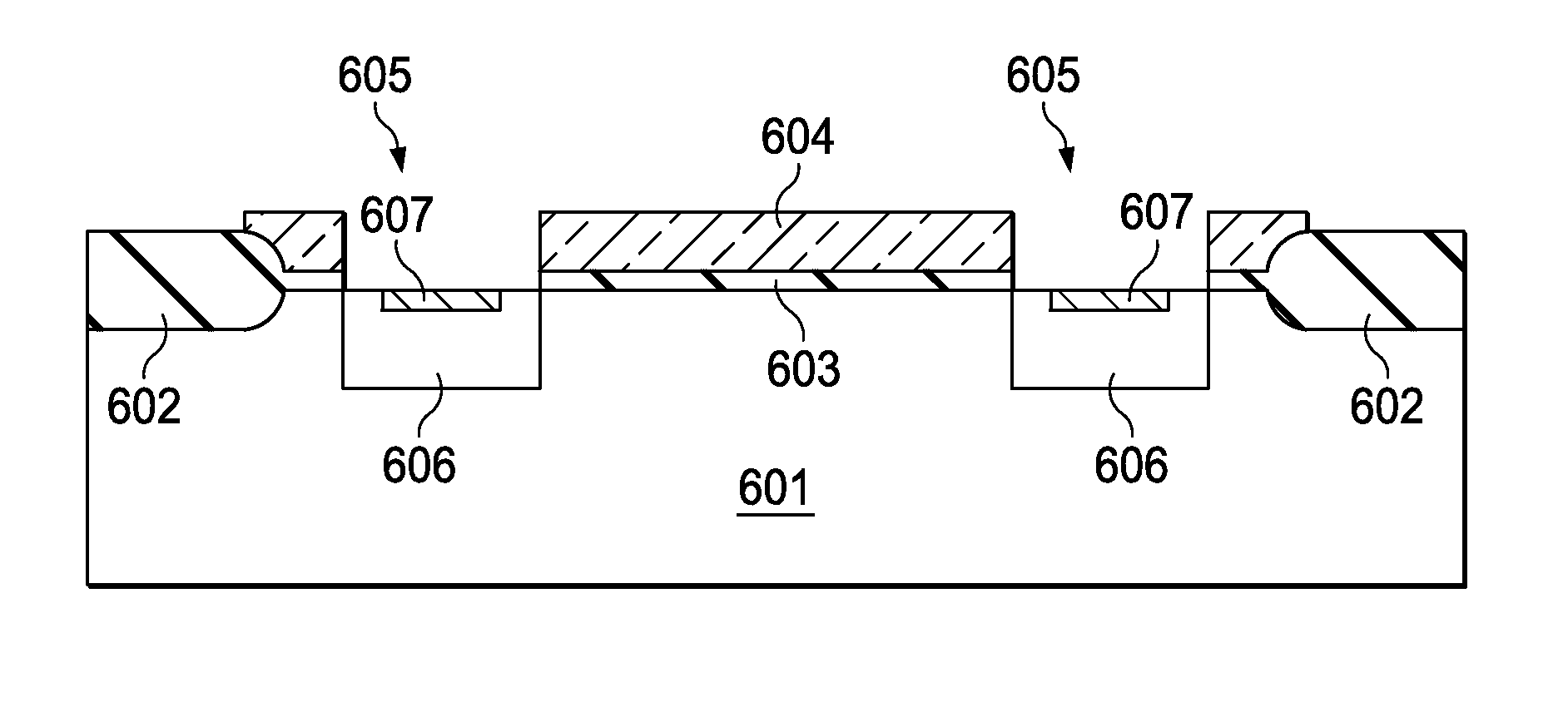

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

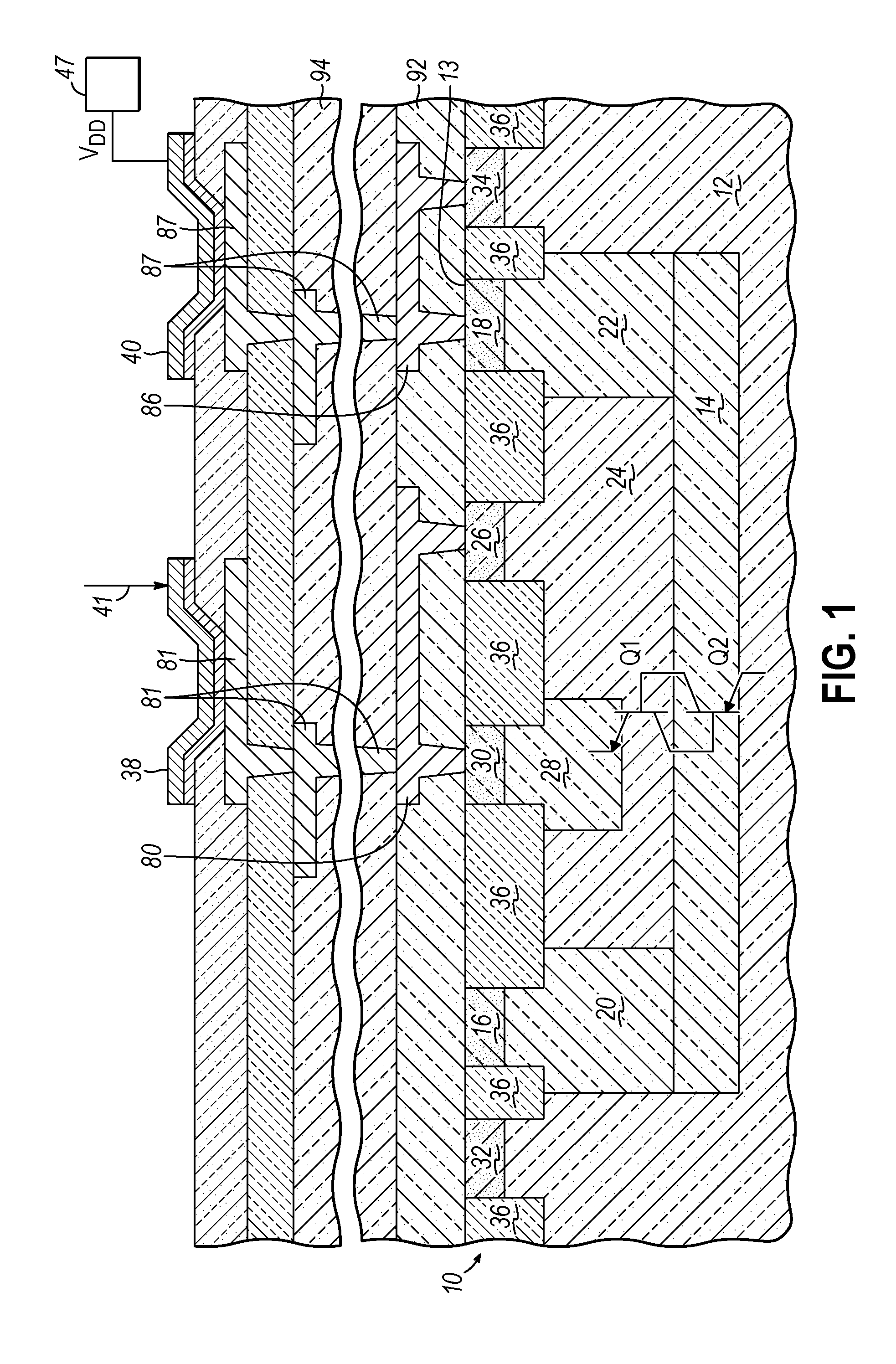

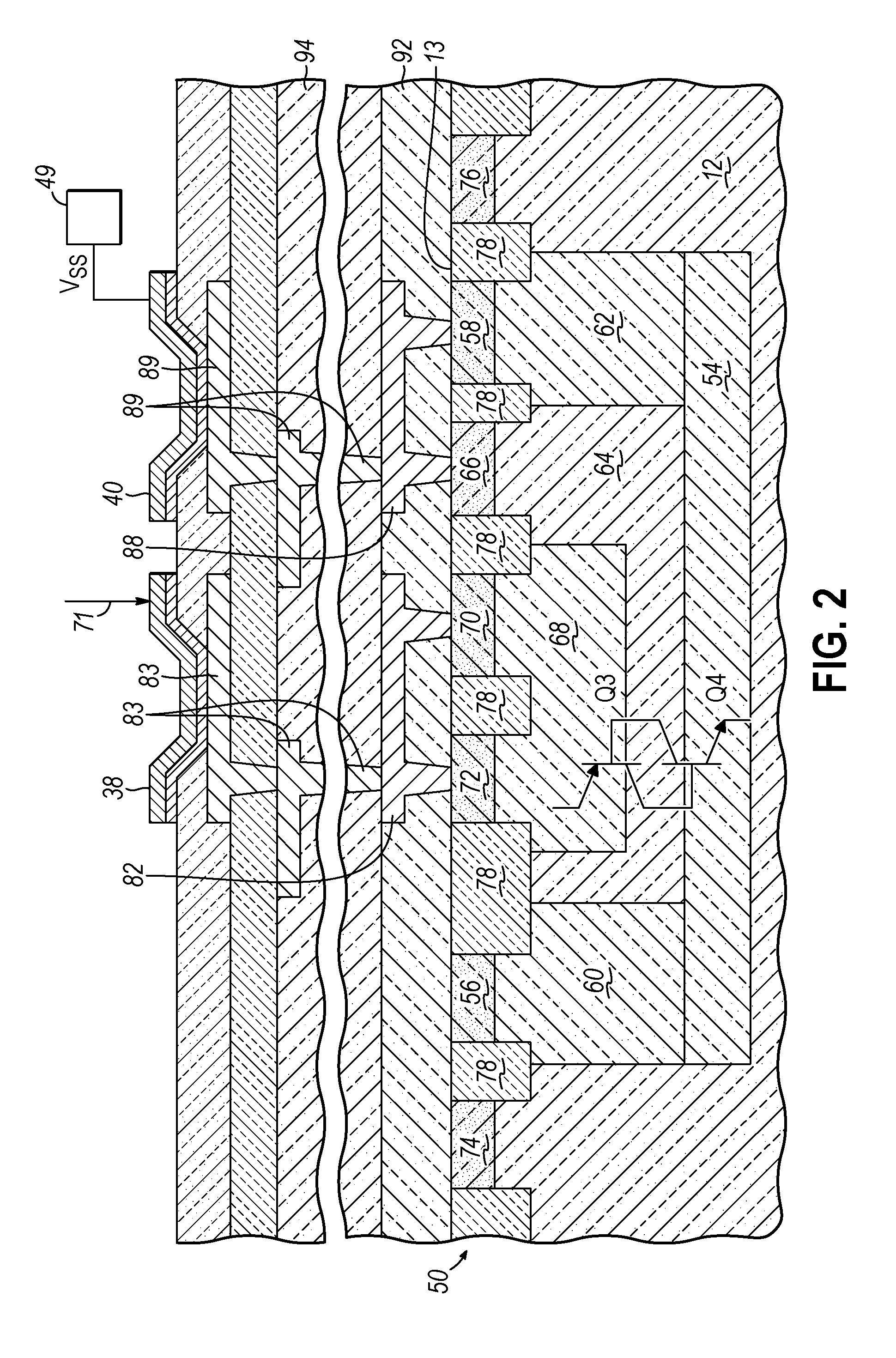

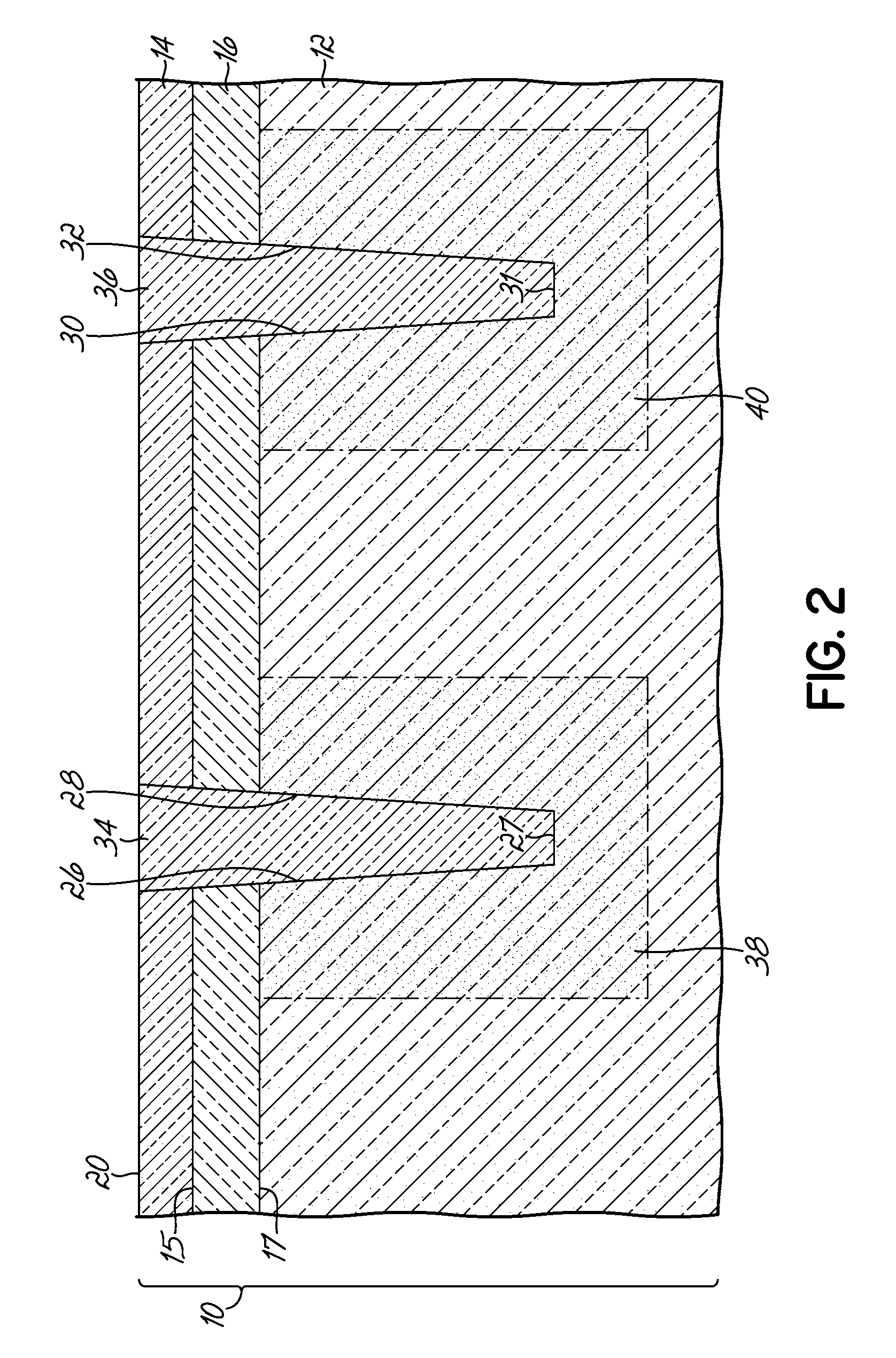

InactiveUS20070007545A1Impaired immunityHigh protection levelTransistorThyristorNon symmetricTransmission-line pulse

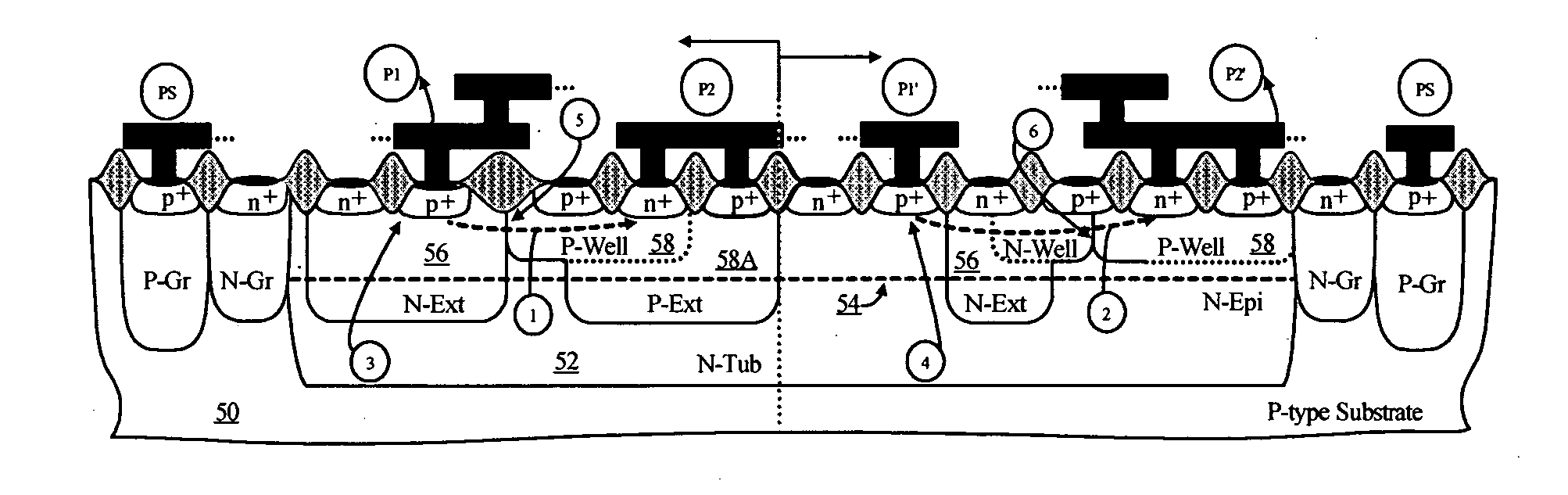

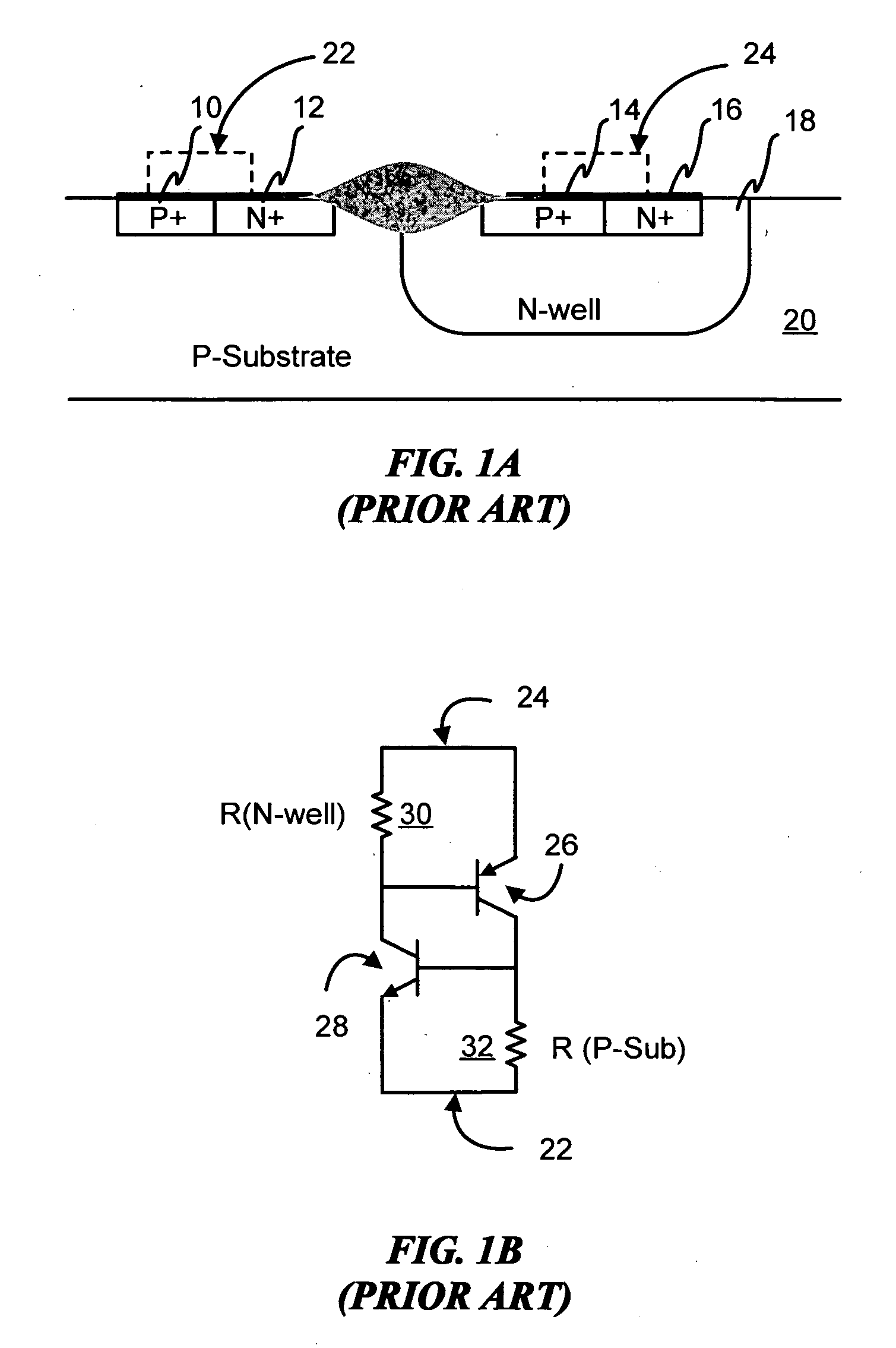

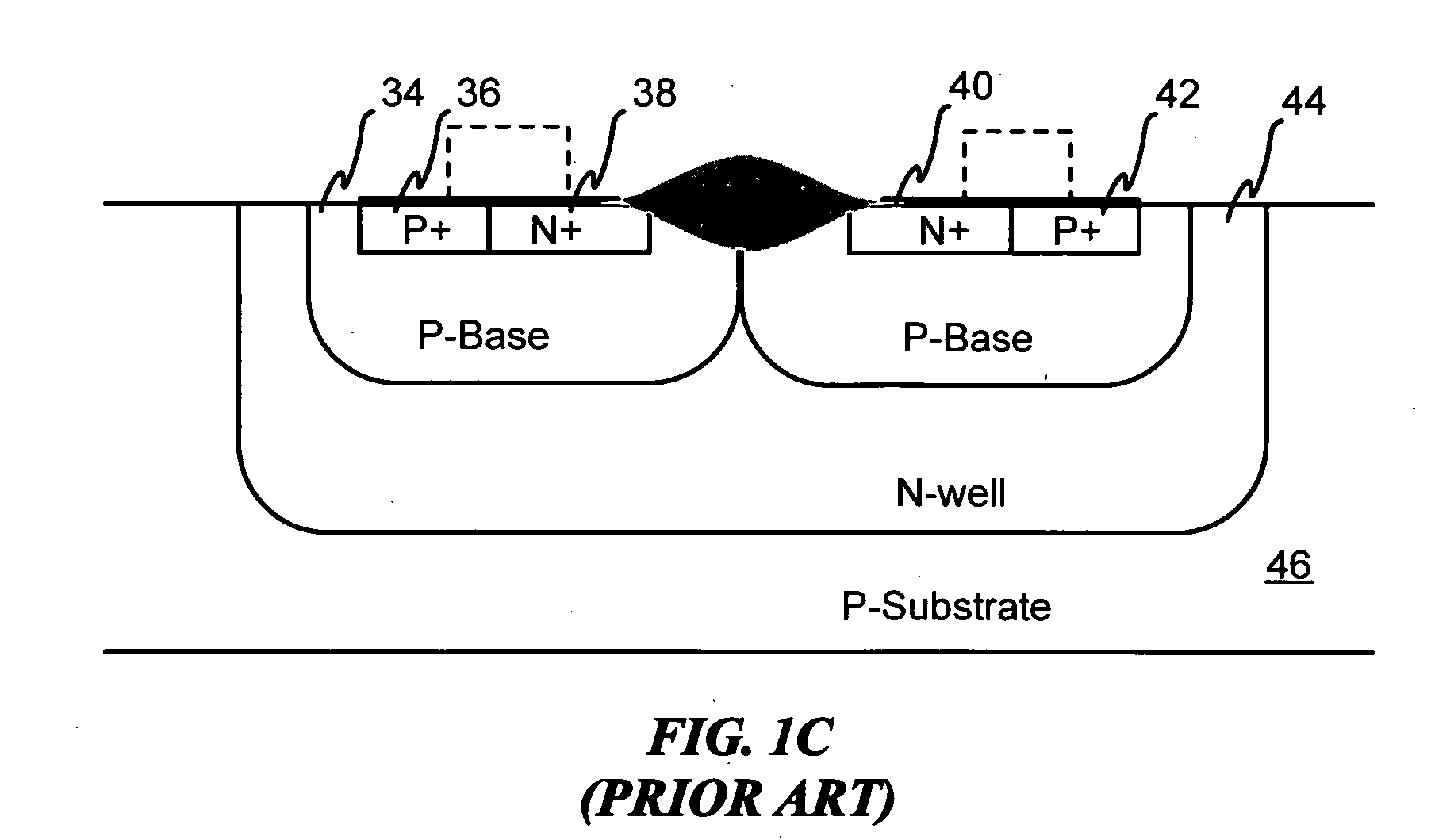

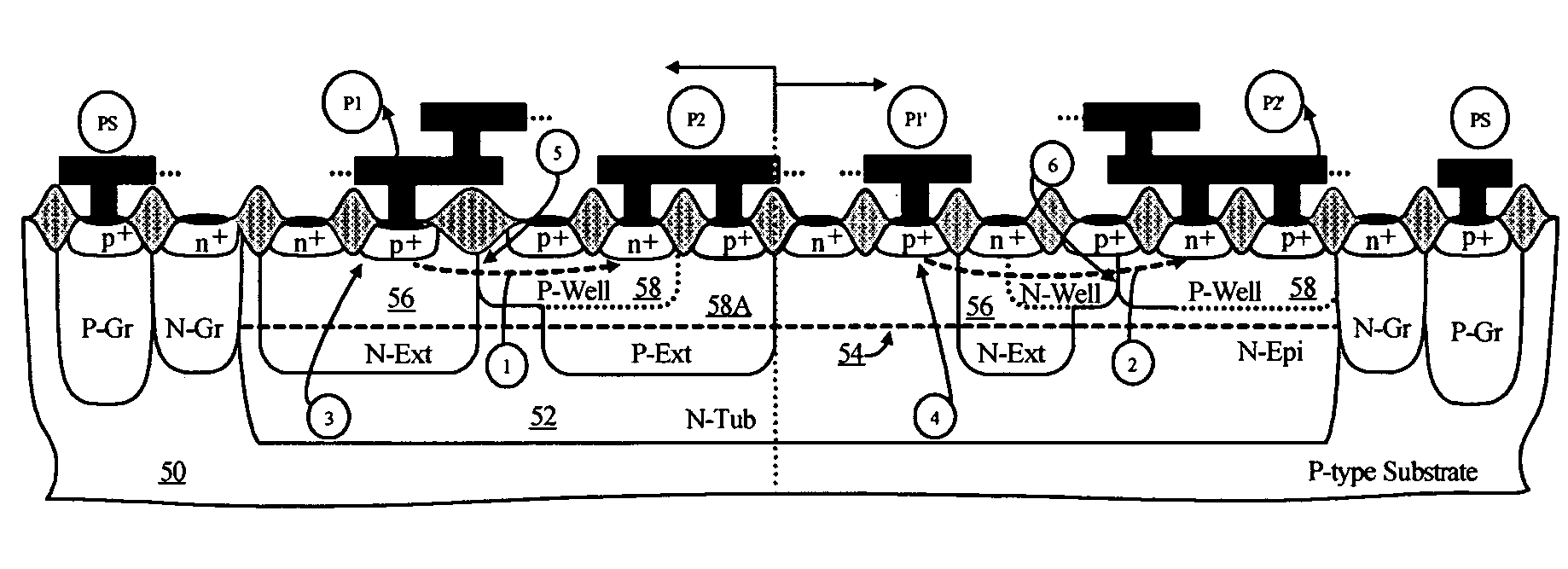

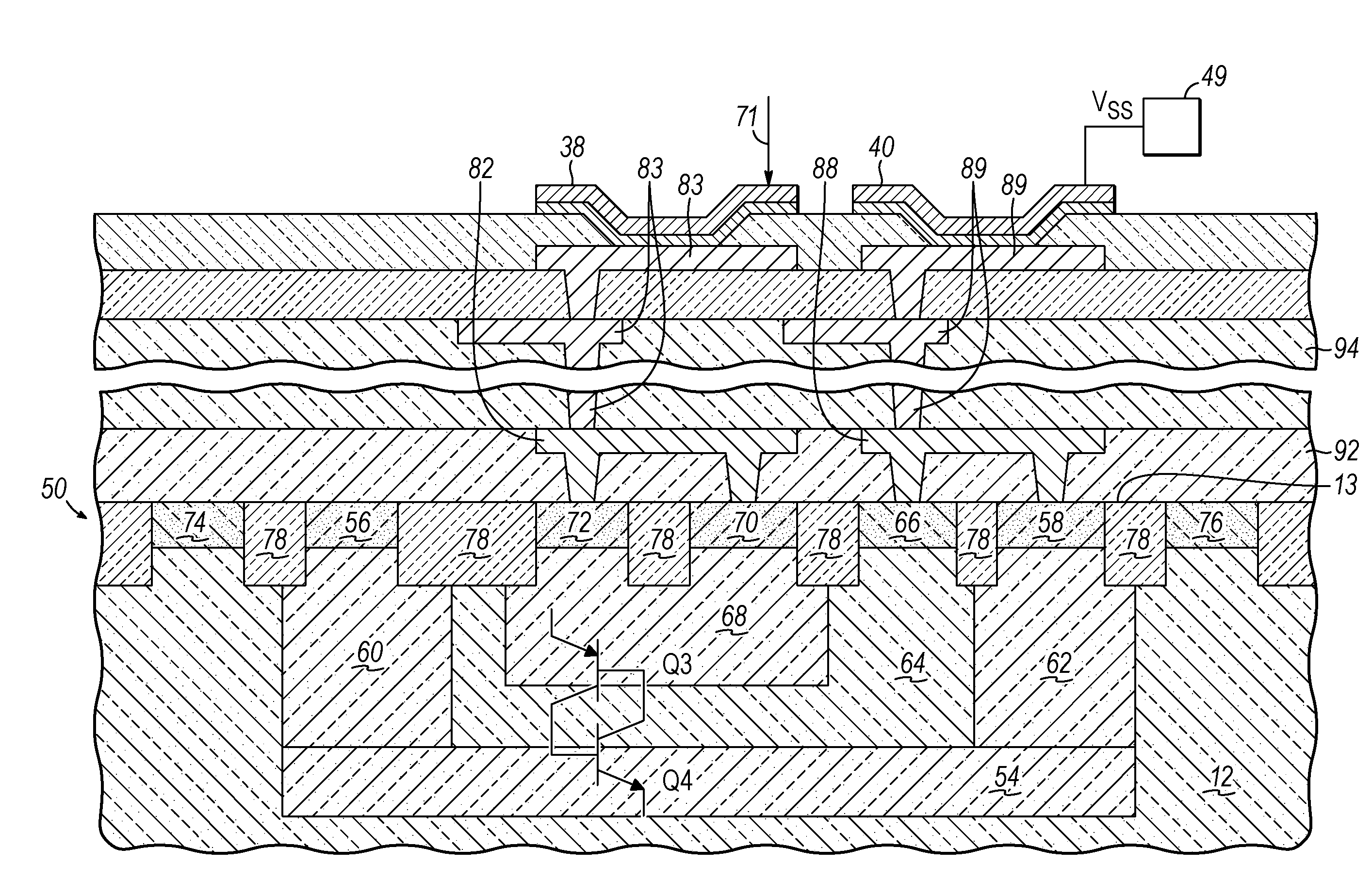

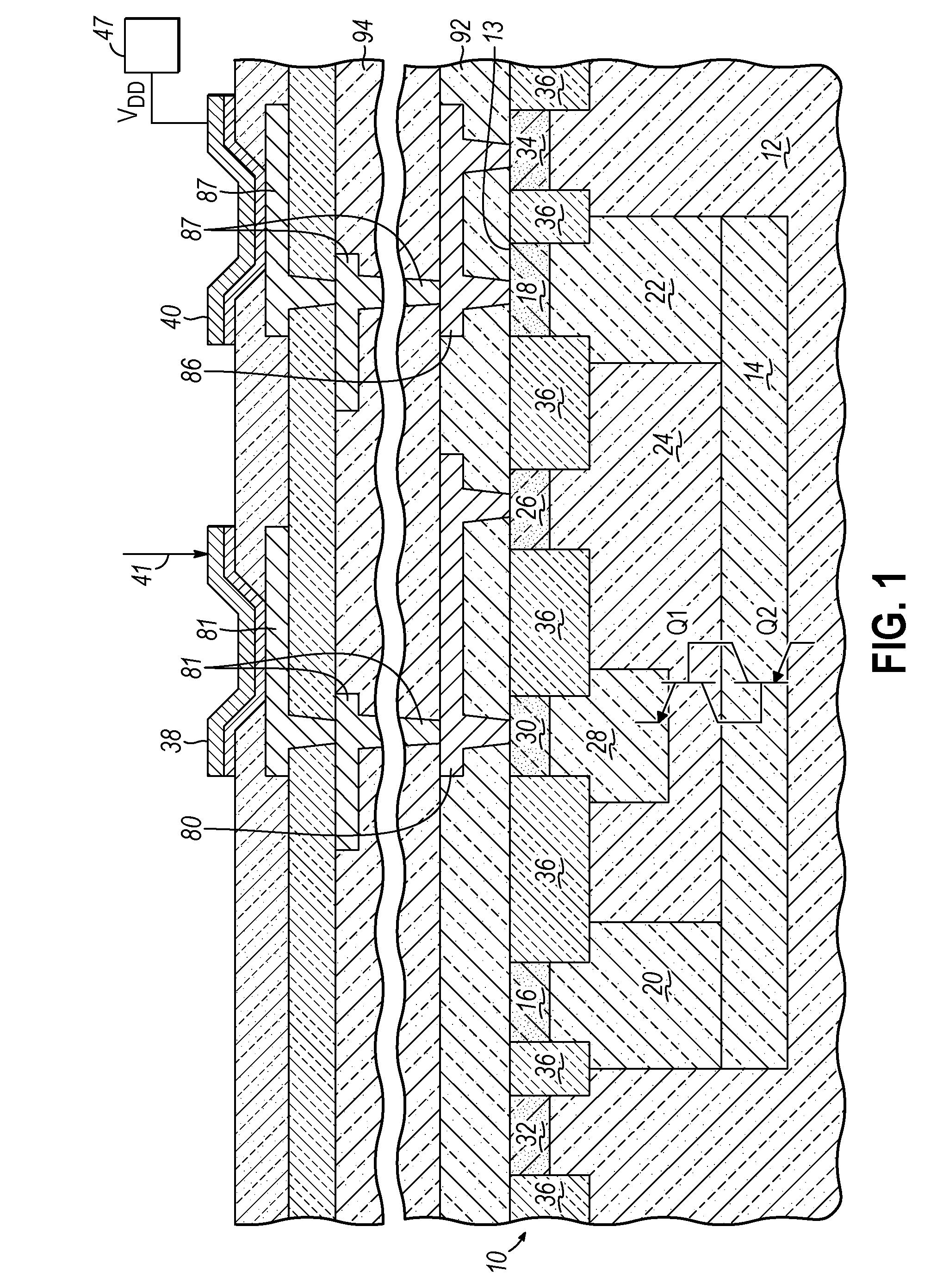

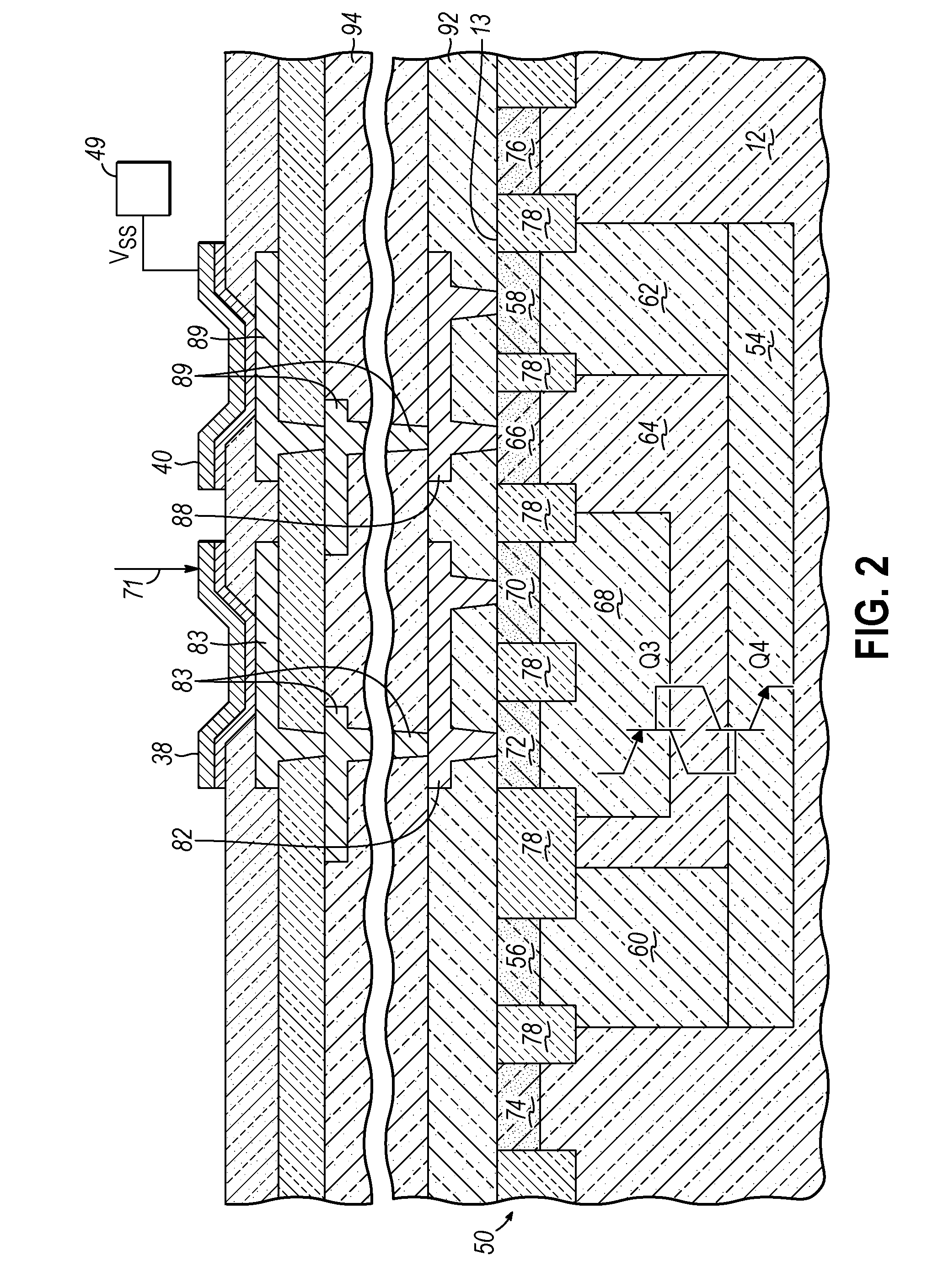

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

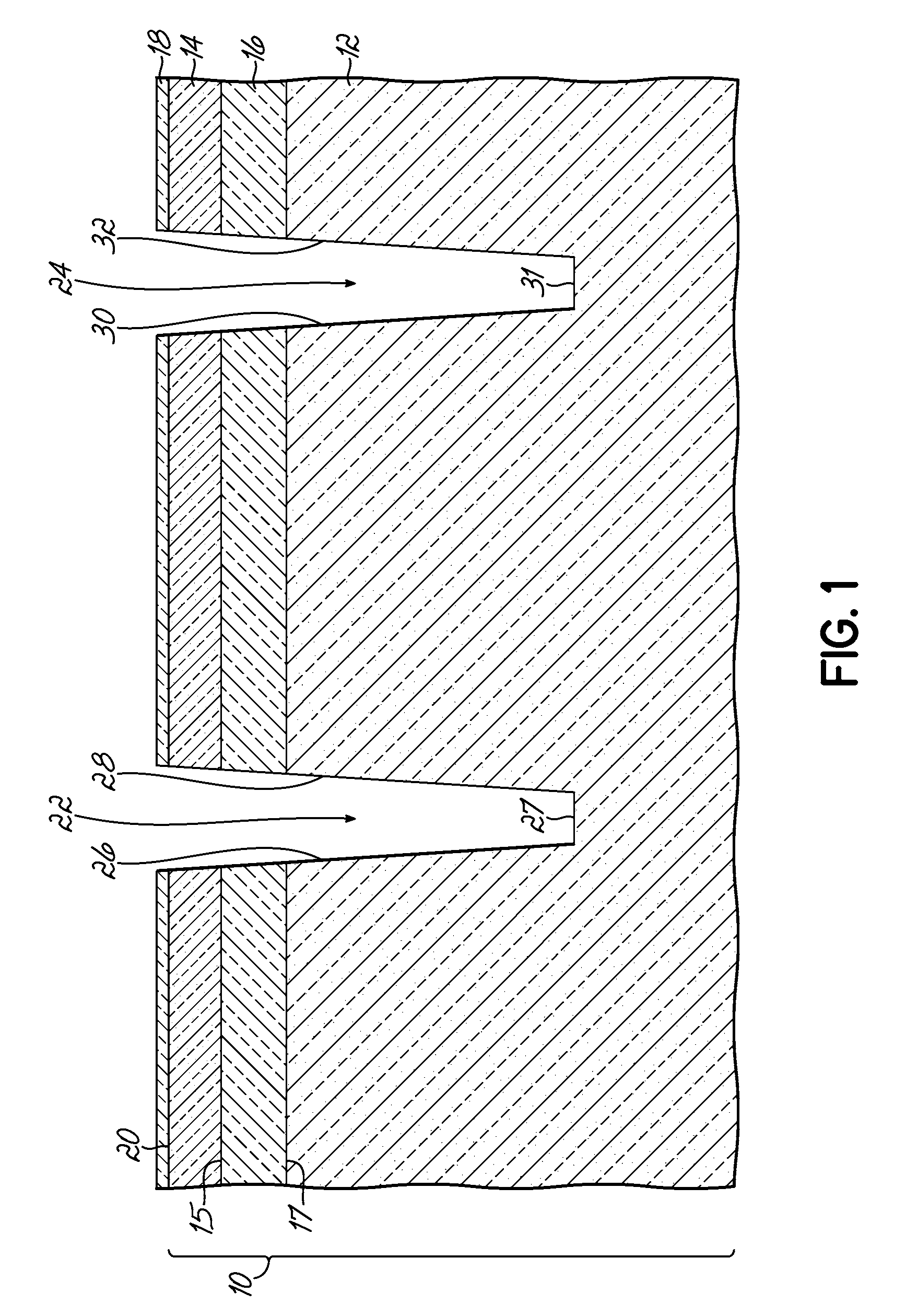

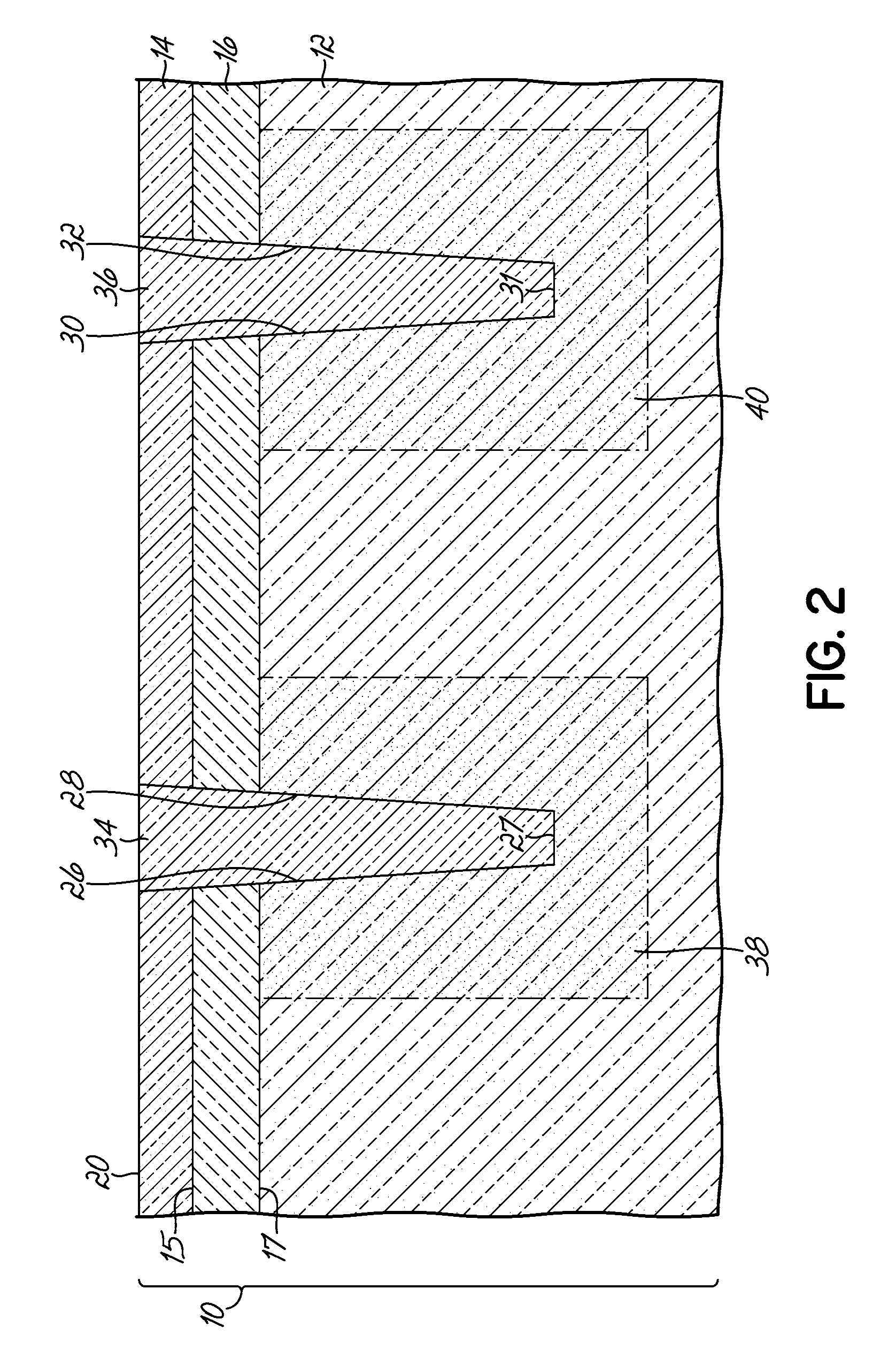

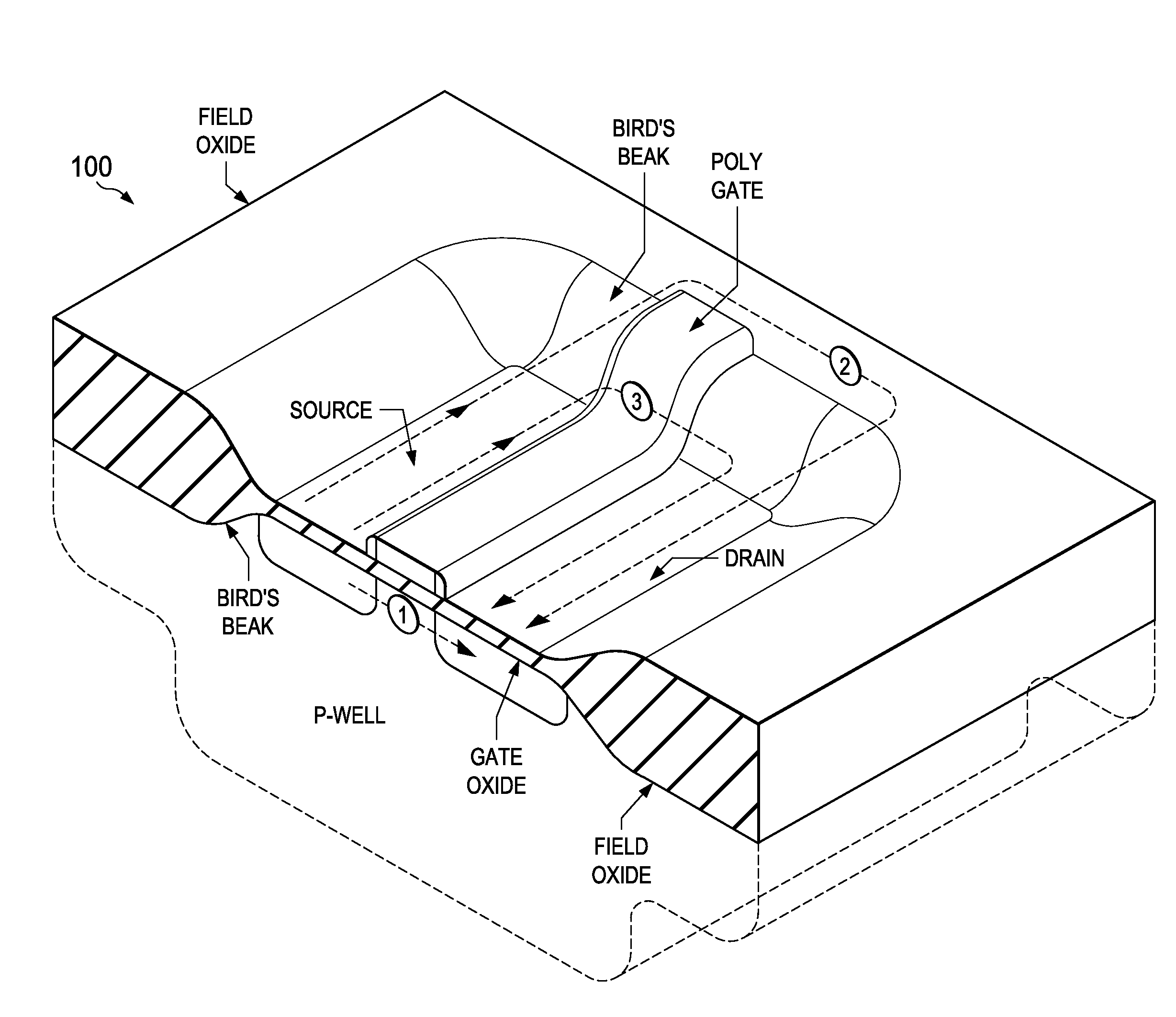

Radiation hardened mos devices and methods of fabrication

InactiveUS20110084324A1Improve radiation hardnessReducing radiation-induced leakageTransistorSolid-state devicesCMOSRadiation resistant

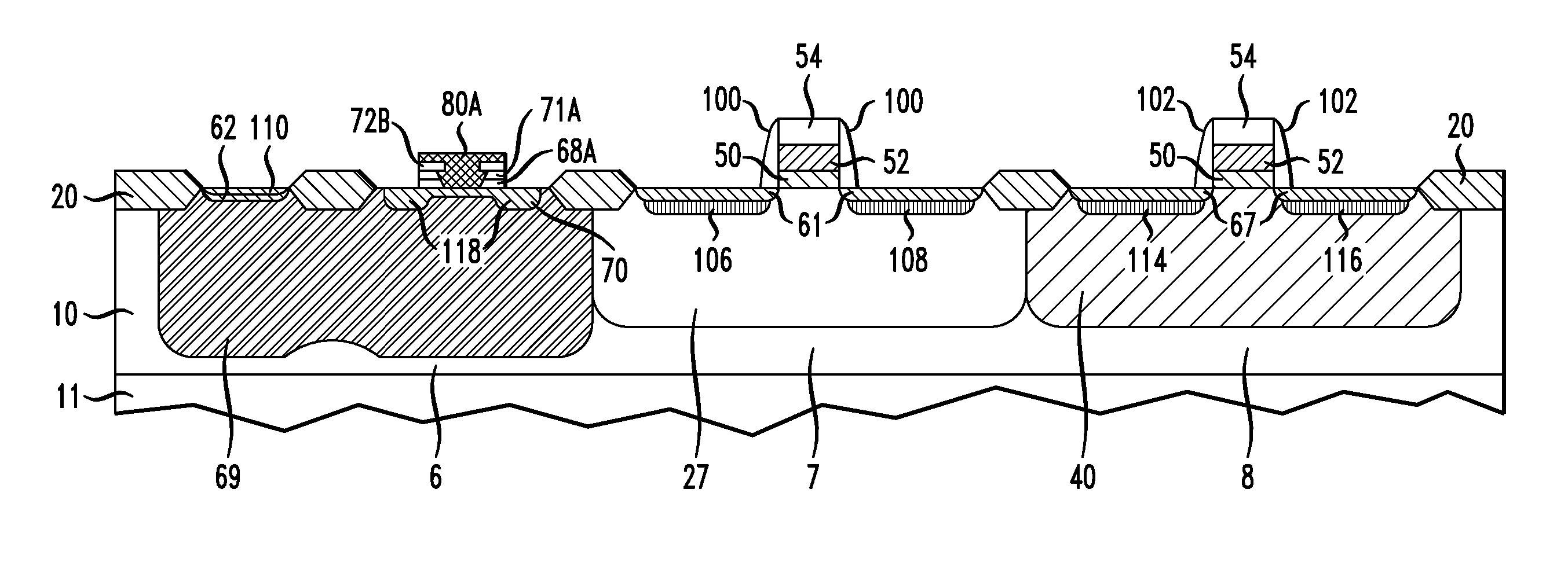

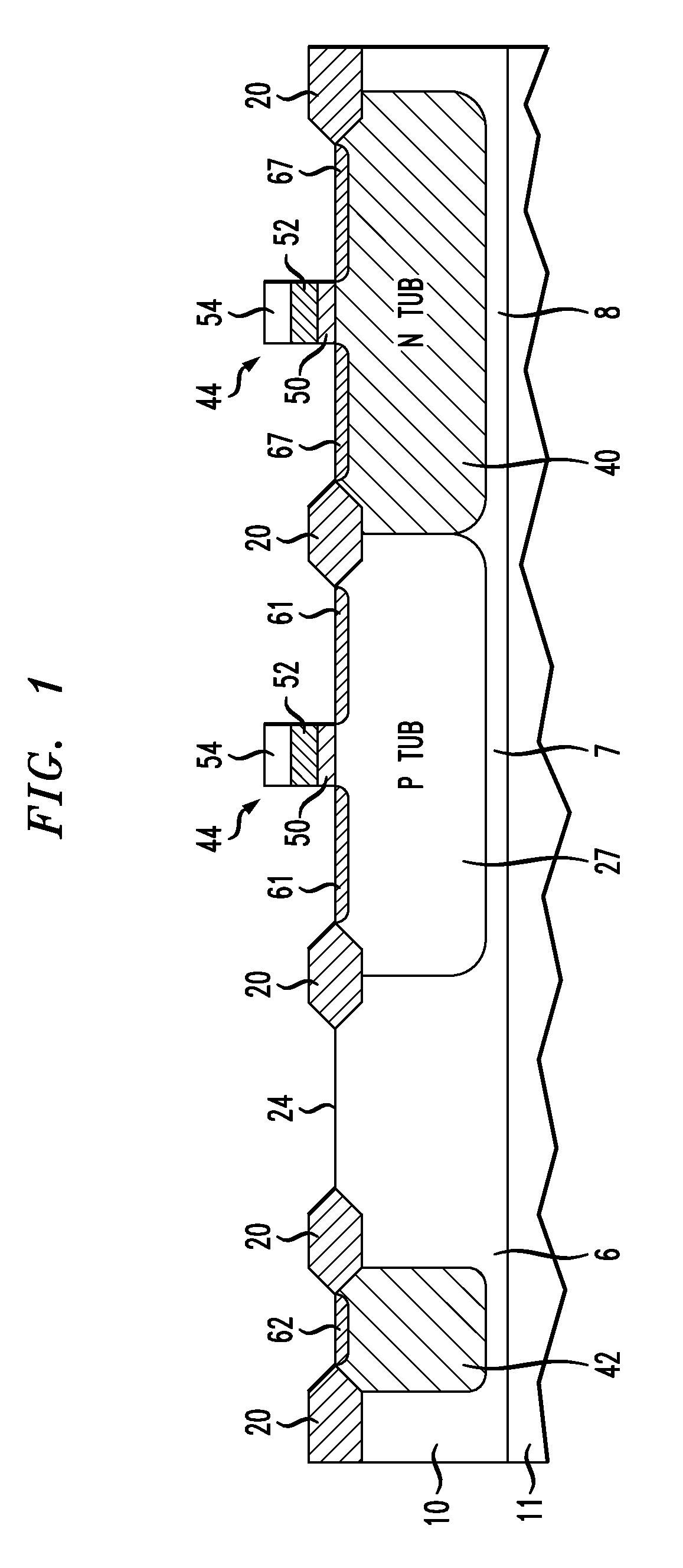

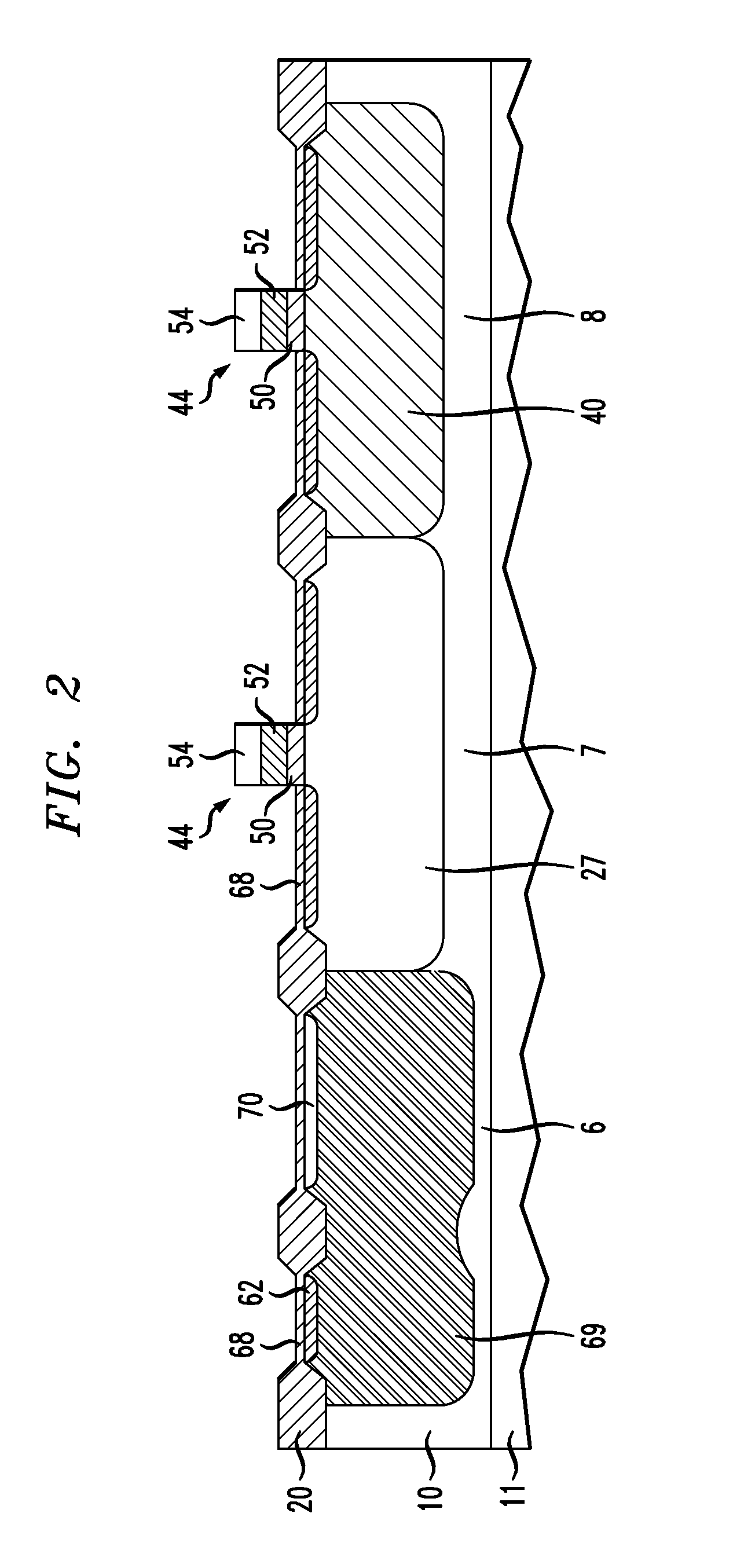

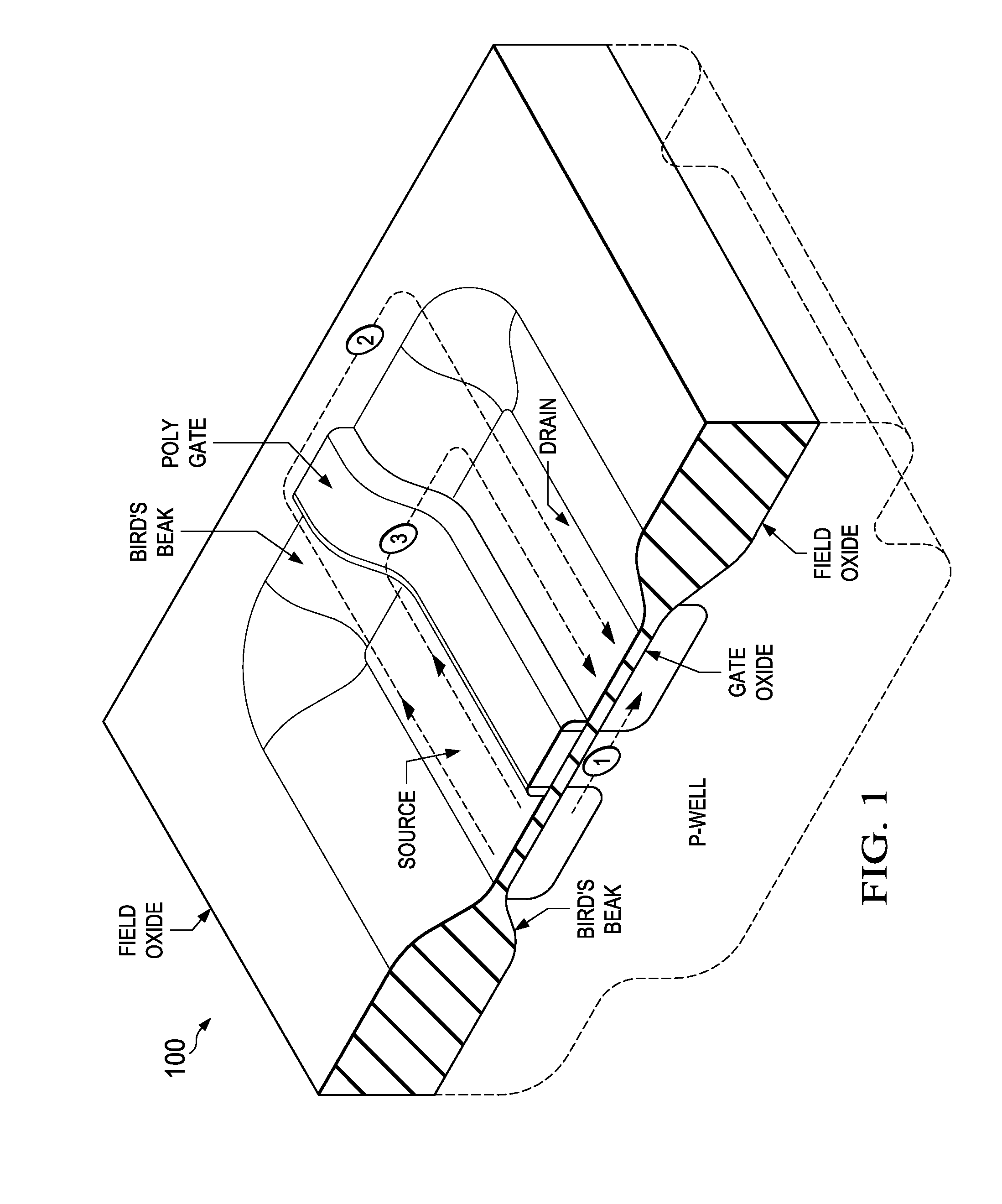

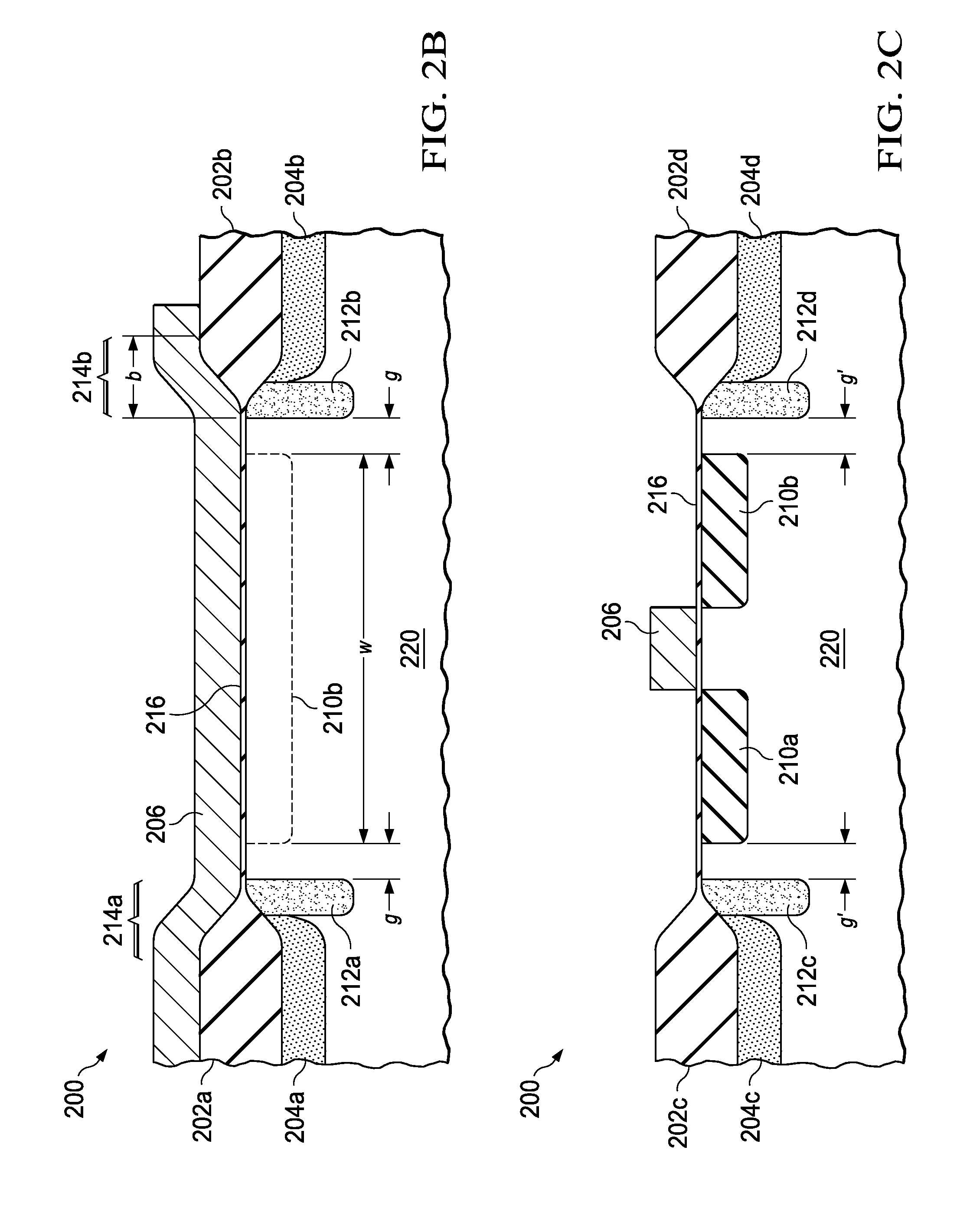

Radiation hardened NMOS devices suitable for application in NMOS, CMOS, or BiCMOS integrated circuits, and methods for fabricating them. A device includes a p-type silicon substrate, a field oxide surrounding a moat region on the substrate tapering through a bird's beak region to a gate oxide within the moat region, a heavily-doped p-type guard region underlying at least a portion of the bird's beak region and terminating at the inner edge of the bird's beak region, a gate crossing the moat region, and n-type source and drain regions spaced by a gap from the inner edge of the guard region. A variation of a local oxidation of silicon process is used with an additional bird's beak implantation mask as well as minor alterations to the conventional moat and n-type source / drain masks. The resulting devices have improved radiation tolerance while having a high breakdown voltage and minimal impact on circuit density.

Owner:TEXAS INSTR INC

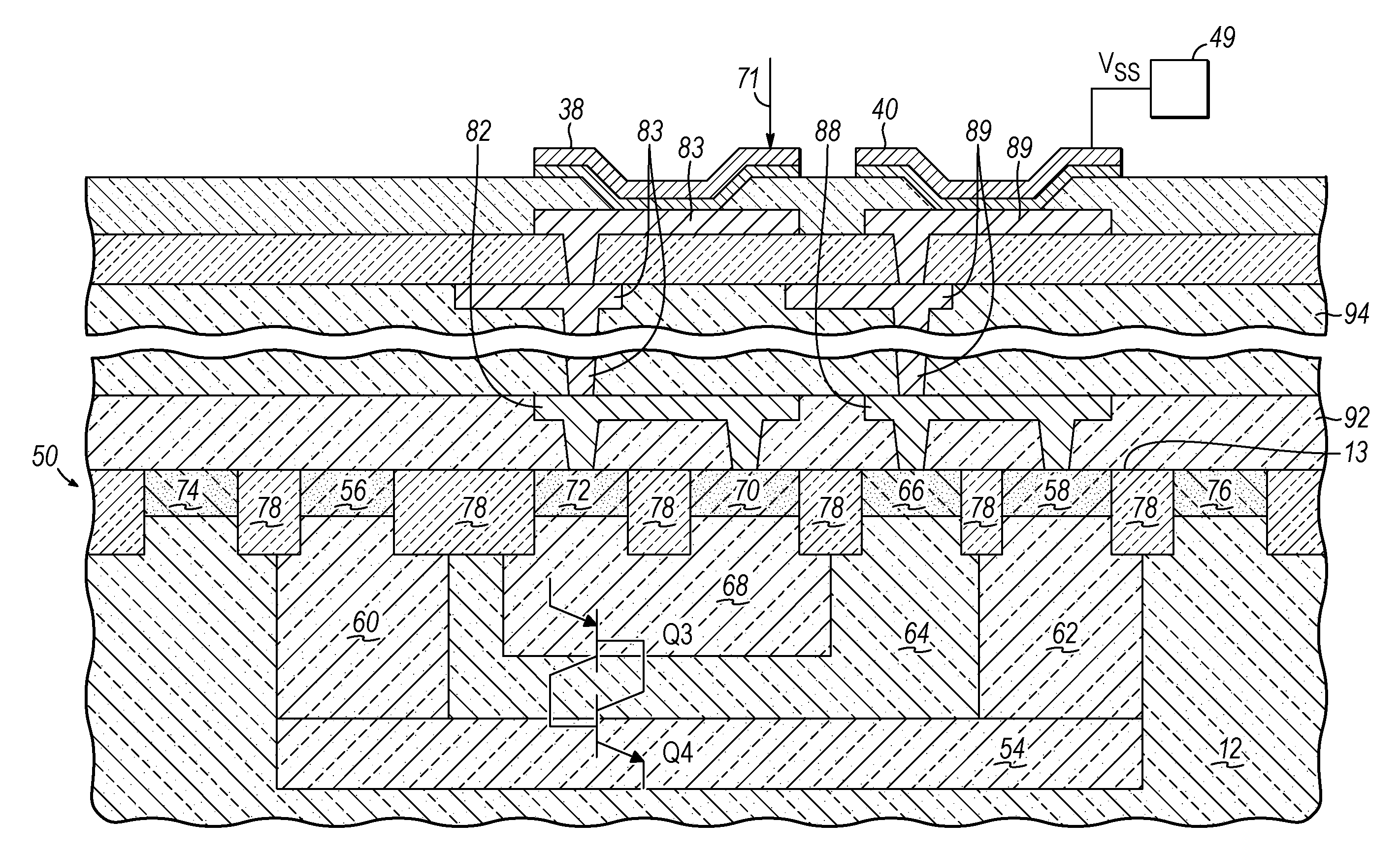

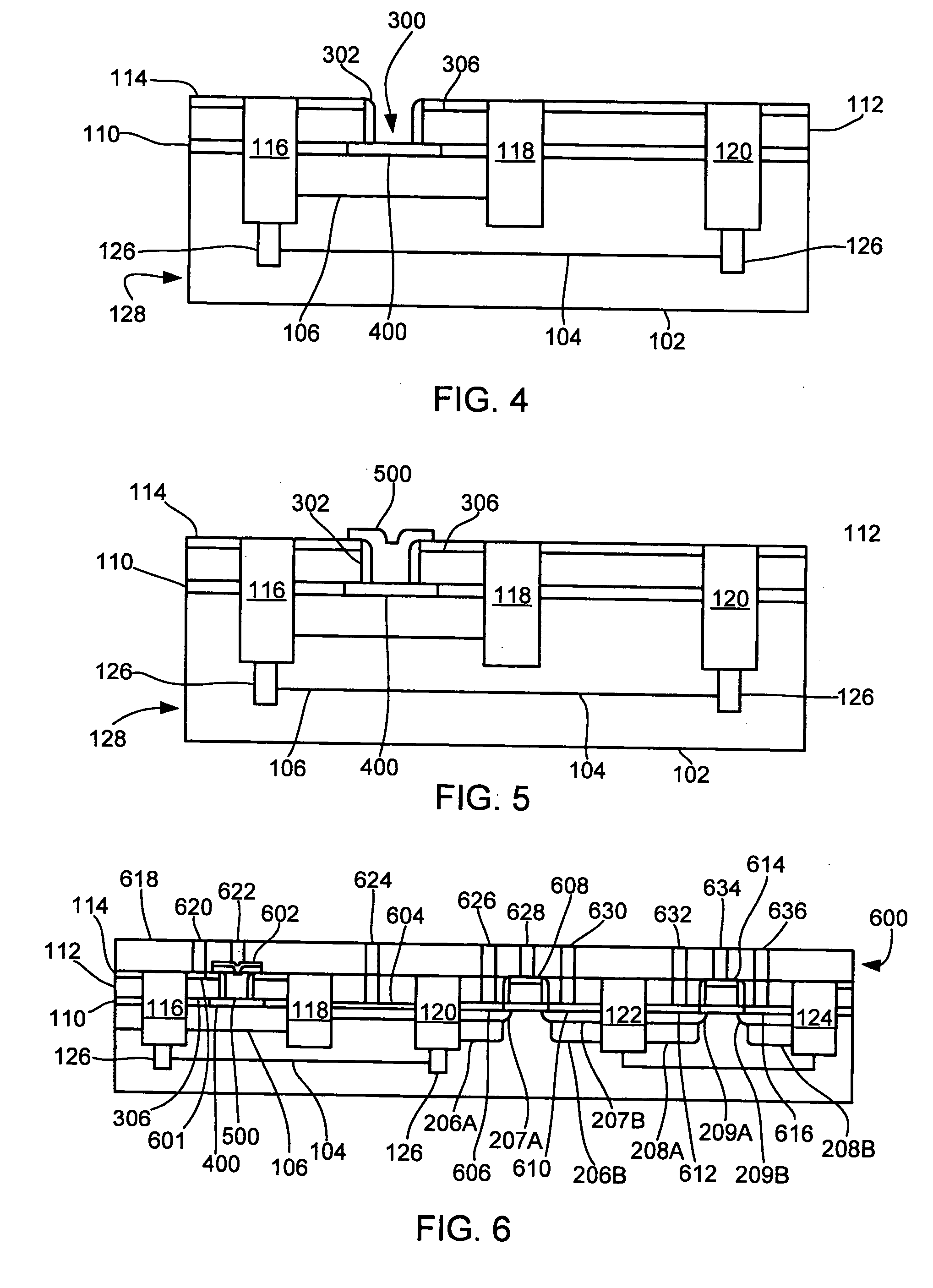

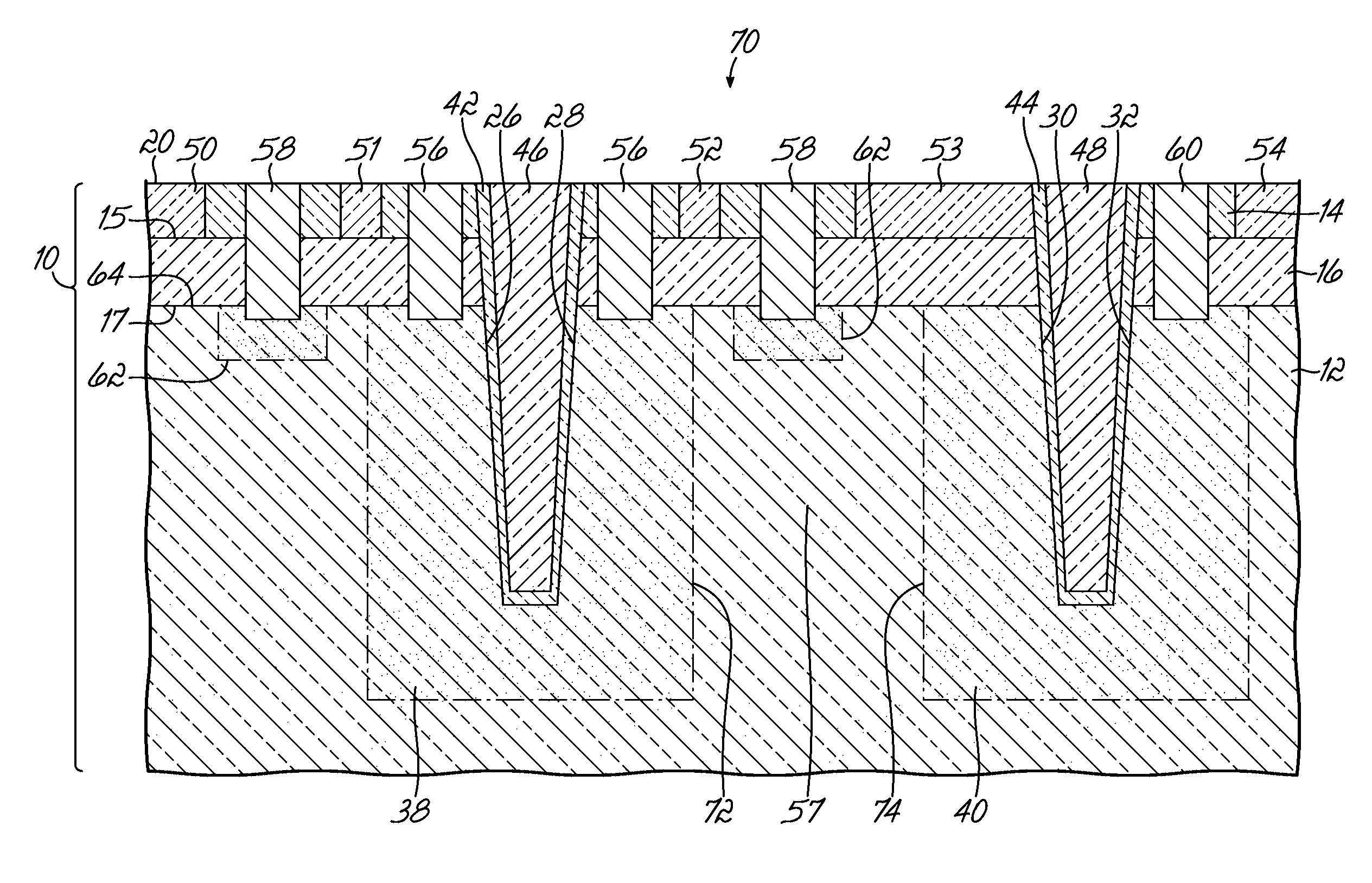

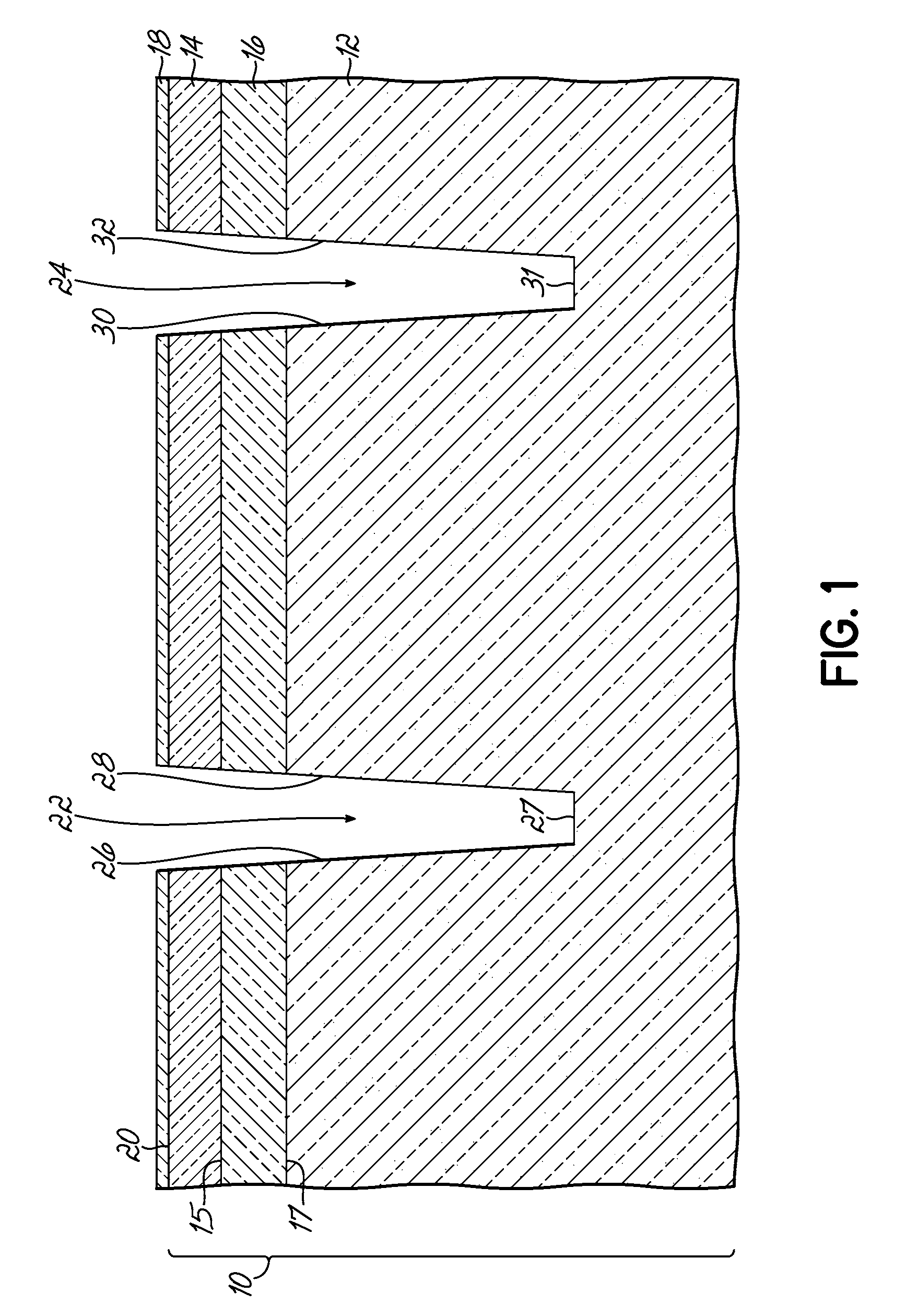

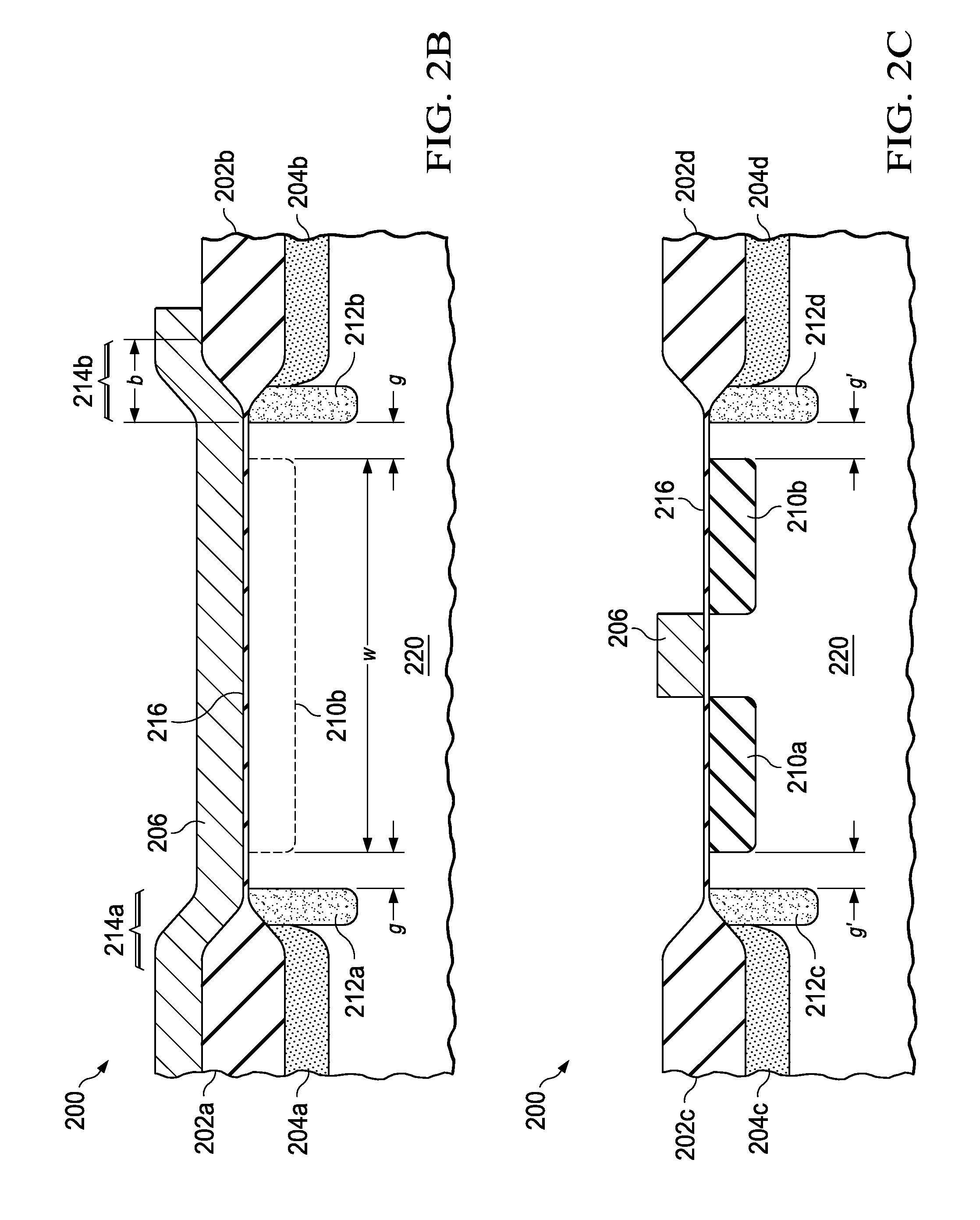

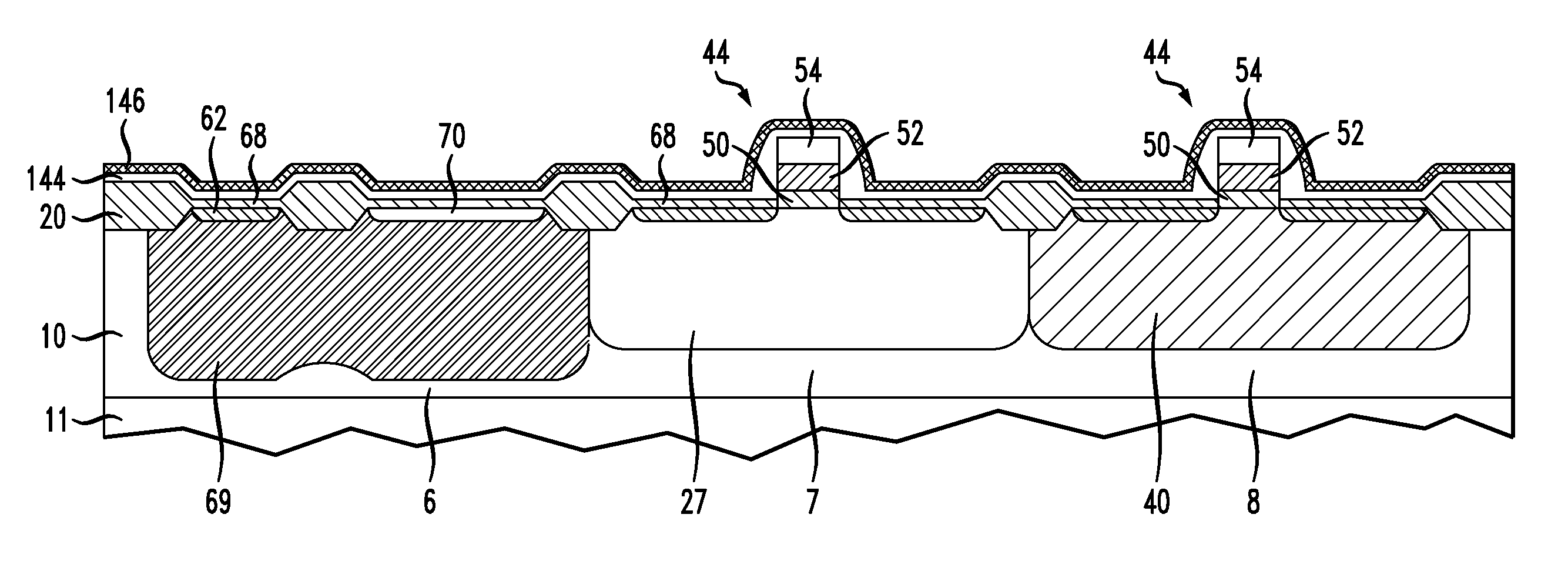

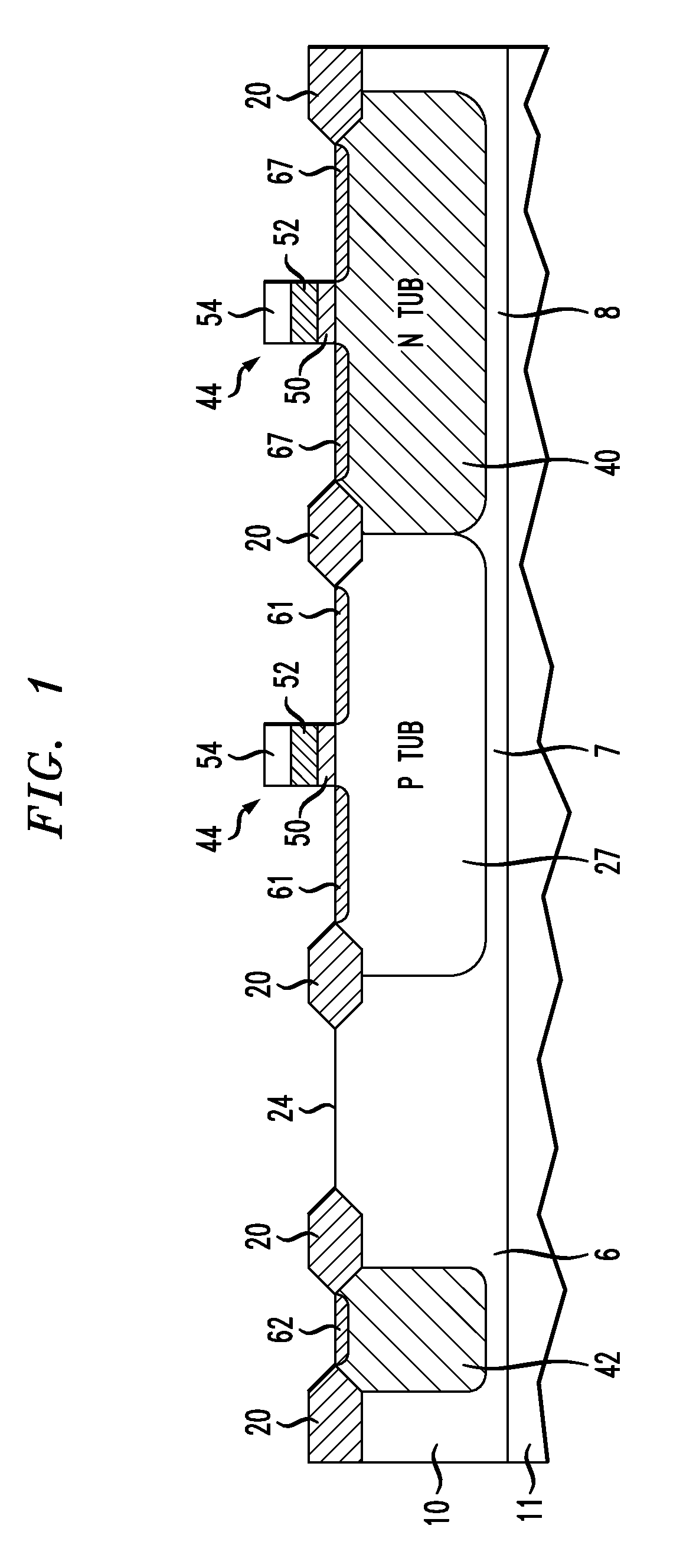

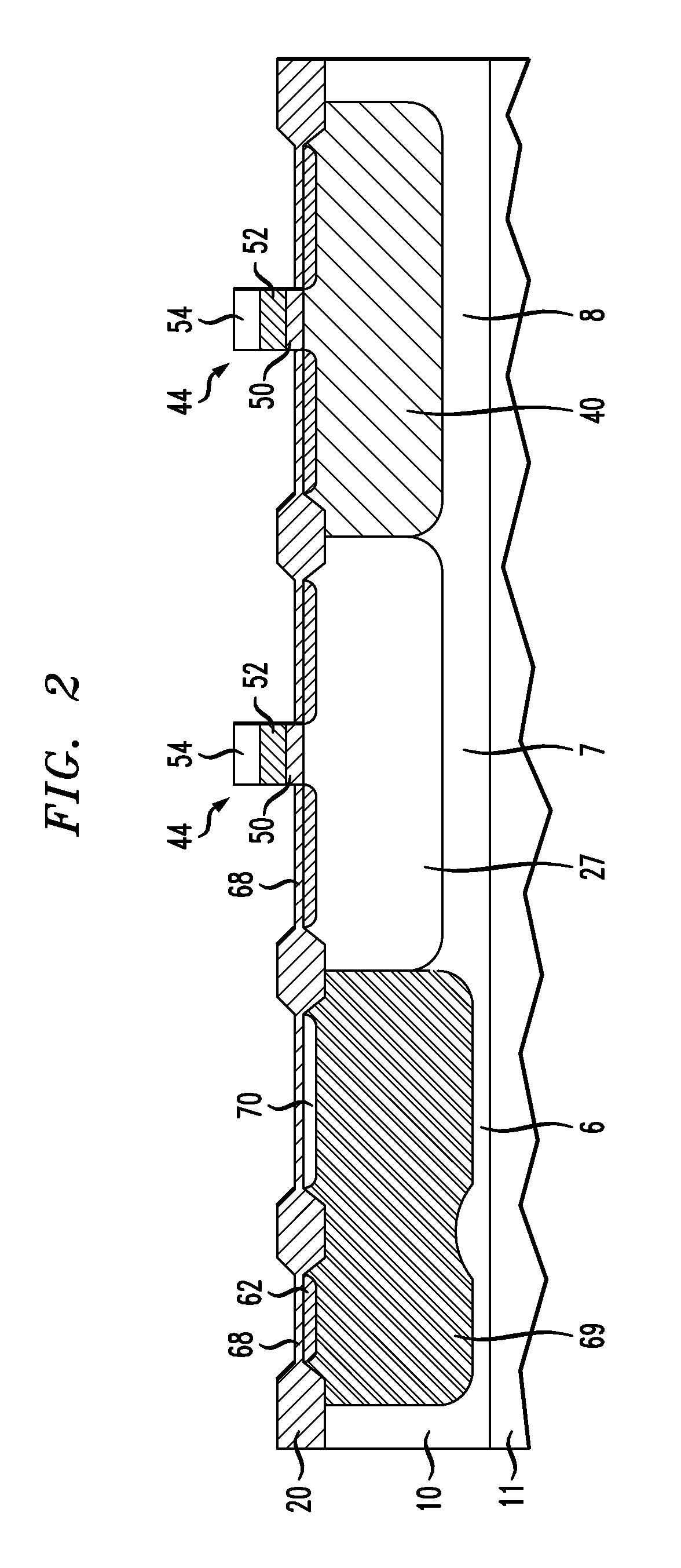

Trench generated device structures and design structures for radiofrequency and bicmos integrated circuits

ActiveUS20100230779A1TransistorSolid-state devicesBicmos integrated circuitsSemiconductor wafer fabrication

Trench-generated device structures fabricated using a semiconductor-on-insulator (SOI) wafer, design structures embodied in a machine readable medium for designing, manufacturing, or testing an integrated circuit, as well as methods for fabricating trench-generated device structures. The device structure includes a trench extending through the semiconductor and insulator layers of the SOI wafer and into the underlying semiconductor substrate, and a first doped region in the semiconductor substrate. The doped region, which extends about the trench, has a second conductivity type opposite to the first conductivity type. The device structure further includes a first contact extending from the top surface through the semiconductor and insulator layers to a portion of the semiconductor substrate outside of the doped region, and a second contact extending from the top surface through the semiconductor and insulator layers to the doped region in the semiconductor substrate.

Owner:GLOBALFOUNDRIES US INC

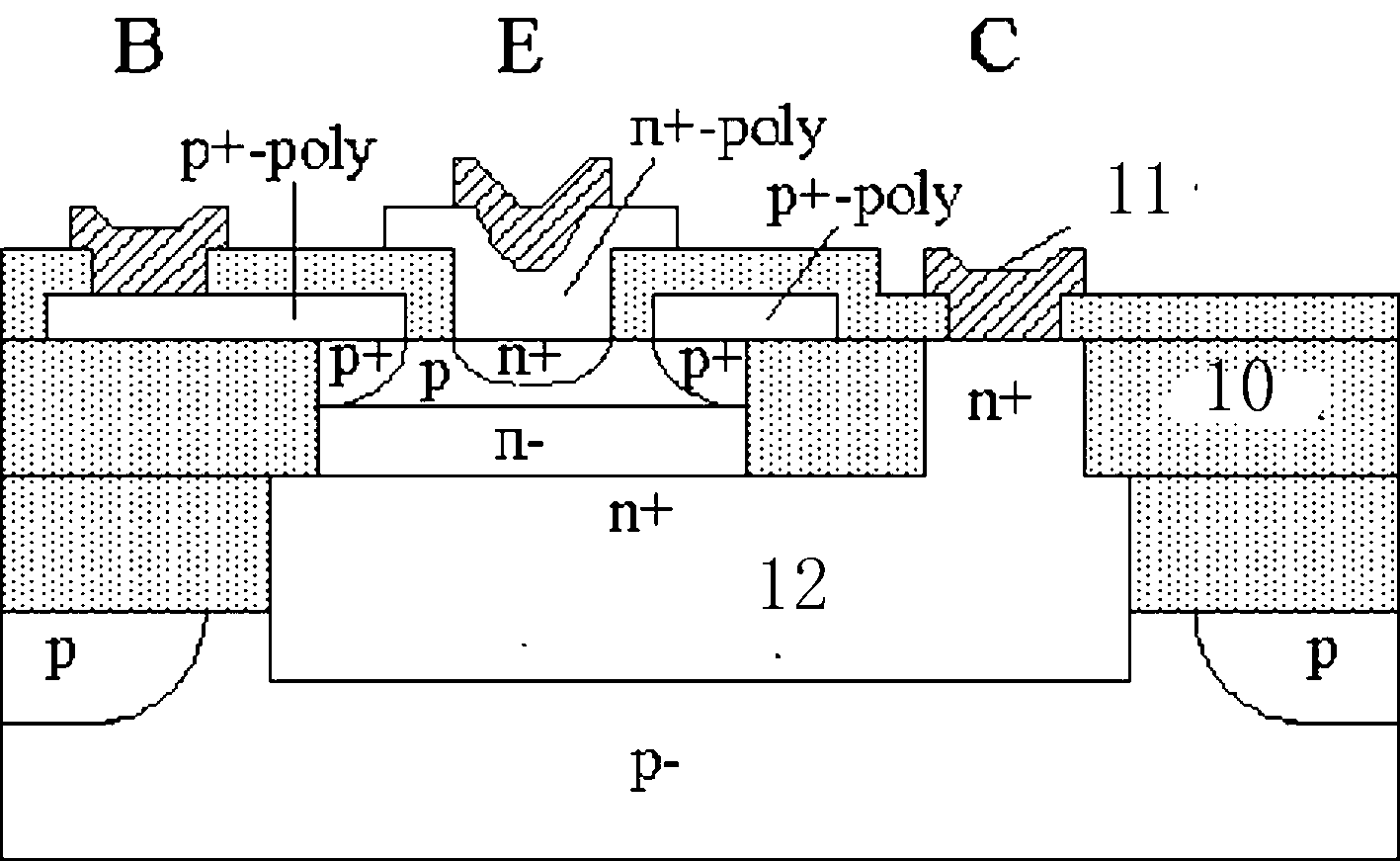

Thermally stable BiCMOS fabrication method and bipolar junction transistors formed according to the method

A method for forming BiCMOS integrated circuits and structures formed according to the method. After forming doped wells and gate stacks for the CMOS devices and collector and base regions for the bipolar junction transistor, an emitter layer is formed within an emitter window. A dielectric material layer is formed over the emitter layer and remains in place during etching of the emitter layer and removal of the etch mask. The dielectric material layer further remains in place during source / drain implant doping and activation of the implanted source / drain dopants. The dielectric material layer functions as a thermal barrier, to limit out-diffusion of the emitter dopants during the activation step.

Owner:BELL SEMICON LLC

Vertical NPNP Structure In a Triple Well CMOS Process

A vertical NPNP structure fabricated using a triple well CMOS process, as well as methods of making the vertical NPNP structure, methods of providing electrostatic discharge (ESD) protection, and design structures for a BiCMOS integrated circuit. The vertical NPNP structure may be used to provide on-chip protection to an input / output (I / O) pad from negative-voltage ESD events. A vertical PNPN structure may be also used to protect the same I / O pad from positive-voltage ESD events.

Owner:ALSEPHINA INNOVATIONS INC

Heterojunction BiCMOS integrated circuits and method therefor

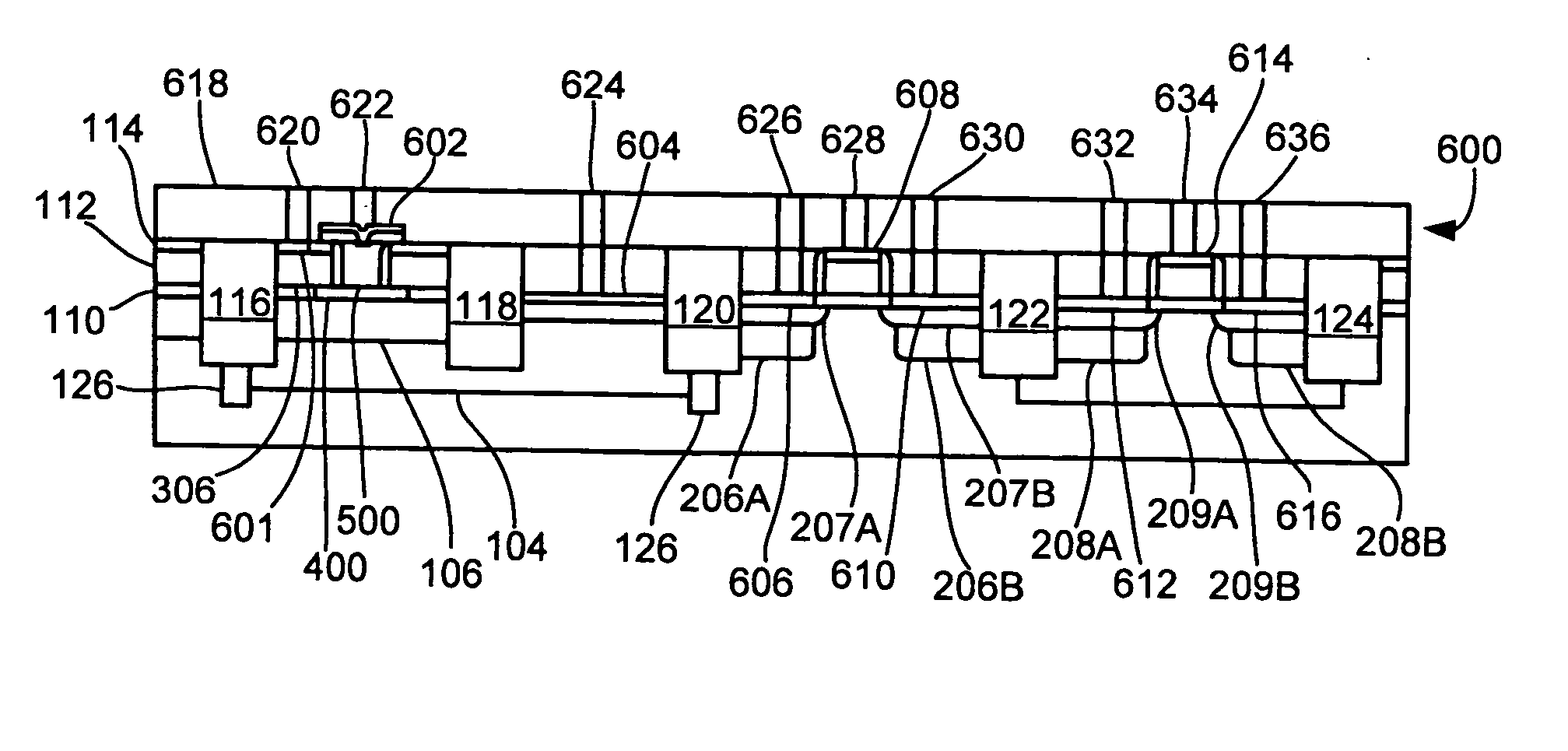

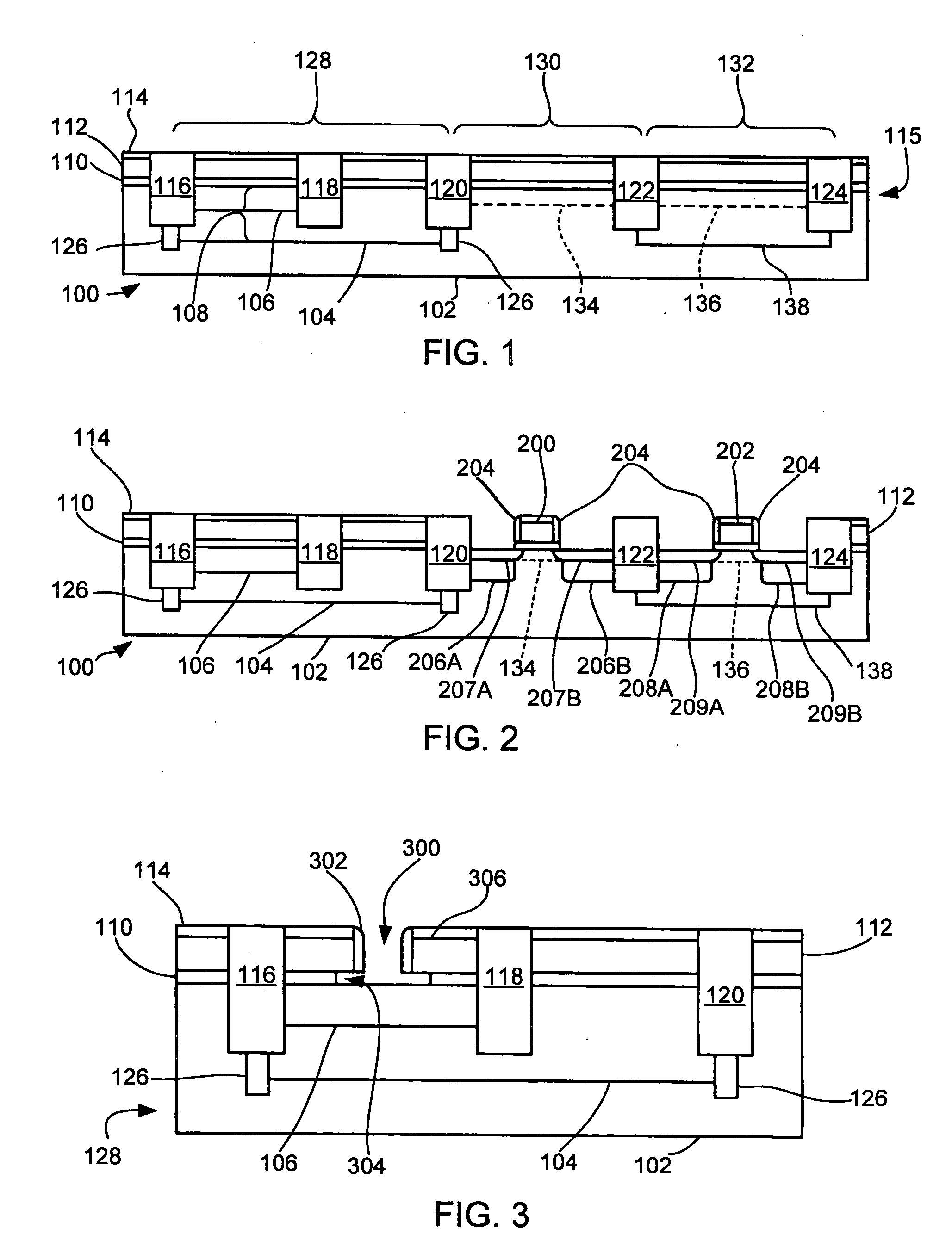

A method of manufacturing a BiCMOS integrated circuit including a CMOS transistor having a gate structure, and a heterojunction bipolar transistor having an extrinsic base structure. A substrate is provided, and a polysilicon layer is formed over the substrate. The gate structure and the extrinsic base structure are formed in the polysilicon layer. A plurality of contacts is formed through the interlevel dielectric layer to the CMOS transistor and the heterojunction bipolar transistor.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

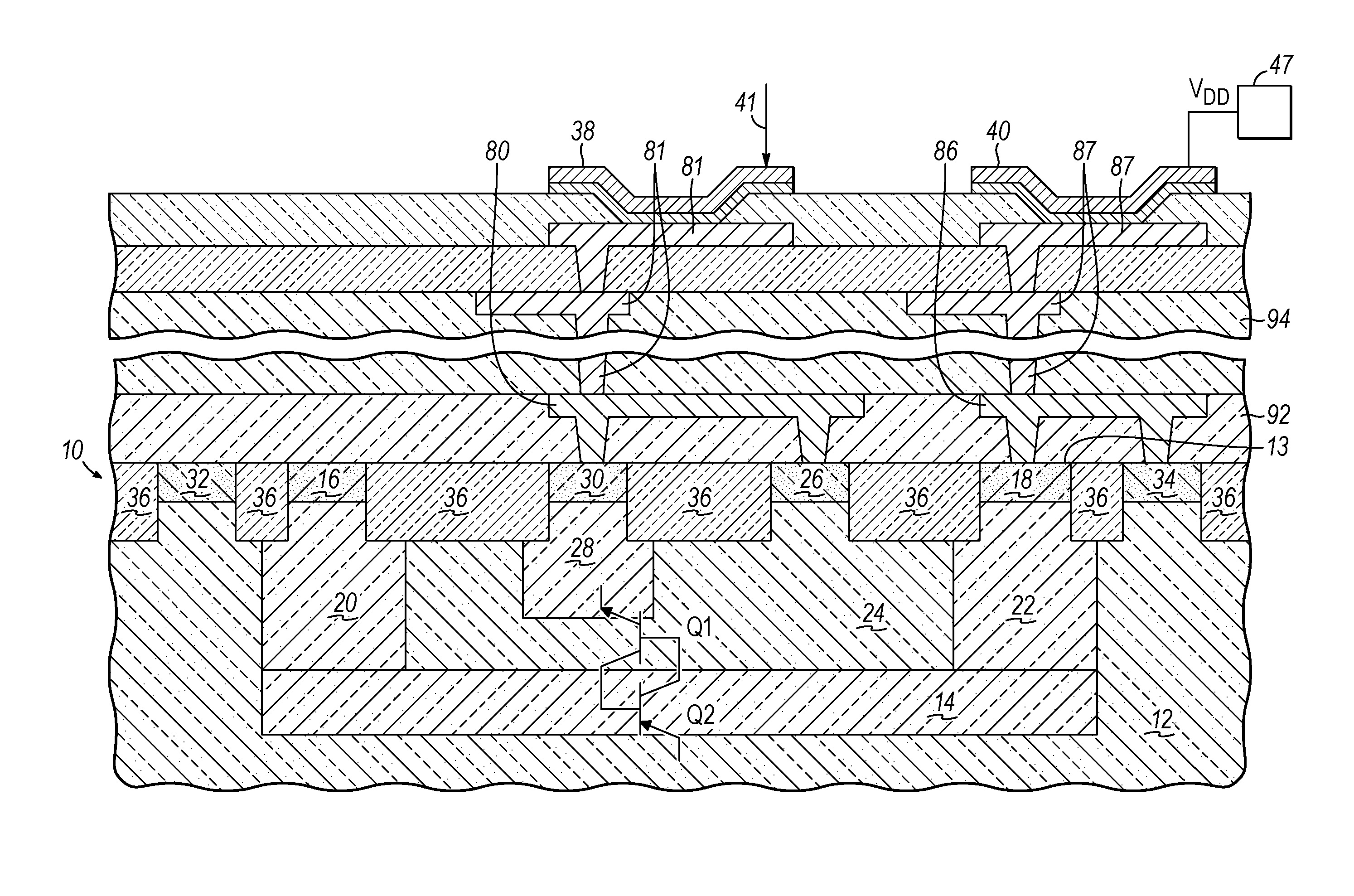

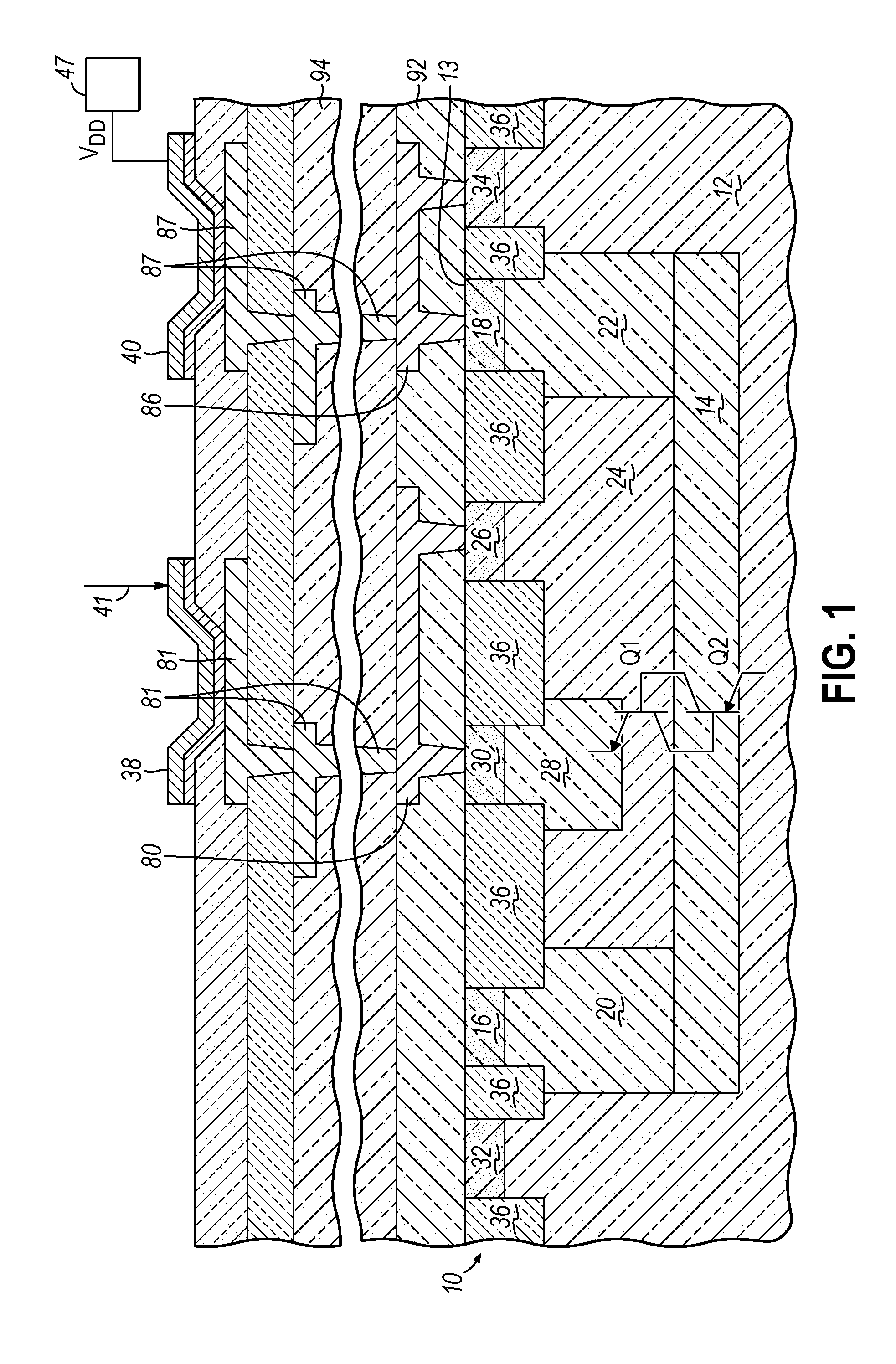

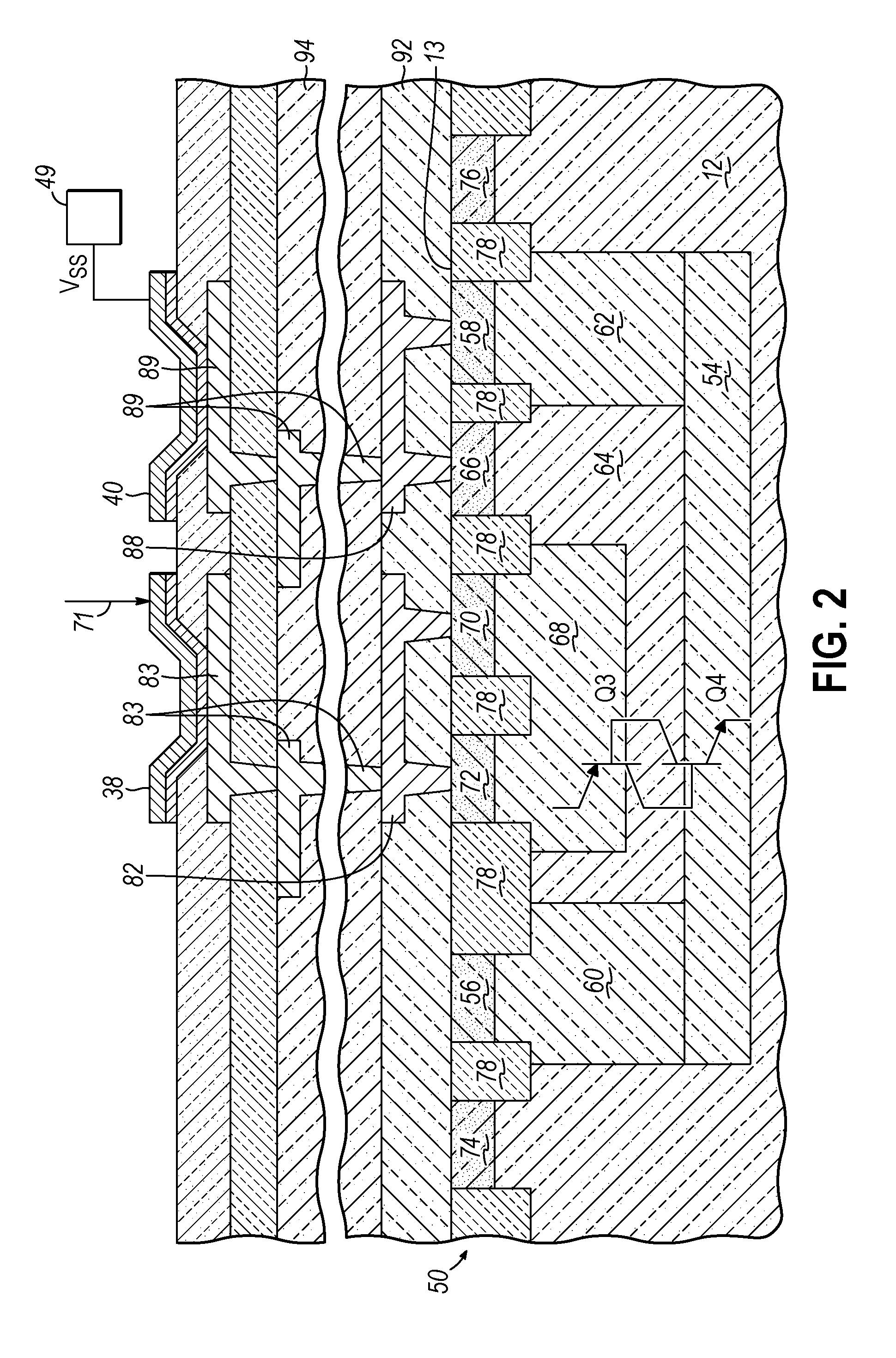

Vertical NPNP structure in a triple well CMOS process

A vertical NPNP structure fabricated using a triple well CMOS process, as well as methods of making the vertical NPNP structure, methods of providing electrostatic discharge (ESD) protection, and design structures for a BiCMOS integrated circuit. The vertical NPNP structure may be used to provide on-chip protection to an input / output (I / O) pad from negative-voltage ESD events. A vertical PNPN structure may be also used to protect the same I / O pad from positive-voltage ESD events.

Owner:ALSEPHINA INNOVATIONS INC

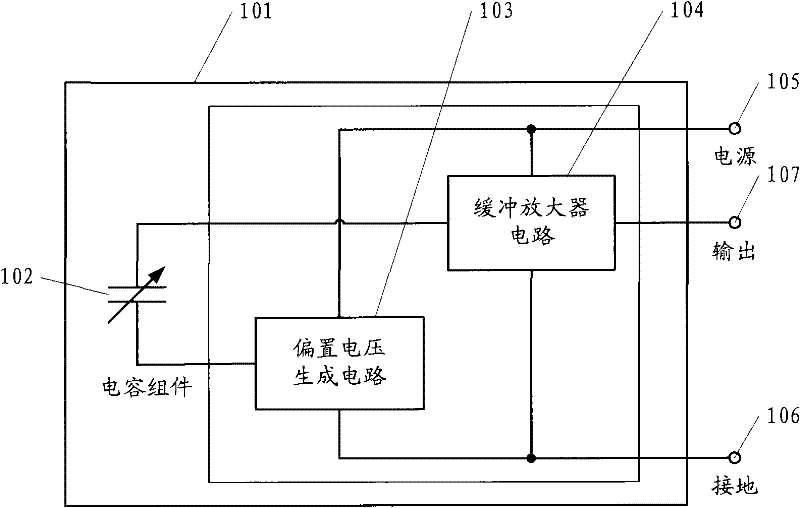

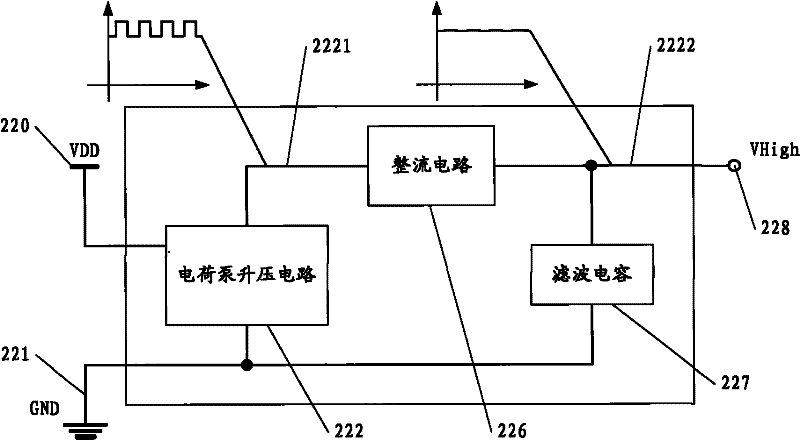

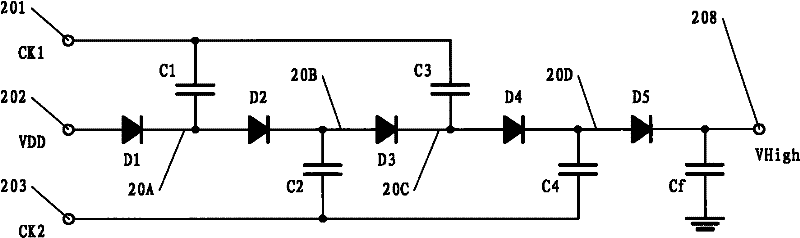

An integrated microphone bias voltage control method and bias voltage generation circuit

ActiveCN102271300AIncrease output impedanceSmall fluctuationTransducer acoustic reaction preventionElectric variable regulationCMOSBicmos integrated circuits

The invention discloses an integrated microphone offset voltage control method and an offset circuit. The method is implemented based on the CMOS (complementary metal-oxide-semiconductor) or BiCMOS (bipolar complementary metal oxide semiconductor) integrated circuit production process, and is applied to an offset voltage generating circuit of a silicon microphone which comprises a charge pump booster circuit, a rectifier circuits and a filter circuits. According to the method, the relationship between output voltages and input currents of the offset voltage generating circuit is controlled, so that the circuit is within a neighboring region with zero current, the input currents of output nodes of the circuit are increased with the increase of output voltages, and the increasing slope rises rapidly with the increase in voltage. The circuit is implemented by connecting a compensation circuit in parallel between the output terminal and the ground terminal of the rectifier circuit; and the compensation circuit has the following functions: in the region of almost zero current and close to the voltage of offset voltage working points of the microphone, the input currents of the output nodes are increased with the increase of voltages applied to the two ends of the compensation circuit, and the current increase rate is higher than the voltage increase rate.

Owner:SHANDONG GETTOP ACOUSTIC

Radiation hardened mos devices and methods of fabrication

ActiveUS20150108588A1Improve radiation hardnessMinimal impactTransistorSemiconductor/solid-state device detailsCMOSBeak

Radiation hardened NMOS devices suitable for application in NMOS, CMOS, or BiCMOS integrated circuits, and methods for fabricating them. A device includes a p-type silicon substrate, a field oxide surrounding a moat region on the substrate tapering through a Bird's Beak region to a gate oxide within the moat region, a heavily-doped p-type guard region underlying at least a portion of the Bird's Beak region and terminating at the inner edge of the Bird's Beak region, a gate included in the moat region, and n-type source and drain regions spaced by a gap from the inner edge of the Bird's Beak and guard regions. A variation of minor alterations to the conventional moat and n-type source / drain masks. The resulting devices have improved radiation tolerance while having a high breakdown voltage and minimal impact on circuit density.

Owner:TEXAS INSTR INC

Trench generated device structures and design structures for radiofrequency and BiCMOS integrated circuits

Trench-generated device structures fabricated using a semiconductor-on-insulator (SOI) wafer, design structures embodied in a machine readable medium for designing, manufacturing, or testing an integrated circuit, as well as methods for fabricating trench-generated device structures. The device structure includes a trench extending through the semiconductor and insulator layers of the SOI wafer and into the underlying semiconductor substrate, and a first doped region in the semiconductor substrate. The doped region, which extends about the trench, has a second conductivity type opposite to the first conductivity type. The device structure further includes a first contact extending from the top surface through the semiconductor and insulator layers to a portion of the semiconductor substrate outside of the doped region, and a second contact extending from the top surface through the semiconductor and insulator layers to the doped region in the semiconductor substrate.

Owner:GLOBALFOUNDRIES U S INC

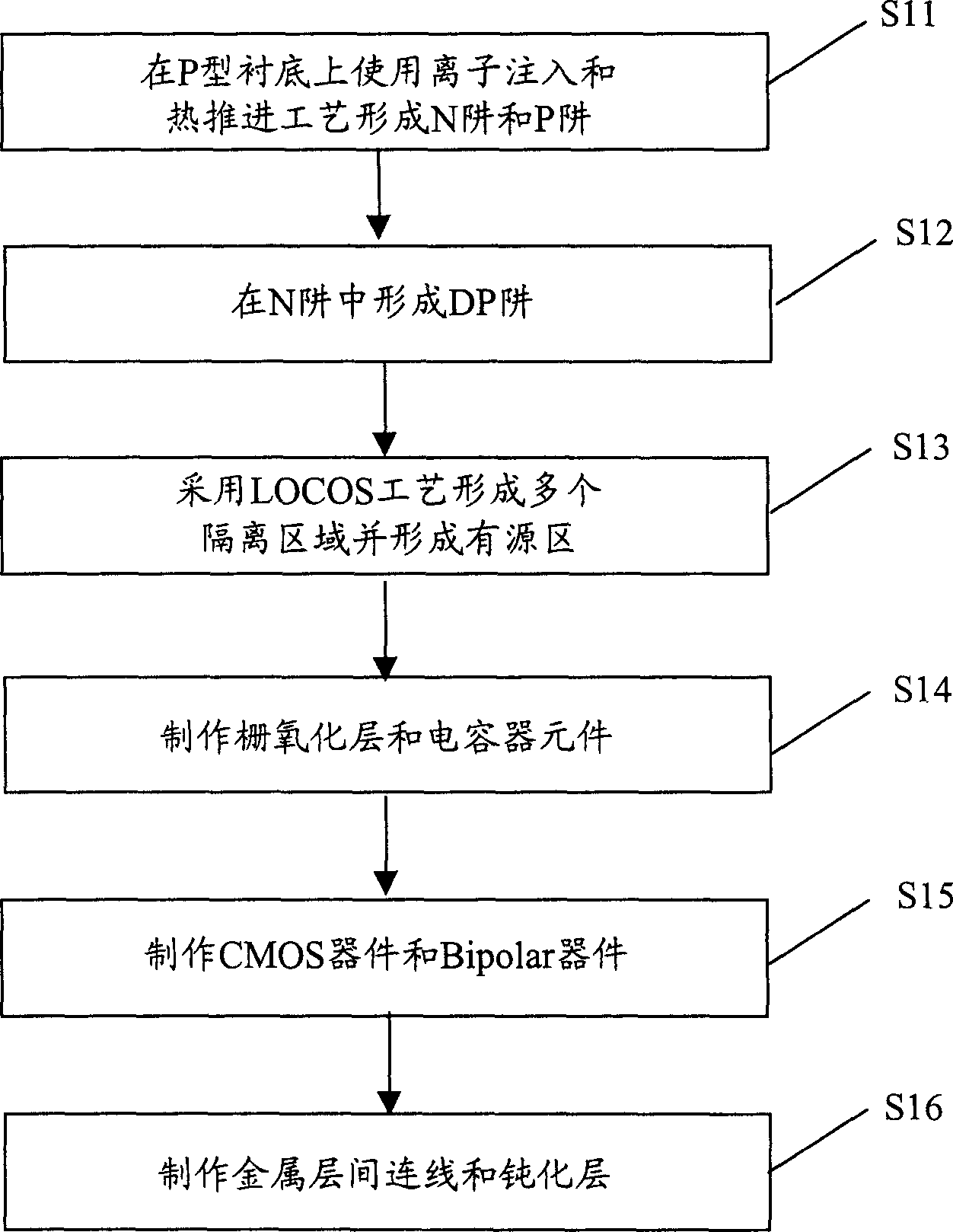

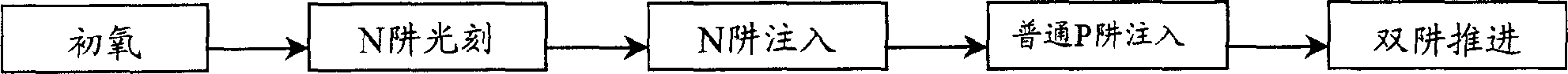

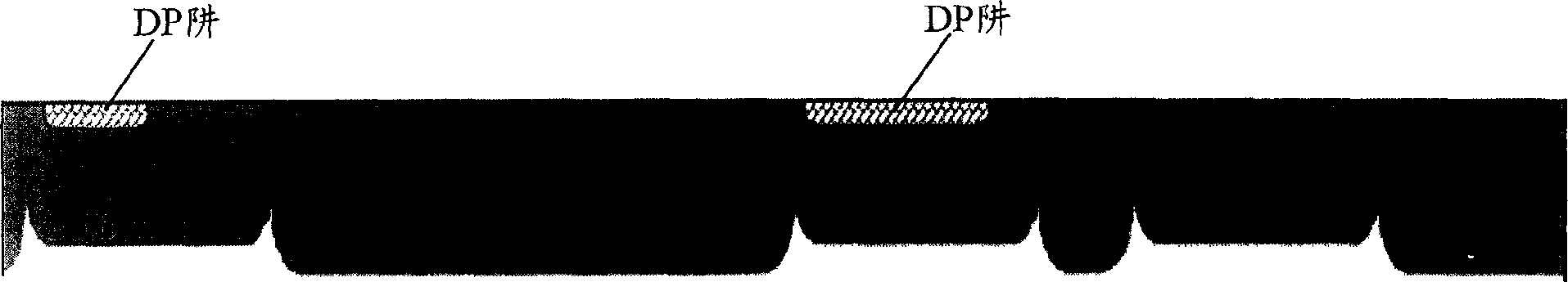

Process for manufacturing 0.8 micron silicon bipolar CMOS integrated circuit

ActiveCN1734748AGood low noise functionIncrease resistanceSemiconductor/solid-state device manufacturingLow voltageLOCOS

This invention discloses a improved 0.8um BICMOS IC manufacture technique to form DP trap in N trap, which comprises following steps: forming N trap and P trap on P-type substrate by ion implantation and thermal propulsion techniques; form DP trap in N trap: first, using photoresist to define the zone for DP trap, then forming DP trap by ion implantation; using LOCOS technique to form a plurality of separation zones with place same to formed trap and active region; preparing grid oxide layer and capacitor, wherein, the oxide layers for high-voltage and low-voltage devices are completed on same step; preparing CMOS device and Bipolar device; forming insulated NMOS and Bipolar NPN device on N trap with DP trap; manufacturing connecting wire between metal layers and passivation layer. The invention can simplify process and decrease cost.

Owner:ADVANCED SEMICON MFG CO LTD

Device having improved radiation hardness and high breakdown voltages

Radiation hardened NMOS devices suitable for application in NMOS, CMOS, or BiCMOS integrated circuits, and methods for fabricating them. A device includes a p-type silicon substrate, a field oxide surrounding a moat region on the substrate tapering through a Bird's Beak region to a gate oxide within the moat region, a heavily-doped p-type guard region underlying at least a portion of the Bird's Beak region and terminating at the inner edge of the Bird's Beak region, a gate included in the moat region, and n-type source and drain regions spaced by a gap from the inner edge of the Bird's Beak and guard regions. A variation of minor alterations to the conventional moat and n-type source / drain masks. The resulting devices have improved radiation tolerance while having a high breakdown voltage and minimal impact on circuit density.

Owner:TEXAS INSTR INC

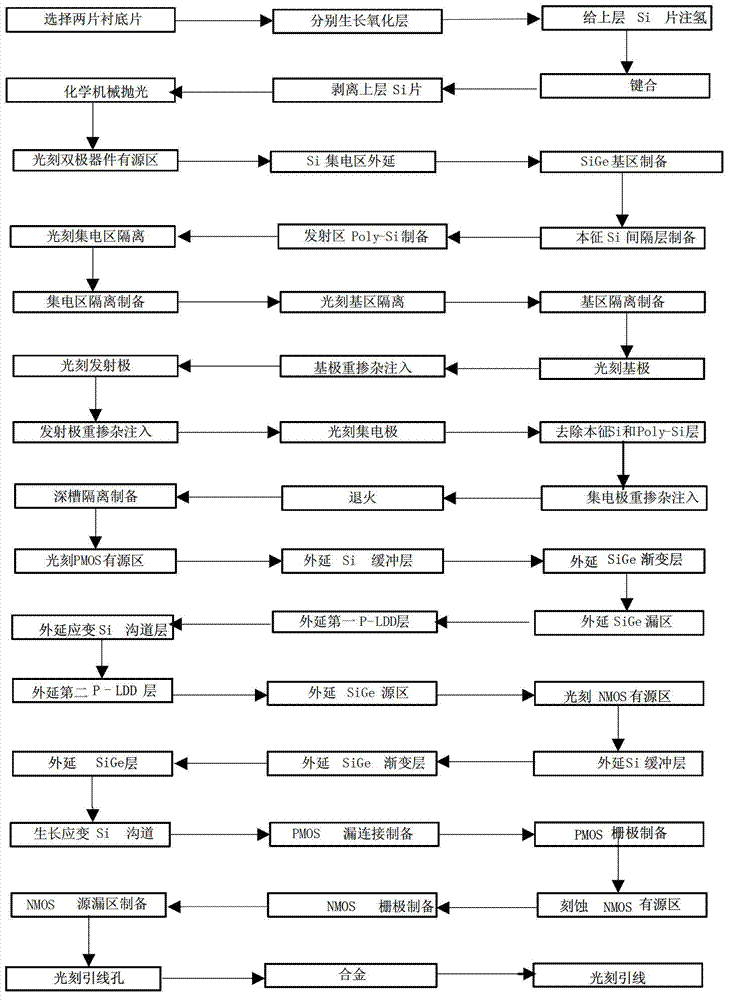

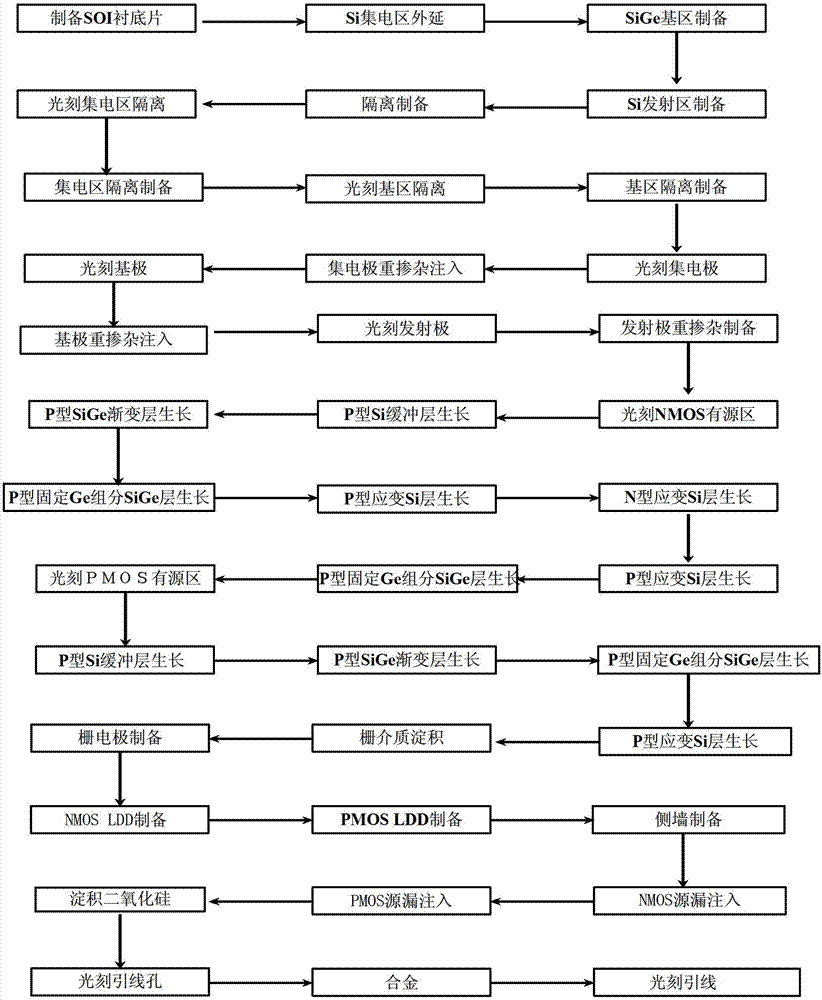

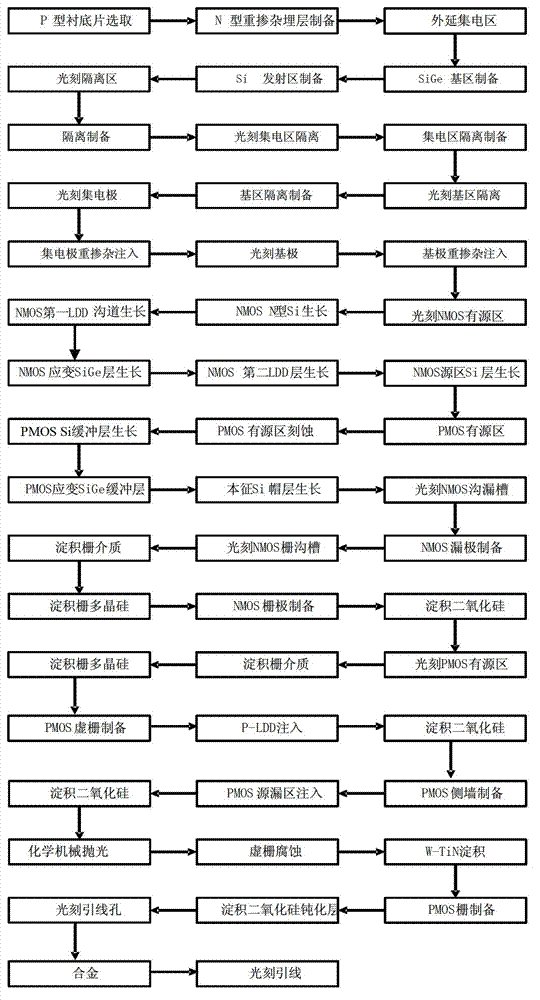

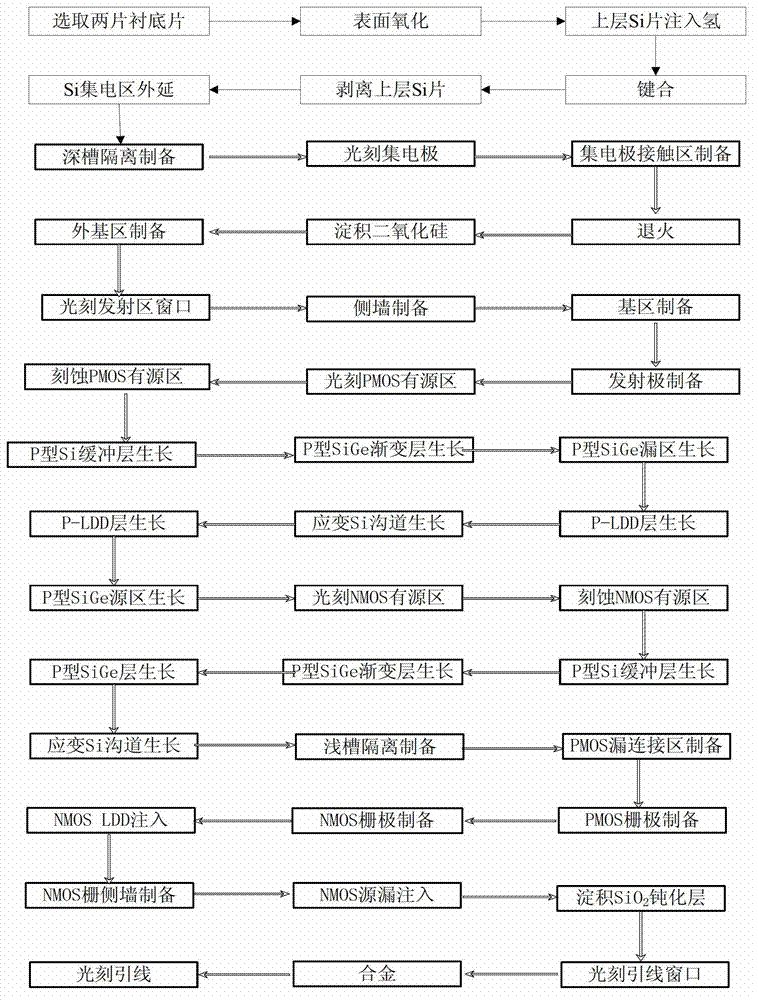

Double-polycrystal and double-strain mixed crystal face Si-base Bi CMOS (complementary metal-oxide-semiconductor transistor) integrated device and manufacturing method thereof

InactiveCN102738161AHigh frequencyImprove current drive capabilitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringP channel

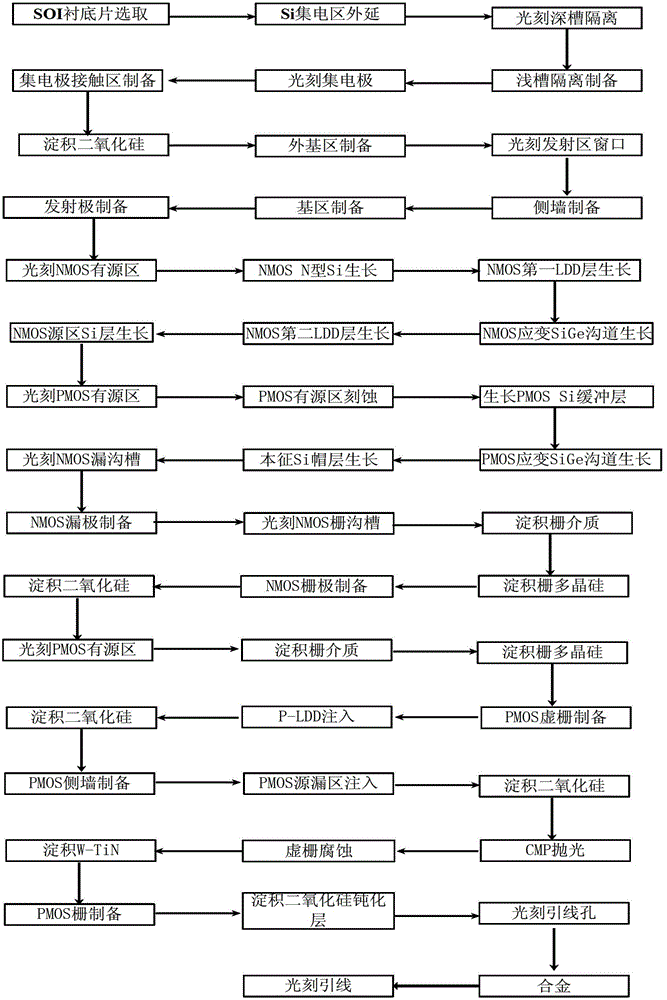

The invention discloses a double-polycrystal and double-strain mixed crystal face Si-base Bi CMOS (complementary metal-oxide-semiconductor transistor) integrated device and a manufacturing method of the double-polycrystal and double-strain mixed crystal face Si-base Bi CMOS integrated device. The method provided by the invention comprises the following steps of: manufacturing an SOI (silicon on insulator) substrate with a crystal face (110) being as an upper base material and a crystal face (100) being as a lower base material; growing N-Si to be as a bipolar device collector region; growing P-SiGe / i-Si / i-Poly-Si in a base region in a photoetching region, manufacturing an emission electrode, a base electrode and a collector electrode, and forming an SiGe Hbt device; manufacturing a deep groove for isolation; selectively growing a PMOS (P-channel metal oxide semiconductor) device active region with the crystal face (110) in a PMOS device region and manufacturing a compression strain Si vertical channel PMOS device; etching a deep groove in an NMOS (N-channel metal oxide semiconductor) device region, selectively growing an NMOS device active region with the crystal face (100) and manufacturing an Si channel NMOS device; and manufacturing the Si-base Bi CMOS integrated device and circuit. According to the invention, the characteristics that electronic mobility of a tensile strain Si is higher than that of a body Si material, the hole mobility of a compression strain Si material is higher than that of the body Si material and mobility is anisotropic are fully used to manufacture the double-polycrystal and double-strain mixed crystal face Si-base Bi CMOS integrated circuit.

Owner:XIDIAN UNIV

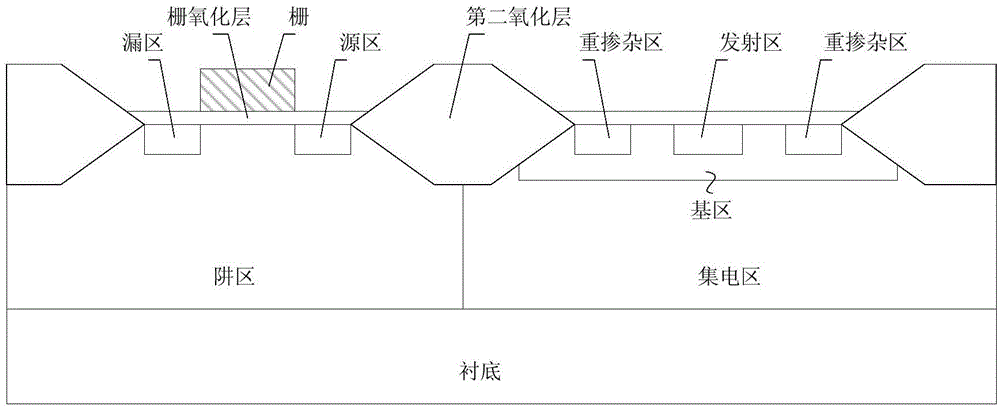

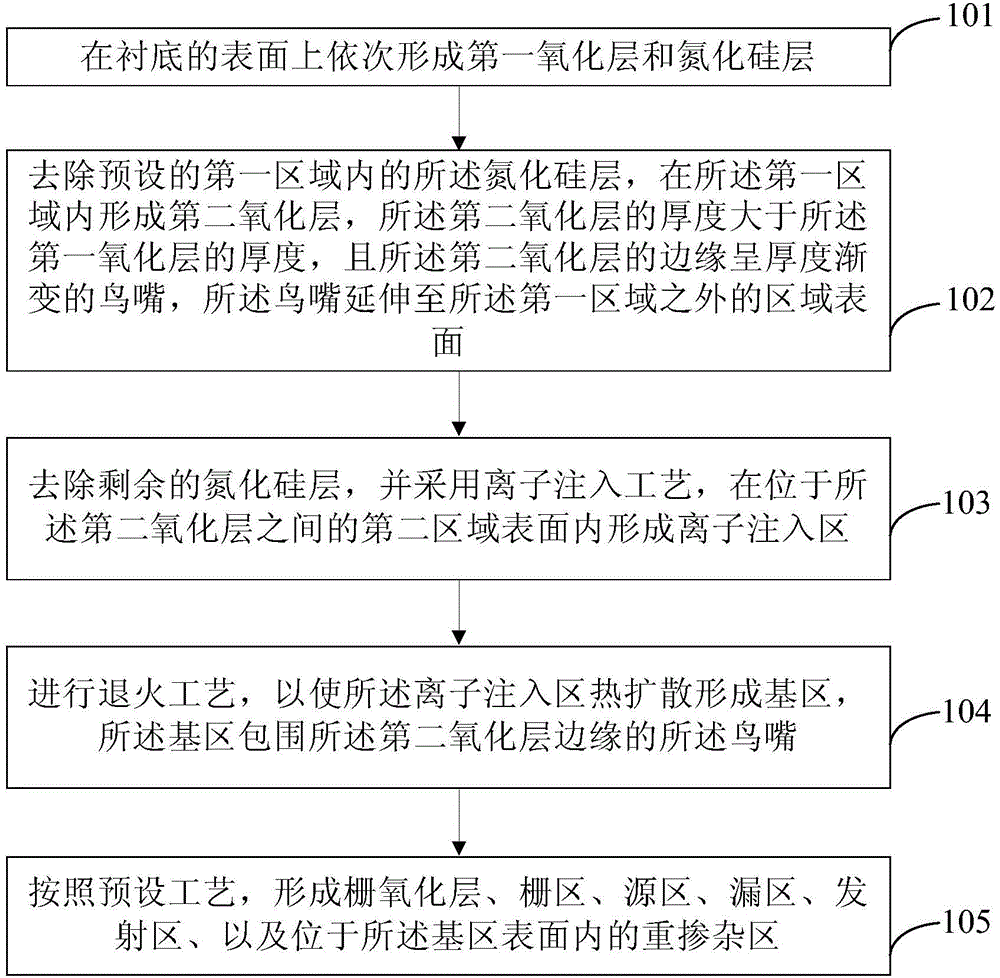

Manufacturing method of BiCMOS integrated circuit

InactiveCN105990254AImprove reverse withstand voltageIncrease working voltageSemiconductor/solid-state device manufacturingSemiconductor devicesBicmos integrated circuitsEngineering

The present invention provides a manufacturing method of a BiCMOS integrated circuit. The method comprises a step of orderly forming a first oxide layer and the silicon nitride layer on the surface of a substrate, a step of removing the silicon nitride layer in a preset first area, forming second oxide layers in the first area, wherein the edges of the second oxide layers are in the shape of a beak with increasing thickness, and the beak extends to the area surface outside the first area, a step of removing the remaining silicon nitride layer and forming ion implanting area in the second area surface between the second oxide layers, a step of carrying out annealing process such that the ion implanting area is allowed to be in thermal diffusion to form a base area which surrounds the beaks of the edges of the second oxide layers. Through the scheme provided by the invention, the base area can laterally spread to an area under the beaks and surrounds the beaks, when a transistor is under high voltage, a wide depletion layer can be realized in the base area, thus the reverse voltage withstanding of the BiCMOS integrated circuit is improved, the highest working voltage of the transistor is raised, and the requirement of a high voltage device is satisfied.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

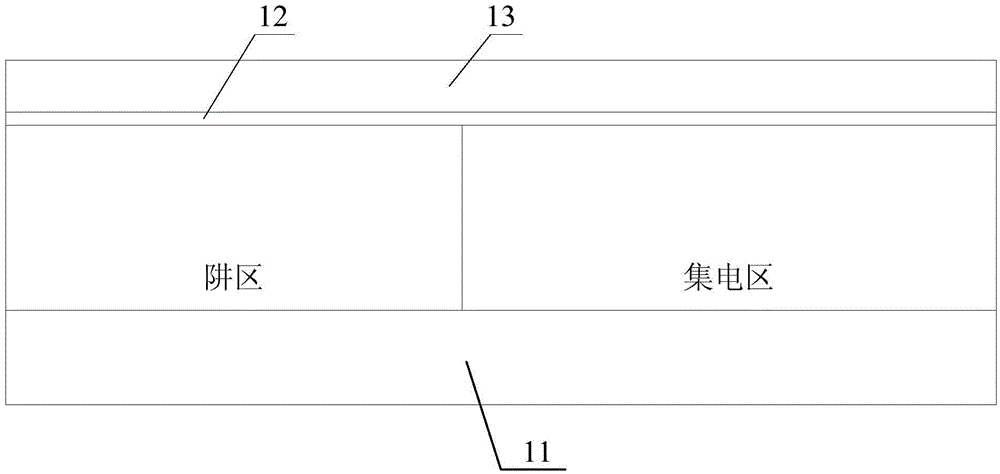

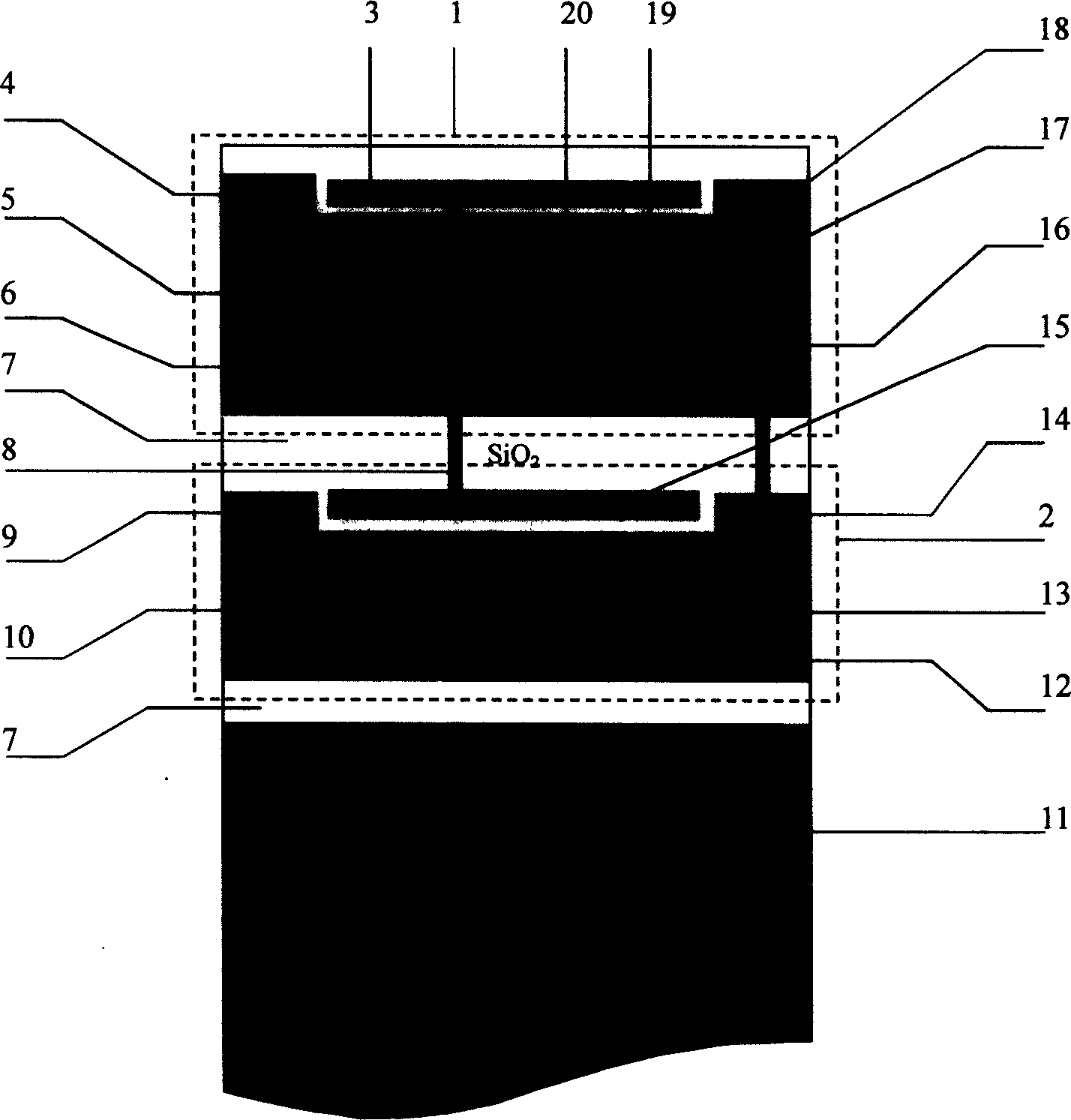

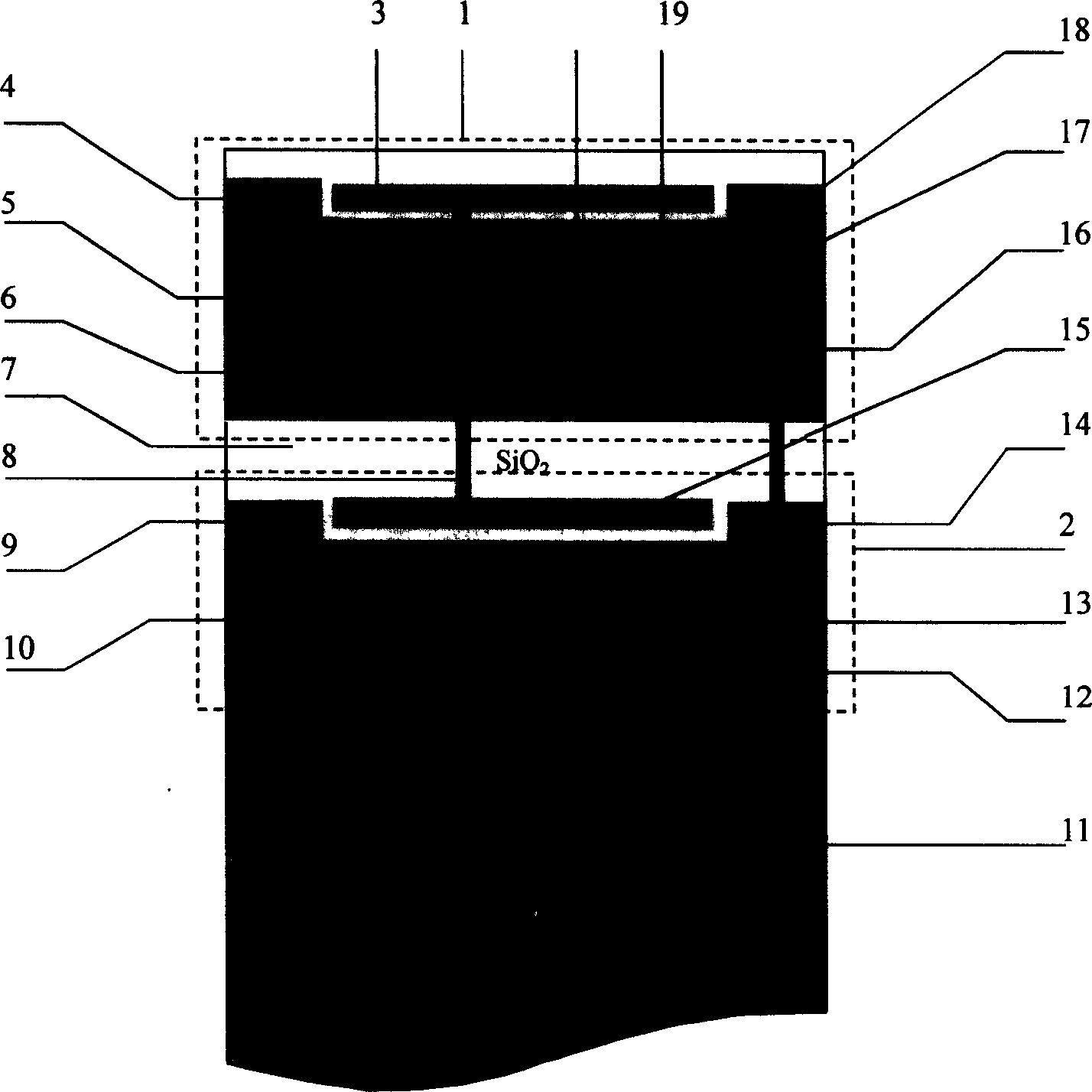

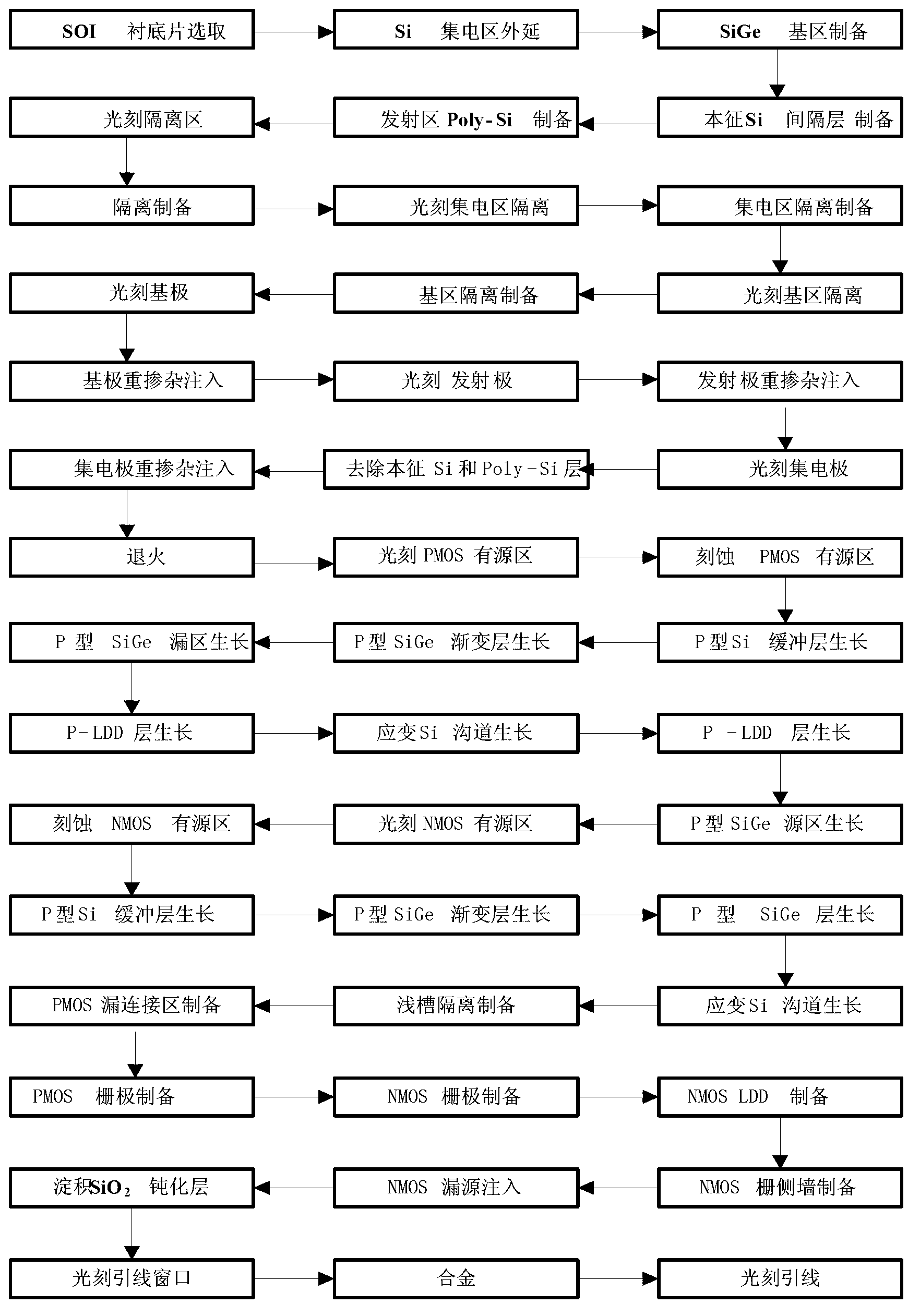

Mixed crystal plane silicon-on-insulator (SOI) bipolar complementary metal oxide semiconductor (BiCMOS) integrated device based on square channel process and preparation method

InactiveCN102738160AImprove performanceHigh hole mobilitySolid-state devicesSemiconductor/solid-state device manufacturingP channelMixed crystal

The invention discloses a mixed crystal plane silicon-on-insulator (SOI) bipolar complementary metal oxide semiconductor (BiCMOS) integrated device based on a square channel process and a preparation method. The method comprises the following steps of: preparing an SOI substrate, continuously growing N-Si, P-SiGe and N-Si layers on the SOI substrate, preparing an deep groove isolator, forming a collector, a base and an emitter contact area, and forming a SiGe heterojunction bipolar transistor (HBT) device; photo-etching an active area of a p-channel metal oxide semiconductor (PMOS) device, continuously growing 7 layers of materials in the active area, preparing a drain and a grid, and forming the PMOS device; photo-etching a groove of an active area of an n-channel metal oxide semiconductor (NMOS) device, continuously growing 4 layers of materials in the active area, preparing a grid dielectric layer and grid polycrystalline, and forming the NMOS device; and photo-etching lead holes, alloying, photo-etching leads, and thus forming the mixed crystal plane SOI BiCMOS integrated device and a mixed crystal plane SOI BiCMOS integrated circuit of which CMOS conductive channels are 22 to 45 nanometers based on the square channel process. By fully using the characteristic of mobility anisotropy of a strain Si material, the mixed crystal plane SOI BiCMOS integrated circuit with enhanced performance is prepared at the temperature between 600 and 800 DEG C.

Owner:XIDIAN UNIV

Thermally stable BiCMOS fabrication method and bipolar junction transistors formed according to the method

A method for forming BiCMOS integrated circuits and structures formed according to the method. After forming doped wells and gate stacks for the CMOS devices and collector and base regions for the bipolar junction transistor, an emitter layer is formed within an emitter window. A dielectric material layer is formed over the emitter layer and remains in place during etching of the emitter layer and removal of the etch mask. The dielectric material layer further remains in place during source / drain implant doping and activation of the implanted source / drain dopants. The dielectric material layer functions as a thermal barrier, to limit out-diffusion of the emitter dopants during the activation step.

Owner:BELL SEMICON LLC

SiGe base vertical channel strain BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device and manufacturing method

InactiveCN102738156ASolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionBicmos integrated circuits

The invention discloses a SiGe base vertical channel strain BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device and a manufacturing method. The method comprises the following steps of: manufacturing a SiGe HBT (Heterojunction Vipolar Transistor) device at a bipolar device area on a Si substrate sheet; etching an active area of an NMOS (N-Channel Metal Oxide Semiconductor) device; extensionally growing five layers of materials at the area so as to form the active area of the NMOS device; manufacturing the NMOS device; etching an active area of the PMOS (P-Channel Metal Oxide Semiconductor) device; extensionally growing three layers of materials at the area so as to form the active area of the PMOS device; forming a virtual grid and accomplishing the manufacturing of the PMOS device; and forming the SiGe base vertical channel strain BiCMOS integrated device and a circuit. The characteristics that the electronic mobility rate at the vertical direction and the hole mobility rate at the horizontal direction of the SiGe material are higher than that of the relaxation Si are utilized; and through a low temperature process, a circuit of the performance-enhanced SiGe base vertical channel strain BiCMOS integrated device is manufactured.

Owner:XIDIAN UNIV

High-speed three-dimension integrated circuit active layer structure and manufacturing method

InactiveCN1599072AHigh hole mobilityHigh speedTransistorSolid-state devicesCryogenic technologyEngineering

The invention discloses an active structure of the high speed three dimensional integrated circuits and its preparation method and aims to increase the speed of today's three dimensional integrated circuits. The invention adopts the single crystal of Si and SiGe / Si to build the two active layers of the new three dimensional integrated circuits. The first active layer chooses the Si SOI or substrate of Si to produce the n-type channel MOS field effect transistor nMOS. The second active layer chooses the substrate of SiGe / Si SOI to produce the p-type channel MOS field effect transistor pMOS. We adopt the low temperature technique to realize the bonding between the two layers and prepare the second active material and device as at low temperature to avoid the effect of the high temperature to the structure of the preliminary active device and to guarantee the alternating current-direct current electric property of the three dimensional integrated circuits. The active structure of he invention can be used in producing the three dimensional CMOS integrated circuits as well as the BiCMOS integrated circuits. Based on the feature of high cavity mobility of SiGe / Sip MOS field effect transistor, compared with today's three dimensional integrated circuits, the three dimensional integrated circuits produced through the active layer of the invention is featured by the high speed and good property.

Owner:XIDIAN UNIV

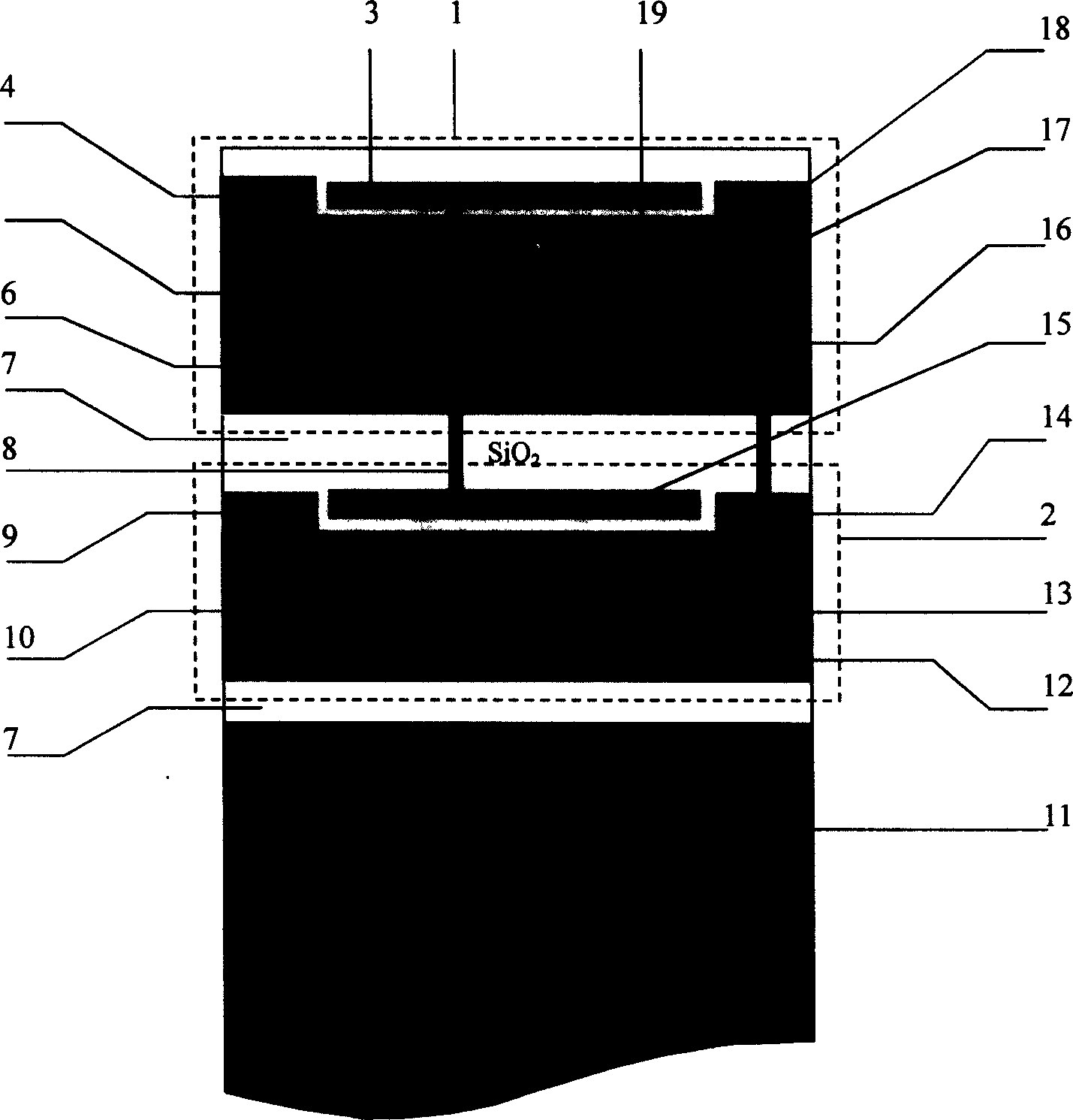

Vertical-channel mixed-lattice-strain BiCMOS (bipolar complementary metal oxide semiconductor) integrated device and preparation method

InactiveCN102738154AImprove performanceHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricP channel

The invention discloses a vertical-channel mixed-lattice-strain BiCMOS integrated device and a preparation method. The preparation method comprises preparing an SOI (silicon on insulator) substrate, epitaxially growing a Si layer on the substrate as a collector region, preparing deep trench isolation, and preparing a double-polysilicon SiGe HBT (heterojunction bipolar transistor) device on the active region of the bipolar device by self-alignment process; etching an active region of a PMOS (p-channel metal oxide semiconductor) device by lithography, continuously growing seven material layers on the active region, andpreparing a drain and a gate to obtain the PMOS device; etching a trench in the active region of an NMOS (n-channel metal oxide semiconductor) device by lithography, continuously growing four material layers on the active region, preparing a gate dielectric layer and gate polysilicon to obtain the NMOS device, etching lead holes by lithography, alloying, and etching leads by lithography to obtain the vertical-channel mixed-lattice-strain BiCMOS integrated device and circuit with a CMOS conductive channel of 22 to 45nm. The preparation method provided by the invention can prepare the performance-enhanced vertical-channel mixed-lattice-strain BiCMOS integrated device at 600 to 800 DEG C by fully utilizing the characteristics of mobility anisotropy of the tensile strained Si material.

Owner:XIDIAN UNIV

Three-polycrystalline SiGe HBT (Heterojunction Bipolar Transistor)-based hybrid crystal face strain BiCOMS integrated device and preparation method thereof

InactiveCN102751292AImprove mobilityImprove electrical performanceSolid-state devicesSemiconductor/solid-state device manufacturingBicmos integrated circuitsSoi substrate

The invention discloses a three-polycrystalline SiGe HBT (Heterojunction Bipolar Transistor)-based hybrid crystal face strain BiCOMS integrated device and a preparation method thereof. The preparation method comprises the steps of: preparing an SOI (Silicon On Insulator) substrate, wherein an upper-layer matrix material is a crystal face (100) and a lower-layer matrix material is a crystal face (110); etching a bipolar device active region, growing an N type Si epitaxial layer, preparing a collector region, and preparing a base region and an emitter region to form a SiGe HBT device; etching an NMOS (N-channel Metal Oxide Semiconductor) device region to form a deep channel, and growing the active region of an NMOS device with the crystal face (100) selectively to prepare a strain Si channel NMOS device; and growing a SiGe epitaxial layer selectively along the crystal face (110) on a PMOS (P-channel Metal Oxide Semiconductor) device region, and preparing a compressive strain SiGe channel PMOS device on the SiGe epitaxial layer; and forming the three-polycrystalline SiGe HBT-based hybrid crystal face strain BiCOMS integrated device and a circuit. According to the invention, by using the characteristics that a mobility of a strain Si material is higher than that of a body Si material and the migration is anisotropic, the three-polycrystalline SiGe HBT-based hybrid crystal face strain BiCOMS integrated circuit with enhanced property is prepared on the basis of the SOI substrate.

Owner:XIDIAN UNIV

Vertical npnp structure in a triple well CMOS process

A vertical NPNP structure fabricated using a triple well CMOS process, as well as methods of making the vertical NPNP structure, methods of providing electrostatic discharge (ESD) protection, and design structures for a BiCMOS integrated circuit. The vertical NPNP structure may be used to provide on-chip protection to an input / output (I / O) pad from negative-voltage ESD events. A vertical PNPN structure may be also used to protect the same I / O pad from positive-voltage ESD events.

Owner:ALSEPHINA INNOVATIONS INC

Special equipment and method for diffusing antimony latex source buried layer

ActiveCN103199009AEasy to operateLarge loading capacitySemiconductor/solid-state device manufacturingDiffusion methodsProduction line

The invention relates to special equipment and a method for diffusing an antimony latex source buried layer. According to the special equipment, a quartz diffusion tube is arranged in a diffusion high-temperature furnace; a gas inlet is formed at the front part of the quartz diffusion tube and connected with a uniform-flow quartz device; an exhaust port is formed at the rear part of the quartz diffusion tube; and the diffusion high-temperature furnace is divided into three areas, and a three-area temperature control device is arranged outside the furnace. According to the antimony latex source buried layer diffusion method, a low-resistance buried layer is prepared by use of a thermal diffusion method generally used on a process line, wherein the gluing speed is 2500-5000rpm; the diffusion conditions are that the optimal diffusion temperature is 1250 DEG C, the constant temperature time is 7 hours and the heating / cooling speed is 5 DEG C per minute; and the ratio of N2 to O2 in the protection atmosphere (diffusion atmosphere) is 8.8:1.8. According to the invention, the bipolar integrated circuit buried layer diffusion technology is optimized and can be popularized and applied to the diffusion of other bipolar discrete device buried layers, and can also be applied to a BiCMOS integrated circuit production line focusing on bipolar technology.

Owner:FUJIAN ANTE MICROELECTRONICS CO LTD

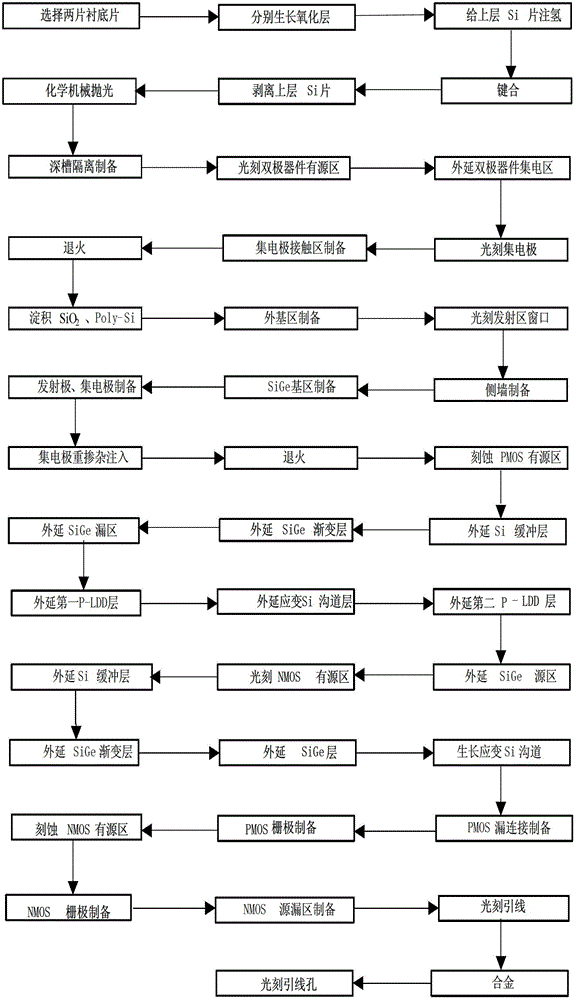

Bi-polycrystal SOI (Silicon On Insulator) Bi CMOS (Complementary Metal Oxide Semiconductor) integrated device with SiGe clip-shaped channel and preparation method thereof

InactiveCN102723336AHigh hole mobilityHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingCharge carrier mobilityP channel

The invention discloses a bi-polycrystal SOI (Silicon On Insulator) Bi CMOS (Complementary Metal Oxide Semiconductor) integrated device with a SiGe clip-shaped channel and a preparation method of the device. The preparation method comprises the steps of conducting epitaxy on a collector region of a bipolar device on an SOI substrate, preparing a deep-trench isolator, a base window and base polycrystal, conducting epitaxy on a SiGe base region and a Poly-Si emitter region to form a SiGe HBT (Heterojuntion Bipolar Transistor) device; conducting photoetching on an active region of an NMOS (N-Channel Metal Oxide Semiconductor) device, growing five layers of materials on the region in an epitaxial manner to form the active region of the NMOS device so as to prepare an NMOS device; conducting photoetching on an active region of a PMOS (P-Channel Metal Oxide Semiconductor) device, growing three layers of materials in an epitaxial manner in the region to form the active region of the PMOS device, preparing a virtual grid electrode, and injecting by utilizing a self alignment process so as to form the drain electrode and the source electrode of the PMOS device; etching a virtual grid to prepare the PMOS device, and thus forming the Bi CMOS integrated with a conducting channel being 22-45nm and a circuit of an MOS (Metal Oxide Semiconductor) device, wherein the device and the circuit are based on the self alignment process. According to the preparation method, the self alignment process is adopted, and the characteristic of the anisotropism of the mobility ratio of strain SiGe material is utilized sufficiently, so that a bi-polycrystal SOI strain Bi COMOS integrated circuit with SiGe clip-shaped channel is prepared, and the performance of the circuit is enhanced.

Owner:XIDIAN UNIV

Bicmos integrated circuit manufacturing method

ActiveCN106033743BImprove pass rateDefects such as induced particles do not appearSemiconductor/solid-state device manufacturingIntegrated circuit manufacturingBicmos integrated circuits

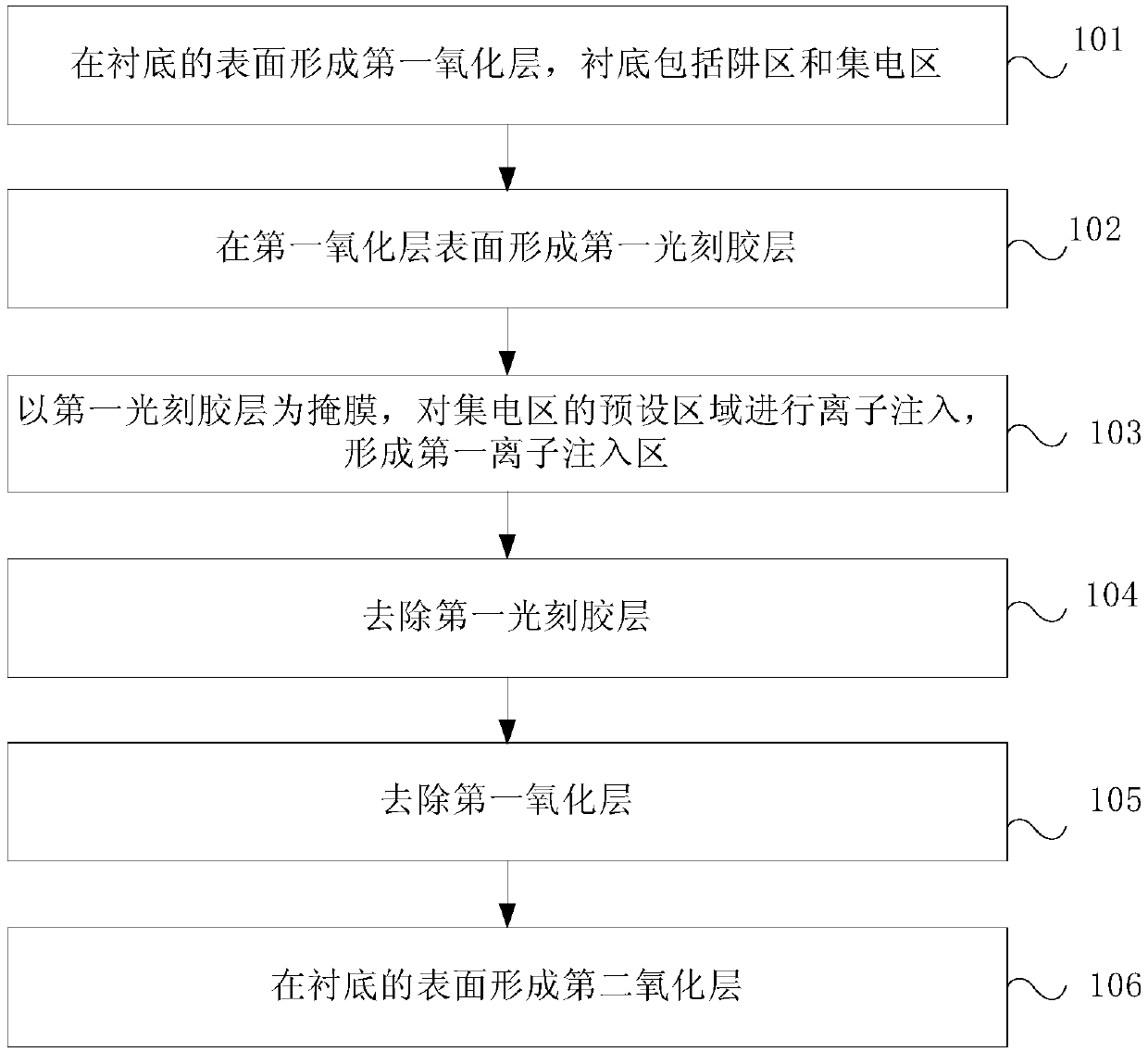

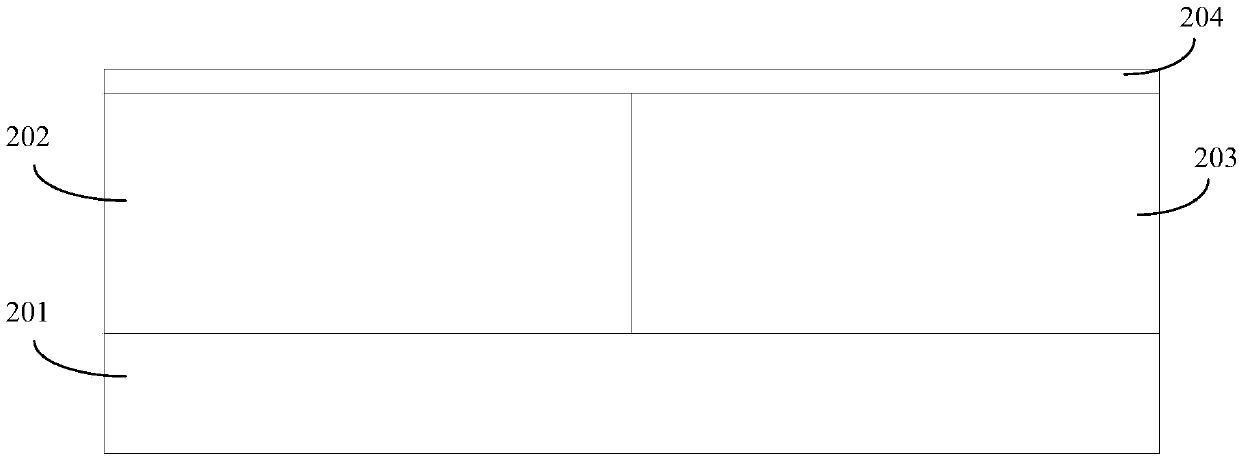

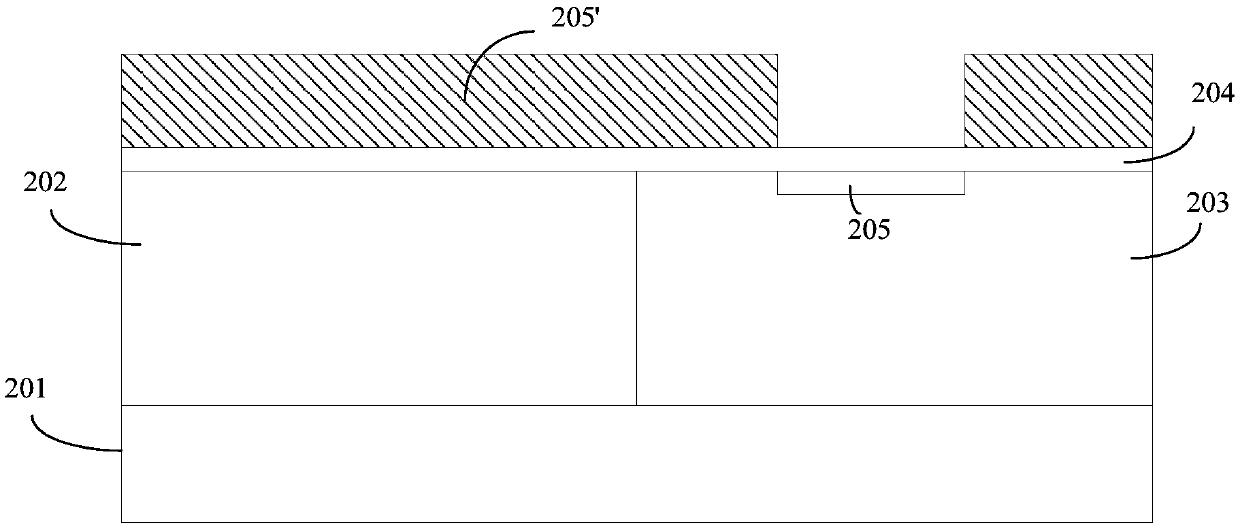

The invention provides a BiCMOS integration circuit manufacturing method. The method comprises the following steps of forming a first oxide layer on a substrate surface, wherein a substrate includes a well region and a collecting area; forming a first photoresist layer on a first oxide layer surface; taking the first photoresist layer as a mask film, and carrying out ion implantation on a preset area of the collecting area so as to form a first ion implantation area; removing the first photoresist layer; removing the first oxide layer; and forming a second oxide layer on the substrate surface. By using the BiCMOS integration circuit manufacturing method of the invention, a qualified rate of a BiCMOS integration circuit can be increased.

Owner:FOUNDER MICROELECTRONICS INT

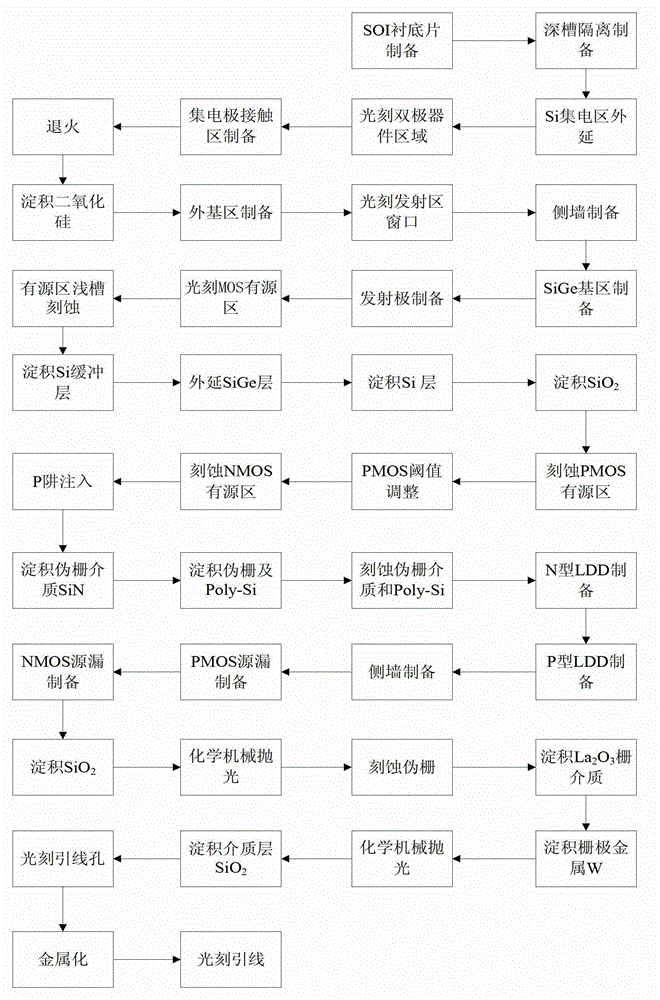

A double polycrystalline strained sige planar bicmos integrated device and its preparation method

InactiveCN102738159BSolid-state devicesSemiconductor/solid-state device manufacturingDielectricChemical vapor deposition

The invention discloses a method for preparing a dual polycrystalline strain SiGe plane bipolar complementary metal oxide semiconductor (BiCMOS) integrated device. The method comprises the following steps of: preparing a silicon-on-insulator (SOI) substrate, etching a bipolar device area on the substrate, preparing a dual polycrystalline SiGe heterojunction bipolar transistor (HBT) device in the area by using a chemical vapor deposition (CVD) method and a self-aligning process, photo-etching a metal oxide semiconductor (MOS) active area, continuously growing a Si buffer layer, a strain SiGe layer and an intrinsic layer in the area, respectively forming active areas of n-channel metal oxide semiconductor (NMOS) and p-channel metal oxide semiconductor (PMOS) devices, depositing SiO2 and polycrystalline silicon in the active areas of the NMOS and PMOS devices, etching a pseudo grid with the length of 22 to 350 nanometers, forming a light doped drain (LDD) and a source drain of the NMOS and PMOS devices by adopting the self-aligning process, then removing the pseudo grid, forming grid dielectric lanthanum oxide (La2O3) and metallic tungsten (W) for forming a grid, metalizing, photo-etching leads, and thus forming a BiCMOS integrated circuit. The self-aligning process is adopted in the preparation method, and the LDD structure is adopted in the MOS structure, so that influence of hot carriers on performance of the device is efficiently inhibited, and the reliability of the device is improved.

Owner:XIDIAN UNIV

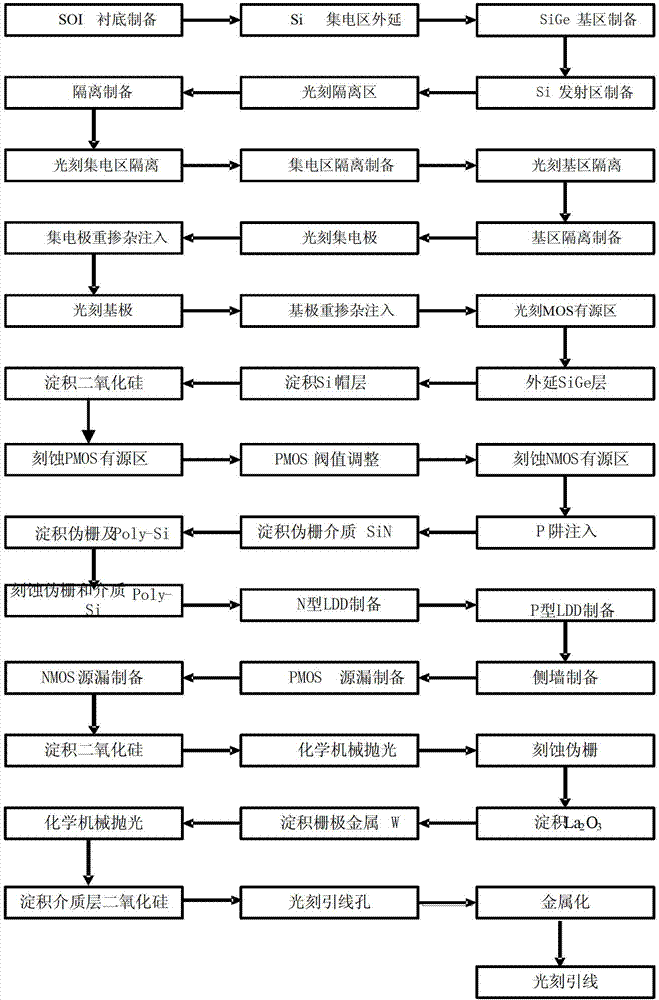

A dual-strain bicmos integrated device based on soi substrate and its preparation method

InactiveCN102810544BSuppress performance impactInhibition effectSolid-state devicesSemiconductor/solid-state device manufacturingPhosphoniumTransmitter

The invention discloses a dual-strain bipolar complementary metal-oxide semiconductor (BiCMOS) integration device based on a silicon on insulator (SOI) substrate and a preparation method thereof. The preparation method comprises following steps that a negative-silicon (N-Si) layer, a positive-silicon germanium (P-SiGe) layer and an N-Si layer continuously grow on the SOI substrate, a deep groove isolator is prepared, a collector zone shallow groove isolator and a base zone shallow groove isolator are prepared, a collector zone is photo-etched, phosphonium ions are injected to form a collector electrode, a base electrode and a transmitter electrode, and a SiGe heterojunction bipolar transistor (HBT) device is formed; a strain SiGe material grow on the substrate, an N-channel MOS (NMOS) device active region and a P-channel MOS (PMOS) device active region are formed, a pseudo grid is prepared, a source drain region of the NMOS and the PMOS devices is respectively generated in a self-aligning way, the pseudo grid is eliminated, a lanthanum oxide (La2O3) material is prepared in a pressing groove at the pseudo grid to form a grid medium and metal tungsten (W) to form a grid electrode, a lead is photo-etched, and a dual-strain plane BiCMOS integration device and a circuit based on the SOI substrate are formed. According to the method, the characteristic that a hole mobility of the strain SiGe material is higher than that of the bulk-Si material is adequately utilized to prepare the dual-strain plane BiCMOS integration circuit based on the SOI substrate, so that the performance of the existing analog and digital-analog mixed integrated circuit is greatly improved.

Owner:XIDIAN UNIV

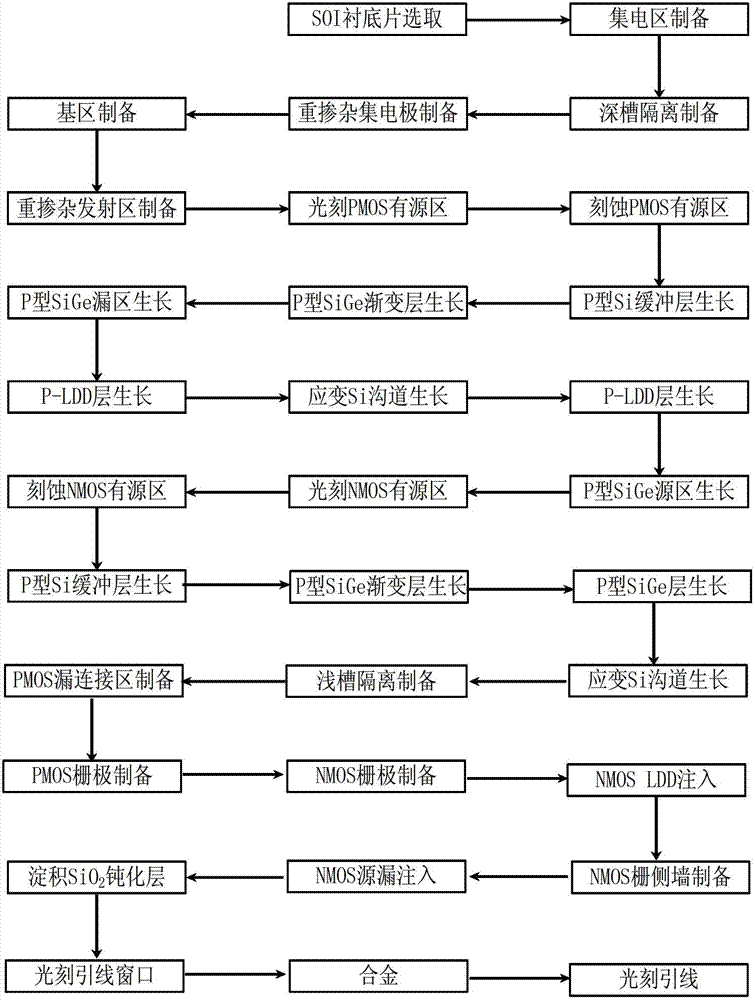

Crystal plane-based Tri-polycrystal-plane Bi CMOS (Complentary Metal-Oxide-Semiconductor) integrated device and preparation method thereof

InactiveCN102723343BImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingCrystal planeElectrode Contact

The invention discloses a crystal plane-based tri-polycrystal-plane Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device and a preparation method of the device. The preparation process is as follows: preparing an SOI (Silicon On Insulator) substrate; growing N type Si epitaxy and preparing a deep-trench isolator so as to form a collector electrode contact region and a nitride side wall, etching a window in a base region, growing a SiGe base region, conducting photoetching on a collector electrode window, depositing N type Poly-Si, and preparing an emitting electrode and the collector electrode to form an HBT (Heterojunction Bipolar Transistor) device; etching a deep trench in an NMOS (N-Channel Metal Oxide Semiconductor) device region, selectively growing a strain Si epitaxial layer with a crystal plane (100) to prepare an NMOS device with a Si channel; selectively growing a strain SiGe epitaxial layer with a crystal plane (110) to prepare a PMOS (P-Channel Metal Oxide Semiconductor) device with a SiGe channel, and thus forming the crystal plane-based tri-polycrystal-plane Bin CMOS integrated device and a circuit. According to the crystal plane-based tri-polycrystal-plane Bi CMOS integrated device and the preparation method, the characteristics that the electronic mobility of tensile strain Si material is higher than that of Si material, the electronic mobility of strain SiGe material is higher than of that of body Si material, and the electronic mobility is anisotropic are utilized, and based on the SOI substrate, the plane Bi CMOS integrated circuit is prepared, and the performance of the Bi CMOS integrated device is enhanced.

Owner:XIDIAN UNIV

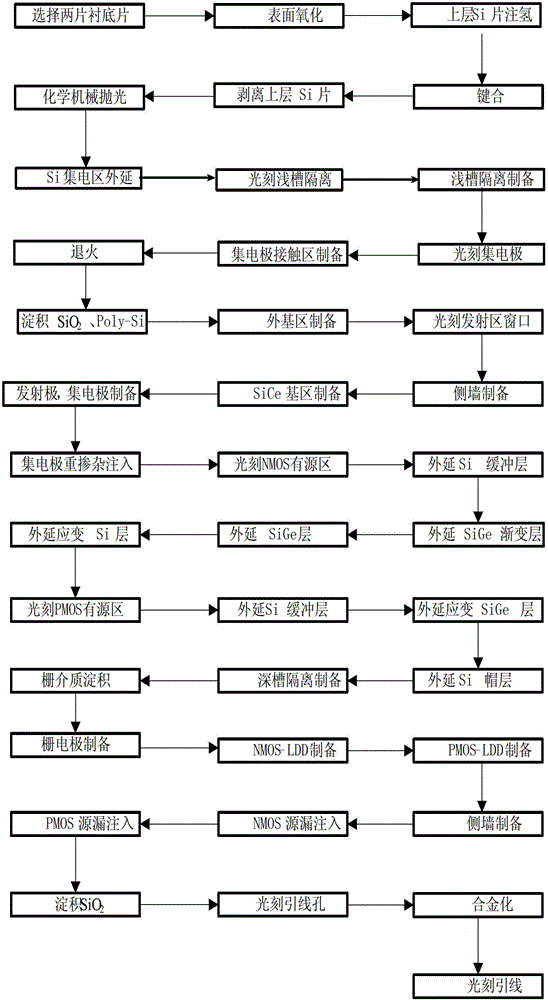

Strain Si BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor) integrated device based on SOI (Silicon on Insulator) substrate and preparation method thereof

InactiveCN102738177AImprove performanceHigh hole mobilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricBicmos integrated circuits

The invention discloses a strain Si BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor) integrated device based on an SOI (Silicon on Insulator) substrate and a preparation method thereof. The preparation method comprises the following steps: growing N-type Si epitaxy on the SOI substrate, preparing trench isolation, and manufacturing a conventional Si bipolar transistor in a bipolar device region; respectively photoetching the ditch grooves of the active regions of an NMOS (Negative-channel Metal Oxide Semiconductor) and a PMOS (Positive-channel Metal Oxide Semiconductor) devices, continuously growing an Si buffer layer, a gradually varied SiGe layer, a fixed component SiGe layer and an N-type strain Si channel layer in the ditch groove of the active region of the NMOS device and continuously growing an Si buffer layer, a gradually varied SiGe layer, a fixed component SiGe layer, a strain Si P-LDD layer, a strain Si channel layer, a strain Si P-LDD layer and a fixed component SiGe layer in the ditch groove of the active region of the PMOS device, and preparing a drain and a grid on the active region of the PMOS device to form the PMOS device; preparing a gate dielectric layer and a gate polycrystal in the active region of the NMOS device to form the NMOS device; and photoetching leads to form an Si BICMOS integrated circuit in which an MOS (Metal Oxide Semiconductor) conducting channel is 22-45nm. According to the invention, based on the full use of the characteristic that tension strain Si material has mobility anisotropism, the strain Si BiCMOS integrated device with strengthened performance based on SOI substrate and the circuit thereof are prepared at the temperature of 600-800 DEG C.

Owner:XIDIAN UNIV

Stress silicon (Si) vertical-groove silicon-on-insulator bipolar complementary metal-oxide semiconductor (SOI BICMOS) integrated device and preparation method

InactiveCN102842584AImprove performanceHigh hole mobilitySolid-state devicesSemiconductor/solid-state device manufacturingPhosphoniumP type silicon

The invention discloses a stress silicon (Si) vertical-groove silicon-on-insulator bipolar complementary metal-oxide semiconductor (SOI BICMOS) integrated device and a preparation method. The preparation method comprises following steps of continuously growing n-type silicon (N-Si), p-type silicon germanium (P-SiGe), amorphous silicon (i-Si), amorphous poly silicon (i-Poly-Si) on an SOI substrate to prepare deep-groove isolation, preparing base-region shallow-groove isolation, photo-etching a base region, injecting boron ions, photo-etching a transmitting region, injecting phosphonium ions to form a collector electrode, and forming a SiGe heterojunction bipolar transistor (HBT) device; respectively photo-etching a N-channel metal-oxide semiconductor (NMOS) device active region groove and a P-channel metal-oxide semiconductor (PMOS) device active region groove, preparing a drain electrode and a grid electrode on the PMOS device active region to form a PMOS device; preparing a grid medium layer and grid polycrystal on the NMOS device active region to form an NMOS device; and photo-etching a lead to form the stress Si vertical-groove SOI BiCMOS integrated device and a circuit. The characteristics of mobility ratio anisotropy of a stress Si material are adequately utilized to prepare a stress Si vertical-groove SOI BiCMOS integrated circuit with enhanced performance under the temperature of 600 to 800 DEG C.

Owner:XIDIAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com