High-speed three-dimension integrated circuit active layer structure and manufacturing method

A technology of integrated circuits and active layers, applied in circuits, electrical components, electric solid-state devices, etc., can solve the problem of low speed of three-dimensional integrated circuits, and achieve the effect of ensuring AC and DC electrical performance and avoiding influence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

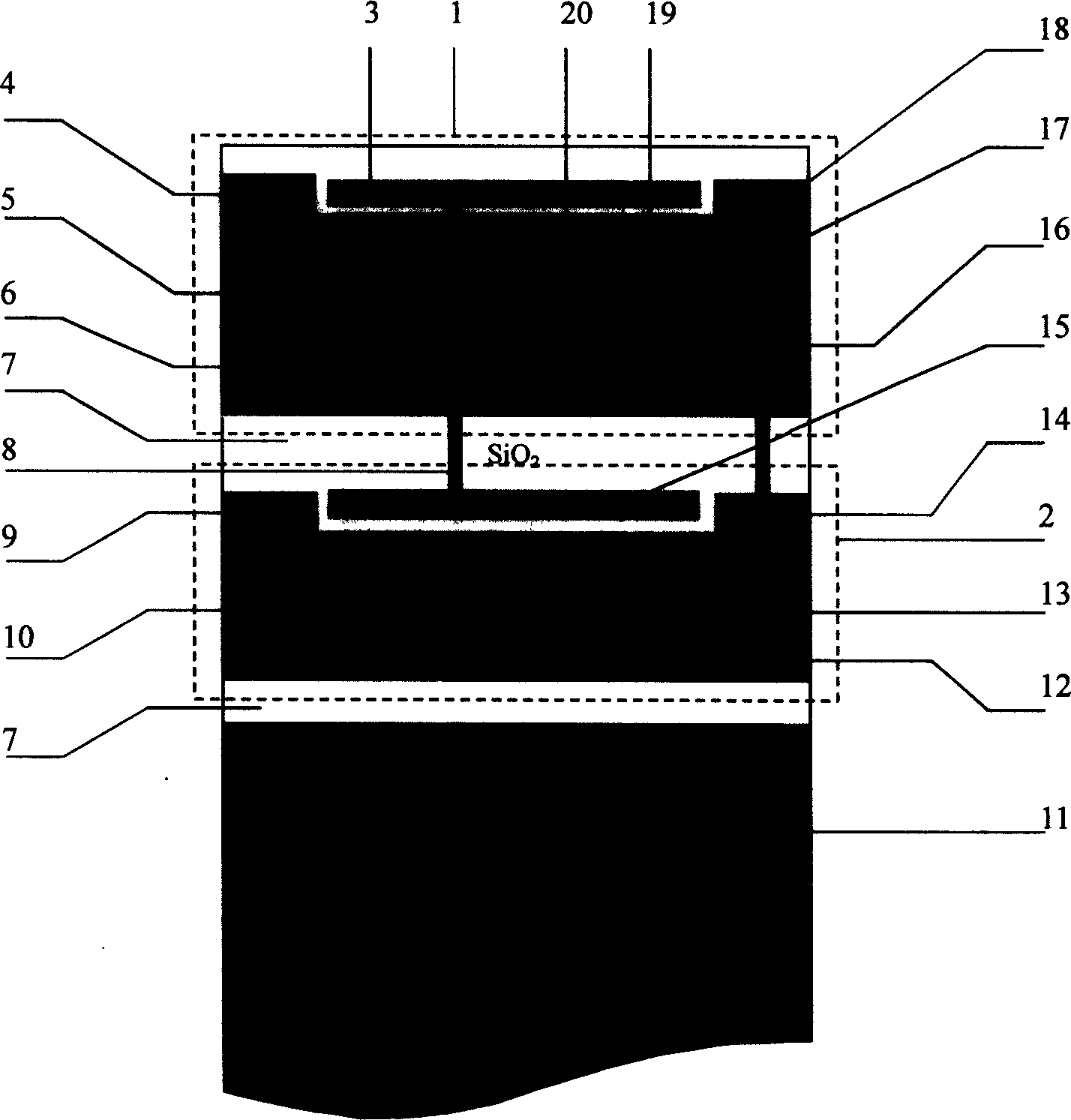

Embodiment 1

[0038] like figure 1 As shown, in the first embodiment of this description, the active layer of the CMOS IC is composed of the SiGe / Si SOI quantum well active layer and the SiSOI active layer. The structure has upper and lower layers, of which 1 is SiGe / Si pMOS field effect transistor; 2 is Si nMOS field effect transistor; 3 is pMOS field effect transistor Ploy-Si gate; 4 is pMOS Ploy-Si source; 5 is pMOS Source region; 6 is pMOS substrate region; 7 is insulating layer; 8 is Ploy-Si interconnection line; 9 is nMOS Ploy-Si source; 10 is nMOS source region; 11 is substrate; 12 is nMOS drain region; 13 is the nMOS channel substrate region; 14 is the nMOS Ploy-Si drain; 15 is the nMOS field effect transistor Ploy-Si gate; 16 is the Ploy-Si interconnection line; 17 is the pMOS drain region; 18 is the pMOS drain ; 19 is the MOS channel region; 20 is the cap layer.

[0039] The pMOS gate 3 , source 4 , source region 5 , substrate region 6 , insulating layer 7 , drain region 17 , dr...

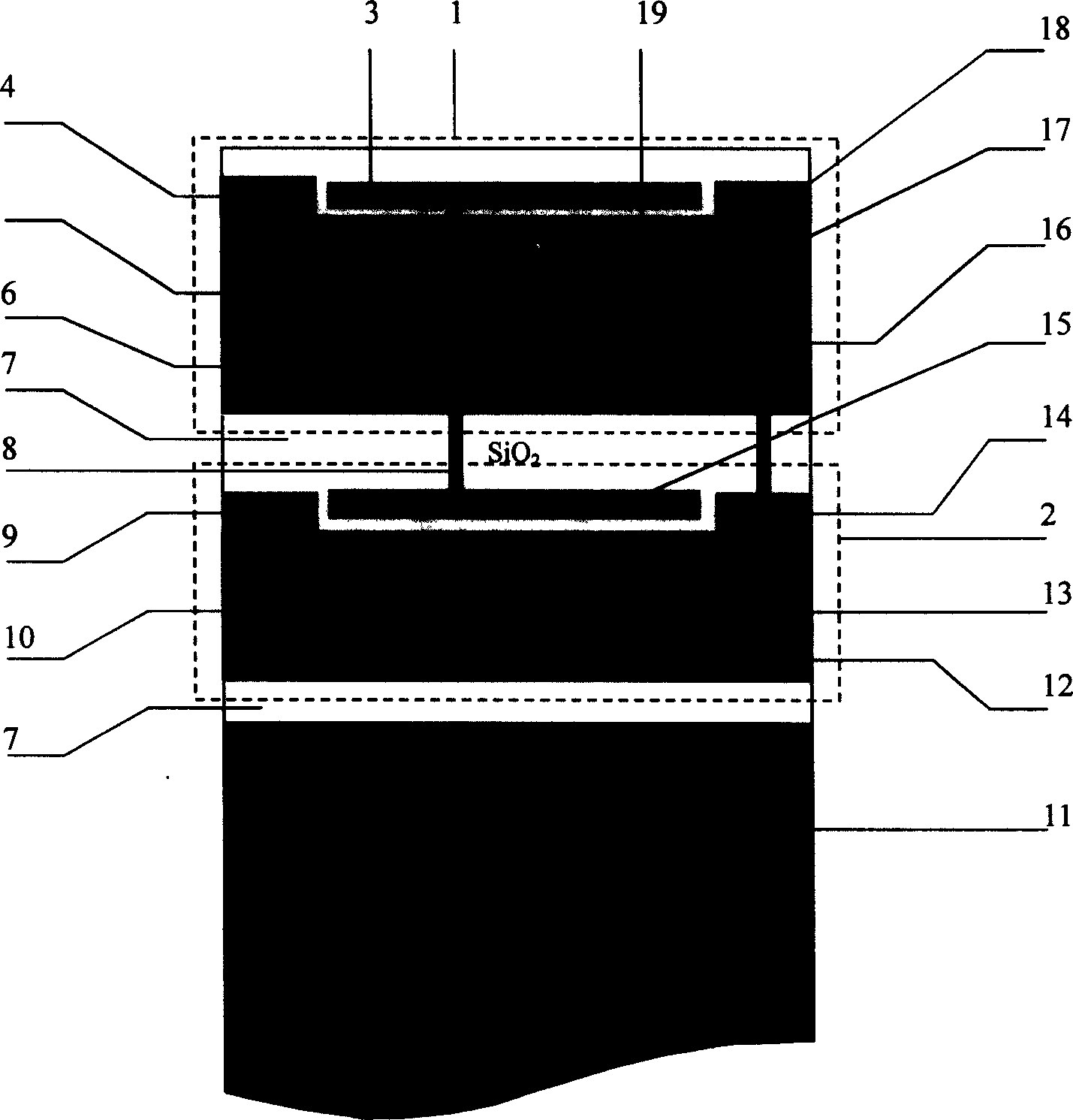

Embodiment 2

[0043] like figure 2 As shown, the second embodiment of this description is a structure in which the active layer of the CMOS IC is formed by the SiGe / Si SOI surface channel active layer and the Si SOI active layer. The structure has upper and lower layers, of which 1 is SiGe / Si pMOS field effect transistor; 2 is Si nMOS field effect transistor; 3 is pMOS field effect transistor Ploy-Si gate; 4 is pMOS Ploy-Si source; 5 is pMOS Source region; 6 is pMOS substrate region; 7 is insulating layer; 8 is Ploy-Si interconnection line; 9 is nMOS Ploy-Si source; 10 is nMOS source region; 11 is substrate; 12 is nMOS drain region; 13 is the nMOS channel substrate region; 14 is the nMOS Ploy-Si drain; 15 is the nMOS field effect transistor Ploy-Si gate; 16 is the Ploy-Si interconnection line; 17 is the pMOS drain region; 18 is the pMOS drain ; 19 is the MOS channel region.

[0044] The pMOS gate 3 , source 4 , source region 5 , substrate region 6 , insulating layer 7 , drain region 17 a...

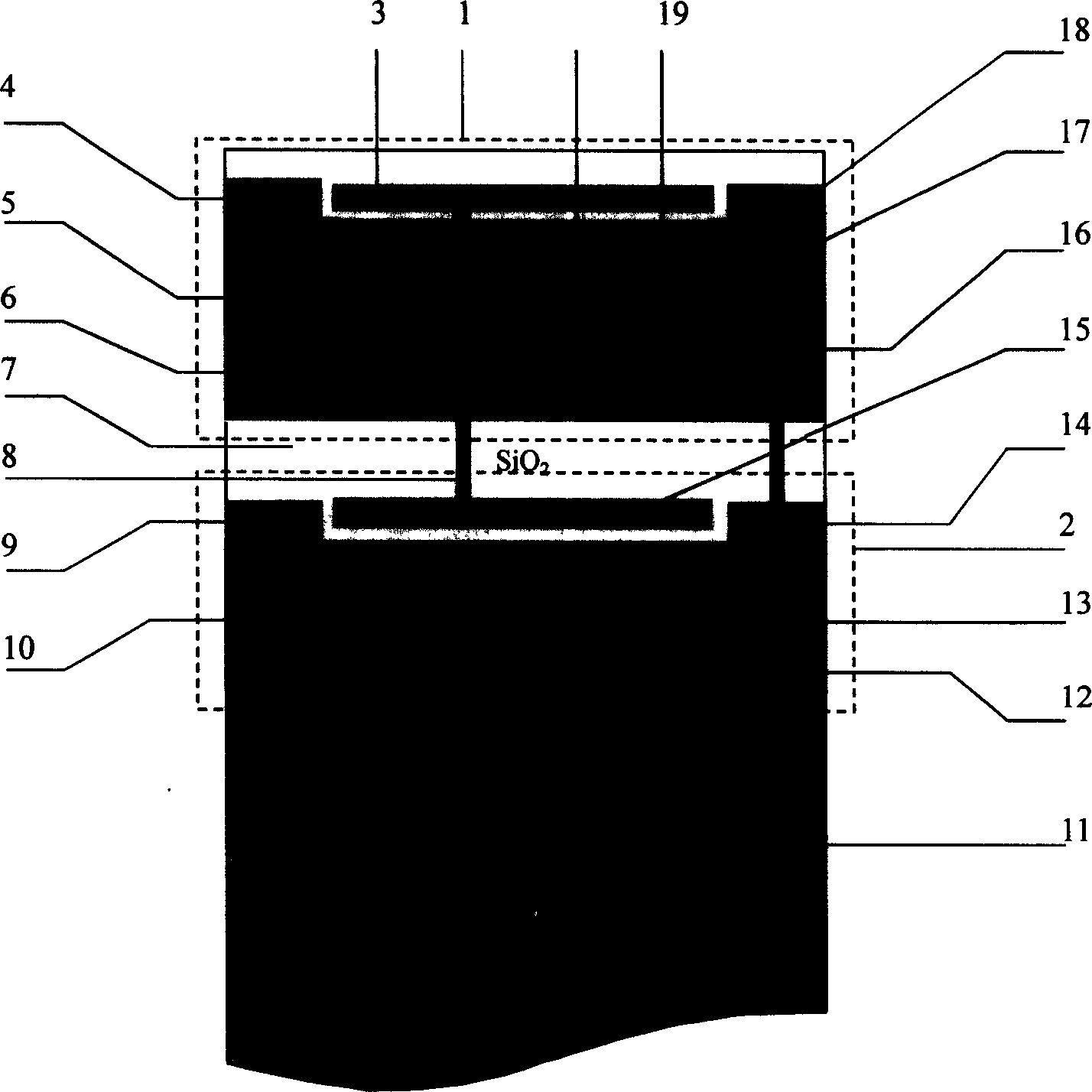

Embodiment 3

[0048] like image 3 As shown, in the third embodiment of this description, the active layer of the CMOS IC is composed of the SiGe / Si SOI quantum well channel active layer and the Si active layer. The structure has two layers, 1 is SiGe / SipMOS field effect transistor; 2 is Si nMOS field effect transistor; 3 is pMOS field effect transistor Ploy-Si gate; 4 is pMOS Poly-Si source; 5 is pMOS source 6 is the pMOS substrate area; 7 is the insulating layer; 8 is the Ploy-Si interconnection line; 9 is the nMOS Ploy-Si source; 10 is the nMOS source area; 11 is the substrate; 12 is the nMOS drain area; 13 14 is nMOS Ploy-Si drain; 15 is nMOS field effect transistor Ploy-Si gate; 16 is Ploy-Si interconnection; 17 is pMOS drain; 18 is pMOS drain; 19 is a MOS channel region; 20 is a cap layer.

[0049] The pMOS gate 3 , source 4 , source region 5 , substrate region 6 , insulating layer 7 , drain region 17 , drain 18 , channel region 19 and cap layer 20 constitute a pMOS field effect tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com