A double polycrystalline strained sige planar bicmos integrated device and its preparation method

An integrated device, dual polycrystalline technology, used in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as difficulty in meeting design, reducing lithography accuracy, and inability to meet low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

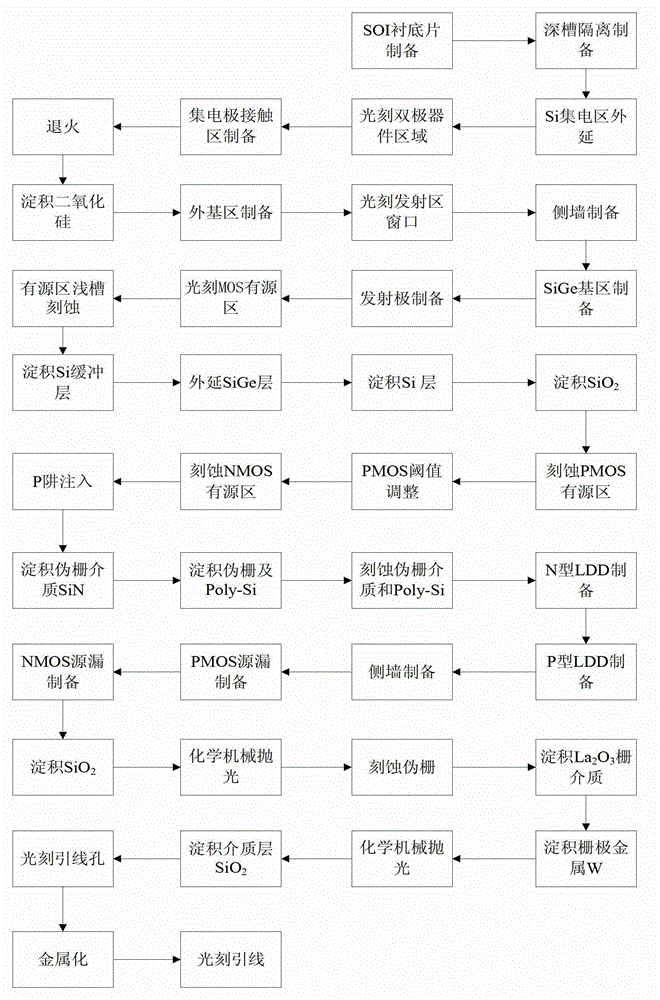

Image

Examples

Embodiment 1

[0120] Embodiment 1: The preparation of a dual-polycrystalline strained SiGe planar BiCMOS integrated device and circuit with a channel length of 22nm, the specific steps are as follows:

[0121] Step 1, SOI substrate material preparation.

[0122] (1a) Select the N-type doping concentration as 1×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 1 μm, which is used as the base material of the upper layer, and hydrogen is injected into the base material;

[0123] (1b) Select the N-type doping concentration as 1×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 1 μm, which is used as the base material of the lower layer;

[0124] (1c) Using a chemical mechanical polishing (CMP) process to polish the surface of the lower layer and the upper layer of substrate material after hydrogen injection;

[0125] (1d) Put the oxide layer on the surface of the polished lower layer and the upper layer o...

Embodiment 2

[0186] Embodiment 2: The preparation of a double polycrystalline strained SiGe planar BiCMOS integrated device and circuit with a channel length of 130nm, the specific steps are as follows:

[0187] Step 1, SOI substrate material preparation.

[0188] (1a) Select the N-type doping concentration as 3×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 0.7 μm, which is used as the base material of the upper layer, and hydrogen is injected into the base material;

[0189] (1b) Select the N-type doping concentration as 3×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 0.7 μm, which is used as the base material of the lower layer;

[0190] (1c) Using a chemical mechanical polishing (CMP) process to polish the surface of the lower layer and the upper layer of substrate material after hydrogen injection;

[0191] (1d) Put the oxide layer on the surface of the polished lower layer and the upper ...

Embodiment 3

[0252] Embodiment 3: the preparation channel length is the dual polycrystalline strained SiGe planar BiCMOS integrated device and the circuit of 350nm, and specific steps are as follows:

[0253] Step 1, SOI substrate material preparation.

[0254] (1a) Select the N-type doping concentration as 5×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 0.5 μm, which is used as the base material of the upper layer, and hydrogen is injected into the base material;

[0255] (1b) Select the N-type doping concentration as 5×10 15 cm -3The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 0.5 μm, which is used as the base material of the lower layer;

[0256] (1c) Using a chemical mechanical polishing (CMP) process to polish the surface of the substrate material of the lower layer and the upper layer of the active layer after injecting hydrogen, respectively;

[0257] (1d) Put the oxide layer on the surface of the p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com