Process for manufacturing 0.8 micron silicon bipolar CMOS integrated circuit

A manufacturing process and process technology, applied in the field of 0.8 micron silicon bipolar complementary metal oxide semiconductor integrated circuit manufacturing process, can solve the problems of high cost and complex process flow, and achieve the effect of high resistance and high gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solution of the present invention will be further described below in conjunction with the embodiments.

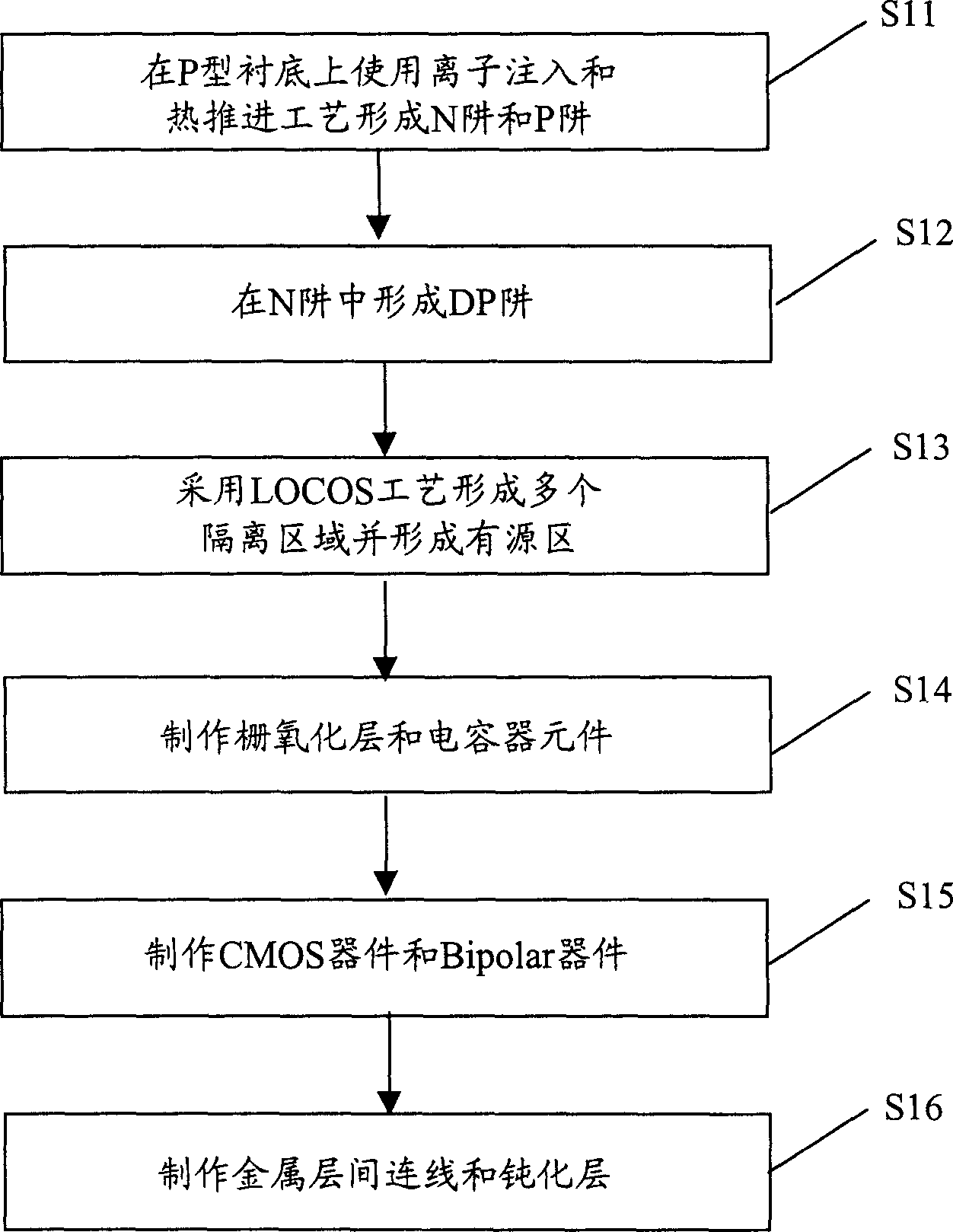

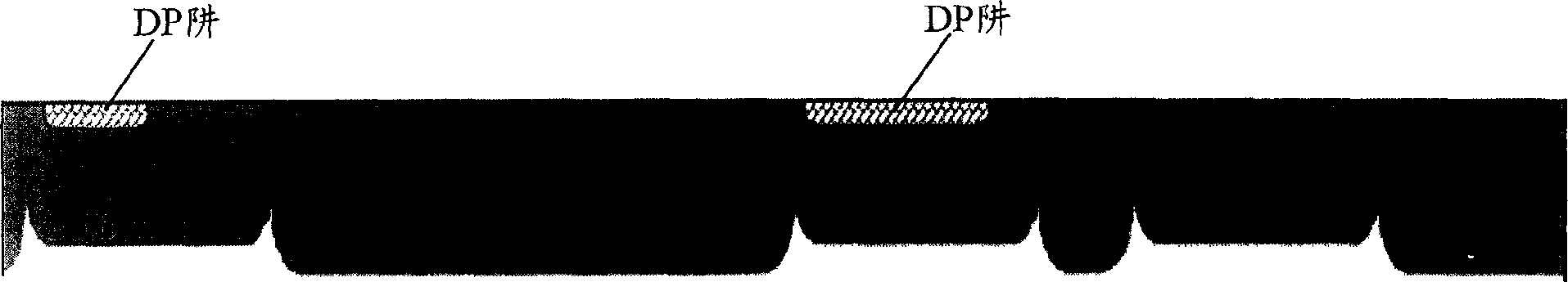

[0025] The flow process of manufacturing process of the present invention is as follows, with reference to figure 1 , the main features of which are that DP wells are also formed in N wells; the gate oxide layers of high-voltage devices and low-voltage devices are completed in the same oxidation step; and isolation NMOS devices and Bipolar NPN devices are formed on N wells with DP wells.

[0026] Such as figure 1 As shown, the process includes the following steps:

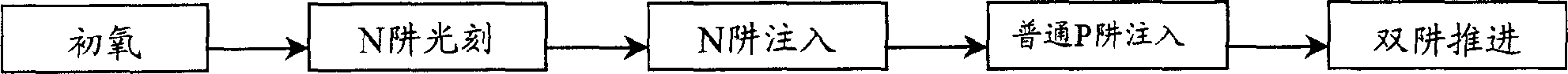

[0027] S11. Forming an N well and a P well on a P-type substrate by using ion implantation and a thermal push process. In this embodiment, the step of making the double wells specifically includes: initial oxygen; using photoresist to locate the N well region and the P well; N well ion implantation; P well ion implantation; double well advance. The above steps refer to figure 2 , these ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com