No-junction field effect transistor and manufacturing method therefor

A production method and junction field effect technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as large contact resistance, small size, and exacerbated MOSFET short channel effect, so as to improve performance and reduce The effect of interface scattering

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

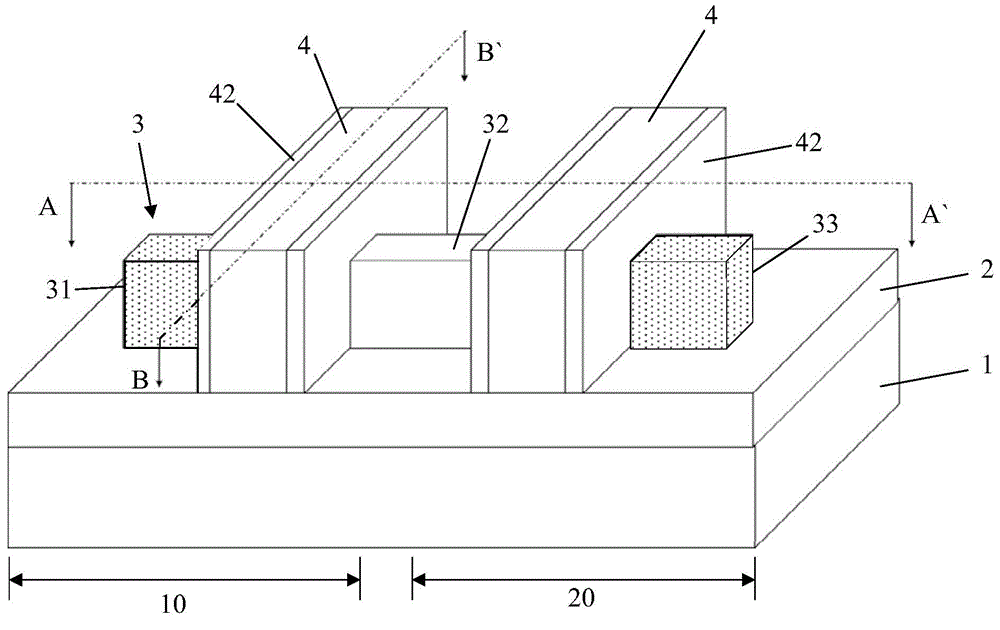

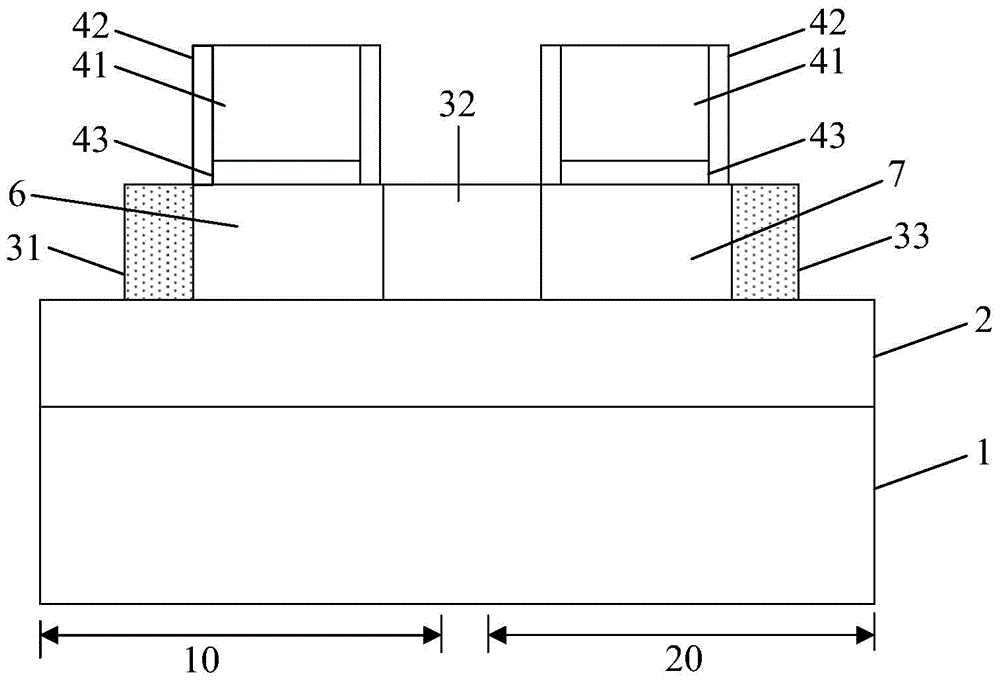

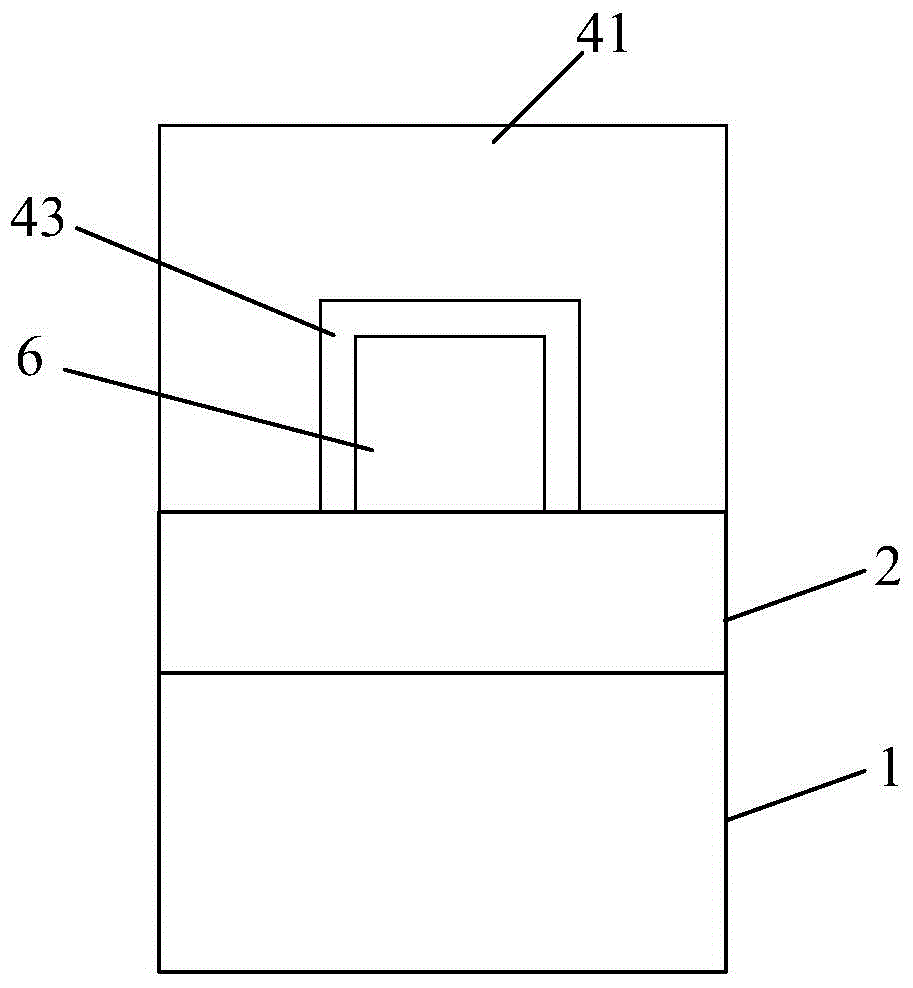

[0067] Since the feature size of existing field effect transistors (such as MOSFETs) decreases gradually, the difficulty of the doping process for making MOSFETs also gradually increases; at the same time, since the source and drain regions of existing MOSFETs are generally semiconductor materials, the source and drain The problem of large resistance between regions has been difficult to improve; and there is a large contact resistance between the semiconductor material and the conductive plug in the interconnect structure, generally requiring additional process steps to form a low contact resistance on the source and drain regions. silicide contact layer.

[0068] In addition, when the MOSFET is working, the interface scattering (surface scattering) phenomenon of carriers in the channel region is relatively serious, which will affect the working performance of the junctionless field effect transistor to a certain extent, such as increased noise.

[0069] Therefore, the presen...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com