Double-strain CMOS (Complementary Metal Oxide Semiconductor) integrated device and preparation method thereof

A dual-strain and device technology, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of incompatibility in technology, wide application and development, difficulty in preparing large-diameter single crystals, and poor heat dissipation performance. Achieve the effect of improving electrical performance, suppressing short channel effect, and excellent circuit performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

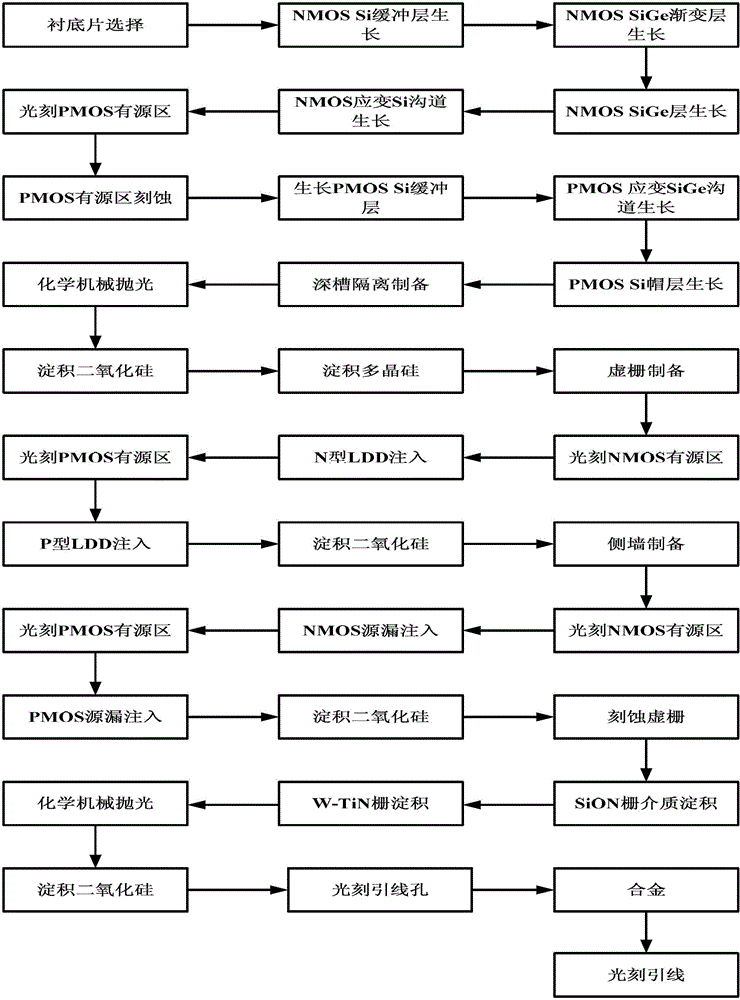

[0050] Embodiment 1: prepare the double-strain CMOS integrated device and the circuit that the conduction channel is 45nm, concrete steps are as follows:

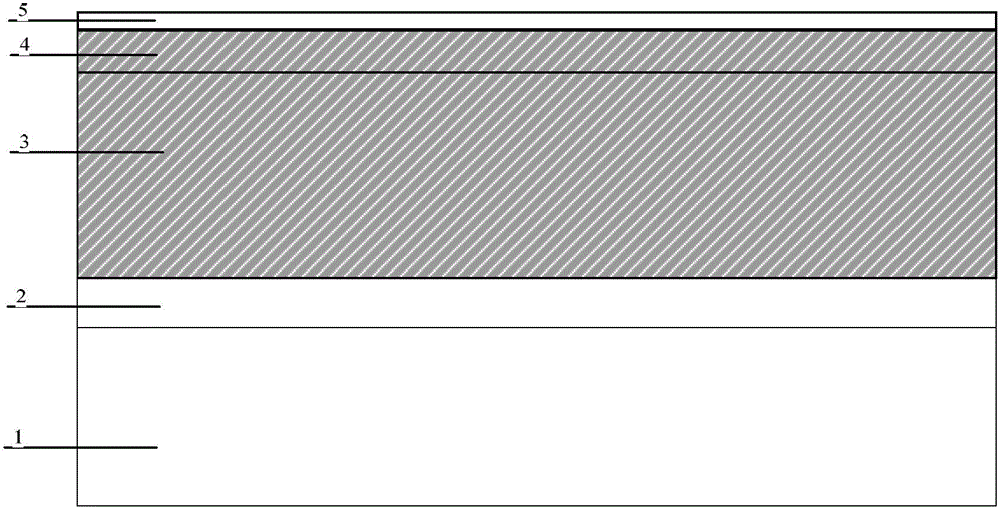

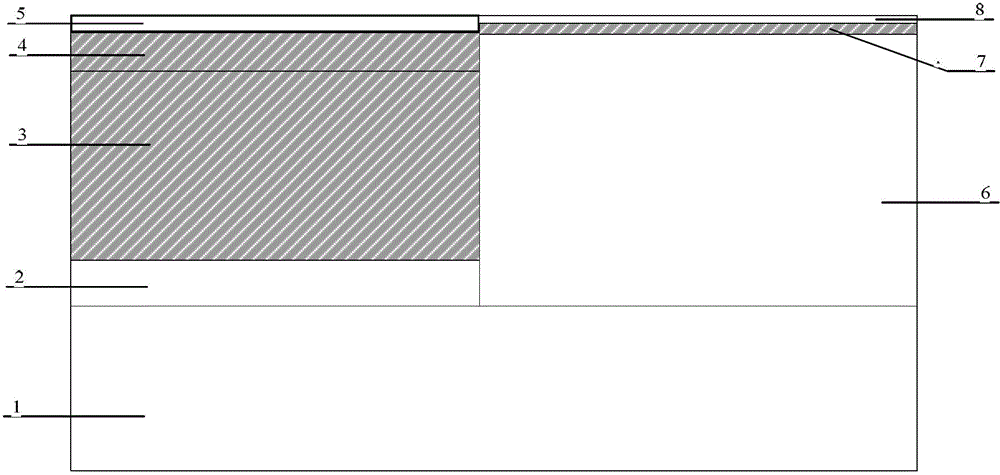

[0051] Step 1, NMOS epitaxial material preparation, such as figure 2 shown.

[0052] (1a) Select the doping concentration as 1×10 16 cm -3 A p-type Si substrate sheet 1;

[0053] (1b) Using chemical vapor deposition (CVD), grow a P-type Si buffer layer 2 with a thickness of 400 nm on the substrate at 600°C, with a doping concentration of 5×10 16 cm -3 ;

[0054] (1c) Using chemical vapor deposition (CVD), grow a P-type SiGe graded layer 3 with a thickness of 2 μm on the substrate at 600°C, with a bottom Ge composition of 0% and a top Ge composition of 15% , with a doping concentration of 5×10 16 cm -3 ;

[0055] (1d) Using the method of chemical vapor deposition (CVD), grow a P-type SiGe layer 4 with a thickness of 400nm on the substrate at 600°C, with a Ge composition of 15% and a doping concentration of 5×10 17...

Embodiment 2

[0091] Embodiment 2: The preparation of a dual-strain CMOS integrated device and circuit with a conductive channel of 30nm, the specific steps are as follows:

[0092] Step 1, NMOS epitaxial material preparation, such as figure 2 shown.

[0093] (1a) Select the doping concentration to be 5×10 15 cm -3 A p-type Si substrate sheet 1;

[0094] (1b) Using chemical vapor deposition (CVD), grow a P-type Si buffer layer 2 with a thickness of 300 nm on the substrate at 700°C, with a doping concentration of 1×10 16 cm -3 ;

[0095] (1c) Using the chemical vapor deposition (CVD) method, grow a P-type SiGe graded layer 3 with a thickness of 1.8 μm on the substrate at 700 ° C, the bottom Ge composition is 0%, and the top Ge composition is 20% %, the doping concentration is 1×10 16 cm -3 ;

[0096] (1d) Using chemical vapor deposition (CVD), grow a P-type SiGe layer 4 with a thickness of 300 nm on the substrate at 700 °C, with a Ge composition of 20% and a doping concentration of...

Embodiment 3

[0132] Embodiment 3: prepare the double-strain CMOS integrated device and the circuit that the conduction channel is 22nm, the specific steps are as follows:

[0133] Step 1, NMOS epitaxial material preparation, such as figure 2 shown.

[0134] (1a) Select the doping concentration as 1×10 15 cm -3 A p-type Si substrate sheet 1;

[0135] (1b) Using chemical vapor deposition (CVD), grow a P-type Si buffer layer 2 with a thickness of 200 nm on the substrate at 750°C, with a doping concentration of 5×10 15 cm -3 ;

[0136] (1c) Using chemical vapor deposition (CVD), grow a P-type SiGe graded layer 3 with a thickness of 1.5 μm on the substrate at 750°C, with a bottom Ge composition of 0% and a top Ge composition of 25% %, the doping concentration is 5×10 15 cm -3 ;

[0137] (1d) Using chemical vapor deposition (CVD), grow a P-type SiGe layer 4 with a thickness of 200 nm on the substrate at 750°C, with a Ge composition of 25% and a doping concentration of 5×10 16 cm -3 ;...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com