Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

60results about How to "Reduce etch depth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

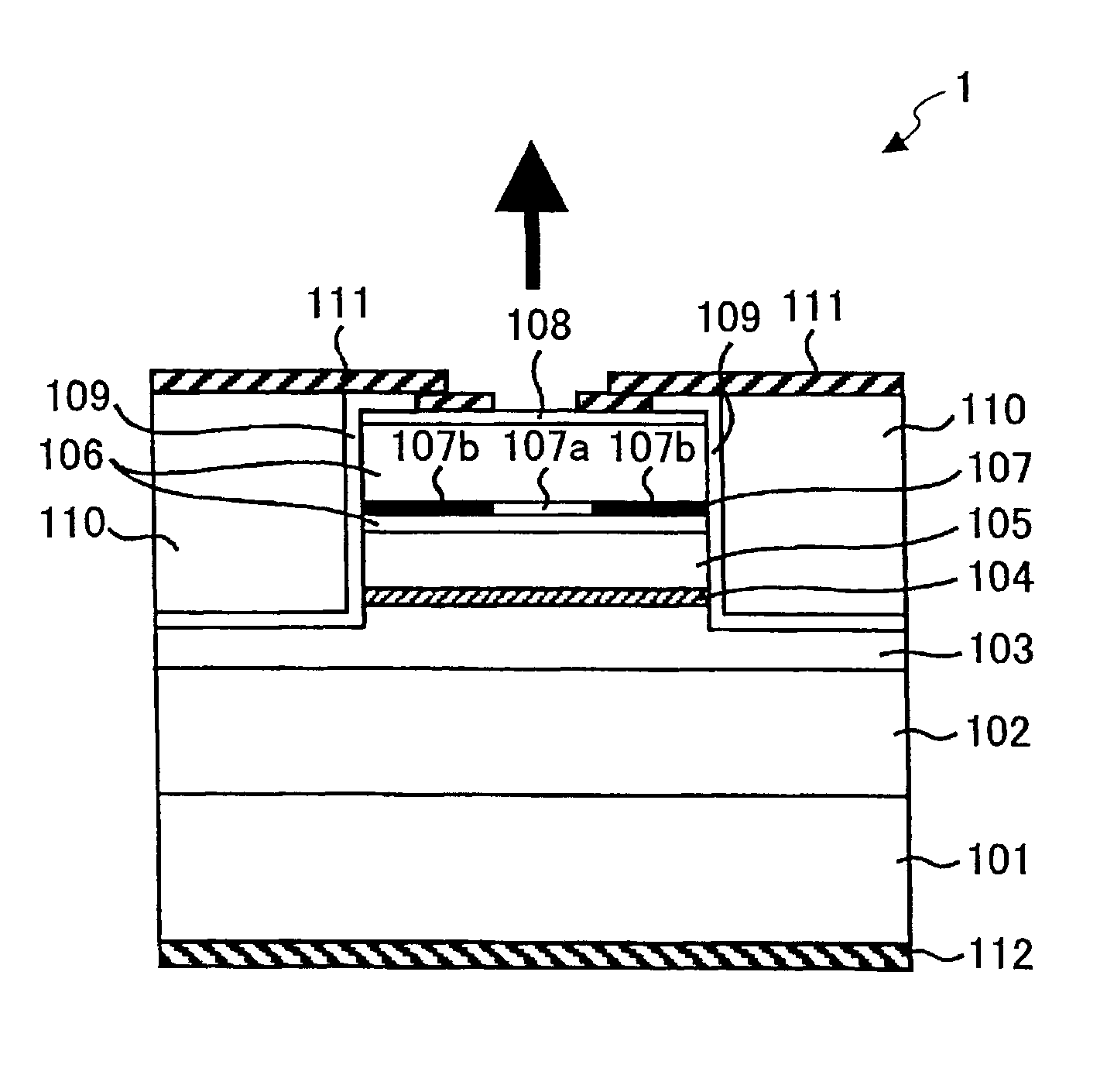

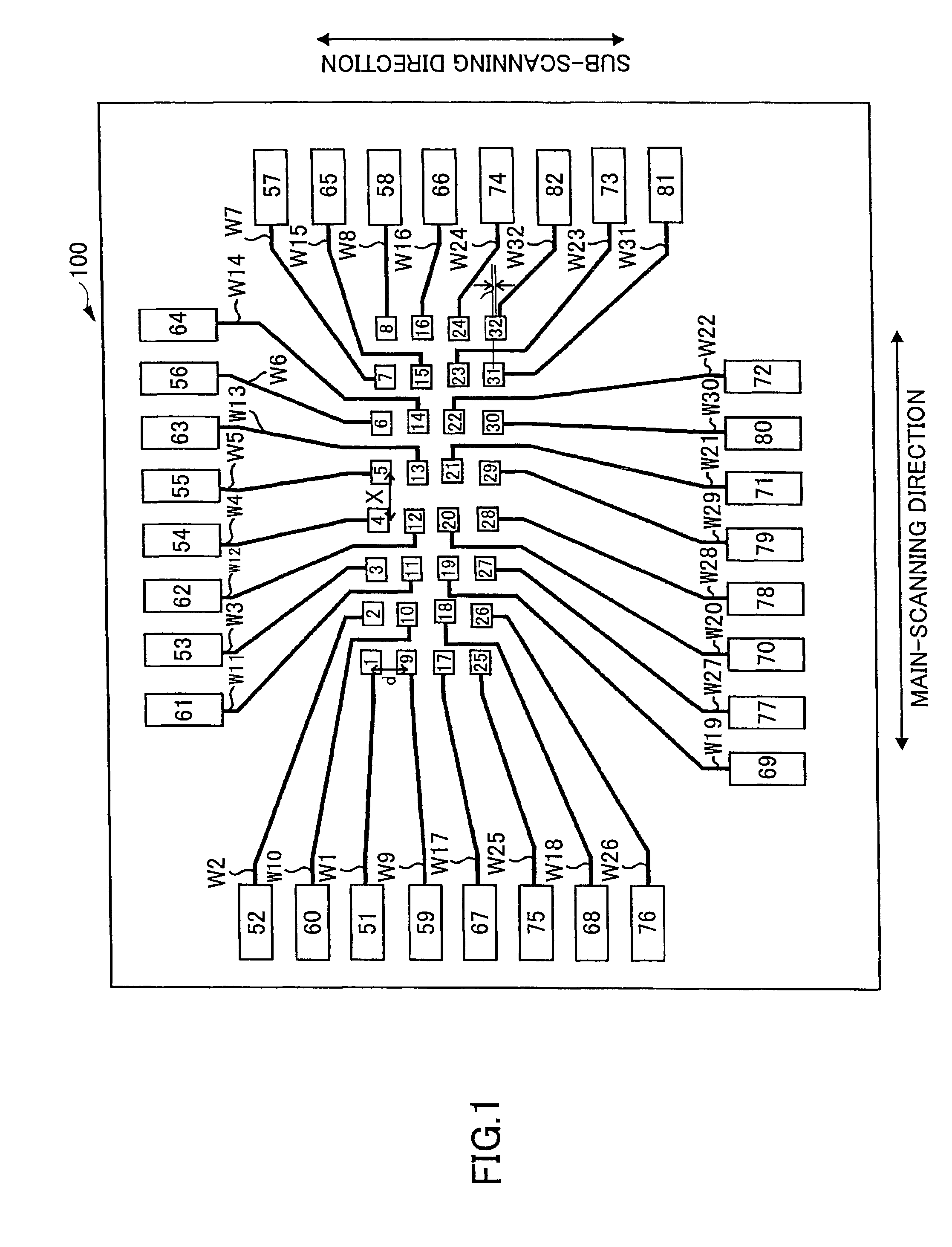

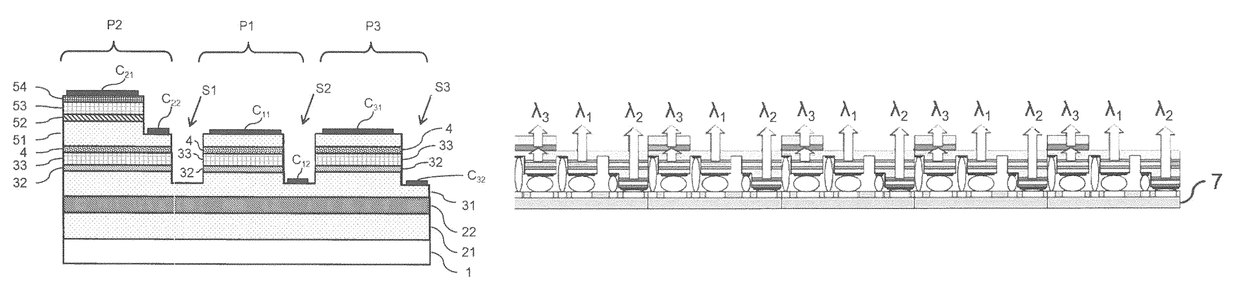

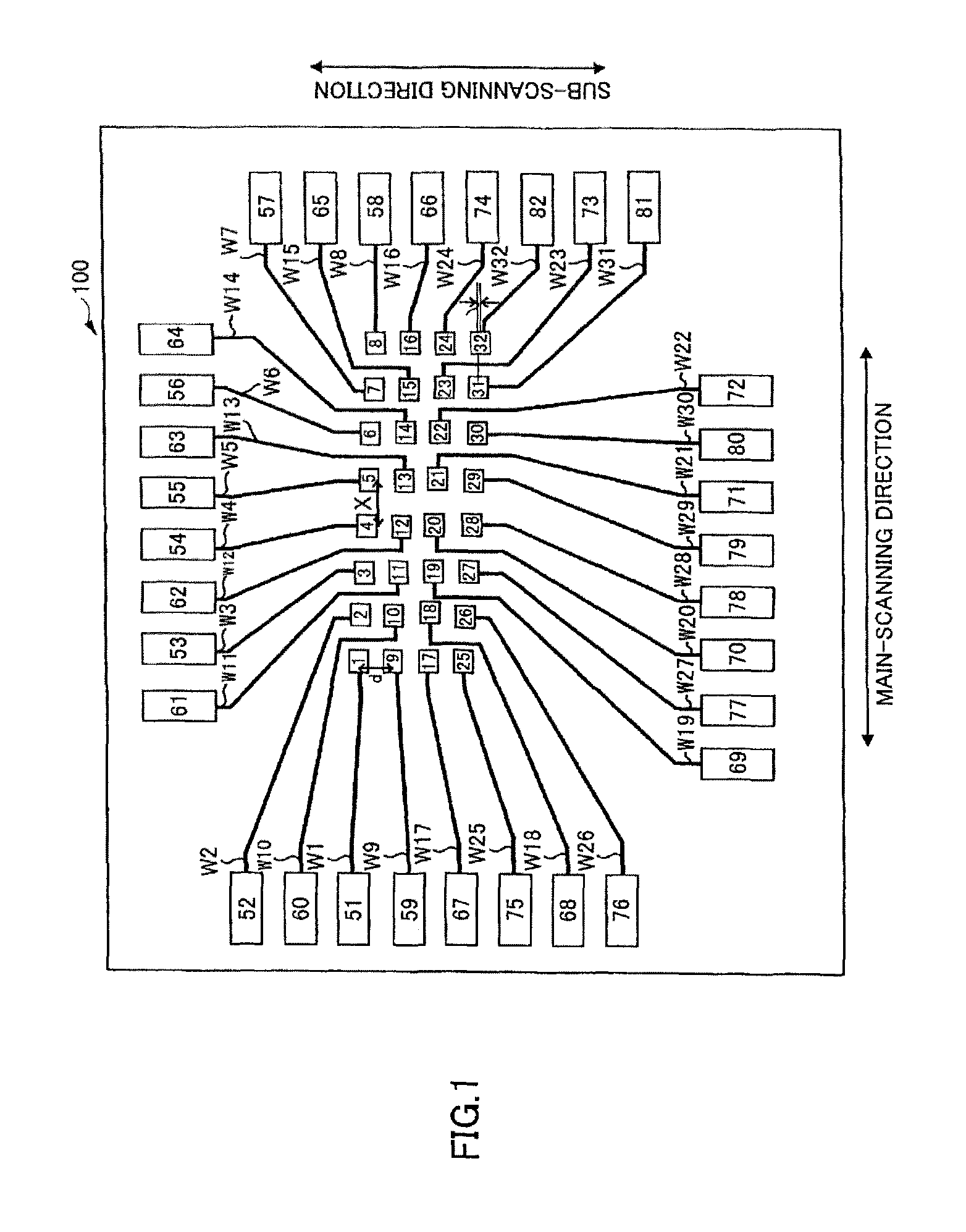

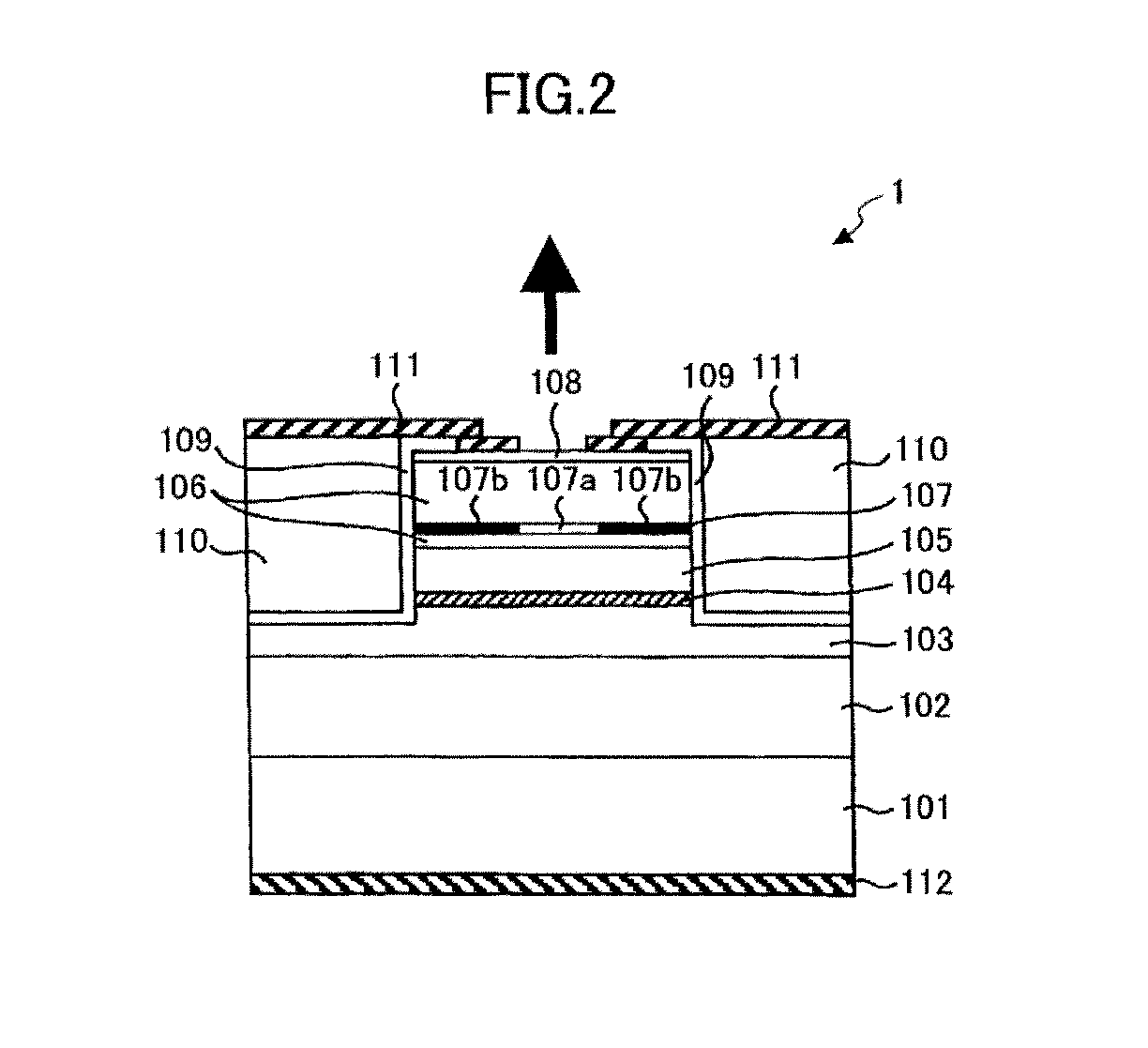

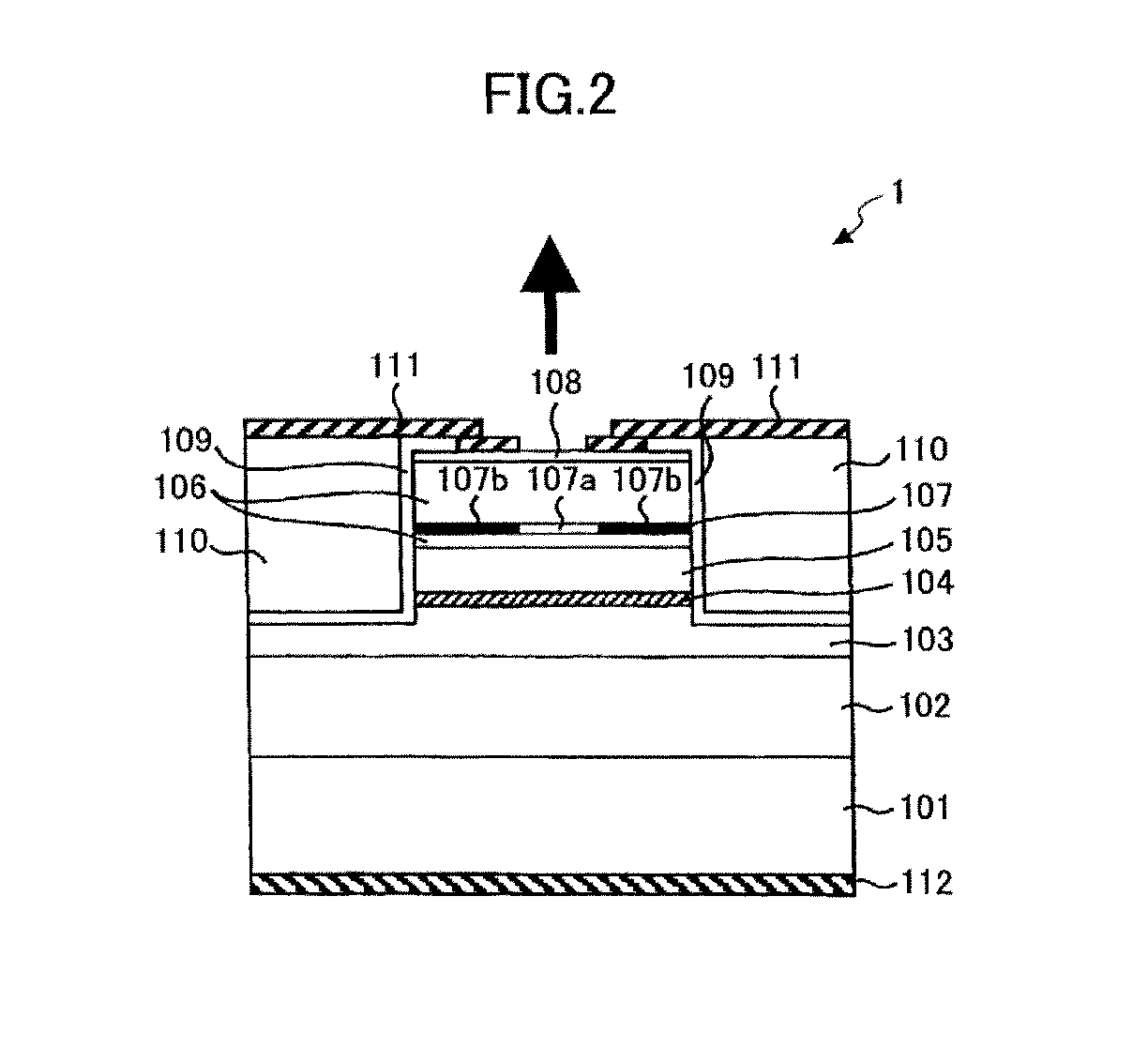

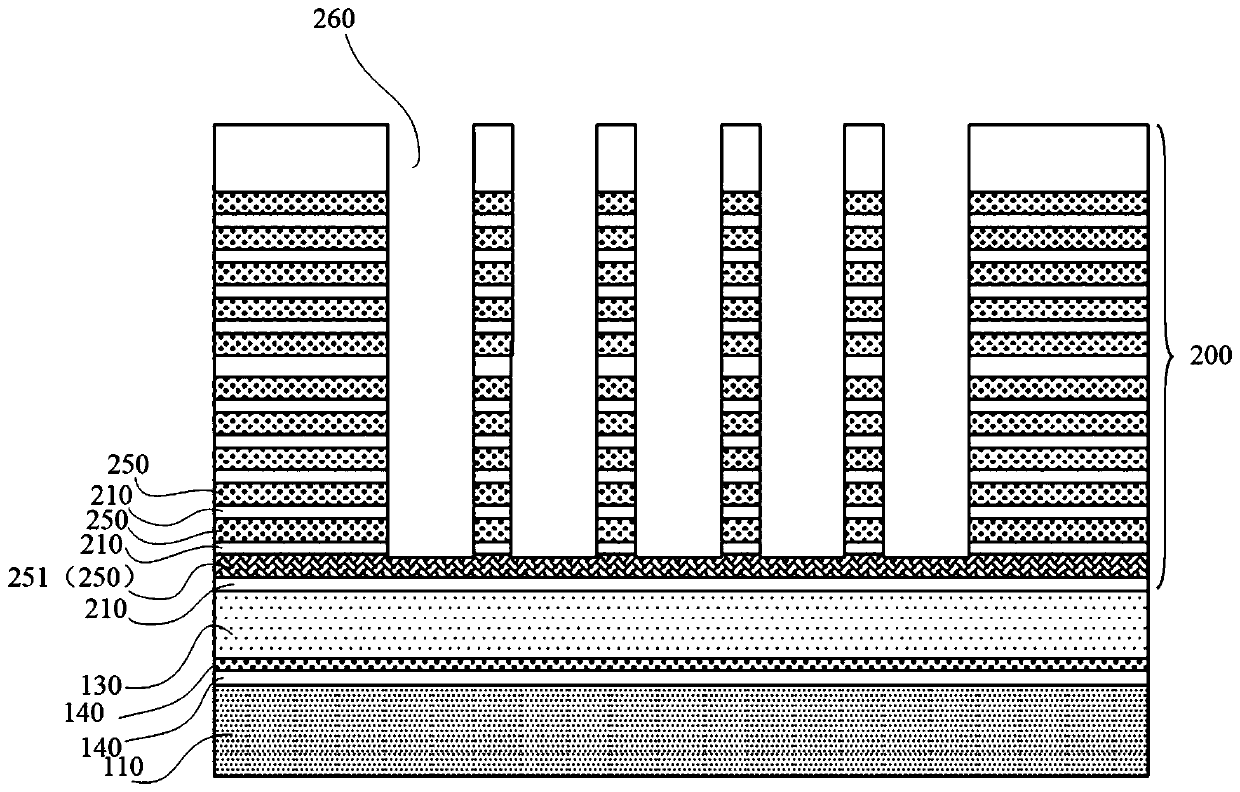

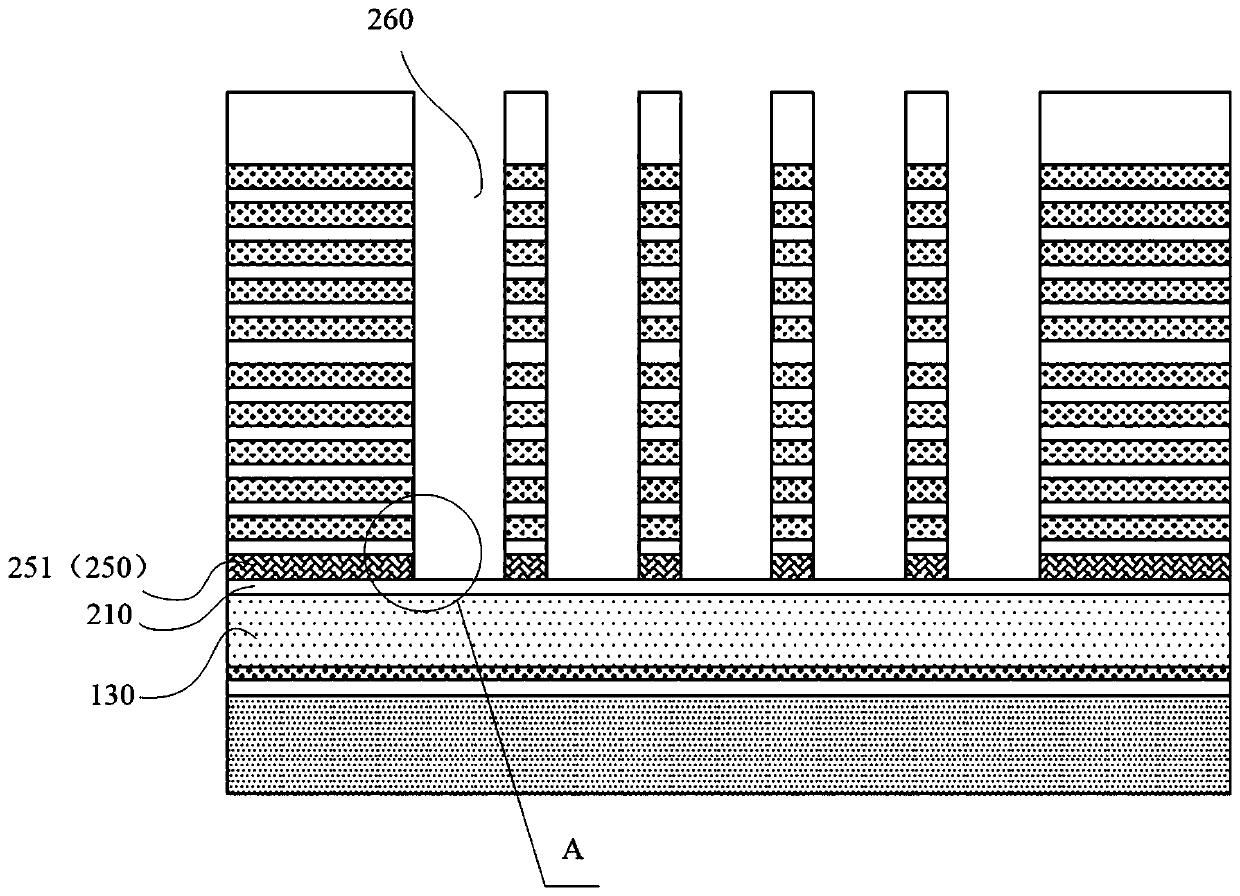

Surface-emitting laser array, optical scanning device, and image forming device

InactiveUS20090295902A1Avoid contactPrevent oxidationRecording apparatusLaser detailsLaser arrayRefractive index

A surface-emitting laser array includes a plurality of surface-emitting laser elements. Each surface-emitting laser element includes a first reflection layer formed on a substrate, a resonator formed in contact with the first reflection layer and containing an active layer, and a second reflection layer formed over the first reflection layer and in contact with the resonator. The second reflection layer contains a selective oxidation layer. The first reflection layer contains on the active layer side at least a low refractive index layer having an oxidation rate equivalent to or larger than an oxidation rate of a selective oxidation layer contained in the second reflection layer. The resonator is made of an AlGaInPAs base material containing at least In. A bottom of a mesa structure is located under the selective oxidation layer and over the first reflection layer.

Owner:RICOH KK

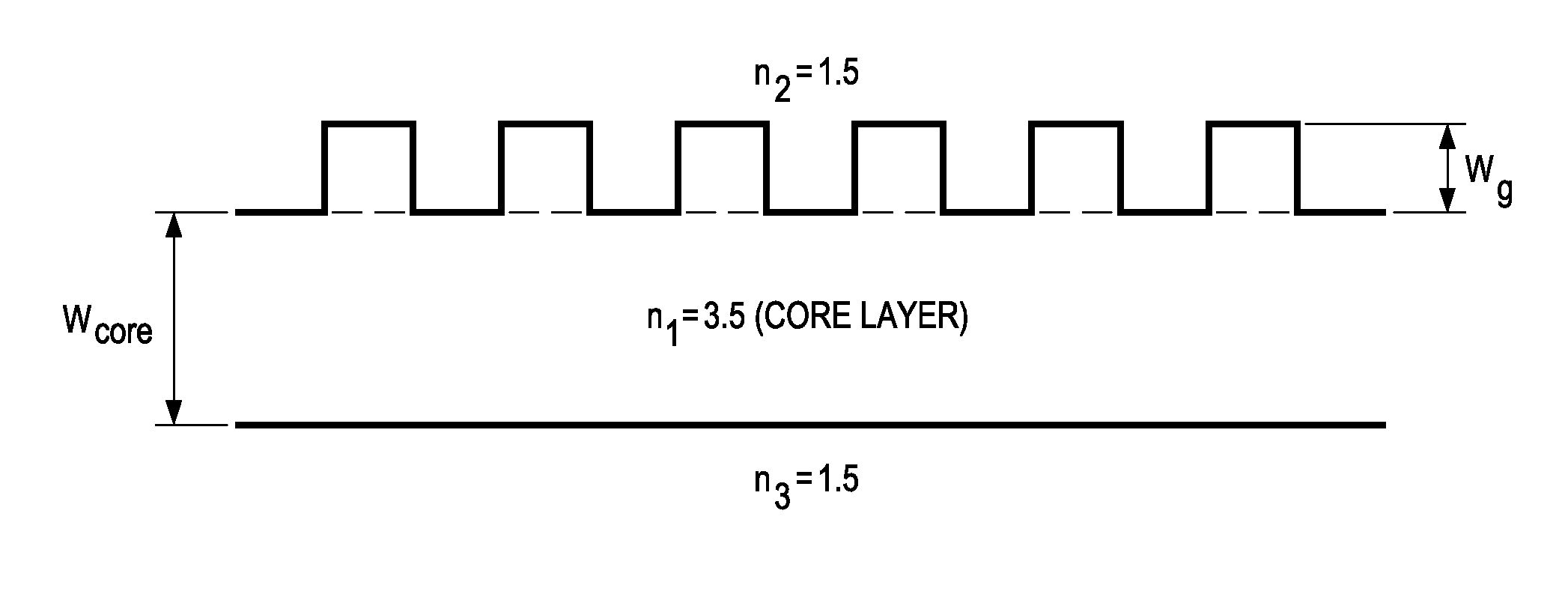

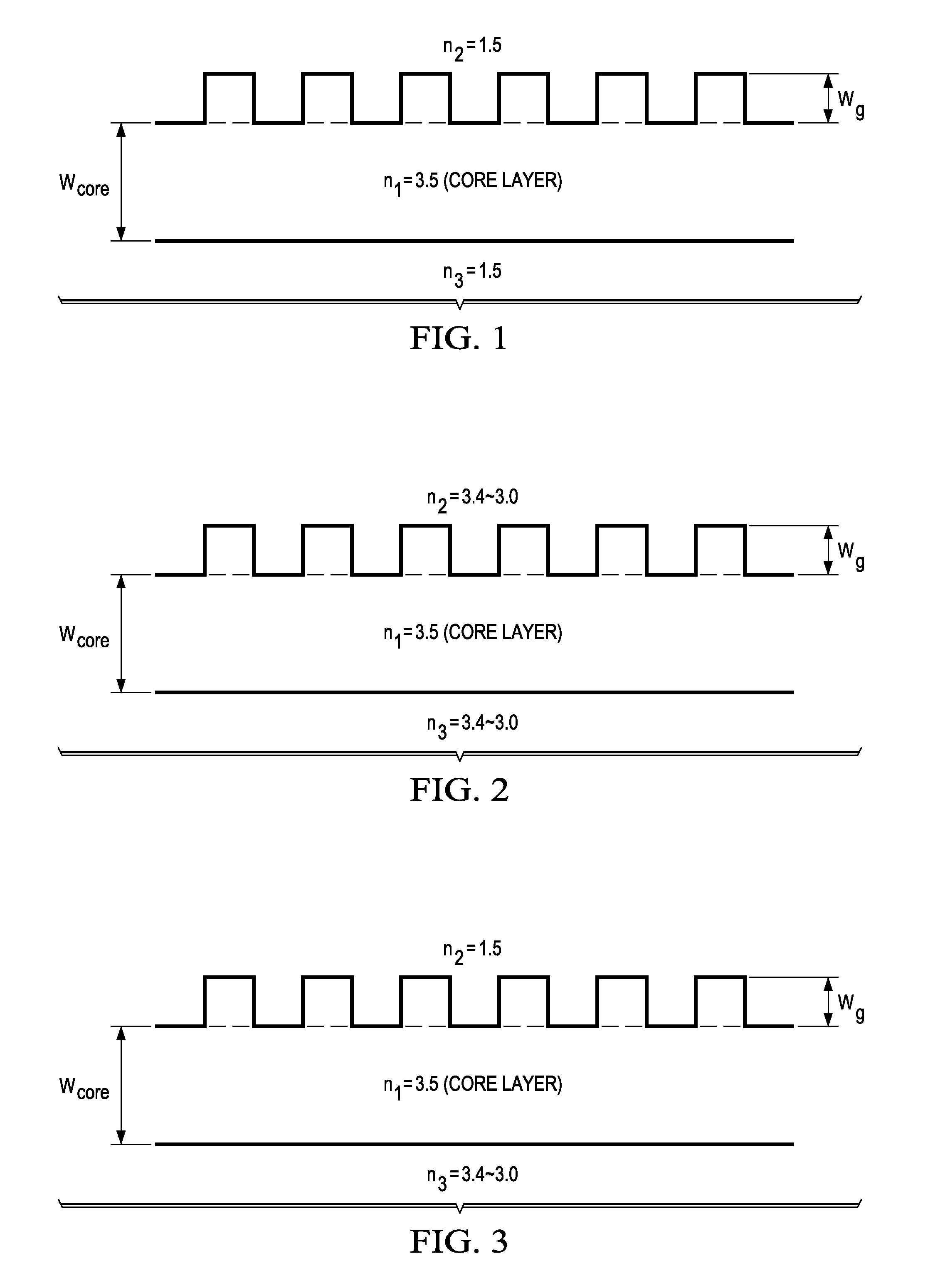

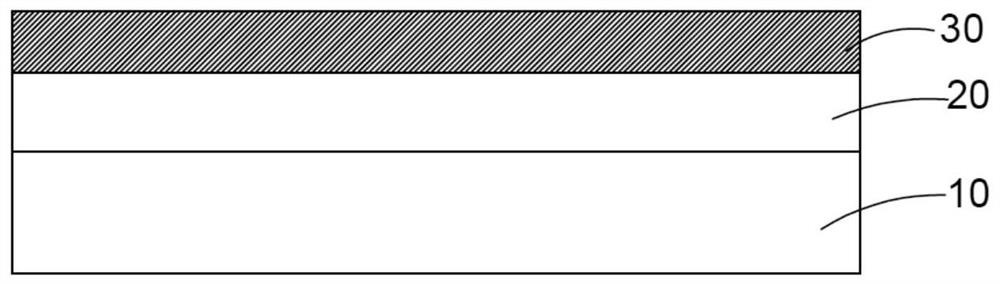

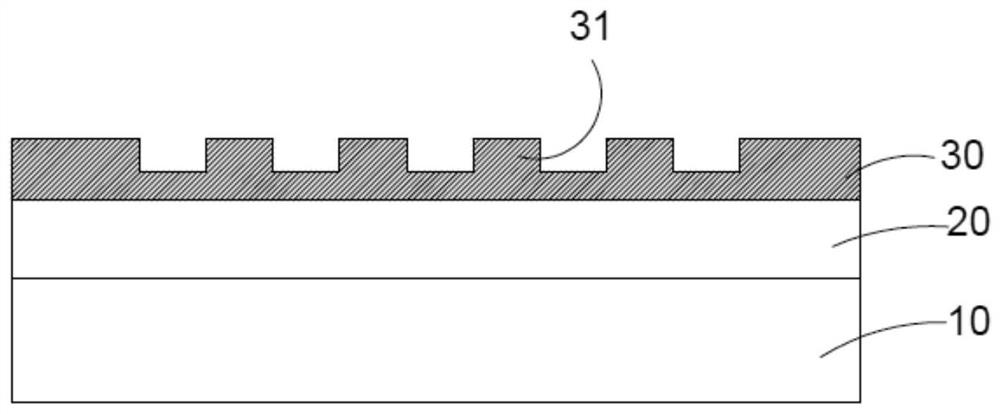

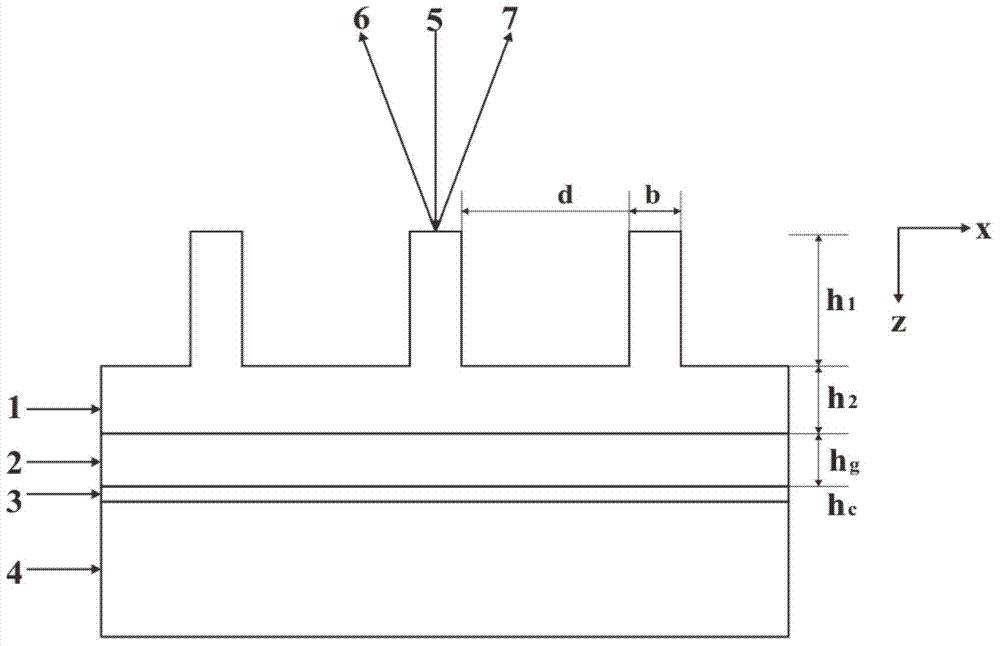

Enhanced coupling strength gratings

ActiveUS20150063753A1Improve coupling strengthHigh indexLaser detailsLaser optical resonator constructionGratingRefractive index

The present invention includes an optical waveguide with a grating and a method of making the same for increasing the effectiveness of the grating. In one example, the grating is at least partially covered by a liner layer disposed on at least a portion of a grating; and a cover layer disposed on the liner layer, wherein a first material selected for the core and ridges and a second material selected for the liner layer are selected to provide a difference in the index of refraction between the first and second material that is sufficient to provide a contrast therebetween.

Owner:ORACLE INT CORP +1

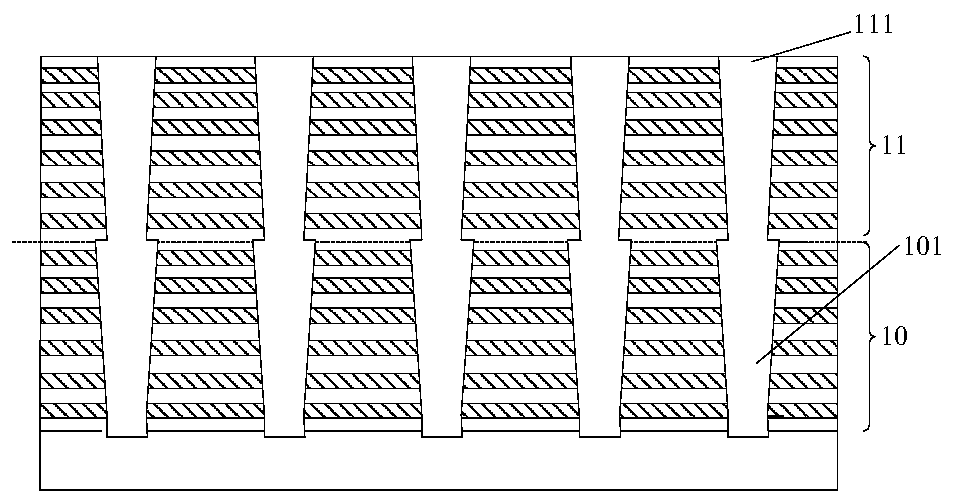

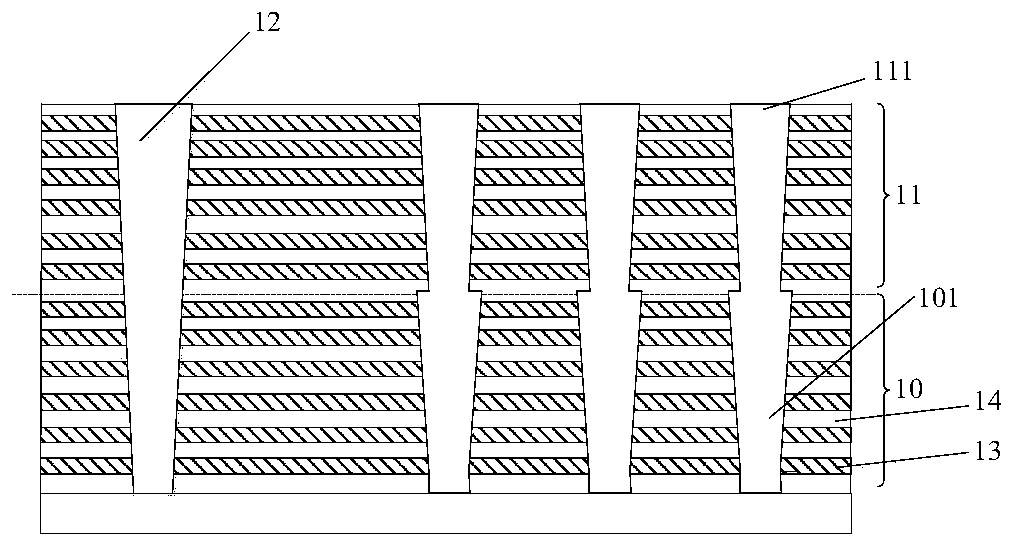

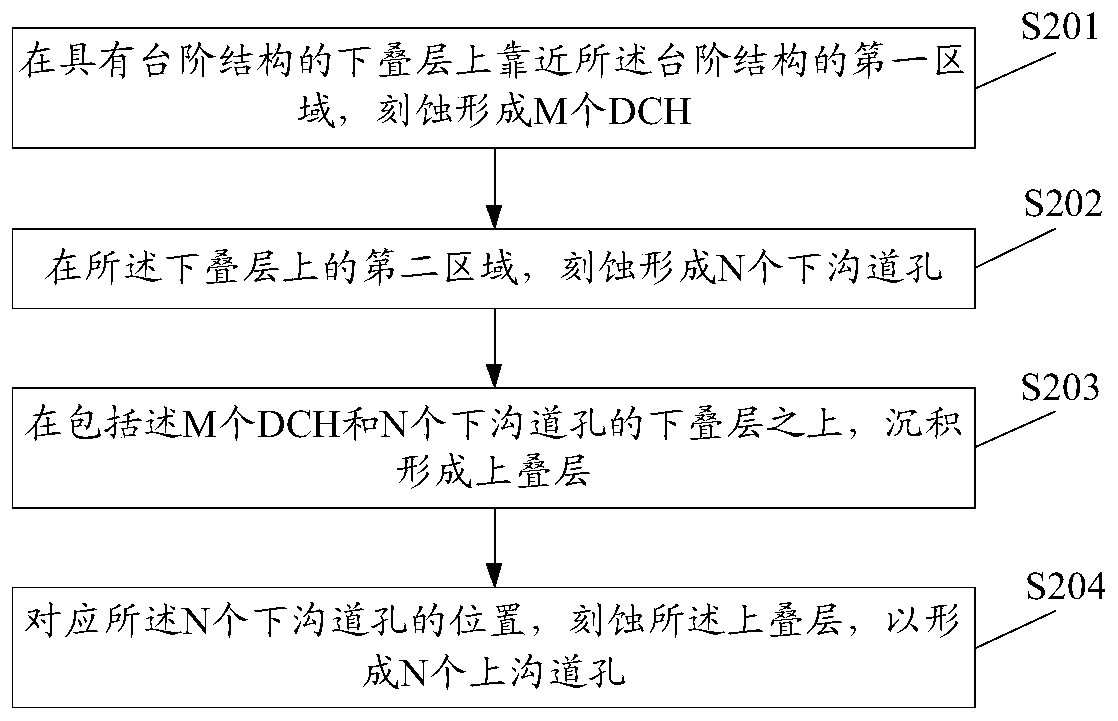

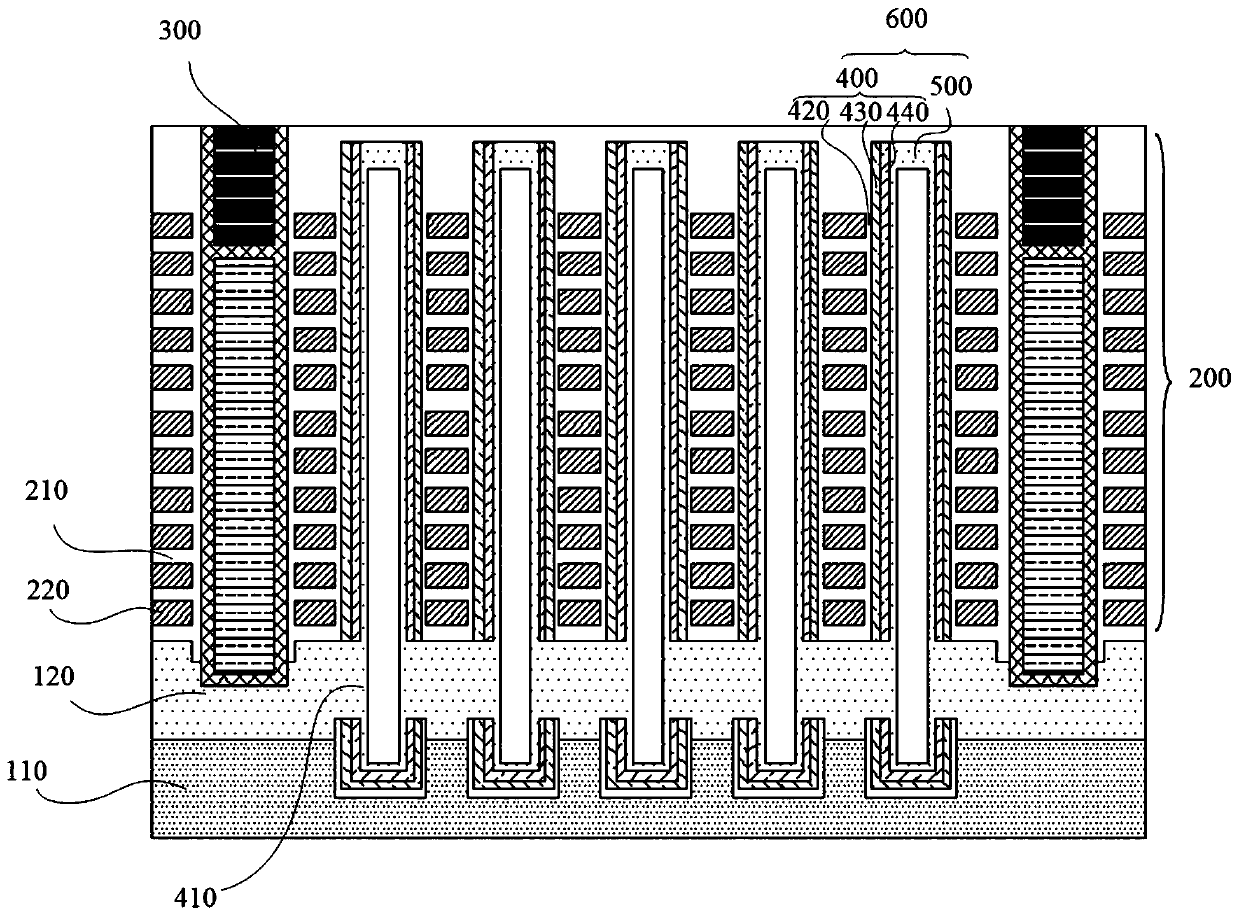

Forming method of three-dimensional memory device, and three-dimensional memory device

ActiveCN109817639AAvoid defectsReduce etch depthSolid-state devicesSemiconductor devicesComputer science

The embodiment of the invention discloses a forming method of a three-dimensional memory device, and the three-dimensional memory device, and the method comprises the steps: etching M DCHs in a firstregion on a lower lamination layer, wherein the lower lamination layer has a step structure, and the first area is close to the step structure; etching N lower channel holes in a second region on thelower lamination layer, wherein the second area is different from the first area, and M and N are positive integers; depositing to form an upper lamination layer on the lower lamination layer comprising the M DCHs and the N lower channel holes; and etching N upper channel holes in the upper lamination layer corresponding to the N lower channel holes in position.

Owner:YANGTZE MEMORY TECH CO LTD

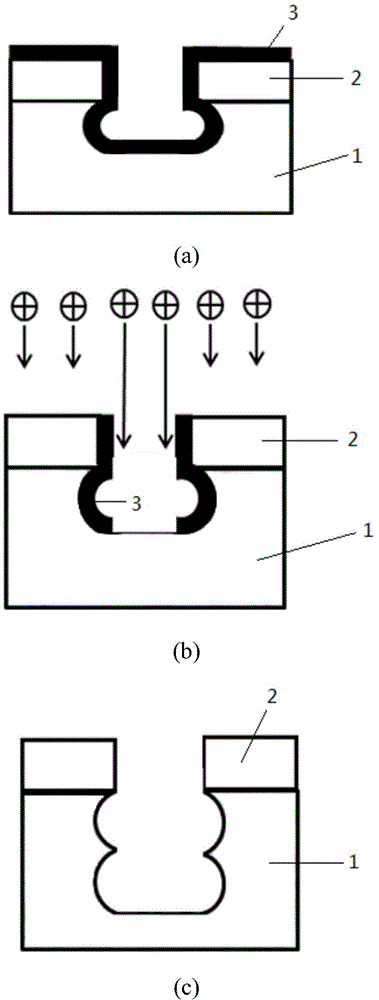

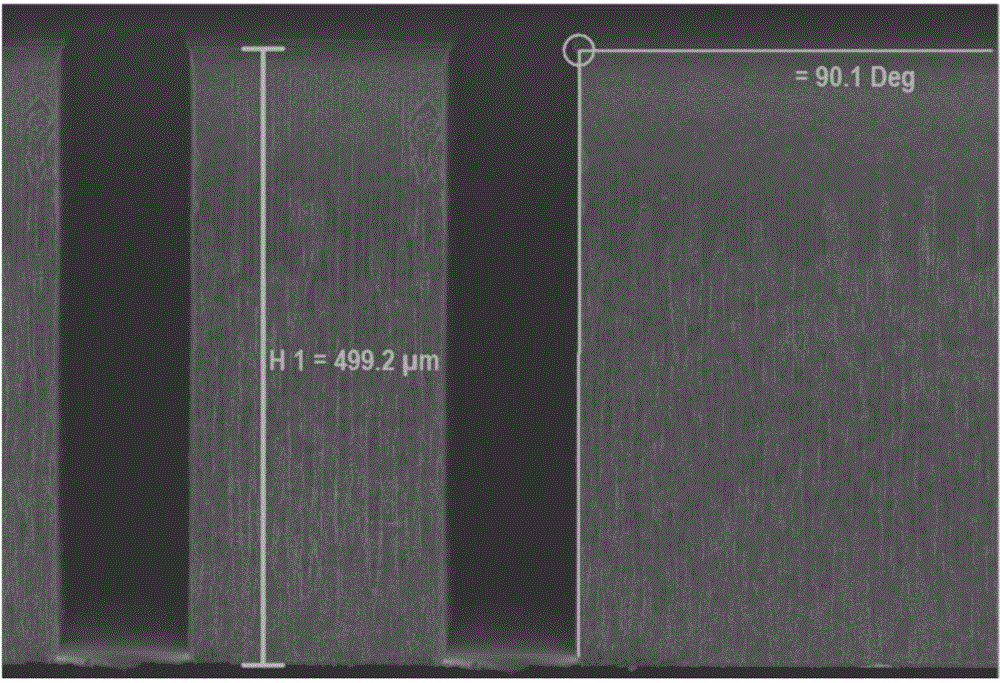

Deep silicon etching method

ActiveCN103950887AAchieve physical bombardmentReduce physical bombardmentDecorative surface effectsChemical vapor deposition coatingInductively coupled plasmaSilicon etching

The invention discloses a deep silicon etching method which comprises the following steps: (1) preparing a graphic photoresist mask on a silicon chip surface; (2) performing deep inductively coupled plasma dry etching of the silicon chip, wherein the etching is divided into several phases, each etching phase is completed in a inductively coupled plasma machine, and is completed through alternate circular processing of three steps of passivation, bombardment, and etching, and with the increase of the etching depth, the bombardment intensity in the bombardment step of each etching phase increases gradually. The method of the invention effectively solves the problems of difficult control of sidewall verticality and roughness, and difficult realization of large etching depth in the prior art, both improves the etching efficiency and increases the selection ratio or photoresist, and is high in etching groove sidewall verticality, low in roughness, and large in etching depth.

Owner:HUAZHONG UNIV OF SCI & TECH

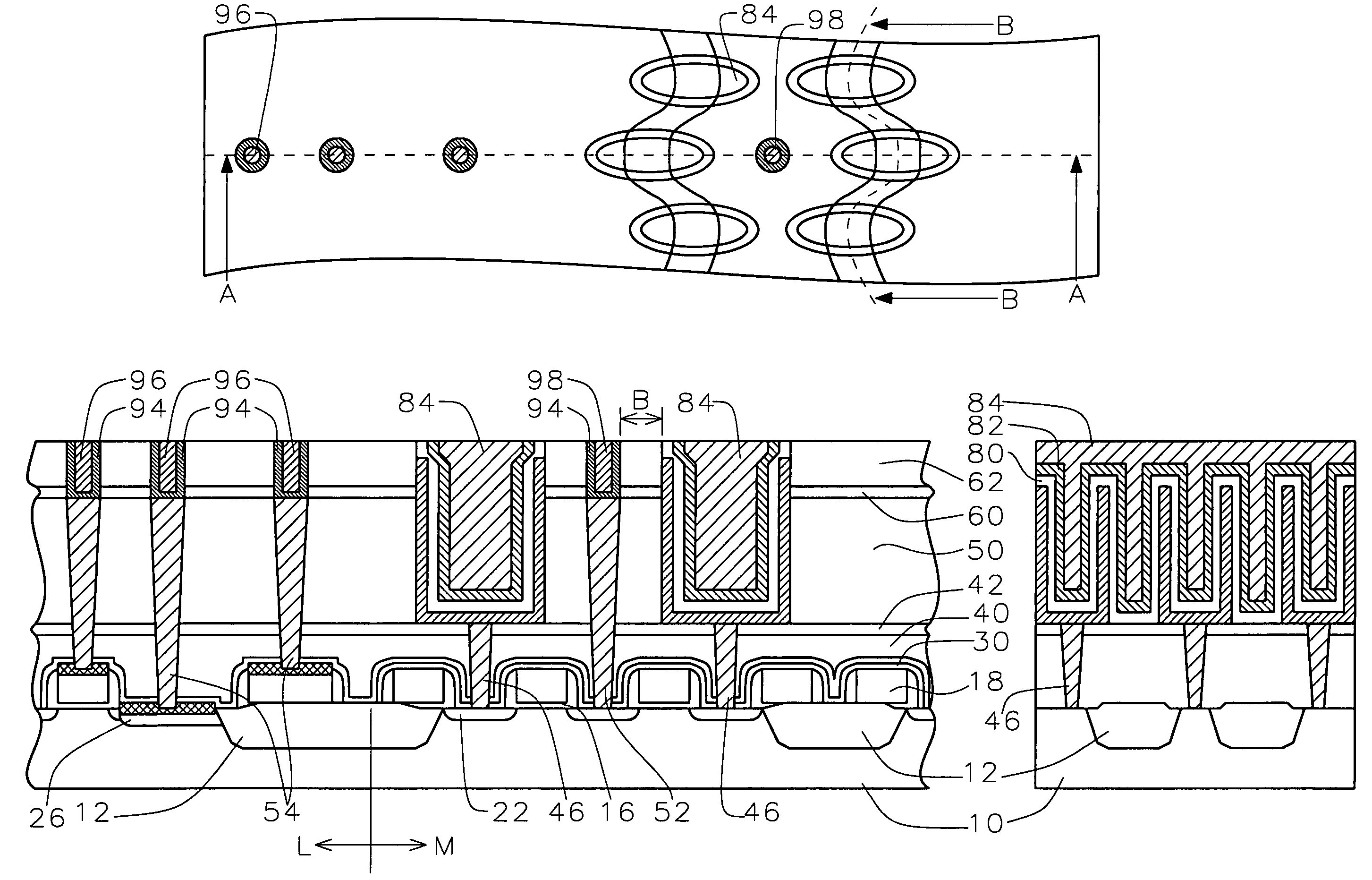

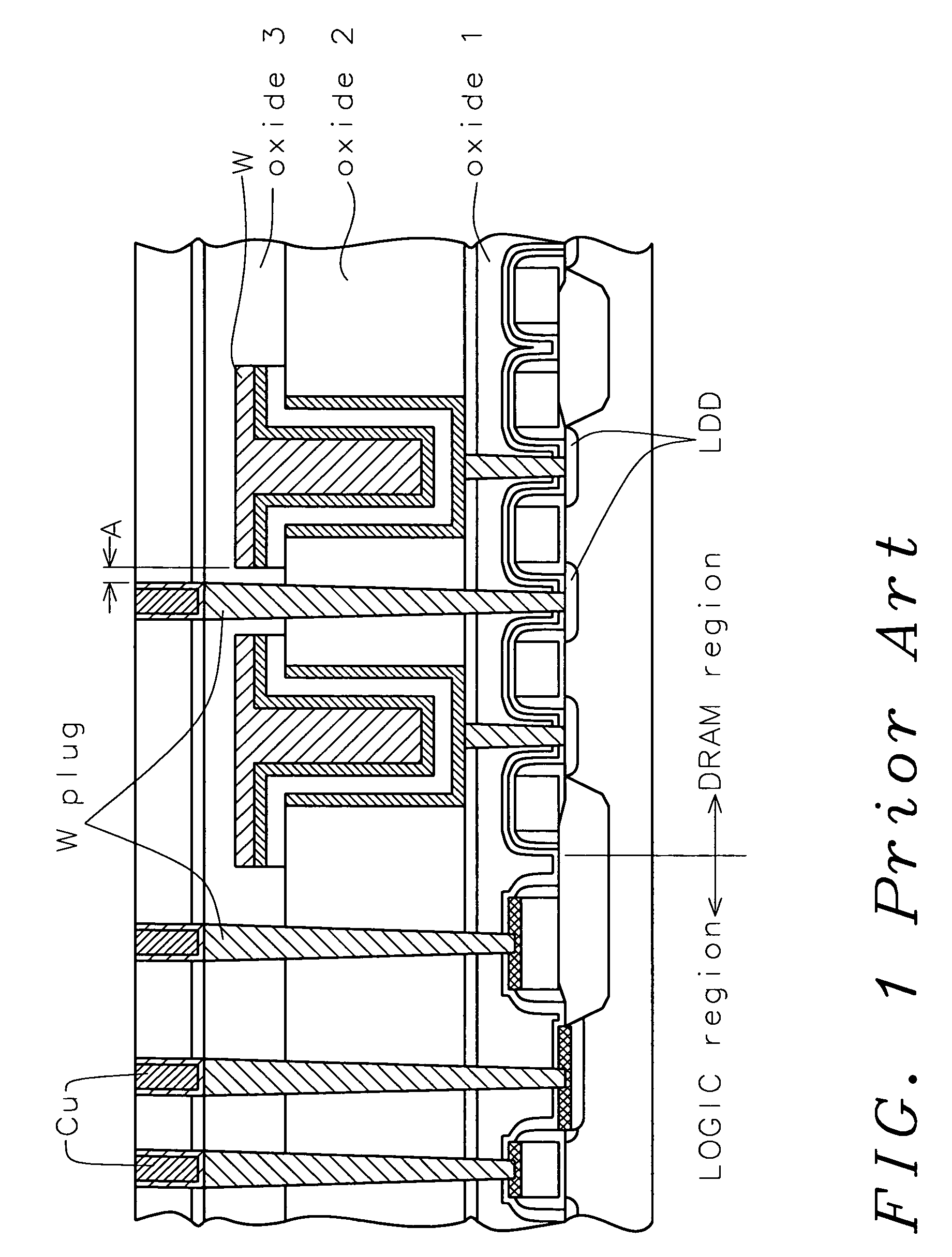

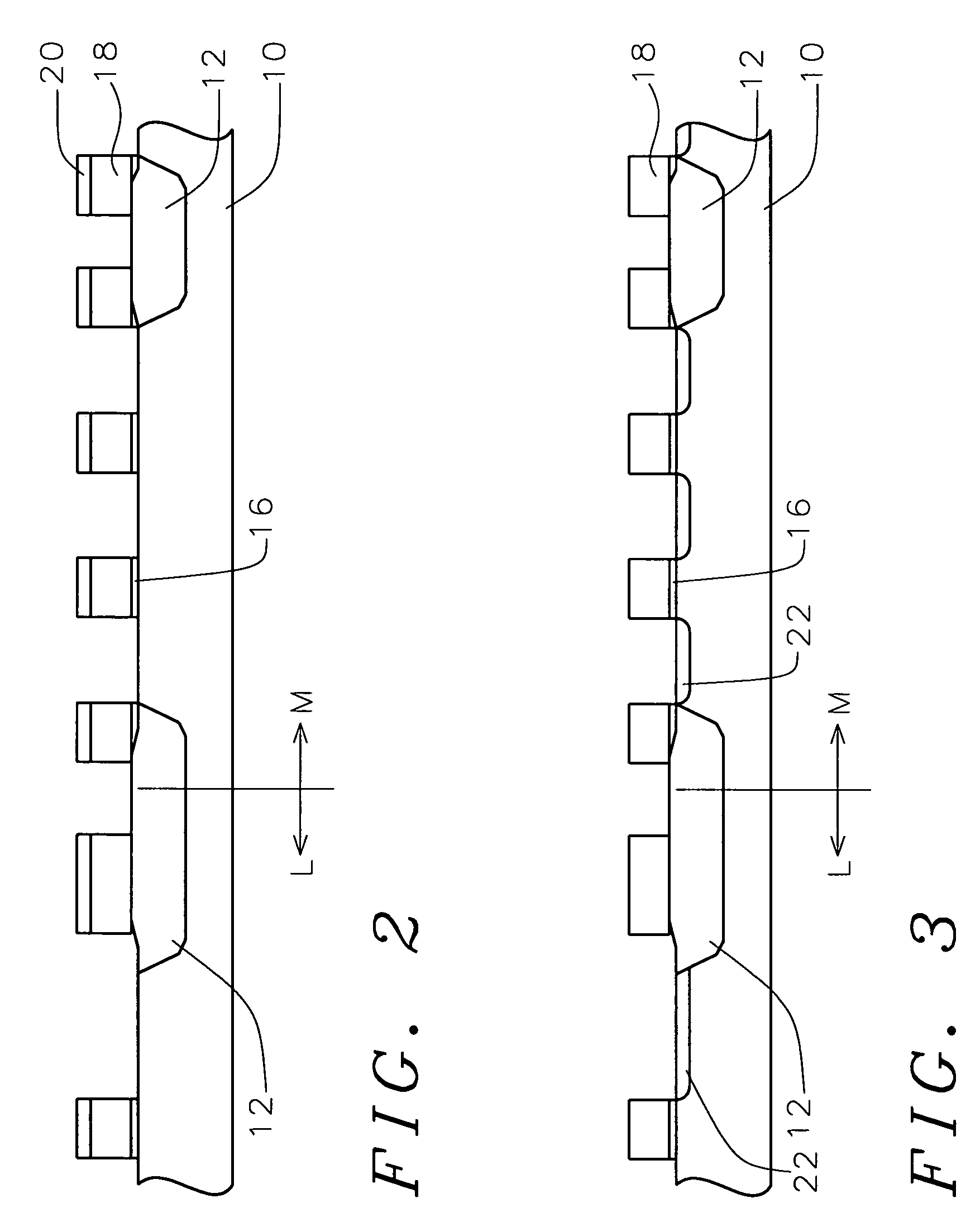

Embedded DRAM for metal-insulator-metal (MIM) capacitor structure

A method for fabricating a metal-insulator-metal capacitor in an embedded DRAM process is described. A plurality of contact plugs are provided through an insulating layer to semiconductor device structures in a substrate wherein the contact plugs are formed in a logic area of the substrate and in a memory area of the substrate and providing node contact plugs to node contact regions within the substrate in the memory area. Thereafter, capacitors are fabricated in a twisted trench in a self-aligned copper process.

Owner:TAIWAN SEMICON MFG CO LTD

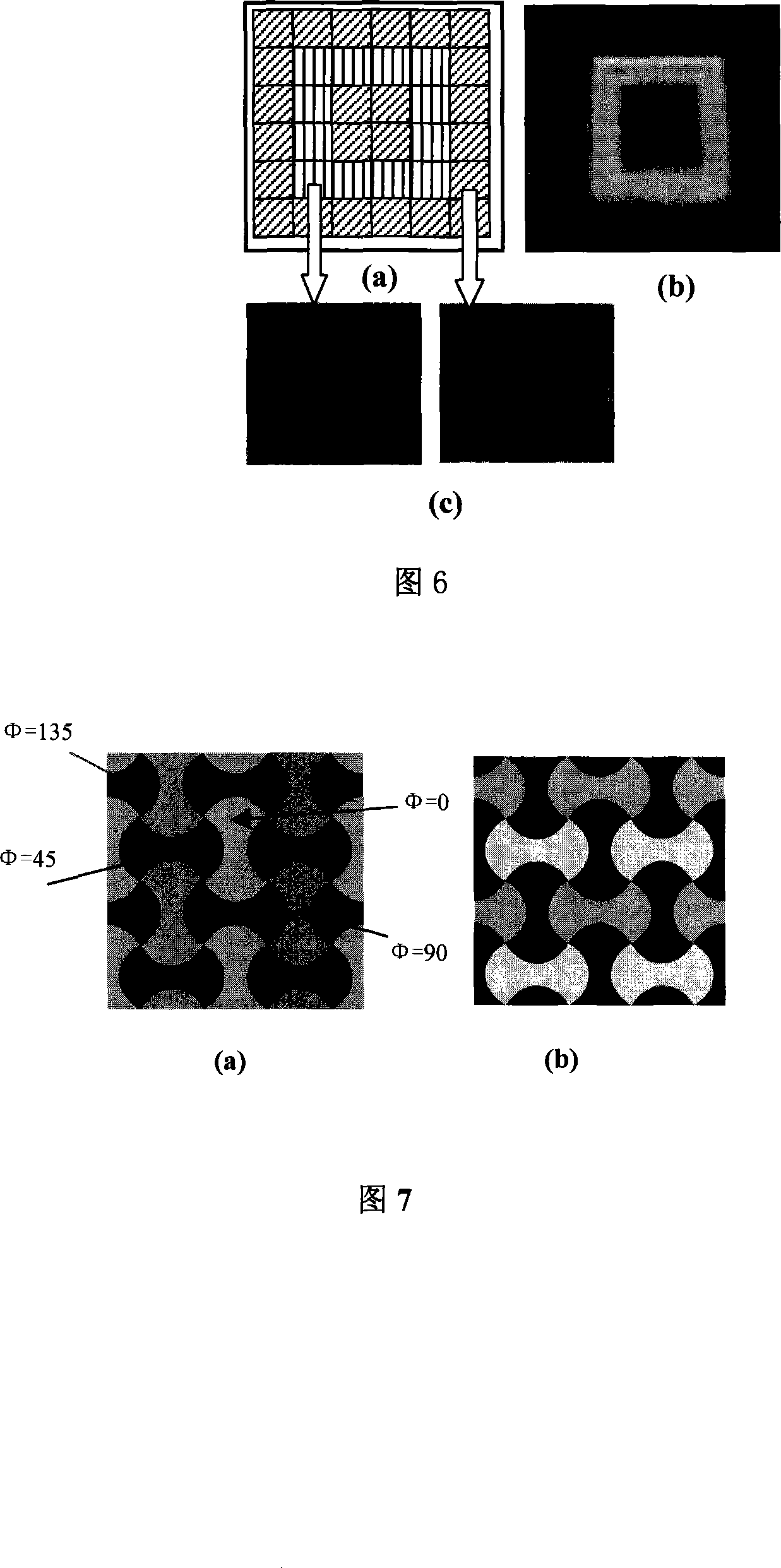

Diffraction color changing laser marking method and apparatus thereof

ActiveCN101135776AHigh-resolutionReduce etch depthLaser detailsDiffraction gratingsLaser power densityImage resolution

The method thereof comprises: using a high power semiconductor pumping solid state laser as light source; the laser beam satisfies the requirement of interference; using a beam-splitting component to generate a beam-splitting light; using a optical lens group to converge the light spot on the material surface to form an even interference fringe optical field; the laser power density on the surface of the materials is over a damage threshold to form the fringe etch; by controlling the scan, realizing the marking of diffracted light color-changed image.

Owner:SVG TECH GRP CO LTD +1

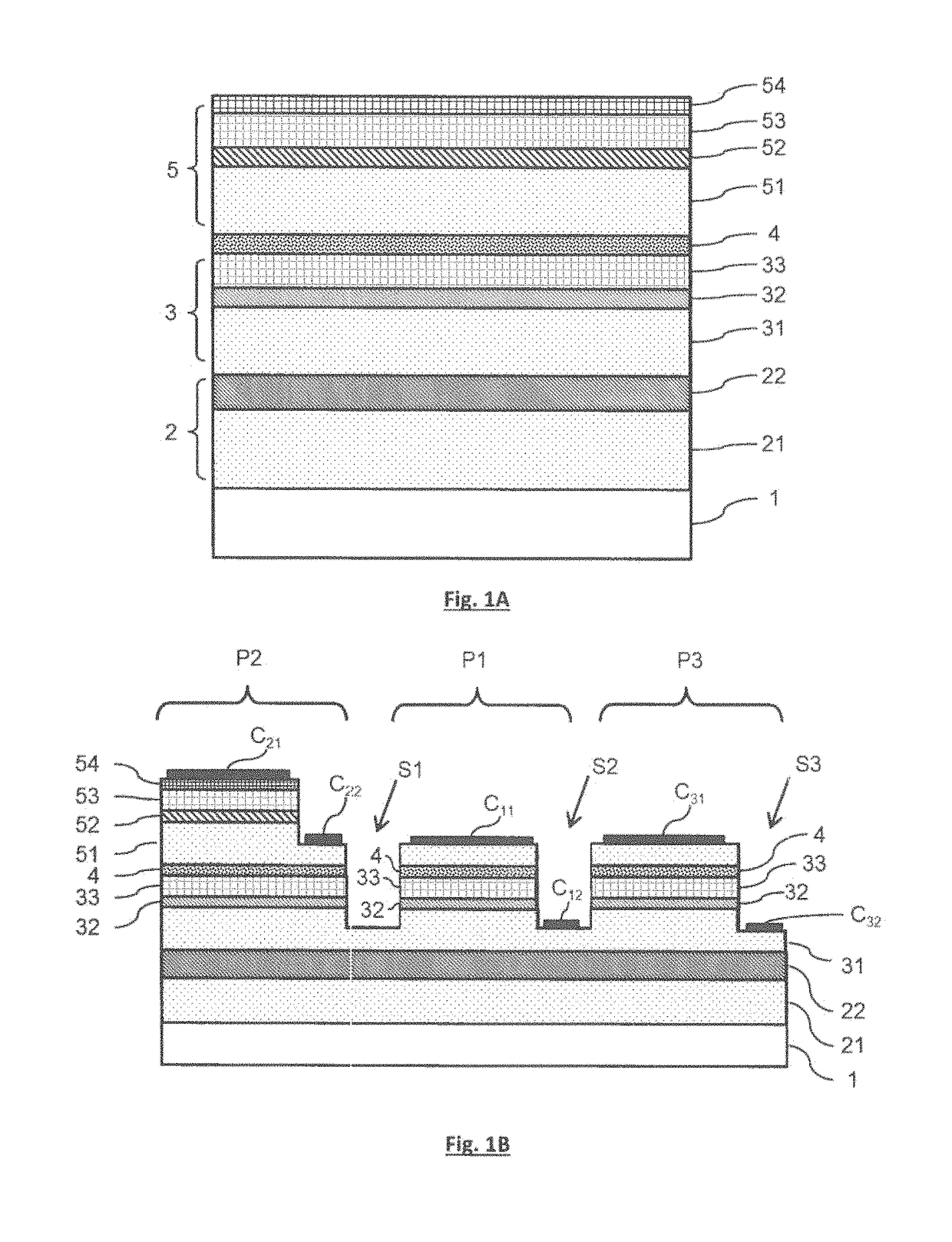

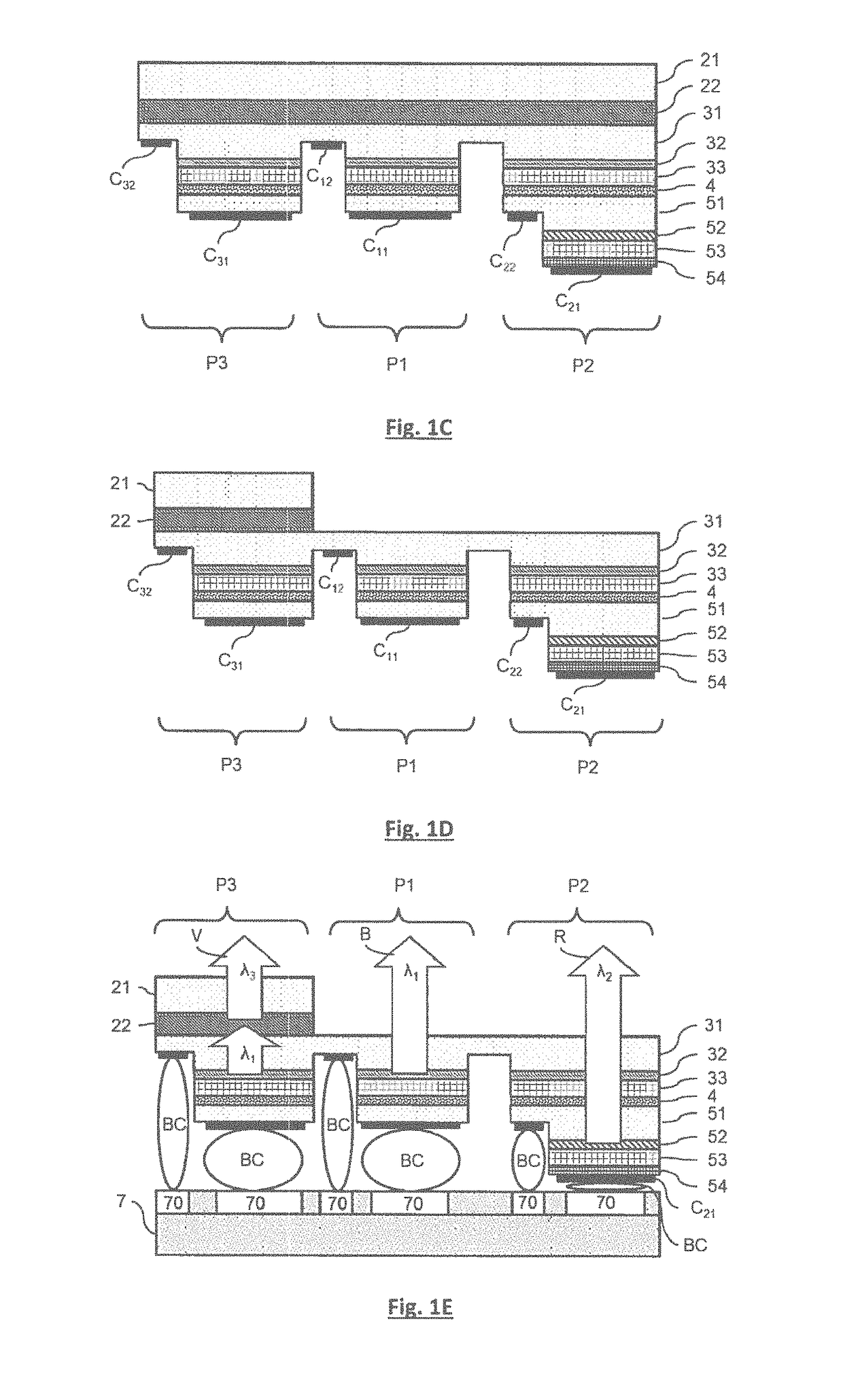

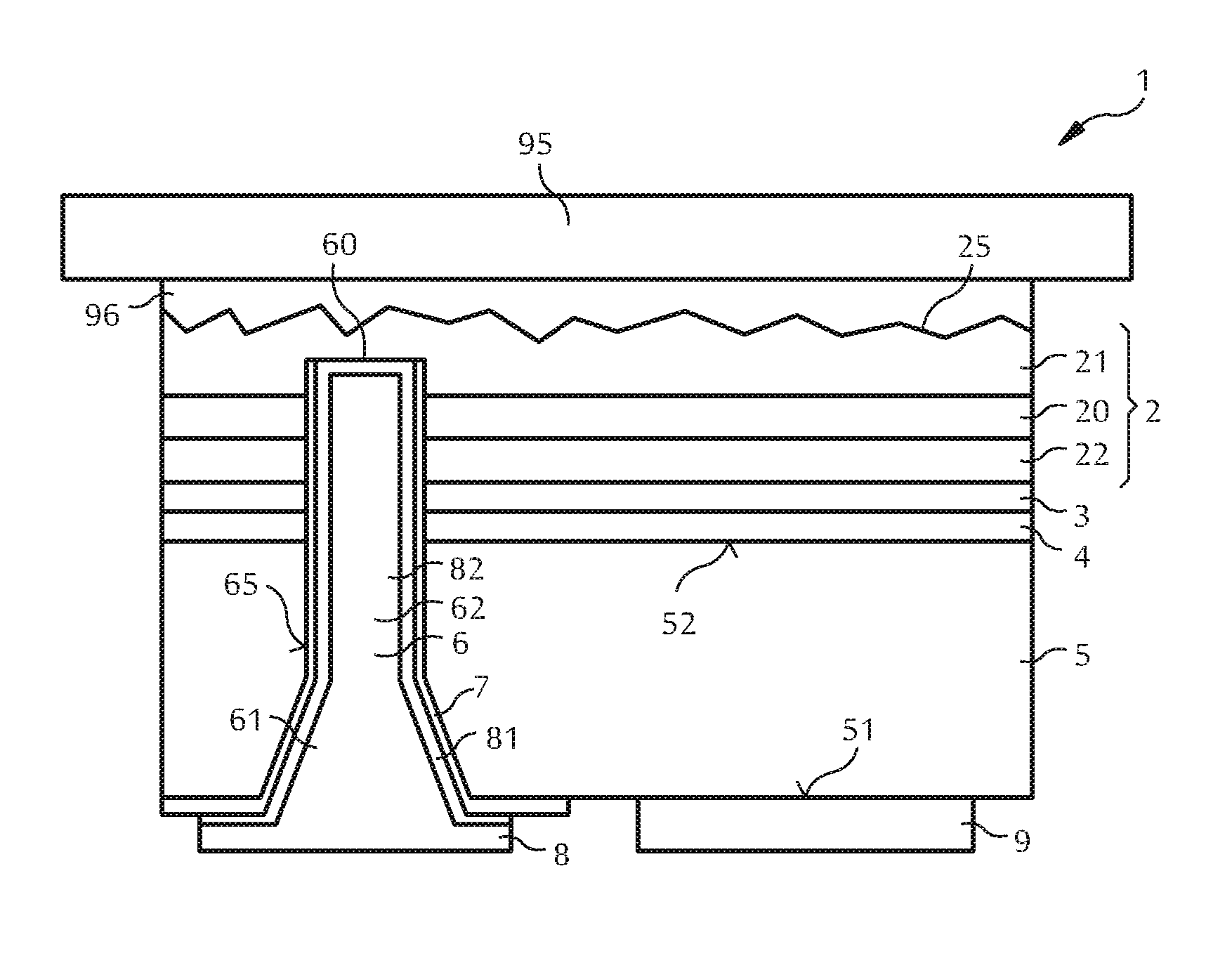

Semiconducting pixel, matrix of such pixels, semiconducting structure for the production of such pixels and their methods of fabrication

ActiveUS10103195B2Increase brightnessHigh degree of miniaturizationSolid-state devicesSemiconductor devicesPower flowSemiconductor structure

A pixel comprises three adjacent sub-pixels, formed by respective stacks of semi-conducting layers wherein: each sub-pixel comprises a first active layer, adapted for emitting a light at a first wavelength when an electric current passes through it; another sub-pixel comprises a second active layer, adapted for emitting a light at a second wavelength greater than the first wavelength; another sub-pixel comprises a third active layer, adapted for emitting a light at a third wavelength greater than the first wavelength and different from the second wavelength; at least one from among the second and third active layers being adapted for emitting light when it is excited by the light at the first wavelength emitted by the first active layer of the same sub-pixel. Semi-conducting structure and methods for the fabrication of such a pixel are provided.

Owner:CENT NAT DE LA RECHERCHE SCI

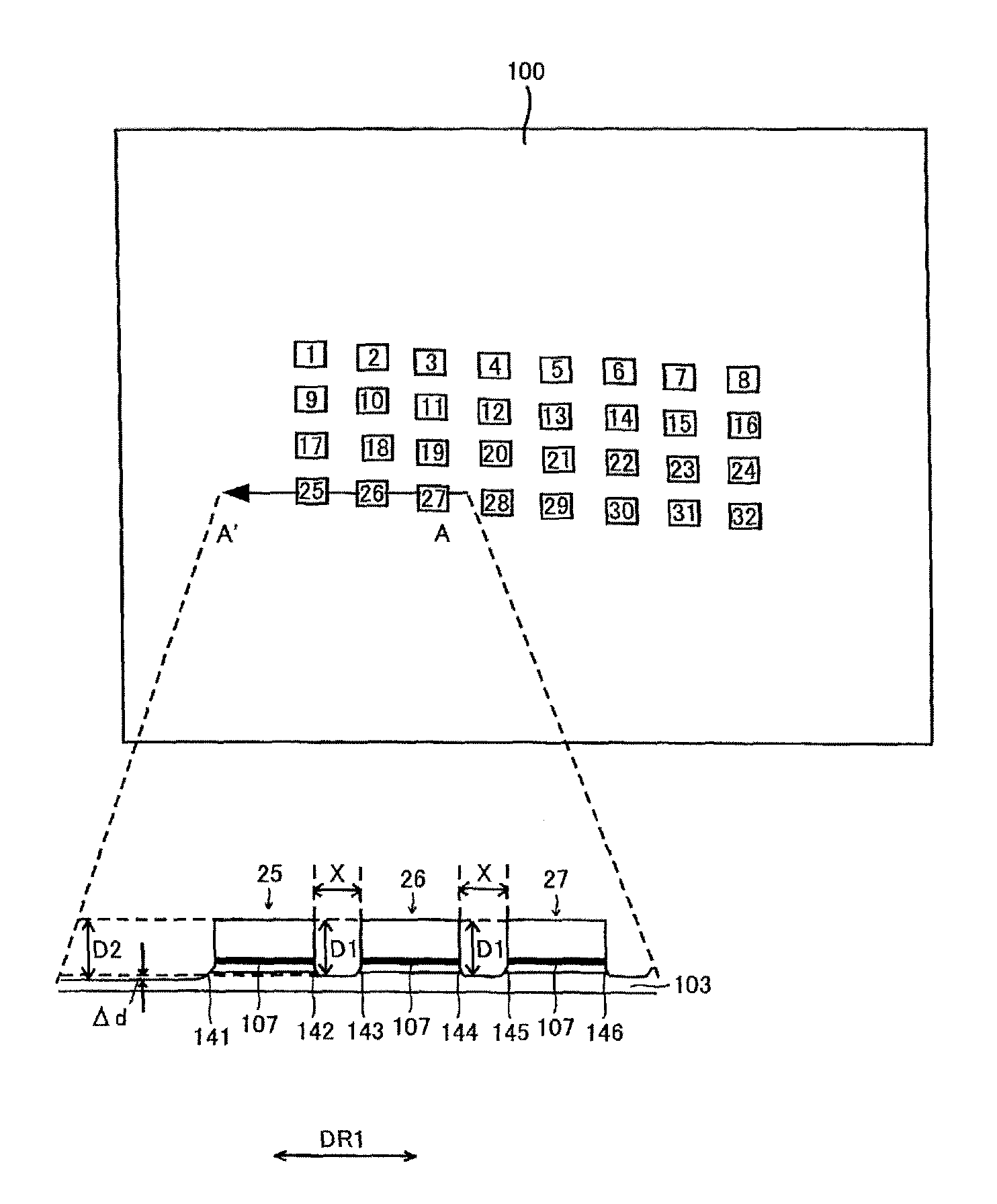

Double-patterned magneto-resistive random access memory (MRAM) for reducing magnetic tunnel junction (MTJ) pitch for increased MRAM bit cell density

ActiveUS20190214554A1Reduce sizeFacilitates MTJsMagnetic-field-controlled resistorsSolid-state devicesStatic random-access memoryRandom access memory

Double-patterned magneto-resistive random access memory (MRAM) for reducing magnetic tunnel junction (MTJ) pitch for increased MRAM bit cell density is disclosed. In one aspect, to fabricate MTJs in an MRAM array with reduced MTJ row pitch, a first patterning process is performed to provide separation areas in an MTJ layer between what will become rows of fabricated MTJs, which facilitates MTJs in a given row sharing a common bottom electrode. This reduces the etch depth and etching time needed to etch the individual MTJs in a subsequent step, can reduce lateral projections of sidewalls of the MTJs, thereby relaxing the pitch between adjacent MTJs, and may allow an initial MTJ hard mask layer to be reduced in height. A subsequent second patterning process is performed to fabricate individual MTJs. Additional separation areas are etched between free layers of adjacent MTJs in a given row to fabricate the individual MTJs.

Owner:QUALCOMM INC

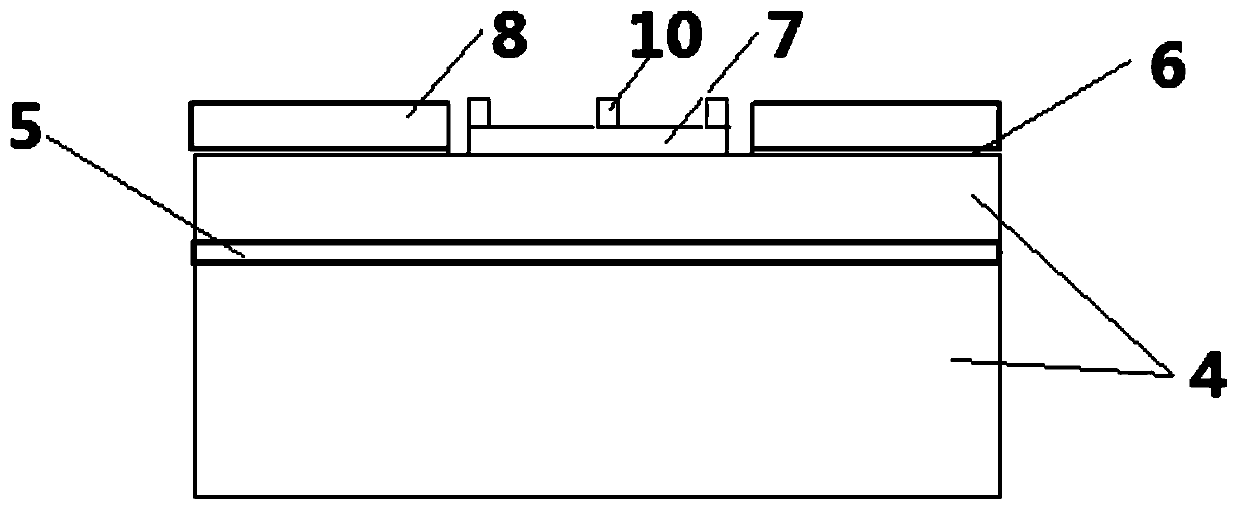

Cavity type bulk acoustic wave resonator with pillar and preparation method thereof

The invention provides a cavity type bulk acoustic wave resonator with a support column and a preparation method of the cavity type bulk acoustic wave resonator. The method comprises the following steps of: taking a piezoelectric single crystal wafer which is subjected to ion implantation and is provided with a bottom electrode; forming a plurality of supporting columns on one side, with the bottom electrode, of the piezoelectric single crystal wafer; forming a cavity at the gap of supporting columns, taking the substrate, bonding the substrate with one side of the piezoelectric single crystalwafer with the cavity, carrying out heat treatment on the substrate after bonding, stripping a film of the piezoelectric single crystal wafer, and producing a top electrode on the stripped side of the piezoelectric single crystal wafer to obtain the piezoelectric single crystal wafer. According to the technical scheme provided by the invention, a sacrificial layer does not need to be grown, etching and trepanning are not carried out on the thin film, the mechanical strength of the device is improved, and the thin film is not easily damaged; the cavity structure is formed before film formation, the rate of finished products is high, residues left by etching after film formation do not exist, and the influence of incomplete release on the device does not need to be considered.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

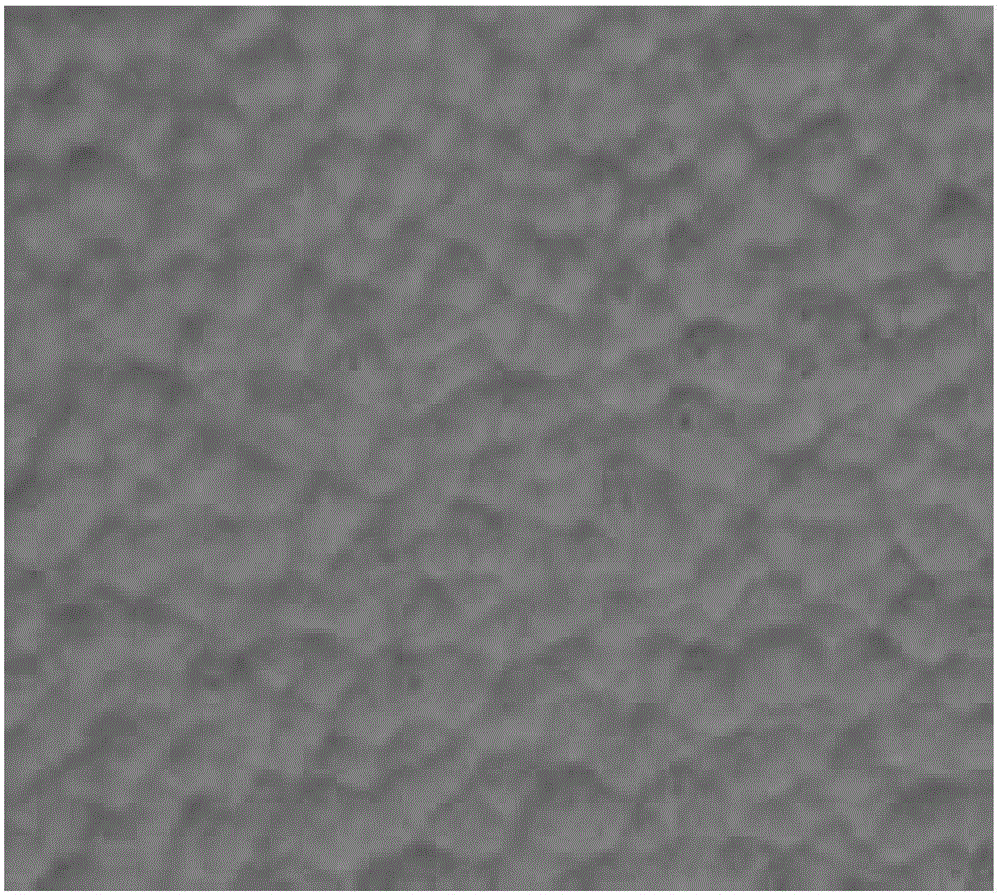

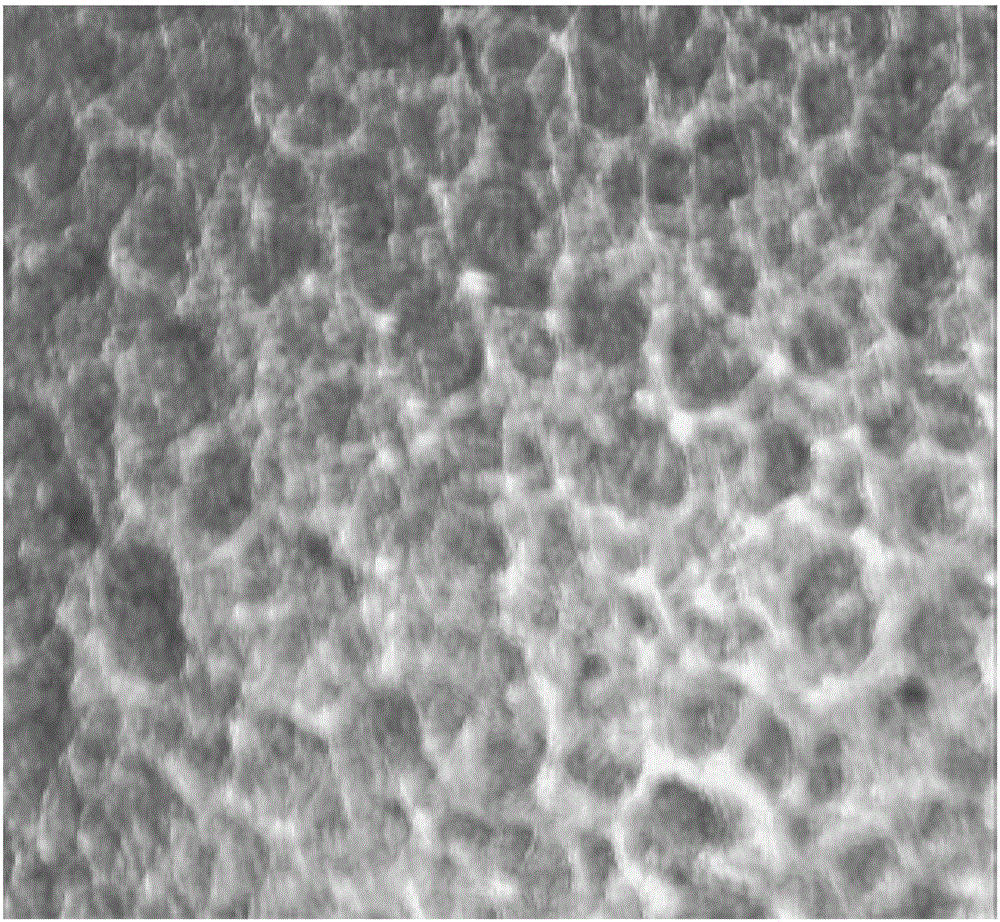

Preparation method of aluminium foil bionic nanostructured super-hydrophobic anti-condensation functional surface

The invention relates to a treatment method of an aluminium foil bionic nanostructured super-hydrophobic anti-condensation functional surface. The method comprises the following steps: firstly performing ultrasonic cleaning of an aluminium foil with acetone and deionized water, blowing to dry, soaking the aluminium foil into a 1 mol / L NaOH aqueous solution for treatment for 30-60 s, cleaning with ethanol and deionized water in order, blowing to dry so as to keep in reserve; soaking the pretreated aluminium foil in liquid which adopts a mixed aqueous solution of phosphoric acid and glycerol as an electrolyte, performing anodization under a room-temperature condition in a constant current density mode for 120-150 min; after the anodization is completed, taking the aluminium foil out, cleaning with ethanol and deionized water, blowing to dry; soaking the anodized aluminium foil in liquid stearic acid at 70 DEG C for 1 h, rinsing in hot ethanol with a temperature of 70 DEG C, curing in an oven with a temperature of 80 DEG C for 30 min so as to prepare the aluminium foil bionic nanostructured super-hydrophobic anti-condensation functional surface. The invention has a simple preparation process, no pollution, less substrate damage, excellent surface quality, and is applicable to popularization and application.

Owner:SOUTHEAST UNIV

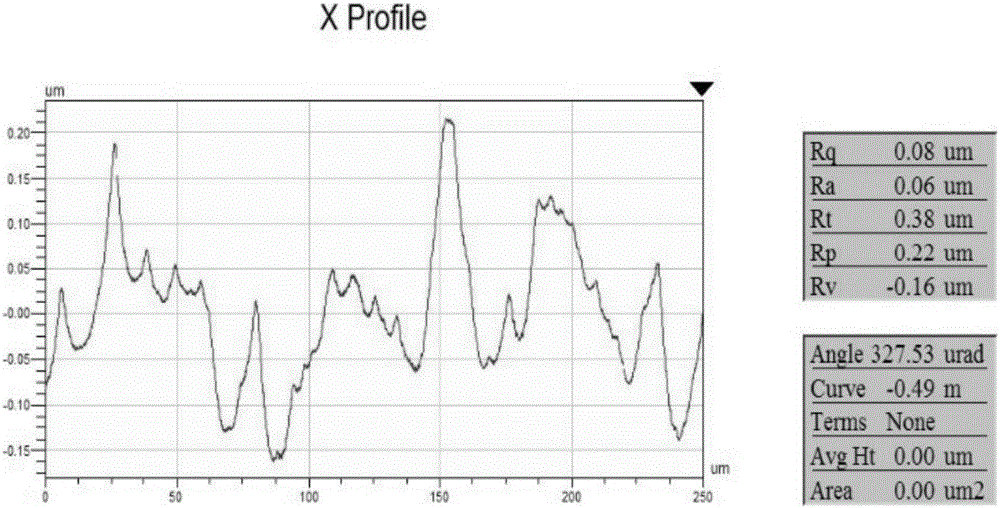

High anti-dazzle glass and preparing technology

The invention discloses high anti-dazzle glass and a preparing technology. An etchant layer with the depth of 0.10 micron to 0.20 micron is arranged on the surface of glass, and comprises compact, regular and honeycomb hexagon etched patterns. The preparing technology includes the following steps of 1, cleaning , wherein the surface of the glass is cleaned with water or deionized water; 2, etching, wherein etching liquid is sprayed to the surface of the glass with the spraying method, and comprises, by weight, 35-45 parts of ammonium bifluoride, 4-15 parts of ammonium sulfate, 5-10 parts of ammonium nitrate, 5-10 parts of barium sulfate, 4-8 parts of potassium sulfate, 60-100 parts of hydrochloric acid and 20-40 parts of water; 4, polishing, wherein the etched surface of the glass is polished through mixed acid liquid of hydrofluoric acid and sulfuric acid. The reflective rate of the high anti-dazzle glass prepared with the technology is smaller than or equal to 3%, the light transmittance is larger than or equal to 90%, the roughness degree is as low as 0.15 micron or below.

Owner:安徽赢赛触控技术有限公司

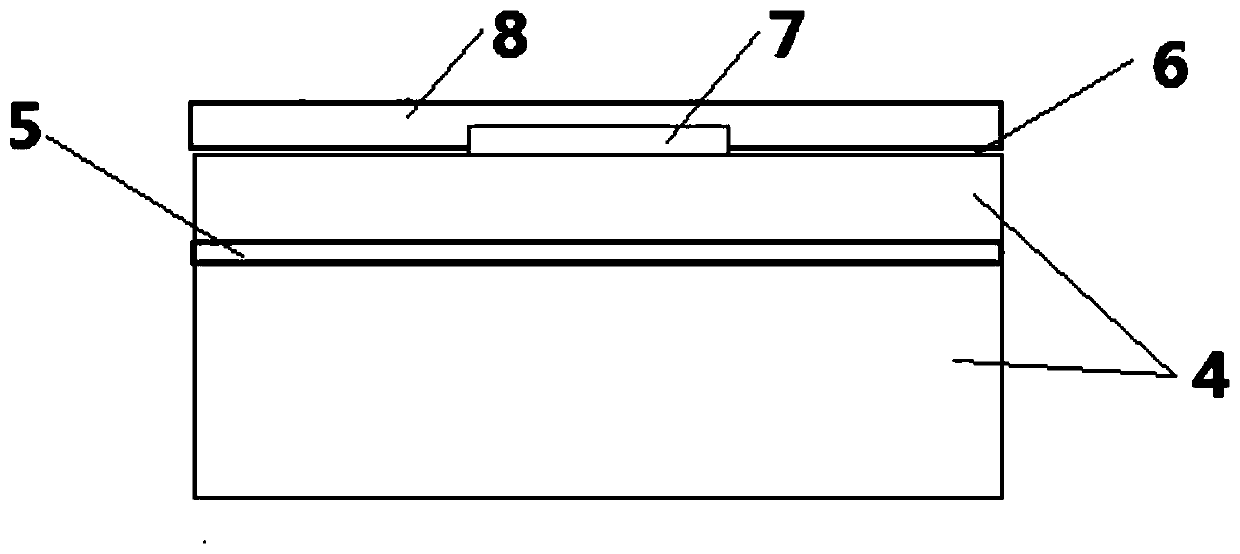

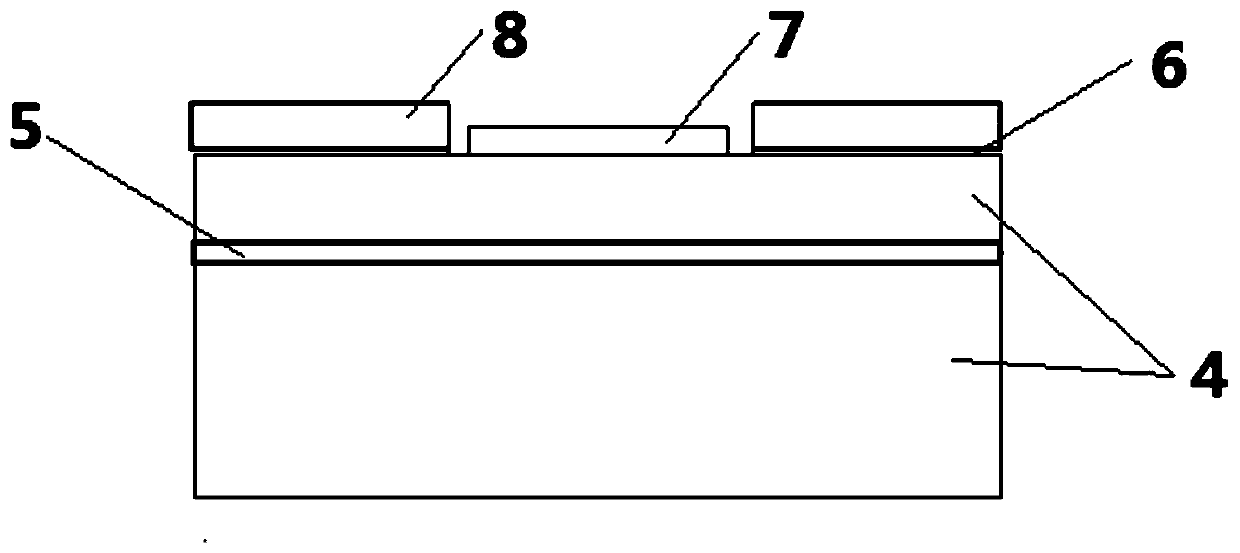

Cavity type bulk acoustic wave resonator without preparing sacrificial layer and preparation method of cavity type bulk acoustic wave resonator

The invention provides a cavity type bulk acoustic wave resonator without preparing a sacrificial layer and a preparation method of the cavity type bulk acoustic wave resonator. The method comprises the following steps that a piezoelectric single crystal wafer which is subjected to ion implantation and provided with a bottom electrode is taken, a cavity is formed in the side, provided with the bottom electrode, of the piezoelectric single crystal wafer, then a substrate is taken, and the substrate and the side, provided with the cavity, of the piezoelectric single crystal wafer are bonded; andheat treatment is carried out on the bonded intermediate product to strip the film of the piezoelectric single crystal wafer, and then a top electrode is produced on one stripped side of the piezoelectric single crystal wafer to obtain the cavity type bulk acoustic wave resonator. According to the preparation method of the cavity type bulk acoustic resonator without the need of preparing the sacrificial layer, the sacrificial layer does not need to be grown, etching and trepanning are not carried out on the thin film, the mechanical strength of the device is improved, and damage to the thin film is not likely to be generated; the cavity structure is formed before film formation, the rate of finished products is high, residues left by etching after film formation do not exist, and the influence of incomplete release on the device does not need to be considered.

Owner:CHIMEMS MICROELECTRONICS CO LTD

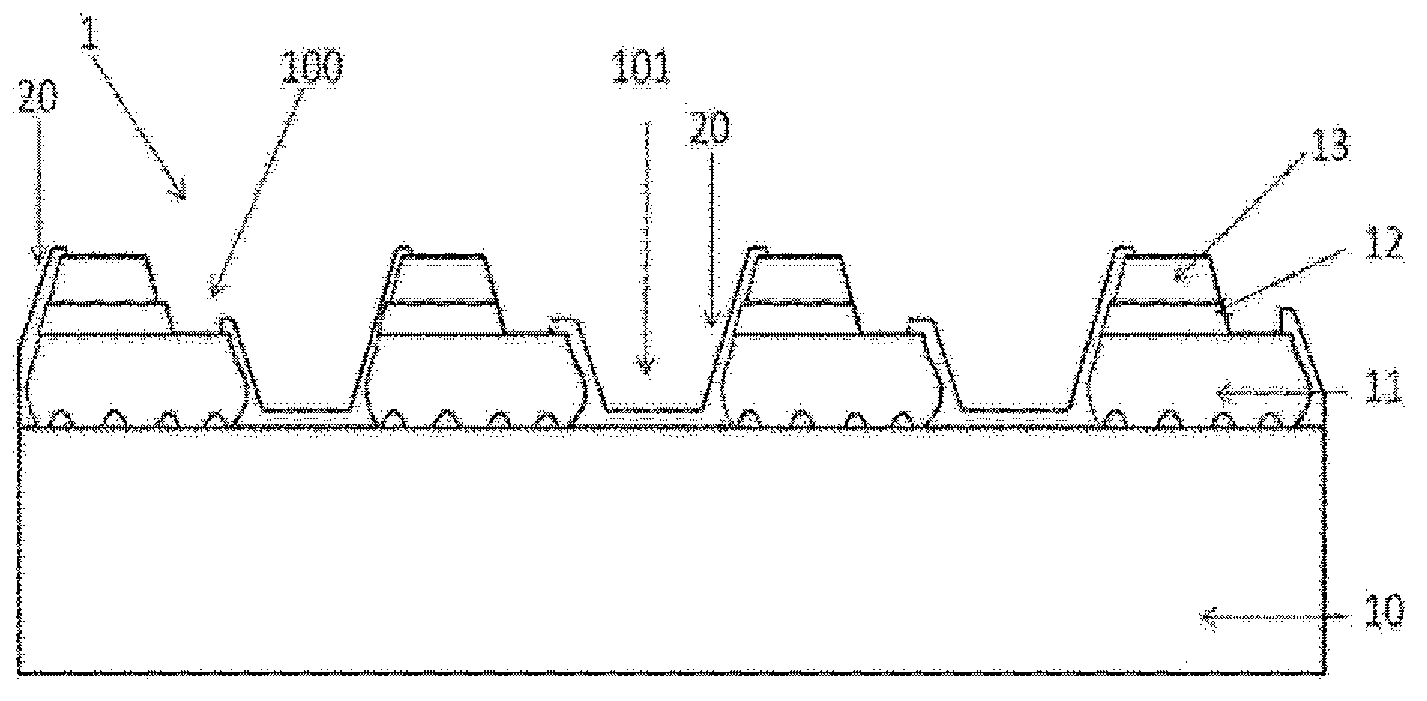

Preparation method of crystalline silicon solar cell textured structure

ActiveCN106098810AReduce the depth of etchingReduce dosageSemiconductor/solid-state device manufacturingNanotechnologySurface etchingCitric acid

The invention discloses a method for preparing a textured surface structure of a crystalline silicon solar cell, which comprises the following steps: (1) forming a porous layer structure on the surface of a silicon chip; (2) etching the surface with a first chemical etching solution to form the textured surface surface structure; the first chemical etching solution is a mixed solution of hydrofluoric acid, an oxidizing agent and an additive; the additive is acetic acid or citric acid. The present invention designs a new chemical etching solution, and uses the chemical etching solution to etch the surface of the porous layer structure to form a suede structure. The experiment proves that the reaction speed of the chemical etching solution of the present invention is controllable, so that the suede surface can be guaranteed. The stability and uniformity of the structure, and the stability of the electrical performance of the solar cell.

Owner:CSI CELLS CO LTD

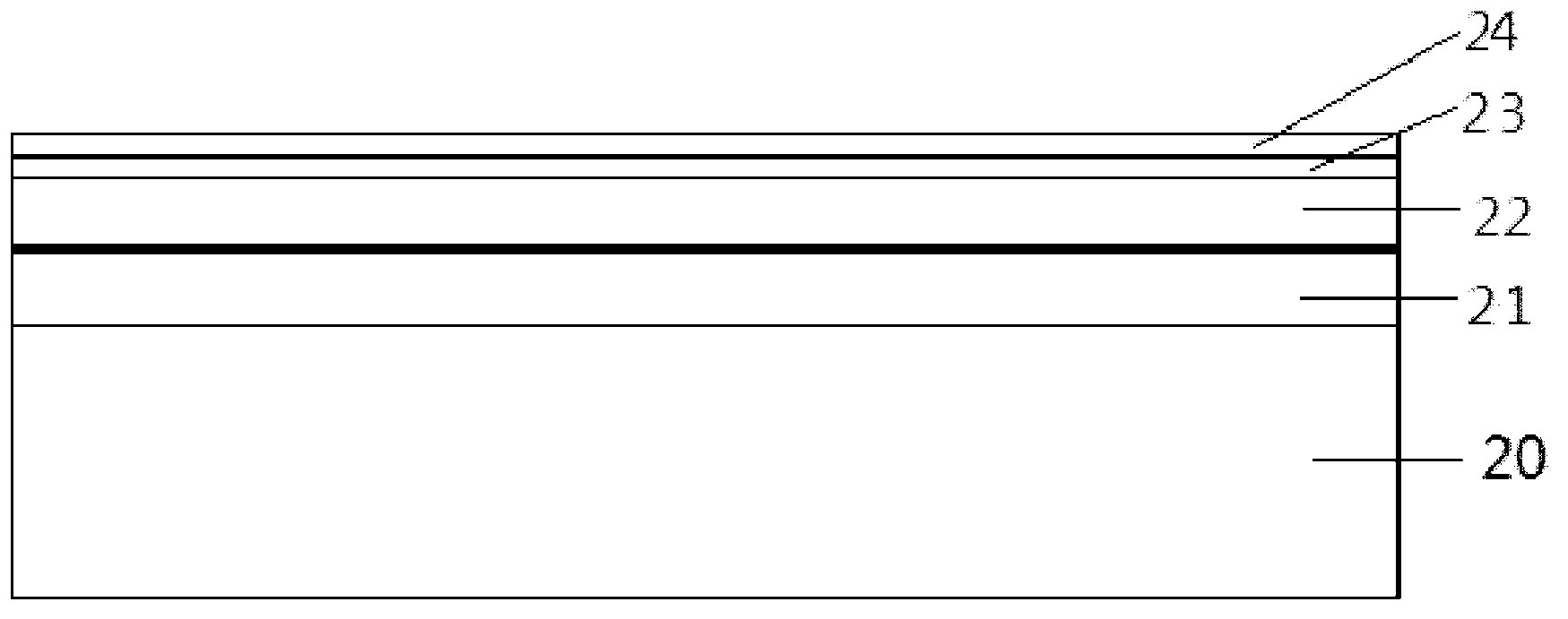

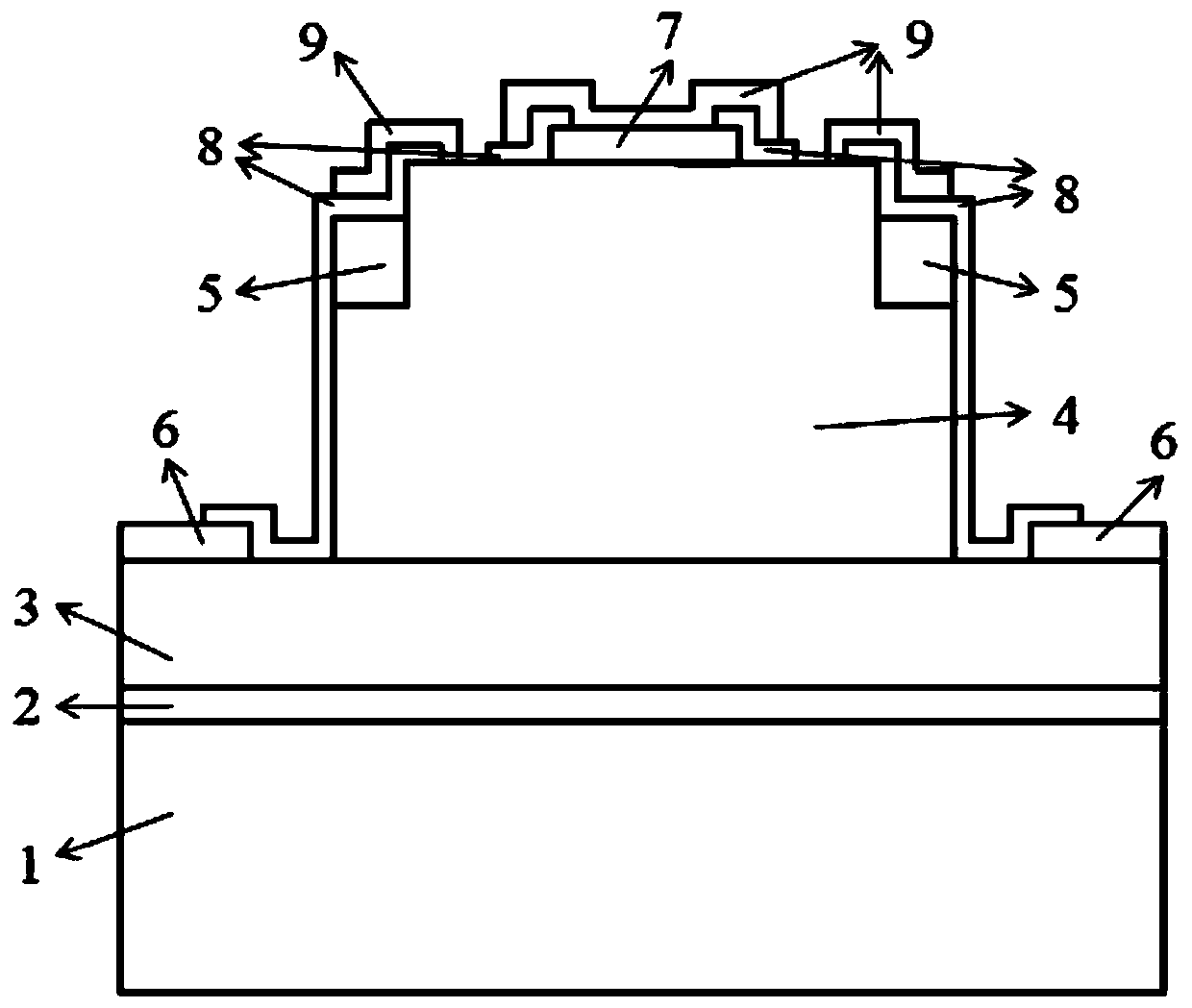

High voltage light-emitting diode and manufacturing method thereof

InactiveCN103187494AAvoid damageReduce etch depthSolid-state devicesSemiconductor devicesHigh pressureMetal

The invention relates to a manufacturing method of a high voltage light-emitting diode. The manufacturing method of the high voltage light-emitting diode comprises the steps of forming an insulating buffer layer on a substrate; forming an n-type semiconductor layer, an active layer and a p-type semiconductor layer on the insulating buffer layer; patterning the n-type semiconductor layer, the active layer and the p-type semiconductor layer, then etching the n-type semiconductor layer, the active layer and the p-type semiconductor layer to form grooves till the insulating buffer layer is exposed out of the bottoms of the grooves, forming a plurality of isolated luminous units through the grooves; and forming metal interconnecting wires, and connecting the adjacent luminous units in series. The manufacturing method is characterized in that the grooves are 2.5mu m-4mu m deep. By adopting the manufacturing method of the high voltage light-emitting diode, the damages to the active area of LED (light-emitting diode), which are caused by the long-term plasma bombardment, are reduced, and the luminous degree of LED is improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

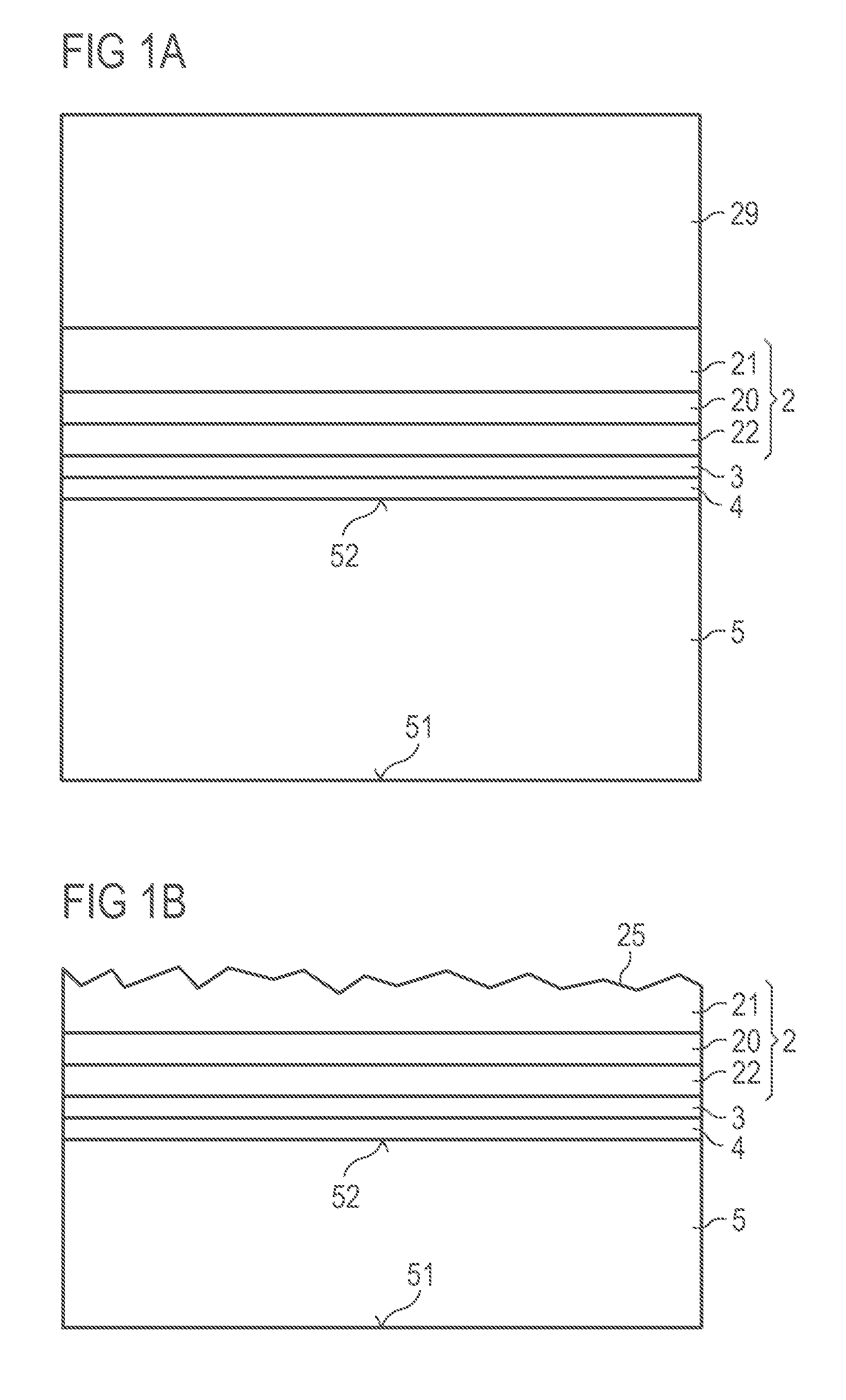

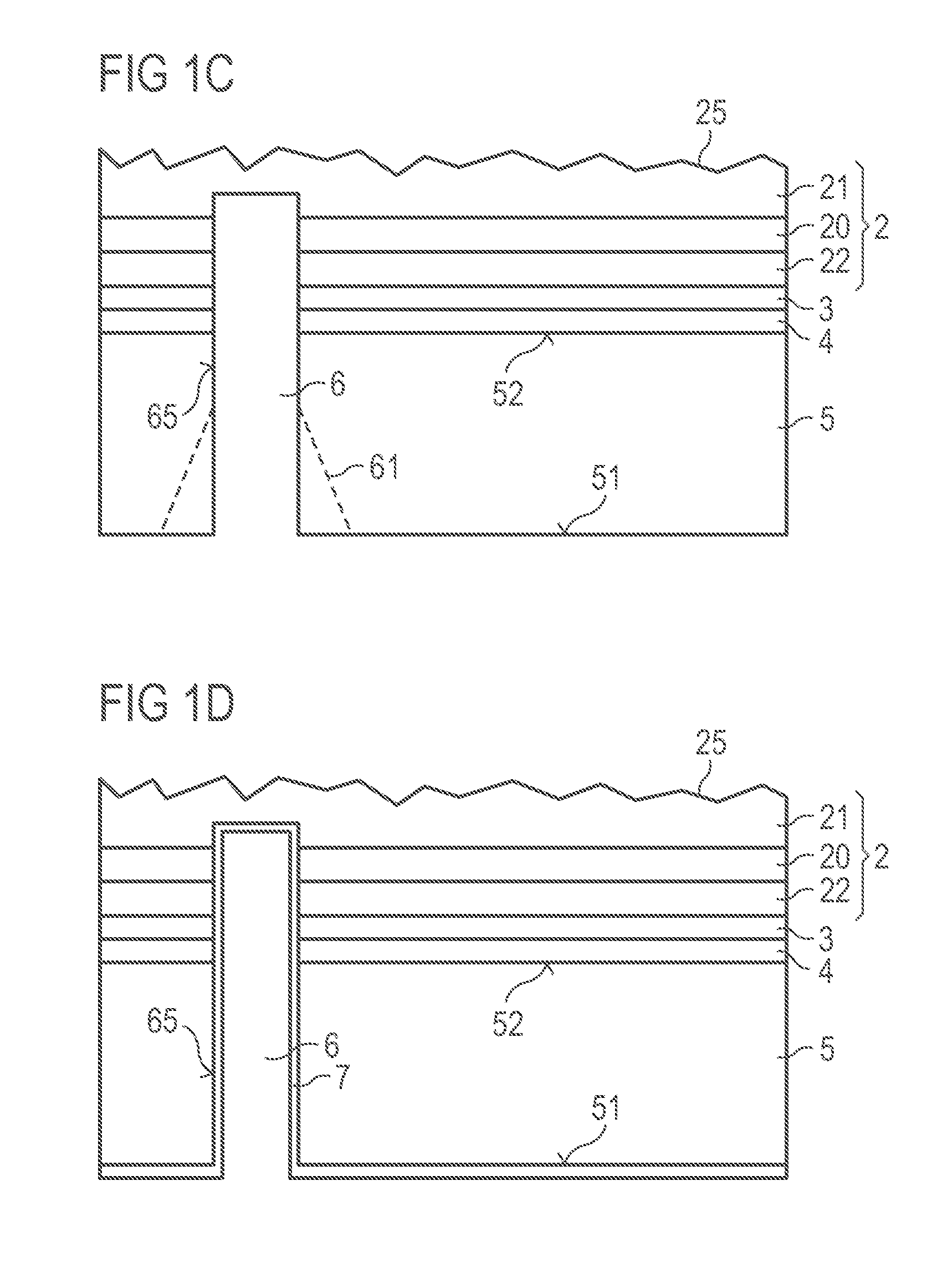

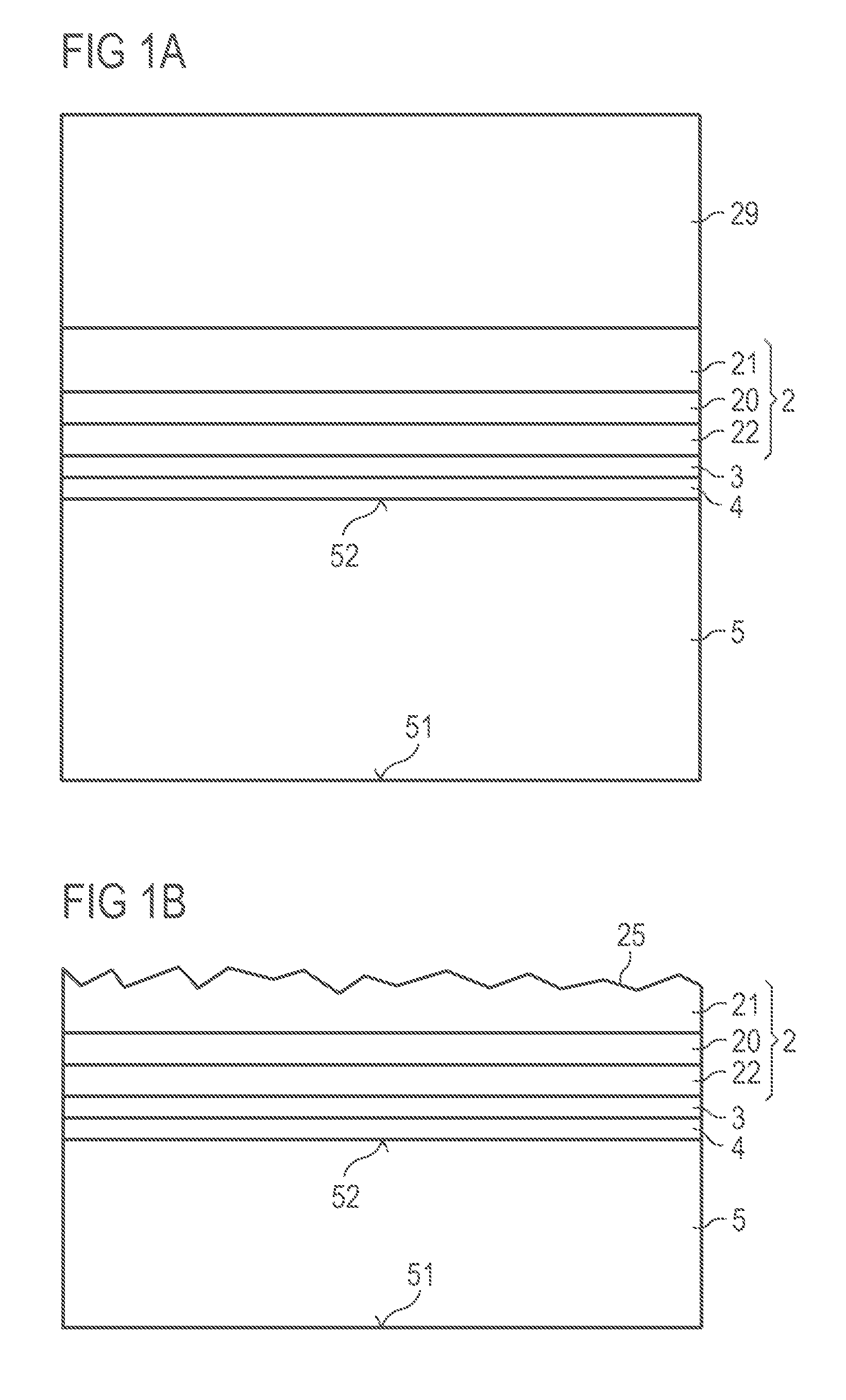

Method for Fabricating a Plurality of Opto-Electronic Semiconductor Chips, and Opto-Electronic Semiconductor Chip

ActiveUS20150270446A1Improve efficiencyMaintain good propertiesSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor chip

A method for fabricating optoelectronic semiconductor chips and optoelectronic semiconductor chips are disclosed. In embodiments the method comprises depositing a semiconductor layer sequence having an active, the active region being arranged between a first semiconductor layer and a second semiconductor layer on a growth substrate, attaching the semiconductor layer sequence to a carrier and forming a plurality of recesses extending through the carrier, the second semiconductor layer and the active region into the first semiconductor layer. The method further comprises forming first contacts on a first main surface of the carrier, the first main surface facing away from the semiconductor layer sequence, wherein the first contacts are electrically conductively connected to the first semiconductor layer in the region of the recesses and singulating the carrier and the semiconductor layer sequence into the plurality of optoelectronic semiconductor chips, wherein each semiconductor chip has at least one recess.

Owner:OSRAM OLED

Surface-emitting laser array, optical scanning device, and image forming device

ActiveUS8705585B2Avoid contactPrevent oxidationLaser optical resonator constructionSemiconductor laser arrangementsLaser arrayRefractive index

A surface-emitting laser array includes a plurality of surface-emitting laser elements. Each surface-emitting laser element includes a first reflection layer formed on a substrate, a resonator formed in contact with the first reflection layer and containing an active layer, and a second reflection layer formed over the first reflection layer and in contact with the resonator. The second reflection layer contains a selective oxidation layer. The first reflection layer contains on the active layer side at least a low refractive index layer having an oxidation rate equivalent to or larger than an oxidation rate of a selective oxidation layer contained in the second reflection layer. The resonator is made of an AlGaInPAs base material containing at least In. A bottom of a mesa structure is located under the selective oxidation layer and over the first reflection layer.

Owner:RICOH KK

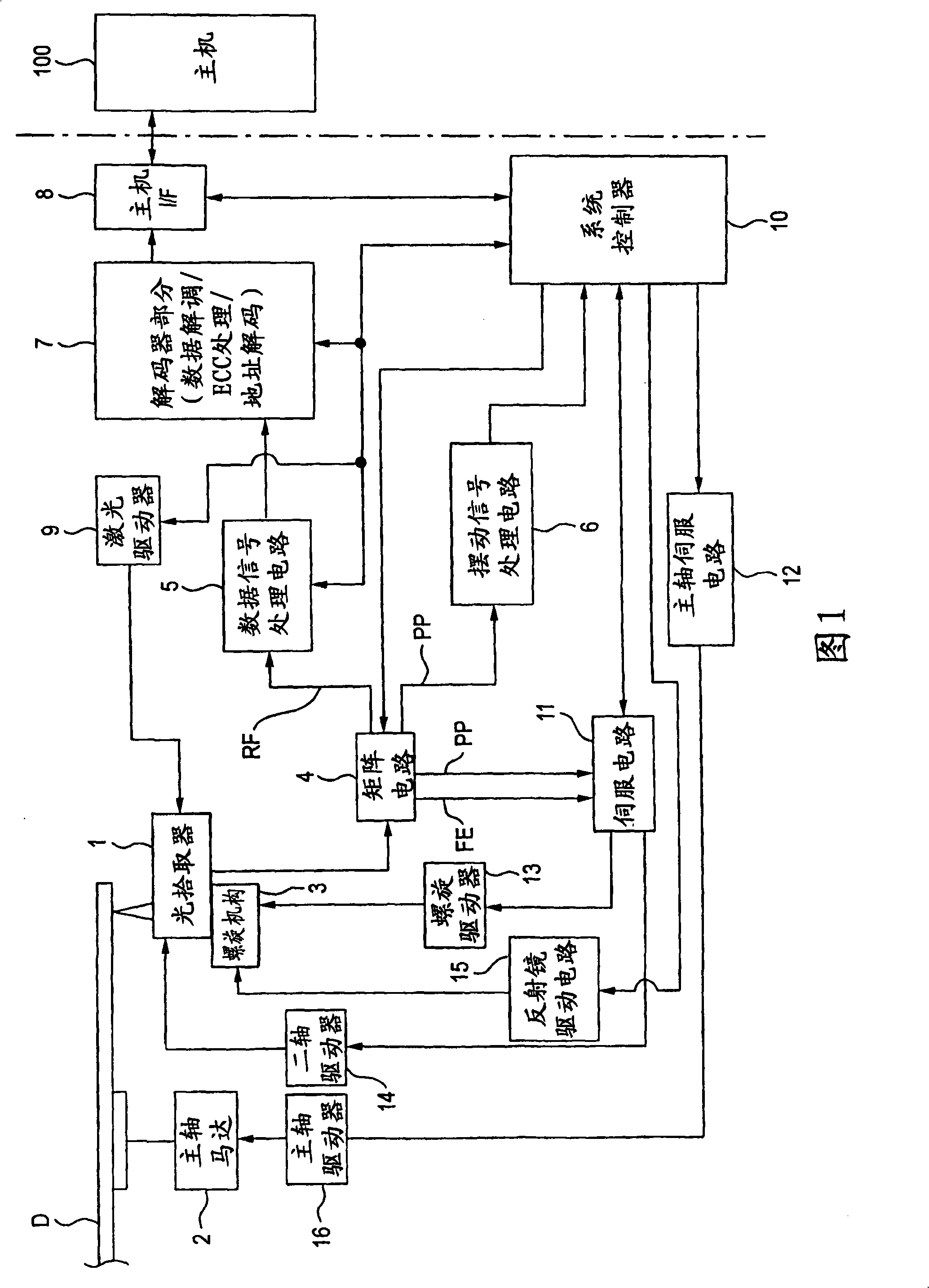

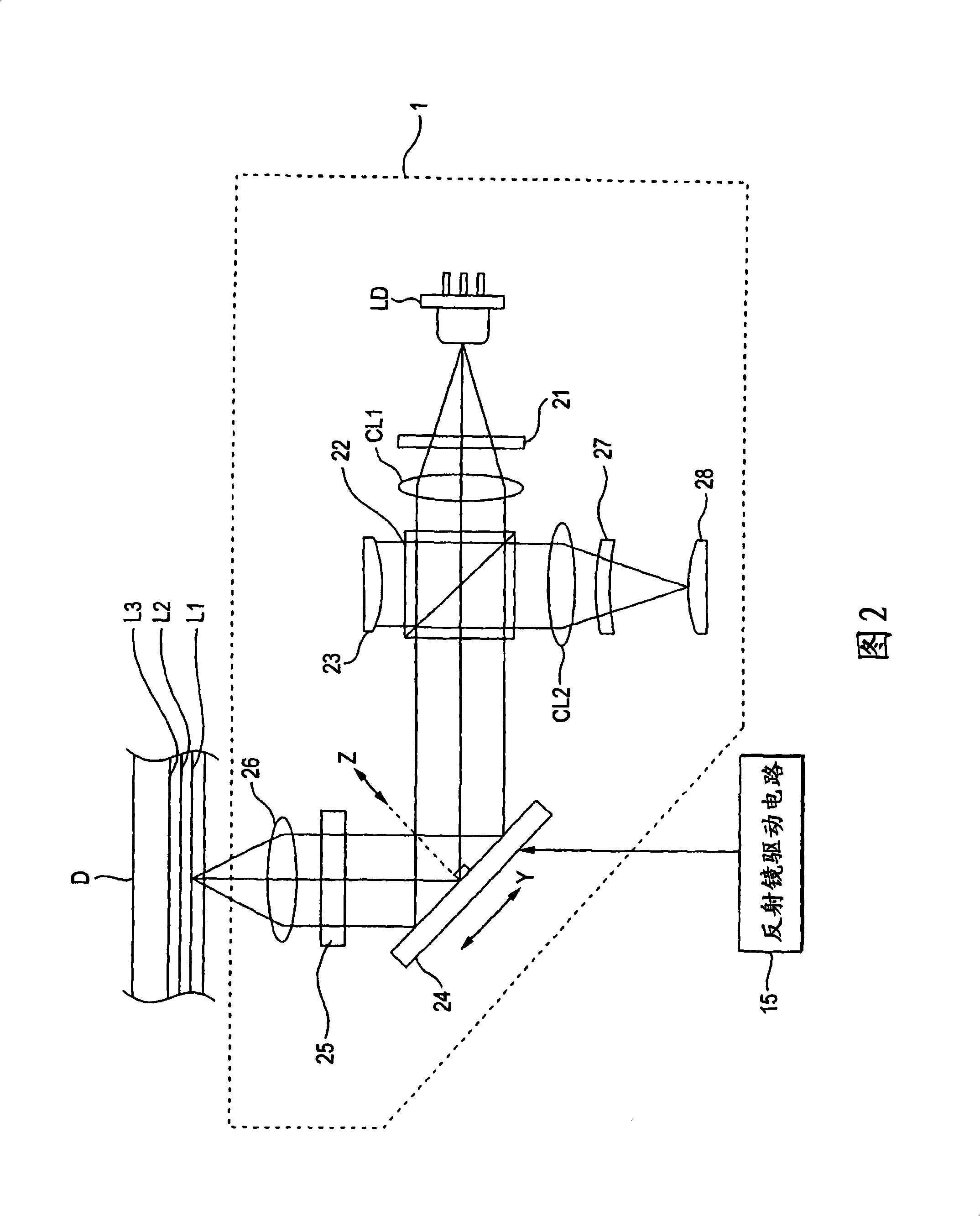

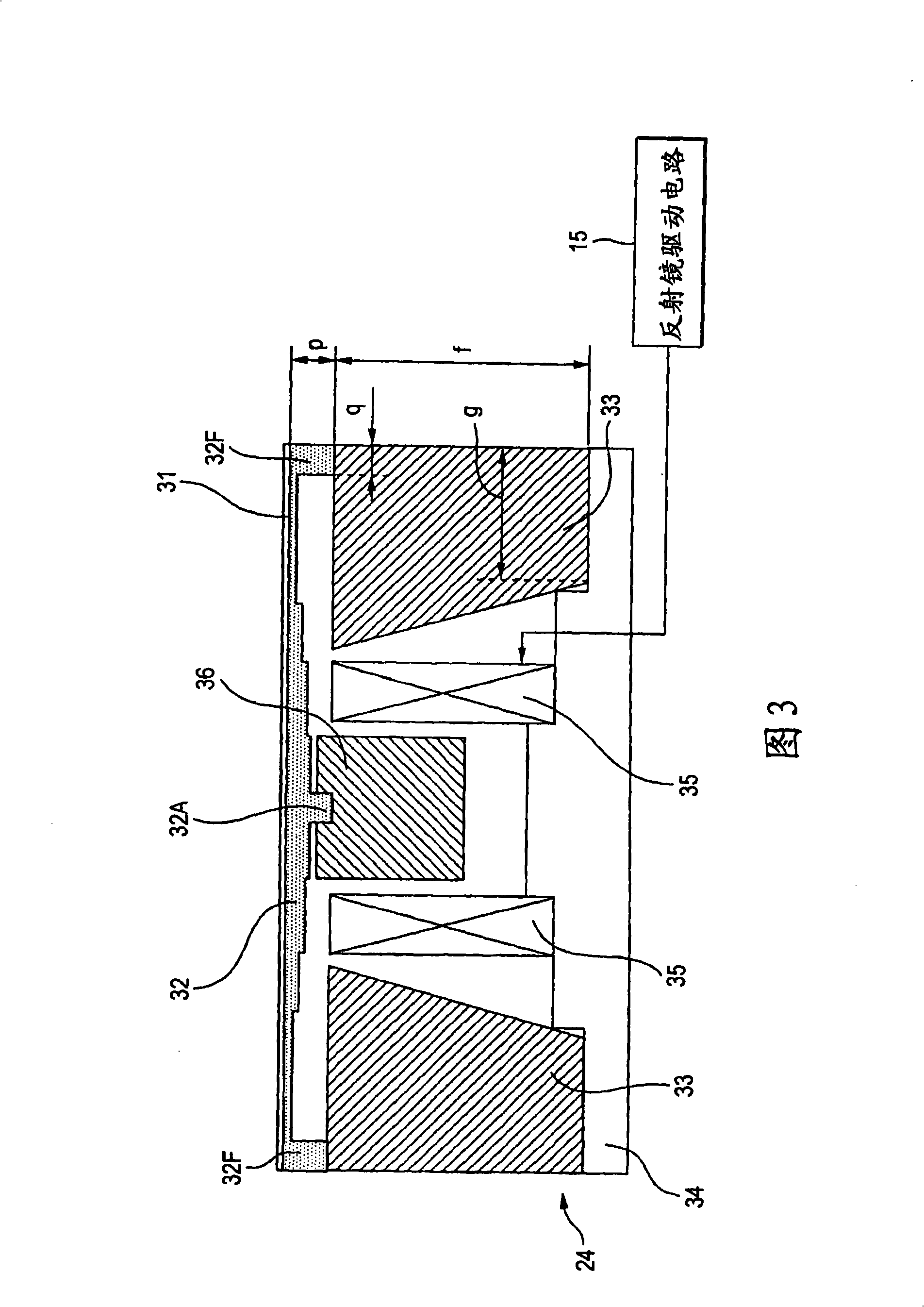

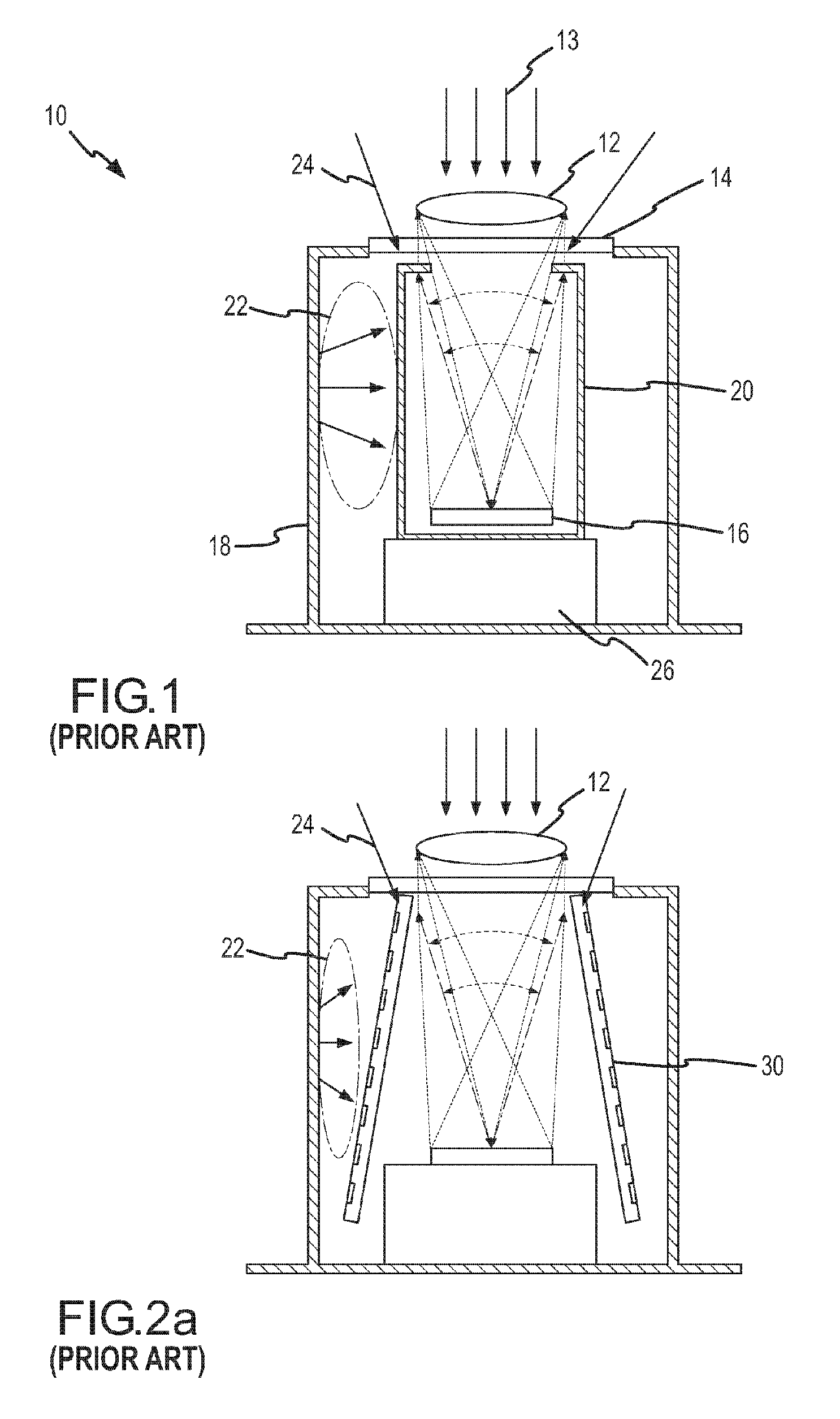

Deformable reflector apparatus, optical pickup device and optical drive apparatus

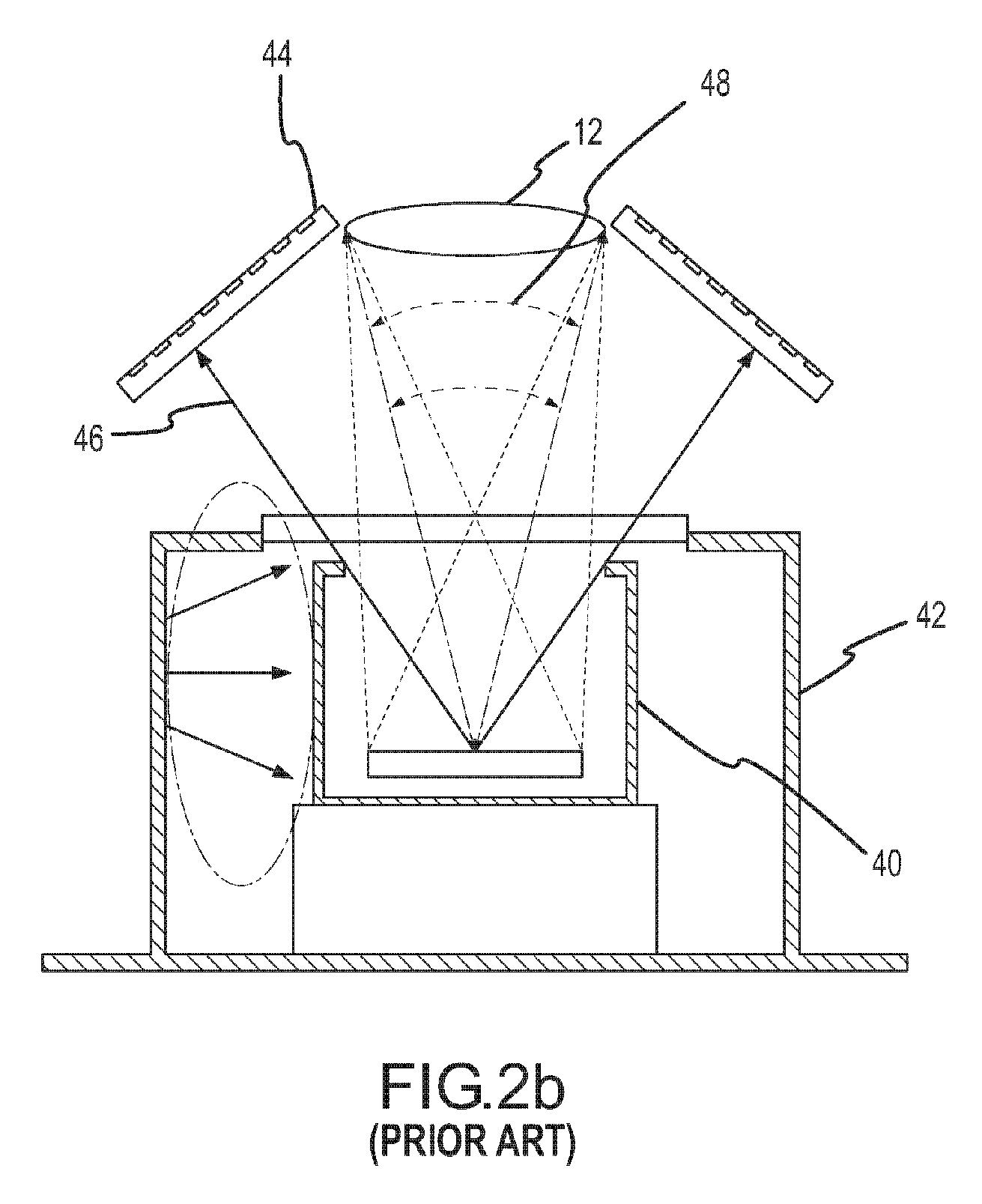

InactiveCN101329447AHigh precisionSmall sizeRecord information storageOptical beam guiding meansOptical pickupEngineering

Disclosed is a deformable mirror apparatus, optical pickup and optical drive apparatus. The deformable mirror apparatus includes a flexible member having a mirror on a surface and having a part having a different section form to form a convex on the opposite surface of the mirror such that a predetermined strength distribution is imparted to the flexible member; a base substrate; a strength securing member provided between the base substrate and the flexible member to support the flexible member from the base substrate side; and a driving section that deforms the form of the mirror by applying driving force to the opposite surface of the mirror of the flexible member.

Owner:SONY CORP

Vertical GaN Schottky device structure with high breakdown voltage and low reverse electric leakage

ActiveCN111192928AImprove breakdown voltageReduce reverse leakage currentSemiconductor devicesEtchingHigh field

The invention discloses a vertical GaN Schottky device structure with high breakdown voltage and low reverse electric leakage. The vertical GaN Schottky device structure comprises a first conductive type highly-doped GaN layer, a first conductive type low-doped GaN layer, a second conductive type NiO filling layer, a SiO2 and Si3N4 mixed dielectric layer, a floating metal field plate, an ohmic cathode, a Schottky anode, a sapphire substrate and an AlN nucleating layer. According to the device structure provided by the invention, a two-step etching process is applied, so that the operability problem of a deep etching technology is solved; the designed second conductive type NiO filling layer overcomes the technical problem of second conductive type doping of a GaN material, effectively shields a high electric field and protects a Schottky barrier, so that the reverse leakage current of the device is effectively reduced; the designed multi-field-plate structure effectively utilizes the advantage of high field plate contact area brought by a two-step etching process, weakens the fringe field concentration effect of the device, and effectively improves the reverse breakdown voltage ofthe device.

Owner:XI AN JIAOTONG UNIV

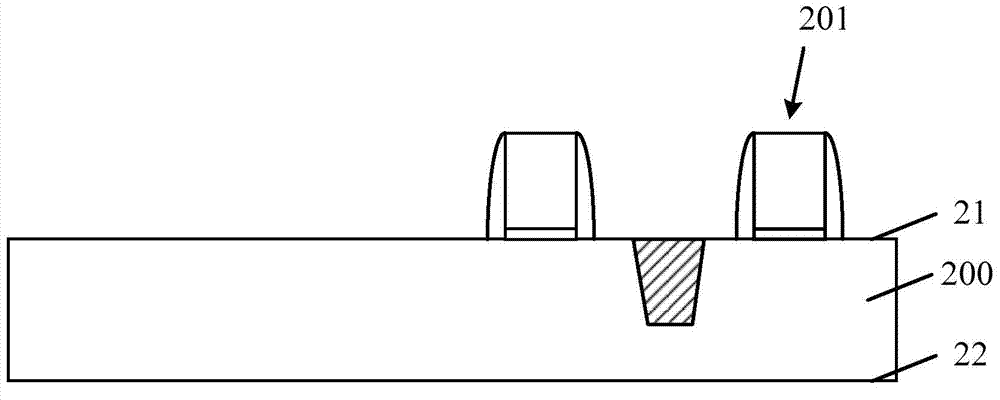

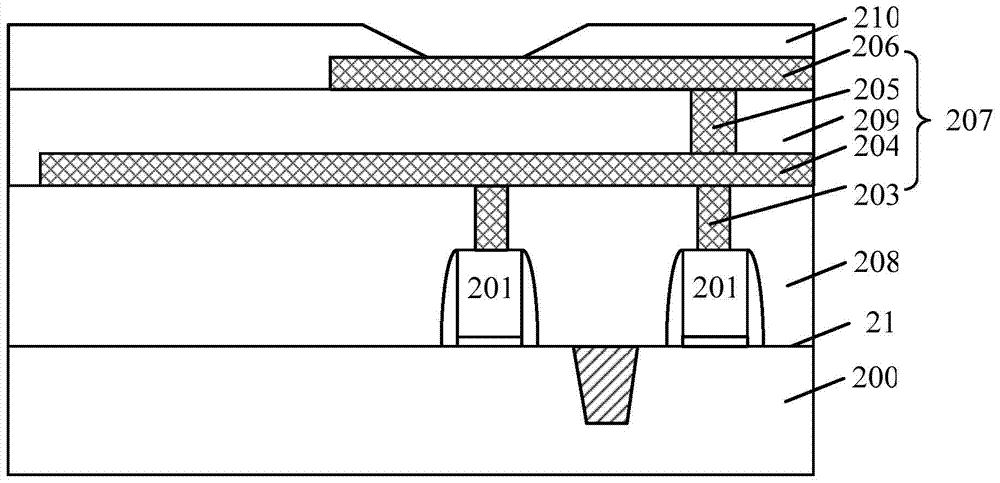

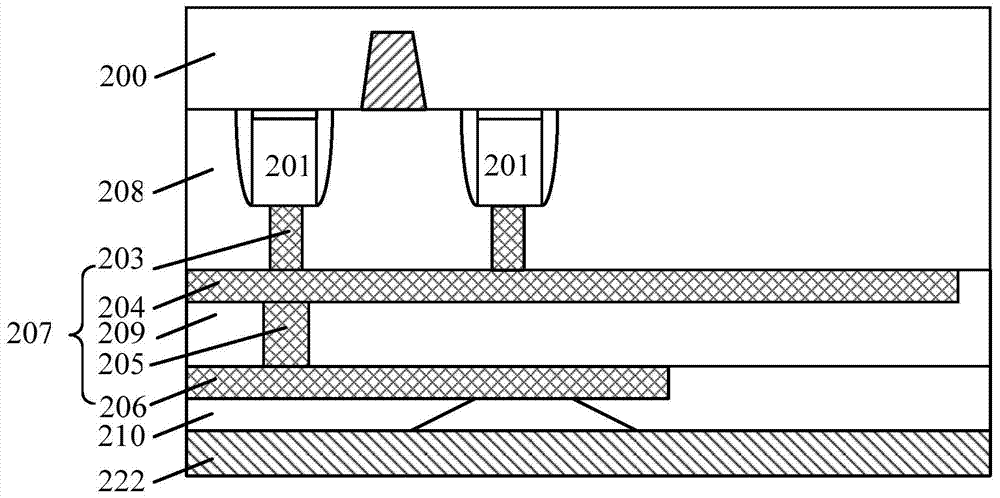

Semiconductor structure and formation method thereof

InactiveCN104517959AHighly integratedReduced occupied volumeSolid-state devicesSemiconductor/solid-state device manufacturingCMOSSemiconductor structure

Disclosed are a semiconductor structure and a formation method thereof. The semiconductor structure comprises a semiconductor substrate, a plurality of CMOS (complementary metal oxide semiconductor) devices, a first medium layer, a first interconnection structure, a through hole, an isolation layer, a second metal interconnection layer, a second medium layer and a plurality of passive devices. The semiconductor substrate comprises a first surface and a second surface, the CMOS devices are arranged on the first surface, the first medium layer covers the first surface and the CMOS device, the first interconnection structure is arranged in the first medium layer and connected with the CMOS devices, the through hole penetrates through the second surface of the semiconductor substrate and a part of the first medium layer, and the surface of the bottom of the first interconnection structure is exposed at the bottom of the through hole; the isolation layer is arranged on the side wall of the through hole and the second surface; the second metal interconnection layer is arranged on the isolation layer and at the bottom of the through hole and is connected with the surface of the bottom of the first interconnection structure; the second medium layer covers the second metal interconnection layer, and the through hole is filled with the second medium layer; the passive devices are arranged on the second medium layer, and one end of each passive device is connected with the second metal interconnection layer. The semiconductor structure is small in occupation space and high in integrity.

Owner:SEMICON MFG INT (SHANGHAI) CORP

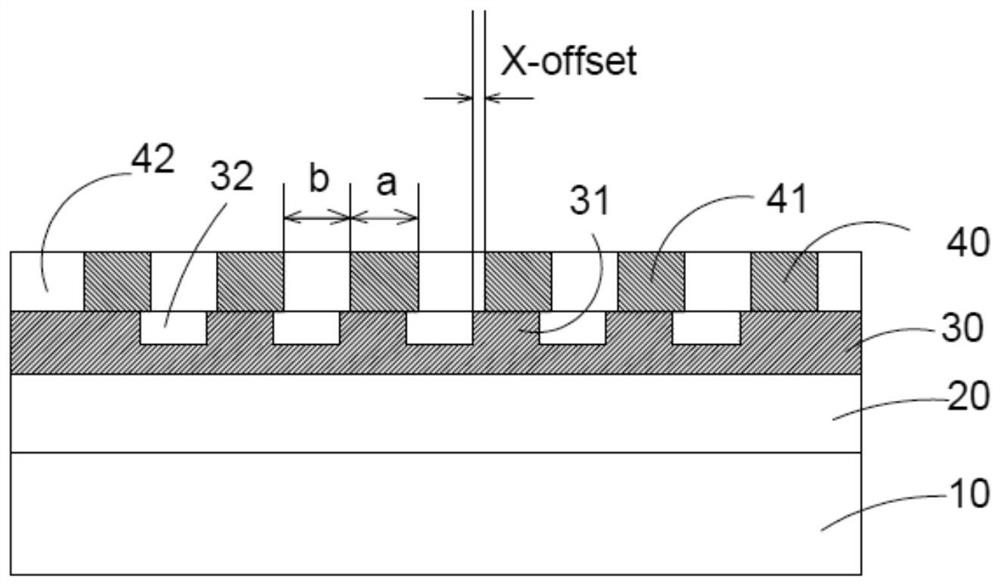

Grating coupler and preparation method thereof

The invention provides a grating coupler and a preparation method thereof. The preparation method of the grating coupler comprises the following steps: providing an SOI substrate, wherein the SOI substrate comprises a silicon substrate layer, a silicon dioxide middle layer and a silicon top layer from bottom to top; etching the silicon top layer to form a first coupling grating; forming a Poly-Silayer on the silicon top layer; etching the Poly-Si layer to form a second coupling grating; stacking the second coupling grating and the first coupling grating in a staggered manner. According to thegrating coupler, the insertion loss of the grating coupler is reduced by forming the Poly-Si layer on the silicon top layer, the insertion loss is further reduced through the offset design of the second coupling grating and the first coupling grating, and the tolerance of a grating preparation process can be improved through the offset design.

Owner:UNITED MICROELECTRONICS CENT CO LTD

Surface-emitting laser array, optical scanning device, and image forming device

ActiveUS20130230070A1Avoid contactPrevent oxidationLaser detailsLaser optical resonator constructionLaser arrayRefractive index

A surface-emitting laser array includes a plurality of surface-emitting laser elements. Each surface-emitting laser element includes a first reflection layer formed on a substrate, a resonator formed in contact with the first reflection layer and containing an active layer, and a second reflection layer formed over the first reflection layer and in contact with the resonator. The second reflection layer contains a selective oxidation layer. The first reflection layer contains on the active layer side at least a low refractive index layer having an oxidation rate equivalent to or larger than an oxidation rate of a selective oxidation layer contained in the second reflection layer. The resonator is made of an AlGaInPAs base material containing at least In. A bottom of a mesa structure is located under the selective oxidation layer and over the first reflection layer.

Owner:RICOH KK

Method for fabricating a plurality of opto-electronic semiconductor chips, and opto-electronic semiconductor chip

ActiveUS9530935B2Improve efficiencyMaintain good propertiesSolid-state devicesSemiconductor devicesElectrical conductorSemiconductor chip

A method for fabricating optoelectronic semiconductor chips and optoelectronic semiconductor chips are disclosed. In embodiments the method comprises depositing a semiconductor layer sequence having an active, the active region being arranged between a first semiconductor layer and a second semiconductor layer on a growth substrate, attaching the semiconductor layer sequence to a carrier and forming a plurality of recesses extending through the carrier, the second semiconductor layer and the active region into the first semiconductor layer. The method further comprises forming first contacts on a first main surface of the carrier, the first main surface facing away from the semiconductor layer sequence, wherein the first contacts are electrically conductively connected to the first semiconductor layer in the region of the recesses and singulating the carrier and the semiconductor layer sequence into the plurality of optoelectronic semiconductor chips, wherein each semiconductor chip has at least one recess.

Owner:OSRAM OLED

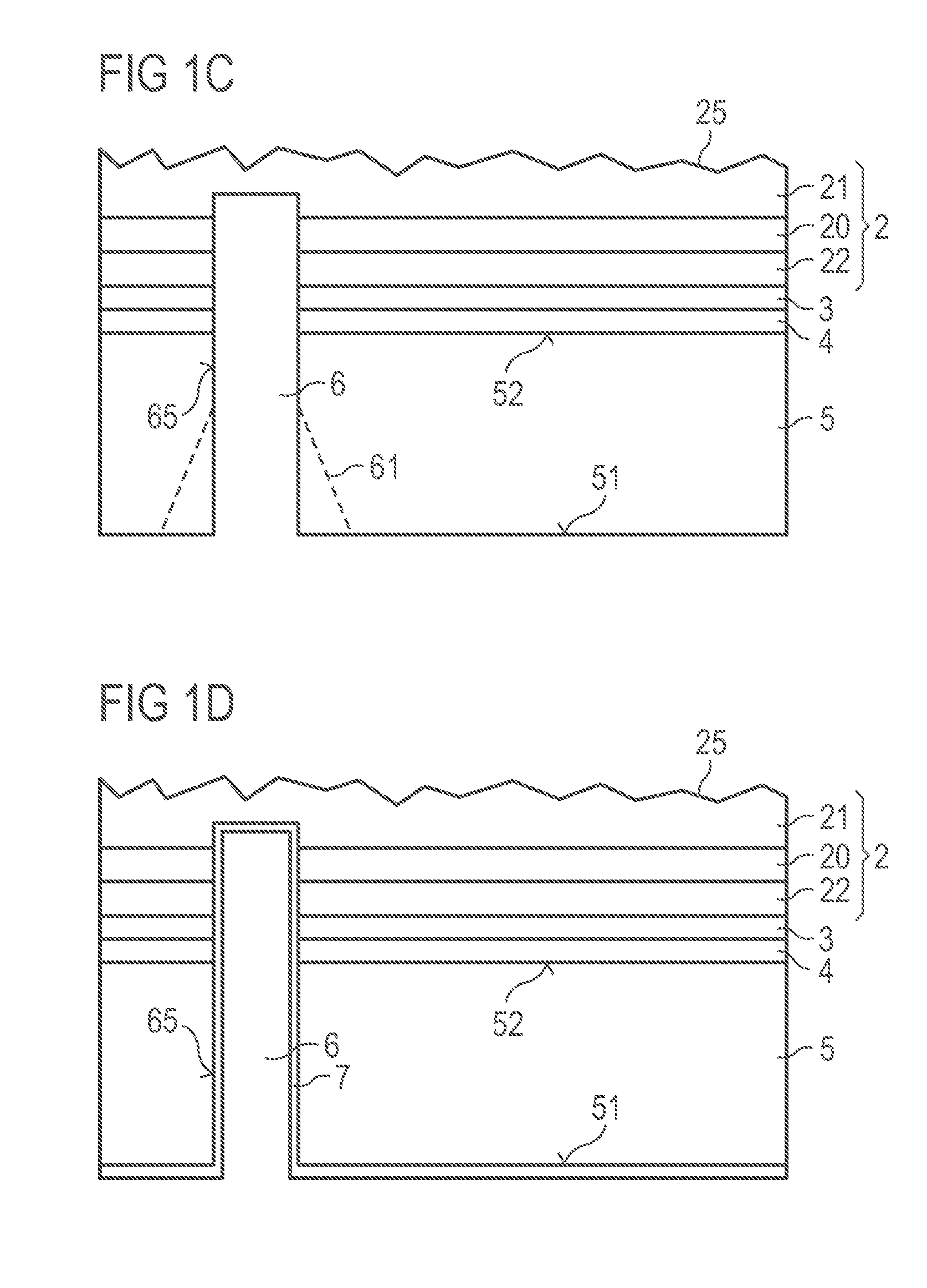

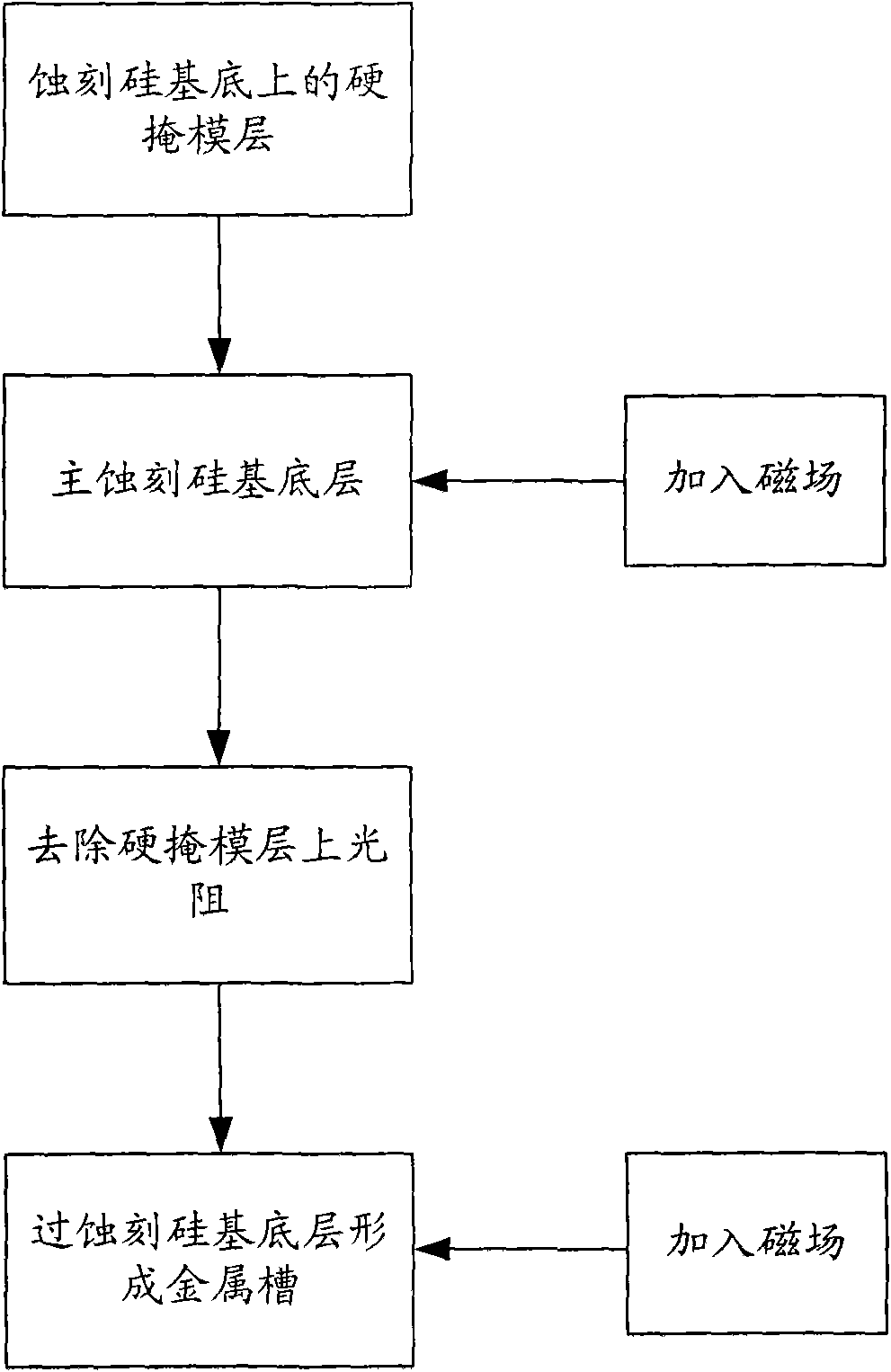

Method for producing metallic channel

ActiveCN101567315AReduce etch depthReduce depth differenceSemiconductor/solid-state device manufacturingTwo stepSilicon

The invention provides a method for producing a metallic channel, in particular a top-layer metallic channel, comprising steps as follows: 1, coating photoresistance on a hard mask layer and etching the hard mask layer by a plasma; 2, form a metallic channel of preset depth a silicon substrate layer under the mask layer etched by the plasma, wherein etching the silicon substrate layer in step 2 comprises the following three steps: 21, performing major etching, i.e. etching the silicon substrate layer to form a metallic channel with a depth less than the preset depth; 22, removing the photoresistance on the hard mask layer; 23, performing over etching, i.e. further etching the silicon substrate layer to form a metallic channel of preset depth, and both the major etching and the over etching are performed in a magnetic field of preset strength. The metallic channel on the silicon substrate layer is etched by utilizing main etching and over etching supported by the magnetic field in two steps, thereby the problem of stripe edge existed in the traditional method for producing metallic channels can be solved and depth evenness of the metallic channel can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Three-dimensional memory manufacturing method and three-dimensional memory

ActiveCN111326522AReduce etch depthReduce machining errorsSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The invention provides a three-dimensional memory manufacturing method and a three-dimensional memory, and the method comprises: forming a semiconductor structure, and enabling a stack structure of the semiconductor structure to be provided with a first structural hole with the bottom located at an etching stop layer; removing the etching stop layer at the bottom of the first structure hole, and exposing the insulating layer at the bottom of the etching stop layer; further extending the bottom of the first structure hole into the sacrificial layer; removing the sacrificial layer to form a sacrificial gap; forming a second substrate in the sacrificial gap; and forming a common source contact in the first structural hole. An etching stop layer is arranged in a stack structure of the three-dimensional memory, the etching stop layer can be used as a stop layer for etching the first structural hole, and the etching depth in the last process step can be reduced due to the fact that the position of the etching stop layer in the stack structure is determined, so that the machining error is reduced, the etching precision is accurately controlled, and the bottom of the first structural holecan be just located in the sacrificial layer and cannot be too deep or too shallow.

Owner:YANGTZE MEMORY TECH CO LTD

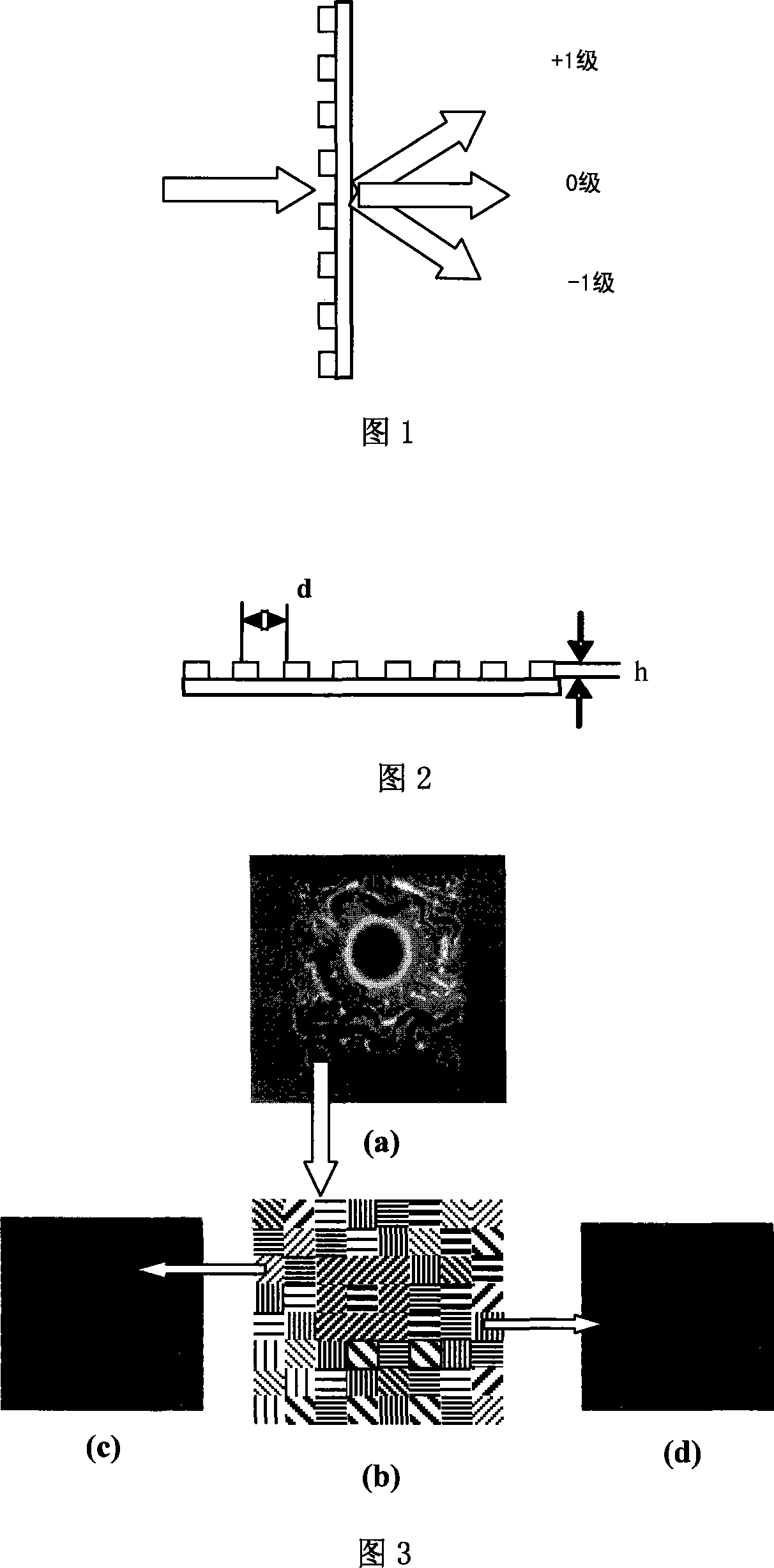

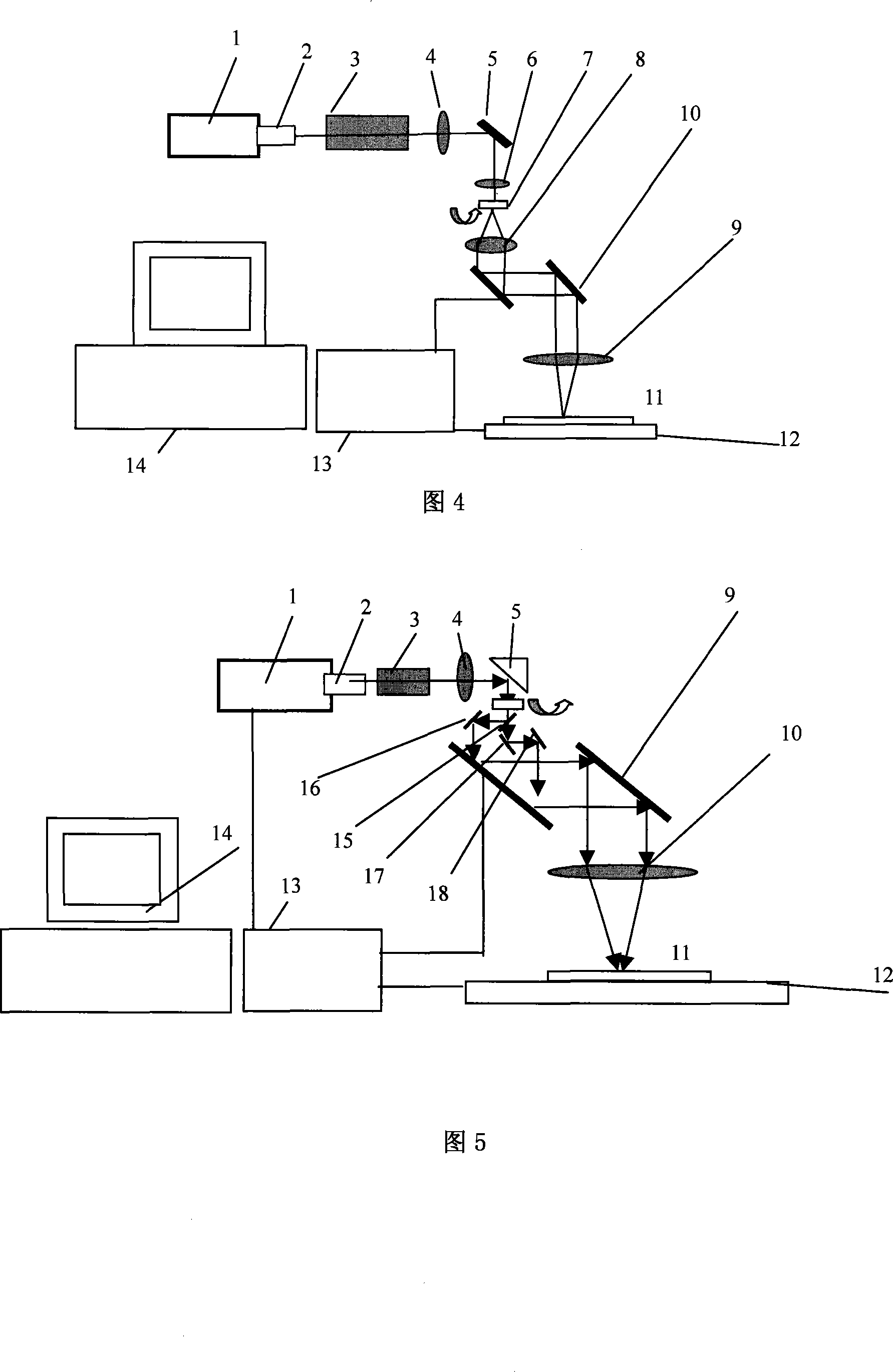

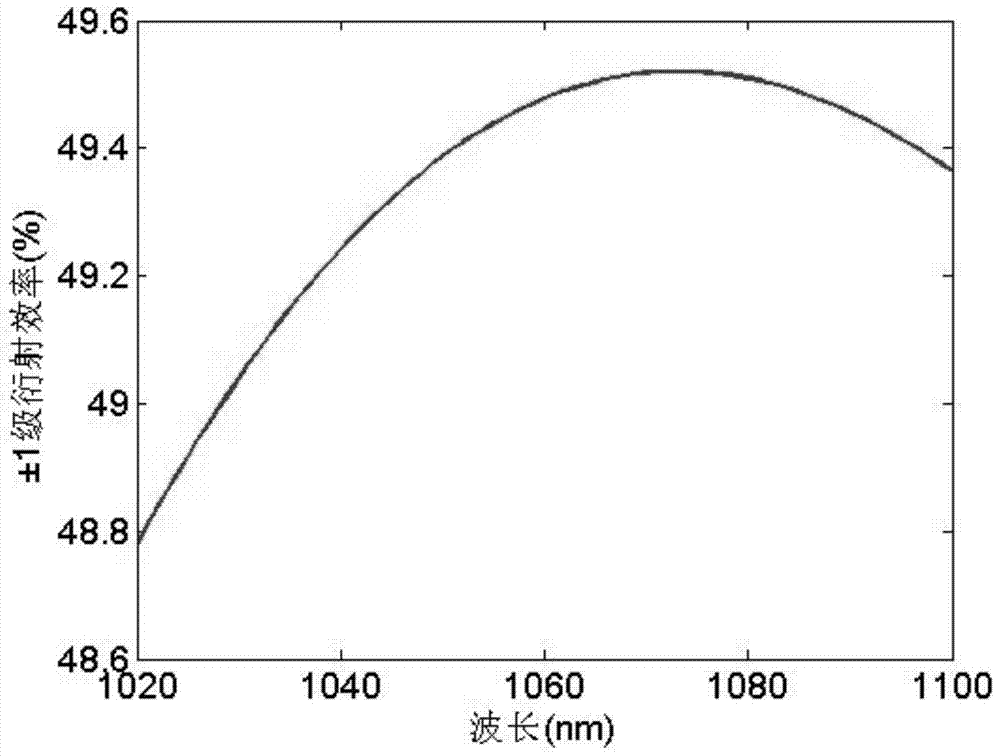

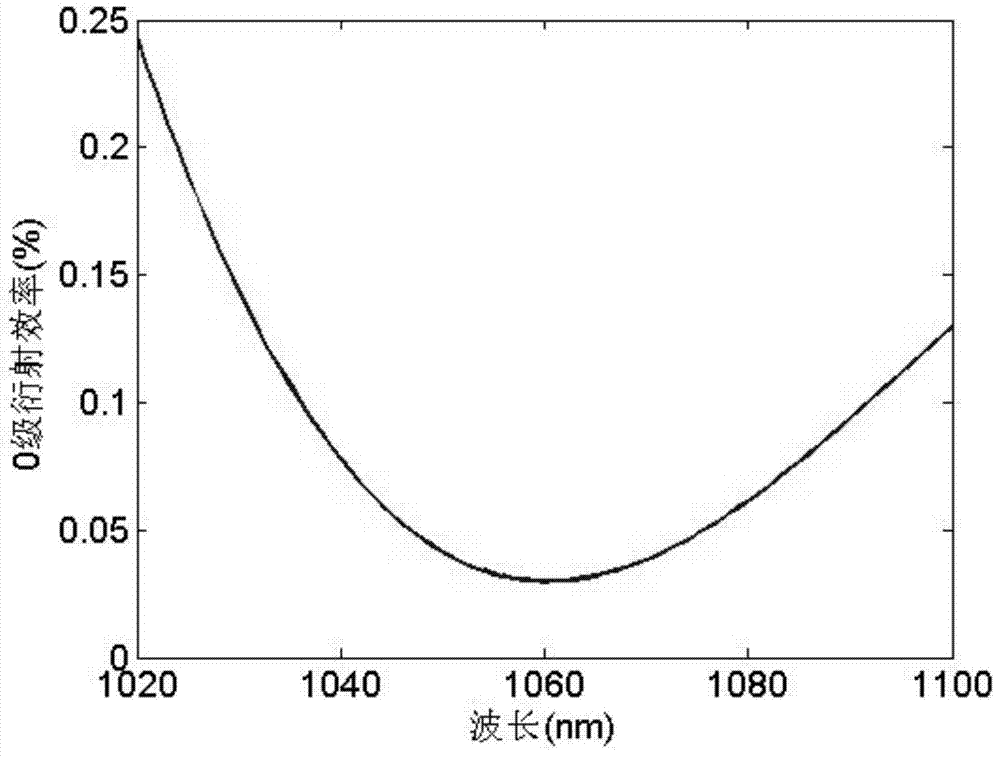

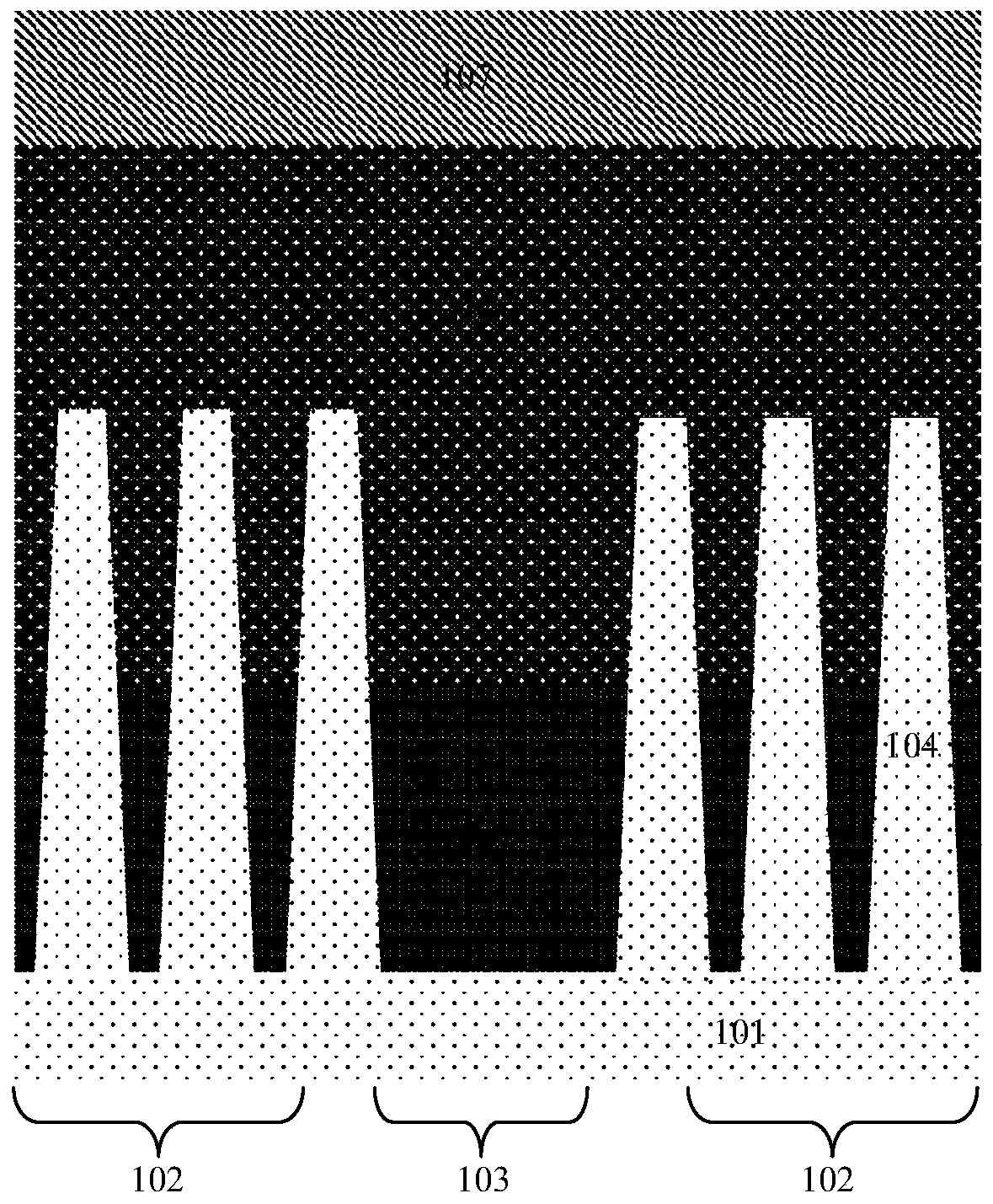

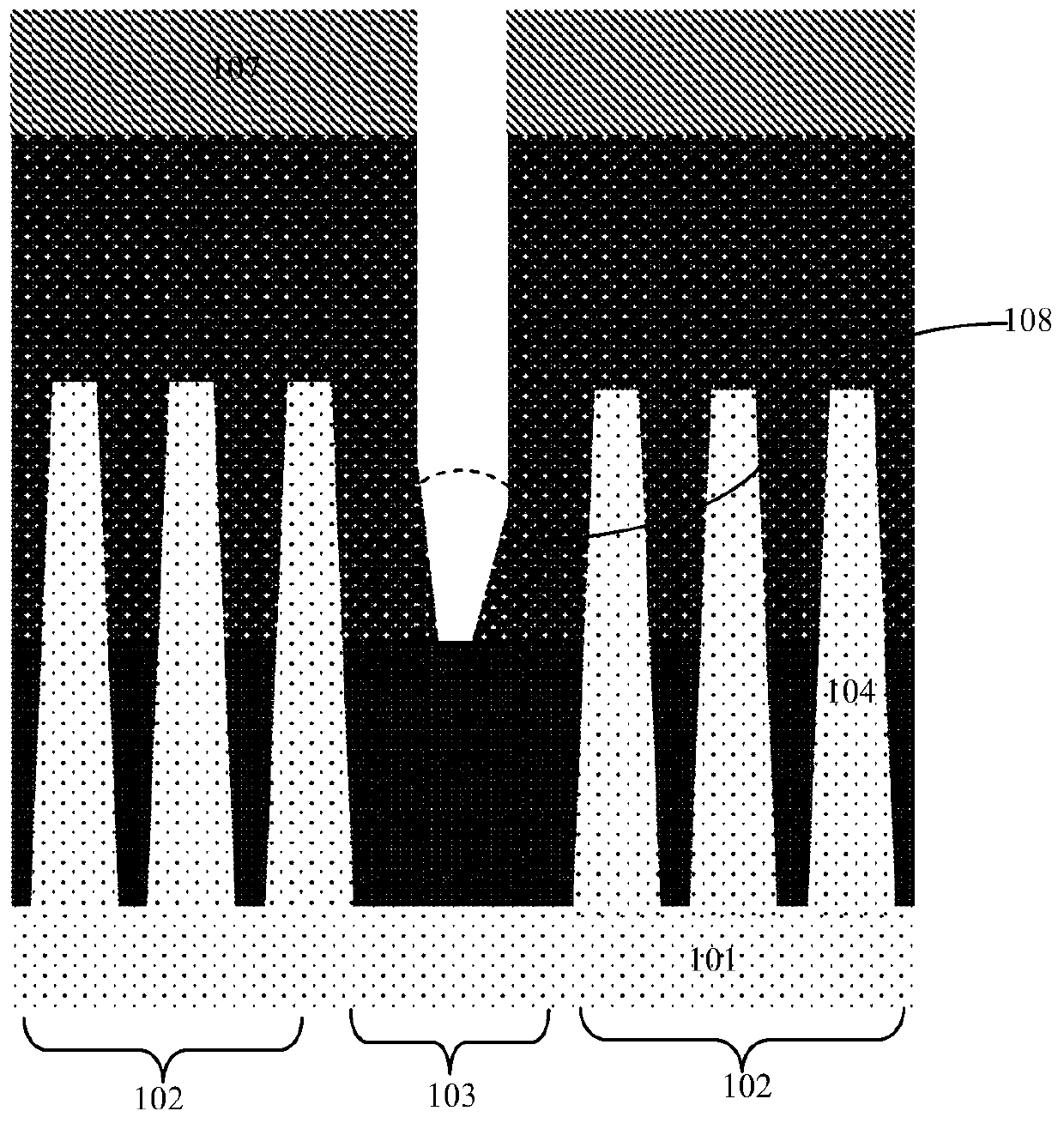

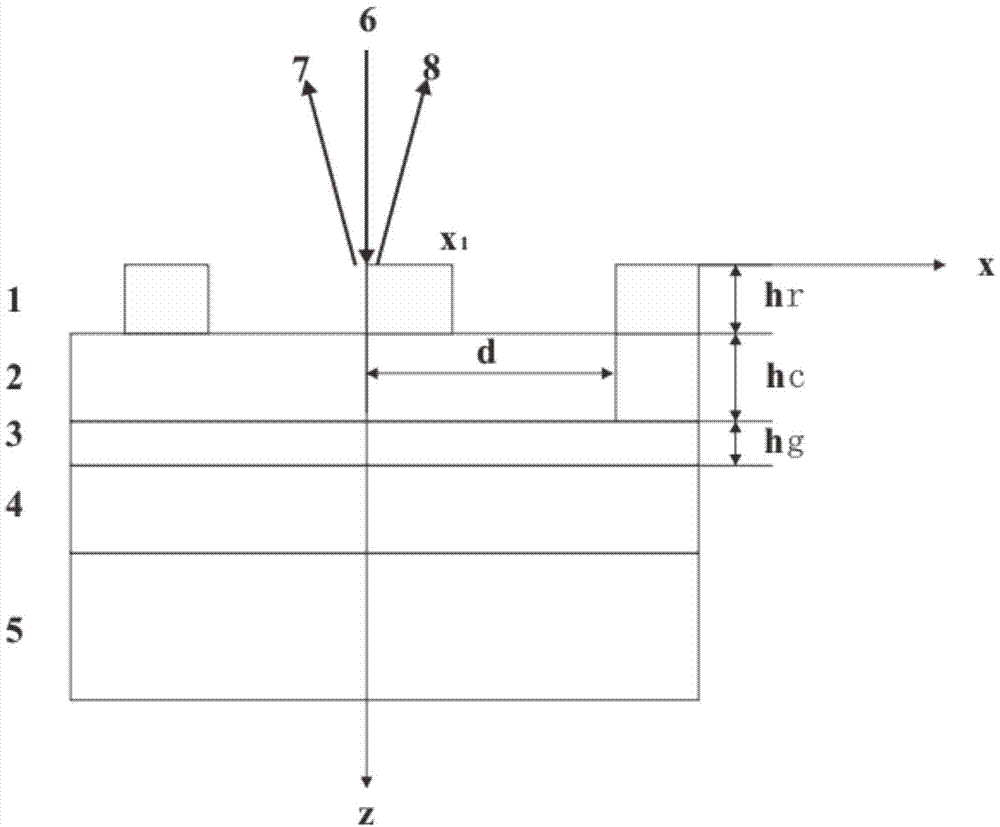

1*2 high-efficiency reflection-type grating

The invention provides a TE (transverse electric) polarized 1*2 high-efficiency reflection-type grating with central wavelength of 1,064 nanometers. The grating is structurally characterized in that a fused quartz substrate is sequentially coated with a chromium film, a gold film and a fused quartz film, a rectangular-groove grating is etched on the fused quartz film layer, the fused quartz film layer without being etched is a connection layer, the grating cycle is 2,304-2,308 nanometers, the duty ratio is 0.34-0.36, the grating depth is 570-590 nanometers, and the connection layer is 133-143 nanometers thick. When TE polarization light performs perpendicular incidence, zero-order elimination of the central wavelength of 1,064 nanometers can be realized, and the positive or negative one order diffraction efficiency is higher than 96%. The grating can be machined through a multi-beam laser parallel direct writing device in combination with a self-induction coupling plasma deep etching process and a film coating technique, materials are convenient to obtain, machining is simple, and the grating has important practical prospect.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

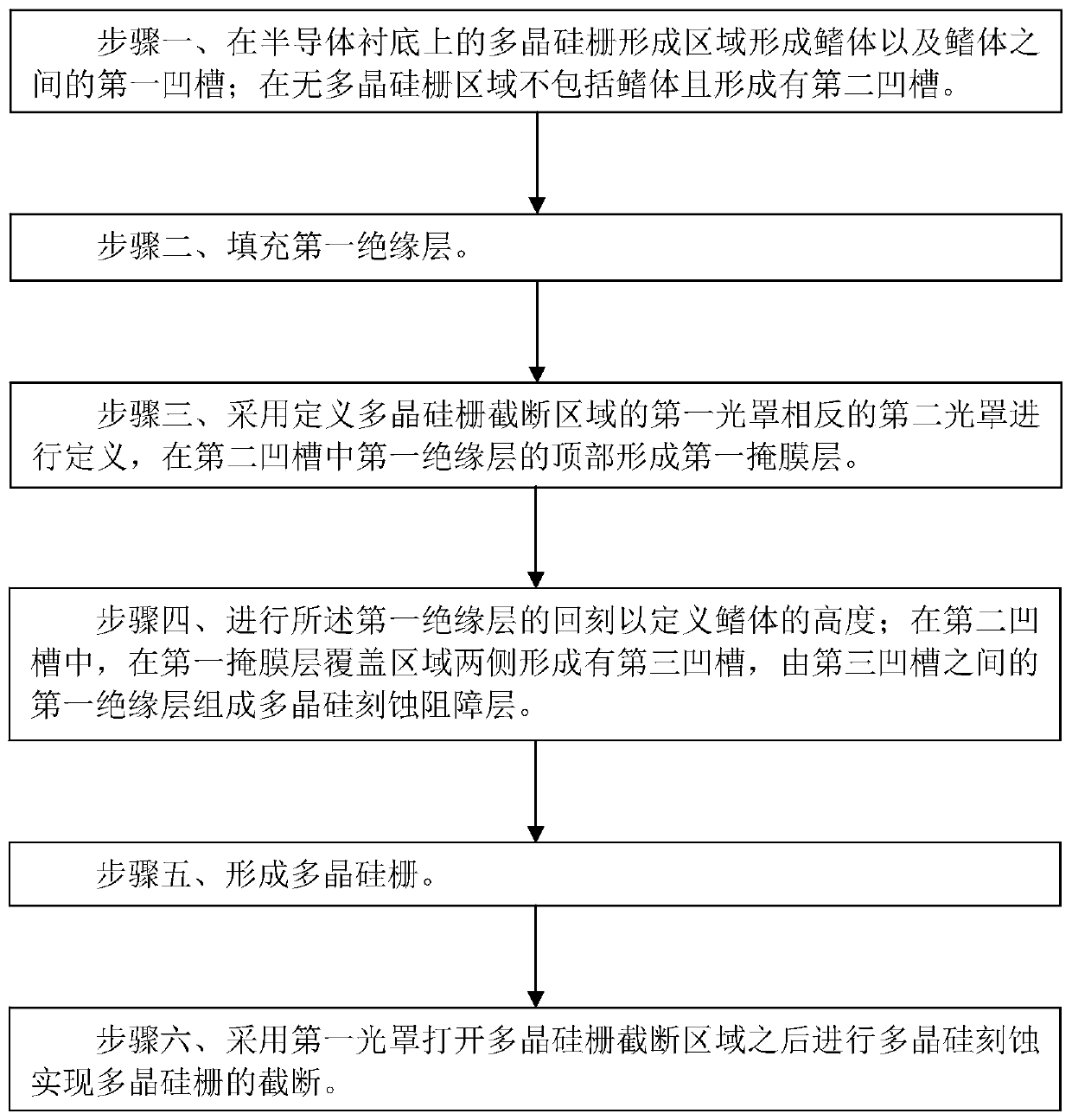

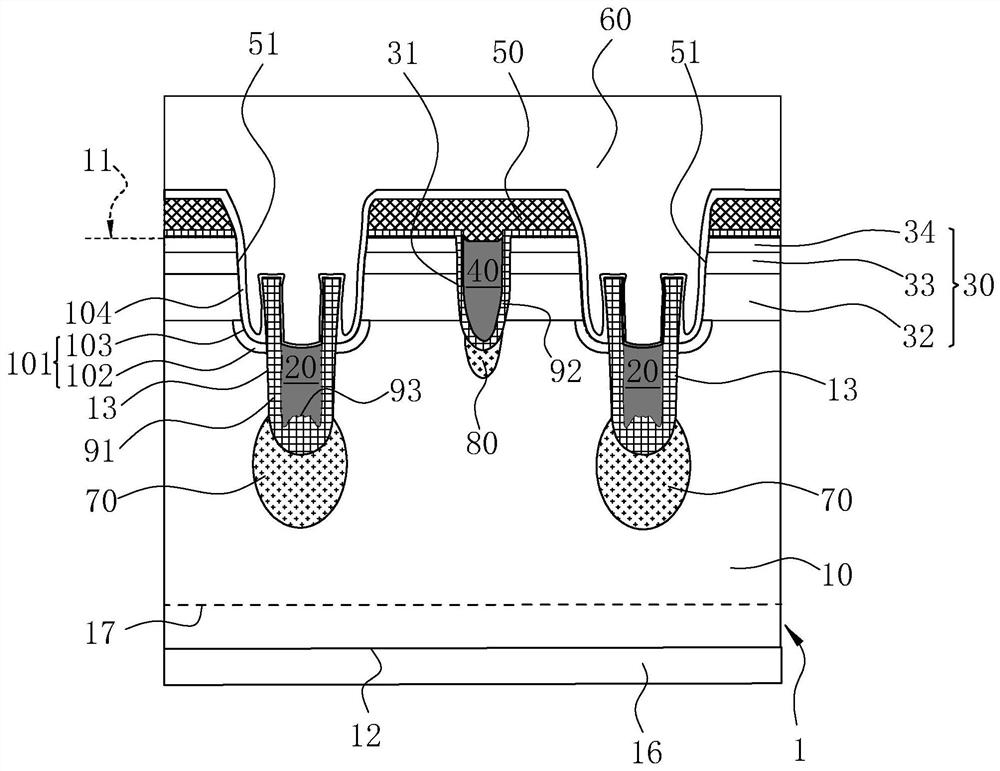

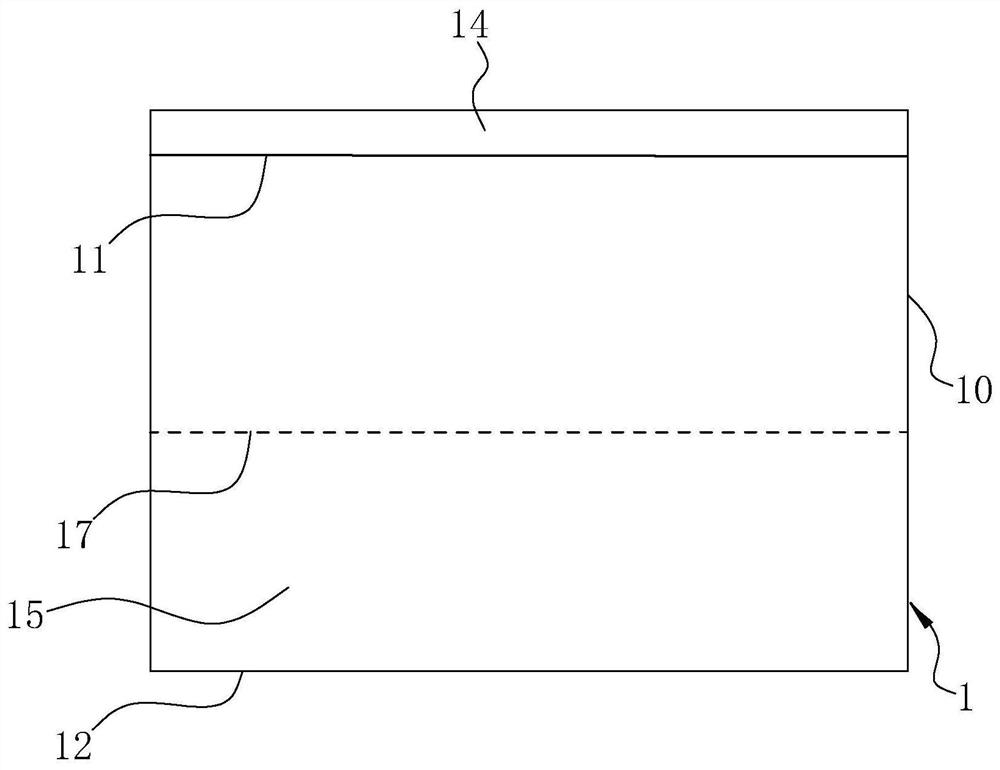

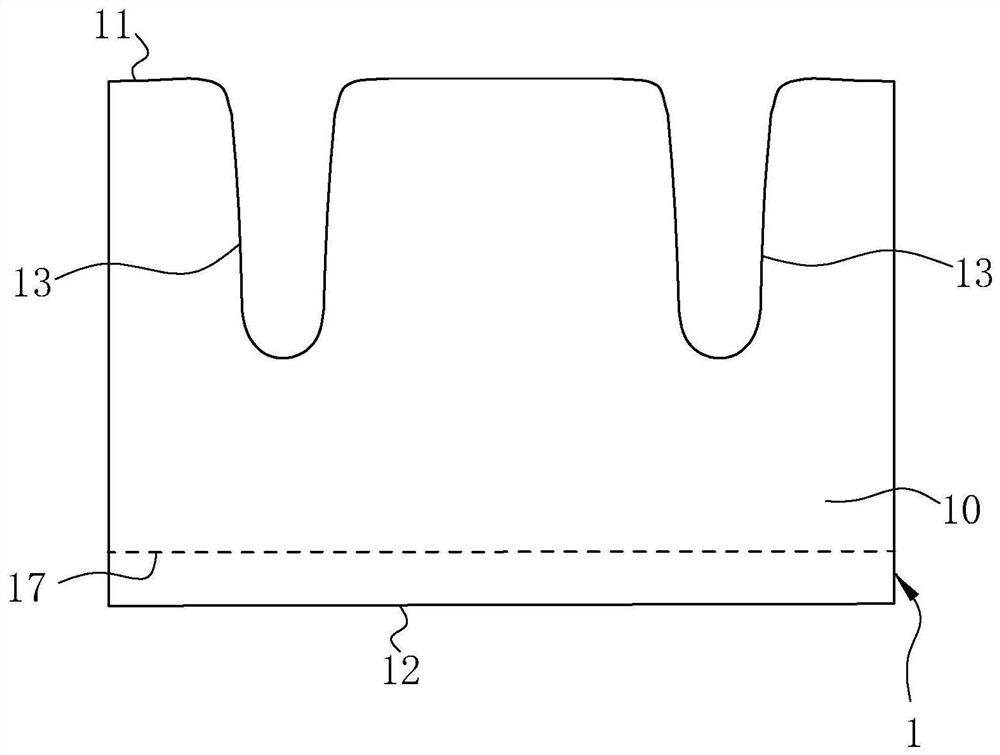

Process method for truncating polysilicon gate of fin transistor

ActiveCN110752152AIncreased process windowImprove yieldSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringPolysilicon gate

The invention discloses a process method for truncating a polysilicon gate of a fin transistor. The process method comprises the following steps of step 1, forming fin bodies and a first groove between the fin bodies in a polysilicon gate formation region on a semiconductor substrate, and the fin bodies are not included in a polysilicon-free gate region and a second groove is formed; step 2, filling a first insulating layer; step 3, using a second photomask opposite to a first photomask that defines a polysilicon gate truncated region to define, and forming a first mask layer at the top of thefirst insulating layer in the second groove; step 4, etching back the first insulating layer, so as to define the height of the fin bodies; in the second groove, forming third grooves at the two sides of a coverage region of the first mask layer, and forming a polysilicon etching barrier layer by the first insulating layer between the third grooves; step 5, forming the polysilicon gate; and step6, after the polysilicon gate truncated region is opened by the first mask, performing polysilicon etching to achieve the truncation of the polysilicon gate. The process method for truncating the polysilicon gate of the fin transistor provided by the invention can increase process windows and improve the product yield.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Field effect transistor structure, manufacturing method thereof and chip device

ActiveCN113410307AImprove cooling effectIncreased current capabilityTransistorSemiconductor/solid-state device manufacturingElectron flowEngineering

The invention relates to a field effect transistor structure, a manufacturing method thereof and a chip device. A transistor comprises a drain electrode epitaxial layer located at the bottom, a source electrode layer located at the top, and a source electrode extension inverted fin and a grid electrode which are embedded in the drain electrode epitaxial layer. The grid electrode is arranged between the source electrode extension inverted fins, and symmetrical channels which are connected in parallel from the source electrode layer to the interior of the drain electrode epitaxial layer in pairs are formed in the two sides of the grid electrode. In a preferable example, paired symmetrical field resistors which are connected in parallel from the source electrode layer to the drain electrode epitaxial layer are also formed above the channels at the two sides of the grid electrode; in a preferable example, the drain epitaxial layer forms an under-gate floating antipole junction at the bottom part corresponding to the grid electrode; in a preferable example, the drain epitaxial layer forms a shield gate bottom floating antipolar column bottom junction at bottom portions corresponding to the source electrode extension inverted fins. According to the invention, a double-inverted-half-fin floating super-junction gate type field effect transistor framework is created for the first time, and the gain effect of uniformizing or helping uniformizing electron flows of the drain electrode on the back surface of the substrate and the source electrode on the top surface of the substrate is achieved.

Owner:深圳真茂佳半导体有限公司

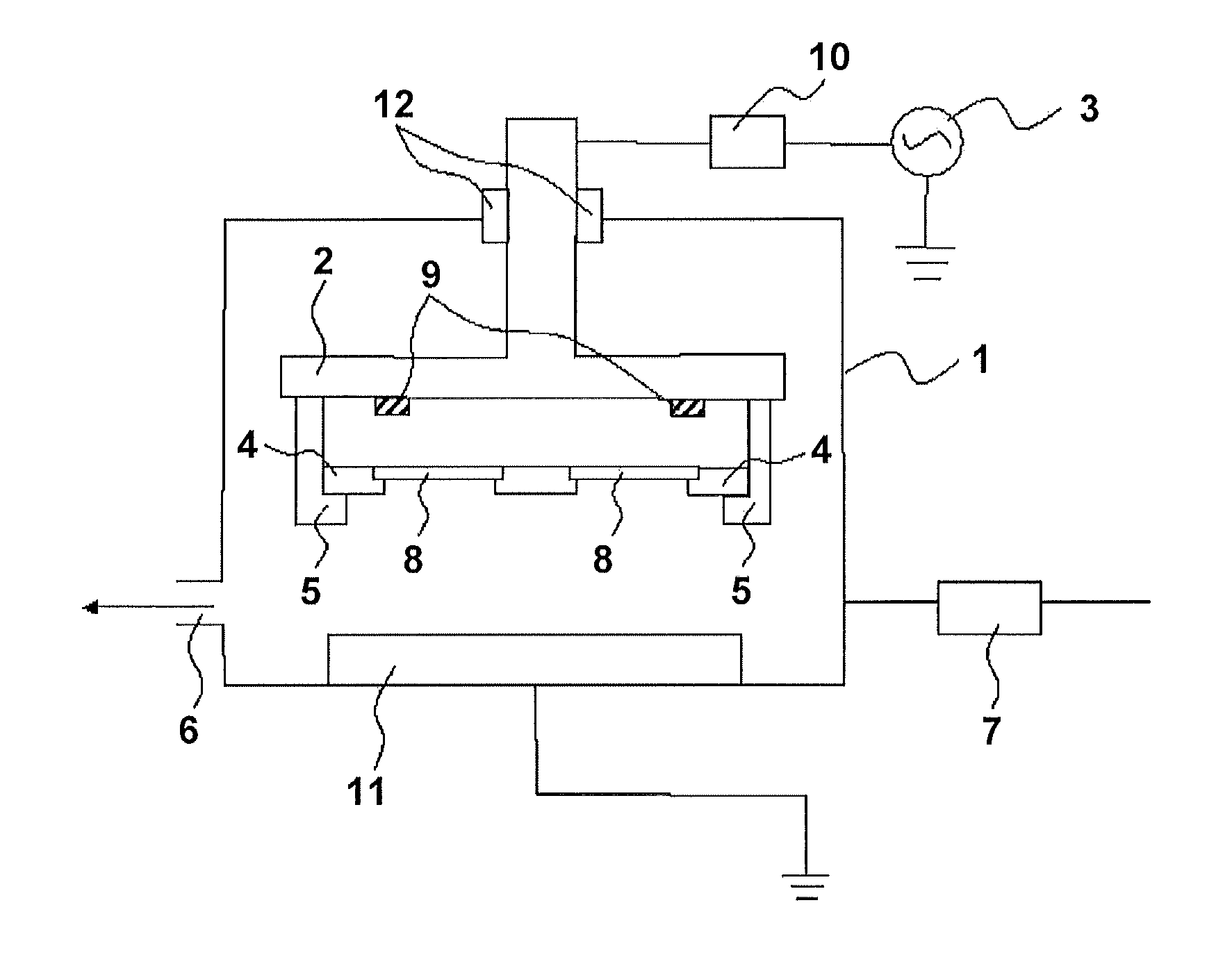

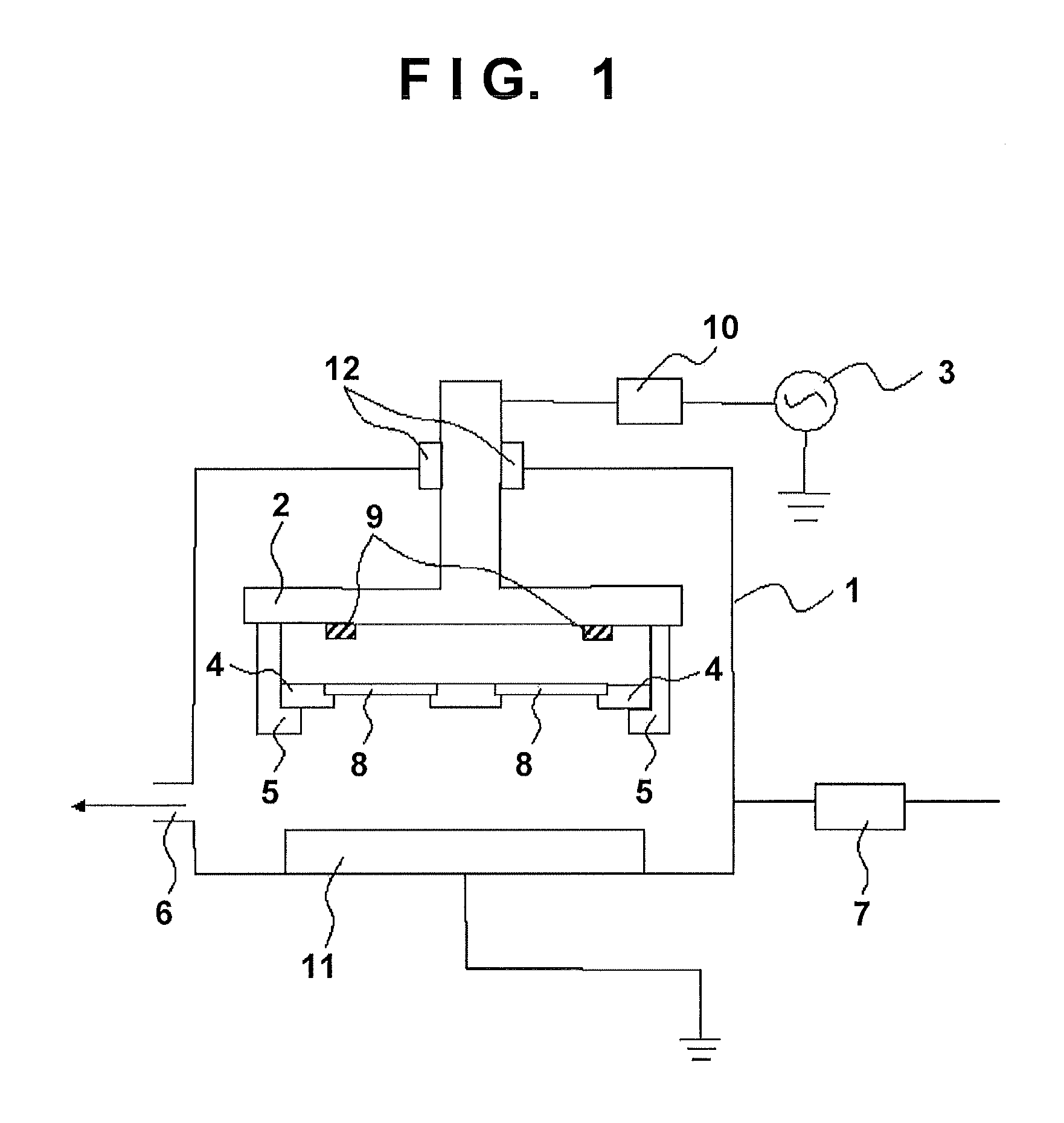

Etching apparatus

ActiveUS20140338836A1Reduce etch depthElectric discharge tubesSemiconductor/solid-state device manufacturingDielectric plateNon targeted

An etching apparatus includes a chamber capable of being evacuated, a first electrode provided in the chamber and including a tray support portion configured to support a tray which can hold a plurality of substrates and load / unload the substrates into / from the chamber, and a voltage applying unit configured to apply a voltage to the first electrode. A dielectric plate is attached to a portion, of an obverse surface of the first electrode, which faces an outer edge portion of a non-target surface of the substrate.

Owner:CANON ANELVA CORP

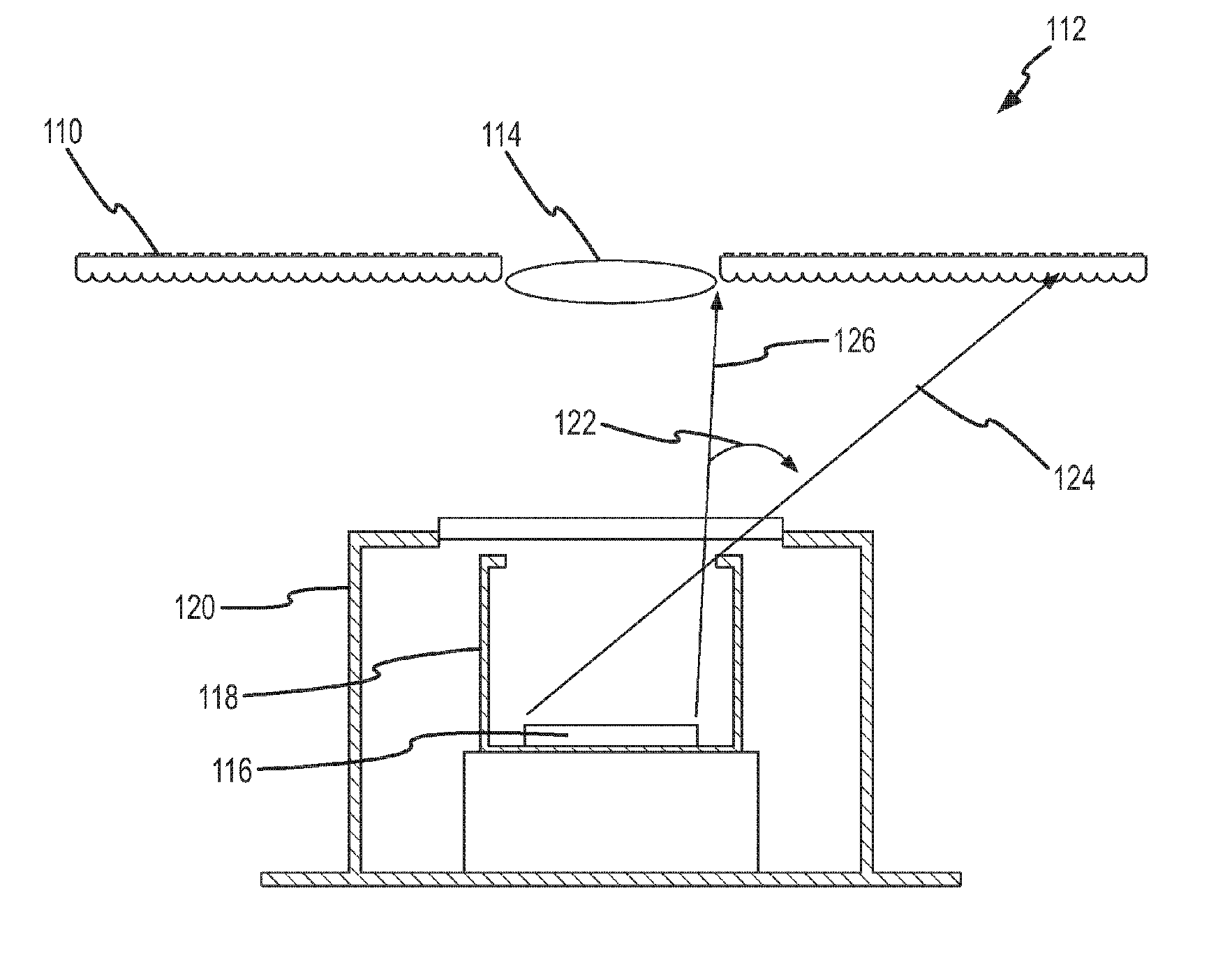

Negative luminescence cold shield (NLCS) with microlenses to magnify the effective area of sparsely populated negative luminescence regions and method of fabrication

ActiveUS7473896B2Cost-effectiveReduce areaTelevision system detailsSolid-state devicesNegative luminescenceCold shield

An array of microlenses magnifies the effective negative luminescence regions of a sparsely populated NLCS so that the NLCS appears cold to a FPA. This approach reduces the total diode area with minimal effect on device processing. The microlenses are fabricated on the backside of the substrate away from the devices, either prior to or after device processing. This ensures high quality devices that maintain NL efficiency without negatively impacting power consumption.

Owner:TELEDYNE SCI & IMAGING

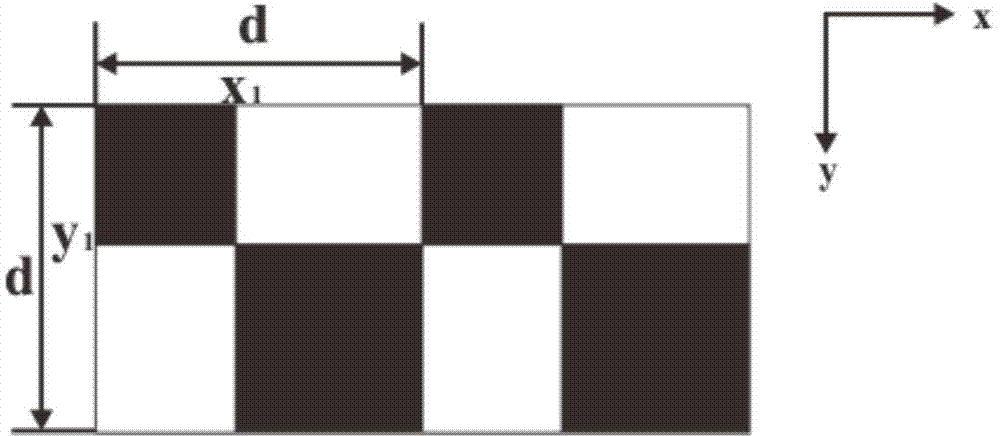

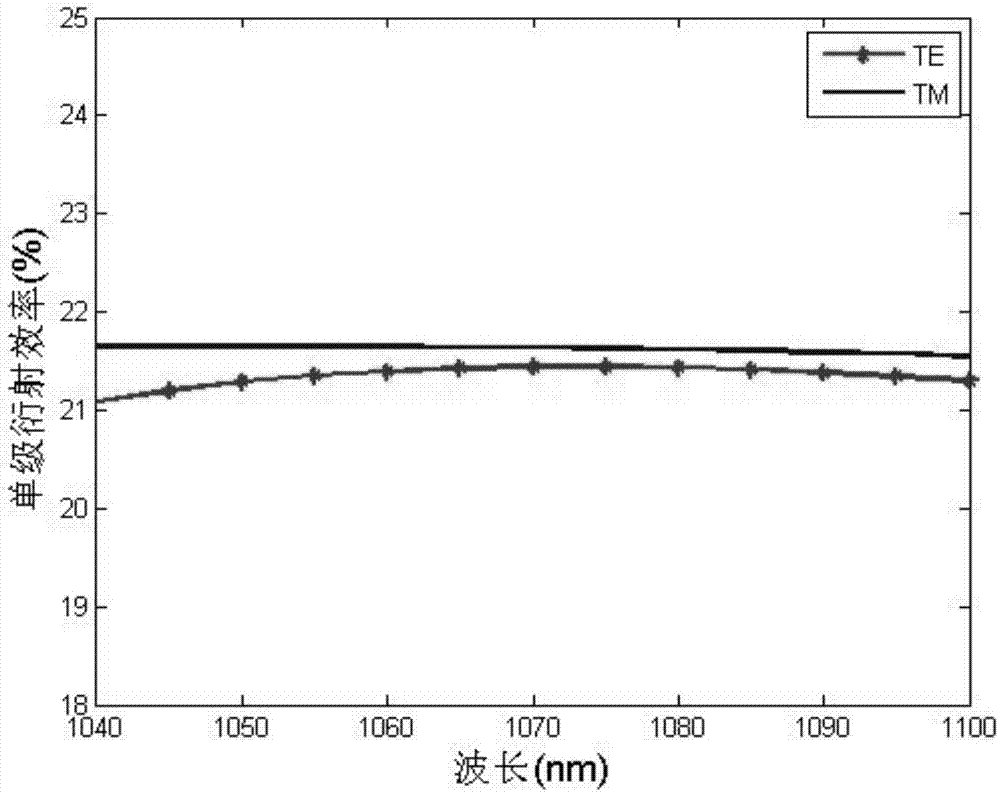

Polarization-independent high-efficiency two-dimensional reflecting Dammann grating for wave band with central wavelength of 1064 nanometers

InactiveCN104777536AImprove performanceLow costDiffraction gratingsBeam splittingOptical polarization

A polarization-independent high-efficiency two-dimensional reflecting Dammann grating for wave band with central wavelength of 1064 nanometers is structurally characterized in that a fused quartz substrate is sequentially coated with an aluminum oxide film, a gold film, an aluminum oxide film and a fused quartz film, the aluminum oxide film between the gold film and the fused quartz film is a connection layer, and a rectangular-groove grating is etched on the fused quartz film layer. The grating cycle is 1,917-1,027 nanometers, the coordinate of a normalized phase mutation point is 0.265-0.275, the grating depth is 730-740 nanometers, and the connection layer is 92-102 nanometers thick. When TE (transverse electric) or TM (transverse magnetic) polarization light of the Dammann grating performs perpendicular incidence, 2*2 beam splitting of the wave band with the central wavelength of 1064 nanometers can be realized, the total diffraction efficiency is larger than 85% basically. The Dammann grating is machined with an optical hologram recording technique or by a laser direct writing device in combination with a microelectronic deep etching process and a film coating technique, materials are convenient to obtain, the manufacturing cost is low, large batch production can be realized, and the Dammann grating has important practical prospect.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com