Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32results about How to "Good gettering effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Photovoltaic conversion device and method of manufacturing the device

InactiveUS20050160970A1Good gettering effectHigh propertyPolycrystalline material growthFinal product manufactureSurface measurementPeak value

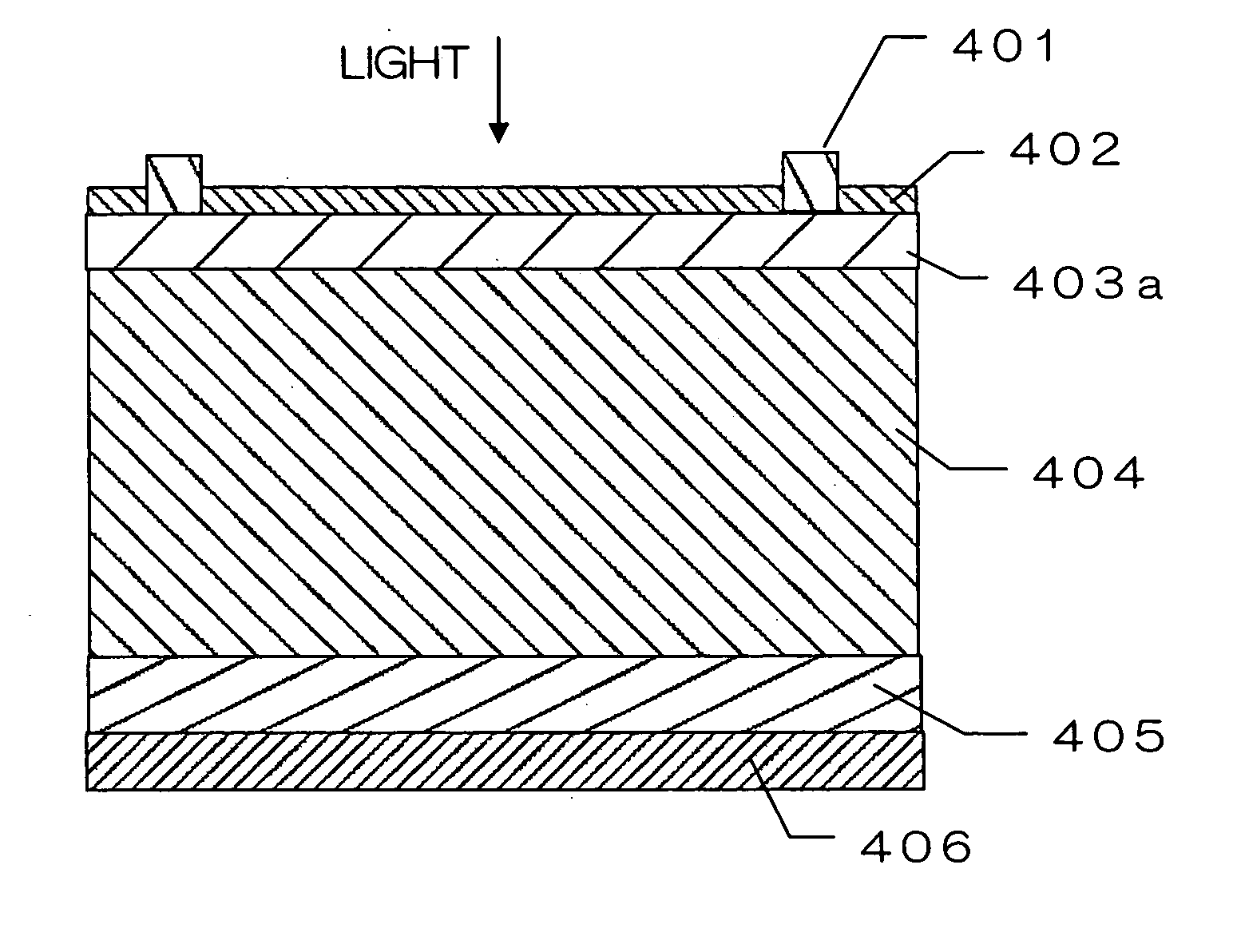

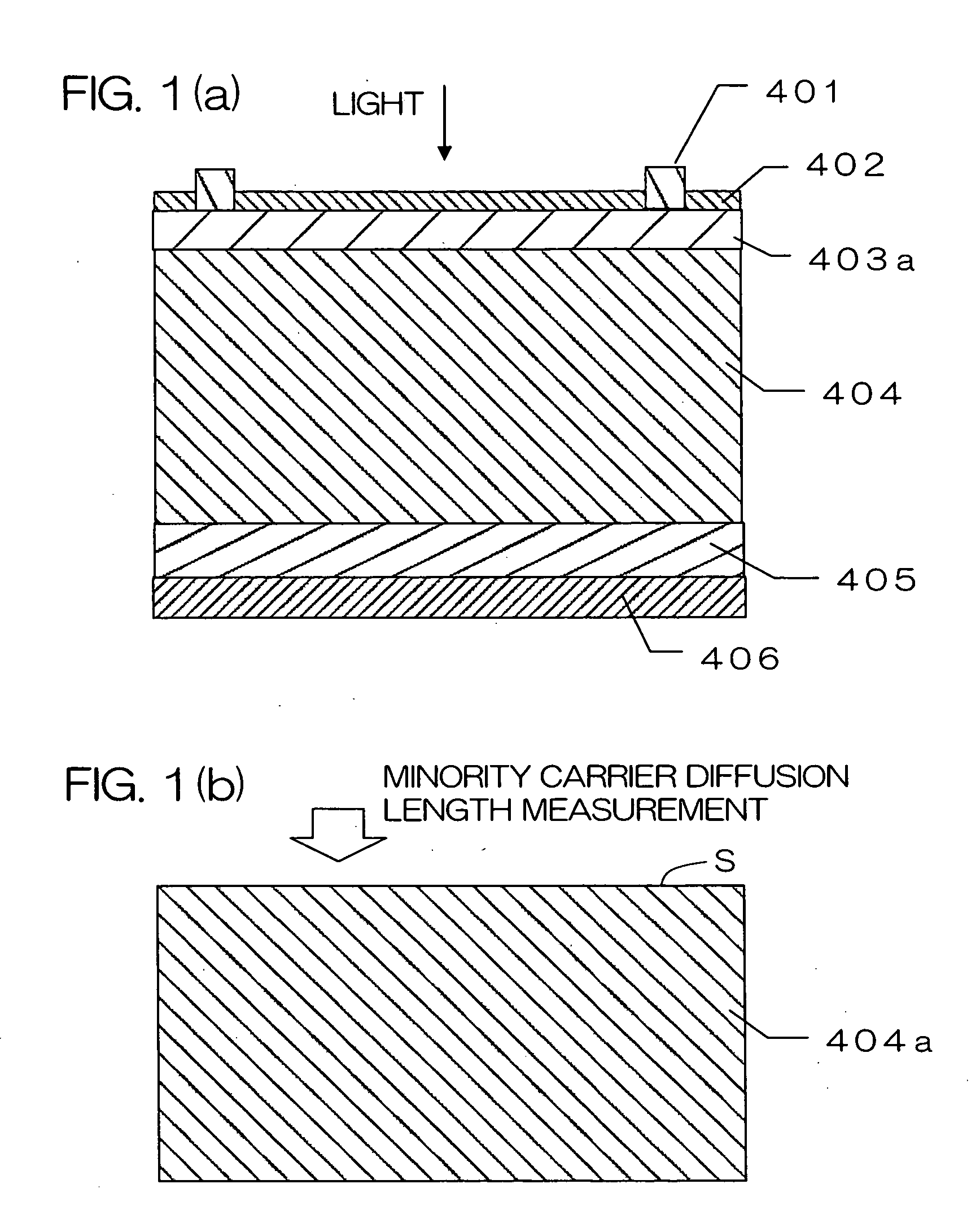

There is disclosed a photovoltaic conversion device constructed using a p-type crystalline silicon substrate 404 doped with boron, which comprises a bulk substrate region 404, regions other than the bulk substrate region including an n-type region 403a joining to a light receiving surface of the bulk surface region, a BSF region 405 joining to a back surface of the bulk surface region, [0001]wherein with regions other than the bulk substrate region 404 being removed, when a minority carrier diffusion length of the bulk substrate region 404 is measured from the light receiving surface of the bulk surface region, 0.5<(L1 / Lpeak)is satisfied, where L1is a minority carrier diffusion length at an arbitrary measuring area of the light receiving surface of the bulk surface region, and Lpeak is a diffusion length corresponding to a maximum peak on the side of higher diffusion length of a histogram, the histogram being formed from data obtained when a minority carrier diffusion length of the light receiving surface of the bulk surface region is measured at a plurality of measurement areas. This structure can reduce influence of impurities such as Fe, and enhances utilization efficiency of silicon ingots. With this structure, a photovoltaic conversion device with high photovoltaic conversion efficiency can be realized.

Owner:KYOCERA CORP

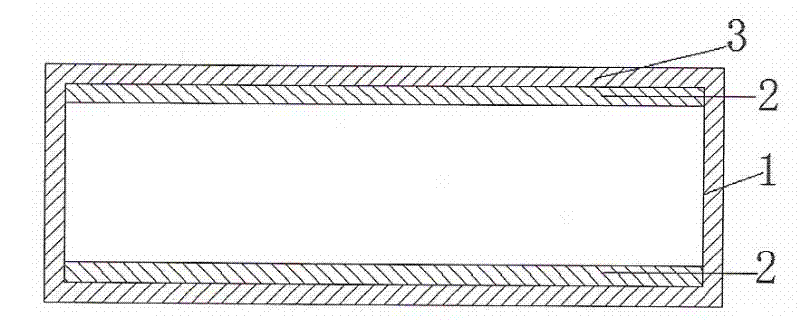

Encapsulation structure for wafer backside

InactiveCN101740525AEasy to adjust bowEasy to adjust warpageSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSilicon dioxide

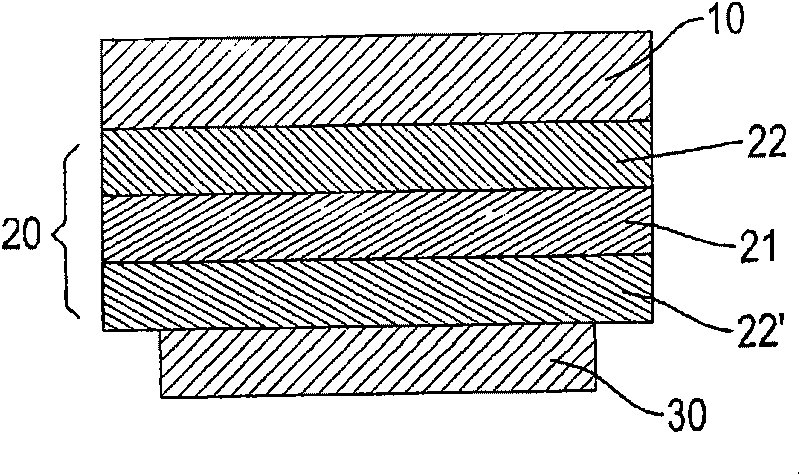

The invention relates to an encapsulation structure for wafer backside. The structure comprises a semiconductor substrate and a multilayered structural layer which is arranged at the bottom of the semiconductor substrate and is formed by combining a polysilicon layer and an insulating layer (such as a silicon dioxide layer); the multilayered structure can promote the effect of impurity absorption, effectively prevents automatic doping, improves the phenomenon of burr, and saves process cost; and through the structure, the bowing degree and the warping degree of the silicon substrate are easily adjusted.

Owner:WAFER WORKS

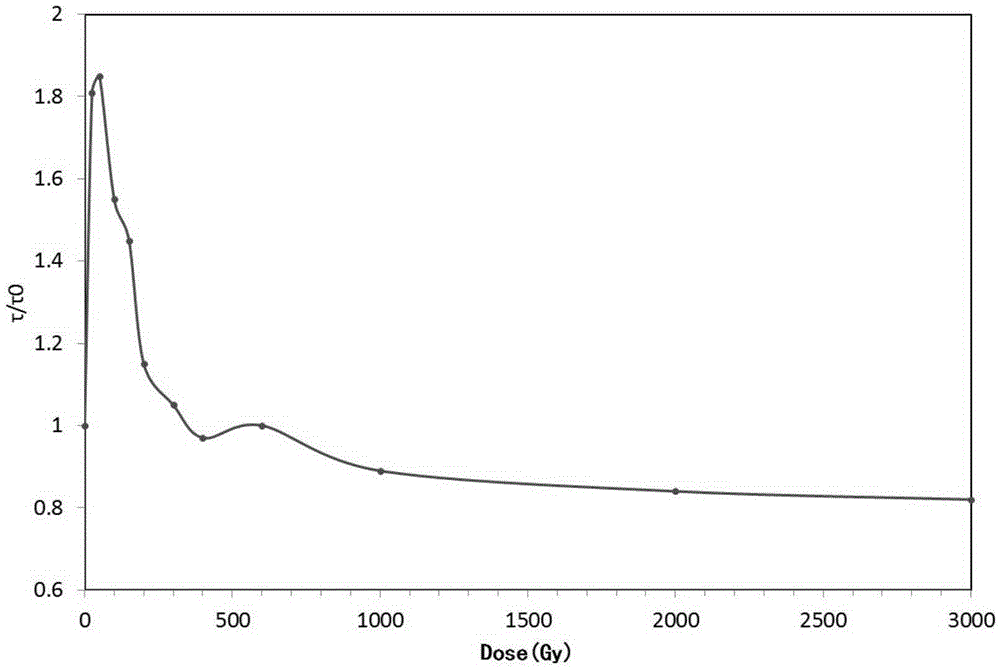

Method for removing transition metal impurities in silicon wafer or silicon device in sucking mode at indoor temperature

ActiveCN103794473AImprove radiation gettering effectChange structureSemiconductor/solid-state device manufacturingSemiconductor materialsSingle crystal

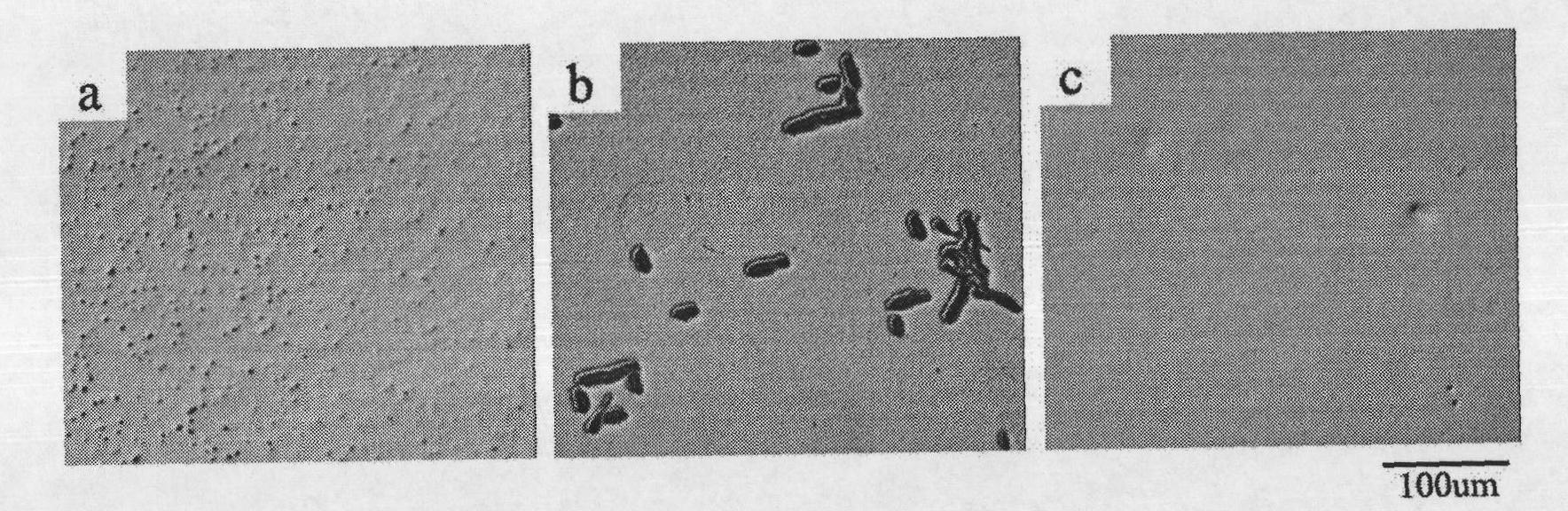

The invention discloses a method for removing transition metal impurities in a silicon wafer or silicon device in a sucking mode at the indoor temperature. Low-dose electron irradiation with the dose smaller than 5000 Gy is carried out on the silicon wafer or silicon device at the indoor temperature to enable the transition metal impurities in a to-be-cleaned area of the silicon wafer or an active area of the silicon device to be diffused to a nearby impurity sucking defect area, and therefore the concentration of the transition metal impurities in the to-be-cleaned area of the silicon wafer or the active area of the silicon device is lowered. Compared with an existing silicon material impurity sucking method, the method is implemented at the indoor temperature, and therefore the method can be used for silicon wafer or silicon device impurity sucking, is not limited to the single-crystal or polycrystalline silicon wafer and the silicon device, and is also suitable for other semiconductor materials such as germanium, and corresponding devices.

Owner:PEKING UNIV

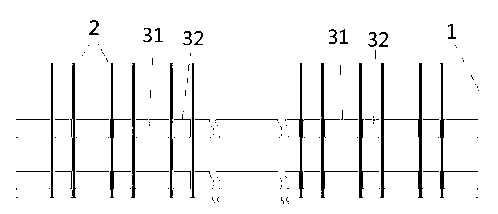

Boron-aluminum common gettering method for silicon slice

ActiveCN101944554AGetterGood repeatabilityFinal product manufactureSemiconductor devicesScreen printingSurface layer

The invention discloses an aluminum-boron common gettering method for a silicon slice, which comprises the following steps of: preparing a boron-doped aluminum source, cleaning the silicon slice, forming a boron aluminum layer on the surface of the silicon slice by using screen printing or spin coating technology, performing annealing with one or more steps, and removing the surface layer of the silicon slice. The boron is doped into the aluminum by using the characteristic that the boron has high solid solubility in silicon compared with the aluminum, and the boron is doped into a heavy doped layer on the back of the silicon by using an alloying process of the aluminum and the silicon to obtain an aluminum-boron common gettering layer with high doping concentration. The aluminum-boron common gettering method can form a deeper and uniform gettering layer with higher doping concentration at the same annealing temperature, achieve the gettering effect of other processes at a low temperature, and reduce the influence of high temperature on the performance of the silicon slice. The aluminum-boron common gettering method has the characteristics of low cost, easy operation and good gettering effect, and has great application prospect.

Owner:ZHEJIANG UNIV

Silicon epitaxial wafer and production method for same

InactiveUS20090017291A1Sufficient IG effectImprove applicabilityPolycrystalline material growthFinal product manufactureSingle crystalIngot

A silicon epitaxial wafer of the invention comprises a silicon single crystal wafer sliced from a CZ silicon ingot doped with carbon in a concentration range of not less than 5×1015 atoms / cm3 and not more than 5×1017 atoms / cm3 and an epitaxial layer consisting of a silicon single crystal epitaxially grown on a front surface of the silicon single crystal wafer. A polycrystalline silicon layer having a thickness of not less than 0.5 μm and not more than 1.5 μm is formed on a back surface of the silicon single crystal wafer.

Owner:SUMCO CORP

Silicon wafer rapid heat treatment phosphorus diffusion gettering technology for manufacture of solar cell

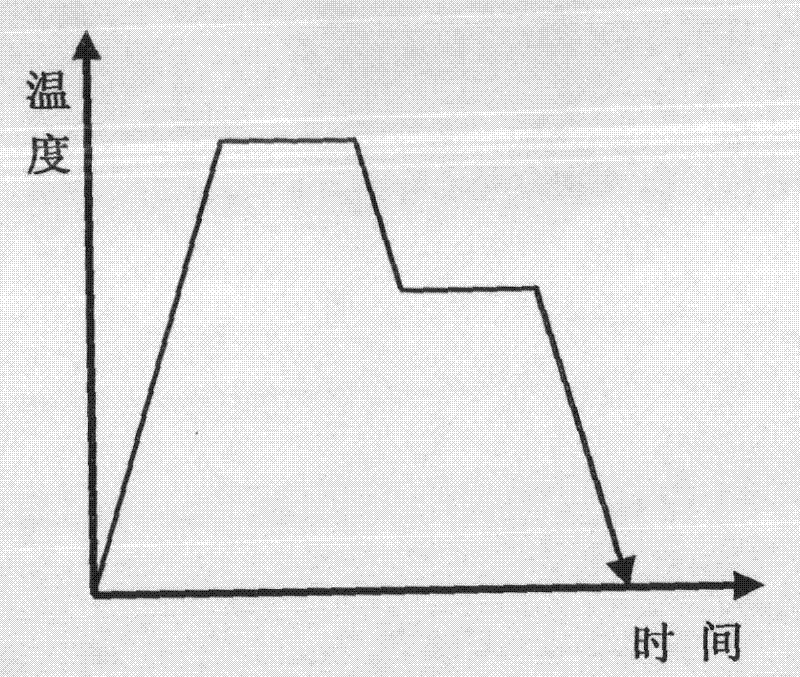

InactiveCN101834224AShort processing timeImprove productivityFinal product manufactureSemiconductor devicesSilicon chipAtmosphere

The invention discloses a silicon wafer phosphorus diffusion gettering technology for manufacture of a solar cell, which comprises the following steps of: coating a phosphorus source on the surface of a silicon wafer; heating the silicon wafer to 800-1,100 DEG C at the rate of 50-200 DEG C / s in the presence of a protective gas atmosphere; preserving the temperature for 1-10 minutes; then cooling to 500-800 DEG C and preserving the temperature for 1-10 minutes; and cooling and then removing a phosphorosilicate glass layer. The invention has short process time, low cost and good gettering effect.

Owner:ZHEJIANG UNIV

Conveying and impurity adsorbing device for melt-blown cloth production

PendingCN112663305AAvoid wrinklesGood for dust removalMechanical cleaningPressure cleaningEngineeringMechanical engineering

The invention discloses a conveying and impurity adsorbing device for melt-blown cloth production. The device comprises a bottom plate, wherein a box body is fixedly mounted at the top of the bottom plate, a first cavity and a second cavity are formed in the box body, a feeding port is formed in the inner wall of the side, away from the second cavity, of the first cavity, the inner walls of the sides, close to each other, of the first cavity and the second cavity are provided with the same communication hole, the inner wall of the side, away from the first cavity, of the second cavity is provided with a discharging port, the two sides of the box body are both rotationally provided with first guide rollers, and two second guide rollers and two third guide rollers are rotationally mounted in the first cavity. The conveying and impurity adsorbing device is reasonable in design and good in practicability, the upper surface and the lower surface of melt-blown cloth can be subjected to impurity adsorbing cleaning at the same time, the impurity adsorbing cleaning effect on the surface of the melt-blown cloth is better, the melt-blown cloth is cleaned more thoroughly, the melt-blown cloth can be flattened, the phenomenon that the melt-blown cloth wrinkles is avoided, and the production quality of the melt-blown cloth is improved.

Owner:ANHUI HONGSHI ENVIRONMENTAL TECH

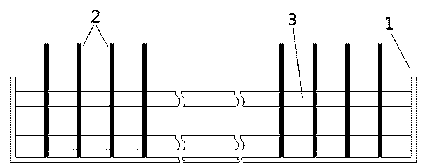

Novel railboat for diffusing silicon wafers

InactiveCN103325720ADoes not affect compatibilityDoes not affect gettering effectFinal product manufactureSemiconductor/solid-state device manufacturingEngineeringSilicon chip

The invention discloses a novel railboat for diffusing silicon wafers. The silicon wafers are placed on the novel railboat. The novel railboat for diffusing the silicon wafers comprises a boat body, at least three clamping grooves for containing the silicon wafers are formed in the boat body, the distances between any one of the clamping grooves and adjacent clamping grooves are L1 and L2, L1 is larger than L2 or L2 is larger than L1, and the clamping grooves are arranged at the intervals of L1, L2, L1, L2 in sequence. L2 is 1 / 2-1 / 7 of L1, or L1 is 1 / 2-1 / 7 of L2. Due to the fact that the distance of the front faces of the silicon wafers is not changed, the uniformity of diffusion is not influenced by the novel railboat. The structure of the novel railboat is combined with an insertion mode, compared with the railboat with an ordinary traditional structure being combined with the insertion mode, the novel railboat has the same gettering effect with a traditional insertion mode a, is higher in battery efficiency and productivity. The ordinary railboat can not meet the requirements of battery efficiency and productivity at the same time, while the novel railboat with the strucuture being combined with the insertion mode can meet the requirements of battery efficiency and productivity at the same.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

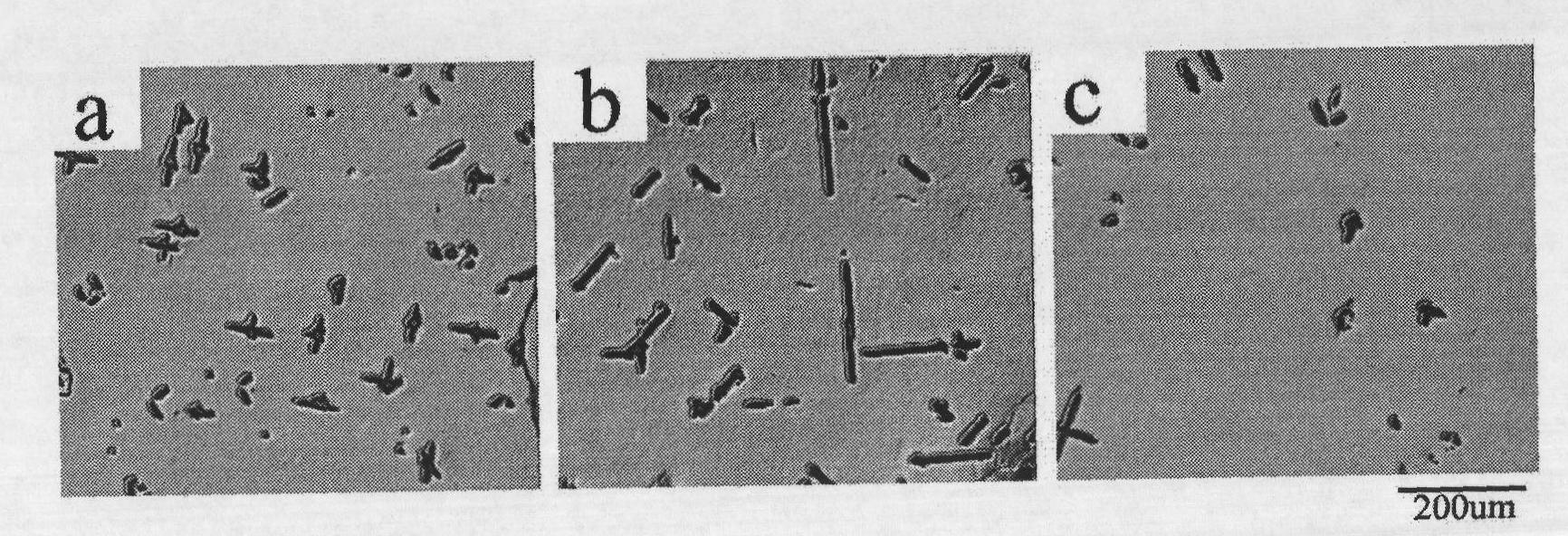

Silicon wafer phosphorus and aluminum combined temperature varying and impurity suction method for preparing solar cells

InactiveCN103928573AImprove life expectancySimple processFinal product manufacturePhotovoltaic energy generationHydrofluoric acidPhysical chemistry

A silicon wafer phosphorus and aluminium combined temperature varying and impurity suction method for preparing solar cells comprises the following steps that after damage layer removing and ultrasonic cleaning are sequentially conducted on a substrate silicon wafer, the front face and the back face of the silicon wafer are coated with phosphorus sources first, and then the silicon wafer is plated with aluminium coatings in an evaporated mode; then under protecting of nitrogen atmosphere, thermal treatment is conducted, and primary impurity suction and secondary impurity suction are sequentially conducted; after the silicon wafer is cooled to the room temperature, the silicon wafer is put in a mixed solution of hydrofluoric acid and nitric acid to be corroded, and an impurity suction layer is removed. The silicon wafer phosphorous and aluminium combined temperature varying and impurity suction method for preparing the solar cells has the advantages that a temperature varying process is introduced on the basis of a phosphorus and aluminium impurity suction process, all the processes of impurity suction are effectively controlled through different temperatures, and the respective advantages of phosphorus impurity suction and aluminium impurity suction are fully utilized; the process is simple and easy to achieve, and other equipment is of no need; an impurity suction effect is obvious, after impurity suction treatment, the minority carrier lifetime of the silicon wafer is obviously prolonged, and the process cycle is reduced under the premise that the requirement for impurity suction effect is met.

Owner:NANKAI UNIV

Gettering method through implantation of carbon ions

InactiveCN103872180AImprove compatibilityGood gettering effectSemiconductor/solid-state device manufacturingSemiconductor devicesCMOS sensorHigh energy

The invention relates to a gettering method through implantation of carbon ions. The method comprises the following steps that high-energy carbon ions are implanted on an exposed layer on the back face of a silicon wafer or a silicon dioxide layer on the back face of the silicon wafer by the adoption of the ion implantation process, and a crystal defect area is formed on the implantation layer of the silicon wafer; the annealing is carried out, the crystal defect area is converted to be a gettering area, and metal ions in the silicon wafer are captured to form an impurity removing area; the impurity removing area is removed according to the chemical and mechanical grinding method. The ion implantation gettering process and the manufacturing process of a photodiode are high in compatibility and can be easily added into the prior art, the carbon ion implantation has no side effect on the performance of a device, and the device is not polluted in the gettering process of the ion implantation; meanwhile, the ion implantation gettering process parameters are optimized and controlled, so that the metal ion gettering effect is good, the performance of the gettered photodiode is better remarkably, dark current and white pixels are reduced remarkably, and the imaging effect of a CMOS sensor is improved.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Multi-functional short-staple rope twisting machine

ActiveCN109281215AAdjust the mobile positionGuaranteed lengthRope making machinesLength measurementEngineering

The invention provides a multi-functional short-staple rope twisting machine. The multi-functional short-staple rope twisting machine comprises anti-slip mats, left supporting legs, right supporting legs, a machine base, a U-shaped supporting frame, a rope twisting motor, a rotary disc, a linear sliding rail, U-shaped sliders, winged screws, rope twisting hooks, a rope taking and wheel replacing structure, a structure for coiling a rope after rope twisting, a rope twisting length measurement determining rail structure and an anti-overflow shield structure, wherein the anti-slip mats are transversely glued to the lower surfaces of the horizontal sections on the lower portions of the left supporting legs and the lower surfaces of the horizontal sections on the lower portions of the right supporting legs respectively. Due to the arrangement of a fixing rod, a movable sleeve, a fixing hook and a square-head bolt, the moving position of the fixing hook is easily adjusted according to the horizontal requirements of rope twisting, and it can be ensured that rope twisting work is smoothly conducted; due to the arrangement of an adjusting slider, a stainless steel sliding rail, a measurement ruler and an adjusting bolt, the rope twisting length is easily ensured, and the rope twisting length consistency can be ensured.

Owner:扬州市新天河绳业有限公司

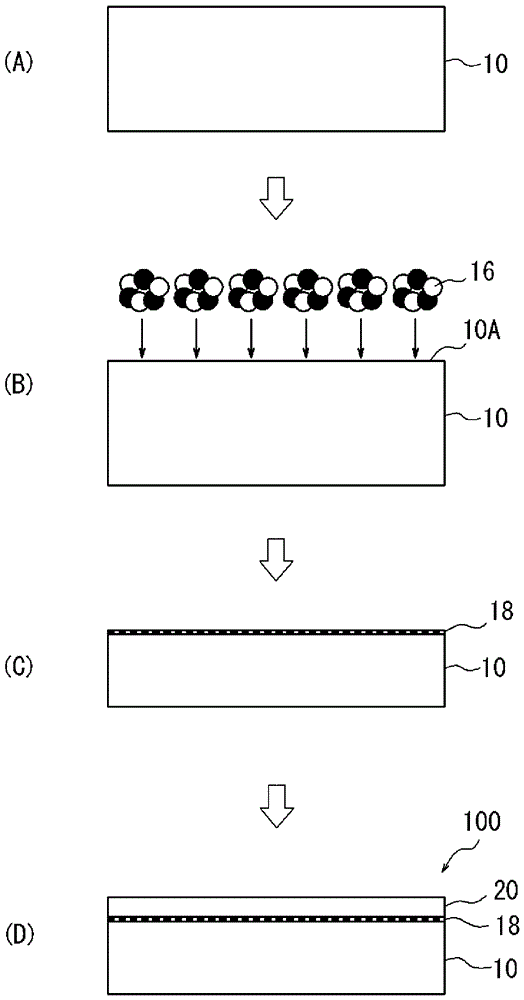

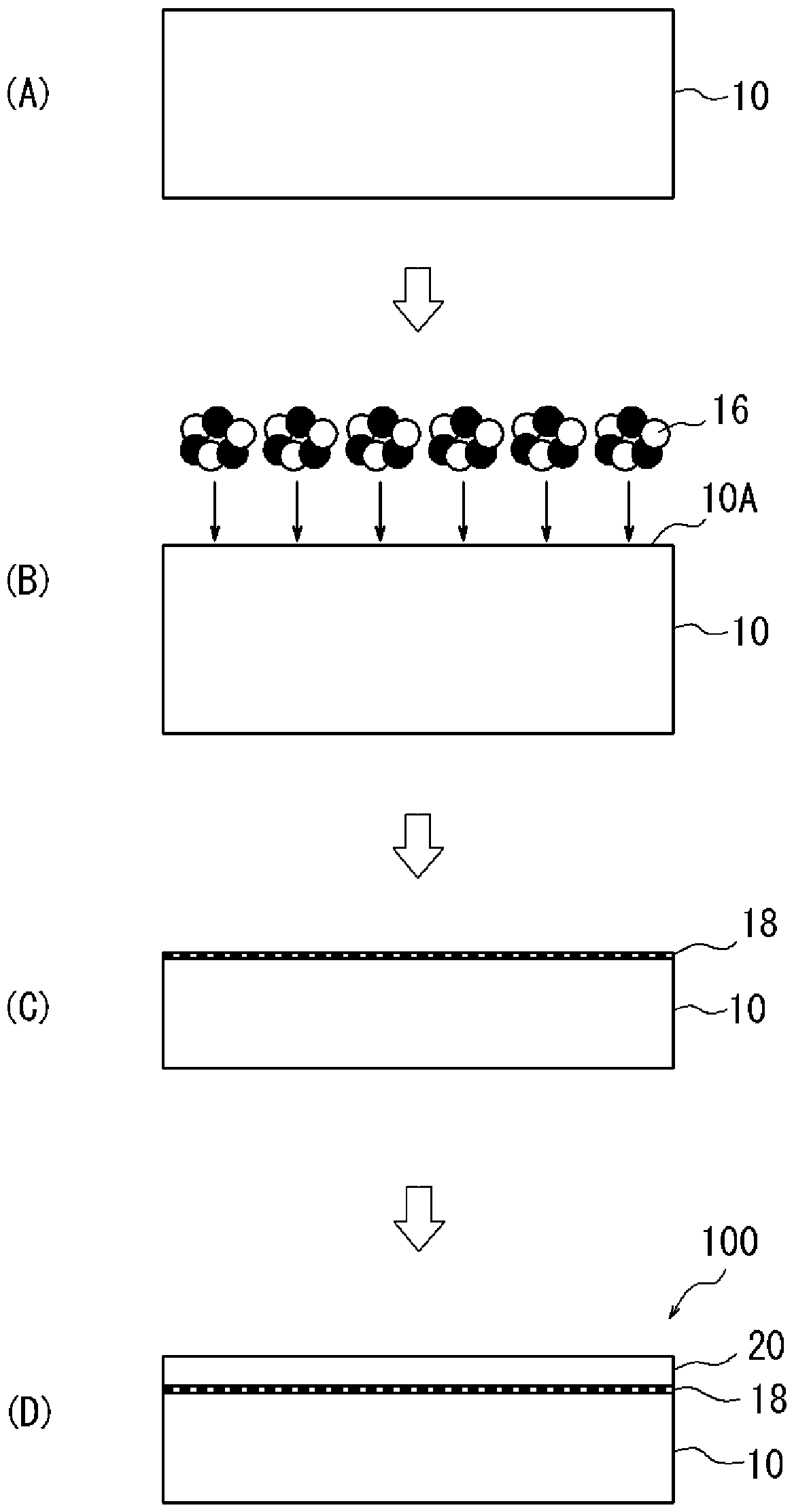

Epitaxial wafer manufacturing method and epitaxial wafer

ActiveCN106062937AGood gettering effectInhibition formationSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistivityOmega

Provided is a method for manufacturing an epitaxial wafer which has excellent gettering capability while suppressing the formation of epitaxial defects. This method is characterized by involving: a cluster ion irradiation step in which cluster ions (16), which contain at least carbon, are irradiated in a dose amount of 2.0*1014 / cm2 to 1.0*1016 / cm2 onto the surface of a silicon wafer (10) having a resistivity of 0.001-0.1 omega*cm, and a modified layer (18) consisting of a solid solution of the constituent elements of the cluster ions (16) is formed on the surface of the silicon wafer (10); and a epitaxial layer forming step in which an epitaxial layer (20) having higher resistivity than the silicon wafer (10) is formed on the modified layer (18) of the silicon wafer (10).

Owner:SUMCO CORP

Preparation method of crystalline silicon solar cell textured structure

InactiveCN106057972AReduce compoundingImprove conversion efficiencyFinal product manufacturePhotovoltaic energy generationHydrofluoric acidPorous medium

The invention discloses a preparation method of a crystalline silicon solar cell textured structure. The preparation method comprises the following steps: (1) forming a porous medium layer structure on the surface of a silicon wafer; (2) and then carrying out surface etching by using a first chemical corrosive liquid so that the crystalline silicon solar cell textured structure can be obtained. The first chemical corrosive liquid is a mixed solution of hydrofluoric acid and an oxidizing agent, wherein the molar ratio of the hydrofluoric acid to the oxidizing agent is 1: (1 to 5). According to the preparation method, the proportion of HF to HNO3 is adjusted, the generation is beneficial for diffusing a gettering loosened porous silicon layer besides hole enlarging and metal particle removal; the loosened porous silicon layer has extremely excellent gettering performance, and the recombination of PN junctions can be greatly reduced through subsequent high-temperature diffusion and gettering, so that the open-circuit voltage and battery conversion efficiency are improved.

Owner:CSI CELLS CO LTD

Silicon wafer rapid heat treatment phosphorus diffusion gettering technology for manufacture of solar cell

InactiveCN101834224BShort processing timeImprove productivityFinal product manufactureSemiconductor devicesSilicon chipAtmosphere

The invention discloses a silicon wafer phosphorus diffusion gettering technology for manufacture of a solar cell, which comprises the following steps of: coating a phosphorus source on the surface of a silicon wafer; heating the silicon wafer to 800-1,100 DEG C at the rate of 50-200 DEG C / s in the presence of a protective gas atmosphere; preserving the temperature for 1-10 minutes; then cooling to 500-800 DEG C and preserving the temperature for 1-10 minutes; and cooling and then removing a phosphorosilicate glass layer. The invention has short process time, low cost and good gettering effect.

Owner:ZHEJIANG UNIV

Boron and aluminum common gettering method for silicon wafer

ActiveCN101944553AGetterGood repeatabilityFinal product manufactureSemiconductor devicesSurface layerBoron

The invention discloses an aluminum and boron common gettering method for a silicon wafer, which comprises the following steps of: preparing a boron-doped aluminum source; cleaning a silicon wafer; forming a boron-aluminum layer on the surface of the silicon wafer by utilizing a film plating technology; annealing at one step or multiple steps; and removing the surface layer of the silicon wafer. The invention utilizes the characteristic that the boron has higher solid solubility in silicon relative to aluminum, dopes the boron into the aluminum and dopes the boron into a heavy doped layer in the alloying process of the aluminum and silicon to obtain an aluminum-boron common gettering layer with high doping concentration. The aluminum and boron common gettering method of the invention can form the gettering layer which is deeper and even and has higher doping concentration at same annealing temperature and achieve the gettering effect of other processes at lower temperature and reduce the influence of high temperature on the performance of the silicon wafer. The aluminum and boron common getteirng method of the invention has the characteristics of low cost, easy operation and good gettering effect and has wider application prospect.

Owner:ZHEJIANG UNIV

Silicon-based heterojunction solar cell structure and preparation method thereof

PendingCN114093963APlay a role in separationReduce compoundingFinal product manufacturePhotovoltaic energy generationHeterojunctionSolar cell

The invention relates to a silicon-based heterojunction solar cell structure and a preparation method thereof, the silicon-based heterojunction solar cell structure comprises an N-type monocrystalline silicon substrate, the front surface of the N-type monocrystalline silicon substrate is provided with an n + doping layer, a first intrinsic amorphous silicon / microcrystalline silicon film is deposited on the surface of the n + doping layer, no less than two layers of n-type amorphous silicon / microcrystalline silicon films are deposited on the surface of the first intrinsic amorphous silicon / microcrystalline silicon film, and a layer of first conductive film is deposited on the surface of the outermost layer of n-type amorphous silicon / microcrystalline silicon film; and a layer of second intrinsic amorphous silicon / microcrystalline silicon film is arranged on the back surface of the N-type monocrystalline silicon substrate, no less than two layers of p-type amorphous silicon / microcrystalline silicon films are deposited on the surface of the second intrinsic amorphous silicon / microcrystalline silicon film, and a layer of second conductive film is deposited on the surface of the outermost layer of p-type amorphous silicon / microcrystalline silicon film. The n + doping layer is formed on the main surface of the N-type monocrystalline silicon substrate to form a high-low junction, so that a certain separation effect on photon-generated carriers is achieved, and recombination of the photon-generated carriers is reduced.

Owner:SUZHOU AIKANG LOW CARBON TECH INST +1

Carbon doped silicon sheet with internal impurity absorbing function and production thereof

InactiveCN1269186CImprove yieldHigh densityAfter-treatment detailsSemiconductor/solid-state device manufacturingNitrogen gasOxygen

The invention was about one kind of C mixed silicon dice that has the function of inner absorbency of impurity, which has the oxygen concentration of 5-15X1017 cm-3, and C concentration was 5-30X1016cm-3. It is produced by: 1) the crystal was grown by method of straight drawing, the oxygen concentration of 5-15X1017cm-3 and C concentration was 5-30X1016cm-3 were obtained by control the processing parameter. 2) the silicon dice that has the oxygen concentration of 5-15X1017cm-3 and C concentration was 5-30X1016cm-3 was put into the furnace for heat treatment, which was thermal retarded 1-3 h on the temperature of 1100-1250 deg.C under the argon shield and helium gas shield. Then, it was thermal retarded 4-50 h on the temperature of 600-900 deg.C. After all, it was thermal retarded 4-30h on the temperature of 1000-1200 deg.C. Its advantages higher function of inner absorbency of impurity; good ability in the absorbency of harmful metal; used to the integrated circuit for improving the ratio of finished products.

Owner:ZHEJIANG UNIV

An oxygen-free diffusion method for crystalline silicon solar cells

ActiveCN109545673BAvoid enteringPrevent proliferationFinal product manufactureSemiconductor/solid-state device manufacturingHigh concentrationPhysical chemistry

An oxygen-free diffusion method for crystalline silicon solar cells, comprising: depositing a silicon wafer whose surface does not contain oxygen and a source layer film containing high-concentration dopant atoms, in a high-temperature furnace with an oxygen-free atmosphere at 810‑1050 Diffusion is carried out in the temperature range of ℃; after the diffusion is completed, the furnace temperature is lowered to 700-800°C, and an atmosphere with an oxygen volume concentration >2% is introduced, and annealing treatment is performed for 20-200min. The invention eliminates the possibility of oxygen entering the silicon wafer through the diffusion step, and can improve the impurity distribution state in the silicon wafer and the minority carrier lifetime of the silicon wafer; prevents the diffusion of oxygen to the silicon wafer and the uncontrollable elements in the doped layer diffusion. The invention is suitable for preparing p-type crystalline silicon diffusion layer and n-type crystalline silicon diffusion layer on n-type crystalline silicon chip, and also suitable for preparing n-type crystalline silicon diffusion layer and p-type crystalline silicon diffusion layer on p-type crystalline silicon chip. It is not only suitable for preparing monocrystalline silicon solar cells, but also suitable for preparing polycrystalline silicon solar cells.

Owner:NANCHANG UNIV

Diffusion process for making solar cells

InactiveCN104900751AReduce spreadReduce concentrationFinal product manufactureSemiconductor/solid-state device manufacturingOhmic contactNitrogen

The invention discloses a diffusion process for making solar cells, comprising the following steps: controlling the temperature inside a furnace at 840 DEG C; feeding oxygen at 200-500ml / min and small nitrogen at 700-1000ml / min under the temperature, and feeding big nitrogen at 10000-15000mL / min, wherein the duration is 8-12min; continuing feeding oxygen at 200-500ml / min and small nitrogen at 700-900ml / min, and feeding big nitrogen at 10000-15000mL / min, wherein processing lasts 11-16min; stopping feeding phosphorus source, reducing the temperature to 700-780 DEG C in 25-40min, continuously feeding oxygen at 2000-2500ml / min and feeding big nitrogen at 10000-15000ml / min in the whole cooling process, and then taking a silicon wafer out. The problem that ohmic contact difference is caused by too much reduction of the phosphorus concentration in the diffusion process and the problem that the uniformity is poor due to the difference between crystal boundary and crystal lattice positions on polycrystalline silicon in phosphorus source absorption in the prior art are solved.

Owner:JETION SOLAR HLDG

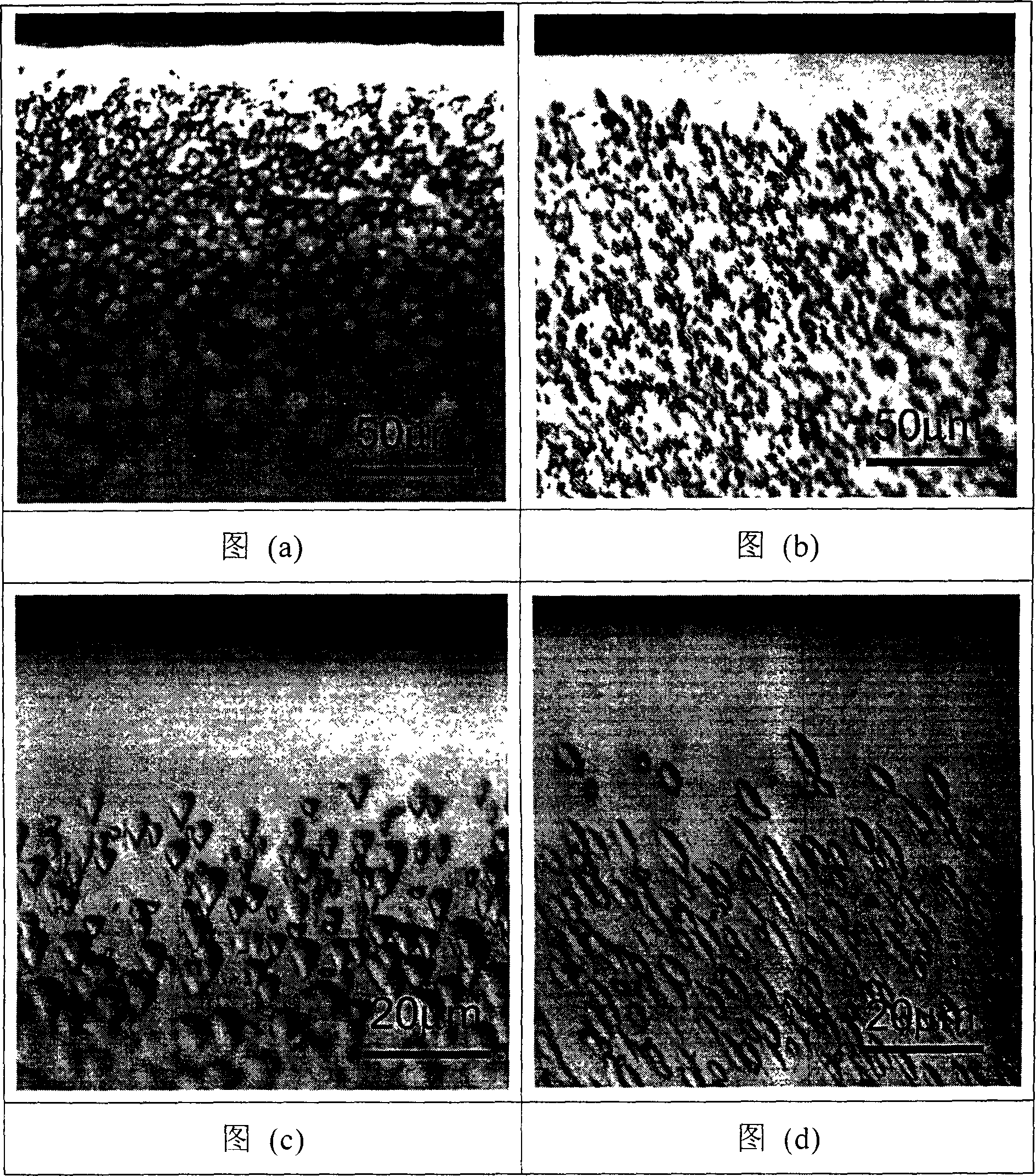

A preparation method of an insulating SOI material

InactiveCN109216255AGood gettering effectLow gettering efficiencySemiconductor/solid-state device manufacturingHigh dosesOxide

The invention discloses a preparation method of an insulating SOI material, which comprises the following steps of: absorbing Cu impurities in bulk silicon and SOI material by a nano cavity caused byhydrogen ion implantation and helium ion implantation, respectively introducing the nano cavity formed by helium ion implantation into the SIMOXSOI material and the Smart Under the oxide buried layerof cut SOI material, there is little difference in the distribution of oxygen-rich buried layer after high temperature annealing. During annealing, the interaction of vacancy and hydrogen induced by hydrogen implantation will increase the diffusion rate of oxygen and form a wider oxygen-enriched region. After oxygen ion implantation, hydrogen ion implantation with high dose will be disadvantageousto the formation of continuous oxidized buried layer. The preparation method of the insulating SOI material has certain gettering effect on Cu due to the buried layer interface of the SIMOX material,but the gettering efficiency is low and the gettering is unstable at high temperature, while Smart The buried interface of cut SOI is more perfect than that of SIMOX SOI, and the gettering effect ofnano cavity layer is more obvious than that of SIMOX SOI. Two gettering sites, cavity layer and Al metal precipitation layer, were introduced into the same silicon substrate for the first time, and the gettering effects of two gettering methods on Cu impurity were compared.

Owner:久耀电子科技(江苏)有限公司

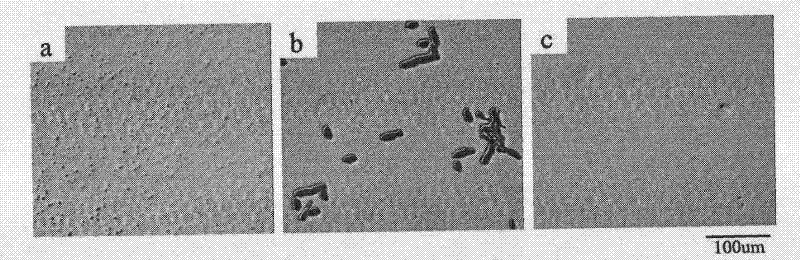

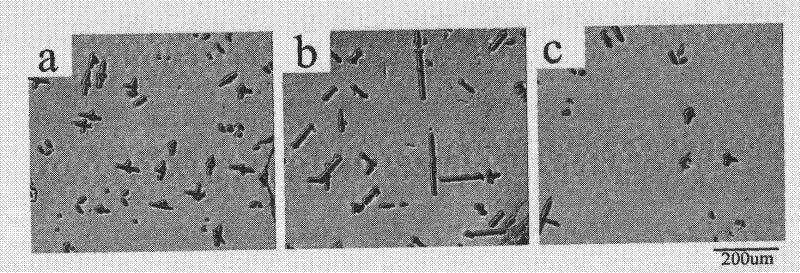

A method for aluminum gettering of ingot polycrystalline silicon wafer

ActiveCN106449873BImprove stabilityHigh industrial production valueFinal product manufactureSemiconductor/solid-state device manufacturingMetal impuritiesIngot

The invention discloses an aluminium gettering method for ingot polycrystalline silicon chips. The method comprises the following main steps of (1) cleaning; (2) vacuum evaporation of an aluminium layer; (3) into a furnace; (4) first annealing; (5) cooling at a constant speed to low temperature; (6) second annealing; (7) cooling; (8) removal of an impurity layer. After a large number of experimental verification, the process of the invention can remove most of the metal impurities (such as iron, nickel, copper, cobalt and the like) in the ingot polycrystalline silicon chips, thereby increasing the lifetime of the minority carrier to improve the photoelectric conversion efficiency of the solar cell. The average minority carrier lifetime of the polycrystalline silicon chips subjected to the aluminium gettering is determined to be about 15.80 [mu]s by an apparatus, and the aluminium gettering process of the present invention is relatively stable and had a high industrial production value.

Owner:HEBEI UNIV OF TECH

Encapsulation structure for wafer backside

InactiveCN101740525BGood gettering effectPrevent auto dopingSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSilicon dioxide

The invention relates to an encapsulation structure for wafer backside. The structure comprises a semiconductor substrate and a multilayered structural layer which is arranged at the bottom of the semiconductor substrate and is formed by combining a polysilicon layer and an insulating layer (such as a silicon dioxide layer); the multilayered structure can promote the effect of impurity absorption, effectively prevents automatic doping, improves the phenomenon of burr, and saves process cost; and through the structure, the bowing degree and the warping degree of the silicon substrate are easily adjusted.

Owner:WAFER WORKS

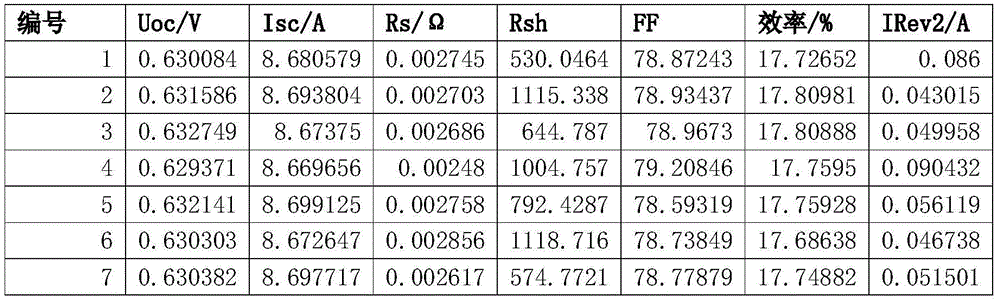

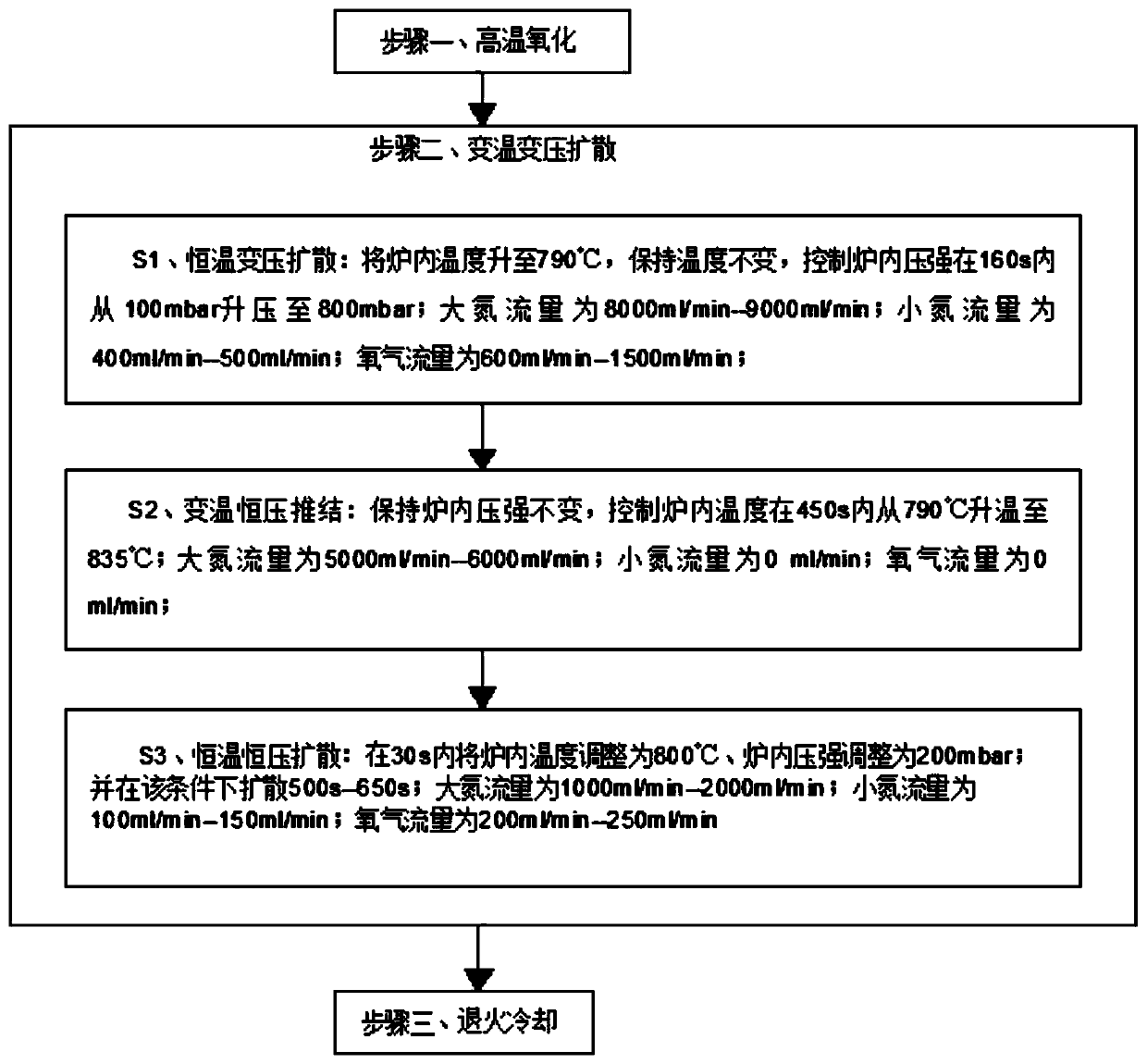

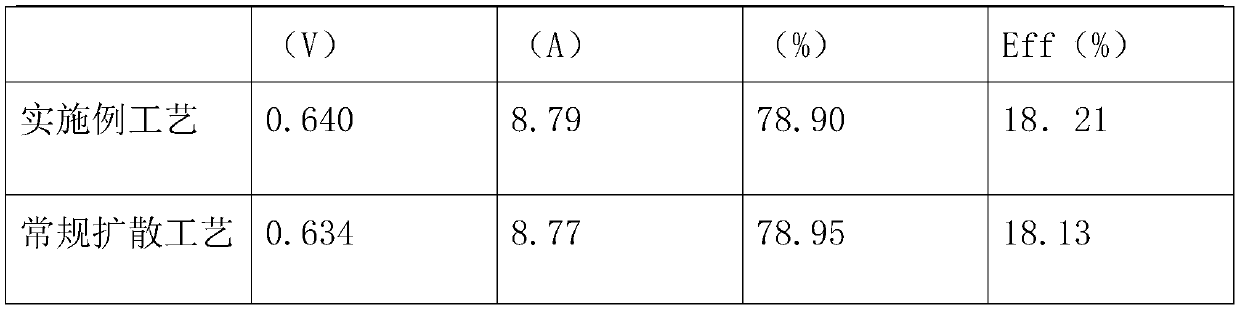

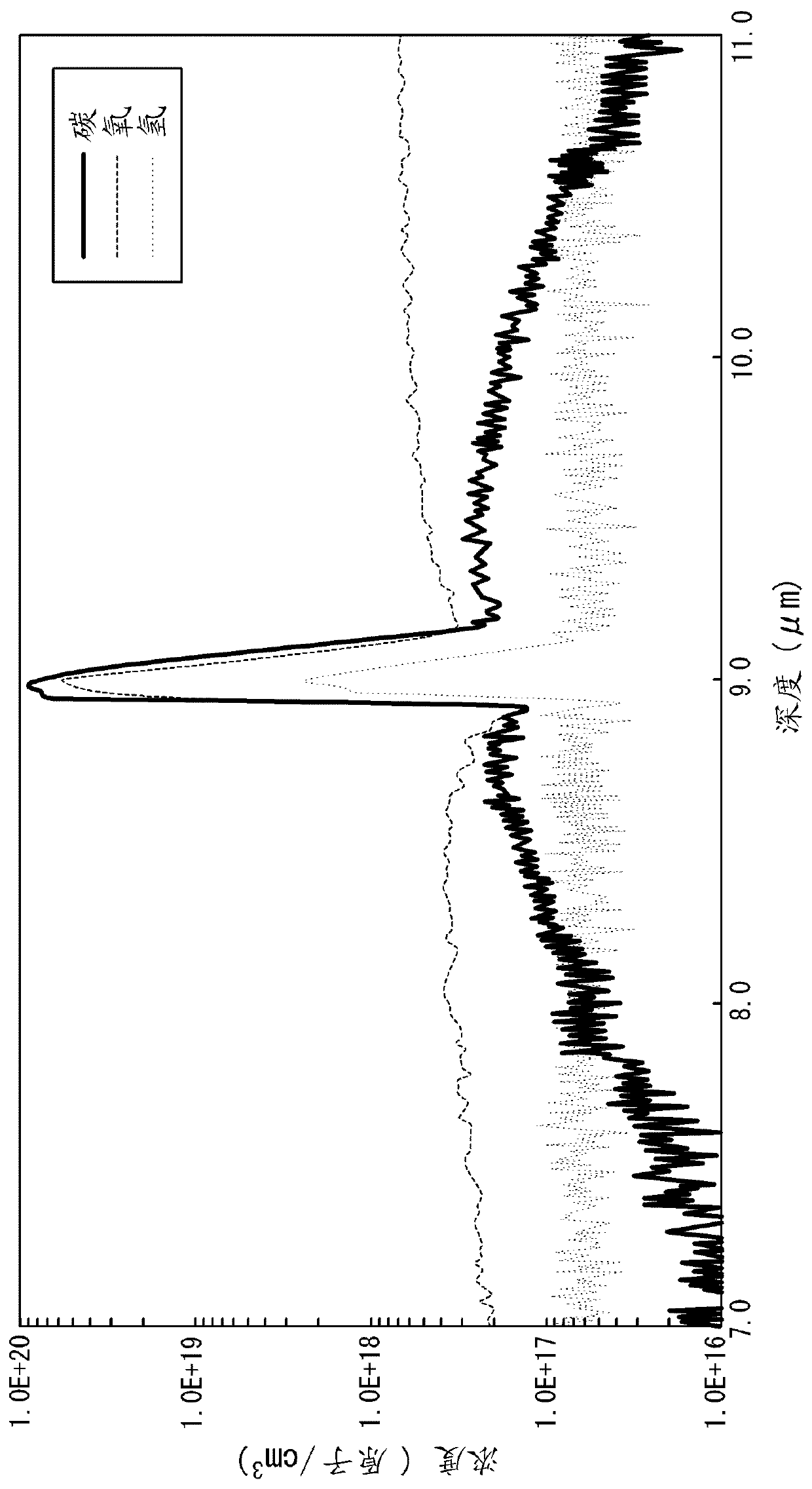

A variable temperature variable pressure diffusion process for improving photoelectric conversion efficiency

ActiveCN108598216BStrong gettering effectStrong push effectFinal product manufactureSemiconductor/solid-state device manufacturingEngineeringHigh-temperature corrosion

The invention discloses a variable temperature and variable pressure diffusion process for improving photoelectric conversion efficiency, comprising the following steps: step one of high temperature oxidation; step two of variable temperature and variable pressure diffusion: S1 of constant temperature and variable pressure diffusion: raising the temperature inside the furnace to 790 degrees centigrade, maintaining the temperature constant, controlling the pressure to increase from 100mbar to 800mbar in 160s; S2 of constant temperature and constant pressure maintaining: keeping the pressure inside the furnace constant, and controlling the temperature in the furnace to rise from 790 to 835 degrees centigrade in 450s; and S3 of constant temperature and constant pressure diffusion: adjusting the temperature in the furnace to 800 degrees centigrade within 30s, adjusting the pressure in the furnace to 200mbar, and diffusing for 500s - 650s under this condition; and step three of annealing and cooling. The invention variably controls the temperature and pressure during the diffusion process, thereby reducing the requirement of the silicon wafer spacing, reducing the phosphorus source dosage of the diffusion process by 20%, reducing the total diffusion process time by more than 10 minutes, and improving the battery yield and battery photoelectric conversion efficiency. Thus, the invention is very worth promoting.

Owner:TONGWEI SOLAR (ANHUI) CO LTD

Outer gettering method for silicon wafer

ActiveCN102142359BEasy to makeEasy to operateSemiconductor/solid-state device manufacturingHydrofluoric acidRoom temperature

The invention discloses an outer gettering method for a silicon wafer, which comprises the following steps of: coating an indium source on a surface of the silicon wafer; and putting the silicon wafer into a conventional heat treatment boiler or a fast heat treatment boiler for heat preservation for a while under the atmosphere of oxygen, cooling the silicon wafer to make the temperature of the silicon wafer equal to room temperature, and soaking the silicon wafer into a hydrofluoric acid to remove a surface glass layer, wherein a heat-preservation temperature is 700-1,000 DEG C, time for heat preservation in the conventional heat treatment boiler is 30-120 minutes, and the time for heat preservation in the fast heat treatment boiler is 1-10 minutes. The method is simple in operation, lowin cost and quite good in gettering effect.

Owner:ZHEJIANG UNIV

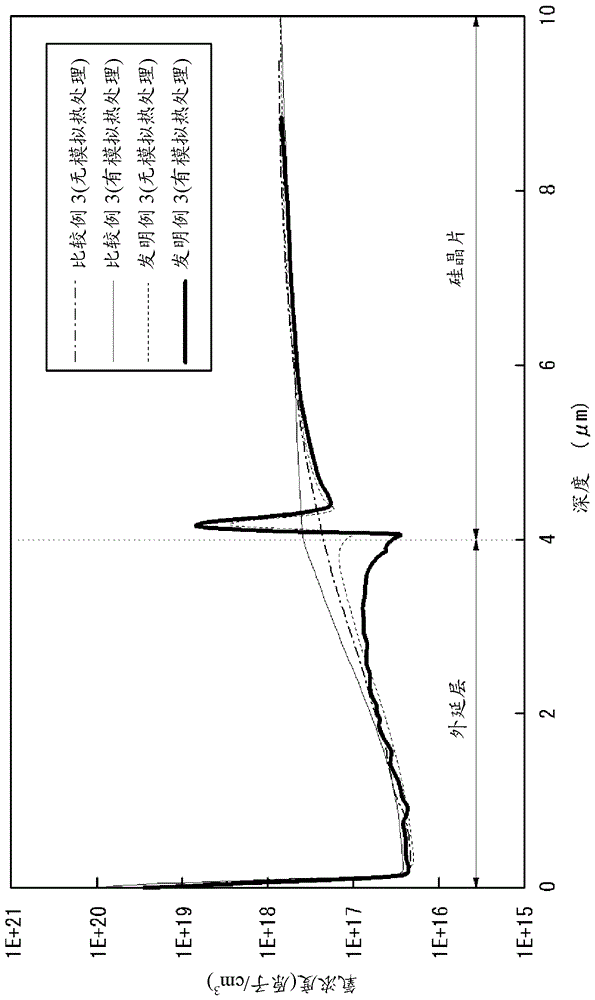

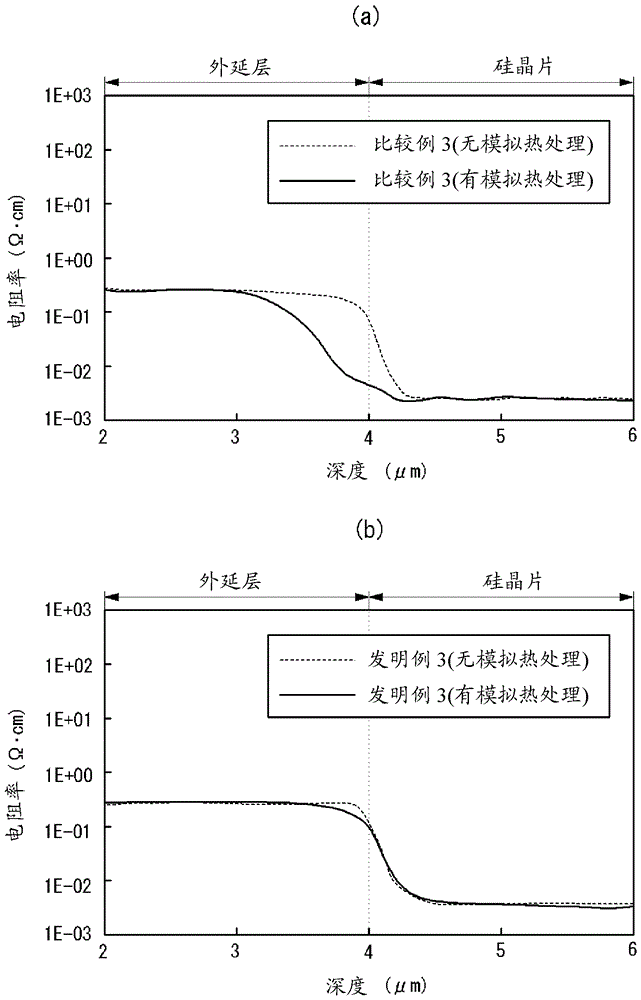

Semiconductor epitaxial wafer, method of manufacturing same, and method of manufacturing solid-state imaging device

ActiveCN107134404BInhibition Manufacturing MethodGood gettering effectSemiconductor/solid-state device manufacturingRadiation controlled devicesWaferingPhysical chemistry

Owner:SUMCO CORP

Epitaxial wafer manufacturing method and epitaxial wafer

ActiveCN106062937BGood gettering effectInhibition formationSemiconductor/solid-state device manufacturingSemiconductor devicesWaferingPhysical chemistry

Provided is a method for manufacturing an epitaxial wafer having excellent gettering capability while suppressing the formation of epitaxial defects. It is characterized in that it has the following process: cluster ion irradiation process, with 2.0×10 14 / cm 2 Above 1.0×10 16 / cm 2 The following dose irradiates cluster ions 16 containing at least carbon to the surface of silicon wafer 10 having a resistivity of 0.001 Ω·cm or more and 0.1 Ω·cm or less, and the constituent elements forming cluster ions 16 form a solid solution on the surface of silicon wafer 10 to form a solid solution. and an epitaxial layer forming step of forming an epitaxial layer 20 having a resistivity higher than that of the silicon wafer 10 on the modified layer 18 of the silicon wafer 10 .

Owner:SUMCO CORP

Boron and aluminum common gettering method for silicon wafer

ActiveCN101944553BIncrease the doping concentrationGood gettering effectFinal product manufactureSemiconductor devicesSurface layerBoron

The invention discloses an aluminum and boron common gettering method for a silicon wafer, which comprises the following steps of: preparing a boron-doped aluminum source; cleaning a silicon wafer; forming a boron-aluminum layer on the surface of the silicon wafer by utilizing a film plating technology; annealing at one step or multiple steps; and removing the surface layer of the silicon wafer. The invention utilizes the characteristic that the boron has higher solid solubility in silicon relative to aluminum, dopes the boron into the aluminum and dopes the boron into a heavy doped layer in the alloying process of the aluminum and silicon to obtain an aluminum-boron common gettering layer with high doping concentration. The aluminum and boron common gettering method of the invention can form the gettering layer which is deeper and even and has higher doping concentration at same annealing temperature and achieve the gettering effect of other processes at lower temperature and reduce the influence of high temperature on the performance of the silicon wafer. The aluminum and boron common getteirng method of the invention has the characteristics of low cost, easy operation and good gettering effect and has wider application prospect.

Owner:ZHEJIANG UNIV

A method for getting rid of transition metal impurities in silicon wafer or silicon device at room temperature

ActiveCN103794473BImprove radiation gettering effectChange structureSemiconductor/solid-state device manufacturingSemiconductor materialsWafering

The invention discloses a method for removing transition metal impurities in a silicon wafer or silicon device in a sucking mode at the indoor temperature. Low-dose electron irradiation with the dose smaller than 5000 Gy is carried out on the silicon wafer or silicon device at the indoor temperature to enable the transition metal impurities in a to-be-cleaned area of the silicon wafer or an active area of the silicon device to be diffused to a nearby impurity sucking defect area, and therefore the concentration of the transition metal impurities in the to-be-cleaned area of the silicon wafer or the active area of the silicon device is lowered. Compared with an existing silicon material impurity sucking method, the method is implemented at the indoor temperature, and therefore the method can be used for silicon wafer or silicon device impurity sucking, is not limited to the single-crystal or polycrystalline silicon wafer and the silicon device, and is also suitable for other semiconductor materials such as germanium, and corresponding devices.

Owner:PEKING UNIV

Method for manufacturing selective emitter solar cell from local laser melting phosphorosilicate glass

ActiveCN102110743BNo damageSimple processFinal product manufactureOther printing apparatusSilver pasteScreen printing

The invention discloses a method for manufacturing a selective emitter solar cell from local laser melting phosphorosilicate glass, which comprises the following steps of: texturing the surface of a chip; performing phosphorous diffusion by utilizing thermal diffusion, and generating the phosphorosilicate glass on the surface; diffusing the phosphorous element in the phosphorosilicate glass on a laser scanning part into the chip through local chip-melting; isolating the boundary; removing a damaged layer formed in the laser chip-melting process; removing the residual phosphorosilicate glass; forming a coating on the front surface; plating silver paste on the front surface of the chip in a screen printing mode, and obtaining a front electrode in a laser scanned area; plating the silver paste on a rear surface of the chip to form a back electrode, and plating aluminum paste on the rear surface of the chip in the screen printing mode to form a back electric field; and sintering the chip to make the metal electrode element and silicon in the chip eutectic. Only one diffusion process is present in the whole process, and the process is simple, has no damage to the silicon chip and has good gettering effect.

Owner:HANWHA SOLARONE QIDONG

A multifunctional short fiber rope making machine

ActiveCN109281215BAdjust the mobile positionGuaranteed lengthRope making machinesFiberMeasuring ruler

The invention provides a multi-functional short-staple rope twisting machine. The multi-functional short-staple rope twisting machine comprises anti-slip mats, left supporting legs, right supporting legs, a machine base, a U-shaped supporting frame, a rope twisting motor, a rotary disc, a linear sliding rail, U-shaped sliders, winged screws, rope twisting hooks, a rope taking and wheel replacing structure, a structure for coiling a rope after rope twisting, a rope twisting length measurement determining rail structure and an anti-overflow shield structure, wherein the anti-slip mats are transversely glued to the lower surfaces of the horizontal sections on the lower portions of the left supporting legs and the lower surfaces of the horizontal sections on the lower portions of the right supporting legs respectively. Due to the arrangement of a fixing rod, a movable sleeve, a fixing hook and a square-head bolt, the moving position of the fixing hook is easily adjusted according to the horizontal requirements of rope twisting, and it can be ensured that rope twisting work is smoothly conducted; due to the arrangement of an adjusting slider, a stainless steel sliding rail, a measurement ruler and an adjusting bolt, the rope twisting length is easily ensured, and the rope twisting length consistency can be ensured.

Owner:扬州市新天河绳业有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com