Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

145results about How to "No thermal deformation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

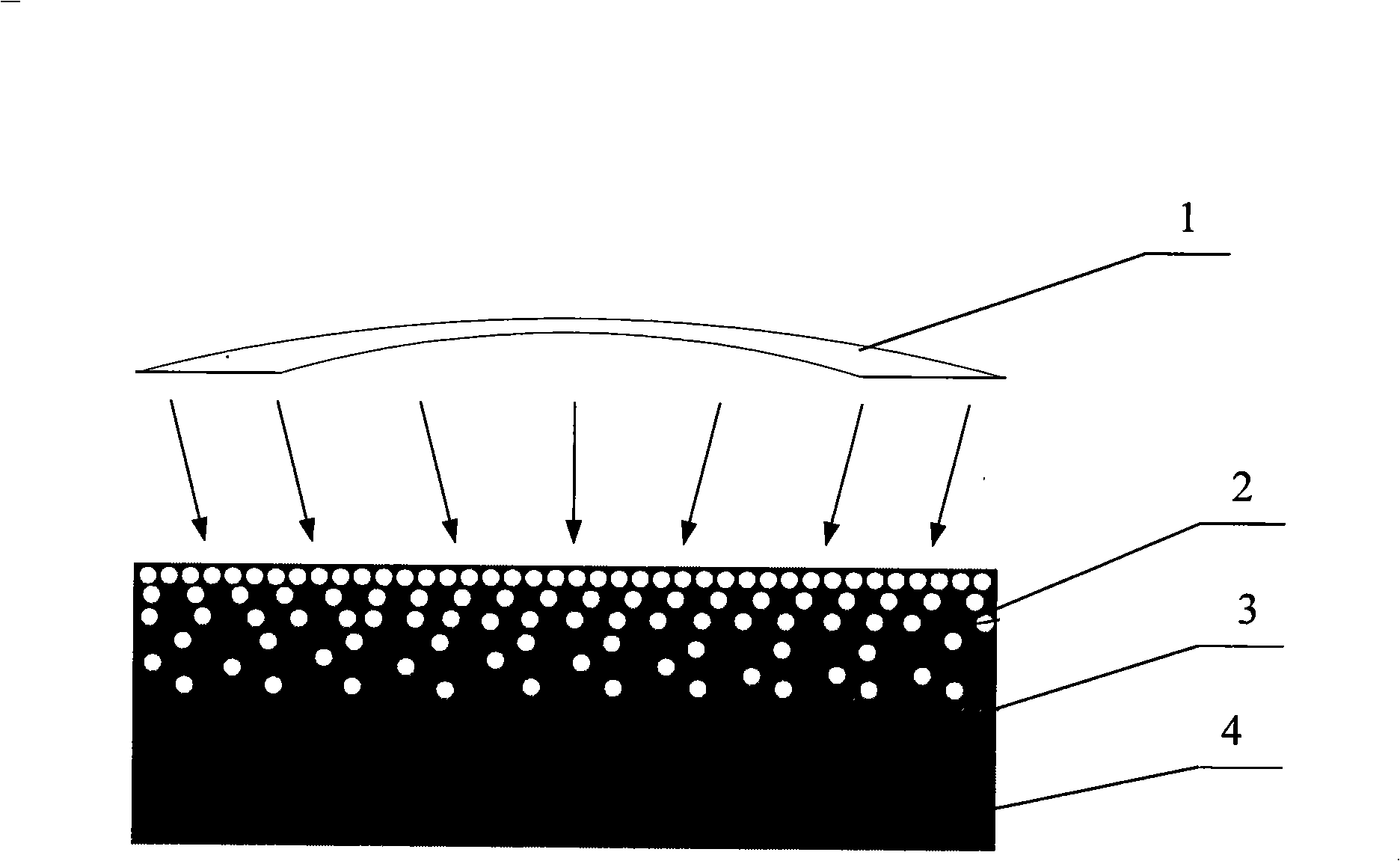

Polymer/porous ceramics structure and function integrated gradient composite material and preparation method thereof

ActiveCN101259766ALow densityAchieve self-protection effectSynthetic resin layered productsCeramic layered productsHeat fluxWashout

The invention relates to a function-integration gradient composite material with polymer / porous ceramic structure and a preparation method. The invention solves the problems that single material can not meet the requirement for the performance of the material made by the application condition in an extreme environment and the multilayer composite-structure material is easily layered and has poor safety and reliability. The product of the invention is made from a polymer layer, a gradient connecting layer and a ceramic layer from the inside to the outside. The preparation method comprises the following steps that: 1. the polymer layer, the gradient connecting layer and the ceramic layer are sequentially paved and then are put into a die to be formed by compression so as to obtain the green body of the composite material; 2. the ceramic layer of the green body of the composite material is loaded with high-density heat flux and then is naturally cooled. The composite-structure material of the invention has the advantages of small weight, strong structural strength and high effective heat insulation, is suitable for being used under the extreme working conditions of high temperature, airflow washout, etc., and is safe as well as reliable. The preparation method of the invention is simple and easy to be operated, and can prepare large-scale products with a complicated shape.

Owner:HARBIN INST OF TECH

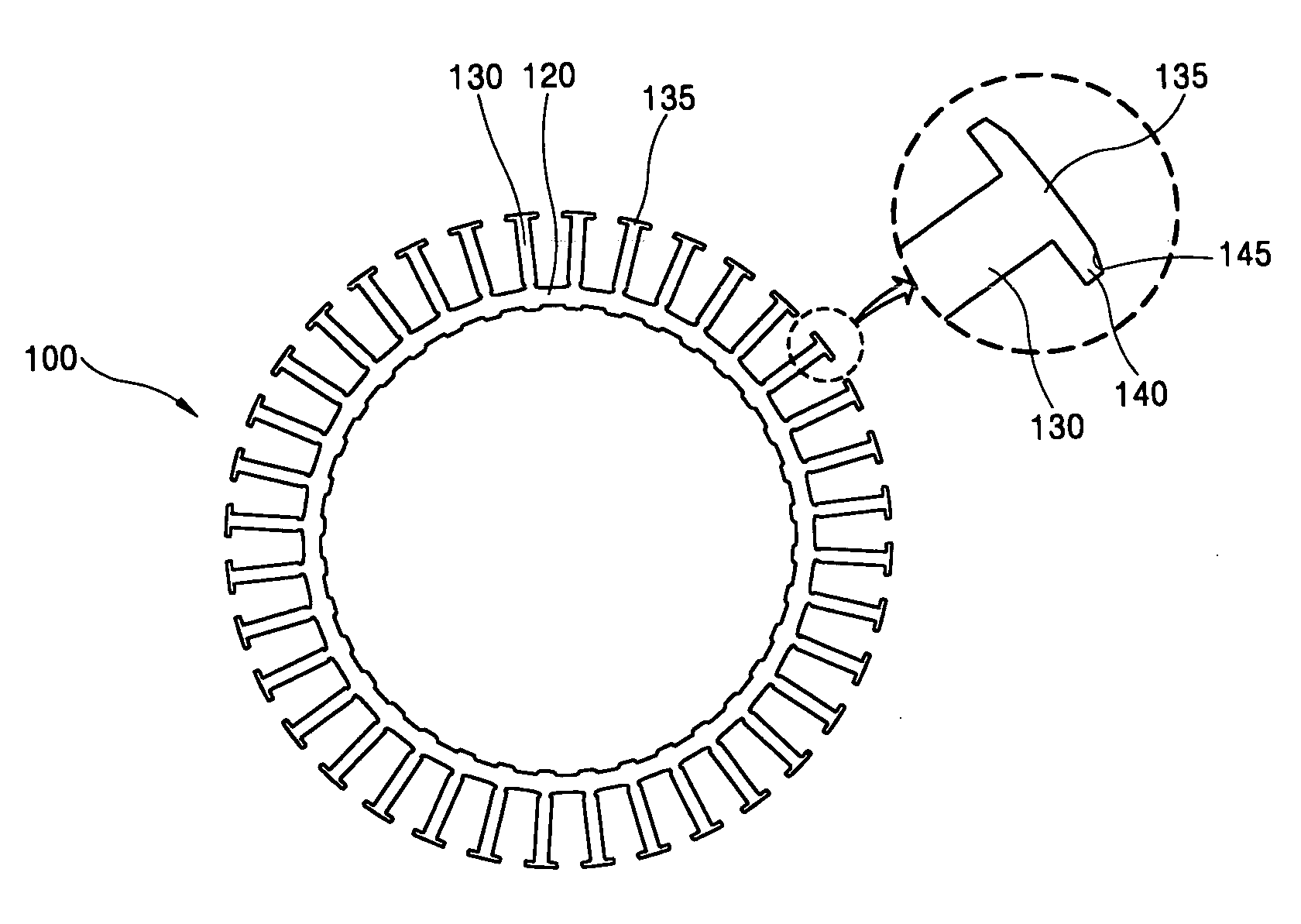

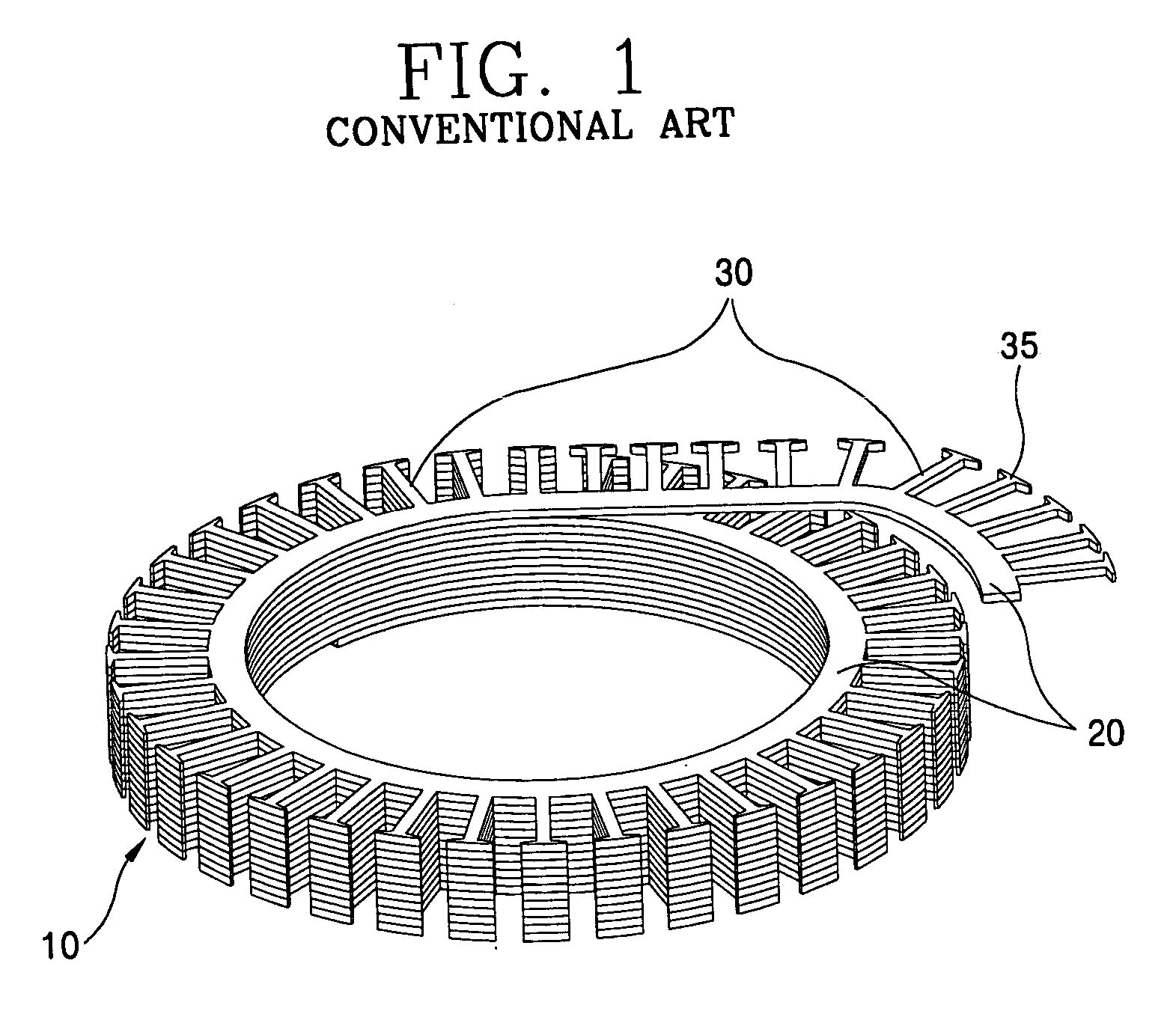

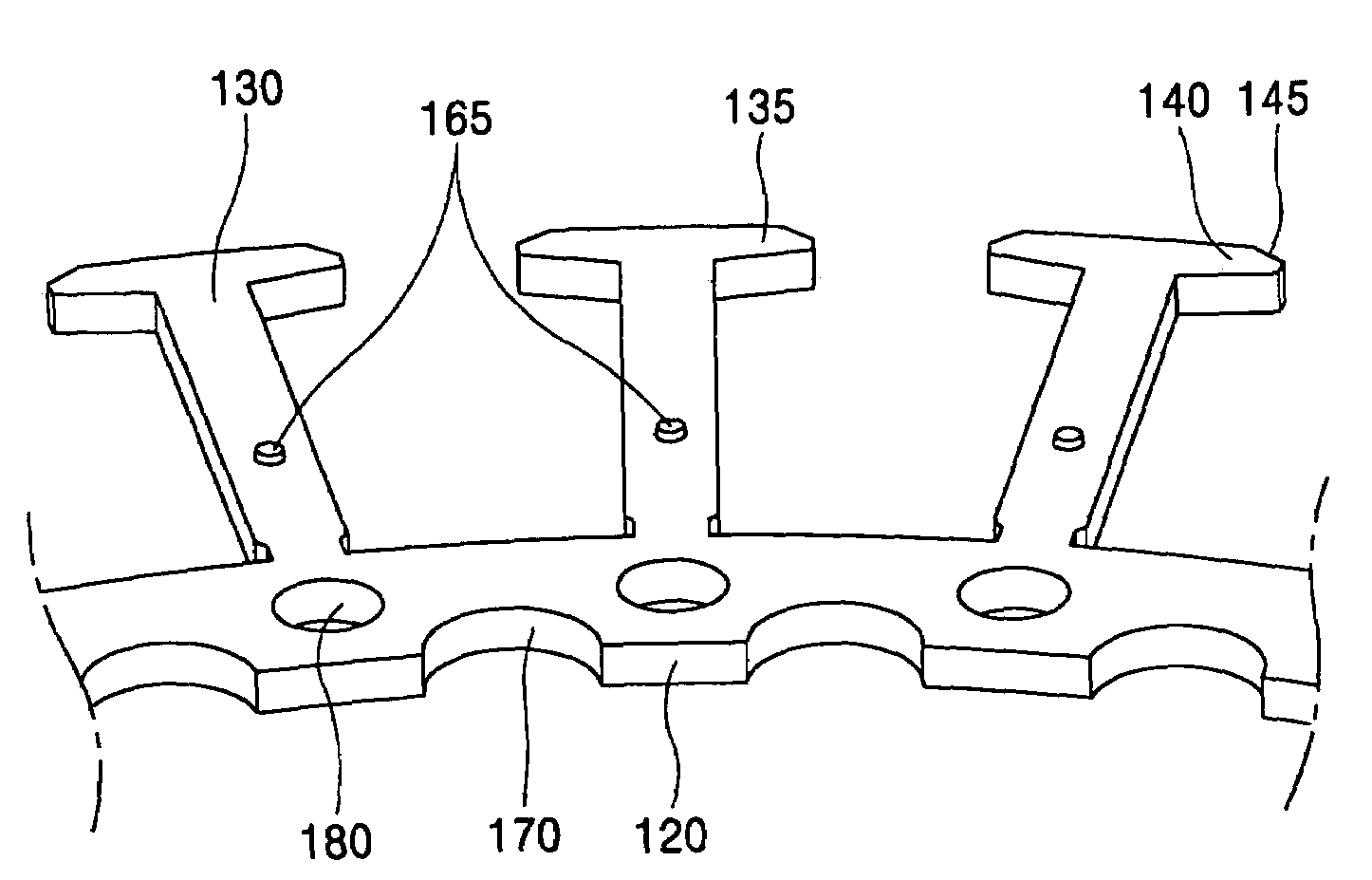

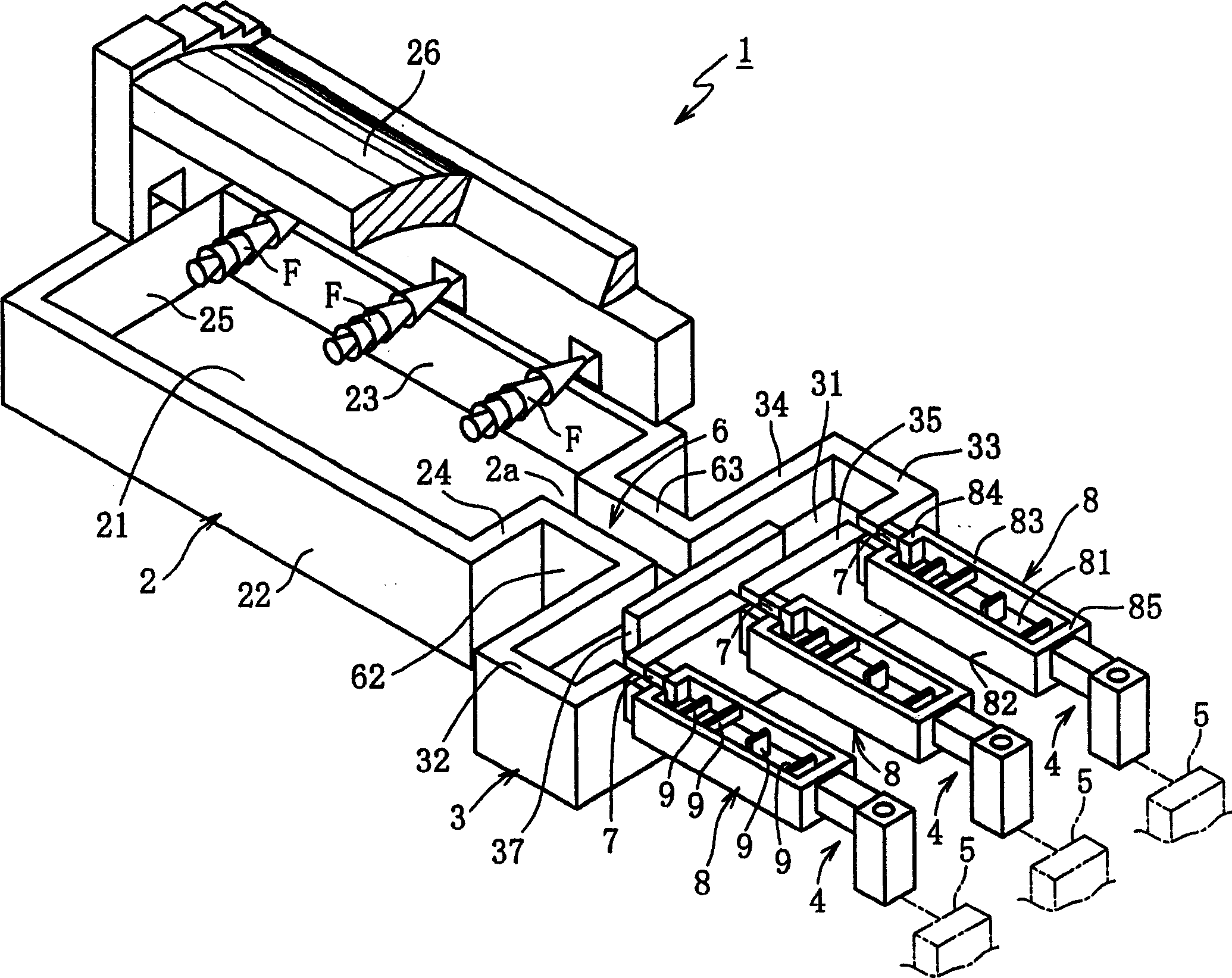

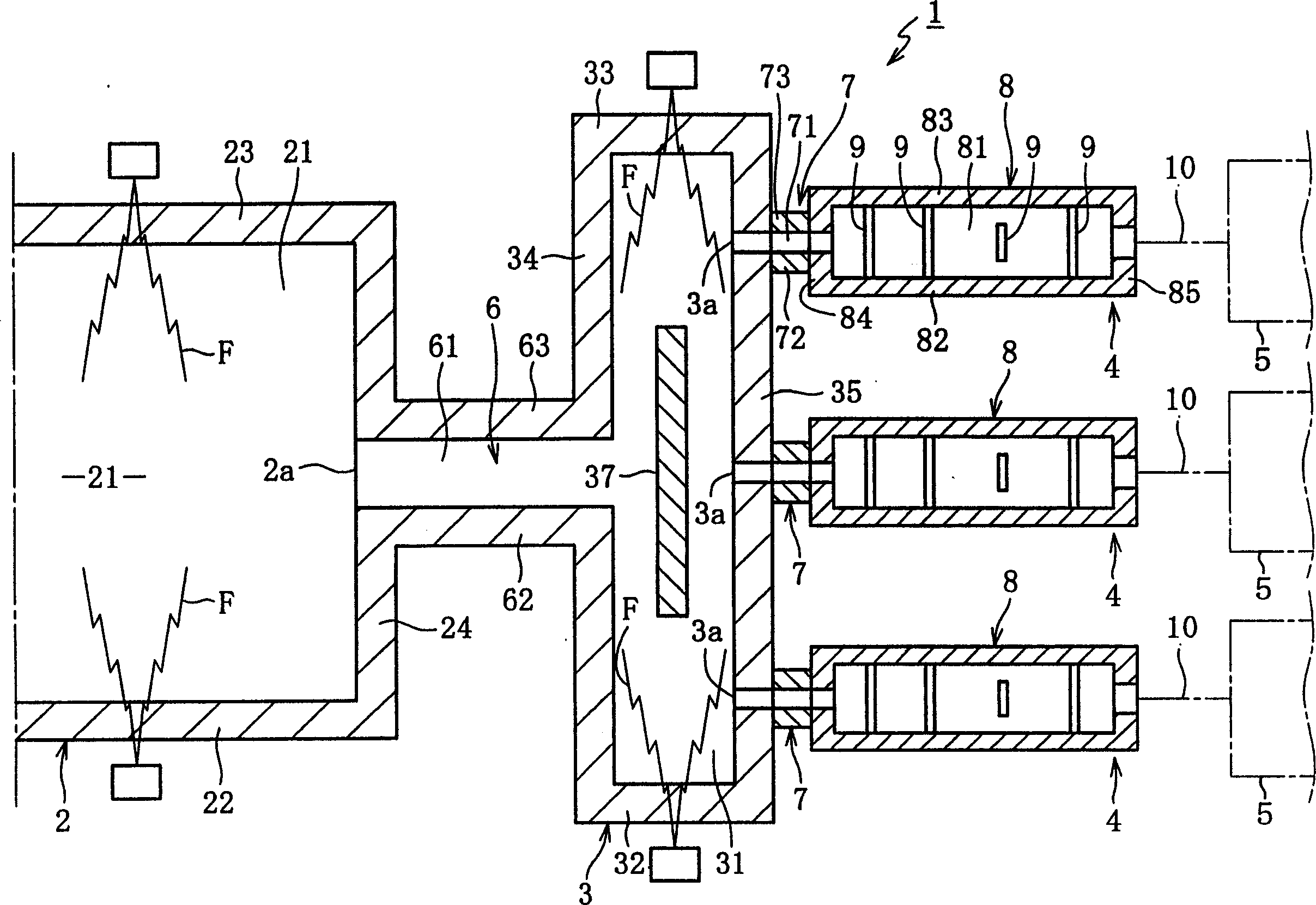

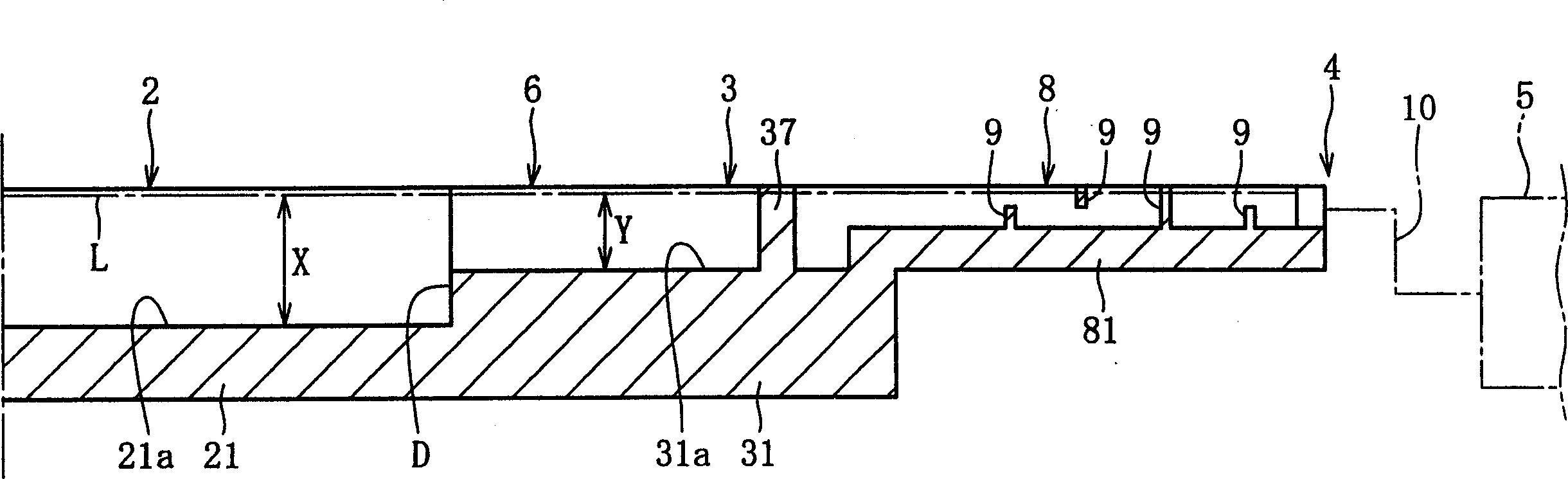

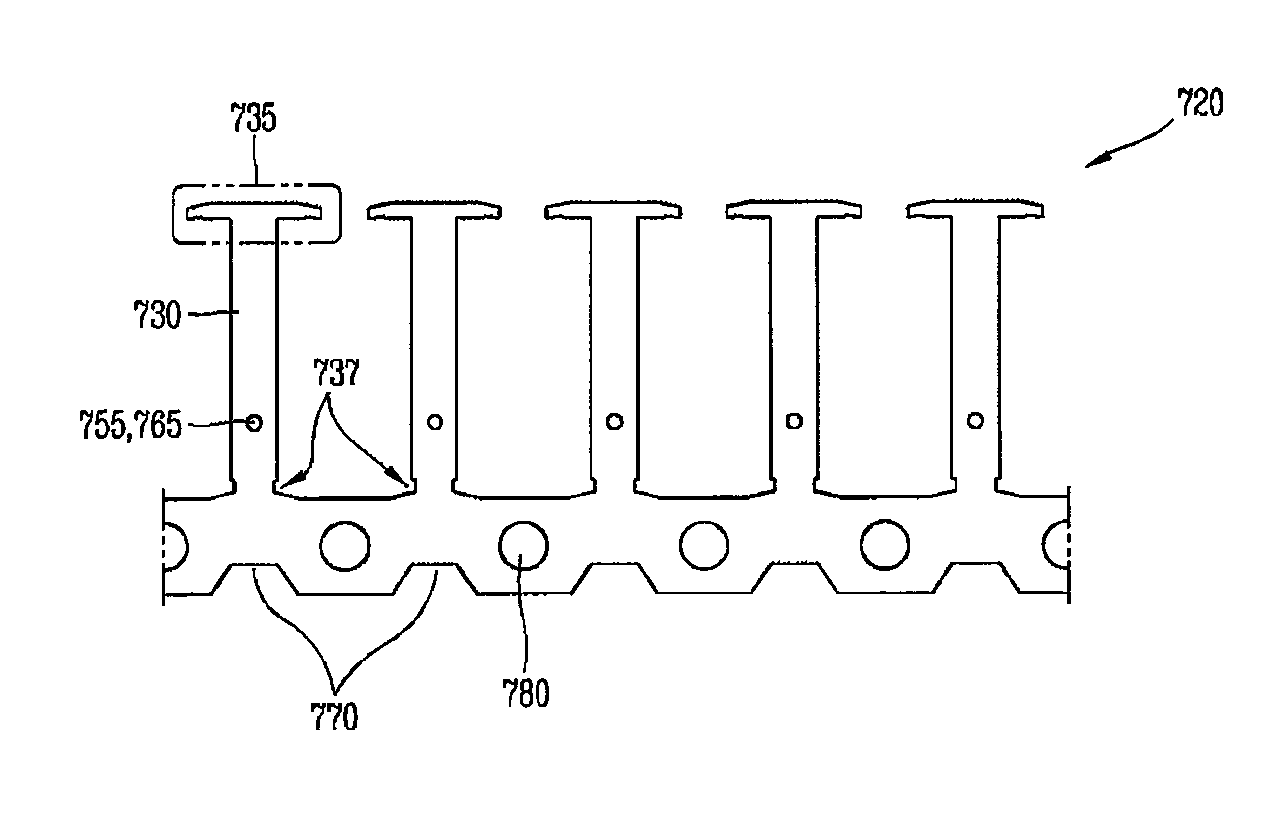

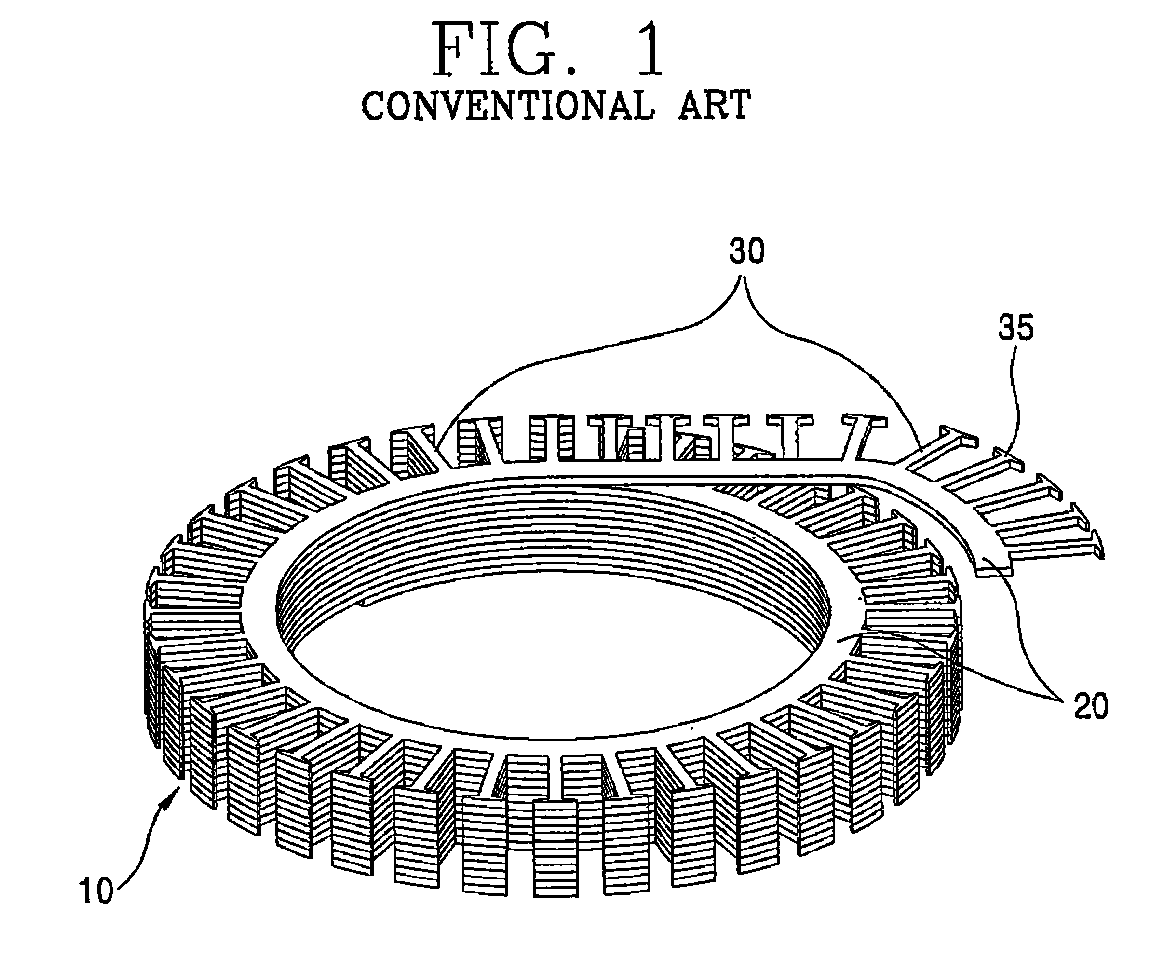

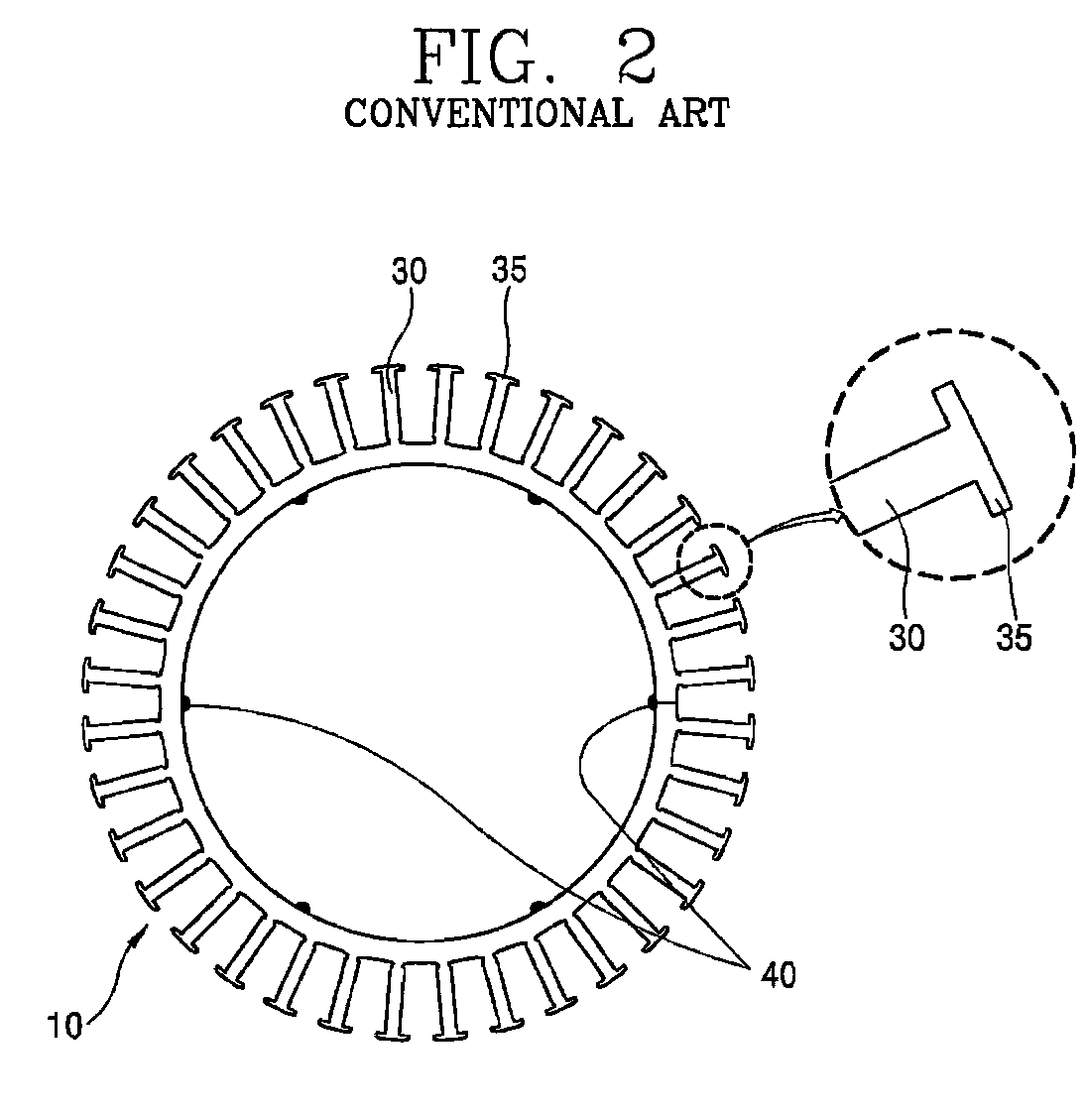

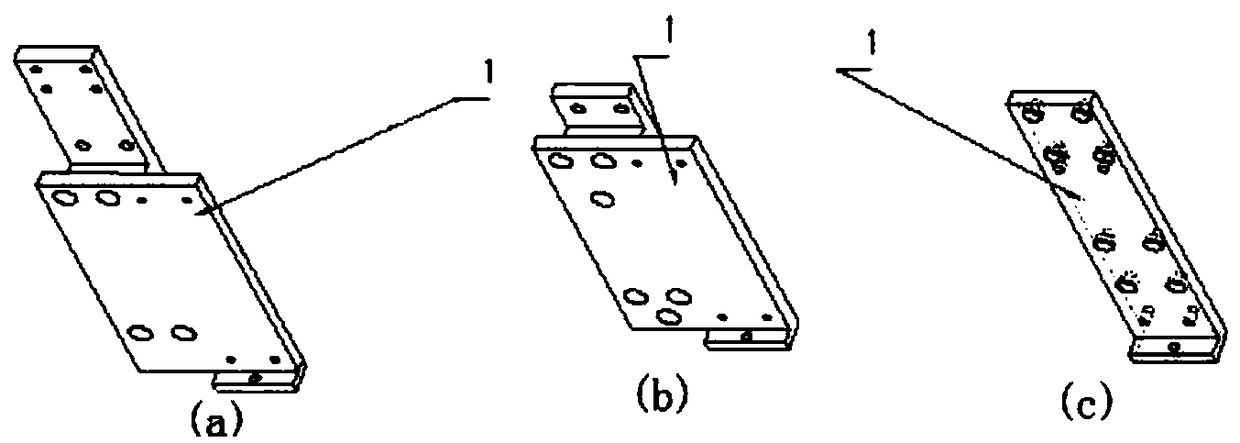

Laminated body of motor and manufacturing method thereof

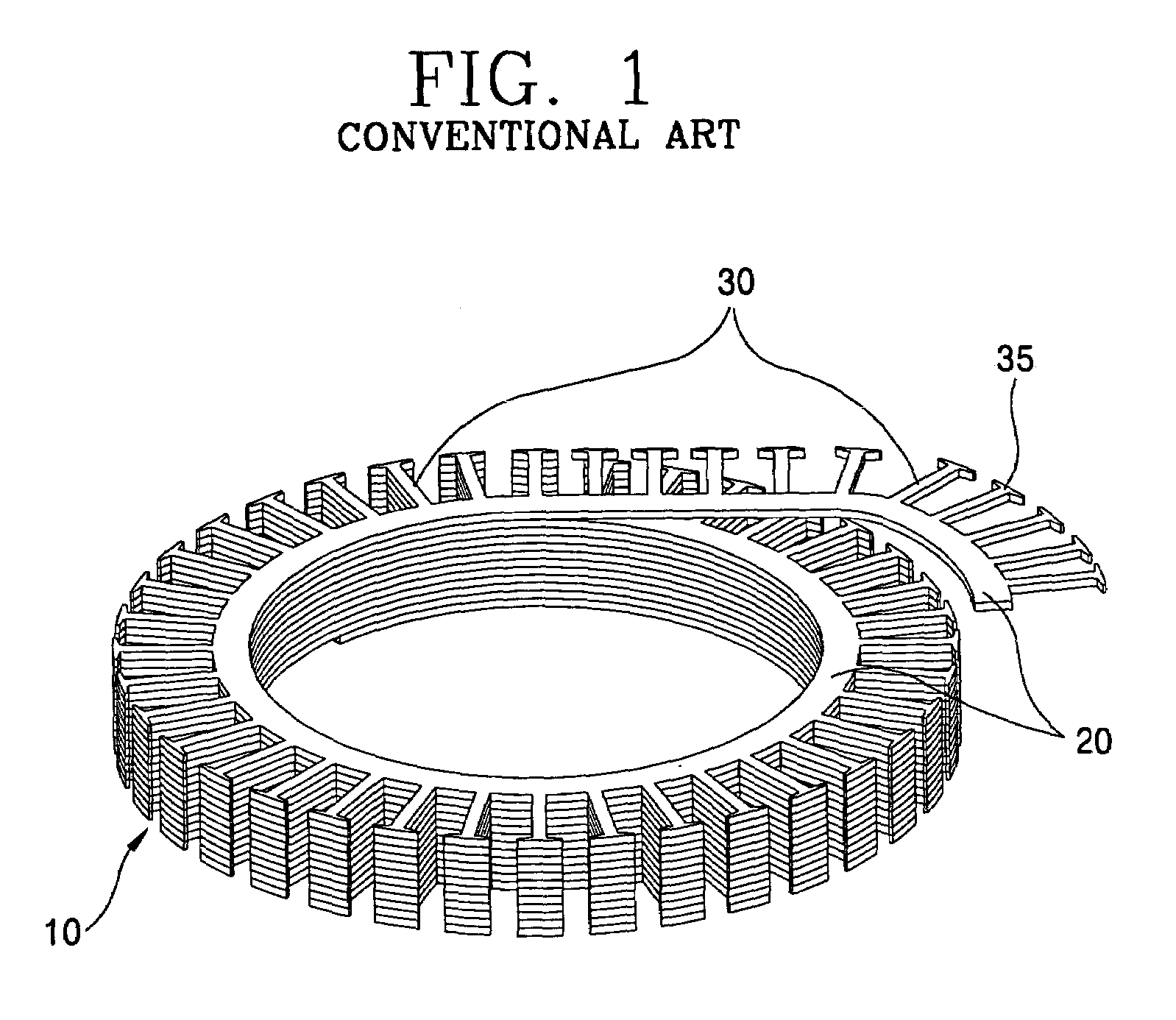

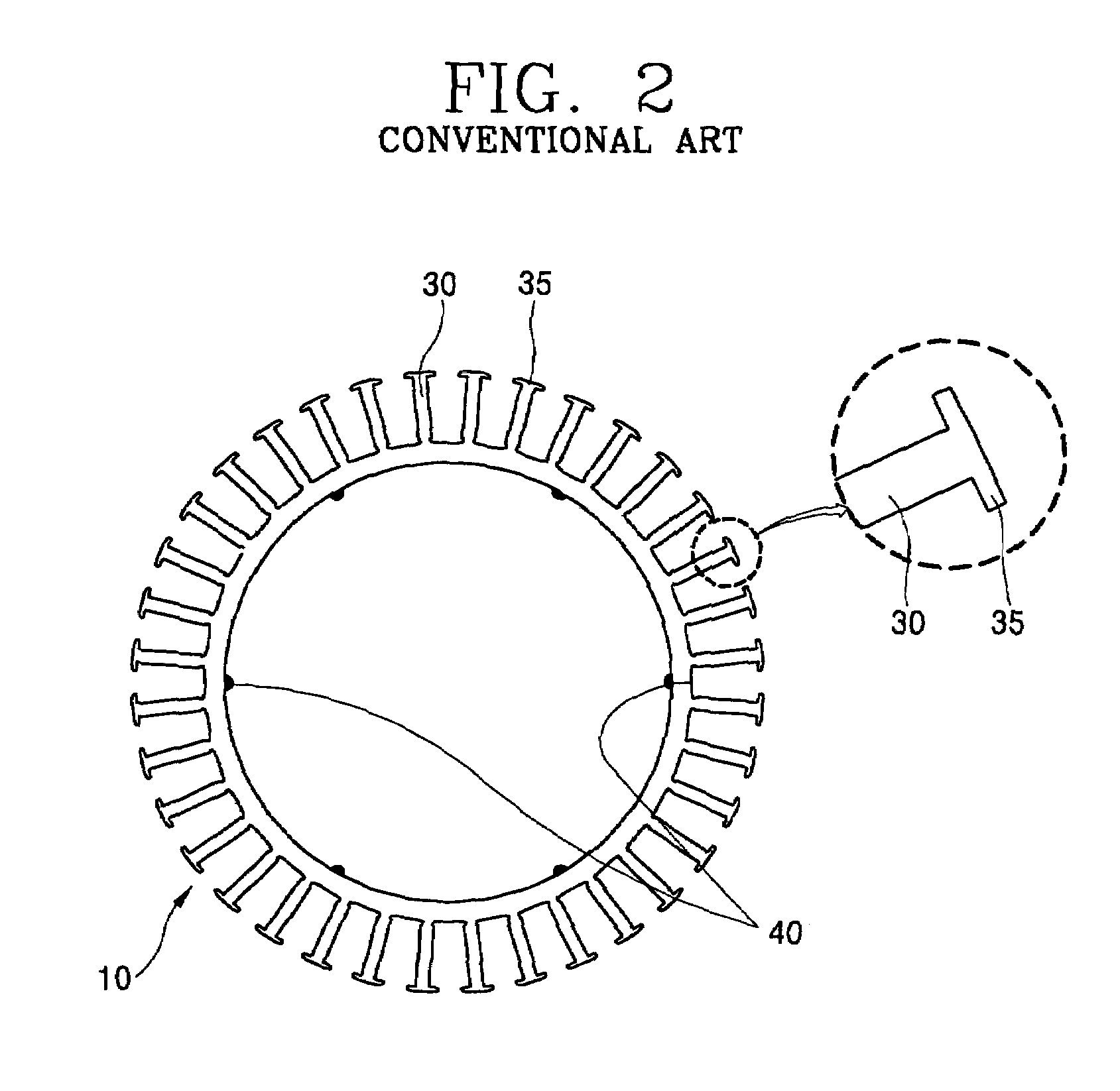

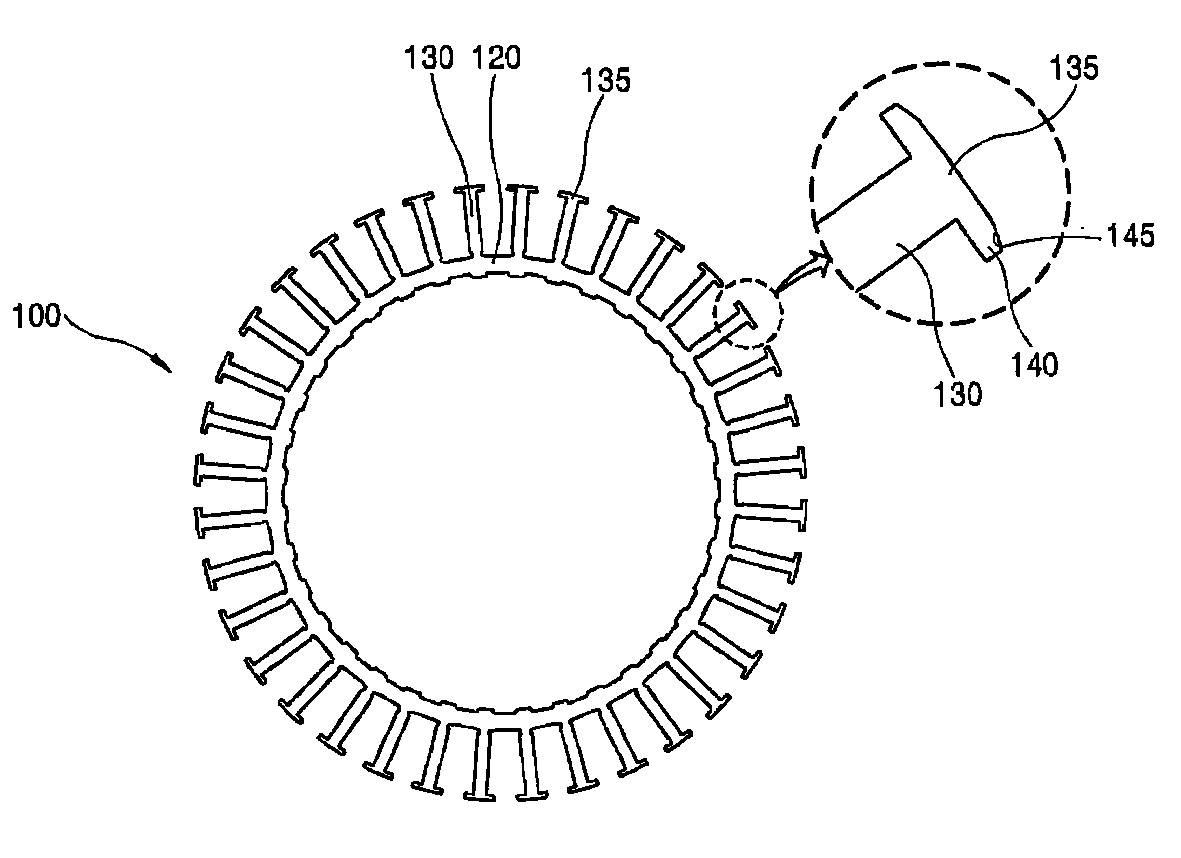

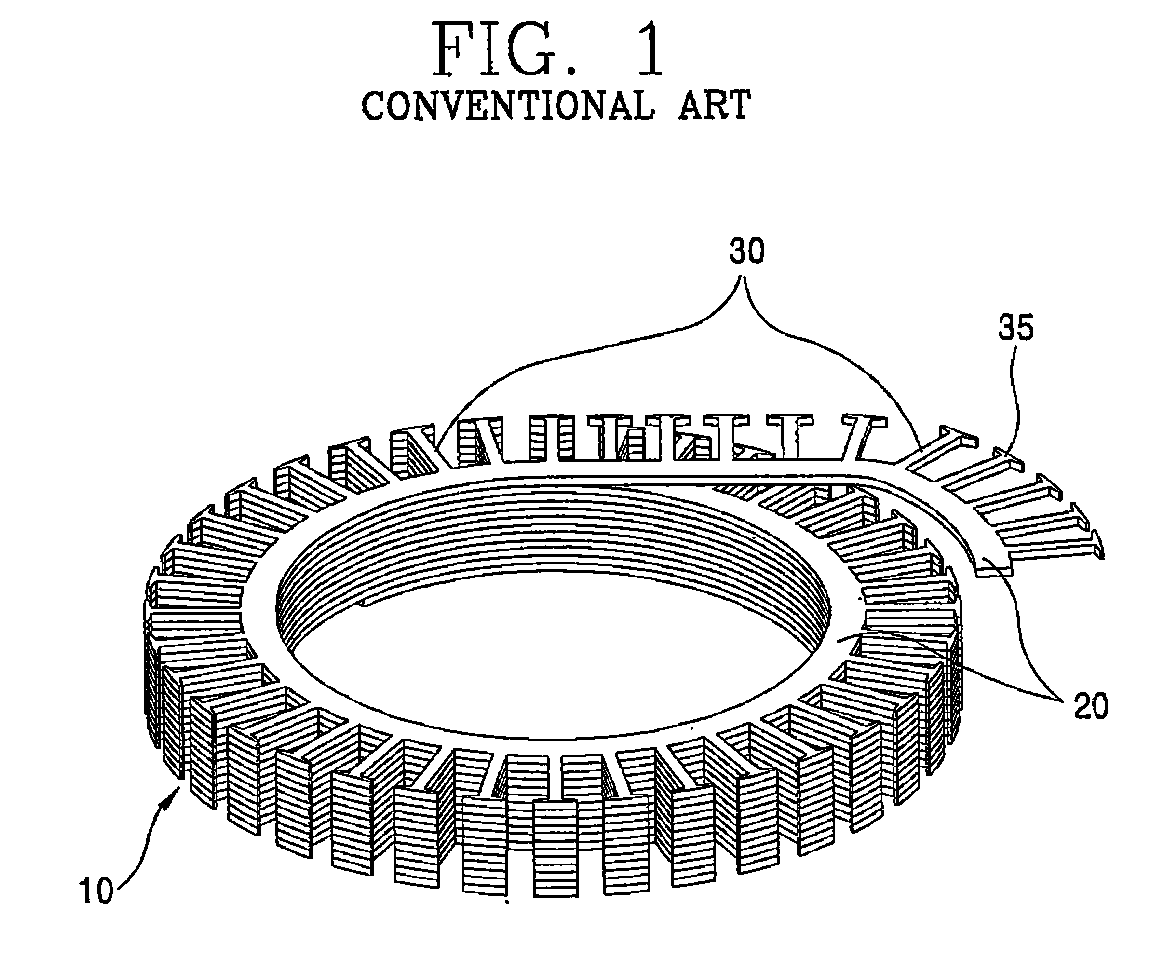

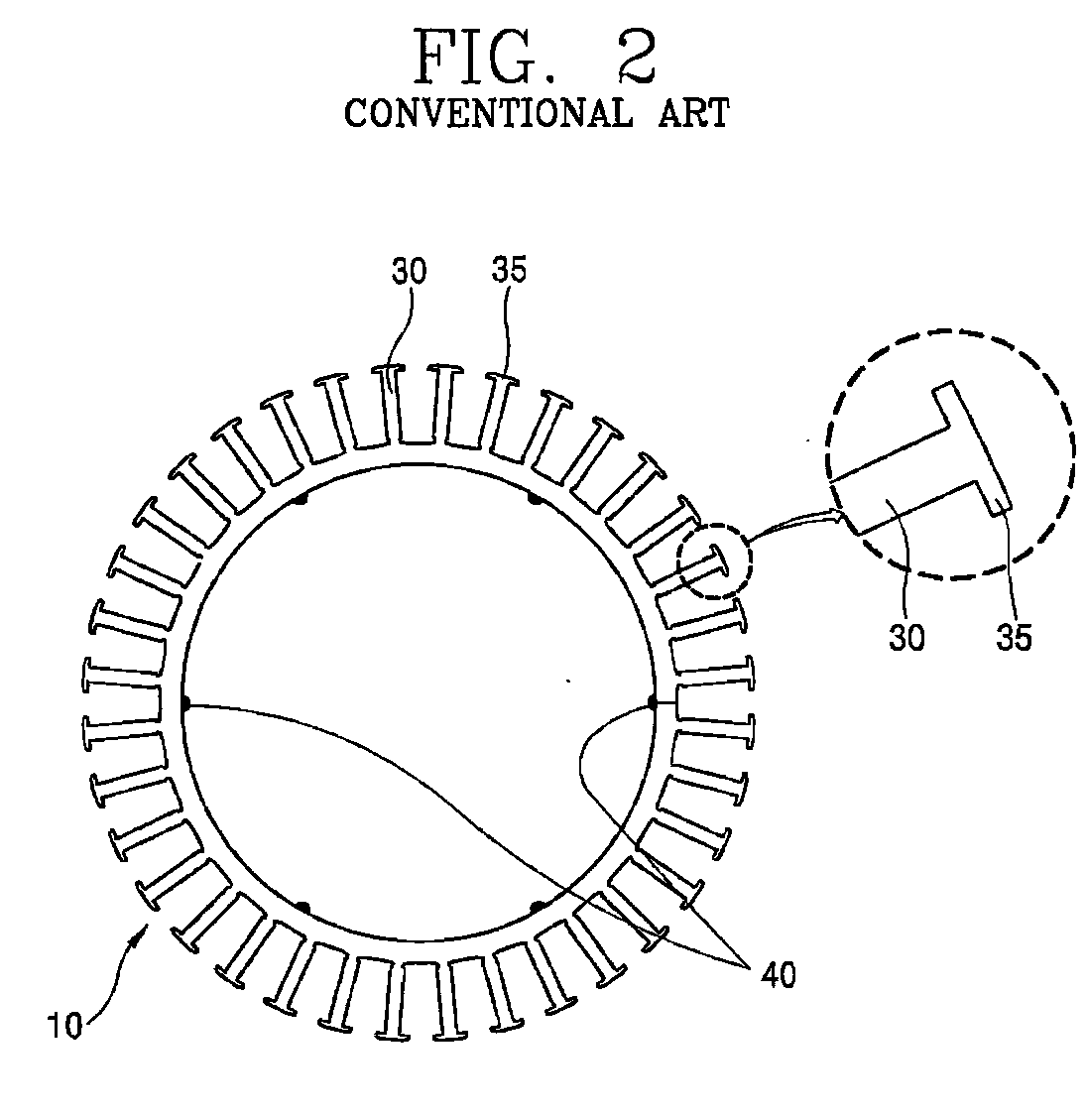

ActiveUS20050073211A1Reducing cogging torque in operation of motorNo thermal deformationMagnetic circuit stationary partsManufacturing stator/rotor bodiesConductor CoilTooth part

A laminated body of a motor includes: a yoke part having a belt shape with a long length in comparison with its width and spirally laminated to form a hollow cylindrical shape; a plurality of teeth parts protruding from one side edge of the yoke part in a width direction and disposed along a longitudinal direction in an isolated manner at a predetermined distance; a stopping protrusion extendingly formed at a protruding end of the teeth part in a longitudinal direction of the yoke part; and an inclined portion having an inclined surface formed by decreasing a width of the stopping protrusion toward its end so as to reduce cogging torque, so that a minimum passage for a winding nozzle is provided while cogging torque is reduced. A laminated body of a motor includes: a yoke part having a belt shape with a long length in comparison with its width and spirally laminated to form a hollow cylindrical shape; a plurality of teeth parts protruding from one side edge of the yoke part in a width direction and disposed along a longitudinal direction in an isolated manner at a predetermined distance; and a protrusion receiving groove recessed in one side of the teeth part along a thickness direction and a coupling protrusion protruding from its other side along the thickness direction of the teeth part to be inserted and fixed by each other, so that defective measurement and an increase in production time caused by welding operation are prevented.

Owner:LG ELECTRONICS INC

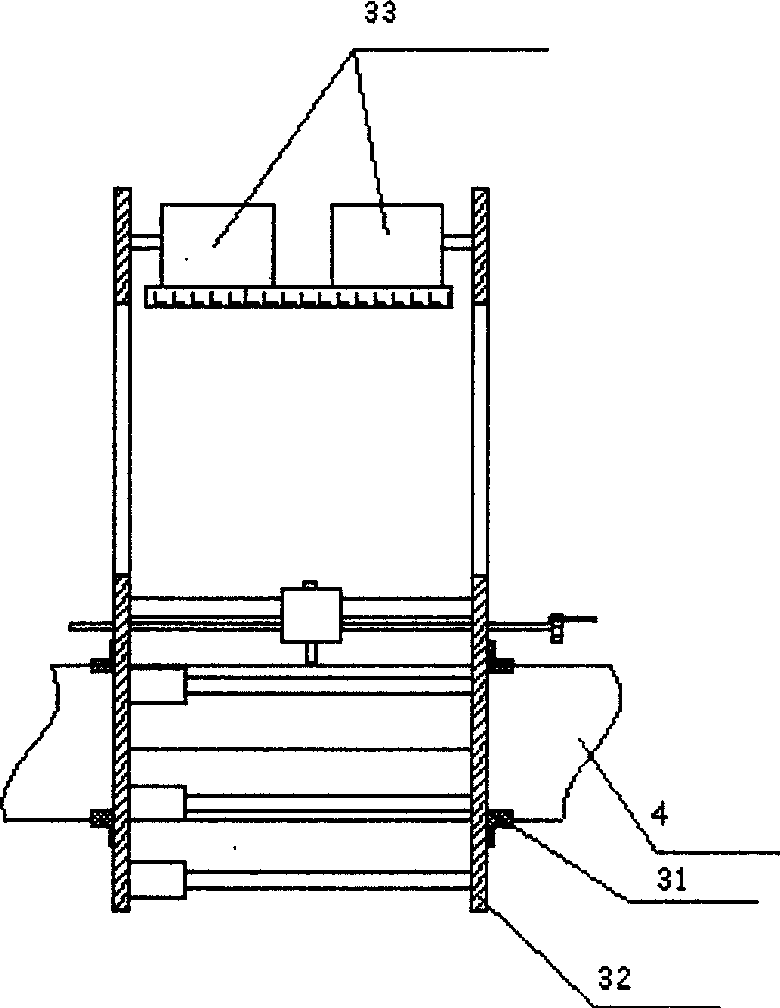

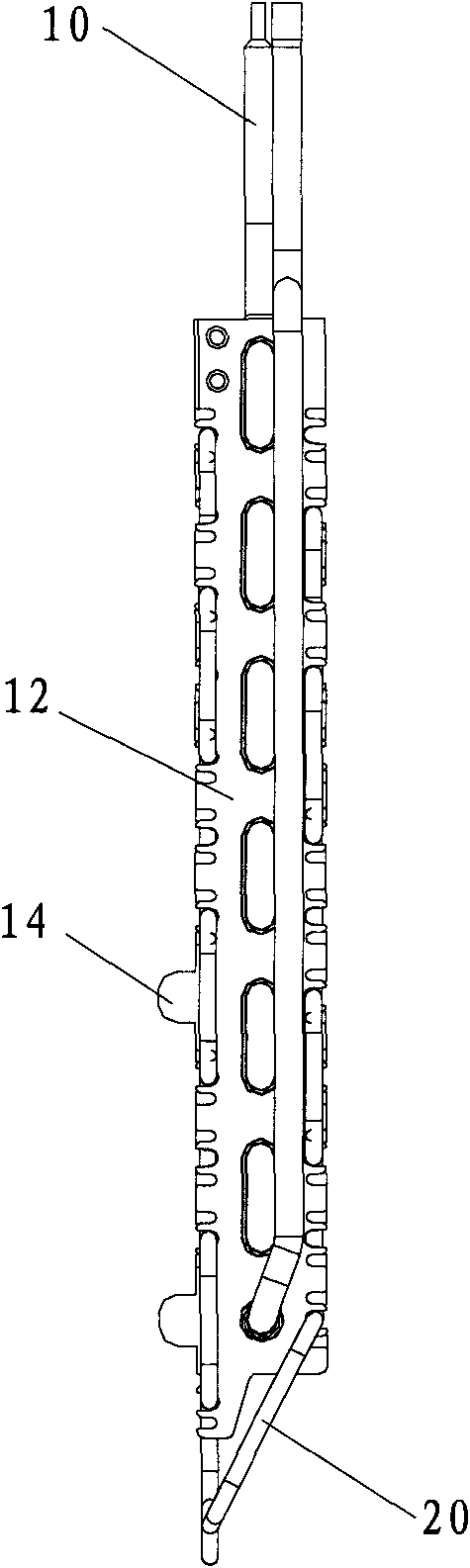

Laser method for repairing rotor shaft of generator and steam turbine and dedicated device

InactiveCN1660538AImprove controllabilityImprove automationMetallic material coating processesOther manufacturing equipments/toolsNondestructive testingElectric generator

Owner:SHENYANG DALU LASER TECH

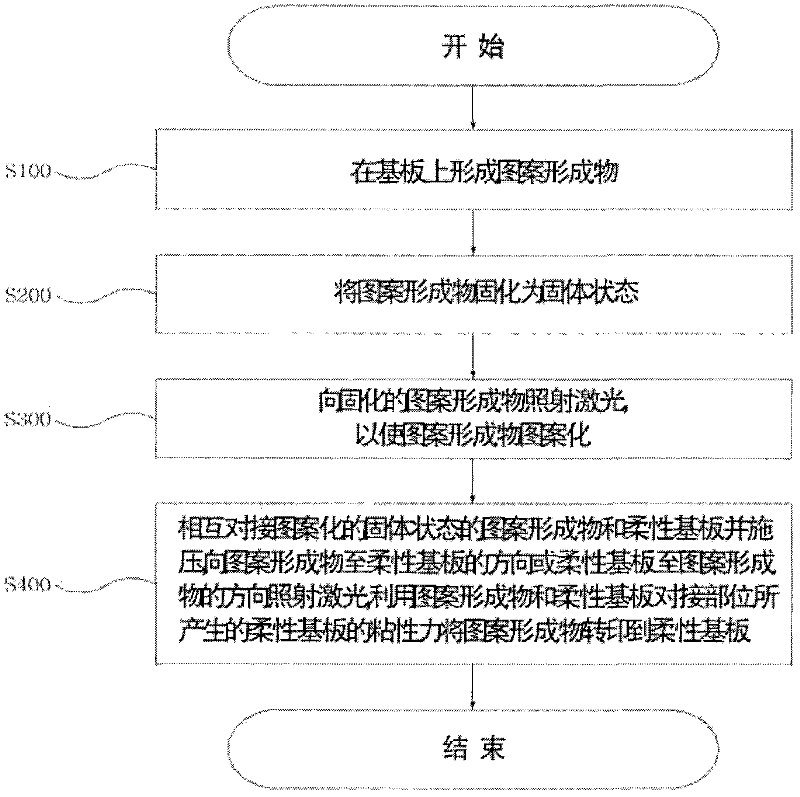

Pattern transfer method and apparatus therefor

InactiveCN102452239AForm evenlyUniform transferTransfer printingDuplicating/marking methodsElectromagnetic shieldingElectronic book

The present invention relates to methods and apparatuses for transferring pattern, a flexible display panel, a flexible solar cell, an electronic book, a thin film transistor, an electromagnetic-shielding sheet, and a flexible printed circuit board applying thereof. A pattern transfer method related to the present invention comprises: a first step of forming a pattern material on a substrate; a second step of hardening the pattern material in the solid state; a third step of patterning the pattern material by irradiating a laser beam to the hardened pattern material in the solid state; and a fourth step of pressing the patterned pattern material in the solid state and a flexible substrate facing each other and transferring the pattern material to the flexible substrate by a viscous force of the flexible substrate occurring in a facing part between the pattern material and the flexible substrate by irradiating the laser beam from the pattern material to the flexible substrate or from the flexible substrate to the pattern material.

Owner:KOREA ADVANCED INST OF SCI & TECH

Laminated body of motor and manufacturing method thereof

ActiveUS7271519B2Reduce stepsNo thermal deformationMagnetic circuit stationary partsManufacturing stator/rotor bodiesEngineeringHelix

A laminated body of a motor includes: a yoke spirally laminated to form a hollow cylindrical shape; a plurality of teeth protruding from one side edge of the yoke disposed along a longitudinal direction of the yoke and being separated apart at a predetermined distance; a plurality of notch portions on an opposite side edge of the yoke, each of the plurality of notch portions being aligned with each of the plurality of teeth; a stopping protrusion extendingly formed at a protruding end of the teeth in the longitudinal direction of the yoke; and an inclined portion having an inclined surface formed by decreasing a width of the stopping protrusion toward an end of the stopping protrusion so as to reduce cogging torque.

Owner:LG ELECTRONICS INC

Fin type evaporator and refrigerator thereof

InactiveCN101936626AReduce defrosting energy consumptionEasy to installEvaporators/condensersDefrostingEngineeringRefrigerant

The invention relates to a fin type evaporator which comprises a fixed plate, single column or multiple columns of refrigerant coil pipes mounted on the fixed plate and a plurality of fins sheathed on the refrigerant coil pipes, wherein a groove is formed on each fin, a heater pipe clamp for defrosting is mounted in each groove, and each fin is provided with a hem for stably clamping a heater pipe along the edge of the groove. The invention further relates to a refrigerator using the evaporator. The fins of the evaporator are provided with the hems for clamping the heater pipes along the edges of the grooves, and the arrangement of the hems change the traditional line contact to the surface contact, thereby reducing the heat transfer resistance between the heater pipes and the fins, shortening the defrosting time, saving the defrosting energy consumption of the evaporator and mounting the heater pipes on the evaporator more firmly.

Owner:HEFEI MIDEA REFRIGERATOR CO LTD +1

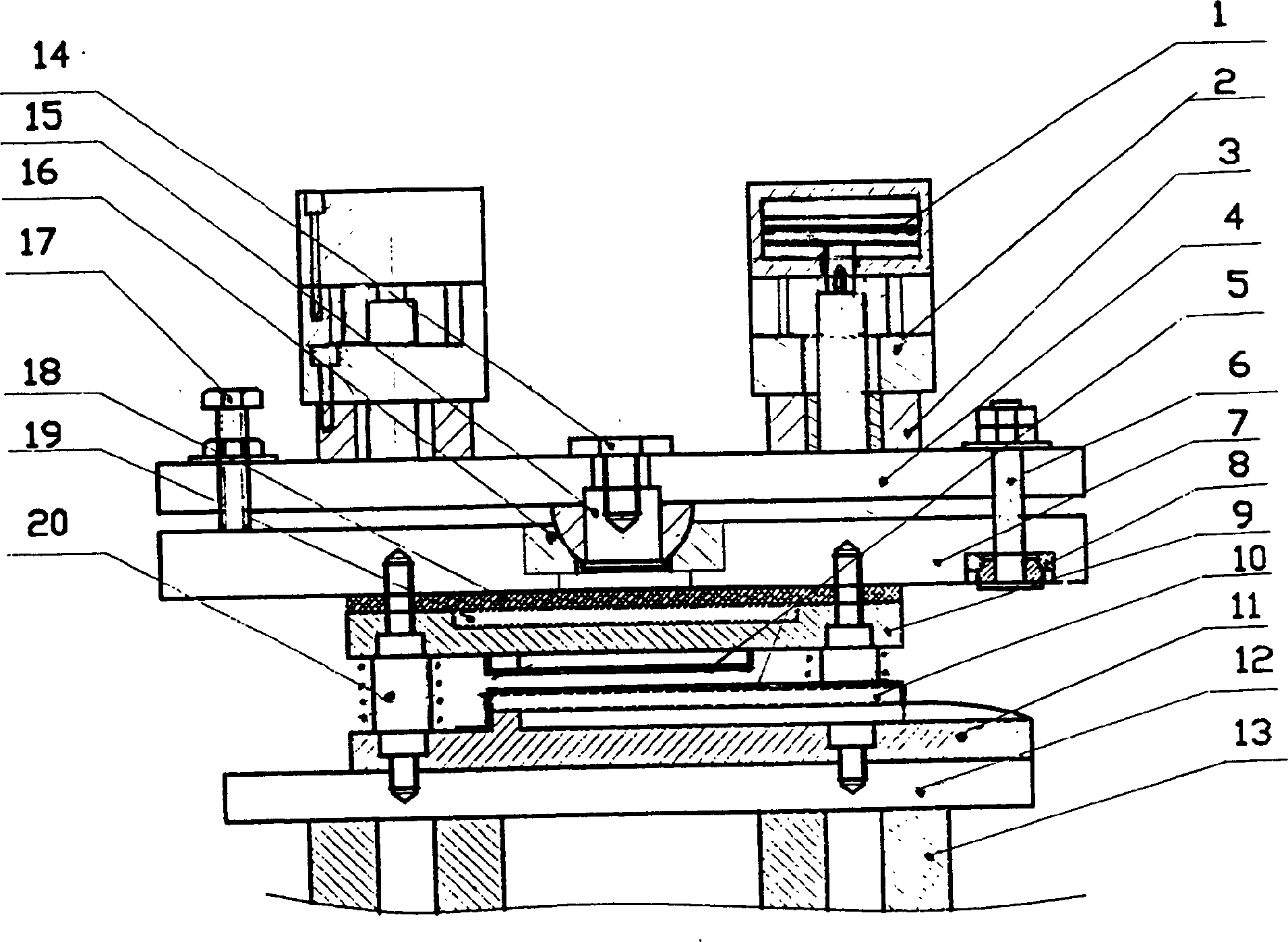

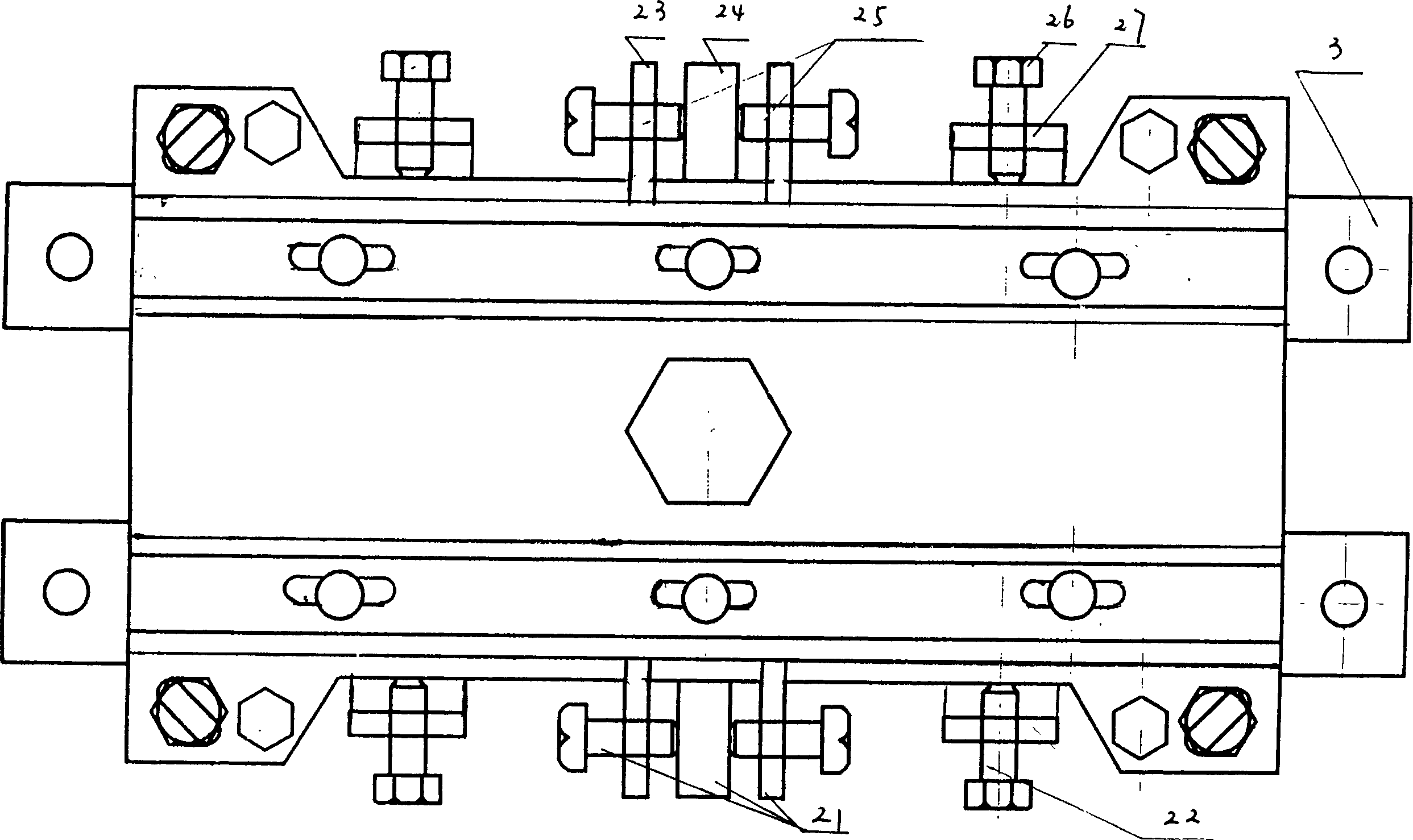

Heat-sealing apparatus for bag-making machine

InactiveCN1422740ASimple structurePrecise positioningEnvelopes/bags making machineryBox making operationsPneumatic pressureHeating element

The heat-sealing device of bagging machine comprises lower die component, upper die component, coupled bar and pneumatic pressure device, the lower end of the coupled bar is connected with power source, its upper end is connected with pneumatic pressure device, its lower die component includes lower die, lower connecting plate and lower cross beam which are connected together from top to bottom, and the upper die component includes upper die, upper die fixing plate and upper cross beam which are connected together from bottom to top. The upper cross beam is connected with pneumatic pressure device, and the upper die is equipped with heating element. Said invention can be used for heat-sealing various plastic bags, and its structure is simple and operation is convenient.

Owner:王飞鸿 +1

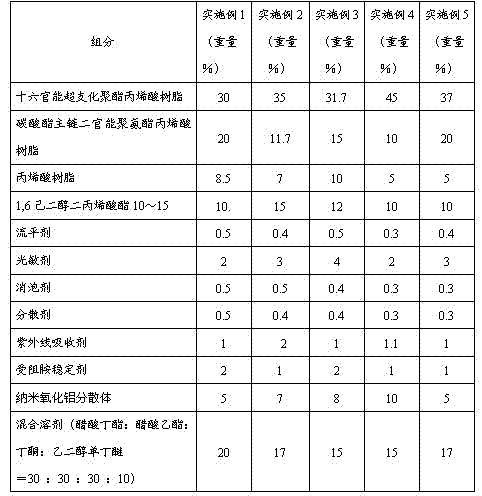

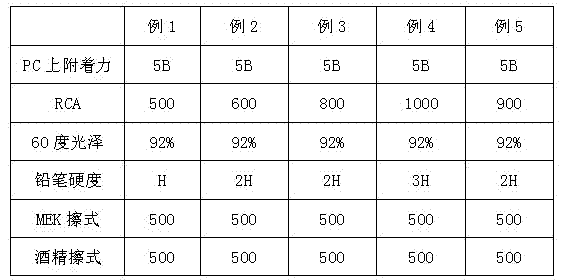

Ultraviolet (UV) cured plastic coating

InactiveCN102533067AAddressing deficiencies in finishing coatingsAvoid defectsPolyurea/polyurethane coatingsPolyester coatingsAcrylic resinNano al2o3

The invention discloses an ultraviolet (UV) cured plastic coating. The coating consists of the following components in percentage by weight: 30 to 45 percent of hexadefunctional hyperbranched polyester acrylic resin, 10 to 20 percent of carbonate main chain bifunctional polyurethane acrylic resin, 5 to 10 percent of acrylic resin, 10 to 15 percent of 1,6-hexanediol diacrylate, 2 to 4 percent of photosensitizer, 1 to 2 percent of ultraviolet absorbent, 1 to 2 percent of hindered amine stabilizer, 0.9 to 1.5 percent of aid, 5 to 10 percent of nano-alumina dispersion and 15 to 20 percent of mixed solvent. When the coating is used, the components are uniformly mixed in a ratio, and the mixture is sprayed on a plastic workpiece and cured by a UV light curing machine. The coating can be used for coating on acrylonitrile-butadiene-styrene (ABS) plastic and polycarbonate (PC) plastic, and the coating layer has the characteristics of high hardness, high wear resistance, hard object scratch resistance, high gloss, yellowing resistance, environment friendliness and the like.

Owner:深圳市美丽华科技股份有限公司

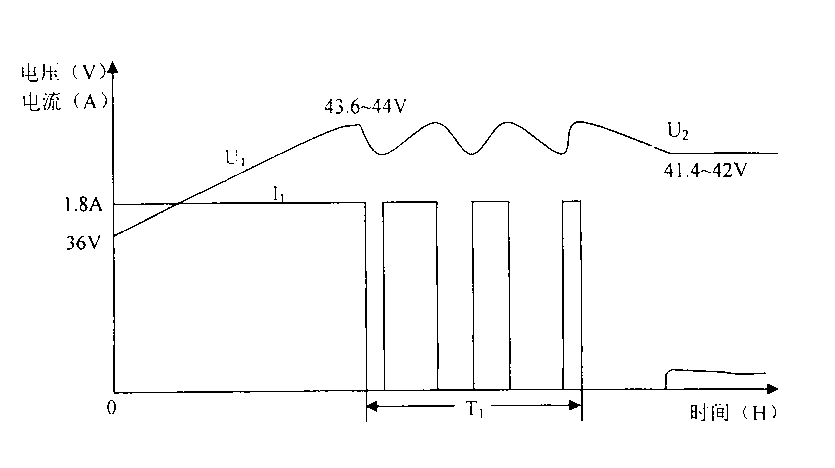

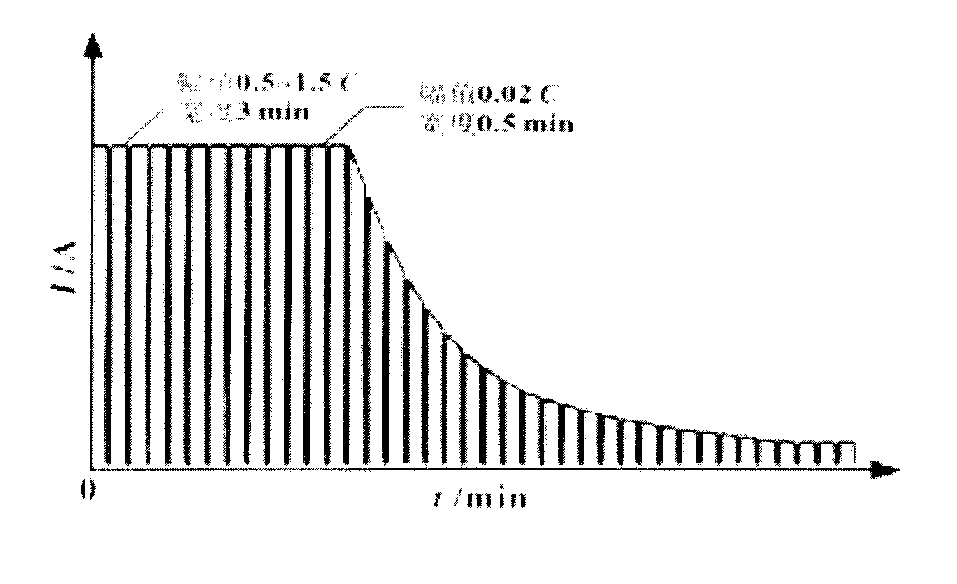

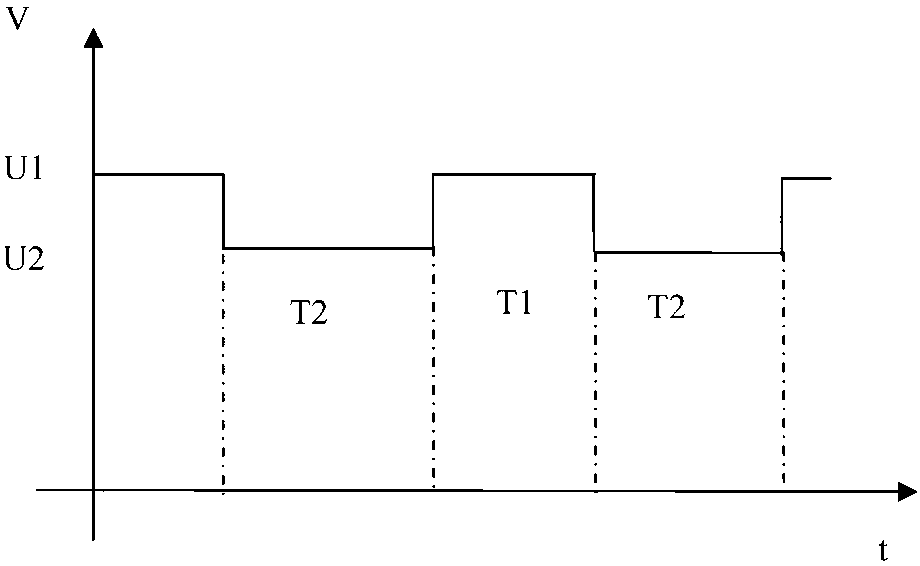

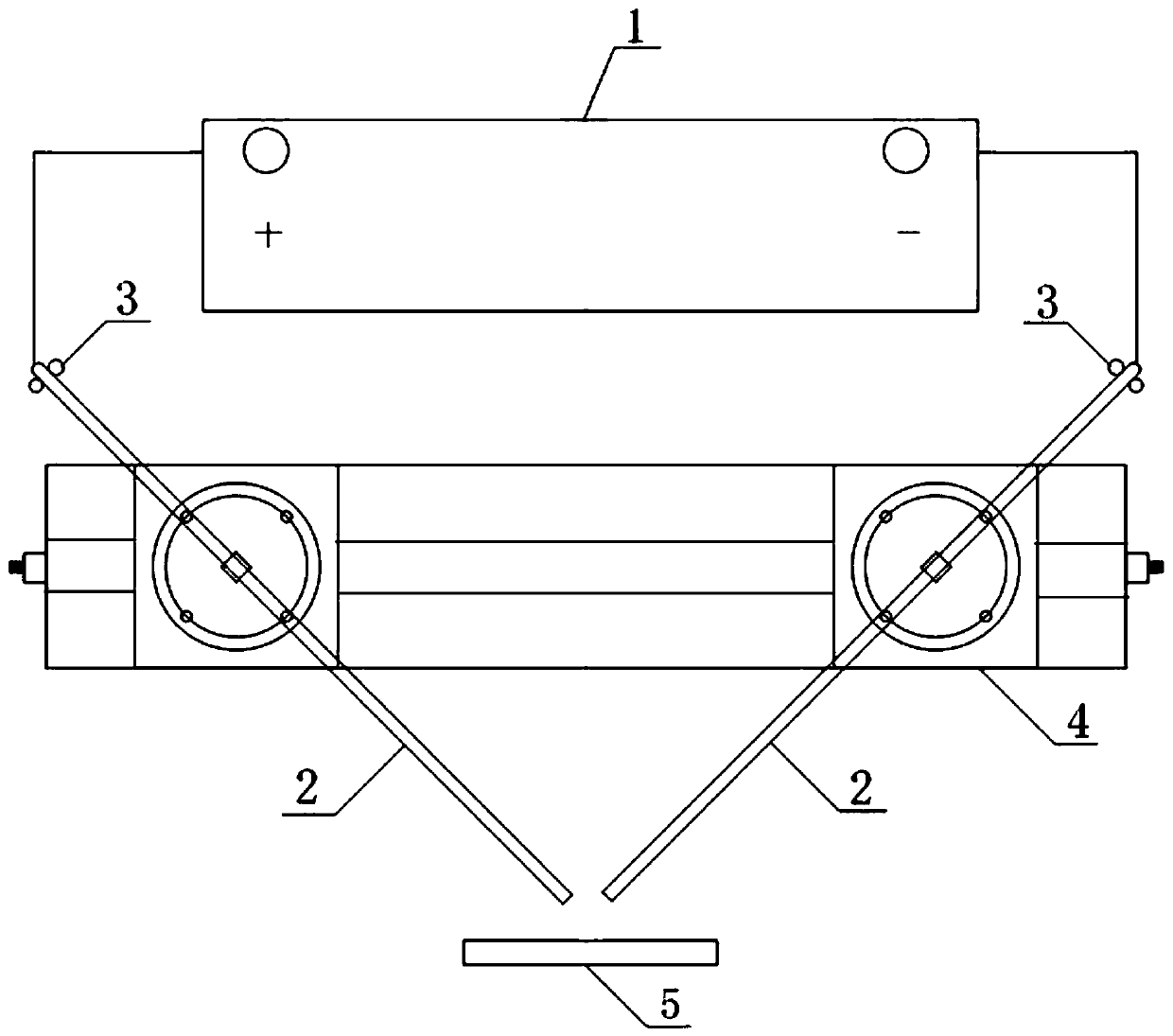

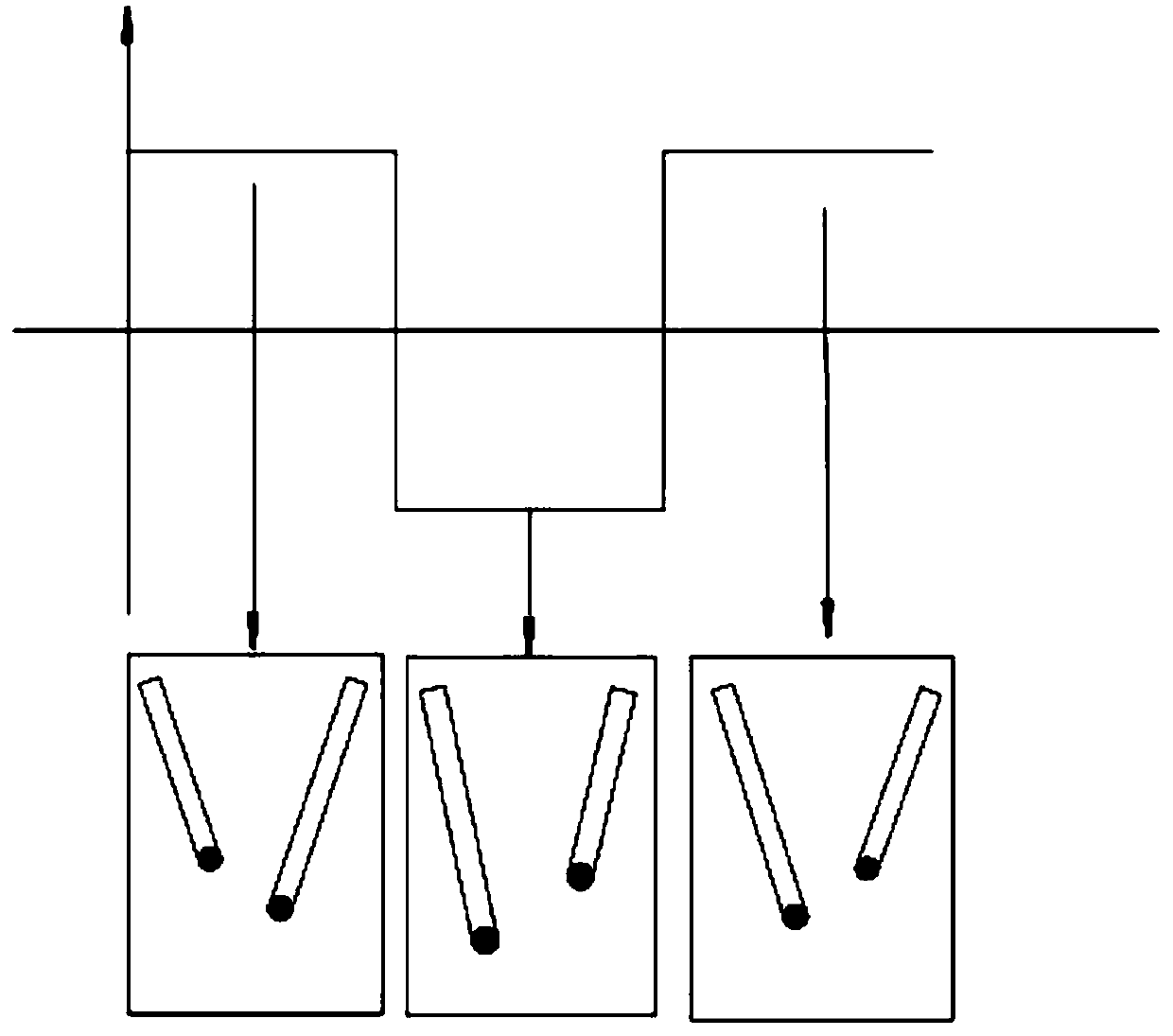

Pulse charging method used for prolonging VRLA battery service life

ActiveCN103227351AHigh porositySmall particle sizeSecondary cells charging/dischargingElectrical batteryPulse charge

The invention relates to a pulse charging method used for prolonging VRLA battery service life. The invention aims at provides a pulse charging method used for prolonging VRLA battery service life, such that the service life of a valve-regulated lead acid battery is prolonged. The invention adopts a technical scheme that, a VRLA battery has an output voltage of U and a capacity of C. The method is characterized in that the method is preceded in three sections which are a section A, a section B, and a section C. In the section A, constant-current charging is carried out with a charging limited current I. In the section B, periodic-change charging is carried out with constant current of the limited current I and constant-voltage of a second charging voltage U2. In the section C, periodic-change charging is carried out with constant-voltage of a first charging voltage U1 and constant-voltage of the charging voltage U2. In the section A, when a voltage is increased to U1, the process turns to the section B. In the section B, when the battery is charged to almost full, the process turns to the section C. The invention is suitable to be used in a field of storage battery charger.

Owner:杭州优联新能源科技有限公司

Molten glass supply device, glass formed product, and method of producing the glass formed product

ActiveCN1524811AAvoid deterioration in qualityEasy to useForehearthsGlass furnace apparatusPoiseMolten glass

Owner:NIPPON ELECTRIC GLASS CO LTD

Laminated body of motor and manufacturing method thereof

ActiveUS7728481B2Reduce stepsNo thermal deformationManufacturing dynamo-electric machinesMagnetic circuit shape/form/constructionEngineeringMechanical engineering

A laminated body of a motor includes: a yoke spirally laminated to form a hollow cylindrical shape; a plurality of teeth protruding from one side edge of the yoke disposed along a longitudinal direction of the yoke and being separated apart at a predetermined distance; a plurality of notch portions on an opposite side edge of the yoke, each of the plurality of notch portions being aligned with each of the plurality of teeth; a stopping protrusion extendingly formed at a protruding end of the teeth in the longitudinal direction of the yoke; and an inclined portion having an inclined surface formed by decreasing a width of the stopping protrusion toward an end of the stopping protrusion so as to reduce cogging torque.

Owner:LG ELECTRONICS INC

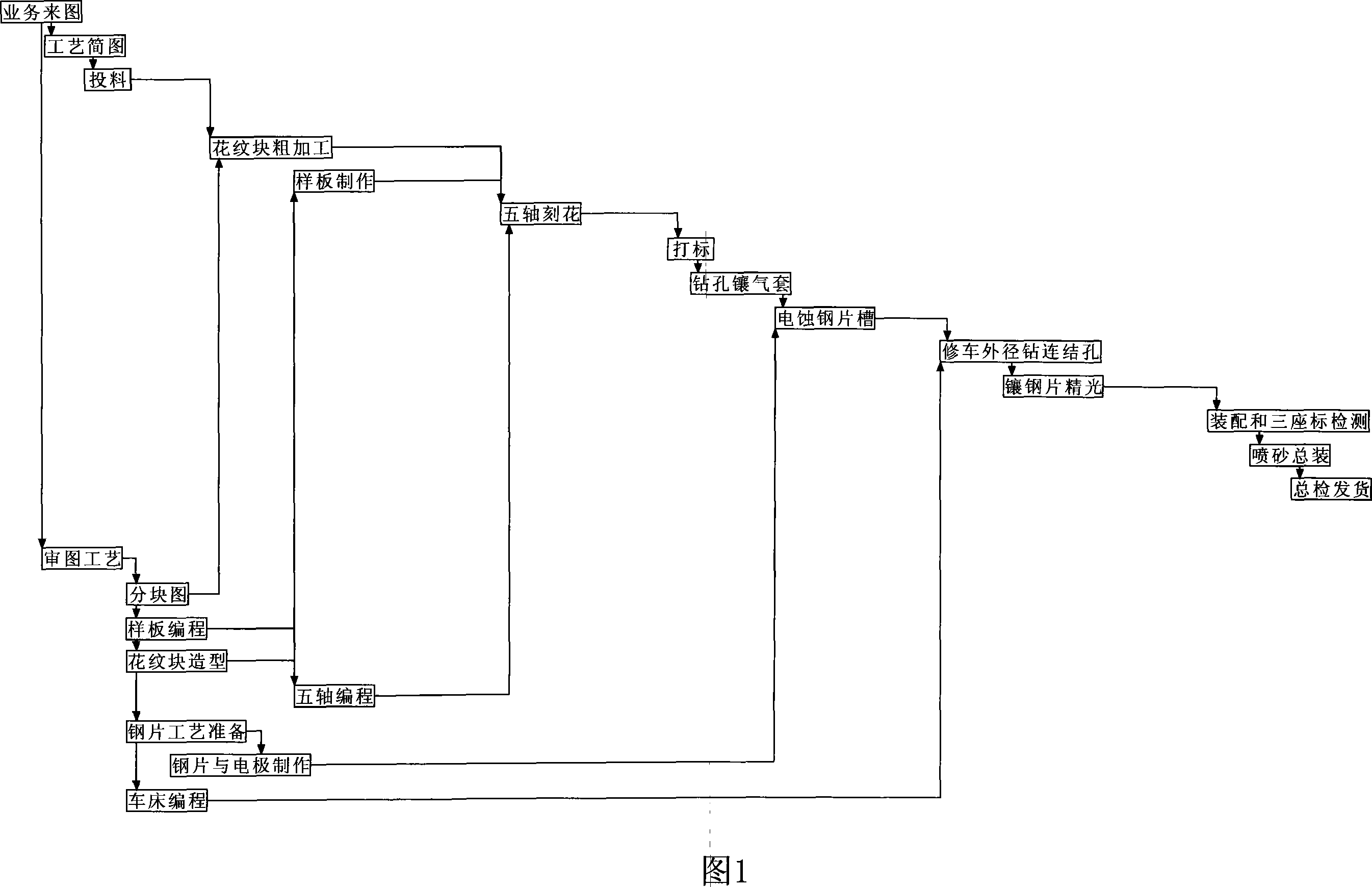

Tire mold high speed high precision parallel machining constitution method

InactiveCN101236416AShorten the design cycleReduce process preparation timeProgramme controlComputer controlNumerical controlEngineering

The invention relates to a high velocity and high precision constituting method for collaterally elaborating a tyre mould, comprising the following steps of a concurrence of designing and manufacture processing; a concurrence of designing and material purchasing; a concurrence of technology planning, rough machining and semifinishing; a concurrence of designing and numerical control process programming; and an elaboration for a single piece with high velocity and high precision. The high velocity and high precision constituting method for collaterally elaborating a tyre mould has the advantages of improving an elaborating precision of a product, shortening a delivery date for the mould and reducing the cost, and is suitable for collaterally elaborating the tyre mould with high velocity and high precision.

Owner:GREATOO INTELLIGENT EQUIP INC

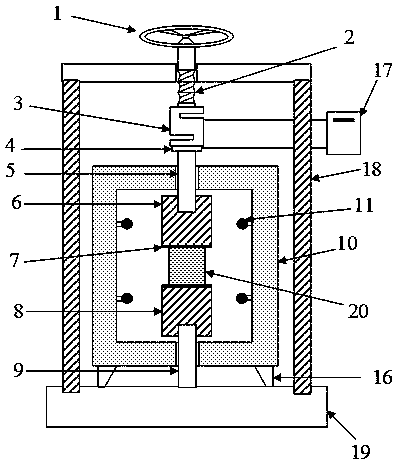

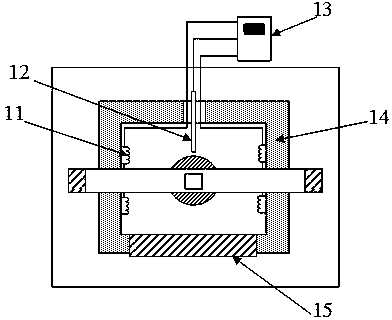

High-temperature tensile testing machine

PendingCN107607411AObtaining tensile strength propertiesImplementing Tensile Strength TestsMaterial strength using tensile/compressive forcesTemperature controlAdhesive

The invention provides a high-temperature tensile testing machine which comprises a hand wheel, an adjusting bolt, a pressure sensor, a displacement sensor, an upper connecting rod, a stretching end,a high-temperature resisting adhesive, a fixing end, a lower connecting rod, a high temperature electric heating furnace, a heating element, a temperature measuring element, a temperature control device, a furnace wall, a furnace door, a support frame, a measuring system, a pressurizing frame, a base and a rock sample. The high-temperature tensile testing machine is capable of realizing the tensile strength test for the rock sample under the high temperature condition, is capable of accurately acquiring the tensile strength of the rock sample under high temperature state and has significance in the construction structure safety on the fire scene.

Owner:XINJIANG UNIVERSITY

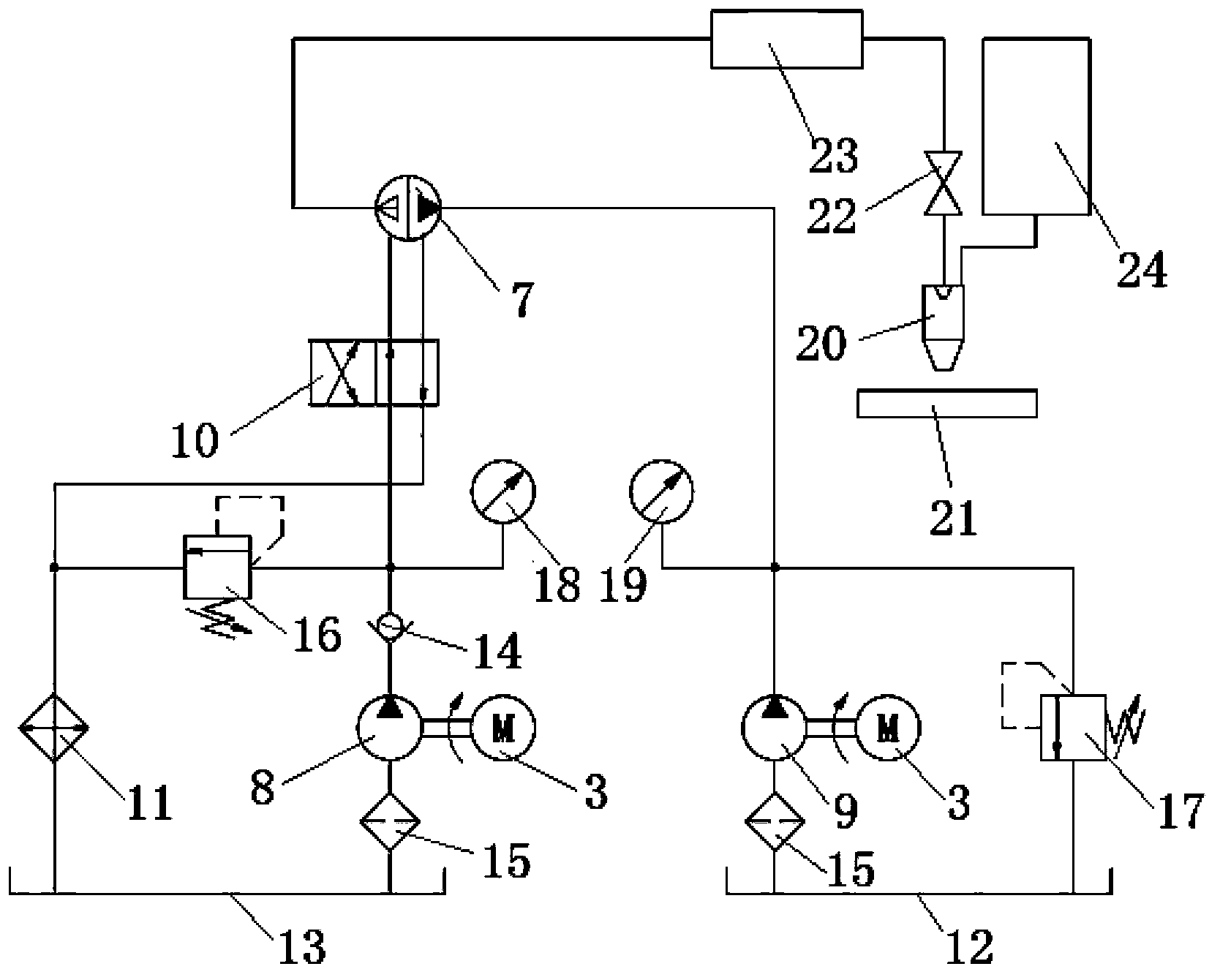

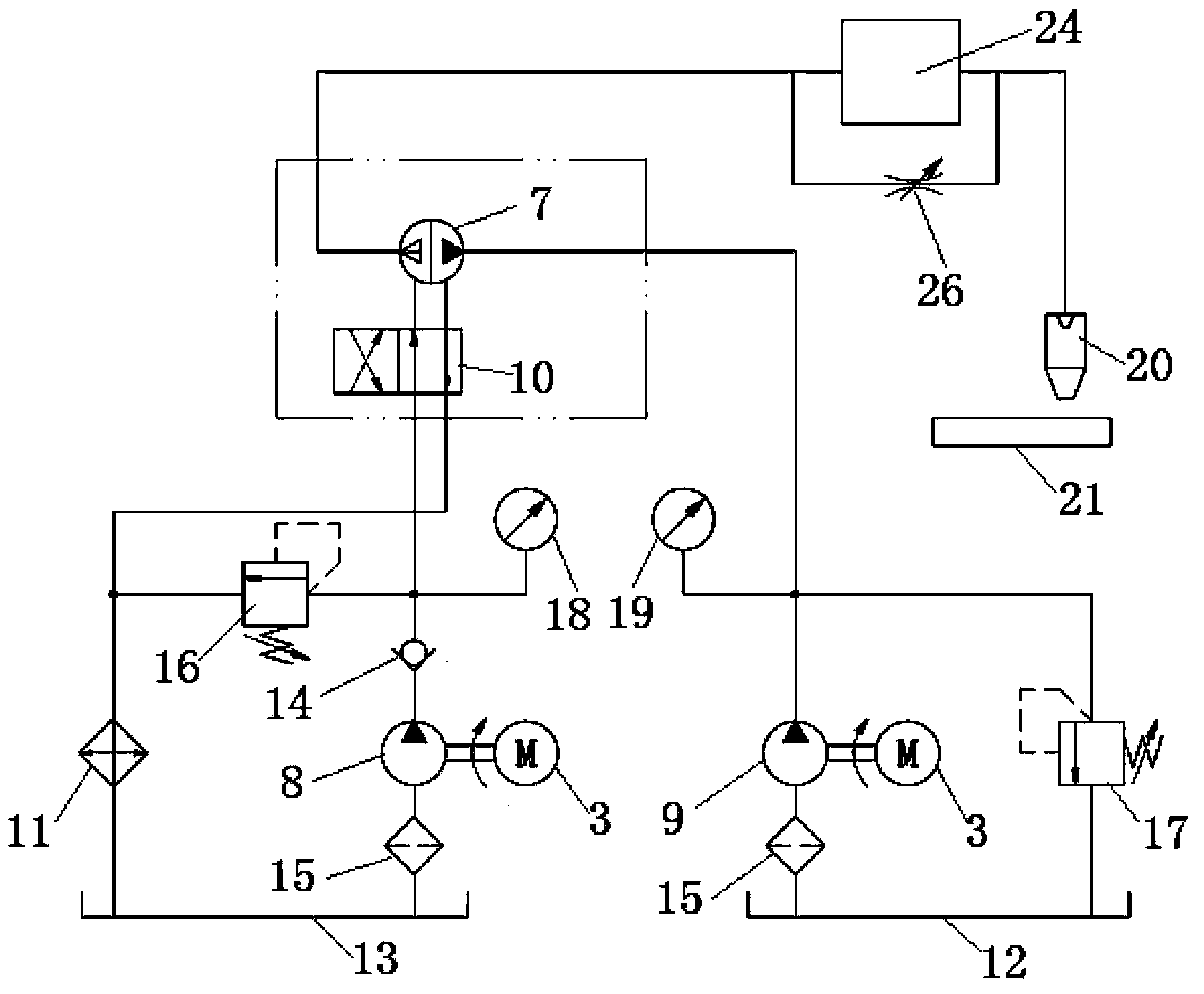

Vehicle-mounted water cutting system

ActiveCN103447970AMove quicklyNo need for high temperatureAbrasive feedersAbrasive machine appurtenancesChemical transformationThermal deformation

Owner:纪新刚

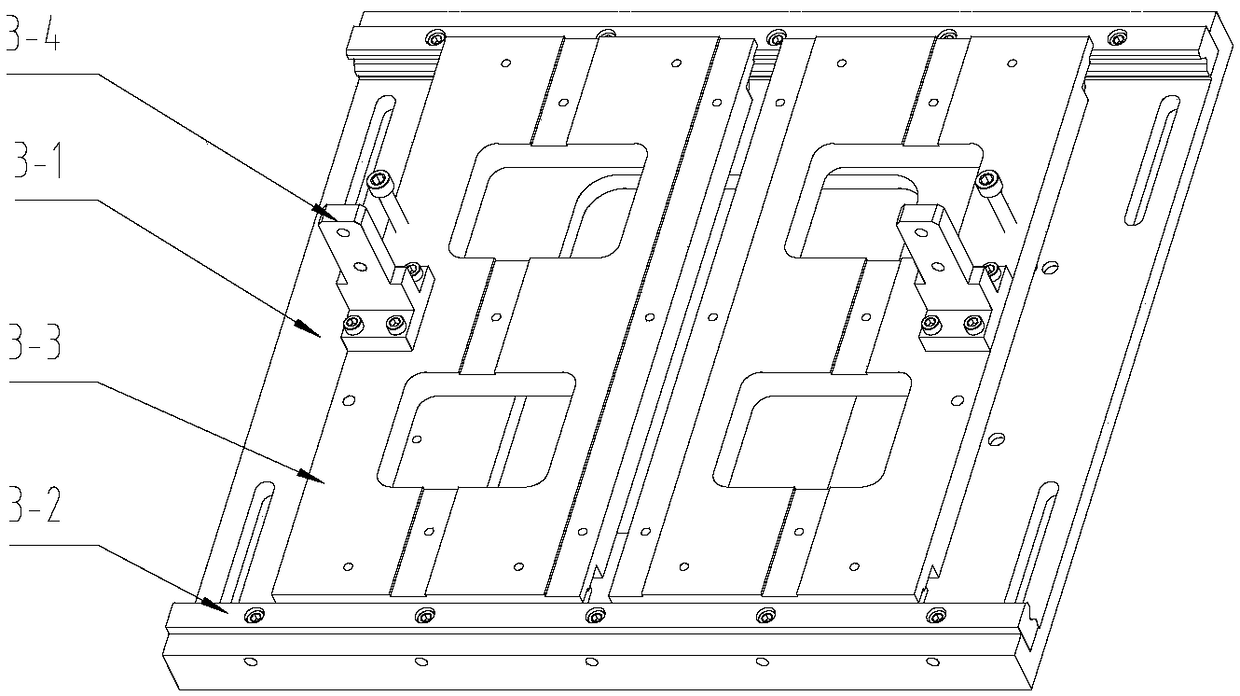

Integrated driving short roller device for pulling glass

The invention provides an integrated driving short roller device for pulling glass. The integrated driving short roller device comprises a baseboard, a baseboard guide rail is arranged on the baseboard, two sliding plates are slidably arranged on the baseboard guide rail, and a clamping mechanism, a driving mechanism and an adjusting mechanism are correspondingly arranged on each sliding plate; each clamping mechanism comprises a short roller mandrel fixed to the corresponding sliding plate; a glass clamping end is arranged at one end of each short roller mandrel, and is sleeved with an asbestos roller wheel, and a driving end is arranged at the other end of the corresponding short roller mandrel and is connected with a driving shaft of the corresponding driving mechanism; the adjusting mechanisms comprise pulling rods for controlling the sliding plates to slide and weights for adjusting clamping force of the asbestos roller wheels. By means of the integrated driving short roller device for pulling the glass, multiple driving short roller devices are installed on a mounting support to form an integrated structure and are installed at the two sides of an annealing furnace. The riving short roller device is independently arranged, one set of rollers oppositely stretch into the hot end annealing furnace from the two sides of the annealing furnace and clamp and pull the substrate glass from the two sides respectively, the manufacturing cost is low, and the integrated driving short roller device is convenient and flexible to adjust, and can be quickly installed and adjusted.

Owner:IRICO

Sealing structure and sealing method of non-welded metal plate single battery

PendingCN112701315AReduce manufacturing costImprove yieldSealing/support meansStructural engineeringBattery cell

The invention relates to a sealing structure and a sealing method of a non-welded metal plate single cell, the sealing structure comprises a single cell formed by stacking an anode plate, a membrane electrode and a cathode plate together, an air main channel is communicated with a cathode flow field through an air side air inlet duct and a negative plate air side boss, and a hydrogen main channel is communicated with an anode flow field through a hydrogen side gas inlet duct by penetrating through a hydrogen side boss of an anode plate; the anode plate air side boss is communicated with the anode plate water side boss through a first channel, a first communication hole is formed in a membrane electrode frame between the anode plate water side boss and the cathode plate water side boss, and the cathode plate water side boss is communicated with the cathode plate hydrogen side boss through a second channel; and sealing rings are formed in the anode plate air side boss, the first channel, the anode plate water side boss, the cathode plate water side boss, the second channel and the cathode plate hydrogen side boss through integrated glue injection. The sealing structure and the sealing method are high in reliability, low in production cost and high in production efficiency.

Owner:FUJIAN YANAN ELECTRIC MACHINE

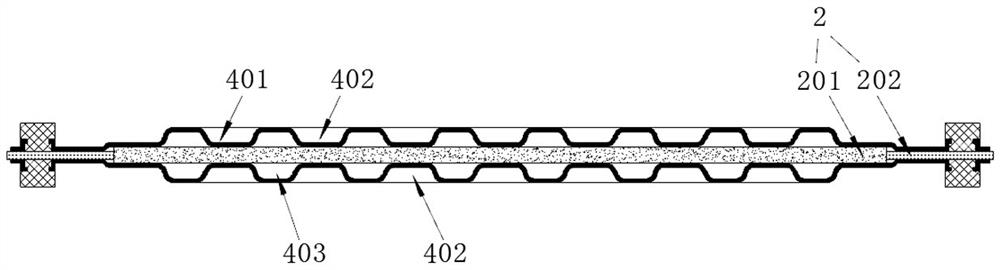

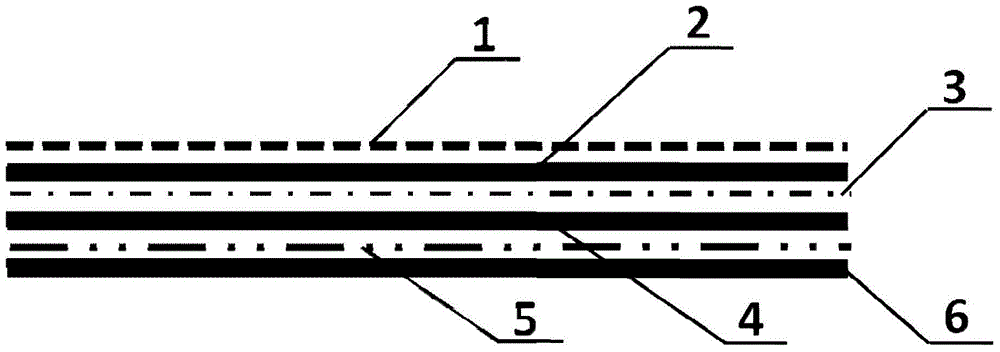

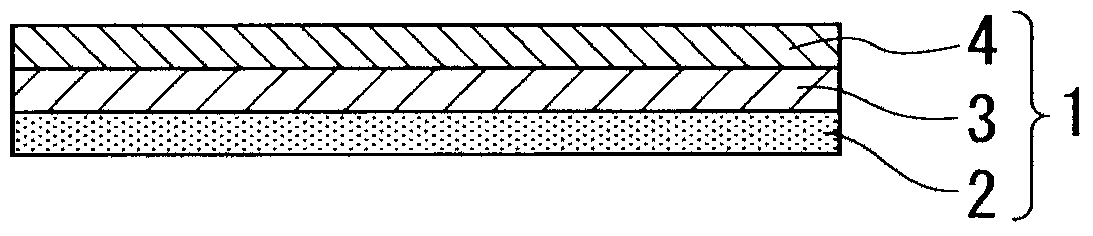

Composite sheet structure for decoration and preparation method of composite sheet structure

ActiveCN104589746ANo thermal deformationBright surfaceSynthetic resin layered productsLaminationPolyesterWeather resistance

The invention discloses a composite sheet structure for decoration by taking PET / PVC as main materials, wherein the composite sheet structure structurally comprises a PVC sheet (6), a tackifying layer (5) on the PVC sheet (6), a hot melting glue layer (4) on the tackifying layer (5), a priming coat layer (3) on the hot melting layer (4), a polyester film layer (2) on the priming coat layer (3) and a surface hardening layer (1) on the polyester film layer (2). The PVC sheet disclosed by the invention cannot deform thermally; the laminated PET surface hardening layer can enable the surface hardness of the PVC sheet to achieve 2H above, and the surface is relatively bright; the composite sheet structure can absorb ultraviolet rays, slow down the light aging speed of the PVC sheet, improve the weather resistance of PVC resin, and prolong the service life, can obstruct micromolecule additives, such as a plasticizing agent in the PVC sheet, from migrating toward the surface, reduce harm to human bodies, and also can greatly improve the tear resistance performance and toughness of the PVC sheet, and improve the mechanical intensity of the PVC sheet.

Owner:张家港保税区康得菲尔实业有限公司

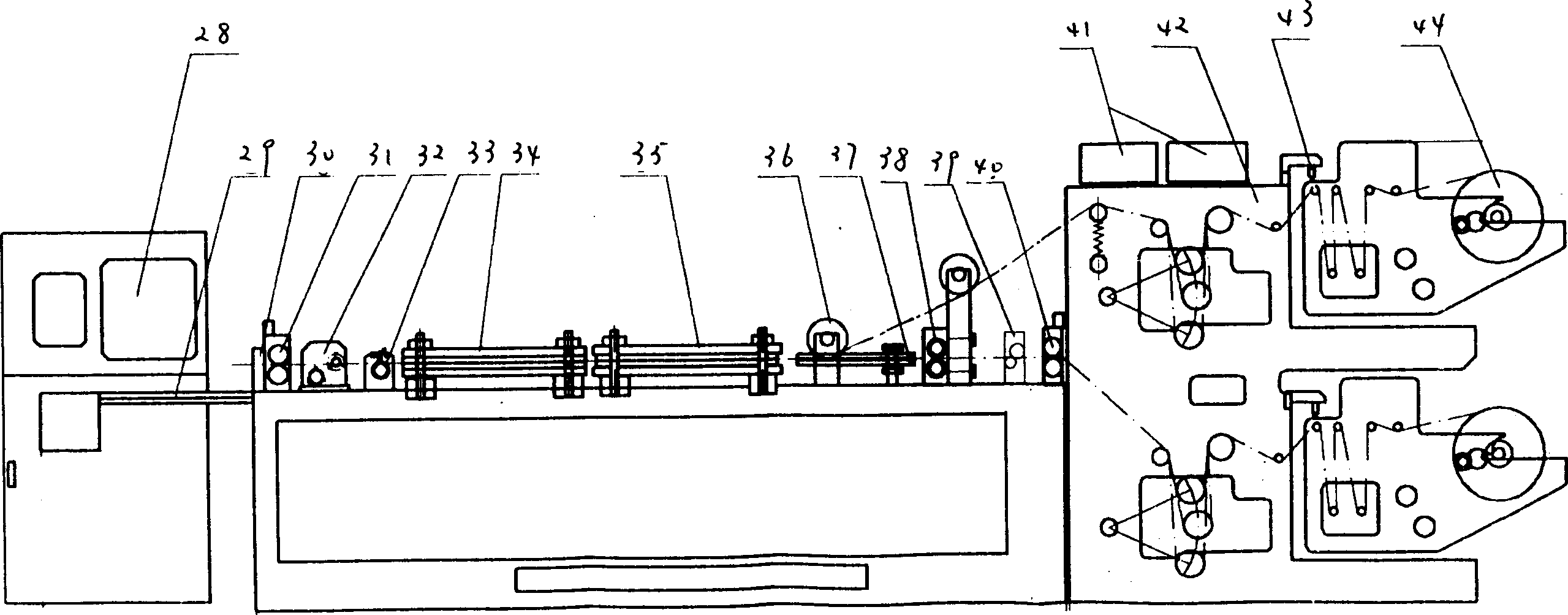

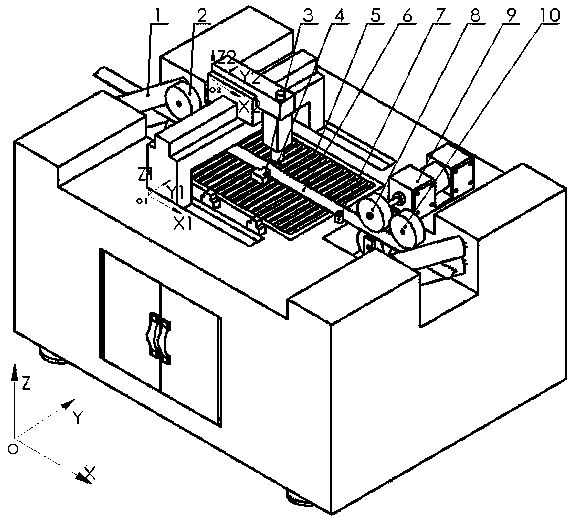

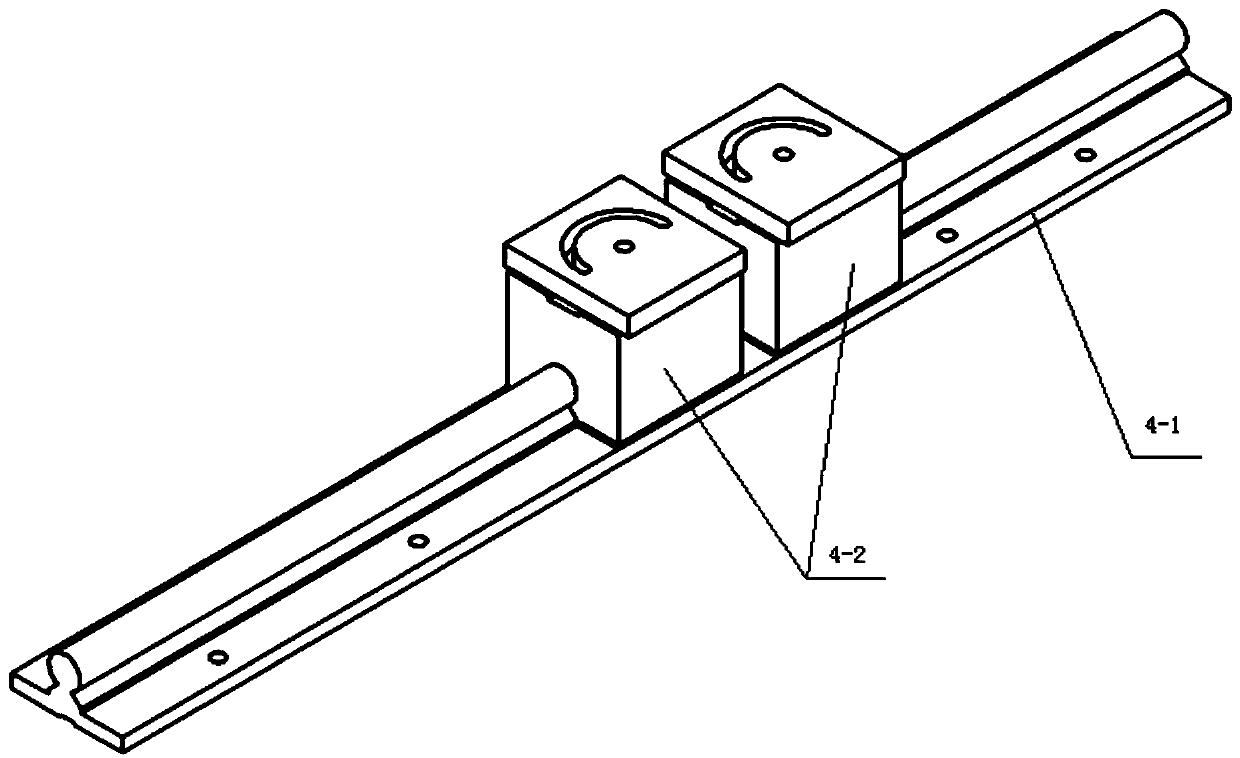

Laser continuous cutting device used for cutting saw belt and cutting method

ActiveCN104014938ANo thermal deformationNo damageWelding/soldering/cutting articlesMetal working apparatusMilling cutterLaser cutting

The invention discloses a laser continuous cutting device used for cutting a saw belt and a cutting method. The laser continuous cutting device aims to solve the problems that continuous cutting and forming of sawteeth can not be achieved, tool auxiliary time accounts for a high percentage, and cutting efficiency is low in the prior art. The laser continuous cutting device comprises a base which is sequentially provided with a driving friction roller used for regulating feeding speed of the saw belt, a pressing wheel set used for pressing the saw belt, a work platform and a driving wheel set driven by a driving device; a laser head which is arranged on a Z shaft for cutting the saw belt is arranged above the work platform; the work platform is provided with a feeler block and a transverse locating mechanism used for locating the saw belt; during cutting work, the speed of a sliding platform X1 is the same as the feeding speed of the saw belt. The laser cutting sawtooth continuous forming technique does not need a milling cutter, and the sawteeth in any two-dimensional shapes can be correspondingly manufactured very rapidly.

Owner:湖南泰嘉智能科技有限公司

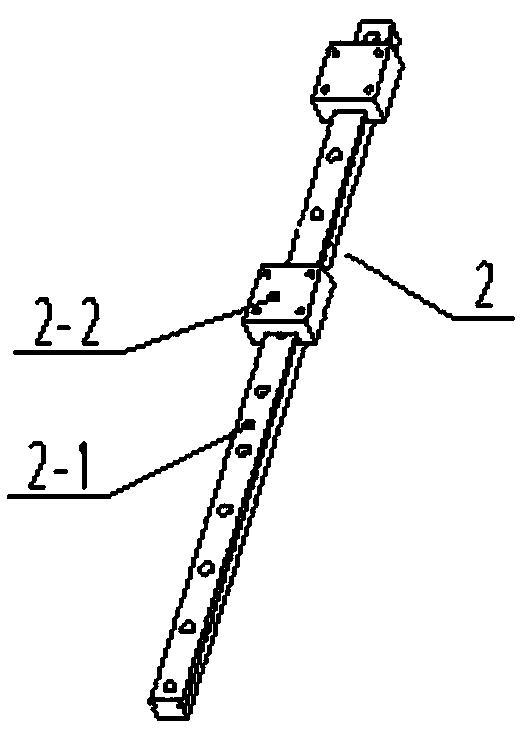

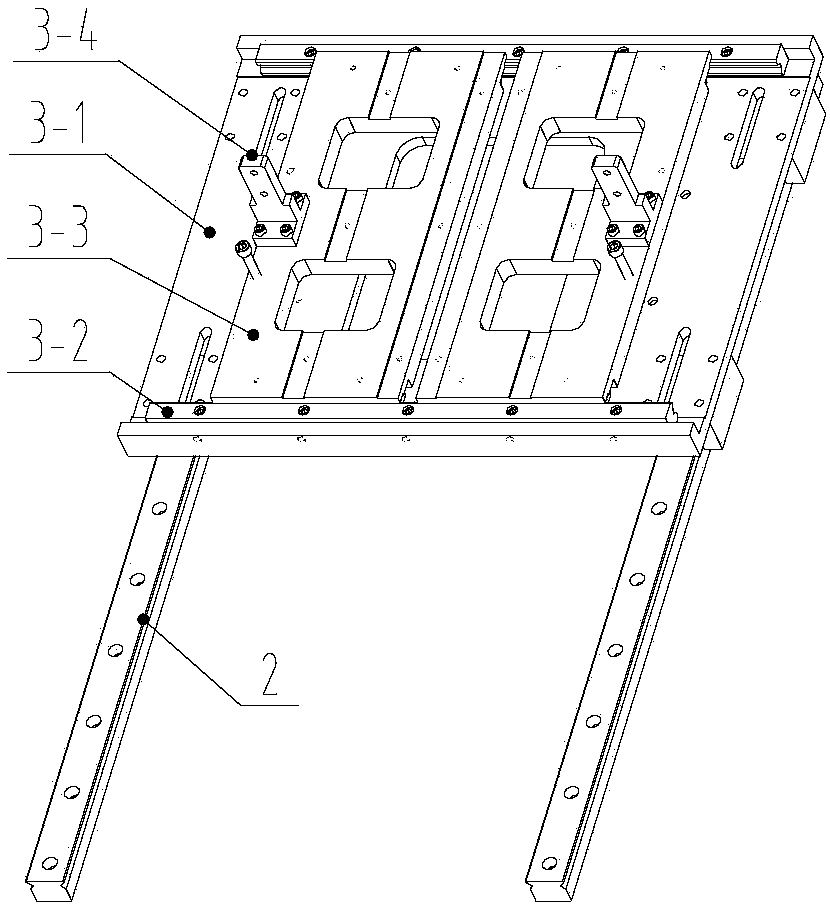

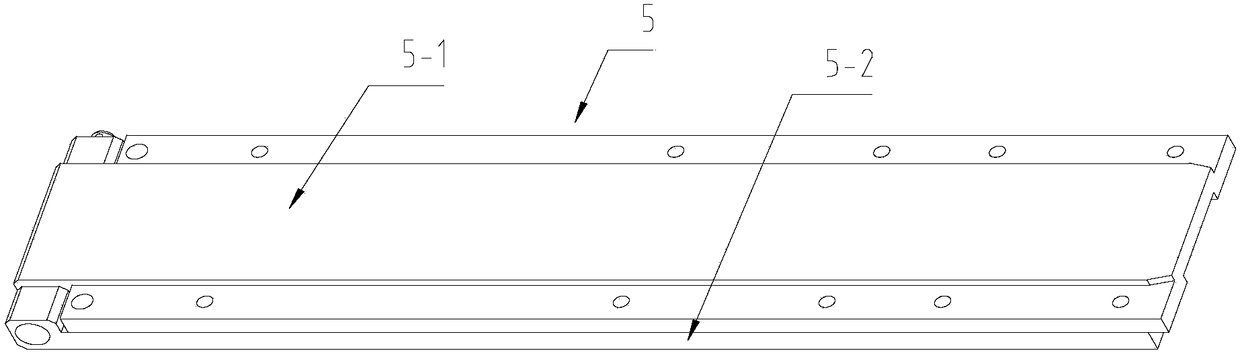

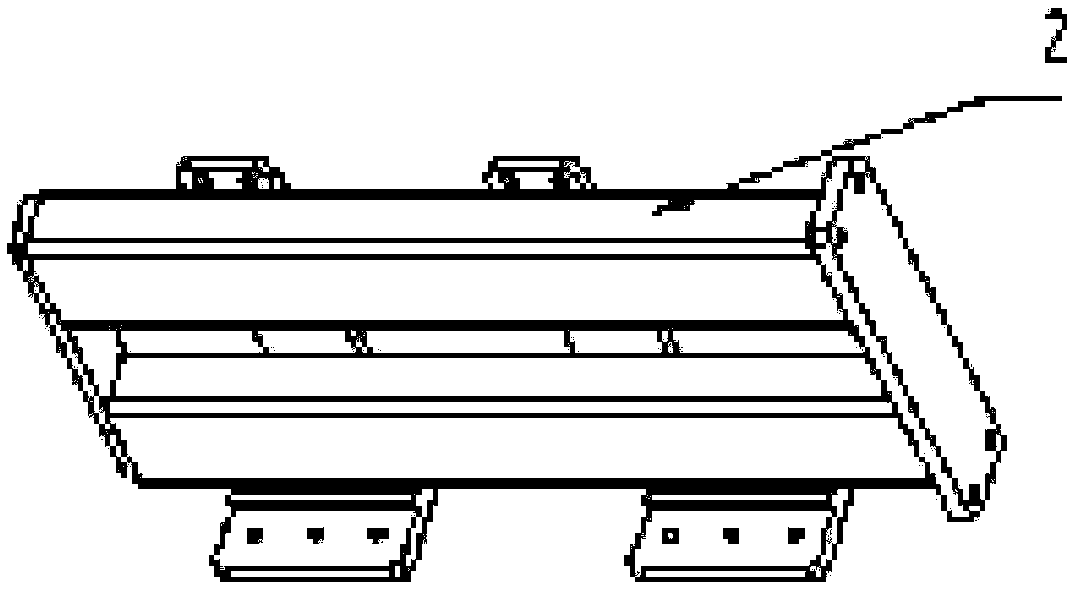

Split type drive short roller device for drawing glass

The invention provides a split type drive short roller device for drawing glass. The split type drive short roller device comprises a horizontal sliding table mechanism, wherein the horizontal slidingtable mechanism comprises a bottom plate, wherein guide rails are arranged on the bottom plate, two sliding plates are arranged on the guide rails in a sliding manner, and a clamping mechanism, a drive mechanism and an adjusting mechanism are arranged corresponding to each sliding plate; each clamping mechanism comprises a short roller mandrel fixed on the corresponding sliding plate, one end ofthe short roller mandrel is a glass clamping end, the other end is a drive end, the glass clamping end of the short roller mandrel is sleeved with an asbestos roll wheel, and the axial direction of the short roller mandrel is vertical to the trend of the guide rails; each drive mechanism is fixed on the corresponding sliding plate, and a drive shaft of the drive mechanism is coaxially connected with the drive end of the corresponding short roller mandrel; each adjusting mechanism comprises a pull rod for controlling sliding of the corresponding sliding plate and counter weight for adjusting clamping force of the corresponding asbestos roll wheel. The drive short roller device is independently arranged, a group of rollers extend into a hot-end annealing furnace from the two sides of the annealing furnace oppositely and clamp and draw substrate glass on the two sides respectively, the manufacturing cost is low, and the flexible adjustment is convenient.

Owner:IRICO

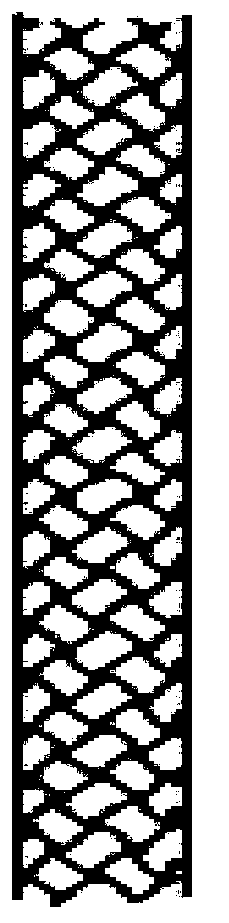

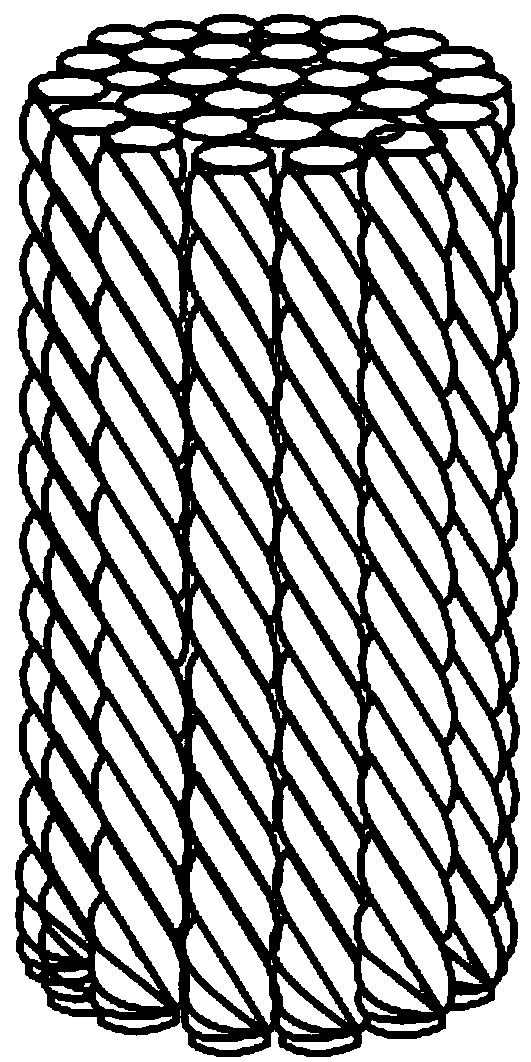

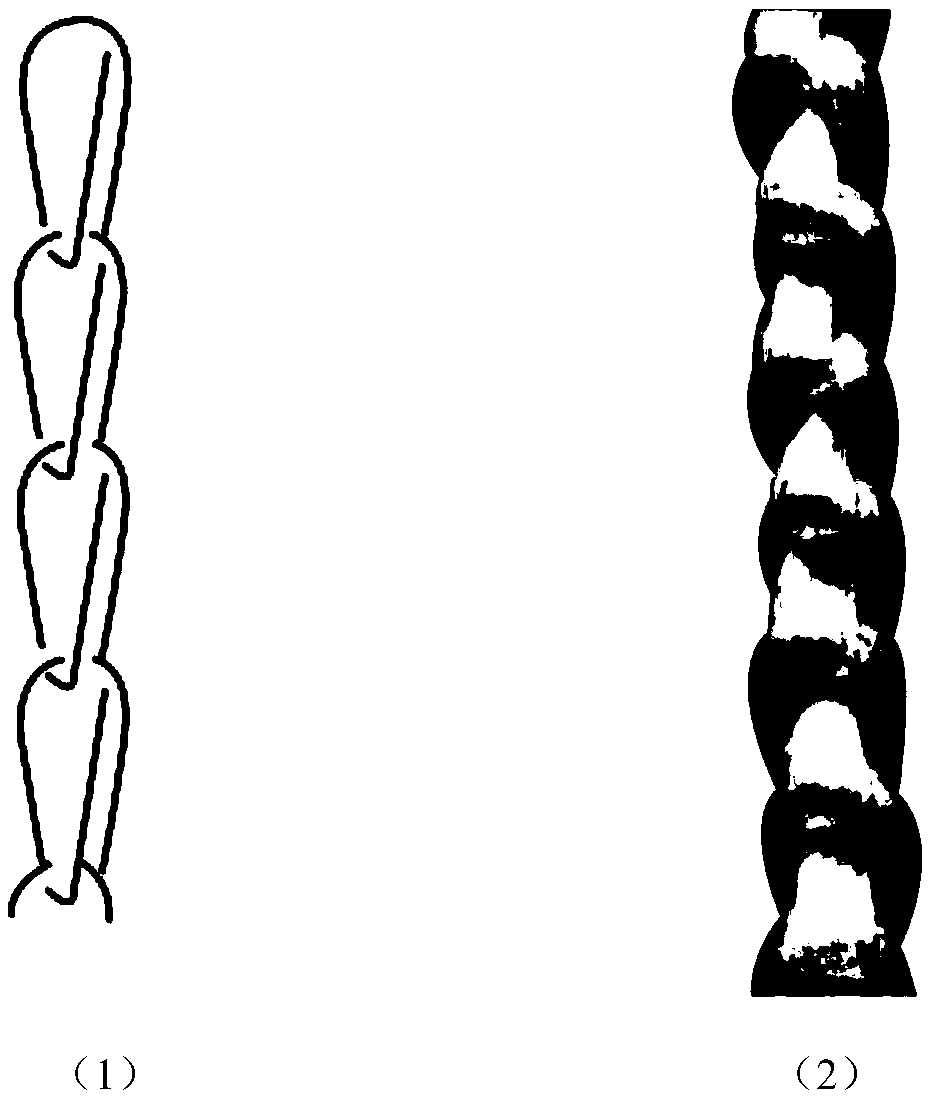

Degradable odor generation element for non-burned cigarette and cigarette product

InactiveCN108685192ASimple processIncrease productivityTobacco devicesEnvironmental chemistryAfter treatment

The invention provides a degradable odor generation element for a non-burned cigarette. The odor generation element is made of biodegradable polylactic acid monofilaments, and is formed by preparing several polylactic acid monofilaments into a rope or knitted fabric structure through one or more processes of weaving, knitting and twisting and then carrying out cutting. The odor generation elementfurther comprises polylactic acid monofilaments without perfume and polylactic acid monofilaments with perfume adhering to the surfaces after treatment, and when a hot airflow passes through a longitudinal extension channel defined by the polylactic acid monofilaments, the original odor of smoke and a generated volatile aroma are kept respectively. The process is simple, and the production efficiency is high; the adopted polylactic acid monofilaments have good biodegradability and environmental friendliness.

Owner:CHANGZHOU LOONG TOP NEW MATERIALS TECH

Method for remedying water-eroded defects on finished surface of engine cylinder block

ActiveCN103192226ANo thermal deformationGuaranteed dimensional accuracyManufacturing technologyEngineering

The invention discloses a method for remedying water-eroded defects on the finished surface of an engine cylinder block and belongs to the technical field of engine cylinder block refabrication. The method includes: polishing the defective surface to expose a cylinder block body; polishing sharp corners or edges on the cylinder block body; removing oil at defective positions; re-polishing; cleaning the defective positions; remedying the defective positions by electric spark ionic microwelding to make the welded positions level to the finished surface of the cylinder block; polishing the welded positions to make the welded positions lower than the finished surface of the cylinder block; remedying the welded positions by pulse cold welding to make the welded positions higher than the finished surface of the cylinder block; and polishing the welded positions to make the welded positions level to the finished surface of the cylinder block. The method effectively guarantees fine bonding of welding material and substrate during welding. The electric spark ionic microwelding is reasonably combined with the pulse cold welding, so that efficiency is increased and the remedied texture is kept dense and non-defective.

Owner:WEICHAI POWER CO LTD

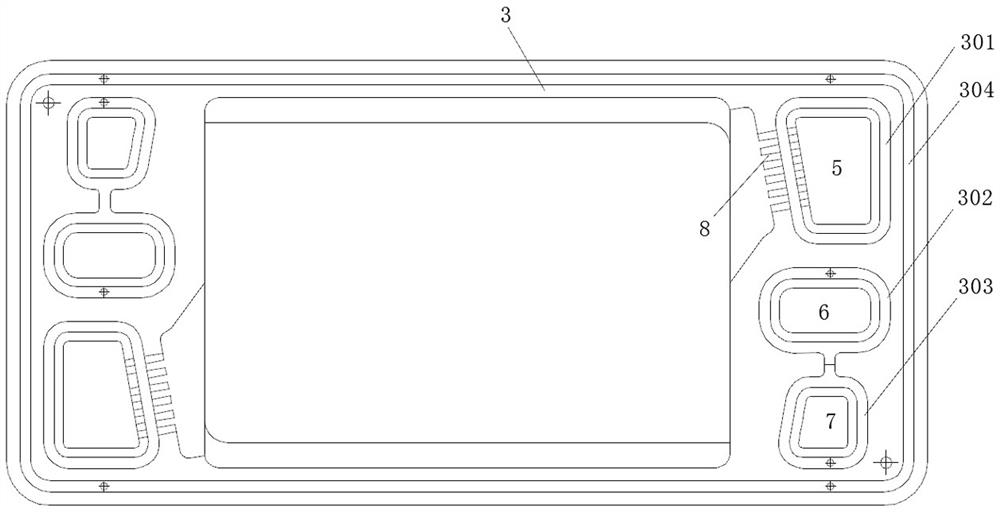

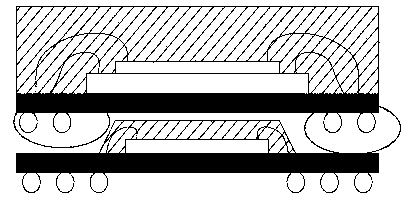

Packaging-after etching three-dimensional system-on-chip upright stacking packaging structure and technology method

ActiveCN103456645AFlexible stackingNo height limitSemiconductor/solid-state device detailsSolid-state devicesSolder ballEngineering

The invention relates to a packaging-after etching three-dimensional system-on-chip upright stacking packaging structure and a technology method. The packaging-after etching three-dimensional system-on-chip upright stacking packaging structure comprises a base island and pins, a chip is arranged in the front of the base island through conducting materials and non-conducting materials; the front of the chip is connected with the fronts of the pins through metal wires; conducting posts are arranged in the fronts of the pins; the region on the periphery of the base island, the region between the base island and the pins, the region between the pins, the region above the base island and the pins, the region below the base island and the pins, the chip, the metal wires and the conducting posts are all wrapped with molding compounds; packaging bodies are arranged on the tops of the conducting posts or the backs of the pins through conducting materials. The e packaging-after etching three-dimensional system-on-chip upright stacking packaging structure and the technology method have the advantages of solving the problem that because a bottom-layer substrate welding disc is lower than a bottom-layer plastic packing surface in a traditional substrate packaging stacking mode, the quality of interconnected welding balls between the packaging bodies is hard to control.

Owner:江苏尊阳电子科技有限公司

Double-fast-curing repair finish paint for car body and preparation method thereof

ActiveCN102775903AFast curingIncrease productivityPolyurea/polyurethane coatingsEpoxy resin coatingsSolventSolid content

The invention relates to a double-fast-curing repair finish paint for a car body and a preparation method of the finish paint. The finish paint comprises the following components by weight: 40-60 parts of low polymer A, 20-30 parts of low polymer B, 3-5 parts of initiator, 0.2-2 parts of assistant, 1-10 parts of solvent and 10-20 parts of additive resin. The preparation method of the finish paint comprises the following steps: 1, according to the requirements of a formula, adding the low polymer A, the low polymer B, the initiator, the assistant, 50-80% by weight of the solvent and all the additive resin into a dispersion cylinder; 2, stirring for 15-30min at constant speed to obtain a coating; and 3, measuring the solid content of the coating and adjusting the solid content of the coating by using the rest solvent till the solid content reaches a theoretical value to finally the finish paint. Compared with the prior art, the double-fast-curing repair finish paint has the advantages of high curing speed, environment friendliness and energy saving.

Owner:ZHANGZHOU XIN ZHAN WANG CHEM IND

Laminated body of motor and manufacturing method thereof

ActiveUS20080024031A1Reduce stepsNo thermal deformationManufacturing dynamo-electric machinesMechanical energy handlingMechanical engineeringCogging torque

A laminated body of a motor includes: a yoke spirally laminated to form a hollow cylindrical shape; a plurality of teeth protruding from one side edge of the yoke disposed along a longitudinal direction of the yoke and being separated apart at a predetermined distance; a plurality of notch portions on an opposite side edge of the yoke, each of the plurality of notch portions being aligned with each of the plurality of teeth; a stopping protrusion extendingly formed at a protruding end of the teeth in the longitudinal direction of the yoke; and an inclined portion having an inclined surface formed by decreasing a width of the stopping protrusion toward an end of the stopping protrusion so as to reduce cogging torque.

Owner:LG ELECTRONICS INC

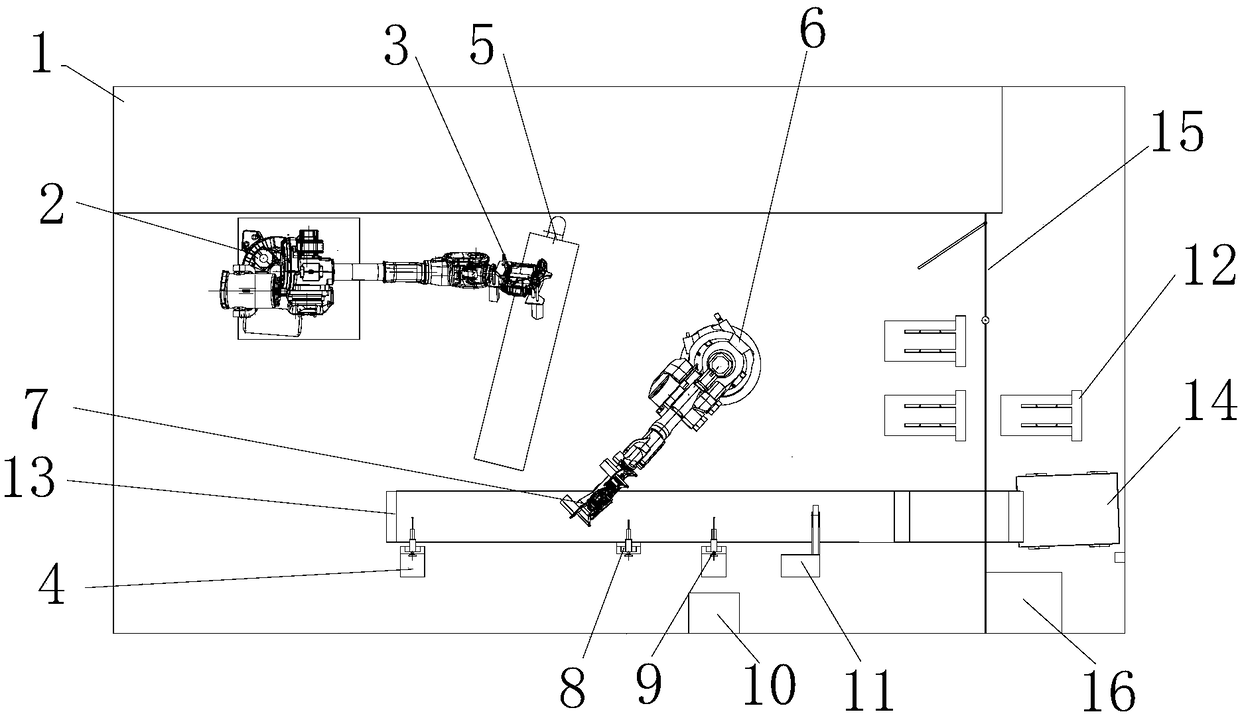

Industrial robot automobile engine end cover machining flexible production automatic line and method

ActiveCN108058023ANovel ideaMeet the process requirementsOther manufacturing equipments/toolsDie castingMachining system

The invention discloses an industrial robot automobile engine end cover machining flexible production automatic line. The industrial robot automobile engine end cover machining flexible production automatic line comprises an end cover taking and cooling system and a machining system which are arranged beside a die casting machine. The end cover taking and cooling system is arranged on one side ofthe die casting machine, a chamfering milling machine and a double-layer cooling frame are arranged with a material taking robot as the center, and the tail end of the material taking robot is connected with a material taking clamp. The machining system is arranged on one side of the double-layer cooling frame with the machining robot as the center, and the tail end of the machining robot is connected with a special clamp. Various devices are connected into the industrial robot automobile engine end cover machining flexible production automatic line from head to tail through a scrap discharging conveying belt according to the machining technology process. A master control cabinet is arranged on one side of the tail end of the scrap discharging conveying belt outside a fence. The inventionfurther discloses a flexible production method. The industrial robot automobile engine end cover machining flexible production automatic line is long in service life and low in maintaining cost, the tool replacing time is saved, meanwhile, one machine has multiple purposes, the production efficiency is improved, and the equipment usage investment cost is reduced as well.

Owner:广东省机械研究所有限公司

A kind of strengthening grinding method of wear-resistant alloy steel workpiece surface

InactiveCN103878703BImprove fatigue lifeNo thermal deformationAbrasion apparatusWear resistantSteel ball

The invention relates to a strengthened grinding method for wear-resisting alloy steel workpiece surface. The method comprises the steps of ejecting a mixture to the surface of a wear-resisting alloy steel workpiece with speed of 100-300 m / s and an ejecting angle of 15-75 degrees, and completely covering the surface of the wear-resisting alloy steel workpiece by ejecting points, wherein the mixture is composed of steel balls, grinding powder and strengthened grinding modified liquid with the mass ratio of the steel balls to the grinding powder to the strengthened grinding modified liquid of (1:1:1) to (5:1:3); the steel balls are cast steel balls or bearing steel balls with the hardness greater than 62 HRC (rockwell hardness) and the diameter of phi1-phi8; the strengthened grinding modified liquid is composed of the following raw materials by weight percentage: 15%-25% of extreme pressure additive, 2-3% of corrosion remover, 10-15% of penetrant, 4-6% of pH conditioning agent, 2-8% of non-ionic surface active agent, 2-5% of pH buffering agent, 0.3-0.8% of softener, 1% of alkali, 0.1-0.2% of defoamer, 0.2-0.5% of antirust agent and the balance of water. By utilizing the strengthened grinding method, strengthened treatment can be carried out on the wear-resisting alloy steel workpiece surface in the grinding process of ejecting a grinding material so as to prolong the fatigue life and improve the surface hardness of a workpiece.

Owner:GUANGZHOU UNIVERSITY

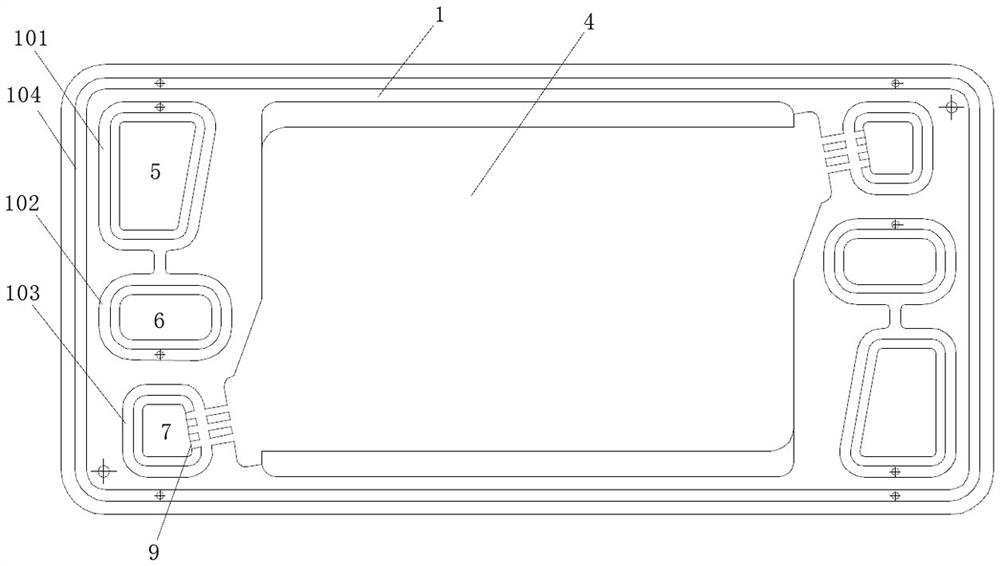

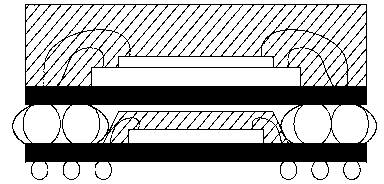

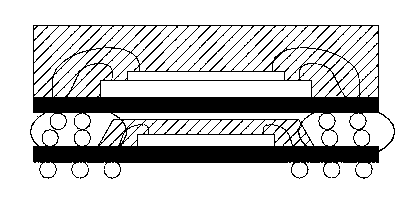

Three-dimensional system-level chip normal installation stacking packaging structure formed by sealing first and then corroding and technique method

ActiveCN103441078AFlexible stackingNo height limitSemiconductor/solid-state device detailsSolid-state devicesEpoxyElectricity

The invention relates to a three-dimensional system-level chip normal installation stacking packaging structure formed by sealing first and then corroding and a technique method. The packaging structure comprises a paddle (1) and pins (2). Electricity conducting columns (3)are arranged on front faces of the pins (2). A chip (4) is arranged on the front face of the paddle (1) through electricity-conducting or non-electricity-conducting adhesive substances. The front face of the chip (4) is connected with front faces of the pins (2) through metal wires (5). Plastic packaging materials or epoxy resin (7) wraps the area of the front face of the paddle (1), areas of the front faces of the paddles (2) and the peripheral area of the electricity conducting columns(3), the peripheral area of the chip (4), and the peripheral area of the metal wires (5). Anti oxidation layers (8) are arranged on the surface, exposing out of the plastic packaging materials or the epoxy resin (7), of the paddle (1), the surfaces, exposing out of the plastic packaging materials or the epoxy resin (7), of the pins (2), and the surfaces, exposing out of the plastic packaging materials or epoxy resin (7), of the electricity conducting columns (3). Packaging bodies (10) are stacked at tops of the electricity conducting columns (3) through electricity conducting substances (9). The packaging structure has the advantages of solving the problem that the quality of interconnected solder balls between packaging bodies is hard to control due to the fact that a lower layer welding disk is lower than a lower layer plastic packaging face in traditional substate packaging stacking.

Owner:江阴芯智联电子科技有限公司

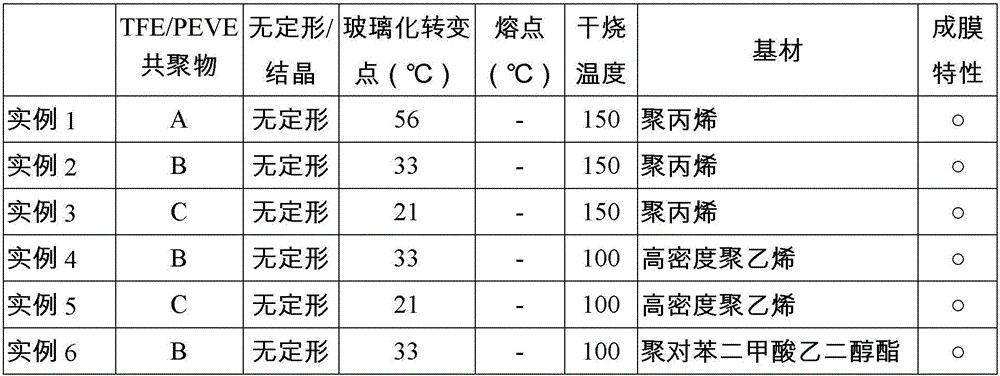

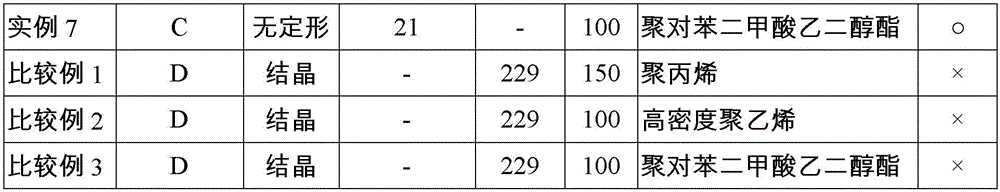

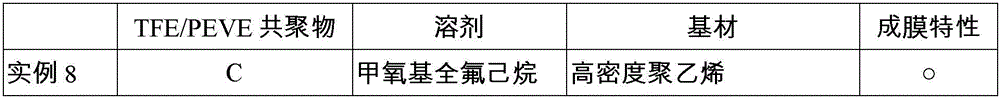

Composite molded body with a layer of a copolymer of tetrafluoroethylene and perfluoro(ethyl vinyl ether)

InactiveCN106459455ADoes not cause meltingIdeal chemical propertiesSynthetic resin layered productsCoatingsTetrafluoroethyleneEthyl vinyl ether

A composite molded body, and its manufacturing method, is provided wherein the composite body contains a layer comprising a copolymer of tetrafluoroethylene (TFE) and perfluoro(ethyl vinyl ether) (PEVE). The composite body can be manufactured under conditions in which an adjoined layer of thermoplastic resin and / or thermosetting resin is not be melted, thermally degraded or decomposed. The copolymer has a PEVE content of 20 to 80 weight percent, based on the total weight of the copolymer, and a melt flow rate of from 0.1 to 100 g / 10 min, as measured in compliance with ASTM D1238 at a temperature of 250 DEG C + / - 0.1 using a 5 kg weight.

Owner:DUPONT MITSUI FLUOROCHEMICALS CO LTD

High-entropy alloy additive manufacturing device and additive manufacturing method

PendingCN110091035ASimple structureEasy to useElectrode supporting devicesWelding/cutting media/materialsHigh entropy alloysAlternating current

The invention relates to the technical field of high-entropy alloy additive manufacturing, and particularly discloses a high-entropy alloy additive manufacturing device and additive manufacturing method. The high-entropy alloy additive manufacturing device comprises a welding wire clamp used for fixing two welding wires, an alternating-current power source and two wire feeders. The two welding wires are located on the same plane, axes of the two welding wires are crossed, the alternating-current power source is provided with two output ends, the two output ends are connected with a conductivenozzle of one welding wire, the two wire feeders are connected with one welding wire, are located on the ends, close to the conductive nozzle, of the welding wires, and are used for enabling the welding wires to be axially fed, the traditional high-entropy alloy additive manufacturing mode is changed, the high-entropy alloy of the complex structure can be manufactured, in the preparing process, the alternating-current double-wire indirect electric arc welding is used, heat transfer and medium transfer decoupling control is achieved, heat input is controlled within a certain range while the deposition rate is improved, and the device is more efficient and energy-saving.

Owner:HEBEI UNIVERSITY OF SCIENCE AND TECHNOLOGY

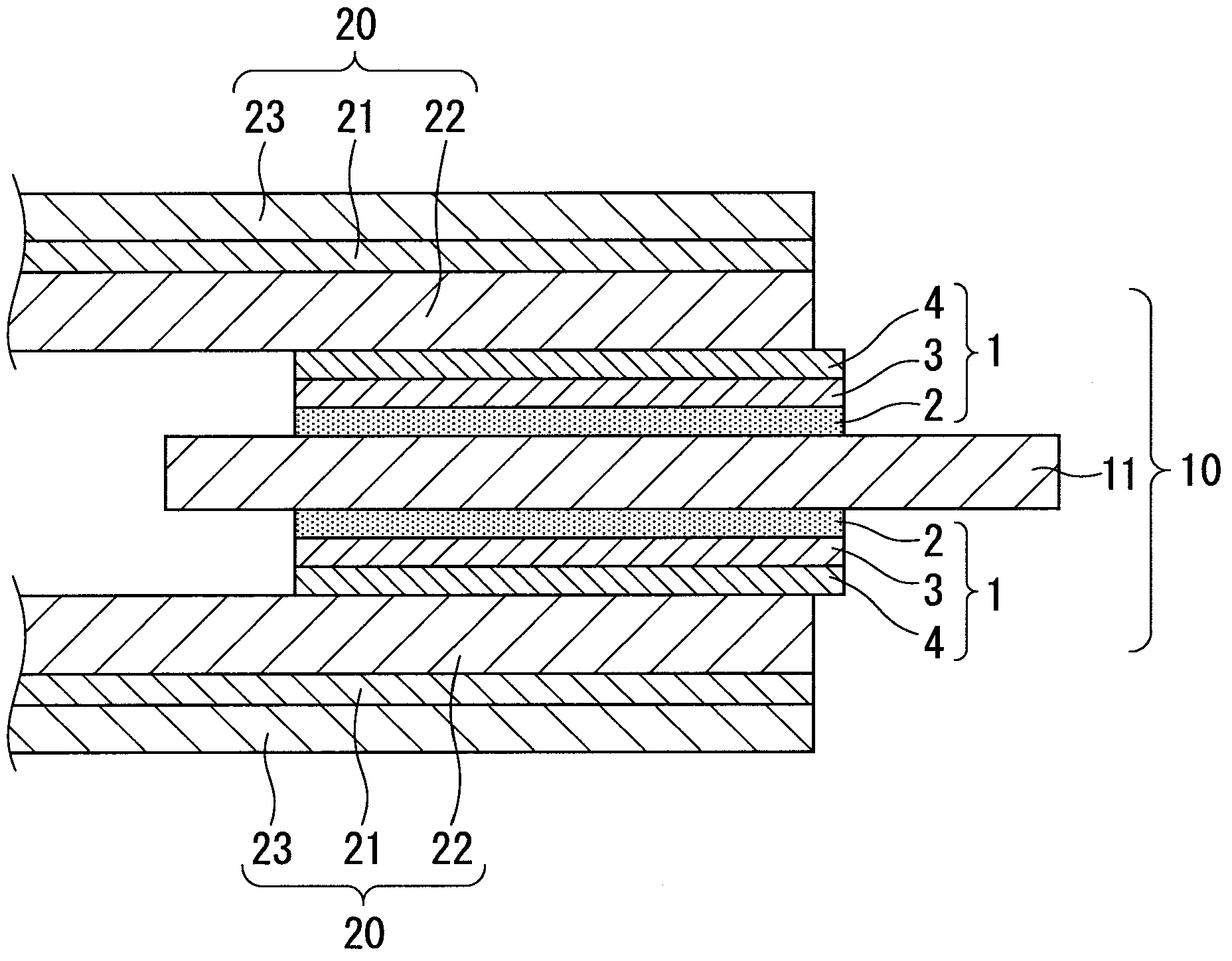

Process for producing sealing film, and sealing film

ActiveCN103222084ANot prone to short circuitImprove joint strengthSynthetic resin layered productsDouble layer capacitorsMolten stateChemical Linkage

A process for producing a sealing film (1) to be interposed between each electrode (11), as a power-generating element, that has been introduced into a bag (20) and the edge of the bag (20), the process comprising: a melt kneading step in which both an acid-modified polyolefin resin A to which a carboxylic acid has been grafted and a resin B having functional groups capable of reacting with the carboxy groups of the resin A are melted and kneaded together to thereby chemically bond the carboxy groups of the resin A to the functional groups of the resin B and convert the resins into a resin C; a heat-resistant-layer formation step in which the resin C is formed into a layer to form a heat-resistant layer (3); an adhesive-layer formation step in which a carboxylic-acid-modified polyolefin resin D is formed into a layer to form an electrode adhesion layer (2) which adheres to electrodes; and a laminating step in which the heat-resistant layer (3) and the electrode adhesion layer (2) are directly laminated to each other when the resin C and / or the resin D is in a molten state.

Owner:FUJIMORI KOGYO CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com