Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

40results about "Dielectric characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

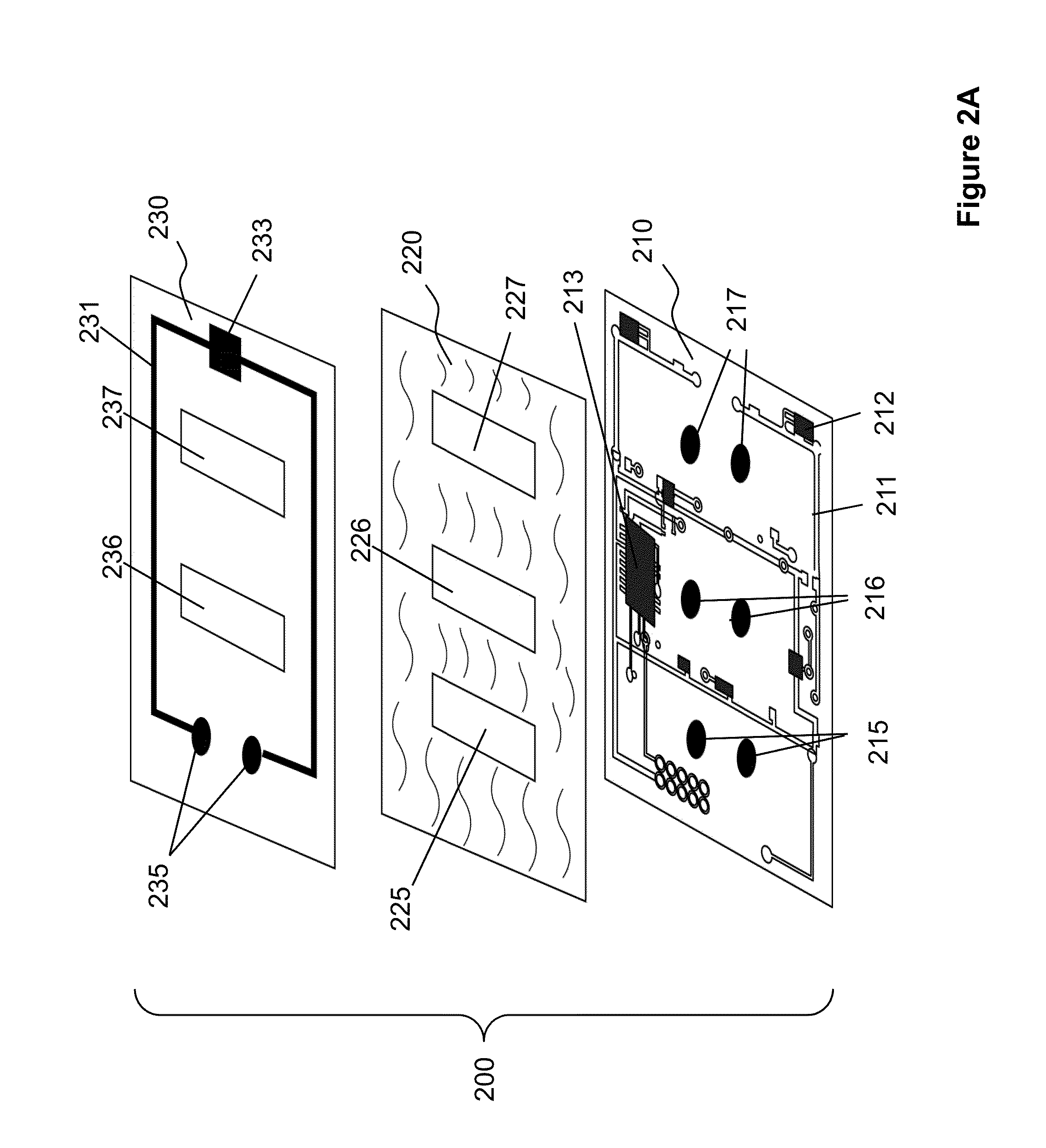

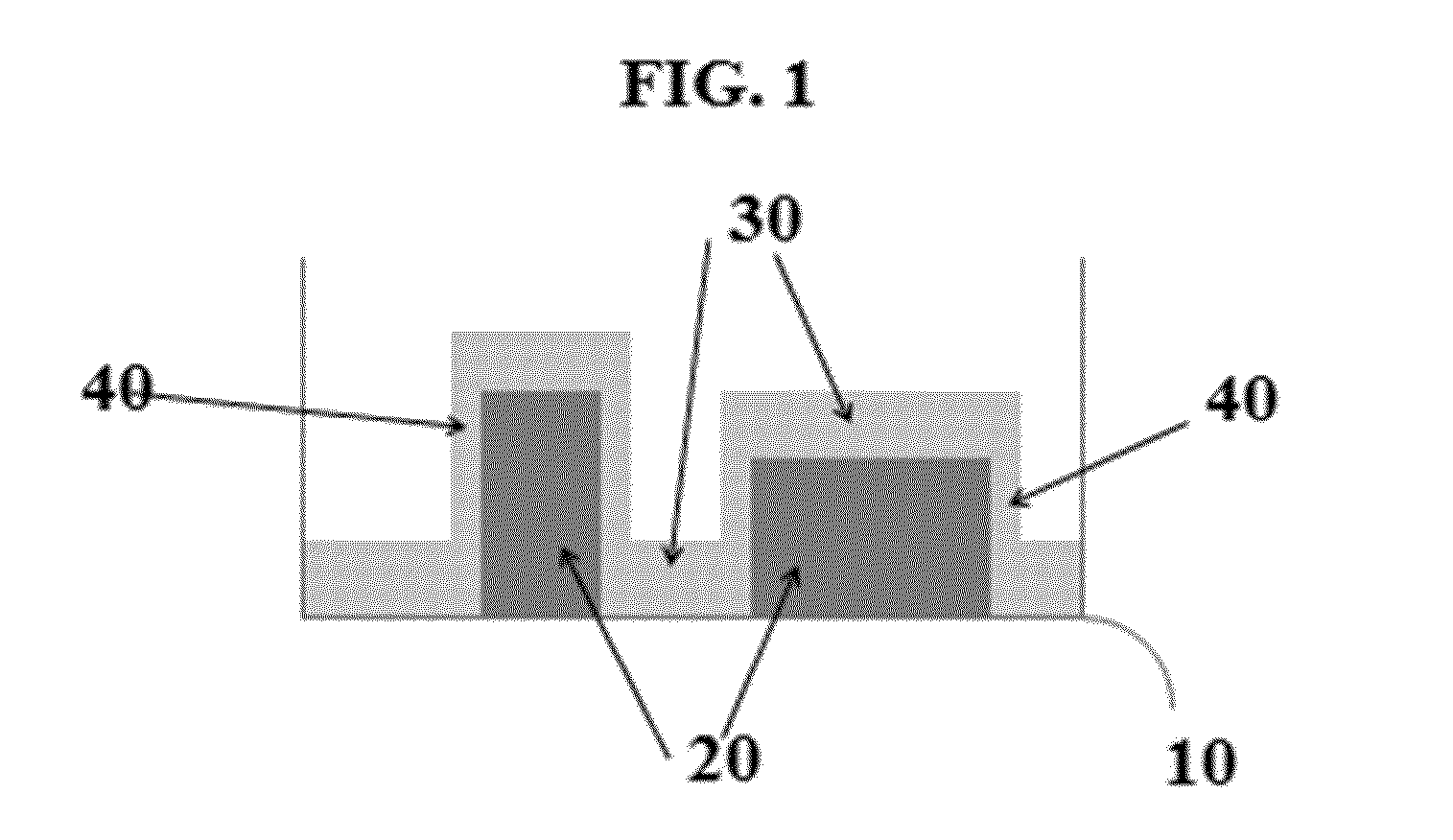

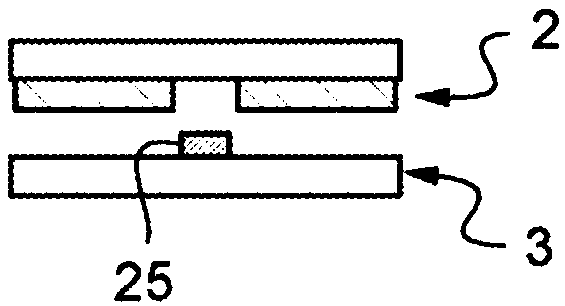

Electronic Stickers with Modular Structures

ActiveUS20160066854A1Highly compliantHighly flexibleBioelectric signal measurementNear-field in RFIDEngineering physicsMaterials science

An electronic sticker assembly includes a first electronic sticker comprising an upper surface, a lower surface, and a first group of conductive connection dots on the upper surface, a first adhesive layer on the first electronic sticker and comprising a first window. The first window is positioned to expose the first group of one or more conductive connection dots. A second electronic sticker on the first adhesive layer includes a lower surface and one or more second conductive connection dots on the lower surface. The first group of conductive connection dots on the upper surface of the first electronic sticker are in contact with the one or more second conductive connection dots on the lower surface of the second electronic sticker through the first window in the first adhesive layer.

Owner:VIVALNK

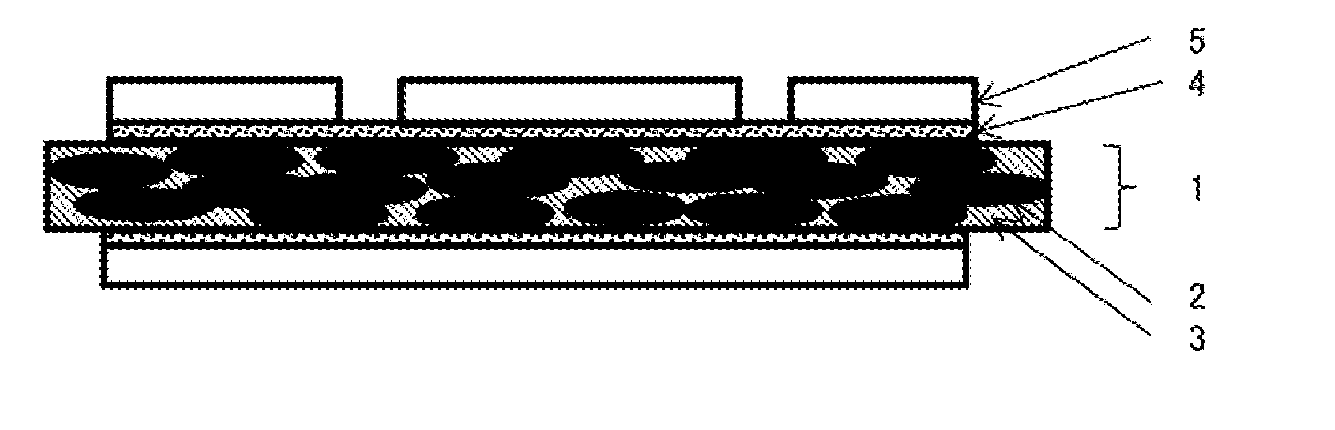

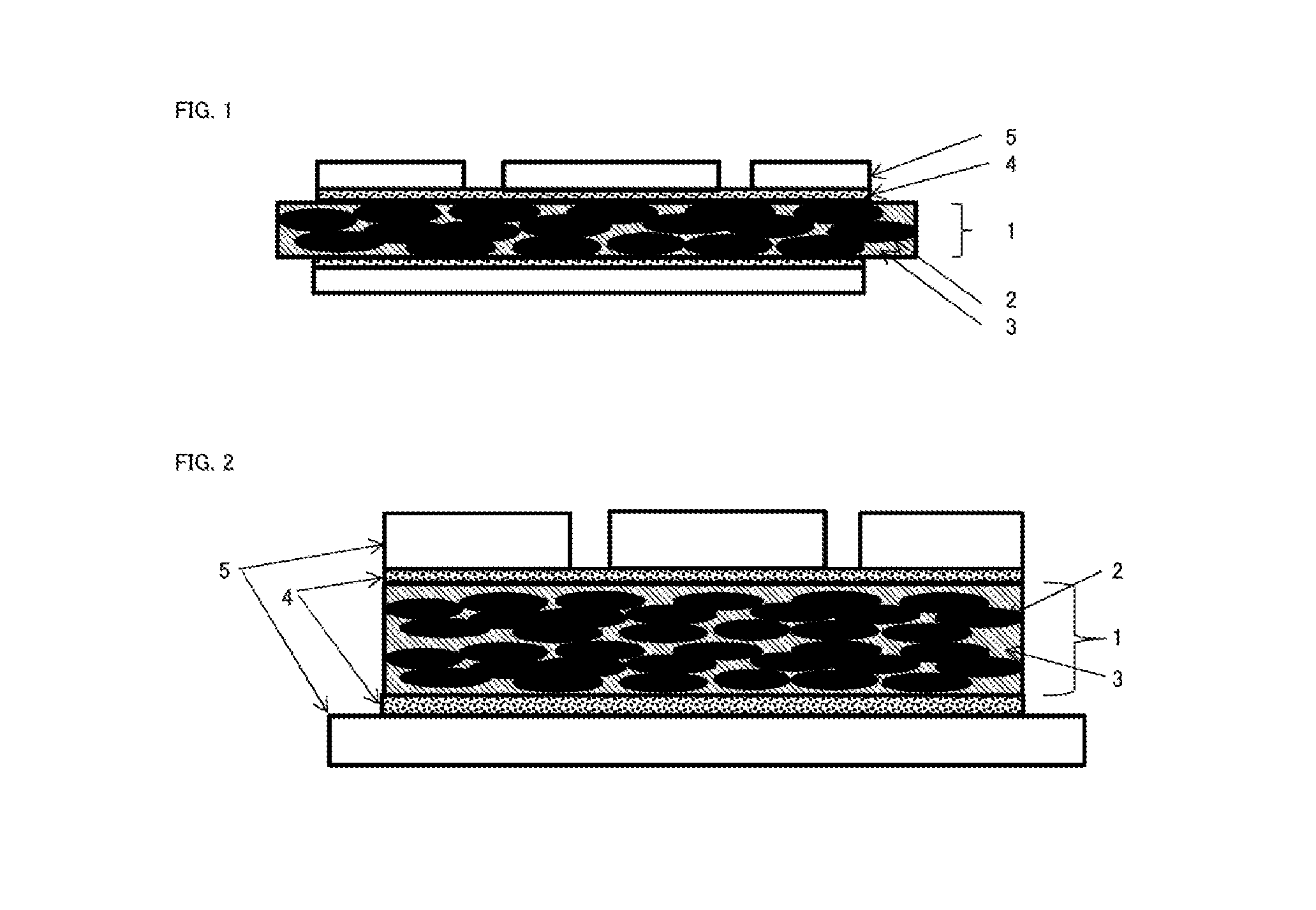

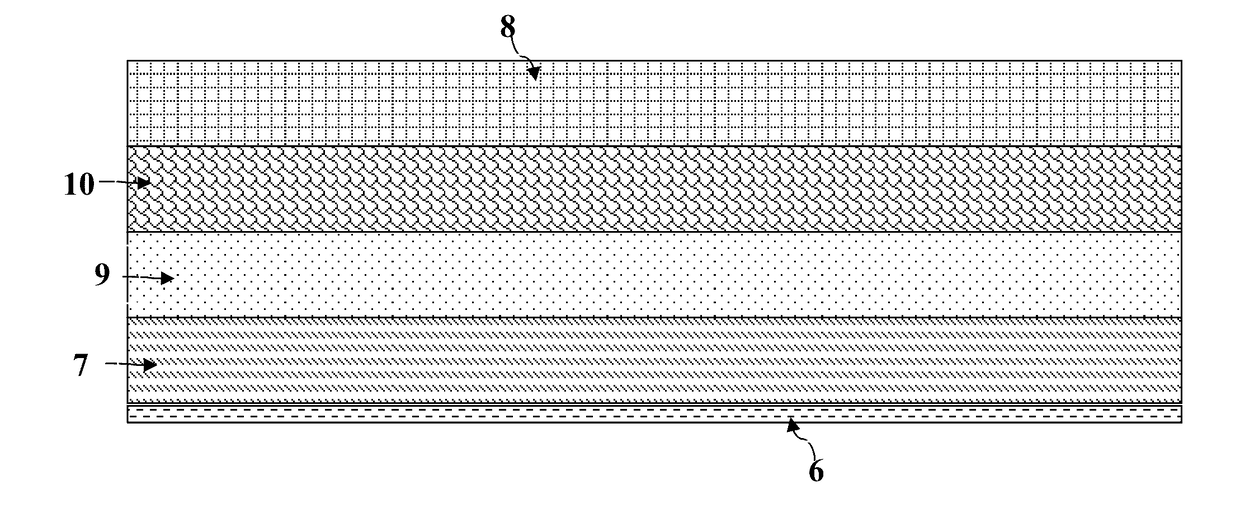

Boron nitride/resin composite circuit board, and circuit board including boron nitride/resin composite integrated with heat radiation plate

ActiveCN105453707AGood heat dissipationInsulating substrate metal adhesion improvementPrinted circuits stress/warp reductionBoron nitrideThermal expansion

Provided is a boron nitride / resin composite circuit board which has high heat radiation properties and high reliability. The boron nitride / resin composite circuit board is characterized by comprising: a platy resin-impregnated sintered boron nitride object which has a plate thickness of 0.2-1.5 mm and comprises 30-85 vol% sintered boron nitride object in which boron nitride particles having an average major-axis length of 5-50 [mu]m have been three-dimensionally bonded and 70-15 vol% resin; and a metal circuit constituted of copper or aluminum and bonded to each of both main surfaces of the sintered object. The circuit board is further characterized in that the ratio of the coefficient of thermal linear expansion (CTE1) at 40-150 DEG C in the plane direction of the resin-impregnated sintered boron nitride object to the coefficient of thermal linear expansion (CTE2) at 40-150 DEG C of the metal circuit, CTE1 / CTE2, is 0.5-2.0.

Owner:DENKA CO LTD

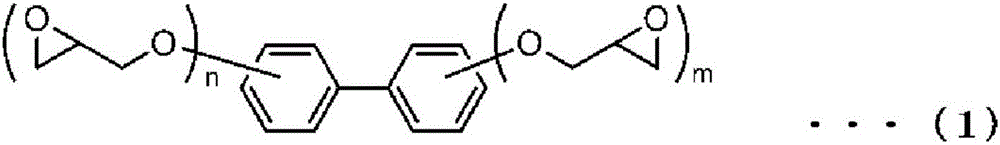

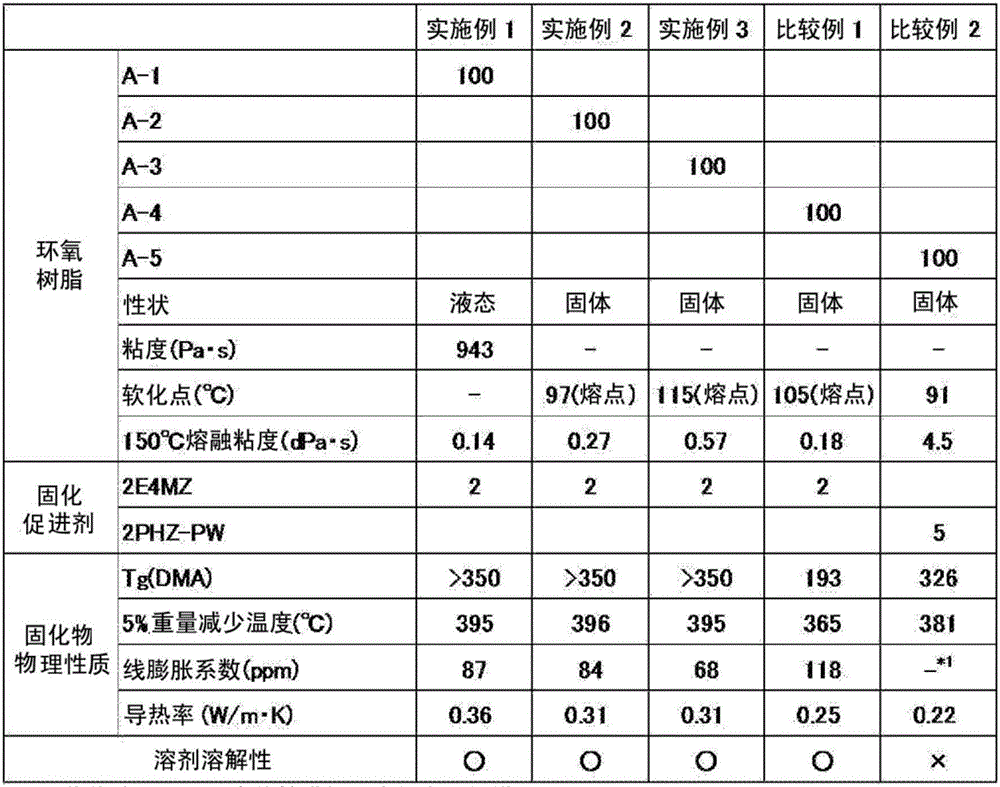

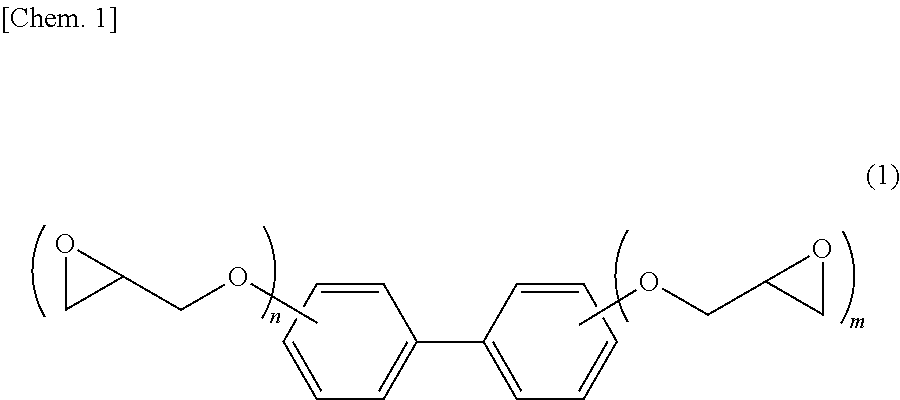

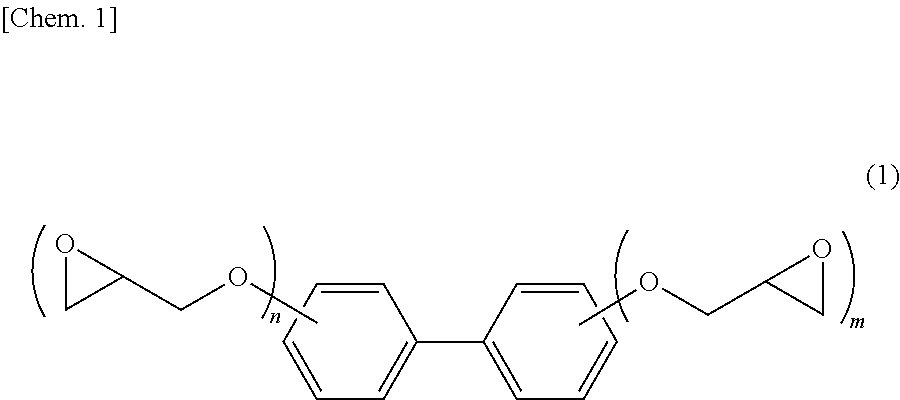

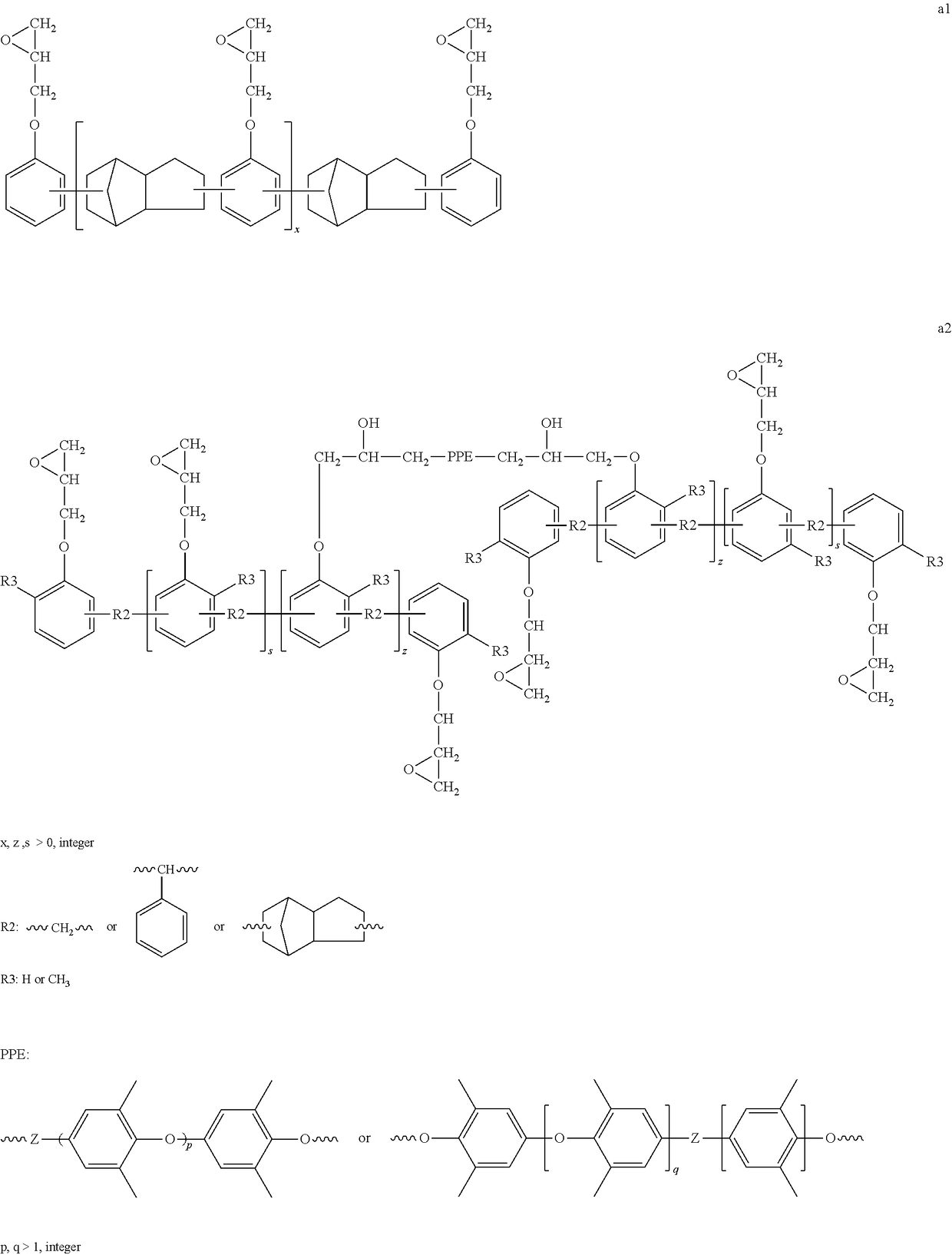

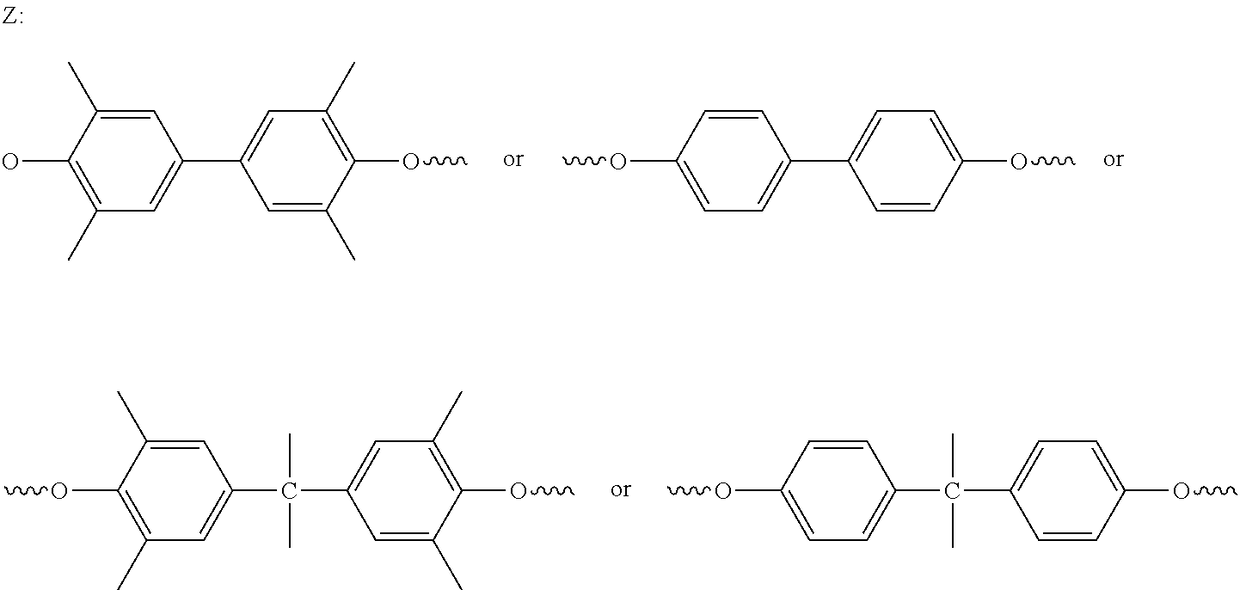

Epoxy resin composition for electronic material, cured product thereof and electronic member

ActiveCN106471035ALow thermal expansionImprove solubilityNon-macromolecular adhesive additivesSemiconductor/solid-state device detailsEpoxyGlycylxylidide

An epoxy resin composition for an electronic material is provided which contains: a multifunctional biphenyl-type epoxy resin which is a triglycidyloxybiphenyl or a tetraglycidyloxybiphenyl; and a curing agent and / or a curing promoting agent. Further, an epoxy resin composition for an electronic material is provided which also contains a filler, specifically a thermally conductive filler. Further, a cured product formed by curing said epoxy resin composition, and an electronic member containing said cured product are provided.

Owner:DIC CORP

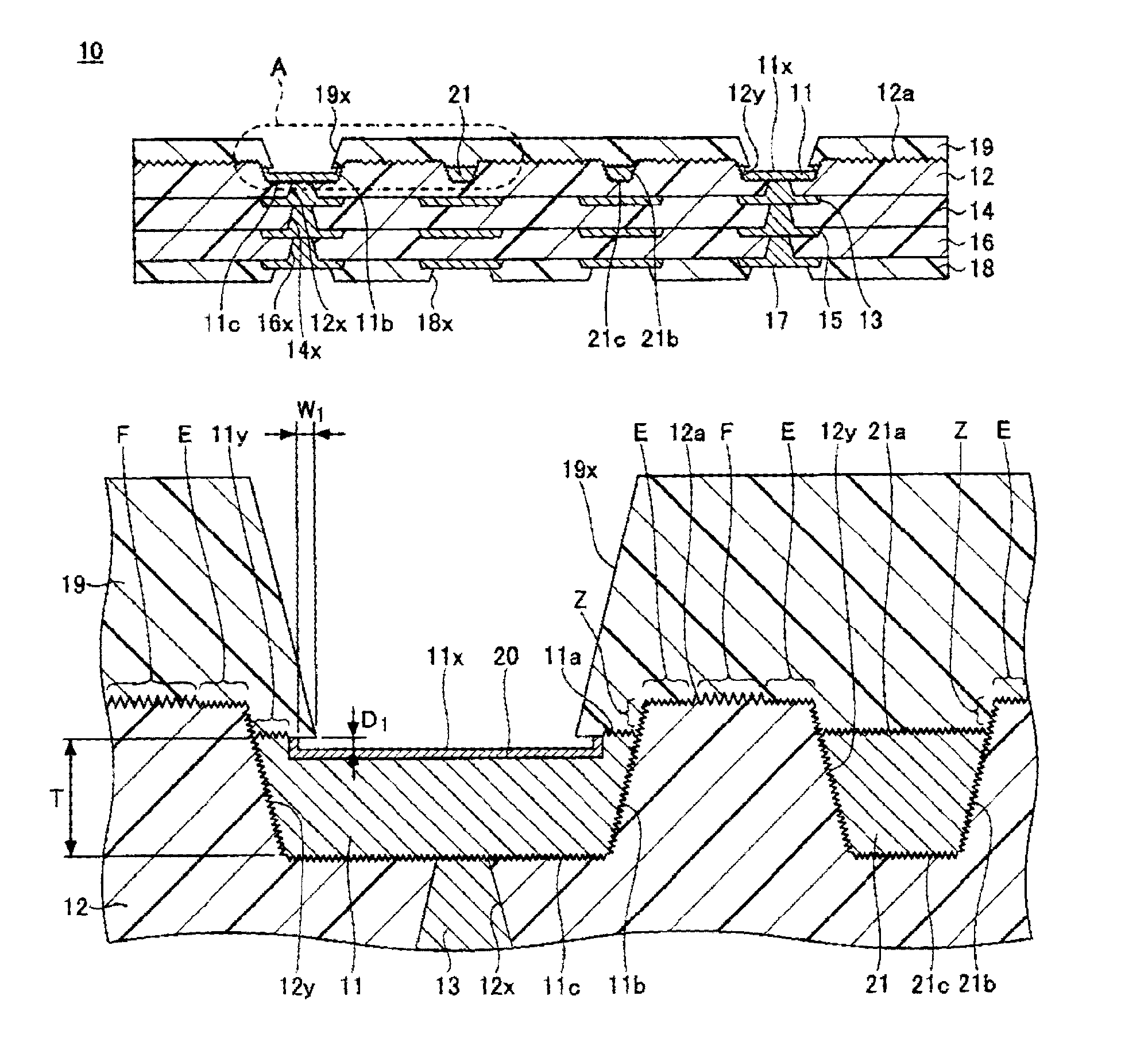

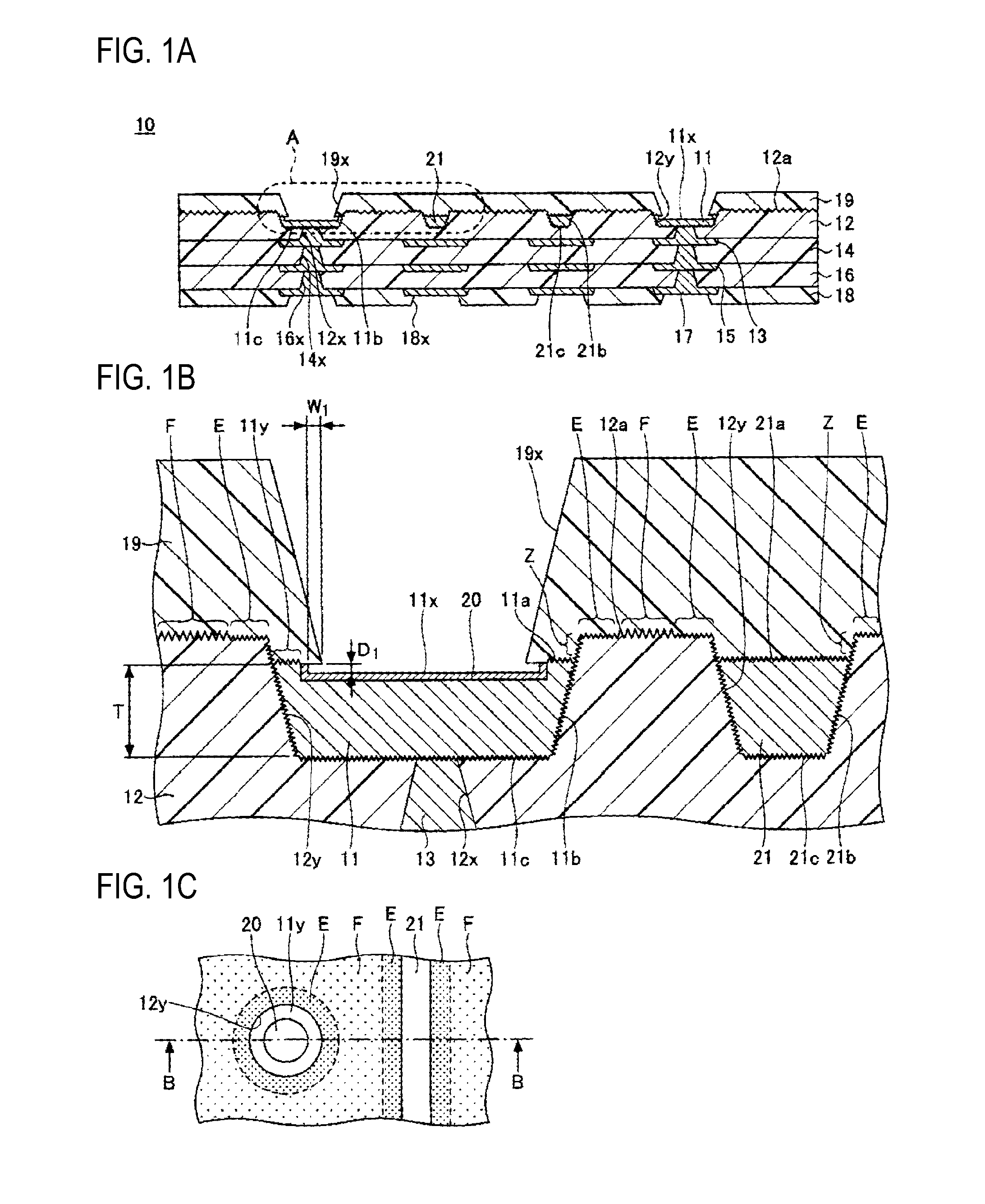

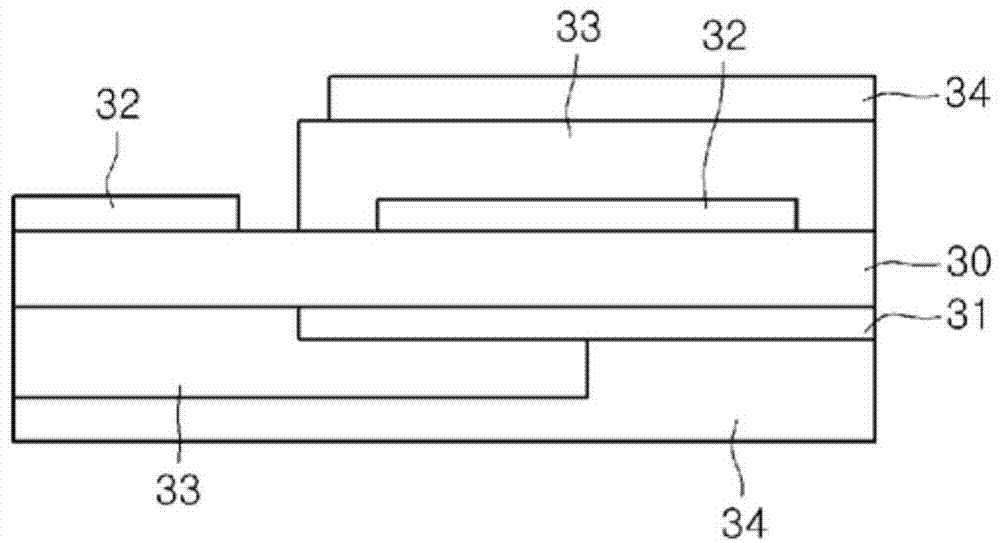

Wiring board and method for manufacturing the same

ActiveUS20150014027A1Improve connection reliabilityDielectric characteristicsPrinted circuit manufactureResistEngineering

A wiring substrate includes an insulating layer, a pad, and a solder resist layer. The insulating layer has a first surface formed with a first recess portion. The pad is embedded in the first recess portion. The pad includes a second surface and a third surface. The third surface that is located at a lower position than the first surface so as to expose an inner wall surface of the first recess portion. The pad is formed with a second recess portion in a center portion of the third surface. The solder resist layer is provided on the first surface. An adjacent portion of the first surface to a peripheral portion of the first recess portion is smaller in roughness than a region of the first surface peripheral to the adjacent portion of the first surface.

Owner:SHINKO ELECTRIC IND CO LTD

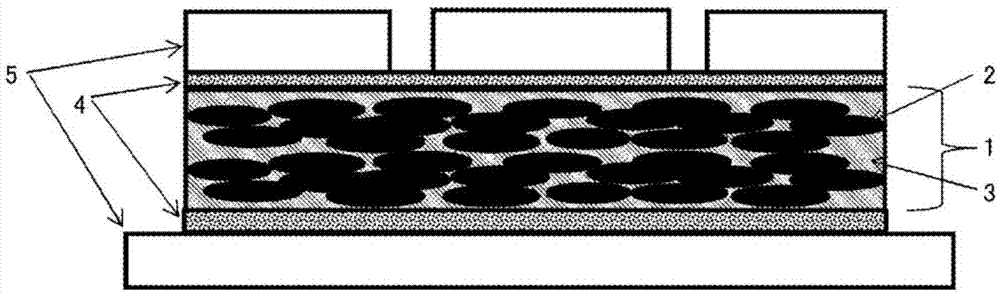

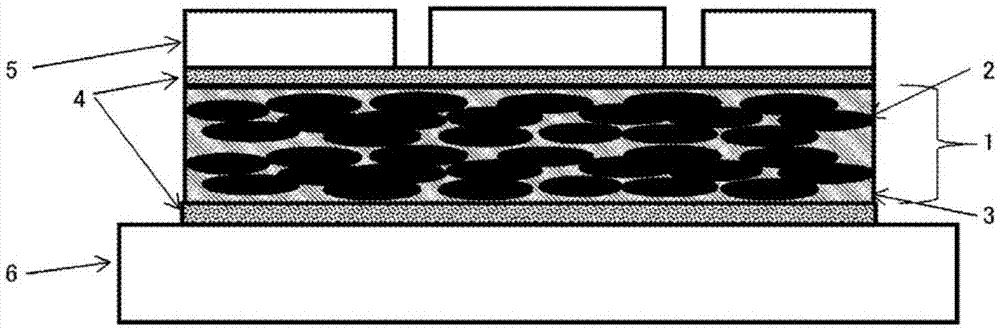

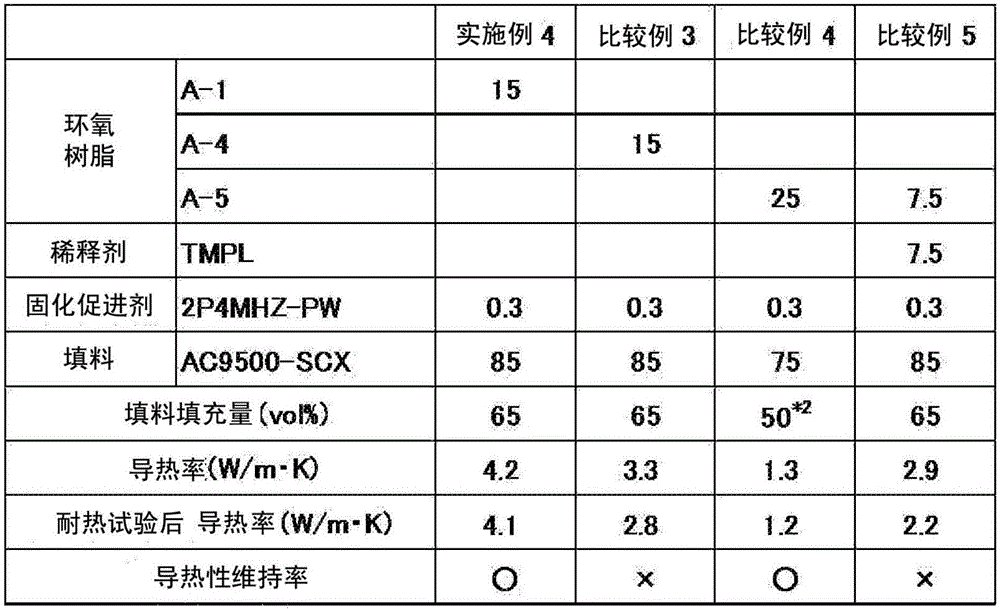

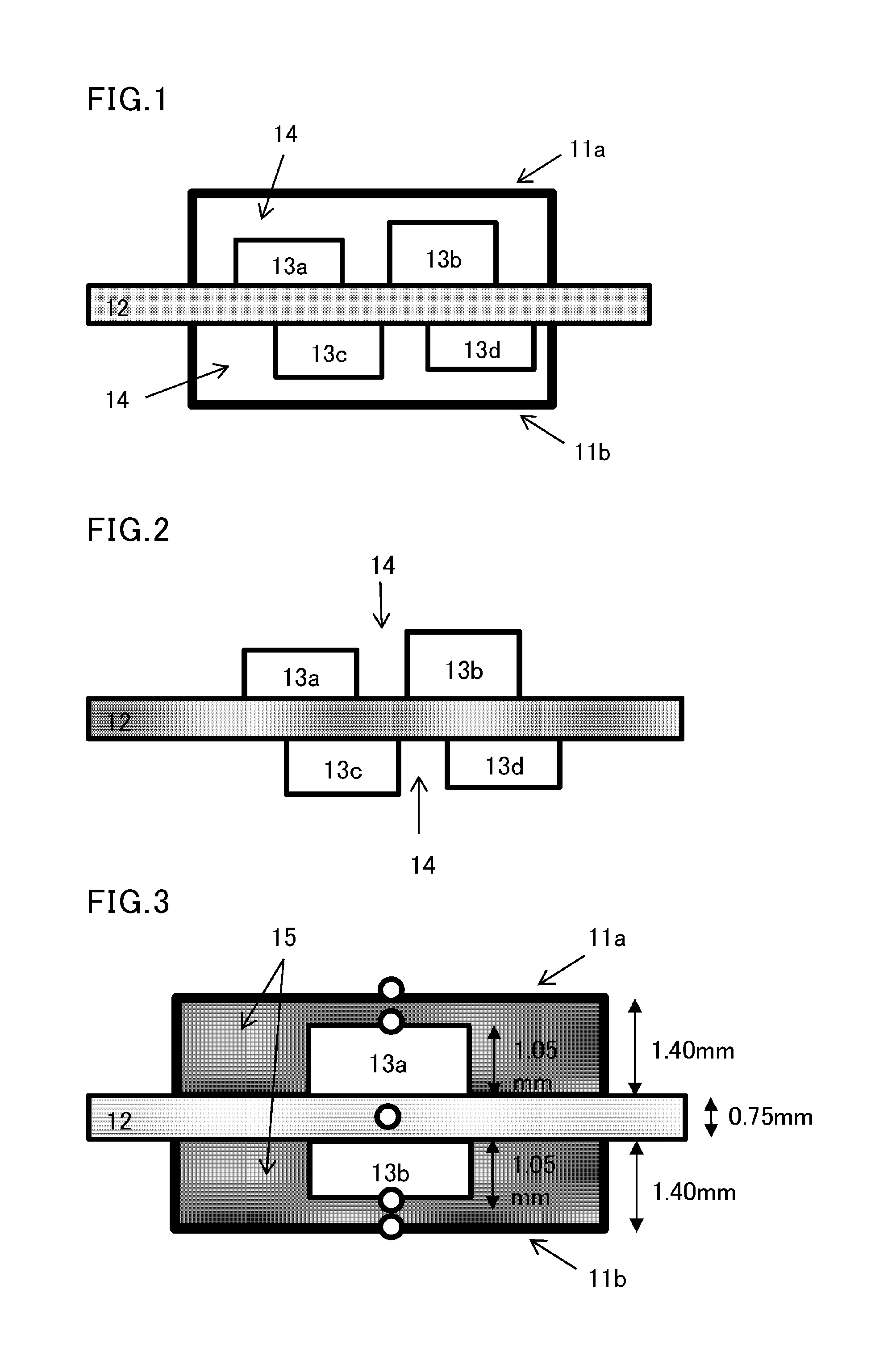

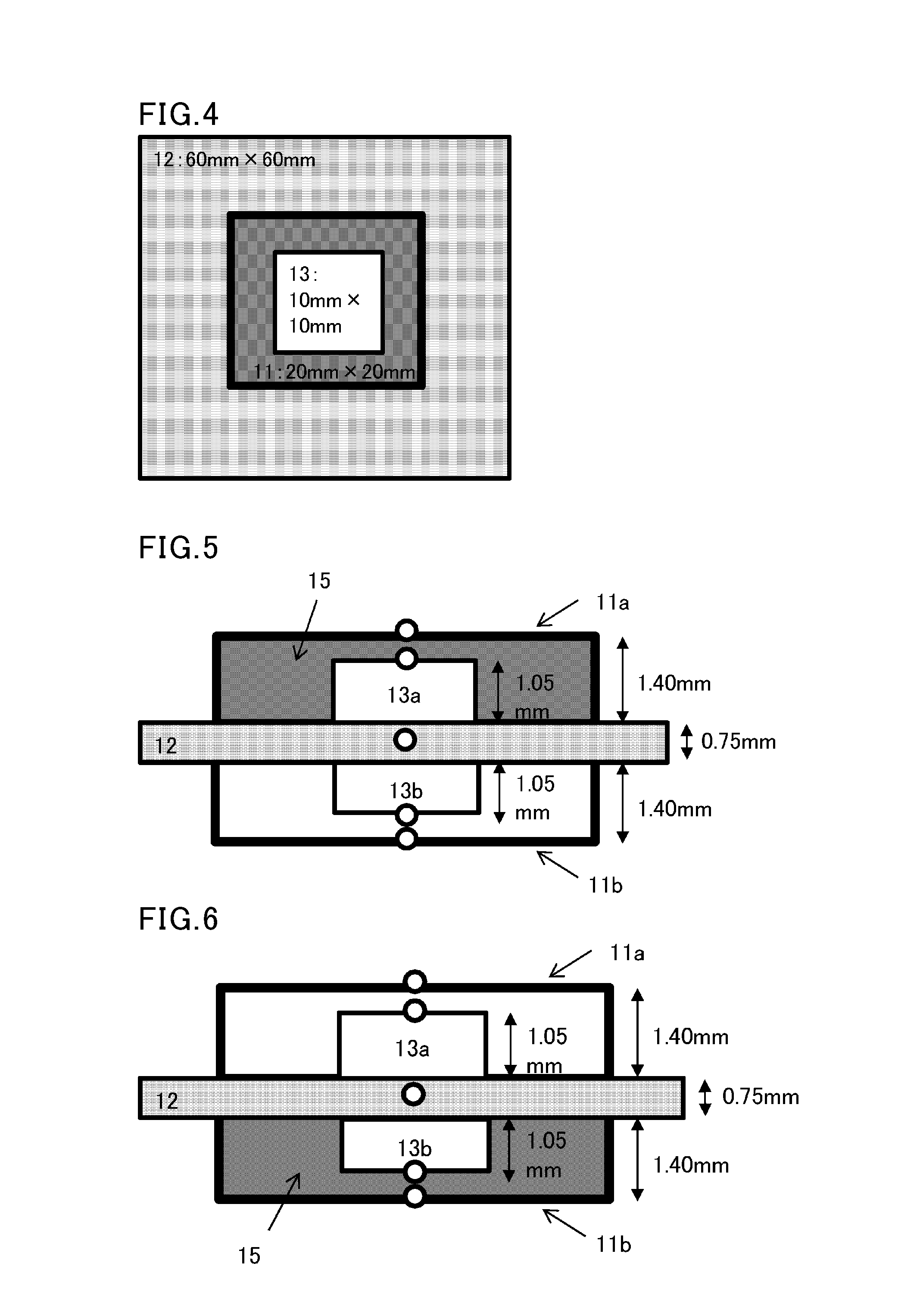

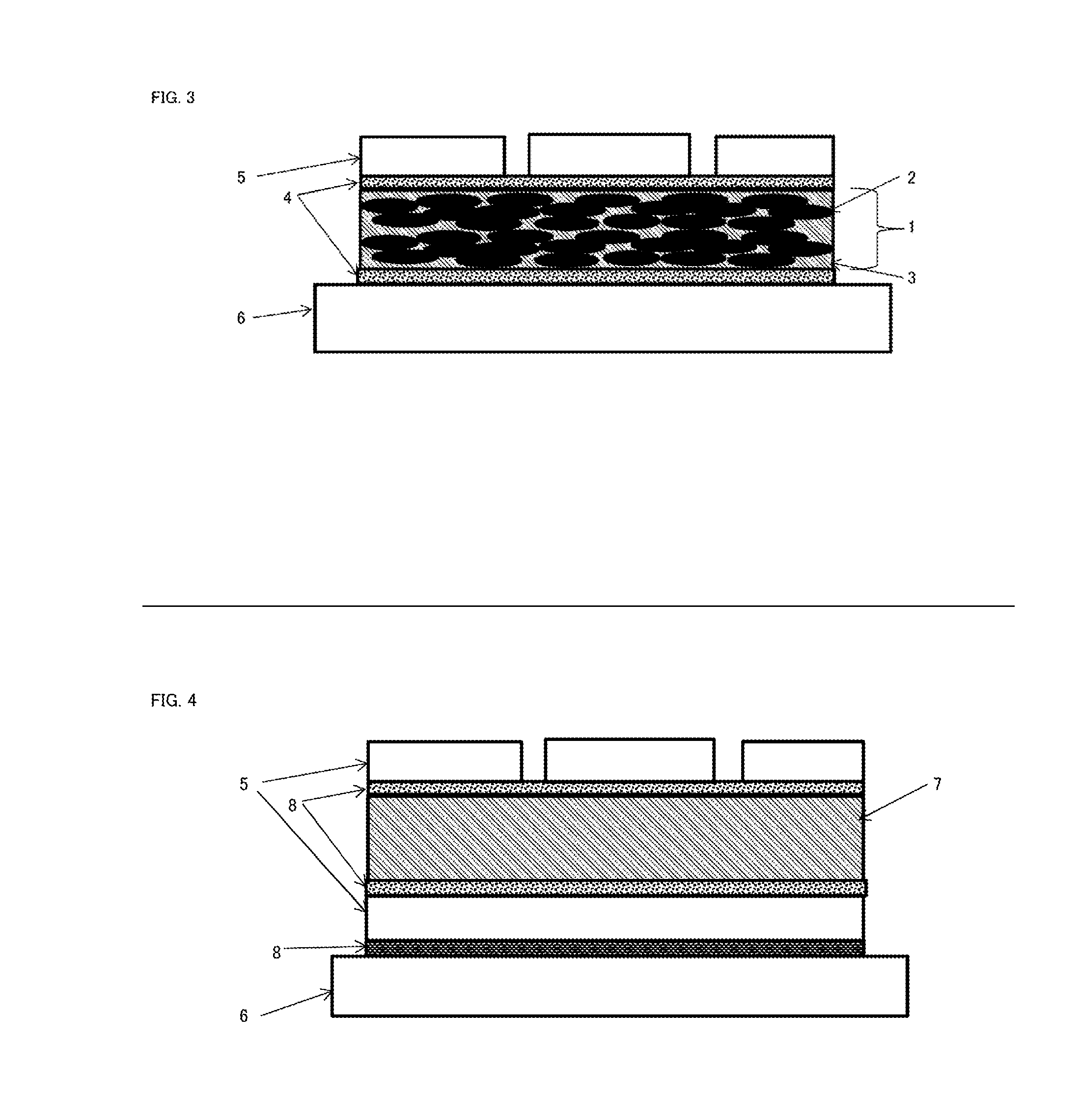

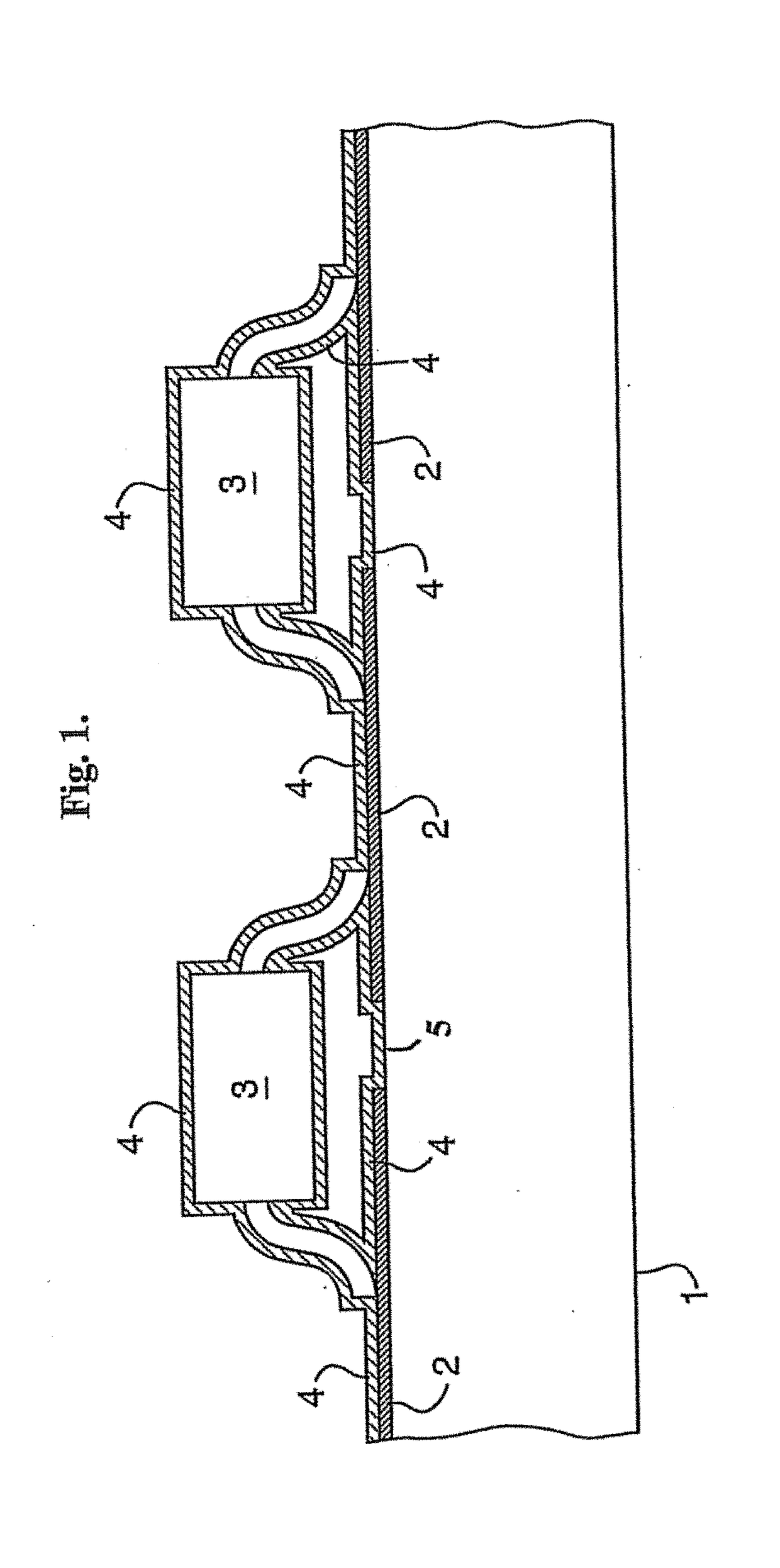

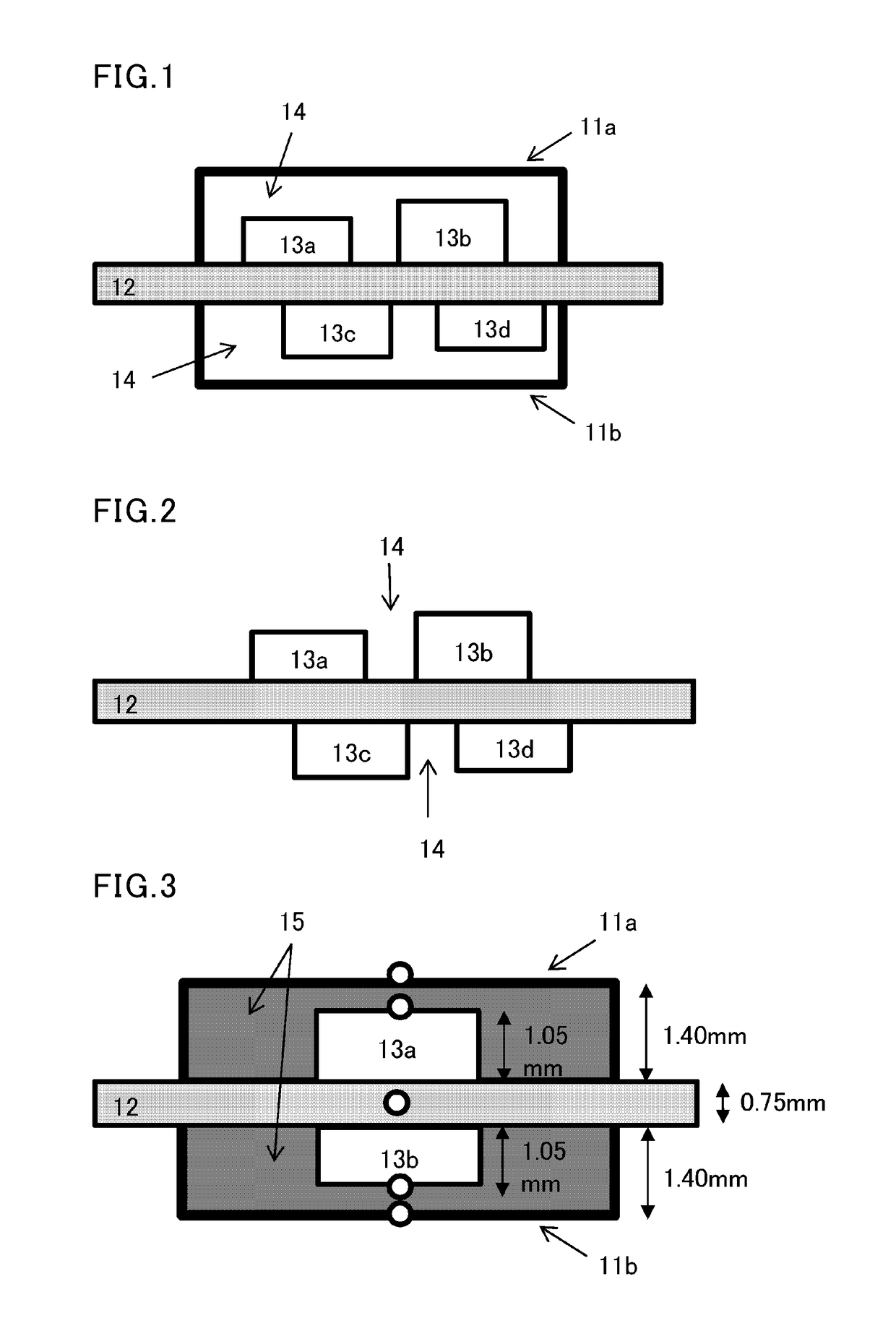

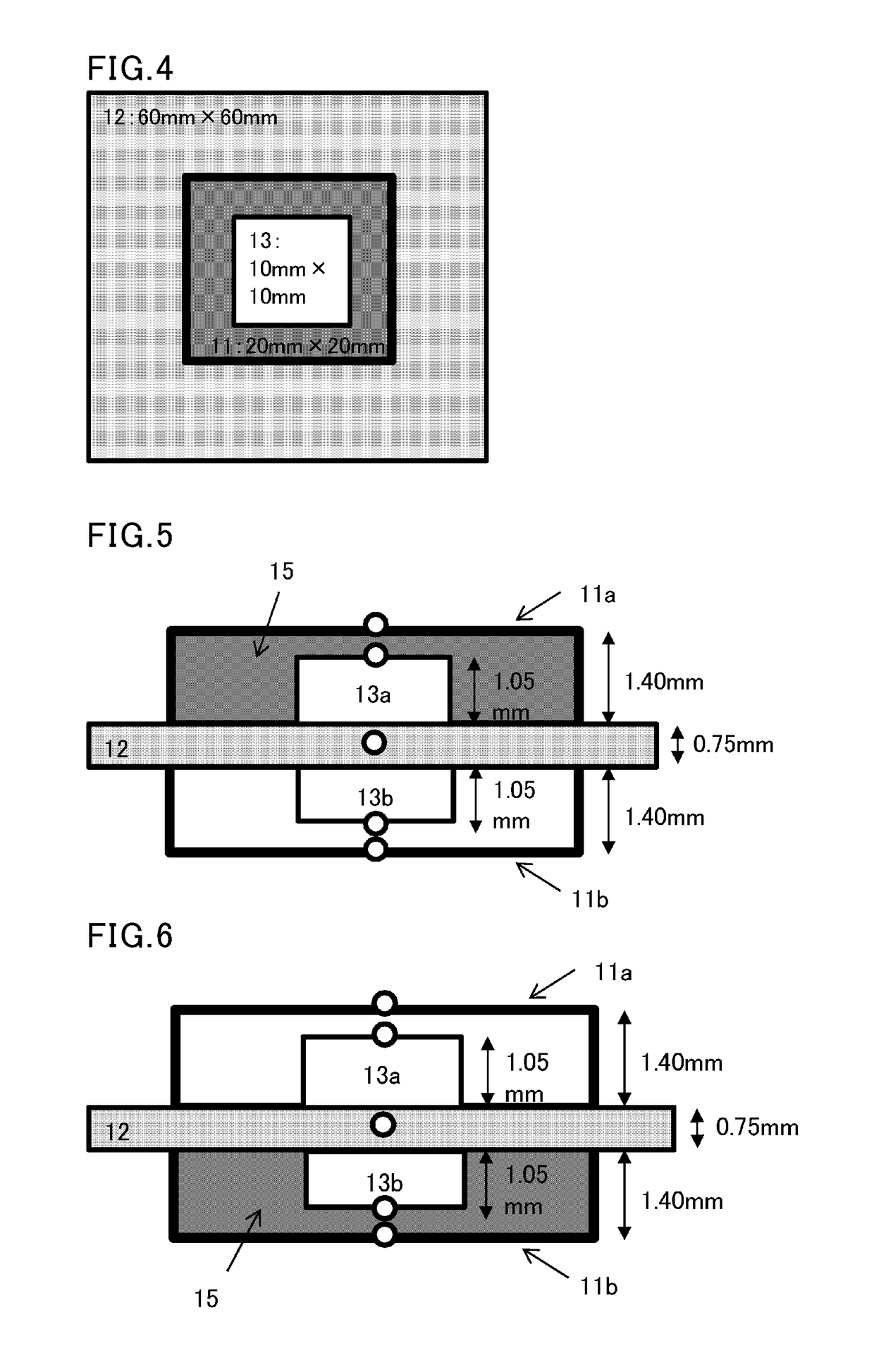

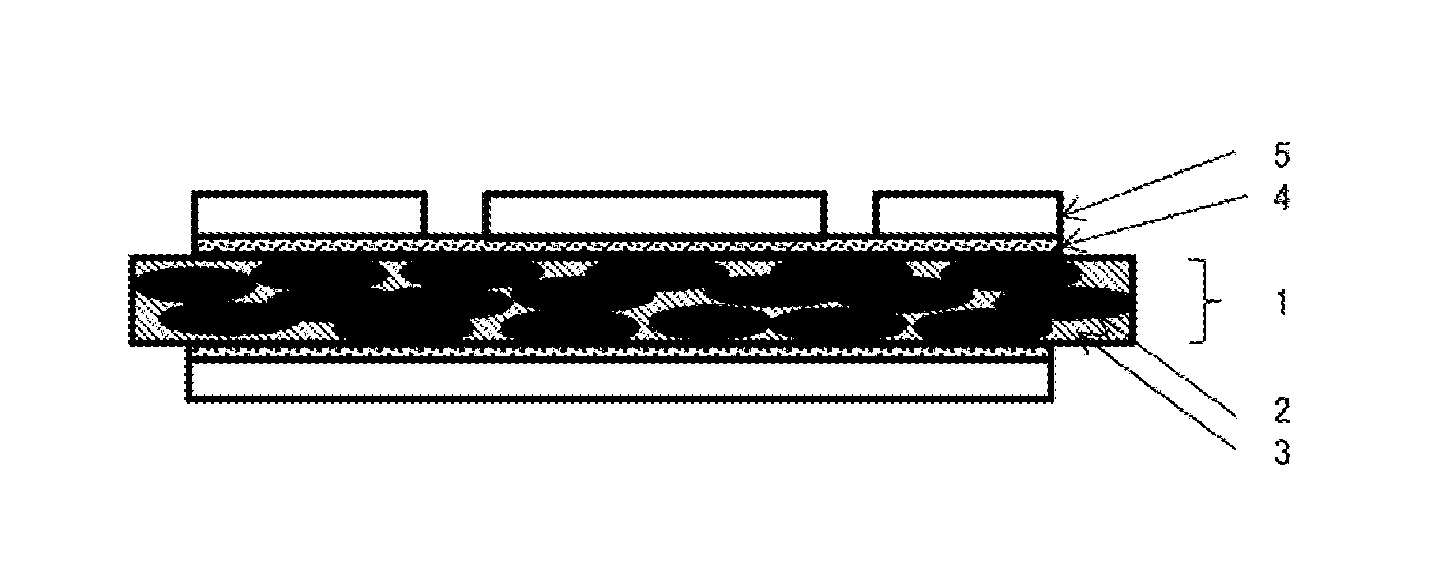

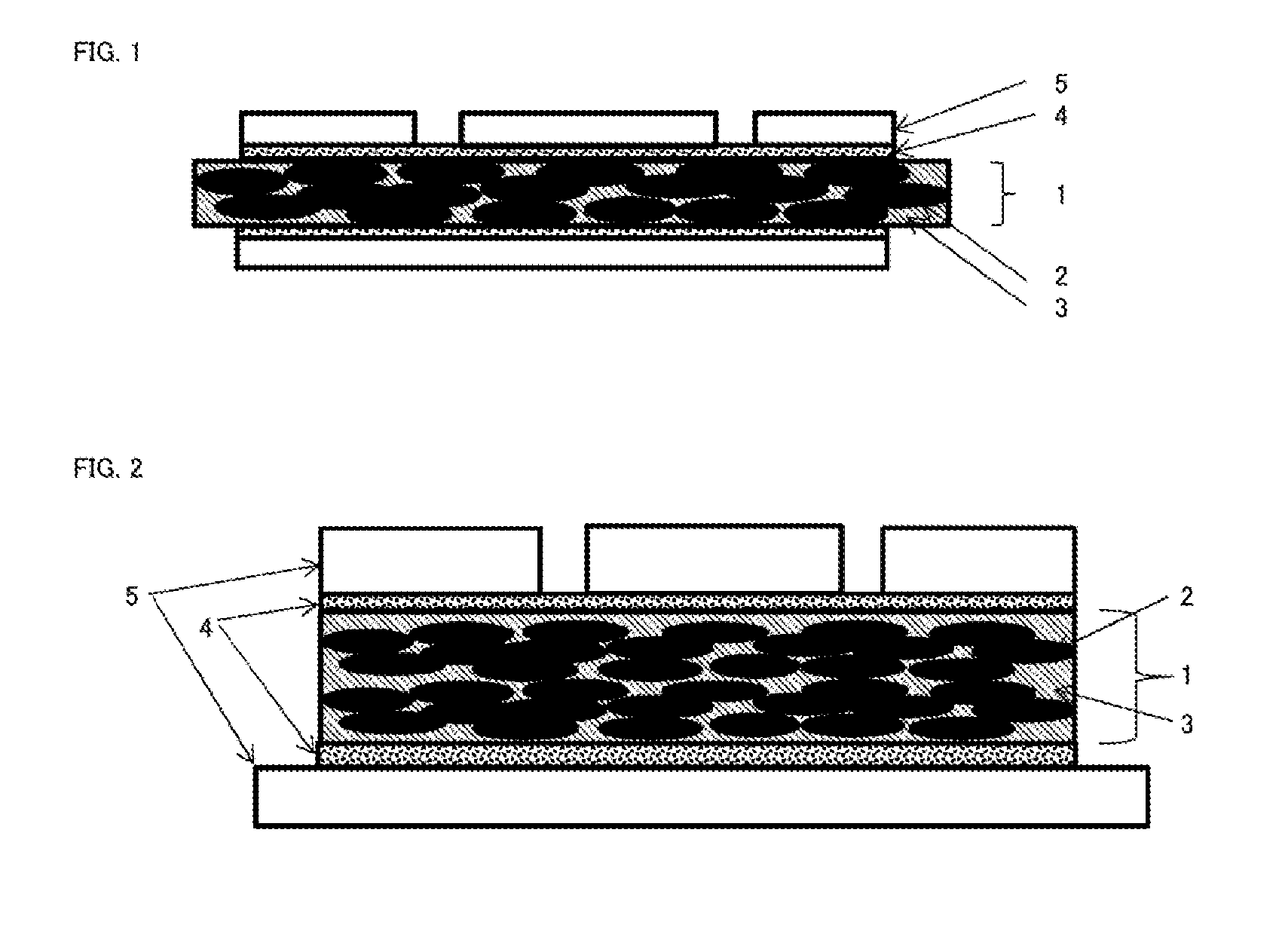

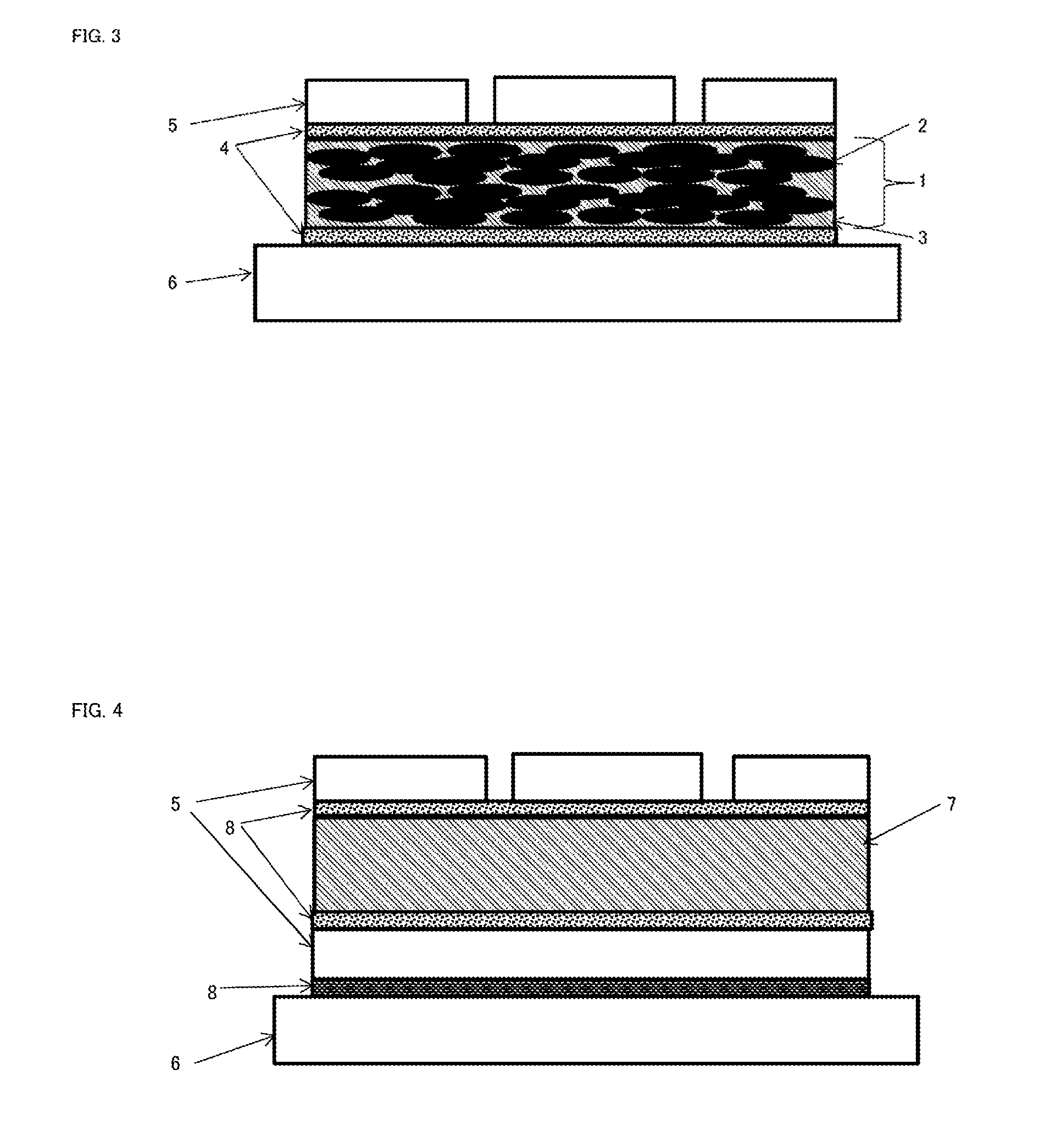

Heat dissipating structure

ActiveUS20160157334A1Avoid overall overheatingAvoid performance degradationCircuit thermal detailsSemiconductor/solid-state device detailsPrinted circuit boardLiquid resin

A heat dissipation structure including: a printed circuit board; a first heat-generating element; a second heat-generating element; and a cured product of a thermally conductive curable liquid resin composition, the printed circuit board having a first surface and a second surface that is opposite to the first surface, the first heat-generating element being placed on the first surface, the second heat-generating element being placed on the second surface, the first heat-generating element generating an equal or greater amount of heat than the second heat-generating element, the second heat-generating element being surrounded by the cured product, the first heat-generating element being surrounded by a layer that has a lower thermal conductivity than the cured product.

Owner:KANEKA CORP

Boron nitride/resin composite circuit board, and circuit board including boron nitride/resin composite integrated with heat radiation plate

ActiveUS20160227644A1Good heat dissipationHeat resistant cycle characteristicsInsulating substrate metal adhesion improvementPrinted circuits stress/warp reductionLongest DiameterBoron nitride

A boron nitride / resin composite circuit board having high heat dissipation characteristics and high relyability is provided. A boron nitride / resin composite circuit board, including: a plate-shaped resin-impregnated boron nitride sintered body having a plate thickness of 0.2 to 1.5 mm, the plate-shaped resin-impregnated boron nitride sintered body including 30 to 85 volume % of a boron nitride sintered body having boron nitride particles bonded three-dimensionally, the boron nitride particles having an average long diameter of 5 to 50 μm, and 70 to 15 volume % of a resin; and a metal circuit adhered onto both principal planes of the plate-shaped resin-impregnated boron nitride sintered body, the metal circuit being copper or aluminum, wherein: a ratio of a linear thermal expansion coefficient in a plane direction of the resin-impregnated boron nitride sintered body at 40 to 150° C. (CTE1) and a linear thermal expansion coefficient of the metal circuit at 40 to 150° C. (CTE2) (CTE1 / CTE2) is 0.5 to 2.0.

Owner:DENKA CO LTD

Epoxy resin composition for electronic material, cured product thereof and electronic member

InactiveUS20170158807A1Excellent solvent solubilityLow viscosityNon-macromolecular adhesive additivesSemiconductor/solid-state device detailsEpoxyElectronic component

An epoxy resin composition for electronic material, containing a polyfunctional biphenyl type epoxy resin that is a triglycidyloxybiphenyl or a tetraglycidyloxybiphenyl and at least one of a curing agent and a curing accelerator is provided. Furthermore, the epoxy resin composition for electronic material, further containing a filler, in particular, a thermal conductive filler, is provided. Furthermore, a cured product obtained by curing the epoxy resin composition for electronic material, and an electronic component containing the cured product are provided.

Owner:DAINIPPON INK & CHEM INC

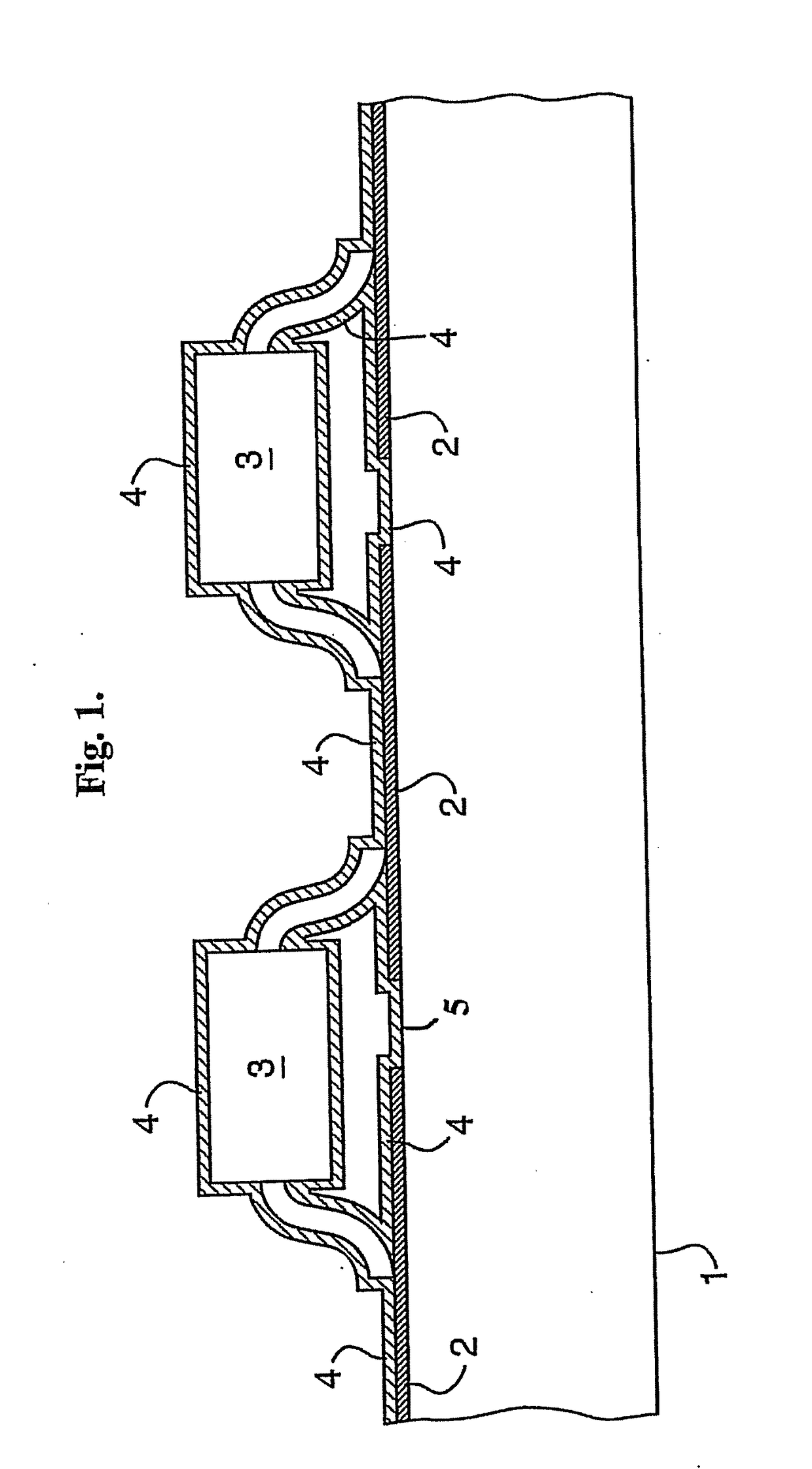

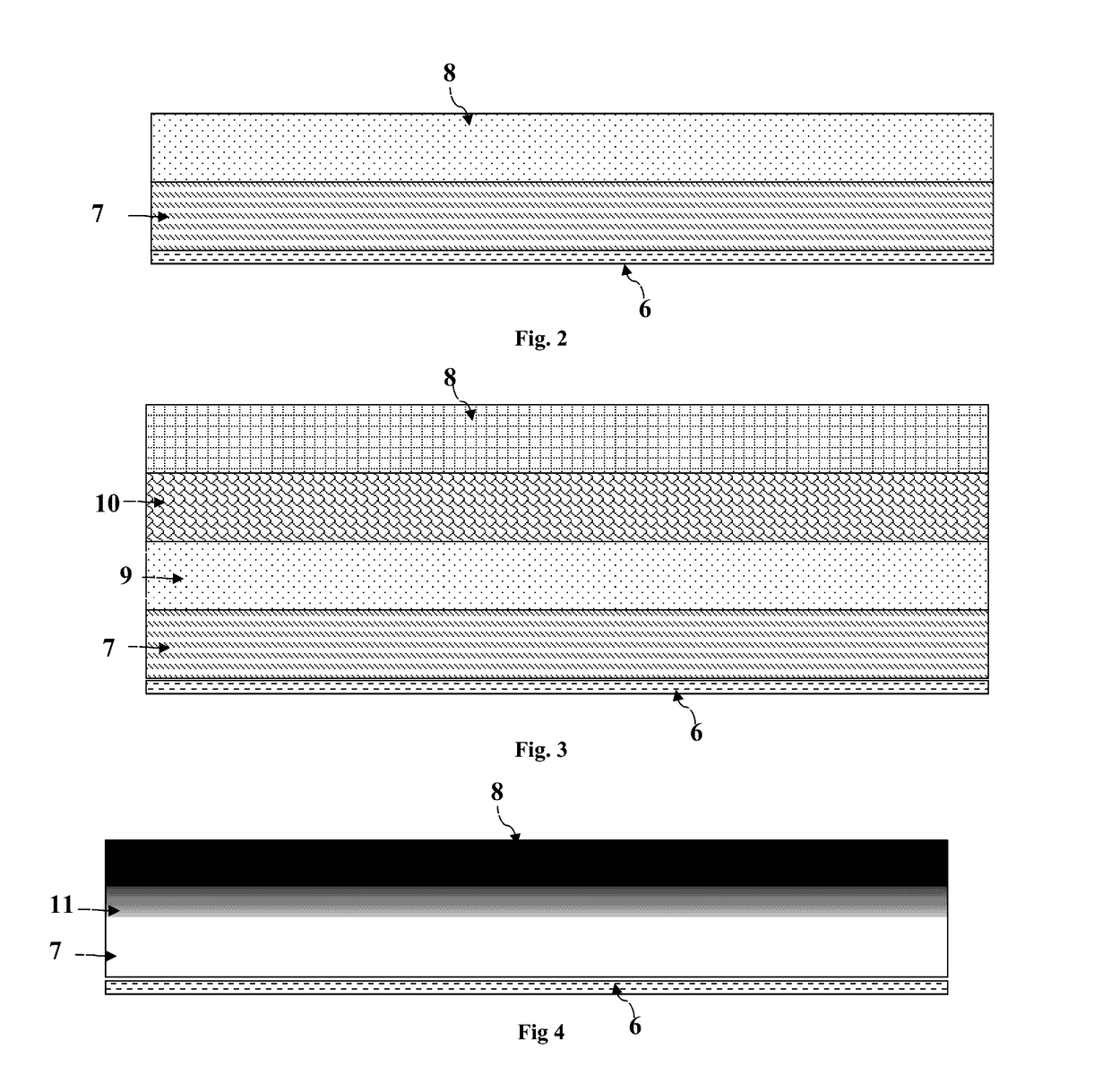

Formulated resin compositions for flood coating electronic circuit assemblies

ActiveUS20150077947A1Printed circuit detailsPrinted circuit board receptaclesHemt circuitsConformal coating

Electrical circuit assemblies flood coated with polymeric flood coat compositions as described or exemplified herein are provided. The flood coat composition is characterized as having a sufficient gel time and thixotropic index as to substantially cover or encapsulate the electrical circuit assembly as a fixed mass upon cure such that the thickness of the polymeric coating on surfaces horizontal to the assembly is from 20 mils to 75 mils, and the thickness on surfaces vertical to the assembly is from 4 mils to 20 mils. Such flood coated assemblies and devices containing same are advantageous over conventional potting materials or conformal coatings because they require less material thereby reducing weight and cost, and they are able to withstand extreme environmental stresses such as from temperature and / or vibrations.

Owner:ELANTAS PDG

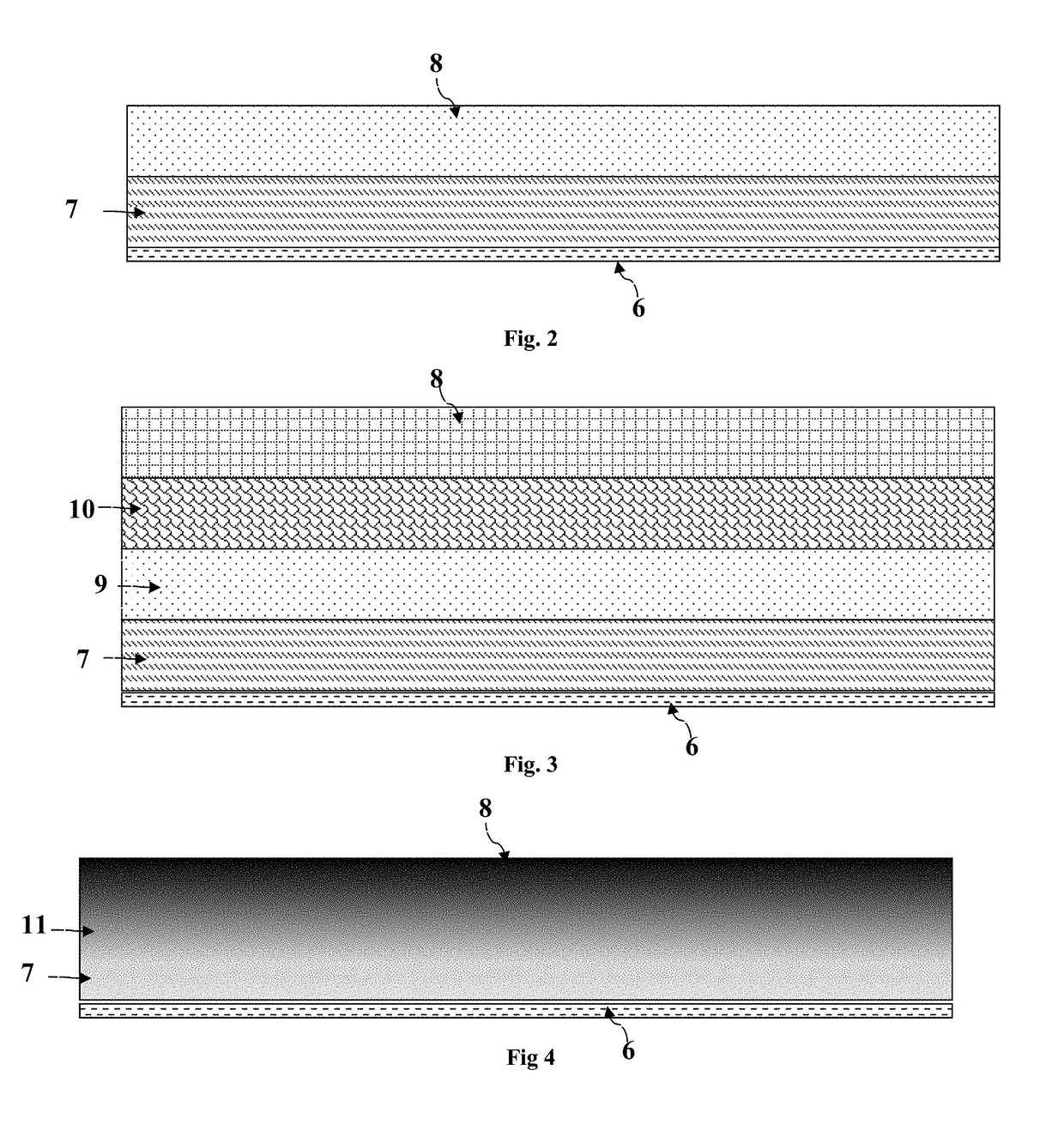

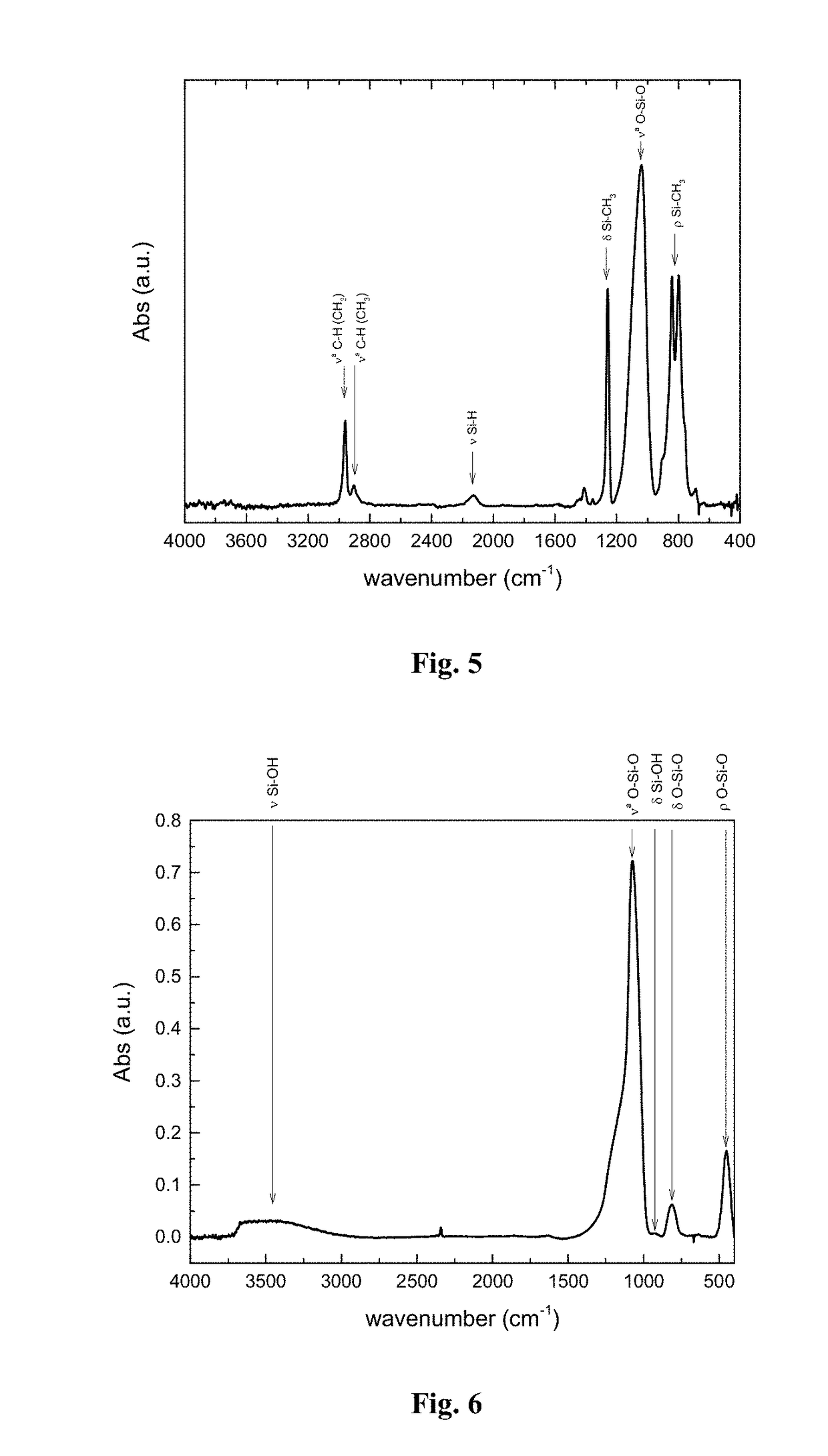

Coated electrical assembly

InactiveUS20170094810A1High of electricalIncreased Physical ProtectionLiquid surface applicatorsDielectric characteristicsHexafluoropropylenePlasma deposition

Owner:SEMBLANT

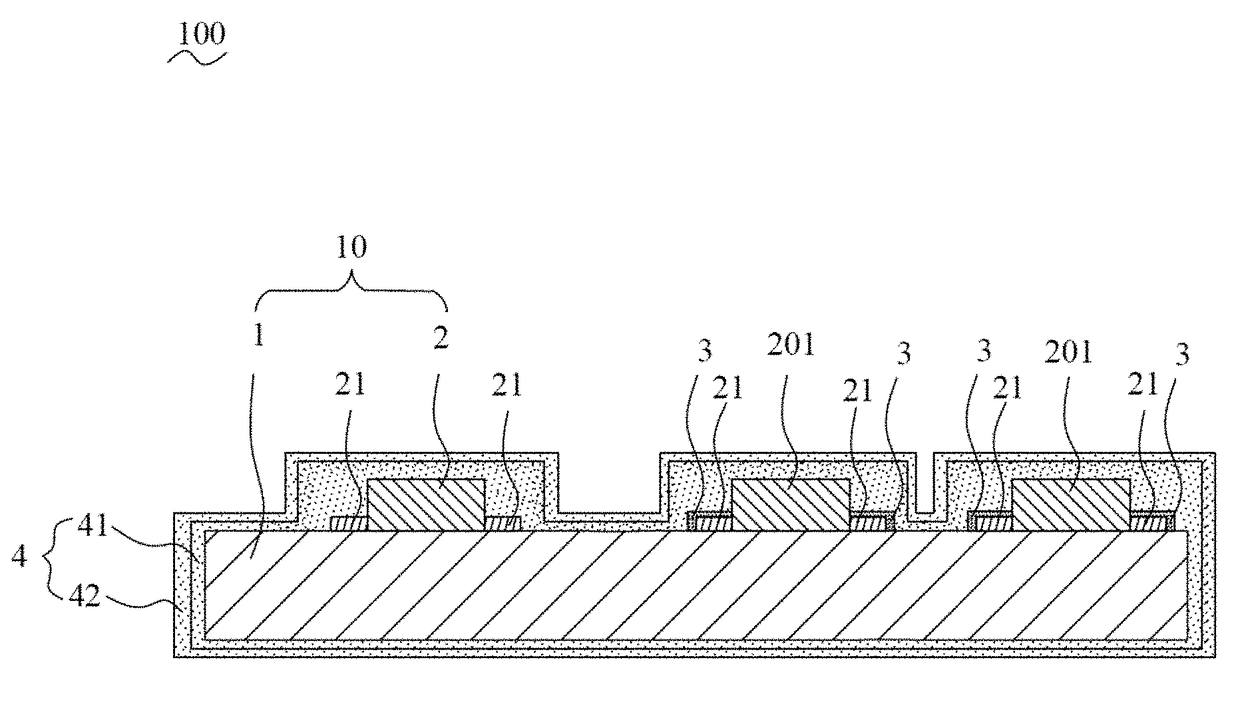

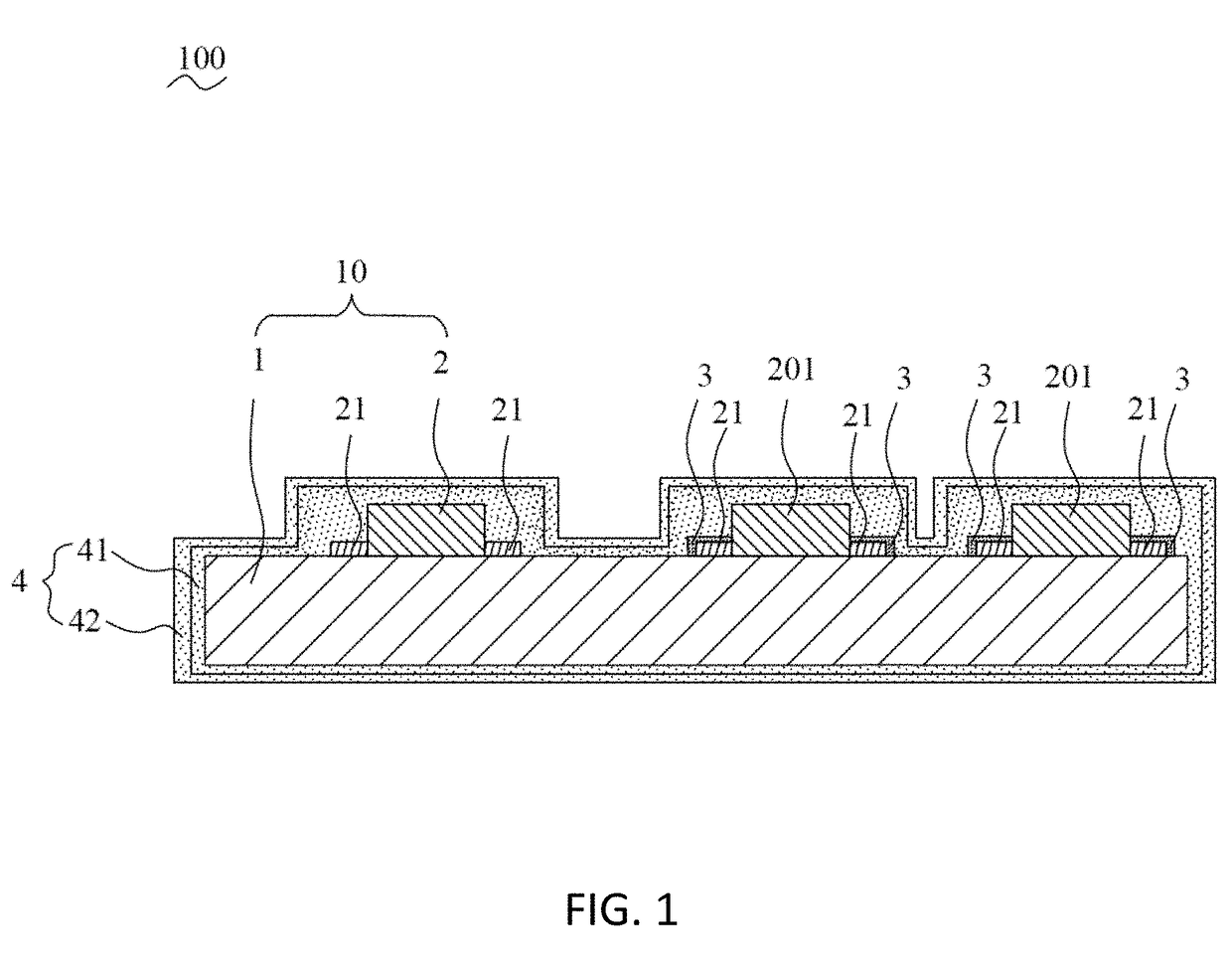

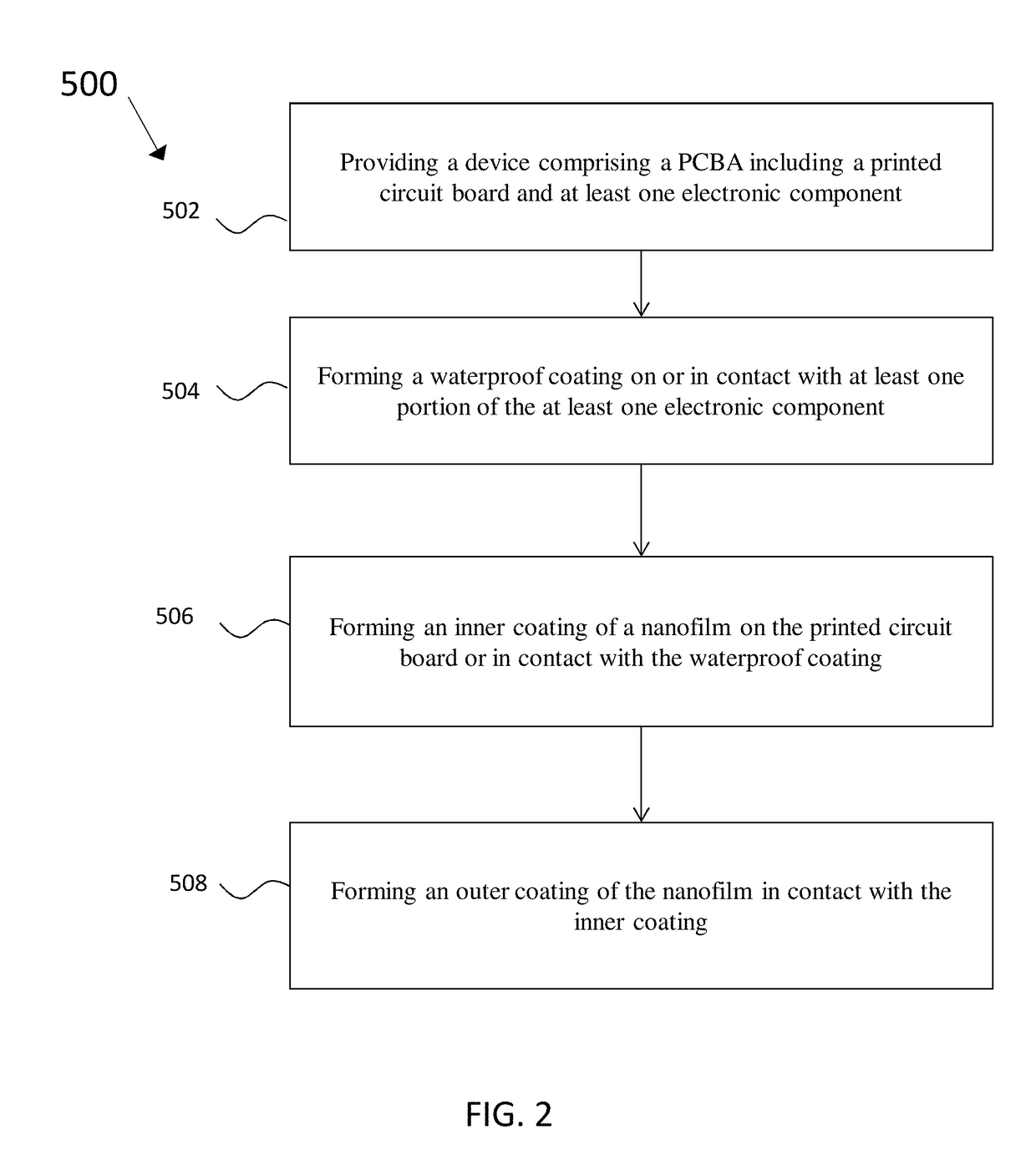

Method for coating devices and resulting products

ActiveUS20170367192A1Avoid excessive frictionLess functionPrinted circuit assemblingDielectric materialsMetal oxide nanoparticlesEngineering

A method for waterproofing a device and the resulting device are provided. The device includes a printed circuit board assembly (PCBA), which includes a printed circuit board, and at least one electronic component disposed on the printed circuit board. A waterproof coating such as a polymer coating is disposed on or in contact with at least one portion of the at least one electronic component. A nanofilm is disposed on the PCBA. The nanofilm includes an inner coating and an outer coating. The inner coating is disposed on the printed circuit board or in contact with the waterproof coating. The inner coating comprises metal oxide nanoparticles having a particle diameter in a range of about 5 nm to about 100 nm. The outer coating in contact with the inner coating, and comprises silicon dioxide nanoparticles having a particle diameter in a range of 0.1 nm to 10 nm.

Owner:NANO SHIELD TECH CO LTD

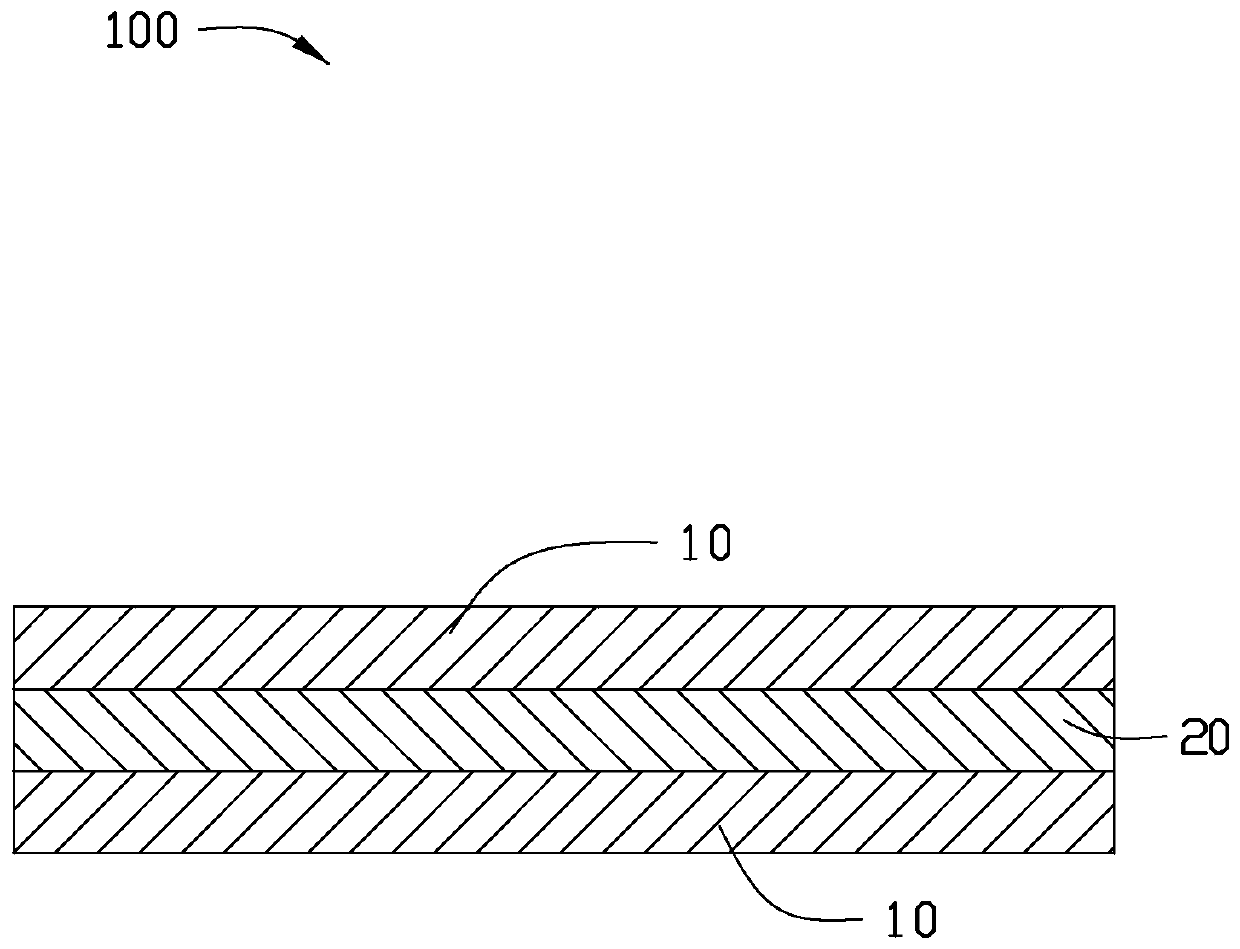

Adhesive film and flexible metal laminate

ActiveUS20160242274A1Film/foil adhesivesHigh frequency circuit adaptationsPolyimide membraneHydroxy group

To provide an adhesive film comprising a polyimide film and a fluorinated resin layer directly laminated, in which blisters (foaming) in an atmosphere corresponding to reflow soldering at high temperature are suppressed, and a flexible metal laminate. An adhesive film having a fluorinated resin layer containing a fluorinated copolymer (A) directly laminated on one side or both sides of a polyimide film, wherein the fluorinated copolymer (A) has a melting point of at least 280° C. and at most 320° C., is melt-moldable, and has at least one type of functional groups selected from the group consisting of a carbonyl group-containing group, a hydroxy group, an epoxy group and an isocyanate group, and the fluorinated resin layer has a thickness of from 1 to 20 μm.

Owner:ASAHI GLASS CO LTD

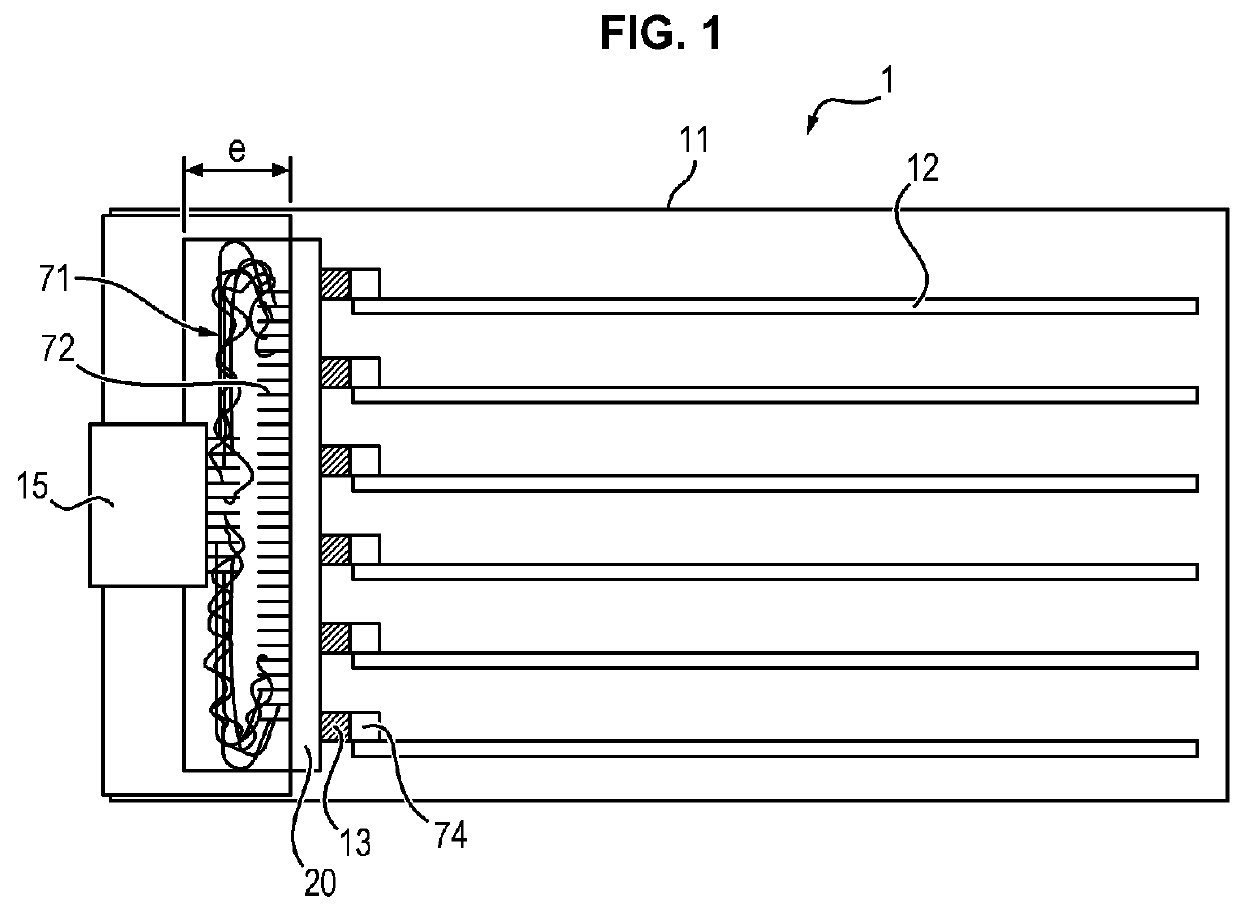

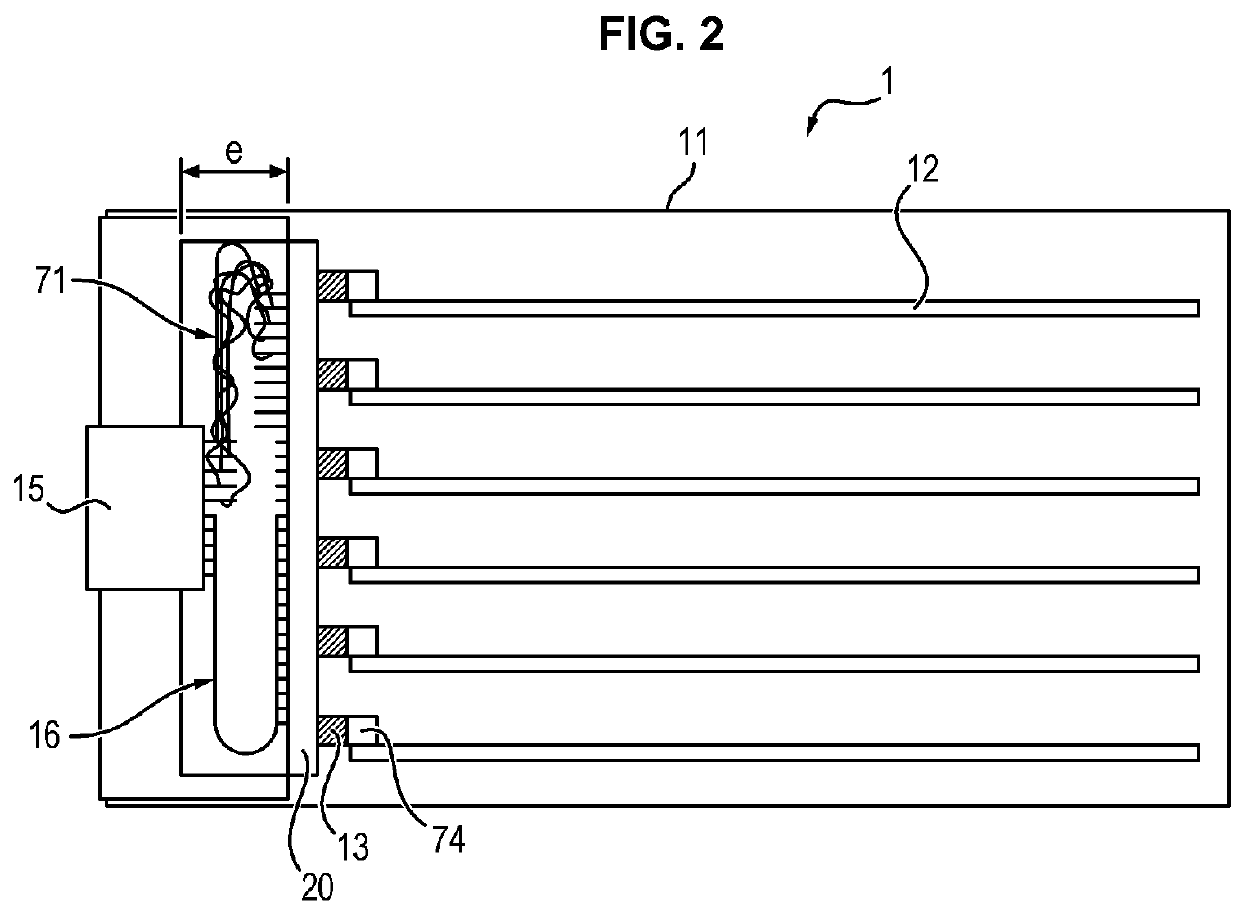

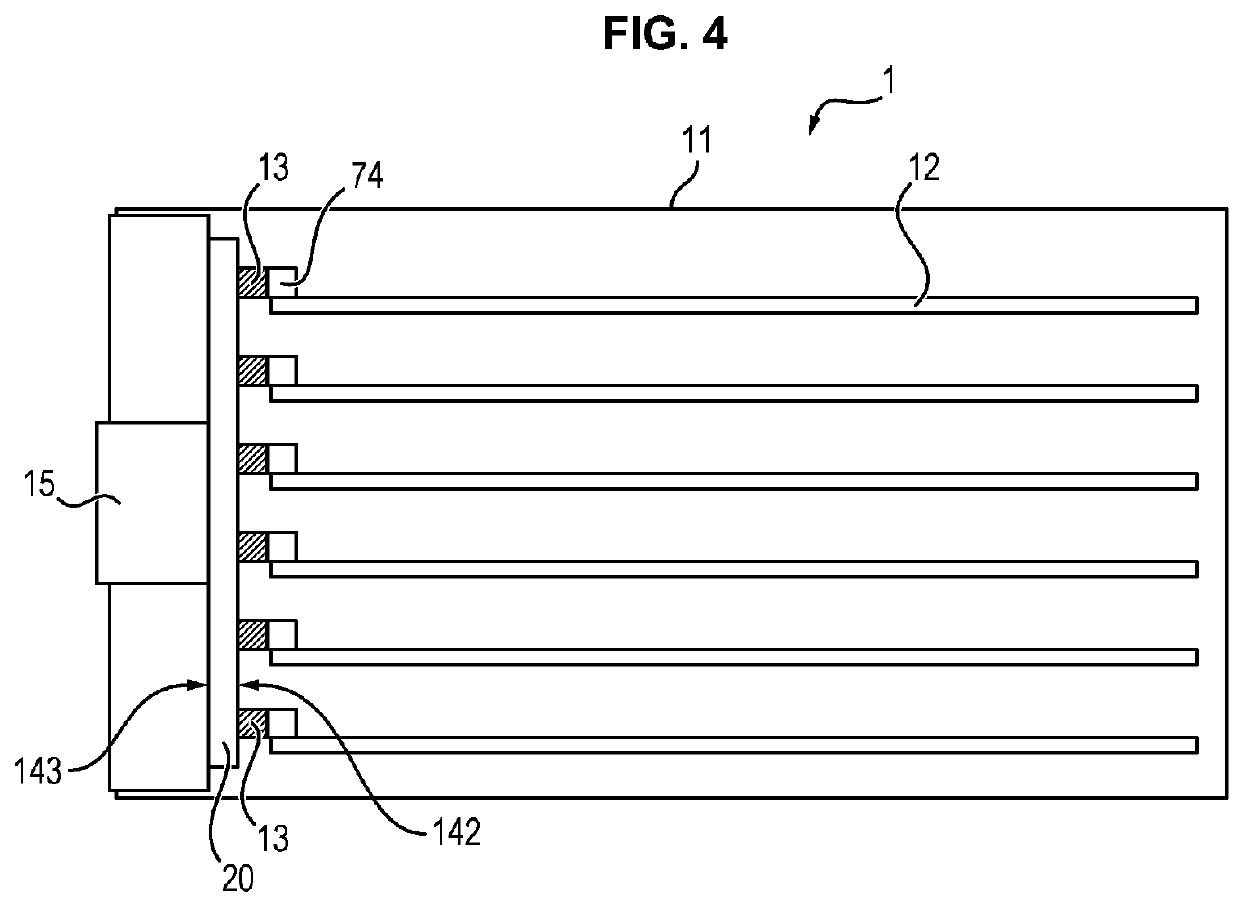

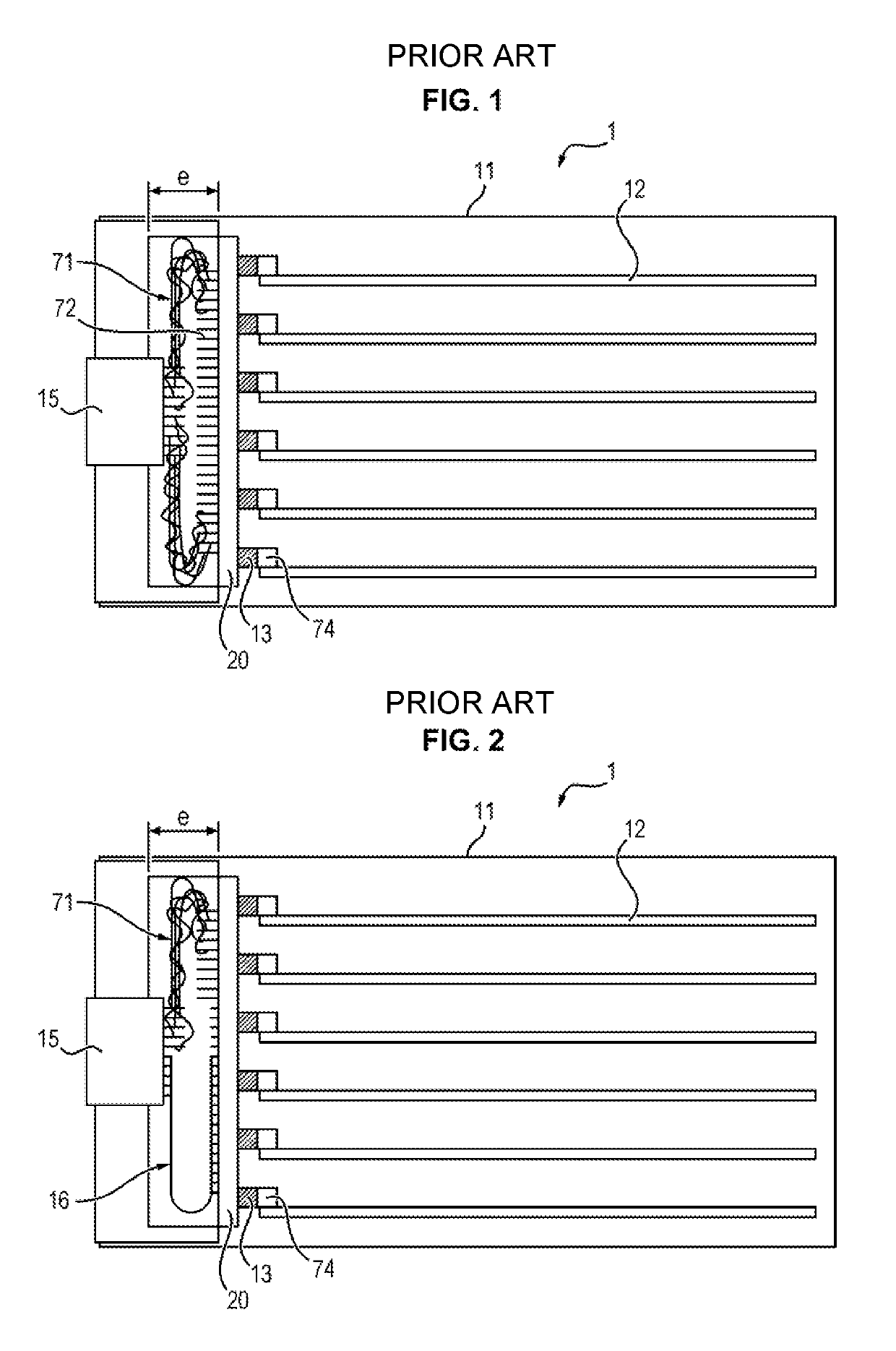

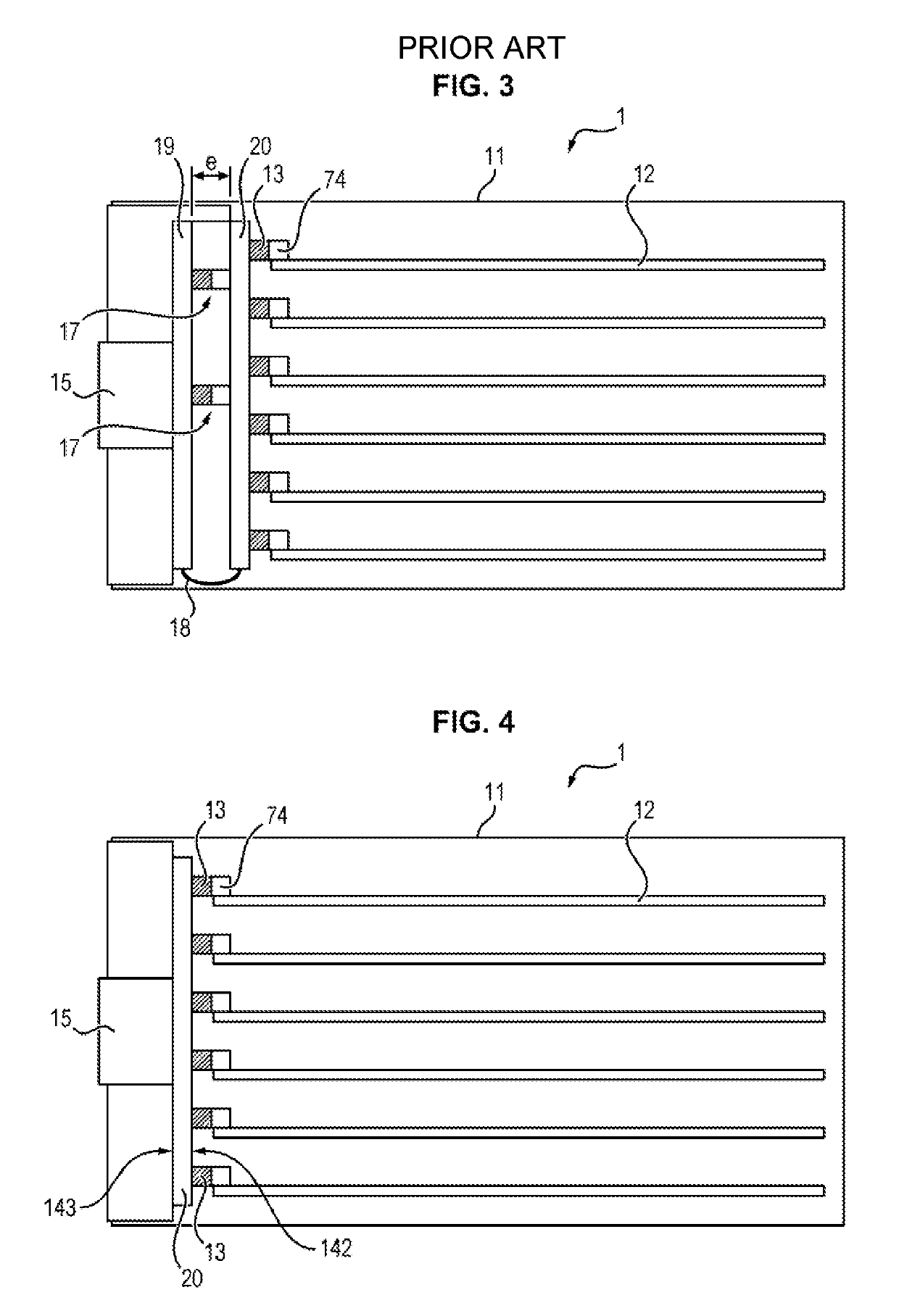

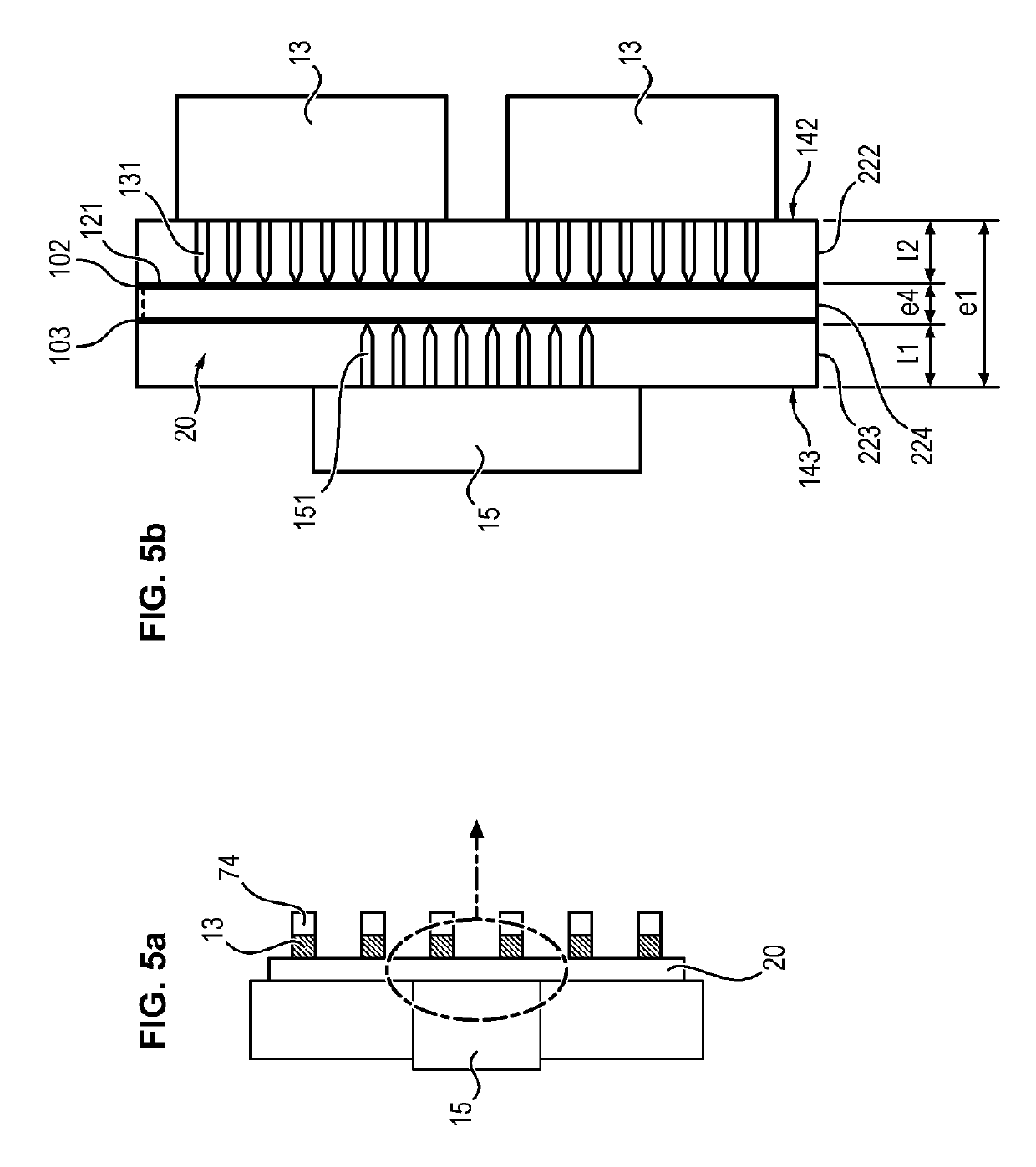

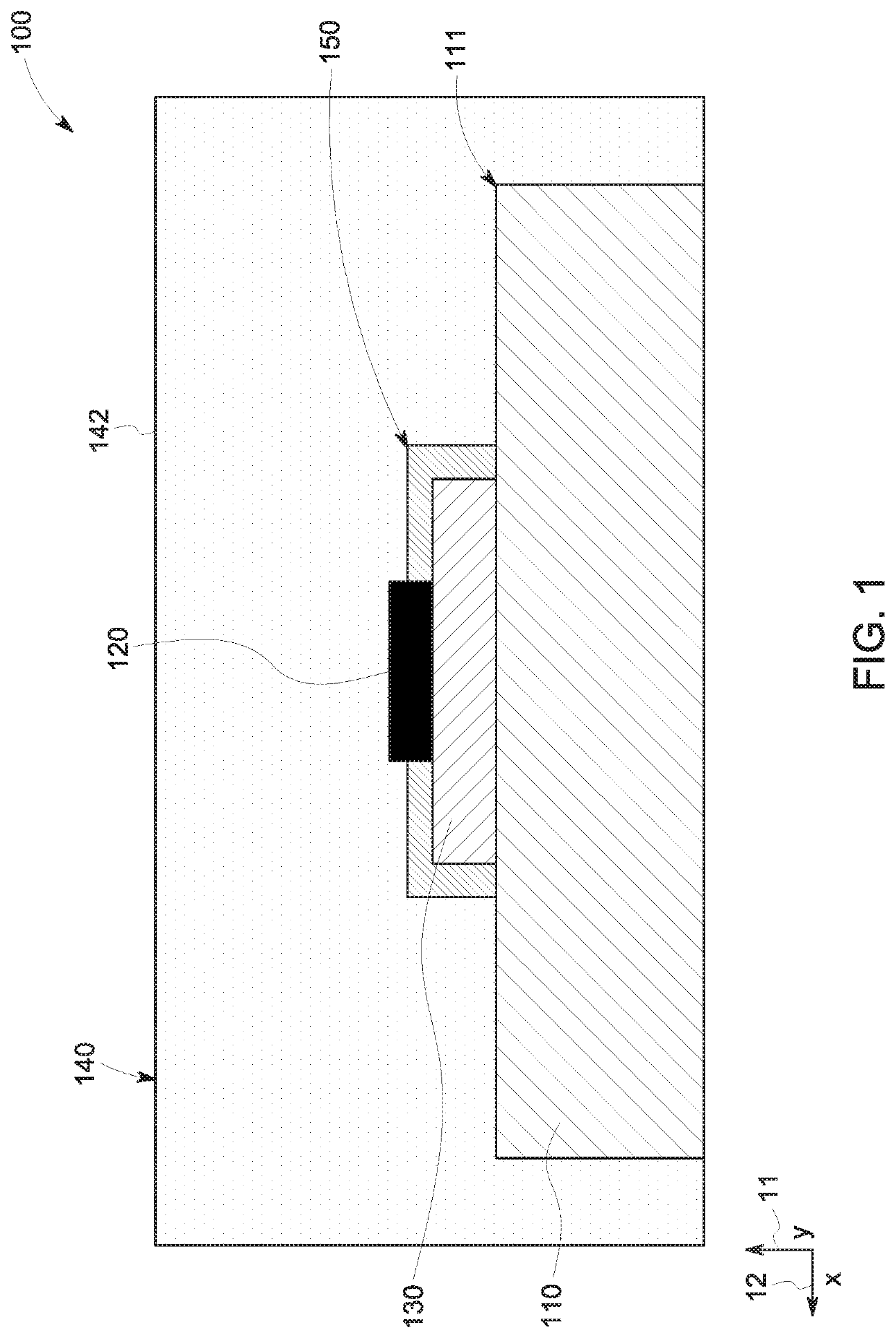

Backplane electronic board and associated electronic control unit

ActiveUS20180110149A1Reduce connection spaceIncrease the lengthCoupling device connectionsClamping/extracting meansElectricityMating connection

The present invention concerns a backplane electronic board (20) having on inner face (142) suitable for bein g connected to electronic board connectors (12) and an outer face (143) suitable for being connected lo an outer connector (15), the backplane board (20) being characterised in that it has blind holes opening on ihe inner face (142) of some, and holes opening on the outer face (143) of same, the holes being suitable for receiving press-fit connection elements and forming therewith an electrical connection point.

Owner:SAFRAN ELECTRONICS & DEFENSE

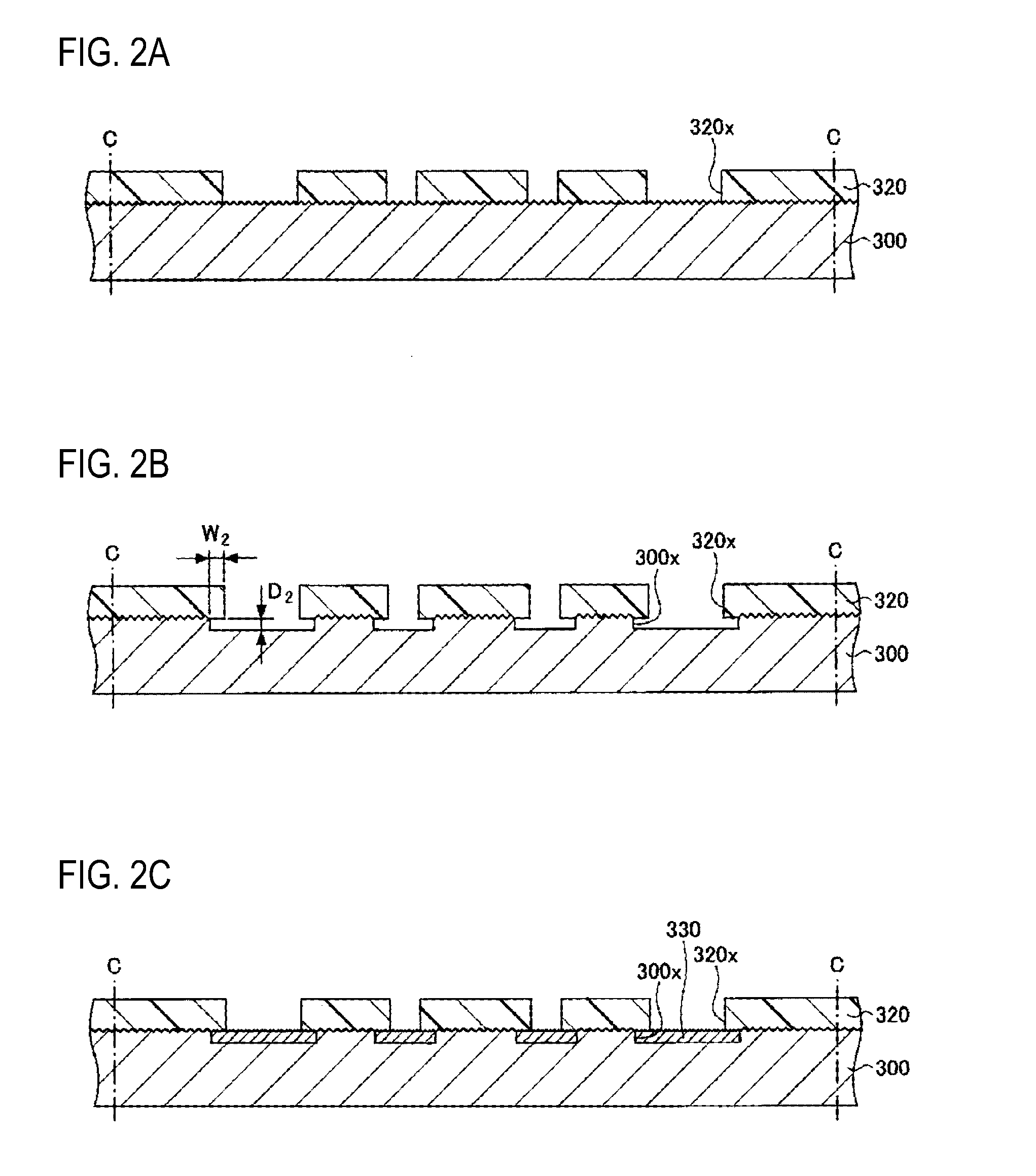

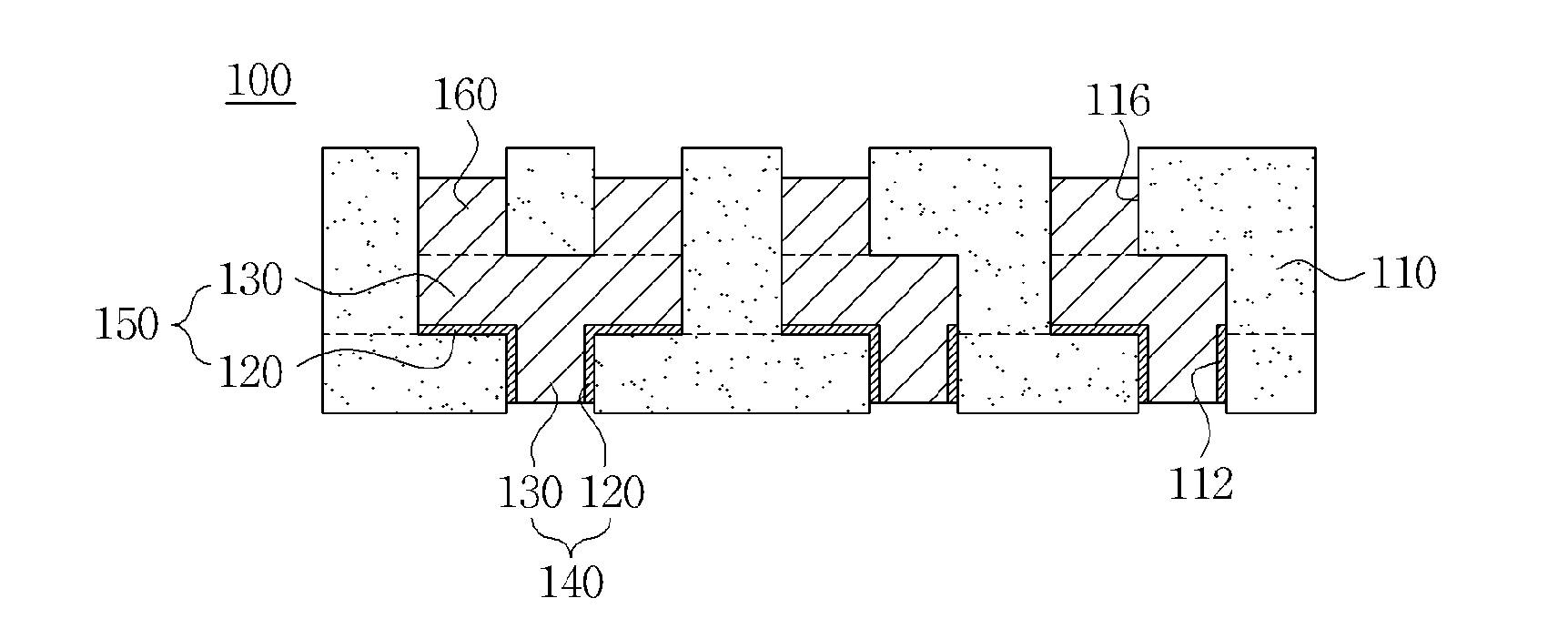

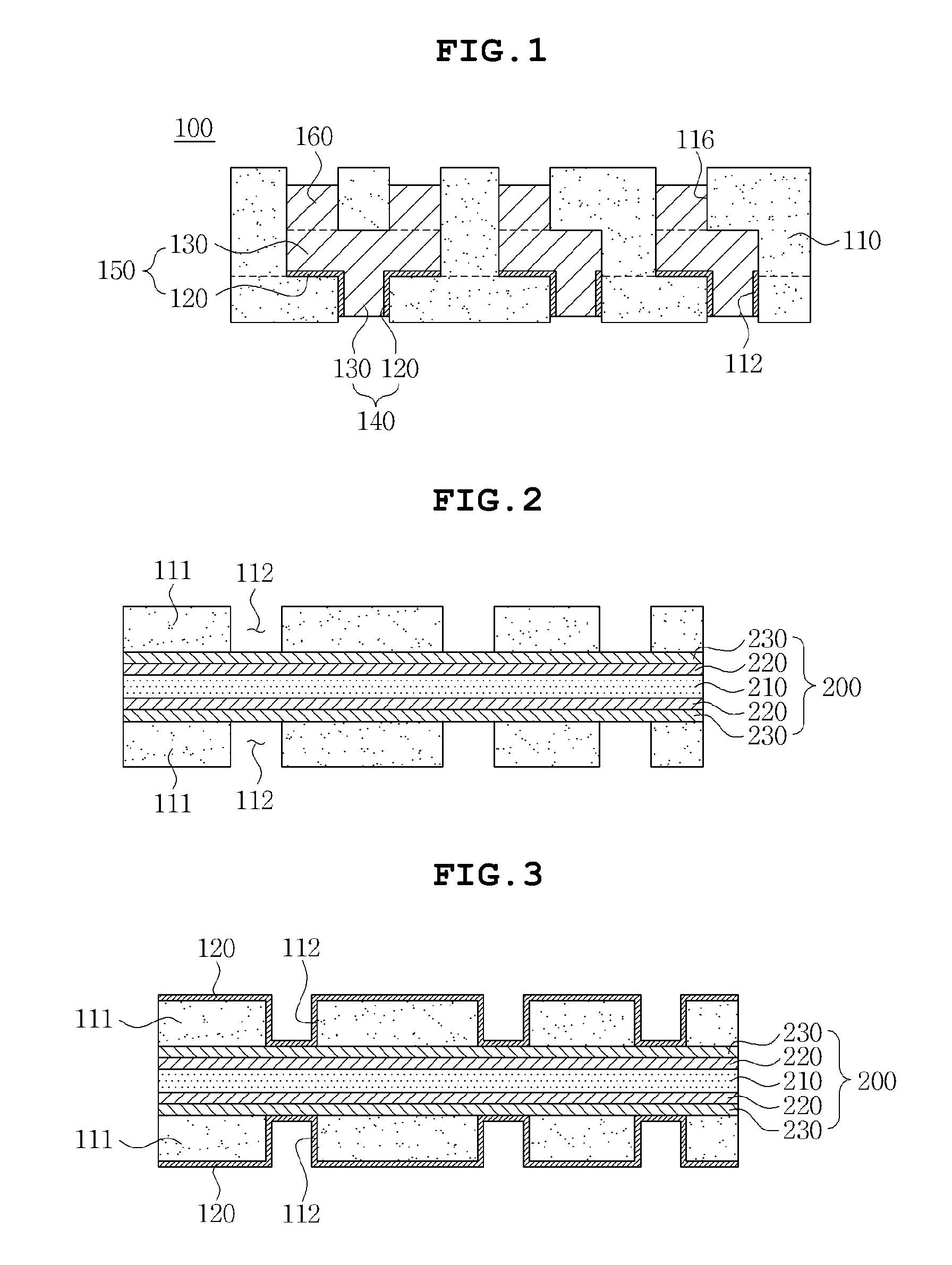

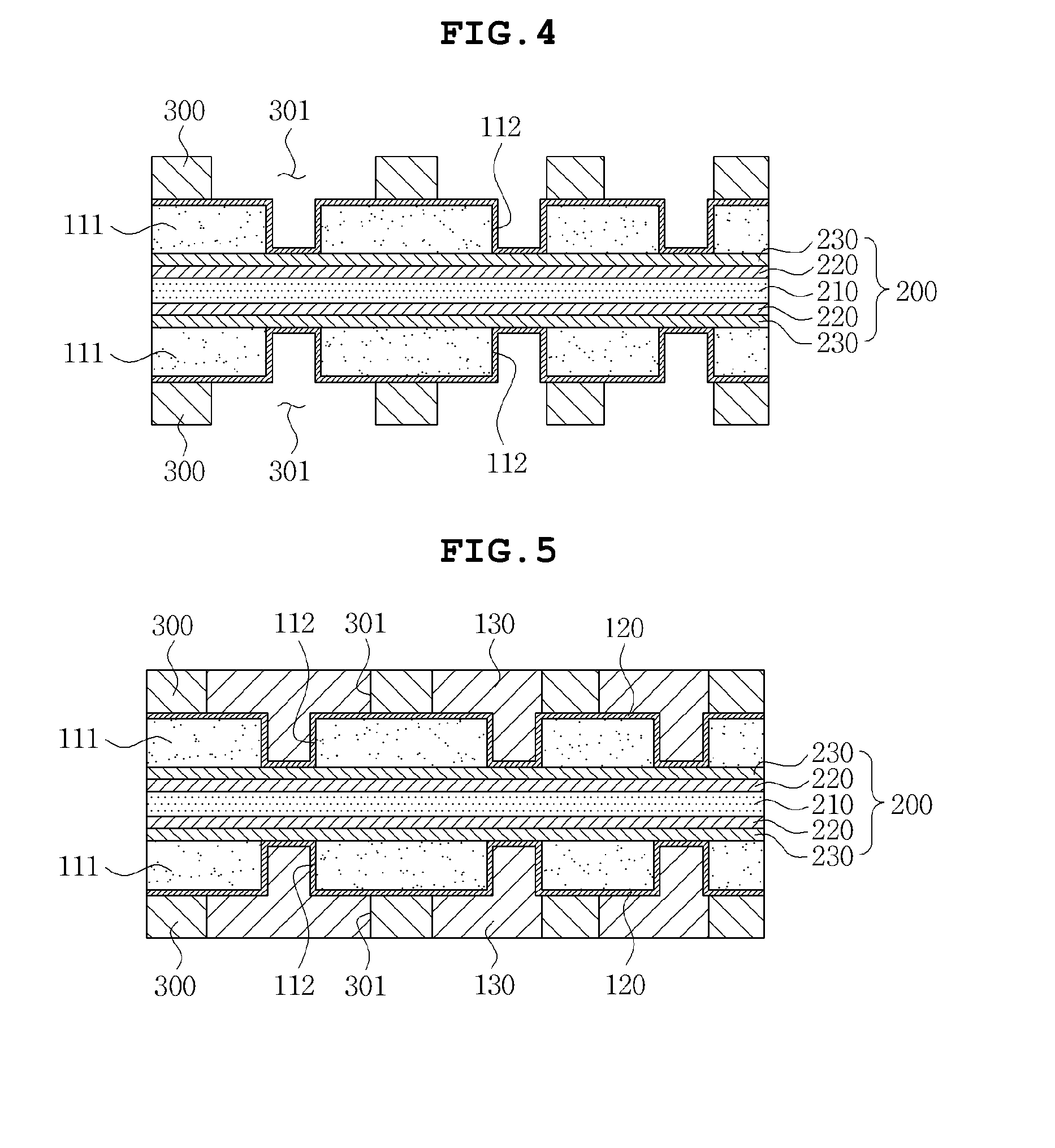

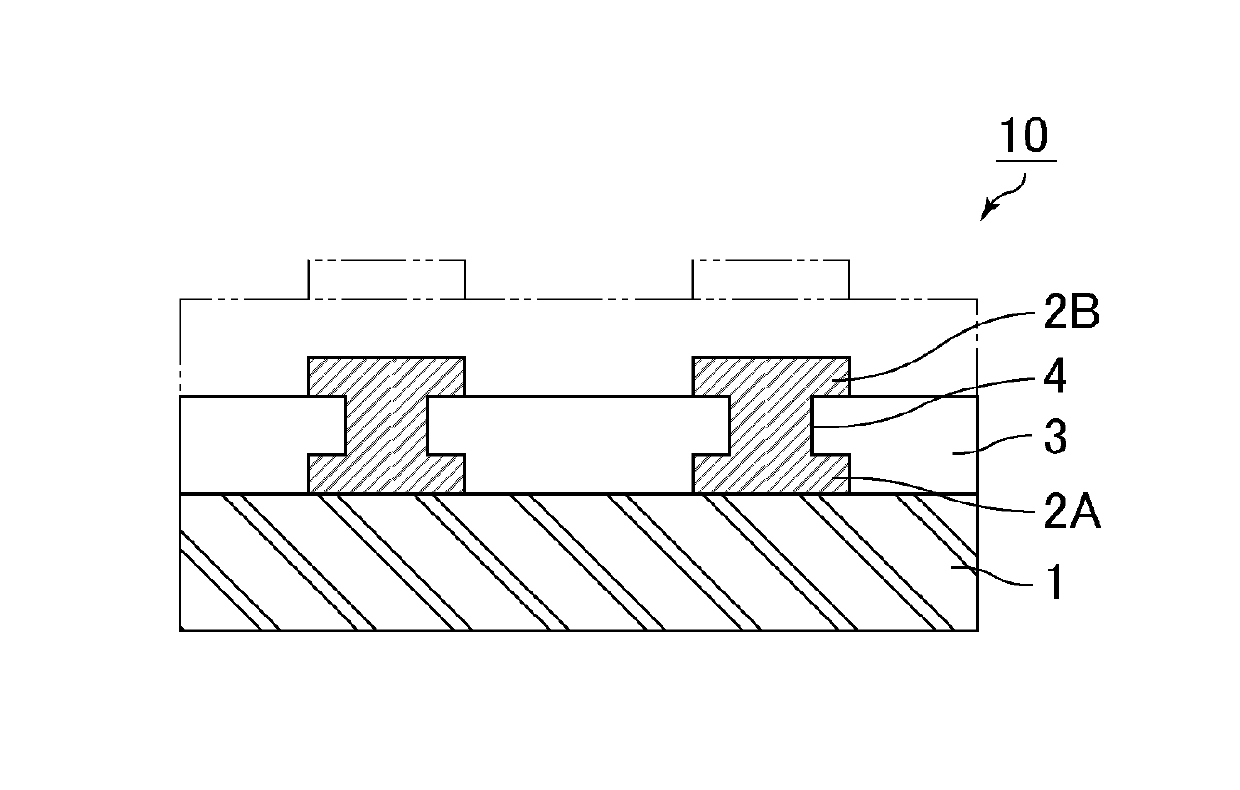

Printed circuit board and method of manufacturing the same

InactiveUS20150101852A1Preventing dimple generationAvoid lossDielectric characteristicsConductive material mechanical removalPrinted circuit boardEngineering

Disclosed herein are a printed circuit board and a method of manufacturing the same.The printed circuit board according to a preferred embodiment of the present invention may include: an insulating layer; a first via depressed from one surface of the insulating layer; a second via depressed from the other surface of the insulating layer; and a circuit pattern formed in the insulating layer and bonded to the first and second vias.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Coated electrical assembly

PendingUS20190090358A1Improve waterproof levelHigh levelLiquid surface applicatorsDielectric characteristicsHexafluoropropylenePlasma deposition

An electrical assembly which has a multi-layer conformal coating on at least one surface of the electrical assembly, wherein each layer of the multi-layer coating is obtainable by plasma deposition of a precursor mixture comprising (a) one or more organosilicon compounds, (b) optionally O2, N2O, NO2, H2, NH3, N2, SiF4 and / or hexafluoropropylene (HFP), and (c) optionally He, Ar and / or Kr. The chemistry of the resulting plasma-deposited material chemistry can be described by the general formula: SiOxHyCzFaNb. The properties of the conformal coating are tailored by tuning the values of x, y, z, a and b.

Owner:HZO INC

Heat dissipating structure

ActiveUS9826623B2Avoid overall overheatingAvoid performance degradationCircuit thermal detailsSemiconductor/solid-state device detailsPrinted circuit boardLiquid resin

A heat dissipation structure including: a printed circuit board; a first heat-generating element; a second heat-generating element; and a cured product of a thermally conductive curable liquid resin composition, the printed circuit board having a first surface and a second surface that is opposite to the first surface, the first heat-generating element being placed on the first surface, the second heat-generating element being placed on the second surface, the first heat-generating element generating an equal or greater amount of heat than the second heat-generating element, the second heat-generating element being surrounded by the cured product, the first heat-generating element being surrounded by a layer that has a lower thermal conductivity than the cured product.

Owner:KANEKA CORP

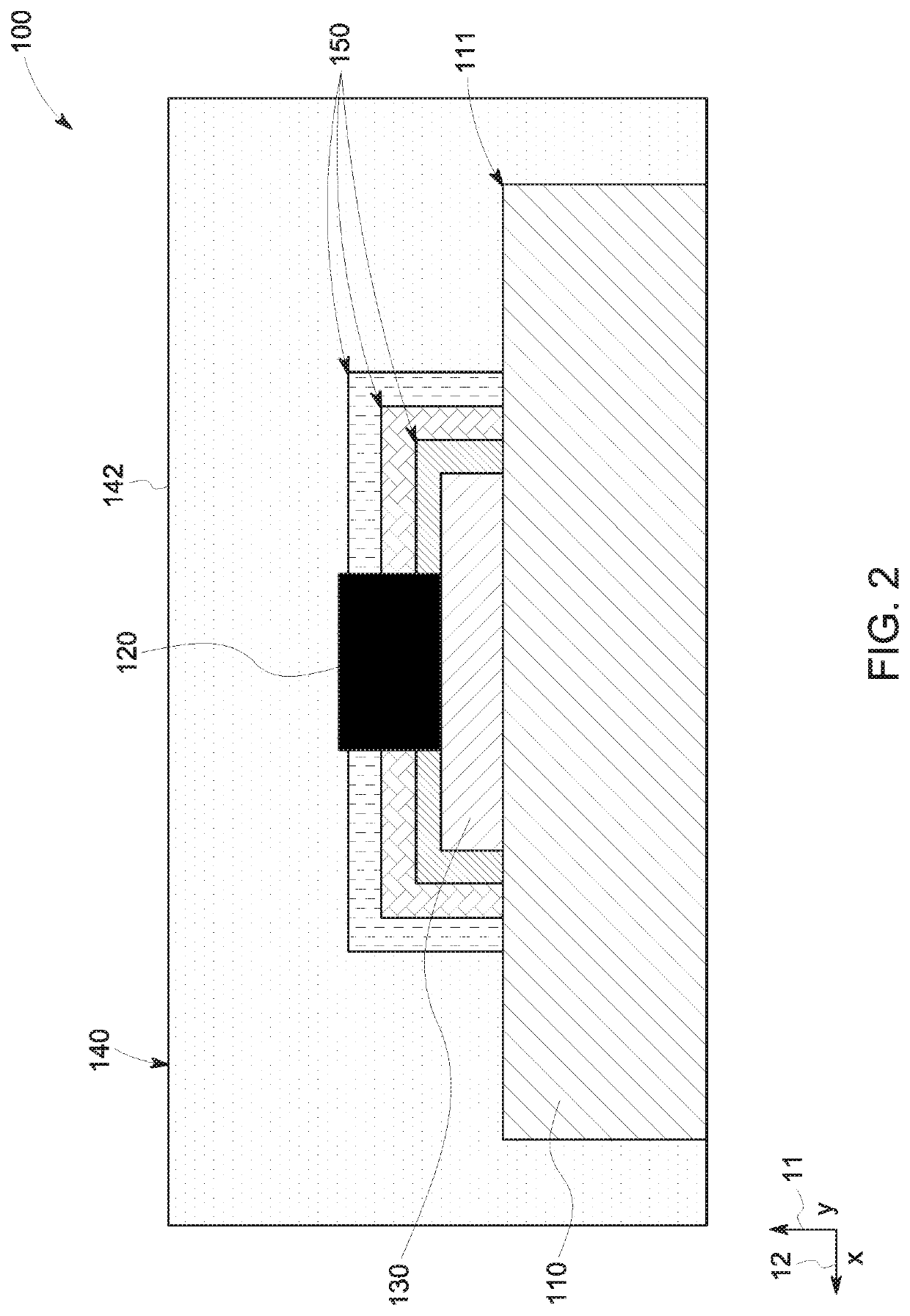

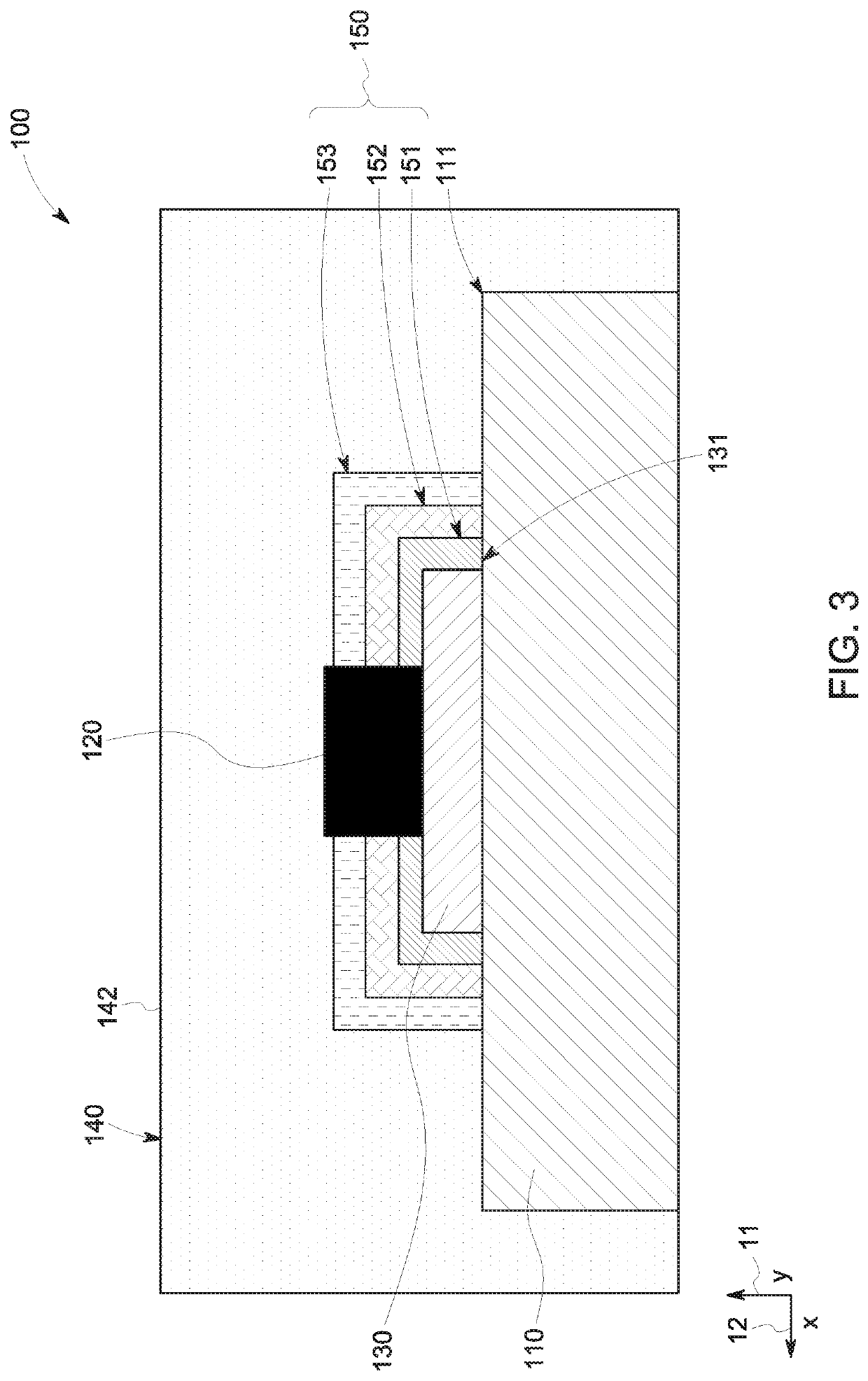

Backplane electronic board and associated electronic control unit

ActiveUS10375849B2Reduce connection spaceIncrease the lengthCoupling device connectionsClamping/extracting meansElectricityElectrical connection

The present invention concerns a backplane electronic board (20) having on inner face (142) suitable for being connected to electronic board connectors (12) and an outer face (143) suitable for being connected to an outer connector (15), the backplane board (20) being characterized in that it has blind holes opening on the inner face (142) of same, and holes opening on the outer face (143) of same, the holes being suitable for receiving press-fit connection elements and forming therewith an electrical connection point.

Owner:SAFRAN ELECTRONICS & DEFENSE

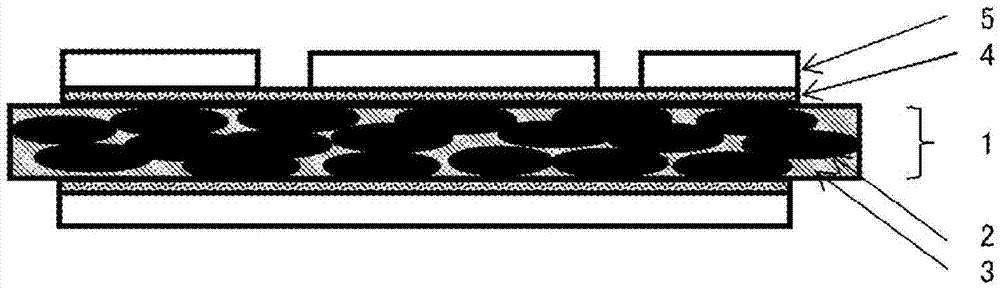

Boron nitride/resin composite circuit board, and circuit board including boron nitride/resin composite integrated with heat radiation plate

ActiveUS9516741B2Good heat dissipationHeat resistant cycle characteristicsInsulating substrate metal adhesion improvementPrinted circuits stress/warp reductionLongest DiameterCarbon nitride

A boron nitride / resin composite circuit board having high heat dissipation characteristics and high reliability is provided. A boron nitride / resin composite circuit board, including: a plate-shaped resin-impregnated boron nitride sintered body having a plate thickness of 0.2 to 1.5 mm, the plate-shaped resin-impregnated boron nitride sintered body including 30 to 85 volume % of a boron nitride sintered body having boron nitride particles bonded three-dimensionally, the boron nitride particles having an average long diameter of 5 to 50 μm, and 70 to 15 volume % of a resin; and a metal circuit adhered onto both principal planes of the plate-shaped resin-impregnated boron nitride sintered body, the metal circuit being copper or aluminum, wherein: a ratio of a linear thermal expansion coefficient in a plane direction of the resin-impregnated boron nitride sintered body at 40 to 150° C. (CTE1) and a linear thermal expansion coefficient of the metal circuit at 40 to 150° C. (CTE2) (CTE1 / CTE2) is 0.5 to 2.0.

Owner:DENKA CO LTD

Printing method using two lasers

ActiveCN107852818AEasy to implementHigh resolutionLaser detailsTransfer patterningLiquid jetOptoelectronics

The invention relates to a laser printing method comprising the following steps: (a) providing a receiving substrate (4); (b) providing a target substrate (5) including a transparent substrate (50), one face of which has a coating (51) formed by a solid metal film; (c) locally irradiating the film (51) through the transparent substrate (50) using a first laser (8) in order to reach the melting point of the metal in a target zone of the film that is in liquid form; (d) irradiating the liquid film through the transparent substrate using a second laser on the target zone defined in step (c), in order to form a liquid jet in the target zone and to eject same from the substrate in the form of molten metal; (e) depositing a drop of molten metal on a defined receiving zone of the receiving substrate, the drop solidifying as it cools.

Owner:CENT NAT DE LA RECHERCHE SCI +1

Photosensitive glass paste and electronic component

ActiveUS10390427B2Avoid warpingAvoid separationDielectric materialsInorganic insulatorsThermal expansionElectronic component

Owner:MURATA MFG CO LTD

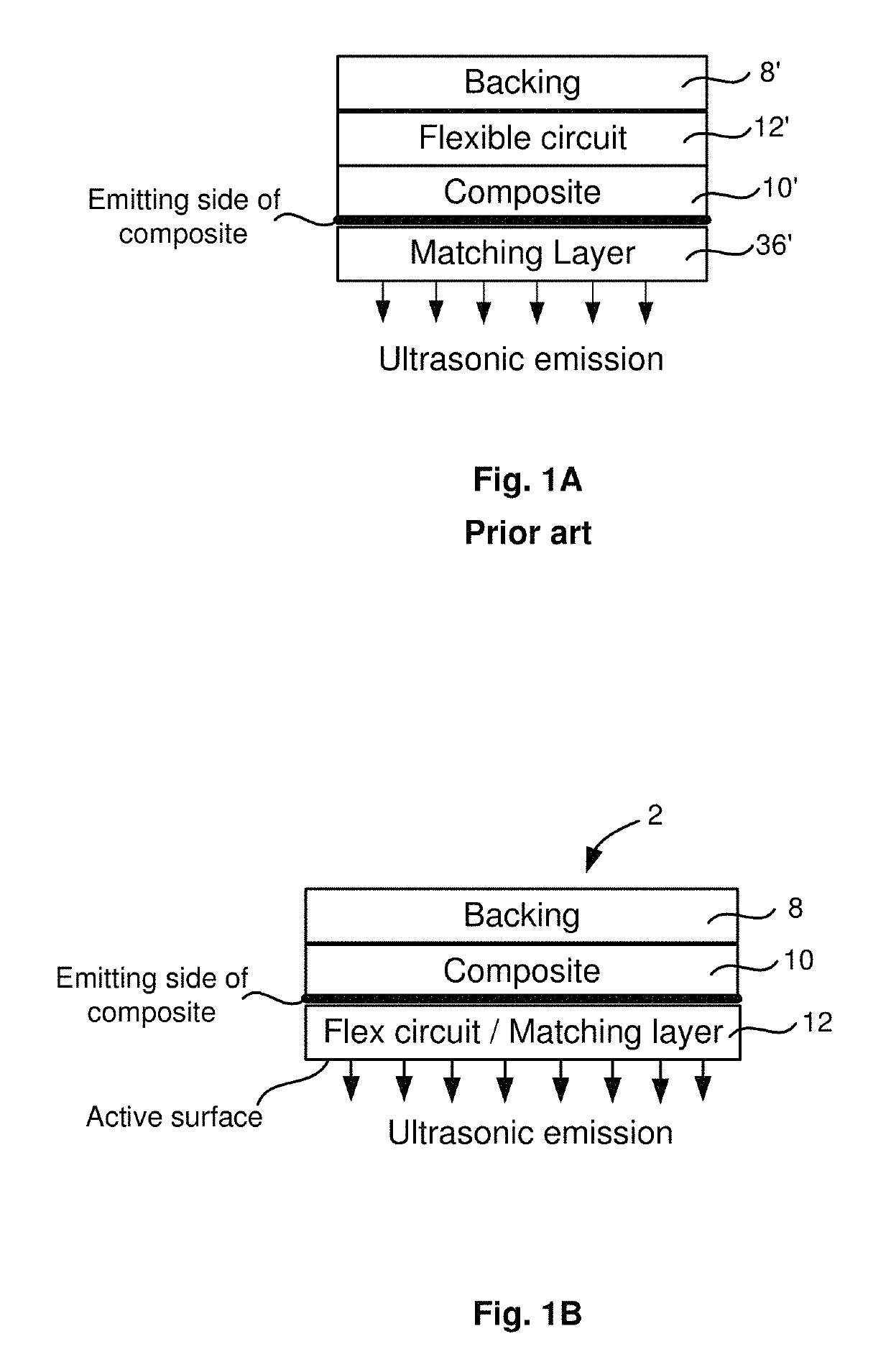

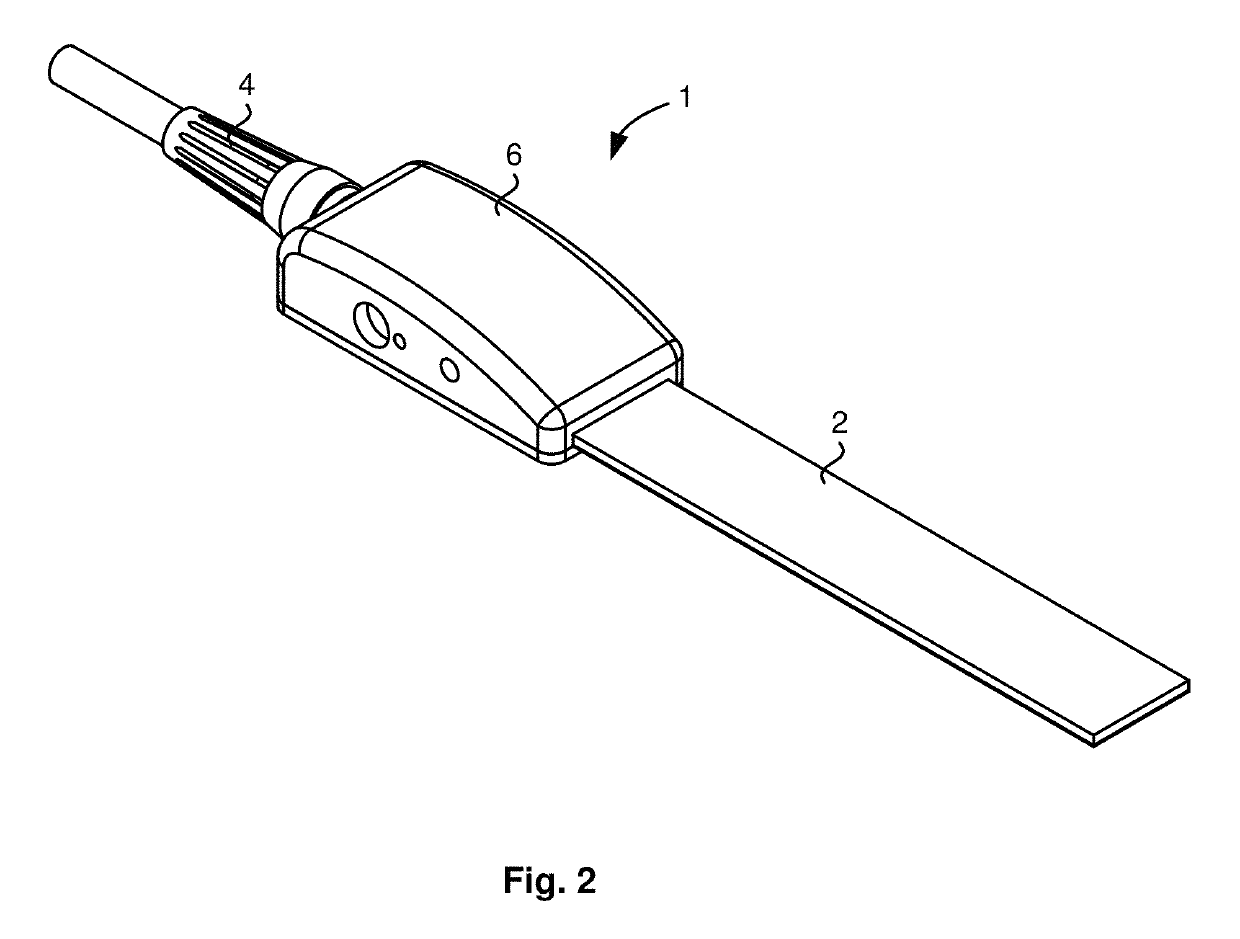

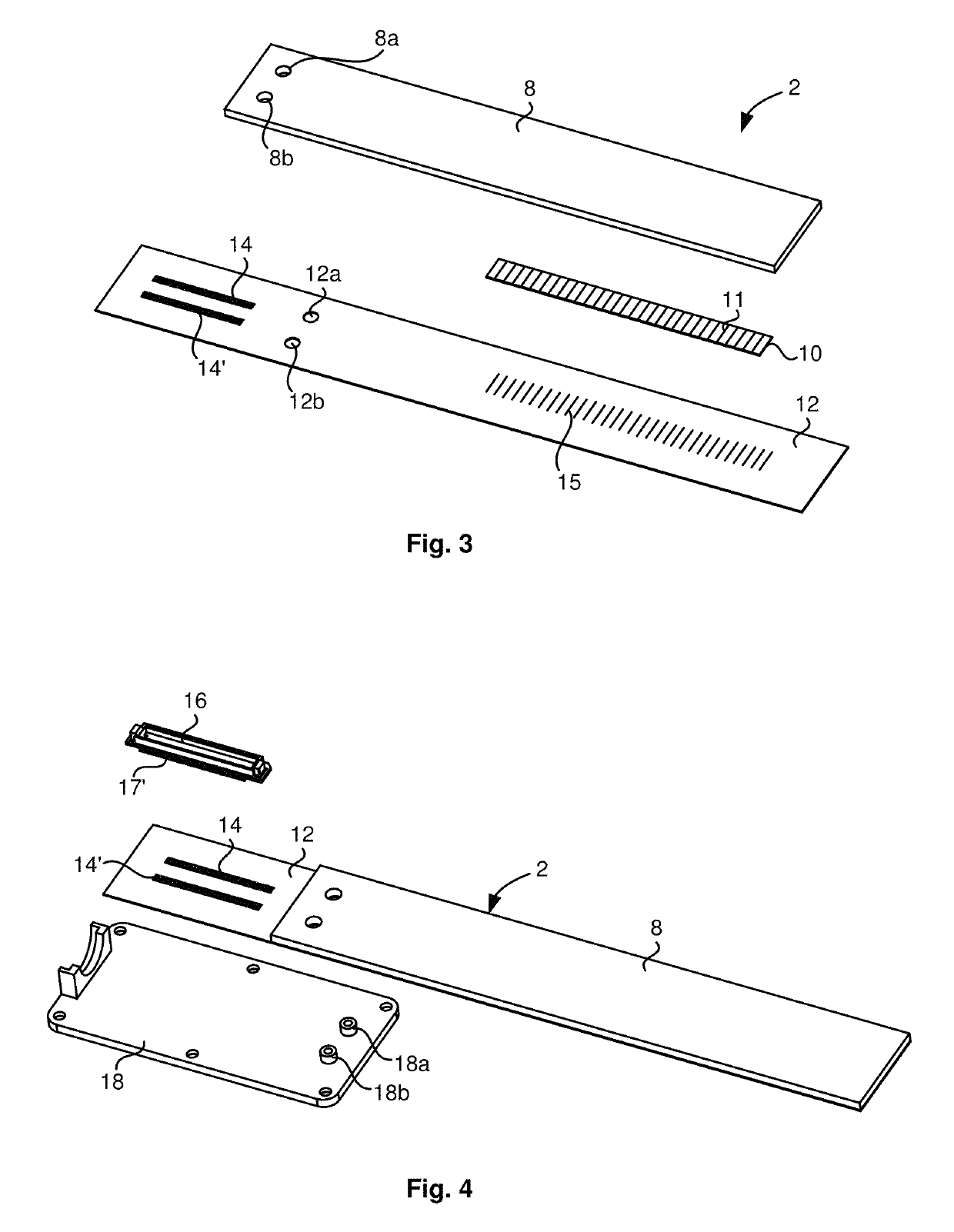

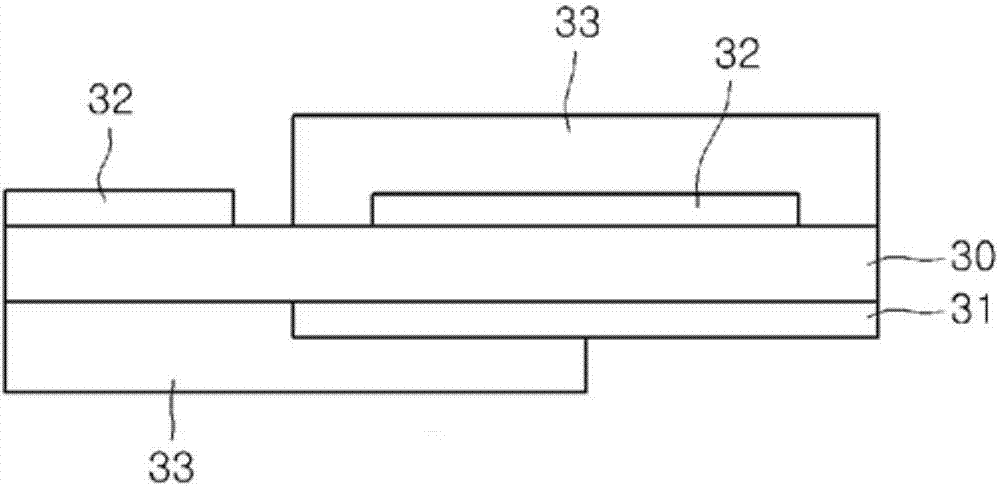

Ultrasonic phased array probe using PCB as matching layer

ActiveUS10576499B2Reduce decreaseSimple manufacturing processPiezoelectric/electrostrictive device manufacture/assemblyMaterial analysis using sonic/ultrasonic/infrasonic wavesUltrasonic sensorFlexible circuits

Disclosed is a flexible ultrasonic transducer in which a single layer serves dual function as both a matching layer and a flexible circuit for making electrical connections, and there is no separate matching layer. Also disclosed is a method of assembling the flexible transducer.

Owner:OLYMPUS SCI SOLUTIONS AMERICAS

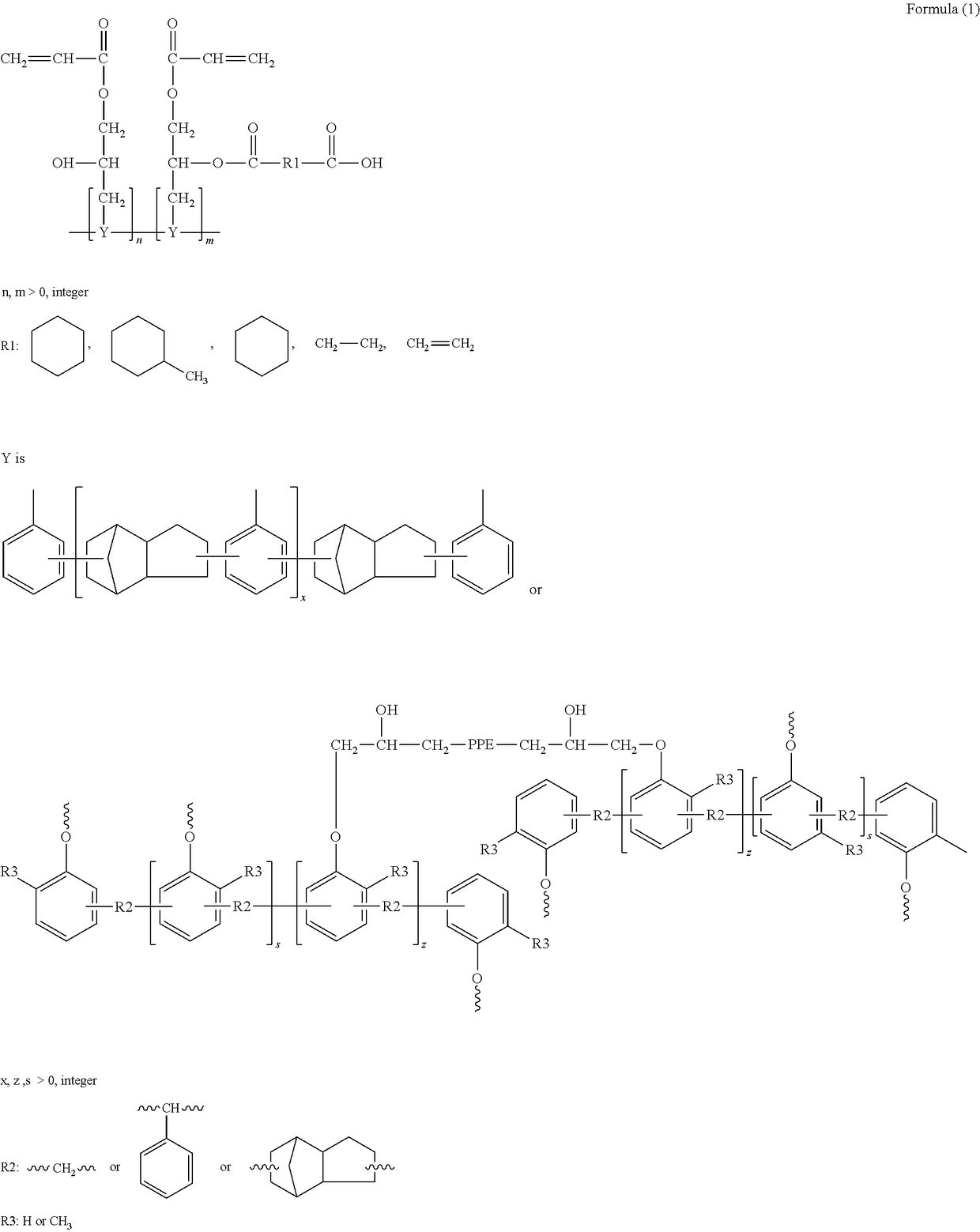

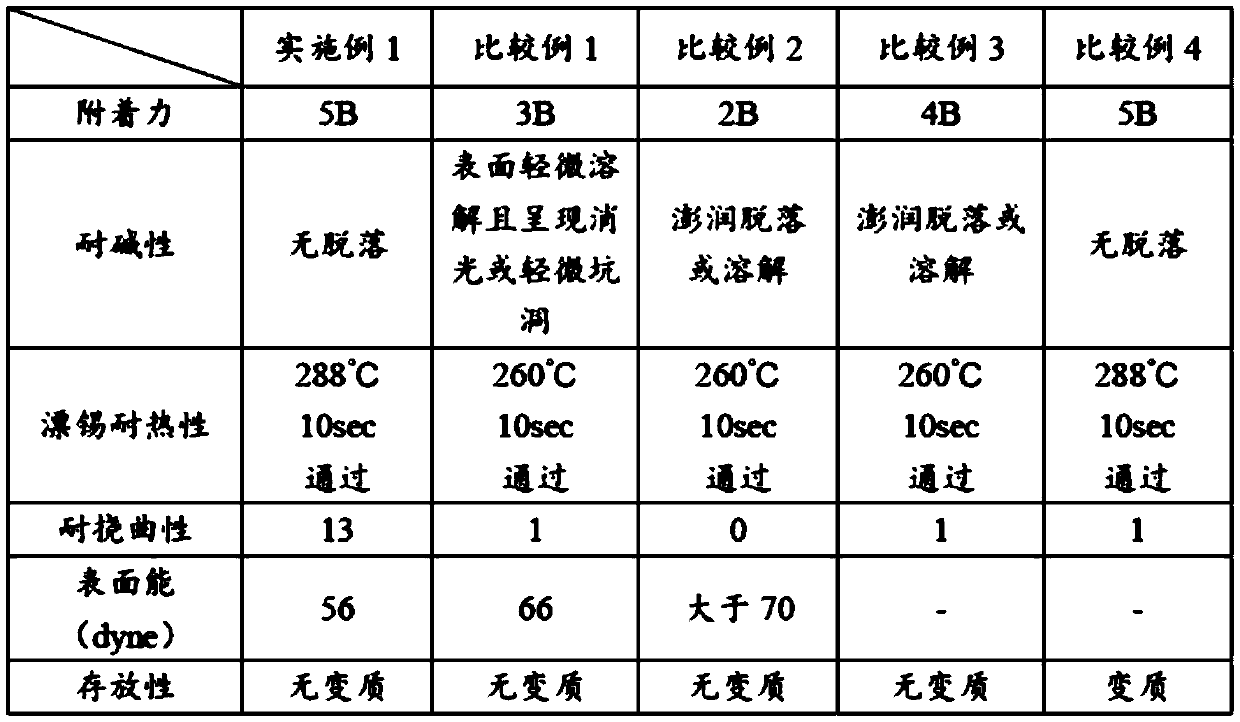

Low dk/df solder resistant composition use for printed circuit board

ActiveUS20170363958A1Improve adhesionExcellent characteristicsHigh frequency circuit adaptationsPhotomechanical apparatusOrganic solventAqueous solution

A low dielectric constant (Dk) and dissipation factor (Df) of solder resistant mask composition having excellent photo and thermocurability, and high developability resolution with an alkaline aqueous solution, wherein the dielectric constant is below 3.20 (1 GHz), and the dissipation factor is less than 0.015 (1 GHz); and wherein the composition comprises (A) a photopolymerizable prepolymer; (B) a photopolymerizable vinyl monomer; (C) an epoxy compound; (D) a photopolymerization initiator; (E) an inorganic filler; (F) a catalyst; and (G) an organic solvent.

Owner:NANYA PLASTICS CORP

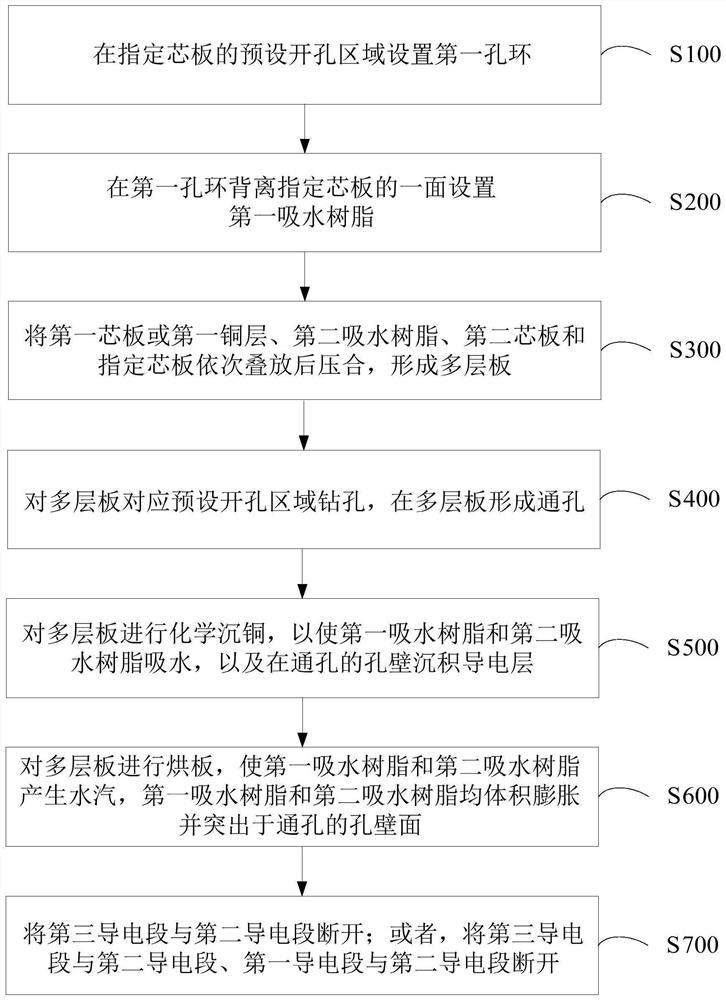

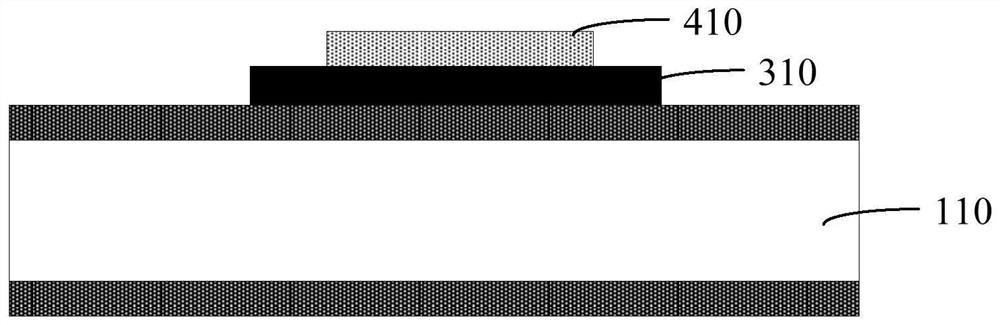

Preparation method of PCB (Printed Circuit Board) and PCB

ActiveCN114206025AEliminate signal transmission effectsTo achieve separation and non-conductionDielectric characteristicsElectrical connection printed elementsEngineeringMechanical engineering

The invention discloses a preparation method of a PCB and the PCB, and the method comprises the steps: setting a first hole ring in a preset hole opening region of a specified core board; first water-absorbent resin is arranged on the face, away from the designated core plate, of the first hole ring; sequentially stacking the first core board or the first copper layer, the second water-absorbent resin, the second core board and the specified core board and then laminating to form a multi-layer board; a hole is drilled in a preset hole opening area corresponding to the multi-layer board, and through holes are formed in the multi-layer board; performing chemical copper deposition on the multi-layer board so as to enable the first water-absorbent resin and the second water-absorbent resin to absorb water, depositing a conductive layer on the hole wall of the through hole, and drying the multi-layer board; disconnecting the third conductive section from the second conductive section; or disconnecting the third conductive section from the second conductive section, and disconnecting the first conductive section from the second conductive section. The technical scheme of the invention provides the PCB preparation method capable of completely eliminating the influence of the stub on signal transmission.

Owner:DONGGUAN SHENGYI ELECTRONICS

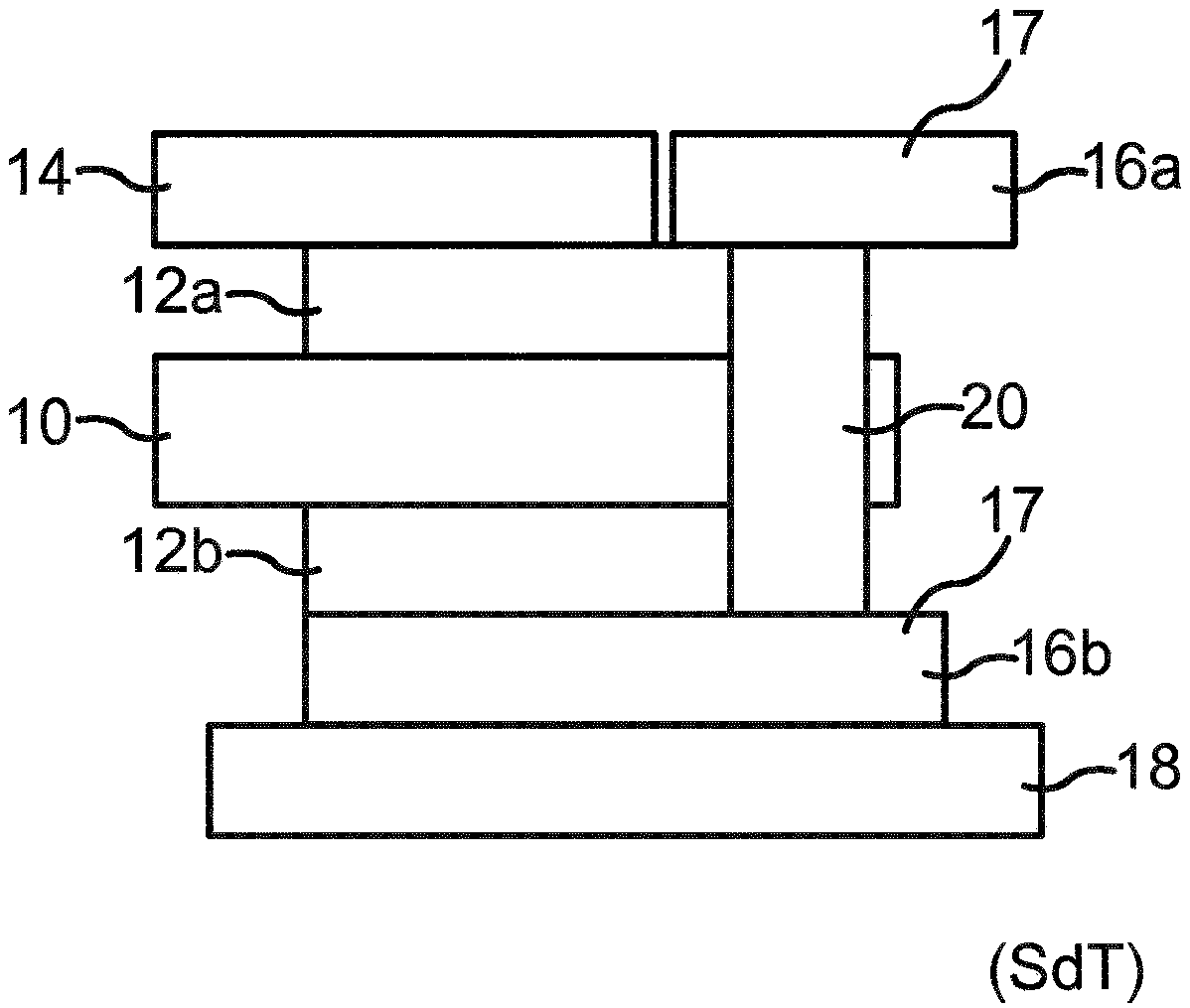

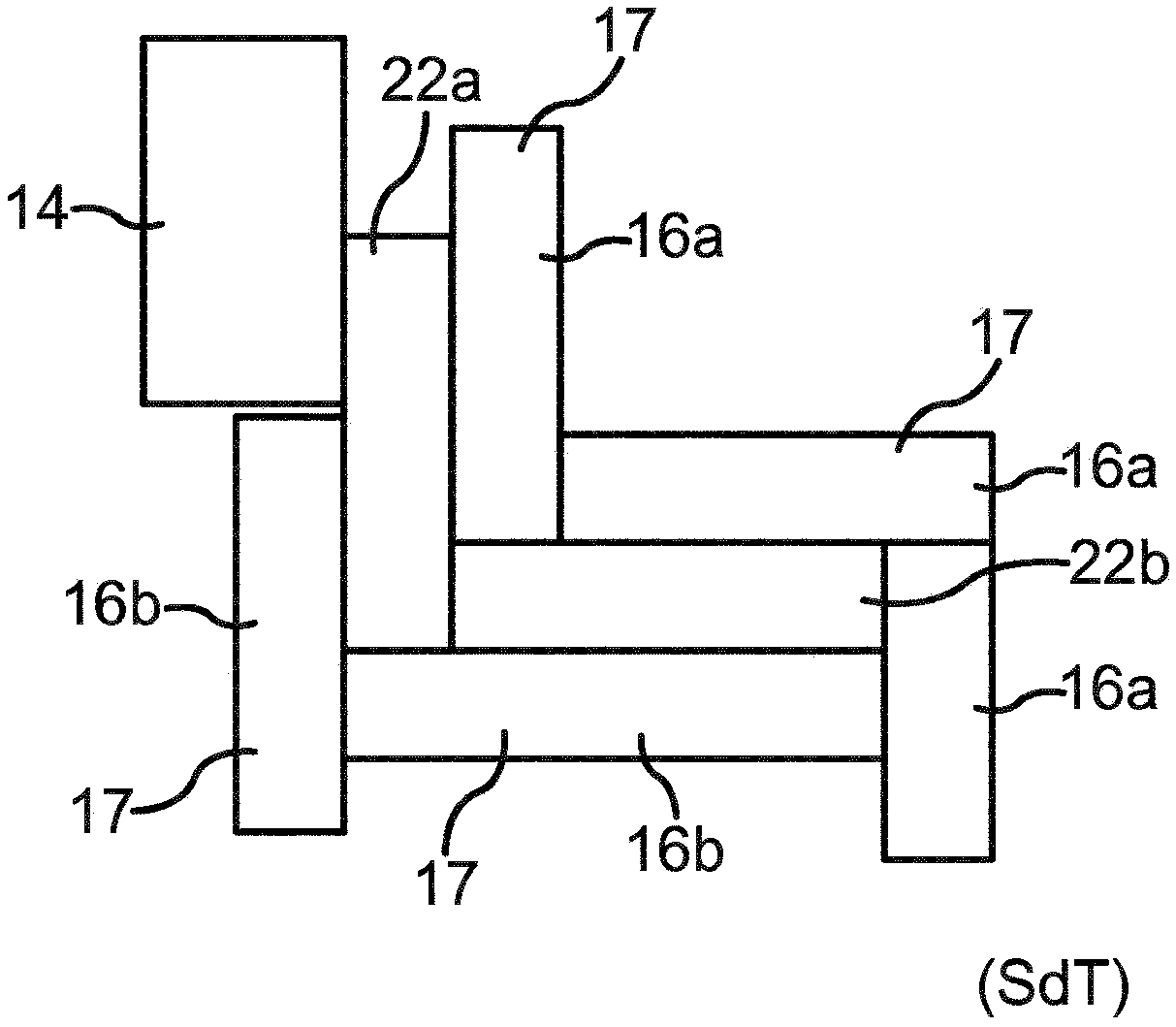

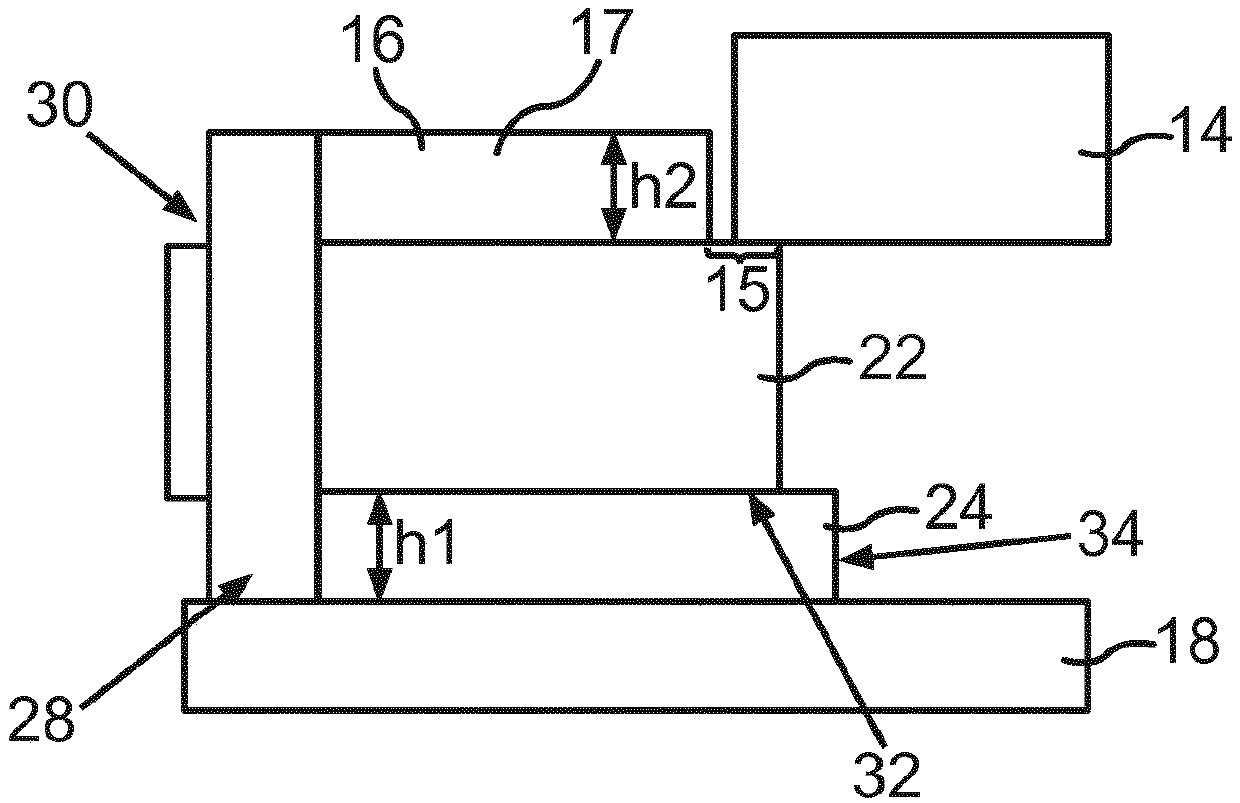

Circuit support for an electronic circuit, and method for manufacturing a circuit support of said type

InactiveCN107750477AReduce thicknessHigh power lossVehicle headlampsLighting and heating apparatusHeat sinkElectronic component

The invention relates to a circuit support for an electronic circuit, comprising: - at least one conductor path (22); - an insulating matrix made of a first insulating material (17) that is injection-molded over the at least one conductor path (22) in such a way as to leave open at least one first region (15) for connecting at least one electronic component (14) of the electronic circuit; - and aheat sink (18); the first insulating material (17) is injection-molded over the at least one conductor path (22) in such a way that the insulating matrix (16) also leaves open at least one second region (34) located between the conductor path (22) and the heat sink (18); the circuit support further comprises a plurality of spacers (28; 36) which are designed and placed in such a way as to adjust aheight (h1) of the second region (34) between the conductor path (22) and the heat sink (18); the circuit support also comprises a second insulating material (24) with which the second region (34) isfilled. The invention further relates to a method for manufacturing said type of circuit support for an electronic circuit.

Owner:OSRAM GMBH

Adhesive film and flexible metal laminate

ActiveUS10716203B2Insulating substrate metal adhesion improvementFilm/foil adhesivesPolymer scienceThin membrane

Owner:ASAHI GLASS CO LTD

Display device

ActiveUS9412726B2The connection is tight and firmPrinted circuit assemblingSolid-state devicesAnisotropic conductive filmDisplay device

A display device includes a substrate on which a plurality of pixels are arranged and a circuit for displaying images with respect to each pixel is formed, a substrate terminal as a terminal formed on the substrate, and an electronic component terminal as a terminal of an electronic component electrically connected to the terminal via an anisotropic conductive film. A conductive region that conducts to the anisotropic conductive film in the substrate terminal has a light transmissive part in which a material having light transmissivity penetrates the substrate surface in a perpendicular direction.

Owner:JAPAN DISPLAY INC

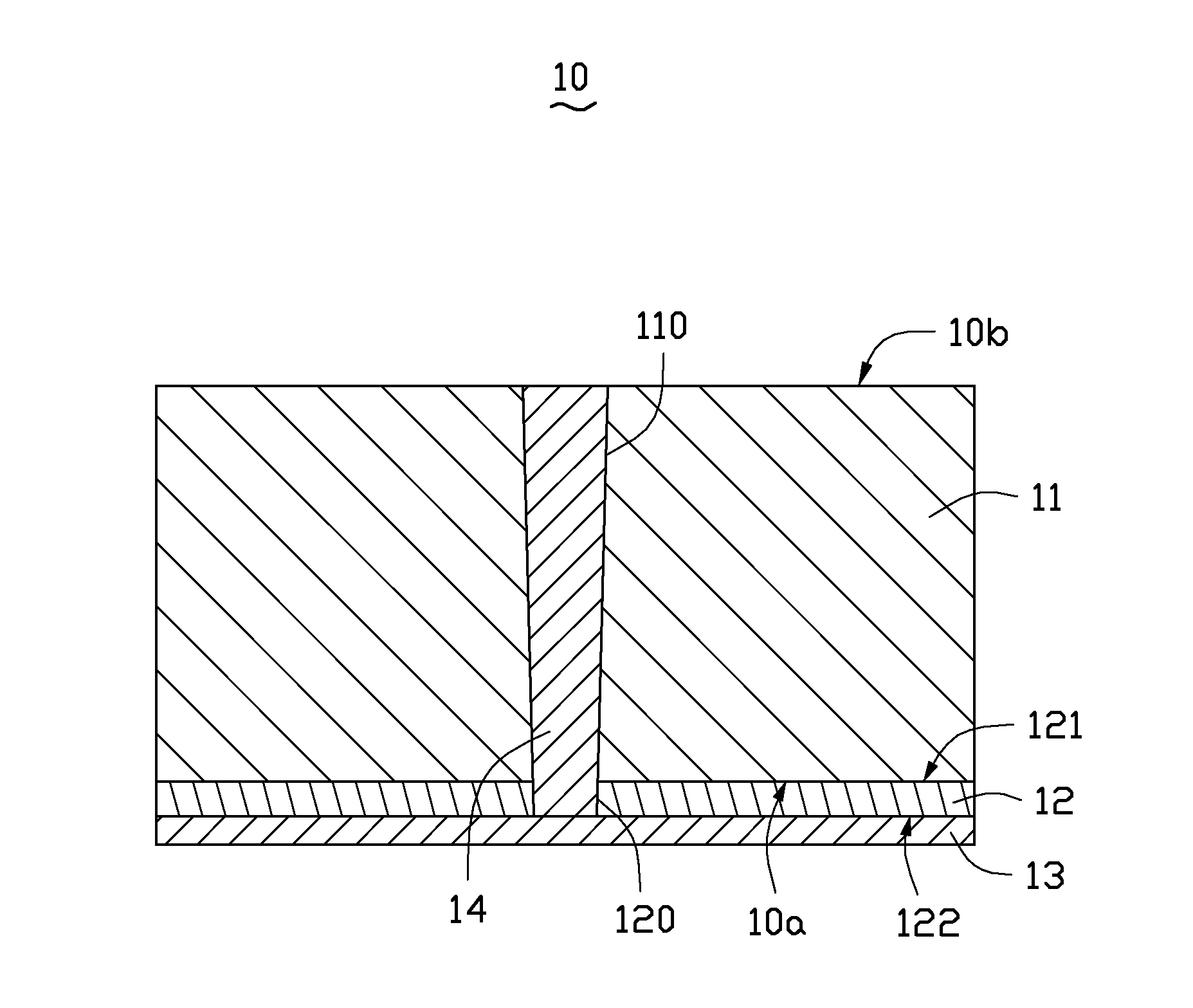

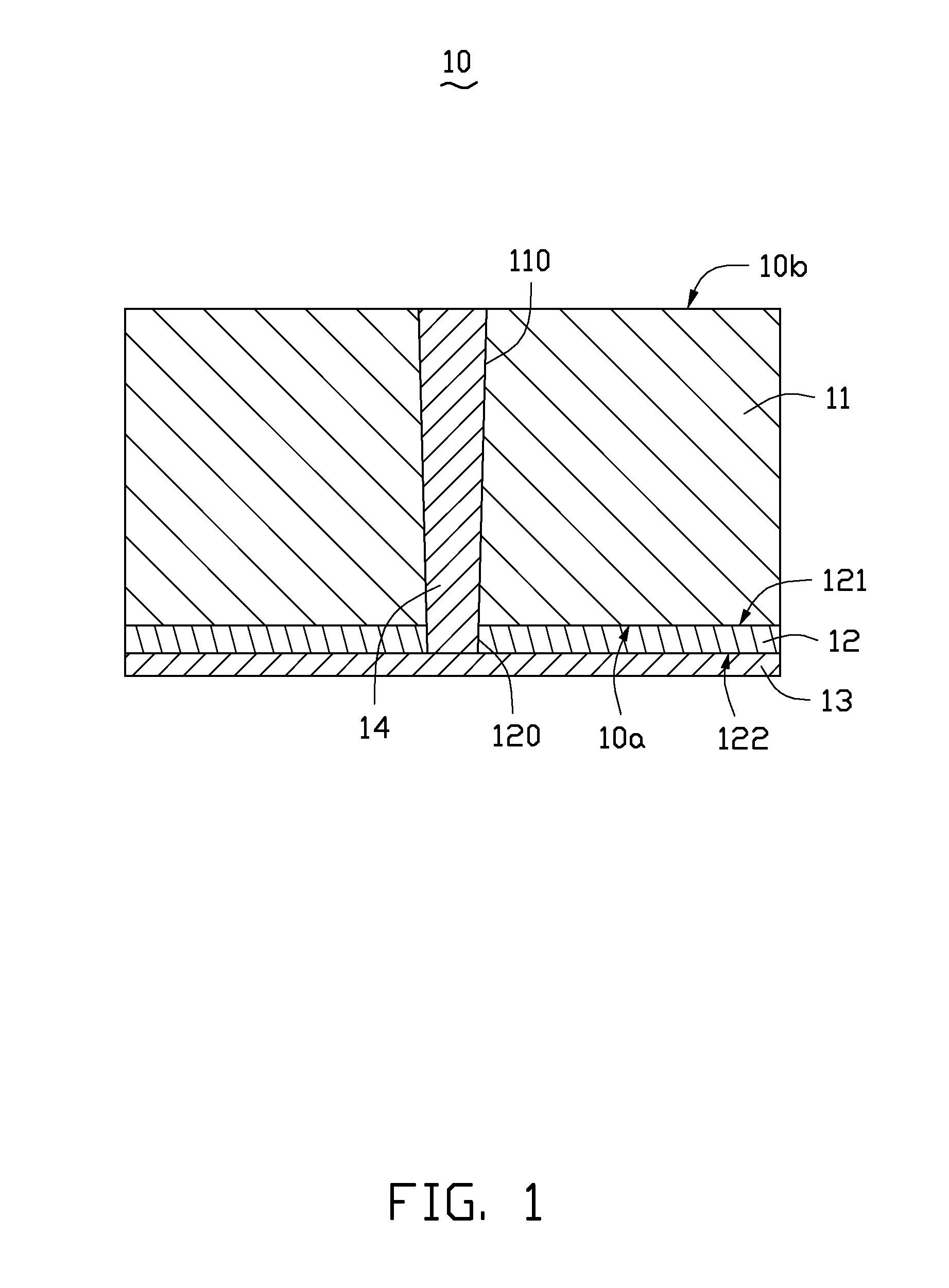

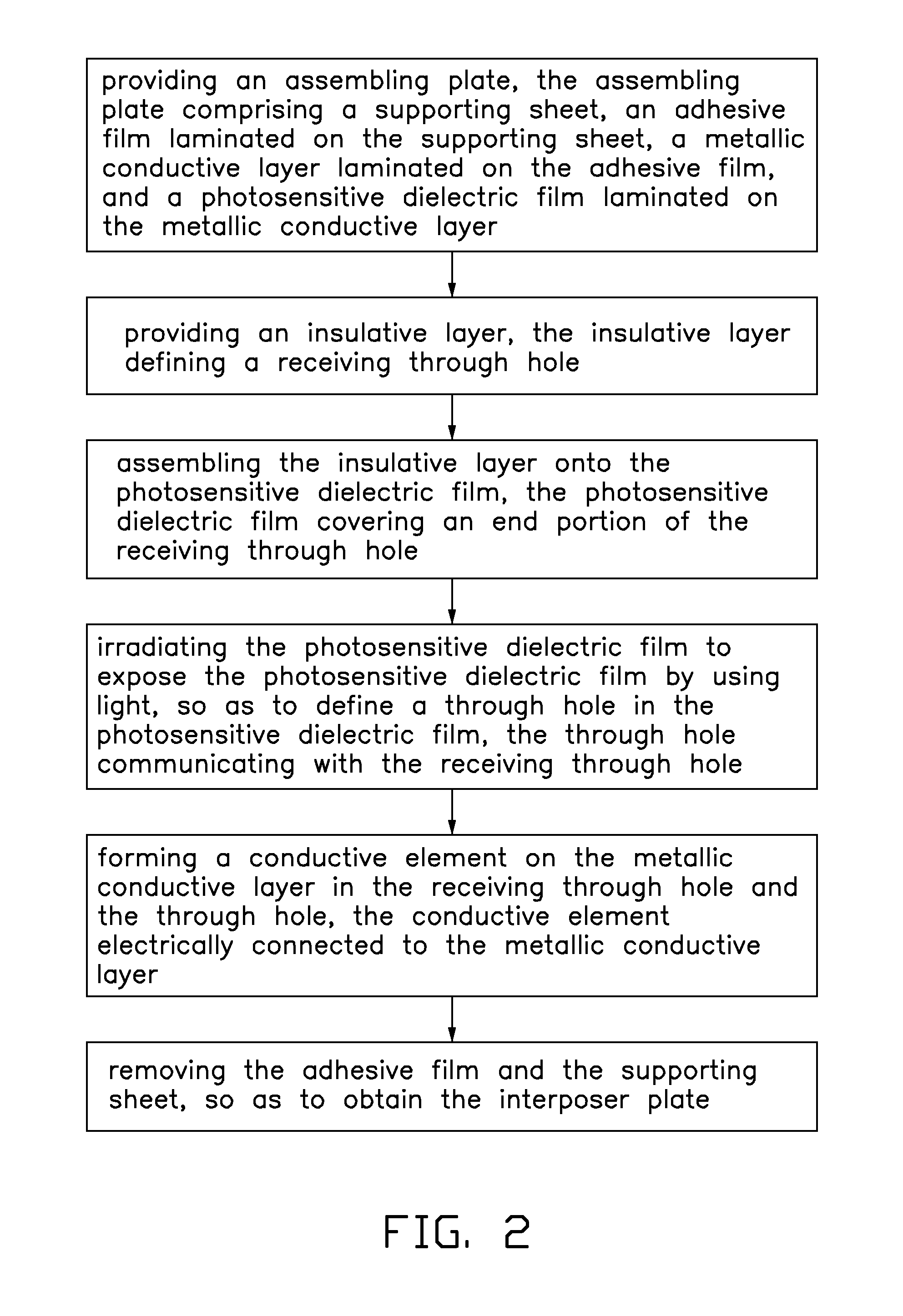

Interposer and method for manufacturing same

ActiveUS20150136457A1Dielectric characteristicsElectrical connection printed elementsDielectricInterposer

An interposer includes an insulating substrate, a photosensitive dielectric film, a conductive layer, and a conductive via. The insulating substrate includes a bottom surface and a top surface, and defines a receiving through hole extending through the bottom surface and the top surface. The photosensitive dielectric film is mounted on the bottom surface. The photosensitive dielectric film defines a through hole spatially corresponding to and communicating with the receiving through hole. The conductive layer is mounted on an end of the photosensitive dielectric film away from the insulating substrate. The conductive layer covers an end of the through hole.The conductive via is received in the receiving through hole and the through hole. The conductive via contacts and electrically connects to the conductive layer.

Owner:LEADING INTERCONNECT SEMICON TECH QINHUANGDAO CO LTD +1

Insulation systems and methods of depositing insulation systems

ActiveUS10968529B2Semiconductor/solid-state device detailsSolid-state devicesElectrophoresesDevice material

This present disclosure generally relates to systems and methods of electrophoretic deposition (EPD) techniques for use in insulation systems at least partially encapsulating a semiconductor device, a conductive component and a substrate, such as insulation systems of semiconductor devices, busbars, or the like. Insulation systems formed using EPD processes may be designed to have a dielectric constant that decreases in a direction away from a substrate of the insulation system. This may improve insulation technologies since depositing coatings with sequentially arranged dielectric constants may improve resistance of the insulation system to high temperature, high electric fields, or the like.

Owner:GENERAL ELECTRIC CO

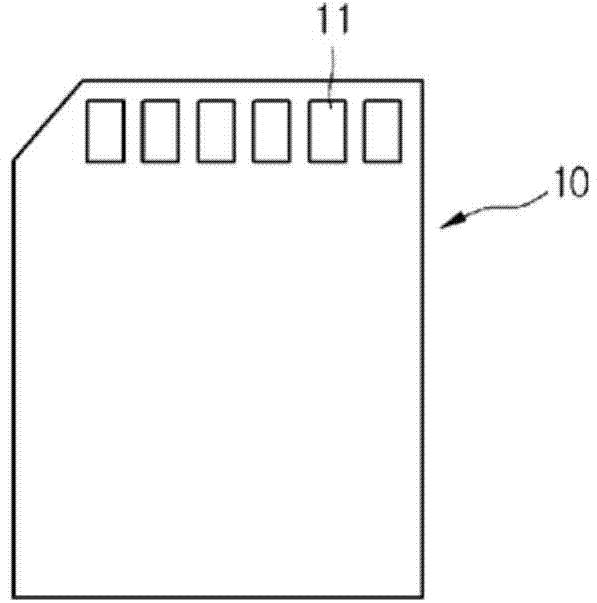

Semiconductor memory card, printed circuit board for memory card and method of fabricating the same

InactiveCN104335230AReduce thicknessReduce hardnessSolid-state devicesLiquid/solution decomposition chemical coatingEngineeringPrinted circuit board

A printed circuit board for a memory card includes an insulating layer; a mounting part on a first surface of the insulating layer, the mounting part being electrically connected to a memory device; and a terminal part on a second surface of the insulating layer, the terminal part being electrically connected to an external electronic appliance, wherein a same metal layer having a same property is formed on exposed surfaces of the mounting part and the terminal part.

Owner:LG INNOTEK CO LTD

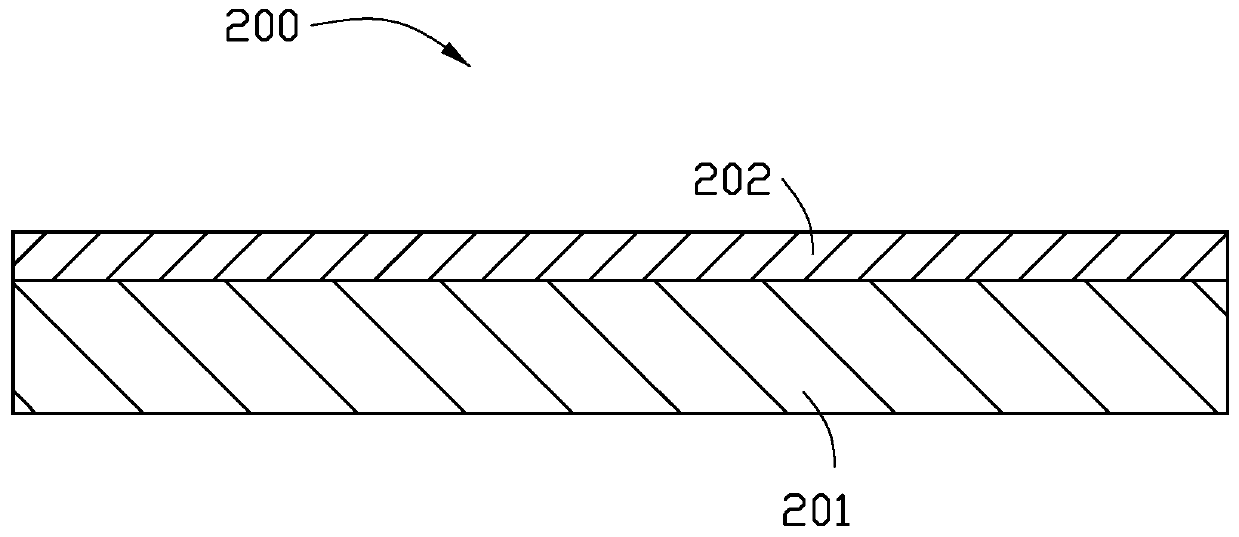

Photosensitive resin composition, cover film and circuit board

ActiveCN107522822BImprove storage effectReduce storage costsDielectric characteristicsCoatingsMethacrylatePolymer science

A kind of photosensitive resin composition, it comprises carboxylic acid modified bisphenol type epoxy (meth) acrylate, photosensitive monomer, photosensitive prepolymer, photoinitiator and colorant, in this photosensitive resin composition Carboxylic acid-modified bisphenol-type epoxy (meth)acrylate, photosensitive monomer, and photosensitive prepolymer will undergo cross-linking reaction under the irradiation of ultraviolet light and solidify to form a dense network structure. The photosensitive resin composition has better storage properties, can be stored at room temperature for a long time, and can reduce the storage cost of the photosensitive resin composition. In addition, the present invention also provides a cover film made of the photosensitive resin composition, and a circuit board made of the cover film.

Owner:ZHEN DING TECH CO LTD

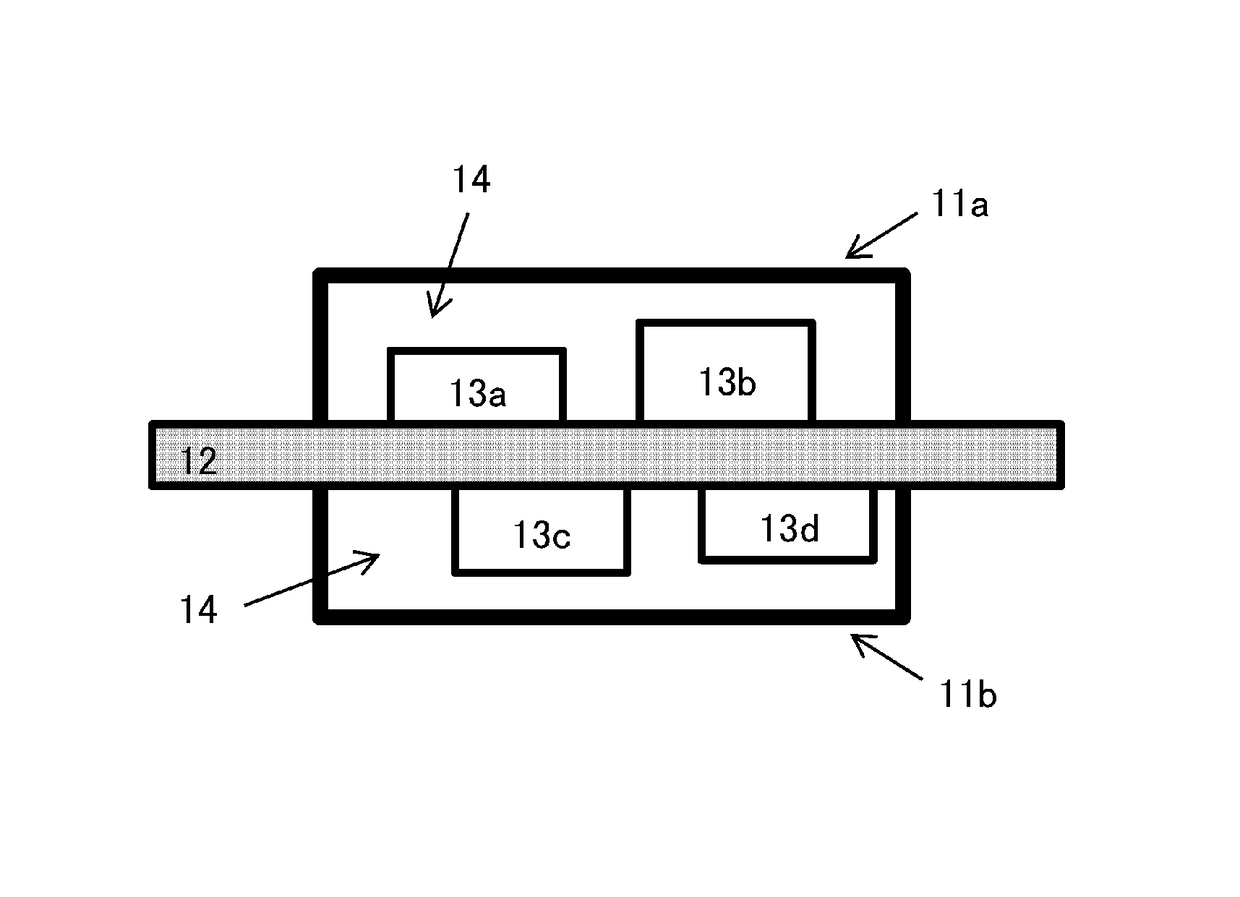

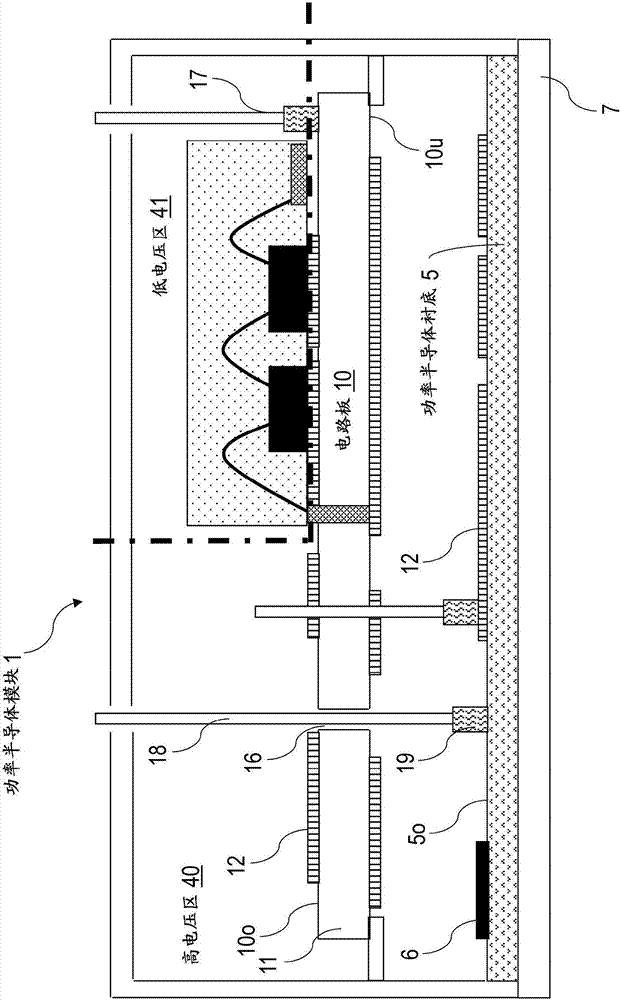

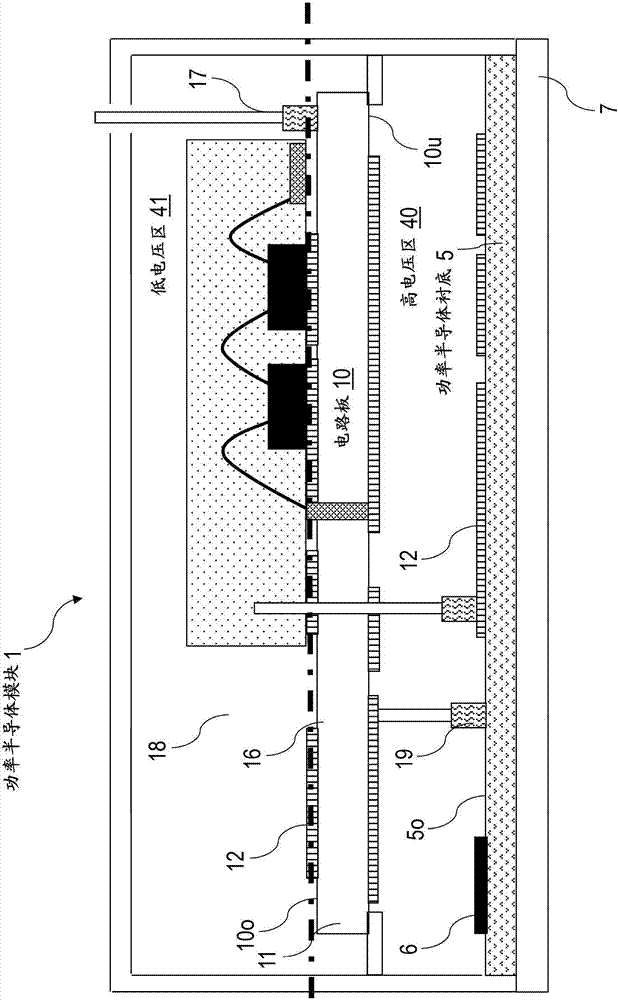

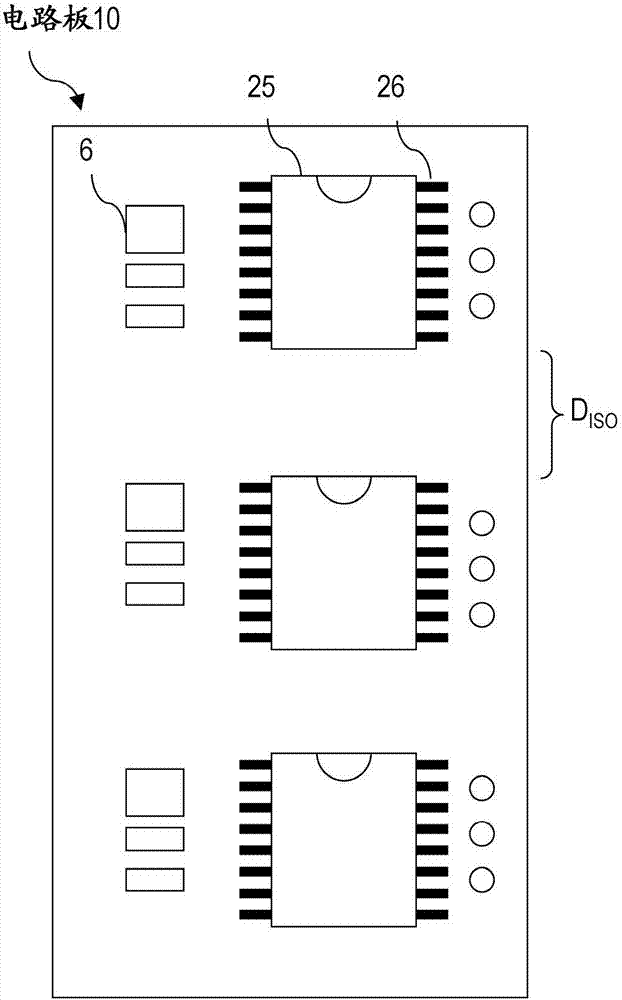

Power semiconductor module and method for producing a power semiconductor module

ActiveCN104517952BSemiconductor/solid-state device detailsSolid-state devicesInsulation layerContact pad

The invention relates to a power semiconductor module. According to one example of the invention, the power semiconductor module has a circuit board with a structured first metal structure and at least one second metal structure arranged on the upper side of the circuit board. At least one housingless semiconductor chip is arranged on the top side of the circuit board, the semiconductor chip has a plurality of contact electrodes, which in turn are connected to corresponding contact pads of the first metal structure on the top side of the circuit board via bonding wires connect. During operation, the contact electrodes and the corresponding first part of the contact lugs are connected to a high voltage. All high-voltage-connected contact lugs are electrically conductively connected to the second metal structure via inner-layer connections. The insulating layer completely covers the chip and the separation area of the circuit board surrounding the chip, wherein all contact pads and inner layer connections for high-voltage switching are completely covered by the insulating layer. The plurality of contact electrodes and the corresponding second portion of the contact pads are at a low voltage during operation.

Owner:INFINEON TECH AG

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com