Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39 results about "Ge element" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

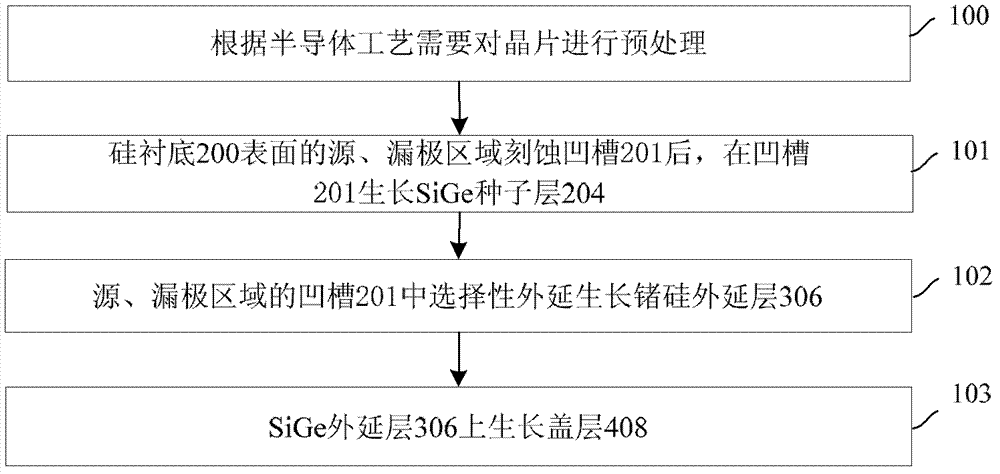

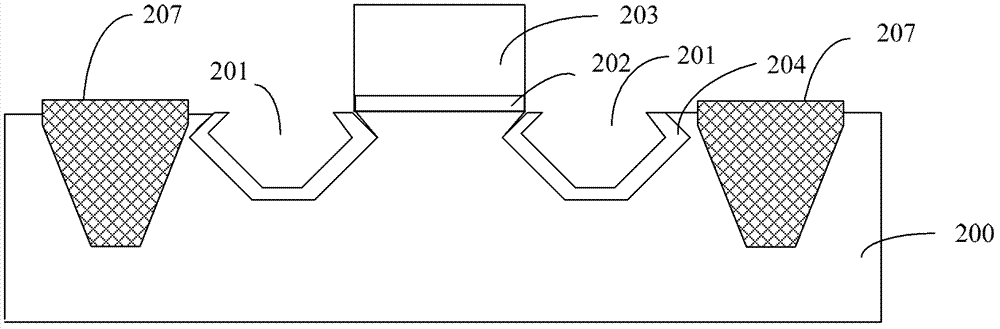

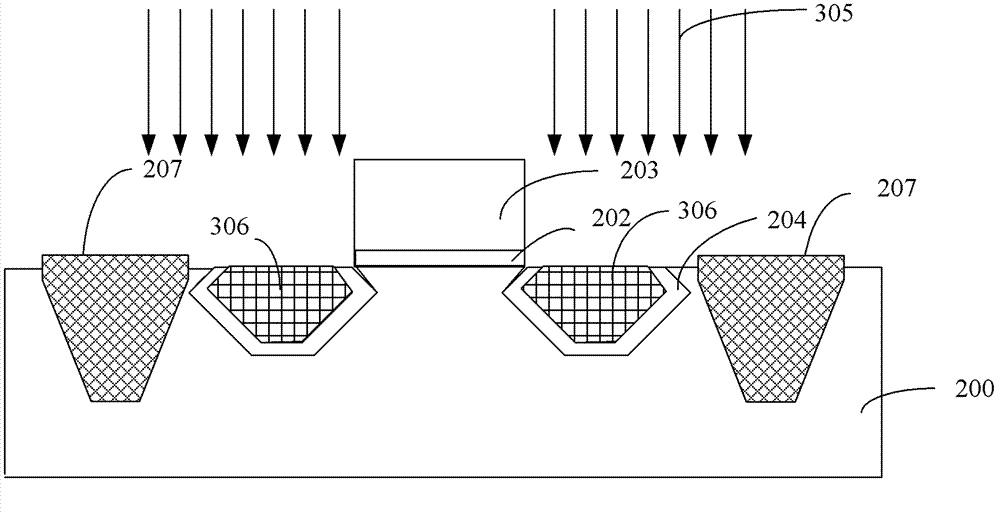

Method for growing germanium-silicon epitaxial layers

InactiveCN102956445AReduced strain relaxationReduce lattice mismatchSemiconductor/solid-state device manufacturingCharge carrier mobilityGe element

The invention provides a method for epitaxially growing SiGe epitaxial layers. The method is applied to filling the SiGe epitaxial layers in source and drain electrode regions of a PMOS (P-channel metal oxide semiconductor), and reaction gas containing Ge elements and carbonaceous gas are simultaneously filled into a reaction chamber, so that the carbonaceous SiGe epitaxial layers are selectively and epitaxially grown on surfaces of source and drain electrode regions of the surface of a silicon substrate. The method has the advantages that on the premise that contents of Ge elements in the SiGe epitaxial layers are guaranteed, critical thicknesses of the SiGe epitaxial layers are increased, strain relaxation is avoided, and the carrier mobility of the PMOS is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

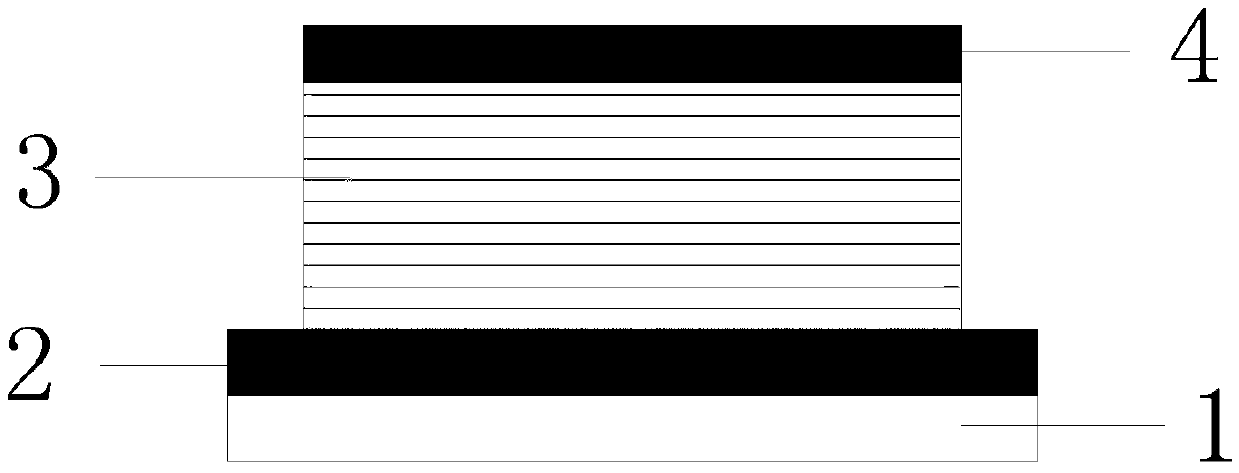

Infrared night-vision goggle based on GeSn infrared detector

InactiveCN105514209AImprove photosensitivityRedshift adjustableTelescopesSemiconductor devicesDisplay deviceGe element

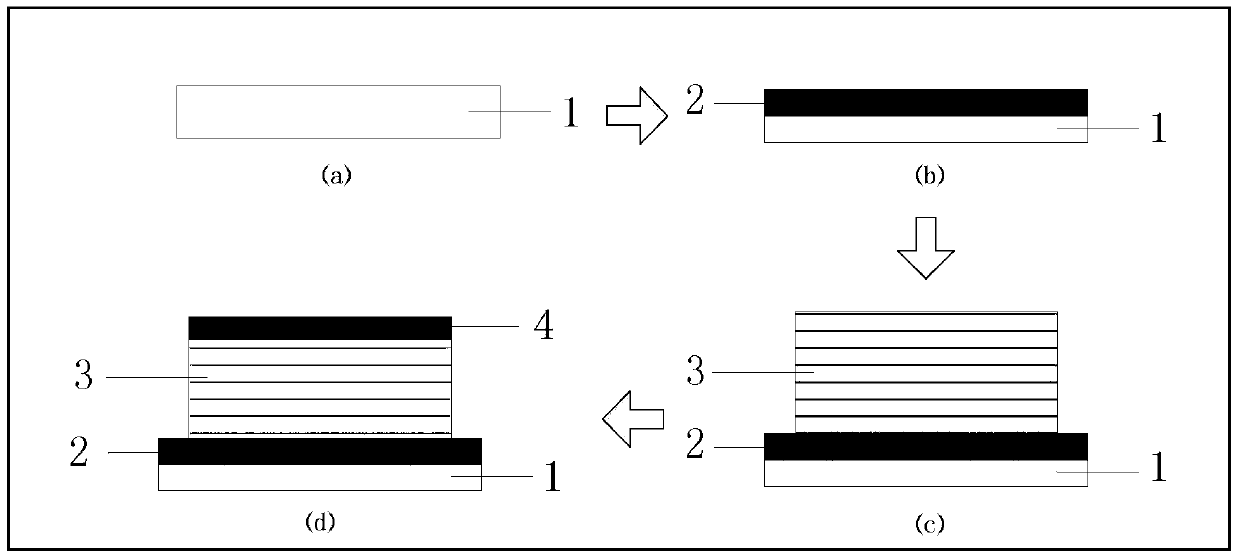

The invention discloses an infrared night-vision goggle based on a GeSn infrared detector, and mainly aims to solve the problem that the existing infrared night-vision goggle is of low light sensing efficiency. The infrared night-vision goggle comprises an optical system, a detector, a signal processor and a display. The detector is a GeSn infrared detector, and comprises a substrate (1), a lower electrode (2), an absorption area (3) and an upper electrode (4), wherein the absorption area (3) is made of a GeSn material of which the general formula is Ge1-xSnx, x is a component of Sn, and 0<=x<=0.25. As the Sn element is added to the Ge element to form a relaxation intrinsic GeSn single crystal, the energy band structure of GeSn is changed from direct band gap to direct band gap while the forbidden bandwidth is decreased. Therefore, the light sensing frequency is increased, the red shift of the absorption edge is adjustable, and the light sensing efficiency and absorption wavelength range of the infrared night-vision goggle are improved.

Owner:XIDIAN UNIV

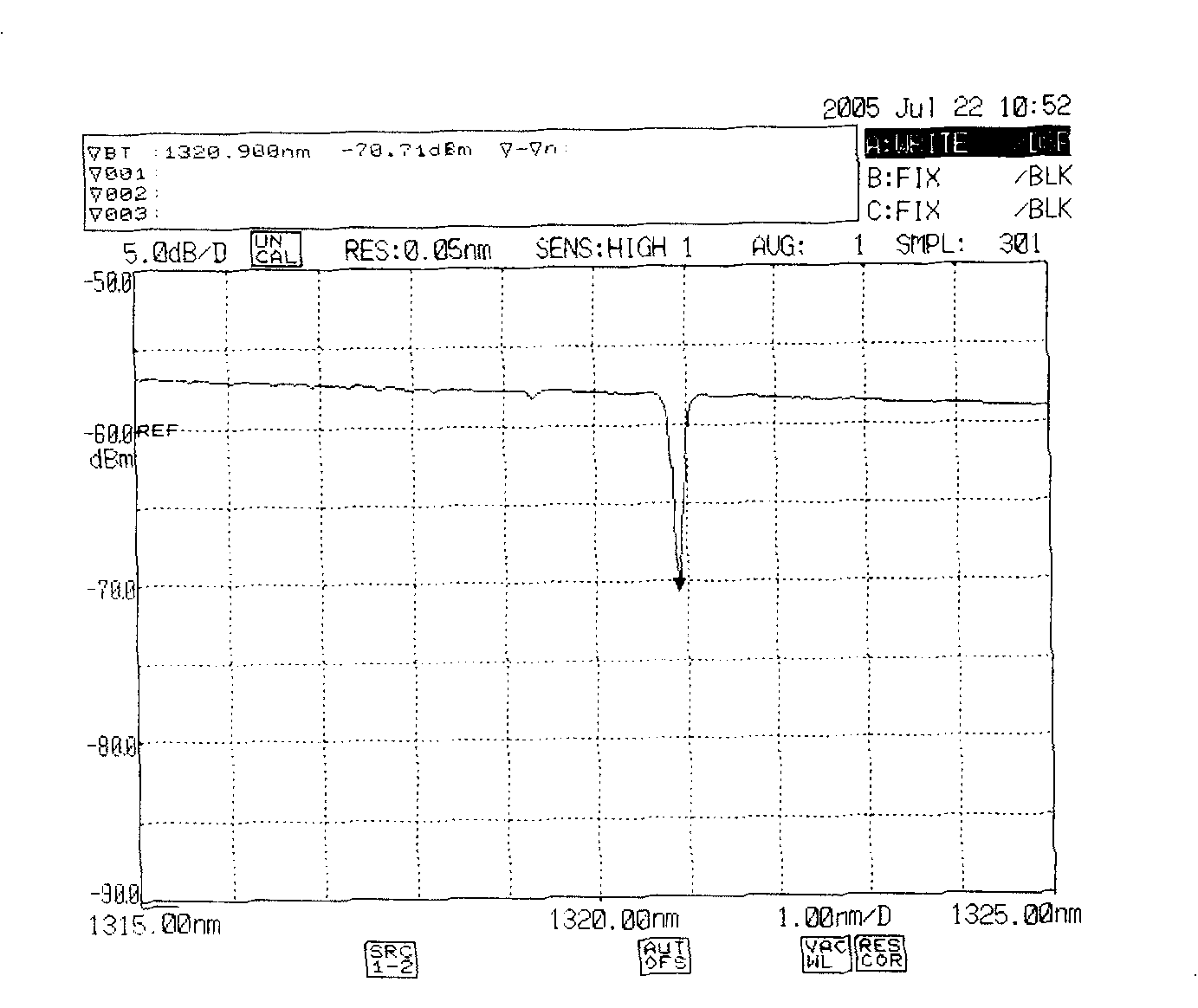

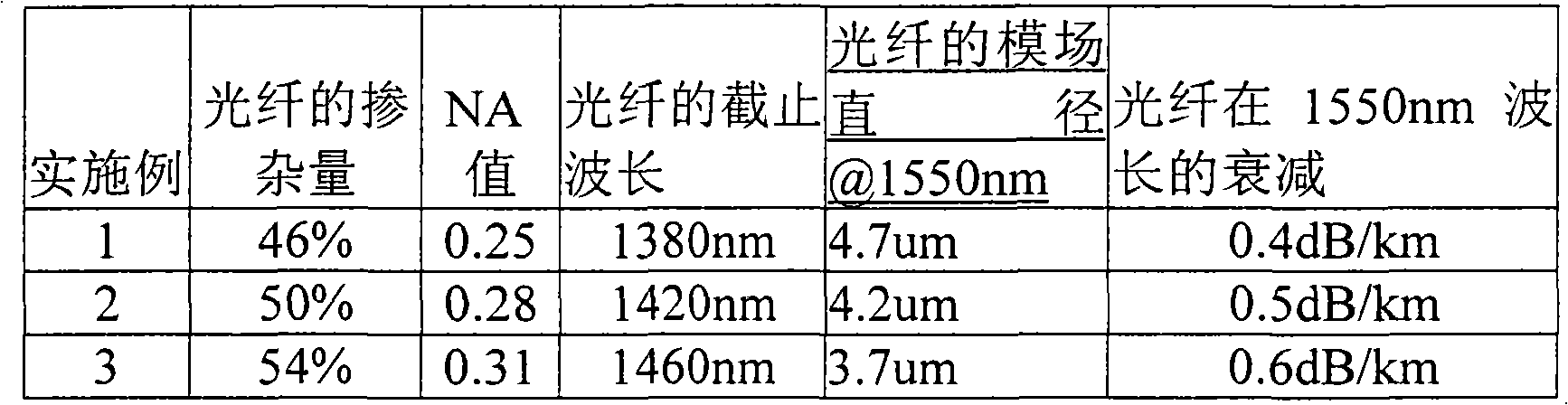

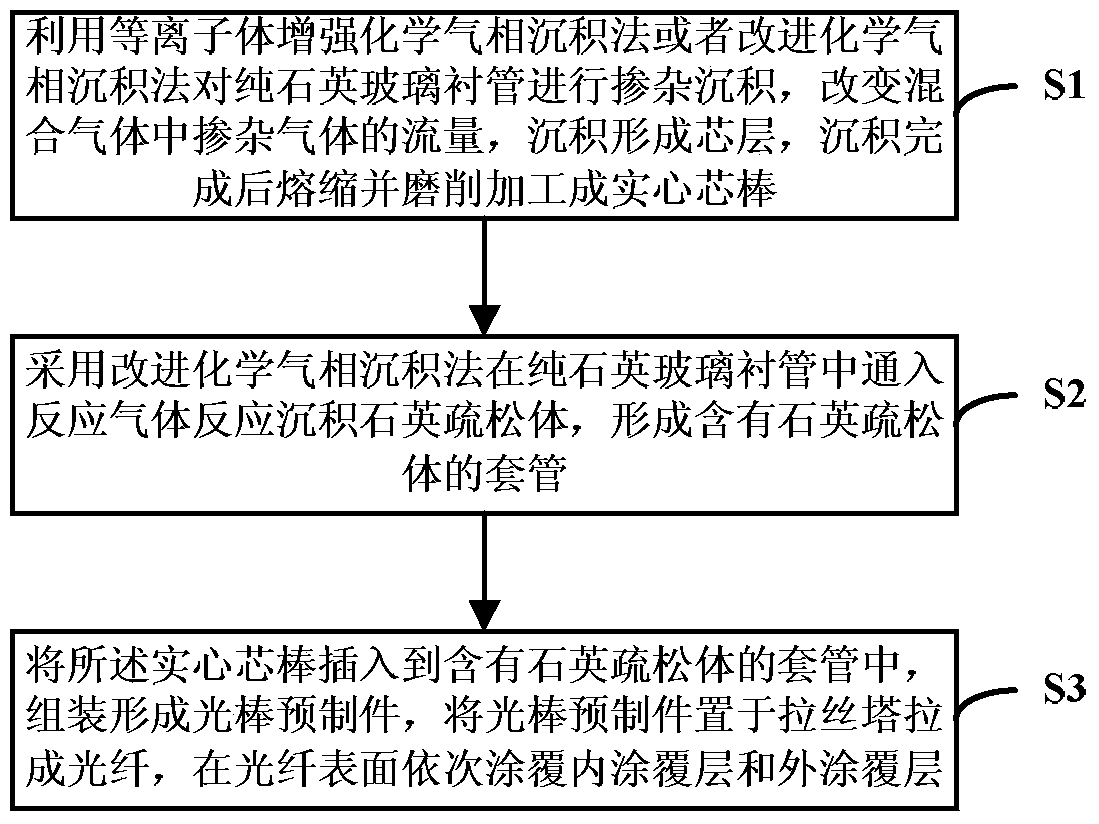

Novel highly germanium-doped -type light-sensitive optical fibre and method for making same

ActiveCN101216574AReduce contentIncrease photosensitivityGlass making apparatusCladded optical fibreFiberUltrasound attenuation

The invention relates to a novel Ge-heavily-doped photosensitive fiber, which is doped with 46% to 54% Ge element in the core layer of an optical fiber with an NA value of 0.25 to 0.31. The Ge-heavily-doped photosensitive fiber has large mode field diameter and small attenuation, and can satisfy the requirement for signal transmission and sensing, so that a fiber grating can be directly etched on a certain section of an optical fiber segment and the rest section serves as the optical fiber for transmitting signal. The invention has a significant characteristic that the photosensitive fiber has very high photosensitive performance, and the fiber grating can be directly etched in the core of the optical fiber without hydrogen loading treatment, etc. The invention can save a great amount of processing program and time and can provide excellent sensing element for an optical fiber sensor system.

Owner:YANGTZE OPTICAL FIBRE & CABLE CO LTD

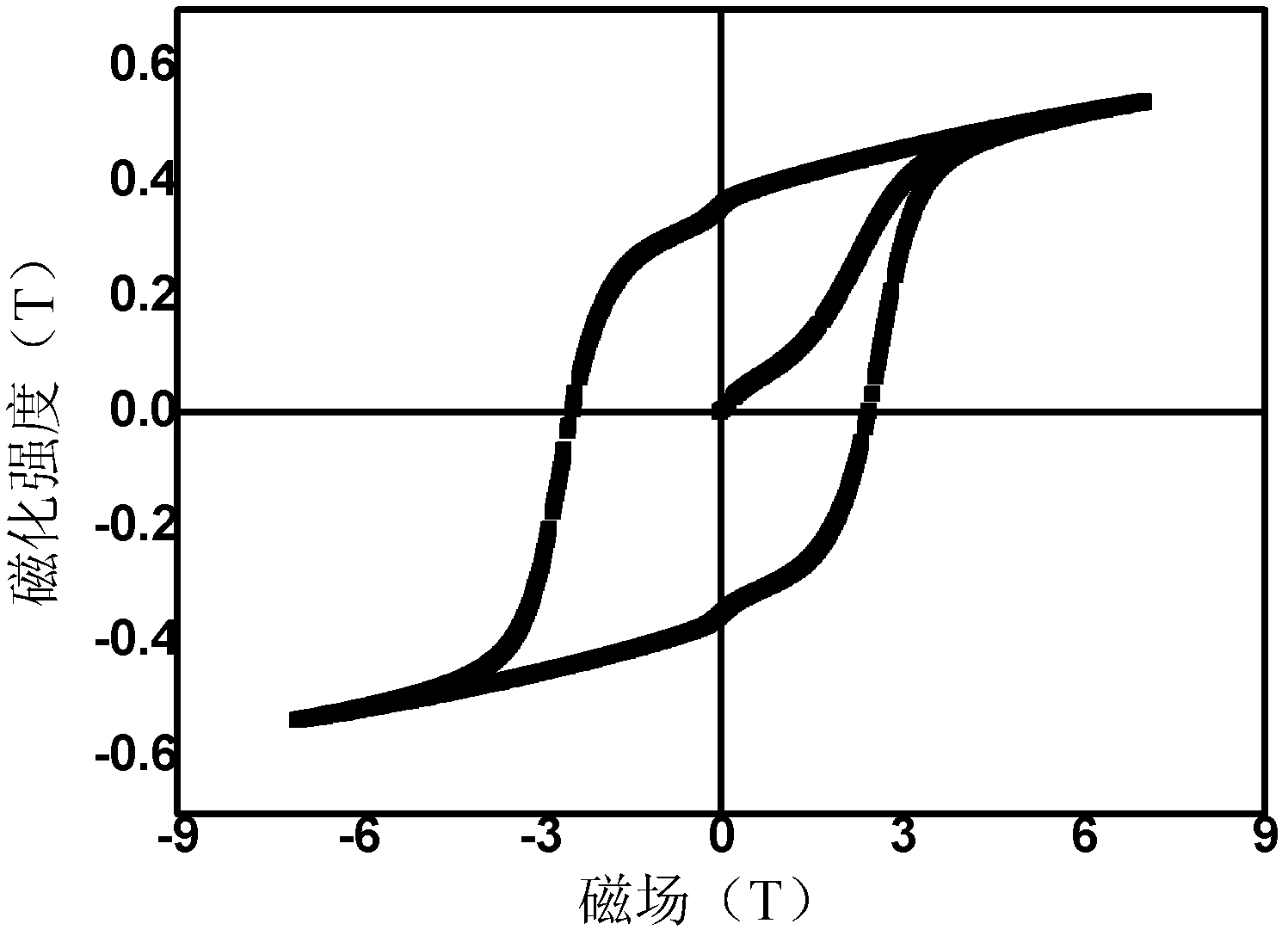

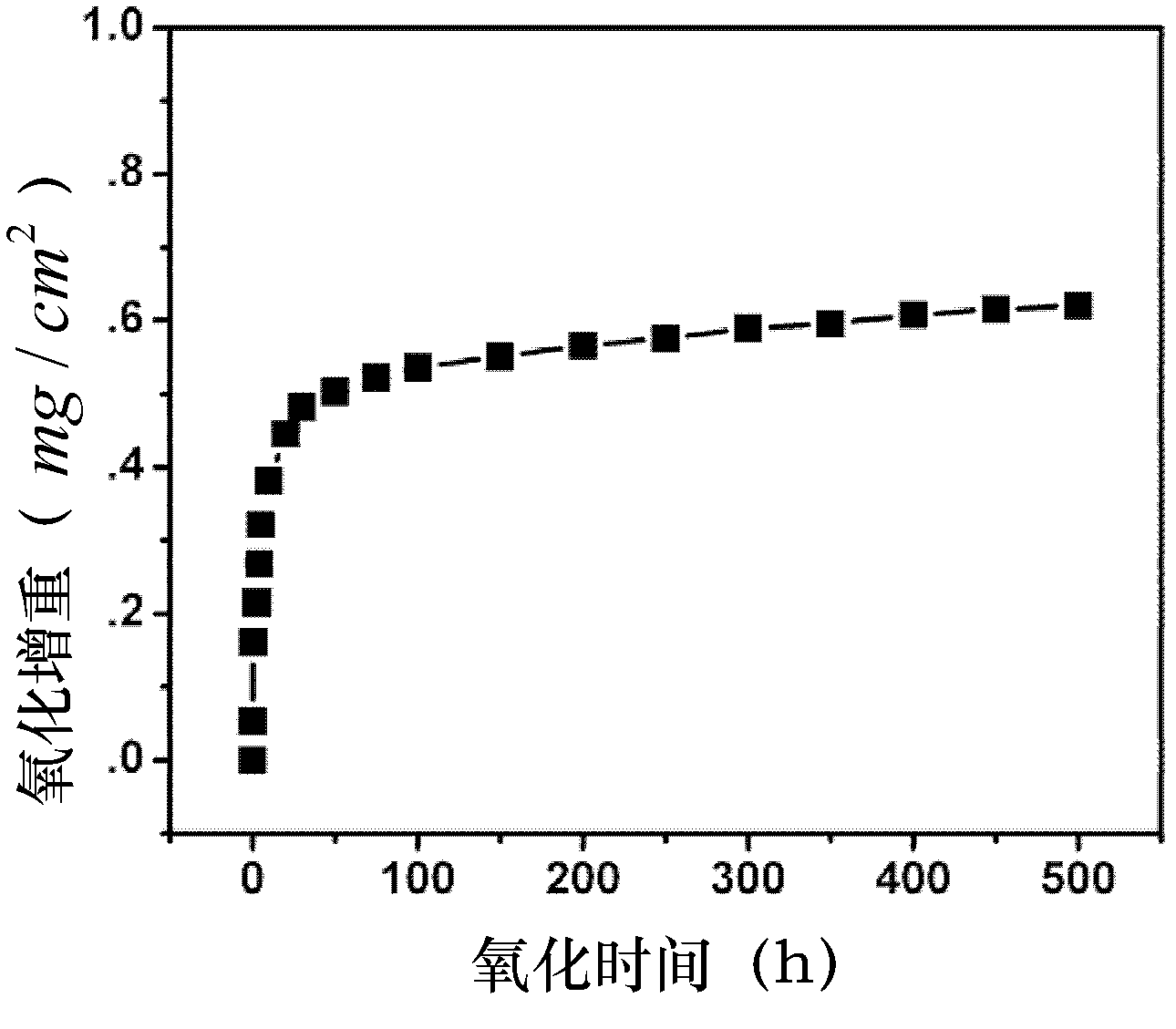

Oxidation-resistant SmCoX-Y(SiaGebSnc)Y high-temperature permanent-magnet material for aeroengine and preparation method thereof

ActiveCN102304646AImprove high temperature oxidation resistanceStable structureMagnetic materialsGe elementOxidation resistant

The invention discloses an oxidation-resistant SmCoX-Y(SiaGebSnc)Y high-temperature permanent-magnet material for an aeroengine and a preparation method thereof. The expression formula of the permanent-magnet material is SmCoX-Y(SiaGebSnc)Y, wherein the atom number of X is 5.0-8.5 and the atom number of Y is 0.01-1.90; and a+b+c=1, the atom number of a is 0.20-0.98, the atom number of b is 0.01-0.70 and the atom number of c is 0.01-0.10. In the invention, Si, Ge and Si elements are doped in SmCo7 alloy, and the ratio of three elements (Si, Ge and Sn) is properly adjusted to achieve the purposes of simultaneously stabilizing the structure of TbCu7 and improving the high-temperature oxidation resistant capacity of a magnet. The Si element is doped, so that the formation of a TbCu7 phase canbe promoted and the high-temperature oxidation resistance of the material can be improved; the Ge element is doped, so that the growth of crystal grains in the sintering process can be inhibited; andthe Sn element is doped, so that the sintering temperature can be reduced, the sintering efficiency can be improved and the mechanical performance of the material can be enhanced at the same time.

Owner:BEIHANG UNIV

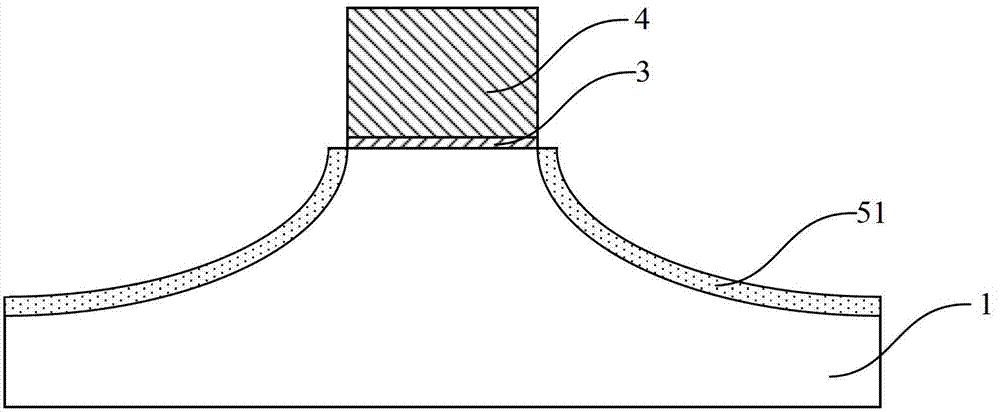

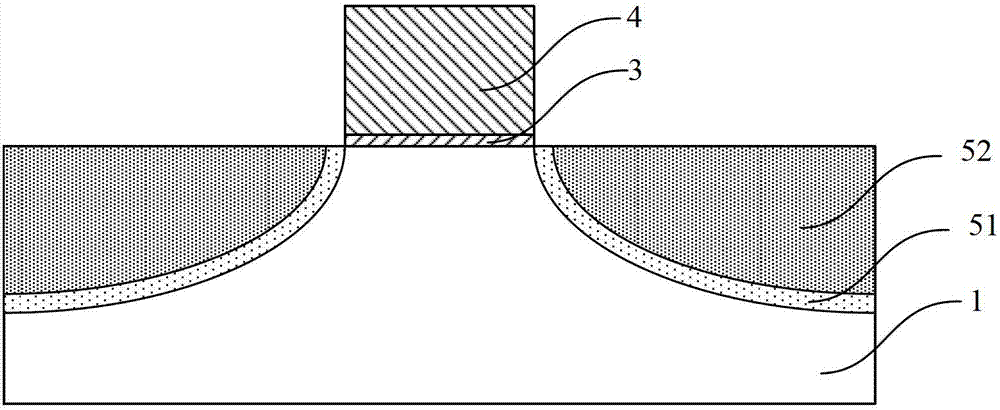

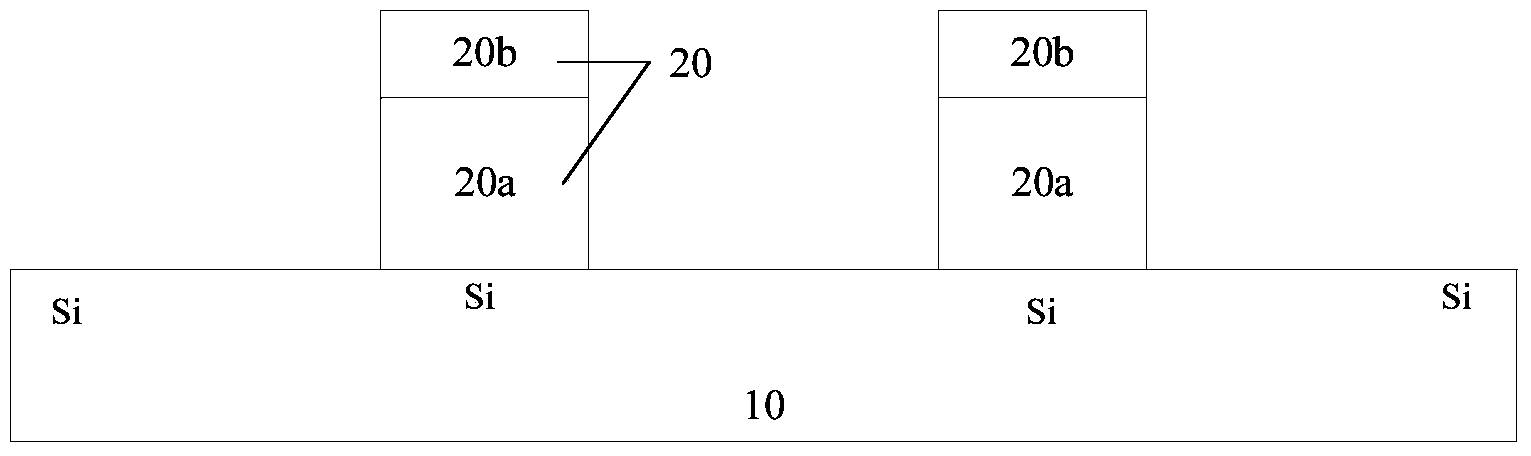

PMOS transistor and manufacturing method thereof

ActiveCN103928336AIncrease compressive stressIncrease working currentSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowLattice mismatch

The invention provides a PMOS transistor and a manufacturing method of the PMOS transistor. When source electrode areas and drain electrode areas of the PMOS transistor are formed, a method that a first stress adjusting layer, a second stress adjusting layer and a stress maintaining layer sequentially grow in an epitaxial mode is adopted. The lattice constant of the first stress adjusting layer and the lattice constant of the second stress adjusting layer gradually increase. When the second stress adjusting layer is formed in an epitaxial mode, an element with the lattice constant larger than that of the Ge element for doping, so that the second stress adjusting layer forms most of the source electrode areas and the drain electrode areas, and larger pressure stress is provided for a channel so that the channel can have higher carrier mobility and work current of a device can be improved; the first stress adjusting layer between the second stress adjusting layer and a substrate serves as a stress buffering layer, and defects caused by too large lattice mismatch between the second stress adjusting layer and the substrate are reduced; a sandwich structure formed by the first stress adjusting layer and the second stress adjusting layer which are spaced is adopted, so that the defects caused by too large lattice mismatch between the second stress adjusting layer and the substrate are further reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

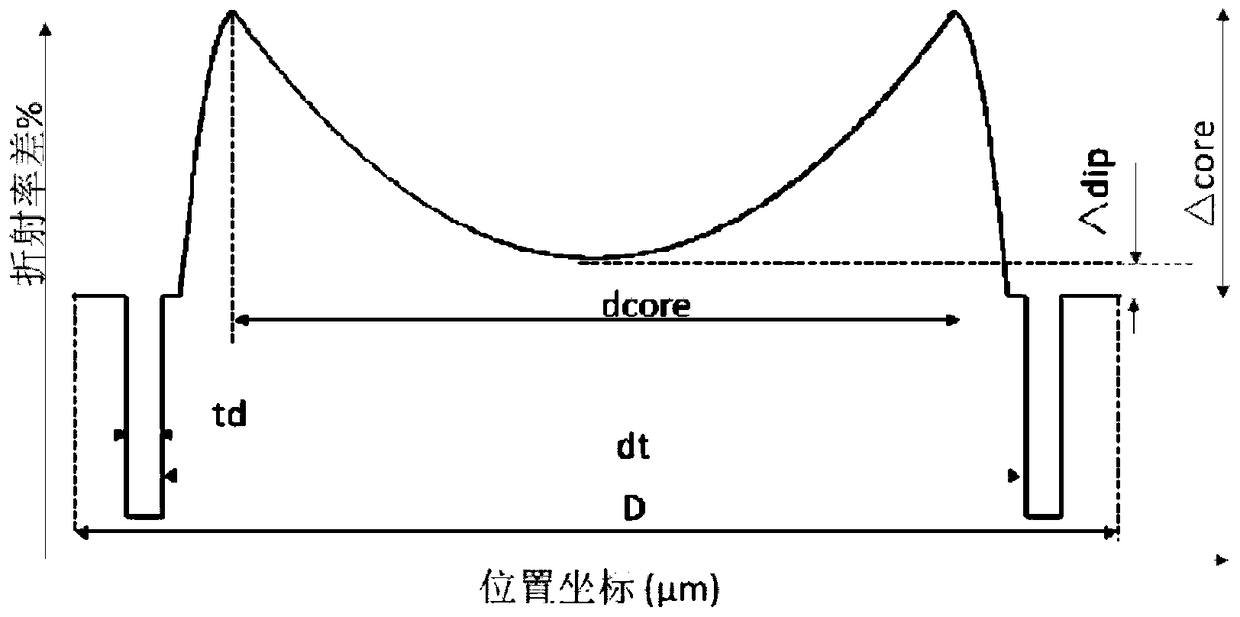

Quartz cladding large-power-transmission dispersion optical fiber and manufacturing method thereof

ActiveCN106033137AImprove stabilityImprove reliabilityGlass making apparatusOptical fibre with multilayer core/claddingRefractive indexGe element

A quartz cladding large-power-transmission dispersion optical fiber and a manufacturing method thereof relate to the technical field of optical communication and related sensing devices. The dispersion optical fiber is composed of a core layer, a first quartz cladding and a second quartz cladding which are successively arranged from inside to outside. The core layer is doped with Ge element; the refractivity of the core layer changes in a gradual manner; and furthermore distribution power exponent is 1.5-3.3. The first quartz cladding contains bubbles and has a light scattering function. The refractivity of the second quartz cladding is higher than that of the first quartz cladding. The quartz cladding large-power-transmission dispersion optical fiber and the manufacturing method have advantages of enduring relatively high power and relatively high temperature, improving stability and reliability of the optical fiber, and effectively settling a color change problem of the optical fiber in illumination.

Owner:WUHAN POST & TELECOMM RES INST CO LTD +1

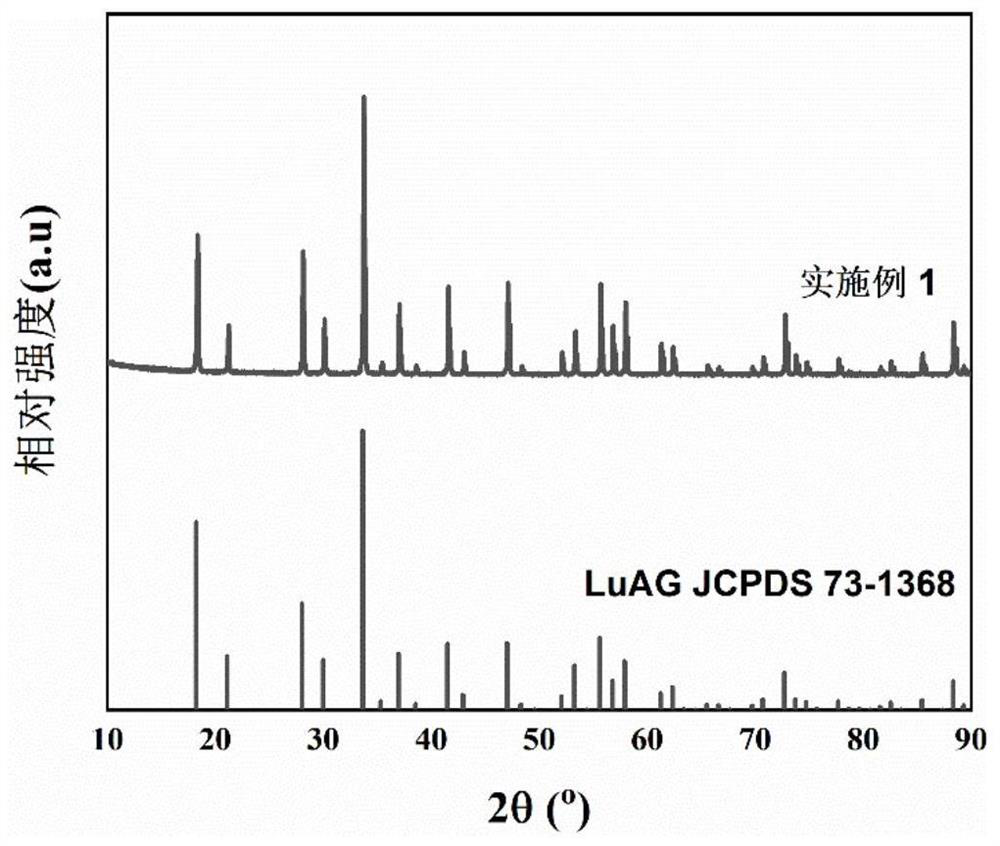

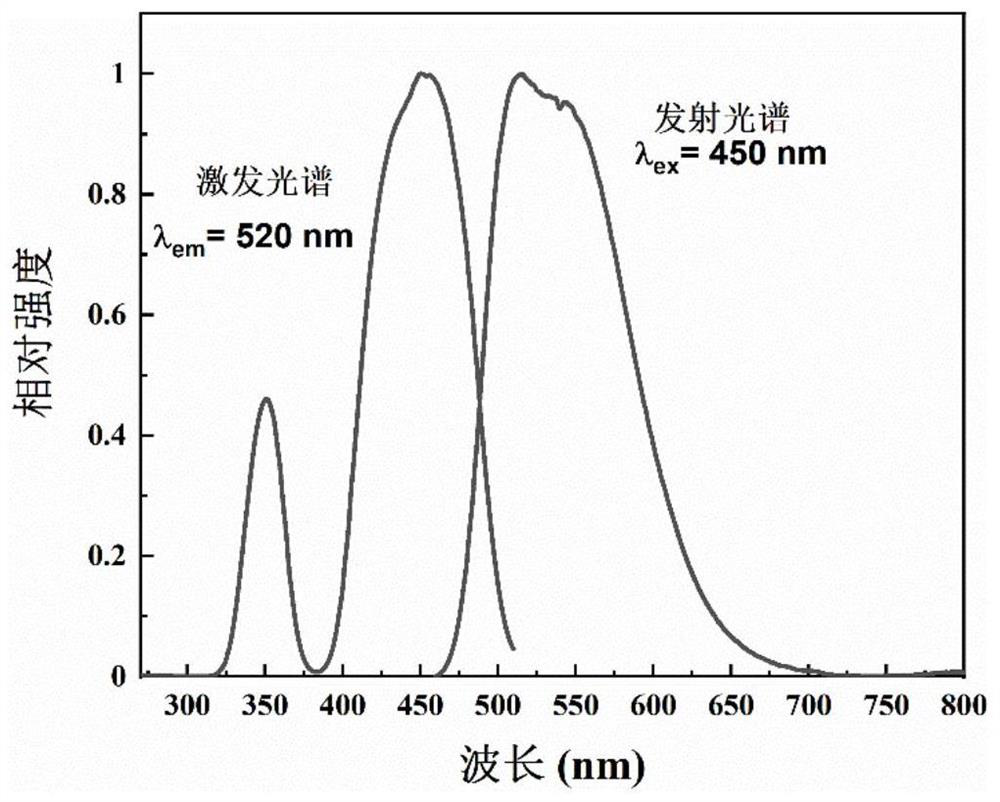

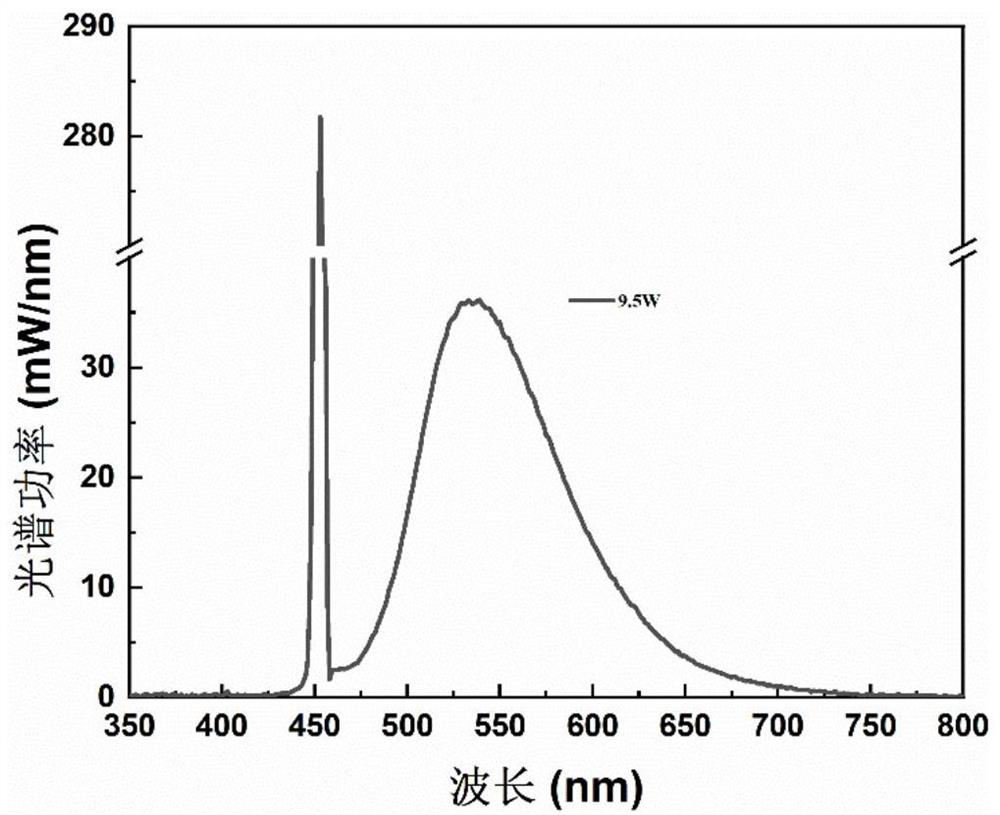

Fluorescent ceramic as well as preparation method and application thereof

InactiveCN111995397AHigh densityLaser wellElectric lightingLuminescent compositionsConvertersAlkaline earth metal

The invention discloses fluorescent ceramic as well as a preparation method and application thereof. The fluorescent ceramic is selected from at least one of substances with a composition general formula shown in a formula I, and the formula I is Lu<3-x-y>Ce<x>M<y>Al<5-y>Q<y>O12, wherein M represents a first co-doped element, the first co-doped element is selected from at least one of alkaline earth metal elements, Q represents a second co-doped element, the second co-doped element is selected from at least one of a Si element and a Ge element, x is more than or equal to 0.0001 and less than or equal to 0.3, and y is more than or equal to 0 and less than or equal to 2. Charge balance is realized through equivalent common doping of doped M<2+> and Q<4+> ions, so that variable-valence Ce<3+>ions in the fluorescent ceramic are inhibited from being converted into Ce<4+> ions, and the fluorescent ceramic is mostly composed of Ce<3+> light-emitting ions. The fluorescent ceramic has the characteristics of high density, good laser saturation performance, high luminous efficiency and the like, can be used as a key material of a color converter, and has a huge application potential in the field of high-power laser illumination.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

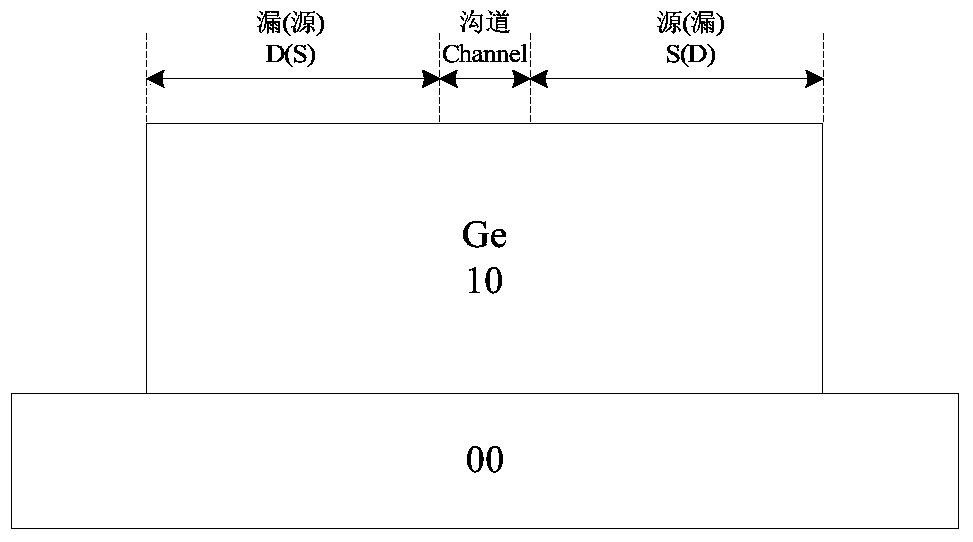

MOSFET with SiGe channel and forming method of MOSFET

InactiveCN103972105AThe overall thickness is thinGood electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSurface layer

The invention provides an MOSFET with a SiGe channel and a forming method of the MOSFET. The forming method includes the following steps of providing a substrate with a Si layer at the top, injecting atoms, molecules, ions or plasmas containing Ge elements into the surface layer of the Si layer so that the SiGe layer can be formed, forming a gate stacking structure on the upper portion of the SiGe layer, and forming a source and a drain on the two sides of the gate stacking structure. According to the forming method of the MOSFET, the MOSFET with the SiGe channel can be formed, the SiGe channel is thin, crystalline quality is good, and accordingly the MOSFET has good electrical property and the method has the advantages of being simple, easy to carry out and low in cost.

Owner:TSINGHUA UNIV

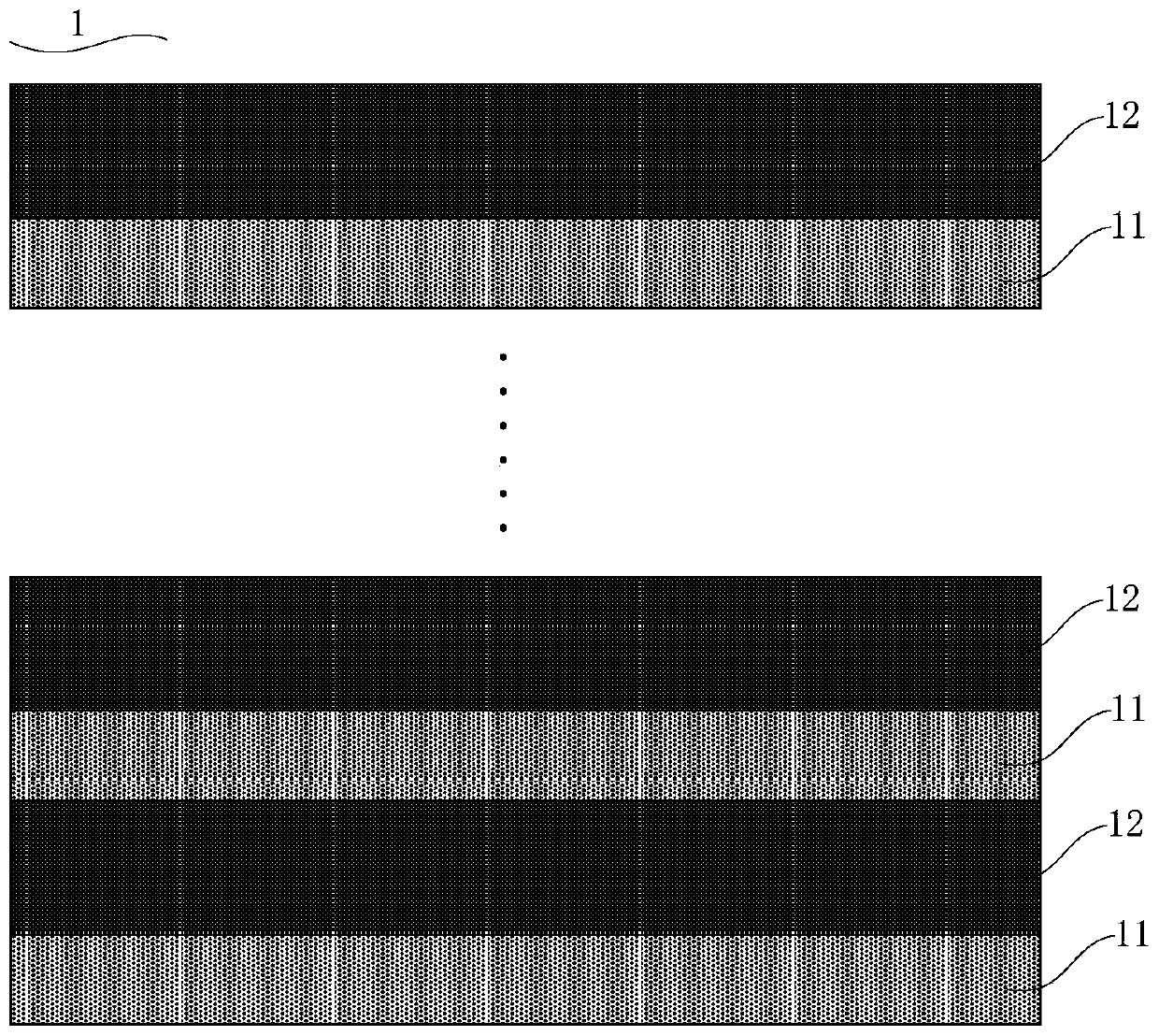

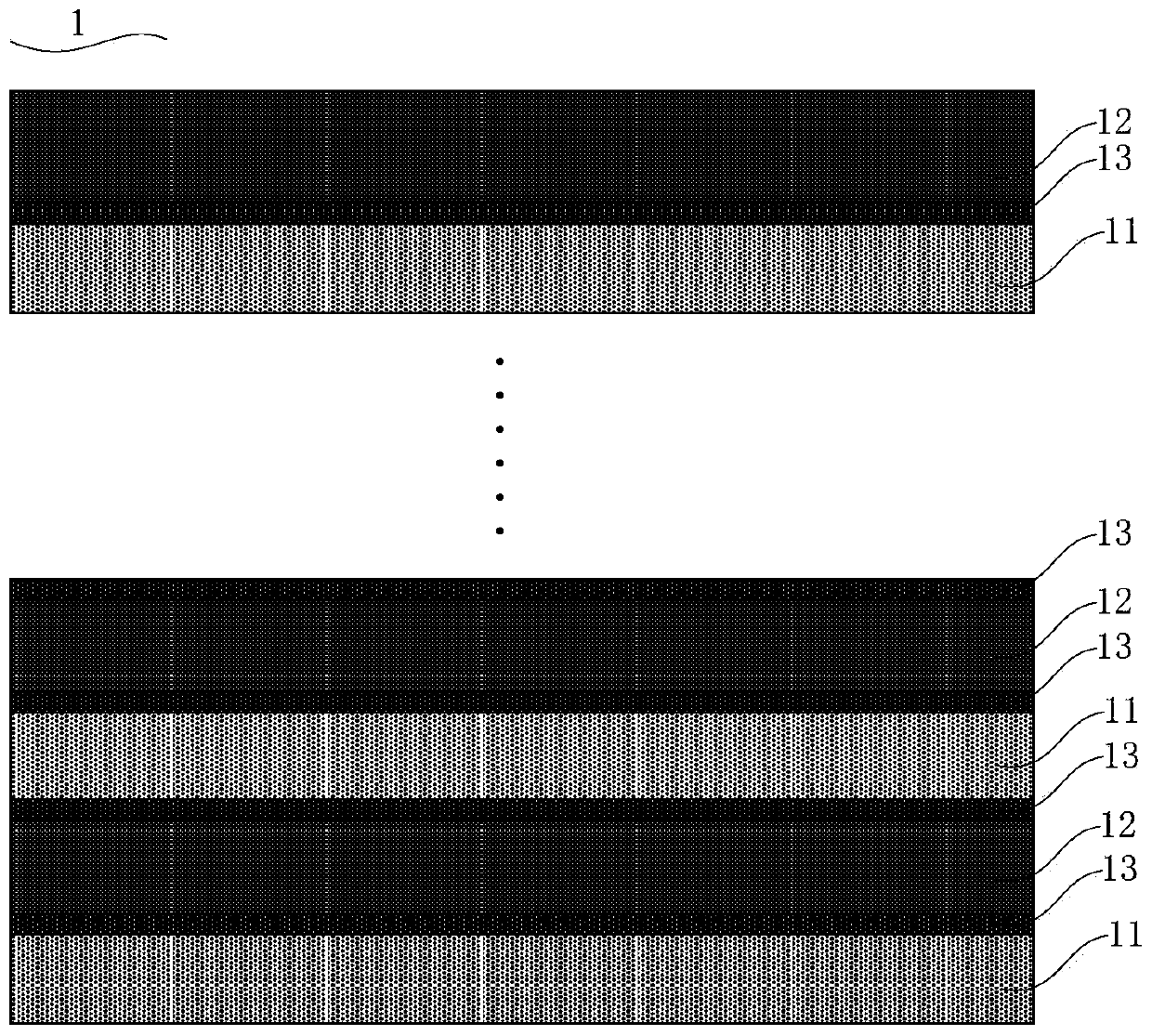

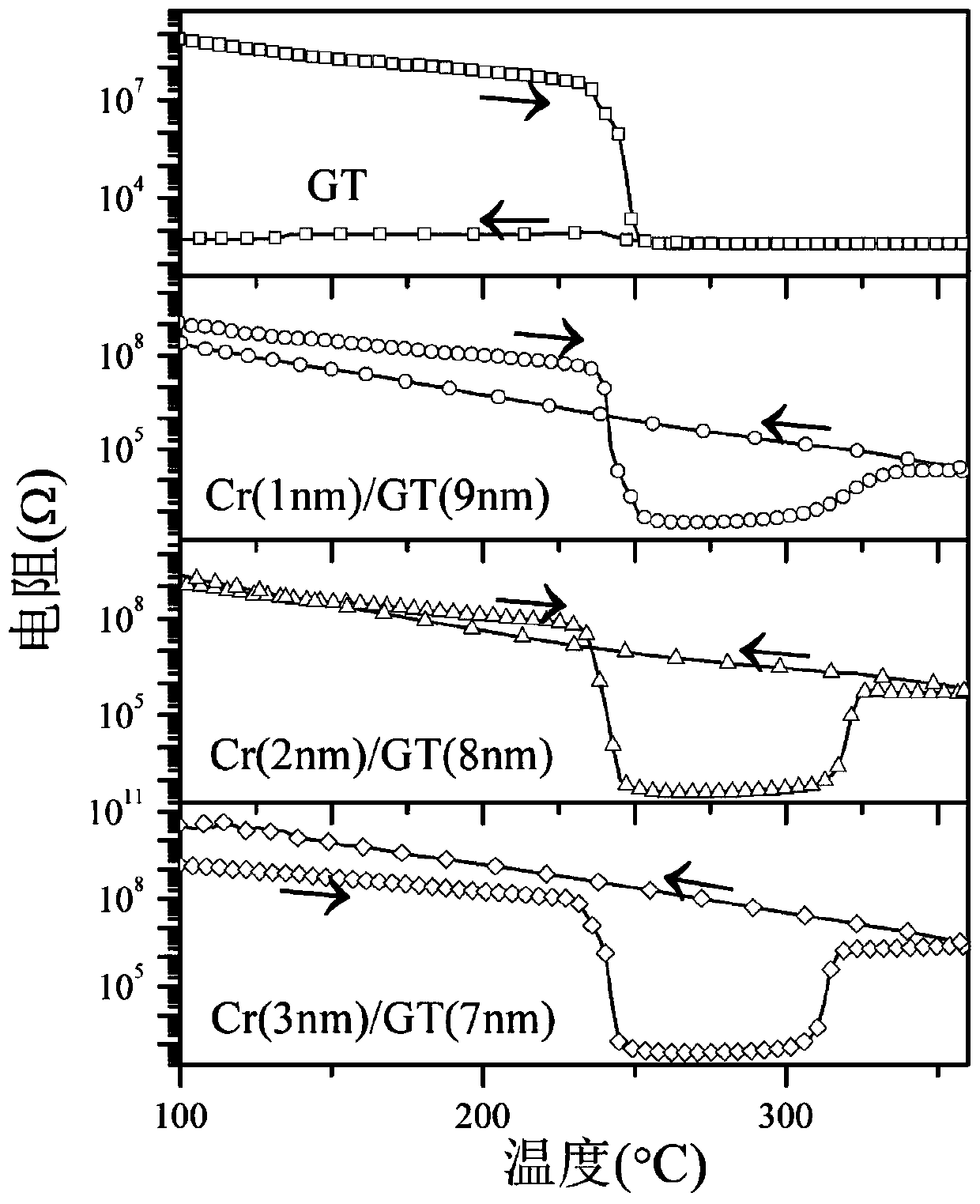

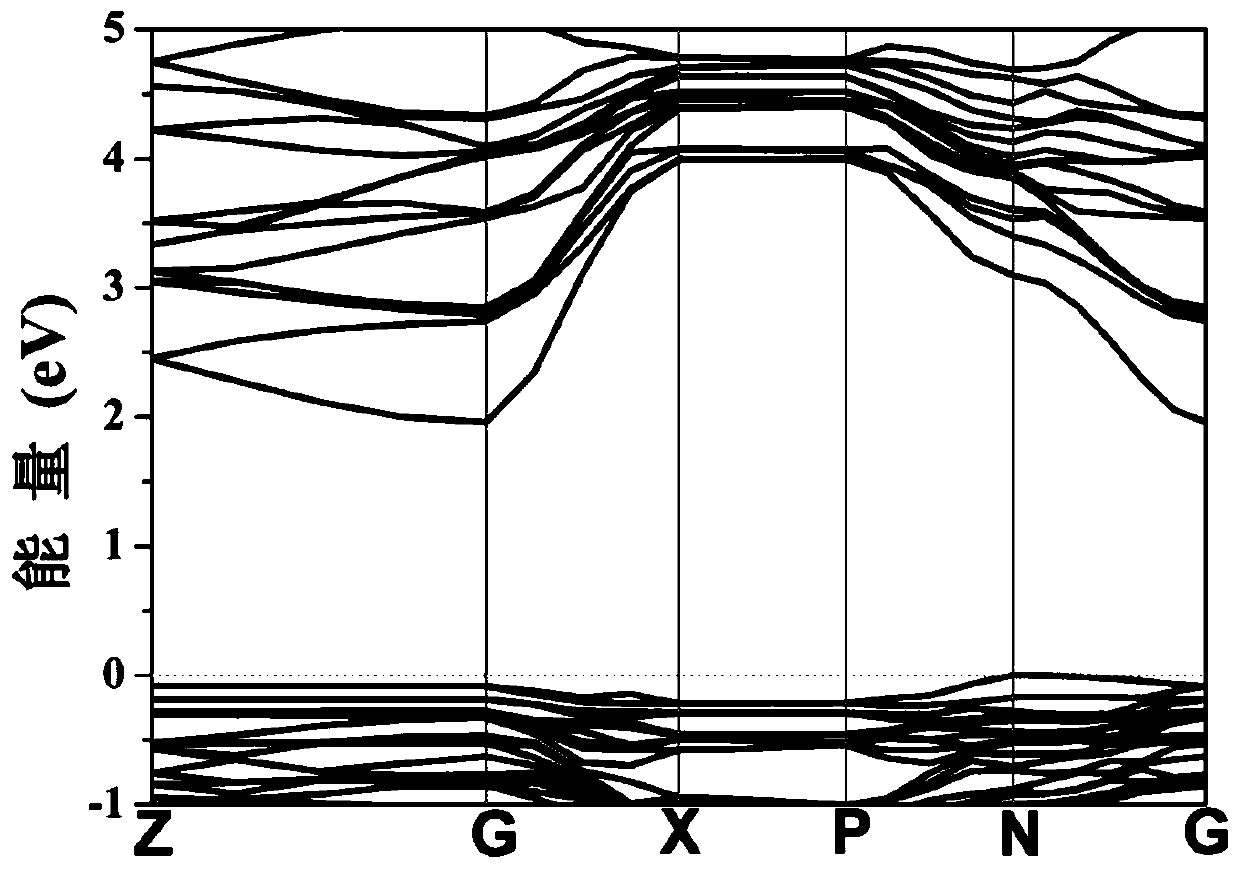

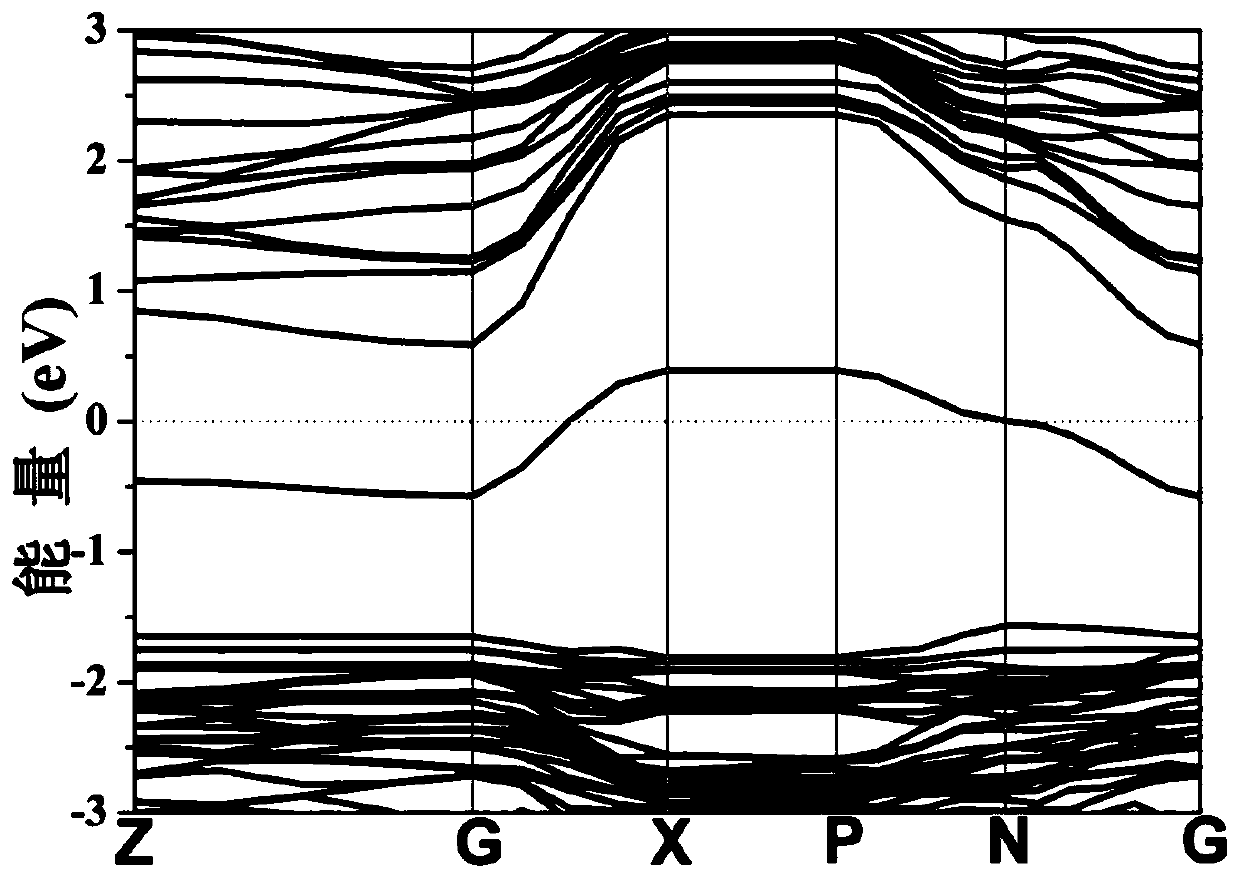

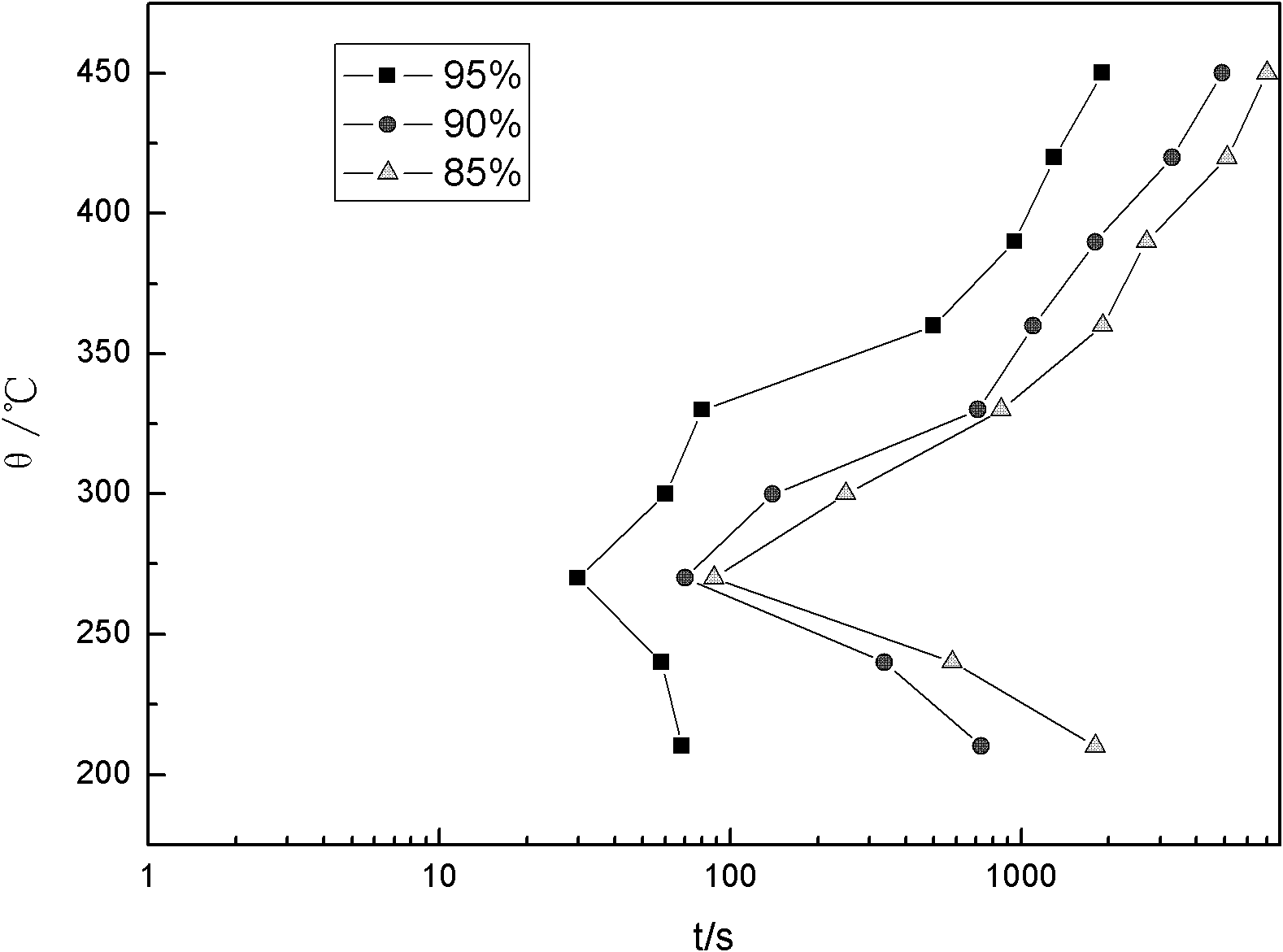

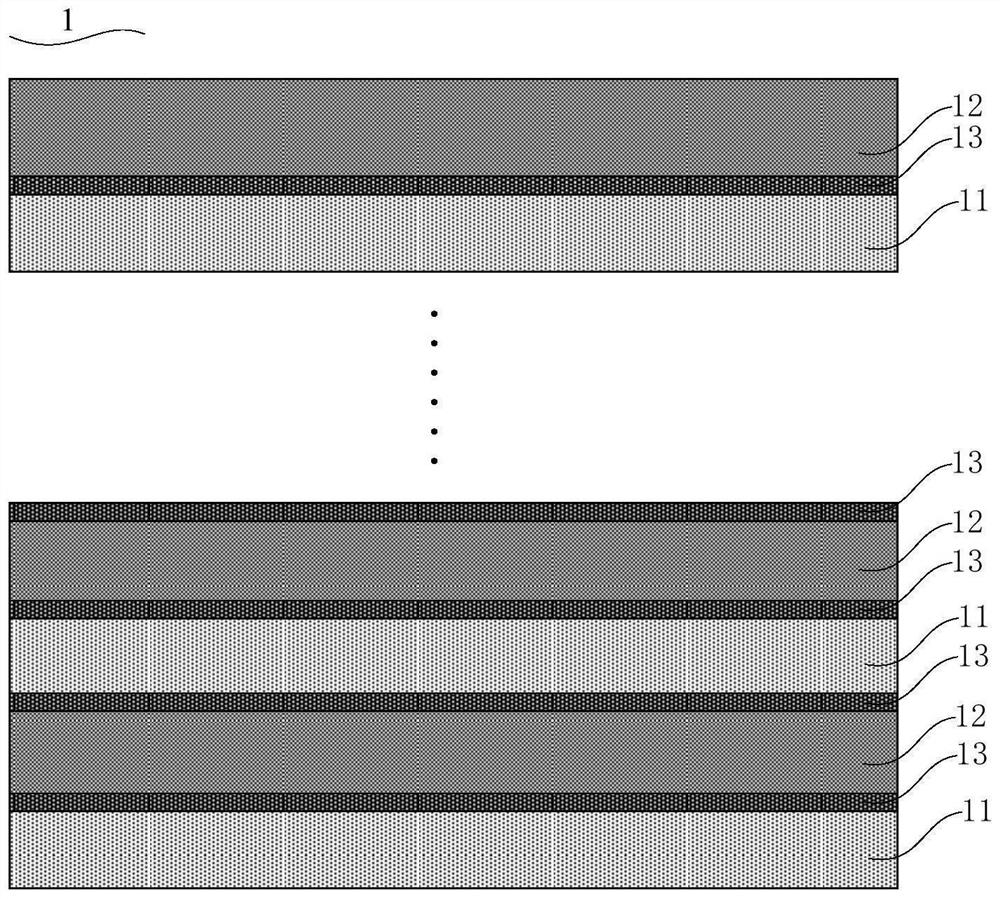

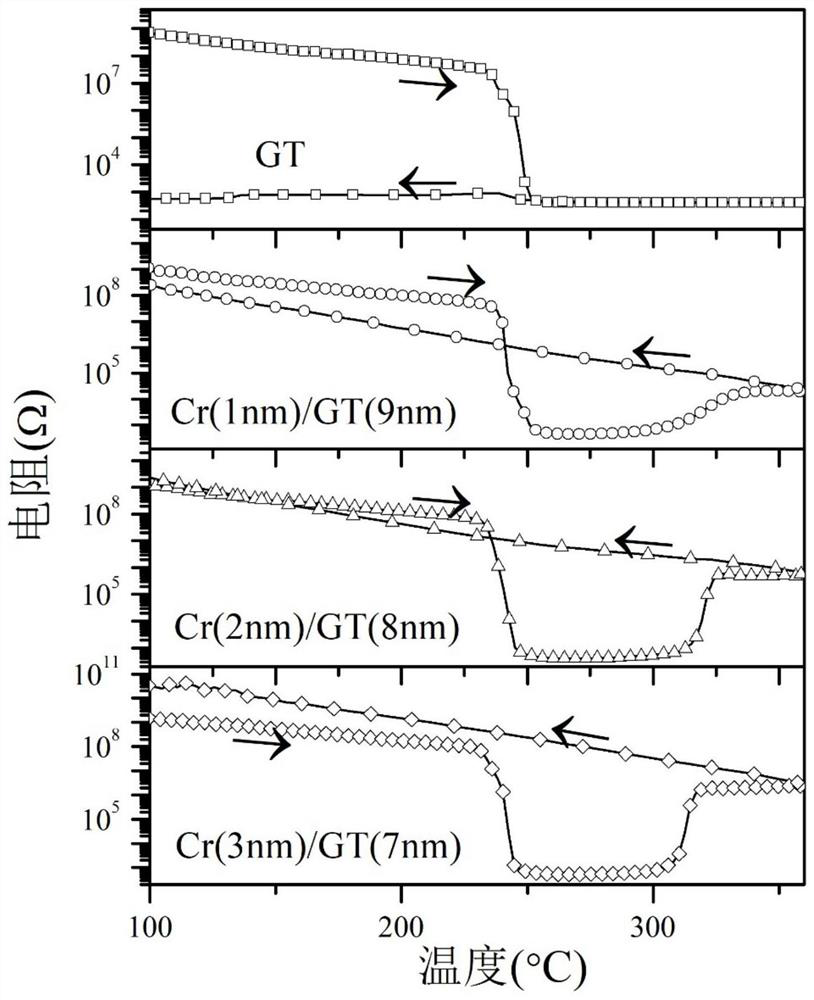

Phase change thin film structure, phase change memory unit, manufacturing method thereof and phase change memory

ActiveCN109935688AWith crystalline resistanceHas polymorphic storageElectrical apparatusHigh resistancePhase-change memory

The invention provides a phase change thin film structure, a phase change memory unit, a manufacturing method thereof and a phase change memory. The phase change thin film structure comprises Cr layers and GexTe100-x layers, wherein 0<x<100, and the Cr layers and the GexTe100-x layers are alternately stacked in turn. The phase change thin film structure disclosed in the invention can continuouslyundergo two phase changes during a temperature rise process; in an early stage of temperature rise, the GexTe100-x layer changes from an amorphous state to a polycrystalline state, and a reversible high-resistance state and low-resistance state change is accompanied; in continuous temperature rise, a Cr2Ge2Te6 layer is formed at the interface between the Cr layer and the GexTe100-x layer, partialCr enters the GexTe100-x layer under interfacial diffusion at high-temperature induction to replace partial Ge elements in the GexTe100-x layer, and a reversible low-resistance state and high-resistance state change is accompanied; and when the temperature rises continuously, high-resistance state GexTe100-x amorphous state can be returned.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

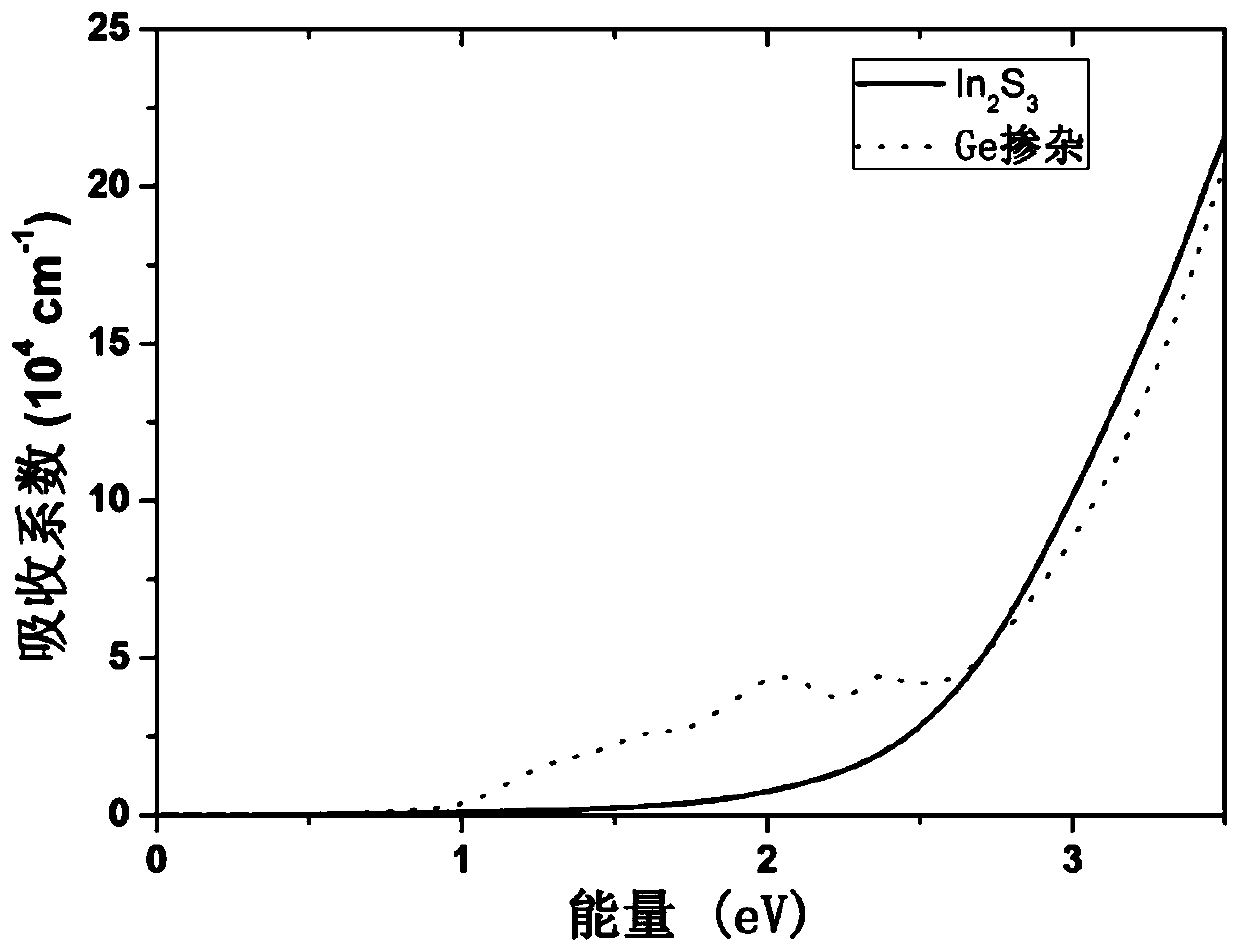

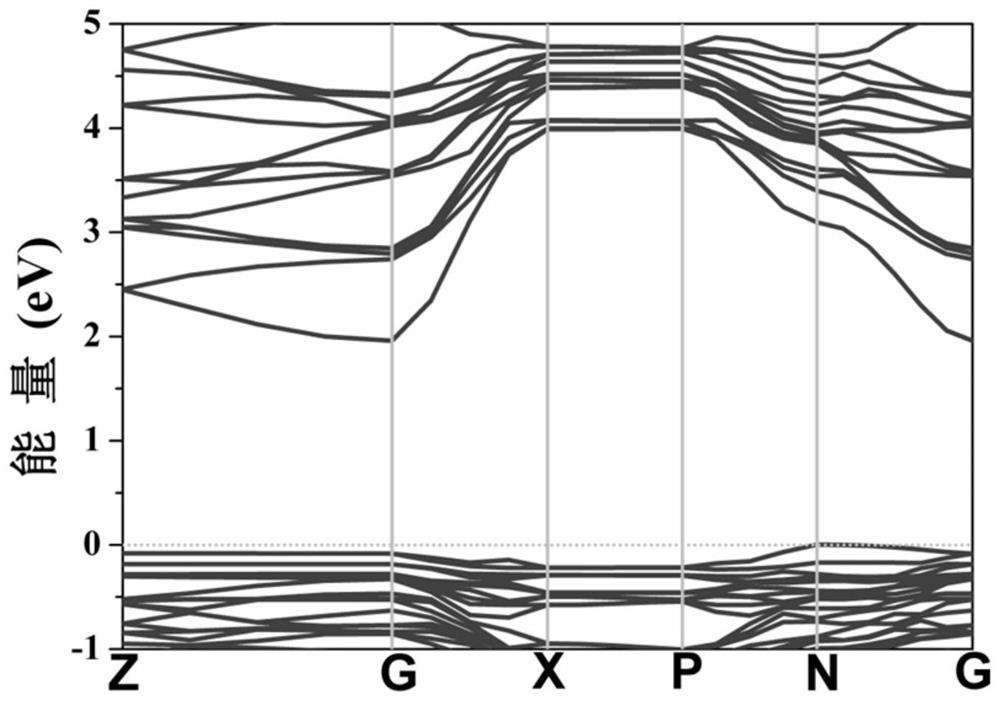

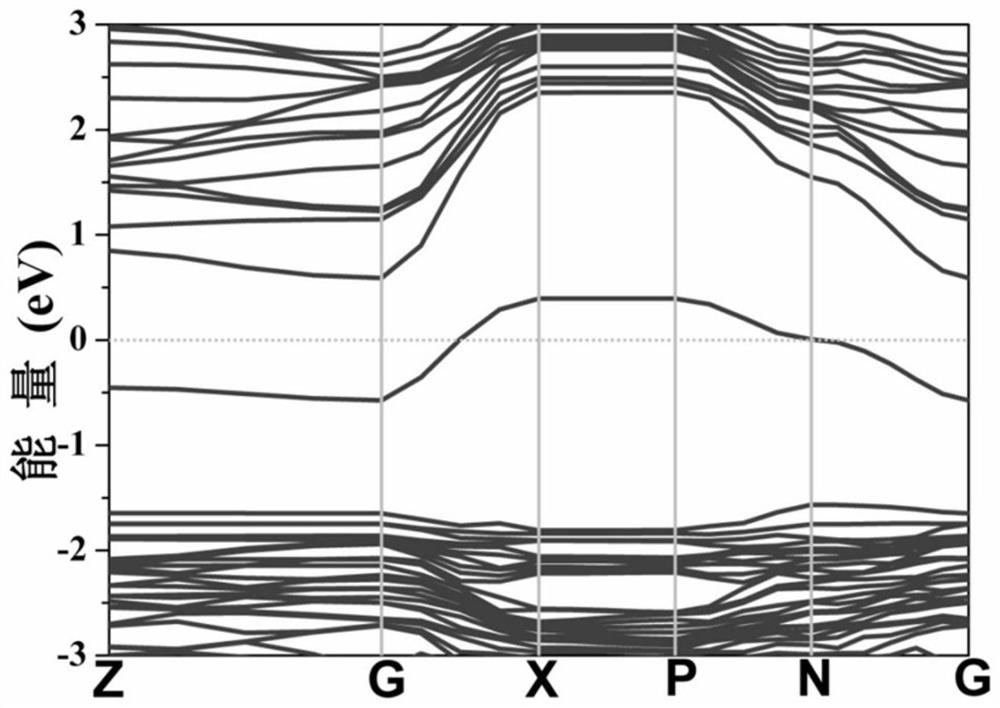

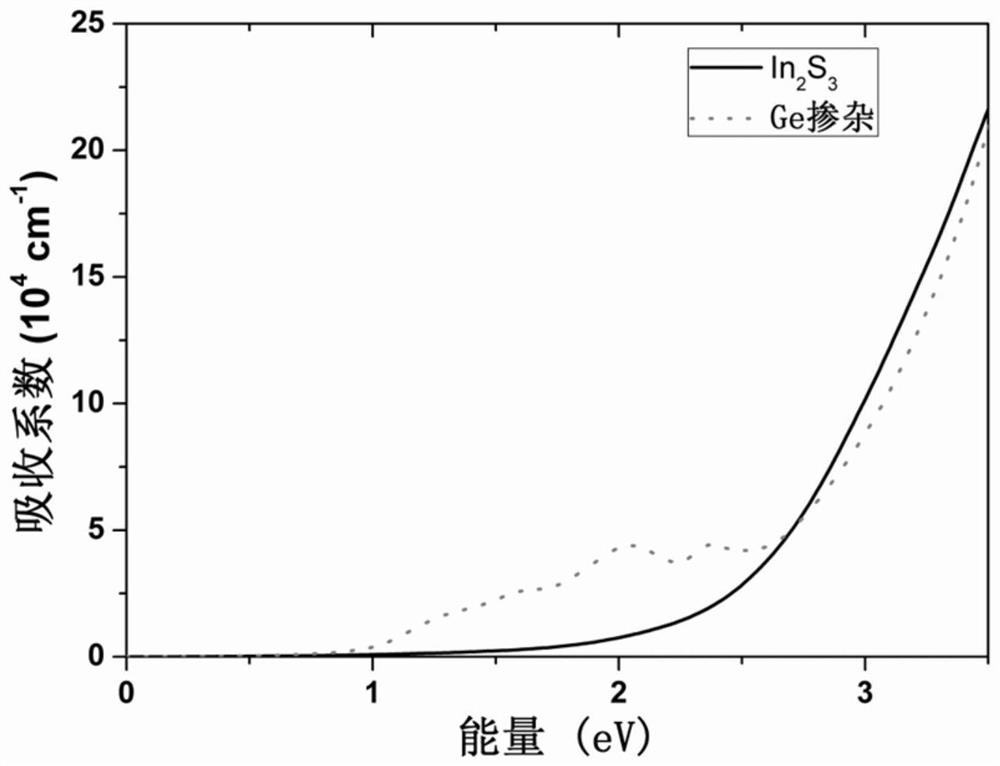

Indium sulfide-based impurity band semiconductor and preparation method and application thereof

ActiveCN110422874APromote absorptionEfficient use ofGallium/indium/thallium compoundsSemiconductor devicesIndiumSemiconductor materials

The invention relates to a method for constructing an In2S3 impurity band semiconductor. An In2S3 semiconductor serves as an index compound, a Ge element is adopted for doping the In position of the In2S3 semiconductor, and the In2S3 impurity band semiconductor is obtained. Compared with the prior art, according to the In2S3 impurity band semiconductor, In2S3 with the excellent performance is adopted as a substrate material, the VI group element Ge is adopted for doping the In positon of the In2S3 semiconductor, thus a strip of an impurity band is introduced in an index band gap, the electrontransition path is increased, the absorption spectrum is broadened, optical absorption of raw materials is enhanced, thus the In2S3 semiconductor can be directly used as a solar cell adsorption material, and practical significance is achieved for development of solar energy sources; the theoretical calculated absorption spectrum of the In2S3 and Ge doped In2S3 shows that an intrinsic semiconductorhas only one absorbing edge, after the Ge is doped, a novel absorbing edge occurs, and an absorbing curve starts being enhanced significantly in the energy area lower than the band gap. According tothe Ge doped In2S3 semiconductor material, the preparation method is simple, and industrial large-scale production can be achieved.

Owner:SHANGHAI DIANJI UNIV

Ge-containing low-quenching sensitive aluminum alloy

The invention relates to a Ge-containing low-quenching sensitive aluminum alloy. Aluminum alloy is subjected to micro-Ge alloying treatment; based on the characteristic that binding energy of Ge element and vacancy is far more than that of elements of Zn, Mg, Cu and the like and the vacancy is utilized, the Ge element, when solid solution is quenched, is added into the inside of the alloy and is preferentially combined with the vacancy to prevent the diffusion of Zn, Mg, Cu and other solute atoms of the alloy at a low solid solution quenching speed and the precipitation of a coarse second phase; and therefore, the full hardening of the aluminum alloy is improved effectively, the quenching sensitivity of the aluminum alloy is reduced, and a quenching tissue with full solid solution is provided for obtaining dispersion-strengthened phase in subsequent aging. The Ge-containing low-quenching sensitive aluminum alloy can effectively reduce the quenching sensitivity of the aluminum alloy and improves the full hardening of the aluminum alloy, the saturation of the solute atom solid solution of the alloy at the low quenching speed and the mechanical property after the aging treatment. The Ge-containing low-quenching sensitive aluminum alloy provides a reliable aluminum alloy structural material for meeting the needs for large-scale heavy plates and large members in aerospace and other fields.

Owner:CENT SOUTH UNIV

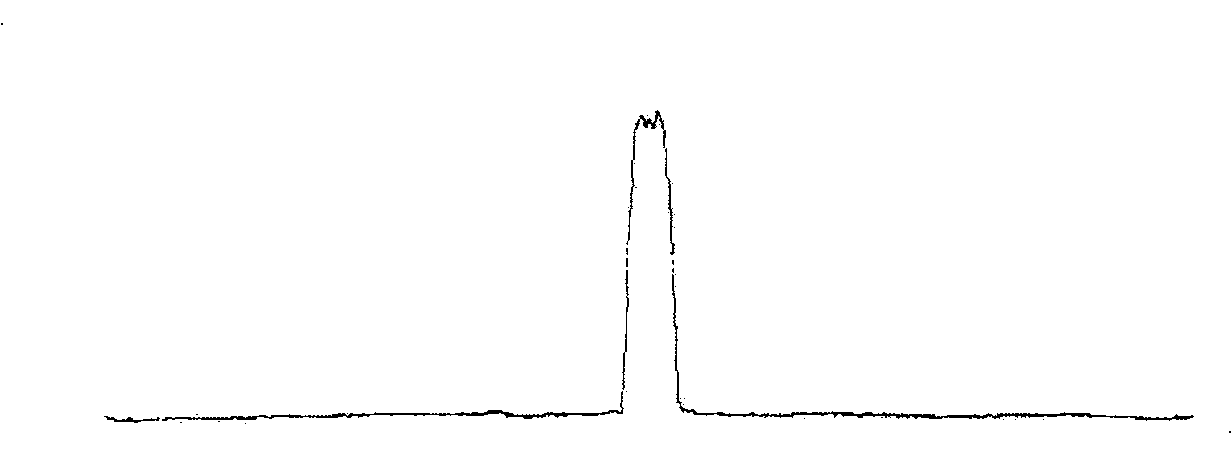

Method for measuring retaining stress double-refraction value of stress deflection fibre-optical

InactiveCN1598522AGuaranteed cleanlinessSimple methodElectromagnetic transmissionTesting optical propertiesPolarization-maintaining optical fiberGe element

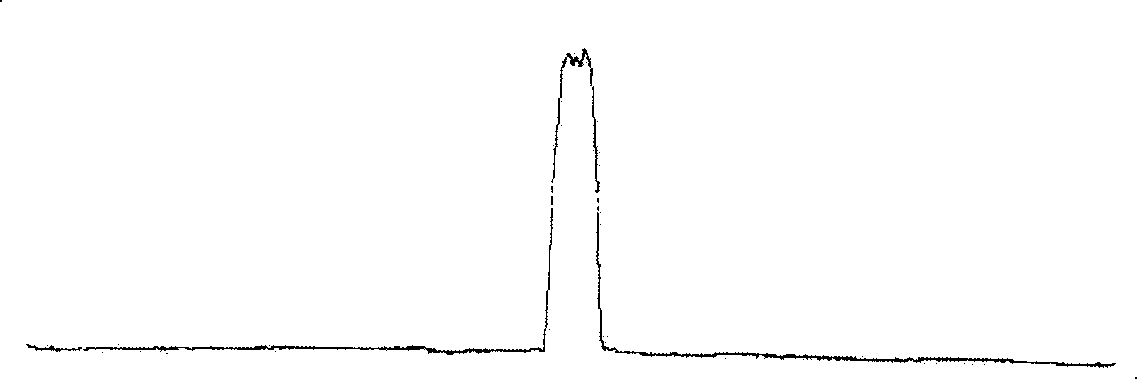

The invention is a measuring method for fiber stress double-refraction value of stress deflection and maintaining fiber in fiber interference communication and fiber sensor fields. The technology includes following steps: selects out the samples in stress area and core area, measures the content of B element in stress sample, measures the content of element Ge in core area; plates conductive film with thickness from 1 micron to 2 micron on the end surface of the fiber, scans the surface used as the atom lining by the electron probe device and carries on line scan to the Ge element, eliminates the impurities and spots on the surface; the image is inputted into the MATLAB project software, works out the stress double-refraction value through stress double-refraction formula and stress area impurities density.

Owner:HARBIN INST OF TECH

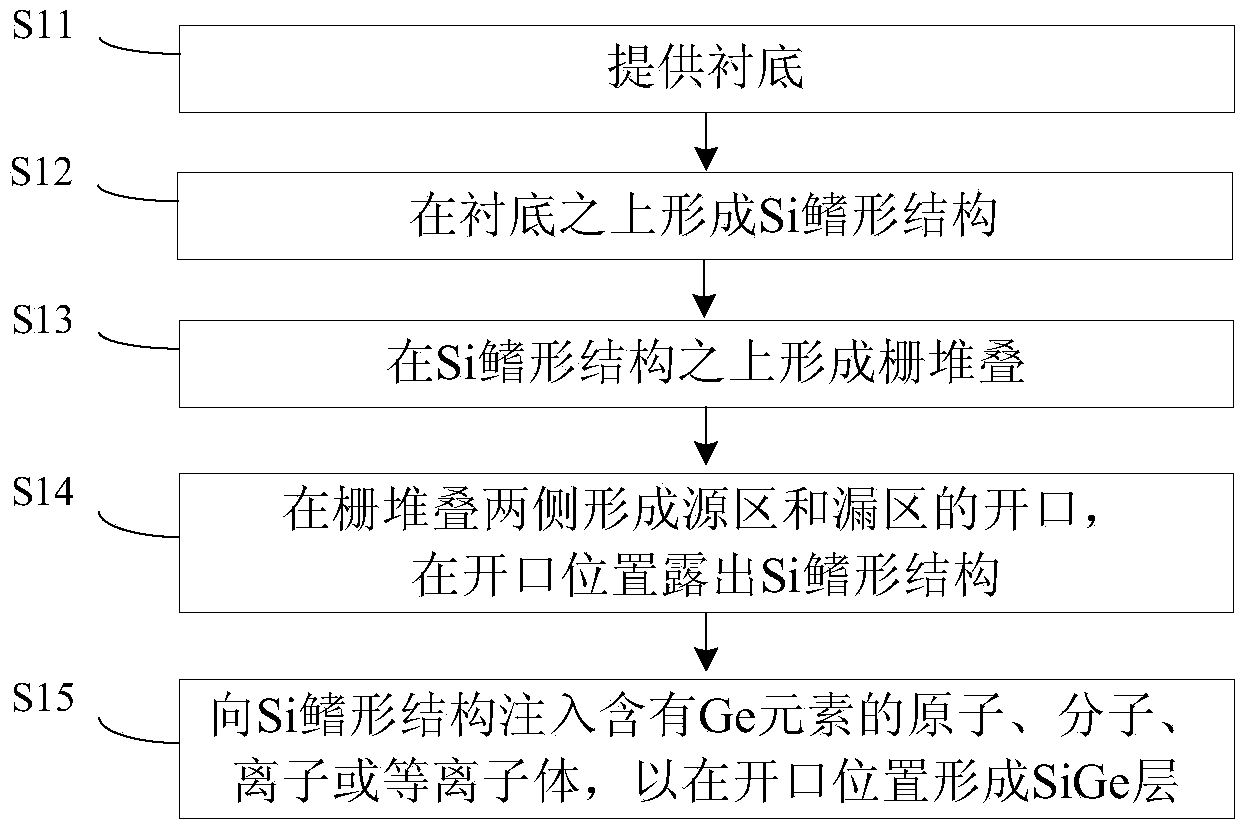

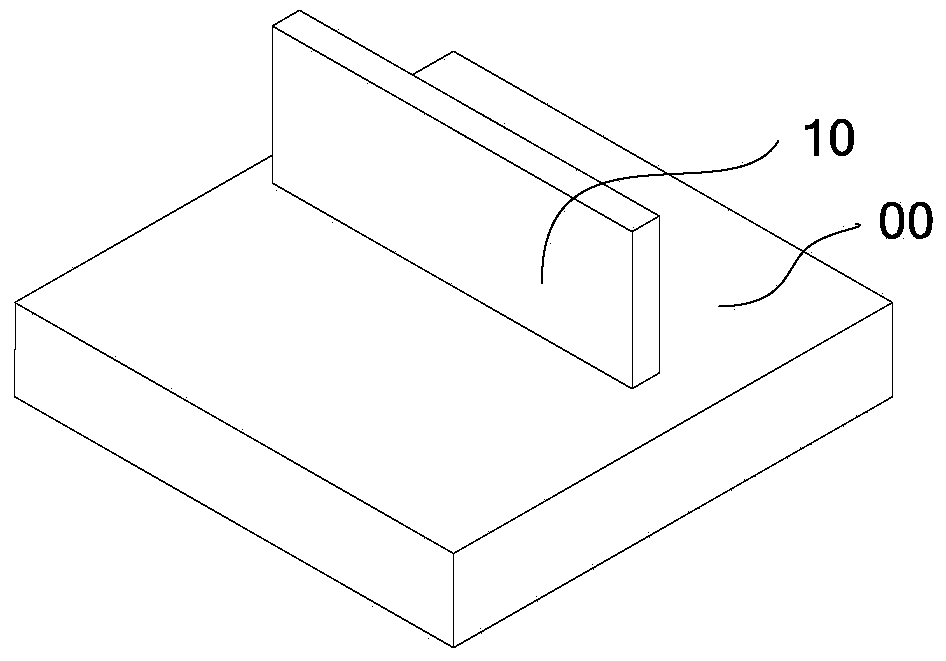

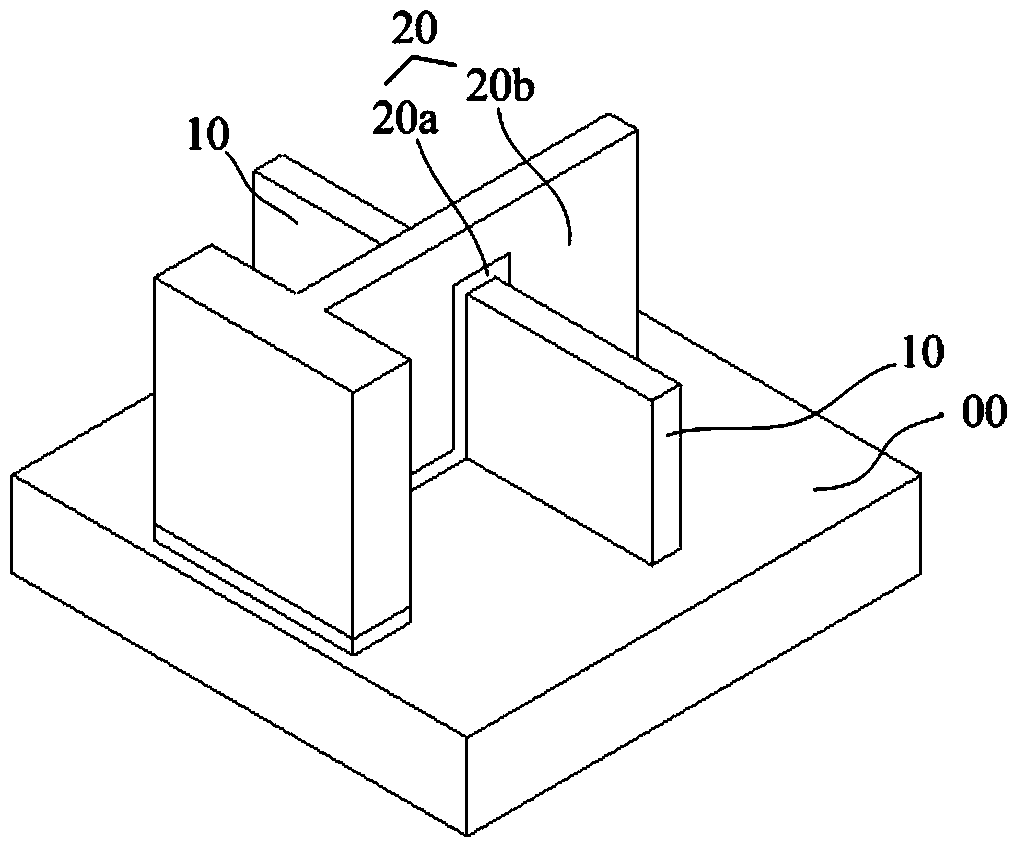

Fin-shaped field effect transistor with SiGe channel and forming method of fin-type field effect transistor

InactiveCN103972104AThe overall thickness is thinQuality improvementSemiconductor/solid-state device manufacturingSemiconductor devicesGe elementGate stack

The invention provides a fin-shaped field effect transistor with a SiGe channel and a forming method of the fin-shaped field effect transistor. The forming method includes the following steps of providing a substrate, forming a Si fin-shaped structure on the upper portion of the substrate, injecting atoms, molecules, ions or plasmas containing Ge elements into the Si fin-shaped structure so that the SiGe layer can be formed, and forming a gate stacking structure on the upper portion of the SiGe layer. According to the forming method, the FinFET with the SiGe channel can be formed, the SiGe channel is thin and good in quality, and accordingly the forming method has the advantages of being simple, easy to carry out and low in cost.

Owner:TSINGHUA UNIV

FinFET with SiGe source region and SiGe drain region and forming method of FinFET

InactiveCN103972107AGood electrical propertiesThe overall thickness is thinSemiconductor/solid-state device manufacturingSemiconductor devicesGe elementGate stack

The invention provides a FinFET with a SiGe source region and a SiGe drain region and a forming method of the FinFET. The method includes the following steps of providing a substrate, forming a Si fin-shaped structure on the upper portion of the substrate, forming gate stacking or a fake gate on the upper portion of the Si fin-shaped structure, forming openings of the source region and the drain region on the two sides of the gate stacking or the fake gate, exposing the Si fin-shaped structure at the opening positions, and injecting atoms, molecules, ions or plasmas containing Ge elements into the Si fin-shaped structure so that SiGe layers can be formed at the opening positions. According to the forming method of the FinFET, the FinFET with the SiGe source region and the SiGe drain region can be formed, the SiGe source region and SiGe drain region are thin, crystalline quality is good, and accordingly the FinFET has good electrical property, and the method has the advantages of being simple, easy to carry out and low in cost.

Owner:TSINGHUA UNIV

Low quenching sensitive aluminum alloy added with Ag and Ge at same time

The invention discloses a low quenching sensitive aluminum alloy added with Ag and Ge at the same time. The aluminum alloy is subjected to alloying treatment of trace Ag and Ge elements. On the one hand, the Ag and a vacancy have higher binding energy by using the characteristic that the binding energy of the Ge element and the vacancy is far greater than that of elements such as Zn, Mg, Cu and the like and the vacancy, and the Ge and Ag elements added into the alloy are first bond with the vacancy during solid solution quenching so as to prevent the dispersion of solvent atoms of Zn, Mg, Cu and the like in the alloy and the separation of a thick second phase at a low solid solution quenching speed, effectively improve the quenching property of the aluminum alloy, reduce the quenching sensitivity of the aluminum alloy and provide a complete solid solution quenching tissue for obtaining a dispersed strengthening phase for follow-up ageing; and on the other hand, the added Ag can play a role in reinforcement when the Ge is added by using the effect that the Ag can produce solid solution reinforcement and separation promotion in the aluminum alloy. A low quenching sensitive aluminum alloy structural material is provided for large-scale thick plates and large members in aerospace and other fields.

Owner:CENT SOUTH UNIV

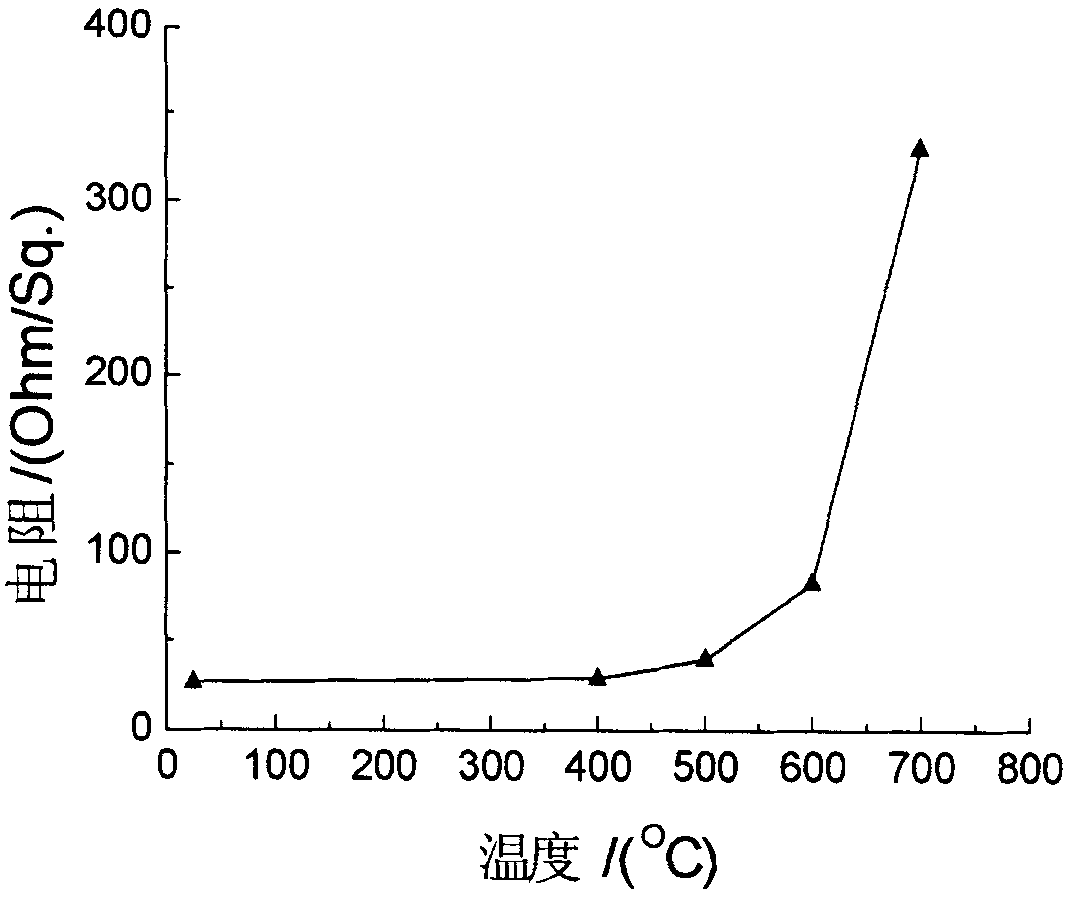

Heating electrode material for phase transformation memory and preparing method

The invention relates to a heating electrode material for phase varying memory and the preparing method thereof, where the heating electrode material is a heating electrode material at least containing Ge element whose general formula is one of GexWyN1-x-y, GexTiyN1-x-y, GexWyO1-x-y and GexTiyO1-x-y, where x and y are atomic percents of elements and 0ú“xíœ1, 0íœyú“1, and 0ú“x+yíœ1; the preparing method adopts any one of the processes: sputtering, evaporating, atomic layer deposition, chemical vapour deposition, and metallic organic matter thermal decomposition or laser auxiliary deposition, and as compared with traditional heating electrode materials such as W, TiN, TiON and TiAlN, the Ge-base heating electrode material of the invention has advantages of adhesive property to phase varying material, high resistance, etc, able to raise heating efficiency of devices and reduce device power losses.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

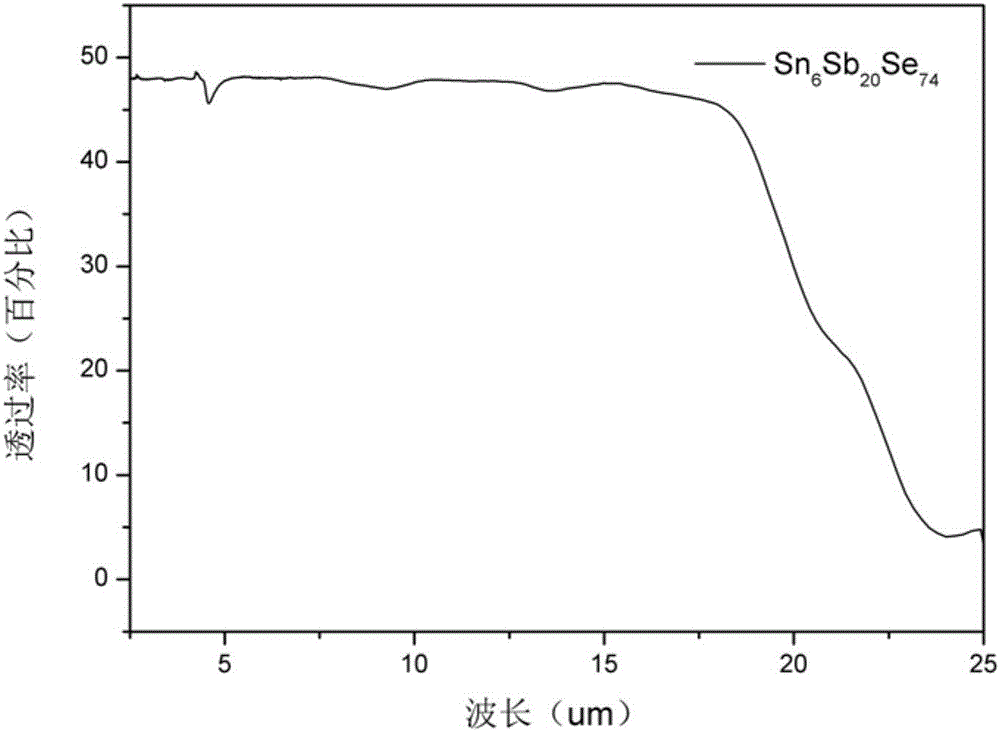

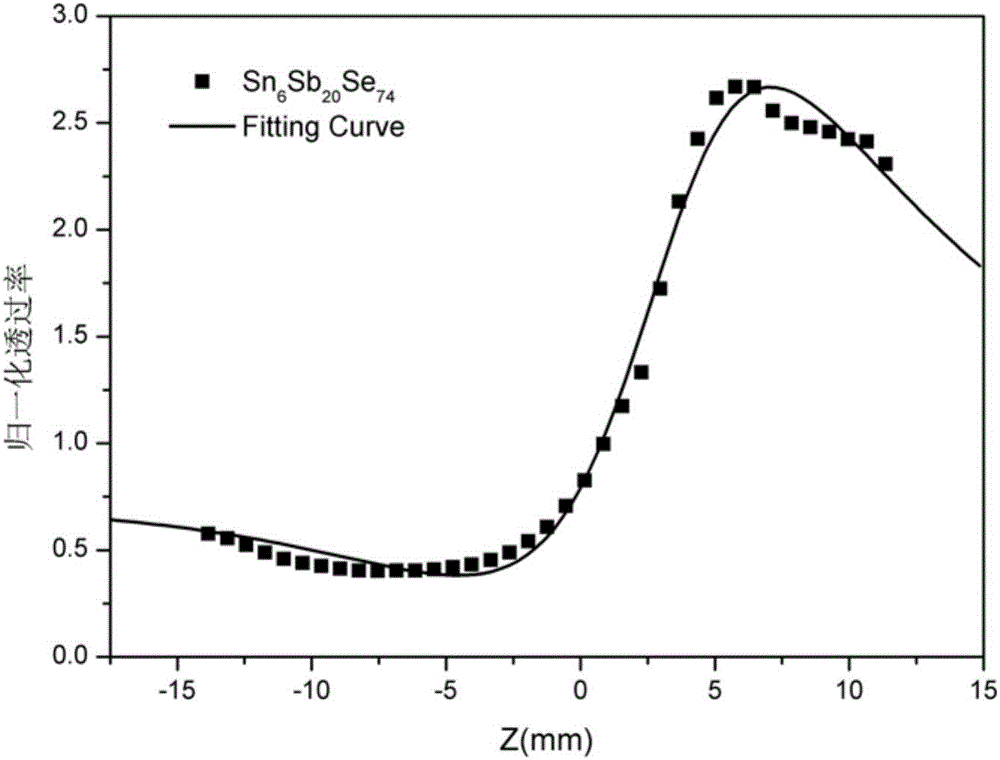

Tin-antimony-selenium chalcogenide glass and preparation method thereof

InactiveCN106746615AExcellent glass forming performanceGood medium and far infrared transmission abilityAs elementChemical Linkage

The invention discloses Sn-Sb-Se chalcogenide glass. The formula of the chalcogenide glass is SnxSbySez, wherein x, y and z respectively represent the mole number of Sn, Sb and Se, x=6-12, y=10-20, and z=68-82. In the microstructure of the chalcogenide glass, the percentage of the bond number of Sn-Se bonds accounting for the total chemical bond number is 16.45-32.67%, the percentage of the bond number of Sb-Se bonds accounting for the total chemical bond number is 20.08-58.37%, and the balance is the percentage of the bond number of Se-Se bonds accounting for the total chemical bond number. The Sn-Sb-Se chalcogenide glass has the advantages that the Sn-Sb-Se chalcogenide glass does not contain toxic As element and expensive Ge element and is simple and practical in preparation method, the forming area of the Sn-Sb-Se chalcogenide glass mainly concentrates on a selenium-rice area, the refractive index of the Sn-Sb-Se chalcogenide glass at a 4-micrometer waveband position is 2.59-2.86, third-order nonlinear refractive index can reach up to 10.15*10<-18>m<2> / W, the Sn-Sb-Se chalcogenide glass is good in mid-infrared and far-infrared transmission capacity and near-infrared transmission capacity, and a foundation is laid for the infrared device design and manufacturing of the Sn-Sb-Se chalcogenide glass and application of the Sn-Sb-Se chalcogenide glass to the optical field.

Owner:NINGBO UNIV

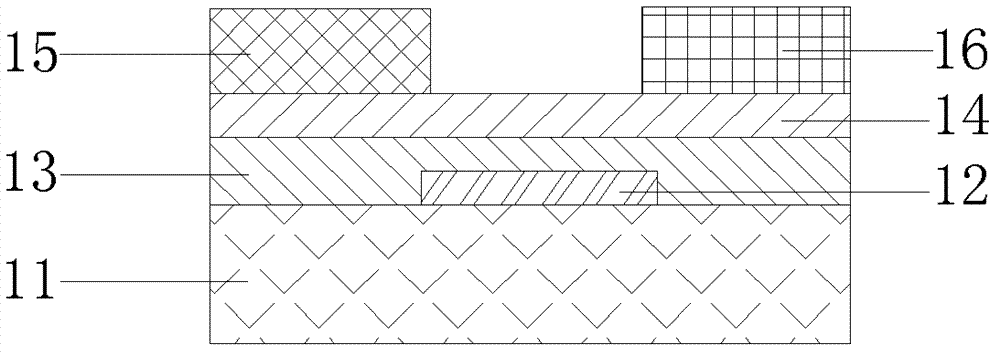

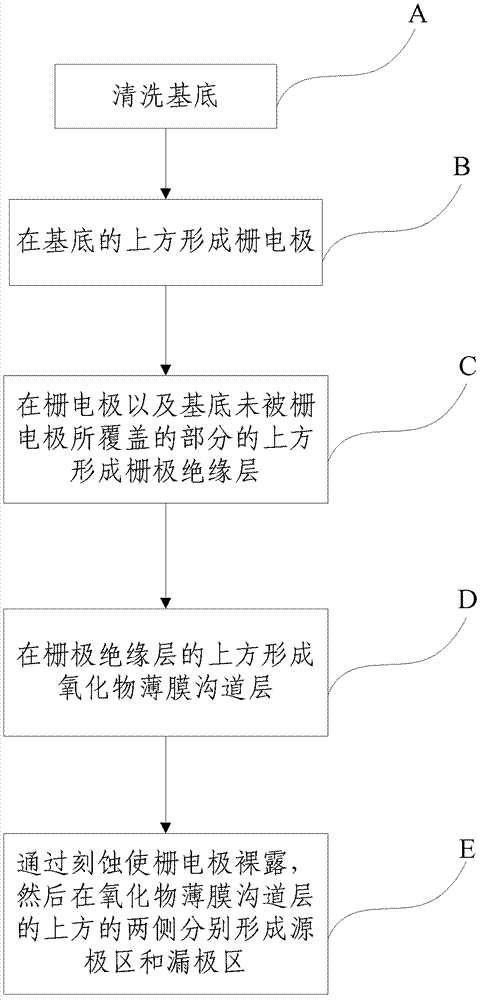

Oxide thin-film, thin-film transistor and preparation method thereof

ActiveCN102709312ALower threshold voltageGuaranteed reliabilityTransistorSemiconductor/solid-state device manufacturingInsulation layerCharge carrier

The invention discloses an oxide thin-film, a thin-film transistor and a preparation method thereof. The invention relates to the technical field of the thin-film transistor. In the thin-film transistor, the chemical general formula of the oxide thin-film of the oxide thin-film channel layer is In-X-Zn-O, wherein X is Si element, Ge element, La element or Y element; a gate electrode is arranged over a substrate; a gate insulation layer is arranged at the gate electrode, and over the portion of the substrate not covered by the gate electrode; the oxide thin-film channel layer is arranged over the gate insulation layer; a source electrode area is arranged at one side of the upper of the oxide thin-film channel layer; and the leakage electrode area is arranged at the side of the upper of the oxide thin-film channel layer. Based on the In-X-Zn-O thin-film transistor, the invention can enhance the inhibiting ability of the oxide thin-film channel layer to the formation of a charge carrier, improves the crystallization temperature of a crystal so as to improve the consistency of element preparation, and weakens the effects of the oxide thin-film channel layer to the threshold voltage, leakage current Ioff and on-off time ratio of the thin-film transistor.

Owner:PEKING UNIV

Preparation method of casting high-strength rapid-corrosion magnesium alloy

The invention relates to the technical field of metal alloy materials, and particularly relates to a preparation method of casting high-strength rapid-corrosion magnesium alloy. The method comprises the following steps: (1) correspondingly preprocessing a magnesium ingot and an aluminum ingot; (2) preprocessing germanium particles; (3) smelting the preprocessed magnesium ingot and the aluminum ingot; (4) adding the germanium particles after smelting so as to obtain a smelted material; and (5) cooling the smelted material; then pouring; and naturally cooling the casting ingots until room temperature is reached, and thus obtaining the casting high-strength rapid-corrosion magnesium alloy, wherein the casting high-strength rapid-corrosion magnesium alloy comprises the following components inpercentage by weight: 2-8% of Al, 0.5-7% of Ge, and the balance magnesium. According to the method, the Al and Ge elements are fully utilized to improve the strength and corrosion rate of the magnesium alloy; the alloy elements of few types are added, and few alloy elements are added, so that the mechanical performance and the corrosion rate can be obviously improved.

Owner:TAIYUAN UNIV OF TECH

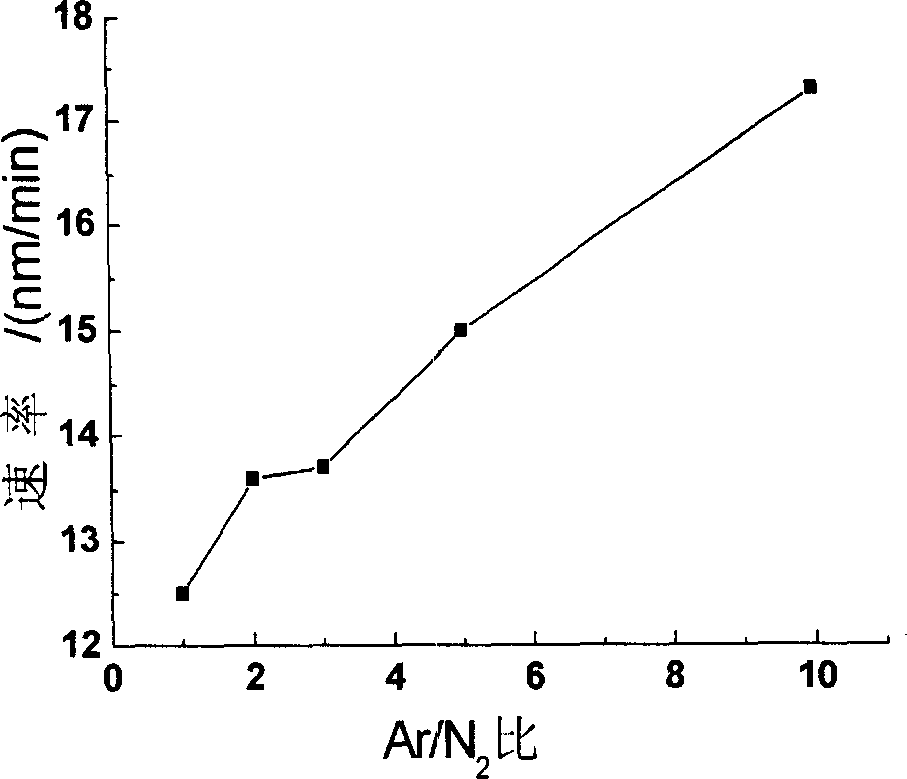

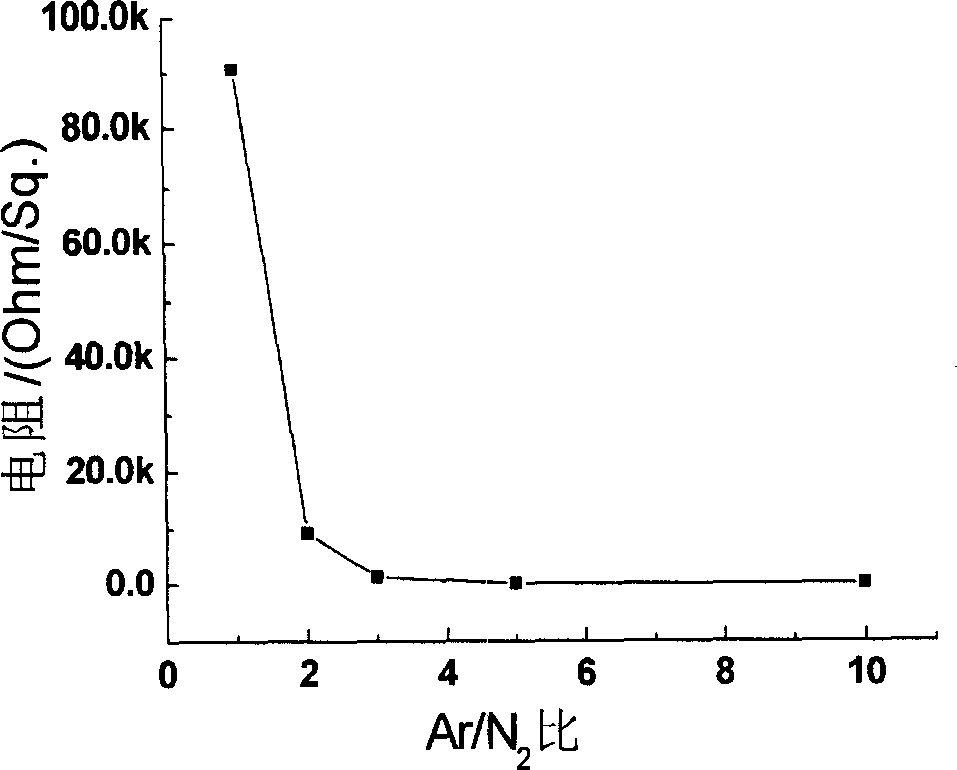

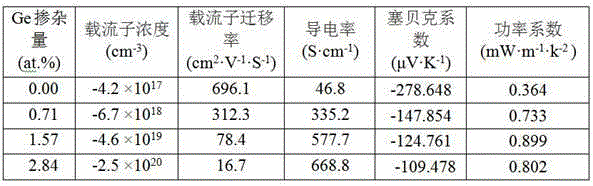

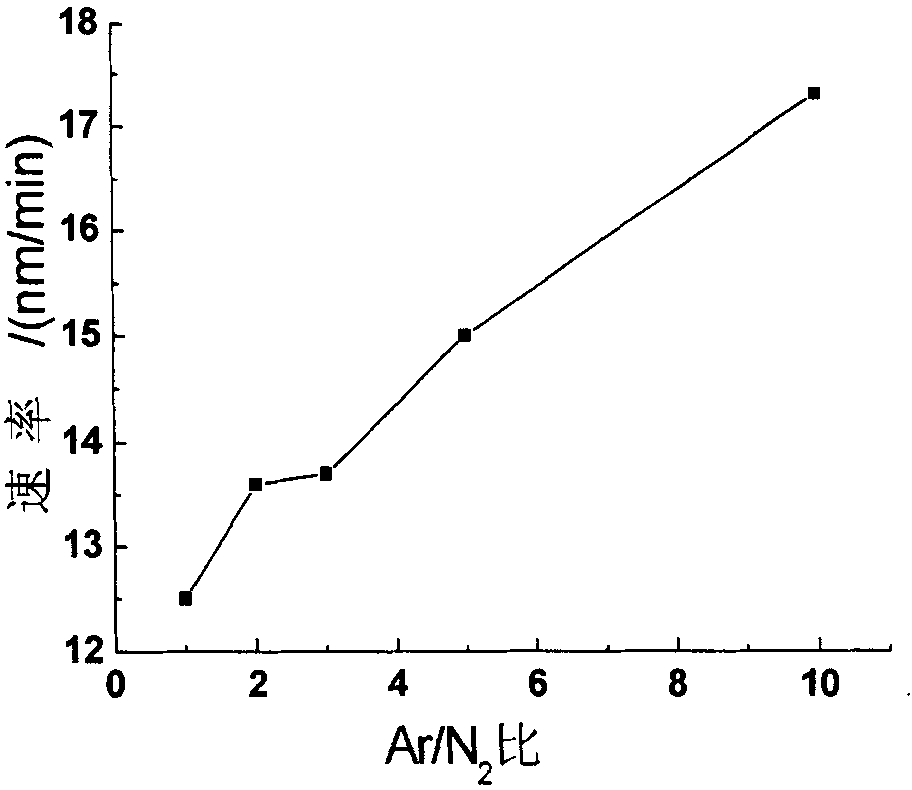

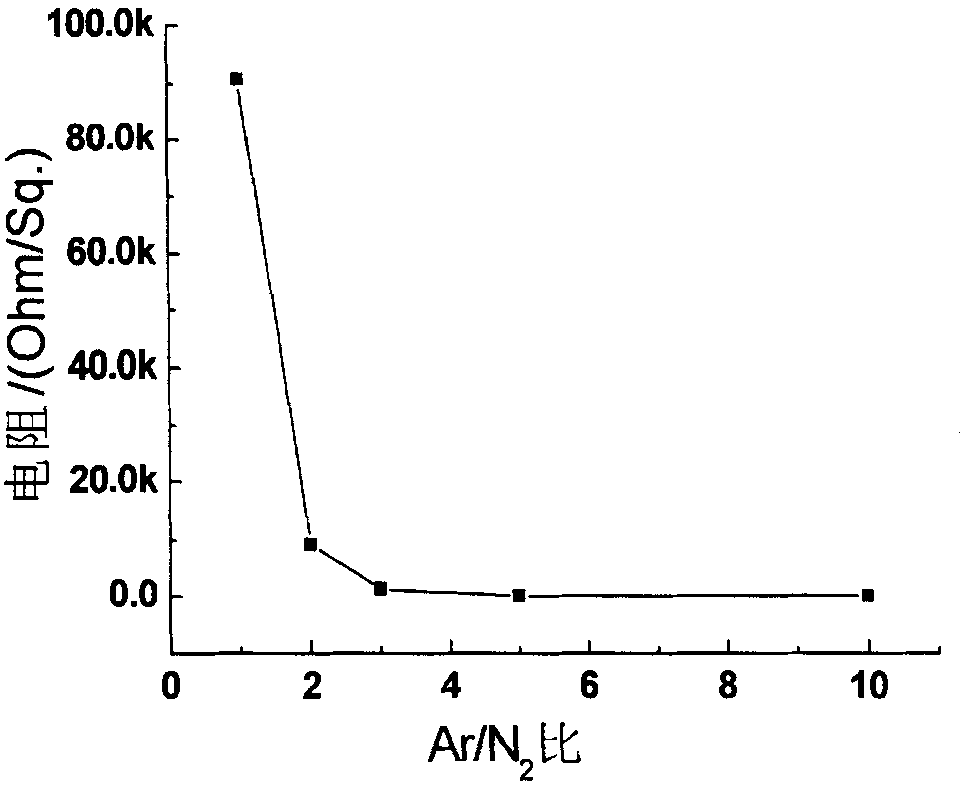

Ge-doped Mg2Si-base thermoelectric film and preparation method thereof

InactiveCN105200382AImprove conductivityImprove thermoelectric performanceVacuum evaporation coatingSputtering coatingGe elementPhysical chemistry

The invention discloses a Ge-doped Mg2Si-base thermoelectric film and a preparation method thereof. A magnetron sputtering deposition process is employed for performing double-target cyclic sputtering and further for preparing a film with a lamination structure, and then vacuum annealing is employed for obtaining the Ge-doped Mg2Si-base thermoelectric film. The thermoelectricity performance of the Mg2Si-based material is improved by utilizing Ge doping and film low-dimension processing, the method is high in controllability. The Ge element doping amount can be adjusted by adjusting the sputtering power, the sputtering time ratio and other parameters. The doped Ge element uniformity is improved by employing heat treatment. The film possesses the advantages of strong binding force between the film and a substrate, uniform compact film, simple technology, low cost and the like, and possesses significant industrial application value.

Owner:FUZHOU UNIV

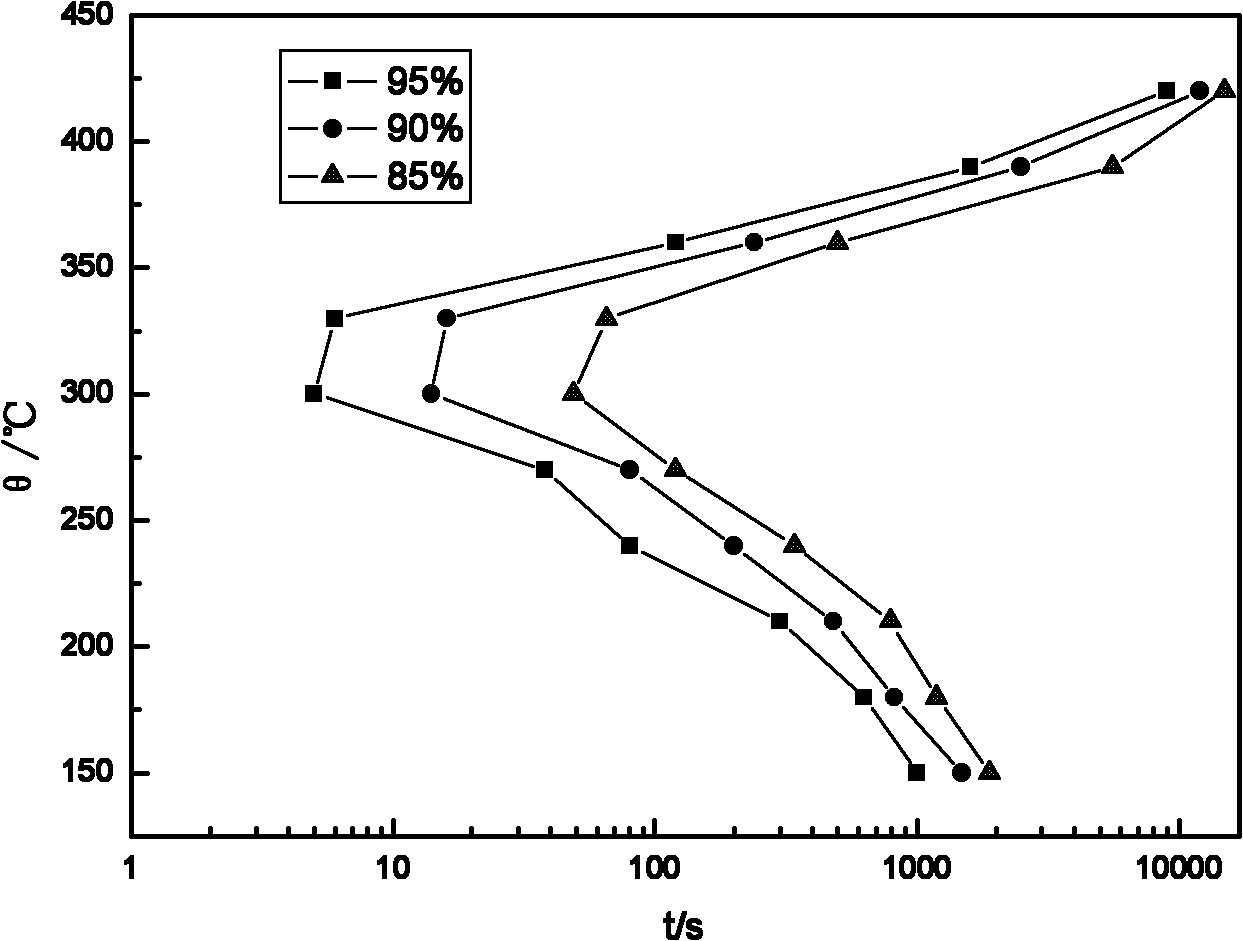

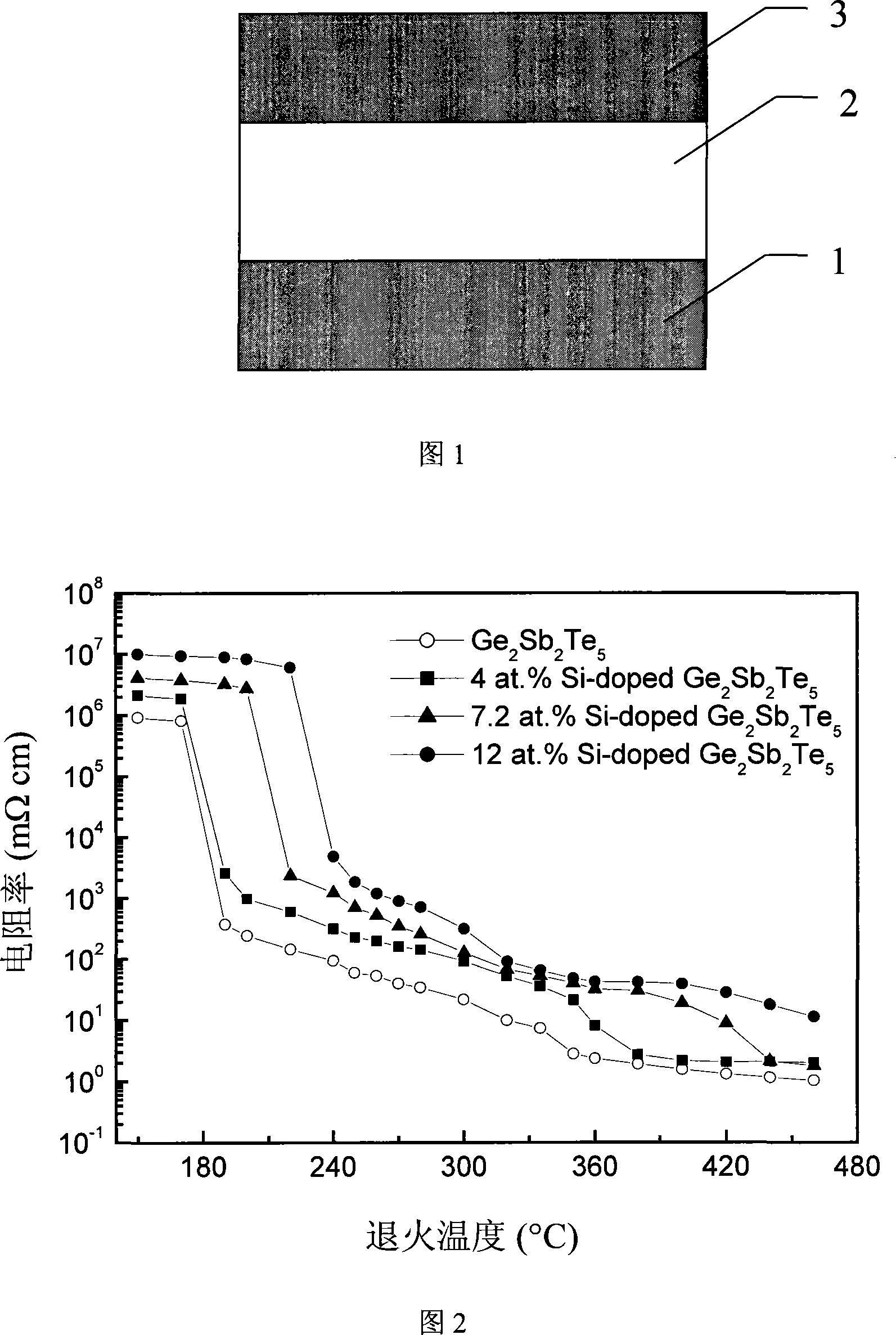

Phase change film material of silicon-adulterated sulfur series for phase change memory

InactiveCN101101966AEasy transferLower write operation currentChalcogenide/metal/alloy compound compositionsElectrical apparatusPhase-change memoryGe element

The invention is concerned with a kind of phase change film material with chalcogenide in silicon series for phase change storage, belonging to micro-electronics technology field. Si element takes place of Ge element of TeaGebSb100-(a+b) alloy to form TeaGeb-cSicSb100-(a+b) alloy film, and a is from 48 to 60, b is from 8 to 40, the replace scalar c of Si is from 1 to 40 atom percent. This invention has higher crystal resistance than common Ge2Sb2Te5 phase change film, and more higher amorphous / crystalline state change ratio of resistance and more lower amorphous / crystalline state film thickness change ratio and lower melting point. This kind of storage has more higher open / close ratio and stability of piece to reduce writing current of storage and get storage multi-value with higher density.

Owner:SHANGHAI JIAO TONG UNIV +1

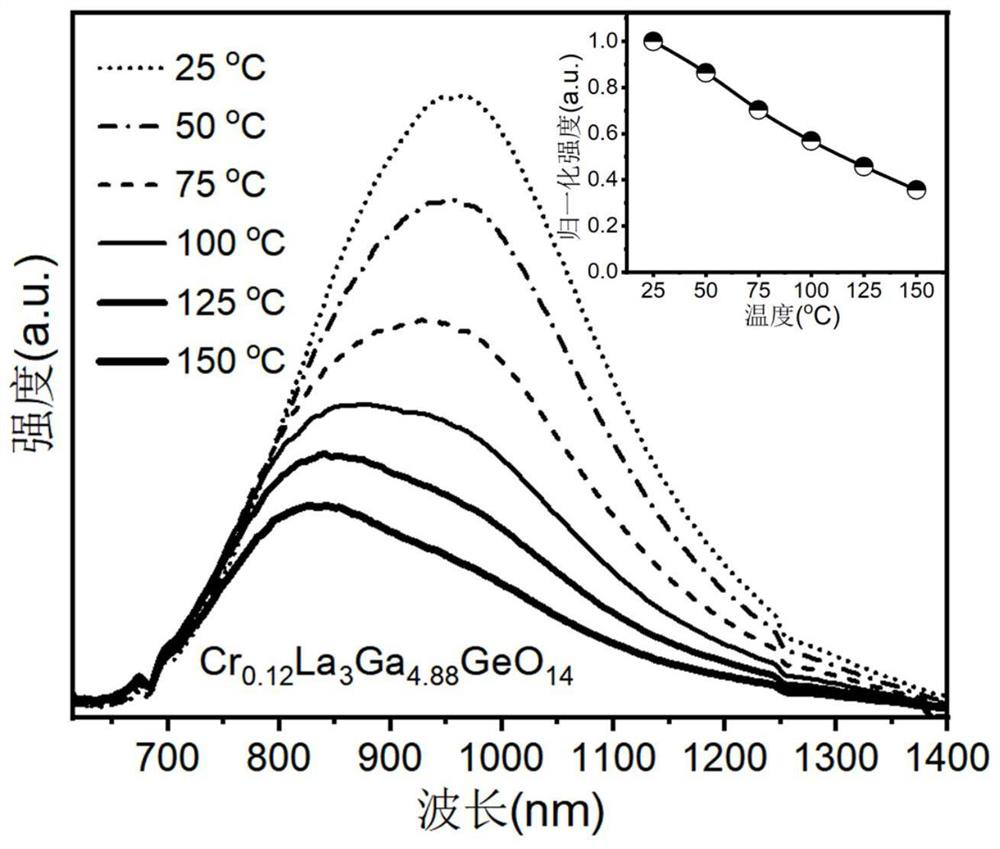

Oxide near-infrared light-emitting material, preparation method thereof and light-emitting device

ActiveCN113817468AImprove luminous efficiencyExcitation widthSaving energy measuresLuminescent compositionsGe elementHeat stability

The invention discloses an oxide near-infrared light-emitting material, a preparation method thereof and a light-emitting device. The near-infrared light-emitting material comprises an inorganic compound, wherein the chemical formula of the inorganic compound is AxByCzOqDp; wherein A is one or a combination of more than two of elements of Mg, Ca, Sr, Ba, Lu, Y, Gd or La; B is one or a combination of more than two of Sc, In, Ga, Mg, Zr, Ti, Hf, Sn, Lu, Y, Gd or La; C is one or a combination of more than two of Al, Si or Ge elements; O is an oxygen element; D is a Cr element; 0.7 < = x < = 1.3, 0.7 < = y < = 1.3, 1 < = Z < = 3, 5 < = q < = 7, and 0 < p < = 0.3. The emission peak wavelength of the near-infrared light-emitting material is about 930 nm, the half-peak width is about 210 nm, the near-infrared light-emitting material can be efficiently excited by blue light, and the chemical stability and the thermal stability are good.

Owner:SOUTH CHINA UNIV OF TECH

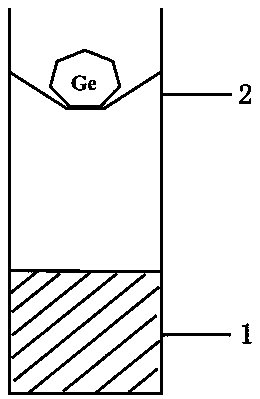

Ge (germanium) element compensation method for CdGeAs2 single crystal growth

InactiveCN109056052AAvoid inconsistenciesImprove availabilityPolycrystalline material growthFrom frozen solutionsTemperature controlCrucible

The invention discloses a Ge (germanium) element compensation method for CdGeAs2 single crystal growth. The method adopts a growth device comprising a single crystal growth crucible, a germanium element compensation device and a six-temperature-zone growth furnace for controlling Ge element compensation for CdGeAs2 single crystal growth. A high-purity CdGeAs2 multi-crystal raw material is put in acrucible provided with a Ge element compensation device for vacuum sealing and then put in the six-temperature-zone growth furnace, CdGeAs2 single crystal growth and Ge element compensation are realized through accurate temperature control, so that Ge elements at the upper and lower ends of the grown single crystal are uniform, and the phenomenon of inconsistent properties formed by different Geelements in the single crystal is avoided. The method is easy to implement, the utilization rate of the single crystal is effectively increased, and the growth cost is reduced.

Owner:CHINA ELECTRONICS TECH GRP NO 46 RES INST

Heating electrode material for phase transformation memory and preparing method

The invention relates to a heating electrode material for phase varying memory and the preparing method thereof, where the heating electrode material is a heating electrode material at least containing Ge element whose general formula is one of GexWyN1-x-y, GexTiyN1-x-y, GexWyO1-x-y and GexTiyO1-x-y, where x and y are atomic percents of elements and 0<x<=1, 0<=y<1, and 0<x+y<=1; the preparing method adopts any one of the processes: sputtering, evaporating, atomic layer deposition, chemical vapour deposition, and metallic organic matter thermal decomposition or laser auxiliary deposition, and as compared with traditional heating electrode materials such as W, TiN, TiON and TiAlN, the Ge-base heating electrode material of the invention has advantages of adhesive property to phase varying material, high resistance, etc, able to raise heating efficiency of devices and reduce device power losses.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Novel highly germanium-doped -type light-sensitive optical fibre and method for making same

ActiveCN101216574BMeet the design requirementsLarge attenuationGlass making apparatusCladded optical fibreFiberUltrasound attenuation

Owner:YANGTZE OPTICAL FIBRE & CABLE CO LTD

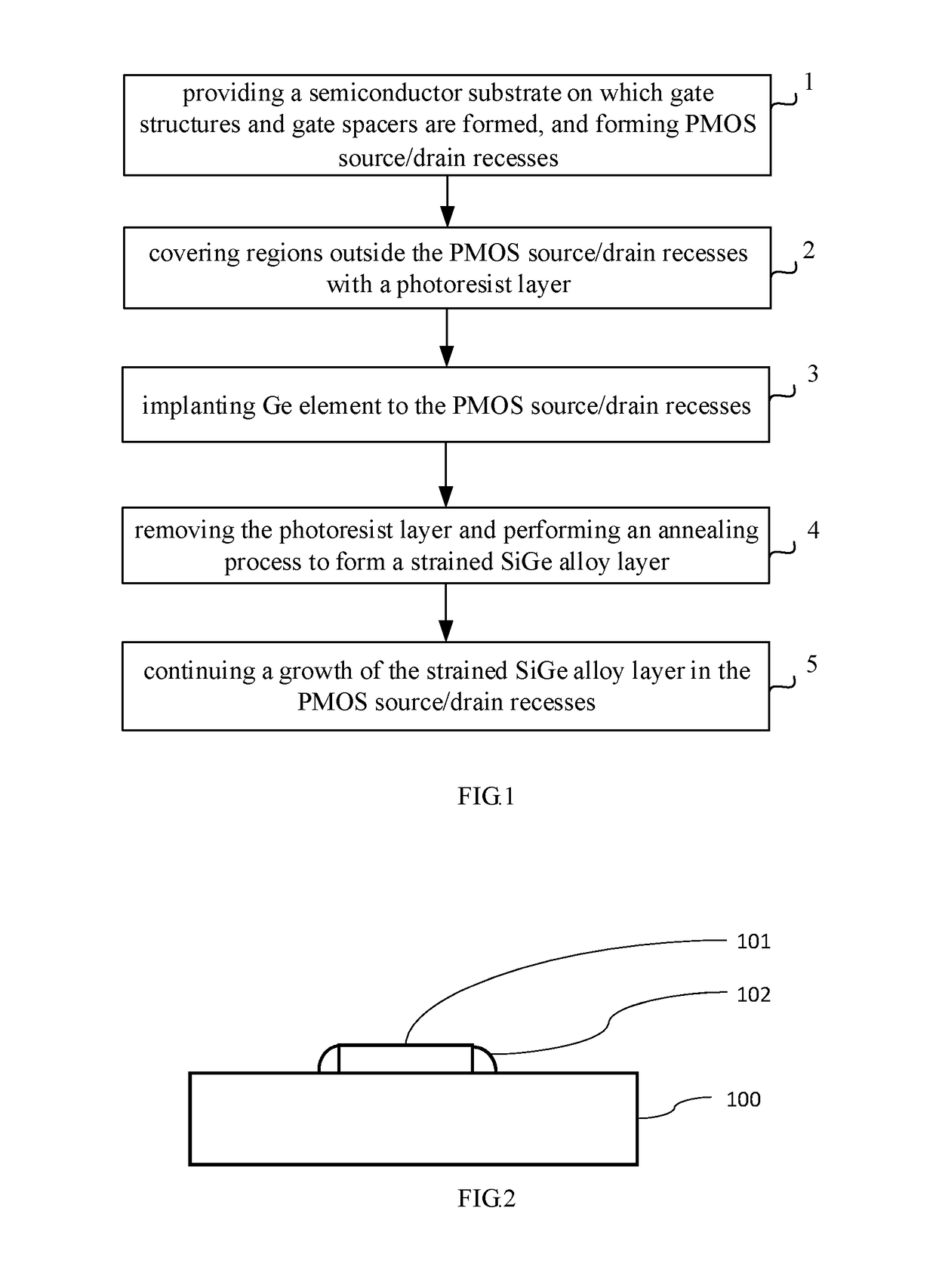

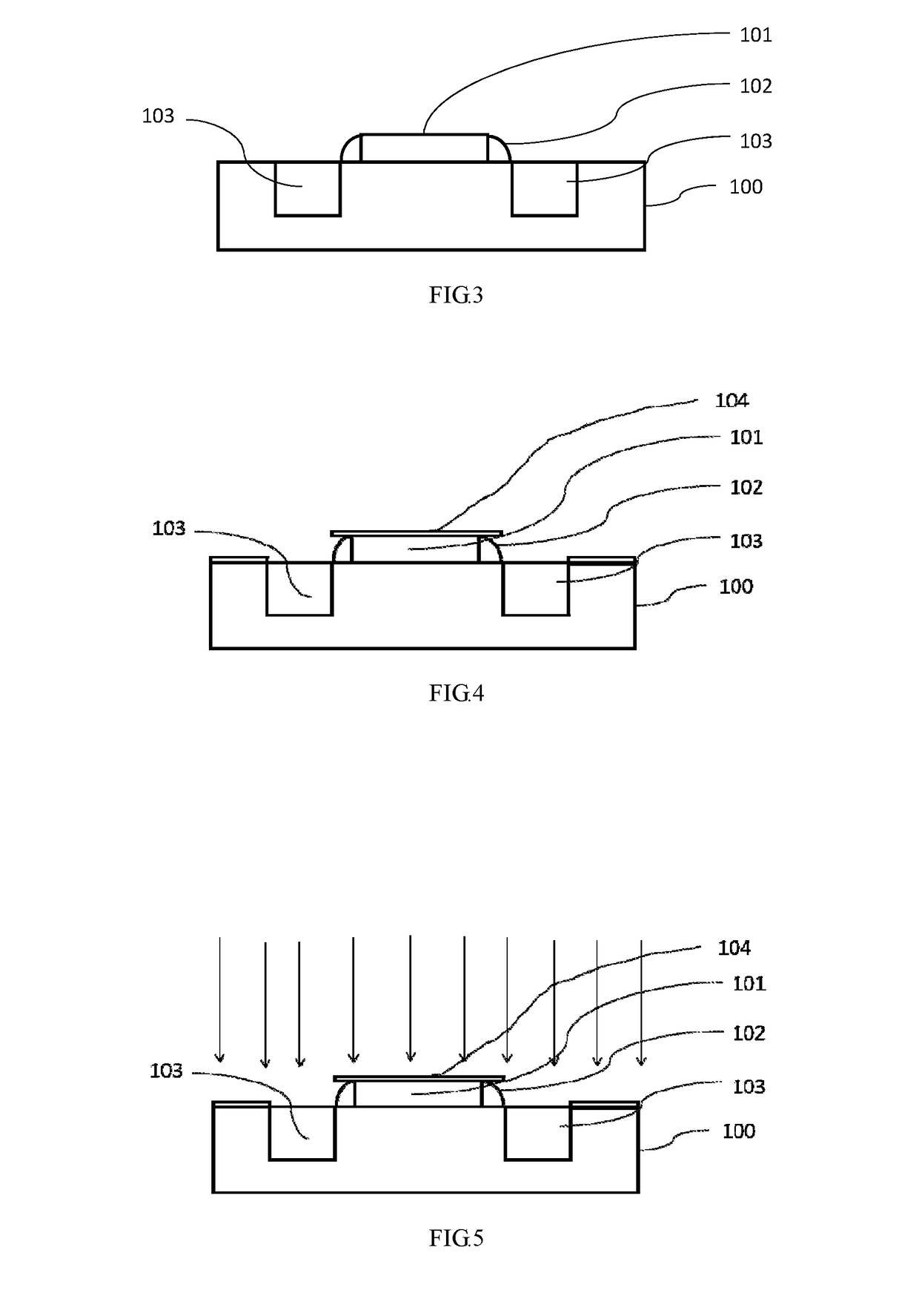

Method of fabricating pmos devices with embedded sige

InactiveUS20170213897A1Improve electrical performanceGood flexibilitySemiconductor/solid-state device manufacturingSemiconductor devicesGe elementElectrical performance

A method of fabricating PMOS devices with embedded SiGe is disclosed. Prior to the selective epitaxial growth of SiGe, Ge element is implanted to the source / drain recesses and an annealing process is performed to form a strained SiGe alloy layer. Then, the strained SiGe alloy layer is used as a base layer on which another strained SiGe alloy layer is grown continually by an selective epitaxy process, so as to avoid a direct contact between the epitaxially grown strained SiGe alloy layer and the silicon substrate and reduce the defects formed at the SiGe / Si interfaces. Therefore, the stress can be applied to the PMOS channel regions without causing junction current leakage due to the defects at the SiGe / Si interfaces, which enhances the electrical performance of the PMOS devices. The fabrication method is also compatible with the conventional CMOS process.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

A kind of indium sulfide-based impurity band semiconductor and its preparation method and application

ActiveCN110422874BIncrease jump pathImprove optical absorptionGallium/indium/thallium compoundsSemiconductor devicesSemiconductor materialsIndium

The present invention relates to a kind of structure In 2 S 3 impurity band semiconductor approach to In 2 S 3 The semiconductor is the parent compound, and the Ge element is used to dope In 2 S 3 In bit of semiconductor, get In 2 S 3 Impurity band semiconductor. Compared with the prior art, the present invention adopts In 2 S 3 As the base material, In is doped with the group IV element Ge 2 S 3 The In site, thus introducing an impurity band in the parent bandgap, increases the transition path of electrons, broadens the absorption spectrum, and enhances the optical absorption of raw materials, so that it can be directly used as solar cell absorption materials, and has a great impact on the development of solar energy. Has practical significance; theoretically calculated In 2 S 3 Doping In with Ge 2 S 3 The absorption spectrum shows that the intrinsic semiconductor has only one absorption edge, and after doping Ge, a new absorption edge appears, and the absorption curve starts to be significantly enhanced in the energy region lower than the band gap; Ge-doped In in the present invention 2 S 3 The preparation method of the semiconductor material is simple, and industrialized mass production can be realized.

Owner:SHANGHAI DIANJI UNIV

Dispersion fiber for high-power transmission with quartz cladding and manufacturing method thereof

ActiveCN106033137BImprove stabilityImprove reliabilityGlass making apparatusOptical fibre with multilayer core/claddingRefractive indexGe element

A quartz cladding large-power-transmission dispersion optical fiber and a manufacturing method thereof relate to the technical field of optical communication and related sensing devices. The dispersion optical fiber is composed of a core layer, a first quartz cladding and a second quartz cladding which are successively arranged from inside to outside. The core layer is doped with Ge element; the refractivity of the core layer changes in a gradual manner; and furthermore distribution power exponent is 1.5-3.3. The first quartz cladding contains bubbles and has a light scattering function. The refractivity of the second quartz cladding is higher than that of the first quartz cladding. The quartz cladding large-power-transmission dispersion optical fiber and the manufacturing method have advantages of enduring relatively high power and relatively high temperature, improving stability and reliability of the optical fiber, and effectively settling a color change problem of the optical fiber in illumination.

Owner:WUHAN POST & TELECOMM RES INST CO LTD +1

Phase-change thin film structure, phase-change memory cell, and preparation method thereof, and phase-change memory

ActiveCN109935688BControllable interfaceControllable growth processElectrical apparatusPhase-change memoryMemory cell

The invention provides a phase change thin film structure, a phase change memory unit, a manufacturing method thereof and a phase change memory. The phase change thin film structure comprises Cr layers and GexTe100-x layers, wherein 0<x<100, and the Cr layers and the GexTe100-x layers are alternately stacked in turn. The phase change thin film structure disclosed in the invention can continuouslyundergo two phase changes during a temperature rise process; in an early stage of temperature rise, the GexTe100-x layer changes from an amorphous state to a polycrystalline state, and a reversible high-resistance state and low-resistance state change is accompanied; in continuous temperature rise, a Cr2Ge2Te6 layer is formed at the interface between the Cr layer and the GexTe100-x layer, partialCr enters the GexTe100-x layer under interfacial diffusion at high-temperature induction to replace partial Ge elements in the GexTe100-x layer, and a reversible low-resistance state and high-resistance state change is accompanied; and when the temperature rises continuously, high-resistance state GexTe100-x amorphous state can be returned.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

MOSFET with SiGe source region and SiGe drain region and forming method of MOSFET

InactiveCN103972106AImprove crystal qualityGood electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSurface layer

The invention provides an MOSFET with a SiGe source region and a SiGe drain region and a forming method of the MOSFET. The forming method includes the following steps of providing a substrate with a Si layer at the top, forming gate stacking or a fake gate on the upper portion of the substrate, forming openings of the source region and the drain region on the two sides of the gate stacking or the fake gate, exposing the Si layer at the opening positions, and injecting atoms, molecules, ions or plasmas containing Ge elements into the surface layer of the Si layer so that SiGe layers can be formed at the opening positions. According to the forming method of the MOSFET, the MOSFET with the SiGe source region and the SiGe drain region can be formed, the SiGe source region and SiGe drain region are thin, crystalline quality is good, and accordingly the MOSFET has good electrical property, and the method has the advantages of being simple, easy to carry out and low in cost.

Owner:TSINGHUA UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com