Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

115 results about "Field programmable gate array chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

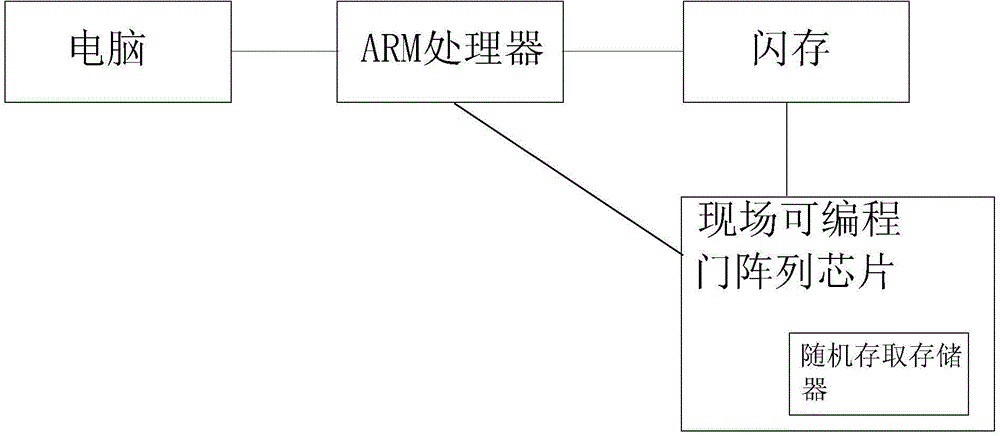

Apparatus used for debugging programmable chip and field programmable gate array chip

InactiveCN101369001AImprove versatilitySimple structureDigital circuit testingSpecial data processing applicationsProgrammable logic deviceComplex programmable logic device

The invention relates to a device for debugging a programmable chip and an FPGA (field programmable gate array) chip. The device comprises: a physics layer which is connected with a debugging main computer outside the programmable chip, a decoding operation module, an encoding operation module, a command operation module, and a debugging port which is used for providing the interface that can obtain signal status information for the command operation module. The FPGA (field programmable gate array) chip comprises a device which is used for debugging the programmable chip and the debugging port. The invention also relates to a complex PLD (programmable logic device) chip, which comprises the device that is used for debugging the programmable chip and the debugging port. In the technical proposal, the device for debugging the programmable chip has simple structure without consuming hardware source, greatly reduces the complexity, and is convenient for realization in low-end programmable chip, and greatly improves the universality of the debugging device.

Owner:BEIJING XINWANG RUIJIE NETWORK TECH CO LTD

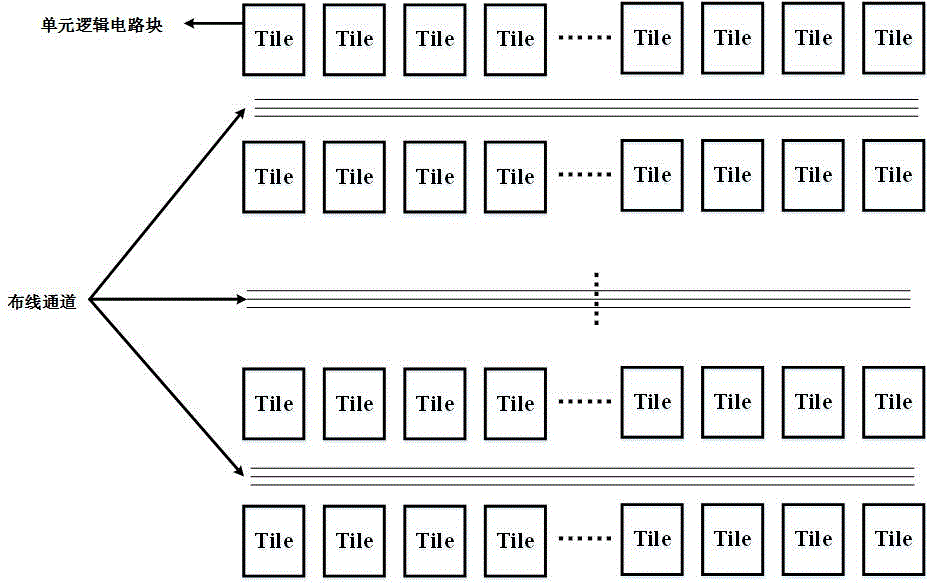

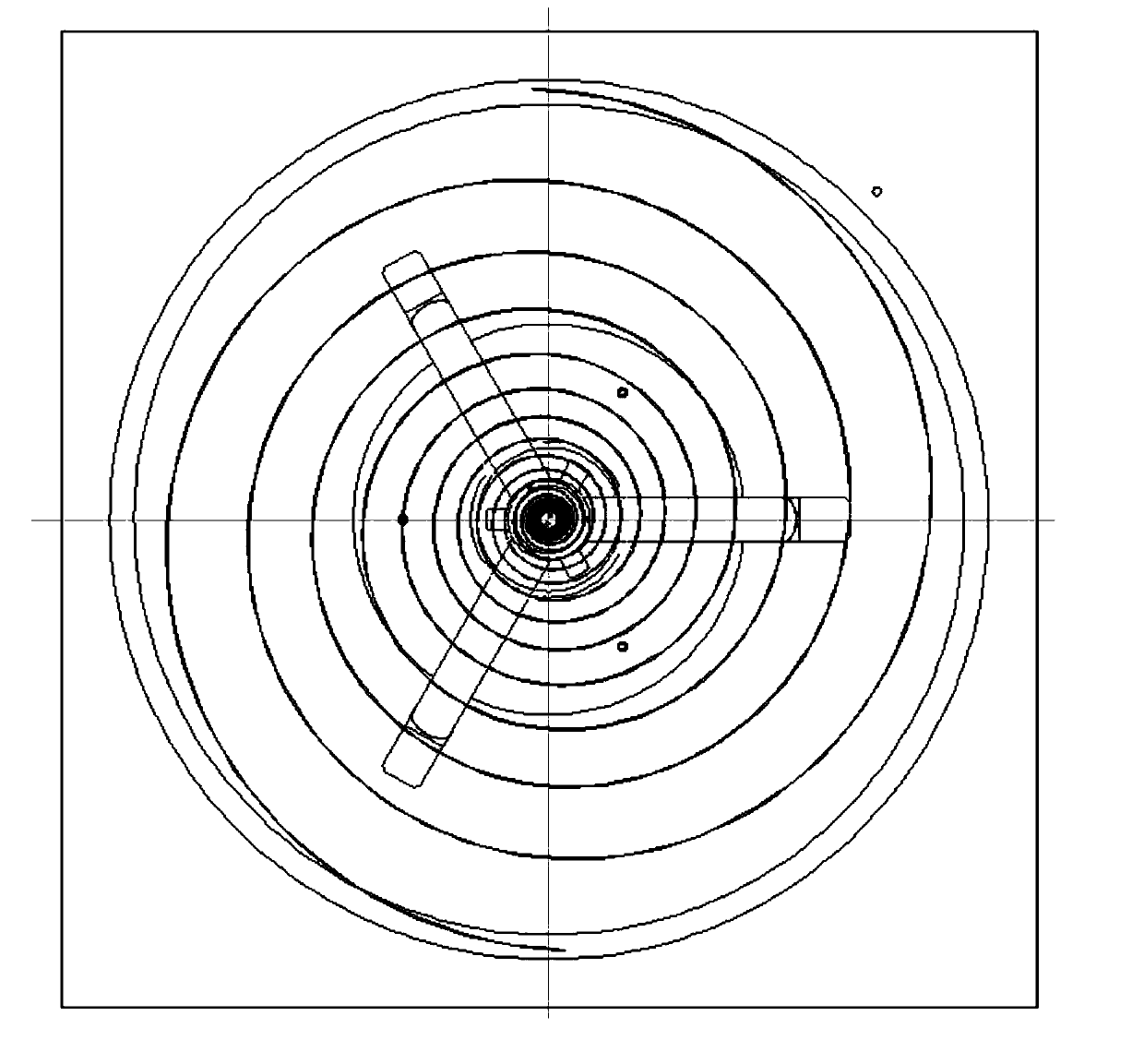

Field programmable gate array chip layout method

ActiveCN103366029ALower latencyQuick layoutSpecial data processing applicationsResource utilizationTime delays

The invention provides a field programmable gate array chip layout method. The method includes providing structural information of a logic unit of a field programmable gate array chip and net list information, generated after packaging, of a logic module; establishing a wiring resource map according to the structural information of the logic unit of the chip; arranging the field programmable gate array chip according to the net list information and the wiring resource map, and quickly wiring simultaneously. By the method, quick wiring is realized in the overall arrangement process according to the wiring resource map, and overall arrangement and wiring are closely combined, so that wiring success rate is increased, time delay of a circuit is reduced, and wiring resource utilization rate is increased.

Owner:SOI MICRO CO LTD

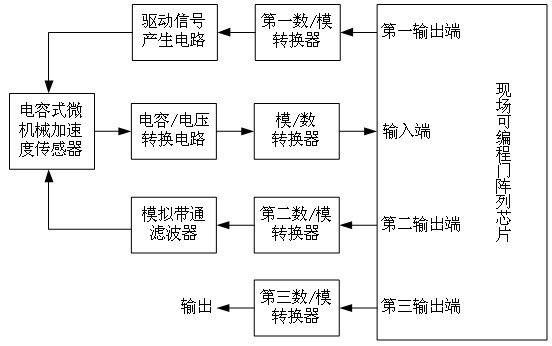

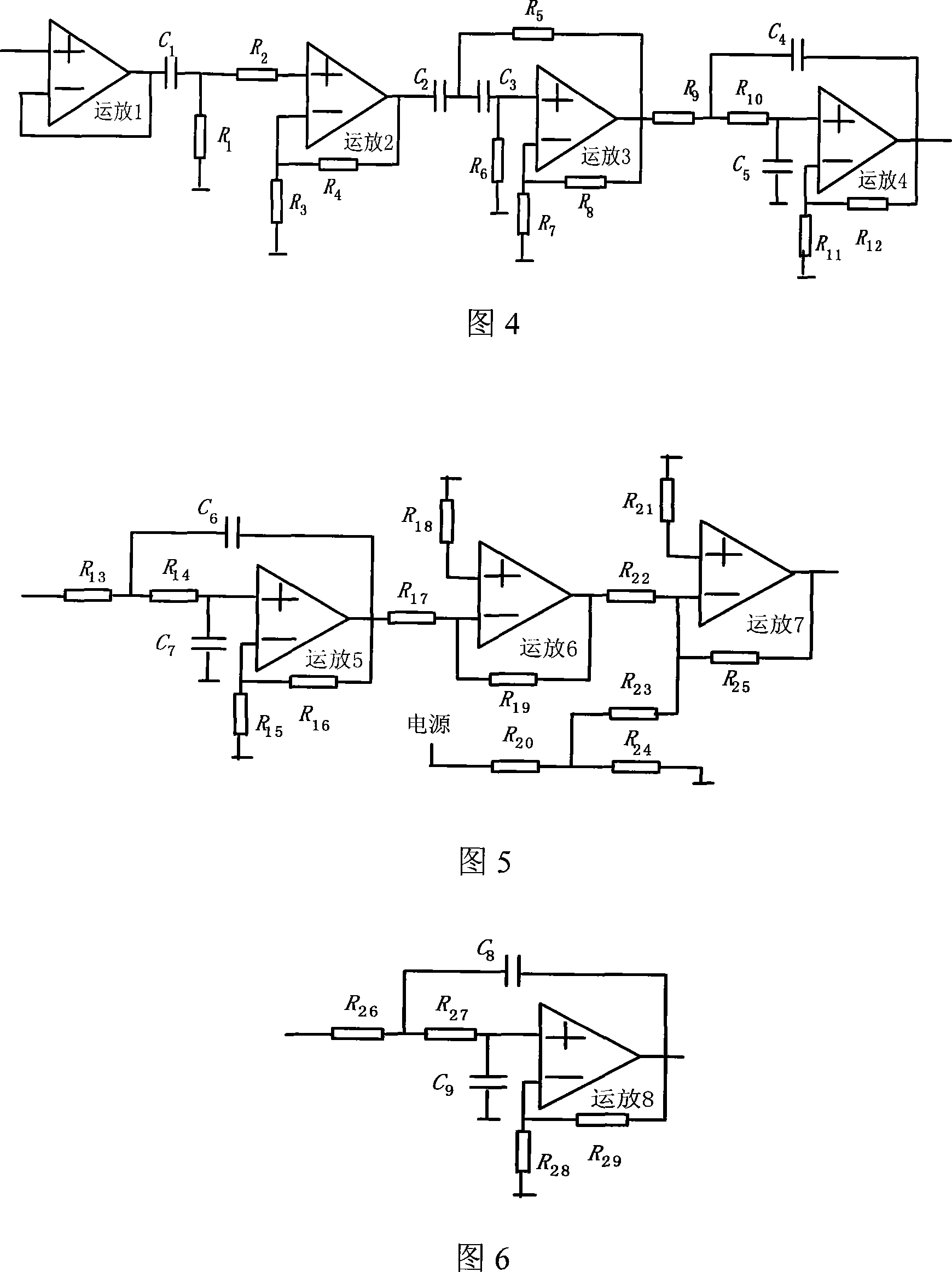

Temperature compensation system and method for capacitance type micro-mechanical accelerometer

ActiveCN102435774AReduce temperature compensation costsEliminate the influence of compensation accuracyAcceleration measurementCapacitanceAccelerometer

The invention discloses a temperature compensation system and a temperature compensation method for a capacitance type micro-mechanical accelerometer. The temperature compensation system for the capacitance type micro-mechanical accelerometer comprises a capacitance type micro-mechanical acceleration sensor, a driving signal generating circuit, a capacitance / voltage switching circuit, an analog band-pass filter, a first digital / analog (D / A) converter, an analog / digital (A / D) converter, a second D / A converter, a third D / A converter and a field programmable gate array chip. The temperature compensation method for the capacitance type micro-mechanical accelerometer comprises three steps of: carrier wave generating / synchronously demodulating, resonance frequency locking and zero offset temperature compensating. According to the invention, the temperature change of a capacitance type micro-mechanical acceleration sensor is detected by the means that the resonance frequency of the capacitance type micro-mechanical acceleration sensor changes along with the change of the temperature, and the temperature compensation system is used for compensating the temperature by the means that the resonance frequency is taken as a compensation reference signal of an output signal of a capacitance type micro-mechanical accelerometer system. Therefore, the temperature compensation cost is reduced, the influence of temperature measurement errors on compensation precision is eliminated, and the temperature compensation precision is improved.

Owner:ZHEJIANG UNIV

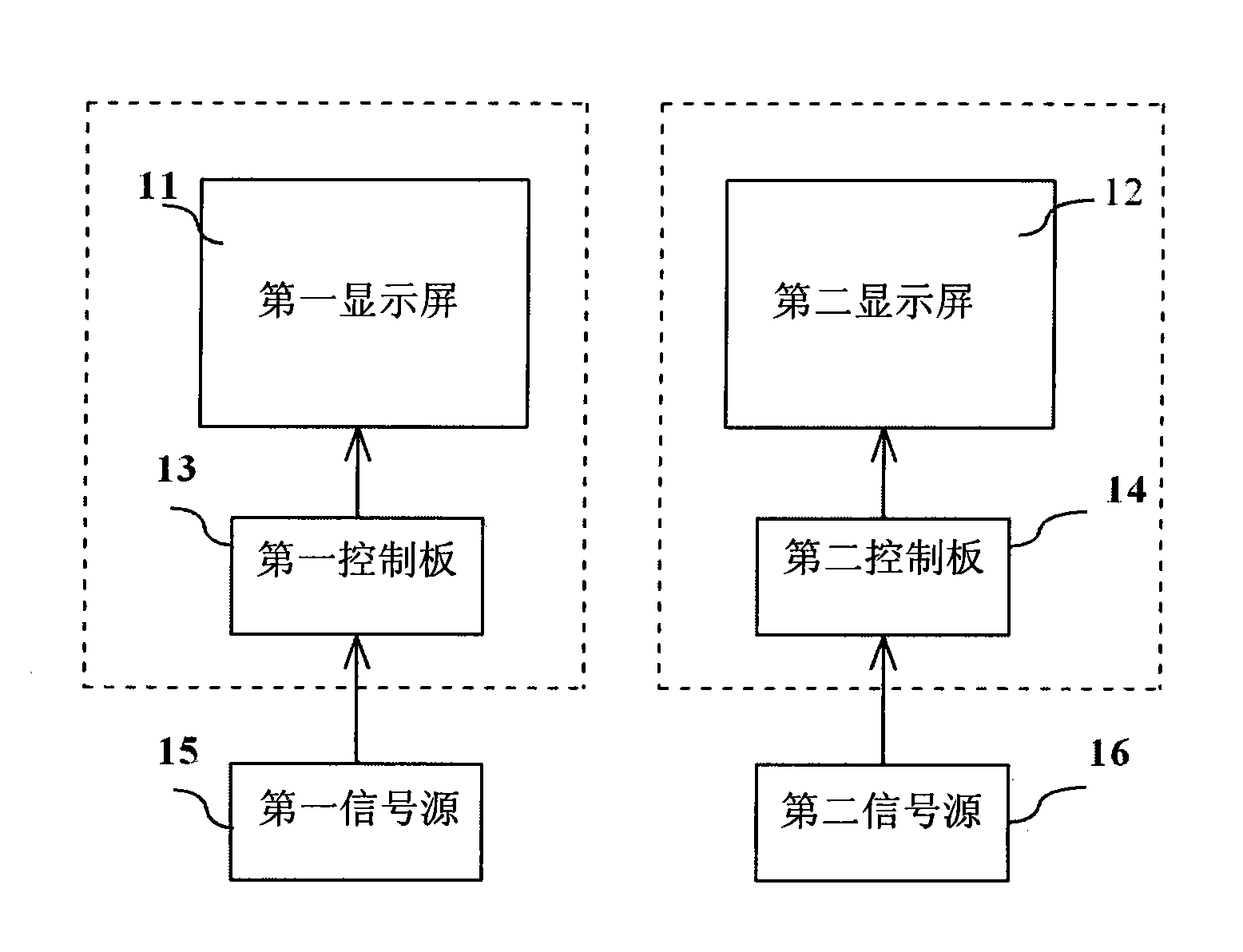

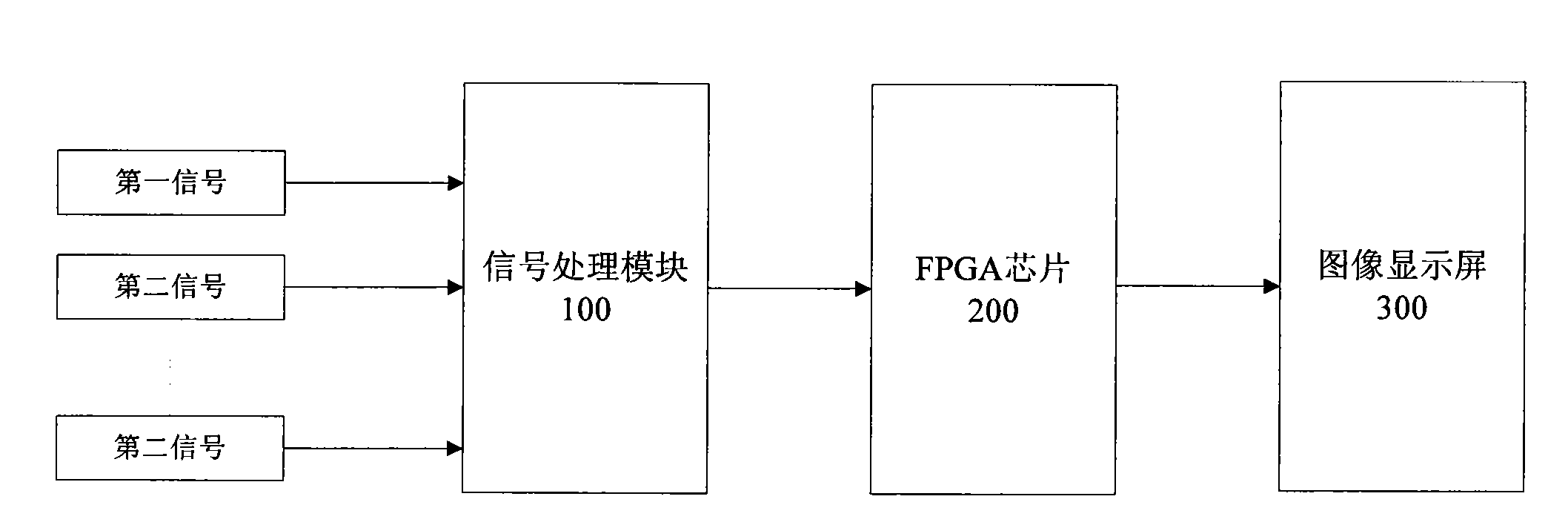

Method and device for seamlessly displaying images

ActiveCN101635137ARealize seamless splicing displayImprove the display effectCathode-ray tube indicatorsComputer graphics (images)Image signal

The invention relates to a device for seamlessly displaying images. The device comprises an image display screen, a signal processing module which is used for receiving a plurality of image signals and a field programmable gate array which integrates at least two image signals received by the signal processing module into one image which needs to be displayed by the display screen. The invention also relates to a method for seamlessly displaying the images. The method is characterized by including the following steps: a. receiving a plurality of image signals; b. selecting two of a plurality of image signals, and synthesizing the two image signals into one image; and c. displaying the synthesized image. The method and the device for seamlessly displaying the image have the advantages that the seamless splicing and the display of two images are realized. As the images have the furthest approach.

Owner:深圳市巨烽显示科技有限公司 +1

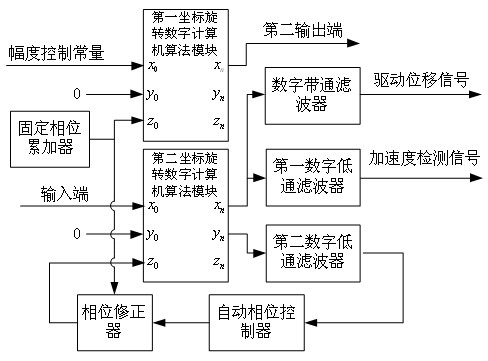

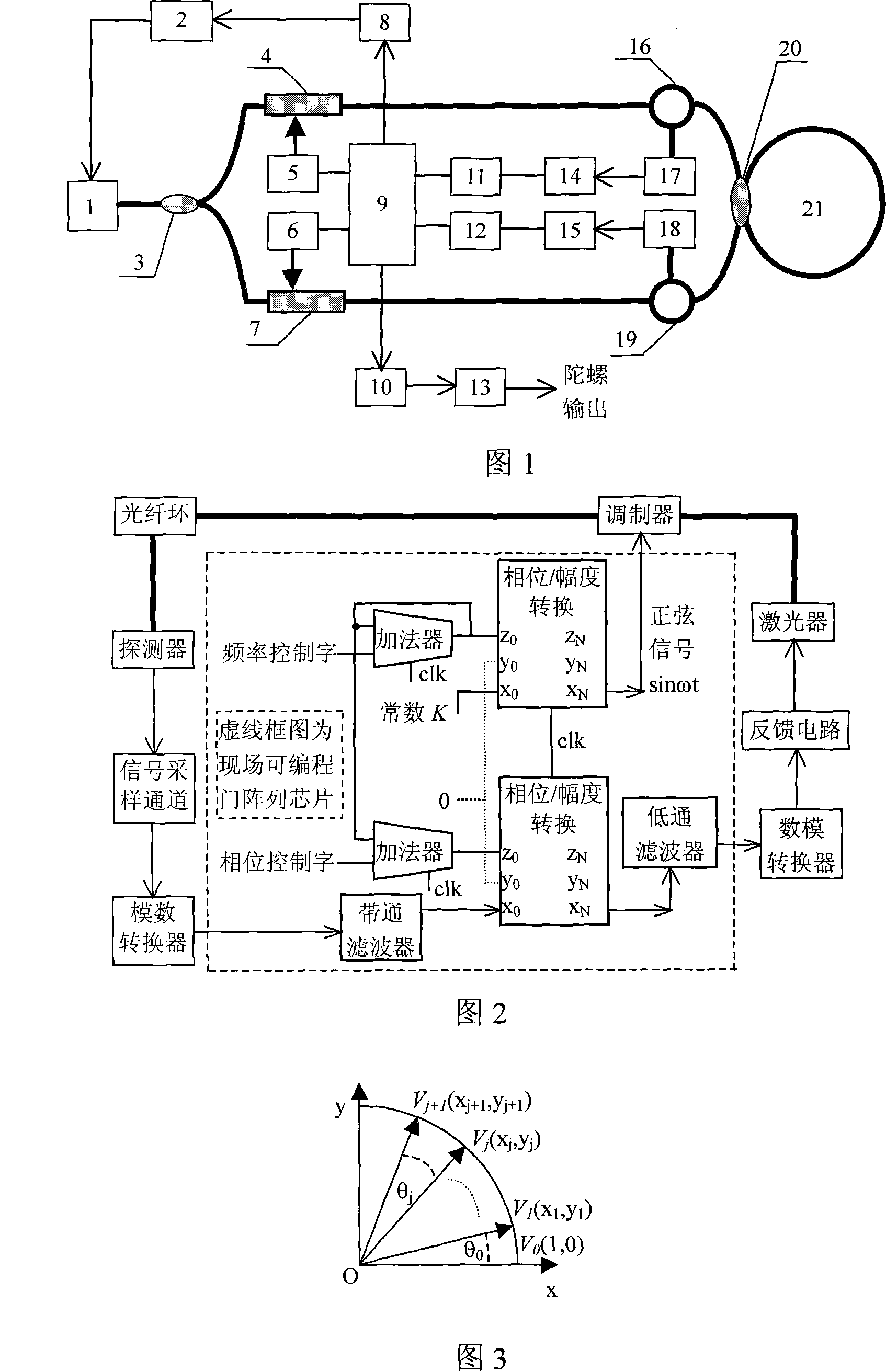

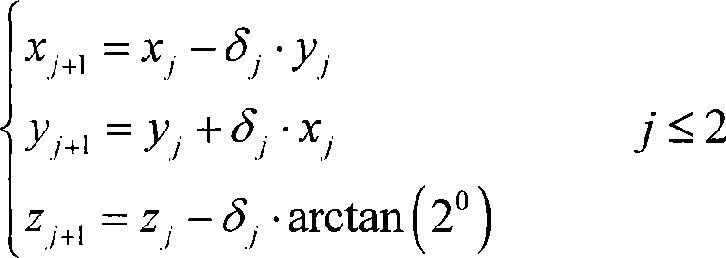

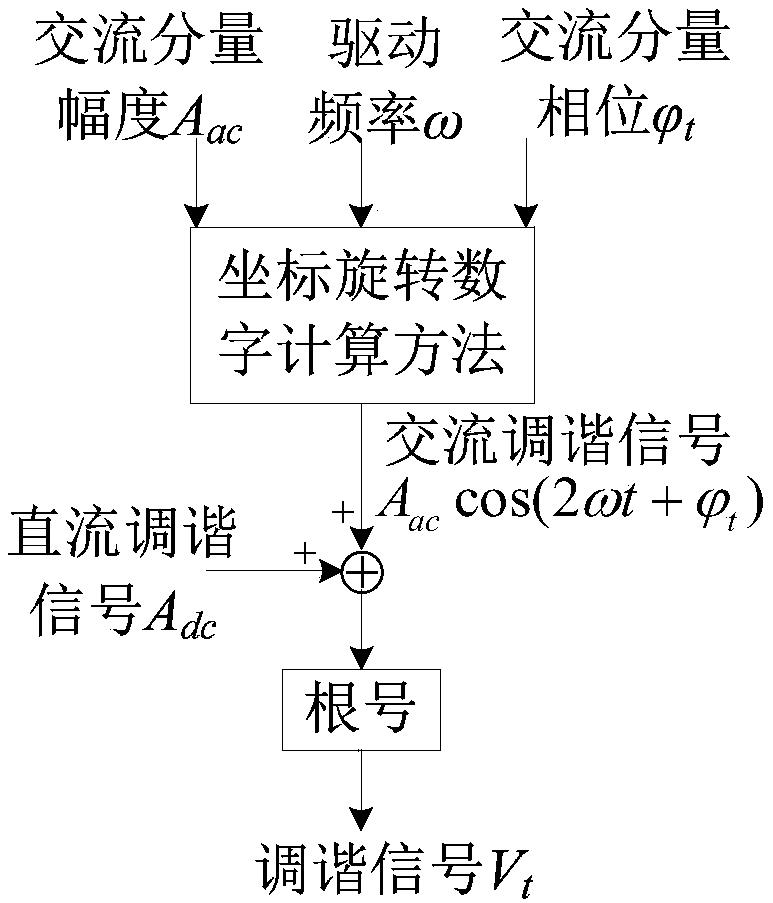

Resonance type optical fiber peg-top signal detection method and device based on coordinate rotation digital computer algorithm

InactiveCN101149264AHigh precisionImprove stabilityDigital data processing detailsSagnac effect gyrometersSignal productionPhotovoltaic detectors

The invention discloses a resonant fibre-optic gyro signal detection method and device based on the coordinate rotary digital computer algorithm. The detection method includes the modulation signal production and the signal demodulation method, which are all reached by the phase bit / scope switch module based on the coordinate rotary digital computer algorithm. The detection device includes the laser, the coupler, the phase bit modulator, the fibre-optic ringer, the photoelectrical detector, the present programme array chip, the digital / module switcher, the sample collecting channel, the reactive circuit and the signal output channel. The invention can reach the two circuits of the modulation signal production, demodulation and treatment by using the coordinate rotary digital computer algorithm; the scope, phase bit and frequency is dispatched by the programme, which is benefit for the detection system stable and assembly; the algorithm is determined by the iterative times and data word length; the fibre-optic ringer can avoid the light wave in fibre-optic back to the laser and influence the laser stable.

Owner:ZHEJIANG UNIV

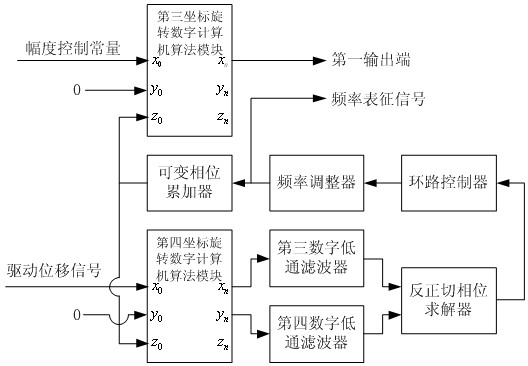

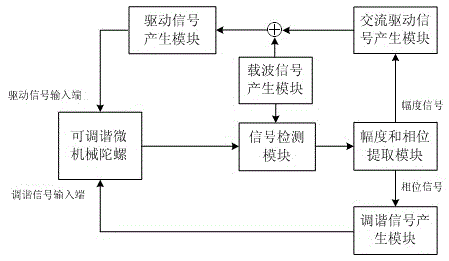

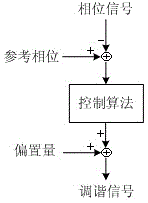

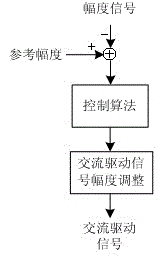

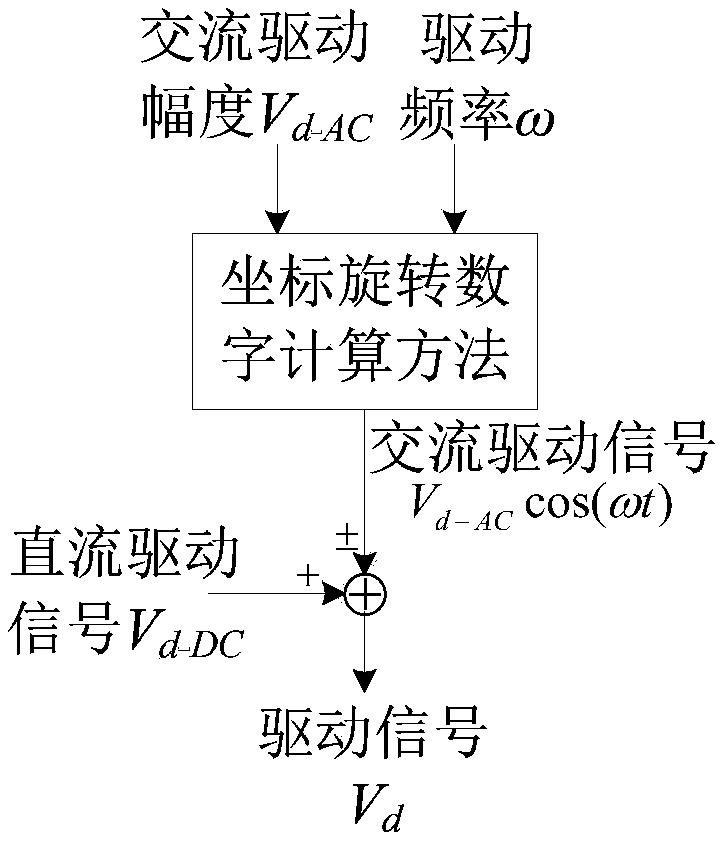

Constant-frequency drive method and constant-frequency drive device of tunable micromechanical gyroscope

ActiveCN102944230AImprove stabilitySimple signal processingTurn-sensitive devicesCapacitanceGyroscope

The invention discloses a constant-frequency drive method and a constant-frequency drive device of a tunable micromechanical gyroscope. The method comprises the steps of generation of a drive signal, generation of a tuning signal, signal detection, amplitude extraction and phase extraction, and the device comprises the tunable micromechanical gyroscope, a drive signal generation circuit, a capacitance / voltage conversion circuit, a tuning signal amplification circuit, a first digital / analog converter, an analog / digital converter, a second digital / analog converter and an in-situ programmable gate array chip. Through the automatic adjustment of the alternative-current drive signal amplitude and the resonant frequency of the tunable micromechanical gyroscope, the frequency and the amplitude of the drive output signal can be maintained constant, and the phase difference of the drive output signal and the alternative-current drive signal can also be maintained constant. The constant-frequency drive method and the constant-frequency drive device are simple to realize, the resonant frequency of a drive modal is unnecessary to track, the influence on the system from the module which is correlated to the frequency in the system under the time-variant frequency can be avoided, the signal processing process of the system can be simplified, and the system stability can be improved.

Owner:ZHEJIANG UNIV

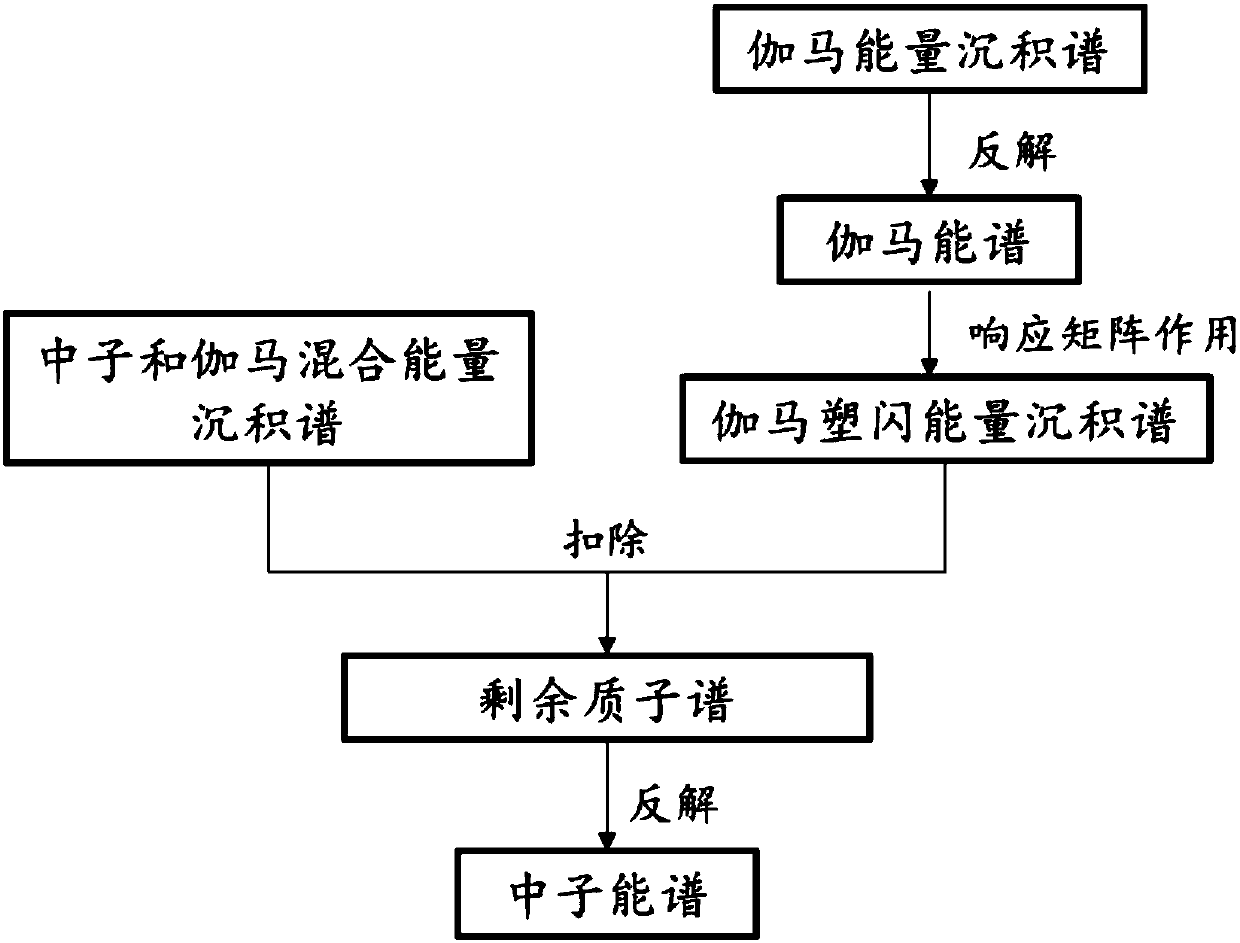

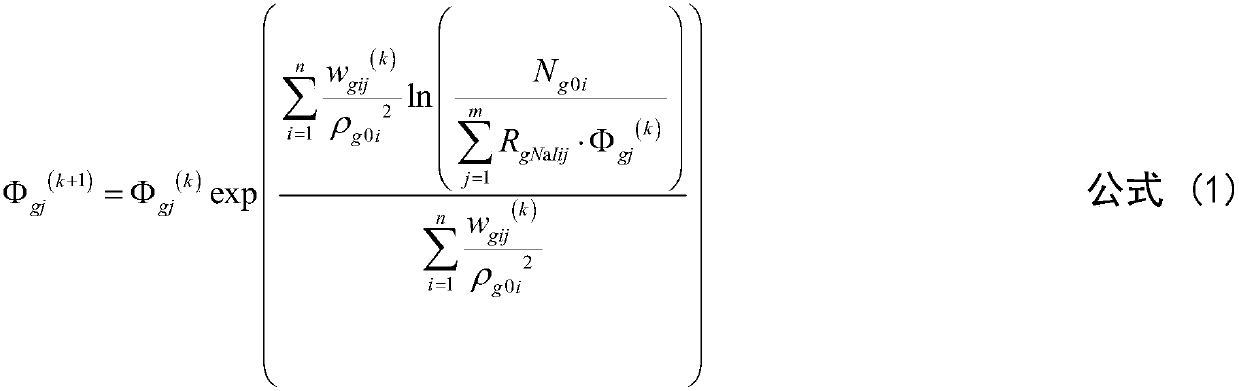

Method and system for measuring neutron, gamma energy spectrum and dosage in nuclear power station

ActiveCN107907901AReduce volumeSimple structureX-ray spectral distribution measurementDosimetersDigital signal processingGamma detection

The invention discloses a method for measuring neutron, gamma energy spectrum and dosage in a nuclear power station. The method comprises the following steps: 1 ) the neutron and gamma rays are inputinto a neutron detection system to output a signal A, and the gamma rays are input into a gamma detection system to output a signal B; 2) the signal A and the signal B are input into a digital signalprocessing circuit to be subjected to operation processing to obtain the neutron, gamma energy spectrum and dosage, wherein the digital signal processing circuit takes a field-programmable gate arraychip as a core chip. Compared with the prior art, the method for measuring neutron, gamma energy spectrum and dosage in the nuclear power station disclosed by the invention has the advantages that thesimulations measurement of the neutron, gamma energy spectrum and dosage can be realized based on the field-programmable gate array technology. In addition, the invention further discloses a system for measuring the neutron, gamma energy spectrum and dosage in nuclear power station.

Owner:中广核工程有限公司 +1

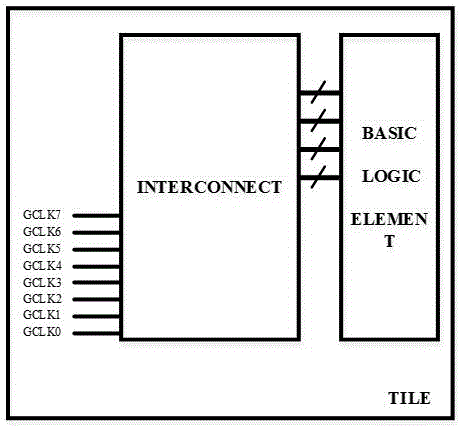

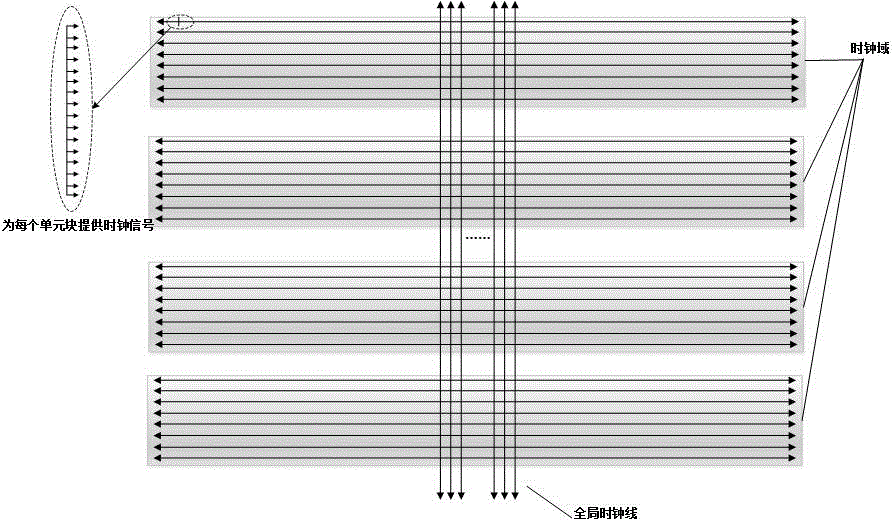

Clock network traversing testing method based on FPGA (Field Programmable Gate Array) hardware structure

ActiveCN104617928AReduce occupancyReduce configuration timesDetecting faulty computer hardwarePulse manipulationHardware structureComputer architecture

The invention belongs to the technical field of testing of integrated circuits, and specially provides a clock network traversing testing method based on the FGPA (Field Programmable Gate Array). The method is that each logic block is configured as that the SLICE in the a CLB logic block circuit (Configurable Logic Block) is configured to be in a logic gate operation form; a BRAM logic block circuit is configured to the read-only ROM address searching mode; a DSP logic block circuit is configured to be in some operation form; all configuration modes above are under the control of a clock signal, and the result is outputted through a register; the faults which can be tested include short circuit, open circuit, general 0 and 1 faults of an FPGA clock end. With the adoption of the method, the clock input ends of all unit block circuits in an FPGA chip and all clock network functions can be tested; the configuration times, configuration difficulty and the testing time for testing are greatly optimized.

Owner:FUDAN UNIV

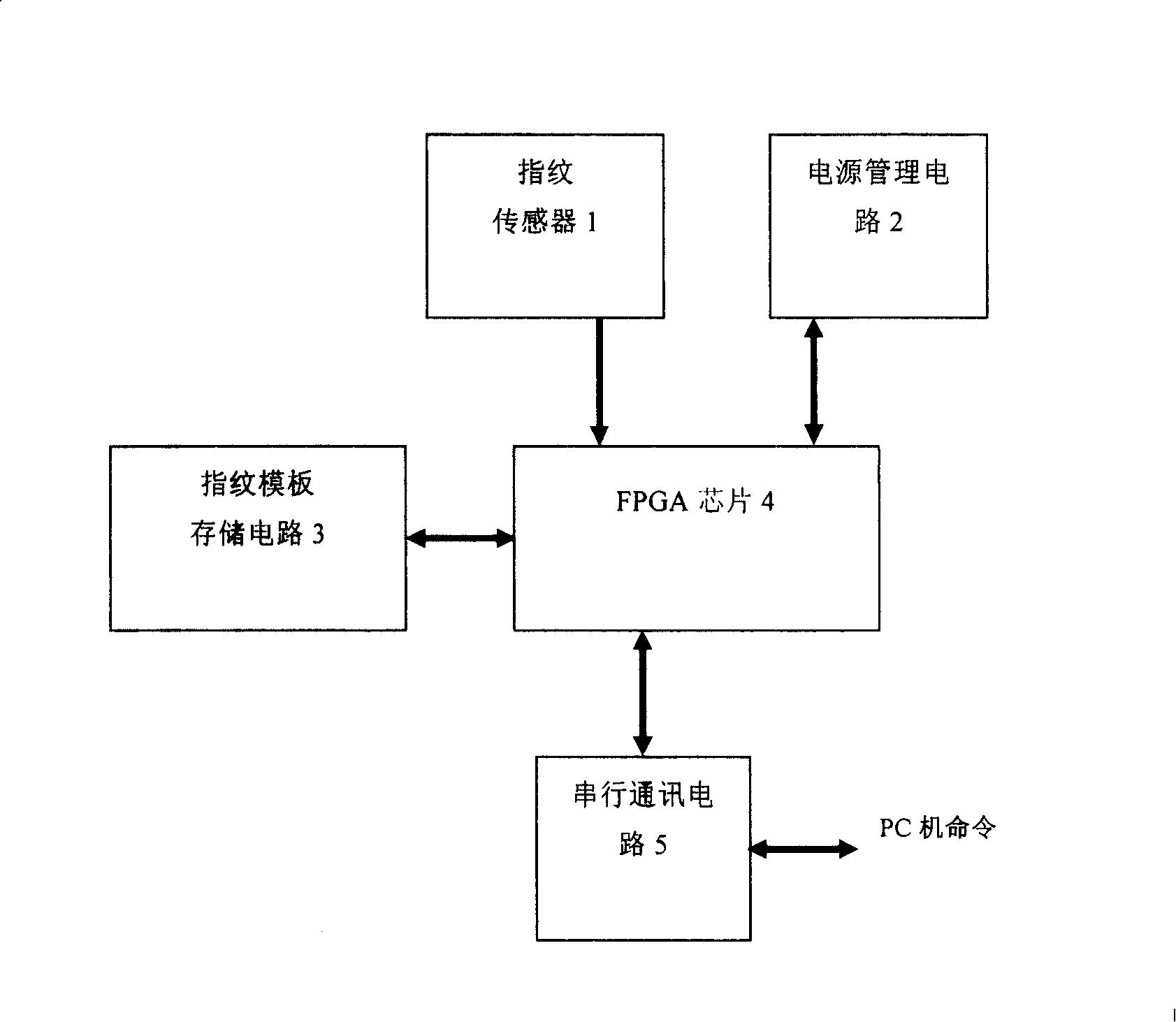

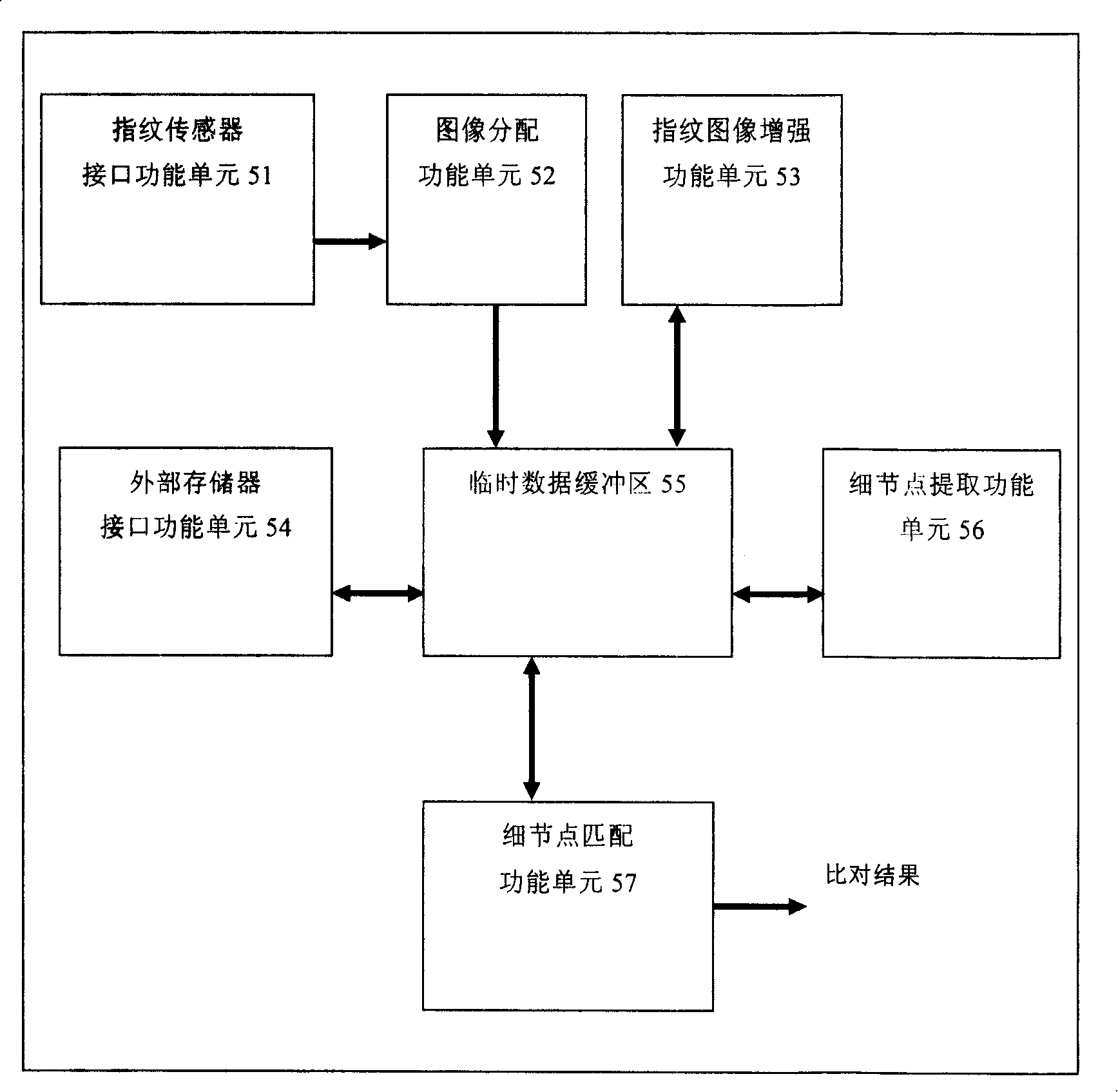

Fingerprint identification method and apparatus based on field programmable gate array chip

InactiveCN101226588ARealize fingerprint registrationRealize functionCharacter and pattern recognitionMemory chipExternal storage

The invention discloses a fingerprint identifying method and a device based on on-site programmable gate array chips. The invention is realized by hardware description language, sequentially carries out image distribution, fingerprint image enhancement and minutiae extracting operation to fingerprint image data read by the interface of a fingerprint sensor, and stores a fingerprint template including the fingerprint minutiae in an external memory chip by an interface of the external memory. In the process of minutiae matching, a minutiae template produced by input fingerprint is matched with the stored minutiae template to verify whether the minutiae templates belong to the same finger. The on-site programmable gate array chip is respectively connected with the fingerprint sensor, a fingerprint template storage circuit, a serial communication circuit and a power management circuit. The invention increases the fingerprint identification speed under embedded systems environment, reduces the temporary data storage space required in the fingerprint identifying process, and decreases the hardware cost of fingerprint identifying system, thereby higher fingerprint identifying property can be realized with lower cost of embedded system.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

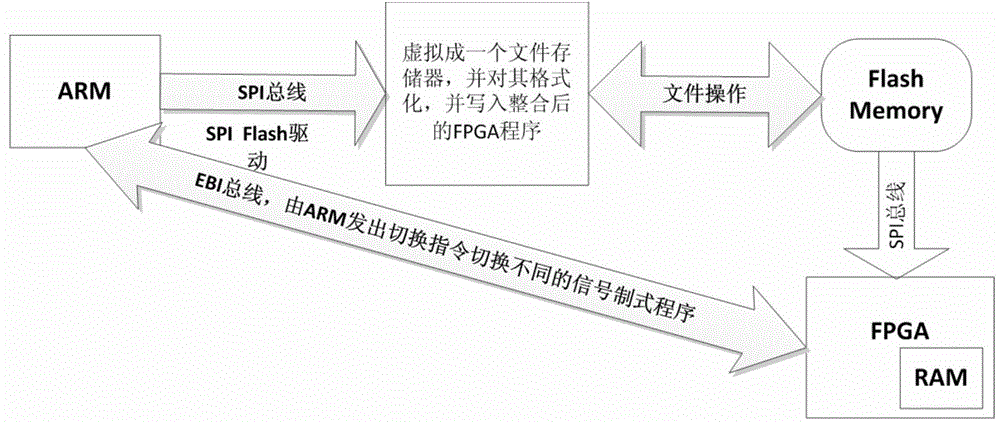

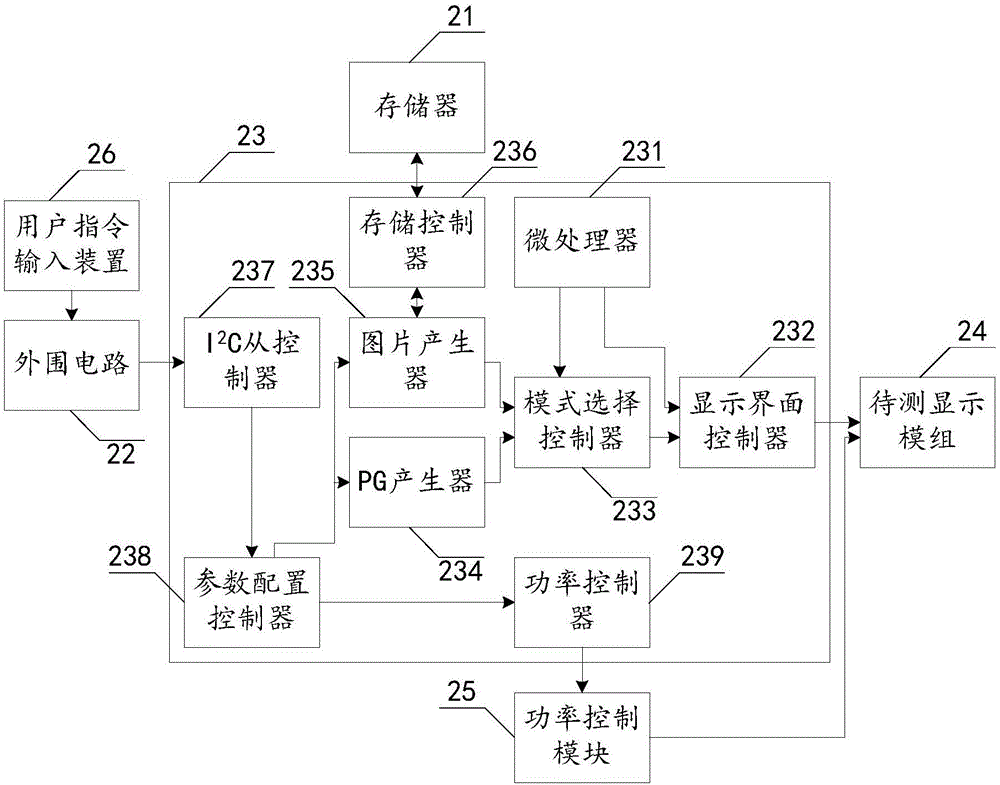

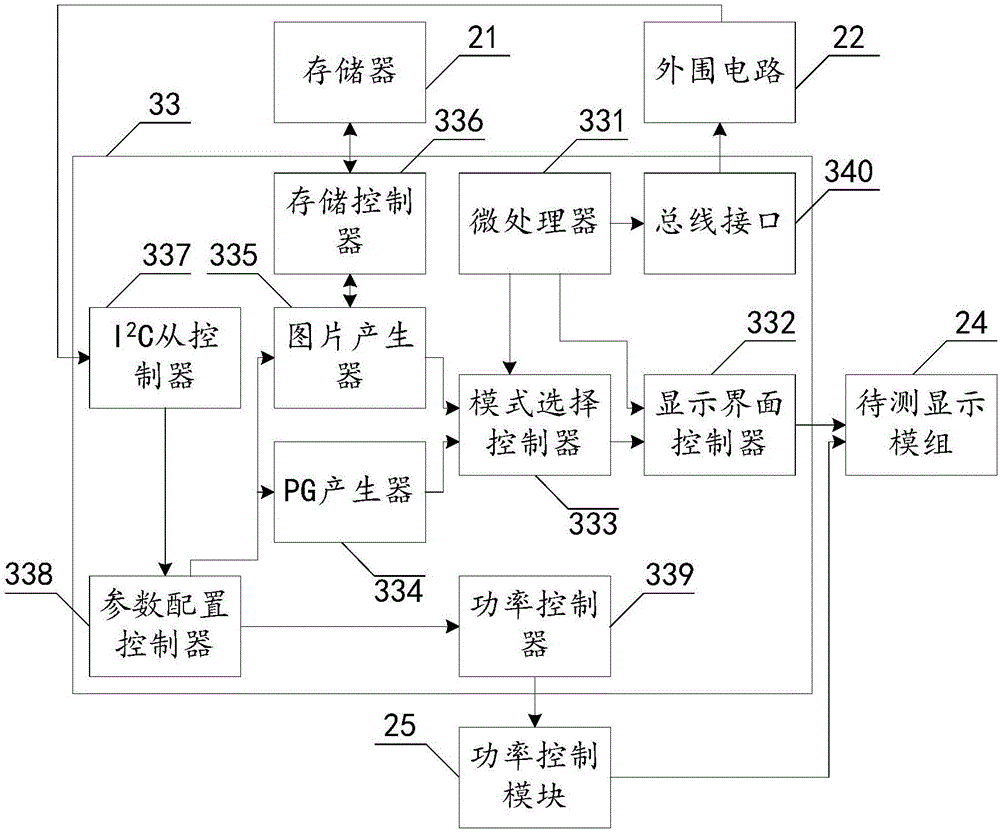

FPGA program multi-image loading method based on ARM

ActiveCN104572211AFast startup timeSatisfy R&DProgram loading/initiatingMulti-imageProcessor register

The invention relates to an FPGA (Field Programmable Gate Array) program multi-image loading method based on an ARM. The loading method comprises the following steps: 1, packing field-programmable gate array files with different signal formats in a computer through a field-programmable gate array compiler; 2, writing the packed field-programmable gate array files into a flash memory in the computer by an ARM processor via a serial peripheral interface; 3, writing external bus interface storage address information and corresponding external bus interface register addresses of the files demanded to be loaded into external bus interfaces by the ARM processor when demanding to load one of the packed field-programmable gate array files, and loading the necessary field-programmable gate array files into the random access memory of the field-programmable gate array chip from the flash memory by the field-programmable gate array chip. Fast switch and power down protection of display module test signals can be simultaneously realized by the loading method.

Owner:WUHAN JINGCE ELECTRONICS GRP CO LTD

Testing apparatus and method for fixed series compensation protection

InactiveCN105242138AImprove versatilityComprehensive and detailed checkElectrical testingEngineeringLow pass filtering

The invention discloses a testing apparatus for fixed series compensation protection. A current transformer is used for converting a current analog quantity into a small voltage signal. A low-pass filtering module is use for filtering the small voltage signal. An analog-digital conversion module is used for sampling and maintaining an analog quantity input by the low-pass filtering module, and sending an obtained digital quantity to a signal processing module. The signal processing module is used for conducting caching, data zooming and communication protocol transformation, and enables data to be packed and written in a field programmable gate array chip. The field programmable gate array chip is used for driving a photoelectric conversion module to convert the data into an optical signal that supports a preset communication protocol, and sends the optical signal to a to-be-tested protection apparatus through a fiber interface. The invention also discloses a testing method for fixed series compensation protection. According to the invention, the protection function of a series compensation protection apparatus can be checked in a quantified manner, and the testing apparatus and method are suitable for debugging an intelligent transformer substation.

Owner:NR ELECTRIC CO LTD

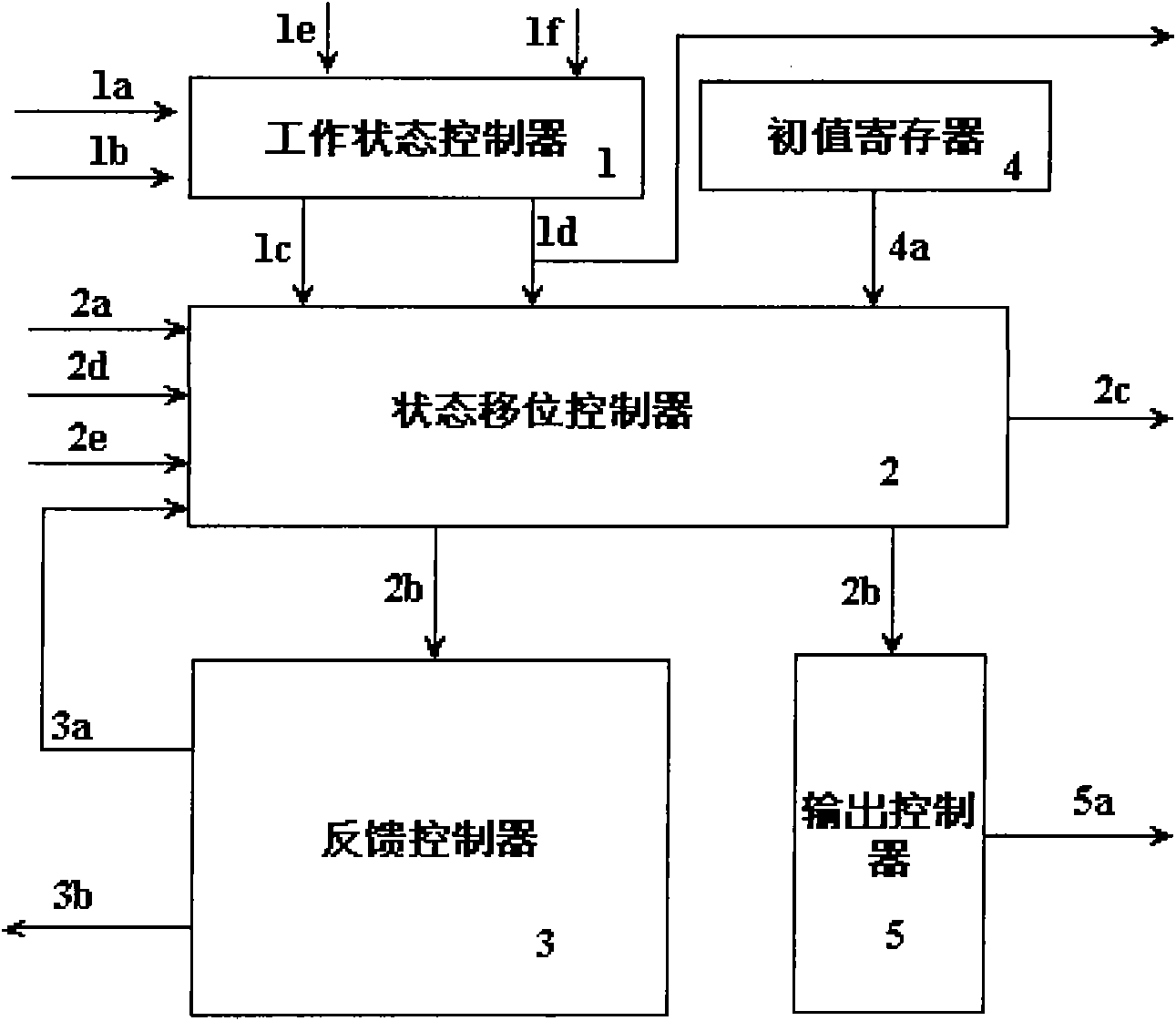

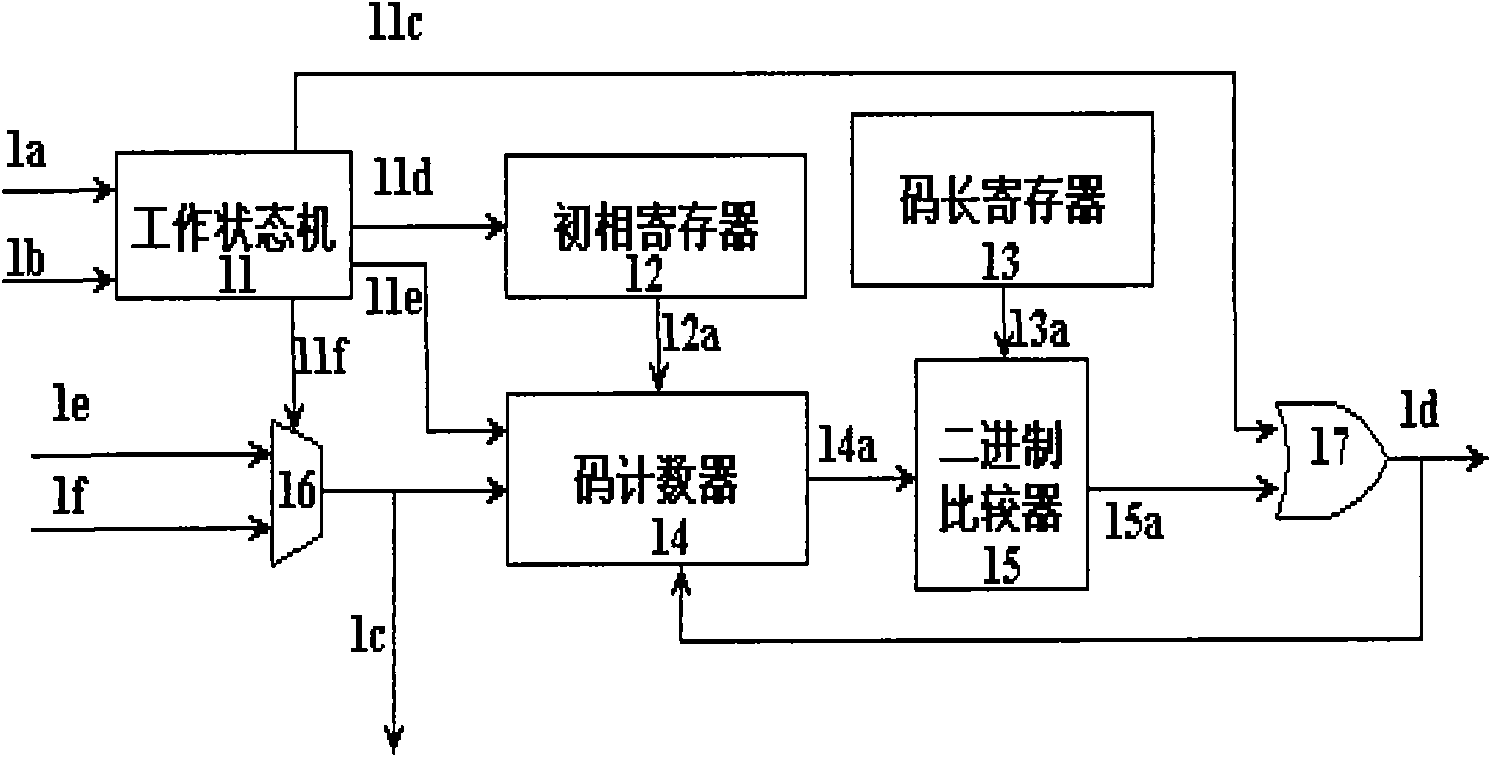

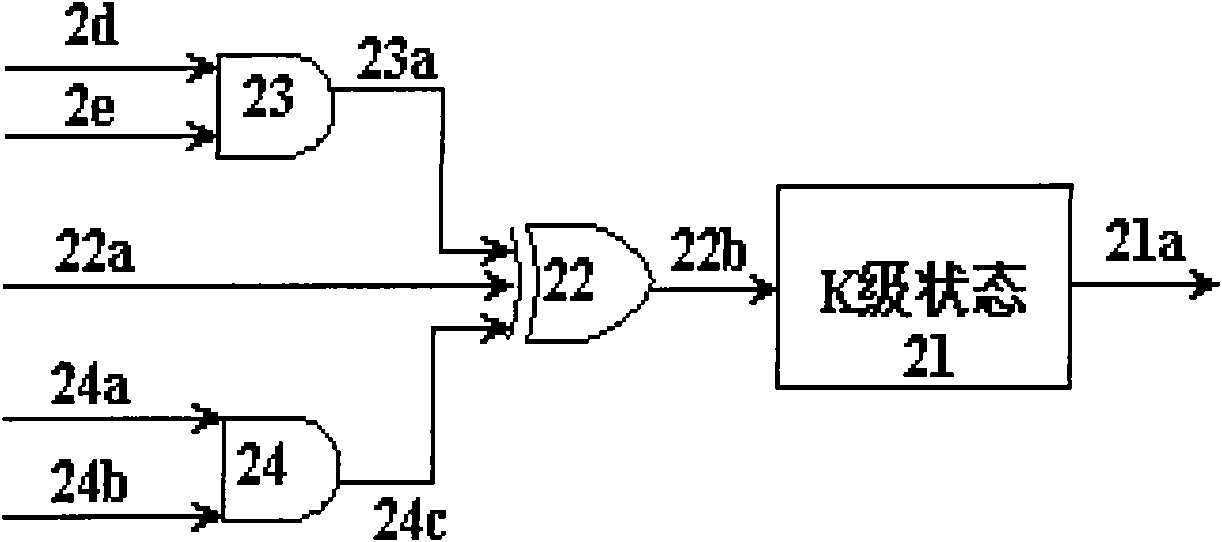

Programmable navigational satellite spread spectrum sequence generator

InactiveCN101887130AReduce overheadReduce workloadSatellite radio beaconingDigital clockFeedback controller

The invention belongs to the technical field of satellite navigation and relates to a programmable navigational satellite spread spectrum sequence generator. The programmable navigational satellite spread spectrum sequence generator comprises input / output modules, a configurable logic unit, a digital clock management module and a block memory which are integrated into a field programmable gate array chip. The programmable navigational satellite spread spectrum sequence generator is characterized in that: different pseudorandom sequence generating methods for different navigation systems by using the spread spectrum sequence generator can be implemented by connecting 1 to 6 code generator units in series or in parallel; and all the code generator units are provided with identical working condition controllers, state shifting controllers, feedback controllers, initial registers and output controllers. The programmable navigational satellite spread spectrum sequence generator is used forgenerating pseudorandom codes in a satellite signal simulator, so the programmable navigational satellite spread spectrum sequence generator has the advantages of greatly reducing expenditure of hardware resources, reserving a larger space for perfecting other functions, and greatly reducing workload of the conventional real-time generating mode, along with easy maintenance.

Owner:PLA SECOND ARTILLERY ENGINEERING UNIVERSITY

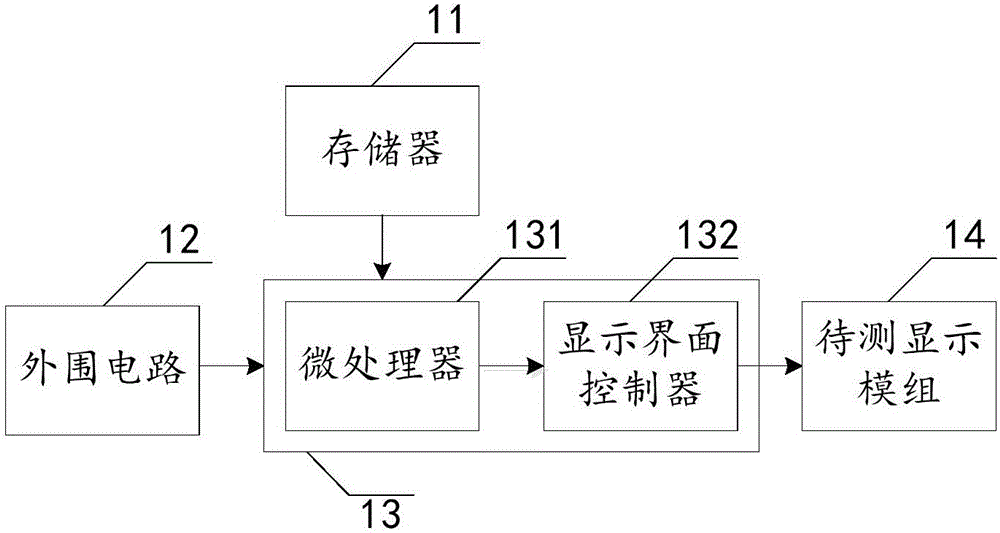

Display module light-on test device and method

ActiveCN106771974ASimplify the hardware partImprove stabilityProgramme controlComputer controlElectronic componentElectron

The invention discloses a display module light-on test device and a display module light-on test method. The device is used for performing light-on test on a to-be-tested display module and comprises a memorizer, a peripheral circuit and a field programmable gate array chip, wherein a microprocessor and a display interface controller are integrated in the field programmable gate array chip; the microprocessor is used for outputting initialization information; the microprocessor is connected with the display interface controller; and the field programmable gate array chip is connected with the to-be-tested display module through the display interface controller to output the initialization information to the to-be-tested display module, so that the to-be-tested display module is subjected to initialization operation, processed picture data is output to the to-be-tested display module, and the to-be-tested display module is subjected to light-on test. By the method, a hardware part of the light-on test device can be simplified, the design of the peripheral circuit is reduced, the use amount of electronic components is reduced, the stability of the light-on device is improved and maintenance of research staff is facilitated.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

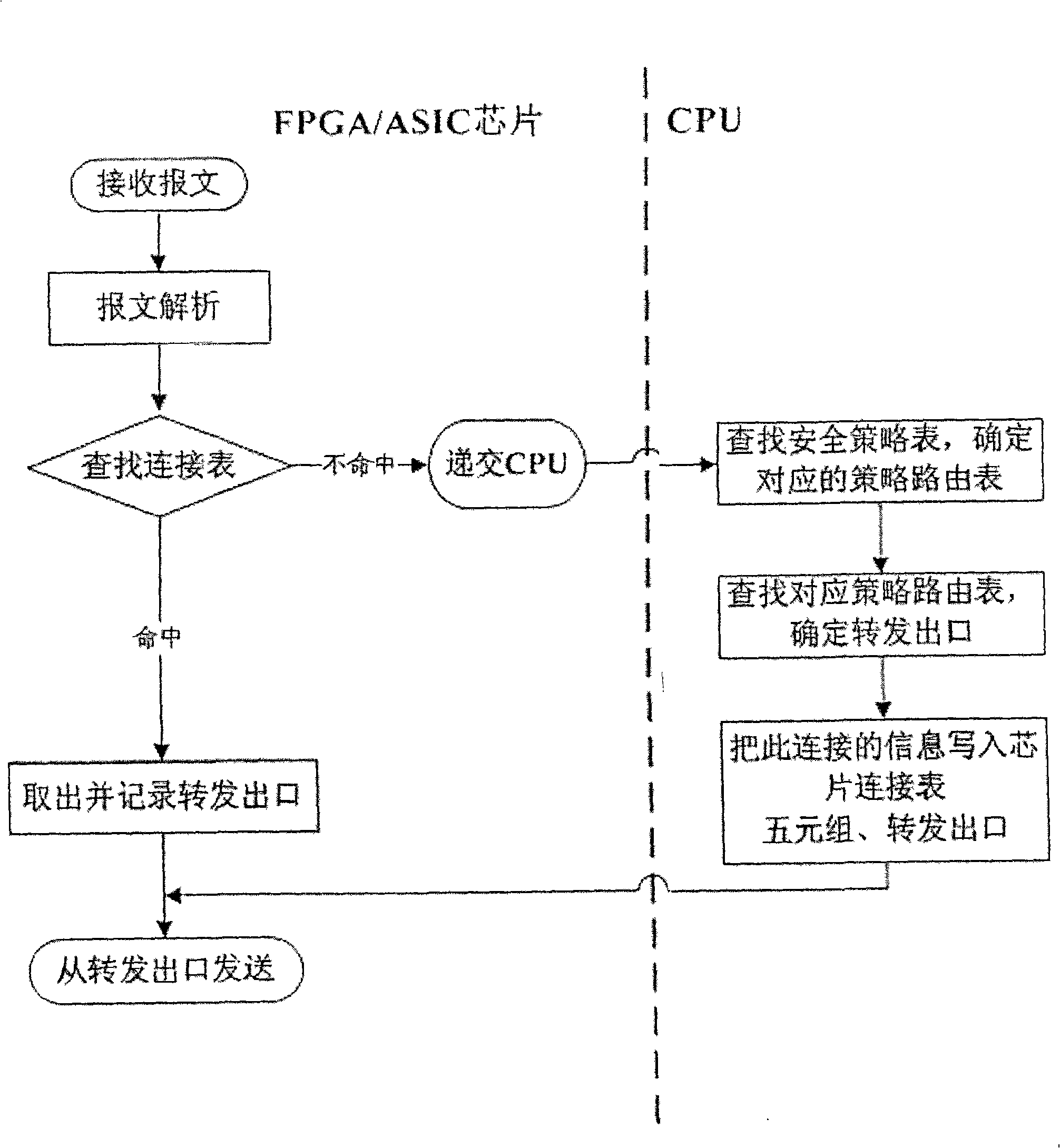

Method for chip internal link list supporting policy routing

InactiveCN101296168AReduce bandwidth requirementsSave resourcesData switching by path configurationSecuring communicationRouting tableConnection table

The invention discloses a method for leading a connection table in a chip to support policy routing, which pertains to the field of network safety and comprises the steps of the application of programmable gate array chips based on field and the connection with a CPU (central processing unit). The method also comprises the following steps: the chip receives messages; resolution is carried out to obtain the quintuple content of input messages; the quintuple is taken out according to the resolution result and a connection table is searched; if the target is hit, information is taken out and a forwarding outlet is recorded; if the target is not hit, the CPU is submitted; a safety strategy table is searched, and a corresponding strategy routing table is used according to a safety strategy rule, the forwarding outlet is determined and the connection information is written into the connection table in the chip and then to the forwarding outlet. The messages are sent out from the specified forwarding outlet. The method reduces the demand of the system on CPU and PCI bus bandwidth, saves CPU resources and improves the performance of the whole system and the high speed processing capacity in the network environment.

Owner:BEIJING TOPSEC NETWORK SECURITY TECH

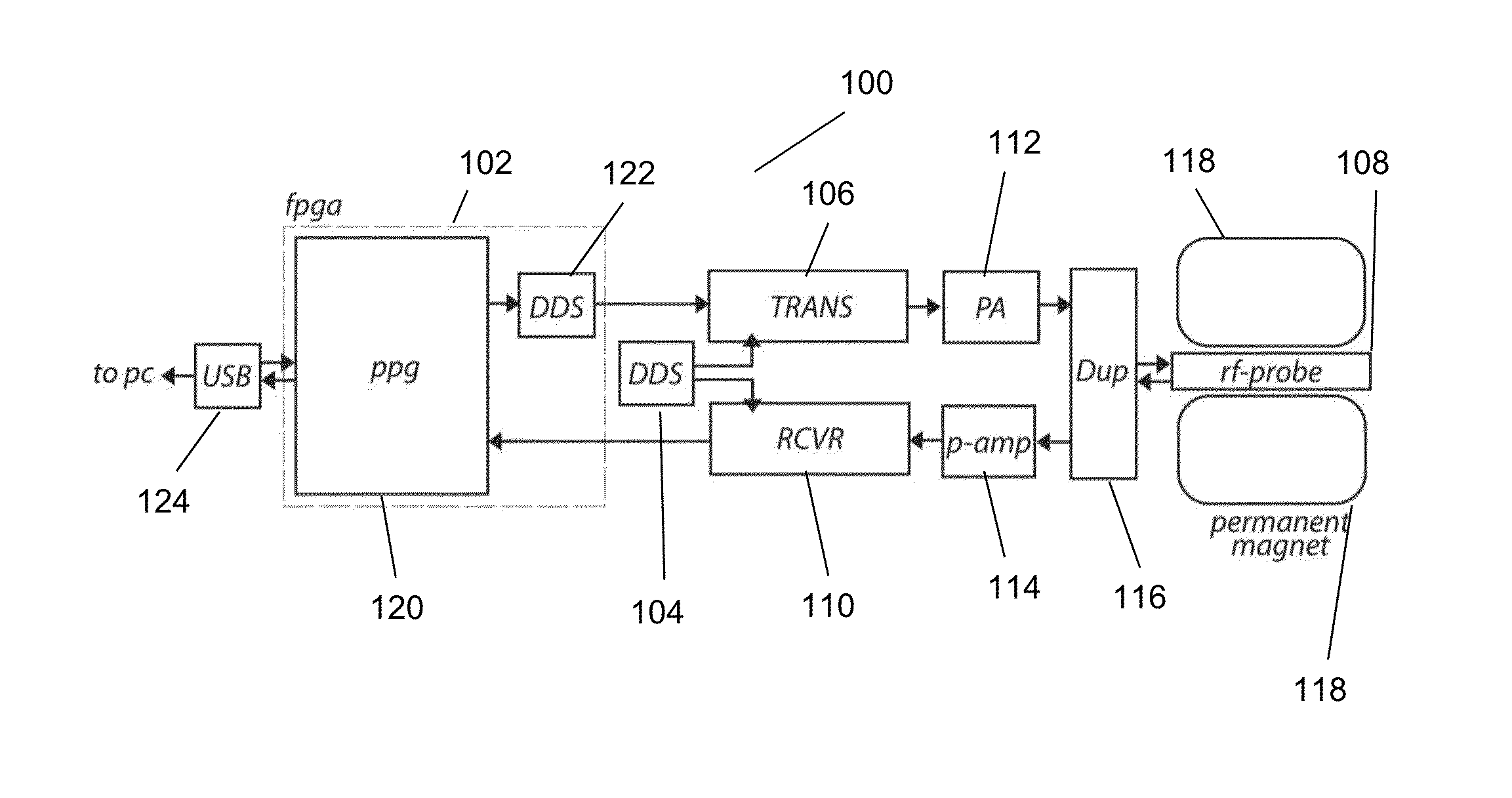

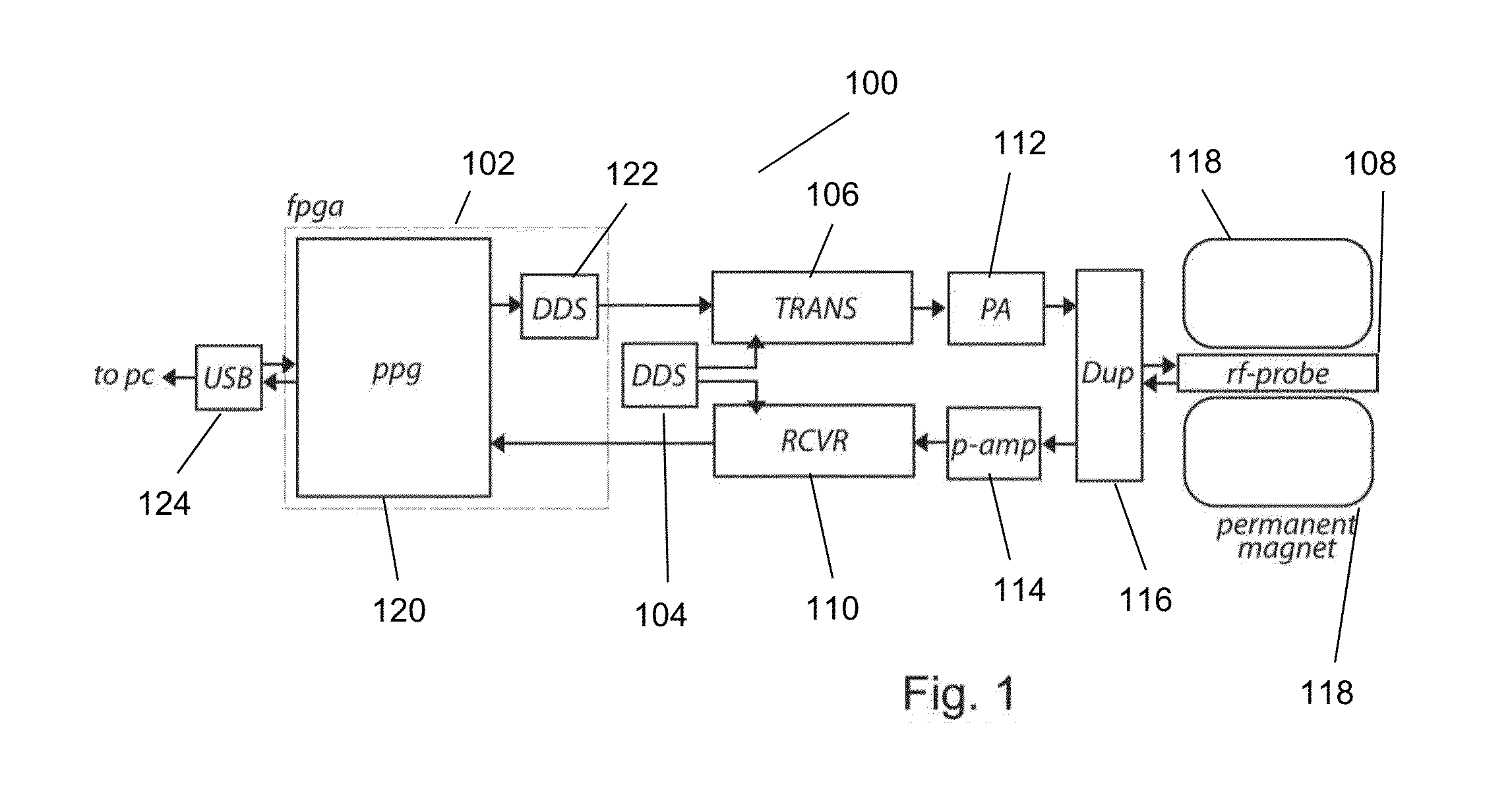

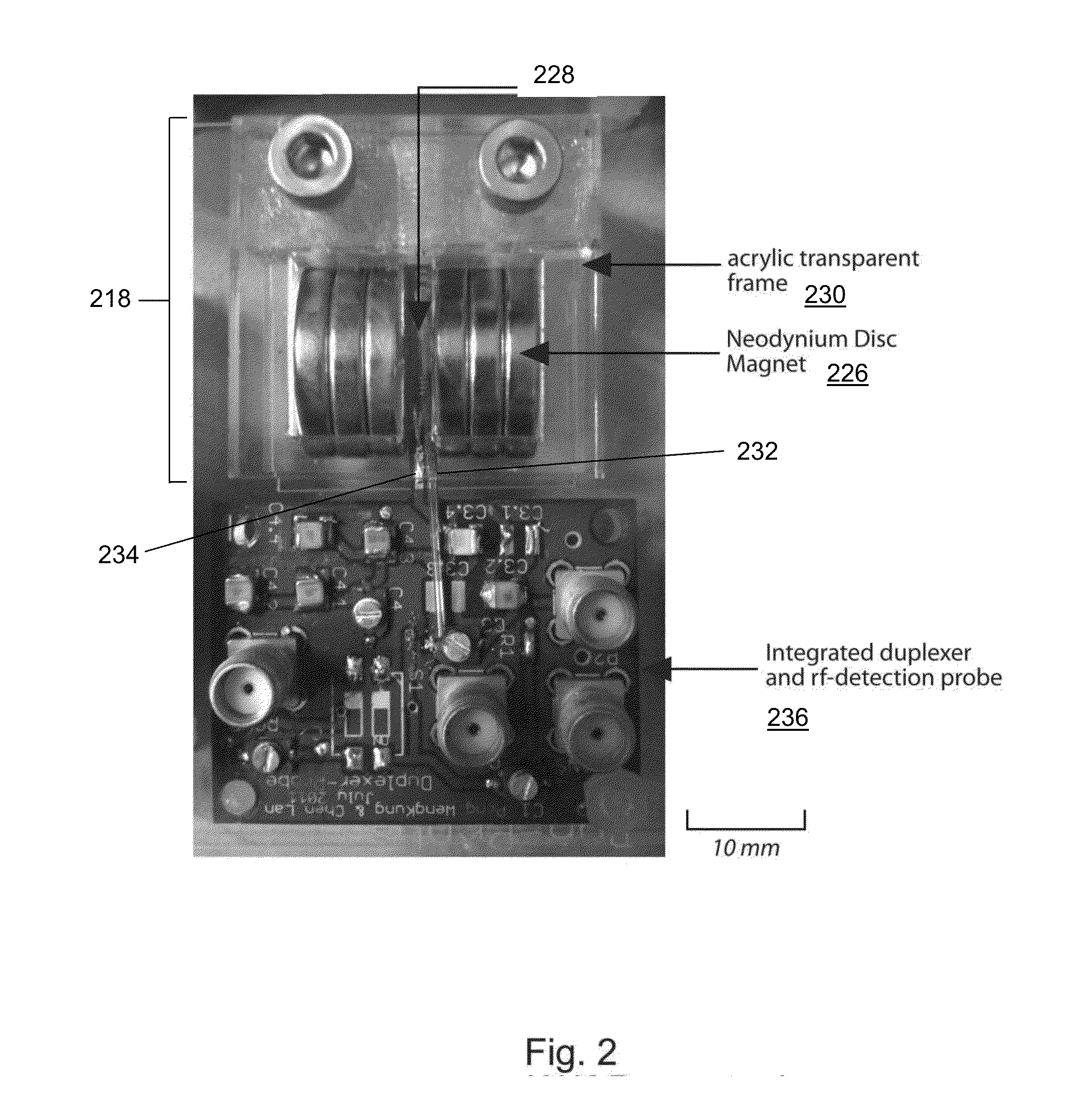

Biosensor, palm-sized device and method based on magnetic resonance relaxometry

ActiveUS20150177348A1Measurements using NMR imaging systemsElectric/magnetic detectionParalemminElectromagnetic radiation

In accordance with one aspect of this disclosure, there is provided a device for performing magnetic resonance relaxometry. The device comprises a radio-frequency spectrometer comprising at least one field-programmable gate array chip; a power amplifier electrically connected with the radio-frequency spectrometer and amplifying an electrical output of the radio-frequency spectrometer, thereby producing an amplified electrical signal comprising between about 0.1 Watts and about 10 Watts power; a duplexer configured to isolate the radio-frequency spectrometer from the amplified electrical signal during a receiving mode of the device; a radio-frequency detection probe configured to transmit radio-frequency electromagnetic radiation to excite nuclei under resonance during a transmission mode of the device, the radio-frequency detection probe comprising a detection coil comprising an inner diameter of less than about 1 millimeter; and at least one magnet supplying an external magnetic field to a detection region of the radio-frequency detection probe, the external magnetic field being less than about 3 Tesla.

Owner:MASSACHUSETTS INST OF TECH

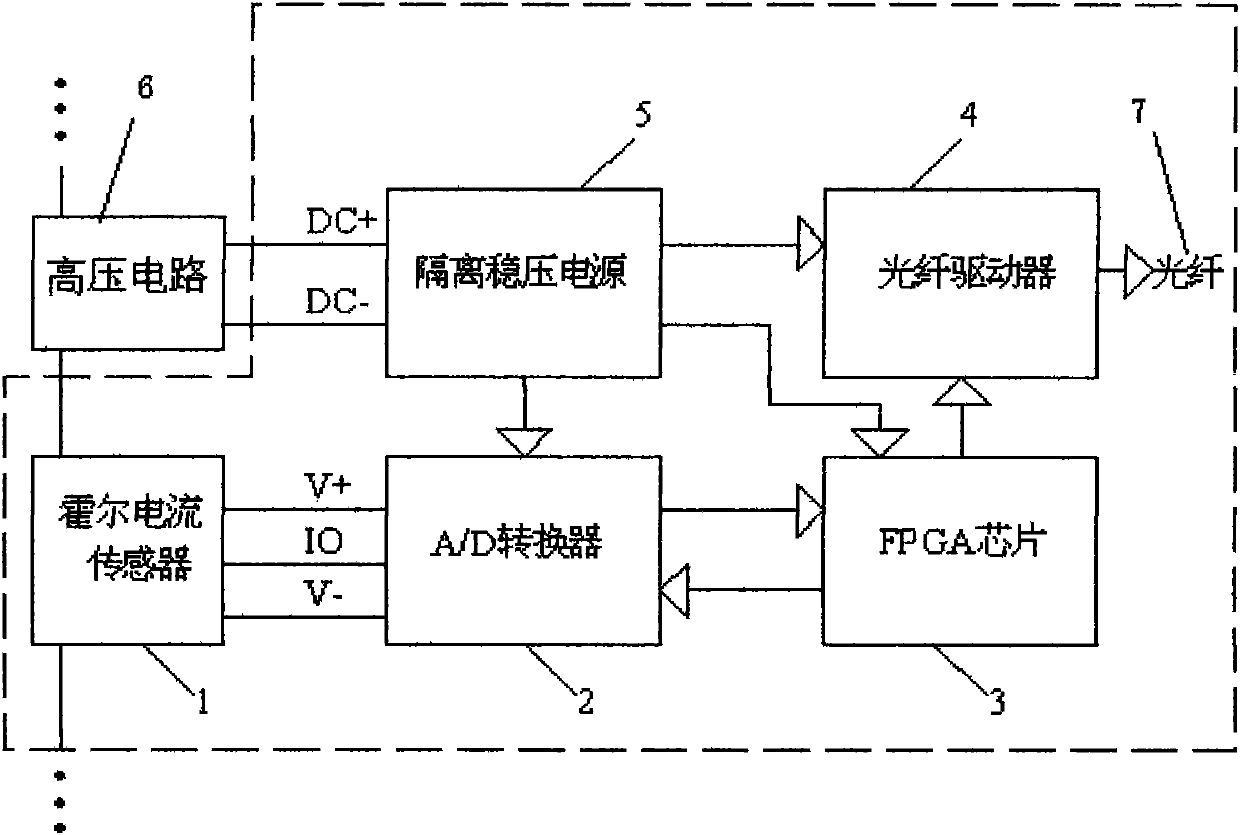

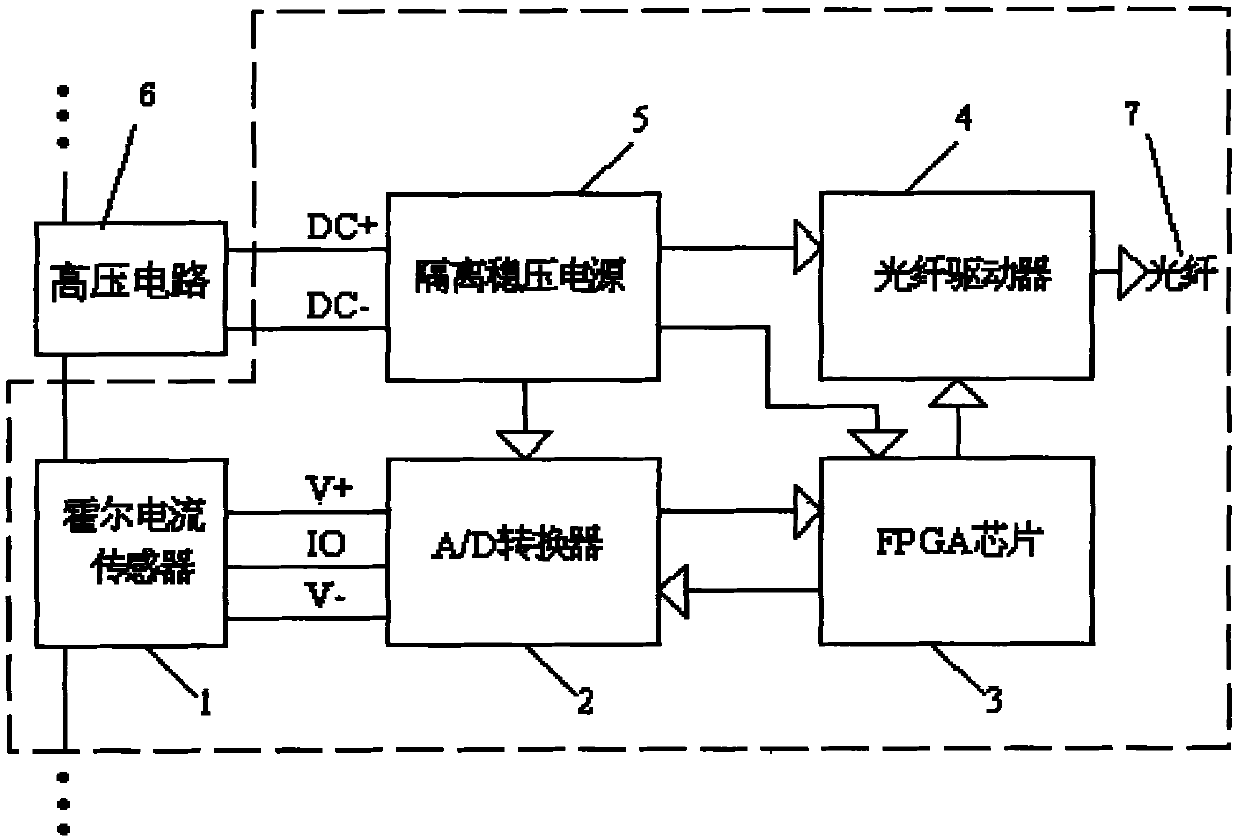

Current measurement device for high-voltage converter

InactiveCN101949972ASolving Quick Measurement ProblemsSolve pressureNon-electrical signal transmission systemsMeasurement using digital techniquesFiberMeasurement device

The invention discloses a current measurement device for a high-voltage converter, which is connected with a high-voltage circuit, and the high-voltage circuit supplies input power supply for the device. The device comprises a current sensor, an A / D converter, a field programmable gate array chip, a fiber driver and an isolation voltage stabilizing power supply, wherein the current sensor is connected with a circuit end of the high-voltage circuit, and is connected with the A / D converter; the A / D converter is connected with the field programmable gate array chip; the field programmable gate array chip is connected with the fiber driver; the fiber driver is connected with the isolation voltage stabilizing power supply; and the isolation voltage stabilizing power supply is connected with the high voltage circuit. The device overcomes the defect of the prior art to solve the problem of quick measurement of current of the high-voltage converter.

Owner:STATE GRID ZHEJIANG ELECTRIC POWER +2

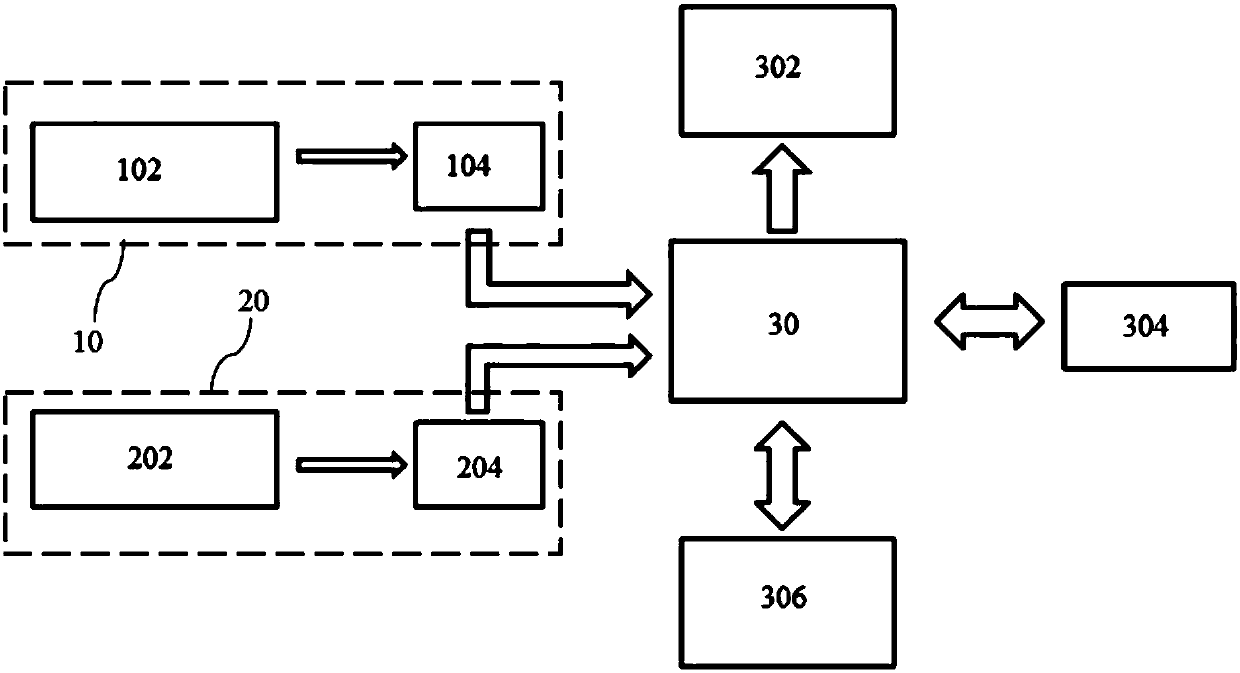

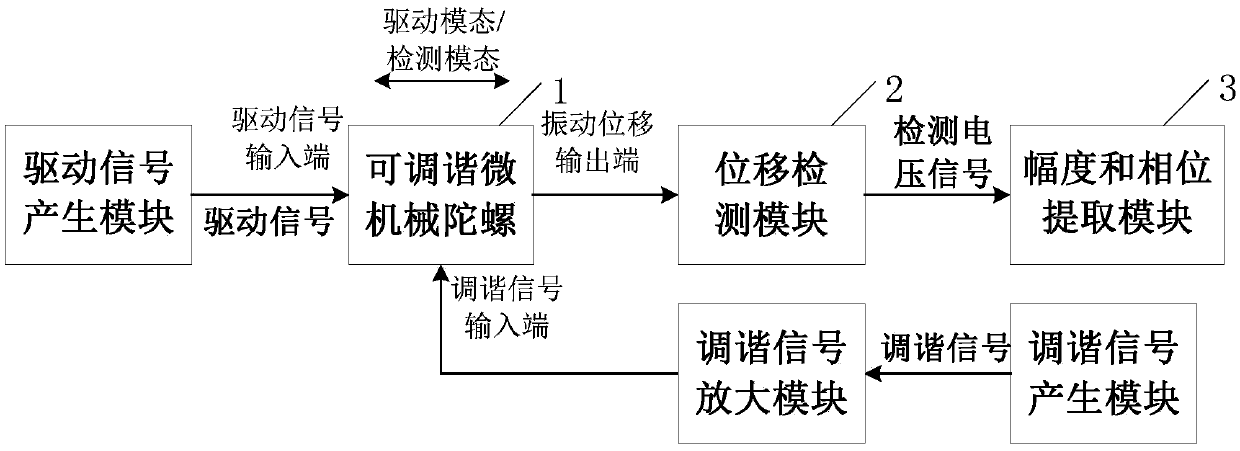

Parameter amplification method in tunable grid structure micro mechanical gyroscope, and device thereof

ActiveCN109029409ALimit working displacementHigh sensitivitySpeed measurement using gyroscopic effectsGyroscopes/turn-sensitive devicesCapacitanceGyroscope

The invention discloses a parameter amplification method in a tunable grid structure micro mechanical gyroscope, and a device thereof. The method comprises the following five steps: driving signal production, tuning signal production, tuning signal amplification, displacement detection, and amplitude and phase extraction; the device comprises a tunable micro mechanical gyroscope, a driving signalproducing circuit, a capacitor / voltage conversion circuit, a tuning signal amplification circuit, a first digital-to-analog converter (DAC), an ADC, a second DAC and a field programmable gate array chip. The tuning structure is realized by utilizing a variable-area type triangular electrode without importing soft spring effect; a tuning voltage signal in a radical form is produced by utilizing thefield programmable gate array chip, the DC tuning capacity and the parameter amplification can be separately arranged. The method can be applied to the driving modal or detection modal of the micro mechanical gyroscope, and can be applied to the micro mechanical resonator of other types.

Owner:ZHEJIANG UNIV

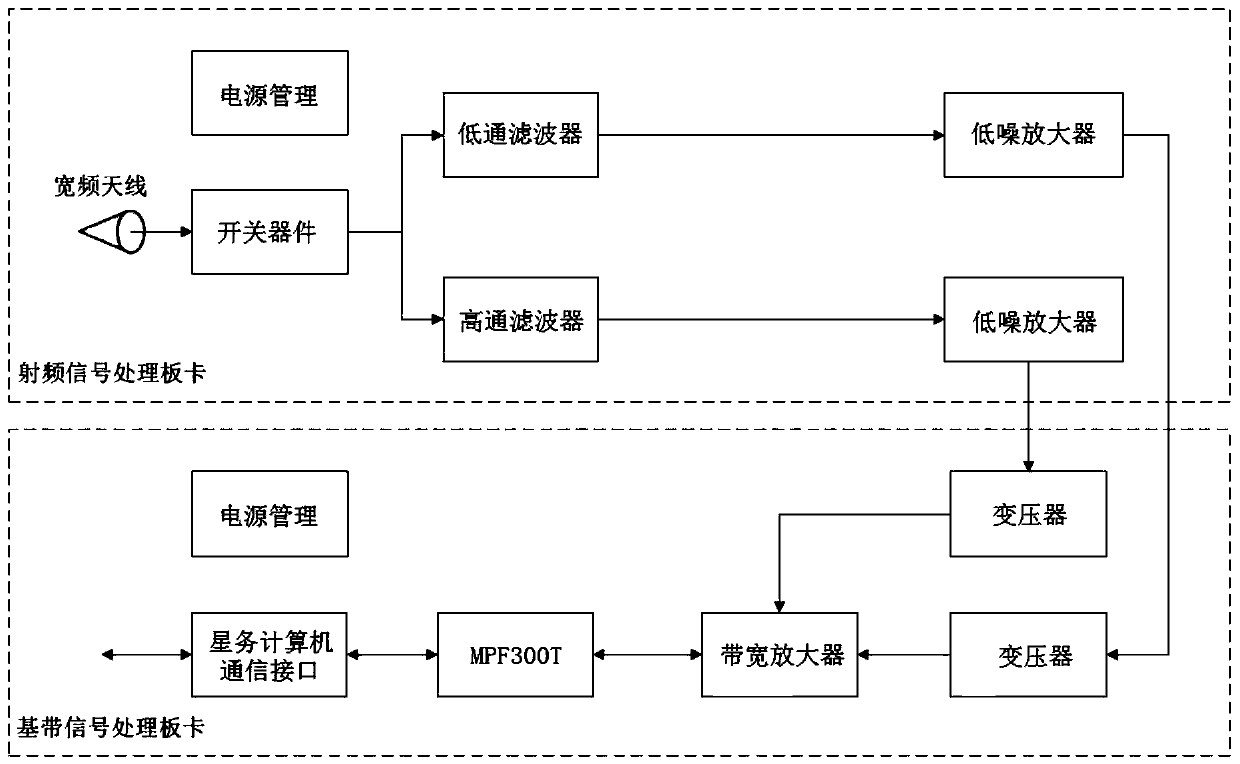

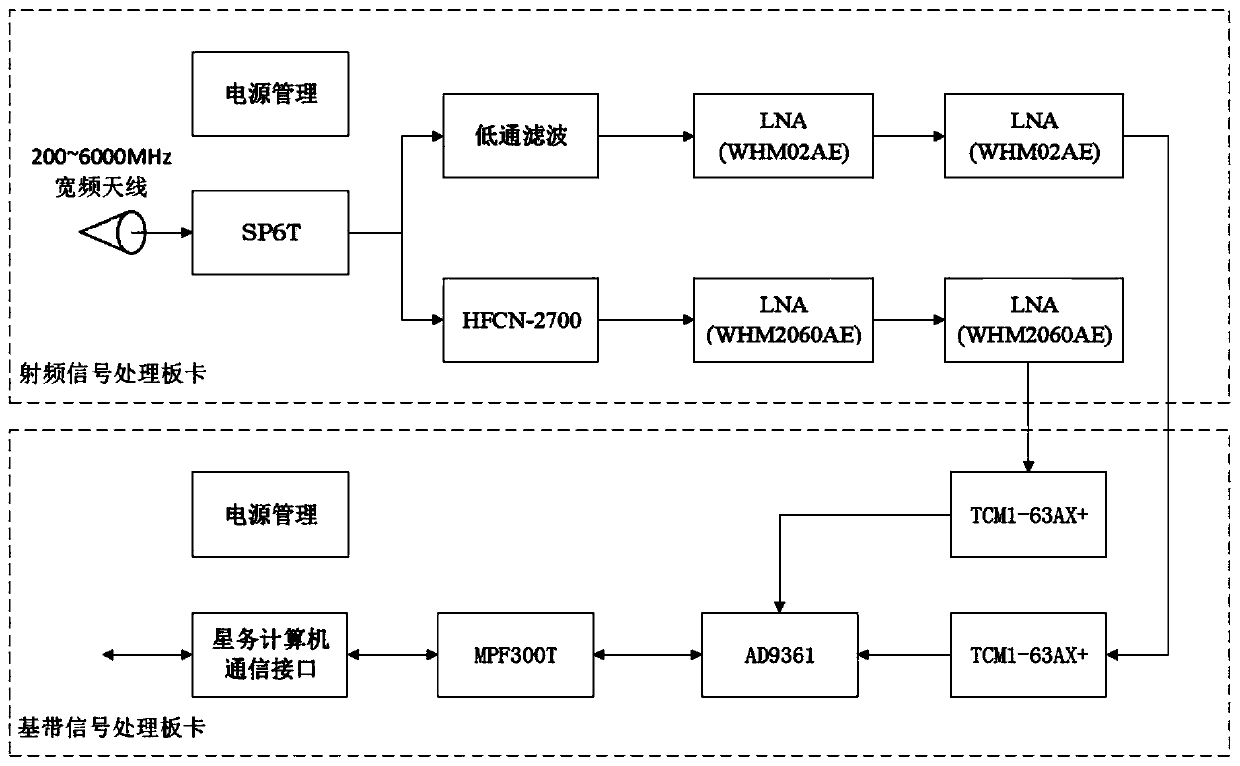

Satellite-borne broadband electromagnetic spectrum sensing device and electromagnetic spectrum sensing algorithm

ActiveCN110166152ALarge receiving rangeReduce the impactTransmission monitoringFrequency spectrumTransformer

Owner:NAT INNOVATION INST OF DEFENSE TECH PLA ACAD OF MILITARY SCI

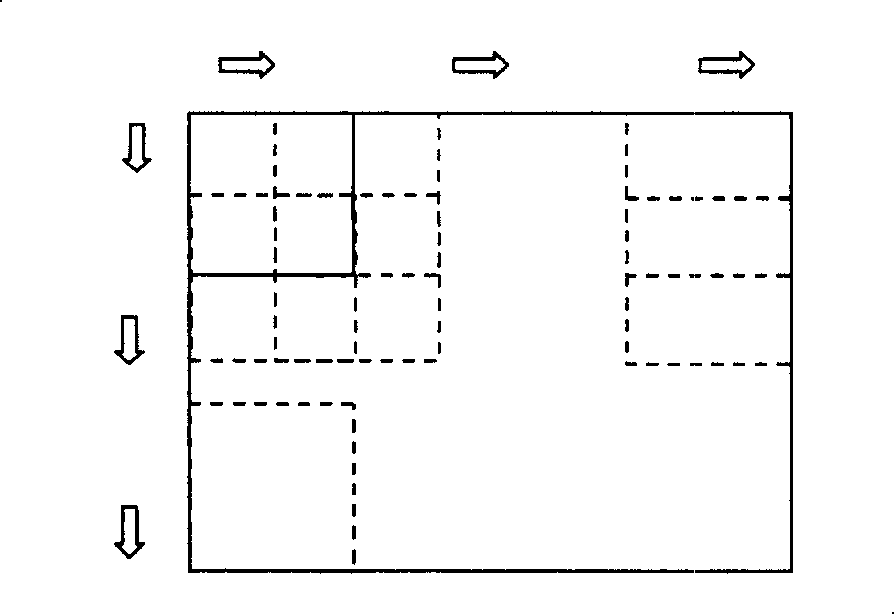

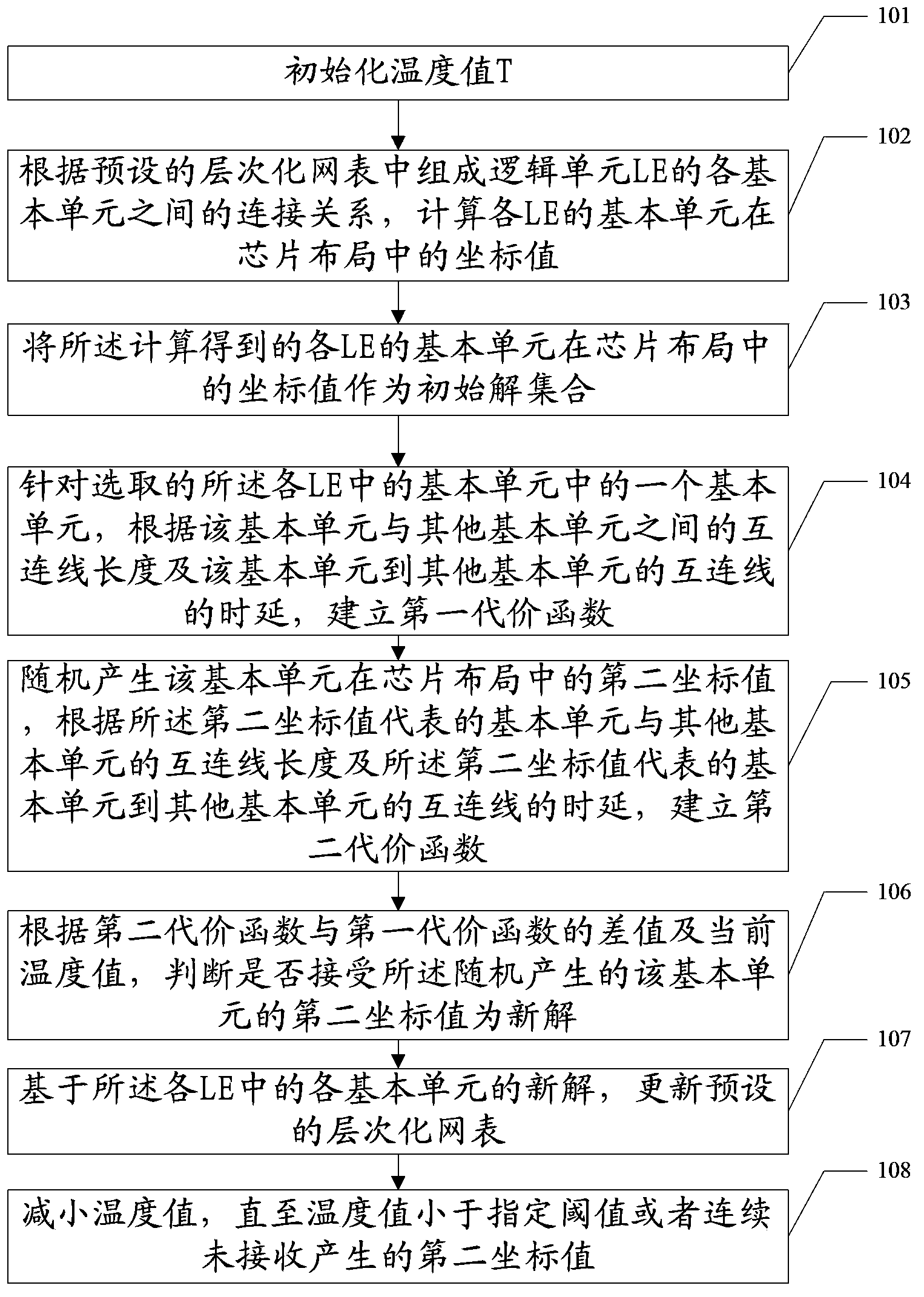

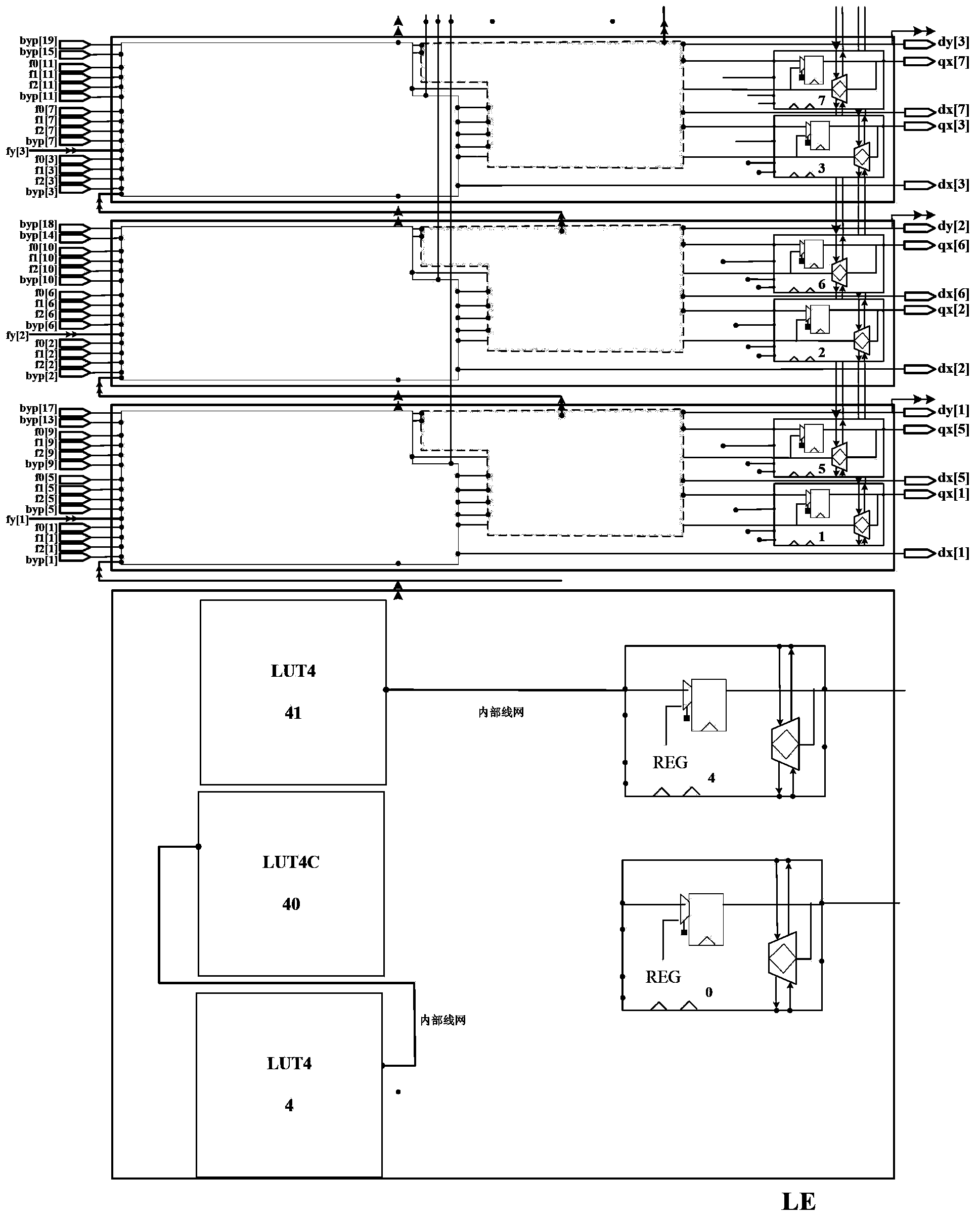

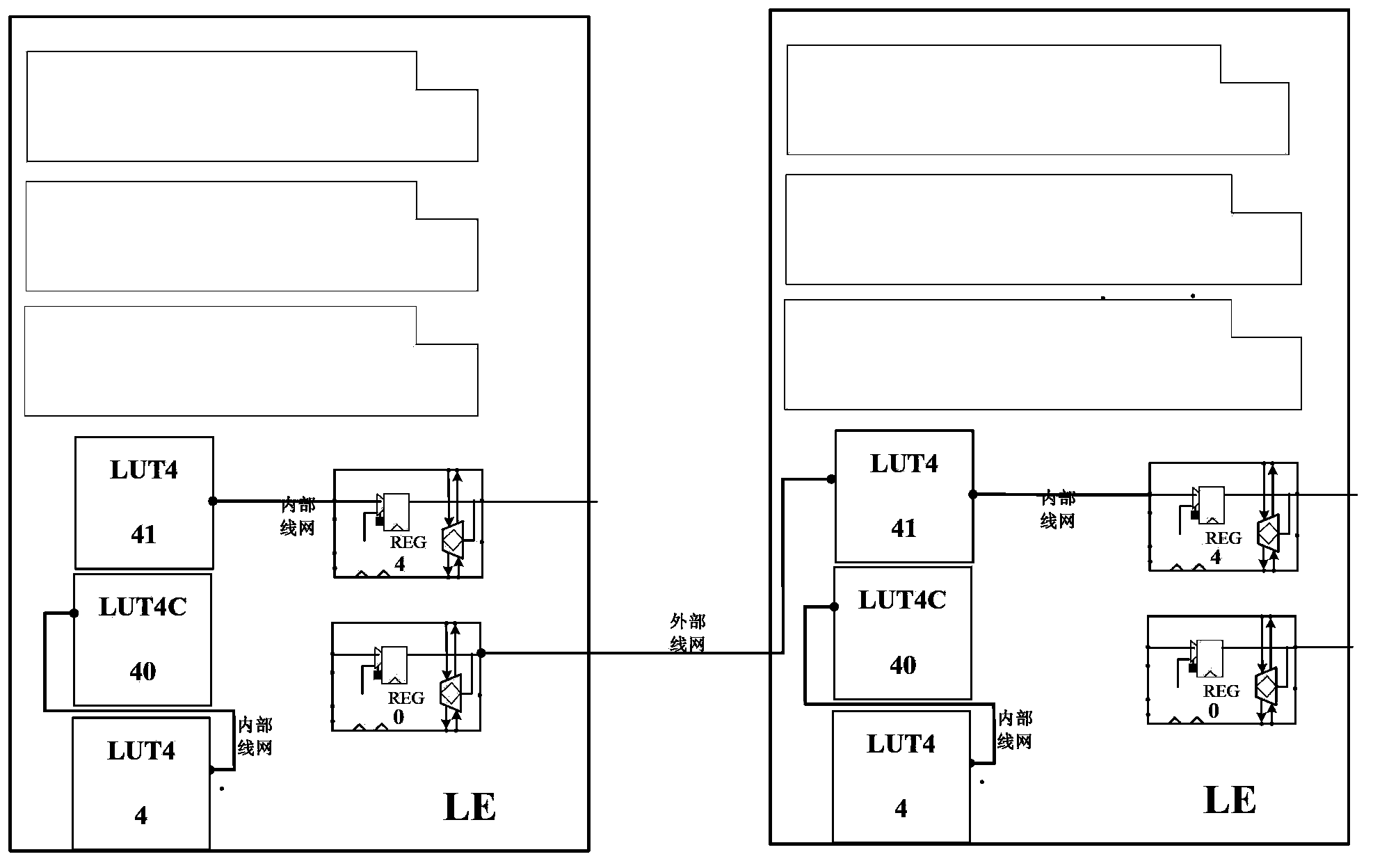

A method for optimizing a field-programmable gate array chip layout

InactiveCN104348479ARun fastShorten the timeLogic circuits using elementary logic circuit componentsTime delaysInterconnection

The invention relates to a method for optimizing a field-programmable gate array chip layout, the method comprising: initiating a temperature value T; selecting a basic unit, creating a first cost function in accordance with a length of an interconnection line between the basic unit and other basic units, and the time delay of the interconnection line; generating in random a second coordinate value of the basic unit, creating a second cost function in accordance with a length of an interconnection line between the basic unit represented by the second coordinate value and other basic units and the time delay of the interconnection line; determining whether the generated second coordinate value is accepted as a new solution according to a difference value of the second cost function from the first cost function and a current temperature value; based on the new solution of each basic unit in said each LE, updating a preset hierarchical net list; reducing the temperature value until the temperature value is less than a designated threshold value or the generated second coordinate value is continuously not received. When processing a layout circuit in a large scale, the method of optimizing a chip layout of the invention can speed up the running speed of the algorithm, and reduce the running time of a program.

Owner:CAPITAL MICROELECTRONICS

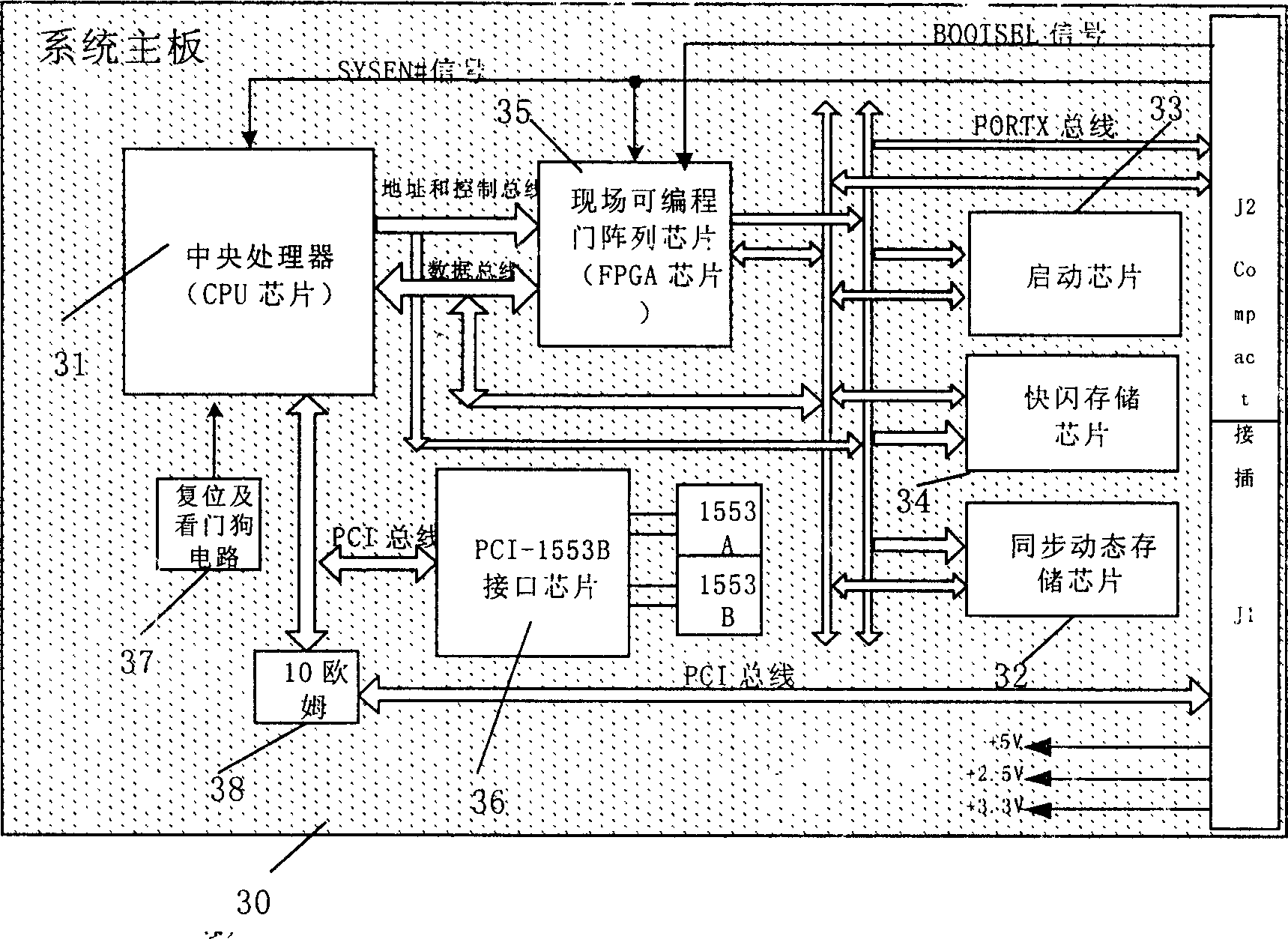

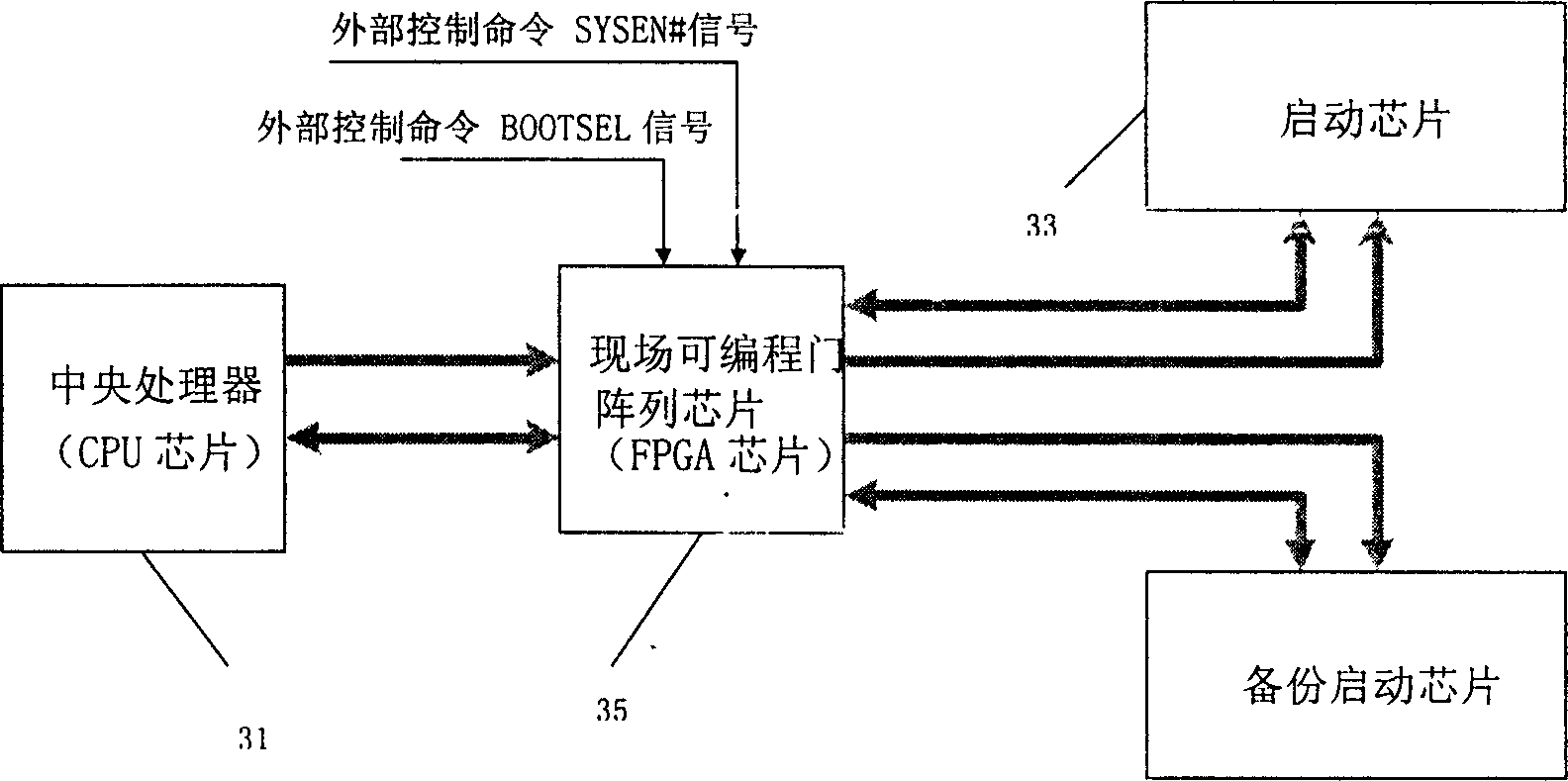

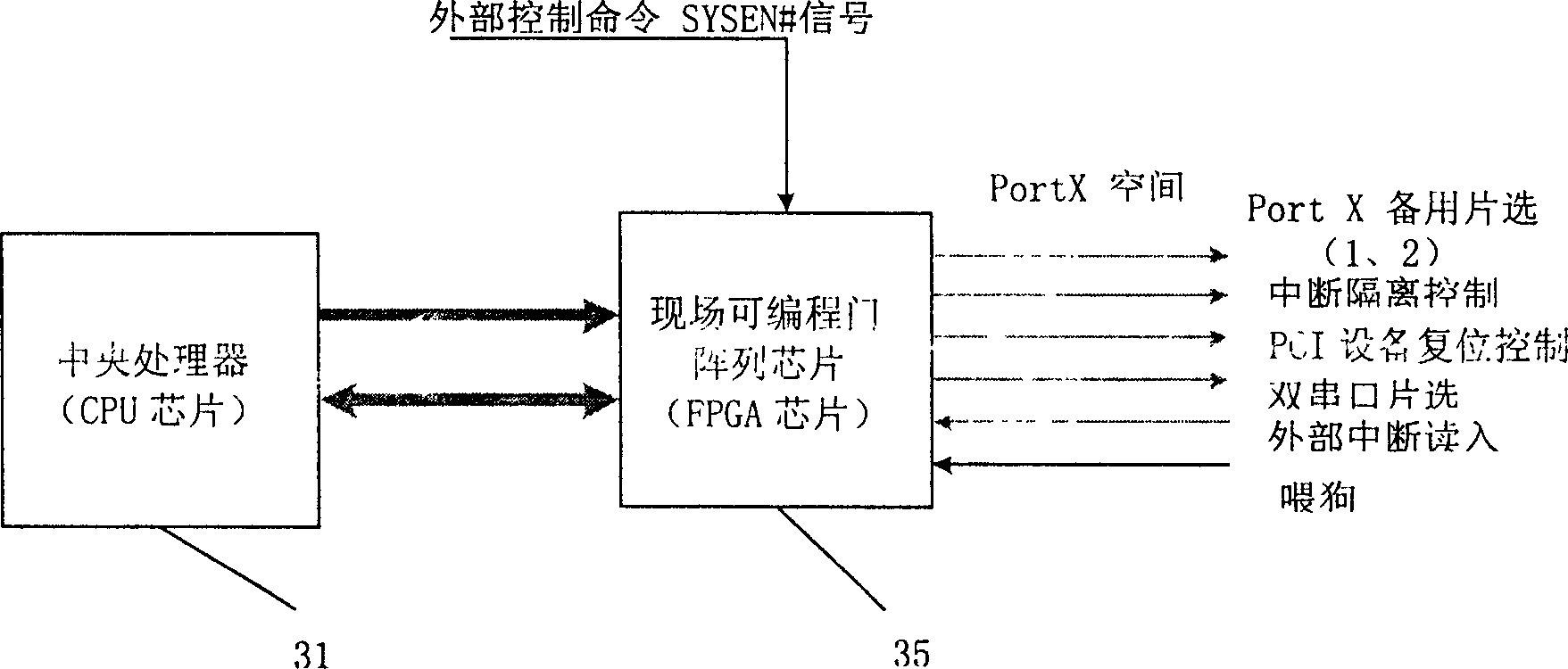

System mainboard for embedded computer systems

InactiveCN1621997AImprove reliabilityPowerfulDigital data processing detailsEnergy efficient computingComputerized systemAddress bus

The system mainboard for embedded computer includes one CPU chip, one sync DRAM chip, one starting chip, one flash memory chip, FPGA chip, etc. and all the chips perform communication via data bus and address bus. The system mainboard also has definied X port and X port bus, and the X port bus is connected to double serial port and spare starting chip outside the system mainboard. The system mainboard is connected to embedded computer based on COMPACT PCI bus and X port bus structure. The high performance computer mainboard of the present invention has powerful function, powerful processing capacity, small size and moderate power consumption, and is suitable for use in aeronautics, astronautics and other fields with high processing capacity requirement.

Owner:NAT SPACE SCI CENT CAS

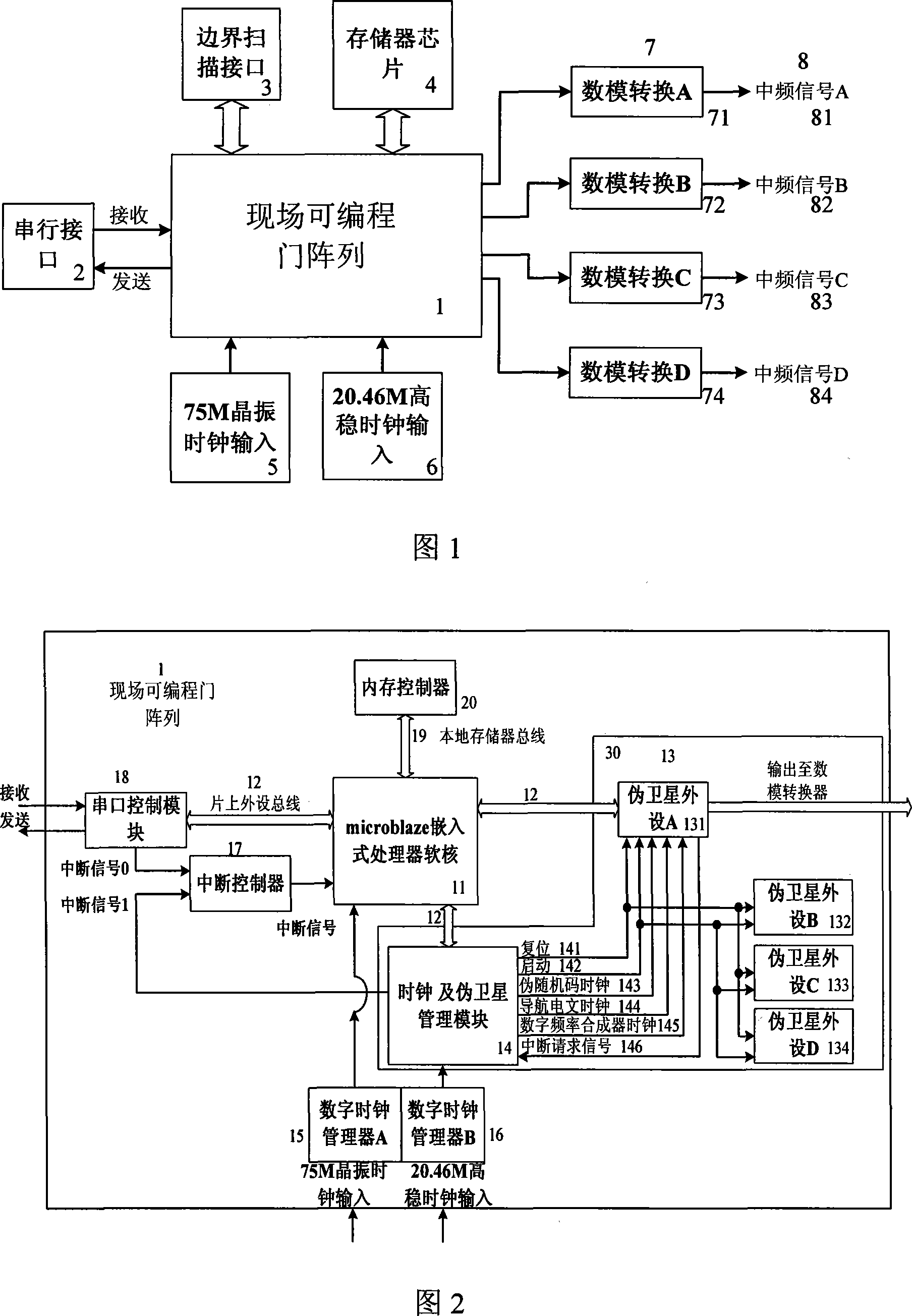

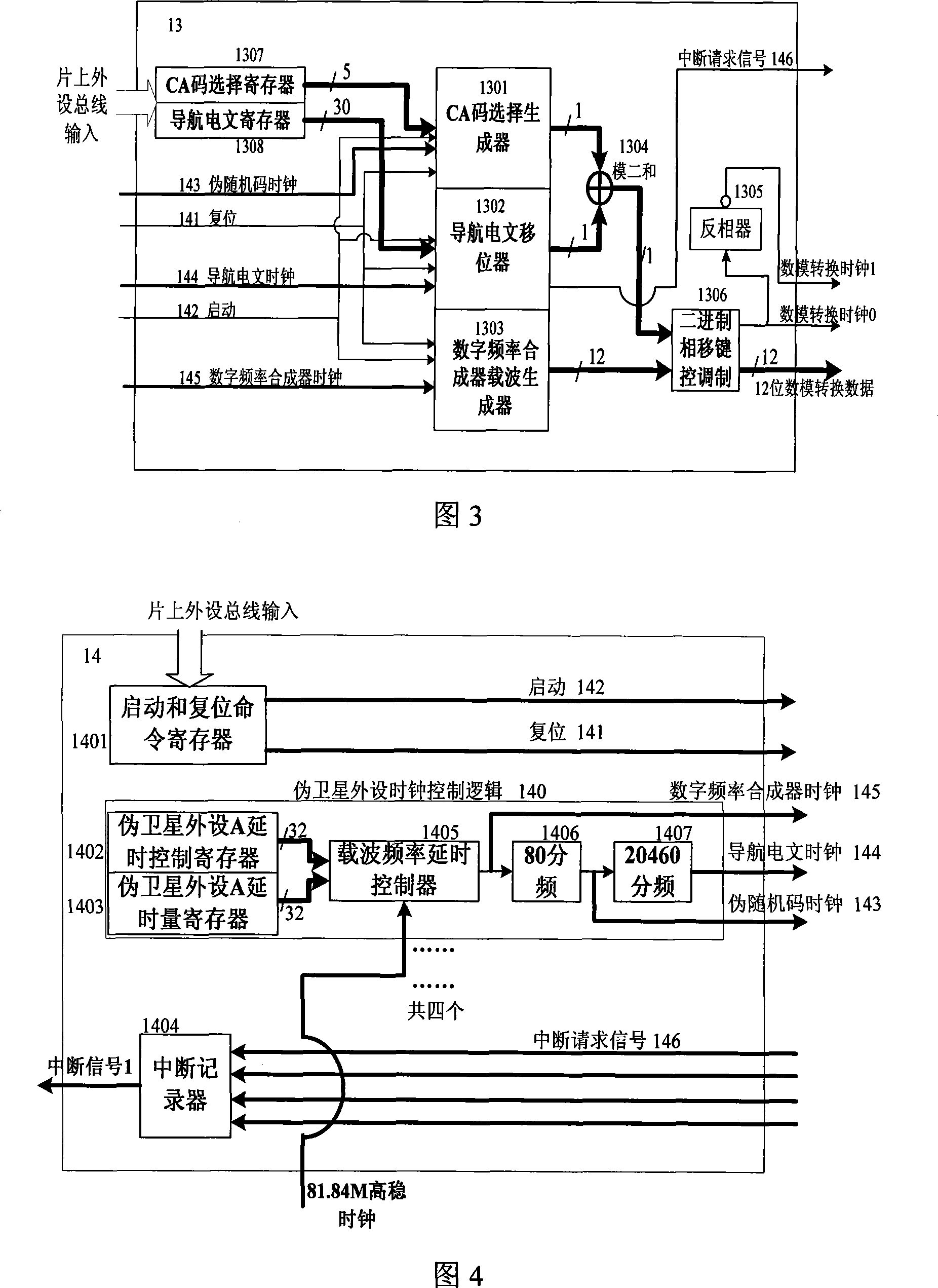

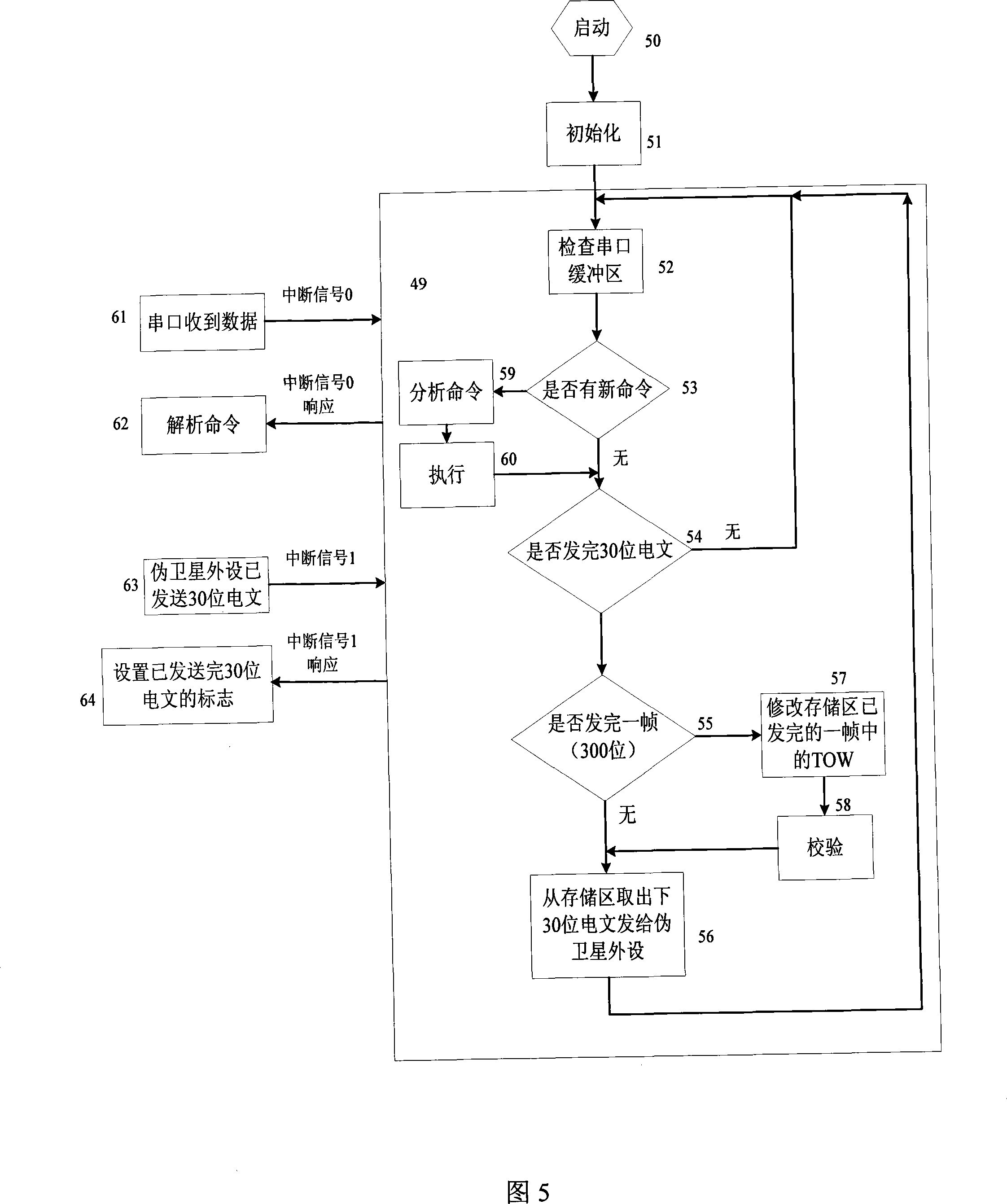

False satellite baseband signal maker and control method of built-in processor thereof

InactiveCN101158717ALow costHigh precisionBeacon systems using radio wavesPosition fixationIntermediate frequencyControllability

The invention relates to a signal transmission equipment in the electronic technical field, in particular to a baseband signal generator of pseudosateilite that adopts modern technological means and is used for satellite signal simulation and the implementation of pseudosateilite location and so on, as well as a control method of the embedded processor of the invention. The equipment comprises a field programmable gate array (FPGA) and a module of intermediate frequency signal, etc, and the baseband signal generator is combined by a soft core and a four-way pseudosateilite peripheral together. By adopting a baseband signal control software of the pseudosateilite designed by the equipment, the method responds to control commands in PC. The method mainly solves the related technical problems of how to integrate the whole system core into a chip of field programmable gate array. The invention has the advantages that the format and content of output signal of the equipment are consistent with that of GPS signal, and according to the defined communication protocol, the method can resolve the command parameters from the data frame and execute the commands, the method improves the reliability and controllability, and has the advantages of low cost and flexible control, etc.

Owner:SHANGHAI BEIGA NAVIGATION TECH CO LTD

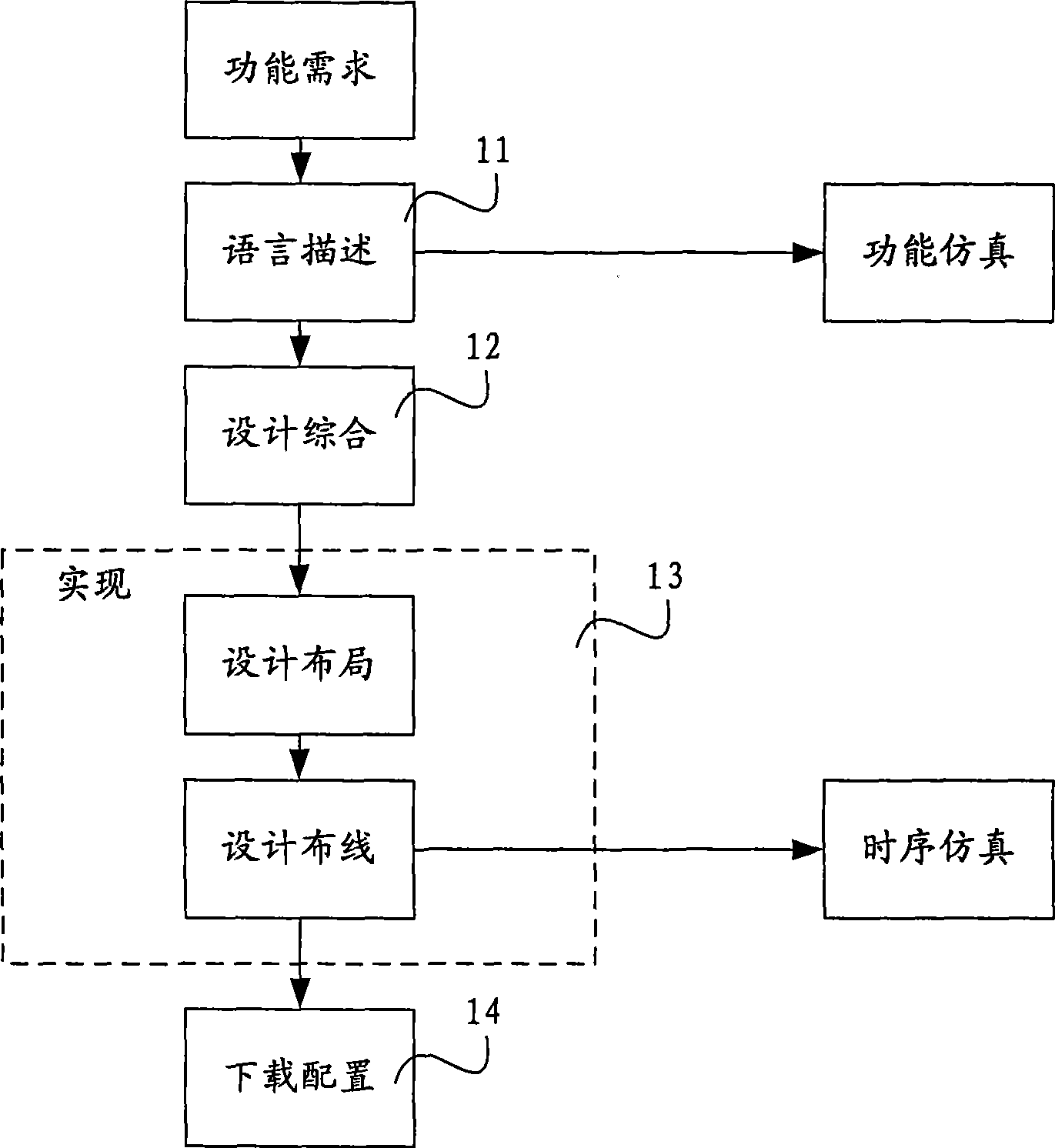

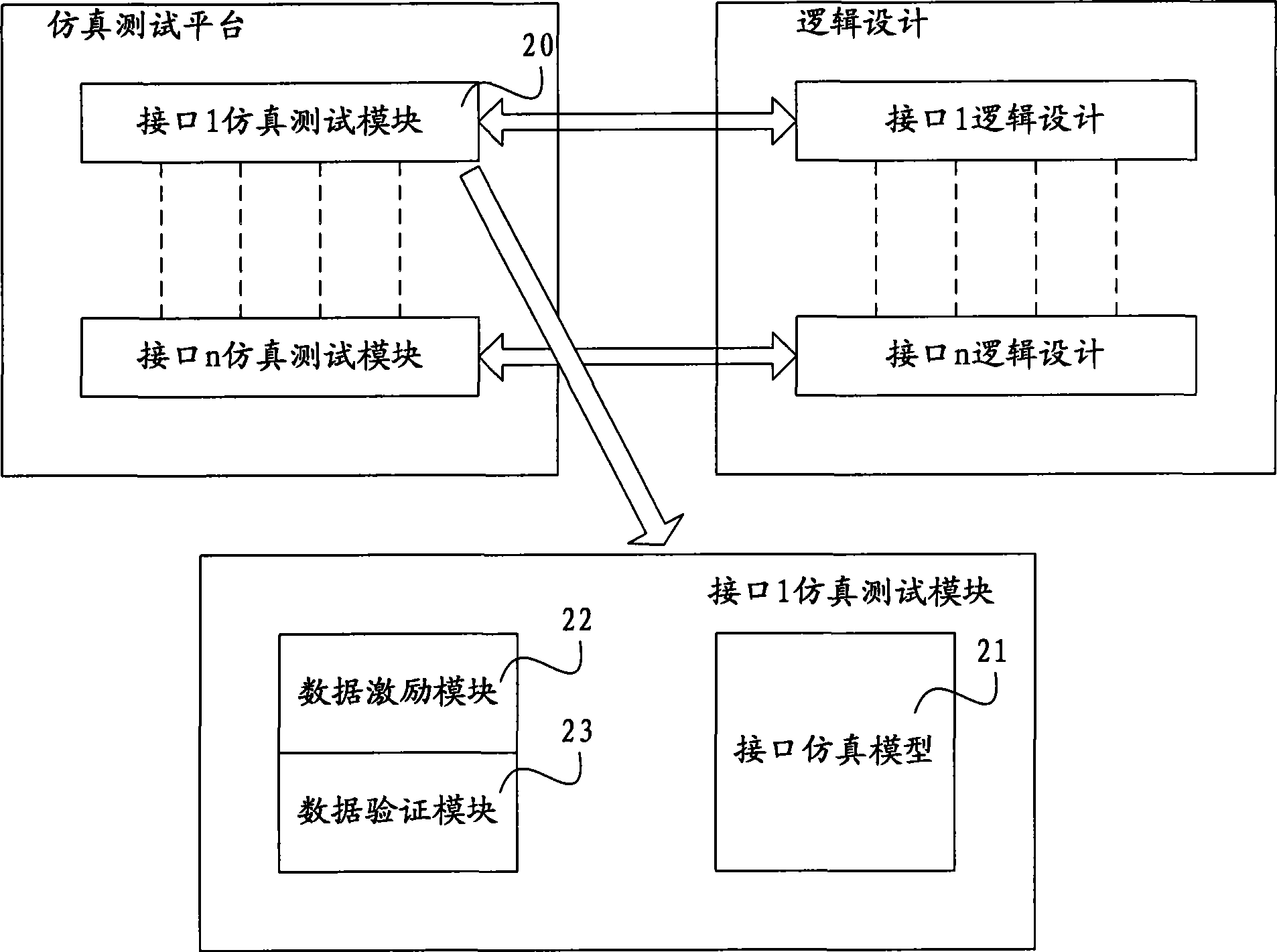

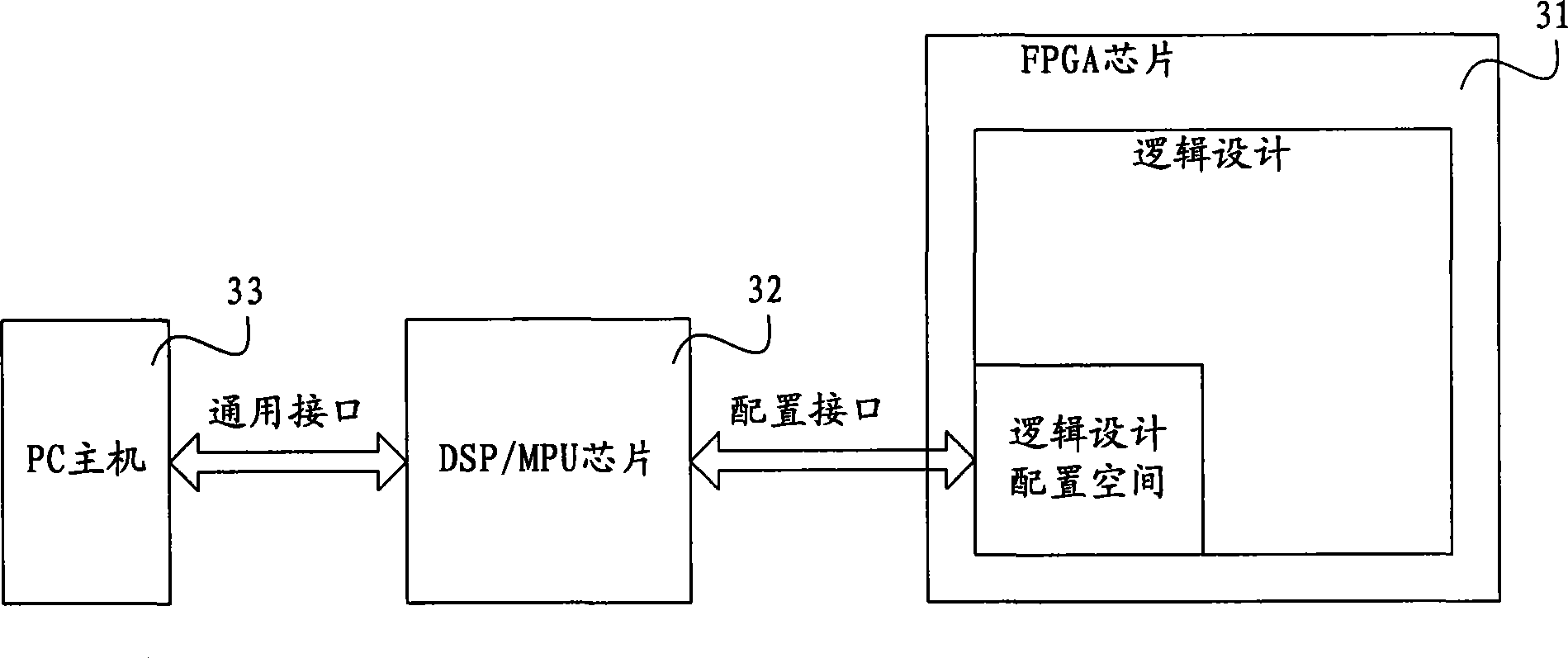

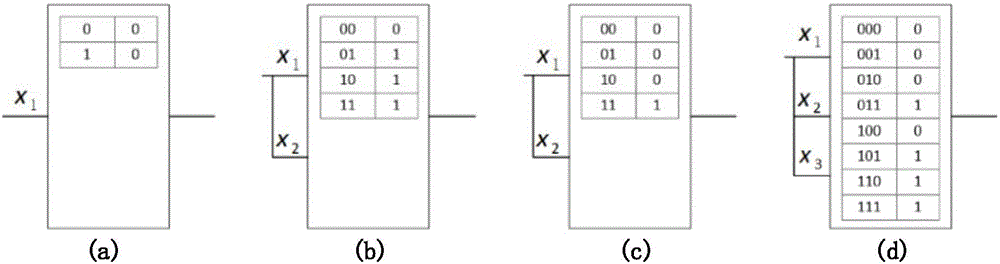

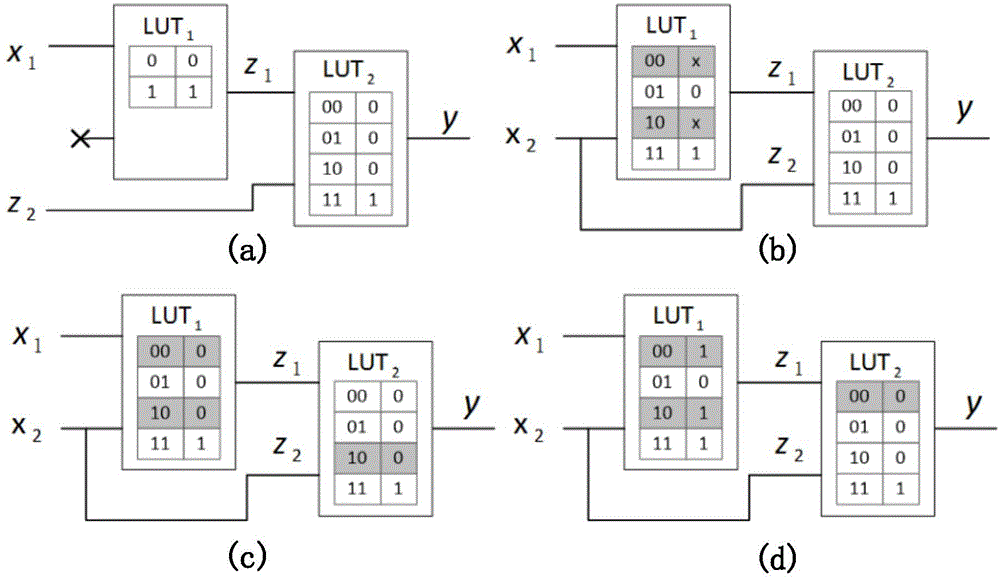

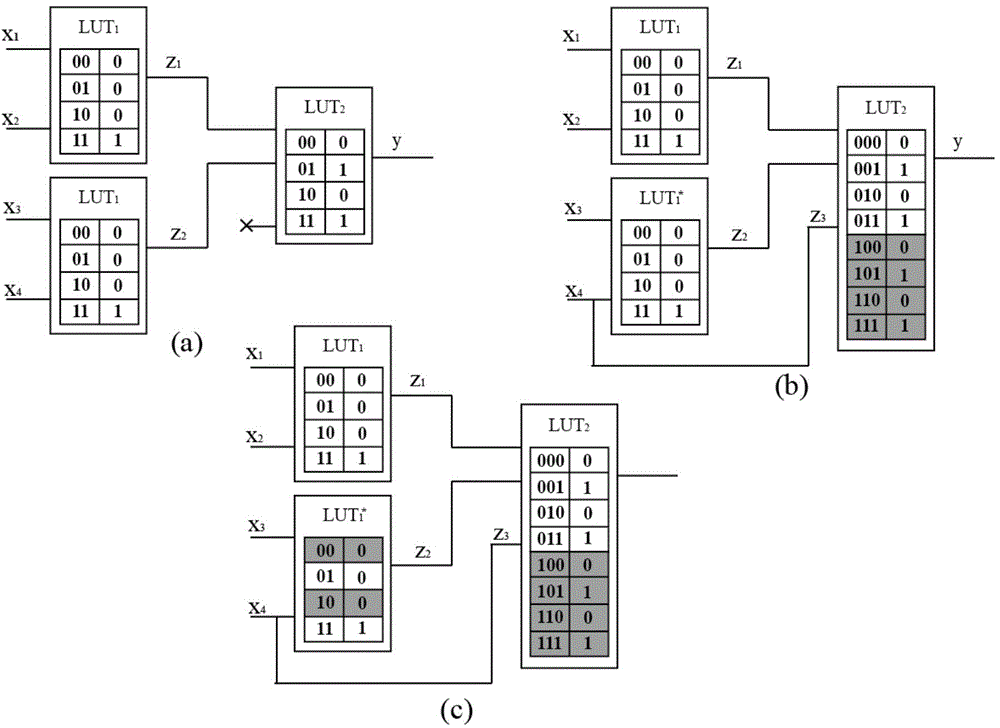

Test method of FPGA chip application circuit

ActiveCN104133747AReduce complexityReduce the amount of resourcesDetecting faulty computer hardwareFpga chipComputer science

The invention relates to a test method of an FPGA (Field Programmable Gate Array) chip application circuit, and belongs to the technical field of circuit design. For two directly connected LUTs (Look Up Tables) in the circuit, if the two LUTs meet a specific condition, a back redundant line can be added to the previous LUT, or a forward redundant line can be added to a posterior LUT under the condition of ensuring the correct logic function of the circuit. The number of test vectors required by a local circuit can be reduced by adding the forward and backward redundant lines, so that the total number of the test vectors required by a whole circuit can be integrally reduced. Meanwhile, the method provided by the invention has the advantages that unknown faults generated during the original circuit test generation can be reduced to a certain degree, and the circuit test generation difficulty is reduced.

Owner:TSINGHUA UNIV

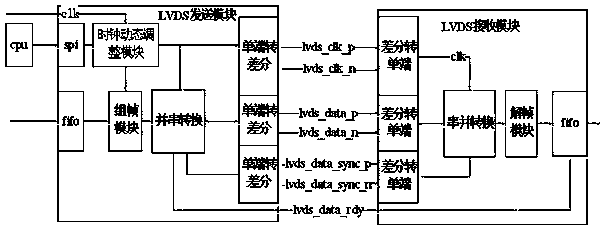

FPGA-based interconnection device among chips

ActiveCN104035904ARealize information transferAdjustable rateElectric digital data processingInformation transmissionLow voltage

The invention relates to the technical field of chip interconnection, in particular to an FPGA-based interconnection device among chips. According to the FPGA-based interconnection device among the chips, a dynamic clock adjusting module, a low-voltage differential signal sending module and a low-voltage differential signal receiving module are arranged in each FPGA chip so that information transmission between the FPGA chips can be achieved. The interconnection device has the advantages of being adjustable in speed and high in flexibility.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD

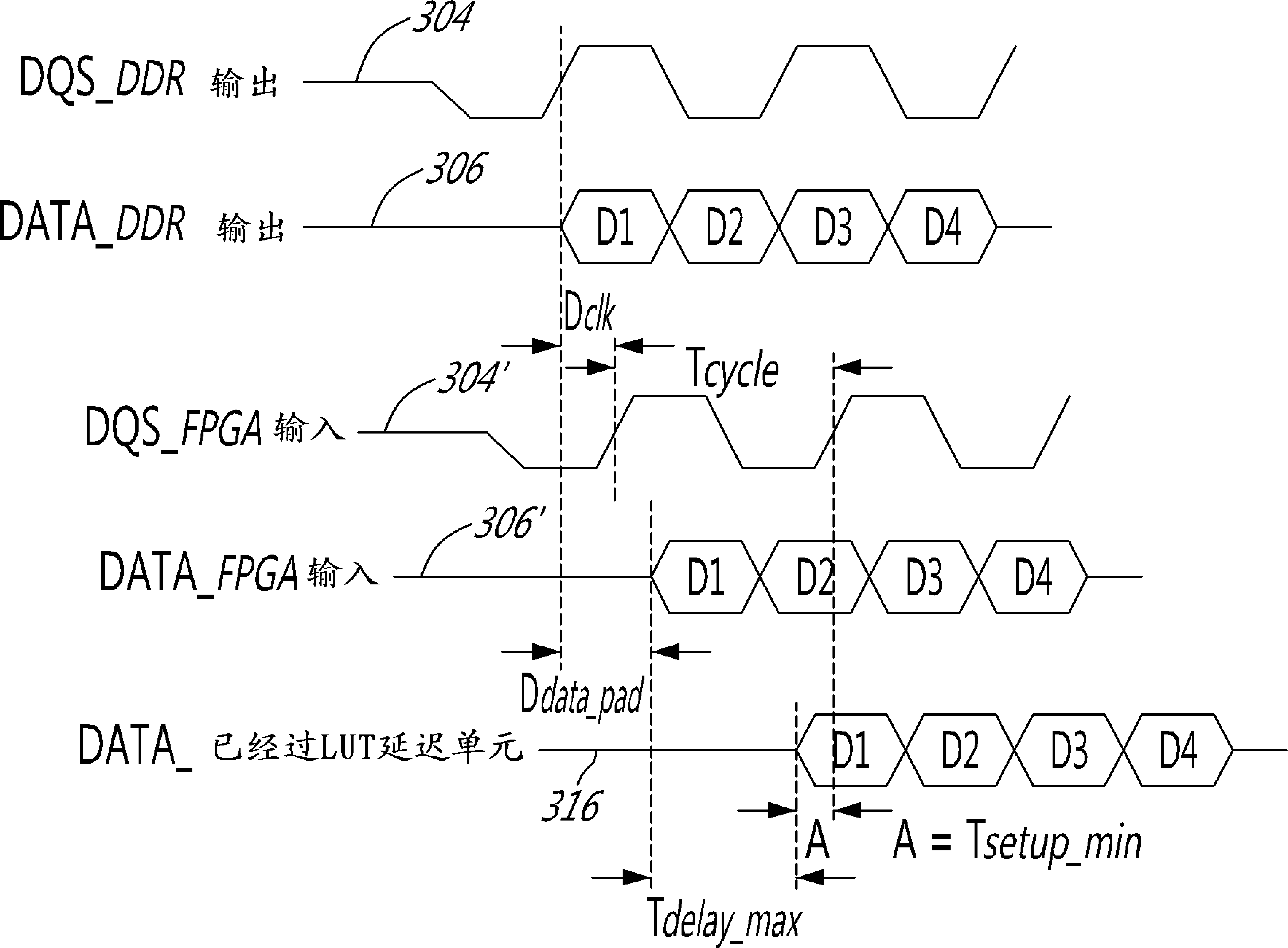

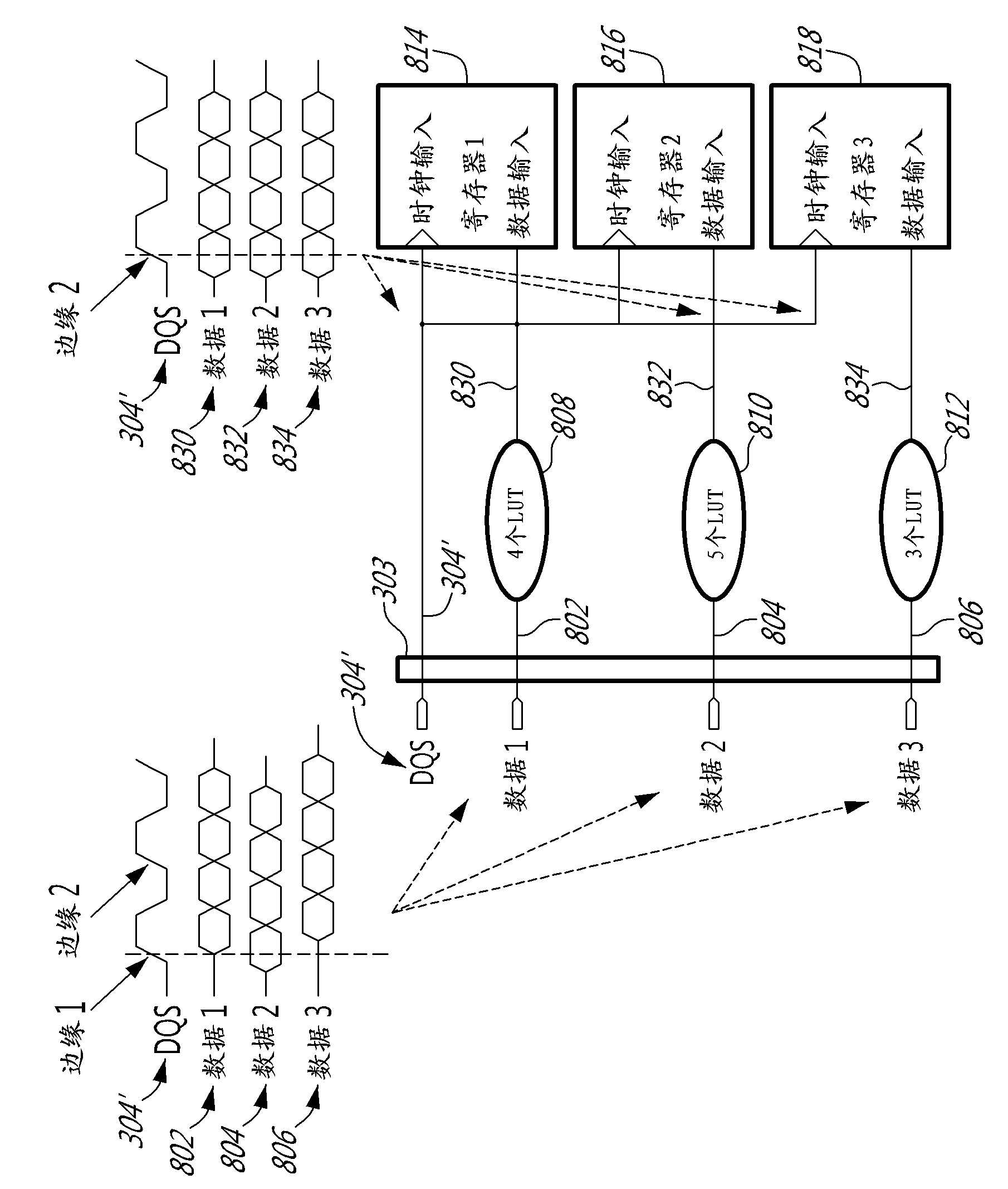

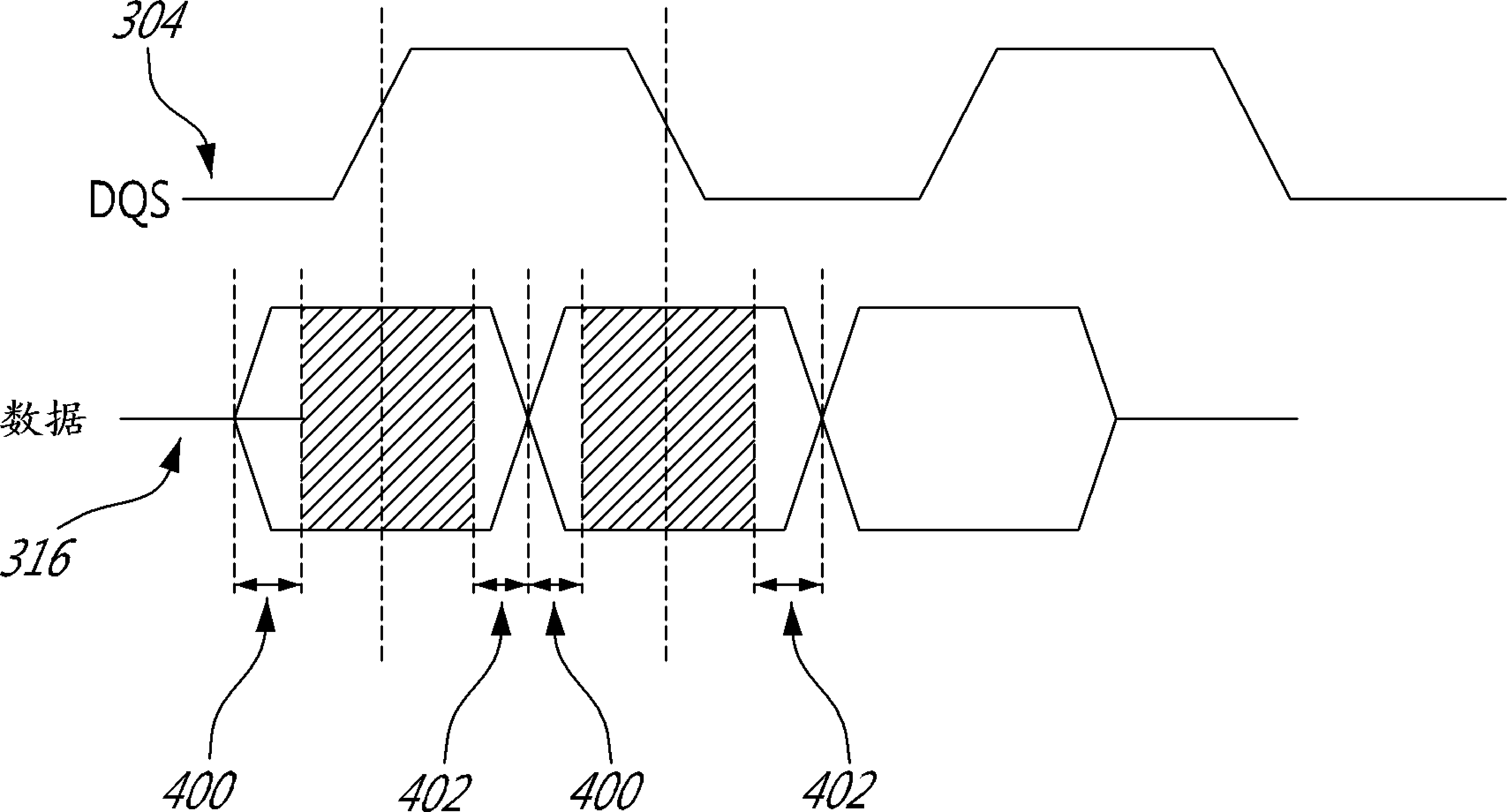

Look-up tables for delay circuitry in field programmable gate array (fpga) chipsets

InactiveCN103155413ASave spaceLow costCAD circuit designSpecial data processing applicationsData signalChipset

A method, new use for Look-Up Tables (LUTs), and a Field Programmable Gate Array (FPGA) chipset are provided for delaying data signals. The FPGA comprises an input and a set of LUTs operationally connected to and receiving from the interface a data signal and a clock signal. The set of LUTs delay the data signal by a delay so that a corresponding first delayed data signal output from the set of LUTs is so synchronized with the clock signal for appropriate sampling of the delayed data signal to be performed by the FPGA chipset. A process of manufacturing of the FPGA chipset comprises calculating a delay for delaying and synchronising the data signal with a clock signal to meet requirements of the chipset, calculating a number of LUTs for delaying the data signal, and implementing in a data path of the data signal the number of LUTs.

Owner:ERICSSON (CHINA) COMMUNICATION COMPANY LTD

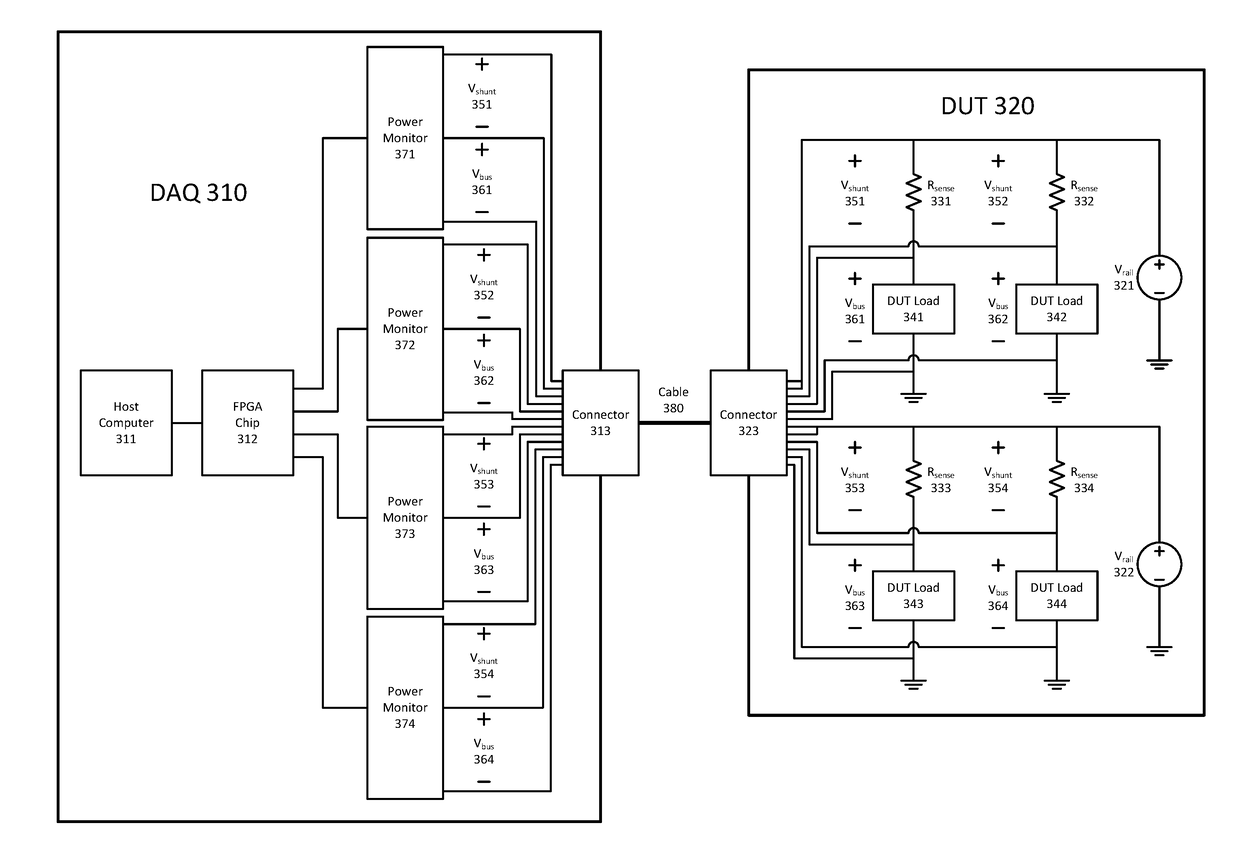

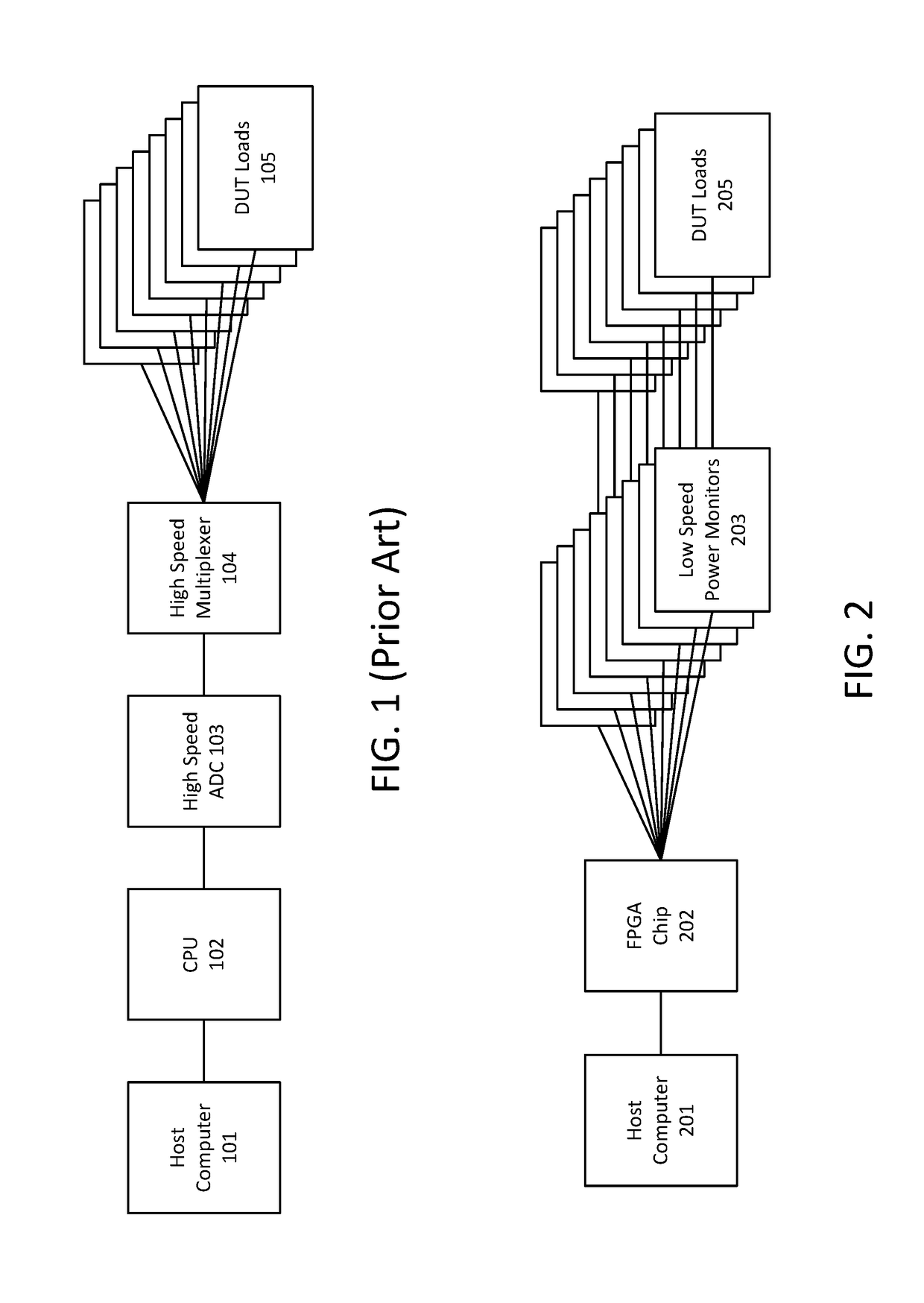

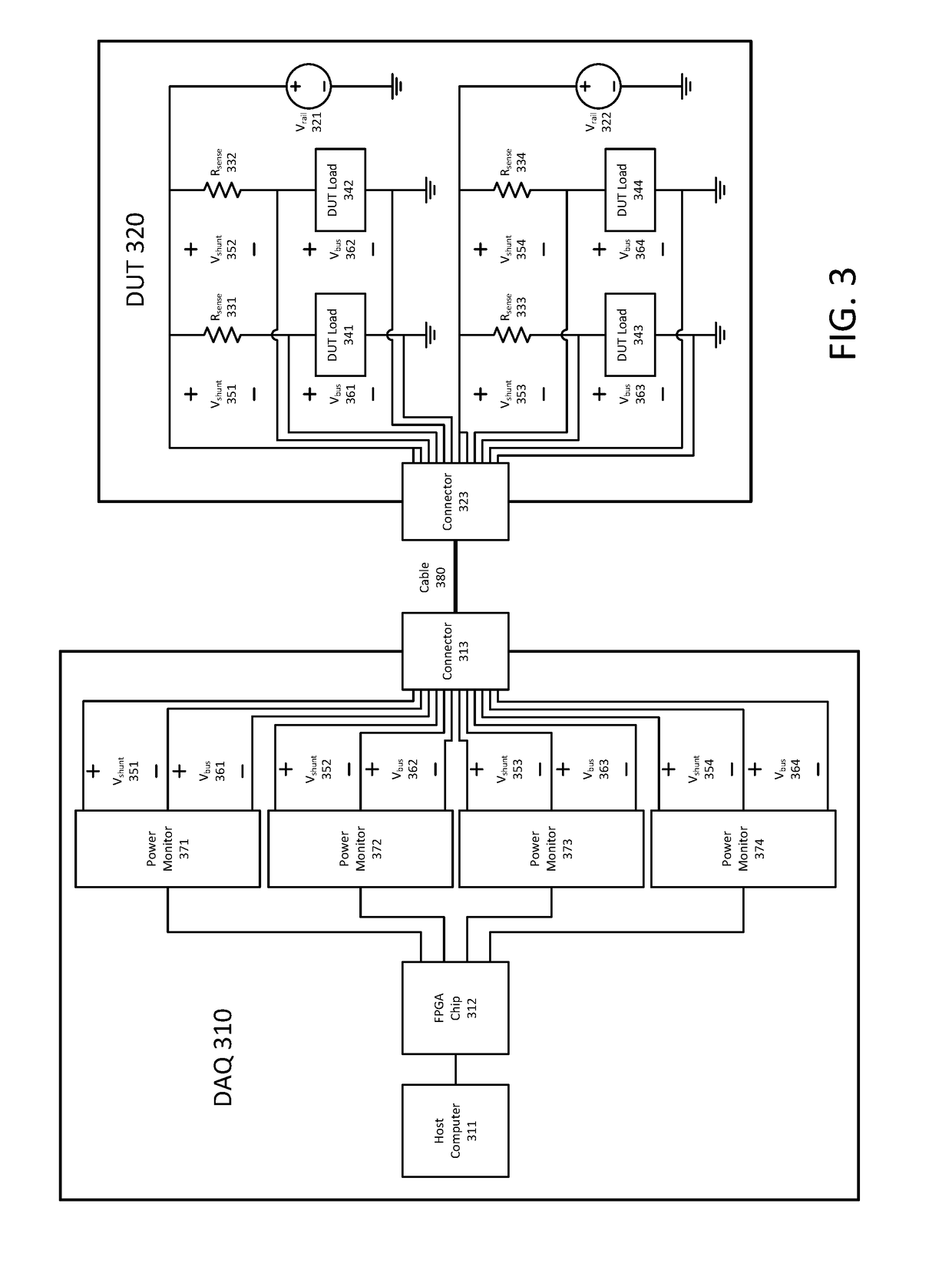

System and method for parallel power monitoring

InactiveUS20180143230A1Highly accurateHighly affordableTelemetry/telecontrol selection arrangementsError detection/correctionNanosecondData acquisition

One aspect of the disclosure provides a data acquisition system (“DAQ”) for monitoring, in parallel, the power consumption of a plurality of subsystems of a device under test (“DUT”). The DAQ comprises a plurality of power monitors and a field-programmable gate array (“FPGA”) chip. The power monitors are employed to gather the power consumption for the subsystems of the DUT. The FPGA chip can independently operate the power monitors via internal logic. By employing a parallel array of power monitors, power consumption data can be collected at the same time, and in some cases down to the tens of nanoseconds or less. Once the data is acquired by the FPGA chip, it timestamps, packages and sends the data to a host computer for further processing and / or presentation to a user.

Owner:GOOGLE LLC

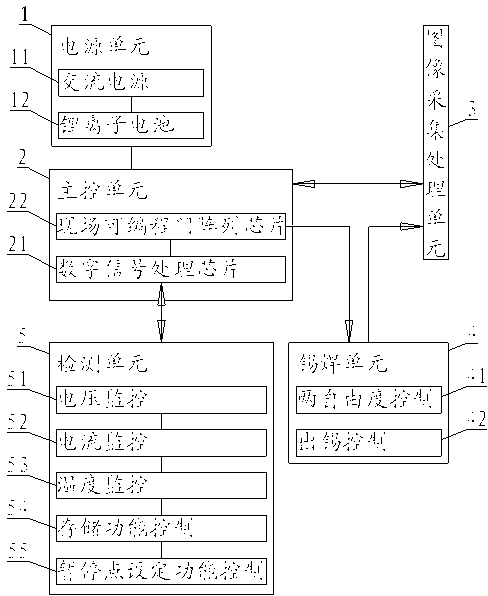

Dual-core two-freedom-degree high-speed full-automatic tin soldering robot servo controller

ActiveCN103252783AHigh degree of automationImprove work efficiencyProgramme-controlled manipulatorMetal working apparatusDigital signal processingElectrical battery

The invention discloses a dual-core two-freedom-degree high-speed full-automatic tin soldering robot servo controller which comprises a power source unit, a main control unit, an image capturing and processing unit and a tin soldering unit. The power source unit comprises an alternating current power source and a battery, the battery is a lithium ion battery, the main control unit comprises a digital signal processing chip and a field-programmable gate array chip which are connected, and the tin soldering unit comprises two-freedom-degree control and tin-discharging control. One end of the main control unit is connected with the power source unit, the other end of the main control unit is connected with the image capturing and processing unit, and the field-programmable gate array chip is connected with the tin soldering unit. According to the method, the dual-core two-freedom-degree high-speed full-automatic tin soldering robot servo controller is high in automation degree, working efficiency and motion accuracy and effectively protects the battery from impact of a large current, and the temperature and the length of tin-feeding are easy to control.

Owner:JIANGSU ROBOBOR ROBOT TECH CO LTD

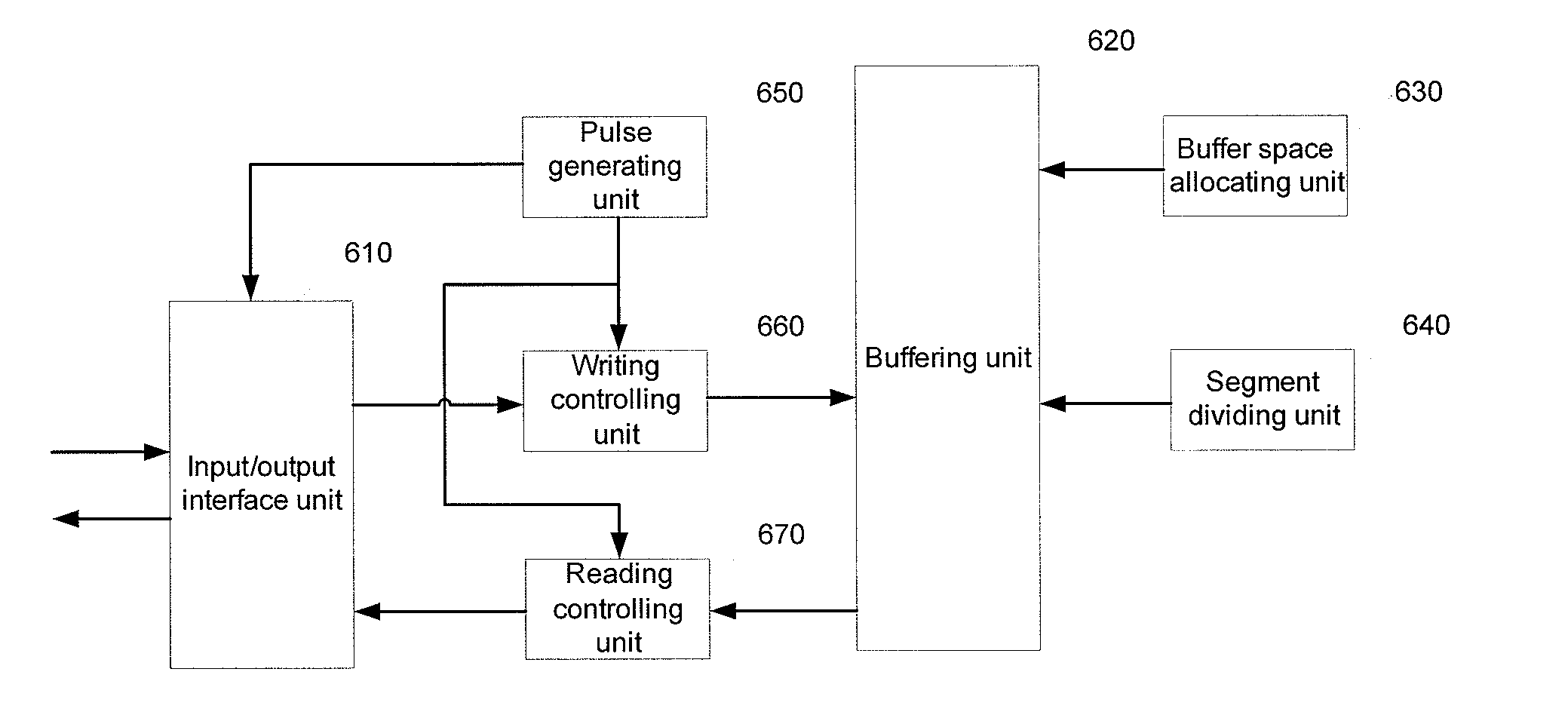

Method and device for video-stream frame rate adaptation, and field programmable gate array chip and video stream processing apparatus

InactiveUS20100104007A1Simple designReduce processing overheadColor television with pulse code modulationColor television with bandwidth reductionRate adaptationFpga chip

This invention provides a method and device for video-stream frame rate adaptation. The method includes: allocating a buffer space for each of at least one video conference room respectively and dividing the buffer space into at least one segment, each segment of which is used for buffering a video frame; and performing following steps for each of the at least one video conference room: generating a pulse signal for the video conference room periodically according to a certain pulse rate; and performing a data writing operation for a segment of the corresponding buffer space at an input-video-stream frame rate of the video conference room, and performing a reading operation for a segment of the buffer space at an output-video-stream frame rate. This invention also provides an FPGA chip and a video stream processing apparatus. The invention simplifies frame rate adaptation design, and reduces system processing overhead during the frame rate adaptation.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

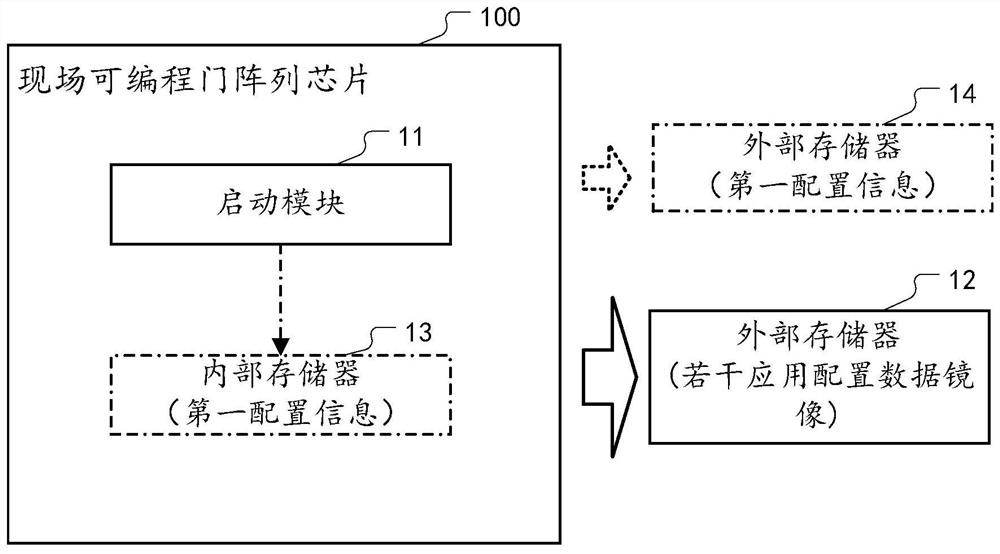

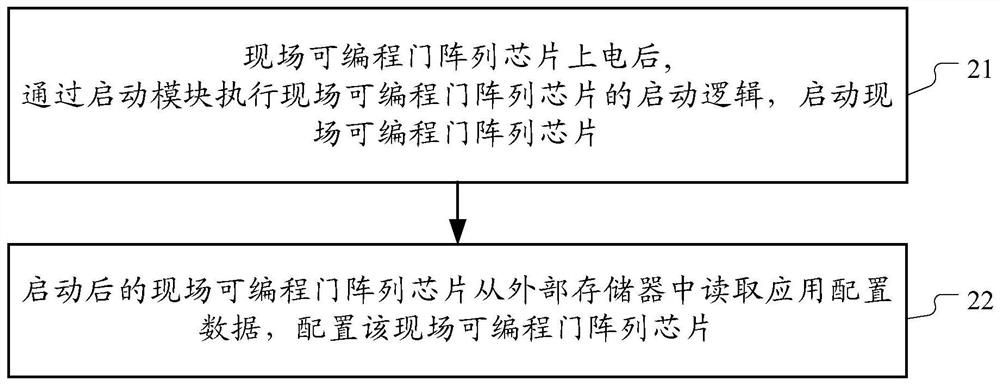

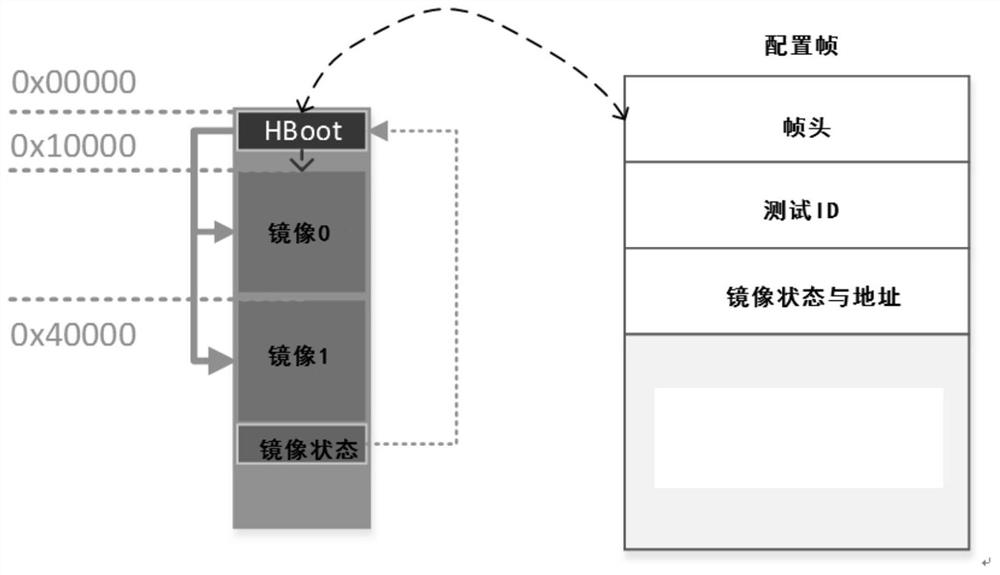

FPGA hard start method and device supporting multiple mirror images

The embodiment of the invention provides a field programmable gate array chip and a configuration method thereof. The field programmable gate array chip at least comprises a starting module. The starting module is used for realizing starting logic of the field programmable gate array chip by hardware in advance, and the method comprises the following steps: after the field programmable gate arraychip is electrified, executing the starting logic of the field programmable gate array chip through the starting module, and starting the field programmable gate array chip; and the started field-programmable gate array chip reading different application configuration data from an external memory, and configuring the field programmable gate array chip. By means of the field programmable gate arraychip and the configuration method thereof, the starting and configuration time of the field programmable gate array chip can be accelerated, meanwhile, the occupation of field programmable gate arraychip starting on field programmable gate array user logic resources is reduced, and the space of an external memory for storing configuration information is saved.

Owner:HERCULES MICROELECTRONICS CO LTD

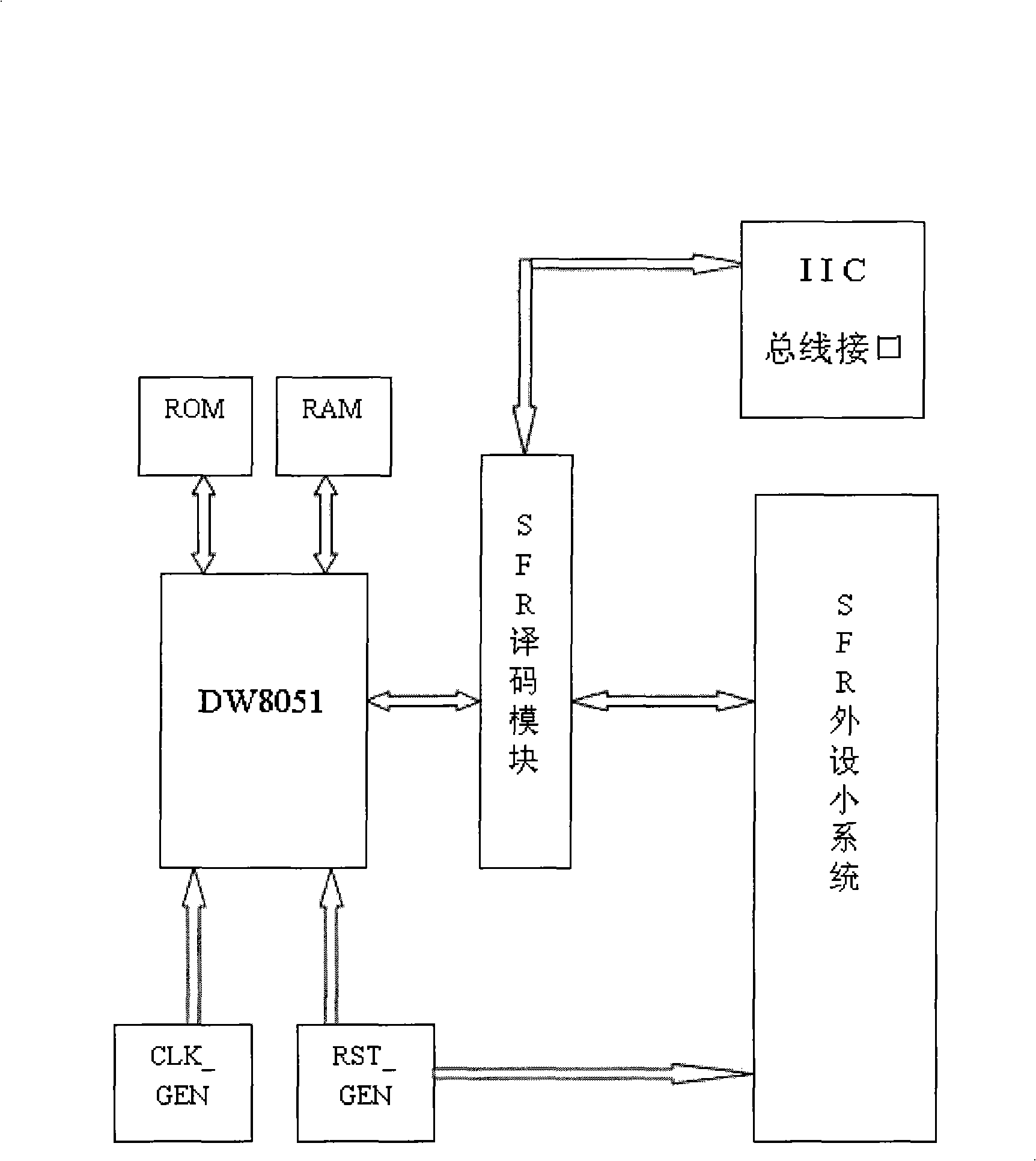

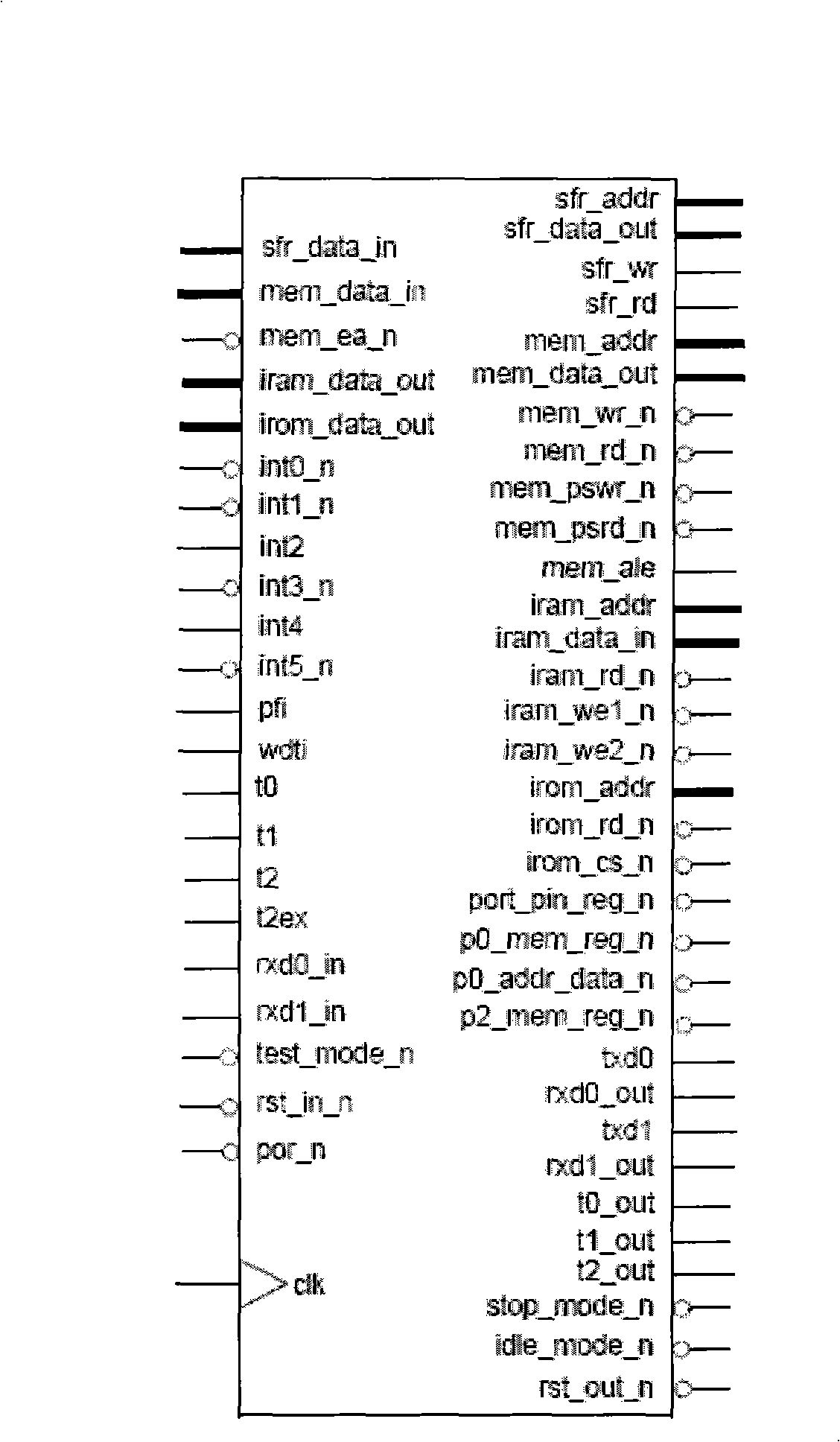

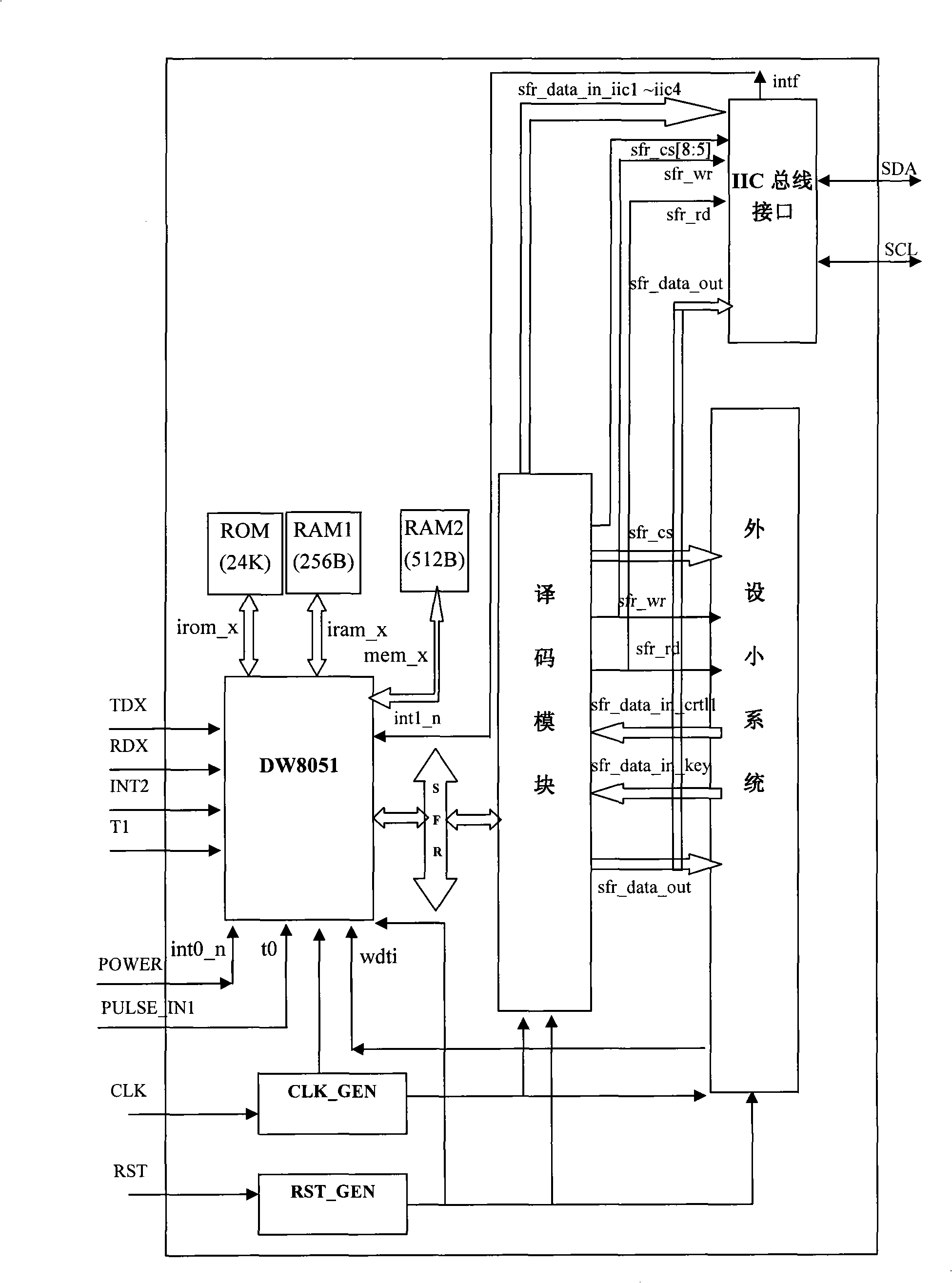

On site programmable gate array on-chip programmable system based on DW8051 core

InactiveCN101286181ARun fastImprove anti-interference abilitySpecial data processing applicationsGate arrayControl system

The invention provides a programmable system on a field programmable gate array chip based on a DW8051 core, the programmable system on the chip takes the DW8051 core as a core, comprising a memory, an external interface circuit and a clock reset circuit to provide a clock and a reset signal to the whole system; the memory comprises three memory spaces of a ROM program memory, an expanding data memory and an internal data memory; the external interface circuit comprises three small modules of an SFR decoding module, an IIC bus interface and an external small system; the clock reset circuit comprises two modules of a clock signal generation module and a reset generation module. The programmable system on the chip of the invention improves the operation speed of the control system due to the integration of the DW8051 core at the interior; as the FPGA realizes the internal control logic, thus enhancing the anti-interference and the stability of the system. The programmable system can modify the corresponding logic algorithm according to the actual needs of the system, thus having great flexibility and configurability.

Owner:SHANDONG UNIV

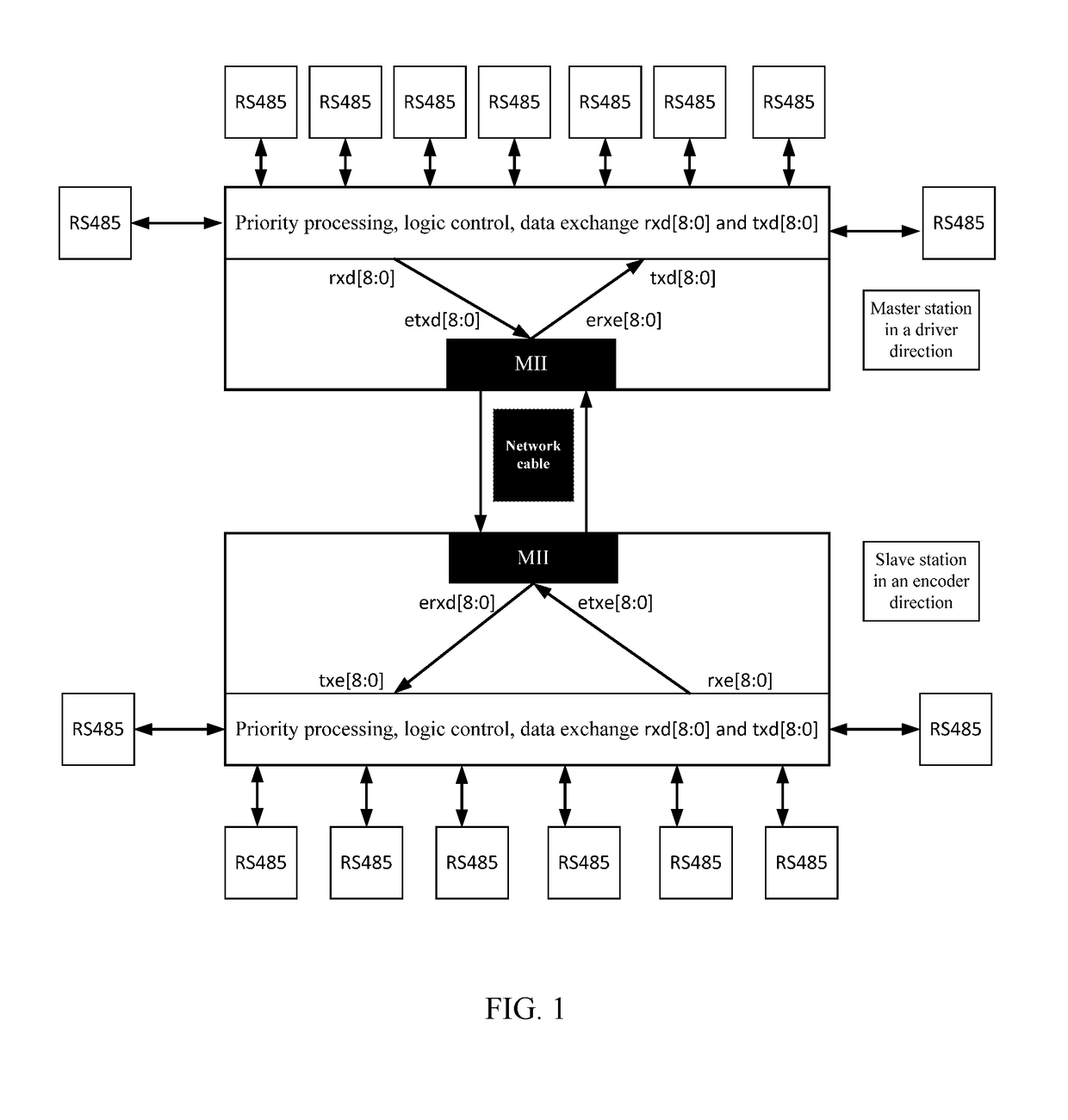

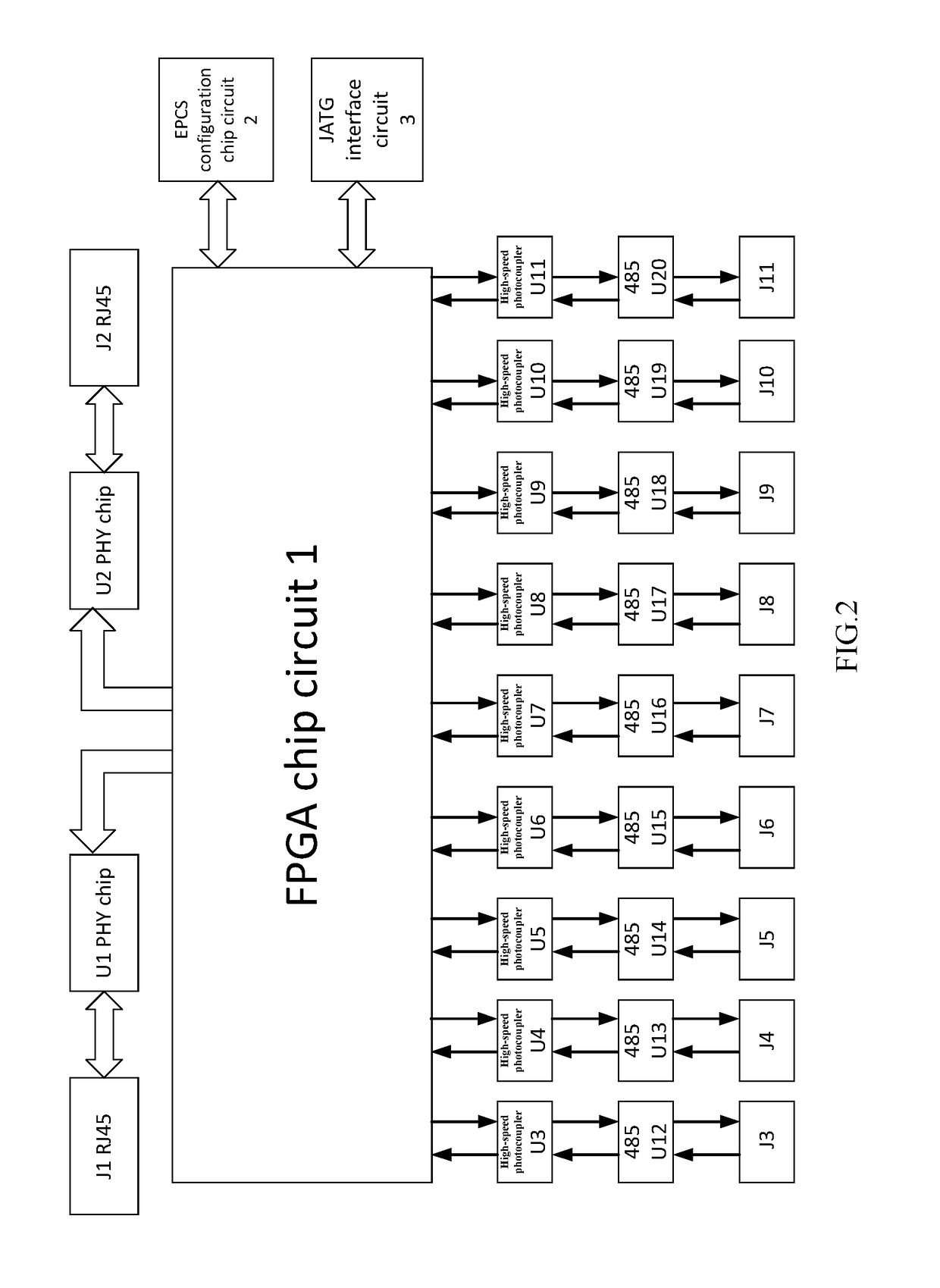

Transmission system for converting signal of 9-channel encoder into 1000mbps phy signal

ActiveUS20180341251A1Complicated cablingLow costProgramme-controlled manipulatorTransmissionTransceiverPHY

A transmission system for converting a signal of a 9-channel encoder into a 1000 Mbps PHY signal, includes a PHY chip circuits U1 and U2, digital photocouplers U3˜U11, 485 transceivers U12˜U20, RJ45 isolation transformer-integrated jacks J1 and J2, a field programmable gate array (FPCiA) chip circuit, an electronic propulsion control system (EPCS) configuration chip circuit, a Jtag interface and SM-6P-PCB jackets J3˜J11, wherein two-channel MII digital signal output and input ends of the FPGA chip circuit are respectively connected with MII digital signal input and output ends of the PHY chip circuits U1 and U2; differential data signal output and input ends of the PHY chip circuits U1 and U2 are respectively connected to the RJ45 isolation transformer-integrated jacks J1 and J2, and a master station and a slave station are arranged at the same time.

Owner:HARBIN BO QIANG ROBOT TECH CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com