A method for optimizing a field-programmable gate array chip layout

A technology of chip layout and programming logic, applied in the direction of logic circuits using specific components, logic circuits using basic logic circuit components, etc., which can solve the problem of long processing time, large layout circuit volume, and failure to meet user requirements for program running time and other problems to achieve the effect of reducing the time and speeding up the running speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

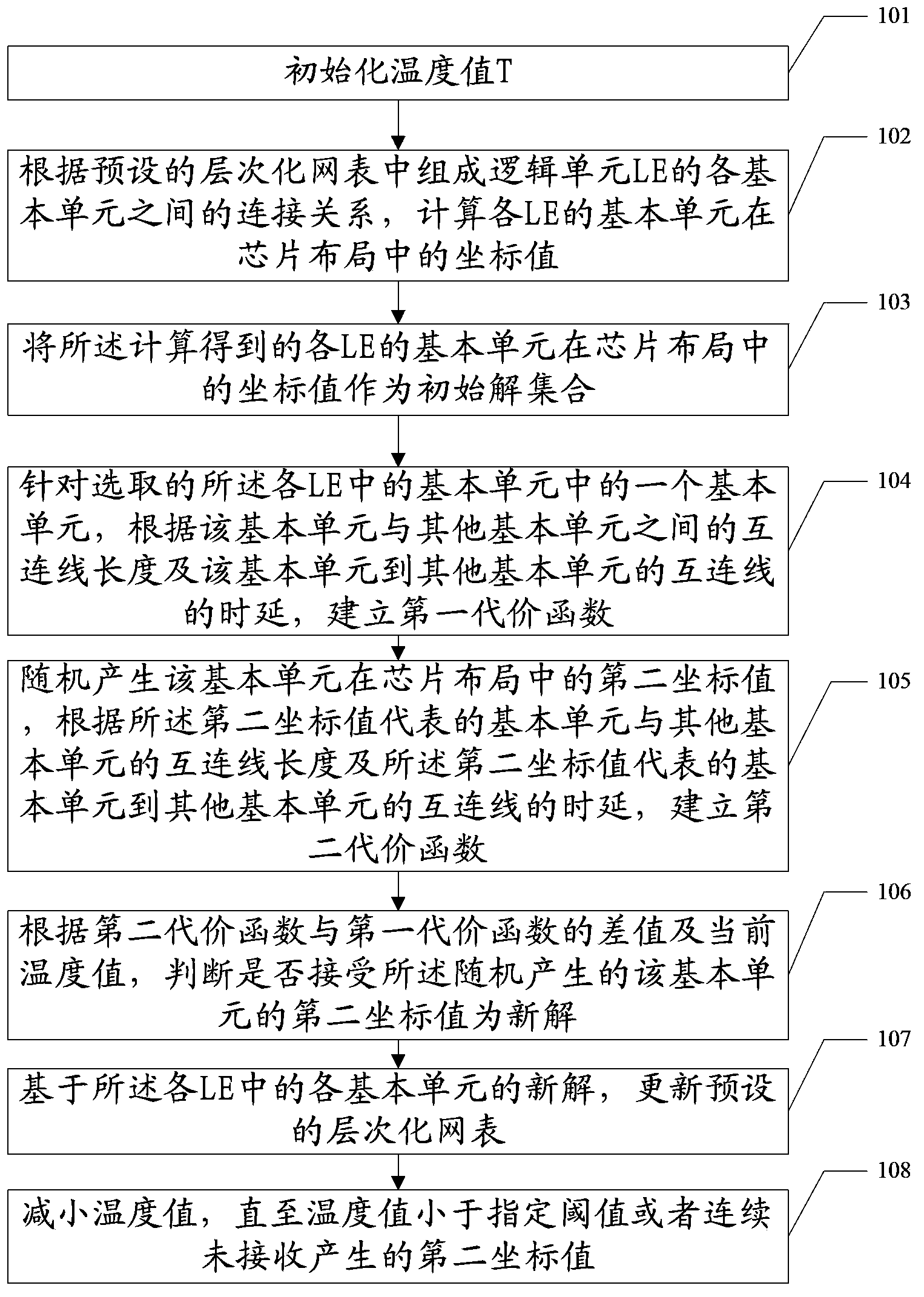

[0034] figure 1 It is a flow chart of the field programmable logic gate array chip layout optimization method of Embodiment 1 of the present invention. In the figure, the field programmable logic gate array chip layout optimization method mainly includes:

[0035] Step 101, initialize the temperature value T.

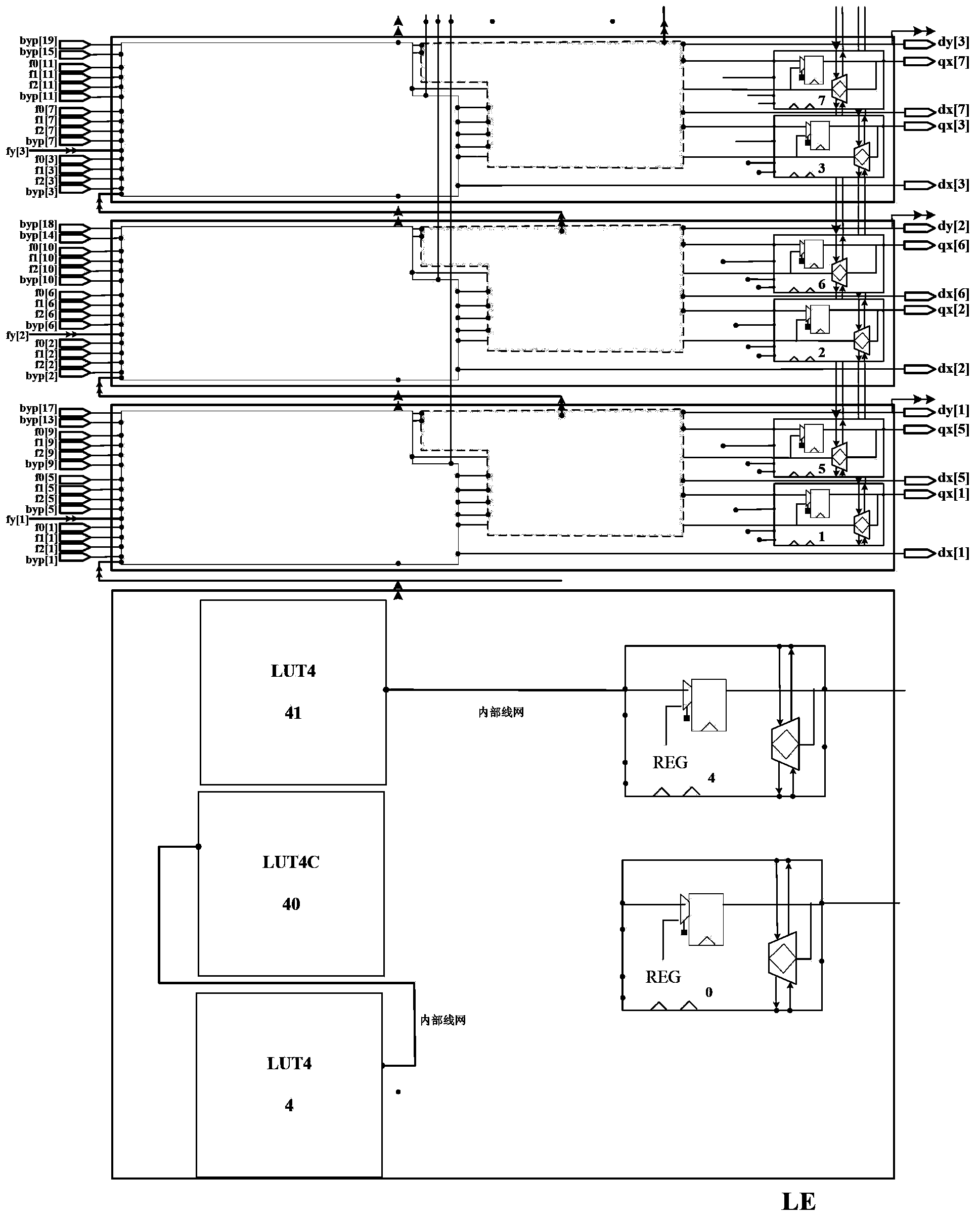

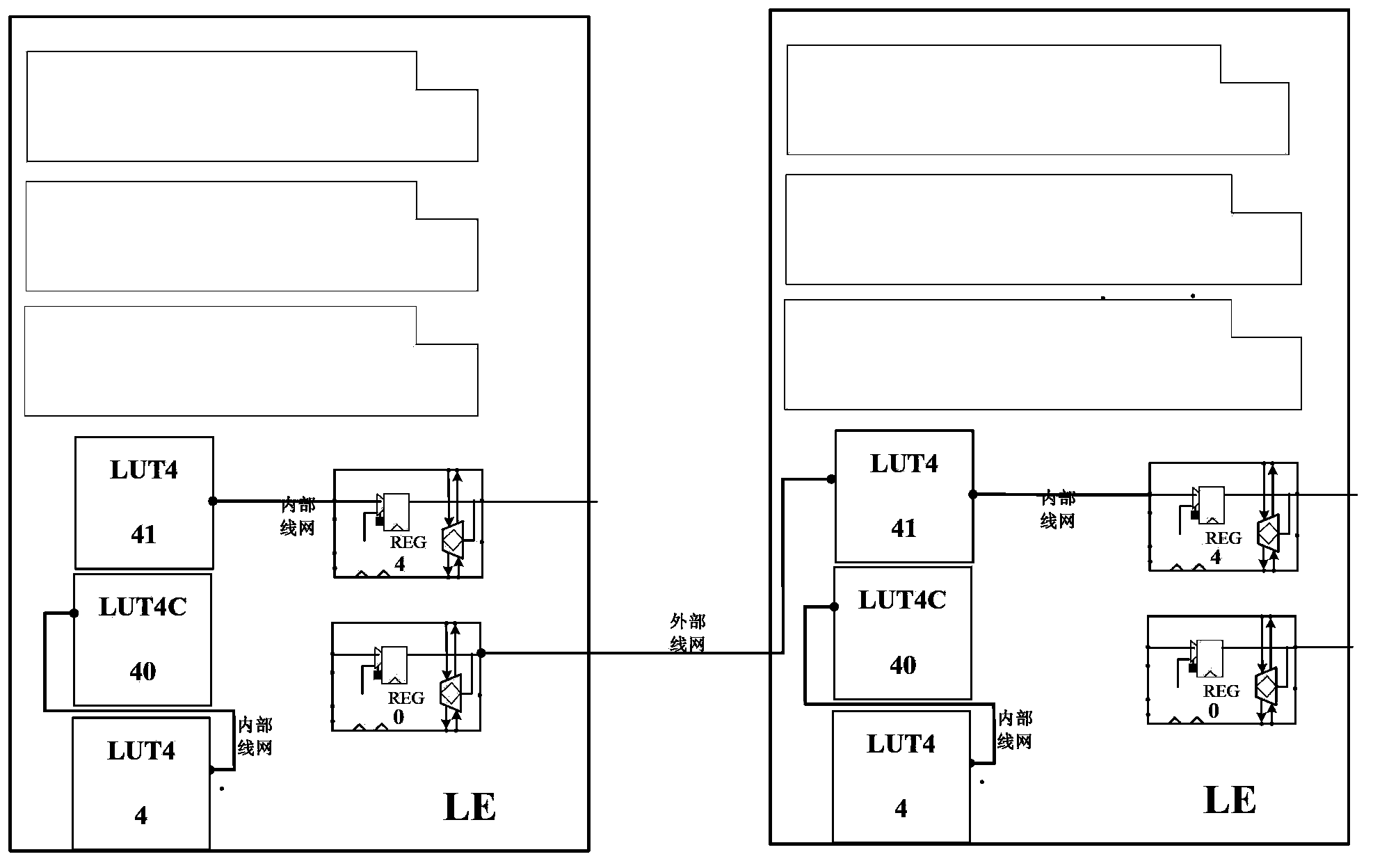

[0036] In step 101, the temperature T needs to be initialized, and the higher the value of the initialization temperature, the larger the search space. Specifically, the preset hierarchical netlist records the lookup table, the register, or the basic unit represented by the lookup table and the register and the logic unit composed of these basic units, and also records the connection relationship between these basic units. Initialize the temperature value T according to the formula Value, where the parameter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com