Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

46results about How to "High level of abstraction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Real time video game uses emulation of streaming over the internet in a broadcast event

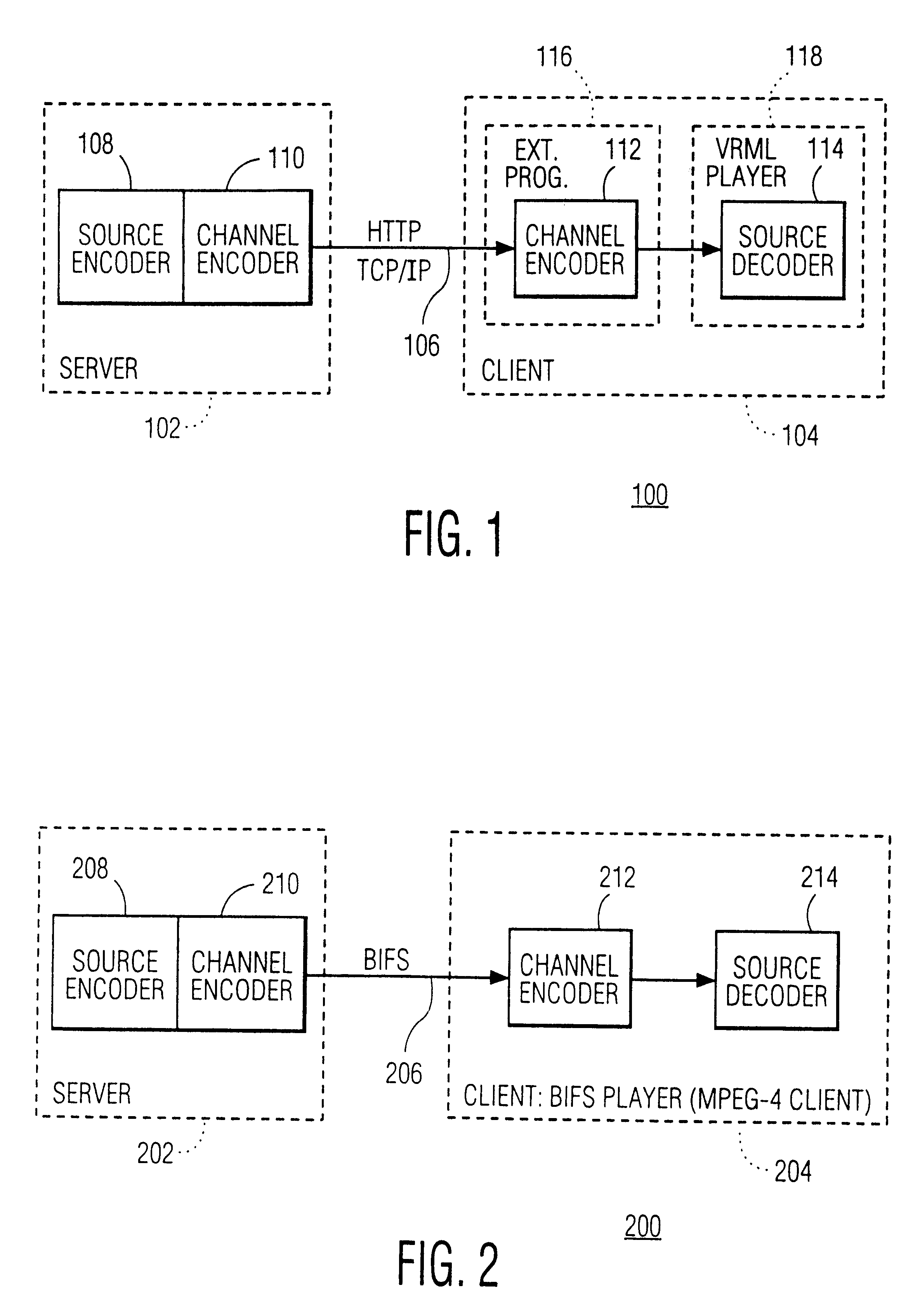

InactiveUS20030037156A1Easy programmingLow bandwidthSpecial service provision for substationPulse modulation television signal transmissionGraphicsAnimation

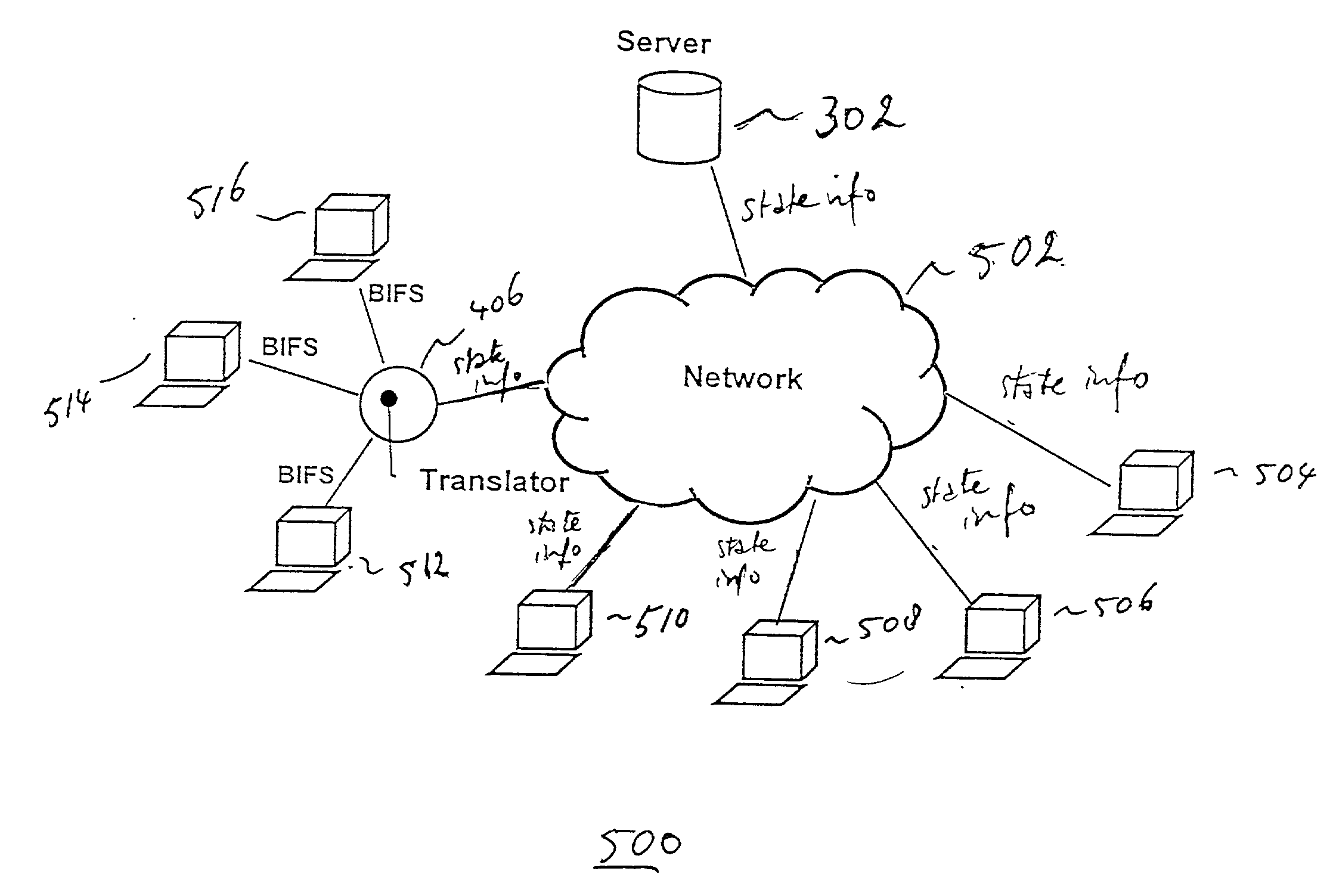

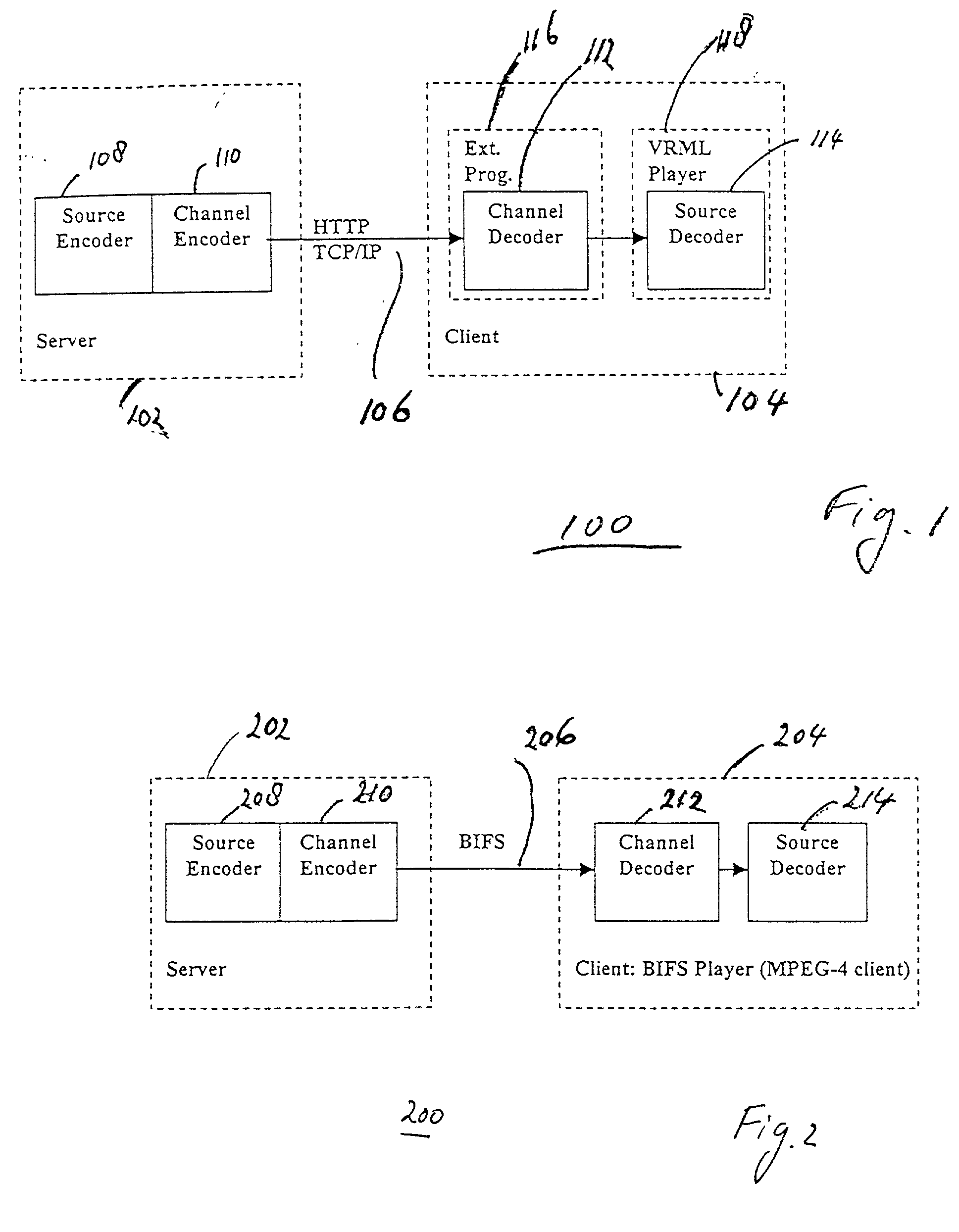

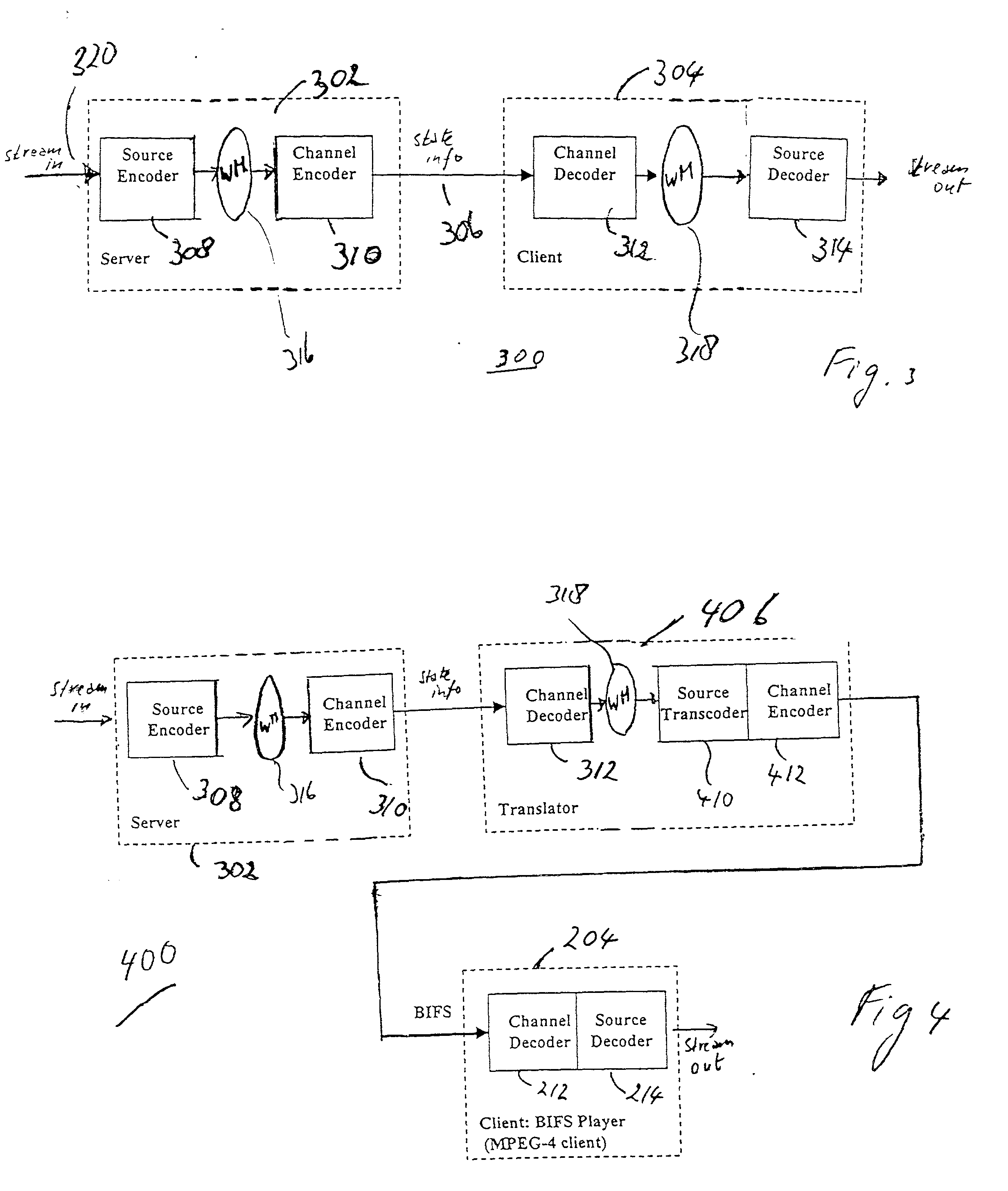

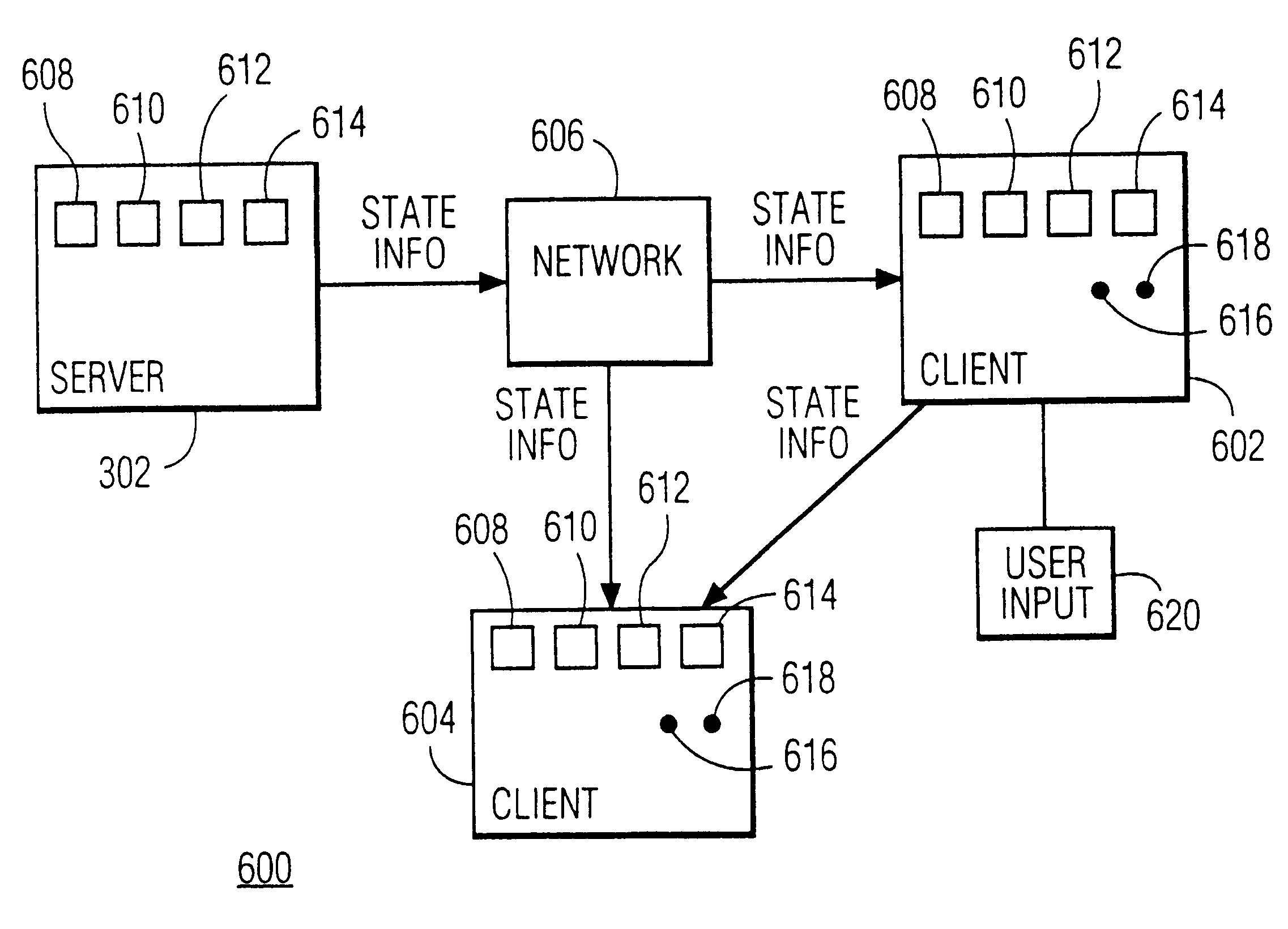

In a broadcast application on a client-server network the streaming is emulated of animation data over the Internet to a large number of clients. The animation is considered a sequence of states. State information is sent to the clients instead of the graphics data itself. The clients generate the animation data itself under control of the state information. The server and clients communicate using a shared object protocol. Thus, streaming is accomplished as well as a broadcast without running into severe network bandwidth problems. This approach is used to map a real life event, e.g., a motor race, onto a virtual environment in order to let the user participate in a virtual race against the real life professionals, the dynamics of the virtual environment being determined by the state changes sent to the user.

Owner:QUALCOMM INC

Real time video game uses emulation of streaming over the internet in a broadcast event

InactiveUS6557041B2Easy programmingLow bandwidthSpecial service provision for substationPulse modulation television signal transmissionGraphicsState variation

In a broadcast application on a client-server network the streaming is emulated of animation data over the Internet to a large number of clients. The animation is considered a sequence of states. State information is sent to the clients instead of the graphics data itself. The clients generate the animation data itself under control of the state information. The server and clients communicate using a shared object protocol. Thus, streaming is accomplished as well as a broadcast without running into severe network bandwidth problems. This approach is used to map a real life event, e.g., a motor race, onto a virtual environment in order to let the user participate in a virtual race against the real life professionals, the dynamics of the virtual environment being determined by the state changes sent to the user.

Owner:QUALCOMM INC

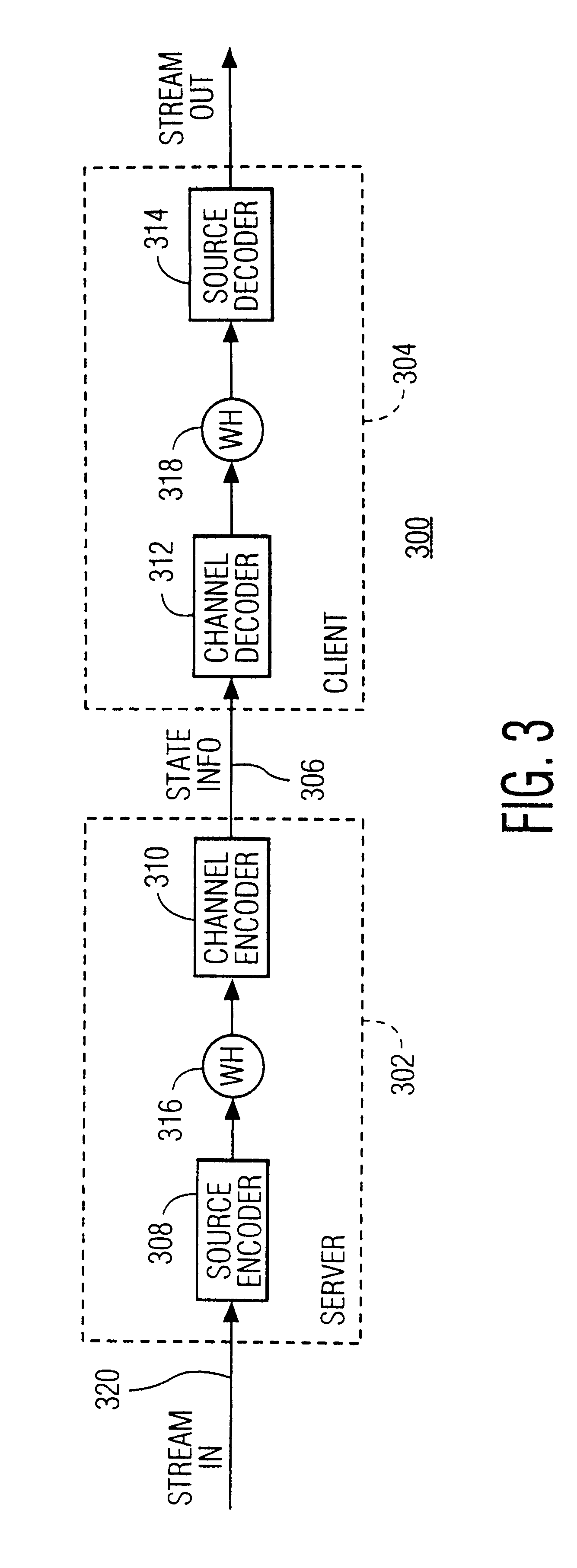

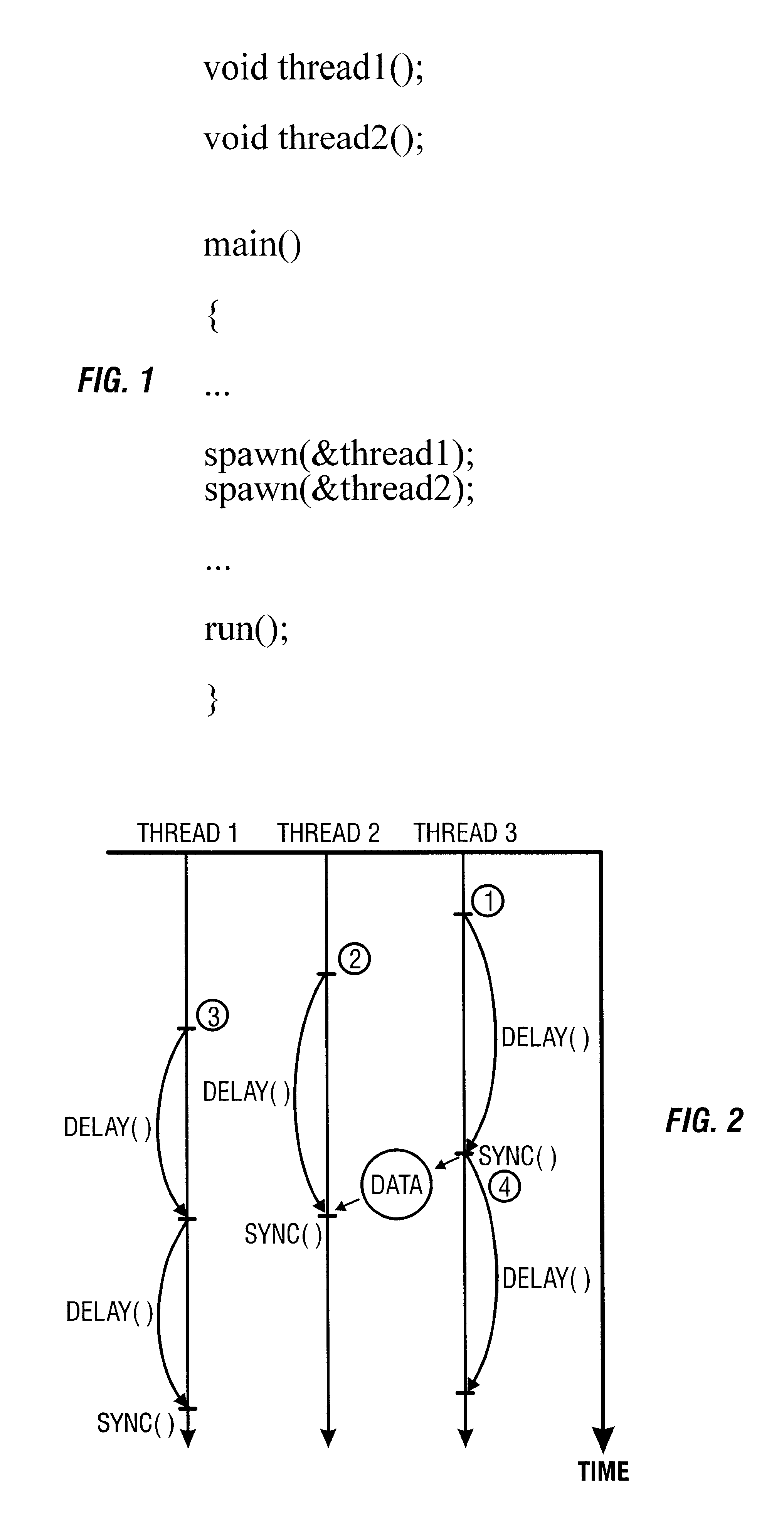

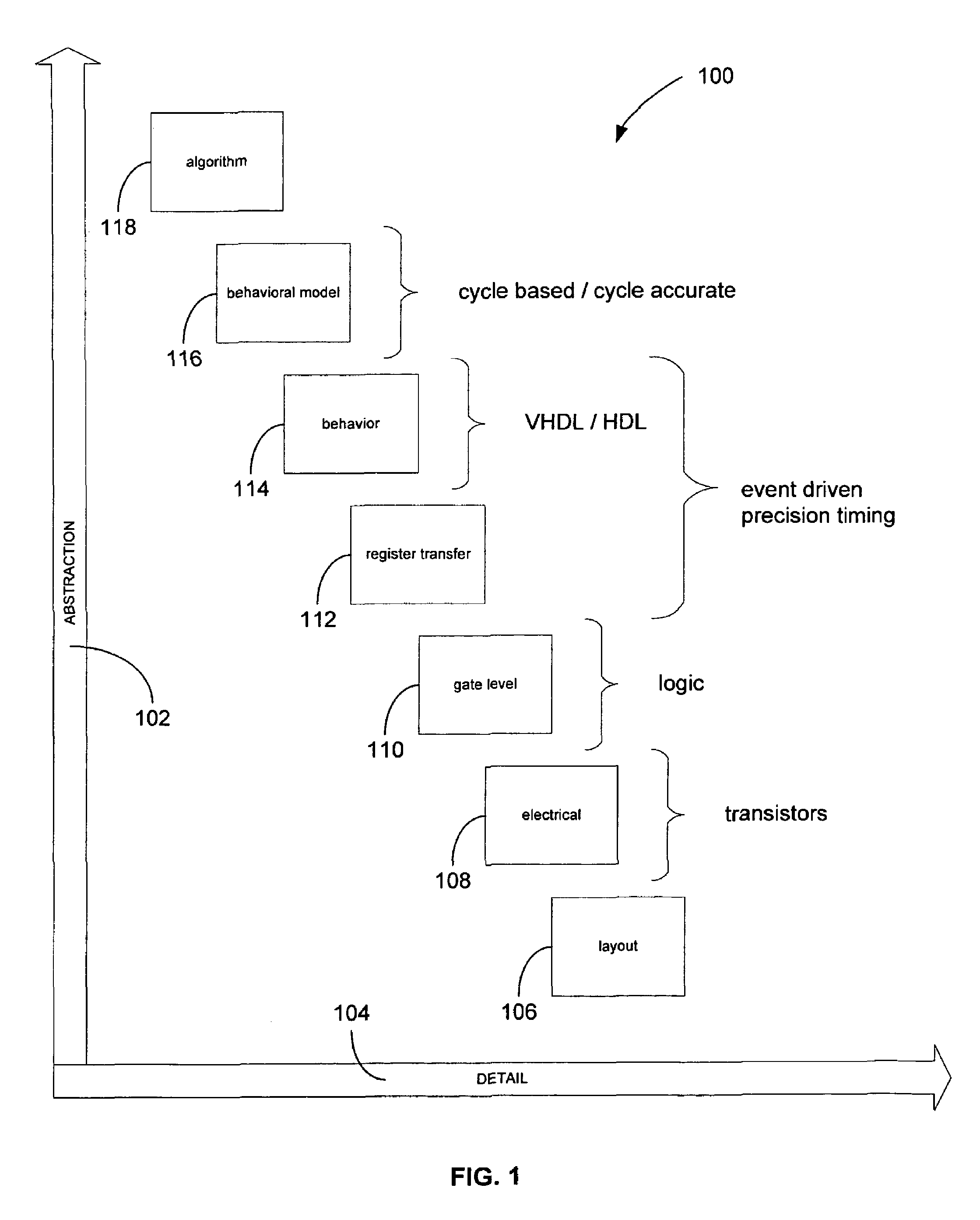

Concurrent timed digital system design method and environment

InactiveUS6952825B1Improve Simulation EfficiencyAvoid switchingMultiprogramming arrangementsSoftware designSystems designCommunications system

The present invention relates to the design of an essentially digital system. As one example of digital systems, these may perform real-time transformations on time discrete digitized samples of analogue quantities. An example of such a system is a digital communication system. The transformations on the data can be specified in a programming language and executed on a processor such as a programmable processor or directly on application specific hardware. In accordance with the present invention the digital system is described as a set of threads in a description language. Alternative names for a thread are tasks and processes. The set of threads defines a representation or model of the digital system. In accordance with the present invention, the representation or model is preferably executable at each stage of the design independent of the current level of abstraction of that representation or model. With description language is meant a programming language. In accordance with the present invention each of the threads has a variable having an assignable value which represents the “local time” of said thread, i.e. a time associated only with that thread, which can be used for sequencing the processing of that thread with respect to other threads. With the word “local” is meant that the time is an attribute of the thread only. In accordance with the present invention a means is provided for the designer to assign a delay to each thread or operation within a thread, this delay representing for instance the processing time for the respective operation or thread on a processing engine, e.g. a computer. By this means, not only can the processing of threads be scheduled but also the designer may assign a value representative of an elapsed time for the processing of a thread or operation on a processing engine. In addition, the threads may be refined concurrently, while still keeping their local time so that after the refining process the new representation of the digital system is executable, i.e. the processing of the refined threads can be scheduled without divergence from the specification.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

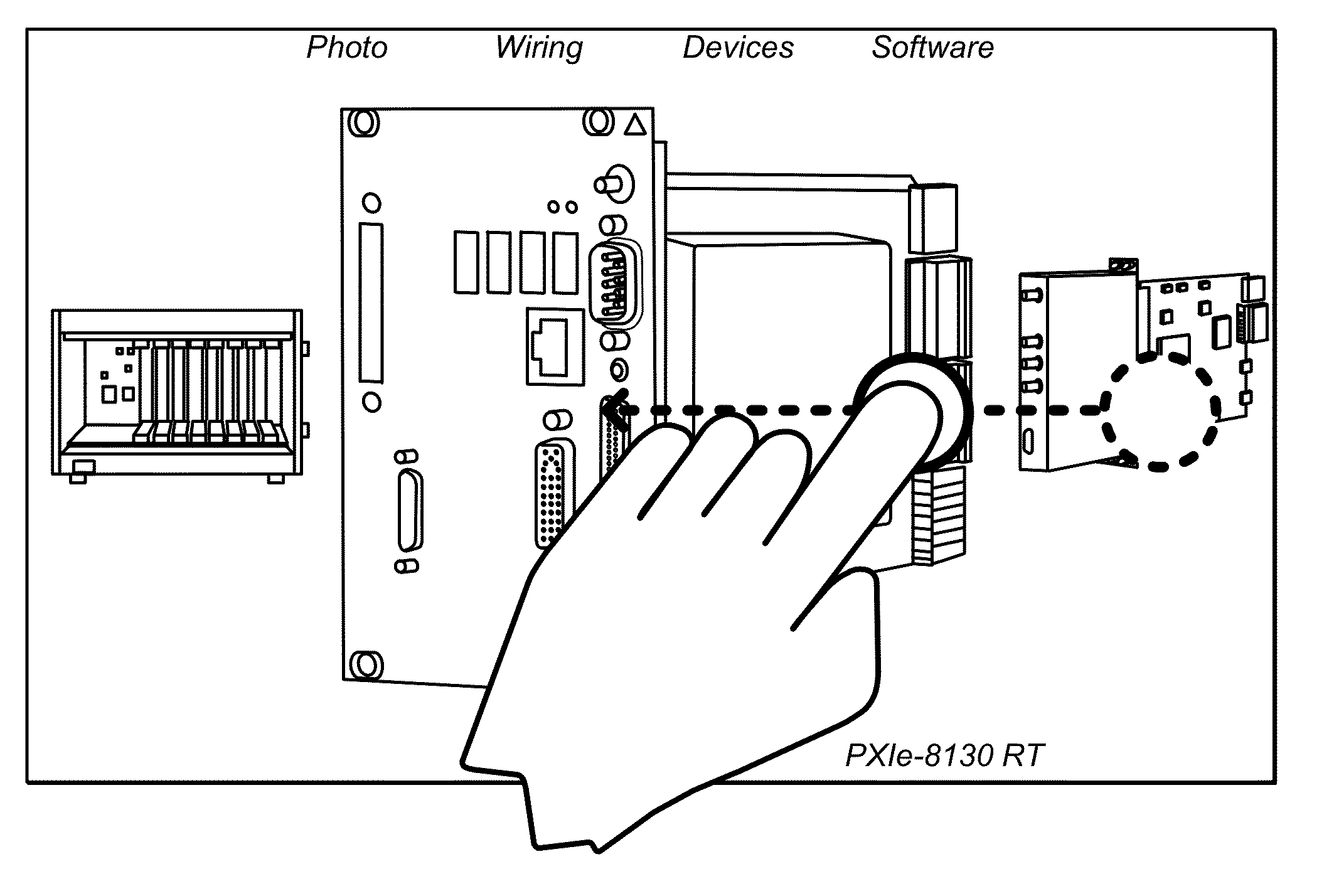

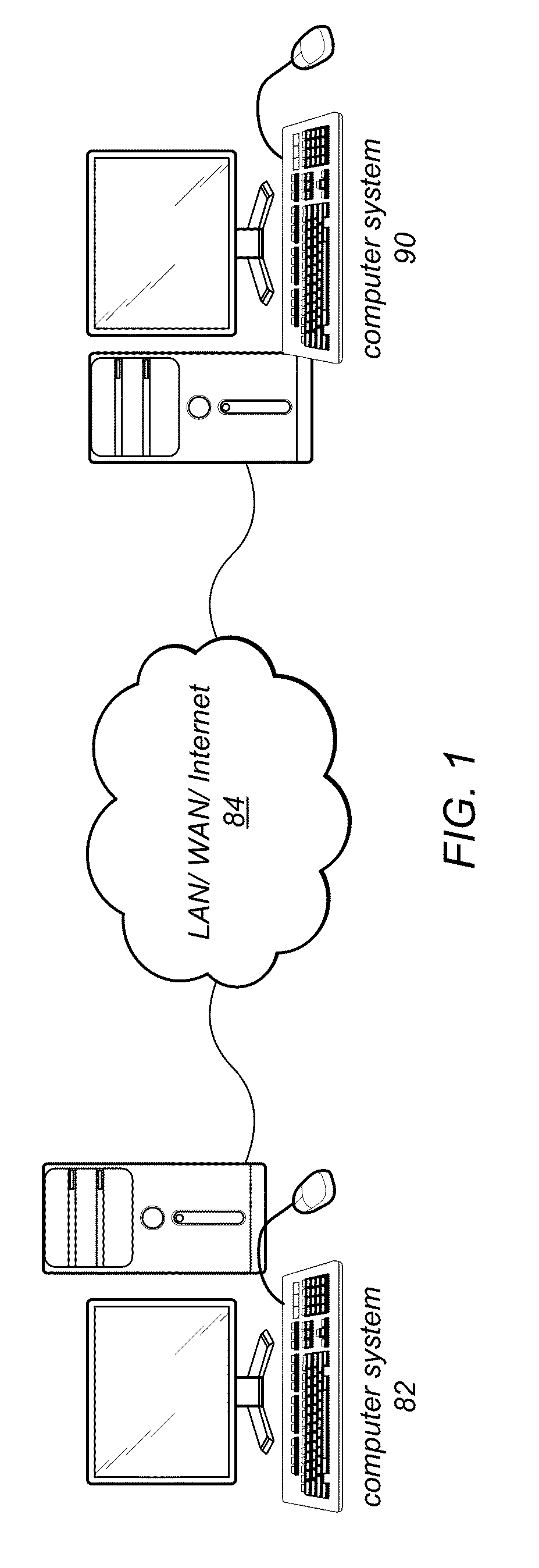

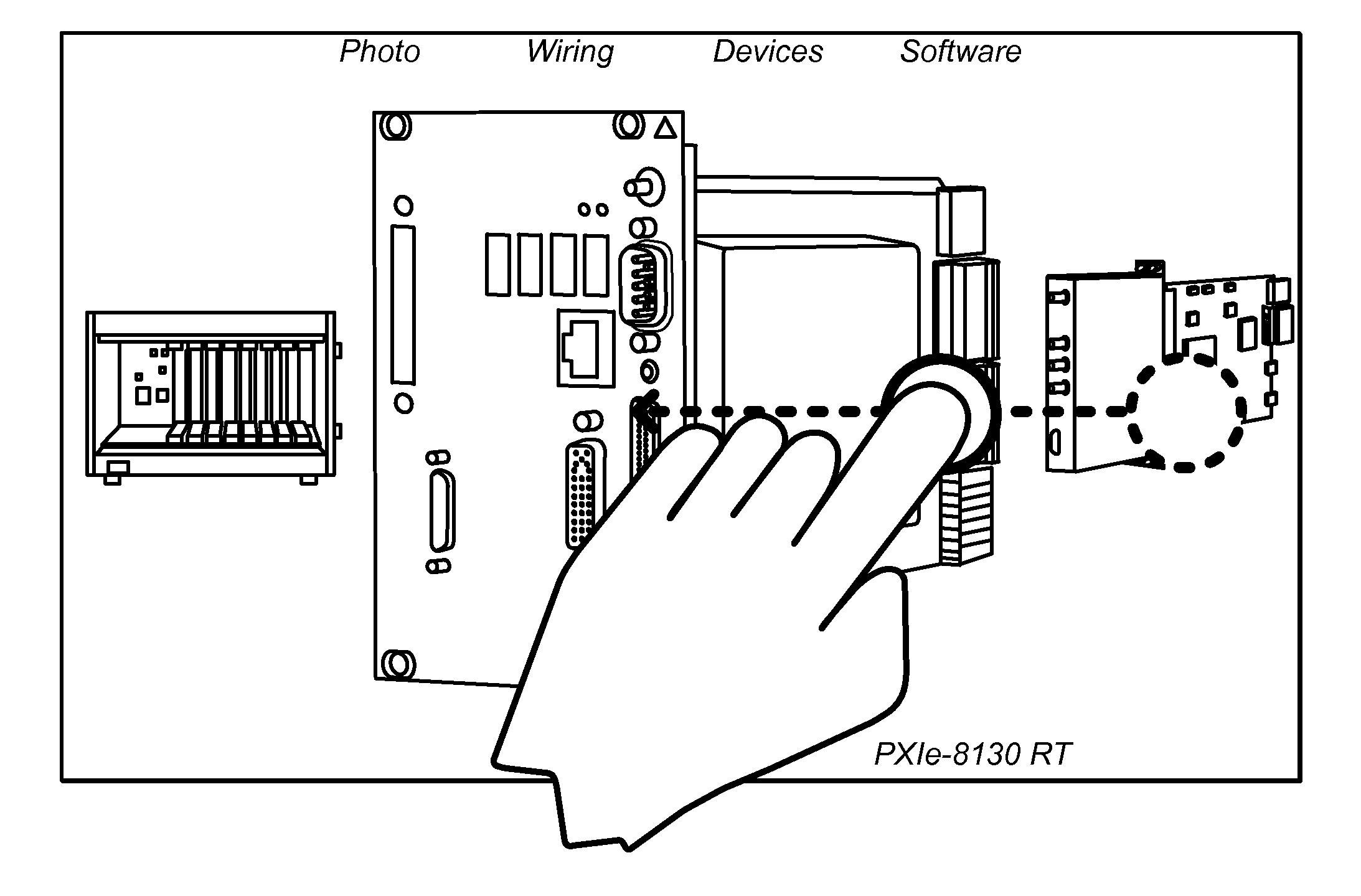

Gestures for Presentation of Different Views of a System Diagram

ActiveUS20130031514A1Level of abstraction may increase and decreaseHigh level of abstractionInput/output processes for data processingUser inputHuman–computer interaction

Presenting different views of a system based on input from a user. A first view of a first portion of the system may be displayed. For example, the first portion may be a device of the system. User input specifying a first gesture may be received. In response to the first gesture, a second view of the first portion of the system may be displayed. For example, the first view may represent a first level of abstraction of the portion of the system and the second view may represent a second level of abstraction of the portion of the system. A second gesture may be used to view a view of a different portion of the system. Additionally, when changing from a first view to a second view, the first view may “morph” into the second view.

Owner:NATIONAL INSTRUMENTS

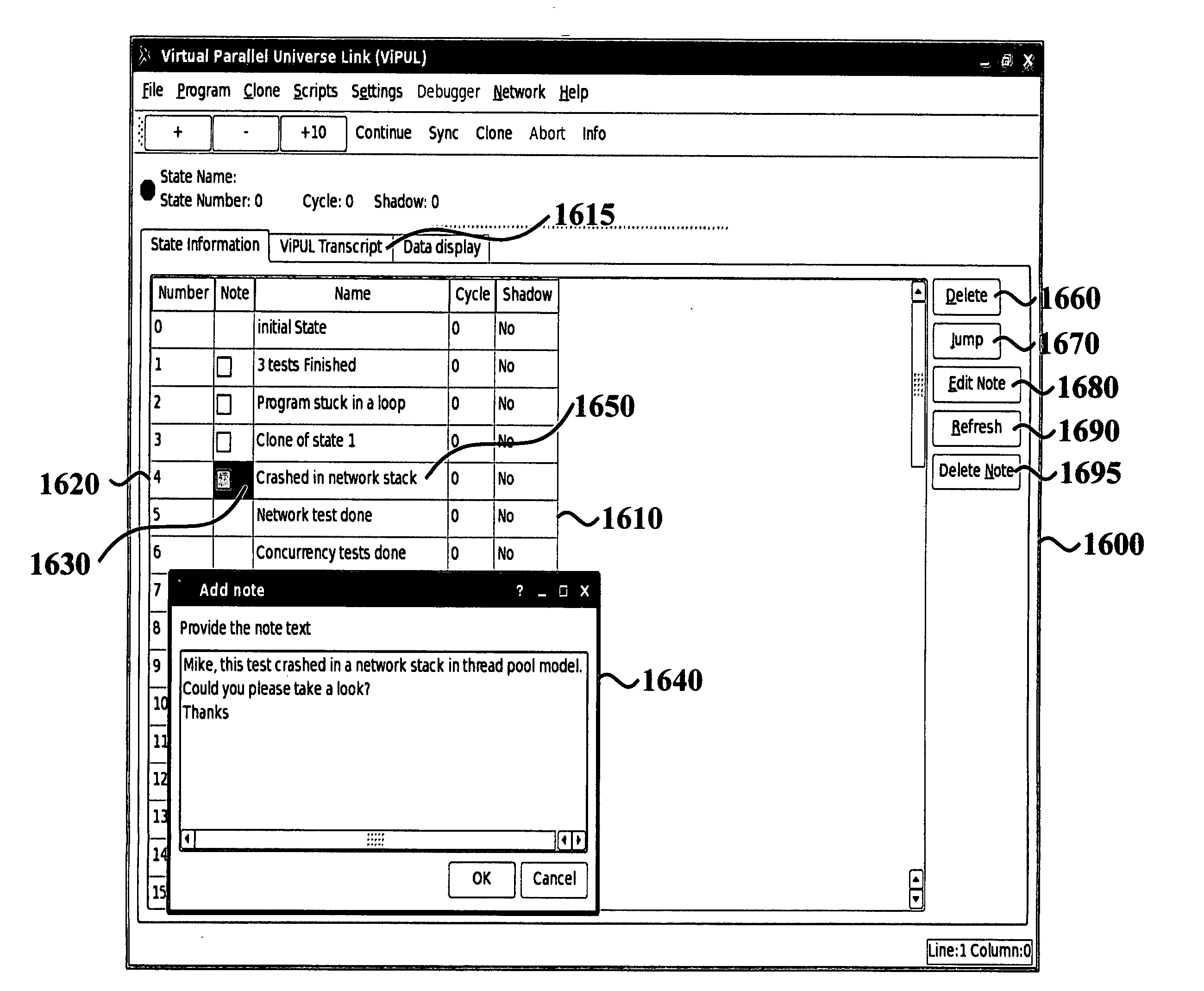

Method and apparatus for execution control of computer programs

InactiveUS20080295114A1High level of abstractionCreate illusionError detection/correctionInterprogram communicationSoftware engineeringExecution control

A method for execution control of a user application program utilizing control program and management software is provided. This execution control is provided without a need to modify or recompile the user application program. The invention provides ability to save states during the execution of an application program and provides a means to jump between them. The invention also provides a means for multiple remote users to interact with the user program and also provide means to control the user application via script and share common portions of execution among multiple execution instances of the same user application program. The invention enables attaching a debugger to a state, maintaining debug context for all the saved states, and means to jump to a state saved at an earlier point in execution to help debug user application programs.

Owner:ARGADE PRAMOD VASANT +1

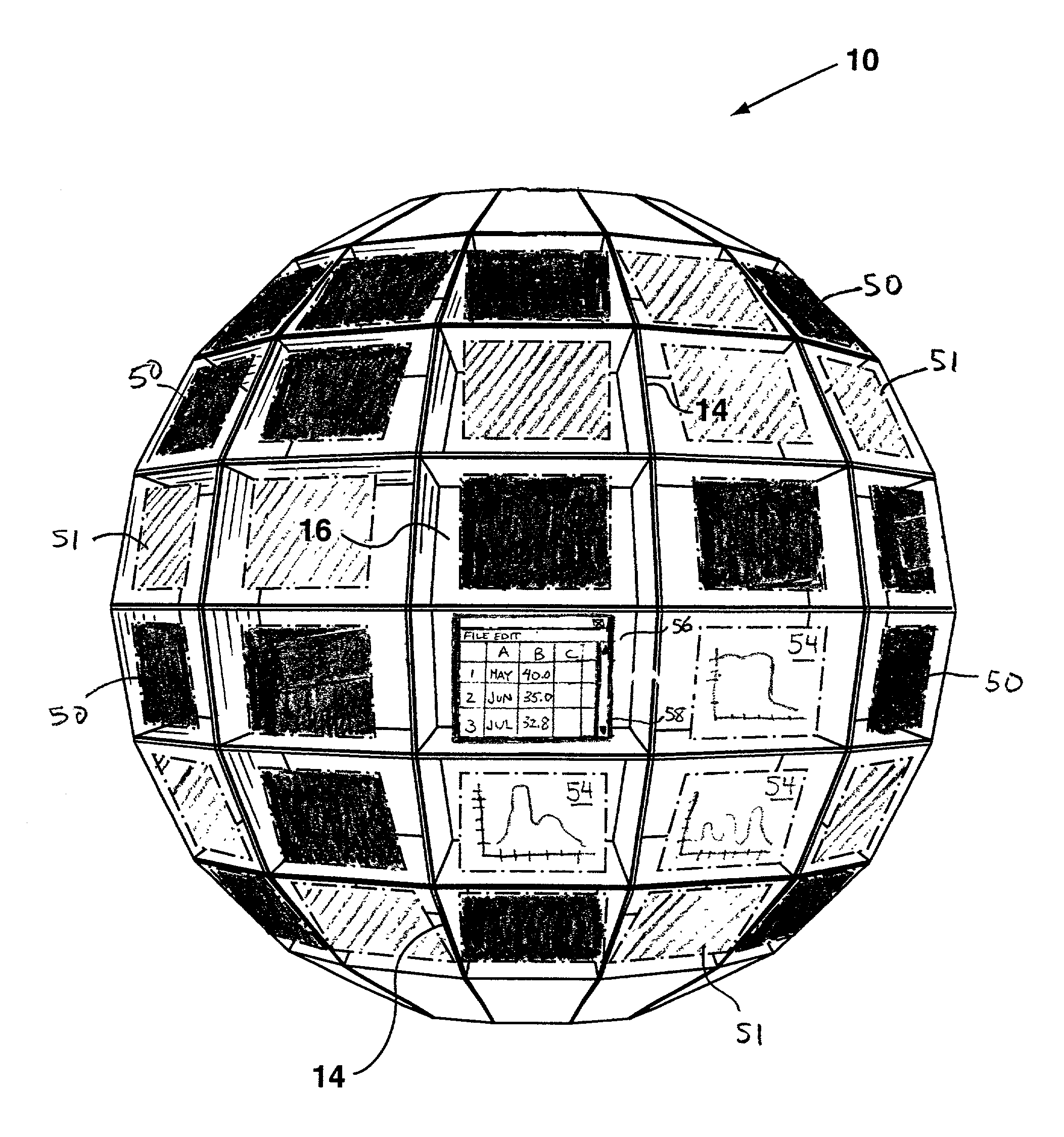

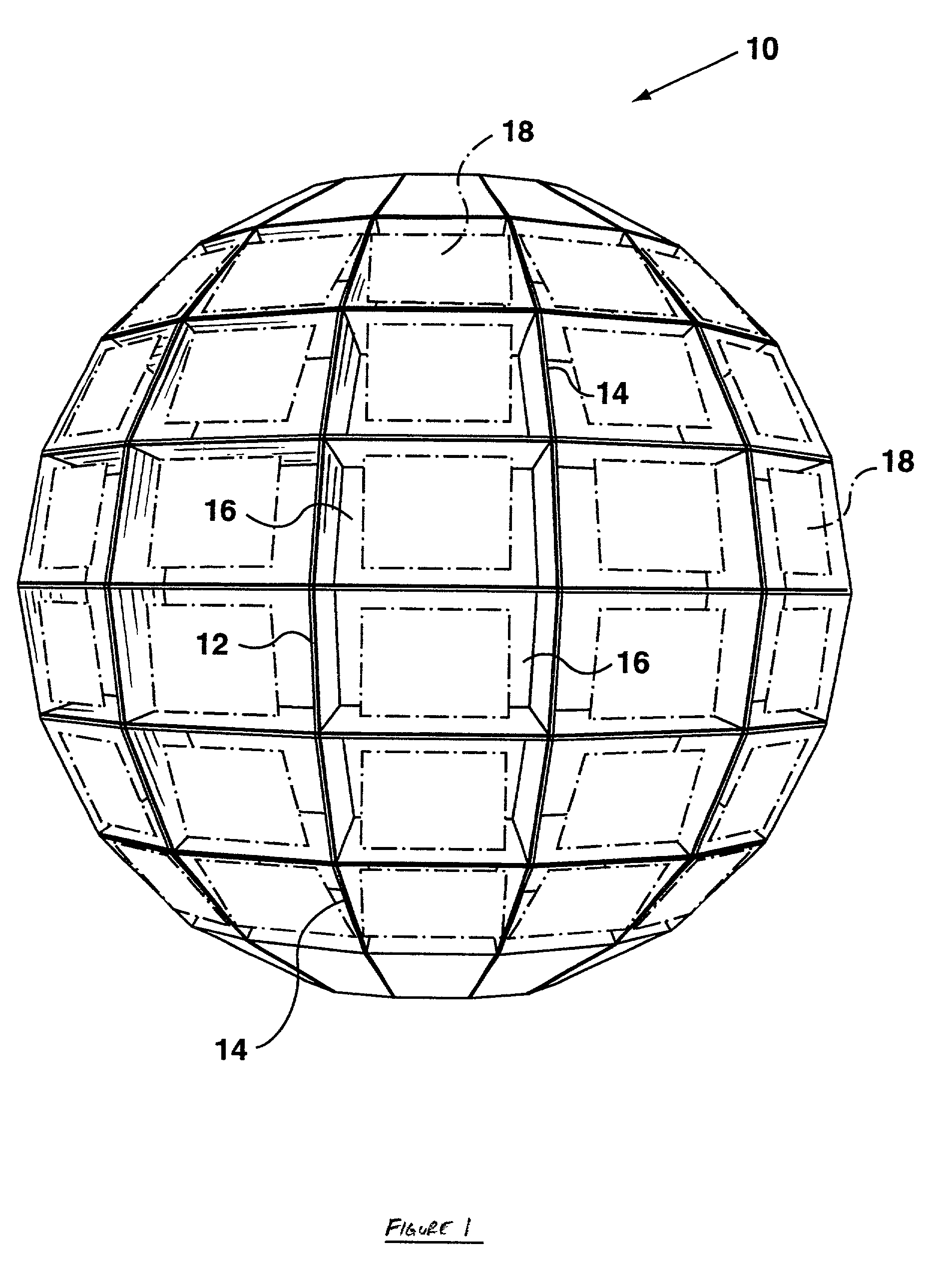

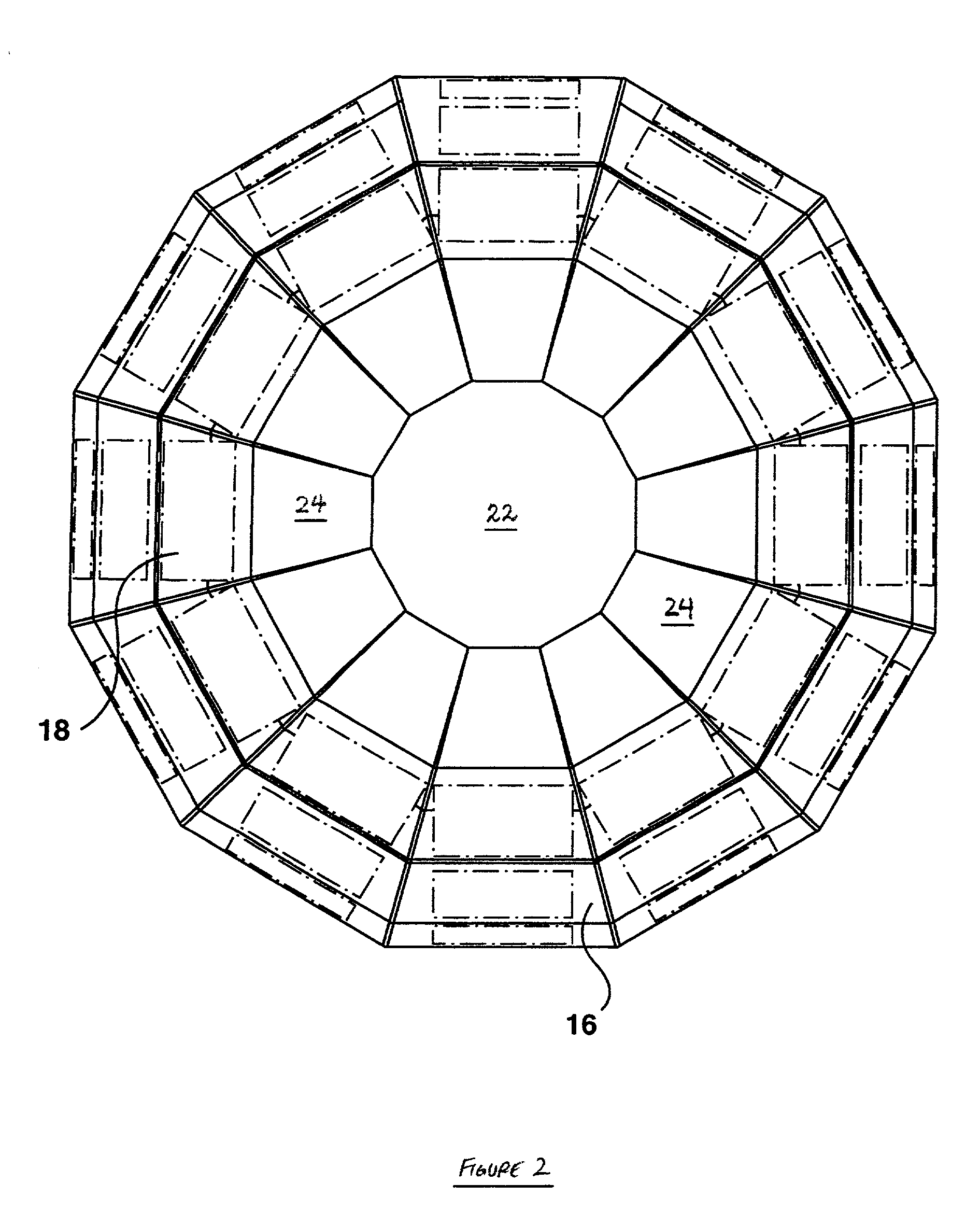

Method of representing information on a three-dimensional user interface

ActiveUS7412650B2Facilitate representation of dataHigh level of abstractionSpecial data processing applicationsDigital output to display deviceColor-codingColor code

The present invention relates to a method of representing information on a three-dimensional user interface having multiple portals, in which data is associated with each of the portals. A symbolic marker is associated with each of the portals according to a pre-specified scheme, and displayed in the respective portals. In a preferred embodiment of the invention, the symbolic marker is a colored marker. By color-coding the portals, data associated with the portals can be classified into a number of categories to provide the user with a summary of the data on the three-dimensional user interface at a high level of abstraction. The three-dimensional user interface may be adapted to update the colored markers more efficiently, and to display them using less computing resources than would be required if more memory-sensitive visual cues were displayed.

Owner:VIZIBLE CORP

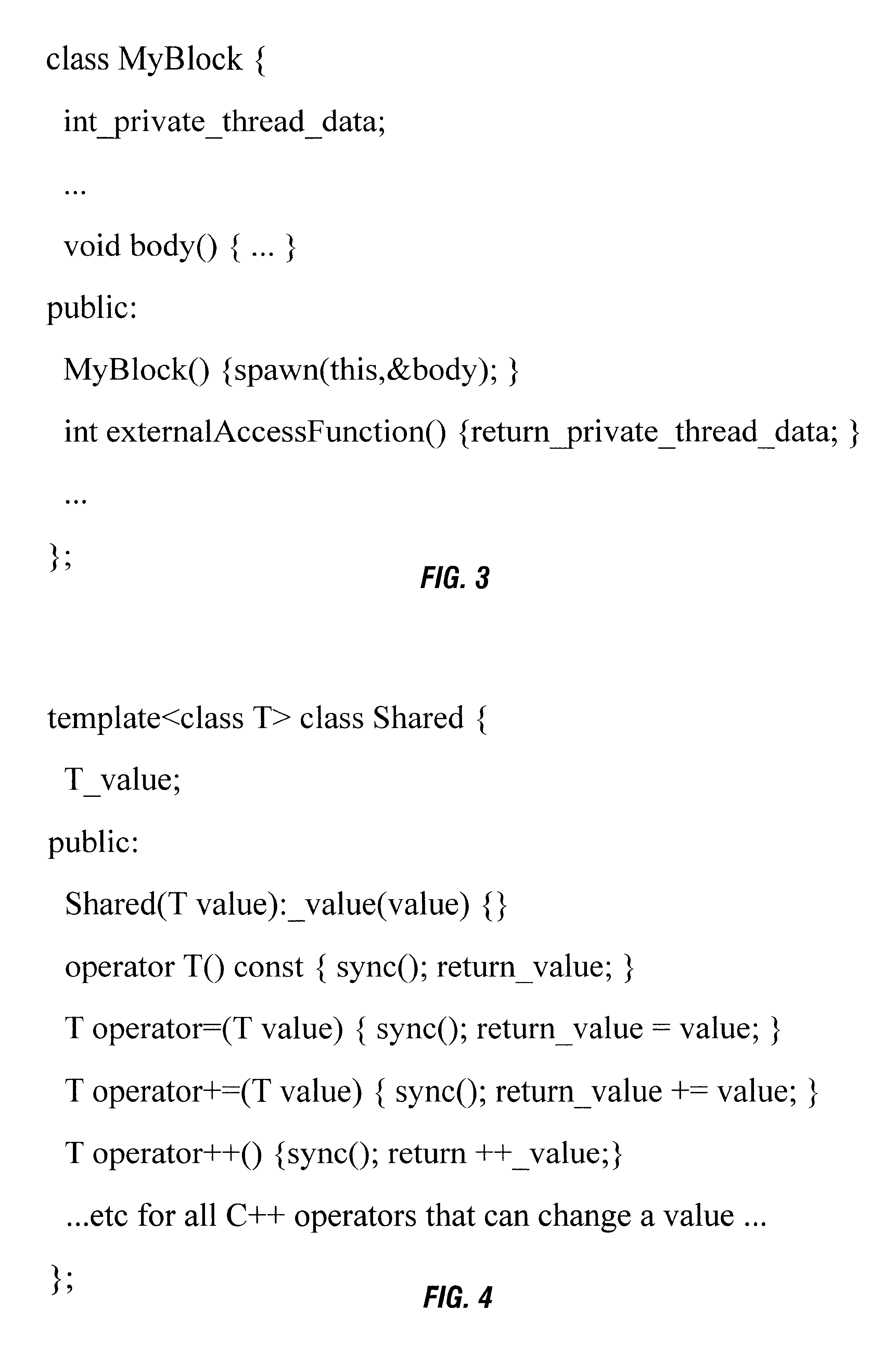

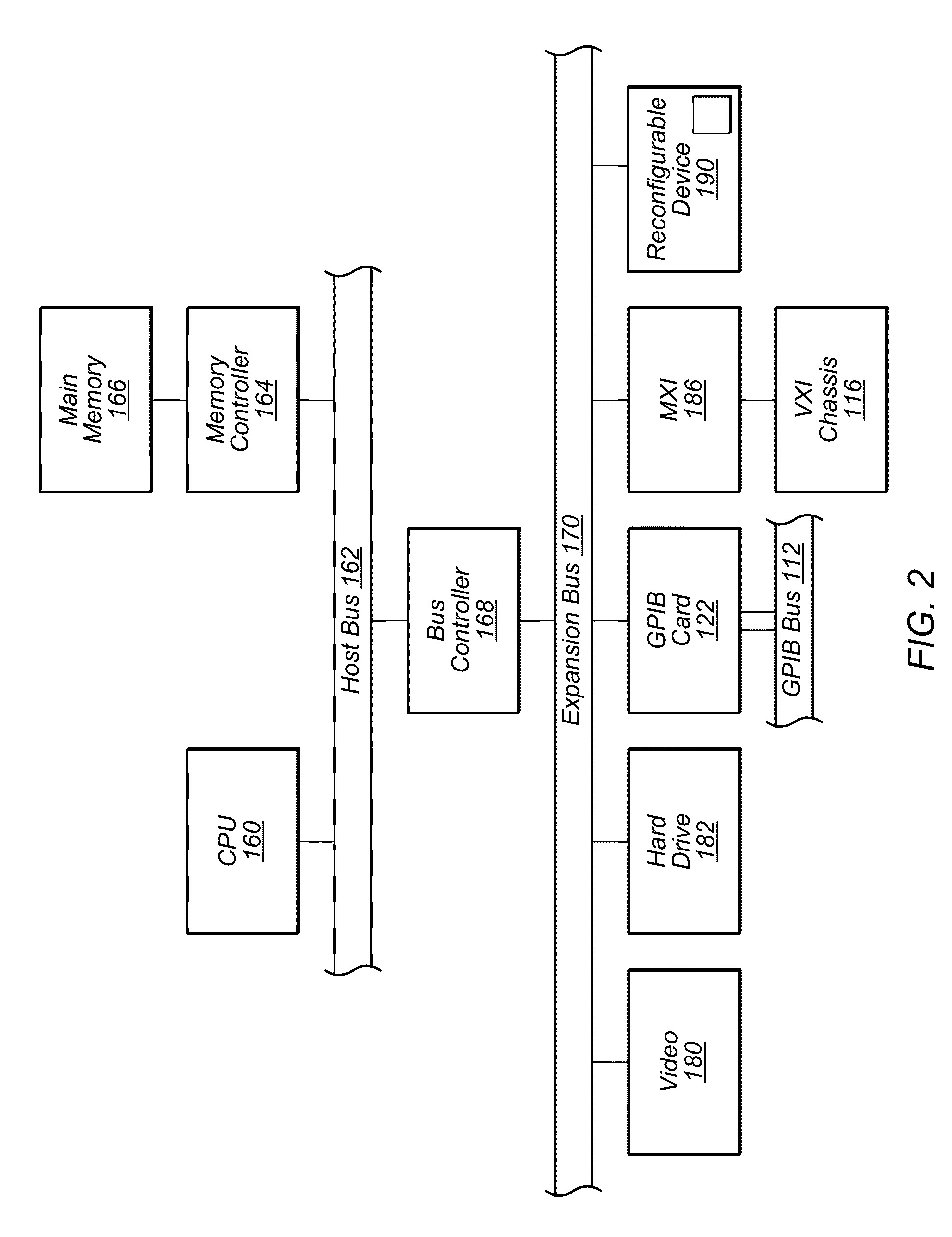

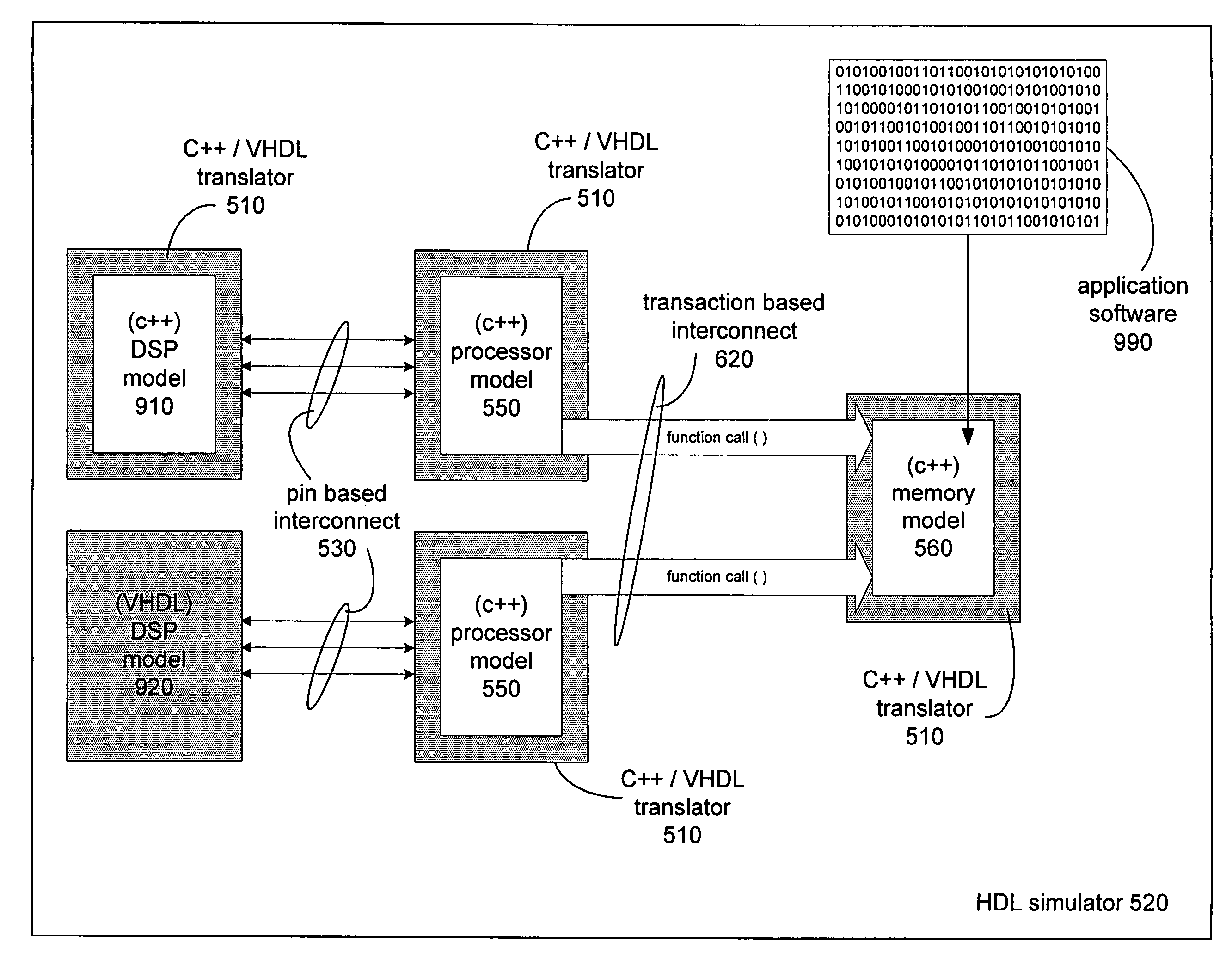

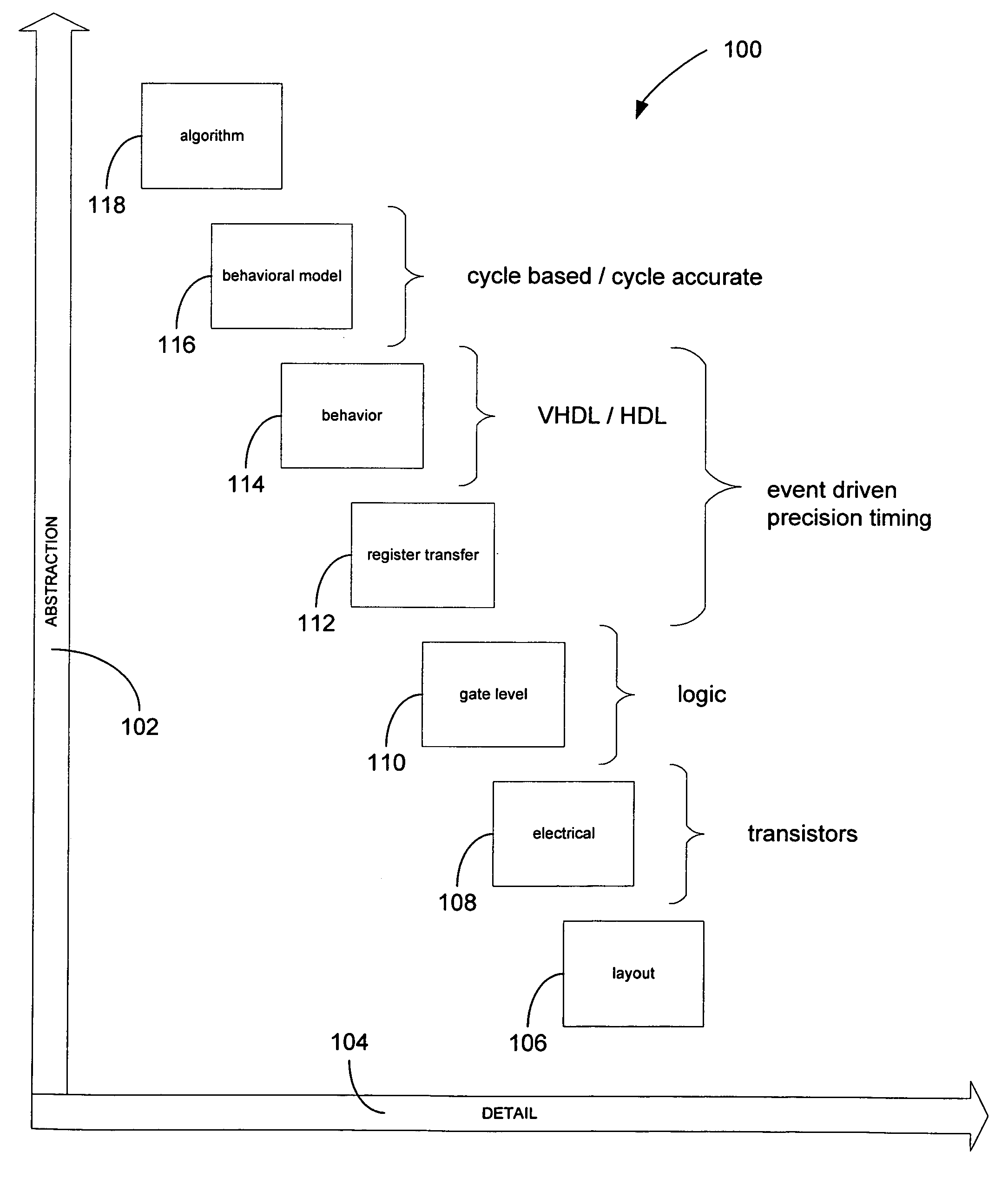

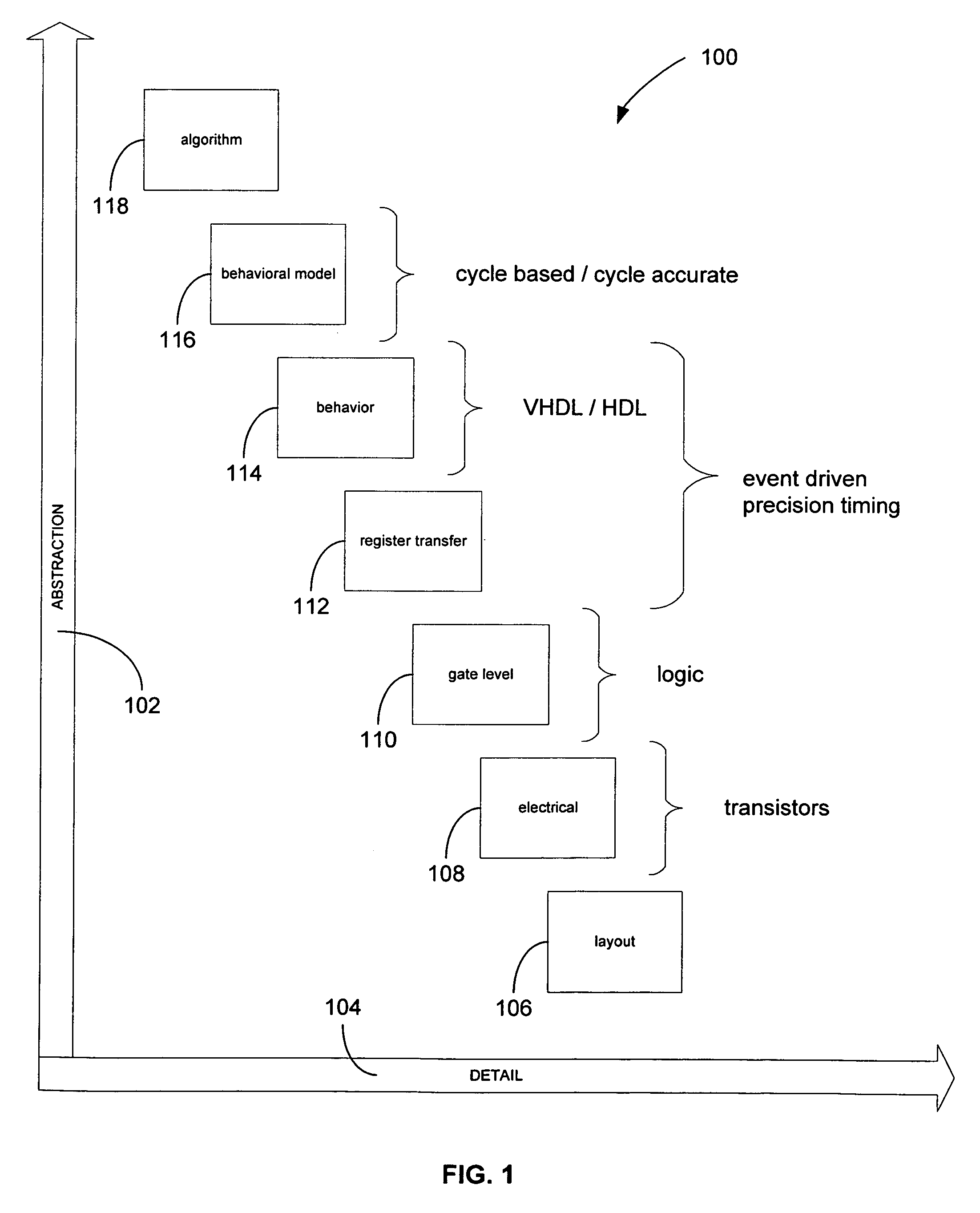

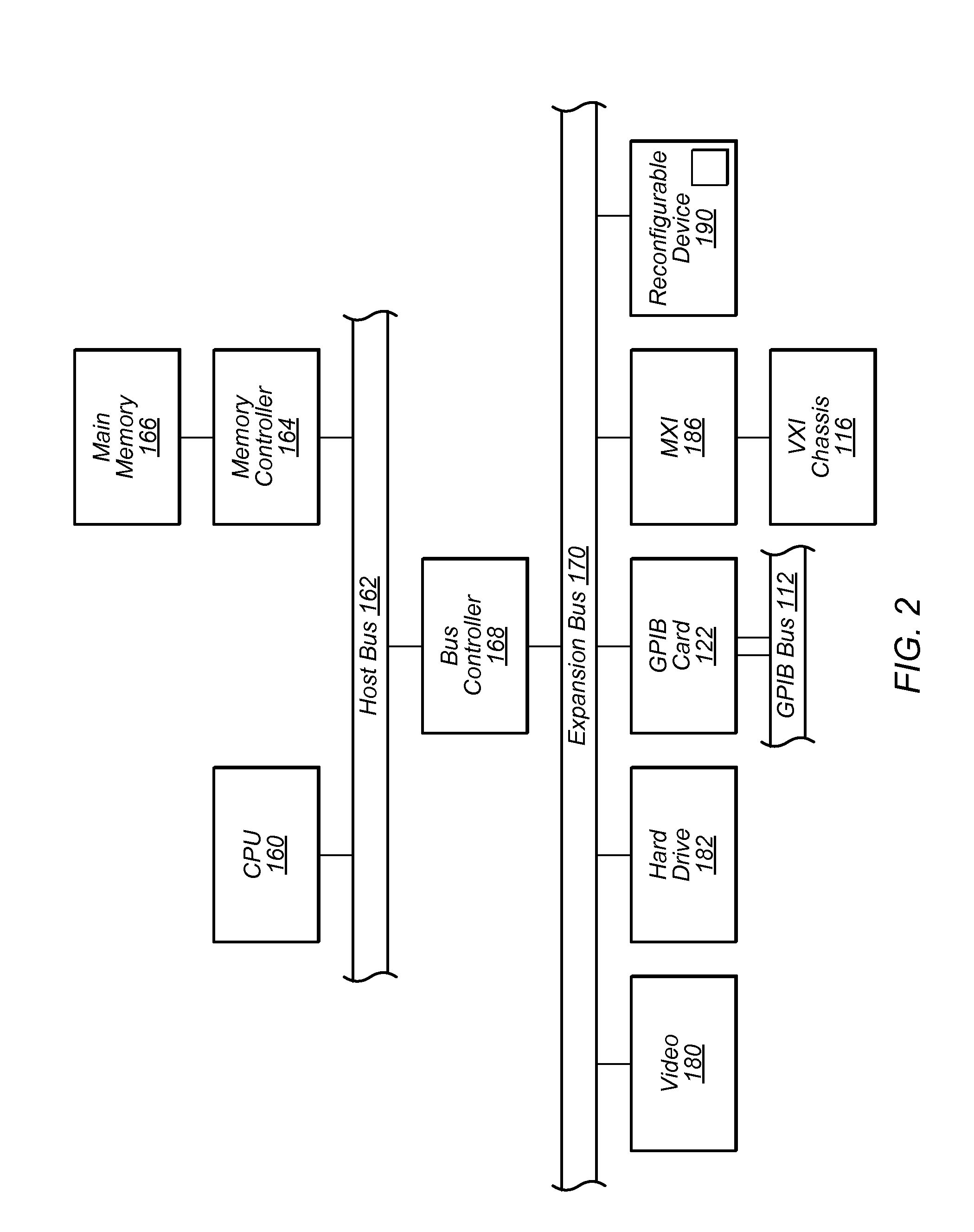

Method and apparatus for unified simulation

InactiveUS6993469B1Improve capacityHigh level of abstractionAnalogue computers for electric apparatusCAD circuit designSingle processSystems design

A significant improvement over current methods for co-simulation of the hardware and software components of embedded digital system designs is provided. The present invention integrates the hardware and software components of a system design into a single unified simulation environment. The unified simulation environment and the various component models of the system design are created in a high level general purpose programming language. This allows inter-component communications and communications with the unified simulation environment to be carried out through the use of function calls, which significantly increases the overall simulation speed. Additionally, the unified simulation environment runs as a single process, which significantly improves debugging capabilities. Furthermore, the present invention employs a higher level of abstraction than conventional simulation environments and thereby significantly increases simulation speed while moving away from the detail saturated event driven simulations of the past.

Owner:ARM LTD

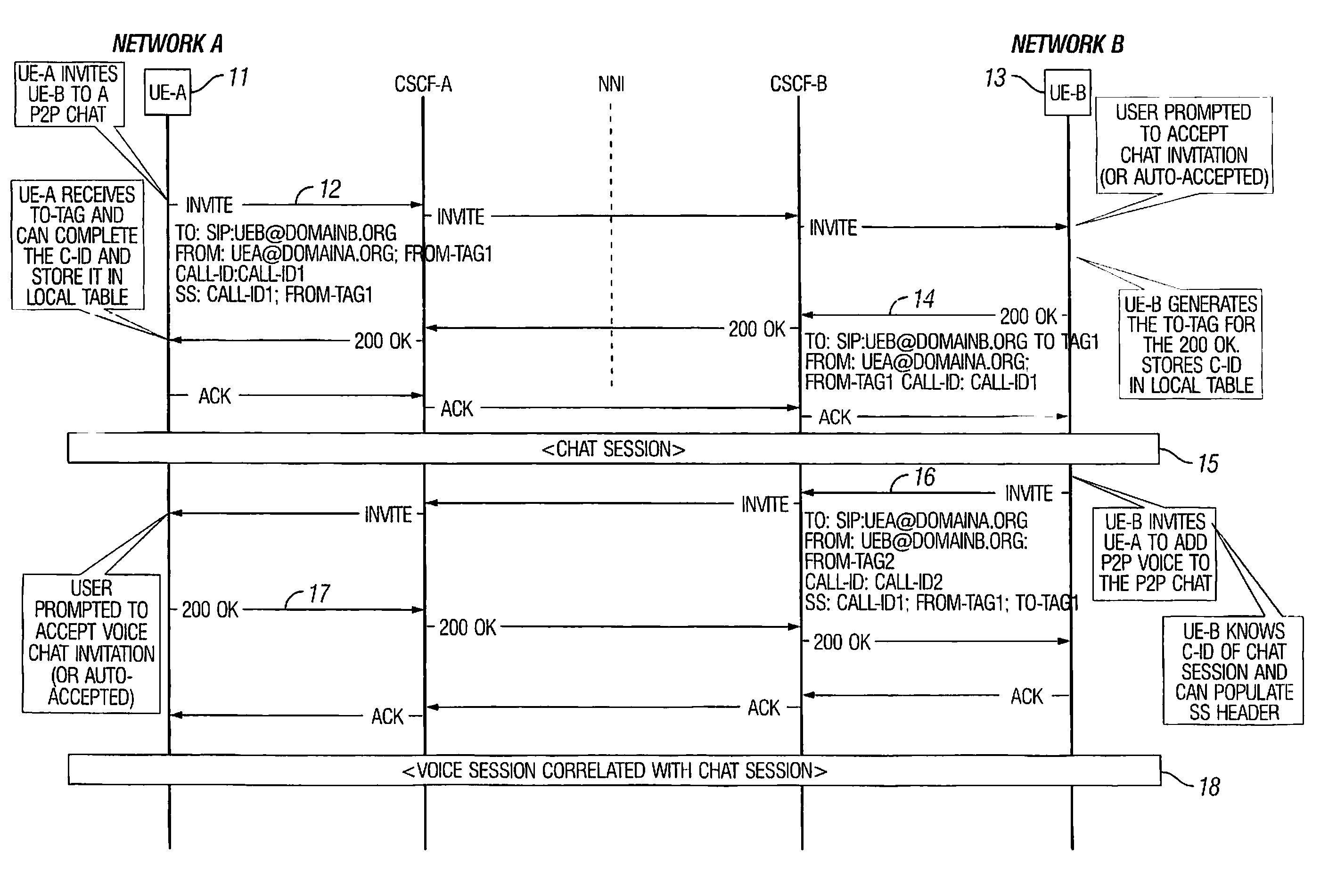

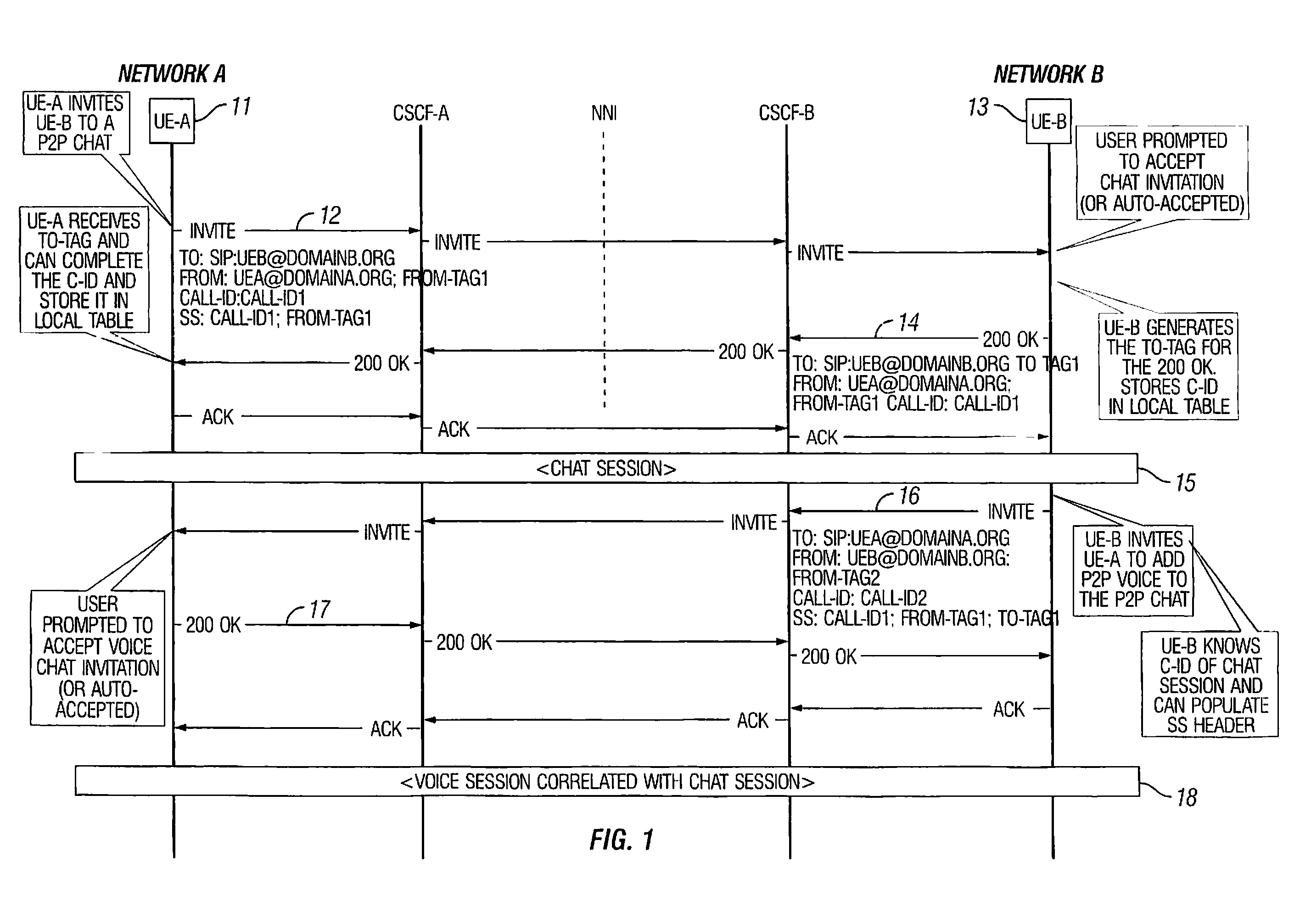

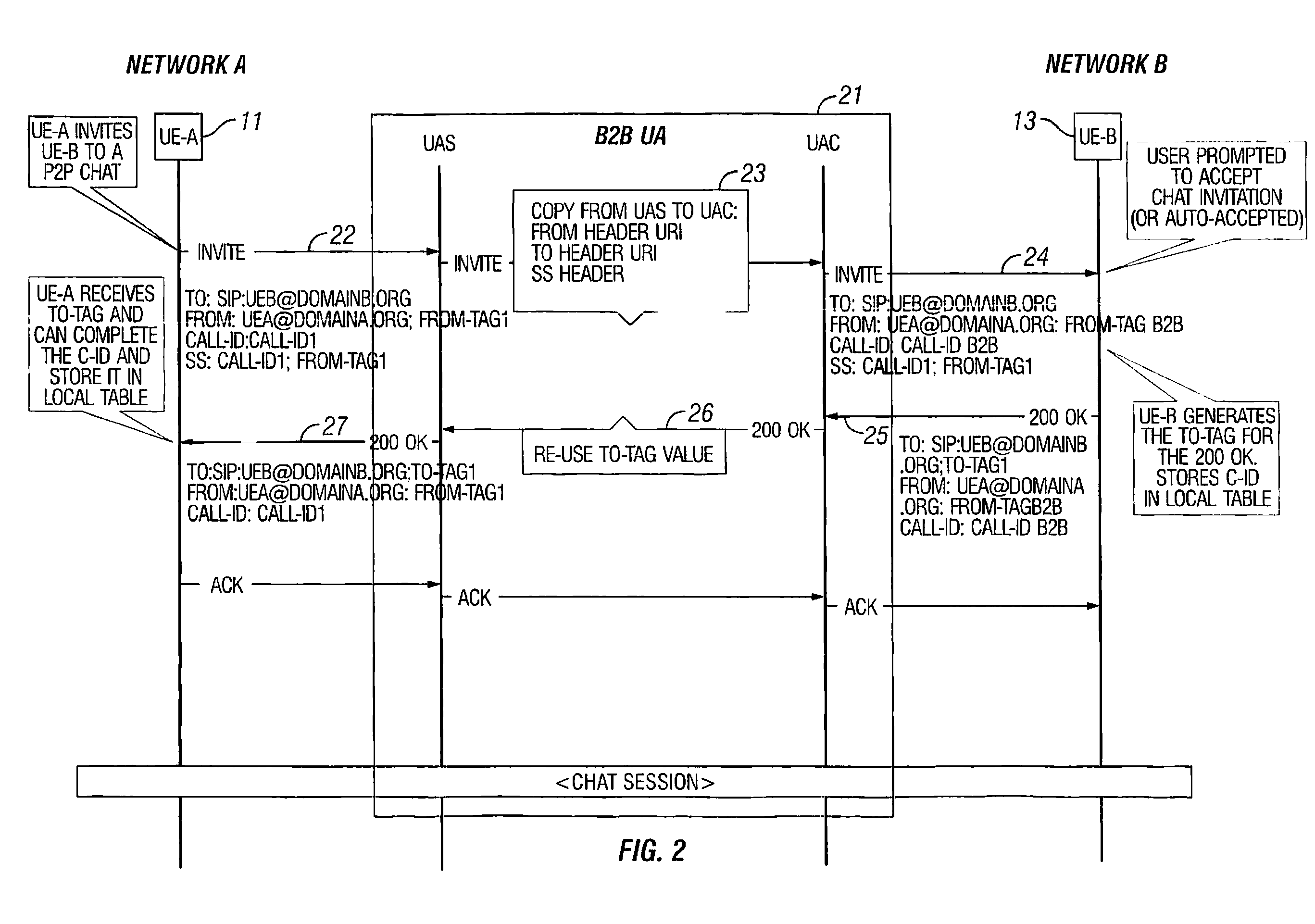

System and method for communication session correlation

InactiveUS20080089344A1High level of abstractionModulated-carrier systemsData switching by path configurationCommunications systemRadio reception

An arrangement and method in a communication system such as an Orthogonal Frequency Division Multiplexing (OFDM) radio receiver for reducing the impact of interference from an intermittent interfering signal transmitted by an interfering system which may be co-located with the OFDM system or may be remotely located. Each OFDM symbol in a received OFDM signal includes a guard interval (GI), a middle portion, and a last portion identical to the GI. The arrangement determines which portion of each OFDM symbol is contemporaneous with the interfering signal and time-shifts a fast Fourier transform (FFT) window in the OFDM receiver to minimize or eliminate FFT processing of samples of the OFDM symbol that are contemporaneous with the interfering signal, thereby minimizing the impact of the interfering signal.

Owner:TELEFON AB LM ERICSSON (PUBL)

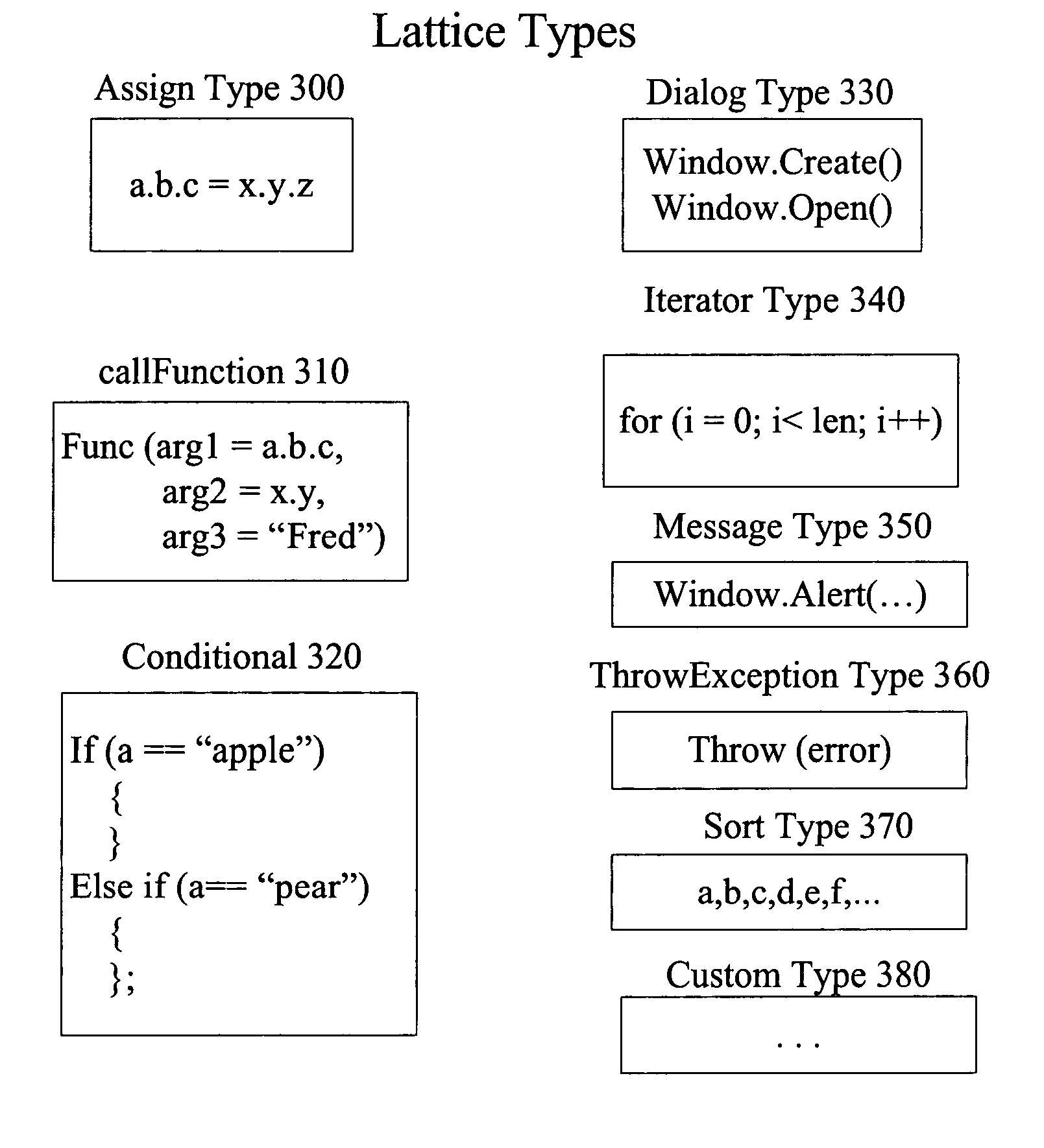

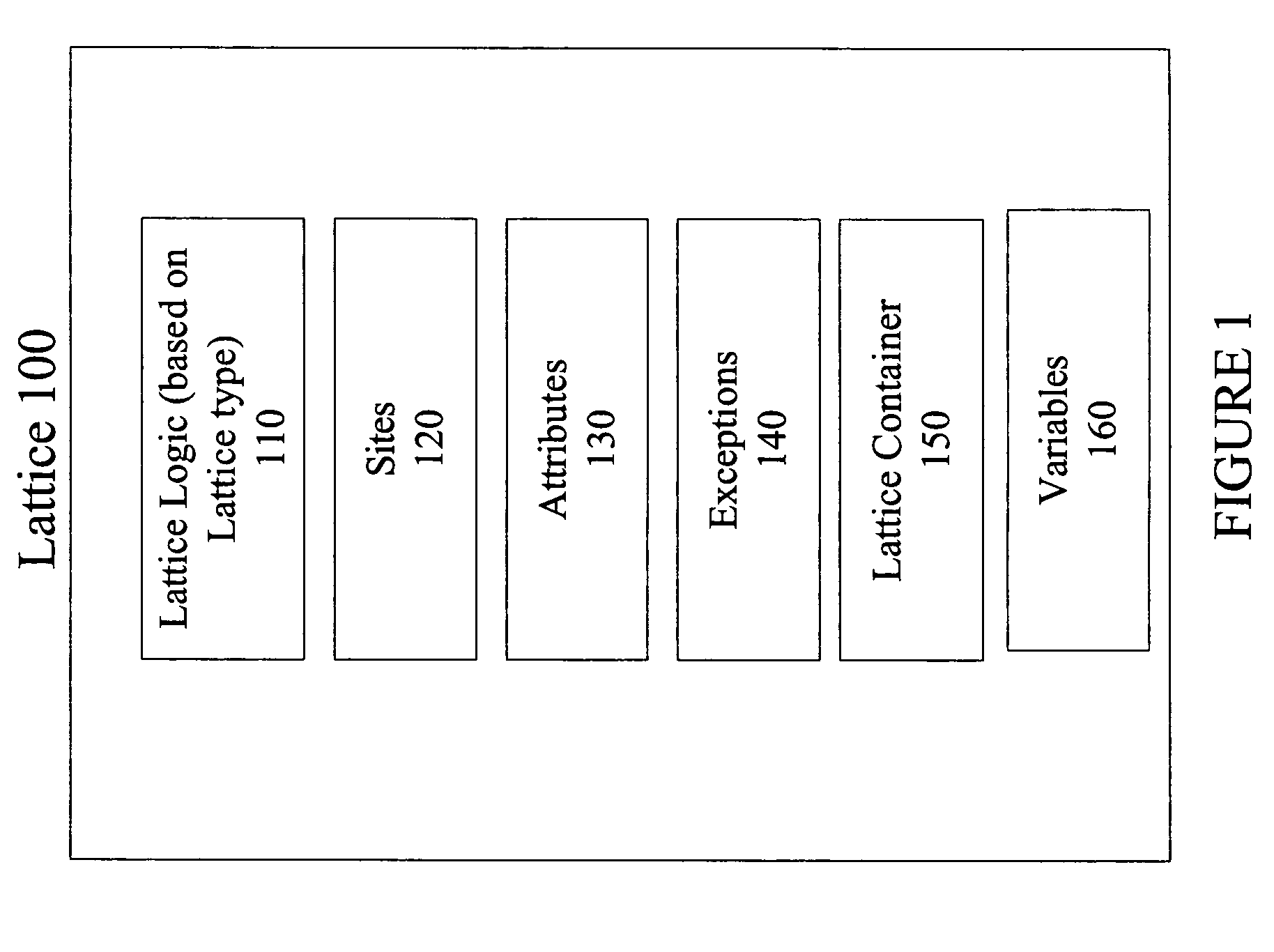

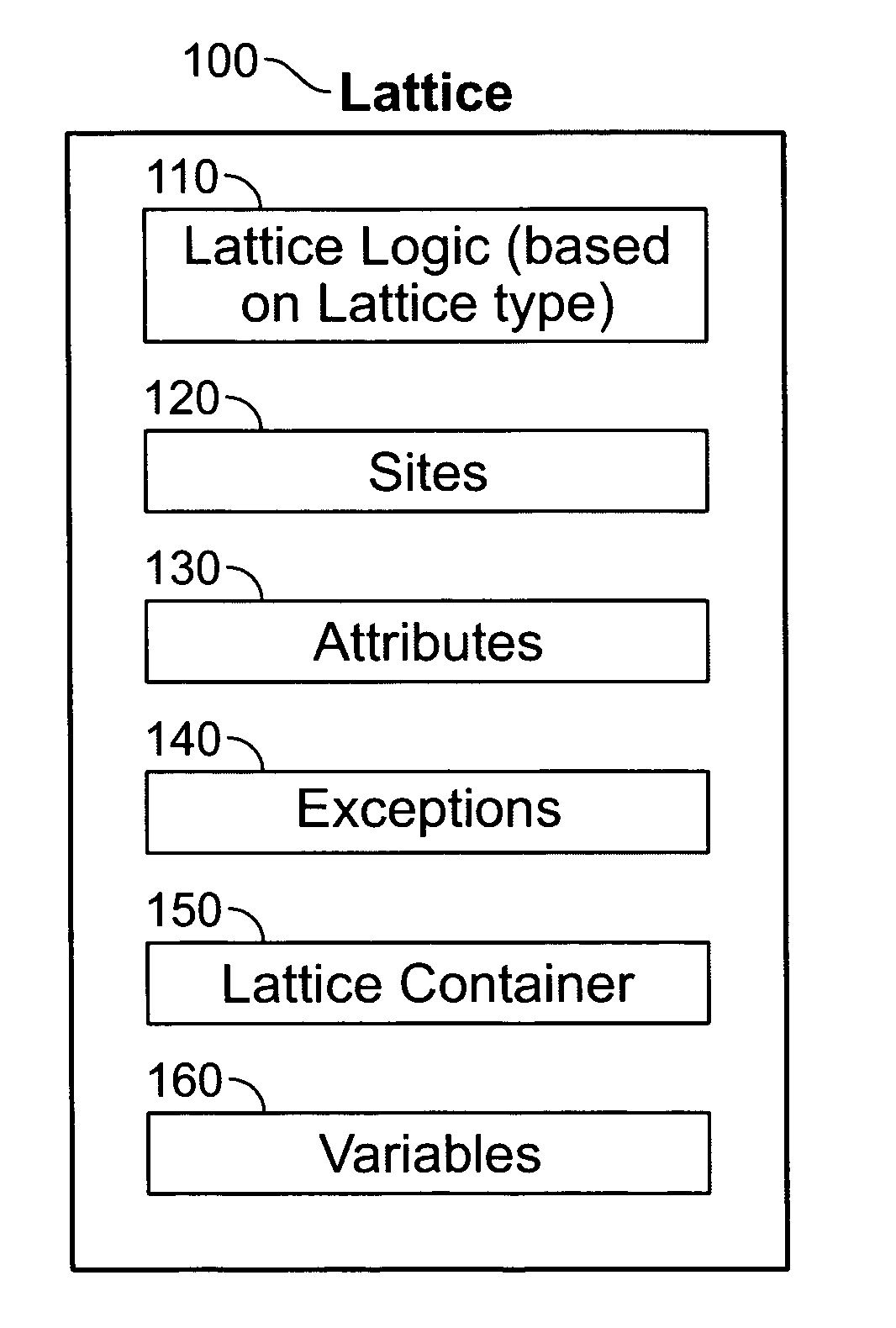

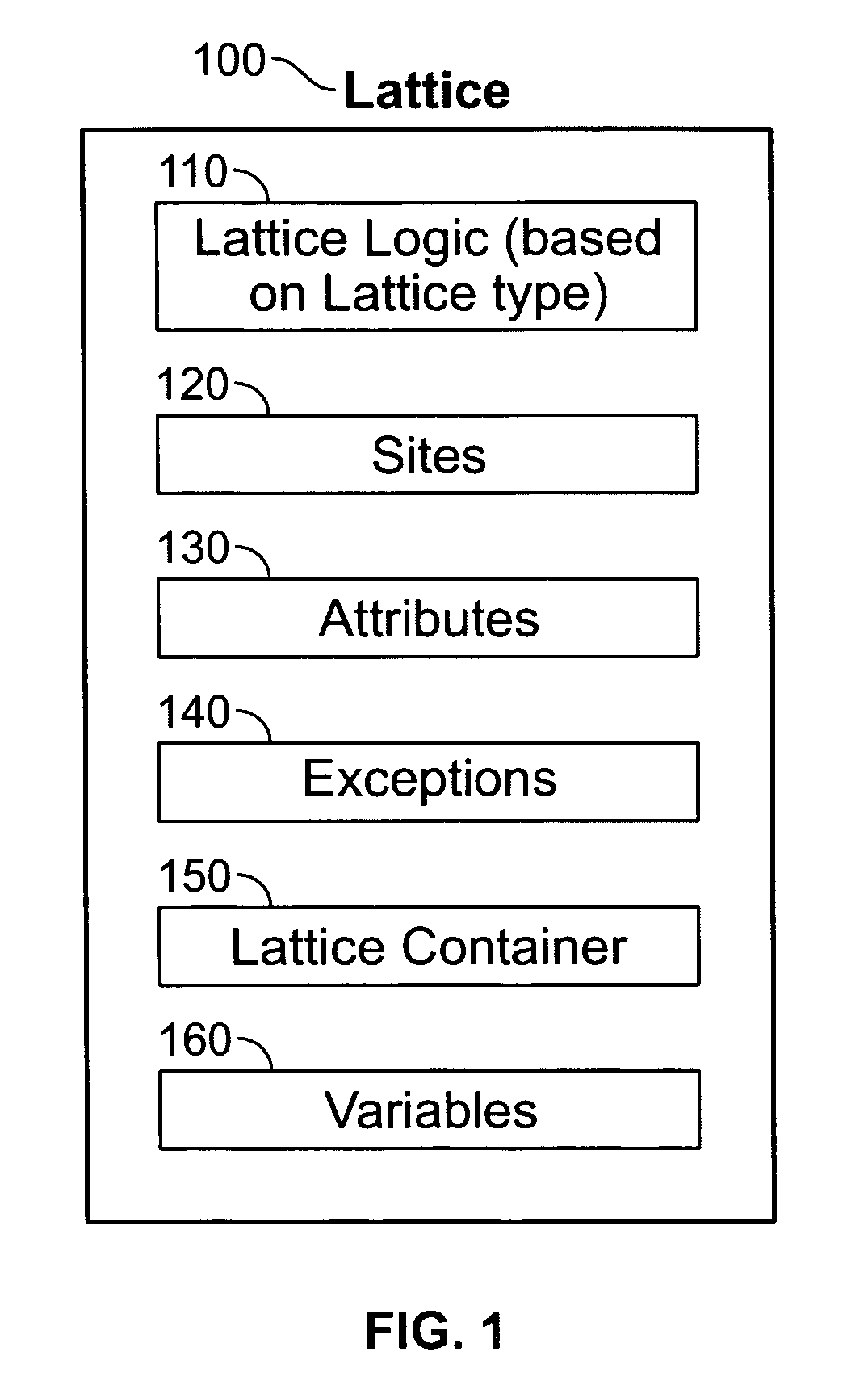

Declarative computer programming language method and system

ActiveUS20050203958A1High level of abstractionGreat degree of power and flexibilitySoftware engineeringSpecific program execution arrangementsDeclarative programmingComputer programming

A method and system for instructing a computer in a system of a declarative computer programming language. Unlike traditional declarative languages, the programming language may be neither relational nor functional, neither procedural nor imperative. The declarative programming elements may be defined as a meta-description of logic and data. The basic morphology of this meta-description may be a data construct known as a Lattice. Lattices derive declarative power from their inclusion of “Attributes” and “Sites”. Attributes are declarative properties that determine the internal behavior of a Lattice; while Sites are declarative data access points that establish the external relationship a Lattice may have with other Lattices, Lattice Containers, and Lattice Elements. Each of these data constructs are highly adaptable, recursive, and expandable, providing the entire language with a degree of flexibility that facilitates a very high level of abstraction.

Owner:III HLDG 3

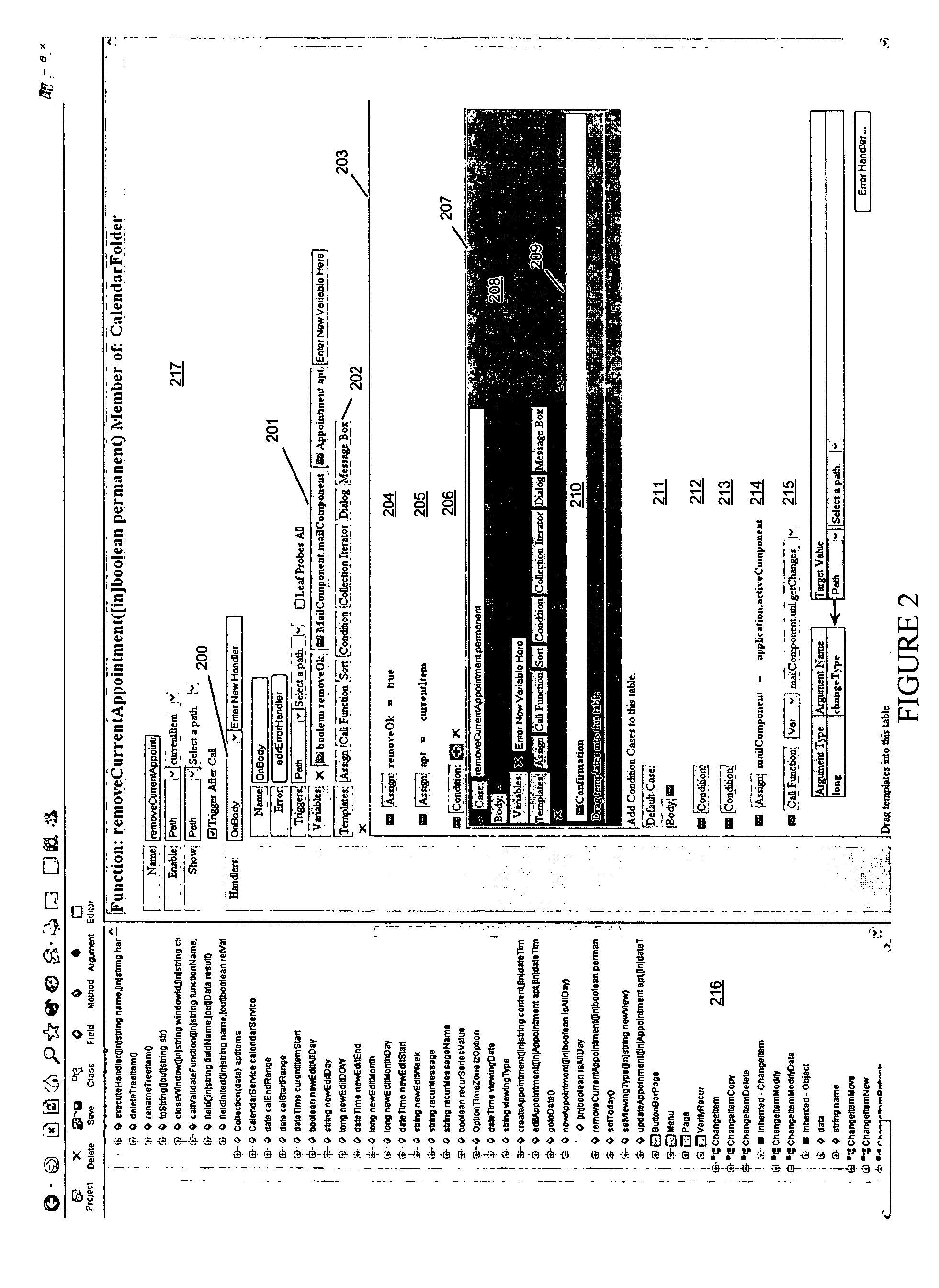

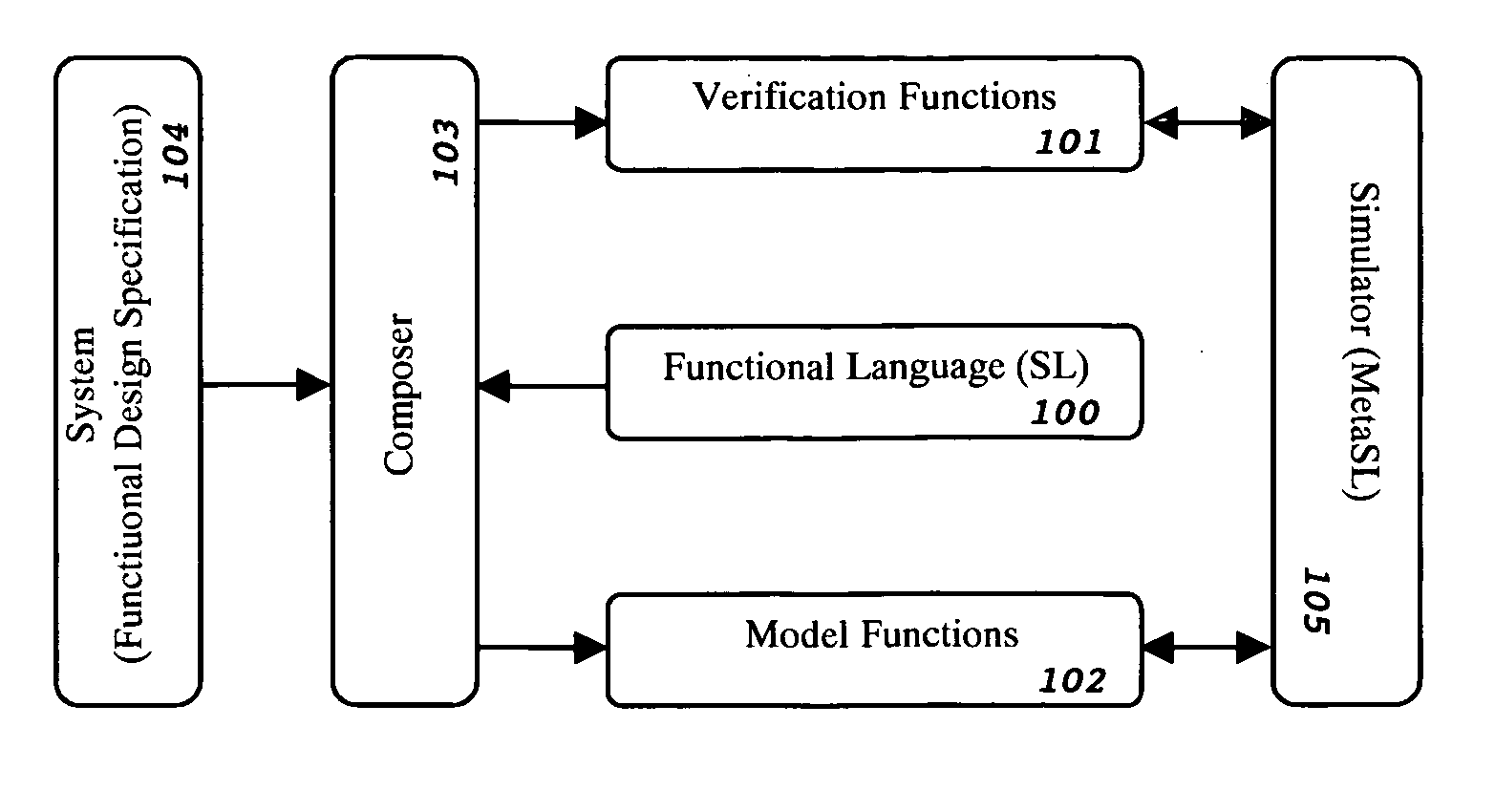

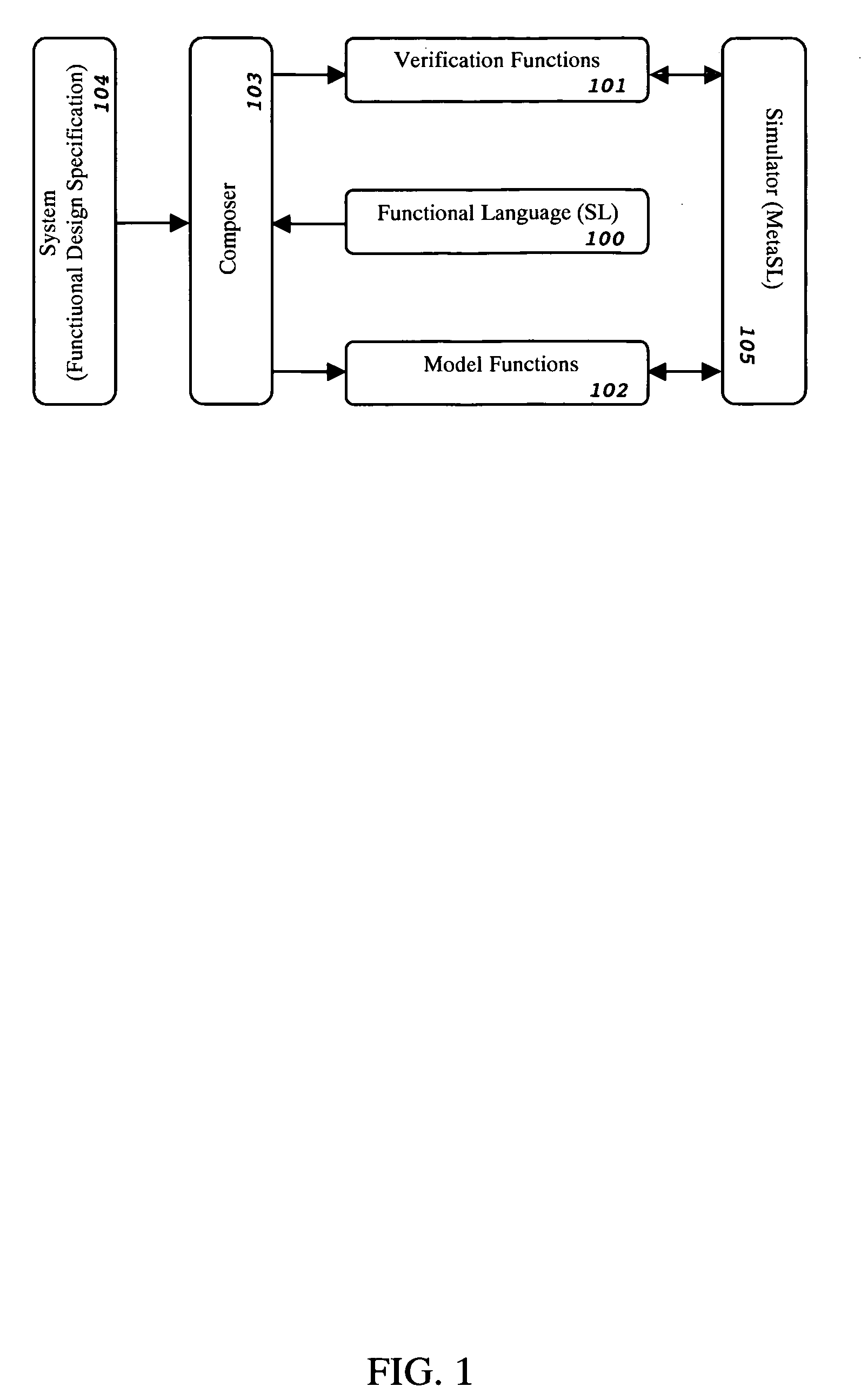

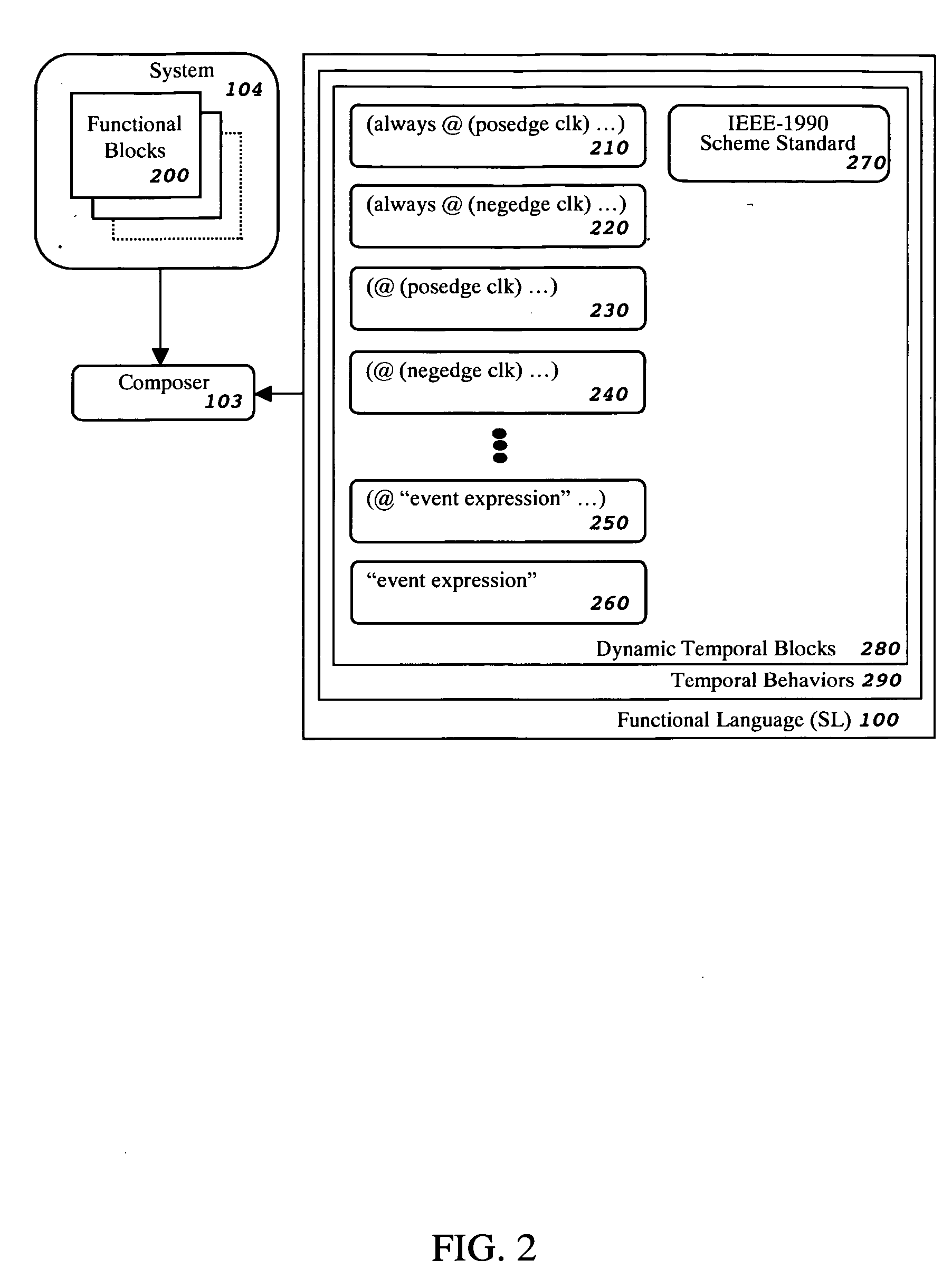

Method and apparatus for functional language temporal extensions, dynamic modeling, and verification in a system-level simulation environment

InactiveUS20050209840A1Easily instructHigh level of abstractionCAD circuit designProgram controlGraphical user interfaceRegister-transfer level

A method and apparatus for functional simulation of a system 104 in a system-level simulation and verification environment using a functional language 100 derived from a selected Scheme Language standard, and a simulator 105 for simulating verification functions 101 and model functions 102 expressed in the functional language 100. The functional language 100 has syntax extensions expressed as dynamic “always @” and “@” blocks, and all other event expressions which are similar to Verilog and other RTL (Register-Transfer Level) HDL (Hardware Description Language) temporal syntax constructs. A composer 103 is further used to connect verification functions 101 with model functions 102. Model functions 102, represented as mutable state functional objects along with selected test, monitor, checker and user-defined functions, sample reactive responses and ensure concurrent drive of abstracted signals for the simulator 105. The simulator 105 can function as a formal verifier to formally verify the model functions 102, or a synthesizer to transform programs written in a restricted subset of the functional language 100 into an internal control and data flow format or any synthesis-ready language. A system-level modeling and simulation environment enhanced with a graphical user interface facilitates the usage of the functional language 100.

Owner:SIMANTIX SYST

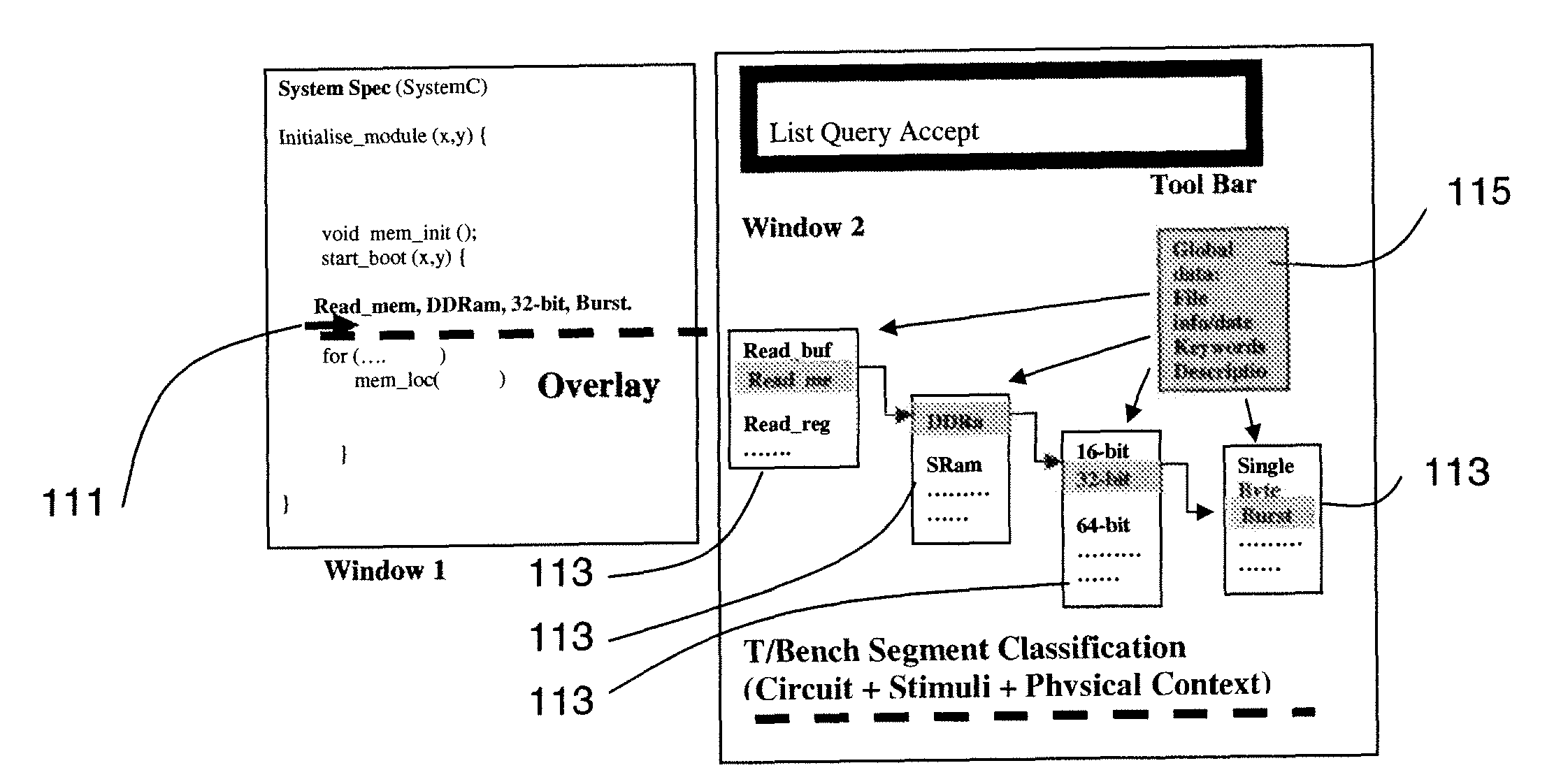

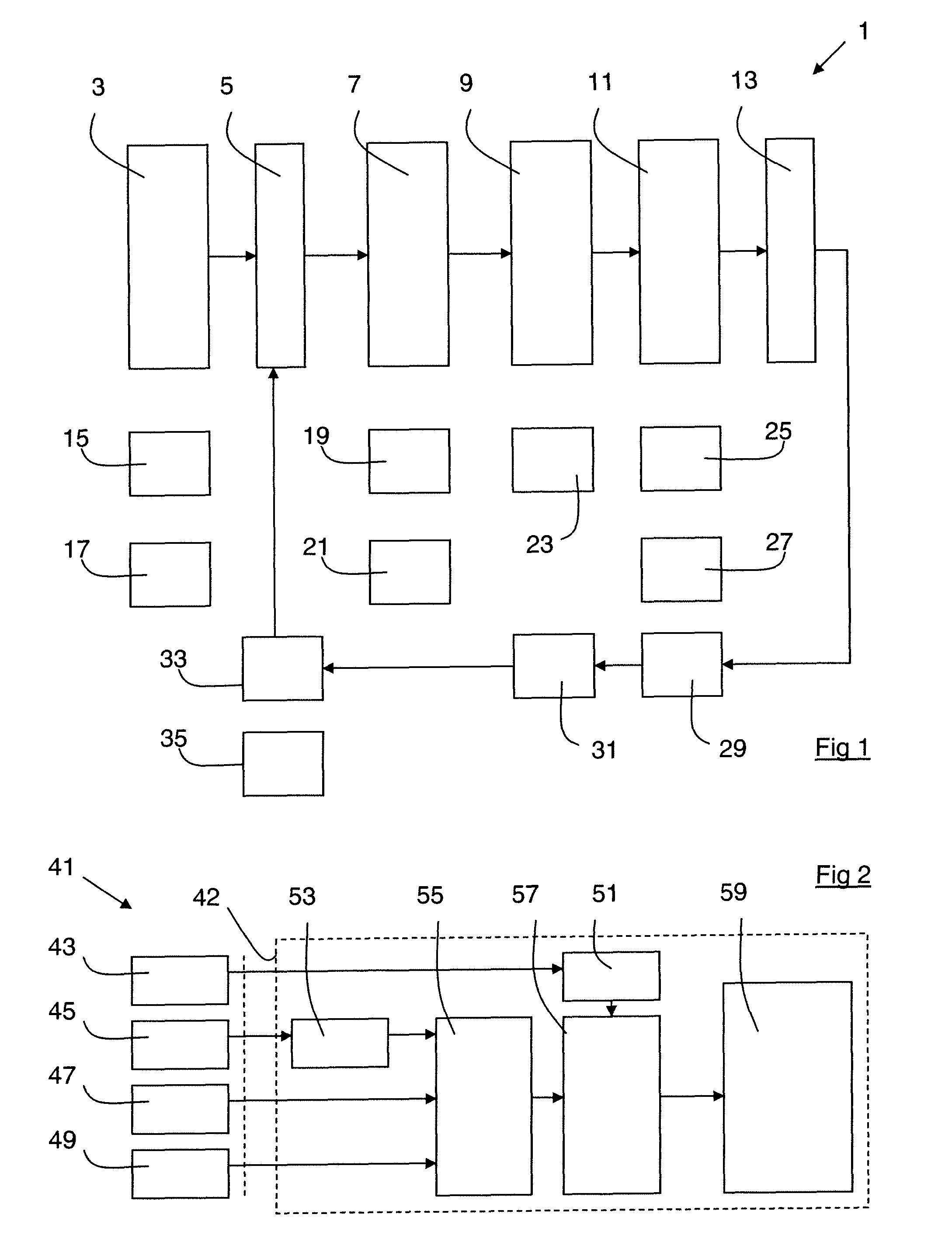

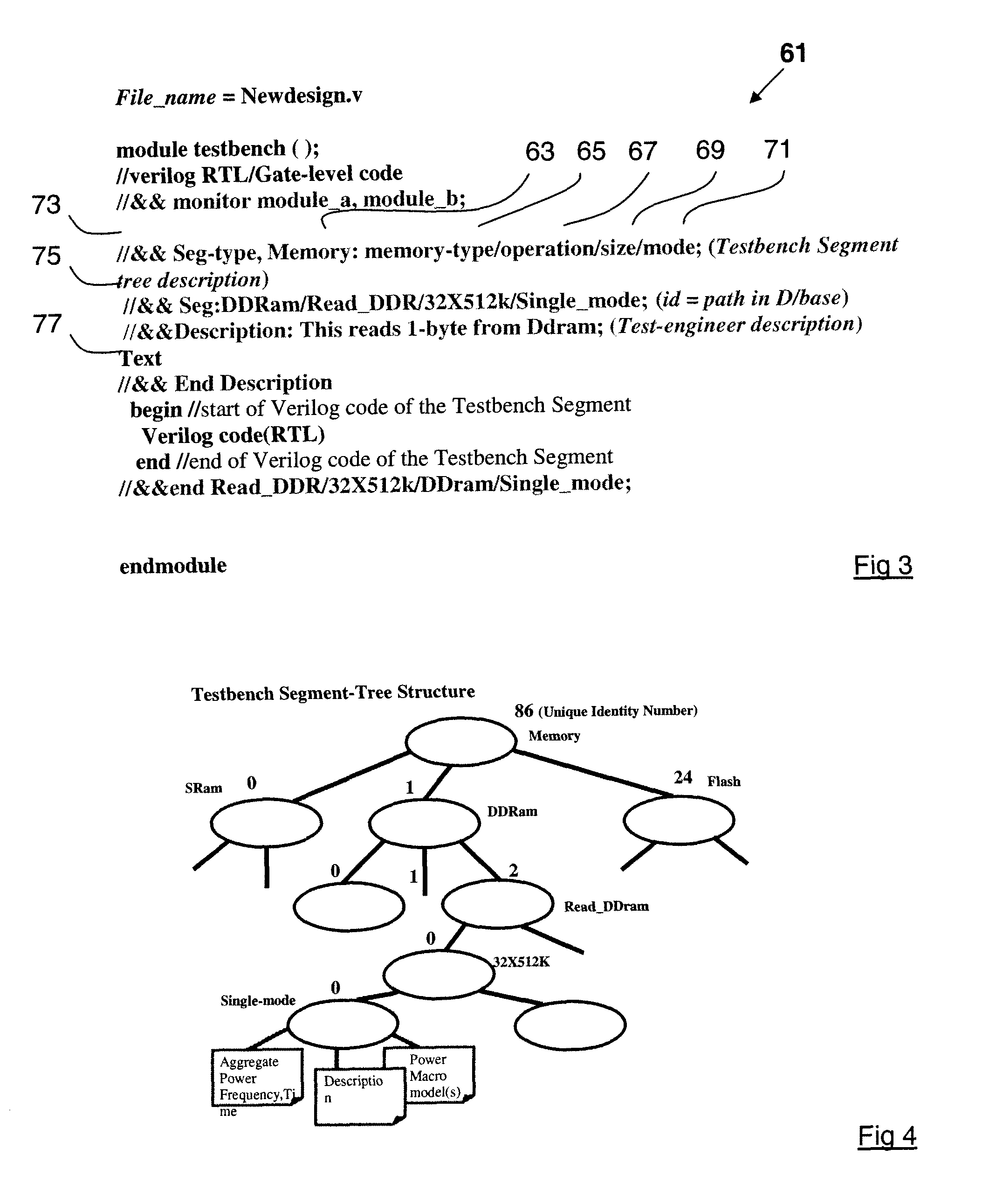

System level power evaluation method

InactiveUS20110035203A1Overcome disadvantagesMinimize power consumptionDesign optimisation/simulationSpecial data processing applicationsSystem levelComputer architecture

This invention relates to a system level power evaluation method in which detailed power macro-models (PMM) are created for operations of modules. These PMMs are stored in memory. A system level circuit description (SLCD) is evaluated using the PMMs stored in memory that are relevant to that SLCD and using other PMMs that are generated for operations of modules that do not have PMMs stored in memory. In this way, a highly accurate and computationally efficient power evaluation of the SLCD is possible. Furthermore, the user implementing the method may define a case, which relates to an operation of a module and has a PMM associated therewith, in a highly flexible manner that allows for more abstract analysis of the SLCD to be carried out. A case may relate to a single operation of a module, a plurality of operations of a module or operation(s) of a plurality of modules.

Owner:UPM RAFLATEC OY

Declarative computer programming language method and system

ActiveUS7836428B2Great degree of power and flexibilityHigh level of abstractionSoftware engineeringSpecific program execution arrangementsExtensibilityWeb site

Owner:III HLDG 3

Method and apparatus for accelerating hardware simulation

InactiveUS7050958B1Reduce in quantityFunction increaseAnalogue computers for electric apparatusCAD circuit designCommunication interfaceSystems design

A method for accelerating hardware simulation is presented wherein cycle based simulations of digital system designs are generated by raising the level of abstraction in a hardware simulation environment. Behavioral models of the digital system components are created in a high level general purpose programming language. Function calls created in a high level general purpose programming language provide a transaction based communication interface. During a simulation of the system design, the behavioral models communicate with each other through the transaction based communication interface. Additionally, the behavioral models employ an execute and update method of instruction processing that generates cycle accurate information for the simulation.

Owner:ARM LTD

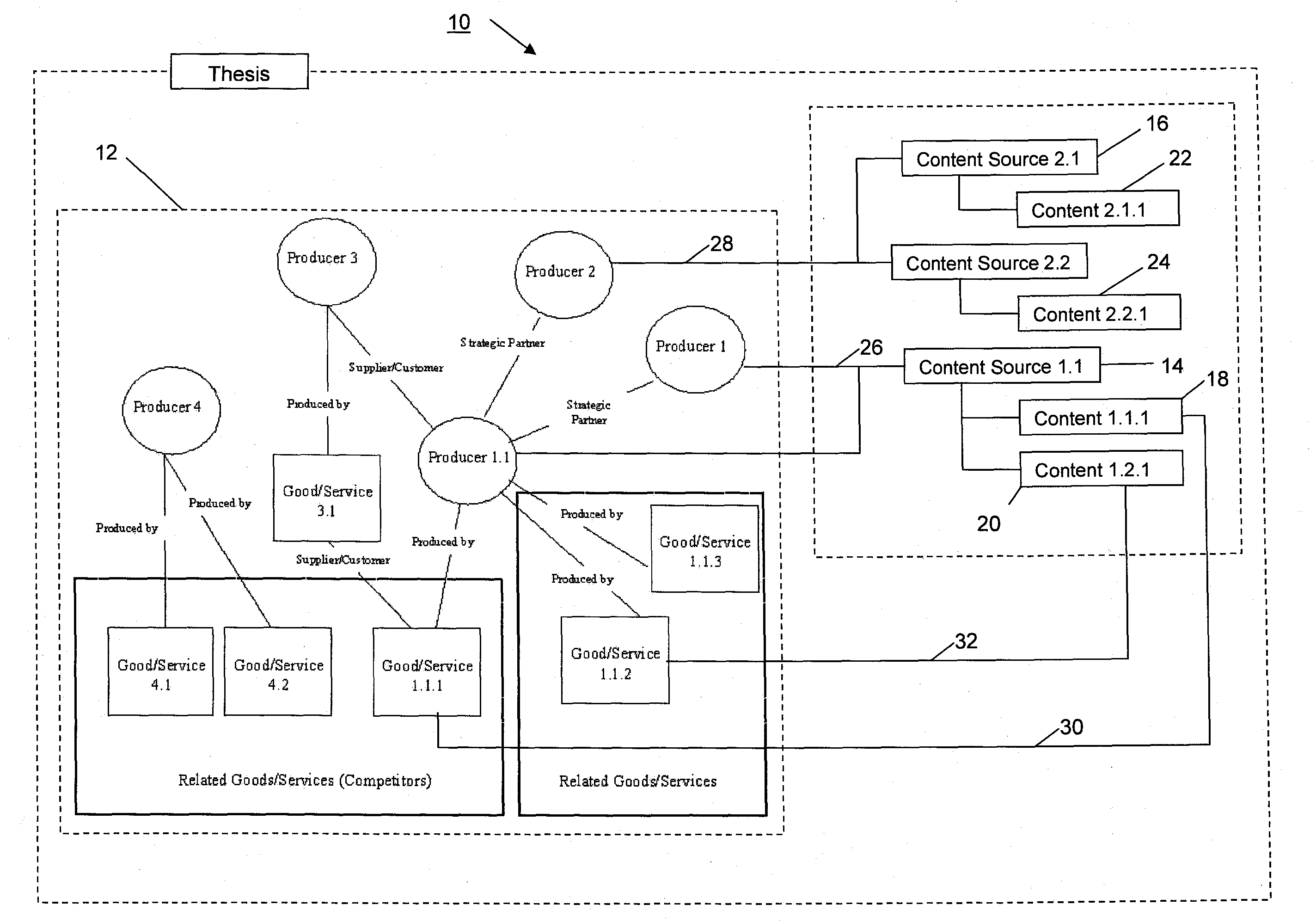

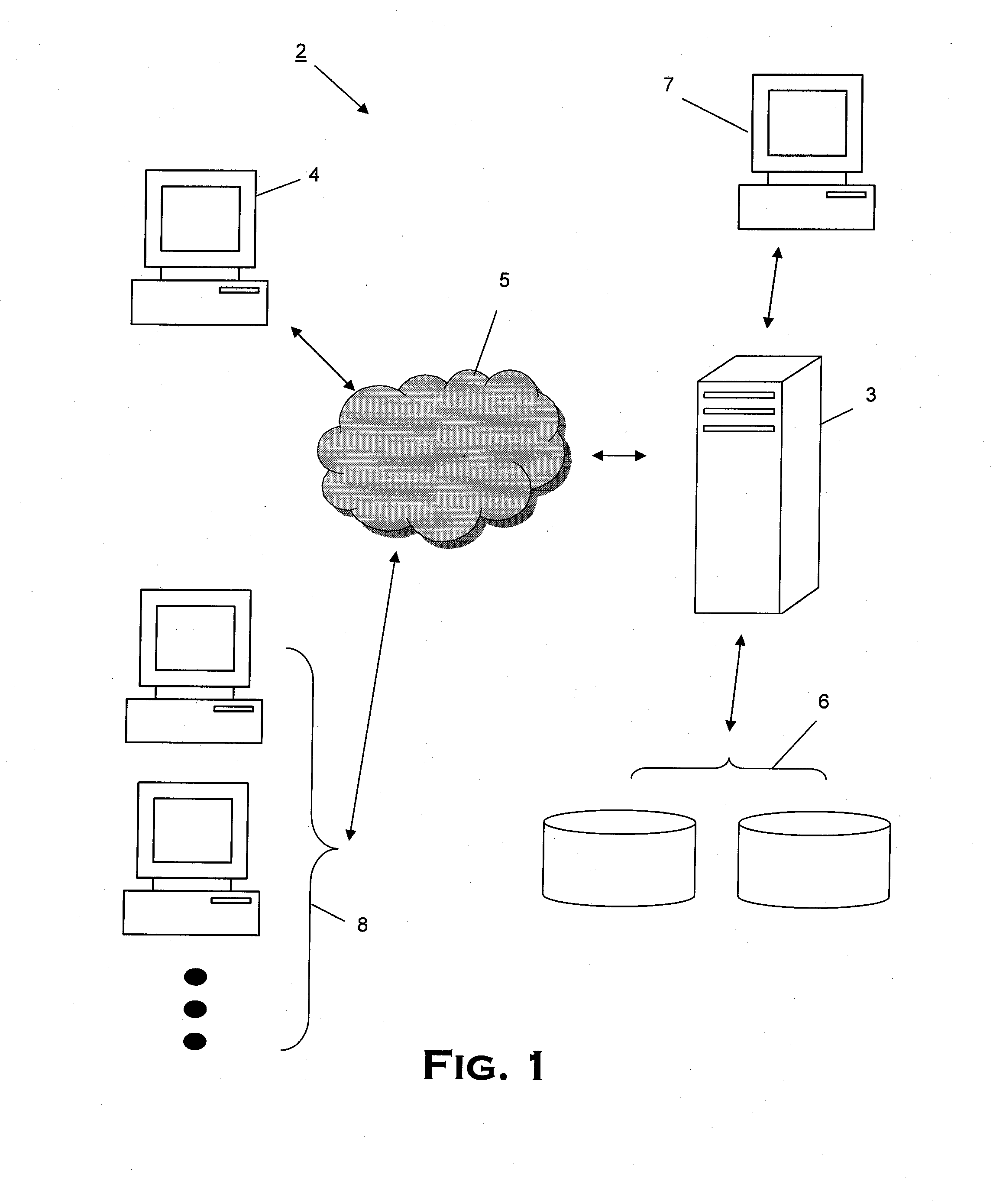

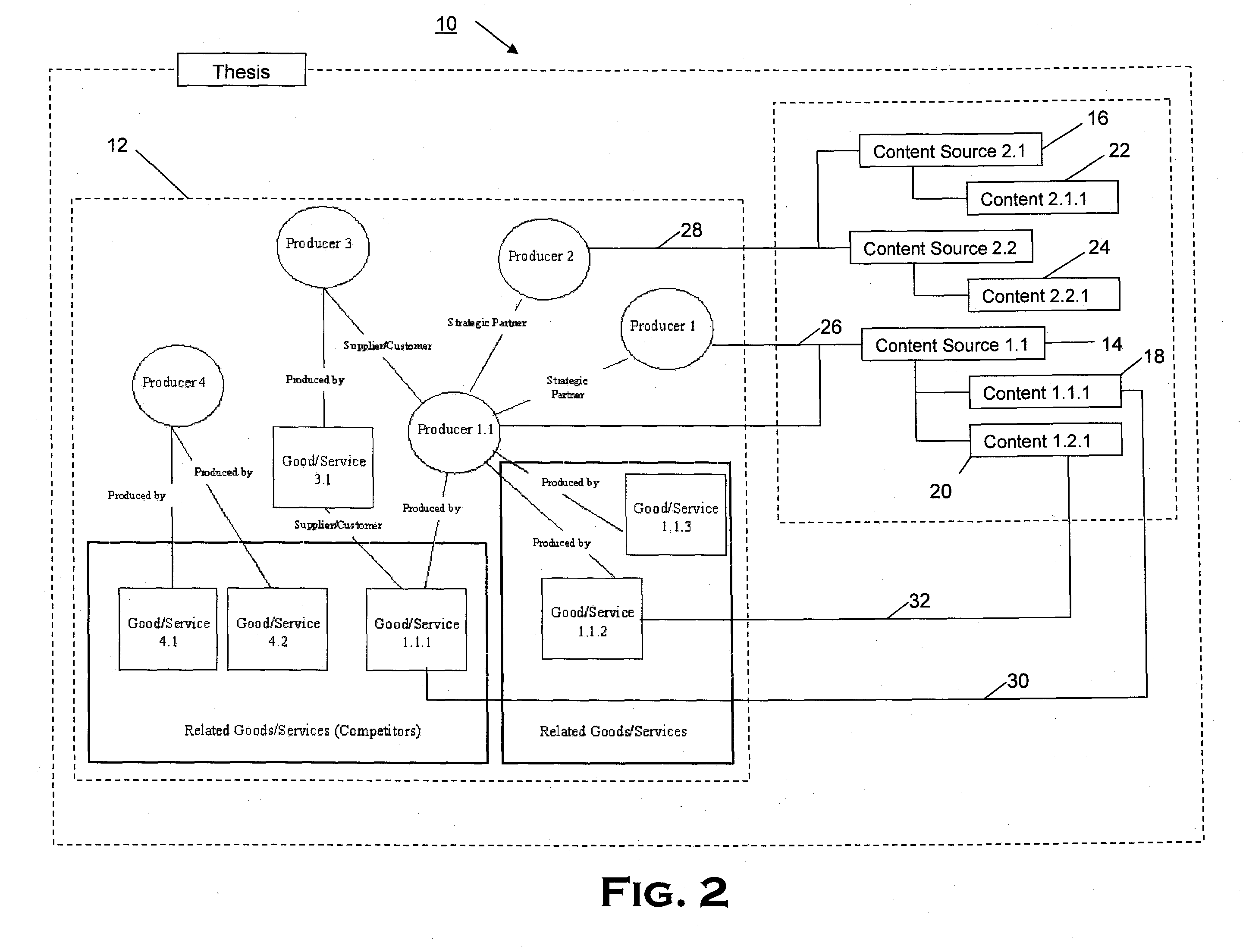

System for storing, displaying, and navigating content data regarding market driven industries

InactiveUS20070276871A1Simplify speed up processEfficient navigationDigital data processing detailsOffice automationMarket drivenResearch model

A model and system employing the model provides an organized structure for storing, displaying, and navigating content data regarding instruments for market driven industries (i.e., securities). A Market Research Model (MRM) paradigm is used to represent elemental concepts, a plurality of specific classes of entities form the MRM, and an interface is used to assemble, maintain, and interact with the model. Information may be added to the model by a research provider and provided to an end user on a subscription basis. The user is provided with an interconnected, navigable model of an item of interest for research and decision-making support.

Owner:PRIMARY GLOBAL RES

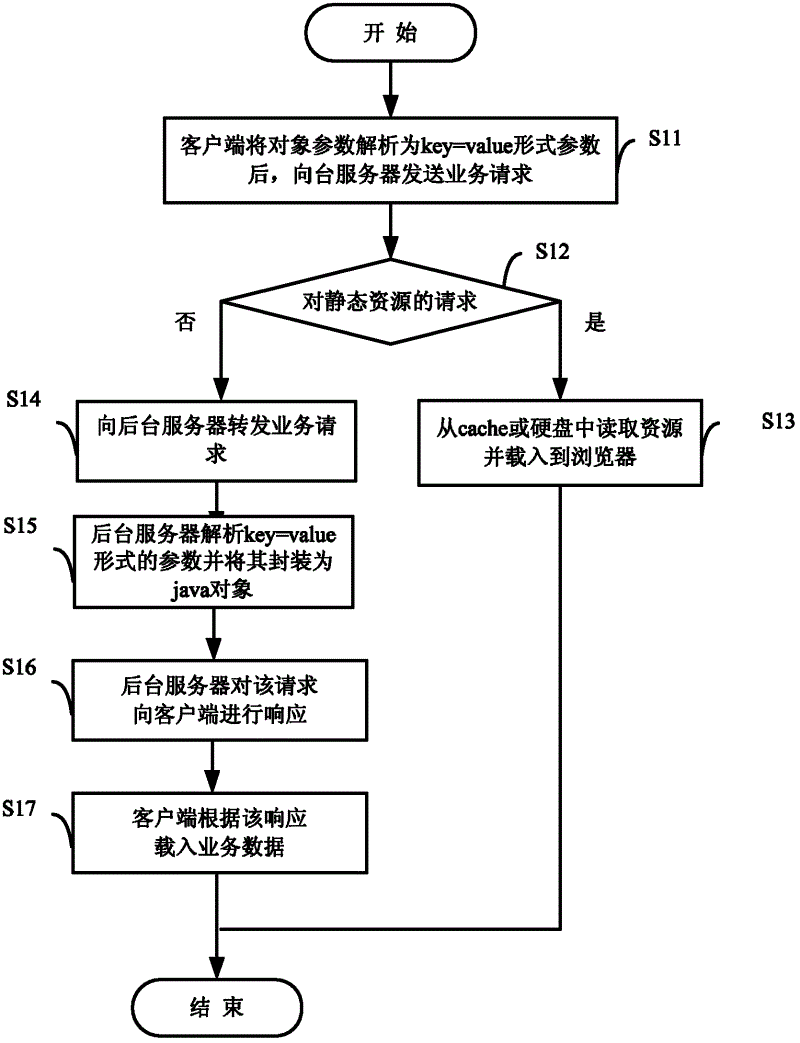

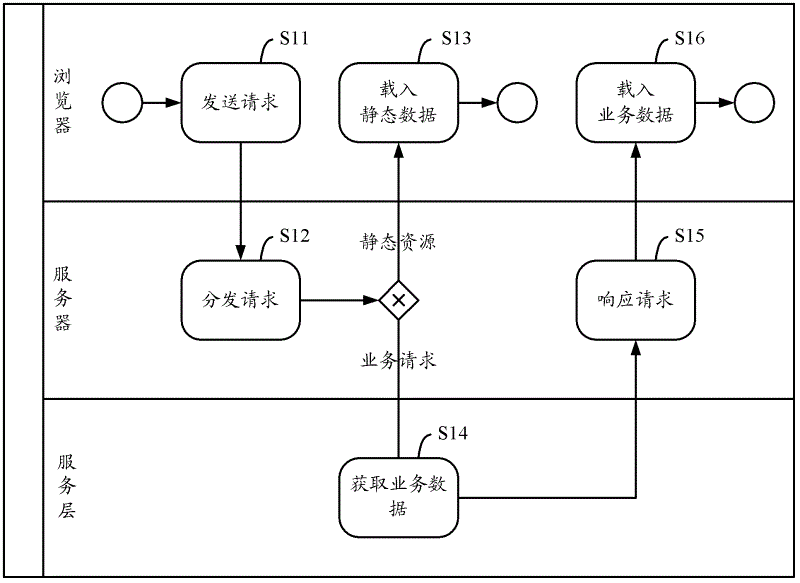

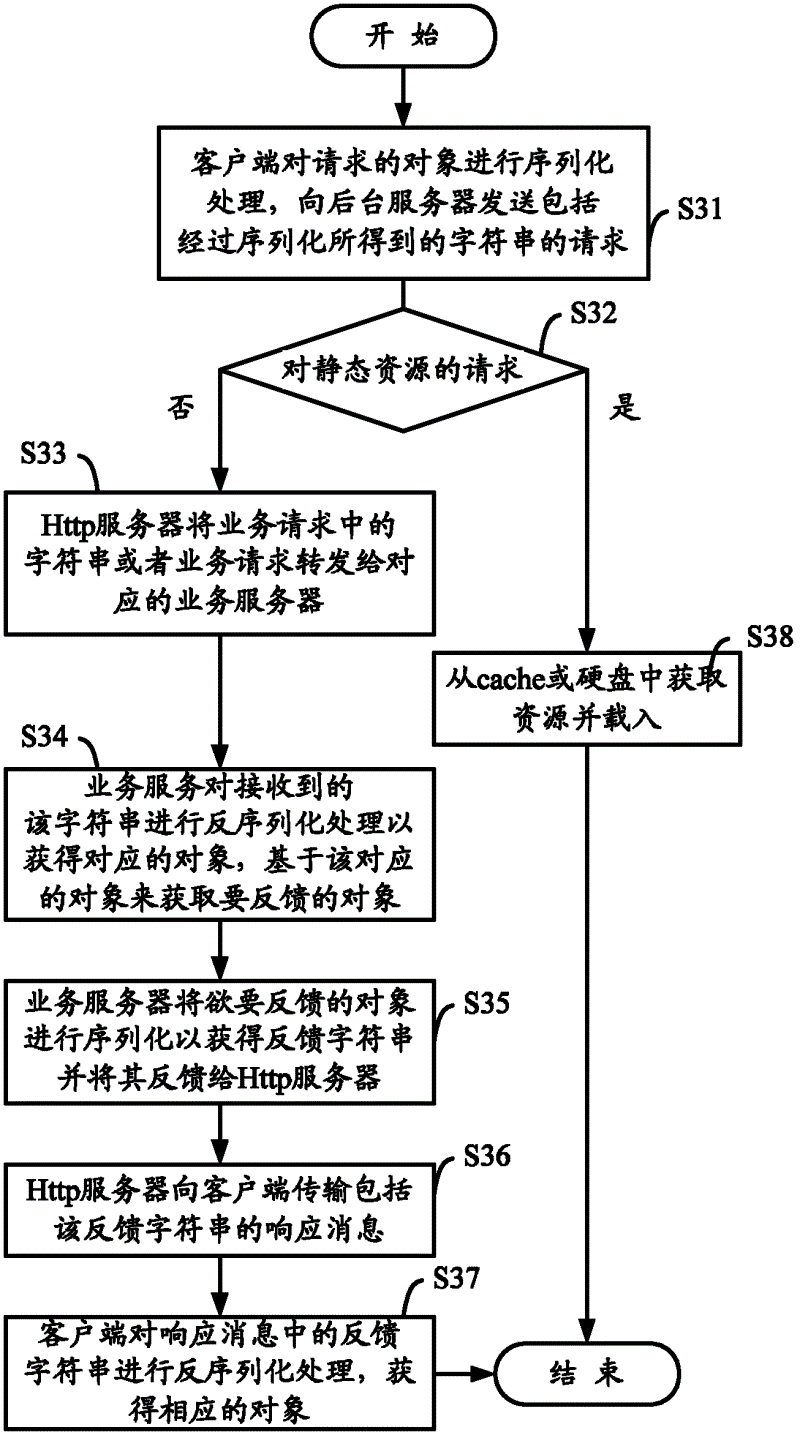

Method and system for processing network service request

InactiveCN102624895AShielding is cumbersomeHigh level of abstractionError prevention/detection by using return channelSerializationNetwork service

The invention discloses a method and a system for processing a network service request. The method comprises the following steps that: a client serializes an object of a request to be transmitted to a background server, and transmits a request taking a request character string obtained by the serialization as a parameter to the background server; the background server receives the request from the client, and de-serializes the request character string in the received request to obtain a corresponding object; the background server acquires an object to be fed back on the basis of the corresponding object, and serializes the object to be fed back to obtain a feedback character string; and the client receives the feedback character string, and de-serializes the feedback character string to obtain corresponding object information. By the method, the operation of the client and / or the background server is simplified.

Owner:亿赞普(北京)科技有限公司

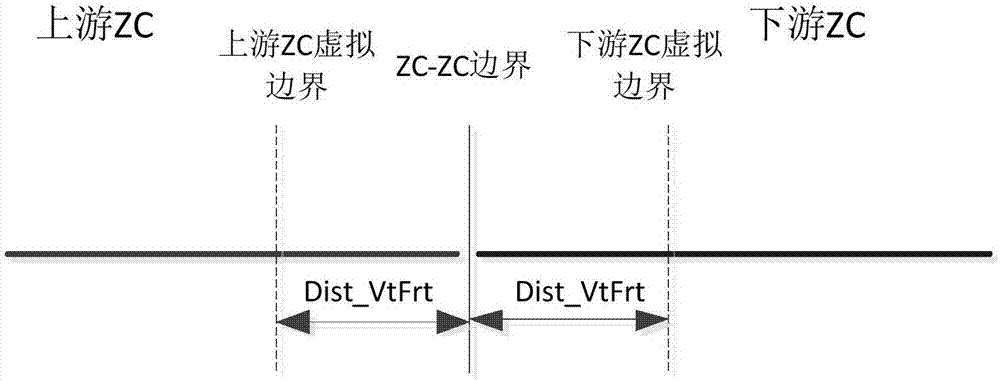

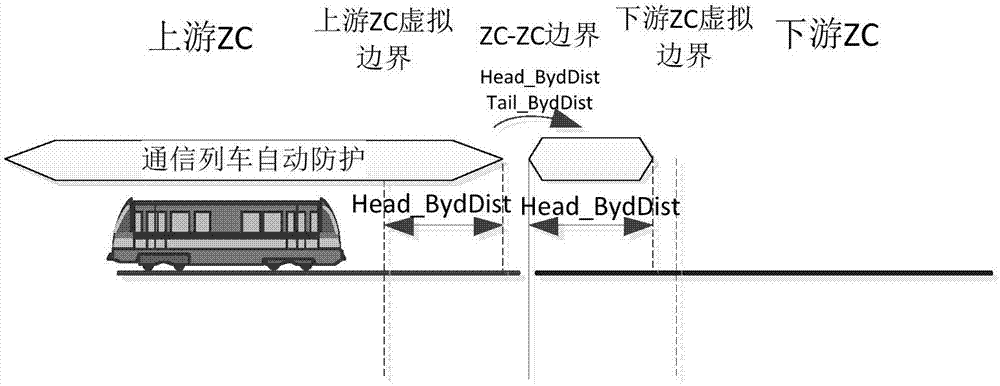

Zone controller train transfer management method based on automatic protection of train

ActiveCN107139974AHigh level of abstractionEasy to implementRailway traffic control systemsProcess mechanismAutomatic train protection

The invention relates to a zone controller train transfer management method based on automatic protection of trains. The zone controller train transfer management method comprises the following steps: A, respectively setting virtual boundaries for an upstream ZC (Zone Controller) and a downstream ZC; B, transmitting a transfer 'automatic train protection' virtual boundary cross distance to the downstream ZC by the upstream ZC; C, establishing receiving 'automatic train protectio' by the downstream ZC; D, updating the receiving 'automatic train protection' by the downstream ZC; E, transmitting a receiving 'automatic train protection' virtual boundary cross distance to the upstream ZC by the downstream ZC; and F, deleting the transfer 'automatic train protection' by the upstream ZC. Compared with the prior art, the method has the advantages of being high in processing mechanism abstract degree, concise in interface, small in line constraint condition, low in processing coupling degree of adjacent ZCs, and the like when being adopted to process train transfer among ZCs.

Owner:CASCO SIGNAL

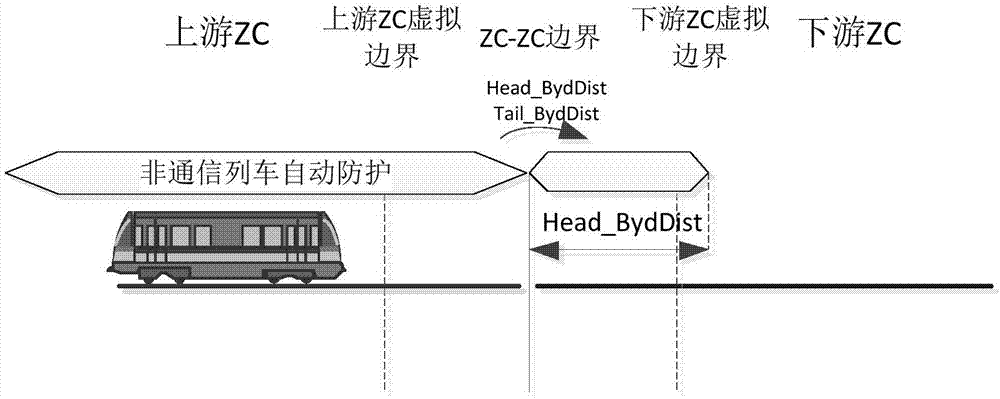

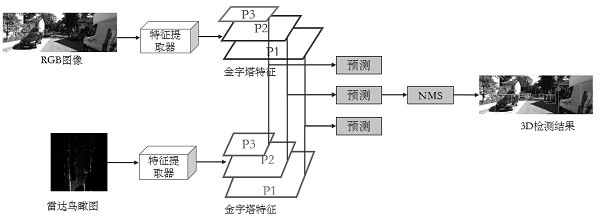

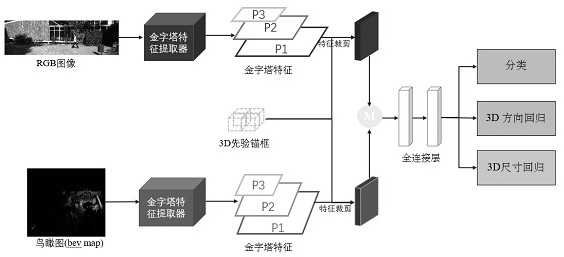

Multi-scale three-dimensional target detection method based on feature pyramid network

The invention discloses a multi-scale three-dimensional target detection method based on a feature pyramid network. The objective of the invention is to solve the problem that a target is easy to loseunder complex conditions (such as target partial occlusion and low long-distance imaging resolution). According to the method, the advantages of RGB images and radar point clouds in a detection taskare combined, 3D point clouds are expressed as multi-channel aerial views, a pyramid feature extractor is designed, and multi-scale and strong semantic feature expressions of the aerial views and theRGB images are constructed respectively; and a prior anchor box is applied to each feature output layer, regional fusion features are obtained through feature cutting operation, the regional fusion features are directly input into a shared classifier and a regression device to complete cross-scale detection, and an optimal target classification and positioning result is obtained. The method is a single-stage detection method, the step of generating a proposal box is omitted, the network structure is simple; the real-time performance, the accuracy and the robustness of detection are guaranteed,and the detection rate and the positioning accuracy of a partially-shielded and long-distance target are effectively improved.

Owner:SICHUAN UNIV

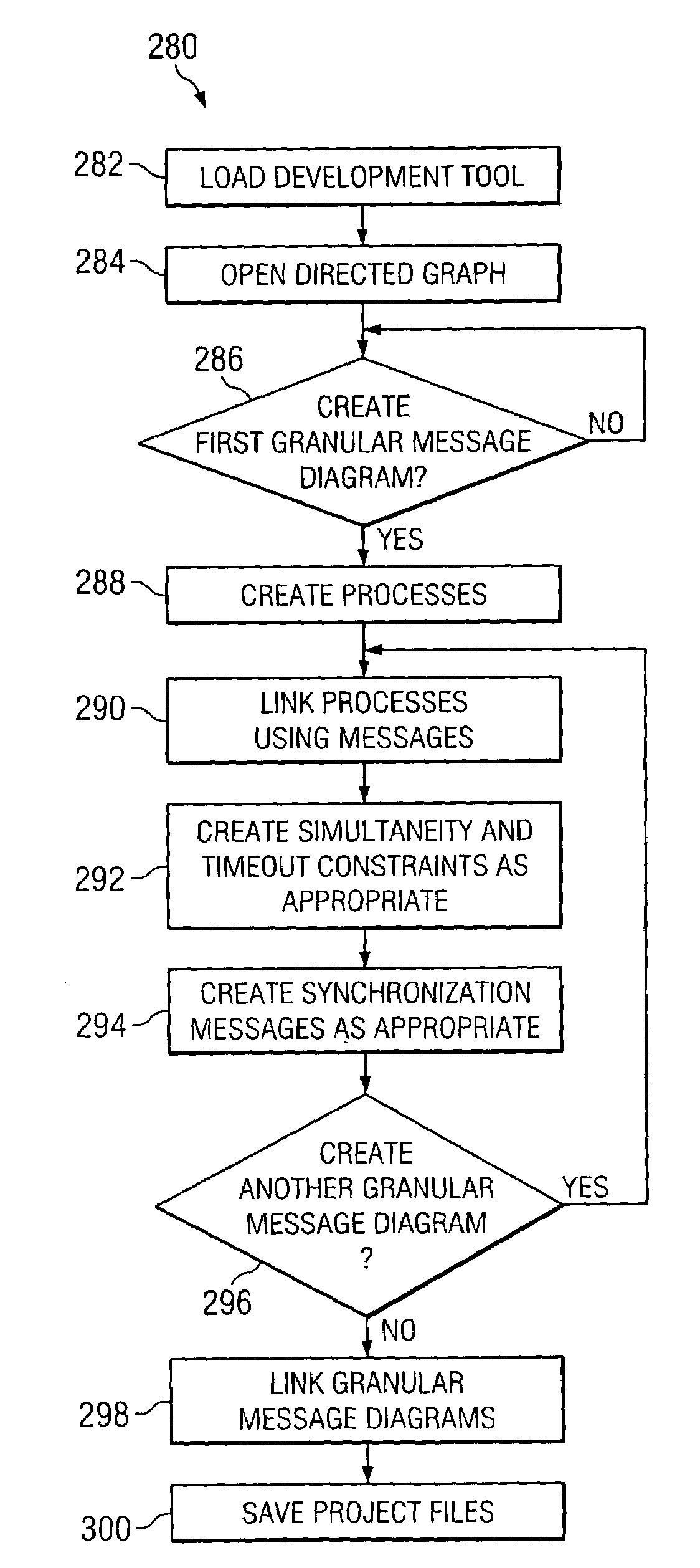

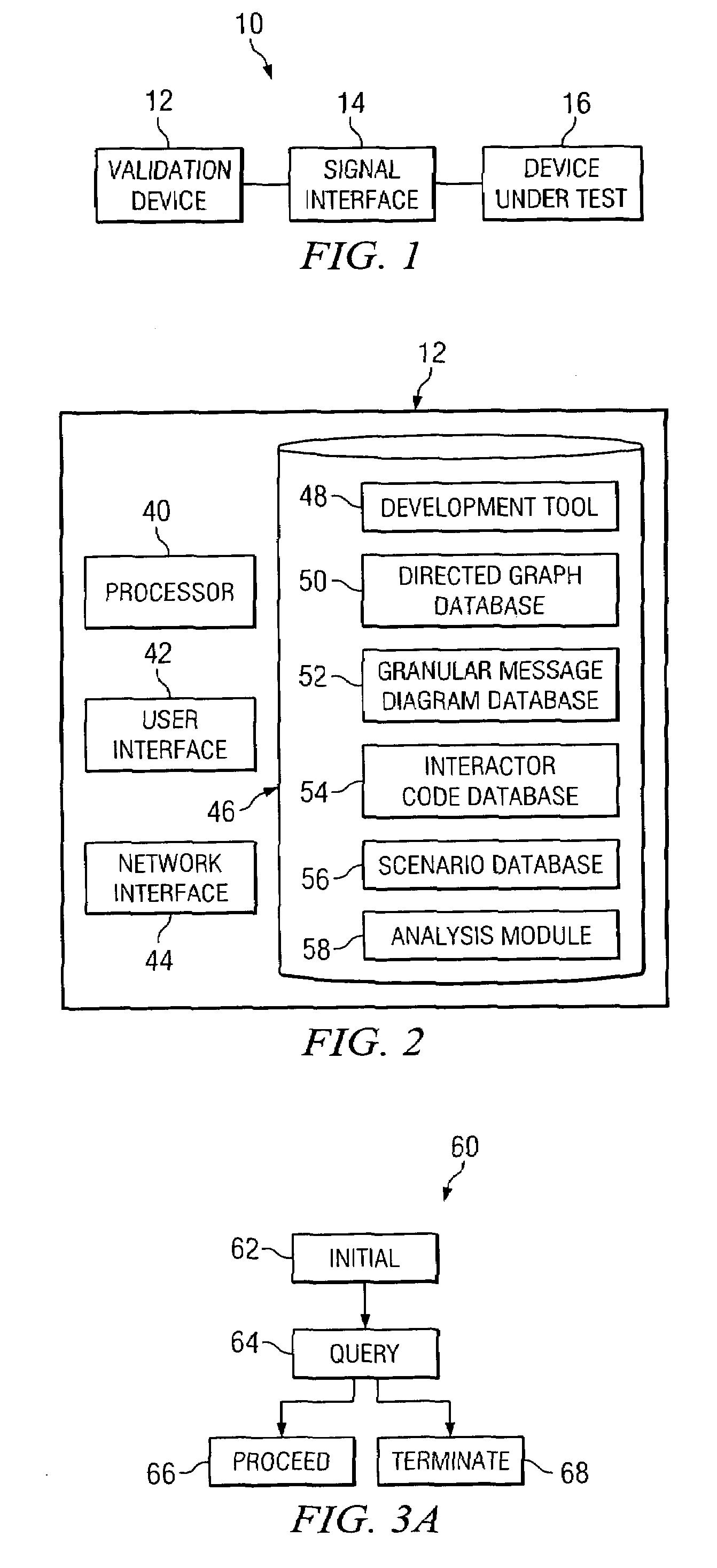

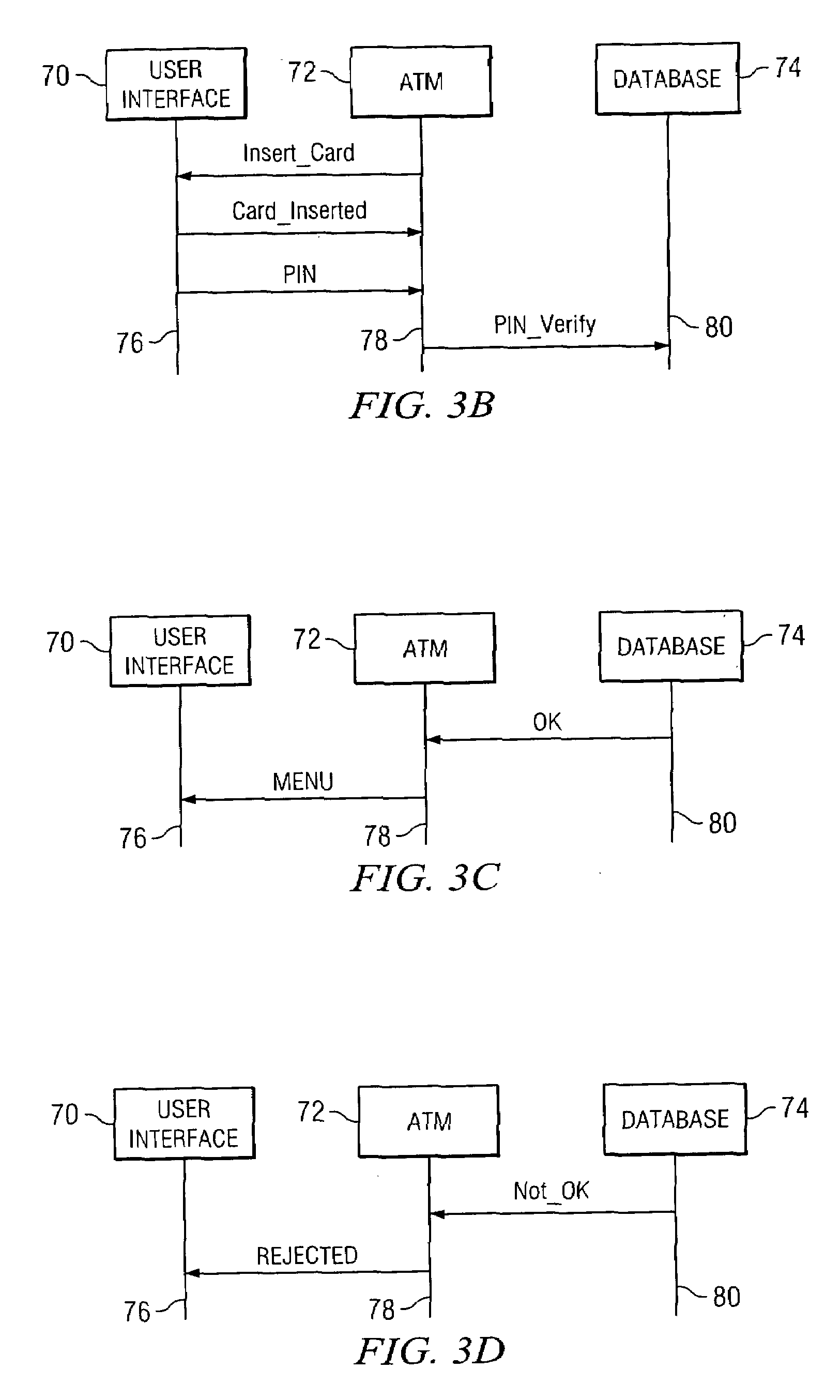

High level validation of designs and products

InactiveUS7275231B2High level validationHigh level of abstractionATM softwaresDesign optimisation/simulationComputer hardwareTest design

A method for high level validation of a design includes receiving input associated with a design; generating a message diagram in response to the input, wherein the message diagram describes a relationship of messages communicated between multiple processes; resolving at least one scenario from the message diagram, wherein the scenario comprises a particular sequence of messages identified by the message diagram; generating a state machine operable to receive and transmit at least some of the messages identified by the message diagram according to the scenario; and testing an implementation of the design using the state machine.

Owner:FUJITSU LTD

Transitioning Between Different Views of a Diagram of a System

InactiveUS20120026173A1Level of abstraction may increase and decreaseHigh level of abstractionProgramme controlCathode-ray tube indicatorsUser inputHuman–computer interaction

Presenting different views of a system based on input from a user. A first view of a first portion of the system may be displayed. For example, the first portion may be a device of the system. User input specifying a first gesture may be received. In response to the first gesture, a second view of the first portion of the system may be displayed. For example, the first view may represent a first level of abstraction of the portion of the system and the second view may represent a second level of abstraction of the portion of the system. A second gesture may be used to view a view of a different portion of the system. Additionally, when changing from a first view to a second view, the first view may “morph” into the second view.

Owner:NATIONAL INSTRUMENTS

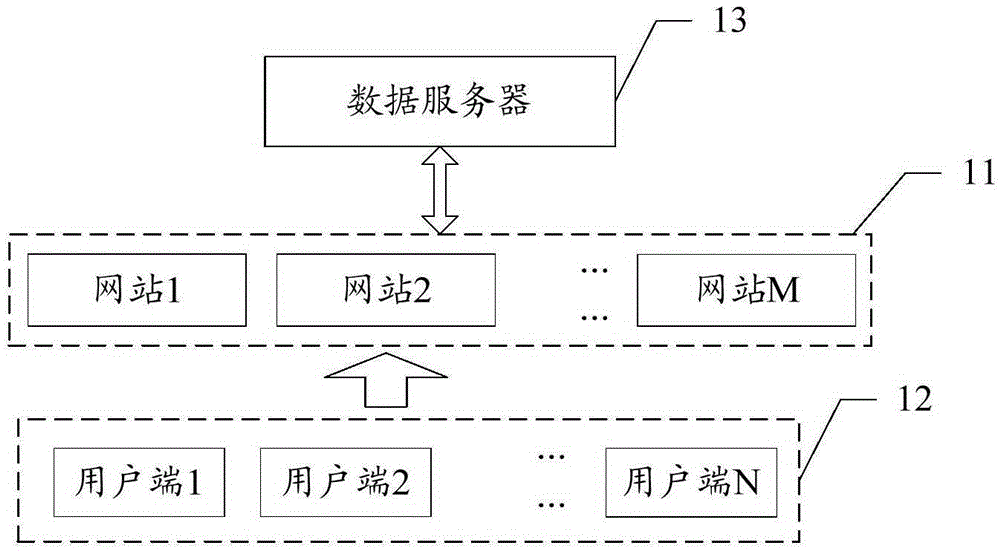

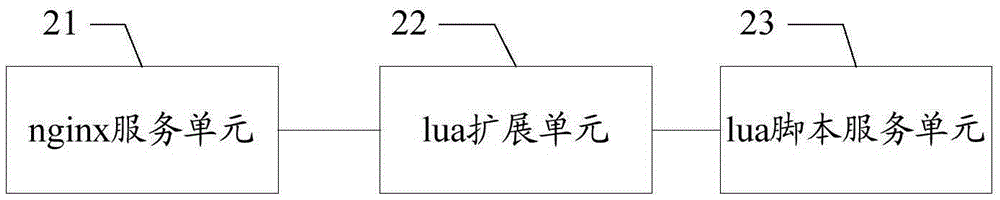

Data server

A data server comprises a Nginx service unit, a lua extension unit and a lua script service unit, wherein the Nginx service unit is suitable for receiving an HTTP request; the lua extension unit is suitable for acquiring the HTTP request and forwarding the HTTP request to the lua script service unit; the lua script service unit is suitable for analyzing the HTTP request to acquire target data. The data server has the advantages of being high in throughput and low in development degree.

Owner:上海晶赞企业管理咨询有限公司

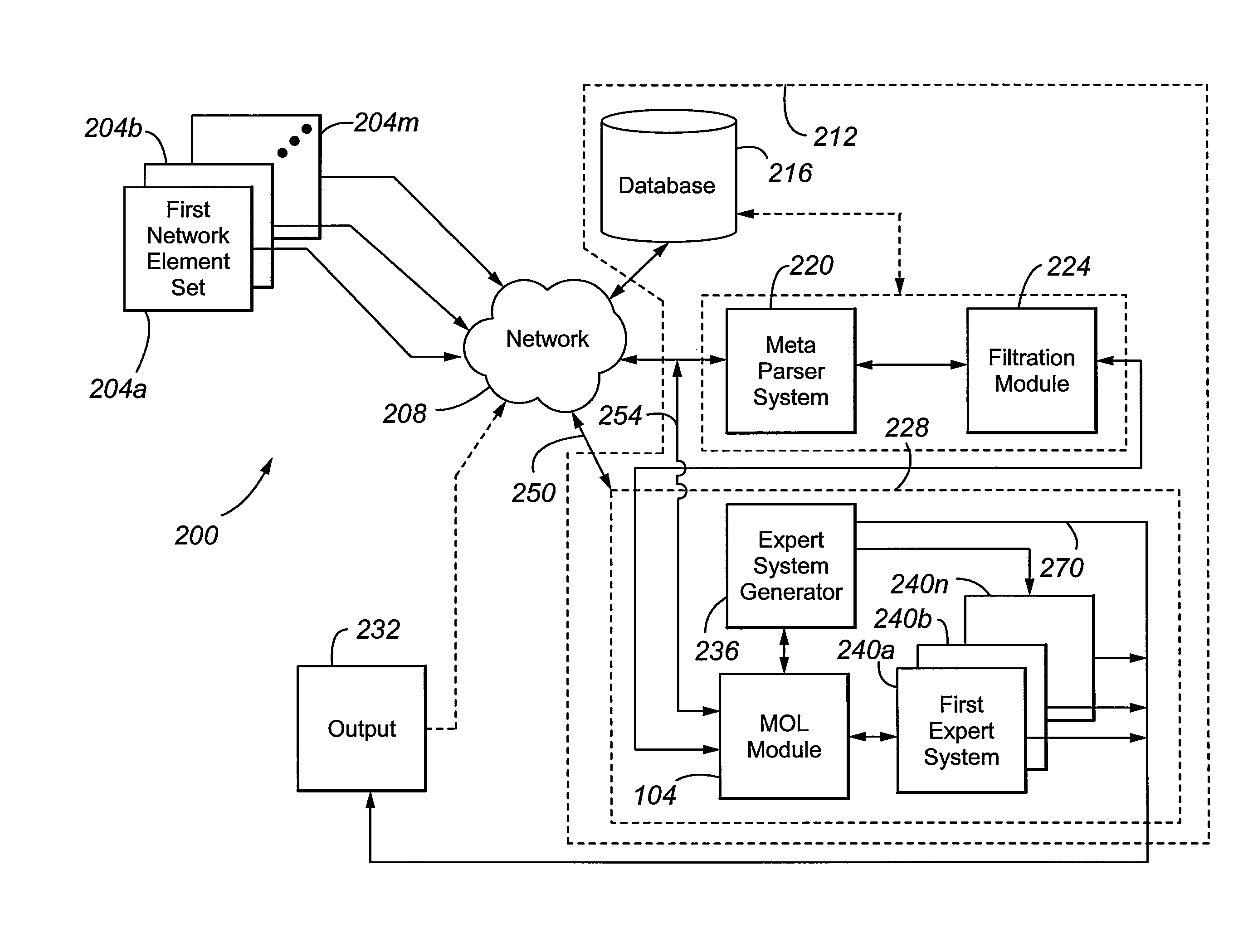

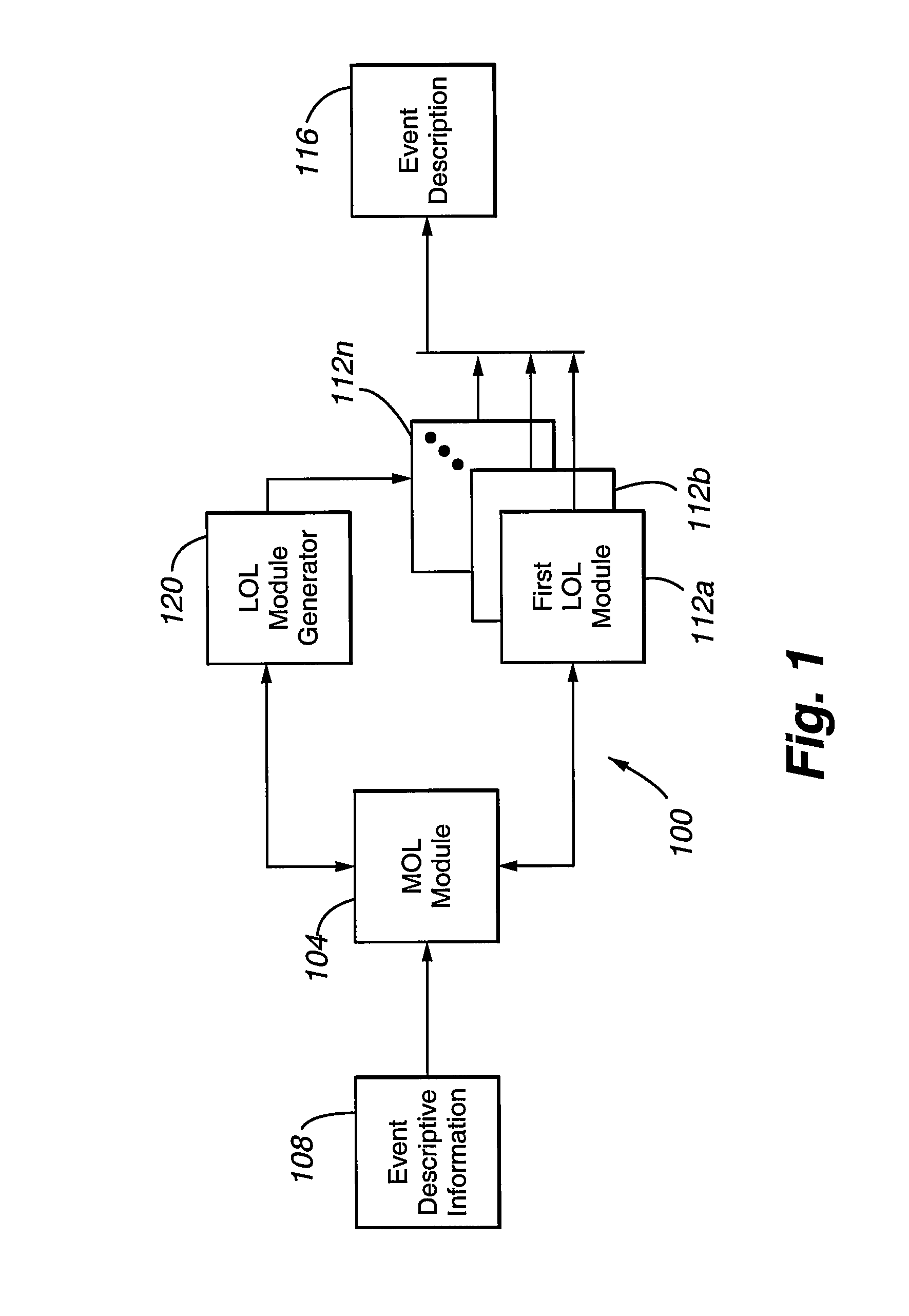

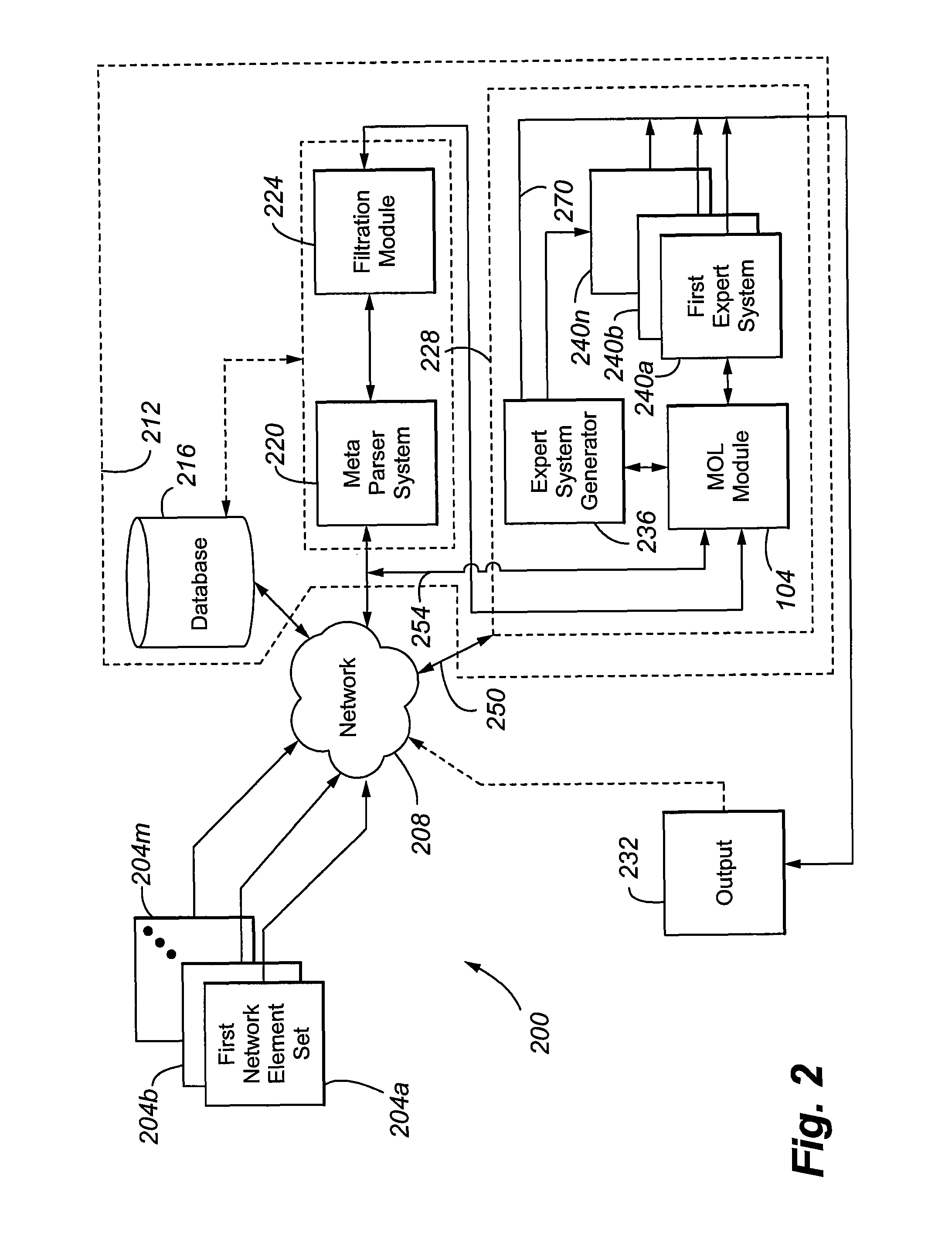

Higher order logic applied to expert systems for alarm analysis, filtering, correlation and root cause

ActiveUS8027946B1High level of abstractionComputationally efficientKnowledge representationSpecial data processing applicationsRoot causeAlarm analysis

The present invention is directed to a system and method for applying second- and higher-order logic to analysis of event descriptive information, such as alarms, error messages, and fault signals.

Owner:AVAYA INC

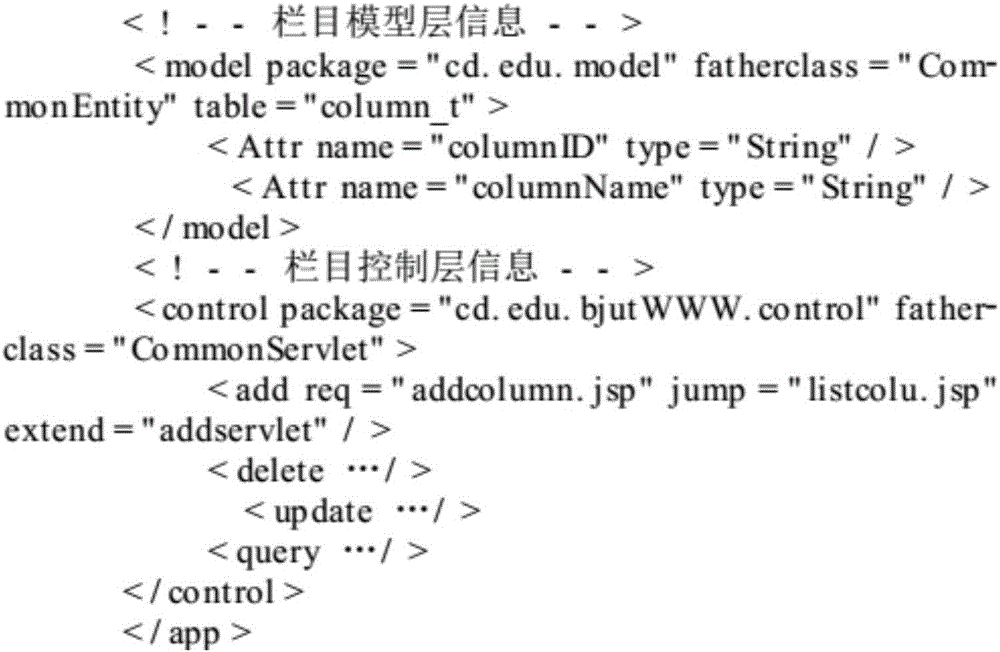

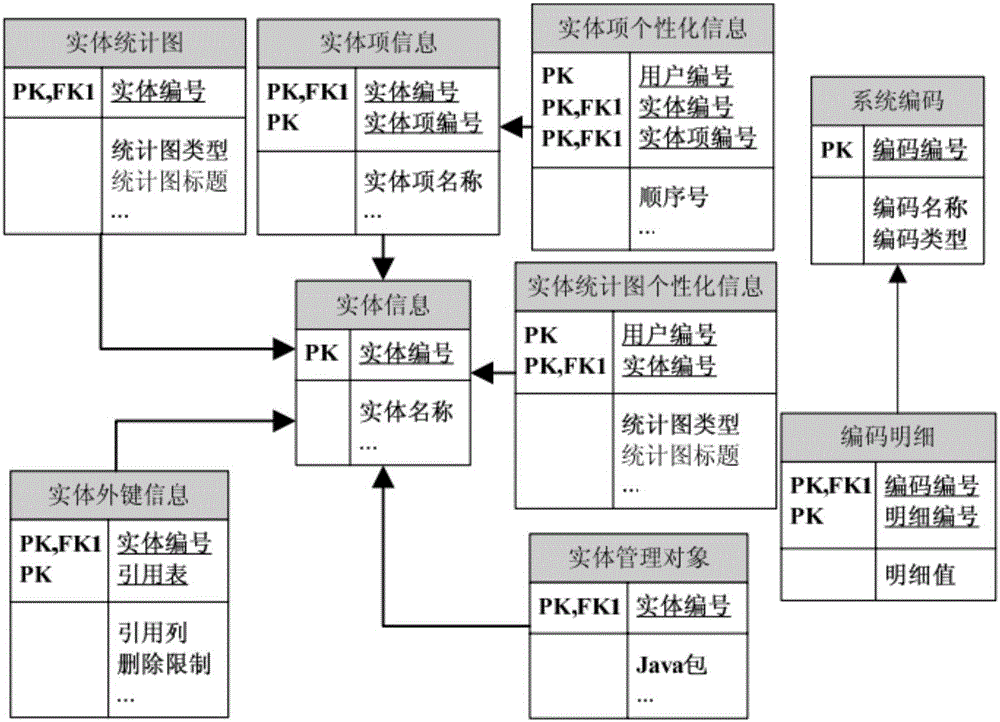

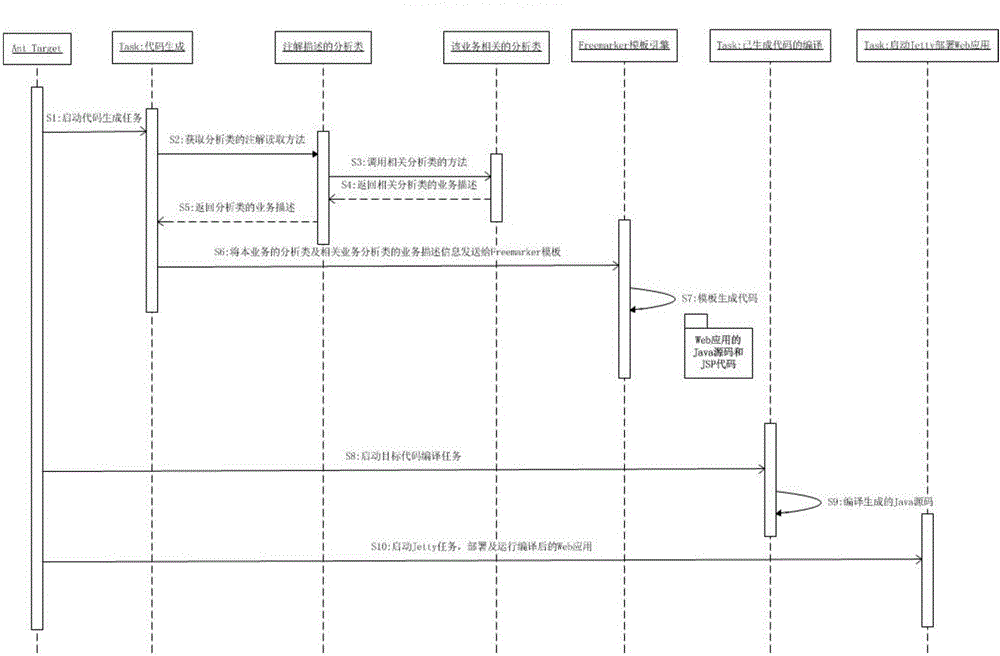

Annotation-based Web application code generation method

InactiveCN106648587AImprove productivityQuality improvementSoftware maintainance/managementSpecific program execution arrangementsWeb applicationObject code

The invention relates to an annotation-based Web application code generation method. The method comprises the following steps of S1: running Ant and starting a code generation technology; S2: applying an annotation reading method of an analysis class; S3: reading annotation contents of related analysis classes; S4: returning the annotation contents to an analysis class of a business module; S5: returning the annotation contents to the code generation technology; S6: sending business description information obtained from annotations to a Freemarker template engine by the code generation technology; S7: generating a source code by the Freemarker template engine; S8: starting a target code compilation task by the Ant; S9: performing compilation and copy on the source code, and generating a jar package or a war package; and S10: starting a Jetty task by the Ant, and releasing a Web application. According to the annotation-based Web application code generation method, an encoding process and detailed design and unit test time related to the encoding process can be greatly shortened.

Owner:福州宇嘉软件科技有限公司

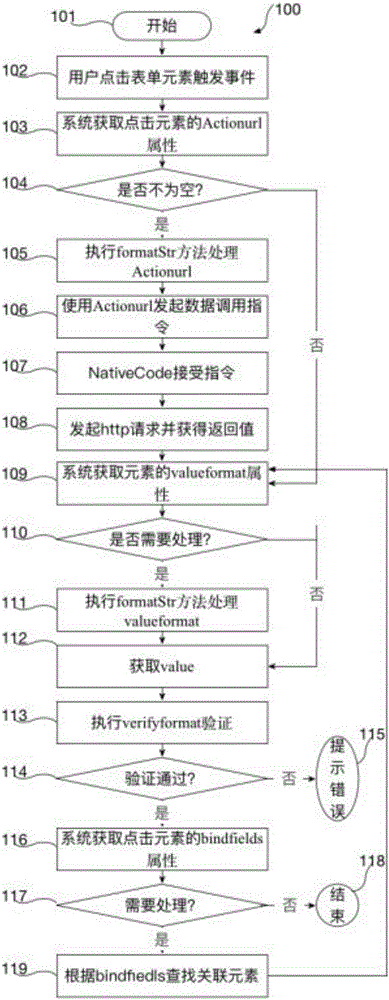

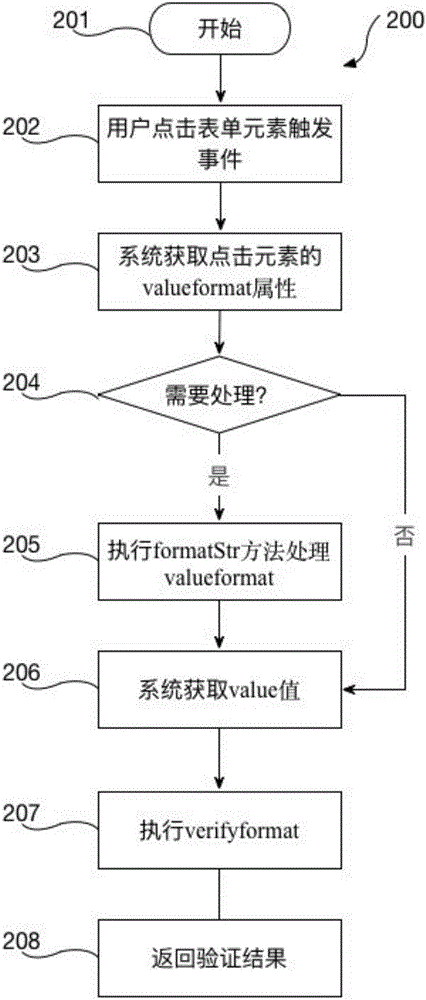

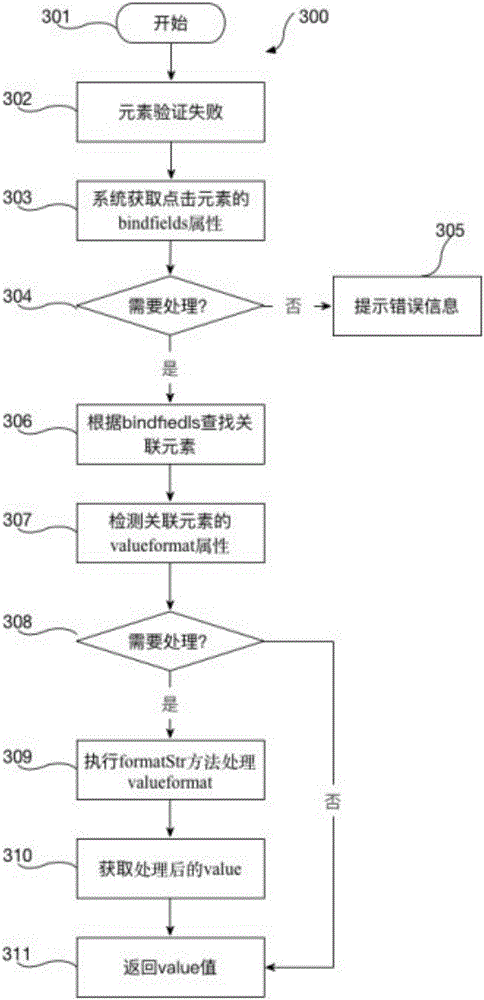

Method and system for realizing automatic verification of form and communication among multiple systems

ActiveCN105808701AForm abstraction is highHigh level of abstractionText processingExecution for user interfacesMultiple platformMulti field

This invention provides a method for realizing automatic verification of a form and communication among multiple systems. The method comprises the following steps: a server side create an html form, and the server side re-draws the form to a display container; a user side clicks a form element, and sends a triggering event for clicking the form element to the server side; according to the triggering event for clicking the form element, the server side realizes multi-field automatic combined verification of the drawn form through a built-in verification process engine, and sets data calling and binds data in the display container; the server side puts the verified form into the display container; and when the user side clicks the form element, the server side achieves remote procedure calling and cross-domain calling of field data through a built-in network service. By adopting the method provided by the invention, the higher degree of abstraction of the form is achieved through the multi-field automatic combined verification, and multiple platforms can be automatically switched; the form is filled automatically according to the associated fields; and thus, the development difficulty is effectively reduced.

Owner:JIANGSU ZHONGWEI TECH SOFTWARE SYST

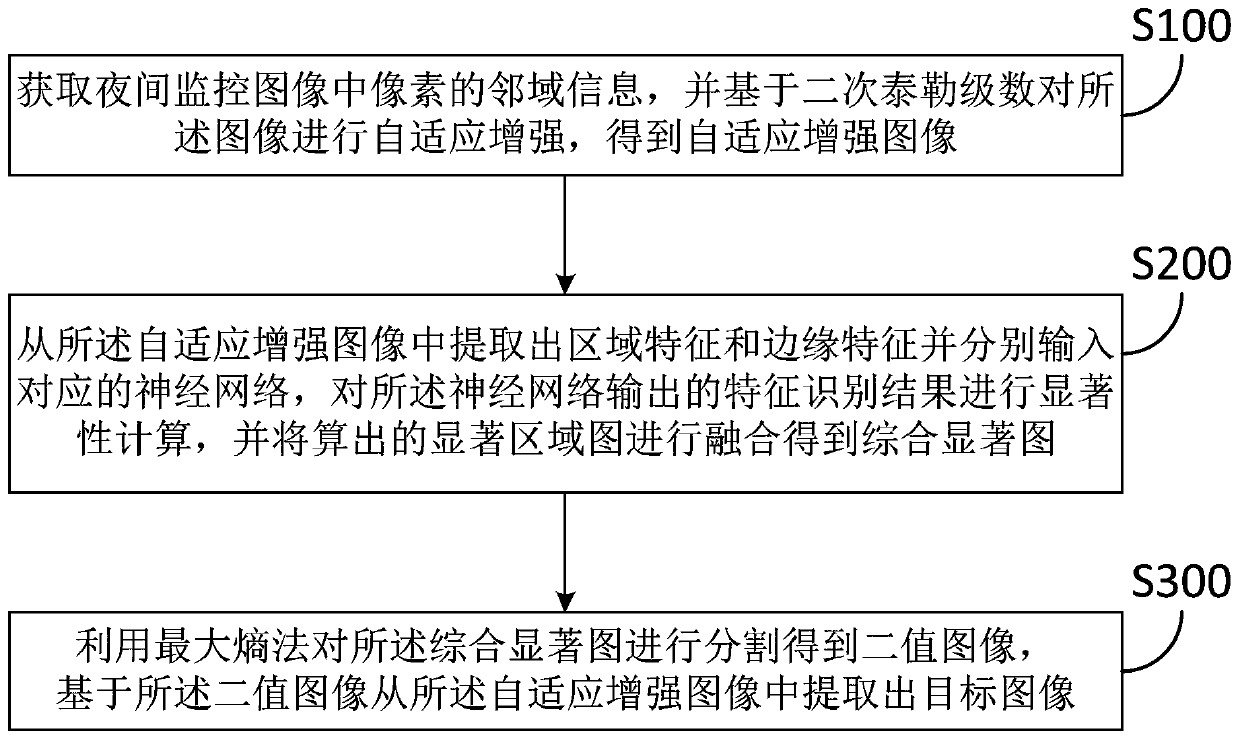

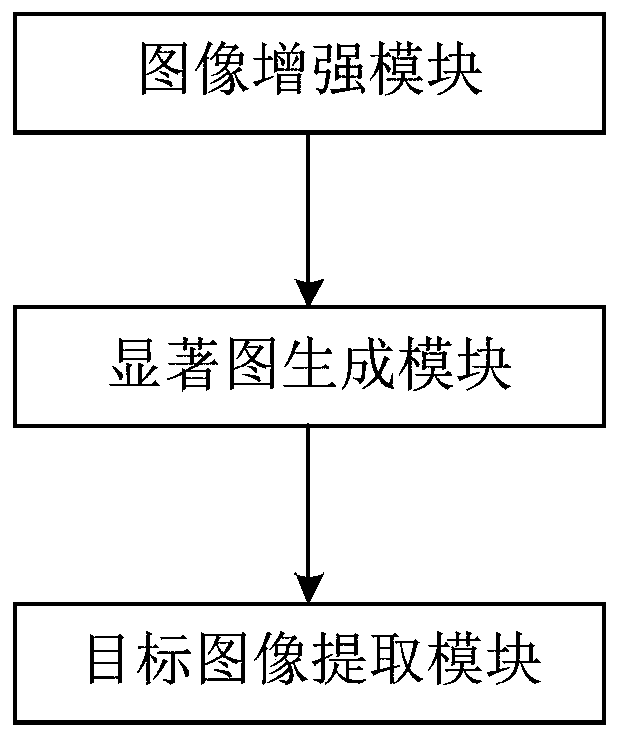

Night monitoring and identification method and system based on neural network enhancement

InactiveCN110598560AQuality improvementIncrease contrastCharacter and pattern recognitionNeural architecturesNerve networkSaliency map

The invention discloses a night monitoring and identification method based on neural network enhancement. The night monitoring and identification method includes the steps: firstly, obtaining neighborhood information of pixels in a night monitoring image; carrying out adaptive enhancement on the image based on the quadratic Taylor series; obtaining adaptive enhanced images, extracting regional features and edge features from the self-adaptive enhanced image and respectively inputting the regional features and the edge features into corresponding neural networks; and performing significance calculation on a feature recognition result output by the neural network, fusing the calculated significance region images to obtain a comprehensive significance image, finally segmenting the comprehensive significance image by using a maximum entropy method to obtain a binary image, and extracting a target image from the adaptive enhanced image based on the binary image. According to the night monitoring and identification method, the contrast of the image can be improved, and self-adaptive image enhancement is performed for the problem of uneven illumination of each part of the image, and the generated saliency map can effectively cover the boundary of the target area and well inhibit the saliency of the background area.

Owner:重庆特斯联智慧科技股份有限公司

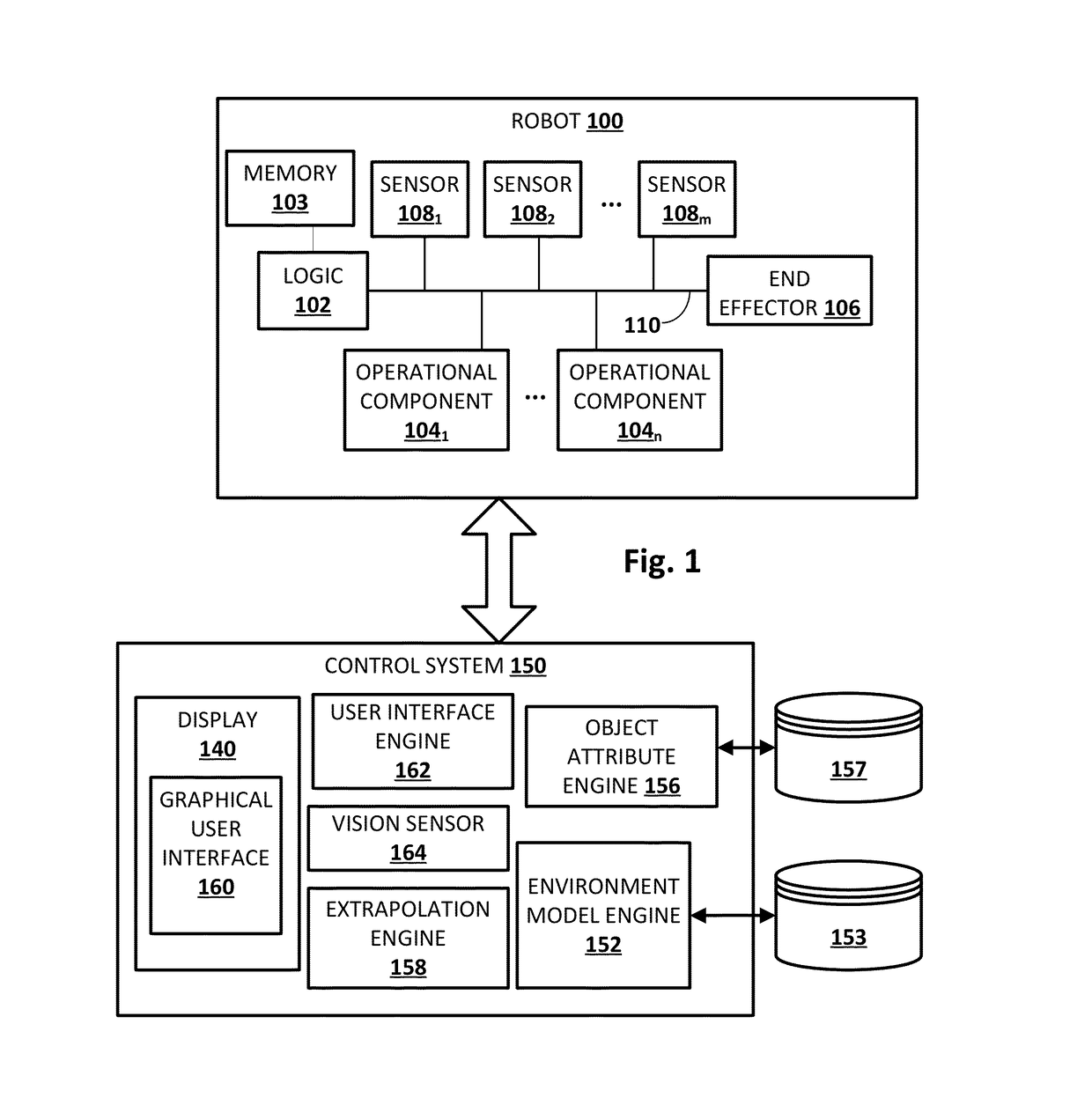

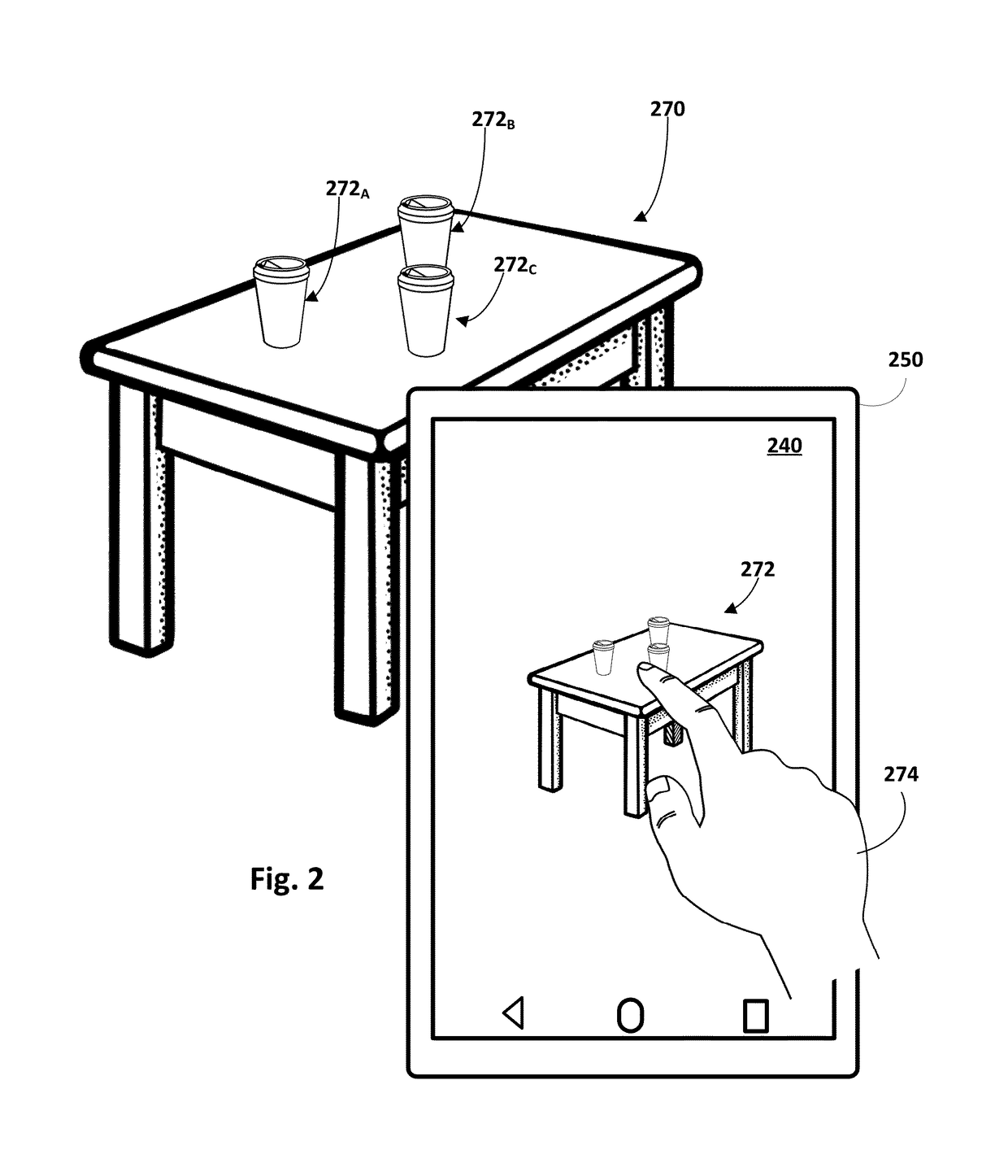

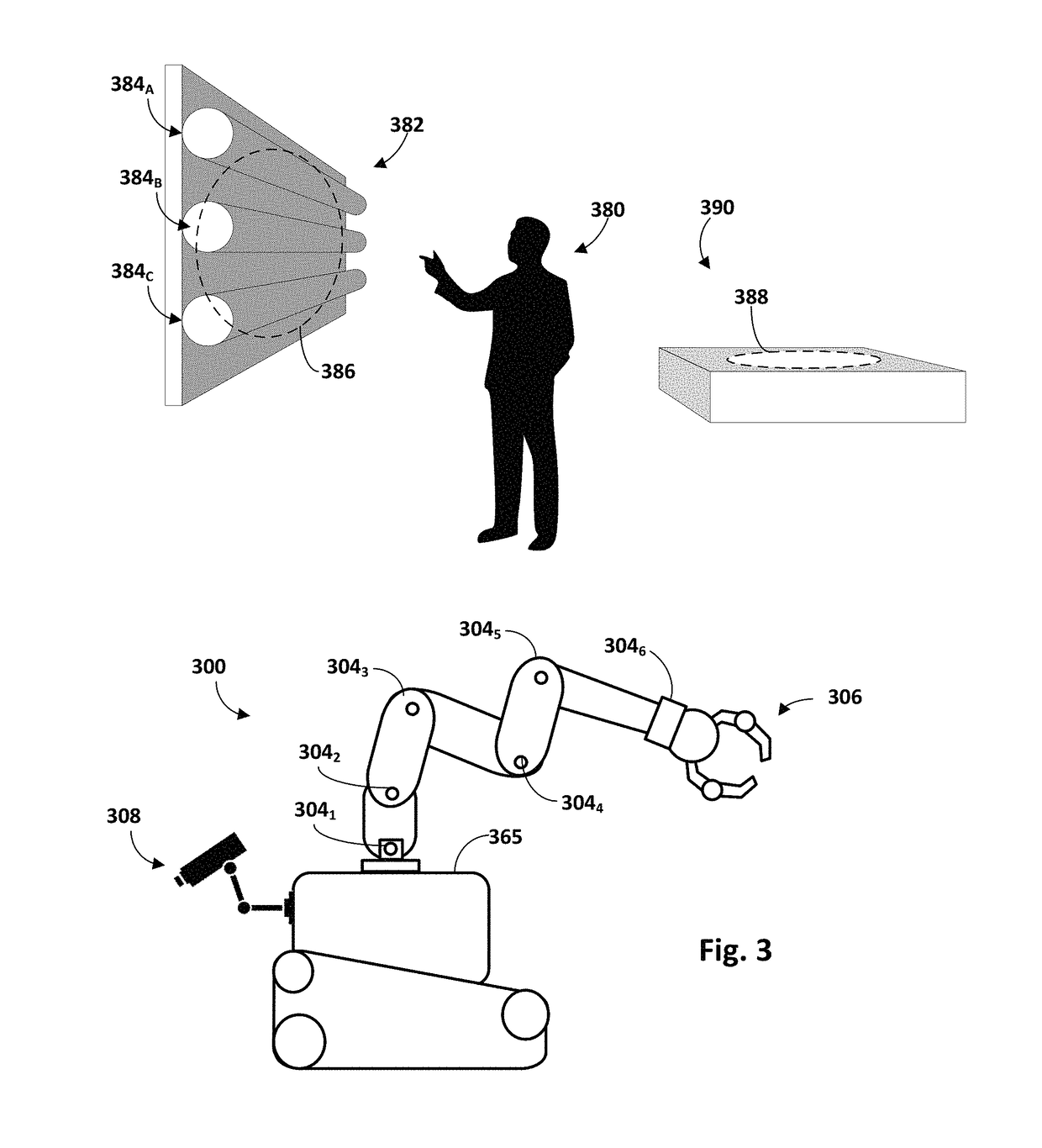

Space extrapolation for robot task performance

ActiveUS10058997B1High level of abstractionInput/output for user-computer interactionProgramme controlUser inputSimulation

Methods, apparatus, systems, and computer-readable media are provided for enabling users to approximately identify a space within an environment inhabited by a plurality of objects that user wishes for a robot to manipulate. In various implementations, an approximation of a space within an environment may be identified based on user input. The actual space within the environment may then be extrapolated based at least in part on the approximation and one or more attributes of the environment. A plurality of objects that are co-present within the space and that are to be manipulated by a robot may be identified. The robot may then be operated to manipulate the identified plurality of objects.

Owner:GOOGLE LLC

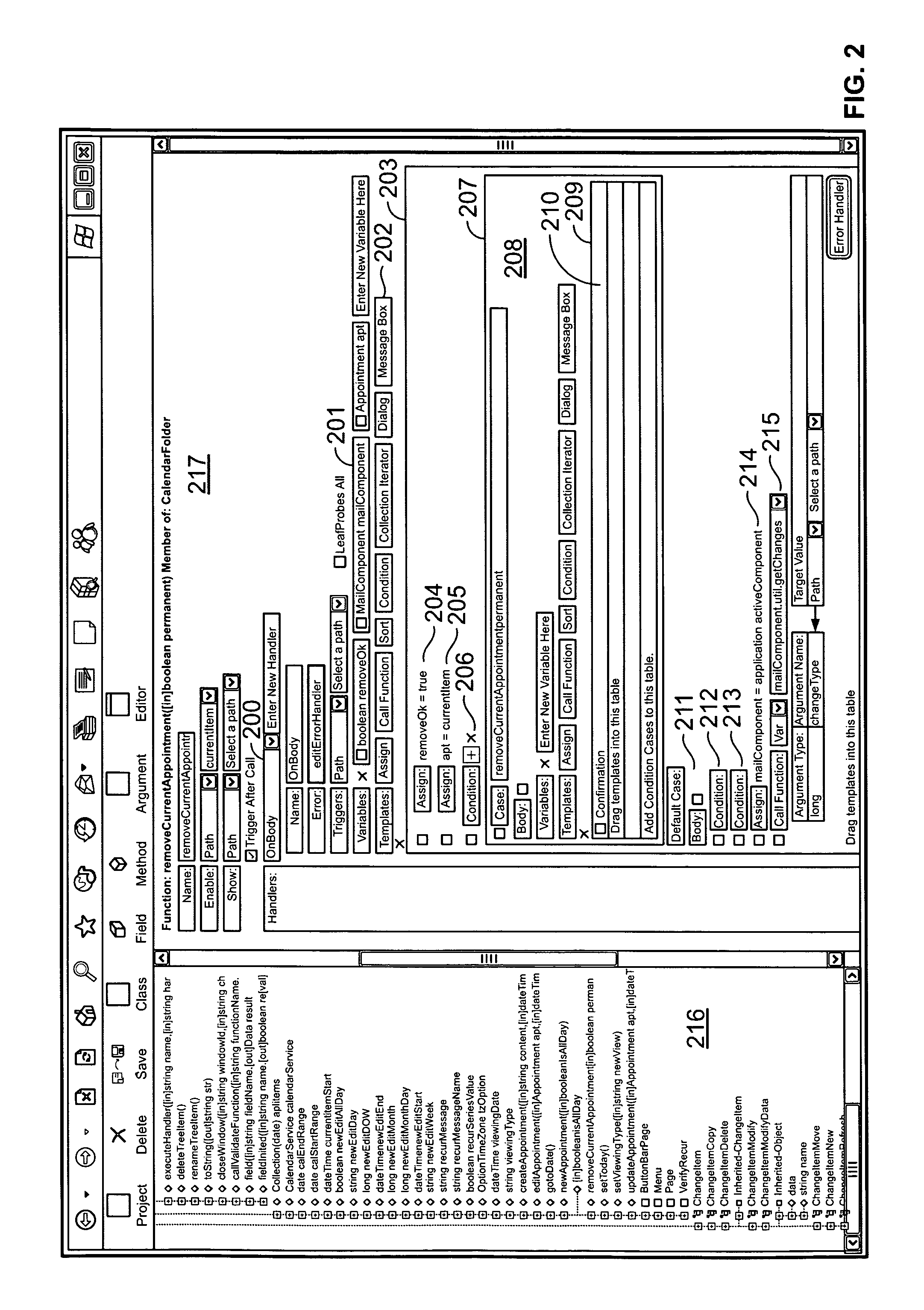

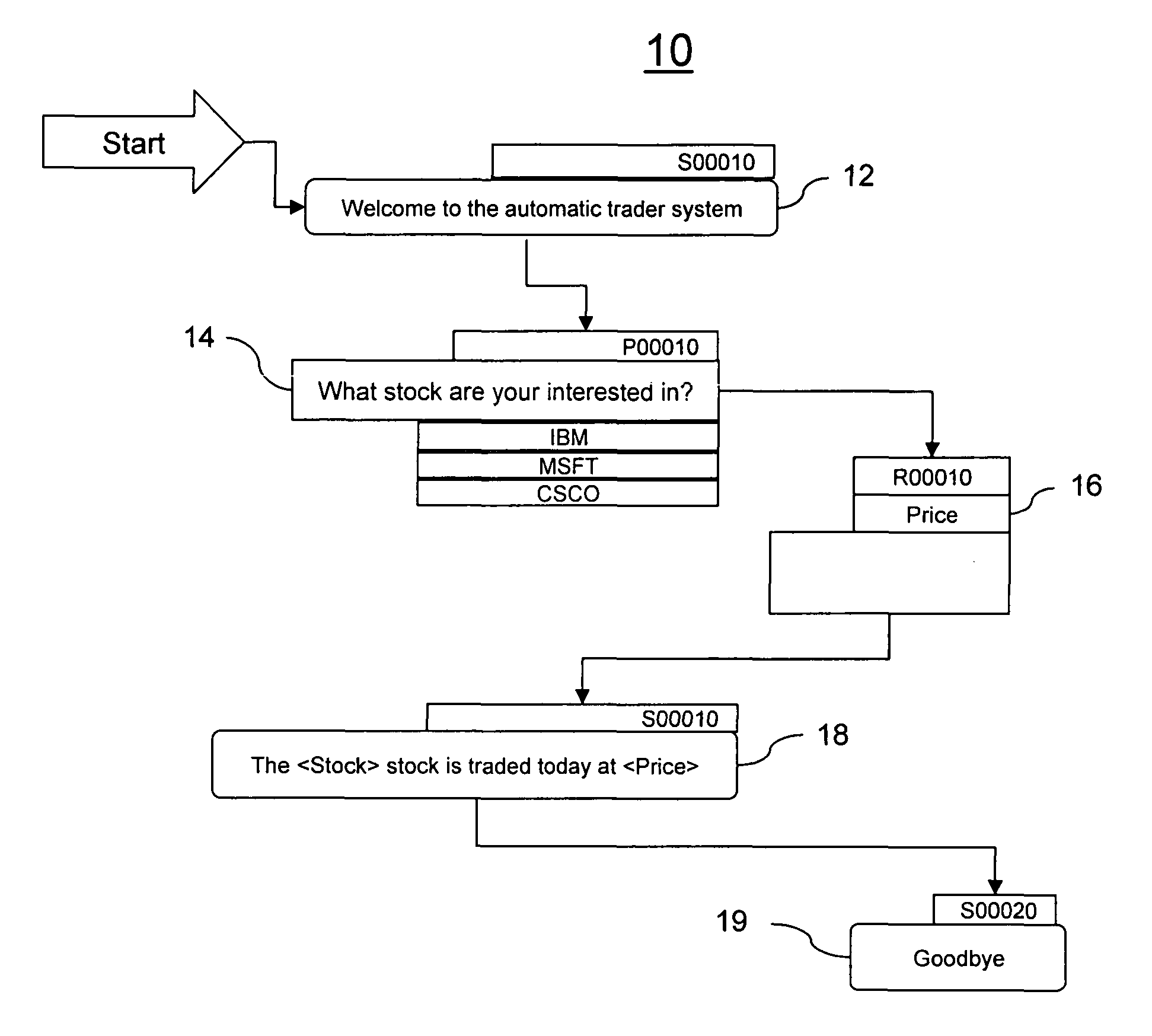

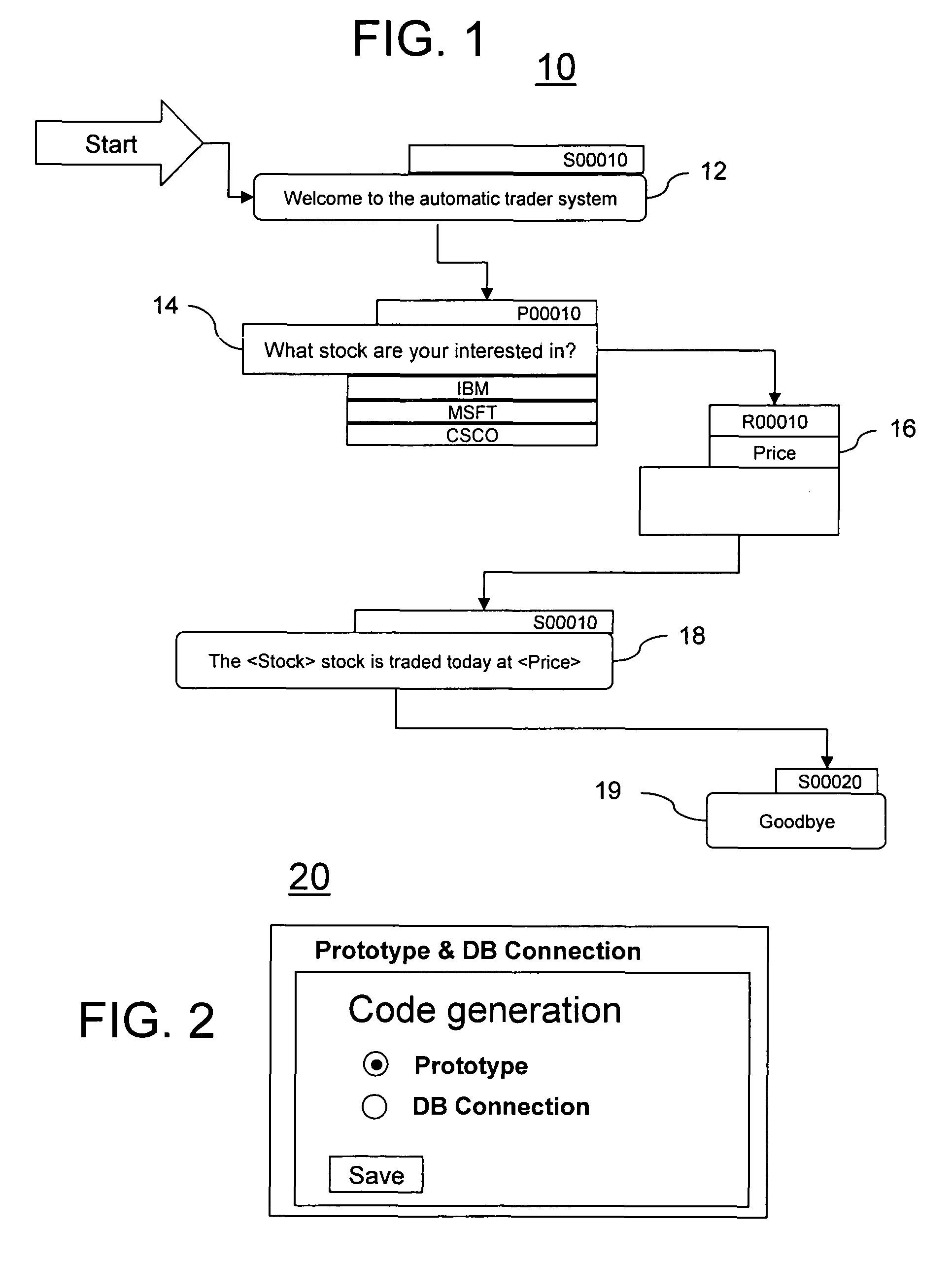

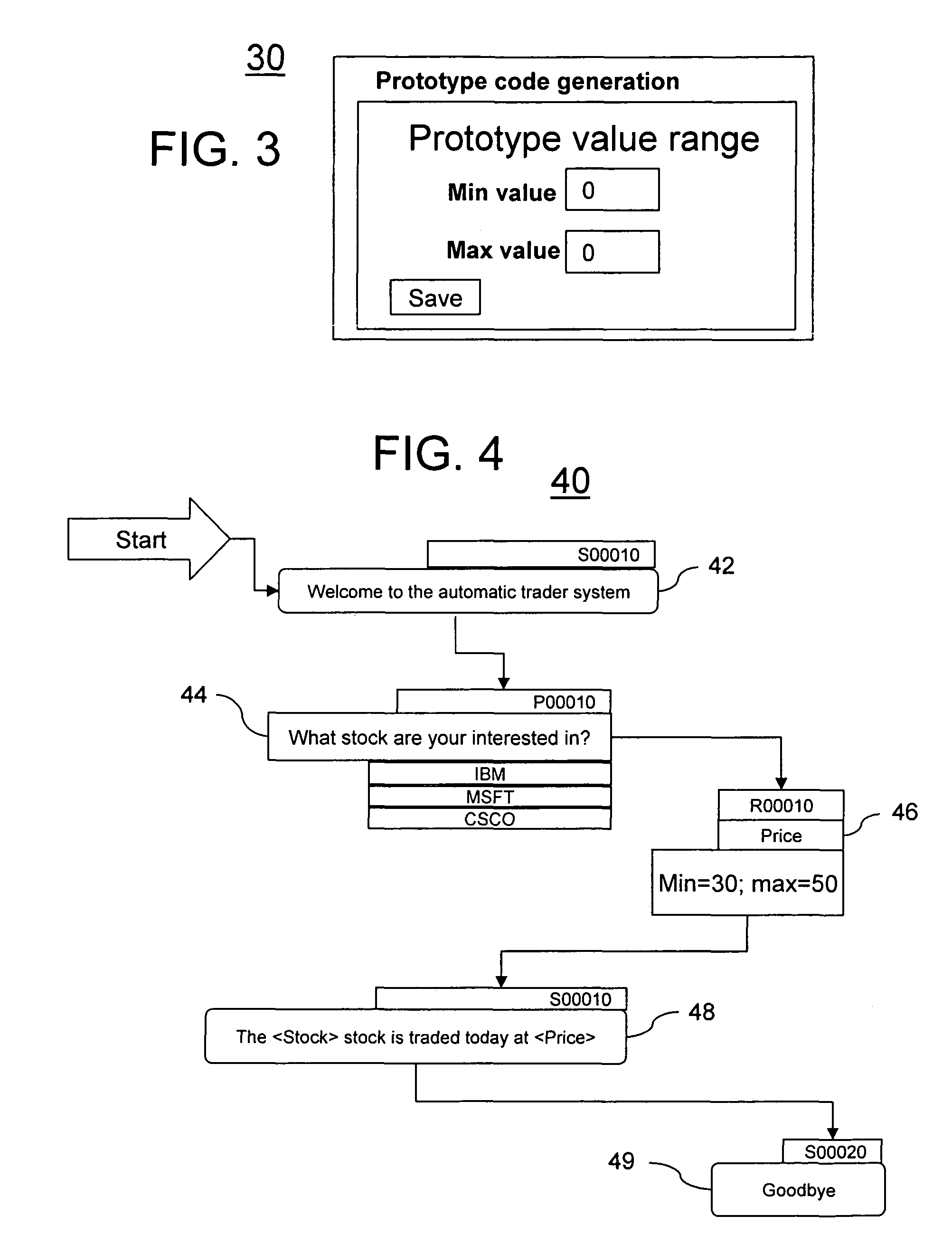

Method and system for switching between prototype and real code production in a graphical call flow builder

InactiveUS7797676B2High level of abstractionResistance/reactance/impedenceDigital data processing detailsProgramming languageGraphics

A method and system for automated code generation in a call flow builder (10) can include a display coupled to a processor. The processor can be programmed to select a real code (database connection) or a prototype code using a graphical interface (20) to provide a selected code and develop a call flow using the selected code. The processor can be programmed to select the prototype code as the selected code, test the call flow in a local development environment and further enable the switching of the selected code from the prototype to the real code to complete a database connection. The processor can be further programmed to enable specification of a default or range of values. Additionally, the processor can be programmed to use a database connection code that replaces a prototype assignment of values to variables when the real code is the selected code.

Owner:LINKEDIN

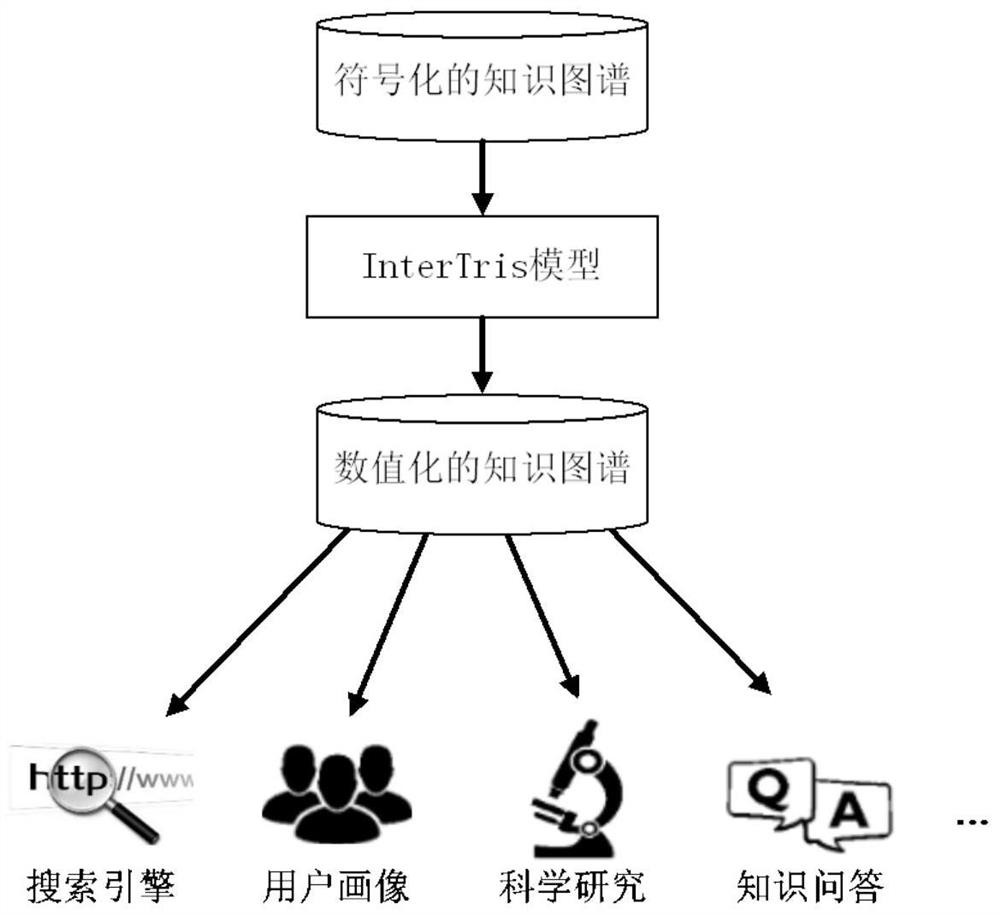

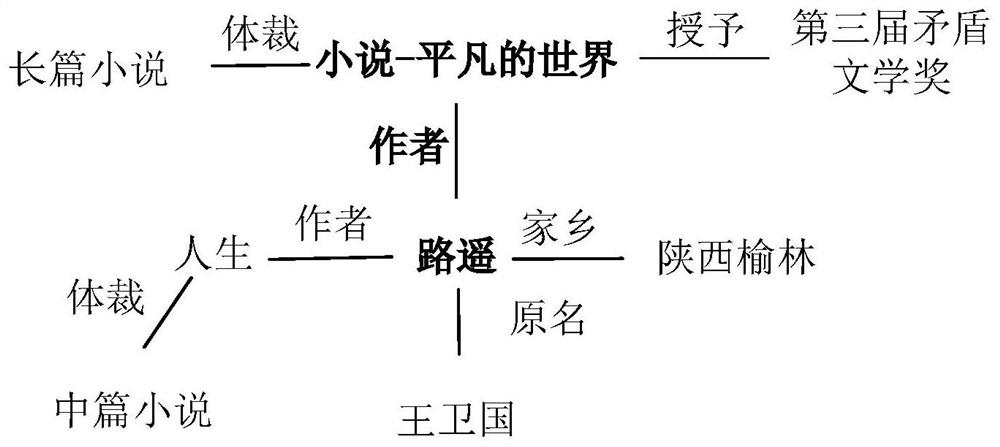

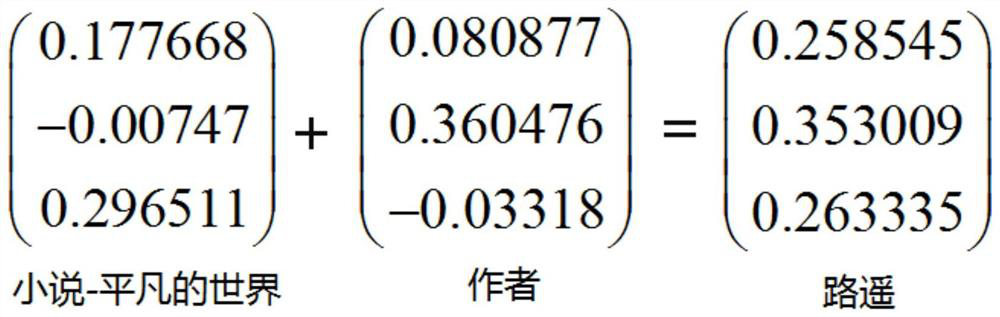

Knowledge graph representation learning method based on ternary interaction

ActiveCN111914094AHigh utility valueReduce dependencySemantic analysisSpecial data processing applicationsData setMedicine

The invention relates to a knowledge graph representation learning method based on ternary interaction, and the method is characterized in that the method comprises the following steps: 1) in a knowledge graph, modeling a head entity, a relationship and a tail entity and the interaction among the head entity, the relationship and the tail entity through employing a triad as a basic unit to acquirean InterTris model; 2) training the constructed InterTris model to acquire a trained InterTris model; and 3) by utilizing the obtained InterTris model, achieving numeralization representation of theknowledge graph so that a foundation is laid for knowledge graph value mining. The essence of semantic relationship construction of the knowledge graph, modeling is performed on the basis of basic unit triples of the knowledge graph. No matter how the data characteristics change, the basic composition unit of the knowledge graph does not change. Therefore, as the abstraction degree is relatively high, the dependence degree of the knowledge graph representation learning model on a data set is reduced, and the invention has higher universality and can be widely applied to the field of knowledgegraph representation learning.

Owner:RENMIN UNIVERSITY OF CHINA

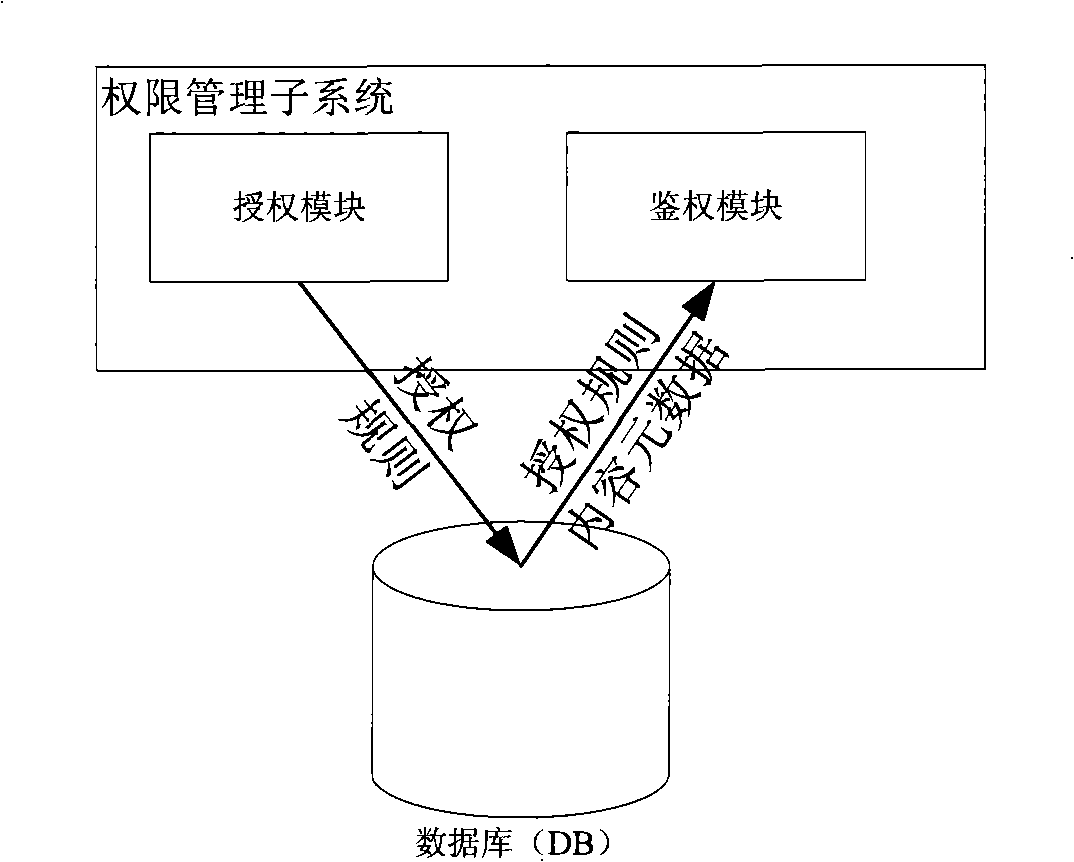

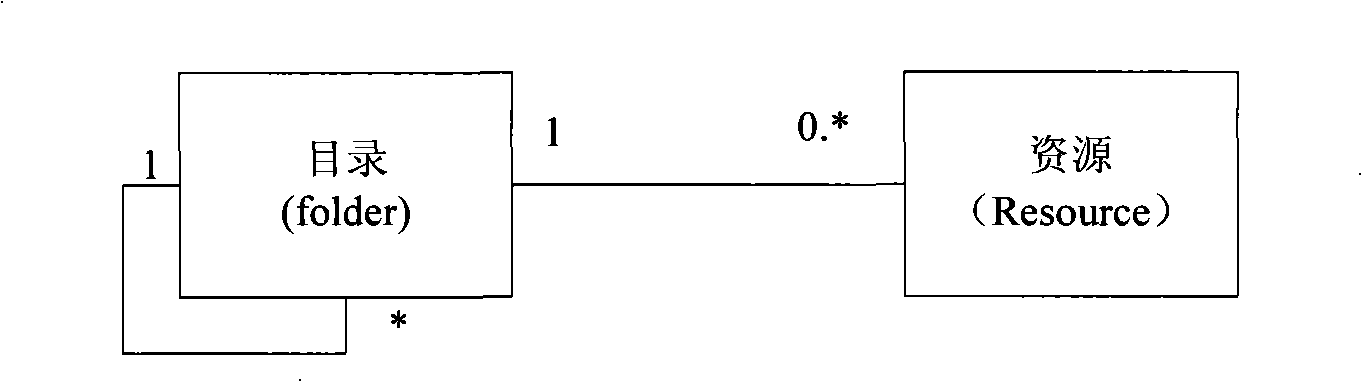

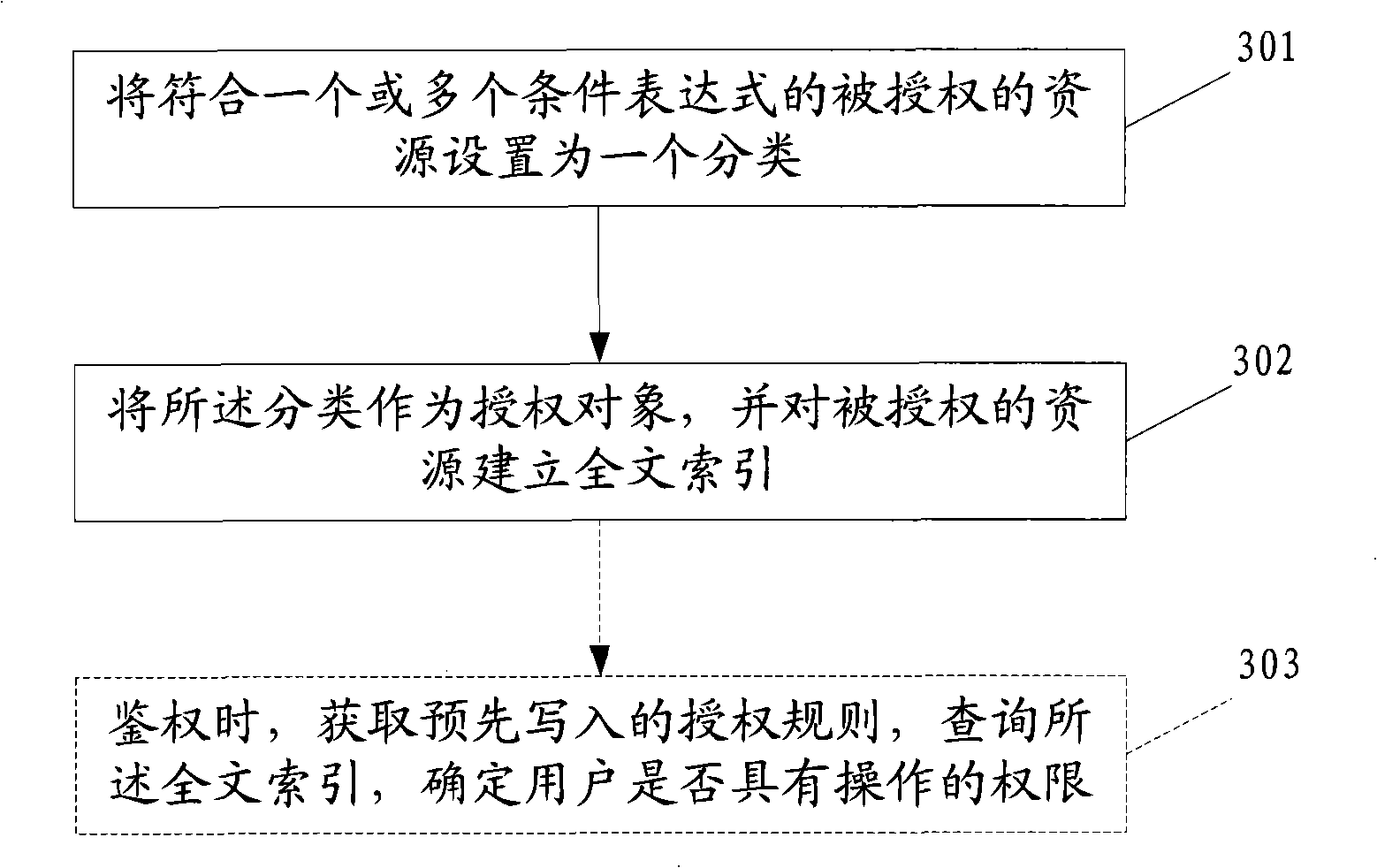

Authority management method, apparatus and system

ActiveCN101299216AImprove experienceImprove performanceProgram/content distribution protectionSpecial data processing applicationsConditional expressionEngineering

The invention discloses an authority management method, including: setting the authorized resource conforming to one or a plurality of conditional expressions as a categorization; taking the categorization as authorization object, and establishing full text indexes to the authorized resource. Furthermore, the invention also discloses an authority management device and system, which can improve the authentication performance of the user data authority and can improve the expandability of the system.

Owner:HUAWEI TECH CO LTD

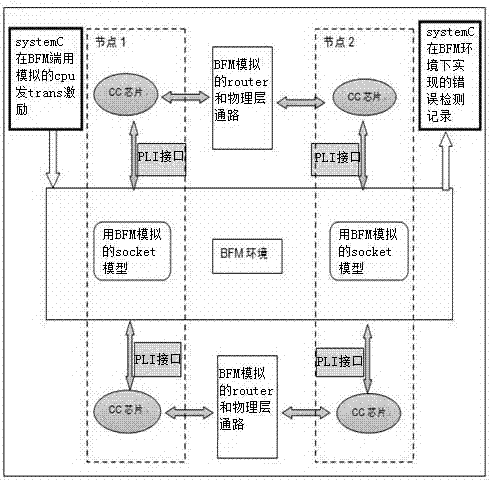

Method for verifying large-scale interconnection chips based on BFM

InactiveCN104714870AImprove verification efficiencyReduce complexityElectronic circuit testingLogical operation testingEmbedded systemSoftware language

The invention discloses a method for verifying large-scale interconnection chips based on a BFM, and belongs to the field of chip design. The method comprises the steps that operation of sending a bus protocol command is achieved through utilizing routers and physical layer accesses of the chips between BFM simulation nodes; the BFM is connected with the chips of the same node through pli interfaces, the BFM simulates socket models between the nodes, and BFM logic verification environment is established; a system C simulates a CPU to send a drive signal to the logic verification environment at the BFM end, the socket models send verification data to chips through the pli interfaces, after the chips respond, chip feedback data are recorded, and error detection records are achieved through the system C. By means of the method for verifying the large-scale interconnection chips based on the BFM, the complexity degree of verification is reduced, the comprehensive validation is guaranteed, the universality of verification drive is improved, and by means of the advantage of taking the system C as a software language, the operation and the data monitoring with higher abstraction degree are achieved.

Owner:INSPUR GROUP CO LTD

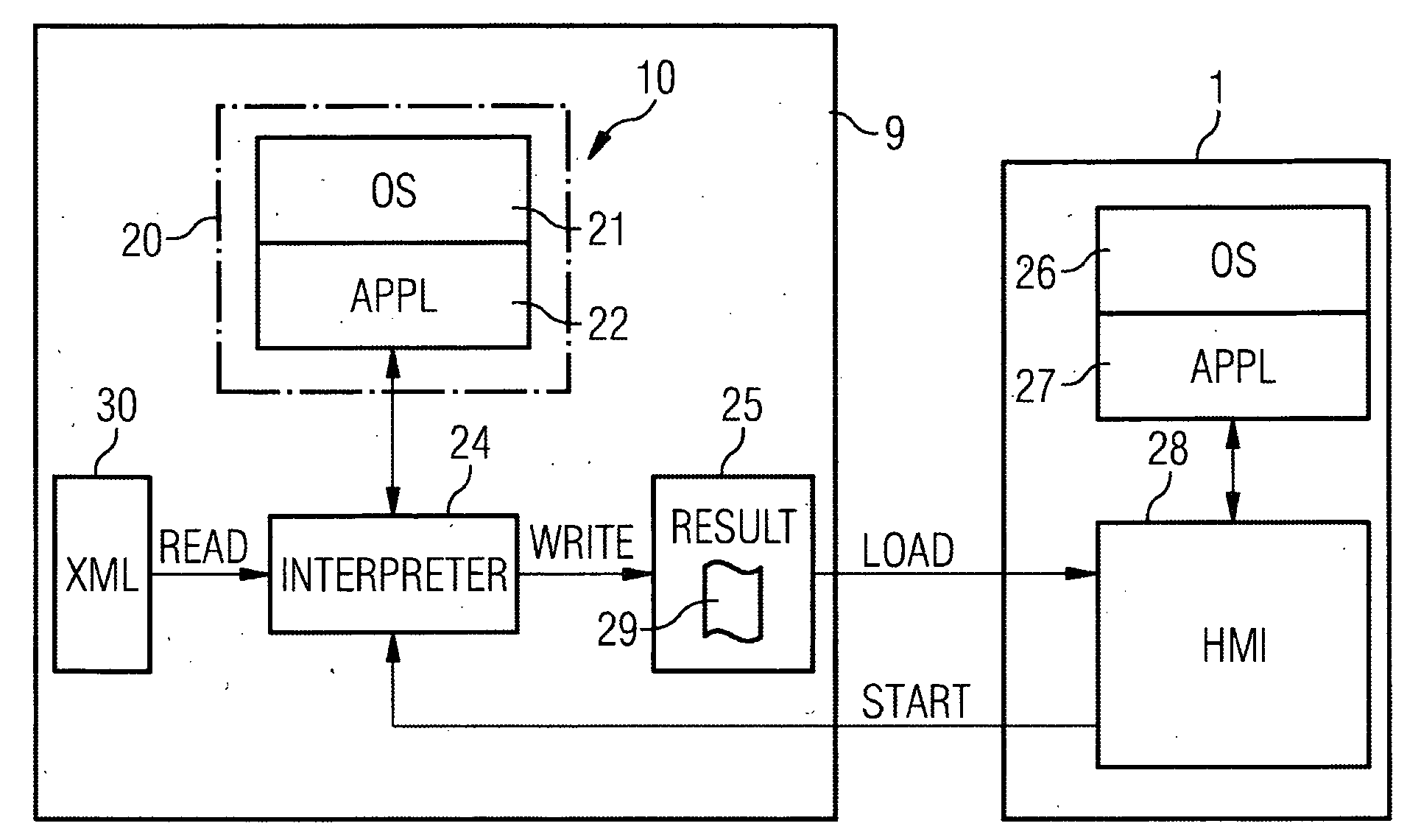

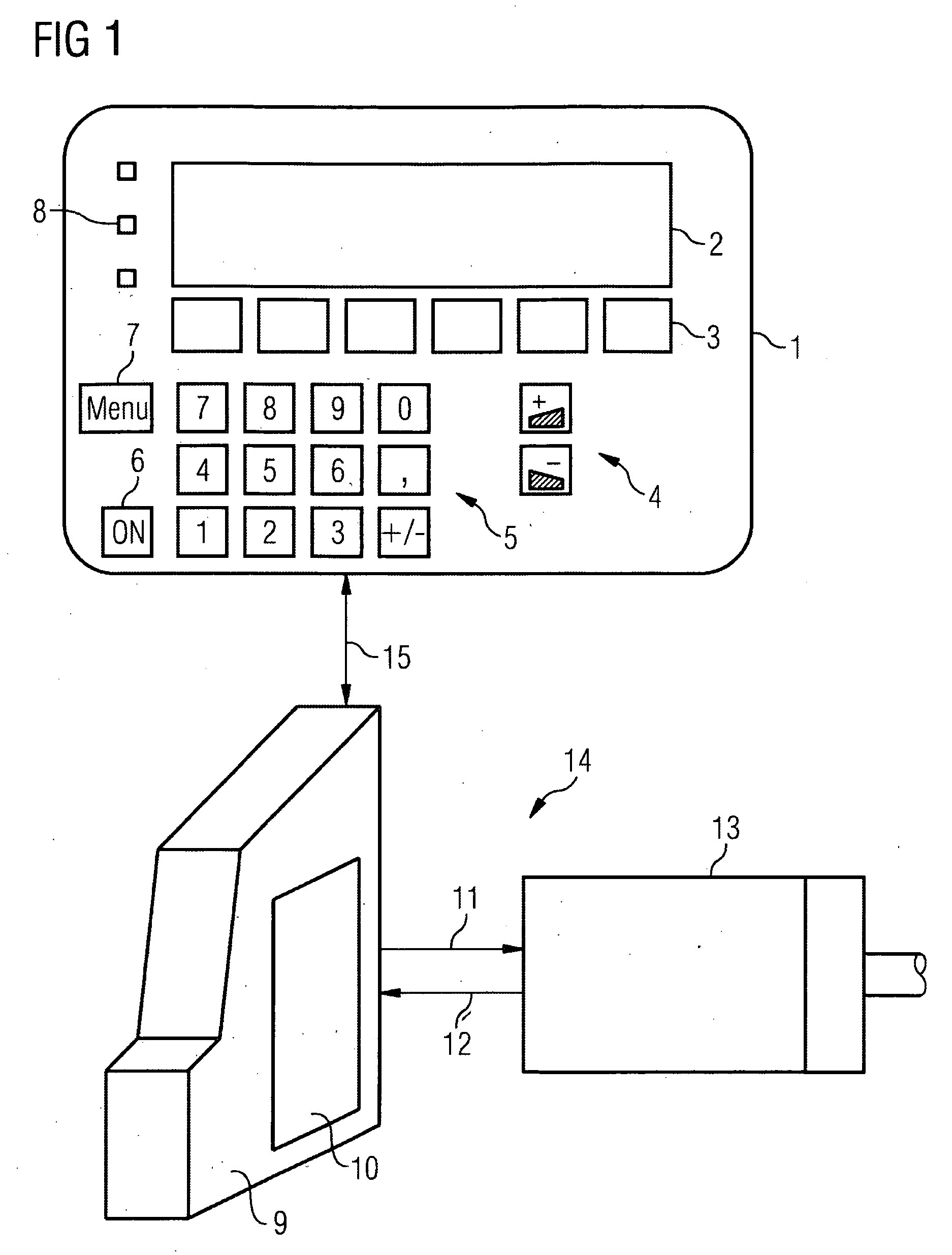

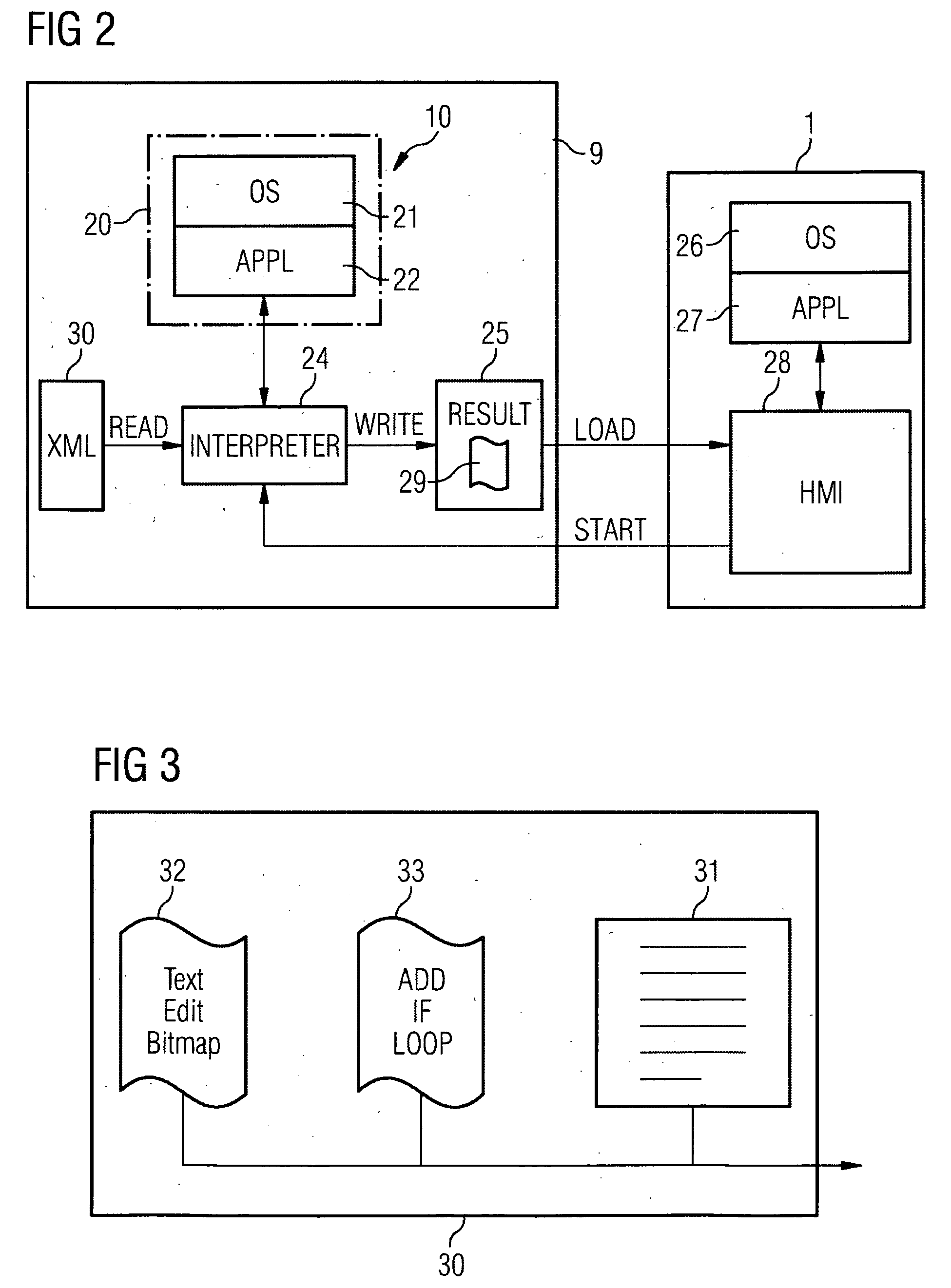

Method for operating and monitoring a control device, corresponding operating/monitoring device, control device and machine with such a control device, and uses of the method together with data storage media

ActiveUS20090182437A1Control unit is damagedEasy to modifyInput/output for user-computer interactionComputer controlApplication softwareData store

There is described a method, wherein an interpreter program is executed on a control device and is adapted to access scripts having display components and program architectures. Said program architectures are enabled to access operating data of the firmware of the control device, said operational data being convertible to display data of a defined display format and vice versa. The scripts are run, the program architectures compiling the corresponding result in the form of display components with optionally the display data in the defined display format and making the result available to the operating / monitoring device. A display program is executed on the reporting / monitoring device in order to display at least the display components in the defined display format. References to at least one script on the control device are deposited in the display components. These references are connected to an event, and the interpreter program initiates and runs the corresponding script when this event occurs. The operating / monitoring device can no longer directly access the sensitive firmware of the control device. Communication is carried out via an interpreter program. Access to the actual control application is no longer possible.

Owner:SIEMENS AG

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com