Clock network traversing testing method based on FPGA (Field Programmable Gate Array) hardware structure

A clock network and traversal test technology, applied in the field of integrated circuits, can solve the problems of increasing test time, test cost, scarcity of resources, etc., and achieve the effect of reducing the number of configurations, reducing the number of configurations, and improving portability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

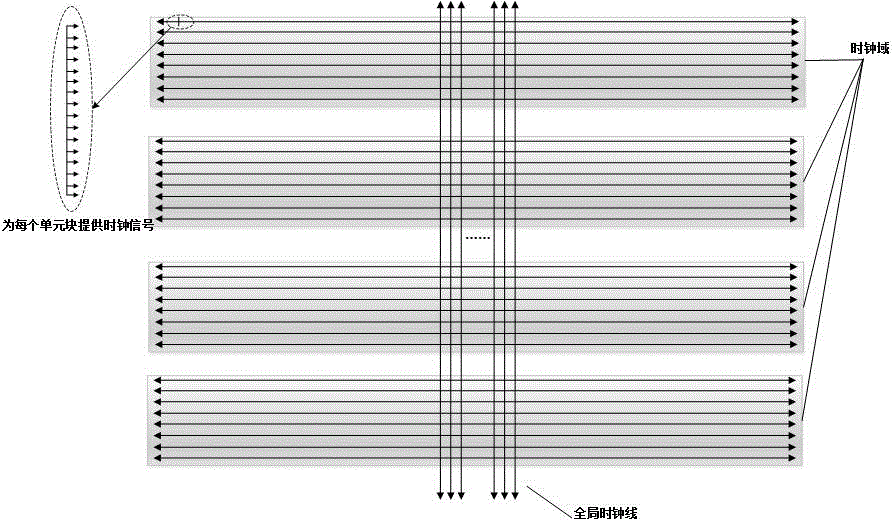

[0024] For the unit circuit whose basic logic block is CLB, all SLICEs are Figure 5 configured as shown. Configure the output of all SLICEs to operate in clock edge-based modes, such as flip-flops. In this mode of operation, short circuit, open circuit, normal 0 and normal 1 faults of the clock signal can be detected. Configure one SLICE in a logic unit as a four-input AND operation unit, and configure the other three as a state where the output is always 1 after the clock signal arrives, and connect it to the three input terminals of the first SLICE, and the other three of the SLICE One input comes from the output of the upper logic unit. After all the CLBs in the FPGA are configured in this way, the entire FPGA is like a shift chain. If all clock terminals can work normally, then after N clock cycles, the input value will be shifted out. Among them, N is the number of all CLB logic blocks in the FPGA. If any clock input terminal in the chip fails, for example, the cloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com